US00D546819S

# (12) United States Design Patent (10) Patent No.:

Oliver

US D546,819 S

(45) Date of Patent: Jul. 17, 2007

#### RADIO FREQUENCY IDENTIFICATION TAG **ANTENNA ASSEMBLY**

- Inventor: Ronald A. Oliver, Seattle, WA (US)

- Assignee: Impinj, Inc., Seattle, WA (US)

- Term: 14 Years

- Appl. No.: 29/254,144

- Filed: Feb. 17, 2006 (22)

| (51) | LOC (8) Cl                                        |

|------|---------------------------------------------------|

| (52) | U.S. Cl D14/230                                   |

| (58) | Field of Classification Search                    |

|      | D14/230-238, 299, 358; D12/42, 43; 343/700 MS,    |

|      | 343/700 R-705, 711-713, 741, 748, 767,            |

|      | 343/795, 819, 840, 846, 866, 871–908; 455/90.2,   |

|      | 455/90.3, 91, 128, 269, 344, 347, 562.1           |

|      | See application file for complete search history. |

#### (56)**References Cited**

## U.S. PATENT DOCUMENTS

| 4,783,783 | A            | 11/1988 | Nagai et al.      |

|-----------|--------------|---------|-------------------|

| 4,935,702 | $\mathbf{A}$ | 6/1990  | Mead et al.       |

| 5,430,441 | $\mathbf{A}$ | 7/1995  | Bickley et al.    |

| 5,528,222 | A            | 6/1996  | Moskowitz et al   |

| 5,572,226 | $\mathbf{A}$ | 11/1996 | Tuttle            |

| 5,719,586 | $\mathbf{A}$ | 2/1998  | Tuttle            |

| 5,805,632 | A            | 9/1998  | Leger             |

| 5,933,039 | A            | 8/1999  | Hui et al.        |

| 5,939,945 | A            | 8/1999  | Thewes et al.     |

| 5,995,048 | A            | 11/1999 | Smithgall et al.  |

| 6,043,746 | $\mathbf{A}$ | 3/2000  | Sorrells          |

| 6,045,652 | A            | 4/2000  | Tuttle            |

| 6,069,564 | $\mathbf{A}$ | 5/2000  | Hatano et al.     |

| 6,118,379 | A            | 9/2000  | Kodukula et al.   |

| 6,130,612 | $\mathbf{A}$ | 10/2000 | Castellano et al. |

| 6,130,632 | A            | 10/2000 | Opris             |

| 6,134,182 | A            | 10/2000 | Pilo              |

| 6,147,655 | A            | 11/2000 | Roesner           |

| 6,166,706    | A   | 12/2000 | Gallagher             |

|--------------|-----|---------|-----------------------|

| 6,184,841    | B1  | 2/2001  | Shober et al.         |

| 6,215,402    | B1  | 4/2001  | Rao Kodukula et al.   |

| 6,266,362    | B1  | 7/2001  | Tuttle et al.         |

| 6,268,796    | B1  | 7/2001  | Gnadinger et al.      |

| 6,271,793    | B1  | 8/2001  | Brady et al.          |

| 6,320,788    | B1  | 11/2001 | Sansbury et al.       |

| 6,340,932    | B1  | 1/2002  | Rodgers et al.        |

| 6,346,922    | B1  | 2/2002  | Proctor et al.        |

| 6,357,025    | B1  | 3/2002  | Tuttle                |

| 6,366,260    | B1  | 4/2002  | Carrender             |

| 6,396,438    | B1  | 5/2002  | Seal                  |

| 6,445,297    | B1  | 9/2002  | Nicholson             |

| 6,517,000    | B1  | 2/2003  | McAllister et al.     |

| 6,571,617    | B2  | 6/2003  | Van Niekerk et al.    |

| 6,677,917    | B2  | 1/2004  | Van Heerden et al.    |

| 6,700,491    | B2  | 3/2004  | Shafer                |

| 6,701,605    | B2  | 3/2004  | Huffer et al.         |

| 6,720,930    | B2  | 4/2004  | Johnson et al.        |

| D492,670     | S   | 7/2004  | Hung et al.           |

| D493,446     | S   | 7/2004  | Hung et al.           |

| 6,830,193    | B2* | 12/2004 | Tanaka 235/492        |

| 2002/0109636 | A1* | 8/2002  | Johnson et al 343/742 |

| 2002/0167405 | A1  | 11/2002 | Shanks et al.         |

| 2005/0134460 | A1* | 6/2005  | Usami 340/572.7       |

| 2006/0044192 | A1* | 3/2006  | Egbert 343/700 MS     |

| 2006/0208897 | A1* | 9/2006  | Chiu et al 340/572.7  |

|              |     |         |                       |

### FOREIGN PATENT DOCUMENTS

| EP | 0 298 618 | 1/1989  |

|----|-----------|---------|

| WO | 01 73854  | 10/2001 |

#### OTHER PUBLICATIONS

Carley, L. Richard, "Trimming Analog Circuits Using Floating-Gate Analog MOS Memory", IEEE Journal of Solid-State Circuits, vol. 24, No. 6, Dec. 1989, pp. 1569-1575.

Raszka et al., "Embedded Flash Memory for Security Applications in a 0.13 µ m CMOS Logic Process", Digest of Technical Papers, IEEE International Solid-State Circuits Conference 2004, p. 46.

Weis, Stephen A., et al., Security and Privacy Aspects of Low-Cost Radio Frequency Identification Systems, Laboratory for Computer Science, Auto-ID Center, Massachusetts Institute of Technology, pp. 1-12.

Yoshida, Junko, EE Times, "RFID "kill" Feature Aims to Soothe Privacy Fears", Apr. 28, 2003.

Jonietz, Erika, Technology Review, "Tracking Privacy", Jul./Aug. 2004, pp. 74-75.

Partial International Search for International Application No. PCT/US03/31792, date mailed Apr. 2, 2004.

Nobel, Carmen, "Symbol Considers RFID Options", eWEEK, vol. 23, No. 7, p. 35, Feb. 13, 2006.

#### \* cited by examiner

Primary Examiner—Louis S. Zarfas

Assistant Examiner—John Windmuller

(74) Attorney, Agent, or Firm—Thelen Reid Brown

Raysman & Steiner LLP; David B. Ritchie

#### (57) CLAIM

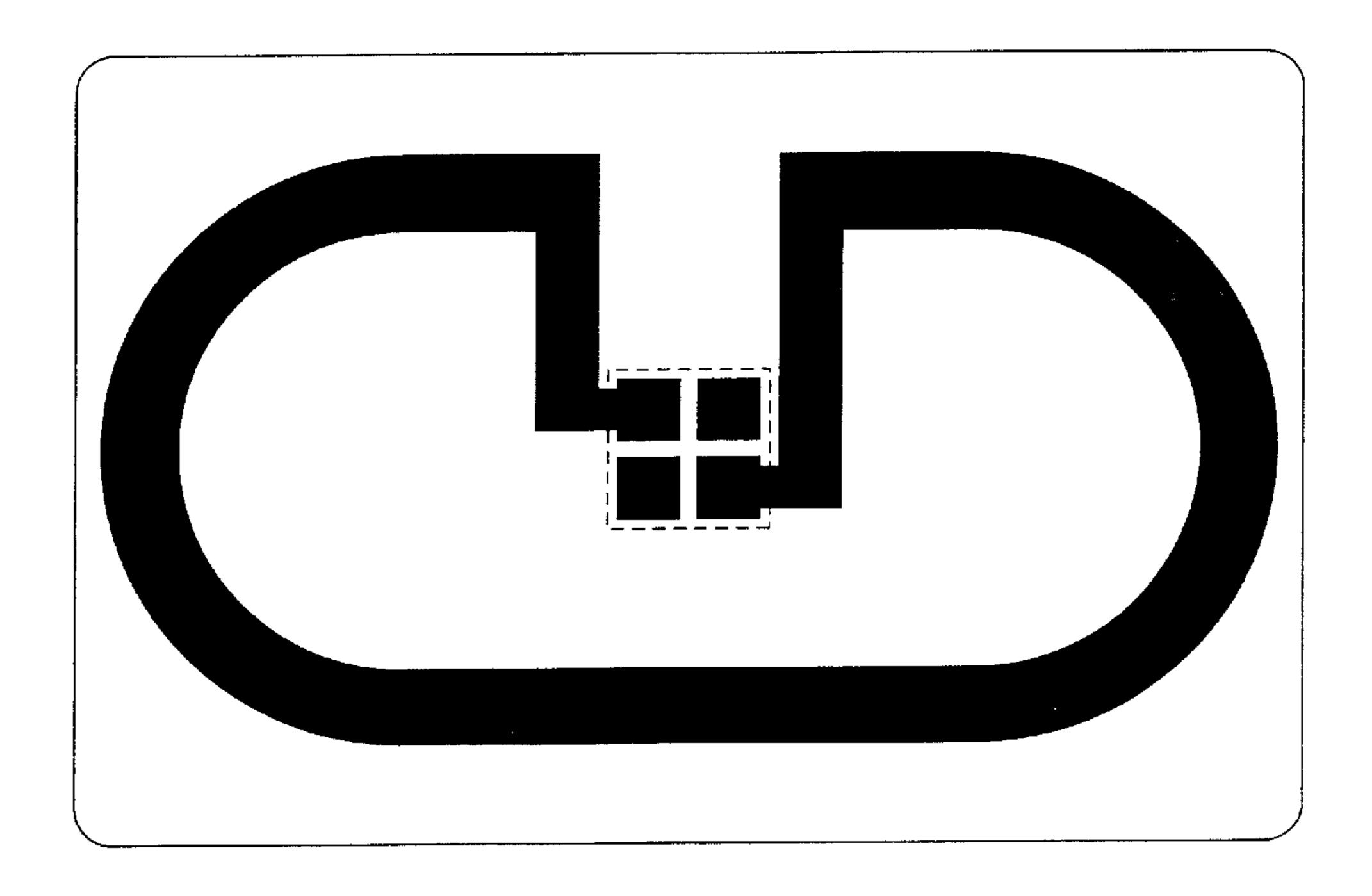

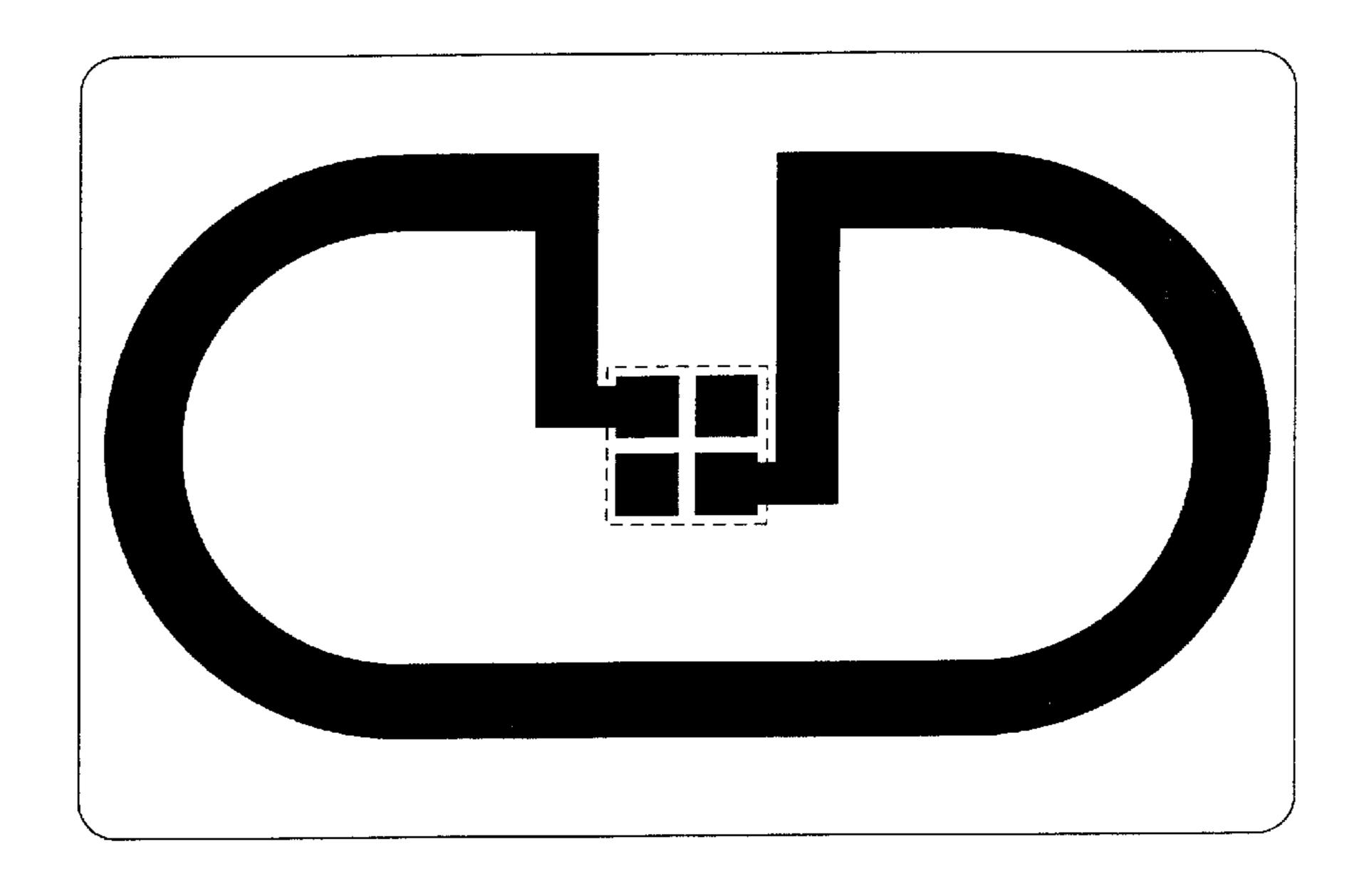

The ornamental design for a radio frequency identification tag antenna assembly, as shown and described.

#### **DESCRIPTION**

The present application may be considered to be related to co-pending U.S. Design patent application Ser. No. 29/220, 504 filed Dec. 30, 2004, in the name of inventor Ronald A. Oliver, entitled "Radio Frequency Identification Tag Antenna Assembly", commonly owned herewith, which is a continuation-in-part U.S. Utility patent application Ser. No. 10/812,493 filed Mar. 29, 2004, in the same of inventors Ronald A. Oliver, Christopher J. Diorio and Todd E. Humes, entitled "Circuits for RFID Tags with Multiple Non-Independently Driven RF Ports", now abandoned, and a continuation-in-part of U.S. Utility patent application Ser. No. 10/815,474 filed Mar. 31, 2004, in the same of inventors John D. Hyde, Omer Onen and Ronald A. Oliver, entitled "RFID Tags Combining Signals Received from Multiple Ports", now abandoned.

The present application may also be considered to be related to co-pending U.S. Design patent application Ser. No. 29/220,493 filed Dec. 30, 2004, in the name of inventor Ronald A. Oliver, entitled "Radio Frequency Identification Tag Antenna Assembly", commonly owned herewith, which is also a continuation-in-part U.S. Utility patent application Ser. No. 10/812,493.

The present application may also be considered to be related to co-pending U.S. Design patent application Ser. No. 29/220,496 filed Dec. 30, 2004, in the name of inventor Ronald A. Oliver, entitled "Conductor for Radio Frequency Identification Tag Antenna Assembly", commonly owned herewith.

The present application may also be considered to be related to co-pending U.S. Design patent application Ser. No. 29/254,156 filed Feb. 17, 2006, in the name of inventor Ronald A. Oliver, entitled "Radio Frequency Identification Tag Antenna Assembly", commonly owned herewith.

The present application may also be considered to be related to co-pending U.S. Design patent application Ser. No. 29/254,159 filed Feb. 17, 2006, in the name of inventor Ronald A. Oliver, entitled "Radio Frequency Identification Tag Antenna Assembly", commonly owned herewith.

The present application may also be considered to be related to co-pending U.S. Design patent application Ser. No. 29/254,158 filed Feb. 17, 2006, in the name of inventor Ronald A. Oliver, entitled "Radio Frequency Identification Tag Antenna Assembly", commonly owned herewith.

The present application may also be considered to be related to co-pending U.S. Design patent application Ser. No. 29/254,157 filed Feb. 17, 2006, in the name of inventor Ronald A. Oliver, entitled "Radio Frequency Identification Tag Antenna Assembly", commonly owned herewith.

The present application may also be considered to be related to co-pending U.S. Design patent application Ser. No. 29/254,143 filed Feb. 17, 2006, in the name of inventor Ronald A. Oliver, entitled "Radio Frequency Identification Tag Antenna Assembly", commonly owned herewith.

The FIGURE is a top plan view of a radio frequency identification tag antenna assembly showing my new design.

The broken line showing of a square integrated circuit chip is included for the purpose of illustrating environment and forms no part of the claimed design.

#### 1 Claim, 1 Drawing Sheet