#### US00D411516S

# United States Patent [19]

## Imafuku et al.

#### [54] GAS DIFFUSION PLATE FOR ELECTRODE OF SEMICONDUCTOR WAFER PROCESSING APPARATUS

[75] Inventors: Kosuke Imafuku, Kofu; Shosuke

Endo, Nirasaki; Kazuo Fukasawa,

Kofu, all of Japan

[73] Assignee: Tokyo Electron Limited, Tokyo-To,

Japan

[\*] Notice: This patent is subject to a terminal dis-

claimer.

[\*\*] Term: 14 Years

[21] Appl. No.: 29/059,398

[22] Filed: **Sep. 10, 1996**

[30] Foreign Application Priority Data

Mar. 15, 1996 [JP] Japan ...... 8-7276

, r 1

156/643, 646; 437/228

[56] References Cited

U.S. PATENT DOCUMENTS

FOREIGN PATENT DOCUMENTS

**Date of Patent:** \*\* Jun. 29, 1999

Des. 411,516

952210 4/1996 Japan . 952210 5/1996 Japan .

Primary Examiner—Brian N. Vinson Attorney, Agent, or Firm—Ladas & Parry

Patent Number:

[11]

[45]

[57] CLAIM

We claim the ornamental design for gas diffusion plate for electrode of semiconductor wafer processing apparatus, as shown and described.

#### **DESCRIPTION**

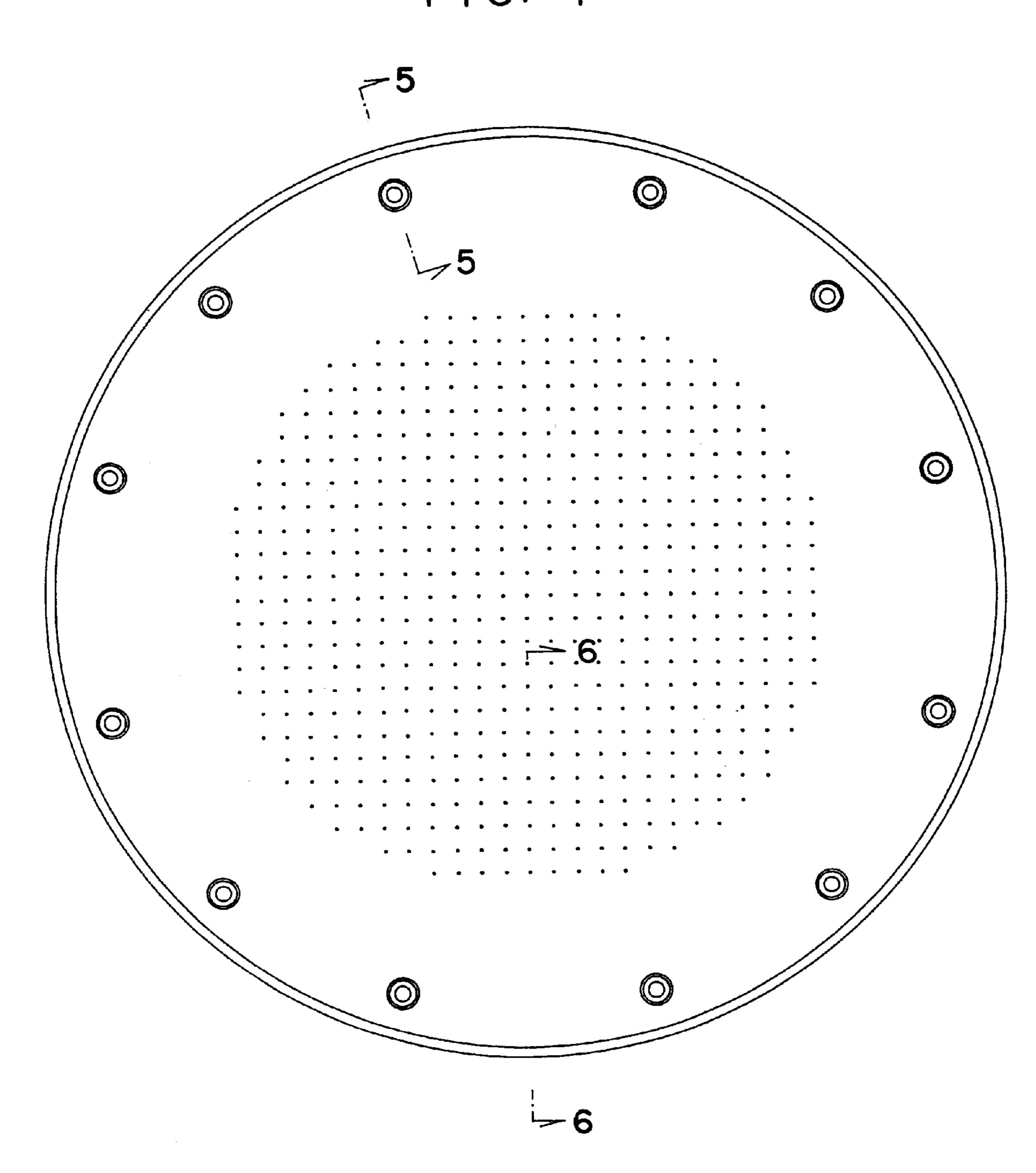

FIG. 1 is a bottom view of a gas diffusion plate for electrode of semiconductor wafer processing apparatus showing our new design;

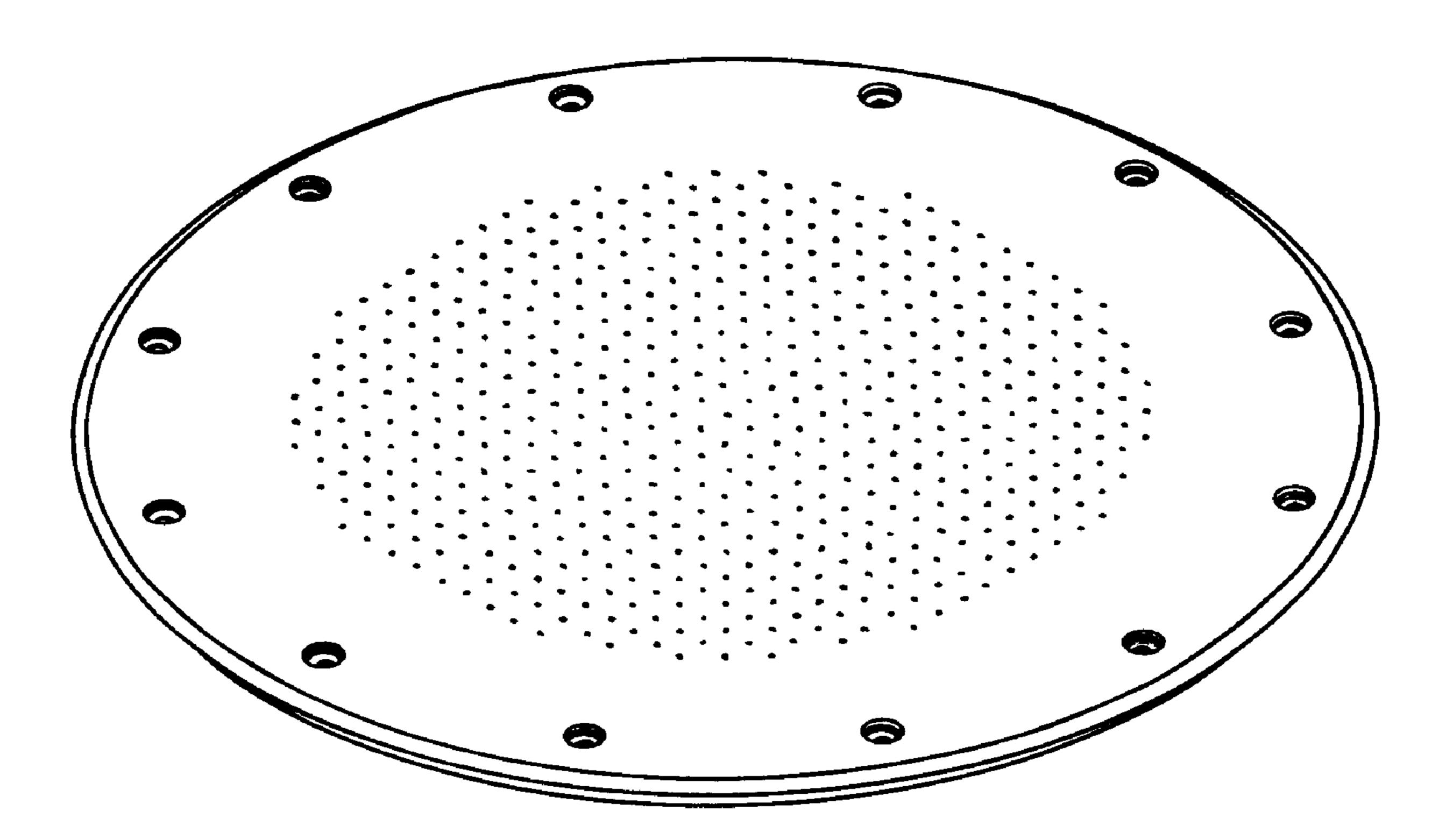

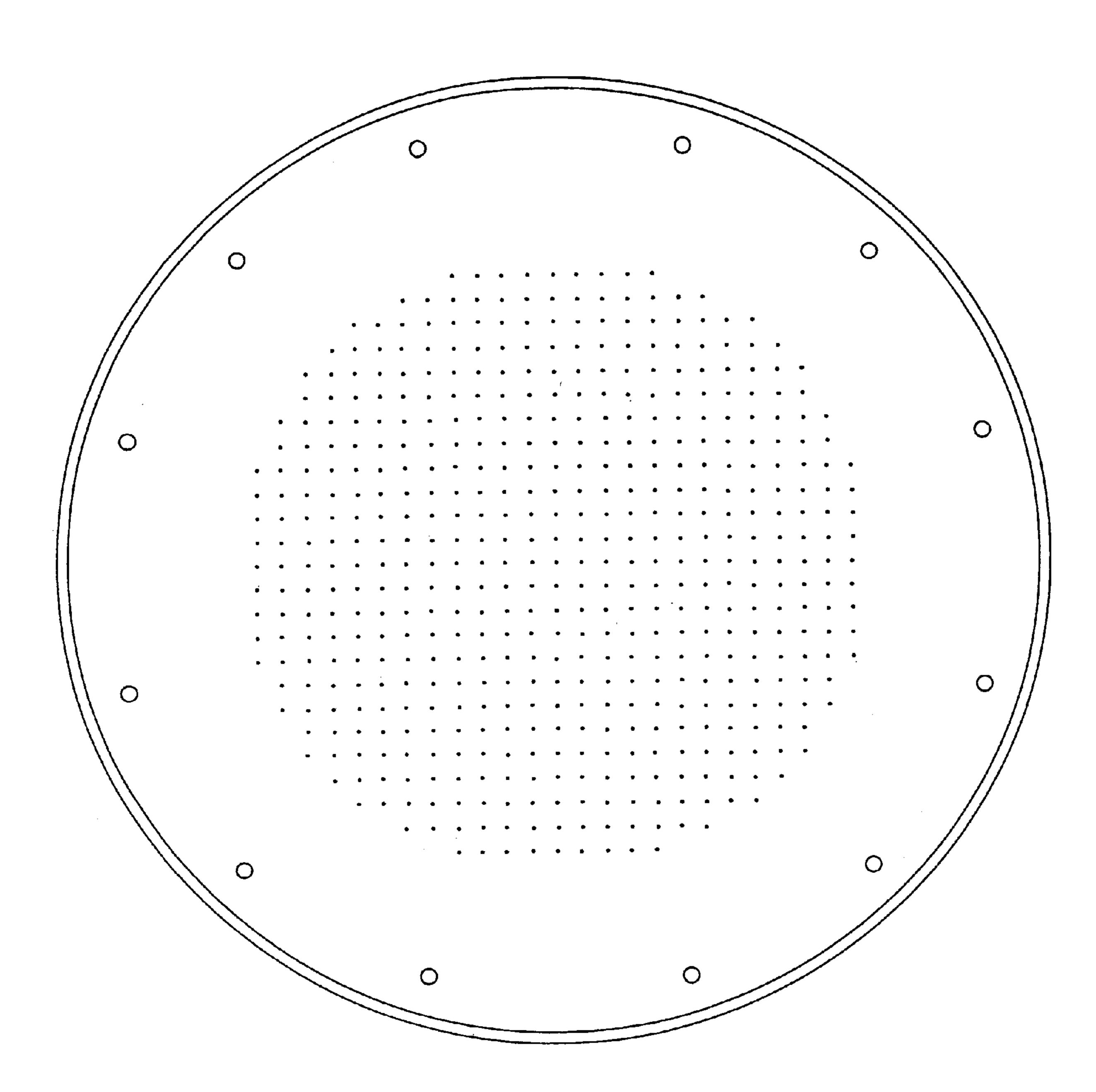

FIG. 2 is a top view thereof;

FIG. 3 is a right elevational view thereof, the left elevational view thereof being a mirror image and, therefore, not shown;

FIG. 4 is a front elevational thereof, the rear elevational view thereof being a mirror image and, therefore, not shown;

FIG. 5 an enlarged sectional view of on section 5—5 in FIG. 1;

FIG. 6 an enlarged sectional view of on section 6—6 in FIG. 1; and,

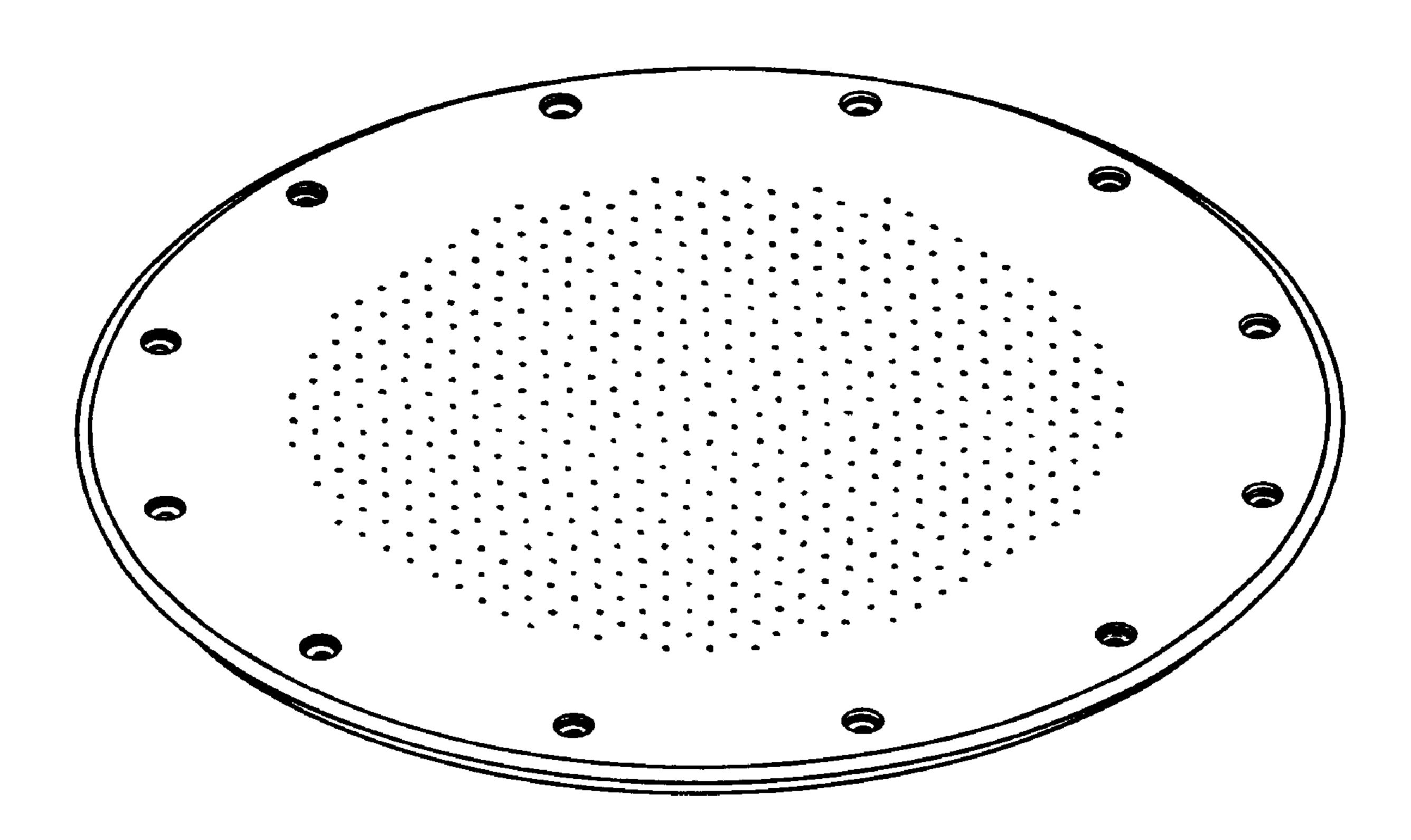

FIG. 7 is a bottom/rear perspective view thereof.

### 1 Claim, 4 Drawing Sheets

FIG. 1

Jun. 29, 1999

FIG. 2

FIG. 4

FIG. 7

Jun. 29, 1999