# United States Patent [19]

### Yoshida et al.

[11] Patent Number: Des. 309,130

[45] Date of Patent: \*\* Jul. 10, 1990

| [54]                    | CENTRAL PROCESSOR FOR AN ELECTRONIC COMPUTER |                                                                                                                                                               |  |  |

|-------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| [75]                    | Inventors:                                   | Atsuo Yoshida, Kokubunji;<br>Koushirou Adachi, Tokorozawa;<br>Tousaku Hattori, Tokyo; Hiroshi<br>Watanabe, Hitachi; Yoshiaki<br>Takahashi, Mito, all of Japan |  |  |

| [73]                    | Assignee:                                    | Hitachi, Ltd., Tokyo, Japan                                                                                                                                   |  |  |

| [**]                    | Term:                                        | 14 Years                                                                                                                                                      |  |  |

| [21]                    | Appl. No.:                                   | 160,077                                                                                                                                                       |  |  |

| [22]                    | Filed:                                       | Feb. 24, 1988                                                                                                                                                 |  |  |

| [30]                    | Foreign Application Priority Data            |                                                                                                                                                               |  |  |

| Sep. 4, 1987 [JP] Japan |                                              |                                                                                                                                                               |  |  |

| <del></del>             |                                              |                                                                                                                                                               |  |  |

| [58]                    |                                              | arch                                                                                                                                                          |  |  |

|                         | •                                            | , 41; 174/50, 52 R; 360/97–99, 132, 133;                                                                                                                      |  |  |

|                         |                                              | /330, 331, 334, 335, 390–395, 399, 415;                                                                                                                       |  |  |

|                         |                                              | 200/5 A, 5 R, 6 A, 6 R; 312/198, 208                                                                                                                          |  |  |

## [56] References Cited

### U.S. PATENT DOCUMENTS

| D. 218,753 | 9/1970 | Lauer                    |

|------------|--------|--------------------------|

| D. 242,926 | 1/1977 | Abrahamsen et al D14/102 |

| D. 267,490 | 1/1983 | LaDue et al              |

| D. 273,866 | 5/1984 | LaDue et al              |

| D. 278,712 | 5/1985 | Adachi et al             |

| D. 283,817 | 5/1986 | Sakamoto                 |

Primary Examiner—Susan J. Lucas Assistant Examiner—Freda S. Nunn

Attorney, Agent, or Firm—Antonelli, Terry & Wands

[57] CLAIM

The ornamental design for a central processor for an electronic computer, as shown.

#### **DESCRIPTION**

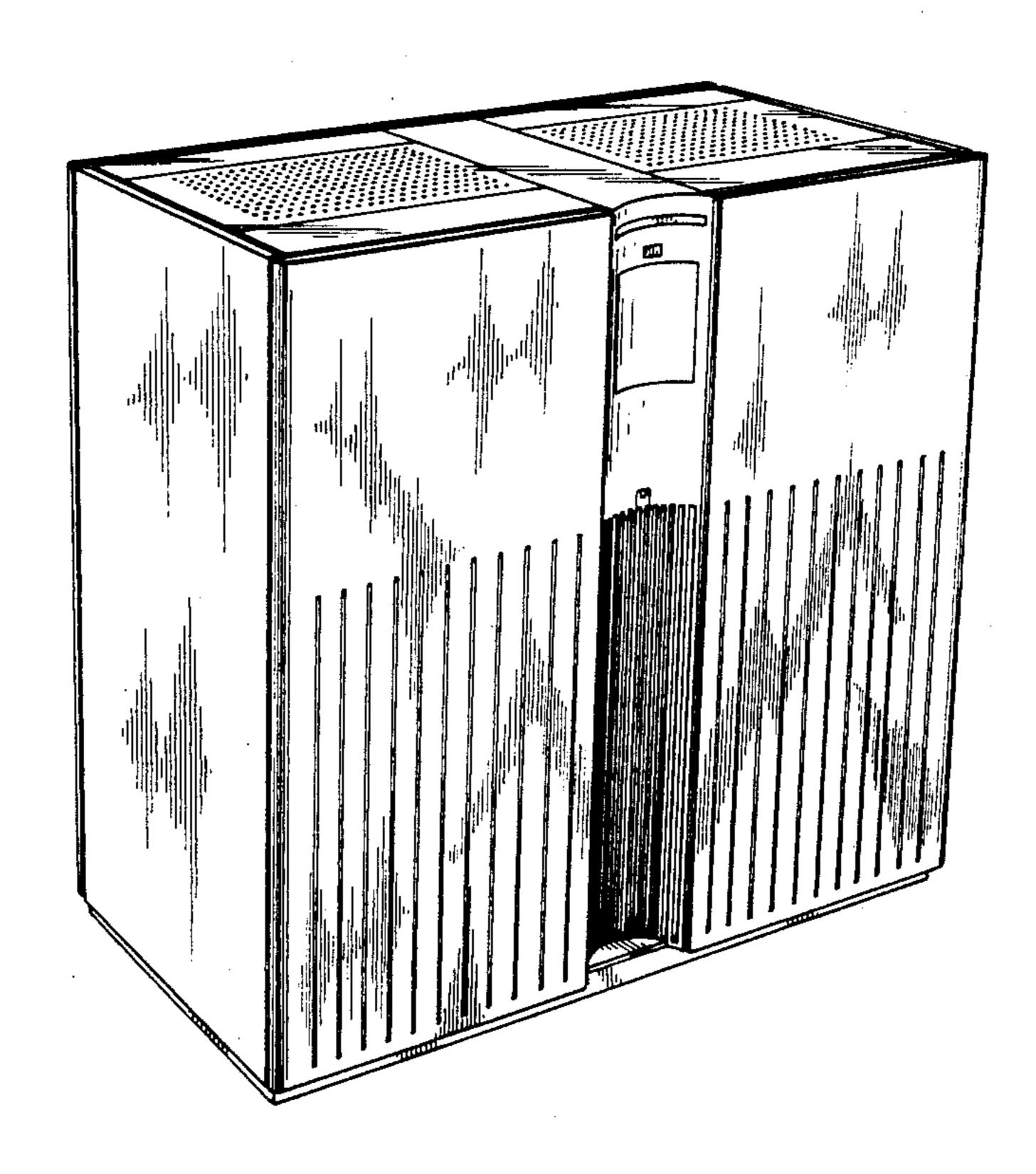

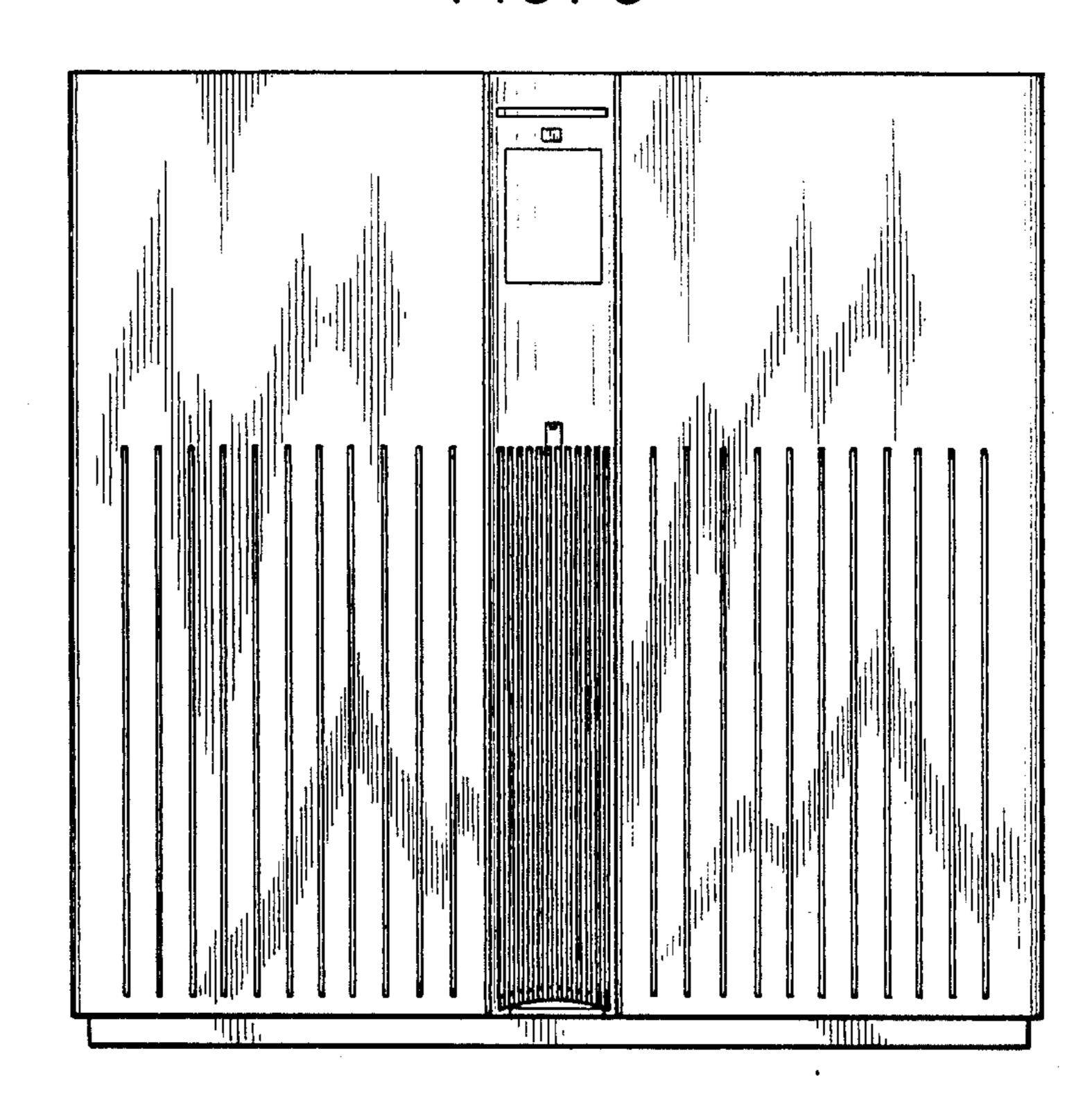

FIG. 1 is a front, top and left side perspective view of a central processor for an electronic computer showing our new design;

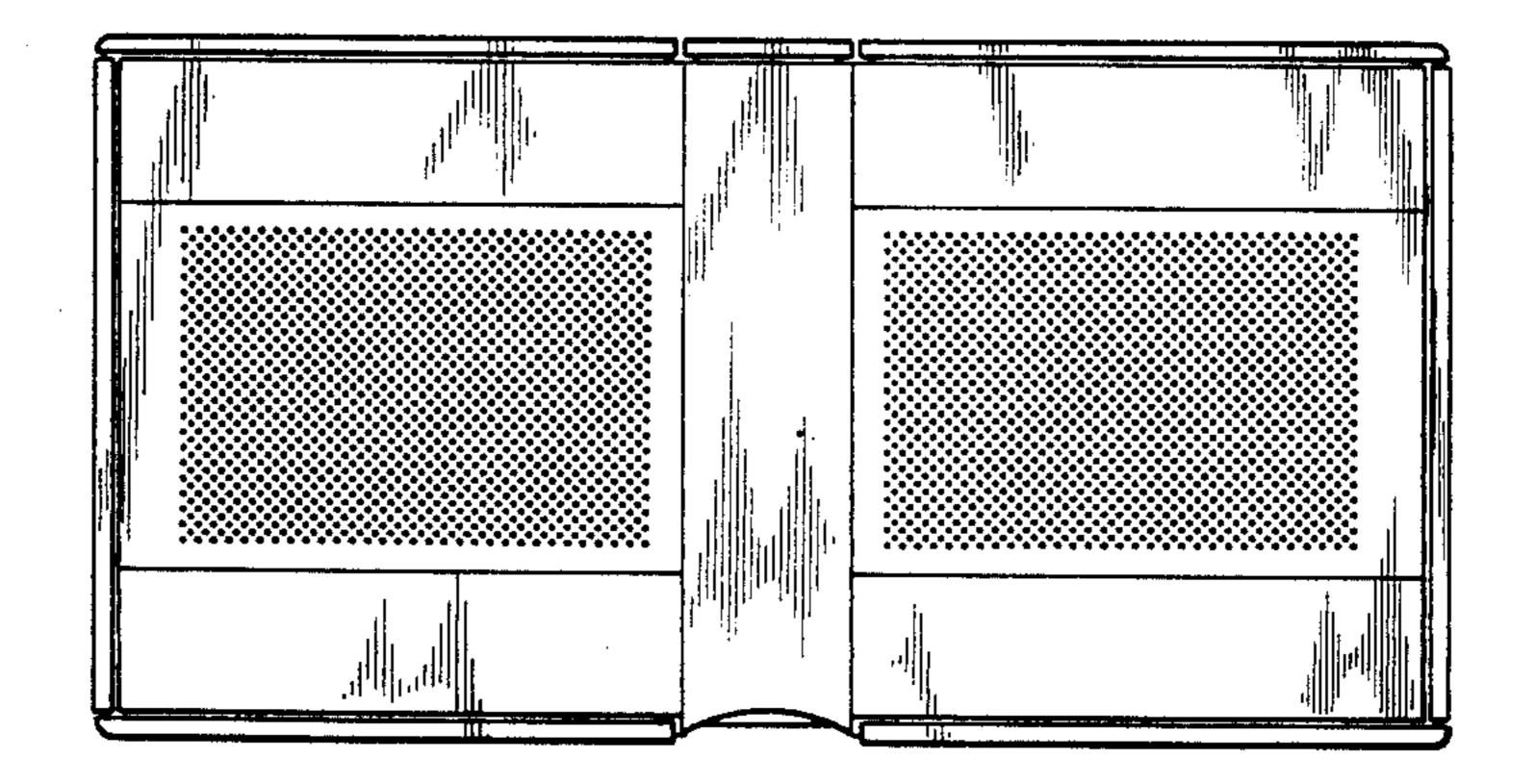

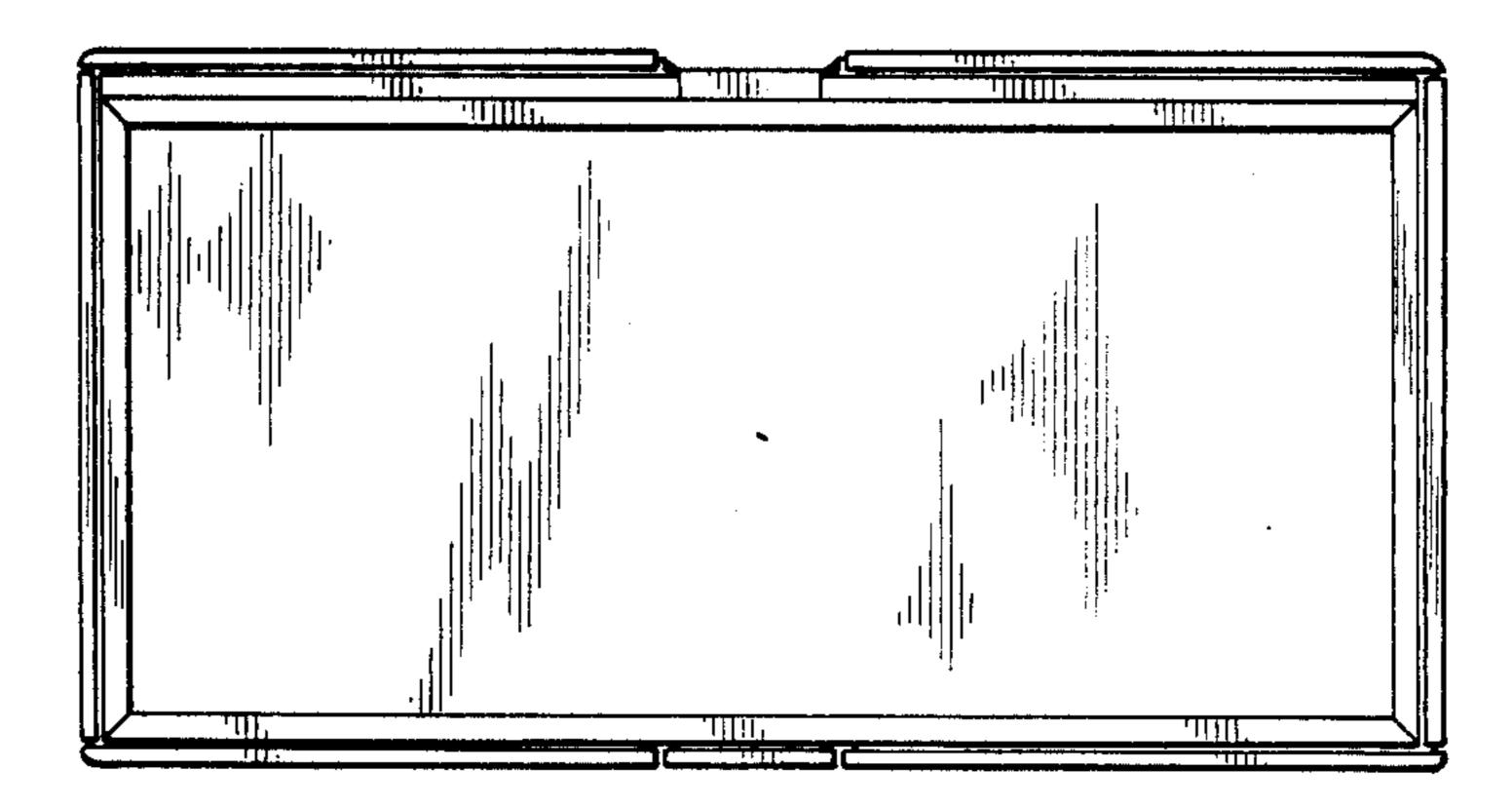

FIG. 2 is a top plan view thereof;

FIG. 3 is a front elevational view thereof;

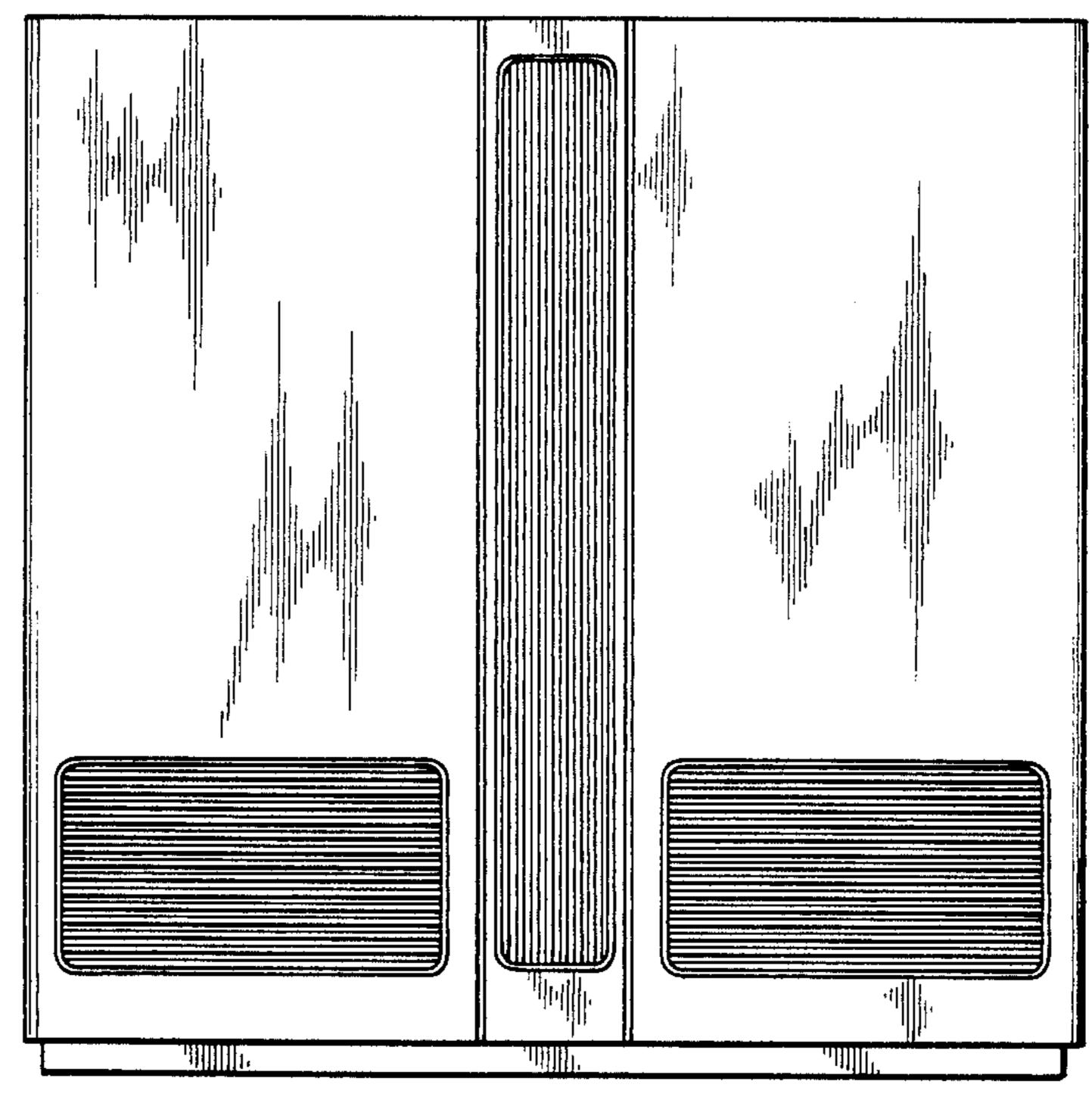

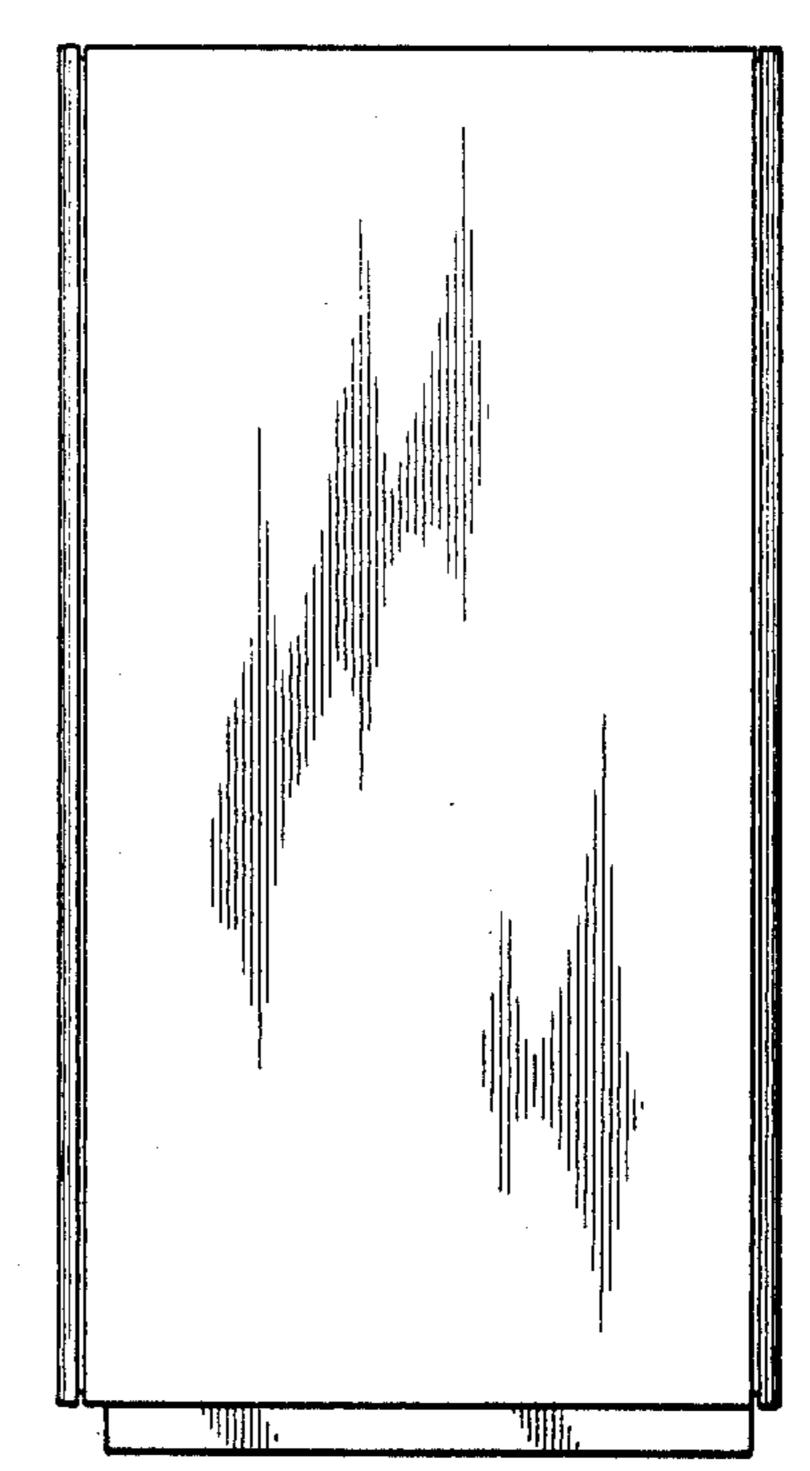

FIG. 4 is a bottom plan view thereof;

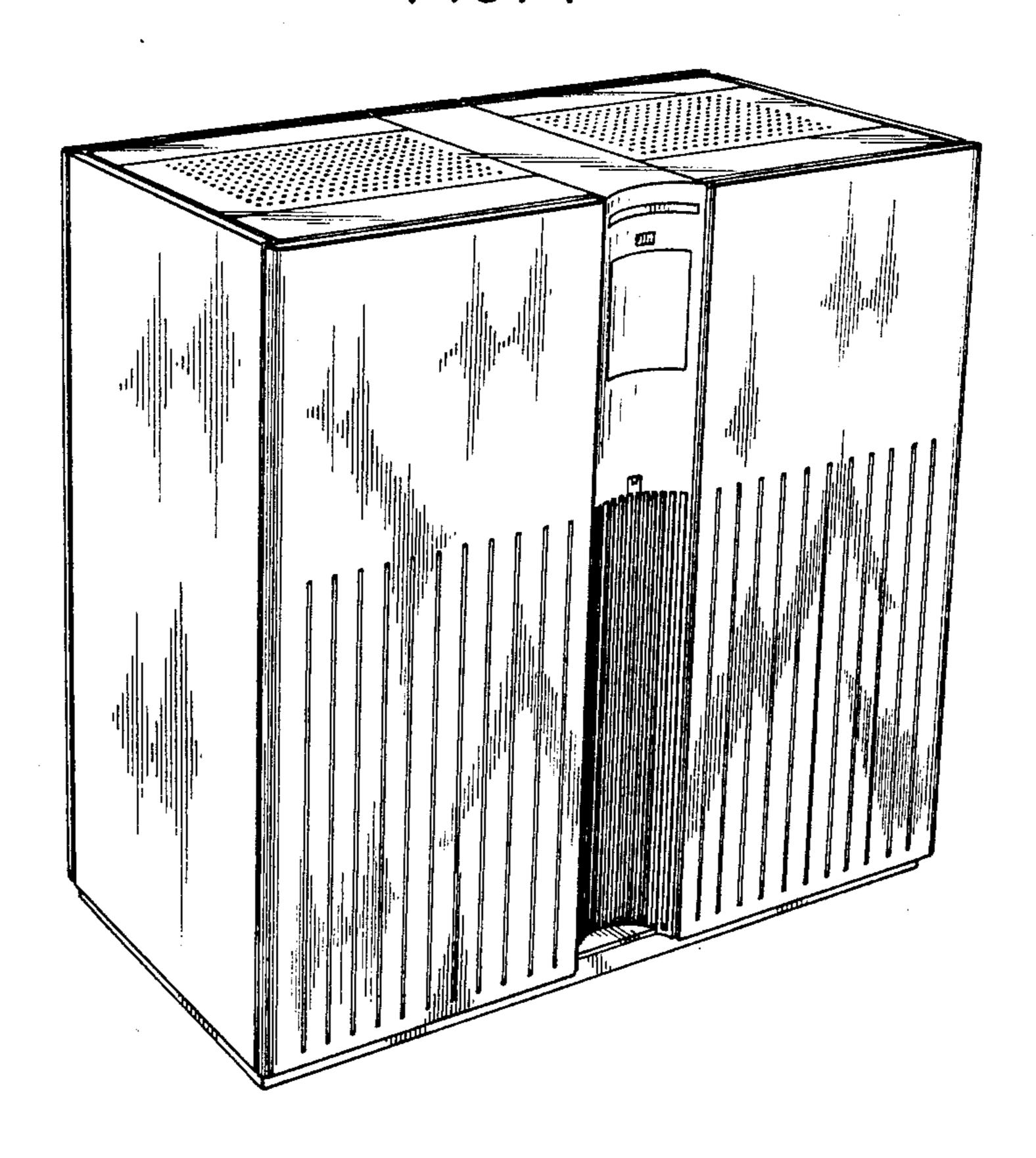

FIG. 5 is a right side elevational view thereof; and

FIG. 6 is a rear elevational view thereof.

FIG. 1

FIG. 2

FIG. 3

FIG. 4

F/G. 5

F1G. 6