## United States Patent [19]

### Du Bois

[11] Patent Number: Des. 288,557

[45] Date of Patent: \*\* Mar. 3, 1987

| [54]                 | SEMICONDUCTOR HOUSING |                                                                                                                  |  |

|----------------------|-----------------------|------------------------------------------------------------------------------------------------------------------|--|

| [75]                 | Inventor:             | Jerry M. Du Bois, Mesa, Ariz.                                                                                    |  |

| [73]                 | Assignee:             | Motorola, Inc., Schaumburg, Ill.                                                                                 |  |

| [**]                 | Term:                 | 14 Years                                                                                                         |  |

| [21]                 | Appl. No.:            | 649,081                                                                                                          |  |

| [22]<br>[52]<br>[58] | Field of Sea          | Sep. 10, 1984  D13/99; D13/41  arch  D13/40, 41, 99;  395, 399, 400, 331; 174/52 R, 52 PE,  52 S; 357/70, 72, 74 |  |

## [56] References Cited

## U.S. PATENT DOCUMENTS

| 3,340,347<br>3,902,148<br>3,918,084<br>3,946,428<br>4,047,197<br>4,067,040<br>4,079,410<br>4,106,052<br>4,213,141<br>4,218,724 | 9/1967<br>8/1975<br>11/1975<br>3/1976<br>9/1977<br>1/1978<br>3/1978<br>8/1978<br>5/1978<br>8/1980 | Spiegler                          |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------|

| 4,213,141<br>4,218,724                                                                                                         | 8/1980                                                                                            | Kaufman 361/395                   |

| 4,278,990<br>4,278,991<br>4,340,900                                                                                            | 7/1981<br>7/1981<br>7/1982                                                                        | Fichot . Ritchie et al Goronkin . |

|                                                                                                                                |                                                                                                   |                                   |

### FOREIGN PATENT DOCUMENTS

2607083 9/1977 Fed. Rep. of Germany ..... 174/525

#### OTHER PUBLICATIONS

IBM Technical Disclosure Bulletin, vol. 21, #1, 6–1978, pp. 99–100, Circuit Chip Support Assembly, Coombs & Larnerd.

Primary Examiner—Susan J. Lucas Attorney, Agent, or Firm—Robert Handy

## [57]

#### **CLAIM**

The ornamental design for a semiconductor housing, as shown and described.

#### **DESCRIPTION**

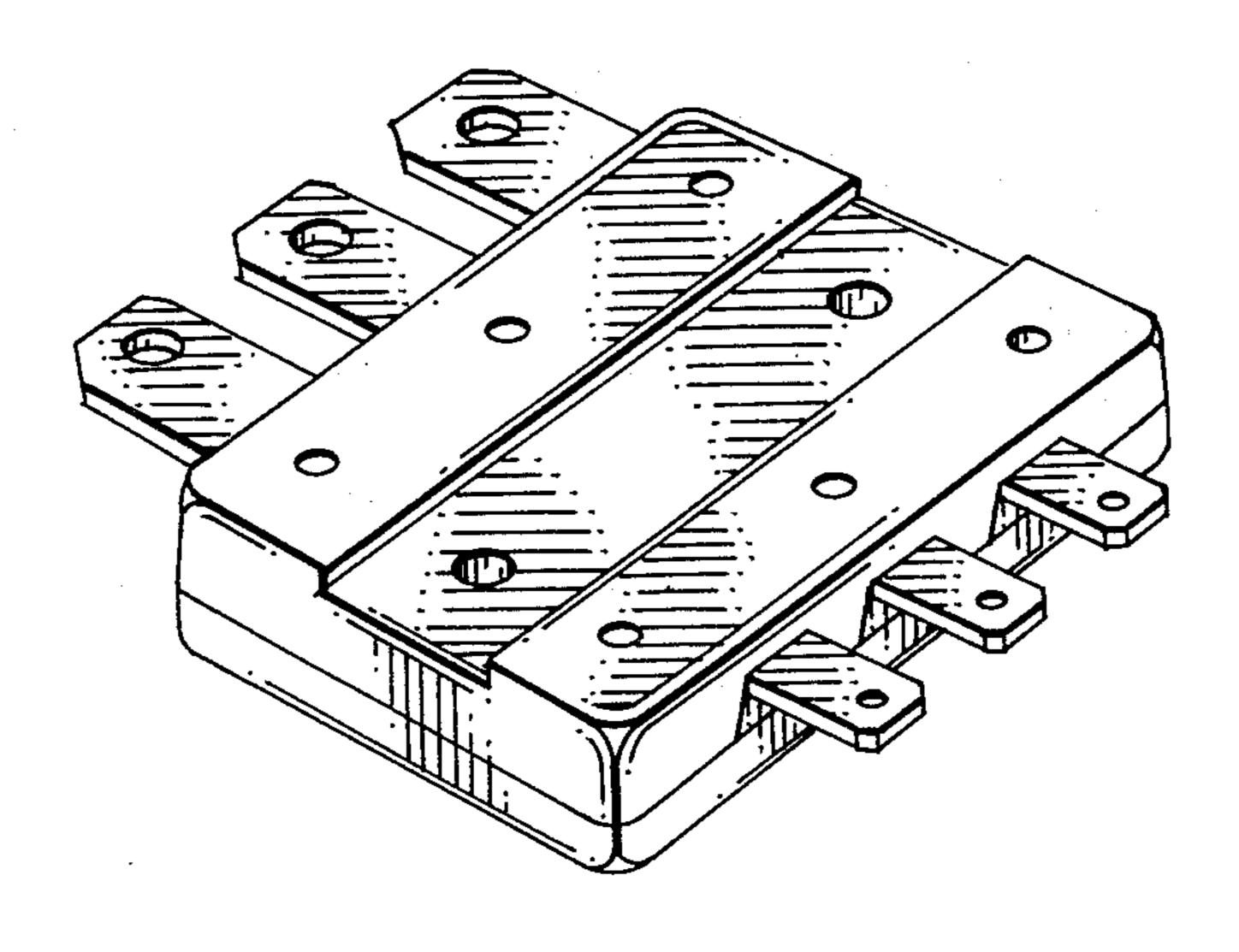

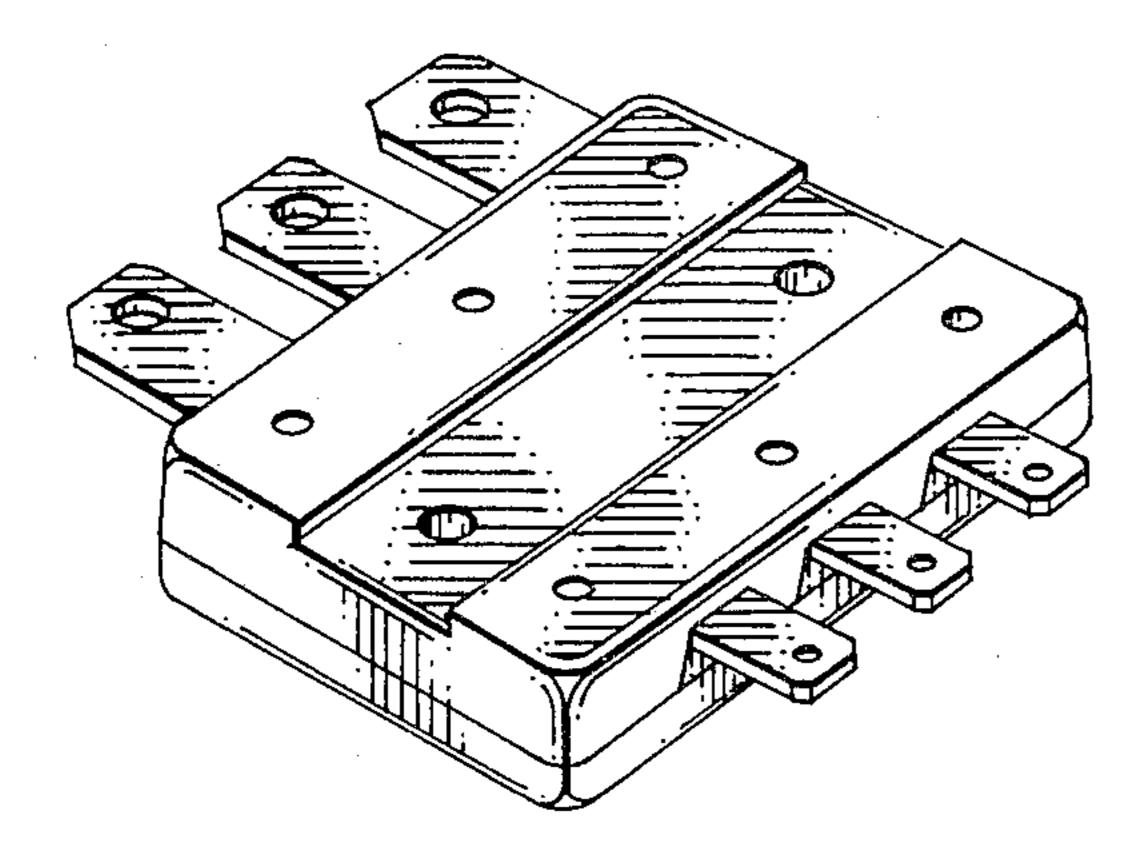

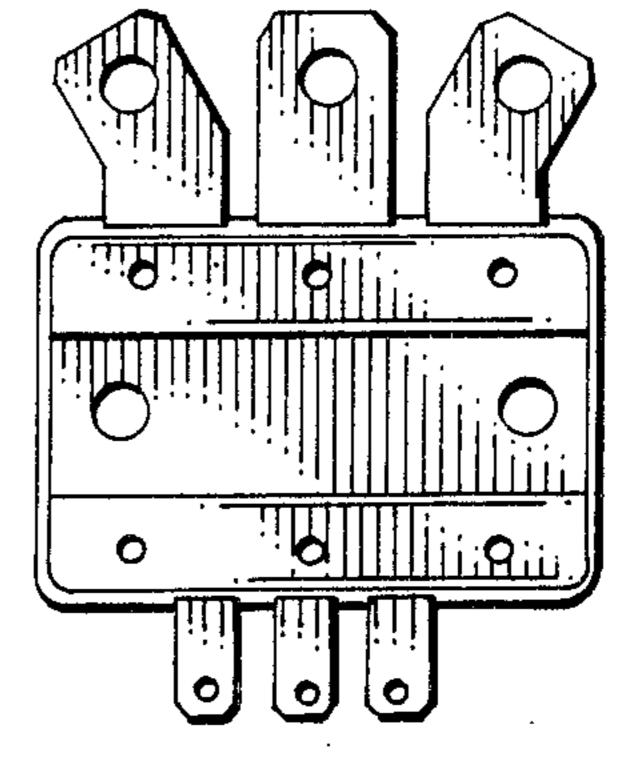

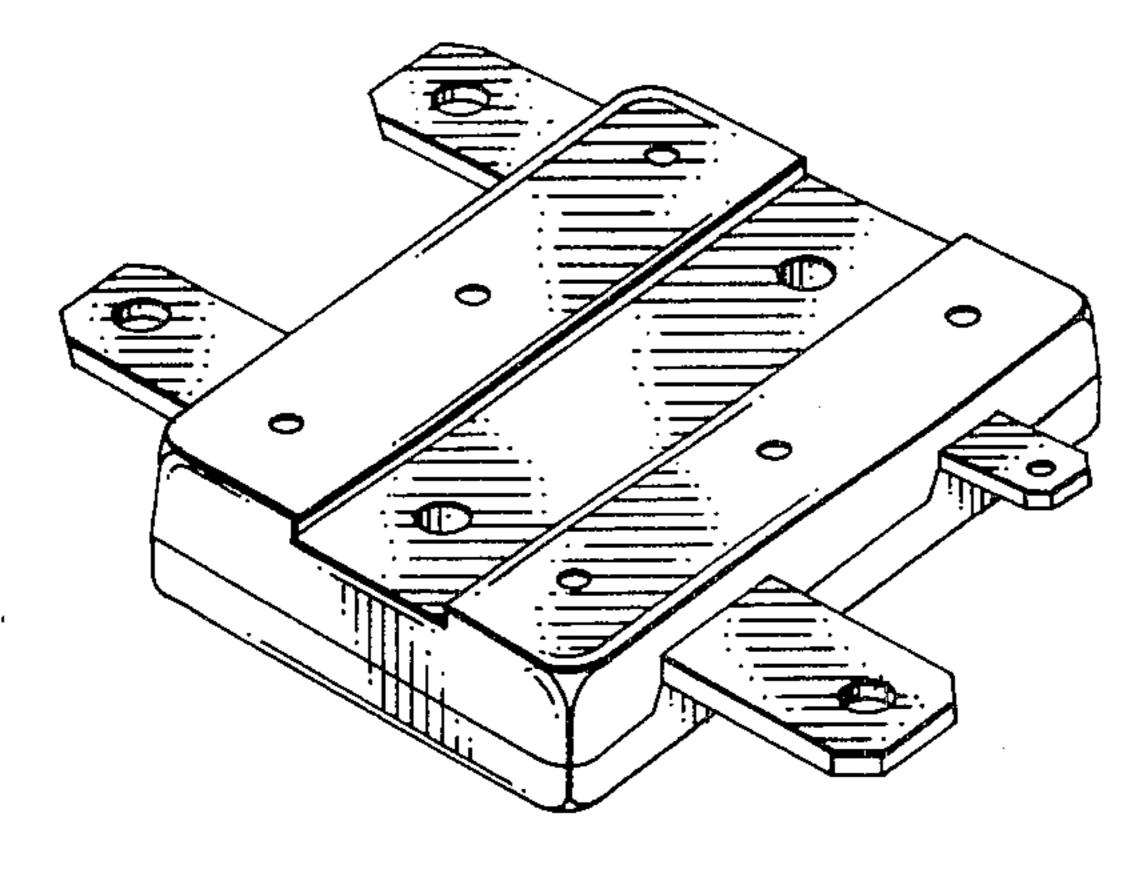

FIG. 1 is a right side, top and front perspective view of a semiconductor housing showing my new design;

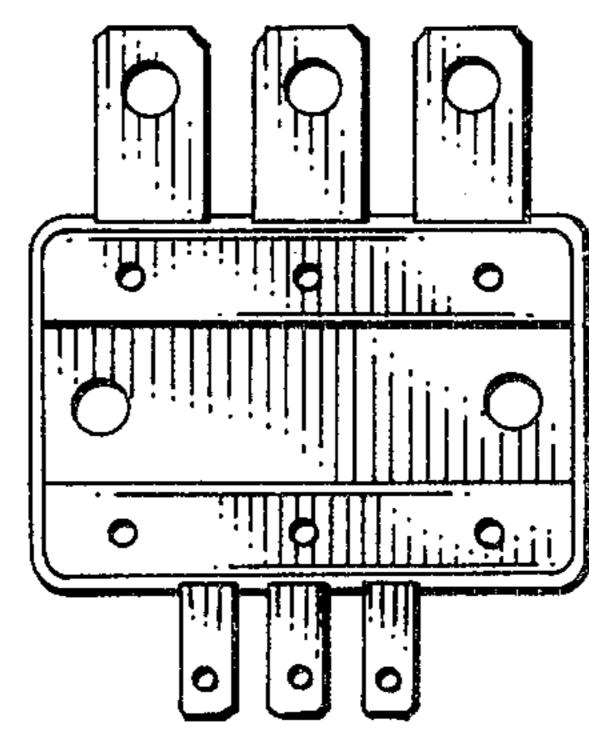

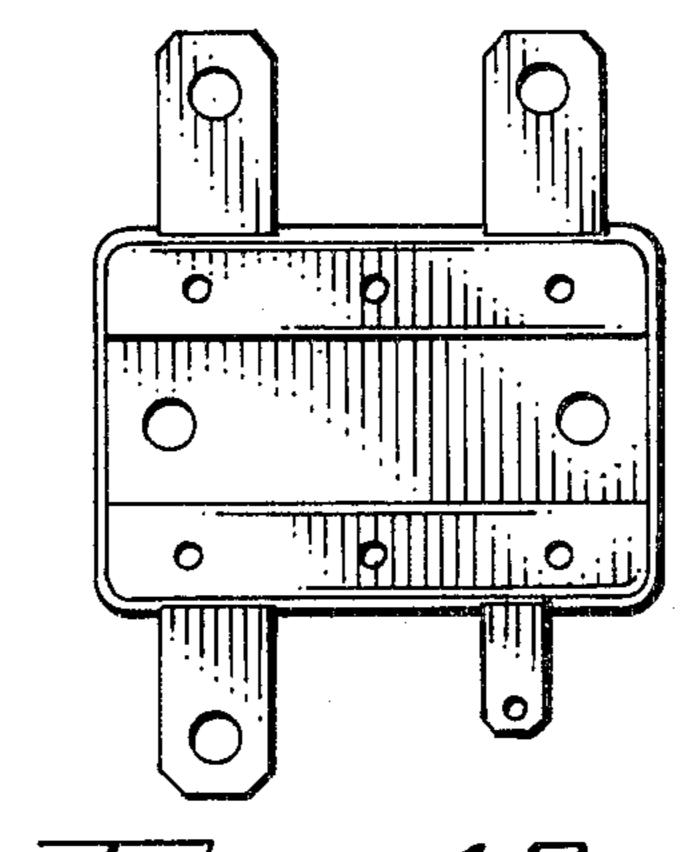

FIG. 2 is a top plan view thereof on a reduced scale;

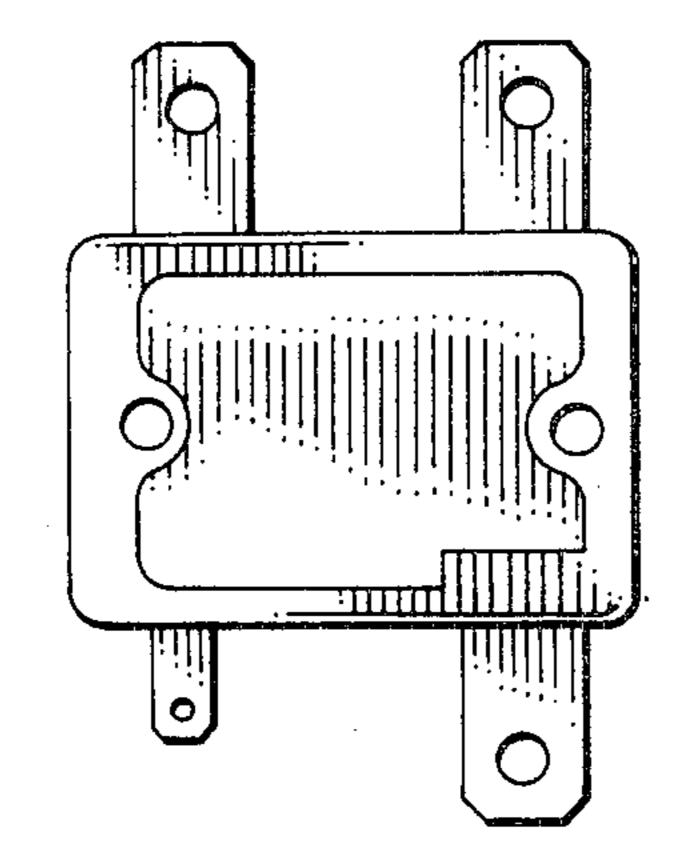

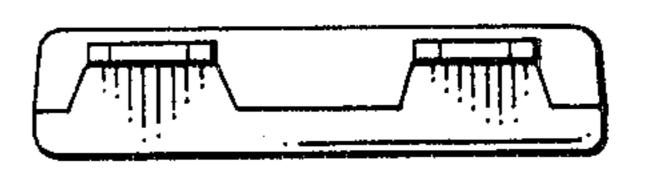

FIG. 3 is a bottom plan view thereof on a reduced scale; FIG. 4 is a left side elevational view thereof on a re-

duced scale;

FIG. 5 is a right side elevational view thereof on a

reduced scale;

FIG. 6 is a front elevational view thereof on a reduced

scale; FIG. 7 is a rear elevational view thereof on a reduced scale;

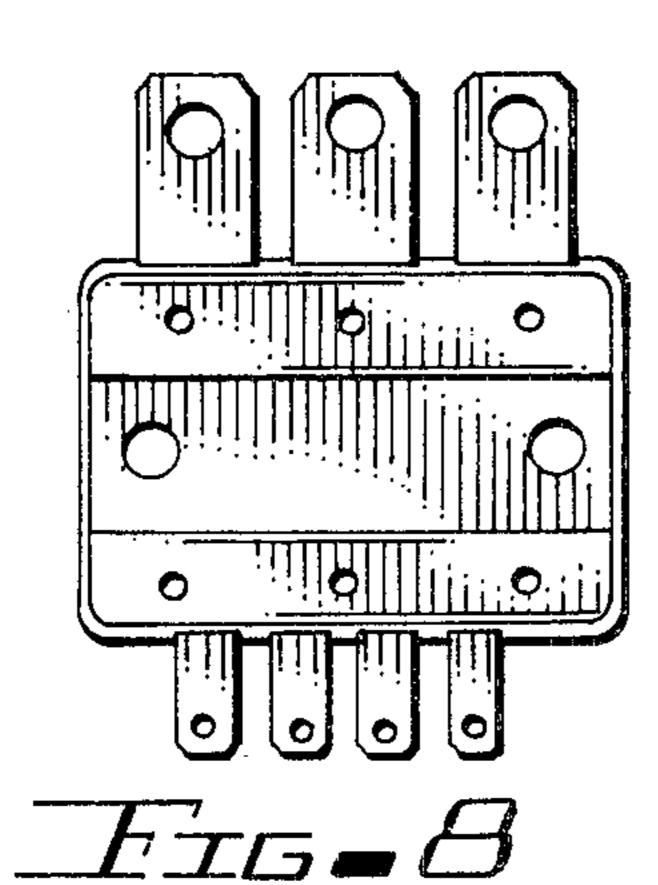

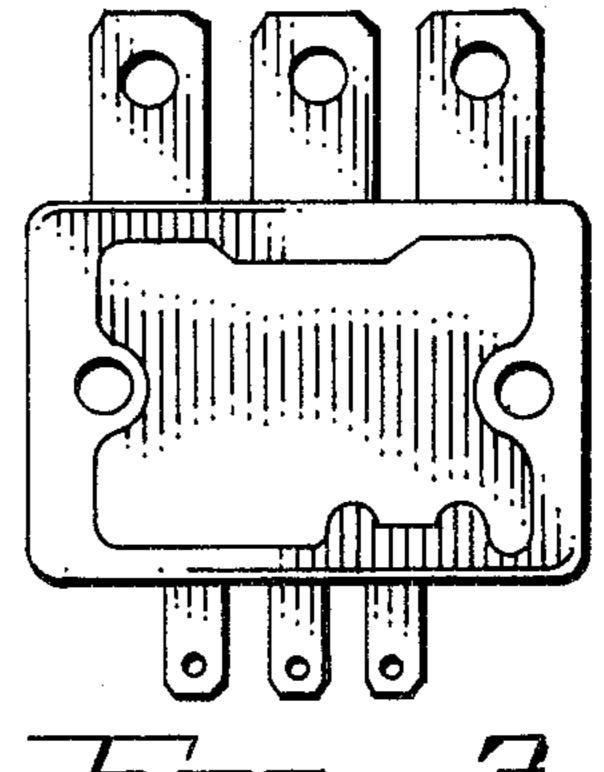

FIG. 8 is a top plan view of second embodiment of my new design, the second embodiment being identical to the first except for the number of leads on the right hand side;

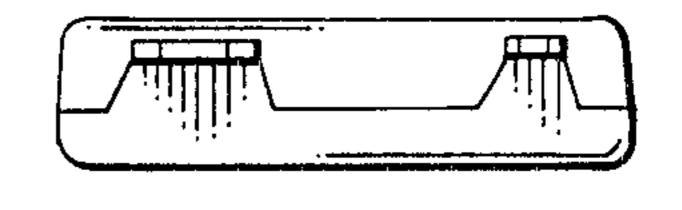

FIG. 9 is a bottom plan view thereof;

FIG. 10 is a top plan view of a third embodiment of my new design, the third design being identical to the first embodiment except for the shape of the two leads on the left hand side;

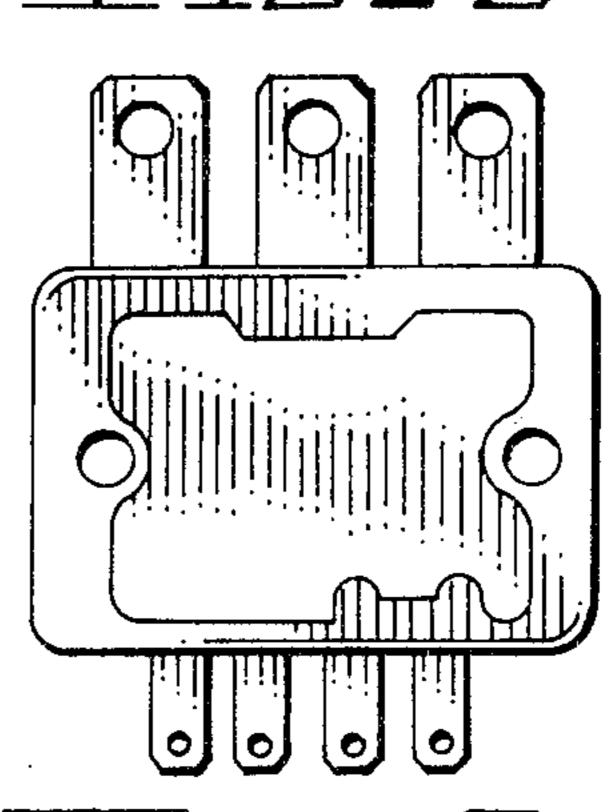

FIG. 11 is a bottom plan view thereof;

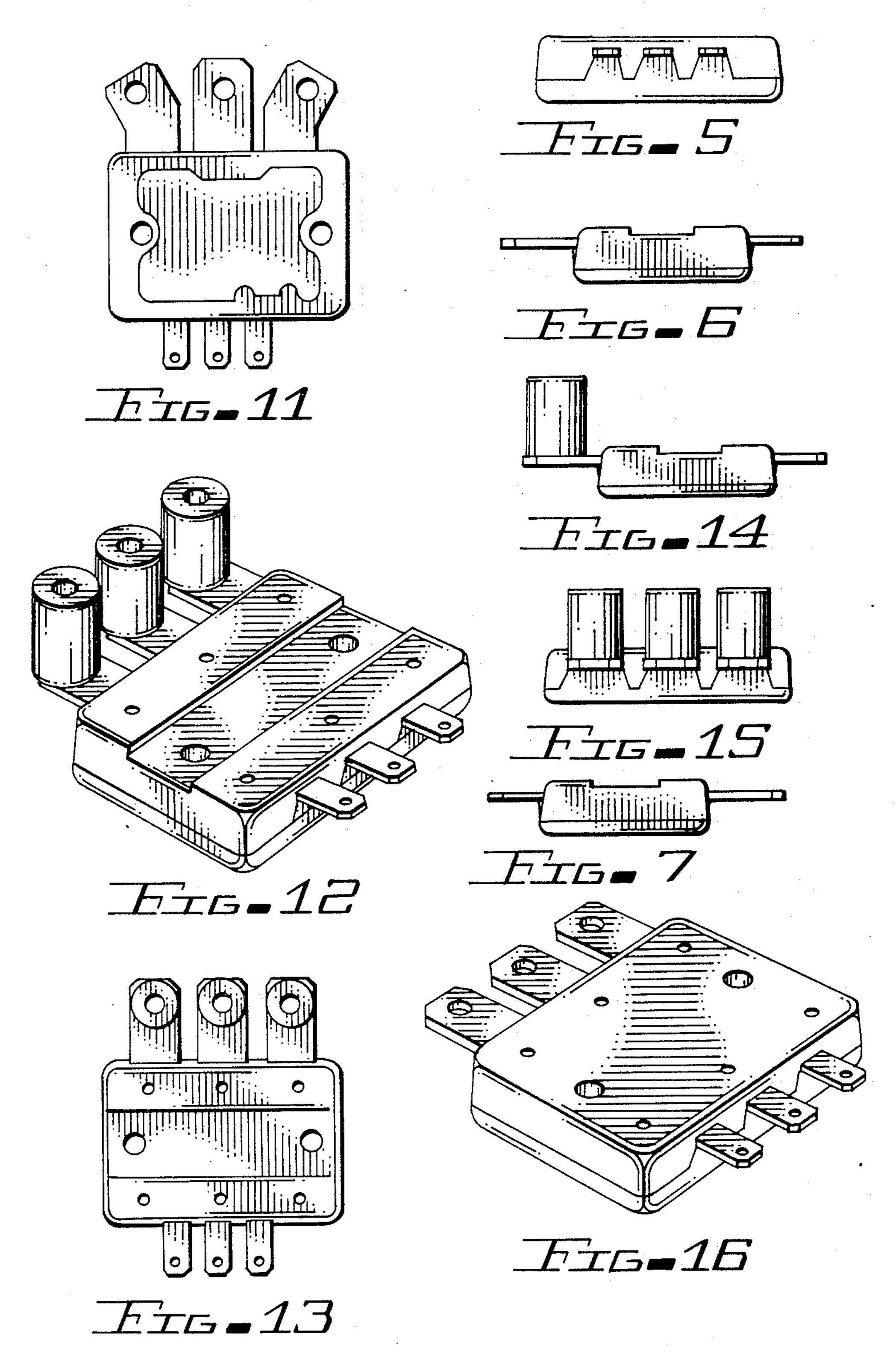

FIG. 12 is a right side, top and front perspective view of a fourth embodiment of my new design;

FIG. 13 is a top plan view thereof on a reduced scale; FIG. 14 is a front elevational view thereof on a reduced scale;

FIG. 15 is a left side elevational view thereof on a reduced scale;

FIG. 16 is a right side, top and front perspective view of a fifth embodiment of my new design, the fifth embodiment being identical to the first embodiment except for the flat top surface;

FIG. 17 is a right side, top and front perspective view of a sixth embodiment of my new design;

FIG. 18 is a top plan view thereof on a reduced scale; FIG. 19 is a bottom plan view thereof on a reduced scale;

FIG. 20 is a left side elevational view thereof on a reduced scale;

FIG. 21 is a right side elevational view thereof on a reduced scale.

Fz5-10

Ezs. 9

U.S. Patent Mar. 3, 1987 Sheet 2 of 3 Des. 288,557

# U.S. Patent Mar. 3, 1987

Sheet 3 of 3 Des. 288,557

\_E\_\_\_1B\_\_\_1B

**Ezs.19**

EIG-20

**Dis** 21