## US009831888B1

US 9,831,888 B1

# (12) United States Patent

# Waltari

# (45) **Date of Patent:** Nov. 28, 2017

(10) Patent No.:

# (54) SORT-AND DELAY TIME-TO-DIGITAL CONVERTER

(71) Applicant: IQ-Analog Corporation, San Diego,

CA (US)

(72) Inventor: Mikko Waltari, Escondido, CA (US)

(73) Assignee: **IQ-Analog Corp.**, San Diego, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 15/614,705

(22) Filed: Jun. 6, 2017

(51) **Int. Cl.**

H03M 1/12 (2006.01) H03M 1/44 (2006.01) H03M 1/06 (2006.01)

(52) **U.S. Cl.**

CPC ..... *H03M 1/1215* (2013.01); *H03M 1/0624* (2013.01); *H03M 1/447* (2013.01)

(58) Field of Classification Search

#### (56) References Cited

# U.S. PATENT DOCUMENTS

| 5,886,660 A  | 3/1999  | Loewenstein     |

|--------------|---------|-----------------|

| 7,557,746 B1 | 7/2009  | Waltari         |

| 7,609,756 B2 | 10/2009 | Wood            |

| 7,667,633 B2 | 2/2010  | Choi et al.     |

| 8,138,843 B2 | 3/2012  | Straayer et al. |

| 8,421,661 B1 | 4/2013  | Jee et al.      |

| 8,433,025 B2 | 4/2013  | Sun et al.      |

| 8,552,901 B2 | 10/2013 | Danesh et al.   |

| 8,896,477 B2 | 11/2014 | Dosho et al.    |

| 8,970,420    | B2  | 3/2015  | Henzler et al.    |  |

|--------------|-----|---------|-------------------|--|

| 8,988,269    | B2  | 3/2015  | Dosho             |  |

| 2011/0304372 | A1* | 12/2011 | Wang G04F 10/005  |  |

|              |     |         | 327/264           |  |

| 2012/0313803 | A1* | 12/2012 | Dosho H03M 1/50   |  |

|              |     |         | 341/166           |  |

| 2013/0234792 | A1* | 9/2013  | Niitsu H03F 3/602 |  |

|              |     |         | 330/124 R         |  |

| 2013/0249627 | A1* | 9/2013  | Kwon H03K 5/1515  |  |

|              |     |         | 330/69            |  |

| (Continued)  |     |         |                   |  |

|              |     | •       | •                 |  |

#### OTHER PUBLICATIONS

H. Chung, H. Ishikuro, T. Kuroda, "A 10-Bit 80-MS/s Decision-Select Successive Approximation TDC in 65-nm CMOS", IEEE Journal of Solid-State Circuits, vol. 47, No. 5, May 2012.

Primary Examiner — Peguy Jean Pierre (74) Attorney, Agent, or Firm — Law Office of Gerald Maliszewski; Gerald Maliszewski

# (57) ABSTRACT

A sort-and-delay time-to-digital converter (TDC) is provided, made up of a plurality of serially connected sort-anddelay circuits. Each sort-and-delay circuit accepts a timedifferential input signal with a first edge separated from a second edge by an input duration of time. The first and second edges are selectively routed as a time-differential output signal with a delayed edge separated from a trailing edge by an output duration of time representing a compression of the input duration of time. Each sort-and-delay circuit also supplies a TDC coded bit (e.g., Gray code) indicating the order in which the first and second edges are routed as leading and trailing edges. The TDC outputs a digital output signal representing the initial input duration of time associated with the initial time-differential input signal received by the initial sort-and-delay circuit. Associated TDC, sort-and-delay, and time amplification methods are also provided.

# 28 Claims, 12 Drawing Sheets

# US 9,831,888 B1

Page 2

# (56) References Cited

# U.S. PATENT DOCUMENTS

2014/0232827 A1 8/2014 Kumar et al. 2015/0041625 A1 2/2015 Dutton et al.

<sup>\*</sup> cited by examiner

Fig. 1 (PRIOR ART)

Fig. 2B

Fig. 1.

Fig. 3A

Fig. 3B

Fig. 4

Fig. 5

Fig. 6

Fig. 8

Fig. 7B

**800-0**~ 70,2-0 RESET 600-0 304-0a 602-0  $S_{\mathsf{FIRST\_IN}}$ TIME - S<sub>LAST\_OUT</sub> **AMP** S<sub>LAST\_IN</sub> 304-0b 802-0 TIME S<sub>FIRST\_OUT</sub> **AMP** <del>-900-0</del>

Fig. 9

Fig. 10A

Fig. 10B

Fig. 13B

Fig. 13A

Fig. 14

Fig. 16

Fig. 15

# SORT-AND DELAY TIME-TO-DIGITAL CONVERTER

#### RELATED APPLICATIONS

The following applications are incorporated herein by reference:

VOLTAGE-TO-TIME-TO-DIGITAL SUB-RANGING CONVERTER, invented by Mikko Waltari, Ser. No. 14/979, 186, filed Dec. 22, 2015; issued as U.S. Pat. No. 9,323,226; 10 and,

TRAVELING PULSE WAVE QUANTIZER, invented by Mikko Waltari, Ser. No. 14/681,206, filed Apr. 8, 2015; issued as U.S. Pat. No. 9,098,072.

### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

This invention generally relates to analog-to-digital con- 20 several samples simultaneously in pipelined fashion. verters (ADCs) and, more particularly, to a system and method for converting measured time durations to digital information.

#### 2. Description of the Related Art

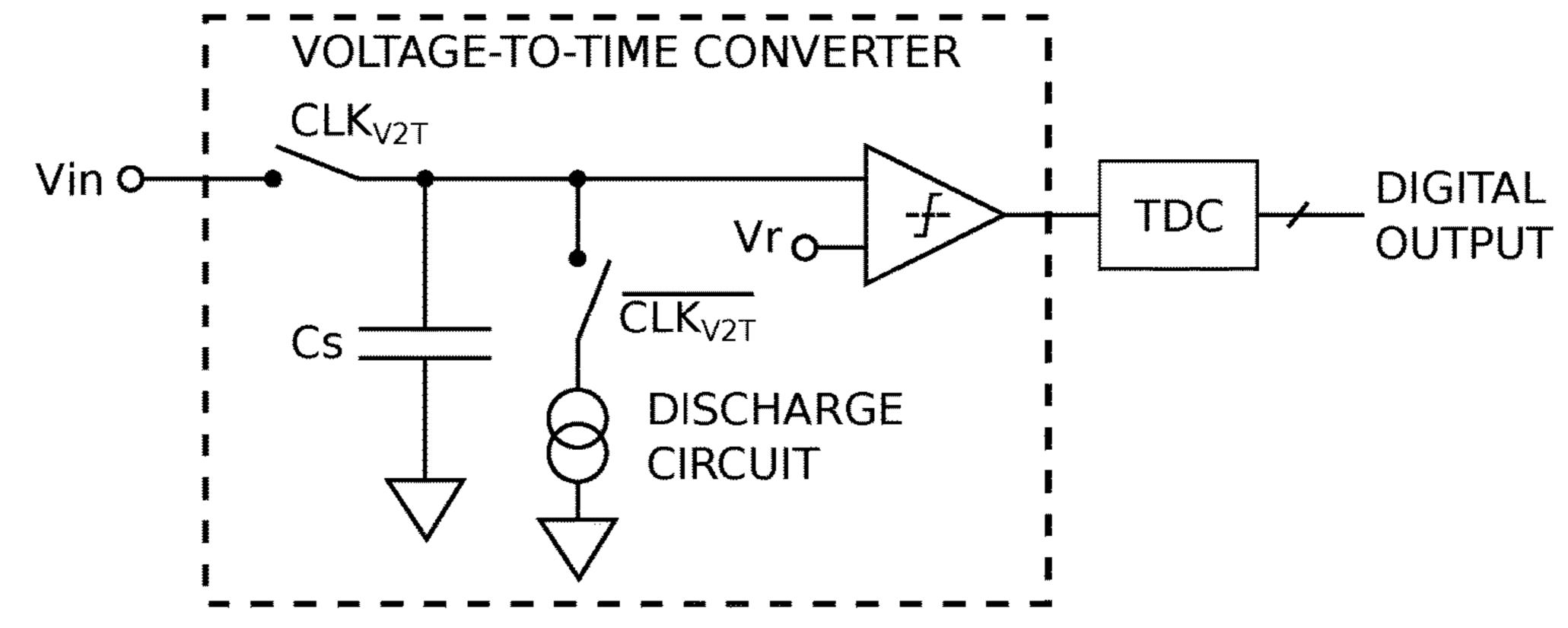

FIG. 1 is a simplified schematic of an ADC comprised of a voltage-to-time (V2T) converter and a time-to-digital converter (TDC) based upon a single slope principle (prior art). One promising way of performing very high speed 30 analog-to-digital (A-to-D) conversion in today's most advanced CMOS technologies is to utilize time domain analog signal processing. There, the A-to-D conversion process is split in two steps. In the first step the input voltage is converted into a time domain signal using pulse position 35 or pulse width modulation. In the second step this signal is digitized using a TDC. The advantage of this method is that most of the complexity of the design is in the TDC part, which can be implemented in digital, or digital-like circuitry that enjoys all the benefits of technology scaling in the 40 CMOS process. A well-known example of this type of ADC is the single-slope ADC, which uses a simple digital counter as the TDC.

One commonly used TDC architecture is the gated ringoscillator. It uses start and stop signals to define the time 45 interval to be digitized. The start signal is used to start the oscillator and the stop signal is used to capture the state of the oscillator, and so determine its state at a sub-period level. A digital counter is used to count the number of full oscillator cycles. The speed of the counter determines the 50 minimum oscillation periods. For instance, in modern CMOS technology the counter can operate on the order of 50 picoseconds (ps). If the desired least significant bit (LSB) size is 1 ps, there is a need for 50 sub-period quantization levels. Typically, the sub-period detection is done with 55 parallel structures yielding a 50 bit output signal that needs to be decoded into a final, in this case 6-bit, word length. Processing these 50 bits at a fast rate is power and circuit area consuming.

Another limitation of the gated ring oscillator is that it 60 cannot start processing the next sample while the current one is still circulating in the oscillator. This limitation can be overcome by unrolling the ring into a delay chain. However, the unrolled architecture suffers from the same parallel detection inefficiency. Yet another limitation in both archi- 65 tectures is that they are not truly time differential. While the measurement interval is defined to be the difference between

the start and the stop signals, the start signal must always arrive before the stop signal. Thus, in a system using a pair of signals (two inputs), the start signal must always be carried on one predetermined line and the stop pulse always carried on the other line. Another popular TDC architecture, the Vernier delay line, suffers from the same issues.

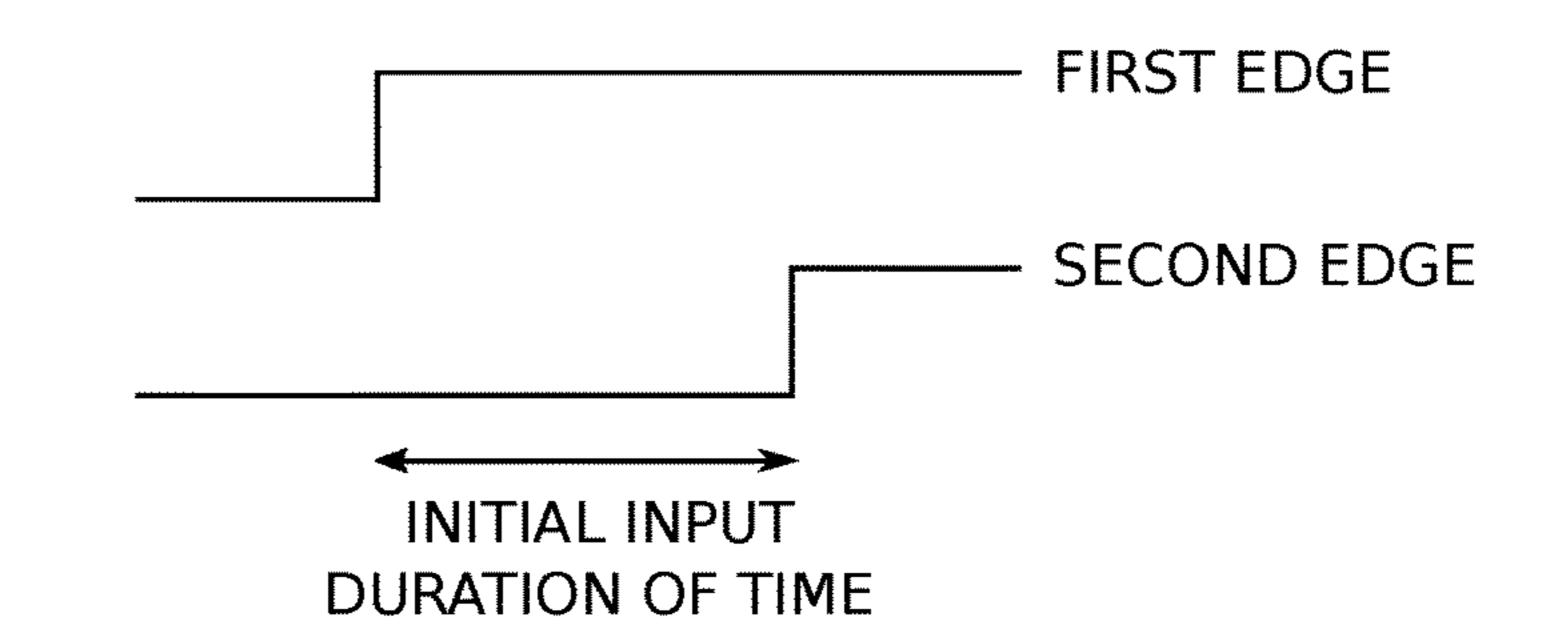

As used herein, a time-differential signal is understood to be a pair of bi-level signals, where one signal (pulse) indicates the start of a time durations to be measured and the other signal indicates the end (stop) of the time duration to be measured, but where there is no predetermined correlation between which signal is the start and which signal is the stop.

It would be advantageous if the number of detectors and 15 raw output bits of a TDC grew in proportion to N, N being the number of output bits, instead of  $2^N$  as it does in parallel type detectors.

It would be advantageous if a TDC could operate with a truly time-differential input, with the capability to process

### SUMMARY OF THE INVENTION

Disclosed herein is a time-to-digital converter (TDC) that 25 has a time-differential input enabled as a pair of bi-level input signals. In one aspect, the time interval to be digitized is defined as the time between the rising edge of the positive input signal and the rising edge of the negative input signal. The maximum time range to be digitized is from -T/2 to T/2. The time interval may be considered to be negative (less than zero duration time) if the stop (negative) input signal has a rising edge that occurs before the start (positive) input signal. As used herein, a time-differential signal is understood to be a pair of bi-level signals, where one signal (start/positive) indicates the start of a time durations to be measured and the other signal (stop/negative) indicates the end of the time duration to be measured, but where there is no predetermined correlation between which signal is the positive, first arriving signal. For the purpose of discussion rising edges are used as triggers, but the same idea can be implemented using negative edges as well.

The TDC consists of several cascaded stages, with the most significant bit (MSB) of the digital output being resolved in the front stage and the other bits in the following stages resolved in descending order. The principle of operation follows the successive approximation method. The time interval is converted into a digital word in several successive steps carried out one bit per TDC stage. Once a stage has completed its task, it passes the signal residue to the next stage. After passing the residue signal, the stage is reset and becomes ready to process the next sample.

Accordingly, a sort-and-delay time-to-digital converter is provided made up of a plurality of serially connected sort-and-delay circuits. Each sort-and-delay circuit accepts a time-differential input signal with a binary level first edge separated from a binary level second edge by an input (first) duration of time. The first and second edges are selectively routed as a time-differential output signal with a binary level delayed edge separated from a binary level trailing edge by an output (second) duration of time representing a compression of the input duration of time. Each sort-and-delay circuit also supplies a TDC coded bit indicating the order in which the first and second edges are routed to the leading and trailing edges. The TDC is also made up of a bit decoder having inputs to receive a plurality of TDC coded bits (e.g., Gray code) from the corresponding plurality of sort-anddelay circuits, and an output to supply a digital output signal

representing the initial input duration of time associated with the initial time-differential input signal received by the initial sort-and-delay circuit.

In one aspect, an nth sort-and-delay circuit in a plurality of n sort-and-delay circuits supplies a time-differential residue signal, so that the bit decoder supplies a digital output signal representing the n most significant bits in a p-bit digital word. In this aspect, the sort-and-delay TDC further includes a backend conventional TDC having an input to accept the time-differential residue signal and an output to supply a digital output signal comprising the (p-n)th least significant bits of the p-bit digital word.

Each sort-and-delay circuit is made up of an edge sort circuit having an input to accept a time-differential input signal. The edge sort circuit determines the order in which the first and second edges are accepted, and has outputs to supply a leading edge, the trailing edge, and the TDC coded bit. Each sort-and-delay circuit also includes a delay circuit having an input operatively connected to the first output of time asso the edge sort circuit, and an output to supply the delayed edge and the trailing edge are the time-differential output signal.

In one variation, the edge sort circuit includes an OR gate having a first input to accept the first edge, a second input to accept the second edge, and an output to supply the leading edge. An AND gate has a first input to accept the first edge, a second input to accept the second edge, and an output to supply the trailing edge. The edge sort circuit also includes an arrival time comparator (ATC) having a first input to accept the first edge, a second input to accept the second edge, and an output to supply an order signal responsive to the order in which the first and second edges are received. Alternatively, multiplexors can be used instead of combination logic, as provided in detail below.

In one aspect, the sort-and-delay circuit further also includes a time amplifier. In one variation a single-ended time amplifier has an input to accept the leading edge and the trailing edge. A pull-down circuit has an input to accept the leading edge and an output to supply a pull-down current to 40 a first node, initially set to a first voltage level, in response to the leading edge. A pull-up circuit has an input to accept the trailing edge and an output to supply a pull-up current to the first node in response to the trailing edge. A capacitor has a first terminal connected to the first node and a second 45 terminal connected to a reference voltage. Finally, a comparator has a first input connected to a threshold voltage, a second input connected to the first node, and an output to supply a time-amplified edge. The leading edge and the trailing edge are separated by a third duration of time, and 50 the leading and the time-amplified edge are separated by an amplified duration of time, directly proportional to the third duration of time. Alternatively, a differential time amplifier may be used, as provided in more detail below.

Addition details of the above described circuitry, as well 55 as successive approximation TDC, time amplification, and sort-and-delay methods, are provided below.

### BRIEF DESCRIPTION OF THE DRAWINGS

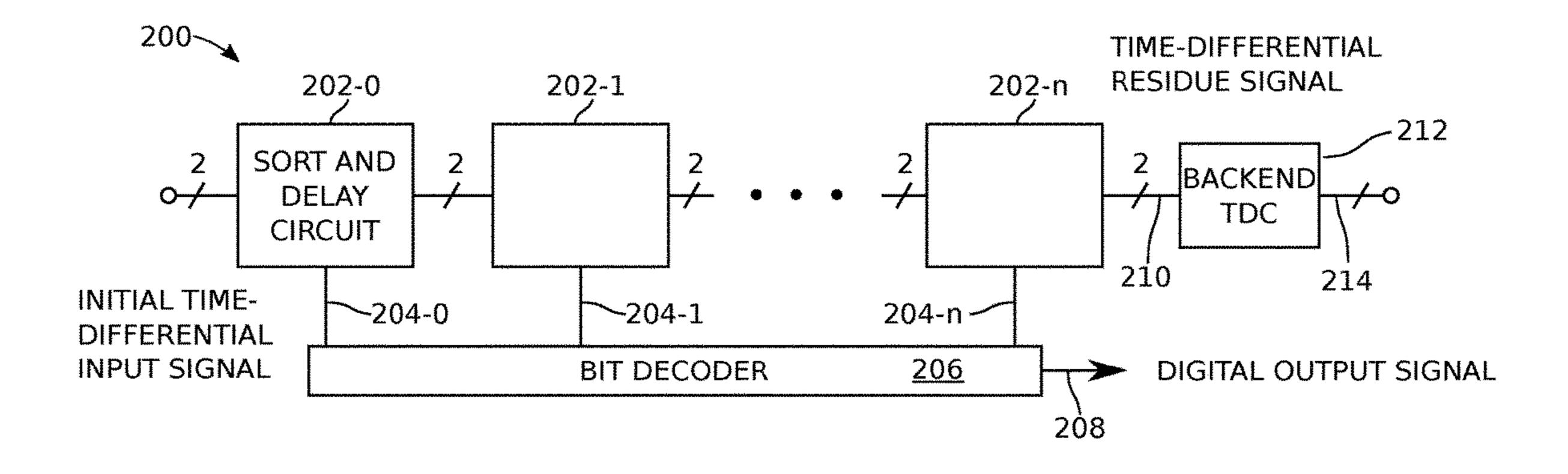

FIG. 1 is a simplified schematic of an ADC comprised of a voltage-to-time (V2T) converter and a time-to-digital converter (TDC) based upon a single slope principle (prior art).

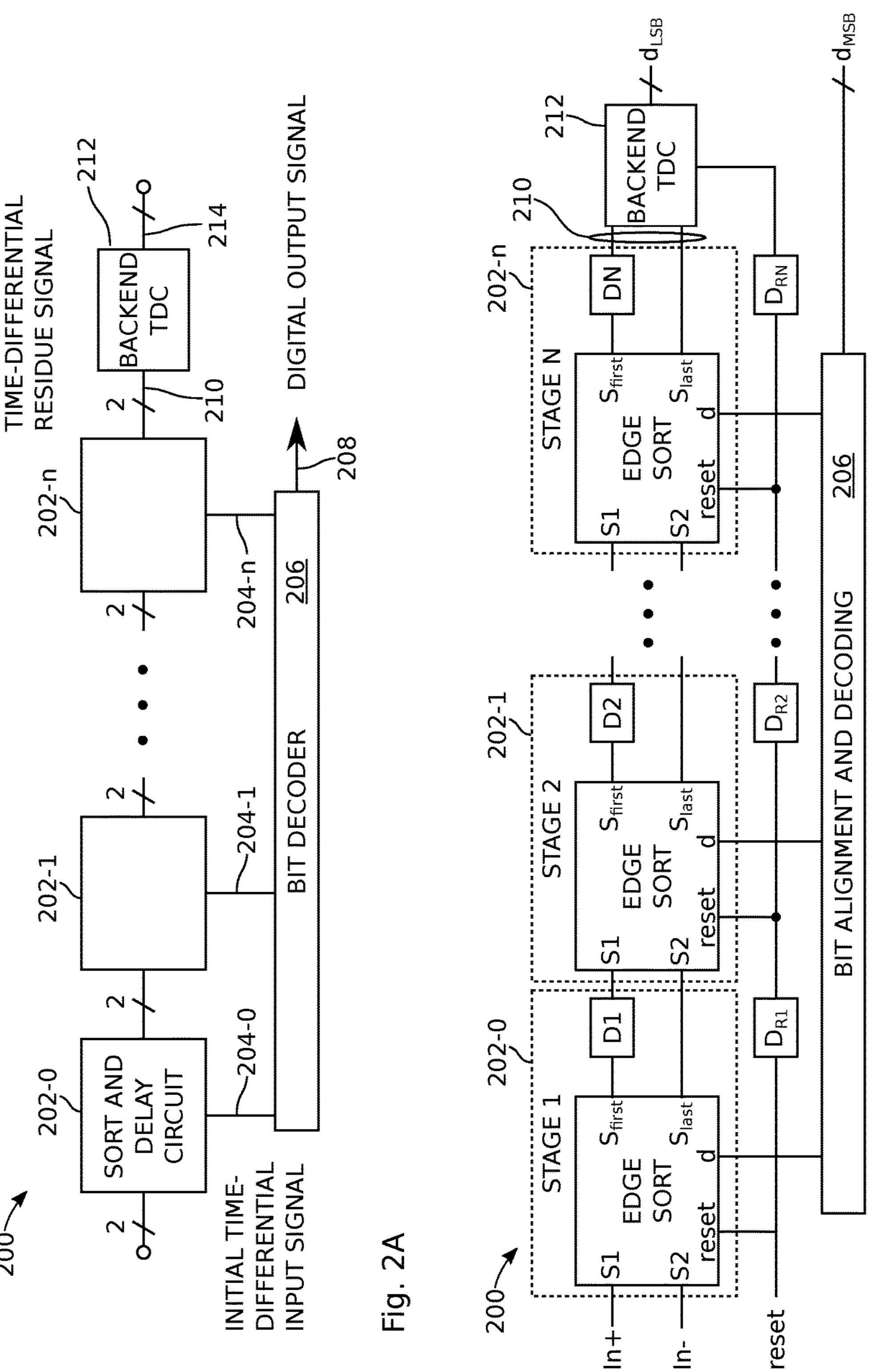

FIGS. 2A and 2B are, respectively, a schematic block 65 diagram depicting a sort-and-delay TDC and an associated timing diagram.

4

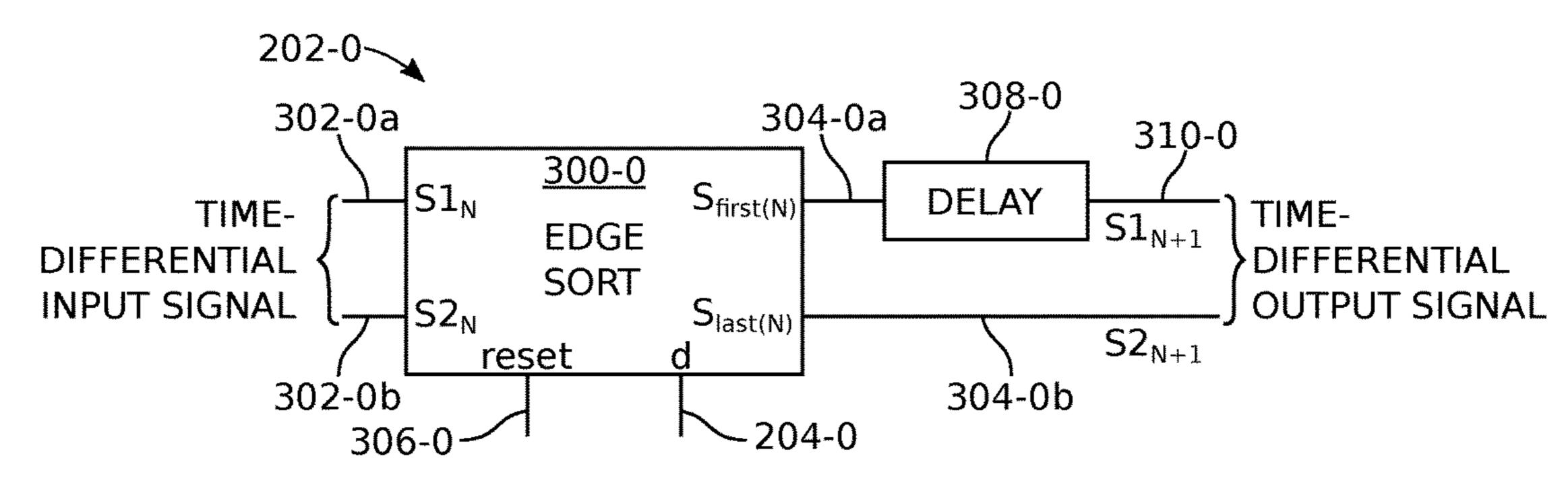

FIG. 3A is a schematic block diagram of a sort- and delay circuit, and FIG. 3B is an associated timing diagram.

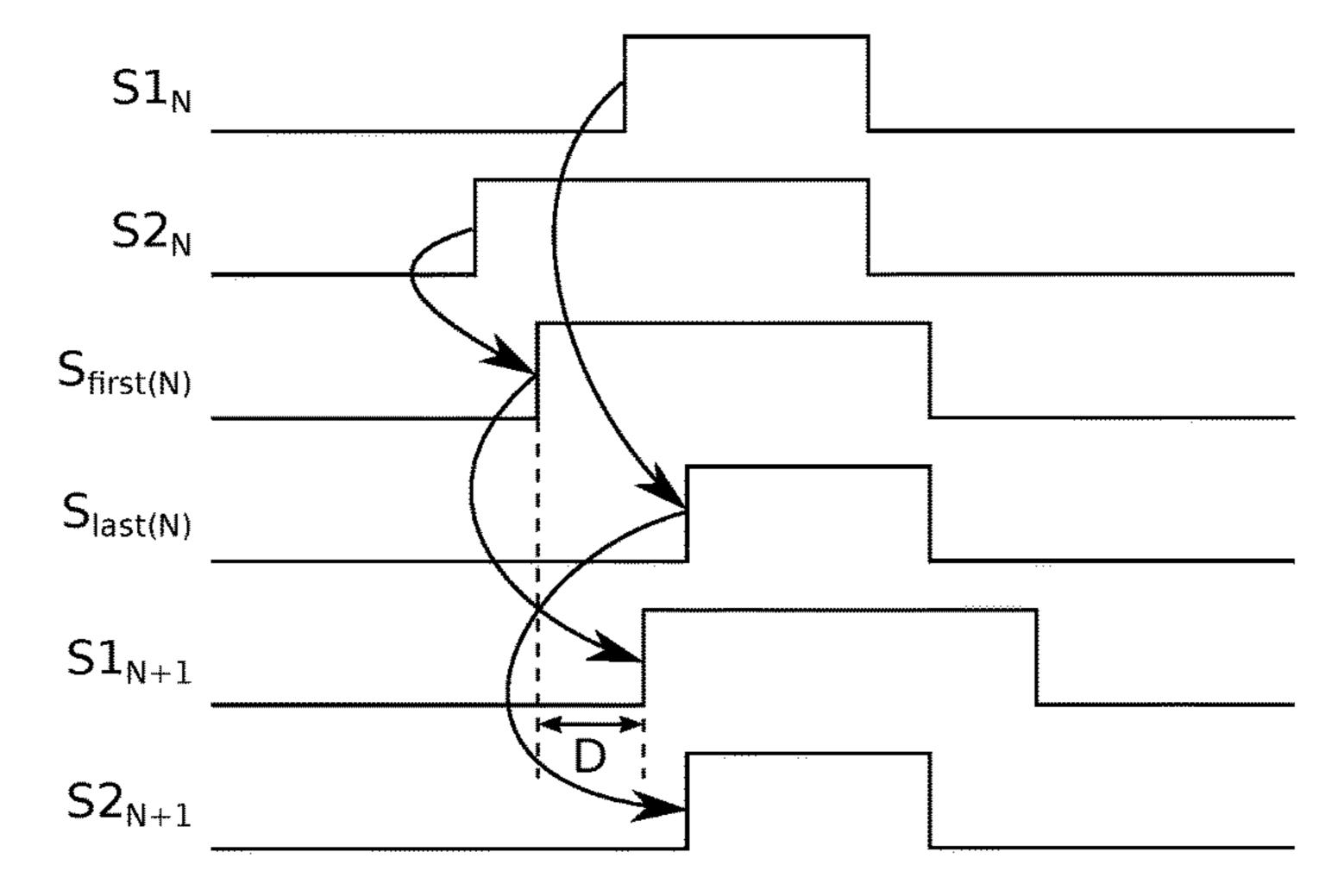

FIG. 4 is a schematic block diagram depicting a first variation of an edge sort circuit.

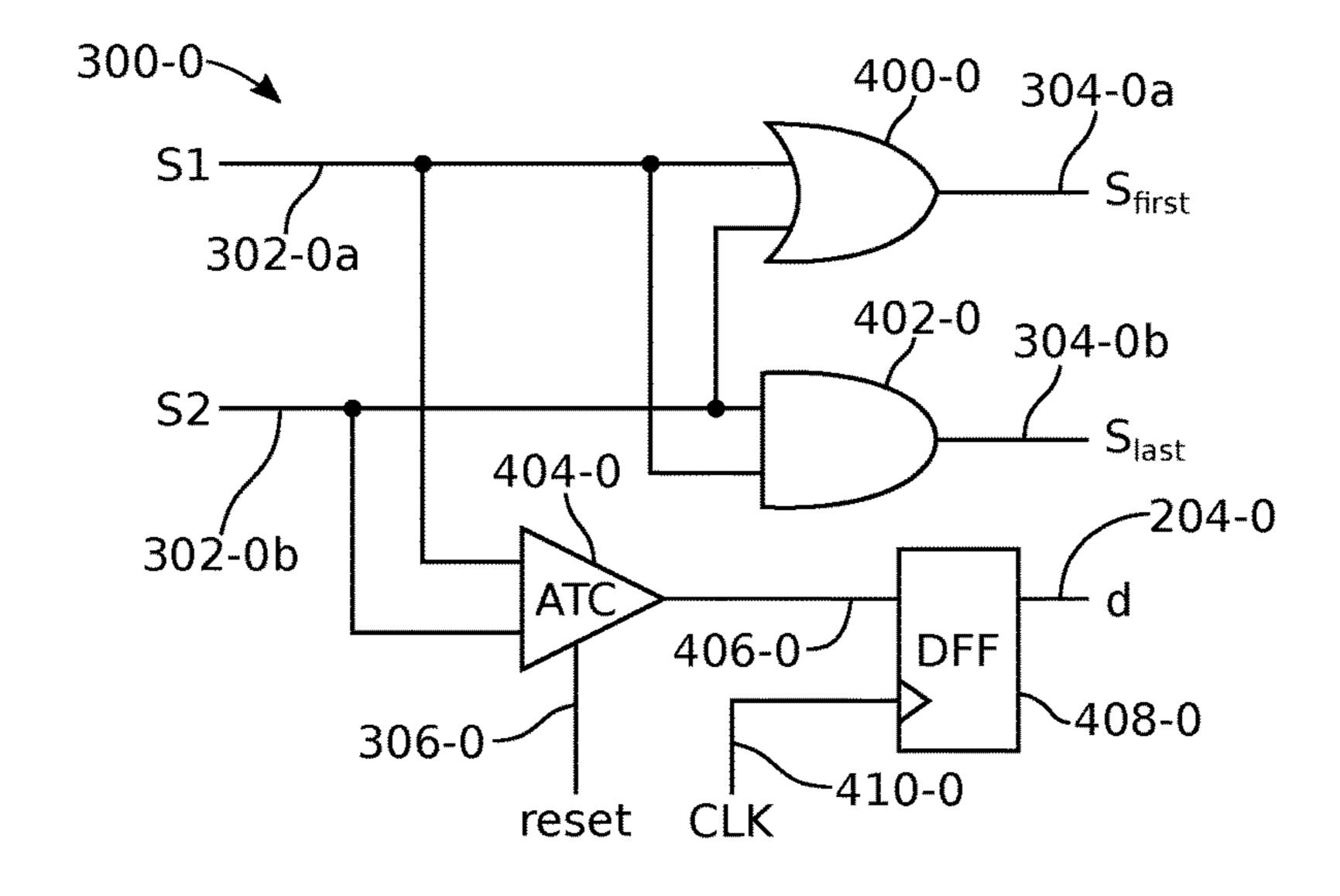

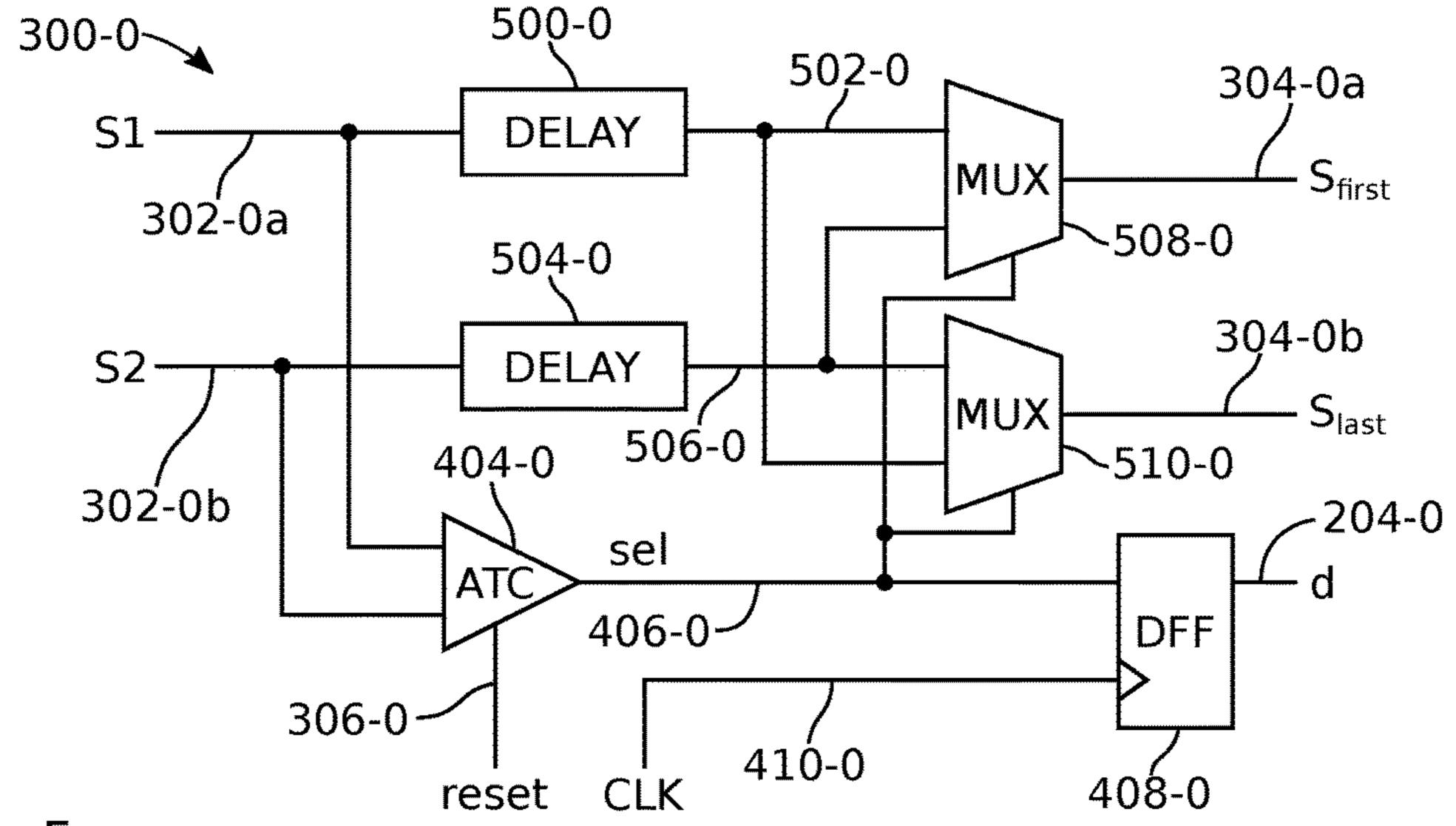

FIG. 5 is a schematic block diagram depicting a second variation of an edge sort circuit.

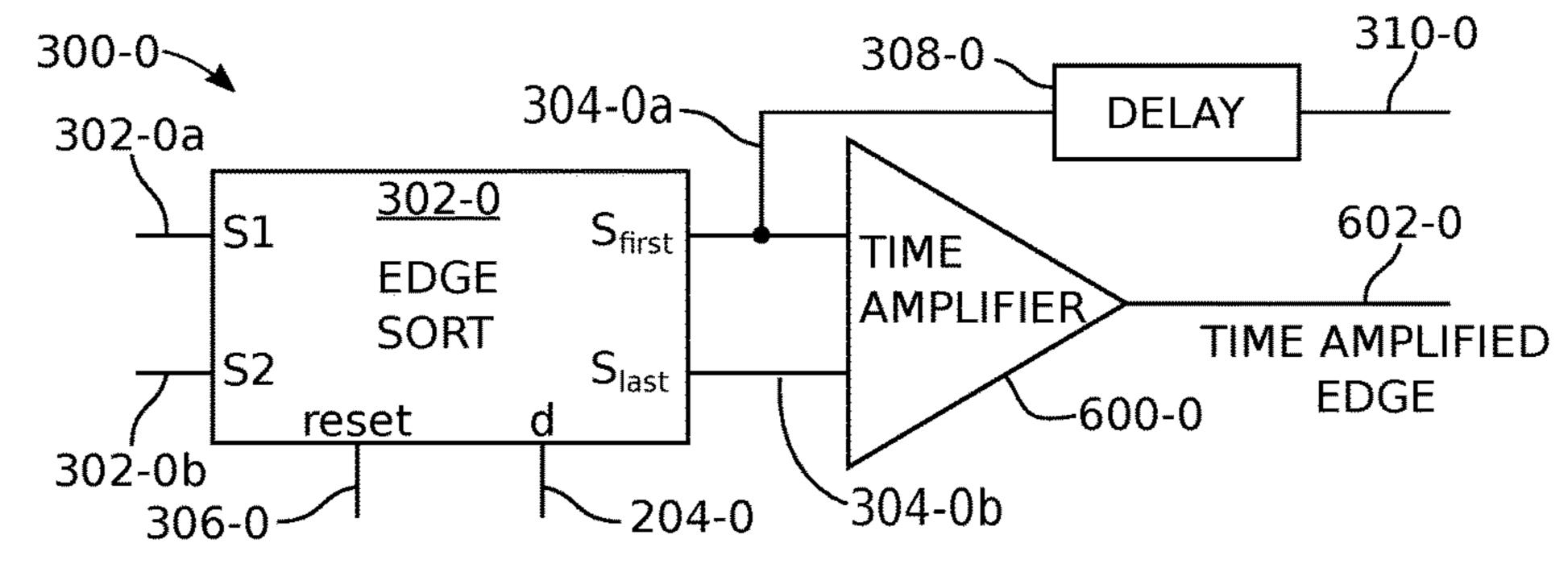

FIG. 6 is a schematic block depicting a variation of the sort-and-delay circuit further comprising a time amplifier.

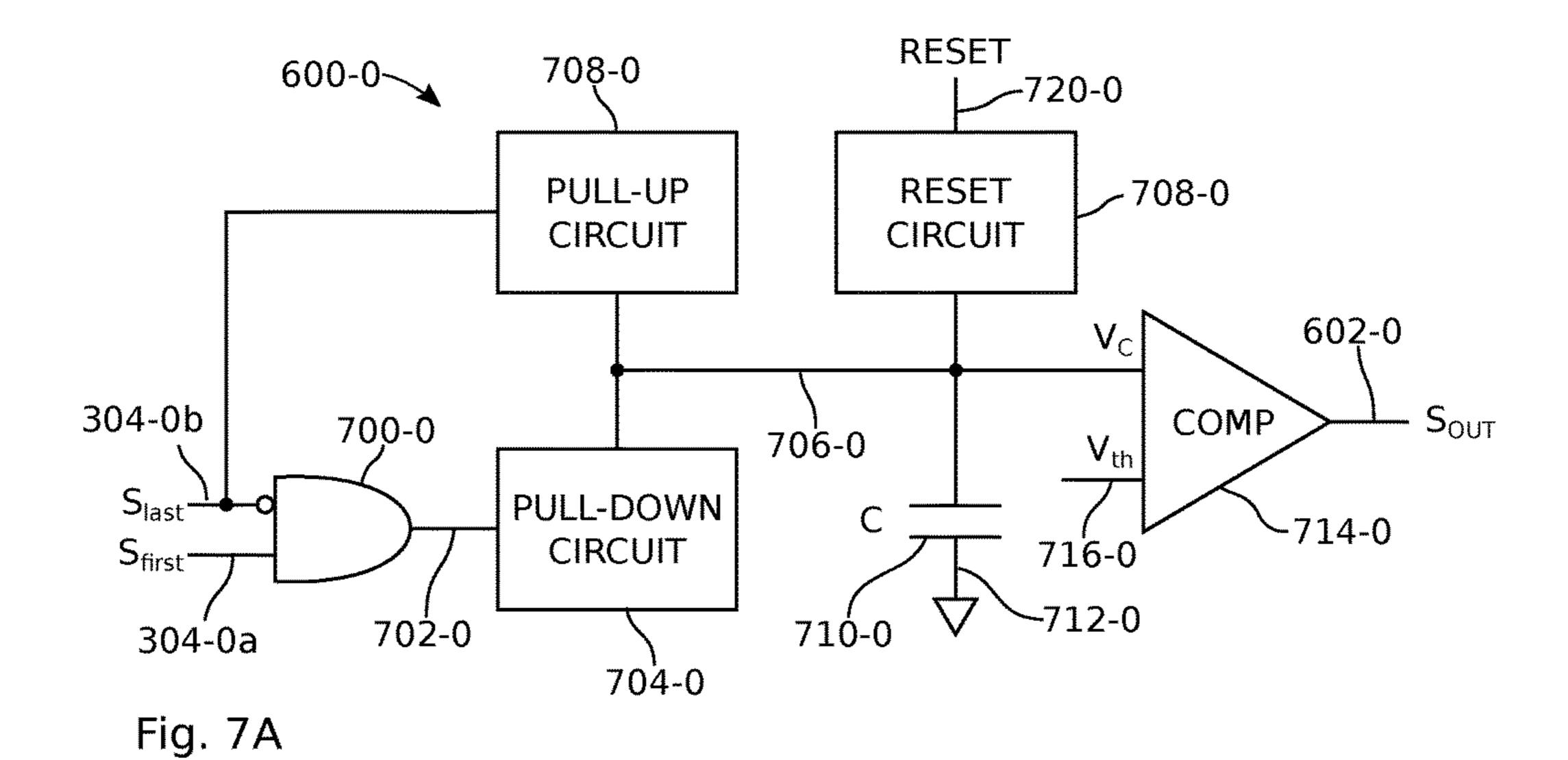

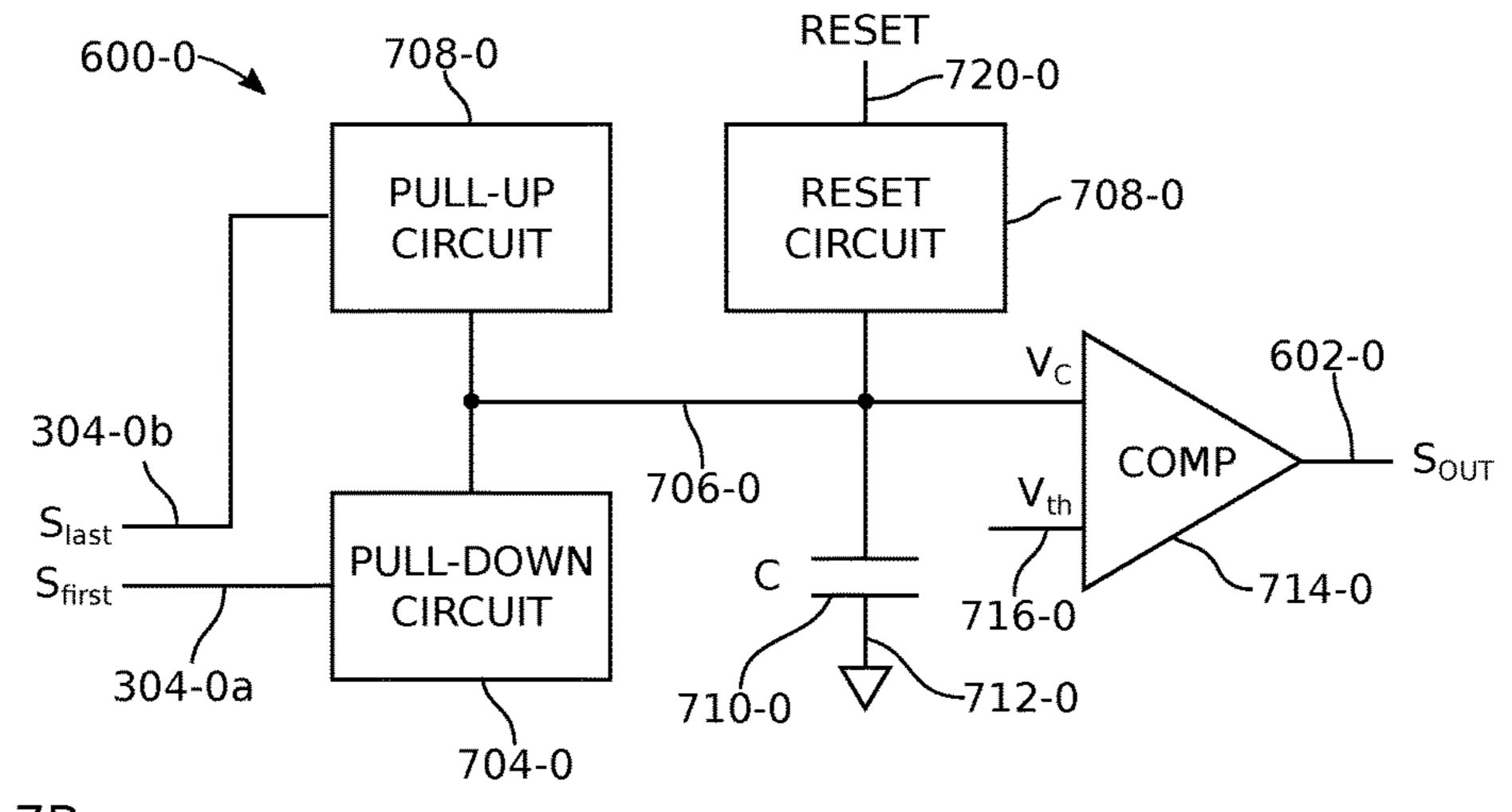

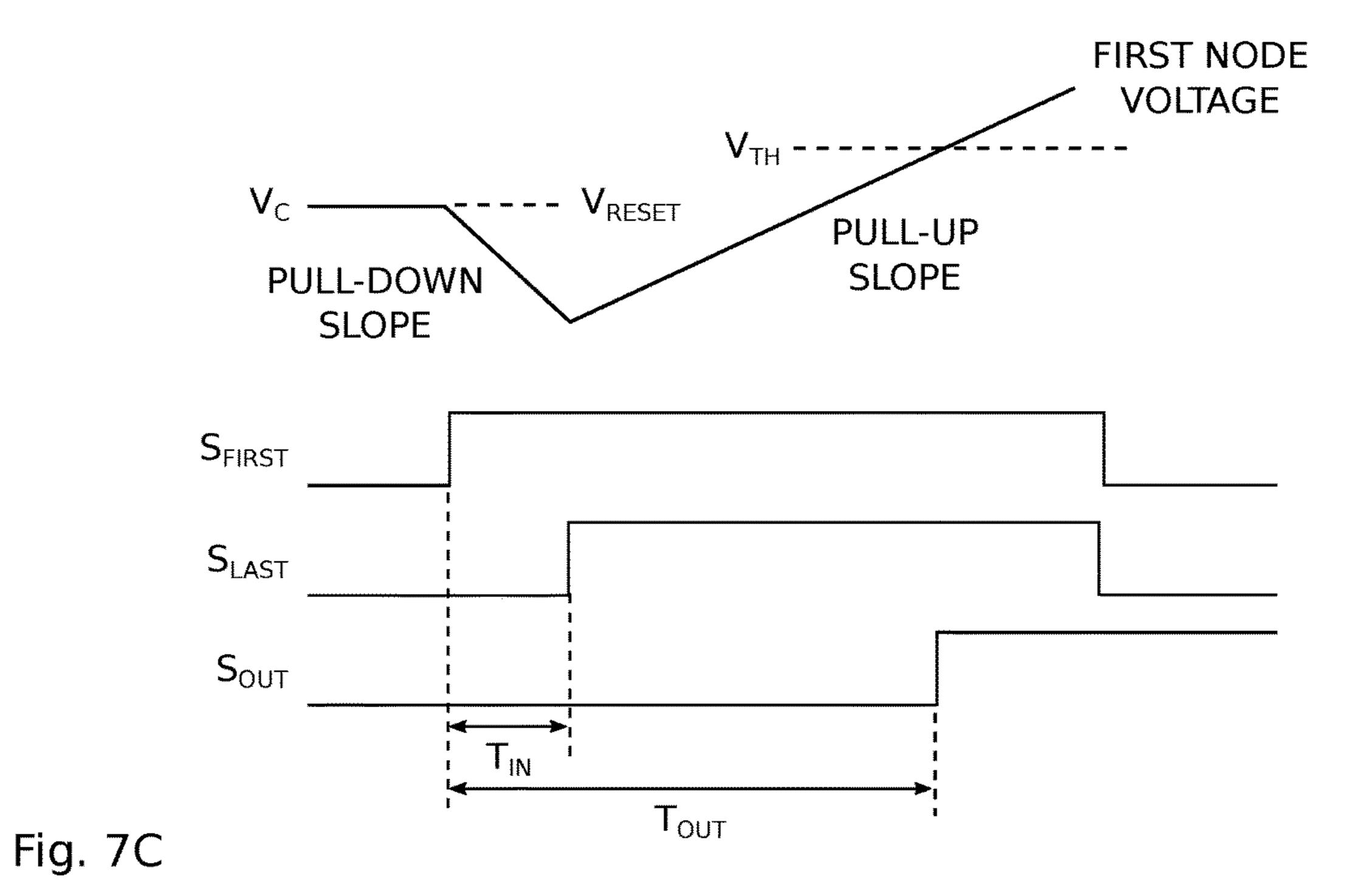

FIGS. 7A and 7B are schematic block diagrams depicting variations of the single-ended time amplifier of FIG. 6 in greater detail, and FIG. 7C is a timing diagram associated with FIG. 7A or 7B.

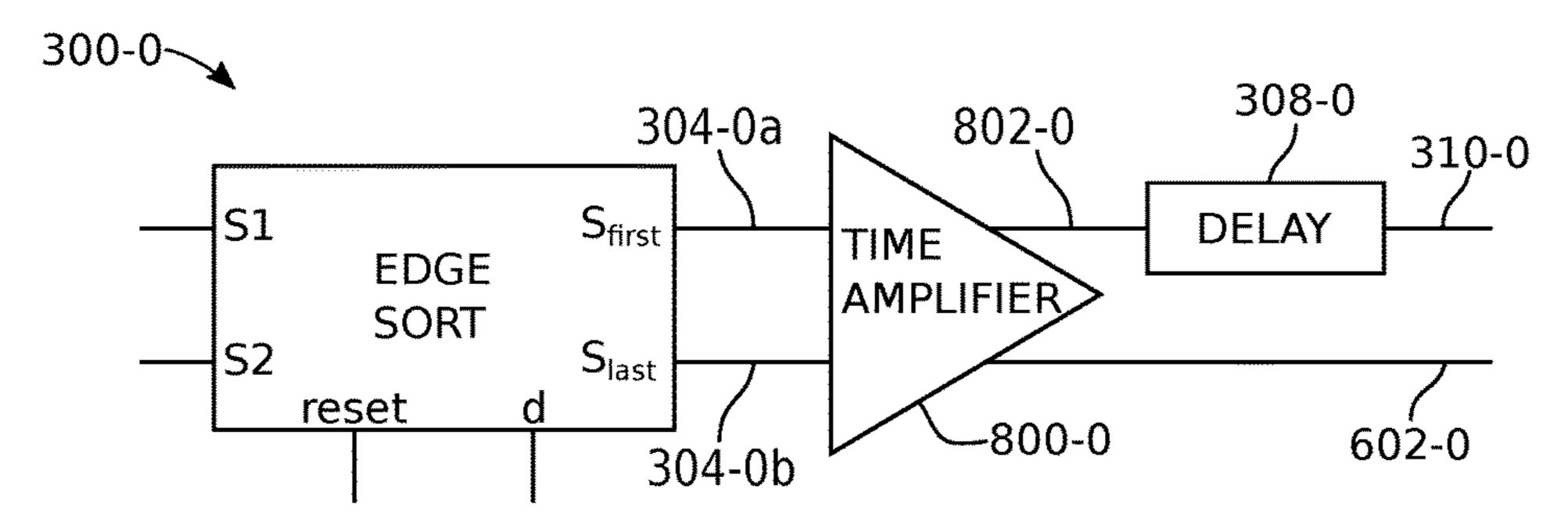

FIG. **8** is a schematic block depicting a variation of the sort-and-delay further comprising a differential time amplifier.

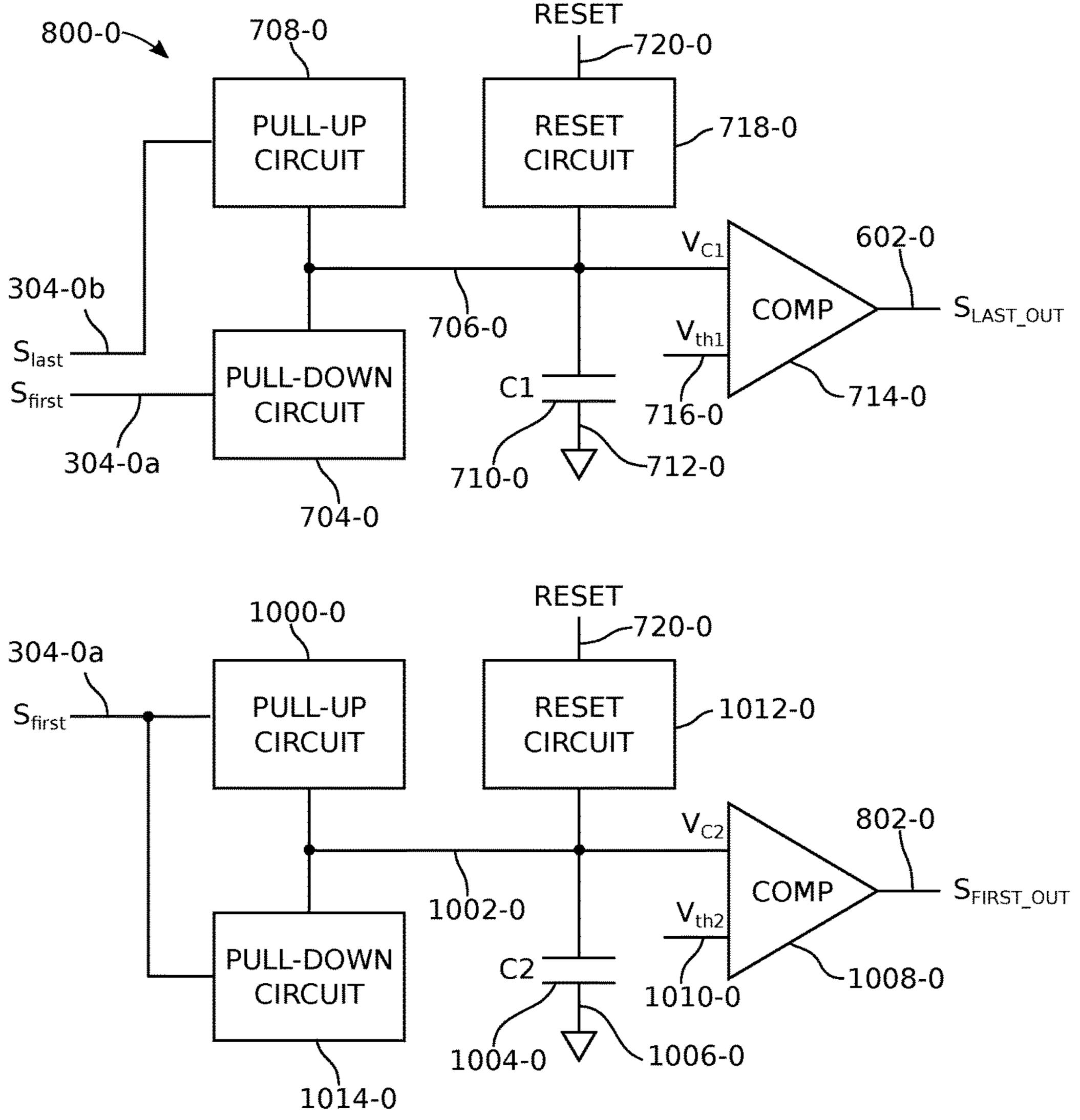

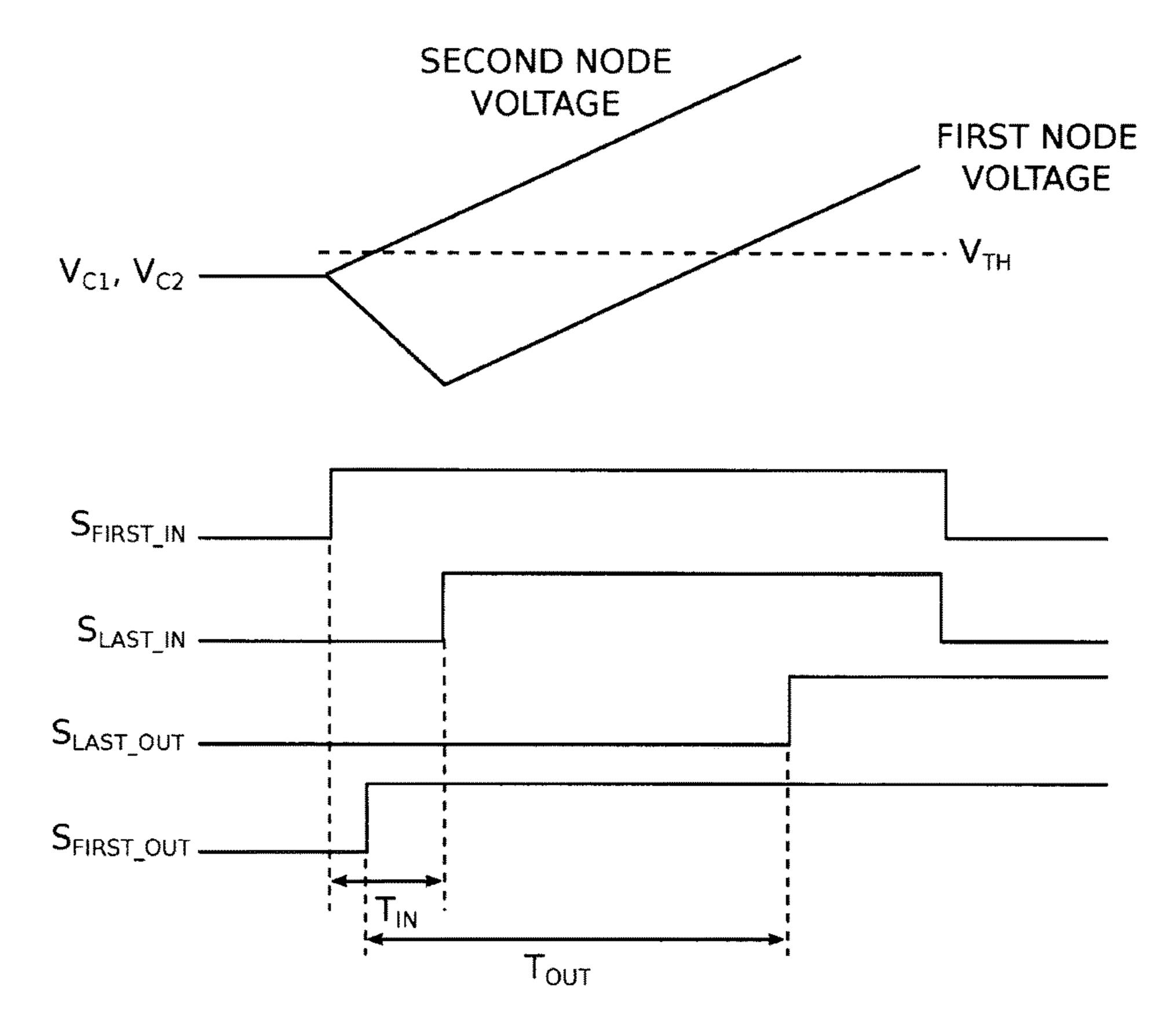

FIG. 9 is a block diagram depicting the differential time amplifier of FIG. 8.

FIG. 10A is a schematic block diagram of the differential time amplifier of FIG. 9 in greater detail, and FIG. 10B is an associated timing diagram.

FIG. 11 is a schematic block diagram depicting the sort-and-delay TDC in slightly greater detail than shown in FIG. 2.

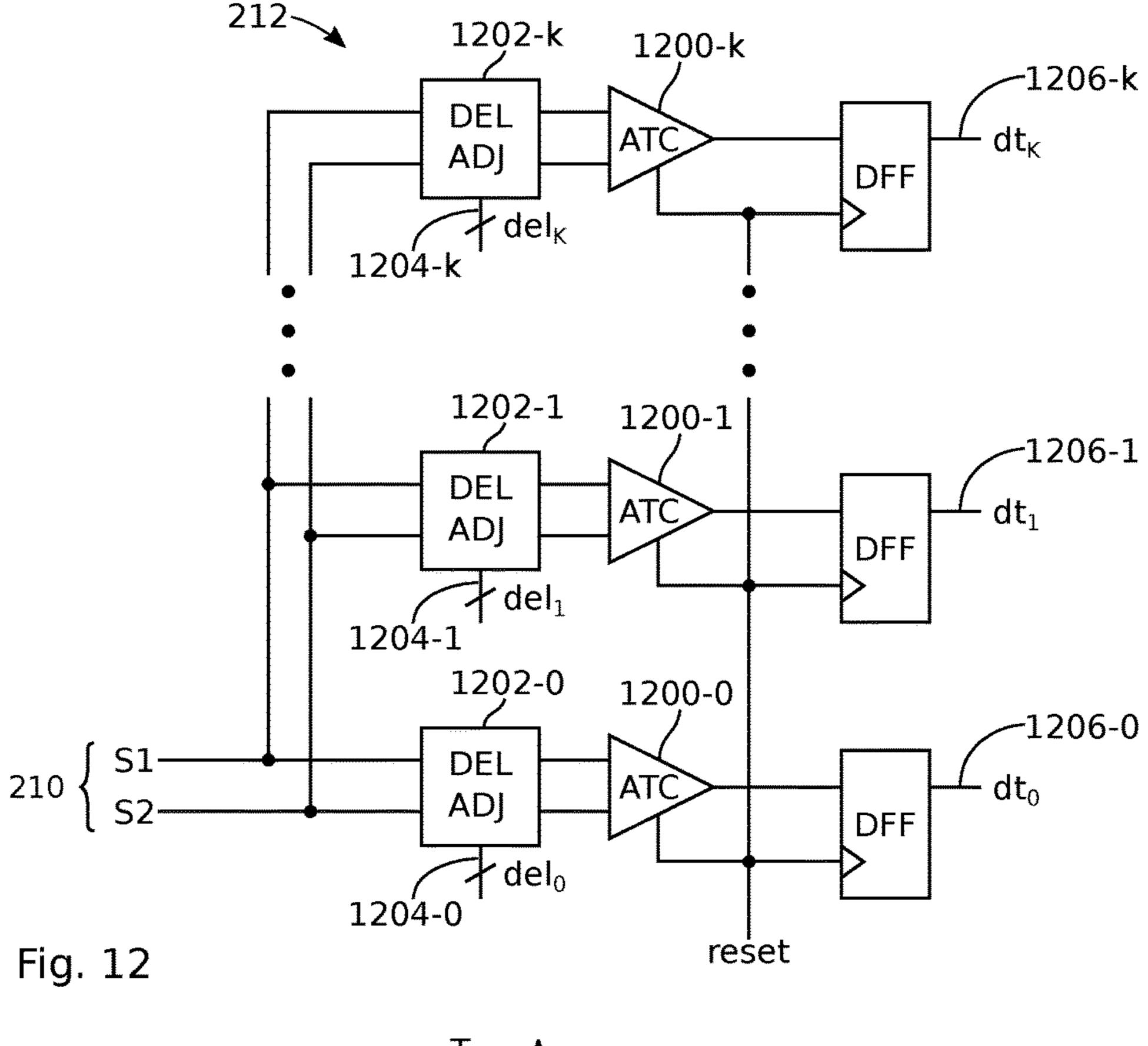

FIG. 12 is a schematic block diagram depicting an exemplary backend TDC.

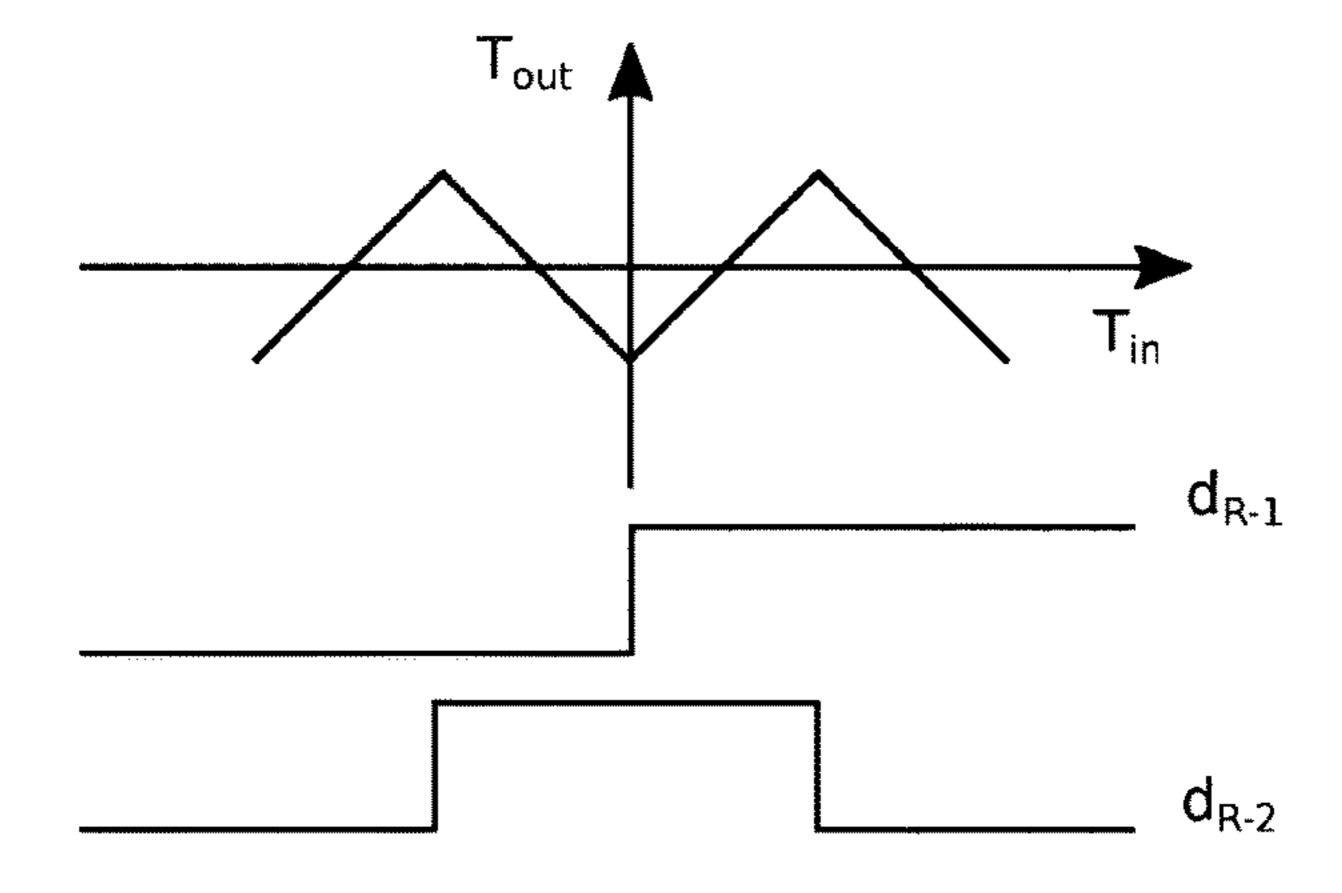

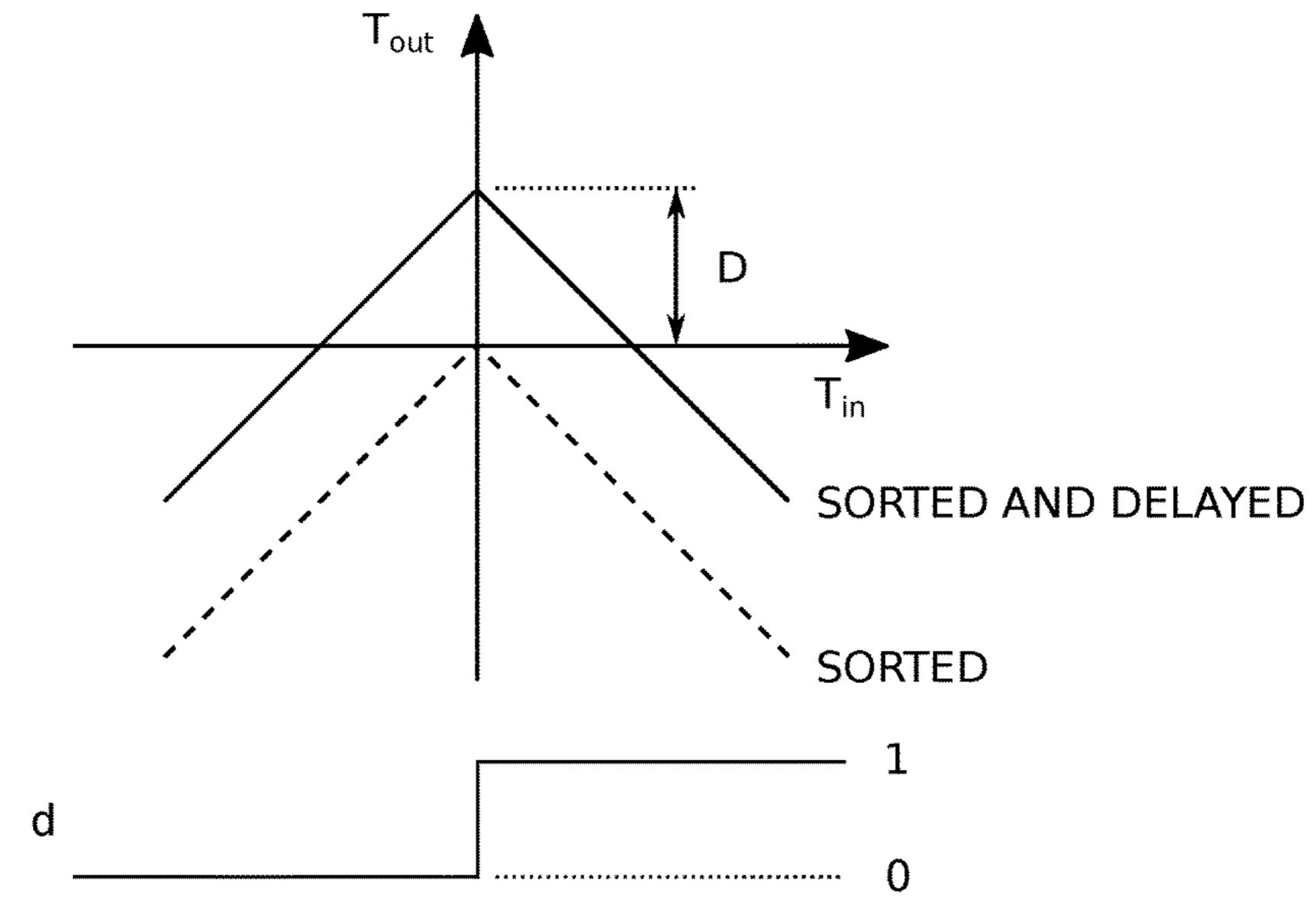

FIGS. 13A and 13B are diagrams depicting sort-and-delay circuit transfer functions.

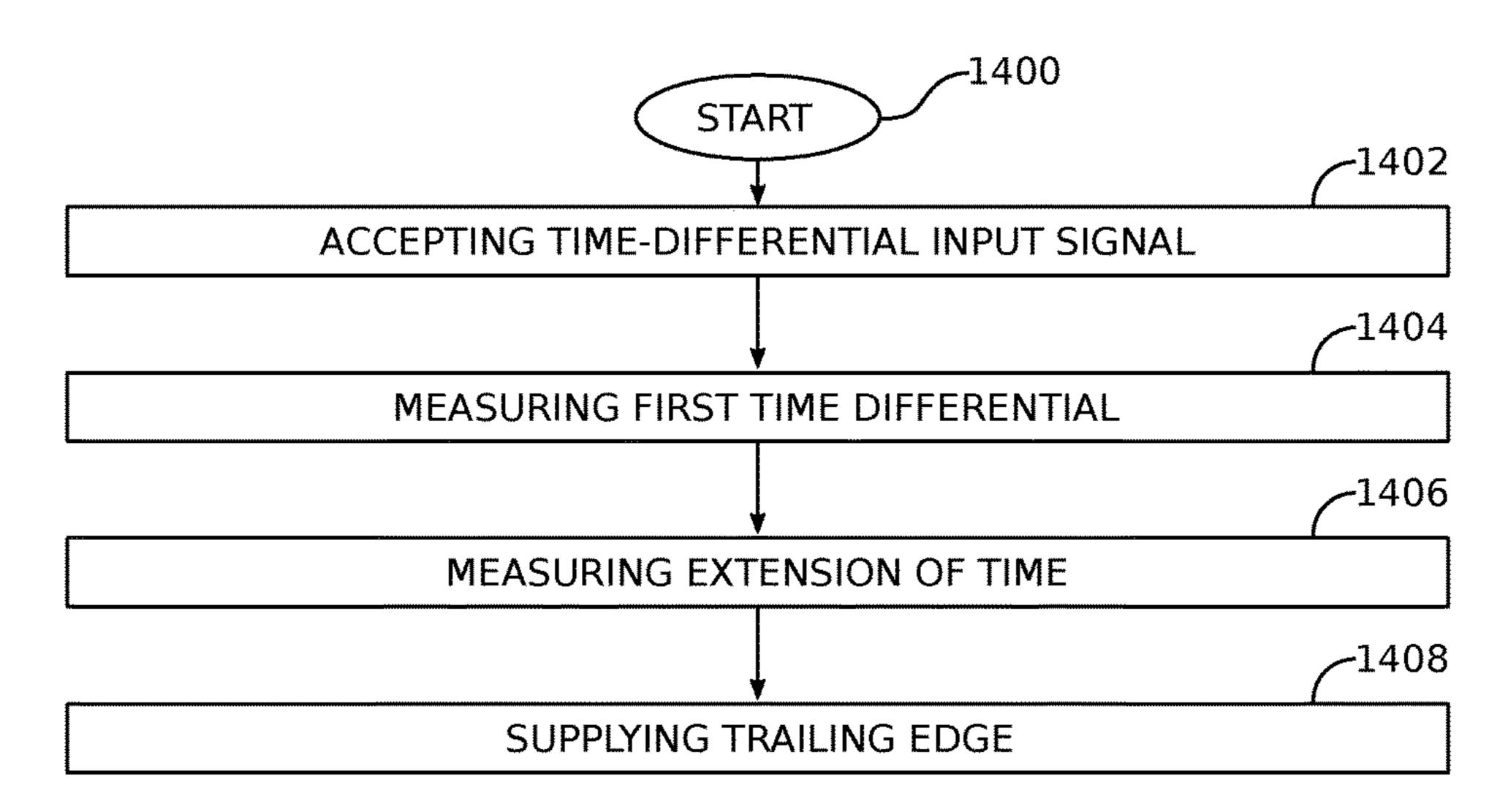

FIG. **14** is a flowchart illustrating a method for amplifying the duration of a time-differential signal.

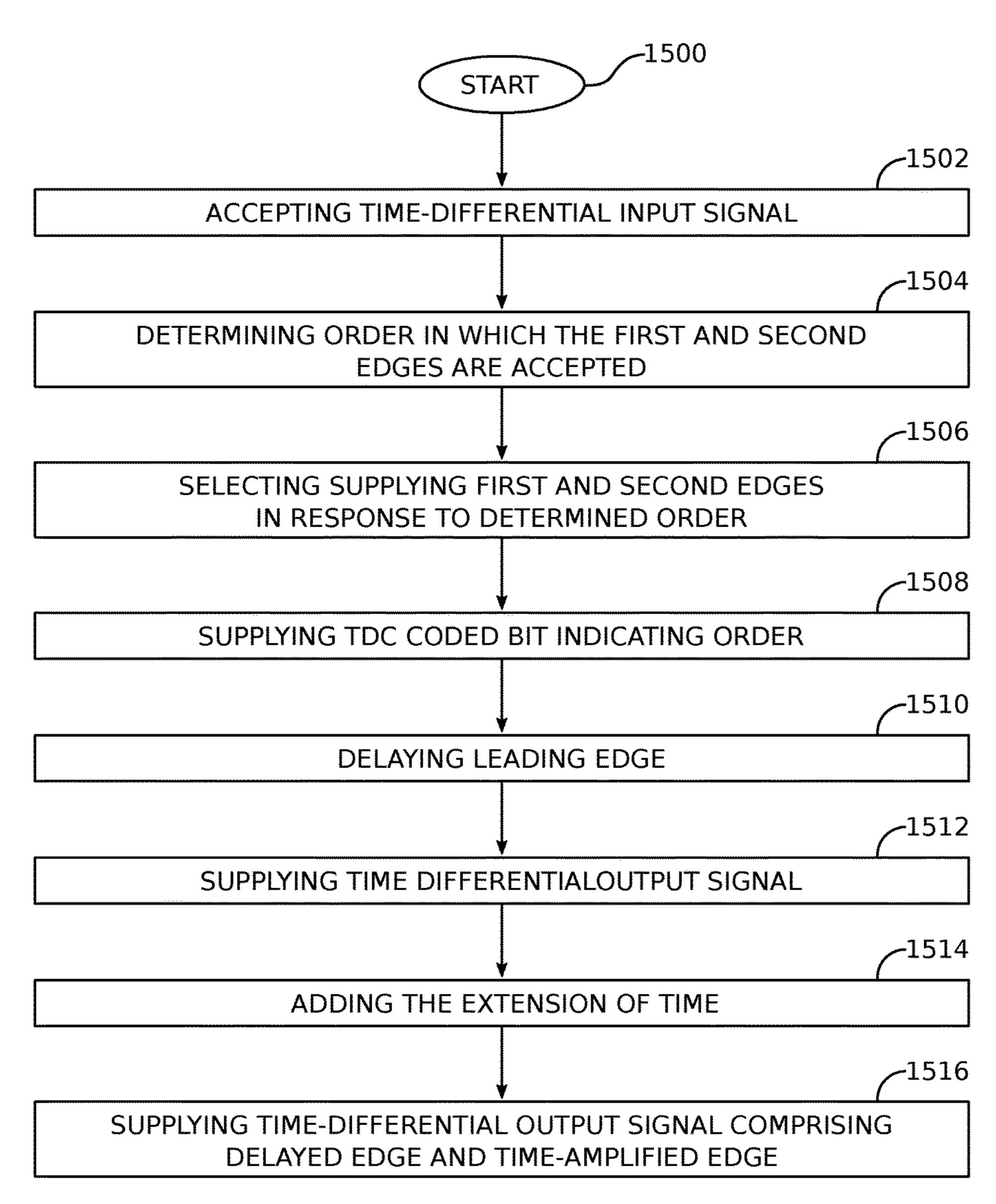

FIG. **15** is a flowchart illustrating a successive approximation TDC method.

FIG. **16** is a flowchart illustrating a sort-and-delay TDC method.

#### DETAILED DESCRIPTION

FIGS. 2A and 2B are, respectively, a schematic block diagram depicting a sort-and-delay TDC and an associated timing diagram. The sort-and-delay TDC 200 comprises a plurality of serially connected sort-and-delay circuits 202-0 through 202-n, where n is an integer greater than zero. Each sort-and-delay circuit accepts a time-differential input signal comprising a binary level first edge separated from a binary level second edge by an input or first duration of time. Each sort-and-delay circuit selectively routes respective first and second edges to a time-differential output signal comprising a binary level delayed edge separated from a binary level trailing edge by an output or second duration of time representing a compression of the input duration of time. As explained in more detail below, a time delay duration (D) is subtracted from time-differential input signal as a means of compression, to supply the time-differential output signal. Each sort-and-delay circuit supplies a TDC coded bit respectively on lines 204-0 through 204-n, indicating the order in which the first and second edges are routed as the leading and trailing edges. As used herein, a time-differential signal is understood to be a pair of bi-level signals on two separate lines, where one signal (the first edge) indicates the start of a time durations to be measured and the other signal (the second edge) indicates the end of the time duration to be measured, but where there is no predetermined correlation between the positive, first arriving signal and the line carrying the positive signal.

A bit decoder 206 has inputs to receive a plurality of TDC coded bits from the corresponding plurality of sort-and-delay circuits, and an output on line 208 to supply a digital output signal representing the initial input duration of time

associated with the initial time-differential input signal received by the initial sort-and-delay circuit **202-0**. For example, taken together the TDC coded bits on lines **204-0** through **204-***n* may be in the form of a Gray code. Although the differential input first and second edges are represented as rising edges, they may also be falling edges, or a combination of rising and falling edges.

In one aspect as shown, the nth sort-and-delay circuit (202-n) in a plurality of n sort-and-delay circuits supplies a time-differential residue signal on line 210. Then, the bit 10 decoder 206 supplies a digital output signal on line 208 representing the n most significant bits in a p-bit digital word. In this aspect, the sort-and-delay TDC 200 further comprises a backend TDC 212 having an input on line 210 to accept the time-differential residue signal and an output on line 214 to supply a digital output signal comprising the (p-n)th least significant bits of the p-bit digital word. The backend TDC 212 may be enabled using a conventional technology, such as Flash, gated ring-oscillator, delay chain oscillator, or Vernier delay line, to name a few examples.

FIG. 3A is a schematic block diagram of a sort- and delay circuit, and FIG. 3B is an associated timing diagram. Each sort-and-delay circuit, for example sort-and-delay circuit 202-0, comprises an edge sort circuit, with edge sort circuit **300-0** being shown as an example. Edge sort circuit **300-0** 25 has an input on lines 302-0a (S1<sub>N</sub>) and 302-0b (S2<sub>N</sub>) to accept a time-differential input signal. The edge sort circuit 300-0 determines the order in which the first and second edges are accepted. Edge sort circuit 300-0 has a first output on line 304-0a ( $S_{first(N)}$ ) to supply the leading edge, a second 30 output on line 304-0b ( $S_{last(N)}$ ) to supply the trailing edge, and a third output on line 204-0 (d) to supply the TDC coded bit. A reset is shown on line 306-0, which is explained in more detail below. A delay circuit 308-0 with a time delay duration of D, has an input operatively connected to the first 35 output of the edge sort circuit on line 304-0a, and an output on line 310-0 to supply a delayed edge.

As used herein, "operatively connected" means directly connected or connected through an intervening element (e.g., a time amplifier, as described below). The delayed 40 edge on line 310-0 (S1<sub>N-1</sub>) and the trailing edge on line 304-0b (S2<sub>N+1</sub>) comprise a time-differential output signal. Typically, the time duration D of each stage is less than the maximum input duration of the time-differential input signal. Further, due to the successive compression of the 45 time-differential signals, the fixed delay D of each successive sort- and delay circuit decreases at a comparable rate. As used herein, a time-differential output signal is compressed when the time-differential input signal is within the range -T1/2 to +T1/2, and the time-differential output signal 50 within the range -T2/2 to +T2/2, and T2 < T1. This concept is illustrated in FIG. 13A, where the sorting operation first compresses the input range from -T1/2 to +T1/2, to the range –T1/2 to 0. A subsequent delay operation shifts the range up by D and the output range becomes -T2/2 to +T2/2. In this example T2 is approximately T112. Alternately considered, "compression" may be considered as a form of subtraction with the time duration of D.

FIG. 4 is a schematic block diagram depicting a first variation of an edge sort circuit. Using the edge sort circuit 60 300-0 as an example, the edge sort circuit comprises an OR gate 400-0 having a first input on line 302-0a to accept the first edge, a second input on line 302-0b to accept the second edge, and an output on line 304-0a to supply the leading edge. An AND gate 402-0 has a first input on line 302-0a to 65 accept the first edge, a second input on line 302-0b to accept the second edge, and an output on line 304-0b to supply the

6

trailing edge. An arrival time comparator (ATC) 404-0 has a first input on line 302-0a to accept the first edge, a second input on line 302-0b to accept the second edge, and an output on line 406-0 to supply an order signal responsive to the order in which the first and second edges are received. In this version the routing is automatic and does not depend on the ATC. One advantage of this edge sort circuit variation is that it is fast and simple, but it suffers from two potential shortcomings: it is not guaranteed that the ATC detection of the order of arrival matches the automatic routing performed by the logic gates. The second issue has to do with the transistor level implementation of the AND and OR gates, which makes the gate delay dependent on the proximity of the signal changes at the two inputs.

In one aspect, the ATC 404-0 has a reset input on line **306-0** to accept a reset signal responsive to the trailing edge, which may occur concurrently with the trailing edge or sometime after the trailing edge, on the condition that it occurs before the arrival of the next time-differential input signal. A register 408-0, such as a D flip-flop (DFF), has an input connected to the ATC output on line 406-0, a clock input to accept a clock (CLK) signal 410-0, and an output to supply the TDC coded bit on line 204-0. The clock on line 410-0 must arrive before or simultaneously with the reset signal on line 306-0. One possibility is to use the leading edge of a common signal to generate the clock and the trailing edge of the common signal to generate the reset. Note: the above-described circuitry can be enabled using other variations of combinational logic, as would be understood by one with ordinary skill in the art.

A multiplexing function is preformed automatically with the AND and OR gates without any control signals. The ATC is used only to provide the digital output bit. This implementation has a shorter propagation delay than the variation depicted in FIG. 5, but may suffer from accuracy problems close to the input zero crossing, due to the offset in the ATC 404-0.

FIG. 5 is a schematic block diagram depicting a second variation of an edge sort circuit. In this variation, the edge sort circuit 300-0 comprises a first delay 500-0 having an input on line 302-0a to accept the first edge and an output on line 502-0 to supply a delayed first edge, delayed a first period of time. A second delay 504-0 has an input to accept the second edge on line 302-0b and an output on line 506-0 to supply a delayed second edge, delayed a second period of time. Typically, the first and second periods of time are the same, or intended to be the same. However, this circuit variation can also be enabled using delays of different durations.

A first multiplexor (MUX) 508-0 has a control input to accept the order (select) signal on line 406-0, a first input on line **502-0** to accept the delayed first edge, a second input on line 506-0 to accept the delayed second edge, and an output on line 304-0a to supply the leading edge in response to the order signal. A second MUX 510-0 has a control input on line 406-0 to accept the order signal, a first input on line **506-0** to accept the delayed second edge, a second input on line 502-0 to accept the delayed first edge, and an output on line 304-0b to supply the trailing edge in response to the order signal. The ATC 404-0 has a first input on line 302-0a to accept the first edge, a second input on line 302-0b to accept the second edge, and an output on line 406-0 to supply the order signal responsive to the order in which the first and second edges are routed. In one aspect, the ATC 404-0 has a reset input on line 306-0 to accept a reset signal responsive to the trailing edge. As above, the reset may occur concurrently with the trailing edge or sometime after

the trailing edge, on the condition that it occurs before the arrival of the next time-differential input signal. The register 408-0 (e.g., DFF) has an input connected to the ATC output on line 406-0, a clock input to accept a clock signal 410-0, and an output to supply the TDC coded bit on line 204-0.

The arrival time comparator **404-0** detects the incoming edge order and sets the output multiplexers accordingly. Nominally equal delays are inserted into the signal path to give the ATC some time to make its decision and to program the MUXs before the signals arrive at the MUX inputs. The 10 ATC has a reset signal to reset its state between different samples. A clocked D flip-flop captures the ATC output and provides the digital output bit. The reset timing is not critical; it just needs to occur between two successive input samples.

FIG. 6 is a schematic block depicting a variation of the sort-and-delay circuit further comprising a time amplifier. The time amplifier 600-0 had an input on line 304-0a to accept the leading edge and an input on line 304-0b to accept the trailing edge, where the leading and trailing edges are 20 separated by a third duration of time. The time amplifier 600-0 has an output on line 602-0 to supply a time-amplified edge. The delayed edge and the time-amplified edge comprise an amplified time-differential output signal, where the leading edge and time-amplified edges are separated by an 25 amplified duration of time, directly proportional to the third duration. Using sort-and-delay circuit 300-0 as an example, a single-ended time amplifier 600-0 is shown, as described in more detail below.

FIGS. 7A and 7B are schematic block diagrams depicting 30 **600-0**. variations of the single-ended time amplifier of FIG. 6 in greater detail, and FIG. 7C is a timing diagram associated with FIG. 7A or 7B. Using single-ended time amplifier 600-0 as an example, the time amplifier comprises a logic circuit 700-0 having an input on lines 304-0a ( $S_{first}$ ) and 35 304-0b ( $S_{last}$ ) to respectively accept the leading edge and the trailing edge, and an output on line 702-0 to supply an enable signal for the third duration of time  $(T_{in})$  in response to accepting the leading edge. Here, the logic circuit 700-0 is enabled as an AND gate with one inverted input, however, 40 the enable signal on line 702-0 can be created using other types of combinational logic. A pull-down circuit 704-0 has an input on line 702-0 to accept the enable signal and an output on line 706-0 to supply a pull-down current to a first node (line 706-0), initially set to a first voltage level (Vc), in 45 response to the enable signal. A pull-up circuit 708-0 has an input on line 302-0b to accept the trailing edge and an output on line 706-0 to supply a pull-up current to the first node in response to the trailing edge.

A capacitor 710-0 (C) has a first terminal connected to the 50 first node on line 706-0 and a second terminal connected to a reference voltage (e.g., ground) on line **712-0**. A comparator 714-0 has a first input connected to a threshold voltage (Vth) on line 716-0, a second input connected to the first node on line 706-0, and an output on line 602-0 ( $S_{out}$ ) to 55 supply a time-amplified edge. The leading edge (304-0a, see FIG. 6) and the time-amplified edge on line 602-0 are separated by an amplified duration of time  $(T_{out})$ , directly proportional to the third duration of time  $(T_{in})$ , which is the difference in time between the leading and trailing edges. 60 The delayed edge and the time-amplified edge are referred to as an amplified time-differential output signal. A reset circuit 718-0 has an input on line 720-0 to accept a reset signal and an output connected to the first node on line 706-0 to supply the first voltage level in response to the reset 65 signal. The reset circuit 718-0 resets the voltage Vc to a reset level, which is below the comparator threshold Vth.

8

FIG. 7B is similar to FIG. 7A except that a logic circuit is not required. The  $S_{first}$  signal on line 304-0a is fed directly to pull-down circuit 704-0, and the  $S_{last}$  signal on line 304-0b is fed directly to pull-up circuit 708-0. In contrast to the circuit of FIG. 7A, the pull-down current is not stopped by the trailing input edge. Instead, the pull-up current is made larger (for instance 2x) to cancel the pull down-current and to make the overall current direction pull-up. This variation overcomes some potential issues in generating very narrow pulses with an AND gate.

When the leading edge arrives it activates the pull-down circuit, which starts to ramp down the voltage Vc. The trailing edge disables the pull-down circuit (FIG. 7A only) and enables the pull-up circuit, which changes the voltage ramp direction to up. Once the first node voltage reaches the comparator threshold level Vth, the comparator output voltage goes high. The gain of the amplifier is defined by the relative up and ramp rates. When the ramp rates are equal, the gain is two.

FIG. 8 is a schematic block depicting a variation of the sort-and-delay further comprising a differential time amplifier. Using sort-and-delay circuit 300-0 as an example, differential time amplifier 800-0 is shown, having outputs on line 802-0 and 602-0.

FIG. 9 is a block diagram depicting the differential time amplifier of FIG. 8. As explained in greater detail below (FIGS. 10A and 10B), the differential time amplifier is essentially a modified single-ended time amplifier 900-0 connected in parallel with the single-ended time amplifier 600-0

FIG. 10A is a schematic block diagram of the differential time amplifier of FIG. 9 in greater detail, and FIG. 10B is an associated timing diagram. Using differential time amplifier 800-0 as an example, the time amplifier has an input on lines 304-0a ( $S_{first}$ ) and 304-0b ( $S_{last}$ ) to respectively accept the leading edge and the trailing edge. A first pull-down circuit 704-0 has an input on line 304-0a to accept the leading edge and an output on line 706-0 to supply a pull-down current to a first node (line 706-0), initially set to a first voltage level (Vc1), in response to the leading edge. A first pull-up circuit 708-0 has an input on line 304-0b to accept the trailing edge and an output on line 706-0 to supply a pull-up current to the first node in response to the trailing edge.

A capacitor 710-0 (C1) has a first terminal connected to the first node on line 706-0 and a second terminal connected to a reference voltage on line 712-0. A comparator 714-0 has a first input connected to a threshold voltage (Vth1) on line 716-0, a second input connected to the first node on line 706-0, and an output on line 602-0 (S<sub>last\_out</sub>) to supply a time-amplified edge. Alternatively, the circuit of FIG. 7A may be used.

A second pull-up circuit 1000-0 has an input to accept the leading edge on line 304-0a and an output on line 1002-0 to supply a pull-up current to a second node, initially set to a second voltage level (Vc2), in response to the leading edge. A second pull-down circuit 1014-0 has an input on line 304-0b to accept the leading edge and an output on line 1002-0 to supply a pull-down current to the second node in response to the leading edge. A second capacitor 1004-0 has a first terminal connected to the second node on line 1002-0 and a second terminal connected to a second reference voltage on line 1006-0. A second comparator 1008-0 has a first input connected to a second threshold voltage (Vth2) on line 1010-0, a second input connected to the second node on line 1002-0, and an output to connected to the input of the delay circuit 308-0 on line 802-0 ( $S_{first\ out}$ ). The leading edge (on line 304-0a, see FIG. 8) and the time-amplified

edge on line 602-0 are separated by an amplified duration of time  $(T_{out})$ , directly proportional to the third duration of time  $(T_{in})$ , which is the difference in time between the leading and trailing edges. The delayed edge and the time-amplified edge are an amplified time-differential output signal. In this 5 example, Vth1=Vth2=Vth. However, in other embodiments the threshold levels may be set to different voltages. Likewise, initial voltages Vc1 and Vc2 are equal in this example, but need not necessarily be so in other embodiments due to design or due to some random or systematic mismatch 10 between the two. The second single-ended amplifier, with its inputs tied together in the differential amplifier, produces the same delay as the first single-ended amplifier for a zero input  $(S_{first\_in} = S_{last\ in})$ . If the two circuits are perfectly matched, a components cancelled.

A reset circuit 718-0 has an input on line 720-0 to accept a reset signal and a output connected to the first node on line 706-0 to supply the first voltage level in response to the reset signal. A second reset circuit 1012-0 has an input to accept 20 a second reset signal (typically the same as the first reset signal on line 720-0) and an output connected to the second node on line 1002-0 to supply the second voltage level in response to the second reset signal. Again, the reset signal is shown as the same for reset circuits 718-0 and 1012-0, but 25 they need not be so. The purpose of the reset is to prepare the amplifier for the next sample. It needs to occur between the output edge (N) and the first input edge (N+1). Whether the reset signal is a clock pulse with regular timing or a self-generated reset pulse based on the output edge doesn't 30 matter. That is, the reset can be generated from a system clock or generated from the trailing edge. If generated from a system clock, it may be the same reset signal used for the ATC in the edge sort circuit, which is a periodic clock-like signal having a period related to the TDC sampling (or 35 fier before the stage delay satisfies the latter requirement. update) rate.

FIG. 11 is a schematic block diagram depicting the sort-and-delay TDC in slightly greater detail than shown in FIG. 2. The TDC consists of several cascaded stages, with the most significant bit (MSB) of the digital output being 40 resolved in the front stage and the other bits in the following stages resolved in descending order. The principle of operation follows the successive approximation method. The time interval is converted into a digital word in several successive steps carried out one bit per TDC stage. Once a stage has 45 completed its task, it passes the signal residue to the next stage. After passing the residue signal, the stage is reset and becomes ready to process the next sample.

After a certain number of stages (e.g., n) the residue output 210 (S1 and S2, see FIG. 12) becomes quite small and 50 it may be advantageous to use another type of TDC (e.g., backend TDC **212**) to further process the residue output to obtain more digital resolution. The digital output of this backend TDC on lines 1206-0 ( $dt_0$ ) through 1206-k ( $dt_{\kappa}$ ) (see FIG. 12) is combined with the MSBs obtained from the 55 cascaded stages (on line 208, see FIG. 3).

The operation carried out by a TDC stage consists of sorting the incoming edges in order of arrival and routing the first to arrive to a first output and the last to arrive to a second output. The first output is further passed through a delay cell. 60 These two signals, the delayed first output and the second output, form a residue signal that is passed on to the next stage. Repeating this process through several stages with decreasing delays has the effect of bringing the residue signal edges closer together. This is somewhat analogous to 65 the operation of a pipelined or successive approximation analog-to-digital converter (ADC). The TDC stage also

**10**

records the routing decision and outputs it as a digital bit. The digital output of the TDC can be calculated from the output bits of the stages using the knowledge of the magnitudes of the delays in each stage.

In its simplest form the TDC consists of stages with binary delays, with the delay in the first stage being T/2, in the second T/4, in the third T/8, and so forth. The digital output is simply calculated by performing a Gray-to-binary conversion to the digital word formed from the stage output bits. In practice, some form of trimming may be required to implement the exact delays with precisely binary weights.

Another alternative is to rely upon digital calibration to implement approximately binary delays, while making sure that the sum of the downstream delays is large enough to zero input produces a zero output with constant delay 15 avoid missing codes. In practice this means scaling the delays from one stage to the next with a factor of slightly less than 2.0. This method requires measuring the actual delays and using the measured values to calculate the final digital output. The measurement can be implemented as a foreground or background calibration, or as a combination of the

> FIG. 12 is a schematic block diagram depicting an exemplary backend TDC. This flash type backend TDC **212** is based on an array of ATCs 1200-0 through 1200-k in series with adjustable delay blocks 1202-0 through 1202-k. A calibration procedure is used to program the delays on lines 1204-0 (del<sub>0</sub>) through 1204-k (del<sub>k</sub>) to achieve the desired quantization levels.

> It is also possible to include gain in one or more of the sort-and-delay TDC stages. This relaxes the LSB size and the noise requirements of the following stages. Implementing a time amplifier can be tricky but the task becomes more practical if the input signal is small and the amplifier only has to deal with positive time intervals. Inserting the ampli-

> FIGS. 13A and 13B are diagrams depicting sort-and-delay circuit transfer functions. The transfer function of a single TDC stage, from the input to the residue output (solid line), is shown in FIG. 13A. The dotted line represents the signal after the edge sort circuit. When the negative (stop) input arrives before the positive (start) one, it is routed to the first output. Once the edges cross, the routing order is changed causing a fold in the transfer function. Adding the delay to the first output (leading edge) shifts the curve up, centering it around zero. This has the desired effect of compressing the incoming signal range to approximately half at the output. In other words, the transfer function of a single stage is  $y=(d\cdot x)\cdot D$ , where d is a digital output bit, either +1 or -1, and D is a fixed delay. When a time amplifier is used, the transfer function is  $y=A\cdot(d\cdot x)\cdot D$ , where "A" is the gain of the time amplifier.

> FIG. 13B depicts the signal transfer function of two cascaded sort-and-delay circuits. The time-differential signal output bits  $d_{R-1}$  and  $d_{R-2}$  form a Gray code that provides some insensitivity against decision metastability. Note:  $d_{R-1}$ is associated with the MSB.

> FIG. 14 is a flowchart illustrating a method for amplifying the duration of a time-differential signal. Although the method is depicted as a sequence of numbered steps for clarity, the numbering does not necessarily dictate the order of the steps. It should be understood that some of these steps may be skipped, performed in parallel, or performed without the requirement of maintaining a strict order of sequence. Generally however, the method follows the numeric order of the depicted steps. The method starts at Step 1400.

> Step 1402 accepts a time-differential input signal comprising a binary level leading edge followed a pre-amplified

duration of time by a binary level trailing edge. Step 1404 measures the pre-amplified duration of time. Step 1406 measures an amplified duration of time that is directly proportional to the pre-amplified duration of time. Step 1408 supplies a time-amplified edge separated from the leading edge by the amplified duration of time. In the case of a time differential amplifier, Step 1408 supplies the leading edge, followed the amplified duration of time by the time-amplified edge.

FIG. **15** is a flowchart illustrating a successive approximation TDC method. The method begins at Step 1500. Step 1502 accepts a time-differential input signal comprising a binary level first edge separated from a binary level second edge by a first (input) duration of time. Step 1504 determines 15 delay TDC, along with the supporting functions of edge the order in which the first and second edges are accepted. Step 1506 selectively supplies the first and second edges as a leading edge and a trailing edge in response to the determined order. Step 1508 supplies a TDC coded bit indicating the order in which the first and second edges are 20 routed. Step 1510 delays the leading edge to supply a delayed edge. Step 1512 supplies a time-differential output signal comprising the delayed edge and the trailing edge, where the delayed and trailing edge signals are separated by a second (output) duration of time representing a compres- 25 sion of the first (input) duration of time.

In one aspect, Step **1514** adds an amplified duration of time to the trailing edge to supply an amplified timeamplified edge. Then, Step **1516** supplies a time-differential output signal comprising the delayed edge and the time- 30 amplified edge, where the leading edge and trailing edge are separated by a third duration of time, and the leading edge and time-amplified edges are separated by an amplified duration of time, directly proportional to the third duration of time.

FIG. **16** is a flowchart illustrating a sort-and-delay TDC method. The method begins at Step 1600. Step 1602 accepts a time-differential input signal comprising a binary level first edge separated from a binary level second edge by an initial input duration of time. Step **1604** successively approximates 40 the input duration of time in a plurality of stages. At each stage, Step 1606 determines a time-differential leading edge and a time-differential trailing edge. At each stage, Step 1608 routes the leading edge through a fixed delay, where the fixed delay of a subsequent stage is less than the fixed 45 delay of a preceding stage. At each stage, Step 1610 supplies a TDC coded bit responsive to the order in which the first and second edges are routed. In other words, the TDC coded bit represents the order in which the leading and the trailing edge are supplied, which in the ideal case is the same as the 50 order of arrival of the input edges. However, if an error is made in determining the arrival order when the edges are very close to one another, the error has no effect in the TDC operation as long as the digital bit represents the actual routing decision.

In contrast to prior art methods, which simply add delay based on the arrival order, the method disclosed herein routes the signal through delay and no-delay paths based on the arrival order. This is a subtle but important difference. The routing has the effect of selectively inverting the timedifferential signal that passes through the TDC stage, which produces Gray coded output bits. The Gray coding makes the TDC less sensitive to ATC metastability errors. The method also provides an always-positive time differential signal at the output of the edge sort circuits. This enables the 65 use of simple time amplifiers capable of operating on positive (start) signals only.

Step 1612 sums the TDC coded bits from each stage to supply a digital output signal representing the initial input duration of time. In one aspect, Step 1602 includes a first stage accepting a first time-differential signal. Then, routing the leading edge through a fixed delay in Step 1608 includes the first stage supplying a second time differential signal to a subsequent second stage, where the difference between the leading edge and the trailing edge is guaranteed to represent a time delay greater than or equal to zero. That is, regardless of any arrival time interpretation errors in the first stage, it is guaranteed that the second time-differential signal first edge can be treated as a start signal by the second stage.

Systems and methods have been provided for a sort-andsorting and time amplification. Examples of particular subcircuits and hardware units have been presented to illustrate the invention. However, the invention is not limited to merely these examples. Other variations and embodiments of the invention will occur to those skilled in the art.

### I claim:

- 1. A time amplifier for extending the duration of a time-differential signal, the time amplifier comprising:

- a first pull-down circuit having an input to accept a binary level leading edge and an output to supply a pull-down current to a first node, initially set to a first voltage level, in response to the leading edge;

- a first pull-up circuit having an input to accept a binary level trailing edge, separated from the leading edge by a pre-amplified duration of time, and an output to supply a pull-up current to the first node, in response to the trailing edge;

- a first capacitor having a first terminal connected to the first node and a second terminal connected to a first reference voltage; and,

- a first comparator having a first input connected to a first threshold voltage, a second input connected to the first node, and an output to supply a time-amplified edge of a binary level time-amplified output signal, where the leading edge and time-amplified edge are separated by an amplified duration of time, directly proportional to the pre-amplified duration of time.

- 2. The time amplifier of claim 1 further comprising;

- a first reset circuit having an input to accept a first reset signal and an output connected to the first node to supply the first voltage level in response to the first reset signal.

- 3. The time amplifier of claim 2 wherein the first comparator output supplies the time-amplified edge of a timedifferential output signal;

the time amplifier further comprising:

55

- a second pull-up circuit having an input to accept the leading edge and an output to supply a pull-up current to a second node, initially set to a second voltage level, in response to the leading edge;

- a second pull-down circuit having an input connected to accept the leading edge and an output to supply a pull-down current to the second node in response to the leading edge;

- a second capacitor having a first terminal connected to the second node and a second terminal connected to a second reference voltage;

- a second comparator having a first input connected to a second threshold voltage, a second input connected to the second node, and an output to supply a binary level leading edge of the time-differential output signal; and,

- a second reset circuit having an input to accept a second reset signal and an output connected to the second node to supply the second voltage level in response to the second reset signal.

- 4. A sort-and-delay circuit comprising:

- an edge sort circuit having an input to accept a time-differential input signal comprising a binary level first edge separated from a binary level second edge by a first duration of time, the edge sort circuit determining the order in which the first and second edges are accepted and having a first output to supply a leading edge, a second output to supply a trailing edge, and third output to supply a time-to-digital converter (TDC) coded bit indicating the order in which the first and second edges are routed;

- a delay circuit having an input operatively connected to the first output of the edge sort circuit, and an output to supply a delayed edge having a time delay duration (D); and,

- wherein the delayed edge and the trailing edge comprise a time-differential output signal, where the delayed and trailing edges are separated by a second duration of time representing a compression of the first duration of time.

- 5. The sort-and-delay circuit of claim 4 wherein the edge sort circuit comprises:

- an OR gate having a first input to accept the first edge, a second input to accept the second edge, and an output to supply the leading edge;

- an AND gate having a first input to accept the first edge, a second input to accept the second edge, and an output to supply the trailing edge; and,

- an arrival time comparator (ATC) having a first input to accept the first edge, a second input to accept the 35 second edge, and an output to supply an order signal responsive to the order in which the first and second edges are received.

- 6. The sort-and-delay circuit of claim 5 wherein the ATC has a reset input to accept a reset signal responsive to the 40 trailing edge; and,

the sort-and-delay circuit further comprising:

- a register having an input connected to the ATC output, a clock input to accept a clock signal, and an output to supply the TDC coded bit.

- 7. The sort-and-delay circuit of claim 4 wherein the edge sort circuit comprises:

- a first delay having an input to accept the first edge and an output to supply a delayed first edge, delayed a first period of time;

- a second delay having an input to accept the second edge and an output to supply a delayed second edge, delayed a second period of time;

- a first multiplexor (MUX) having a control input to accept an order signal, a first input to accept the delayed first 55 edge, a second input to accept the delayed second edge, and an output to supply the leading edge in response to the order signal;

- a second MUX having a control input to accept the order signal, a first input to accept the delayed second edge, 60 a second input to accept the delayed first edge, and an output to supply the trailing edge in response to the order signal; and,

- an ATC having a first input to accept the first edge, a second input to accept the second edge, and an output 65 to supply the order signal responsive to the order in which the first and second edges are routed.

**14**

8. The sort-and-delay circuit of claim 7 wherein the ATC has a reset input to accept a reset signal responsive to the trailing edge; and,

the sort-and-delay circuit further comprising:

- a register having an input connected to the ATC output to accept the order signal, a clock input to accept a clock signal, and an output to supply the TDC coded bit.

- 9. The sort-and-delay circuit of claim 4 further comprising:

- a time amplifier having an input to accept the leading edge an input to accept the trailing edge, and an output to supply a time-amplified edge; and,

- wherein the delayed edge and the time-amplified edge comprise an amplified time-differential output signal, where the leading edge and trailing edge are separated by a third duration of time, and the leading edge and time-amplified edge are separated by an amplified duration of time, directly proportional to the third duration of time.

- 10. The sort-and-delay circuit of claim 9 wherein the time amplifier is a single-ended time amplifier comprising:

- a pull-down circuit having an input to accept the leading edge and an output to supply a pull-down current to a first node, initially set to a first voltage level, in response to the leading edge;

- a pull-up circuit having an input to accept the trailing edge and an output to supply a pull-up current to the first node in response to the trailing edge;

- a capacitor having a first terminal connected to the first node and a second terminal connected to a reference voltage; and,

- a comparator having a first input connected to a threshold voltage, a second input connected to the first node, and an output to supply the time-amplified edge.

- 11. The sort-and-delay circuit of claim 10 wherein the single-ended time amplifier further comprises;

- a reset circuit having an input to accept a reset signal and a output connected to the first node to supply the first voltage level in response to the reset signal.

- 12. The sort-and-delay circuit of claim 9 wherein the time amplifier is a differential time amplifier comprising:

- a first pull-down circuit having an input to accept the leading edge and an output to supply a pull-down current to a first node, initially set to a first voltage level, in response to the leading edge signal;

- a first pull-up circuit having an input to accept the trailing edge and an output to supply a pull-up current to the first node in response to the trailing edge;

- a first capacitor having a first terminal connected to the first node and a second terminal connected to a first reference voltage;

- a first comparator having a first input connected to a first threshold voltage, a second input connected to the first node, and an output to supply the time-amplified edge;

- a second pull-up circuit having an input to accept the leading edge and an output to supply a pull-up current to a second node, initially set to a second voltage level, in response to the leading edge;

- a second pull-down circuit having an input connected to accept the leading edge and an output to supply a pull-down current to the second node in response to the leading edge;

- a second capacitor having a first terminal connected to the second node and a second terminal connected to a second reference voltage; and,

- a second comparator having a first input connected to a second threshold voltage, a second input connected to the second node, and an output connected to the input of the delay circuit.

- 13. The sort-and-delay circuit of claim 12 wherein the 5 differential time amplifier further comprises:

- a first reset circuit having an input to accept a first reset signal and a output connected to the first node to supply the first voltage level in response to the first reset signal; and,

- a second reset circuit having an input to accept a second reset signal and a output connected to the second node to supply the second voltage level in response to the second reset signal.

- 14. A sort-and-delay time-to-digital converter (TDC) comprising:

- a plurality of serially connected sort-and-delay circuits, each sort-and-delay circuit accepting a time-differential input signal comprising a binary level first edge sepa- 20 rated from a binary level second edge by an input duration of time, and selectively routing the first and second edges as a time-differential output signal comprising a binary level delayed edge separated from a binary level trailing edge by an output duration of time 25 representing a compression of the input duration of time, each sort-and-delay circuit supplying a TDC coded bit indicating the order in which the first and second edges are routed as the leading and trailing edges; and,

- a bit decoder having inputs to receive a plurality of TDC coded bits from the corresponding plurality of sort-anddelay circuits, and an output to supply a digital output signal representing an initial input duration of time associated with an initial time-differential input signal received by an initial sort-and-delay circuit.

- **15**. The sort-and-delay TDC of claim **14** wherein the nth sort-and-delay circuit in a plurality of n sort-and-delay circuits supplies a time-differential residue signal;

- wherein the bit decoder supplies a digital output signal representing the n most significant bits in a p-bit digital word; and,

the sort-and-delay TDC further comprising:

- a backend TDC having an input to accept the time- 45 differential residue signal and an output to supply a digital output signal comprising the (p-n)th least significant bits of the p-bit digital word.

- 16. The sort-and-delay TDC of claim 14 wherein the bit decoder accepts TDC coded bits in the form of a Gray code. 50

- 17. The sort-and-delay TDC of claim 14 wherein each sort-and-delay circuit comprises:

- an edge sort circuit having an input to accept a timedifferential input signal, the edge sort circuit determining the order in which the first and second edges are 55 accepted, and having a first output to supply the leading edge, a second output to supply a trailing edge, and a third output to supply the TDC coded bit; and,

- a delay circuit having an input operatively connected to the first output of the edge sort circuit, and an output to 60 amplifier is a single-ended time amplifier comprising: supply the delayed edge having a time delay duration (D).

- **18**. The sort-and-delay TDC of claim **17** wherein the edge sort circuit comprises:

- an OR gate having a first input to accept the first edge, a 65 second input to accept the second edge, and an output to supply the leading edge;

**16**

- an AND gate having a first input to accept the first edge, a second input to accept the second edge, and an output to supply the trailing edge; and,

- an arrival time comparator (ATC) having a first input to accept the first edge, a second input to accept the second edge, and an output to supply an order signal responsive to the order in which the first and second edges are received.

- 19. The sort-and-delay TDC of claim 18 wherein the ATC has a reset input to accept a reset signal responsive to the trailing edge; and,

the edge sort circuit further comprising:

- a register having an input connected to the ATC output, a clock input to accept a clock signal, and an output to supply the TDC coded bit.

- 20. The sort-and-delay TDC of claim 17 wherein the edge sort circuit comprises:

- a first delay having an input to accept the first edge and an output to supply a delayed first edge, delayed a first period of time;

- a second delay having an input to accept the second edge and an output to supply a delayed second edge, delayed a second period of time;

- a first multiplexor (MUX) having a control input to accept an order signal, a first input to accept the delayed first edge, a second input to accept the delayed second edge, and an output to supply the leading edge in response to the order signal;

- a second MUX having a control input to accept the order signal, a first input to accept the delayed second edge, a second input to accept the delayed first edge, and an output to supply the trailing edge in response to the order signal; and,

- an ATC having a first input to accept the first edge, a second input to accept the second edge, and an output to supply the order signal responsive to the order in which the first and second edges are received.

- 21. The sort-and-delay TDC of claim 20 wherein the ATC has a reset input to accept a reset signal responsive to the trailing edge; and,

the edge sort circuit further comprising:

- a register having an input connected to the ATC output, a clock input to accept a clock signal, and an output to supply the TDC coded bit.

- 22. The sort-and-delay TDC of claim 17 further comprising:

- a time amplifier having an input to accept the leading edge, an input to accept the trailing edge, and an output to supply a time-amplified edge; and,

- wherein the delayed edge and the time-amplified edge comprise an amplified time-differential output signal, where the leading edge and trailing edge are separated by a third duration of time, and the leading edge and time-amplified edge are separated by an amplified duration of time, directly proportional to the third duration of time.

- 23. The sort-and-delay TDC of claim 22 wherein the time

- a pull-down circuit having an input to accept the leading edge and an output to supply a pull-down current to a first node, initially set to a first voltage level, in response to the leading edge;

- a pull-up circuit having an input to accept the trailing edge and an output to supply a pull-up current to the first node in response to the trailing edge;

- a capacitor having a first terminal connected to the first node and a second terminal connected to a reference voltage; and,

- a comparator having a first input connected to a threshold voltage, a second input connected to the first node, and 5 an output to supply the time-amplified edge.

- 24. The sort-and-delay TDC of claim 23 wherein the single-ended time amplifier further comprises;

- a reset circuit having an input to accept a reset signal and a output connected to the first node to supply the first voltage level in response to the reset signal.

- 25. The sort-and-delay TDC of claim 22 wherein the time amplifier is a differential time amplifier comprising:

- a first pull-down circuit having an input to accept the leading edge and an output to supply a pull-down current to a first node, initially set to a first voltage <sup>15</sup> level, in response to the leading edge;

- a first pull-up circuit having an input to accept the trailing edge and an output to supply a pull-up current to the first node in response to the trailing edge;

- a first capacitor having a first terminal connected to the 20 first node and a second terminal connected to a first reference voltage;

- a first comparator having a first input connected to a first threshold voltage, a second input connected to the first node, and an output to supply the time-amplified edge; 25

- a second pull-up circuit having an input to accept the leading edge and an output to supply a pull-up current to a second node, initially set to a second voltage level, in response to the leading edge;

- a second pull-down circuit having an input connected to accept the leading edge and an output to supply a pull-down current to the second node in response to the leading edge;

- a second capacitor having a first terminal connected to the second node and a second terminal connected to a 35 second reference voltage; and,

- a second comparator having a first input connected to a second threshold voltage, a second input connected to the second node, and an output connected to the input of the delay circuit.

- 26. The sort-and-delay TDC of claim 25 wherein the differential time amplifier further comprises:

- a first reset circuit having an input to accept a first reset signal and a output connected to the first node to supply the first voltage level in response to the first reset signal; and,

- a second reset circuit having an input to accept a second reset signal and an output connected to the second node to supply the second voltage level in response to the second reset signal.

- 27. A sort-and-delay time-to-digital converter (TDC) method, the method comprising:

- accepting a time-differential input signal comprising a binary level first edge separated from a binary level second edge by an initial input duration of time;

- successively approximating the input duration of time in a plurality of stages;

- at each stage, determining a time-differential leading edge and a time-differential trailing edge;

- at each stage, routing the leading edge through a fixed delay, where the fixed delay of a subsequent stage is less than the fixed delay of a preceding stage;

- at each stage, supplying a TDC coded bit responsive to the order in which the first and second edges are routed; and,

- summing the TDC coded bits from each stage to supply a digital output signal representing the initial input duration of time.

- 28. The method of claim 27 wherein accepting the time-differential input signal includes a first stage accepting a first time-differential signal; and,

- wherein routing the leading edge through a fixed delay includes the first stage supplying a second time differential signal to a subsequent second stage, where the difference between the leading edge and the trailing edge is guaranteed to represent a time delay greater than or equal to zero.

\* \* \* \*