#### US009819581B2

## (12) United States Patent

## Chanda et al.

## (10) Patent No.: US 9,819,581 B2

## (45) **Date of Patent:** Nov. 14, 2017

## (54) CONFIGURING A HARDWARE SWITCH AS AN EDGE NODE FOR A LOGICAL ROUTER

- (71) Applicant: Nicira, Inc., Palo Alto, CA (US)

- (72) Inventors: **Anupam Chanda**, San Jose, CA (US); **Bruce Davie**, Menlo Park, CA (US)

- (73) Assignee: NICIRA, INC., Palo Alto, CA (US)

- (\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 59 days.

- (21) Appl. No.: 14/815,849

- (22) Filed: Jul. 31, 2015

## (65) Prior Publication Data

US 2017/0034052 A1 Feb. 2, 2017

(51) Int. Cl.

H04L 12/713 (2013.01)

H04L 12/46 (2006.01)

H04L 12/931 (2013.01)

H04L 12/751 (2013.01)

(52) **U.S.** Cl.

CPC ...... *H04L 45/586* (2013.01); *H04L 12/4633* (2013.01); *H04L 45/02* (2013.01); *H04L 49/70* (2013.01)

## (58) Field of Classification Search

CPC ... H04L 45/586; H04L 12/4633; H04L 45/02; H04L 49/70

See application file for complete search history.

## (56) References Cited

#### U.S. PATENT DOCUMENTS

6,243,394 B1 6/2001 Deng 6,640,251 B1 10/2003 Wiget et al.

| 6,850,529   |      |         | ~                    |  |  |  |  |  |  |

|-------------|------|---------|----------------------|--|--|--|--|--|--|

| 7,463,639   | B1 * | 12/2008 | Rekhter H04L 12/4641 |  |  |  |  |  |  |

|             |      |         | 370/409              |  |  |  |  |  |  |

| 8,161,095   | B2   | 4/2012  | Manion et al.        |  |  |  |  |  |  |

| 8,345,688   | B2   | 1/2013  | Zhou et al.          |  |  |  |  |  |  |

| 8,589,919   | B2   | 11/2013 | Smith et al.         |  |  |  |  |  |  |

| 8,874,876   | B2   | 10/2014 | Bhadra et al.        |  |  |  |  |  |  |

| 8,897,134   | B2   | 11/2014 | Kern et al.          |  |  |  |  |  |  |

| 8,943,490   | B1   | 1/2015  | Jain et al.          |  |  |  |  |  |  |

| 8,964,528   | B2   | 2/2015  | Casado et al.        |  |  |  |  |  |  |

| 9,014,181   | B2   | 4/2015  | Lakshman et al.      |  |  |  |  |  |  |

| 9,032,095   | B1*  | 5/2015  | Traina H04L 29/06    |  |  |  |  |  |  |

|             |      |         | 370/389              |  |  |  |  |  |  |

| 9,100,285   | B1   | 8/2015  | Choudhury et al.     |  |  |  |  |  |  |

| (Continued) |      |         |                      |  |  |  |  |  |  |

## FOREIGN PATENT DOCUMENTS

EP 1154601 11/2001

Primary Examiner — Noel Beharry

Assistant Examiner — Nicole King

(74) Attorney, Agent, or Firm — Adeli LLP

## (57) ABSTRACT

A method for configuring an edge MHFE for a logical network to communicate with other networks is described. The method receives data for the logical network that defines a logical router and a set of logical switches for logically connecting several end machines that operate on different host machines. The method, based on the received logical network data, identifies a physical port of the MHFE to bind a logical uplink port of the logical router to the identified physical port. The uplink port is for connecting the logical router to the external network. The method then binds the logical uplink port to the identified physical port by defining an uplink logical switch with a logical port that is associated with the identified physical port and assigning network and data link addresses of the logical uplink port to the logical port of the uplink logical switch.

## 20 Claims, 19 Drawing Sheets

# US 9,819,581 B2 Page 2

| (56)                  |                |             | Referen | ces Cited           | 2013/0121209         |      |                    | Padmanabhan et al. |

|-----------------------|----------------|-------------|---------|---------------------|----------------------|------|--------------------|--------------------|

|                       |                |             |         | 2013/0132533        |                      |      | Padmanabhan et al. |                    |

|                       | U              | .S. I       | PATENT  | DOCUMENTS           | 2013/0287026         |      | 10/2013            |                    |

|                       |                |             |         |                     | 2013/0315246         |      |                    | Zhang et al.       |

| 9,154                 | <b>1,433</b> B | 32          | 10/2015 | Koponen et al.      | 2013/0322453         |      | 12/2013            |                    |

| 9,306                 | 5,843 B        | 32          | 4/2016  | Koponen et al.      | 2014/0029451         |      | 1/2014             | <b>.</b>           |

| 9,319                 | 9,375 B        | 32          | 4/2016  | Gross, IV et al.    | 2014/0029618         |      |                    | Janardhanan        |

| 9,331                 | l,940 B        | 32          | 5/2016  | Balus et al.        | 2014/0071986         |      | 3/2014             |                    |

| 9,369                 | 9,426 B        | 32          | 6/2016  | Koponen et al.      | 2014/0101467         | A1   | 4/2014             | Jubran et al.      |

| 9,397                 | 7,946 B        | 31 *        | 7/2016  | Yadav H04L 41/0806  | 2014/0195666         | A1   | 7/2014             | Dumitriu et al.    |

| 9,455                 | 5,901 B        | 32          | 9/2016  | Davie et al.        | 2014/0229605         | A1   | 8/2014             | Besser et al.      |

| 9,485                 | 5,149 B        | 31          | 11/2016 | Traina et al.       | 2014/0269709         | A1   | 9/2014             | Benny et al.       |

| 9,577                 | 7,927 B        | 32          | 2/2017  | Hira et al.         | 2014/0301391         | A1   | 10/2014            | Krishnan et al.    |

| 9,621                 | l,461 B        | 32          | 4/2017  | Sun                 | 2015/0009992         | A1   | 1/2015             | Zhang              |

| ,                     | 3,040 B        |             | 4/2017  |                     | 2015/0100560         | A1   |                    | Davie et al.       |

|                       | 7,541 B        |             | 5/2017  |                     | 2015/0100675         | A1   | 4/2015             | Davie et al.       |

| 2002/006              |                |             |         | Taylor et al.       | 2015/0100704         |      |                    | Davie et al.       |

| 2003/004              |                |             | 2/2003  |                     | 2015/0124809         |      |                    | Edsall et al.      |

| 2006/009              |                |             |         | Ansari et al.       | 2015/0124821         |      |                    | Chu et al.         |

| 2008/018              |                |             |         | Casado et al.       | 2015/0379150         |      | 12/2015            |                    |

| 2008/021              |                |             | 9/2008  |                     | 2016/0014073         |      |                    | Reddy et al.       |

| 2011/007              |                |             |         | Li et al.           | 2016/0173535         |      |                    | Barabash et al.    |

| 2011/009              |                |             |         | Hao et al.          | 2016/0197824         |      |                    | Lin et al.         |

| 2011/020              |                |             |         | Donthamsetty et al. | 2016/0137824         |      |                    | Shah et al.        |

| 2011/028              |                |             |         |                     | 2010/0232019         |      | 2/2017             |                    |

| 2011/029              |                |             |         | Saraiya et al.      |                      |      |                    |                    |

|                       |                |             |         | Kern et al.         | 2017/0085502         |      |                    | Biruduraju         |

|                       |                |             |         | Reid et al.         | 2017/0093617         |      |                    | Chanda et al.      |

| 2012/023              |                |             |         | Yang et al.         | 2017/0093646         |      |                    | Chanda et al.      |

| 2012/027              |                |             |         | Nilakantan et al.   | 2017/0093758         |      |                    | Chanda             |

|                       |                |             |         | Kempf et al.        | 2017/0171055         | Al   | 6/2017             | Wang et al.        |

| ZU13/UU4 <sup>(</sup> | 4030 A         | <b>XI</b> ' | 2/2013  | Koponen             | * aited have area    | mino | <b>1</b> 2         |                    |

|                       |                |             |         | 370/254             | * cited by example * | mme  | L                  |                    |

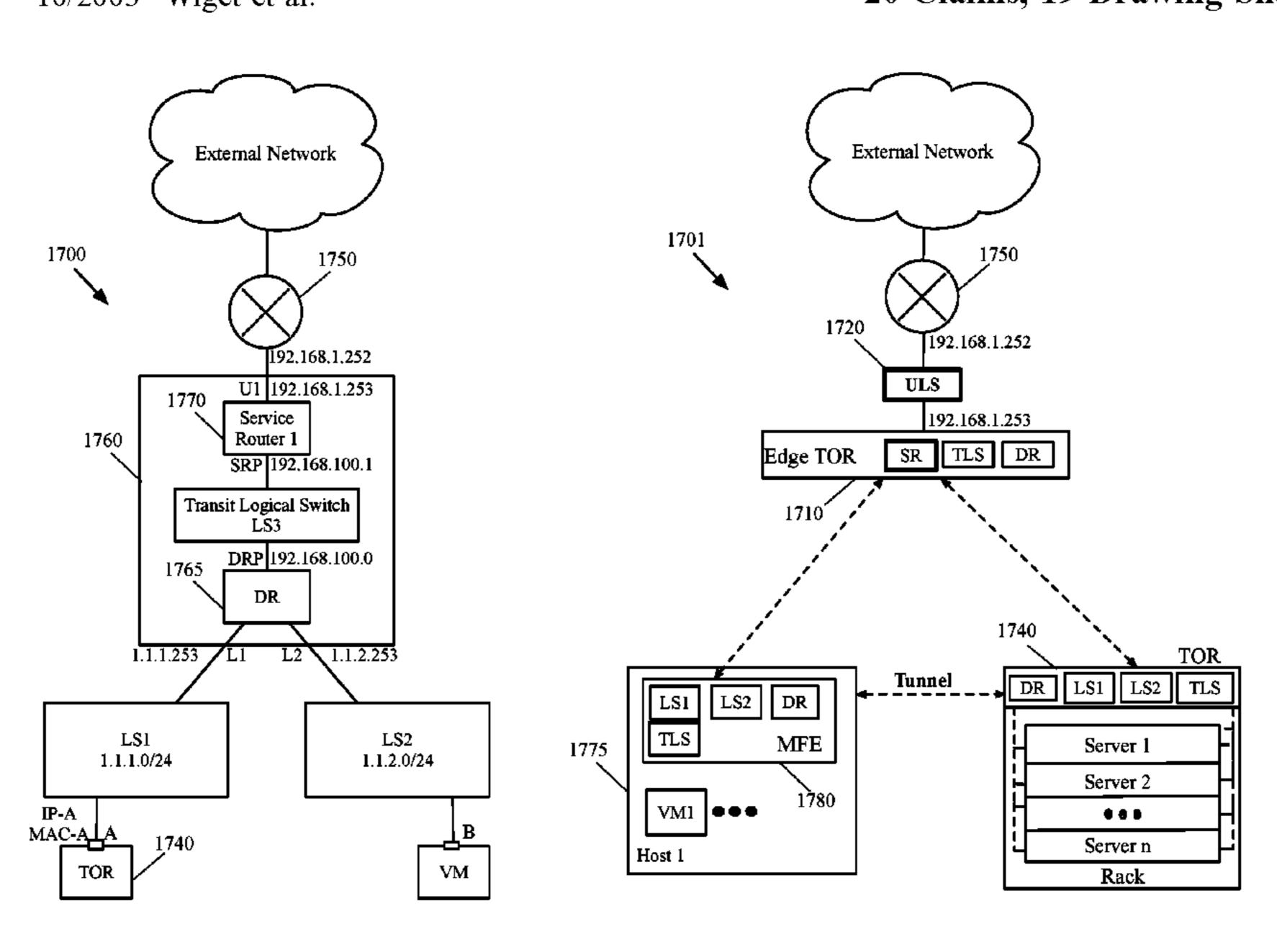

Figure 1

Figure 2

Figure 3

Figure 7

Figure 8

Nov. 14, 2017

Nov. 14, 2017

Nov. 14, 2017

Figure 18

## CONFIGURING A HARDWARE SWITCH AS AN EDGE NODE FOR A LOGICAL ROUTER

#### BACKGROUND

There is a growing movement, driven by both industry and academia, towards a new network control paradigm called Software-Defined Networking (SDN). In Software-Defined Networking (SDN), a control plane implements and maintains the control logic that governs the forwarding 10 behavior of shared network switching elements on a per user basis. A virtual network that is implemented for a tenant of a hosting system is a good example of an SDN. The virtual (logical) network of a tenant of the hosting system connects a set of data compute nodes (e.g., virtual machines) that are 15 assigned to the tenant, to each other and to other virtual and/or physical networks through a set of logical switches and logical routers.

One of the challenges in today's hosting system networks is extending the virtual networks (e.g., of one or more 20 tenants) to other physical networks through hardware switches (e.g., third-party hardware switches).

## BRIEF SUMMARY

Some embodiments provide a novel method of configuring a logical router of a logical network on a managed hardware forwarding element (MHFE) in order for the MHFE to implement the logical network and to perform logical routing functionalities. In some embodiments, the 30 method is performed by a control plane that configures and manages one or more logical networks for one or more tenants of a hosting system (e.g., a datacenter). In some embodiments, a logical network of the hosting system switches and routers) that logically connects different end machines (e.g., virtual machines, containers, etc.) that run on different host machines. Some embodiments configure a logical router of a logical network on the MHFE (e.g., a third-party hardware switch such as a top-of-rack or TOR 40 switch or other appliances such as firewalls, load balancers, etc.) to enable the physical workloads connected to the MHFE (e.g., third-party servers connected to a TOR switch) to exchange network data with other end machines and/or external networks that are connected to the logical network. 45

In some embodiments, the control plane receives a definition of a logical router (e.g., through an application programming interface or API) and defines several routing components for the logical router. Each of these routing components is separately assigned a set of routes and a set 50 of logical interfaces. Each logical interface (also referred to as logical port) of each routing component is also assigned a network layer (e.g., Internet Protocol or IP) address and a data link layer (e.g., media access control or MAC) address. In some embodiments, the several routing components 55 defined for a logical router include a single distributed router (also referred to as distributed routing component) and several different service routers (also referred to as service routing components). In addition, the control plane of some embodiments defines a transit logical switch (TLS) for 60 handling communications between the components internal to the logical router (i.e., between the distributed router and the service routers).

The control plane of some embodiments configures and manages one or more logical networks for one or more 65 tenants of a hosting system (e.g., a datacenter). In some embodiments, a logical network of the hosting system

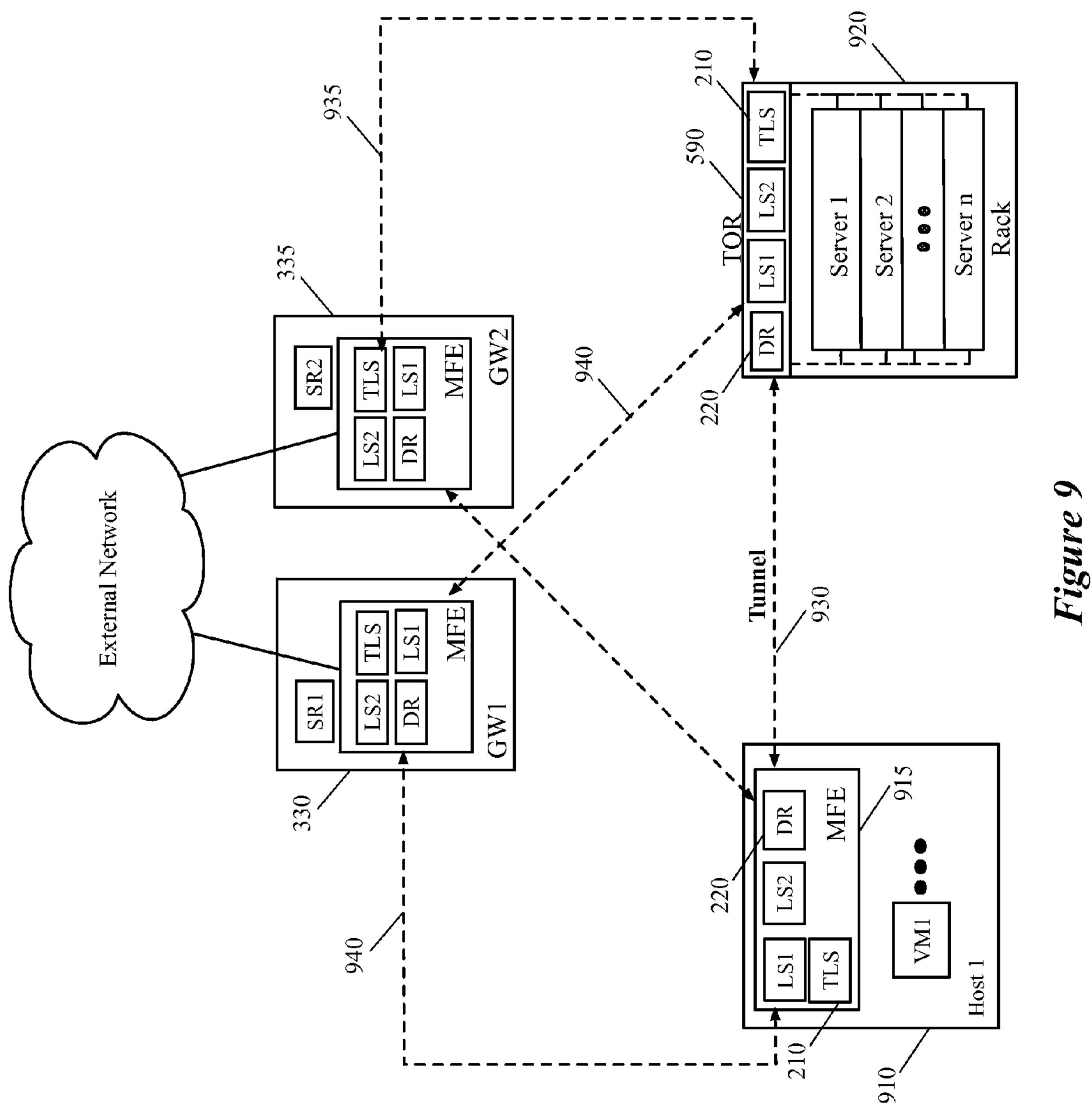

logically connects a set of end machines (e.g., virtual machines, physical servers, containers, etc.) and a set of physical machines using a set of logical forwarding elements (e.g., logical L2 and L3 switches). In some embodiments, different subsets of end machines reside on different host machines that execute managed forwarding elements (MFEs). The MFEs implement the logical forwarding elements of the logical network to which the local end machines are logically connected. Additionally, the logical forwarding elements are implemented by one or more MHFEs in order to connect the physical machines that are connected to the MHFEs to the other end machines of the logical network. In other words, each of the host machines executes an MFE that processes packets sent to and received from the end machines residing on the host machine, and exchanges these packets with other MFEs operating on other host machines as well as the MHFEs (e.g., through tunnels). The MFE of some embodiments is a software instance that is implemented in the virtualization software (e.g., a hypervisor) of the host machine.

Some embodiments implement the distributed routing component of the logical router in a distributed manner across the different MFEs and the MHFE. Some embodiments implement each of the service routing components of 25 the logical network on an edge node (e.g., a gateway), which is a machine at the edge of the network (e.g., the datacenter network), in order to communicate with one or more external networks. Each of the service components has an uplink interface (port) for communicating with an external network as well as a TLS interface (port) for connecting to the transit logical switch and communicating the network data with the distributed routing component of the logical router that is also connected to the transit logical router.

Some embodiments configure both the distributed comincludes a set of logical forwarding elements (e.g., logical 35 ponent and the service components of the logical router on an MHFE. In other words, in some embodiments, the MHFE acts as the edge node of the logical router by implementing the service routers (components) of the logical router for exchanging network data with the external networks. When the control plane receives a definition of a logical router, in which, the uplink port of the logical router is bound to a physical port of an MHFE (i.e., the physical port is assigned the same IP and MAC addresses of the uplink port), the control plane instantiates both the distributed component and service components of the logical router on the MHFE. The control plane further defines a new uplink logical switch (ULS) for handling the communications between the SRs implemented on the MHFE and the external networks.

> In some embodiments, the control plane defines the southbound interface of the uplink logical switch (ULS) to be associated with the physical port of the edge MHFE that is assigned the MAC and IP addresses of the uplink port of the logical router. In some such embodiments, the control plane defines the northbound interface of the ULS to be associated with an external network (e.g., a southbound port of a next hop physical router that connects the logical network to one or more external networks).

> In order to configure and manage the different components of a logical router as well as other logical forwarding elements (e.g., logical L2 switches) of a logical network, some embodiments configure a set of database tables (e.g., forwarding tables of the forwarding elements) on the MHFE using an open source protocol (e.g., an open vSwitch database management (OVSDB) protocol), which is recognizable by the MHFE. Such an open source protocol requires minimal software to execute on the MHFE (e.g., TOR switch) and to enable the MHFE to implement the logical

network forwarding elements (e.g., logical L2 and L3 forwarding elements) in order to communicate with the other machines connected to the logical network as well as other external networks.

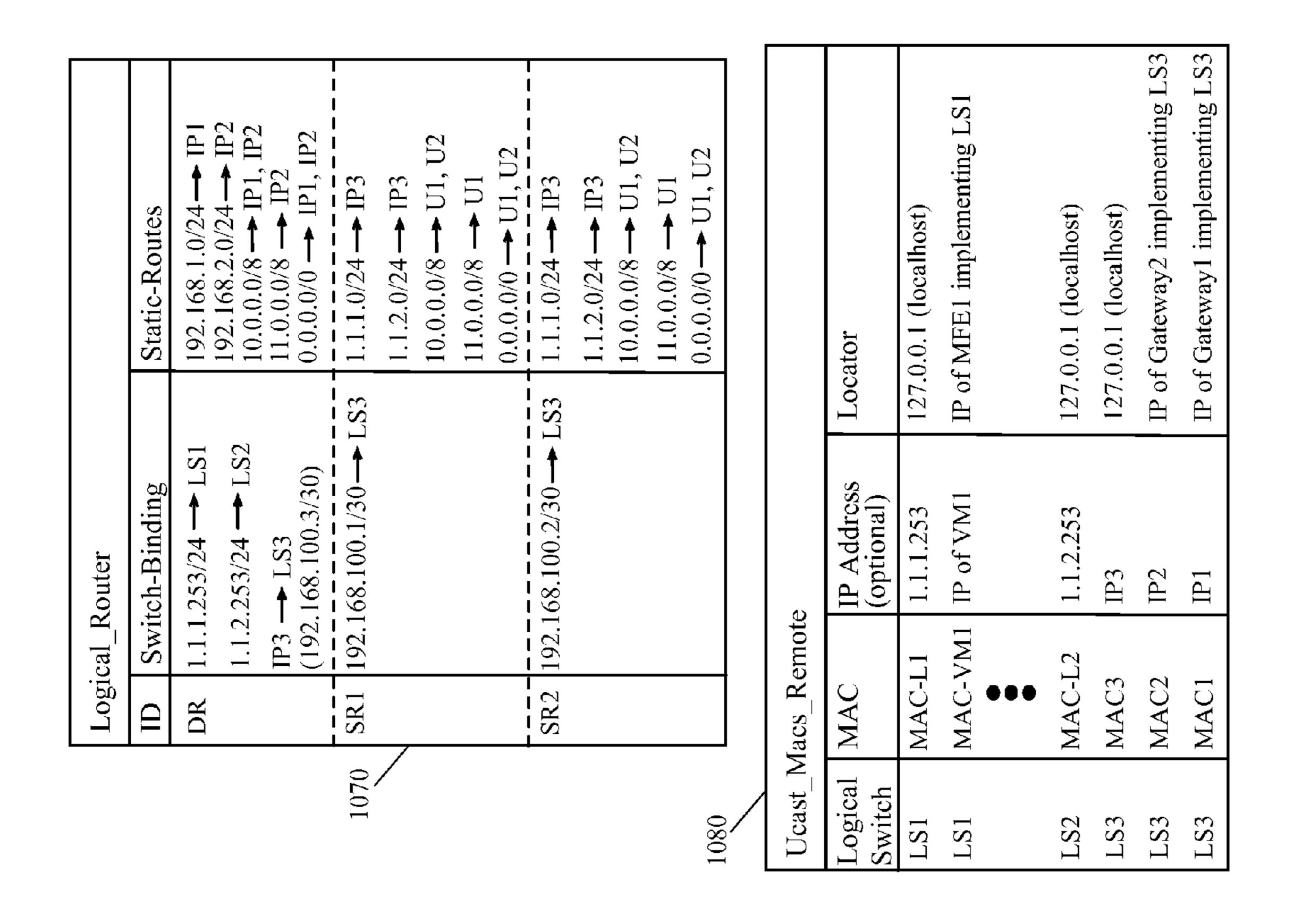

After generating the database tables on the MHFE using 5 the open source protocol (e.g., OVSDB), some embodiments use the database schema to propagate a particular one of the tables with the physical locator information of the logical ports of the different routing components (i.e., distributed and service routers) of the logical router. The physical 10 locator information, in some embodiments, specifies the tunnel (e.g., Virtual Extensible LAN (VXLAN) tunnel) endpoint addresses (i.e., IP addresses) of the MFEs and MHFEs that implement the different logical forwarding elements (e.g., logical L2 and L3 switches). This table (the 15 tunnel endpoint locator table), in some embodiments, specifies the network layer (IP) addresses of the MFEs and MHFEs that implement the logical ports of logical switches to which the machines (e.g., end machines, physical machines, etc.) and/or logical ports of the logical routers are 20 connected. By locating the endpoints, the MFEs and MHFEs are able to establish tunnels between themselves and exchange the network data through the established tunnels (VXLAN tunnels).

In some embodiments, the generated tunnel endpoint 25 locator table has several fields including (i) a logical switch field that species the logical switch to which a port of a machine or logical router is connected, (ii) a MAC address field that specifies the corresponding MAC address of the port, and (iii) a locator field that specifies the IP address of 30 the tunnel endpoint for the corresponding MAC address. In order to configure the locator data of the logical ports of the different routing components on the table, some embodiments populate a record for each logical port of the distributed routing component in the table in a first manner a record 35 for each logical port of the service routing component in a second different manner.

For each port of the distributed component that is connected to a logical forwarding element (e.g., an L2 logical switch), some embodiments generate a record and stores (i) 40 in the logical switch field, the logical switch to which the port is connected, (ii) in the MAC address field, the MAC address of the port, and (iii) in the locator field, a fixed IP address of 127.0.0.1, or the localhost. The localhost is a loopback interface address (127.0.0.1) in networking which 45 can be used to access the machine's own network services. In other words, when the MHFE (e.g., the VXLAN tunnel endpoint (VTEP) of the MHFE) realizes that the destination MAC address of a packet belongs to a port of the distributed routing component, the VTEP does not establish a tunnel for 50 routing the packet. This is because the distributed routing component is implemented by every single MFE, MHFE, and gateway that participates in the logical network. As such, a packet with a destination MAC address of the logical router is not required to be routed to any other node in the 55 network.

Some embodiments, on the other hand, populate the tunnel endpoint locator table with the tunnel endpoint data of each logical port of the service routing components that is connected to a logical forwarding element (e.g., an L2 60 logical switch). That is, for each logical port of the service routers, some embodiment store (i) in the logical switch field, the logical switch to which the port is connected (e.g., the transit logical switch to which the southbound port of the service component is connected), (ii) in the MAC address 65 field, the MAC address of the port, and (iii) in the locator field, the IP address of the tunnel endpoint that implements

4

the logical switch port to which the service component port is connected (e.g., the IP address of the gateway machine that implements the service routing component).

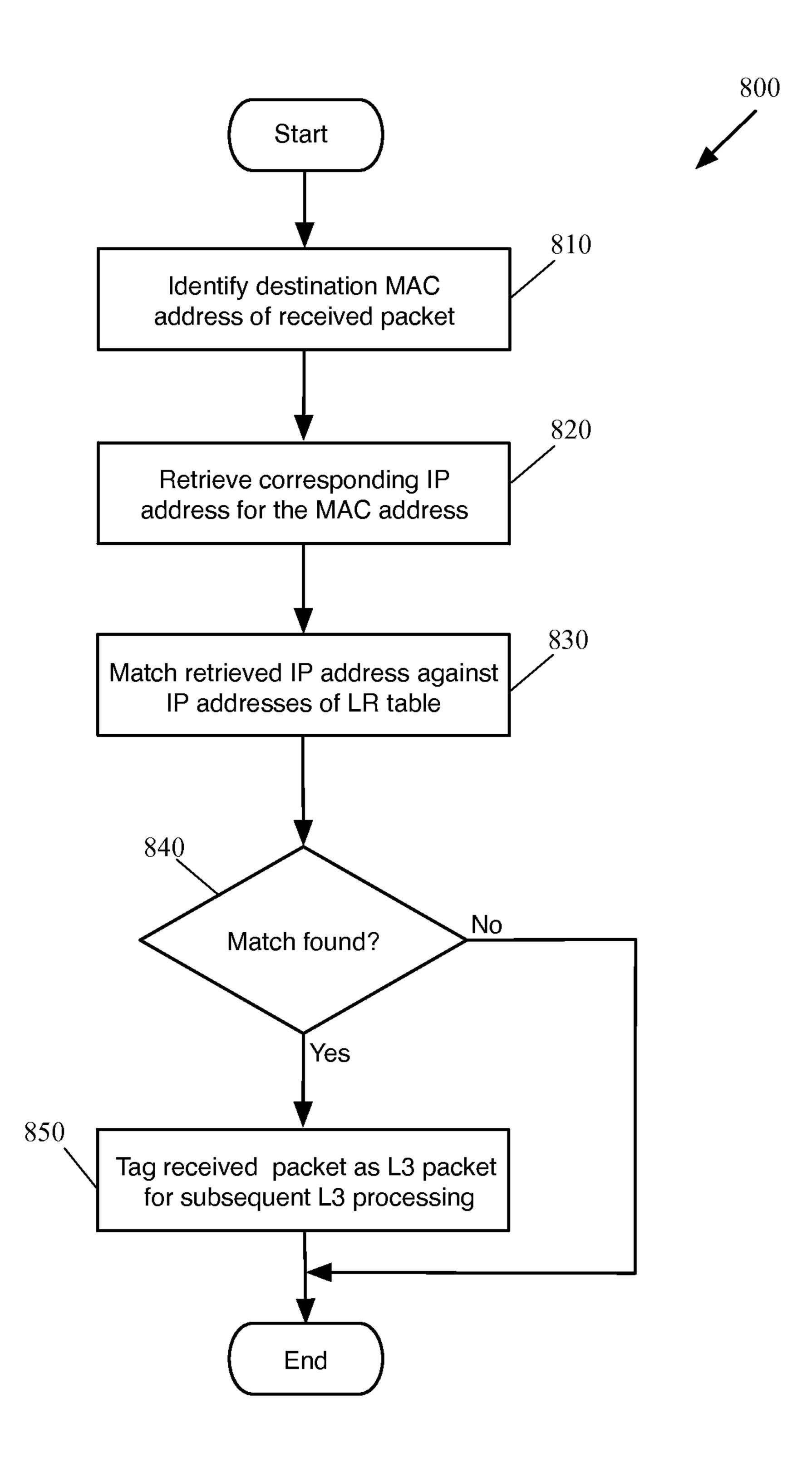

Some embodiments enable an MHFE (e.g., the hardware VTEP of the MHFE) to perform L3 routing functionalities on the packets that are destined for the logical router implemented by the MHFE. In order for the hardware VTEP to realize that a packet is destined for the logical router, the hardware VTEP must be able to identify the destination MAC address of the packet as a MAC address that belongs to a logical port of a routing component of the logical router. In order to enable the hardware VTEP to make such a determination, some embodiments use the database schema (e.g., OVSDB schema) to propagate configuration data that links the different database tables generated on the MHFE.

Linking the different tables allows the hardware VTEP to search the MAC address of the received packet against a logical router table that has all the MAC addresses of the different ports of the different routing constructs of the logical router. In OVSDB schema, among the different tables (e.g., forwarding tables) that are generated and configured on the MHFE, the control plane generates a logical router table on the MHFE that maps the IP addresses of the different ports of the distributed and service routing components of the logical router to the logical switches with which they are associated. On the other hand the tunnel endpoint locator table described above, includes the MAC addresses of all the different logical ports of the routing components of the logical router. In order to link these two tables together, some embodiments store the IP addresses of the ports of the logical router in an optional field of the tunnel endpoint locater table while configuring this table. In other words, the control plane uses a field of the table that has optional data (i.e., the field may or may not be used) to propagate the linking configuration data in the field.

By doing so, in some embodiments, the control plane is able to tag the MAC addresses of the logical ports of the logical router during the configuration of the tunnel endpoint locator table. That is, while the control plane is configuring the tunnel endpoint locator table, the control plane looks up the corresponding IP address of each port's MAC address in the logical router table, and when a match found, the control plane tags the corresponding MAC address of the port, in the tunnel endpoint locator table, as a logical router port's MAC address. As such, when a hardware VTEP receives a packet, the hardware VTEP simply looks up the destination MAC address of the packet in the tunnel endpoint locator table, and if the MAC address in the table is tagged as a logical router port MAC address, the hardware VTEP realized that the packet is an L3 packet and starts L3 processing on the packet.

In some other embodiments, the control plane, although populates the linking IP address in the tunnel endpoint locator table, does not tag the MAC addresses during the configuration of this table. In some such embodiments the hardware VTEP retrieves a corresponding IP address of the destination MAC address of the packet from the tunnel locator table and matches the corresponding IP address against the IP addresses of all the logical ports of the routing components that are stored in the logical router table in the OVSDB schema (i.e., the logical router table configured on the MHFE). When the hardware VTEP finds a match for the IP address in the logical router table, the hardware VTEP realizes that the destination MAC address of the packet is in fact a MAC address of one of the logical router ports. As such, the hardware VTEP starts to perform routing functionalities on the packet (e.g., the hardware VTEP modifies

the source and destination MAC addresses in the packet headers to route the packet to the next hop).

The preceding Summary is intended to serve as a brief introduction to some embodiments of the invention. It is not meant to be an introduction or overview of all of the 5 inventive subject matter disclosed in this document. The Detailed Description that follows and the Drawings that are referred to in the Detailed Description will further describe the embodiments described in the Summary as well as other embodiments. Accordingly, to understand all the embodiments described by this document, a full review of the Summary, Detailed Description and the Drawings is needed. Moreover, the claimed subject matters are not to be limited by the illustrative details in the Summary, Detailed Description and the Drawing, but rather are to be defined by the appended claims, because the claimed subject matters can be embodied in other specific forms without departing from the spirit of the subject matters.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The novel features of the invention are set forth in the appended claims. However, for purposes of explanation, several embodiments of the invention are set forth in the 25 following figures.

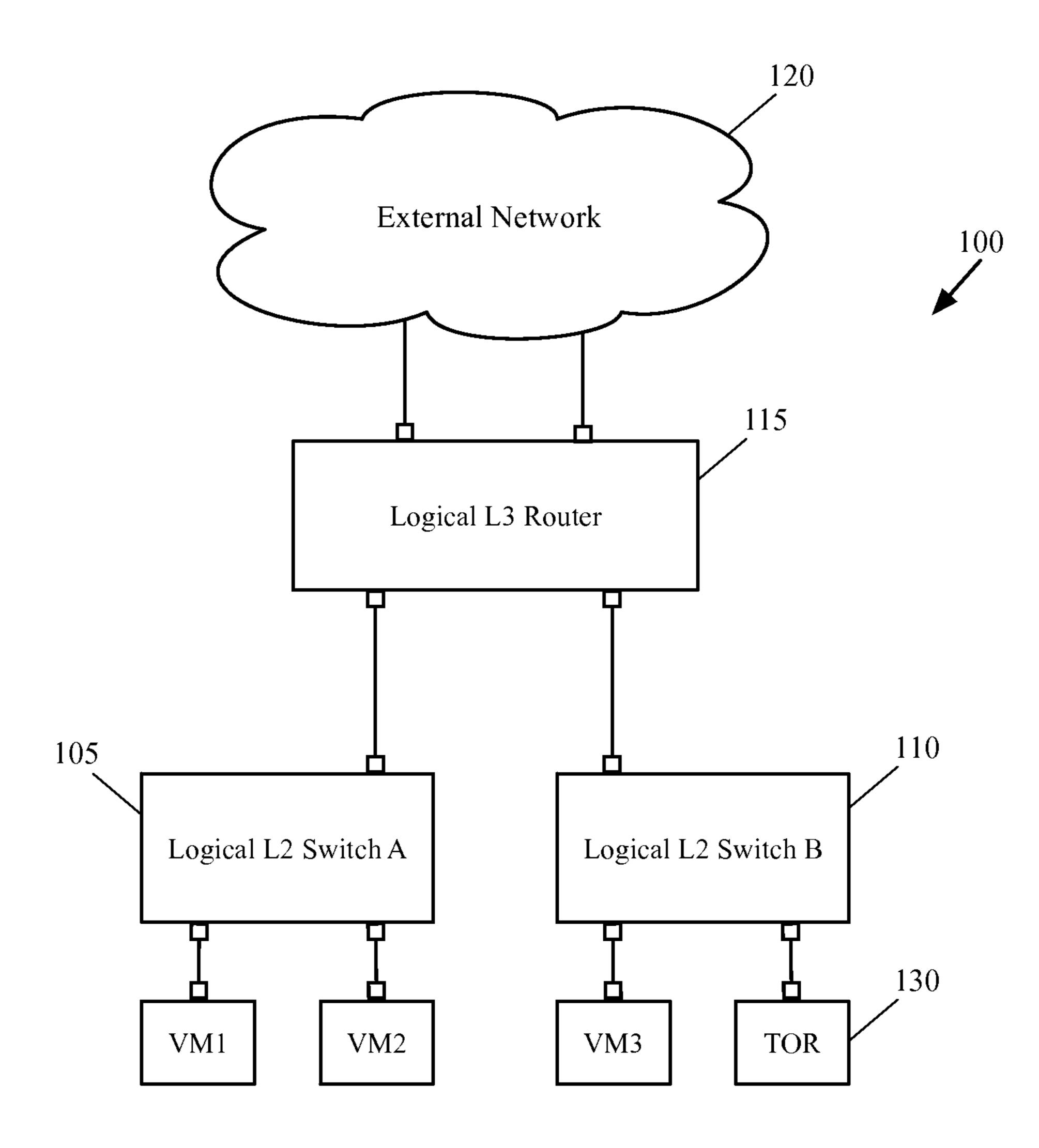

- FIG. 1 illustrates a configuration view of a logical router, which represents a logical network as designed by a user.

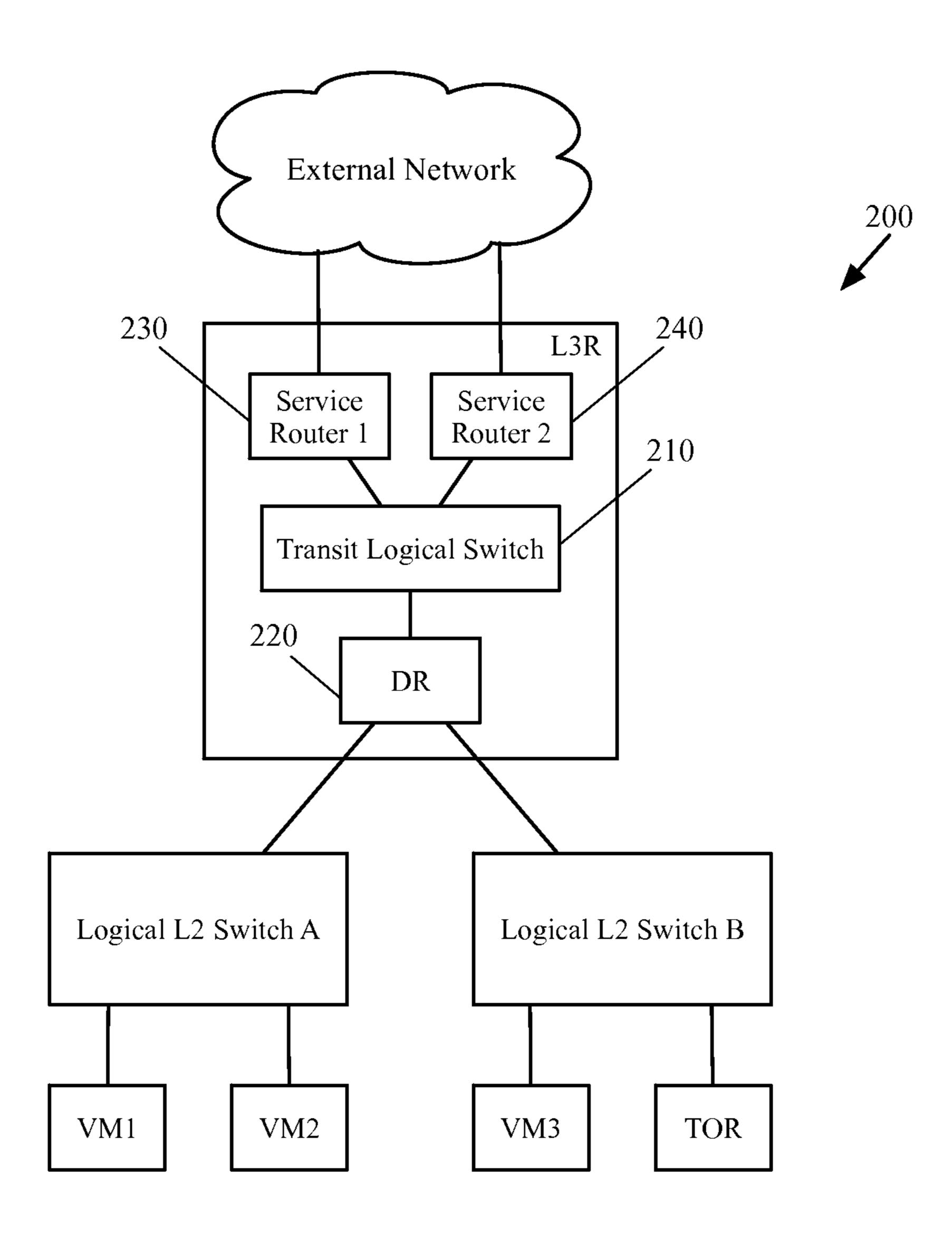

- FIG. 2 illustrates a control plane view of a logical network when the logical router is implemented in a distributed 30 manner.

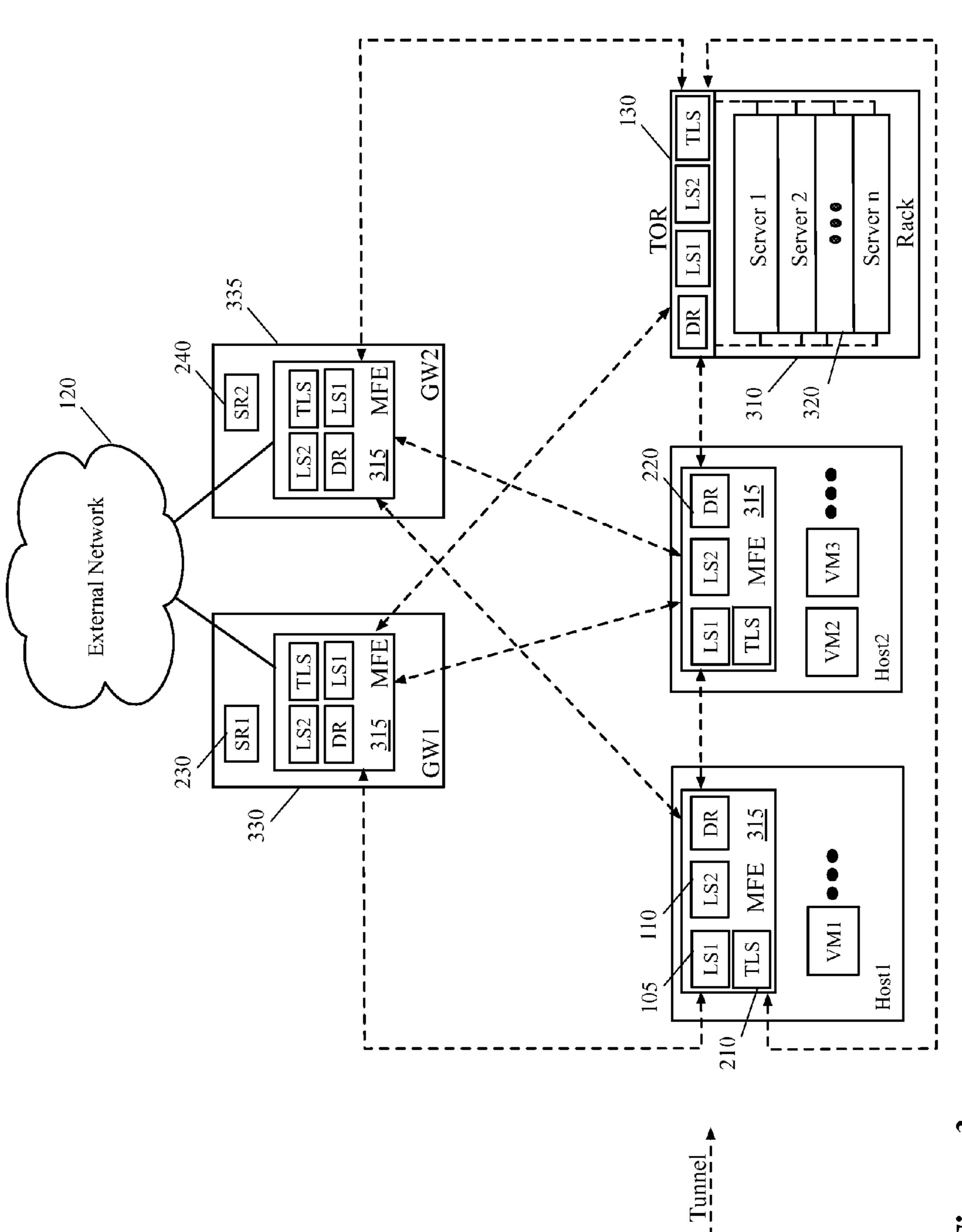

- FIG. 3 illustrates a physical distributed implementation of a logical router defined for a logical network.

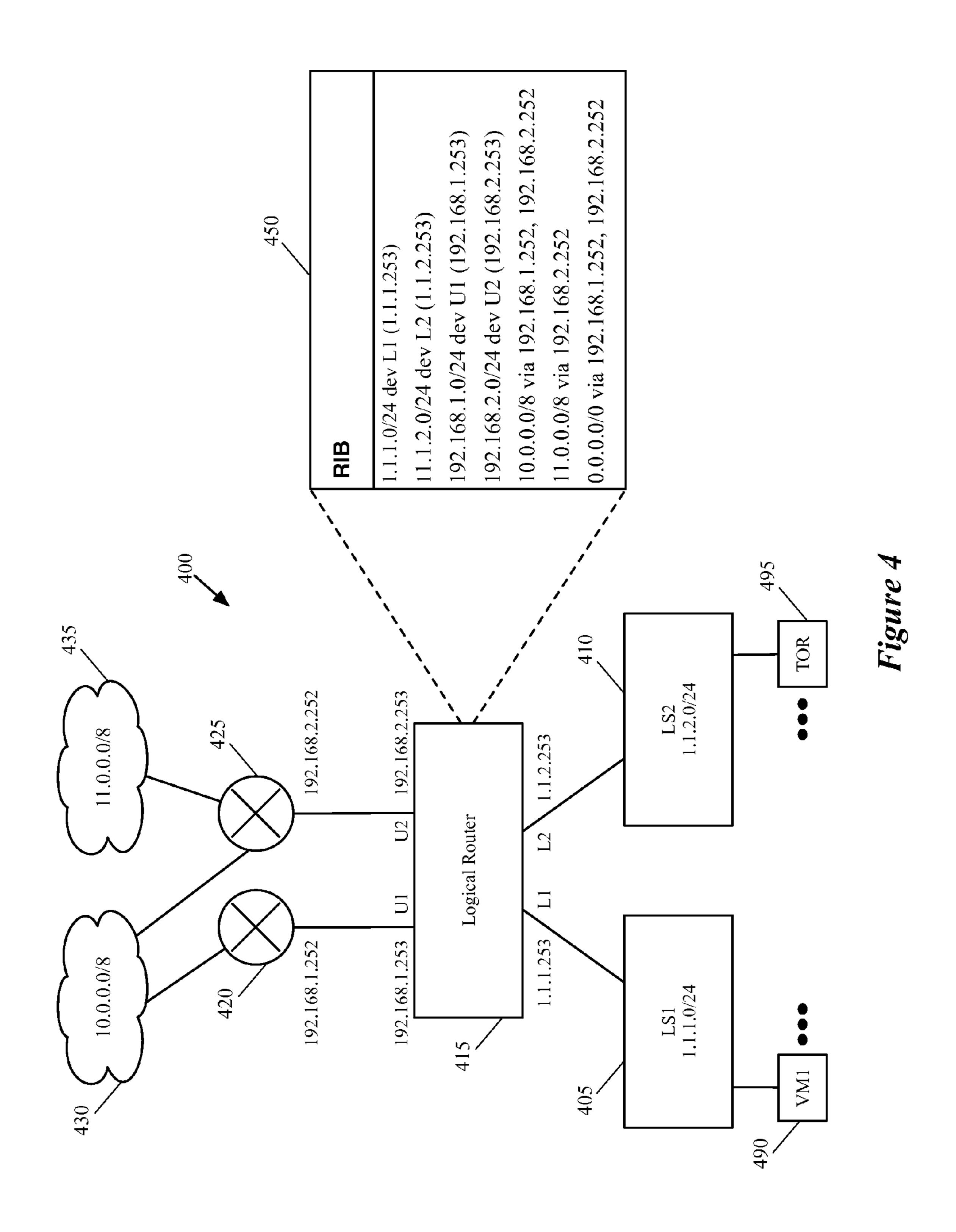

- FIG. 4 conceptually illustrates a more detailed configuration of a logical network topology, including the network 35 addresses and interfaces assigned by an administrator.

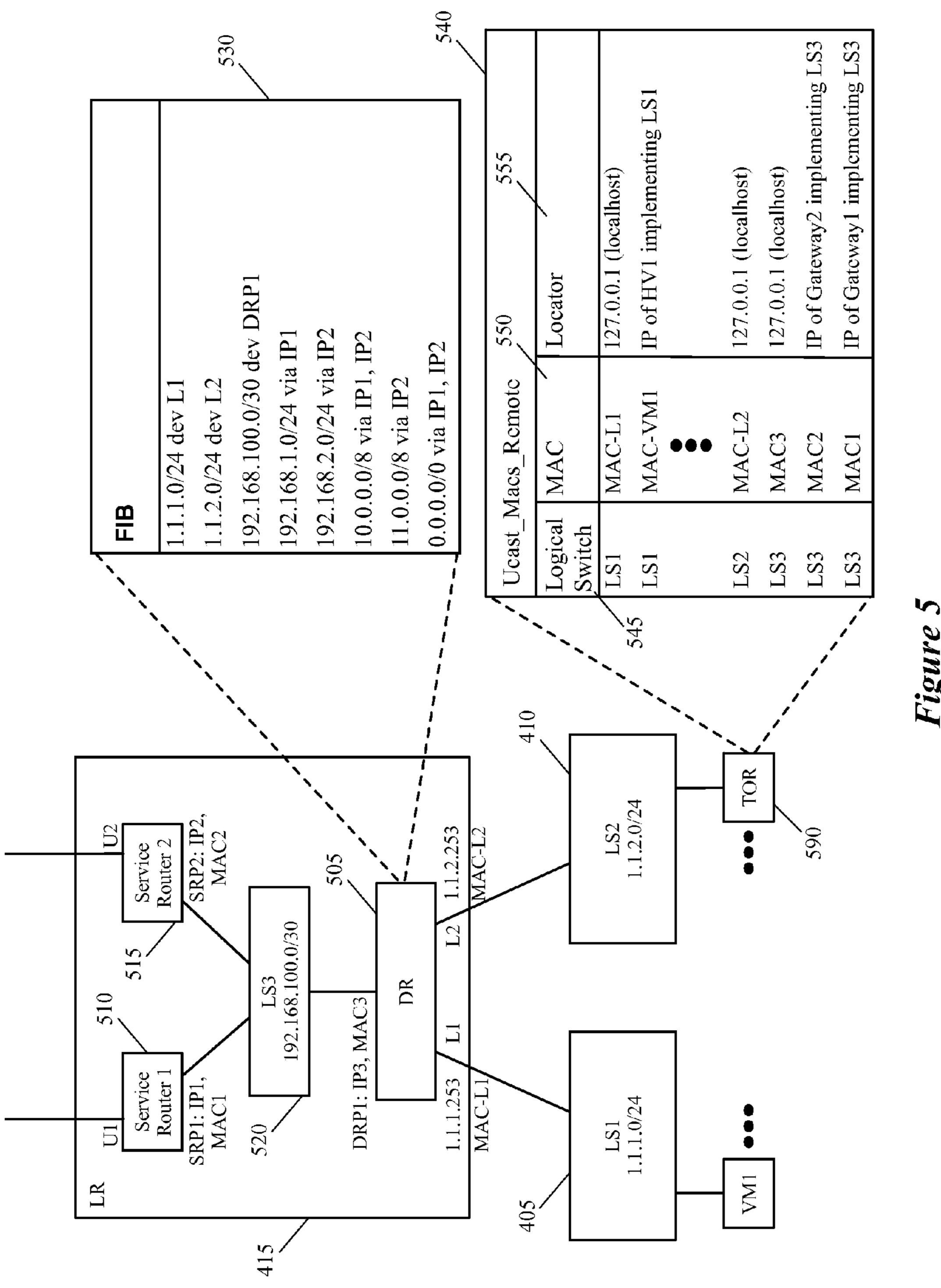

- FIG. 5 illustrates the configuration of a logical router and how the control plane configures the tunnel endpoint locators on an MHFE that implements the logical router.

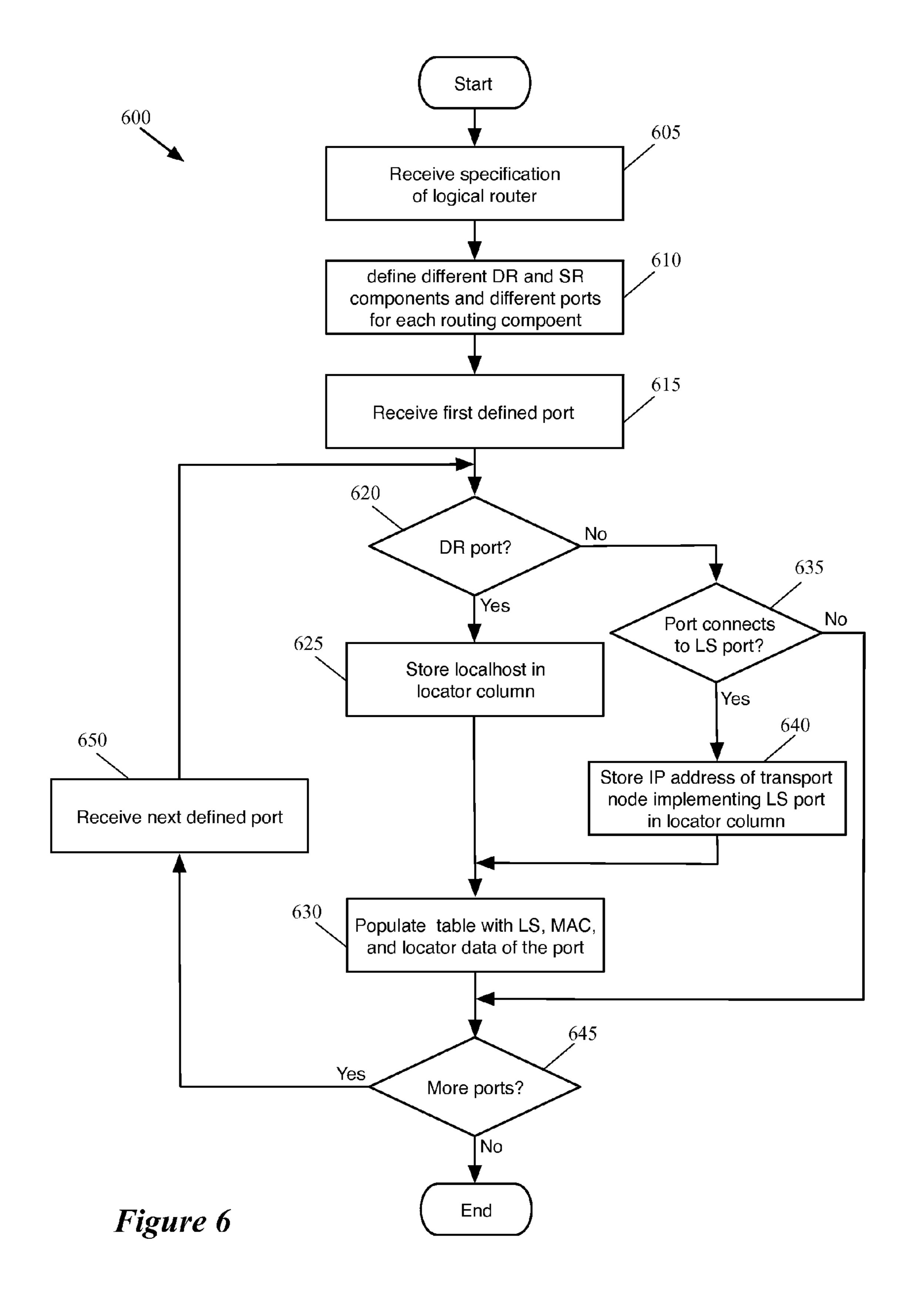

- FIG. 6 conceptually illustrates a process of some embodi- 40 ments for configuring the tunnel endpoint locators for different ports of the logical router on an MHFE.

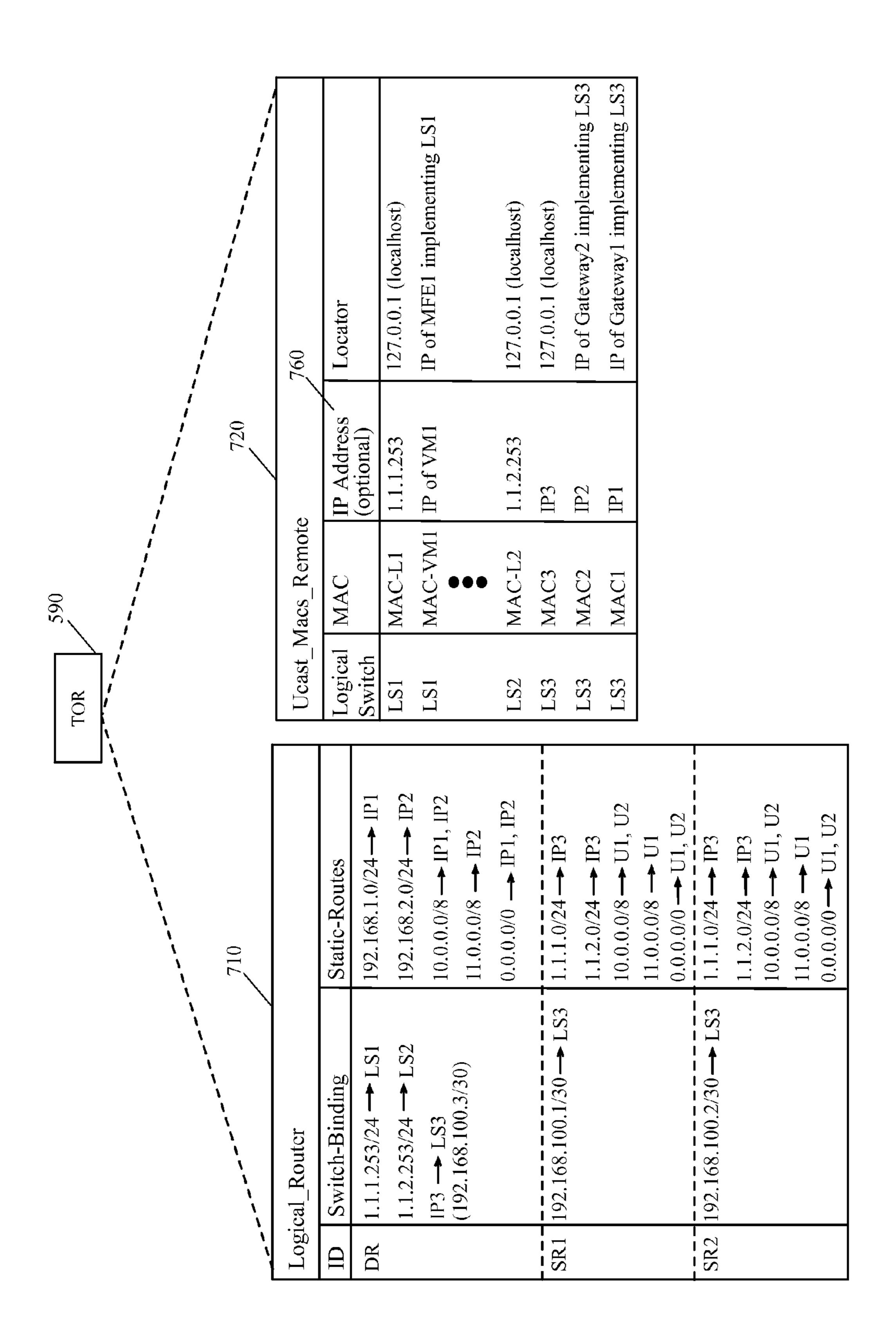

- FIG. 7 illustrates the configuration data propagated in different database tables stored on an MHFE using the OVSDB schema in order to enable the MHFE to infer the 45 data link layer (MAC) address of logical ports of a logical router.

- FIG. 8 conceptually illustrates a process that the MHFE of some embodiments performs for identifying logical ports of a logical router configured on the MHFE.

- FIG. 9 illustrates a physical network implementation logical router that routes the logical network traffic.

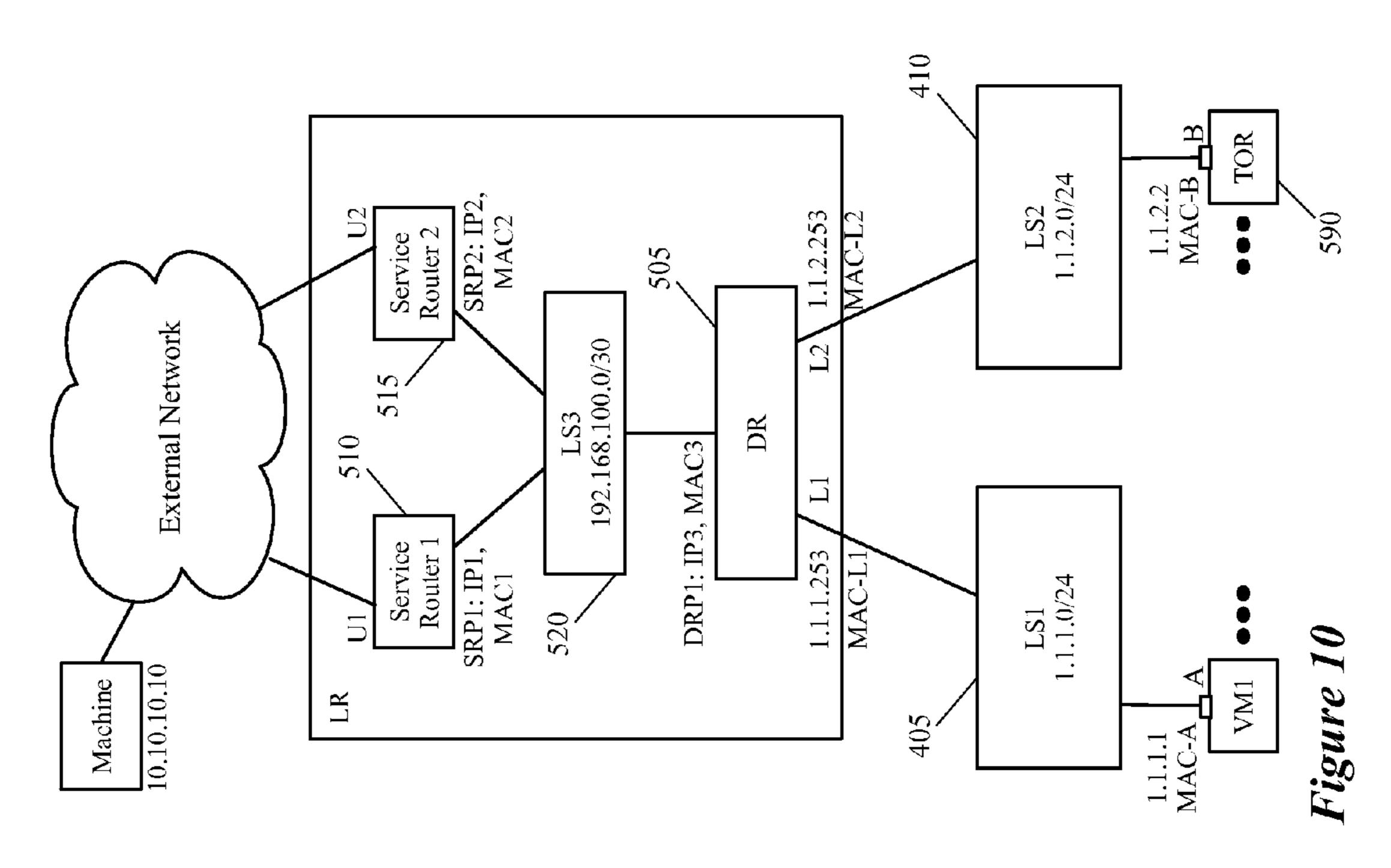

- FIG. 10 illustrates a control plane view for the physical network implementation shown in FIG. 9.

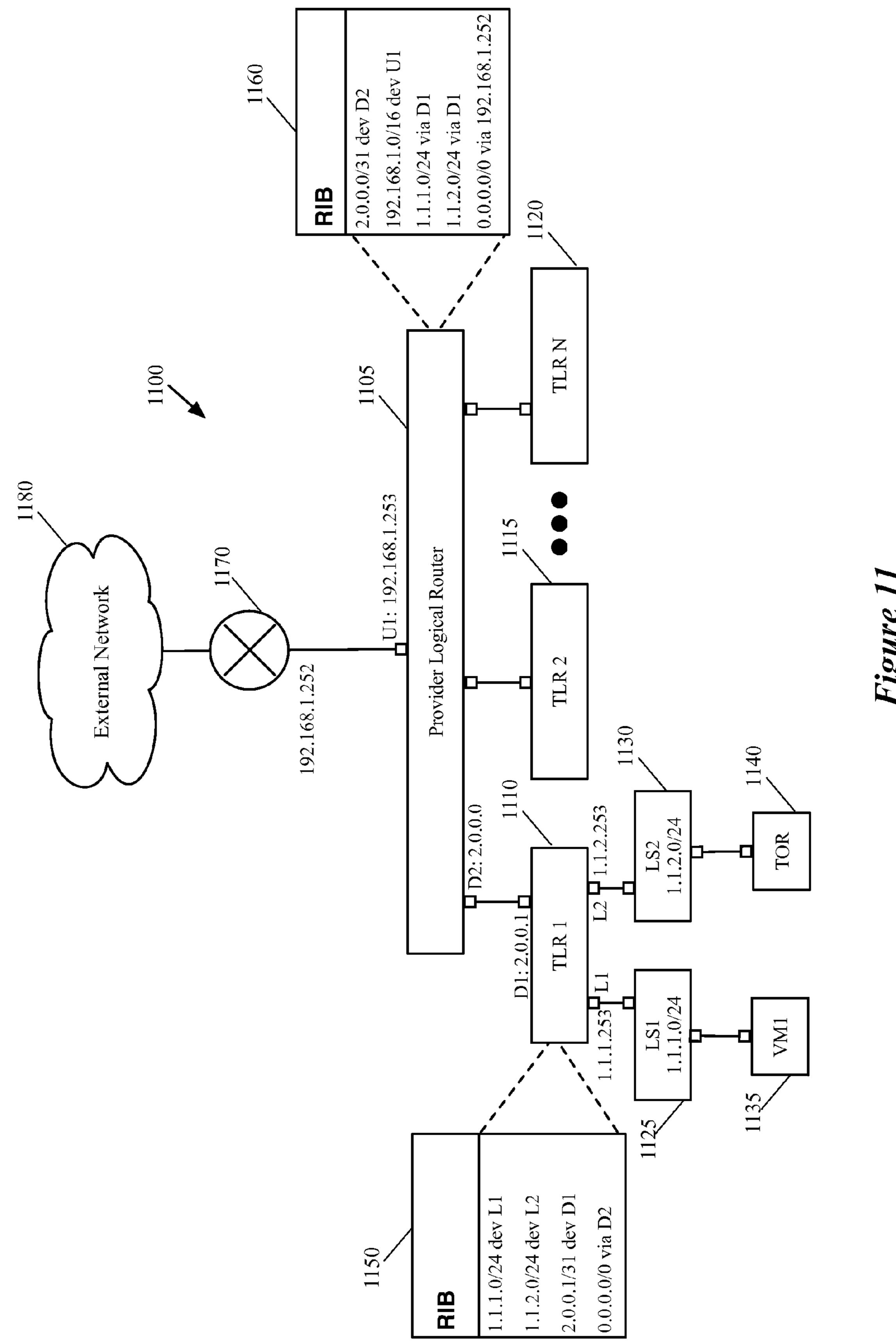

- FIG. 11 conceptually illustrates a multi-tier logical router 55 in a logical network of some embodiments.

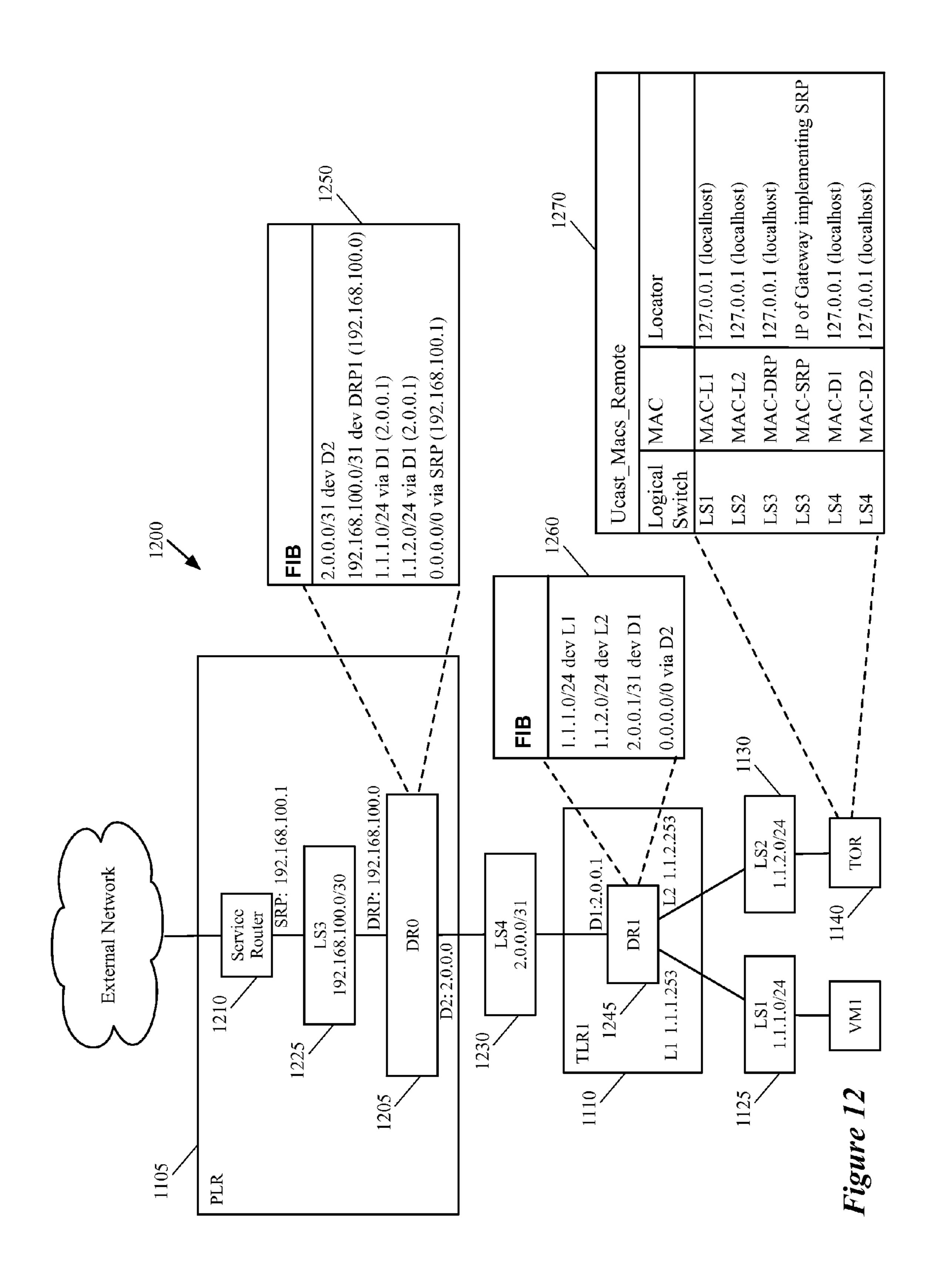

- FIG. 12 illustrates the control plane view for the logical topology of FIG. 11 when a TLR in the logical network is completely distributed.

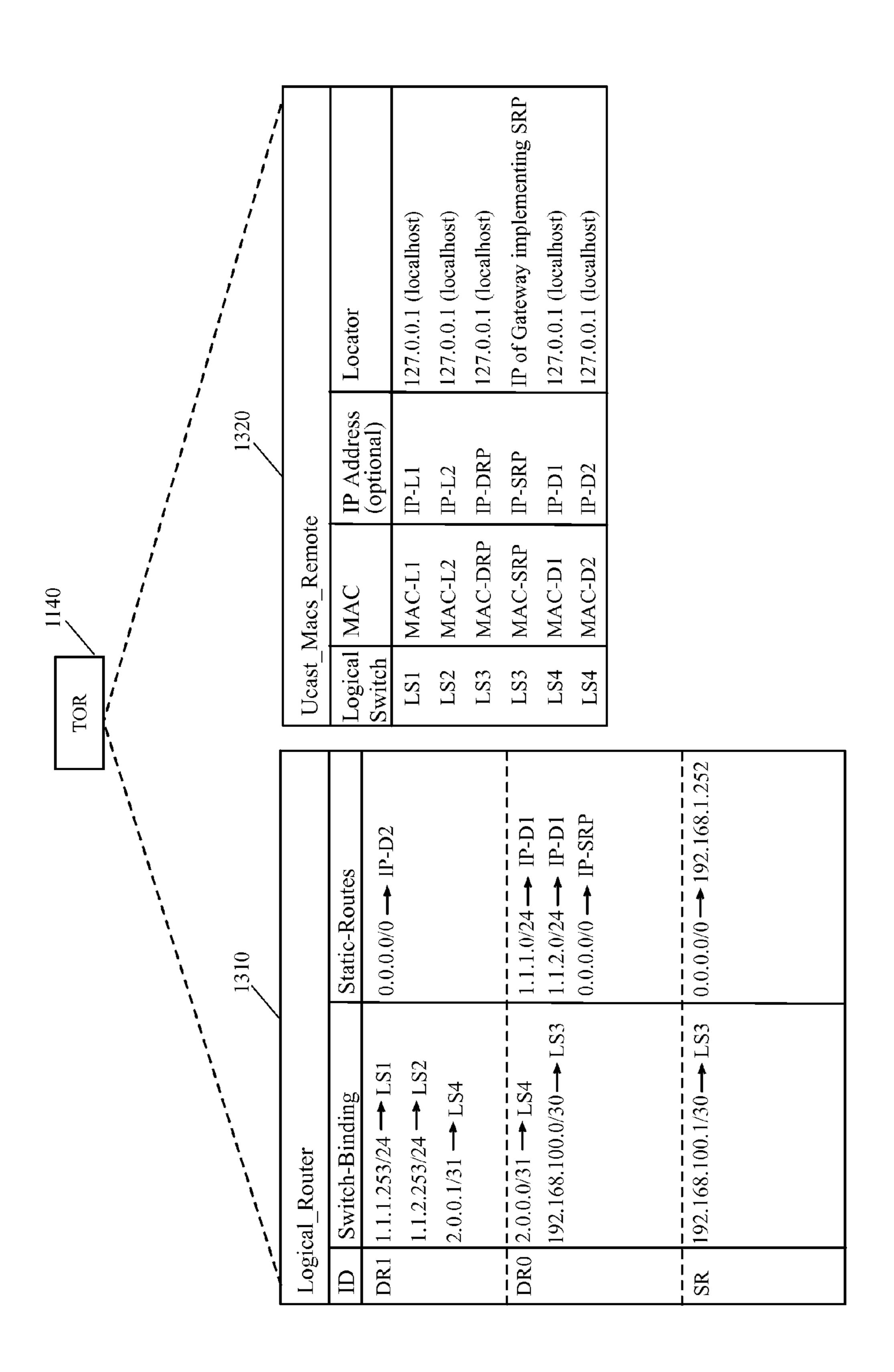

- data propagated in different database tables stored on an MHFE using the OVSDB schema in order to enable the MHFE to infer the MAC address of logical ports of multitier logical routers.

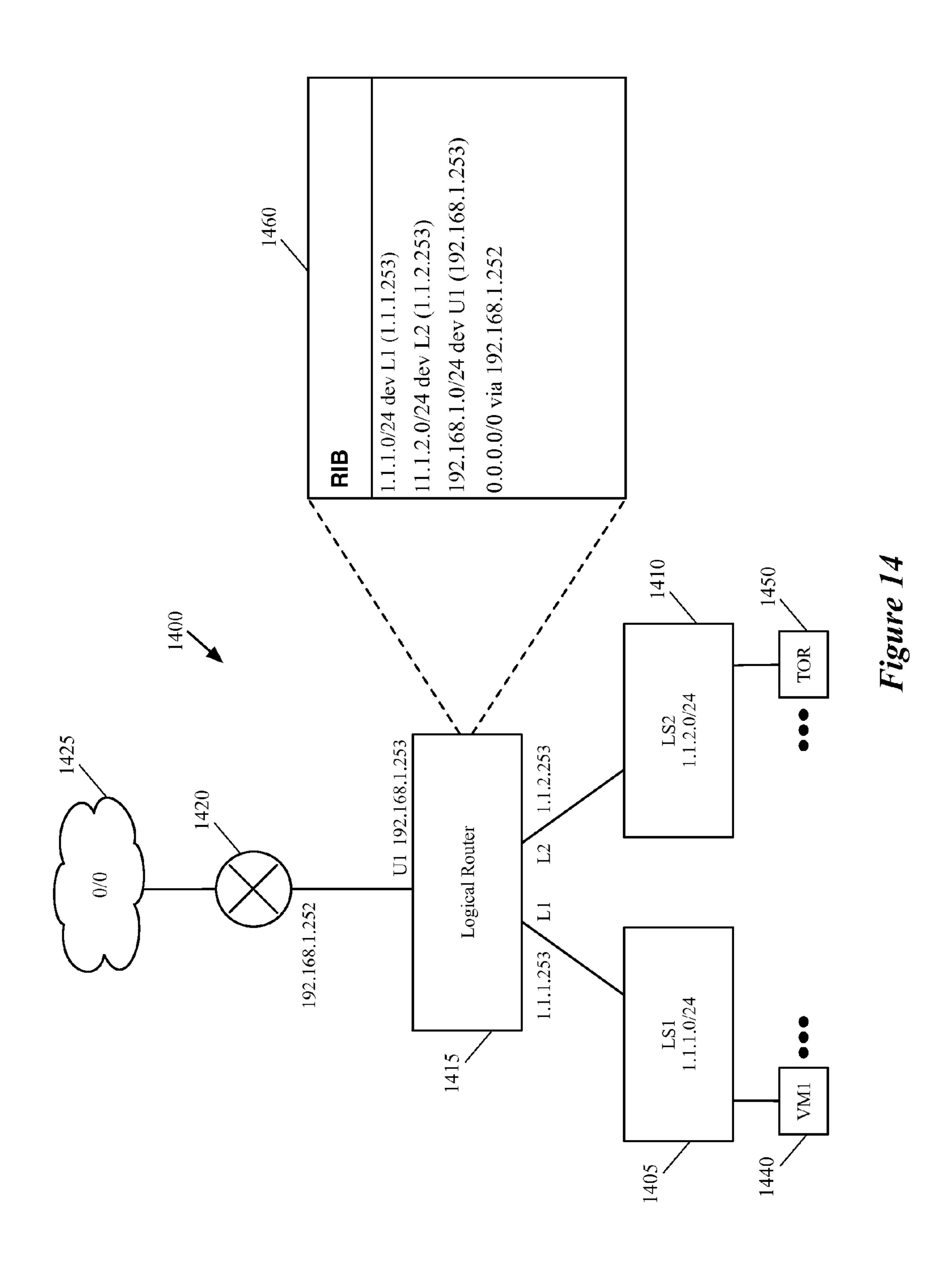

- FIG. 14 illustrates an example of a logical network 65 topology that includes single-tier logical router and a RIB that defines the routes of the logical router.

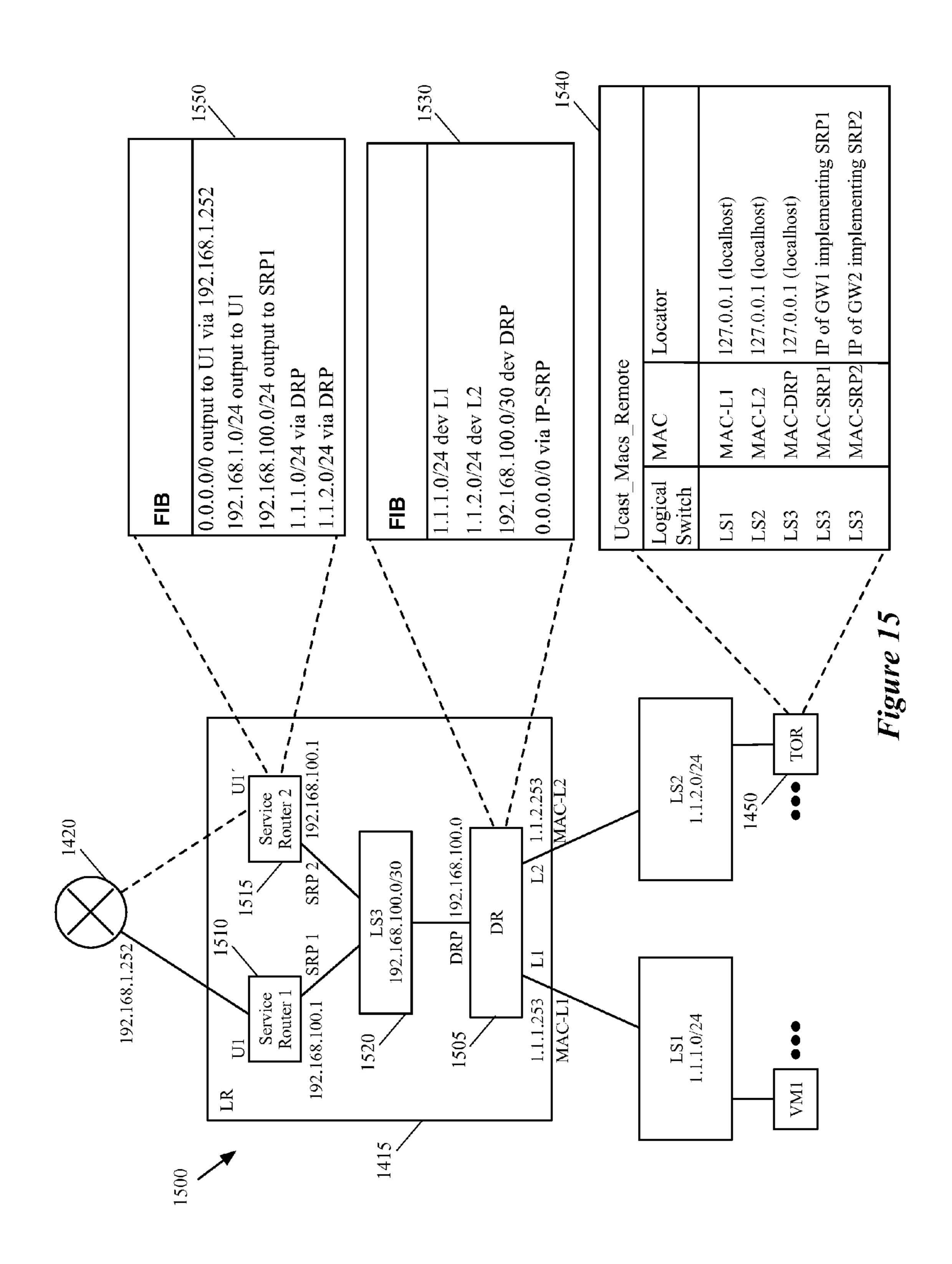

- FIG. 15 illustrates a control plane view of the logical network topology of FIG. 14 when the logical router is configured in active-standby mode, rather than active-active (ECMP) mode.

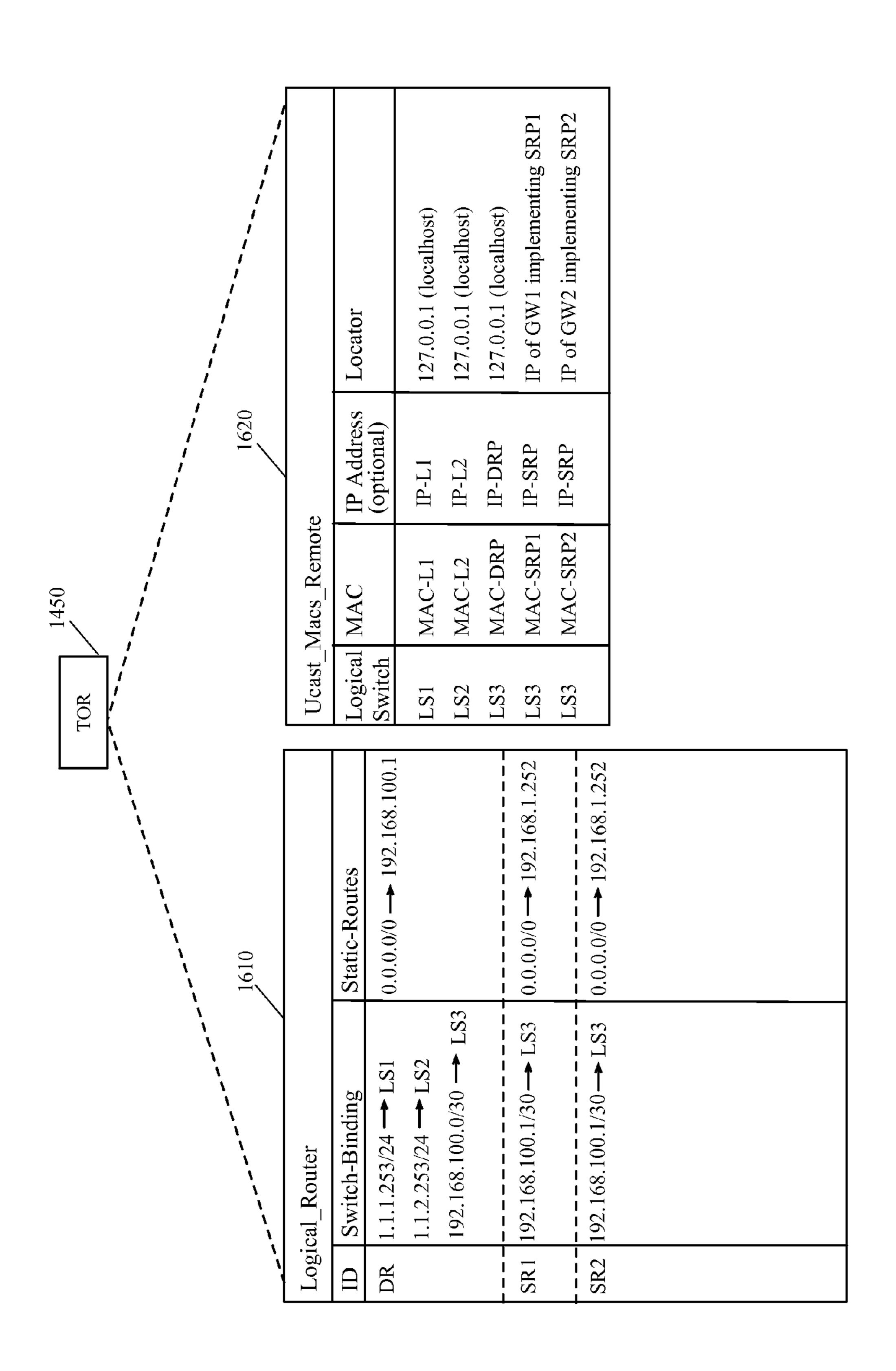

- FIG. 16 illustrates another example of the configuration data propagated in different database tables stored on an MHFE using the OVSDB schema in order to enable the MHFE to infer the MAC address of logical ports of the logical router.

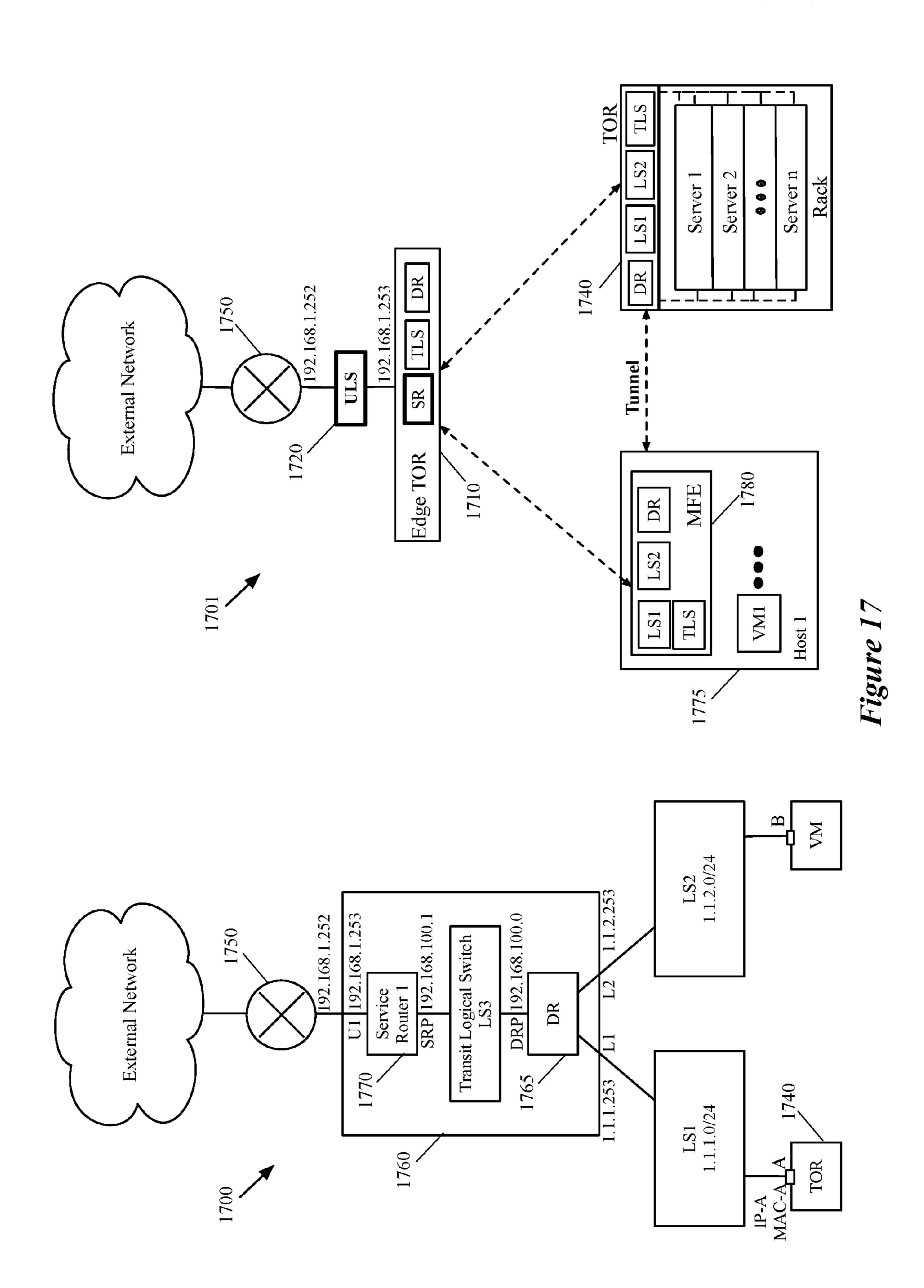

- FIG. 17 illustrates a control plane view and physical realization of a logical network topology, in which an edge MHFE implements the service component of the logical router and communicates with external networks through the service component.

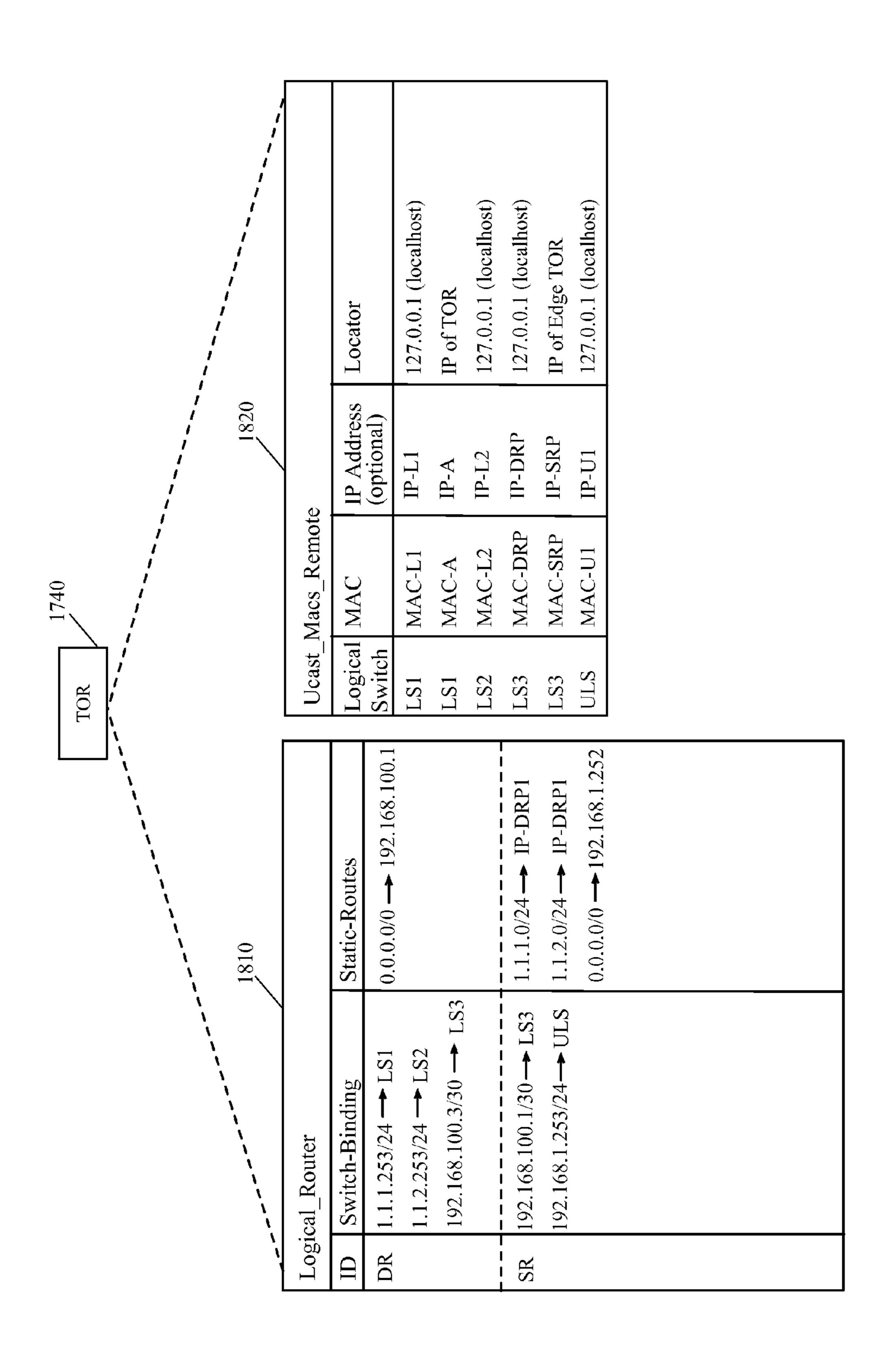

- FIG. 18 illustrates an example of the configuration data propagated in different database tables stored on an MHFE using the OVSDB schema in order to configure the MHFE as an edge node of the logical router.

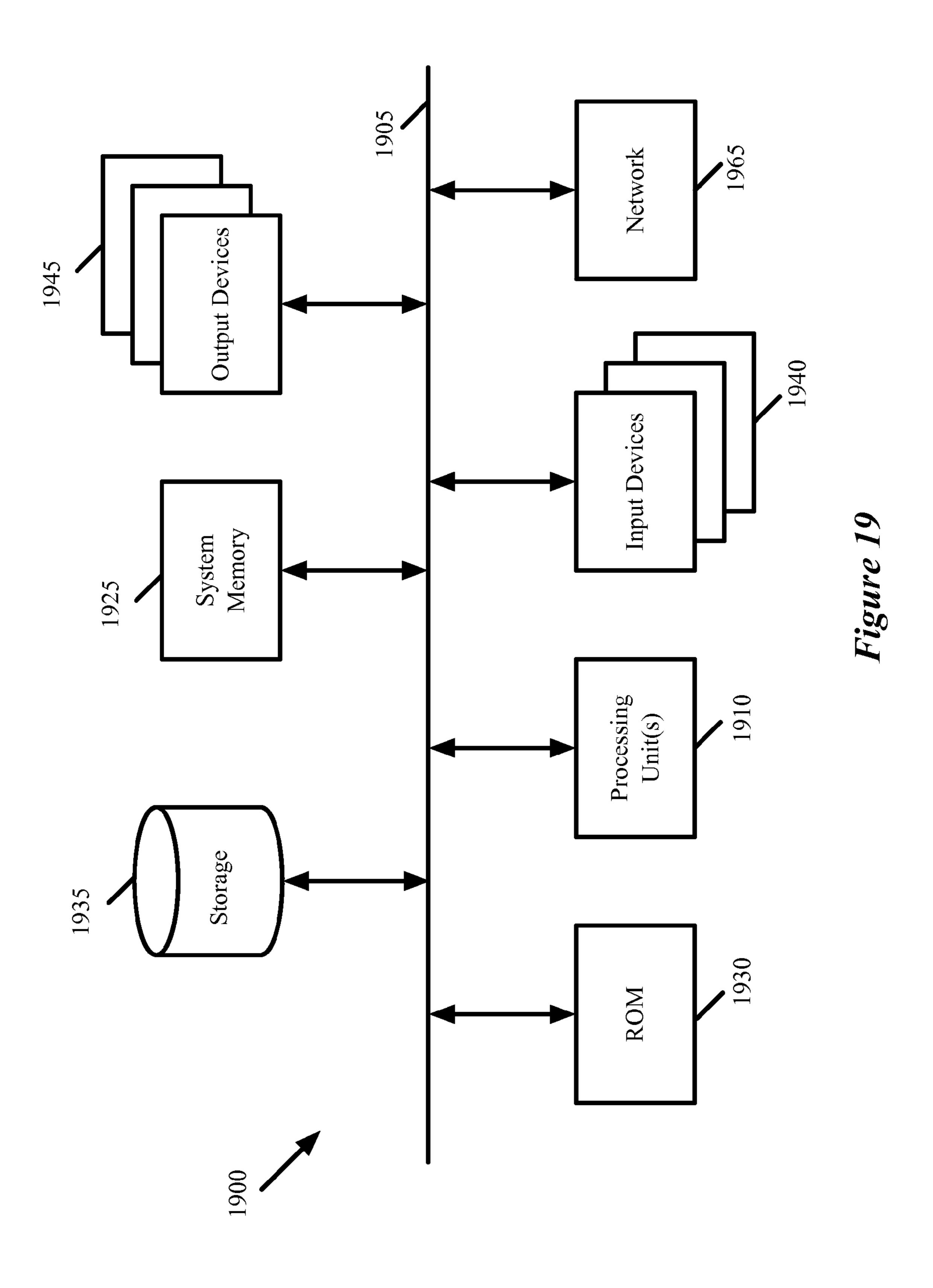

- FIG. 19 conceptually illustrates an electronic system with 20 which some embodiments of the invention are implemented.

## DETAILED DESCRIPTION OF THE INVENTION

In the following detailed description of the invention, numerous details, examples, and embodiments of the invention are set forth and described. However, it should be understood that the invention is not limited to the embodiments set forth and that the invention may be practiced without some of the specific details and examples discussed.

A new schema (i.e., OVSDB schema) that allows the control plane to configure hardware switches to implement different logical networks (for different tenants) has recently been introduced to the market. Some embodiments provide methods to improve this new schema in order to implement different logical network elements (e.g., logical routers) on the hardware switches.

Some embodiments provide a novel method of configuring a logical router of a logical network on a managed hardware forwarding element (MHFE) in order for the MHFE to implement the logical network and to perform logical routing functionalities. In some embodiments, the method is performed by a control plane that configures and manages one or more logical networks for one or more tenants of a hosting system (e.g., a datacenter). In some embodiments, a logical network of the hosting system includes a set of logical forwarding elements (e.g., logical switches and routers) that logically connects different end machines (e.g., virtual machines, containers, etc.) that run on 50 different host machines.

Some embodiments configure a logical router of a logical network on the MHFE (e.g., a third-party hardware switch such as a top-of-rack (TOR) switch or other appliances such as firewalls, load balancers, etc.) to enable the physical workloads connected to the MHFE (e.g., third-party servers connected to a TOR switch) to exchange network data with other end machines and/or external networks that are connected to the logical network.

In some embodiments, the control plane receives a defi-FIG. 13 illustrates another example of the configuration 60 nition of a logical router (e.g., through an application programming interface (API)) and defines several routing components for the logical router. Each of these routing components is separately assigned a set of routes and a set of logical interfaces. Each logical interface (also referred to as logical port) of each routing component is also assigned a network layer (e.g., Internet Protocol (IP)) address and a data link layer (e.g., media access control (MAC)) address.

In some embodiments, the several routing components defined for a logical router include a single distributed router (also referred to as distributed routing component) and several different service routers (also referred to as service routing components). In addition, the control plane of some 5 embodiments defines a transit logical switch (TLS) for handling communications between the components internal to the logical router (i.e., between the distributed router and the service routers).

The service components of a logical router, in some 10 embodiments, may be configured in active-active or activestandby mode. In active-active mode, all of the service components are fully functional at the same time, and traffic can ingress or egress from the logical network through the service components using equal-cost multi-path (ECMP) 15 forwarding principles (balancing the traffic across the various service routing components). In this mode, each logical interface of each separate service component has unique IP and MAC addresses for communicating with an external network and/or with the distributed component (through the 20) transit logical switch).

In some embodiments, the logical router is part of a two-tier logical network structure. The two-tier structure of some embodiments includes (1) a single logical router (referred to as a provider logical router (PLR) and admin- 25 istrated by, e.g., the owner of the datacenter) for connecting the logical network to a network external to the datacenter, and (2) multiple logical routers (each referred to as a tenant logical router (TLR) and administrated by, e.g., different tenants of the datacenter) that connect to the PLR and do not 30 separately communicate with the external network. In some embodiments, the control plane defines a transit logical switch between the distributed component of the PLR and the service components of the TLR.

active mode whenever possible, and only use active-standby mode when stateful services (e.g., NAT, firewall, load balancer, etc.) are configured for the PLR. In active-standby mode, only one of the service routing components is active, i.e., fully operational at a time, and only this active routing 40 component sends out messages to attract traffic. All the other service routing components is in standby. In some embodiments, the active service component and a standby service component use the same IP address, but different MAC addresses, for communicating with the distributed compo- 45 nent. However, only the active component replies to address resolution protocol (ARP) requests from this distributed component. Furthermore, only the active service component advertises routes to the external network to attract traffic.

For a TLR logical router, some embodiments either use no 50 service components or two service components in activestandby mode when stateful services are configured for the TLR. The TLR operates internally in the same manner as a PLR in active-standby mode, i.e., having an active component and a standby component sharing the same network 55 layer address, but only the active component responding to ARP requests. To connect to the PLR, some embodiments assign each of the two service components of the TLR a same network layer address (though different from the IP address used to connect to its own distributed component). 60

The logical router described above is a distributed logical router implemented by a single distributed routing component and a set of service routing components. Some embodiments provide other types of logical router implementations in a physical network (e.g., a datacenter network) such as a 65 centralized logical router. In a centralized logical router, L3 logical routing functionalities are performed in only gateway

machines, and the control plane of some embodiments does not define any distributed routing component and instead only defines multiple service routing components, each of which is implemented in a separate gateway machine. Different types of logical routers with multiple routing components for end machines of a datacenter are described in greater detail in U.S. Provisional Patent Application 62/110, 061, filed Jan. 30, 2015, which is incorporated herein by reference.

The above introduced the general concepts of a logical router configuration as well as certain aspects of the logical router configuration and implementation of some embodiments. In the following, Section I describes how the different routing components of a logical router is configured on a managed hardware forwarding elements (e.g., a TOR switch) in order for the MHFE to implement these components. Section II then describes configuring the logical router on the MHFE in such a way to enable the MHFE to perform routing functionalities. Next, Section III describes configuration of the MHFEs in other types of logical network topologies and for other types of logical routers. Section IV then describes configuring an MHFE as an edge node of a logical router. Finally, Section V describes the electronic system with which some embodiments of the invention are implemented.

## I. CONFIGURING LOGICAL ROUTER ON MHFE

Some embodiments use a distributed logical router implementation that enables first-hop routing in a distributed fashion (rather than concentrating all of the routing functionality at the gateways). In the physical realization, the logical router of some embodiments includes a single distributed routing component (also referred to as a distributed router (DR)) and one or more service routing components For a PLR logical router, some embodiments use active- 35 (also referred to as service routers (SRs)). The DR, in some embodiments, spans managed forwarding elements (MFEs) that couple directly with virtual machines (VMs) or other data compute nodes that are logically connected, directly or indirectly, to the logical router. The DR of some embodiments also spans the gateways to which the logical router is bound as well as one or more MHFEs (e.g., third-party physical machines). The DR of some embodiments is responsible for first-hop distributed routing between logical switches and/or other logical routers that are logically connected to the logical router.

> The service routers (SRs) of some embodiments are responsible for delivering services that are not implemented in a distributed fashion (e.g., some stateful services) as well as connecting the logical network to external network(s). A distributed logical router will have SRs if either (i) the logical router is a provider logical router (PLR), and therefore connects to external physical networks or (ii) the logical router has services configured that do not have a distributed implementation (e.g., NAT, load balancing, DHCP in some embodiments). Even if there are no stateful services configured on a PLR, some embodiments use SRs for failure handling and for ECMP.

> Logical routers, in some embodiments, can be viewed from three different perspectives. The first of these views is the API view, or configuration view, which is how the user (e.g., a datacenter provider or tenant) views and defines the logical router. The second view is the control plane or management plane view, which is how the controller computer internally defines the logical router. Finally, the third view is the physical realization, or implementation of the logical router, which is how the logical router is actually implemented in the physical network.

FIG. 1 illustrates the configuration view of a distributed logical router in a logical network as designed by a user (e.g., a network administrator, a tenant of a datacenter, etc.). As shown, the logical router 115 is part of the logical network 100 which also includes two other logical switches 105 and 110. The logical router 115 has two logical ports that are connected to the logical switches 105 and 110.

Logical switch 105 has logical ports that are connected to virtual machines VM1 and VM2 while the logical switch 110 has logical ports connected to the virtual machine VM3 and TOR switch 130. The logical router 115 also includes two logical ports that connect to the external physical network 120. The TOR switch 130 connects one or more physical machines (e.g., physical servers, etc.) to the VMs of the logical network 100 through the logical switches 105 and 110, and the logical router 115.

While shown as VMs in this figure and other figures below, it should be understood that other types of data compute nodes (e.g., namespaces, containers, etc.) may 20 connect to logical forwarding elements (e.g., logical switches 105 or logical routers 115) in some embodiments. It should also be understood that although a TOR switch in the example figures is shown as a managed hardware forwarding element (MHFE), the MHFE can be any other 25 third-party forwarding elements (e.g., other physical switches and routers, appliances such as firewalls, load balancers, etc.). Additionally, although in the illustrated example, as well other examples below, only one TOR switch is shown to connect to the logical network, one of 30 ordinary skill in the art would realize that many more TOR switches or other third-party hardware switches can connect to the logical network in the same manner. The illustrated examples include only one TOR switch in order to simplify the figures and the descriptions.

FIG. 2 illustrates the management (control) plane view of the logical network 100 shown in FIG. 1. The control plane view 200 for the distributed implementation illustrates that the control plane, after receiving the configuration data of the distributed logical router, creates a distributed router 40 220, two service routers 230 and 240, and a transit logical switch 210 based on the received logical router data. In some embodiments, the control plane generates separate routing information bases (RIBs) and/or forwarding information bases (FIBs) for each of the routing components 220, 230, 45 and 240. That is, in addition to having separate objects created in the management/control plane, each of the routing components is treated as a separate router with separate routes.

The transit logical switch 210 has different logical ports 50 for each of the created routers, and each of the routing components 220-240 has an interface to logically connect to the transit logical switch 210. The configuration of the northbound and southbound interfaces of the various routing components 220-240 and their connections with the transit 55 logical switch 210 will be described in further detail below by reference to FIGS. 3 and 4.

FIG. 3 illustrates the physical distributed implementation of the logical router 115 of FIG. 1. As shown, the virtual machine VM1, which couples to the logical switch 105 60 (LS1) in the logical network 100, operates on the host machine Host1, while VM2 and VM3 that couple to logical switches 105 and 110, respectively, operate on the host machine Host2. Additionally, the TOR switch 130 that couples to the logical switch 110 is part of a third-party rack 65 310 which also includes a set of servers 320 that are connected to the TOR switch 130. The virtual machines

**10**

VM1-VM3 and servers 320 communicate (e.g., exchange network data) with each other and other entities via the logical network 100.

Each host machine is operating a managed forwarding element (MFE) 315. In some embodiments, the MFEs 315 operating on the host machines are software switches provided by the hypervisors or other virtualization software on the host machines. The TOR 130 is operating as a managed hardware forwarding element (MHFE). A MHFE in some 10 embodiments is a third-party hardware switch that implements one or more logical networks and logically connects the physical workload attached to it (e.g., hardware and physical machines connected to the TOR 130) to the end machines and other devices in the logical network. The 15 MFEs and MHFE implement the logical switches 105, 110, and 210 as well as the distributed routing component 220. The MFEs of some embodiments perform first-hop switching for the logical switches 105 and 110 for packets sent by the VMs of the logical network 100 (unless the pipeline of the transit logical switch 210 of the MFE specifies to send the packet to a SR). The MFEs **315** (or a subset of them) may also implement logical switches (and distributed logical routers) for other logical networks if the other logical networks have VMs that reside on the host machines Host1 and Host2 as well.

The control plane of some embodiments configures and manages one or more logical networks for one or more tenants of a hosting system (e.g., a datacenter). In some embodiments, a logical network of the hosting system logically connects a set of end machines (e.g., virtual machines, physical servers, containers, etc.) and a set of physical machines using a set of logical forwarding elements (e.g., logical L2 and L3 switches). In some embodiments, different subsets of end machines reside on different host 35 machines that execute managed forwarding elements (MFEs). The MFEs implement the logical forwarding elements of the logical network to which the local end machines are logically connected. These MFEs may be flow-based forwarding elements (e.g., Open vSwitch) or code-based forwarding elements (e.g., ESX), or a combination of the two, in various different embodiments. These different types of forwarding elements implement the various logical forwarding elements differently, but in each case they execute a pipeline for each logical forwarding element that may be required to process a packet.

In some embodiments, the logical forwarding elements are implemented by one or more MHFEs (e.g., TOR switches) in order to connect the physical machines that are connected to the MHFEs to the other end machines of the logical network. In other words, each of the host machines executes an MFE that processes packets sent to and received from the end machines residing on the host machine, and exchanges these packets with other MFEs operating on other host machines as well as the MHFEs (e.g., through tunnels established by overlay encapsulation).

In some embodiments, when the MFE receives a packet from a VM that is coupled to the MFE, it performs the processing for the logical switch to which that VM logically couples, as well as the processing for any additional logical forwarding elements (e.g., logical router processing if the packet is sent to an external network, logical router processing and processing for the other logical switch in the network if the packet is sent to an end machine coupled to the other logical switch, etc.).

In some embodiments, the MFEs implement the logical forwarding elements through a set of flow entries. These flow entries are generated by a local controller operating on

each host machine (not shown). The local controller of each host machine generates the flow entries by receiving the logical forwarding data from the control plane and converting the logical forwarding data to the flow entries for routing the packets of the logical network in the host machine. That 5 is, the local controller, operating on a host machine, converts the universal logical forwarding data that is computed and sent by the control plane to every local controller operating on different host machines, to a customized set of forwarding behaviors that is recognizable and used by the MFE that 10 operates on the same host machine as the local controller.

The MFE then uses the customized set of forwarding data to forward the packets of the logical network between the end machines operating on the host machine. In other words, by using the generated flow entries, the MFEs are able to 15 forward and route packets between network elements of the logical network that are coupled to the MFEs. In some embodiments, however, some or all of the MFEs are not flow-based software forwarding elements, but instead process packets based on configuration data that is generated by 20 their respective local controllers. In some embodiments, the local controllers receive the same data from the control plane irrespective of the type of MFEs they manage, and perform different data conversions for different types of MFEs.

Additionally, the control plane distributes the logical forwarding data of the logical forwarding elements to the TOR switch 130 in order for the TOR switch to implement these logical forwarding elements and connect the physical workload to the virtual machines VM1-VM3. In some 30 embodiments, the control plane distributes the logical forwarding data of the logical forwarding elements to the TOR switch using an open source database schema such as OVSDB. In some other embodiments the control plane distributes the forwarding data to a particular MHFE con- 35 troller using the NETCPA protocol, which is a proprietary protocol (a VXLAN control plane protocol). In some such embodiments, the MHFE controller subsequently translate the logical forwarding data to the open source protocol that is recognizable by the TOR switch and distributes the 40 forwarding data to the TOR switch using the open source protocol.

The distributed router 220, as shown in FIG. 3, is implemented across the MFEs 315, the TOR switch 130, and the gateway machines 330 and 335. That is, the datapaths (e.g., 45 in the MFEs 315, or in a different form factor on the gateways and MHFEs) all include the necessary processing pipelines for the DR 220 (and the transit logical switch 210 illustrated in FIG. 2). Unlike the distributed router 220, each of the two service routers 230 and 240 operates on a single 50 gateway machine. Specifically, the SR 230 shown in the figure operates on the gateway machine 330, while the SR 240 operates on the gateway machine 335.

In some embodiments, the gateway machines 330 and 335 (also called edge nodes in some embodiments) are host 55 machines similar to the host machines Host1 and Host2, which host service routers rather than user VMs. As shown in the figure, each of the gateway machines 330 and 335 includes an MFE 315 as well, which are similar to the other MFEs operating on the other host machines that implement 60 the logical forwarding elements of the logical network 100. In the illustrated gateway machines 330 and 335, the SRs are shown as separate from the MFEs that operate on the gateway machines.

Different embodiments, however, may implement the SRs 65 differently. Some embodiments implement the SRs as VMs (e.g., when the MFE is a software switch integrated into the

12

virtualization software of the gateway machine), in which case the SR processing is performed outside of the MFE. As will be discussed in more detail below in Section IV, some embodiments implement the SRs on an edge MHFE (e.g., a hardware VTEP). In some such embodiments, the edge hardware VTEP plays the role of a gateway machine and connects the logical network (also implemented by the VTEP) to external network(s).

On the other hand, some embodiments implement the SRs as virtual routing and forwarding (VRFs) elements within the MFE datapath (when the MFE uses DPDK for the datapath processing). In either case, the MFE treats the SR as part of the datapath, but in the case of the SR being a VM (or other data compute node) separate from the MFE, the MFE sends the packet to the SR for processing by the SR pipeline (which may include the performance of various services). As with the MFEs on the host machines Host1 and Host2, the MFEs of the gateway machines, as described above, are configured to perform all of the distributed processing components of the logical network.

The SRs of some embodiments may operate in an active-active or active-standby mode, depending on whether any stateful services (e.g., firewalls) are configured on the logical router. When stateful services are configured, some embodiments require only a single active SR. In some embodiments, the active and standby service routers are provided with the same configuration, but the MFEs operating on the host machines are configured to send packets via a tunnel to the active SR (or to the MFE of the gateway machine that implements the active SR). Only if the tunnel is down will the MFE send packets to the standby SR.

As described above, in order to exchange the network data between the different elements of the logical network 100, the different MFEs and MHFE that implement the logical forwarding elements establish tunnels between themselves. In some embodiments, the control plane (e.g., one or more controller computers of a centralized controller system) distributes configuration data to the MFEs and MHFE (e.g., through separate controllers of MFEs and MHFE), which includes instructions on how to set up tunnels between the MFEs and MHFE. For instance, the configuration data specifies the location (e.g., IP address) of each tunnel endpoint. In some embodiments, the TOR switch is also one of the tunnel endpoints.

The TOR switch of some embodiments, after receiving the endpoint addresses (in the configuration data), stores the tunnel endpoint addresses of the other MFEs and MHFEs that implements the logical forwarding elements and their different logical ports in a particular tunnel endpoint locator table. The tunnel endpoint locator table is one of several database tables that are configured on the TOR switch through a database schema (e.g., OVSDB). The distributed configuration data, therefore, enables the TOR switch to locate other tunnel endpoints (through their IP addresses) and establish the tunnels between the TOR switch and the other endpoints. Configuring the TOR switch to enable the switch to locate these other endpoints is discussed in further detail below.

When a user configures a logical router, the control plane uses this configuration to configure the SRs and the DR of the logical router. For instance, the logical router 115 of FIG. 1 has four interfaces (two ports connected to the logical switches' ports, and two uplink ports). However, as shown in FIG. 2, the distributed control plane implementation of the logical router includes a DR with three logical ports (two of which are connected to the logical switches and one connected to the TLS 210) and two SRs that each has two

logical ports (a total of seven interfaces). The IP and MAC addresses and other configuration details assigned to the four interfaces as part of the logical router configuration are used to generate the configuration for the various components of the logical router.

In addition, as part of the configuration, some embodiments generate a routing information base (RIB) for each of the logical router components. That is, although the administrator defines only a single logical router, the management (control) plane of some embodiments generates separate 10 RIBs and/or FIBs for the DR and for each of the SRs. For the SRs of a PLR, the control plane in some embodiments generates the RIB initially, but the physical implementation of the SR also runs a dynamic routing protocol process (e.g., BGP, OSPF, etc.) to supplement the RIB locally.

In some embodiments, the DR is always located on the southbound side (i.e., facing the data compute nodes of the logical network, rather than facing the external physical network) of the logical router implementation. The southbound ports of the DR, therefore, are connected to different 20 logical switches that have their other ports connected to different virtual and physical machines that reside in host machines or connected to managed hardware forwarding elements, or alternatively have their ports connected to other forwarding elements. The northbound interface of the DR, 25 on the other hand, couples to the transit logical switch that is part of the logical router.

FIG. 4 conceptually illustrates a detailed configuration of a logical network topology 400 that includes the network addresses and interfaces assigned by a user. As shown, the 30 logical switches 405 and 410 are each assigned their own subnets, 1.1.1.0/24 and 1.1.2.0/24, and all of the data compute nodes and MHFEs attached to the logical switches 405 and **410** have IP addresses in the corresponding subnet. The switch **405**. The interface L1 has an IP address of 1.1.1.253 that is the default gateway for the data compute nodes and MHFEs in the subnet 1.1.1.0/24, which includes the VM **490**. The logical router **415** also has a second interface L**2** to the second logical switch 410. The interface L2 has an IP 40 address of 1.1.2.253 that is the default gateway for the data compute nodes and MHFEs in the subnet 1.1.2.0/24, which includes the TOR switch 495.

The northbound side of the logical router **415** has two uplinks, U1 and U2. The first uplink U1 has an IP address of 45 192.168.1.253 and connects to a first physical router 420 with an IP address of 192.168.1.252. The second uplink U2 has an IP address of 192.168.2.253 and connects to a second physical router **425** with an IP address of 192.168.2.252. The physical routers 420 and 425 are not actually part of the 50 logical network (e.g., logical network 100), but rather connect the logical network to the external networks 430 and 435. The first physical router 420 connects to the subnet 10.0.0.0/8, while the second physical router 425 connects to both of the subnets 10.0.0.0/8 and 11.0.0.0/8. Although not shown, each of the logical ports of the logical router **415** is also assigned a separate data link layer (MAC) address.

Based on these example addresses, the RIB 450 defines the different routings performed by the router 415. Specifically, the RIB includes four connected routes based on the 60 subnets configured on the southbound and northbound interfaces of the logical router. These four connected routes include a route that egresses from logical port L1 for any packet that has a destination IP address that is in the subnet of LS1; a route that egresses from the logical port L2 for 65 packets with destination IP addresses that belong to the subnet of LS2; a route that egresses the logical port U1 for

14

packets with destination IP addresses that belong to the subnet of U1 and/or physical router 420; and a route that egresses from the logical port U2 for packets with destination IP addresses that belong to the subnet of U2 and/or physical router 425. The RIB also includes three other static routes: any packet with the subnet IP address of 10.0.0.0/8 is to be routed from either logical port U1 or logical port U2; any packet with the subnet IP address of 11.0.0.0/8 is to be routed from logical port U2; and a default route which is either through the logical port U1 or the logical port U2 of the router.

FIG. 5 illustrates the configuration of the logical router 415 of FIG. 4 and how the control plane configures the tunnel endpoint locators on an MHFE that implements the 15 logical router **415**. As shown, the logical switches **405** and 410 are configured as indicated by the user configuration. However, the control plane defines a distributed routing component (DR) **505**, two service routing components (SRs) 510 and 515, and a transit logical switch (TLS or L3) 520 for the logical router **415**. The DR is assigned the two southbound interfaces of the logical router 415, which connect to the logical switches 405 and 410. The transit logical switch **520** (L3) is assigned a subnet of 192.168.100.0/30. Some embodiments require the subnet assignment of each logical switch be unique among the logical switches that logically connect (directly or indirectly) the logical router 415. Each of the three control plane router constructs (the DR 505, the SR 510, and the SR 515) also includes an interface that connects to the TLS **520**, and has an IP address in the subnet of the transit logical switch. The northbound interfaces U1 and U2 are assigned to the two SRs 510 and 515, the configuration of which is described below.

A DR (e.g., 505) of a logical router (e.g., 415) in some embodiments is configured as follows. The southbound logical router 415 has an interface L1 to the first logical 35 interfaces of the DR are configured in the same way as the southbound interfaces of the logical router. These interfaces are those that connect to a logical switch in the logical topology. The DR of some embodiments is allocated a single northbound interface, which is assigned an IP address and a MAC address. Assuming the logical router has one or more SRs, the northbound interface of the DR connects to a transit logical switch.

> The RIB of the DR is assigned connected routes based on the subnets configured on its various southbound and northbound interfaces. These are the subnets configured for (i) the transit logical switch configured between the DR and SR components of the logical router, and (ii) any logical switches on its southbound interfaces. These logical switches on the southbound interfaces are user-defined logical domains to which data compute nodes connect (or other transit logical switches located between the DR of a PLR and any TLRs that connect to the PLR as described below is Section III below).

> In addition, any static routes that egress from an uplink of the logical router are included in the RIB of the DR; however, these routes are modified such that the next-hop IP address is set to that of the uplink's SR. For example, a static route "a.b.c.0/24 via 192.168.1.252" (192.168.1.252 being an address of an external physical network router) is modified to be "a.b.c.0/24 via [IP of SR's southbound interface]". Static routes that egress from a southbound interface of the logical router, on the other hand, are included in the RIB of the DR unmodified.

> The control plane in some embodiments generates the FIB 530 based on the configuration data and the RIB of logical router 415 which includes the different routes illustrated in the figure. The illustrated routes include three connected

routes, for the logical switch domains connected to the DR (1.1.1.0/24, 1.1.2.0/24, and 192.168.100.0/24). In addition, the subnet on which the first uplink is located (192.168.1.0/ 24) is reached via the southbound interface of the first SR **510** (IP1), while the subnet on which the second uplink is located (192.168.2.0/24) is reached via the southbound interface of the second SR **515** (IP**2**). In addition, three static routes have been added by the user for the logical router 415, which the control plane automatically modifies for the DR 505. Specifically, the static routes include the network 10 10.0.0.0/8 via the southbound interface of either of the SRs, and the network 11.0.0.0/8 via the southbound interface of SR2. Lastly, default routes pointing to these same southbound interfaces are included. As shown, the IP addresses IP1, IP2, and IP3 that are created by the control plane for the 15 ports of the logical router constructs that interface the TLS are all in the subnet 192.168.100.0/24.

In addition to configuring the FIB of the DR, the control plane also assigns MAC addresses to the DR interfaces in some embodiments. In some embodiments, some or all of 20 the physical routing elements (e.g., software modules) in the physical network that implement the DR functionality only support a single MAC address. In this case, because the MAC of a DR port may come from that of a logical router port visible to users, this imposes requirements on how the 25 control plane allocates MAC addresses for the logical router ports. Thus, in some embodiments, all DR/SR ports that connect to any logical switch that has user data compute nodes or SRs must share a common MAC address. In addition, if a DR/SR port is connected to another DR/SR or 30 to a physical network, this port is assigned a unique MAC address.

Similar to the DR of a logical router, the control plane also configures each SR of the logical router with a separate FIB and interfaces. As described above, in some embodiments 35 SRs may deliver services (i.e., functionalities beyond simply routing, such as NAT, firewall, load balancing, etc.) and provide the connection between the logical network and external physical networks. As shown in FIG. 5, since the logical router 415 has two uplinks, the control plane defines 40 two service routers 510 and 515. Each of these SRs is assigned a southbound interface, with different IP and MAC addresses (as the SRs are in an active-active configuration). The IP addresses IP1 (for the first SR 510) and IP2 (for the second SR 515) are in the subnet 192.168.100.0/30, as is IP3 45 (the northbound interface of the DR 505).

For each southbound interface of the logical router, some embodiments add a route for the corresponding network to the RIB of each SR. This route points to the northbound DR interface as its next-hop IP address. Furthermore, any other routes configured for the logical router that egress from the southbound interface are copied to the SR with the same northbound DR interface as the next-hop IP address. On the other hand, a static route of the logical router that egresses from an uplink (e.g., U1 or U2) is copied to the FIB of the SR. In addition, the SRs (of a top-level logical router) may learn dynamic routes and place the learned dynamic routes in their FIB (though some embodiments perform this locally, without involving the centralized controller system in the control plane).

As described above, some embodiments implement the distributed routing component of the logical router in a distributed manner across the different MFEs and the MHFE. Some of these embodiments implement each of the service routing components of the logical network on an 65 edge node (e.g., a gateway machine), which is a machine at the edge of the network (e.g., the datacenter network), in

**16**

order to communicate with one or more external networks. The control plane of some embodiments distributes configuration data of the logical forwarding elements to the MFEs in a manner that is different than to the MHFEs.

In some embodiments, the control plane computes and distributes the logical configuration and forwarding data to each local controller that operates on a host machine using a proprietary protocol (e.g., NETCPA). In some such embodiments, the local controller operating on a host machine generates a set of forwarding tables for the MFE that runs on the same host machine and distributes the generated data to the MFE for implementing the logical forwarding elements of the logical network (e.g., by forwarding the logical network data to other end machines executed on the same host machine, or establishing tunnels to other MFEs and/or MHFEs and forwarding the network data through the established tunnels to those MFEs and MHFEs).

In some embodiments, the control plane computes and distributes the logical configuration and forwarding data to each MHFE using an open source protocol that is recognizable and used by the MHFE (e.g., an open vSwitch database management (OVSDB) protocol). In some other embodiments, the control plane distributes the logical network data to a particular controller that manages the MHFE using a proprietary protocol (e.g., NETCPA) and the particular controller distributes the data to the MHFE using an open source protocol such as OVSDB. The controllers (local controller operating on the host machine, particular controller managing the MHFE, etc.) of some embodiments are applications that are instantiated on either the host machines or other dedicated controller machines.

In order to configure and manage the different components of a logical router as well as other logical forwarding elements (e.g., logical L2 switches) of a logical network on a MHFE, some embodiments configures the MHFE with a set of database tables (e.g., forwarding tables of the forwarding elements) that is populated by using a database schema (e.g., OVSDB schema) that is recognizable and used by the MHFE. Such an open source protocol requires minimal software on the MHFE to enable the implementation of the logical network forwarding elements (e.g., logical L2 and L3 forwarding elements) in order to communicate with the other machines connected to the logical network as well as other external networks.

After generating the database tables on the MHFE using the OVSDB schema, some embodiments propagate a particular one of these tables with the physical locator information of the logical ports of the different routing components (i.e., distributed and service routers) of the logical router. The physical locator information, in some embodiments, specifies the tunnel endpoint locations (e.g., VXLAN) tunnel endpoints or VTEPs). This tunnel endpoint locator table (also referred to as a Ucast\_Macs\_Remote table in some embodiments) specifies the network layer (IP) addresses of the MFEs and MHFEs that implement the logical ports of logical switches to which the machines (e.g., end machines, physical machines, etc.) and/or logical ports of the logical routers are connected. By locating the endpoints, the MFEs and MHFEs are able to establish tunnels between themselves and exchange the network data through the established tunnels. In some embodiments, a MHFE (i.e., a TOR) is also referred to as a hardware VTEP.

FIG. 5 illustrates a tunnel endpoint locator (Ucast\_Macs\_Remote) table 540 that is generated on the TOR switch 590 (e.g., by the OVSDB schema). Each record of the table 540 has several different fields (or table columns) that include (i)

a logical switch field **545** that species the logical switch to which a port of a machine or a logical router is connected, (ii) a MAC address field **550** that specifies the corresponding MAC address of the port, and (iii) a locator field **555** that specifies the IP address of the tunnel endpoint for the 5 corresponding MAC address. The tunnel endpoint locator table is therefore also referred to as a tunnel endpoint table.

In order to configure the logical router on this table 540 (i.e., configure the locator data of the logical ports of the different routing components on the table), some embodi- 10 ments populate a record for each logical port of the distributed routing component in the table in a first manner and a record for each logical port of the service routing component in a second different manner. For each port of the distributed routing component (e.g., DR 505) that is connected to a 15 logical forwarding element (e.g., LS1 405 and LS2 410), some embodiments generate a record and stores (i) in a logical switch field, the logical switch to which the port is connected, (ii) in a MAC address field, the MAC address of the port, and (iii) in a locator field, a fixed IP address of 20 127.0.0.1, or the local host. The local host is a loopback interface address (127.0.0.1) in networking which can be used to access the machine's own network services.

In other words, when the MHFE realizes that the destination MAC address of a packet belongs to a port of the 25 distributed routing component, the VTEP of the MHFE does not establish a tunnel for routing the packet. This is because the distributed routing component, as described above, is implemented by every single MFE, MHFE, and gateway that participates in the logical network. As such, a packet 30 whose destination MAC address is that of the logical router is not required to be routed to any other node in the network.

Some embodiments, on the other hand, populate the tunnel endpoint locator table with the tunnel endpoint data of each logical port of the service routing components that 35 is connected to a logical forwarding element (e.g., an L2 logical switch). That is, for each logical port of the SRs, some embodiments store (i) in the logical switch field, the logical switch to which the port is connected (e.g., the transit logical switch to which the southbound port of the service 40 component is connected), (ii) in the MAC address field, the MAC address of the port, and (iii) in the locator field, the IP address of the tunnel endpoint that implements the logical switch port to which the service component port is connected (e.g., the IP address of the gateway machine that 45 implements the service routing component).

As for the end machines connected to the logical switches, some embodiments store (i) in the logical switch field, the logical switch to which the end machine's port is connected, (ii) in the MAC address field, the MAC address of the port, 50 and (iii) in the locator field, the IP address of the tunnel endpoint that implements the logical switch port to which the end machine is connected (e.g., the IP address of the MFE that implements the port of the logical switch). For instance, the tunnel endpoint locator table 540 shown in the 55 FIG. 5 includes the MAC address of virtual machine VM1 (MAC-VM) in the MAC address field **550**. The port of this virtual machine is connected to the logical port of switch LS1 which is stored in the logical switch field **545**. Since the MFE is operated by hypervisor HV1 (not shown in the 60 figure), the control plane stores the IP address of this hypervisor in the locator field 555.

For the different logical ports of the different logical routing constructs, the tunnel endpoint locator table **540** includes the three different logical switches (LS1, LS2, and 65 LS3) of the logical network in the logical switch field **545**, the MAC addresses of the ports to which the logical

18

switches' corresponding ports are connected in the MAC address field **550**, and the locator (IP address) of the MFEs and MHFEs that implement the corresponding ports in the tunnel endpoint locator field **555**. As mentioned above though, the control plane configures the tunnel endpoint locator table differently for different routing components of the logical router.

For example, for the MAC address of the logical port L1 of the DR (MAC-L1) which is connected to the logical switch LS1, the control plane stores 127.0.0.1 (localhost) as the IP address of the tunnel endpoint locator field 555. As described above, this is because the distributed component of the logical router is implemented by every MFE, MHFE, and gateway of the logical network and as such no tunnel is required to be established for any port of the DR. Therefore, MAC-L2 and MAC3 which are the MAC addresses of the other ports of the DR that are connected to the logical switches LS2 and LS3, respectively, also have the same loopback IP address of 127.0.0.1 (localhost) stored in their corresponding tunnel endpoint locator field 555.

For the service components of the logical router, however, the control plane stores the IP addresses of the gateway machines that implement (e.g., through the MFEs that the gateway machines execute) the logical switch ports that are connected to the SR ports. That is, the SR port SRP1 with the MAC address MAC1 is implemented by the MFE of the gateway machine Gateway1 (not shown in the figure). As such, the control plane stores, in the locator field, the IP address of MFE of Gateway1 (the hypervisor on which the MFE runs). Similarly, the logical port SRP2 of the service component 515 is connected to a logical port of the TLS 520 (LS3). This port is implemented by the gateway machine Gateway2 and as such the table stores the IP address of this gateway machine (the IP address of the hypervisor that implements the logical switch connected to the SRP2 port).

FIG. 6 conceptually illustrates a process 600 of some embodiments for configuring the tunnel endpoint locators for different ports of the logical router on an MHFE. In some embodiments, process 600 is uses a control plane of a datacenter (e.g., a set of modules at a centralized controller that manages the networks of a datacenter). The control plane of some embodiments performs the configuration process and then uses a centralized control plane of the controller to distribute the data to the MHFE (or to a different controller that manages the MHFE to be subsequently distributed to the MHFE) that implements the configured logical router.

As shown, the process 600 begins by receiving (at 605) a specification of a logical router. The specification of the logical router is based on a user (network administrator, tenant, etc.) input to define the logical router. In some embodiments, this specification includes definitions of any services the logical router should provide, whether the logical router will be configured in active-active or active-standby mode (though some embodiments automatically use active-active mode unless stateful services are configured), how many uplinks are configured for the logical router, the IP and MAC addresses of the uplinks, the L2 and L3 connectivity of the uplinks, the subnets of any southbound interfaces of the logical router, any static routes for the RIB of the logical router, as well as other data.

The process then defines (at **610**) the different routing components of the logical router based on the received specification. Specifically, the process defines a distributed router (DR) and a set of service routers (SRs) based on the specification of the logical router and assigns different MAC and IP addresses for the different ports of these routing

components. Defining the different routing components and assigning network data link layers addresses to the different ports of the routing components is described in greater detail in the U.S. Provisional Patent Application 62/110,061, filed Jan. 30, 2015. Essentially, the process of some embodiments 5 uses the southbound interface configuration of the logical router for the southbound interface of the DR. That is, the IP addresses and MAC addresses for the different southbound ports of the DR are those specified for the logical router.

The process **600** also assigns each uplink specified for the 10 logical router to a gateway machine and defines a SR on the gateway machine. For each SR, the process uses the configuration for the uplink assigned to that gateway machine as the configuration for the northbound interface of the SR. This configuration information includes the IP and MAC 15 address of the uplink, as well as any uplink-specific policies. In defining the different routing components, the process additionally defines a unique transit logical switch to connect the defined SRs and DR. Some embodiments require that the subnet assigned to the transit logical switch be 20 unique among the logical network topology. The process also assigns a northbound interface to the DR and assigns both a MAC address and an IP address to this interface. The process also assigns southbound interfaces to the SRs with separate MAC and IP addresses (only the active-standby 25 SRs may share the same IP address). In some embodiments, the IP addresses of the northbound port of the DR and the southbound ports of the SRs are in the same subnet that is assigned to the transit logical switch.

The process 600 receives (at 615) the first defined port 30 (e.g., a port that is defined for the DR or one of the SRs). This is done in order to configure the defined ports of different routing components on the MHFE. The process then determines (at 620) whether the port belongs to a service component of the logical router. If the port belongs to the DR, the process proceeds to 625. Otherwise, the process proceeds to 635.