#### US009728952B2

## (12) United States Patent

#### McMahon et al.

### (10) Patent No.: US 9,728,952 B2

### (45) **Date of Patent:** Aug. 8, 2017

## (54) ELECTRICAL WIRING DEVICE WITH PROTECTIVE FEATURES

(71) Applicant: Pass & Seymour, Inc., Syracuse, NY

(US)

(72) Inventors: Michael F. McMahon, East Syracuse,

NY (US); Kent R. Morgan, Groton,

NY (US)

(73) Assignee: Pass & Seymour, Inc., Syracuse, NY

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 290 days.

(21) Appl. No.: 14/512,769

(22) Filed: Oct. 13, 2014

#### (65) Prior Publication Data

US 2015/0043109 A1 Feb. 12, 2015

#### Related U.S. Application Data

(63) Continuation of application No. 12/972,106, filed on Dec. 17, 2010, now Pat. No. 8,861,146.

(51) Int. Cl. *H02H 3/16*

H02H 3/16 (2006.01) H01H 47/22 (2006.01) G01R 31/02 (2006.01) H02H 3/33 (2006.01)

(52) **U.S. Cl.**

#### (58) Field of Classification Search

CPC ...... H02H 3/162; H02H 3/335; H01H 47/22; G01R 31/025

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 3,872,354 A | 3/1975      | Nestor       |  |  |  |

|-------------|-------------|--------------|--|--|--|

| 3,953,766 A | 4/1976      | Howell et al |  |  |  |

| 4,309,681 A | 1/1982      | Draper       |  |  |  |

| 4,345,289 A | 8/1982      | Howell       |  |  |  |

| 4,359,626 A | 11/1982     | Potter       |  |  |  |

|             | (Continued) |              |  |  |  |

#### FOREIGN PATENT DOCUMENTS

| WO | 2007027908 A3 | 3/2007  |

|----|---------------|---------|

| WO | 2007056668    | 5/2007  |

|    | (Con          | tinued) |

Primary Examiner — Zeev V Kitov (74) Attorney, Agent, or Firm — Bond Schoeneck & King, PLLC; George McGuire; Frederick Price

#### (57) ABSTRACT

The present invention is directed to an electrical wiring device that includes an automatic test circuit configured to commence an automatic test at a predetermined time such that a test current propagates on a test conductor. The sensor assembly provides a sensor test output responsive to the test current only if both the differential transformer and the grounded neutral transformer are operative. A fault detector circuit is configured to generate a test detection signal in response to the sensor test output only if the fault detector circuit is operable and the at least one power supply is substantially charged. A device integrity evaluation circuit includes a timer that effects a tripped state when a time measurement exceeds a threshold, the test detection signal resetting the time measurement when properly wired before the time measurement exceeds the predetermined threshold but does not reset the time measurement when miswired.

#### 26 Claims, 11 Drawing Sheets

# US 9,728,952 B2 Page 2

| (56)                         | Referer            | nces Cited                                   | 7,154,71             |       |                    | Finlay, Sr.                        |

|------------------------------|--------------------|----------------------------------------------|----------------------|-------|--------------------|------------------------------------|

| U.S.                         | PATENT             | DOCUMENTS                                    | 7,164,56             | 53 B2 | 1/2007<br>1/2007   |                                    |

| 4,412,193 A                  |                    | Bienwald et al.                              | 7,167,06             | 66 B2 | 1/2007             | Wang                               |

| 4,477,857 A<br>4,574,324 A   |                    |                                              | 7,173,75<br>7,184,25 |       | 2/2007             | Weeks et al.<br>Bonilla            |

| 4,598,331 A                  | 7/1986             | Legatti                                      | 7,187,52<br>7,195,50 |       | 3/2007<br>3/2007   |                                    |

| 4,618,907 A<br>4,931,761 A   | 6/1990             | Leopold<br>Kijima                            | 7,196,88             | 86 B2 | 3/2007             | Chan                               |

| 4,979,070 A<br>5,177,657 A   | 12/1990<br>1/1993  |                                              | 7,209,33             |       | 4/2007<br>5/2007   | DiSalvo<br>Finlay, Sr.             |

| 5,202,662 A                  | 4/1993             | Bienwald                                     | 7,227,43             |       | 6/2007<br>7/2007   | Germain<br>Morgan                  |

| 5,363,083 A<br>5,363,269 A   | 11/1994<br>11/1994 | Fischer<br>McDonald                          | 7,253,62             | 29 B1 | 8/2007             | Richards et al.                    |

| 5,418,678 A<br>5,477,412 A   | 5/1995<br>12/1995  | McDonald<br>Neiger                           | 7,256,97<br>7,265,95 |       | 8/2007<br>9/2007   | Radosavljevic<br>Huang             |

| 5,541,800 A                  | 7/1996             | Misencik                                     | 7,268,55<br>7,283,34 | 59 B1 | 9/2007             | Chen et al.                        |

| 5,594,398 A<br>5,600,524 A   |                    | Marcou<br>Neiger et al.                      | 7,289,30             | )6 B2 | 10/2007            |                                    |

| 5,638,243 A                  | 6/1997             | Torezan                                      | 7,292,41<br>7,295,41 |       | 11/2007<br>11/2007 |                                    |

| 5,661,623 A<br>5,706,155 A   | 1/1998             | McDonald<br>Neiger                           | 7,295,41             | 15 B2 | 11/2007            | Huang                              |

| 5,715,125 A<br>5,729,417 A * |                    | Neiger et al.<br>Neiger H02H 3               | 7.007.00             |       | 11/2007<br>12/2007 | -                                  |

|                              |                    | 36                                           | 7,312,96<br>7,315,22 |       | 12/2007<br>1/2008  | Radosavljevic                      |

| 5,923,239 A<br>5,963,408 A   |                    | Krueger<br>Neiger et al.                     | 7,315,43             | 87 B2 | 1/2008             | Bonilla et al.                     |

| 6,040,967 A                  | 3/2000             | DiSalvo                                      | 7,317,60<br>7,336,45 |       | 1/2008<br>2/2008   | Huang<br>Liscinsky                 |

| 6,043,966 A<br>6,052,265 A   | 4/2000             | Krueger<br>Zaretsky                          | 7,336,45             | 58 B2 | 2/2008             | Ziegler                            |

| 6,111,733 A<br>6,226,161 B1  |                    | Neiger et al.<br>Neiger et al.               | 7,355,49<br>7,355,82 | 27 B2 | 4/2008             | <b>O</b>                           |

| 6,246,558 B1                 | 6/2001             | DiSalvo                                      | 7,365,62<br>7,372,67 |       |                    | Germain<br>DiSalvo et al.          |

| 6,262,871 B1<br>6,317,307 B1 | 11/2001            | Nemir<br>Bone                                | 7,375,93             | 88 B1 | 5/2008             | Radosavljevic                      |

| 6,370,001 B1<br>6,381,112 B1 |                    | Macbeth<br>DiSalvo et al.                    | 7,400,47<br>7,400,47 |       | 7/2008<br>7/2008   | Campolo<br>DiSalvo                 |

| 6,407,893 B1                 | 6/2002             | Neiger                                       | 7,403,08<br>7,408,43 |       | 7/2008<br>8/2008   |                                    |

| 6,433,977 B1<br>6,437,953 B2 |                    | Macbeth<br>DiSalvo                           | 7,411,76             | 66 B1 | 8/2008             | Huang                              |

| 6,442,007 B1<br>6,492,894 B2 | 8/2002<br>12/2002  |                                              | 7,414,49<br>7,414,81 |       | 8/2008<br>8/2008   | Germain<br>Shi                     |

| 6,522,510 B1                 | 2/2003             | Finlay                                       | 7,439,83<br>7,439,83 |       |                    | Radosavljevic et al.<br>Germain    |

| 6,587,319 B1<br>6,590,753 B1 |                    | Finlay<br>Finlay                             | 7,443,30             | 9 B2  | 10/2008            | Baldwin et al.                     |

| 6,621,388 B1<br>6,628,486 B1 | 9/2003             | Macbeth<br>Macbeth                           | 7,463,12<br>7,492,55 |       | 12/2008<br>2/2009  |                                    |

| 6,670,870 B2                 | 12/2003            | Macbeth                                      | 7,492,55<br>7,498,90 | 59 B2 | 2/2009<br>3/2009   |                                    |

| 6,674,289 B2<br>6,721,156 B2 |                    | Macbeth<br>Masghati                          | 7,498,91             | l0 B2 | 3/2009             | Gallas                             |

| 6,724,590 B1                 | 4/2004             | Radosavljevic                                | 7,515,02<br>7,518,84 |       | 4/2009<br>4/2009   |                                    |

| 6,734,769 B1<br>6,788,508 B2 |                    | Germain<br>Papallo, Jr.                      | 7,522,06             | 54 B2 | 4/2009             | Zhang et al.                       |

| 6,807,035 B1<br>6,807,036 B2 |                    | Baldwin et al.<br>Baldwin                    | 7,525,40<br>7,525,44 |       | 4/2009<br>4/2009   | Zhang                              |

| 6,831,819 B2                 | 12/2004            | Nemir et al.                                 | 7,535,37<br>7,538,64 |       | 5/2009<br>5/2009   | Wang<br>Leopold                    |

| 6,842,095 B2<br>6,850,394 B2 | 2/2005             | Macbeth<br>Kim                               | 7,538,99             | 93 B2 | 5/2009             | Huang                              |

| 6,856,498 B1<br>6,867,954 B2 |                    | Finlay, Sr.<br>Wu et al.                     | 7,538,99<br>7,542,25 |       | 6/2009             | Bonilla<br>Chan                    |

| 6,873,158 B2                 | 3/2005             | Macbeth                                      | 7,545,24<br>7,573,69 |       |                    | DiSalvo<br>Weeks et al.            |

| 6,900,972 B1<br>6,937,452 B2 | 5/2005<br>8/2005   | _                                            | 7,576,95             | 59 B2 | 8/2009             | Huang et al.                       |

| 6,952,150 B2<br>6,958,895 B1 |                    | Radosavljevic et al.<br>Radosavljevic et al. | 7,576,96<br>7,586,71 |       |                    | Gao et al.<br>Radosavljevic et al. |

| 6,980,005 B2                 | 12/2005            | Finlay, Sr. et al.                           | 7,592,92<br>7,598,82 |       |                    | Zhang et al.<br>Weeks et al.       |

| 7,009,473 B2<br>7,068,481 B2 |                    | Zhang<br>Radosavljevic et al.                | 7,626,78             | 88 B2 | 12/2009            | Wang et al.                        |

| 7,082,021 B2                 | 7/2006             | Chan et al.                                  | 7,642,45<br>7,719,80 |       |                    | Weeks et al.<br>Morgan et al.      |

| 7,084,725 B2<br>7,088,205 B2 | 8/2006             | Richter<br>Germain                           | 7,733,61             | 17 B2 | 6/2010             | Baldwin et al.                     |

| 7,088,206 B2<br>7,098,761 B2 |                    | Germain<br>Germain                           | 7,751,16<br>7,791,84 |       |                    | Packard et al.<br>Baldwin et al.   |

| 7,099,129 B2                 | 8/2006             | Neiger                                       | 7,791,85             | 50 B2 | 9/2010             | Chen                               |

| 7,116,191 B2<br>7,133,266 B1 | 10/2006<br>11/2006 | Wang<br>Finlay, Sr.                          | 7,800,87 $7,800,87$  |       |                    | Batko et al.<br>DiSalvo et al.     |

| 7,149,065 B2                 | 12/2006            | Baldwin                                      | 7,852,60             | )6 B2 | 12/2010            | Mernyk et al.                      |

| 7,154,715 B2                 | 12/2006            | Yamanaka et al.                              | 7,859,36             | o8 B2 | 12/2010            | Huang et al.                       |

# US 9,728,952 B2 Page 3

| (56)         | Refere      | nces Cited      | 2008/0123227   | 7 A1    | 5/2008  | Bonasia            |

|--------------|-------------|-----------------|----------------|---------|---------|--------------------|

| `            |             |                 | 2008/0170341   | A1      | 7/2008  | Huang              |

| Į            | U.S. PATENT | Γ DOCUMENTS     | 2008/0186642   | 2 A1    | 8/2008  | Campolo            |

|              |             |                 | 2008/0225448   | 3 A1    | 9/2008  | Li                 |

| 7,911,746    | B2 3/2011   | Zaretsky et al. | 2008/0272925   | 5 A1    | 11/2008 | Griffin            |

| 8,054,590    |             | Li et al.       | 2009/0040667   | 7 A1    | 2/2009  | DiSalvo et al.     |

| 8,081,001    |             | Hooper et al.   | 2009/0052098   | 3 A1    | 2/2009  | DiSalvo            |

| 2004/0223272 |             | Germain         | 2009/0086389   | ) A1    | 4/2009  | Huang              |

| 2005/0063109 |             | Baldwin         | 2009/0086390   | ) A1    | 4/2009  | Huang              |

| 2006/0139132 |             | Porter          | 2009/0091869   | ) A1    | 4/2009  | Huang              |

| 2006/0181373 |             | Germain         | 2009/0128264   | 1 A1    | 5/2009  | DiSalvo            |

| 2006/0268472 |             | Winch           | 2009/0147416   | 5 A1    | 6/2009  | Zheng              |

| 2006/0279886 |             | Huang           | 2009/0147418   | 3 A1    | 6/2009  | Li et al.          |

| 2006/0285262 |             | Neiger          | 2009/0161271   | A1      | 6/2009  | Huang et al.       |

| 2007/0014058 |             | Chan            | 2009/0180222   | 2 A1    | 7/2009  | Chen et al.        |

| 2007/0030608 |             | Baldwin         | 2009/0251148   | 3 A1    | 10/2009 | Finlay, Sr. et al. |

| 2007/0035898 |             | Baldwin         | 2009/0262472   | 2 A1    | 10/2009 | Weeks et al.       |

| 2007/0053118 |             | Germain         | 2010/0013491   | A1      |         | Hooper et al.      |

| 2007/0133136 | A1 6/2007   | Germain         | 2010/0053826   | 5 A1    |         | Finlay, Sr. et al. |

| 2007/0188955 |             | Elms            | 2010/0073178   | 3 A1    |         | Huang et al.       |

| 2007/0215576 |             | Chung           | 2010/0134306   | 5 A1    |         | Zeng et al.        |

| 2007/0230072 |             | Zhang           | 2010/0238597   | 7 A1    |         | Baldwin et al.     |

| 2007/0268635 |             | Bonasia         | 2010/0295568   | 3 A1    | 11/2010 | Ostrovsky et al.   |

| 2007/0274012 | A1 11/2007  | Bonasia         |                |         |         |                    |

| 2008/0007879 | A1 1/2008   | Zaretsky        | FC             | DREIG   | N PATE  | NT DOCUMENTS       |

| 2008/0013227 |             | Mernyk et al.   |                |         |         |                    |

| 2008/0022153 |             | Wang            | WO 2           | 2007093 | 3885    | 8/2007             |

| 2008/0024252 |             | Gallas          |                | 2007137 |         | 11/2007            |

| 2008/0024945 | A1 1/2008   | Gao             |                | 2007143 |         | 12/2007            |

| 2008/0088992 | A1 4/2008   | Williamson      |                | 2008005 |         | 10/2008            |

| 2008/0094765 | A1 4/2008   | Huang           |                |         |         |                    |

| 2008/0112099 |             |                 | * cited by exa | aminer  | •       |                    |

## ELECTRICAL WIRING DEVICE WITH PROTECTIVE FEATURES

## CROSS-REFERENCE TO RELATED APPLICATIONS

This is a continuation of U.S. patent application Ser. No. 12/972,106 filed on Dec. 17, 2010, the content of which is relied upon and incorporated herein by reference in its entirety, and the benefit of priority under 35 U.S.C. §120 is 10 hereby claimed.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates generally to electrical wiring devices, and particularly to electrical wiring devices having protective features.

#### 2. Technical Background

An electric distribution system transmits AC power from 20 a breaker box to one or more load circuits disposed in a structure to provide electrical power throughout. A load circuit may include any number of electrical devices such as electrical outlets, lighting devices, appliances, or other such devices. An electric circuit typically includes at least one 25 protection device. Examples of electric circuit protection devices include ground fault circuit interrupters (GFCIs), arc fault circuit interrupters (AFCIs), or devices that include both GFCIs and AFCIs in one protective device.

A protective device is mounted in an upstream outlet box 30 within the electric circuit and non-protective devices, such as receptacles, are mounted downstream of the protective device within the electric circuit. Electrical wiring is placed within the structure between the breaker box and the various outlet boxes in the circuit. At the protective device location, 35 a portion of the electrical wiring is fed into the outlet box. The portion of the electrical wiring is cut into two pieces. For example, the upstream portion of the electrical wiring (i.e., the line cable) is connected to the line terminals of the protective device such that the protective device is con- 40 nected to the AC power source. The downstream portion of the cable (i.e., the load side cable) is connected to the load terminals of the protective device. The remainder of the load side cable extends to the remainder of the electrical devices (e.g., electrical receptacles) in the electric circuit. A connec- 45 tion process is performed at each outlet box until the terminals of the last device are connected to the electrical wiring.

A protective device typically includes one or more integral face receptacles accessible to a user via the front face of 50 the device. Thus, an electrical appliance with a corded plug may be plugged into the receptacle to obtain power. The electrical loads that may be serviced by the protective device include loads connected to the face receptacles, the downstream wiring, downstream receptacles, user attachable 55 loads plugged into the downstream receptacles, and permanently connected loads (e.g., lighting). When everything in the electric circuit is operating properly, the protective device provides power from the AC power source to the loads in the electric circuit.

As its name suggests, a protective device protects the load circuit from one or more fault conditions. One type of fault condition is known as a ground fault condition. A ground fault may occur, for example, by frayed or missing insulation on a hot conductor disposed somewhere in the load 65 circuit. If a human being (or some other conductive element) were to simultaneously contact the hot conductor and a

2

ground path a current would flow to ground through the person. This current is potentially lethal. Fortunately, the protective device (GFCI) is configured to detect and interrupt the resulting current flow through the body before there is serious injury or even electrocution. Another type of fault condition is a parallel arc fault. This type of fault occurs when there is damaged insulation between a hot conductor and an adjacent conductor (that is at a different potential). The damaged insulation allows a sputtering current to flow across the compromised insulation. A series arc fault represents another type of fault condition. A series arc fault occurs because a termination in the load circuit is loose. For example, a wire nominally terminated by the screw terminal of an electrical device (e.g., an outlet receptacle or a switch) may be loose because the screw terminal is not completely tightened; a small gap may be formed between the wire and the screw terminal. As another example, when a wire is accidentally severed, a small gap may be formed at the cut such that adjacent ends of wire are almost touching. In each instance, a sputtering arc fault may bridge the small gap. The fault current is limited by the impedance of the load. Series arc fault conditions can also occur in the line cable or elsewhere upstream of the AFCI. The protective device (AFCI) senses and detects at least one of these types of arcing conditions and interrupts the current flowing through the fault before there an electrical fire is started. There are other types of protective devices other than the ones described above, such TVSS devices, GFEP devices, etc. The aforementioned protective devices are non-limiting examples of such devices.

One drawback to all prior art electrical devices is that they are subject to one or more end of life conditions. An end-of-life condition refers to a failure that should render the device unusable or unsafe for use. For example, some end of life conditions may make a protective device non-protective. This drawback may be addressed by providing an end-of-life monitoring circuit that is configured to detect the end of life condition and interrupt any unprotected power to the load circuit. A device of this type may also include an end-of-life display that provides a signal to the user indicative of the end-of-life state. Upon learning of the condition, the user would be required to replace the device to resume service to the load circuit. An end-of-life indicator of this type may provide either a visual or audible indication that warns the user that the protective device needs to be replaced.

Another drawback to prior art protective devices relates to the fact that can be miswired during installation. Since the protective device has line terminals and load terminals it is possible to make the mistake of connecting the line cable to the load terminals and the load cable to the line terminals; this condition is commonly referred to a miswiring or reverse wiring. When reverse wired, some prior art GFCIs are not capable of protecting the face receptacles. One approach for solving the problem has been to provide product labeling and installation instructions sheets that warn against miswiring. These have lessened the chances for miswiring but unfortunately some installers choose to ignore installation instruction sheets. Another approach to the aforementioned problem is to include a miswire detection circuit configured to detect a miswired condition and automatically prevent the protective device from resetting. As a result, no power is provided to the downstream circuit or the face terminals. The lack of power eventually induces the installer to correct the miswired condition. While this approach may be successful for an initial GFCI installation, it may not be operative for subsequent reinstallations. Pro-

tective devices that do include miswire detection for subsequent installations often include relatively expensive solutions to the problem.

What is needed, therefore, is a protective system that inexpensively detects end of life conditions and miswire 5 conditions in first and subsequent installations.

#### SUMMARY OF THE INVENTION

The present invention addresses the needs described 10 above by providing a protective system that inexpensively detects both end of life conditions and miswire conditions in first and subsequent installations.

One aspect of the present invention is an electrical wiring device for use in an electrical distribution system including 15 a plurality of line conductors coupled to a source of AC power and a plurality of load conductors. A housing includes a plurality of line terminals and a plurality of load terminals, the plurality of line terminals being configured to terminate the plurality of line conductors and the plurality of load 20 terminals being configured to terminate the plurality of load conductors. The electrical wiring device is in a properly wired condition when the plurality of line conductors are terminated to the plurality of line terminals and in a miswired condition when the plurality of line conductors are 25 terminated to the plurality of load terminals. An internal line conductor and an internal neutral conductor are disposed in the interior of the housing and coupled between the plurality of line terminals and the plurality of load terminals in a reset state and decoupled in a tripped state. A sensor assembly 30 includes a differential transformer and a grounded neutral transformer, the internal line conductor and the internal neutral conductor being routed through the differential transformer and the grounded neutral transformer. An automatic test circuit includes a test conductor routed through the 35 differential transformer and the grounded neutral transformer, the automatic test circuit being configured to commence an automatic test at a predetermined time such that a test current propagates on the test conductor. The sensor assembly provides a sensor test output responsive to the test 40 current only if both the differential transformer and the grounded neutral transformer are operative. A protective circuit includes a fault detector circuit and a power supply circuit coupled to the plurality of line terminals. The power supply circuit is charged in the reset state or charged in the 45 tripped state and in the properly wired condition. The fault detector circuit is configured to generate a test detection signal in response to the sensor test output only if the fault detector circuit is operable and the at least one power supply is substantially charged. A device integrity evaluation circuit 50 is coupled to the plurality of load terminals. The device integrity evaluation circuit includes a timing circuit configured to provide a time measurement and a tripping stimulus to effect the tripped state when the time measurement exceeds a predetermined threshold. The test detection signal 55 resets the time measurement in the properly wired condition before the time measurement exceeds the predetermined threshold but does not reset the time measurement in the miswired condition.

Additional features and advantages of the invention will 60 be set forth in the detailed description which follows, and in part will be readily apparent to those skilled in the art from that description or recognized by practicing the invention as described herein, including the detailed description which follows, the claims, as well as the appended drawings.

It is to be understood that both the foregoing general description and the following detailed description are merely

4

exemplary of the invention, and are intended to provide an overview or framework for understanding the nature and character of the invention as it is claimed. The accompanying drawings are included to provide a further understanding of the invention, and are incorporated in and constitute a part of this specification. The drawings illustrate various embodiments of the invention and together with the description serve to explain the principles and operation of the invention.

#### BRIEF DESCRIPTION OF THE DRAWINGS

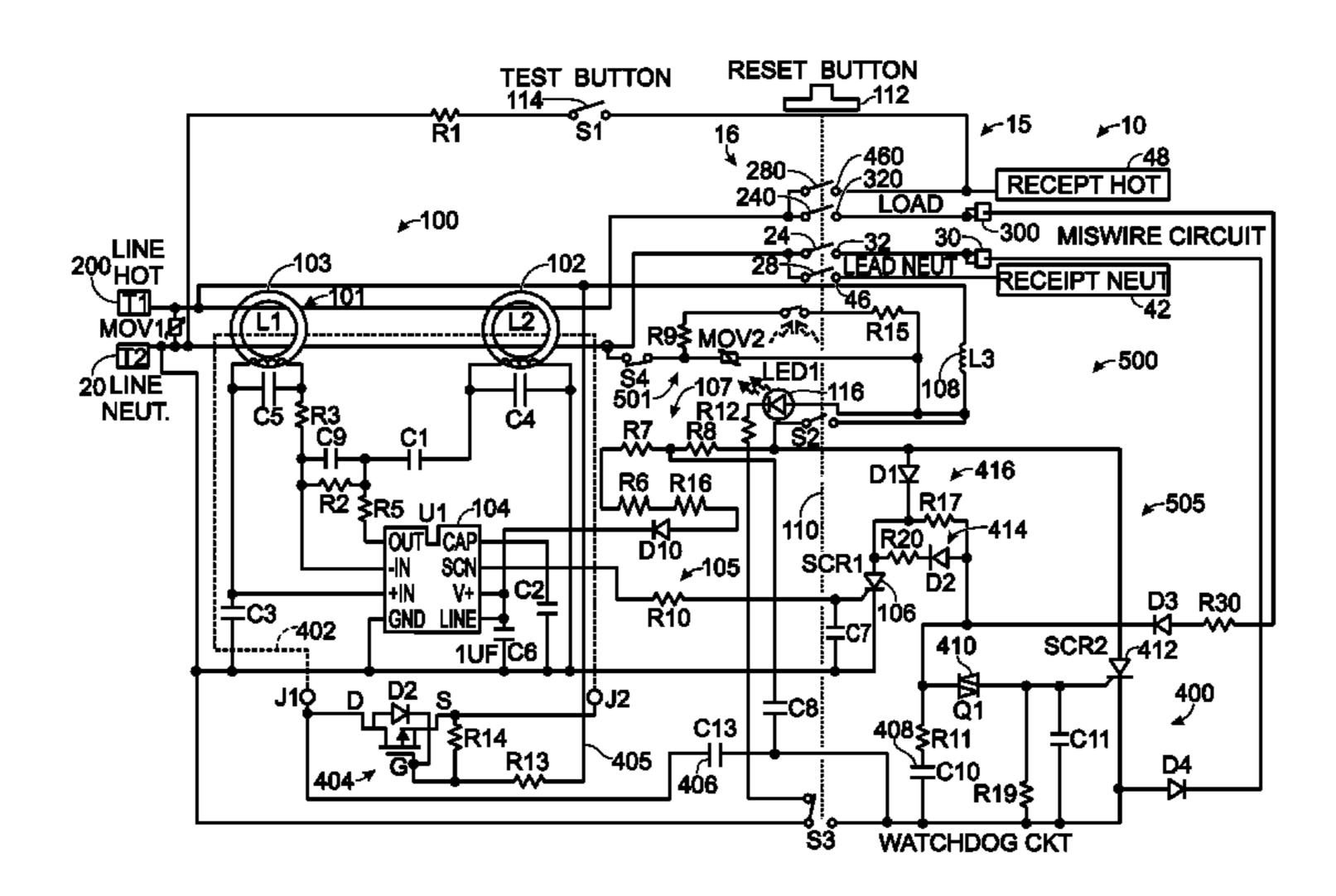

FIG. 1 is a schematic diagram of a protective electrical device in accordance with a first embodiment of the present invention;

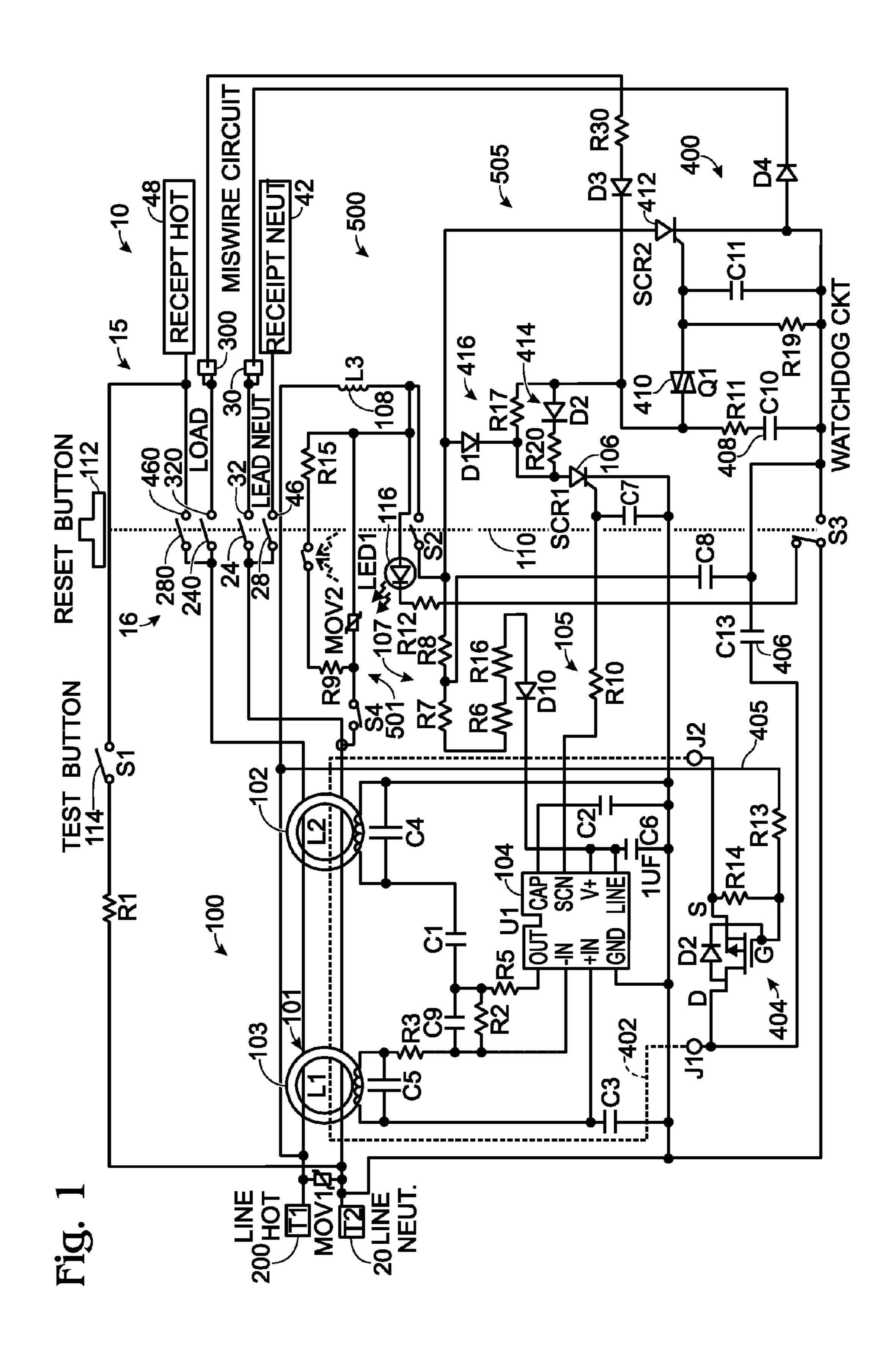

FIG. 2 is a schematic diagram of a protective electrical device in accordance with an alternate embodiment of the present invention;

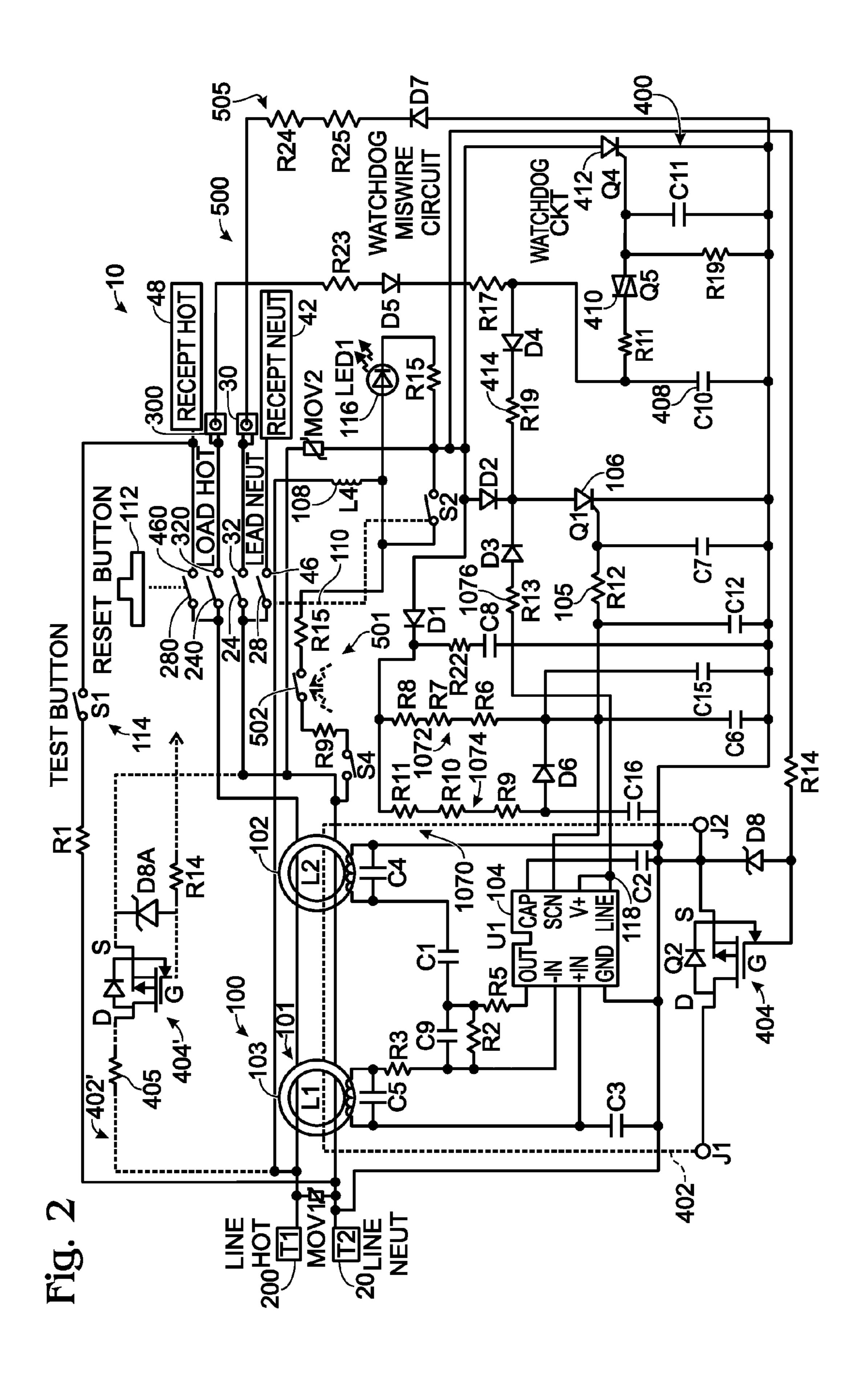

FIG. 3 is a schematic diagram of a protective electrical device in accordance with an alternate embodiment of the present invention;

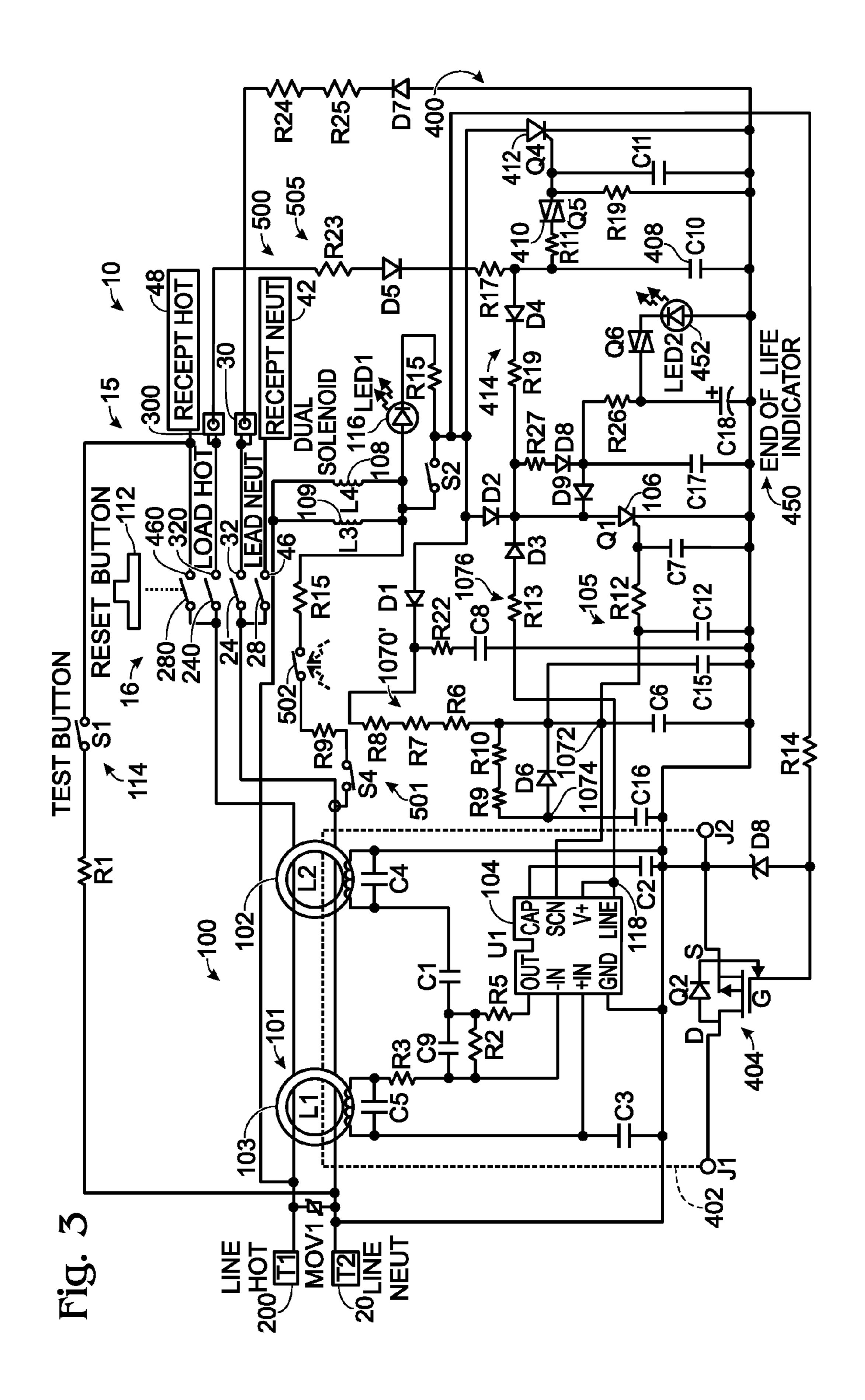

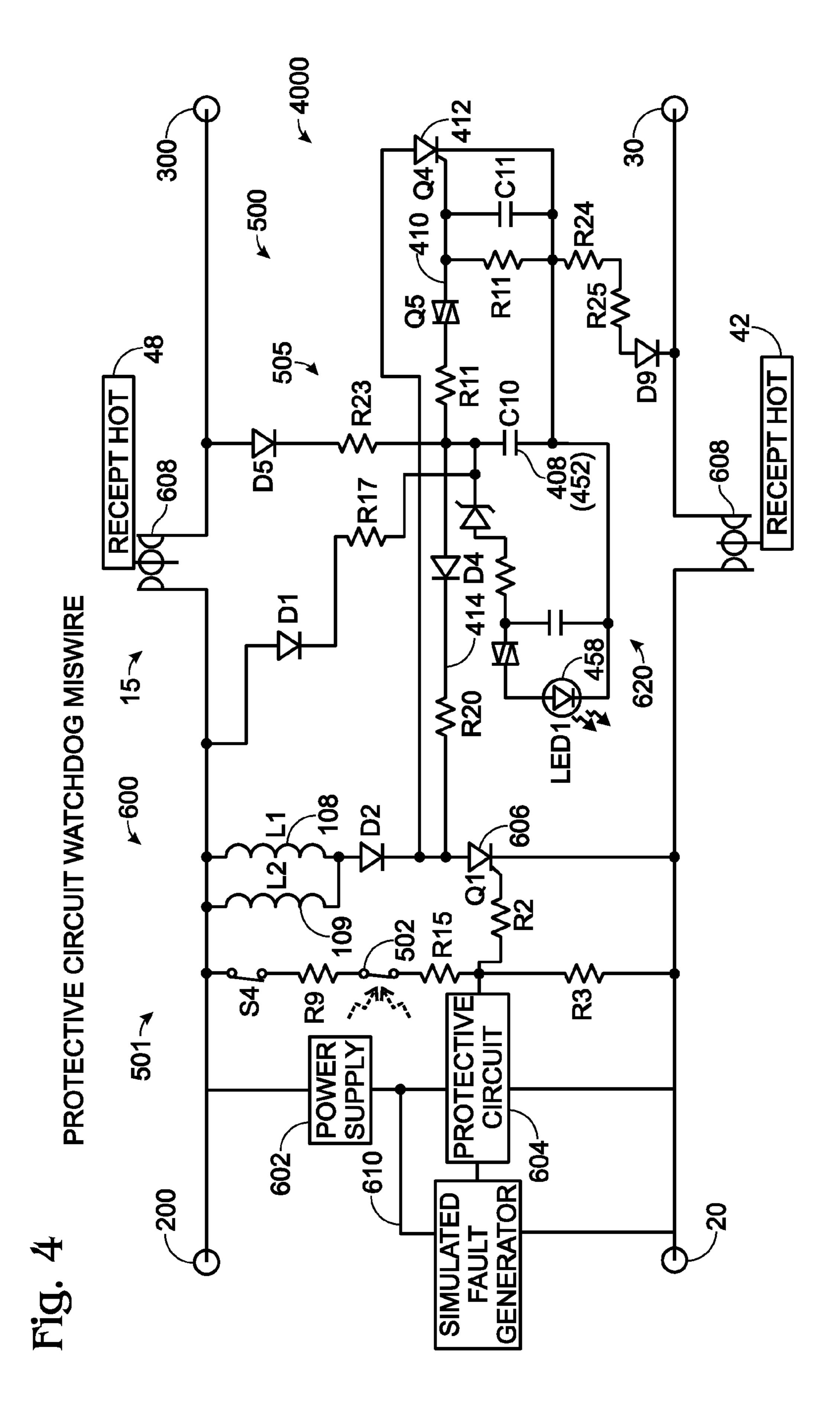

FIG. 4 is a diagrammatic depiction of a circuit for protective electrical devices in accordance with another alternate embodiment of the present invention;

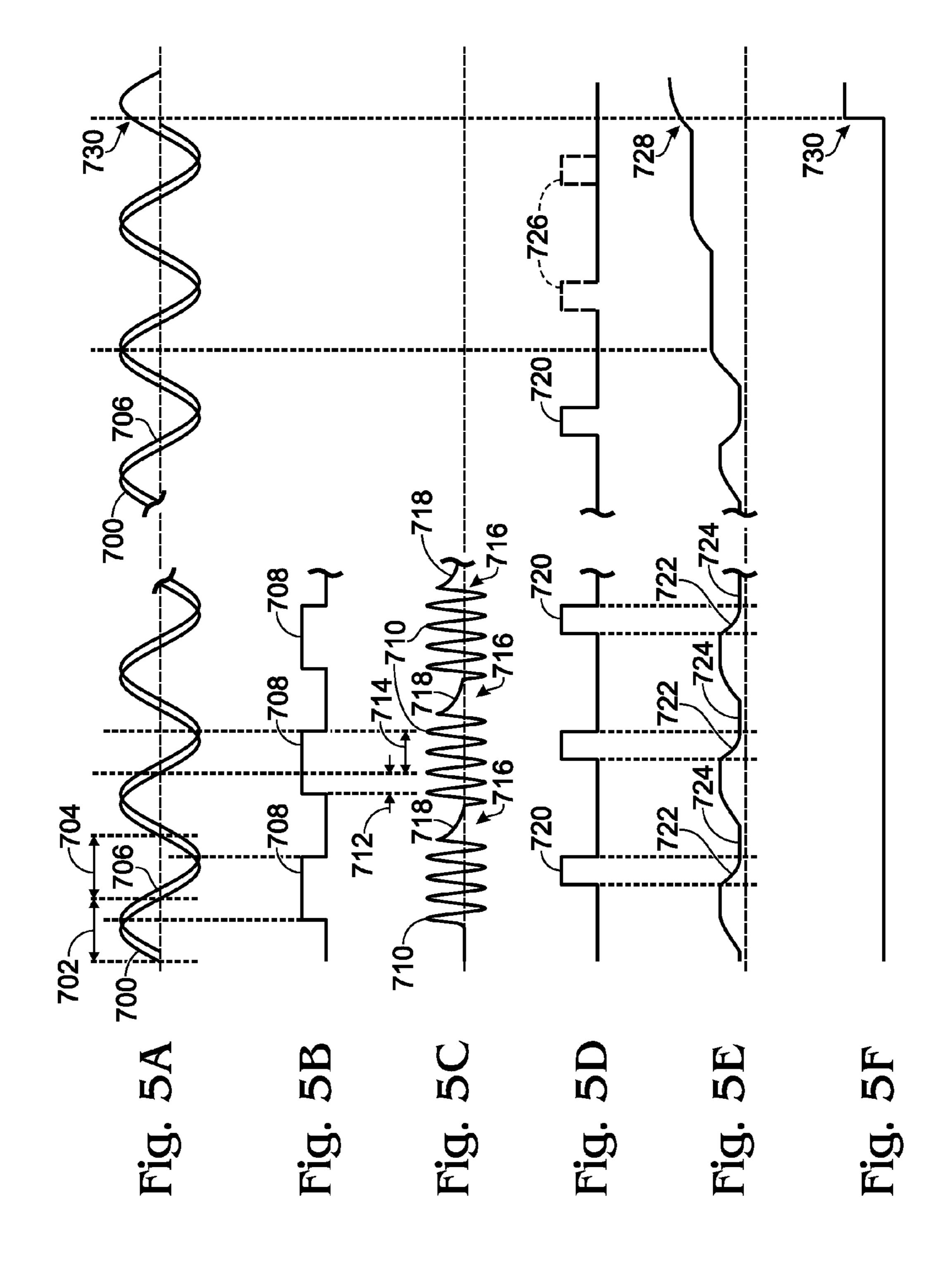

FIGS. **5**A-**5**F include a set of timing diagrams for a watchdog circuit in accordance with the embodiment depicted in FIG. **1**;

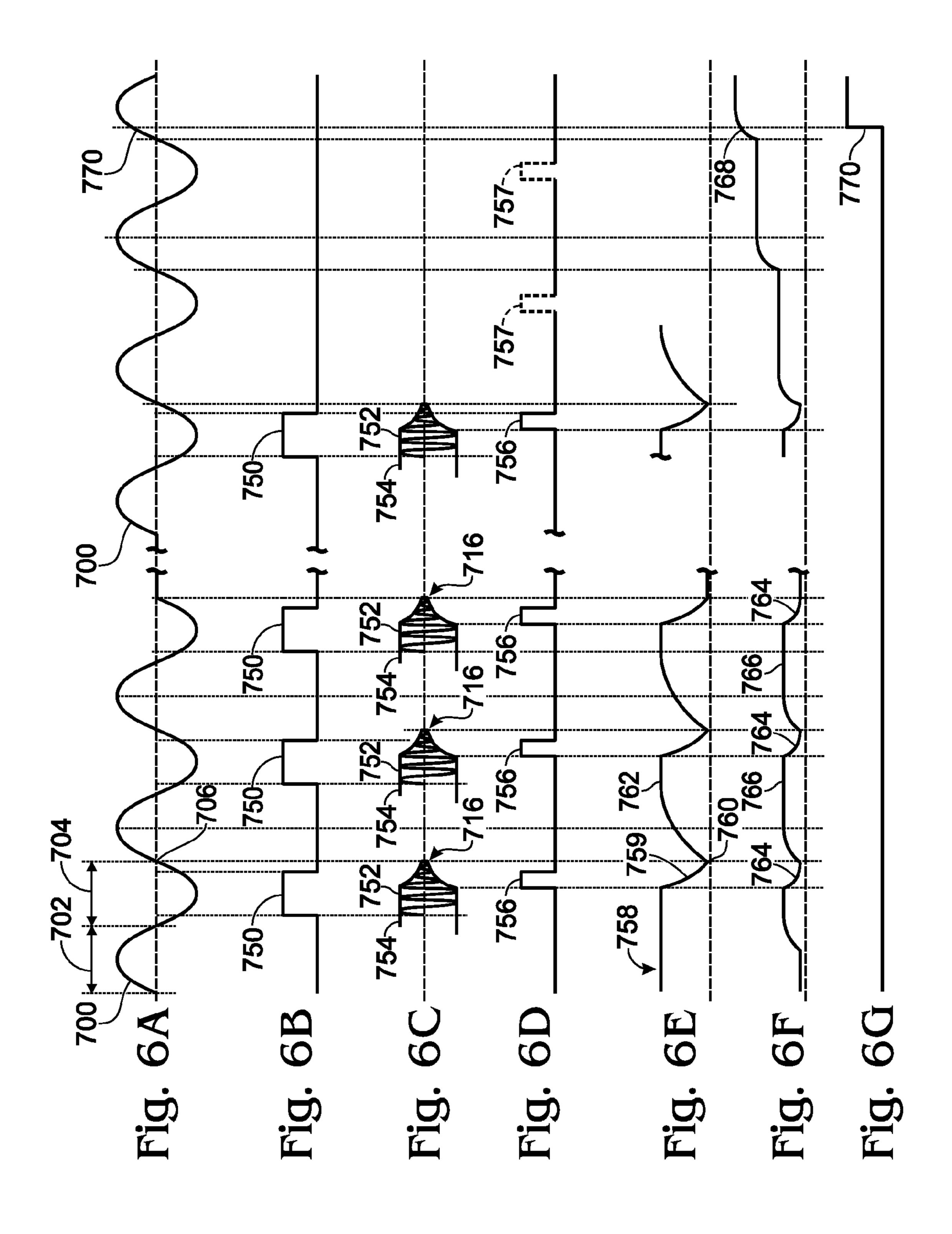

FIGS. 6A-6G include a set of timing diagrams for a watchdog circuit in accordance with the embodiments depicted in FIGS. 2-3;

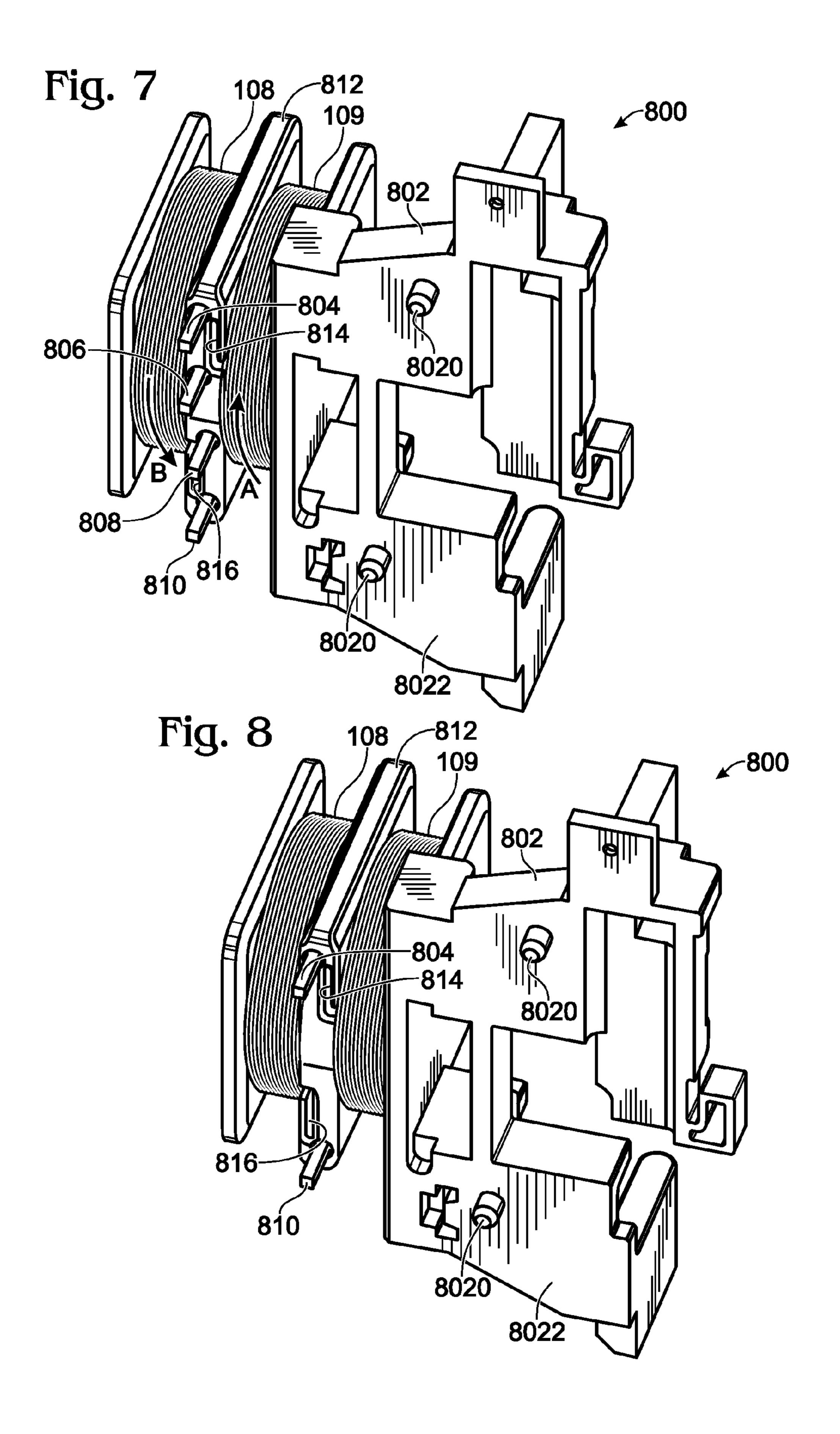

FIG. 7 is a perspective view of a dual solenoid in accordance with embodiments of the present invention;

FIG. **8** is a perspective view of a dual solenoid in accordance with alternate embodiments of the present invention;

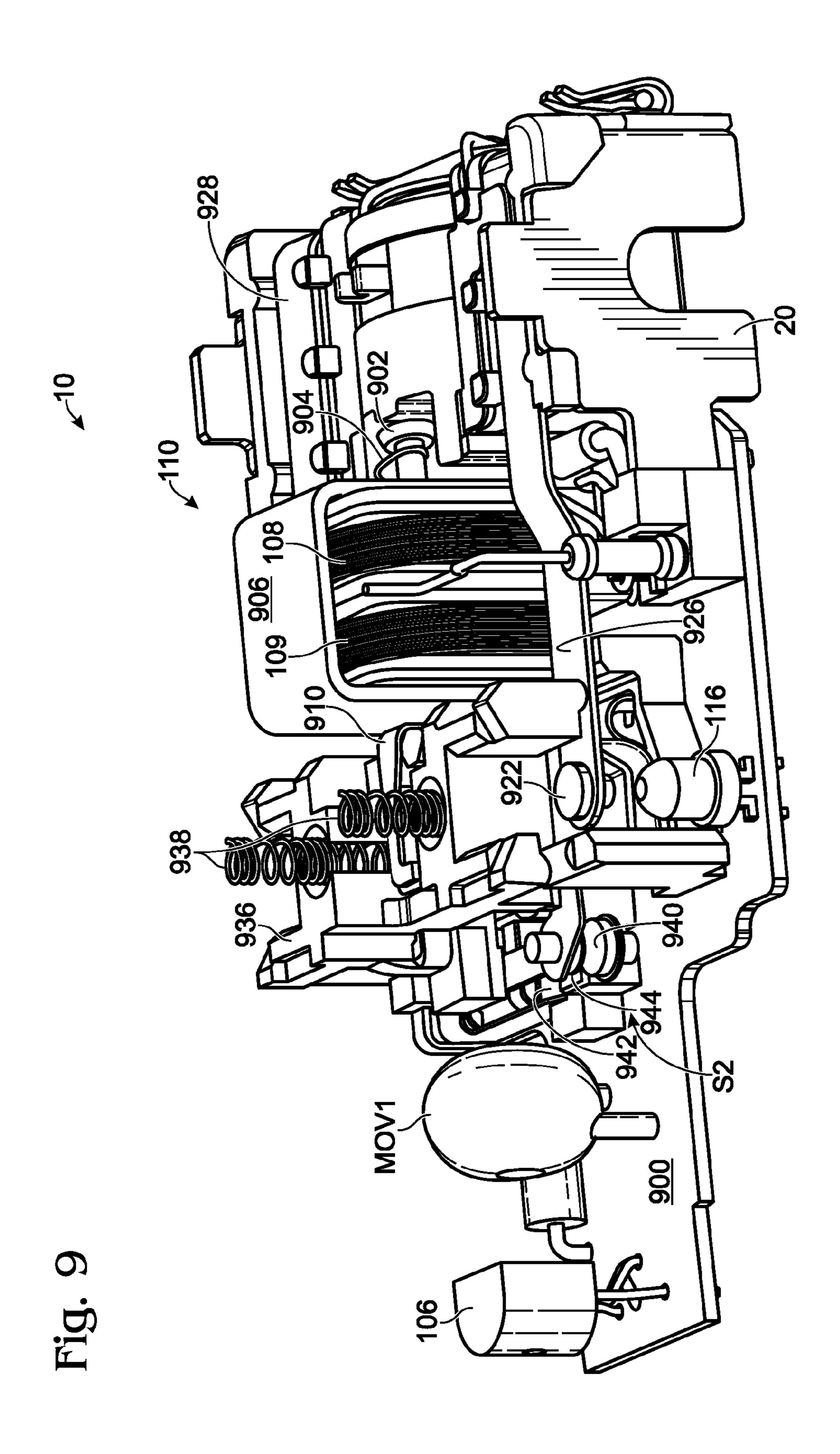

FIG. 9 is a perspective view of a printed circuit board assembly in accordance with an embodiment of the present invention;

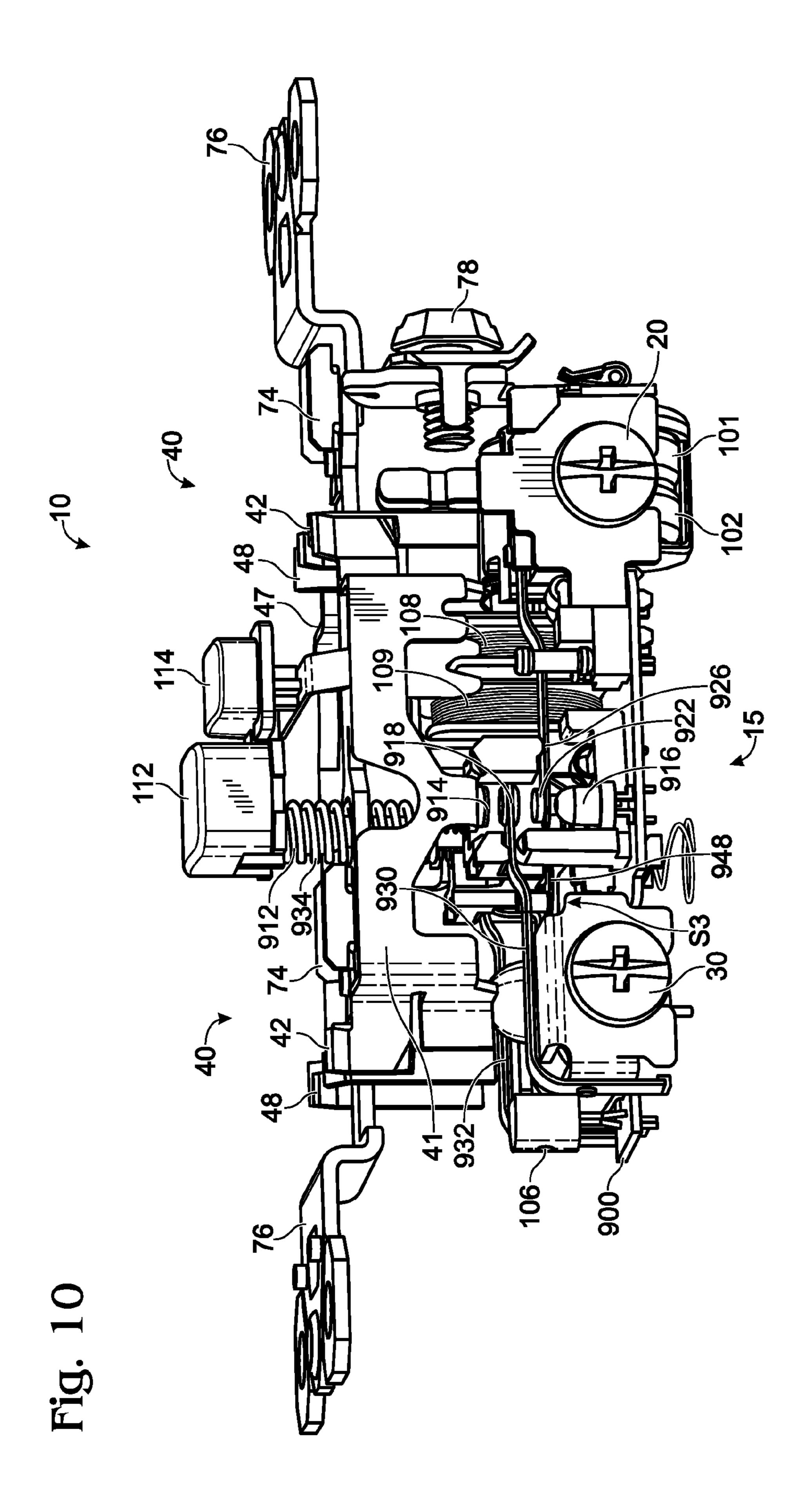

FIG. 10 is a perspective view of a partially assembled protective device in accordance with the embodiment depicted in FIG. 9;

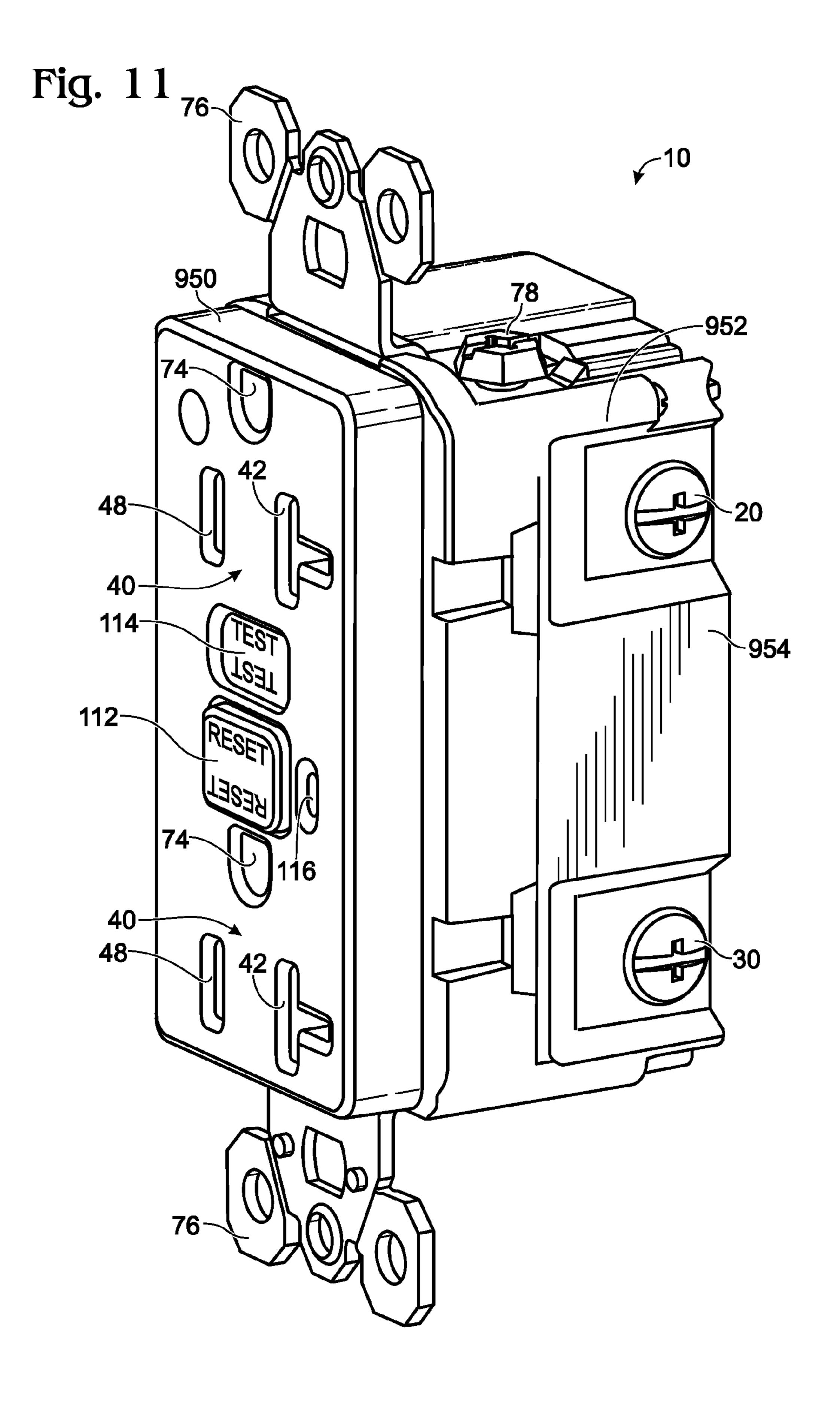

FIG. 11 is a perspective view of a fully assembled protective device in accordance with the embodiment depicted in FIG. 9 and FIG. 10; and

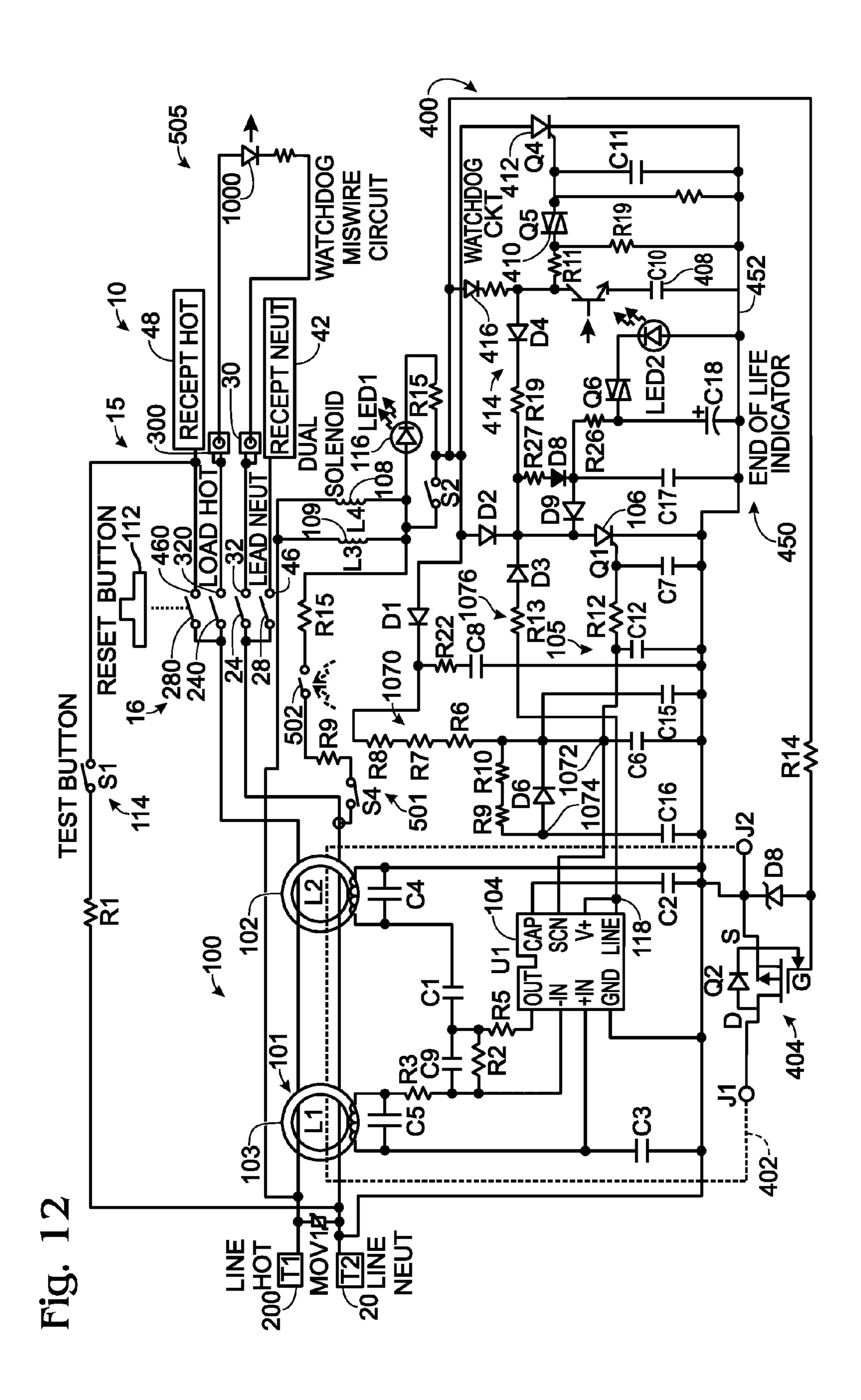

FIG. 12 is a schematic diagram of a protective electrical device in accordance with yet another embodiment of the present invention.

#### DETAILED DESCRIPTION

Reference will now be made in detail to the present exemplary embodiments of the invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers will be used throughout the drawings to refer to the same or like parts. An exemplary embodiment of the protective device of the present invention is shown in FIG. 1, and is designated generally throughout by reference numeral 10.

As embodied herein and depicted in FIG. 1, a schematic diagram of a protective electrical device in accordance with a first embodiment of the present invention is disclosed. As an initial point, while FIG. 1 shows a GFCI embodiment, the teachings of the present invention are also applicable to AFCIs or other protective devices.

The protective electrical wiring device 10 includes a hot line terminal 200, neutral line terminal 20, hot load terminal 300, neutral load terminal 30, hot receptacle terminal 48 and

-5

neutral receptacle 42. The protective device 10 is properly wired when the upstream line cable is connected to line terminals (20,200) and the downstream load cable is connected to load terminals (30,300). The receptacles (48, 42), of course, provide power via the face receptacle openings of the wiring device to the user when a corded plug is inserted therein. Again, when the device 10 is properly wired, AC power is directed from the line terminals to the receptacle terminals (42, 48) and the load terminals (30, 300).

The wiring device 10 depicted in FIG. 1 includes a GFCI 10 circuit 100 that includes differential transformer 101 and grounded neutral transformer 102 coupled to detector 104. The line hot conductor and the line neutral conductor are routed through the differential transformer 101 and condition occurs, the current flowing through the line hot conductor and the current flowing through the line neutral conductor are not equal because a portion of the current in the line hot conductor is diverted to ground instead of returning to the power source via the neutral conductor. As 20 its name implies, differential transformer 101 provides a differential current signal to detector 104; the differential current signal represents the difference between the line hot conductor current and the neutral conductor current. If the magnitude of the differential current signal exceeds a pre- 25 determined threshold level monitored by the fault detector **104**, the detector **104** is configured to turn the SCR **106** ON. The SCR 106 energizes trip solenoid 108 in turn. When the solenoid 108 is energized, the solenoid armature provides an actuation force that trips the circuit interrupter 16 and 30 opening its switch contacts. Note that the fault detector 104 is coupled to silicon controlled rectifier (SCR) 106 by way of a noise filter 105. The noise filter 105 substantially prevents spurious noise signals propagating on the detector **104** output from turning SCR **106** ON.

Circuit interrupter 16 includes line hot switch elements (240, 280) and line neutral switch elements (24, 28). When the device is reset, the line hot switch elements (240, 280) close the hot electrical switch contacts (320, 460) to make the line hot conductor 200 electrically continuous with the 40 load hot terminal 300 and the receptacle load terminal 48. Likewise, the line neutral switch elements (24, 28) close the neutral electrical switch contacts (32, 46) to make the line neutral conductor 20 electrically continuous with the load neutral terminal 30 and the receptacle load neutral terminal 45 42. As noted above, the solenoid armature provides an actuation force that trips the circuit interrupter 16 such that the line hot switch elements (240, 280) and the movable line neutral switch elements (24, 28) are opened.

The tripping and resetting actions of the circuit interrupter 16 are performed by movement of the latch block 110 (which is depicted in the schematic of FIG. 1 as a dotted line). The line hot switch elements (240, 280) and the line neutral switch elements (24, 28) are coupled to latch mechanism 110. When a user depresses the reset button 112, the 155 latch block is engaged by a reset pin such that the switch elements (24, 28, 240, and 280) are closed (reset). When the solenoid 108 is energized, the solenoid armature applies an actuation force to a latch mechanism causing the reset pin to disengage from the latch block 110; as a result, the switch 60 elements (24, 28, 240, and 280) are opened (tripped).

The switch elements (24, 28, 240 and 280) of circuit interrupter 16 may be implemented using cantilevers, bus bars, solid state switch devices and the like. Reference is made to U.S. Pat. Nos. 6,958,895 and 7,154,718, which are 65 incorporated herein by reference as though fully set forth in its entirety, for a more detailed explanation of various

6

four-pole circuit interrupter arrangements. Reference is made to U.S. Pat. No. 5,594,398, which is incorporated herein by reference as though fully set forth in its entirety, for a more detailed explanation of a bus bar circuit interrupter arrangement.

Device 10 also includes a manual test circuit that includes test button 114 (S1) and test resistor R1. TEST button switch 114 is accessible to the user and introduces a simulated ground fault and provides a convenient method for the user to periodically test the GFCI operation. When the test button 114 is closed by a user's depression thereof, current is diverted from receptacle hot 48 to line neutral 20 to thereby generate a simulated ground fault condition. The simulated fault condition tests the entire GFCI. If the GFCI apparatus grounded neutral transformer 102. When a ground fault 15 passes the test, the latch mechanism 110 will drive the circuit interrupter 16 into the tripped state. The GFCI response to the simulated fault may be deemed a "test acceptance signal." Wire loop 402 (as explained in greater detail below) may be employed to induce a sensor (101, 102) response. Thus, a simulated fault may be generated by either the test signal or the induced fault signal. Hereinafter, both of these signals will be referred to as simulated fault conditions.

Device 10 further includes a trip indicator 116 comprising an LED1 in series with current limiting resistor R12 and switch S3. As shown, switch S3 is a single pole double throw (SPDT) switch. When device 10 is tripped, trip indicator 116 is illuminated because the coupling contacts (in switch S3) connect the indicator 116 to line neutral. When device 10 is reset, there is little or no potential difference across LED1 and R32 because the coupling contacts (in switch S3) disconnect the indicator 116 from line neutral. Those of ordinary skill in the art will recognize that indicator 130 may include an audible annunciator as well as an illumination device.

GFCI circuit 100 includes a grounded neutral transmitter 102 that is configured to detect grounded neutral conditions. As an initial point, the line neutral conductor (i.e., the conductor that is connected to neutral line terminal 20) is deliberately grounded in the electrical circuit. On the other hand, a grounded neutral condition occurs when the load neutral conductor (i.e., the conductor that is connected to load neutral terminal 300) is accidentally grounded. The grounded neutral condition creates a parallel conductive path relative to the neutral return path disposed between neutral line terminal 20 and neutral load terminal 200. Since these two paths are in parallel, they may be thought of as comprising a wire loop. When a grounded neutral condition is not present, grounded neutral transmitter 102 is configured to couple equal signals into the hot and neutral conductors. As noted above, differential transformer 101 senses a current differential; thus, the equal signals provided by grounded neutral transmitter 102 effectively cancel each other. However, when a grounded neutral condition is present, the signal coupled onto the neutral conductor circulates as a current around the parallel conductive path and the return path, forming a conductive loop. Since the circulating current conducts through the neutral conductor but not the hot conductor, a differential current condition is created. Differential transformer 101 senses the differential current between the hot and neutral conductors and the detector 104 generates a fault detection signal in response thereto. The fault detection signal ultimately trips the circuit interrupter **16**.

Device 10 also includes an auxiliary switch S2 that is coupled to circuit interrupter 16; the auxiliary switch S2 is open when circuit interrupter 16 is tripped and is closed when circuit interrupter 16 is reset. Auxiliary switch S2 is

used to protect the solenoid. Under normal operating conditions one embodiment of the GFCI of the present invention trips out in response to a ground fault within about 25 milliseconds. As a result, solenoid **108** is only momentarily energized. If SCR 106 short circuits due to an end of life 5 condition, solenoid 108 will also be energized indefinitely and ultimately will burn out. The auxiliary switch S2, therefore, is used to protect the solenoid from being burned out if the SCR becomes shorted by an end-of-life condition. Once the SCR 106 fires and energizes the solenoid, the 10 auxiliary switch will open with the tripping of the circuit interrupter 16; the solenoid energizing current ceases when the circuit interrupter trips. Even if the device is reset, switch S2 interrupts the current again and prevents burn-out.

The protective device 10 also includes an end-of-life 15 (EOL) "watchdog" circuit 400. The watchdog circuit 400 periodically determines whether or not GFCI 100 is operational by generating a periodic test signal that is fed-back into the GFCI. In general, if GFCI 100 is in an EOL (end-of-life) state, i.e., incapable of properly responding to 20 the test signal, the watchdog circuit ensures that the device 10 will trip or indicate that the EOL state is extant.

By way of overview, the self-test assembly includes a watchdog circuit 400, a test circuit 401, and a test timing circuit 403. The test circuit 401 includes a wire loop 402 and 25 FET 404. The test timing circuit 403 includes capacitor 406 and resistor 405. The watchdog circuit 400 includes a second SCR 412 that is disposed in parallel with SCR 106; in other words, if an EOL state is extant such that the GFCI circuitry is non-functional, SCR **412** will energize solenoid **108**. The control input of SCR 412 is coupled to diac 410 and charging capacitor 408. Essentially, if a self-test is conducted and SCR 106 fails to respond within a predetermined period of time, the charging capacitor 408 will cause diac such that the circuit interrupter 16 is tripped.

The self-test circuit **401** generates a simulated grounded neutral test signal by way of wire loop 402 when FET 404 is turned ON. The ON state resistance of FET 404 is less than about 4 Ohms. The wire loop **402** in combination with 40 the FET (in the ON state) forms a loop that passes through the differential transformer 101 and neutral transmitter 102 to simulate a grounded neutral condition. In an alternate embodiment, instead of having a third wire passing through the transformers (101, 102) the wire loop 402 may incor- 45 porate a portion of the neutral conductor that is disposed between line neutral terminal 20 and load neutral terminal 30. One advantage for using the third wire technique, i.e., not incorporating a portion of the neutral conductor in the wire loop, relates to noise immunity. In particular, when the 50 third wire is employed the wire loop 402 and the neutral conductor are isolated; thus, the current propagating in wire loop 402 during the self-test is not affected by voltage drops or electrical noise propagating in the neutral conductor. Under certain circumstances, noise propagating on the neu- 55 tral conductor could impair the test signal and the GFCI's detection thereof.

In one embodiment of the present invention, the FET 404 is turned ON near the conclusion of the positive half cycle of the AC power source and remains ON through a portion 60 of the negative half cycle. The grounded neutral transformer 102 provides a differential current to the sensor 101 in response to the current propagating in wire loop 402. When operating properly, the fault detector 104 provides a fault detection signal that typically turns SCR 106 ON. However, 65 during the test, current flow through SCR 106 is either limited or completely restricted to prevent nuisance tripping

of the circuit interrupter. This is accomplished by performing the testing during the negative half cycle or late in the positive half cycle. If the SCR 106 is turned ON late in the positive half-cycle of the AC line cycle, the amount of current propagating through the SCR is not sufficient to energize the solenoid 108. If the SCR 106 is turned ON during the negative half cycle, it is only ON long enough to discharge positive voltage that happens to be on capacitor 408. In any event, SCR 106 cannot conduct current through solenoid 108 during the negative half cycle; diode D1 is also used to block current through the solenoid during the negative half cycle.

As noted above, the timing circuit 403 includes resistor 405 and capacitor 406. The test timing circuit 403 provides the timing for the test circuit, i.e., it determines when FET 404 is turned ON. Resistor 405 and capacitor 406 are coupled across line terminals 20,200 and establish the voltage at the gate of FET **404**. Since they are coupled across line terminals 20, 200, the gate signal approximates the AC power source waveform but is phase shifted by the RC time constant established by resistor 405 and capacitor 406. In one embodiment of the present invention, the time constant is about 1 millisecond. The phase shift is responsible for FET **404** turning on late in the positive half cycle and turning off before the end of the negative half cycle. The test signal is turned OFF early in the negative half cycle to give the flux in the core 103 portion of transformer 101 time to decay to prevent nuisance tripping. If the test signal is not turned OFF at this time the resultant flux generated within the core 103 could linger into the start of the positive half cycle and be misinterpreted as a ground fault condition. The timing circuit waveforms are depicted in FIG. 5.

The watchdog circuit 400 operates as follows. If the GFCI 410 to turn SCR 412 ON to thereby energize solenoid 108 35 is operating properly, the sensor circuit (101, 102), detector 104 and SCR 106 will respond to the test signal. The fault detector 104 will generate a fault detection signal late in the positive half-cycle or relatively early in the negative halfcycle and the SCR 106 will be turned ON. Moreover, the watchdog circuit 400 is configured such that SCR 106 is discharged via a discharging circuit 414. The SCR 106 remains ON until the voltage on capacitor 408 falls to a predetermined level. During the following positive half cycle, capacitor 408 is recharged by way of charging circuit **416**. Thus, the process of testing the GFCI and discharging capacitor 408 repeats every line cycle until the GFCI enters an EOL condition. When that happens, capacitor 408 fails to discharge. Thus, the capacitor 408 voltage reaches the breakover voltage of diac 410 when there is an EOL condition but not when the GFCI is operating properly.

An EOL condition, e.g., may include inter alia, an opencircuited grounded neutral transmitter 102, a faulty detector **104** circuit, a damaged SCR **106**, etc. When there is an EOL condition in a GFCI 100 component, the SCR 106 does not turn ON in response to the test signal and capacitor 408 is not discharged. On the other hand, capacitor 408 will continue to receive additional charge from charging circuit 416 every positive half-cycle. After a predetermined number of line cycles have elapsed, charging circuit 416 will cause diac 410 to break over and diac 410 will provide the necessary current to turn SCR 412 ON. SCR 412 energizes solenoid 108 which in turn trips the latch mechanism 110. If the user resets the circuit interrupter, the testing process will be repeated such that the circuit interrupter is tripped again. Thus, once device 10 is in an EOL state, the device may be reset only momentarily. The repeated tripping functions as a means for indicating device 10 failure.

As embodied herein and depicted in FIG. 2, a schematic diagram of a protective electrical device in accordance with an alternate embodiment of the present invention is disclosed. In this embodiment, an alternate test circuit 401' may replace or supplement the test circuit 401 described above. 5 Test circuit 401' is a ground fault simulation circuit that generates a simulated ground fault test signal instead of a simulated grounded neutral test signal. Test circuit 401' includes FET 404' and conductive path 402'. When FET 404' is turned ON, the ground fault simulation circuit generates 10 a simulated ground fault current through conductive path 402' and portions of the hot and neutral conductors that interconnect line terminals 20, 200 to load terminals 30, 300. Unlike one embodiment of test circuit 401, test circuit 401' is not isolated from the internal hot and neutral conductors 15 because it need not be. Voltage drops and other electrical noise occur in the internal conductors; however they have little or no effect due to the large impedance value presented by resistor 405. In one embodiment of the invention, resistor **405** is about 15 k-Ohms FET **404**' is turned on by a signal 20 provided by resistor R14. FET 404' is selectively turned ON and OFF to prevent nuisance tripping. In the embodiment depicted in FIG. 2, FET 404' is turned ON during the negative half-cycle and turned OFF later in the negative half cycle, allowing time for the flux in core 103 to decay before 25 the next zero crossing of the AC line cycle is reached. In accordance with the teachings of the present invention, any number of suitable simulated differential signals may be used by the watchdog circuit 400 to determine the operative status of the protective device. For example, a differential 30 signal may be derived from a power supply terminal to provide a pulsed DC differential signal.

Referring back to FIG. 1, the present invention includes both line side miswire protection and load side miswire protection. As noted previously, the term miswiring or 35 reverse wiring refers to a condition wherein the hot and neutral wires in the line cable (and hence the source of AC power) are improperly connected to the load terminals. The line side miswire circuit 501 is coupled to the ground fault detector and simulates a ground fault condition to prevent 40 reset when miswired. Each time there is an attempt to reset the circuit interrupter, it trips. Once the installer corrects the reverse wiring condition and applies source voltage to the line terminals for a certain amount of time, the line-side miswire circuit becomes permanently disabled and the cir- 45 cuit interrupter can be reset. Of course, it is possible that a protective device, having been properly wired, is then removed from the installation and miswired upon re-installation.

The load side miswire circuit **505** is coupled to the end of life detection circuit and simulates an end of life condition to prevent reset when miswired. In contrast to the line side miswire circuit, the load-side miswire protection circuit is not disabled after the device is properly wired and power is applied. Each time a device is removed from service and 55 miswired during reinstallation, the load side miswire circuit will function to prevent reset. Thus, the present invention provides multi-use miswire protection.

In reference to FIGS. 1-3, the miswire protection circuit 500 includes a line side miswire circuit 501 that includes a 60 switch S4 connected to the line neutral conductor; switch S4, resistors (R9, R15) and fusible element 502 are connected to line hot via solenoid 108. Again, all of these components are on the line side of circuit interrupter 16. In another embodiment of the present invention, the line-side miswire protective circuit 501 may be coupled to the line terminals (20, 200) without being in series with solenoid 108. In any event,

**10**

the line side miswire protection circuit **501** simulates a ground fault such that the differential current transformer **101** creates a differential current output signal in excess of the GFCI trip threshold (which is typically about 6 milliamperes). Resistors (R**9**, R**15**) establish the magnitude of this differential current in accordance with Ohm's Law.

The line side miswire protection circuit **501** operates as follows. When device **10** is miswired and reset, the circuit **501** will generate the simulated fault and the device will trip (if the GFCI is not at EOL) in the manner described above. After the device is tripped and miswired, nothing visible happens because the current flowing through the fault resistance (R**9**, R**15**) is interrupted when the device trips. If one attempts to reset the device in the miswired condition, the device immediately trips out again, and this continues until such time as the device is wired correctly, i.e., when AC power is applied to the GFCI at the line terminals (**20**, **200**). Thus, device **10** cannot substantially be reset until the device **10** is properly wired.

The estimated time it take for the fault resistance (R9, R15) to "clear" or burn out, or generate enough heat to open fusible element 52 is greater than 50 ms. The trip time of the GFCI is less than or equal to about 25 msec. Thus, when device 10 is miswired, the fault result resistance (R9, R15) does not have enough time to generate an open circuit condition before the circuit interrupter 16 is tripped. Once the device is properly wired, the device will trip once and either the fault resistor(s) or the fusible element 52 will open circuit to thereby disable the miswire circuit 501 permanently (the fault resistance is on the line side of circuit interrupter 16 and current continues to flow through fault resistance despite circuit interrupter 16 being open).

The fusible element 502 or the resistor(s) are open circuited within a predetermined time frame (i.e., typically about 50 msec). This may be implemented by selecting one or more resistors (e.g., R9, R15) having a power rating that is greatly exceeded by the current such that the resistor or resistors open. Another option is to provide a fusible element 502 in series with the fault resistance (R9, R15) with a properly selected I<sup>2</sup>t rating so that the fusible element blows instead of the fault resistance (R9, R15.) Once the fusible element is melted, the present invention may also include a release mechanism that dislodges the fusible element 502, creating an open circuit condition. Another option is to position resistors R9, R15 near the fusible element 502. They generate enough heat when the device is properly wired to open the fusible element. Fusible element **502** may be realized as a link of solder that melts open. In each of the alternate embodiments described above and contemplated by the present invention, once the device has been properly wired such that AC power is connected to the line terminals and the circuit **501** cleared, the device **10** may be reset to provide its normal protective functions.

Two interesting issues that arise in conjunction with the above described line side miswire protection circuit 501 relate to (1) performing required Underwriters Laboratories (UL) tests; and (2) keeping circuit 501 intact during manufacturing and testing. In particular, various tests showing that the device conforms to UL standard 943 must be performed during manufacturing of the protective device. In reference to the first point, the differential current produced by the fault resistors (R9, R15) cannot affect the test results. With respect to the second point, manufacturing testing cannot cause the miswire protection circuit 501 to clear. One solution is to place a switch S4 in series with the fault

resistance (R9, R15). Switch S4 is open until testing is completed and closed just before the device 10 enters the stream of commerce.

Switch S4 may be implemented using a flexible conductive spring arm that is flexed against a contact on the top side 5 of the printed circuit board to complete the miswire circuit **501**. A hole is formed in the printed circuit board directly below the spring arm of switch S4. Another hole is formed in the plastic back body of the GFCI device that is in alignment with the hole formed in the printed circuit board. 10 Subsequently, when the GFCI under test is loaded into a piece of test equipment designed to perform the required manufacturing tests, a mechanical test probe is guided through the two aforementioned holes to open switch S4. The test probe engages the spring arm of switch S4 and 15 pushes it away from the contact to open the line side miswire circuit **501**. Once this is achieved, manufacturing testing is performed without any of the above identified issues being a factor. The last test performed on the GFCI device in the test sequence is to close switch S4, miswire the device, and 20 apply AC power. This last test, of course, checks the integrity and operability of the line side miswire circuit 501.

In another embodiment of the present invention, switch S4 is implemented using solder. After the manufacturing tests have been performed, the solder is introduced through 25 a port in the housing to short the terminals of S4 together. Afterwards, the port may be sealed with a door piece.

To reiterate, the line side miswire circuit portion **501** becomes non-operational after the first time the device has been properly wired. The load side miswire protection 30 circuit 505 is included to provide miswire protection during a subsequent reinstallation of device 10.

In reference to FIG. 1, the load side miswire protective circuit 505 includes a diode D3 in series with resistor R30 coupled between load hot terminal 300 and diac 410 of the 35 miswire circuit 505 provides redundant miswire protection watchdog circuit 400. The load side miswire protective circuit **505** also includes a diode D**4** connected between load neutral terminal 30 and the cathode of SCR 412. As its name implies, the load side miswire circuit 505 derives power from the load terminals 30, 300. The load side miswire 40 protection circuit operates as follows.

If the protective device 10 is properly wired and in the reset condition, then diode D3, resistor R30, and diode D4 conduct a current derived from the voltage across load terminals 30, 300 to charge the watchdog charging capacitor 45 408. Note that the load side charging path is a redundant charging path; the charging circuit 416 described above provides charging capacitor 408 with charging current on the positive half-cycle of the AC line cycle. Thus, the watchdog circuit 400 receives charge from the line side and the load 50 side when the device 10 is properly wired and reset. The watchdog circuit 400 only receives charge from the line side charging circuit 416 when device 10 is properly wired and the circuit interrupter 16 is in the tripped condition because there is no voltage across the load terminals and D3, R30 and 55 D4 are not providing charging current; line side path 416 continues to do so. On the other hand, the watchdog circuit 400 only receives charge from the load side when device 10 is reverse wired and the circuit interrupter 16 is in the tripped condition because there is no voltage across the line terminals. Of course, it is in this last state (miswired and tripped) that the load side miswire protection circuit 505 is needed.

When device 10 is in the miswired and tripped state, the watchdog circuit 400 is powered by the load side miswire circuit portion 505 and is configured to respond to a mis- 65 wired condition in the same way it responds to an end of life condition (when properly wired). In this state, current flows

from load hot to load neutral via the circuit path that includes diode D3, resistor R30 and diode D4 to thereby charge capacitor 408. In the description provided above, it was noted that the line side charging circuit 416 charged on the positive half cycle and SCR 106 discharged capacitor 408 on the negative half cycle. In this state (miswired and tripped), SCR 106 cannot be turned ON because the circuit interrupter 16 contacts are open. Thus, the load side miswire circuit continues to charge capacitor 408 until the breakover voltage of diac 410 is attained; at this point, diac 410 is activated but SCR 412 cannot turn on due to the fact that there is no anode voltage. Once a user depresses reset button 112, the circuit interrupter is closed and now there is anode voltage. The signal through diac 410 then turned SCR 412 ON. With SCR 412 turned on, the solenoid 108 is energized and the circuit interrupter 16 is tripped. The above stated sequence repeats every time reset is attempted ad infinitum. At some point, the user will recognize the repeated tripping of the circuit interrupter means that the device is improperly wired (miswired). Unlike miswire circuit portion 501, there is no fusible element in the load side miswire protection circuit **505**. Thus, the load side miswire circuit portion **505** affords miswire protection after the initial installation is complete and the line side miswire circuit **501** is cleared. In fact, the load side miswire circuit may be employed for repeated reinstallations.

In yet another embodiment of the present invention, one end of the load side miswire circuit 505 may be connected across the face terminals (42, 48); this configuration will operate in a manner that is similar to what has been described above.

Those skilled in the art will understand that many GFCIs, once installed, may never be reinstalled. Thus, the combination of the line side miswire circuit **501** and the load side for the initial installation. If the device is in the tripped and miswired state, the line side miswire circuit 501 is configured to trip the circuit interrupter 16 via SCR 106. The trip signal is delayed through filter 105 by about 25 msec. The load side miswire circuit 505 has no such delay signal and so is the first to provide the trip signal. If there is an EOL condition in either miswire circuit, the other will still provide miswire protection. However, only line side circuit **501** assures complete miswire protection during the first installation; circuit 505 provides protection only when the device is in the tripped state. Thus primary miswire protection is afforded by circuit 501 whereas secondary protection is afforded by circuit **505**.

Those skilled in the art will also understand that the presence of a load side circuit implicates certain UL test requirements. For example, the present Underwriters Laboratories standard includes a high voltage dielectric test requirement. This test is performed by applying a high voltage potential between the hot terminals 200, 300 and neutral terminals 20, 30, or both sets of terminals at the same time, while the device 10 is in the tripped state. The typical dielectric test voltage is 1500 VAC. The device fails the test if a leakage current greater than about 0.5 mA is detected. Thus, the load side miswire circuit must be sufficiently isolated from the line side terminals in order for device 10 to pass this test.

The required isolation is achieved by the combination of diode D3, resistors R17 and R30, auxiliary switch S2 and SPDT switch S3. In one embodiment of the invention, resistors R17, R30 are chosen to have resistance values greater than 1 MOhm. For example, resistors R17, R30 may have resistance values of 1.5 MOhm. Diode D3 may be

selected to have a break-over voltage greater than 1500 Volts such that there is little or no current passing through it in the reverse direction. In the tripped state, SPDT switch S3 disconnects the neutral connection of the watchdog circuit 400 (e.g., SCR 412 cathode) from line neutral. Diode D4 5 isolates terminals 20, 30 during the reset state. Without diode D4, note that terminals 20, 30 would be directly connected by switch S3 creating a simulated grounded neutral condition. Moreover, if enough load current was diverted through the short circuit, a ground fault condition 10 could be created. Either condition would cause the device to nuisance trip.

In reference to FIGS. 1-3, the protective device 10 includes an indicator circuit 116 having LED1 in series with an impedance. The indicator circuit **116** provides multiple 15 indicator meanings: when the device is properly wired, LED1 functions as a trip indicator; and when the device is miswired, LED1 functions as a miswire indicator. A more detailed explanation of the indicator circuit **116** is as follows.

In reference to FIG. 1, when the device 10 is wired 20 be employed together (FIG. 1) or separately. properly, i.e., power from the supply source is connected to the line terminals, and the device is in the reset condition, indicator LED1 is OFF because the coupling contacts S3 are open and such that resistor R12 and indicator LED 1 are disconnected from the line terminals 20, 200. As a result, 25 there is little or no voltage across LED 1 and resistor R12. If the GFCI trips for any reason, contacts S3 close such that the resistor R12 and LED1 are connected to the line terminals (20,200); as a result, LED1 is illuminated. When the device is reset, contacts S3 again decouple indicator LED1 30 from the line terminals, so the indicator again turns off. When the device is miswired, indicator LED1 is always OFF. When the device is in the reset condition and miswired, contacts S3 are open (turning LED1 OFF). When the device line terminals because the circuit interrupter 16 is tripped (and open).

The indicator circuit **116** is described above as a visual indicator, but the present invention should not be construed as being limited to visual indication. In other embodiments 40 of the invention, indicator LED1 may be replaced by, or supplemented with, an audible indicator. In other alternate embodiments of the present invention, the indicator 116 may provide a non-steady form of indication, e.g., a flashing visual indication and/or a beeping audible indication.

Device 10 also includes one or more surge suppression circuits that protect the device circuitry from voltage surges propagating in the electrical distribution system. One typical cause of a surge event is lightning. In reference to FIG. 1, a MOV1 is disposed across the line terminals (20, 200). Surge 50 suppression MOV1 limits the voltage across line terminals (20,200) to a predetermined value. A surge event, such as a lightening strike my propagate voltages that might otherwise be large enough to damage device 10. Those skilled in the art will appreciate the fact that MOV1 can be located 55 elsewhere in the device and provide similar benefits. For example, MOV1 may be disposed across the load terminals (30, 300) or the face terminals (42, 48).

Although the surge suppressor has been symbolized as a metal oxide varistor (MOV), those skilled in the art will 60 recognized that the MOV1 may comprise a plurality of surge suppression devices connected in series or in parallel. For example, a plurality of metal oxide varistors may be employed in both series and parallel configurations. Moreover, a metal oxide varistor may be connected in parallel 65 with a spark gap, capacitor or any other suitable type of surge suppression device.

14

As contemplated by the present invention and depicted in FIG. 1, a surge suppressor (e.g., MOV) may be disposed within the device at a location other than across the line terminals. This arrangement may be employed to take advantage of certain device synergies or to merely protect a limited portion of the GFCI circuit that is vulnerable to surge events. For example, the surge suppressor MOV2 shown in FIG. 1 is configured to protect GFCI 100 including upstream miswire circuit **501**. With respect to the device synergies mentioned above, MOV2 is located behind the trip solenoid **108**. One benefit of this arrangement relates to the fact that the inductive reactance of the solenoid 108 effectively decouples MOV2 from the line terminals during all or a portion of the voltage surge event. Because of the impedance characteristic of solenoid 108, MOV2 is required to dissipate considerably less energy. The energy reduction translates to a substantially reduction is movistor size, i.e., from 12 mm to 7 mm. In accordance with the teachings of the present invention, surge suppressors MOV1 and MOV2 may

As embodied herein and depicted in FIG. 2, a schematic diagram of a protective electrical device in accordance with an alternate embodiment of the present invention is disclosed. This embodiment is similar to the one depicted in FIG. 1. One difference is that charging circuit **416** has been omitted from the device of FIG. 2. While the watchdog circuit 400 of FIG. 2 operates in a manner much like the watchdog circuit of FIG. 1, the charging path is now entirely associated with the load terminals. The charging path includes resistor R23, diode D5, and resistor R17 disposed between the load hot terminal 300 and charge capacitor 408. When the device is in the reset state and properly wired, the watchdog circuit 400 provides end-of-life protection in the manner described above. If the device is miswired, i.e., is tripped and miswired, there is no line voltage across the 35 when the AC source voltage is connected to the load terminals, the charging circuit comprises resistor R23, diode D5, resistor R17, diode D7, and resistors R25 and R24 connected across the load terminals (30,300). Thus, capacitor 408 is charged and SCR 412 of the watchdog circuit 400 will energize solenoid 108 to thereby trip the circuit interrupter 16 in response to a miswire condition, when reset is attempted. In other words, the watchdog circuit prevents reset.

> Another difference between the embodiments of FIG. 1 and FIG. 2 is that the device depicted in FIG. 2 does not include SPDT switch S3; thus, there are no contacts serving to isolate the line from the load when the device 10 is in the tripped state. However, isolation between load hot terminal 300 and line terminals (20,200) is fully provided by resistors R17, R23, and diode D5. Similarly, resistors R24, R25, and diode D7 fully isolate the line neutral terminal 20 from the load neutral terminals 30. Diodes D5 and D7 have breakover voltages that provide isolation during the half cycles (of the AC line cycle) in which they are reverse biased. In the neutral isolation circuit, note that the resistors R24, R25 have a combined resistance that is greater than about 500 KOhms, which is less than the 1.5 MOhms employed in FIG. 1. The diode D7 permits the combined resistance to be somewhat reduced (relative to FIG. 1) while still passing the dielectric test. The combined resistances in the hot isolation circuit (i.e., resistors R17, R23) may be different than the combined resistance of resistors R24, R25 (neutral isolation circuit). The reason for the difference relates to the time constant governing the charging of the watchdog circuit 400. In particular, resistors R17, R23 govern the charging time constant of capacitor 408 when the device 10 is properly wired and reset.

Another difference in the circuit depicted in FIG. 2 is that indicator 116 is connected across auxiliary switch S2 since it is not being relied upon for isolation. The indicator circuit 116 depicted in FIG. 2 is illuminated when the device 10 is properly wired and in the tripped condition.

Another difference in the circuit depicted in FIG. 2 is that surge suppressor MOV2 is coupled to the hot line terminal 200 by way of the solenoid 108 and the auxiliary switch S2. Like the indicator circuit 116, MOV2 is connected across the auxiliary switch S2. Again, this is possible because the 10 auxiliary switch is not being relied upon for isolation in FIG. 2. Like FIG. 1, MOV2 is connected differentially such that if it develops a sufficient leakage current at end of life, it will be sensed by transformer 101 and detected by detector 104. Detector 104, of course, will signal SCR 106 to trip the 15 device. Thus, the differentially connected MOV 2 provides another means for detecting an EOL event. Moreover, because the device 10 is tripped, solenoid burnout is prevented.

In reference to FIG. 2, device 10 includes a dual power 20 supply 1070. As the name suggests, the dual power supply 1070 includes two power supply portions; power supply portion 1072 and power supply portion 1074. Dual power supply 1070 is configured to provide power to the supply terminal 118 of detector 104. Dual power supply 1070 25 includes a diode D1 that is connected to line hot via solenoid 108 and the parallel circuit that includes indicator 116 and auxiliary switch S2. Diode D1 is further connected to power supply portion 1072 including resistor R22 disposed in series with capacitor C8. Resistor R22 and capacitor C8 are 30 disposed in parallel with resistors R8, R7 R6 and parallel capacitors C15 and C6. Power supply portion 1074 includes resistors R9, R10, and R11. R11 is connected to resistor R8 and resistor R9 is connected to power supply 1072 via diode D6.

As an initial point, the GFCI 100 is configured to interrupt circuit interrupter 16 during the positive half-cycle of the AC line cycle. In order to meet the trip time requirements, power supply portion 1072 is configured to charge to the full supply voltage in less than about 2 milliseconds whereas power 40 supply portion 1074 takes longer to come up to full charge. The purpose of supply portion 1074 is to sustain the supply voltage during the negative half cycles when diode D1 is reverse biased and not providing energy. Power supply portion 1074 charges and discharges in accordance with a 45 time constant that is approximately 15 milliseconds. Note that supply portion 1072 is slaved via diode D6 to supply portion 1074; thus, it is discharged at the same rate as supply portion 1074.

The dual power supply provides for certain modifications to the grounded neutral test circuit. In the embodiment of FIG. 2, the timing resistor R14 is arranged such that turn FET 404 is turned ON for a substantial portion of the negative half cycle. One reason for increasing the time duration of the simulated fault signal generated by loop 402 55 relates to improving the efficacy of the self-test detection. One drawback to this approach relates to the duration of the magnetic flux in core 103. Specifically, if the magnetic flux in core 103 carries over into the subsequent positive half cycle, the resultant sensor output would cause detector 104 to improperly turn SCR 106 ON and nuisance trip the device 10. The dual power supply 1070 substantially prevents nuisance tripping by collapsing the power supply output voltage before the conclusion of the negative half cycle.

One reason why the collapsible power supply voltage 65 prevents nuisance tripping relates to the inability of grounded neutral oscillations to persist in the absence of the

**16**

oN, there is substantially no magnetic flux in core 103 once the power supply voltage collapses. Thus, if the power supply voltage is collapsed before the conclusion of the negative half cycle, the grounded neutral oscillations that otherwise would be generated by FET 404, cannot carry over into the positive half cycle. Thus, the dual power supply 1070 prevents nuisance tripping.

The details regarding the collapsible power supply voltage are as follows. During the self test, the SCR 106 is turned ON at about 225°-280° of the AC line cycle (i.e., during a portion of the negative half cycle). As a result, capacitor C6 and capacitor C16 (by way of diode D6) are dump-discharged via discharge circuit 1076 and SCR 106 to thereby collapse the output voltage of the power supply. The discharging process occurs gradually because of the C16, R13 time constant. Accordingly, when FET 404 is turned ON, the grounded neutral transmitter 102 produces an oscillating signal that is a function of the full power supply voltage. As the power supply voltage gradually collapses in accordance with the aforementioned RC time constant, the magnitude of the oscillating signal produced by the grounded neutral transmitter 102 also diminishes. In response, the grounded neutral simulation current propagating around loop 402 diminishes. Finally, the flux in core 103 diminishes such that the sensor signal provided to detector 104 does not represent a fault condition. This process occurs before the conclusion of the negative half cycle; thus, little or no flux is present in core 103 at the start of the subsequent positive half cycle. In one embodiment of the present invention, the C16, R13 time constant is about 0.5 milliseconds and the period of the grounded neutral oscillation is about 0.15 milliseconds.

In FIG. 1, the self test nuisance trip issue was addressed by controlling by the RC time constant of capacitor 406 and resistor R14, which in turn, controlled FET timing. In FIG. 2, the input terminal of FET is only coupled to the line terminal by via resistance R14 because the self test nuisance trip issue has been addressed by reconfiguring the power supply. Specifically, the resistor R14 is coupled to the hot line terminal 200 by way of solenoid 108. Thus, like MOV2, FET 404 is also protected by the impedance of the solenoid 108 during a surge event. Moreover, FET 404 is additionally protected by surge suppressor MOV2.

As embodied herein and depicted in FIG. 3, a schematic diagram of a protective electrical device in accordance with an alternate embodiment of the present invention is disclosed. The embodiment of FIG. 3 is similar to the embodiment of FIG. 2, except that it includes an end of life (EOL) indication circuit 450 as well as a dual solenoid arrangement. The embodiment of FIG. 3 also includes a modified dual power supply.

The EOL indication circuit 450 includes a charging capacitor 452 coupled to diac 456 and LED 458. The charging capacitor 452 is charged by charging circuit 454 and operates in much the same way that the charge capacitor 408 operates in the watchdog circuit 400. Power is derived from the load hot terminal via diode D5 and resistor R23; these components are coupled to diode D4, resistors R19 and R27, Diode D8, and resistor R26. As noted above, the self-test circuit 402 is turned ON every negative half cycle to test the GFCI 100 circuitry. When SCR 106 is turned ON every negative half cycle, capacitor 452 discharges to a voltage at or near zero. When there is an end of life condition in the GFCI circuitry, SCR 106 will not turn ON and capacitor 452 will not be discharged. Thus, capacitor 452 continues to accumulate charge until it reaches the break-

over voltage of diac 456; thus, diac 456 turns on and LED 458 emits light. Subsequently, the current through LED 458 drains the voltage on the capacitor, diac 456 turns OFF and LED **458** ceases to emit light. Because the GFCI is at EOL, the charge again accumulates on capacitor **452** and the cycle 5 repeats. Thus, LED **458** functions as a flashing end of life indicator. In an alternate embodiment, LED 458 is replaced by an annunciator that makes an audible beeping sound at end of life.

The device of FIG. 3 includes two redundant trip solenoids 108, 109 that are capable of tripping circuit interrupter 16 when energized by SCR 106 or SCR 412. The redundancy ensures that if one of the solenoids has an opencircuited end of life condition, device 10 will continue to afford protection because the second solenoid is operative. 15 Perspective views of the dual solenoid embodiments of the present invention are shown in FIGS. 7 and 8.

The dual power supply 1070' of FIG. 3 is similar to the power supply 1070 of FIG. 2, with the exception that it includes only one set of resistors to charge the supply 20 capacitors C6 and C16.

As embodied herein and depicted in FIG. 4, a diagrammatic depiction of a watchdog circuit for a protective electrical device in accordance with another alternate embodiment of the present invention is disclosed. The 25 embodiment of FIG. 4 is generalized to apply to different protective devices such as ground fault circuit interrupters (GFCIs), ground-fault equipment protectors (GFEPs), arc fault circuit interrupters (AFCIs), or combination AFCI/ GFCI. This list includes representative examples and is not 30 meant to be exhaustive. Reference is made to U.S. Pat. No. 6,798,628, which is incorporated herein by reference as though fully set forth in its entirety, for a more detailed explanation of an AFCI device.