#### US009691339B2

## (12) United States Patent

#### Furihata et al.

### (10) Patent No.: US 9,691,339 B2

#### (45) **Date of Patent:** Jun. 27, 2017

# (54) DISPLAY APPARATUS AND DISPLAY APPARATUS CONTROL CIRCUIT

(75) Inventors: **Hirobumi Furihata**, Kanagawa (JP);

Takashi Nose, Kanagawa (JP)

(73) Assignee: Renesas Electronics Corporation,

Koutou-ku, Tokyo (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 196 days.

(21) Appl. No.: 14/007,228

(22) PCT Filed: Feb. 20, 2012

(86) PCT No.: PCT/JP2012/053942

§ 371 (c)(1),

(2), (4) Date: Sep. 24, 2013

(87) PCT Pub. No.: WO2012/132624

PCT Pub. Date: Oct. 4, 2012

#### (65) Prior Publication Data

US 2014/0022221 A1 Jan. 23, 2014

#### (30) Foreign Application Priority Data

(51) **Int. Cl.**

G09G 3/36 (2006.01) G09G 3/00 (2006.01)

(Continued)

(52) **U.S. Cl.**

(Continued)

#### (58) Field of Classification Search

CPC .. G09G 2370/08; G09G 3/003; G09G 3/3611; H04N 19/115; H04N 19/136; H04N 5/66 (Continued)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

5,388,209 A \* 2/1995 Akagiri ...... G11B 11/10502 704/201 6,208,689 B1 \* 3/2001 Ohira ...... H04N 19/159 375/240.03 (Continued)

#### FOREIGN PATENT DOCUMENTS

JP 2007-067531 A 3/2007 JP 2007-306545 A 11/2007 (Continued)

#### OTHER PUBLICATIONS

Communication dated Jun. 18, 2014, from the Japanese Patent Office in counterpart Japanese Patent Application No. 2013507255. (Continued)

Primary Examiner — Tony Davis

(74) Attorney, Agent, or Firm — Sughrue Mion, PLLC

#### (57) ABSTRACT

A display apparatus includes: a display device; a display device driver which drives the display device; a compression section adapted to an operation of generating compression data by compression processing performed on image data; and a transmission section which, when receiving compressed data from the compression section, transmits the compressed data to the display device driver by using a serial data signal. The compression section performs the compression processing with a data compression ratio selected in response to a frame rate with which the display device driver drives the display device. The display device driver receives the serial data signal from the transmission section, generates decompressed data by decompressing the compressed data transmitted by the serial data signal, and drives the display device in response to the decompressed data. The data compression ratio used in the compression processing is set so that the transmission rate of the serial data signal from the transmission section to the display (Continued)

| aevice an | iver is k | tept cons | tant indepei | ndently of | the frame |

|-----------|-----------|-----------|--------------|------------|-----------|

| rate.     |           |           |              |            |           |

#### 9 Claims, 26 Drawing Sheets

| (51) | Int. Cl.             |                                                              |

|------|----------------------|--------------------------------------------------------------|

|      | H04N 5/66            | (2006.01)                                                    |

|      | H04N 19/136          | (2014.01)                                                    |

|      | H04N 19/115          | (2014.01)                                                    |

| (52) | U.S. Cl.             |                                                              |

| . ,  | CPC <i>G09G</i> .    | 2370/08 (2013.01); H04N 19/115                               |

|      |                      | (2014.11)                                                    |

| (58) | Field of Classificat | tion Search                                                  |

| . ,  | USPC 375/2           | 240; 348/207.1, 240.25; 382/282;                             |

|      |                      | 345/204                                                      |

| (58) | Field of Classificat | (2014.11)<br>tion Search<br>240; 348/207.1, 240.25; 382/282; |

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

See application file for complete search history.

|              | U.S.    | FAIENI  | DOCUMENTS               |

|--------------|---------|---------|-------------------------|

| 6,229,852    | B1*     | 5/2001  | Hoang H04N 19/61        |

| c c 1 1 100  | 75.4 di | 0 (0000 | 375/240.14              |

| 6,614,483    | B1 *    | 9/2003  | Lee G06T 9/00           |

|              |         |         | 348/391.1               |

| 6,989,773    | B2 *    | 1/2006  | Wee H04N 21/234         |

|              |         |         | 341/51                  |

| 7,333,929    | B1 *    | 2/2008  | Chmounk G10L 19/24      |

|              |         |         | 704/200                 |

| 8,705,635    | B2 *    | 4/2014  | Lee G06T 9/00           |

|              |         |         | 375/240.23              |

| 2002/0064314 | A1*     | 5/2002  | Comaniciu et al 382/239 |

| 2002/0080881 | A1*     | 6/2002  | Honda H04N 19/172       |

|              |         |         | 375/240.16              |

| 2002/0094031 | A1*     | 7/2002  | Ngai H04N 21/23655      |

|              |         |         | 375/240.27              |

| 2003/0038883 | A1*     | 2/2003  | Takahashi H04N 5/232    |

|              |         |         | 348/207.1               |

| 2004/0196903 | A1*     | 10/2004 | Kottke H04N 19/147      |

|              |         |         | 375/240.03              |

| 2005/0190872 | A1*     | 9/2005  | Seong et al 375/354     |

|              |         |         | Shimazaki H04N 5/772    |

|              |         |         | 386/240                 |

| 2005/0243190 | A1*     | 11/2005 | Ogikubo G11B 27/005     |

|              |         |         | 348/231.99              |

| 2006/0018553 | A1*     | 1/2006  | Lee H04N 19/172         |

| 2000,0010555 |         | 1, 2000 | 382/232                 |

|              |         |         | 502/232                 |

| 2007/0046620 | <b>A</b> 1 | 3/2007  | Ugajin                |

|--------------|------------|---------|-----------------------|

| 2008/0279275 | A1*        |         | Suzuki H04N 19/176    |

|              |            |         | 375/240.03            |

| 2009/0097764 | A1*        | 4/2009  | Sung H04N 19/172      |

|              |            |         | 382/239               |

| 2009/0102807 | <b>A</b> 1 | 4/2009  | Kashiwa et al.        |

| 2009/0116563 | A1*        | 5/2009  | Kawamura H04N 7/152   |

|              |            |         | 375/240.26            |

| 2009/0245760 | A1*        | 10/2009 | Kawano H04N 9/7921    |

|              |            |         | 386/241               |

| 2009/0322713 | <b>A1</b>  | 12/2009 | Furihata et al.       |

| 2010/0046607 | A1*        | 2/2010  | Tseng H04N 19/172     |

|              |            |         | 375/240.01            |

| 2010/0110285 | A1*        | 5/2010  | Nobori                |

| 2010/0231736 | A1*        | 9/2010  | Hosokawa H04N 5/2351  |

|              |            |         | 348/222.1             |

| 2010/0253853 | <b>A</b> 1 | 10/2010 | Sakashita             |

| 2011/0150330 | A1*        | 6/2011  | Jannard H04N 19/30    |

|              |            |         | 382/166               |

| 2011/0176054 | A1*        | 7/2011  | Omae H04N 7/147       |

|              |            |         | 348/384.1             |

| 2011/0267452 | A1*        | 11/2011 | Notsu G06K 9/00798    |

|              |            |         | 348/116               |

| 2012/0044375 | A1*        | 2/2012  | Lin H04N 19/146       |

|              |            |         | 348/222.1             |

| 2012/0086818 | A1*        | 4/2012  | Yamamoto H04N 5/23293 |

|              |            |         | 348/207.1             |

| 2015/0078431 | A1*        | 3/2015  | Sung H04N 19/172      |

|              |            |         | 375/240.02            |

|              |            |         |                       |

#### FOREIGN PATENT DOCUMENTS

| JP | 2008-039890 | A            | 2/2008  |

|----|-------------|--------------|---------|

| JP | 2009-098504 | $\mathbf{A}$ | 5/2009  |

| JP | 2010-096951 | A            | 4/2010  |

| JP | 2010113012  | A            | 5/2010  |

| JP | 2010-141775 | A            | 6/2010  |

| JP | 4507265     | B2           | 7/2010  |

| JP | 2010-243608 | $\mathbf{A}$ | 10/2010 |

|    |             |              |         |

#### OTHER PUBLICATIONS

International Preliminary Report on Patentability issued Oct. 2, 2013 in PCT/JP2012/053942.

Communication dated May 20, 2015 from the State Intellectual Property Office of the P.R.C. in counterpart application No. 201280016020.7.

<sup>\*</sup> cited by examiner

SOURCE CLOCK PHASE COMPARATOR VCO OUTPUT

FREQUENCY DIVIDER

FREQUENCY DIVIDER

FREQUENCY DIVIDING RATIO ADJUSTMENT CIRCUIT 123a

Fig. 3B

Fig. 5

Fig. 6

| P  | IXEL | A  | P  | IXEL | В  | P  | IXEL | C  | Р  | IXEL | D  |

|----|------|----|----|------|----|----|------|----|----|------|----|

| RA | GA   | BA | RB | GB   | Вв | Rc | Gc   | Bc | Ro | GD   | BD |

Fig. 7A

Fig. 7B

Jun. 27, 2017

TOTAL 48 BITS

(DATA COMPRESSION

RATIO 50%)

BoDATA (3 bits)

GDDATA (4bits)

RDDATA (4bits)

BcDATA (4bits)

| BBDATA<br>(4bits)                                |

|--------------------------------------------------|

| GBDATA<br>(4bits)                                |

| RBDATA<br>(4bits)                                |

| BADATA<br>(4bíts)                                |

| GADATA<br>(4bíts)                                |

| RADATA<br>(4bits)                                |

| COMPRESSION<br>TYPE<br>RECOGNITION BIT<br>(1bit) |

6 . . . .

о О О

TOTAL 64 BITS (DATA COMPRESSION RATIO 66.7%)

BDDATA (5bits)

GDDATA (5bíts)

RDDATA (5bíts)

BcDATA (5bits)

ROUNDING: TRUNCATE LOWER 5 BITS AFTER ADDING 16 FOR TRUNCATE LOWER 4 BITS AFTER ADDING 8 FOR OTHER SUBPIXELS

8 8 8 2

1-|2|

2 2 2

A B C B

4-

100

(1 × 4) PIXEL COMPRESSION

æ

INAGE DATA)

(ORIGINAL

9

DATA

ಭ

0 70

8

(1 × 4) PIXEL DECOMPRESSION

|               |   |     | ,         |            |          |   |

|---------------|---|-----|-----------|------------|----------|---|

| (DECOMPRESSED | 8 | 48  | 29        | 9          | 26       |   |

| (DECOM        |   | A   | В         | 9          | D        |   |

|               |   |     | SUBTRACT  | 3↑         |          | • |

|               | 8 | 35  | 48        | 112        | 35       |   |

|               | Э | 0   | 112       | 16         | 16       |   |

|               | 8 | 48  | 64        | <b>9</b> { | 112      |   |

|               |   | A   | В         | 3          |          |   |

|               |   | THE | BIT SHIFT | 1          |          |   |

|               | В | 7   | 3         | L          | <b>*</b> |   |

| DATA          | 9 | 0   | 7         | •          | •        |   |

| SSED          | æ | 3   | 4         | <b>~~~</b> | 7        |   |

| (COMPRE       |   | A   | 83        | ပ          | _        |   |

LEFT BIT SHIFT: 5-BIT LEFT SHIFT FOR B SUBPIXEL OF PIXEL D 4-BIT LEFT SHIFT FOR OTHER SUBPIXELS

COMPRESSION FORM RECOGNITION REPRESENTA-REPRESENTA-RECOGNITION BIT DATA TIVE VALUE TIVE VALUE TIVE VALUE (1bit x2) (50r6bits) (50r6bits) (50r6bits) (50r6bits) (50r6bits) (50r6bits)

WITH LOW CORRELATION

TOTAL 48 BITS

(DATA COMPRESSION

RATIO 50%)

DATA FOR TWO PIXELS

BjDA1

RjDATA (4bits)

BiDATA (4bits)

GiDATA (4bits)

RiDATA (4bits)

| FORM REPRESENTA-REPRESENTA-REPRESENTA-RE (3bits) (7or8its) (7or8bits) |

|-----------------------------------------------------------------------|

|                                                                       |

| FORM FORM DATA DATA (3bits)                                           |

|                                                                       |

|       | 101     |         | ) i mam |         | 71.40   |         |

|-------|---------|---------|---------|---------|---------|---------|

| ~~~~~ | BjDATA  | GjDATA  | RjDATA  | BiDATA  | GiDATA  | RiDATA  |

|       | (5bits) | (6bìts) | (5bits) | (5bits) | (6bíts) | (5bíts) |

TOTAL 64 BITS

(DATA COMPRESSION

RATIO 66 70%)

COMPRESS I ON 2) PIXEL

|                       |           |    | 7177 | JE UMIR     | <u></u>      | 4             |                   |                       | B            | 7   | <b></b>  |

|-----------------------|-----------|----|------|-------------|--------------|---------------|-------------------|-----------------------|--------------|-----|----------|

|                       |           |    |      | 12          | <u>ප</u><br> | -             |                   |                       | G            | -   |          |

|                       |           |    | 2    | 3 1         | <u>~~</u>    | <u> </u>      |                   |                       |              |     | , l      |

|                       |           |    |      |             |              | [ATIV         | <u>13</u>         |                       |              | ပ   |          |

|                       |           |    |      | DING        | /TRUNCATION  | → REPRESENTAI | VALU              |                       | TRUNCATION I | 1   |          |

|                       |           |    |      | <b>8</b>    | TRU          | <b>}</b>      | ì                 |                       | B            | 130 | 17       |

|                       |           |    |      |             | <u></u>      | 35            |                   |                       | ß            | 14  | 16       |

|                       |           |    |      |             | හ            | 2             |                   |                       | 22           | 14  | 115      |

|                       |           |    |      |             | ∝            | 55            |                   |                       |              | ပ   | ದ        |

|                       |           |    |      | ,           | $ADD\alpha$  | 1             |                   |                       | ADDa         | 1   |          |

|                       |           | B  | 30   | 39          |              | 35            | <br>~             | İ                     | В            | 100 | 2        |

|                       |           | G  | 2    | <del></del> | >            | 2             | SMALER            | 1                     | 9            | 4   | <b>,</b> |

|                       |           | ~~ | 20   | 59          | <b></b> >    | 55            | LARGER :          | മ                     | ~            | 4   | 100      |

|                       |           |    | A    | മ           |              | 1)/2          | COMPARISON WITH B | MHICH IS LARGER?      |              | ပ   | ۵        |

| NO IS                 |           |    |      |             |              | (A+B+1)/2     | RISON             | 1<br>1<br>1<br>1<br>1 |              |     |          |

| COMPRESSION           | DATA      | 8  | 30   | 39          | 100          | 2             | COMPA             | SE SE                 |              |     |          |

|                       | IMAGE DA' | 9  | 2    | ,           | 4            | <b>*</b> ~~   | ÿ                 |                       |              |     |          |

| 2) P1X                |           | 22 | 50   | 59          | 4            | 100           | A A A             | CORRELATION           |              |     |          |

| $(2+1 \times 2)$ PIXE | (ORIGINAL |    | <<   | മ           | ပ            | <b>a</b>      | DIVELO            | HIGH CO               |              |     |          |

$\widehat{\widehat{\mathbf{a}}}$

(DECOMPRESSE

5 BASED LARGER AND B ED DATA (A, 4 32 4 32 32

51

DATA (C, 102 32  $\alpha$ S S S SMILER (DECOMPRESSED  $\mathfrak{Q}$  $\varpi$ 4 |₩| ARGER  $\odot$ 97 SUBTRACT & SUBTRACT &  $\infty$  $\alpha$ SMALLER 16  $\mathfrak{Q}$ ARGER  $\alpha$ EET BIT SHIFT LEFT BIT SHIFT  $\widehat{\widehat{\mathbf{a}}}$ DECOMPRESS 10N DATA (C, D) > DATA (A, SMALLER REPRESENT R G TATTIVE (COMPRESSED  $(2+1 \times 2)$  PIXEL (C)

7 . . .

COMPRESSION FORM REPRESENTA-REPRESENTA-REPRESENTA-REPRESENTA-REPRESENTA-REPRESENTA-REPRESENTA-REPRESENTA-REPRESENTA-REPRESENTA REPRESENTA-REPRESENTA-REPRESENTA-REPRESENTA-REPRESENTA-REPRESENTA REPRESENTA REPRE

ري الما الما

A-REPRESENTA-REPRESENTA-REPRESENTA-REPRESENTA-RECOGNITION COMPARISON #1(8 or #1(8 or #1(8 or #2(8 or #2(8 or #2(7 or 0.000)))) = 101 or 1

T%0

RECOGNITION DATA

A A A

ಥ

COMPRESS 10N

2) PIXEL

SMALLER ARGER 56 ET BIT SEIF LARGER WITH B  $\widehat{\widehat{\mathbf{a}}}$ DATA (A. SMALLER (COMPRESSED Ç  $(2 \times 2)$  PIXEL ARGER REPRESENTATIVE VALUES #1

OMPARISON L

WITH B

WHIGH IS

LARGER?

(C, D) B 177 DATA (A. DATA 2 4 4 (DECOMPRESSED (DECOMPRESSED 102 51 5 BASED LARGER AND D OR -5 BASED H IS LARGER EN A AND B < B |ပ|င N WEIGH I LARGER む ADD +5 O SMIGHT RETWEED SMALLER ARGER LARGER ADD  $\infty$  $\circ$ 33 8  $\mathfrak{A}$ ဗြ SMALLER 82 M  $\Box$  $\hat{\boldsymbol{\Omega}}$ ARGER. 102 56  $\mathfrak{a}$  $\alpha$ LARGER COMPARISON L COMPARISON WITH B MARGER? MAICH IS LARGER? SUBTRACT & SUBTRACT & ARGER 9{  $\Diamond$  $\infty$ SMALLER ARGERL 92  $\infty$ EFT BIT SAIFT SMALLER ARGERSMALLER WITH B WHICH IS LARGER? (COMPRESSED DATA(C, D)) B 2 23  $\mathfrak{S}$ 28 REPRESEN-TATIVE VALUES #2 WITH B WITH B

Cr' (10bits)

Cb/ (10bits)

ADDRESS (2bits)

Ydist2 (4bits)

Ydist1 (4bits)

Ymin (10bits)

COMPRESSION TYPE RECOGNITION BITS (4bits)

(DATA COMPRESSION RATIO 50%)

1 S A

(DATA COMPRESSION RATIO 66, 7%)

REDING (1bit) **Cr**′ (12bits) Cb/ (12bits) ADDRESS (2bits) Ydist2 (7bits) Ymin (12bits) COMPRESSION TYPE RECOGNITION BITS

- CO

Ydist

Ydist0,

Ydist2,

IMAGE DATA)

(ORIGINAL

A B O D

(8bits/subpixel) 4-0 2 9

▼ B C D

COMPRESS 10N  $(4 \times 1)$  PIXEL

DATA (8bits/sub 2 2 ~ 4 -(DECOMPRESSED 0 3 0 T 0 < m ∪ □ 82 82 4 A B O D

DECOMPRESSION

Fig. 17

|      |    | X1X0 |    |    |    |

|------|----|------|----|----|----|

|      |    | 00   | 01 | 10 | 11 |

| Y1Y0 | 00 | 15   | 05 | 01 | 11 |

|      | 01 | 00   | 10 | 14 | 04 |

|      | 10 | 07   | 09 | 13 | 02 |

|      | 11 | 08   | 06 | 03 | 12 |

Fig. 18

# DISPLAY APPARATUS AND DISPLAY APPARATUS CONTROL CIRCUIT

# CROSS REFERENCE TO RELATED APPLICATIONS

This is a National Stage of International Application No. PCT/JP2012/053942, filed Feb. 20, 2012, claiming priority from Japanese Patent Application No. 2011-073478, filed Mar. 29, 2011, the contents of all of which are incorporated herein by reference in their entirety.

#### TECHNICAL FIELD

The present invention relates to a display apparatus and a display apparatus control circuit, more particularly, to data transmission from a display apparatus control circuit to a display device driver.

#### BACKGROUND ART

Recently, panel display apparatuses, such as liquid crystal display apparatuses, have become required to display various contents. Examples of contents displayed on panel 25 display apparatuses include still images, 2D (2-dimensional) moving images and 3D (3-dimensional) moving images.

The inventors consider that, in displaying various contents thus described, it is appropriate to switch the frame rate (the number of frame images per unit time) in response to 30 the contents. In the case that a liquid crystal display apparatus is used as a television, use of a frame rate corresponding to the double speed (120 Hz) successfully results in displaying images with reduced blur when contents consisting of still images or including many still images (for 35 example, web contents) are displayed. For displaying a 2D moving image, on the other hand, it is preferable to use a higher frame rate, such as a frame rate corresponding to the triple speed (180 Hz) in order to reduce blur. For displaying a 3D moving image, in which left- and right-eye images are 40 alternatively displayed, it is preferable to use a further higher frame rate, such as a frame rate corresponding to the quadruple speed (240 Hz). Use of a high frame rate independent of the contents may be acceptable if only the image quality is considered; however, the inventors consider that it 45 is preferable that the frame rate is variable, instead of displaying images permanently with a high frame rate, since a high frame rate undesirably increases the power consumption of the display apparatus.

One issue the inventors have recognized in developing a 50 display apparatus configured to vary the frame rate is that the necessary transmission rate of the display data widely varies depending on the frame rate. For example, the transmission rate of the display data for displaying images at the frame rate corresponding to the triple speed is one and a half times 55 as much as that for displaying images at the frame rate corresponding to the double speed. The change in the transmission rate of the display data causes two problems. One is that the anti-EMI design of the printed circuit board and the transmission cables is made difficult. The changes in 60 the transmission rate of the display data enlarge the frequency range of the EMI and this makes it difficult to take anti-EMI measures. Another problem is that, when a clock signal used in the data transmission is generated by a PLL (phase locked loop) or a DLL (delay locked loop), it is 65 necessary to re-lock the PLL or DLL when the transmission rate of the display data is changed. The transmission of the

2

display data is not allowed until the re-lock of the PLL or DLL is completed and this is not preferable for displaying images.

A disclosure of transmission of display data in a display apparatus is found, for example, in Japanese Patent Application Publication No. 2010-141775 A. This publication discloses a technique in which display data are stored in a frame memory after the display data are compressed and a display panel is driven in response to decompressed data obtained by decompressing the compressed data read from the frame memory. In this technique, the data compression ratio is adjusted depending on the display image. The data compression ratio is set high for reducing the power consumption for a display image which does not experience severe image quality deterioration even when the data compression ratio is large. For a display image which suffers from severe image quality deterioration when the data compression ratio is large, the data compression ratio is set 20 low to maintain a sufficient image quality in displaying images in response to the decompressed data.

Also, Japanese patent gazette No. 4,507,265 B also discloses a technique in which display data are stored in a memory after the display data are compressed. This gazette discloses that the compression method is selected in response to the correlation among pixel data of four pixels.

The above-described techniques, however, do not address the changes in the necessary transmission rate of the display data, which are accompanied by the changes in the frame rate.

#### CITATION LIST

#### Patent Literature

[Patent Literature 1] Japanese Patent Application Publication No. 2010-141775 A

[Patent Literature 2] Japanese Patent Gazette No. 4507265

[Patent Literature 2] Japanese Patent Gazette No. 4507265

#### **SUMMARY**

Therefore, an objective of the present invention is to provide a display apparatus and a display apparatus control circuit which address the problem of changes in the transmission rate of the display data accompanied by changes in the frame rate.

In one aspect of the present invention, a display apparatus includes: a display device; a display device driver which drives the display device; a compression section adapted to an operation of generating compression data by compression processing performed on image data; and a transmission section which, when receiving compressed data from the compression section, transmits the compressed data to the display device driver by using a serial data signal. The compression section performs the compression processing with a data compression ratio selected in response to a frame rate with which the display device driver drives the display device. The display device driver receives the serial data signal from the transmission section, generates decompressed data by decompressing the compressed data transmitted by the serial data signal, and drives the display device in response to the decompressed data. The data compression ratio used in the compression processing is set so that the transmission rate of the serial data signal from the transmission section to the display device driver is kept constant independently of the frame rate.

In another aspect of the present invention, a display apparatus control circuit which controls a display device driver driving a display device includes: a compression section adapted to an operation of generating compression data by compression processing performed on image data; 5 and a transmission section which, when receiving compressed data from the compression section, transmits the compressed data to the display device driver by using a serial data signal. The compression section performs the compression processing with a data compression ratio selected in response to a frame rate with which the display device driver drives the display device. The display device driver receives the serial data signal from the transmission section, generates decompressed data by decompressing the 15 data; compressed data transmitted by the serial data signal, and drives the display device in response to the decompressed data. The data compression ratio is set so that the transmission rate of the serial data signal from the transmission section to the display device driver is kept constant inde- 20 pendently of the frame rate.

The present invention provides a display apparatus and a display apparatus control circuit which address a problem of changes in the transmission rate of display data accompanied by changes in the frame rate.

#### BRIEF DESCRIPTION OF DRAWINGS

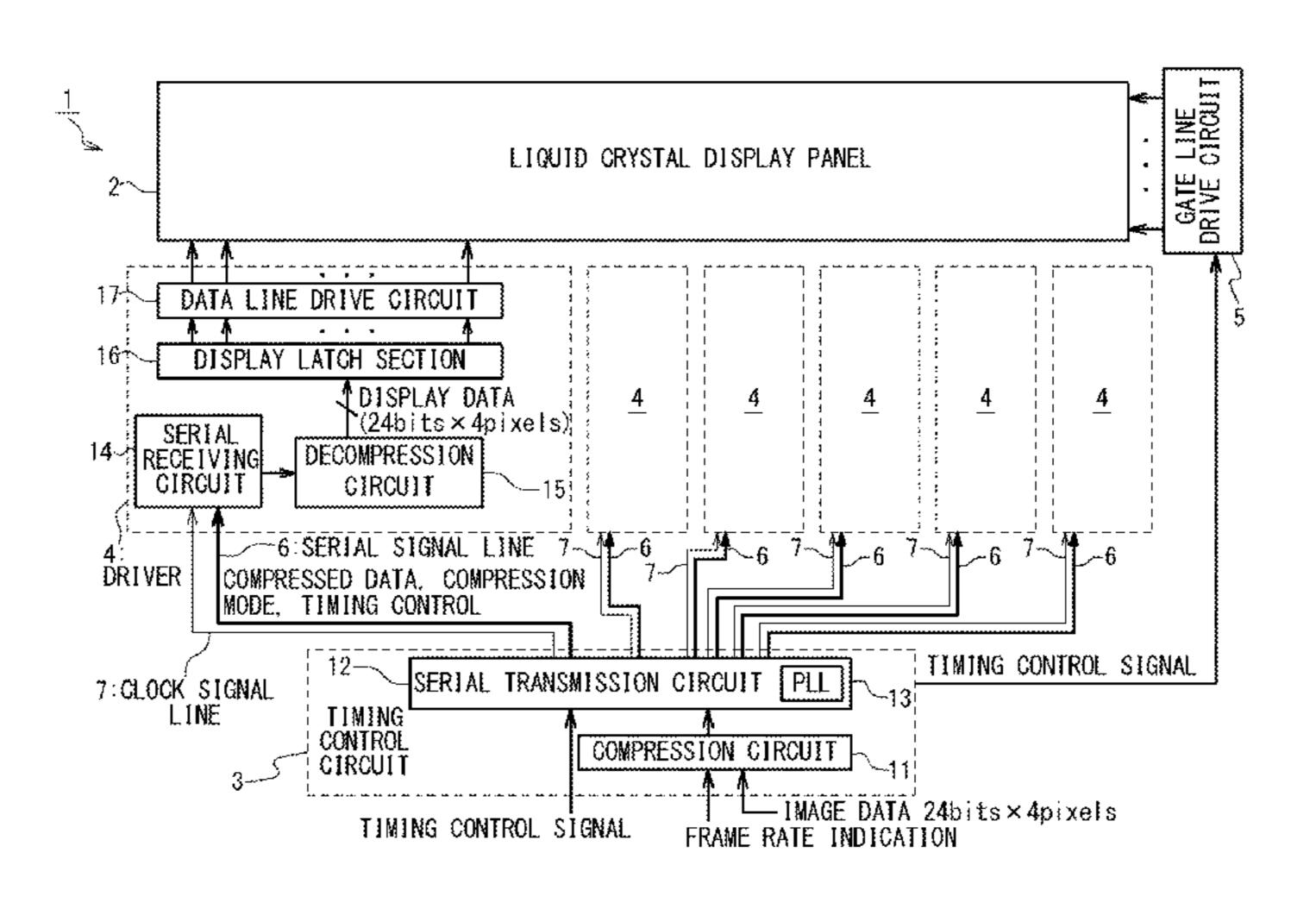

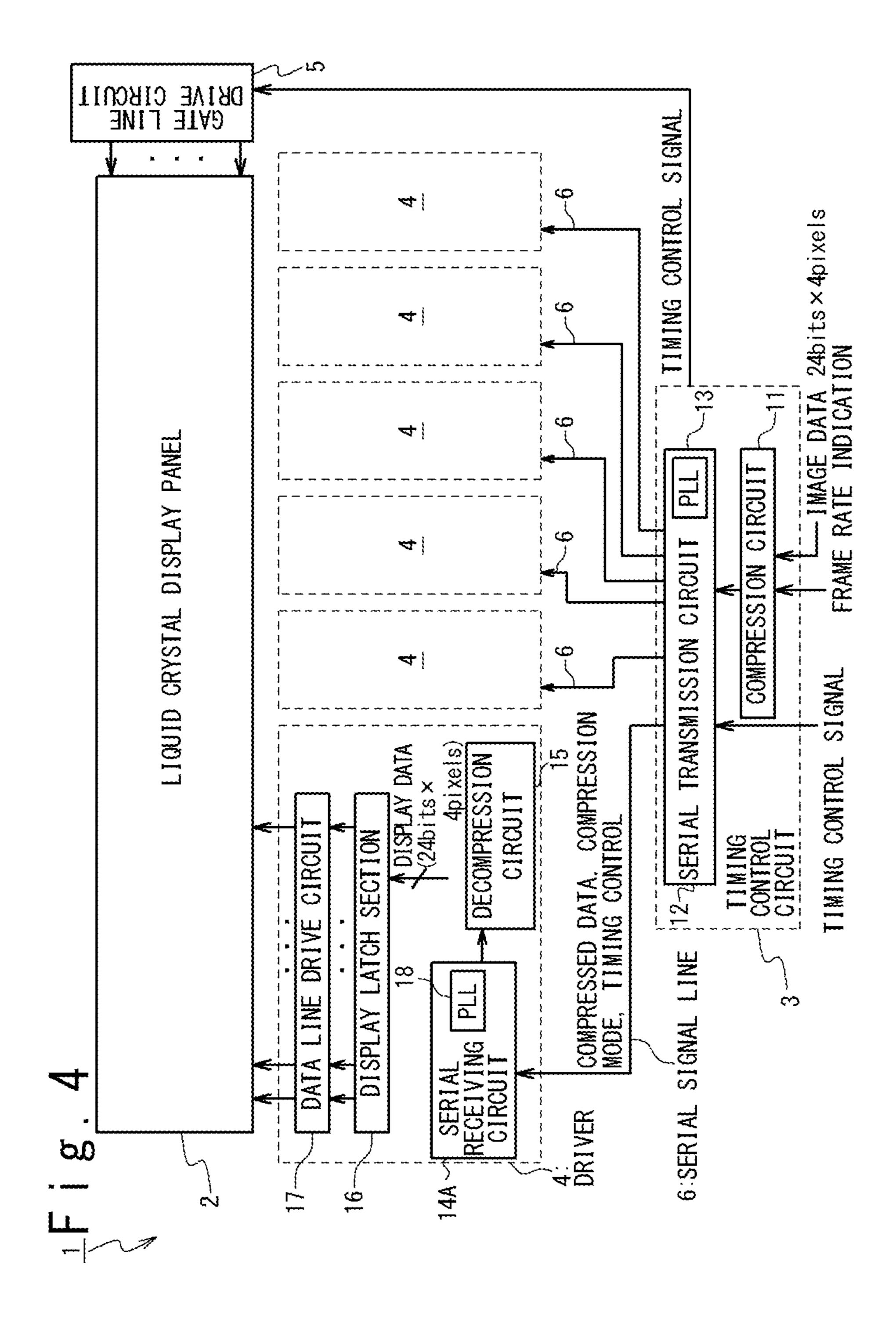

- FIG. 1 is a block diagram illustrating the configuration of a display apparatus of a first embodiment of the present 30 invention;

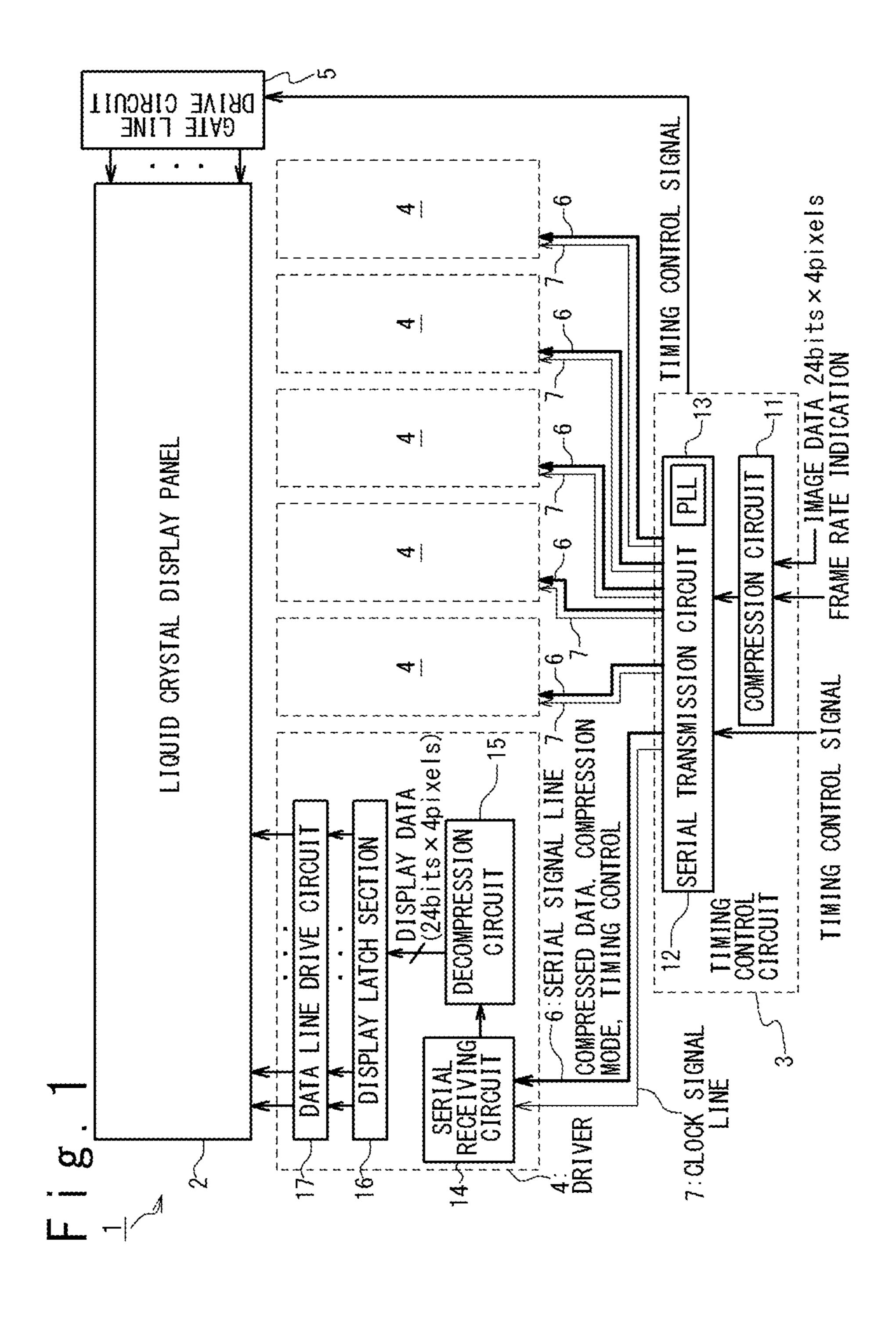

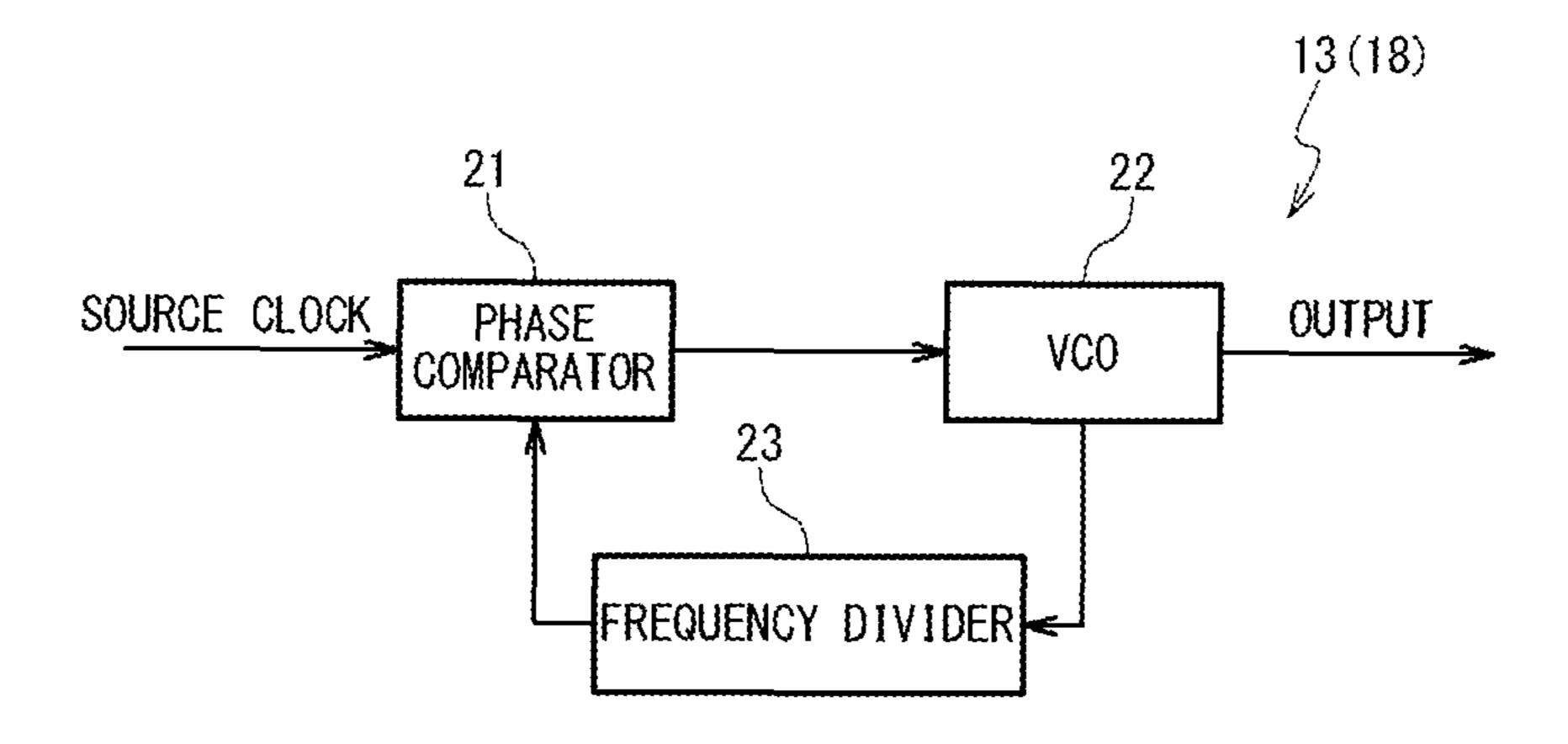

- FIG. 2 is a conceptual illustration illustrating the relation among kinds of contents, the frame rate and the data compression ratio;

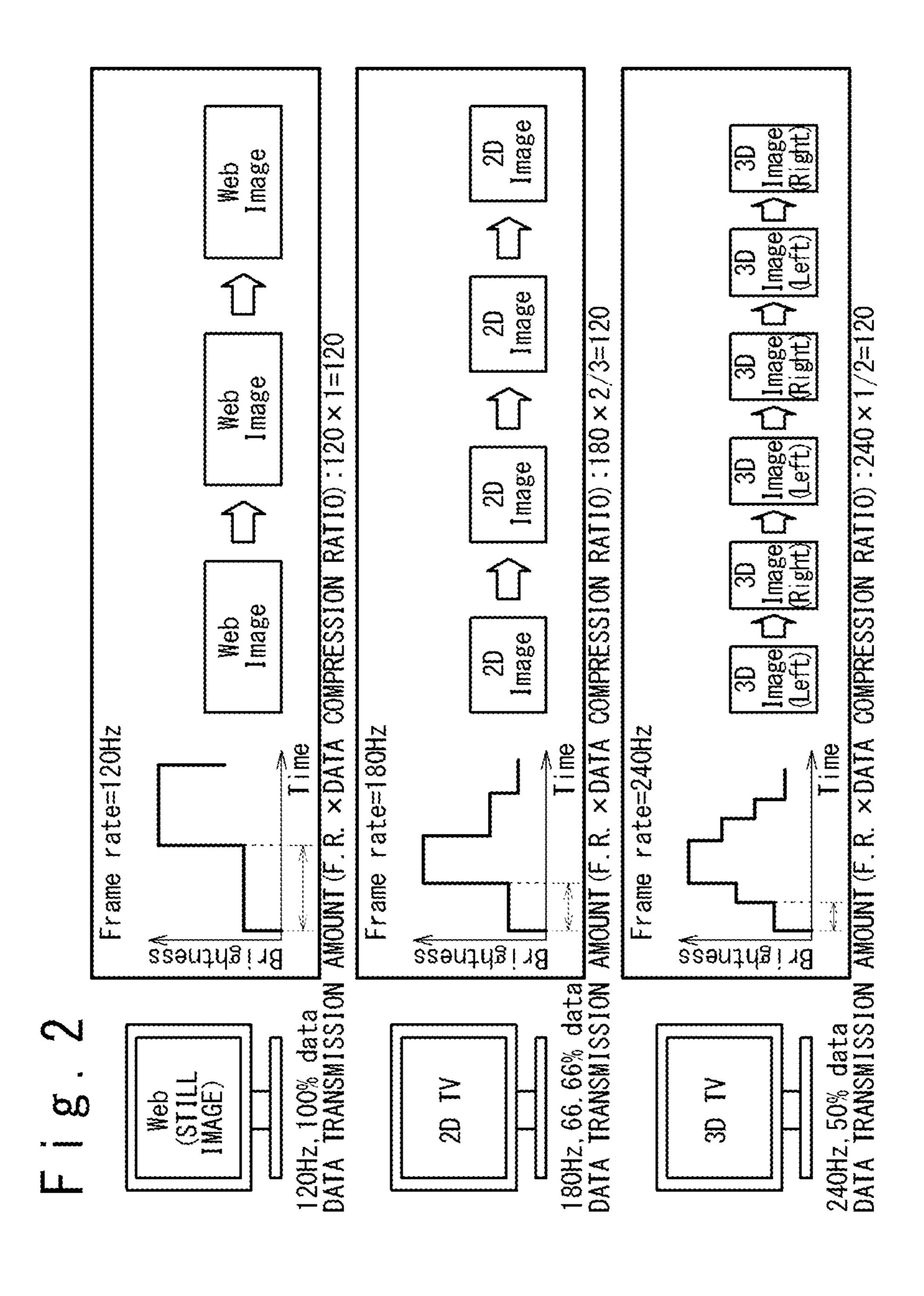

- FIG. 3A is a block diagram illustrating a circuit configu- 35 ration of a commonly used PLL circuit;

- FIG. 3B is a block diagram illustrating a preferred circuit configuration of a PLL circuit of the first embodiment;

- FIG. 4 is a block diagram illustrating the configuration of a display apparatus of a second embodiment of the present 40 invention;

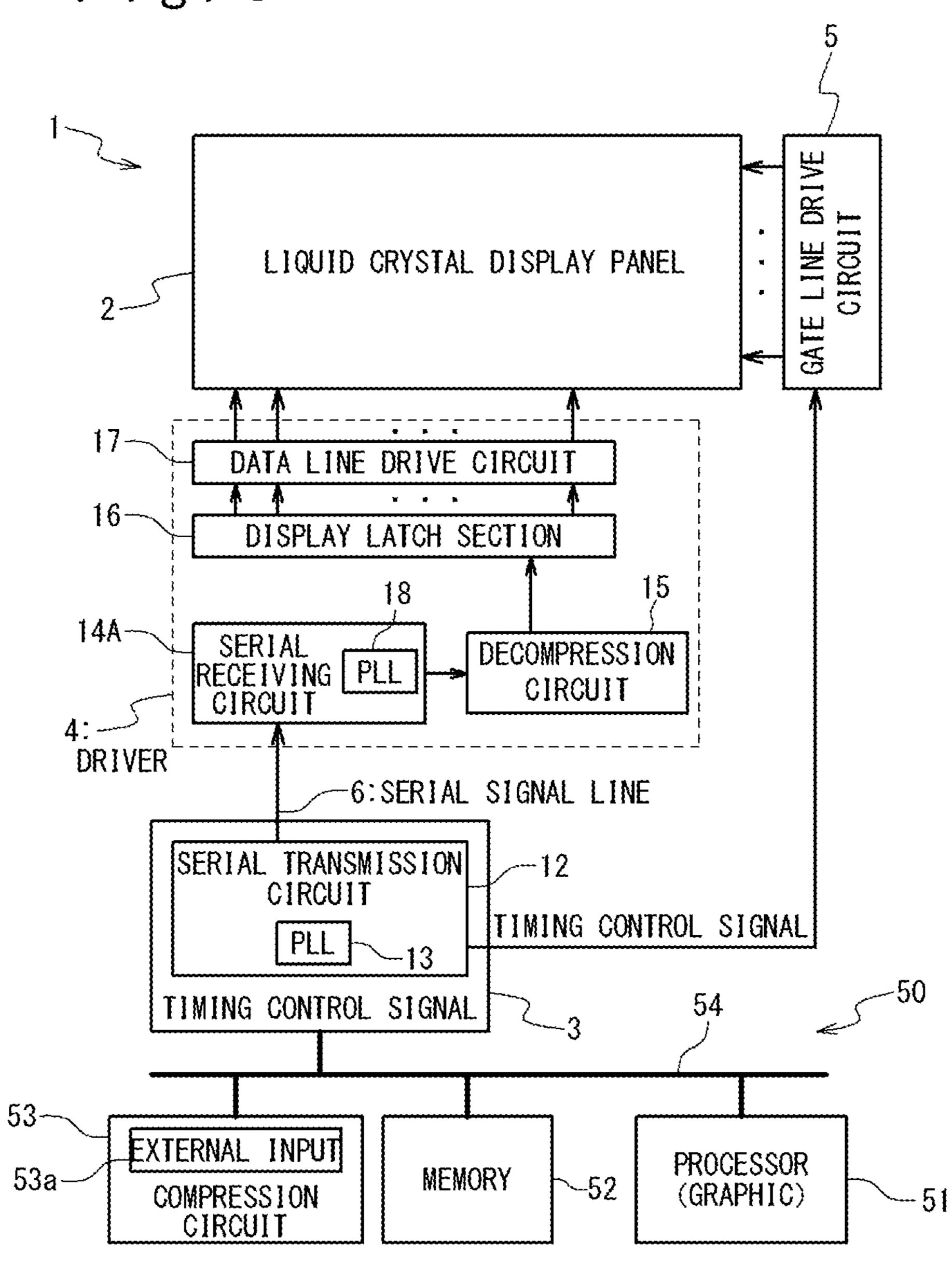

- FIG. 5 is a block diagram showing the configuration of a display apparatus of a third embodiment of the present invention;

- FIG. 6 is a conceptual illustration showing an example of 45 the configuration of a block, which is unit data of compression processing;

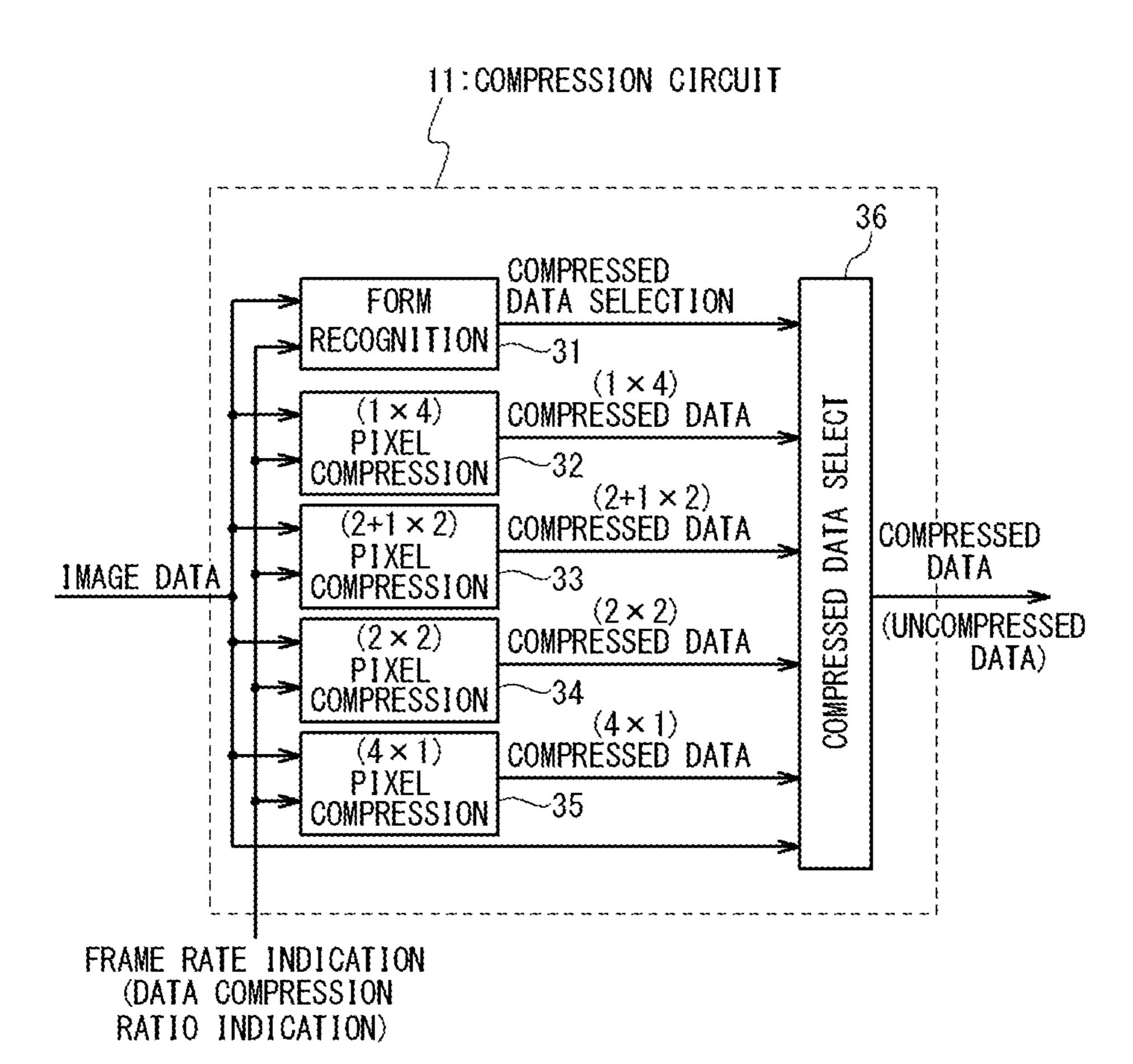

- FIG. 7A is a block diagram illustrating an example of the configuration of a compression circuit;

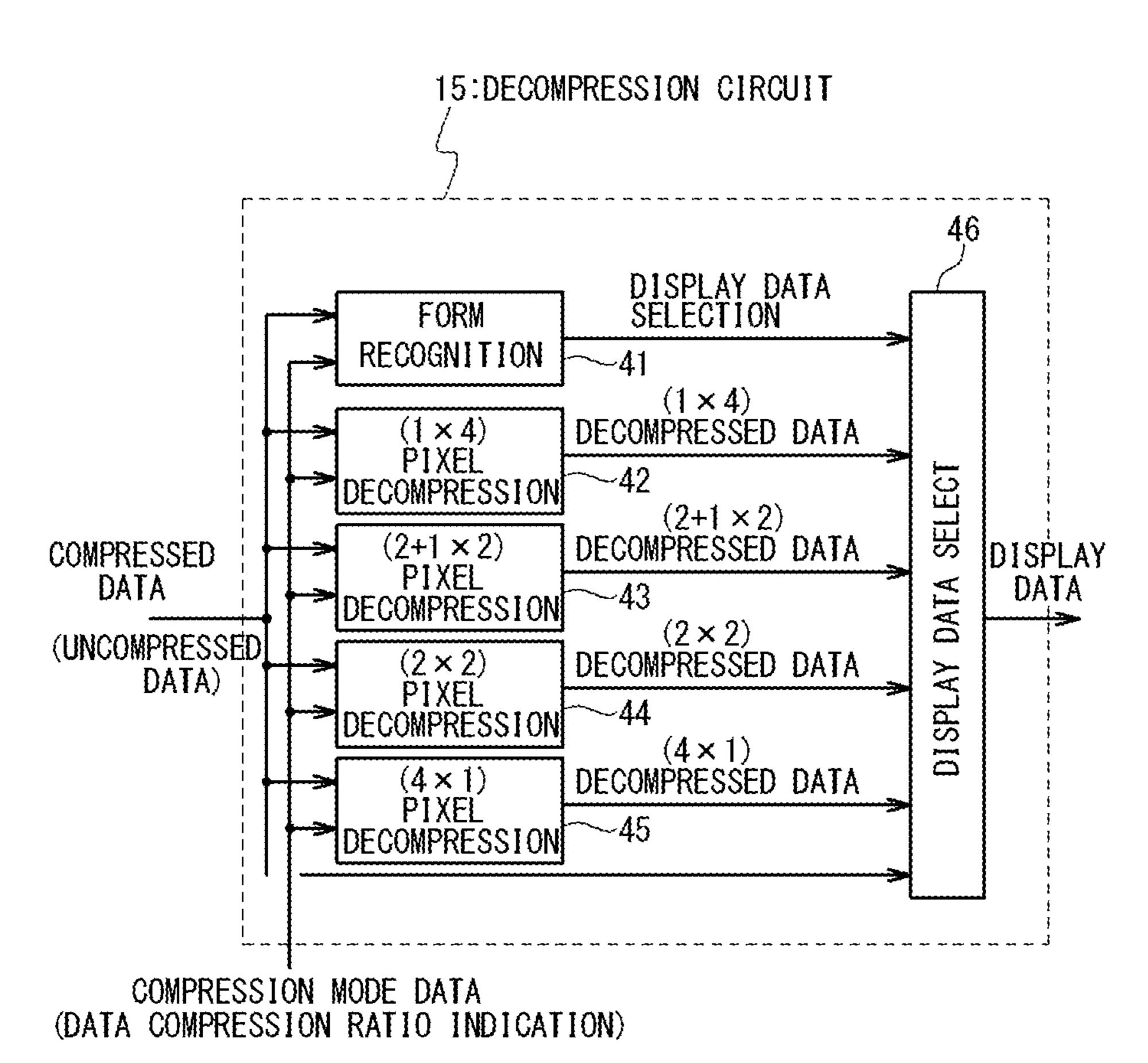

- FIG. 7B is a block diagram illustrating an example of the 50 configuration of a decompression circuit;

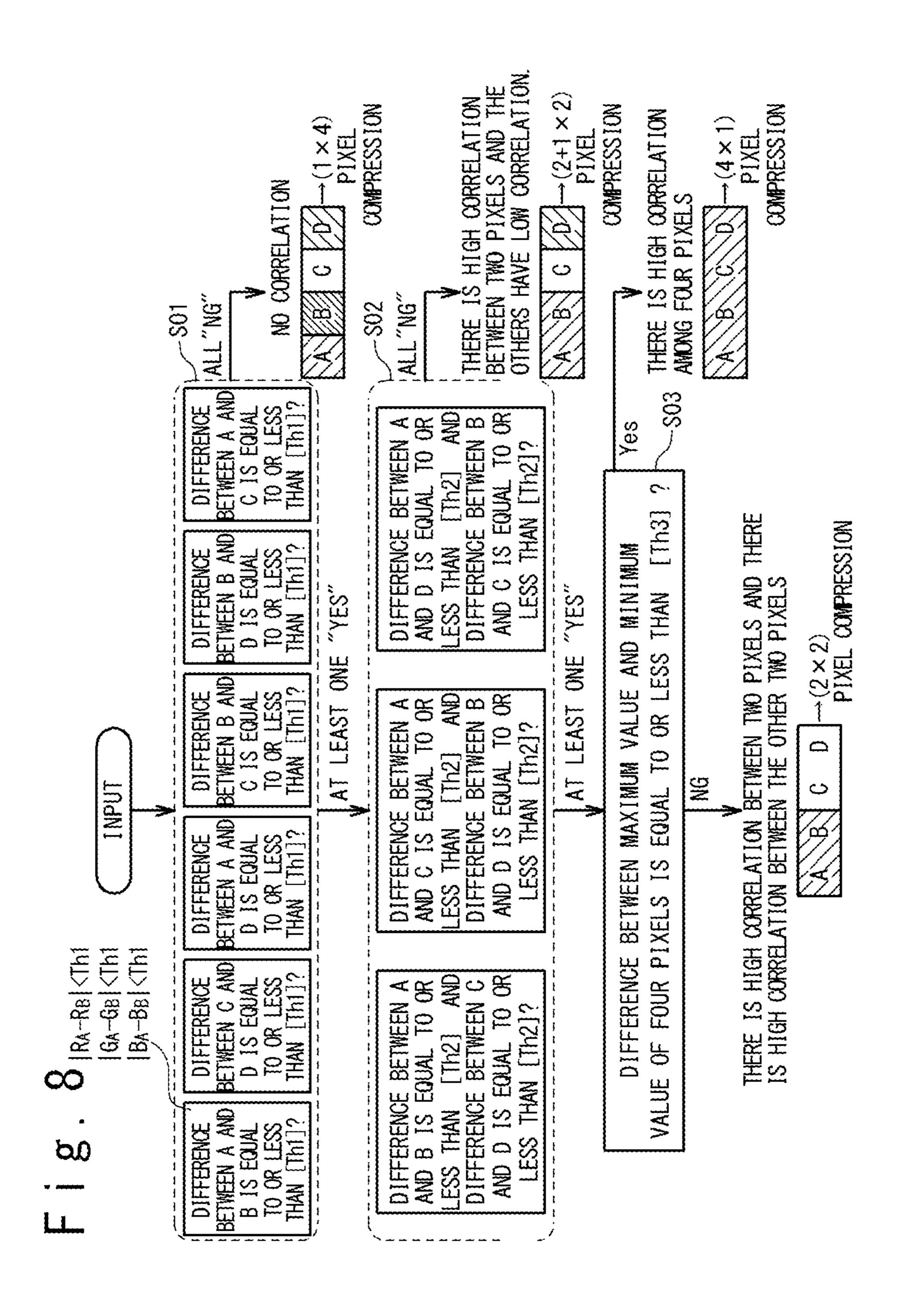

- FIG. 8 is a flowchart illustrating an example of the procedure of selecting a compression method;

- FIG. 9A is a diagram illustrating the format of  $(1\times4)$  pixel compressed data for a data compression ratio of 50%;

- FIG. 9B is a diagram showing the format of (1×4) pixel compressed data for a data compression ratio of 66.7%;

- FIG. 10A is a conceptual illustration illustrating the processing contents of  $(1\times4)$  pixel compression;

- FIG. 10B is a conceptual illustration illustrating the 60 contents of decompression processing of (1×4) compressed data;

- FIG. 11A is a diagram illustrating the format of  $(2+1\times2)$  pixel compressed data for a data compression ratio of 50%;

- FIG. 11B is a diagram illustrating the format of (2+1×2) 65 pixel compressed data for a data compression ratio of 66.7%;

4

- FIG. 12A is a conceptual illustration illustrating the processing contents of  $(2+1\times2)$  pixel compression;

- FIG. 12B is a conceptual illustration illustrating the contents of decompression processing of (2+1×2) compressed data;

- FIG. 13A is a diagram illustrating the format of  $(2\times2)$  pixel compressed data for a data compression ratio of 50%;

- FIG. 13B is a diagram illustrating the format of (2×2) pixel compressed data for a data compression ratio of 66.7%;

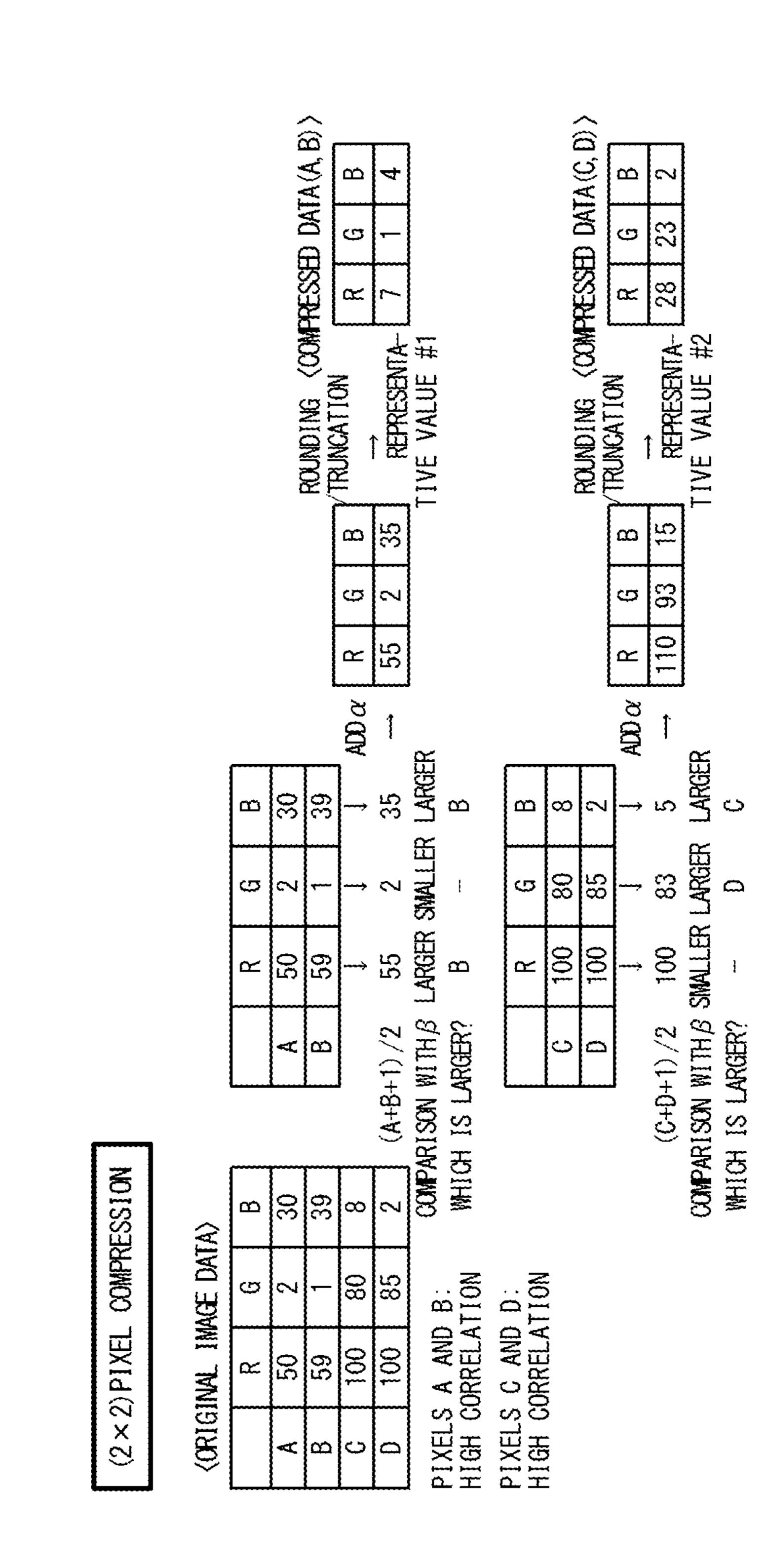

- FIG. 14A is a conceptual illustration illustrating the processing contents of  $(2\times2)$  pixel compression;

- FIG. 14B is a conceptual illustration illustrating the contents of decompression processing of (2×2) compressed data:

- FIG. 15A is a diagram illustrating the format of  $(4\times1)$  pixel compressed data for a data compression ratio of 50%;

- FIG. **15**B is a diagram illustrating the format of (4×1) pixel compressed data for a data compression ratio of 66.7%;

- FIG. 16A is a conceptual illustration illustrating the processing contents of  $(4\times1)$  pixel compression;

- FIG. **16**B is a conceptual illustration illustrating decompression processing of compressed data compressed by (4×1) pixel compression;

- FIG. 17 is a diagram illustrating an example of a basic matrix used for the generation of error data  $\alpha$ ; and

- FIG. 18 is a conceptual illustration illustrating another example of a block, which is unit data of compression processing.

#### DESCRIPTION OF EMBODIMENTS

#### First Embodiment

FIG. 1 is a block diagram showing the configuration of a display apparatus according to a first embodiment of the present invention. In this embodiment, a display apparatus according to the present invention is applied to a liquid crystal display apparatus 1. Although an embodiment in which the present invention is applied to the liquid crystal display apparatus 1 is described in the following, it would be apparent to the person skilled in the art that the present invention is applicable to other display apparatuses (such as, PDP (plasma display panel) display apparatuses and organic EL (electroluminescence) display apparatuses).

The liquid crystal display apparatus 1 is configured to display images on a liquid crystal display panel 2 in response to image data transmitted from an external device. Placed in the liquid crystal display panel 2 are pixels, data lines (or signal lines) and gate lines (or scan lines). Each pixel includes an R subpixel (a subpixel for displaying red), a G subpixel (a subpixel for displaying green) and a B subpixel (a subpixel for displaying blue). Each subpixel is placed at the intersection of the corresponding data line and gate line. In the following, pixels corresponding to the same gate line are referred to as pixel line.

In this embodiment, image data are fed as data representing the grayscale level of each of the R subpixel, the G subpixel and the B subpixel with eight bits, that is, data representing the grayscale levels of each pixel with 24 bits. It should be noted that the number of bits of the image data is not limited to these numbers.

The liquid crystal display apparatus 1 includes a timing control circuit 3, drivers 4 and a gate line drive circuit 5. The timing control circuit 3 controls the drivers 4 and the gate line drive circuit 5 so that desired images are displayed on

the liquid display panel 2. The drivers 4 drive the data lines of the liquid crystal display panel 2 and the gate line drive circuit 5 drives the gate lines of the liquid crystal display panel 2. In this embodiment, the timing control circuit 3, the drivers 4 and the gate line drive circuit 5 are mounted as 5 separate ICs (integrated circuits). The drivers 4 are adapted to vary the frame rate of image display on the liquid crystal display panel 2. As described above, the configuration in which the frame rate is variable is useful for appropriately displaying various contents (such as, the WWW, 2D (2-dimensional) moving images and 3D (3-dimensional) moving images) with reduced power consumption.

In this embodiment, a plurality of drivers 4 are provided in the liquid crystal display apparatus 1, and the timing control circuit 3 and each driver 4 is connected with a 15 peer-to-peer connection. Specifically, the timing control circuit 3 and each driver 4 is connected via a serial signal line 6 and a clock signal line 7 which are dedicated to each driver 4. The data transmission between the timing control circuit 3 and each driver 4 is achieved by serial data 20 transmission via the serial signal line 6. Although an architecture in which a timing controller and drivers are connected by a bus is commonly known with respect to a liquid crystal display apparatus incorporating a plurality of drivers, the architecture of this embodiment in which the timing 25 control circuit 3 and each driver 4 is connected with a peer-to-peer connection is useful, since such architecture allows reducing the transmission rate necessary for data transmission between the timing control circuit 3 and each driver 4.

Schematically, the timing control circuit 3 has two roles. First, the timing control circuit 3 performs an overall timing control of the liquid crystal display apparatus 1 in response to timing control signals fed from an external device. In detail, the timing control circuit 3 controls the operation 35 timings of the drivers 4 and the gate line drive circuit 5 by transmitting various control data to each driver 4 via the serial signal line 6 and transmitting timing control signals to the gate line drive circuit 5. The transmission of the control data from the timing control circuit 3 to each driver 4 is 40 performed in the blanking period of each horizontal synchronization period. The control data transmitted from the timing control circuit 3 to each driver 4 include polarity reversal data and timing control data. Here, the polarity reversal data are data which specifies polarities of drive 45 signals fed to the data lines. On the other hand, the timing control data include data which notify each driver of the starts of each vertical synchronization period and each horizontal synchronization period, data which indicate a data start (that is, data instructing each driver 4 to latch 50 image data) and data which indicate to start driving the data lines. Each driver 4 operates at operation timings in response to the timing control data. The control of the frame rate of image display on the liquid crystal display panel 2 is achieved by using these timing control data.

Second, the timing control circuit 3 feeds image data to each driver 4 via the serial signal line 6. Here, the timing control circuit 3 has the function of feeding image data to each driver 4 after performing compression processing on the image data. The compression processing on image data 60 will be described later in detail. The image data are fed to each driver 4 in the display period in each horizontal synchronization period. A detailed description is given below of the timing control circuit 3 and the drivers 4.

The timing control circuit 3 includes a compression 65 circuit 11 and a serial transmission circuit 12. The compression circuit 11 generates compressed data by performing

6

compression processing on the image data. In this embodiment, the image data are compressed in units of four pixels. This implies that image data are compressed in units of 96 bits, since image data corresponding to one pixel consists of 24 bits as described above.

As described above, the data compression ratio of the compression processing in the compression circuit 11 is variable. In this Specification, the data compression ratio is defined as the ratio of the number of bits of compressed data to the number of bits of the original image data. When compressed data of 48 bits are generated from image data of 96 bits, the data compression ratio is 50% (=1/2). In this embodiment, the data compression ratio of the compression processing is selected from 100% (=1), 66.7% (=2/3) and 50% (=1/2). The data compression ratio of 100% means that the compression circuit 11 outputs the image data as they are without performing compression processing; in the following, however, the data outputted from the compression circuit 11 are referred to as compressed data, including the case that the data compression ratio is 100%.

The compression circuit 11 is fed with frame rate indication data which indicate the frame rate, and the data compression ratio of the compression processing is selected in response to the frame rate indication data. In other words, the data compression ratio is adjusted in response to the frame rate of the image display on the liquid crystal display panel 2. This aims at keeping the transmission rate of the serial data transmission constant by varying the data compression ratio in response to the frame rate as described later. When the frame rate is high, for example, it is required to feed image data of a large data amount to each driver 4 and therefore the data compression ratio is set high to keep the transmission rate of the serial data transmission constant. The compression circuit 11 feeds the compressed data generated by the compression processing and compression mode data indicating the data compression ratio to the serial transmission device 12.

The serial transmission circuit 12 generates a serial data signal which incorporates the compressed data, the compression mode data received from the compression circuit 11, and timing control data to be transmitted to each driver 4, and transmits the serial data signal with a serial data communication. In this embodiment, the serial transmission circuit 12 includes a PLL circuit 13 generating a clock signal and transmits the serial data signal to each driver 4 via the serial signal line 6 in synchronization with the generated clock signal. Additionally, the serial transmission circuit 12 transmits the clock signal generated by the PLL circuit 13 to each driver 4 via the clock signal line 7.

On the other hand, each driver 4 includes a serial receiving circuit 14, a decompression circuit 15, a display latch section 16 and a data line drive circuit 17. The serial receiving circuit 14 receives the serial data signal transmitted from the serial transmission circuit 12 in synchronization 55 with the clock signal fed via the clock signal line 7, and performs sampling on the serial data signal to extract the compressed data, the compression mode data and the timing control data. The extracted compressed data compression mode data and timing control data are forwarded to the decompression circuit 15. The decompression circuit 15 decompresses the received compressed data to generate display data and sequentially forwards the generated display data to the display latch section 16. In this operation, the decompression circuit 15 recognizes the data compression ratio from the compression mode data and decompresses the compressed data in response to the recognized data compression ratio. The display latch section 16 sequentially

latches the display data received from the decompression circuit 15. The display latch section 16 of each driver 4 stores the display data of pixels corresponding to the each driver 4 out of pixels of a pixel line. The data line drive circuit 17 drives the data lines in response to the display data latched by the display latch section 16. In response to the display data stored in the display latch section 16, the respective data lines corresponding to the display data are driven in each horizontal synchronization period. It should be noted that, although the configuration of only one driver 1 4 is illustrated in FIG. 1, other drivers 4 are similarly structured.

Various known compression processing and decompression process may be used as the compression processing performed in the compression circuit 11 and the decompression processing performed in the decompression circuit 15. It should be noted, however, that compression processing and decompression processing preferred for the liquid crystal display apparatus 1 of this embodiment are described in detail later.

Next, the operation of the liquid crystal display apparatus 1 of this embodiment is described. As illustrated in FIG. 2, the frame rate of the image display on the liquid crystal display panel 2 is variable in the liquid crystal display apparatus 1 of this embodiment. In this embodiment, the 25 frame rate is selected from 120 Hz (the double speed), 180 Hz (the triple speed) and 240 Hz (the quadruple speed). The frame rate is indicated by the frame rate indication data fed to the timing control circuit 3 and the timing control circuit 3 and the drivers 4 operate to display images at the frame 30 rate indicated by the frame rate indication data.

In this embodiment, the frame rate is switched in response to the contents displayed on the liquid crystal display panel 2. When still images or contents frequently including still images such as the web are displayed, the frame rate is set 35 to 120 Hz. Still images, which do not cause a severe problem in terms of image blur, are displayed at a relatively low frame rate in order to reduce the power consumption. When 2D moving images are displayed, on the other hand, the frame rate is set to a higher value, more specifically, 180 Hz 40 to reduce blur. When 3D moving images, which require alternately displaying left- and right-eye images, are displayed, the frame rate is set to a further higher value, more specifically, 240 Hz.

configured to switch the data compression ratio of the compression circuit 11 in response to the switching of the frame rate, and thereby the transmission rate of the serial data transmission from the timing control circuit 3 to each driver 4 is kept constant. In this embodiment, the data 50 compression ratio is switched so that the product of the data compression ratio and the frame rate is kept constant independently of the frame rate. In detail, the data compression ratio is set to 100% (=1) for the frame rate of 120 Hz, to 66.7% (=2/3) for the frame rate of 180 Hz and to 50% (=1/2) 55 for the frame rate of 240 Hz. It should be noted that the product of the frame rate and the data compression ratio is kept to a constant value of 120. The combination of the data compression ratio and the frame rate may be variously modified; it is important that the product of the data compression ratio and the frame rate is kept constant independently of the frame rate.

There are two advantages to keeping the transmission rate of the serial data transmission constant by adjusting the data compression ratio in response to the frame rate. First, 65 anti-EMI designs of the printed circuit board and transmission cables are facilitated. In this embodiment, since the

transmission rate of the serial data transmission is kept constant, the frequency range of the EMI is narrowed and this makes it easy to take anti-EMI measures.

Second, the need of re-locking the PLL circuit 13 is eliminated, since it is not necessary to switch the frequency band of the clock signal generated by the PLL circuit 13 in response to the frame rate. If the frame rate is switched without adjusting the data compression ratio, this necessitates increasing or decreasing the data transmission rate in the serial data transmission, causing a necessity of switching the frequency band of the clock signal. When the frame rate is switched from 120 Hz to 180 Hz with the data compression rate kept constant, the data transmission amount in the serial data transmission is increased up to one and a half times and the data transmission rate is also increased up to one and a half times. This necessitates switching the frequency band of the clock signal generated by the PLL circuit 13 to a frequency band including the frequency of one and a half times of the original frequency. One issue is that it is 20 necessary to re-lock the PLL circuit 13 when the frequency band of the clock signal generated by the PLL circuit 13 is switched. This implies the display data cannot be transmitted until the re-lock is completed, which is not preferable for displaying images. In this embodiment, it is not necessary to switch the frequency band of the clock signal generated by the PLL circuit 13, since the transmission rate of the serial data transmission is kept constant even when the frame rate is switched. This offers an advantage of eliminating the necessity of re-locking the PLL circuit 13.

The elimination of the necessity of switching the clock signal generated by the PLL circuit 13 also offers an advantage that the circuit configuration of the PLL circuit 13 can be simplified. FIG. 3A illustrates the circuit configuration of a commonly used PLL circuit and FIG. 3B illustrates the circuit configuration of the PLL circuit 13 of this embodiment. Known as a commonly known PLL circuit is a configuration which includes a phase comparator 21a VCO (voltage-controlled oscillator) 22 and a frequency divider 123 as shown in FIG. 3A. The phase comparator 21 outputs an output voltage corresponding to the phases of a source clock and an output signal of the frequency divider 123 and The VCO 22 outputs an output clock signal in response to the output voltage received from the phase comparator 21. The frequency divider 123 outputs the output signal by In addition, the liquid crystal display apparatus 1 is 45 performing frequency-dividing on the output clock signal. In general, a low pass filter (LPF) is often provided between the phase comparator 21 and the VCO 22; however, the low pass filter is not illustrated in FIG. 3A.

> In general, the frequency band of the output clock signal outputted from the VCO 22 is not so wide. Accordingly, the frequency dividing ratio of the frequency divider 123 is switched by a frequency dividing ratio adjustment circuit 123 provided in the frequency divider 123, when the frequency of the output clock signal is to be widely changed. This implies that the use of the configuration in which the frequency band of the clock signal generated by the PLL circuit 13 is switched in response to the switching of the frame rate necessitates using such a circuit configuration that the frequency dividing ratio of the frequency divider 123 is switchable as illustrated in FIG. 3A.

> In this embodiment, on the other hand, the frequency band of the clock signal generated by the PLL circuit 13 is not switched even when the frame rate is switched. This allows using a circuit configuration using a frequency divider 23 which does not have the function of switching the frequency dividing ratio as illustrated in FIG. 3B. The configuration of the frequency divider 23 can be simplified by removing the

function of switching the frequency dividing ratio from the frequency divider 23. This is advantageous in implementation of the PLL circuit 13. It should be noted that the frequency divider 23 is not necessary when a clock signal having the same frequency as the source clock is generated. In this case, the output of the VCO 22 is directly connected to the input of the phase comparator 21 or a signal of the same frequency as the output of the VCO 22 is fed to the input of the phase comparator 21 via a certain circuit (for example, a delay circuit).

A DLL (delay locked loop) circuit may be used in place of the PLL circuit **13**. Also in this case, it is not necessary to provide the DLL circuit with the function of switching the frequency band, since the transmission rate of the serial data transmission is kept constant. This contributes the simplification of the configuration of the DLL circuit.

As described above, the frame rate is switched in response to the contents displayed on the liquid crystal display panel 2 in the liquid crystal display apparatus 1 of this embodiment. Furthermore, the data compression ratio of the compression circuit 11 is switched in response to the switching of the frame rate and thereby the transmission rate of the serial data transmission from the timing control circuit 3 to each driver 4 is kept constant. This facilitates taking anti-EMI measures and also eliminates the necessity of relocking the PLL circuit 13. In addition, this embodiment eliminates the necessary of switching the frequency band of the clock signal generated by the PLL circuit 13, allowing simplification of the circuit configuration of the PLL circuit 30 13.

#### Second Embodiment

FIG. 4 is a block diagram illustrating the configuration of the display apparatus according to a second embodiment of the present invention. Used in this embodiment is an architecture in which a clock recovery is performed in each driver 4 from the serial data signal transmitted to the driver 4 via the serial signal line 6. The clock signal line 7 is not 40 provided in this embodiment. The architecture in which a clock recovery from the serial data signal is performed is effective for reducing the number of signal lines of the cable which provides connection between the timing control circuit 3 and each driver 4. One example of a serial data 45 transmission technique adapted to such architecture is LVDS (low voltage differential signaling).

In connection with such modification, a PLL circuit 18 is provided in the serial receiving circuit 14a of each driver 4 in this embodiment. The PLL circuit 18 generates a clock 50 signal synchronous with the serial data signal transmitted to the driver 4. The serial receiving circuit 14A performs sampling on the serial data signal at timings synchronous with the clock signal generated by the PLL circuit 18 to extract the compressed data, the compression mode data and 55 the timing control data. It should be noted that a DLL circuit may be used in place of the PLL circuit 18.

The configuration and operation of the liquid crystal display apparatus 1 except for those described above are same as the first embodiment. That is, as is the case with the 60 first embodiment, the frame rate is also switched in response to the contents displayed on the liquid crystal display panel 2 in this embodiment. Furthermore, the data compression ratio of the compression circuit 11 is switched in response to the switching of the frame rate and thereby the transmission 65 rate of the serial data transmission from the timing control circuit 3 to each driver 4 is kept constant.

**10**

This embodiment, in which PLL circuits are provided not only in the serial transmission circuit 12 but also the serial receiving circuit 14A, offers a larger advantage by the transmission rate of the serial data transmission being kept constant. In this embodiment, in which the transmission rate of the serial data transmission is kept constant, it is not necessary to switch the frequency band of the clock signal in any of the PLL circuit 13 of the serial transmission circuit 12 and the PLL circuit 18 of the serial reception circuit 14A. This implies that an operation of re-locking is not necessary for any of the PLL circuits 13 and 18 (as long as no malfunction occurs). Since both of the PLL circuit 13 of the serial transmission circuit 12 and the PLL circuit 18 of the serial receiving circuit 14A are required to normally operate in order to achieve the serial data transmission between the timing control signal 3 and each driver 4, it is very advantageous that it is not necessity to re-lock any of the PLL circuits 13 and 18. In addition, the simple circuit configuration illustrated in FIG. 3B, which does not provide the function of switching the frequency dividing ratio, can be used for the PLL circuit 18 as well as the PLL circuit 13. When the circuit configuration illustrated in FIG. 3B is used for the PLL circuit 18, a recovery signal obtained by performing a waveform recovery on the serial data signal is inputted to the phase comparator 21 in place of the source clock signal.

#### Third Embodiment

FIG. 5 is a block diagram illustrating the display apparatus according to a third embodiment of the present invention. In this embodiment, a display apparatus according to the present invention is applied to an image processing apparatus 50 including the liquid crystal display apparatus 1. The image processing apparatus 50 includes a processor 51, a memory 52 and an external input interface 53. A CPU (central processing unit) or a DSP (digital signal processor) may be used as the processor 51, for example. The processor 51 performs graphic processing, using the memory 52 as a work area. The external input interface 53 is connected to an external device, such as an optical disk drive. In this embodiment, the external input interface 53 includes a compression circuit 53a and the compression circuit 53aperforms compression processing on image data received by the external input interface 53 from the external device. The operation of the compression circuit 53a is same as that of the compression circuit 11 in the first and second embodiments. The compression circuit 53a is fed with the frame rate indication data which indicates the frame rate and the compression circuit 53a performs compression processing on the image data with the data compression ratio selected in response to the frame rate indication data. The data generated by the compression processing are forwarded to the timing control circuit 3 via a bus 54 and then transmitted to the drivers 4 by the serial data transmission.

Also in this embodiment, as is the case with the first and second embodiments, the frame rate is switched in response to the contents displayed on the liquid crystal display panel 2. Furthermore, the data compression ratio of the compression circuit 11 is switched in response to the switching of the frame rate; this allows the transmission rate of the serial data transmission from the timing control circuit 3 to the drivers 4 to be kept constant.

Although the frame rate is set depending on the kind of the contents to be displayed in the above-described embodi-

ments, the present invention is applicable to the case when the frame rate is adjusted depending on a factor other than the kind of the contents.

(Compression Processing and Decompression Processing)

In the following, a description is given of the compression processing performed in the compression circuit 11 and the decompression processing performed in the decompression circuit 15 in the above-described embodiments.

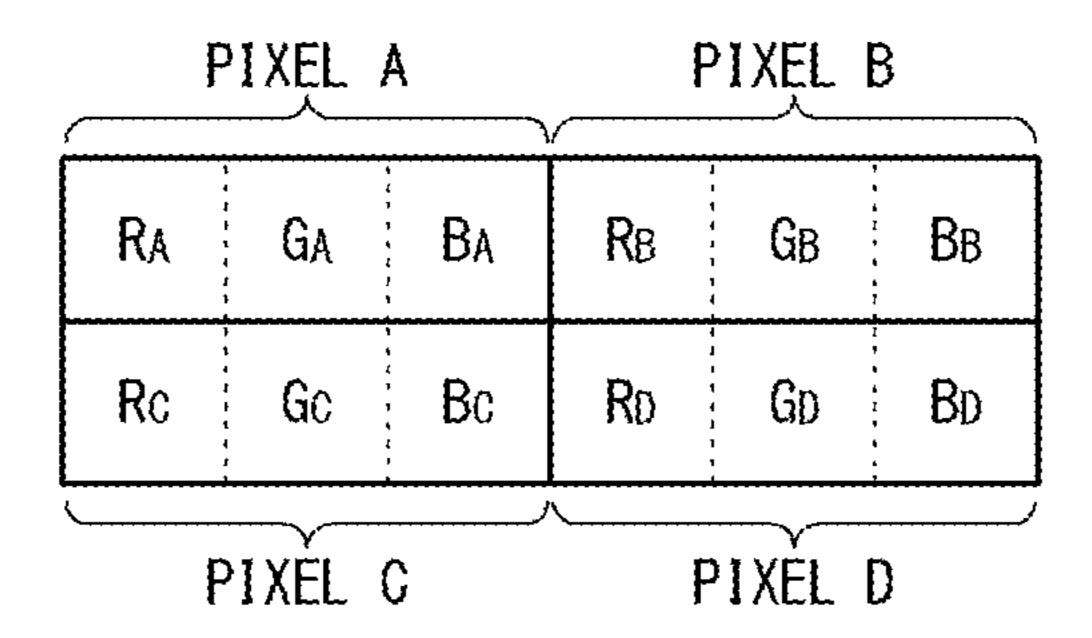

#### 1. Configuration of Block

As described above, block coding, in which compression is performed in units of blocks each consisting of a plurality of pixels, is used as the compression processing in the present embodiments. More specifically, in the present to the same pixel line, and image data of the four pixels (total 96 bits) are collectively compressed. FIG. 6 illustrates the arrangement of four pixels in each block; four pixels included in each block may be referred to as pixel A, pixel B, pixel C and pixel D, respectively, in the following. Each 20 of pixels A to D includes an R subpixel, a G subpixel and a B subpixel. The R subpixel, G subpixel and B subpixel of pixel A are denoted by symbols  $R_A$ ,  $G_A$  and  $B_A$ , respectively. The same goes for pixels B to D. In the present embodiments, the subpixels  $R_A$ ,  $G_A$ ,  $B_A$ ,  $R_B$ ,  $R_B$ ,  $R_B$ ,  $R_C$ ,  $R_D$ ,  $G_D$  and  $B_D$  of four pixels of each block are positioned in the same pixel line and connected to the same gate line. In the following, a block to be subjected to compression processing is referred to as target block.

2. Overview of Configurations and Operations of Compression Circuit and Decompression Circuit

In the present embodiments, the compression circuit 11 is adapted to compress image data with any of the following five compression methods:

No-compression

(1×4) pixel compression

$(2+1\times2)$  pixel compression

(2×2) pixel compression

(4×1) pixel compression

As described above, the no-compression is a method of outputting image data as compressed data as they are, and used to set the data compression ratio to 100% (=1). The (1×4) pixel compression is a method in which a process to reduce the number of bit planes is performed on each of the 45 four pixels of the target block, independently. The  $(1\times4)$ pixel compression is advantageous when the correlation among image data of the four pixels is low. The  $(2+1\times2)$ pixel compression is a method in which a representative value representing image data of two pixels out of the four 50 pixels of the target block is determined and a process to reduce the number of bit planes is performed on each of the other two pixels. The  $(2+1\times2)$  pixel compression is advantageous when the correlation of image data of two pixels out of the four pixels is high, and the correlation of the image 5: data of the other two pixels is low. The  $(2\times2)$  pixel compression is a method in which four pixels of the target block is classified into two pairs each consisting of two pixels, and representative values for representing the image data for each pair are calculated to thereby compress the image data. 60 The  $(2\times2)$  pixel compression is advantageous when the correlation of image data of two pixels out of four pixels is high, and the correlation of the image data of the other two pixels is also high. As described above, the  $(4\times1)$  pixel compression is a method in which representative values for 65 representing the imaged data of the four pixels of the target block are calculated to thereby compress the image data. The

$(4\times1)$  pixel compression is advantageous when the correlation among the image data of the four pixels of the target block is high.

The data compression ratio is variable for the four compression method other than the no-compression (that is,  $(1\times4)$  pixel compression,  $(2+1\times2)$  pixel compression,  $(2\times2)$ pixel compression and  $(4\times1)$  pixel compression). In any of these four compression methods, the data compression ratio is set to 66.7% (=2/3) for the frame rate of 180 Hz (corresponding to the triple speed), and to 50% (=1/2) for the frame rate of 240 Hz (corresponding to the quadruple speed) in the present embodiments.

In addition, when the data compression ratio is not 100%, the compression method is selected from the  $(1\times4)$  pixel embodiments, each block consists of four pixels belonging 15 compression, the (2+1×2) pixel compression, the (2×2) pixel compression and the  $(4\times1)$  pixel compression, in response to the correlation among image data of the four pixels which form the target block. For example, the  $(4\times1)$  pixel compression is used when the correlation among the image data of the four pixels is high, and the  $(2\times2)$  pixel compression is used when the correlation of the image data of two pixels out of the four pixels is high, and the correlation of the image data of the other two pixels is also high. When the data compression ratio is 100%, the no-compression is selected independently of the correlation among the four pixels forming the target block.

> To perform the operation as described above, as illustrated in FIG. 7A, the compression circuit 11 includes a form recognition section 31, a  $(1\times4)$  pixel compression section 32, a  $(2+1\times2)$  pixel compression section 33, a  $(2\times2)$  pixel compression section 34, a  $(4\times1)$  pixel compression section 35, and a compressed data selection section 36.

When receiving the image data of the pixels of the target block, the form recognition section 31 recognizes the cor-35 relation among the received image data of the pixels. For example, the form recognition section 31 recognizes which combination of the pixels arranged in one row and four columns has a high correlation in the image data or which pixel has a low correlation with other pixels in the image data. Furthermore, the form recognition section **31** generates compressed data selection data which indicate which of the five compression methods: the no compression, the  $(1\times4)$ pixel compression, the  $(2+1\times2)$  pixel compression, the  $(2\times2)$ pixel compression, and the  $(4\times1)$  pixel compression should be used in response to the result of the recognition and the data compression ratio to be used.

The  $(1\times4)$  pixel compression section 32, the  $(2+1\times2)$  pixel compression section 33, the  $(2\times2)$  pixel compression section 34, and the  $(4\times1)$  pixel compression section 35 perform the above-described  $(1\times4)$  pixel compression,  $(2+1\times2)$  pixel compression,  $(2\times2)$  pixel compression, and  $(4\times1)$  pixel compression, respectively, and thereby generate  $(1\times4)$  compressed data,  $(2+1\times2)$  compressed data,  $(2\times2)$  compressed data, and  $(4\times1)$  compressed data, respectively. In the present embodiments, the  $(1\times4)$  pixel compression section 32, the  $(2+1\times2)$  pixel compression section 33, the  $(2\times2)$  pixel compression section 34, and the  $(4\times1)$  pixel compression section 35 are fed with the frame rate indication data, and switch the data compression ratio of the compression processing in response to the frame rate. As described above, the data compression ratio is set to 66.7% (=2/3) for the frame rate of 180 Hz (corresponding to the triple speed) and the data compression ratio is set to 50% (=1/2) for the frame rate of 240 Hz (corresponding to the quadruple speed).

The compressed data selection section 36 selects any of the original image data, the  $(1\times4)$  compressed data, the  $(2+1\times2)$  compressed data, the  $(2\times2)$  compressed data, and

the (4×1) compressed data in response to the compressed data selection data received from the form recognition section 31, and outputs the selected data as the resultant compressed data. When any one of the (1×4) compressed data, the (2+1×2) compressed data, the (2×2) compressed data, and the (4×1) compressed data is selected as the resultant compressed data, the resultant compressed data include one or more compression type recognition bits indicating which one is used out of the four compression methods. The compressed data outputted from the compressed data selection section 36 are forwarded to the serial transmission circuit 12.

The decompression circuit **15**, which is provided on the receiving side (that is, in the driver **4**), determines which one of the above-described five compression methods is used to perform the compression processing for the compressed data received from the serial receiving circuit **14** (**14A**), recognizes the data compression ratio from the compression mode data, and decompresses the compressed data by the decompression method adapted to the used compressed method and the data compression ratio. To perform such an operation, as shown in FIG. **7B**, the decompression circuit **15** includes the form recognition section **41**, an (1×4) pixel decompression section **42**, and a (2+1×2) pixel decompression section **44**, a (4×1) pixel decompression section **45**, and the display data selection section **46**.

The  $(1\times4)$  pixel decompression section 42, the  $(2+1\times2)$ pixel decompression section 43, the  $(2\times2)$  pixel decompression section 44, and the  $(4\times1)$  pixel decompression section 45 has the function of decompressing the compressed data generated by the  $(1\times4)$  pixel compression, the  $(2+1\times2)$  pixel compression, the  $(2\times2)$  pixel compression, and the  $(4\times1)$ pixel compression, respectively. The  $(1\times4)$  pixel decompression section 42, the  $(2+1\times2)$  pixel decompression section 43, the  $(2\times2)$  pixel decompression section 44, and the  $(4\times1)$ pixel decompression section 45 recognizes the data compression ratio from the compression mode data and performs the decompression processing in accordance with the rec- 40 ognized data compression ratio. Hereinafter, the decompressed data obtained by decompressing the compressed data by the  $(1\times4)$  pixel decompression section 42, the  $(2+1\times2)$  pixel decompression section 43, the  $(2\times2)$  pixel decompression section 44, and the  $(4\times1)$  pixel decompres- 45 sion section 45 are referred to as  $(1\times4)$  decompressed data,  $(2+1\times2)$  decompressed data,  $(2\times2)$  decompressed data and (4×1) decompressed data, respectively.

The form recognition section 41 recognizes the compression method actually used for the compression processing 50 from the compression type recognition bits and the compression mode data, and generates display data selection data specifying which of the  $(1\times4)$  decompressed data, the  $(2+1\times2)$  decompressed data, the  $(2\times2)$  decompressed data, the  $(4\times1)$  decompressed data and the compressed data is to 55 be selected as the display data. The display data selection section 46 outputs any of the  $(1\times4)$  decompressed data, the  $(2+1\times2)$  decompressed data, the  $(2\times2)$  decompressed data, the (4×1) decompressed data and the compressed data in response to the display data selection data. It should be noted 60 that the compressed data are selected as the display data as they are, only when the data compression ratio is 100% (that is, when the no-compression is used as the compression method). The display data outputted from the decompression circuit 15 are fed to the display latch section 16 and the 65 data line drive circuit 17 and used to drive the liquid crystal display panel 2.

14

In the following, a description is given of the recognition method of the correlation among the image data of pixels arranged in one row and four columns and details of the four compression methods other than the no-compression. In the following description, the grayscale values of the R subpixels of the pixels A, B, C, and D are denoted by R<sub>A</sub>, R<sub>B</sub>, R<sub>C</sub>, and R<sub>D</sub>, respectively. Also, the grayscale values of the G subpixels of the pixels A, B, C, and D are denoted by G<sub>A</sub>, G<sub>B</sub>, G<sub>C</sub>, and G<sub>D</sub>, respectively, and the grayscale values of the B subpixels of the pixels A, B, C, and D are denoted by B<sub>A</sub>, B<sub>B</sub>, B<sub>C</sub>, and B<sub>D</sub>, respectively.

3. Selection of Compression Method in Response to Correlation Among Pixels

When the data compression ratio is not 100% (that is, when a compression method other than the no-compression is selected), the compression method is selected in response to the correlation among the four pixels. More specifically, the compression circuit 11 determines which of the following cases is valid for the image data of the four pixels, which are arranged in one row and four columns, of the target block:

Case A: The correlation is low for any combinations of the image data of the four pixels.

Case B: There exists a high correlation between the image data of two pixels, while the image data of the other two pixels have a low correlation with the preceding two pixels and are mutually low in the correlation.

Case C: There exists a high correlation among the image data of the four pixels.

Case D: There exists a high correlation between the image data of two pixels, and there exists a high correlation between the image data of the other two pixels.

FIG. 8 is a flowchart illustrating the procedure of selecting the compression methods in response to the correlation among the pixels.

First, if the following condition (A) is not established for any combination of i and j satisfying:

$$i \in \{A, B, C, D\},\$$

$j \in \{A, B, C, D\},\$  and  $i \neq j,$

the compression circuit 11 determines case A is valid (that is, the correlation among the image data of the four pixels of arbitrary combinations of the four pixels is low) (step S01).

$$|Ri-Rj| \le Th1$$

,

$|Gi-Gj| \le Th1$ , and

$|Bi-Bj| \le Th1$ .

Condition (A)

When case A is valid, the compression circuit 11 determines that the  $(1\times4)$  pixel compression is to be performed.

When determining that case A is not valid, the compression circuit 11 defines a first set of two pixels and a second set of two pixels for the four pixels, and determines for all the allowed first and second sets whether a condition that the difference of the image data between the two pixels of the first set is smaller than the predetermined value, and the difference of the image data between the two pixels of the second set is smaller than the predetermined value is satisfied (Step S02). More specifically, the compression circuit 11 determines whether any of the following conditions (B1) to (B3) holds true:

$$|R_A - R_B| \le Th2$$

,

$|G_A - G_B| \le Th2$

$$\begin{split} |B_A - B_B| &\leq Th2, \\ |R_C - R_D| &\leq Th2, \\ |G_C - G_D| &\leq Th2, \text{ and} \\ |B_C - B_D| &\leq Th2. \\ |R_A - R_C| &\leq Th2, \\ |G_A - G_C| &\leq Th2, \\ |B_A - B_C| &\leq Th2, \\ |R_B - R_D| &\leq Th2, \\ |R_B - R_D| &\leq Th2, \\ |R_B - R_D| &\leq Th2, \\ |R_A - R_D| &\leq Th2, \\ |R_D - R_C| &\leq Th2, \\ |R_D - R_C| &\leq Th2, \\ |R_D - R_C| &\leq Th2, \\ |R_D - R_D| &\leq Th2, \\ |R_D - R_C| &\leq Th2, \\ |R_D - R_D| &\leq Th2, \\ |R_D - R_C| &\leq Th2, \\ |R_D - R_D| &\leq Th2, \\ |R_D - R_D$$

When none of the above-described conditions (B1) to (B3) holds true, the compression circuit 11 determines that case B is valid (that is, there exists a high correlation between the image data of the two pixels, and the image data of the other two pixels are mutually low in the correlation). In this case, the compression circuit 11 determines that the  $(2+1\times2)$  pixel compression is to be performed.

When determining that none of cases A and B is valid, the compression circuit 11 determines whether a condition that the difference between the maximum value and the minimum value of the image data of the four pixels with respect to all colors of the four pixels is smaller than a predetermined value is satisfied. More specifically, the compression circuit 11 determines whether the following condition (C) holds true (Step S03):

$$\max(R_{A},R_{B},R_{C},R_{D})-\min(R_{A},R_{B},R_{B},R_{D}) < Th3,$$

$$\max(G_{A},G_{B},G_{C},G_{D})-\min(G_{A},G_{B},G_{C},G_{D}) < Th3, \text{ and}$$

$$\max(B_{A},B_{B},B_{C},B_{D})-\min(B_{A},B_{B},B_{C},B_{D}) < Th3.$$

Condition (C)

When condition (C) does not hold true, the compression circuit 11 determines that case C is valid (that is, there exists a high correlation among the image data of the four pixels). In this case, the form recognition section 61 determines that the  $(4\times1)$  pixel compression is to be performed.

When condition (C) does not hold true, on the other hand, the compression circuit 11 determines that case D is valid (that is, there exists a high correlation between image data of two pixels and there exists a high correlation between image data of the other two pixels). In this case, the 60 compression circuit 11 determines that the (2×2) pixel compression is to be performed.

Based on the result of the above-described recognition of the correlation, the form recognition section 31 of the compression circuit 11 selects any of the  $(1\times4)$  pixel compression, the  $(2+1\times2)$  pixel compression, the  $(2\times2)$  pixel compression, the (3+1) pixel compression, and the  $(4\times1)$

pixel compression. As described later, the image data of the target block are compressed by using the selected compression method.

4. Details of Respective Compression Methods and Decom-5 pression Methods

Next, details of the compression methods and decompression methods are described for the  $(1\times4)$  pixel compression, the  $(2+1\times2)$  pixel compression, the  $(2\times2)$  pixel compression and the  $(4\times1)$  pixel compression, individually.

10 4-1. (1×4) Pixel Compression

FIGS. 9A and 9B are conceptual illustrations illustrating the formats of the (1×4) compressed data. As described above, the (1×4) pixel compression is a compression method used in the case that the correlation among the image data of the pixels is low for any combinations of the four pixels. Here, FIG. 9A illustrates the format of the compressed data in the case that the data compression ratio of 50% (=½) and FIG. 9B illustrates the format of the compressed data in the case that the data compression ratio of 66.7% (=½). Except that the total number of bits and the bit allocation are different, the basic format is common for these data compression ratios.

As illustrated in FIG. 9A, the (1×4) compressed data are comprised of: a header (attribute data) including a compression type recognition bit; R<sub>A</sub>, G<sub>A</sub> and B<sub>A</sub> data corresponding to the image data of the pixel A; R<sub>B</sub>, G<sub>B</sub> and B<sub>B</sub> data corresponding to the image data of the pixel B; R<sub>C</sub>, G<sub>C</sub>, and B<sub>C</sub> data corresponding to the image data of the pixel C; and R<sub>D</sub>, G<sub>D</sub>, and B<sub>D</sub> data corresponding to the image data of the pixel D. Here, the compression type recognition bit is data indicating the type of the compression method used for the compression type recognition bit in the (1×4) compressed data. In the present embodiments, the value of the compression type recognition bit of the (1×4) compressed data is "0".

The R<sub>A</sub>, G<sub>A</sub> and B<sub>A</sub> data are bit-plane reduced data obtained by performing reduction of the number of the bit planes for the grayscale values of the R, G and B subpixels of pixel A, and the R<sub>B</sub>, G<sub>B</sub> and B<sub>B</sub> data are bit-plane reduced data obtained by performing reduction of the number of bit planes for the grayscale values of the R, G, and B subpixels of pixel B. Correspondingly, the R<sub>C</sub>, G<sub>C</sub>, and B<sub>C</sub> data are bit-plane reduced data obtained by performing reduction of the number of the bit planes for the grayscale values of the R, G, and B subpixels of pixel C, and the R<sub>D</sub>, G<sub>D</sub>, and B<sub>D</sub> data are bit-plane reduced data obtained by performing reduction of the number of the bit planes for the grayscale values of the R, G, and B subpixels of pixel D.

In the present embodiments, when the data compression ratio is 50% (FIG. 9A), only the B<sub>D</sub> data, which correspond to the B subpixel of pixel D, are three-bit data and other data are four-bit data. In such a bit allocation, the total number of bits including the compression type recognition bit is 48 bits. When the data compression ratio is 66.7% (FIG. 9B), on the other hand, the G<sub>A</sub>, G<sub>B</sub> and G<sub>C</sub> data, which correspond to the G subpixels of pixels A, B and C, are six-bit data and other data are five-bit data. In such a bit allocation, the total number of bits including the compression type recognition bit is 64 bits.

FIG. 10A is a schematic illustration explaining the (1×4) pixel compression. Although FIG. 10A illustrates the (1×4) pixel compression for the data compression ratio of 50%, a similar compression processing is performed for the data compression ratio of 66.7%, except that the number of bits is different. In the (1×4) pixel compression, dithering using a dither matrix is performed for each of pixels A to D to thereby reduce the number of bit planes of the image data of

pixels A to D. In detail, error data  $\alpha$  is first added to each of the image data of pixel A, B, C, and D. In this embodiment, the error data  $\alpha$  of each pixel is determined from the coordinates of the pixel of interest, by using a basic matrix which is a Bayer matrix. The calculation of the error data  $\alpha$  5 will be described separately later. In the following, a description will be made assuming that the error data  $\alpha$  defined for pixels A, B, C and D are 0, 5, 10, and 15, respectively.

Furthermore, rounding processing are performed to 10 thereby generate the  $R_A$ ,  $G_A$  and  $B_A$  data, the  $R_B$ ,  $G_B$  and  $B_B$ data, the  $R_C$ ,  $G_C$  and  $B_C$  data, and the  $R_D$ ,  $G_D$  and  $B_D$  data. It should be noted that rounding processing means adding a value of  $2^{(n-1)}$  and then truncating the lower n bits, where n is a desired value. When the data compression ratio is 50%, 15 and Rj, Gj and Bj data. the grayscale value of the B subpixel of pixel D is subjected to a process of adding a value of 16 and then truncating the lower five bits, and the other grayscale values are subjected to a process of adding a value of 8 and then truncating the lower four bits. When the data compression ratio is 66.7%, 20 on the other hand, the grayscale value of the G subpixels of pixels A, B and C are subjected to a process of adding a value of 2 and then truncating the lower two bits, and the other grayscale values are subjected to a process of adding a value of 4 and then truncating the lower three bits. The 25 (1×4) compressed data are generated by attaching a value "0" as the compression type recognition bit to the  $R_A$ ,  $G_A$ and  $B_A$  data, the  $R_B$ ,  $G_B$  and  $B_B$  data, the  $R_C$ ,  $G_C$  and  $B_C$  data, and the  $R_D$ ,  $G_D$  and  $B_D$  data, which are generated in the above-described manner.