### US009648260B2

## (12) United States Patent Machida

## (54) SOLID-STATE IMAGE TAKING DEVICE WITH UNIFORM NOISE DISTRIBUTION

(71) Applicant: Sony Corporation, Tokyo (JP)

(72) Inventor: Takashi Machida, Kanagawa (JP)

(73) Assignee: SONY SEMICONDUCTOR SOLUTIONS CORPORATION,

Kanagawa (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 14/856,064

(22) Filed: Sep. 16, 2015

(65) Prior Publication Data

US 2016/0006959 A1 Jan. 7, 2016

### Related U.S. Application Data

(60) Continuation of application No. 14/087,281, filed on Nov. 22, 2013, now Pat. No. 9,167,184, which is a (Continued)

### (30) Foreign Application Priority Data

(51) Int. Cl.

H04N 5/363 (2011.01)

H01L 27/146 (2006.01)

(Continued)

(52) **U.S. Cl.**CPC ....... *H04N 5/363* (2013.01); *H01L 27/1463* (2013.01); *H01L 27/14603* (2013.01); (Continued)

### (10) Patent No.: US 9,648,260 B2

(45) Date of Patent: May 9, 2017

### (58) Field of Classification Search

CPC ..... H04N 5/363; H04N 5/2353; H04N 5/378; H04N 5/3595; H04N 5/37452;

(Continued)

### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,942,474 A 7/1990 Akimoto et al. 6,091,793 A 7/2000 Kamashita (Continued)

### FOREIGN PATENT DOCUMENTS

CN 101355094 1/2009 CN 101562707 10/2009 (Continued)

### OTHER PUBLICATIONS

Chinese Office Examination Report issued in connection with related Chinese patent application No. CN 201110075897.01 dated Dec. 1, 2014.

(Continued)

Primary Examiner — Gevell Selby (74) Attorney, Agent, or Firm — Dentons US LLP

### (57) ABSTRACT

A solid-state image taking device including a pixel section and a scan driving section wherein on each pixel column included in the pixel area determined in advance to serve as a pixel column having the unit pixels laid out in the scan direction, the opto-electric conversion section and the electric-charge holding section are laid out alternately and repeatedly, and on each of the pixel columns in the pixel area determined in advance, two the electric-charge holding sections of two adjacent ones of the unit pixels are laid out disproportionately toward one side of the scan direction with respect to the optical-path limiting section or the opto-electric conversion section.

### 5 Claims, 31 Drawing Sheets

### US 9,648,260 B2

Page 2

### Related U.S. Application Data

division of application No. 13/043,913, filed on Mar. 9, 2011, now Pat. No. 8,625,011.

| (51) | Int. Cl.    |           |

|------|-------------|-----------|

| , ,  | H04N 5/359  | (2011.01) |

|      | H04N 5/374  | (2011.01) |

|      | H04N 5/235  | (2006.01) |

|      | H04N 5/3745 | (2011.01) |

|      | H04N 5/378  | (2011.01) |

# (52) **U.S. Cl.**CPC .. *H01L 27/14612* (2013.01); *H01L 27/14623*(2013.01); *H04N 5/2353* (2013.01); *H04N*5/3595 (2013.01); *H04N 5/378* (2013.01); *H04N 5/37452* (2013.01)

## (58) Field of Classification Search CPC ........... H01L 27/1463; H01L 27/14612; H01L 27/14623; H01L 27/14603 See application file for complete search history.

### (56) References Cited

### U.S. PATENT DOCUMENTS

| 7,399,951    | B2         | 7/2008  | Morimoto et al.     |

|--------------|------------|---------|---------------------|

| 2004/0130757 | <b>A</b> 1 | 7/2004  | Mabuchi             |

| 2009/0251582 | <b>A</b> 1 | 10/2009 | Oike                |

| 2009/0256230 | <b>A</b> 1 | 10/2009 | Watanabe            |

| 2009/0278031 | A1*        | 11/2009 | Kitano H01L 27/1462 |

|              |            |         | 250/208.1           |

| 2010/0060762 | A1*        | 3/2010  | Takada H04N 5/238      |

|--------------|------------|---------|------------------------|

|              |            |         | 348/300                |

| 2010/0097514 | A1*        | 4/2010  | McCarten H01L 27/14634 |

|              |            |         | 348/340                |

| 2010/0176272 | A1         | 7/2010  | Itahashi               |

| 2010/0330723 | A1         | 12/2010 | Okabe et al.           |

| 2011/0032379 | A1         | 2/2011  | Kobayashi et al.       |

| 2011/0085066 | <b>A</b> 1 | 4/2011  | Sugawa et al.          |

|              |            |         |                        |

### FOREIGN PATENT DOCUMENTS

| CN | 101588506   | 11/2009  |             |

|----|-------------|----------|-------------|

| JP | 01-243675   | 9/1989   |             |

| JP | 08-111821   | 4/1996   |             |

| JP | 11-177076   | 7/1999   |             |

| JP | 2004-140149 | 5/2004   |             |

| JP | 2005-129965 | 5/2005   |             |

| JP | 2006-311515 | 11/2006  |             |

| JP | 2007-116356 | 5/2007   |             |

| JP | 2008-004692 | 1/2008   |             |

| JP | 2010021450  | * 7/2008 | H01L 27/146 |

| JP | 2009-268083 | 11/2009  |             |

| JP | 2009-272539 | 11/2009  |             |

| JP | 2010-045083 | 2/2010   |             |

|    |             |          |             |

### OTHER PUBLICATIONS

Japanese Office Examination Report issued in connection with related Japanese patent application No. JP 2010-070252 dated Feb. 12, 2014.

<sup>\*</sup> cited by examiner

F I G . 1

FIG 2

F I G . 3

F I G . 4

F I G . 5

F I G . 6

FIG.7

F I G . 8

F I G . 9

FIG. 10

FIG.11A

FIG. 11B

FIG. 12

FIG. 13

FIG. 14

F I G . 15

FIG. 16

FIG. 17

### FIG. 18

FIG. 19

FIG. 20

FIG. 21

F I G . 22

FIG. 23

FIG. 24

FIG. 25

FIG. 26

FIG. 27

FIG. 28

FIG.29

FIG.30

FIG. 31

FIG.32

## FIG. 33

FIG. 34

F I G . 35

FIG.36A

FIG.36C

FIG.36D

FIG.36E

FIG.36F

FIG.36G

FIG.37

FIG. 38

FIG.39

1

### SOLID-STATE IMAGE TAKING DEVICE WITH UNIFORM NOISE DISTRIBUTION

### RELATED APPLICATION DATA

This application is a continuation of U.S. patent application Ser. No. 14/087,281 filed Nov. 22, 2013, which is a division of U.S. patent application Ser. No. 13/043,913 filed Mar. 9, 2011 now U.S. Pat. No. 8,625,011 issued Jan. 7, 2014, the entireties of which are incorporated herein by reference to the extent permitted by law. The present application claims the benefit of priority to Japanese Patent Application No. JP 2010-070252 filed on Mar. 25, 2010 in the Japan Patent Office, the entirety of which is incorporated by reference herein to the extent permitted by law.

### BACKGROUND OF THE INVENTION

### 1. Field of the Invention

The present invention relates to a solid-state image taking 20 device adopting an all-pixel read method for reading out pieces of electric charge at the same time from opto-electrical conversion elements each employed in one of all unit pixels forming a pixel array and relates to an electronic apparatus in which the device is embedded.

### 2. Description of the Related Art

One of typical examples of the solid-state image taking device is a CMOS image sensor for reading out opto-electric charge, which has been accumulated in a PN junction capacitor of a photodiode serving as the opto-electric conversion element (also referred to hereafter as an opto-electric conversion section) of every unit pixel employed in the CMOS image sensor, through a MOS transistor of the pixel. The CMOS image sensor carries out an operation to read out pieces of opto-electric charge, which each have been accumulated in a photodiode, for every predetermined unit such as a pixel or a row of pixels. Opto-electric charge is signal electric charge obtained as a result of an opto-electric conversion process carried out by the photodiode. Thus, an exposure period during which opto-electric charge is accu- 40 mulated cannot be made uniform for all pixels employed in the CMOS image sensor. As a result, a distortion is generated at an image taking time typically for a case in which an image taking object moves.

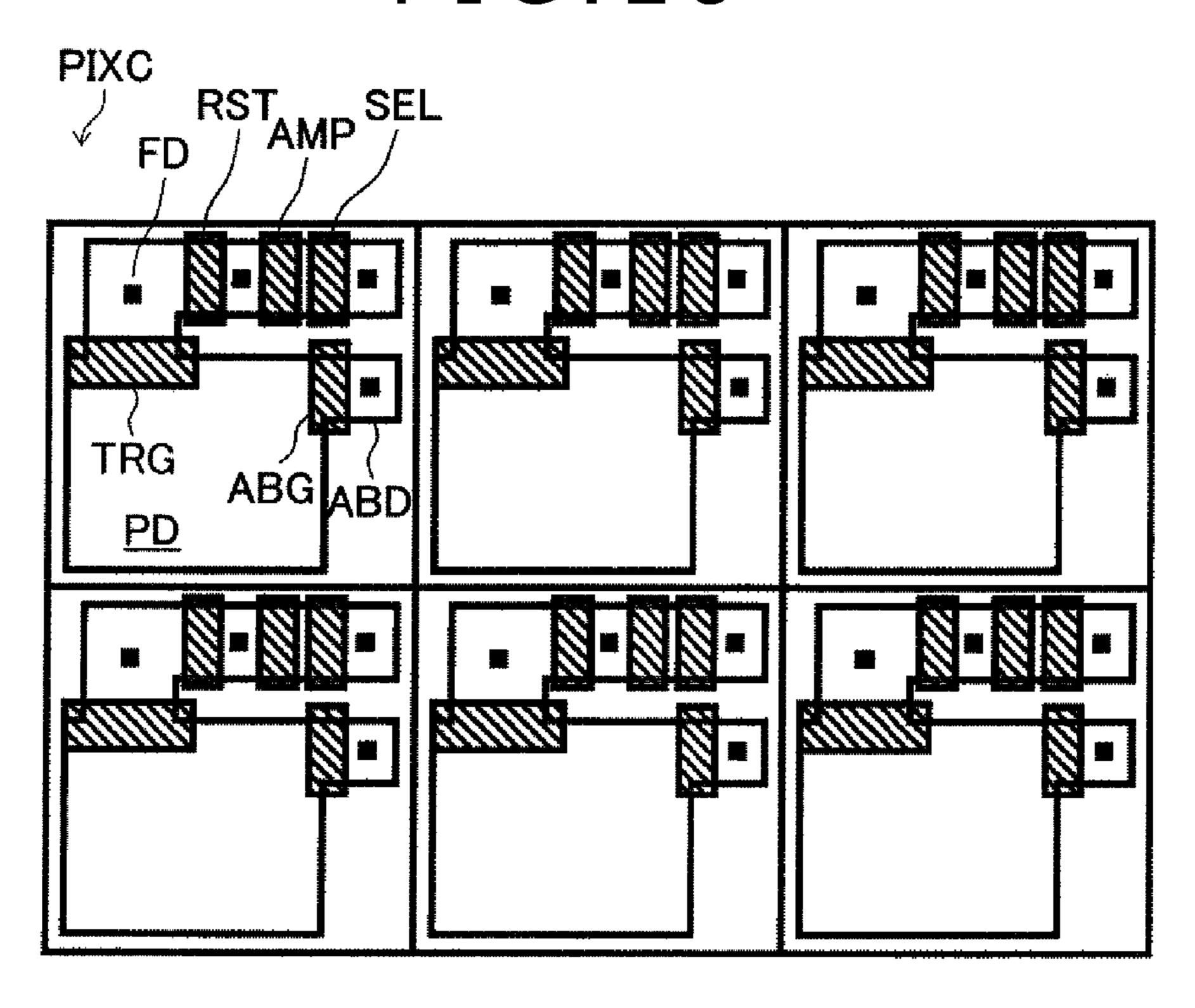

Typical Configuration of a Unit Pixel of the CMOS Image 45 Sensor

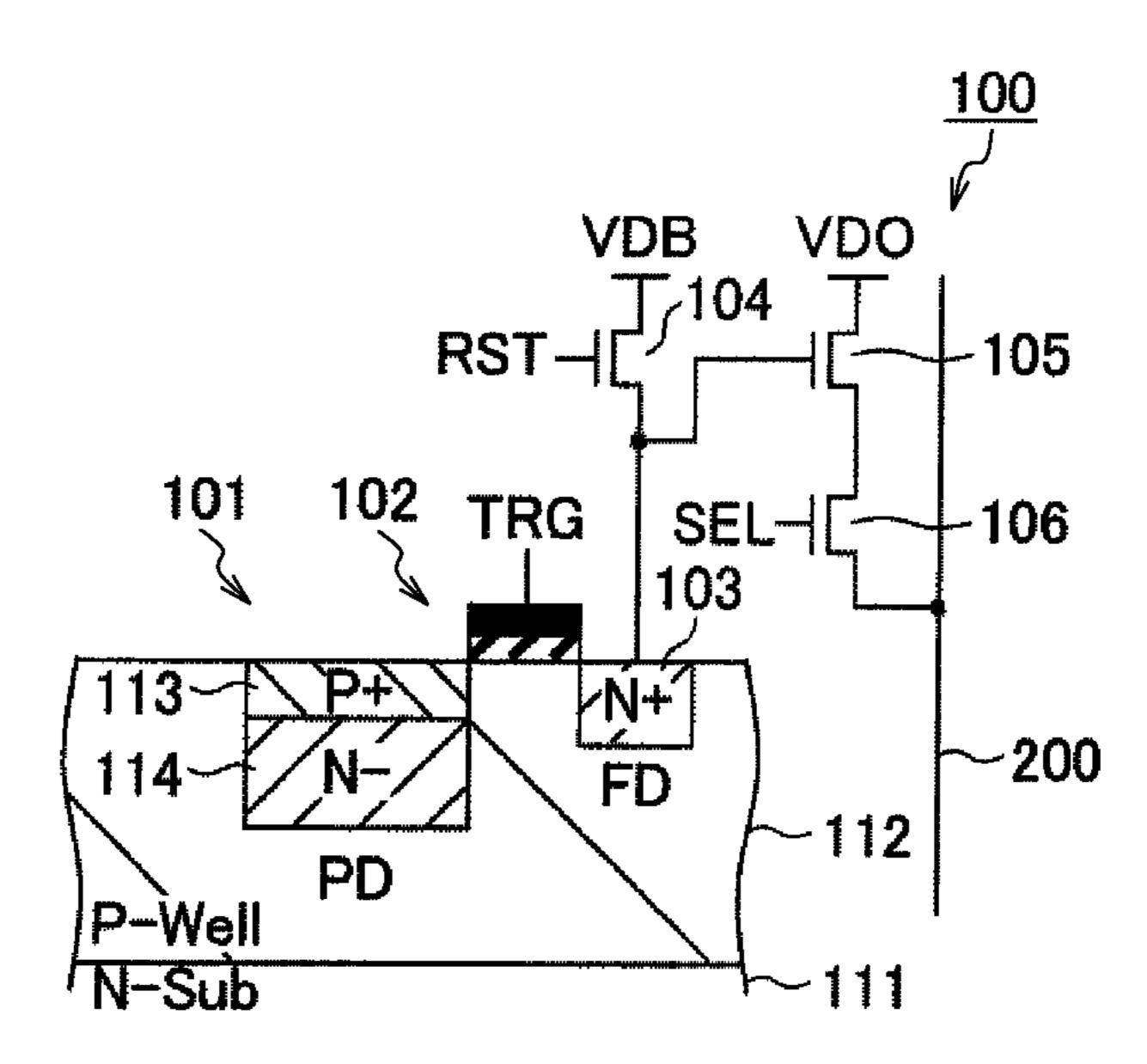

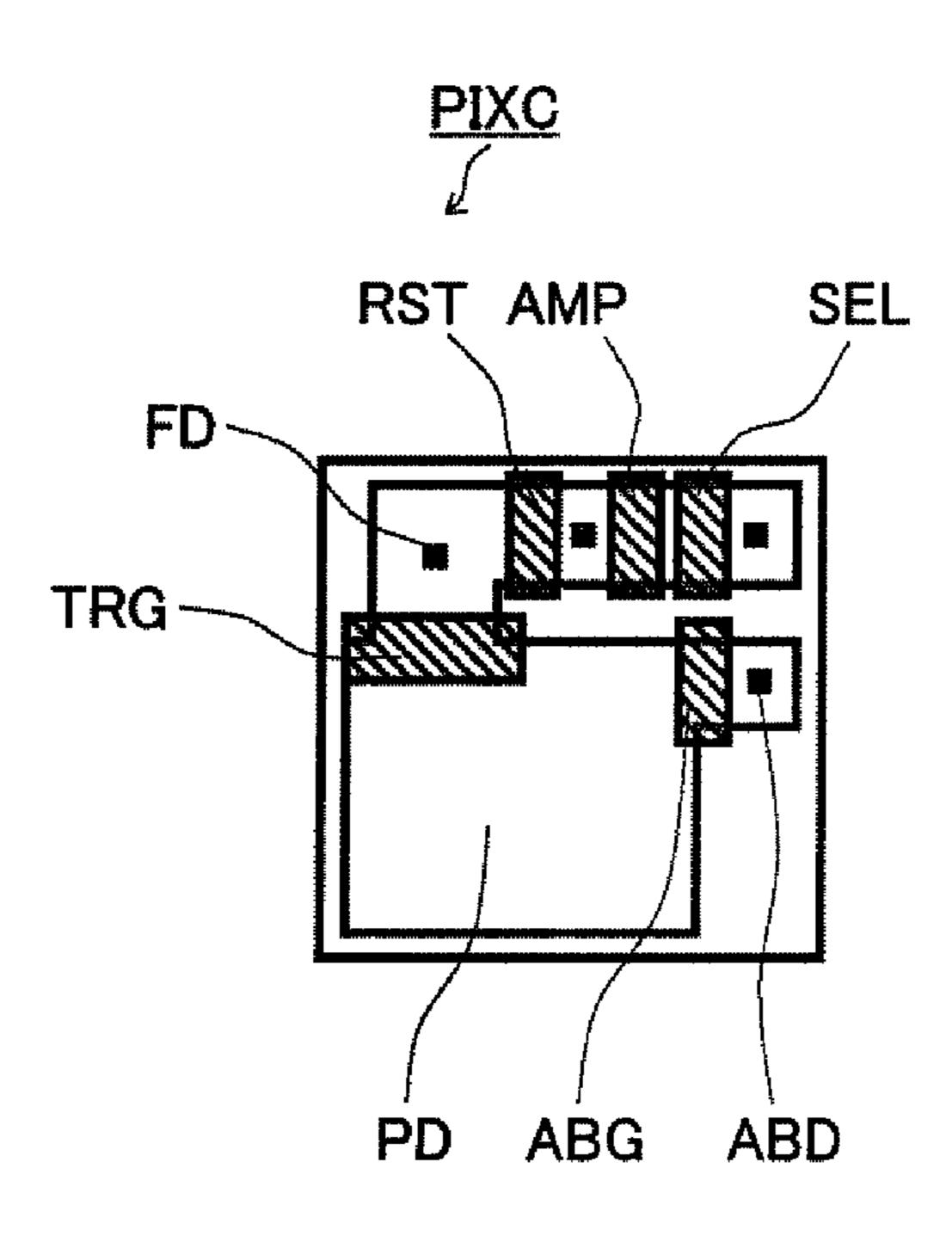

FIG. 1 is a diagram showing the configuration of a unit pixel 100 employed in a CMOS image sensor according to an existing technology disclosed in Japanese Patent Laidopen No. 2009-268083 (hereinafter referred to as Patent 50 Document 1).

As shown in FIG. 1, the unit pixel 100 employs a PD (photodiode) 101, a transfer gate transistor 102 denoted by reference symbol TRG and an N-type area 103 composing an FD (floating diffusion) capacitor denoted by reference 55 symbol FD in the figure. In addition, the unit pixel 100 also has a reset transistor 104, an amplification transistor 105 and a select transistor 106.

In the unit pixel 100, the photodiode 101 is an embedded photodiode created by typically forming a P-type layer 113 60 on the surface of a P-type well layer 112 constructed on a semiconductor substrate 111 and embedding an N-type embedded layer 114 beneath the P-type layer 113. The transfer gate transistor 102 transfers electric charge accumulated in the PN junction of the photodiode 101 to the 65 N-type area 103 composing the floating diffusion capacitor FD.

2

In the CMOS image sensor, the unit pixels 100 each having the configuration described above are laid out to form a unit-pixel matrix serving as an image taking section.

In the image taking section, the amount of signal electric charge transferred by the transfer gate transistor 102 from the photodiode 101 to the N-type area 103 is determined by a timing to apply a transfer pulse TRG to the gate electrode of the transfer gate transistor 102. A method of applying the transfer pulse TRG to the gate electrode of the transfer gate transistor 102 employed in every unit pixel at the same time is known as the all-pixel read method mentioned before. Mechanical-Shutter Method

By the way, a typical example of a method for implementing an exposure operation of an image taking operation during almost simultaneous exposure periods for all pixels is a widely utilized mechanical-shutter method making use of a mechanical shutter serving as mechanical light shielding means.

This mechanical light shielding means carries out the exposure operation by starting the exposure period almost at the same time for all pixels and terminating the exposure period also almost at the same time for all the pixels.

In accordance with the mechanical-shutter method, the exposure periods are mechanically controlled in order to 25 make the exposure periods all but uniform for all unit pixels. The exposure period is a period during which light incident to the photodiode **101** is converted into opto-electric charge serving as signal electric charge. Then, when the mechanical shutter is closed, the unit pixel enters a state in which actually no opto-electric charge is generated in the photodiode 101. After the mechanical shutter has been closed, the signal electric charge is sequentially read out from the photodiode 101. Since the mechanical-shutter method requires that the mechanical light shielding means be used, however, it is difficult to reduce the size of the CMOS image sensor. In addition, since there is a limit on the mechanical driving speed of the mechanical light shielding means, the simultaneity of mechanical-shutter method is inferior to that of an electrical method.

All-Pixel Simultaneous Read Operation Using an Electronic Shutter (Global Exposure)

In order to prevent a distortion from being generated at an image taking time as described above, an image taking operation is carried out by making use of an electronic shutter to execute electrical control for setting an all-pixel simultaneous exposure period. The operation carried out for setting this all-pixel simultaneous exposure period is referred to as the so-called global exposure operation. By referring to FIG. 1, the following description explains steps (1) to (6) of a procedure of the global exposure operation disclosed in documents such as Patent Document 1. Step (1)

Light incident to the photodiode 101 is subjected to an opto-electric conversion process of converting the light into signal electric charge in the semiconductor substrate 111. In the case of the configuration shown in FIG. 1 for example, electrons serving as the signal electric charge are accumulated in the N-type embedded layer 114 whereas holes are discarded from a P-type area not shown in the figure to the outside. Some holes are caught by the P-type layer 113 so that the signal electric charge is not trapped at a substrate surface level introduced by a defect and the caught holes serve as fixed electric charge having an effect on the electrons accumulated in the N-type embedded layer 114. As a result, the quantity of the saturated electric charge accumulated in the N-type embedded layer 114 is stabilized. Step (2)

When a transfer pulse TRG is applied to the gate electrode of the transfer gate transistor 102, an electric-charge exhausting operation is carried out at the same time on all unit pixels in order to discard electric charge accumulated in the photodiode **101** employed in every unit pixel, that is, in <sup>5</sup> order to make the photodiode 101 empty.

Then, in an exposure operation, on the other hand, signal electric charge (that is, opto-electric charge) obtained as a result of an opto-electric conversion process is accumulated in the PN junction capacitor of the photodiode 101. Step (3)

At the end of the exposure period during which the exposure operation described above is carried out, the transfer pulse TRG is again applied to the gate electrode of the 15 transfer gate transistor 102 in order to turn on the transfer gate transistor 102 of every unit pixel 100 for all unit pixels 100 at the same time. With the transfer gate transistor 102 turned on, all the electric charge accumulated in the photodiode 101 employed in every unit pixel 100 is transferred to 20 the N-type area 103 serving as the floating diffusion capacitor FD of the unit pixel 100 for all unit pixels 100 at the same time. On the falling edge of the transfer pulse TRG applied to the transfer gate transistor 102 for the second time, the transfer gate transistor 102 is turned off, entering a closed 25 state. Thereafter, the opto-electric charge accumulated in the photodiode 101 of every unit pixel 100 during the same exposure period for all the unit pixels 100 is held in the floating diffusion capacitor FD employed in the same unit pixel **100**.

Step (4)

The amplification transistor 105 amplifies a signal level representing the amount of the signal electric charge held in the N-type area 103. When a select pulse SEL is applied to the gate electrode of the select transistor **106**, the amplified 35 signal level is asserted on a vertical signal line 200 in the so-called D phase read operation. The D phase read operation to read out the amplified signal can be carried out for every unit pixel 100. In this procedure, however, the operation to read out the amplified signal is carried out for every 40 row of unit pixels 100 on a one-row-after-another basis. Step (5)

Then, when a reset pulse RST is applied to the gate electrode of the reset transistor 104, the amount of electric charge held in the N-type area 103 is reset. Step (6)

Thereafter, the select pulse SEL is again applied to the gate electrode of the select transistor 106 in order to assert a reset level on the vertical signal line 200 in the so-called P phase read operation.

After the signal level and the reset level have been asserted on the vertical signal line 200, in signal processing carried out at a later stage, the reset level is used to eliminate noises from the signal level.

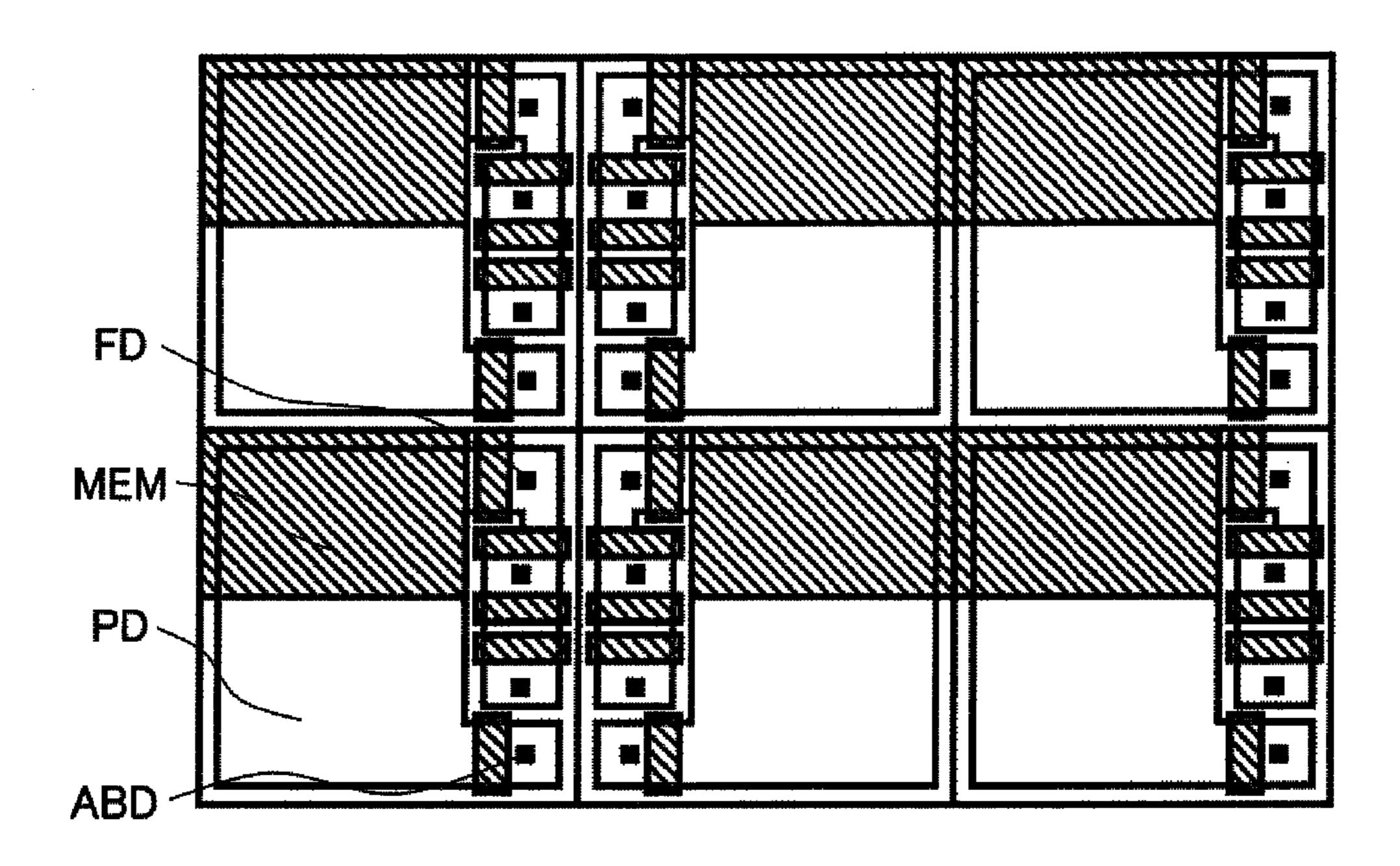

Structure of Unit Pixel Having a Memory

Patent Document 1 and Japanese Patent Laid-open No. Hei 11-177076 (hereinafter referred to as Patent Document 4), Japanese Patent Laid-open No. 2006-311515 (hereinafter referred to as Patent Document 5), and Japanese Patent Laid-open No. 2008-004692 (hereinafter referred to as Pat- 60 ent Document 6) disclose the structure of a unit pixel further having a memory section added to the configuration shown in FIG. 1. In some cases, the memory section is also referred to as an electric-charge storage section.

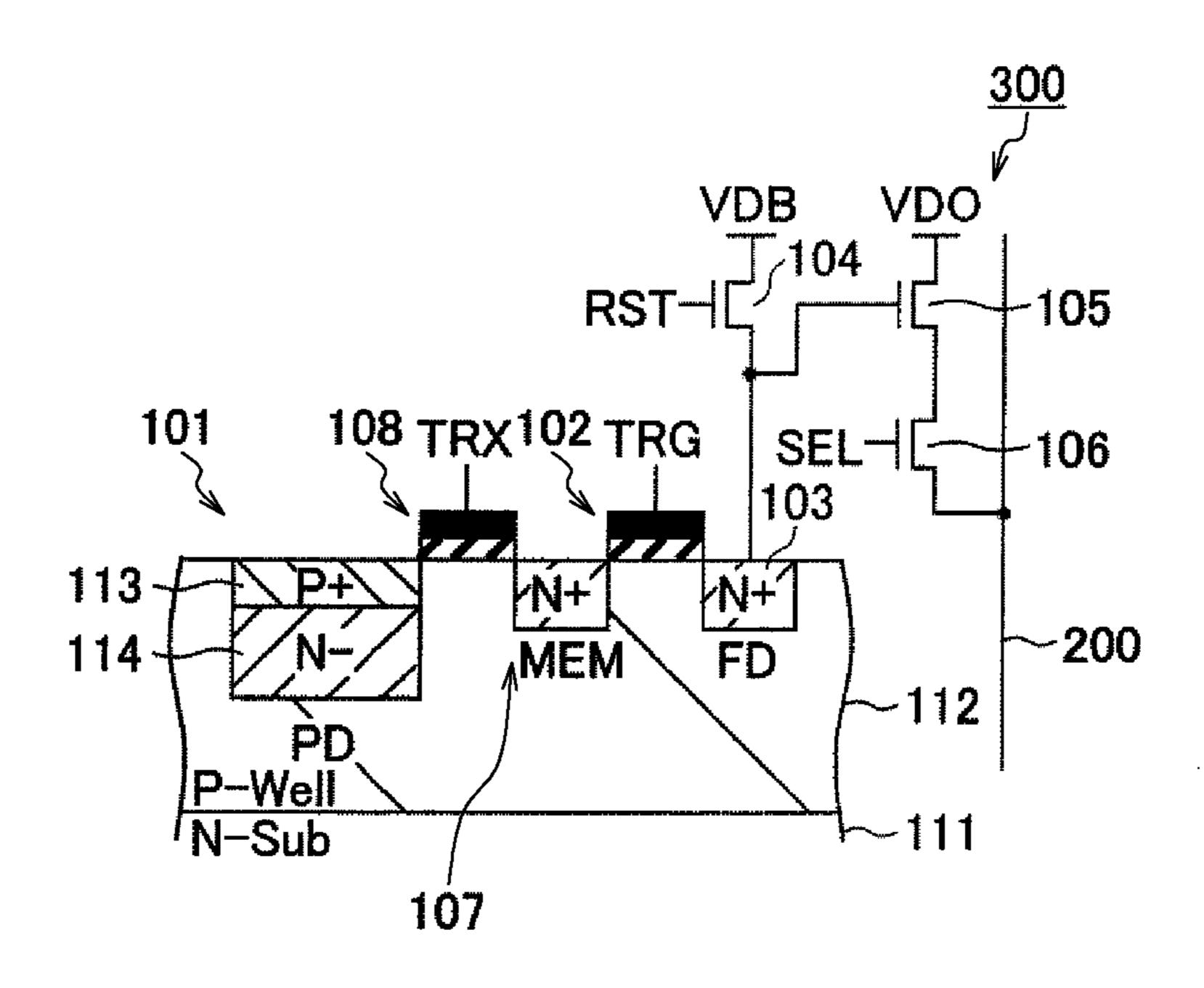

pixel 300 including a memory section 107 described in Patent Document 1.

In addition to the N-type area 103 created in the P-type well layer 112 on a silicon substrate serving as the semiconductor substrate 111 to serve as the floating diffusion capacitor FD, the unit pixel 300 shown in FIG. 2 also employs the memory section 107 denoted by reference symbol MEM in the figure. In the same way as the N-type area 103, the memory section 107 is created from an N-type semiconductor area. The memory section 107 is used for temporarily stored opto-electric charge accumulated in the photodiode **101** and transferred from the photodiode **101**. A transfer gate transistor 108 denoted by reference symbol TRX is provided between the photodiode 101 and the memory section 107 to function as means for controlling a transfer channel between the photodiode 101 and the memory section 107. To put it concretely, opto-electric charge accumulated in the photodiode 101 is transferred to the memory section 107 by way of the transfer gate transistor **108**.

### SUMMARY OF THE INVENTION

In the so-called rolling shutter method for determining the amount of electric charge accumulated in unit pixels provided on a row for every unit-pixel row for example, an image distortion causing an image to be seen as an inclined image is generated with ease in typically a moving-image taking operation. For more information, the reader is advised to refer to documents such as Japanese Patent Laid-open No. 2004-140149 (hereinafter referred to as Patent Document 2). 30 Thus, if an all-pixel read method generating no image distortion is adopted, by merely applying the existing technology described in the document, the following demerits will be encountered.

Let noise elimination processing be carried out by making use of a D phase level (also referred to as a signal level) and a P phase level (also referred to as a noise level or a reset level) which are read out in the D phase read operation and the P phase read operation respectively in the pixel circuit configuration shown in FIG. 1 as described above. In this case, after the D phase read operation has been carried out to read out the signal level, the P phase read operation is performed after resetting the N-type area 103 in order to read out the noise level. Thus, kTC noises generated in the reset operation carried out to reset the N-type area 103 cannot be eliminated. As a result, the quality of the image deteriorates. The kTC noises can be considered to be a sort of thermal noise.

The kTC noise generated in the reset operation is a random noise caused by a switching operation carried out by 50 the reset transistor **104** during the reset operation. Thus, if a level prior to the transfer of electric charge from the photodiode 101 to the floating diffusion capacitor FD is not used, the noise of the signal level cannot be eliminated with a high degree of accuracy. This is because the noise of the 55 signal level is eliminated by carrying out the reset operation after the signal level has been read out as a level representing the amount of electric charge transferred from the photodiode 101 to the floating diffusion capacitor FD for all unit pixels at the same time. By getting rid of the noise in this way, a noise caused by an offset error or the like can be eliminated. However, the kTC noise cannot.

In the following description, the period of the operation carried out to read out the signal level is referred to as a D period whereas the period of the operation carried out to read FIG. 2 is a diagram showing the configuration of a unit 65 out the reset level is referred to as a P period. On the boundary surface between an Si material used for making the semiconductor substrate 111 and an SiO<sub>2</sub> material used

5

for making a gate insulation film or the like, there are a number of crystal defects so that a dark current is generated with ease and added to the signal level. A variety of quantities such as the magnitude of the dark current vary. In particular, the magnitude of the dark current varies in accordance with the order in which electric charge held in the floating diffusion capacitor FD is read out from the floating diffusion capacitor FD. For more information, the reader is advised to refer to documents such as Patent Document 2 and Japanese Patent Laid-open No. Hei 01-243675 (hereinafter referred to as Patent Document 3). The variations in dark-current magnitude cannot be cancelled too by merely adopting the noise elimination method making use of the reset level.

In order to solve such problems raised by the reset-noise elimination methods disclosed in documents such as Patent Documents 2 and 3, there have been provided technologies disclosed in Patent Documents 1 and 4 to 6 mentioned before. In accordance with these technologies, a memory 20 section 107 also referred to as an electric-charge storage section is provided between the opto-electric conversion section PD and the floating diffusion capacitor FD in the pixel circuit as shown for example in FIG. 2.

The memory section 107 is provided as shown in FIG. 2 25 in order to make the levels of the reset noise (or, strictly speaking, the kTC noise) uniform for all unit pixels 300.

The kTC noises are electric-potential fluctuations left in the floating diffusion capacitor FD during the control of the MOS transistor even after induction noises have been 30 absorbed. The kTC noises are thermal noises generated in the channel resistor of the MOS transistor.

If the memory section 107 is not provided, a sequence of read operations is carried out as follows. First of all, the signal level is read out from the N-type area 103 and, then, the reset level is read out from the N-type area 103 as described earlier.

pixels. Thus, by merely applying the existing technologies disclosed in the Patent Documents, it is difficult to eliminate the noise having a quantity not uniform for all unit pixels. The fact that the quantity of a noise including the smear component as a main component increases as the memory

With the memory section 107 newly added to the pixel circuit, on the other hand, the signal electric charge also referred to as the opto-electric charge can be stored tempo-40 rarily in the memory section 107. Thus, even in the case of an all-pixel read operation, a reversed sequence of read operations can be adopted and carried out as follows. First of all, the reset level is read out from the N-type area 103 and, then, the signal level is read out from the N-type area 45 103. By carrying out the reversed sequence of read operations in this way, a reset noise having a level about equal to the reset level read out earlier is superposed on the signal level in the electric-charge transfer through the same transistor. Thus, the reset noise can be eliminated with ease in 50 noise elimination processing carried out later.

By adoption of the pixel configuration including the memory section 107, it is possible to eliminate the reset noise which is relatively large in comparison with a variety of random noises.

On the presumption that the pixel configuration including the memory section 107 is adopted, in order to further eliminate noises, it is necessary to eliminate noise components such as smear components having an effect on accumulated electric charge and causing an alias signal. In general, smear components are noise components superposed on signal electric charge also referred to as optoelectric charge read out from an opto-electric conversion element such as a photodiode and accumulated temporarily in a memory before being transferred to a destination in a way similar to an operation carried out by for example a vertical transfer register employed in a CCD image sensor.

6

If a memory section used for temporarily accumulating signal electric charge also referred to as opto-electric charge is provided in the pixel configuration, a countermeasure against the smear noise is required.

As a countermeasure against the smear noise, Patent Documents 1 and 4 to 6 disclose a configuration in which a light shielding film is used to shield the memory section against light. In addition, patent reference 6 discloses a structure in which a P-type embedded layer is provided on the substrate deeper side of an N-type electric-charge storage section corresponding to the memory section 107 employed in the unit pixel 300 shown in FIG. 2. The electric-potential barrier of the P-type embedded layer prevents electric charge, which causes smear noises to be generated on the substrate deeper side, from diffusing into the N-type electric-charge storage section.

By adoption of such a configuration, it is possible to get rid of smear components generated in each individual unit pixel.

The memory electric accumulation period is a period between an operation to transfer opto-electric charge from the opto-electric conversion section PD to the memory section at the same time for all unit pixels and an operation to transfer the opto-electric charge from the memory section to the floating diffusion capacitor FD. Relative to the signal component, the quantity of a noise including the smear component as a main component increases as the memory electric accumulation period becomes longer. Thus, if the memory electric accumulation period varies from pixel to pixel, the quantity of such a noise also varies from pixel to pixel as well. In addition, an inclined light component causing the smear component is also not uniform for all unit pixels. Thus, by merely applying the existing technologies disclosed in the Patent Documents, it is difficult to eliminate the noise having a quantity not uniform for all unit pixels.

The fact that the quantity of a noise including the smear component as a main component increases as the memory electric accumulation period becomes longer and the fact that there is an effect of an inclined light component causing the smear component as described above can be said to hold true for not only the memory section, but also to the floating diffusion capacitor FD, which is used for temporarily holding signal electric charge, as well. In addition, in some configurations, a plurality of floating diffusion capacitors FD may exist along a route through which signal electric charge is read out from the memory section (or the opto-electric conversion section PD).

In accordance with what is written in this invention specification, signal electric charge is transferred from the opto-electric conversion section at the same time for all unit pixels. In addition, an area used for holding electric charge is referred to as an electric-charge holding section or simply as a holding section. That is to say, in accordance with a single FD method to be described later, an FD area playing a role as a section for converting electric charge into a voltage expressed in terms of variations in electric potential and a memory section MEM provided between the opto-electric conversion section and the FD area are each referred to as an electric-charge holding section or simply as a holding section.

The present invention proposes a pixel internal layout structure capable of making noise components such as smear noise components, which have an effect on accumulated opto-electric charge, uniform throughout the layout surface of all unit pixels. In addition, the proposed pixel internal layout structure is also capable of sufficiently eliminating the noise components. The present invention also provides a

solid-state image taking device employing unit pixels each having such a pixel internal layout structure. On top of that, the present invention also provides electronic apparatus each employing a solid-state image taking device capable of sufficiently eliminating noise components such as smear 5 noise components.

A solid-state image taking device according to a first mode of the present invention employs a pixel section and a scan driving section. The pixel section includes a plurality of unit pixels laid out to form a pixel matrix and to serve as unit pixels which have read sections and are each provided with a pixel opening prescribed by an optical-path limiting section created on a semiconductor substrate and with an opto-electric conversion section as well as an electric-charge holding section. On the other hand, the scan driving section to controls an operation to transfer electric charge from the opto-electric conversion section to the electric-charge holding section at the same time for the unit pixels in a pixel area determined in advance in the pixel matrix. The scan driving section also scans and drives the read sections in one scan 20 direction.

On each pixel column included in the pixel area determined in advance to serve as a pixel column having the unit pixels laid out in the scan direction, the opto-electric conversion section and the electric-charge holding section are 25 laid out alternately and repeatedly.

In addition, on each of the pixel columns in the pixel area determined in advance, two aforementioned electric-charge holding sections of two adjacent ones of the unit pixels are laid out disproportionately toward one side of the scan 30 direction with respect to the optical-path limiting section or the opto-electric conversion section.

In accordance with the configuration described above, the scan driving section scans the read sections of all the unit pixels in a scan direction of the pixel column during a scan 35 operation and drives the read sections. In this scan operation, electric charge generated in the opto-electric conversion section is transferred to the electric-charge holding section at the same time for all the pixel units. The scan operation is started with a pixel row at one end of the scan direction and 40 carried out toward a pixel row at the other end of the scan direction sequentially on a one-row-after-another basis.

In every unit pixel, on the scan-start side of the scan direction of the scan operation, the opto-electric conversion section of the unit pixel or the electric-charge holding 45 section of the unit pixel is placed whereas, on the scan-end side of the scan direction of the scan operation, the electriccharge holding section of the unit pixel or the opto-electric conversion section of the unit pixel is placed. For example, on the scan-start side of the scan direction of the scan 50 operation, the electric-charge holding section of the unit pixel is placed whereas, on the scan-end side of the scan direction of the scan operation, the opto-electric conversion section of the unit pixel is placed. In addition, two aforementioned electric-charge holding sections are laid out 55 disproportionately toward one side of the scan direction with respect to the optical-path limiting section or the optoelectric conversion section. For example, in comparison with the distance between the opto-electric conversion section of a certain unit pixel and the electric-charge holding 60 section of the same unit pixel located on the scan start side, the distance between the opto-electric conversion section of the unit pixel and the opto-electric conversion section of another unit pixel located on the scan end side is set at a large value.

Thus, in a unit pixel placed on the scan end side of a pixel column oriented in the scan direction as a unit pixel includ-

8

ing an electric-charge holding section with a long electriccharge holding period, the magnitude of a light component entering from a side at a short distance is greater than the magnitude of a light component entering from a side at a long distance. This is because, when the solid-state image taking device is being used, in the optical lens, there are generally a number of light components dispersed from the optical axis of the optical lens to the outer side. Thus, in the pixel section, the number of light components most inclined on the scan start row and the scan end row generally increases in comparison with the total quantity of incident light. Accordingly, the quantity of light causing noises in the electric-charge holding section decreases due to inclined leak light and, the closer the location of the unit pixel to the scan end side, the larger the decrease, so that the number of smear components is reduced.

This relation is reversed on the scan start side with relatively short electric-charge accumulation periods. Thus, more leak light hits the electric-charge holding section. Since the electric-charge accumulation period is short from the beginning, however, an abrupt increase in smear-component count (that is, an abrupt increase in noise count) is not observed.

As a result, in accordance with the pixel internal layout structure proposed by the present invention, by virtue of the electric-charge accumulation period and the reversed relation, the quantity of leak light is adjusted so that, as a whole, the number of noise components is reduced uniformly to a low level.

A solid-state image taking device according to a second mode of the present invention is different from the solid-state image taking device according to the first mode of the present invention in that, in the case of the solid-state image taking device according to the second mode of the present invention, in every unit pixel of the pixel matrix, the electric-charge holding section is placed on the start side of the scan direction whereas the opto-electric conversion section is placed on the end side of the scan direction.

An electronic apparatus according to a third mode of the present invention includes an optical system employing the solid-state image taking device according to the first mode of the present invention.

In particular, a small or thin electronic apparatus in which light incident to the solid-state image taking device includes a number of inclined components has a big merit of being capable of eliminating noises by virtue of the distance prescriptions described above.

In accordance with the present invention, there is provided a solid-state image taking device capable of making noise components such as smear noise components, which have an effect on accumulated opto-electric charge, uniform throughout the layout surface of all unit pixels and also capable of sufficiently eliminating the noise components. In addition, also in accordance with the present invention, there are provided electronic apparatus each employing a solid-state image taking device capable of sufficiently eliminating noise components such as smear noise components.

# BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a diagram showing the configuration of a unit pixel employed in a CMOS image sensor according to an existing technology;

FIG. 2 is a diagram showing the configuration of a unit pixel including a memory section in accordance with an existing technology;

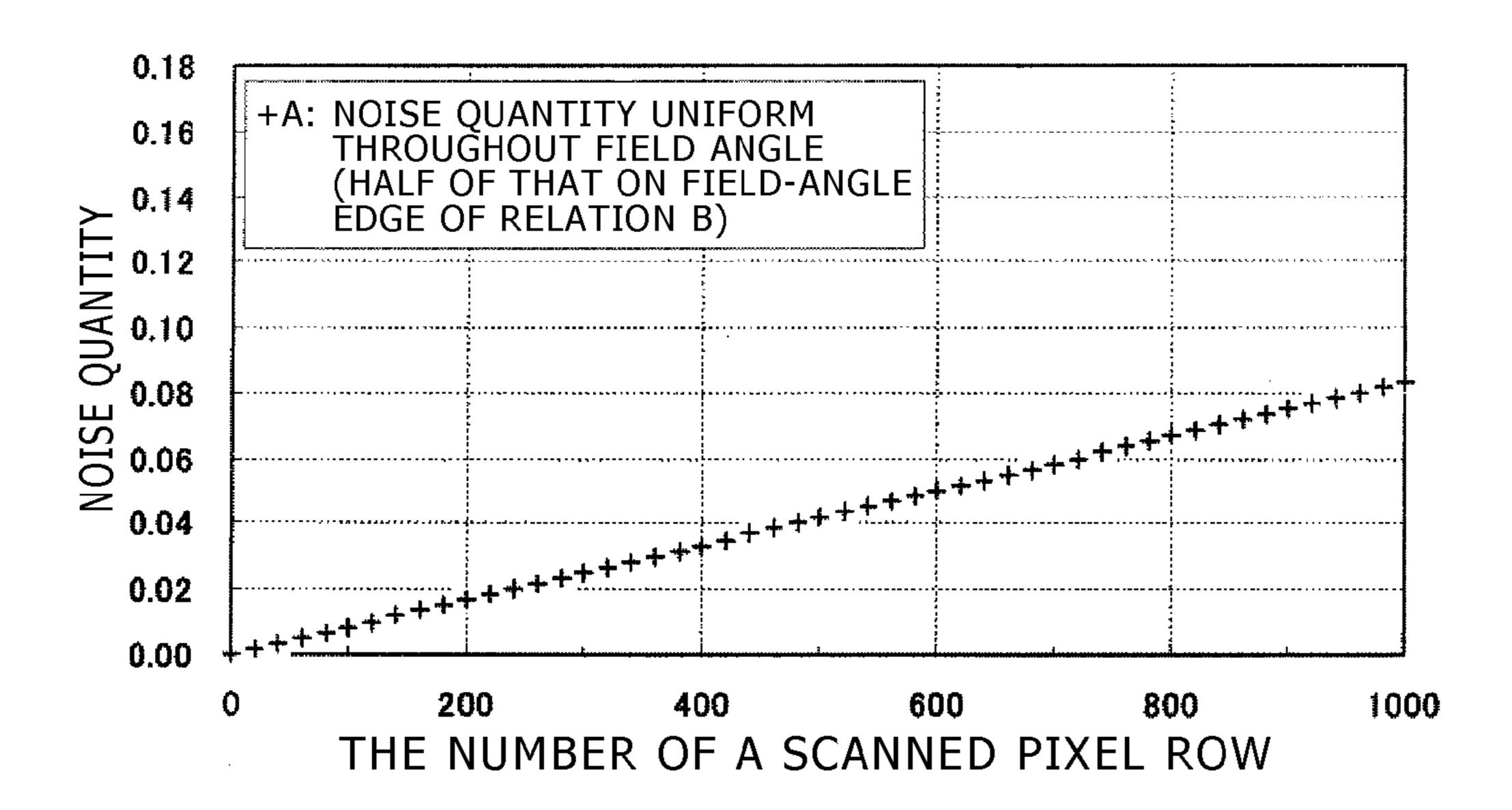

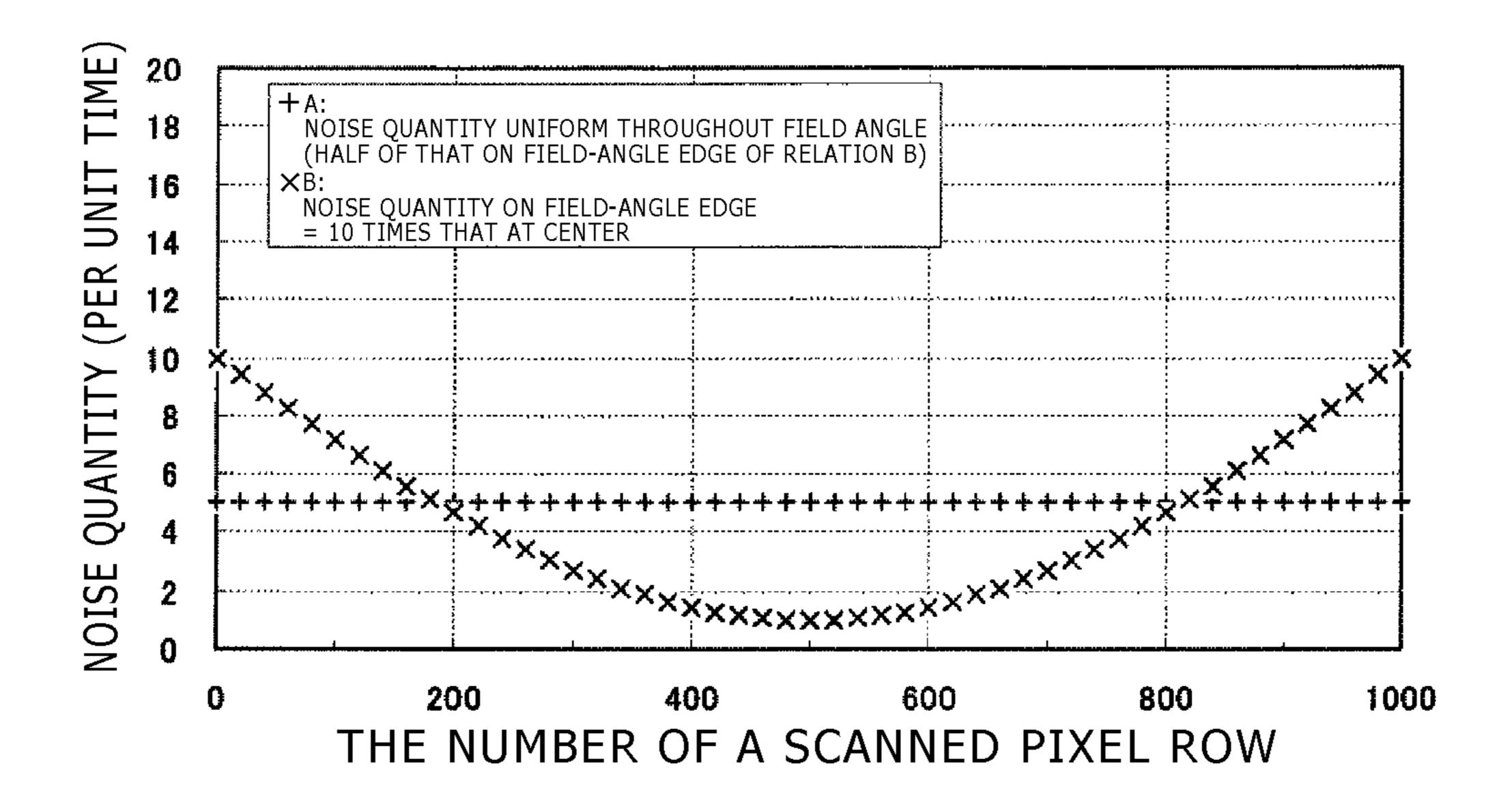

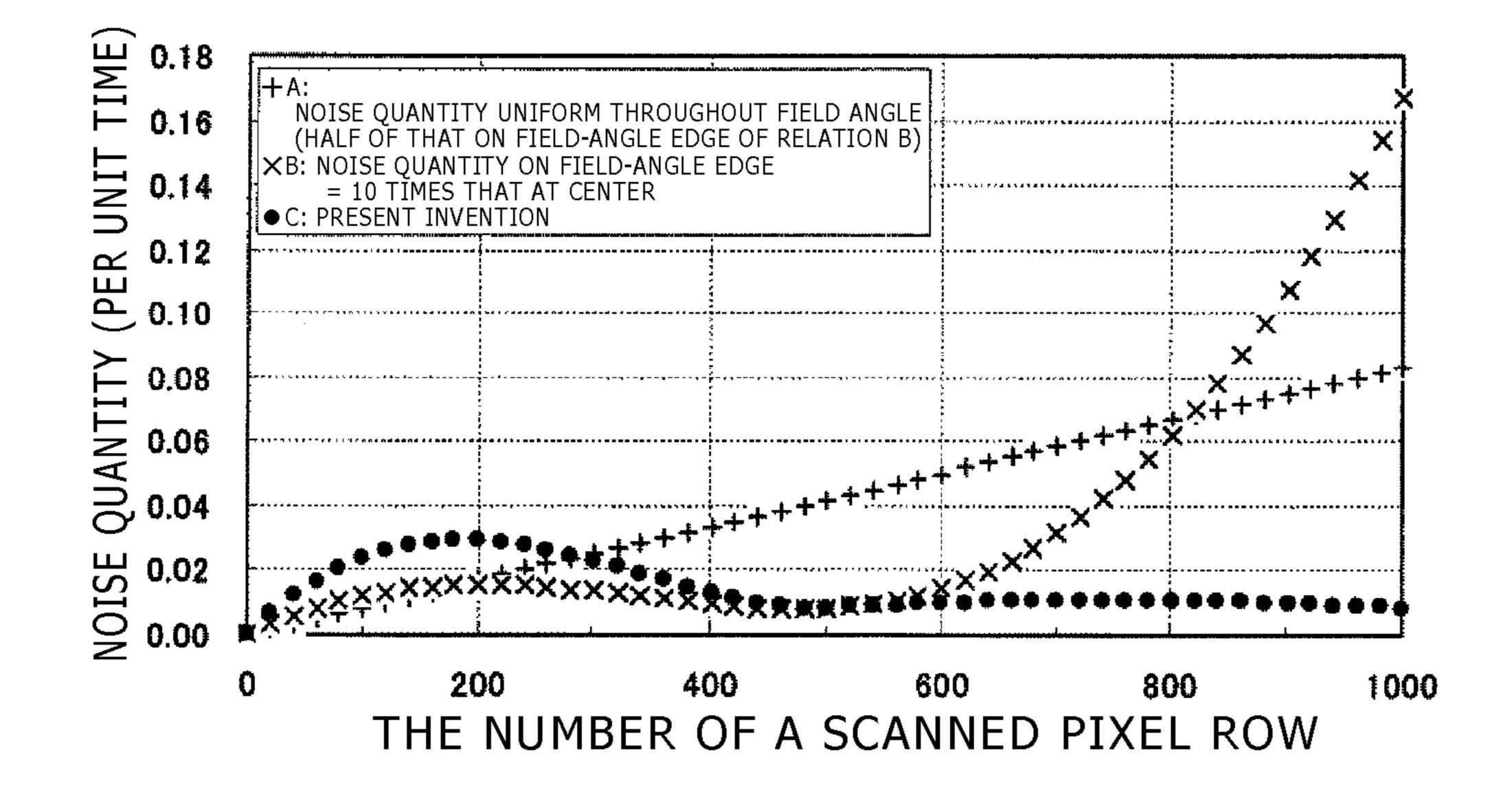

- FIG. 3 is a correlation diagram showing a relation between the number of a scanned pixel row and the noise quantity per unit time;

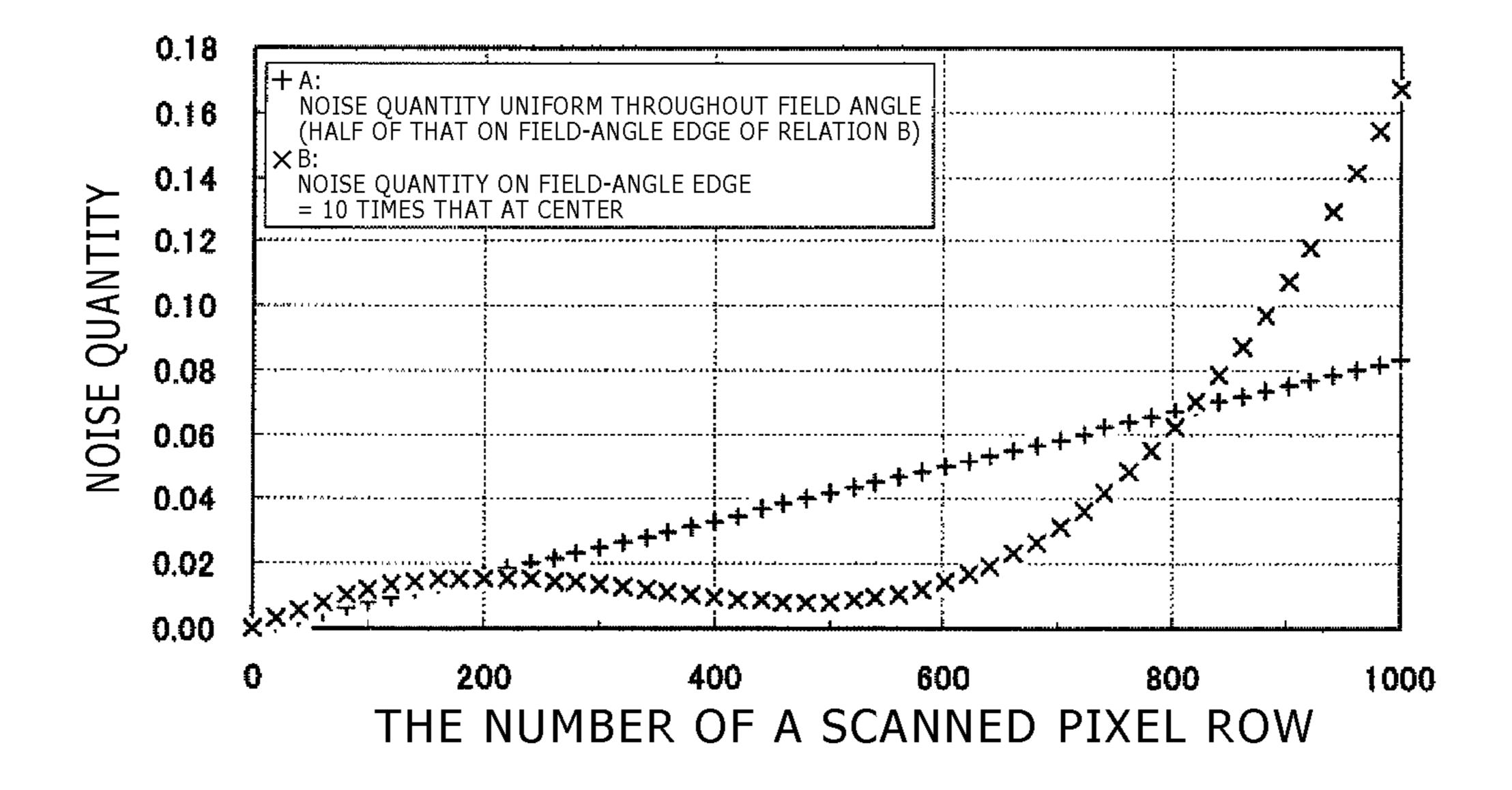

- FIG. 4 is a correlation diagram showing a relation between the number of a scanned pixel row and the noise 5 quantity of the noise actually accumulated during an electric-charge holding period;

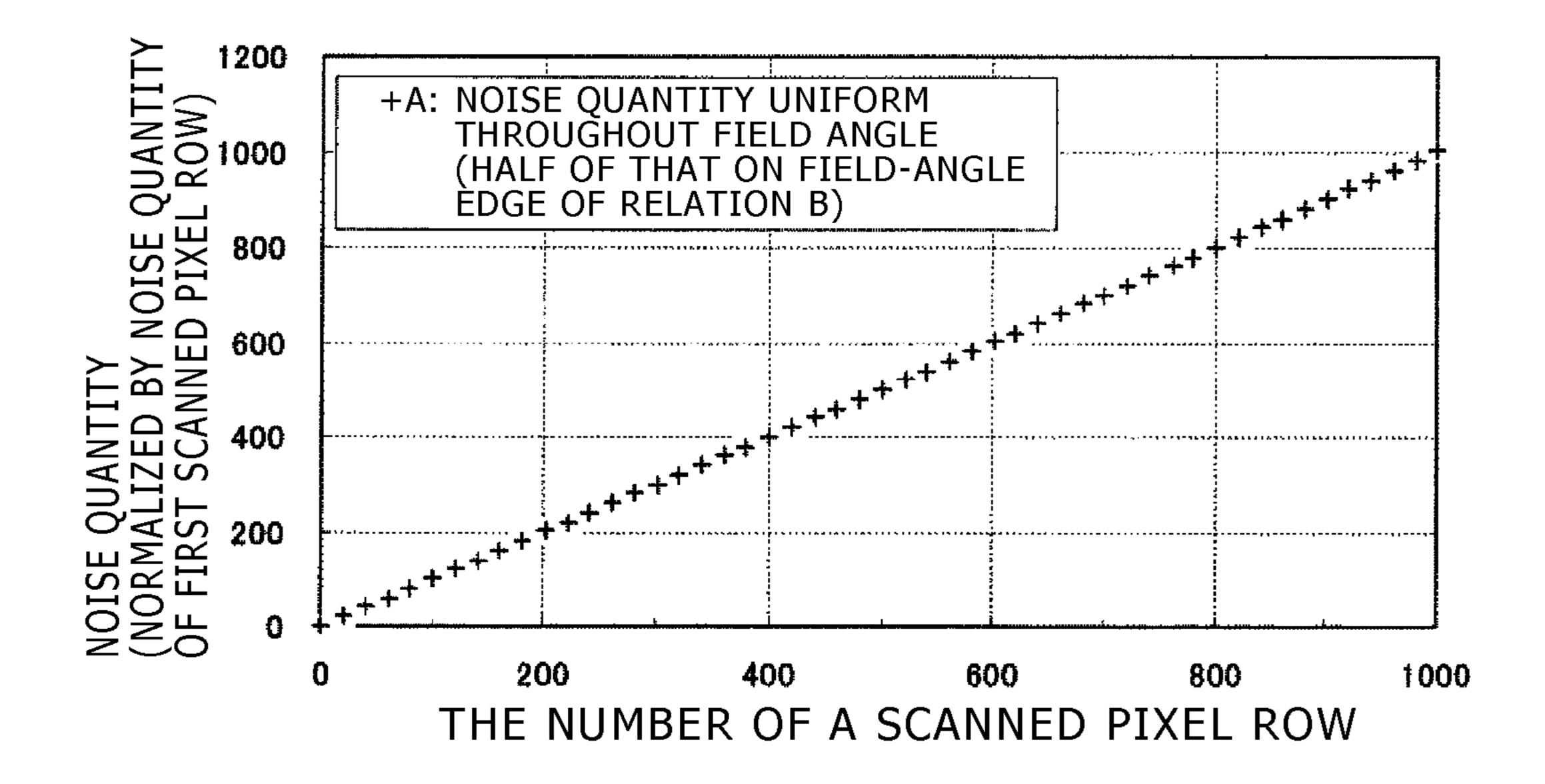

- FIG. 5 is a correlation diagram showing a relation between the number of a scanned pixel row and a normalized noise quantity of the noise accumulated during an 10 electric-charge holding period;

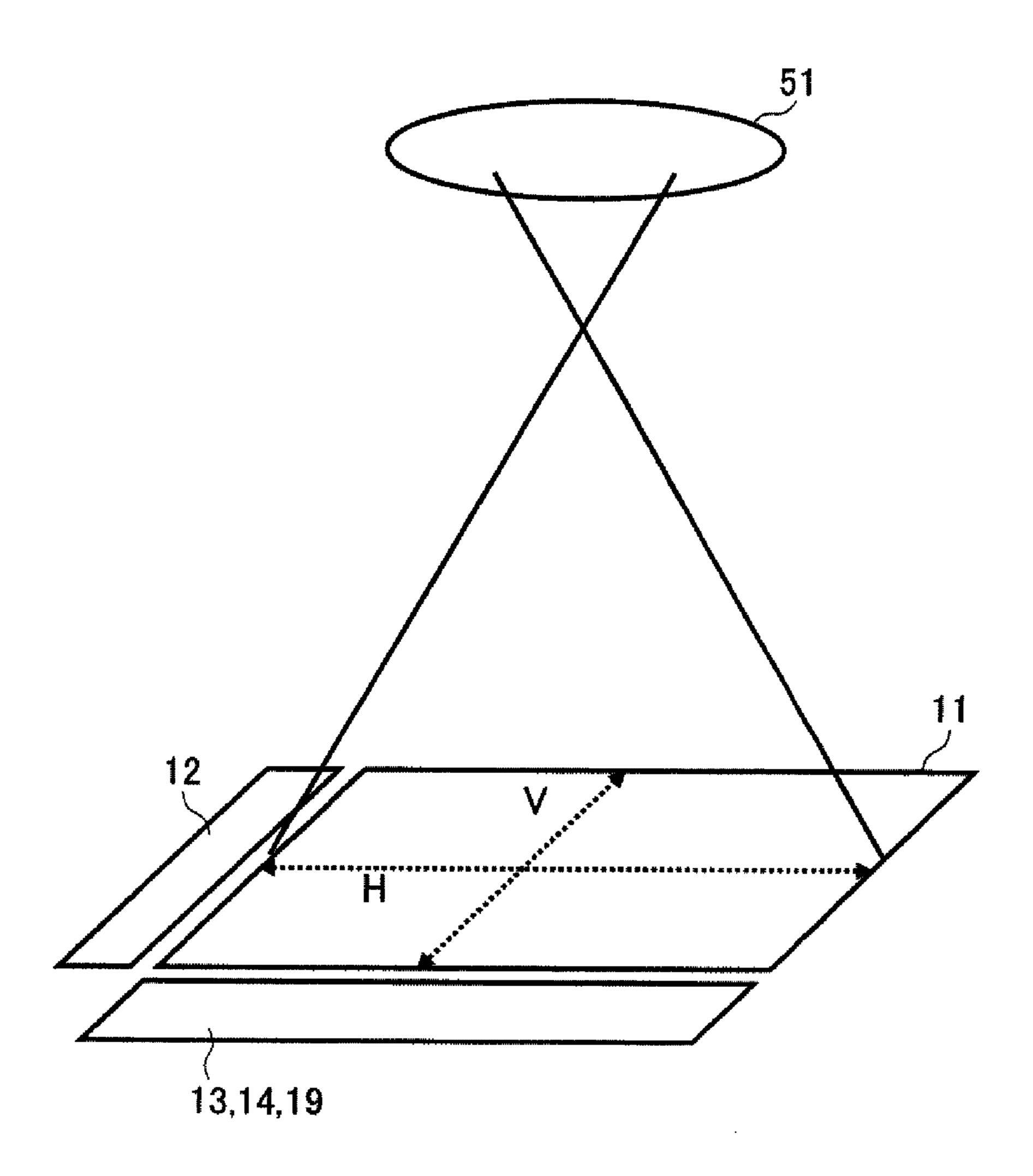

- FIG. 6 is an image diagram for a case in which a lens group converges incident light toward a pixel array;

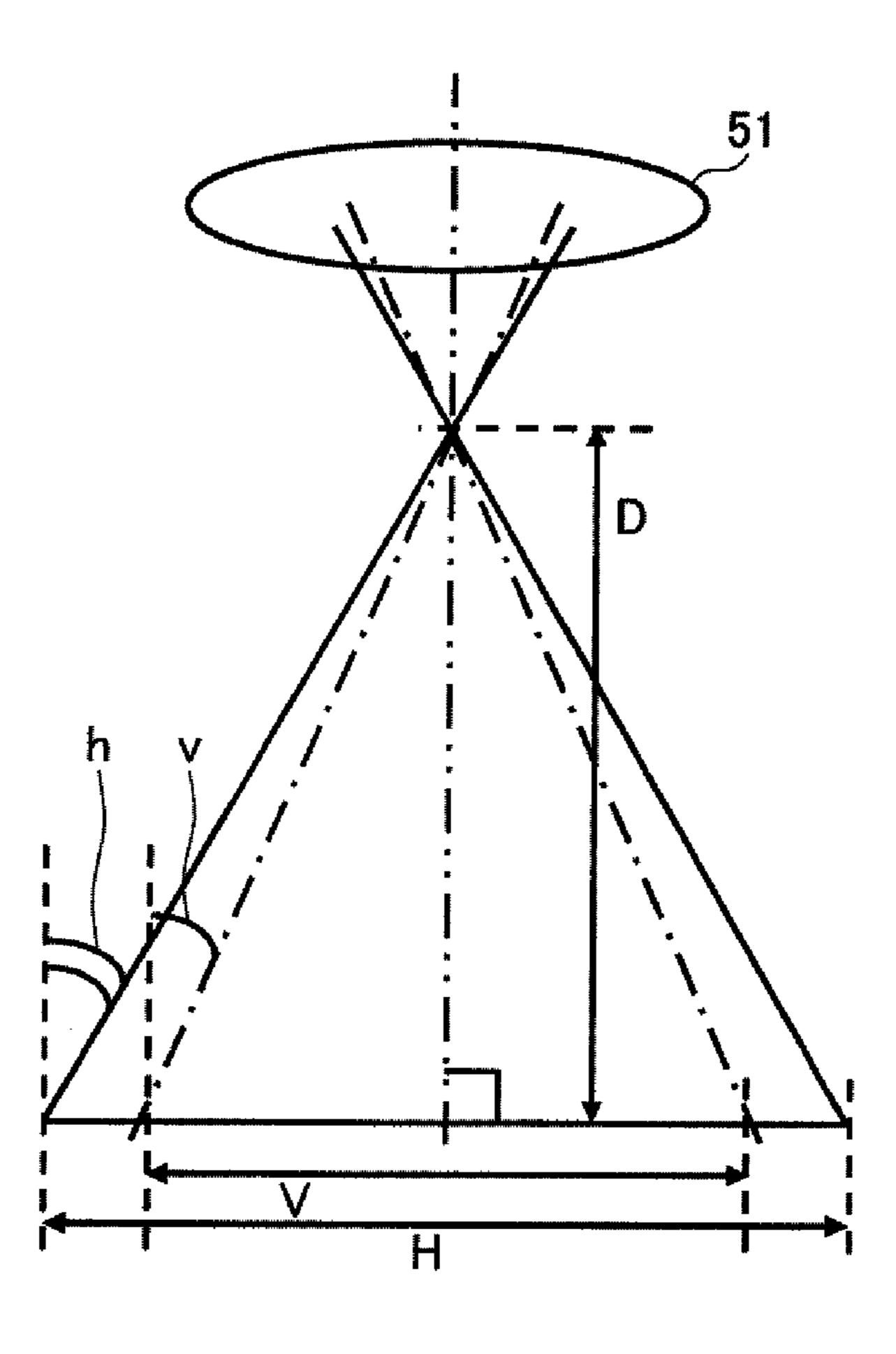

- FIG. 7 is a model diagram showing how the lens group converges incident light toward the pixel array represented 15 by its cross sections spread in the H (horizontal) and V (vertical) directions;

- FIG. 8 is a correlation diagram showing the relation shown in FIG. 3 and another relation obtained by re-plotting the relation of FIG. 3 by taking the incidence angle of light 20 into consideration;

- FIG. 9 is a correlation diagram showing the relation shown in FIG. 4 and another relation obtained by re-plotting the relation of FIG. 4 by taking the incidence angle of light into consideration;

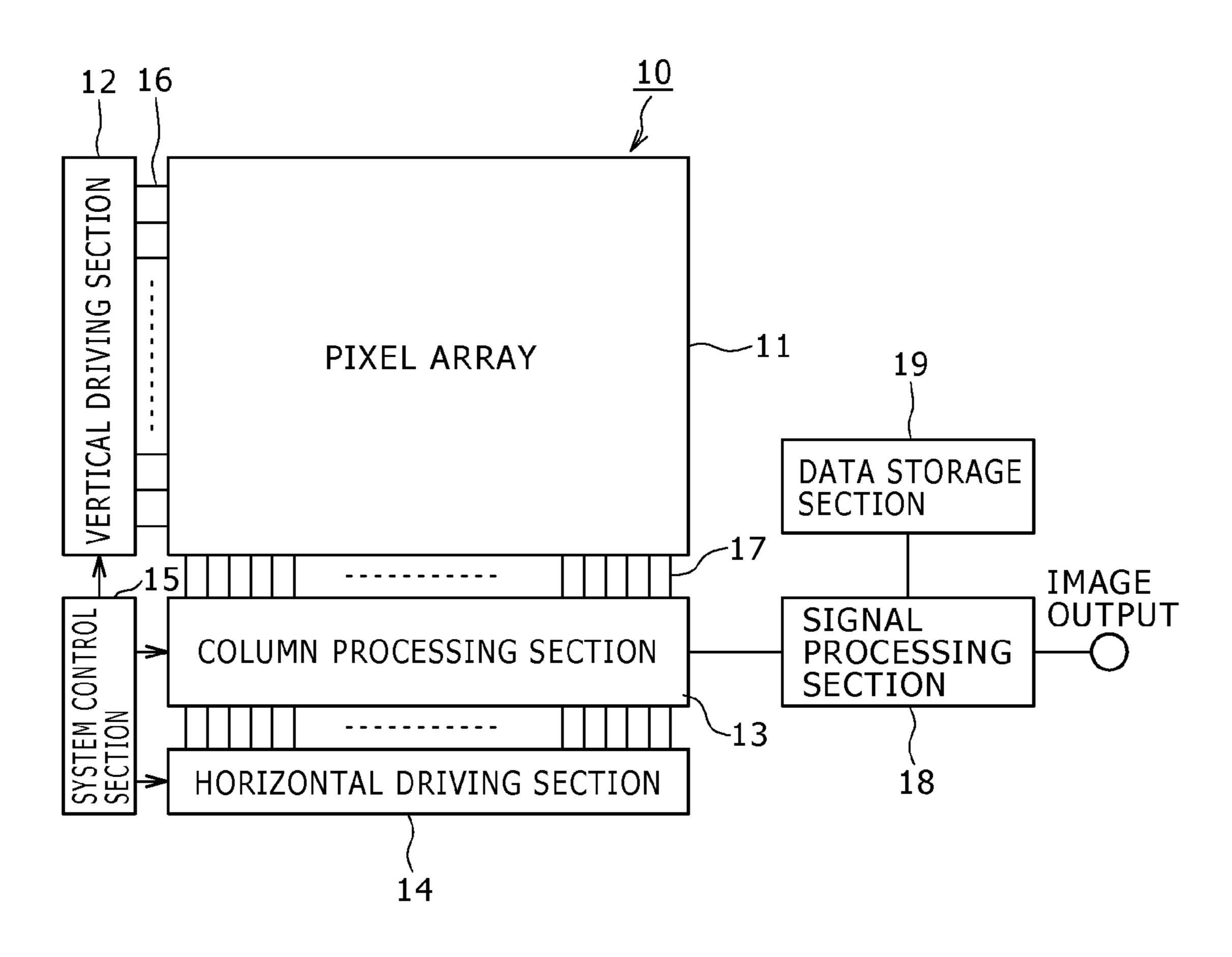

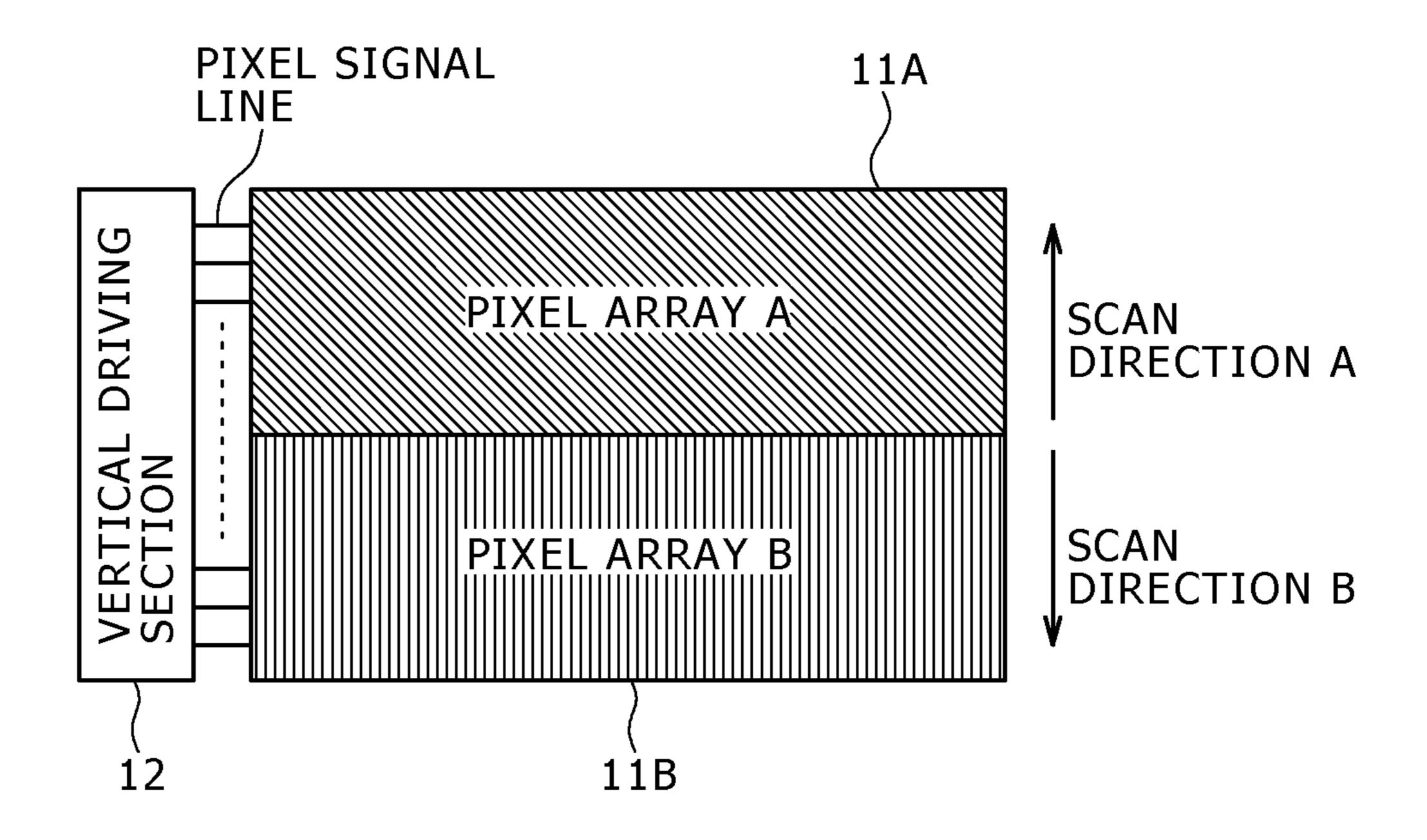

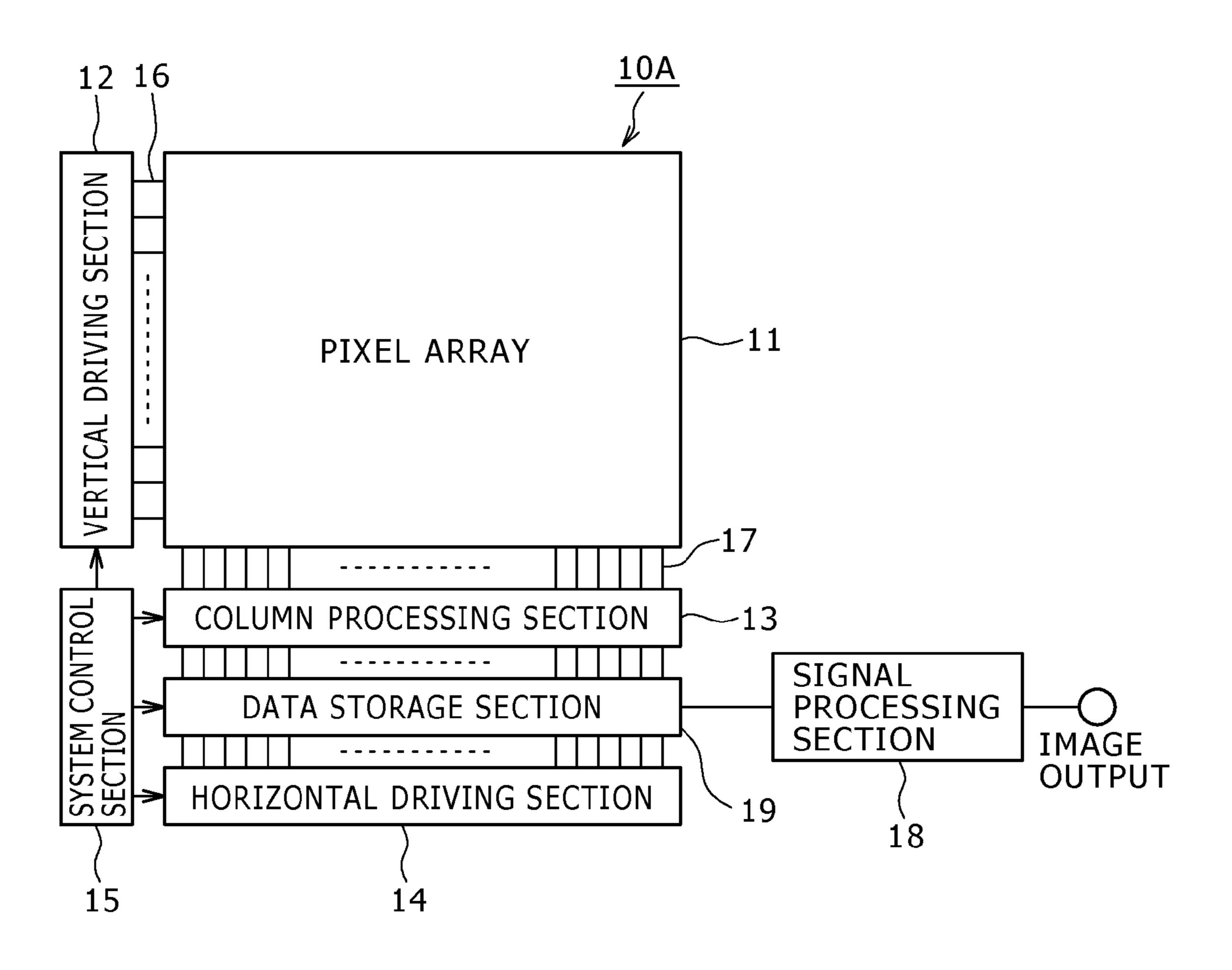

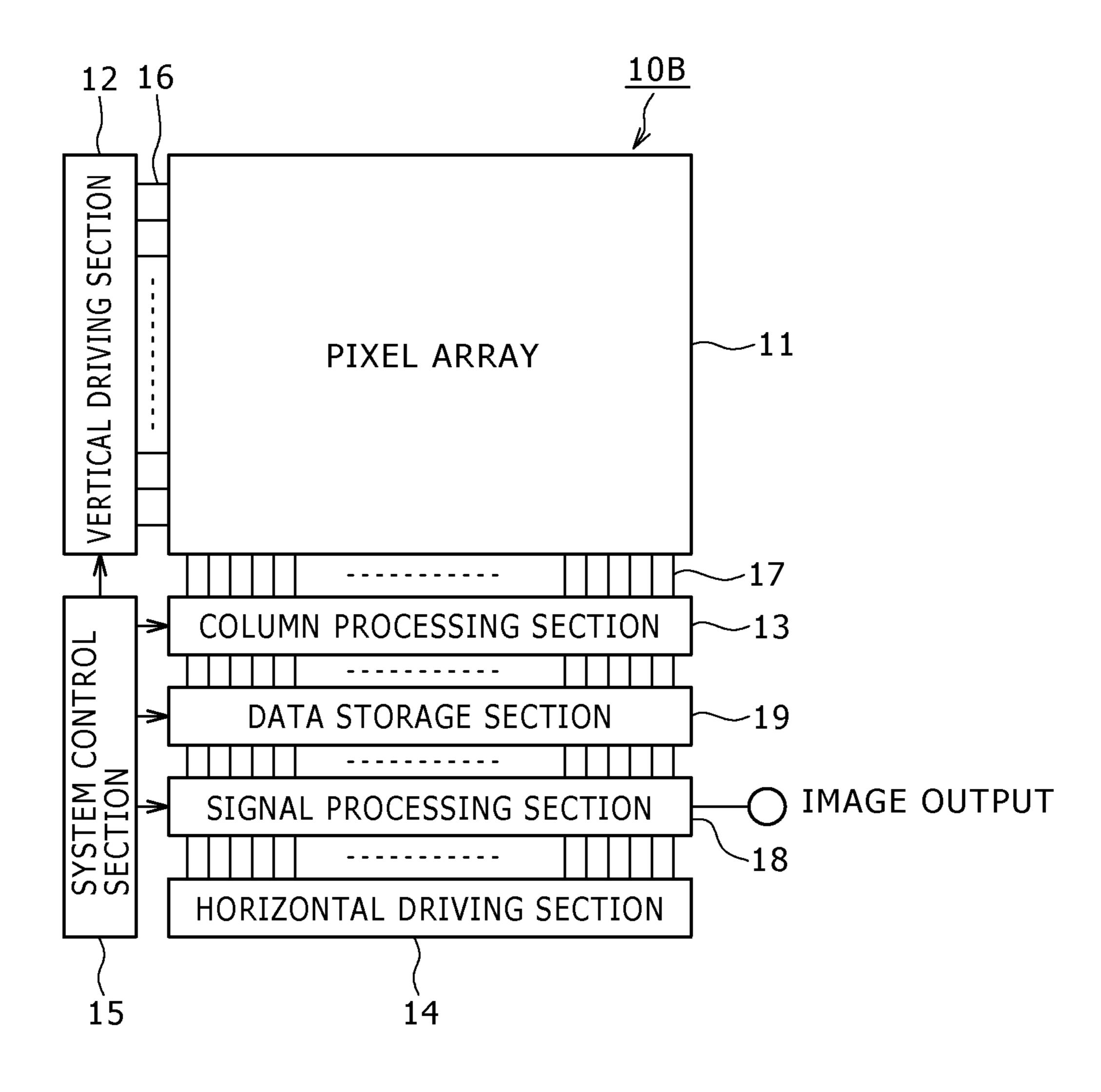

- FIG. 10 is a diagram showing the system configuration of a CMOS image sensor according to an embodiment;

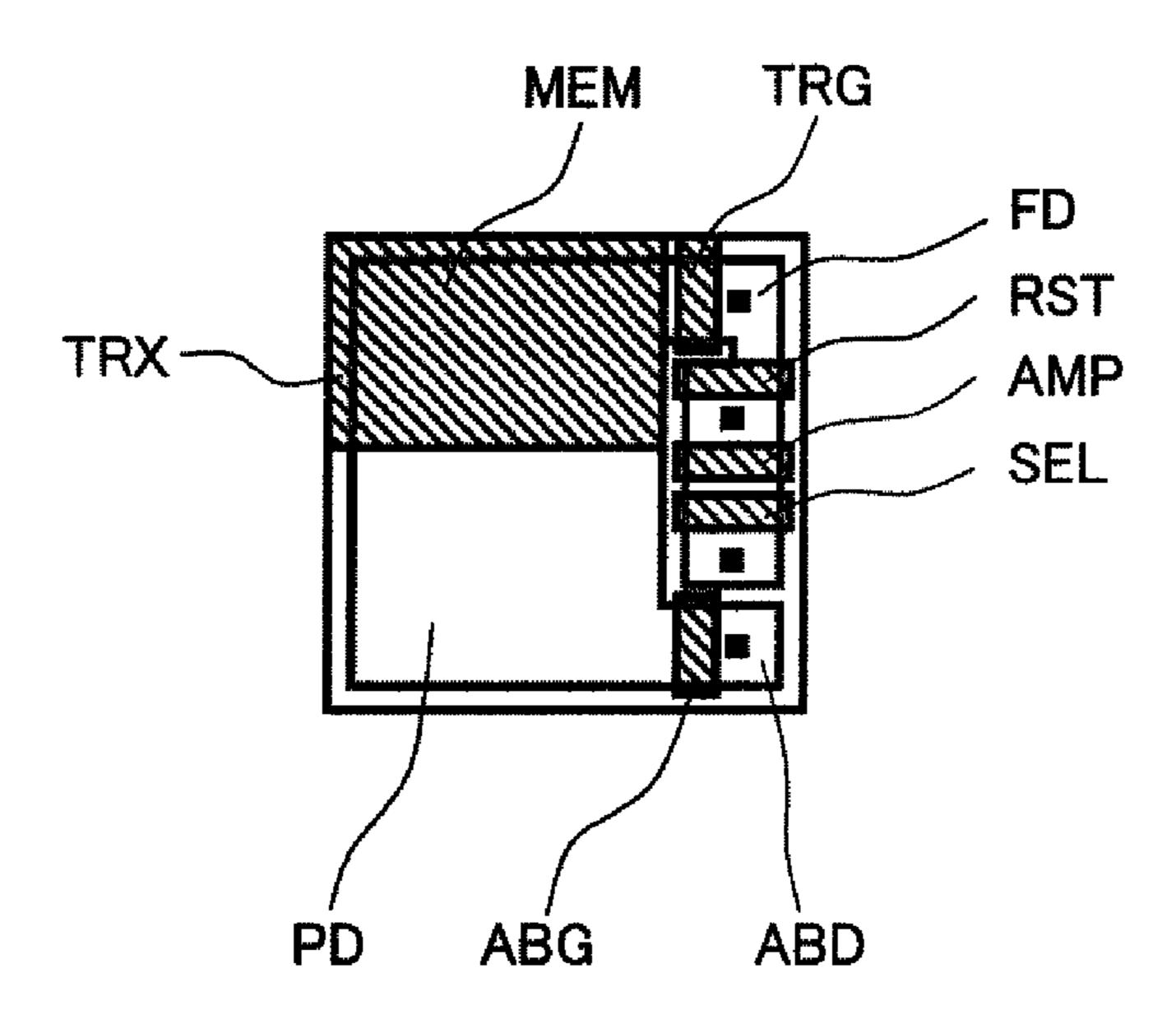

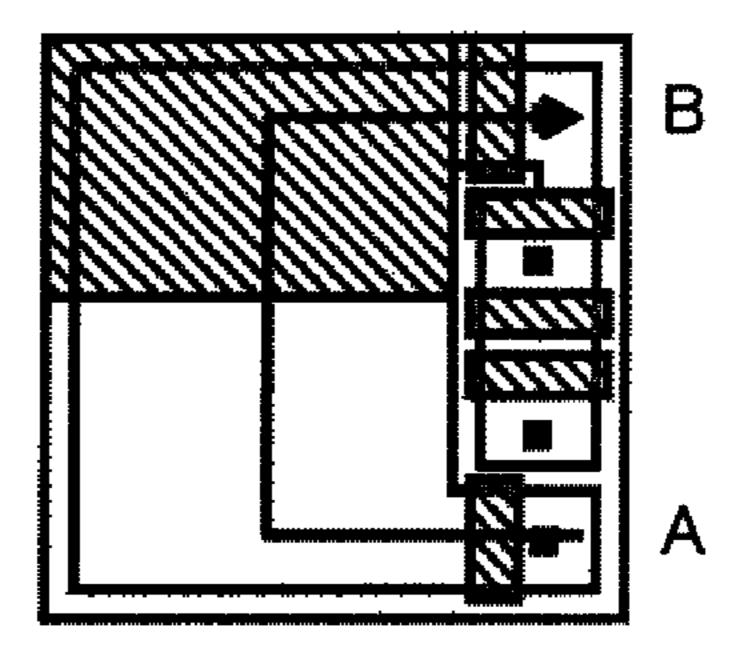

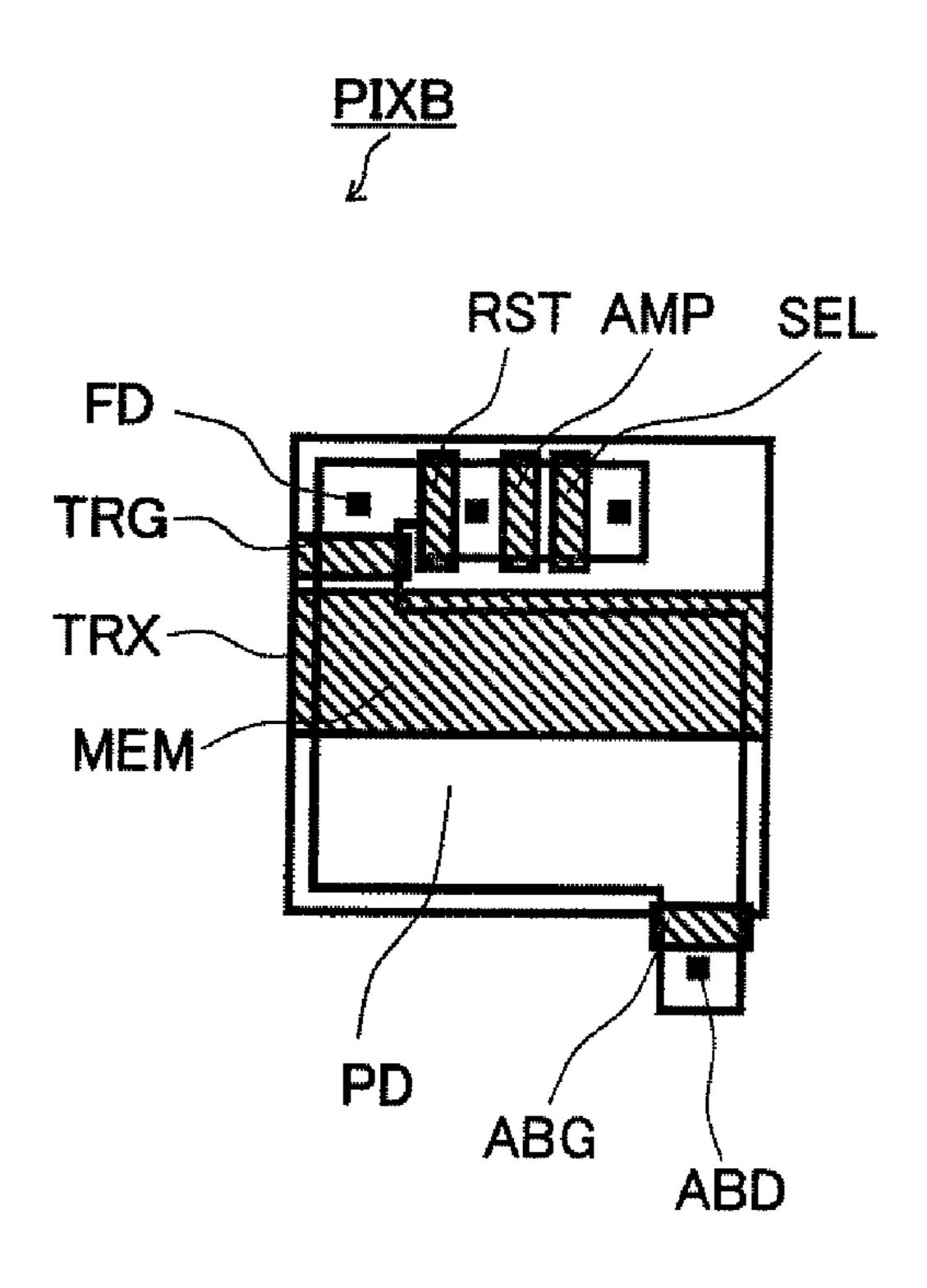

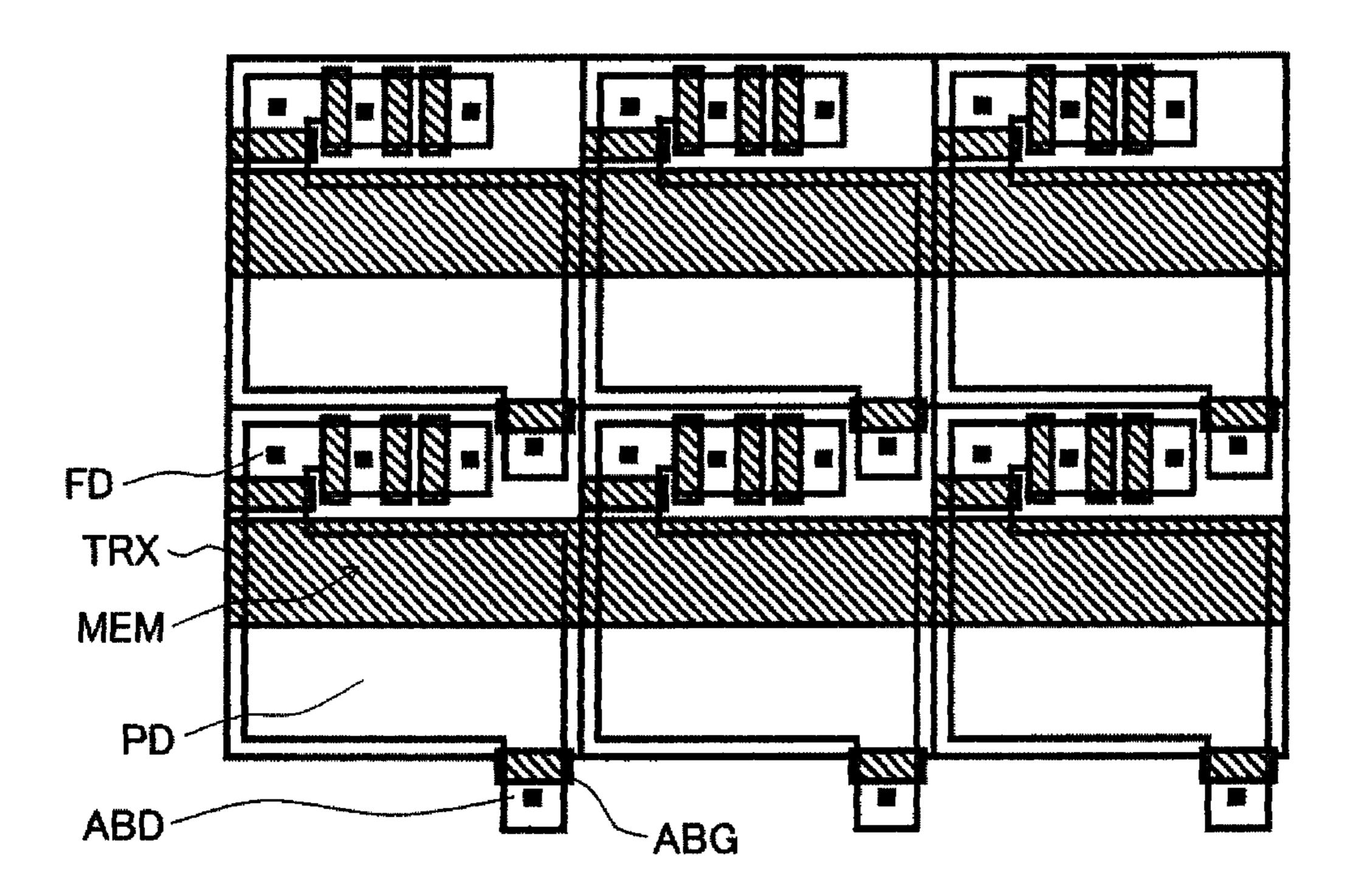

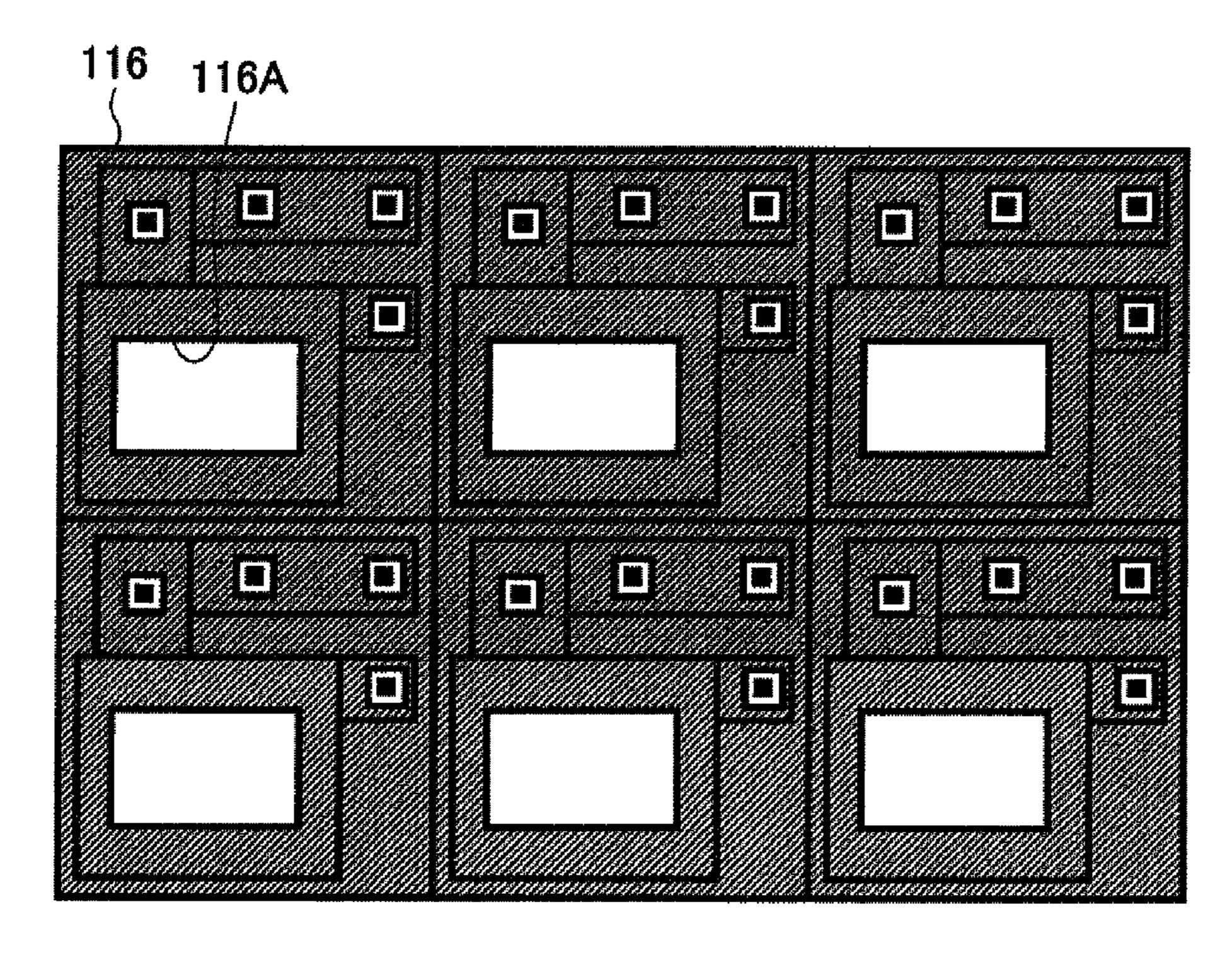

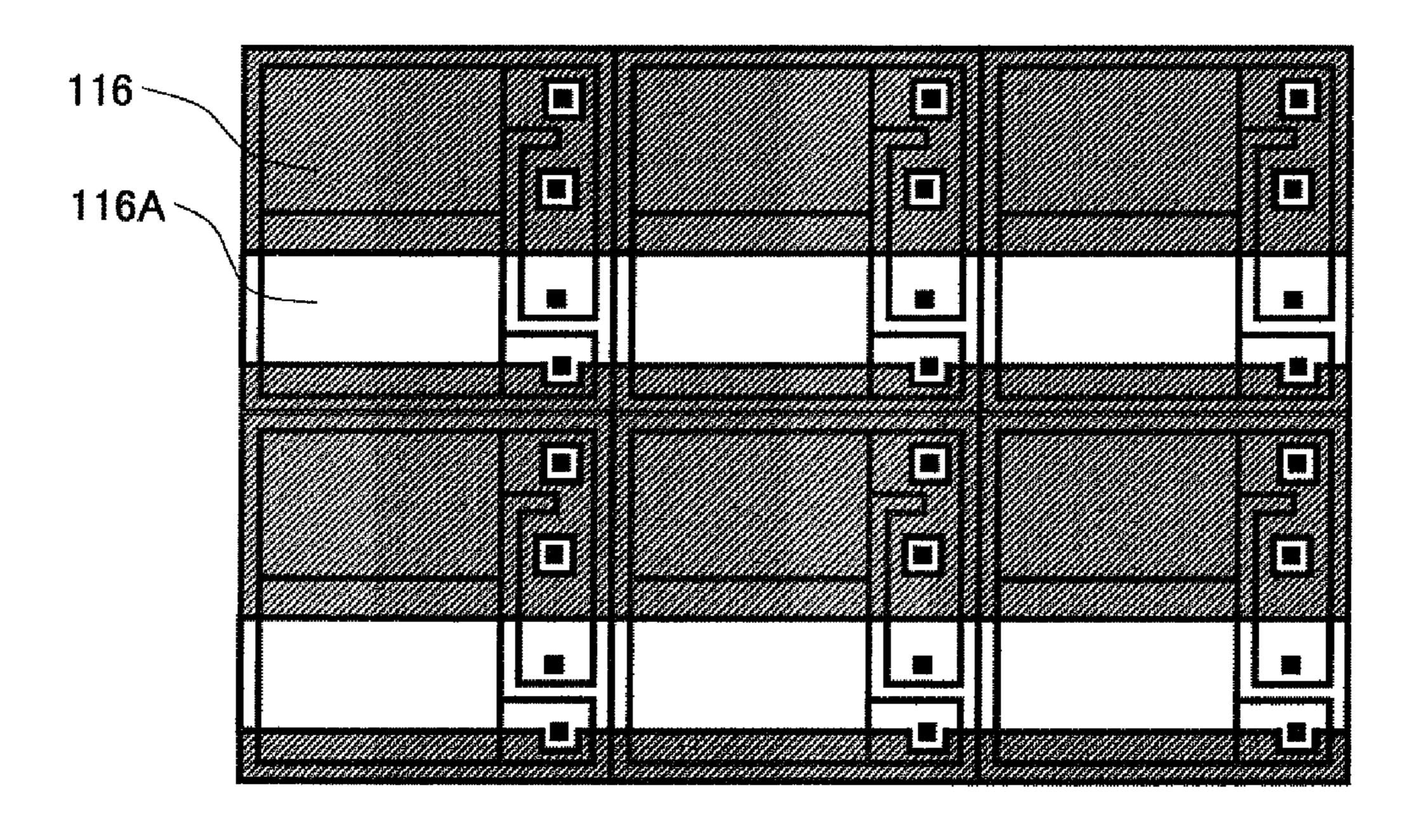

- FIGS. 11A and 11B are a plurality of top-view diagrams showing the configuration of a unit pixel according to a first embodiment;

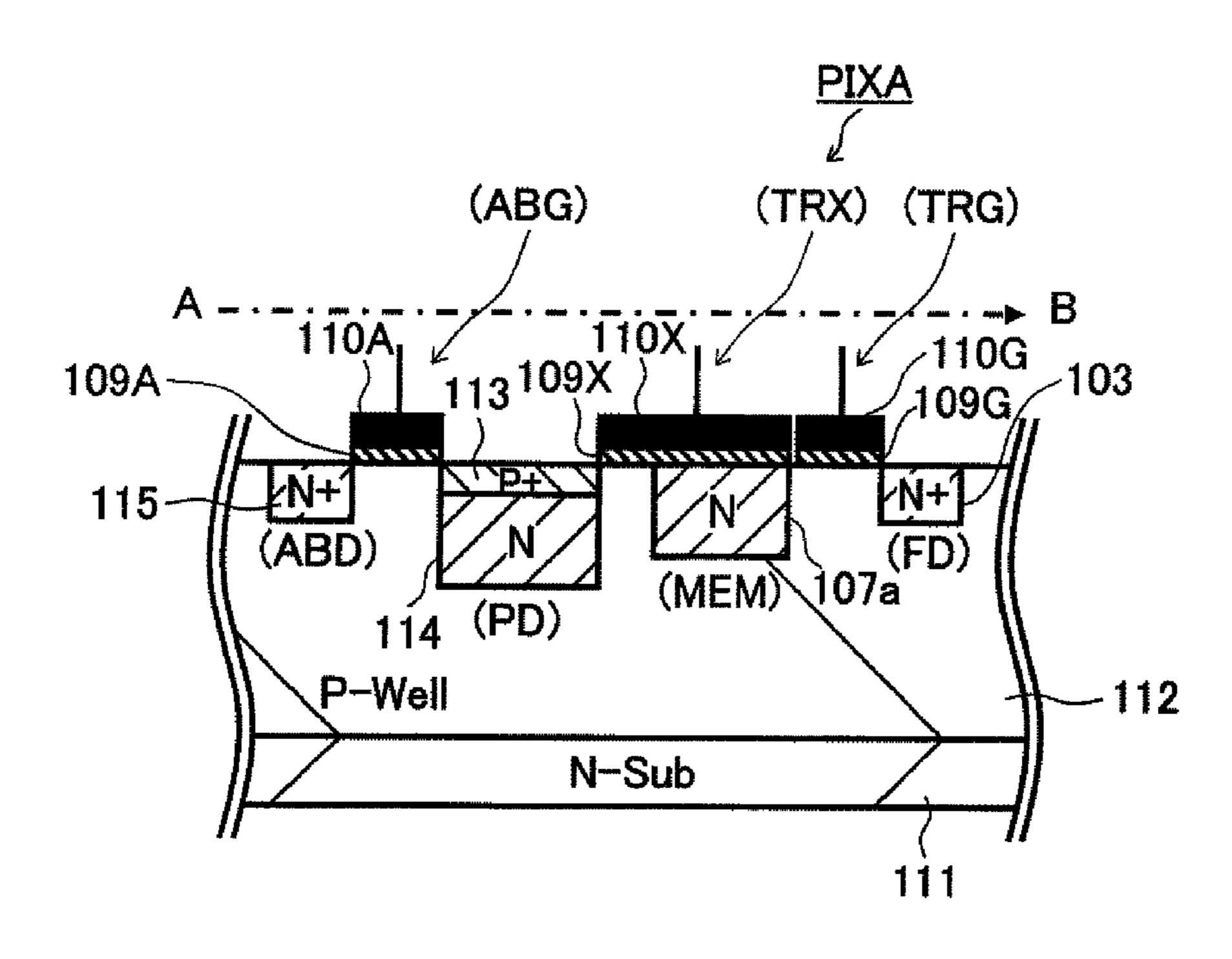

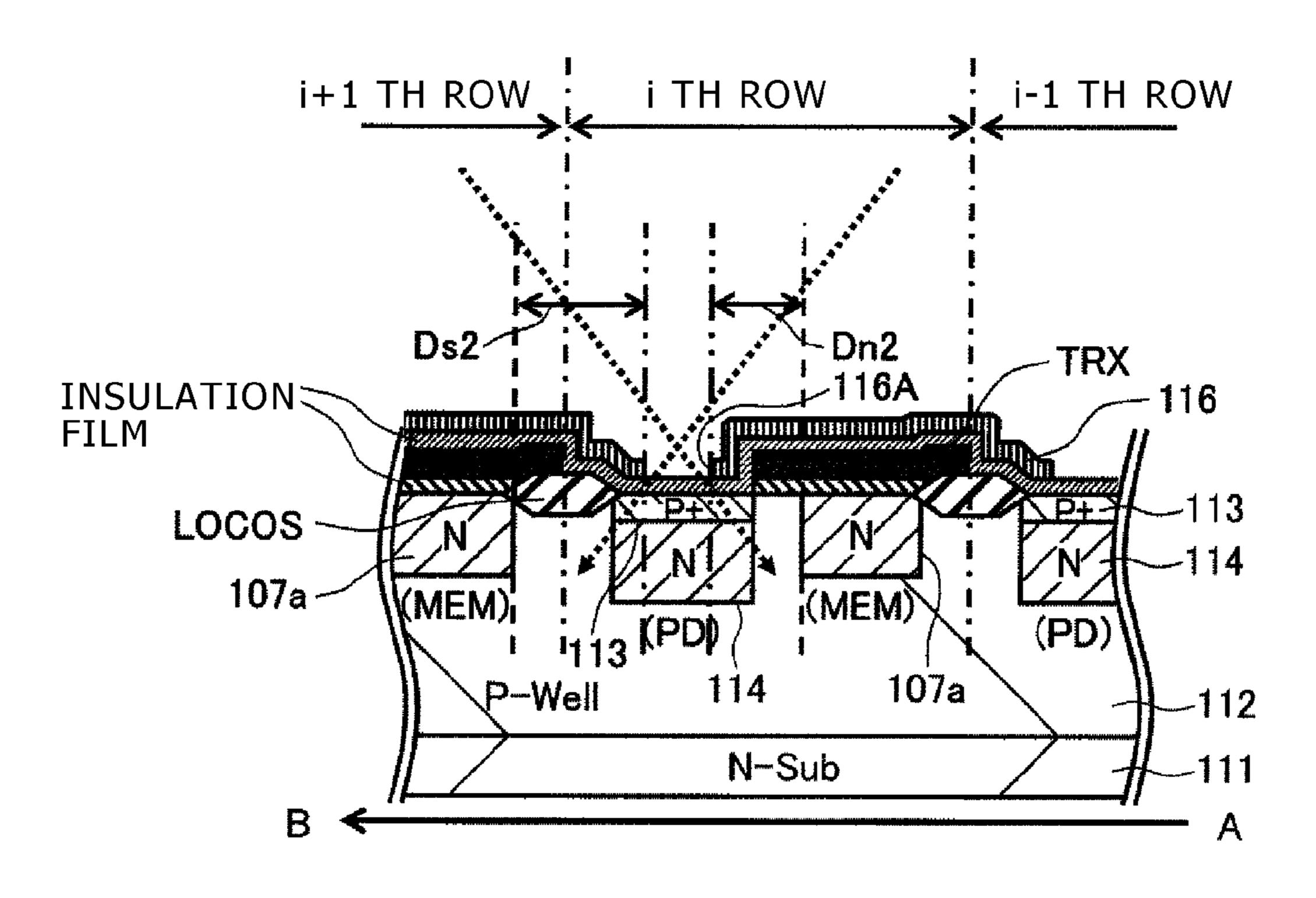

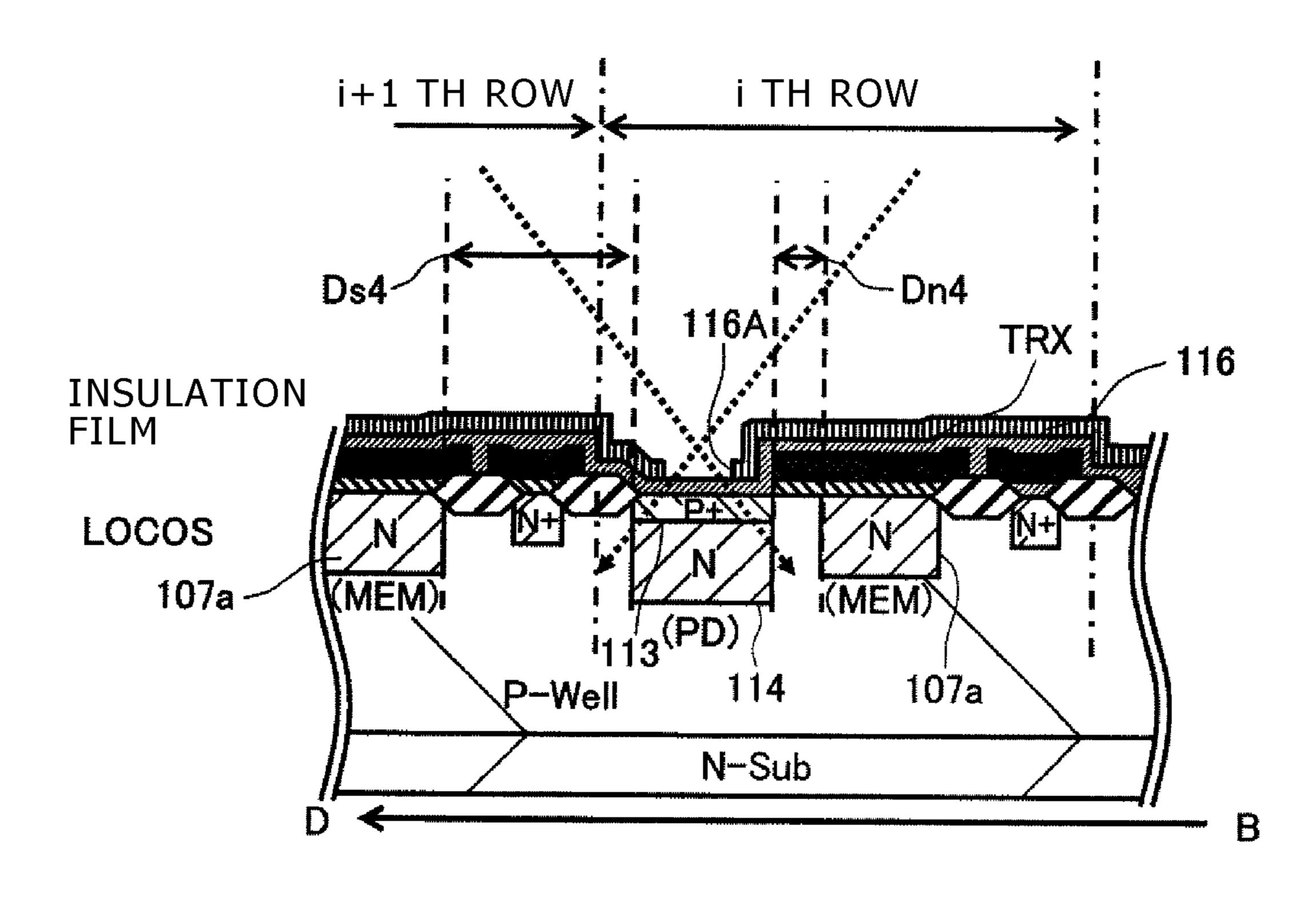

- FIG. 12 is a cross-sectional diagram showing the structure of the unit pixel according to the first embodiment;

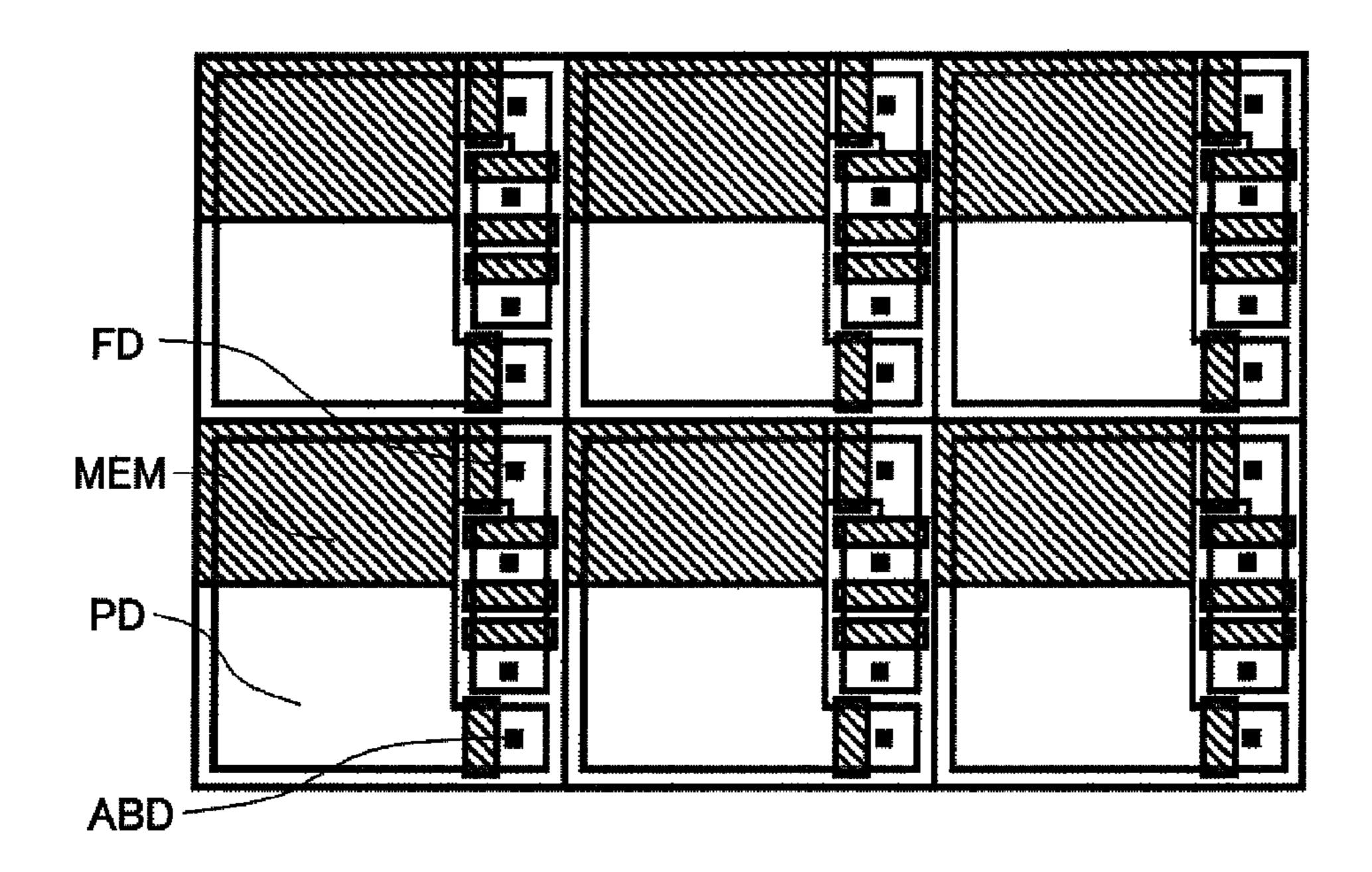

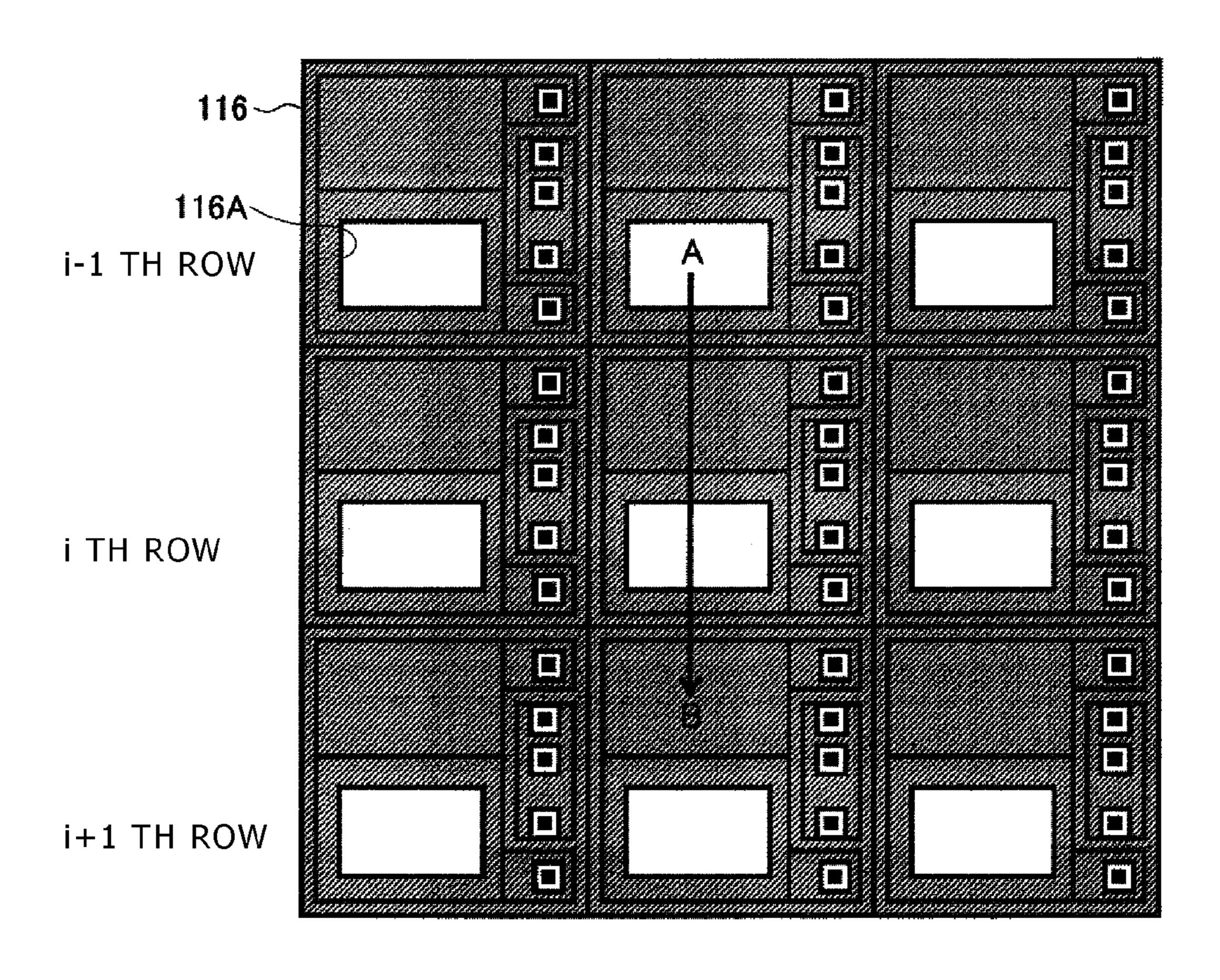

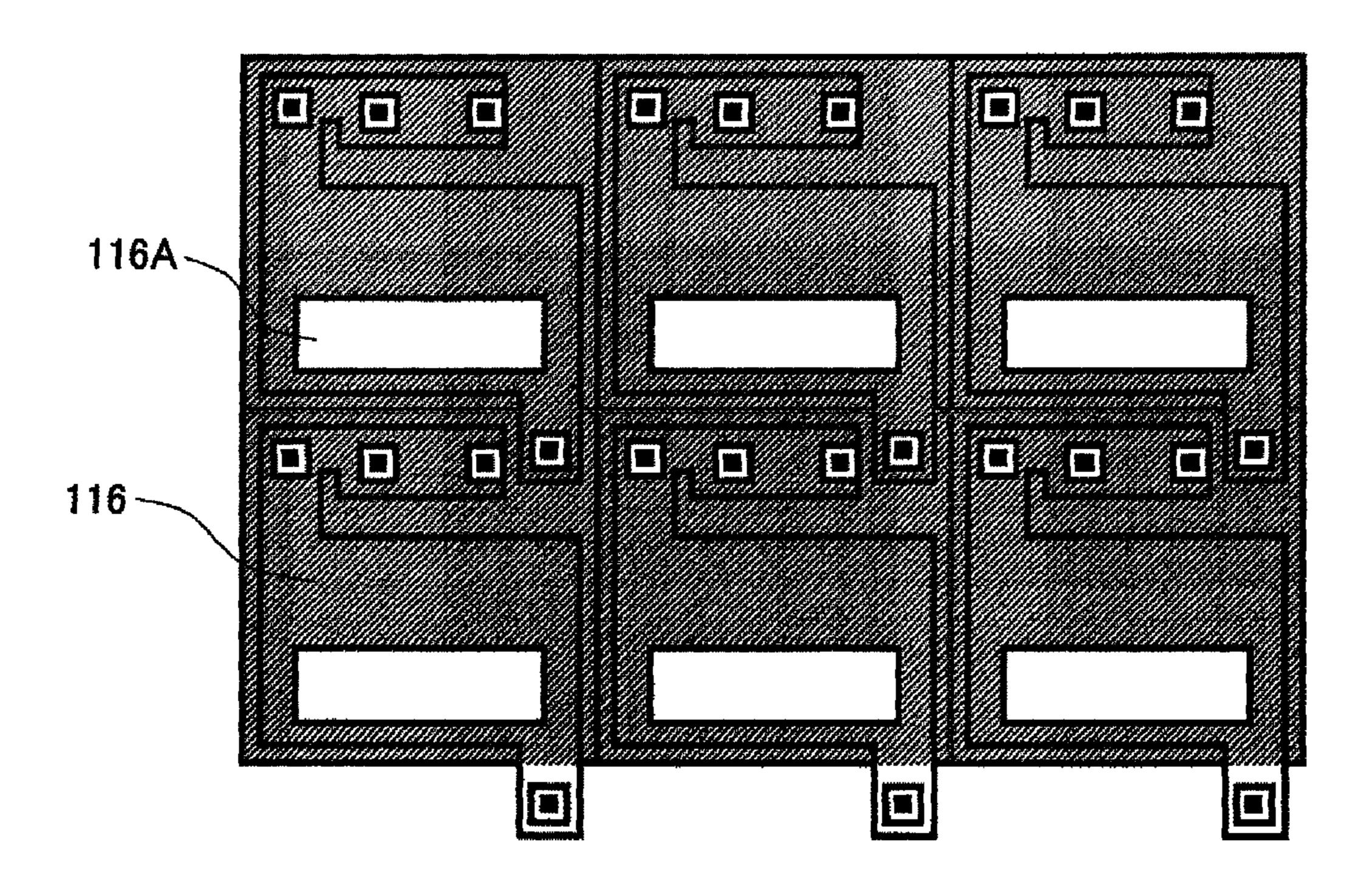

- FIG. 13 is a top-view diagram showing the basic configuration of a pixel array according to the first embodiment;

- FIG. 14 is a top-view diagram showing a layout of field 35 shielding films for shielding the basic configuration of the pixel array 11 shown in FIG. 13 against light and a layout of PD openings;

- FIG. 15 is a top-view diagram showing the pixel array shown in FIG. 13 and a variety of signal lines;

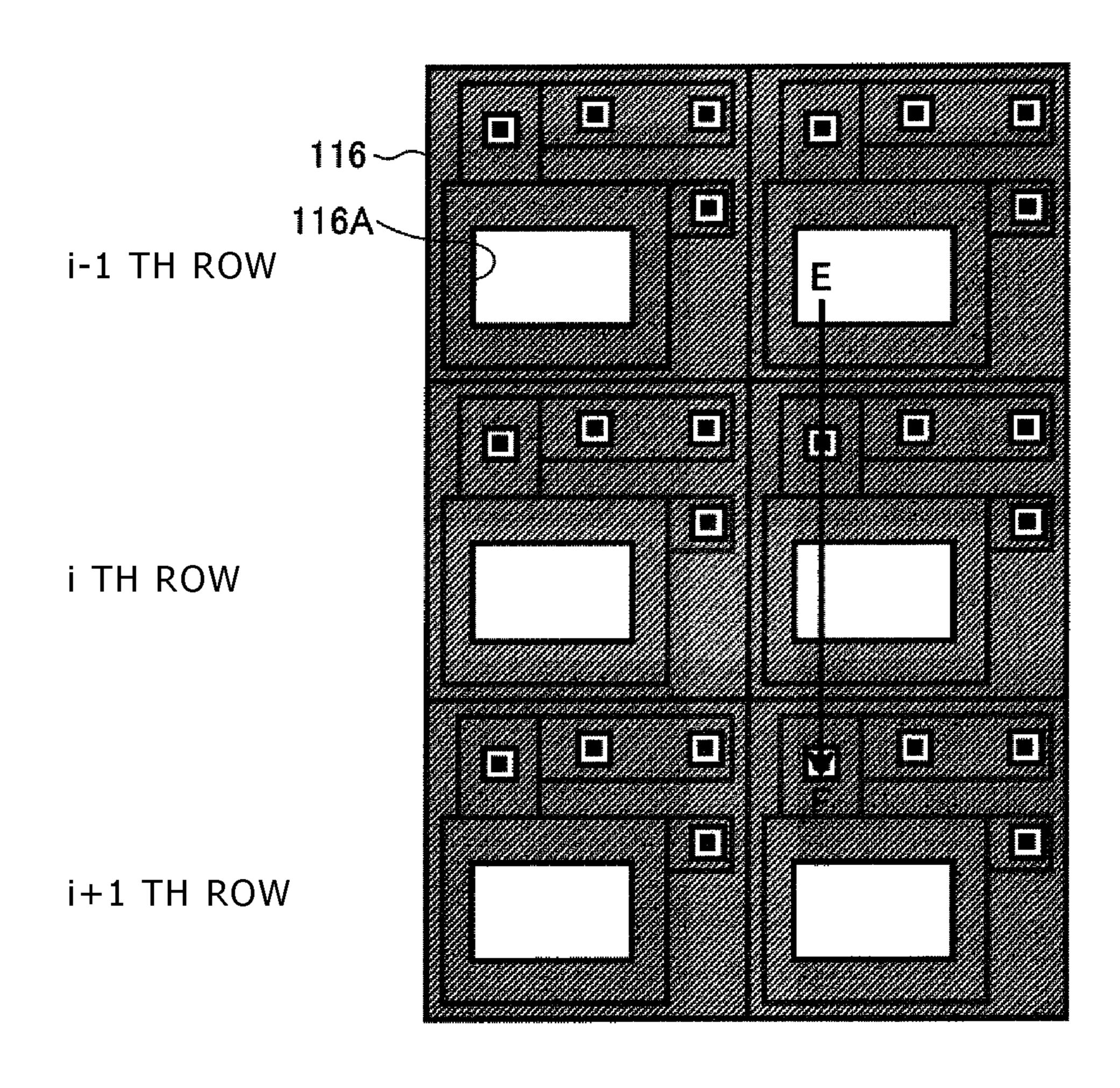

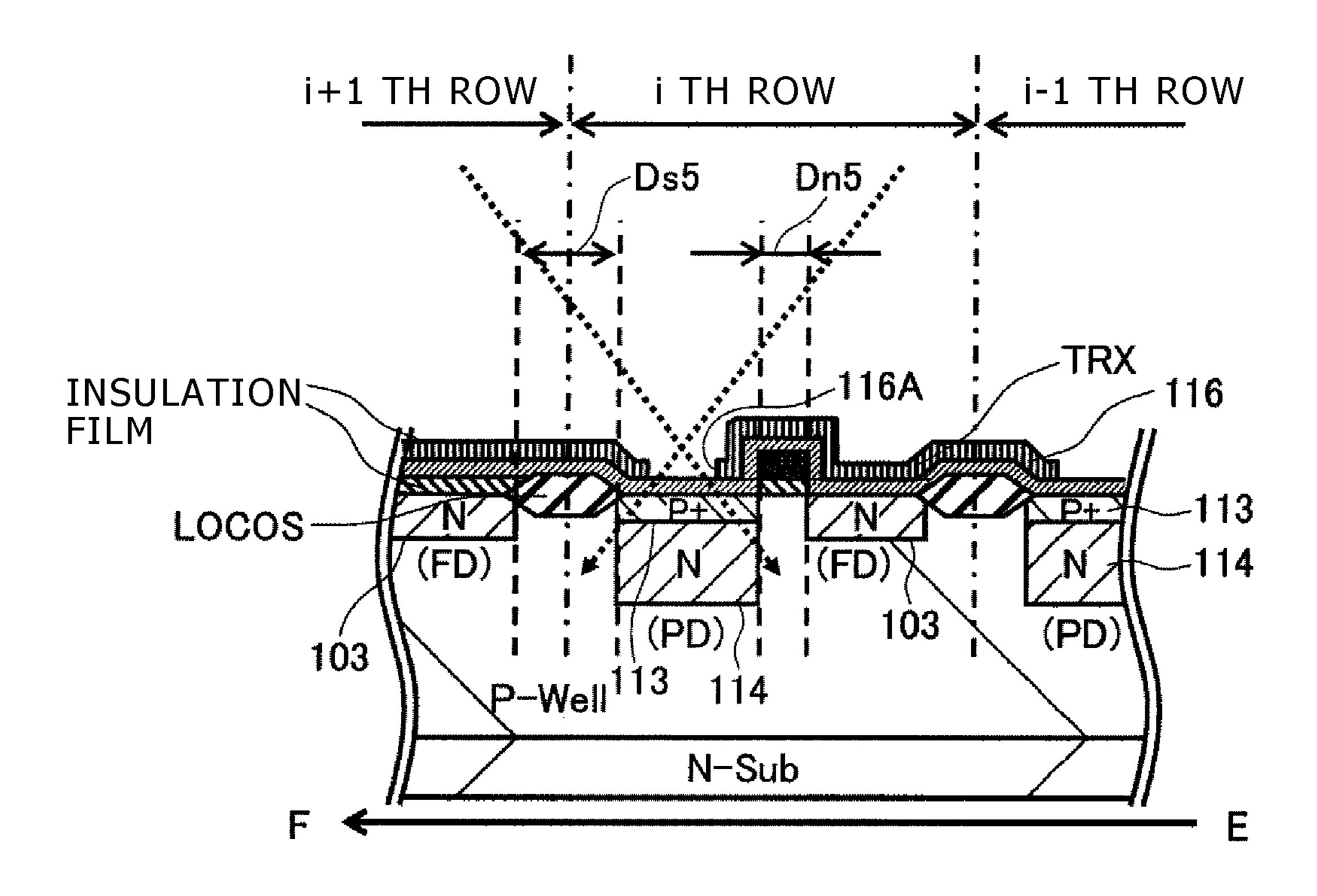

- FIG. 16 is a top-view diagram showing the basic configuration of the pixel array for three scanned pixel rows;

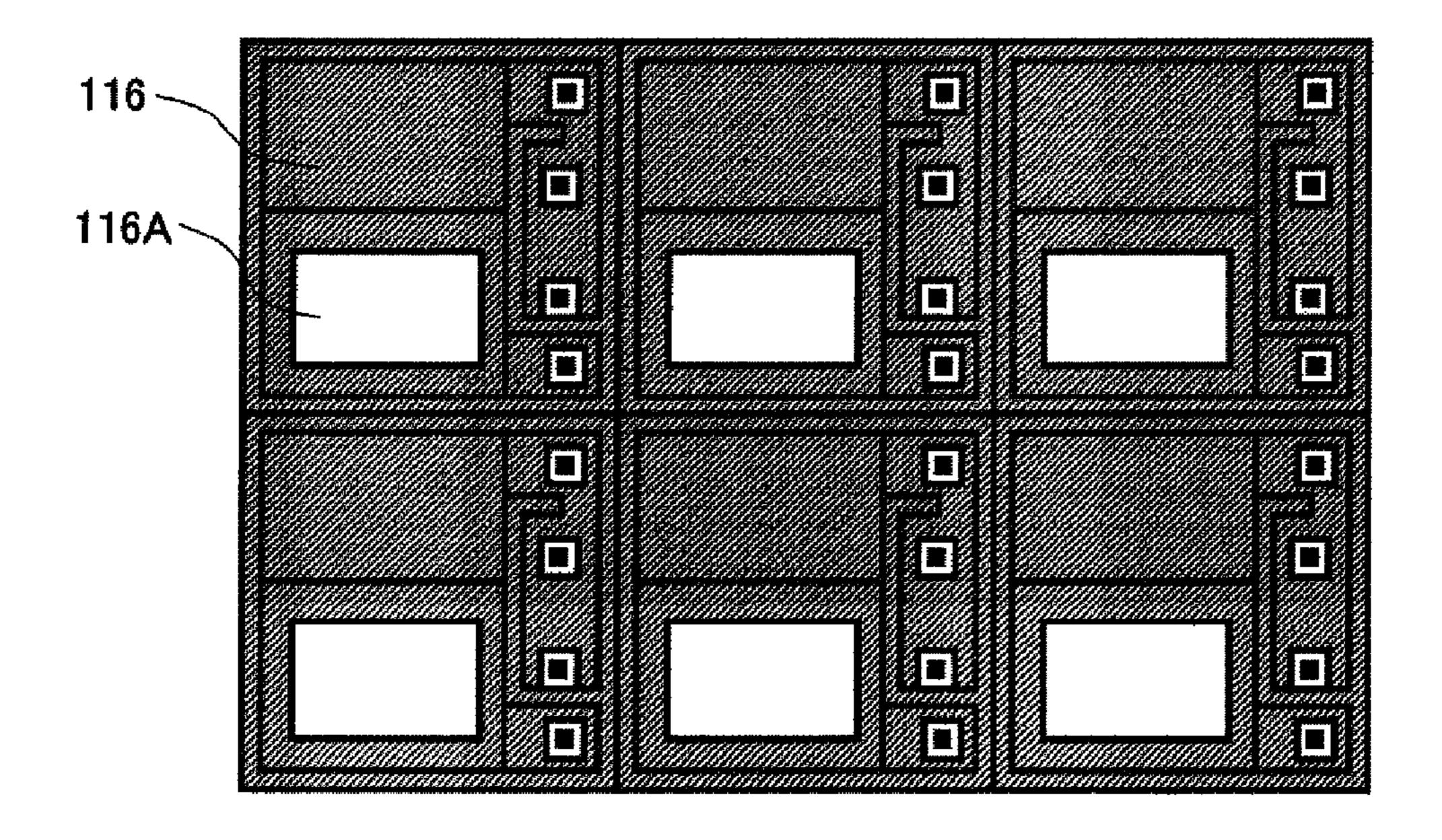

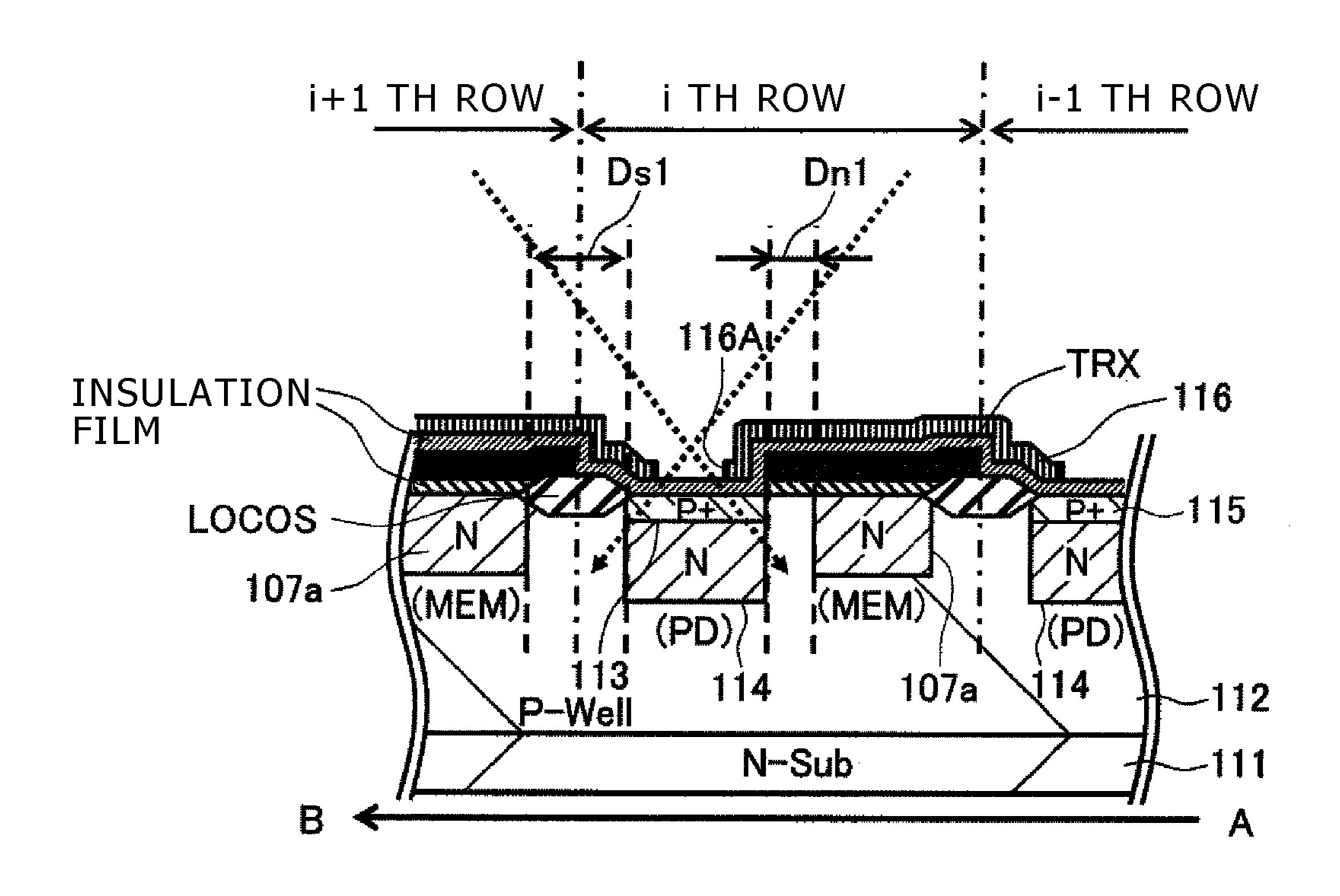

- FIG. 17 is a cross-sectional diagram showing a structure along a line A-B shown in FIG. 16;

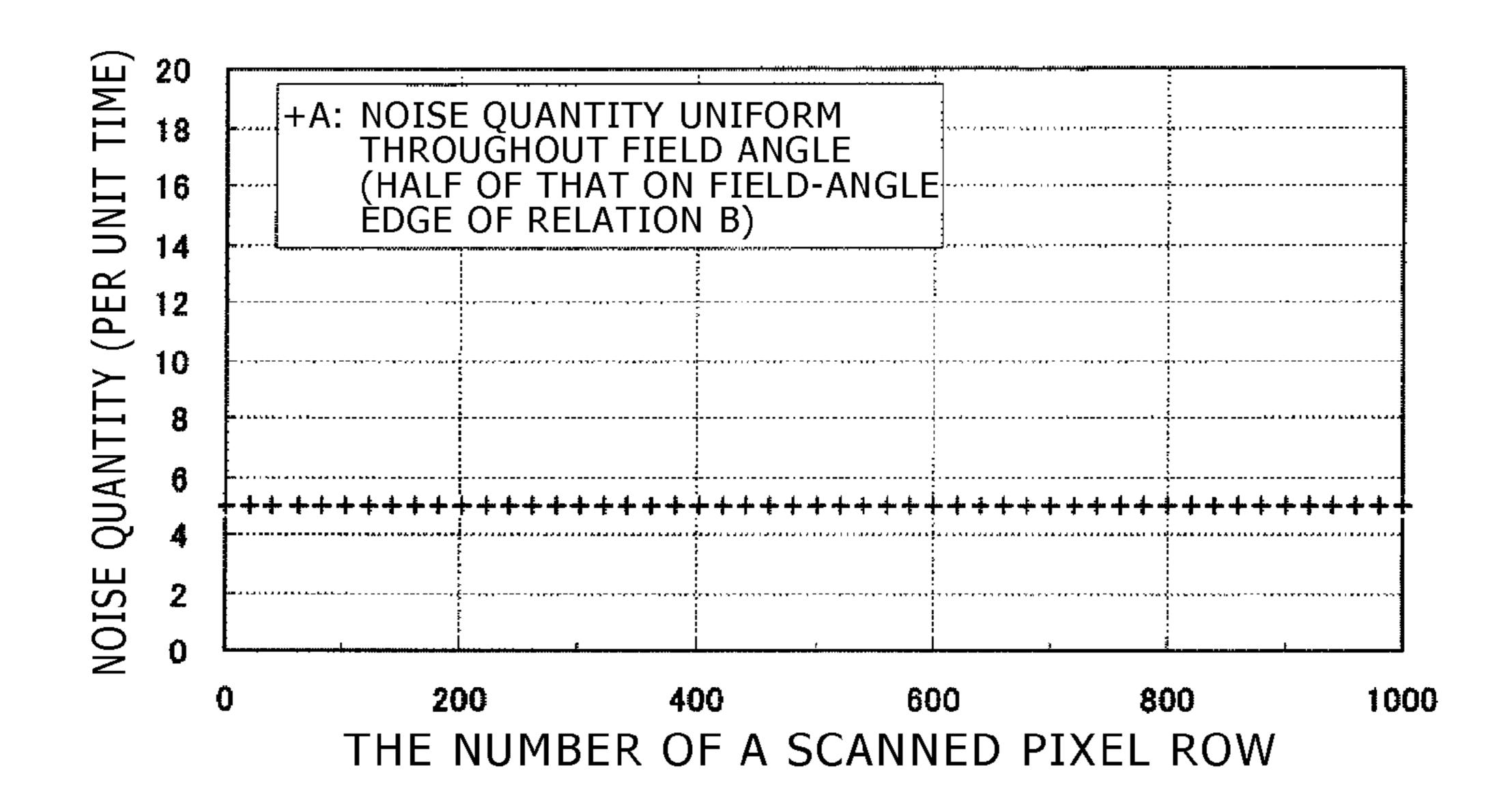

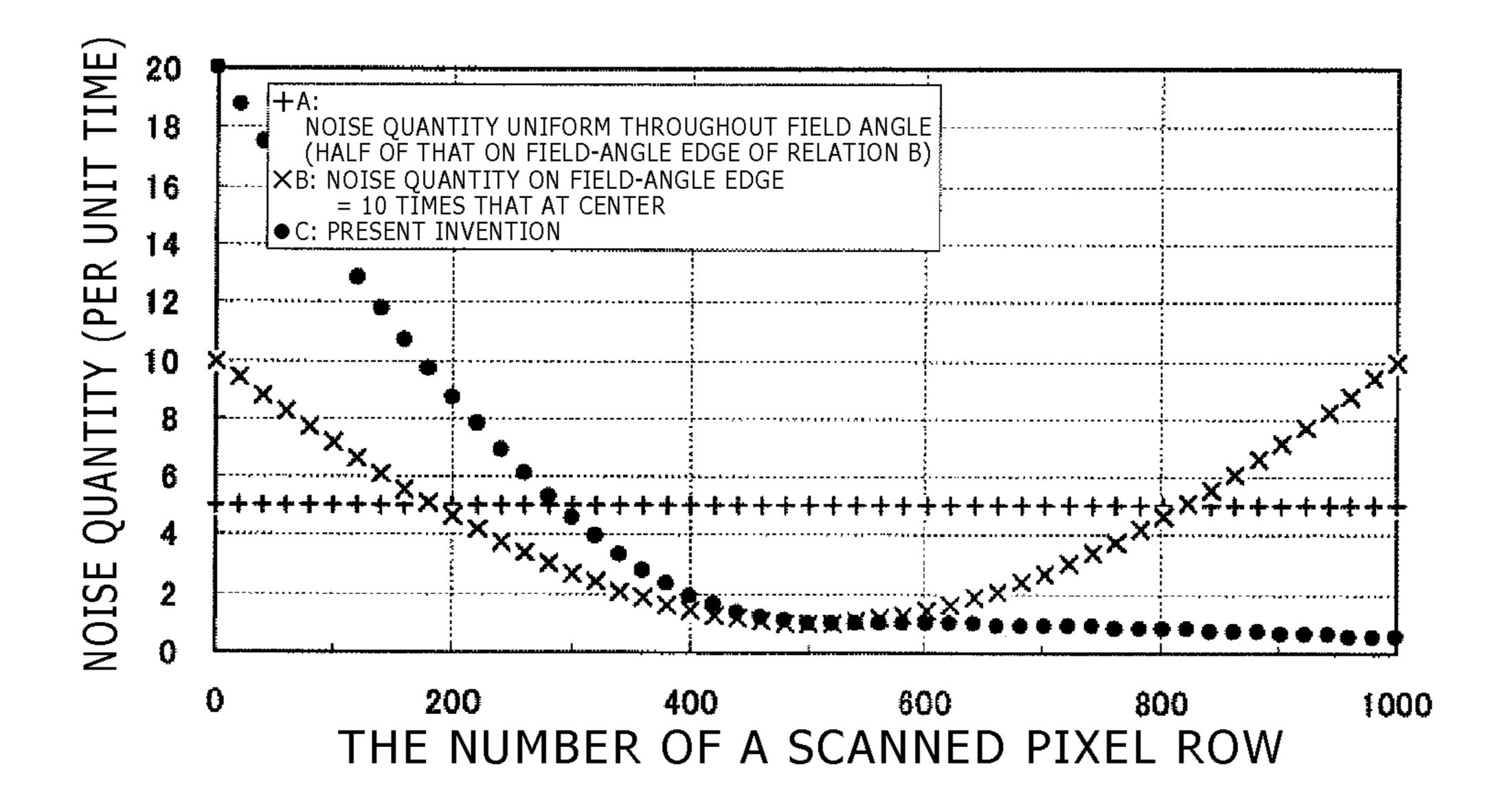

- FIG. 18 is a correlation diagram showing the relations 45 shown in FIG. 8 and a relation between the number of a scanned pixel row and the noise quantity per unit time for the first embodiment;

- FIG. 19 is a correlation diagram showing the relations shown in FIG. 9 and another relation between the number of 50 a scanned pixel row and the actually accumulated noise quantity for the first embodiment;

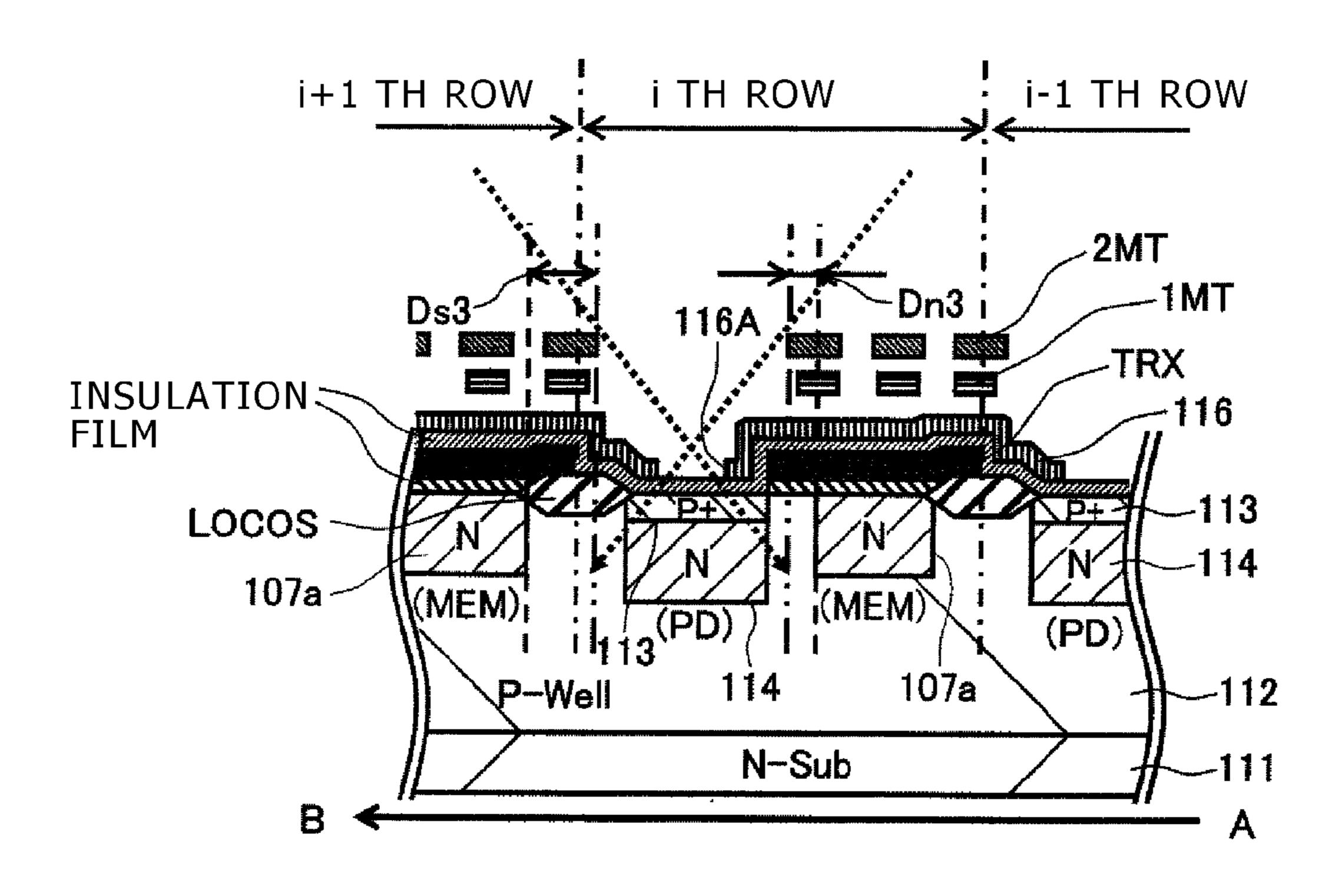

- FIG. 20 is a pixel-structure cross-sectional diagram to be referred to in description of a method for prescribing distances in accordance with a second embodiment;

- FIG. 21 is a pixel-structure cross-sectional diagram to be referred to in description of a method for prescribing distances in accordance with a third embodiment;

- FIG. 22 is a top-view diagram showing the configuration of a unit pixel according to a fourth embodiment;

- FIG. 23 is a top-view diagram showing the basic configuration of a pixel array according to the fourth embodiment;

- FIG. 24 is a top-view diagram showing a layout of field shielding films for shielding the basic configuration of the 65 3: Third Embodiment pixel array shown in FIG. 23 against light and a layout of PD openings;

- FIG. 25 is a top-view diagram showing the basic configuration of the pixel array for three scanned pixel rows;

- FIG. 26 is a pixel-structure cross-sectional diagram to be referred to in description of a method for prescribing distances in accordance with the fourth embodiment;

- FIG. 27 is a top-view diagram showing the configuration of a pixel according to a fifth embodiment;

- FIG. 28 is a top-view diagram showing the basic configuration of a pixel array according to the fifth embodiment;

- FIG. 29 is a top-view diagram showing a layout of field shielding films for shielding the basic configuration of the pixel array shown in FIG. 28 against light and a layout of PD openings;

- FIG. 30 is a top-view diagram showing the basic configuration of the pixel array for three scanned pixel rows;

- FIG. 31 is a pixel-structure cross-sectional diagram to be referred to in description of a method for prescribing distances in accordance with the fifth embodiment;

- FIG. 32 is a top-view diagram showing a layout of field shielding films for shielding the basic configuration of a pixel array according to a sixth. embodiment against light and a layout of PD openings;

- FIG. 33 is a top-view diagram showing the basic configuration of a pixel array according to a seventh embodi-25 ment;

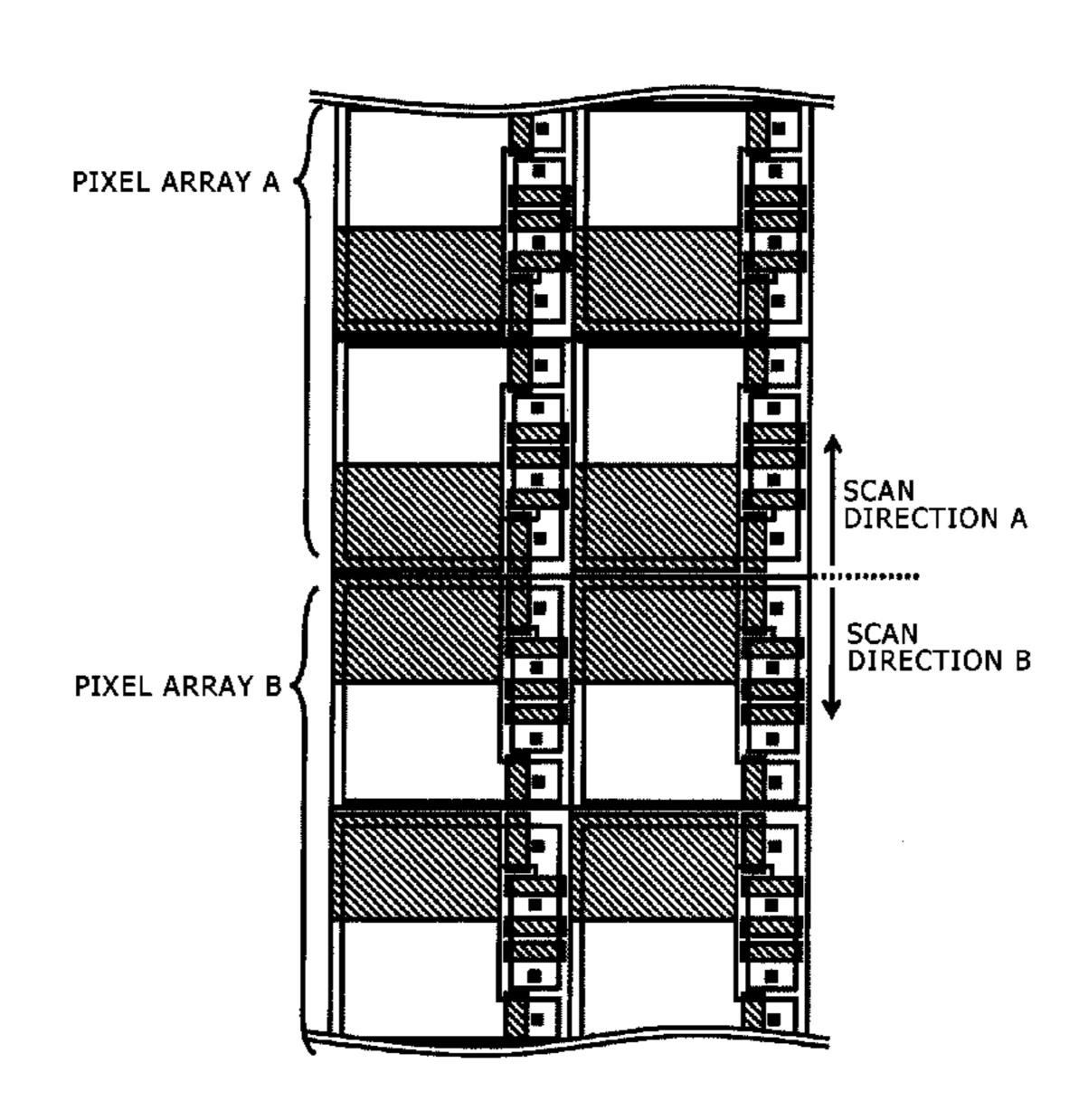

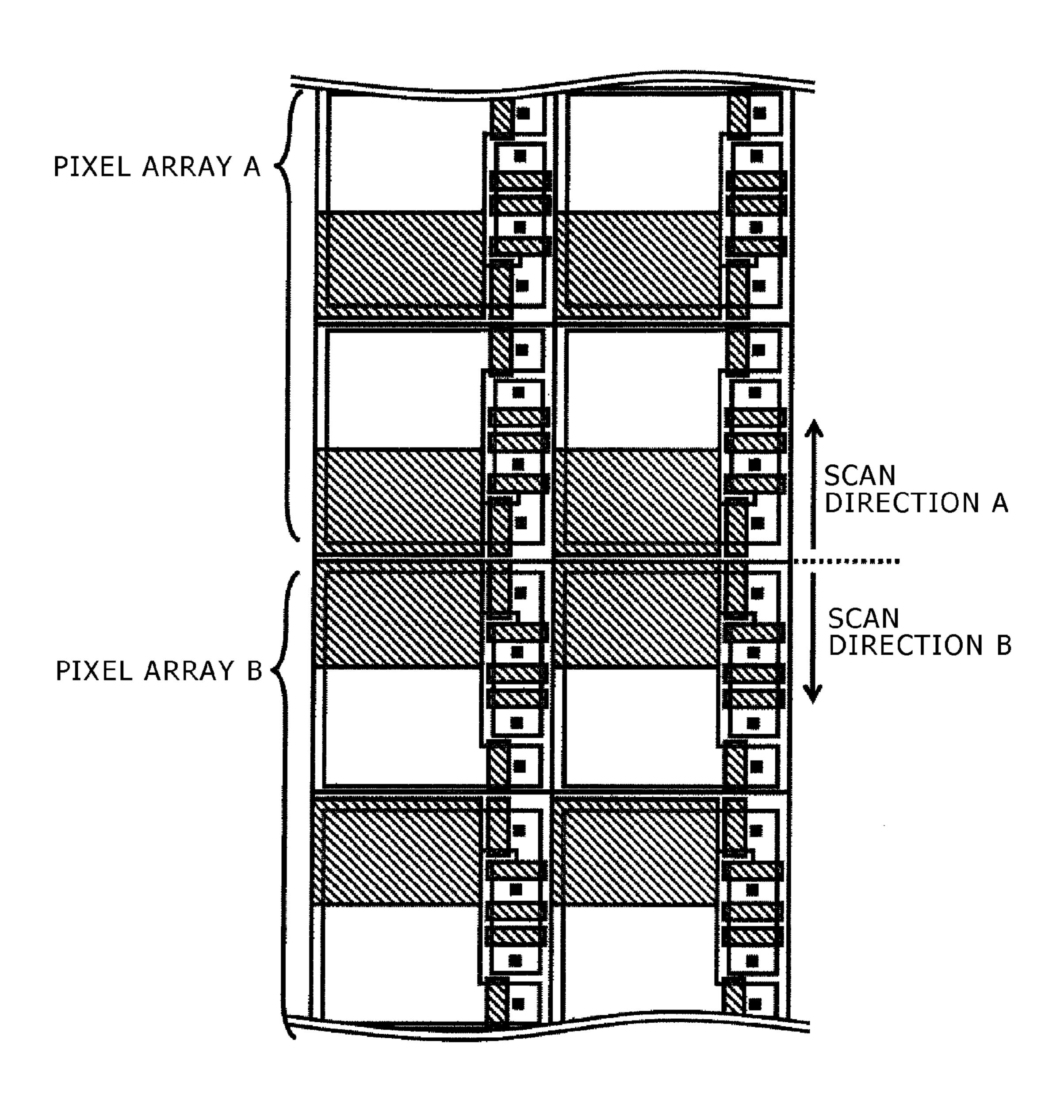

- FIG. **34** is a diagram showing the basic configuration of two pixel arrays according to an eighth embodiment;

- FIG. 35 is an enlarged diagram obtained by enlarging a portion of the basic configuration shown in FIG. 34;

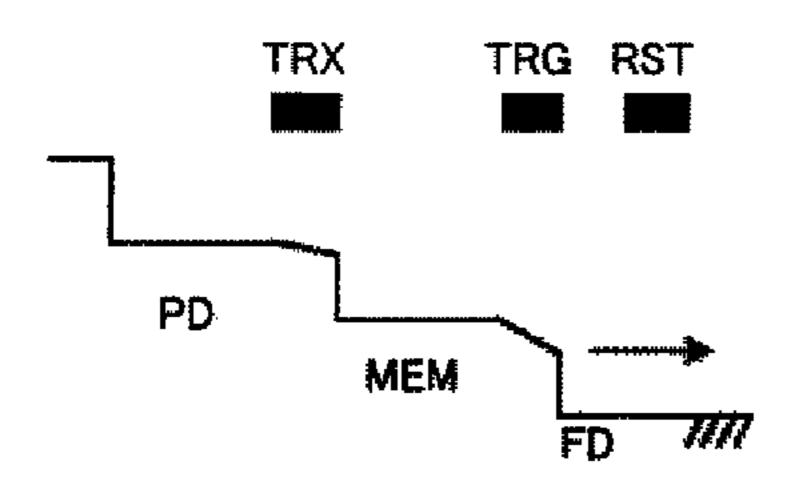

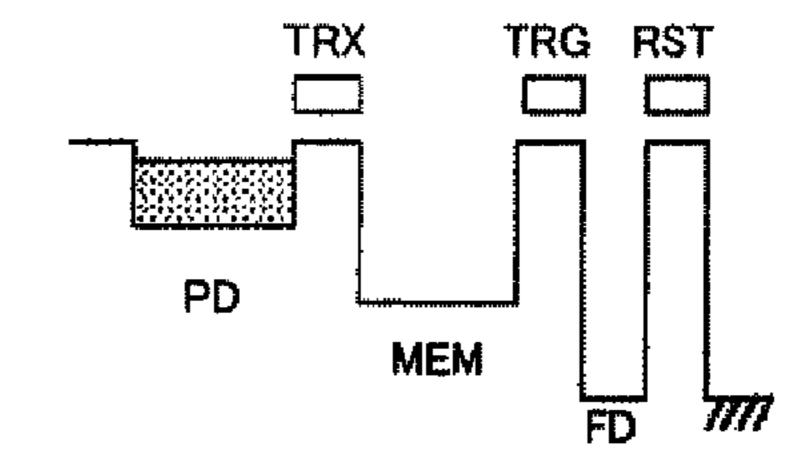

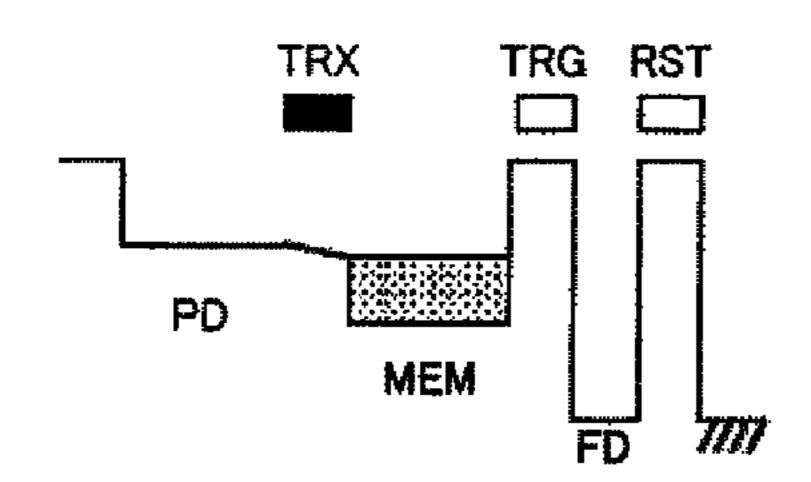

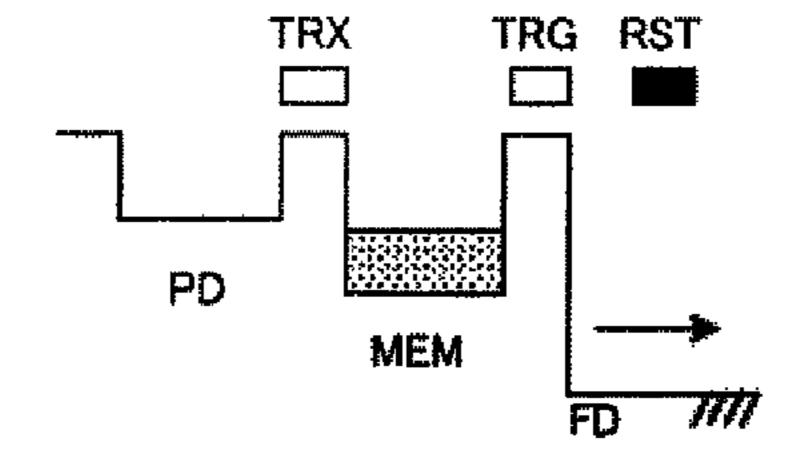

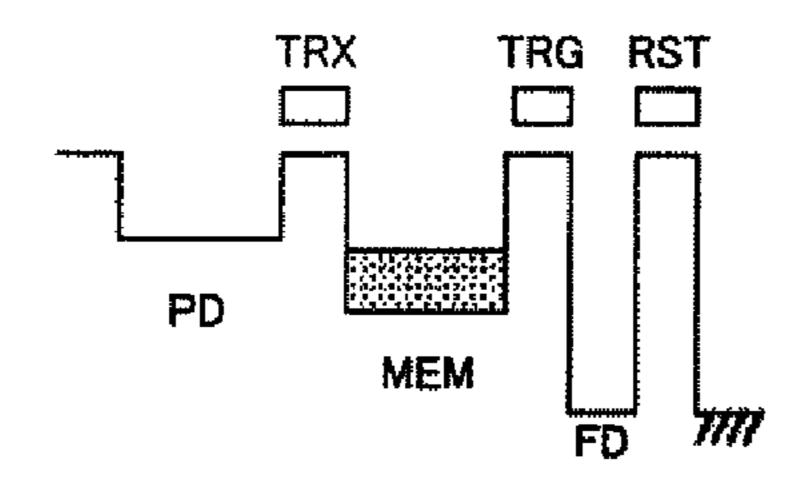

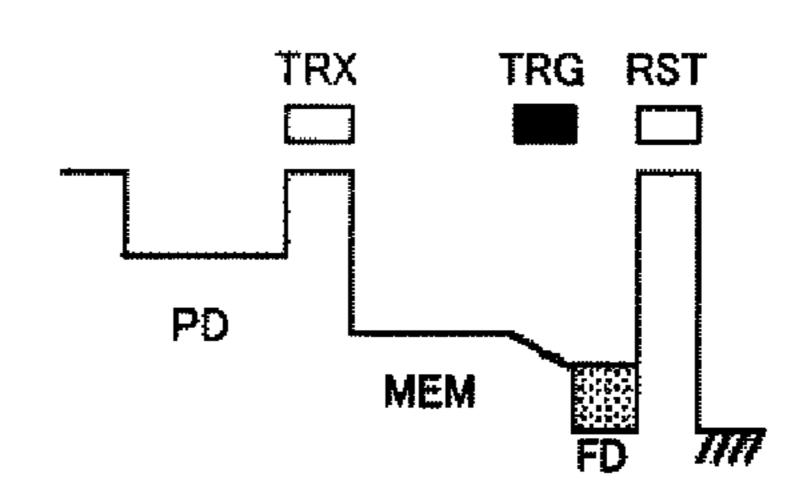

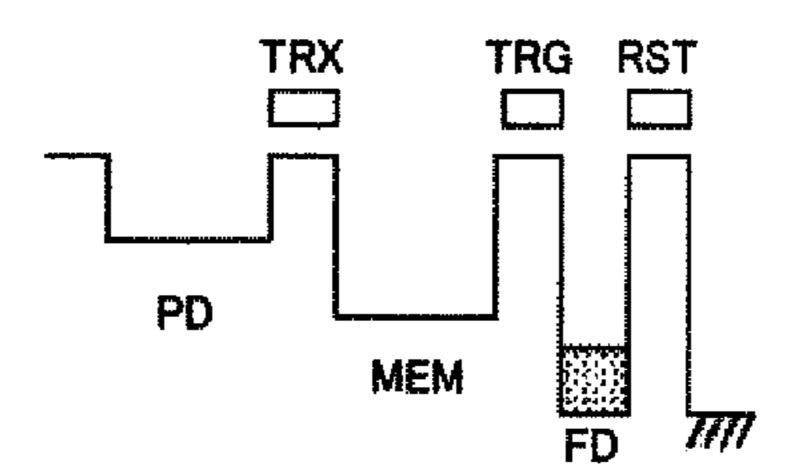

- FIGS. 36A to 36G are a plurality of model diagrams to be referred to in description of electric-charge exhausting, global-exposure, electric-charge accumulation, read and electric-charge transfer operations carried out by a unit pixel employing a memory section;

- FIG. 37 is a block diagram showing a first typical modified system;

- FIG. 38 is a block diagram showing a second typical modified system; and

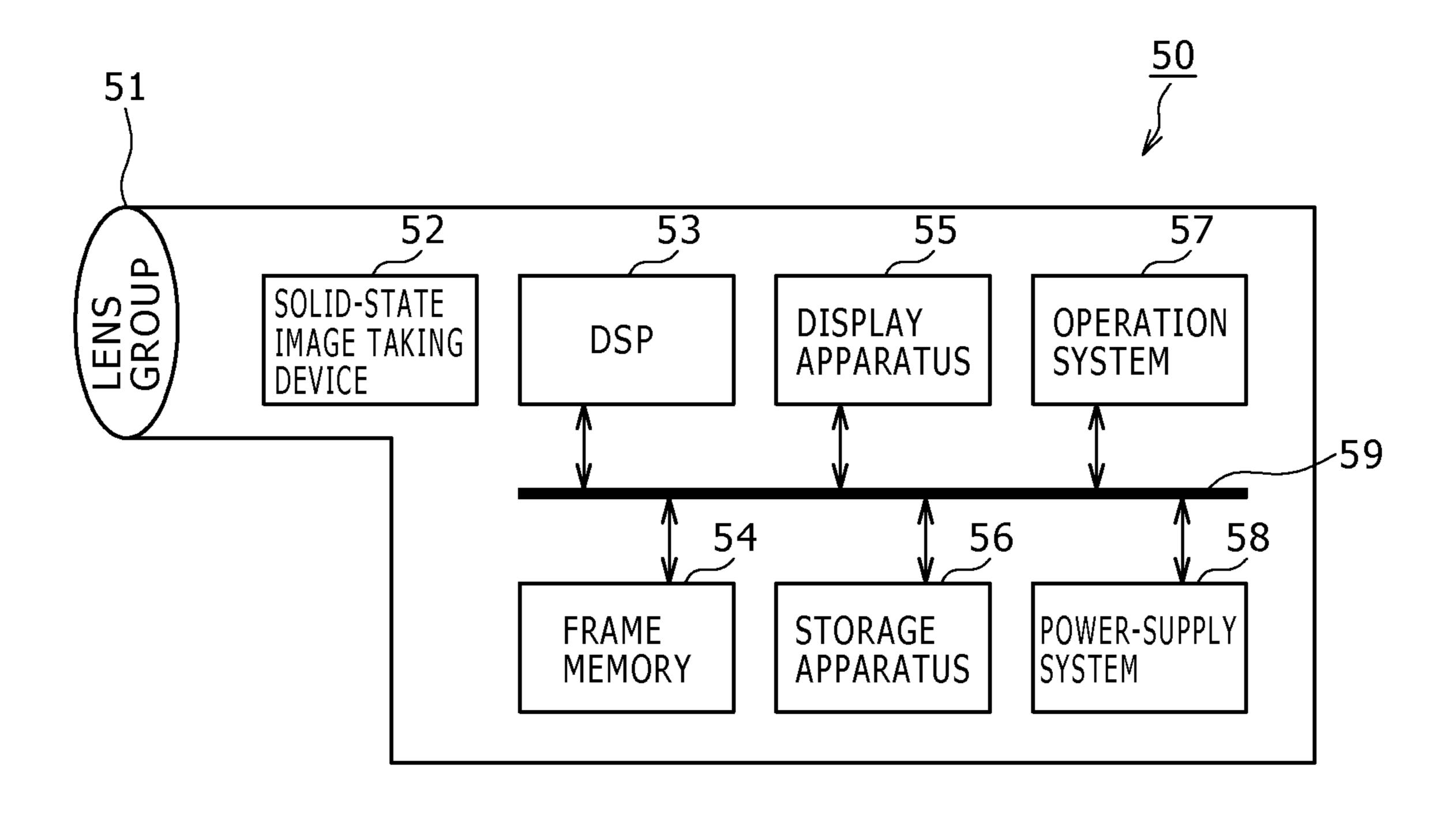

- FIG. **39** is a block diagram showing a typical configura-40 tion of an electronic apparatus such as an image taking apparatus to which the embodiments of the present invention are applied.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

With the CMOS image sensor taken as an example, embodiments of the present invention are explained by referring to diagrams in chapters arranged as follows.

## 1: First Embodiment

In the first embodiment, the shifts of electric-charge holding sections on the two scan-direction sides of an opto-electric conversion section from the opto-electric conversion section are expressed in terms of the magnitudes of 55 distances between the electric-charge holding sections and the opto-electric conversion section.

## 2: Second Embodiment

In the second embodiment, the shifts of electric-charge holding sections on the two scan-direction sides of an 60 incident light path limiting section from the incident light path limiting section are expressed in terms of the magnitudes of distances between the electric-charge holding sections and the light shielding edges of the incident light path limiting section.

In the third embodiment, the shifts of electric-charge holding sections on the two scan-direction sides of an

incident light path limiting section from the incident light path limiting section are expressed in terms of the magnitudes of distances between the electric-charge holding sections and the wire-layer edges of the incident light path limiting section.

#### 4: Fourth Embodiment

The fourth embodiment implements a pixel internal layout in which a pixel transistor area serving as a read section is provided between a memory section and an opto-electric conversion section.

#### 5: Fifth Embodiment

The fifth embodiment implements a pixel internal layout in which no memory section is used and an floating diffusion capacitor FD functions as an electric-charge holding section.

6: Sixth Embodiment

The sixth embodiment implements a pixel internal layout in which a light shielding section is also capable of serving as a wire.

#### 7: Seventh Embodiment

The seventh embodiment implements a pixel internal 20 layout in which a gate electrode driven by a pixel driving line is shared by two unit pixels.

## 8: Eighth Embodiment

In the eighth embodiment, the pixel array is split into two portions and a typical scan operation is carried out on the 25 portions.

- 9: Read Method Common to the Embodiments

- 10: Modified System Configurations

- 11: Other Modified Versions

- 12: Typical Applications (Embodiments of Electronic Appa- 30 ratus)

- 13: Effects of the Embodiments (Conclusion)

# 1: First Embodiment

A first embodiment has been proposed on the basis of results of paying attention to the fact that unevenness of 35 smear components is seen in the scan direction and determining causes of the unevenness. The first embodiment of the present invention is an embodiment implementing an internal layout structure adopted by a unit pixel to serve as a structure capable of reducing smear components uniformly 40 and sufficiently throughout all unit pixels.

First of all, the following description explains the results of determining the causes of the unevenness seen in the scan direction as the unevenness of smear components. Then, as a typical application of the present invention, the following 45 description explains a CMOS image sensor including countermeasures taken by the first embodiment in the form of the internal layout structure of the unit pixel.

Noise Unevenness in the Scan Direction

A global shutter driving operation is carried out in a pixel 50 structure including an opto-electric conversion section PD and an electric-charge holding section which can be a memory section MEM or a floating diffusion capacitor FD. In this case, if a signal read operation is carried out after a reset operation in accordance with the existing technologies 55 disclosed in Patent Documents 1 and 4 to 6 explained earlier, the noise per unit pixel can be reduced to a value lower than those of the existing structures according to the existing technologies.

If the entire pixel array is seen, however, a phenomenon 60 has been observed from results of analyses of noises. Observation of this phenomenon has led to a finding that, the larger the order number of a pixel row being scanned, selected and subjected to a read operation by a vertical driving section, undesirably, the larger the noise quantity. 65 This phenomenon is further explained by referring to FIGS. 1 and 2 as follows.

12

In the global shutter driving operation, the transfer gate transistor 102 is turned on at the same time for all unit pixels in order to transfer opto-electric charge from the photodiode 101 serving as the opto-electric conversion section PD to the electric-charge holding section by way of the transfer gate transistor 102. In the case of the unit pixel 100 shown in FIG. 1, the electric-charge holding section is the floating diffusion capacitor FD whereas, in the case of the unit pixel 300 shown in FIG. 2, the electric-charge holding section is the memory section 107. After this electric-charge transfer operation, the vertical driving section scans pixel rows in the scan direction and selects one of the pixel rows on a one-row-after-another basis in order to output opto-electric charge from the electric-charge holding sections of the selected pixel row.

In the case of a typical pixel array having 1,000 pixel rows for example, the electric-charge holding period of unit pixels on the 1,000th pixel row selected last is about 1,000 times the electric-charge holding period of unit pixels on the 1st pixel row selected first.

FIGS. 3 to 5 are each a correlation diagram showing a relation between the numbers assigned to a scanned pixel row also referred to hereafter simply as a pixel row and a noise quantity. For the sake of simplicity, the relation shown in each of these correlation diagrams is drawn on the assumption that light is radiated to all unit pixels uniformly.

The X axis of each of FIGS. 3 to 5 represents a number assigned to a scanned pixel row which is a pixel row subjected to a scan operation. In this case, the pixel array has 1,000 pixel rows. That is to say, the pixel row provided with a row number of 1 is the pixel row scanned first whereas the pixel row provided with a row number of 1,000 is the pixel row scanned last.

Since it is assumed that light is radiated to all unit pixels uniformly, the noise quantity per unit time such as 1 second is a constant not dependent on the number of the pixel row as shown in FIG. 3. In the case of the relation shown in this figure, the constant is set at 5 (without a unit).

If the frame rate is assumed to be 60 fps, the pixel row scanned last has an electric-charge holding period of 1/60 seconds. In this case, the difference in electric-charge holding period between a pixel row provided with a row number of i and a pixel row provided with a row number of (i+1) where i is an integer in the range 1 to 999 is 1/60/1000 seconds. In addition, the electric-charge holding period of a pixel row provided with a row number of i is 1/60/1000×i seconds.

As is obvious from the above description, the noise quantity of the noise accumulated during the electric-charge holding period of a pixel row is a product obtained as a result of multiplying the noise quantity per unit time by the electric-charge holding period. As described above, the noise quantity per unit time is a constant set at 5/second. Thus, the noise quantity of the noise accumulated during the electric-charge holding period of a pixel row increases linearly with the number of the pixel row as shown in FIG. 4. That is to say, the noise quantity of the noise accumulated during the electric-charge holding period of a pixel row is proportional to the number of the pixel row or, the later the time at which a pixel row is scanned, the larger the noise quantity.

FIG. 5 is a correlation diagram showing a relation between the number of a scanned pixel row and a normalized noise quantity of the noise accumulated during an electric-charge holding period. The normalized noise quantity is obtained as a result of normalizing the noise quantity

shown in FIG. 4 by dividing the noise quantity shown in FIG. 4 by the noise quantity of the pixel row scanned first.

As shown in FIG. 5, the noise quantity of a pixel row provided with a row number of i is i times the noise quantity of a pixel row provided with a row number of 1 where i is 5 an integer in the range 1 to imax which is 1,000. That is to say, on the assumption that light is radiated to all unit pixels at the same level, the quantity of the noise accumulated in the electric-charge holding section of each unit pixel on a pixel row scanned last is 1,000 times the quantity of the 10 noise accumulated in the electric-charge holding section of each unit pixel on a pixel row scanned first.

The relations shown in FIGS. 3 to 5 are obtained on the assumption that light is radiated to all unit pixels uniformly so that the noise quantity per unit time such as 1 second is 15 a constant not dependent on the number assigned to the pixel row. In the case of an actual pixel array, however, depending on the position (or the field angle) of the pixel row in the pixel array, the noise quantity per unit time varies.

Next, the field angle cited above and an incidence angle 20 are explained.

FIG. 6 is an image diagram for a case in which a lens group converges incident light toward a pixel array. In FIG. 6, reference numeral 11 denotes the pixel array whereas reference numeral 12 denotes a vertical driving section. 25 Reference numerals 13, 14 and 19 denote a column processing section, a horizontal driving section and a data storage section respectively. Reference numeral 51 denotes the lens group employed in a camera section included in an electronic apparatus having the CMOS image sensor.

As shown in FIG. 6, unit pixels are laid out on the pixel array 11 in the H (horizontal) and V (vertical) directions. In general, the V-direction size of the pixel array 11 is smaller than the H-direction size thereof. The ratio of the V-direction size of the pixel array 11 to the H-direction size thereof is 35 referred to as the aspect ratio of the displayed image. A main reason why the V-direction size of the pixel array 11 is made smaller than the H-direction size thereof is that a small vertically driven pixel-row count is advantageous to improvement of the frame rate.

FIG. 7 is a model diagram showing how the lens group 51 converges incident light toward the pixel array 11 represented by its cross sections spread in the H (horizontal) and V (vertical) directions.

As shown in FIG. 7, the V-direction size of the pixel array 11 is smaller than the H-direction size thereof. Thus, the following relation holds true: h>v. In this relation, reference symbol h denotes the incidence angle on each H-direction edge of the pixel array 11 whereas reference symbol v denotes the incidence angle on each V-direction edge of the pixel array 11. It is to be noted that the incidence angle v on each V-direction edge of the pixel array 11 and the incidence angle h on each H-direction edge of the pixel array 11 can be expressed by the following equations as follows:

Incidence angle  $v=\tan((V/2)/D)$

Incidence angle  $h=\tan((H/2)/D)$

In the above equations, reference symbol V denotes the V-direction size of the pixel array 11 whereas reference 60 symbol H denotes the H-direction size of the pixel array 11. On the other hand, reference symbol D denotes the distance between the focal point of the lens group 51 and the pixel array 11.

The row scan direction (also referred to simply the scan 65 direction) cited before is the V direction mentioned above. Normally, the start pixel row is positioned on a V-direction

**14**

edge of the pixel array 11. An operation to scan pixel rows on the pixel array 11 is begun at the start pixel row in the V direction toward the center pixel row. The operation to scan pixel rows on the pixel array 11 is carried out sequentially on a one-row-after-another basis. The operation to scan pixel rows on the pixel array 11 is terminated at the end pixel row which is positioned on a V-direction edge of the pixel array 11. Thus, the farther the scanned pixel row from the center pixel row, the larger the incidence angle. In other words, the closer the scanned pixel row to the start or end pixel row, the larger the incidence angle. That is to say, due to these differences in incidence angle, the quantity of light incident to the opto-electric conversion section in the periphery of the pixel array 11 is small in comparison with the quantity of light incident to the opto-electric conversion section at the center of the pixel array 11. Thus, the optical sensitivities of unit pixels in the periphery of the pixel array 11 decrease but the noise quantities of unit pixels in the periphery of the pixel array 11 increase as described as follows.

The noise quantity of a unit pixel in the periphery of the pixel array 11 increases mainly because of a first reason described as follows. The incidence angle of light hitting the unit pixel in the periphery of the pixel array 11 is large. At a large incidence angle, the light directly hits the electriccharge holding section shielded against light and is subjected to an opto-electric conversion process in the electriccharge holding section. Thus, the amount of electric charge generated in the opto-electric conversion process also rises as well. The noise quantity of a unit pixel in the periphery of the pixel array 11 increases also because of a second reason described as follows. The number of components obtained as a result of the opto-electric conversion process carried out outside the opto-electric conversion section increases, raising the probability that electric charge obtained as a result of the opto-electric conversion process is diffused from the location of the opto-electric conversion process to the electric-charge holding section.

FIG. 8 is a correlation diagram showing the relation shown in FIG. 3 and another relation obtained by re-plotting the relation shown in FIG. 3 by taking the incidence angle of light into consideration whereas FIG. 9 is a correlation diagram showing the relation shown in FIG. 4 and another relation obtained by re-plotting the relation shown in FIG. 4 by taking the incidence angle of light into consideration. In each of FIGS. 8 and 9, the relation obtained by not taking the incidence angle of light into consideration is shown as a plot A whereas the relation obtained by taking the incidence angle of light into consideration is shown as a plot B. In each of FIGS. 8 and 9, the plot B is superposed on the plot A.

Much like FIGS. 3 to 5, the X axes of FIGS. 8 and 9 represent a number assigned to the pixel row. The Y axis of FIG. 8 represents the noise quantity per unit time which is 1 second in this case. The incidence angle for the 500th pixel row serving as the center pixel row of the 1,000 pixel rows arranged in the V direction is 0 degrees. Thus, the noise quantity on the 500th pixel row is smallest, being set at 1. As the number assigned to the pixel row decreases or increases toward the numbers assigned to pixel rows in the periphery of the pixel array 11, the noise quantity rises in accordance with a quadratic curve to reach the largest value at the 1st pixel row serving as the start pixel row and the 1,000th pixel row serving as the end pixel row.

In general, the noise quantity per unit time on the center pixel line differs from that on a peripheral pixel line by at least one order of magnitude. Thus, since the noise quantity per unit time on the center pixel row is set at 1, the noise quantity per unit time on a peripheral pixel row can be

assumed to have a value of 10. It is to be noted that, as a matter of course, due to the structure of the unit pixel and/or the optical structure of the lens group 51 included in the configurations shown in FIGS. 6 and 7, there is a good chance that the noise quantity per unit time on the start pixel 5 row is different from that on the end pixel row. In addition, there is also a good chance that the noise quantity per unit time on the center pixel row is not smallest.

It is to be noted that, in the relations shown in FIG. **8**, the noise quantity per unit time for the plot A has a value of 5 10 which is approximately the average of the largest noise quantity of 10 per unit time and the smallest noise quantity of one per unit time for the plot B.

The plot B shown in FIG. 8 represents a relation between the noise quantity per unit time of 1 second and the number 15 assigned to the pixel row whereas the plot B shown in FIG. 9 represents a relation between the quantity of the noise actually accumulated during the electric-charge holding period of a pixel row and the number assigned to the pixel row. The plot B shown FIG. 9 is obtained from the plot B 20 shown in FIG. 8.

As shown by the plot B of FIG. **8**, in the early part of the row scan operation, the noise quantity per unit time is large. In the early part of the row scan operation, however, the electric-charge holding period is short. Thus, in the early 25 part of the row scan operation, the quantity of the noise actually accumulated during the electric-charge holding period is not so large as shown by the plot B of FIG. **9**.

In the middle part of the row scan operation, the noise quantity per unit time is small as shown by the plot B of FIG. 30 8 even though the electric-charge holding period becomes relatively longer. Nevertheless, in the middle part of the row scan operation, the quantity of the noise actually accumulated during the electric-charge holding period is still not so large as shown by the plot B of FIG. 9.

A problem is raised in the later part of the row scan operation as follows. In the later part of the row scan operation, the noise quantity per unit time is again large as shown by the plot B of FIG. 8 and, in addition, the electric-charge holding period becomes longer. Thus, in the 40 later part of the row scan operation, the quantity of the noise actually accumulated during the electric-charge holding period is undesirably very large as shown by the plot B of FIG. 9.

As described above, in a unit pixel implementing a global 45 exposure operation by making use of the floating diffusion capacitor FD as the electric-charge holding section as is the case with the unit pixel 100 shown in FIG. 1 or making use of the memory section 107 as the electric-charge holding section as is the case with the unit pixel 300 shown in FIG. 50 2, it has been discovered that, during the period of holding electric charge in the floating diffusion capacitor FD or the memory section 107, noise is cumulatively added undesirably to the electric charge with the lapse of time. This noise is generated in accordance with the same principle as the 55 smear noise of the CCD sensor. In addition, it has also been discovered a characteristic indicating that, as shown by the plot B of FIG. 8, the quantity of the noise held in the electric-charge holding section per unit time on each of the scan-direction start pixel row and scan-direction end pixel 60 row is large whereas the quantity of the noise held in the electric-charge holding section per unit time on a scandirection middle pixel row is smallest.

The noise includes mainly a noise of a first kind and a noise of a second kind. The noise of the first kind is a noise 65 generated as a result of an opto-electric conversion process carried out by the electric-charge holding section such as the

**16**

floating diffusion capacitor FD or the memory section 107 to convert light incident directly to the electric-charge holding section. The noise of the second type is electric charge originating from the opto-electric conversion section or a source other than the opto-electric conversion section and flowing undesirably to the electric-charge holding section in a diffusion process.

System Configuration

FIG. 10 is a diagram showing the system configuration of a CMOS image sensor 10 serving as a solid-state image taking device according to the first embodiment of the present invention. This system configuration is also adopted by embodiments other than the first embodiment.

As shown in FIG. 10, the CMOS image sensor 10 according to the embodiment of the present invention is configured to employ a pixel array 11 created on a semiconductor substrate (or chip) not shown in the figure and a peripheral circuit integrated on the same substrate as the pixel array 11. The peripheral circuit typically includes a vertical driving section 12, a column processing section 13, a horizontal driving section 14 and a system control section 15.

The CMOS image sensor 10 is further provided with a signal processing section 18 and a data storage section 19.

The signal processing section 18 and the data storage section 19 can be implemented as an external signal processing section created on a substrate other than the semiconductor substrate of the CMOS image sensor 10. A typical example of the external signal processing section is a DSP (Digital Signal Processor). The external signal processing section can also be implemented by carrying out processing based on hardware and software for controlling the hardware which is typically the hardware of a DSP or a CPU (Central Processing Unit). The external signal processing section normally employs memory means for implementing the data storage section 19.

It is to be noted that the external signal processing section can also be created on the same semiconductor substrate as the CMOS image sensor 10.

The pixel array 11 is configured to include unit pixels laid out in row and column directions to form a 2-dimensional pixel matrix. In the following description, the unit pixel is also referred to simply as a pixel in some cases. Each of the unit pixels employs an opto-electric conversion element for converting light incident to the element into opto-electric charge also referred to hereafter as signal electric charge or simply as electric charge in some cases. That is to say, the opto-electric conversion element is an element for generating opto-electric charge having an amount proportional to the quantity of the light incident to the element. The generated opto-electric charge is accumulated in the opto-electric conversion element.

The basic cross section (and the circuit configuration) of this unit pixel can be made the same as those shown in FIG. 2 or can be partially modified as will be described later. The shape of a planar pattern of the unit pixel will be described later.

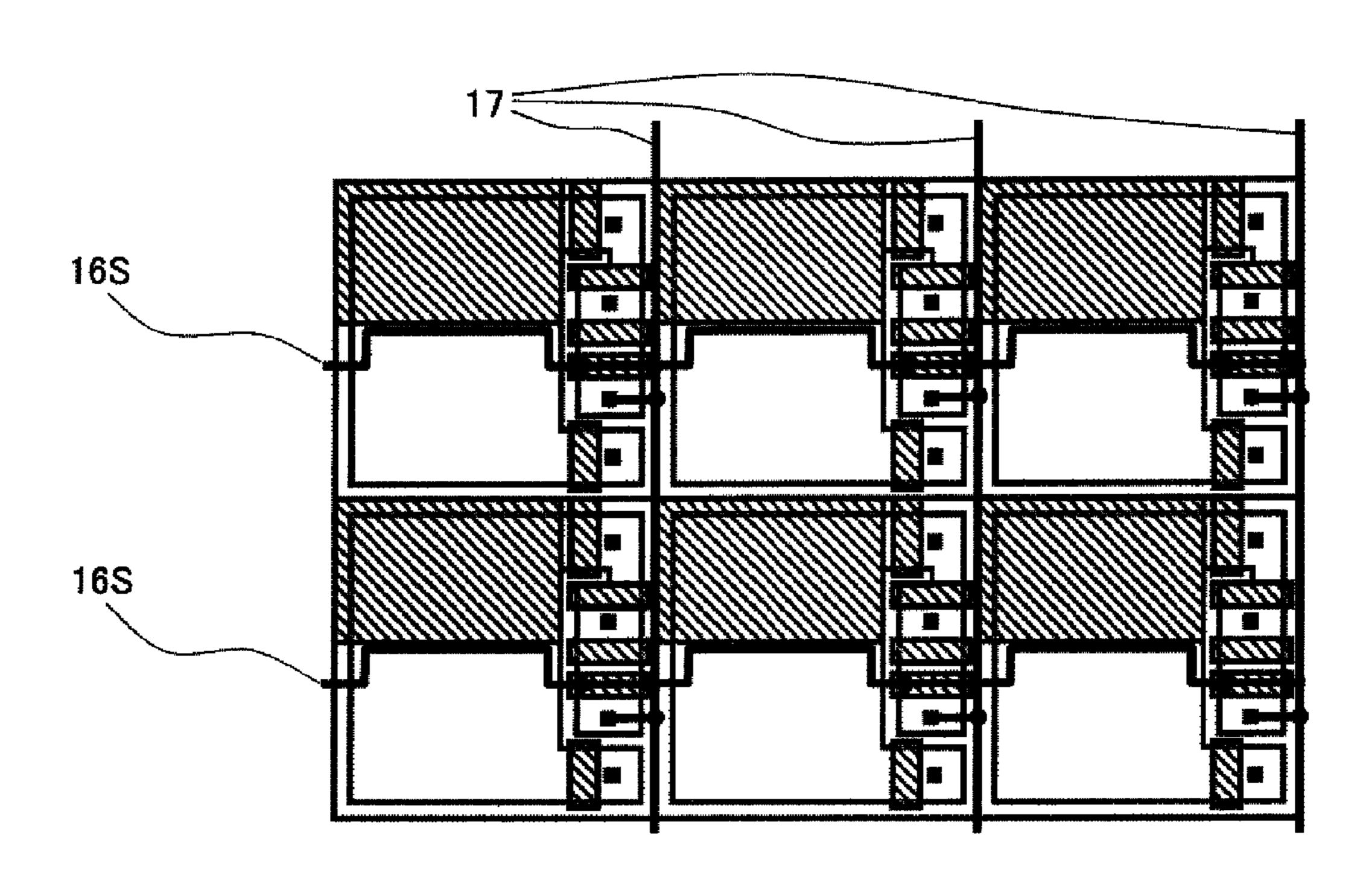

In the pixel array 11, a pixel driving line 16 is created in the horizontal direction of the figure for every pixel row of the pixel matrix which is a 2-dimensional array of unit pixels. The horizontal direction is the row direction in which every pixel row is oriented. In addition, a vertical signal line 17 is created in the vertical direction of the figure for every pixel column of the pixel matrix. The vertical direction is the column direction in which every pixel column is oriented. FIG. 10 shows only one pixel driving line 16 per pixel row. In actuality, however, every pixel row is not necessarily

provided with only one pixel driving line 16. That is to say, every pixel row can also be provided with a plurality of pixel driving lines 16. For example, as shown in FIG. 2, every pixel row is provided with two pixel driving lines 16, i.e., a reset line for supplying a reset pulse RST to the gate 5 electrode of the reset transistor 104 and a select line for supplying a select pulse SEL to the gate electrode of the select transistor 106. In this invention specification, the select line is also referred to as a scan line.

One end of the pixel driving line 16 is connected to an 10 output terminal of the vertical driving section 12. The output terminal of the vertical driving section 12 is associated with a pixel row for which the pixel driving line 16 is provided.

The vertical driving section 12 is configured to include components such an address decoder and a shift register. The 15 vertical driving section 12 is a pixel driving section for driving the unit pixels of the pixel array 11 at the same time in certain units each of which can be typically a pixel area determined in advance or a pixel row. In the case of this embodiment, the vertical driving section 12 drives all the 20 rarily in an internal memory. unit pixels of the pixel array 11 at the same time.

A concrete configuration of the vertical driving section 12 is not shown in the figure. In general, however, the vertical driving section 12 is configured to include two scan systems, i.e., a read scan system and a sweep scan system. Each of the 25 read scan system and the sweep scan system is a circuit for individually driving the scan lines of the pixel rows on a one-row-after-another basis. A typical example of the scan line is the select line for supplying a select pulse SEL to the gate electrode of the select transistor 106 as shown in FIG. 30

In order to read out signals from unit pixels in the pixel array 11, the read scan system sequentially scans and selects the unit pixels in row units in a read scan operation. The pixel row to be subjected to a read scan operation carried out by the read scan system. The sweep scan operation leads ahead of the read scan operation by a time the length of which is determined by the speed of a shutter. The read scan operation is carried out by the read scan system synchro- 40 nously with the sweep scan operation carried out by the sweep scan system in accordance with control based on a clock signal.

The sweep scan operation carried out by the sweep scan system sweeps (or resets) unnecessary electric charge from 45 an opto-electric conversion element employed in a unit pixel being subjected to the sweep scan operation, resetting the opto-electric conversion element.

The sweep scan system sweeps (or resets) unnecessary electric charge in order to carry out the so-called electronic 50 register. shutter operation. The electronic shutter operation is an operation to discard opto-electric charge of the opto-electric conversion element such as the photodiode 101 employed in the unit pixel 300 shown in FIG. 2 and newly start an exposure operation, that is, newly start an operation to 55 accumulate opto-electric charge.

As is obvious from the above description, in the case of the unit pixel 300 shown in FIG. 2 for example, the reset transistor 104 is driven by the sweep scan system.

A signal read out from an opto-electric conversion ele- 60 ment employed in a unit pixel in a read operation carried out by the read scan system has a magnitude determined by the quantity of incident light hitting the opto-electric conversion element during the immediately preceding read operation or hitting the opto-electric conversion element since the elec- 65 tronic shutter operation. In the case of the unit pixel 300 shown in FIG. 2 for example, the select transistor 106 is

**18**

driven by the read scan system. A period between the read timing of the immediately preceding read operation or the sweep timing of the electronic shutter operation and the read timing of the present read operation is referred to as the period of accumulation of opto-electric charge in the unit pixel. In the following description, the period of accumulation of opto-electric charge is referred to as an exposure period.

Signals read out from unit pixels on a pixel row selected and scanned by the vertical driving section 12 are supplied to the column processing section 13 for each pixel column through the vertical signal line 17 corresponding to the vertical signal line 200 connected to the unit pixel 300 as shown in FIG. 2.

The column processing section 13 carries out signal processing determined in advance on signals output by unit pixels on the selected pixel row of the pixel array 11 through the vertical signal lines 17 for every pixel column and stores signals obtained as a result of the signal processing tempo-

To put it concretely, the signal processing carried out by the column processing section 13 includes at least noise elimination processing such as CDS (Correlated Double Sampling) processing. By carrying out the CDS processing, the column processing section 13 is capable of eliminating reset noises and fixed pattern noises caused by, among others, variations of the threshold voltage of the amplification transistor 105 as noises inherent in the unit pixel. In addition to the function to eliminate such noises, the column processing section 13 is also provided with typically an AD (analog-to-digital) conversion function to convert the analog input signal into an output digital signal.

The horizontal driving section 14 is also configured to include components such an address decoder and a shift sweep scan system carries out a sweep scan operation on a 35 register. The horizontal driving section 14 sequentially selects unit circuits each employed in the column processing section 13 as a circuit corresponding to a pixel column. The horizontal driving section 14 selects and scans the unit circuits in order to sequentially supply a signal completing the signal processing carried out by the column processing section 13 for every unit circuit to the signal processing section 18.

> It is to be noted that the shift register employed in the horizontal driving section 14 may be configured to allow conversion scan processing to convert input parallel pixel data representing signal electric charge into output serial pixel data or into an output consisting of bits the number of which is determined in advance. In this case, an AD converter may be connected to the output terminal of the shift

> The system control section 15 is configured to include a timing generator for generating a variety of timing signals. The system control section 15 controls operations to drive sections such as the vertical driving section 12, the column processing section 13 and the horizontal driving section 14 on the basis of the timing signals generated by the timing generator.

> The signal processing section 18 has at least an addition processing function to be executed for carrying out various kinds of signal processing including addition processing on a pixel signal output by the column processing section 13. A purpose of the addition processing is elimination of random noises caused by an averaging process. Another purpose of the addition processing is addition.

> The data storage section 19 is used for temporarily storing data required in the signal processing carried out by the signal processing section 18. The signal processing may not

require data to be stored temporarily in a memory in some cases. In such cases, the data storage section 19 can be omitted.

Pixel Structures and Layouts

The structures of the unit pixel and the layouts thereof are 5 explained by referring to FIGS. 11A to 17.

FIG. 11A is a top-view diagram showing a structure of the unit pixel. FIG. 12 is a cross-sectional diagram showing the cross section of the pixel unit along a line A-B shown in FIG. 11B. FIGS. 11A and 11B show the same top-view pattern. In 10 the following description, FIG. 11A showing a variety of reference numerals and reference symbols is referred to.

First of all, a cross-sectional structure of the unit pixel is explained by referring to FIG. 12.

pixel PIXA shown in FIG. 12 is typically constructed in the P-type well layer 112 created on the N-type semiconductor substrate 111. In the case of this embodiment, the semiconductor substrate 111 is a silicon substrate.

Much like the unit pixel 300 shown in FIG. 2, in the 20 P-type well layer 112, an opto-electric conversion section PD is created. The opto-electric conversion section PD has a P+-type hole accumulation layer 113 on the surface side of the P-type well layer 112 and the N-type embedded layer 114 on the inner side of the P-type well layer 112. The P+-type 25 hole accumulation layer 113 corresponds to the P-type layer 113 employed in the unit pixel 300 shown in FIG. 2. On one side of the opto-electric conversion section PD, a first transfer gate transistor and a second transfer gate transistor are created, being connected to each other in series. The first transfer gate transistor has a circuit function equivalent to that of the transfer gate transistor 108 employed in the unit pixel 300 shown in FIG. 2 whereas the second transfer gate transistor has a circuit function equivalent to that of the transfer gate transistor 102 employed in the unit pixel 300 35 shown in FIG. 2.

In the following description as well as FIGS. 11A and 11B and subsequent figures, reference symbol TRX denotes a first transfer gate which is the gate electrode of the first transfer gate transistor whereas reference symbol TRG 40 denotes a second transfer gate which is the gate electrode of the second transfer gate transistor. In addition, reference symbol TRX is also used for denoting a pulse signal applied to the gate electrode of the first transfer gate transistor whereas reference symbol TRG is also used for denoting a 45 pulse signal applied to the gate electrode of the second transfer gate transistor.

The first transfer gate TRX also denoted by reference numeral 110X is placed to cover the surface of an area separating a semiconductor area forming the opto-electric 50 conversion section PD and the N-type area 107a of the memory section 107 also denoted by reference symbol MEM from each other. As described earlier, the opto-electric conversion section PD has the P+-type hole accumulation layer 113 and the N-type embedded layer 114. In addition, 55 the first transfer gate TRX also covers the surface of the N-type area 107a itself. A gate insulation film 109X is provided between the first transfer gate TRX and these covered surfaces which are a part of the surface of the P-type well layer 112 created on the semiconductor substrate 111. 60

The impurity profile of the memory section MEM in the substrate depth direction has the face of a junction between the memory section MEM and the P-type well layer 112 created on the semiconductor substrate 111 at a position which is shallow in comparison with the face of a junction 65 between the opto-electric conversion section PD and the P-type well layer 112. In the following description, the

**20**

position at which the face of the junction is placed is referred to simply as a junction position.

The opto-electric conversion section PD employed in the CMOS image sensor receives light having a variety of large wavelengths in a range up to a small wavelength of 700 nm in the red color region. Thus, the opto-electric conversion section PD has to be an area which is sensitive to the depth of about 3  $\mu$ m.

On the other hand, the memory section MEM is used for eliminating noises including the smear noises described earlier as main components. Thus, it is nice to prevent light incident to the opening of the opto-electric conversion section PD in an inclined direction from directly hitting the memory section MEM. To put it concretely, it is desirable to Much like the unit pixel 300 shown in FIG. 2, the unit 15 have a narrowest possible face of the junction and a shallowest possible junction position which satisfy other characteristics such as the amount of electric charge that can be accumulated. Thus, the junction position of an N-type area 107a forming the memory section MEM is made shallow in comparison with the junction position of the N-type area 103 forming the opto-electric conversion section PD.

> The second transfer gate TRG also denoted by reference numeral 110G is placed to cover the surface of an area separating the N-type area 107a of the memory section 107 and the N-type area 103 serving as the floating diffusion capacitor FD from each other. A gate insulation film 109G is provided between the second transfer gate TRG and the covered surface which is also a part of the surface of the P-type well layer 112.

> The N-type area 103 serving as the floating diffusion capacitor FD is created in an area included in the P-well layer 112 as an area adjacent to the second transfer gate TRG. In the same way as the unit pixel 300 shown in FIG. 2, the floating diffusion capacitor FD is typically connected to a read section including the reset transistor 104, the amplification transistor 105 and the select transistor 106. The reader is advised to keep in mind that it is also possible to provide a configuration in which the select transistor 106 is placed between the line supplying the voltage Vdd and the amplification transistor 105 to serve as a switch for connecting the amplification transistor 105 to the line or disconnecting the amplification transistor 105 from the line. It is also to be noted that this configuration can be adopted as well in the unit pixel 300 shown in FIG. 2.

> The unit pixel PIXA shown in FIG. 12 also includes an electric-charge exhausting drain ABD even though the electric-charge exhausting drain ABD is not an absolutely required element.

> The electric-charge exhausting drain ABD is an N+-type area 115 created on the P-type well layer 112 separately from the opto-electric conversion section PD. On a substrate area between the opto-electric conversion section PD and the electric-charge exhausting drain ABD, an electric-charge exhausting gate ABG is created, being separated from the substrate area by a gate insulation film 109A.