### US009558917B2

# (12) United States Patent

Finley et al.

### ADJUSTABLE NON-DISSIPATIVE VOLTAGE (54)**BOOSTING SNUBBER NETWORK FOR** ACHIEVING LARGE BOOST VOLTAGES

Applicant: Advanced Energy Industries, Inc., Fort Collins, CO (US)

Inventors: **Kenneth W. Finley**, Fort Collins, CO

(US); **Hendrik Walde**, Fort Collins, CO

(US)

Assignee: Advanced Energy Industries, Inc., (73)

Fort Collins, CO (US)

Subject to any disclaimer, the term of this Notice:

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

Appl. No.: 15/222,597

Jul. 28, 2016 Filed: (22)

#### (65)**Prior Publication Data**

US 2016/0336148 A1 Nov. 17, 2016

### Related U.S. Application Data

- Continuation of application No. 14/945,331, filed on Nov. 18, 2015, which is a division of application No. 14/185,213, filed on Feb. 20, 2014, now Pat. No. 9,224,579, which is a continuation of application No. 13/867,907, filed on Apr. 22, 2013, now Pat. No. 9,129,776, which is a continuation-in-part of application No. 13/666,668, filed on Nov. 1, 2012, now Pat. No. 9,226,380.

- Int. Cl. (51)H01J 37/32 (2006.01)

H01J 37/34 (2006.01)

U.S. Cl. (52)

> (2013.01)

US 9,558,917 B2 (10) Patent No.:

(45) Date of Patent: Jan. 31, 2017

#### Field of Classification Search (58)

CPC H01J 37/3417; H01J 37/3438; H01J 37/3444; H01J 37/3467; H05H 1/46 See application file for complete search history.

#### **References Cited** (56)

### U.S. PATENT DOCUMENTS

| 2005/0092596 A1 | 5/2005 | Kouznetsov      |

|-----------------|--------|-----------------|

| 2006/0192774 A1 | 8/2006 | Yasumura        |

| 2007/0217093 A1 | 9/2007 | Xue et al.      |

| 2008/0203070 A1 | 8/2008 | Ilic et al.     |

| 2011/0011737 A1 | 1/2011 | Wu et al.       |

| 2011/0075445 A1 | 3/2011 | Drummond et al. |

|                 | (Con   | tinued)         |

### (Commuca)

### FOREIGN PATENT DOCUMENTS

EP 2316123 A1 5/2011

### OTHER PUBLICATIONS

King, Monica C., "Restriction Requirement re U.S. Appl. No. 14/184,968", Jul. 23, 2015, p. 5 Published in: US. (Continued)

Primary Examiner — Monica C King (74) Attorney, Agent, or Firm — Neugeboren O'Dowd PC

#### (57)**ABSTRACT**

This disclosure describes a non-dissipative snubber circuit configured to boost a voltage applied to a load after the load's impedance rises rapidly. The voltage boost can thereby cause more rapid current ramping after a decrease in power delivery to the load which results from the load impedance rise. In particular, the snubber can comprise a combination of a unidirectional switch, a voltage multiplier, and a current limiter. In some cases, these components can be a diode, voltage doubler, and an inductor, respectively.

## 32 Claims, 30 Drawing Sheets

## (56) References Cited

### U.S. PATENT DOCUMENTS

| 2011/0120861 | A1* | 5/2011  | Horishita C23C 14/3464 |

|--------------|-----|---------|------------------------|

|              |     |         | 204/298.08             |

| 2011/0248633 | A1* | 10/2011 | Nauman C23C 14/3485    |

|              |     | - (     | 315/111.21             |

| 2012/0025726 | Al* | 2/2012  | Watanabe H01J 37/32027 |

| 2014/0150640 | A 1 | 6/2014  | 315/205                |

| 2014/0159648 | ΑI  | 6/7014  | Sadwick                |

### OTHER PUBLICATIONS

Gruber, Stephen S., "Response to Restriction Requirement re U.S. Appl. No. 14/184,968", Sep. 23, 2015, p. 7, Published in: US. King, Monica C., "Office Action re U.S. Appl. No. 15/055,761", Sep. 2, 2016, p. 7 Published in: US. King, Monica C., "Office Action re U.S. Appl. No. 14/945,324", Jun. 10, 2016, p. 24 Published in: US. Gruber, Stephen S., "Response to Office Action re U.S. Appl. No. 14/945,324", Jul. 8, 2016, p. 9 Published in: US.

Belkind, A. et al., "Characterization of Pulsed DC Magnetron Sputtering Plasmas", Apr. 6, 2005, p. 19 vol. 7, No. 1, Publisher: New Journal of Physics.

Christie, et al., "High performance pulsed current source supplies for large area", Nov. 2, 2000, p. 12 Published in: US.

King, Monica C., "Office Action re U.S. Appl. No. 13/666,668", Jan. 30, 2015, p. 6 Published in: US.

O'Dowd, Sean R., "Response to Office Action re U.S. Appl. No. 13/666,688", Mar. 27, 2015, p. 8 Published in: US.

Koh, Eugene, "International Search Report and Written Opninion re Application No. PCT/US2013/068033", Feb. 3, 2014, p. 17 Published in: AU.

Sittinger, et al., "Position and Time Resolved Optical Emission Spectroscopy and Film Properties of", 2007, p. 6, Published in: US. Todd, Philip C., "Snubber Circuits: Theory, Design and Application", "Unitrode Corporation", May 1993, pp. 2-1 through 2-17, Publisher: Texas Instruments, Published in: US.

Wittmann-Regis, Agnes, "International Preliminary Report on Patentability re Application No. PCT/US2013/068033", May 14, 2015, p. 12, Published in: US.

<sup>\*</sup> cited by examiner

FG. 16

FIG. 26

FIG. 27

FIG. 30

## ADJUSTABLE NON-DISSIPATIVE VOLTAGE **BOOSTING SNUBBER NETWORK FOR** ACHIEVING LARGE BOOST VOLTAGES

### CLAIM OF PRIORITY UNDER 35 U.S.C. §120

The present Application for Patent is a Continuation of U.S. Patent Publication No. 2016/0071697 entitled "ADJUSTABLE NON-DISSIPATIVE VOLTAGE BOOST-ING SNUBBER NETWORK FOR ACHIEVING LARGE 10 BOOST VOLTAGES," filed Nov. 18, 2015, which is a Divisional of U.S. Pat. No. 9,224,579 entitled "ADJUST-ABLE NON-DISSIPATIVE VOLTAGE BOOSTING SNUBBER NETWORK FOR ACHIEVING LARGE BOOST VOLTAGES," filed Feb. 20, 2014, which is a 15 Continuation of U.S. Pat. No. 9,129,776 entitled "DIFFER-ING BOOST VOLTAGES APPLIED TO TWO OR MORE ANODELESS ELECTRODES FOR PLASMA PROCESS-ING," filed Apr. 22, 2013, which is a Continuation in Part of U.S. Pat. No. 9,226,380 entitled "ADJUSTABLE NON-DISSIPATIVE VOLTAGE BOOSTING SNUBBER NET-WORK" filed Nov. 1, 2012. All applications are assigned to the assignee hereof and hereby expressly incorporated by reference herein.

### FIELD OF THE DISCLOSURE

The present disclosure relates generally to power supplies. In particular, but not by way of limitation, the present disclosure relates to systems, methods and apparatuses for 30 limiting voltage and current spikes in a power supply.

## BACKGROUND

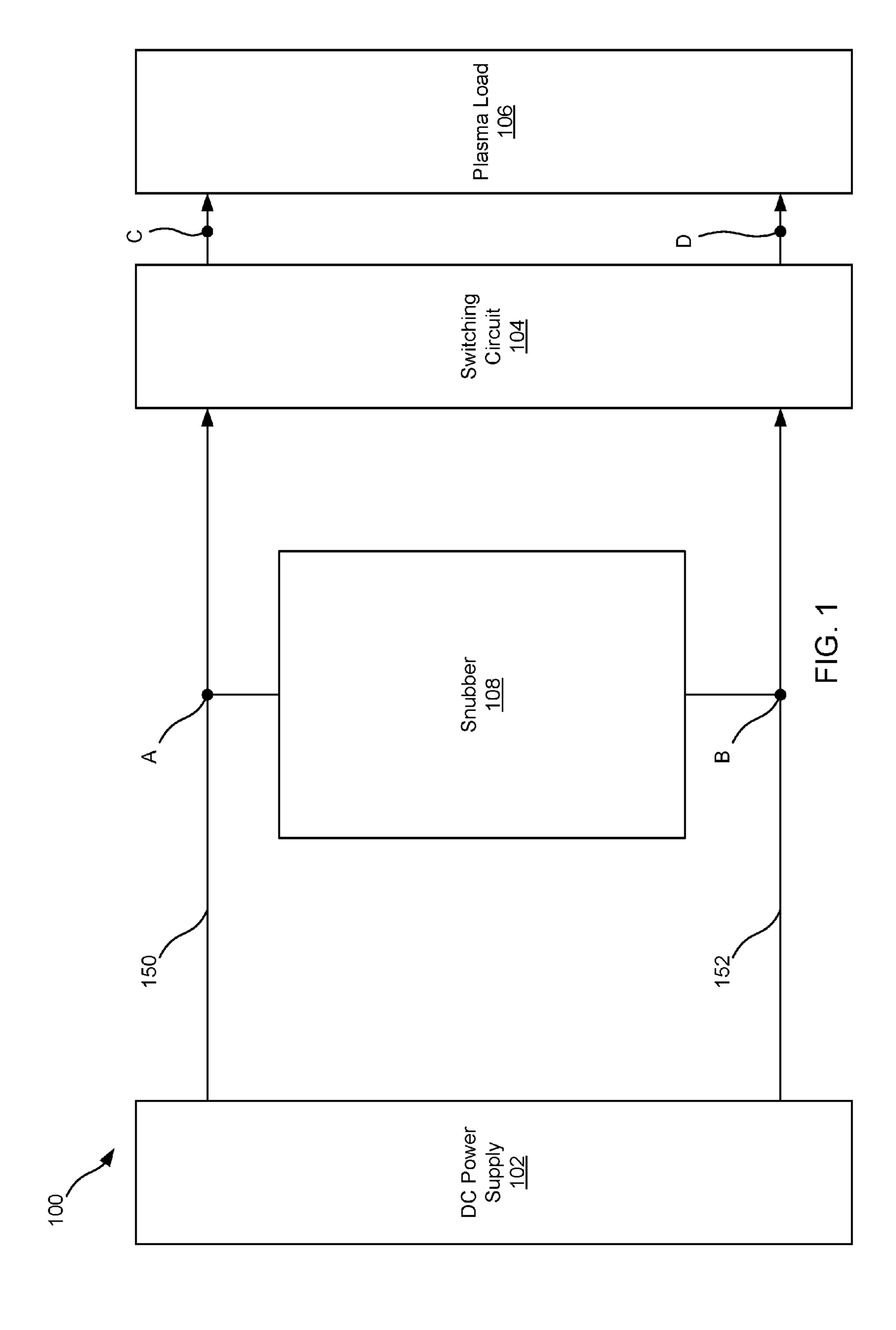

system 100 used for plasma processing. The power supply system 100 includes a DC power supply 102 providing DC power to a switching circuit **104** that converts the DC power into pulsed DC and provides the pulsed DC to a plasma load **106**. When switching, the potential between nodes C and D 40 passes through a potential of zero, and the plasma can be extinguished or can dim to an extent that it becomes highly resistive and acts like an unfluxed inductor or an open circuit for a short time after this transition. Immediately after this transition, the DC power supply 102 continues to provide 45 power to the switching circuit 104, but most of that power can no longer be delivered to the plasma load 106. Instead, the power predominantly passes through the switching circuit 104 potentially damaging the switching circuit 104.

A snubber 108 can be used to mitigate damage to the 50 switching circuit 104 by absorbing power from the DC power supply 102 during the period after the switching circuit **104** transitions through 0 V. However, existing snubbers are typically dissipative snubbers and/or dissipate significant power.

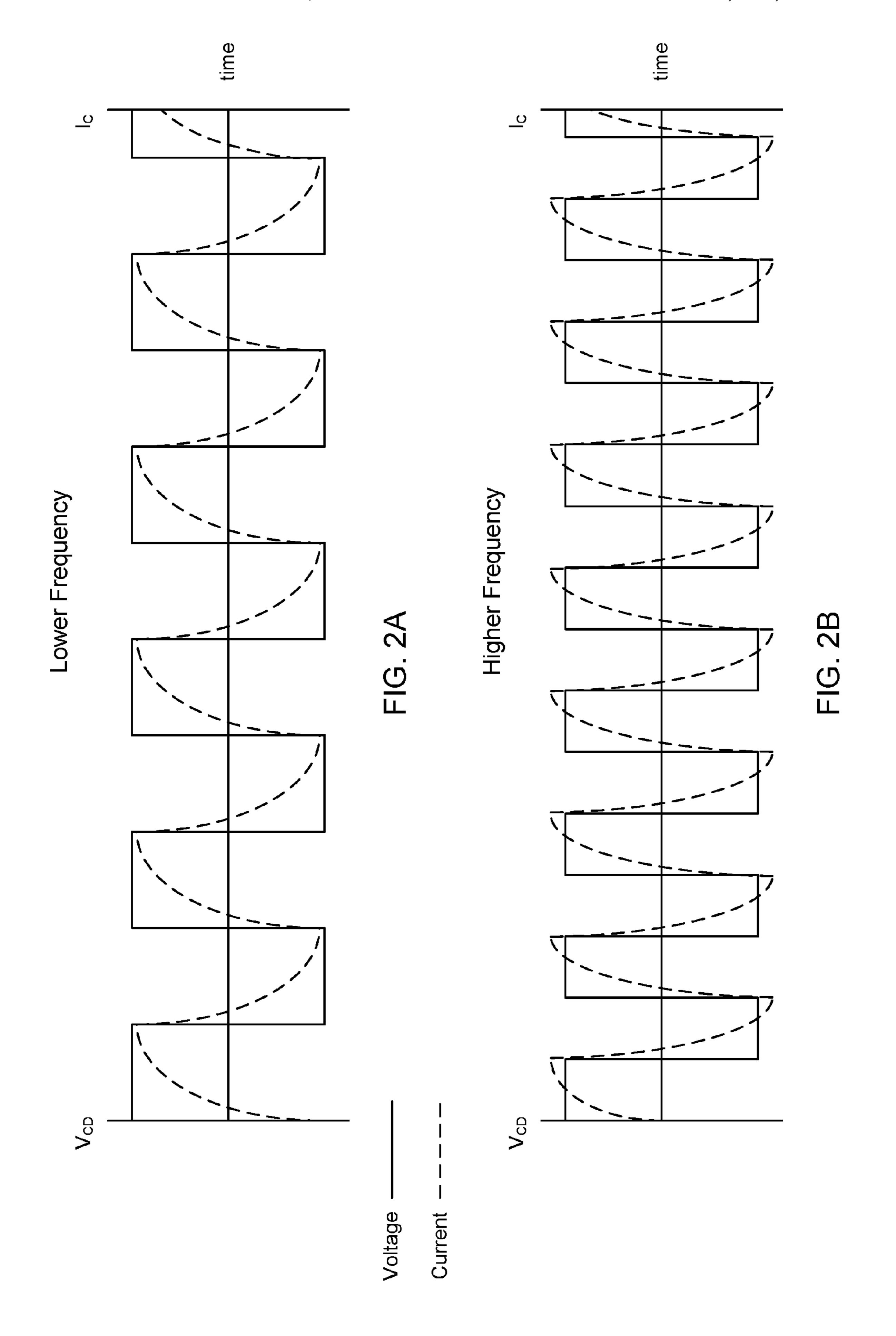

Additional challenges to known power supply systems include slow processing throughput and further inefficiencies from power dissipation. For instance, and as seen in FIG. 2A, while voltage between nodes C and D can switch with negligible ramp time, current ramps at a much slower 60 pace thus providing an average power that is significantly lower than the power output from the DC power supply 102. This leads to longer processing periods and decreased throughput, since many processes can only end when a predetermined total power has been delivered.

There is also a desire to increase DC pulse frequency provided to the plasma load 106 since this reduces arcing.

However, the above-noted problems become more acute at higher frequencies, as illustrated in FIG. 2B. Furthermore, since each pulse is shorter at higher frequency, the current at high frequency may end up larger (in a power-regulated system) than at lower frequency. Since power dissipation is proportional to I<sup>2</sup>, these larger currents lead to larger power losses. Additionally, switching losses, which are proportional to the current at the moment of switching, are accentuated at higher frequencies since switching current is larger.

### SUMMARY OF THE DISCLOSURE

Exemplary embodiments of the present invention that are shown in the drawings are summarized below. These and other embodiments are more fully described in the Detailed Description section. It is to be understood, however, that there is no intention to limit the invention to the forms described in this Summary of the Invention or in the Detailed Description. One skilled in the art can recognize that there are numerous modifications, equivalents and alternative constructions that fall within the spirit and scope of the invention as expressed in the claims.

Some embodiments of the disclosure may be characterized as a power system comprising a DC power supply, a 25 switching circuit, and a snubber circuit. The DC power supply can supply DC power to first and second rails having a voltage between the first and second rails. The switching circuit can receive the DC power via the first and second rails and converting the DC power to a pulsed DC voltage, the pulsed DC voltage configured for application to a plasma load. The snubber circuit can be coupled to the first and second rails such that the voltage between the first and second rails falls across the snubber circuit. Furthermore, the snubber circuit can comprise a first unidirectional switch, a FIG. 1 illustrates one example of a typical power supply 35 voltage multiplier, an electrical node, and a current limiter. The first unidirectional switch can be configured to allow current to pass from the first rail. The voltage multiplier can be coupled between the first unidirectional switch and the second rail. The voltage multiplier can be configured to absorb and store energy from the DC power supply via the first unidirectional switch when an impedance seen by the switching circuit increases. It can also be configured to boost the voltage between the first and second rails by virtue of absorbing and storing the energy from the DC power supply. It can further be configured to then apply at least a portion of the stored energy to the switching circuit when the impedance seen by the switching circuit decreases and thereby decrease the voltage between the first and second rails. The electrical node can be arranged between the first unidirectional switch and the voltage multiplier. The current limiter can be coupled between the electrical node and the first rail and can limit rises in current that the voltage multiplier discharges to the switching circuit

Other embodiments of the disclosure may also be char-55 acterized as a snubber circuit comprising a voltage multiplier, a first unidirectional switch, and a first current-limiter. The voltage multiplier can be coupled between a first power rail and a second power rail and it can absorb and store energy from the first rail and consequently boost a voltage between the first and second rail, and then discharge at least some of the energy and consequently reduce the voltage between the first and second rail. The first unidirectional switch can allow current to pass from the first power rail to the voltage multiplier, but can block current attempting to pass back to the first power rail through the first unidirectional switch. The first current-limiter can be coupled between the first power rail and the voltage multiplier. The

first current-limiter can provide a low-resistance current path from the voltage multiplier to the first power rail and can limit a rate of change of current that the voltage multiplier discharges to the first power rail.

Other embodiments of the disclosure can be characterized as a method comprising passing power from a power supply to a load having an impedance. The method can also include absorbing at least some of the power when the impedance of the load substantially increases and thereby increasing a voltage and a current reaching the load. The method finally includes discharging at least some of the absorbed power into the load when the impedance of the load decreases, such that the discharge is substantially non-dissipative.

### BRIEF DESCRIPTION OF THE DRAWINGS

Various objects and advantages and a more complete understanding of the present invention are apparent and more readily appreciated by referring to the following 20 detailed description and to the appended claims when taken in conjunction with the accompanying drawings:

- FIG. 1 illustrates one example of a typical power supply system used for plasma processing;

- FIGS. 2A and 2B illustrate plots of voltage and current for 25 a traditional power supply system;

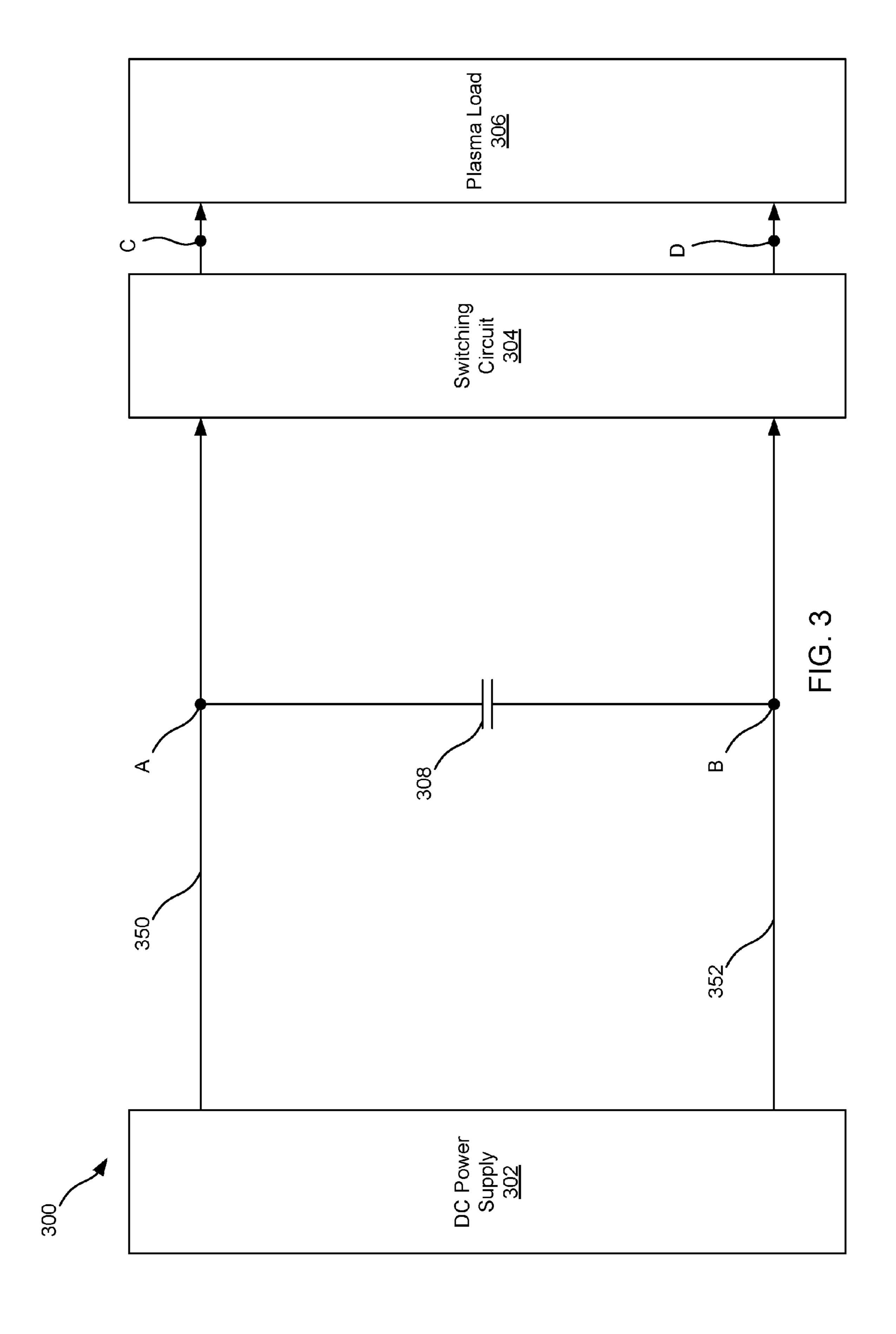

- FIG. 3 illustrates a power supply system including a DC power supply, a switching circuit, a plasma load, and an embodiment of a non-dissipative snubber circuit;

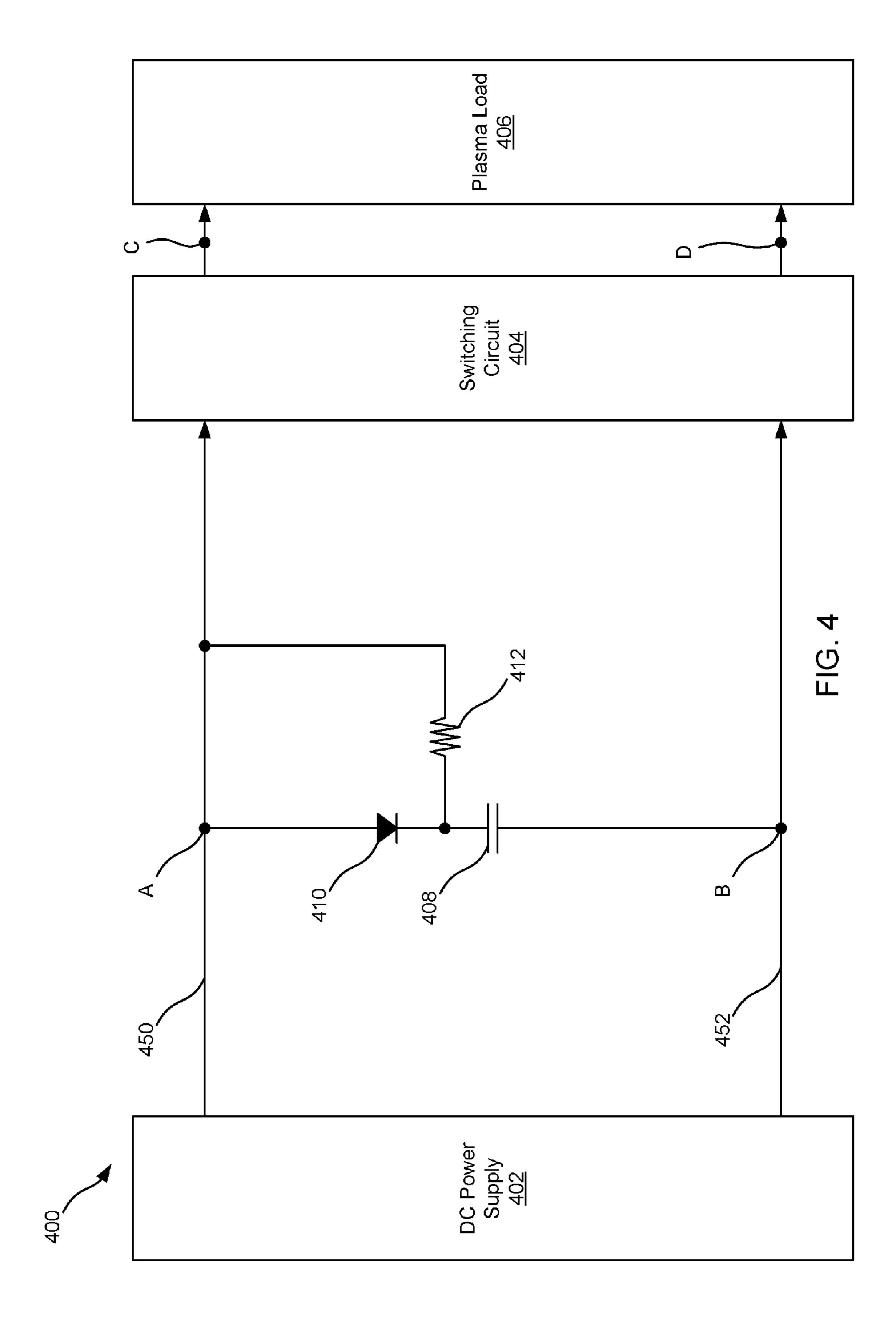

- FIG. 4 illustrates a power supply system including a DC power supply, a switching circuit, a plasma load, and another embodiment of a dissipative snubber circuit;

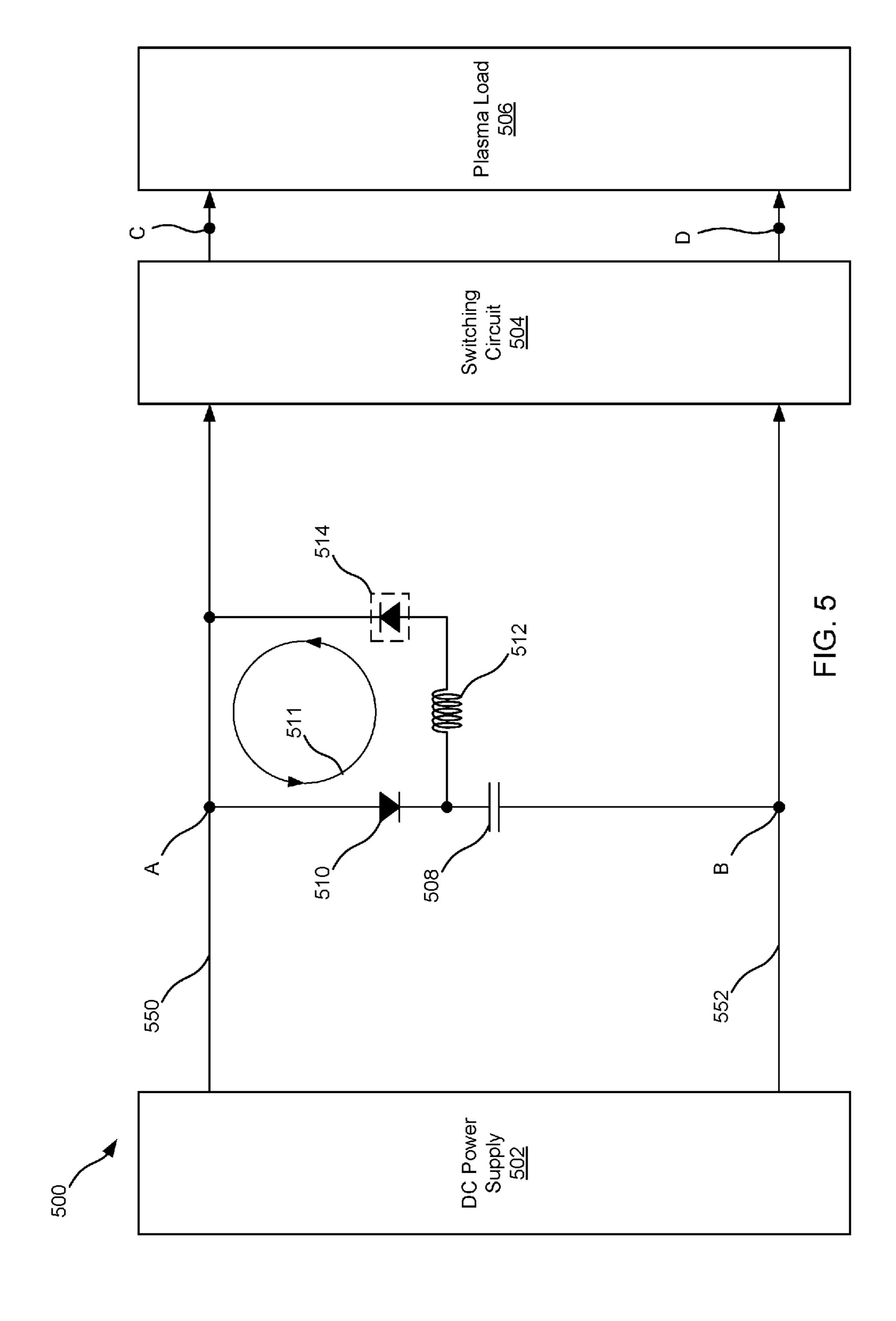

- FIG. 5 illustrates a power supply system including a DC power supply, a switching circuit, a plasma load, and yet another embodiment of a non-dissipative snubber circuit;

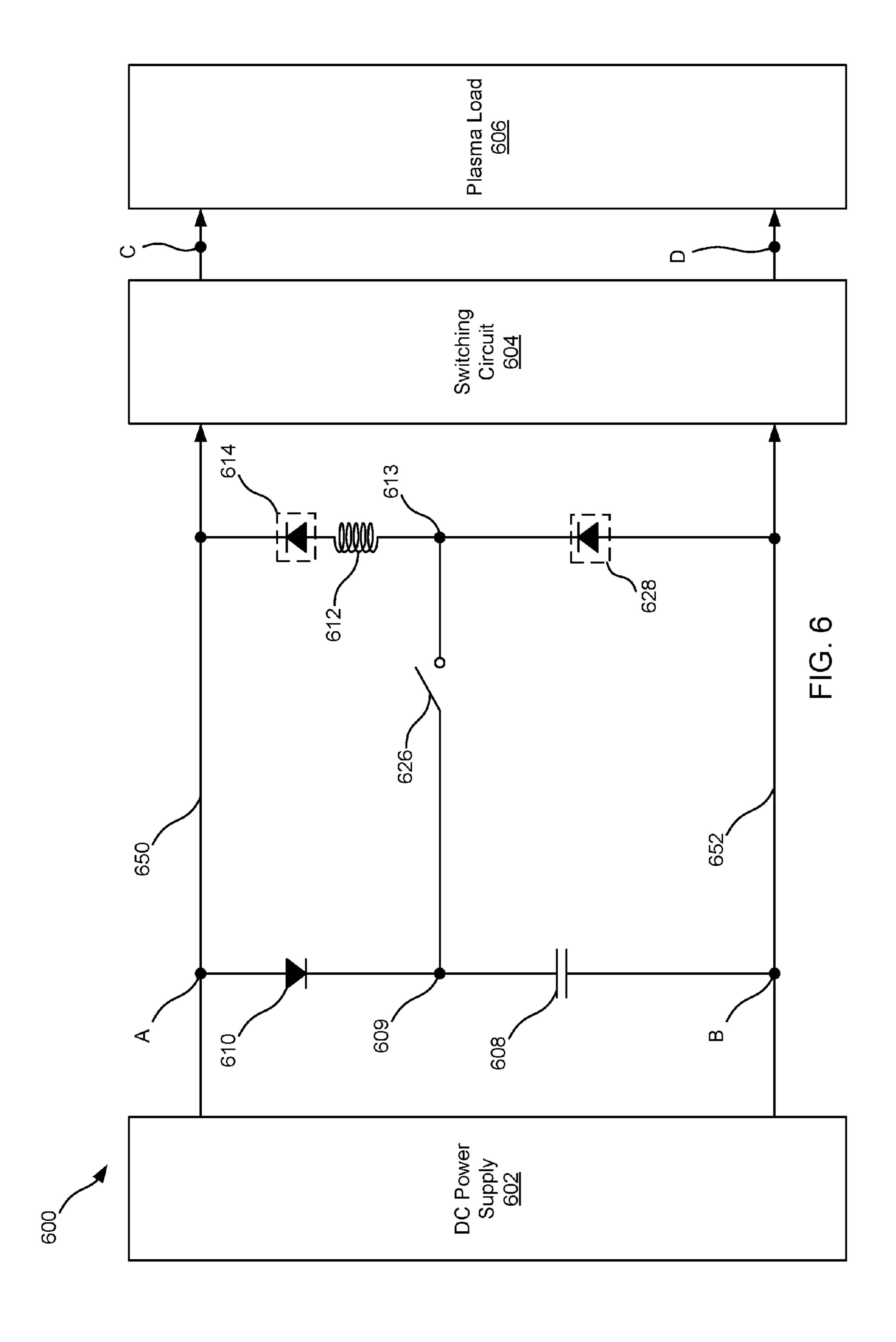

- FIG. 6 illustrates a power supply system including a DC power supply, a switching circuit, a plasma load, and yet another embodiment of a non-dissipative snubber circuit;

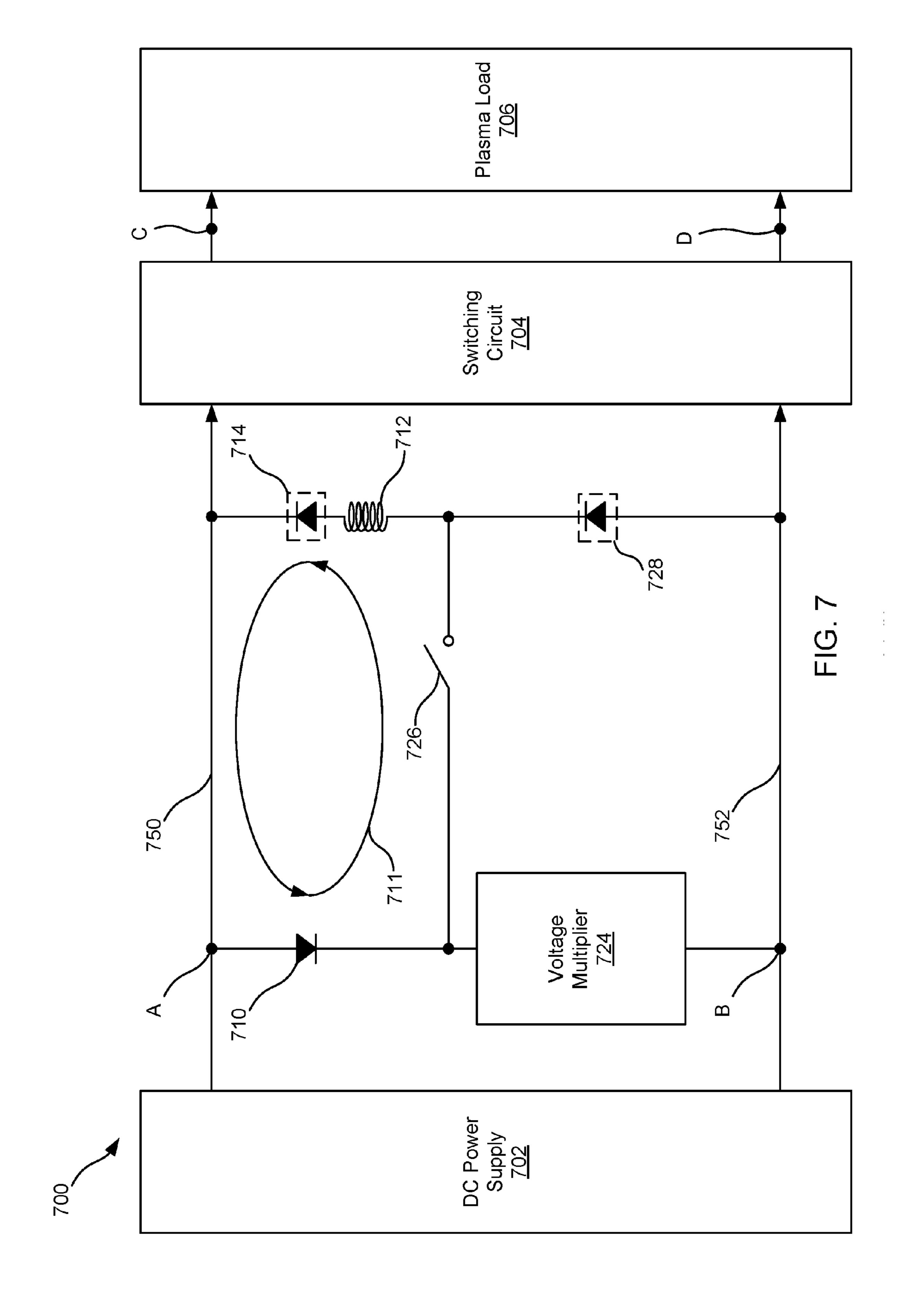

- FIG. 7 illustrates a power supply system including a DC power supply, a switching circuit, a plasma load, and yet another embodiment of a non-dissipative snubber circuit;

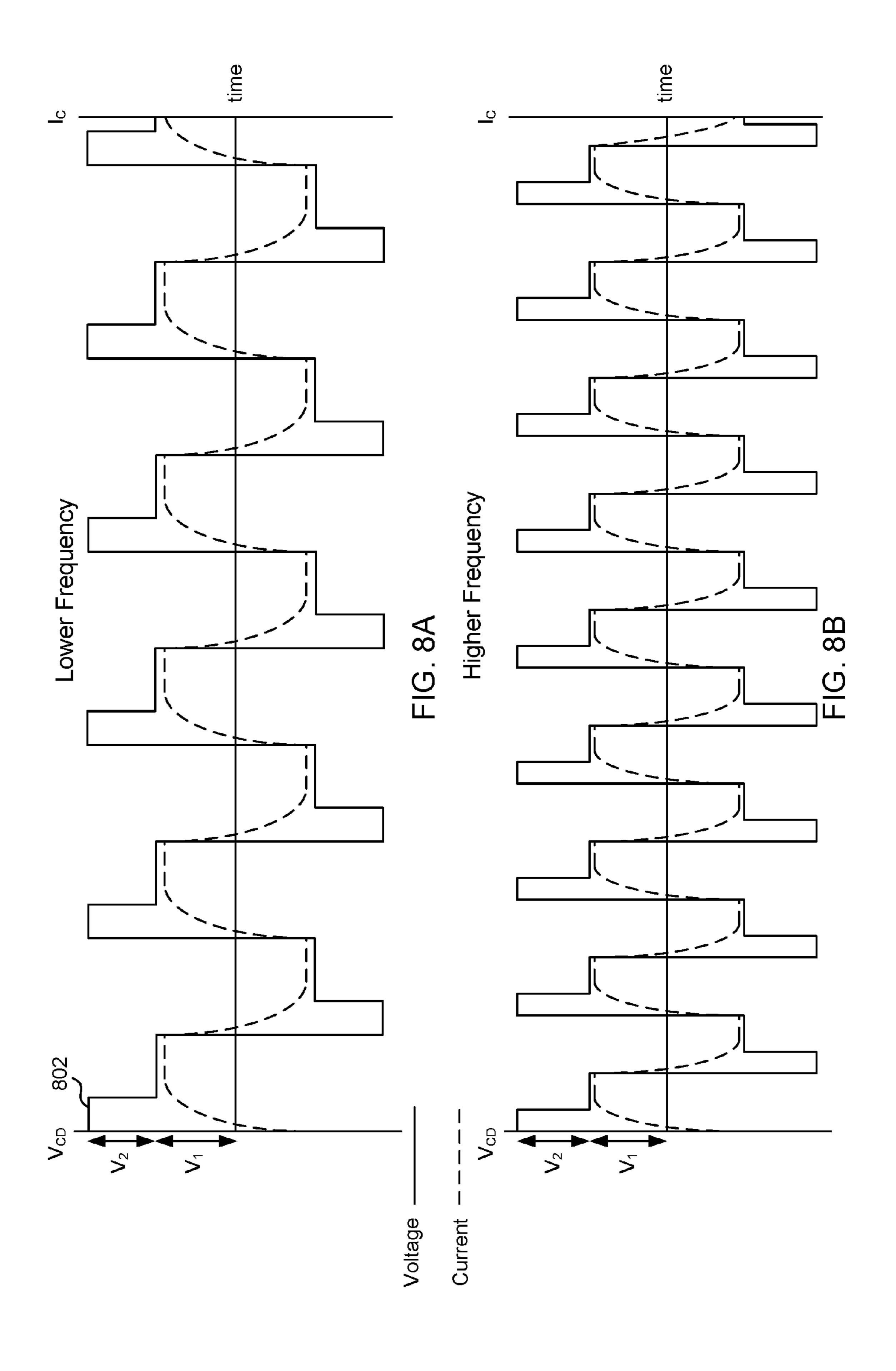

- FIGS. 8A and 8B illustrate plots of voltage and current for a power supply system according to one embodiment of this disclosure;

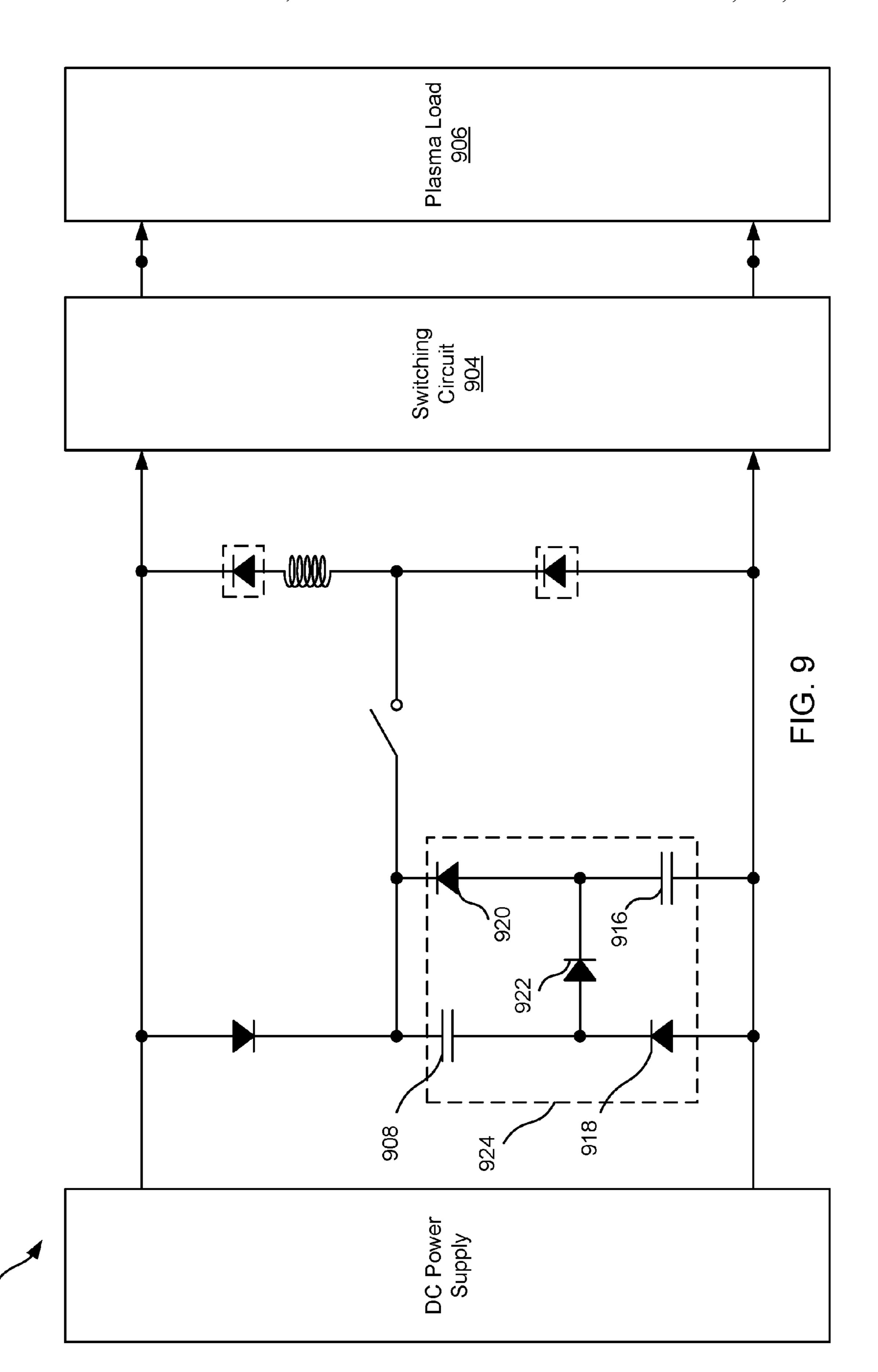

- FIG. 9 illustrates an embodiment of a power supply system showing details of a voltage multiplier;

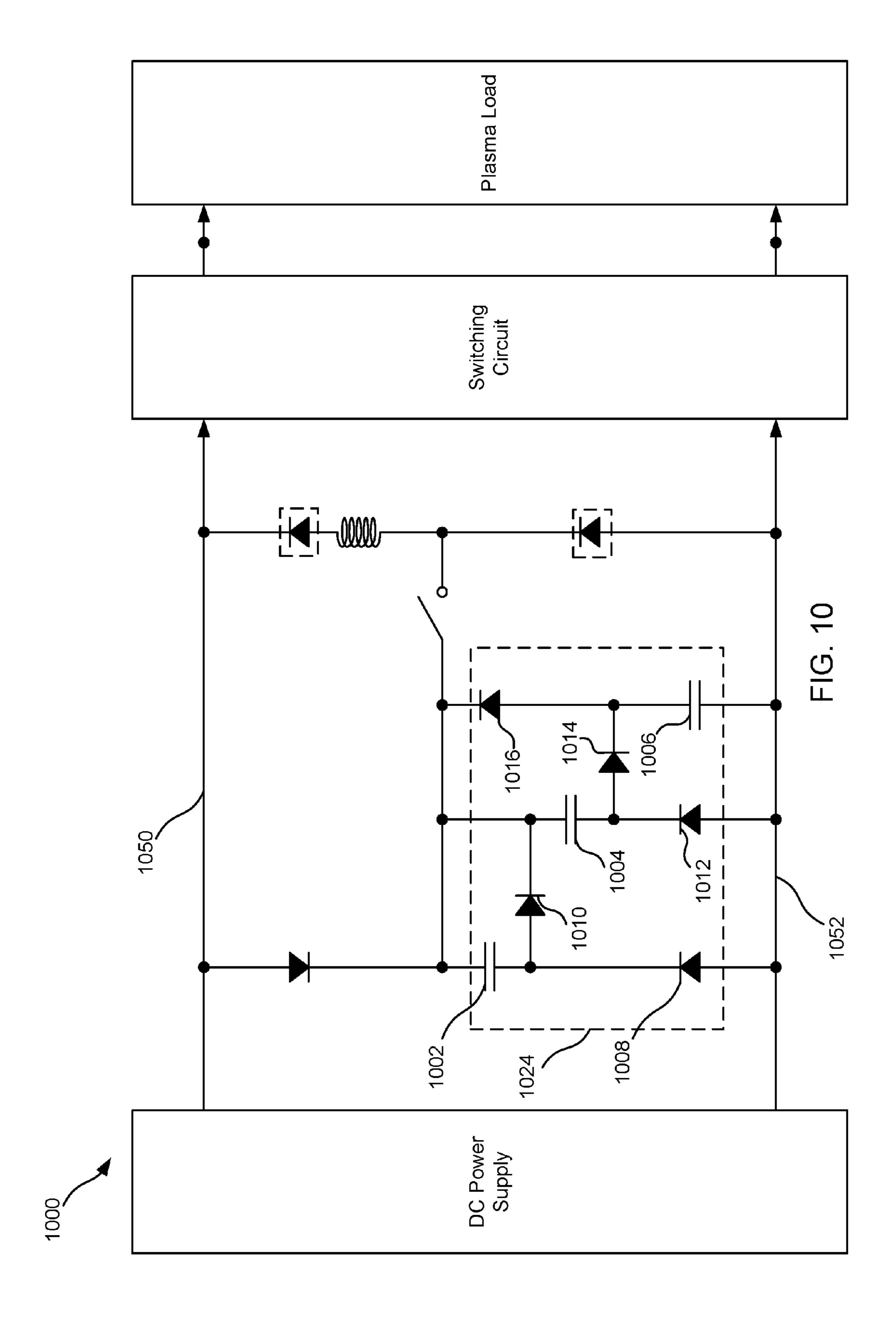

- FIG. 10 illustrates an embodiment where the voltage multiplier of the snubber is a voltage tripler;

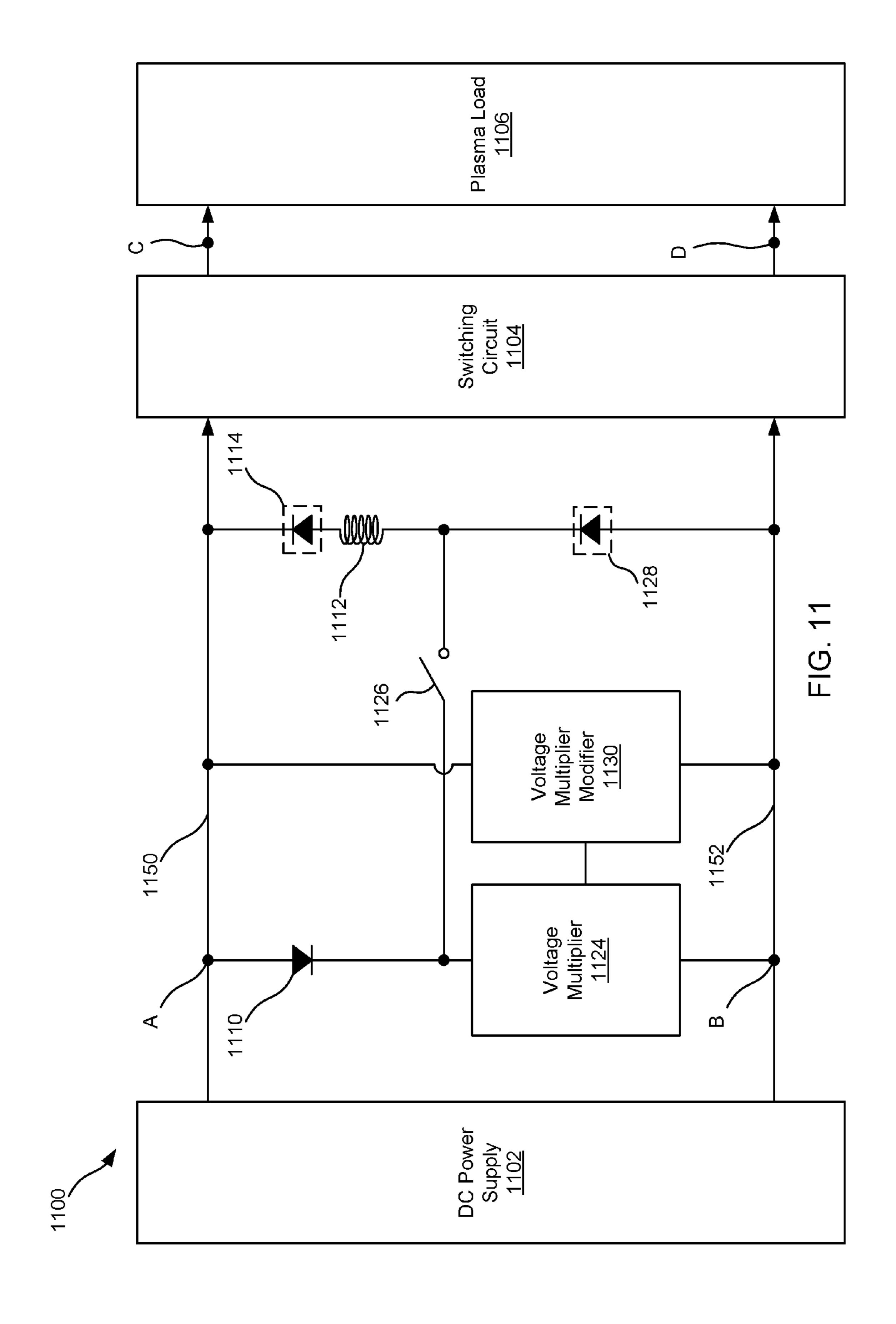

- FIG. 11 illustrates a power supply system including a DC 50 power supply, a switching circuit, a plasma load, yet another embodiment of a snubber circuit, and a voltage multiplier modifier;

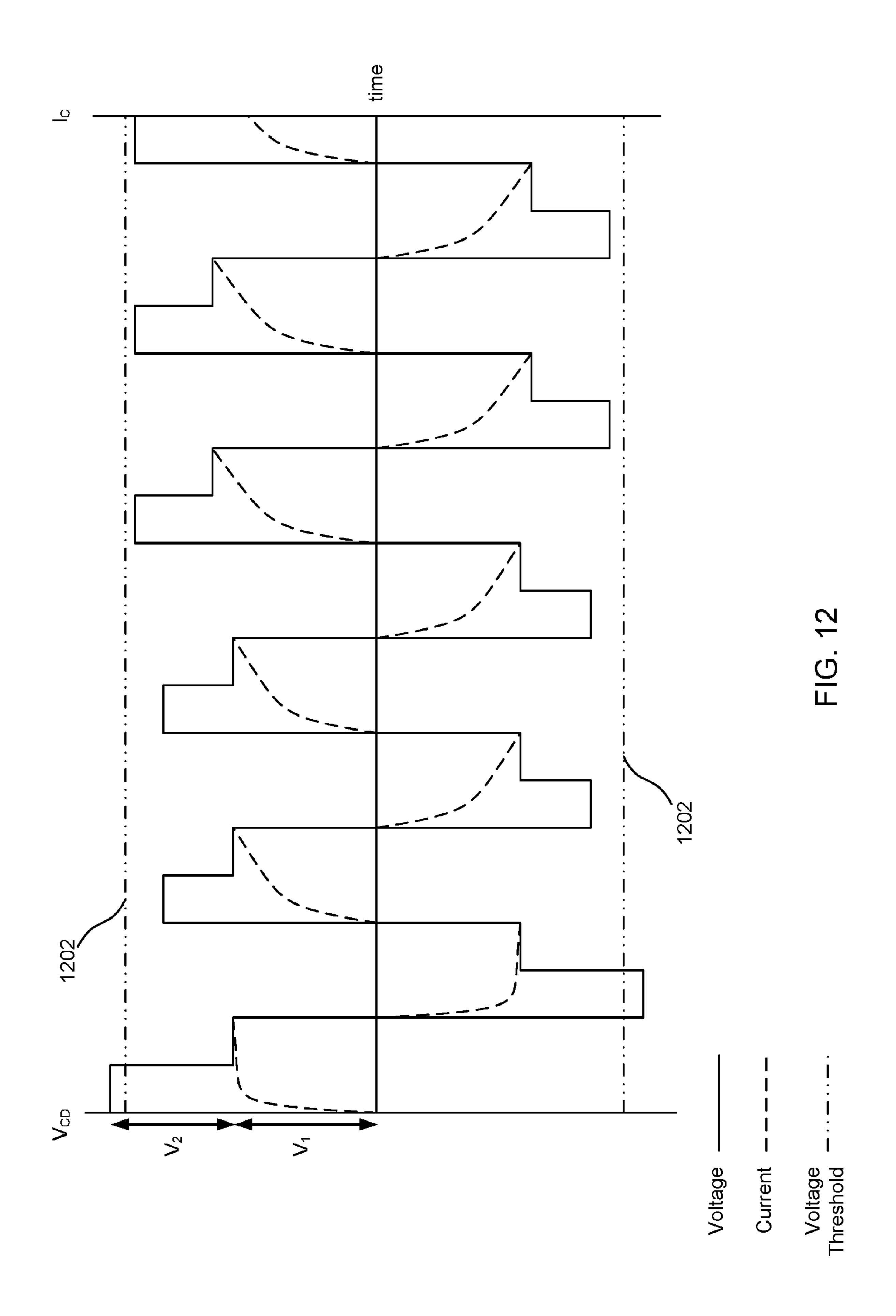

- FIG. 12 illustrates a plot of voltage and current for a power supply system according to one embodiment of this 55 disclosure;

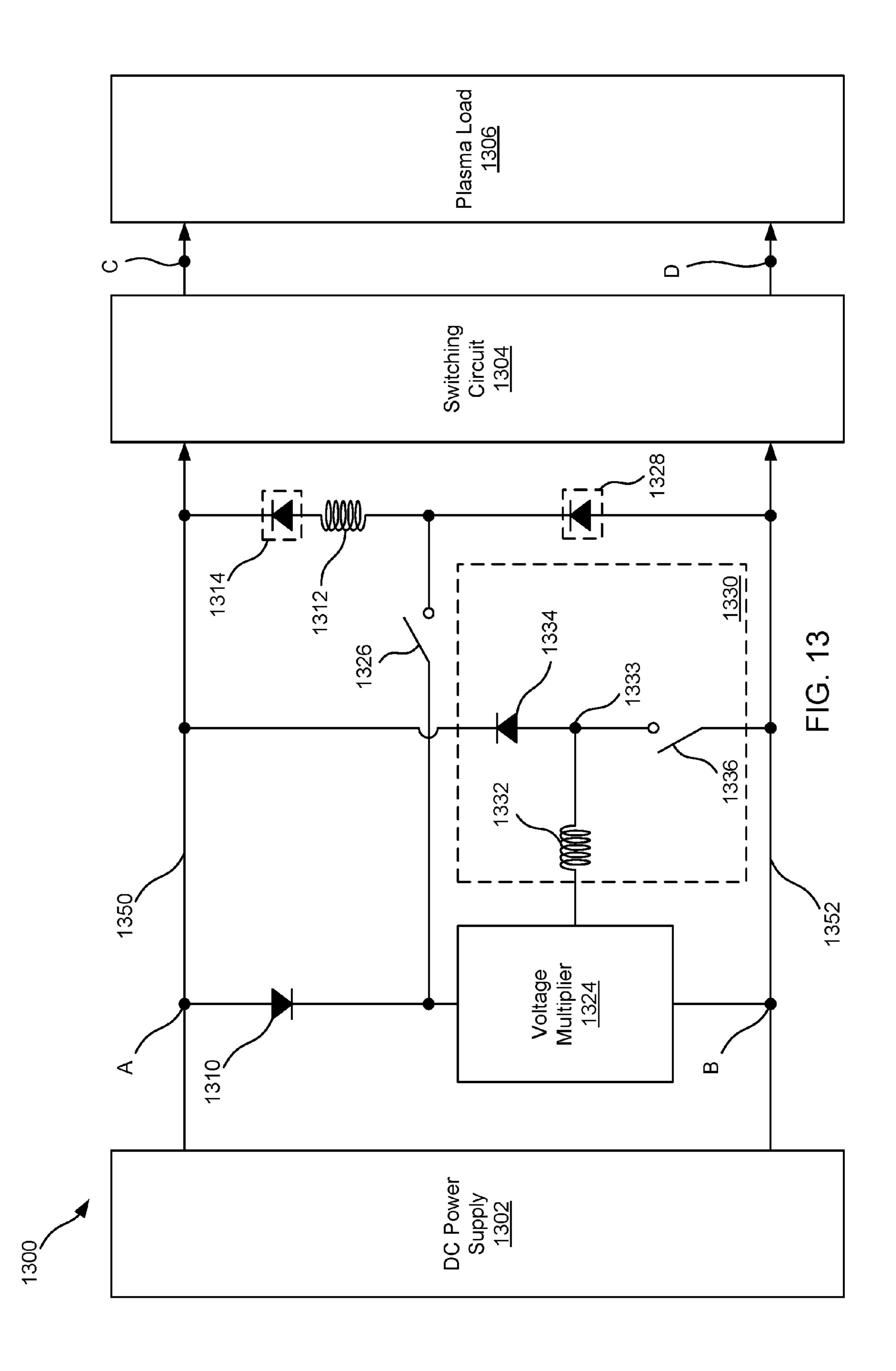

- FIG. 13 illustrates a power supply system showing details of one embodiment of a voltage multiplier modifier;

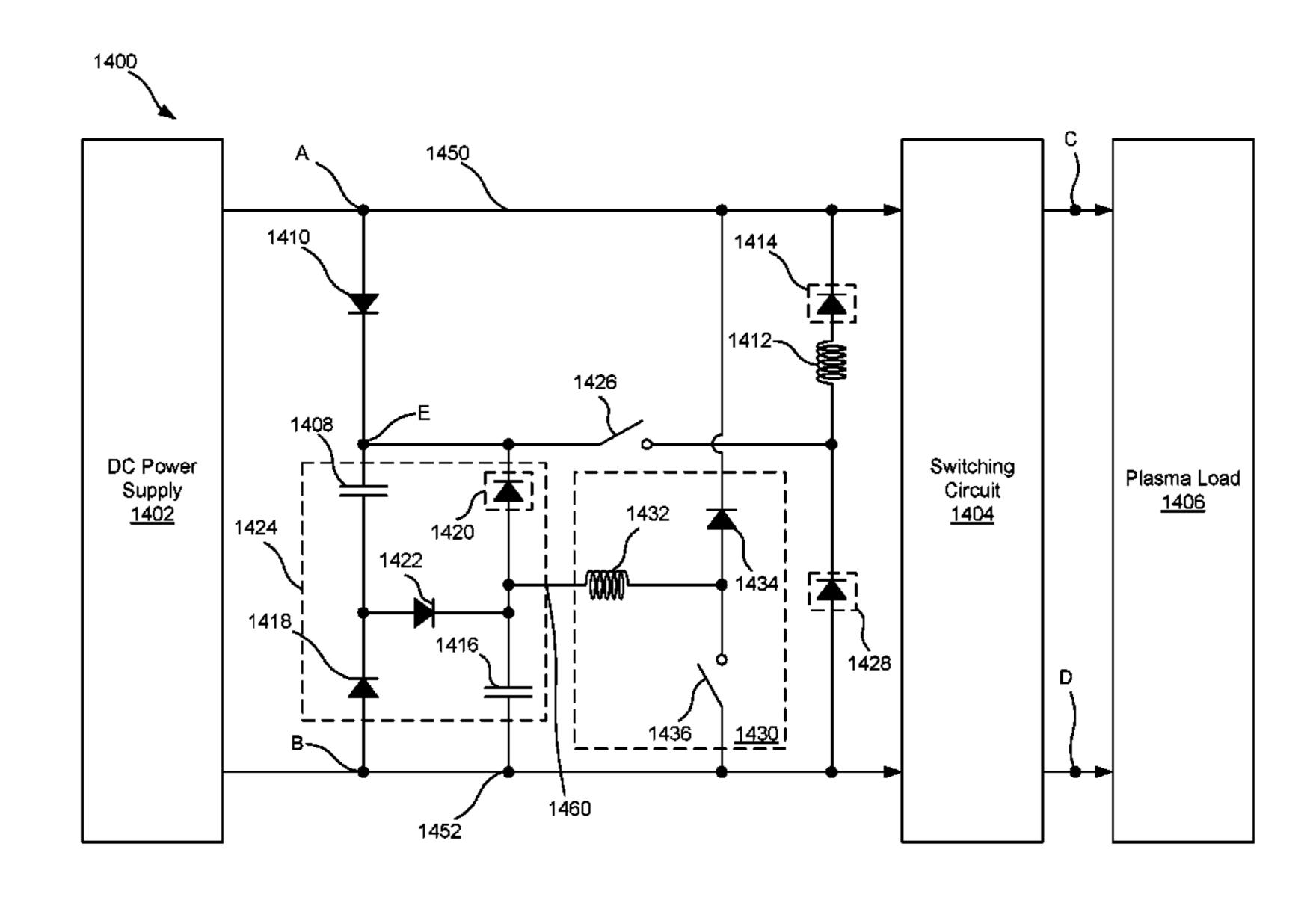

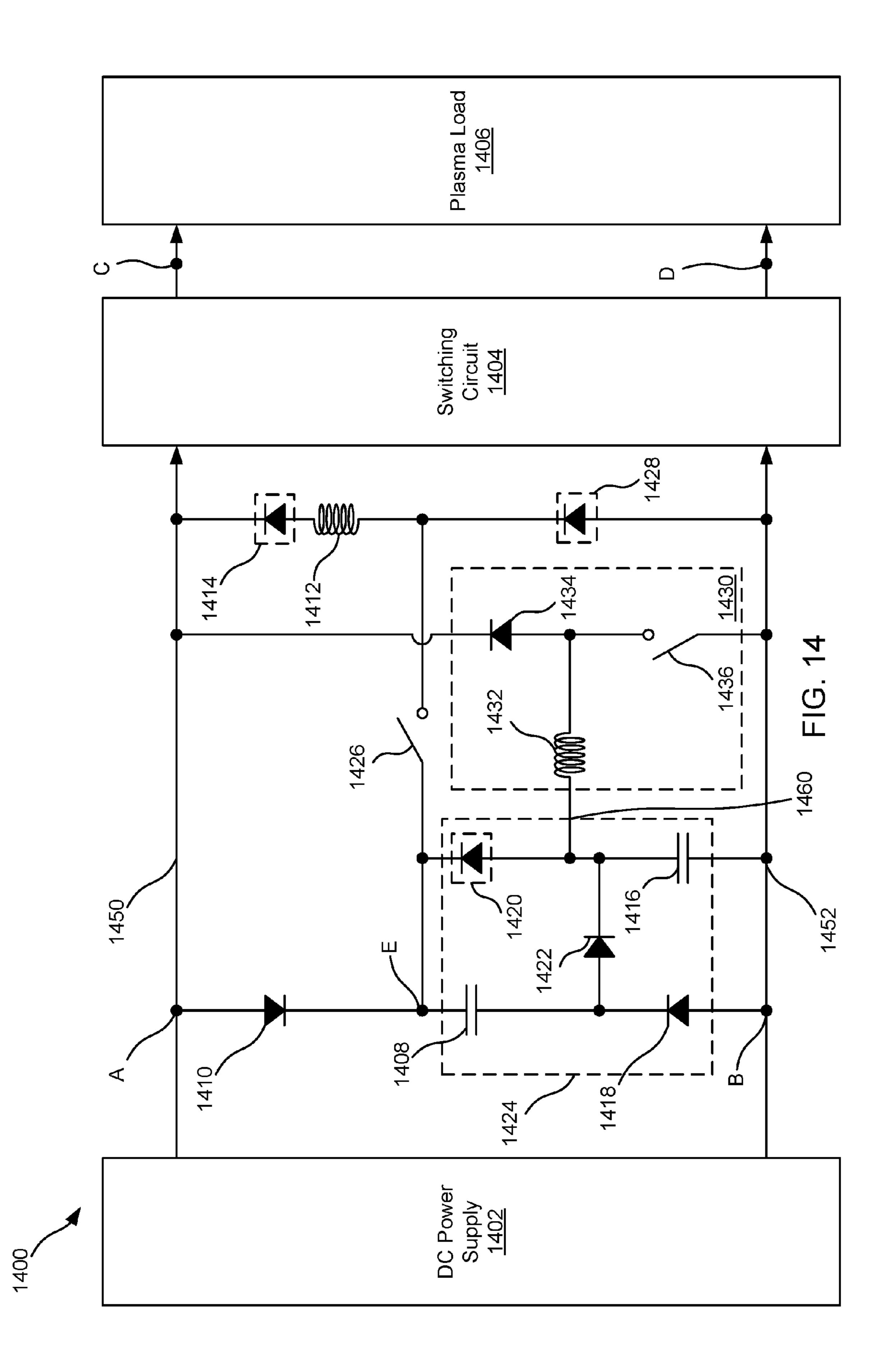

- FIG. 14 illustrates a power supply system showing details of one embodiment of a voltage multiplier and of a voltage 60 multiplier modifier;

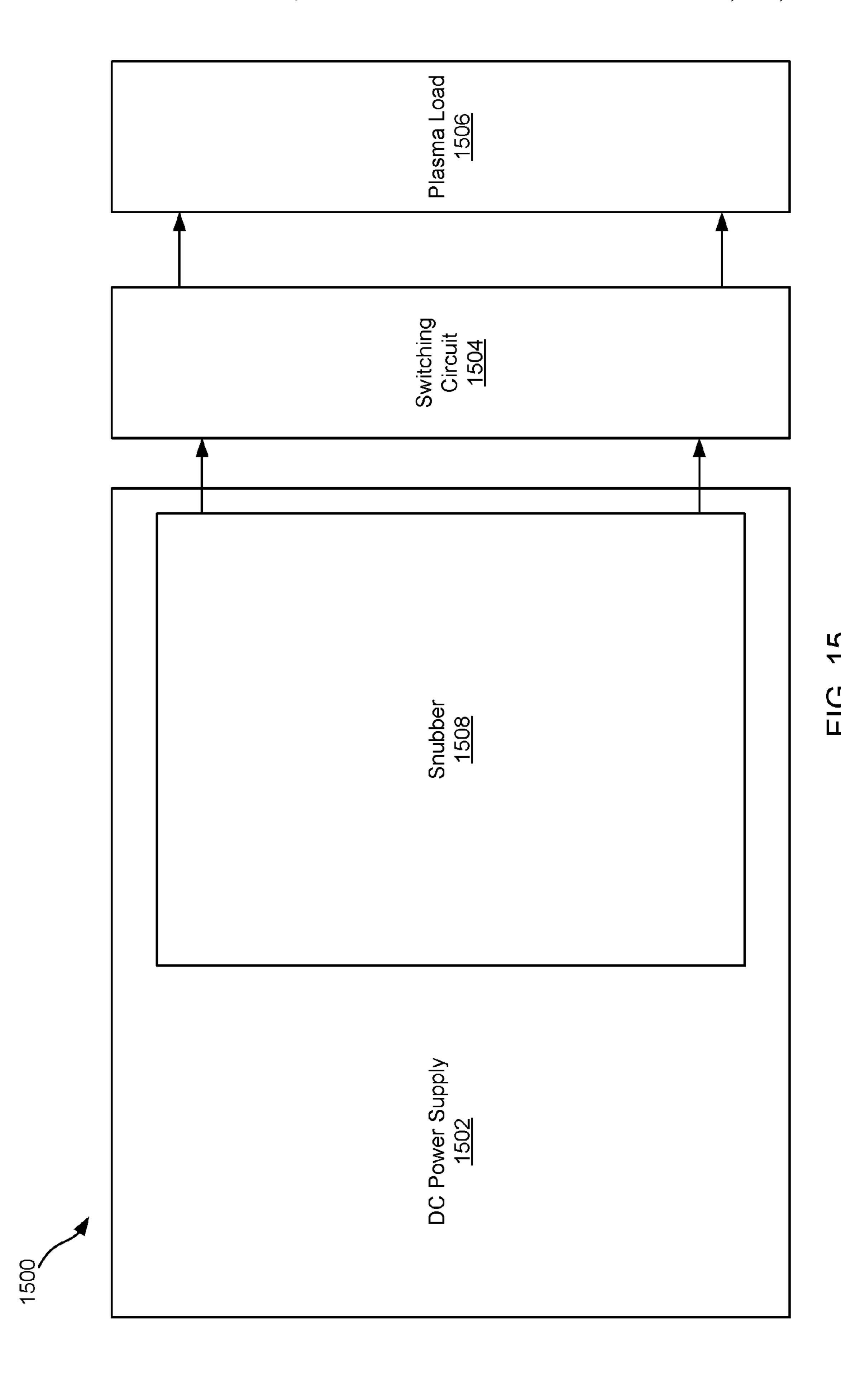

- FIG. 15 illustrates a power supply system including a DC power supply providing power to a switching circuit, which then provides pulsed DC power to a plasma load;

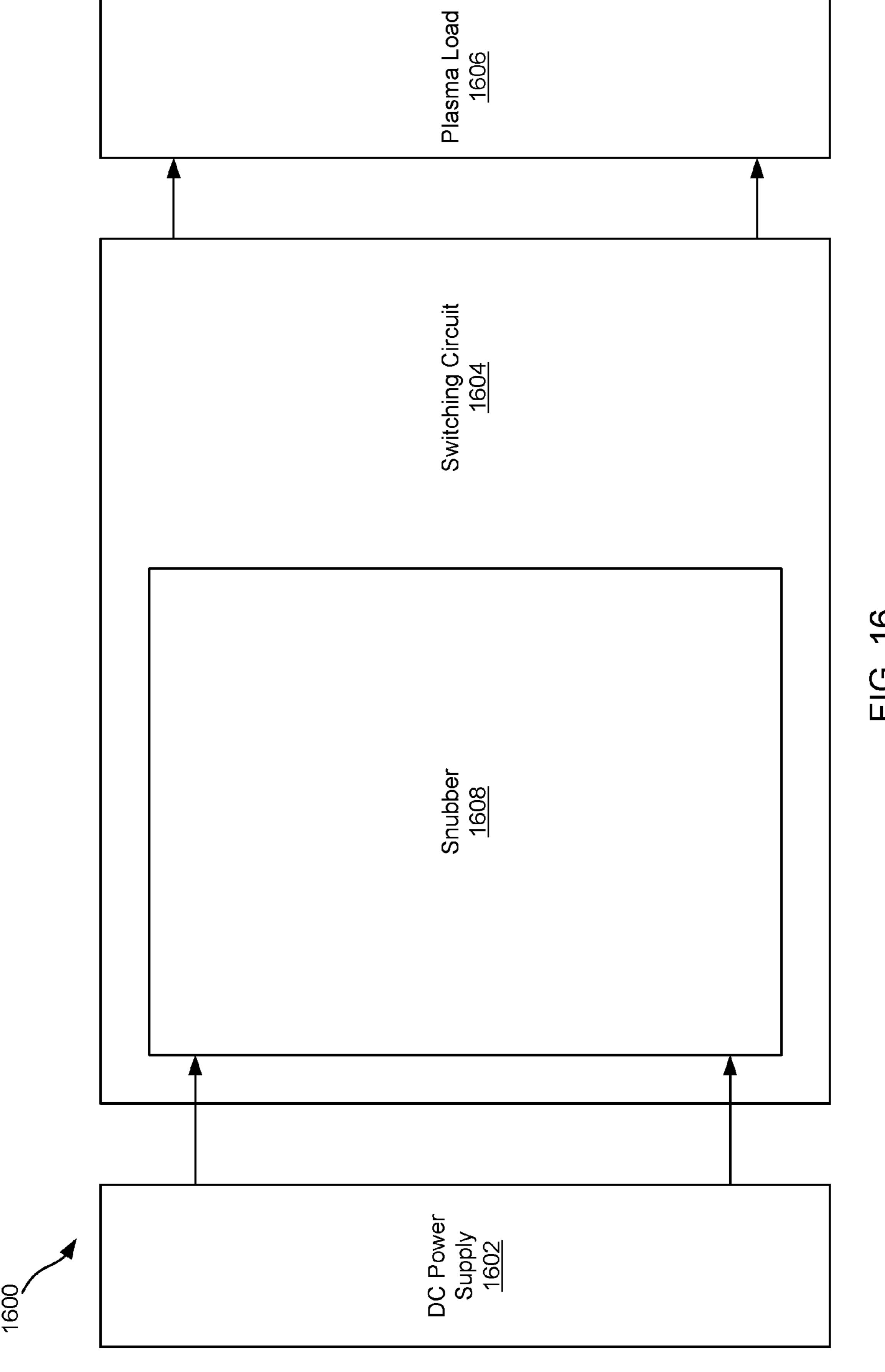

- FIG. 16 illustrates a power supply system including a DC 65 power supply providing power to a switching circuit, which then provides pulsed DC power to a plasma load;

4

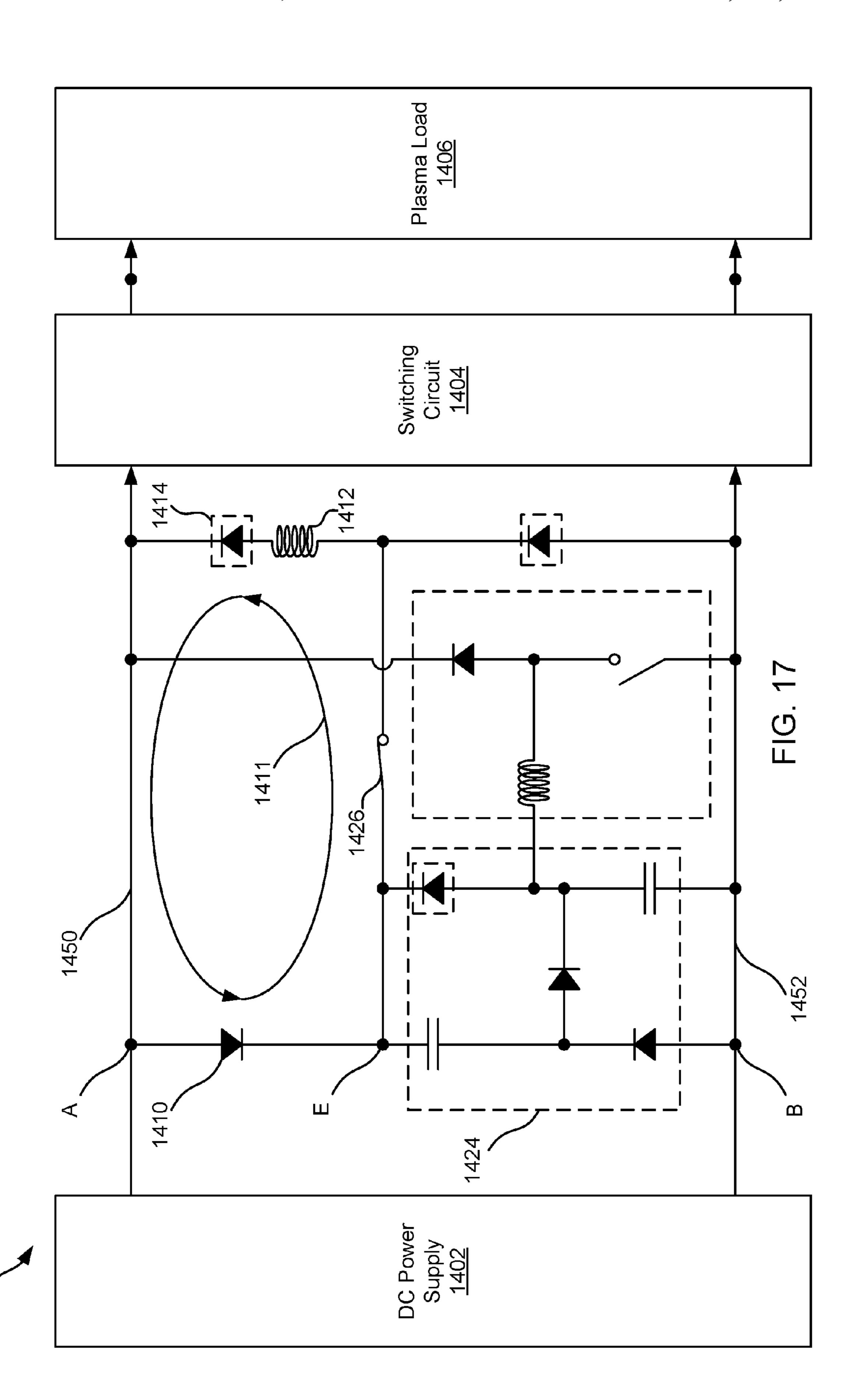

- FIG. 17 illustrates a power supply system including a DC power supply providing power to a switching circuit, which then provides pulsed DC power to a plasma load;

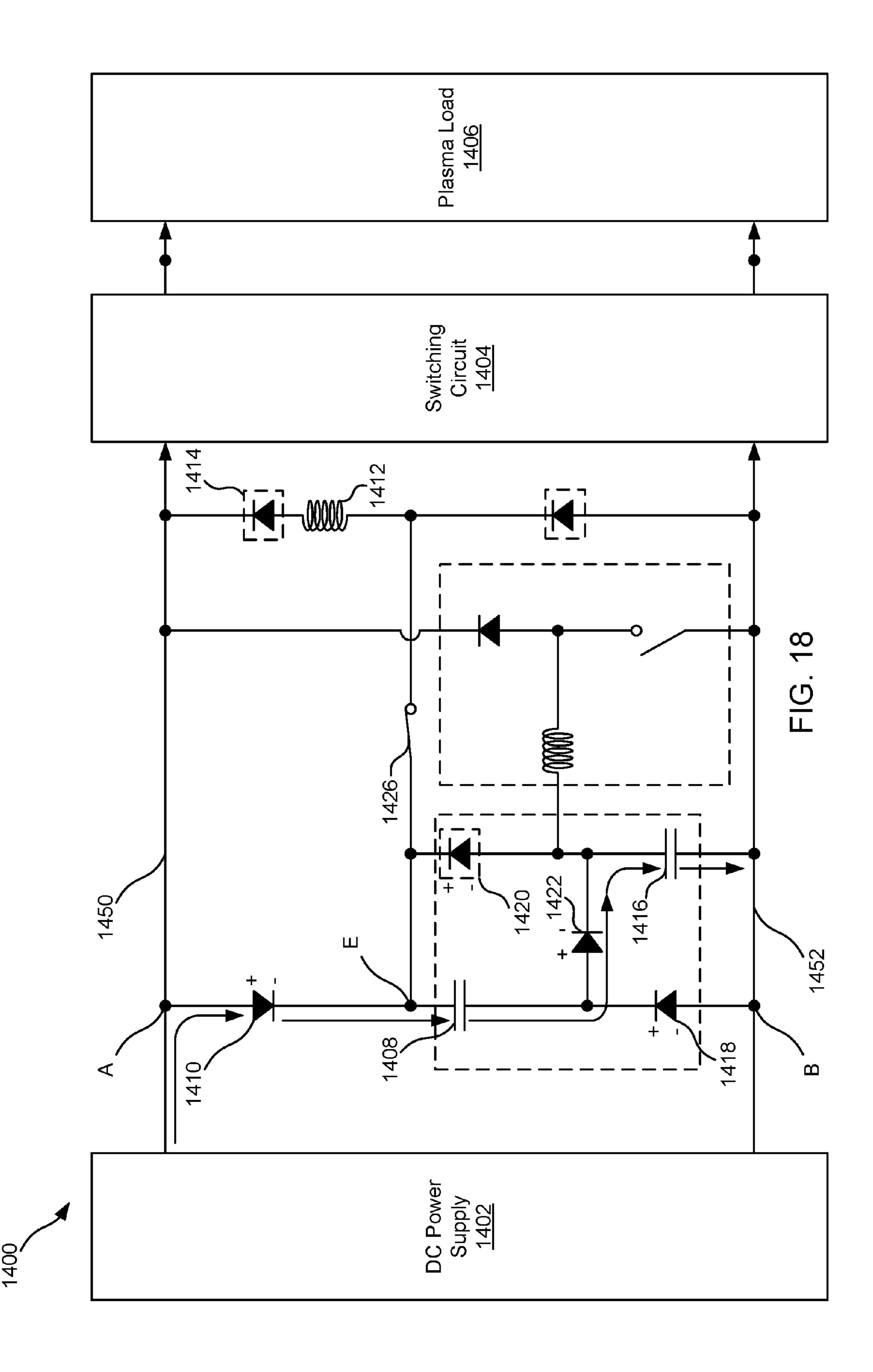

- FIG. 18 illustrates the power supply system of FIG. 14 just after a 0 V transition of the switching circuit;

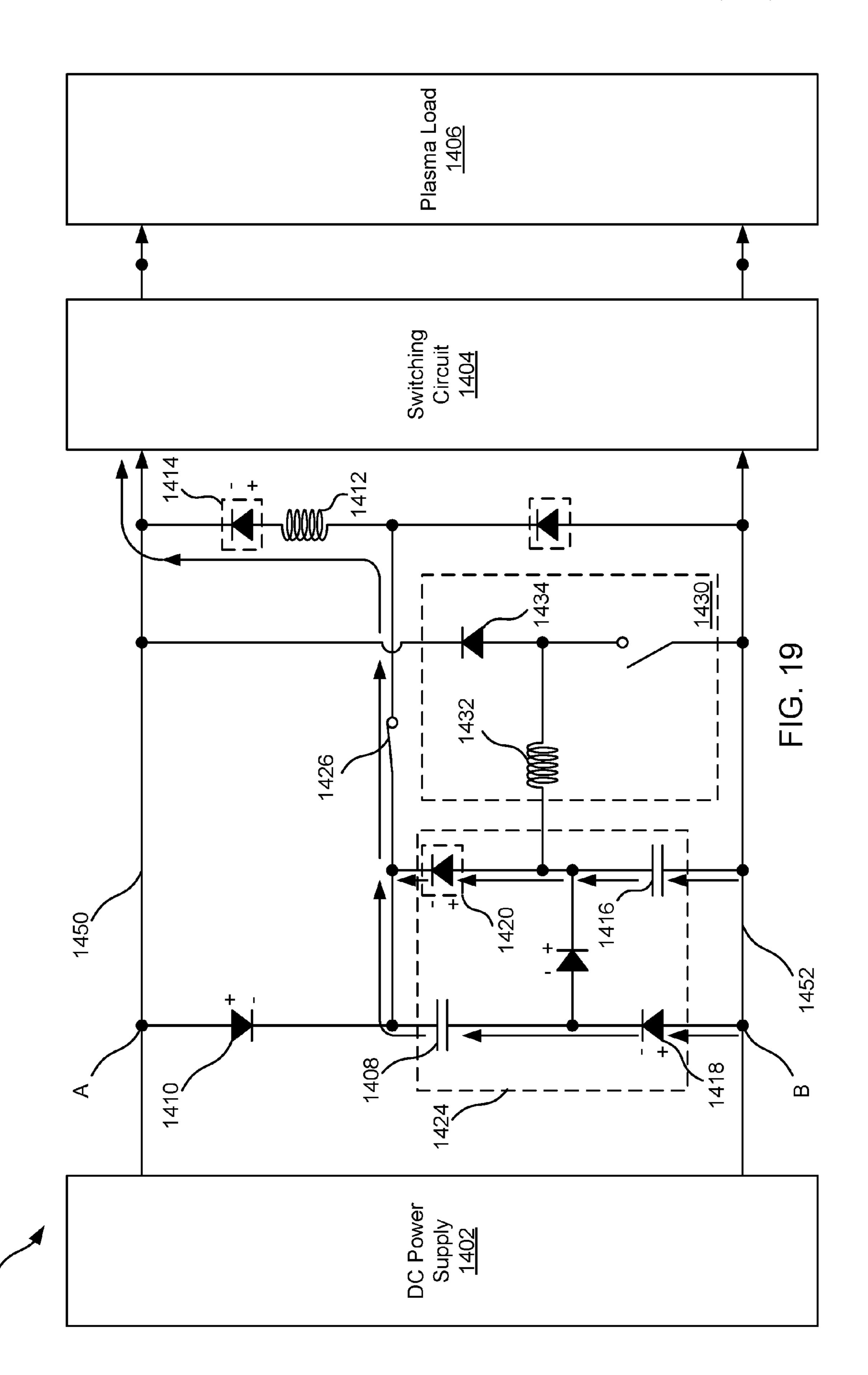

- FIG. 19 illustrates the power supply system of FIG. 14 during a falling edge of a voltage boost from the snubber;

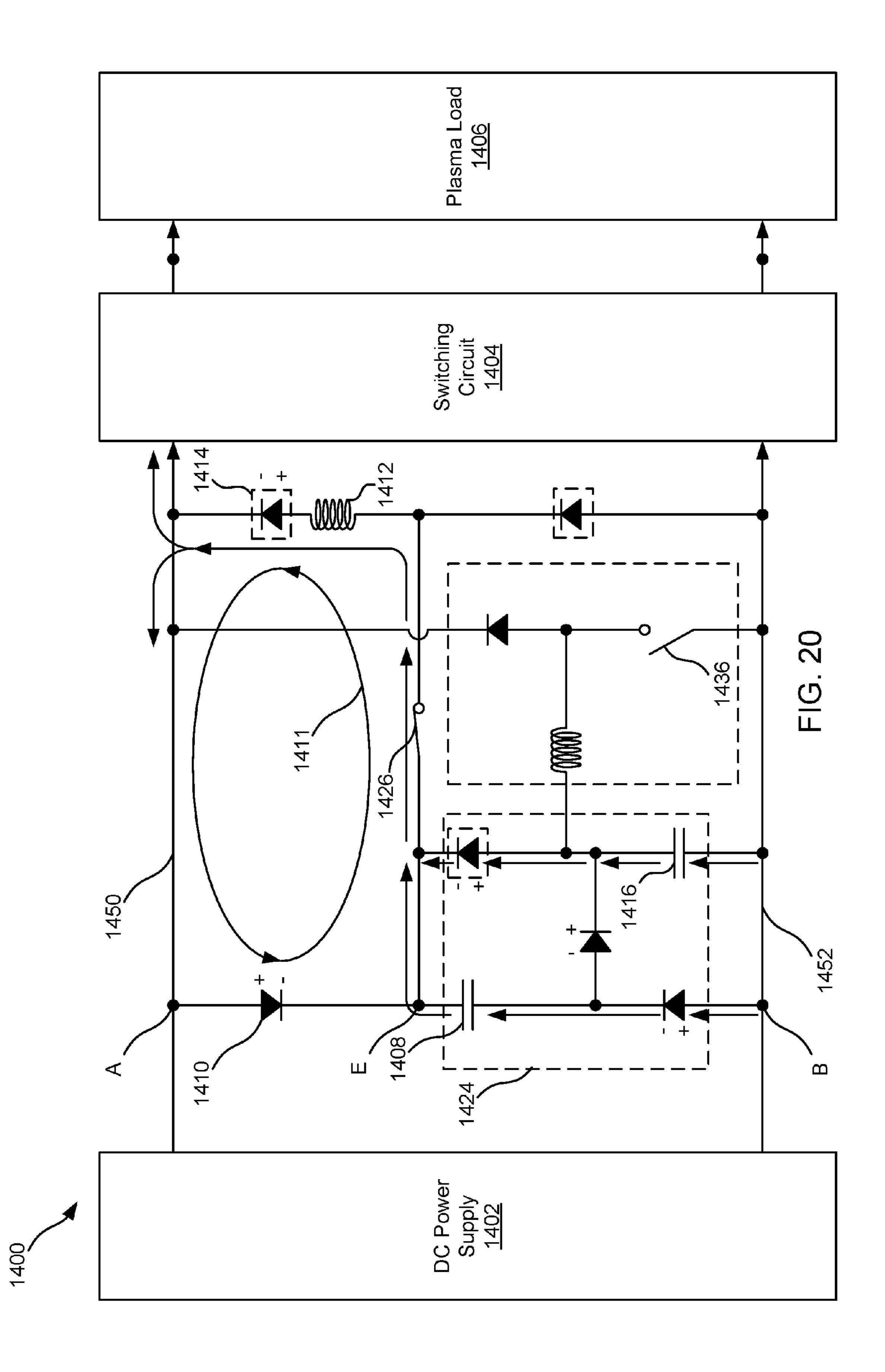

- FIG. 20 illustrates the current paths and diode biases in the power supply system of FIG. 14 during a single arc event;

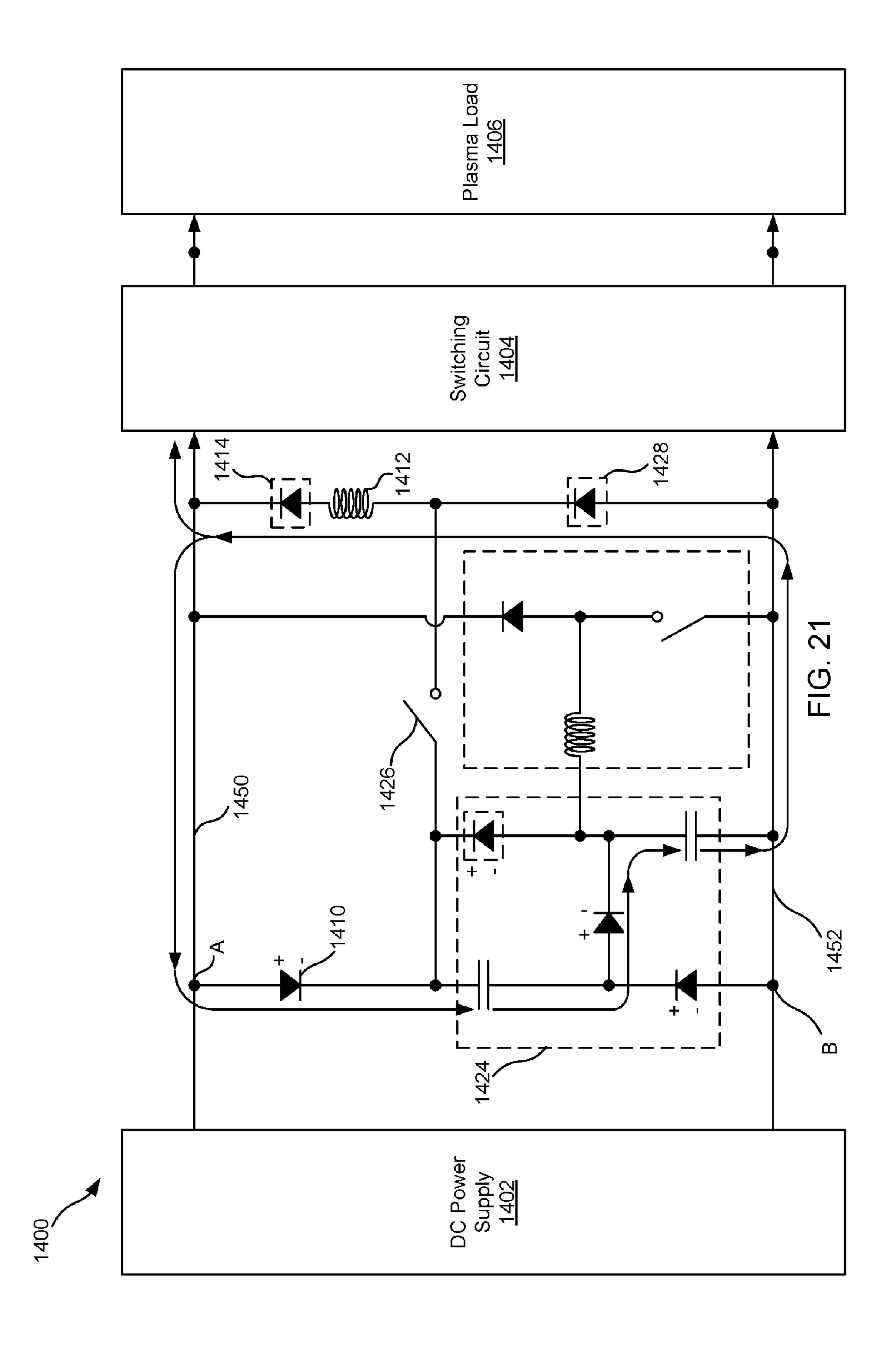

- FIG. 21 illustrates the current paths and diode biases in the power supply system of FIG. 14 during a succession of high-frequency arcs;

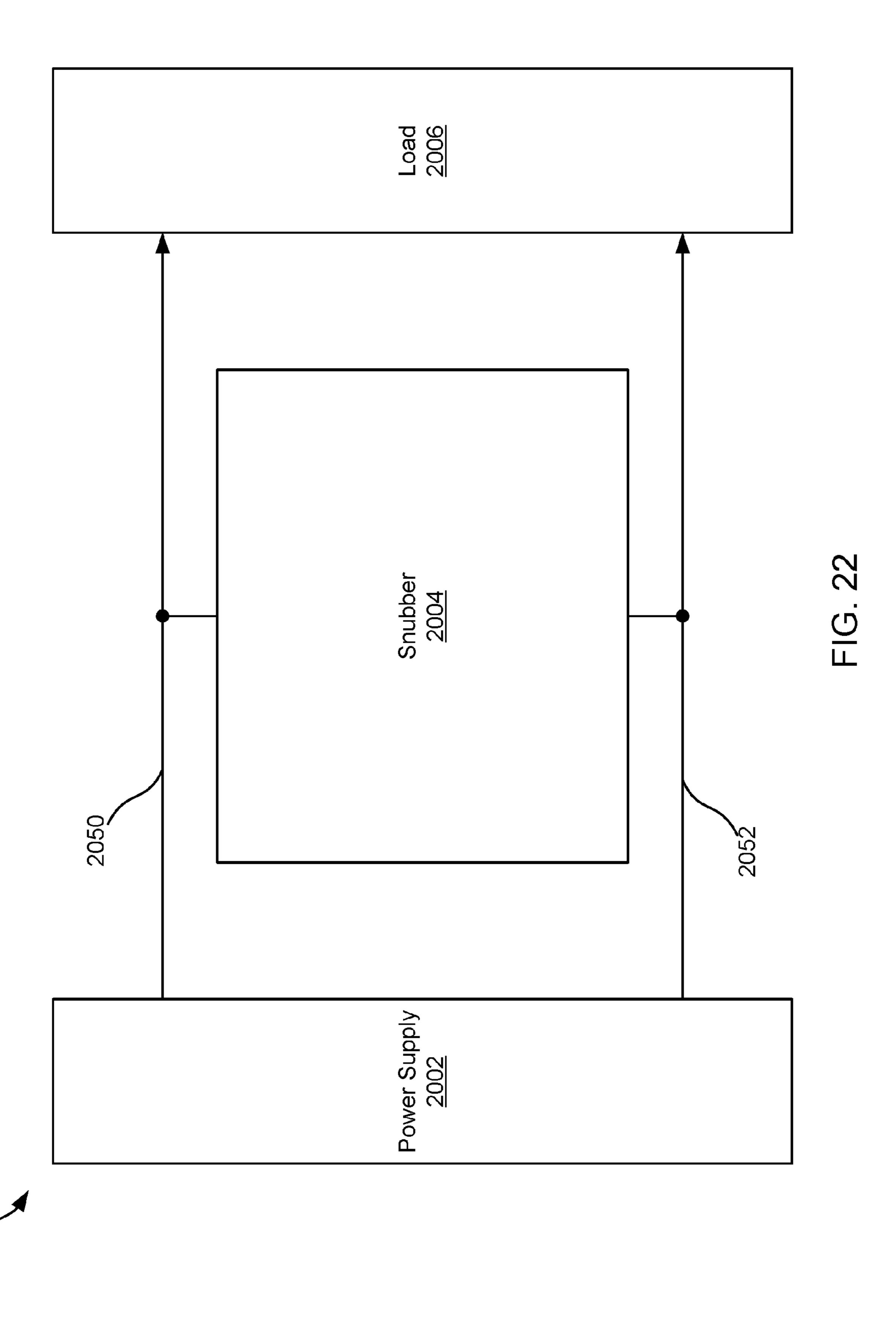

- FIG. **22** illustrates another embodiment of a power supply system;

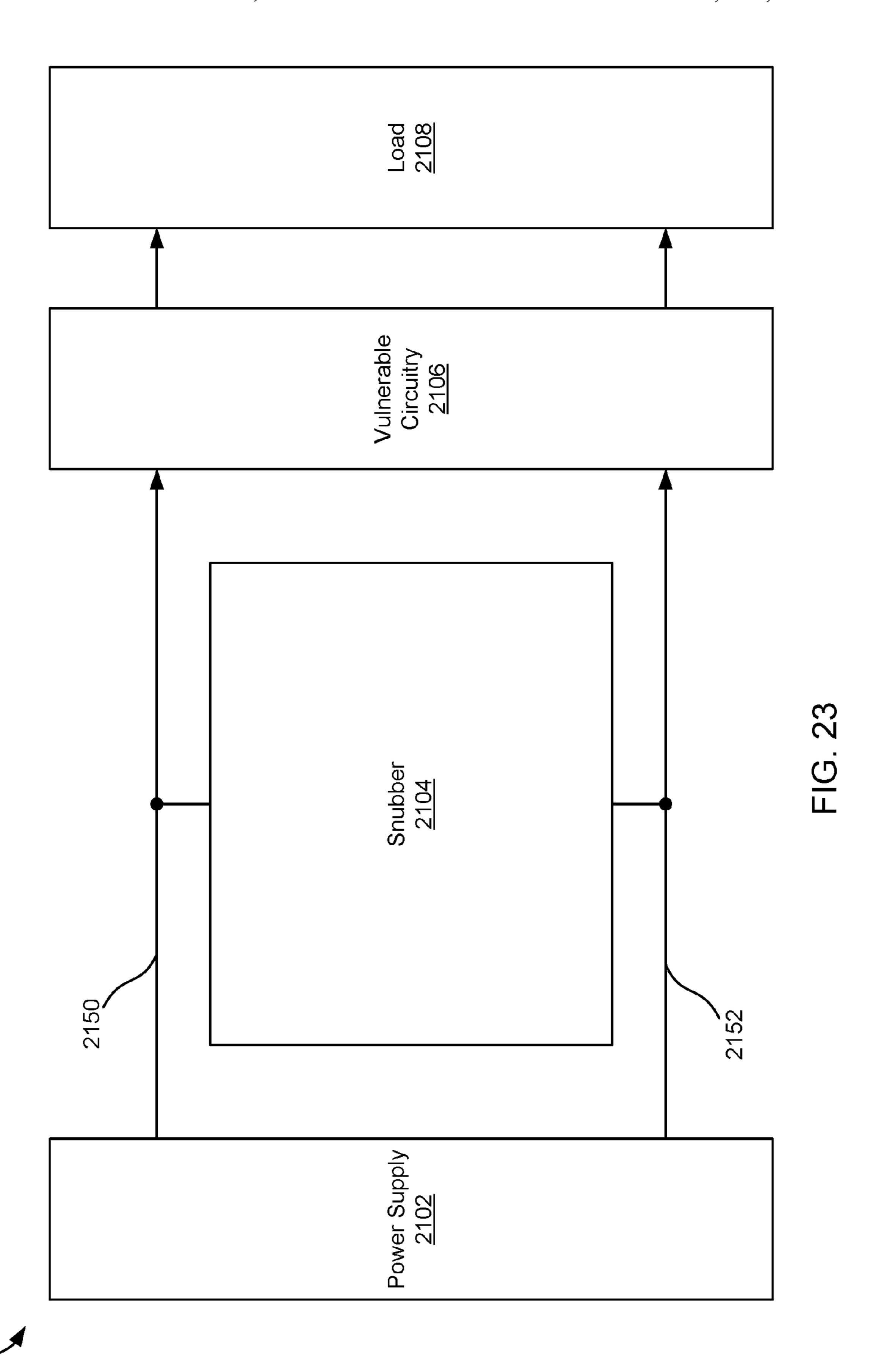

- FIG. 23 illustrates yet another power supply system;

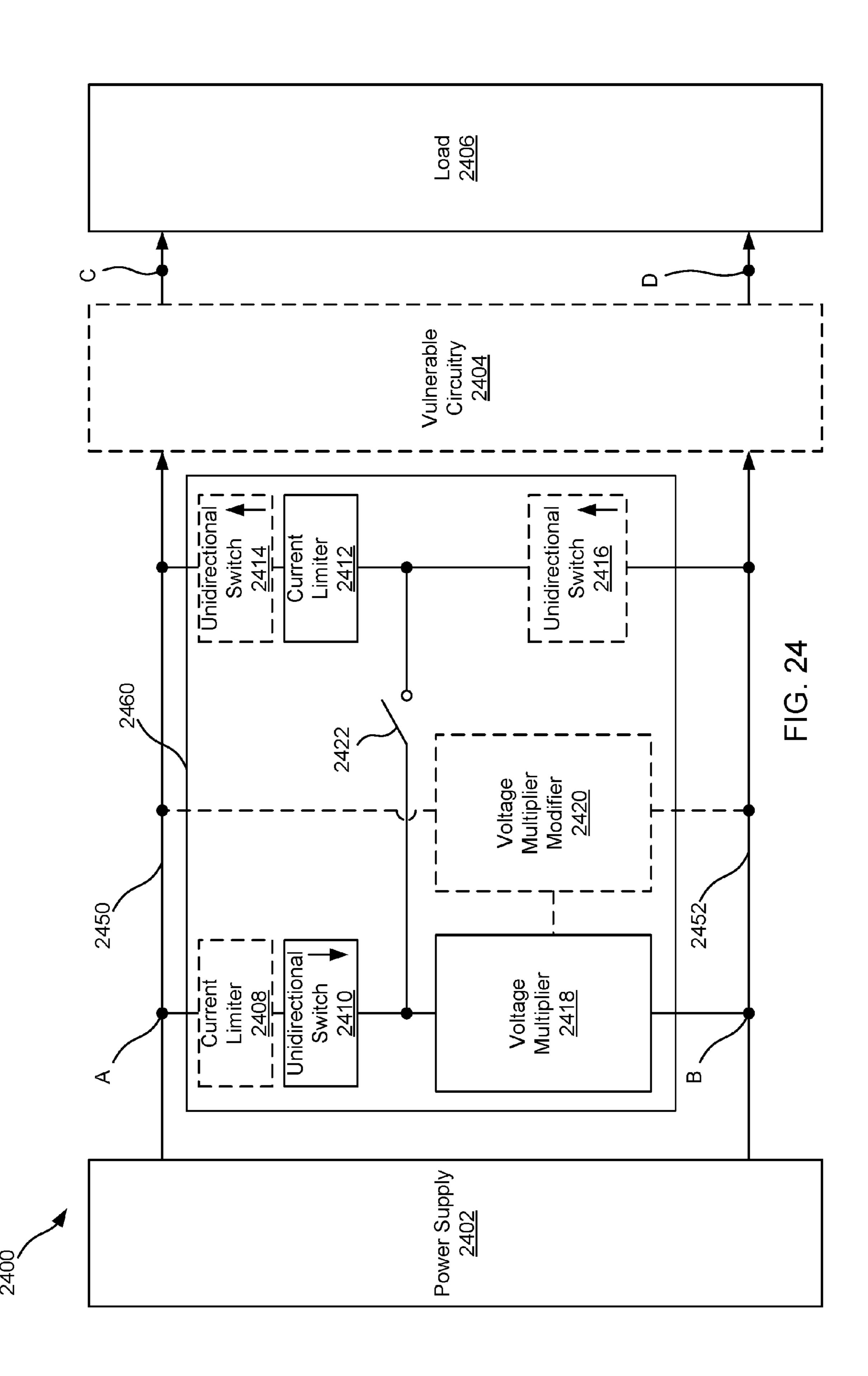

- FIG. 24 illustrates yet a further power supply system;

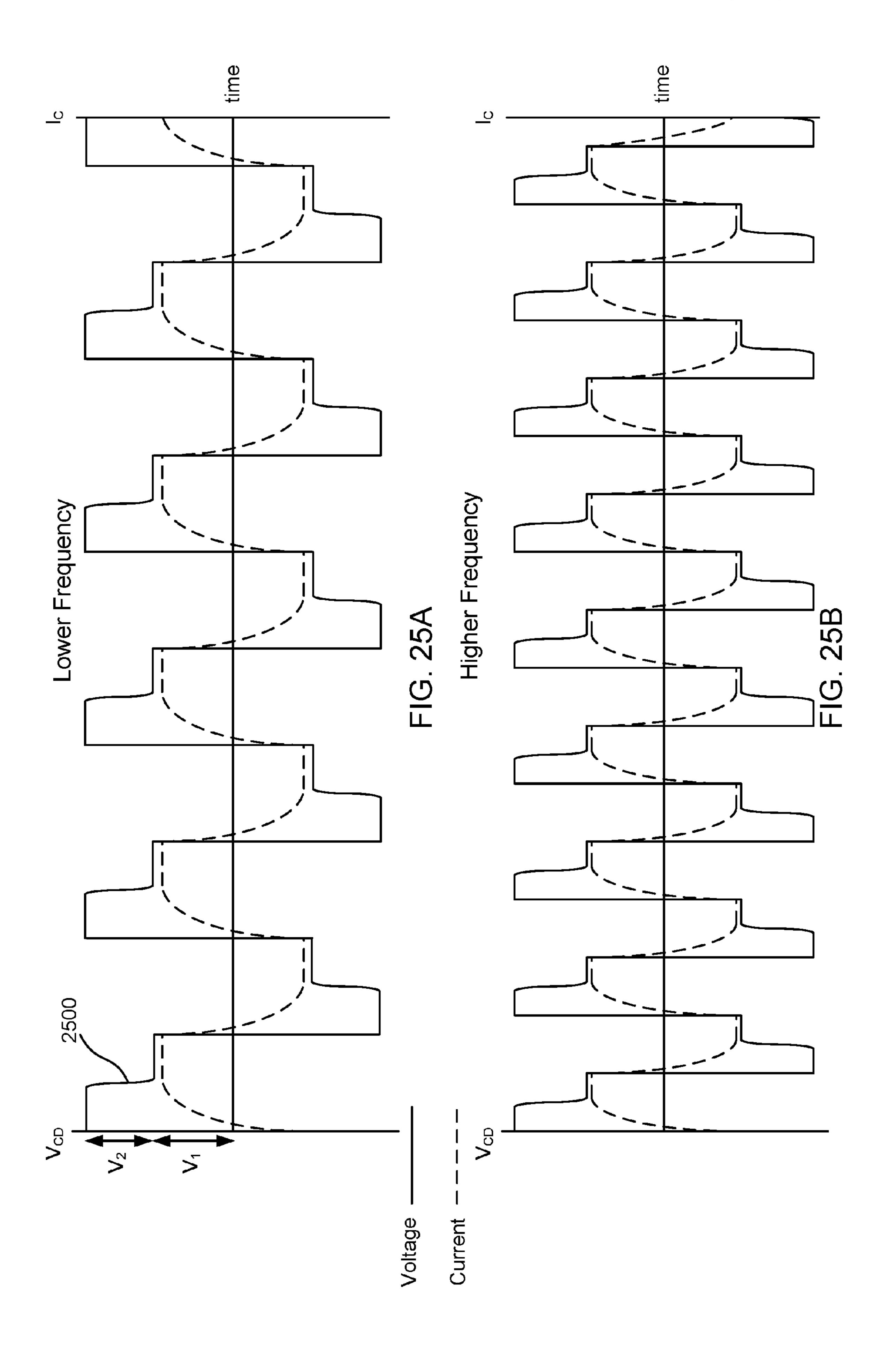

- FIGS. 25A and 25B illustrate plots of voltage and current for a power supply system according to one embodiment of this disclosure;

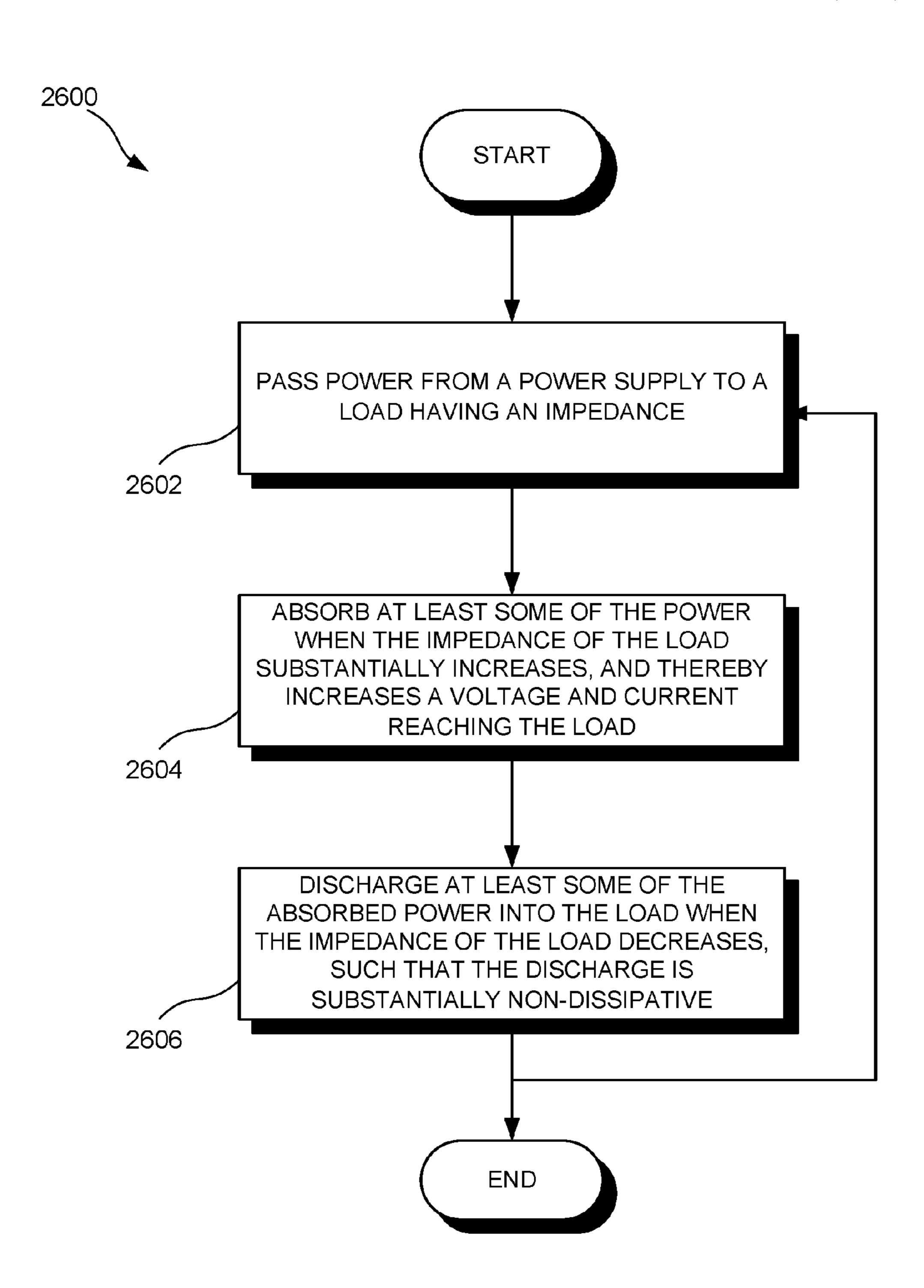

- FIG. 26 illustrates a method of controlling power in a power supply system; and

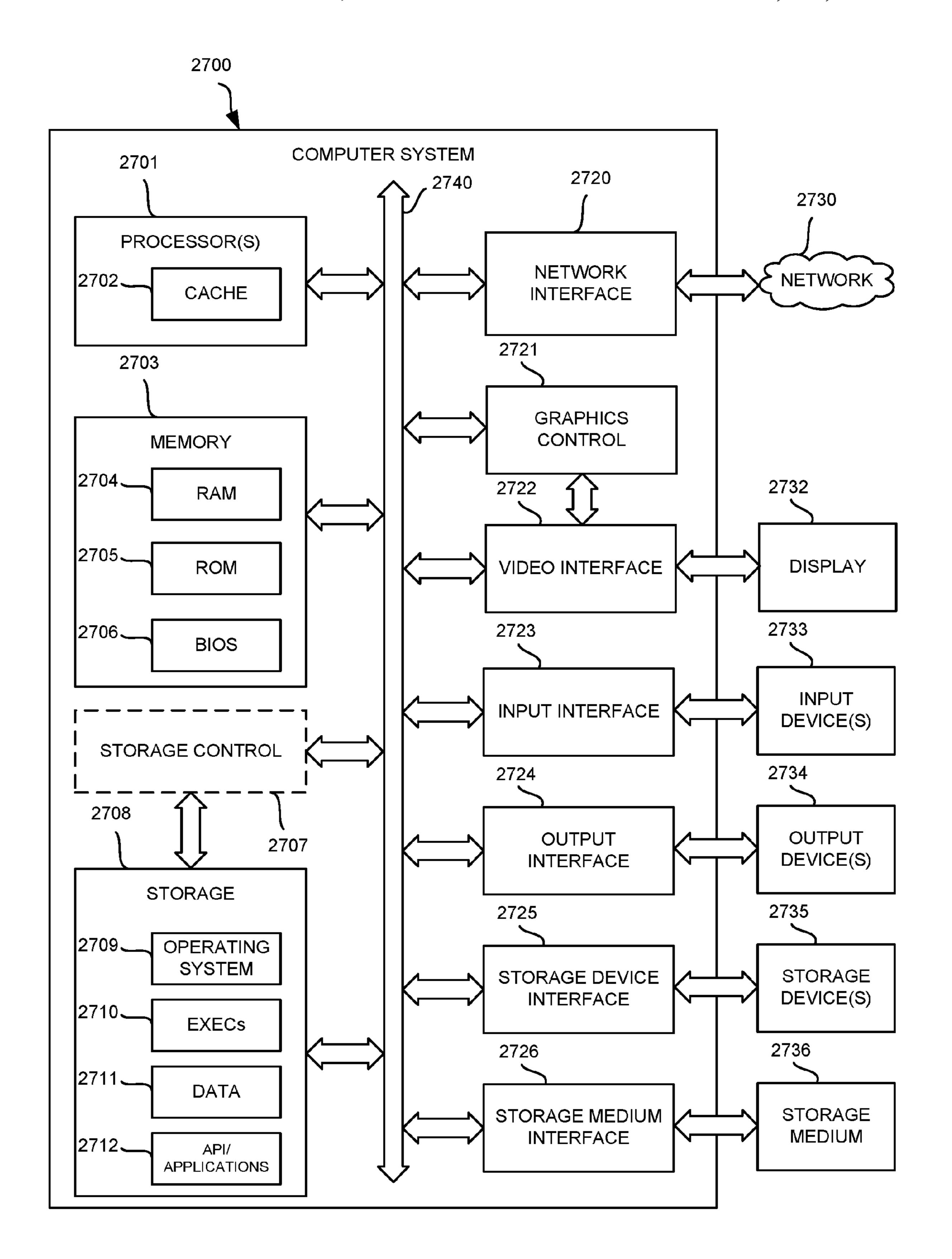

- FIG. 27 shows a diagrammatic representation of one embodiment of a machine in the exemplary form of a computer system;

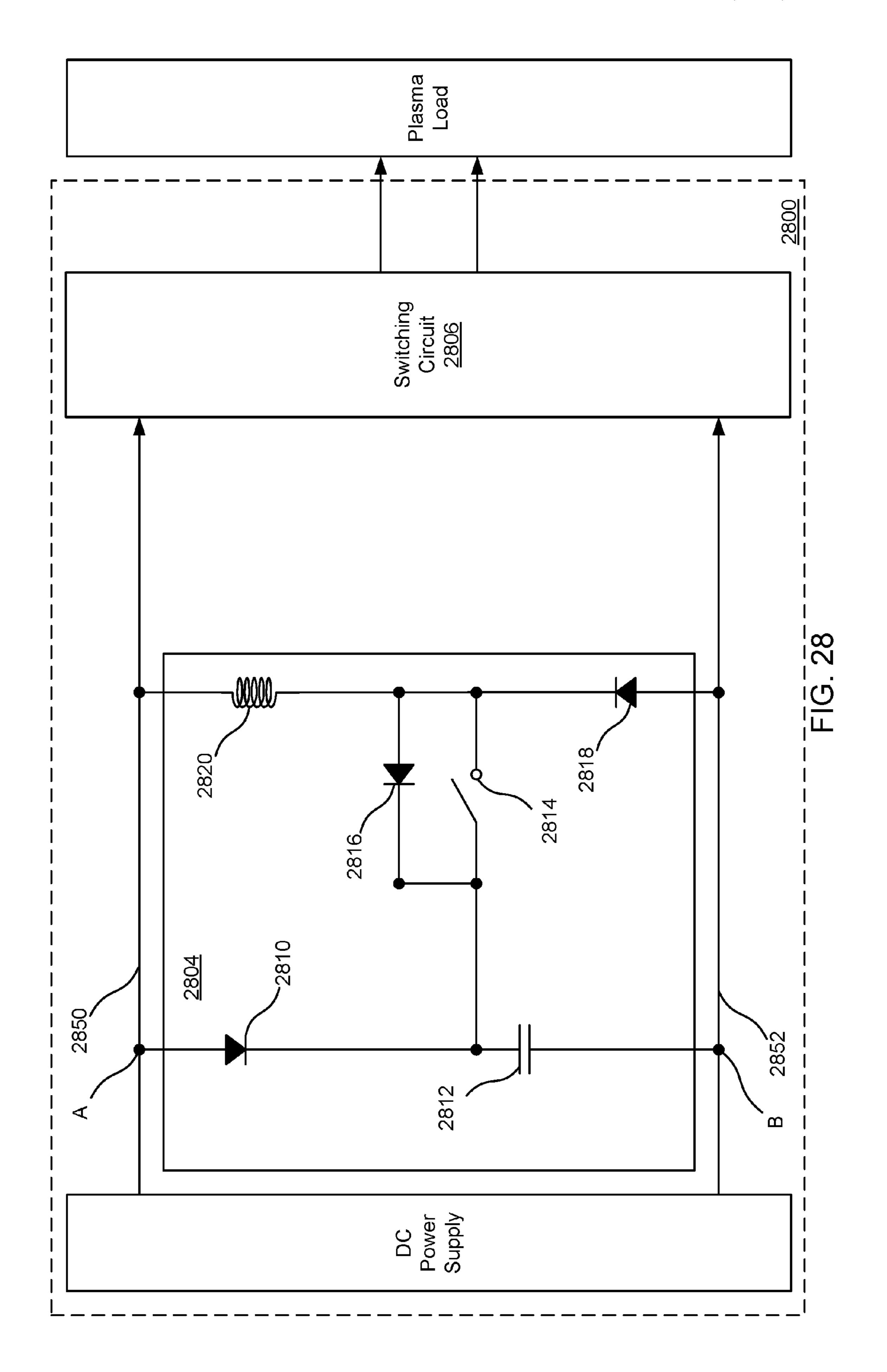

- FIG. 28 illustrates an alternative topology for a voltage-boosting circuit;

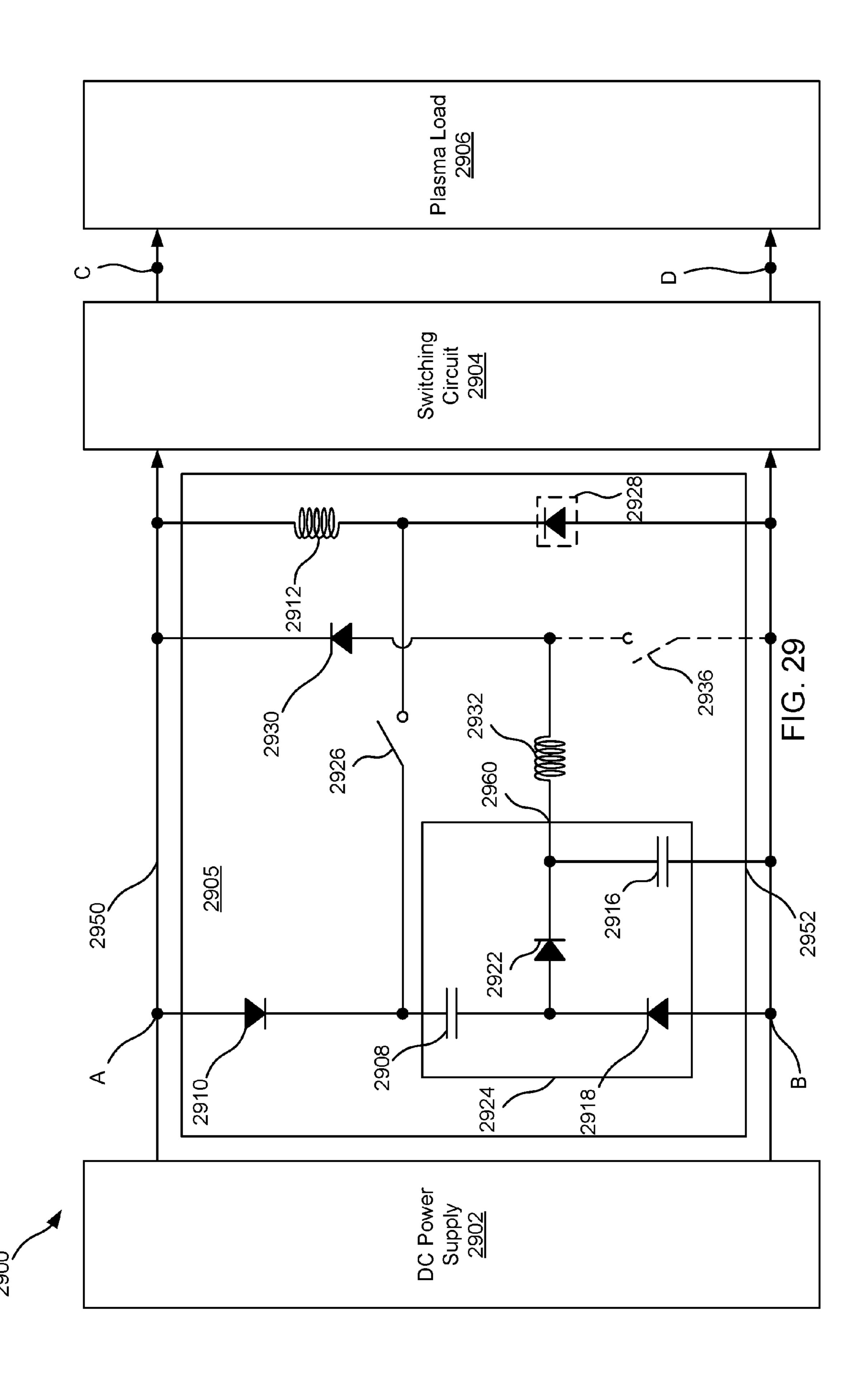

- FIG. **29** illustrates another embodiment of a voltage boosting circuit having snubber functionality; and

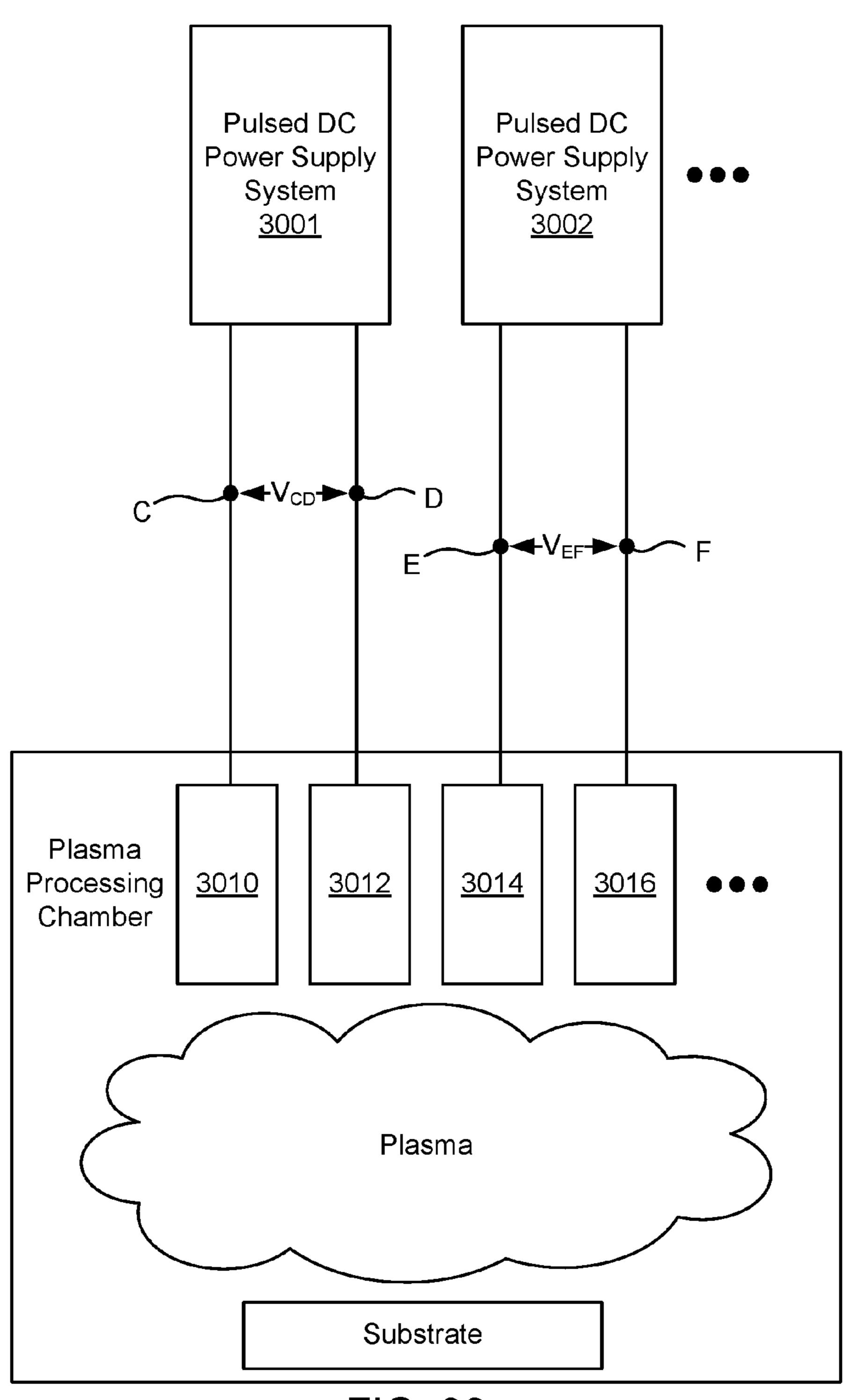

- FIG. 30 illustrates an embodiment of a power supply system including two or more pulsed DC power supply systems providing pulsed DC power to four or more anodeless electrodes in a plasma processing chamber.

### DETAILED DESCRIPTION

The present disclosure relates generally to power supply systems. More specifically, but without limitation, the present disclosure relates to a non-dissipative snubber for use in a power supply system.

The word "exemplary" is used herein to mean "serving as an example, instance, or illustration." Any embodiment described herein as "exemplary" is not necessarily to be construed as preferred or advantageous over other embodiments.

For the purposes of this disclosure, a current limiter is any device or circuit that limits a current that can pass through the current limiter or that limits a rate at which current passing through the current limiter can rise or fall. In some embodiments, a current limiter can limit both the rate of increase and an upper bound of the current passing through the current limiter. An inductor, resistor, JFET, MOSFET, and IGBT are all examples of current-limiting elements since each are able to limit the rate of change of and amount of current.

For the purposes of this disclosure, a switch includes any circuit or device that stops the passage of current when in an off or open state. For instance, transistors (e.g., MOSFET, BJT, IGBT) can be a switch, and in some cases, where a current limiter is operated so as to reduce current to 0 A, a current limiter can be a switch.

For the purposes of this disclosure, a unidirectional switch includes any device or circuit that only passes current in a single direction. For instance, both a diode and a transistor can be considered a unidirectional switch, depending on operation.

The challenges noted in the background can be dealt with via use of a non-dissipative snubber **2460** as illustrated in FIG. 24, comprising a first unidirectional switch 2410, a voltage multiplier **2418**, and a first current limiter **2412**. The snubber 2460 can be arranged between a first power rail 5 2450 and a second power rail 2452, wherein the power rails 2450 and 2452 transfer power from a power supply 2402 to a load 2406 (e.g., a plasma of a plasma processing chamber), and optionally transfer said power through vulnerable circuitry 2404 (e.g., a switching circuit). The first unidirec- 10 tional switch **2410** can be arranged between a first power rail 2450 and the voltage multiplier 2418 and allows current to pass from the first power rail 2450 to the voltage multiplier 2418 (optionally through a current limiter 2408), but prevents current from traveling a reverse path through the 15 unidirectional switch 2410. The first current limiter 2412 can couple the voltage multiplier 2418 to the first power rail 2450 in parallel to the unidirectional switch 2410 and provides a low-loss current path from the voltage multiplier 2418 to the first power rail 2450. The snubber 2460 may 20 further include a switch **2422** between the voltage multiplier 2418 and the first current limiter 2412, wherein the switch 2422 remains closed during most operations, but is opened when a current in the current limiter **2412** reaches a threshold, and then closes when the current in the current limiter 25 **2412** falls below the threshold.

One advantage of the snubber 2460 is its ability to non-dissipatively absorb energy from the power supply 2402 when an impedance of the load 2406 increases, or substantially increases. For instance, where the load 2406 is a 30 plasma, and the plasma dims or is extinguished, the plasma impedance increases substantially. When the load 2406 impedance increases substantially, the power supply 2402 continues to deliver the same power, and this power would dissipate largely in the vulnerable circuitry 2404. However, 35 the snubber 2460, and in particular, the voltage multiplier 2418, absorbs a large portion of this energy, thus protecting the vulnerable circuitry 2404.

Another advantage of the snubber 2460 is to avoid rapid discharges of the stored energy in the voltage multiplier 40 2418 when the load 2406 impedance suddenly drops. For instance, where the load 2406 is a plasma, and an arc in the plasma occurs, the arc creates a low impedance current path for the energy in the voltage multiplier 2418. However, the current limiter 2412 prevents rapid discharge of the voltage 45 multiplier 2418. In the case of plasma arcs, this aspect helps prevent the snubber 2460 from exacerbating arcs.

A third advantage of the snubber 2460 is an ability to boost a voltage that the power supply 2402 provides to the load 2406, and consequently boosts a current ramp rate 50 provided to the load 2406. When the voltage multiplier 2418 absorbs energy from the power supply 2402, a voltage across the voltage multiplier 2418 can be raised to some multiple of a voltage between nodes A and B,  $V_{AB}$ , generated by the power supply **2402**. In this way, the voltage multiplier 55 2418 can boost a voltage, and thus a current ramp rate, provided to the load 2406 after the load 2406 impedance rises. Where there is a desire to control or limit the multiplying effect of the voltage multiplier **2418**, (e.g., where one or more devices have a voltage threshold that can be 60 exceeded if the voltage multiplier's full effect is enabled) an optional voltage multiplier modifier 2420 may be utilized (see FIGS. 11-14). The voltage multiplier modifier acts as a 'control knob' over the voltage boost provided by the voltage multiplier **2418**.

The power supply 2402 can be embodied by a current source or other current-regulating power supply. In one

6

embodiment, the power supply 2402 can be any power supply having an output current that is limited to slow changes in current. For instance, the power supply 2402 can be any power supply having an inductive output behavior. The power supply 2402 may be able to raise its compliance voltage, and hence the voltage  $V_{AB}$ . The ability to raise the compliance voltage, and hence,  $V_{AB}$ , can further enable turn-on of the unidirectional switch 2410.

The snubber **2460** has particular application to pulsed DC power systems providing pulsed DC power to a plasma load during plasma processing. For instance, and as illustrated in FIG. 7, a non-dissipative snubber can be arranged between a DC power supply 702 (e.g., power supply 2402) and a switching circuit 704 (e.g., vulnerable circuitry 2404) providing pulsed DC voltage to a plasma load 706 (e.g., load 2406). In this application, the non-dissipative snubber absorbs power from the DC power supply 702 when the plasma load 706 impedance rises such that power would otherwise damage the switching circuit 704 (e.g., immediately after the switching circuit voltage transitions through 0 V), avoids excessive current discharge during arc events in the plasma, and increases a ramp rate of current provided to the plasma load 706 during each voltage pulse. These advantages can be especially beneficial for high frequency pulsing and high power applications.

The non-dissipative snubber includes a voltage multiplier 724 that temporarily boosts a voltage  $V_{AB}$  and thus a current provided to the switching circuit 704 in order to increase an average power delivered to the plasma load 706, thereby increasing throughput, and decreasing losses from excessive currents. The non-dissipative snubber can also include an inductor 712 to prevent the voltage multiplier 724 from rapidly discharging stored energy into the switching circuit 704 and the plasma load 706 when the plasma load 706 drops (e.g., during an arc). The snubber circuit may further include a switch 726 between the voltage multiplier 724 and the inductor 712 to help stop runaway current ramping in the inductor 712 caused by high-frequency multiple arc events in the plasma (e.g., rapid succession of arcs). Various diodes 710, 714, and 728 and capacitors can be interleaved with the above-noted components in order to control the direction of currents in the non-dissipative snubber and various capacitors can be used to store energy.

In one embodiment, a capacitor can replace the voltage multiplier 724 (see FIG. 6). In one embodiment, the voltage multiplier 724 can be a voltage doubler (see FIG. 9), a voltage tripler (see FIG. 10), or any other multiplier having an integer or fractional multiplying effect.

Before delving deeper into FIGS. 7 and 24, a discussion of the development of these circuits and power systems may be helpful. FIG. 3 illustrates a power supply system 300 including a DC power supply 302, a switching circuit 304, a plasma load 306, and an embodiment of a non-dissipative snubber circuit. The DC power supply 302 provides DC power to the switching circuit 304 (e.g., a half-bridge switching circuit) which converts the DC power to pulsed DC that is then provided to the plasma load 306. In order to prevent damage to the switching circuit 304 during switching, when the plasma load 306 appears as a capacitor or open circuit, a snubber circuit including a capacitor 308 coupled between a first rail 350 (positive rail) and a second rail 352 (negative rail) can be implemented. While the capacitor 308 can limit current and/or voltage spikes in the switching 65 circuit 304, it unfortunately also quickly discharges stored energy into arcs in the plasma, thus exacerbating such events.

FIG. 4 illustrates a power supply system 400 including a DC power supply 402, a switching circuit 404, a plasma load 406, and another embodiment of a dissipative snubber circuit. In this embodiment the snubber circuit includes a diode 410, a capacitor 408, and a resistor 412. During 5 switching circuit 404 switching, when the plasma load 406 appears as a capacitor or open circuit, a majority of power from the DC power supply 402 passes through the diode 410 and charges the capacitor 408. The capacitor 408 can discharge its energy through the resistor 412 to the switching circuit 404 in the plasma load 406 when the plasma load 406 impedance returns to typical levels. Unlike the snubber illustrated in FIG. 3, the snubber of FIG. 4 limits the current that the capacitor 408 discharges to the first rail 450 via the maximum current threshold. However, power is dissipated as current passes through the resistor 412, and thus this design is merely a dissipative snubber.

FIG. 5 illustrates a power supply system 500 including a DC power supply **502**, a switching circuit **504**, a plasma load 20 **506**, and yet another embodiment of a non-dissipative snubber circuit. However this design replaces the resistor 412 in FIG. 4 with an inductor 512, thus enabling the capacitor 508 to discharge stored energy in a non-dissipative fashion. In this case, power from the DC power supply 502 can pass 25 through the diode 510 (or any unidirectional switch) and charge the capacitor 508 (or any capacitive circuit or device, such as a capacitor) when the switching circuit **504**'s switching of the plasma load 506 appears as a capacitor or an open circuit. Energy stored in the capacitor **508** can be discharged 30 through the inductor **512** (or any inductive circuit or device), the switching circuit **504**, and to the plasma load **506** without the losses incurred by passing said energy through a resistor. At the same time, like the resistor 412, the inductor 512 limits the rate of increase in current thus preventing the 35 capacitor 508 from dangerously discharging its energy during arcing events.

In an optional embodiment the snubber can include a diode 514 (or any unidirectional switch) arranged between the inductor and the first rail 550 that prevents current from 40 charging the capacitor 508 through the inductor 512. This diode 514 may be required since the inductor 512, rather than the diode 510, is the path of least resistance from the first rail 550 to the capacitor 508. The inductor-capacitor (512, 508) combination can also lead to ringing, and thus the 45 optional diode 514 helps to alleviate this ringing.

However, since the inductor **512** and diode **510** (and optionally the diode **514**) are arranged in a near-lossless current loop **511**, current in the inductor **512** continues to flow with little or no dissipation. Every time an arc occurs, 50 the capacitor **508** discharges some energy in the form of current through the inductor **512**, and then recharges after the arc. The added current builds upon the already looping current, and if the rate of arcing is high enough, then the current in the inductor **512** can step wise build in a runaway 55 current ramp until the current in this loop **511** damages or destroys either or both of the diodes **510** and **514**.

In some embodiments, a bank of capacitors can replace the capacitor **508** such that smaller and less expensive capacitors can be used to achieve a large capacitance.

FIG. 6 illustrates a power supply system 600 including a DC power supply 602, a switching circuit 604, a plasma load 606, and yet another embodiment of a non-dissipative snubber circuit. In this case, a switch 626 can be arranged between an electrical node 609 (between a diode 610 and a 65 capacitor 608) and an inductor 612. The switch 626 can remain closed during normal processing, but be opened

8

during arc events in order to cut the near-lossless current loop formed by the inductor 612 and the diode 610 (and optionally a diode 614). Thus, when high-frequency arc events occur, a current in the inductor 612 may stepwise rise as a result of each successive discharge from the capacitor 608. When the current reaches a threshold, the switch 626 opens, and the current passes into the capacitor 608 via diode 610 thus providing a current path for the inductor to discharge through until the energy stored in the inductor's magnetic field falls and the current in the inductor 612 drops below the threshold. This prevents the runaway current ramp in the inductor 612 that was described with reference to FIG. 5

Optionally, the snubber can include a diode 628 (or other resistor 412, whose resistance can be selected to meet a maximum current threshold. However, power is dissipated as current passes through the resistor 412, and thus this design is merely a dissipative snubber.

FIG. 5 illustrates a power supply system 500 including a DC power supply 502, a switching circuit 504, a plasma load 506, and yet another embodiment of a non-dissipative snubber circuit. However this design replaces the resistor 412 in FIG. 4 with an inductor 512, thus enabling the capacitor 508 to discharge stored energy in a non-dissipative fashion. In this case, power from the DC power supply 502 can pass 25

In some embodiments, a bank of capacitors can replace the capacitor 608 such that smaller and less expensive capacitors can be used to achieve a large capacitance.

FIG. 7 illustrates a power supply system 700 including a DC power supply 702, a switching circuit 704, a plasma load 706, and yet another embodiment of a non-dissipative snubber circuit. Here, a voltage multiplier 724 replaces the capacitor seen in earlier snubber embodiments. The voltage multiplier 724 is designed to improve the efficiency of the system 700, while still enabling the snubber to absorb power from the DC power supply 702 and thus protect the switching circuit 704.

In particular, and recalling FIGS. 2A and 2B, pulsed DC power systems often suffer from slow current ramp rates during each pulse. The voltage multiplier 724 absorbs power from the DC power supply 702 after the switching circuit 704 voltage switches, but also boosts process voltage,  $V_1$ , to a boosted voltage,  $V_1+V_2$ , for a first portion 802 of each pulse so that current ramps faster as illustrated in FIG. 8A. For instance, the DC power supply 702 provides sufficient power to enable the process voltage  $V_1$ , but the voltage multiplier 724 boosts this voltage by  $V_2$  during the first portion 802 of each pulse.

This voltage boost is actually a byproduct of the snubber circuit absorbing power from the DC power supply 702 immediately after 0 V transitions of the switching circuit 704. When the switching voltage reaches 0 V, the plasma density drops substantially and the plasma acts more like an open circuit or an unfluxed inductor than as a low resistance current path. The DC power supply 702 is current or power regulated and thus continues to drive the same current level. The snubber circuit absorbs this power, which otherwise would be directed into the switching circuit 704 and potentially damage that circuit.

As current passes into the voltage multiplier 724, energy is stored within the voltage multiplier 724 and accumulates along with a voltage that is increasingly larger than the process voltage  $V_2$  until the current in the plasma has ramped sufficiently to raise the plasma density back to a level where power can again be largely provided to the plasma load 706 rather than to the snubber. This time is long enough that the voltage across the voltage multiplier 724

builds to greater than the process voltage,  $V_1$ , and thus for a first portion 802 of each DC pulse, there is a voltage boost of  $V_2$  as seen in FIG. 8A.

This increased voltage causes the current to ramp faster than seen in the art (e.g., FIG. 2A). As a result, the current 5 flattens out sooner in each pulse meaning that greater average power is delivered and thus less time is required for a given process. The increased current ramp rate also means that current does not rise as high as it would given a slower ramp rate, which results in less overall losses (proportional 10 to I<sup>2</sup>) and less switching losses (proportional to I at the moment of switching). These improvements in efficiency are especially noticeable at higher frequencies (see FIG. 8B and compare to FIG. 2B).

It should be noted that FIG. **8**A is a simplification of the voltage and current waveforms, and in practice the vertical rises and falls may have non-infinite slopes caused by capacitive and inductive effects.

If the voltage between the first rail 750 and the second rail 752 falls below approximately the process voltage,  $V_1$ , then 20 the voltage multiplier 724 can partially discharge and supplement the current provided from the DC power supply 702 at approximately the process voltage,  $V_1$ .

During arcs, the voltage multiplier **724** can also discharge some of its energy through the closed switch **726** and the 25 inductor **712**. A near-lossless current loop **711** may then be established through the inductor **712**, the diode **710**, and the closed switch **726** (and optionally the diode **714**) until the switch **726** is opened, thus forcing the current to recharge the voltage multiplier **724**.

In some embodiments,  $V_2=V_1$  (e.g., the voltage multiplier 724 is a voltage doubler). However, in other embodiments,  $V_2$  can be less than or greater than the process voltage,  $V_1$ . In some embodiments,  $V_2$  can even be variable (see FIGS. 11-14).

In some embodiments, the first diode 710 can be arranged in series with a current limiter such as an inductor (not illustrated) so as to limit not only the direction of current into the voltage multiplier 724, but to also limit the amount and rate of change of current entering the voltage multiplier 724. 40 Such a current limiter may be implemented to prevent current overload in the voltage multiplier 724. In embodiments, where two or more of the herein disclosed snubbers are arranged in parallel, the current limiter may limit the current entering each of the snubbers so that voltage can 45 remain at a reasonable level while still sending current to each of the two or more snubbers.

In such an embodiment, the current limiter in series with the first diode 710 can be selected so that current is able to rapidly enter and charge the voltage multiplier 724, while 50 the inductor 712 can be selected so that the voltage multiplier 724 discharges at a lower current. This can lead to a rapid boosting of voltage to  $V_1+V_2$  at the start of each DC pulse (see the first portion 802 of FIGS. 8A and 8B) while the voltage multiplier 724 supplements the DC power supply 55 702 current at  $V_1$  over a longer second portion of each DC pulse.

In one embodiment, the first and second rails 750 and 752 are floating, such that neither is referenced to ground.

The diode **714** can be optional where the LC time constant 60 is long. A "long" LC time constant is one where the inductor **712** current is prevented from reversing direction. In particular, the inductor **712** is sinusoidal without the optional diode **714**, and so the LC time constant is equal to the inverse resonant frequency of the inductor **712** and the 65 capacitor of the voltage multiplier **724** and preferably an order of magnitude greater than the inverse switching fre-

10

quency of the switching circuit 704. The LC time constant can be calculated from the inductance of the inductor 712 and any capacitance of the voltage multiplier 724.

The switching circuit 704 takes either DC voltage or constant power from the DC power supply 702 and generates pulsed DC power. Two non-limiting examples of the switching circuit 704 are an H-bridge (half or full bridge) or a double-pole double-throw switch network. In one embodiment, the switching circuit 704 can include two or more half or full bridge H-bridge circuits coupled in parallel (e.g., one pair of H-bridge outputs is parallel to the next pair of H-bridge outputs).

The plasma load **706** can be part of a plasma processing chamber, such as those used in plasma processing (e.g., sputtering or etching). Power can be provided to the plasma load **706** via one or more electrodes such as those in dual-magnetron sputtering (one or more magnetrons can also be used).

FIG. 9 illustrates an embodiment of a power supply system 900 showing details of a voltage multiplier 924. The voltage multiplier 924 includes a first capacitor 908 (or a capacitor bank or any capacitive element or system), a second capacitor 916, a first diode 918, a second diode 922, and a third diode 920. The first and second capacitors 908 and 916 can be charged in series when the second diode 922 is forward biased. The first and second capacitors 908 and 916 can then discharge in parallel when the first and third diodes 918 and 920 are forward biased, and the second diode 922 is reverse biased.

FIG. 10 illustrates an embodiment where the voltage multiplier of the snubber is a voltage tripler. The voltage multiplier 1024 includes a first capacitor 1002, a second capacitor 1004, and a third capacitor 1006. The voltage multiplier 1024 further includes a first diode 1008, a second diode 1010, a third diode 1012, a fourth diode 1014, and a fifth diode 1016. Each of the capacitors 1002, 1004, 1006 can be charged to near or greater than the process voltage, and therefore when all three are charged, a voltage drop across all three is around three times the process voltage.

Thus, the voltage multiplier 1024 is able to boost the voltage across the first and second rails 1050, 1052 by a factor of about three and can therefore be referred to as a voltage tripler.

In some embodiments, a bank of capacitors can replace the capacitors 1002, 1004, and 1006 such that smaller and less expensive capacitors can be used to achieve a large capacitance.

FIG. 11 illustrates a power supply system 1100 including a DC power supply 1102, a switching circuit 1104, a plasma load 1106, yet another embodiment of a voltage multiplier 1124, and a voltage multiplier modifier 1130. Here, the snubber sees the addition of a voltage multiplier modifier 1130 coupled between a first and second rail 1150, 1152, and having an electrical connection to the voltage multiplier 1124. The voltage multiplier modifier 1130 can control the effect of the voltage multiplier 1124 on the voltage,  $V_{AB}$ , between the rails 1150 and 1152. In this way the boost voltage V<sub>2</sub> (see FIG. 12) can be tailored to a desired amplitude that is less than the maximum boost that the voltage multiplier 1124 is capable of. Furthermore, the voltage V<sub>2</sub> can be varied in time. This embodiment has particular application where the voltage multiplier 1124 has a fixed multiplying effect (e.g., a voltage doubler or a voltage tripler).

One application of such control is illustrated in FIG. 12, where a voltage threshold 1202 shows a threshold above which circuitry in the power supply system 1100 can be

damaged. As such the voltage multiplier modifier 1130 can be used to lower  $V_2$  so that the total voltage  $(V_2+V_1)$  of the first portion 802 of the pulses remains below the voltage threshold 1202. As seen, V<sub>2</sub> can be adjusted in time so long as the sum is kept below the voltage threshold 1202.

FIG. 13 illustrates a power supply system showing details of one embodiment of a voltage multiplier modifier. The voltage multiplier modifier 1330 can include a diode 1334, an inductor 1332, and a switch 1336. The combination of the inductor 1332, the switch 1336, and the diode 1334 can function as a discontinuous conduction mode (DCM) boost converter, where the inductor 1332 current can fall to zero for at least a portion of operation. The combination can also converter, where the inductor 1332 current never falls to zero.

The inductor 1332 can be arranged between the voltage multiplier 1324 and an electrical node 1333, where the electrical node 1333 is arranged between the diode 1334 and 20 the switch 1336. In particular the electrical node 1333 can be arranged between an anode of the diode 1334 and the switch 1336. The switch 1336 can be arranged between the electrical node 1333 and a second rail 1352. When the switch 1336 closes, stored energy in the voltage multiplier 1324 is 25 removed through the inductive component 1332 and the unidirectional switch 1334 to the first rail 1350, thus lowering the voltage across the voltage multiplier 1324 and hence lowering the voltage boost V<sub>2</sub> caused by energy storage in the voltage multiplier 1324.

The switch 1334 can be turned on and off according to a duty cycle, where a larger duty cycle decreases the voltage boost  $V_2$  from the voltage multiplier **1324**. For instance, a 0% duty cycle (the switch **1334** open 100% of the time) 1324 to reach the switching circuit 1304.

FIG. 14 illustrates a power supply system showing details of one embodiment of a voltage multiplier **1424** and of a voltage multiplier modifier **1430**. The details of the voltage multiplier modifier **1430** are the same as those illustrated in 40 FIG. 13, and the details of the voltage multiplier 1424 are the same as those illustrated in FIG. 9. The voltage multiplier 1124 can include a first capacitor 1408, a second capacitor 1416, a first diode 1418, a second diode 1422, and an optional third diode 1420.

During switching of the switching circuit **1404** when the plasma load 1406 appears as an inductor or an open circuit, power from the DC power supply 1402 passes through the diode **1410** and into the voltage multiplier **1424**. Due to the arrangement of the diodes 1418, 1422, 1420 the current 50 charges the first capacitor 1408 and the second capacitor 1416 in series while passing through the diodes 1410 and **1422**. The diode **1418** and the optional diode **1420** are reverse biased during charging of the first and second capacitors 1408, 1416.

When the voltage multiplier 1424 discharges, and the voltage multiplier module 1430 is not active, the second diode **1422** is reverse biased and the first diode **1418** and the optional third diode 1420, if implemented, are forward biased. As a result, the first and second capacitors 1408 and 60 **1416** discharge in parallel. The voltage that the first and second capacitors 1408 and 1416 are each charged to can be equivalent to the process voltage, V<sub>2</sub>, minus a forward bias voltage drop across the diode 1410. In other words, the voltage multiplier 1424 approximately doubles the voltage 65 provided by the DC power supply 1402, and can be referred to as a voltage doubler.

The voltage multiplier modifier 1430 can control how much of the voltage doubling effect the voltage multiplier **1424** has on  $V_{AB}$ . For instance, where the switch **1426** has a maximum safe operating voltage threshold of 1700 V, and 5  $V_1$  is 1000 V, the voltage multiplier module **1424** by itself would generate a 2000 V rail voltage on the first rail 1450 and thus damage the switch **1426**. However, via proper control of the voltage multiplier modifier 1430 the multiplying effect of the voltage modifier 1424 can be tailored such that  $V_{AB}$  is kept below 1700 V, thus avoiding damage to the switch 1426.

In particular, when the switch **1436** is closed, energy from the capacitor 1416 is removed to the second rail 1452 via an output 1460 of the voltage multiplier, the inductor 1432, and function as a continuous conduction mode (CCM) boost 15 the closed switch 1436. As such, the more often the switch 1436 is closed (e.g., a higher duty cycle), the lower the voltage on the capacitor **1416**. The voltage multiplier modifier 1430 does not affect the voltage on the capacitor 1408. In this fashion, the voltage multiplier modifier 1430 can control the boost voltage V<sub>2</sub> provided by the voltage multiplier **1424**.

> When the first and second capacitors 1408, 1416 discharge, and the voltage multiplier modifier 1430 is active, the first capacitor 1408 discharges via the switch 1426, the inductor **1412**, and the optional diode **1414**. Because charge has been removed from the second capacitor 1416, the optional diode 1420 is reverse biased, and can be removed from the circuit when the voltage multiplier modifier 1430 is used. The second capacitor **1416** discharges through the voltage multiplier modifier 1430, and in particular through the inductor 1432 and the diode 1434.

Discussion will now be directed to current paths, voltages, and forward or reverse biases existing on the various components illustrated in FIG. 14 during different phases of allows the full voltage boost V<sub>2</sub> of the voltage multiplier 35 operation of one embodiment of a power supply system. The DC power supply 1402 can be power or current-regulated. During non-arcing conditions, current passes along first rail 1450 from the DC power supply 1402 to the switching circuit 1404. The switch 1426 is closed (or on), and the diodes 1410 and 1414 are also on, and thus current also passes in a near-lossless loop 1411 (see FIG. 17) through the inductor 1412, the diode 1410, the closed switch 1426, and the diode 1414 (optional). A voltage,  $V_{AB}$ , is equal to a process voltage during this phase of operation. The process 45 voltage is a voltage across the plasma load **1406** given a steady state plasma impedance. This occurs when the plasma is ignited and sustained and thus is conducting, but can vary to some extent depending on plasma stability and process conditions (e.g., when reactive gas flow enters the plasma processing chamber). A voltage,  $V_{EB}$ , as measured from electrical node E to electrical node B is equal to the process voltage minus the forward conduction voltage drop across diode **1410** (e.g.,  $V_{EB} = V_{AB} - V_{AE}$ ).

> The constant current loop **1411** (see FIG. **17**) maintains 55 the diodes 1410 and 1414 (optional) in an on state, thus providing the first rail 1450 instant access to the voltage multiplier 1424 should the plasma load impedance 1406 rise for any reason. Thus, the voltage multiplier **1424** is ready to absorb power from the DC power supply 1402 after every 0 V transition of the switching circuit 1404 as well as after any malfunction caused by an impedance spike in the plasma load 1406. For instance, where there is a leak in the plasma chamber that suddenly extinguishes the plasma, power from the DC power supply 1402 can be shunted into the voltage multiplier 1424.

FIG. 18 illustrates the power supply system of FIG. 14 just after a 0 V transition of the switching circuit. After the

0 V transition, the plasma load 1406 impedance rises substantially such that the path of least resistance for most of the current is through diode 1410, first capacitor 1408, diode 1422, and capacitor 1416 to the second rail 1452 (1452 is mislabeled in FIG. 18 as 1442). Diode 1418 is reverse 5 biased, as is optional diode 1420 if implemented. The voltage between the rails,  $V_{AB}$ , when the current begins to take this route, is equal to the process voltage,  $V_1$ . The current charges the capacitors 1408 and 1416 and in doing so increases  $V_{AB}$  above the process voltage,  $V_1$ . With the 10 illustrated voltage multiplier 1424 (a voltage doubler),  $V_{AB}$ can be boosted to substantially twice the processing voltage,  $V_1$ . In other embodiments, the voltage can be boosted to three, four, or any integer or fractional multiplier of the process voltage,  $V_1$ .

The current running along this path and the corresponding charging of the first and second capacitors 1408 and 1416 gradually falls off as the capacitors 1408 and 1416 are charged. Eventually the current flow tapers to a negligible amount or the current in the plasma ramps sufficiently to 20 draw down the plasma load 1406 impedance to normal levels, such that power again is delivered to the plasma load **1406**. When this happens, the voltage across the voltage multiplier,  $V_{EB}$ , is typically large enough to forward bias diode 1418 as well as optional diode 1420 if implemented, 25 and diode **1422** turns off. The resulting current flow and diode biasing is illustrated in FIG. 19. Here, the capacitors **1408** and **1416** discharge in parallel through the closed switch 1426, the inductor 1412, and the optional diode 1414 until the capacitors 1408 and 1416 return to a voltage at 30 which diodes 1418 and 1420 turn off (e.g., near process voltage).

In embodiments, where the voltage multiplier modifier 1430 is used to remove some portion of charge on the second such embodiments the optional diode **1420** is reverse biased even if implemented. Either way, the second capacitor **1416** discharges via the inductor 1432 and diode 1434 rather than via the illustrated current path through optional diode 1420.

As the capacitors 1408 and 1416 discharge, the voltage 40  $V_{AB}$  drops from  $V_1+V_2$  to  $V_1$  or the process voltage as seen in FIGS. 8A and 8B. However, this current flow can also cause the voltage fall time to be finite as illustrated in FIGS. 25A and 25B. FIGS. 25A and 25B illustrate the plots in FIGS. 8A and 8B, but include detail of the sloped voltage 45 decrease 2500 attributable to the discharge of the capacitors 1408 and 1416 after the plasma impedance falls to normal levels.

As seen, diode 1410 is still forward biased, thus continuing to provide an instant shunt for power from the DC power 50 supply 1402 to the voltage multiplier 1424 should it be needed. Even small amounts of power from the DC power supply 1402 can be directed into the voltage multiplier 1424, where the energy builds until the diodes 1418 and 1420 turn on and begin to discharge the capacitors 1408 and 1416. In 55 this way, the capacitors 1408 and 1416 remain at voltages near or slightly above process voltage.

FIG. 20 illustrates the current paths and diode biases in the power supply system of FIG. 14 during a single arc event. During an arc, the plasma load impedance 1406 drops 60 causing the voltage  $V_{AB}$  to drop. When this happens, the voltage  $V_{AB}$  typically falls below the voltage  $V_{EB}$ , which reverse biases the diode 1410 (illustrated as forward biased). While the voltage multiplier 1424 does discharge energy into the arc, the discharge is not large since the inductor 65 **1412** limits the rise in current. In some cases, the inductor 1412 can be selected to be so large, that even during such an

14

arc, the current does not appreciably rise. Thus, the voltage multiplier 1424 does not threaten to exacerbate arcs.

The current leaves the snubber and heads to the switching circuit 1404 as well as back into the near-lossless loop 1411. If two arcs occur back-to-back, then the current in the inductor 1412 may step upwards due to multiple discharges from the capacitors in the voltage multiplier **1424**. A series of arcs in rapid succession can stepwise increase the current to levels that could damage the diodes 1410 and 1414. Thus, when the current in the inductor 1412 reaches a threshold, the switch 1426 opens as seen in FIG. 21. The opening of the switch 1426 cuts the near-lossless loop 1411 and forces the inductor 1412 current to discharge into the voltage multiplier 1424. The inductor 1412 current ramps down and thus opening of the switch **1426** avoids runaway stepwise current ramping in the near-lossless loop 1411.

The current is illustrated as leaving the optional diode **1414** and heading either back to the diode **1410** or to the switching circuit 1404. In some cases, both current paths will be used. However, where the switching circuit **1404** is open, current does not pass to the switching circuit 1404 and instead all current passes through diode 1410 to the voltage multiplier 1424. In cases where the switching circuit 1404 is closed and there is an arc, current will prefer the path into the switching circuit **1404** and the arc. However, after the arc has ceased, or at least diminished, current may be more equally split between the two paths.

Optional diode **1428** can be included between the inductor **1412** and the second rail **1452** to provide a current path to the inductor 1412 when the switch 1426 opens, thereby avoiding voltage spikes in the inductor **1412**.

Duty cycle control can be used to control the switch 1426, limiting the voltage between the rails 1450, 1452 as a protection of the snubber circuit 108 (FIG. 1) and the capacitor 1416, optional diode 1420 is not needed, and in 35 switching circuit 104. If the voltage increases above a set level  $V_{max}$ , the switch 1426 closes and the voltage across capacitors 1408 and 1416 drops towards the process voltage of the plasma. If the voltage across the rails 1450, 1452 is below set minimum voltage  $V_{min}$  then switch 1426 opens. The control range is between the voltage across capacitor **1408** and the voltage across the capacitor **1416**. The advantage of this control using the switch 1426 is that the voltage boost is independent from this control.

> Similar control could be used to control the switch 1436 to keep the voltage across the capacitor **1416** within a range. It requires an additional measurement of that voltage to be applied. It would replace duty cycle control and allows automatic synchronization of the switching frequency of switch 1436 to the switching frequency of the circuit 1404. The value  $V_{max}$  – $V_{min}$  defines the duty cycle of the switches 1436, 1426 as a multiple of the double of the switches 1436, 1426, because the first and second capacitors 1408, 1416 are only charged during a first portion of each pulse from the switching circuit 1404, when the plasma has a high impedance and thus cannot draw the full current delivered from the DC power supply 1402, the inductor 1412, and the inductor **1432**.

> A voltage sensor (not illustrated) can monitor a voltage across the second capacitor 1416 and provide feedback to a control of the switch 1436 to control opening and closing of the switch 1436 or a duty cycle of the switch 1436. In other words, the switch 1436 can open and close, or have a duty cycle, responsive to feedback from a voltage sensor monitoring the voltage across the second capacitor 1416.

> FIG. 15 illustrates a power supply system including a DC power supply providing power to a switching circuit, which then provides pulsed DC power to a plasma load. A snubber

1508 can be incorporated into the DC power supply 1502, and power can be provided from the snubber 1508 to the switching circuit 1504.

FIG. 16 illustrates a power supply system including a DC power supply providing power to a switching circuit, which 5 then provides pulsed DC power to a plasma load. A snubber 1608 can be incorporated into the switching circuit 1604, and power can be provided from the DC power supply 1602 to the snubber 1608.

FIG. 26 illustrates a method of controlling power in a 10 power supply system. The method 2600 can begin with the passage of power from a power supply (e.g., DC power supply) to a load via a pass power operation 2602. The load can have an impedance, and the impedance can change in time. When the impedance substantially increases, an 15 absorbing at least some of the power operation 2604 can absorb at least some of the power from the power supply. Absorption of the power can cause a boost or increase to voltage and current reaching the load (e.g., 8A, 8B, 12, 25). After absorption of the power, the method **2600** can include 20 a discharging at least some of the absorbed power operation 2606 where at least some of the absorbed power is discharged into the load. This discharge can be activated by a decrease in the load impedance and can take place in a substantially non-dissipative fashion. After the discharge 25 operation 2606, the method 2600 can end or return to the passing power operation 2602.

Although this disclosure has focused on embodiments where snubbers are used to mitigate voltage and current spikes (or ramps) in a power supply system, and in particular 30 for pulsed DC applications, it is envisioned that the disclosed snubber can be used in a variety of other voltage and/or current clamping situations.

FIG. 22 illustrates another embodiment of a power supply system. A power supply (DC or AC) 2002 provides power to 35 a load 2006 via first and second rails 2050 and 2052. The load 2006 can be a plasma load or any other type of load (e.g., a DC or AC electrical motor). A single magnetron sputtering system is one implementation of such a power supply system. A snubber 2004 can be coupled to the rails 40 2050 and 2052 between the power supply 2002 and the load 2006 and can be configured to absorb power from the power supply 2002 when an impedance of the load 2006 increases. As the load 2006 impedance decreases, the snubber 2004 can discharge some of its stored energy into the load 2006 45 to supplement power from the power supply 2002. Because little to no energy is dissipated in the snubber 2004, the snubber can be referred to as a non-dissipative snubber.

The snubber 2004 is further configured to temporarily boost a voltage as measured from the first rail 2050 to the 50 second rail 2052, again in a non-dissipative Omanner. If the power supply 2002 is a power-regulated supply, then the voltage boost will result in faster current ramping when the power is first applied, or when power is reapplied in a pulsing context. This can decrease power turn on time, 55 which can be useful in semiconductor fabrication applications, to name one example. For instance, where there is a problem with the load 2006 that drives the load 2006 impedance high (e.g., loss of plasma conductivity in a plasma processing chamber), power can be more quickly 60 reapplied to the load 2006 after the problem has been resolved than with known snubbers.

FIG. 23 illustrates yet another power supply system. A power supply (DC or AC) 2102 provides power to a load 2106 via first and second rails 2150 and 2152 and via 65 vulnerable circuitry 2106. Vulnerable circuitry includes any circuitry that can be damaged by excessive voltages, cur-

**16**

rents or power and in particular can be damaged when an impedance of the load 2108 increases. A snubber 2104 can be coupled to the rails 2150 and 2152 between the power supply 2102 and the vulnerable circuitry 2106 and can be configured to absorb power from the power supply 2102 when an impedance of the load 2108 increases. In this way the snubber 2104 can prevent excessive power, voltages or currents from passing through the vulnerable circuitry 2106 and damaging components therein.

Returning to FIG. 24 illustrates yet a further power supply system. The power supply system 2400 can include a power supply 2402, a load 2406, a non-dissipative snubber 2460, and optionally vulnerable circuitry 2404. The snubber 2460 can be arranged between the power supply 2402 and the load 2406. The optional vulnerable circuitry 2404 can be arranged between the snubber 2460 and the load 2406.

The snubber 2460 functions much like the snubbers disclosed throughout this disclosure. However, the snubber 2460 does so using more generalized components, in order to show applications outside of the pulsed DC environment. For instance, rather than diodes, the snubber 2460 can include unidirectional switches 2410, 2414, and 2416. The snubber 2460 can also include an optional current limiter 2408 in series with the unidirectional switch 2410 as well as a current limiter 2412 in series with the unidirectional switch 2414. The snubber 2460 includes a switch 2422 and a voltage multiplier 2418. Optionally, the snubber 2460 can include a voltage multiplier modifier 2420. The snubber 2460 may further include an optional unidirectional switch 2404 arranged between the current limiter 2412 and the second rail 2452.

In some embodiments, the unidirectional switch 2410 can be arranged in series with the optional current limiter 2408, such as an inductor, so as to limit not only the direction of current into the voltage multiplier 2424, but to also limit the amount and rate of change of current entering the voltage multiplier 2424. Such an optional current limiter 2408 may be implemented to prevent current overload in the voltage multiplier 2424. In embodiments, where two or more of the herein disclosed snubbers 2460 are arranged in parallel, the optional current limiter 2408 may limit the current entering each of the snubbers so that voltage can remain at a reasonable level while still sending current to each of the two or more snubbers.

In such an embodiment, the optional current limiter 2408 in series with the first unidirectional switch 2410 can be selected so that current is able to rapidly enter and charge the voltage multiplier 2418, while the current limiter 2412 can be selected so that the voltage multiplier 2418 discharges at a lower current. This can lead to a rapid boosting of voltage to  $V_1+V_2$  at the start of each DC pulse (see the first portion 802 of FIGS. 8A and 8B) while the voltage multiplier 2418 supplements the power supply 2402 current at  $V_1$  over a longer second portion of each DC pulse.

In one embodiment, the first and second rails 2450 and 2452 are floating, such that neither is referenced to ground. The optional unidirectional switch 2414 can be excluded where an LC time constant is long. A "long" LC time constant is long enough to prevent the current limiter 2412 current from reversing direction. In particular, current in the current limiter 2412 would be sinusoidal without the optional unidirectional switch 2414, and so the LC time constant is preferably equal to a switching frequency of the vulnerable circuitry 2404 includes a switching frequency. In a further preferred embodiment, the LC time constant is an order of magnitude greater than the switching frequency of the vulnerable

circuitry 2404, assuming the vulnerable circuitry 2404 includes a switching frequency. The LC time constant can be calculated from the inductance of the current limiter 2412 and any capacitance of the voltage multiplier 2424. Two non-limiting examples of the vulnerable circuitry 2404 are 5 an H-bridge (half or full bridge) and a double-pole double-throw switch network.

The load **2406** can be part of a plasma processing chamber, such as those used in plasma sputtering. Power can be provided to the load **2406** via one or more electrodes such 10 as those in dual-magnetron sputtering (one or more magnetrons can also be used).

One of skill in the art will recognize that the plots of voltage and current (e.g., FIGS. 2A, 2B, 8A, 8B, 25A, and 25B are not necessarily drawn to scale, and that the shape 1 and scale of different features of the waveforms can change depending on the circuits used to generate these waveforms. For instance, the pulse width of the voltage increase at the start of each pulse may vary depending on the power passing to the snubber and depending on capacitance values within 20 the snubber (e.g., the capacitances of the first capacitor 1408 and the second capacitor 1416 in FIG. 14). As another example, vertical aspects of the voltage pulses illustrated in FIGS. 8A and 8B may have less than infinite slope in practice. For instance, the falling edge of the boosted voltage 25 (the first portion of each pulse) can have a negative slope that is a function of inductance and capacitance. The front vertical aspect of each pulse can in practice include an exponentially increasing portion for  $V_2$  where the boost voltage rises above  $V_1$  as a function of charge accumulation 30 on the capacitors 1408 and 1416 in FIG. 14. Furthermore, while the current waveforms show a flat or near flat portion during a latter portion of each pulse, in practice the slope of this portion of the current waveform can vary and be voltage and current in the figures are meant as illustrations and generalizations only, and that variations on these specific waveforms can be made without departing from the scope of this disclosure.

FIG. 28 illustrates an alternative topology for a voltage- 40 boosting circuit of a pulsed DC power supply system. The voltage-boosting circuit **2804** can have functionality of a snubber and can be used to both boost the rail voltage  $V_{AB}$ as well as to absorb current and/or power from a DC power supply providing power to the rails 2850, 2852. The voltage-45 boosting circuit 2804 includes a first diode 2810, a capacitor 2812, a switch 2814, a second diode 2816, a third diode **2818**, and an inductor **2820**. Unlike other voltage-boosting circuits having snubber functionality, here the switch **2814** remains open (off) until the capacitor 2812 charges to a 50 desired boosted voltage  $(V_1+V_2)$ . Other voltage-boosting circuits can be limited to a boosted voltage equal to twice the process voltage  $(V_1)$  and greater than twice the average rail voltage  $V_{AB}$ . Because the switch **2814** of the illustrated voltage-boosting circuited **2804** can be left open indefinitely, 55 the capacitor 2812 can charge to greater than twice the process voltage  $(V_1)$  and greater than twice the average rail voltage  $V_{AB}$ . Charge and voltage on the capacitor **2812** is in part a function of a duty cycle of the switch 2814.

When the switching circuit 2806 switches and plasma 60 impedance rises, so does the rail voltage  $V_{AB}$ . This rise in rail voltage  $V_{AB}$  forward biased the first diode 2810 allowing current to run into the capacitor 2812 and charge the voltage across the capacitor 2812. When the switch 2814 is open (off) the capacitor 2812 can be charged as long as the rail 65 voltage  $V_{AB}$  is greater than the capacitor 2812 voltage plus a diode voltage drop across the first diode 2810. The

**18**

capacitor **2812** voltage can therefore be charged to voltages greater than twice a process voltage  $V_1$  and twice an average rail voltage  $V_{AB}$ .

When the switch is closed (on) the capacitor **2812** discharges through inductor **2820** raising the instantaneous rail voltage  $V_{AB}$ . As the capacitor **2812** discharges, the instantaneous rail voltage  $V_{AB}$  decreases until the instantaneous rail voltage  $V_{AB}$  is lower than a voltage across the capacitor **2812**, at which point the first diode **2810** becomes reverse biased and current ceases to charge the capacitor **2812**. The rail voltage  $V_{AB}$  then remains at this voltage, a process voltage  $V_{AB}$ , until switching occurs and the plasma impedance again rises and forward biases the first diode **2810**. When the switch **2814** opens, the third diode **2818** provides a current path to the inductor **2820** to enable current to continue flowing through the inductor **2820** as the current ramps down.

One of skill in the art will recognize that the voltage-boosting circuit **2804** can be implemented for the snubbers described with reference to FIGS. **1-27**.

FIG. 29 illustrates another embodiment of a voltage-boosting circuit 2905 having snubber functionality. The voltage-boosting circuit 2905 includes a first diode 2910, a first switch 2926, a second and optional switch 2936, a first inductor 2912, a second inductor 2932, a second diode 2930, a third and optional diode 2928, and a voltage multiplier 2924. The voltage multiplier 2924 includes a first capacitor 2908, a second capacitor 2916, a fourth diode 2918, and a fifth diode 2922.

The optional second switch 2936 is typically open, or in its absence, the second inductor 2932 is merely coupled to a first rail 2950 via the second diode 2930. The first switch 2926 typically is closed (on).

this portion of the current waveform can vary and be non-zero. These examples demonstrate that the plots of voltage and current in the figures are meant as illustrations and generalizations only, and that variations on these specific waveforms can be made without departing from the scope of this disclosure.

When the switching circuit 2904 switches, the plasma impedance rises as does the rail voltage  $V_{AB}$ , which forward biases the first diode 2910 and sends current into the voltage multiplier 2924. In particular, the current charges the first capacitor 2908 and charges the second capacitor 2916. Both capacitors 2908, 2916 charge until an average rail voltage  $V_{AB}$  is seen across each capacitor 2908, 2916.

Although the capacitors 2908, 2916 each charge to the average rail voltage  $V_{AB}$ , they can see instantaneous voltage in excess of the average rail voltage  $V_{AB}$ , and for safety, there is a desire to mitigate these overvoltages. This is where the optional second switch **2936** can be used. The optional second switch 2936 can operate according to a hysteresis control algorithm. The second capacitor **2916** can discharge via an output 2960 of the voltage multiplier 2924 and through the second inductor 2932 and the second diode 2930. The optional second switch 2936 can close when a voltage across the second capacitor 2916 rises above a maximum voltage threshold  $V_{max}$  in order to lower the voltage across the second capacitor **2916**. In an alternative, the second optional switch 2936 can begin switching at a defined duty cycle configured to lower a voltage across the second capacitor **2916**. Alternatively, the second optional switch 2936 may already be switching when the voltage across the second capacitor 2916 rises above the maximum voltage threshold  $V_{max}$ . In this case the second optional switch 2936 can increase its duty cycle so as to lower the voltage across the second capacitor **2916**.

Whichever of these methods is implemented, the second optional switch 2936 persists in operation (e.g., closed, defined duty cycle, or an increased duty cycle) until the voltage across the second capacitor 2916 falls below a minimum voltage threshold  $V_{min}$ . The second optional switch 2936 can then open, or decrease its duty cycle. The

second optional switch 2936 can remain open or maintain the decreased duty cycle until the voltage across the second capacitor 2916 again exceeds the maximum voltage threshold  $V_{max}$ . This overvoltage hysteresis control prevents transient voltages from damaging the electronics or generating unwanted high energy ions in the plasma.

The value  $V_{max}$ - $V_{min}$  defines the duty cycle of the second optional switch 2936 as a multiple of the double of the second optional switch 2936, because the first and second capacitors 2908, 2916 are only charged during a first portion of each pulse from the switching circuit 2904, when the plasma has a high impedance and thus cannot draw the full current delivered from the DC power supply 2902, the first inductor 2912, and the second inductor 2932.

A voltage sensor (not illustrated) can monitor a voltage across the second capacitor 2916 and provide feedback to a control of the optional second switch **2936** to control opening and closing of the optional second switch **2936** or a duty cycle of the optional second switch **2936**. In other words, the 20 optional second switch 2936 can open and close, or have a duty cycle, responsive to feedback from a voltage sensor monitoring the voltage across the second capacitor 2916.

As noted earlier, while this discussion has focused on embodiments where a single pulsed DC power supply 25 system powers a single anodeless electrode pair, in other embodiments, multiple anodeless electrode pairs can be implemented. In some cases, a single pulsed DC power supply system can provide pulsed DC power to each anodeless electrode pair, while in other embodiments, there may 30 be a separate pulsed DC power supply system for each anodeless electrode pair.

In one embodiment, the use of a plurality of pulsed DC power supply systems each feeding one of a plurality of voltages V<sub>2</sub> to each electrode pair so as to effectuate a desired processing effect including a desired film property (e.g., optical characteristic, resistance, and stress) or processing characteristic (e.g., sputtering rate).

For instance, an embodiment could include a first pulsed 40 DC power supply system providing a first pulsed DC power to a first anodeless electrode pair, the first pulsed DC power having a first boost voltage V2, and a second pulsed DC power supply system providing a second pulsed DC power to a second sputtering cathode and a second anode, the 45 second pulsed DC power having a second boost voltage V2'. In another embodiment, the first boost voltage V2 can be provided to a first anodeless electrode while the second boost voltage V2' can be provided to a second anodeless electrode. The first and second anodeless electrodes can both 50 operate as an anode, a cathode, and a sputtering target and may be adjacent to each other (e.g., no targets or electrodes separate the first and second anodeless electrode). V2 and V2' can be non-equal and thus effectuate a desired processing effect. In this way, not only can different process 55 voltages, different duty cycles, and different frequencies be applied to different electrodes, but additional control over the boost voltages to different anodeless electrode pairs is now possible.

FIG. 30 illustrates an embodiment of a power supply 60 system including two or more pulsed DC power supply systems providing pulsed DC power to four or more anodeless electrodes in a plasma processing chamber. Each pulsed DC power supply 3001, 3002 can embody any of the circuits and functionality as described earlier with reference to 65 various embodiments of pulsed DC power supply systems (e.g., FIGS. 1-28). The pulsed DC power supply systems

**20**

3001, 3002 can generate pulsed DC power having a boosted voltage  $(V_1+V_2)$  during a first portion of each pulse (e.g., FIG. **12**).

Each pulsed DC power supply system 3001, 3002 can power a pair of anodeless electrodes. For instance, the first pulsed DC power supply system 3001 provides pulsed DC voltage having a voltage  $V_{CD}$  to first and second anodeless electrodes 3010, 3012. The second pulsed DC power supply system 3002 provides pulsed DC voltage having a voltage  $V_{EF}$  to third and fourth anodeless electrodes 3014, 3016. The anodeless electrodes operate as anodes, cathodes, and sputtering targets.

The boost voltage V<sub>2</sub> provided by each pulsed DC power supply system 3001, 3002 can be selectable and differ from one pulsed DC power supply to another. For instance, a first boost voltage V<sub>2</sub> can be applied to the first and second anodeless electrodes 3010, 3012, while a second boost voltage  $V_{2'}$  can be applied to the third and fourth anodeless electrodes 3014, 3016.

The systems and methods described herein can be implemented in a computer system in addition to the specific physical devices described herein. FIG. 27 shows a diagrammatic representation of one embodiment of a computer system 2700 within which a set of instructions can execute for causing a device to perform or execute any one or more of the aspects and/or methodologies of the present disclosure. The non-illustrated controllers or other control components described above are one implementation of the computer system 2700. The components in FIG. 27 are examples only and do not limit the scope of use or functionality of any hardware, software, firmware, embedded logic component, or a combination of two or more such components implementing particular embodiments of this disclosure. Some or all of the illustrated components can be anodeless electrode pairs, can be paired with different boost 35 part of the computer system 2700. For instance, the computer system 2700 can be a general purpose computer (e.g., a laptop computer) or an embedded logic device (e.g., an FPGA), to name just two non-limiting examples.