#### US009484746B2

## (12) United States Patent

Tang et al.

## (10) Patent No.: US 9,484,746 B2

### (45) Date of Patent: No

Nov. 1, 2016

## (54) POWER CONVERTER CIRCUIT WITH AC OUTPUT

(75) Inventors: Yi Tang, Singapore (SG); Gerald

Deboy, Klagenfurt (AT)

(73) Assignee: Infineon Technologies Austria AG,

Villach (AT)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 989 days.

(21) Appl. No.: 13/352,202

(22) Filed: Jan. 17, 2012

## (65) Prior Publication Data

US 2013/0181529 A1 Jul. 18, 2013

(51) Int. Cl.

H02J 1/00 (2006.01)

H02J 3/38 (2006.01)

H02M 7/5387 (2007.01)

H02M 1/00 (2006.01)

(52) U.S. Cl.

CPC ....... *H02J 3/383* (2013.01); *H02M 7/53871* (2013.01); *H02M 2001/0074* (2013.01); *H02M 2001/0074* (2013.01); *H02M 2001/0077* (2013.01); *Y02E 10/563* (2013.01); *Y10T 307/707* (2015.04)

(58) Field of Classification Search

CPC ...... H02J 3/383; H02M 7/53871; H02M 2001/0074; H02M 2001/0077; Y10T 307/707; Y02E 10/563 USPC ..... 307/82

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

3,466,456 A 9/1969 Tolworthy 4,719,550 A 1/1988 Powell et al. 5,518,624 A 5/1996 Filson et al. 5,837,594 A 11/1998 Honma et al. 6,542,344 B1 4/2003 Mashiko

#### (Continued)

#### FOREIGN PATENT DOCUMENTS

CA 2702392 4/2009 CN 102148509 A 8/2011 (Continued)

#### OTHER PUBLICATIONS

Alonso, O., et al., "Cascaded H-Bridge Multilevel Converter for Grid Connected Photovoltaic Generators with Independent Maximum Power Point Tracking of each Solar Array," IEEE 34<sup>th</sup> Annual Power Electronics Specialist Conference (PESC '03), vol. 2, Jun. 15-19, 2003, pp. 731-735.

(Continued)

Primary Examiner — Daniel Cavallari (74) Attorney, Agent, or Firm — Slater Matsil, LLP

#### (57) ABSTRACT

A power converter circuit includes output terminals configured to receive an external AC voltage. At least one series circuit has at least two converter units. Each converter unit includes input terminals configured to be coupled to a DC power source. Output terminals provide an AC output current. The at least one series circuit is connected between the output terminals of the power converter circuit. A voltage measurement circuit is connected between the output terminals of the power converter circuit and configured to provide at least one measurement signal that includes information related to phase and frequency of the external AC voltage. At least one of the converter units is configured to receive the at least one measurement signal and is configured to regulate the generation of the AC output current dependent on the at least one measurement signal.

## 27 Claims, 15 Drawing Sheets

| DE   20210007960 T1   10/2010   10/2010   10/2010   10/2010   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10/2017   10   | (56) References Cited |               |         |                 | FOREIGN PATENT DOCUMENTS                                         |                                       |            |                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------|---------|-----------------|------------------------------------------------------------------|---------------------------------------|------------|-----------------------------------|

| Fig. 2   477   73   8   2   72012                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       | U.S.          | PATENT  | DOCUMENTS       | DE                                                               | 202010007960 U                        | J <b>1</b> | 10/2010                           |

| 6764.888   Bil   7/2004   Ent et al.   JP   11089242   3/1999   7,126.315   B2   10/2006   Fan et al.   JP   11089242   3/1999   7,126.315   B2   10/2006   Sachdeva et al.   JP   2000166097   A 6/2000   A 6/   |                       |               |         |                 |                                                                  | 2 477 318 A                           | λ2         | 7/2012                            |

| 7,037,787   B2   5/2006   Sco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6,764,898             | B1            | 7/2004  | En et al.       |                                                                  |                                       |            |                                   |

| 7,126,315 B2   10/2006   Sech   JP   2000166007 A   6,2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | , ,                   |               |         |                 |                                                                  |                                       |            |                                   |

| 7,808,125 BI   0/2010   Sachdewa et al.   P   20081188/09 A   5/2008   S. 2008   S. 2008   S. 2008   S. 2008   S. 2008   S. 2007   S. 20 | 7,126,315             | B2            | 10/2006 | Seo             |                                                                  |                                       |            |                                   |

| Assistance   Ass   | 7,808,125             | B1            | 10/2010 | Sachdeva et al. |                                                                  |                                       |            |                                   |

| Section   Sect   | 7,962,249             | B1            | 6/2011  | Zhang et al.    |                                                                  |                                       |            |                                   |

| 9,143,036 B2 9, 9215   lie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8,026,704             | B2            |         | -               |                                                                  |                                       |            |                                   |

| WO WO 2012/016285 Al 2/2012                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |               |         | <b>-</b>        |                                                                  |                                       |            |                                   |

| 2004/0051134   Al   3/2004   Jang et al   2004/0187866 Al   9/2004   Bucur et al   2006/0181212   Al   1/2006   Davies et al   2006/0281212   Al   1/2006   Davies et al   1/2006   Confederation of Grid-Connected   Photovoltaic System with Power Factor Control and Islanding   Detection," Jun. 20-25, 2004, 35th Annual IEEE Power Electronics   Specialists Conference, pp. 1409-1412.   Ranade et al   2008/030530   Al   1/2008   Roger et al   2008/030530   Al   1/2009   Roger et al   2009/02053250   Al   1/2009   Roger et al   | , ,                   |               |         |                 |                                                                  |                                       |            |                                   |

| 2004/01/57836 A1   3/2004   Bucur et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |               |         |                 |                                                                  |                                       |            |                                   |

| 2004/0178766 Al   9/2004 Bucur et al.   2006/0281212 Al   7/2005 Davies et al.   2006/0281212 Al   7/2006 Moriceau et al.   2006/0281212 Al   7/2006 Moriceau et al.   2006/0281212 Al   2/2007 September 2007/0197048 Al   8/2007 September 2007/0197048 Al   8/2007 September 2007/0197048 Al   8/2007 September 2007/0224813 Al   9/2007 Shen et al.   2007/0246752 Al   1/2008 Takami et al.   2008/0303767 Al   1/2008 Takami et al.   2008/0303763 Al   1/2008 Takami et al.   2008/0305303 Al   1/2008 Takami et al.   2008/0305303 Al   1/2008 Takami et al.   2009/018298 Al   7/2009 Molfs   2009/018298 Al   7/2009 Subme et al.   2009/018298 Al   7/2009 Subme et al.   2009/018293 Al   7/2009 Subme et al.   2010/018353 Al   6/2011 Lee   2011/0242857 Al   1/2011 Deboy   2011/0242857 Al   1/2012 Carletti   2011/0242857 Al   1/2012 Carletti   2011/0242857 Al   1/2012 Carletti   2011/0242857 Al   1/2012 Carletti   2011/0243857 Al   1/2013 Deboy et al.   2013/03181530 Al   7/2013 Deboy et al.   2013/03181533 Al   7/2013 Deboy et al   |                       |               |         |                 | WO                                                               | WO 2013/030236 A                      | 12         | 3/2013                            |

| 2006/081212 A1   7/2006   Davies et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                       |               |         |                 |                                                                  |                                       |            |                                   |

| 2006/0181212 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |               |         |                 |                                                                  | OTHER E                               | PUR        | LICATIONS                         |

| 2006/02861212 A1   12/2006   Moriceau et al.   Mckhilef, S. et al.   "Implementation of Grid-Connected Photovoltaic System with Power Factor Control and Islanding Detection," Iun. 20-25, 2004, 35th Annual IEEE Power Electronics Specialists Conference, pp. 1409-1412.   Ranade, S., et al., "A Study of Islanding in Utility-Connected Methods," 8047d IEEE Transactions on Energy Conversion Sep. 4, 1989, No. 3, New York, US, 11 pgs.   Wolfs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |               |         |                 | OTTER TODLICATIONS                                               |                                       |            |                                   |

| Photovoltaic System with Power Factor Control and Islanding 2007/0023812 A1 2/2007 Sekime et al. Sung et al. 2007/0024813 A1 9/2007 Sekime et al. Short of al. 2007/024813 A1 9/2007 Sekime et al. Short of al. 2007/024875 A1 1/2007 Cheng et al. 2008/0003765 A1 1/2008 Wolfs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |               |         |                 | Mekhi                                                            | lef S et al "Ir                       | mnlei      | mentation of Grid-Connected       |

| 2007/0234822 A1   2/2007   Sung et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |               |         |                 | -<br>-                                                           |                                       |            |                                   |

| 2007/02/24813 A1 9/2007 Sekin et al. 2007/02/24813 A1 9/2007 Shen et al. 2007/02/246752 A1 10/2007 Cheng et al. 2008/030376 A1 1/2008 Radmi et al. 2008/0303503 A1* 12/2008 Wolfs G05F 1/67 323/301 A1 2008/0303503 A1* 12/2008 Radmi et al. 2009/02/2323 A1 1/2009 Shum et al. 2009/02/2323 A1 1/2009 Shum et al. 2009/02/2323 A1 1/2009 Paull Shum et al. 2009/02/2323 A1 1/2009 Paull Shum et al. 2011/0149535 A1 6/2011 Choi et al. 2011/02/2857 A1 1/2011 Deboy Endironment et al. 2011/0149535 A1 1/2012 Seymour et al. 2011/02/25375 A1 1/2012 Deboy Endironment et al. 2012/01/26623 A1 5/2012 Voscovich et al. 2012/01/35964 A1 7/2012 Seymour et al. 2012/01/35964 A1 7/2013 Deboy et al. 2013/0155735 A1 6/2011 lic et al. 2013/0155735 A1 6/2011 lic et al. 2013/0155735 A1 7/2013 Deboy et al. 2013/0181530 A1 7/2013 Deboy et al. 2013/0181530 A1 7/2013 Deboy et al. 2013/0181531 A1 7/2013 Deboy et al. 2013/0181533 A1 7/2013 Deboy et al. 2013/018153 A1 7/2013 De |                       |               |         | •               |                                                                  |                                       |            |                                   |

| 2007/0224813 A1 9/2007 Shen et al. 2007/0246752 A1 10/2007 Cheng et al. 2007/0246752 A1 10/2007 Cheng et al. 2007/0252191 A1 11/2007 Kim et al. 2008/0303503 A1* 12/2008 Takami et al. 2008/0303503 A1* 12/2008 Wolfs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |               |         |                 | Detection," Jun. 20-25, 2004, 35th Annual IEEE Power Electronics |                                       |            |                                   |

| 2007/0252191 Al 10/2007 Cheng et al. 2007/0252191 Al 11/2007 Kim et al. 2008/003776 Al 1/2008 Wolfs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |               |         |                 | Specialists Conference, pp. 1409-1412.                           |                                       |            |                                   |

| 2007/0252191 A1   11/2007 Kim et al.   2008/0003776 A1   1/2008   Takami et al.   2008/0003776 A1   1/2008   Takami et al.   2008/00037303 A1 * 12/2008   21/2008   2008/0033530 A1 * 12/2008   21/2008   2008/0033531   21/2008   Rachmady et al.   2009/0023259 A1   1/2009   Shum et al.   2009/0023259 A1   7/2009   Shum et al.   2010/0195361 A1   8/2010   Stem   2011/0140535 A1   6/2011   Lec   2011/0242857 A1   10/2011   Kim et al.   2011/0242857 A1   10/2011   Kim et al.   2012/0087157 A1   4/2012   Seymour et al.   2012/016623 A1   7/2012   Solution   2012/0300515 A1 * 1/2012   Carletti   H02M 1/4225   2013/00185735 A1   6/2013   Ric et al.   2013/0155735 A1   6/2013   Ric et al.   2013/0185735 A1   6/2013   Ric et al.   2013/0181530 A1   7/2013   Deboy et al.   2013/0181531 A1   7/2013   Deboy et al.   2013/0187473 A1   7/2013   Deboy et al.   2013/0187473 A1   7/2013   Deboy et al.   2013/0187473 A1   7/2013   Deboy et al.   2014/0169053 A1   6/2014   Ric et al.   2014/0169053 A1   2014/0169053 A1   6/2014   Ric et al.   2014/0169053 A1     |                       |               |         |                 | _                                                                |                                       |            |                                   |

| 2008/0003776                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                       |               |         |                 |                                                                  | •                                     | -          |                                   |

| 2008/0303503                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                       |               |         |                 |                                                                  | _                                     |            |                                   |

| 323/301                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                       |               |         |                 |                                                                  | ·                                     |            |                                   |

| 2008/0315310   Al   12/2008   Rachmady et al.   2009/023259   Al   17/2009   Shum et al.   2009/0212629   Al   8/2009   Paull   2009/0284232   Al   2019/0915361   Al   8/2010   Stem    | 2000,0505505          | 111           | 12,2000 |                 | •                                                                | ·                                     | -          | _                                 |

| 2009/023259 A1 1/2009 Shum et al. 2009/0189280 A1 7/2009 Shum et al. 8/2009 Paull 6-8, 2012, Proceedings of the International Conference of Integrated 2009/0284232 A1 11/2009 Zhang et al. 2011/0149535 A1 8/2010 Stem 6/2011 Choi et al. 2011/0148195 A1 6/2011 Lee 7/2011/0284857 A1 10/2011 Lee 7/2012/0287157 A1 11/2011 Deboy 7/2012/0087157 A1 1/2011 Deboy 7/2012/0087157 A1 4/2012 Seymour et al. 2012/0126623 A1 5/2012 Koehl 7/2013 Deboy et al. 2012/0300515 A1* 11/2012 Carletti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2008/0315310          | <b>A</b> 1    | 12/2008 |                 |                                                                  |                                       |            | _                                 |

| 2009/0284232 Al 1/2009 Zhang et al. 2010/0195361 Al 8/2010 Stem Sci                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |               |         |                 |                                                                  | ·                                     |            |                                   |

| 2009/0284232 A1 11/2009 Zhang et al. 2010/0195361 A1 8/2010 Stem   2011/0140535 A1 6/2011 Choi et al. 2011/0148195 A1 6/2011 Lee   2011/0242857 A1 10/2011 Deboy   2012/085375 A1 11/2011 Deboy   2012/0097187 A1 4/2012 Huang et al. 2012/0126623 A1 5/2012 Koehl   2012/0175964 A1 7/2012 Voscovich et al. 2012/0300515 A1* 11/2012 Carletti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2009/0189280          | <b>A</b> 1    | 7/2009  | Shum et al.     | Kolar,                                                           | J.W. et al., "Extreme                 | Effic      | eiency Power Electronics," Mar.   |

| 2010/0195361 A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2009/0212629          | <b>A</b> 1    | 8/2009  | Paul1           | 6-8, 20                                                          | 12, Proceedings of the 1              | Interi     | national Conference of Integrated |

| 2011/0140535 A1 6/2011 Choi et al. 6/2011 Lee Applications," Sep. 12-16, 2010, IEEE, pp. 2803-2811. Yang, B. et al., "LLC Resonant Converter for Front End DC/DC Conversion," Mar. 10-14, 2002, IEEE, 5 pages. Ertl, H., et al., "A Novel Multicell DC-AC Converter for Applications in Renewable Energy Systems," IEEE Transactions on Industrial Electronics, vol. 49, No. 5, Oct. 2002, pp. 1048-1057. Walker, G., et al., "Cascaded DC-DC Converter Connection of Photovoltaic Modules," IEEE Transactions on Power Electronics, vol. 19, No. 4, Jul. 2004, pp. 1130-1139. Sahan, B., "Wechselrichtersysteme mit Stromzwischenkreis zur Netzanbindung von PV-Generatoren," ISBN 978-3-89958-912-2, 2013/0181533 A1 7/2013 Deboy et al. 2013/0181533 A1 7/2013 Deboy et al. 2013/0181533 A1 7/2013 Deboy et al. 2013/0187473 A1 7/2013 Deboy et al. 2013/0187473 A1 7/2013 Deboy et al. 2013/0187473 A1 7/2013 Deboy et al. 2014/0169053 A1 2014/0169053 A1 6/2014 Lic et al. 2014/0169053 A1 2014/0157588 A1 6/2014 Deboy 4 Lobby 2014/0169053 A1 2014/0157588 A1 6/2014 Deboy 4 Lobby 2014/0169053 A1 2014/0169053 A1 7/2014 Deboy et al. 2014/0169053 A1 6/2014 Deboy 4 Lobby 2014/0169053 A1 7/2014 Deboy et al. 2014/0 | 2009/0284232          | $\mathbf{A}1$ | 11/2009 | Zhang et al.    | Power                                                            | Electronics Systems (                 | CIPS       | 2012), 23 pages.                  |

| 2011/0148195 A1 6/2011 Choi et al. 6/2011 Choi et al. 2011/0242857 A1 10/2011 Kim et al. 2011/0285375 A1 11/2011 Deboy 2012/0087157 A1 4/2012 Huang et al. 2012/0126623 A1 2012/0175964 A1 7/2012 Voscovich et al. 2012/0300515 A1* 11/2012 Carletti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2010/0195361          | $\mathbf{A}1$ | 8/2010  | Stem            | Trubits                                                          | syn, A. et al., "High-                | Effic      | iency Inverter for Photovoltaic   |

| 2011/0242857 A1 10/2011 Kim et al. 2011/0285375 A1 11/2011 Deboy 2 2012/0087157 A1 4/2012 Huang et al. 2012/0091817 A1 4/2012 Seymour et al. 2012/0175964 A1 2012/0300515 A1* 11/2012 Carletti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |               | 6/2011  | Choi et al.     |                                                                  |                                       |            |                                   |

| 2011/0285375 A1 11/2011 Deboy 2012/0887157 A1 4/2012 Huang et al. 2012/0991817 A1 4/2012 Seymour et al. 2012/0126623 A1 5/2012 Koehl 2012/0300515 A1* 11/2012 Yoscovich et al. 2013/009700 A1 1/2013 Deboy et al. 2013/0155735 A1 6/2013 Ilic et al. 2013/0181530 A1 7/2013 Deboy et al. 2013/0181573 A1 7/2013 Deboy et al. 2013/0187473 A1 7/2013 Deboy et al. 2014/0169053 A1 6/2014 Ilic et al. 2014/0175888 A1 6/2014 Deboy 2014/0191582 A1 7/2014 Deboy et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                       |               |         |                 |                                                                  | · •                                   |            | · • •                             |

| 2012/0087157 A1 4/2012 Huang et al. 2012/0091817 A1 4/2012 Seymour et al. 2012/0126623 A1 5/2012 Koehl 2012/0300515 A1* 7/2012 Yoscovich et al. 2013/009700 A1 1/2013 Deboy et al. 2013/0155735 A1 6/2013 Ilic et al. 2013/0181530 A1 7/2013 Deboy et al. 2013/0181573 A1 2013/0181573 A1 2013/01887473 A1 2013/0187473 A1 2014/019588 A1 6/2014 Deboy et al. 2014/0191582 A1 7/2014 Deboy et al. 2016 Thuang et al. 4/2012 Huang et al. 4/2013 Poscovich et al. 1/2013 Deboy et al. 8/2013 Deboy et al. 9/2013 Deboy et al. 9/2014 Deboy et al. 9/2013 Deboy et al. 9/2014 Deboy et al. 9/2013 Deboy et a |                       |               |         |                 | •                                                                | ·                                     |            |                                   |

| 2012/0091817 A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |               |         |                 |                                                                  | · ·                                   | •          | , 1 0                             |

| 2012/0126623 A1 5/2012 Koehl 2012/0175964 A1 7/2012 Yoscovich et al. 2012/0300515 A1* 11/2012 Carletti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |               |         |                 | •                                                                |                                       |            | <b>*</b> *                        |

| 2012/0300515 A1 * 7/2012 Yoscovich et al. 2012/0300515 A1 * 11/2012 Carletti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                       |               |         |                 |                                                                  |                                       |            |                                   |

| 2012/0300515 A1* 11/2012 Carletti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |               |         |                 |                                                                  |                                       | •          | ' <b>L L</b>                      |

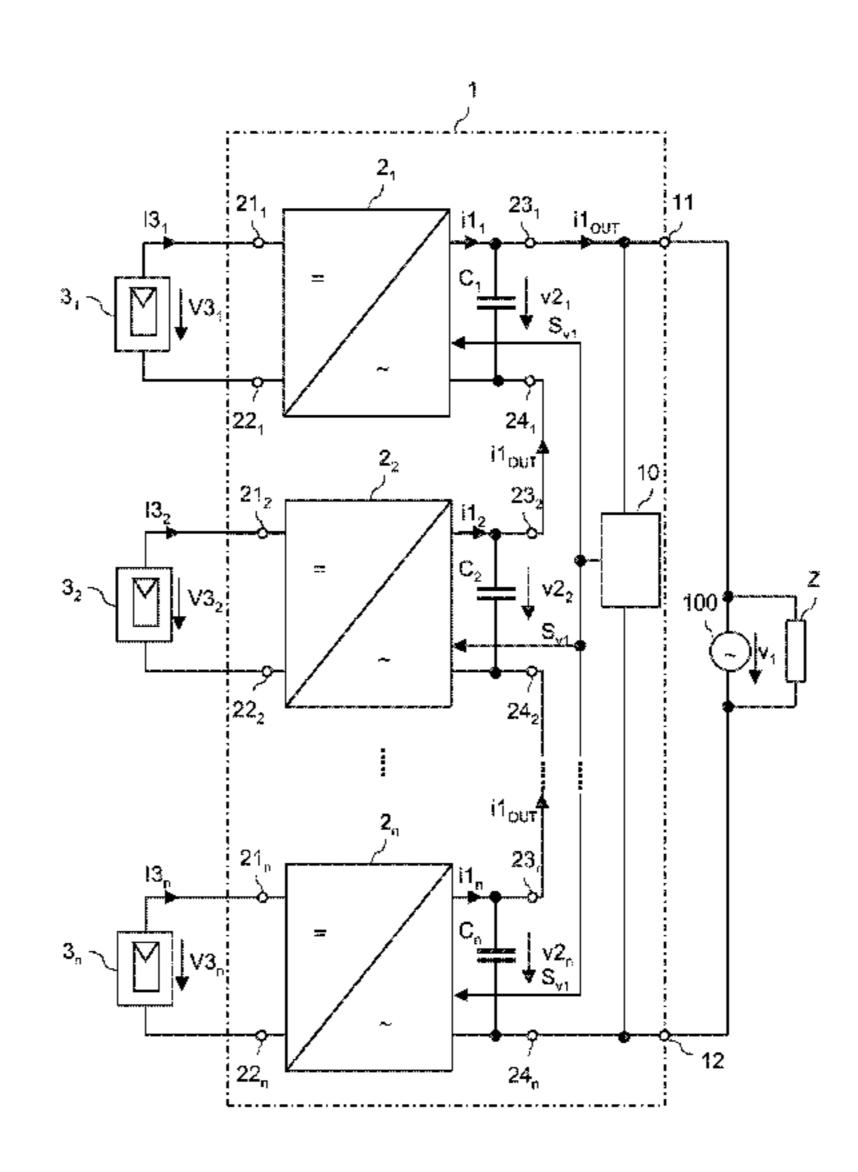

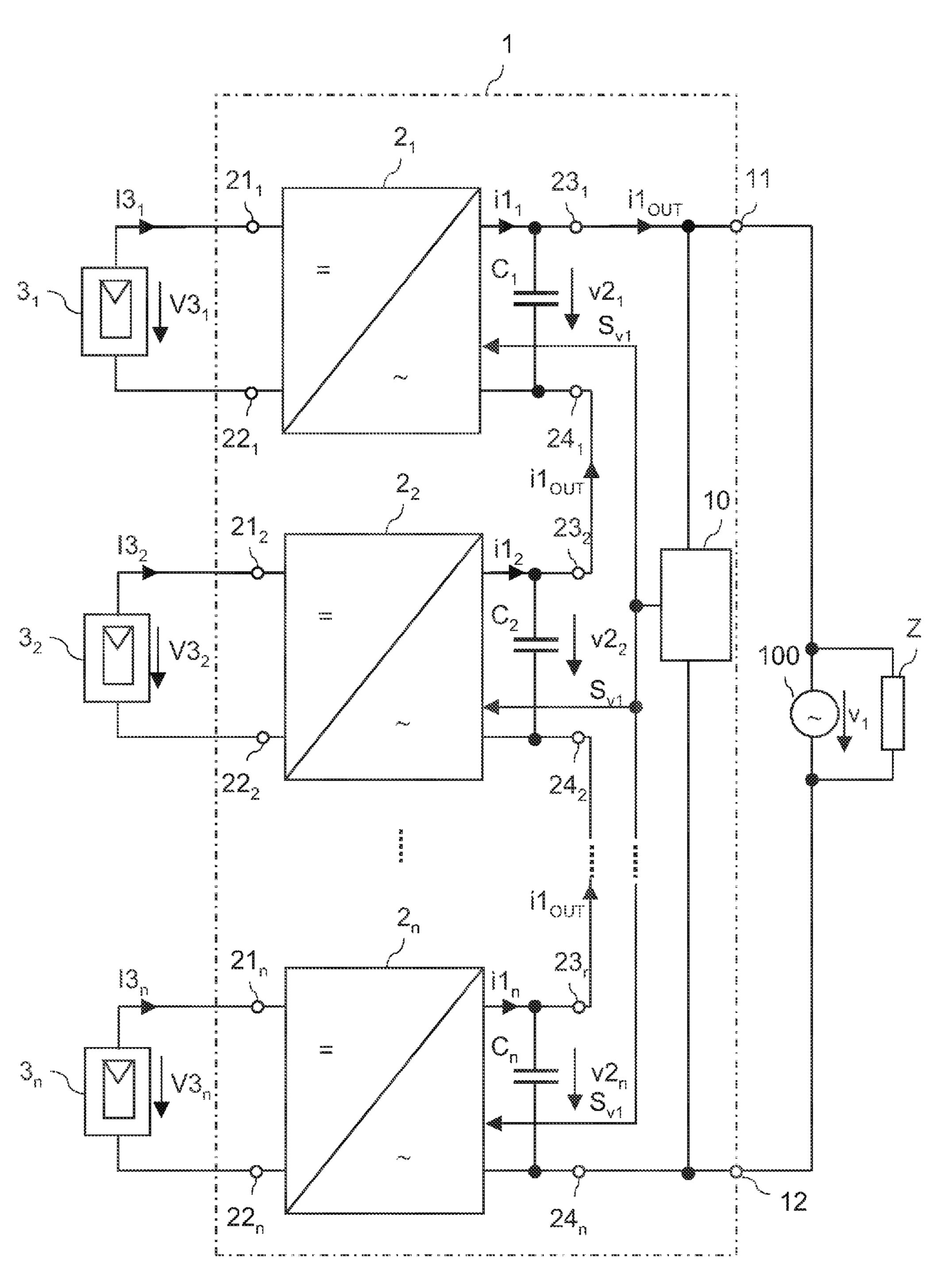

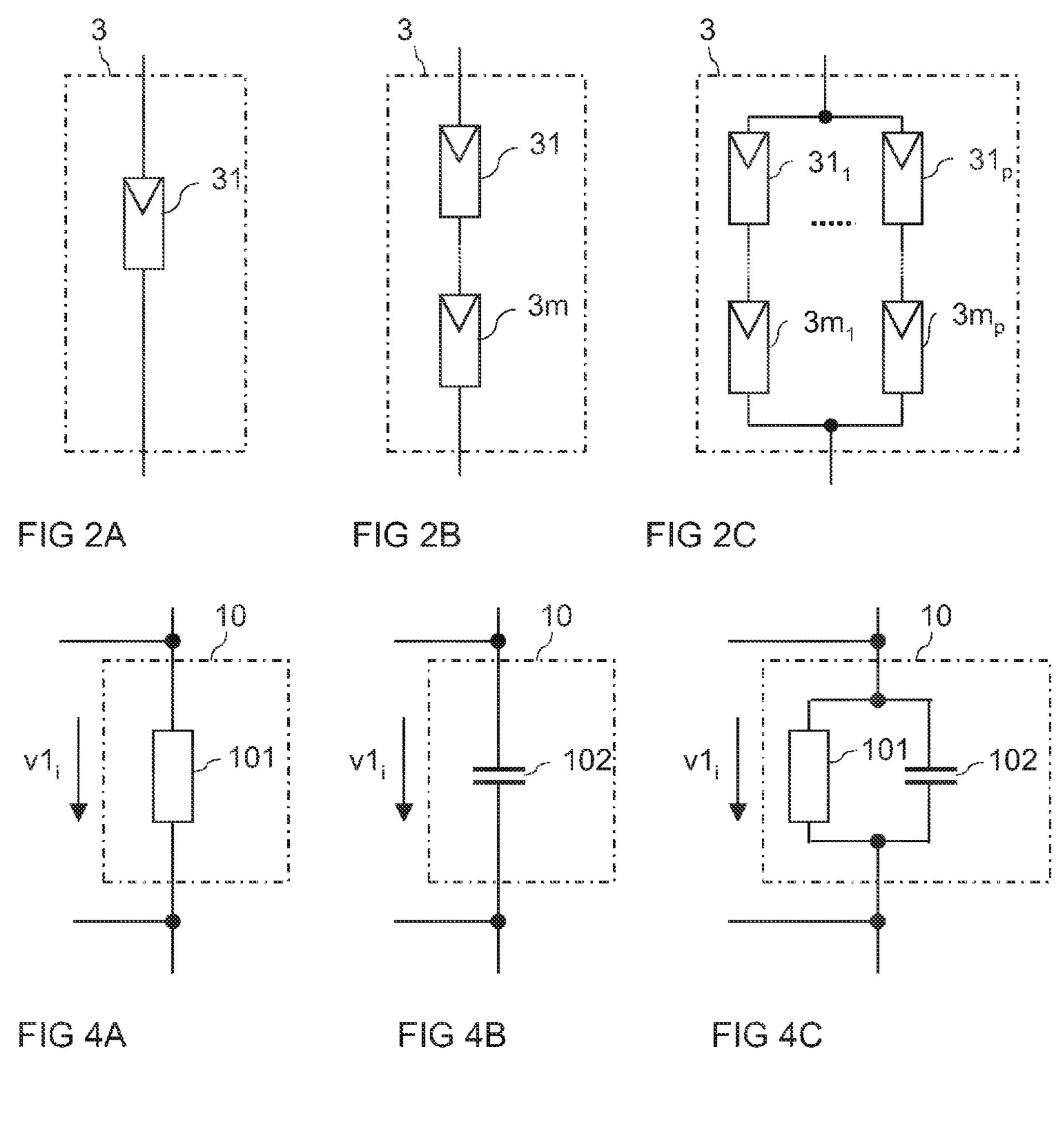

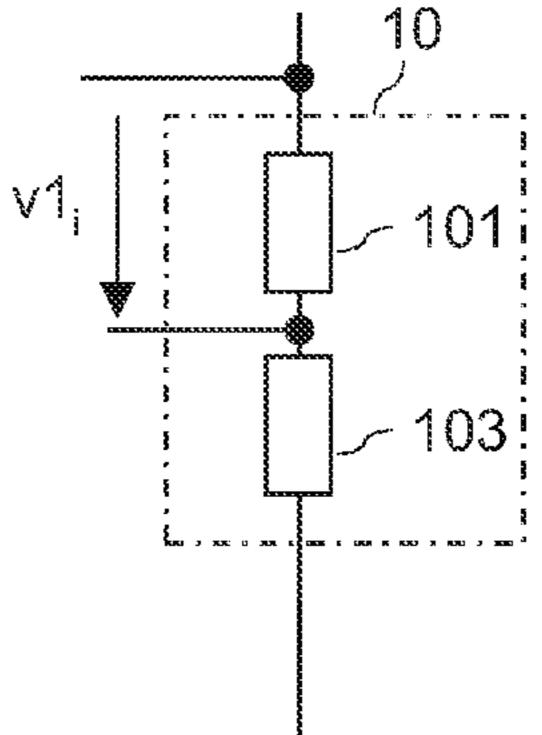

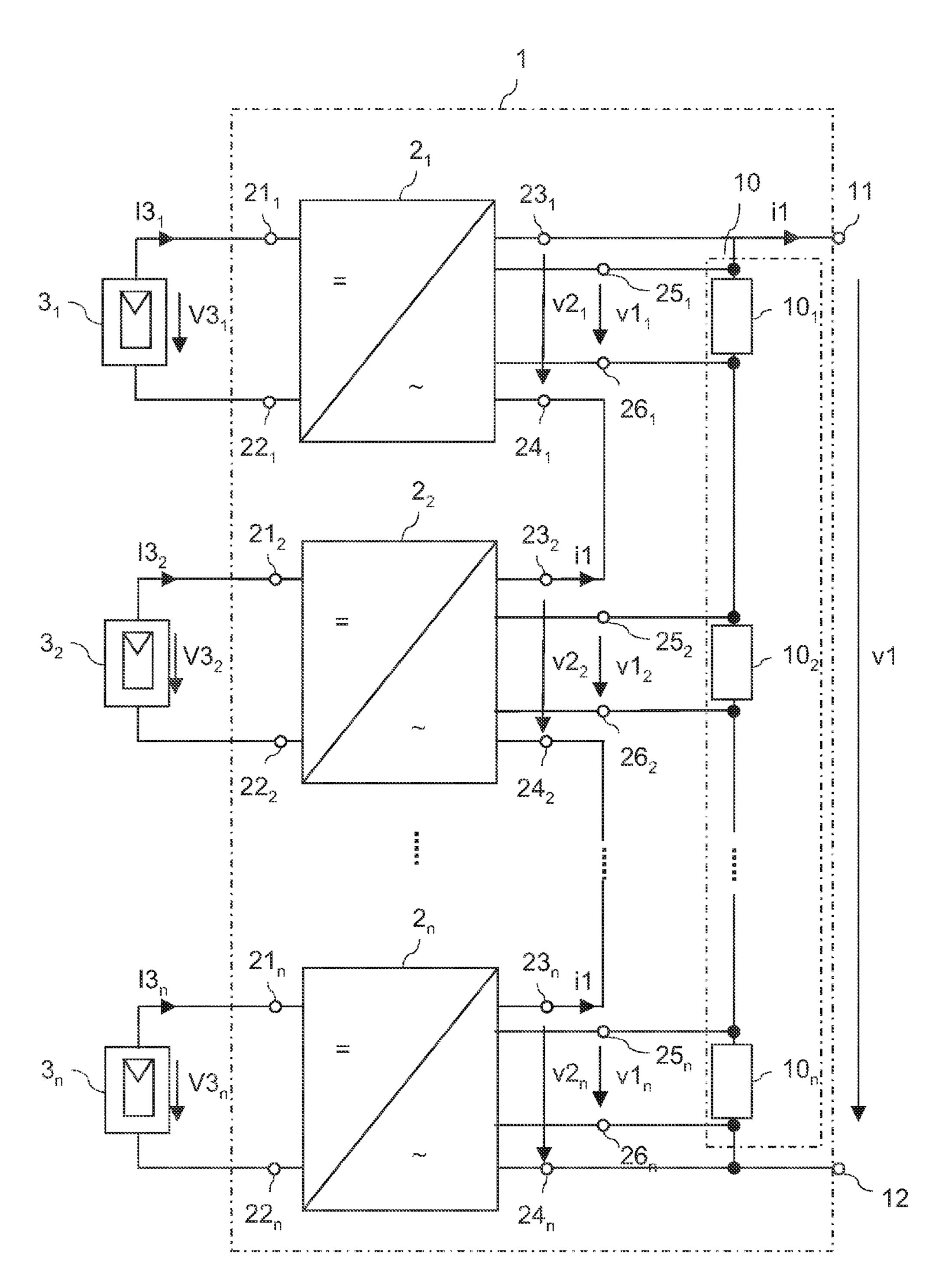

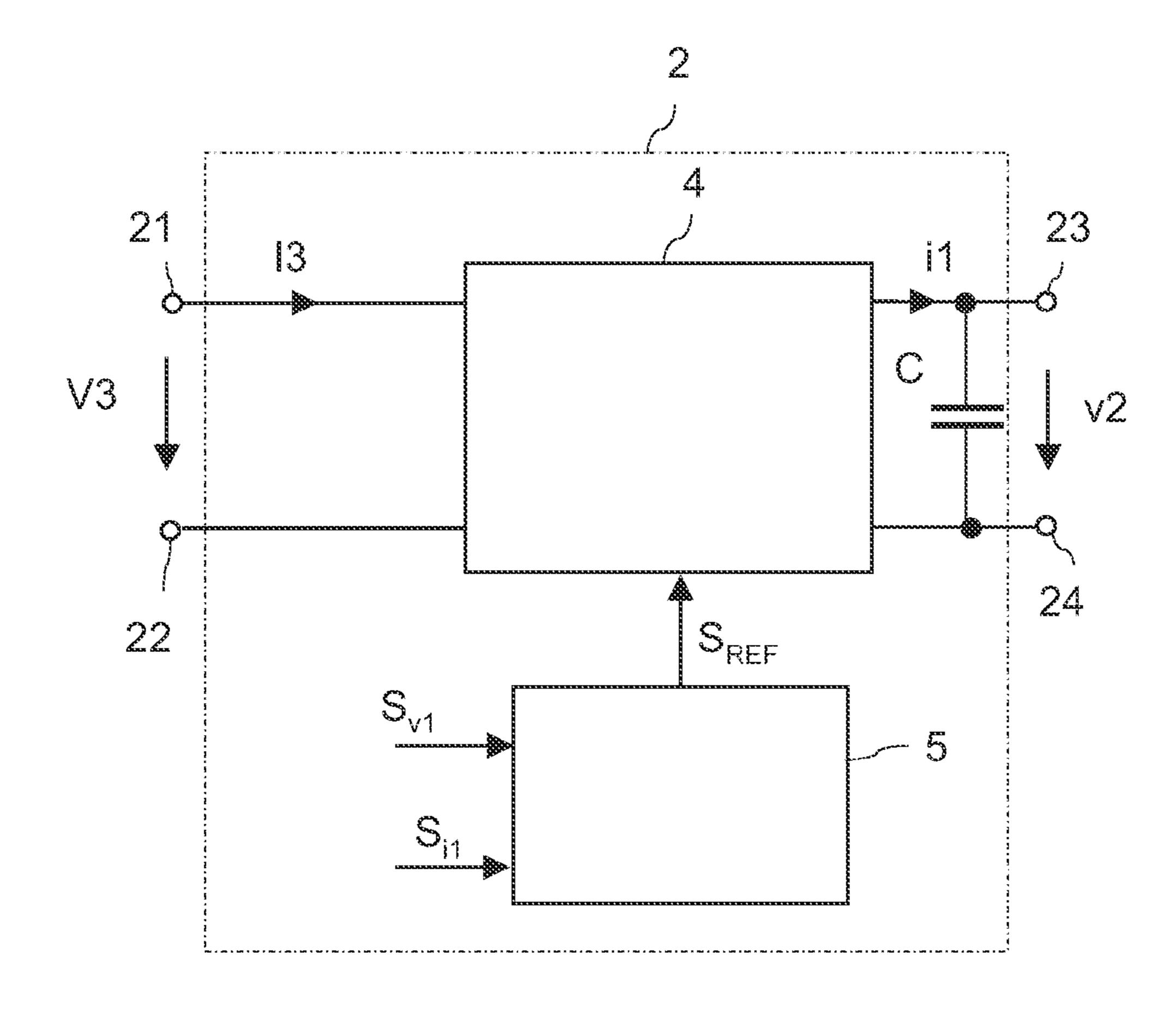

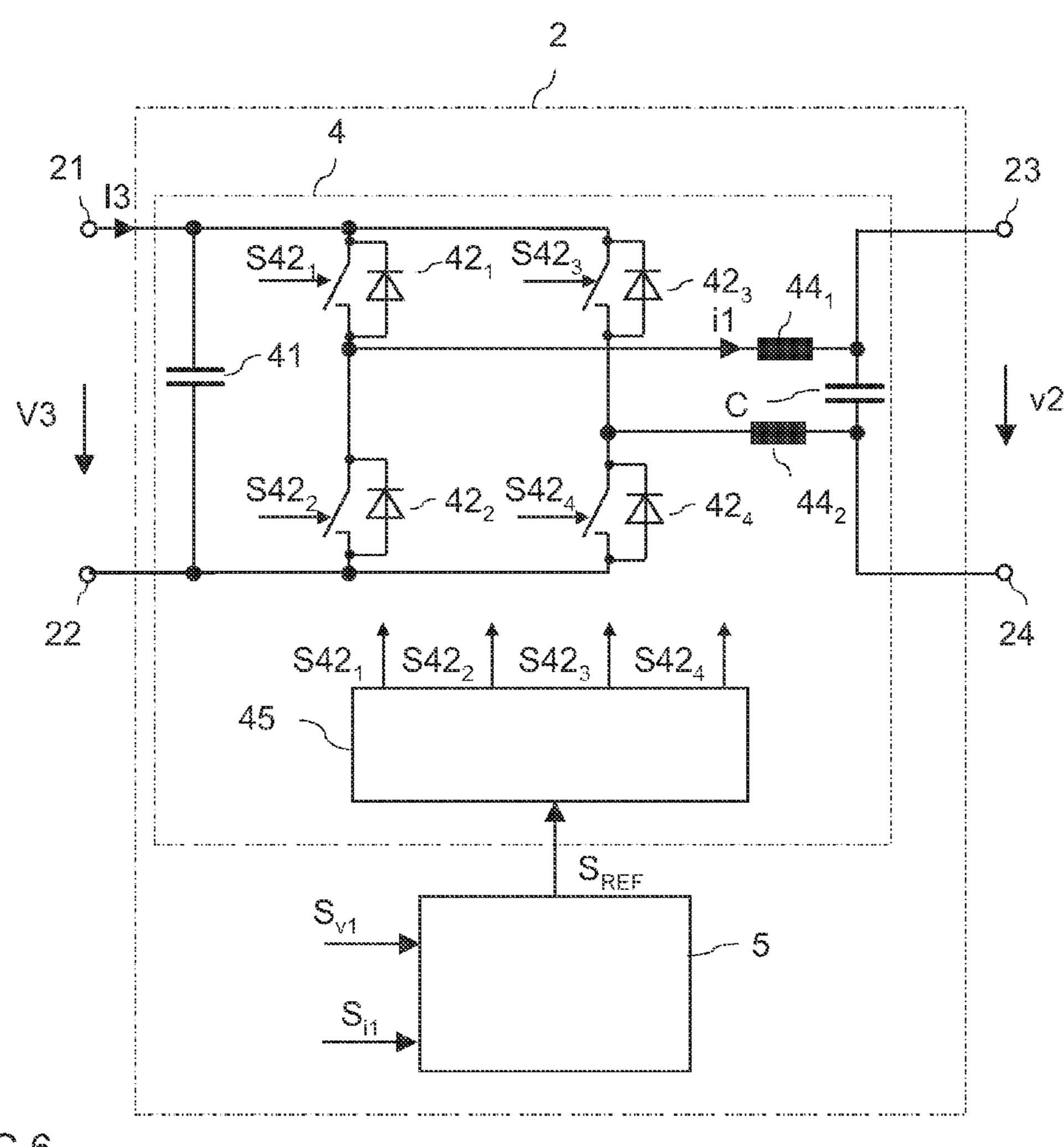

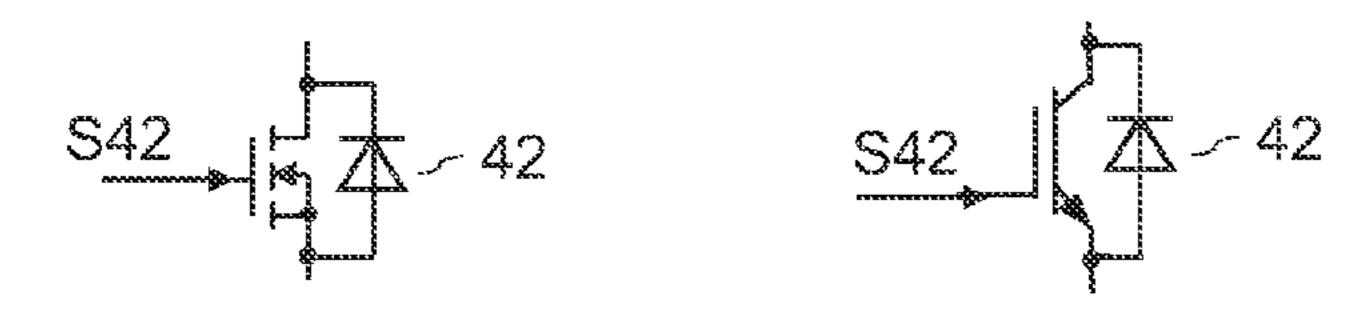

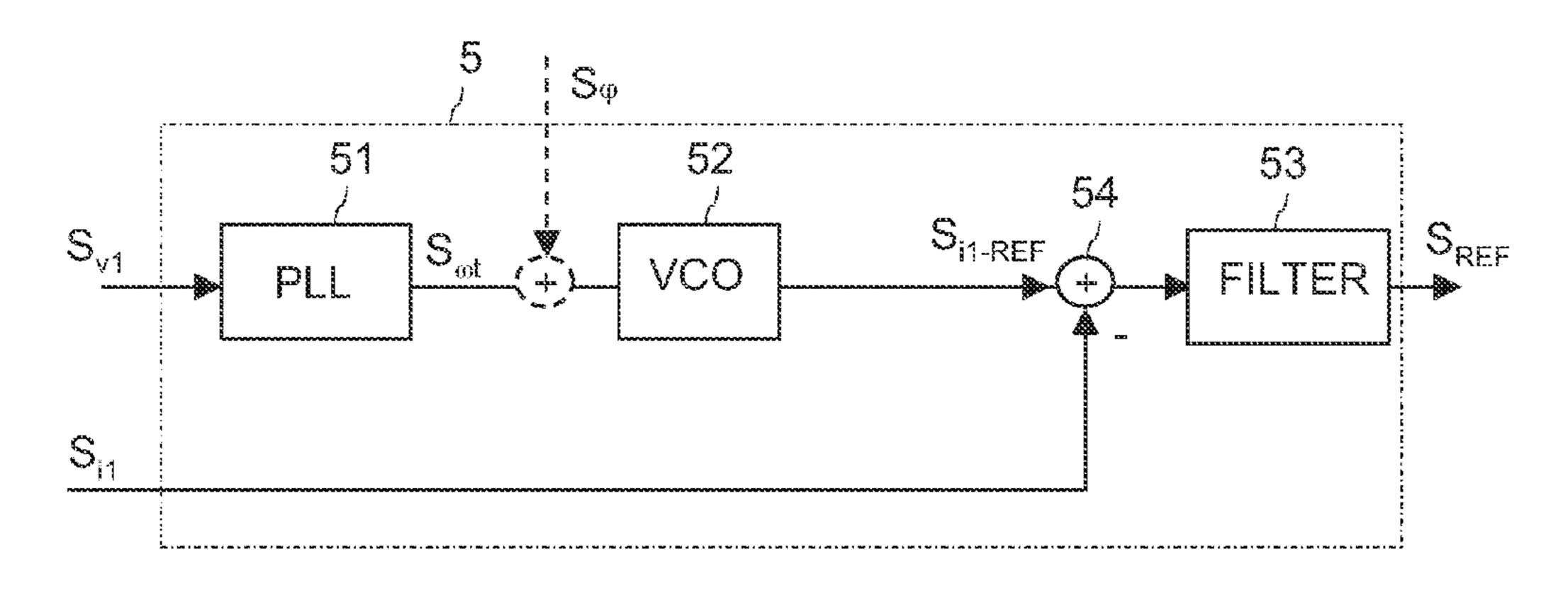

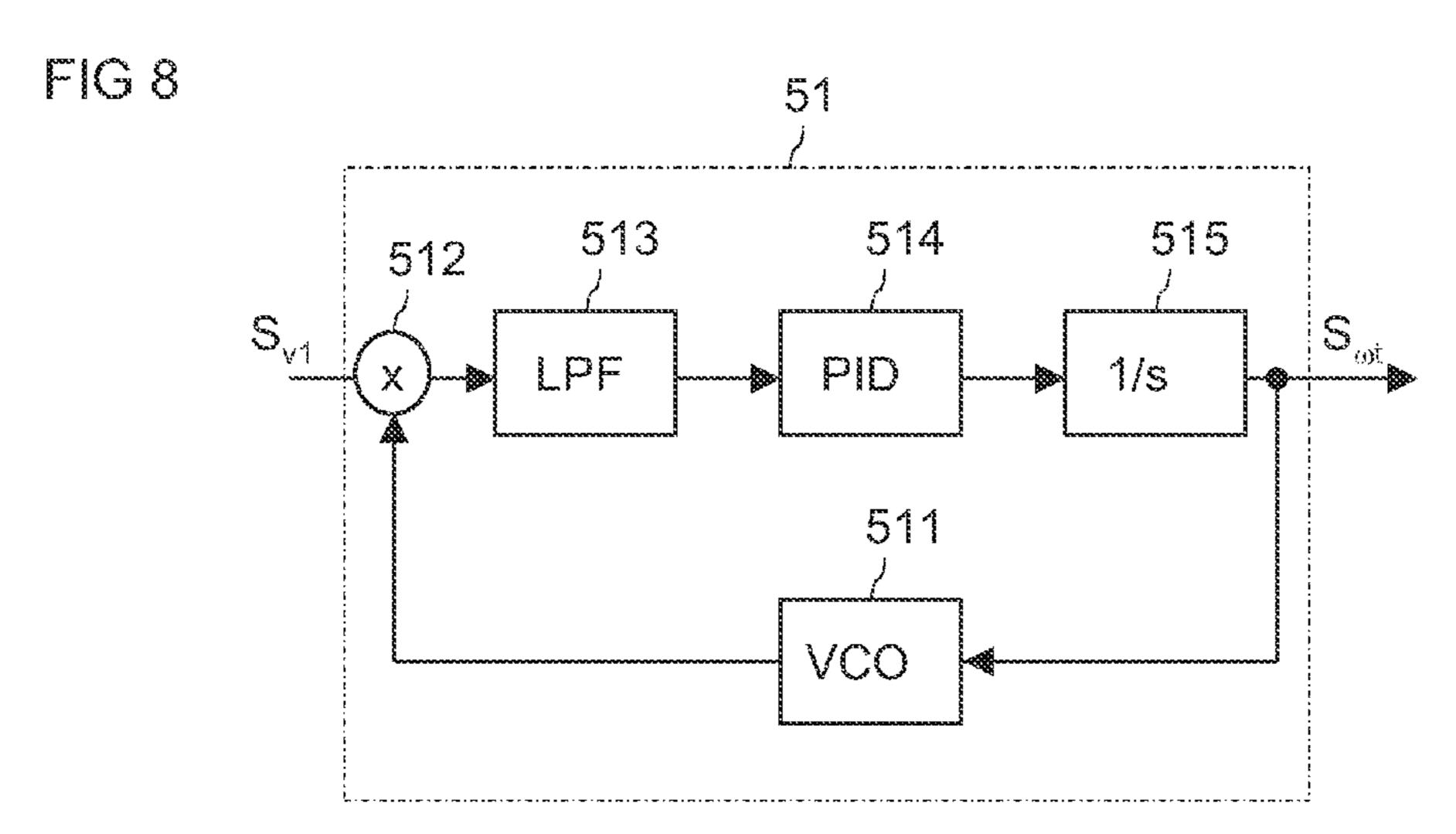

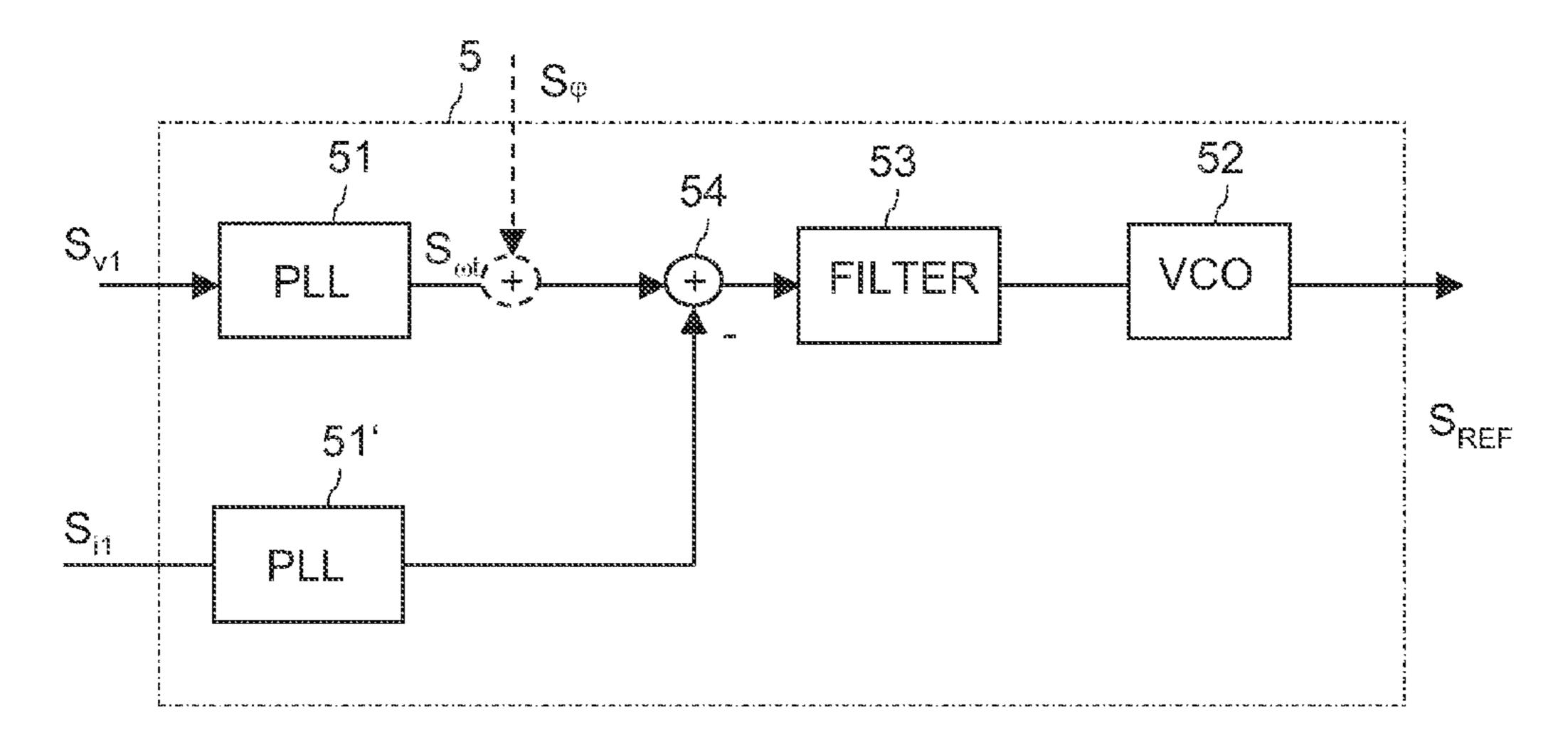

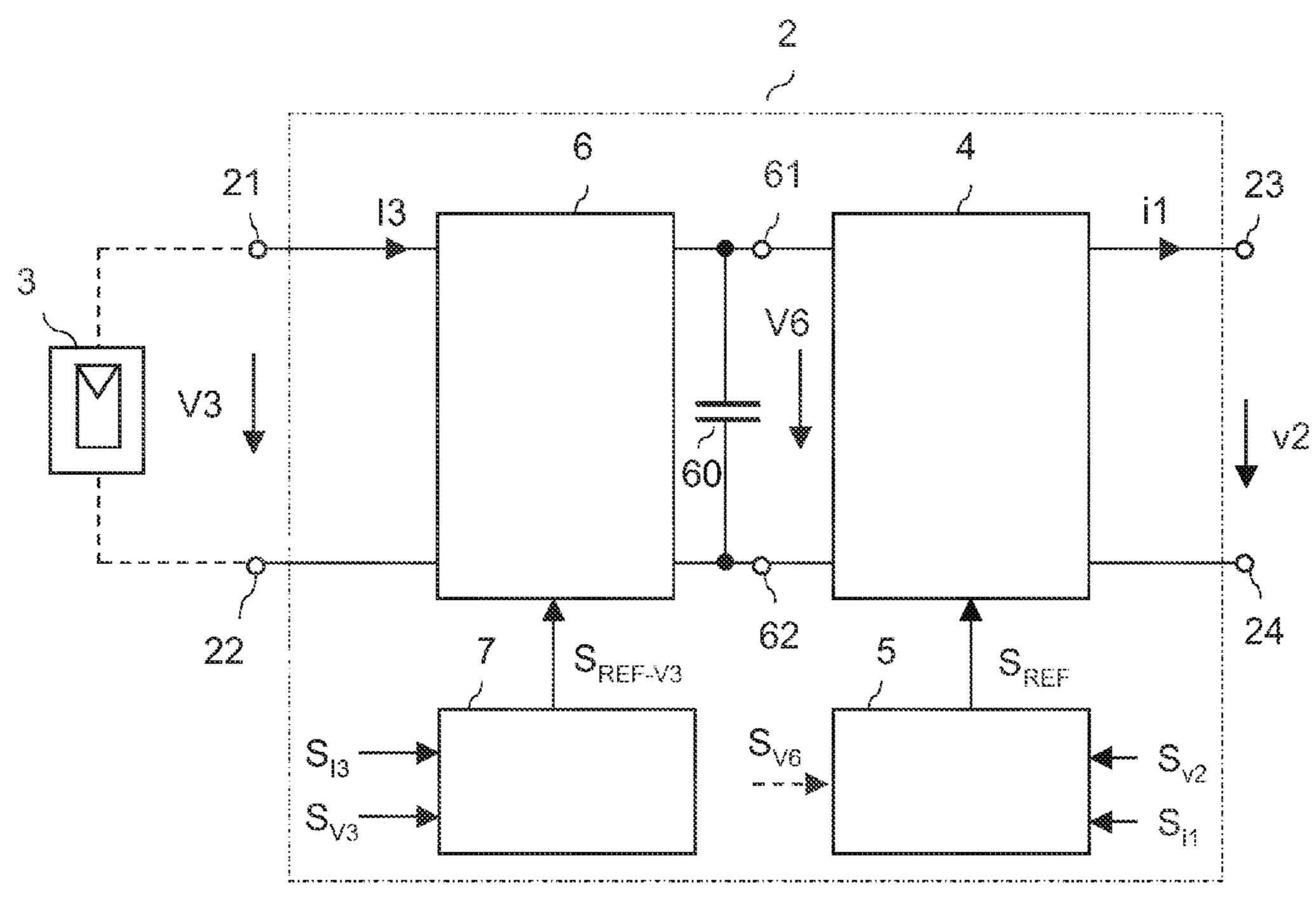

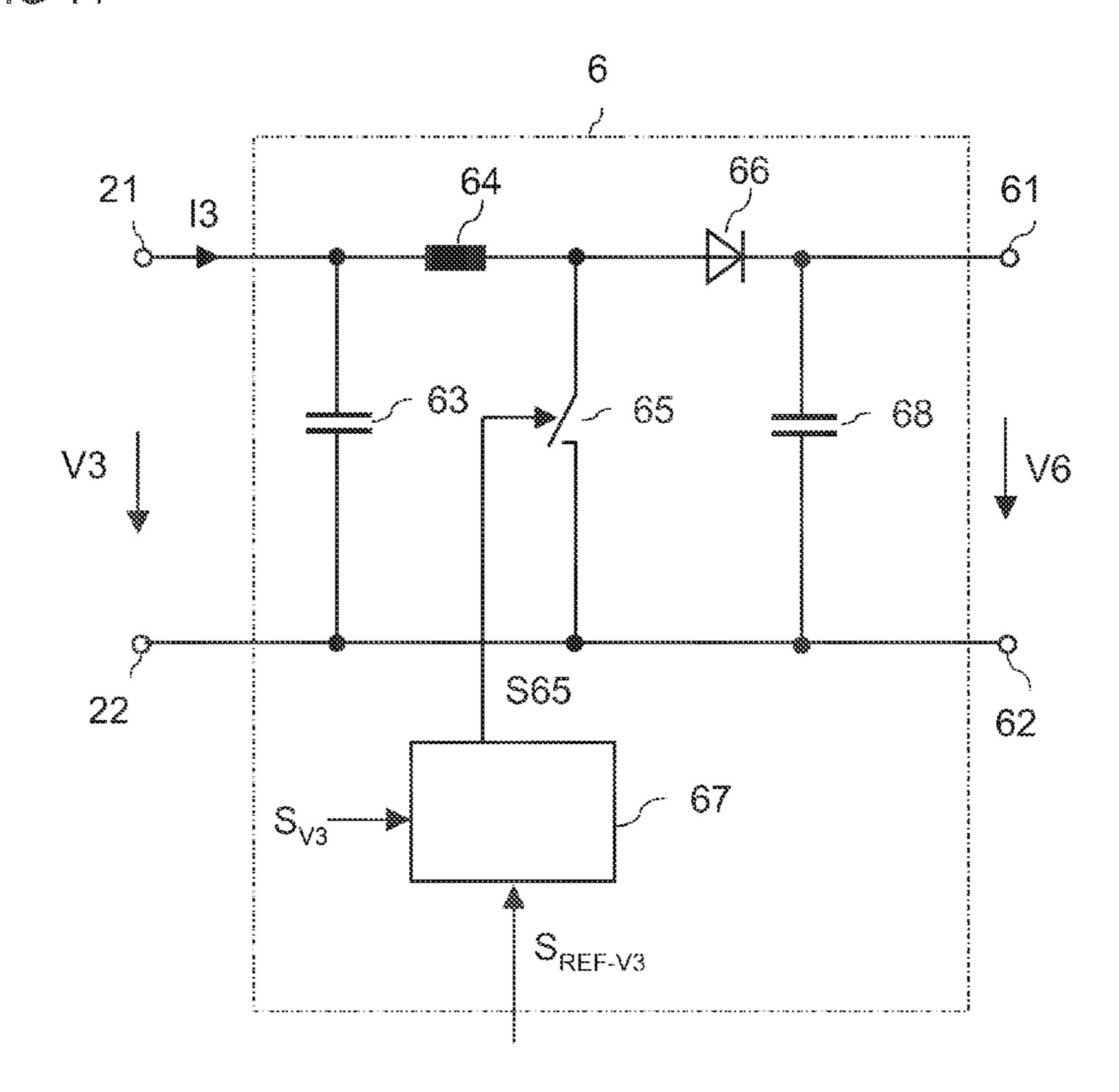

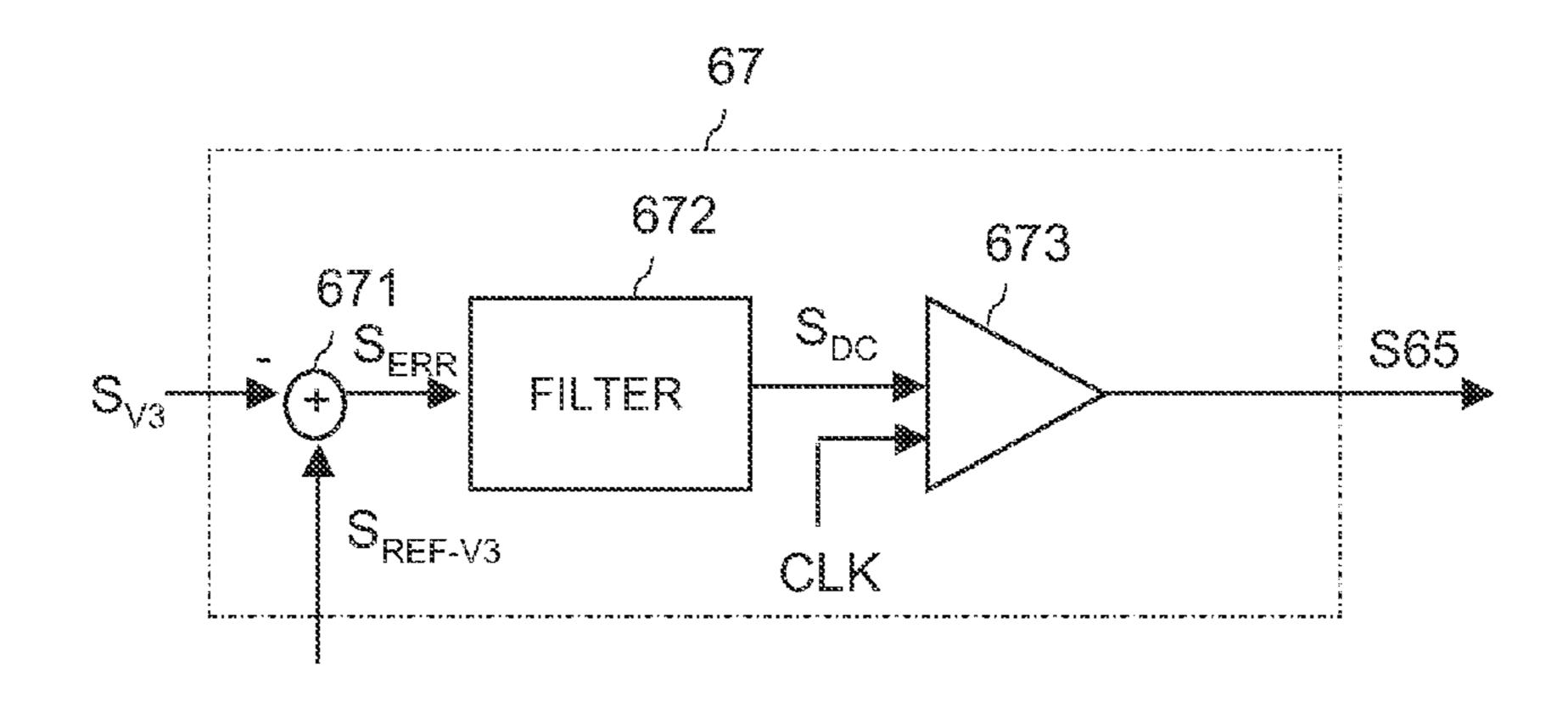

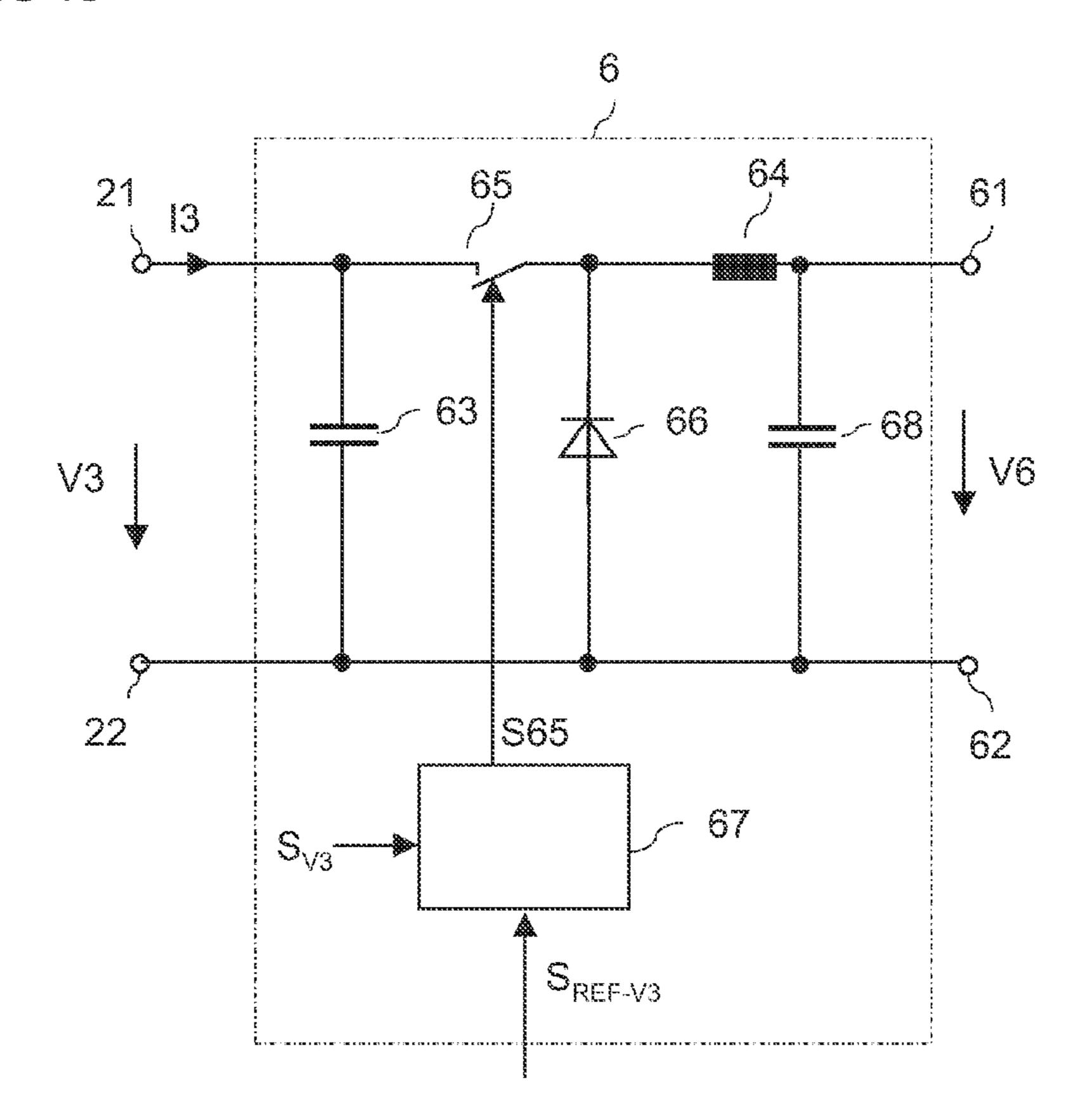

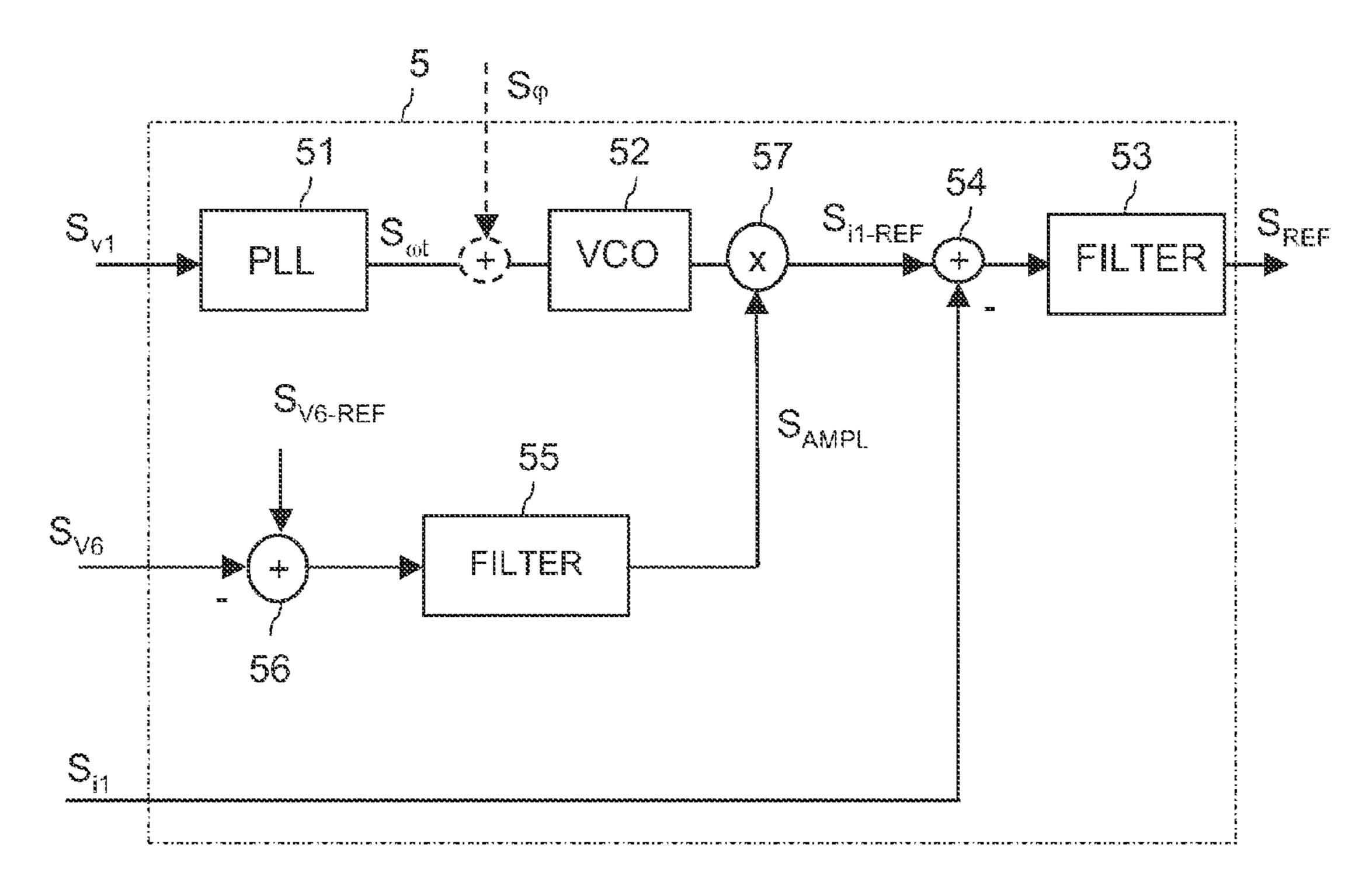

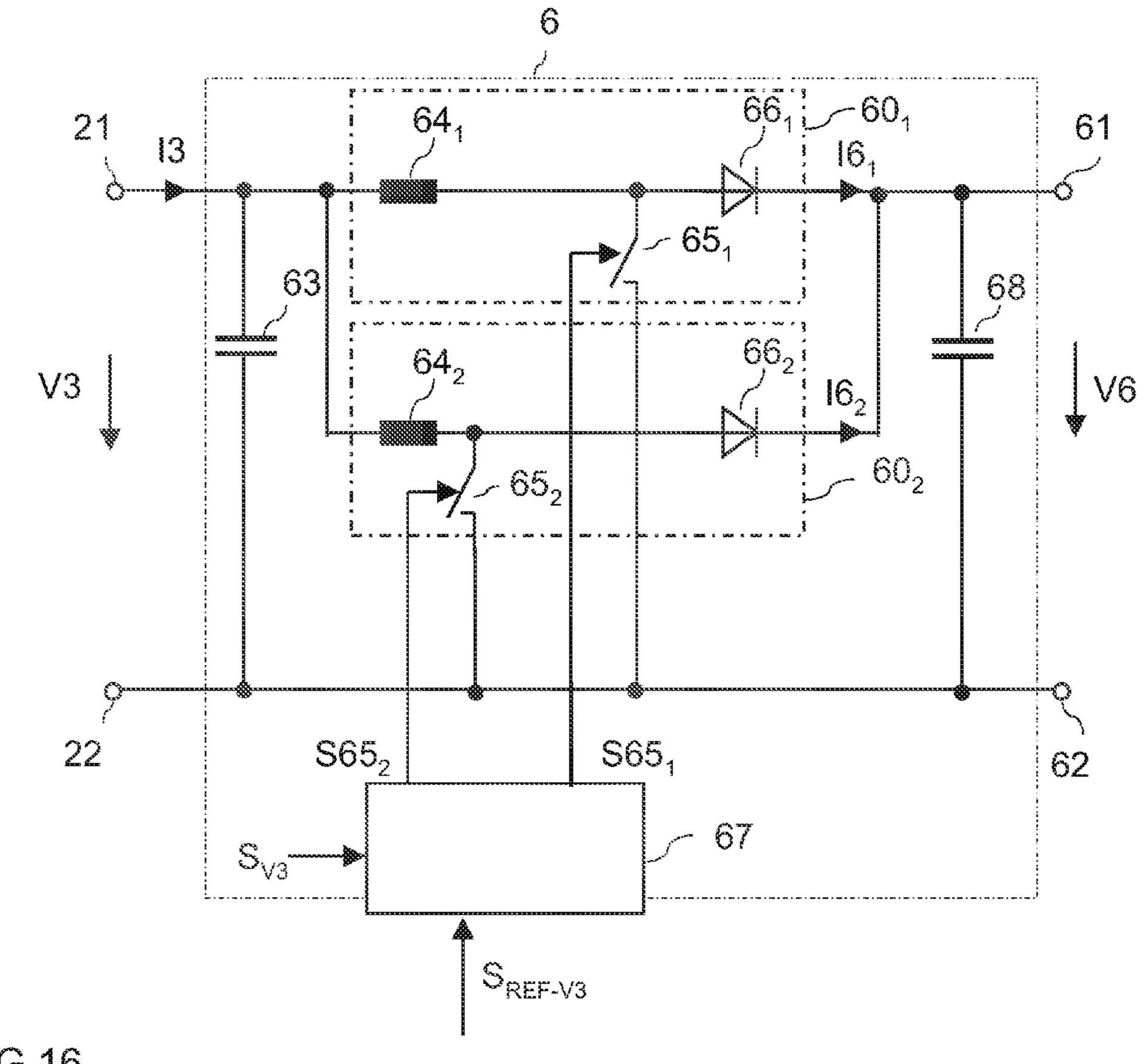

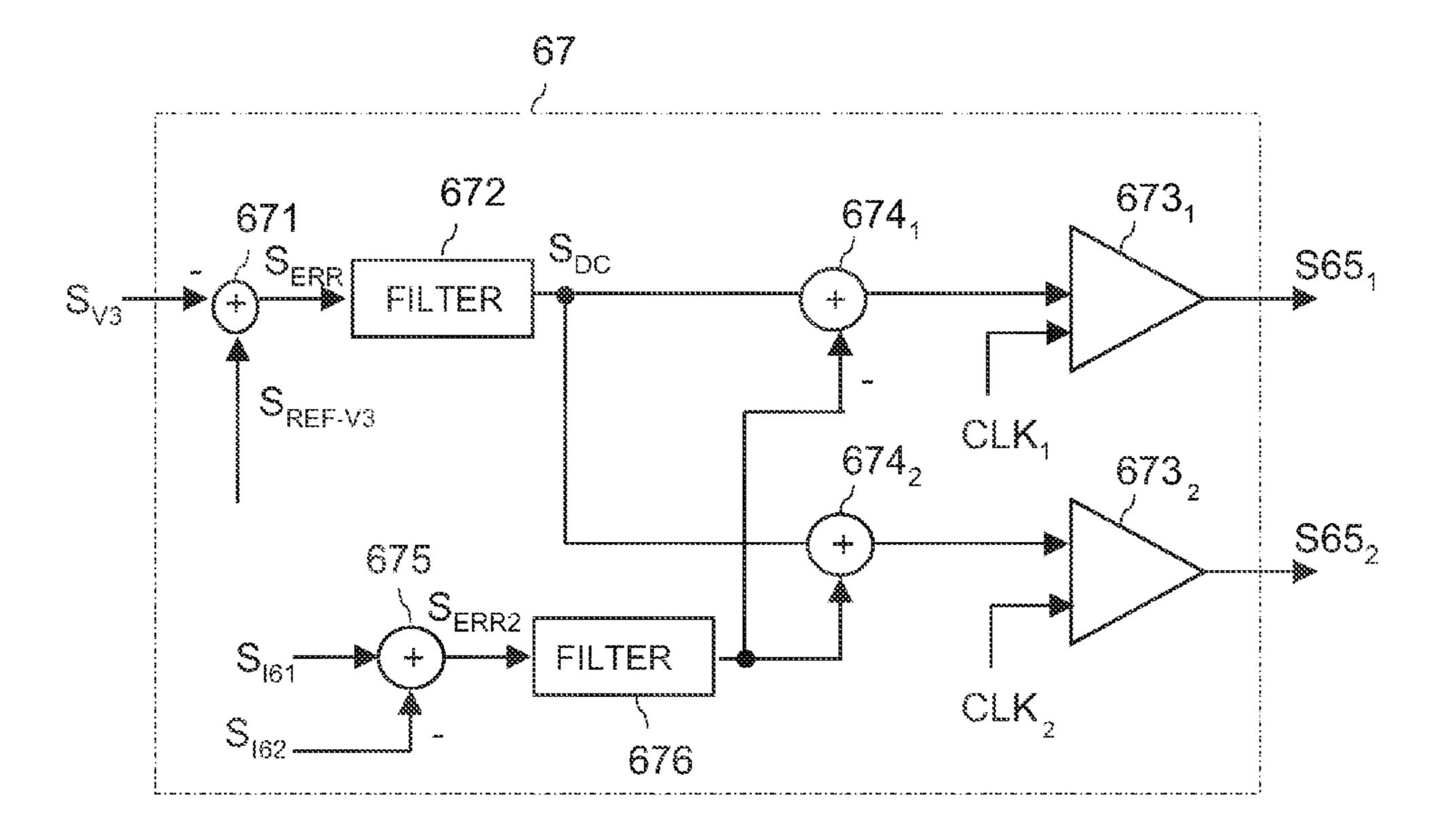

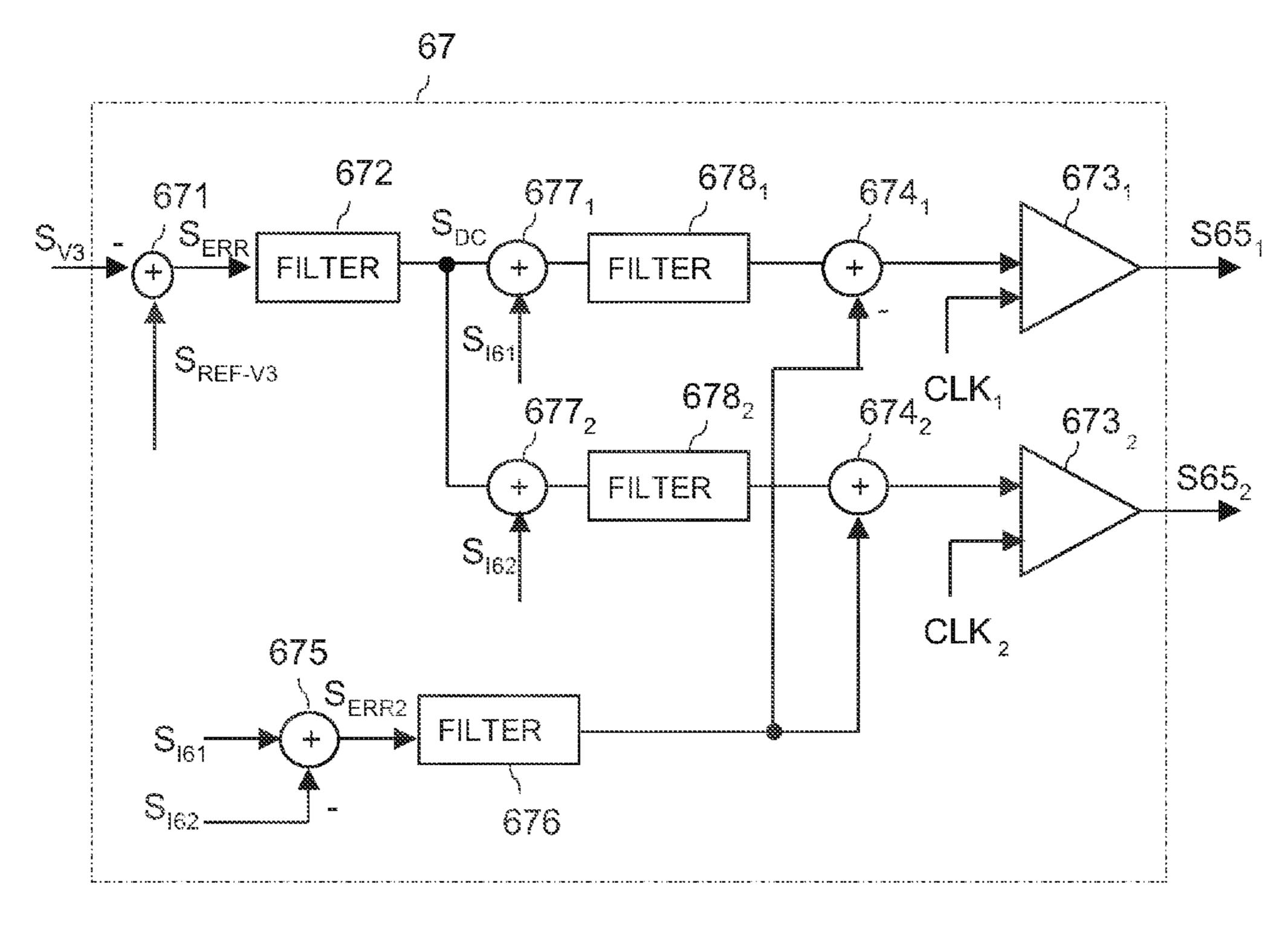

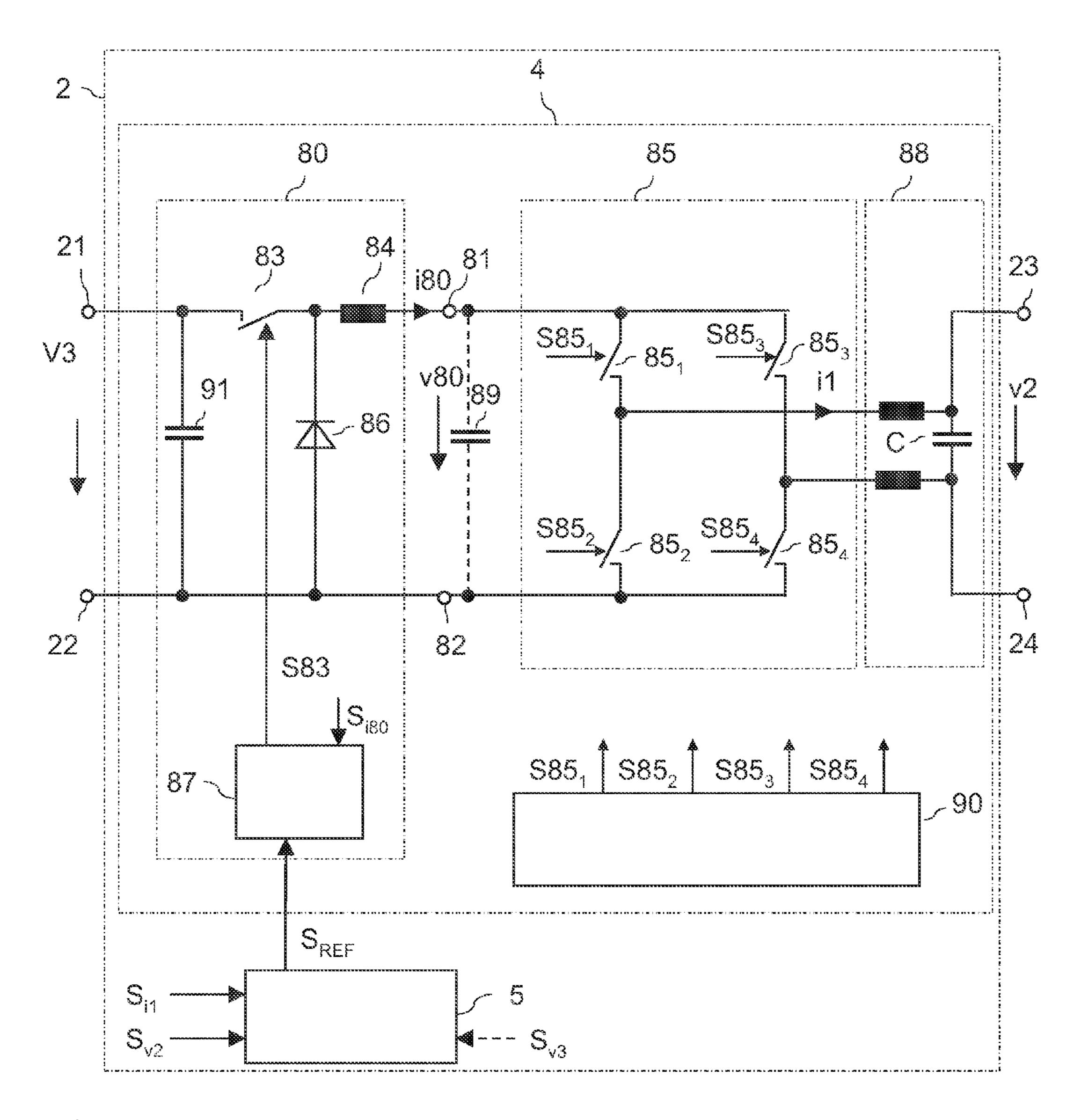

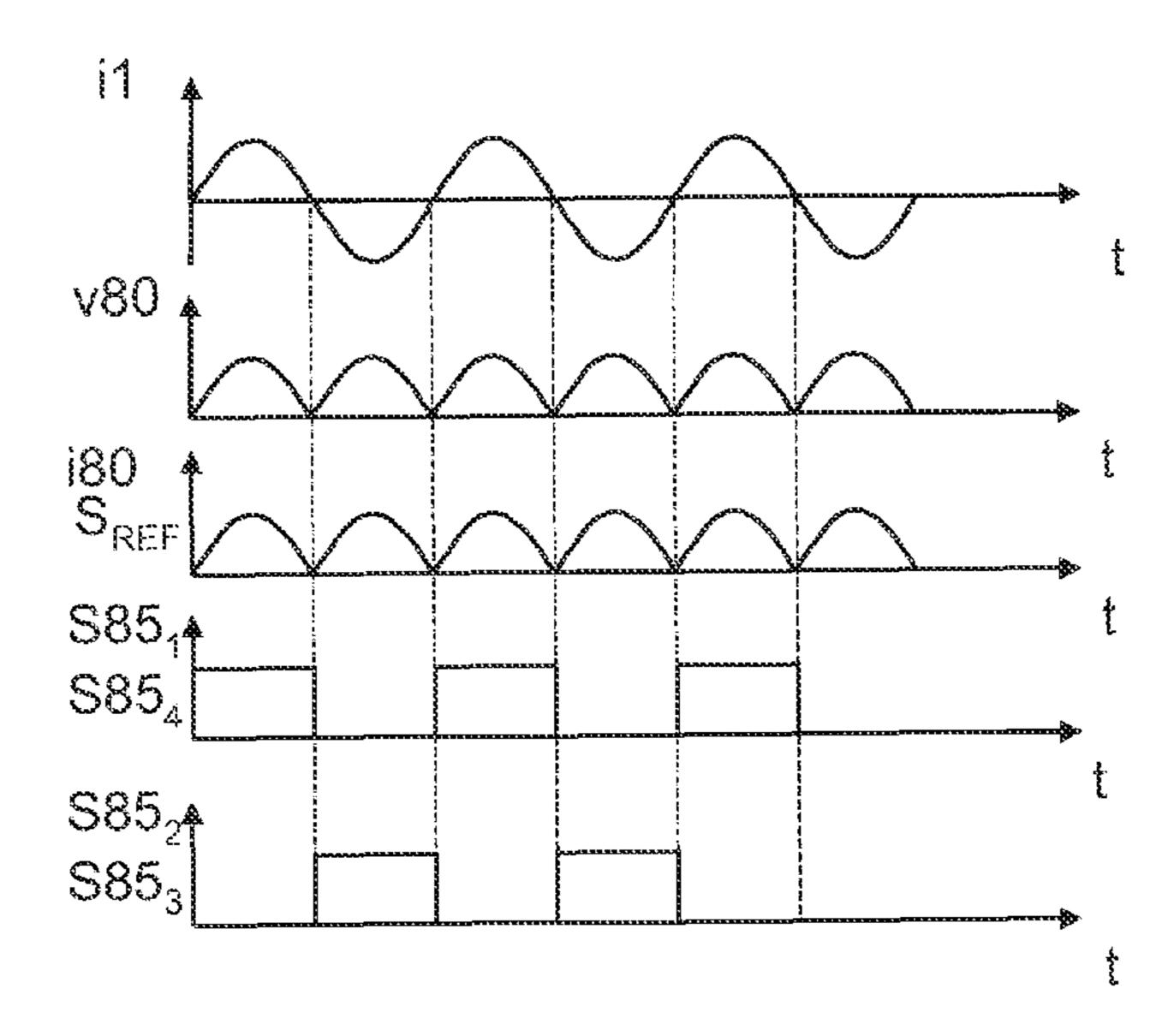

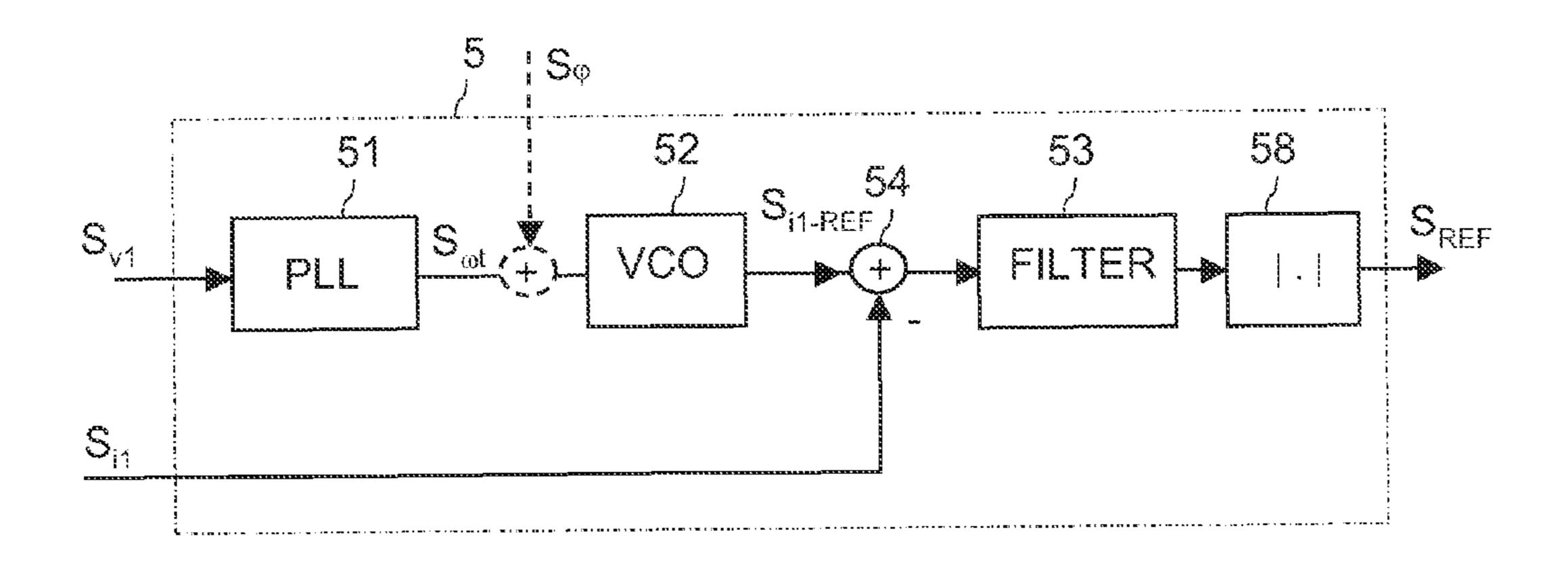

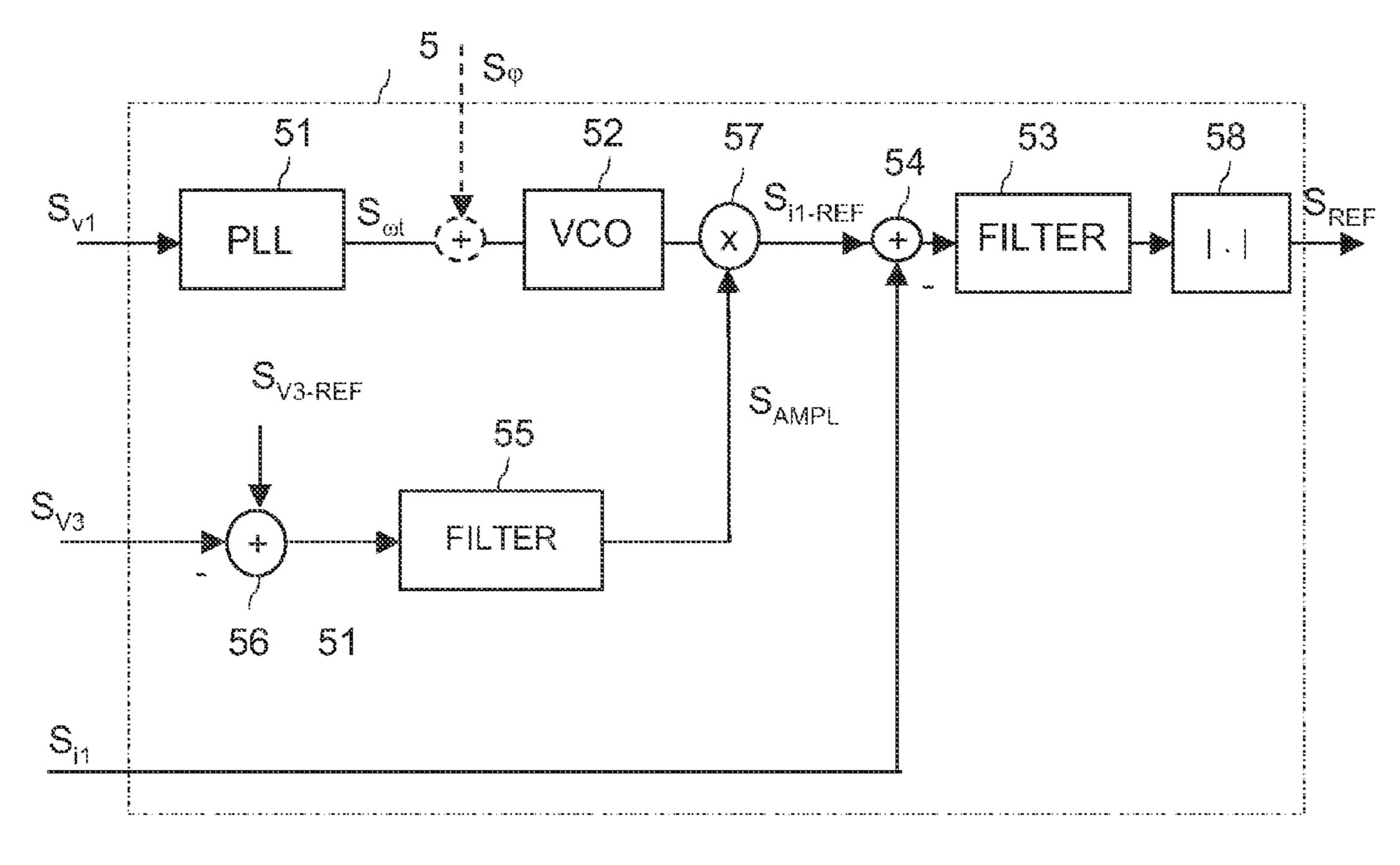

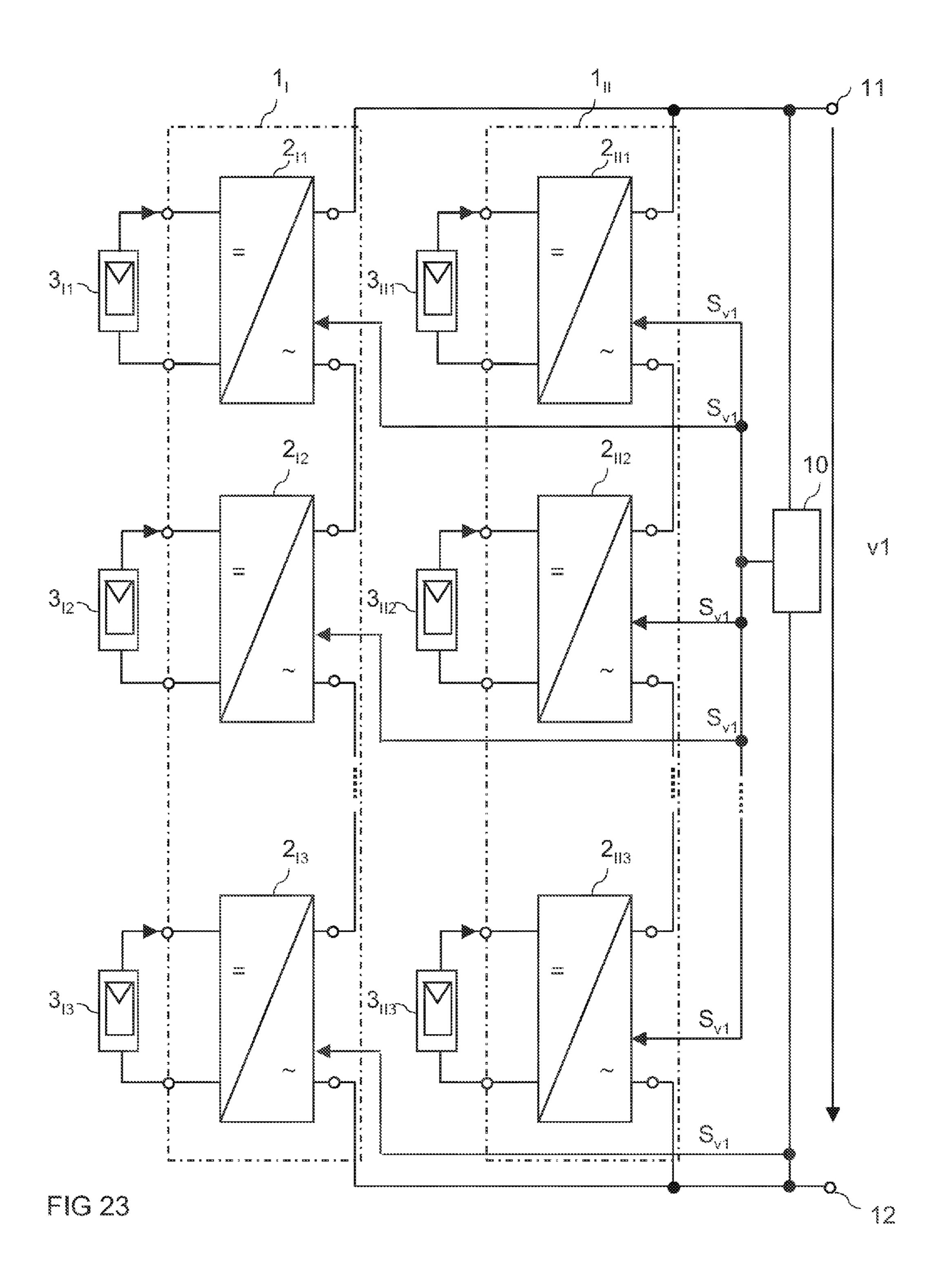

| 2013/0009700 A1 1/2013 Deboy et al. 2013/0155735 A1 6/2013 Ilic et al. 2013/0155736 A1 6/2013 Ilic et al. 2013/0181530 A1 7/2013 Deboy et al. 2013/0181531 A1 7/2013 Deboy et al. 2013/0181573 A1 7/2013 Deboy et al. 2013/0181573 A1 7/2013 Deboy et al. 2013/0187473 A1 7/2013 Deboy et al. 2014/0169053 A1 6/2014 Ilic et al. 2014/0175888 A1 6/2014 Deboy et al. 2014/0191582 A1 7/2014 Deboy et al. 2014/0191582 A1 7/2014 Deboy et al. 363/74 vol. 19, No. 4, Jul. 2004, pp. 1130-1139. Sahan, B., "Wechselrichtersysteme mit Stromzwischenkreis zur Netzanbindung von PV-Generatoren," ISBN 978-3-89958-912-2, 2010, 10 pages. Johnson, B., et al., "Photovoltaic AC Module Composed of a Very Large Number of Interleaved Inverters," Twenty-Sixth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Mar. 6-11, 2011, pp. 976-981, Fort Worth, Texas.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |               |         |                 | Walke                                                            | r, G., et al., "Cascade               | ed Do      | C-DC Converter Connection of      |