#### US009379971B2

### (12) United States Patent

Sem-Jacobsen et al.

### (10) Patent No.:

US 9,379,971 B2

(45) Date of Patent:

Jun. 28, 2016

# (54) METHOD AND APPARATUS FOR DETERMINING PATHS BETWEEN SOURCE/DESTINATION PAIRS

#### (71) Applicant: Simula Innovation AS, Lysaker (NO)

(72) Inventors: Frank O. Sem-Jacobsen, Minnesund

(NO); Olav Lysne, Bekkestua (NO); Hung Quoc Vo, Oslo (NO); Amund

Kvalbein, As (NO)

#### (73) Assignee: Simula Inovation AS, Lysaker (NO)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 368 days.

0.S.C. 134(b) by 30

#### (21) Appl. No.: 13/630,826

(22) Filed: **Sep. 28, 2012**

#### (65) Prior Publication Data

US 2013/0308444 A1 Nov. 21, 2013

#### Related U.S. Application Data

(60) Provisional application No. 61/645,937, filed on May 11, 2012.

| (51) | Int. Cl.    |           |

|------|-------------|-----------|

| ` /  | H04L 12/721 | (2013.01) |

|      | H04L 12/931 | (2013.01) |

|      | H04L 12/751 | (2013.01) |

|      | H04L 12/705 | (2013.01) |

|      | H04L 12/703 | (2013.01) |

|      | H04L 12/803 | (2013.01) |

(52) U.S. Cl.

CPC ...... *H04L 45/34* (2013.01); *H04L 45/02* (2013.01); *H04L 47/125* (2013.01); *H04L* 49/358 (2013.01); *H04L 45/12* (2013.01); *H04L 45/18* (2013.01); *H04L 45/28* (2013.01)

#### (58) Field of Classification Search

USPC ...... 370/218, 229, 235, 237, 238, 241, 248, 370/252, 254, 255, 392, 465; 709/224, 238 See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,812,549 A *    | ° 9/1998 | Sethu 370/389          |  |  |  |

|------------------|----------|------------------------|--|--|--|

| 6,874,032 B2 *   |          | Gersht et al 709/235   |  |  |  |

| 7,724,674 B2 *   | 5/2010   | Lysne 370/238          |  |  |  |

| 2002/0067693 A1* | 6/2002   | Kodialam et al 370/216 |  |  |  |

| 2002/0067720 A1* | 6/2002   | Garcia-Luna-Aceves     |  |  |  |

|                  |          | et al 370/389          |  |  |  |

| 2002/0101869 A1* | 8/2002   | Garcia-Luna-Aceves     |  |  |  |

|                  |          | et al 370/389          |  |  |  |

| 2002/0141346 A1* | 10/2002  | Garcia-Luna-Aceves     |  |  |  |

|                  |          | et al 370/238          |  |  |  |

| 2004/0193729 A1* | 9/2004   | Saraph 709/241         |  |  |  |

| 2005/0111465 A1* |          | -                      |  |  |  |

| (Continued)      |          |                        |  |  |  |

#### OTHER PUBLICATIONS

Vo et al., Permutation Routing for Increased Robustness in IP Networks, May 21-25, 2012, Springer, Networking 2012: 11th International IFIP TC 6 Networking Conference, Prague, Czech Republic, Proceedings, Part I, pp. 217-231.\*

Glass et al., The Turn Model for Adaptive Routing, Computer Architecture, 1992, IEEE, Proceedings., The 19th Annual International Symposium on, pp. 278-287.\*

#### (Continued)

Primary Examiner — Benjamin H Elliott, IV

Assistant Examiner — Eric Nowlin

(74) Attorney, Agent, or Firm — Oblon, McClelland, Maier

#### (57) ABSTRACT

& Neustadt, L.L.P.

Described herein are a method and device for determining paths in a network topology. The method and device provide a source/destination pair representing a source and a destination in the network topology, provide a channel list comprising a topological ordering of channel identifiers representing communication channels in the network topology, and provide at least one path connecting the source and the destination based on the channel list.

#### 44 Claims, 33 Drawing Sheets

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 2007/0053342 A1*                                         | 3/2007 | Sierecki H04L 45/10<br>370/351                                                        |

|----------------------------------------------------------|--------|---------------------------------------------------------------------------------------|

| 2007/0070883 A1*<br>2007/0253403 A1*                     |        | Lysne et al                                                                           |

| 2008/0049609 A1*<br>2008/0232347 A1*                     |        | 370/351<br>Chao et al                                                                 |

| 2010/0232347 A1*<br>2010/0182934 A1*<br>2012/0044837 A1* | 7/2010 | Dobbins et al                                                                         |

| 2012/0140631 A1*<br>2012/0170582 A1*                     |        | et al.       370/256         Klausler       370/235         Abts et al.       370/392 |

#### OTHER PUBLICATIONS

Dally et al.; Deadlock-Free Adaptive Routing in Multicomputer Networks Using Virtual Channels, Apr. 1993, IEEE, IEEE Transactions on Parallel and Distributed Systems, vol. 4, No. 4, pp. 466-475.\*

Starobinki et al., Application of Network Calculus to General Topologies Using Turn-Prohibition, Jun. 2003, IEEE, IEEE/ACM Transactions on Networking, vol. 11, No. 3, pp. 411-421.\*

Skeie et al., LASH-TOR: A Generic Transition-Oriented Routing Algorithm, Proceedings. Tenth International Conference on Parallel and Distributed Systems, 2004. ICPADS 2004, IEEE, pp. 595-604, Jul. 7-9, 2004.\*

Extended European Search Report issued Sep. 17, 2013 in European Patent Application No. 12189314.3.

William J. Dally, et al., "Deadlock-Free Adaptive Routing in Multicomputer Networks Using Virtual Channels", IEEE Transactions on Parallel and Distributed Systems, vol. 4, No. 4, XP 000381816, Apr. 1, 1993, pp. 466-475.

William J. Dally, et al. "Deadlock-Free Message Routing in Multi-processor Interconnection Networks", IEEE Transactions on Computers, vol. C-36, No. 5, May 1987, 7 pgs.

Olav Lysne, et al. "A Methodology for Deriving Deadlock-Free Dynamic Network Reconfiguration Processes", 30 pgs.

<sup>\*</sup> cited by examiner

Т. Э.

Fig. 3

Fig. 4

Fig. 5

Fig. 6

Fig. 7

Fig. 8

Fig. 9A

Fig. 9B

Fig. 10

Fig. 11

Fig. 13

Fig. 14

Fig. 15

Fig. 16

Fig. 18

Fig. 19B

Fig. 20

Fig. 21

Fig. 24

Fig. 27A

Fig. 27B

1

# METHOD AND APPARATUS FOR DETERMINING PATHS BETWEEN SOURCE/DESTINATION PAIRS

## CROSS-REFERENCE TO RELATED APPLICATIONS

This application is based upon and claims the benefit of priority under 35 U.S.C. §119(e) from U.S. Ser. No. 61/645, 937, filed May 11, 2012, the entire contents of which are <sup>10</sup> incorporated herein by reference.

## FIELD OF THE EMBODIMENTS OF THE INVENTION

The present embodiments of the invention relates to a method and apparatus for determining paths between source/destination pairs.

#### DISCUSSION OF THE BACKGROUND

Intelligent routing has been applied to various fields in recent years. For example, such routing has been implemented for large area networks such as the Internet and to small area networks such as (on-chip) networks for super- 25 computers.

In the field of large area networks, the last few years have witnessed the adoption of the Internet as the preferred transport medium for services of critical importance for business and individuals. In particular, an increasing number of timecritical services such as trading systems, remote monitoring and control systems, telephony and video conferencing place strong demands on timely recovery from failures. For these applications, even short outages in the order of a few seconds will cause severe problems or impede the user experience. 35 This has fostered the development of a number of proposals for more robust routing protocols, which are able to continue packet forwarding immediately after a component failure, without the need for a protocol re-convergence. Such solutions add robustness either by changing the routing protocol 40 so that the routing protocol installs more than one next-hop towards a destination in the forwarding table, or by adding backup next-hops a posteriori to the forwarding entries found by a standard shortest path routing protocol. Unfortunately, few of these solutions have seen widespread deployment, due 45 to added complexity or incompatibility with existing routing protocols.

In the field of small area networks, high-performance and cluster computing systems have become more common. These systems rely heavily on the efficiency of the interconnection network. In latter years, the sizes of such systems have become so big that the network also needs to be able to function in the presence of faulty components. This has led to the study and implementation of various methods for routing around faults that appear while the system is running.

Such fault tolerant routing consists of two elements. The first is a method for finding a routing function that is efficient for semi-regular topologies, i.e. topologies such as meshes, tori, and fat-trees where some components have been removed due to malfunctions. Ideally this method should be fast—so that the system can commence normal operation as soon as possible after the fault. Furthermore, it should be efficient, so that the degradation of performance in the presence of the fault is minimal. Finally, it should not require more virtual channels for deadlock freedom than the routing algorithm needs for the fault free case. The second element of fault tolerant routing is a method for transitioning between the

2

old and the new routing function without causing deadlock. It is well known that even if the old and the new routing functions are deadlock free by themselves, an uncontrolled transition between the two can cause deadlocks.

Unfortunately, there is a huge gap between the ideal described above and the current state of the art. Computing a new routing function when a fault has occurred is not at all fast. For systems such as Ranger, Atlas, and JuRoPa that are based on InfiniBand and use the OFED OpenSM subnet manager, the execution time for the routing algorithms (minhop, Up\*/Down\*) is in the range of hundreds of seconds to 15 min. Furthermore, the routing functions that come out of the recalculation are based on Topology Agnostic methods, that disregard the carefully planned routing strategies, which have been made for the fault free case. For this reason, they either require additional virtual channels, or they lead to a severe drop in performance, or both. Regarding reconfiguration between the old and the new routing function, the picture is equally bleak. Even though several mechanisms for deadlock 20 free dynamic reconfiguration have been proposed, none of them are implemented in current hardware. Runtime reconfiguration in Infiniband simply updates the forwarding tables in the switches in the network with the values calculated by the routing function and makes no provisions for guaranteeing a deadlock free transition. A common solution to this problem is to use static reconfiguration. This requires the entire fabric to be drained of all traffic and shut down before the reconfiguration commences. A far more efficient solution is to change the routing tables in the network on-the-fly. This requires careful handling by the routing algorithm of the transient dependencies that occur when the routing tables are updated.

#### SUMMARY OF THE INVENTION

With regard to the field of large area networks, the present embodiments presents an intelligent routing method designated as Permutation Routing as novel and flexible approach for calculating multiple loop-free next-hops in networks with traditional hop-by-hop forwarding.

Permutation Routing is based on the observation that routing in any network consists of using a set of resources (links and nodes) in sequence. A routing strategy can therefore be expressed as a permutation of the nodes that are involved in traffic forwarding to a destination. Routing will be loop-free as long as traffic can only be forwarded in one direction with respect to the node ordering in this permutation. One important goal is to use Permutation Routing to create a routing that maximizes single link fault coverage.

Permutation Routing can be used to create various routing strategies. For instance, Permutation Routing can provide a simple backtracking algorithm that constructs a permutation of routers for each destination, and a simple forwarding rule that enables generation of forwarding tables based on the permutations. The properties of the resulting routing are determined by the constraints that are used at each step in the permutation construction. The input to the construction algorithm is the topology information that is collected by a standard link state routing protocol, and hence no new control plane signaling is needed with Permutation Routing.

Remarkably, permutation routing can easily be integrated with existing intradomain routing protocols, and can be used to augment the shortest path routing tables with additional forwarding entries. The constraints in the permutation construction can be designed so that the resulting routing is compatible with normal shortest path routing, while still offering significantly more forwarding options than the exist-

ing LFA. With multiple loop-free alternates for a given primary next-hop, OSPF or IS-IS may employ some of them as unequal-cost primary paths and the rest as back-up paths. In the case of multiple primary paths, packets can be distributed evenly among paths or with more intelligent load balancing methods.

With regard to the field of small area networks, the present embodiments present a novel mechanism for intelligent routing. The mechanism is in essence topology agnostic, and it is designed with a plug-in architecture to enable topology specific additions that increase the fault tolerance for the specific topology. For meshes, tori, and fat-trees it is able to guarantee toleration of one link fault, and it has a good probability distribution for the toleration of multiple faults. The mecha-  $_{15}$ nism is able to quickly react and reconfigure the network after a topology change. Another characteristic of the mechanism is that it only changes the paths for the flows that are directly disconnected by the change. Finally, the mechanism does not require any additional virtual channels, and the new paths for 20 the disconnected flows are compatible with the existing paths in the network in such a way that deadlock free dynamic reconfiguration is guaranteed. The reconfiguration mechanism is compatible with existing technology such as Infini-Band as it requires no specific functionality in the network 25 elements. The algorithm is completely contained in the node responsible for configuring the network, and it can therefore easily be implemented and be put into production.

Accordingly, the present invention provides, inter alia, in an embodiment, a method of determining paths in a network topology. The method includes a step of providing a source/destination pair representing a source and a destination in the network topology, providing a channel list comprising a topological ordering of channel identifiers representing communication channels in the network topology, and providing at least one path connecting the source and the destination based on the channel list.

In an embodiment of the method the step of providing a channel list further includes the steps of selecting from the topology a first path connecting the source and destination, 40 identifying channel identifiers for channels along the first path, determining dependencies between the channel identifiers based on a deadlock-free routing algorithm, and constructing the channel list by topologically ordering the channel identifiers according to the dependencies.

In an embodiment of the method, any dependency from one channel to another in the channel list only points to a channel identifier with a higher position in the channel list.

In an embodiment of the method the steps of selecting and identifying further includes the steps of receiving an indica- 50 tion of a failure of the first path in the topology, and identifying channel identifiers for the failed path.

In an embodiment of the method the second path avoids the failure.

In an embodiment of the method the step of providing a 55 source/destination pair includes the step of selecting the source/destination pair from the topology based on a predefined traffic pattern provided by an application.

In an embodiment of the method the step of providing a source/destination pair includes the step of selecting the 60 source/destination pair from the topology based on traffic load for at least one network router or switch.

An embodiment of the method further includes storing the at least one provided path in a routing table.

An embodiment of the method further includes replacing, 65 node list. in a routing table, the first path with the at least one provided In an path.

4

In an embodiment of the method the step of determining dependencies further includes steps of generating a new valid channel list in which channels dependencies from the first path are removed, and generating at least one path based on the new valid channel list.

In an embodiment of the method the step of generating the new valid channel list further includes the step of moving the target channel of a dependency to a higher position in the channel list, and repeating the step of moving for any following dependencies.

In an embodiment of the method the step of providing at least one path further includes the step of searching the topology to create a route around the first path using only legal turns.

In an embodiment of the method, the searching utilizes a shortest path algorithm.

In an embodiment of the method the step of providing at least one path further includes the step of searching the topology to create a route around the first path using legal turns, and if necessary illegal turns.

In an embodiment of the method the shortest path algorithm is Dijkstra shortest path algorithm.

In an embodiment of the method the shortest path algorithm obtains the shortest path between the source and the destination considering constraints of the channel list and any pre-existing routing table entries for the source and destination.

In an embodiment of the method the shortest path algorithm is implemented on a reverse path from the destination to the source.

In an embodiment of the method the shortest path algorithm utilizes a cost function which considers a number of hops, a number of illegal turns performed on the path from the source to the destination, and an index of all illegal turns utilized by the shortest path algorithm.

In an embodiment of the method the step of providing at least one path further includes the steps of selecting, from a pre-computed set of paths, at least one path compatible with the channel list.

The present invention provides, inter alia, in an embodiment, an additional method of determining paths in a network topology. The additional method including steps of providing at least one source/destination pair, each pair representing a source and a destination in the topology, providing a node list comprising a topological ordering of node identifiers representing communication nodes in the network topology, and providing at least one path connecting the source and the destination based on the node list.

In an embodiment of the additional method the step of providing a node list further includes the steps of a) selecting a first position in the node list, b) selecting a destination from the at least one source/destination pairs, c) associating the selected destination with the first position, d) determining a subset of nodes, the subset comprising nodes directly connected to the destination, e) selecting a current position in the node list higher than the first position, f) selecting, based on a constraint function, a next node from the subset, g) associating the next node with the current position, h) for each selected node in the subset, extending the subset with a next subset including further nodes connected to the selected node, i) selecting a further position in the node list higher than the first and current positions, the further position hereafter being the current position, and j) repeating steps f)-i) until all nodes in the topology have been associated with a position in the

In an embodiment of the additional method further includes the steps of selecting a source from the topology,

-5

identifying the position of the source in the node list, generating at least one path from the selected source to the destination based on traversing the node list from the identified position to the first position.

In an embodiment of the additional method, the constraint 5 function is defined to realize a routing objective.

In an embodiment of the additional method the step of generating the at least one path further includes the step of generating a plurality of paths.

In an embodiment of the additional method, the routing objective comprises an objective to maximize routing choices at each node.

In an embodiment of the additional method, the routing objective comprises an objective to balance the traffic load of each link at each node.

An embodiment of the additional method further includes the step of storing the at least one path connecting the source and the destination in one or more routing tables in at least one network router or switch.

In an embodiment of the additional method the step of 20 network router or switch.

providing at least one path further includes the step of generating at least one path connecting the source and the destination of each pair based additionally on a predefined traffic pattern utilizing the at least one path.

In an embodiment of the method the step of generating at least one providing at least one path of providing at least one path generating at least one path destination of each pair be additionally on a predefined traffic generating at least one path destination of each pair be additionally on a predefined traffic generating at least one path destination of each pair be additional method the step of generating at least one path connecting the source and the destination of providing at least one path generating at least one path connecting the source and the destination of providing at least one path generating at least one path

In an embodiment of the additional method the step of 25 providing at least one path further includes the step of generating at least one path connecting the source and the destination of each pair based additionally on a traffic load utilizing the at least one path.

In an embodiment of the additional method the step of 30 providing at least one path further includes the step of selecting, from a pre-computed set of paths, at least one path compatible with the node list.

In an embodiment of the additional method the step of associating further includes the step of storing an identifier of 35 the node at the current position in the node list.

The present invention provides, inter alia, in an embodiment, a further additional method of determining paths in a network topology. The further additional method including the steps of providing at least one source/destination pair, 40 each pair representing a source and a destination in the topology, providing a channel list comprising a topological ordering of channel identifiers representing communication channels in the network topology, and providing at least one path connecting the source and the destination based on the channel list.

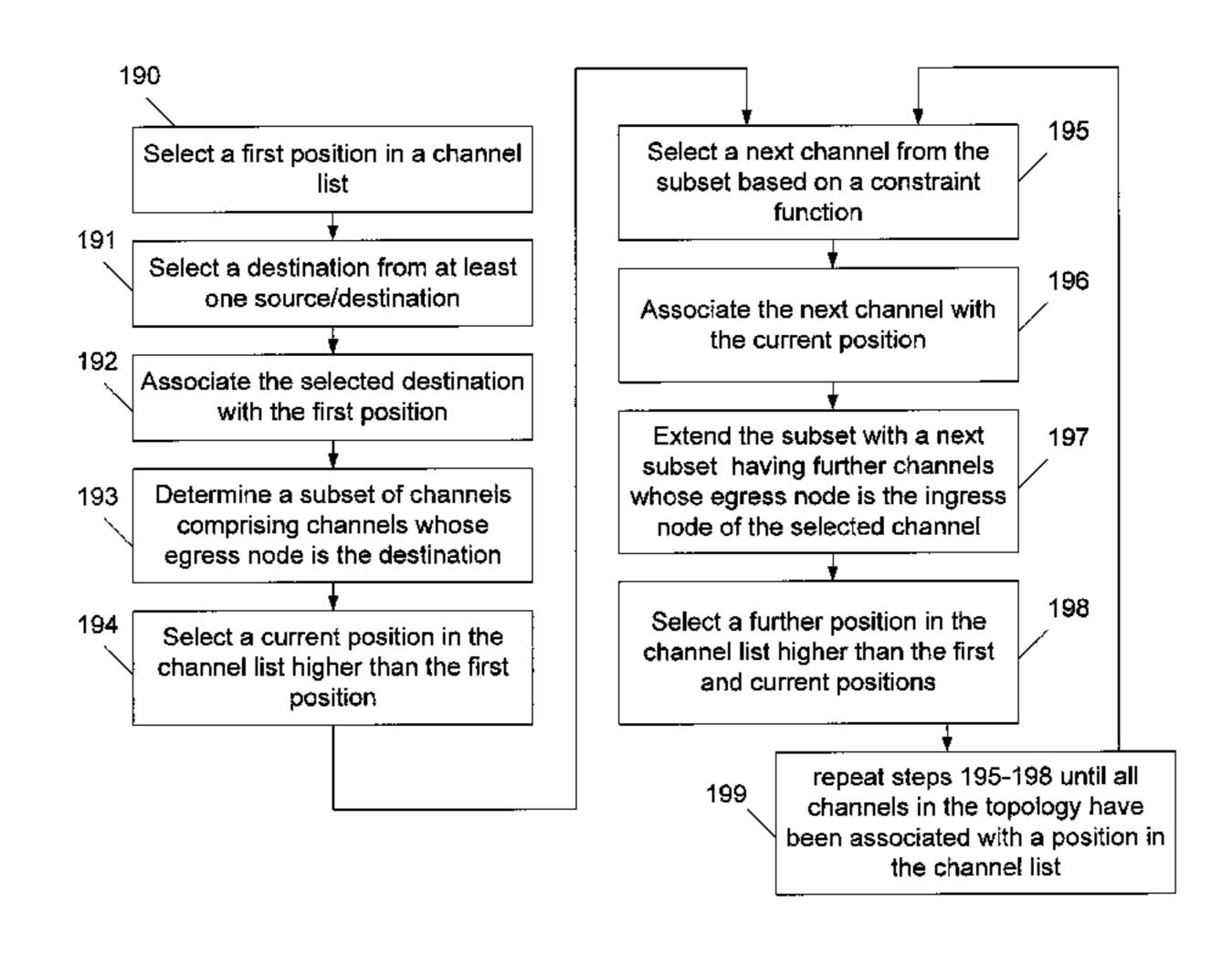

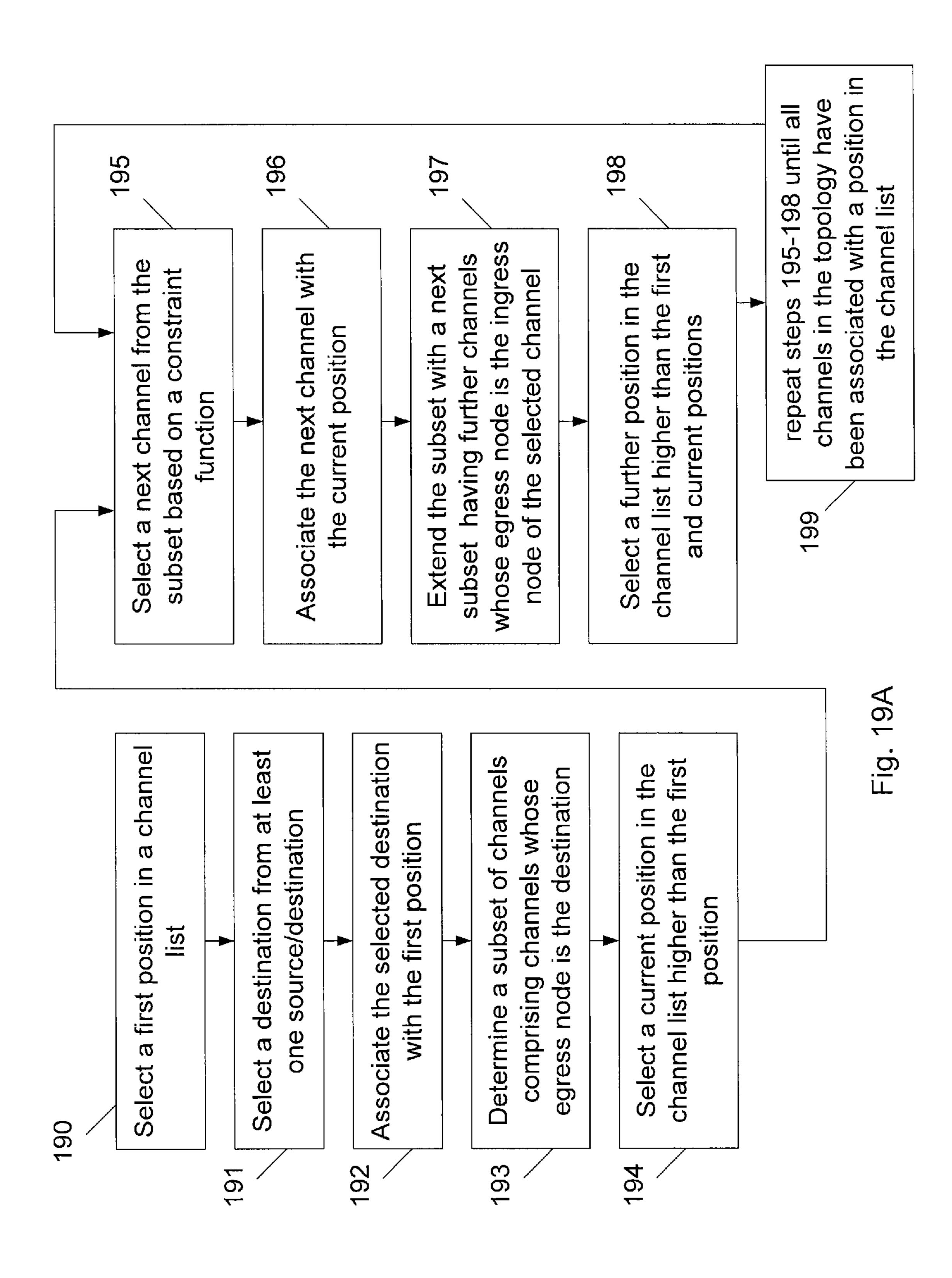

In an embodiment of the further additional method the step of providing a channel list further includes the steps of a) selecting a first position in the channel list, b) selecting a destination from the at least one source/destination pairs, c) 50 associating the selected destination with the first position, d) determining a subset of channels, the subset comprising channels whose egress node is the destination, e) selecting a current position in the channel list higher than the first position, f) selecting, based on a constraint function, a next channel 55 from the subset, g) associating the next channel with the current position, h) for each selected channel in the subset, extending the subset with a next subset including further channels whose egress node is the ingress node of the selected channel, i) selecting a further position in the channel list 60 higher than the first and current positions, the further position hereafter being the current position, and j) repeating steps f)-i) until all channels in the topology have been associated with a position in the channel list.

An embodiment of the further additional method further 65 comprises the steps of selecting a source from the topology, identifying channels whose ingress node is the source, iden-

6

tifying positions associated with the identified channels, and generating at least one path from the selected source to the destination based on traversing the channel list from the identified positions to a position associated with a channel whose egress node is the destination.

In an embodiment of the further additional method the constraint function is defined to realize a routing objective.

In an embodiment of the further additional method the step of generating the at least one path includes the further step of generating a plurality of paths.

In an embodiment of the further additional method the routing objective comprises an objective to maximize routing choices at each node.

In an embodiment of the further additional method the routing objective comprises an objective to balance the traffic load of each channel.

An embodiment of the further additional method includes the step of storing the at least one path connecting the source and the destination in one or more routing tables in at least one network router or switch.

In an embodiment of the further additional method the step of providing at least one path further includes the step of generating at least one path connecting the source and the destination of each pair based additionally on a predefined traffic pattern utilizing the at least one path.

In an embodiment of the further additional method the step of providing at least one path further includes the step of generating at least one path connecting the source and the destination of each pair based additionally on a traffic load utilizing the at least one path.

In an embodiment of the further additional method the step of providing at least one path further includes the step of selecting, based on the channel list, the at least one path from a pre-computed set of paths.

In an embodiment of the further additional method each associating comprises storing an identifier of the channel at the current position in the channel list.

The present invention provides, inter alia, in an embodiment, an additional method of determining paths in a network topology including providing a plurality of source/destination pairs, each pair representing a source and a destination in the network topology, providing a channel list comprising a topological ordering of channel identifiers representing communication channels in the network topology, and providing at least one path connecting the source and the destination based on the channel list.

The present invention provides, inter alia, in an embodiment, an additional method of determining paths in a network topology including the steps of providing a plurality of source/destination pairs representing at least one source and a plurality of destinations in the topology, for each destination: providing a node list comprising a topological ordering of node identifiers representing communication nodes in the network topology, and providing at least one path connecting the source and the destination based on the node list.

The present invention provides, inter alia, a device for determining paths in a network topology. The device provides a source/destination pair representing a source and a destination in the network topology, provides a channel list comprising a topological ordering of channel identifiers representing communication channels in the network topology, and provides at least one path connecting the source and the destination based on the channel list.

The present invention provides, inter alia, a device for determining paths in a network topology. The device provides at least one source/destination pair, each pair representing a source and a destination in the topology, provides a node list

comprising a topological ordering of node identifiers representing communication nodes in the network topology, and provides at least one path connecting the source and the destination based on the node list.

The present invention provides, inter alia, a device for determining paths in a network topology. The device provides at least one source/destination pair, each pair representing a source and a destination in the topology, provides a channel list comprising a topological ordering of channel identifiers representing communication channels in the network topology, and provides at least one path connecting the source and the destination based on the channel list.

It is to be understood that both the foregoing general description of the invention and the following detailed description are exemplary, but are not restrictive, of the invention.

## BRIEF DESCRIPTION OF SEVERAL VIEWS OF THE DRAWINGS

Other objects, features and advantages of the present invention will become more apparent from the following detailed description when read in conjunction with the accompanying drawings, in which:

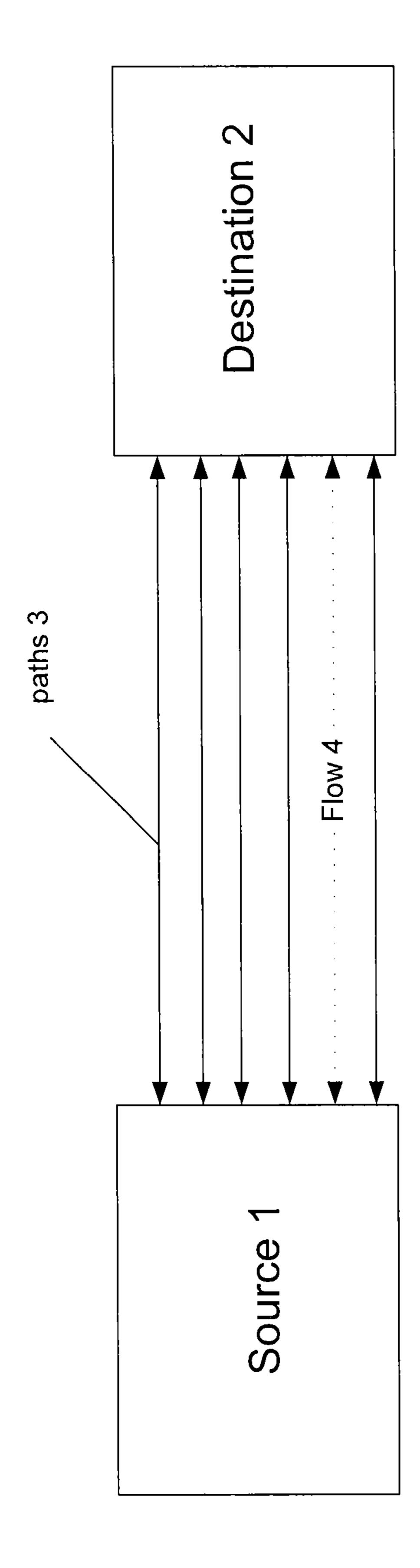

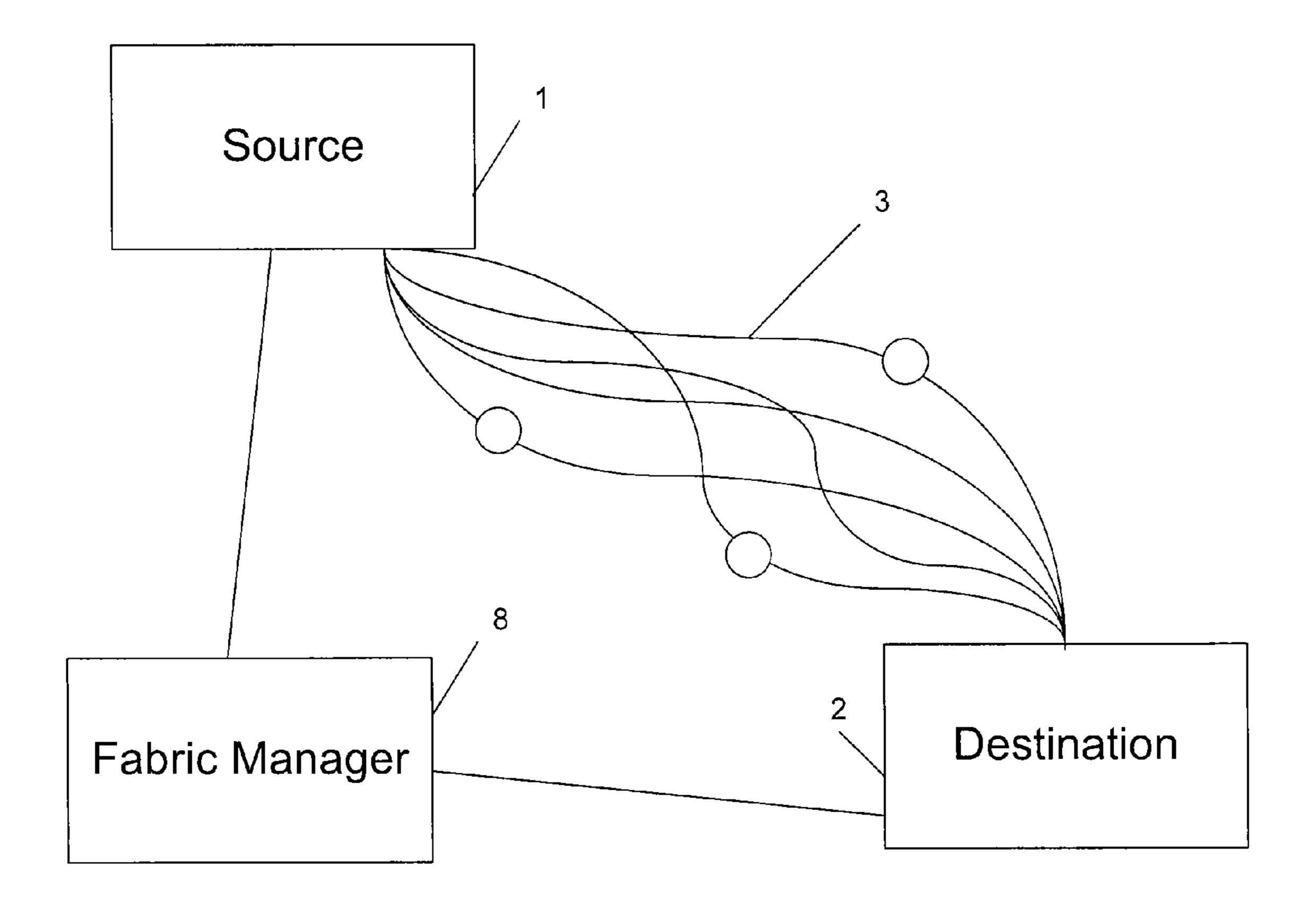

FIG. 1 illustrates a view of a source/destination pair;

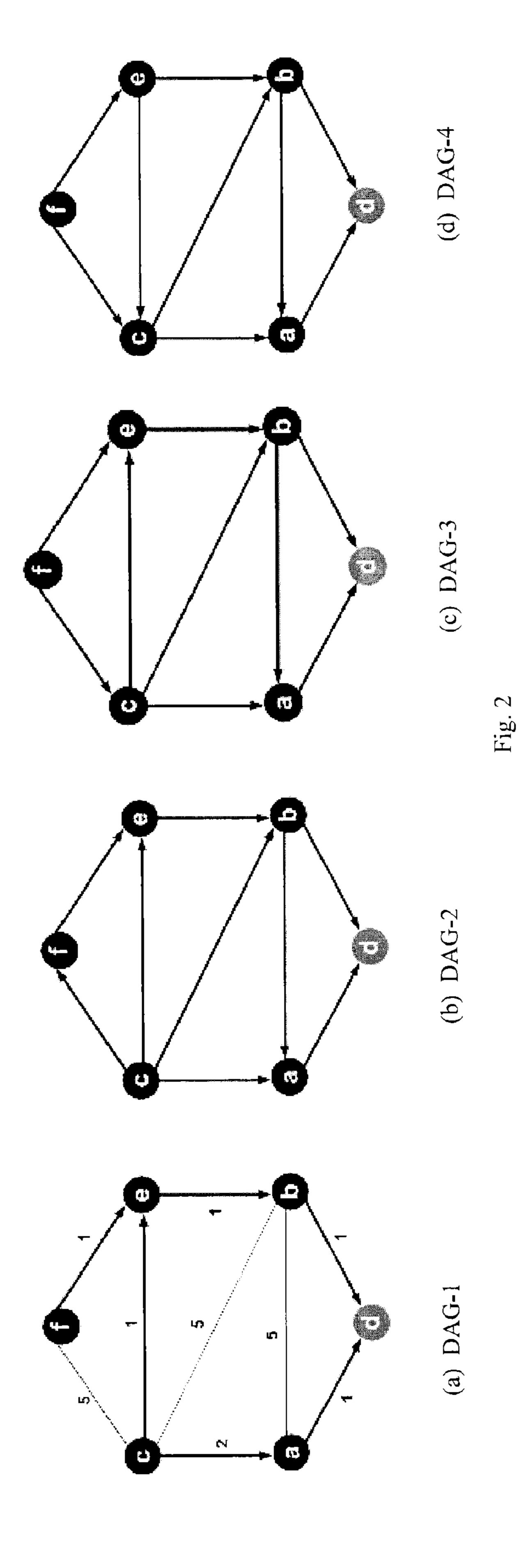

FIGS. 2*a-d* illustrate a network topology with different Directed Acyclic Graphs;

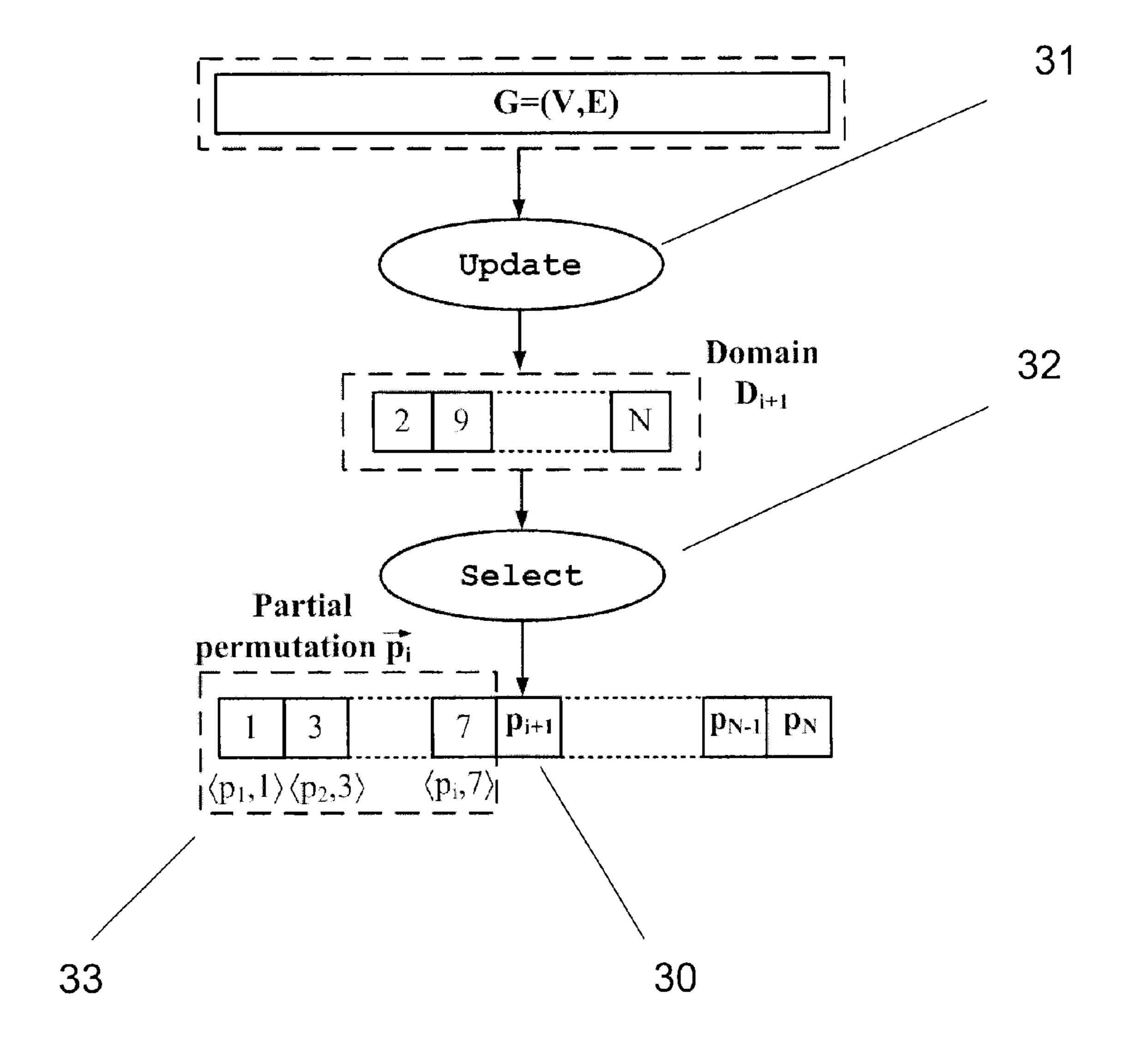

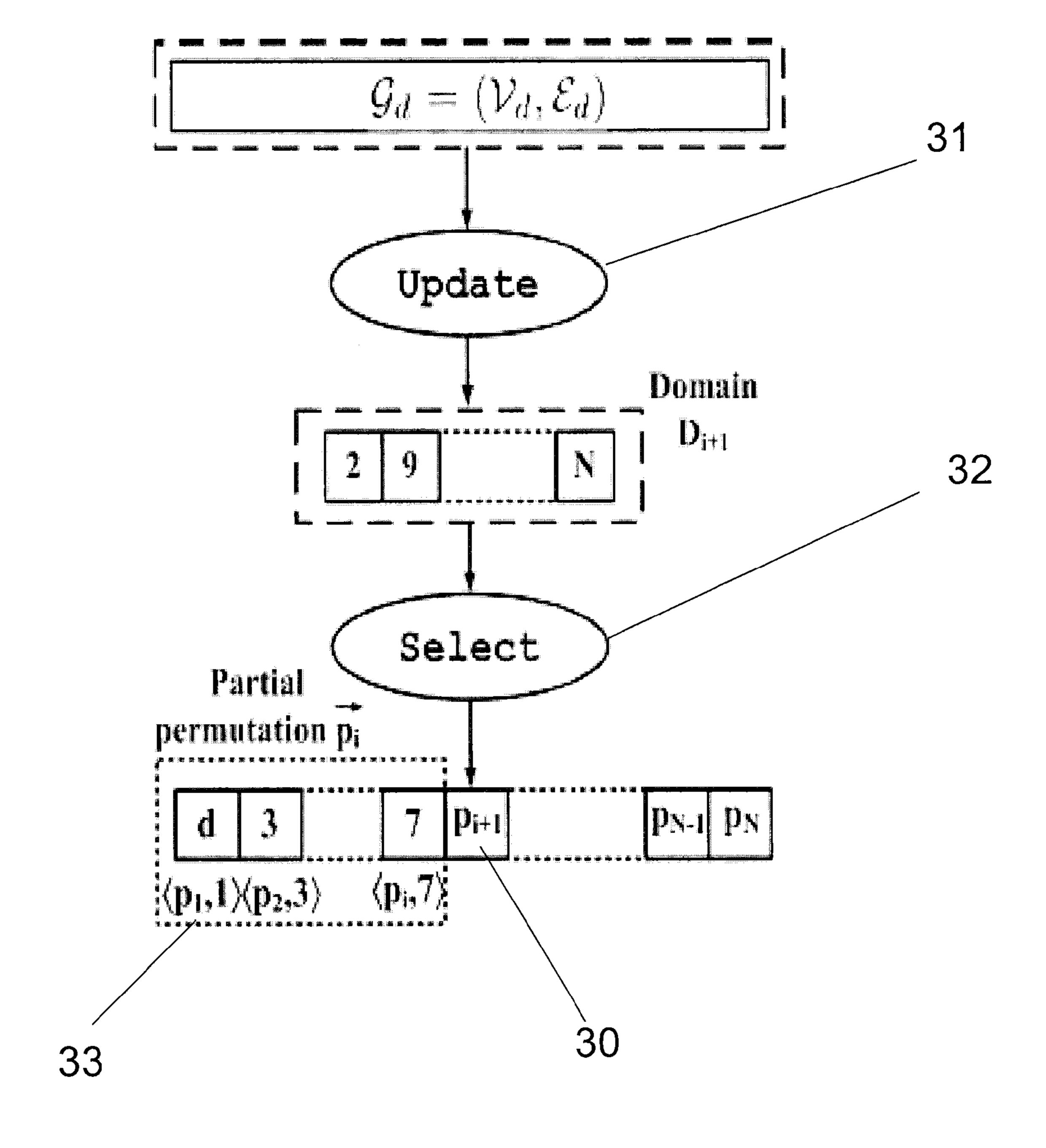

FIG. 3 illustrates the basic assignment procedure for a backtracking algorithm;

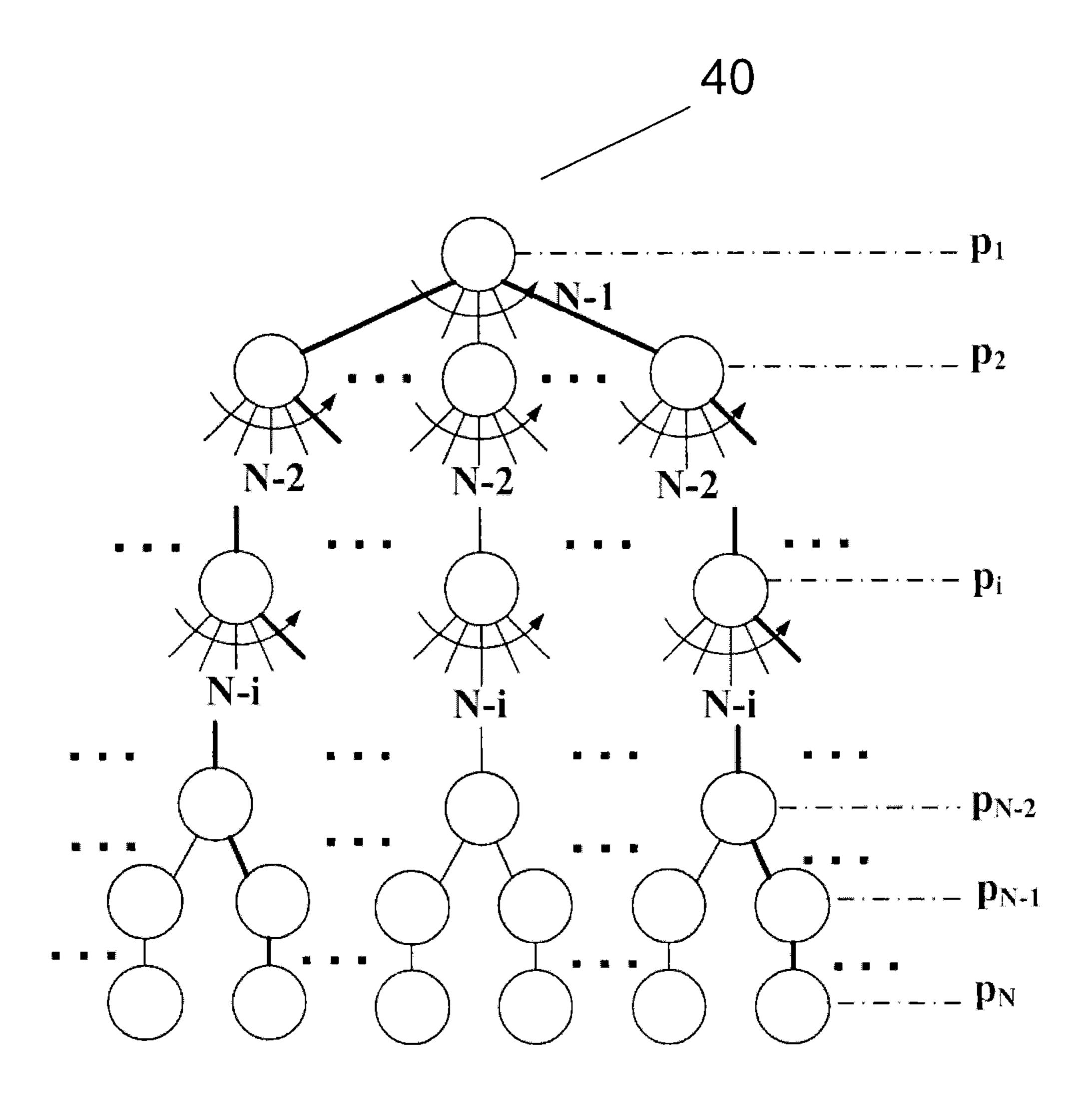

FIG. 4 illustrates a tree representing the search space S of 30 a permutation assignment problem;

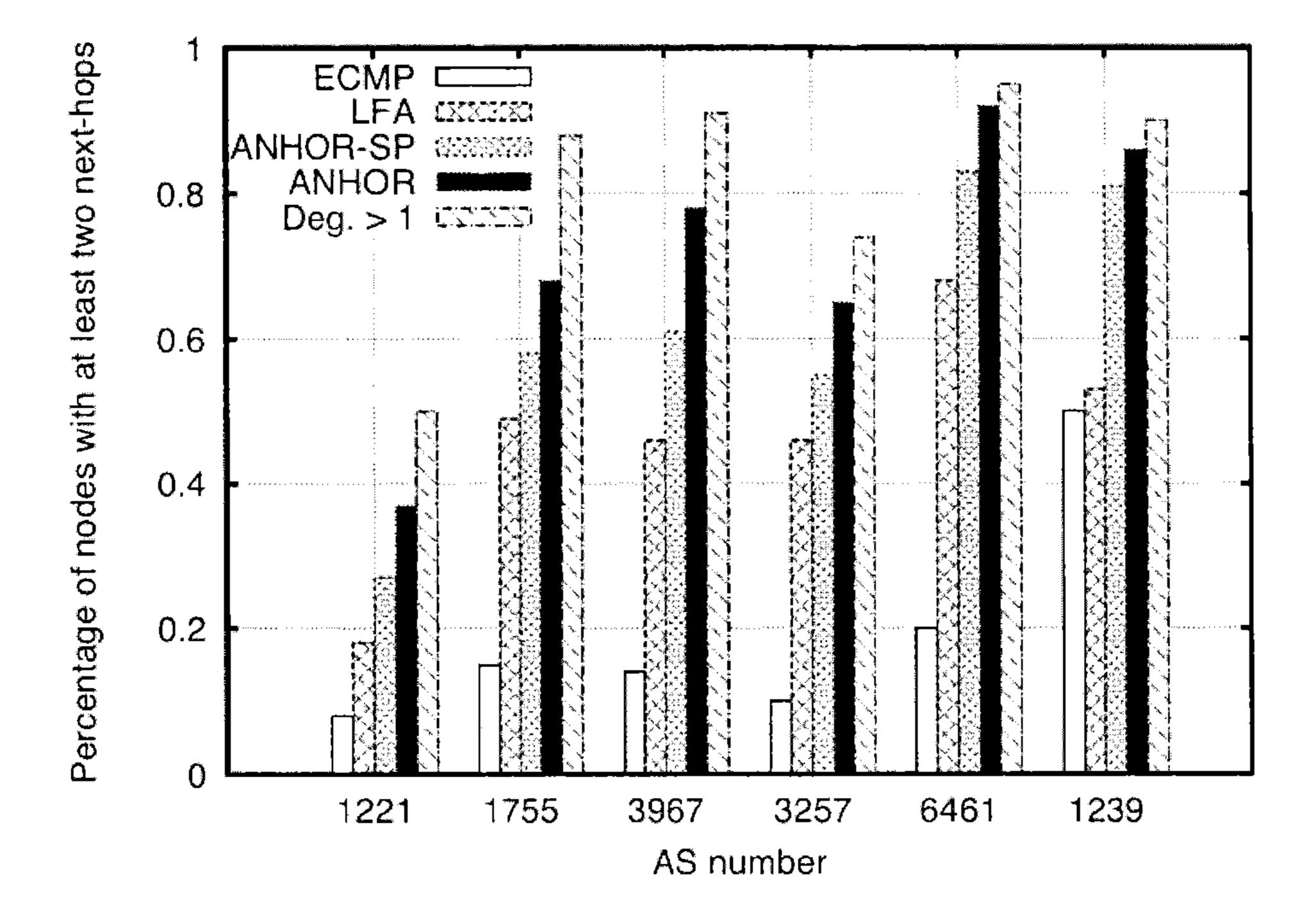

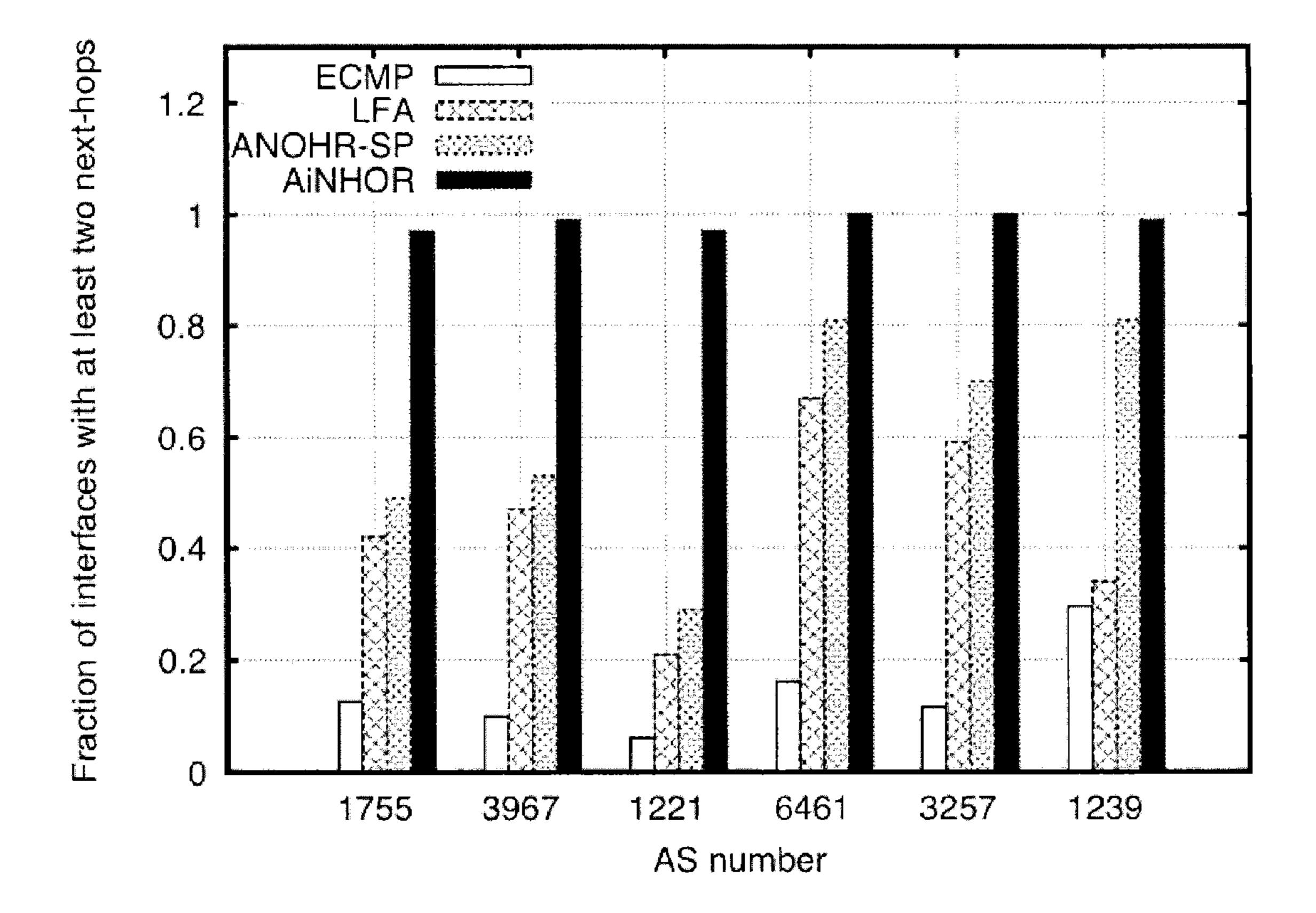

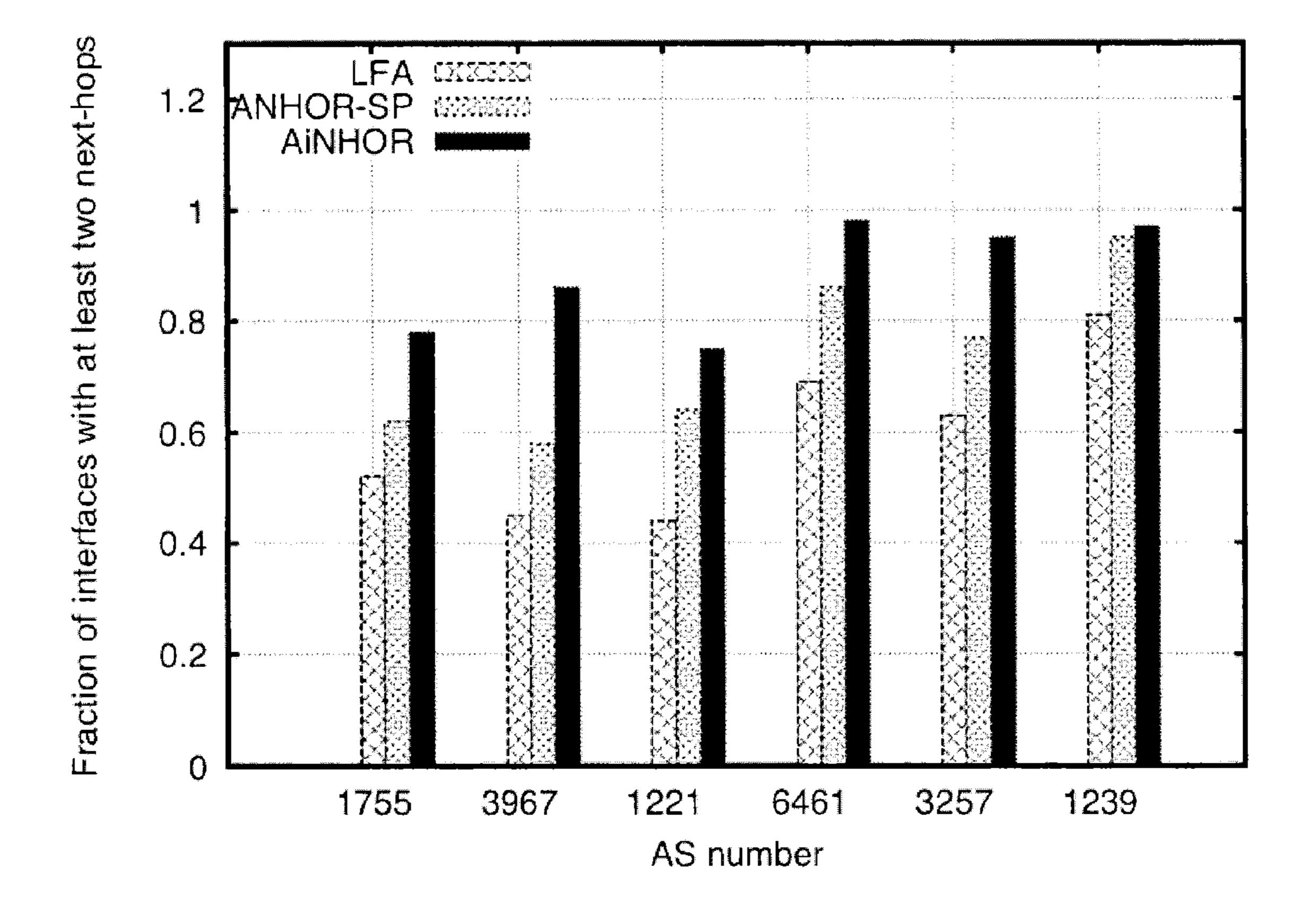

FIG. 5 illustrates the percentage of nodes having at least two next-hops for different routing methods;

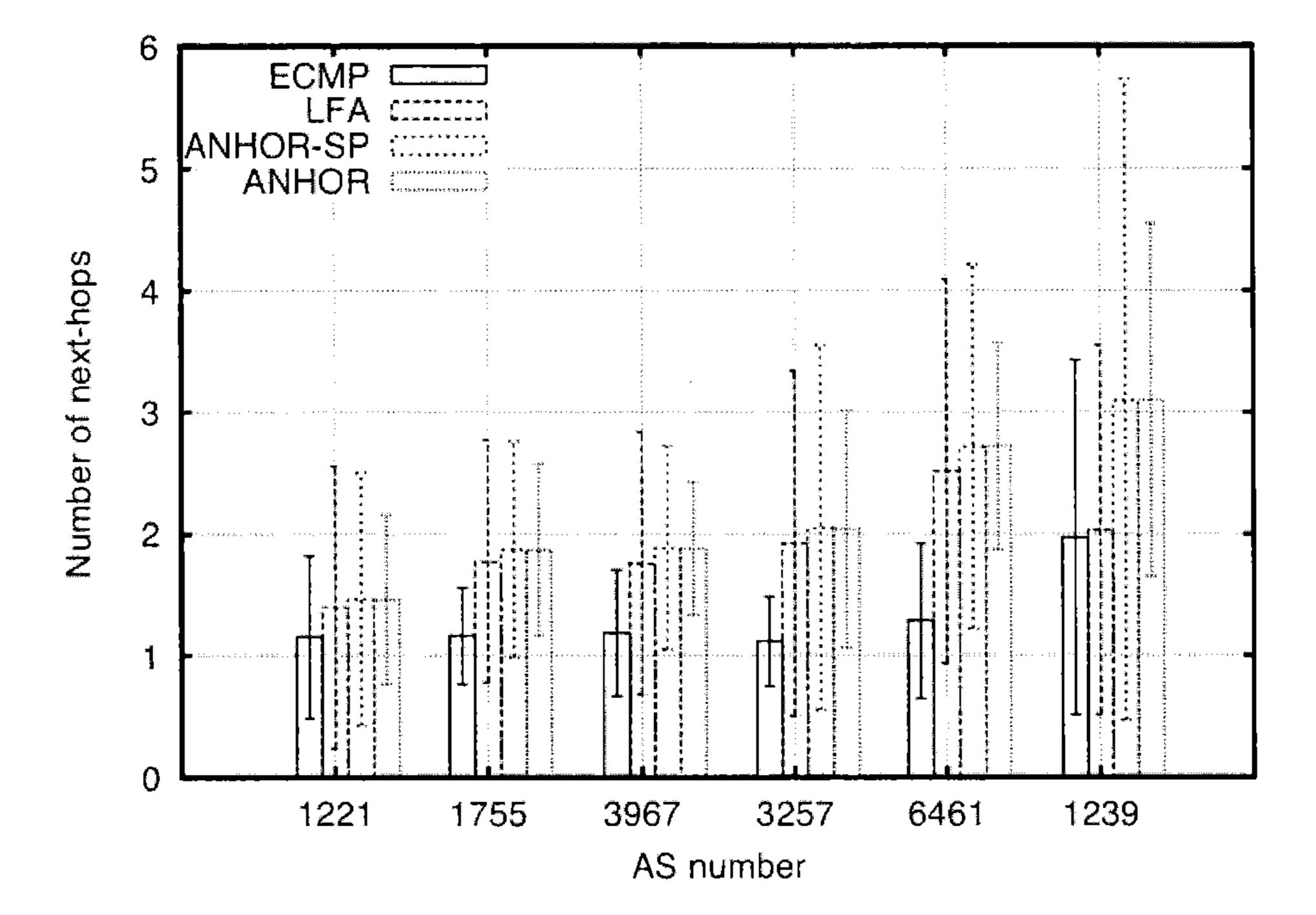

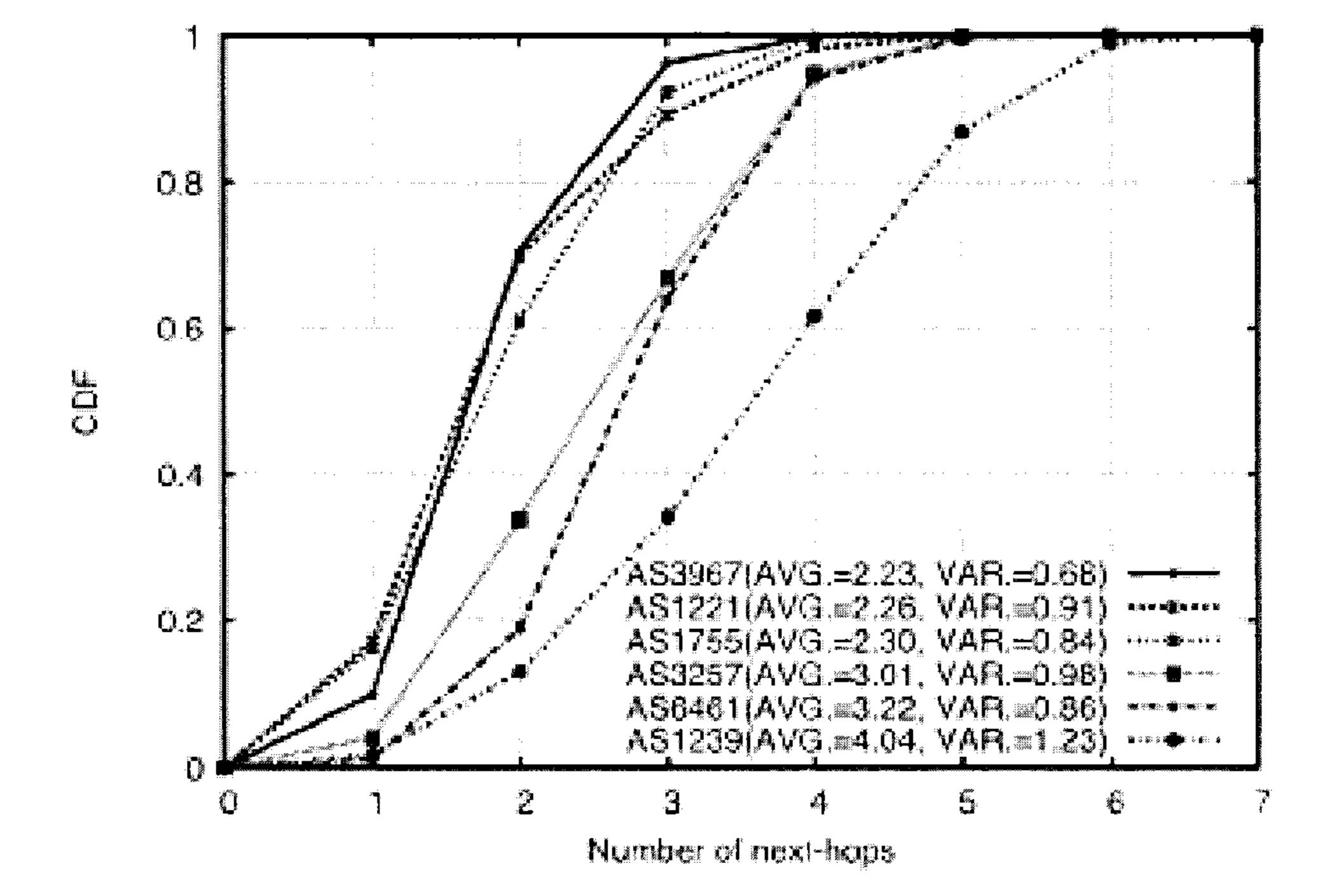

FIG. 6 illustrates the mean and variance for the number of next-hops for different topologies;

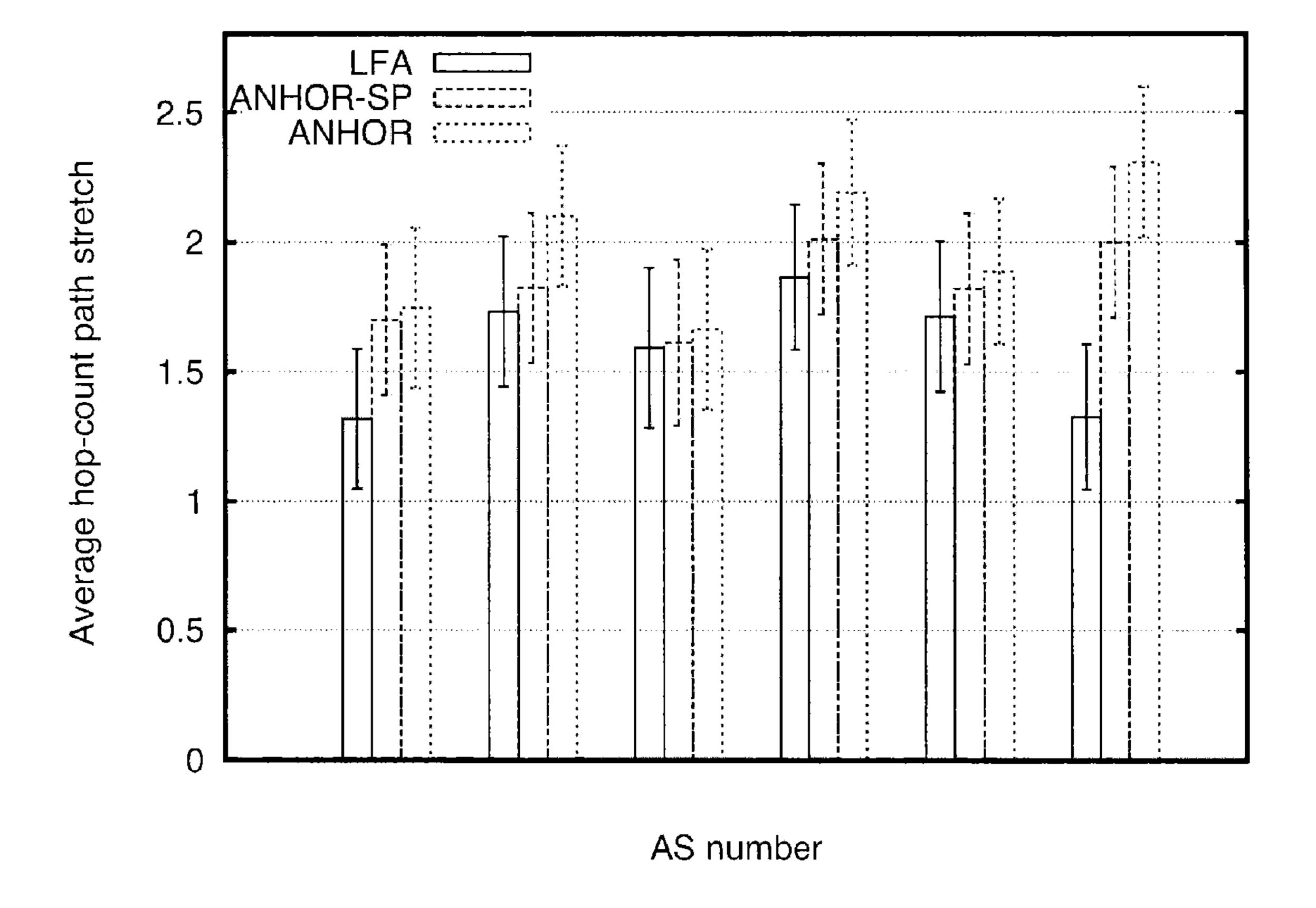

FIG. 7 illustrates the average path stretch regarding for different routings;

FIG. 8 illustrates the relative running time for different topologies;

FIG. 9A illustrates a method of implementing permutation 40 routing according to one embodiment of the present disclosure;

FIG. 9B illustrates a block diagram according to one embodiment of the present disclosure;

FIG. 10 illustrates fast rerouting in node base routing and 45 interface based routing;

FIG. 11 illustrates routing tables of incoming interfaces of two exemplary nodes;

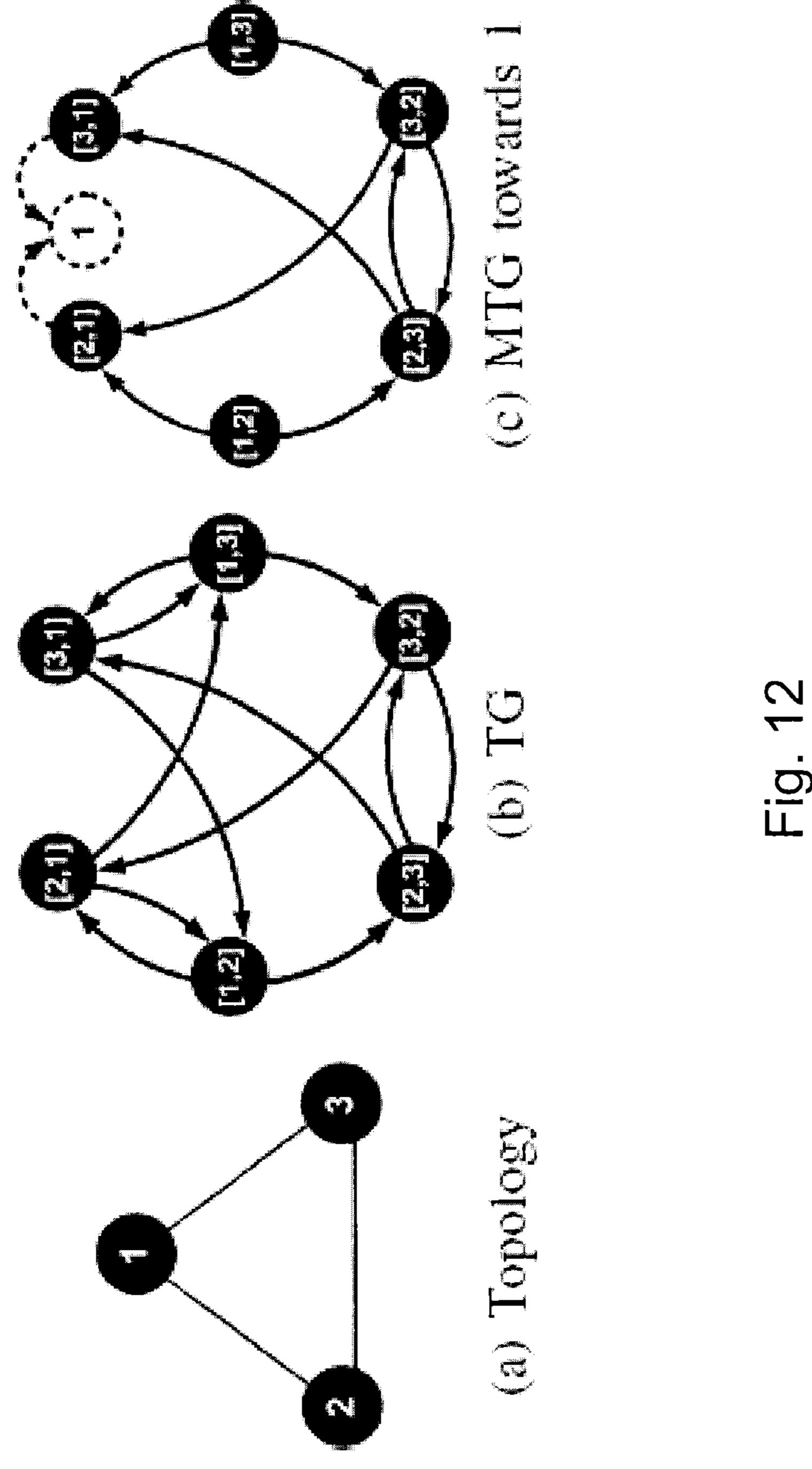

FIG. 12 illustrates a topology and a corresponding transformed graph and modified transformed graph;

FIG. 13 illustrates the basic assignment procedure for a backtracking algorithm in the present embodiment;

FIG. 14 illustrates a graph showing the next-hop distribution of all interface destination (I-D) pairs;

FIG. 15 illustrates a fraction of primary interface destina- 55 tion pairs with at least two routing options;

FIG. 16 illustrates a fraction of secondary interface destination pairs with at least two routing options;

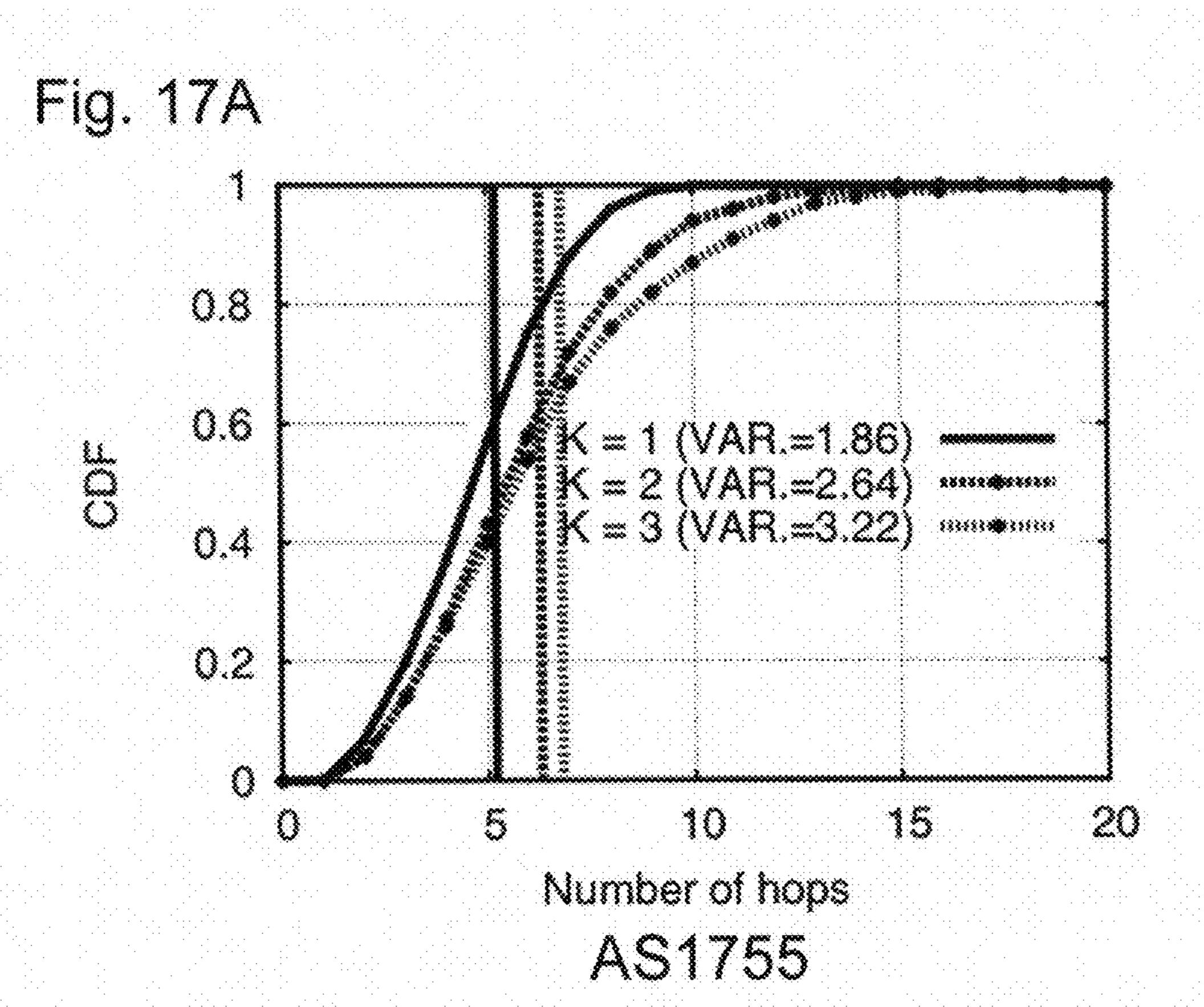

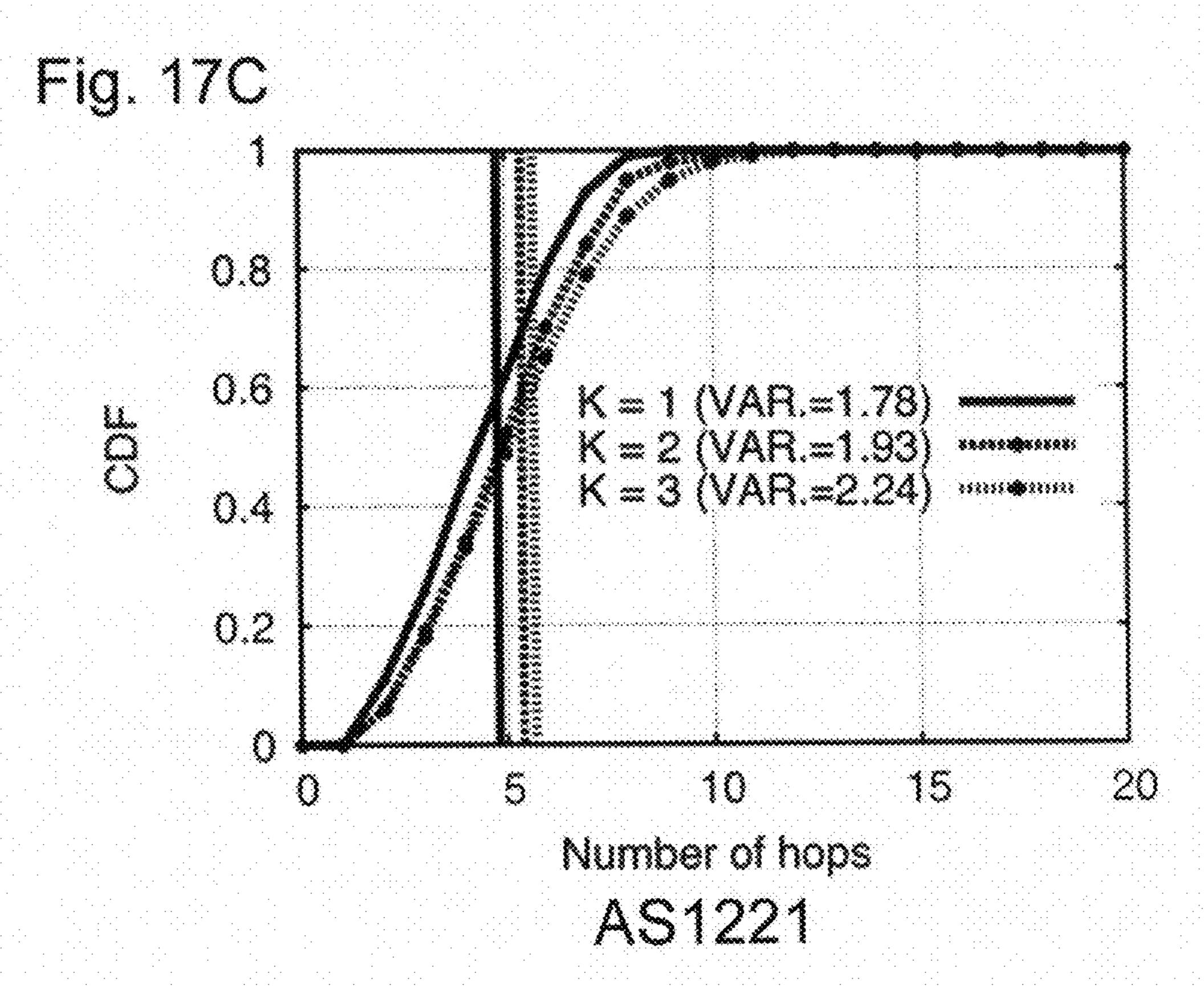

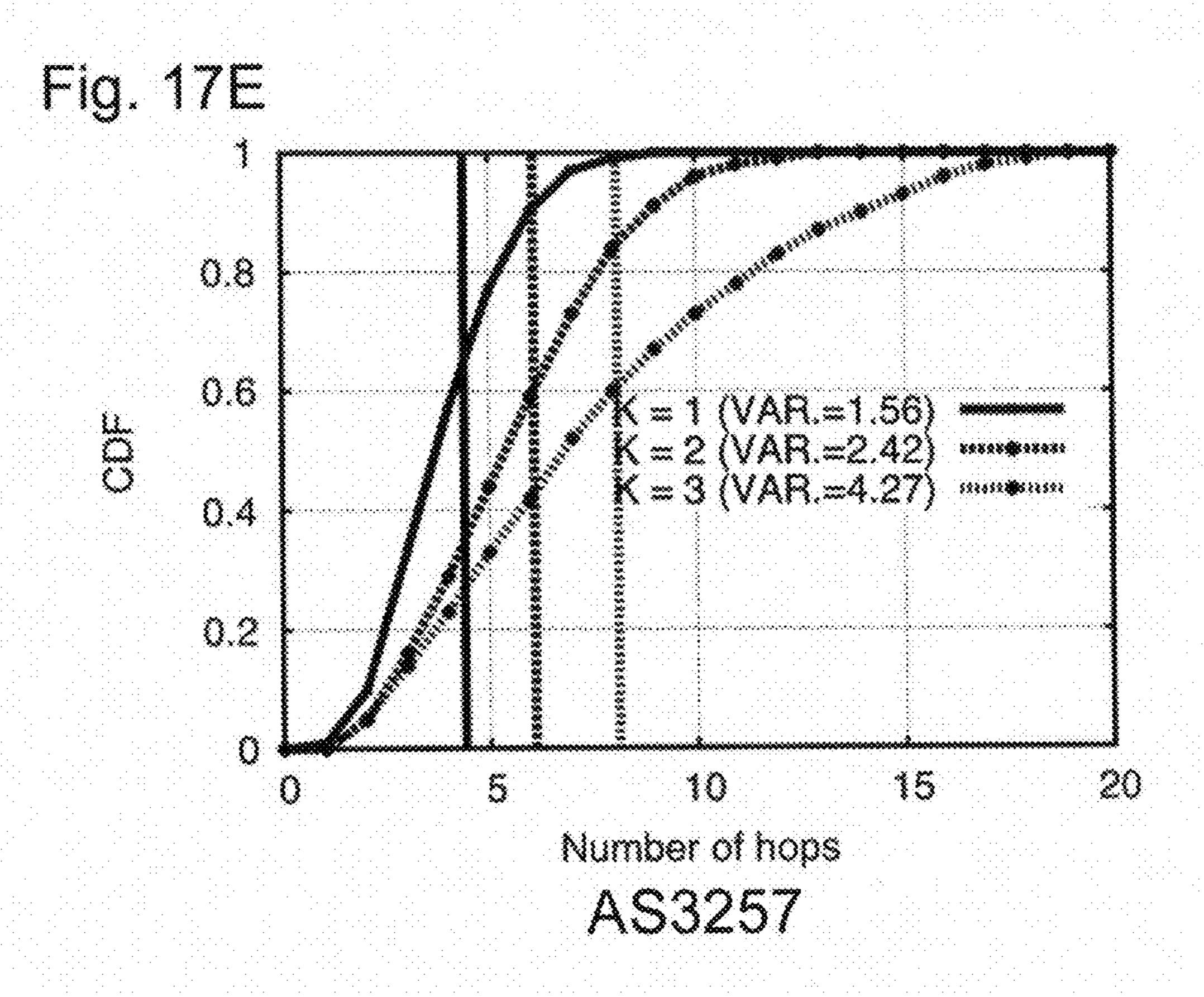

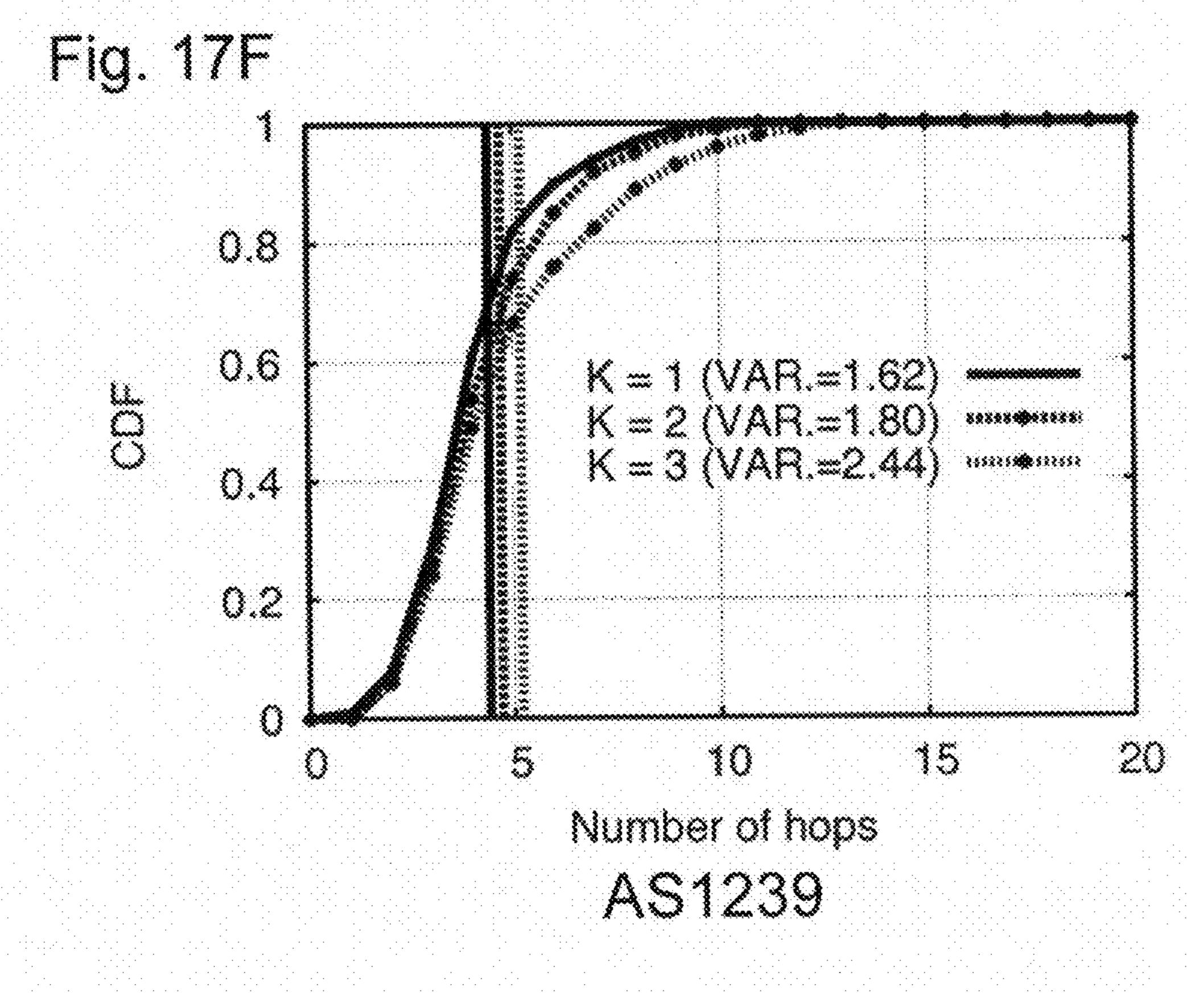

FIGS. 17A-F illustrate the path length distribution and average path length in hops;

FIG. 18 illustrates a comparison of running time between two different routing schemes across multiple topologies;

FIG. 19A illustrates a method of implementing permutation routing according to one embodiment of the present disclosure;

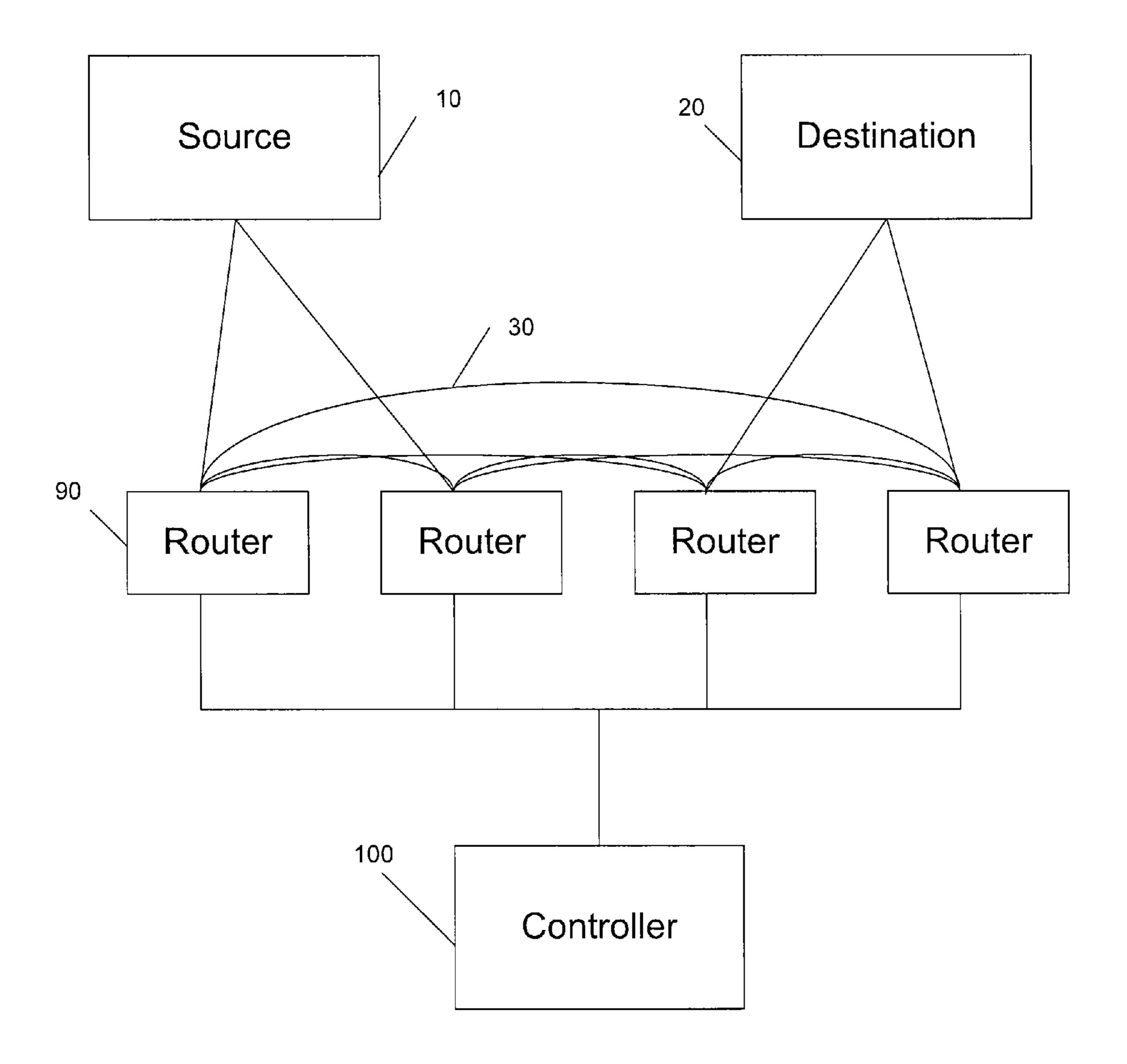

FIG. 19B illustrates a block diagram according to one embodiment of the present disclosure;

8

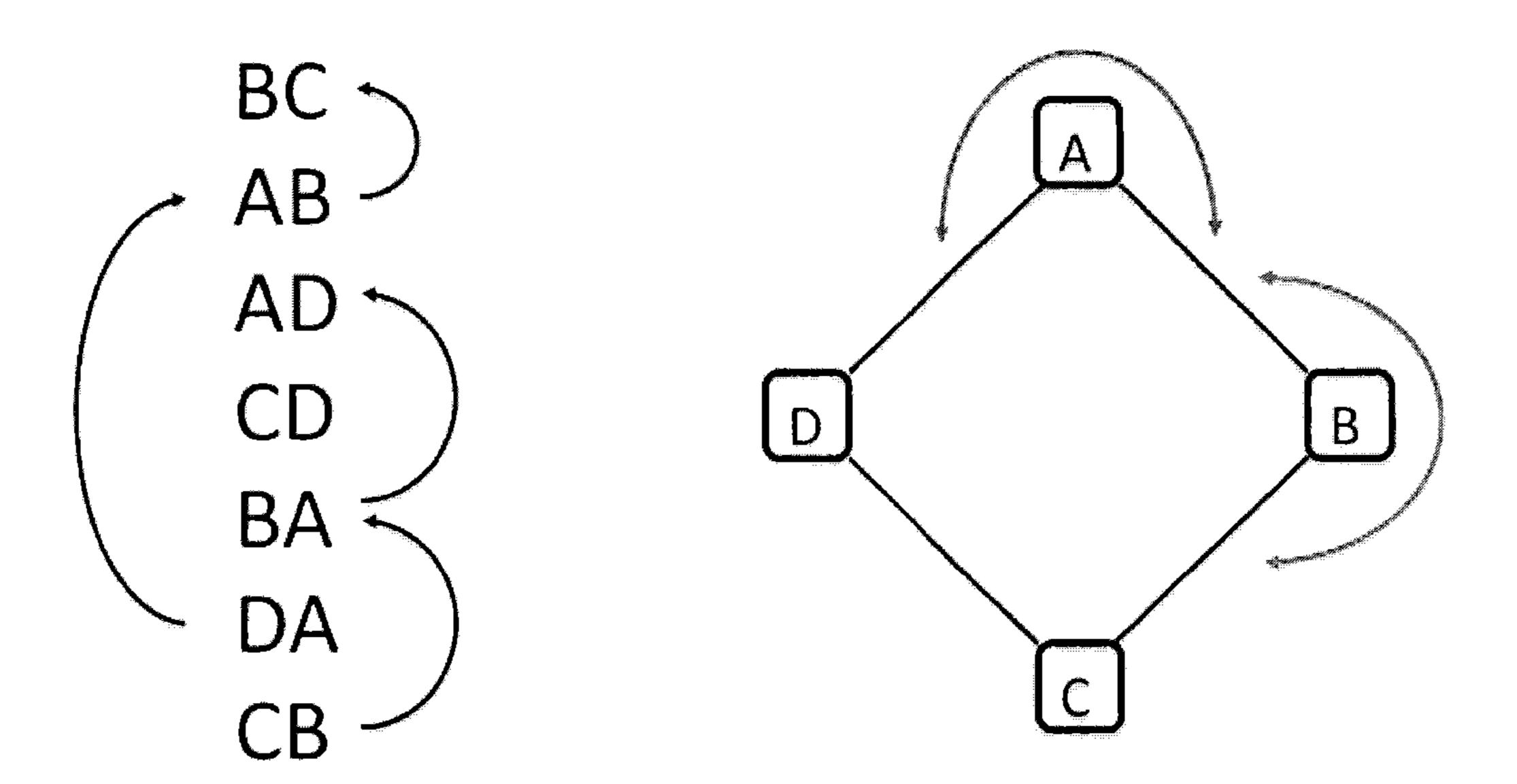

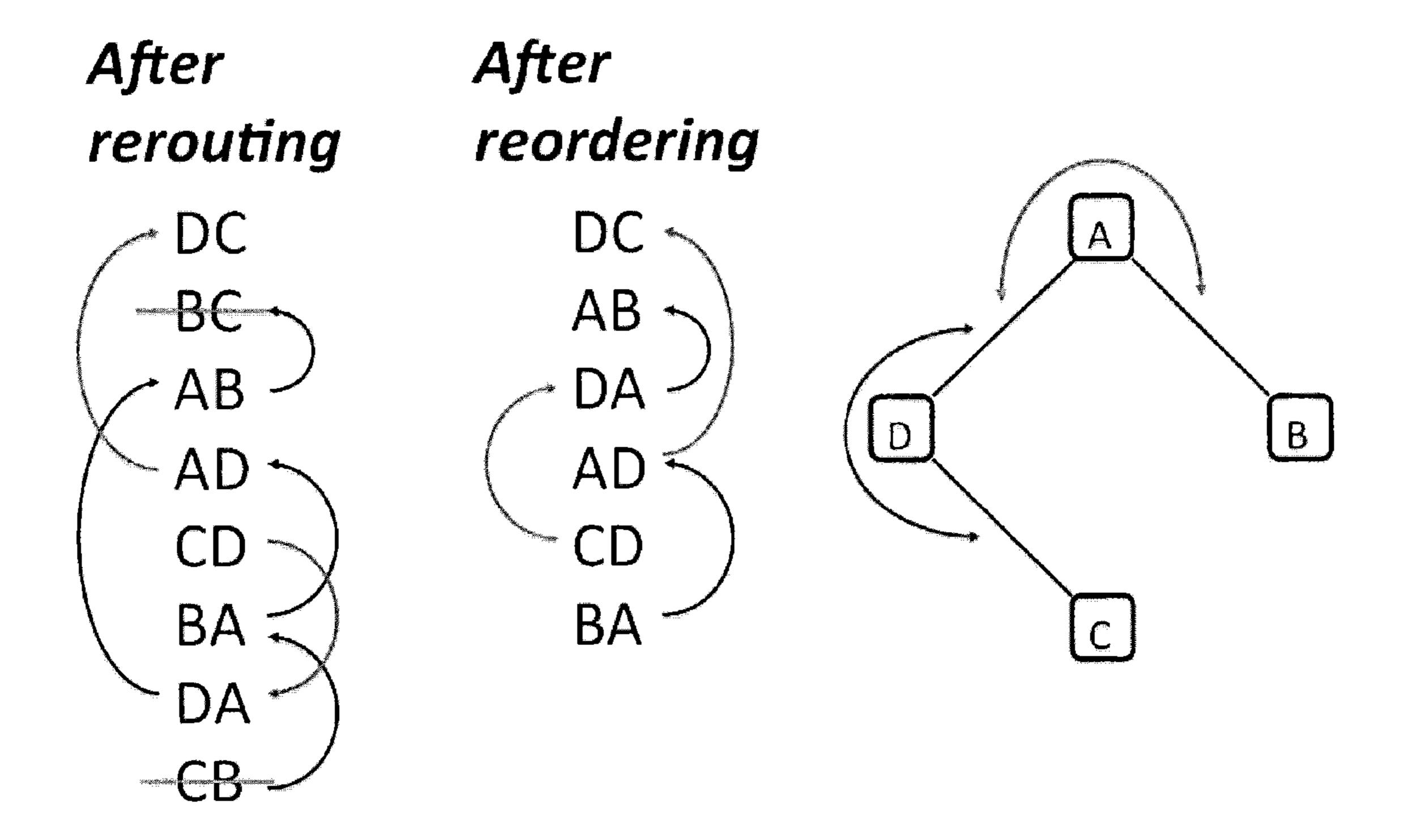

FIG. 20 illustrates a channel list formed based on dependencies from a 4-node ring;

FIG. 21 illustrates an example of reordering of the channel list to allow the turns necessary to connect the topology after a failure;

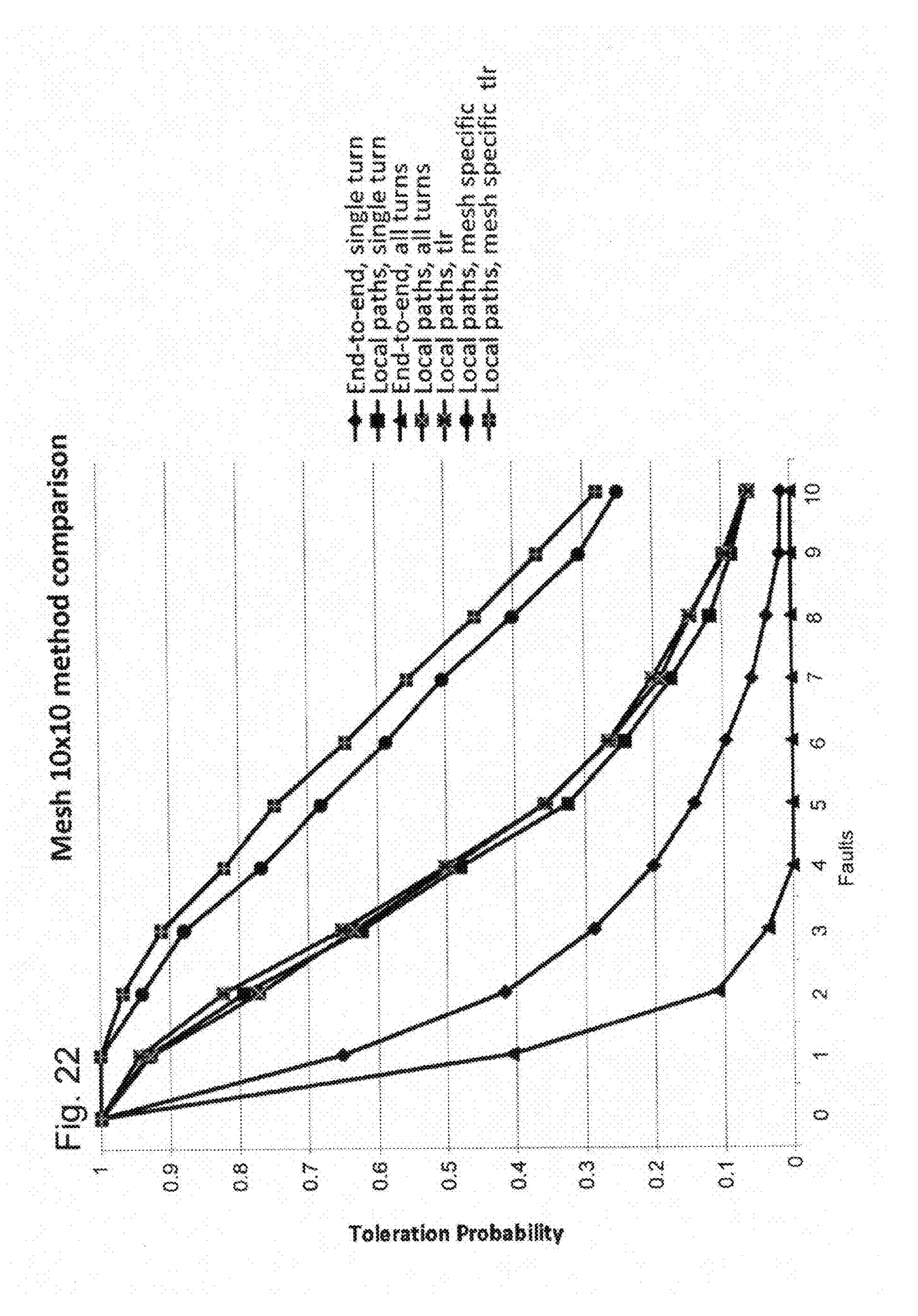

FIG. 22 illustrates a comparison between different variations of the dynamic quick reconfiguration mechanism in a 10×10 mesh;

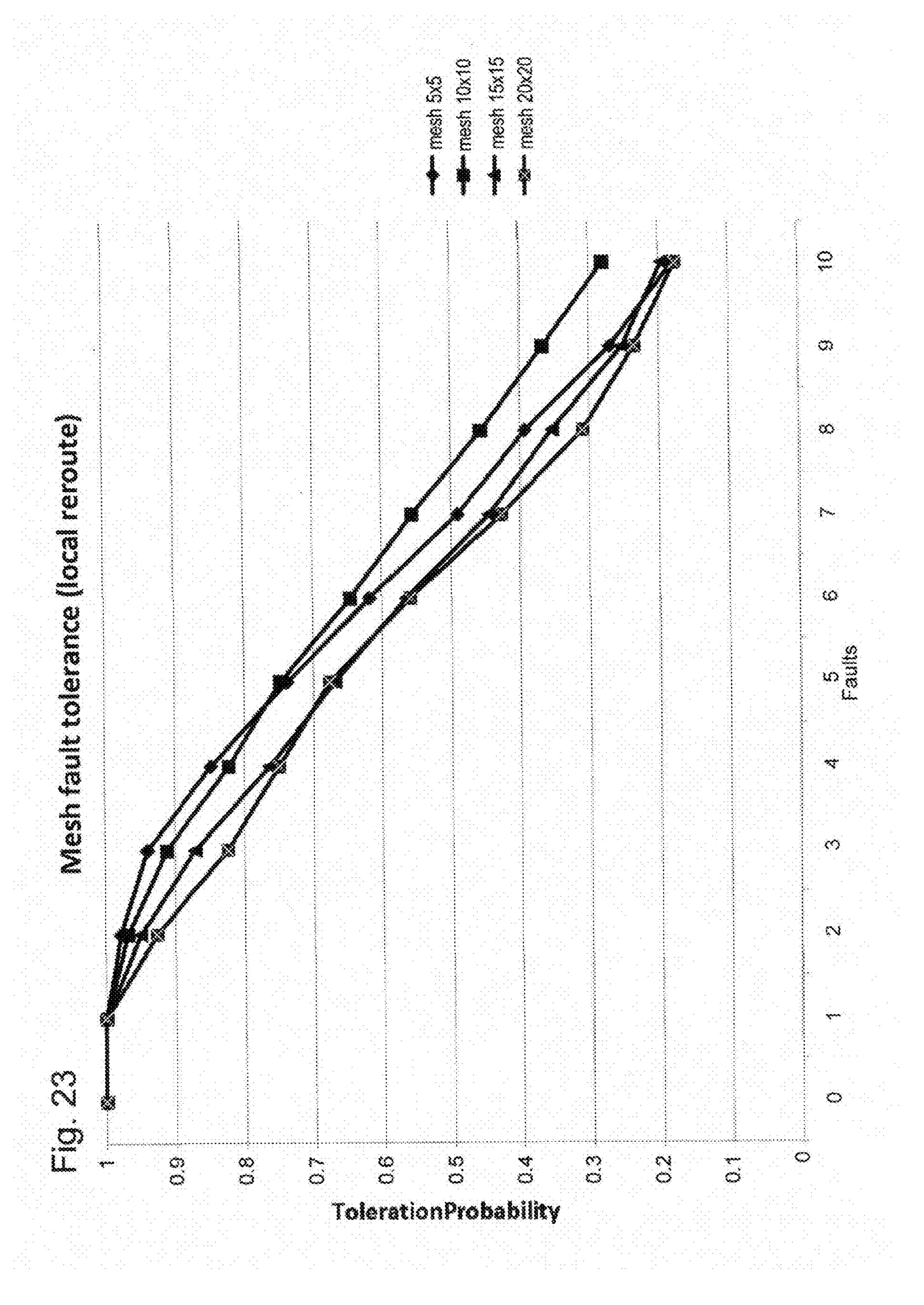

FIG. 23 illustrates an evaluation of the scalability of a solution for a mesh using different mesh sizes;

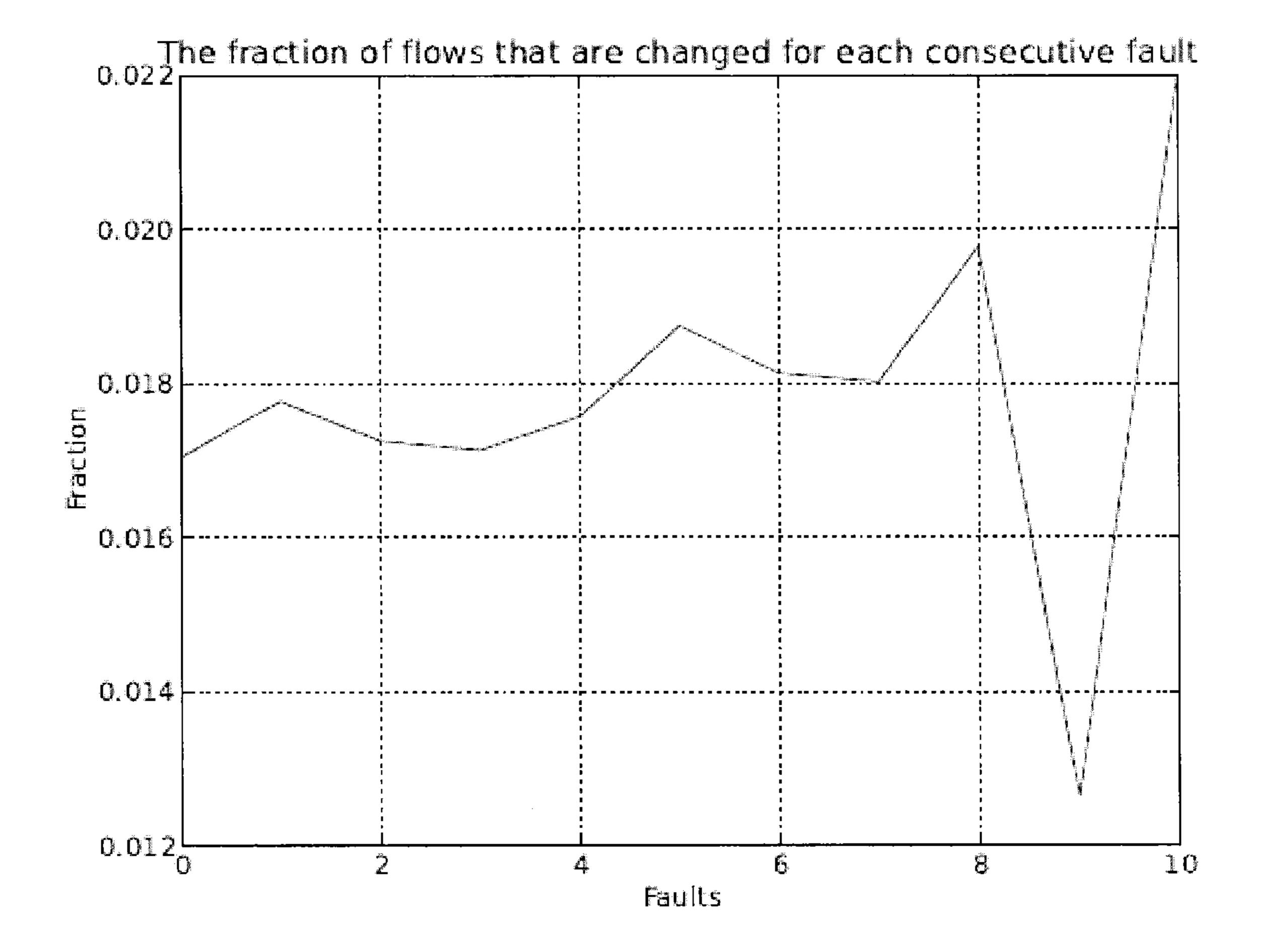

FIG. **24** illustrates the fraction of flows that are affected by the reconfiguration for each fault;

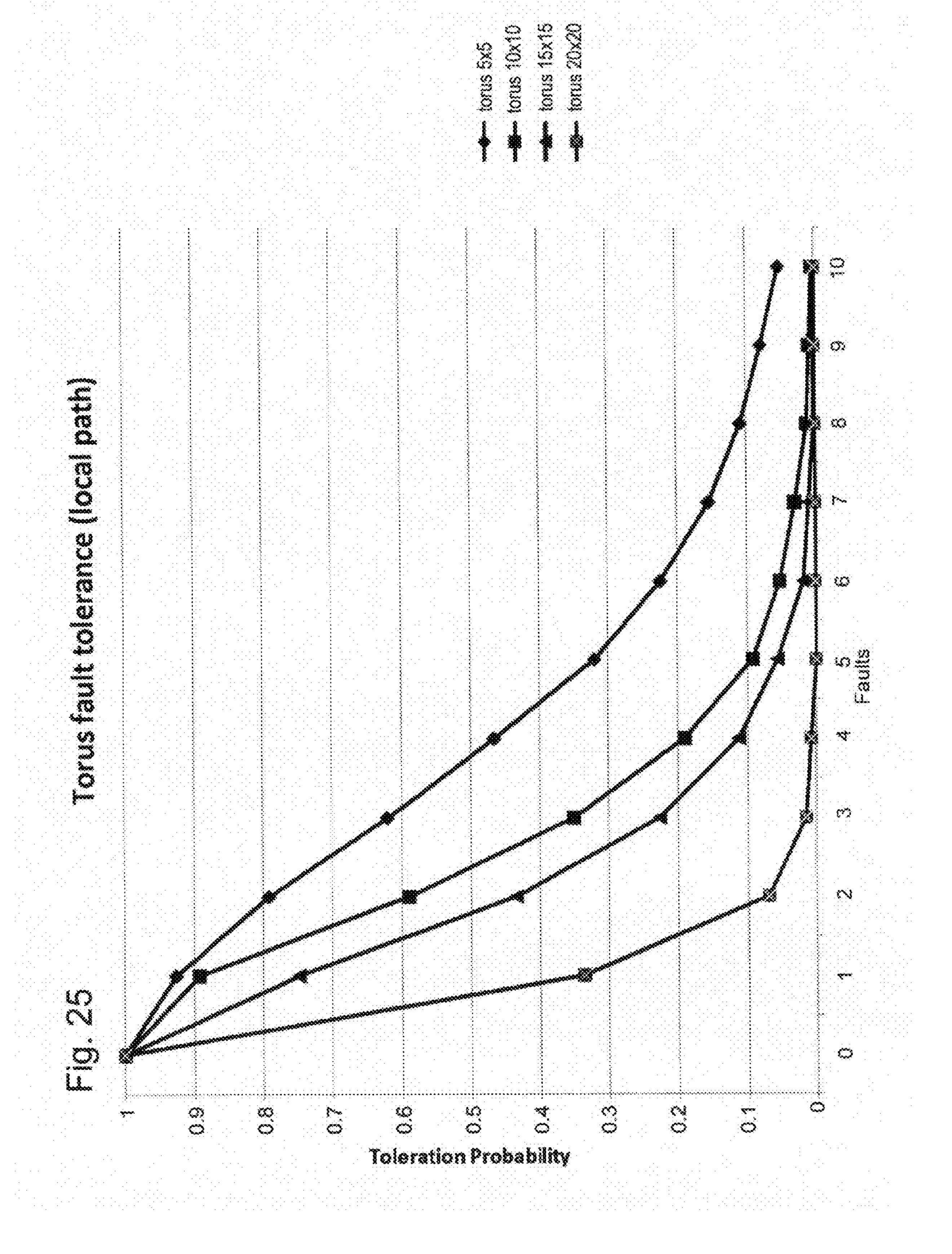

FIG. 25 illustrates a torus fault-tolerant capability;

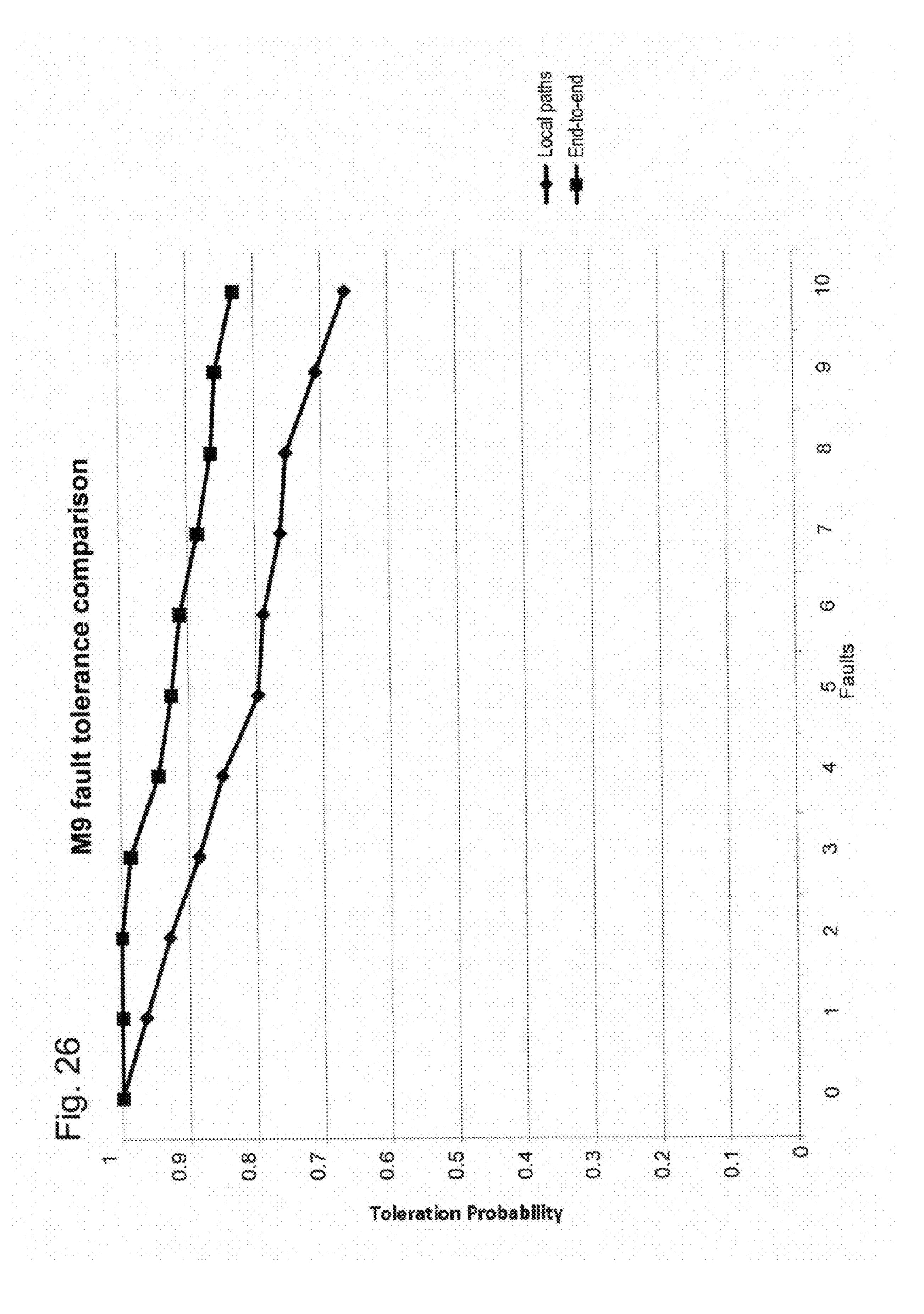

FIG. 26 illustrates a fat tree fault tolerance comparison;

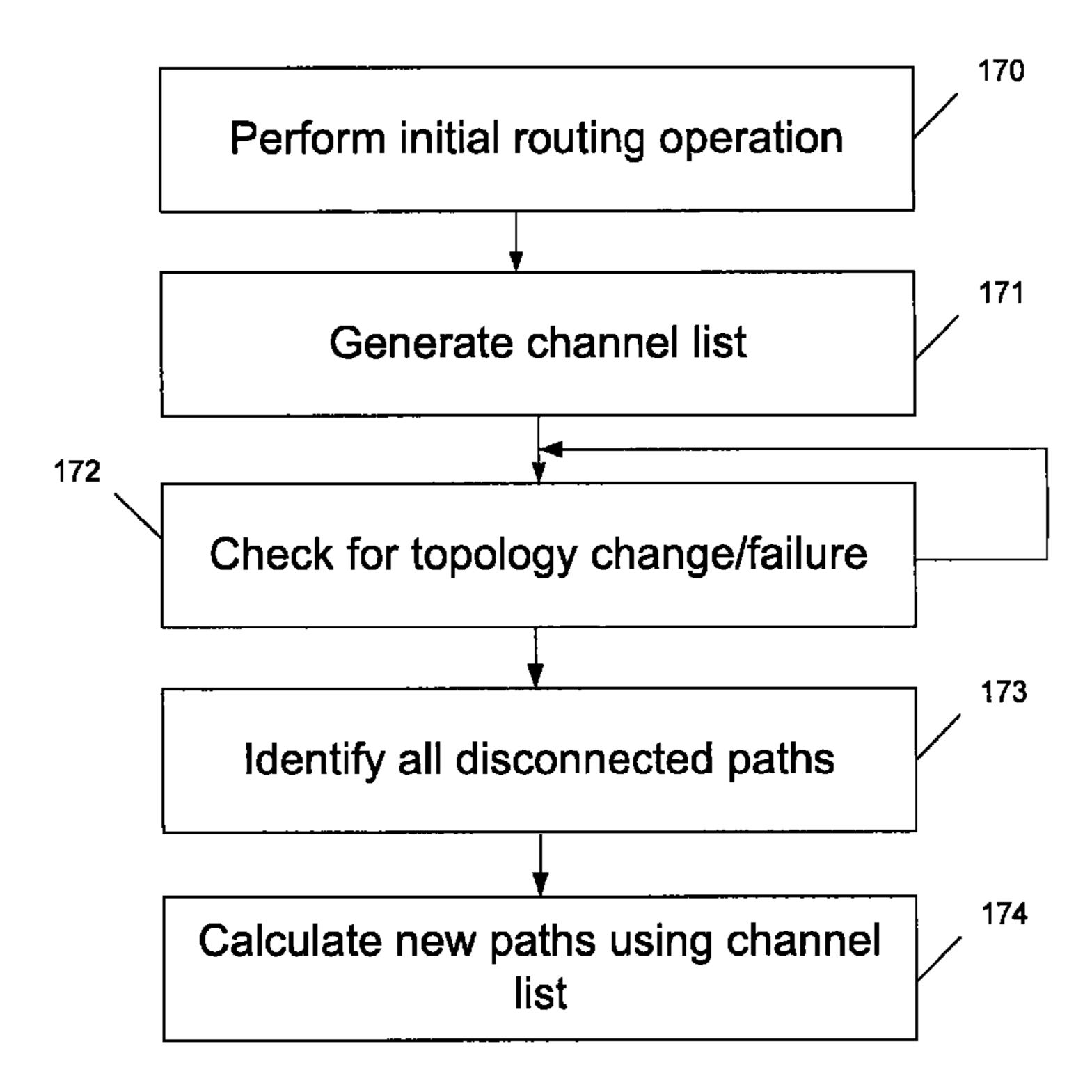

FIG. 27A illustrates a method of implementing dynamic quick reconfiguration according to one embodiment of the present disclosure;

FIG. 27B illustrates a block diagram according to one embodiment of the present disclosure; and

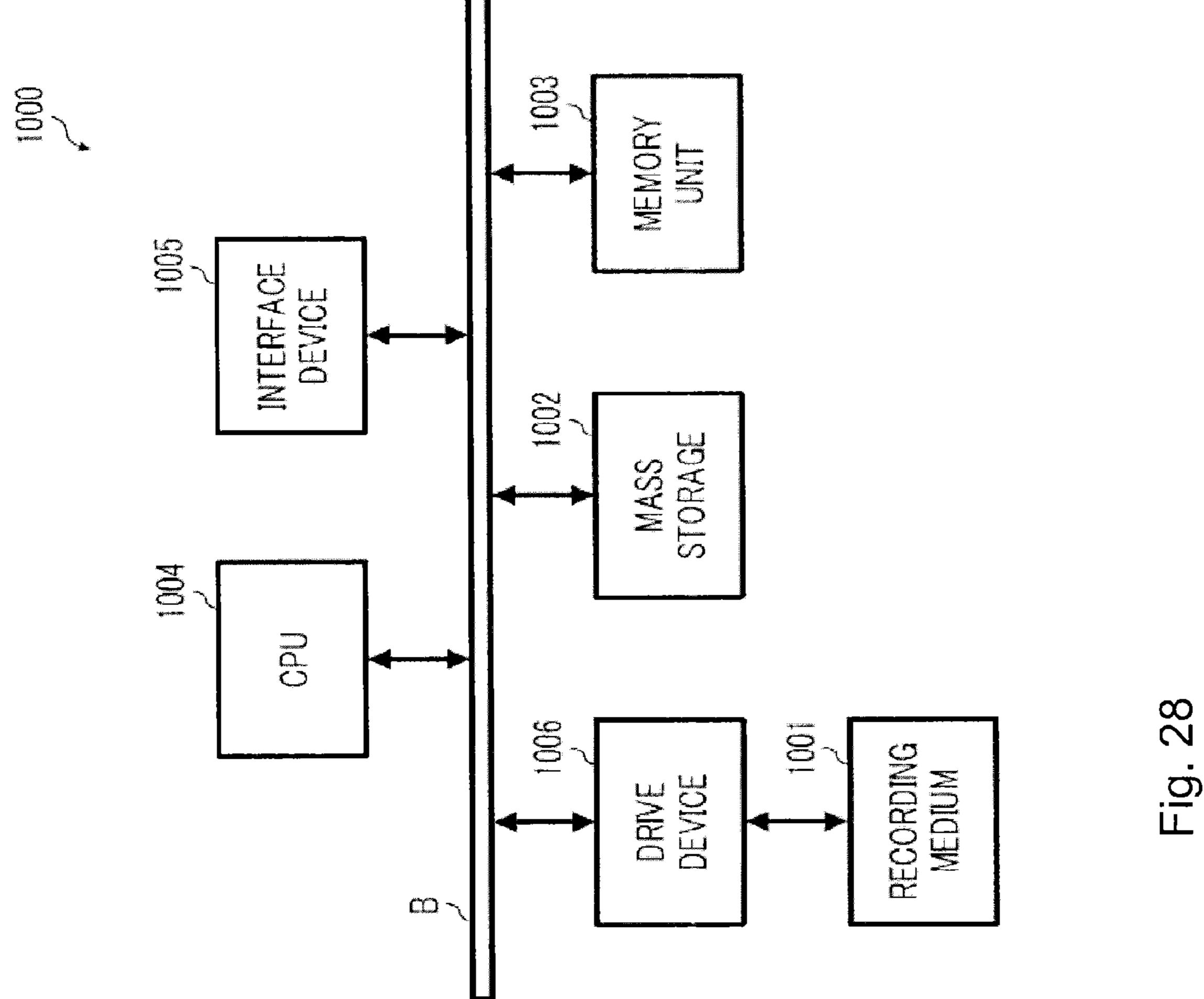

FIG. 28 illustrates computer hardware implementation according to one embodiment of the disclosure.

# DETAILED DESCRIPTION OF THE INVENTIONS

Referring now to the drawings wherein like reference numbers designate identical or corresponding parts throughout the several views and more particularly to FIG. 1 thereof, there is illustrated a general illustration of a source/destination pair 1,2. Between the source/destination pair 1,2 are shown multiple paths 3, some paths having a flow 4.

A path 3 is a sequence of links and switches that connect a source/destination pair 1,2. The data that is sent from the source to the destination along a path 3 is a flow 4. A source/destination pair 1,2 may have more than one path 3 between them, and they may have zero or more active flows 4.

The present disclosure includes multiple embodiments covering both the field of small area networks and the field of large area networks.

In one embodiment applicable to, at least, the field of large area networks, the concepts of source/destination pairs are discussed in the context of capturing scenarios where source/destination pairs need to have more than one path.

In another embodiment applicable to, at least, the field of small area networks, the concepts of source/destination pairs are discussed in the context situations where source/destination pairs have 0 or 1 flows.

In the first embodiment, which can be applied to the field of large area networks, for example, there is described the example of Permutation Routing, which can be used to create various routing strategies. For instance, Permutation Routing can provide the ability to implement robust routing schemes such as Next-Hop Optimal Routing.

Routing, in the present context, refers to the assignment of a set of next-hops for each destination node in each switch or router node. In this example, traffic transiting a node is treated in the same way as traffic originating at the node. In the present example, routing is designed to be loop-free, and hence a given routing corresponds to a Directed Acyclic Graph (DAG) rooted at each destination node consisting of the links and nodes involved in packet forwarding. With multipath routing, each node may have several outgoing links in the DAG for a destination. A routing where all links are included in each DAG is referred to as a full connectivity routing. With a given network topology, many different high or full connectivity routings can normally be constructed.

However, they will have different properties with respect to failure recovery and load balancing.

FIGS. 2a-d show a simple network topology, with 4 different DAGs for the destination node d. In FIG. 2a, DAG-1 is given by shortest path routing with equal-cost multi-path 5 routing ("ECMP") using the link weights indicated in the figure. Node c can split its traffic over two next-hops, while the other nodes have only a single next-hop towards d. Links (a, b), (c, b) and (c, f) are left idle, and are neither used for backup or load balancing. The DAGs in FIG. 2b, FIG. 2c and 10 FIG. 2d are all full-connectivity routing graphs, where all links can be used for packet forwarding. They differ, however, in their distributions of next-hops. In DAG-2, shown in FIG. 2b, there are three nodes (a, e and f) that have only a single next-hop towards d. DAG-3, shown in FIG. 2c, has only two 15 such nodes (a and e). DAG-2 and DAG-3, shown in FIGS. 2b and 2c, respectively, are both compatible with shortest path routing, because they contain all directed links of DAG-1 shown in FIG. 2a. DAG-4, shown in FIG. 2d, is not compatible with shortest path routing. In particular, by changing the 20 direction of the link (c, e), the number of nodes with a single next-hop has been reduced to one (the minimum value).

To maximize the single link fault coverage and load-balancing capabilities of a network, it is helpful to ensure that there is more than one next-hop available for as many S-D 25 pairs (i.e. source-destination pairs) as possible. This leads to the following optimization criterion for Next-Hop Optimal Routing (NHOR).

An NHOR is a full-connectivity routing that maximizes number of S-D pairs that have at least two next-hops towards 30 a destination.

As illustrated by the example above, an NHOR will not always be compatible with shortest path routing. For that reason, the Shortest-Path compatible NHOR (NHOR-SP), which is a full-connectivity routing that maximizes number of 35 S-D pairs that have at least two next-hops while containing the DAG calculated by a shortest path algorithm, can be used.

Permutation Routing can be described by a series of functions which illustrate the operation of this novel routing scheme.

For instance, considering a network modeled as a connected graph G=(V, E) where V is a set of nodes and  $E\subseteq V\times V$  is the set of links (edges) in the network's topology. A connected link from node i to node j is denoted by (i,j).

The assignment of next-hops for each destination can be 45 considered individually. For a destination  $d \in V$ , let  $R_d = (V, E_d)$  be a routing function for packets destined to destination d, where  $E_d$  is a set of directed links constructed on E. In  $R_d$ , node j is called a next-hop of node i if there exists a directed link between node i and node j, denoted by  $(i \rightarrow j)$ . Thus,  $R_d$  is 50 a DAG rooted at destination d.

The routing function  $R_d$  contains all valid paths to d, and each path can be considered as a sequence of nodes from a specific source to d. At each node, packet forwarding is the process of sending packets to a next-hop in such a sequence. 55

Permutation Routing can be used as a tool to find such sequences with the goal of realizing NHOR.

For a given network topology G=(V, E), a permutation P of nodes is an arrangement of all nodes in V into a particular order.

Node j<node i is set to denote that node j occurs before node i in permutation P. The goal is to construct permutations that realize a certain routing strategy.

A permutation P is a routing permutation for  $R_d$  if all next-hops of each node occur before it in P:  $\forall (i \rightarrow j) \in E_d$ : j<i. 65

According to this definition, the destination node d will always be the first node in a routing permutation for  $R_d$ .

**10**

Nodes further out in the routing permutation will be topologically farther from the destination.

In addition, any loop-free routing function  $R_d$  can always be represented by a routing permutation in which d is at the left-most position.

This is the case because a loop-free routing function  $R_d$ =  $(V, E_d)$  is a DAG, rooted at d. When  $i \in V$  is arranged into a sequence such that if  $E_d$  contains a directed link  $(i \rightarrow j)$ , then j appears before i in that sequence, such an arrangement can be calculated by a topological sort algorithm. Destination  $d \in V$  is the only node that does not have any outgoing link. Following the above ordering, node d, hence, has been placed at the first position of the sequence.

In general, there can be more than one valid routing permutation for one routing function  $R_d$ . Starting with a routing permutation P, another valid routing permutation P' can be generated by swapping two consecutive nodes that are not connected by a directed link to each other. For instance, both permutations  $\{d \ a \ b \ e \ c \ f\}$  and  $\{d \ b \ a \ e \ c \ f\}$  are valid routing permutations for DAG-1, shown in FIG. 2a.

In the reverse process, routing tables can be generated from a routing permutation, given a forwarding rule that defines the relationship between neighboring nodes. In the present example a greedy forwarding rule is utilized for constructing the routing table, in which all topological neighbors of a node that occur before the node, in the routing permutation, are installed as next-hops. Note that this forwarding rule will result in a full connectivity routing, where all links in the topology are potentially used for traffic forwarding to all destinations. This will maximize the potential for load balancing and failure recovery. More restrictive forwarding rules could also be considered, which would result in a sparser DAG. This can sometimes be beneficial in order to avoid excessively long paths, or to limit the number of next-hops for a particular destination.

With the given forwarding rule, different routing permutations will result in routing functions with different robustness characteristics.

Finding a routing permutation that can realize NHOR is considered to be NP-hard (non-deterministic polynomial-time hard). However, the present embodiment presents an algorithm that produces routing permutations that approximate NHOR.

In the algorithm, which can be implemented by a microprocessor, a topology G=(V, E) of N nodes (|V|=N) is considered. All of the N nodes are uniquely identified by a number from 1 to N. In addition,  $P=\{p_1, p_2, \ldots, p_N\}$  is a set of N variables in a fixed order from  $p_1$  to  $p_N$ , with respective domains  $D=\{D_1, D_2, \ldots, D_N\}$ .  $D_1$  is set as the candidate set for each variable  $p_i$ . A candidate set consists of the nodes that can be assigned to variable  $p_i$ .

A routing permutation P is constructed by successively assigning a node  $u \in D_i$  to each variable  $p_i \in P$ . Such assignment is said to be valid if it satisfies a specific constraint function C(u) which is defined to realize the selected routing objective.

FIG. 3 illustrates the basic assignment procedure for variable  $p_{i+1}$  30 in which two key functions Update 31 and Select 32 work as filters to control the assignment. In the figure, each pair  $\langle p_i, u_i \rangle$  33 represents an assignment of the node  $u_i$  to variable  $p_i$ . The assignment of nodes to a subset of variables  $\{p_1, p_2, \ldots, p_i\} \subseteq P$  given by  $\{\langle p_1, u_1 \rangle, \ldots, \langle p_i, u_i \rangle\}$  is called partial routing permutation with i nodes. For simplicity, this is abbreviated to  $\overrightarrow{p}_i$ .

This basic assignment procedure has been embedded into the backtracking algorithm to obtain the routing permutation

P. The algorithm calls function Select 32 (with built-in constraint function C(u)) which goes through  $D_i$  to find a valid node for the current variable  $p_i$ . If Select 32 succeeds in finding a valid assignment, the algorithm calls function Update 31 to generate domain  $D_{i+1}$  and proceeds to next variable  $p_{i+1}$ . Otherwise, a backtrack step will be executed to revisit the variable  $p_{i-1}$ . The algorithm terminates if a routing permutation P of N nodes, also denoted by  $\overrightarrow{p}_N$ , is found or a failure notification returns if all backtracks are examined but no solution is found under C(u).

If the constraint function C allows it, the backtracking algorithm will find one routing permutation P among all possible solutions by searching through the search space shaped by the number of variables in P and their domains of 15 values. In a naïve implementation, the domain for variable

$p_{i+1}$  consists of (N-i) nodes that have not been placed in  $p_i$ . Based on that observation, the search space S of the permutation assignment problem has a form of a tree of depth N 40 rooted at the initial state  $\langle p_1, d \rangle$  as illustrated in FIG. 4.

Solutions  $\overrightarrow{p}_N$  are located at the tree's leaves. Two connected states in the search space refer to two instances of  $p_i$  and  $p_{i+1}$ . Assume that t operations are needed on average to move from state  $p_i$  to state  $p_{i+1}$ . The complexity in the best case when no backtrack step is needed (backtrack-free) is  $O(t \times N)$ . In the other extreme, if there is only one solution and the "wrong" choice is always made, the complexity would be  $O(t \times N!)$ .

The naïve implementation described above results in high computational complexity, and is only feasible for small  $^{30}$  topologies. Hence, it is useful to guide the search in order to avoid exploring the entire search space. For instance, in one aspect of the present embodiment, the constraint function C(u) may be simple, in order to reduce computational complexity. In another aspect of the present embodiment, the  $^{35}$  domain  $D_i$  may be limited by taking C(u) into account.

The aspects of the present embodiment described above can be used to construct two high robustness routings that approximate NHOR and NHOR-SP. Specifically, these routing schemes are labeled approximate NHOR and approximate NHOR-SP.

With Permutation Routing using greedy forwarding, a node in  $p_i$  (i>2) has at least two next-hops if it has at least two topological neighbors that occur before it in the routing permutation. The Approximate NHOR ("ANHOR") algorithm  $^{45}$  maximizes the number of nodes where this is the case.

The partial routing permutation  $\overrightarrow{p}_i$  represents a loop-free routing sub-graph towards destination d, denoted by  $R_d^i = (V(\overrightarrow{p}_i), E_d(\overrightarrow{p}_i))$  where  $V(\overrightarrow{p}_i)$  is the set of i nodes in  $\overrightarrow{p}_i$  and  $E_d(\overrightarrow{p}_i)$  50 is the set of directed edges formed by applying the greedy forwarding rule defined in section 3 on  $\overrightarrow{p}_i$ . To achieve highly robust routing, the node selected for variable  $p_{i+1}$  to form the partial routing permutation  $\overrightarrow{p}_{i+1}$  is the node with the maximum number of topological neighbors already placed in  $\overrightarrow{p}_i$ . Correspondingly, the number of directed edges of the routing sub-graph formed by the partial routing permutation  $\overrightarrow{p}_{i+1}$ , resulted from the assignment  $p_{i+1}$ ,  $p_i$  is maximized:

$$|E_d(\vec{p}_{i+1})| = \max_{\forall u \in D_{i+1}} |E_d(\vec{p}_i, < \vec{p}_{i+1}, u >)|$$

(1)

For a more efficient implementation, a counter c[u] can be maintained for each node u. This counter denotes the number

12

of outgoing links from u to  $\overrightarrow{p}_i$ . In other words, c[u] corresponds to the number of next-hops node u will have if it is selected as the next assignment in the routing permutation. The constraint function  $C_{ANHOR}(u)$  is derived to realize the expression (1) noted above as follows:

$$C_{ANHOR}(u) = \begin{cases} \text{True} & \text{if } c[u] = \max_{\forall v \in D_{i+1}} c[v] \\ \text{False} & \text{otherwise} \end{cases}$$

The constraint function  $C_{ANHOR}(u)$  implies that the domain  $D_{i+1}$  includes all nodes that have at least one topological neighbor in  $\overrightarrow{p}_i$ . The domain is, therefore, updated following the recursive relation:

$$D_{i+1} = D_i \cup \{v \in V | (u,v) \in E\} \setminus \{u\}$$

(2)

where u is the node that has been assigned to variable  $p_i$  in the i-th assignment.

The computational complexity of ANHOR is the product of the average number of operations to make a move between two successive states and the total number of states visited in the search space.

The constraint function  $C_{ANHOR}(u)$  gives a backtrack-free algorithm for all connected input topologies.

This reality can be illustrated by contradiction. For instance, when the algorithm with the constraint function  $C_{ANHOR}(u)$  is not backtrack-free, this means that constraint function returns False for all  $u \in D_{i+1}$  at some iteration. That can not happen because all nodes in domain  $D_{i+1}$  always have at least one next-hop in  $\overrightarrow{p}_i$  and that would always accord with  $c[u]=\max_{v\in D_{i+1}}c[v]=1$ .

Given the backtrack-free property of the present algorithm, the complexity of calculating a permutation for each destination is  $O(|E|+N\times|D|)$ , where |D| denotes the average size of the domain. Typically, |D| depends solely on the average node degree of the network topology. In dense topologies, the total complexity of calculating routing permutations for all destinations can approach  $O(N^3)$ . The backtrack-free property also provides low memory consumption because it does not need to store temporary partial routing permutations.

In the example of Approximate NHOR-SP (ANHOR-SP),  $R_d^{SP}$ =(V, $E_d^{SP}$ ) denotes the shortest path tree towards destination d. A routing permutation P whose routing function  $R_d$ =(V,  $E_d$ ) is an ANHOR-SP if  $R_d$  satisfies two constraints in following order:

- 1.  $R_d$  contains  $R_d^{SP}$ , meaning all routing choices for any node in  $R_d^{SP}$  are also valid routing choices for the same node in  $R_d$ .

- 2. ANHOR-SP uses the same selection criterion as ANHOR in order to maximize the number of S-D pairs with at least two next-hops.

The construction of such a routing permutation P is based on the assignment procedure described in FIG. 3. To this end, the shortest path compatibility constraint is implemented in function Update 31 to limit the size of domain  $D_{i+1}$  for variable  $p_{i+1}$  and the connectivity constraint will be formalized by a constraint function  $C_{ANHOR-SP}(u)$  and realized in function Select 32. Clearly, the constraint function  $C_{ANHOR-SP}(u)$  is identical to  $C_{ANHOR}(u)$ .

The next node in routing permutation P is selected among nodes that have all their shortest path next hops towards d already placed in  $\overrightarrow{p}_i$ . Formally,  $R_d^{SP,i}=(V(\overrightarrow{p}_i), E_d^{SP}(\overrightarrow{p}_i))$  is the shortest path tree of  $V(\overrightarrow{p}_i)$  nodes and  $R_d^{SP,i} \subseteq R_d^{SP}$ . The

domain  $D_{i+1}$  for variable  $p_{i+1}$  includes all nodes u such that the assignment  $\langle p_{i+1}, u \rangle$ , resulting in  $\overrightarrow{p}_{i+1}$ , fulfills:

$$R_d^{SP,i+1} \subseteq R_d^{SP}$$

$c_{sp}[v]$  is the number of shortest path next-hops placed in  $\overrightarrow{p}_i$ and  $n_{sp}[v]$  is the total number of shortest path next-hop that can be calculated from  $R_d^{SP}$  of node v. The domain  $D_{i+1}$  for variable  $p_{i+1}$  follows the recursive relation:

$$D_{i+1} = D_i \cup \{v \in V | c_{sp}[v] = n_{sp}[v]\} \setminus \{u\}$$

(3)

where u is the node that has been assigned to variable  $p_i$ .

The constraint function  $C_{ANHOR-SP}(u)$  gives backtrack-free 15 algorithm for all connected input topologies.

For instance, constraint function  $C_{ANHOR-SP}(u)$  always returns True unless  $D_i$  is empty.  $D_i$  can never be empty before all nodes have been placed in the permutation. If  $D_i$  is empty,  $z_0$ there is no node that has all its shortest path descendants in  $\overrightarrow{p}_i$ . In other words, the shortest path DAG R<sub>d</sub> SP can be followed from any node that has not been placed and a next-hop node being empty is impossible. Specifically, since R<sub>d</sub><sup>SP</sup> is connected and loop-free, any path along the shortest path DAG will eventually reach the destination, which is the first node that was placed in the permutation.

The computational complexity of ANHOR-SP towards 30 one destination includes two parts: the shortest path calculation using Dijkstra's algorithm and routing permutation construction. Due to the property of backtrack-freedom, with sparse topologies the complexity of second part towards one destination would be  $O(|E| + |E_d^{SP}| + N \times |D|)$  where |D|denotes the average size of the domain. In dense topologies, the total complexity of calculating routing permutations for all destinations can approach  $O(N^3)$ .

Thus, with a low computational complexity, ANHOR-SP 40 can be implemented on a per-router basis in Open Shortest Path First (OSPF) or Intermediate System To Intermediate System (IS-IS) networks. To ensure a consistent permutation routing in the entire network, constraint function  $C_{ANHOR-SP}$ (u) will return the same node in each assignment among 45 possible selections. This tie can be broken by letting the highest router ID be selected. The highest router ID denotes the largest number numerically. For instance, 192.168.1.2 would be higher than 172.16.3.2, and 172.16.3.2 would also be higher than 172.16.2.1.

The presently disclosed algorithms have been applied to a large area network scenario and the advantageous results have be measured. In particular, the performance of the proposed algorithms have been evaluated by measuring how well the 55 algorithms realize NHOR with respect to NHOR being a full-connectivity routing that maximizes number of S-D pairs that have at least two next-hops towards a destination.

Since multipath routing leads to path inflation, the path length distribution is also measured. ANHOR and ANHOR-SP are compared to standard shortest path routing with ECMP, and to Loop Free Alternate Routes ("LFA").

In the present example, six representative network topologies from the Rocketfuel project have been selected for the 65 evaluation. The topologies are listed in Table 1 in increasing order of their average node degrees.

14 TABLE 1

|     | Network topologies |                  |       |       |              |

|-----|--------------------|------------------|-------|-------|--------------|

| · _ | AS                 | Name             | Nodes | Links | Avg. Degree  |

|     | 1221               | Telstra TM (au)  | 104   | 151   | 2.90         |

|     | 1755               | Ebone TM (eu)    | 87    | 161   | 3.70         |

|     | 3967               | Exodus TM (us)   | 79    | 147   | 3.72         |

|     | 3257               | Tiscali TM (eu)  | 161   | 328   | 4.07         |

|     | 6461               | Abovenet TM (us) | 138   | 372   | <b>5.4</b> 0 |

| 0   | 1239               | Sprint TM(us)    | 315   | 972   | 6.17         |

The results for ECMP and LFA depended heavily on the link weight settings used in the topologies. To obtain realistic link weight settings, a local search heuristic was run with a link load objective function, using a traffic matrix generated by a gravity model. For AS1239 (Sprint<sup>TM</sup>), unit link weights were used, because the above noted local search heuristic did not scale to a topology of this size.

In order to evaluate the robustness, multipath capability was considered. FIG. 5 shows the fraction of nodes with at least two next-hops with the different routing methods. It can be observed that the multipath capability varies strongly between topologies; it is generally higher in more well-conthat is not placed in  $\overrightarrow{p}_i$  can always be found. However  $\overrightarrow{D}_i$  25 nected networks. ANHOR achieves a significant improvement over ECMP and LFA in all networks.

> It should be noted that the number of next-hops achieved with ANHOR is independent of the link weight settings, while ANHOR-SP is constrained to including the shortest paths in the routing. ANHOR-SP performance is close to ANHOR, and gives a clear improvement over LFA (by up to 28% in AS1239). This shows that Permutation Routing can give a significant gain compared to existing solutions, while being compatible with shortest path routing with realistic link weight settings.

> For reference, FIG. 5 also shows the fraction of nodes in each topology with a node degree larger than 1. Nodes with a degree of 1 can not have more than 1 next-hop to any destination.

> FIG. 6 shows the mean and variance for the number of next-hops at each router in the six topologies reviewed in the present example. For increased robustness and load-balancing, it is generally good to have a high mean and a low variance in the number of next-hops. If this variance is high, it means that a few nodes have a high number of next-hops, while others might be left with only one.

Both ANHOR and ANHOR-SP produce full connectivity routings, which means that the mean number of next-hops across all S-D pairs will be equal to half the average node degree in the topology. The mean is somewhat lower for LFA and ECMP, meaning that some links are not used for packet forwarding. The variance, however, is lower with ANHOR than with ANHOR-SP and LFA. This shows how ANHOR achieved a better (more uniform) next-hop distribution than the other routings.

There are good reasons to limit the number of next-hops that are installed in the forwarding table for a particular destination. Installing more than a few next-hops will not give much benefit with respect to robustness or load-balancing. It will, however, require faster memory in the forwarding table, and may lead to the unnecessary inclusion of paths that are much longer than the shortest path.

Hence, an example is considered in which the number of next-hops for a particular destination is limited to at most K. A Routing Efficiency coefficient is defined, which denotes the fraction of bidirectional links that are used for traffic forwarding with a given K.

(4)

$RE=2\times |E_d(K)|/|E|$

**16**

where  $|E_{\lambda}(K)|$  is the number of directed links in the routing DAG when each node can have at most K next-hops and |E| is the number of bidirectional links in the network topology. According to this definition,  $0 \le RE \le 1$ .

Table 2 shows the RE values for three values of K in the selected topologies. The given value is the average over all S-D pairs. It can be seen that for all routing methods, a higher K gives a higher RE value. ANHOR and ANHOR-SP give the highest RE values, sometimes with a significant improvement 10 over ECMP and LFA even for K=2. The RE values in more well-connected topologies (AS1239) are lower than in sparse topologies. Such topologies contain a high number of nodes with a very high degree (39% nodes has their degrees greater than 15 in AS1239), and a low K will hence exclude many 15 valid (but often unnecessary) paths.

The present embodiment presents Permutation Routing as a method for increased robustness in IP networks with traditional hop-by-hop forwarding. The present embodiment can also be used to generate routings that give a significant boost in number of nodes that have at least two forwarding options to a destination. The present embodiment is able to add robustness. This is the case, at least, because Permutation Routing bases its construction solely on topology information and hence no new control plane signaling is required. In addition, Permutation Routing allows a tunable K where K≥1 while still being compatible with traditional link-state routing protocols. In the same category, Protection Routing presents a two-phase heuristic to produce a routing for a given traffic demand in a centralized routing system. In phase 1, the heuristic seeks to minimize number of unprotected nodes towards a destination while minimizing a cost function. Although

TABLE 2

|       |          | Routi  | ng Efficien | cy coefficie | nt     |        |        |

|-------|----------|--------|-------------|--------------|--------|--------|--------|

|       |          | AS1221 | AS1755      | AS3967       | AS3257 | AS6461 | AS1239 |

| K = 2 | ECMP     | 0.74   | 0.61        | 0.61         | 0.54   | 0.43   | 0.49   |

|       | LFA      | 0.80   | 0.79        | 0.77         | 0.77   | 0.62   | 0.49   |

|       | ANHOR-SP | 0.86   | 0.84        | 0.85         | 0.76   | 0.67   | 0.58   |

|       | ANHOR    | 0.94   | 0.90        | 0.95         | 0.81   | 0.81   | 0.60   |

| K = 3 | ECMP     | 0.76   | 0.62        | 0.62         | 0.54   | 0.46   | 0.56   |

|       | LFA      | 0.86   | 0.90        | 0.87         | 0.82   | 0.77   | 0.57   |

|       | ANHOR-SP | 0.92   | 0.95        | 0.94         | 0.88   | 0.85   | 0.75   |

|       | ANHOR    | 0.98   | 0.99        | 1.00         | 0.95   | 0.95   | 0.80   |

| K = 4 | ECMP     | 0.77   | 0.62        | 0.63         | 0.54   | 0.47   | 0.60   |

|       | LFA      | 0.90   | 0.94        | 0.91         | 0.88   | 0.85   | 0.61   |

|       | ANHOR-SP | 0.96   | 0.99        | 0.97         | 0.93   | 0.93   | 0.65   |

|       | ANHOR    | 1.00   | 1.00        | 1.00         | 0.99   | 0.99   | 0.92   |

more load balancing. However, it has a cost in terms of path inflation and increased load in the network if traffic is sent over non-shortest paths. When considering the distribution of path lengths, hop counts should be considered since this metric is independent of the link weight settings. FIG. 7 40 shows the average path stretch regarding K=3 with different routings, where the length of each valid path has been normalized with the shortest path length for that S-D pair. The superior path diversity in ANHOR and ANHOR-SP can be observed but comes at the cost of some path inflation. Nev- 45 ertheless, the average path lengths are still comparable to those of shortest path routing. It should be noted that the path inflation introduced with multipath routing can be ameliorated with more intelligent load balancing methods.

The complexity of the disclosed algorithms depends on the number of nodes, links and on how efficiently the size of the candidate set can be reduced. The average size of candidate set turns out to be approximately 5 times (AS1755) to 12 times (AS1239) higher than their corresponding average 55 node degrees in the exemplary topologies.

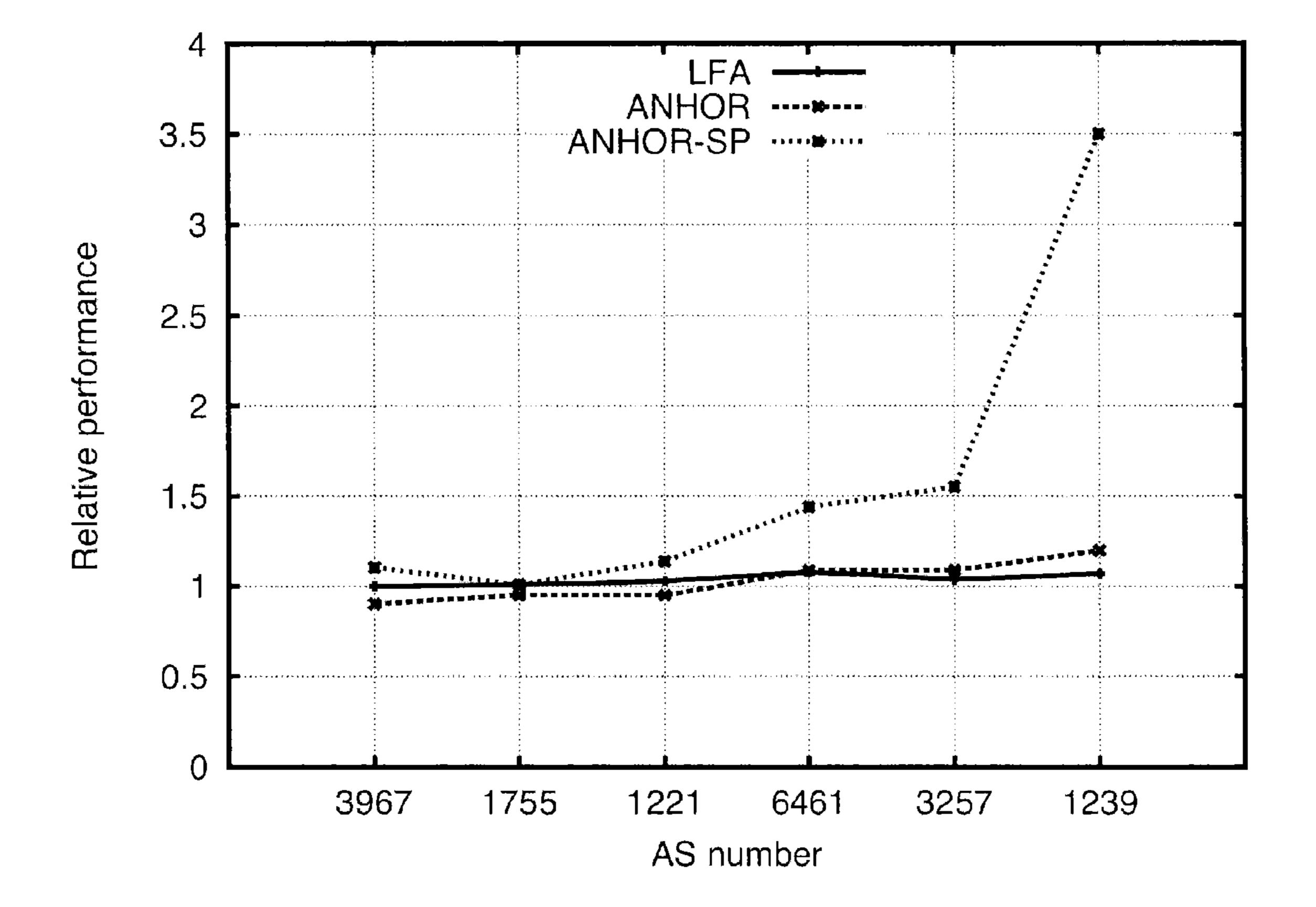

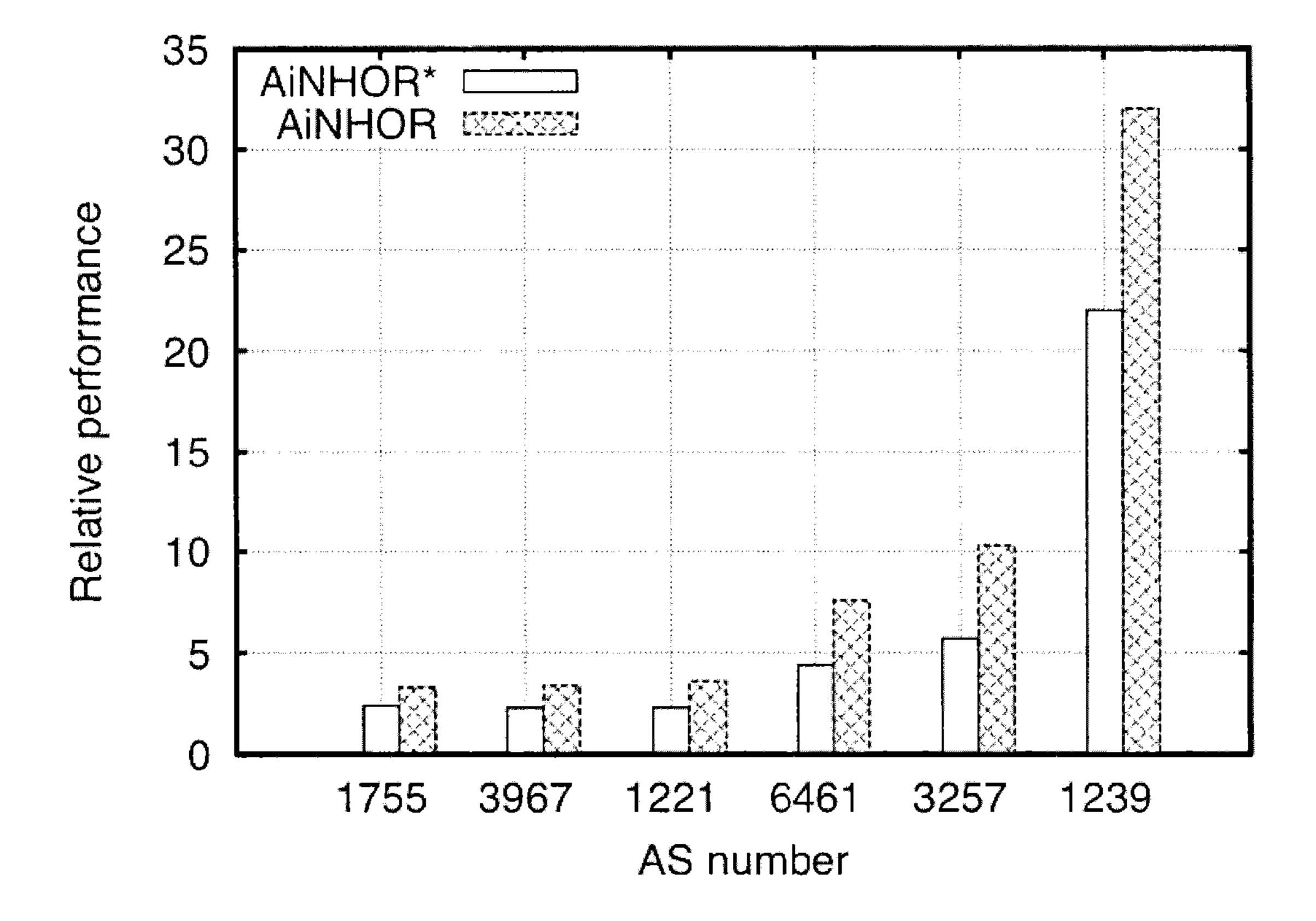

FIG. 8 shows the relative running time of each routing method as compared with ECMP, across six topologies. The AS topologies are listed in an increasing order of number of nodes. The results are achieved with an Intel Core 2 CPU 60 6300 @ 1.86 GHz machine. ANHOR has a low running time that is comparable to a normal ECMP routing computation. For all destinations, the total time difference is less than 10% for all topologies. As for ANHOR-SP, calculating routing permutations for all destinations takes four times less time 65 than ECMP. Across all topologies, the memory consumption never exceeds 6 MB.

High path diversity increases robustness and allows for 35 Routing Permutations share the goal of minimizing the number of nodes with only one forwarding option, next-hops can be evenly distributed among nodes rather than performing traffic optimization for a specific traffic demand. Finding a routing that optimizes for a given load function is less important for the Internet where traffic matrix elements vary significantly with time. Instead, in the Internet context, the available forwarding options can be optimized for more intelligent load balancing methods that are more responsive to traffic variation.

> The Permutation Routing is an approach for calculating more robust routing while being compatible with existing links state routing protocols. An algorithm can be used to construct routing permutations. Routings that optimize different objectives can be implemented by modifying the selec-50 tion criteria that are used in the construction algorithm.

Permutation Routing is to maximize the survivability in a network with traditional hop-by-hop forwarding. In addition, as is noted above, permutation routings outperform existing multipath approaches such as ECMP and LFA in terms of robustness and path diversity. In addition, the complexity of calculating routing permutations is comparable to that of standard link state routing.

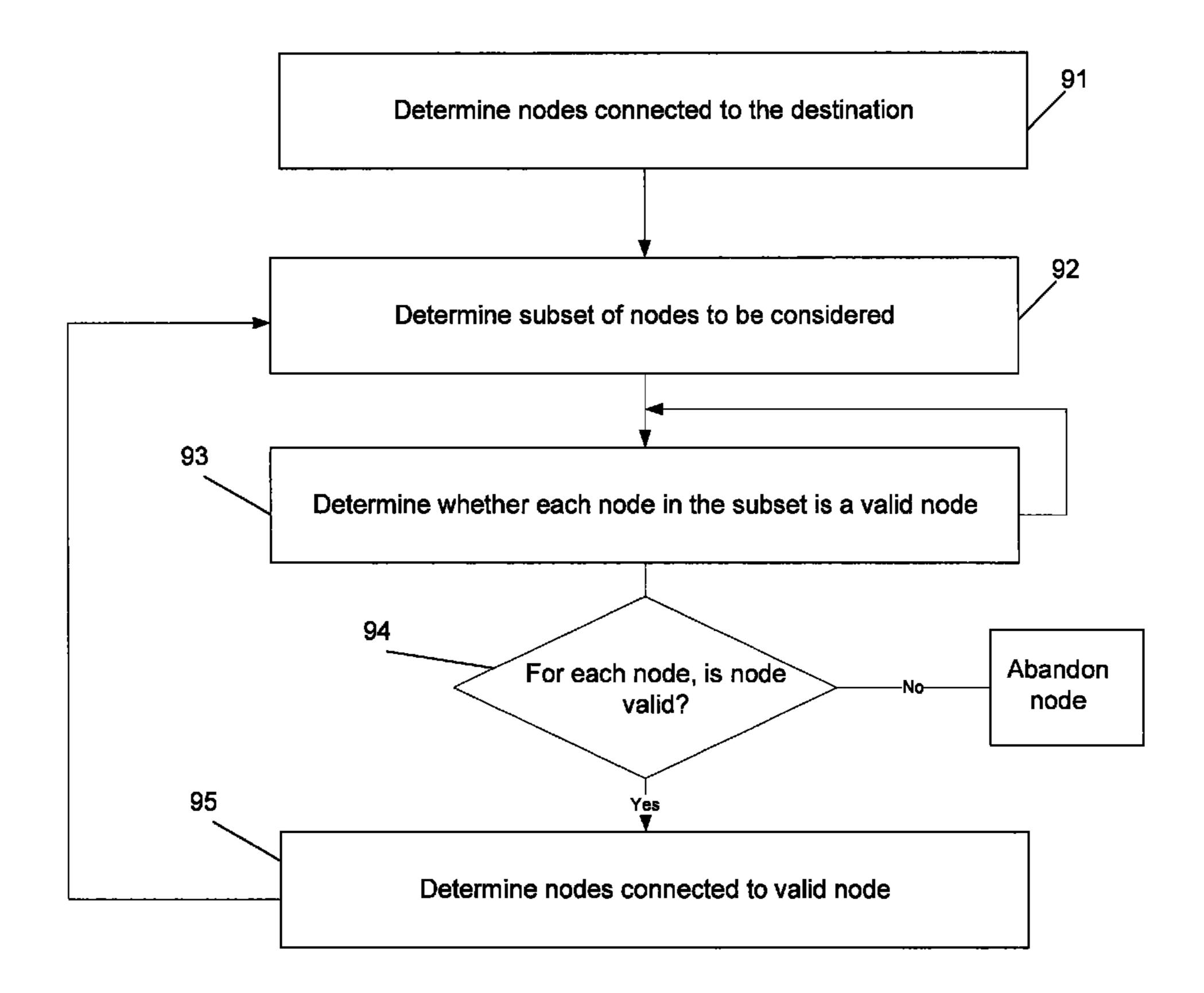

The method of implementing permutation routing is described with respect to the flow chart illustrated in FIG. 9A. In step 91, determine the nodes connected to the destination.

In step **92**, determine the subset of nodes to be considered. In step 93, determine for each of the nodes in the subset, whether the node is a valid node, if so, proceed to next step, if not, abandon the respective node.

In step 94, for each valid node in the subset, determine a next step set of nodes connected thereto.

In step 95, for each next step node in the next step set of node return to step 92.

In the ANHOR and ANHOR-SP schemes, the subset of nodes to be considered in step 92 is reduced. In addition, the determination of whether the node is a valid node in step 93 is based on a further function  $C_{ANHOR}(u)$  or  $C_{ANHOR-SP}(u)$ .

Once the paths are determined they can be stored in one or more routing tables in respective routers/switches. The permutations can be obtained using a distributed algorithm that creates the routing tables in the routers/switches. Hybrid solutions of this is also available. For instance, the paths can be decided by applications using the paths. For example, an application for streaming media data, e.g. a film, or a sports event, may result in a choice of different paths than an application for transferring files, such as Dropbox<sup>TM</sup>.

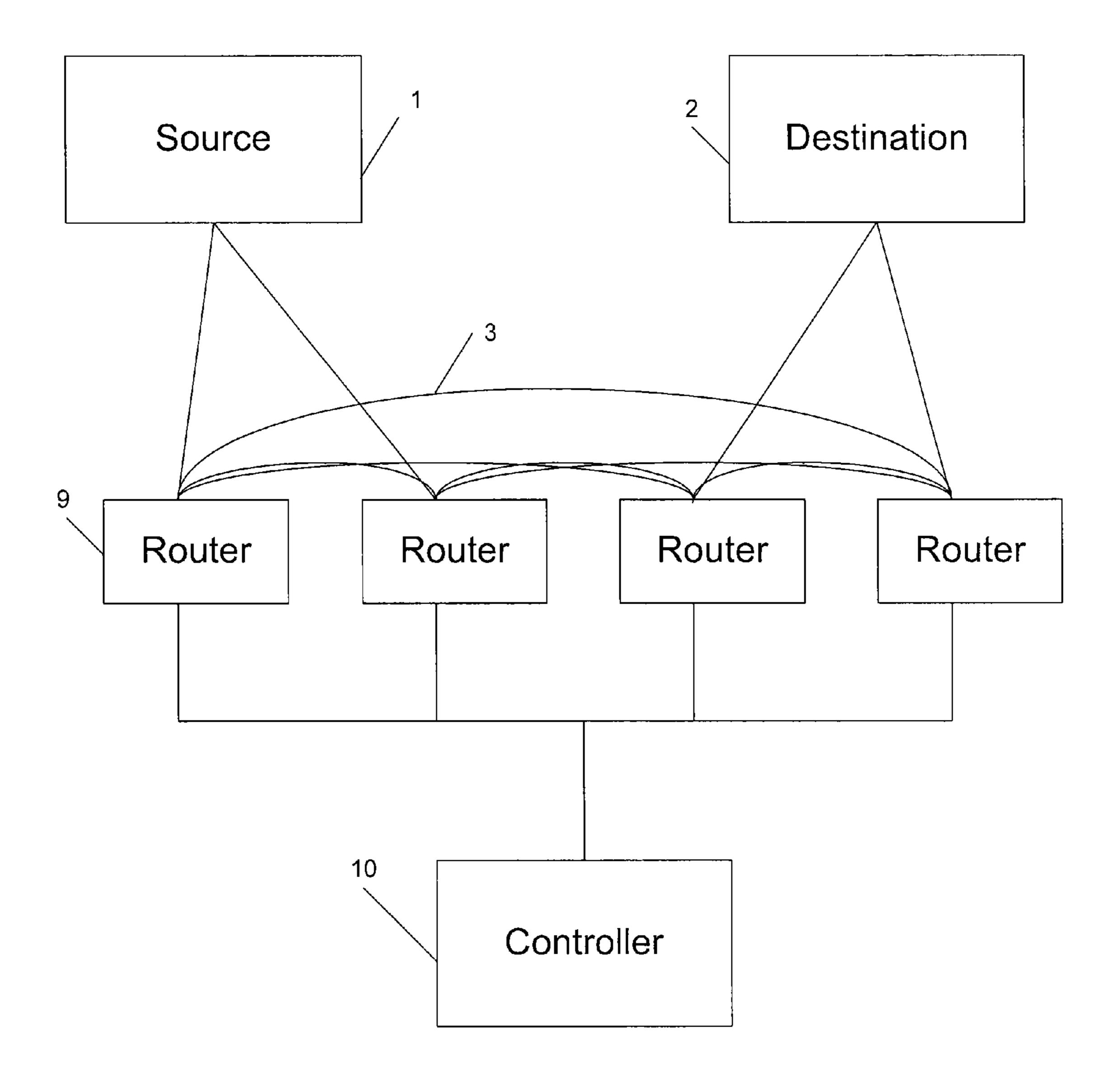

FIG. 9B illustrates a microprocessor implemented controller 10 which determines the routes based on the ANHOR and ANHOR-SP schemes. For instance, the controller 10 determines the routes between the source 1 and destination 2 and 20distributes the determined paths to the routers 9. The controller 10 thus maximizes the number of paths between each source 1 and destination 2 pair, such that packets do not loop in the network. This maximization provides toleration of faults in the network and avoids problems created by looping.

As is noted above, in the field of large area networks, Permutation Routing can provide the ability to implement additional robust routing schemes. In the present embodiment, there is described a new routing method that combines the concept of routing permutations with interface-specific 30 forwarding. This interface based Permutation Routing aims to maximize the fast rerouting coverage for IP networks by giving multiple loop-free alternates for each incoming interface of the router. In addition, the interface based Permutation For instance, the present interface based Permutation Routing method does not require the network operator to change the traditional hop-by-hop forwarding strategy that is optimized for the fault free case. Further, the method does not require addition of fault-information included in the packet header 40 and does not suffer from routing loops, even when there are multiple faulty components in the network. Finally, the interface based Permutation Routing method works with the existing standard link state routing protocols such as OSPF or IS-IS.

As is noted above, Permutation Routing is a highly flexible approach for calculating multiple loop-free next-hops in networks with the traditional hop-by-hop forwarding. Permutation Routing is based on the fact that any routing strategy can be expressed as a permutation (sequence) of nodes that are 50 involved in traffic forwarding to a destination. The routing ensures that loops are avoided when packets are forwarded in one direction towards destination regarding to node ordering in the permutation. Correspondingly, a simple forwarding rule is proposed to generate forwarding tables based on per- 55 mutations. Permutation Routing only takes the topology information that is collected by a standard link state routing protocol as the input for its construction, and hence no new control plane signaling is needed.

This Permutation Routing is used in the present embodi- 60 ment to create a robust routing that maximizes the number of interface-destination (I-D) pairs that have more than one available next-hop. A backtracking algorithm is used to construct the ordering of nodes in the permutation. The properties of the resulting routing are determined by defined constraints 65 which are used to govern the creation of the permutation. Permutation Routing is a powerful abstraction that can be

**18**

used to implement many different routing objectives for IP networks with either node specific forwarding or interface specific forwarding.

Conventional topologies are inconvenient for directly calculating an interface based routing, where next-hops associate with an incoming interface. According, in the present embodiment the given topology is pre-processed to achieve a new directed graph, from which routing tables for incoming interfaces are easily computed. Specifically, each node in the new graph represents a directed link of the original topology and the connectivity among those nodes is induced from the connectivity of the given topology. The graph transformation allows existing routing algorithms, e.g. ECMP and LFA, and Permutation Routing to be reused to construct routing tables for incoming interfaces with different degree of robustness.

Interface specific forwarding has the ability to increase routing robustness for IP networks. The present embodiments implement interface specific forwarding using Interface Next-hop Optimal Routing (iNHOR) as the main objective function for a robust interface based routing.

To help ease the description, networking terms are introduced herewith that will be used in the following embodiment. A directed link from node i to node j, denoted by  $(i \rightarrow j)$ , is an incoming interface to node j and an outgoing interface of node i. A routing is an assignment of a set of next-hops for each destination node for each traffic source. A routing is loop-free in the present embodiment and hence a given routing corresponds to a Directed Acyclic Graph (DAG) rooted at each destination node consisting of the links and nodes involved in packet forwarding. With multipath routing, each node may have several outgoing links in the DAG for a destination.

In IP networks with interface-specific forwarding, packets Routing method shares with ECMP and LFA certain features. 35 are routed based on both the incoming interface and the destination address in the IP header. To do that, each line-card in the router will maintain its own distinct forwarding table that maps each network destination to eligible outgoing interfaces. These forwarding tables are distributed by a routing controller 100 shown in FIG. 19B, where routing protocols (e.g. OSPF or IS-IS) are used to populate the routing tables. In one embodiment, the forwarding engines are integrated into interface cards in the distributed mode. In interface based routing, packets for a given destination can be forwarded in 45 both directions of a bidirectional link without necessarily causing loops. This ability can help increase robustness over traditional IP routing especially when the network topologies are not well-connected.

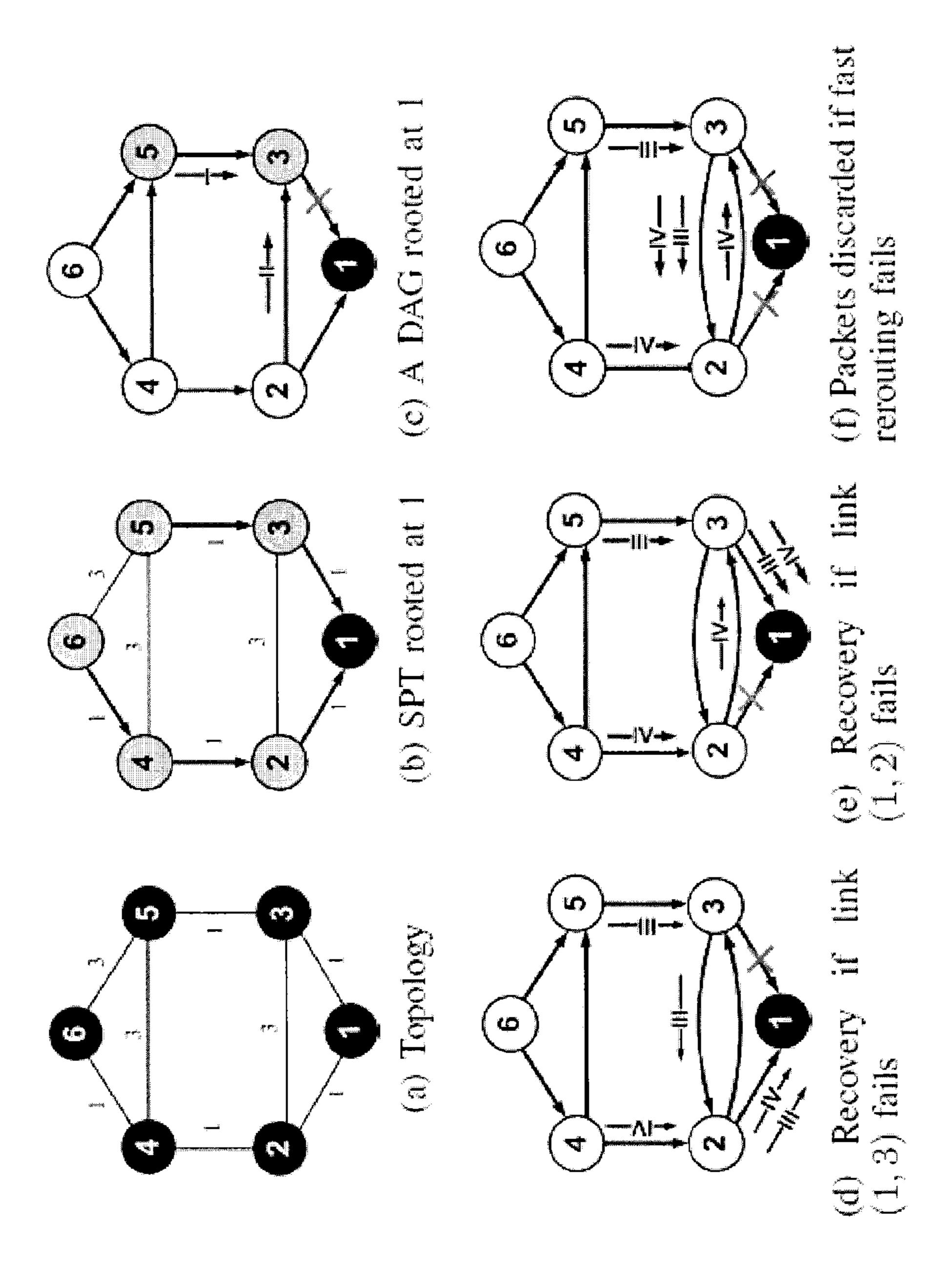

For instance, FIG. 10a illustrates a simple topology with six nodes and eight bidirectional links with their corresponding link weights. FIG. 10b is a shortest path tree (SPT) rooted at destination 1. Shortest path trees are usually sparse and thus less robust against network component failures. Provided that a node is fast reroute protected if it has at least two next-hops, no node in FIG. 10b is protected (gray shadowed nodes). Other routing methods, e.g. LFA, can improve SPT by growing non-shortest path branches to form a better-connected routing graph, mandatorily a DAG. FIG. 10c illustrates such a DAG rooted at node 1. FIG. 10c is the most robust loop-free routing graph that traditional IP routing can provide on the given topology because growing any more directed link will cause loops. For example, if link (1, 3) fails, node 3 must discard its incoming traffic. Any attempt to reroute packets to node 2 would form a loop between node 2 and node 3, until link (1, 3) recovers from the failure. Consequently, node 3 and node 5 are not protected for possible single failures in the example of FIG. 10c.

These problems are addressed and rerouting accomplished successfully in the network using interface-specific forwarding as shown in FIG. 10d and FIG. 10e. In FIG. 10d, the failure of link (1, 3) does not interrupt data flow III from node 5. Instead, node 3 routes flow III to node 2. Being aware of the incoming interface of flow III, node 2 forwards it to destination 1. Similarly, the failure of link (1, 2), in FIG. 10e, triggers node 2 to reroute incoming flow IV to node 3, from which it would be successfully delivered at node 1. The two scenarios, FIG. 10d and FIG. 10e, will be fulfilled if routing tables towards destination 1 are installed at interfaces of node 2 and node 3 as in FIG. 11. Note that those next-hops indicated as primary are used when they are available.

If both link (1, 3) and link (1, 2) fail at the same time, both flows will be discarded at node 2. Flow IV travels on path  $4\rightarrow2\rightarrow3\rightarrow2$  before it would be stopped at node 2. Loops will not occur when each interface is equipped with loop-free next-hops towards the destination and the incoming flow is discarded when there is no available next-hop for the corresponding incoming interface.

In order to maximize the fault tolerance and load-balancing capabilities of a network, a routing should provide more than one available next-hop for as many I-D pairs as possible. In addition, such routing will contain the shortest path tree to be compatible with the standard link state routing protocols. In light of the features, the following optimization criterion has been developed for Interface Next-hop Optimal Routing (iN-HOR).

#### Definition 1:

Given a routing, the outgoing interface on the shortest path tree is called the primary interface (pI) and the outgoing interfaces not on the shortest path tree are called secondary interfaces (sI). An iNHOR is an interface based routing that contains the shortest path tree and satisfies the two following conditions in order:

- 1) The number of pI-D pairs that have at least two next-hops is maximized.

- 2) The number of sI-D pairs that have at least two next-hops is maximized.

Nodes employ their primary interfaces to forward packets when the network is fault-free. The secondary interfaces are used as back-ups for fast rerouting purposes when a primary interface fails. The definition implies that fault tolerance capability is maximized for primary interfaces first and thereafter for secondary interfaces.

iNHOR is able to increase robustness for IP networks especially when line-cards have loop-free routing forwarding tables. Therefore a method is discussed herewith that helps construct DAGs for interfaces directly from given a topology.

The network topology is modeled as a directed graph G=(V, E) where V is the set of nodes and E is the set of directed links (edges). Let N and M denote the cardinality of set V and E, respectively. The directed link  $(u\rightarrow v)$  consists of the head node u and the tail node v. Let  $\mathcal{G}=(v, \mathcal{E})$  be the directed graph generated from G by employing two following transformation definitions.

## Definition 2:

Each directed link in E has been transformed into a node in  $\mathcal V$  .

The node in  $\mathcal{V}$ , which is directed link  $(u \rightarrow v)$  in E, is denoted by [u, v]. Let  $\mathcal{H}(|u, v|)$  and  $\mathcal{T}(|u, v|)$  be two operators which apply on the node [u, v] to extract head node and tail node of the corresponding directed link  $(u \rightarrow v)$ .

**20**

Definition 3:

Two nodes i,  $j^1 \in V$  form a directed edge  $(i \rightarrow j)$  in  $\mathcal{E}$  if and only if  $\mathcal{H}(i) = \mathcal{T}(j)$ .

<sup>1</sup> For convenience, nodes are sometimes denoted in the new directed graphs with single letters.

Following Def. 2 and Def. 3 in that sequence, the directed graph  $\mathcal{G} = (\nu, \mathcal{E})$  has been identified thoroughly. Let A  $\mathcal{G} = (a_{ij})$  be the adjacency-matrix that represents for  $\mathcal{G}$ :

$$a_{ij} = \begin{cases} 1 & H(i) = T(j) \\ 0 & \text{otherwise} \end{cases}$$

Following theorems describe some consequences of the defined graph transformation. Theorem 1 and Theorem 2 prove that the transformation rules preserve subset relationship and acyclic property of a directed graph while Theorem 3 provides the cardinalities of the sets of nodes and links of the transformed graph for the given topology.

Theorem 1:

Let  $G_1$ =( $V_1$ ,  $E_1$ ) and G=(V, E) be two directed graphs and  $\mathcal{G}_1$ =( $\mathcal{V}_1$ ,  $\mathcal{E}_1$ ) and  $\mathcal{G}$ =( $\mathcal{V}$ ,  $\mathcal{E}$ ) be two transformed graphs, with respect to Def. 2 and Def. 3 in such order, of  $G_1$  and G, respectively. If  $G_1 \subseteq G$ , then  $\mathcal{G}_1 \subseteq \mathcal{G}$ .

Proof:

It is proved that  $\nu_1 \subseteq \nu$  and  $\mathcal{E}_1 \subseteq \mathcal{E}$  hold.

(i) It is trivial that  $\gamma_1 \subseteq \gamma$  because  $\mathcal{E}_1 \subseteq \mathcal{E}$ .

(ii) Assuming that arbitrary directed links  $(a \rightarrow b) \in E_1$  and  $(b \rightarrow c) \in E_1$ ,  $(|a,b| \rightarrow |b,c|) \in \mathcal{E}_1$  are present in the transformed domain. Because  $E_1 \subseteq E$ , then  $(a \rightarrow b) \in E$  and  $(b \rightarrow c) \in E$  and  $(|a,b| \rightarrow |b,c|) \in \mathcal{E}$  in the transformed domain. That means  $\mathcal{E}_1 \subseteq \mathcal{E}$ .

Theorem 2:

The transformed graph, with respect to Def. 2 and Def. 3 in such order, of a directed acyclic graph is also a directed acyclic graph.

Proof:

The proof is by contradiction. D is denoted by the given directed acyclic graph and  $\mathcal{D}$  by the directed graph generated from D with respect to Def. 2 and Def. 3 in such order. It is assumed that  $\mathcal{D}$  contains a loop, namely the loop is  $|a, b| \rightarrow |b$ ,  $c| \rightarrow \ldots \rightarrow [y, z] \rightarrow [z, a]$  where  $a, b, c \ldots y, z$  are nodes in D. In addition, the loop implies that there exists a path  $a \rightarrow b \rightarrow c \ldots \rightarrow y \rightarrow z \rightarrow a$  which is another loop in D. Since D is directed acyclic graph, the assumption is broken.

Theorem 3: