#### US009276019B2

### (12) United States Patent

#### Yamada et al.

## (54) METHOD OF MANUFACTURING ELEMENT SUBSTRATE

(75) Inventors: Takaharu Yamada, Osaka (JP); Ryohki

Itoh, Osaka (JP); Masahiro Yoshida, Osaka (JP); Hidetoshi Nakagawa, Osaka (JP); Takuya Ohishi, Osaka (JP); Masahiro Matsuda, Osaka (JP); Kazutoshi Kida, Osaka (JP)

(73) Assignee: SHARP KABUSHIKI KAISHA, Osaka

(JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 170 days.

(21) Appl. No.: 14/131,232

(22) PCT Filed: Jul. 12, 2012

(86) PCT No.: **PCT/JP2012/067778**

§ 371 (c)(1),

(2), (4) Date: **Jan. 7, 2014**

(87) PCT Pub. No.: **WO2013/011911**

PCT Pub. Date: Jan. 24, 2013

(65) Prior Publication Data

US 2015/0044789 A1 Feb. 12, 2015

(30) Foreign Application Priority Data

Jul. 19, 2011 (JP) ...... 2011-157882

(51) **Int. Cl.**

*H01L 27/12* (2006.01) *G02F 1/1333* (2006.01)

(Continued)

(52) U.S. Cl.

CPC ...... *H01L 27/1262* (2013.01); *G02F 1/1309* (2013.01); *H01L 22/14* (2013.01); *H01L 22/32* (2013.01); *H01L 27/124* (2013.01); *G02F 1/1345* (2013.01)

(10) Patent No.: US 9,276,019 B2 (45) Date of Patent: Mar. 1, 2016

(58) Field of Classification Search

See application file for complete search history.

(56) References Cited

#### U.S. PATENT DOCUMENTS

2008/0088760 A1 4/2008 Kawano et al.

(Continued)

#### FOREIGN PATENT DOCUMENTS

JP 2000-10063 A 1/2000 JP 2002-9407 A 1/2002

(Continued)

Primary Examiner — Marvin Payen Assistant Examiner — Jeremy Joy

(74) Attorney, Agent, or Firm — Keating & Bennett, LLP

#### (57) ABSTRACT

A method of manufacturing an array substrate 20 according to the present invention includes a line forming step, and line forming step includes following performances. A plurality of source lines 27 are formed on a glass substrate GS so as to extend from a first region A1 on the glass substrate GS to a second region A2 that is adjacent to the first region on an outer side thereof. A plurality of source driver side check lines 45A are formed on the glass substrate GS so as to extend from the second region A2 to a third region that is adjacent to the first region A1 on an outer side thereof and adjacent to the second region A2. A plurality of first line connection portions 49 are formed in the second region A2 and the first line connection portions 49 connect the source lines 27 and the first source driver side check lines 45A. A capacity stem line 43 and a common line 44 are formed to extend from the first region A1 to the third region A3. A second source driver side check line 45B and a second line connection portion 50 that connects each of the capacity stem line 43 and the common line 44 and the source driver side check line 45B are formed in the third region A3.

#### 20 Claims, 34 Drawing Sheets

# US 9,276,019 B2 Page 2

| (51)                                                 | Int. Cl.  G09G 3/36 (2006.01)  G02F 1/13 (2006.01) |                        | 2010/0149473 A1* 6/2010 Guo   |                  |              |

|------------------------------------------------------|----------------------------------------------------|------------------------|-------------------------------|------------------|--------------|

|                                                      | H01L 21/66<br>G02F 1/1345                          | (2006.01)<br>(2006.01) |                               | FOREIGN PATEN    | NT DOCUMENTS |

| (56)                                                 | References Cited                                   |                        | JP                            | 2002-090424 A    | 3/2002       |

| U.S. PATENT DOCUMENTS                                |                                                    | JP<br>JP               | 2008-70806 A<br>2010-181741 A | 3/2008<br>8/2010 |              |

| 2009/0294771 A1* 12/2009 Kim G02F 1/136204<br>257/59 |                                                    |                        | * cited                       | by examiner      |              |

FIG.2

FIG.3

25

FIG.7

45Aa 49 20 (65) 45Ab 51 RA2 (RA) 45Ba (52) 53 45B (45) 53 45A (45) 45A (45) 27b

FIG.9

FIG. 11

Mar. 1, 2016

US 9,276,019 B2

下(G.15)

FIG.14

FIG. 16

FIG. 17

FIG.18

FIG.19

FIG.20

FIG.21

FIG.22

FIG.23

FIG.24

FIG.25

FIG.26

FIG.27

FIG.30

FIG.33

Mar. 1, 2016

FIG.34

# METHOD OF MANUFACTURING ELEMENT SUBSTRATE

#### TECHNICAL FIELD

The present invention relates to a method of manufacturing an element substrate.

#### **BACKGROUND ART**

A liquid crystal panel used in a liquid crystal display device includes a pair of glass substrates and a liquid crystal layer sandwiched between the glass substrates. One of the glass substrates is an array substrate including TFTs as an active element that controls operations of each pixel. A plurality of gate lines and source lines are arranged in a matrix in a display area of the array substrate and the TFT is arranged at each intersection of the gate lines and the source lines. A check line, a line connection portion, and a check signal input portion are arranged in a non-display area that surrounds the 20 display area of the array substrate. The check line is used for checking disconnection or short-circuit of the gate lines or the source lines in the process of manufacturing the array substrate. The line connection portion connects the check line and each line. The check signal input portion is connected to 25 the check line and a check signal is input from via the check signal input portion. The check line, the line connection portion and the check signal input portion are removed after a checking step in the process of manufacturing the array substrate. The method of manufacturing the array substrate is <sup>30</sup> described in Patent Document 1.

Patent Document 1: Japanese Unexamined Patent Application Publication No. 2002-90424

# Problem to be Solved by the Invention

If an area of the non-display area of the array substrate is reduced, an area of the display area is increased, and this is useful for increasing a screen size. A plurality of array substrates are manufactured from a large-size mother glass. If an area of the non-display area of each array substrate is reduced, an outer size of each array substrate is also reduced and this increases the number of array substrates obtained from one mother glass. However, if the area of the non-display area is simply reduced, an arrangement space in which the check lines, the line connection portions and the check signal input portions are arranged is also reduced. Accordingly, an enough line width of the check line and an enough area for the check signal input portions may not be ensured, and there are limitations to reduce the area of the non-display area.

# DISCLOSURE OF THE PRESENT INVENTION

The present invention was accomplished in view of the foregoing circumstances. An object of the present invention is 55 to provide a method of manufacturing an element substrate having a reduced outer peripheral-side area.

# Means for Solving the Problem

To solve the above problem, according to the present invention, a method of manufacturing an element substrate includes a line forming step of forming lines on a substrate, a checking step, and a removing step. The line forming step includes forming a plurality of first lines extending from a 65 first region of the substrate to a second region that is adjacent to the first region on an outer side of the first region, forming

2

a plurality of first check lines extending from the second region to a third region that is adjacent to the first region on the outer side of the first region and adjacent to the second region, forming a plurality of first line connection portions in the second region, the first line connection portions connecting the first lines and the first check lines, forming a second line extending from the first region to the third region, and forming a second check line and a second line connection portion in the third region, the second line connection portion connecting the second line and the second check line. The checking step includes inputting a check signal to the plurality of first check lines and the second check line, and checking the plurality of first lines and the second line. The removing step includes removing at least a part of one of the first check line and the second check line in the second region and the third region, and disconnecting the first line and the first check line and disconnecting the second line and the second check line.

Accordingly, after the lines, check lines, and the line connection portions are formed in the line forming step, it is checked whether disconnection or short-circuit occurs in each line in the checking step. After the checking step, at least a part of each of the check lines is removed in the removing step and the lines and the check lines are disconnected from each other.

In the line forming step, the first check lines are formed to extend from the second region to the third region on the substrate. The first lien connection portions that connect the first check lines and the first lines are formed in the second region, and the second check lines that are connected to the second line and the second line connection portions are formed in the third region. Therefore, compared to a case in which the first check lines, the first line connection portions, and the second check line and the second line connection portion are concentrated in the same region, a distance between the outer end of each of the second region and the third region and the outer end of the first region is maintained to be short. This reduces a size of the second region and the third region, and the first region is increased in its size by the reduced size. In other words, an outer size of the substrate is

The following configurations may be used in a first aspect of the method of manufacturing an electrode substrate according to the present invention.

- (1) In the line forming step, the first check lines may be formed of a same material and formed in a same layer, and the second check line may be formed of a material different from the first check line and may be formed in a layer different from a layer in which the first check line is formed with having an insulation layer between the second check line and the first check line. Accordingly, at least a part of each of the first check line and the second check line may overlap with each other, and therefore, the first check lines and the second check lines may be arranged at a higher density. Accordingly, the second region and the third region may be reduced in size effectively.

- (2) In the line forming step, the first lines and the second line may be formed of a same material as the second check line and they may be formed in a same layer, an opening may be formed at a portion of the insulation layer overlapping one

60 of the first line and the first check line, and the first line connection portion may be formed so as to cover the opening. The first line connection portion connects the first line and the first check line that are formed in different layers. Accordingly, the first line connection portion may be formed to cover

65 the opening formed in the insulation layer, and this may effectively connect the first line and the first check line that are formed in different layers. The second line and the second

check line may be formed of a same material in a same layer, and therefore they may be effectively connected to each other via the second line connection portion.

(3) In the line forming step, pixel electrodes may be formed and the first line connection portions may be formed with a 5 same material and in a same layer as the pixel electrodes. Accordingly, the first line connection portion may be formed in forming the pixel electrodes, and this may reduce a manufacturing cost.

(4) In the line forming step, an ESD protection circuit that 10 is connected to the plurality of first check lines and the second check line may be formed. Accordingly, the ESD protection circuit may protect the first check line and the second check lines from the ESD (electrostatic discharge).

the ESD protection circuit. The transistor may connect the first check lines each other and connect the first check line and the second check line, and the transistor may have a threshold voltage value relatively higher than a voltage value of the check signal that is input to the first check line and the second 20 check line in the checking step. Accordingly, if a check signal may be input to one of the first check line and the second check line, the voltage value of the check signal may be relatively lower than a threshold voltage value of the transistor that is the ESD protection circuit. Therefore, the check 25 signal may not be supplied to another one of the first check line and the second check line. Accordingly, the lines may be correctly checked. On the other hand, if the ESD voltage that is greater than the threshold voltage value of the transistor may be applied to one of the check lines, the ESD voltage may 30 be also applied to the other one of the check lines via the transistor. Accordingly, a potential difference may be less likely to be generated between the check lines and between the lines.

may be formed so as to be parallel to an outer end of the second region as the plurality of the first check lines, and the plurality of first line connection portions may be arranged between the pair of first check lines that are parallel to the outer end of the second region and along an extending direc- 40 tion in which the first check lines extend. This may shorten a distance between the outer end of the second region and the outer end of the first region and this may further reduce a size of the second region.

(7) In the line forming step, at least a pair of first check lines 45 may be formed so as to be parallel to an outer end of the second region as the plurality of the first check lines, and the plurality of first line connection portions may be formed so as to sandwich at least one of the pair of first check lines that are parallel to the outer end of the second region. Accordingly, the 50 first line connection portions may be arranged at small intervals in an extending direction in which at least the pair of first check lines extend. The pair of first check lines may be parallel to the outer end of the second region. This may reduce a size of the second region in the extending direction in which 55 the pair of first check lines extend.

A second method of manufacturing an element substrate according to the present invention includes a line forming step of forming lines on a substrate, a checking step, and a removing step. The line forming step includes forming a line 60 extending from a non-removing area of the substrate to a first removing area that is adjacent to the non-removing area on an outer side, forming a check line extending from the first removing area to a second removing area that is adjacent to the non-removing area on an outer side and adjacent to the 65 first removing area, forming a line connection portion in the first removing area, the line connection portion connecting

the line and the check line, and forming a check signal input portion extending from the non-removing area to the second removing area, the check signal input portion being connected to the check line. In the checking step, a check signal is input to the check signal input portion and checking the line via the check line. In the removing step, at least a part of at least the line check line and the line connection portion is removed and the line is disconnected from the check line and a part of the check signal input portion is removed.

Accordingly, after forming the lines, the check lines, the line connection portion, and the check signal input portion in the line forming step, the checking step is performed to check whether disconnection or short-circuit occurs in each of the lines. After performing the checking step, the removing step (5) In the line forming step, a transistor may be formed as 15 is performed to remove at least a part of the line connection portion of at least the check line. Accordingly, the line and the check line are disconnected from each other and a part of the check signal input portion is removed.

In the line forming step, the check line is formed to extend from the first removing area to the second removing area, and the line connection portion connecting the check line and the line is formed in the first removing area, and the check signal input portion is formed in the second removing area. Therefore, compared to a case in which the check line, the line connection portion, and the check signal input portion are concentrated in the same area, a distance between an outer end of each of the first removing area and the second removing area and an outer end of the non-removing area is shortened. This reduces the first removing area and the second removing area and this increases the non-removing area by the reduced size. In other words, the outer size of the substrate is reduced. Further, the check signal input portion extends from the first removing area to the non-removing area, and therefore, compared to a case in which the check signal input (6) In the line forming step, at least a pair of first check lines 35 portion is formed only in the first removing area, a sufficient large area is provided for the check signal input portion. This improves workability of inputting the check signal to the check signal input portion in the checking step and this effectively reduces a cost for equipments used in the checking step.

> A third method of manufacturing an element substrate according to the present invention includes a line forming step of forming lines on a substrate, a checking step, and a removing step. The line forming step includes forming at least a pair of lines extending from an inner peripheral side area of the substrate to a pair of outer peripheral side areas that are located to sandwich the inner peripheral side area from outer sides, forming one check line in one of the pair of outer peripheral side areas, the one check line being connected to one end side of one of the pair of lines, and forming another check line in another one of the pair of outer peripheral side areas, the other check line being connected to another end side of the pair of lines. In the checking step, a check signal is input to the one check line and the other check line and at least the pair of lines are checked. In the removing step, at least a part of each of the one check line and the other check line in the pair of outer peripheral side areas is removed and the one line is disconnected from the one check line and the other line is disconnected from the other check line.

> Accordingly, after the lines and the check lines are formed on the substrate via the line forming step, it is checked whether disconnection or short-circuit occurs in each of the lines in the checking step. After performing the checking step, at least a part of each of the check lines is removed in the removing step, the line is disconnected from the check line.

> In the line forming step, one check line that is connected to one end of one line is formed in one of the pair of outer peripheral side areas that are located to sandwich the inner

peripheral area of the substrate from both outer sides, and another check line that is connected to another end side of the other line is formed in another one of the pair of outer peripheral side areas. Therefore, compared to a complicated connection structure in which the check lines are concentrated in one-side outer peripheral side area, the connection structure of the check lines and the lines is simplified and a distance between the outer end of the outer peripheral side area and the outer end of the inner peripheral side area is kept to be small. This is likely to reduce the outer peripheral side area the inner peripheral side area is increased by the reduced size. In other words, the outer size of the substrate is reduced.

The following configurations may be used in a third aspect of the method of manufacturing an electrode substrate according to the present invention.

- (1) A substrate cutting step of cutting a substrate parent material into a plurality of substrates may be performed between the line forming step and the checking step. In the line forming step, at least one of the one check line and the other check line may be formed so as to cross a cutting 20 position of the substrate in the substrate cutting step. Accordingly, before performing the substrate cutting step, the check line that is formed to cross the cutting position of the substrate parent material may have a sufficient line width and a low line resistance. This may be effective for dealing with the electrostatic discharge (ESD). After performing the substrate cutting step, the check line may be located at the outer end of the outer peripheral side area, and the check line may have a sufficient line width and this may be effective for dealing with the ESD.

- (2) In the line forming step, a second line may be formed in 30 one of the pair of outer peripheral side areas, a second check line connected to the second line may be formed to cross the cutting position of the substrate in the substrate cutting step, and a check line connection portion may be formed in an area that is on an outer side from the cutting position of the substrate in the substrate cutting step, the check line connection portion being connected to the second check line and one of the one check line and the other check line. In the substrate cutting step, the check line connection portion may be removed from the substrate according to the cutting of the 40 substrate parent material into the substrates. Accordingly, before performing the substrate cutting step, one of the one check line and the other check line that are formed to cross the cutting position of the substrate may be connected to the second check line via the check line connection portion. This 45 lowers a line resistance between the second check line and one of the one check line and the other check line that are connected to each other. This is further effective for dealing with the ESD.

The following configurations may be used in the first to the 50 third aspect of the method of manufacturing an electrode substrate according to the present invention.

(1) In the line forming step, a plurality of removal check signal input portions may be formed in an area of the substrate in which apart of the substrate is not to be removed in the removing step, and a removal check connection line may be formed in a part of the substrate that is to be removed in the removing step, the removal check connection line connecting the removal check signal input portions each other. After the removing step, the removal checking step may be performed and in the removal checking step, it may be judged whether the removing step is correctly performed based on a current flowing state between the removal check signal input portions. Accordingly, if the removing step is correctly performed, the removal check connection line may be removed, 65 and therefore, a current does not flow between the removal check signal input portions in the removal checking step. If

6

the removing step is not correctly performed, the removal check connection line may not be completely removed, and therefore, a current flows between the removal check signal input portions in the removal checking step. The number of defective products is reduced via the removal checking step.

- (2) In the removing step, a part of the substrate having a predetermined area ranging from an outer end may be chamfered. Accordingly, compared to a case in which the outer end side portion of the substrate is cut off and removed from the substrate in the removing step, the second region and the third region of the substrate, the first removing area and the second removing area, or the outer peripheral side areas are effectively reduced in size. Further, this reduces a cost for the devices used in the removing step.

- (3) A polarizing plate mounting step may be performed prior to the removing step and a polarizing plate may be mounted on a surface of the substrate opposite to a line forming surface thereof. Accordingly, in the polarizing plate mounting step, static electricity may be easily generated in mounting the polarizing plate. However, the check lines formed on the substrate may protect the lines from the electrostatic discharge (ESD).

#### Advantageous Effects of the Invention

According to the present invention, a method of manufacturing an element substrate having a reduced outer peripheral-side area is provided.

#### BRIEF DESCRIPTION OF THE DRAWINGS

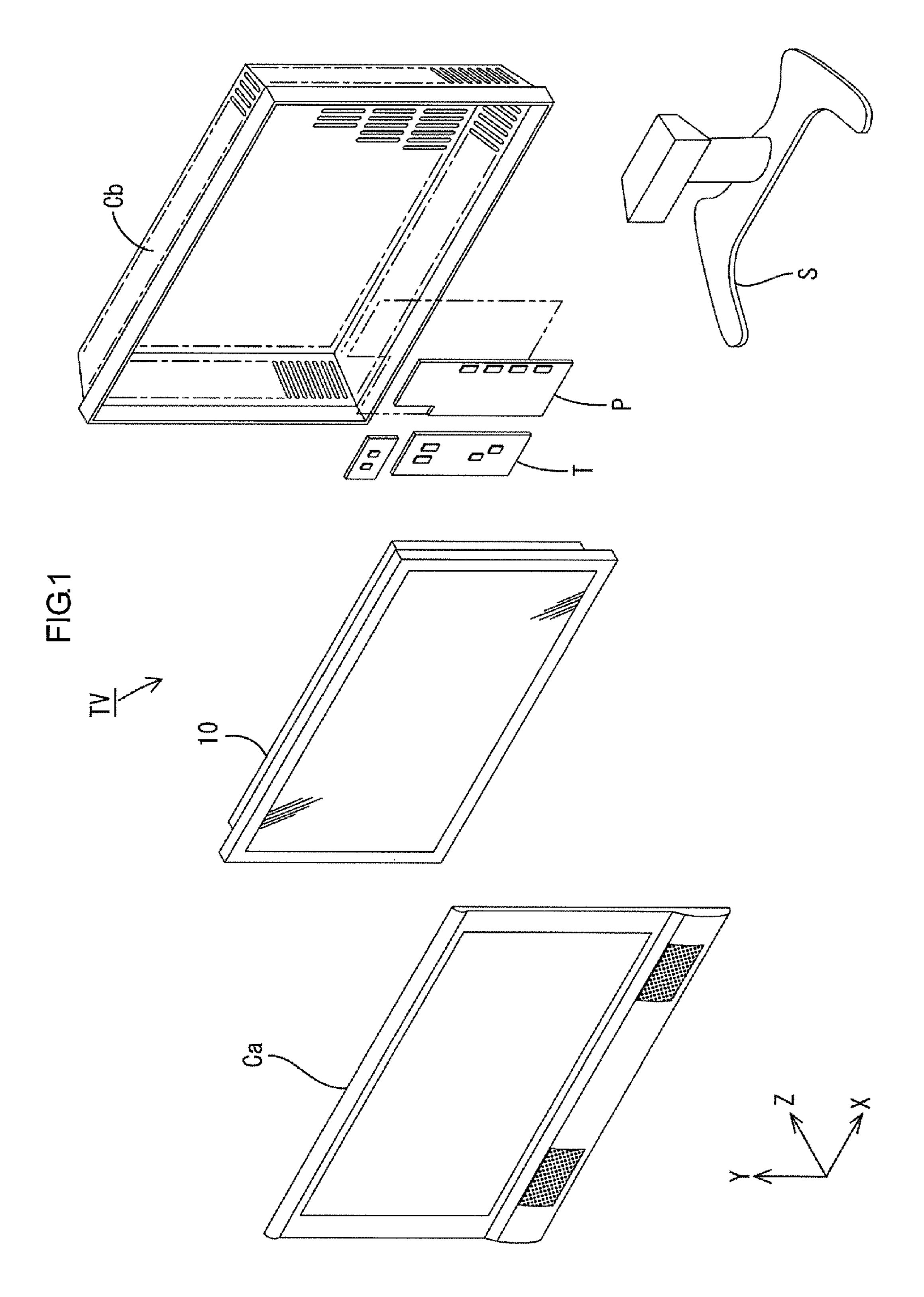

- FIG. 1 is an exploded perspective view illustrating a general construction of a television device according to a first embodiment of the present invention.

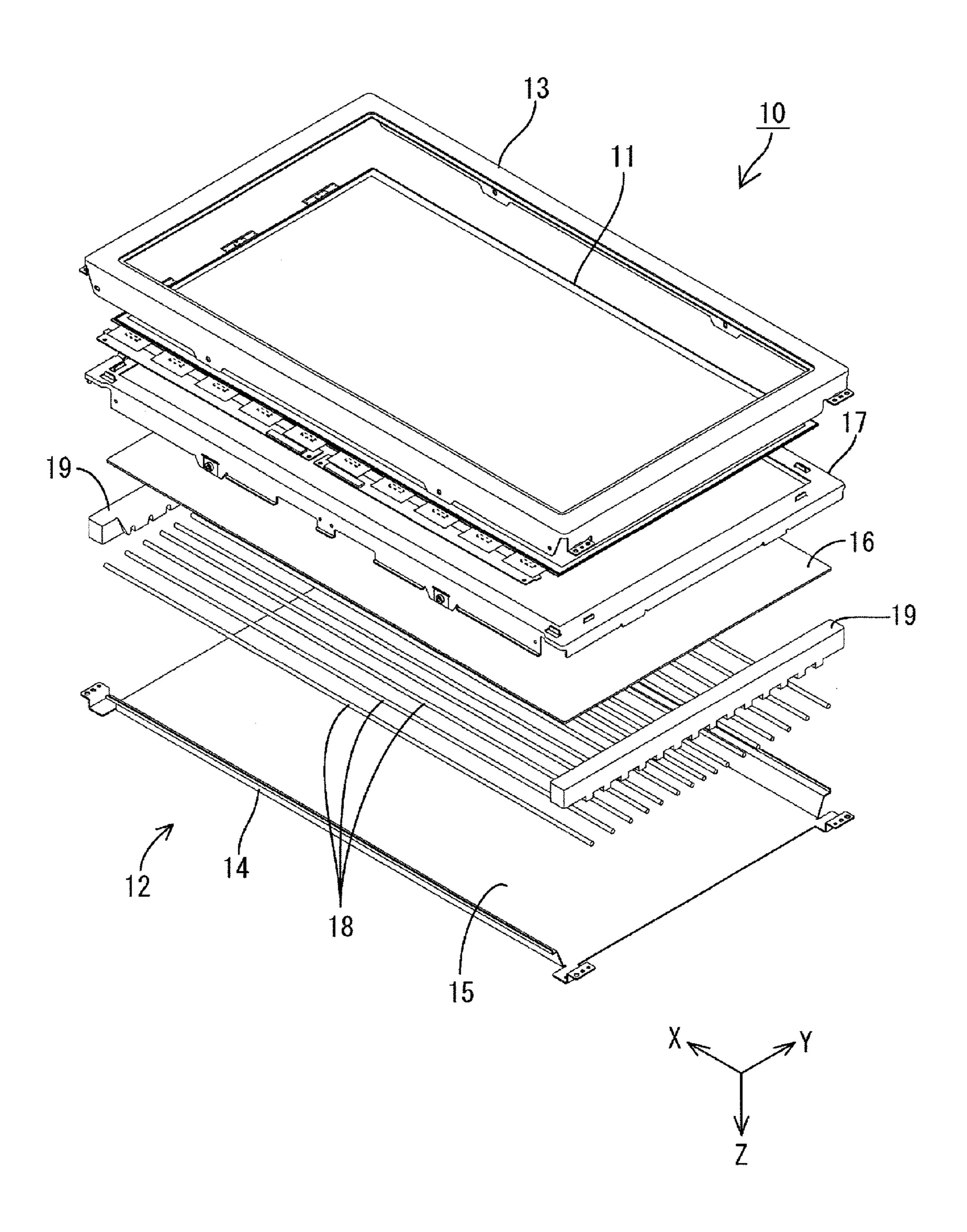

- FIG. 2 is an exploded perspective view illustrating a general construction of a liquid crystal display device included in the television device.

- FIG. 3 is a cross-sectional view generally illustrating a cross-sectional configuration of the liquid crystal display device.

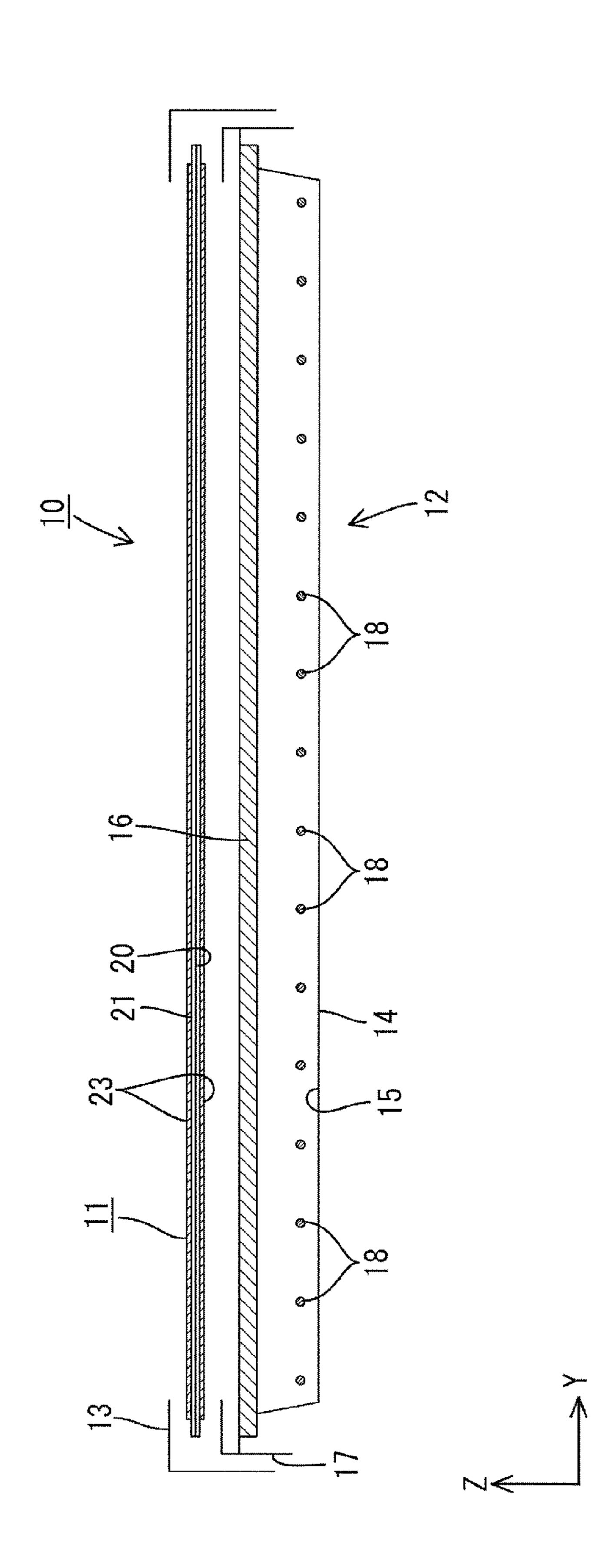

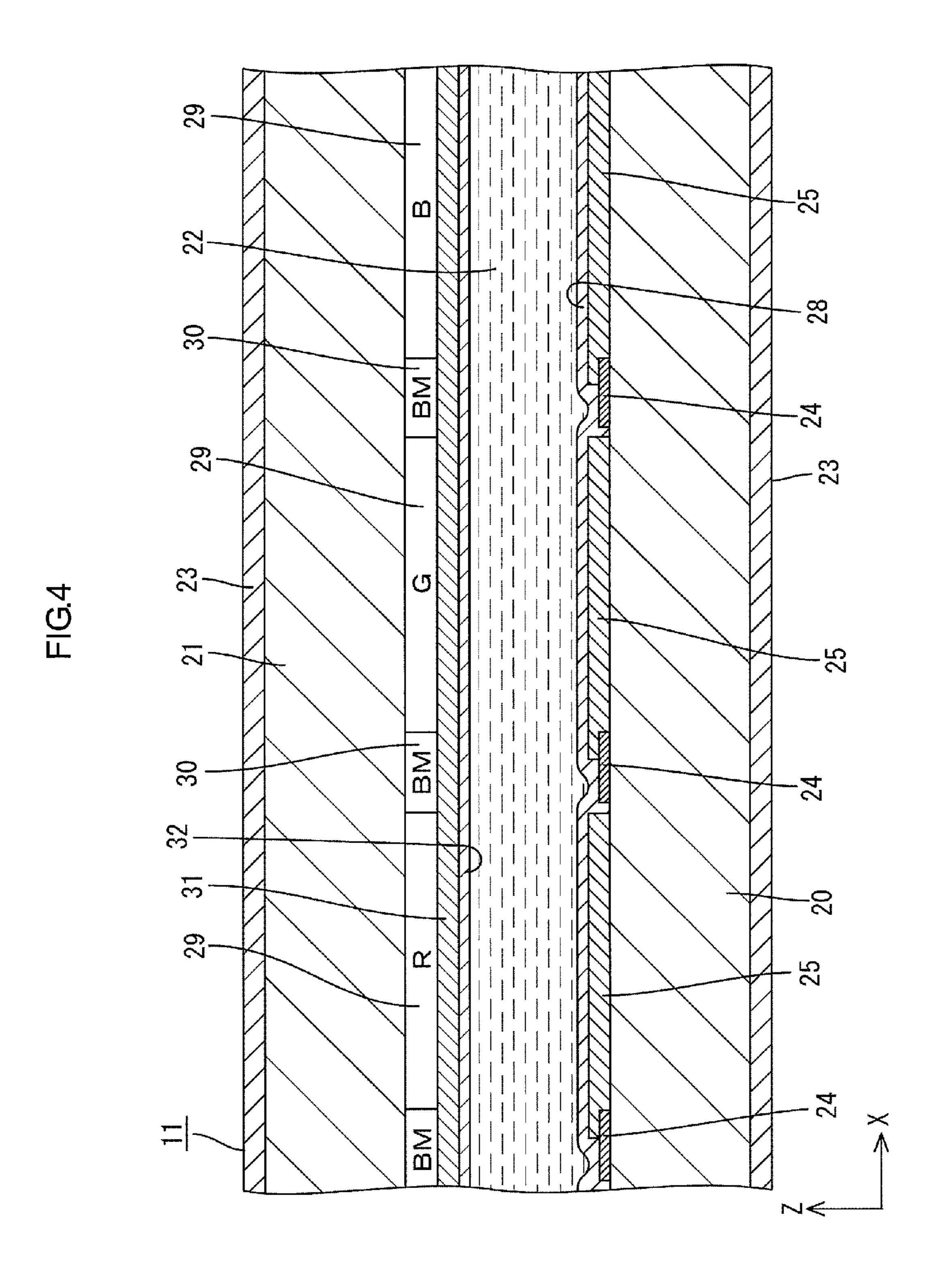

- FIG. 4 is a cross-sectional view generally illustrating a cross-sectional configuration of a liquid crystal panel.

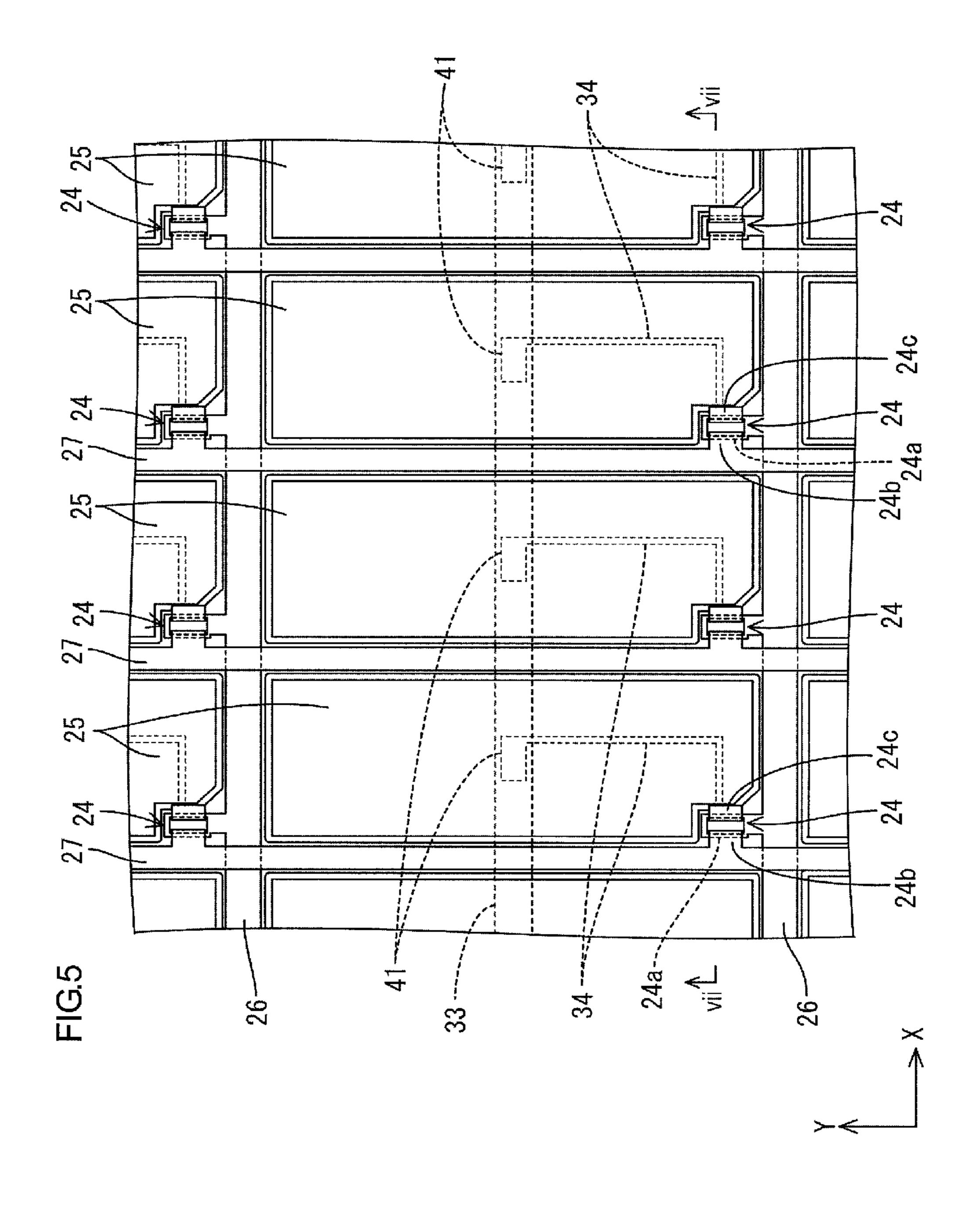

- FIG. 5 is a plan view illustrating a plan configuration of a display area of an array substrate included in the liquid crystal panel.

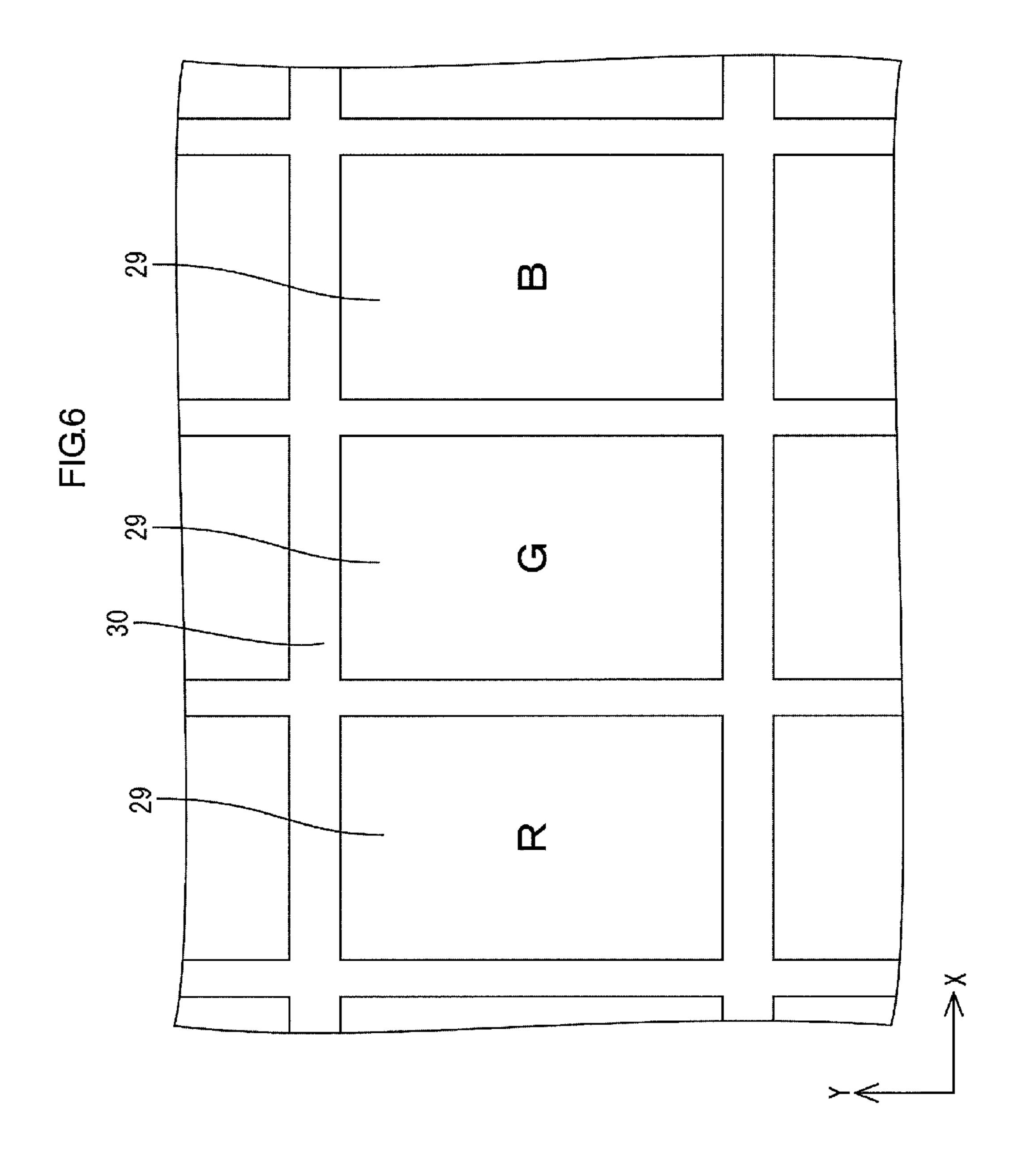

- FIG. 6 is a plan view illustrating a plan configuration of a display area of a CF substrate included in the liquid crystal panel.

- FIG. 7 is a cross-sectional view taken along a vii-vii line in FIG. 5.

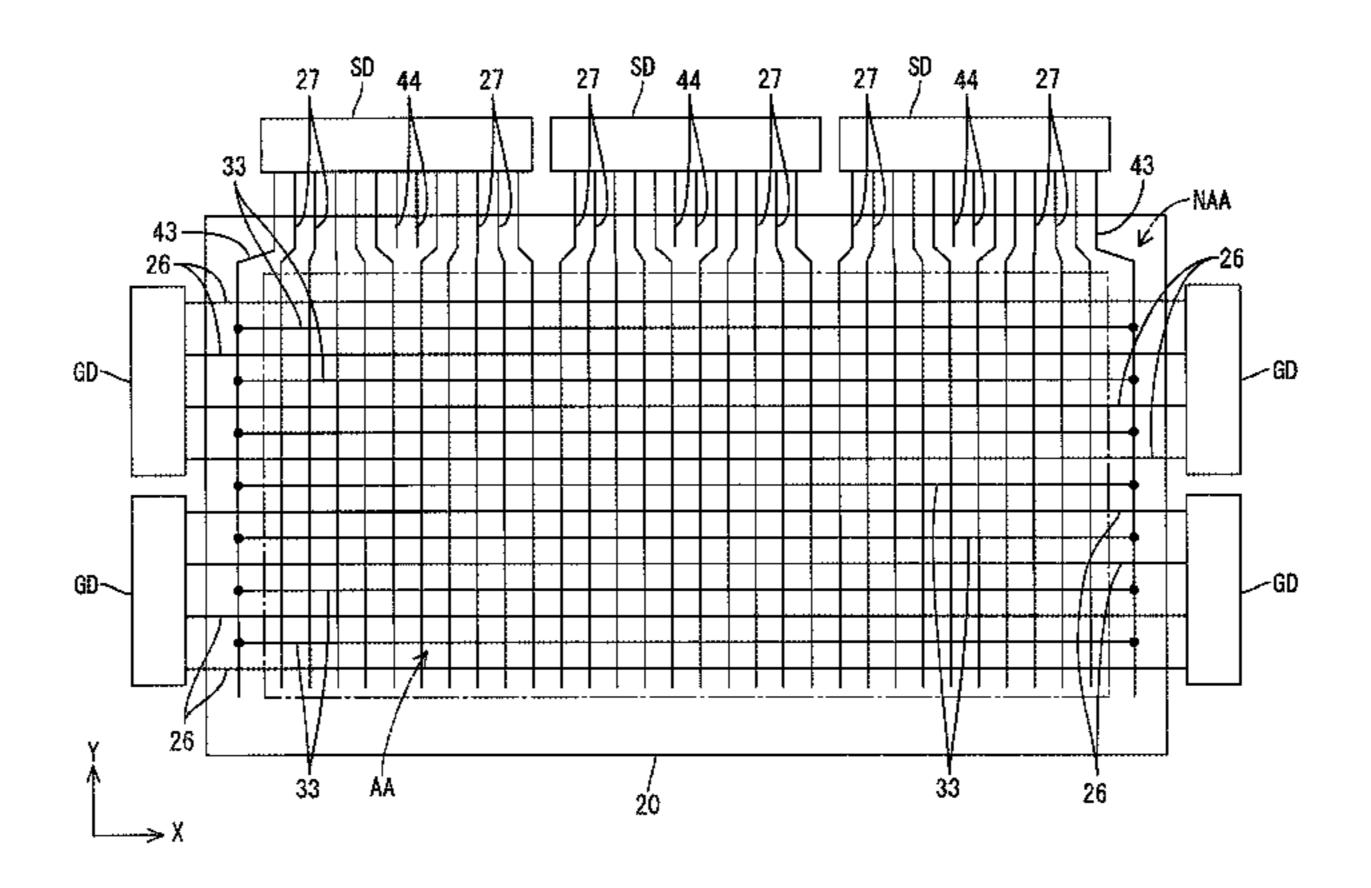

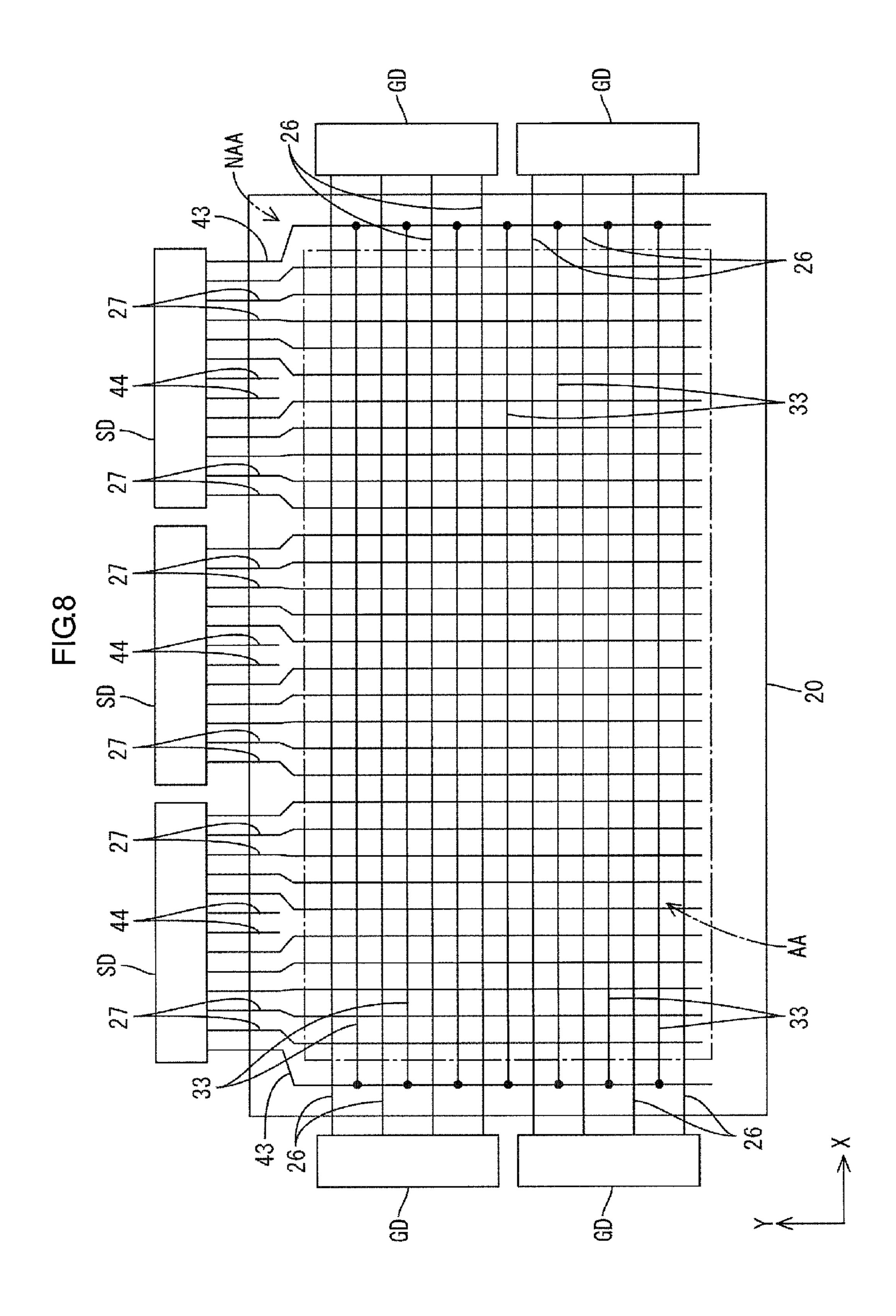

- FIG. 8 is a plan view generally illustrating a wiring configuration on the array substrate included in the liquid crystal panel.

- FIG. 9 is a plan view illustrating a wiring configuration on a source driver side end portion of the array substrate.

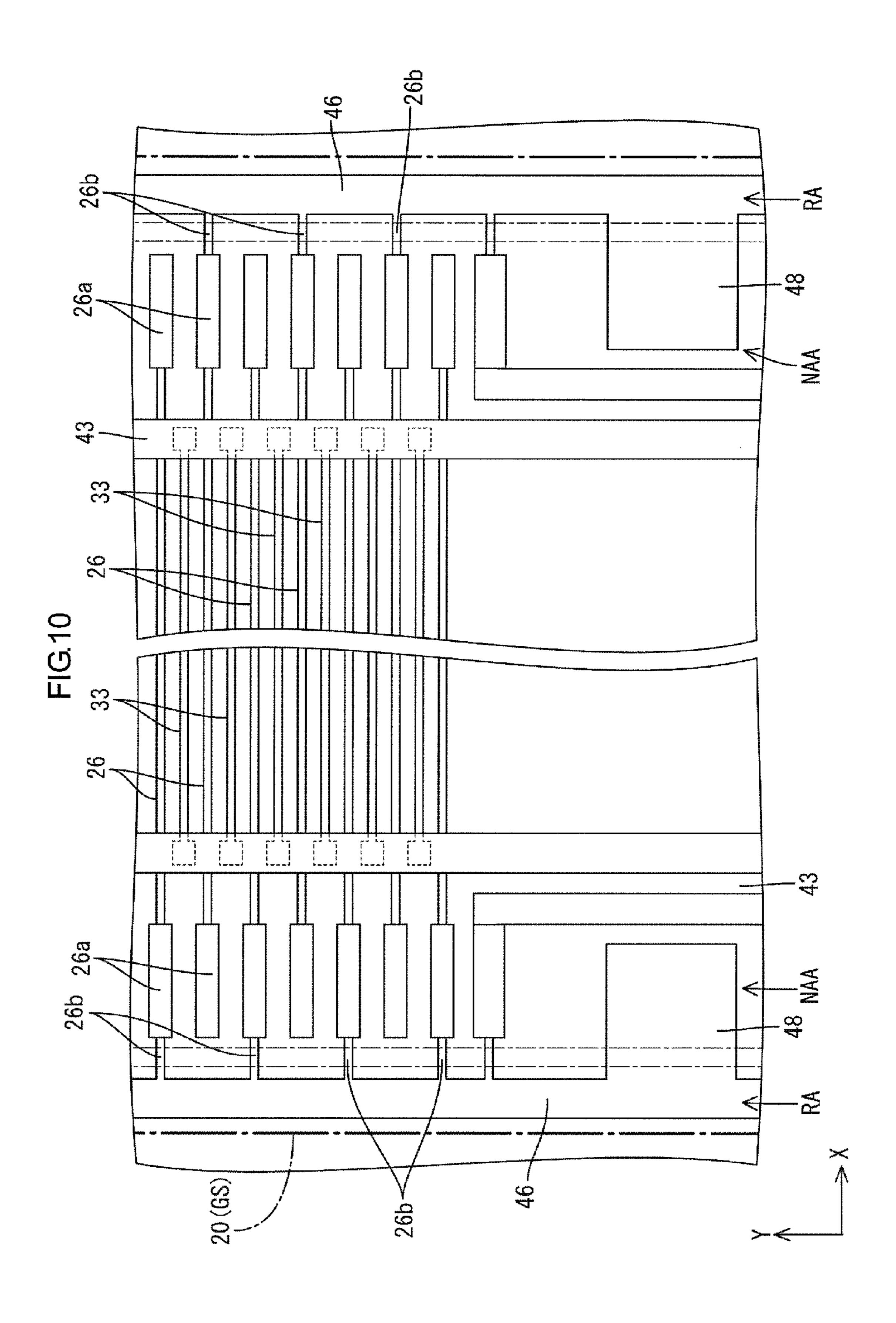

- FIG. 10 is a plan view illustrating a wiring configuration on a gate driver side end portion of the array substrate.

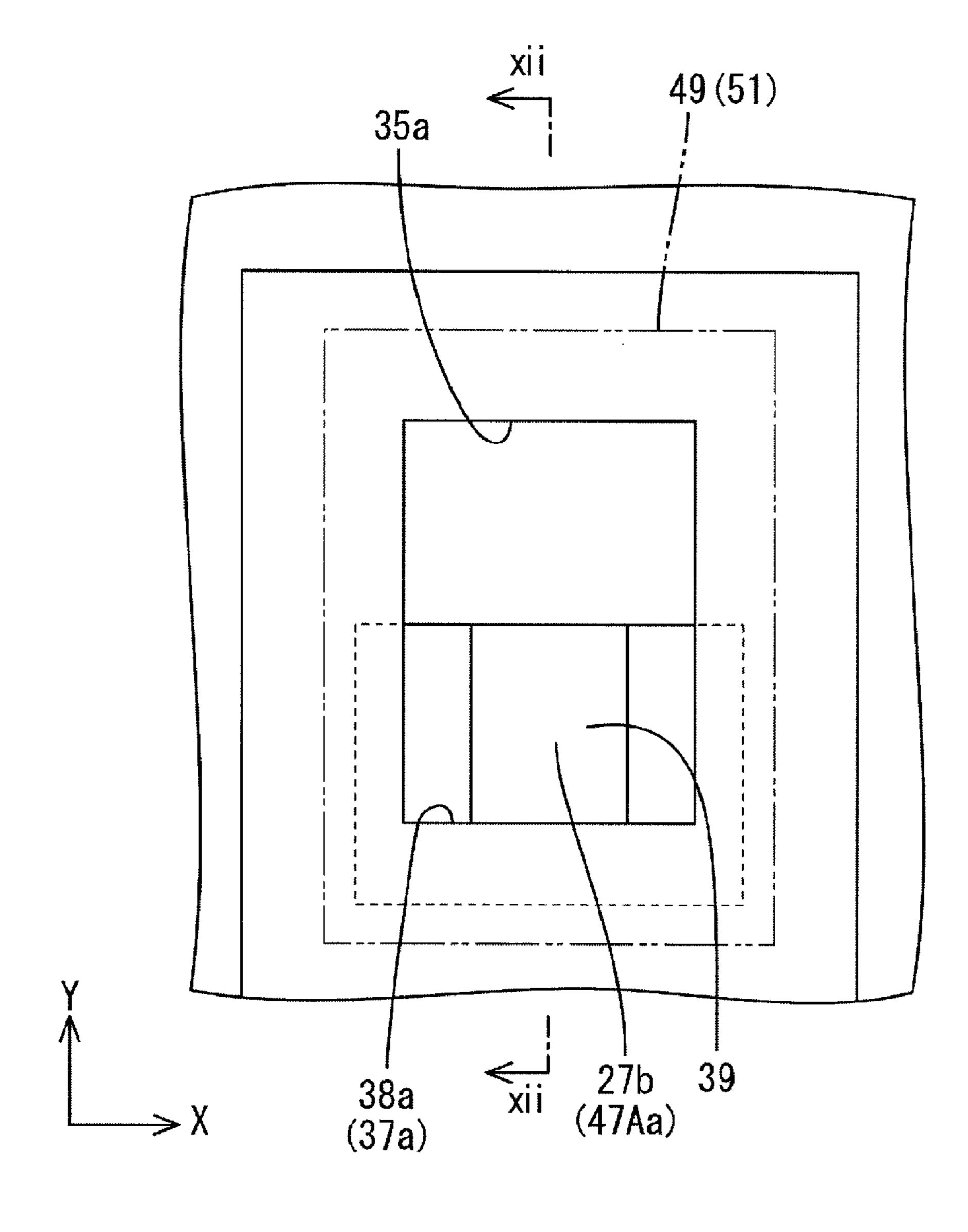

- FIG. 11 is a plan view illustrating a plan configuration of a first line connection.

- FIG. 12 is a cross-sectional view taken along a xii-xii line in FIG. 11.

- FIG. 13 is a circuit generally illustrating a circuit configuration of an ESD protection circuit.

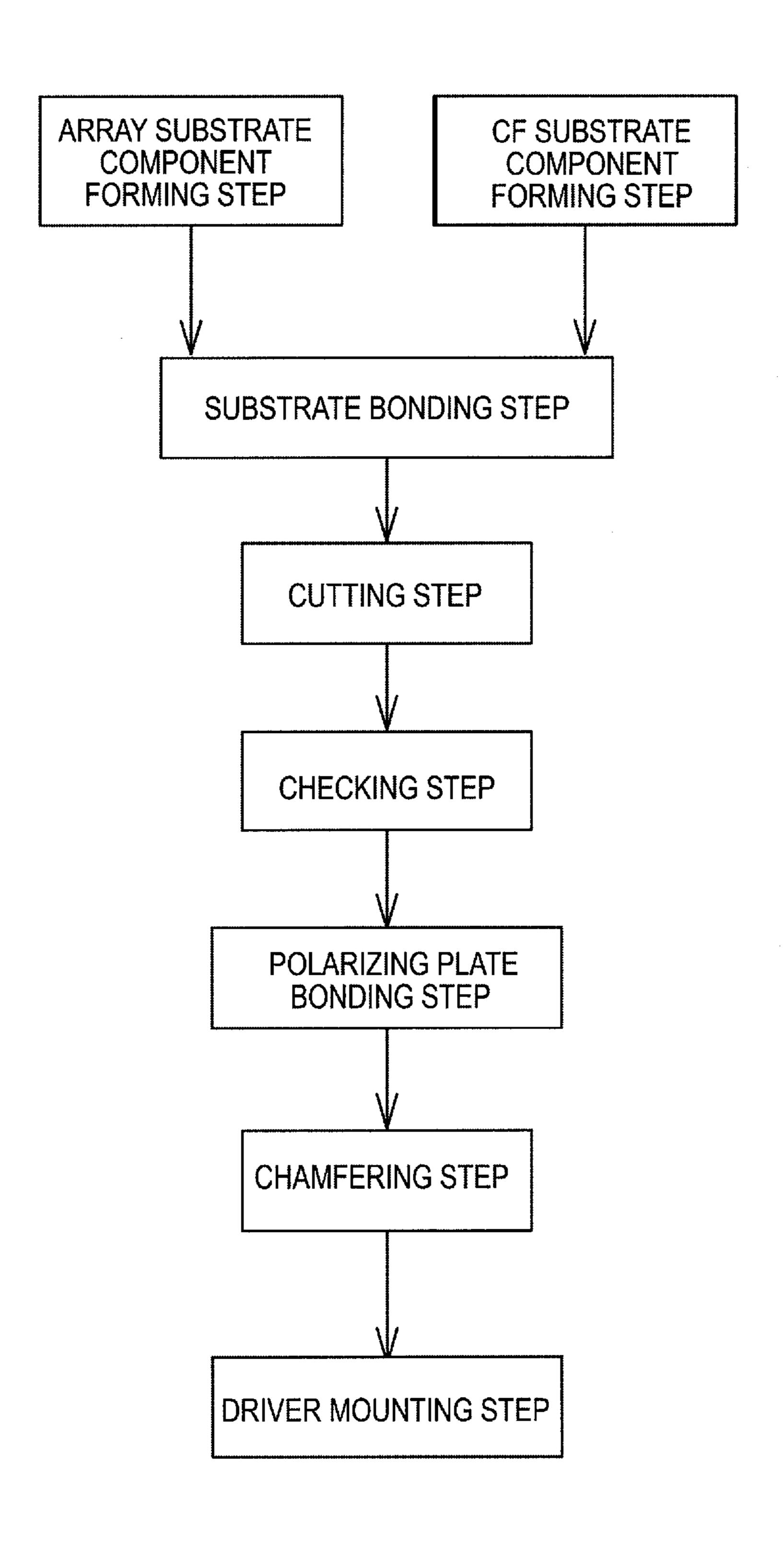

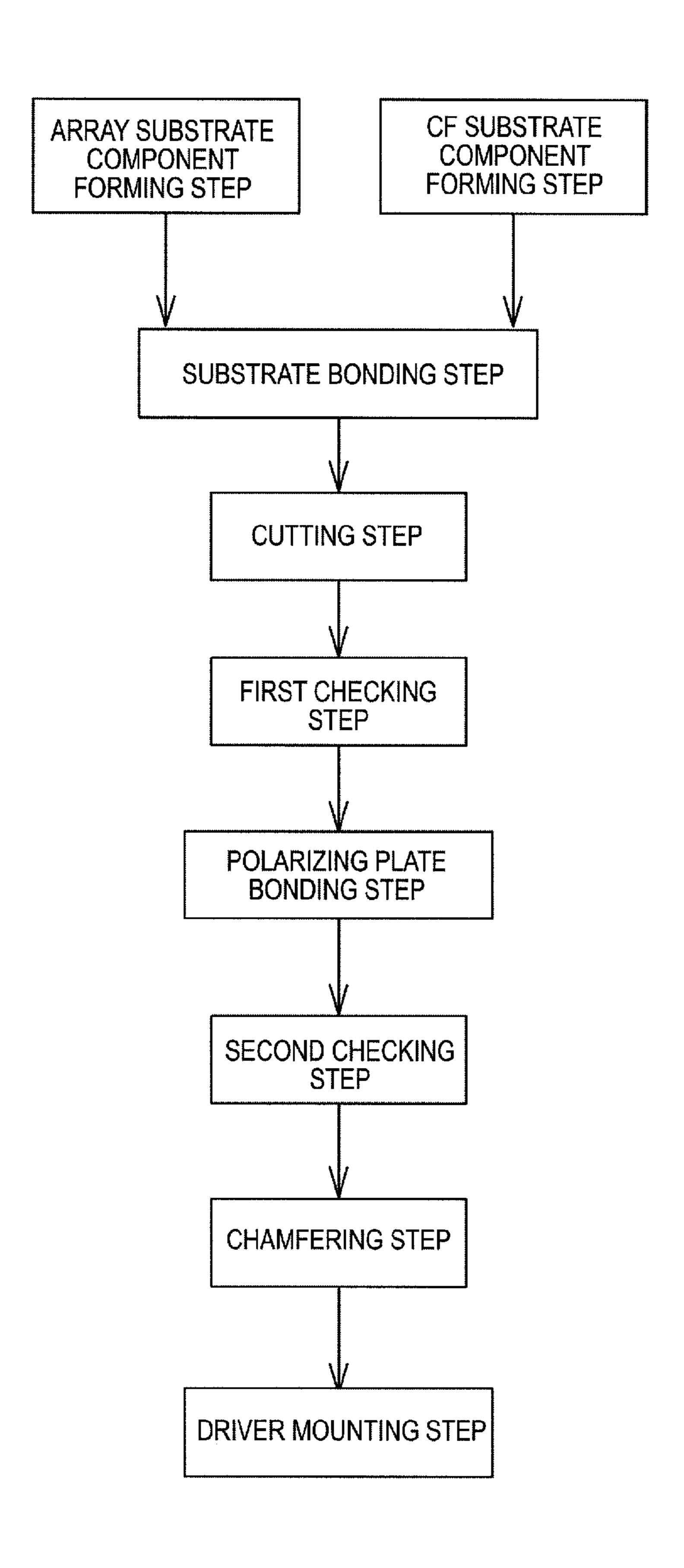

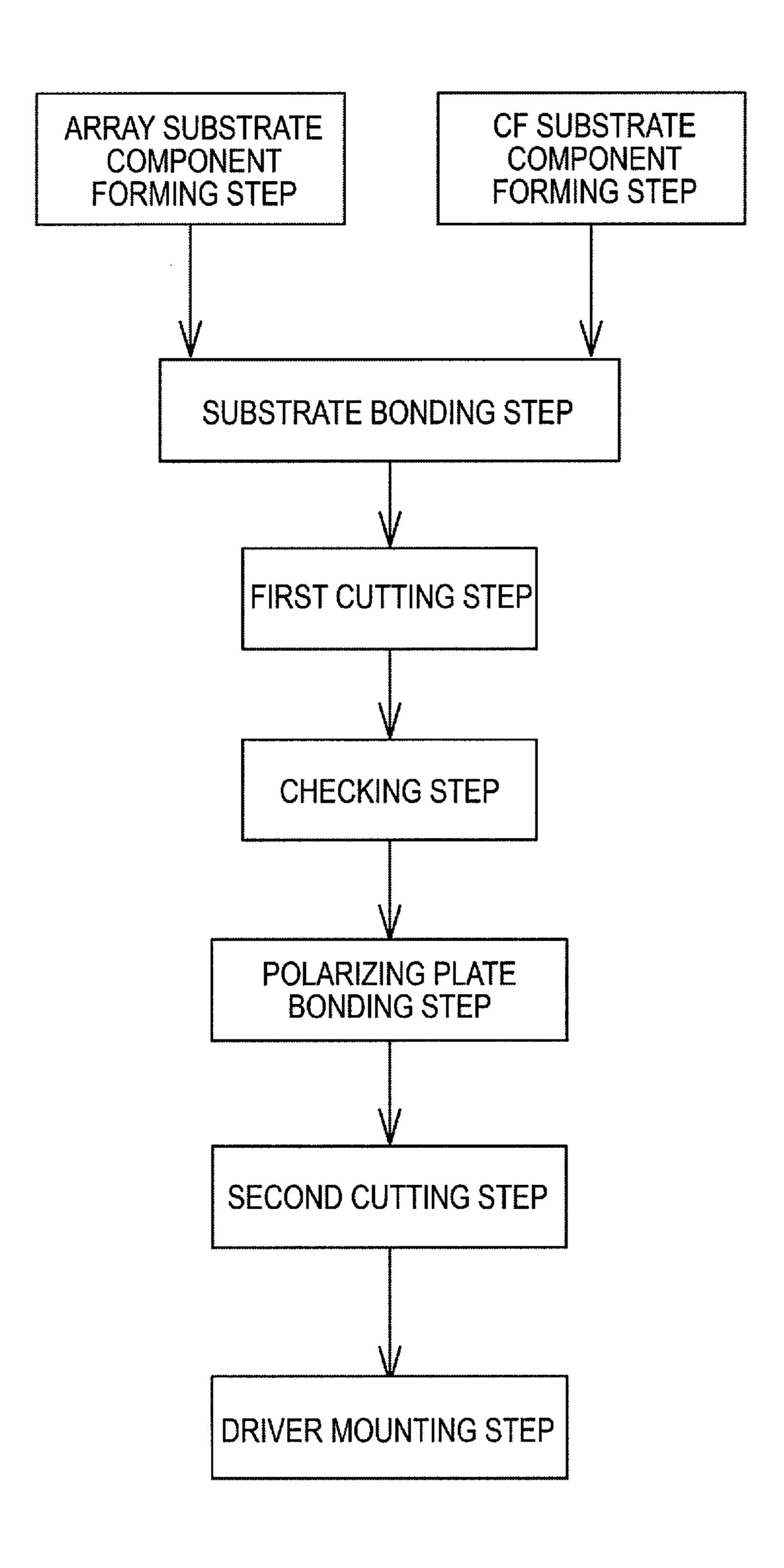

- FIG. 14 is a flowchart illustrating a method of manufacturing the liquid crystal panel.

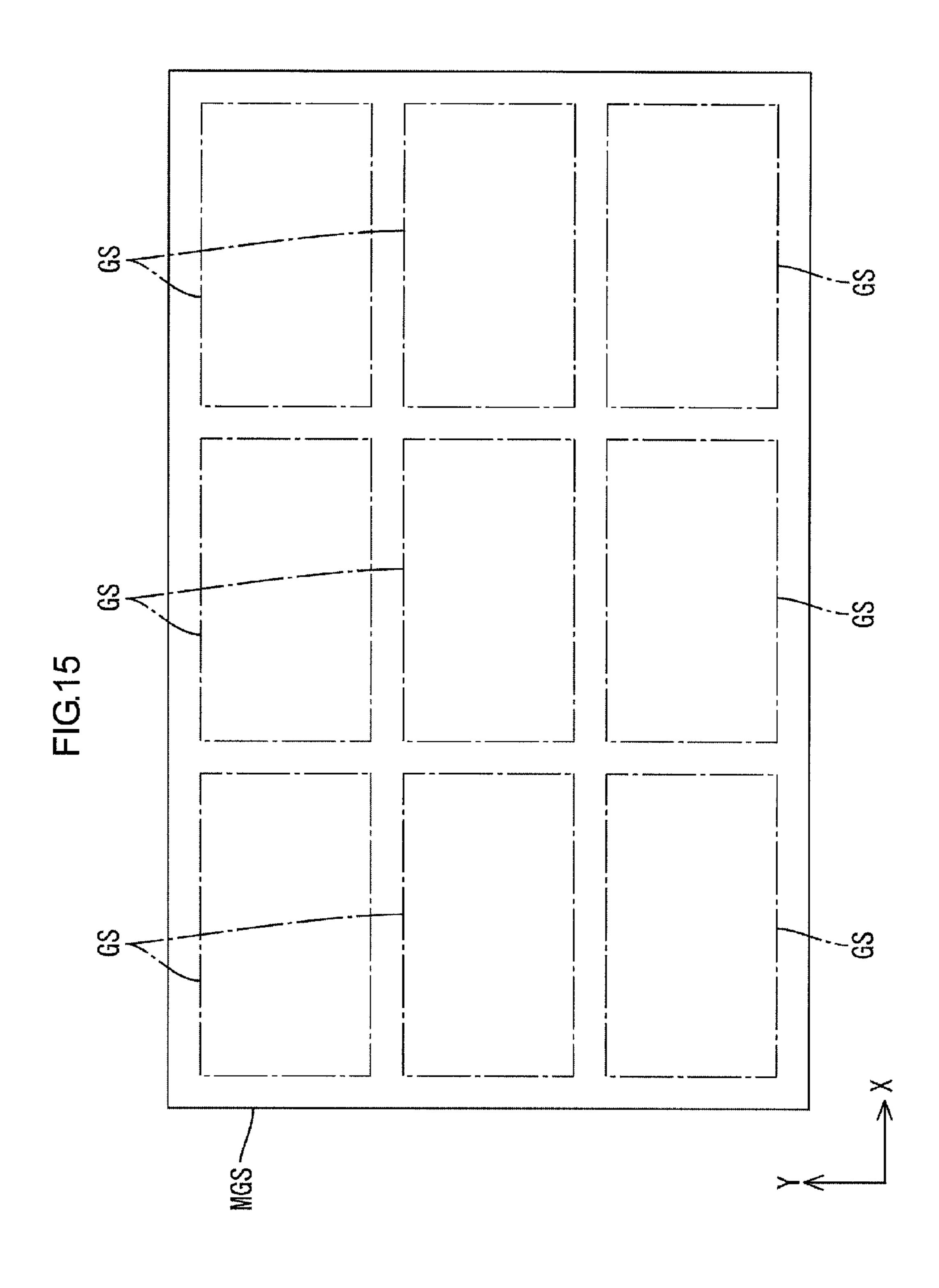

- FIG. 15 is a plan view illustrating a mother glass.

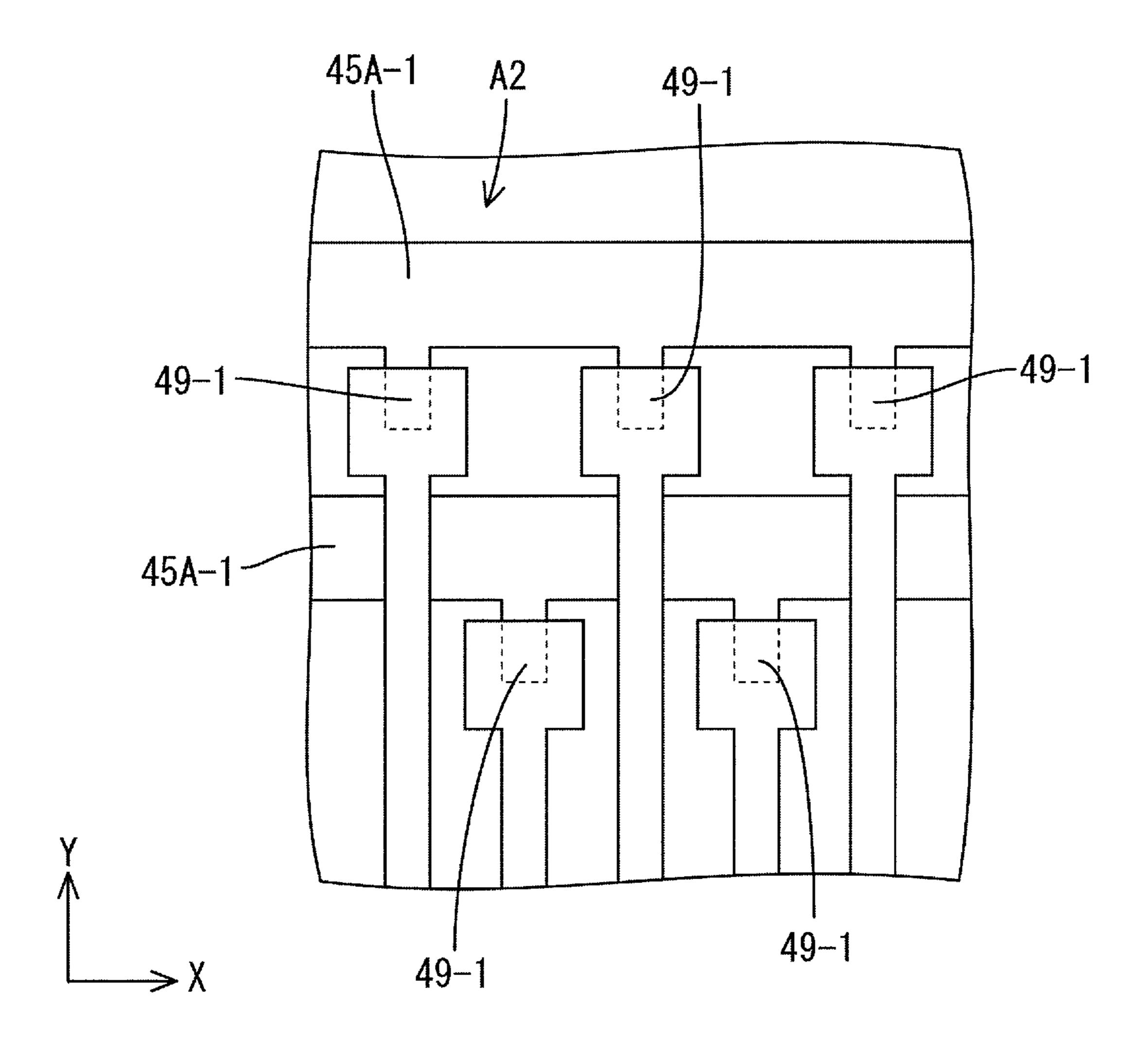

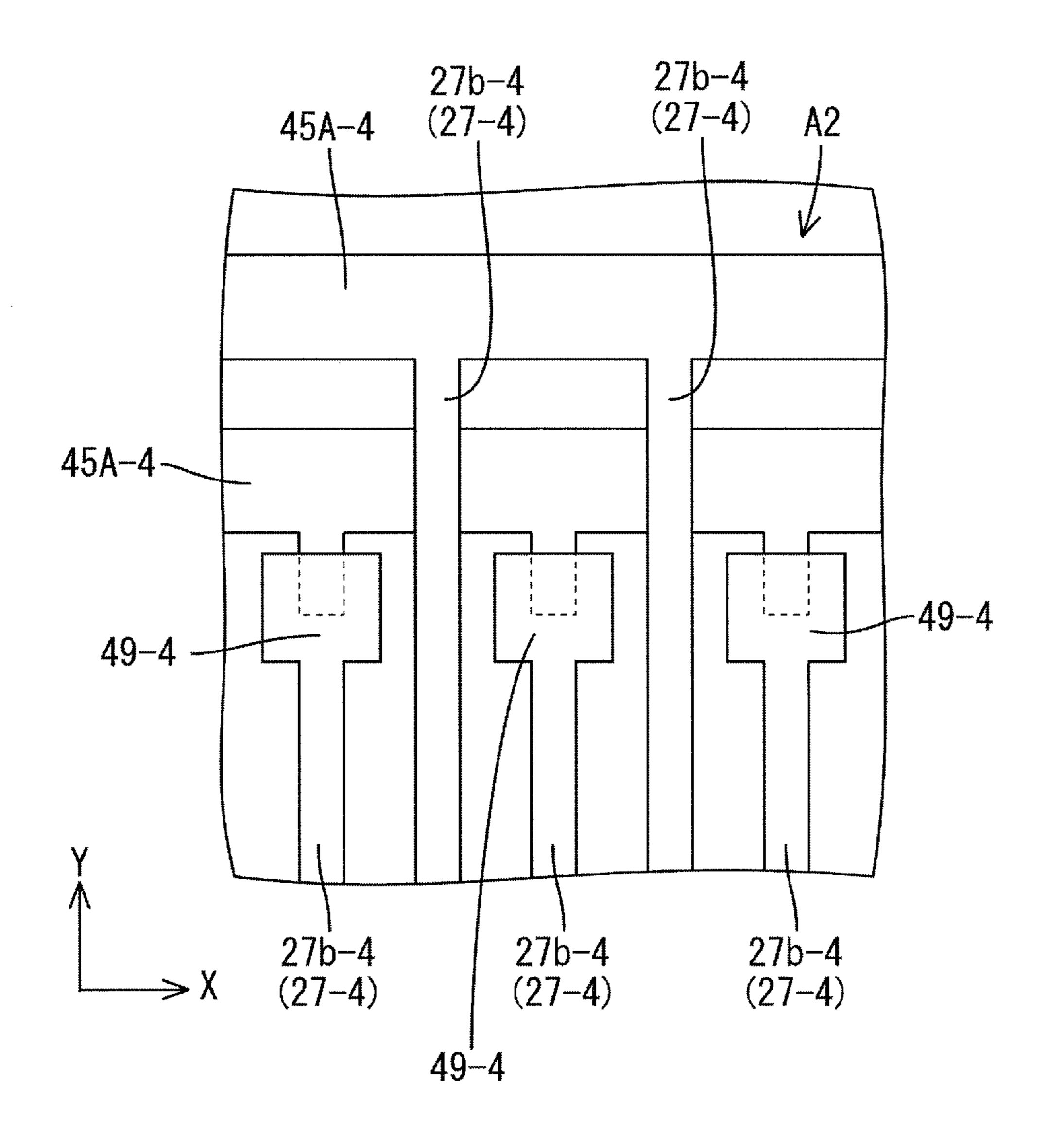

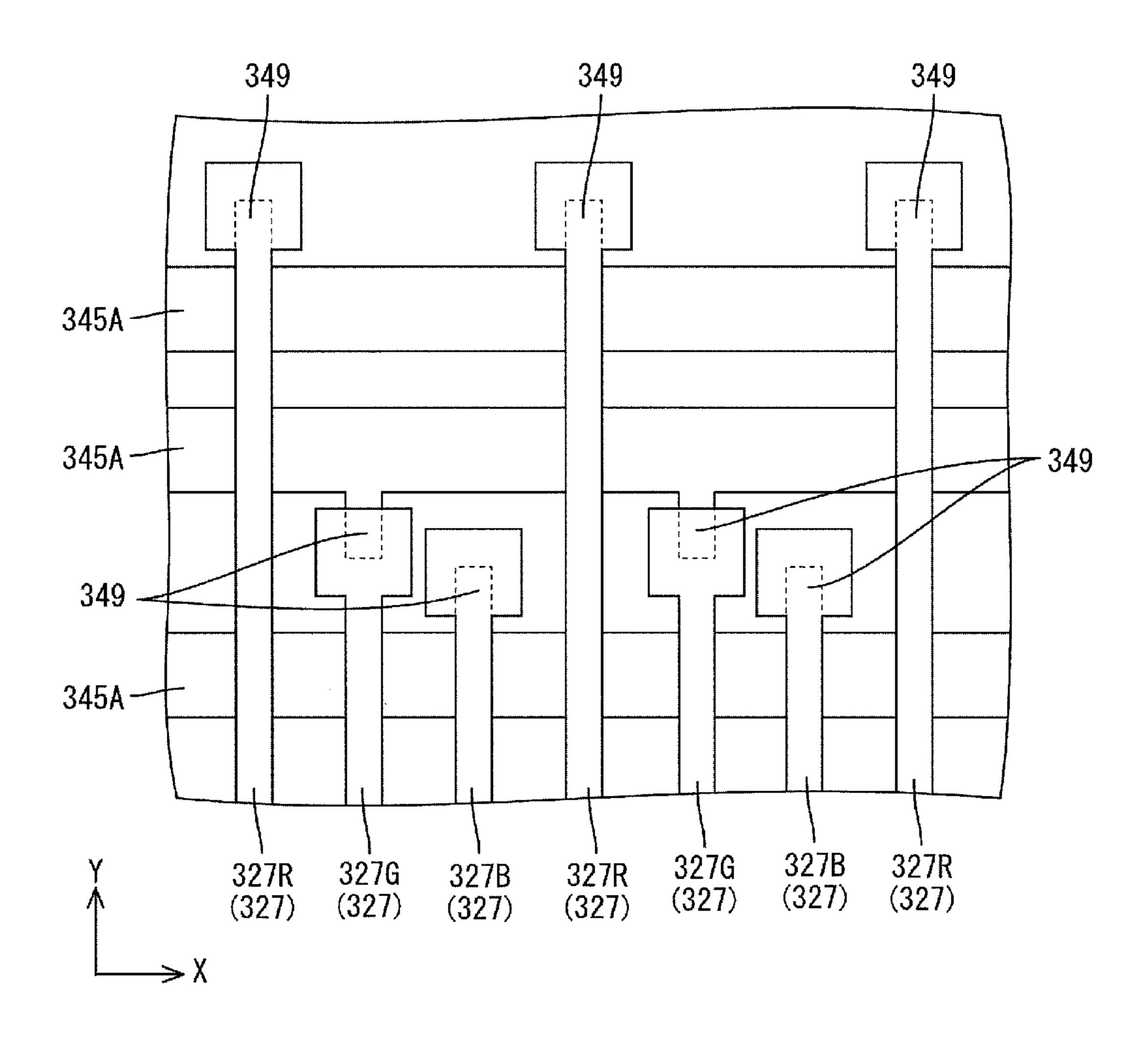

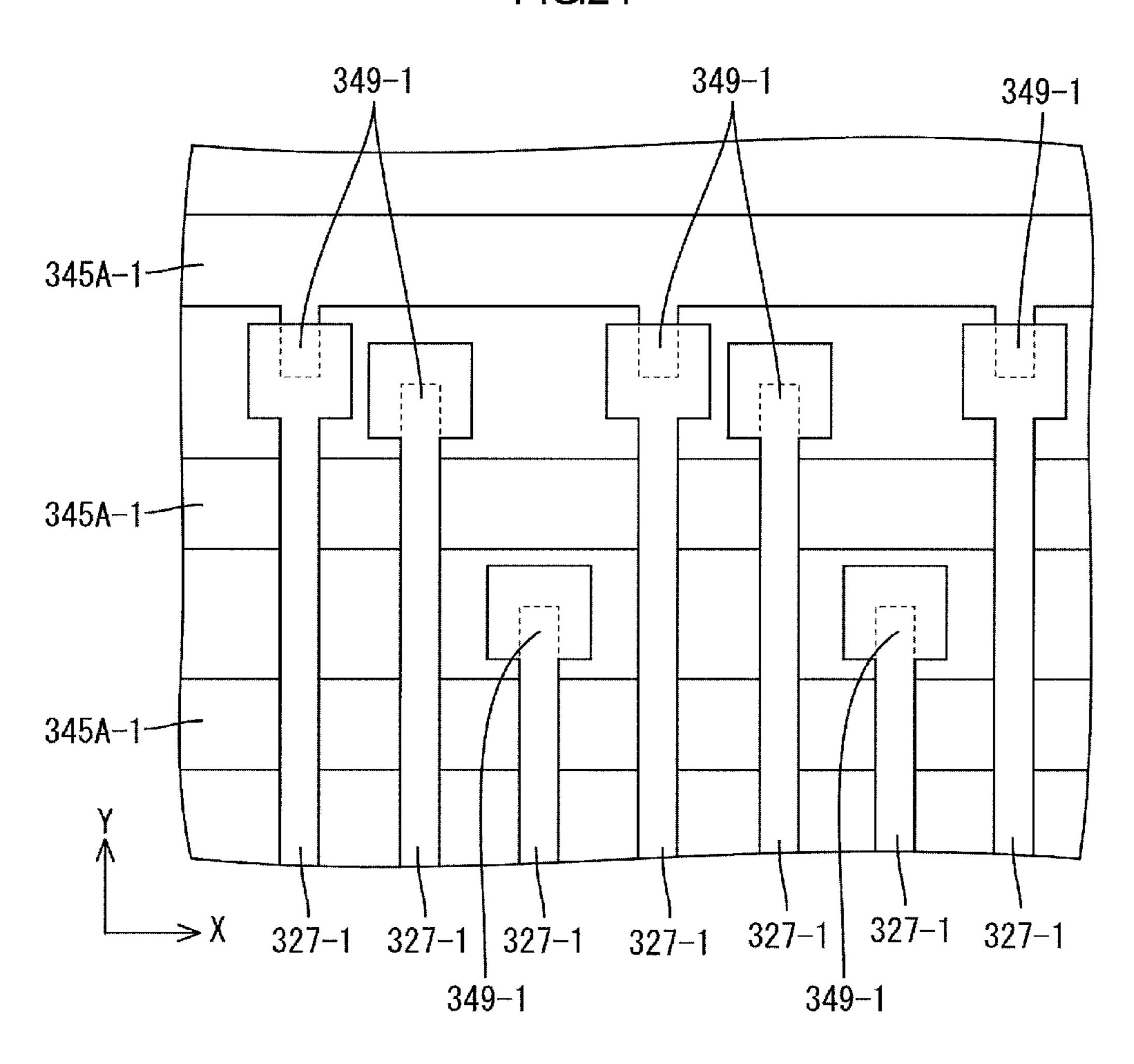

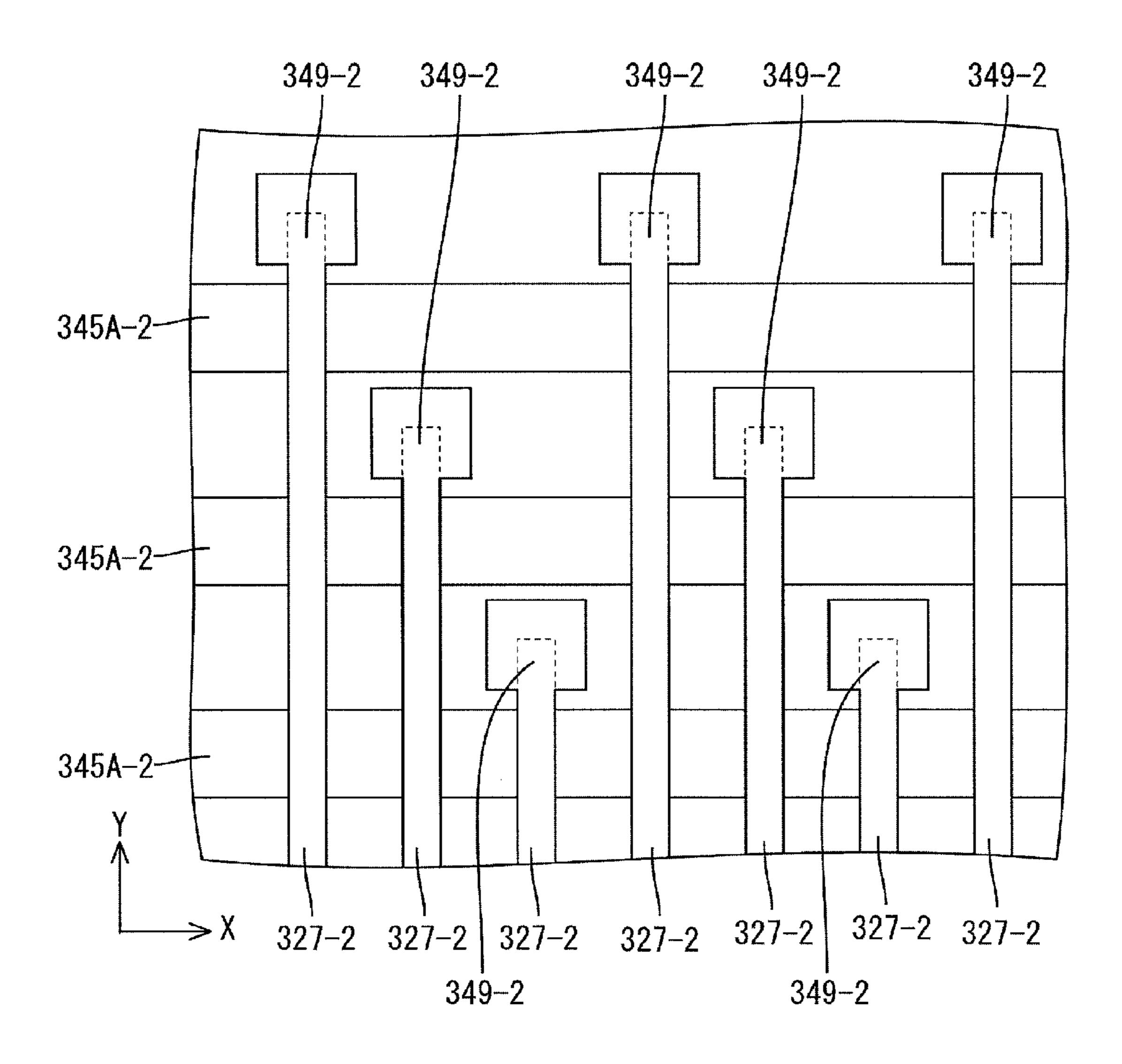

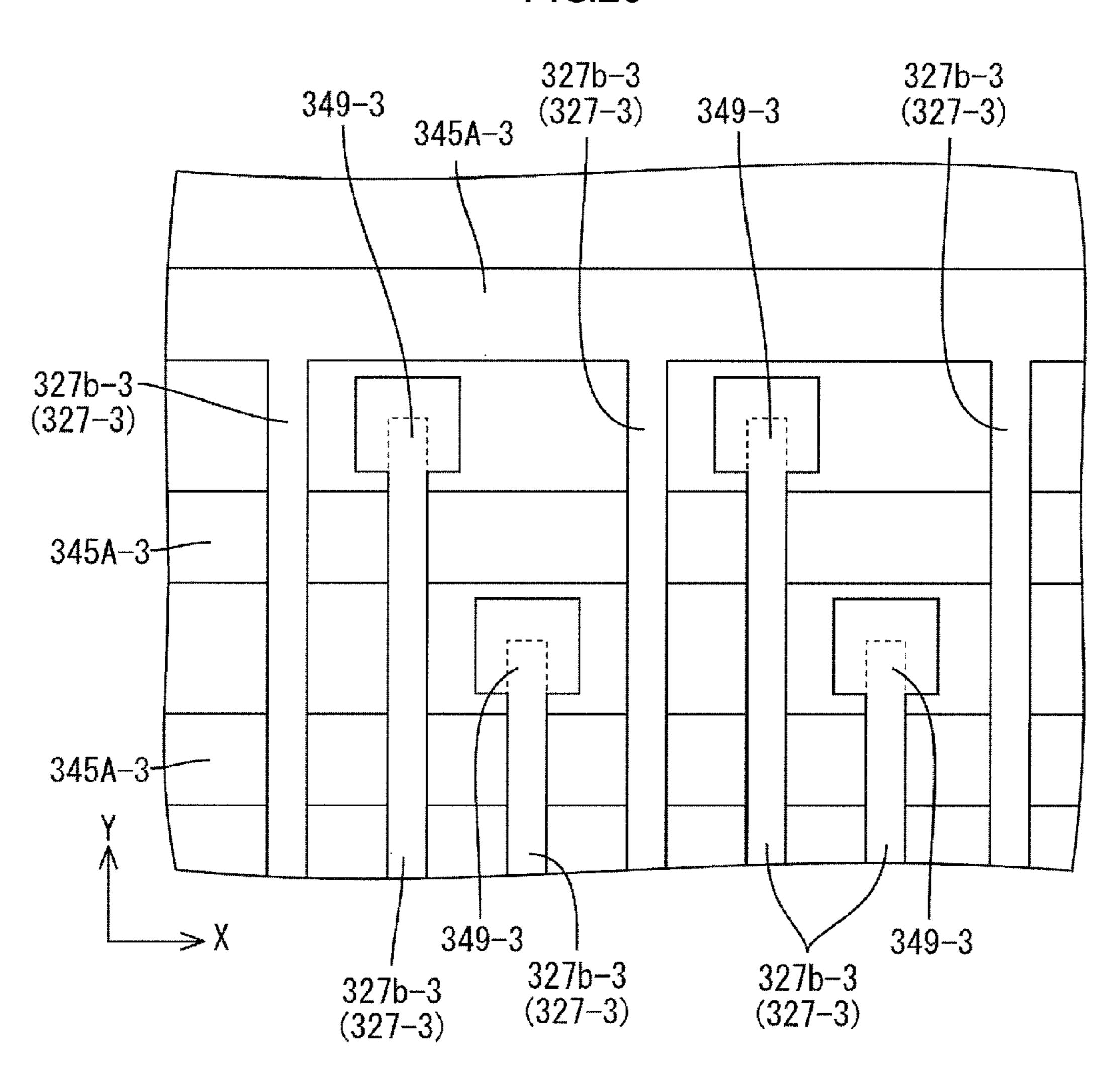

FIG. 16 is a plan view illustrating a plan configuration of a first source driver-side check line and a first wiring connection according to a first modification of the first embodiment.

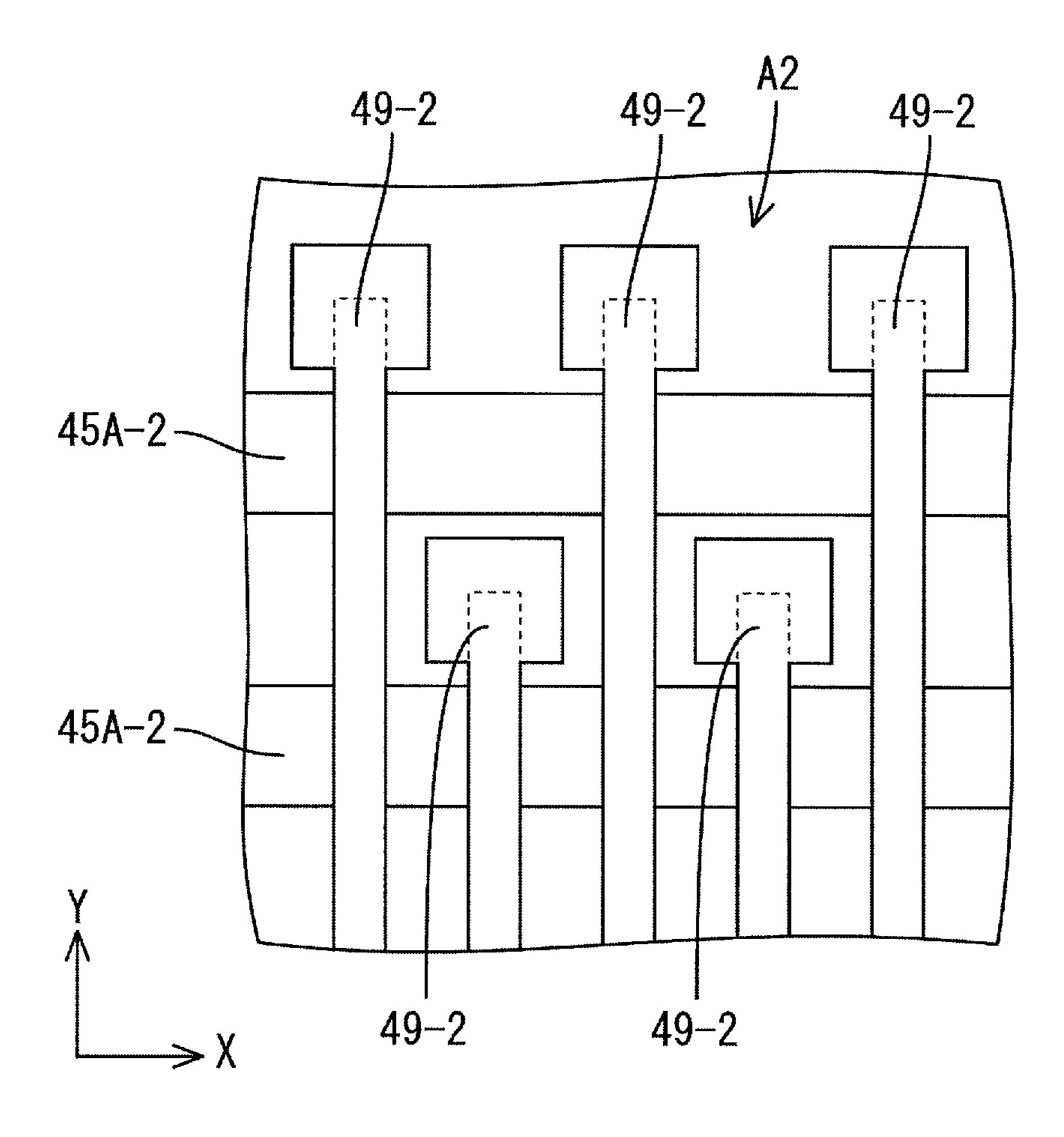

FIG. 17 is a plan view illustrating a plan configuration of a first source driver-side check line and a first wiring connection according to a second modification of the first embodiment.

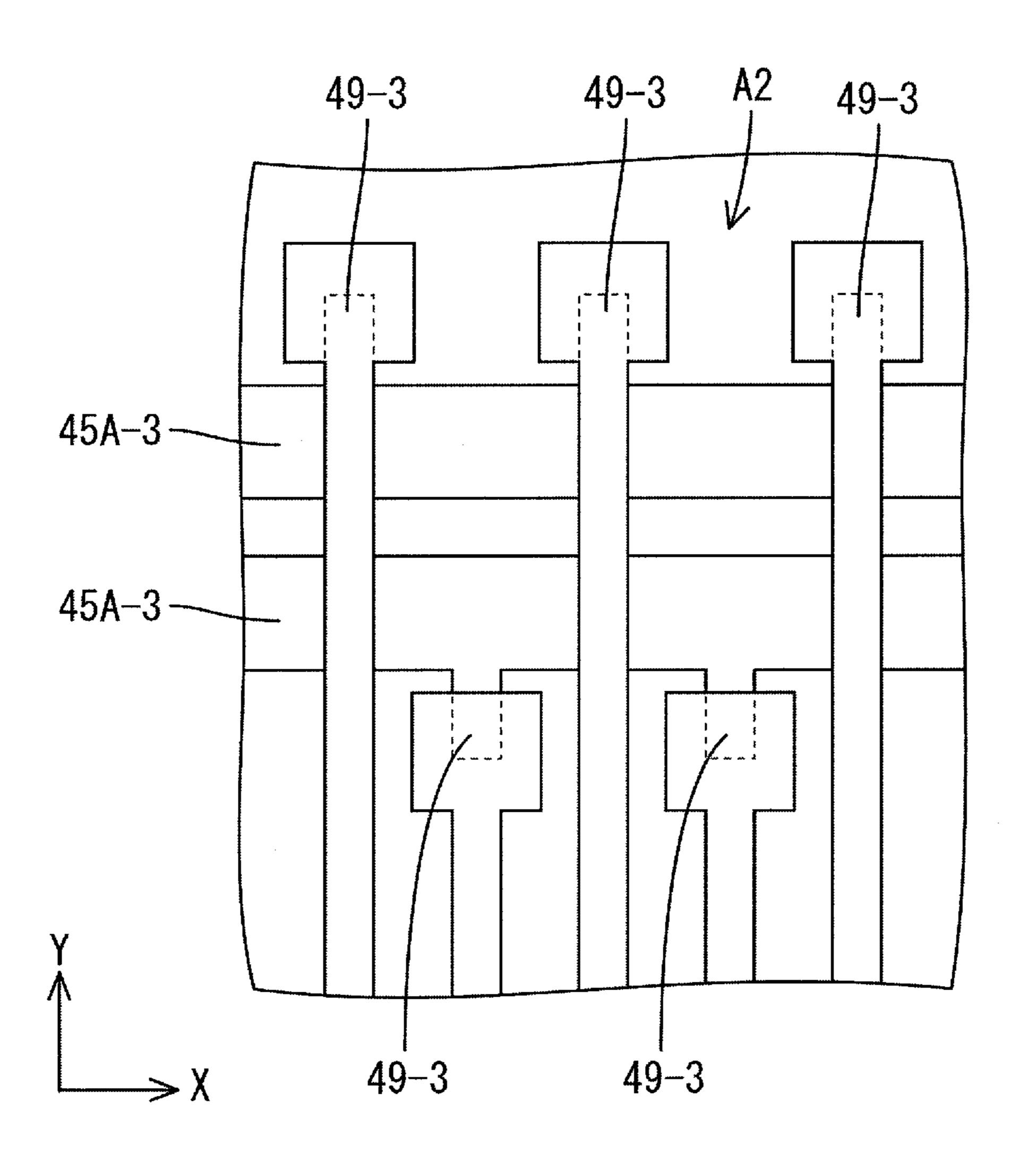

FIG. 18 is a plan view illustrating a plan configuration of a first source driver-side check line and a first wiring connection according to a third modification of the first embodiment.

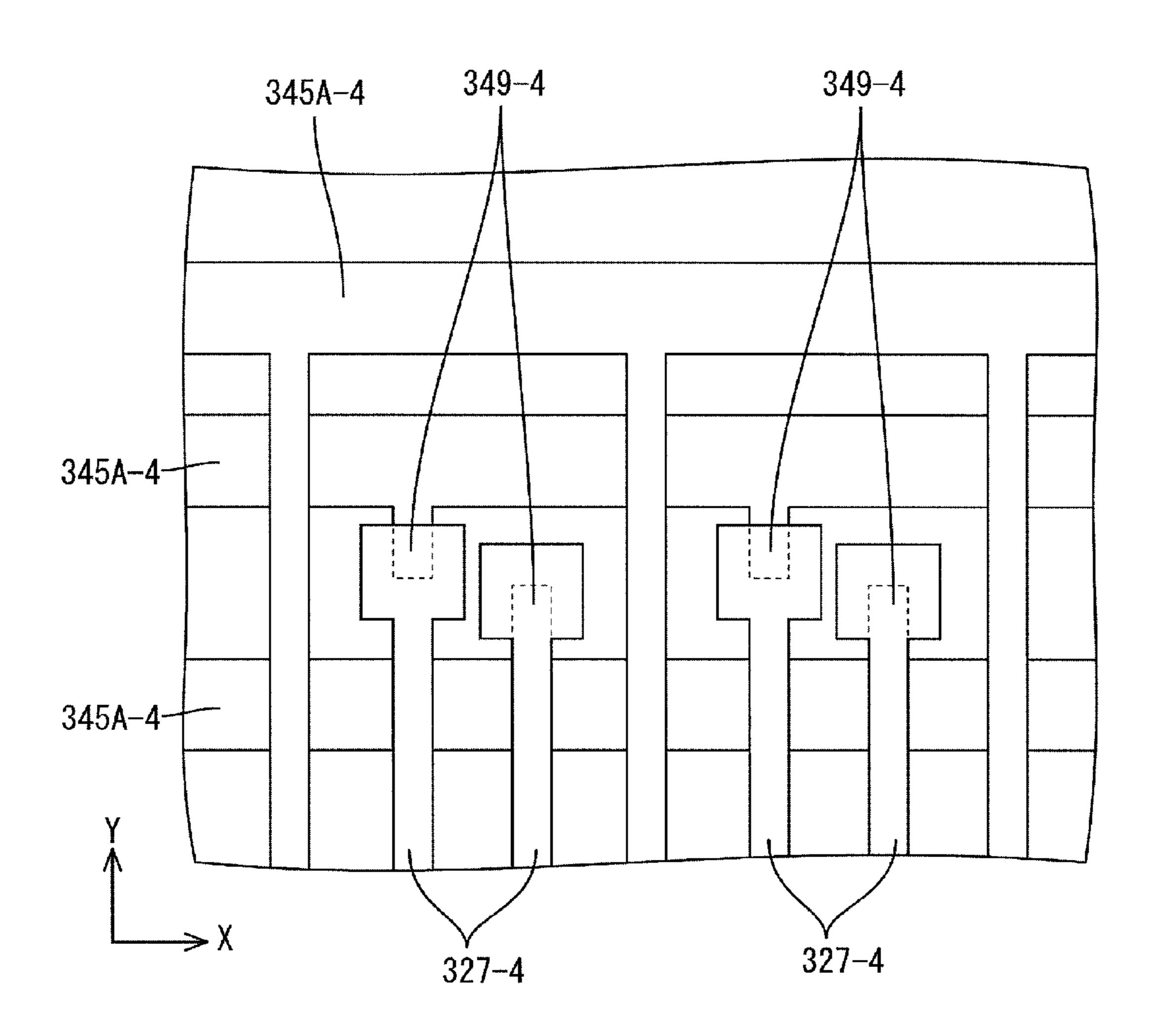

FIG. 19 is a plan view illustrating a plan configuration of a first source driver-side check line and a first wiring connection according to a fourth modification of the first embodiment

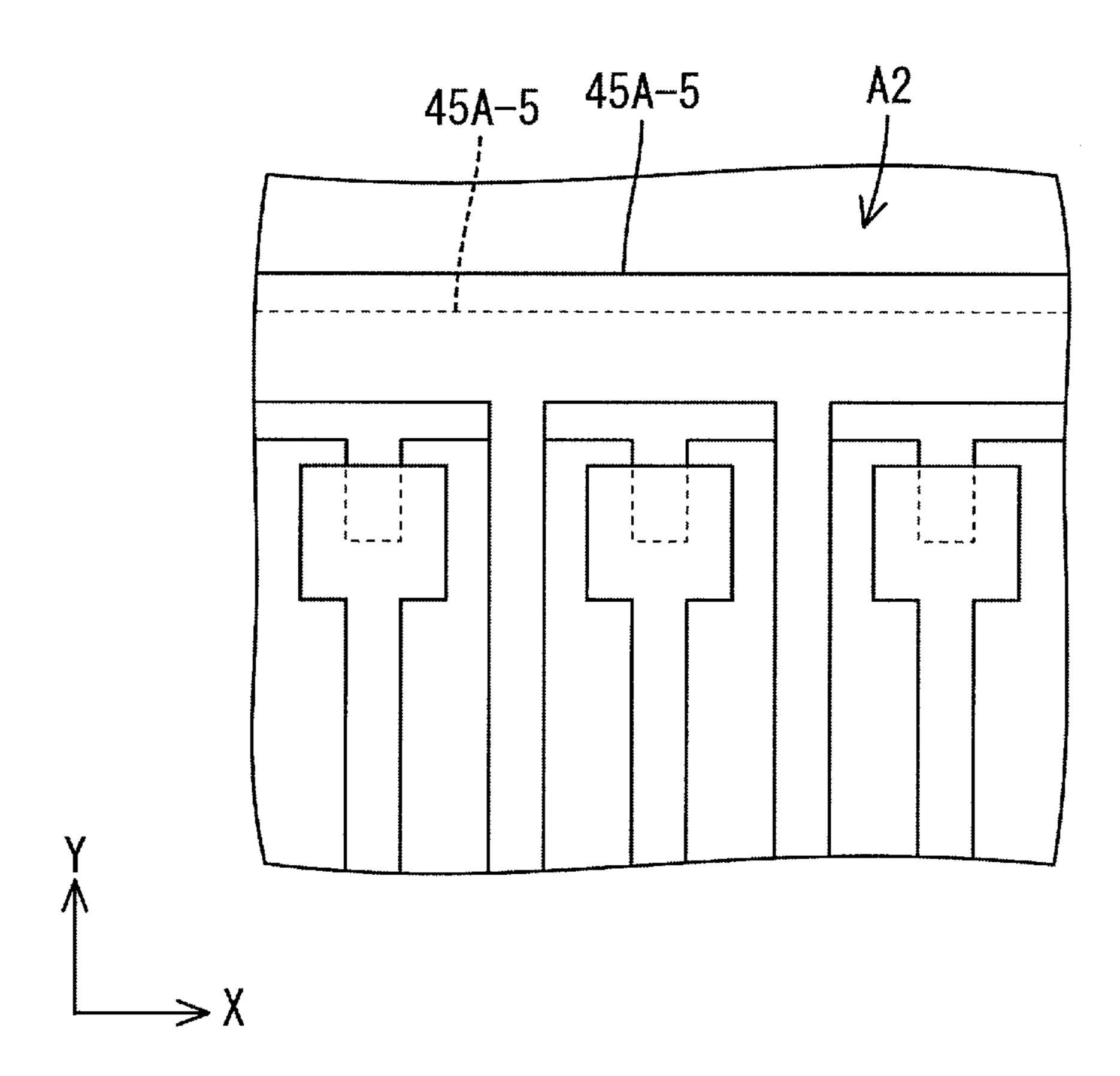

FIG. 20 is a plan view illustrating a plan configuration of a first source driver-side check line and a first wiring connection according to a fifth modification of the first embodiment.

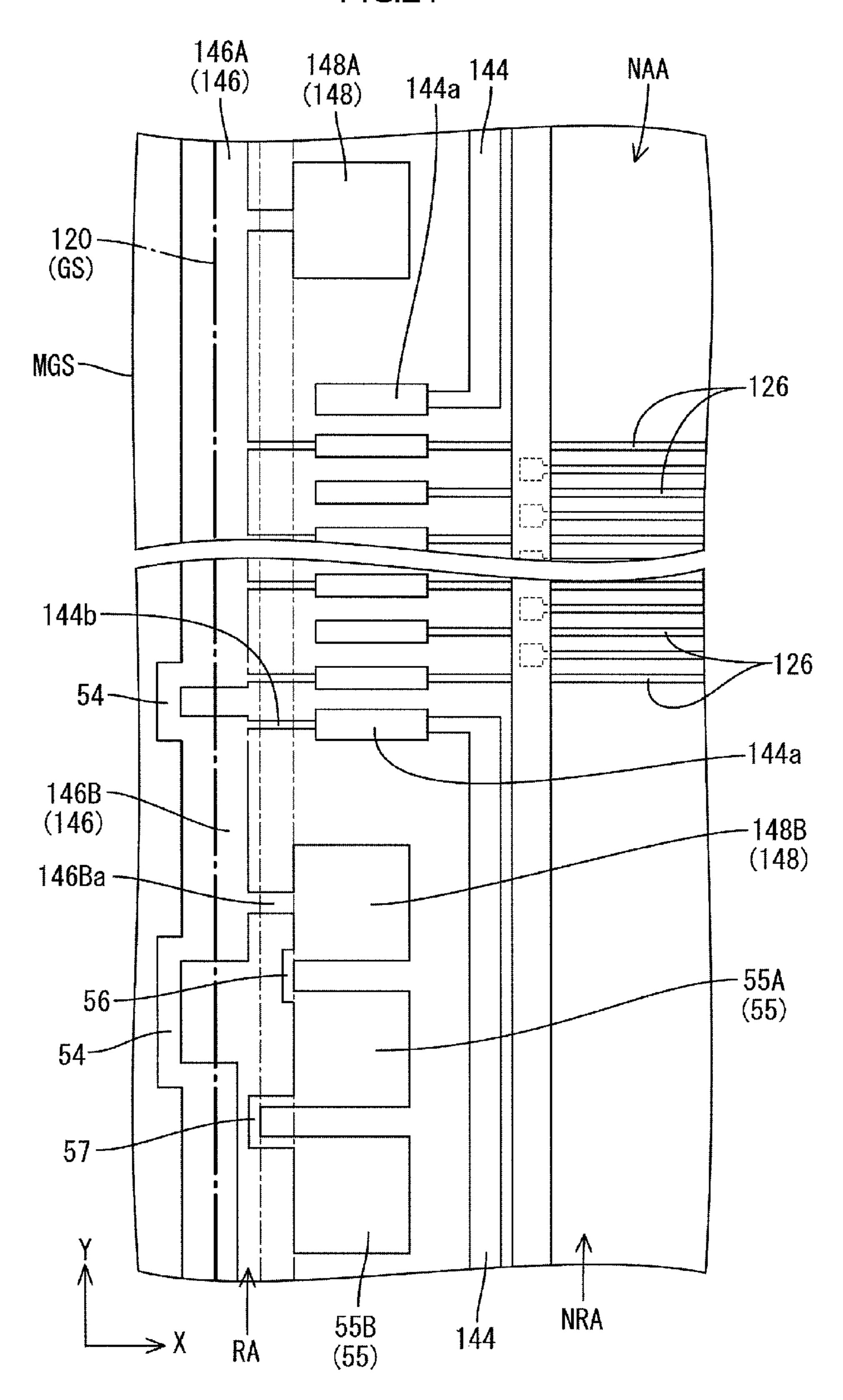

FIG. 21 is a plan view illustrating a wiring configuration of a gate driver-side end portion of an array substrate according to a second embodiment of the present invention.

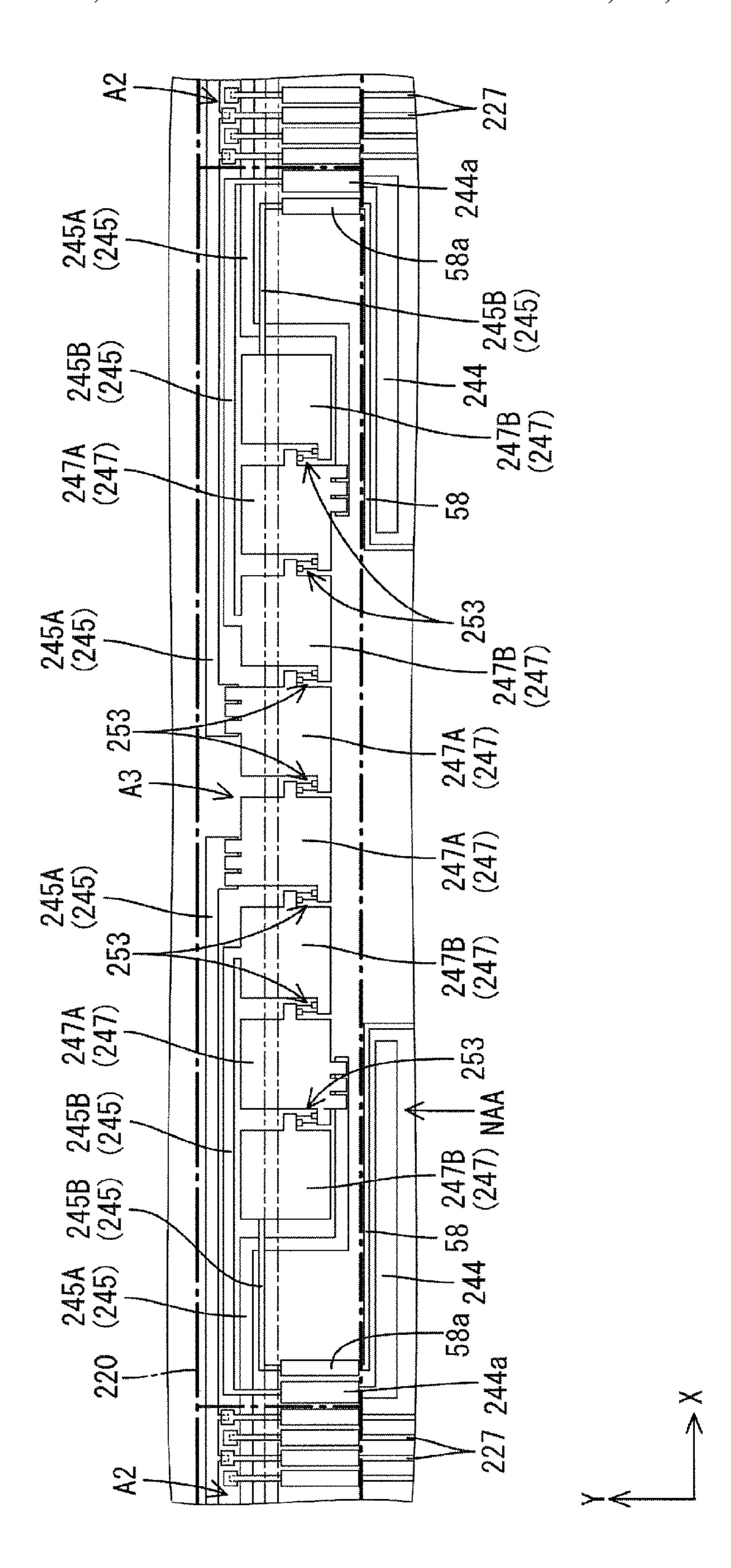

FIG. 22 is a plan view illustrating a wiring configuration of 20 a source driver-side end portion of an array substrate according to a third embodiment of the present invention.

FIG. 23 is a plan view illustrating a plan configuration of a first source driver-side check line and a first wiring connection according to a fourth embodiment of the present invention.

FIG. 24 is a plan view illustrating a plan configuration of a first source driver-side check line and a first wiring connection according to a first modification of the fourth embodiment of the present invention.

FIG. 25 is a plan view illustrating a plan configuration of a first source driver-side check line and a first wiring connection according to a second modification of the fourth embodiment of the present invention.

FIG. **26** is a plan view illustrating a plan configuration of a first source driver-side check line and a first wiring connection according to a third modification of the fourth embodiment of the present invention.

FIG. 27 is a plan view illustrating a plan configuration of a first source driver-side check line and a first wiring connection according to a fourth modification of the fourth embodi- 40 ment of the present invention.

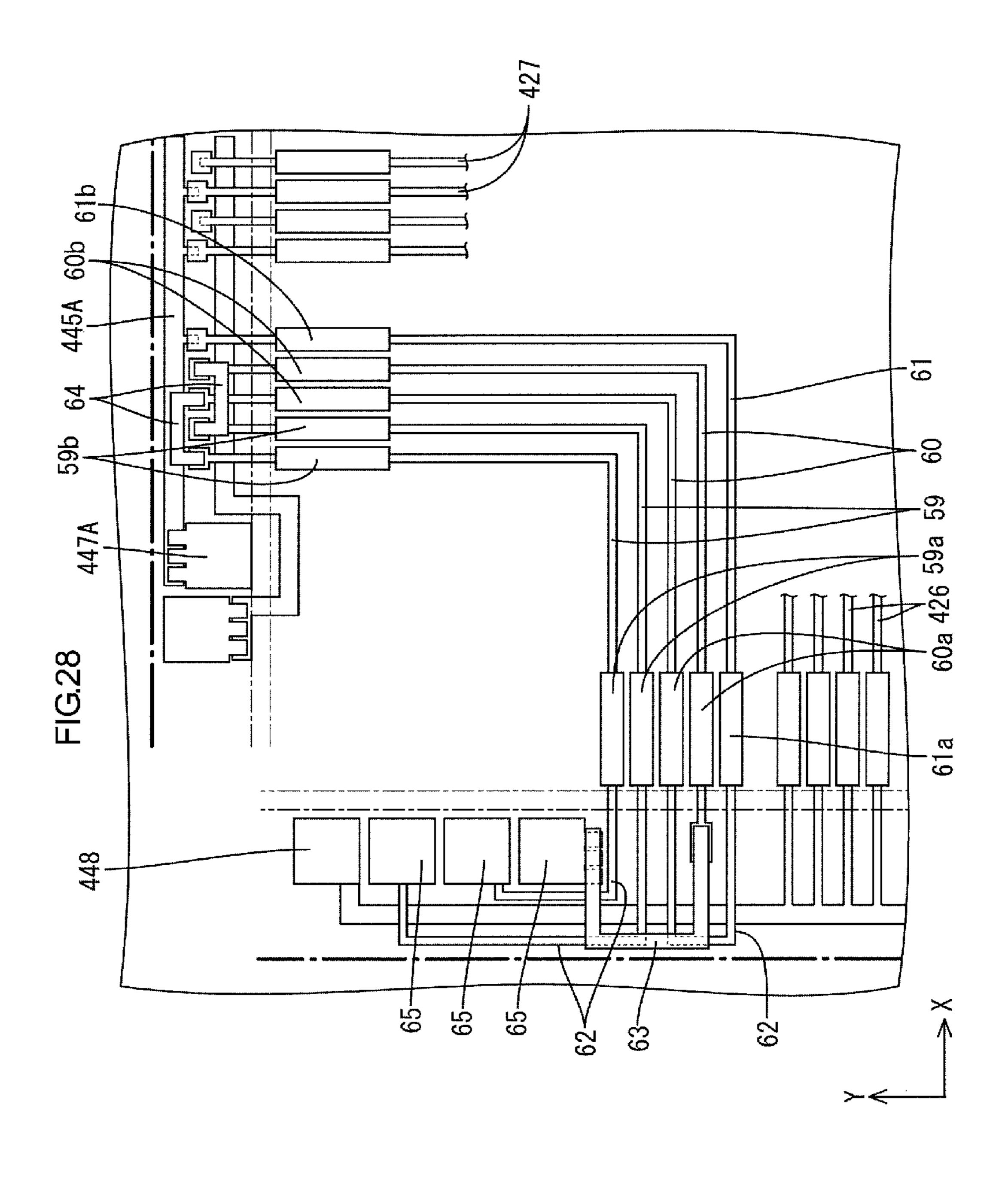

FIG. 28 is a plan view illustrating a wiring configuration of a corner of an array substrate according to a fifth embodiment of the present invention.

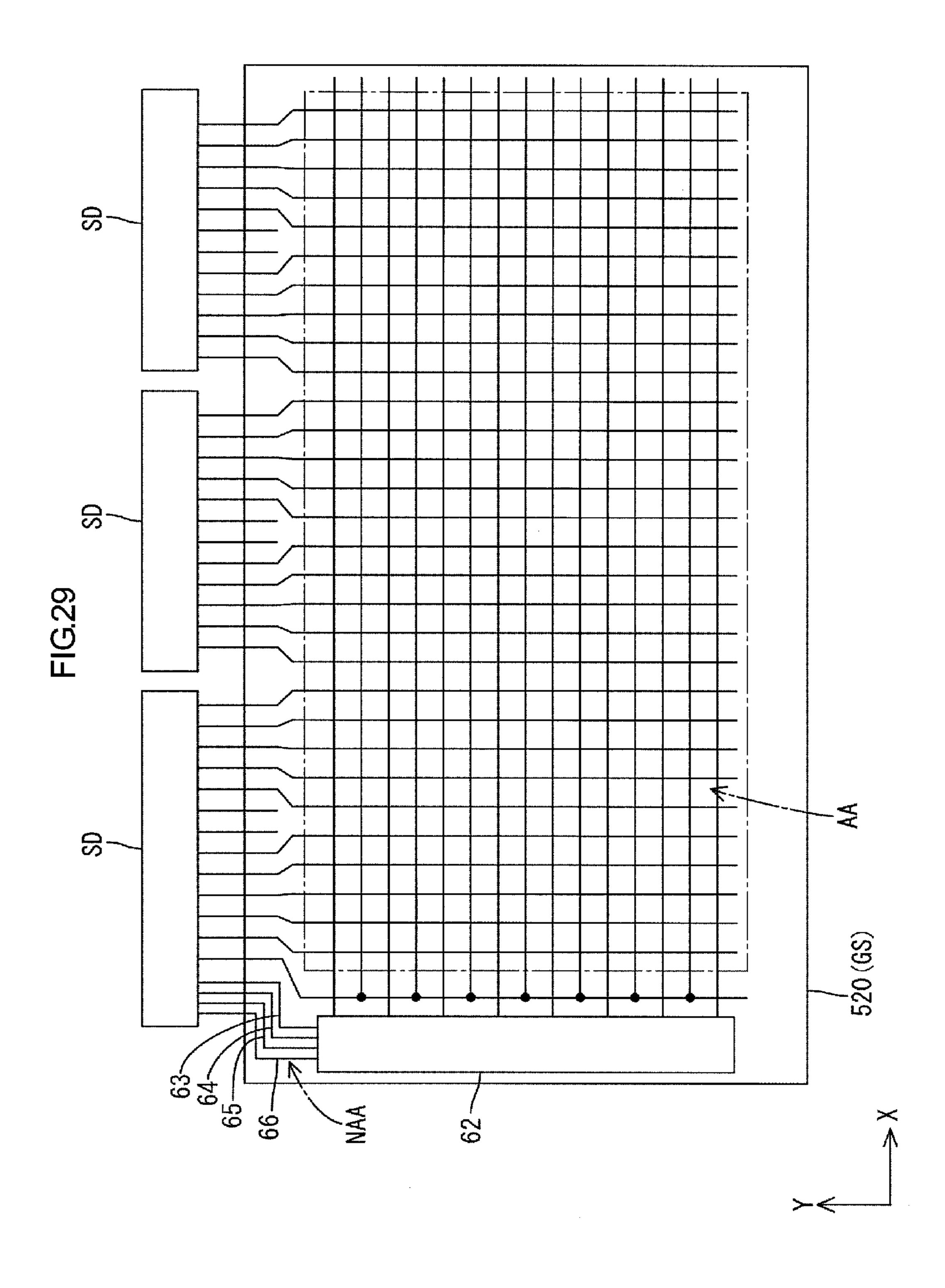

FIG. 29 is a plan view generally illustrating a wiring configuration of an array substrate according to a sixth embodiment of the present invention.

FIG. 30 is a plan view illustrating a wiring configuration of a source driver-side end portion of the array substrate.

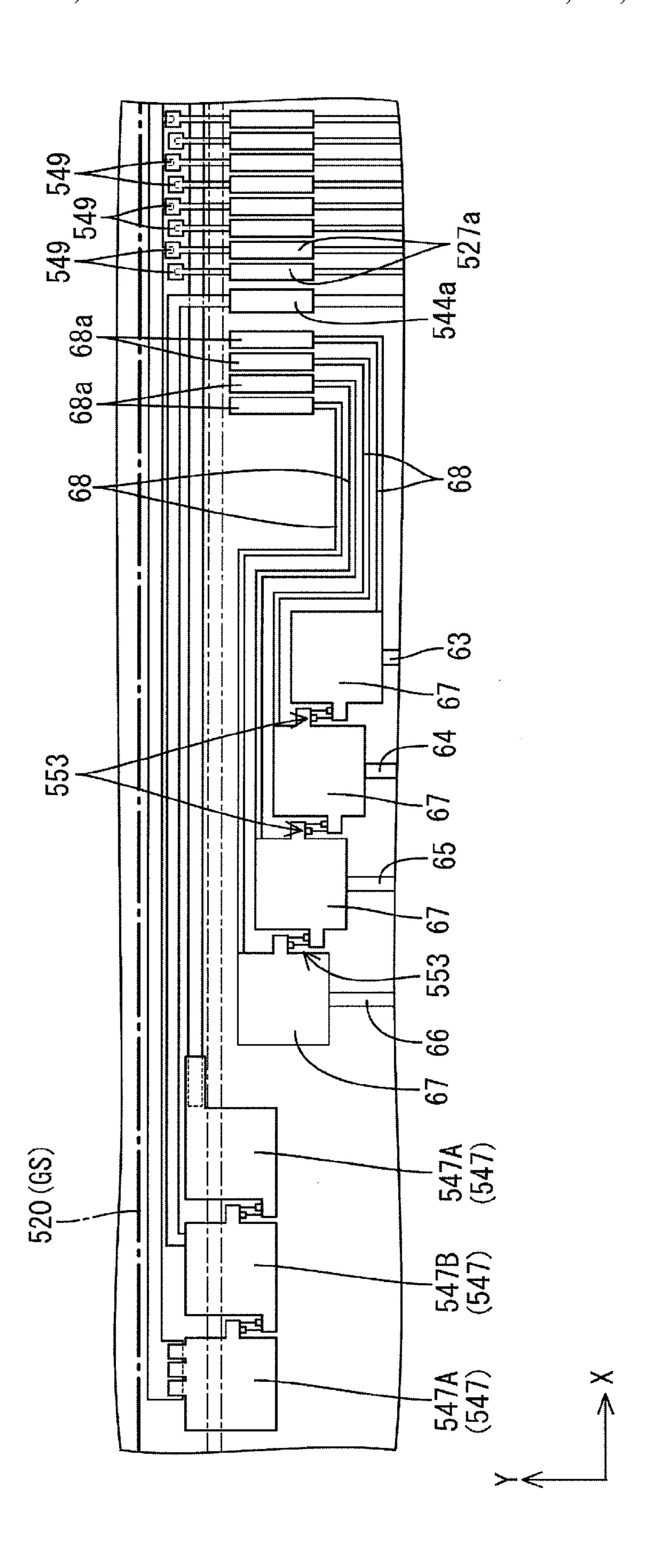

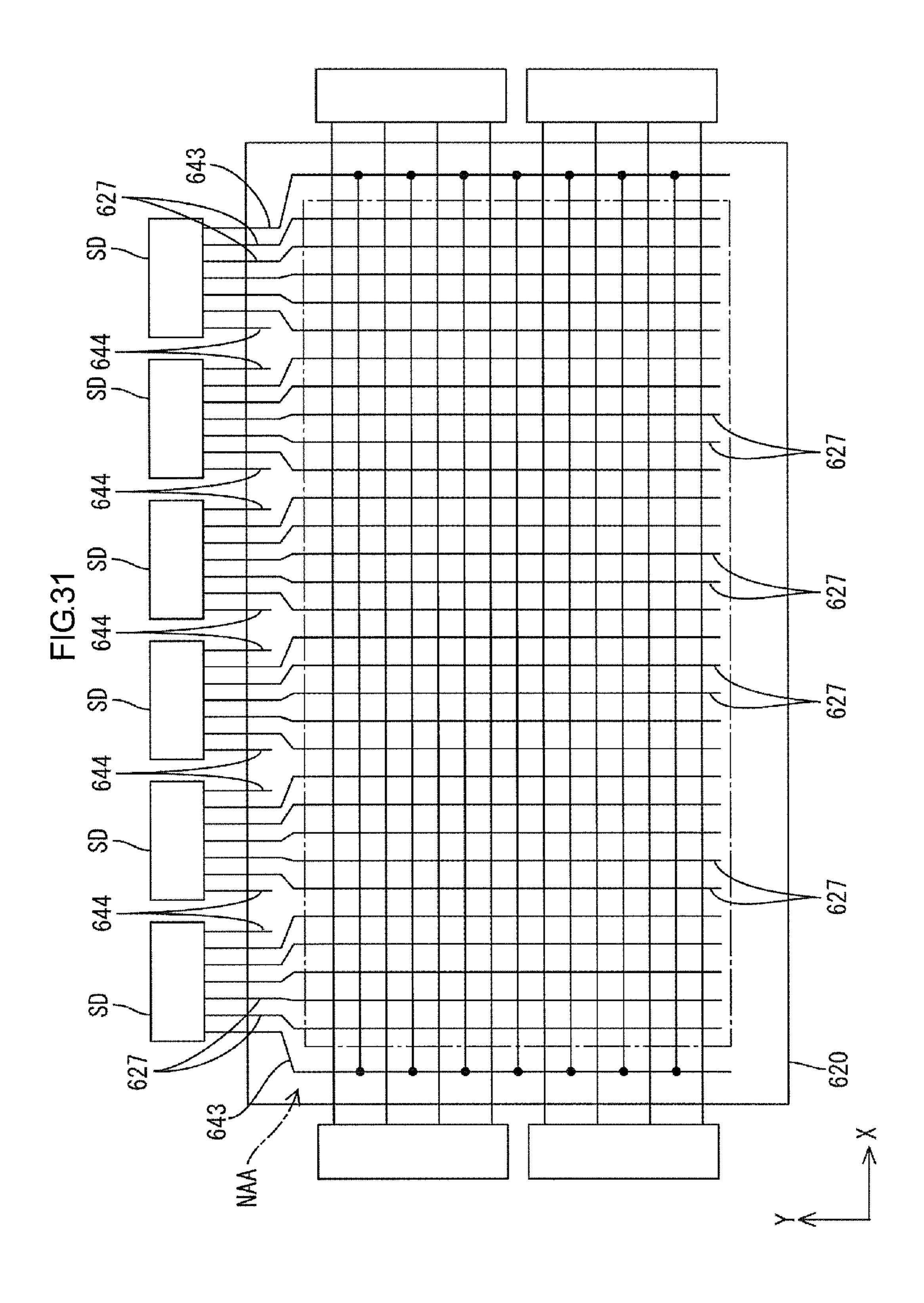

FIG. 31 is a plan view generally illustrating a wiring configuration of an array substrate according to a seventh embodiment of the present invention.

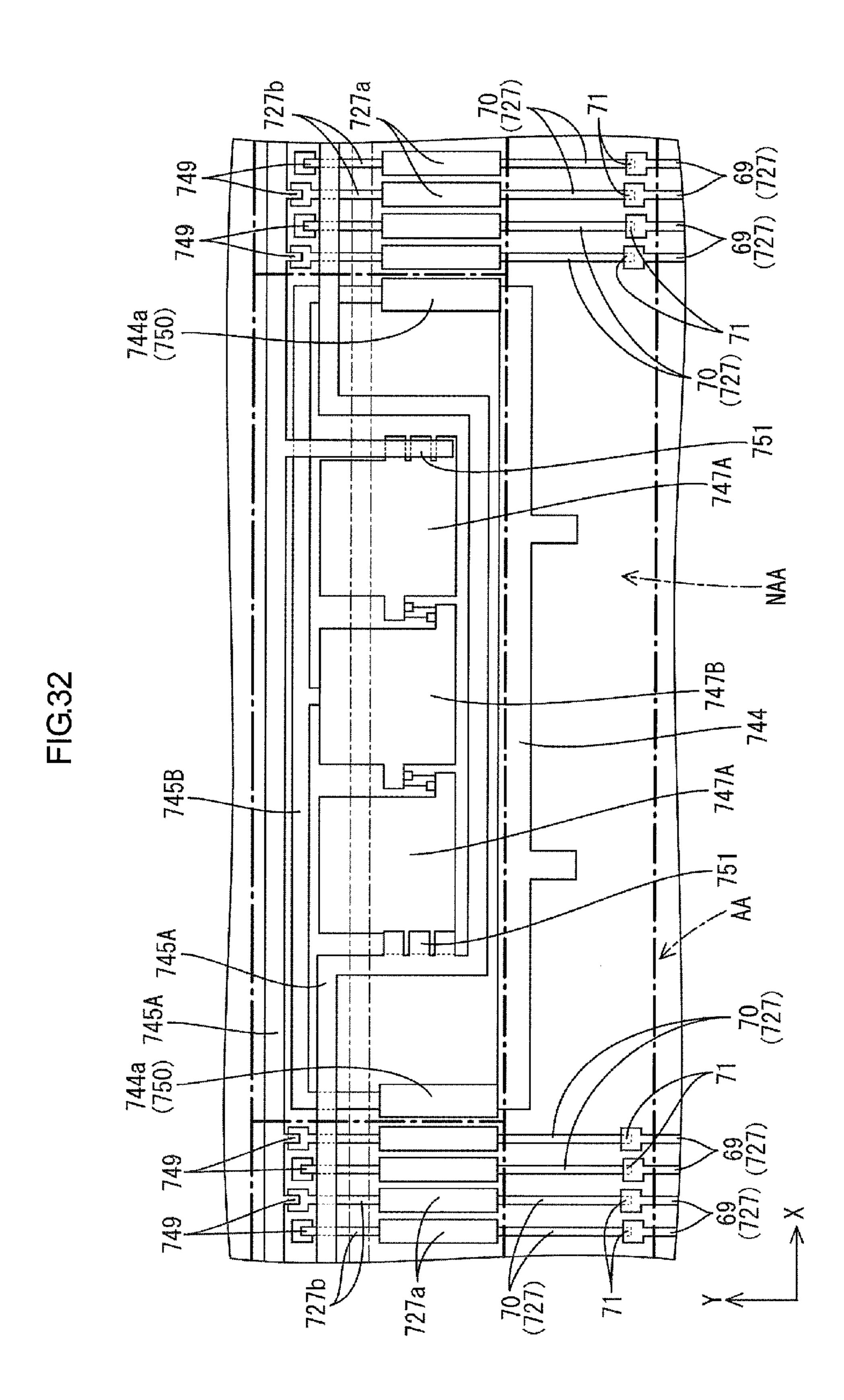

FIG. 32 is a plan view illustrating a wiring configuration of a source driver-side end portion of an array substrate according to a eighth embodiment of the present invention.

FIG. 33 is a flowchart illustrating a method of manufacturing a liquid crystal panel according to another embodiment (1) of the present invention.

FIG. **34** is a flowchart illustrating a method of manufacturing a liquid crystal panel according to another embodiment (2) of the present invention.

#### MODES FOR CARRYING OUT THE INVENTION

# First Embodiment

A first embodiment of the present invention will be explained with reference to FIGS. 1 to 15. In this embodi-

8

ment, a method of manufacturing an array substrate 20 included in a liquid crystal panel (a display panel) 11 of a liquid crystal display device 10 will be described as an example. In a part of each drawing, an X-axis, a Y-axis, and a Z-axis are described as necessary and a direction of each axis matches a direction illustrated in each drawing. An upper side in FIG. 3 is a front side and a lower side in FIG. 3 is a rear side.

As illustrated in FIG. 1, a television device TV according to this embodiment includes the liquid crystal display device (the display device) 10, front and rear cabinets Ca, Cb that sandwich the liquid crystal display device 10 therebetween, a power source P, a tuner T, and a stand S. The liquid crystal display device 10 is formed in a rectangular square shape as a whole. As illustrated in FIGS. 2 and 3, the liquid crystal display device 10 includes the liquid crystal panel 11 as a display panel and a backlight device (a lighting device) 12 that is an external light source, and the components are integrally held by a bezel 13.

A general configuration of the backlight device 12 will be explained. The backlight device 12 includes a light source arranged directly below the liquid crystal panel 11 and the backlight device 12 is a so-called direct-type backlight device. The backlight device 12 includes a chassis 14, a reflection sheet (a reflection member) 15, an optical member 16, a frame 17, a plurality of cold cathode tubes (light source) 18, and a lamp holder 19. The chassis 14 has a light exit portion that is open to a front side (a light exit side, a liquid crystal panel 11 side). The reflection sheet 15 is arranged in the chassis 14. The optical member 16 is arranged to cover the light exit portion of the chassis 14. The frame 17 holds the optical member 16. The cold cathode tubes 18 are aligned with each other and arranged in the chassis 14. The lamp holder 19 shields end portions of the cold cathode tubes 18 from light and has light reflectivity.

Next, the liquid crystal panel 11 will be explained. As illustrated in FIG. 4, the liquid crystal panel 11 includes a pair of substrates 20, 21 and a liquid crystal layer 22 enclosed between the substrates 20, 21. The liquid crystal layer 22 contains liquid crystal materials that change optical characteristics according to impression of an electric field. The liquid crystal layer 22 is enclosed between the substrates 20, 21. The liquid crystal panel 11 includes a display area (an inner peripheral side area) AA and a non-display area (an outer peripheral side area) NAA (refer to FIG. 8). The display area AA is located in a central area in a screen and capable of displaying images. The non-display area NAA is located on an outer peripheral end side of the screen and formed in a frame shape that surrounds the display area AA. The nondisplay area is incapable of displaying images. In FIG. 8, an 50 area surrounded by an alternate long and short dash line represents the display area AA. A pair of polarizing plates are adhered to outer surfaces of the substrates 20, 21, respectively.

One of the pair of substrates 20, 21 included in the liquid crystal panel 11 that is arranged on a rear-surface side (the back light device 12 side) is an array substrate (an element substrate, an active matrix substrate) 20, as illustrated in FIG. 4. Another one of the pair of substrates 20, 21 that is arranged on a front-surface side (a light exit side) is a CF substrate (a counter substrate) 21. Each of the array substrate 20 and the CF substrate GS made of glass and various structures (thin films) that are laminated on the substrate GS. As illustrated in FIG. 15, in manufacturing the array substrate 20 and the CF substrate 21, a large mother glass (substrate parent material) MGS is used such that a plurality of glass substrates GS are obtained from the large mother glass. Accordingly, manufac-

turing efficiency is likely to be improved and a cost for manufacturing equipments is likely to be reduced. Specifically, one mother glass MGS is divided into nine pieces and nine glass substrates GS are obtained. A frame surrounded by an alternate long and short dash line in FIG. 15 represents an outer shape of each glass substrate GS.

A general configuration of the display area AA in the array substrate 20 will be explained. As illustrated in FIG. 5, in the display area AA on an inner side (the liquid crystal layer 22 side, a surface facing the CF substrate 21, a surface on which 10 lines are arranged) of the array substrate 20, a plurality of TFTs (thin film transistor) **24** that are switching components and each of which includes three electrodes 24a to 24c and a plurality of pixel electrodes 25 are arranged. Gate lines 26 and source lines 27 that are arranged in a matrix are arranged to 15 surround the TFTs 24 and the pixel electrodes 25. The pixel electrode 25 is formed of a light transmissive conductive material (transparent conductive material) such as ITO (Indium Tin Oxide) or IZO (Indium Zinc Oxide). The gate lines 26 and the source lines 27 are formed of a conductive metal 20 material. Specifically, each source line 27 includes different kinds of metal films 39, 40 that are laminated and is formed in a two-layer structure. A lower side metal film **39** is made of titanium (Ti) and an upper side metal film 40 is made of aluminum (Al) (refer to FIG. 7). The gate line 26 and the 25 source line 27 are connected to the gate electrode 24a and the source electrode 24b of the TFT 24, respectively. Accordingly, the pixel electrode 25 is connected to the drain electrode **24***c* of the TFT **24** via a drain line **34**. The array substrate 20 includes capacity lines (auxiliary capacity lines, storage 30 capacity lines, Cs lines) 33 that are parallel to the gate lines 26 and overlap the pixel electrodes 25 in a plan view. The capacity line 33 is formed of the same material as the gate line 26 and they are formed in the same layer in the same step of the manufacturing process. The capacity lines 33 and the gate 35 lines 26 are arranged alternately with respect to the Y-axis direction. The gate line 26 is arranged between the pixel electrodes 25 that are arranged adjacent to each other in the Y-axis direction. Each capacity line **33** is arranged to cross a substantially middle portion of each pixel electrode 25 in the 40 line 34. Y-axis direction. An alignment film 28 is formed on an inner surface side of the array substrate 20 (FIG. 4). The alignment film 28 aligns liquid crystal molecules included in the liquid crystal layer 22.

Next, a general configuration of the display area AA in the 45 CF substrate 21 will be explained. As illustrated in FIGS. 4 and 6, in the display area AA on an inner side (the liquid crystal layer 22 side, a surface facing the array substrate 20) of the CF substrate 21, a plurality of color filters are arranged to overlap the pixel electrodes 25 on the array substrate 20, 50 respectively. The color filters includes coloring sections 29 each provides colors of red (R), green (G), and blue (B) that are arranged in the X-axis direction. Each coloring section 29 has an elongated rectangular outer shape similar to an outer shape of the pixel electrode 25 with a plan view. A light 55 blocking section (a black matrix) 30 is formed between the coloring sections 29 included in the color filter. The light blocking sections 30 are formed in a matrix and prevent the colors from being mixed. The light blocking sections 30 are arranged to overlap the gate lines 26, the source lines 27 and 60 the capacity lines 33 on the array substrate 20 side with a plan view. A counter electrode 31 is arranged on a surface of each coloring section 29 and the light blocking sections so as to face the pixel electrode 25 on the array substrate 29 side. An alignment film 32 is provided on an inner side surface of the 65 CF substrate 21. The alignment film. 32 aligns the liquid crystal molecules included in the liquid crystal layer 22.

**10**

The alignment films 28, 32 that are formed on the substrate 20, 21, respectively are vertical alignment films that align the liquid crystal molecules included in the liquid crystal layer 22 to be vertical and are light alignment films. Surfaces of the light alignment films are subjected to light alignment processing and alignment restriction force is applied to the liquid crystal molecules. In the manufacturing process of manufacturing each substrate 20, 21, the light alignment processing is performed. Specifically, after each alignment film 28, 32 is formed, light having a specific wavelength range such as a ultraviolet light (UV light) is irradiated to a surface of each alignment film 28, 32 at a specific angle, and accordingly, the liquid crystal molecules are aligned along a light irradiation direction. In the light alignment processing, the light irradiation direction is changed in some ranges on a plane of each of the alignment films 28, 32. Accordingly, while the alignment films 28, 32 are arranged to face each other, one pixel area (for example, one transparent electrode 25) is divided into four areas each having a different alignment direction of the liquid crystal molecules. Namely, the pixel area is divided into four domains. Accordingly, viewing angle characteristics are averaged and good display quality is obtained. Regarding the light alignment processing, for example, the technology described in Japanese Unexamined Patent Application Publication No. 2008-145700 is used.

The TFT 24 that is one of the structures included in the array substrate 20 will be explained in detail. The TFT 24 is a switching component. As illustrated in FIG. 7, the TFT 24 includes the glass substrate GS that is the array substrate 20 and a plurality of thin films laminated sequentially on the glass substrate GS. Specifically, the gate electrode 24a that is connected to the gate line 26, a gate insulation film 35, a semiconductor film 36, a doping semiconductor film 42, the source electrode 24b and the drain electrode 24c, an in-between insulation film 37 between layers (a passivation film) and a protection film. 38 are laminated on the glass substrate GS in this order from the lower layer side (the glass substrate GS side). The source electrode 24b is connected to the source line 27 and the drain electrode 24c is connected to the drain line 34.

The gate electrode **24***a* is formed of the same material as the gate lines 26 and is formed by patterning directly on the glass substrate GS in the same manufacturing step of the gate lines 26. For example, the gate electrode 24a is formed of a single metal film or a layered film including a plurality of metal films made of aluminum (Al), chrome (Cr), tantalum (Ta), titanium (Ti), copper (Cu). As illustrated in FIG. 5, a branch line extends along the Y-axis direction from a portion in the vicinity of a cross section of the gate line **26** extending in the X-axis direction and the source line 27. The gate electrode 24a is configured with an extended distal end portion of the extended branch line. The gate insulation film 35 is formed of a silicone nitride film (SiNx) and keeps the gate electrode 24a to be insulated from the semiconductor film 36 that will be described later. The gate insulation film **35** is formed over substantially an entire area of the glass substrate GS including an area in which the TFTs 24 are formed.

The semiconductor film 36 is formed of amorphous silicon (a-Si), for example. As illustrated in FIG. 7, one end of the semiconductor film 36 is connected to the source electrode 24b and another end thereof is connected to the drain electrode 24c. This forms a channel area CH that communicates the source electrode 24b and the drain electrode 24c. The doping semiconductor film 42 is made of amorphous silicone (n+Si) that is obtained by doping n-type impurity such as phosphorous (P) at a high density. The doping semiconductor film 42 extends along the semiconductor film 36 and is not

formed on the channel area CH. The portions of the doping semiconductor film **42** arranged to sandwich the channel area CH configure portions of the source electrode **24***b* and the drain electrode **24***c*.

As illustrated in FIG. 7, the source electrode 24b and the drain electrode 24c include a same material as the source line 27 and the drain line 34 and are formed by patterning on the glass substrate GS in a same manufacturing step as the source lines 27 and the drain lines 34. The source electrode 24b and the drain electrode 24c are arranged to face with each other and have a predetermined distance therebetween in the X-axis direction. The source electrode **24***b* and the drain electrode **24**c are arranged on an upper layer side with respect to the gate electrode 24a to have the gate insulation film 35 and the semiconductor film 36 therebetween. A part of the source electrode **24***b* and a part of the drain electrode **24***c* (the facing portions) are located to overlap the gate electrode 24a with a plan view and the overlapped portions are arranged over the gate electrode **24***a*. Each of the source electrode **24***b* and the 20 drain electrode 24c includes a first conductive film 24b1, 24c1 on a lower layer side (the semiconductor film 36 side) and a second conductive film 24b2, 24c2 on an upper layer side (the in-between insulation film 37 side), and the first conductive film and the second conductive film are laminated. The first 25 conductive films 24b1, 24c1 on the lower layer side are configured with end portions of the doping semiconductor film 42 and function as an Ohmic contact layer that is contact with the semiconductor film 36 on the lower layer side with the Ohmic contact. Each of the second conductive films 24b2, 30 **24**c2 on the upper layer side includes two laminated metal layers. The metal film **39** on the lower layer side is made of titanium (Ti) and the metal film 40 on the upper layer side is made of aluminum (Al). Namely, the source electrode 24band the drain electrode 24c are similar to the source line 27 in 35that they include the second conductive films 24b2, 24c2 each of which includes two layered metal films 39, 40. However, the source electrode 24b and the drain electrode 24c have a different structure from the source line 27 in that they include the first conductive films 24b1, 24c1 configured with the 40 doping semiconductor film 42. As illustrated in FIG. 5, a branch line extends along the X-axis direction from a portion in the vicinity of a cross section of the gate line 26 and the source line 27 extending in the Y-axis direction. The source electrode **24***b* is configured with an extended distal end por- 45 tion of the extended branch line.

The in-between insulation film **37** is formed of a silicone nitride film (SiNx) that is a same material as the gate insulation film 35. The protection film is made of an acrylic resin (for example, polymethylmethacrylate resin (PMMA)) or 50 polyimide resin that are an organic material. Therefore, the protection film 38 has a film thickness greater than the gate insulation film **35** and the in-between insulation film **37** that are made from other inorganic material and functions as a flattening film. The in-between insulation film **37** and the 55 protection film 38 are formed on substantially an entire surface area of the glass substrate GS including an area in which the TFTs **24** are formed. In areas other than the areas in which the TFTs 24 are formed, the in-between insulation film 37 and the protection film **38** are located between the source line **27** 60 on the relatively lower layer side and the pixel electrode 25 on the relatively upper layer side and between the drain line 34 on the relatively lower layer side and the pixel electrode 25 on the relatively upper layer side. The in-between insulation film 37 and the protection film 38 keep the upper layer side pixel 65 electrode 25 to be insulated from the upper layer side source line 27 and the drain line 34.

12

Among the above-structured TFTs 24, the drain line 34 connected to the drain electrode **24***c* is formed in substantially an L-shape with a plan view as illustrated in FIG. 5. One end of the drain line 34 is connected to the drain electrode 24c and another end thereof is connected to a pixel connection portion 41 that is connected to the pixel electrode 25. As illustrated in FIG. 7, the drain line **34** is formed on the gate insulation film 35 and formed of the same material as the source line 27 and is configured with two-layered structure similar to the source line 27. The drain line 34 includes an lower layer side metal film 39 made of titanium (Ti) and a upper layer side metal film 40 made of aluminum (Al). Therefore, similar to the source line 27, the drain line 34 is configured with only the second conductive films 24b2, 24c2 (39, 40) of the source electrode 15 **24**b and the drain electrode **24**c and does not include the first conductive films 24b1, 24c1 (42). Accordingly, the drain line **34** has a configuration different from the source electrode **24***b* and the drain electrode **24***c*.

Next, a configuration of the non-display area NAA in the array substrate 20 will be explained. The non-display area NAA is located on an inner surface side of the glass substrate GS of the array substrate 20. As illustrated in FIG. 8, gate drivers (gate side drive components) GD for driving the TFTs 24 and source drivers (source side drive components) SD are connected to the non-display area NAA via an anisotropic conductive film. The gate drivers GD and the source drivers SD are connected to a control board (not illustrated) and supply various signals output from the control board to each line of the array substrate 20 and drive the TFTs 24. Three source drivers SD are arranged along the X-axis direction and along a long-side (X-axis direction) end portion (a source driver SD side end portion) of the array substrate 20. The two gate drivers GD are arranged along the Y-axis direction and along each of two short-side (Y-axis direction) end portions (gate driver GD side end portions) of the array substrate 20.

As illustrated in FIG. 8, the gate lines 26, the source lines 27, and the capacity lines 33 arranged in the display area AA extend to the non-display area NAA of the array substrate 20. The gate lines 26 reach connection portions of the gate drivers GD and the source lines 27 reach connection portions of the source drivers SD. Namely, the gate lines 26, the source lines 27, and the capacity lines 33 are arranged over the display area AA and the non-display area NAA. Extended ends of the capacity lines 33 are located in the non-display area NAA and on an inner side (a display area AA side) from the connection portions of the gate drivers GD and connected to a capacity stem line 43. The capacity stem line 43 is arranged on each of the short-side end portions in the non-display area NAA of the array substrate 20. Each capacity stem line 43 extends along the Y-axis direction (to be parallel to the source lines 27) so as to cross all the capacity lines 33. The end portion of each capacity stem 43 reaches the connection portion of each source driver SD that is arranged on each end in the X-axis direction. The end portion of each capacity stem 43 is connected to the source driver SD. Common lines 44 are formed in an end portion of the non-display area NAA of the array substrate 20 that is close to the source drivers SD and on an inner side (the display area AA side) from the connection portions of each source driver SD. The common lines 33 supply a common potential to the counter electrodes 31 on the CF substrate 21 side. The common lines 44 are arranged in a portion of the array substrate 20 corresponding to a middle portion of each source driver SD. One end of each common line 44 is connected to each source driver SD and another end of each common line 44 is connected to the counter electrode 31 on the CF substrate 21 side via conductive particles (not illustrated) that are arranged to penetrate through the liquid

crystal layer 22. Therefore, a group of the source lines 27 that are connected to one source driver SD are arranged in the connection portion of the source driver SD on a left side and a right side having the common lines 44 therebetween that are arranged in the middle portion of the source driver SD (refer 5 to FIG. 9). The capacity stem lines 43 and the common lines 44 are made of the same material as the source lines 27 and they are formed in the same layer in the same step of the manufacturing process. The capacity stem lines 43 and the common lines 44 include the lower layer side metal film 39 and the upper layer side metal film 40. Thus, the gate driver GD supplies various signals to the gate lines 26 and the source driver SD supplies various signals to the source lines 27, the capacity lines 33, and the common lines 44. Two ends of each gate line 26 are connected to the gate drivers GD, respectively, 15 and the gate lines 26 are driven at the two ends thereof. Only one end of each source line 27 is connected to the source driver SD and the source lines 27 are driven at one end thereof.

As illustrated in FIGS. 9 and 10, the check lines 45, 46 are 20 formed in the non-display area (an outer peripheral side area) NAA of the array substrate 20. The check lines 45, 46 are used to check whether an error occurs in the gate lines 26, the source lines 27, the capacity stem lines 43 (the capacity lines 33) and the common lines 44 such as disconnection or shortcircuit. The check lines 45, 46 are used in the check step of the manufacturing process of the liquid crystal panel 11. Therefore, at least a part of the check lines 45, 46 is removed from the glass substrate GS in a chamfering step (a removing step) that is executed after the checking step. Further, the check 30 signal input portions 47, 48 are formed in the non-display area NAA of the array substrate 20. Check signals are input from outside to the check lines 45, 46 via the check signal input portions 47, 48. The check lines 45, 46 include source driver side check lines **45** and gate driver side check lines **46**. The source driver side check lines 45 are connected to the source lines 27, the capacity stem lines 43, and the common lines 44. The gate drive side check lines **46** are connected to the gate lines 26. The check signal input portions 47, 48 include source driver side check signal input portions 47 and gate 40 driver side check signal input portions 48. The source driver side check signal input portions 47 are connected to the source driver side check lines 45, and the gate driver side check signal input portions 48 are connected to the gate driver side check lines 46. As illustrated in FIG. 9, the source driver 45 side check lines 45 and the source driver side check signal input portions 47 are arranged on a long-side end portion in the non-display area NAA of the array substrate 20 (an end portion close to the source driver SD). As illustrated in FIG. 10, the gate driver side check lines 46 and the gate driver side 50 check signal input portions 48 are arranged in each short-side end portion in the non-display area NAA of the array substrate 20 (an end portion close to the gate driver GD). In FIGS. 9 and 10, an outer shape (an outer end position, a separated position) of the glass substrate GS is represented by an alter- 55 nate longer and short bold dash line.

The source driver side check lines 45 and the source driver side check signal input portions 47 will be explained in detail. As illustrated in FIG. 9, the source driver side check lines 45 includes first source driver side check lines 45A that are 60 connected to the source lines 27 and second source driver side check lines 45B that are connected to the capacity stem lines 43 or the common lines 44. The source drive side check signal input portion 47 includes first source driver side check signal input portions 47A that are connected to the first source driver 65 side check lines 45A and second source driver side check signal input portions 47B that are connected to the second

**14**

source driver side check lines 45B. A pair of first source driver side check lines 45A is arranged for each source driver SD and one first source driver check line 45A is arranged for each source line 27 group. Six first source drier side check lines **45**A are arranged (refer to FIG. 8). Namely, a pair of source line 27 groups connected to one source driver SD is connected to a pair of first source driver side check lines 45A. Two second source driver side check lines 45B are arranged for each of the source drivers SD arranged on the long-side ends of the array substrate 20. Each of the second source driver side check lines 45B is arranged for each of the capacity stem lines 43 and the common lines 44 connected to each of the source drivers SD that are arranged on the long-side ends of the array substrate 20. One second source driver side check line 45B is arranged for the source driver SD located in a middle portion, and the one second source driver side check line 45B is arranged for the common line 44 that is connected to the source driver SD located in the middle portion. Five second source driver side check lines **45**B are arranged (refer to FIG. 8). The number of the first source driver side check signal input portions 47A is same as that of the first source driver side check lines 45A that are connected to the first source driver side check signal input portions 47A. Similarly, the number of the second source driver side check signal input portions 47B is same as that of the second source driver side check lines 45B that are connected to the second source driver

side check signal input portions 47B. As illustrated in FIG. 9, one first source driver side check line 45A is connected to a plurality of source lines 27 and a plurality of first line connection portions 49 are arranged for the source lines 27. The first source driver side check line 45A is connected to each source line 27 via the corresponding first line connection portion 49. The second source driver side check line 45B is connected to the capacity stem line 43 or the common line 44 via a second connection portion 50. Specifically, the source line 27 has a source terminal 27a that is formed in an elongated rectangular shape and extends to the connection portion of the source driver SD in the non-display area NAA and connected to the source driver SD and also has an extended portion 27b that extends outwardly from the source terminal 27a. Branch lines 45Aa extend from the first source driver side check line 45A so as to overlap the extended portion 27b. A first line connection portion 49 is formed in an overlapped portion in which the extended portion 27b and the branch line 45Aa overlap. The source terminal 27a is configured to cover a surface of the lower layer-side metal film 39 (titanium) with a transparent electrode material such as ITO or IZO similar to the pixel electrode 25. The lower layer-side metal film 39 is included in the two-layered metal films 39, 40 of the source line 27. The source terminal 27a does not include the upper layer-side metal film 40 (aluminum). A detailed connection structure of the first line connection portion 49 will be explained later. The capacity stem line 43 has a capacity terminal (not illustrated) and the common line 44 has a common terminal 44a. The capacity terminal and the common terminal 44a extend to the connection portion of the source driver SD in the non-display area NAA and are connected to the source driver SD. The capacity terminal and the common terminal 44a are directly connected to the second source driver side check line 45B and function as a second line connection portion **50**. The capacity terminal and the common terminal 44a are configured to cover a surface of the lower layer-side metal film 39 (titanium) with a transparent electrode material such as ITO or IZO similar to the pixel electrode 25. The lower layer-side metal film 39 is included in the two-layered metal films 39, 40 of the capacity stem line 43 and the common line 44. The capacity terminal

and the common terminal 44a do not include the upper layerside metal film 40 (aluminum). A connection structure of the capacity stem line 43 and the second line connection portion 50 is similar to the connection structure of the common line 44 and the second line connection portion 50 illustrated in FIG. 9, and the connection structure of the capacity stem line 43 and the second line connection portion 50 is not illustrated.

As illustrated in FIG. 9, each source driver side check signal input portion 47 is formed in substantially a square shape with a plan view and has an area relatively greater than 10 the source terminal 27a. The first source driver side check signal input portion 47A is connected to the first source driver side check line 45A via a third line connection portion 51. Specifically, the first source driver side check line 45A that is located on a relatively outer side (close to an outer end of the 15 glass substrate GS) includes extended lines 45Ab that extend toward the first source driver side check signal input portion 47A that is on a right side in FIG. 9 and an object to be connected. The first source driver side check signal input portion 47A has an extended portion 47Aa that extends there- 20 from to overlap the extended lines 45Ab and has a third line connection portion 51 in an overlapped portion in which the extended lines 45Ab and the overlap portion 47Aa overlap. A detailed connection structure of the third line connection portion 51 will be explained later. The first source driver side 25 check line 45A that is located on a relatively inner side also includes the extended lines 45Ab that extend toward the first source driver side check signal input portion 47A that is on a left side in FIG. 9 and an object to be connected. The first source driver side check signal input portion 47A also has the 30 extended portion 47Aa and is connected to the first source driver side check line 45A via the third line connection portion **51**. On the other hand, the second source driver side check signal input portion 47B is connected to the second source driver side check line 45B via a fourth line connection 35 portion **52**. Specifically, the second source driver side check line **45**B has a branch line **45**Ba that extends therefrom toward the second source driver side check signal input portion **46**B and is connected directly to the second source driver side check signal input portion 47B. The branch line 45Ba con- 40 figures a fourth line connection portion **52**.

Next, an arrangement of the source driver side check lines 45, the source driver side check signal input portions 47, the first line connection portions 49, the second line connection portions 50, the third line connection portions 51, and the 45 fourth line connection portions 52 in the non-display area NAA of the array substrate 20 will be explained in detail. As illustrated in FIG. 9, one end portion of the non-display area NAA of the array substrate 20 that extends along a long-side direction and is connected to the source drivers SD is divided 50 into three regions including a first region (an inner region) A1, a second region (an outer region) A2, and a third region (an outer region) A3. The first region A1 is located adjacent to the display area AA on an outer side. The second region A2 located adjacent to the first region A1 on an outer side. The 55 third region A3 is located adjacent to the first region A1 on an outer side and adjacent to the second region A2. Namely, the first region is formed in a belt-like shape that extends in the X-axis direction over an entire length of the long side of the array substrate 20. The second regions A2 and the third 60 regions A4 are arranged alternately in the X-axis direction. In FIG. 9, a definition line that defines each of the first region A1, the second region A2, and the third region A3 is illustrated by an alternate long and short dash line having a long line that is shorter than the alternate longer and short dash line represent- 65 ing the outer shape of the glass substrate GS. The source lines 27 are located over the first region A1 and the second region

**16**

A2. The capacity stem lines 43 and the common lines 44 are located over the first region A1 and the third region A3. The first source driver side check lines 45A are located over the second region A2 and the third region A3. Thus, the first line connection portions 49 are located in the second region A2, and the second source driver side check line 45B, each source driver side check signal input portion 47, and the second line connection portions 50 are located in the third region A3. The third line connection portions 51 and the fourth line connection portion 52 are located in the third region A3. A position relationship between the second region A2 and the third region A3 is as follows. The third region A3 in which a part of the common line 44 is located is located in substantially a middle portion of each source driver SD. Two second regions A2 are located to sandwich the third region A3 from both sides in the X-axis direction. The third region A3 in which a part of the capacity stem line 43 is located is located on an end portion of each of the two source drivers SD arranged on two ends of the array substrate 20.

As illustrated in FIG. 9, the source driver side check signal input portions 47 are arranged in the X-axis direction in a middle portion of the third region A3. The second source driver side check signal input portion 47B is arranged in the middle portion and the two first source driver side check signal input portions 47A are arranged to sandwich the second source driver side check signal input portion 47B therebetween from both ends. The two first source driver side check lines 45A extend in the X-axis direction (along an outer end of the second region A2 and the third region A3, along the outer shape of the glass substrate GS) to be parallel to each other with having a predetermined distance therebetween in the Y-axis direction in the second region A2. In the third region A3, the first source driver side check line 345A that is located relatively on an inner side (close to the first region A1, on a lower side in FIG. 9) is bent around the source driver side check signal input portions 47 to be arranged in an inner portion from the source driver side check signal input portions 47. The bent portion of the first source driver side check line 45A that is arranged on a relatively inner side is formed to follow the outer shape of a group of the three source driver side check signal input portions 47 and extends through a space between the group of the three source driver side check signal input portions 47 and the capacity stem line 43 or the common line 44. The first source driver side check line 45A that is arranged on a relatively outer side (on a side opposite from the first region A1, on an upper side in FIG. 9) extends in the X-axis direction without being bent in the third region A3 and is formed in substantially a straight line over its entire length. Most of the middle part of the second source driver side check line 45B extends in the X-axis direction in the third region A3 and extends through a space between the first source driver side check line 45A on a relatively outer side in the Y-axis direction and each source driver side check signal input portion 47 and a space between the two first source driver side check lines 45A. Two end portions of the second source driver side check line 45B are bent inwardly and extend across the relatively inner side first source driver side check line 45A and connected to the second line connection portions **50**.

As illustrated in FIG. 9, the first line connection portions 49 are arranged in a space between the two first source driver side check lines 45A with respect to the Y-axis direction and arranged in the X-axis direction (a direction in which the first source driver side check line 45A extends). Therefore, the adjacent first line connection portions 49 partially overlap each other with respect to the Y-axis direction. Compared to a case in which the adjacent first line connection portions 49 do

not overlap, an arrangement space for the first line connection portions 49 is reduced in the Y-axis direction. This reduces a width dimension of the second region A2 that is formed in a belt-like shape extending in the X-axis direction, that is, a distance between the outer end of the second region A2 and 5 the outer end of the first region A1, and this reduces the second region A2 in size. The pair of first source driver side check lines 45A are arranged to sandwich the arranged first line connection portions 49 and the first line connection portions 49 (the source lines 27) are connected alternately to the 10 two first source driver side check lines 45A. Namely, one of the two first source driver side check lines 45A is connected to the odd-numbered first line connection portions 49 (the source lines 27) among the arranged first line connection portions 49. Another one of the two first source driver side 15 check lines 45A is connected to the even-numbered first line connection portions 49 (the source lines 27). The second line connection portion 50 is arranged adjacent to the first line connection portion 49 in the X-axis direction that is located closest to the third region A3. Namely, the second line con- 20 nection portion 50 is located in an end portion of the third area A3 close to the second region A2.

As described before, as illustrated in FIG. 9, the first source driver side check lines **45**A and the second source driver side check line 45B partially overlap in plane. However, they are 25 formed in different layers and insulated from each other via the gate insulation film **35**. Therefore, short-circuit does not occur. Specifically, the first source driver side check line **45**A is formed of the same material as the gate lines 26 and they are formed in the same layer in the same step of the manufactur- 30 ing process. The second source driver side check line 45B is formed of the same material as the source line 27, the capacity stem line 43, and the common line 44 and they are formed in the same layer in the same step of the manufacturing process and include the lower layer-side metal film **39** and the upper 35 layer-side metal film **40**. Each of the three source driver side check signal input portions 47 includes a same material as the second source driver side check line 45B and the source line 27 and they are formed in the same layer in the same step of the manufacturing process. Specifically, each source driver 40 side check signal input portion 47 is configured such that a surface of the lower layer-side metal film 39 (titanium) is covered with a transparent electrode material such as ITO or IZO similar to the pixel electrode 25. The source line 27 includes two-layered metal films **39**, **40**. However, the source 45 driver side check signal input portion 47 does not include the upper layer-side metal film 40 (aluminum).

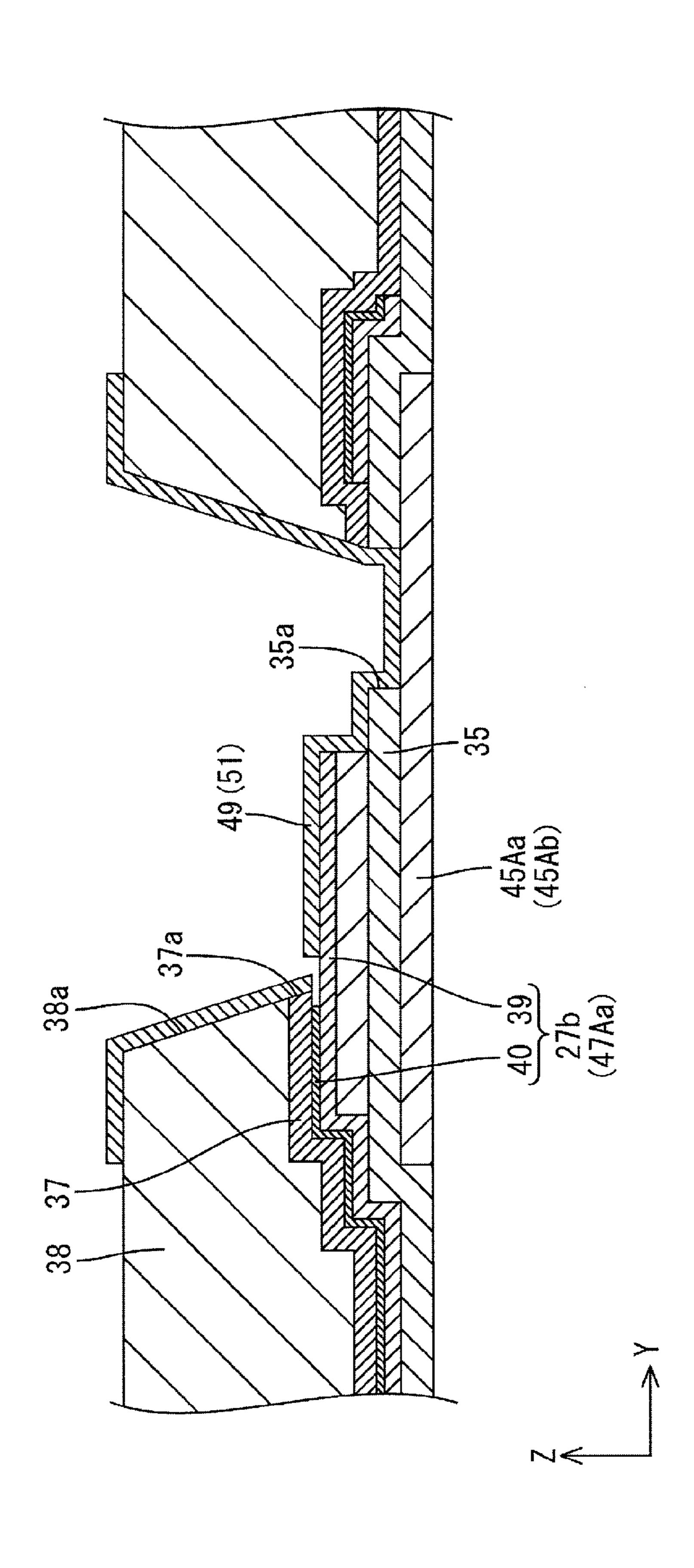

Accordingly, the first source driver side check lines 45A are formed in a different layer from the source lines 27 and the first source driver side check signal input portions 47A via the 50 gate insulation film 35. The source lines 27 and the first source driver side check signal input portions 47A are objects to which the first source driver side check lines 45A are connected. Therefore, the first line connection portions 49 that connect the source lines 27 and the first source driver side 55 check line 45A and the third line connection portions 51 that connects the first source driver side check signal input portions 47A have a connection structure as follows. As illustrated in FIGS. 11 and 12, the first line connection portion 49 is formed to cover openings 35a, 37a, 38a formed in the gate 60 insulation film 35, the in-between insulation film 37 and the protection film 38. Accordingly, the branch line 45Aa of the first source driver side check line 45A that is exposed through each opening 35a, 37a, 38a is connected to the extended portion 27b of the source line 27. The first line connection 65 portion 49 is formed of the same material as the pixel electrode 25 that is layered on the protection film 38 and they are

**18**

formed in the same layer in the same step of the manufacturing process. The first line connection portion 49 and each opening 35a, 37a, 38a are located in a position of the overlap portion in which the branch line 45Aa of the first source river side check line 45A overlap the extended portion 27b of the source line 27. Among the openings 35a, 37a, 38a, the opening 37a of the in-between insulation film 37 and the opening **38***a* of the protection film **38** are formed over an area that is relatively greater than the opening 35a of the gate insulation film 35. The extended portion 27b of the source line 27 is partially removed in an area that is greater than the opening 35a of the gate insulation film 35. The upper layer-side metal film 40 made of aluminum (Al) is removed in an area greater than the lower layer-side metal film 39 made of titanium (Ti). Accordingly, the first line connection portion 49 made of ITO similar to the pixel electrode 25 is in contact only with the lower layer-side metal film 39 made of titanium and is not in directly contact with the upper layer-side metal film 40 made of aluminum. Therefore, galvanic corrosion is less likely to occur and connection reliability is enhanced.

The third line connection portion 51 also has a connection structure substantially similar to the first line connection portion 49. The extended lines 45Ab of the first source driver side check line 45A are connected to the extended portion 47Aa of the first source driver side check signal input portion 47A via the openings 35a, 37a, 38a. The third line connection portion 51 is different from the first line connection portion 49 in that three openings 35a, 37a, 38a are arranged and three connection portions connecting the extended lines 45Ab and the extended portion 47Aa are provided (refer to FIG. 9). In FIGS. 11 and 12, numbers with parentheses are applied to the connection structure of the third line connection portion 51. As is not illustrated in details in the drawings, the capacity stem lines 43 arranged in the same layer as the source lines 27 are connected to the capacity lines 33 that are arranged in the same layer as the gate lines 26 with the same connection structure as the first line connection portion 49 (refer to FIG. **10**).

As illustrated in FIG. 9, the source driver side check signal input portions 47 that are arranged in the X-axis direction are connected to each other via an ESD protection circuit 53. Accordingly, the first source driver side check line 45A that is connected to the first source driver side check signal input portion 47A is connected to the second source driver side check line 45B that is connected to the second source driver side check signal input portion 47B via the ESD protection circuit 53. The source lines 27 are connected to the first source driver side check line 45A and the capacity stem line 43 or the common line **44** is connected to the second driver side check line 45B. Accordingly, with the connection between the source driver side check lines 45 via the ESD protection circuit 53, the TFTs 24 connected to the source lines 27, the capacity stem line 43 and the common line 44 are protected from high voltage (surge voltage) caused by ESD (electrostatic discharge).

As illustrated in FIG. 13, the ESD protection circuit 53 includes two protection circuit TFTs 53a that are transistor components and are connected in parallel between the adjacent source driver side check signal input portions 47. The protection circuit TFT 53a has a same structure as the TFT 24 arranged in the display area AA of the array substrate 20 and the TFTs 53a, 24 are collectively formed in the same step. The two protection circuit TFTs 53a that are connected in parallel have a same potential with the gate electrodes and the source electrodes being connected on a same line. The two protection circuit TFTs 53a are connected in parallel to each other such that the gate electrode and the source electrode of one

protection circuit TFT 53a have a same potential as the drain electrode of the other protection circuit TFT 53a and the gate electrode and the source electrode of the other protection circuit TFT 53a have a same potential as the drain electrode of the one protection circuit TFT 53a. A threshold voltage value of each protection circuit TFT 53a is higher than a voltage value of a check signal and is lower than a voltage value (a surge voltage value) that is applied at the occurrence of ESD. Accordingly, if the check signal is input to each source driver side check signal input portion 47 in the check step, the 10 protection circuit TFTs 53a are not activated and therefore, a current is not less likely to flow between the adjacent source driver side check signal input portions 47 via the ESD protection circuit 53. If a high voltage is applied to the source driver side check signal input portion 47 according to the 15 occurrence of the ESD, the protection circuit TFTs 53a are activated and a current flows between the adjacent source driver side check signal input portions 47 via the ESD protection circuit 53. Accordingly, the current flows through all the source driver side check lines 45 and this protects the 20 TFTs 24 that are connected to the source lines 27, the capacity stem lines 43 and the common lines 44.

Next, the gate driver side check line 46 and the gate driver side check signal input portion 48 will be explained in detail. As illustrated in FIG. 10, a pair of gate driver side check lines 25 46 are arranged in short-side end portions in the non-display area (an outer side area) NAA of the array substrate 20 and are arranged to sandwich the gate lines 26 extending in the X-axis direction from both ends therebetween. One gate driver side check line 46 is arranged for a group of the gate lines 26 that are connected to one gate driver GD and a total number of the gate driver side check lines 46 is four. Specifically, the gate driver side check line 46 is located on an outer side from the connection portion (the gate terminal 26a) of the gate driver GD in the non-display area NAA and extends substantially 35 linearly along the Y-axis direction (along the source line 27 or the capacity stem line 43) so as to cross the gate lines 26. The gate lines 26 extend to the connection portion of each gate driver GD in the non-display area NAA. Each gate line 26 has the elongated rectangular gate terminal **26***a* that is connected 40 to each gate driver GD and has the extended portion **26***b* that is extended outwardly from the gate terminal 26a. The extended portion 26b is connected to the gate driver side check line 46. The gate terminal 26a is formed at each end of each gate line 26 and the gate terminals 26a are connected to 45 each of the gate drivers GD that are arranged on two ends of the array substrate 20 in the X-axis direction. Accordingly, the gate lines 26 are driven at two ends thereof. The gate driver side check lines 46 are formed of the same material as the gate lines 26 and they are formed in the same layer in the same step 50 of the manufacturing process. Therefore, the extended portions 26b of the gate lines 26 are directly connected to the gate driver side check line **46**.