### US009270604B2

## (12) United States Patent

### Tokutsu et al.

# (10) Patent No.: US 9,270,604 B2 (45) Date of Patent: Feb. 23, 2016

### (54) BUS SYSTEM AND ROUTER

(71) Applicant: Panasonic Corporation, Osaka (JP)

(72) Inventors: Satoru Tokutsu, Saitama (JP); Tomoki

Ishii, Kyoto (JP); Atsushi Yoshida, Osaka (JP); Takao Yamaguchi, Osaka (JP); Takashi Yamada, Hyogo (JP)

(73) Assignee: PANASONIC INTELLECTUAL

PROPERTY MANAGEMENT CO.,

LTD., Osaka (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 76 days.

(21) Appl. No.: 14/221,619

(22) Filed: **Mar. 21, 2014**

(65) Prior Publication Data

US 2014/0204740 A1 Jul. 24, 2014

### Related U.S. Application Data

(63) Continuation of application No. PCT/JP2013/004449, filed on Jul. 22, 2013.

### (30) Foreign Application Priority Data

(51) Int. Cl.

H04L 12/28 (2006.01)

H04L 12/851 (2013.01)

(Continued)

(58) Field of Classification Search

### (56) References Cited

### U.S. PATENT DOCUMENTS

### FOREIGN PATENT DOCUMENTS

JP 2002-185503 A 6/2002 JP 2007-510345 T 4/2007

(Continued)

OTHER PUBLICATIONS

International Search Report for corresponding International Application No. PCT/JP2013/004449 mailed Oct. 22, 2013.

(Continued)

Primary Examiner — Dmitry H Levitan (74) Attorney, Agent, or Firm — Renner, Otto, Boisselle & Sklar, LLP.

### (57) ABSTRACT

In an NoC bus system, data is transmitted between first and second nodes through a router. The data includes performance-ensuring data which guarantees throughput and/or a permitted time delay. The first node generates packets, each including the data to be transmitted and classification information that indicates the class of that data to be determined according to its required performance, and controls transmission of the packets. The router includes a buffer section configured to store the received packets separately after having classified the packets according to their required performance by reference to the classification information, and a relay controller configured to control transmission of the packets stored in the buffer section at a transmission rate which is equal to or higher than the sum of transmission rates to be guaranteed for every first node associated with the classification information by reference to each piece of the classification information.

## 19 Claims, 41 Drawing Sheets

# US 9,270,604 B2 Page 2

| (51) Int. Cl.  H04L 12/863 (2013.01)  H04L 12/873 (2013.01)  H04L 12/801 (2013.01) | JP 2008-294865 A 12/2008<br>JP 2009-253949 A 10/2009<br>JP 2011-229192 A 11/2011<br>OTHER PUBLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| U.S. PATENT DOCUMENTS  7,016,366 B2 * 3/2006 Kawarai et al                         | Form PCT/ISA/237 for corresponding International Application No. PCT/JP2013/004449 dated Oct. 22, 2013 and partial English translation.  John Dielissen et al., "Concepts and Implementation of the Philips Network-on-Chip", 2003.  E. Rijpkema et al., "Trade-offs in the design of a router with both guaranteed and best-effort services for networks on chip", Computers and Digital Techniques, IEE Proceedings—(vol. 150,Issue:5), Sep. 22, 2003.  Jean-Jacques Lecler and Gilles Baillieu, "Application Driven Network on Chip Architecture Exploration and Refinement for a Complex SoC", Springer Verlag's Design Automation for Embedded Systems Journal, vol. 15, No. 2, pp. 133-158; Apr. 7, 2011. |

| JP 2008-109534 A 5/2008                                                            | * cited by examiner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## FIG.1A

## FIG.1B

D SECOND Ø **BUS SYSTEM** ROUTER 03 ROUTER FIRST NODE

FIG. 4

FIG. 7.4

FIG. 10

| MASTER ID | REQUESTED<br>BANDWIDTH | PERMITTED<br>TIME DELAY | PACKET<br>LENGTH | DESTINATION<br>SLAVE ID | ACCESS TYPE (READ OR WRITE) |

|-----------|------------------------|-------------------------|------------------|-------------------------|-----------------------------|

| 0         | 800MB/s                | 0.2usec                 | 10flit           | 0                       | Write                       |

| 1         | 100MB/s                | 1.5usec                 | 8flit            | 1                       | Write                       |

| 2         | 400MB/s                | 1.0usec                 | 8flit            | 0                       | Read                        |

## *FIG.11*

| CLASS                             |         | SPECIFIC EXAMPLE OF CLASS                                                   |  |  |

|-----------------------------------|---------|-----------------------------------------------------------------------------|--|--|

| TIME-DELAY-<br>GUARANTEED CLASS B |         | CLASS WHICH GENERATES TRAFFIC FLOW WITH BURST PROPERTY                      |  |  |

|                                   |         | CLASS IN WHICH DELAY AND THROUGHPUT NEED TO BE<br>TAKEN INTO CONSIDERATION  |  |  |

|                                   | CLASS C | CLASS IN WHICH DATA IS TRANSMITTED AT RATE EXCEEDING<br>REQUESTED BANDWIDTH |  |  |

| NON-TIME-<br>DELAY-<br>GUARANTEED | CLASS Z | CLASS WHICH NEEDS TO GENERATE TRAFFIC FLOW ONLY WHEN BUS IS NOT OCCUPIED    |  |  |

FIG. 12

FIG.20

## FIG.21A

FIG.21B

FIG.23

| CLASS<br>DEFINITION | CLASS' TRANSMISSION<br>PRIORITY LEVEL |  |  |  |  |

|---------------------|---------------------------------------|--|--|--|--|

| CLASSA              | 1                                     |  |  |  |  |

| CLASS B             | 2                                     |  |  |  |  |

| CLASS C             | 3                                     |  |  |  |  |

|                     |                                       |  |  |  |  |

| CLASS Z             | N                                     |  |  |  |  |

## FIG.24

|                          | OUTPUT  |          |                                           |                                |

|--------------------------|---------|----------|-------------------------------------------|--------------------------------|

| OUTPUT<br>PORT<br>NUMBER | CLASS   | DEADLINE | TRANS-<br>MISSION<br>PERMISSION<br>SIGNAL | TRANSMISSION<br>PRIORITY LEVEL |

| 0                        | CLASS A | 100      | READY                                     | 1                              |

| 0                        | CLASS A | 120      | READY                                     | 2                              |

| 0                        | CLASS B | 200      | READY                                     | 3                              |

| 0                        | CLASS B | 200      | READY                                     | 4                              |

| 0                        | CLASS C | 4000     | READY                                     | 5                              |

| 0                        | CLASS C | 3000     | NOTREADY                                  | 6                              |

| 0                        | CLASS Z | N/A      | NOT READY                                 | 7                              |

| 1                        | CLASS A | 100      | READY                                     | 1                              |

| 1                        | CLASS B | 200      | READY                                     | 2                              |

| 1                        | CLASS C | 4000     | READY                                     | 3                              |

| 1                        | CLASS C | 3000     | READY                                     | 4                              |

| 1                        | CLASS C | 4000     | READY                                     | 5                              |

| 1                        | CLASS Z | N/A      | NOTREADY                                  | 6                              |

Feb. 23, 2016

US 9,270,604 B2

FIG. 22

FIG.27

FIG.30

| OUTPUT PORT<br>NUMBER | CLASS   | TIMER VALUE OF EACH CLASS' OUTPUT PORT |  |  |  |

|-----------------------|---------|----------------------------------------|--|--|--|

| 0                     | CLASS A | 0                                      |  |  |  |

| 0                     | CLASS B | 6                                      |  |  |  |

| 0                     | CLASS C | 0                                      |  |  |  |

|                       |         |                                        |  |  |  |

| 0                     | CLASS Z | 0                                      |  |  |  |

| 1                     | CLASS A | 5                                      |  |  |  |

| 1                     | CLASS B | 19                                     |  |  |  |

| 1                     | CLASS C | 0                                      |  |  |  |

|                       |         |                                        |  |  |  |

| 1                     | CLASS Z | 0                                      |  |  |  |

## FIG.32

| CLASS   | TRANSMISSION INTERVAL |  |  |  |  |

|---------|-----------------------|--|--|--|--|

| CLASS A | 10                    |  |  |  |  |

| CLASS B | 20                    |  |  |  |  |

| CLASS C | 5                     |  |  |  |  |

|         |                       |  |  |  |  |

| CLASS Z | 0                     |  |  |  |  |

FIG.35

| <u> </u>                | T.OO                  |         |                              |                    | _             |                          |                                                              |

|-------------------------|-----------------------|---------|------------------------------|--------------------|---------------|--------------------------|--------------------------------------------------------------|

| INPUT<br>PORT<br>NUMBER | INPUT<br>BUFFER<br>ID | CLASS   | DESTINA-<br>TION<br>SLAVE ID | PACKETS<br>STORED? | DEAD-<br>LINE | OUTPUT<br>PORT<br>NUMBER | SLAVE<br>ROUTER'S<br>INPUT<br>BUFFER<br>ALLOCATION<br>RESULT |

|                         | 0                     | CLASS A | 0                            | YES                | 100           | 0                        | 0                                                            |

| :                       | 1                     | CLASS A | 1                            | NO                 | N/A           | N/A                      | N/A                                                          |

|                         | 2                     | CLASS B | 0                            | NO                 | N/A           | N/A                      | N/A                                                          |

|                         | 3                     | CLASS B | 1                            | YES                | 200           | 1                        | 3                                                            |

| 0                       | 4                     | CLASS C | 0                            | NO                 | N/A           | N/A                      | N/A                                                          |

|                         | 5                     | CLASS C | 1                            | NO                 | N/A           | N/A                      | N/A                                                          |

|                         | u<br>u<br>=           |         |                              |                    |               |                          |                                                              |

|                         | N                     | CLASS Z | 1                            | NO                 | N/A           | N/A                      | N/A                                                          |

|                         | 0                     | CLASS A | 0                            | NO                 | N/A           | N/A                      | N/A                                                          |

|                         | 1                     | CLASS A | 1                            | NO                 | N/A           | N/A                      | N/A                                                          |

|                         | 2                     | CLASS B | 0                            | YES                | 210           | 0                        | 2                                                            |

|                         | 3                     | CLASS B | 1                            | NO                 | N/A           | N/A                      | N/A                                                          |

| 1                       | 4                     | CLASS C | 0                            | NO                 | N/A           | N/A                      | N/A                                                          |

|                         | 5                     | CLASS C | 1                            | NO                 | N/A           | N/A                      | N/A                                                          |

|                         |                       |         |                              |                    |               |                          |                                                              |

|                         | N                     | CLASS Z | 1                            | NO                 | N/A           | N/A                      | N/A                                                          |

FIG.36

*FIG.37*

## FIG.38A

## IF BUFFERS ARE SEPARATED

## FIG.38B

## UNLESS BUFFERS ARE SEPARATED

HIG. 45

FIG. 46

FIG.47

# **BUS SYSTEM AND ROUTER**

This is a continuation of International Application No. PCT/JP2013/004449, with an international filing date of Jul. 22, 2013, which claims priority of Japanese Patent Applica-5 tion No. 2012-163833, filed on Jul. 24, 2012, the contents of which are hereby incorporated by reference.

### **BACKGROUND**

#### 1. Technical Field

The present application relates to a technology for controlling a network of communications buses (distributed buses) provided for a bus system in a semiconductor integrated circuit.

### 2. Description of the Related Art

An NoC (Network-on-Chip) is a network of communications buses to be provided on a semiconductor chip which is a semiconductor integrated circuit. In an NoC, buses are connected together via routers and traffic flows are transmit-20 ted from a plurality of masters through the same bus shared. As a result, the number of buses to use can be cut down and the buses can be used more efficiently.

In an NoC, however, a bus is shared by traffic flows coming from multiple masters, and therefore, it is difficult to ensure 25 performance (more specifically, to ensure throughput and delay).

Those multiple masters pass traffic flows which require mutually different kinds of performances independently of each other. As a result, a traffic flow which needs to be transmitted with as short a time delay as possible (i.e., a traffic flow of time-delay-guaranteed type), a traffic flow which always needs to be transmitted in a constant transmission quantity for sure (i.e., a traffic flow of throughput guaranteed type) and a traffic flow which needs to transmit a huge size of data at 35 irregular intervals will be transmitted through the same bus as a mix.

As for an NoC, it is important to realize a performance ensuring scheme for satisfying the performance required by each traffic flow (in terms of at least one of throughput and 40 time delay) at a minimum required bus bandwidth. If the performance of an NoC is ensured, the buses can be used more efficiently and the NoC can be designed at the minimum required bus bandwidth to satisfy the required performance. As a result, the hardware design and development of buses 45 can be carried out more easily.

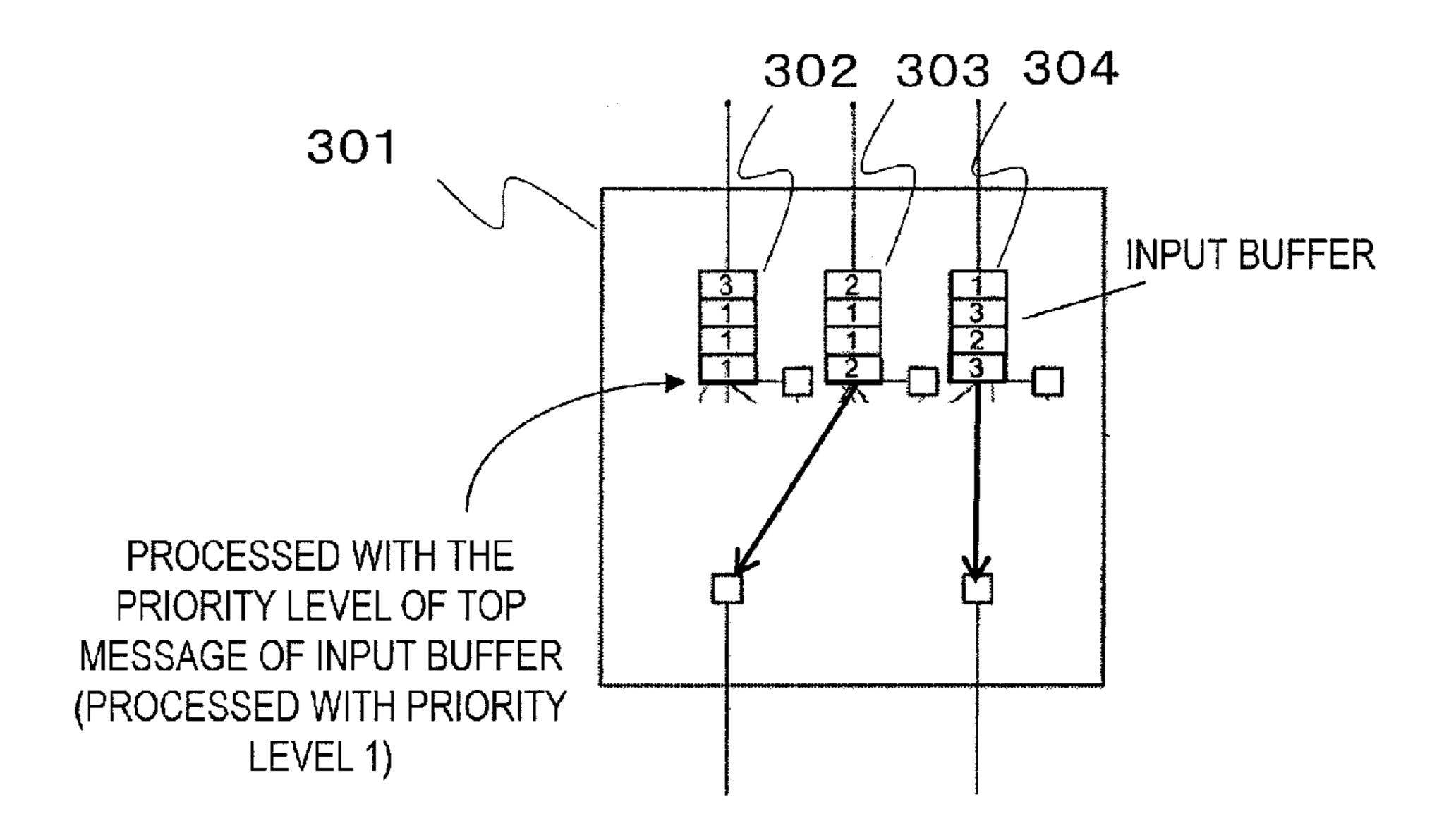

Some conventional routers determine the levels of priority of a given traffic flow. If the data of a traffic flow of a high level of priority is stored in a buffer, then such a router performs transmission processing with the level of priority of that 50 buffer switched to a high level. FIG. 1A illustrates an exemplary configuration for a router 301 which outputs the data of traffic flows with high levels of priorities that are stored in buffers 304 and 303 earlier than the traffic flow stored in the other buffer 301. In FIG. 1A, the numerals indicate the 55 respective levels of priorities, and the larger a numeral, the higher the level of priority indicated by the numeral is. The router 301 determines, according to the levels of priorities of the data that are stored at the respective tops of the input buffers, which traffic flows should be provided as output data. 60

In such a router, however, traffic flows with mutually different levels of priorities can be present in the same buffer. As a result, a traffic flow with a high level of priority will be interfered with by a traffic flow with a low level of priority, which is a problem.

Techniques for coping with such a problem are disclosed in, for example,:

2

United States Laid-Open Patent Publication No. 2005/0117589; and

Jean-Jacques Lecler and Gilles Baillieu, "Application Driven Network on Chip Architecture Exploration and Refinement for a Complex SoC", Springer Verlag's Design Automation for Embedded Systems Journal, Volume 15, Number 2, pp. 133-158.

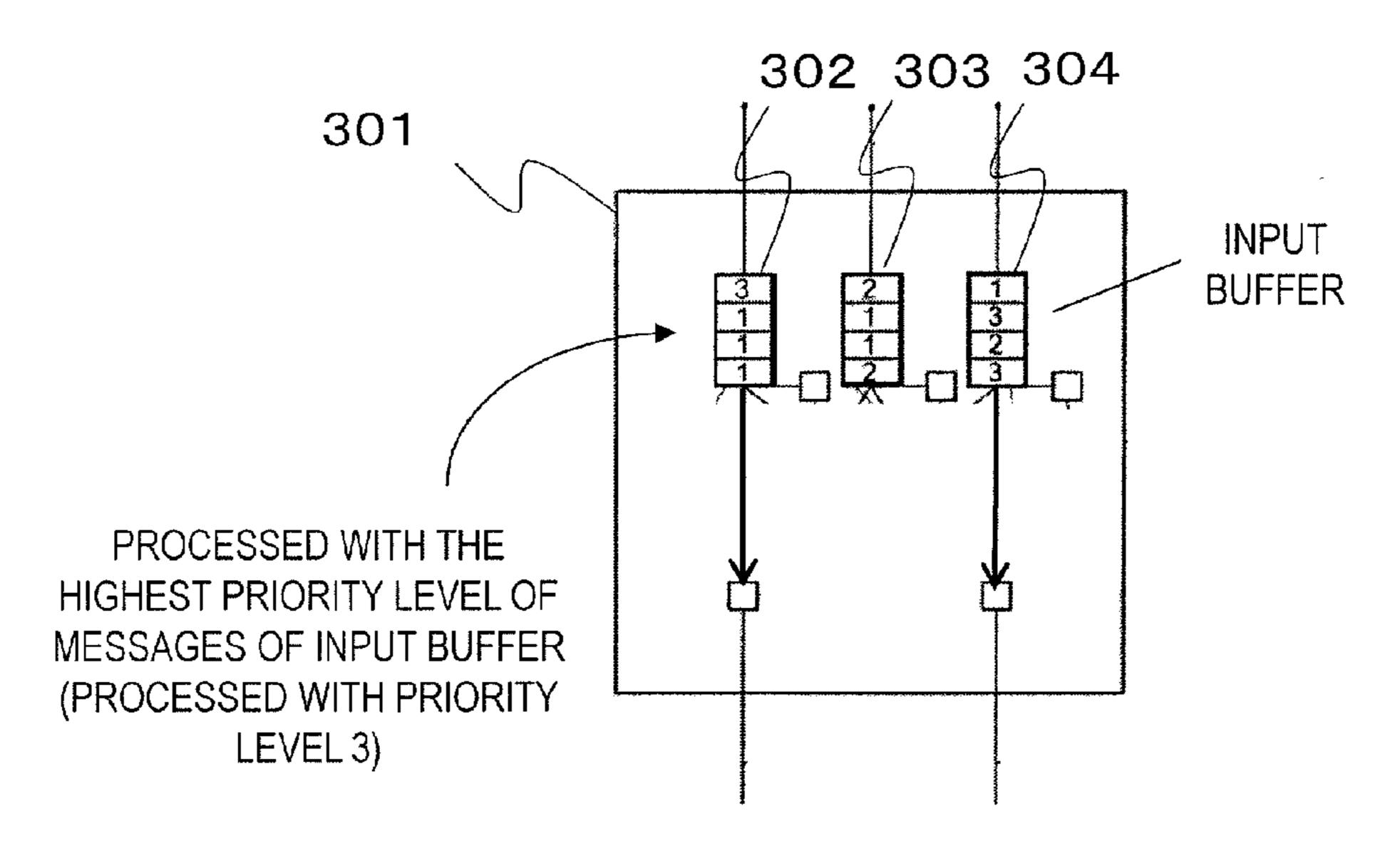

FIG. 1B illustrates a modified configuration for the router 301 shown in FIG. 1A. Specifically, in the router 301 shown in FIG. 1B, the level of priority of each input buffer is determined by the highest level of priority of the messages stored there, and the data is output according to the respective levels of priorities of the input buffers.

In the example illustrated in FIG. 1B, one message, of which the level of priority is Level 3, and three messages, of which the level of priority is Level 1, are stored in the input buffer 302. Two messages, of which the level of priority is Level 2, and two messages, of which the level of priority is Level 1, are stored in the input buffer 303. And one message, of which the level of priority is Level 1, one message, of which the level of priority is Level 2, and two messages, of which the level of priority is Level 3, are stored in the input buffer 304.

The priority level of each input buffer is determined by the highest priority level of the messages stored in that input buffer. That is why the priority levels of the input buffers 302, 303 and 304 become Levels 3, 2 and 3, respectively. Since the messages are sent in the descending order of priorities, the messages stored at the respective tops of the input buffers 302 and 304 are sent as a result.

Thus, the input buffer 302 that stores a message, of which the level of priority is Level 3, can advance the transmission processing preferentially without depending on the levels of priorities of the preceding messages stored. Consequently, the time delay of such a message with a high level of priority can be reduced even if the preceding space of the buffer is occupied with messages with a low level of priority.

## **SUMMARY**

The prior art technique needs further improvement in view of performance on an NOC.

One non-limiting, and exemplary embodiment provides a technique to improve higher performance on an NOC.

In one general aspect, disclosed herein is a bus system for a semiconductor circuit to transmit data between a first node and at least one second node through a network of buses and at least one router which is arranged on any of the buses. The data to be transmitted includes performance-ensuring data which guarantees at least one of throughput and a permitted time delay. The first node includes: a packet generator which generates a plurality of packets, each of which includes the data to be transmitted and classification information that indicates the class of the data to be transmitted to be determined according to its required performance; and a transmission controller which controls transmission of the packets. The at least one router includes: a buffer section which stores the received packets separately after having classified the packets according to their required performance by reference to the classification information; and a relay controller which controls transmission of the packets that are stored in the buffer section at a transmission rate which is equal to or higher than the sum of transmission rates to be guaranteed for every first node associated with the classification information by reference to each piece of the classification information.

According to the above aspect, by adopting a buffer which is configured to change the data to be transmitted according to

the required performance and by adjusting the transmission schedule between a master and a router, the router can minimize mutual interference and the bus' operating frequency to ensure the required performance can be estimated to be a low value. For example, since a traffic flow in a performance 5 ensured class with a high priority level can be transmitted without being interfered with by a traffic flow in a nonperformance-ensured class with a low priority level, the rate of the traffic flow to interfere when the bus bandwidth is estimated can be reduced. As a result, a bus of which the 10 performance can be ensured at a low operating frequency can be established without making overestimation. In addition, the extra bus band to be produced by worst estimation can be reduced as much as possible by adjusting the transmission 15 control are different. schedule between the master and the router. In other words, the extra bus band can be used more efficiently.

These general and specific aspects may be implemented using a system, a method, and a computer program, and any combination of systems, methods, and computer programs.

Additional benefits and advantages of the disclosed embodiments will be apparent from the specification and Figures. The benefits and/or advantages may be individually provided by the various embodiments and features of the specification and drawings disclosure, and need not all be 25 provided in order to obtain one or more of the same.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1A illustrates an exemplary configuration for a router 30 301 which outputs the data of traffic flows with high levels of priorities that are stored in buffers 304 and 303 earlier than the traffic flow stored in the other buffer 301.

FIG. 1B illustrates a modified configuration for the router 301 shown in FIG. 1A in which the level of priority of each 35 input buffer is determined by the highest level of priority of the messages stored there, and the data is output according to the respective levels of priorities of the input buffers.

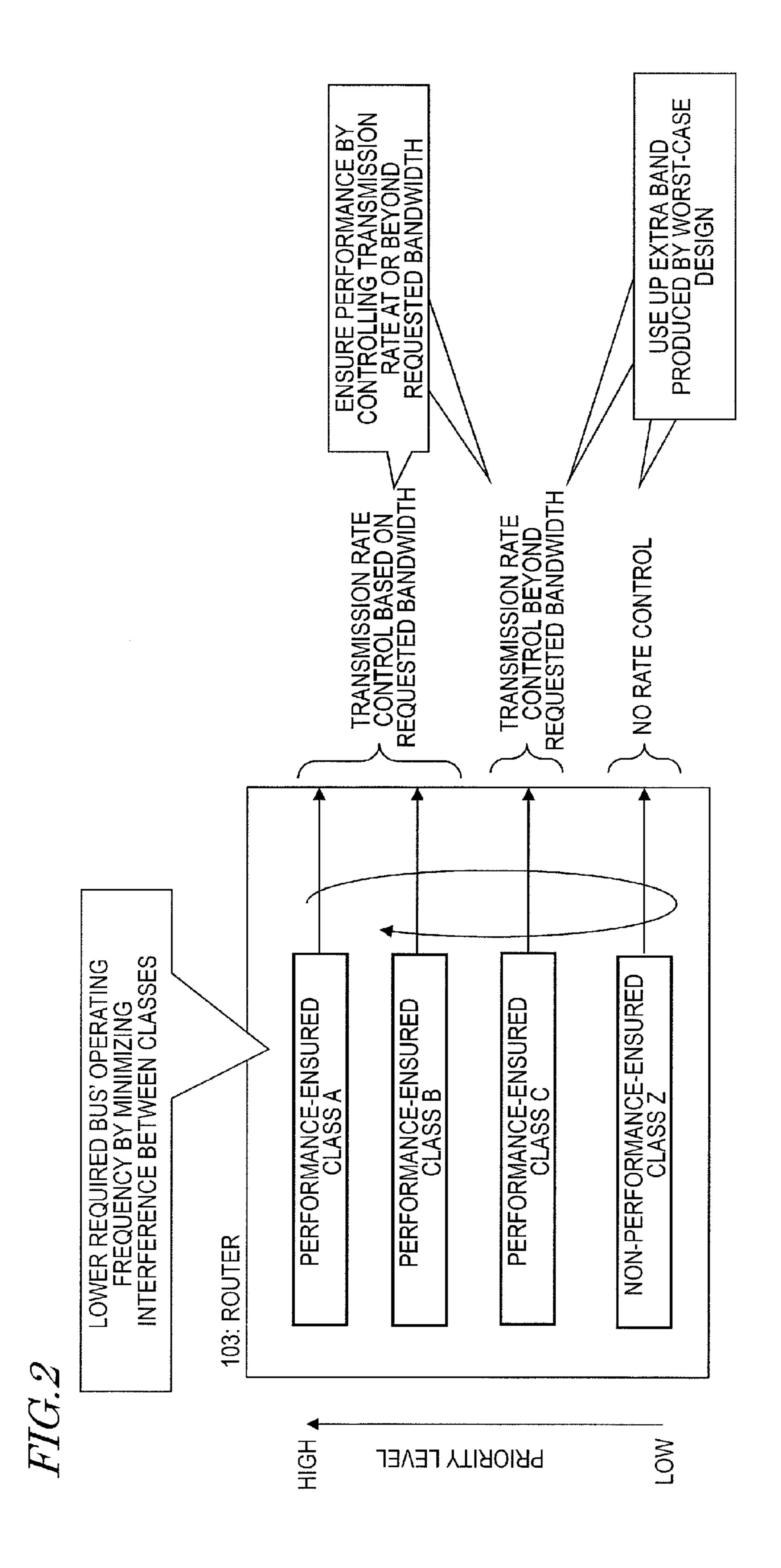

FIG. 2 shows a processing policy according to this embodiment to be applied to the performance-ensured class and the 40 1410. non-performance-ensured class.

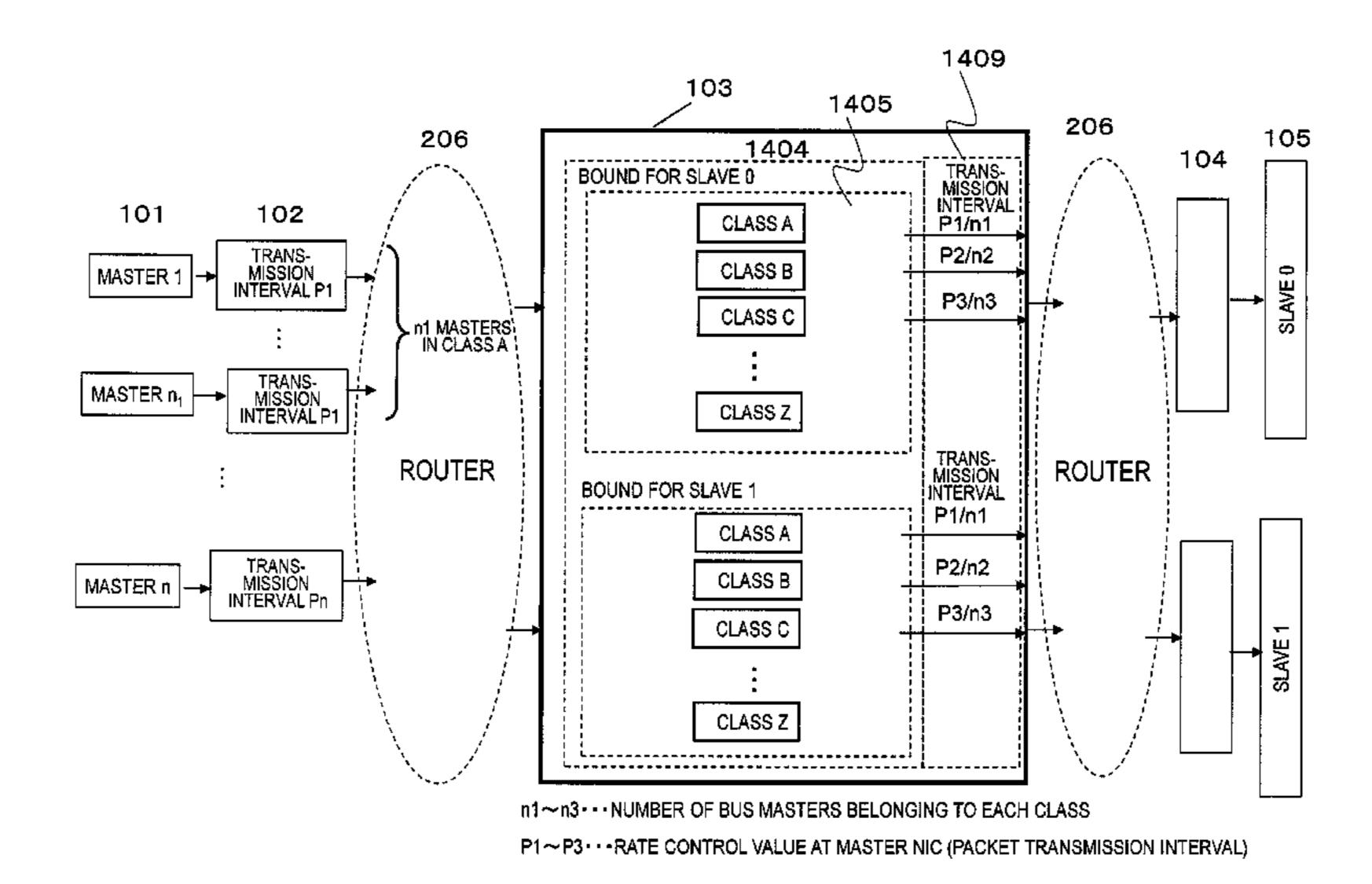

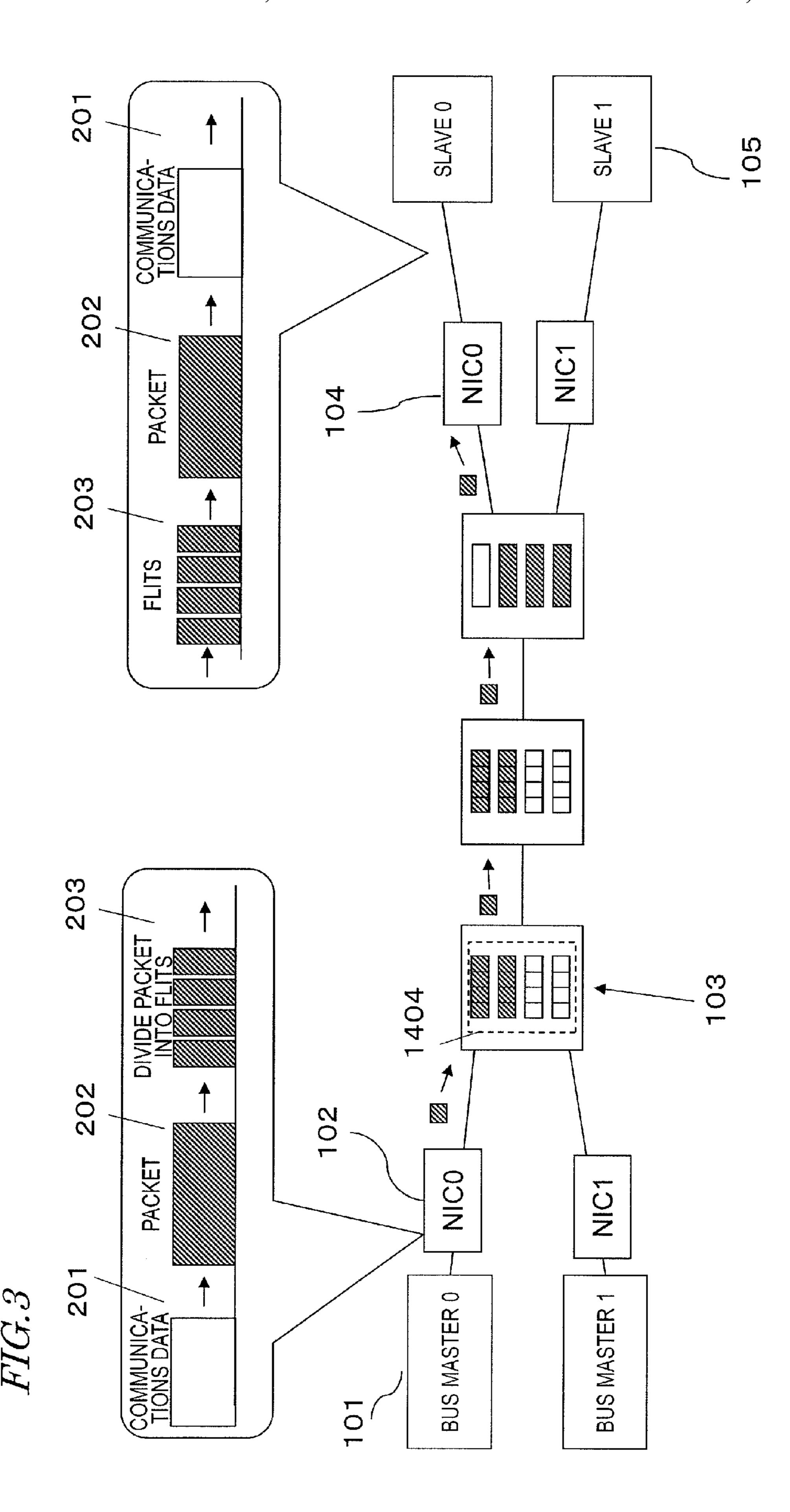

FIG. 3 illustrates an exemplary NoC which is implemented using routers 103 as an embodiment of the present invention.

FIG. 4 shows the concepts of respective components of an NoC.

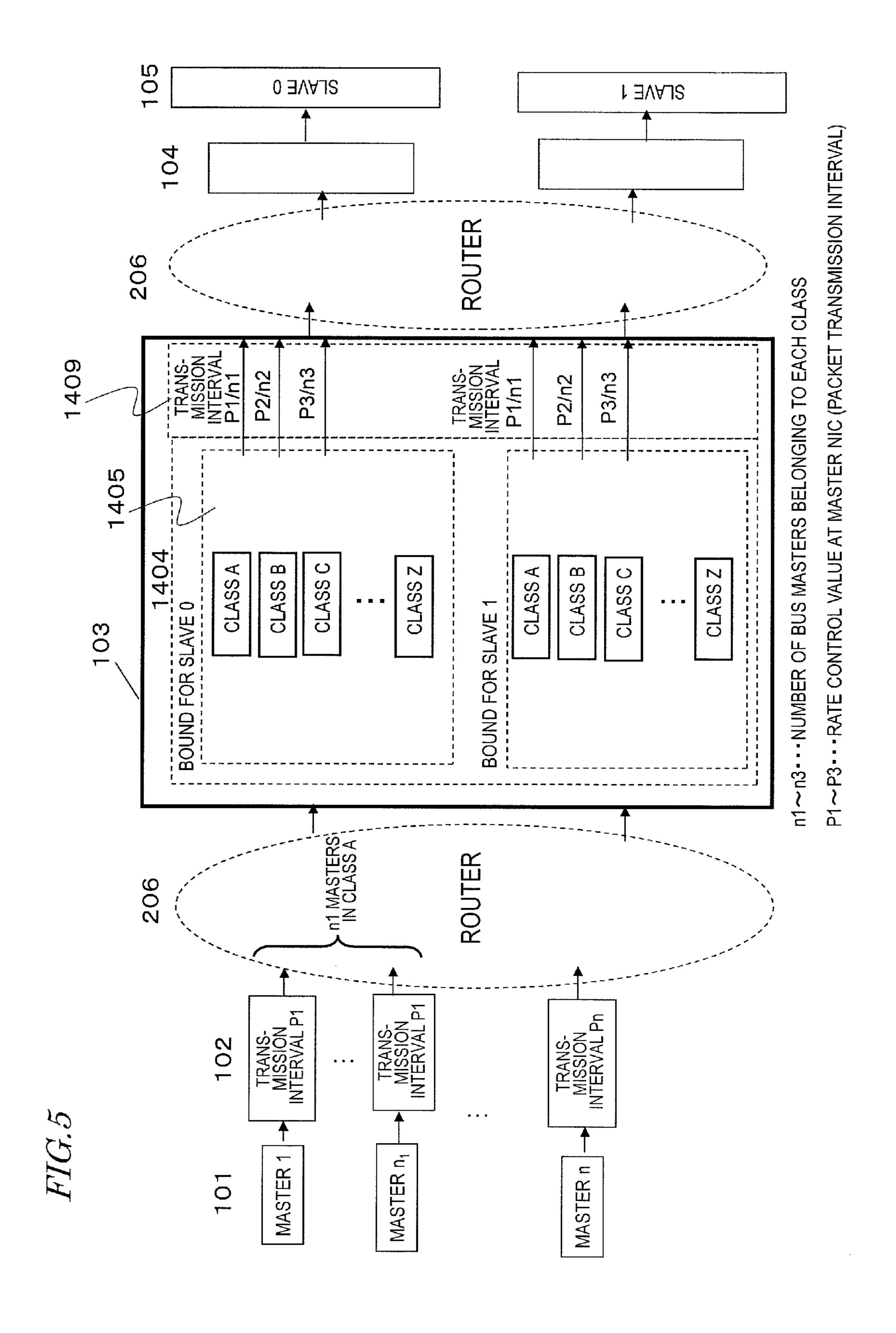

FIG. **5** schematically illustrates a configuration for the NoC shown in FIG. **3**.

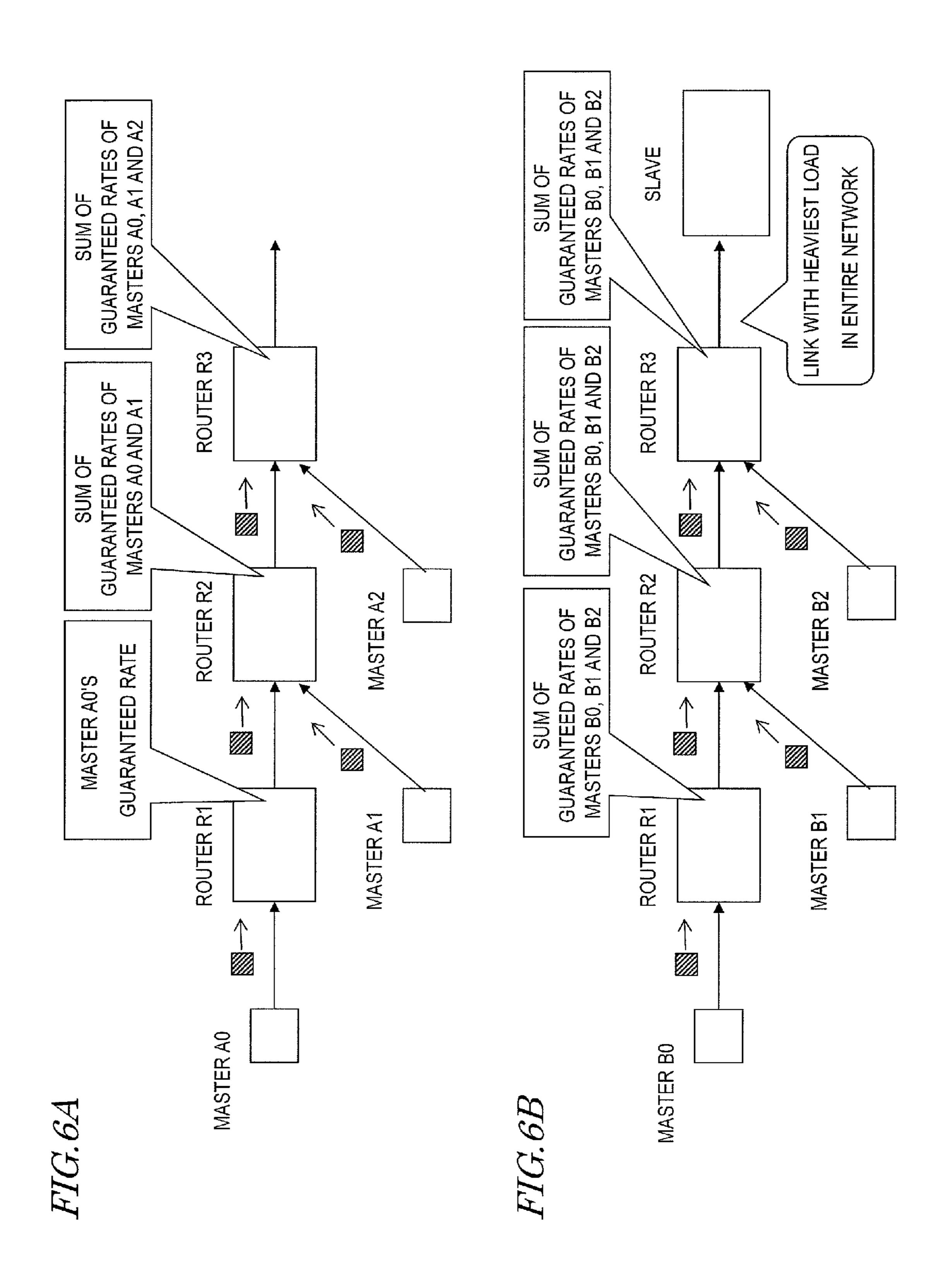

FIGS. 6A and 6B show exemplary transmission rate values

to be set for respective routers.

FIGS. 7A and 7B show how the effect achieved varies 50 depending on whether the configuration of the router 103 is

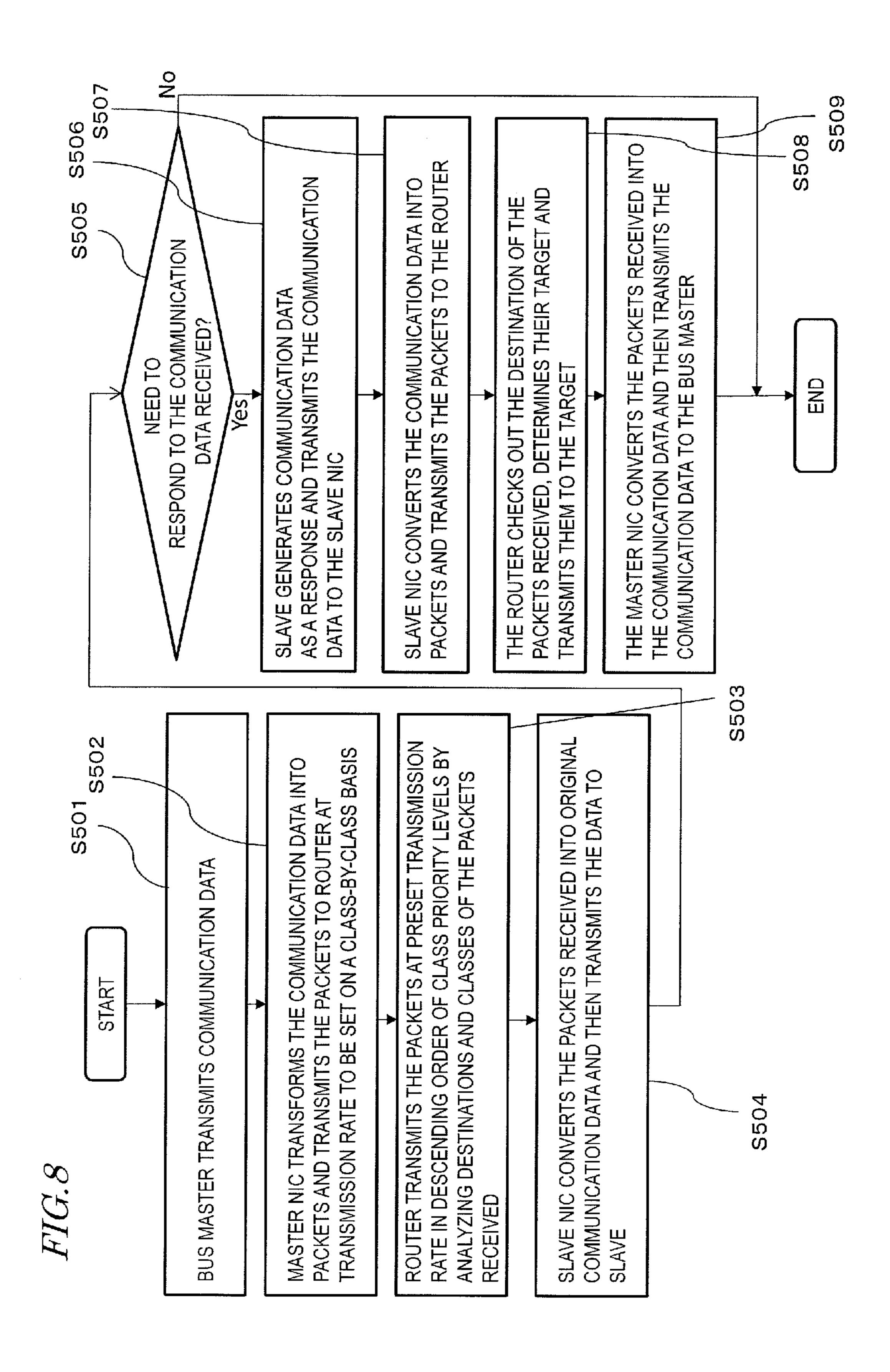

applied to the Internet or to a semiconductor bus system. FIG. 8 is a flowchart showing the procedure of operation of an NoC including routers according to an embodiment of the present invention.

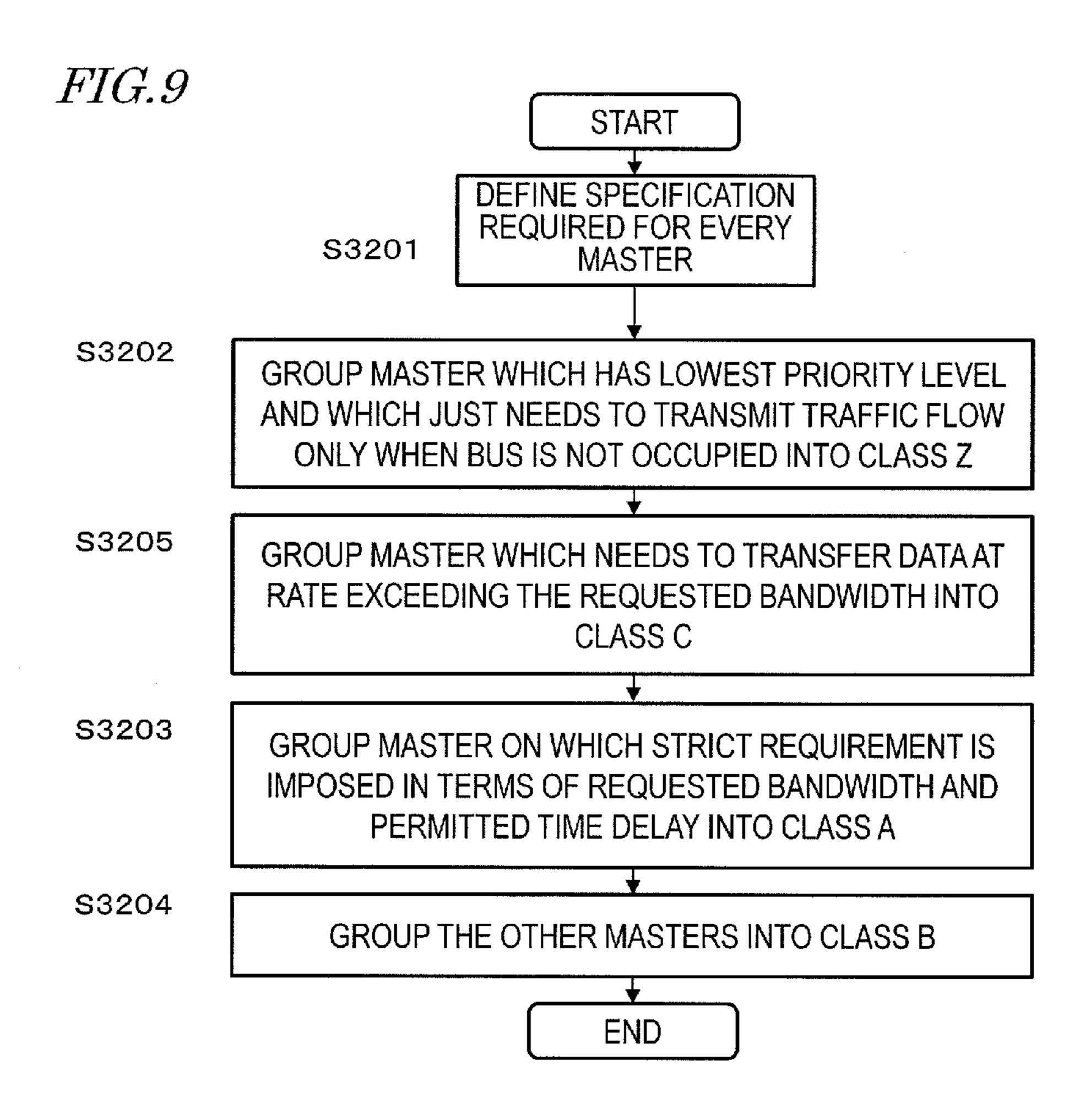

FIG. 9 shows the rule of classifying bus masters so that performance-ensuring data and non-performance-ensuring data can be distinguished from each other, to say the least, in order to lower an estimated bus' operating frequency required.

FIG. 10 shows specific exemplary definitions of specifications required for traffic flows to be generated by masters.

FIG. 11 shows respective classes to which the bus masters 101 are grouped and their specific examples.

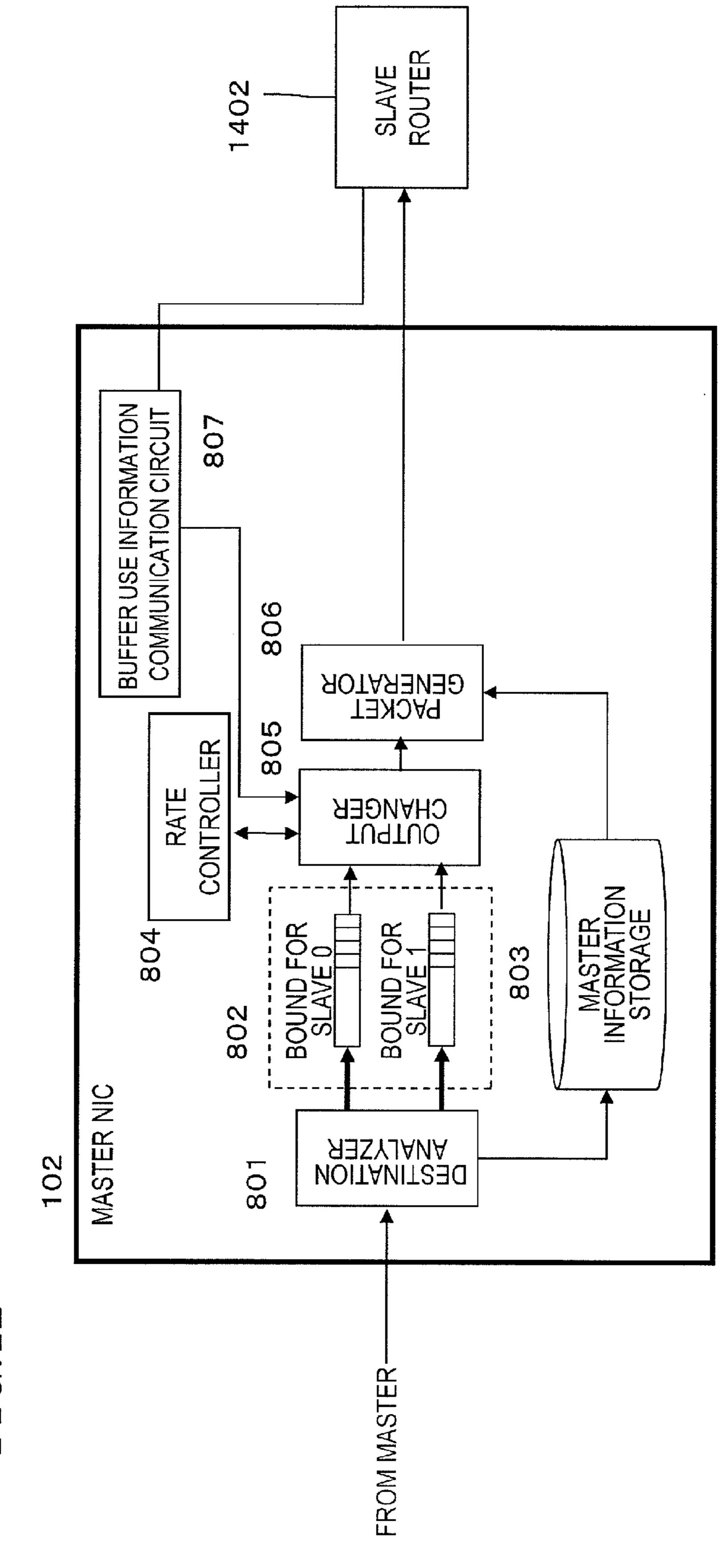

FIG. 12 illustrates a configuration for a master NIC 102.

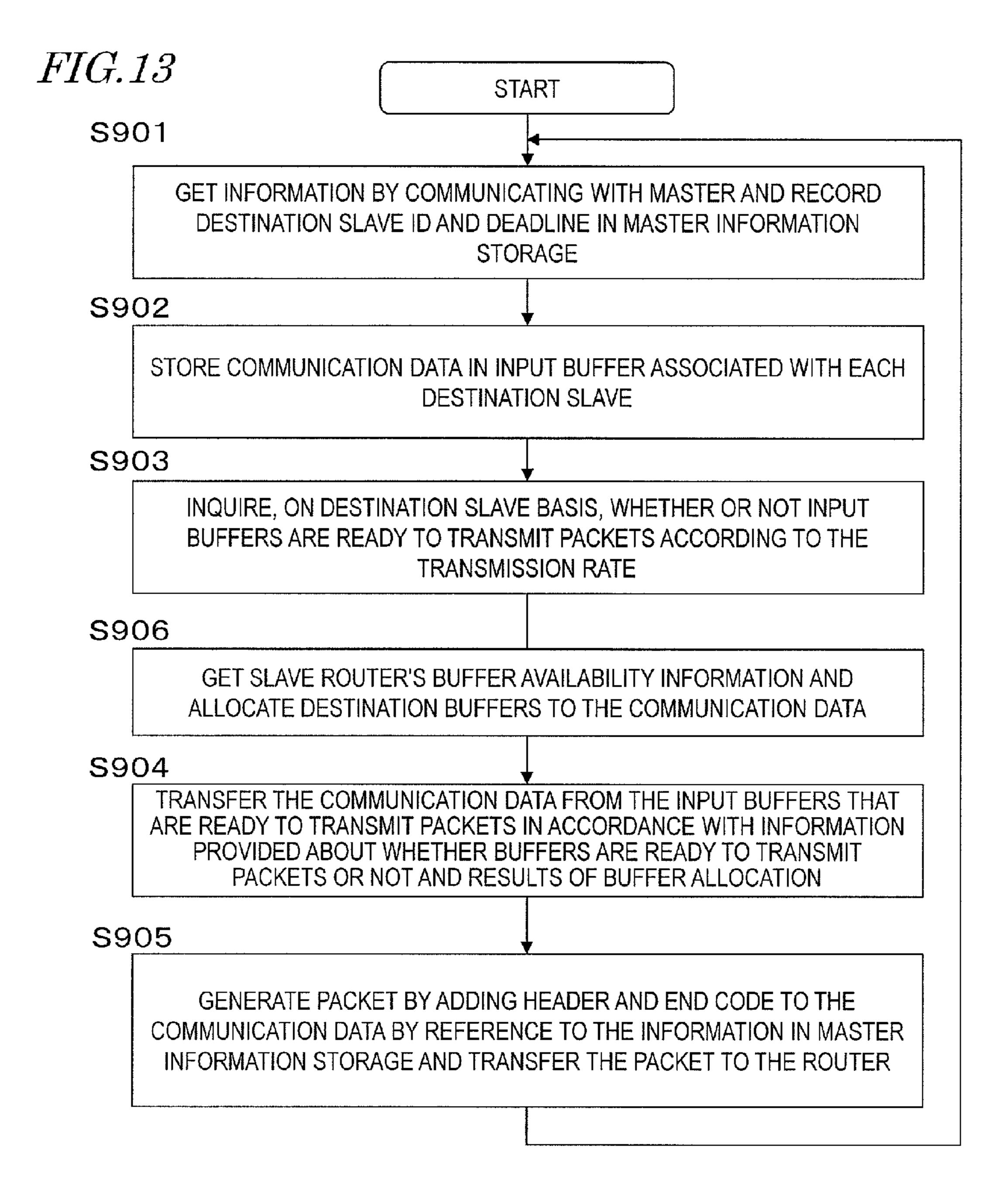

FIG. 13 shows the flow of operation of the master NIC 102.

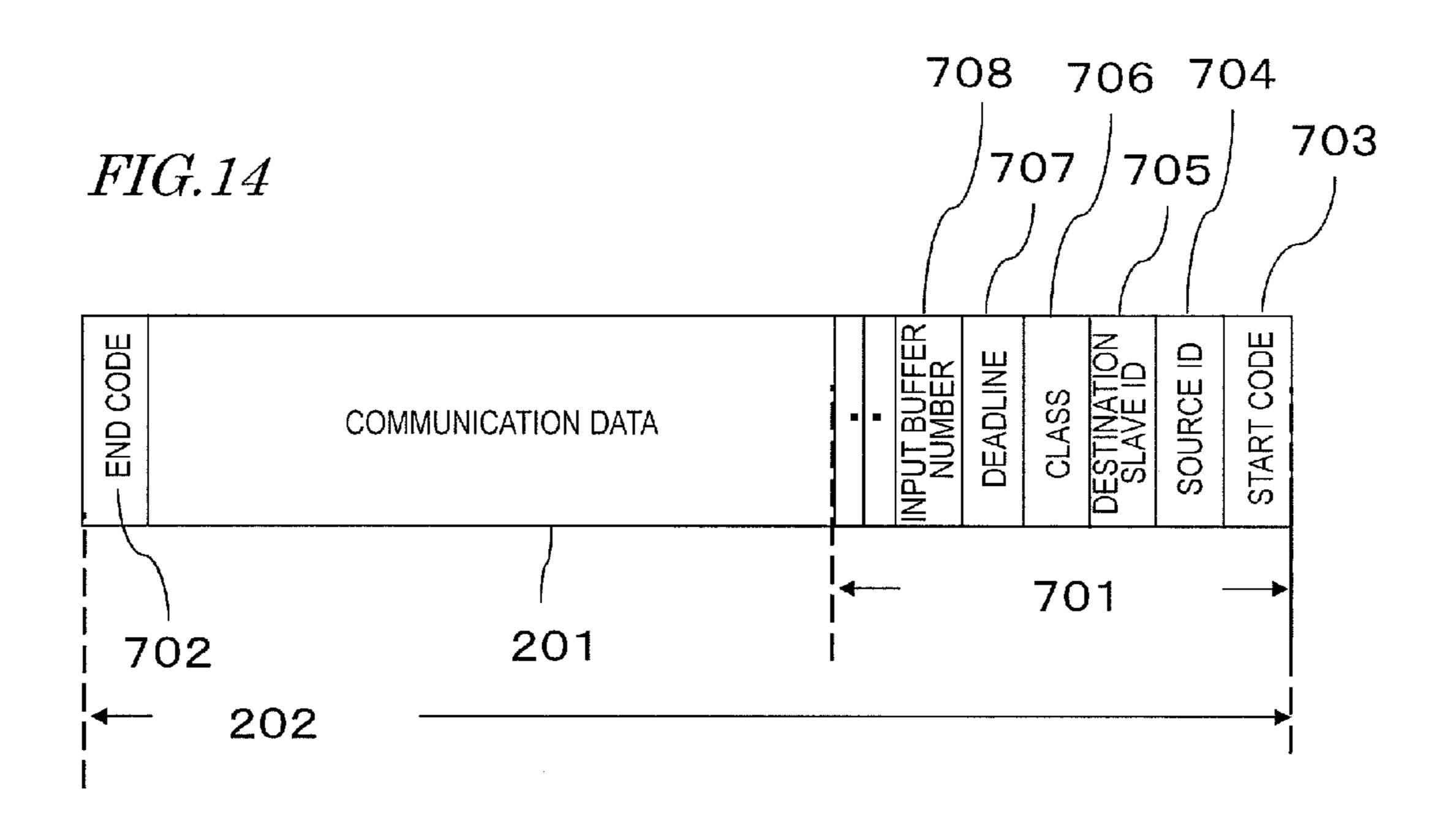

FIG. 14 illustrates a data structure for each packet 202.

4

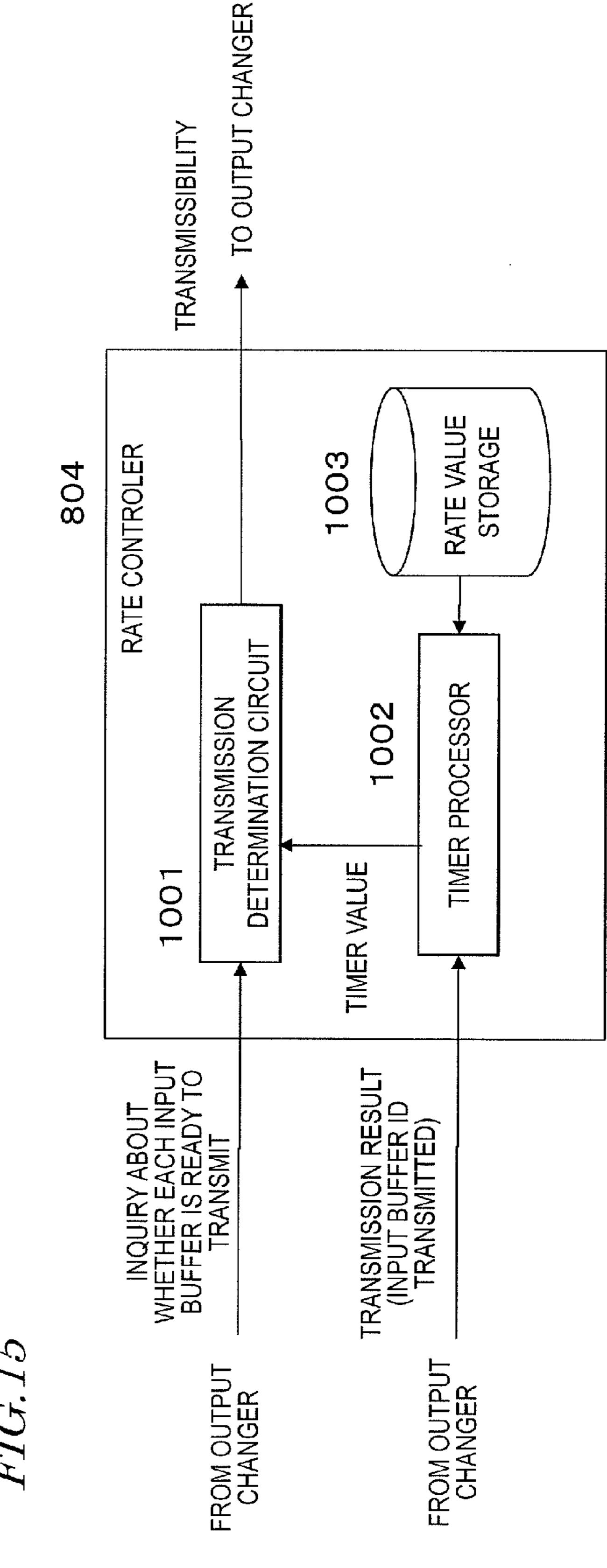

FIG. 15 illustrates a configuration for a rate controller 804 provided for the master NIC 102.

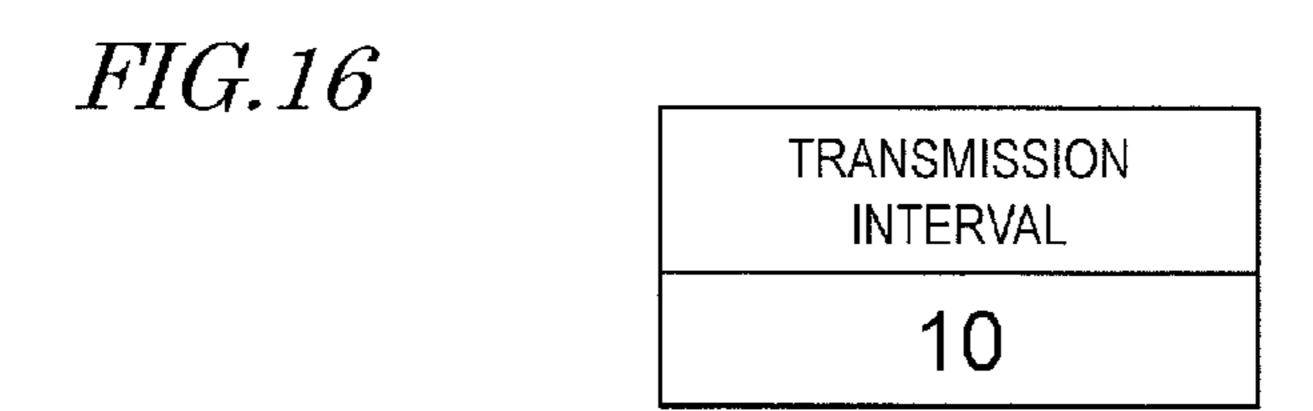

FIG. 16 shows a rate value stored in a rate value storage 1003.

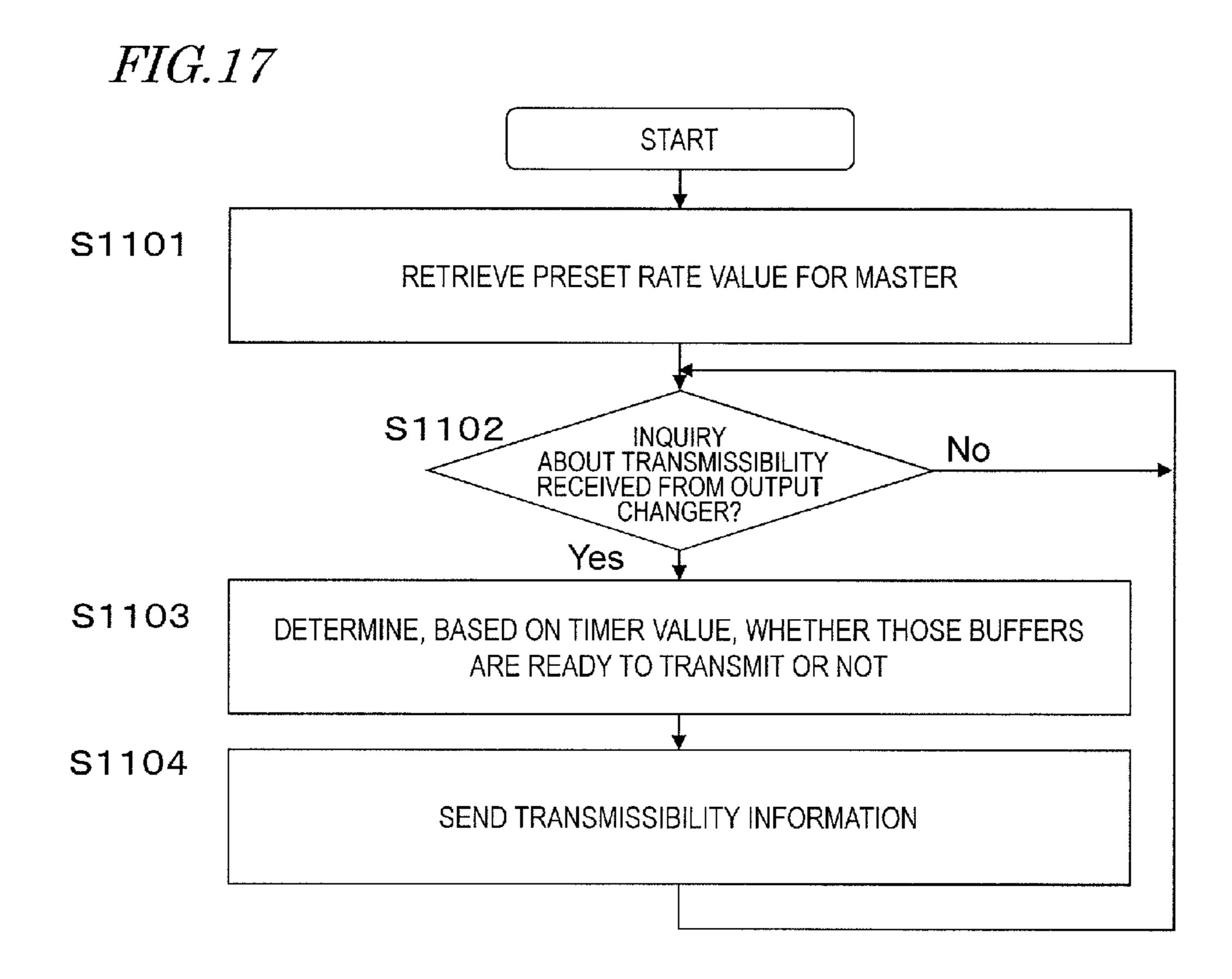

FIG. 17 shows the flow of operation of a rate controller 804.

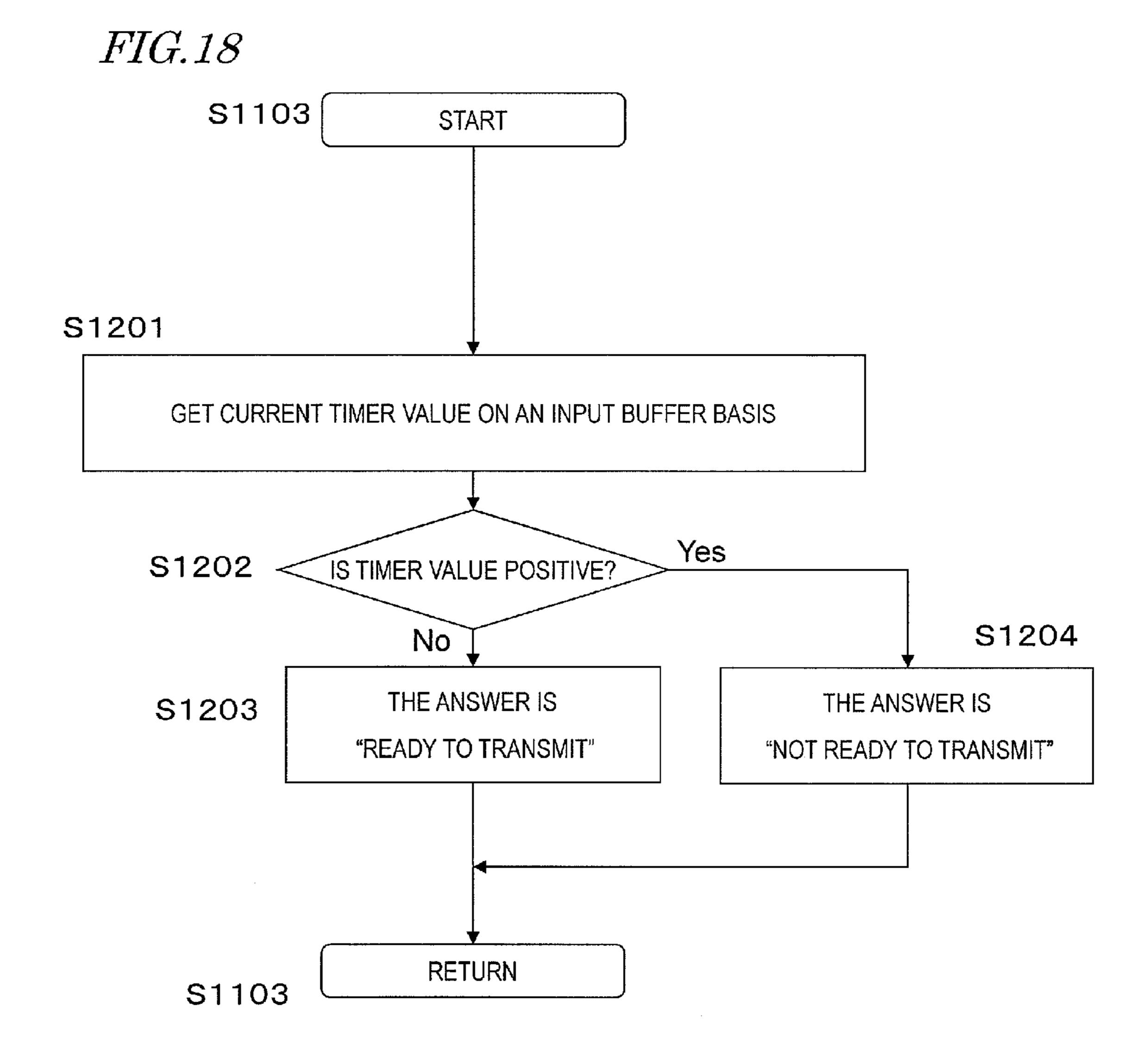

FIG. 18 shows how a transmission determination circuit 1001 performs transmission determining processing step S1103.

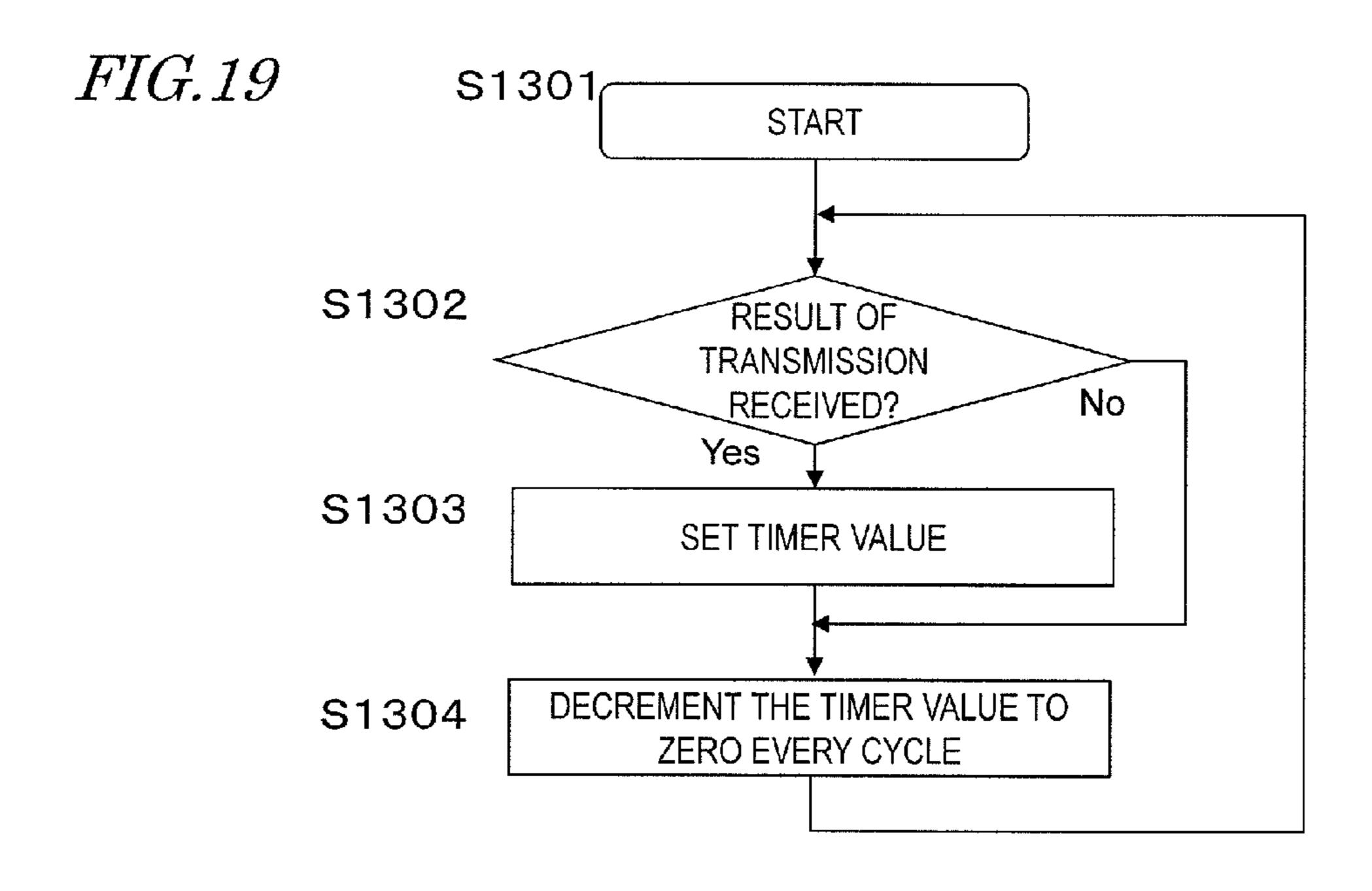

FIG. 19 shows the flow of operation of a timer processor 1002.

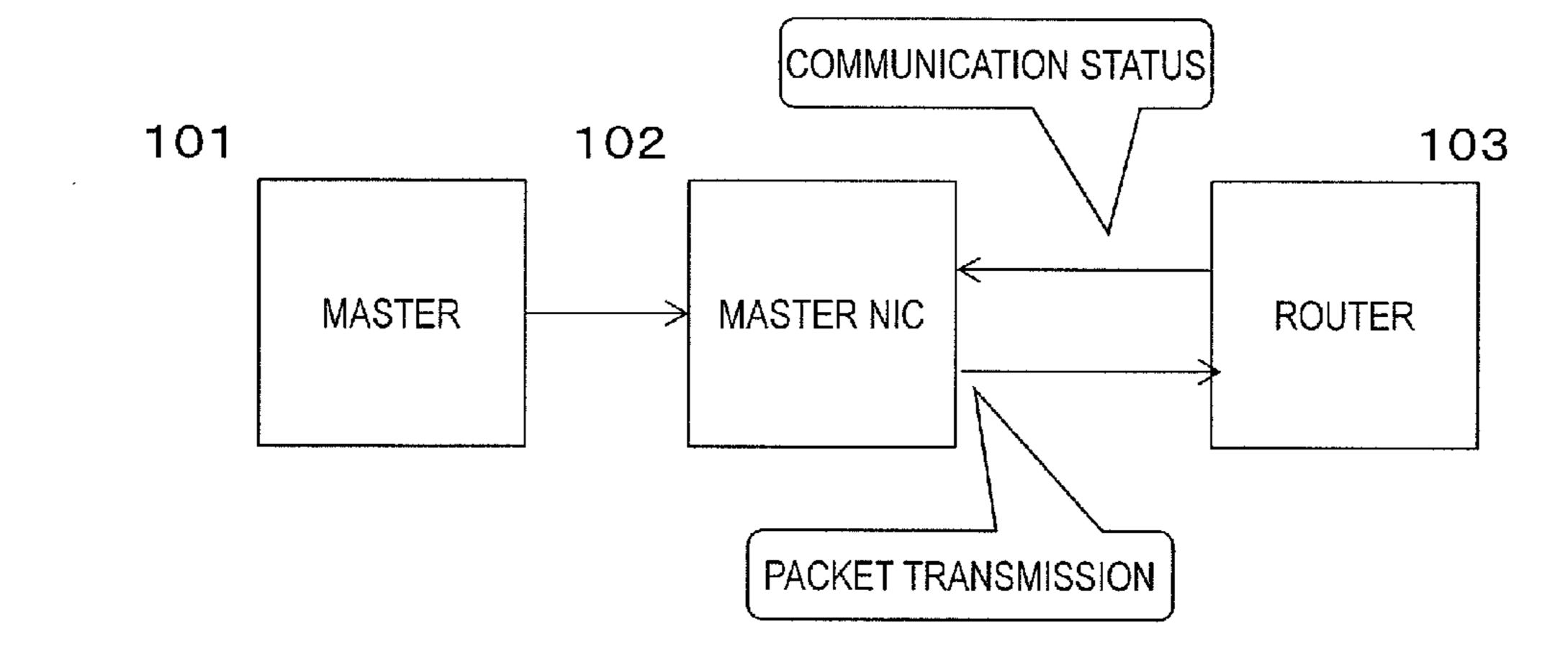

FIG. 20 illustrates how to carry out a general flow control between the master NIC 102 and the router 103.

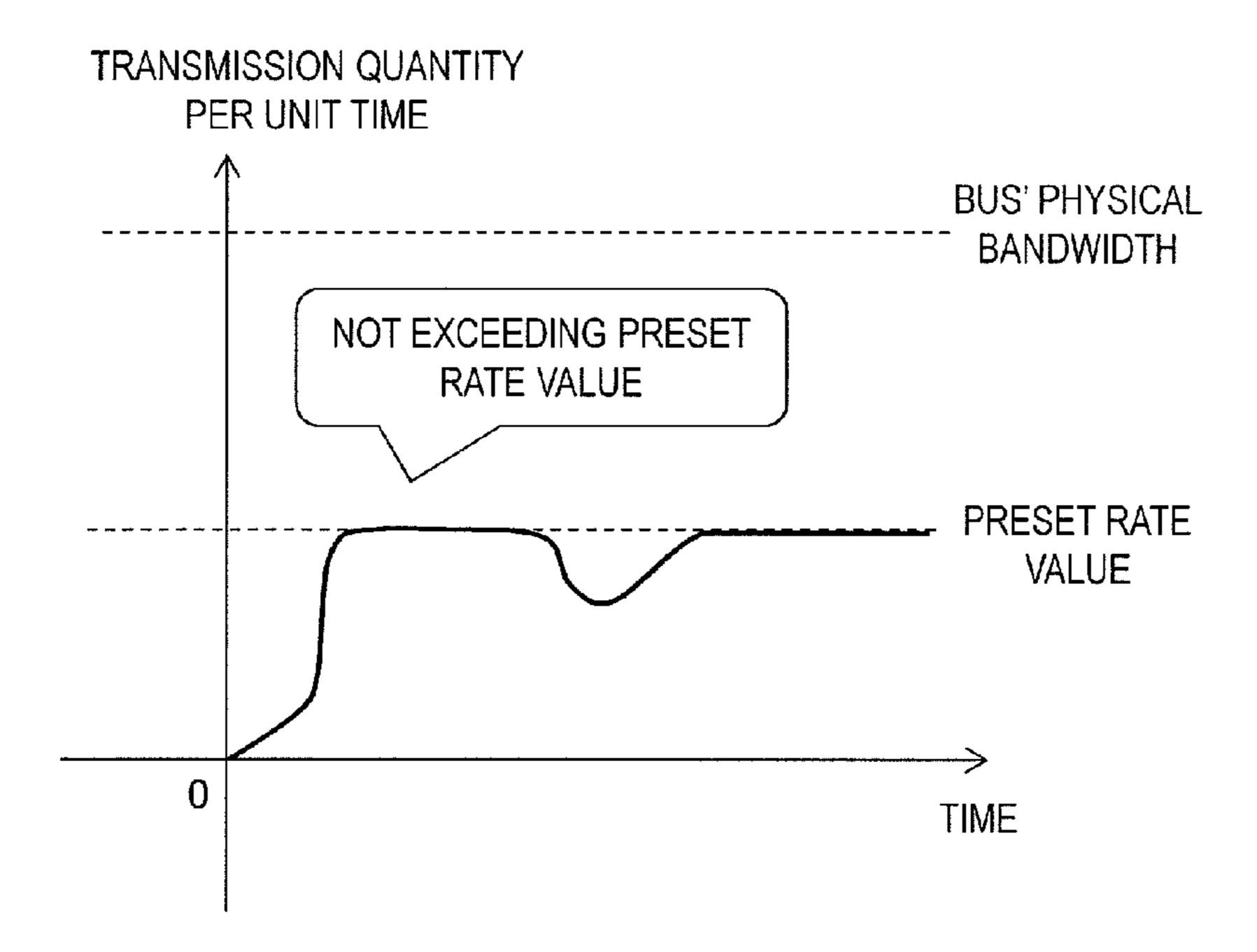

FIGS. 21A and 21B show how a flow control and a rate control are different.

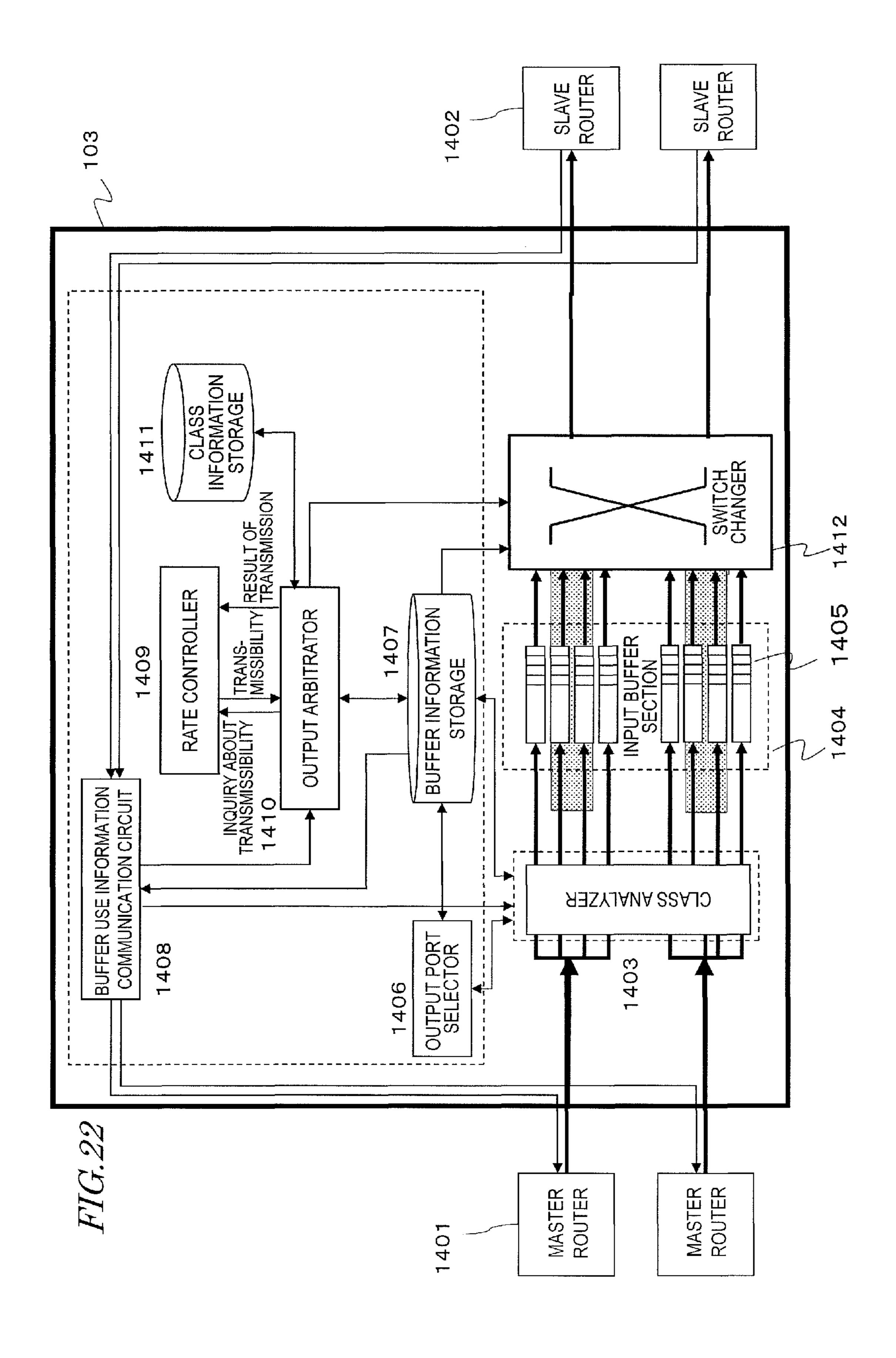

FIG. 22 illustrates a configuration for the router 103.

FIG. 23 shows class priority level information to be stored in class information storage 1411.

FIG. 24 shows a specific example of the results of arbitration conducted by the output arbitrator 1410 of the router 103 between respective buffers to transmit packets from in order to determine their order of priorities.

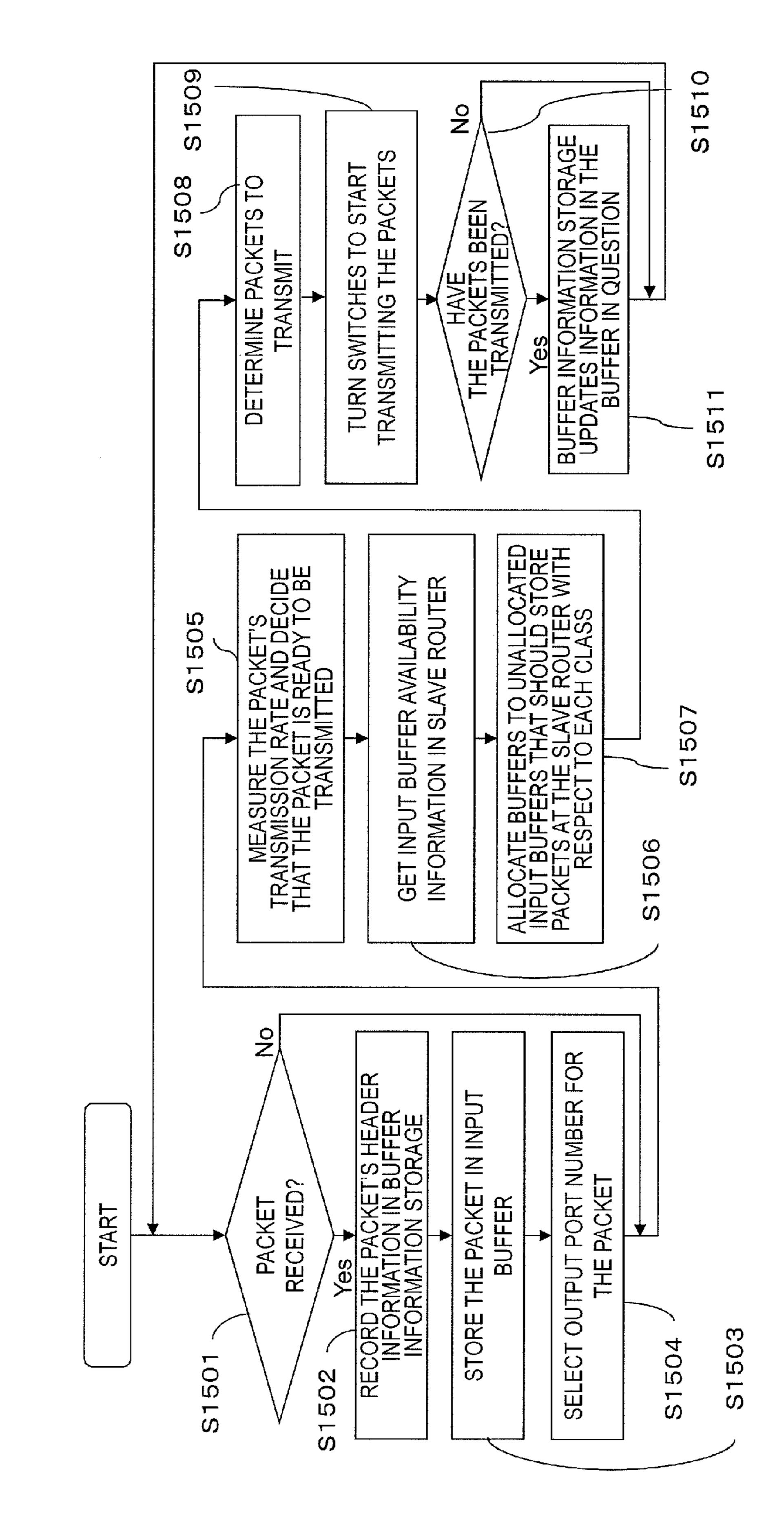

FIG. 25 shows the flow of operation of the router 103.

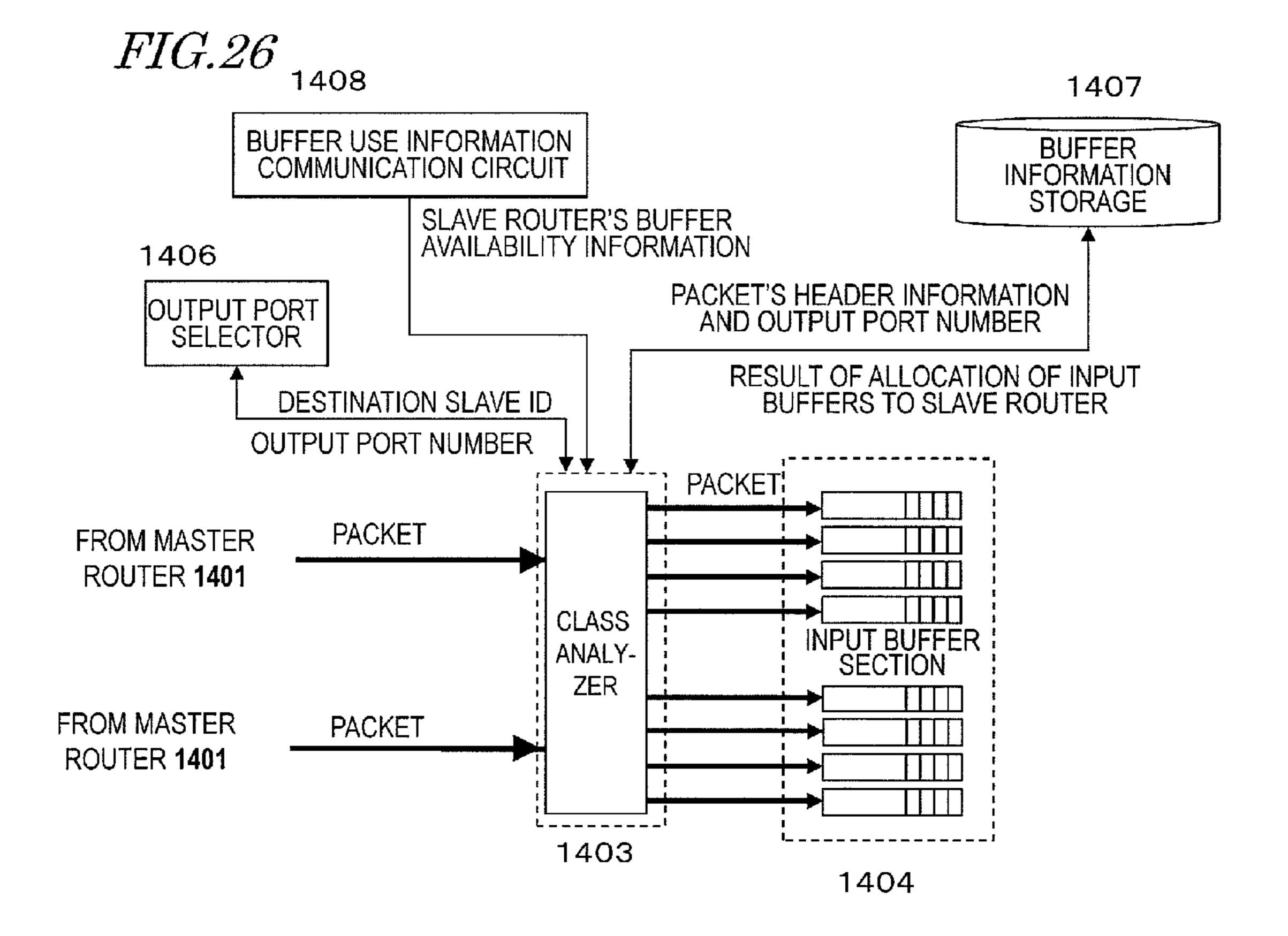

FIG. 26 shows what is input to, and output from, the class analyzer 1403 of the router 103.

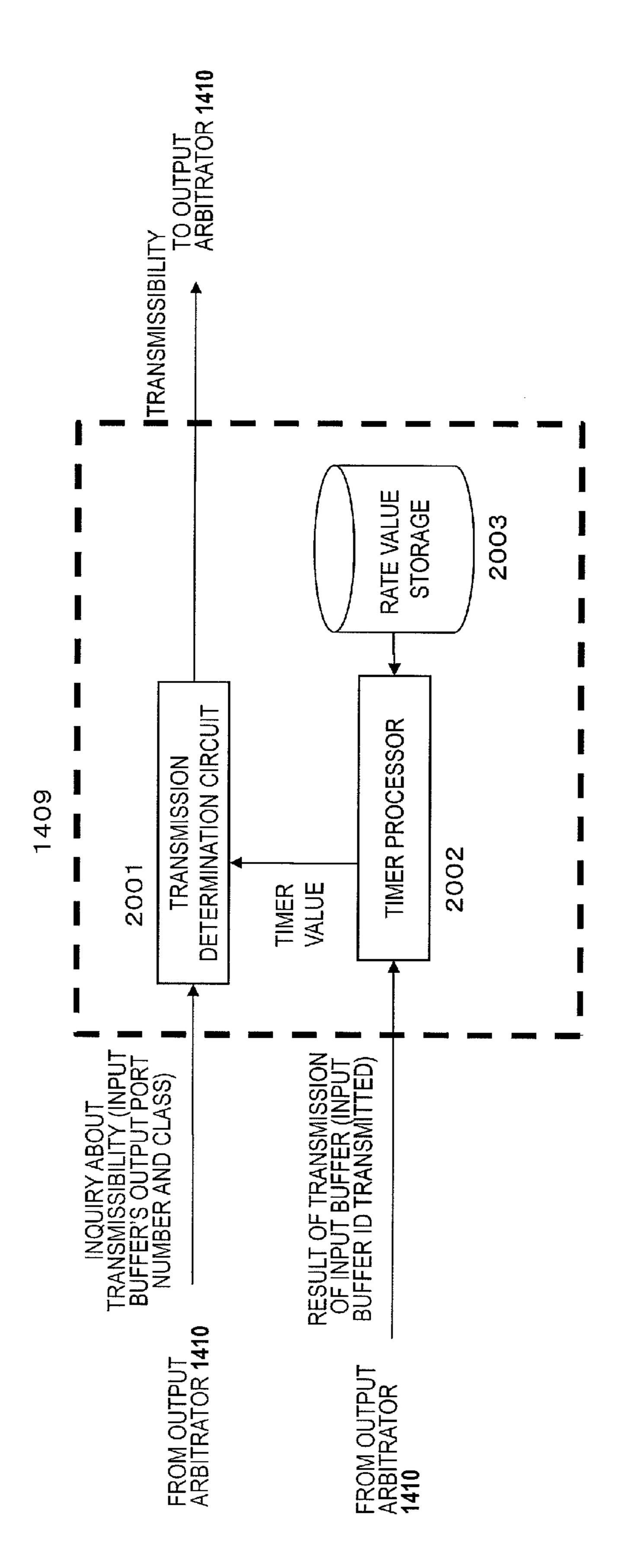

FIG. 27 illustrates a configuration for the rate controller 1409 of the router 103.

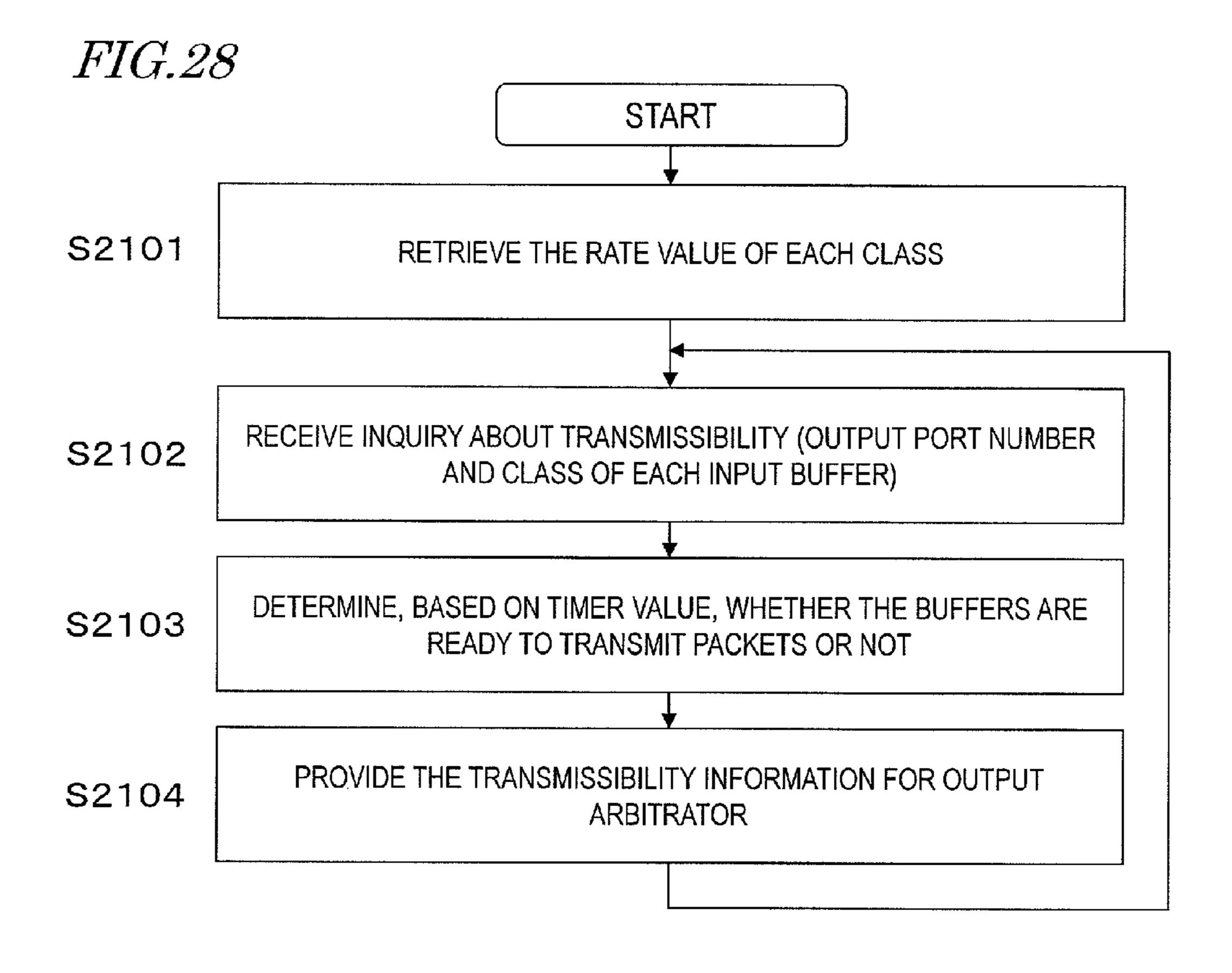

FIG. 28 shows the flow of operation of the rate controller 1409.

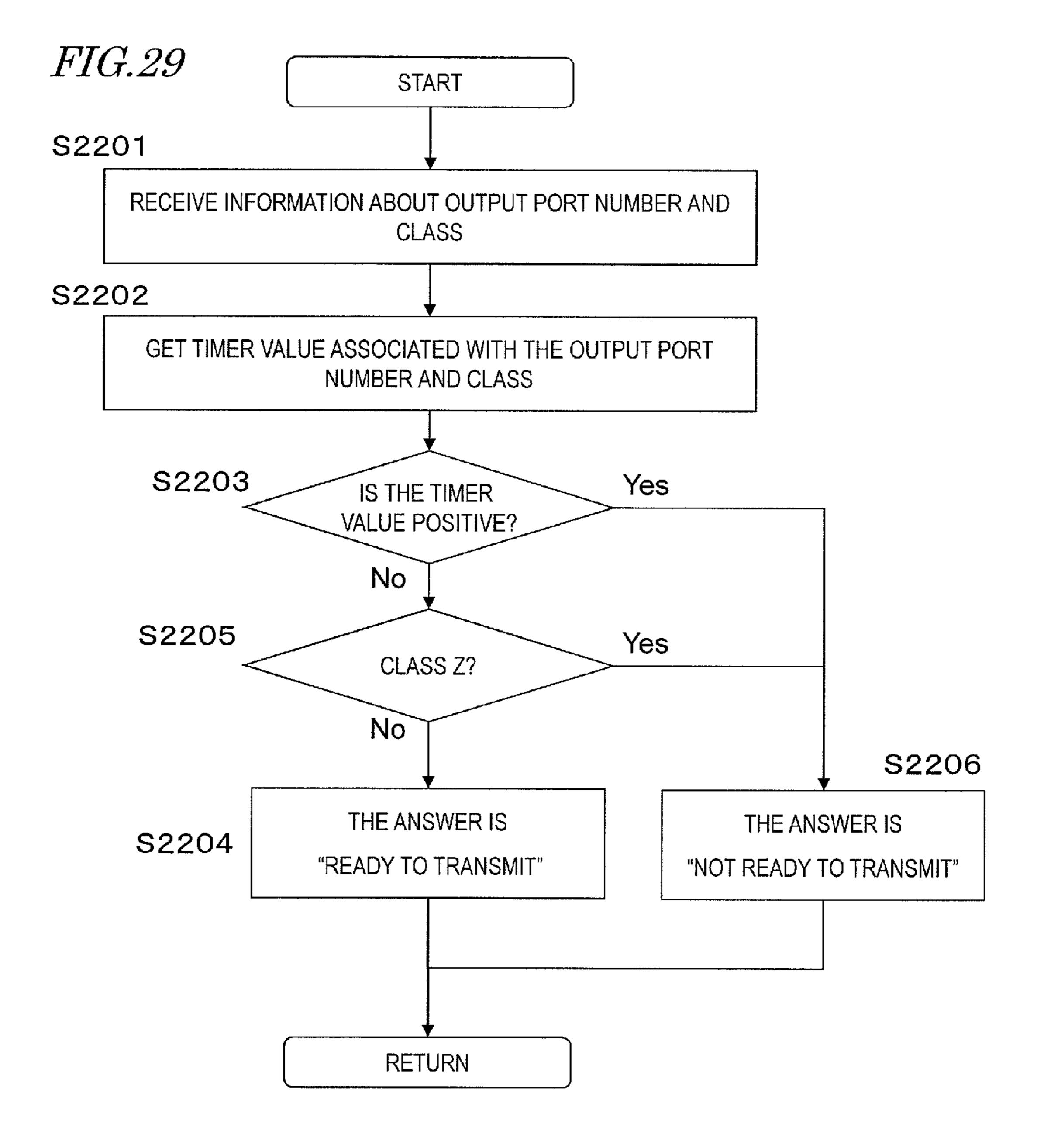

FIG. 29 shows the procedure in which the rate controller 1409 performs transmission determining processing step.

FIG. 30 shows a specific example of the management information for the timer processor.

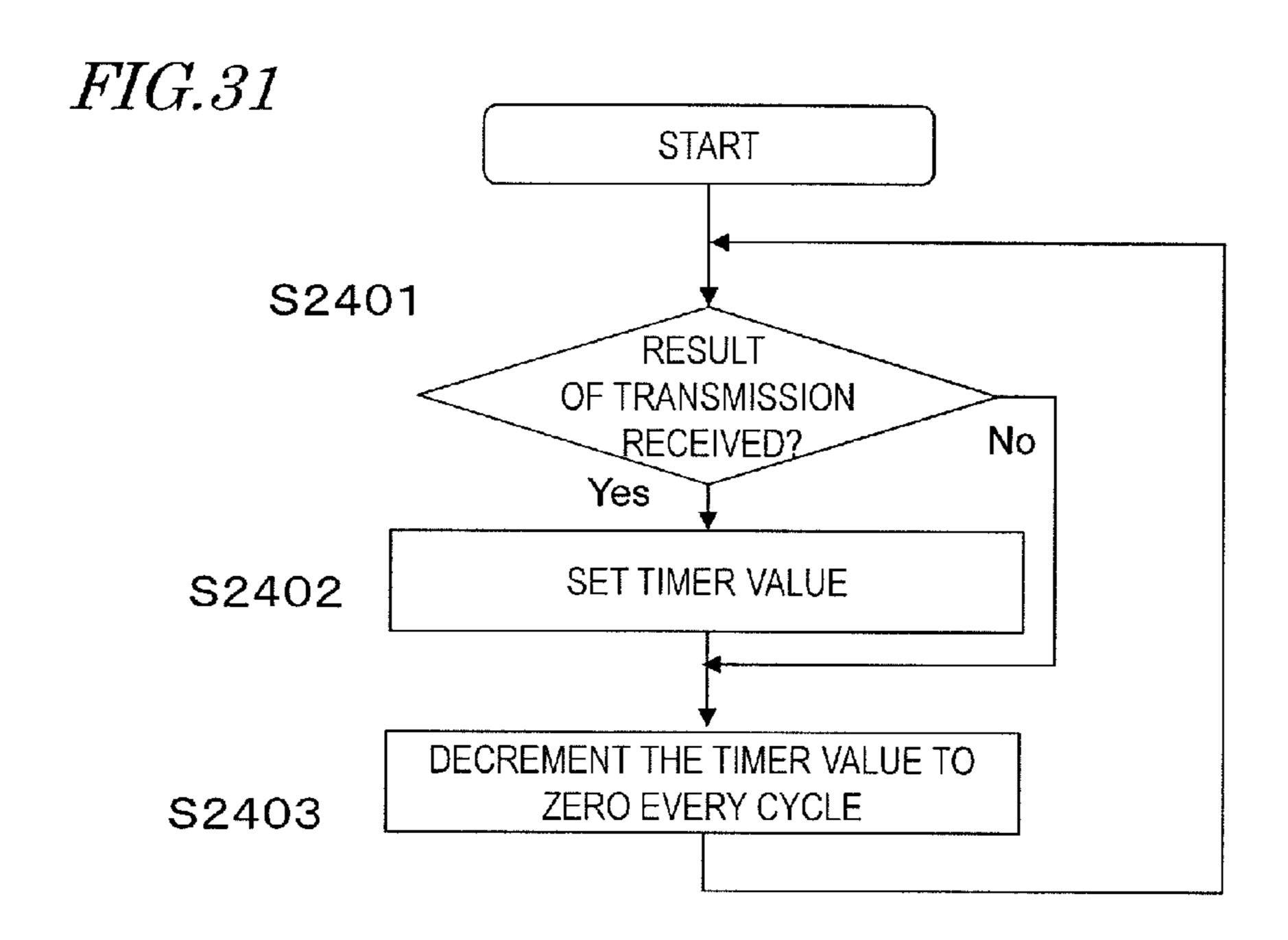

FIG. 31 shows the flow of operation of the timer processor 2002 of the rate controller 1409.

FIG. 32 shows exemplary transmission rate values that are managed by the rate value storage 2003 on a class-by-class basis.

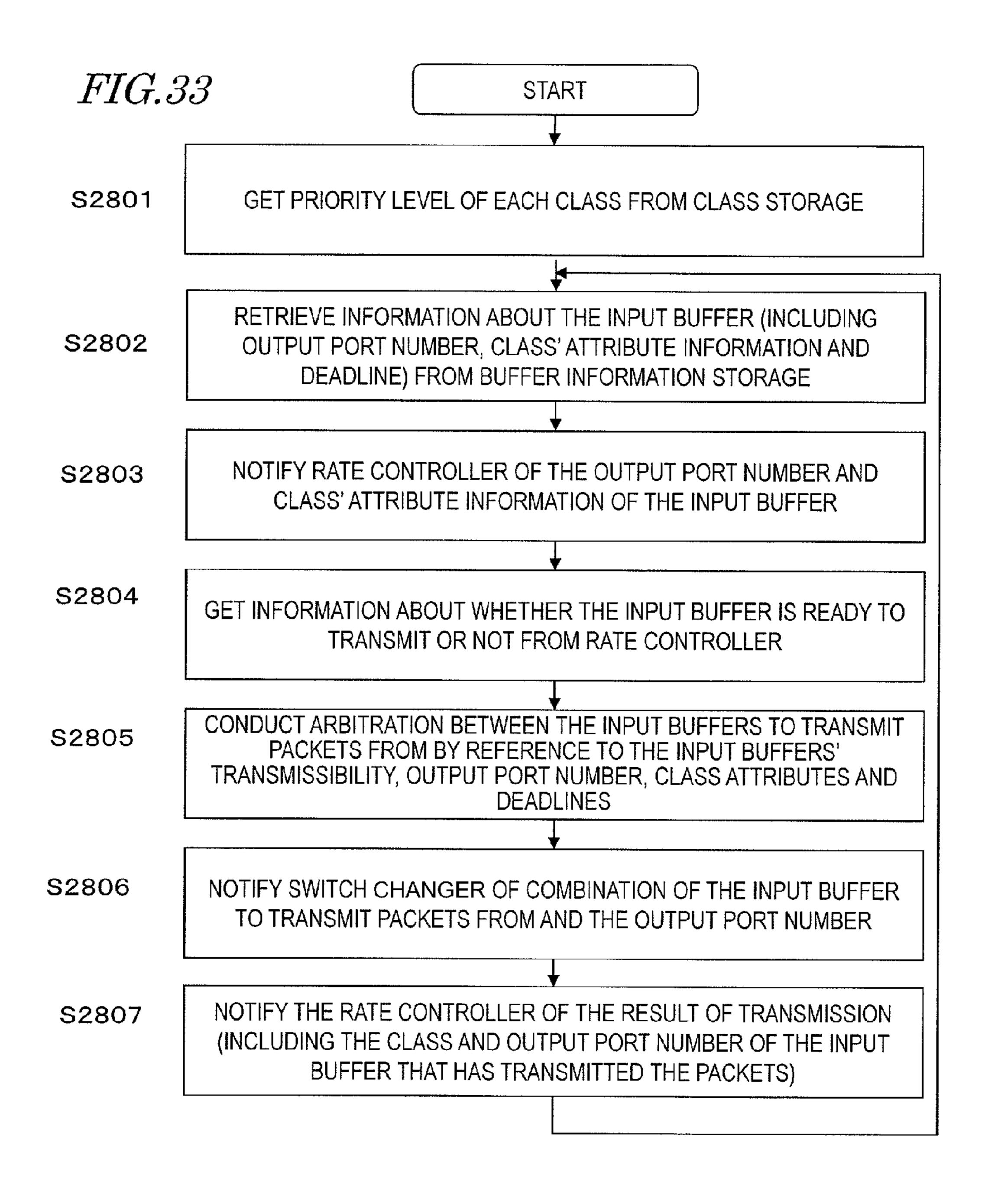

FIG. 33 shows the flow of operation of an output arbitrator 1410

FIG. 34 is a flowchart showing how the output arbitrator 1410 carries out the processing step S2805 of conducting arbitration between the input buffers 1415 to transmit packets from.

FIG. 35 shows a specific exemplary format for management information to be stored in the buffer information storage 1407 of the router 103.

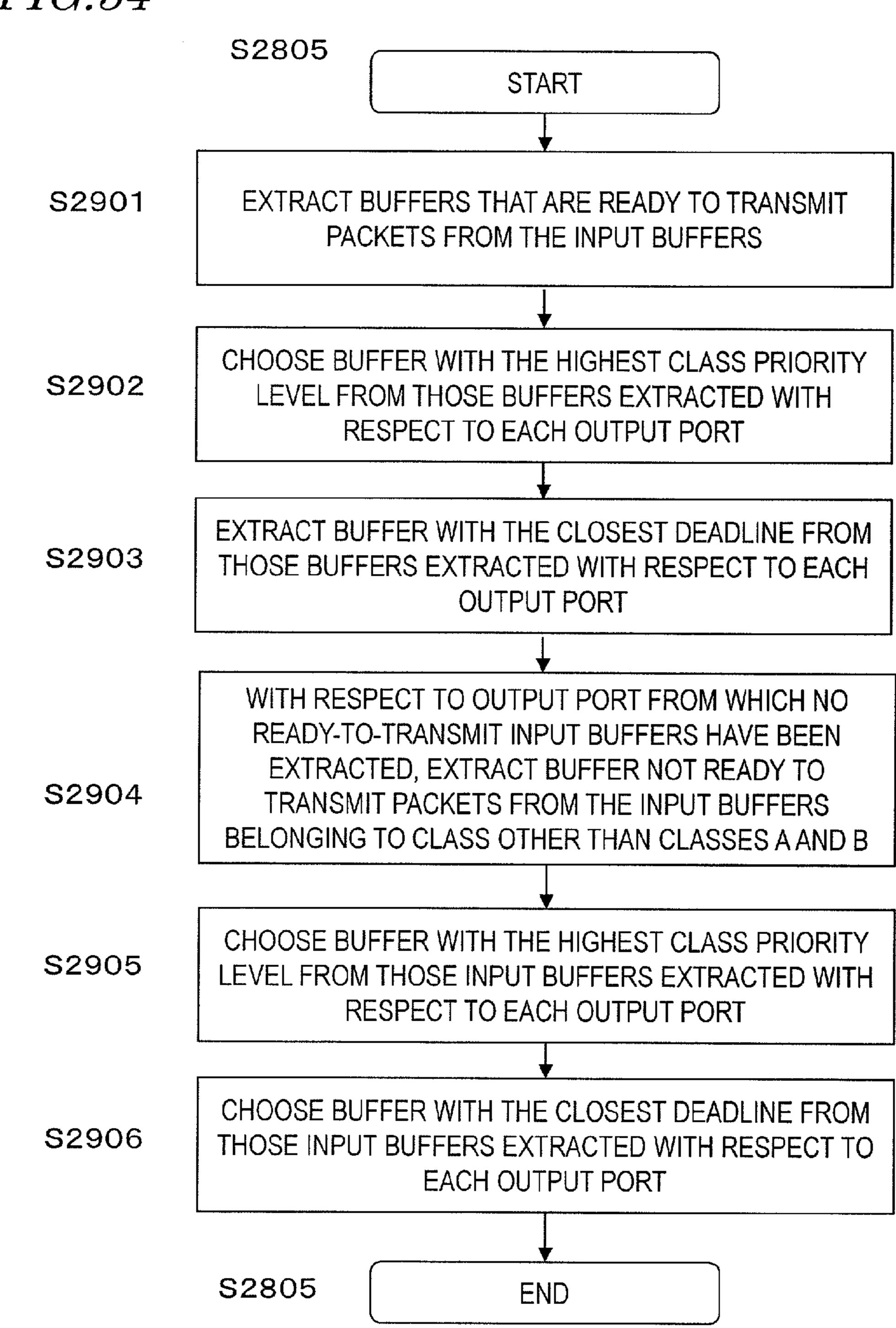

FIG. **36** illustrates exemplary NoCs which can be used as other embodiments of the present invention.

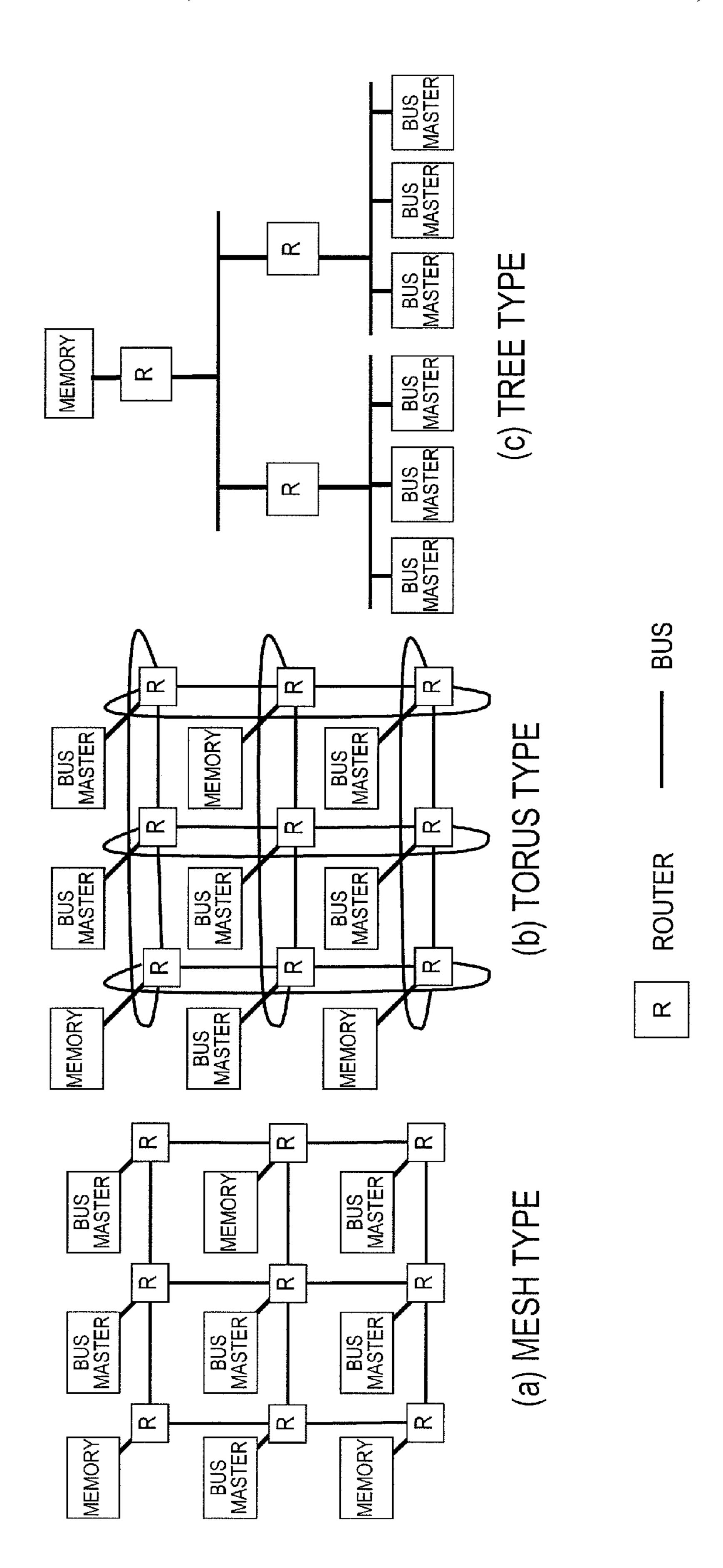

FIG. 37 illustrates an exemplary buffer arrangement to be adopted in a situation where a command and data are separated from each other.

FIGS. **38**A and **38**B show how the delay involved with a command can be shortened, which is an effect to be achieved by separating the command and data from each other.

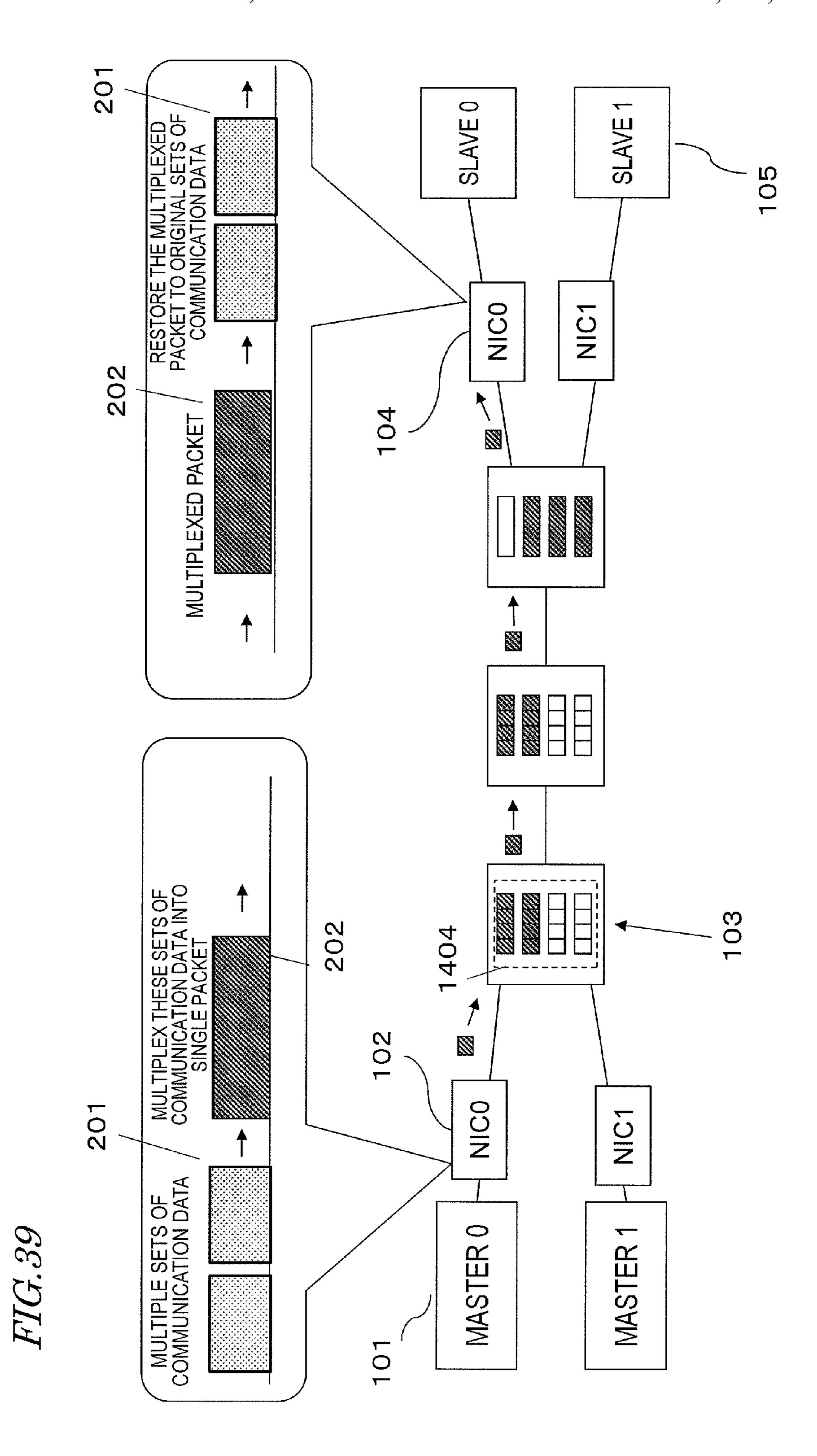

FIG. 39 shows generally how to multiplex and transmit a packet.

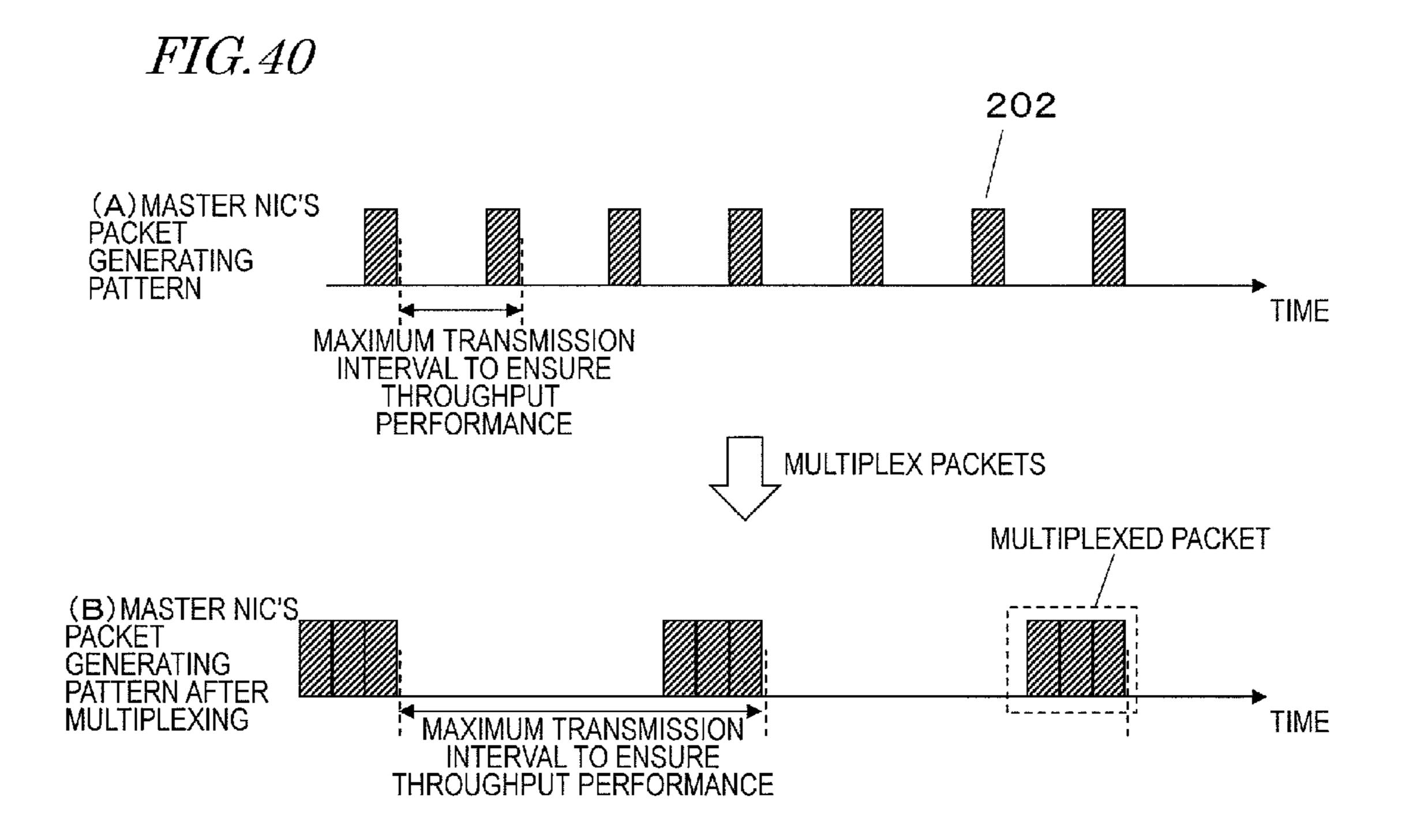

FIG. 40 illustrates how packets may be transmitted depending on whether the packets are multiplexed or not.

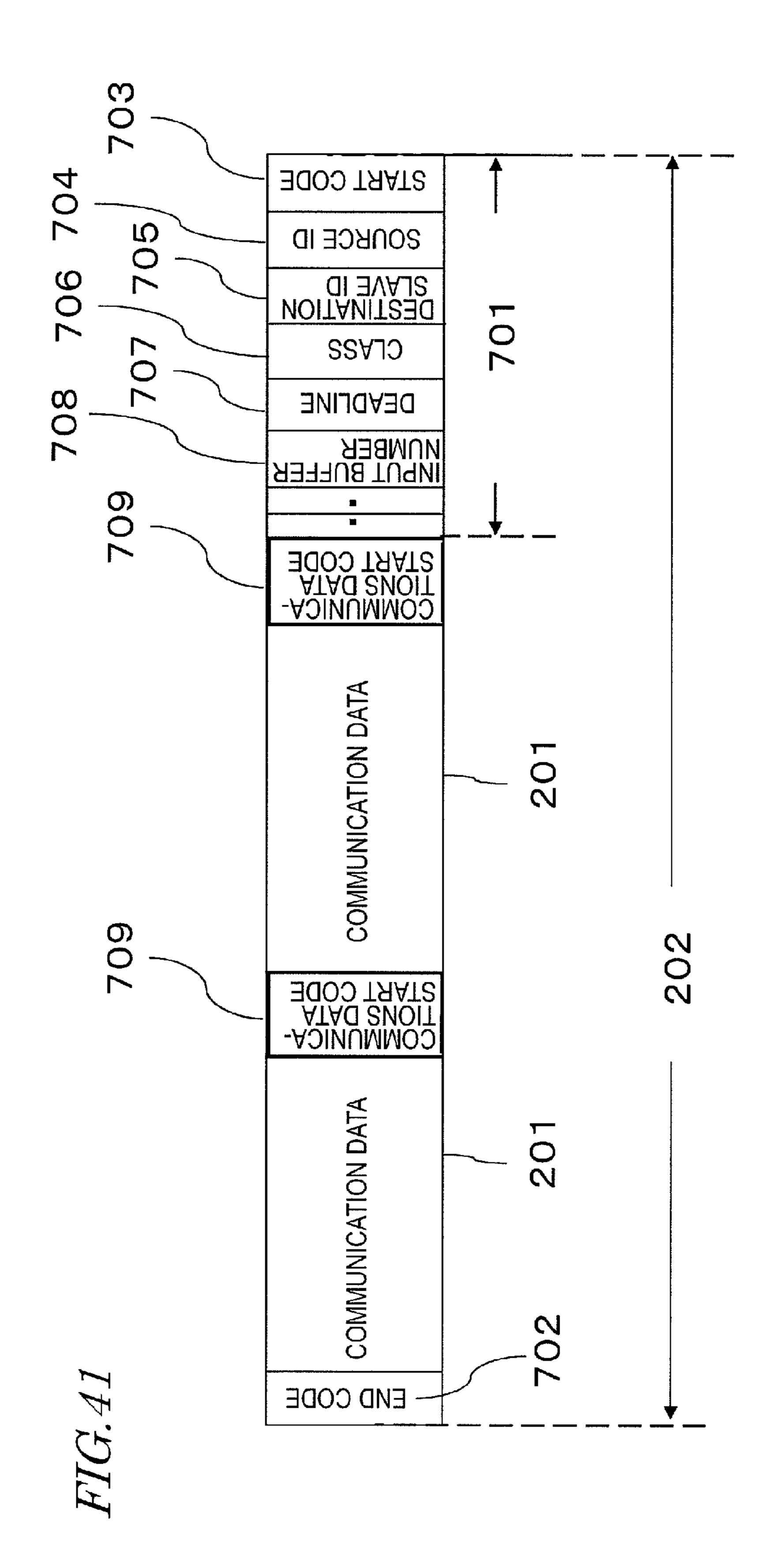

FIG. 41 illustrates a packet multiplexing format for a packet 202.

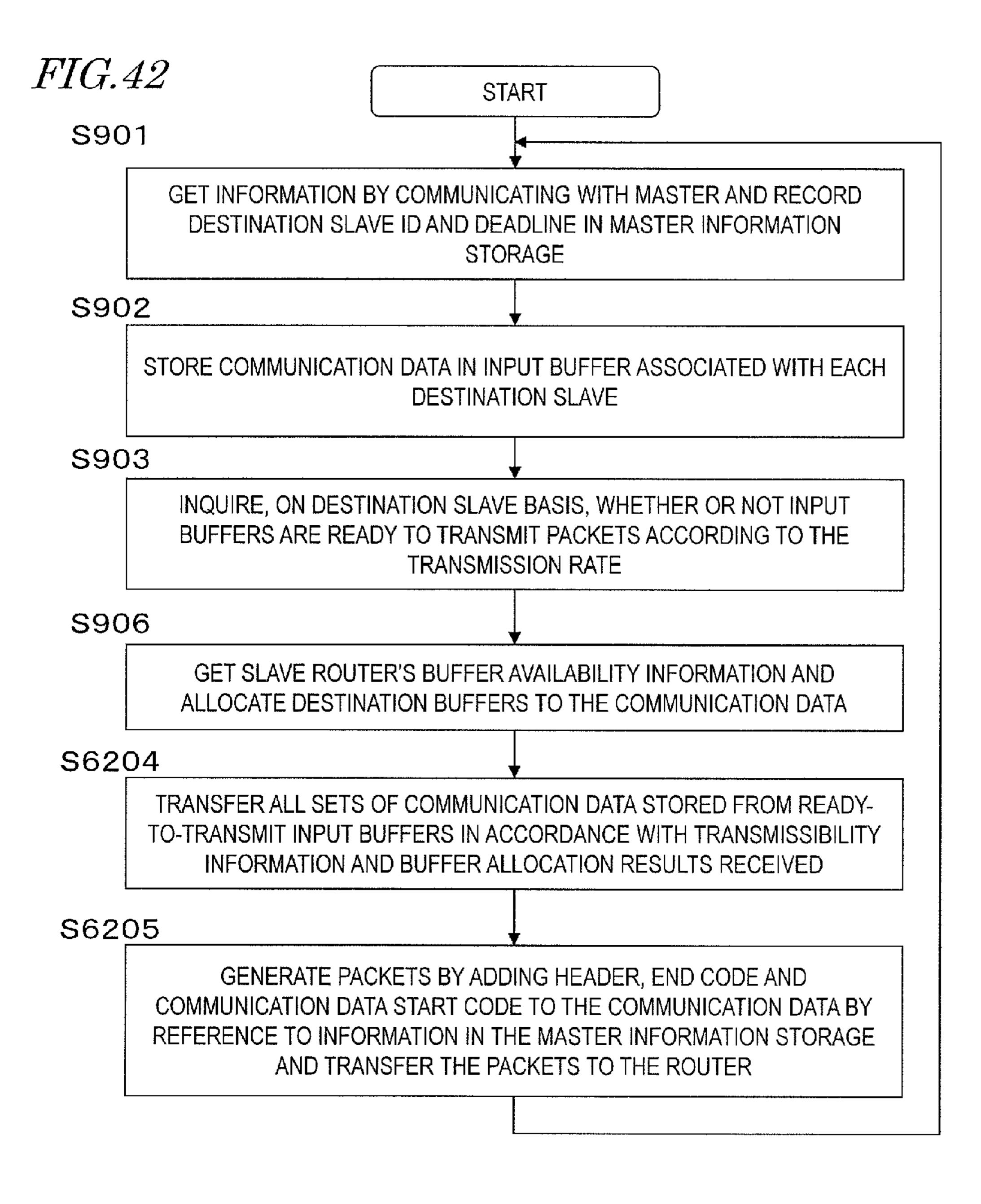

FIG. 42 is a flowchart showing how the master NIC 102 operates to get packet multiplexing done.

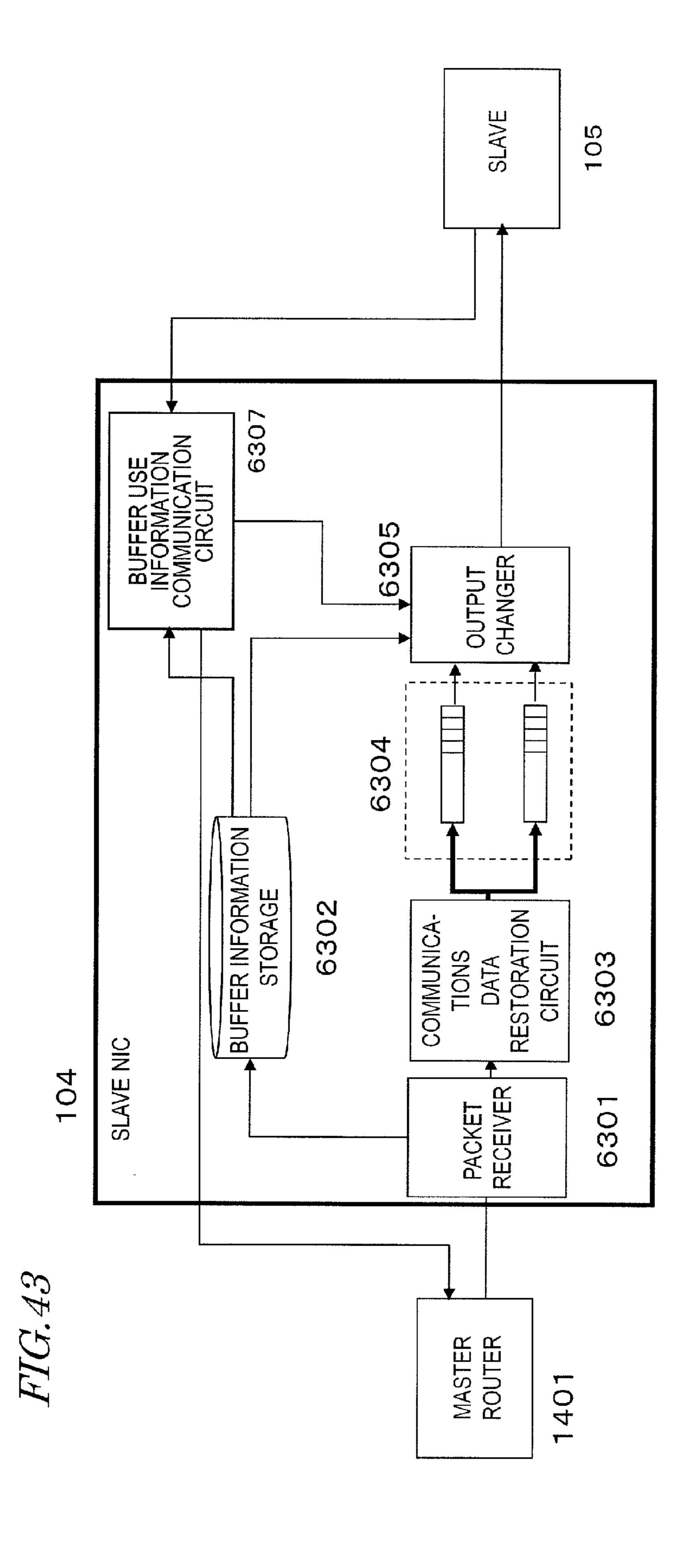

FIG. **43** illustrates a packet multiplexing configuration for a slave NIC **104**.

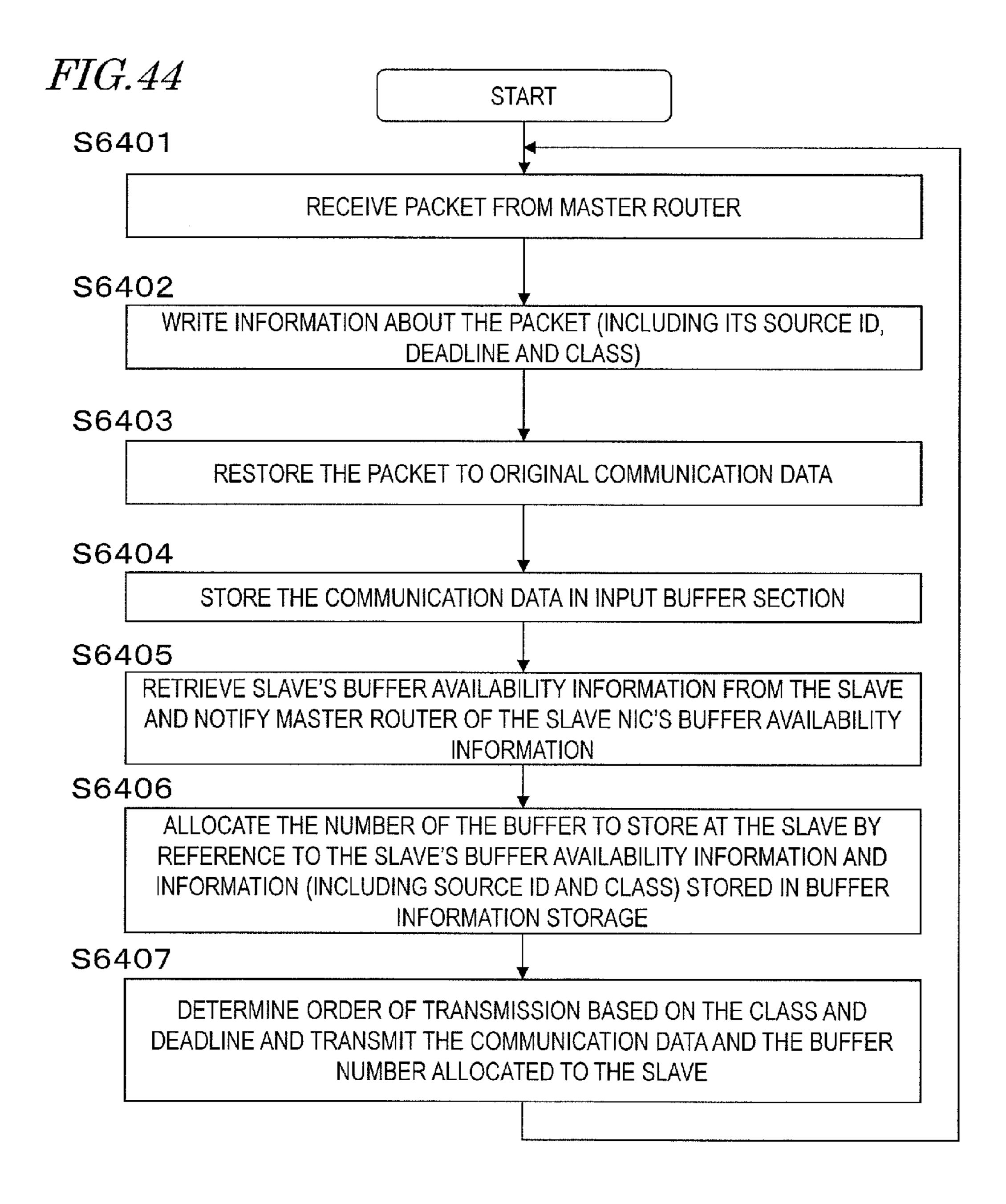

FIG. 44 shows the flow of packet multiplexing operation of the slave NIC 104.

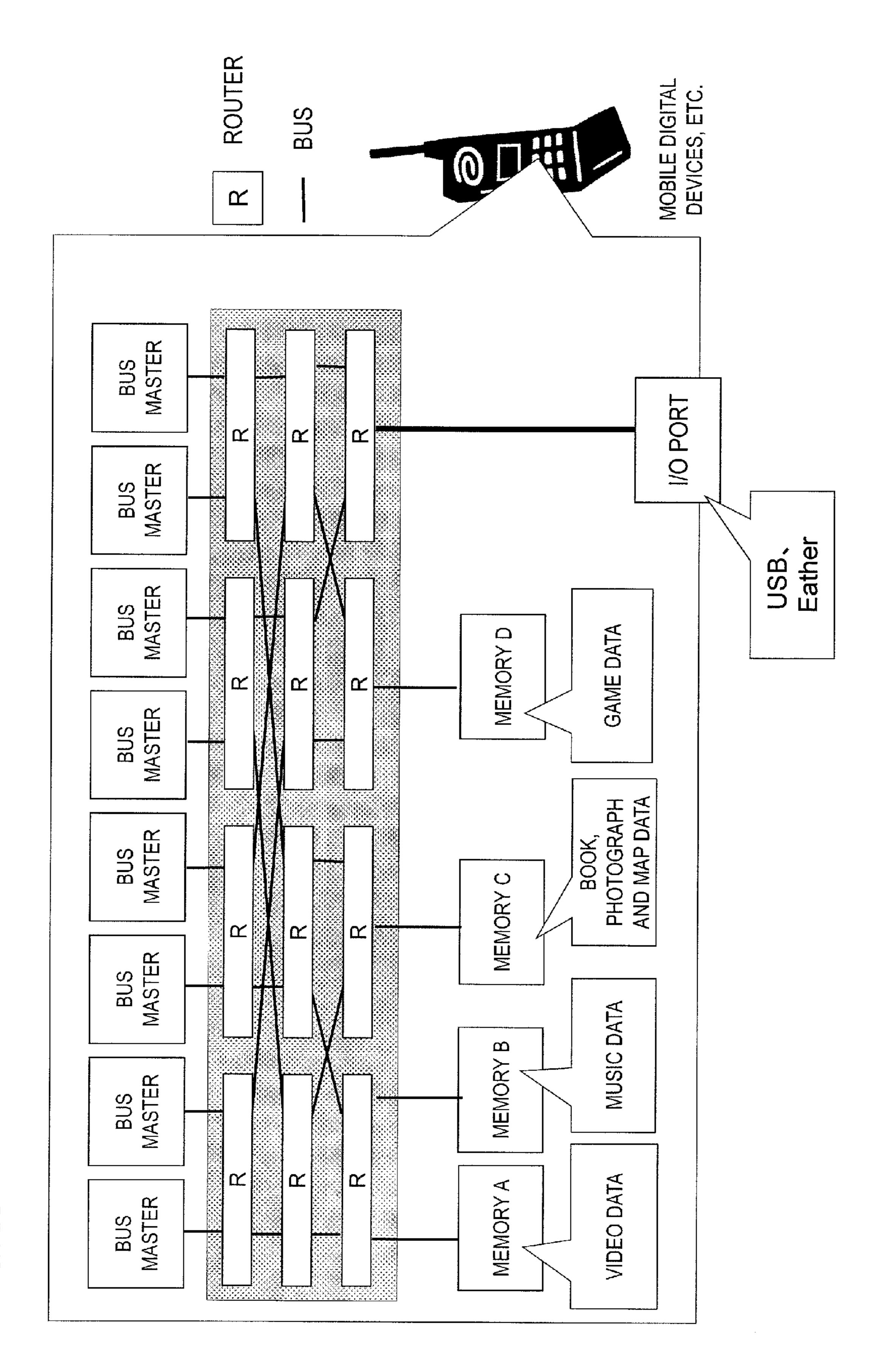

FIG. **45** illustrates an example in which multiple masters and multiple memories on a semiconductor circuit and common input/output (I/O) ports to exchange data with external devices are connected together with distributed buses.

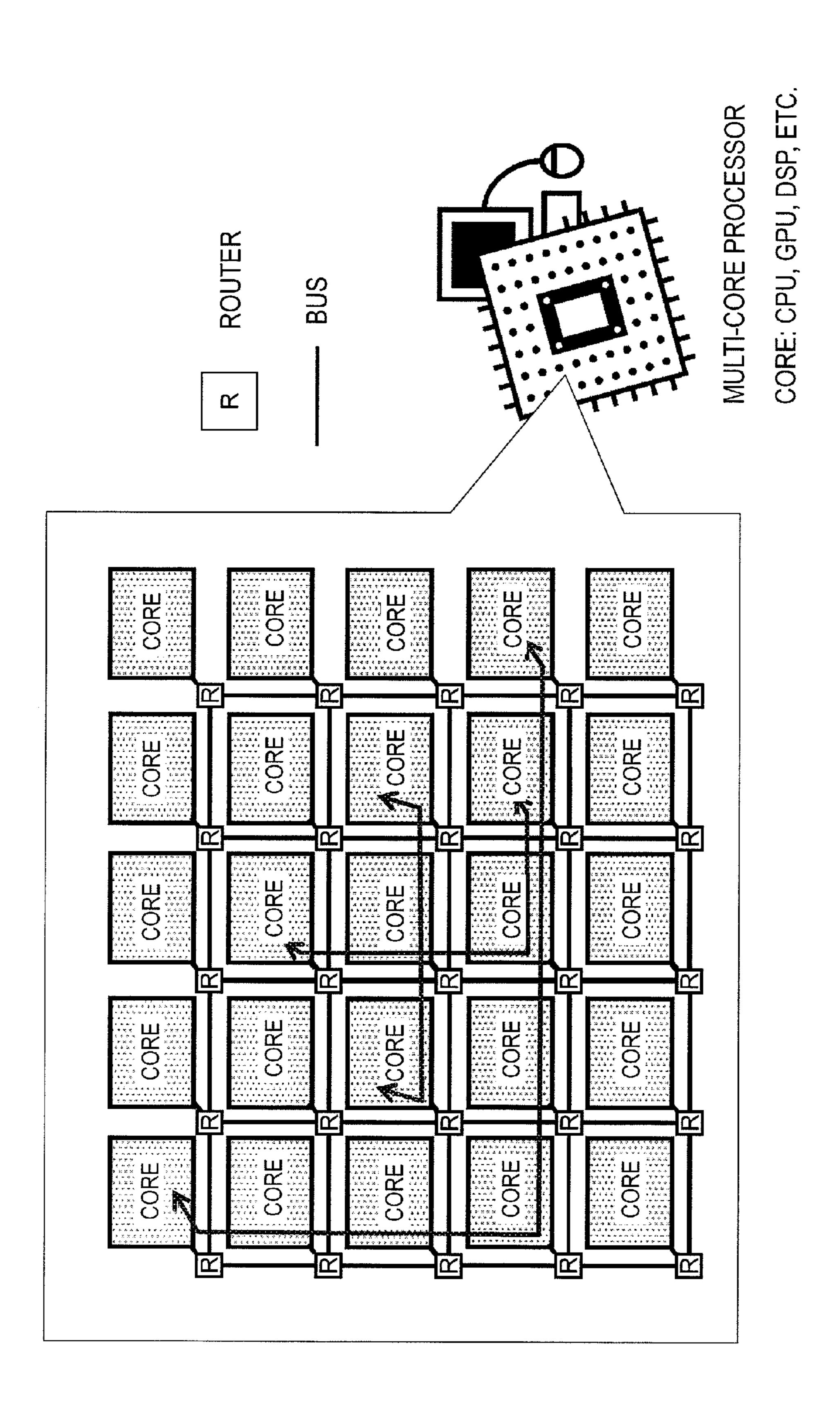

FIG. **46** illustrates a multi-core processor in which a number of core processors such as a CPU, a GPU and a DSP are arranged in a mesh pattern and connected together with distributed buses in order to improve the processing performance of these core processors.

FIG. 47 illustrates how classification may be done according to the priority level of a time-delay-guaranteed class.

#### DETAILED DESCRIPTION

According to the conventional method, however, it is not until the other messages that have been stored in advance have been transmitted, to say the least, that such a message with a high level of priority is transmitted. For that reason, the time delay caused by a router to such a message with a high level of priority is affected by other messages with a low level of priority, and therefore, tends to be a significant one.

To ensure performance under such a condition, the band-width provided should be significantly broader than what is actually needed. In addition, the transmission bandwidth required varies according to the ratio of high and low levels of 25 priorities in a buffer.

According to an exemplary embodiment of the present invention, a bus' band is obtained so as not to be overestimated with respect to the performance required for each traffic flow running through the bus. After that, the bus' extra 30 band to be produced by being estimated in a worst case scenario is cut down as much as possible.

Before exemplary embodiments of the present disclosure are described, the terms to be used in this description will be defined. It should be noted that some terms other than the 35 following ones will also be defined as needed in the following description of embodiments.

"To have a burst property" refers herein to a situation where while a bus master is transmitting the communication data of traffic flows continuously, those traffic flows have only a short 40 permitted time delay or request a broad bandwidth. As such communication data to be transmitted by a bus master with a burst property, video based data may be classified, for example. On the other hand, as communication data in a time-delay-guaranteed class with no burst property, USB data 45 may be classified. It is determined from a designer's point of view whether given data has a burst property or not.

The "non-performance-ensuring data" is data which needs to guarantee neither throughput nor time delay.

The "requested bandwidth" refers herein to the transmis- 50 sion quantity per unit time of a traffic flow, of which the throughput is guaranteed.

The "deadline" of a traffic flow refers herein to a time by which the traffic flow is supposed to arrive at its destination (i.e., slave) as specified by a bus master that has started to 55 transmit the traffic flow.

For example, according to exemplary embodiments of the present invention, the bus system and router to be described below can be obtained.

Specifically, an embodiment provides a bus system for a 60 semiconductor circuit to transmit data between a first node and at least one second node through a network of buses and at least one router which is arranged on any of the buses. The data to be transmitted includes performance-ensuring data which guarantees at least one of throughput and a permitted 65 time delay. The first node includes: a packet generator configured to generate a plurality of packets, each of which

6

includes the data to be transmitted and classification information that indicates the class of the data to be transmitted to be determined according to its required performance; and a transmission controller configured to control transmission of the packets. The at least one router includes: a buffer section configured to store the received packets separately after having classified the packets according to their required performance by reference to the classification information; and a relay controller configured to control transmission of the packets that are stored in the buffer section at a transmission rate which is equal to or higher than the sum of transmission rates to be guaranteed for every first node associated with the classification information by reference to each piece of the classification information.

In one embodiment, the at least one router includes a plurality of routers. The plurality of routers operate at the same operating frequency, and the respective relay controllers provided for those routers control transmission of the packets at the same transmission rate. And the same transmission rate is set to be equal to or higher than the maximum one of the transmission rates to be guaranteed by the plurality of routers.

In another embodiment, a transmission rate to be guaranteed has been set in advance with respect to each performance-ensuring data. The transmission controller controls transmission of packets of the performance-ensuring data either at a predetermined rate which exceeds a transmission rate to be guaranteed by the performance-ensuring data or without imposing a limit to the transmission rate. The at least one router is able to transmit the packets of the performanceensuring data at a rate exceeding the transmission rate to be guaranteed by using a first band in which the transmission rate to be guaranteed is able to be maintained and a second band which is an extra band. The relay controller classifies, by reference to the classification information, the respective packets of the performance-ensuring data among the plurality of packets that are stored in the buffer section into packets to be transmitted using the first band and packets to be transmitted using the first and second bands, and transmits preferentially the packets to be transmitted using the first band.

In another embodiment, the data to be transmitted further includes non-performance-ensuring data which guarantees neither throughput nor permitted time delay. The transmission controller controls transmission of packets of the non-performance-ensuring data without imposing a limit to their transmission rate. The buffer section stores the received packets of the non-performance-ensuring data separately. And the relay controller transmits the packets of the performance-ensuring data and the packets of the non-performance-ensuring data in this order.

In another embodiment, the packet generator further gives time information about the deadlines of the packets to the packets, and as for packets to which the same piece of classification information is given, the relay controller determines the order of transmission of the packets according to their deadlines.

In another embodiment, the time information about the deadlines is information about a deadline by which the packets are supposed to arrive at the at least one second node, information about a time when the first node transmitted the packets, information about an accumulated value of processing times by the first node and the router, or information about the value of a transmission counter indicating the order of transmission of the packets from the first node.

In another embodiment, if the time information about the deadlines does indicate the deadlines, the relay controller transmits packets with closer deadlines more preferentially than the other packets.

In another embodiment, as for each of the packets to be transmitted using the first and second bands, the relay controller and the transmission controller determine a rate exceeding a transmission rate to be guaranteed based on the processing ability of a node or link that is going to cause a 5 bottleneck for the bus system.

In another embodiment, the performance-ensuring data includes burst data with a burst property and non-burst data with no burst property. The classification information given by the packet generator is able to distinguish the burst data 10 from the non-burst data. The buffer section of the at least one router stores the burst data and the non-burst data in the multiple buffers separately. And the relay controller of the at least one router transmits the packets of the burst data and then the packets of the non-burst data.

In another embodiment, the transmission controller of the first node transmits the burst data at a predetermined transmission rate, and the relay controller transmits at least the burst data at a predetermined transmission rate.

includes a plurality of second nodes, and the buffer section of the at least one router stores the packets of the respective second nodes in the plurality of buffers separately from each other.

In another embodiment, the packets include command- 25 sending packets and data-sending packets, and the relay controller transmits the command-sending packets without imposing any limit to their transmission rate.

In another embodiment, the packets include commandsending packets and data-sending packets, and the buffer section of the at least one router stores the command-sending packets and the data-sending packets in the plurality of buffers separately from each other.

In another embodiment, the packet generator of the first node multiplexes the packets and transmits a resultant multiplexed packet.

In another embodiment, the first node that transmits the multiplexed packet and the at least one router include a signal line to transmit information indicating division positions at which the multiplexed packet is restored to respective data.

A router according to another embodiment of the present invention is arranged on any of buses that form a network in a bus system for a semiconductor circuit to relay data to be transmitted between a first node and at least one second node of the bus system. The first node generates and transmits a 45 plurality of packets, each of which includes the data to be transmitted and classification information that indicates the class of the data to be transmitted to be determined according to its required performance. The data to be transmitted includes performance-ensuring data which guarantees at least 50 one of throughput and a permitted time delay. And the router includes: a buffer section which stores the received packets separately after having classified the packets according to their required performance by reference to the classification information; and a relay controller which controls transmis- 55 sion of the packets that are stored in the buffer section at a transmission rate which is equal to or higher than the sum of transmission rates to be guaranteed for every first node associated with the classification information by reference to each piece of the classification information.

Hereinafter, a router as an embodiment of the present invention will be described with reference to the accompanying drawings.

What will be described in the following description is a technique for increasing the transmission efficiency of dis- 65 tributed buses (NoC) in a semiconductor integrated circuit at as low a bus' operating frequency as possible based on quan-

titative tentative calculations while minimizing mutual interference between multiple traffic flows running through the buses with mutually different required performances. What will also be described in the following description is a configuration for a router that ensures performance (in terms of throughput and permitted time delay) for use in the NoC and the QoS (Quality of Service) of the distributed buses.

The present inventors set "classes", into any of which a given traffic flow is to be grouped according to its required performance. That is to say, a traffic flow running out of a bus master as an output node is grouped into any of those classes that have been set and a buffer to store the traffic flow is provided separately in a router for each of those classes in order to reduce interference between the classes. For 15 example, in this description, roughly two major classes, namely, a performance-ensured class and a non-performance-ensured class, are set. And each of these classes may be subdivided into sub-classes according to its required performance. It will be described in further detail later with In another embodiment, the at least one second node 20 respect to exemplary embodiments how to set such classes and sub-classes.

> In one embodiment of the present invention, with respect to a traffic flow of the performance-ensured class, on which a relatively strict performance requirement is imposed, routers and bus masters perform transmission processing at a high priority level and at a controlled rate. On the other hand, a traffic flow of the performance-ensured class, on which a less strict performance requirement is imposed, and a traffic flow of the non-performance-ensured class, on which no performance requirement is imposed at all, are transmitted at a low priority level but at a rate exceeding the requested band. As a result, the traffic flow of the performance-ensured class can definitely have its performance ensured. On the other hand, the traffic flow of the performance-ensured class with less strict performance requirement and the traffic flow of the non-performance-ensured class can be transmitted using the bus' extra band to be produced by worst estimation. By reducing the interference between those classes of performance requirement and using the bus more efficiently, there is no need to overestimate the required bus bandwidth to ensure the performance, and a performance-ensured bus can be established at a low bus' operating frequency. On top of that, since the bus' operating frequency can be decreased, the power dissipation by the bus and the required chip area can be both reduced, the flexibility of layout can be increased, and the restriction of bus lines (e.g., distance of bus lines to be wired) can be relaxed.

> FIG. 2 shows a processing policy according to this embodiment to be applied to the performance-ensured class and the non-performance-ensured class.

> Suppose Performance-Ensured Classes A, B and C and Non-Performance-Ensured Class Z have been defined as traffic flow classes as shown in FIG. 2.

As for traffic flows of Classes A and B, routers and bus masters set a transmission rate (upper limit value) based on the requested bandwidth and control the transmission rate of the traffic flows, thereby ensuring their performance. In particular, a traffic flow of Class A needs to satisfy a more strict performance requirement than a traffic flow of Class B does, and therefore, is transmitted at a higher priority level.

A traffic flow of Class C is transmitted by routers and bus masters at a transmission rate exceeding the requested band. As a result, the bus' extra band can be used with the performance ensured.

A traffic flow of Class Z is processed at a lower priority level than a traffic flow of any of the other classes described above. In this case, non-performance-ensuring data can be

transmitted without putting an upper limit to the transmission rate and the bus' extra band can be used. In addition, the routers can group the buffers into the respective classes, can reduce the interference between the classes by performing the transmission control on a class-by-class basis, and can transmit a traffic flow with a high priority level at a shorter time delay. As a result, the bus can be used more efficiently with the performance ensured at a lower bus' operating frequency.

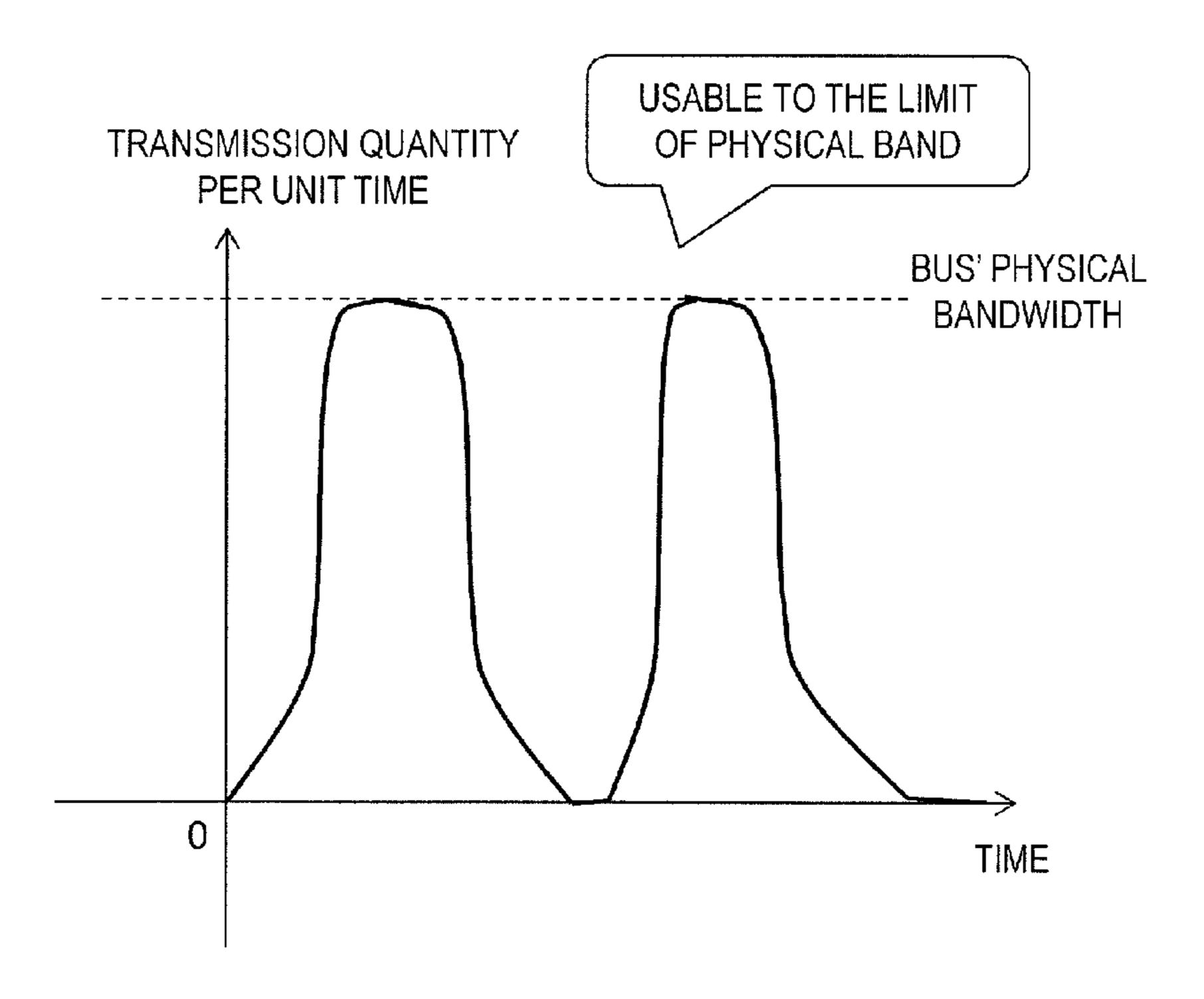

In this description, the "worst estimation" refers herein to calculating the bus bandwidth at which the performance can be ensured by expecting, during the design process, the traffic flow status when the bus system is in the worst-case scenario. Actually, however, the traffic flow rate may sometimes be lower than in the worst-case scenario, and there will be an extra band, i.e., a margin, in the bus.

<Overall Configuration>

FIG. 3 illustrates an exemplary NoC which is implemented using routers 103 as an embodiment of the present invention.

In FIG. 3, illustrated are an exemplary buffer configuration for the routers 103 and how a packet may be transmitted.

to satisfy the performance to satisfy the performance

This NoC includes a bus master 101, a master network interface controller (NIC) 102, at least one router (such as the router 103), a slave NIC 104, and a slave 105.

The bus master 101 (which will be sometimes simply 25 referred to herein as a "master") is connected to the master NIC 102. The master and slave NICs 102 and 104 are connected together via the at least one router (such as the router 103). The slave NIC 104 is connected to the slave 105. In the following description, each of the routers is supposed to have 30 the same configuration and perform the same operation. Thus, the router 103 will be described as an example of the at least one router.

The router 103 includes an input buffer section 1404 to store the packets 202. Specifically, the input buffer section 35 1404 stores the packets 202 on a class-by-class basis according to the class of each of those packets 202 to relay. The router 103 includes such an input buffer section 1404, and therefore, can arrange the order of priorities of the packets 202 to transmit as will be described in detail later. Also, since 40 the master NIC 102 and the router 103 transmit the packets at rates that have been set in advance for the respective classes, each of the NIC 102 and router 103 includes a rate controller (to be described later).

The master NIC 102 generates one or more packets 202 45 based on the communication data 201 received from the bus master 101, divides the packet 202 into data units, of which the size is small enough to send it in one cycle of the bus' operating frequency, and transmits those data units. In this description, such data units, of which the size is small enough 50 to send them in one cycle of the bus' operating frequency, will be referred to herein as "flits". In FIG. 3, illustrated are a number of such flits 203.

The packet to be transmitted is stored in the input buffer section 1404 of the router 103, is sent on a flit-by-flit basis 55 from the router 103 and other routers, and then arrives at the slave NIC 104. In response, the slave NIC 104 reconstructs each packet based on those flits 203 received, restores the original communication data based on a plurality of packets, and transmits the original communication data to the slave 60 105.

FIG. 4 shows the concepts of respective components of an NoC.

In this description, some of these components will be collectively referred to as follows.

The bus master 101 and the master NIC 102 will be collectively referred to herein as a "first node 211".

10

The slave 105 and the slave NIC 104 will be collectively referred to herein as a "second node 215".

More than one router 103 will be regarded herein as a single router macroscopically, and will be referred to herein as a "router 206".

And the first and second nodes 211 and 215 and the entire router 206 will be collectively referred to herein as a "bus system 5501".

Hereinafter, a router **206** according to an exemplary embodiment of the present invention will be described with reference to the accompanying drawings.

FIG. 5 schematically illustrates a configuration for the NoC shown in FIG. 3.

First of all, the master NIC **102** receives data about each traffic flow in the input buffer section (not shown) from the master **101** and transmits the packets **202** at a transmission rate which has been set for each master **101** to be high enough to satisfy the performance requirement on each traffic flow.

The router 103 includes an input buffer section 1404 and a rate controller 1409

The input buffer section **1404** (will be simply referred to herein as a "buffer section") includes input buffers 1405, which store traffic flows that have been grouped according to their destinations and their classes. In the example illustrated in FIG. 5, each of those input buffers 1405 is implemented as an FIFO (First In, First Out) buffer. By being provided with such an input buffer section 1404, the router 103 can change the traffic flows to transmit so as to prevent a traffic flow of a high priority level class from being affected by a traffic flow of a low priority level class. Even though the buffer is supposed to be an input buffer in this embodiment, this configuration is also applicable in the same way, even if the buffer is included as an output buffer. The reason is that the packets just need to be stored separately according to the performance requirement and the rate of transmission of the packets to an adjacent router or slave NIC just needs to be controlled, no matter where the buffers are arranged.

The rate controller **1409** transmits the packets at a transmission rate that has been set on a class-by-class basis. For example, the rate controller **1409** may set the transmission rate in the form of a transmission interval. In this description, the rate controller will be sometimes referred to herein as a "relay controller".

As the transmission rate set by the rate controller 1409 of the router 103, a transmission rate value which is equal to or greater than the transmission rate guaranteed for the master NIC 102 needs to be set on a class-by-class basis, because the packets issued by a plurality of masters are confluent there. For example, if there are N masters that have been grouped into the same class and if the transmission rate is set at a predetermined transmission interval, the transmission interval is set to be equal to or smaller than the value obtained by dividing the transmission interval of the master NIC by N. That is to say, the packets are transmitted at a transmission rate that is equal to or greater than the sum of the transmission rates to be guaranteed by the respective masters. Optionally, if such a rate control is performed in the routers, not just in the master NICs, the time delay and throughput of each class can be guaranteed end-to-end.

Specifically, as a method for getting the transmission rate set by a router, an individual transmission rate value may be set for each router based on the rate to be guaranteed for the traffic flow running through that router.

FIGS. 6A and 6B show exemplary transmission rate values to be set for respective routers.

FIG. 6A illustrates an example in which a minimum guaranteed transmission rate value is set based on the traffic flows

running through the respective routers. For example, as shown in FIG. 6A, the sum of the transmission rates to be guaranteed for the respective traffic flows coming from the masters A0 and A1 is set to be the traffic flow transmission rate for the router R2 and controlled. If the transmission rates 5 of the respective routers are set by such a method, the bus operating frequencies of the respective routers can be minimized. However, the implementation cost will rise, because the respective routers should be designed to have the best frequencies.

According to another exemplary embodiment, the same transmission rate value may also be set for the respective routers. In that case, the traffic flow transmission rates of the respective routers may be set, with respect to each class, to be the transmission rate of a router where traffic flows to be 15 guaranteed are confluent with each other most heavily in the overall system, and controlled.

For example, as shown in FIG. 6B, the router R2 sets the traffic flow transmission rate of each router based on the transmission rate value (i.e., the sum of the rates guaranteed 20 for the masters B0, B1 and B2) of the router R3 where traffic flows are confluent with each other most heavily. By setting the transmission rate that is the highest in the entire system to be the transmission rate of each router, a bottleneck will be hardly created in the entire network. Consequently, the per- 25 formance can be ensured more easily and the hardware can be laid out more easily, because the bus system can be designed at a single operating frequency.

In this exemplary embodiment, the highest transmission rate in the entire system is supposed to be set in common to be 30 the transmission rate at the relay controller of each router. However, this is just an example. Alternatively, the transmission rate may even be set to be higher than the highest transmission rate in the entire system.

operating frequency and if the transmission rate were set to be the same in every relay controller, an excessively high transmission rate would be set for some routers. In that case, those routers should operate at a more than necessarily high operating frequency.

It should be noted that if the operating frequency that makes the routers operate at the sum of the respective transmission rates to be guaranteed is excessively high, then not every router has to be driven at the same operating frequency. Alternatively, as in a system bus or a local bus, the operating 45 frequency may be changed on a bus role basis, a router with the highest transmission rate may be selected, and the transmission rate may be set. In this manner, it is possible to prevent the operating frequency of a router on a local bus which is relatively close to a master from going excessively 50 high.

The classes in the input buffer section 1404 may be grouped into a time-delay-guaranteed class which needs to take the time delay into consideration and a non-time-delayguaranteed class which does not have to take the time delay 55 into consideration. The time-delay-guaranteed class is subdivided into Class A with a burst property and Class B with any other property. In this embodiment, the input buffers are allocated according to those subdivided low-order classes.

As for the low-order classes of the time-delay-guaranteed 60 class and the non-time-delay-guaranteed class, any arbitrary number of input buffers may be allocated to any arbitrary number of classes.

In this embodiment, the "time-delay-guaranteed class" is supposed to be subdivided based on a permitted time delay. 65 However, the "time-delay-guaranteed class" may also be subdivided based on throughput, not on time delay. That is to say,

according to this embodiment, the time-delay-guaranteed class may be subdivided based on at least one of time delay and throughput.

The input buffer section 1404 of the router 103 and the input buffer section (not shown) of the master NIC 102 are configured so that buffers are separated according to their destinations. By separating the buffers not only on a classby-class basis but also according to their destinations, interference between traffic flows with mutually different destinations can be reduced. Also, even if the bus is congested with traffic flows bound for a certain destination, traffic flows bound for another destination can secure buffers for sure, and can be transmitted just as intended.

In addition, if the buffers are separated as described above, interference between traffic flows with mutually different priority levels and interference between traffic flows with mutually different destinations can be reduced by changing the transmission rate according to the class and the destination in a situation where those buffers are implemented as FIFOs. Nevertheless, if the transmission rate can be changed and if the buffers to use can be managed on a class-by-class basis or on a destination basis by using randomly accessible memories, for example, then those buffers do not have to be physically separated from each other.

For example, not only randomly accessible memories but also an address table as data may be provided for the router 103. The address table is a table with which the storage addresses and stored packets are managed on a destination slave basis for each class in the memory. By using those memories and such an address table, any arbitrary packet stored in the input buffer of the router 103 can be freely read from and written to. As a result, effects to be obtained by logically separating the buffers can be achieved. Even if packets with low priority levels or bound for a certain destination Nevertheless, if every router were operating at the same 35 are stored in a buffer, packets with high priority levels or bound for another destination can be transmitted without interfering with the former packets.

> Still alternatively, the bus system may also be configured so that buffers to be used by a traffic flow with a low priority level are usable for a traffic flow with a high priority level. In that case, the buffers usable for the traffic flow with the high priority level will include both buffers not to be interfered with by the traffic flow with the low priority level and buffers to be interfered with by the traffic flow with the low priority level. However, just at least one buffer not to be interfered with by the traffic flow with the low priority level needs to be secured. In that case, interference by the traffic flow with the low priority level can be reduced.

> Furthermore, as a method for controlling the transmission rate between the rate controller 1409 of the router 103 and the rate controller (not shown) of the master NIC 102, the packet transmission interval is controlled according to this embodiment, because such a method can be implemented easily. For example, if a traffic flow needs to be transmitted at a higher transmission rate, the transmission rate can be increased by setting the transmission interval to be a narrower one. Specifically, if the traffic flow transmission rate needs to be doubled, then the transmission interval may be halved. On the other hand, if the traffic flow transmission rate needs to be halved, then the transmission interval may be doubled. However, the transmission rate may also be controlled by any other method such as a technique for measuring the size or length of data that has been transmitted per unit time or in a unit cycle. Furthermore, even though the slave is generally implemented as a memory or a memory controller, the slave does not have to be a memory but may also be any other arbitrary node such as a master, an I/O or a router.

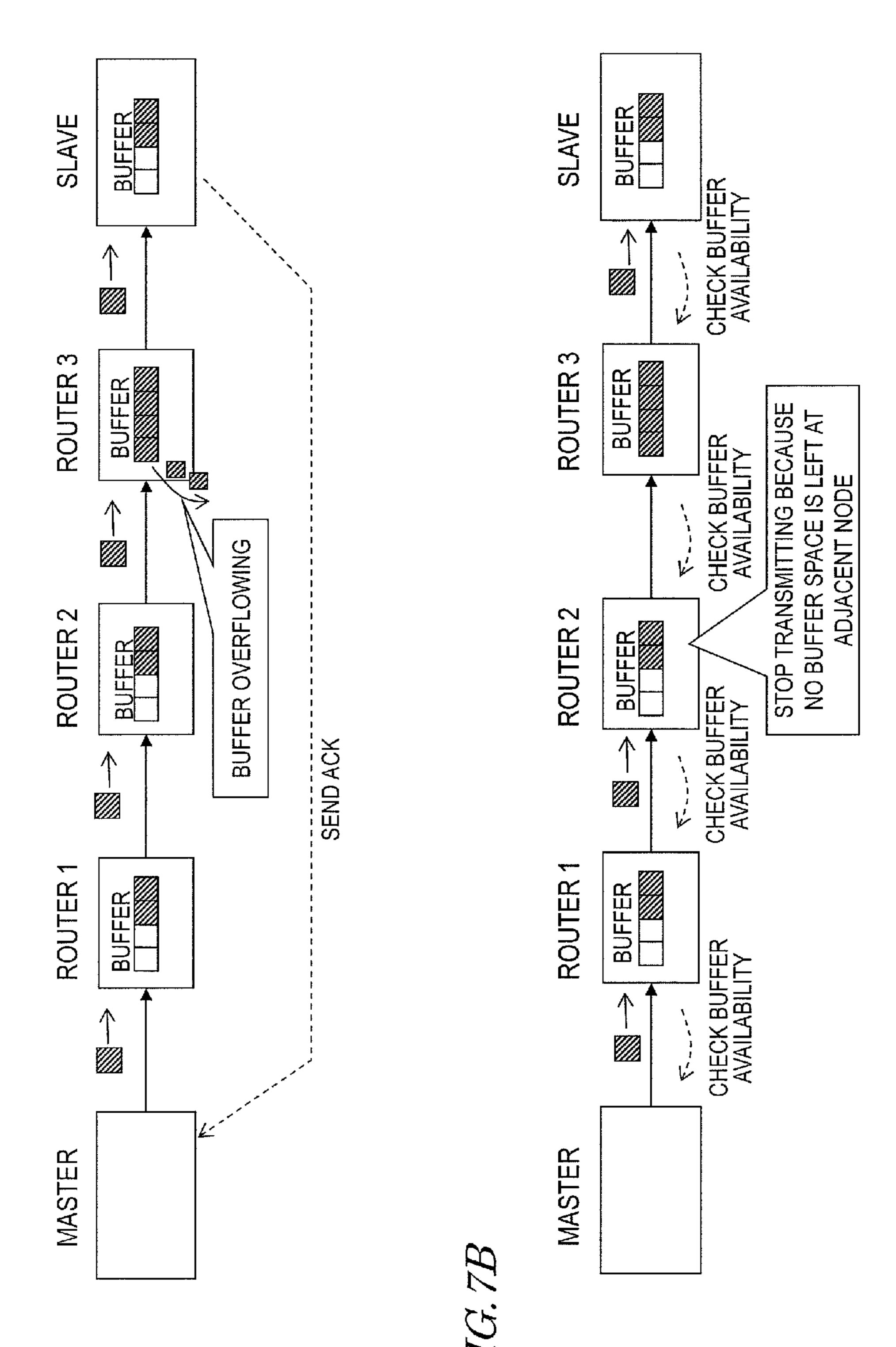

The flow control to be carried out by the router 103 of this embodiment is quite different from a flow control to be applied to the Internet. Hereinafter, the reason will be described with reference to FIGS. 7A and 7B.

FIGS. 7A and 7B shows how the effect achieved varies 5 depending on whether the configuration of the router 103 described above is applied to the Internet or to a semiconductor bus system.

On the Internet (as shown in FIG. 7A), the flow control of data transmitted from a master is carried out based on the 10 exchange between the master and a slave compliant with the TCP (Transmission Control Protocol). Meanwhile, each router on the transmission route performs a routing control for determining the transmission route or the QoS control. However, no routers on the Internet carry out any flow control. Instead, since data is just transmitted through the Internet, no matter how much space is left in a buffer at an adjacent node, data could be lost due to buffer overflowing.

In the example illustrated in FIG. 7A, each of Routers 1 and 2 and Slave, of which the buffer still has a space left, can 20 receive data that has been transmitted from the adjacent node. On the other hand, Router 3, of which the buffer has no space left, cannot store the data in its buffer and causes buffer overflowing. In addition, even if packets are discarded on the router end in order to avoid convergence before the buffer 25 overflows, data could be lost, too.

On the other hand, in the semiconductor bus system to which this embodiment is applied (see FIG. 7B), the flow control is carried out between every pair of nodes on the transmission route. Specifically, for that purpose, before sending data, each node sees if there is any space left in the buffer of the adjacent destination node. And the node transmits the data only if there is still a space left in the buffer.

processed at the highest prioric ence in priority level and a difference in priority level

That is why by stopping transmitting the data if there is no space left in the buffer at the destination node, buffer overflowing can be avoided. In the example illustrated in FIG. 7B, only Master and Routers 1 and 3 which have confirmed that there is still a space left in the buffer at the adjacent destination node (which may also be a router) transmit data, while Router 2 which has failed to confirm that there is a space left in the buffer at the adjacent destination node stops transmitting the data. As a result, the data loss due to buffer overflowing can be avoided. As can be seen, the semiconductor bus system to which this embodiment is applied is quite different from the Internet technology in the respect that no data is 45 supposed to be lost on the transmission route.

If the disclosure of the embodiments described above were applied to the Internet, then excessive amounts of data would be sent on a non-rate-controlled traffic flow or on a traffic flow to be transmitted at a rate exceeding the requested bandwidth 50 to cause buffer overflowing and packet loss on the route. On sensing that packet loss, the transmission node would retransmit the data with the data size cut down dynamically. Consequently, in that case, it should be difficult to maximize the efficiency to use the extra band and to ensure the performance 55 in terms of time delay and throughput.

On the other hand, the semiconductor bus system described above does not lose, but accumulates, the excessive amounts of data that has been transmitted. That is why each router can transmit low priority level data that has been accumulated in 60 the buffer by taking advantage of a time interval in which no high priority level data is being transmitted, and therefore, can use the bus more efficiently. Each router will have such a time interval in which no high priority level data is being transmitted and in which there is a margin in the bus band. The 65 router of this embodiment can make data flow by using that extra band as will be described later.

**14**

<General Flow>

FIG. **8** is a flowchart showing the procedure of operation of an NoC including routers according to an embodiment of the present invention.

The bus master 101 transmits communication data 201 to the master NIC 102 (in Step S501). In response, the master NIC 102 transforms the communication data 201 received into packets 202 and transmits the packets 202 to the router 103 at a transmission rate to be set on a class-by-class basis (in Step S502).

The master NIC 102 sets the transmission rates of time-delay-guaranteed classes A and B to be a transmission rate at which the performance required by each of these classes in terms of the requested bandwidth and time delay is satisfied. As for the transmission rate of Class C, on the other hand, the master NIC 102 may or may not set the transmission rate to be an upper limit value exceeding the requested bandwidth in order to use the extra band while ensuring the performance in terms of requested bandwidth and delay.

And as for the transmission rate of the non-time-delay-guaranteed class (i.e., Class Z), the master NIC **102** does not put an upper limit to the transmission rate in order to use the extra band. It should be noted that the transmission priority levels of these four classes are supposed to decrease in the order of Classes A, B, C and Z. That is to say, Class A is processed at the highest priority level. FIG. **2** shows a difference in priority level and a difference in rate control between the performance ensured classes A, B and C and the non-performance ensured class Z.

The more than one router 103 transmits the packets at a preset rate value in the descending order of the class priority levels according to the destination slave IDs and classes of the packets 202 received (in Step S503).

The slave NIC 104 converts the packets 202 received from the router 103 into the original communication data 201 and then transmits the communication data to the slave 105 (in Step S504). In response, the slave 105 interprets the communication data 201 received to determine whether or not the slave 105 needs to respond to the communication data 201 received (in Step S505). If the answer is YES, the slave 105 generates communication data as a response and transmits the communication data to the slave NIC 104 (in Step S506). The slave NIC 104 converts the communication data 201 which has been received as a response from the slave into packets 202 and transmits the packets 202 to the router 103 (in Step S507). The router 103 checks out the destination of the packets 202 received, determines their target and transmits them to the target (in Step S508). Meanwhile, the master NIC 102 converts the packets 202 received into the communication data 201 and then transmits the communication data 201 to the bus master 101 (in Step S509).

FIG. 9 shows the rule of classifying bus masters so that the performance-ensuring data and the non-performance-ensuring data can be distinguished from each other, to say the least, in order to lower the estimated bus' operating frequency required. The designer of a bus system sets the class of a given bus master according to this classification rule. Although this is not an operation to be performed by a router, it will be described anyway in the following description.

In order to classify respective masters in advance, first of all, the designer defines the specification required for a traffic flow generated by every master during the design process (in Step S3201).

The designer groups a master which has a low priority level and which just needs to make a traffic flow run only when the bus is not occupied into Class Z (in Step S3202). Such a

master grouped into Class Z generates a non-performanceensured traffic flow, which may be data output from a processor, for example.

The designer groups a master which needs to transfer data at a rate exceeding the requested bandwidth into Class C (in Step S3205), to which masters in charge of some processoror graphics-related processing belong. Class C further includes a master that outputs a traffic flow which should be transmitted at rates that vary with time but that are always equal to or higher than a certain rate as in filter processing, for example, and which may be transmitted as a preceding flow at a rate that is equal to or higher than an average requested bandwidth time wise.

The designer groups a master which belongs to the time-delay-guaranteed class, on which a strict requirement is imposed in terms of requested bandwidth and permitted time delay, and which has a burst property into Class A (in Step S3203). A traffic flow generated by such a master in Class A is subjected to transmission processing most preferentially, and therefore, is transmitted by a router without interfering with a traffic flow in any other class. Consequently, the performance of each traffic flow can be ensured in terms of time delay and throughput at an even lower bus' operating frequency.

The designer groups the other masters into Class B (in Step S3204).

FIG. 10 shows specific exemplary definitions of specifications required for traffic flows to be generated by masters.

The required specifications are defined by various parameters. Examples of those parameters include a master ID, a traffic flow requested bandwidth, a permitted time delay, the length of a packet when generated, and a destination slave ID. If the slave is a memory, the type of the communication data, which may be Read access or Write access, for example, is also defined. For example, the item on the second row of the table shown in FIG. 10 indicates the attributes of a traffic flow generated by a master of which the master ID is 0. This traffic flow has a requested bandwidth of 800 megabytes per second (MB/s), a permitted time delay of 0.2 µs and one packet length of 10 flits, and is a Write access with respect to a slave of which the slave ID is 0.

<Respective Components>

FIG. 11 shows respective classes to which the bus masters 101 are grouped and their specific examples. In this embodiment, once a bus master 101 is determined, its class is supposed to be determined automatically. However, if a certain bus master performs multiple kinds of processing and sends a traffic flow, the class may be determined on a traffic flow basis.

One of the following two methods may be adopted as a method for defining classes on a traffic flow basis.

For example, the classes may be defined on a traffic flow basis by having a bus master add class specifying information to data that forms a traffic flow and send such data to a master 55 47. NIC. As described above, the specification required for a traffic flow to be generated by each bus master is defined by the designer. The bus master naturally knows the specifications required for a traffic flow and therefore can specify the class.

Alternatively, the master NIC may define the classes on a traffic flow basis. The master NIC stores, in a memory in advance, a table (not shown) in which the identifier of each traffic flow is associated with a class. A bus master adds an identifier associated with the specifications required for a 65 traffic flow to the data that forms the traffic flow and then sends the data to the master NIC. In response, the master NIC

**16**

can determine the class of that traffic flow by reference to the table with the identifier of the traffic flow received.

According to this embodiment, the bus masters 101 are grouped into respective classes following the classification rule shown in FIG. 9. Specifically, the classes are grouped into time-delay-guaranteed classes (i.e., Classes A, B and C) in which the time delay needs to be taken into consideration and a non-time-delay-guaranteed class (i.e., Class Z) in which the permitted time delay is so long that the time delay can be guaranteed even without taking the delay into consideration.

The time delay guaranteed class is subdivided into a class in which a traffic flow is transmitted at a rate exceeding the requested bandwidth (i.e., Class C), a class which generates a traffic flow with a burst property and of which the permitted time delay is particularly short or the requested bandwidth is particularly broad (i.e., Class A), and the other class in which delay and throughput need to be taken into consideration (i.e., Class B).

For example, masters such as encoders and decoders which need to transmit a huge size of data in a short period are grouped into Class A, masters such as peripherals and I/Os are grouped into Class B, and masters in charge of some processor- or graphics-related processing, involving a data transfer of which the performance needs to be ensured, are grouped into Class C.

Into the non-time-delay-guaranteed class (i.e., Class Z), grouped is a master that generates a traffic flow for which the performance does not have to be ensured in terms of throughput and time delay and which has a low priority level and may just need to be transmitted only when the bus is not occupied. Naturally, the classes may also be grouped on a traffic flow basis as described above. For example, a traffic flow for graphics related processing, for which the performance does not have to be ensured, and a traffic flow including the output data of a processor are grouped into Class Z. It should be noted that if the processor or graphics related traffic flow includes data for which the performance needs to be guaranteed in terms of time delay or throughput, such a traffic flow may also be grouped into a performance-ensured class, instead of Class Z.

Optionally, a class with an even higher priority level may be provided for a traffic flow or master for which a particularly strict performance requirement (on a permitted time delay or a requested bandwidth) is imposed among other classes, and such a traffic flow or master may be grouped into such a class.

Portions (a), (b) and (a) of FIG. 47 illustrate how classification may be done according to the priority level of a time-delay-guaranteed class. In FIG. 47, the closer to the top of the paper a class is located, the higher the priority level of that class is. In each of these portions (a), (b) and (c) of FIG. 47, classification is supposed to be done independently of each other. It should be noted that there is no correspondence in priority level between these portions (a), (b) and (c) of FIG. 47

Portion (a) of FIG. **47** illustrates an exemplary set of priority levels for Classes A, B and C as described above. As far as the priority level is concerned, Class A has the highest priority level, and the priority level decreases in the order of Classes B and C.

In another example, to shorten the time delay to be caused by some processor related traffic flow belonging to Class C, another high-priority-level class D may be provided for such a traffic flow, separately from the other traffic flows belonging to the same Class C. Portion (b) of FIG. 47 illustrates such Class D, of which the priority level is lower than that of Class B but higher than that of Class C. Some processor related

traffic flow is grouped into such Class D. In order to shorten the time delay, at least a traffic flow with a requested bandwidth that has been set with respect to Class D is transmitted at a higher priority level than a traffic flow belonging to Class C

In still another example, traffic flows to be grouped into Class D described above may also be grouped into subdivided classes. Portion (c) of FIG. 47 illustrates exemplary classes which have been subdivided with a traffic flow to be transmitted at a rate exceeding the requested bandwidth taken into consideration. In this example, Classes A, B, D, C1, C and C2 have been set in the descending order of priorities.

First of all, among traffic flows to be grouped into Class D, a class to which traffic flows exceeding the requested bandwidth belong is set to be Class C1. As a result, those traffic 15 flows exceeding the requested bandwidth are transmitted at a higher priority level than traffic flows also exceeding the requested bandwidth but belonging to Class C.

Alternatively, among traffic flows to be grouped into Class D, a class to which traffic flows exceeding the requested 20 bandwidth belong may also be set to be Class C2. As a result, those traffic flows exceeding the requested bandwidth are transmitted at a lower priority level than traffic flows belonging to Class C.

If all of those traffic flows that have been grouped into Class D at first need to be transmitted at as high a priority level as possible, the time delay to be caused by a traffic flow belonging to Class D may be set to be shorter than what is caused by a traffic flow belonging to Class C. On the other hand, if those traffic flows exceeding the bandwidth requested for Class D 30 need to be transmitted at a low priority level, those traffic flows exceeding the requested bandwidth may be grouped into Class C2, and the time delay to be caused by a traffic flow belonging to Class C2 may be shorter than what is caused by a traffic flow belonging to Class C. 35

Optionally, in order to transmit a traffic flow belonging to Class D preferentially, an extra band may be secured in advance for such a traffic flow. For example, in a time interval in which traffic flows are transmitted at a bandwidth requested for Class C but no traffic flows belonging to Class 40 D are transmitted, traffic flows belonging to Class C are transmitted in advance using the extra band. As a result, there will be no need to transmit those traffic flows belonging to Class C that have already been transmitted in advance. That is to say, this means reserving an extra band for the future. 45 Specifically, in a time interval in which no traffic flows belonging to Class D are transmitted, traffic flows belonging to Class C are transmitted at a rate exceeding the requested bandwidth. As a result, the sum of the traffic flows belonging to Class C to be transmitted in the future can be reduced and 50 the extra band can be used to transmit other traffic flows. Consequently, the interference with traffic flows belonging to Class C can be reduced and the time delay to be caused by traffic flows belonging to Class D can be shortened.

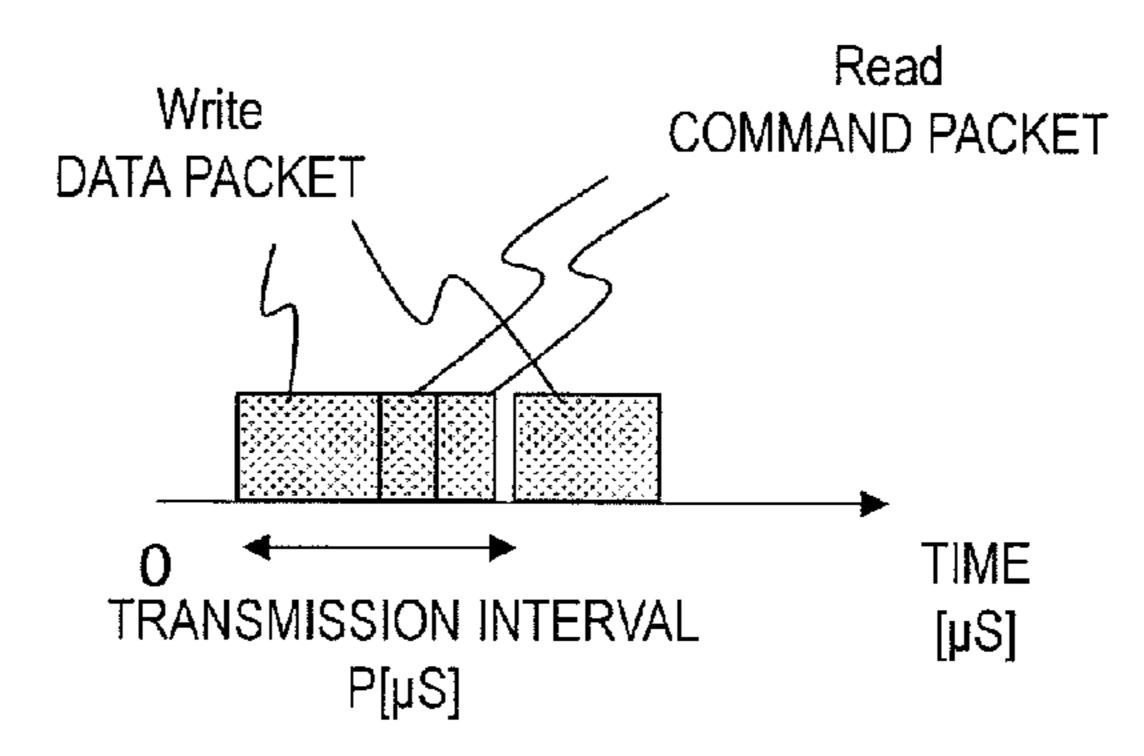

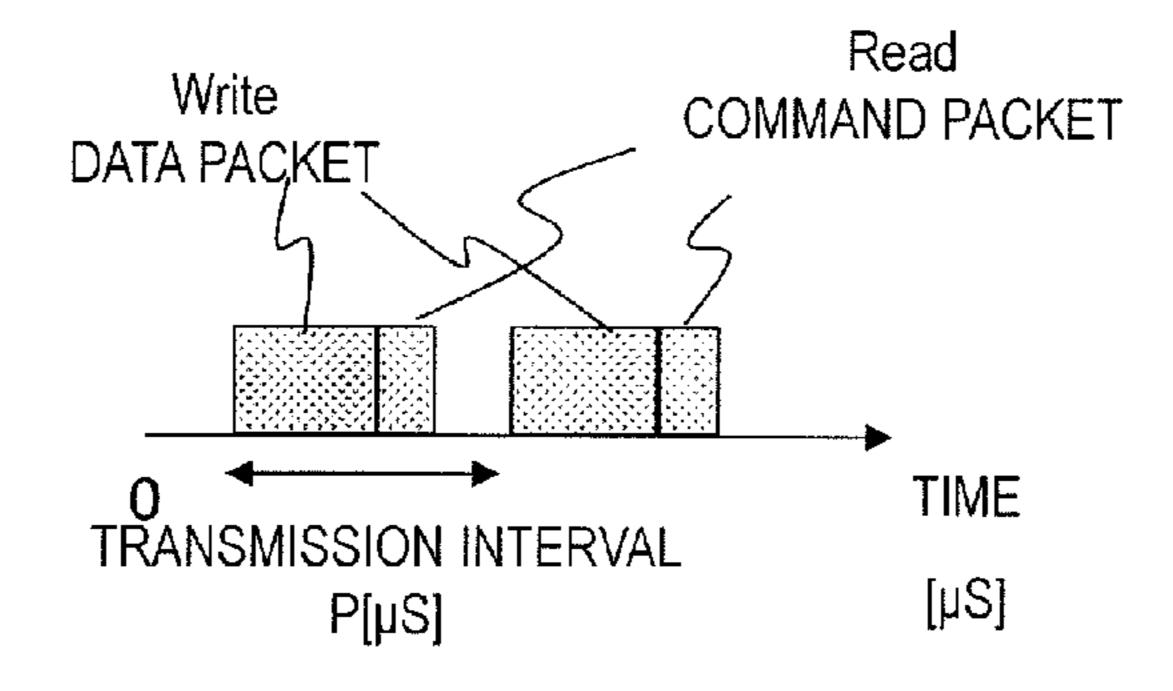

FIG. 12 illustrates a configuration for the master NIC 102, 55 which is comprised mostly of hardware circuits. Each component of the master NIC 102 is implemented as a combination of multiple circuit elements. Alternatively, each component may also be implemented as either a single integrated circuit or multiple integrated circuits.