#### US009235542B2

# (12) United States Patent

## Liu et al.

# (10) Patent No.: US 9,235,542 B2 (45) Date of Patent: Jan. 12, 2016

# (54) SIGNAL SWITCHING CIRCUIT AND PERIPHERAL COMPONENT INTERCONNECT EXPRESS CONNECTOR ASSEMBLY HAVING THE SIGNAL SWITCHING CIRCUIT

(71) Applicant: Zhongshan Innocloud Intellectual Property Services Co., Ltd., Zhongshan

(CN)

(72) Inventors: Lei Liu, Shenzhen (CN); Guo-Yi Chen,

Shenzhen (CN)

(73) Assignee: Zhongshan Innocloud Intellectual

Property Services Co., Ltd., Zhongshan

(CN)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 297 days.

- (21) Appl. No.: 13/957,536

- (22) Filed: Aug. 2, 2013

## (65) Prior Publication Data

US 2014/0223070 A1 Aug. 7, 2014

### (30) Foreign Application Priority Data

Jan. 30, 2013 (CN) ...... 2013 1 00354514

(51) **Int. Cl.**

G06F 13/00 (2006.01) G06F 13/38 (2006.01) G06F 11/00 (2006.01)

(52) **U.S. Cl.**

(58) Field of Classification Search

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,913,045 A * | 6/1999  | Gillespie G06F 13/24              |

|---------------|---------|-----------------------------------|

| 7,340,557 B2* | 3/2008  | 710/266<br>Kong G09G 5/363        |

| 7,539,801 B2* | 5/2009  | 710/306<br>Xie G06F 13/4221       |

| 7,573,295 B1* | 8/2009  | 710/104<br>Stadler H03K 19/17732  |

| 7,657,663 B2* | 2/2010  | 326/38 Freimuth G06F 13/4022      |

| 8,055,934 B1* | 11/2011 | 710/5<br>Blinick G06F 11/0727     |

| 8,473,663 B2* | 6/2013  | 714/10<br>Somervill G06F 13/4095  |

| 8,560,774 B2* | 10/2013 | 710/110<br>Cleveland G06F 11/2089 |

|               |         | 710/301                           |

#### (Continued)

Primary Examiner — Christopher Shin (74) Attorney, Agent, or Firm — Novak Druce Connolly Bove + Quigg LLP

#### (57) ABSTRACT

A signal switching circuit allows a PCIe card access to additional data channels when installation of the PCIe cards on first and second PCIe connectors are detected. First and second PCIe connectors output a first detection signal when each of the first and second PCIe connectors receives a PCIe card. The first and second PCIe connectors output a second detection signal when each of the first and second PCIe connectors does not receive a PCIe card. A first multiplexer receives the first or second detection signal and connects an input terminal to first or second output terminal of the first multiplexer, to transmit PCIe signals to the first or second detection signal and connects an input terminal to first or second output terminal of the second multiplexer, to transmit PCIe signals to the first or second output terminal of the second multiplexer, to transmit PCIe signals to the first or second PCIe connectors.

#### 4 Claims, 1 Drawing Sheet

present2#

PCle X16 Connector

# US 9,235,542 B2 Page 2

| (56) References Cited    |                     | 2011/0320666 A1*                  | 12/2011            | Gregg G06F 13/4027 |                               |

|--------------------------|---------------------|-----------------------------------|--------------------|--------------------|-------------------------------|

|                          |                     | 2011(0220571                      | 40(0044            | 710/300            |                               |

| U.S. PATENT DOCUMENTS    |                     |                                   | 2011/0320674 A1*   | 12/2011            | Gregg G06F 13/385             |

|                          |                     |                                   | 0044(0000555       | 10(0011            | 710/314                       |

| 8,605,879 E              | 32 * 12/2013        | Wellard H04M 3/42371              | 2011/0320675 A1*   | 12/2011            | Gregg G06F 13/404             |

|                          |                     | 379/201.01                        | 2012/0120005 41%   | 5/0010             | 710/315                       |

| 8,615,622 E              | 32 * 12/2013        | Gregg G06F 13/404                 | 2012/0120805 A1*   | 5/2012             | Maze H04L 1/1835              |

|                          |                     | 710/313                           | 2012/0144007 41%   | C/2012             | 370/235<br>December 12/4069   |

| 8,645,606 E              | 32 * 2/2014         | Gregg G06F 13/385                 | 2012/0144087 A1*   | 0/2012             | Buckland G06F 13/4068         |

|                          |                     | 710/306                           | 2012/0144220 41*   | 6/2012             | 710/316 Dualdand C06E 12/4022 |

| 8,677,176 E              | 32 * 3/2014         | Buckland G06F 13/4022             | 2012/0144230 A1*   | 0/2012             | Buckland G06F 13/4022 714/4.5 |

|                          |                     | 714/4.1                           | 2012/0072750 A1*   | 3/2013             | Gregg G06F 13/385             |

| 8,677,180 E              | 32 * 3/2014         | Bayer G06F 11/2033                | 2013/00/3/39 AT    | 3/2013             | 710/106                       |

| 0.545.000 E              | 20 % 6/2014         | 714/11<br>COSE 12/4022            | 2013/0073767 A1*   | 3/2013             | Gregg G06F 13/4027            |

| 8,745,292 E              | 32 * 6/2014         | Lais G06F 13/4022                 | 2013/00/3/07 A1    | 3/2013             | 710/300                       |

| 0.760.100 E              | 20 * 7/2014         | 710/313                           | 2013/0076766 A1*   | 3/2013             | Yamagishi G01C 21/32          |

| 8,769,180 E              | 32 * //2014         | Gregg G06F 13/385                 | 2013/00/00 A1      | 3/2013             | 345/522                       |

| 9 0 1 9 <i>5 7 2</i> - D | 22 * 12/2014        | 710/306<br>Cross                  | 2013/0080678 A1*   | 3/2013             | Buckland G06F 13/4068         |

| 8,918,373 E              | 32 ' 12/2014        | Gregg G06F 13/4027                | 2013/0000078 A1    | 3/2013             |                               |

| 2011/0213910 A           | <b>4.1</b> * 0/2011 | 710/313<br>Samarill C06E 12/4005  | 2012/0000025 41*   | 2/2012             | 710/316 Dualdand C06E 12/4022 |

| Z011/0Z13910 A           | 41 9/2011           | Somervill G06F 13/4095<br>710/316 | 2013/0080825 A1*   | 3/2013             | Buckland G06F 13/4022         |

| 2011/0220652 4           | <b>11</b>           | Lais G06F 13/4022                 |                    |                    | 714/4.5                       |

| Z011/03Z0033 P           | 12/2011             | 710/65                            | * cited by examine | •                  |                               |

|                          |                     | /10/03                            | ched by chamme     | •                  |                               |

1~

1

# SIGNAL SWITCHING CIRCUIT AND PERIPHERAL COMPONENT INTERCONNECT EXPRESS CONNECTOR ASSEMBLY HAVING THE SIGNAL SWITCHING CIRCUIT

#### **BACKGROUND**

#### 1. Technical Field

The present disclosure relates to a peripheral component interconnect express connector assembly having a signal switching circuit.

#### 2. Description of Related Art

In general, a chipset arranged on a motherboard can provide sixteen pairs of data channels to two peripheral component interconnect express (PCIe) X16 connectors, which are arranged on the motherboard. Thus each PCIe X16 connector can transmit data through eight pairs of channels only. For example, when the chipset provides sixteen pairs of data 20 channels, eight pairs of data channels are provided to a first PCIe X16 connector, and the other eight pairs of data channels are provided to a second PCIe X16 connector. When the first PCIe X16 connector receives a PCIe X16 card, and the second PCIe X16 connector is free, the added PCIe X16 card 25 is able to communicate with the motherboard only through the original eight pairs of data channels. At the same time, the eight pairs of data channels of the second PCIe X16 connector are not used. Therefore, there is room for improvement in the art.

## BRIEF DESCRIPTION OF THE DRAWING

Many aspects of the embodiments can be better understood with reference to the following drawing. The components in 35 the drawing are not necessarily drawn to scale, the emphasis instead being placed upon clearly illustrating the principles of the present embodiments.

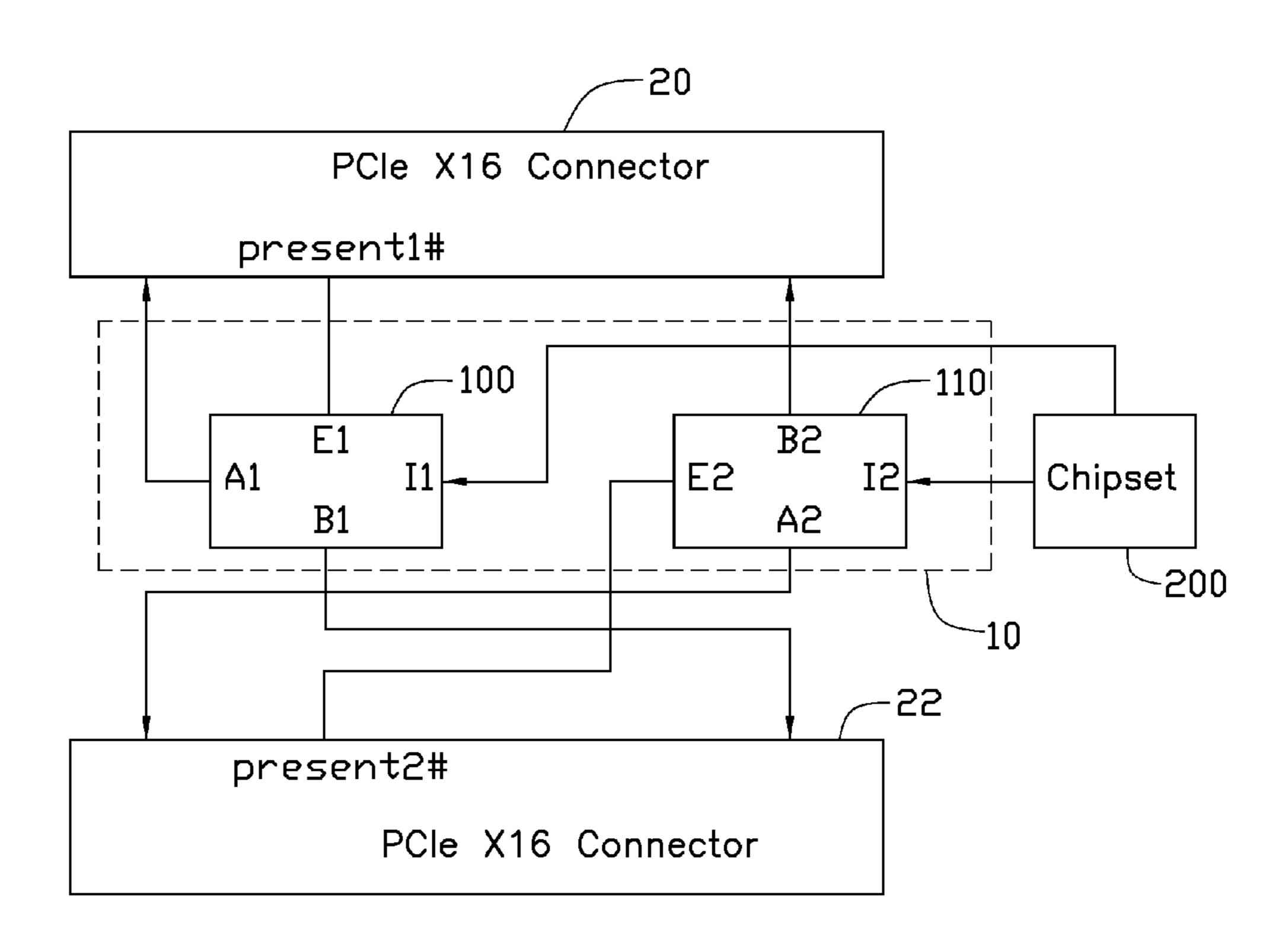

The FIGURE is a circuit diagram of a signal switching circuit in accordance with an embodiment.

### DETAILED DESCRIPTION

The disclosure, including the drawing, is illustrated by way of example and not by way of limitation. References to "an" 45 or "one" embodiment in this disclosure are not necessarily to the same embodiment, and such references mean "at least one."

The FIGURE shows a signal switching circuit 10 in accordance with an embodiment. The signal switch circuit 10 is 50 arranged on a motherboard 1. A chipset 200 is arranged on the motherboard 1 and provides sixteen pairs of data channels, which accord with peripheral component interconnect express (PCIe) protocol. In one embodiment, two PCIe X16 connectors 20 and 22 are arranged on the motherboard 1.

The signal switch circuit 10 includes two multiplexers 100 and 110. Input terminals I1 and I2 of the multiplexers 100 and 110 are connected to the chipset 200, each of the input terminals I1 and I2 receiving eight pairs of the data channels from the chipset 200. A first output terminal A1 of the multiplexer 60 100 is connected to the PCIe X16 connector 20, and a second output terminal B1 of the multiplexer 100 is connected to the PCIe X16 connector 22, to output the eight pairs of data channels to the PCIe X16 connector 20 or to the PCIe X16 connector 22. A first output terminal A2 of the multiplexer 65 110 is connected to the PCIe X16 connector 22, and a second output terminal B2 of the multiplexer 110 is connected to the

2

PCIe X16 connector **20**, to output the eight pairs of data channels to the PCIe X16 connector **22** or the PCIe X16 connector **20**.

An enable terminal E1 of the multiplexer 100 is connected to a detection pin Present1# of the PCIe X16 connector 20. An enable terminal E2 of the multiplexer 110 is connected to a detection pin Present2# of the PCIe X16 connector 22. The multiplexer 100 can connect the input terminal I1 to the first output terminal A1 or to the second output terminal B1, according to voltage level of signals received by the enable terminal E1, to output eight pairs of data channels received from the chipset 200 to the PCIe X16 connectors 20 and 22. The multiplexer 110 can connect the input terminal I2 to the first output terminal A2 or to the second output terminal B2, according to voltage level of signals received by the enable terminal E2, to output eight pairs of data channels received from the chipset 200 to the PCIe X16 connectors 20 and 22.

When the PCIe X16 connector 20 receive a PCIe X16 card, and the PCIe X16 connector **22** does not receive a PCIe X16 card, the detection pin Present1# of the PCIe X16 connector 20 receives a low level signal, such as logic 0, and the detection pin Present2# of the PCIe X16 connector 22 receives a high level signal, such as logic 1. Thus the enable terminal E1 of the multiplexer 100 receives a low level signal, and the enable terminal E2 of the multiplexer 110 receives a high level signal. The input terminal I1 is connected to the first output terminal A1 of the multiplexer 100, and the input terminal I2 is connected to the second output terminal B2 of the multiplexer 110. Eight pairs of data channels received from the chipset 200 by the multiplexer 100 are outputted to the PCIe X16 connector 20, and eight pairs of channel data received from the chipset 200 by the multiplexer 110 are also outputted to the PCIe X16 connector **20**. The PCIe X16 connector 20 thus receives sixteen pairs of data channels.

When the PCIe X16 connector 20 does not receives a card, and the PCIe X16 connector 22 receives a PCIe X16 card, the detection pin Present1# of the PCIe X16 connector 20 receives a high level signal, and the detection pin Present2# of the PCIe X16 connector 22 receives a low level signal. The enable terminal E1 of the multiplexer 100 thus receives a high level signal, and the enable terminal E2 of the multiplexer 110 receives a low level signal. The input terminal I1 is connected to the second output terminal B1 of the multiplexer 100, and the input terminal I2 is connected to the first output terminal A2 of the multiplexer 110. The eight pairs of data channels received from the chipset 200 by the multiplexer 100 are thus outputted to the PCIe X16 connector 22, and eight pairs of data channels received from the chipset 200 by the multiplexer 110 are also outputted to the PCIe X16 connector 22. The PCIe X16 connector 22 thus receives sixteen pairs of data channels.

When the PCIe X16 connector 20 receives a PCIe X16 card, and the PCIe X16 connector 22 also receives a PCIe X16 card, the detection pin Present1# of the PCIe X16 connector 20 receives a low level signal, and the detection pin Present2# of the PCIe X16 connector 22 also receives a low level signal. Thus the enable terminal E1 of the multiplexer 100 and the enable terminal E2 of the multiplexer 110 both receive low level signals. The input terminal I1 is connected to the first output terminal A1 of the multiplexer 100, and the input terminal I2 is connected to the first output terminal A2 of the multiplexer 110. Eight pairs of data channels received from the chipset 200 by the multiplexer 100 are outputted to the PCIe X16 connector 20, and eight pairs of data channels received from the chipset 200 by the multiplexer 110 are

outputted to the PCIe X16 connector 22. In this case, each of the PCIe X16 connectors 20 and 22 receives eight pairs of data channels.

The multiplexers 100 and 110 detect when the PCIe X16 connectors 20 and 22 receive PCIe X16 cards through the 5 enable terminals E1 and E2 and the detection pins Present1# and Present2#, and connect the input terminal to the corresponding first output terminal or to the corresponding second output terminal, to output a further eight pairs of data channels to the PCIe X16 connector **20** or to the PCIe X16 connector 22.

In other embodiments, the PCIe X16 connectors 20 and 22 may be replaced by PCIe X8 and PCIe X32 connectors. That is, the input terminal I1 of the multiplexer 100 is connected to a first group of pins of the chipset 200, to receive a first group 15 of data channels from the chipset 200. The input terminal I2 of the multiplexer 110 is connected to a second group of pins of the chipset 200, to receive a second group of data channels from the chipset 200. The first output terminal A1 of the multiplexer 100 is connected to a first group of pins of a first 20 PCIe connector, and the second output terminal B1 of the multiplexer 100 is connected to a first group of pins of a second PCIe connector, to transmit the first group of data channels from the chipset 200 to the first group of pins of the first PCIe connector or to the second PCIe connector. The first 25 output terminal A2 of the multiplexer 110 is connected to the second group of pins of the second PCIe connector, and the second output terminal B2 of the multiplexer 110 is connected to the second group of pins of the first PCIe connector, to transmit the second group of data channels from the chipset 30 200 to the second group of pins of the first PCIe connector or to the second PCIe connector. The enable terminals E1 and E2 of the multiplexer 100 and 110 are respectively connected to the detection pins of the first and second PCIe connectors.

Even though numerous characteristics and advantages of 35 the disclosure have been set forth in the foregoing description, together with details of the structure and function of the disclosure, the disclosure is illustrative only, and changes may be made in detail, especially in the matters of shape, size, and the arrangement of parts within the principles of the 40 disclosure to the full extent indicated by the broad general meaning of the terms in which the appended claims are expressed.

What is claimed is:

- 1. A signal switching circuit connected between a first 45 minal of the second multiplexer. peripheral component interconnect express (PCIe) connector and a second PCIe connector, the signal switching circuit comprising:

- a first multiplexer comprising an input terminal, a first output terminal, a second output terminal, and an enable 50 terminal, wherein the input terminal is connected to a first group of pins of a chipset of a motherboard, to receive a first group of PCIe signals, the first output terminal is connected to a first group of pins of the first PCIe connector, the second output terminal is connected 55 to a first group of pins of the second PCIe connector, the enable terminal is connected to a detection pin of the first PCIe connector; and

- a second multiplexer comprising an input terminal, a first output terminal, a second output terminal, and an enable 60 terminal, wherein the input terminal of the second multiplexer is connected to a second group of pins of the chipset, to receive a second group of PCIe signals, the first output terminal of the second multiplexer is connected to a second group of pins of the second PCIe 65 connector, the second output terminal of the second multiplexer is connected to a second group of pins of the

first PCIe connector, the enable terminal of the second multiplexer is connected to a detection pin of the second PCIe connector;

- wherein the detection pin of each of the first and second PCIe connectors outputs a first detection signal when each of the first and second PCIe connectors receives a PCIe card, the detection pin of each of the first and second PCIe connectors outputs a second detection signal when each of the first and second PCIe connectors does not receive a PCIe card, the first multiplexer receives the first or second detection signal through the enable terminal and connects the input terminal to the first or the second output terminal of the first multiplexer, to transmit the received PCIe signals to the first or the second PCIe connector, the second multiplexer receives the first or second detection signal through the enable terminal and connects the input terminal to the first or the second output terminal of the second multiplexer, to transmit the received PCIe signals to the first or the second PCIe connectors.

- 2. The signal switch circuit of claim 1, wherein the first and second PCIe connectors are PCIe X16 connectors, the first and second groups of PCIe signals each are eight pairs of channel data; when the first PCIe connector receives a PCIe X16 card, the detection pin of the first PCIe connector outputs a low level signal, when the first PCIe connector does not receive a PCIe card, the detection pin of the first PCIe connector outputs a high level signal; when the second PCIe connector receives a PCIe X16 card, the detection pin of the second PCIe connector outputs a low level signal, when the second PCIe X16 connector does not receive a PCIe card, the detection pin of the second PCIe connector outputs a high level signal; when the enable terminal of the first multiplexer receives the low level signal, the first multiplexer connects the input terminal to the first output terminal of the first multiplexer, when the enable terminal of the first multiplexer receives the high level signal, the first multiplexer connects the input terminal to the second output terminal of the first multiplexer; when the enable terminal of the second multiplexer receives the low level signal, the second multiplexer connects the input terminal to the first output terminal of the second multiplexer, when the enable terminal of the second multiplexer receives the high level signal, the second multiplexer connects the input terminal to the second output ter-

- 3. A peripheral component interconnect express (PCIe) connector assembly comprising:

- a first multiplexer comprising an enable terminal, an input terminal, a first output terminals, and a second output terminal, wherein the input terminal is connected to a first group of pins of a chipset of a motherboard, to receive a first group of PCIe signals from the chipset;

- a second multiplexer comprising an enable terminal, an input terminal, a first output terminals, and a second output terminal, wherein the input terminal is connected to a second group of pins of the chipset, to receive a second group of PCIe signals from the chipset;

- a first PCIe connector, wherein a first group of pins of the first PCIe connector is connected to the first output terminal of the first multiplexer, a second group of pins of the first PCIe connector is connected to the second output terminal of the second multiplexer, a detection pin of the first PCIe connector is connected to the enable terminal of the first multiplexer, to output a detection signal to the enable terminal of the first multiplexer according to the first PCIe connector receiving a PCIe card or not; and

5

a second PCIe connector, wherein a first group of pins of the second PCIe connector is connected to the second output terminal of the first multiplexer, a second group of pins of the second PCIe connector is connected to the first output terminal of the second multiplexer, the detection pin of the second PCIe connector is connected to the enable terminal of the second multiplexer, to output a detection signal to the enable terminal of the second multiplexer according to the second PCIe connector receiving a PCIe card or not;

wherein the first multiplexer connects the input terminal to the first output terminal or the second output terminal according to the detection signal received by the enable terminal of the first multiplexer, the first multiplexer outputs the first group of PCIe signals received from the chipset to the first group of pins of the first or the second PCIe connector; the second multiplexer connects the input terminal to the first output terminal or the second output terminal according to the detection signal received by the enable terminal of the second multiplexer, the second multiplexer outputs the second group of PCIe signals received from the chipset to the second group of pins of the first or the second PCIe connector.

4. The PCIe connector assembly of claim 3, wherein the first and second PCIe connectors are PCIe X16 connectors,

6

the first and second groups of PCIe signals each are eight pairs of channel data; when the first PCIe connector receives a PCIe X16 card, the detection pin of the first PCIe connector outputs a low level signal, when the first PCIe connector does not receives a PCIe card, the detection pin of the first PCIe connector outputs a high level signal; when the second PCIe connector receives a PCIe X16 card, the detection pin of the second PCIe connector outputs a low level signal, when the second PCIe X16 connector does not receive a PCIe card, the detection pin of the second PCIe connector outputs a high level signal; when the enable terminal of the first multiplexer receives the low level signal, the first multiplexer connects the input terminal to the first output terminal of the first multiplexer, when the enable terminal of the first multiplexer receives the high level signal, the first multiplexer connects the input terminal to the second output terminal of the first multiplexer; when the enable terminal of the second multiplexer receives the low level signal, the second multiplexer connects the input terminal to the first output terminal of the second multiplexer, when the enable terminal of the second multiplexer receives the high level signal, the second multiplexer connects the input terminal to the second output terminal of the second multiplexer.

\* \* \* \* \*