#### US009230858B2

# (12) United States Patent Kim et al.

## (10) Patent No.: US 9,230,858 B2 (45) Date of Patent: Jan. 5, 2016

## (54) SEMICONDUCTOR DEVICE AND METHOD FOR MANUFACTURING THE SAME

(71) Applicant: SK HYNIX INC., Icheon (KR)

(72) Inventors: Jae Young Kim, Anyang (KR); Mi

Hyune You, Cheongju (KR)

(73) Assignee: SK HYNIX INC., Icheon (KR)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 24 days.

(21) Appl. No.: 14/155,286

(22) Filed: Jan. 14, 2014

(65) Prior Publication Data

US 2014/0127903 A1 May 8, 2014

#### Related U.S. Application Data

(62) Division of application No. 13/327,614, filed on Dec. 15, 2011, now Pat. No. 8,659,111.

#### (30) Foreign Application Priority Data

Dec. 15, 2010 (KR) ...... 10-2010-0128572

(51) **Int. Cl.**

**H01L 21/44** (2006.01) **H01L 21/768** (2006.01) H01L 27/108 (2006.01)

(52) **U.S. Cl.**

CPC ..... *H01L 21/76879* (2013.01); *H01L 21/7685* (2013.01); *H01L 21/76897* (2013.01); *H01L 27/10888* (2013.01); *H01L 27/10858* (2013.01); *H01L 27/10855* (2013.01)

(58) Field of Classification Search

CPC ...... C23C 16/045; C23C 16/402; H01L

21/02126; H01L 21/022; H01L 21/02211; H01L 21/02222; H01L 21/02274; H01L 21/02282; H01L 21/02304; H01L 21/02337; H01L 21/0234; H01L 21/3105; H01L 21/3125; H01L 21/31612; H01L 21/76837; H01L 27/10885

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,251,746<br>2008/0128800 |     |         | Hong et al                              |

|---------------------------|-----|---------|-----------------------------------------|

| 2008/0318377              | A1* | 12/2008 | 257/330<br>Lee H01L 27/10876<br>438/243 |

| 2009/0267126              | A1* | 10/2009 | Wang H01L 21/823437                     |

| 2011/0024811              | A1* | 2/2011  | Kim 257/296                             |

#### FOREIGN PATENT DOCUMENTS

| KR | 1020060128349 A | 12/2006 |

|----|-----------------|---------|

| KR | 1020080061856 A | 7/2008  |

<sup>\*</sup> cited by examiner

Primary Examiner — Colleen A Matthews Assistant Examiner — Junaiden Mirsalahuddin

#### (57) ABSTRACT

A semiconductor device is manufactured by etching a semiconductor substrate including an active region, forming a bit line contact hole from which the active region is protruded, forming a first spacer exposing a top of the active region at each of an inner wall and a bottom of the bit line contact hole, forming a bit line contact plug and a bit line over the exposed active region, and forming a second spacer over the semiconductor substrate including not only the bit line contact plug but also the bit line.

#### 15 Claims, 7 Drawing Sheets

Fig.1a <Prior Art>

Fig.1b <Prior Art>

Fig.1c <Prior Art>

Fig.1d <Prior Art>

Fig.2

Fig.3a

Fig.3b

Fig.3c

Fig.3d

Fig.3e

Fig.3f

Fig.3g

1

## SEMICONDUCTOR DEVICE AND METHOD FOR MANUFACTURING THE SAME

### CROSS-REFERENCE TO RELATED APPLICATION

The present application is a divisional application of U.S. patent application Ser. No. 13/327,614 filed on Dec. 15, 2011, which claims the priority of Korean Patent Application No. 10-2010-0128572 filed on 15 Dec. 2010, the disclosures of which are hereby incorporated in their entirety by reference.

#### BACKGROUND OF THE INVENTION

Embodiments of the present invention relate to a semiconductor device and a method for manufacturing the same, and more particularly to a semiconductor device including a Global Bit Line (GBL) and a method for manufacturing the same.

In recent times, technologies of 40 nm or less have been 20 applied to semiconductor devices so that a Global Bit Line (GBL) process has been proposed. However, if misalignment between a bit line contact and a bit line occurs, the GBL process unavoidably generates a poor self-aligned contact (SAC) between a bit line contact and a storage node contact. 25 If a thick bit line spacer is formed to solve the above-mentioned problem, a Not-Open phenomenon of a storage node contact occurs. In addition, if the bit line contact spacer is formed thick, resistance of the bit line contact is increased. In order to prevent the increasing resistance of the bit line contact, an inner GBL process has been proposed. However, the inner GBL process is disadvantageous in that it makes difficult a SAC contact process, and increases parasitic capacitance (Cb) between the bit line and a plate electrode. Increased parasitic capacitance (Cb) has a negative influence upon a sensing margin of the entire semiconductor device, resulting in deterioration of device characteristics.

#### BRIEF SUMMARY OF THE INVENTION

Various embodiments of the present invention are directed to providing a semiconductor device and a method for manufacturing the same that substantially obviate one or more problems due to limitations and disadvantages of the related 45 art.

An embodiment of the present invention relates to a semiconductor device and a method for manufacturing the same, which can improve a process for forming an inner bit line so as to improve device characteristics.

In accordance with an aspect of the present invention, a semiconductor device includes a bit line contact hole including a protruded active region; a first spacer formed over a sidewall and bottom of the bit line contact hole so as to expose a top of the active region; a bit line contact plug and a bit line formed over the exposed active region; and a second spacer formed over the semiconductor substrate including not only the bit line contact plug but also the bit line.

Each of the first spacer and the second spacer may include a nitride film.

The first spacer formed over the bottom of the bit line contact hole may be formed to be level to the protruded active region.

A critical dimension (CD) of the bit line contact hole may be larger than a short-axis-directional CD of the active region. 65 A critical dimension (CD) of the bit line contact plug may be smaller than a CD of the bit line contact hole.

2

The bit line contact plug may include polysilicon. The bit line may be formed in a laminated structure of a barrier metal layer, a bit line conductive layer, and a hard mask layer.

The second spacer may fill a space between the bit line contact plug and the bit line contact hole.

The portion of the first spacer formed over the bottom of the bit line contact hole may be formed to have a larger thickness than the portion of the first spacer formed over the sidewall of the bit line contact hole.

In accordance with another aspect of the present invention, a method for manufacturing a semiconductor device includes etching a semiconductor substrate including an active region, and forming a bit line contact hole from which the active region is protruded; forming a first spacer exposing a top of the active region over sidewalls and a bottom of the bit line contact hole; forming a bit line contact plug and a bit line over the exposed active region; and forming a second spacer over the semiconductor substrate including not only the bit line contact plug but also the bit line.

In the forming of the bit line contact hole, a critical dimension (CD) of the bit line contact hole may be larger than a short-axis-directional CD of the active region.

The forming of the first spacer may include depositing an insulation film in the bit line contact hole including the protruded active region; and performing an etch process until the top of the protruded active region is exposed, so that the insulation film remains over an sidewall and bottom of the bit line contact hole.

The etch process may be a lateral etch process. The lateral etch process may be performed using a Light Etch Treatment (LET) scheme, The lateral etch process may be performed using a wet etch scheme. The etch process may be performed using a gas including any of SF<sub>6</sub>, O<sub>2</sub>, N<sub>2</sub>, HBr and a combination thereof.

The forming of the bit line contact plug and the bit line may include forming a polysilicon layer, a barrier metal layer, a bit line conductive layer, and a hard mask layer over the bit line contact hole in which the first spacer is formed; forming a mask pattern defining a bit line over the hard mask layer; and etching the hard mask layer, the bit line conductive layer, the barrier metal layer, and the polysilicon layer using the mask pattern defining the bit line as an etch mask.

The barrier metal layer may be formed of any of a titanium (Ti) film, a titanium nitride (TiN) film, and a combination thereof. The bit line conductive layer may be formed of a material including tungsten (W). The bit line hard mask layer may be formed of a material including a nitride film.

In the etching of the polysilicon layer, the polysilicon layer may be the bit line contact plug. In the forming of the second spacer, the second spacer may be formed to bury the bit line contact hole formed over sidewalls of the bit lie contact plug.

The insulation film may be formed of a material including a nitride film. The method may further include, after forming the second spacer, forming a storage node contact plug adjacent to the bit line.

In accordance with another aspect of the present invention,

A semiconductor device comprising: a trench disposed in a

substrate, wherein a bottom of the trench is at a first level, an

uplifted active region disposed in the trench, wherein a top of

the uplifted active region is at a second level higher than the

first level, a bit line pattern disposed over the uplifted active

region and coupled to the uplifted active region, a first spacer

disposed over a bottom of the trench and extending over a

sidewall of the trench, wherein a top of the first spacer formed

over the bottom of the trench is at a third level, and a second

spacer disposed between the first spacer and the bit line pattern. The third level is substantially the same as the second level.

It is to be understood that both the foregoing general description and the following detailed description of the 5 present invention are exemplary and explanatory and are intended to provide further explanation of the invention as claimed.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIGS. 1A to 1D are cross-sectional views illustrating a general semiconductor device and a method for manufacturing a semiconductor device according to the related art.

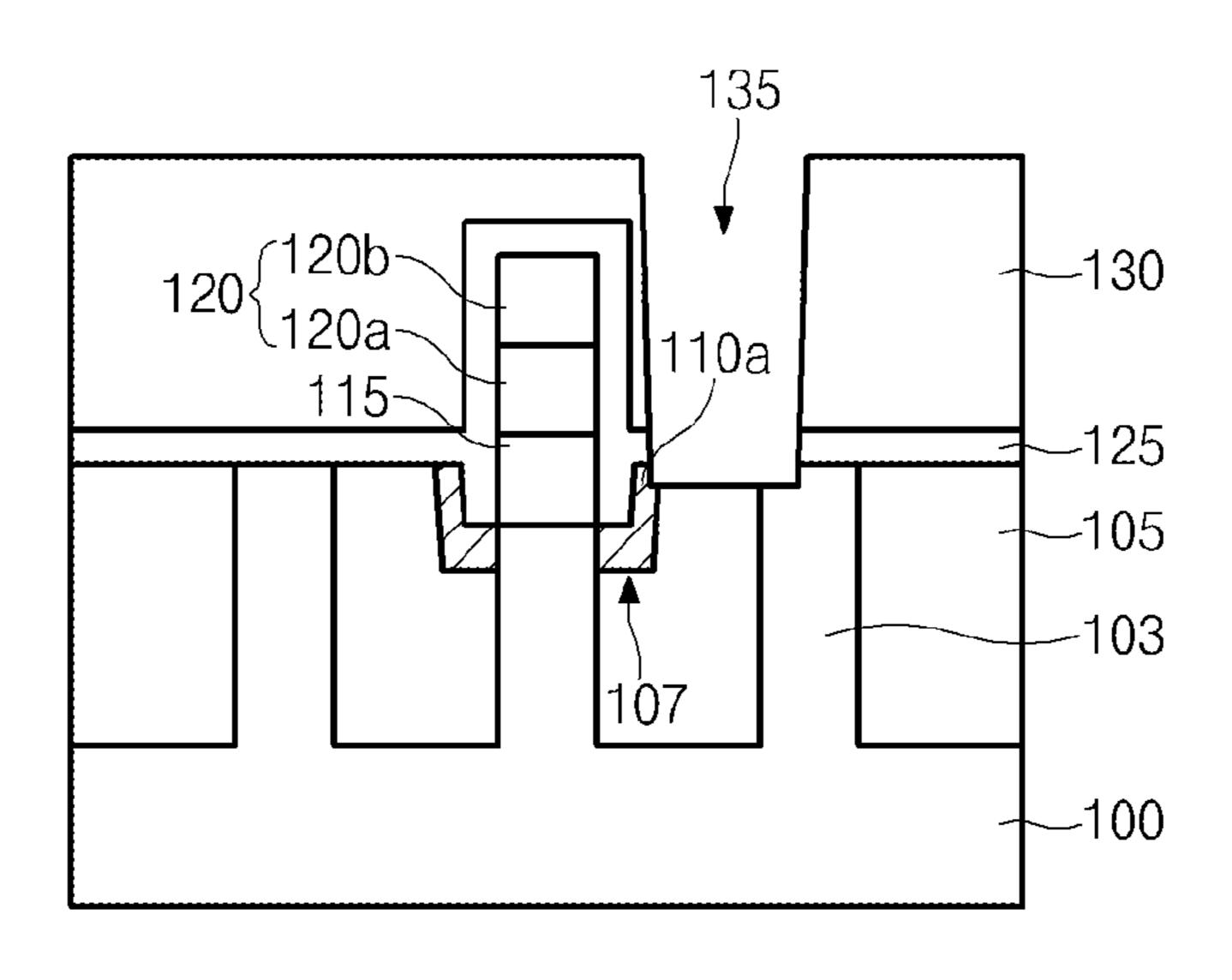

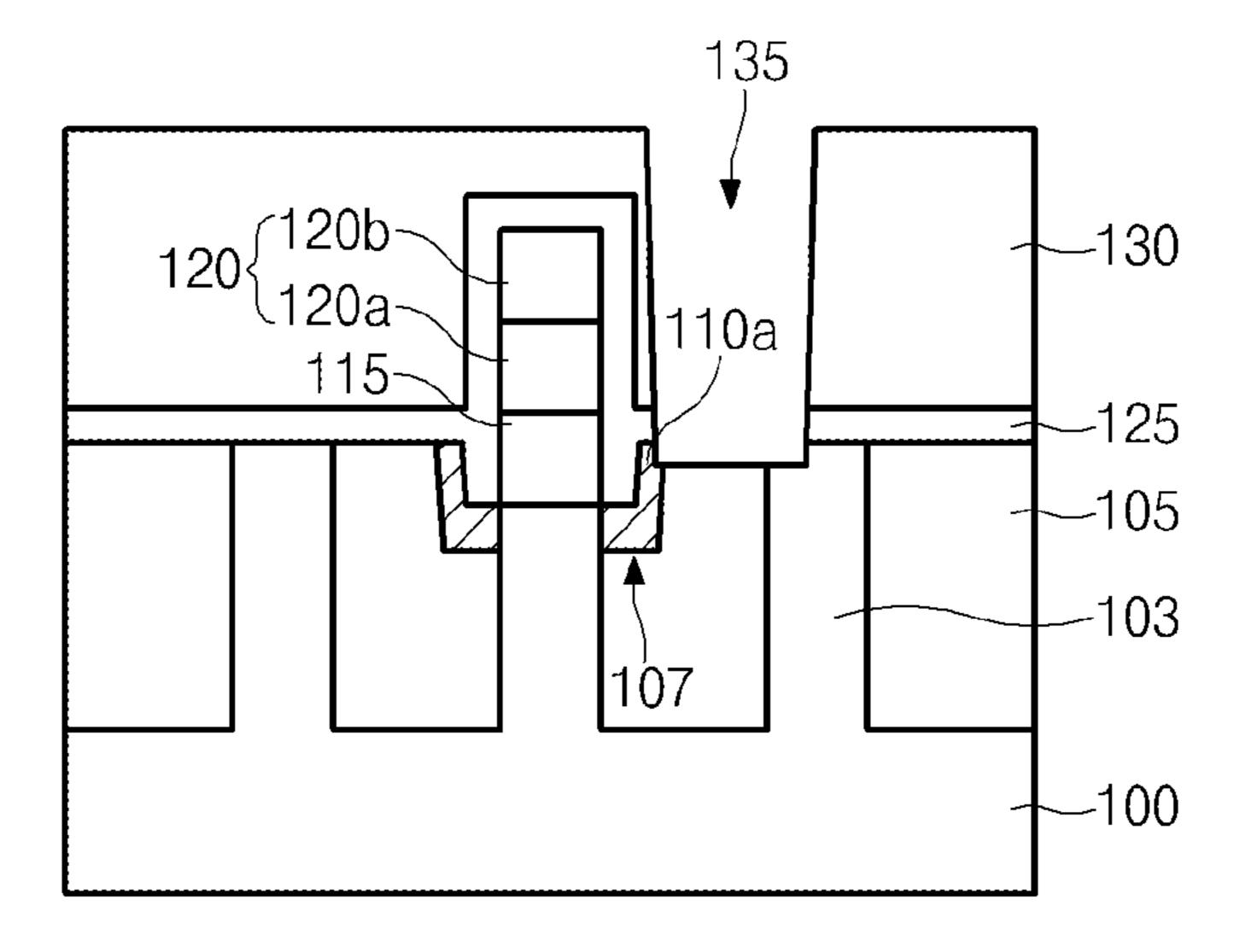

FIG. 2 is a cross-sectional view illustrating a semiconduc- 15 tor device according to an embodiment of the present invention.

FIGS. 3A to 3G are cross-sectional views illustrating a method for manufacturing the semiconductor device shown in FIG. 2.

#### DESCRIPTION OF EMBODIMENTS

Reference will now be made in detail to the embodiments of the present invention, examples of which are illustrated in 25 the accompanying drawings. Wherever possible, the same reference numbers will be used throughout the drawings to refer to the same or like parts. A semiconductor device and a method for manufacturing the same according to embodiments of the present invention will hereinafter be described 30 with reference to the accompanying drawings.

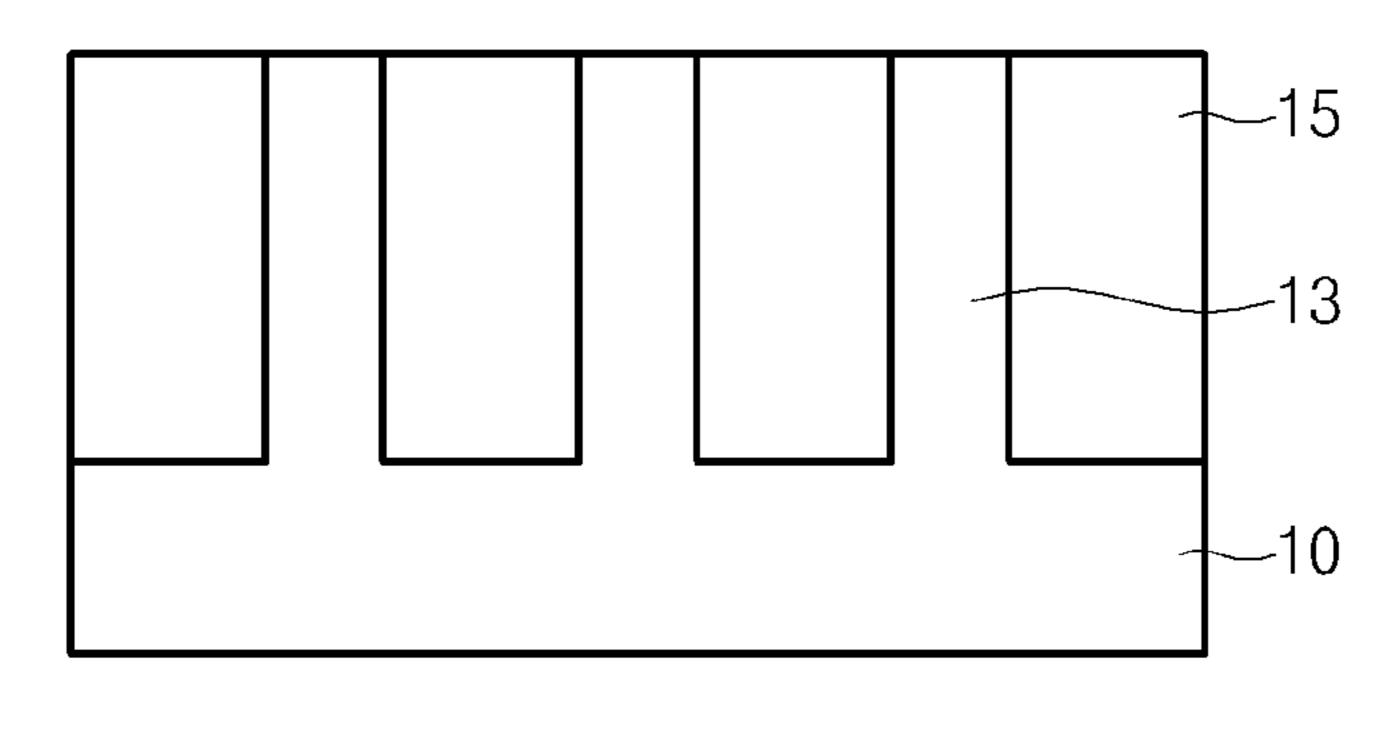

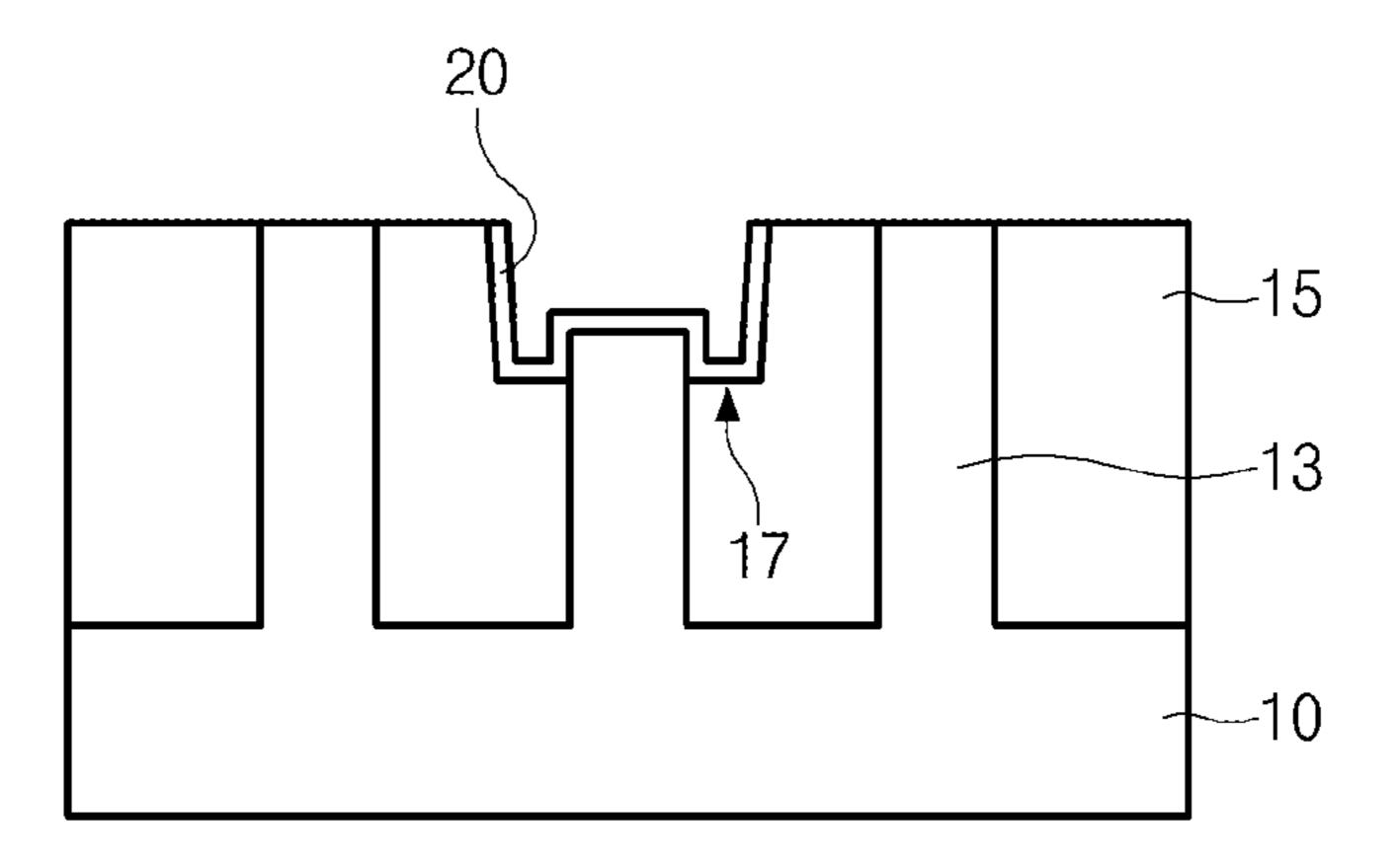

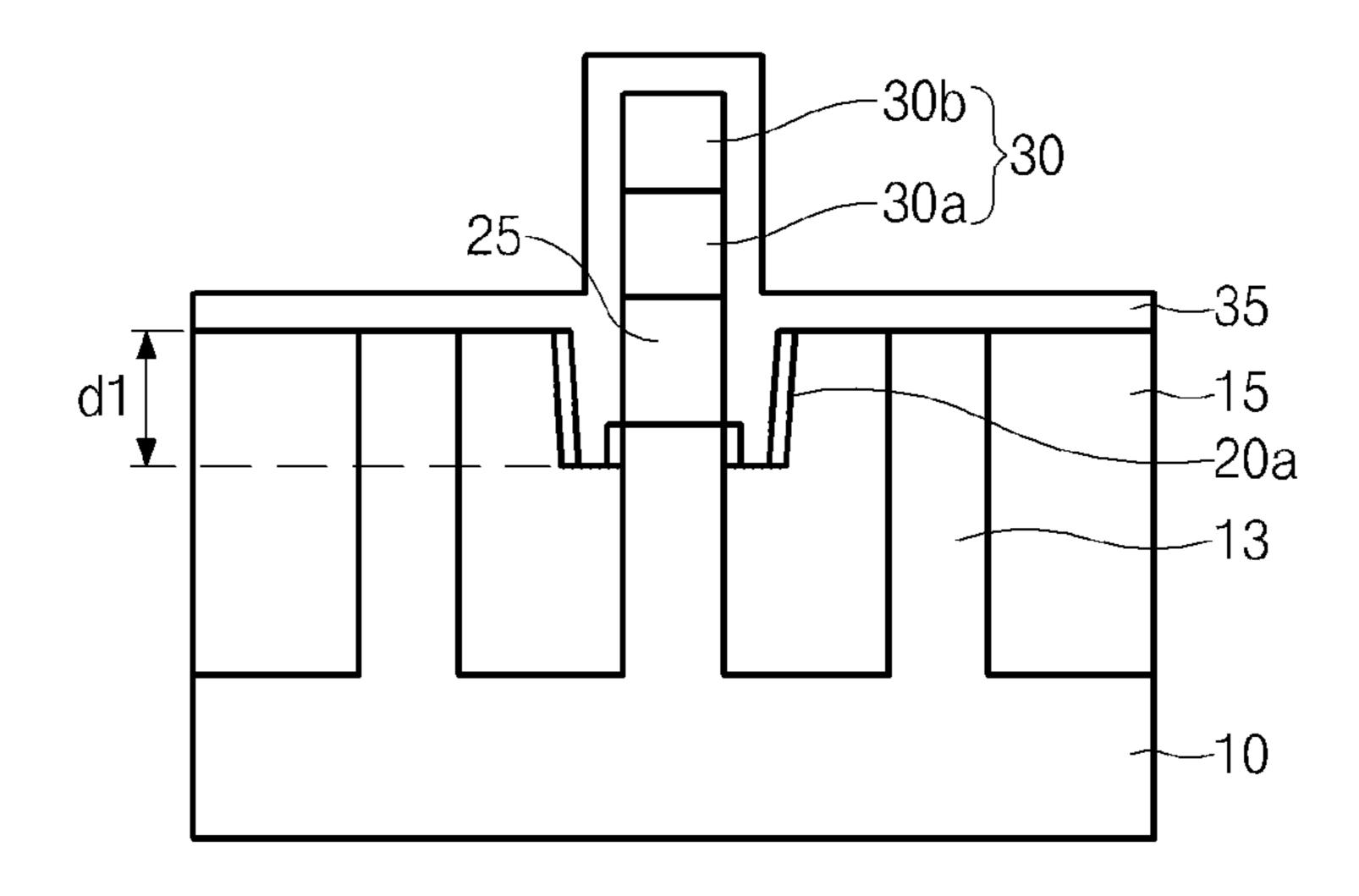

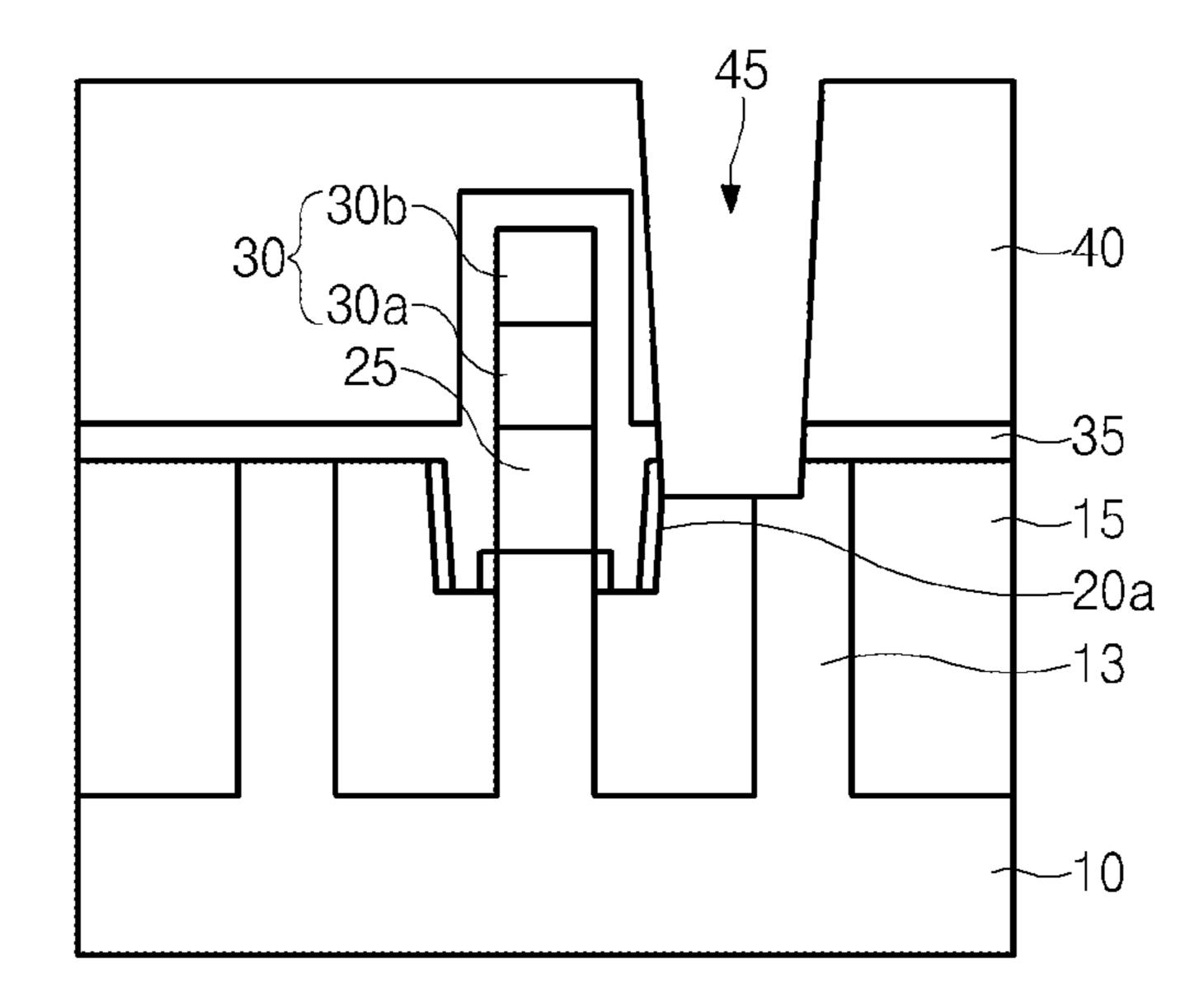

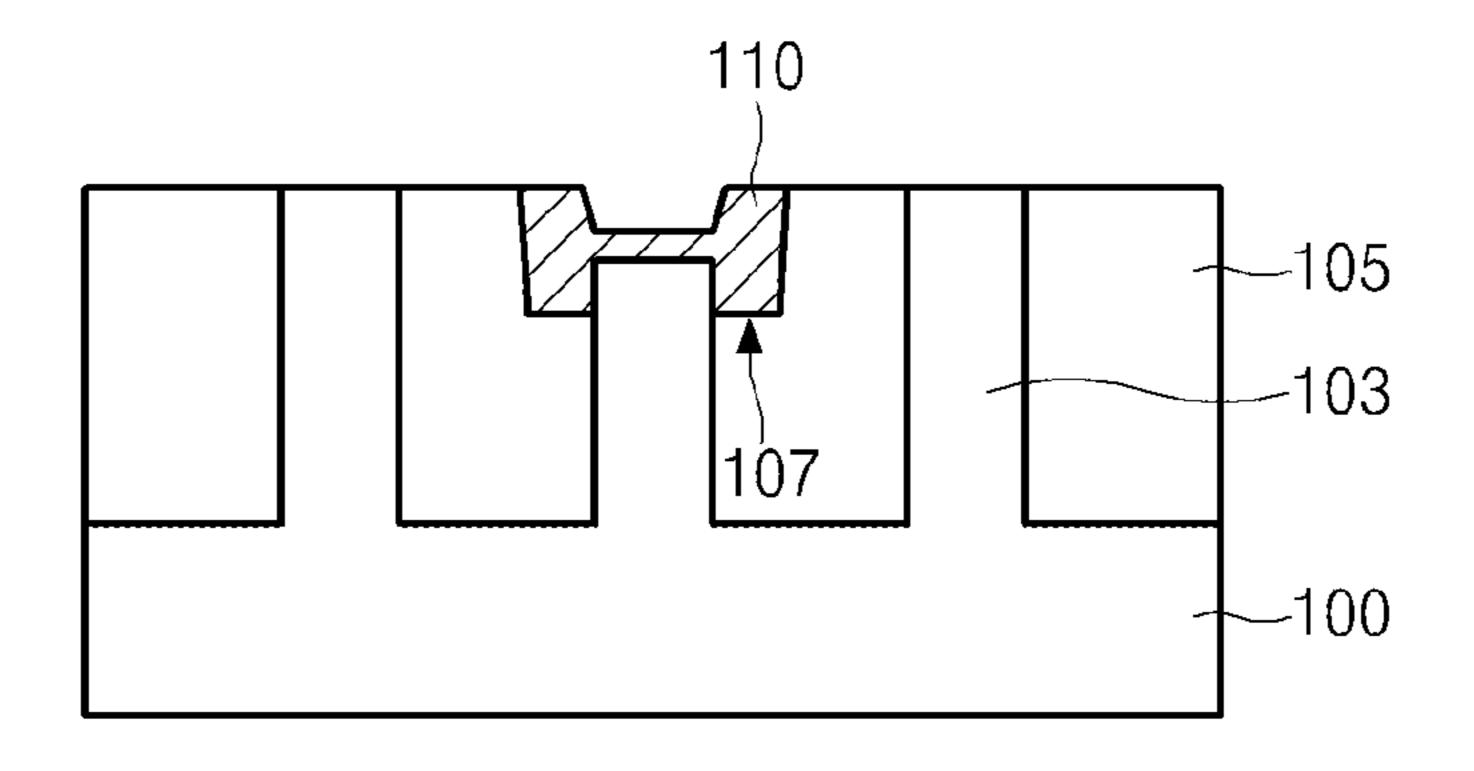

FIGS. 1A to 1D are cross-sectional views illustrating a general semiconductor device and a method for forming the same according to the related art.

active region 13 is formed by etching a semiconductor substrate 10. An oxide film fills the device isolation trench so that a device isolation film **15** is formed. Referring to FIG. **1**B, the semiconductor substrate 10 including the active region 13 and the device isolation film 15 is etched so that a bit line contact 40 hole 17 is formed. In this case, an active region 13 protrudes from a center part of the bit line contact hole 17 is formed because of a difference in etch selection ratio between the active region 13 and the device isolation film 15. Subsequently, a spacer insulation film 20 is deposited along the 45 protruded active region 13 and an inner surface of the bit line contact hole 17. The spacer insulation film 20 may be formed of a nitride film.

Referring to FIG. 1C, the spacer insulation film 20 is etched by an etch-back process, so that a spacer **20***a* is formed at an 50 inner wall of the bit line contact hole 17 and sidewalls of the protruded active region 13. A laminated structure of a polysilicon layer, a barrier metal layer (not shown), a bit line conductive layer 30a, and a bit line hard mask layer 30b is formed over the entire surface including the bit line contact 55 hole 17 including the spacer 20a. Thereafter, after a mask pattern (not shown) defining a bit line is formed over the bit line hard mask layer 30b, and the above-mentioned laminated structure is etched using the mask pattern (not shown) as an etch mask, so that a bit line contact plug 25 and a bit line 30 60 are formed.

Subsequently, a second spacer 35 is formed over the entire surface including the bit line 30 and the bit line contact plug 25. The second spacer 35 fills in an empty space formed at a side of the bit line contact plug **25**. However, as the depth of 65 the bit line contact hole 17 increases, the corresponding depth (d1) (See FIG. 1C) of the second spacer 35 also increases.

Therefore, the second spacer 35 is unlikely to completely fill the bit line contact hole 17, resulting in a void.

Referring to FIG. 1D, an interlayer insulation film 40 is formed over the second spacer 35, and a storage node contact hole 45 is formed by etching the interlayer insulation film 40 and the second spacer 35 formed over the semiconductor substrate 10.

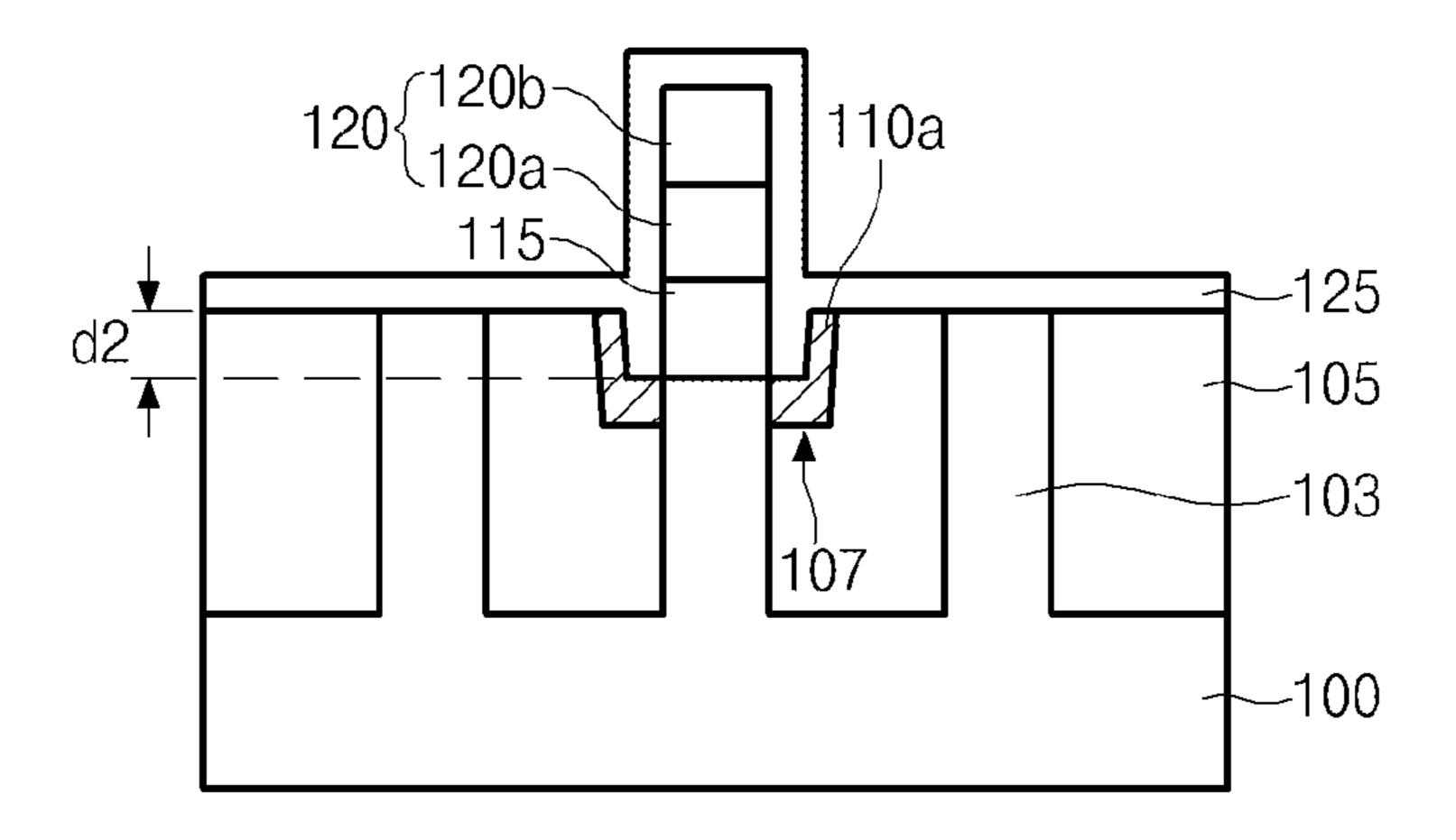

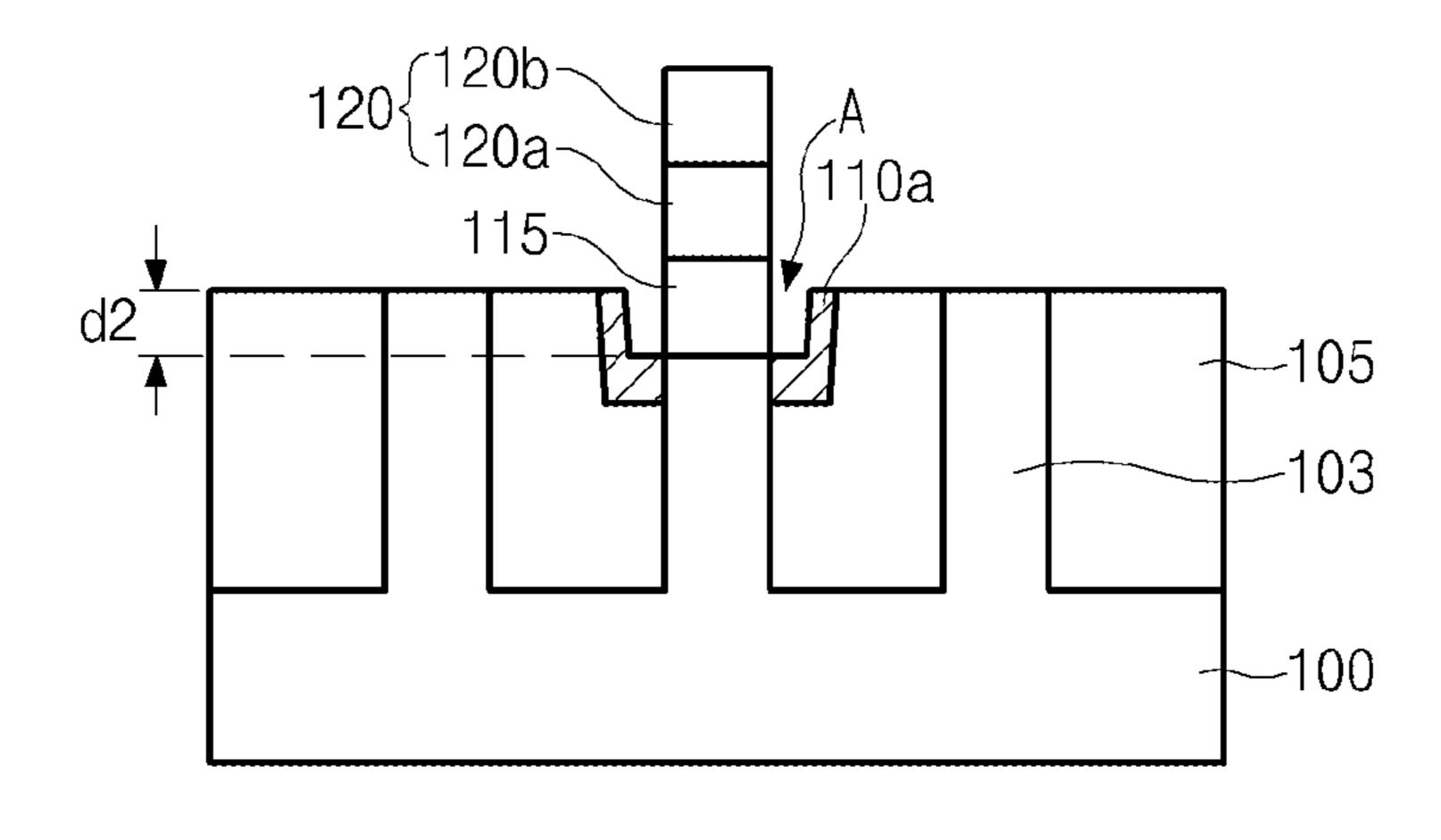

FIG. 2 is a cross-sectional view illustrating a semiconductor device according to an embodiment of the present inven-10 tion.

Referring to FIG. 2, a bit line contact hole 107 is formed in the semiconductor substrate 100 including the active region 103 and the device isolation film 105. The active region 103 may protrude from a center part of the bit line contact hole 107. The active region 103 shown in FIG. 2 shows a crosssectional view of the active region 103 taken along a shortaxis of the active region 103.

In addition, a first spacer 110a is formed over sidewalls and the bottom of the bit line contact hole 107. In an embodiment, the first spacer 110a may include a nitride film. The portion of the first spacer 110a that is formed at the bottom of the bit line contact hole 107 is formed to be thicker than the portion of the first spacer 110a that is formed over the sidewalls of the bit line contact hole 107. In addition, the portion of the first spacer 110a that is formed at the bottom of the bit line contact hole 107 is formed in such a manner that a surface of the protruded active region 103 is exposed. That is, in an embodiment, the portion of the first spacer 110a that is formed at the bottom of the bit line contact hole 107 may be formed to be level with a top of the protruded active region 103.

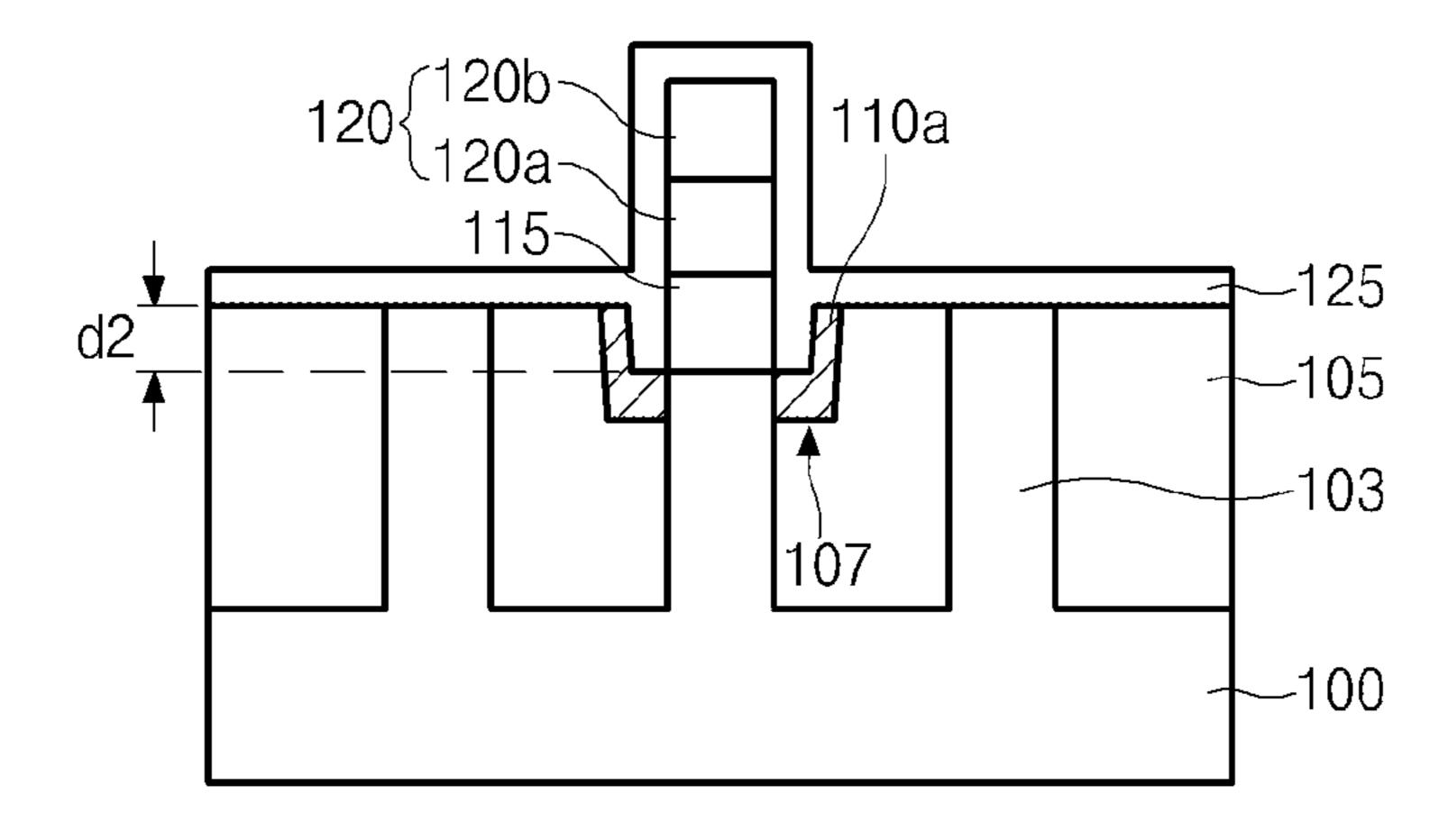

In addition, a bit line contact plug 115 and a bit line 120 are formed over the active region 103. The bit line contact plug 115 may include polysilicon, and the bit line 120 may include a barrier metal layer (not shown), a bit line conductive layer Referring to FIG. 1A, a device isolation trench defining an 35 120a and a bit line hard mask layer 120b. In an embodiment, the bit line contact hole 107 may not be completely filled, resulting in a void at a side of the bit line contact plug 115. A second spacer 125 is formed over the entire surface of the semiconductor substrate 100 including the bit line contact plug 115 and the bit line 120. In an embodiment, the second spacer 125 may include a nitride film, and may fill in the void which may be formed at a side of the bit line contact plug 115.

> As described above, since the first spacer 110a is formed at the bottom of the bit line contact hole 107, the depth (d2) corresponding to a gap-filled depth of the second spacer 125 is reduced. As a result, when a storage node contact hole is formed in a subsequent process, a SAC fail can be prevented.

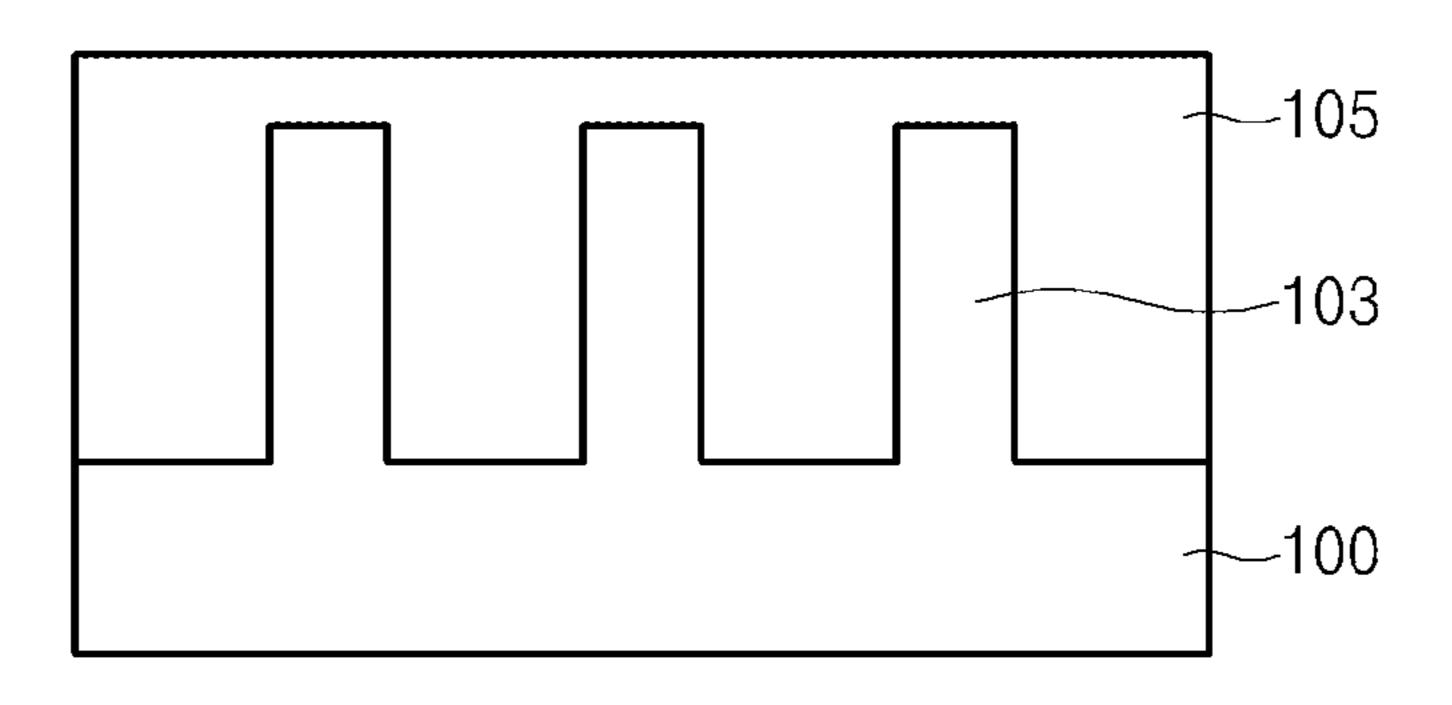

> FIGS. 3A to 3G are cross-sectional views illustrating a method for manufacturing a semiconductor device shown in FIG. 2 according to an embodiment of the present invention.

> Referring to FIG. 3A, a semiconductor substrate 100 is etched so that a device isolation trench for defining the active region 103 is formed. Thereafter, the device isolation trench is filled with an oxide film, and a planarization etching process is performed, so that a device isolation film 105 is formed.

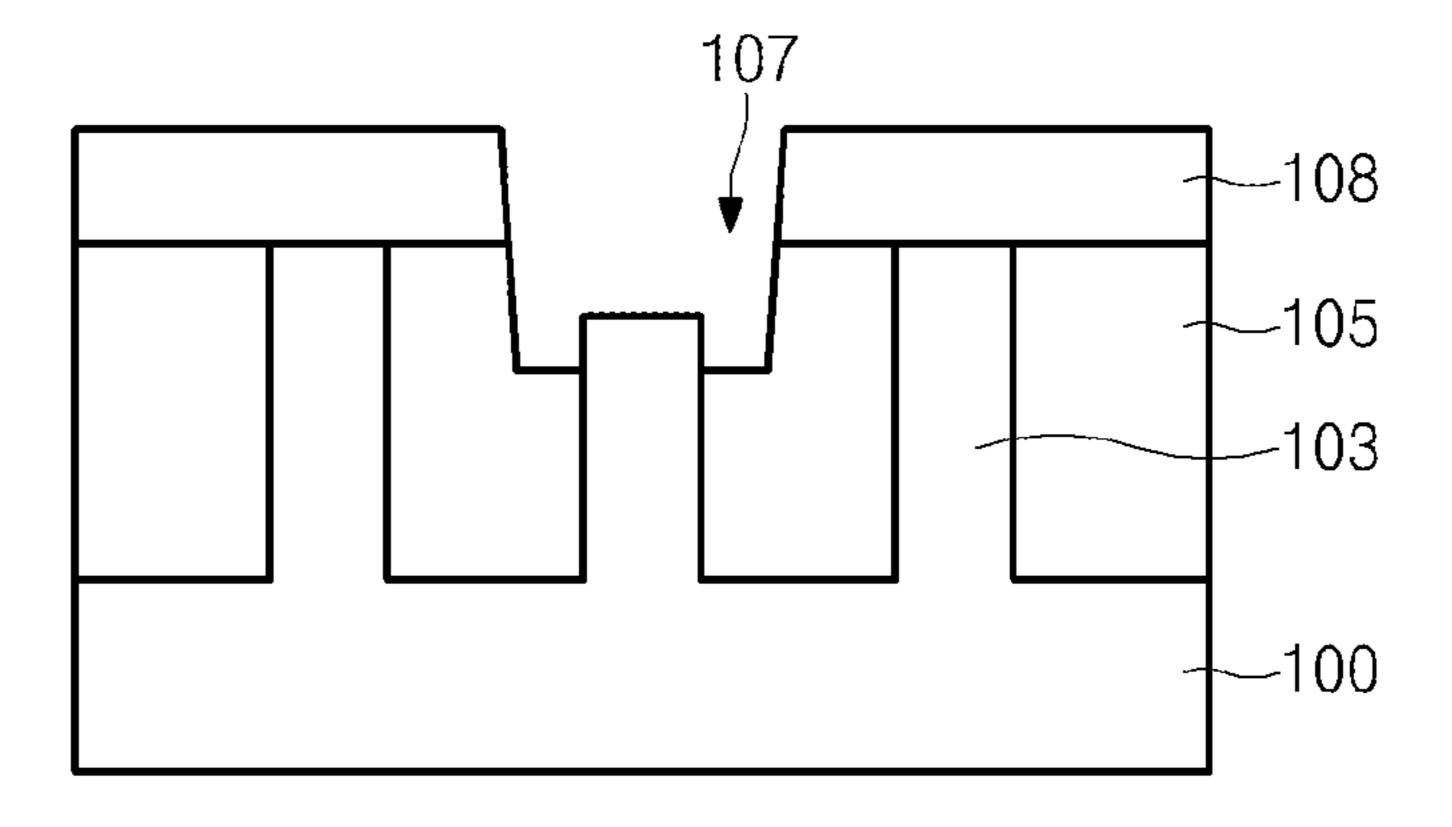

> Referring to FIG. 3B, a mask pattern 108 is formed over the semiconductor substrate 100. Thereafter, the semiconductor substrate 100 is etched using the mask pattern 108 as an etch mask so that a bit line contact hole 107 is formed. In an embodiment, the active region 103 may protrude from a center part of the bit line contact hole 107 due to a difference in etch selection ratio between the active region 103 and the device isolation film 105. The active region 103 shown in FIGS. 3A to 3G is a cross-sectional view taken along a shortaxis of the active region 103.

Referring to FIG. 3C, after the mask pattern 108 is removed, a spacer insulation film 110 is deposited in the bit 5

line contact hole 107. Preferably, the spacer insulation film 110 may be formed of a material including a nitride film. In an embodiment, the spacer insulation film 110 is deposited along sidewalls of the bit line contact hole 107 and over the protruded active region 103, so as to form a recess over the 5 protruded active region 103 as shown in FIG. 3C.

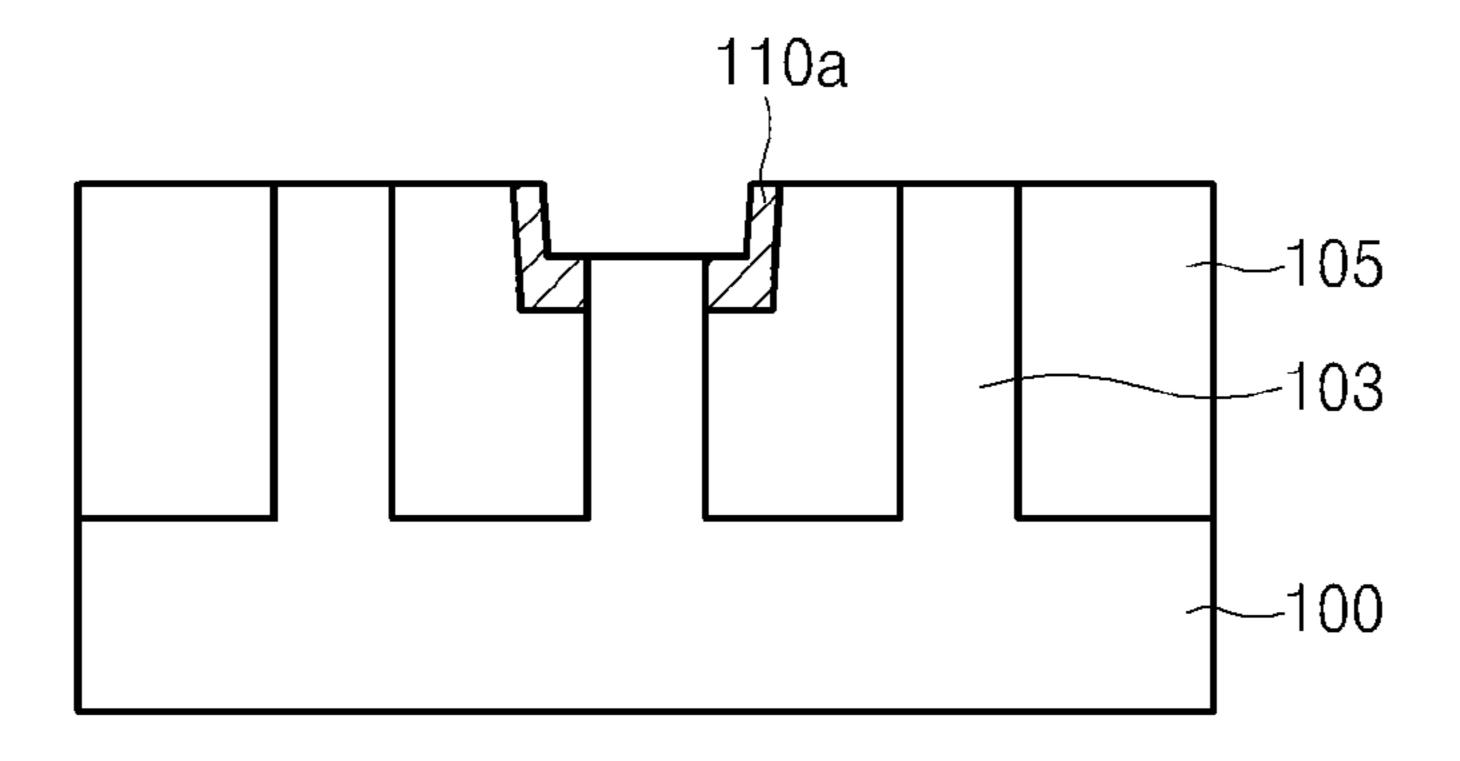

Referring to FIG. 3D, a lateral etch process is performed so that the spacer insulation film 110 remains only over the sidewalls and bottom of the bit line contact hole 107. The remaining spacer insulation film **110** is referred to as a first 10 spacer 110a. The spacer insulation film 110 may be etched until the top of the active region 103 is exposed during the lateral etch process. Therefore, the first spacer 110a may be formed at a sidewall of the bit line contact hole 107. A light etch treatment (LET) scheme may be employed for the lateral 15 etch process. More preferably, a wet etch scheme may be employed, or a lateral etch process may be performed using a gas, including any of SF, O<sub>2</sub>, N<sub>2</sub>, HBr and a combination thereof. In this case, the LET scheme may be performed using a mixed gas of CF<sub>4</sub> and O<sub>2</sub> through a downstream-based 20 etching device. A LET process is advantageous because it cures a substrate surface, which is damaged in the etching process.

In addition, the lateral etch process is performed until the top of the active region 103 is exposed. That is, the first spacer 25 110a is formed to expose the top surface of the active region 103, which protrudes in the bit line contact hole 107. Preferably, the first spacer 110a formed at the bottom of the bit line contact hole 107 may be formed to be the level to a top surface of the protruded active region 103. Preferably, the portion of 30 the first spacer 110a formed at the bottom of the bit line contact hole 107 may be formed to have a larger thickness than the portion of the first spacer 110a formed at a sidewall of the bit line contact hole 107.

layer (not shown), a bit line conductive layer 120a, and a bit line hard mask layer 120b are sequentially formed over the entire surface of the semiconductor substrate 100 including the bit line contact hole 107 in which the first spacer 110a is formed. After that, a mask pattern (not shown) defining a bit 40 line is formed over the bit line hard mask layer 120b. The bit line hard mask layer 120b, the bit line conductive layer 120a, the barrier metal layer (not shown) and the polysilicon layer are etched using the above-mentioned mask pattern (not shown) as an etch mask, so that the bit line 120 and the bit line 45 contact plug 115 are formed. In other words, the bit line 120 and the bit line contact plug 115 are simultaneously etched. The bit line contact plug 115 may be formed by etching the polysilicon layer. Thus, an inner GBL (Global Bit Line), including the bit line contact plug 115, is formed in the bit line 50 contact hole 107, and an empty space, denoted as 'A', is formed between a lateral surface of the bit line contact plug 115 and the first spacer 110a formed at a sidewall of the bit line contact hole 107.

Referring to FIG. 3F, a second spacer 125 is formed over the entire surface of the semiconductor substrate 100 including the bit line contact plug 115 and the bit line 120. The second spacer 125 fully fills the empty space A shown in FIG. 3E. In this case, since the first spacer 110a is formed to a predetermined thickness at the bottom of the bit line contact hole 107, the depth (d2) filled by the second spacer 125 becomes shallower, so that a gap-filling problem caused by a high aspect ratio during the formation of the second spacer 125 can be solved. The second spacer 125 may be formed of the same material as the first spacer 110a. For example, the 65 second spacer 125 may be formed of a material including a nitride film.

6

Referring to FIG. 3G, an interlayer insulation film 130 is formed over the entire surface including the second spacer 125. Thereafter, a mask pattern (not shown) defining a storage node contact hole is formed over the interlayer insulation film 130, and the interlayer insulation film 130 and the second spacer 125 are etched using the above-mentioned mask pattern (not shown) as an etch mask, so that a storage node contact hole 135 is formed and a cleaning process is then performed. The interlayer insulation film 130 is formed of a material, such as an oxide film, that has an etch selectivity ratio different from that of the spacer insulation film 125. As a result, the second spacer 125 formed at sidewalls of the bit line 120 is not damaged and damage to the bit line 120 and the bit line contact plug 115 can be prevented. As can be seen from FIG. 3F, the second spacer 125 can fill a void between the bit line contact plug 115 and the first spacer 110a, preventing a Self Align Contact (SAC) fail from occurring in the course of formation of the storage node contact hole 135.

As is apparent from the above description, a semiconductor device and a method for forming the same according to an embodiment of the present invention, the first spacer is formed at the bottom of the bit line contact hole, and the resultant first spacer is increased in thickness, so that the depth of the second spacer, which is deposited after the formation of the bit line and the bit line contact plug and fills a void between the bit line contact plug and the first spacer, is reduced. As a result, formation of a void can be prevented in the formation of the second spacer, and a SAC fail can also be prevented in the formation of the storage node contact hole, which is formed in a subsequent process.

The above embodiments of the present invention are illustrated hole 107 may be formed to have a larger thickness and the portion of the first spacer 110a formed at a sidewall the bit line contact hole 107.

Referring to FIG. 3E, a polysilicon layer, a barrier metal yer (not shown), a bit line conductive layer 120a, and a bit he hard mask layer 120b are sequentially formed over the tire surface of the semiconductor substrate 100 including

What is claimed is:

1. A method for manufacturing a semiconductor device comprising:

forming a bit line contact hole in which a portion of an active region protrudes from a device isolation film by etching the active region and the device isolation film;

forming a first spacer over a sidewall and an entire bottom surface of the bit line contact hole such that a surface of the active region is exposed, the first spacer being formed between the portion of the active region that protrudes from the device isolation film and the etched device isolation film;

forming a bit line contact plug and a bit line over the exposed active region; and

forming a second spacer between the bit line contact plug and the first spacer.

- 2. The method according to claim 1, wherein, in the forming of the bit line contact hole, a width of the bit line contact hole is larger than a short-axis length of the active region.

- 3. The method according to claim 1, wherein the forming of the first spacer includes:

- depositing an insulation film over the bit line contact hole including the protruded portion of the active region; and performing an etch process until a surface of the protruded portion of the active region is exposed and the insulation film remains over the sidewall and bottom of the bit line contact hole.

- 4. The method according to claim 3, wherein the etch process is a lateral etch process.

7

- 5. The method according to claim 4, wherein the lateral etch process is performed using a Light Etch Treatment (LET) scheme.

- 6. The method according to claim 4, wherein the lateral etch process is performed using a wet etch scheme.

- 7. The method according to claim 3, wherein the etch process is performed using a gas including any of  $SF_6$ ,  $O_2$ ,  $N_2$ , HBr, and a combination thereof.

- 8. The method according to claim 1, wherein the forming of the bit line contact plug and the bit line includes:

- forming a polysilicon layer, a barrier metal layer, a bit line conductive layer and a hard mask layer over the substrate in the bit line contact hole;

- forming a mask pattern defining a bit line over the hard mask layer; and

- etching the hard mask layer, the bit line conductive layer, the barrier metal layer, and the polysilicon layer using the mask pattern defining the bit line as an etch mask.

- 9. The method according to claim 8, wherein the barrier metal layer is formed of any of a titanium (Ti) film, a titanium nitride (TiN) film, and a combination thereof.

8

- 10. The method according to claim 8, wherein the bit line conductive layer is formed of a material including tungsten (W).

- 11. The method according to claim 8, wherein the bit line hard mask layer is formed of a material including a nitride film.

- 12. The method according to claim 8, wherein, in the etching of the polysilicon layer, the polysilicon layer is patterned to form the bit line contact plug.

- 13. The method according to claim 1, wherein the second spacer is formed to fill the bit line contact hole formed at sidewalls of the bit line contact plug.

- 14. The method according to claim 3, wherein the insulation film is formed of a material including a nitride film.

- 15. The method according to claim 1, the method further comprising:

after forming the second spacer, forming a storage node contact plug adjacent to the bit line.

\* \* \* \*