#### US009197137B2

# (12) United States Patent

Saito et al.

## (10) Patent No.: US 9,197,137 B2

(45) Date of Patent: \*Nov. 24, 2015

#### (54) **POWER CONVERSION DEVICE**

(75) Inventors: Masao Saito, Tokyo (JP); Takamasa

Nakamura, Atsugi (JP); Kouji Yamamoto, Chigasaki (JP); Junichi Itoh, Nagaoka (JP); Yoshiya Ohnuma,

Nagaoka (JP)

(73) Assignees: NISSAN MOTOR CO., LTD.,

Yokohama-shi (JP); NAGAOKA UNIVERSITY OF TECHNOLOGY,

Nagaoka-shi (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 14/342,842

(22) PCT Filed: Sep. 6, 2012

(86) PCT No.: PCT/JP2012/072729

§ 371 (c)(1),

(2), (4) Date: Mar. 5, 2014

(87) PCT Pub. No.: WO2013/035782

PCT Pub. Date: Mar. 14, 2013

(65) Prior Publication Data

US 2014/0226382 A1 Aug. 14, 2014

#### (30) Foreign Application Priority Data

Sep. 6, 2011 (JP) ...... 2011-194163

(51) **Int. Cl.**

H02M 5/293 (2006.01) H02M 7/217 (2006.01) H02M 5/297 (2006.01)

(52) **U.S. Cl.**

CPC ...... *H02M 5/297* (2013.01); *H02M 5/293* (2013.01); *H02M 7/217* (2013.01); *H02M*

2005/2932 (2013.01)

| (58) | Field of Classification | on Search                   |

|------|-------------------------|-----------------------------|

|      | CPC                     | H02M 5/293; H02M 7/217      |

|      | USPC                    |                             |

|      |                         | or complete search history. |

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

|      | WidmayerBernet |  |

|------|----------------|--|

| (Con | tinued)        |  |

#### FOREIGN PATENT DOCUMENTS

| CN               | 101951168 A  | 1/2011     |

|------------------|--------------|------------|

| $\Xi \mathbf{P}$ | 1 708 350 A3 | 12/2008    |

|                  | (Cont        | inued)     |

|                  | OTHER PUE    | BLICATIONS |

U.S. Appl. No. 14/342,858, filed Mar. 5, 2014, Saito et al. U.S. Appl. No. 14/342,878, filed Mar. 5, 2014, Saito et al. Koji Kato et al., Development of a Novel Commutation Method Which Drastically Suppresses Commutation Failure of a Matrix Converter, Heisi 19 Electrical Engineering Society Paper, 2007, pp. 829-836, vol. 127, No. 8.

(Continued)

Primary Examiner — Timothy J Dole

Assistant Examiner — Bryan R Perez

(74) Attorney, Agent, or Firm — Foley & Lardner LLP

#### (57) ABSTRACT

An electric power conversion device comprises a conversion circuit having bi-directionally switchable plural pairs of switching elements connected to respective phases and converting an inputted AC power into an AC electric power. A first switching time is calculated using detected voltages detected by voltage sensors and an output command value. A second switching time is calculated using a carrier and the calculated first switching time. The second switching time is such that, in one period of the alternating current electric power outputted from the conversion circuit, the second switching time included in a first half period of the one period is equal to the second switching time included in a second half period of the one period.

#### 6 Claims, 15 Drawing Sheets

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,330,170    | B1   | 12/2001 | Wang et al.           |

|--------------|------|---------|-----------------------|

| 7,701,740    | B2 * | 4/2010  | Yamanaka 363/149      |

| 2003/0095424 | A1   | 5/2003  | Oates                 |

| 2009/0231896 | A1*  | 9/2009  | Barbosa et al 363/131 |

| 2009/0323380 | A1*  | 12/2009 | Harrison 363/126      |

| 2014/0226386 | A1*  | 8/2014  | Saito et al 363/132   |

| 2014/0233280 | A1*  | 8/2014  | Saito et al 363/37    |

|              |      |         |                       |

#### FOREIGN PATENT DOCUMENTS

| JP | 02-131368   | $\mathbf{A}$ | 5/1990  |

|----|-------------|--------------|---------|

| JP | 07-007944   | A            | 1/1995  |

| JP | 08-107672   | $\mathbf{A}$ | 4/1996  |

| JP | 2000-299984 | A            | 10/2000 |

| JP | 2001-298953 | $\mathbf{A}$ | 10/2001 |

| JP | 2003-528562 | $\mathbf{A}$ | 9/2003  |

| JP | 2006-020384 | $\mathbf{A}$ | 1/2006  |

| JP | 2006-246673 | $\mathbf{A}$ | 9/2006  |

| JP | 2010-263702 | $\mathbf{A}$ | 11/2010 |

| RU | 2 265 947   | C2           | 12/2005 |

| RU | 2 349 019   | C1           | 3/2009  |

| RU | 2 414 043   | C1           | 3/2011  |

#### OTHER PUBLICATIONS

Yoshiya Onuma et al., 50kVA, 125A Sanso Tanso Matrix Converter o Tekiyo Shita Koshuha Link AC-DC Converter no Jikki Kensho, Heisei 23 Nen National Convention Record, I.E.E. Japan, Industry Applications Society, Sep. 6, 2011, 1-80, pp. I-403 to I-406.

Young Li, "Direct Duty Ratio Pulse Width Modulation Method for Matrix Converters", *Chonnam National University*, 2009, 186 pgs. Korean Office Action dated Jan. 21, 2015, 6 pgs.

M. Saito, USPTO Non-final Office Action U.S. Appl. No. 14/342,858 dated Jan. 23, 2015, 16 pgs.

M. Saito, USPTO Non-final Office Action U.S. Appl. No. 14/342,878 dated Feb. 5, 2015, 14 pgs.

U.S. PTO Notice of Allowance, U.S. Appl. No. 14/342,858, dated Jun. 2, 2015, 10 pages.

U.S. PTO Notice of Allowance, U.S. Appl. No. 14/342,878, dated Jun. 19, 2015, 9 pages.

Hara, H. et al., "Improvement of output voltage control performance for low speed operation of matrix converter", 2004 35<sup>th</sup> Annual IEEE Power Electronics Specialists Conference, Aachen, Germany, Jun. 20-25, 2004, pp, 2910-2916.

<sup>\*</sup> cited by examiner

YABITTA8 to reference concernment in in in in an entitle after an incommendation of , in more and the commence of the commence of

| A MARKA                                 | #<br>#<br>#<br>#           |                  | ద్ద<br>భ               | eç<br>Ç       | CE<br>CE<br>CE | S<br>S      | Ç.              | ű               |                                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | (A)            | ທົ              | W)          | ري<br>ش        | S<br>S          | Ś            |

|-----------------------------------------|----------------------------|------------------|------------------------|---------------|----------------|-------------|-----------------|-----------------|------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|-------------|----------------|-----------------|--------------|

|                                         | Arren<br>Arren<br>Arren    |                  | şm                     | <b>\\\\\</b>  | <b>\tag{1}</b> | ~           | <b>~</b>        | igossi          | AZ<br>AZ<br>AZ                           | Joseph<br>Joseph<br>June | A CONTRACTOR OF THE PARTY OF TH | <b>\tag{2}</b> | · Quan          | c           | $\Box$         | · kun           | <b>~</b>     |

|                                         |                            |                  |                        |               | Speec          | <b>C</b>    |                 | - Appense       |                                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>~</b>       |                 | <b>©</b>    | Soor           | ş               | <b>~</b>     |

|                                         | (2)                        | , 200<br>, 200   |                        | 83            | dooo           | - Ann       | <b>c</b>        | <b>~</b>        |                                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>~</b>       |                 | ***         | <b>1900</b> 00 | <b>~</b>        | <b>©</b>     |

| *************************************** | 664<br>664                 | \$1.20<br>\$1.20 | <b>6.3</b>             | <b>\$</b>     | <b>~</b>       | 19000       | ·p.v.           | C               |                                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                | <b>~</b>        | · jane      |                | co              | şw           |

| ••••••                                  | £3.                        |                  |                        | gev.          | <b>~</b>       | $\Box$      | <b>&amp;</b>    | 800             |                                          |                          | Sec.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Áice           | c:              | ***         | <b>\_</b>      | <b>C</b>        | <b>Š</b> ver |

|                                         | ٤                          | P.A.             | ą                      | · ·           | <b>\tag{2}</b> | <b>\C</b>   |                 | æ               | **************************************   |                          | A Service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | doco           | 9 <b>200</b> 0: | Cons        | <b>~</b>       | $\varpi$        | <b>\$</b>    |

|                                         | Ann<br>Ann                 | 7.47<br>5.47     | 8                      |               | ngooc          | <b>~</b>    | <b>\$</b>       | dew.            | ST S | year,<br>jann<br>jann    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>\tag{2}</b> | <b>~</b>        |             | doo            | apani           | <b>-</b>     |

|                                         |                            |                  |                        | yee           | gen            | $\Box$      | <b>C</b>        |                 |                                          |                          | (X)<br>(X)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | , <b>ò</b> coc | <b>~</b>        |             | opooc          | <b>~</b>        | <b>\\</b>    |

|                                         | 23                         | Service.         | 13000                  | <b>6</b> ···· |                |             | <b>\$</b>       |                 |                                          | 64.3<br>                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | - Spine        | Space:          | <b>\$3</b>  |                | <b>(11)</b>     | <b>~</b>     |

|                                         | 1.000.                     |                  | good                   |               |                | 4000        | <b>\tau</b>     |                 |                                          | 2003y                    | Sarah<br>Citie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b></b>        | goo             | Secon       | <b>~</b>       |                 | C            |

|                                         | W.                         |                  | <b>~</b>               |               |                | эроос       | -               | <b>\$</b>       |                                          |                          | Service of the Servic |                | <b>~</b>        | Acre        | <b>\tag{2}</b> |                 | ayaax        |

|                                         |                            | (3)              | <b>~</b>               | <b>~</b>      | <b>\$</b>      | <b>~</b>    | gypon.          |                 |                                          | (C)                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>~</b>       | <b>~</b>        | <b>\$\$</b> |                | JOSE            | igoso        |

| 44<br>44<br>44<br>44<br>44<br>44        | Second<br>Second<br>Second |                  | <b>\(\tau_{\tau}\)</b> |               | <i>b</i> ~~    |             | <b>\tag{2}</b>  | <b>C</b>        | ######################################   | produce.                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | · Arre         | ۵               | <b>~</b>    | <b>3</b> ~~~   | <b>\(\tau\)</b> | $\Box$       |

|                                         |                            | on the second    | 8                      | ****          | ~              |             | doir            | <b>~</b>        |                                          |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -Second        |                 | <b>~</b>    |                | Ci              | · Paris      |

|                                         |                            |                  |                        | ~~            |                |             | ****            | 10000           | *********                                |                          | COS<br>COS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                | <b>~</b>        | <b>~</b>    | <b>~</b>       | ķw              | <b>QCCC</b>  |

|                                         |                            |                  | · Serve                |               |                |             | <b>\(\tau\)</b> | 9900x           |                                          | Section 1                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>~</b>       | - Jew           |             | <b>\$</b>      | św              | <b>~</b>     |

|                                         |                            |                  | św                     | <b>~</b> 3    | ~>             | · Serve     | <b>a</b>        |                 | *********                                |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>\tau</b>    | , free          | ****        | <b>~</b>       | <b>~</b>        | 0            |

| *************************************** | <b>3</b>                   |                  | Con                    |               | 2000           | <b>~</b> ~~ | <b>\(\tau\)</b> | <b>\(\omega</b> |                                          | Œ.                       | and a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>\\\\\</b>   |                 | ******      | Som            | <b>\\\\</b>     | C)           |

#### POWER CONVERSION DEVICE

#### TECHNICAL FIELD

The present invention relates to an electric power conversion device.

#### **BACKGROUND ART**

A control apparatus for controlling an electric power converter is known which comprises: a PWM rectifier which performs a conversion of an alternating current to a direct current; and an inverter connected to the PWM rectifier to perform an inversion of the direct current to the alternating current, the control apparatus including: bi-phase modulation 15 means for generating an output voltage command to perform a bi-phase modulation for the inverter; first compensation quantity calculating means for calculating a compensation quantity correcting the output voltage command in order to compensate for an output voltage error generated when the 20 bi-phase modulation for the inverter is carried out; inverter PWM pattern generating means for generating PWM pulses for semiconductor switching elements of the PWM rectifier on a basis of an input current command; switching detecting means for detecting a presence or absence of a switching of 25 the PWM rectifier; voltage magnitude detecting means for detecting a voltage of a maximum phase, a voltage of a middle phase, and a voltage of a minimum phase from an input voltage of each phase; and polarity determination means for determining a polarity of a load current, wherein the first <sup>30</sup> compensation quantity calculating means calculates the compensation quantity correcting the output voltage command using an output of the voltage magnitude detecting means, an output of the polarity determination means, an output of the switching detecting means, a switching frequency of the <sup>35</sup> inverter, and a dead time.

However, such a problem occurs that the known control apparatus for the electric power conversion device compensates only a voltage error generated according to a commutation but cannot prevent a commutation failure itself.

#### PRE-PUBLISHED DOCUMENT

Patent Document 1: Japanese Patent Application First Publication (tokkai) No. 2006-20384.

### DISCLOSURE OF THE INVENTION

It is an object of the present invention to provide an electric power conversion device which can prevent the commutation 50 failure.

The above-described object can be achieved by the present invention such that a switching time calculating section and a control signal generating section configured to generate control signals for switching elements on a basis of a first switch- 55 ing time and a second switching time are provided, wherein the switching time calculating section calculates the first switching time which is a time during which one of the switching elements of an upper arm circuit of the plural pairs of switching elements included in one phase from among the 60 respective phases is turned on, the other switching elements of the upper arm circuit of the plural pairs of switching elements included in the other phases are turned off, at least one switching element of a lower arm circuit of the plural pairs of switching elements included in the other phases is turned on, 65 and the other switching elements of the lower arm circuit of the plural pairs of switching elements included in the one

2

phase are turned off using detected voltages detected by voltage detecting means and an output command value and calculate the second switching time during which the plural pairs of switching elements included in the one phase from among the respective phases are turned on and the plural pairs of switching elements included in the other phases from among the respective phases are turned off using a carrier and the first switching time and wherein, in one period of the alternating current electric power outputted from the conversion circuit, the second switching time included in a first half period of the period is made equal to the second switching time included in a second half period of the period.

According to the present invention, the second switching time is equally allocated to the first half period and the second half period. Thus, an overlap of the switching operations between a first time point of the second switching time and a last time point of the second switching time can be avoided. Consequently, the commutation failure can be prevented from occurring.

#### BRIEF DESCRIPTION OF THE DRAWINGS

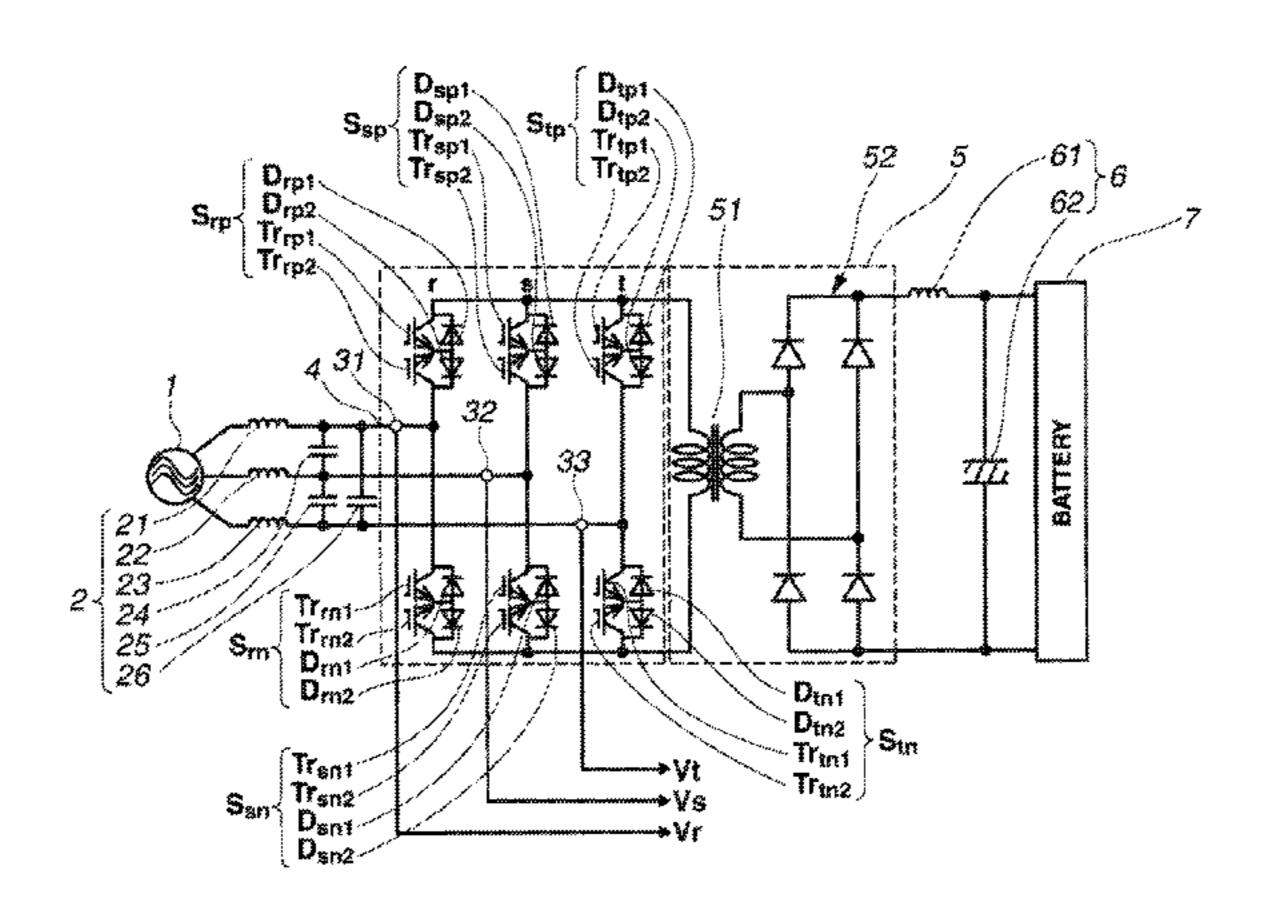

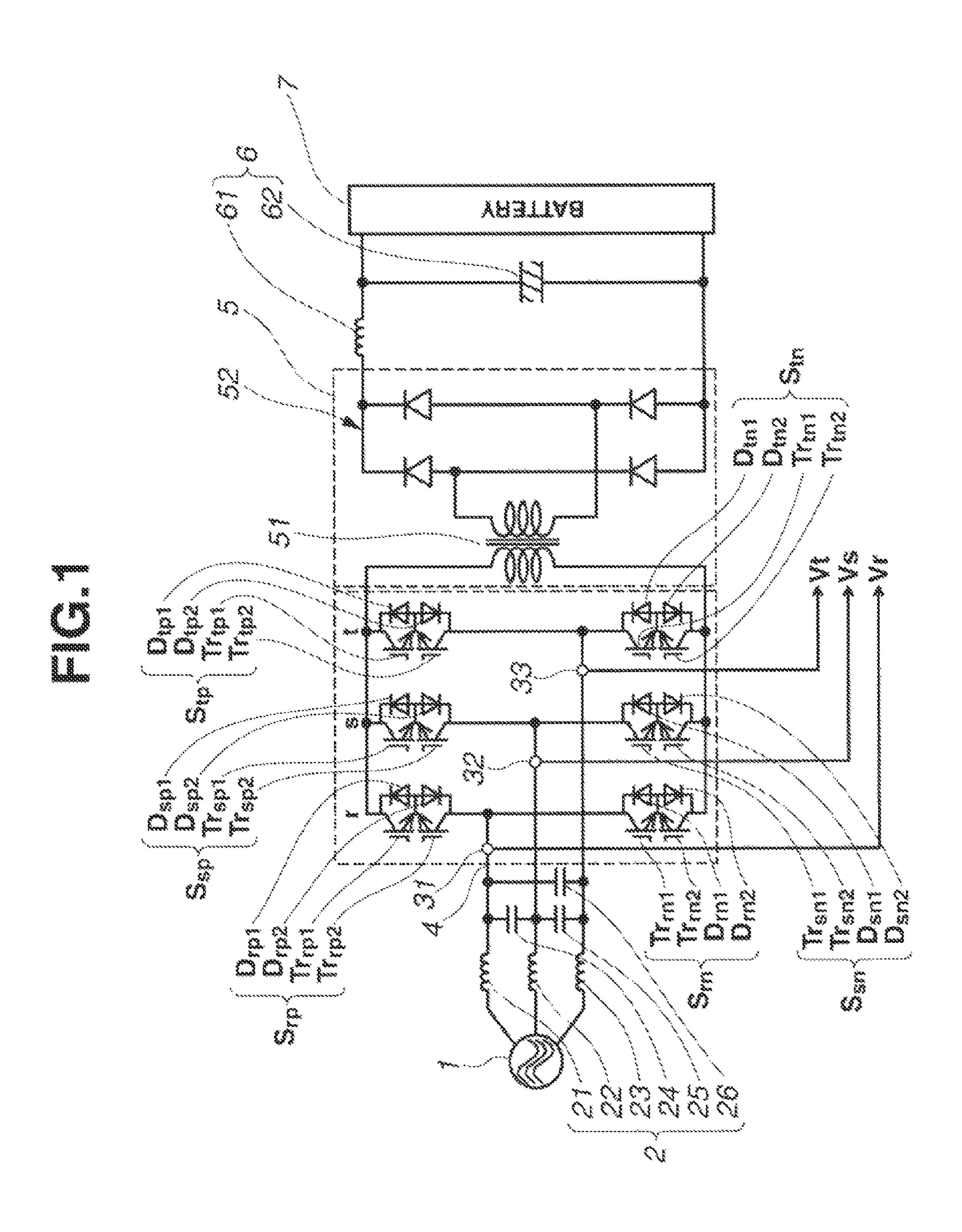

FIG. 1 is a block diagram of a charging system including an electric power conversion device in a preferred embodiment according to the present invention.

FIG. 2 is a block diagram of a charging system in a first comparative example.

FIG. 3 is a block diagram of a charging system in a second comparative example.

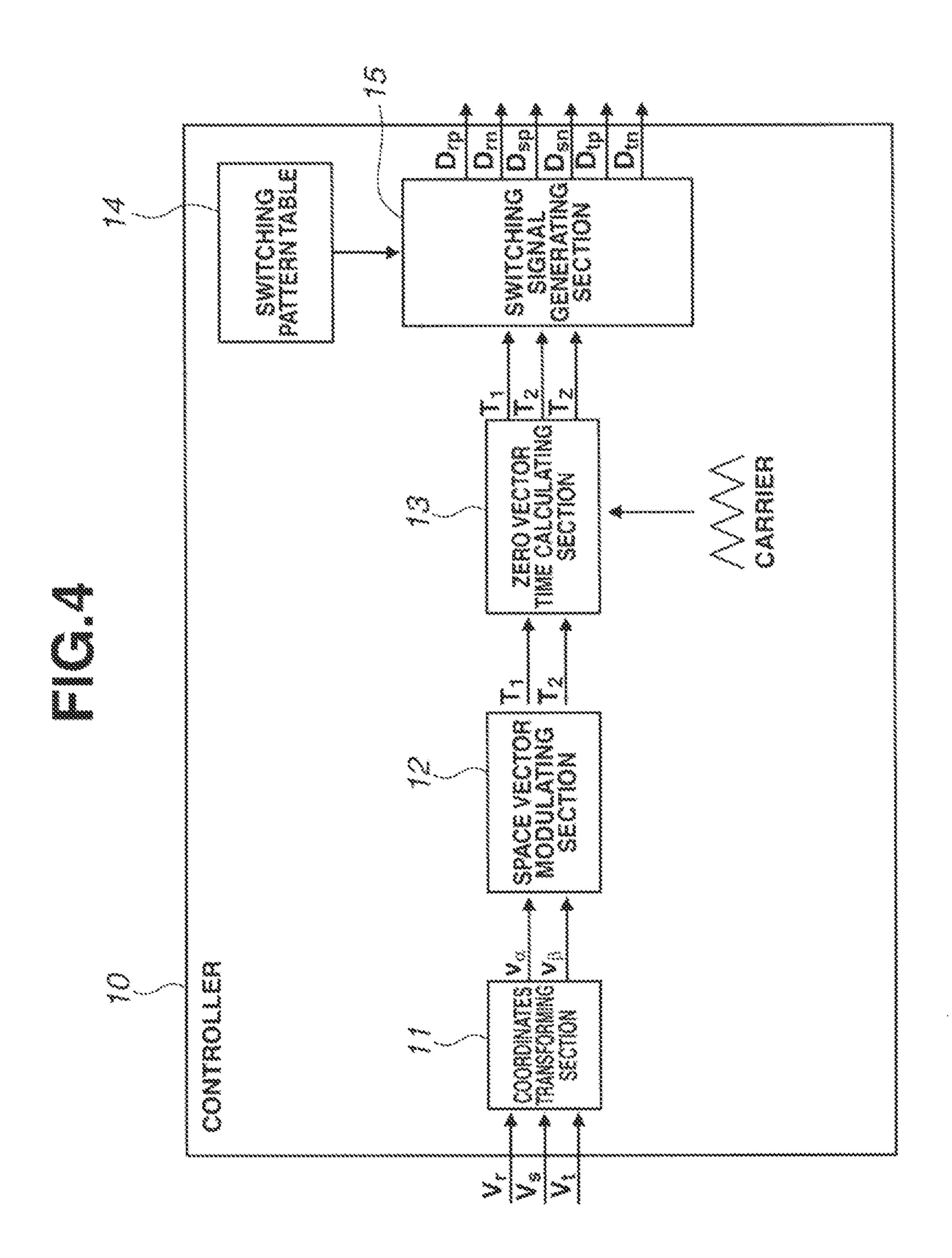

FIG. 4 is a block diagram of a controller controlling the electric power conversion device shown in FIG. 1.

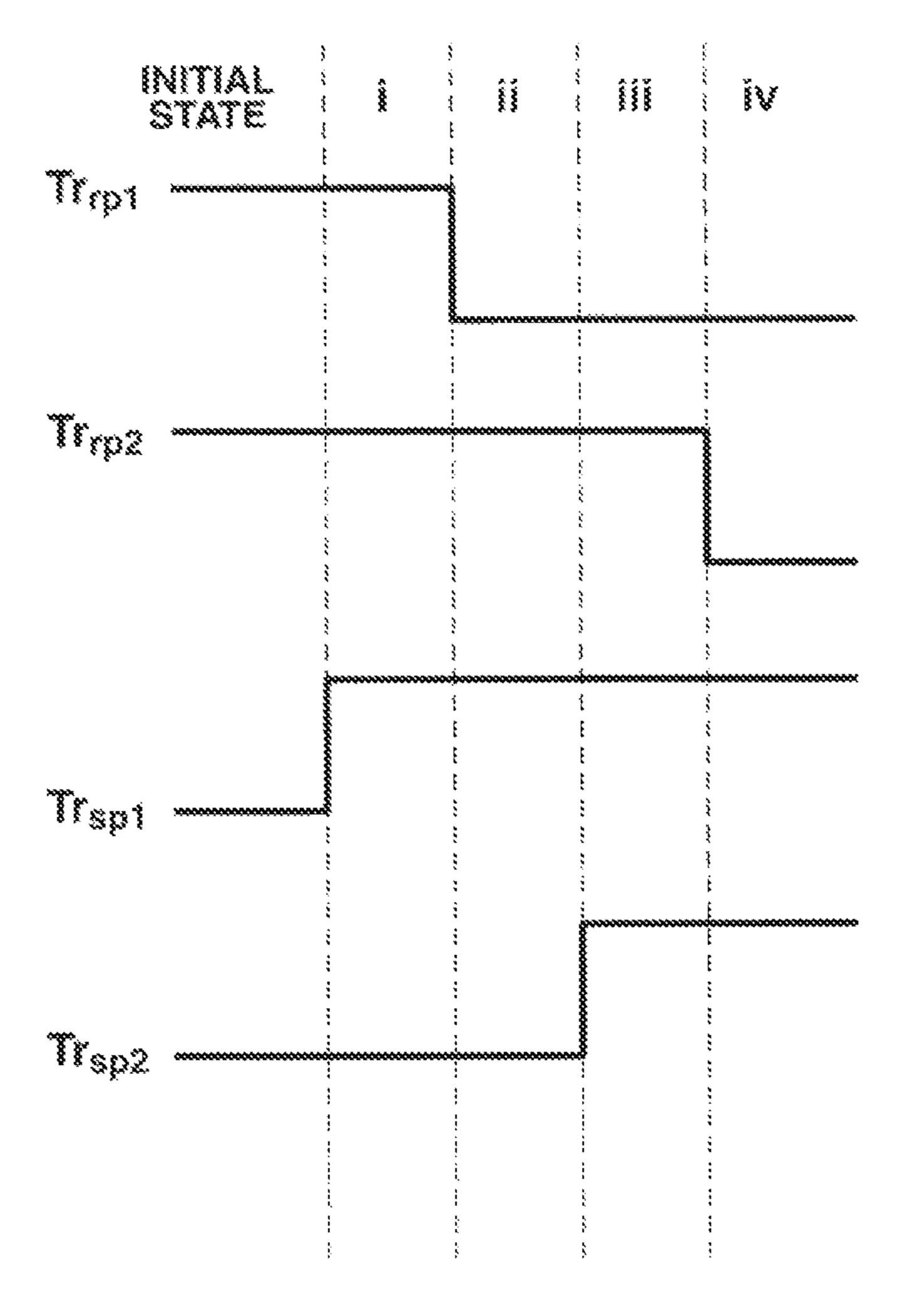

FIG.  $\hat{\bf 5}$  is a graph representing a switching sequence of an r phase switching element shown in FIG.  $\bf 1$ .

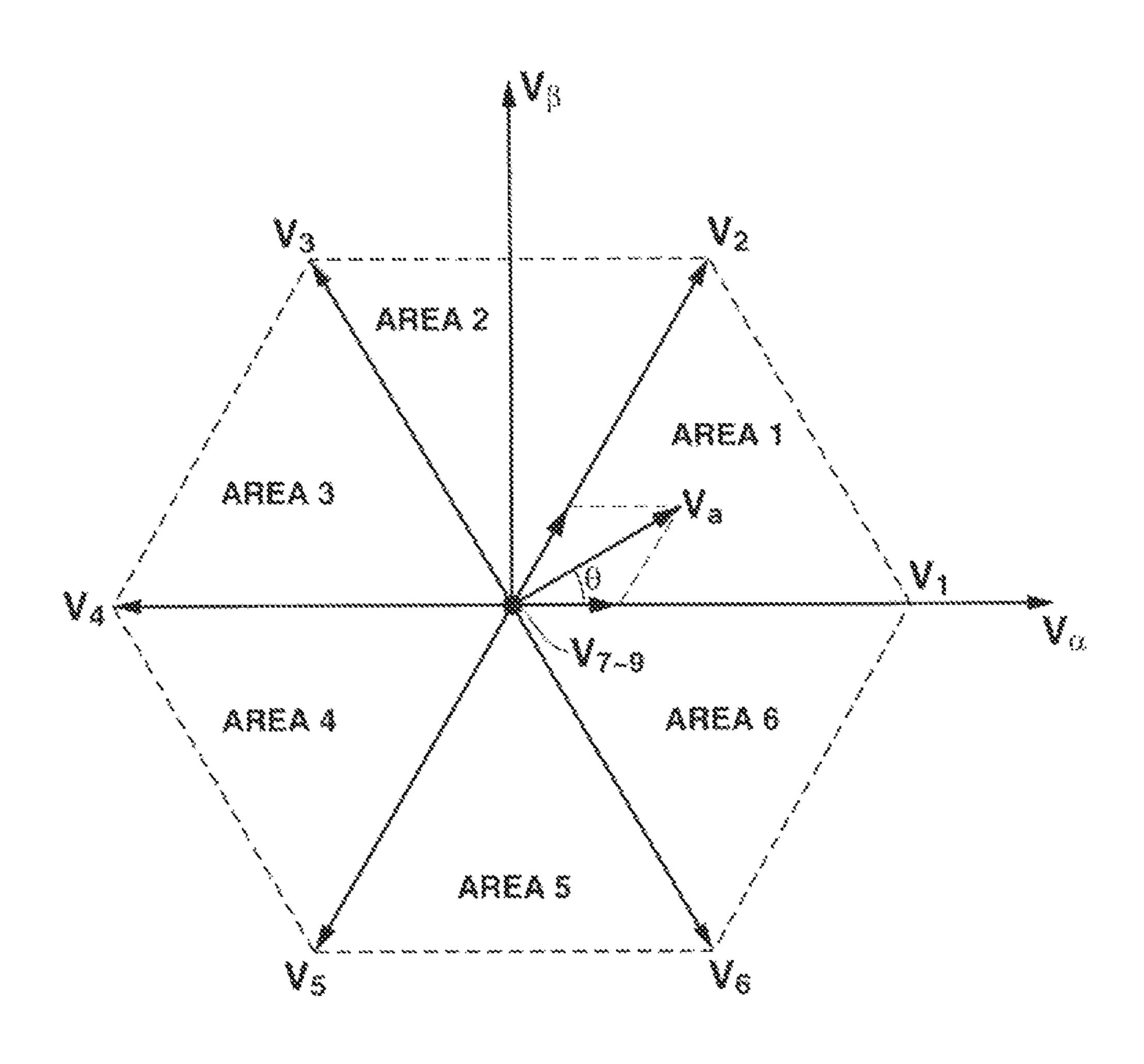

FIG. 6 is a diagram representing a relationship between a base vector and a voltage vector in a space vector modulating section shown in FIG. 4.

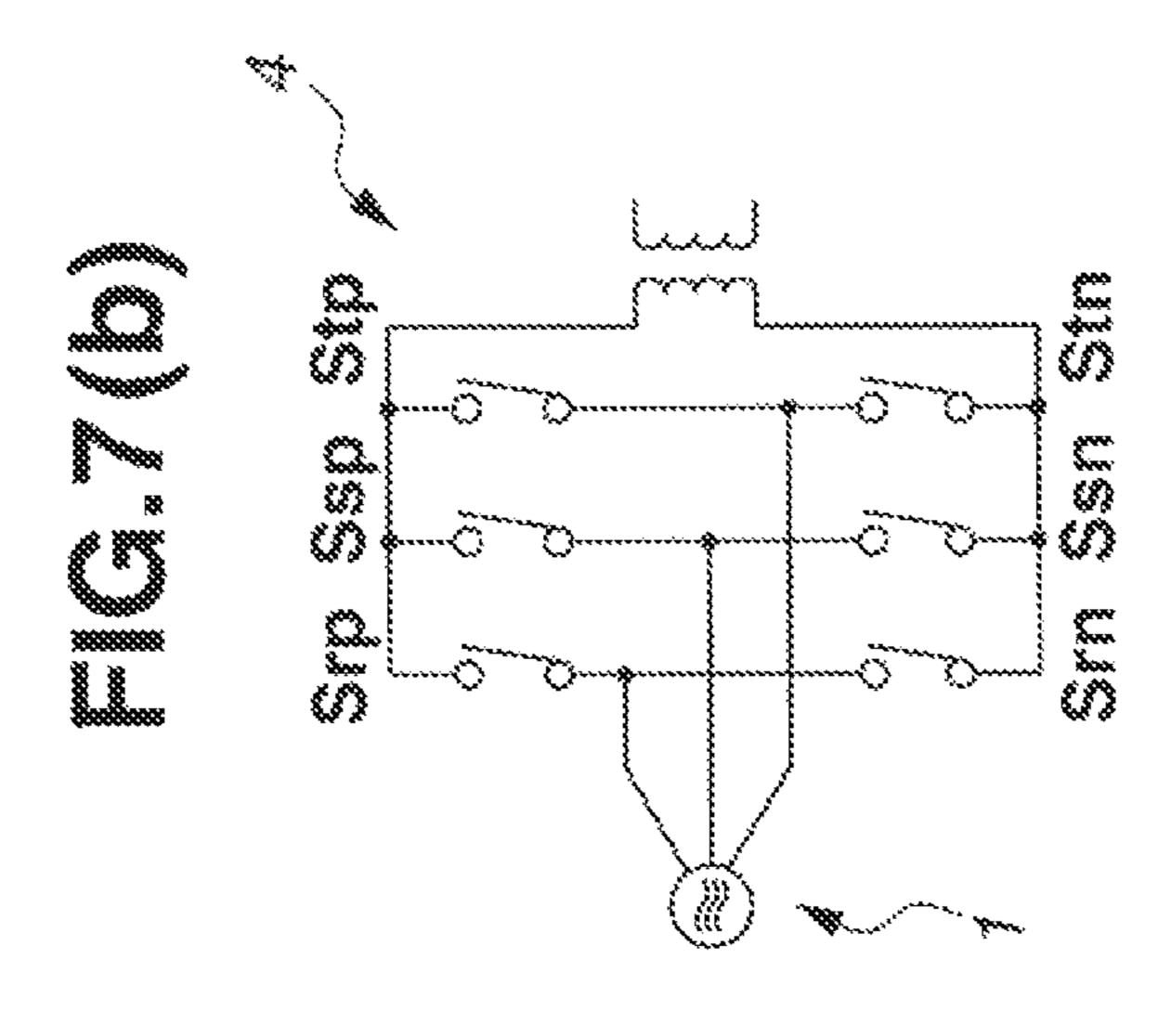

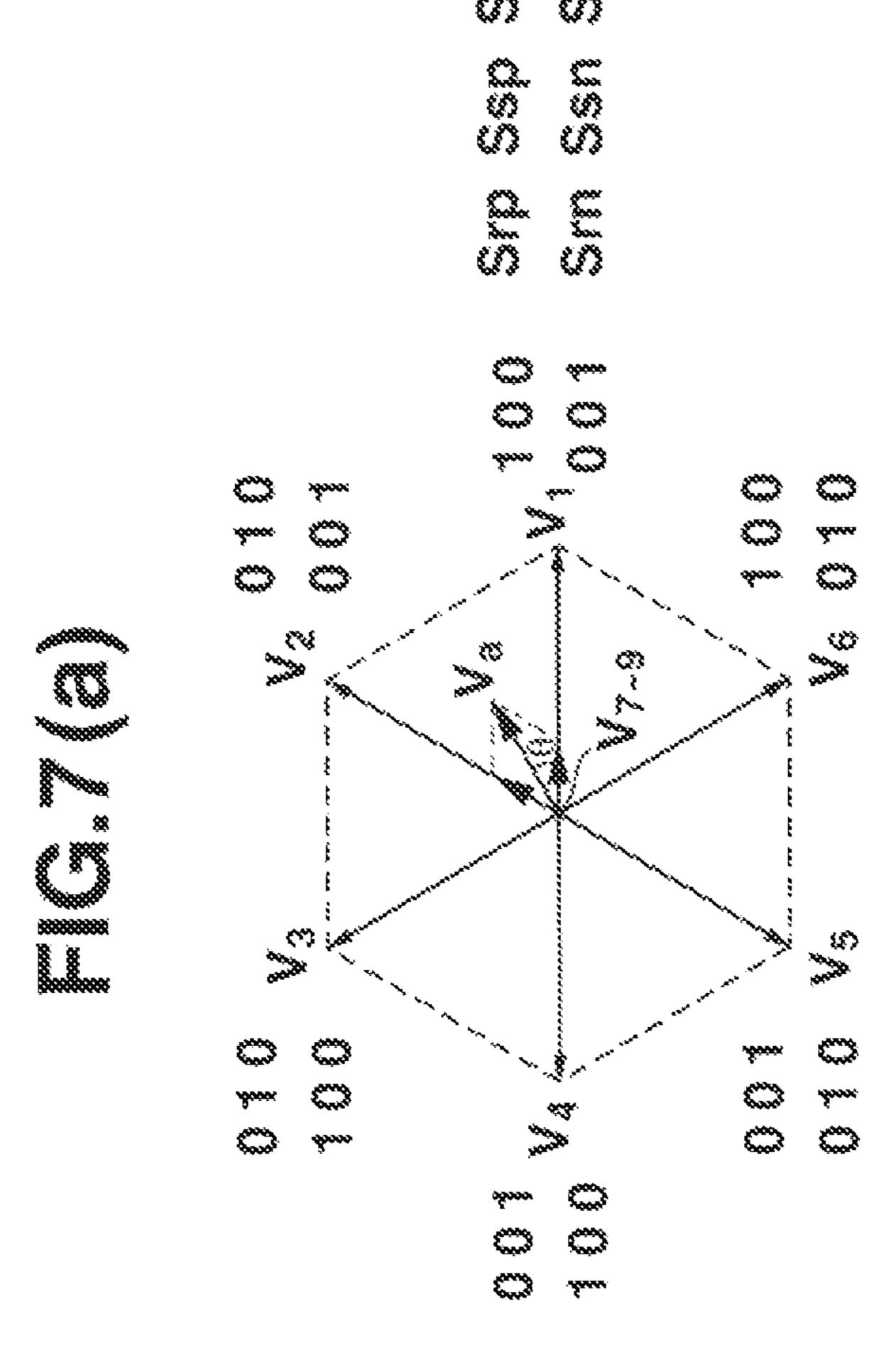

FIG. 7(a) is a diagram which is an addition of a switching pattern to a vector diagram of FIG. 6 and FIG. 7(b) is a circuit diagram of an alternating current power supply 1 and a matrix converter 4 in the charging system shown in FIG. 1.

FIG. 8 is a conceptual diagram of the switching pattern table of FIG. 4.

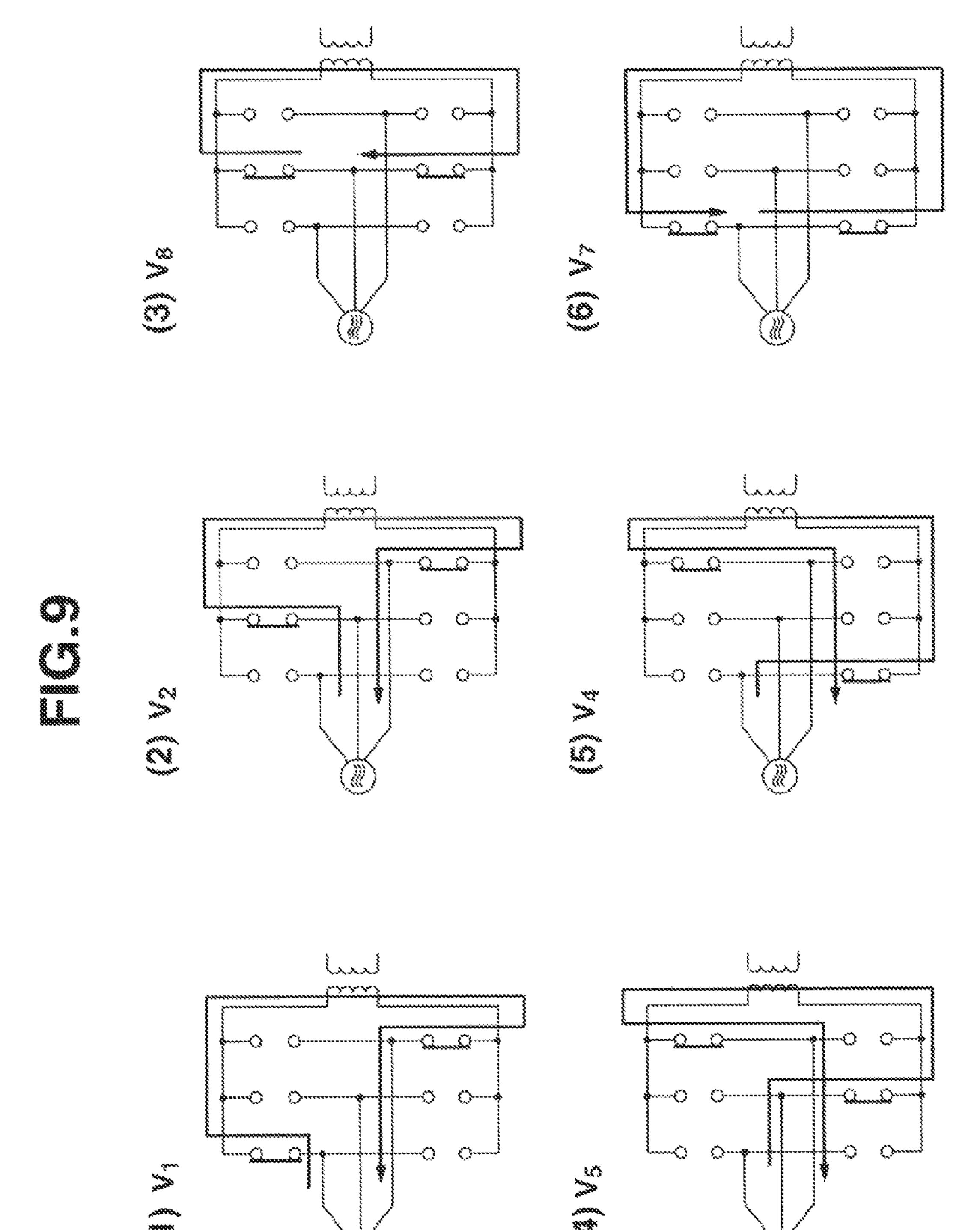

FIGS. 9 (1) through 9 (6) are diagrams for explaining transitions of the switching elements in FIG. 1.

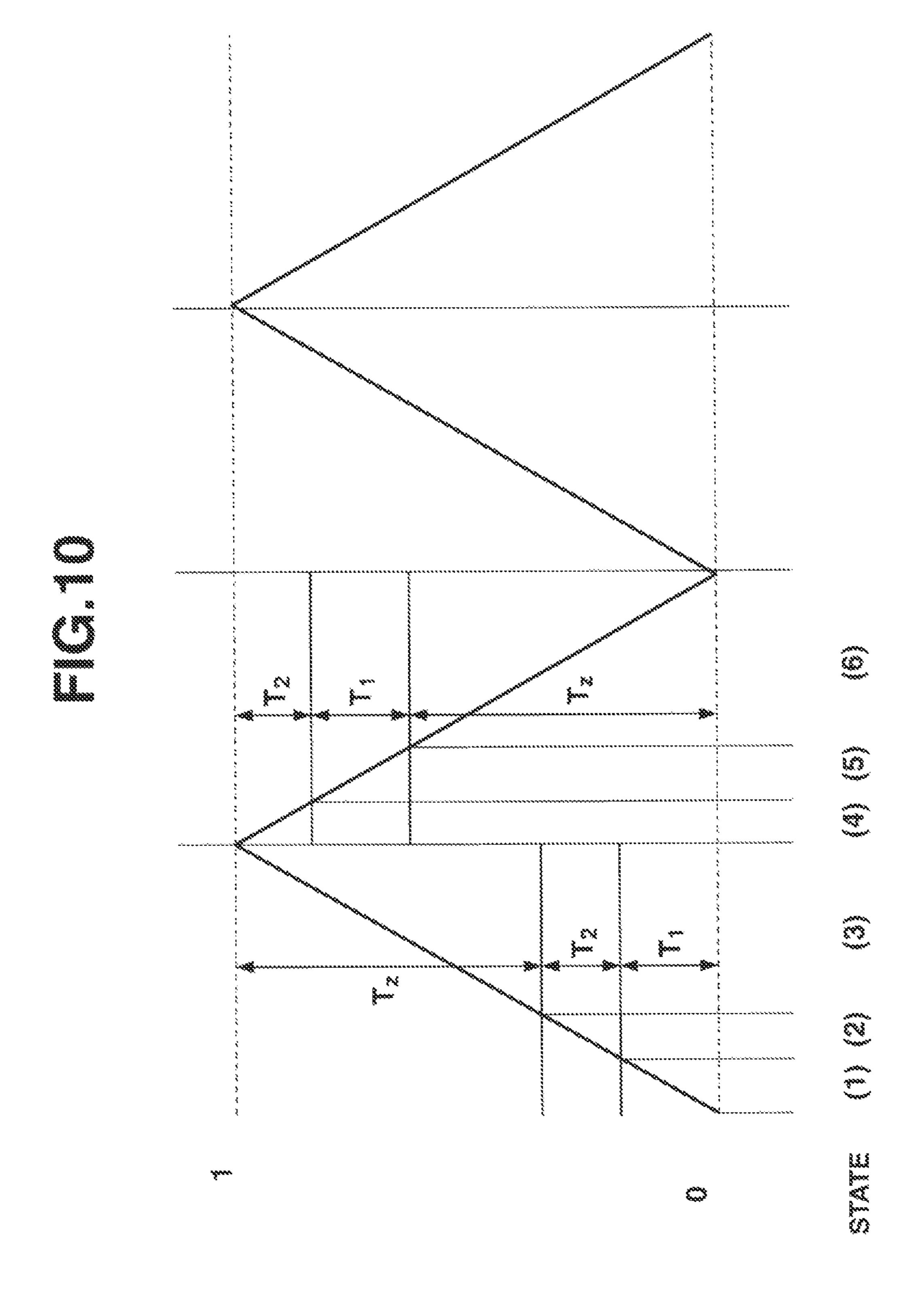

FIG. 10 is a graph representing a relationship between a carrier and an output time in the controller in FIG. 4.

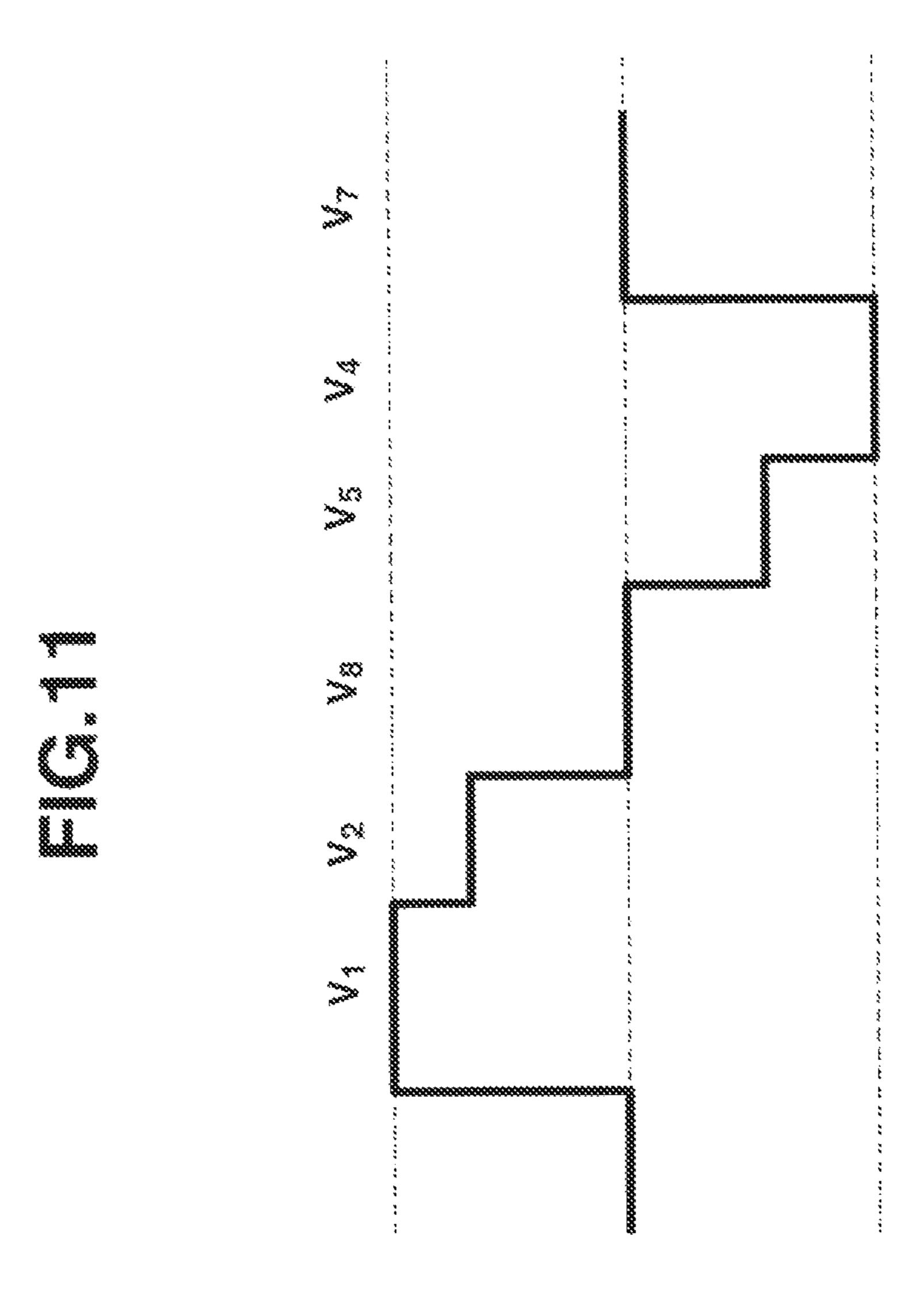

FIG. 11 is a graph representing an output voltage waveform of a matrix converter in FIG. 1.

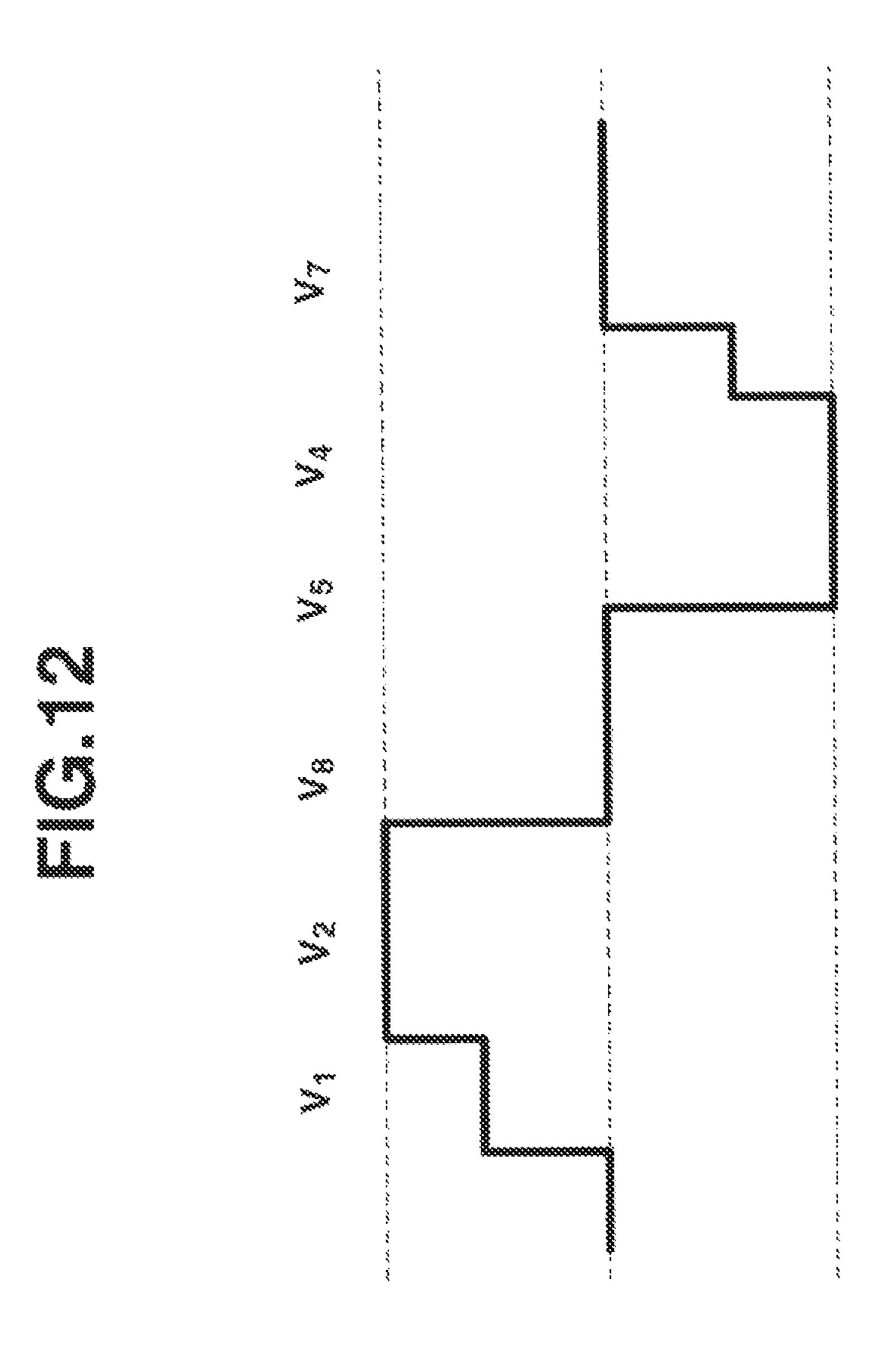

FIG. 12 is a graph representing another output voltage waveform of the matrix converter in FIG. 1.

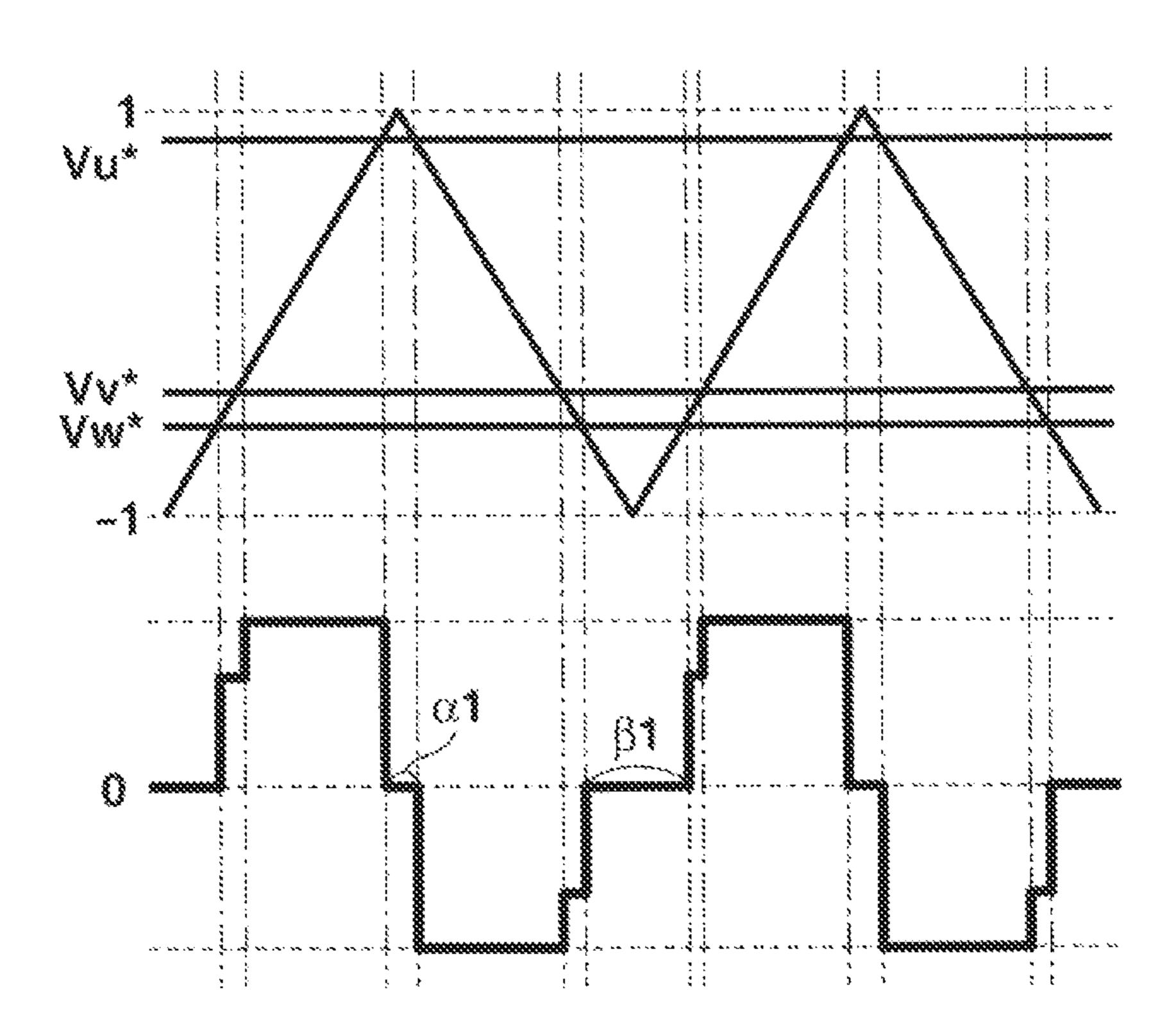

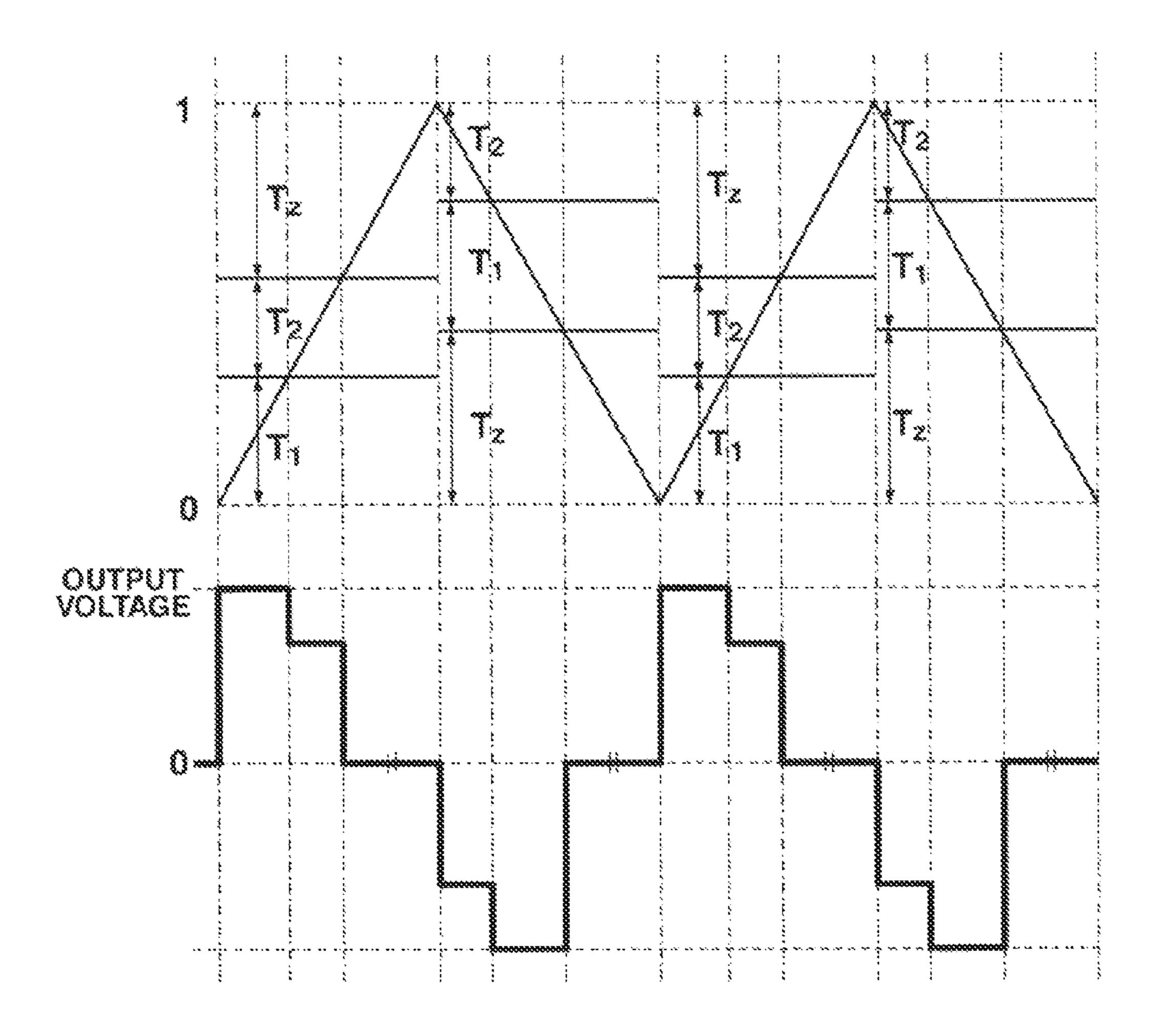

FIG. 13 is graphs representing a relationship between the carrier and a command value and an output voltage waveform in an inverter apparatus in a third comparative example.

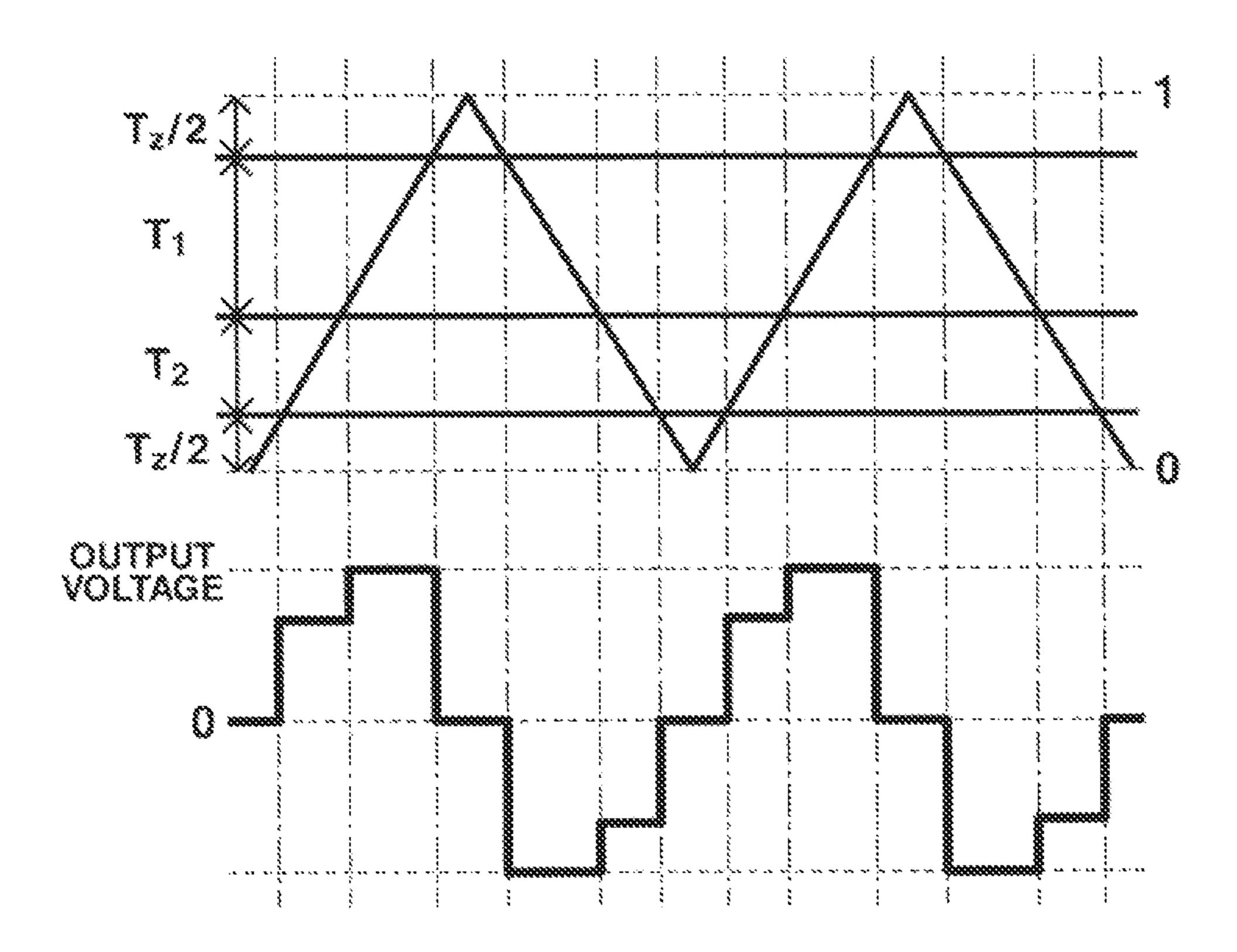

FIG. 14 is graphs representing a relationship between the carrier and the output time and an output voltage waveform, in a controller shown in FIG. 4.

FIG. 15 is graphs representing a relationship between the carrier and the output time and an output voltage waveform in the electric power conversion device in a modification of the preferred embodiment according to the present invention.

### EMBODIMENTS FOR CARRYING OUT THE INVENTION

Hereinafter, a preferred embodiment according to the present invention will be described on a basis of drawings.

#### First Preferred Embodiment

FIG. 1 is a block diagram of a battery system including an electric power conversion device related to a preferred embodiment according to the present invention. Hereinafter, a case in which the electric power conversion device in this embodiment is applied to a charging system is explained as an example but this embodiment may be applied to a vehicle or so forth including a motor and a control apparatus controlling the motor or so forth.

The charging system in this embodiment includes: an alternating current power supply 1; an input filter 2; voltage sensors 31~33; a matrix converter 4; a high frequency transformer circuit 5; an output filter 6; and a battery 7.

Alternating current power supply 1 is a three-phase alternating current power supply and provides an electric power source for the charging system. Input filter 2 is a filter for rectifying an alternating current electric power inputted from alternating current power supply 1 and is constituted by LC circuits having coils 21, 22, 23 and capacitors 24, 25, 26. 20 Coils 21, 22, 23 are connected between respective phases of alternating current power supply 1 and of a matrix converter 4. Capacitors 24, 25, 26 are connected between coils 21, 22, 23 and are connected between the respective phases.

Voltage sensors 31, 32, 33 are connected between alternating current power supply 1 and matrix converter 4 to detect an input voltage  $(V_r, V_s, V_t)$  of each phase from alternating current power supply 1 to matrix converter 4 and outputs the detected voltages to a controller 10 as will be described later. Voltage sensor 31 is connected to a middle point of an r phase 30 of matrix converter 4, voltage sensor 32 is connected to a middle point of an s phase of matrix converter 4, and voltage sensor 33 is connected to a middle point of at phase of matrix converter 4.

elements  $S_{rp}$ ,  $S_{rn}$ ,  $S_{sp}$ ,  $S_{sn}$ ,  $S_{tp}$ ,  $S_{tp}$  bi-directionally switchable, converts the alternating current electric power inputted from alternating current electric power supply 1 into a high frequency alternating current electric power, and outputs the high frequency alternating current electric power to high frequency transformer circuit 5. Matrix converter 4 is connected between input filter 2 and high frequency transformer circuit 5. Switching element  $S_{rp}$ , in order to provide the element bi-directionally switchable, includes: transistor  $Tr_{rp1}$  such as a MOSFET or IGBT; transistor  $Tr_{rp2}$  such as the MOSFET or 45 IGBT; a diode  $D_{rP1}$ ; and diode  $\bar{D}_{rP2}$ . Transistor  $Tr_{rp1}$  and transistor  $Tr_{rp2}$  are serially connected to each other in mutually opposite directions and diode  $D_{rP1}$ , and diode  $D_{rp2}$  are serially connected to each other in mutually opposite directions, transistor  $T_{rp1}$  and diode  $D_{rp1}$  are connected in parallel 50 to each other in mutually opposite directions, transistor  $Tr_{rp2}$ and diode  $D_{rp2}$  are connected in parallel to each other in mutually opposite directions. Similarly, other switching elements  $S_{rn}$ ,  $S_{sp}$ ,  $S_{sn}$ ,  $S_{tp}$ ,  $S_{tn}$  are constituted by a bridge circuit of transistors  $Tr_{rn1}$ ,  $Tr_{rn2}$  and diodes  $D_{rn1}$ ,  $D_{rn2}$ , a bridge 55 circuit of transistors  $Tr_{sp1}$ ,  $Tr_{sp2}$  and diodes  $D_{sp1}$ ,  $D_{sp2}$ , a bridge circuit of transistors  $Tr_{sn1}$ ,  $Tr_{sn2}$  and diodes  $D_{sn1}$ , Dabridge circuit of transistors  $Tr_{sn1}$ ,  $Tr_{sn2}$  and diodes  $D_{sn1}$ ,  $D_{sn2}$ , a bridge circuit of transistors  $Tr_{tp1}$ ,  $Tr_{tp2}$  and diodes  $D_{tp1}$ ,  $D_{tp2}$ , and a bridge circuit of transistors  $Tr_{n1}$ ,  $Tr_{tn2}$  and diodes  $D_{tn1}$ , 60  $D_{tn2}$ .

That is to say, three of a pair of circuits in which two switching elements  $S_{rp}$ ,  $S_{rn}$ ,  $S_{sp}$ ,  $S_{sn}$ ,  $S_{tp}$ ,  $S_{tn}$  are serially connected are connected in parallel to a primary side of a transformer **51**. Then, a bridge circuit in which three lines 65 connected between the respective pairs of switching elements  $S_{rp}$ ,  $S_{rn}$ ,  $S_{sp}$ ,  $S_{sn}$ ,  $S_{tp}$ ,  $S_{tn}$  are electrically connected to three

4

phase output sections of alternating current power supply 1 constitutes three-phase-to-single-phase matrix converter 4.

High-frequency transformer circuit 5 is provided with transformer 51 and a rectifying bridge circuit 52 and is connected between matrix converter 4 and output filter 6. Highfrequency transformer circuit 5 converts the high-frequency alternating current electric power inputted from matrix converter 4 into a direct current electric power and supplies the direct current electric power to a battery 7 via output filter 6. Transformer 51 boosts the high-frequency alternating current voltage inputted from matrix converter 4 and outputs this boosted alternating current to rectifying bridge circuit **52**. It should be noted that, since the alternating current electric power outputted from matrix converter 4 is the high frequency, a small sized transformer can be used as transformer 51. Rectifying bridge circuit 52 is a circuit in which a plurality of diodes are connected in a bridge configuration and serves to convert a secondary side alternating current of transformer **51** into the direct current.

Output filter 6 is constituted by an LC circuit of a coil 61 and a capacitor 62 and is connected between high-frequency transformer circuit 5 and battery 7. Output filter 6 rectifies the direct current electric power outputted from high frequency transformer circuit 5 and supplies the direct current electric power to battery 7. Battery 7 is a secondary cell charged by the charging system in this embodiment and is constituted by, for example, an lithium-ion rechargeable battery. Battery 7 is, for example, mounted in the vehicle and provides a dynamical (power) source of the vehicle.

Thus, the charging system in this embodiment converts the alternating current from alternating current power supply 1 into the high-frequency alternating current, boosts the high-frequency alternating current through high frequency transforwerter 4 is provided with a plurality of switching and S<sub>rp</sub>, S<sub>rp</sub>, S<sub>sp</sub>, S<sub>sp</sub>,

Features of the charging system shown in FIG. 1 using the electric power conversion device in this embodiment will be explained while comparing with a comparative example 1 and another comparative example 2 described below. FIG. 2 shows a block diagram of the charging system related to comparative example 1 and FIG. 3 shows a block diagram of the charging system related to comparative example 2.

As the charging system different from the preferred embodiment according to the present invention, such a system, as shown in FIG. 2, that the alternating current electric power supplied from alternating current power supply 1 is passed through a transformer 101 and is converted into the direct current electric power through a rectifier 102 is known (comparative example 1).

In addition, as another charging system different from the charging system in this embodiment, such a system, as shown in FIG. 3, that the alternating current from alternating current power supply 1 is converted into the direct current through a PWM rectifier 201, the direct current is inverted into the alternating current through an inverter circuit 203 of a primary side of high frequency transformer circuit 202, the converted alternating current is boosted by means of a transformer 204, the boosted alternating current is converted into the direct current through a rectifying bridge circuit 205 of high-frequency transformer circuit 202, and the direct current is supplied to battery 7 is known (comparative example 2).

In a case of comparative example 1, a circuit structure is simple but transformer 101 becomes a large size. In addition, there is a problem such that it becomes necessary to connect a large capacity electrolyte capacitor between rectifier 102 and voltage boosting chopper 103. In a case of comparative

example 2, although a small sized transformer can be used as transformer 204, a loss becomes large since a number of times of conversions are many. In addition, there is a problem such that it is necessary to connect a large capacity electrolyte capacitor between PWM rectifier 201 and high-frequency 5 transformer 202.

In this embodiment, since, as described above, a use of matrix converter 4 can reduce the loss caused by the electric power conversion, can make the large capacity electrolyte capacitor at the primary side of transformer 51 unnecessary, and can achieve the small sizing of transformer 51.

Next, controller 10 controlling matrix converter 4 included in the electric power conversion device in this embodiment will be explained below with reference to FIG. 4. FIG. 4 shows a block diagram of controller 10. Controller 10 15 switches on and off of switching elements  $S_{rp}$ ,  $S_{rn}$ ,  $S_{sp}$ ,  $S_{sn}$ ,  $S_{tp}$ ,  $S_{tn}$  and controls matrix converter 4 through a PWM control. Controller 10 includes: a coordinates transforming section 11; a space vector modulating section 12; a zero vector time calculating section 13; a switching pattern table 14; and 20 a switching signal generating section 15.

Coordinates transforming section 11 compares detected voltages detected by means of voltage sensors 31, 32, 33, grasps a magnitude relationship therebetween, performs a three-phase to two-phase conversion for detected voltages  $(V_r, V_s, V_t)$  in a fixed coordinates system to be converted into voltages  $(v_\alpha, v_\beta)$  in a static coordinates system, and outputs voltages  $(v_\alpha, v_\beta)$  to space vector modulating section 12. Space vector modulation section 12 replaces three phase voltage waveforms into a vector utilizing a space vector modulation. Thus, output times  $(T_1, T_2)$  of the voltage vectors are calculated utilizing a phase angle  $(\theta)$  of voltages  $(v_\alpha, v_\beta)$ .

Zero vector time calculating section 13 calculates an output time  $(T_2)$  of zero vector using a carrier signal such as a triangular wave and the time calculated by space vector 35 modulating section 12. A frequency of the carrier signal is set to be higher than a frequency of the alternating current electric power of alternating current power supply 1. A switching pattern table 14 stores a switching pattern preset to perform switching of switching elements  $S_{rp}$ ,  $S_{rn}$ ,  $S_{sp}$ ,  $S_{sn}$ ,  $S_{tp}$ ,  $S_{tn}$  40 corresponding phase angle  $(\theta)$  in a form of a table.

Switching signal generating section **15** extracts the switching pattern corresponding to the phase angle (**8**) by referring to switching pattern table **14** and outputs control signals ( $D_{rp}$ ,  $D_{rm}$ ,  $D_{sp}$ ,  $D_{sm}$ ,  $D_{tp}$ ,  $D_{tm}$ ) to switch on or off of switching 45 elements ( $S_{rp}$ ,  $S_{rm}$ ,  $S_{sp}$ ,  $S_{sm}$ ,  $S_{tp}$ ,  $S_{tm}$ ) using the extracted switching pattern, output times ( $T_1$ ,  $T_2$ ) of the voltage vector, and output time ( $T_2$ ) of the zero vector to a drive circuit (not shown) included in matrix converter **4**. Switching elements  $S_{rp}$ ,  $S_{rm}$ ,  $S_{sp}$ ,  $S_{sm}$ ,  $S_{tp}$ ,  $S_{tm}$  are controlled by pulse signals. Thus, 50 on and off of switching elements  $S_{rp}$ ,  $S_{rm}$ ,  $S_{sp}$ ,  $S_{sm}$ ,  $S_{tp}$ ,  $S_{tm}$  included in matrix converter **4** are switched to turn on and off by means of the control of controller **10** and the electric power is converted.

Next, a switching control of switching elements  $S_{rp}$ ,  $S_{rm}$ ,  $S_{sp}$ ,  $S_{sn}$ ,  $S_{tp}$ ,  $S_{tm}$  will be described using FIG. **5**. FIG. **5** shows a graph representing a sequence of the switching to switching elements  $S_{rp}$ ,  $S_{rm}$ ,  $S_{sp}$ ,  $S_{sn}$ ,  $S_{tp}$ ,  $S_{tm}$ . In FIG. **5**, a high level denotes an on state and a low level denotes an off state. A voltage commutation system (method) is used for the switching of switching elements  $S_{rp}$ ,  $S_{rm}$ ,  $S_{sp}$ ,  $S_{sm}$ ,  $S_{tp}$ ,  $S_{tm}$ . Controller **10** monitors a magnitude relationship of input voltages from detected voltages ( $V_r$ ,  $V_s$ ,  $V_t$ ) to perform the commutation. Suppose that the state of  $Tr_{rp1}$ ,  $Tr_{rp2}$ ,  $Tr_{sp1}$ ,  $Tr_{sp2}$  are transited from an initial state in a sequence of i, ii, iii, and iv.

Hereinafter, a specific example of the voltage commutation system (method) will be described below. For simplicity of

6

explanation, only the commutation control for an upper arm circuit of matrix converter 4 will be described below.

Suppose that transistors  $Tr_{rp1}$ ,  $Tr_{rp2}$  included in switching element  $S_{rp}$  are in an on state and transistors  $Tr_{sp1}$ ,  $Tr_{sp2}$  included in switching element  $S_{sp}$  are in an off state. Then, a case in which, in a state in which the voltage of switching element  $S_{rp}$  is higher than the voltage of switching element  $S_{sp}$ , the commutation is performed from switching element  $S_{rp}$  to the voltage to switching element  $S_{sp}$  will be explained below

First, when the state is transited from the initial state to state (i), transistor  $\text{Tr}_{sp1}$  is turned on, when the state is transited from state (i) to state (ii), transistor  $\text{Tr}_{rp1}$  is turned off, when the state is transited from state (ii) to state (iii), transistor  $\text{Tr}_{sp2}$ , is turned on, and when the state is transited from state (iii) to state (iv), transistor  $\text{Tr}_{rp2}$  is turned off. This causes the switching of the switching elements such that alternating current power supply 1 is not short-circuited. Thus, a commutation failure is suppressed.

Next, the control in controller 10 will be described below using FOGS. 1, 4, and 6 through 12.

When the voltage  $(V_{\alpha}, V_{\beta})$  in the static coordinates system coordinates transformed and calculated by coordinates transforming section 11 is inputted to space vector modulating section 12, space vector modulating section 12 calculates phase angle ( $\beta$ ) of voltage ( $v_{\alpha}$ ,  $v_{\beta}$ ) from the inputted voltage  $(v_{\alpha}, v_{\beta})$ . It should be noted that the voltage  $(v_{\alpha}, v_{\beta})$  and phase angle  $(\theta)$  are represented by a vector as shown in FIG. 6. FIG. **6** shows a vector diagram in which the detected voltages  $(V_r)$  $V_s, V_t$ ) are converted into two-phase  $\alpha\beta$  coordinates system and the input voltages are observed as voltage vectors in the static coordinates system. V<sub>a</sub> in FIG. 6 represents a base vector and corresponds to an output command value having the phase angle ( $\theta$ ) of the input voltage in the  $\alpha\beta$  coordinates system. The base vector is rotated with a center point shown in FIG. 6 as a center in accordance with a magnitude relationship among the input voltages of the respective phases.

In this embodiment, in the static coordinates system, the coordinates are divided with 60 degrees into six areas from  $\alpha$ axis in the counterclockwise direction. Axes of V<sub>1</sub> through V<sub>6</sub> are allocated to boundary lines of the respective areas. The area between  $V_1$  and  $V_2$  is assumed as "area 1", the area between  $V_2$  and  $V_3$  is assumed as "area 2", the area between  $V_3$  and  $V_4$  is assumed as "area 3", the area between  $V_4$  and  $V_5$ is assumed as "area 4", the area between  $V_5$  and  $V_6$  is assumed as "area 5", and the area between  $V_5$  and  $V_1$  is assumed as "area 6". In addition,  $V_7$  through  $V_9$  are allocated to an origin. Then, vectors of  $V_1$  through  $V_9$  are vectors of voltages outputted from matrix converter 4. Vectors of V<sub>1</sub> through V<sub>6</sub> having magnitudes as the vectors (not zero) represent that the voltages not zero are outputted from matrix converter 4. That is to say, vectors of  $V_1$  through  $V_6$  correspond to voltage vectors not zero (hereinafter, referred to as voltage vectors). On the other hand, vectors of  $V_7$  through  $V_9$  represent vectors of voltage zero (zero voltage) (hereinafter, referred to as zero vectors).

In addition, in this embodiment, voltage vectors  $V_1$  through  $V_9$  are made correspond to the mutually different switching patterns of switching elements  $S_{rp}$ ,  $S_{rm}$ ,  $S_{sp}$ ,  $S_{sn}$ ,  $S_{tp}$ ,  $S_{tm}$  and the switching patterns to operate switching elements  $S_{rp}$ ,  $S_{rm}$ ,  $S_{sp}$ ,  $S_{sn}$ ,  $S_{tp}$ ,  $S_{tm}$  are determined dependent upon which area the input voltages belong to. It should be noted that a relationship between voltage vectors  $V_1$  through  $V_9$  and the switching pattern will be described later.

Then, space vector modulating section 12 determines which area the input voltage at a time point of detection belongs to from the phase angle  $(\theta)$  of base vector  $\mathbf{v}_a$ . In the

example shown in FIG. 6, since base vector va is within area 1, space vector modulating section 12 determines that the input voltage belongs to area 1 from the phase angle ( $\theta$ ) of voltage  $(v_{\alpha}, v_{\beta})$ . In addition, for example, in a case where the magnitude relationship of the input voltages  $(V_r, V_s, V_t)$  of the 5 respective phases is changed and the phase angle ( $\theta$ ) of a  $\beta$ axis voltages  $(v_{\alpha}, v_{\beta})$  coordinates transformed according to coordinates transforming section 11 indicates 90 degrees, space vector modulating section 12 identifies an area 2 including phase angle of 90 degrees.

Space vector modulating section 12 calculates an output time of the voltage vector from an area axis component of base vector  $(V_a)$  when the area is identified. In the case of example shown in FIG. 6, base vector  $(V_a)$  belongs to area 1. Space vector modulating section 12 calculates a component 15  $(V_{a1})$  along  $V_1$  axis and a component  $(V_{a2})$  along  $V_2$  axis using  $V_1$  axis and  $V_2$  axis which are axes of area 1. Then, the magnitude  $(V_{a1})$  of the  $V_1$  axis component is the output time of the switching pattern corresponding to  $V_1$  and the magnitude  $(V_{a2})$  of the  $V_2$  axis component is the output time of the 20 switching pattern corresponding to  $V_2$ . It should, herein, be noted that the output times of voltage vectors  $V_1$  through  $V_6$ are assumed as  $T_1$ ,  $T_2$  and output time of zero vectors ( $V_7$ ) through  $V_9$ ) are assumed as  $T_z$ . As will be described later, in this embodiment, two voltage vectors are outputted for a half 25 3c period of a first half of a carrier. Hence, the output time of a first voltage vector from the two voltage vectors is assumed as  $T_1$  and the output time of a second voltage vector is assumed as  $T_2$ .

Each output time  $(T_1, T_2, T_z)$  is represented by a normalized time corresponding to the period of the carrier. As will be described later, in this embodiment, in order to secure the output time  $(T_7)$  of zero vectors  $(V_7 \text{ through } V_9)$  per half period of the carrier, a limitation is placed on output times  $(T_1,$ times  $(T_1, T_2)$  such that each of output times  $(T_1, T_2)$  during which the corresponding one of the two voltage vectors is outputted is equal to or below a predetermined lowest limit value. It should be noted that the predetermined lowest limit value corresponds to a time for which output time  $(T_z)$  is 40 secured and is set to a time shorter than the time corresponding to the half period of the carrier.

Area 1 is a region between the phase angle of 0 degree to 60 degrees. For example, in a case where the phase angle of base vector  $(v_a)$  falls between 0 degree and 30 degrees, the mag- 45 nitude  $(V_{11})$  of  $V_1$  axis component is larger than magnitude  $(V_{a2})$  of the  $V_2$  axis component. Hence, output time  $(T_1)$  of the  $V_1$  switching pattern is longer than output time  $(T_2)$  of the V<sub>2</sub> switching pattern. Area 4 is a region between phase angle of 180 degrees and phase angle of 240 degrees. For example, 50 the phase angle of base vector  $(v_a)$  ranges from 210 degrees to 240 degrees, the magnitude  $(V_{aS})$  of the  $V_5$  axis component is larger than the magnitude  $(V_{a4})$  of the  $V_4$  axis component. Hence, output time  $(T_2)$  of the switching pattern  $V_5$  is longer than output time  $(T_1)$  of the switching pattern of  $V_4$ . Thus, 55 space vector modulating section 12 calculates the phase angle ( $\theta$ ) using  $v_{\alpha}$ ,  $v_{\beta}$  corresponding to the detected voltages of the respective phases, calculates output times  $(T_1, T_2)$  of the voltage vectors from the base vector V<sub>a</sub> having the calculated phase angle  $(\theta)$  as the directional component, and outputs the 60 calculated output times  $(T_1, T_2)$  to zero vector time calculating section 13.

Zero vector time calculating section 13 subtracts a total time of output time  $(T_1)$  and output time  $(T_2)$  from a predetermined half period of the period of the carrier to calculate 65 the time of zero vector  $(T_z)$ . Since space vector modulating section 12 calculates output time  $(T_1)$  and output time  $(T_2)$

such that the above-described total time is equal to or below the predetermined lowest limit time, zero vector time calculating section 13 can calculate the time of zero vector  $(T_z)$ . In this embodiment, in order to provide the alternating current for the output electric power of matrix converter 4, the time at which the non-zero voltage outputted and the time at which the zero voltage is outputted are periodically provided.

Since the period of the carrier corresponds to the period of the output voltage, the output time  $(T_z)$  of the zero vector is a subtraction of the output time  $(T_1)$  and the output time  $(T_2)$ from the time corresponding to the half period of the carrier. Zero vector time calculating section 13 outputs the time  $(T_z)$ of the zero vector and the times  $(T_1, T_2)$  of the voltage vectors to a switching signal generating section 15.

Switching signal generating section 15 generates switching signals to drive switching elements  $S_{rp}$ ,  $S_{rn}$ ,  $S_{sp}$ ,  $S_{sn}$ ,  $S_{tp}$ ,  $S_{tn}$  using the switching pattern stored in switching pattern table 14, the time of zero vector  $(T_z)$ , and the times  $(T_1, T_2)$  of the voltage vectors.