#### US009196738B2

# (12) United States Patent

# Sakata et al.

# (10) Patent No.: US 9,196,738 B2 (45) Date of Patent: Nov. 24, 2015

# (54) SEMICONDUCTOR DEVICE AND METHOD FOR MANUFACTURING THE SAME

(75) Inventors: Junichiro Sakata, Atsugi (JP);

Tetsunori Maruyama, Atsugi (JP); Yuki

Imoto, Atsugi (JP)

(73) Assignee: Semiconductor Energy Laboratory

Co., Ltd., Atsugi-shi, Kanagawa-ken

(JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 1123 days.

(21) Appl. No.: 12/965,197

(22) Filed: Dec. 10, 2010

(65) Prior Publication Data

US 2011/0140205 A1 Jun. 16, 2011

# (30) Foreign Application Priority Data

Dec. 11, 2009 (JP) ...... 2009-281505

(51) **Int. Cl.**

**H01L 21/336** (2006.01) **H01L 29/786** (2006.01)

(52) **U.S. Cl.**

(58) Field of Classification Search

See application file for complete search history.

# (56) References Cited

# U.S. PATENT DOCUMENTS

5,731,856 A 3/1998 Kim et al. 5,744,864 A 4/1998 Cillessen et al.

| 6,294,274 | B1 | 9/2001 | Kawazoe et al.  |

|-----------|----|--------|-----------------|

| 6,563,174 | B2 | 5/2003 | Kawasaki et al. |

| 6,727,522 | B1 | 4/2004 | Kawasaki et al. |

| 7,049,190 | B2 | 5/2006 | Takeda et al.   |

| 7,061,014 | B2 | 6/2006 | Hosono et al.   |

| 7,064,346 | B2 | 6/2006 | Kawasaki et al. |

|           |    | (Cont  | tinued)         |

#### FOREIGN PATENT DOCUMENTS

EP 1737044 A 12/2006 EP 1770788 A 4/2007 (Continued)

### OTHER PUBLICATIONS

International Search Report (Application No. PCT/JP2010/072595) Dated Feb. 1, 2011.

(Continued)

Primary Examiner — Colleen A Matthews

Assistant Examiner — Colleen E Snow

(74) Attorney, Agent, or Firm — Eric J. Robinson; Robinson Intellectual Property Law Office, P.C.

# (57) ABSTRACT

Many of the physical properties of a silicon semiconductor have already been understood, whereas many of the physical properties of an oxide semiconductor have been still unclear. In particular, an adverse effect of an impurity on an oxide semiconductor has been still unclear. In view of the above, a structure is disclosed in which an impurity that influences electrical characteristics of a semiconductor device including an oxide semiconductor layer is prevented or is eliminated. A semiconductor device which includes a gate electrode, an oxide semiconductor layer, and a gate insulating layer provided between the gate electrode and the oxide semiconductor layer and in which the nitrogen concentration in the oxide semiconductor layer is  $1 \times 10^{20}$  atoms/cm<sup>3</sup> or less is provided.

# 16 Claims, 16 Drawing Sheets

# US 9,196,738 B2 Page 2

| (56)                                | Referer            | nces Cited                                 |                |                                      |       | Chang                               |

|-------------------------------------|--------------------|--------------------------------------------|----------------|--------------------------------------|-------|-------------------------------------|

| U.S.                                | . PATENT           | DOCUMENTS                                  |                |                                      |       | Nakagawara et al.<br>Iwasaki        |

|                                     |                    |                                            |                |                                      |       | Pan et al.                          |

| 7,105,868 B2<br>7,211,825 B2        |                    | Nause et al.<br>Shih et al                 |                |                                      |       | Kawase<br>Lee et al.                |

| 7,211,823 B2<br>7,262,463 B2        |                    |                                            | 2008           | /0129195 A1 6/2                      | 2008  | Ishizaki et al.                     |

| 7,282,782 B2                        |                    | Hoffman et al.                             |                |                                      |       | Kim et al.<br>Cowdery-Corvan et al. |

| 7,297,977 B2<br>7,323,356 B2        |                    | Hoffman et al.<br>Hosono et al.            |                | /0224133 A1 9/2                      | 2008  | Park et al.                         |

| 7,368,067 B2                        | 5/2008             | Yata et al.                                |                | /0254569 A1 10/2<br>/0258139 A1 10/2 |       | Hoffman et al.                      |

| 7,385,224 B2<br>7,402,506 B2        |                    | Ishii et al.<br>Levy et al.                |                |                                      |       | Lee et al.                          |

| 7,411,209 B2                        | 8/2008             | Endo et al.                                |                | /0258141 A1 10/2                     |       |                                     |

| 7,453,065 B2<br>7,453,087 B2        |                    |                                            |                | /0258143 A1 10/2<br>/0296568 A1 12/2 |       |                                     |

| , ,                                 |                    | Hoffman et al.                             | 2009           | /0045397 A1 2/2                      | 2009  | Iwasaki                             |

| 7,468,304 B2<br>7,501,293 B2        |                    | •                                          |                |                                      |       | Lai et al.<br>Kuwabara et al.       |

| 7,561,295 B2<br>7,564,055 B2        |                    |                                            | 2009           | /0090914 A1 4/2                      | 2009  | Yano et al.                         |

| , ,                                 |                    | Akimoto et al.                             |                |                                      |       | Chang<br>Sakakura et al.            |

| 7,732,819 B2<br>7,791,074 B2        |                    | Akimoto et al.<br>Iwasaki                  |                | /0152541 A1 6/2                      |       |                                     |

| 7,935,582 B2                        | 5/2011             | Iwasaki                                    |                | /0278122 A1 11/2<br>/0280600 A1 11/2 |       | Hosono et al.                       |

| 7,956,361 B2<br>8,154,024 B2        |                    | Iwasaki<br>Iwasaki                         |                |                                      |       | Watanabe                            |

| 8,188,467 B2                        | 5/2012             | Itagaki et al.                             |                |                                      |       | Nakata et al                        |

| 8,207,063 B2<br>8,735,229 B2*       |                    | Cowdery-Corvan et al.<br>Son et al 438/149 |                | /0276689 A1 11/2<br>/0279462 A1 11/2 |       | Iwasaki<br>Iwasaki                  |

| 8,785,240 B2                        |                    | Watanabe                                   |                |                                      |       | Yano et al.                         |

| , , ,                               |                    | Watanabe<br>Tai et al                      |                | EODEICN D                            | ATE   | NIT DOCLIMENTS                      |

| 2001/0046027 A1<br>2002/0056838 A1  |                    | Tai et al.<br>Ogawa                        |                | FOREIGN P                            | AIE.  | NT DOCUMENTS                        |

| 2002/0132454 A1                     | 9/2002             | Ohtsu et al.                               | EP             | 1950177                              |       | 7/2008                              |

| 2003/0189401 A1<br>2003/0218222 A1  |                    | Kido et al.<br>Wager et al.                | EP<br>EP       | 2226847<br>2339639                   |       | 9/2010<br>6/2011                    |

| 2004/0038446 A1                     | 2/2004             | Takeda et al.                              | JP             | 60-198861                            |       | 10/1985                             |

| 2004/0127038 A1<br>2005/0017244 A1  |                    | Carcia et al.<br>Hoffman et al.            | JP<br>JP       | 63-210022<br>63-210023               |       | 8/1988<br>8/1988                    |

| 2005/0017211 711<br>2005/0017302 A1 |                    | Hoffman                                    | JP             | 63-210023                            |       | 8/1988                              |

| 2005/0199959 A1<br>2006/0035452 A1  |                    | Chiang et al.<br>Carcia et al.             | JP             | 63-215519                            |       | 9/1988                              |

| 2006/0033432 A1<br>2006/0043377 A1  |                    | Hoffman et al.                             | JP<br>JP       | 63-239117<br>63-265818               |       | 10/1988<br>11/1988                  |

| 2006/0091793 A1                     |                    | Baude et al.                               | JP             | 05-251705                            |       | 9/1993                              |

| 2006/0108529 A1<br>2006/0108636 A1  |                    | Saito et al.<br>Sano et al.                | JP<br>JP       | 08-264794<br>11-505377               |       | 10/1996<br>5/1999                   |

| 2006/0110867 A1                     |                    | Yabuta et al.                              | JP             | 2000-044236                          | A     | 2/2000                              |

| 2006/0113536 A1<br>2006/0113539 A1  |                    | Kumomi et al.<br>Sano et al.               | JP<br>JP       | 2000-150900<br>2002-076356           |       | 5/2000<br>3/2002                    |

| 2006/0113549 A1                     | 6/2006             | Den et al.                                 | JP             | 2002-070350                          |       | 10/2002                             |

| 2006/0113565 A1<br>2006/0169973 A1  |                    | Abe et al.<br>Isa et al.                   | JP<br>JP       | 2003-086000<br>2003-086808           |       | 3/2003<br>3/2003                    |

| 2006/0170111 A1                     |                    | Isa et al.                                 | JP             | 2003-080808                          |       | 4/2004                              |

| 2006/0197092 A1<br>2006/0208977 A1  |                    | Hoffman et al.<br>Kimura                   | JP             | 2004-273614                          |       | 9/2004                              |

| 2006/0208977 A1<br>2006/0228974 A1  |                    | Thelss et al.                              | JP<br>JP       | 2004-273732<br>2005-217038           |       | 9/2004<br>8/2005                    |

| 2006/0231882 A1<br>2006/0238135 A1  |                    | Kim et al.<br>Kimura                       | JP             | 2007-103918                          |       | 4/2007                              |

| 2006/0238133 A1<br>2006/0244107 A1  |                    | Sugihara et al.                            | JP<br>JP       | 2007-123861<br>2007-519256           |       | 5/2007<br>7/2007                    |

| 2006/0284171 A1                     |                    | Levy et al.                                | JP             | 2007-311404                          |       | 11/2007                             |

| 2006/0284172 A1<br>2006/0292777 A1  | 12/2006<br>12/2006 | Isnii<br>Dunbar                            | JP<br>JP       | 2008-281988<br>2008-283046           |       | 11/2008<br>11/2008                  |

| 2007/0024187 A1                     | 2/2007             | Shin et al.                                | JP             | 2008-300518                          | A     | 12/2008                             |

| 2007/0046191 A1<br>2007/0052025 A1  | 3/2007<br>3/2007   |                                            | JP<br>WO       | 2009-141221<br>WO-2004/114391        |       | 6/2009<br>12/2004                   |

| 2007/0054507 A1                     | 3/2007             | Kaji et al.                                | WO             | WO-2005/015643                       |       | 2/2005                              |

| 2007/0072439 A1<br>2007/0090365 A1  |                    | Akimoto et al.<br>Hayashi et al.           | WO<br>WO       | WO-2005/074038<br>WO-2007/029844     |       | 8/2005<br>3/2007                    |

| 2007/0090303 AT<br>2007/0108446 A1  | 5/2007             |                                            | WO             | WO-2007/029844<br>WO-2007/058248     |       | 5/2007                              |

| 2007/0152217 A1<br>2007/0172591 A1  |                    | Lai et al.<br>Seo et al.                   | WO             | WO-2008/091504                       |       | 7/2008                              |

| 2007/0172391 A1<br>2007/0187678 A1  |                    | Hirao et al.                               | WO<br>WO       | WO-2008/126879<br>WO-2008/143021     |       | 10/2008<br>11/2008                  |

| 2007/0187760 A1                     |                    | Furuta et al.                              | WO             | WO-2008/149754                       |       | 12/2008                             |

| 2007/0194379 A1<br>2007/0252928 A1  | _                  | Hosono et al.<br>Ito et al.                |                | OTHER                                | R PUI | BLICATIONS                          |

| 2007/0232323 AT                     | 11/2007            | Kim et al.                                 | 787 ·          |                                      |       |                                     |

| 2007/0287296 A1                     | 1/2008             | •                                          | Writte: 1, 201 |                                      | on No | o. PCT/JP2010/072595) Dated Feb.    |

| 2008/0006877 A1<br>2008/0038882 A1  |                    | Mardilovich et al.<br>Takechi et al.       | ŕ              |                                      | Bandg | gap High-Mobility ZnO Thin-Film     |

|                                     |                    |                                            |                |                                      | _     |                                     |

# (56) References Cited

### OTHER PUBLICATIONS

Transistors Produced at Room Temperature,", Appl. Phys. Lett. (Applied Physics Letters), Sep. 27, 2004, vol. 85, No. 13, pp. 2541-2543.

Dembo.H et al., "RFCPUS on Glass and Plastic Substrates Fabricated by TFT Transfer Technology,", IEDM 05: Technical Digest of International Electron Devices Meeting, Dec. 5, 2005, pp. 1067-1069.

Ikeda.T et al., "Full-Functional System Liquid Crystal Display Using CG-Silicon Technology,", SID Digest '04 : SID International Symposium Digest of Technical Papers, 2004, vol. 35, pp. 860-863.

Nomura.K et al., "Room-Temperature Fabrication of Transparent Flexible Thin-Film Transistors using Amorphous Oxide Semiconductors,", Nature, Nov. 25, 2004, vol. 432, pp. 488-492.

Park.J et al., "Improvements in the Device Characteristics of Amorphous Indium Gallium Zinc Oxide Thin-Film Transistors by Ar Plasma Treatment,", Appl. Phys. Lett. (Applied Physics Letters), Jun. 26, 2007, vol. 90, No. 26, pp. 262106-1-262106-3.

Takahashi.M et al., "Theoretical Analysis of IGZO Transparent Amorphous Oxide Semiconductor,", IDW '08: Proceedings of the 15th International Display Workshops, Dec. 3, 2008, pp. 1637-1640. Hayashi.R et al., "42.1: Invited Paper: Improved Amorphous In—Ga—Zn—O TFTs,", SID Digest '08: SID International Symposium Digest of Technical Papers, May 20, 2008, vol. 39, pp. 621-624.

Prins.M et al., "A Ferroelectric Transparent Thin-Film Transistor,", Appl. Phys. Lett. (Applied Physics Letters), Jun. 17, 1996, vol. 68, No. 25, pp. 3650-3652.

Nakamura.M et al., "The phase relations in the In2O3—Ga2ZnO4—ZnO system at 1350° C.,", Journal of Solid State Chemistry, Aug. 1, 1991, vol. 93, No. 2, pp. 298-315.

Kimizuka.N et al., "Syntheses and Single-Crystal Data of Homologous Compounds, In2O3(ZnO)m (m = 3, 4, and 5), InGaO3(ZnO)3, and Ga2O3(ZnO)m (m = 7, 8, 9, and 16) in the In2O3—ZnGa2O4—ZnO System,", Journal of Solid State Chemistry, Apr. 1, 1995, vol. 116, No. 1, pp. 170-178.

Nomura.K et al., "Thin-Film Transistor Fabricated in Single-Crystalline Transparent Oxide Semiconductor,", Science, May 23, 2003, vol. 300, No. 5623, pp. 1269-1272.

Masuda.S et al., "Transparent thin film transistors using ZnO as an active channel layer and their electrical properties,", J. Appl. Phys. (Journal of Applied Physics), Feb. 1, 2003, vol. 93, No. 3, pp. 1624-1630.

Asakuma.N et al., "Crystallization and Reduction of Sol-Gel-Derived Zinc Oxide Films by Irradiation with Ultraviolet Lamp,", Journal of Sol-Gel Science and Technology, 2003, vol. 26, pp. 181-184. Osada.T et al., "15.2: Development of Driver-Integrated Panel using Amorphous In—Ga—Zn—Oxide TFT,", SID Digest '09: SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 184-187.

Nomura.K et al., "Carrier transport in transparent oxide semiconductor with intrinsic structural randomness probed using single-crystalline InGaO3(ZnO)5 films,", Appl. Phys. Lett. (Applied Physics Letters), Sep. 13, 2004, vol. 85, No. 11, pp. 1993-1995.

Li.C et al., "Modulated Structures of Homologous Compounds InMO3(ZnO)m (M=In,Ga; m=Integer) Described by Four-Dimensional Superspace Group,", Journal of Solid State Chemistry, 1998, vol. 39, pp. 347-355.

Son.K et al., "42.4L: Late-News Paper: 4 Inch QVGA AMOLED Driven by the Threshold Voltage Controlled Amorphous GIZO (Ga2O3—In2O3—ZnO) TFT,", SID Digest '08: SID International Symposium Digest of Technical Papers, May 20, 2008, vol. 39, pp. 633-636.

Lee.J et al., "World's Largest (15-Inch) XGA AMLCD Panel Using IGZO Oxide TFT,", SID Digest '08: SID International Symposium Digest of Technical Papers, May 20, 2008, vol. 39, pp. 625-628.

Nowatari.H et al., "60.2: Intermediate Connector With Suppressed Voltage Loss for White Tandem OLEDs,", SID Digest '09: SID International Symposium Digest of Technical Papers, May 31, 2009, vol. 40, pp. 899-902.

Kanno.H et al., "White Stacked Electrophosphorecent Organic Light-Emitting Devices Employing MOO3 as a Charge-Generation Layer,", Adv. Mater. (Advanced Materials), 2006, vol. 18, No. 3, pp. 339-342.

Tsuda.K et al., "Ultra Low Power Consumption Technologies for Mobile TFT-LCDs,", IDW '02: Proceedings of the 9th International Display Workshops, Dec. 4, 2002, pp. 295-298.

Walle.C, "Hydrogen as a Cause of Doping in Zinc Oxide,", Phys. Rev. Lett. (Physical Review Letters), Jul. 31, 2000, vol. 85, No. 5, pp. 1012-1015.

Fung.T et al., "2-D Numerical Simulation of High Performance Amorphous In—Ga—Zn—O TFTs for Flat Panel Displays,", AM-FPD '08 Digest of Technical Papers, Jul. 2, 2008, pp. 251-252, The Japan Society of Applied Physics.

Jeong.J et al., "3.1: Distinguished Paper: 12.1-Inch WXGA AMOLED Display Driven by Indium—Gallium—Zinc Oxide TFTs Array,", SID Digest '08: SID International Symposium Digest of Technical Papers, May 20, 2008, vol. 39, No. 1, pp. 1-4.

Park.J et al., "High performance amorphous oxide thin film transistors with self-aligned top-gate structure,", IEDM 09: Technical Digest of International Electron Devices Meeting, Dec. 7, 2009, pp. 191-194.

Kurokawa. Y et al., "UHF RFCPUS on Flexible and Glass Substrates for Secure RFID Systems,", Journal of Solid-State Circuits, 2008, vol. 43, No. 1, pp. 292-299.

Ohara.H et al., "Amorphous In—Ga—Zn—Oxide TFTs with Suppressed Variation for 4.0 inch QVGA AMOLED Display,", AM-FPD '09 Digest of Technical Papers, Jul. 1, 2009, pp. 227-230, The Japan Society of Applied Physics.

Coates.D et al., "Optical Studies of the Amorphous Liquid-Cholesteric Liquid Crystal Transition: The "Blue Phase",", Physics Letters, Sep. 10, 1973, vol 45A, No. 2, pp. 115-116.

Cho.D et al., "21.2:Al and Sn-Doped Zinc Indium Oxide Thin Film Transistors for AMOLED Back-Plane,", SID Digest '09: SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 280-283.

Lee.M et al., "15.4:Excellent Performance of Indium—Oxide-Based Thin-Film Transistors by DC Sputtering,", SID Digest '09: SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 191-193.

Jin.D et al., "65.2:Distinguished Paper: World-Largest (6.5") Flexible Full Color Top Emission AMOLED Display on Plastic Film and its Bending Properties,", SID Digest '09: SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 983-985.

Sakata.J et al., "Development of 4.0-In. AMOLED Display With Driver Circuit Using Amorphous In—Ga—Zn—Oxide TFTs,", IDW '09: Proceedings of the 16th International Display Workshops, 2009, pp. 689-692.

Park. J et al., "Amorphous Indium—Gallium—Zinc Oxide TFTs and Their Application for Large Size AMOLED,", AM-FPD '08 Digest of Technical Papers, Jul. 2, 2008, pp. 275-278.

Park.S et al., "Challenge to Future Displays: Transparent AM-OLED Driven by Peald Grown ZnO TFT,", IMID '07 Digest, 2007, pp. 1249-1252.

Godo.H et al., "Temperature Dependence of Characteristics and Electronic Structure For Amorphous In—Ga—Zn—Oxide TFT,", AM-FPD '09 Digest of Technical Papers, Jul. 1, 2009, pp. 41-44.

Osada.T et al., "Development of Driver-Integrated Panel Using Amorphous In—Ga—Zn—Oxide TFT,", AM-FPD '09 Digest of Technical Papers, Jul. 1, 2009, pp. 33-36.

Hirao.T et al., "Novel Top-Gate Zinc Oxide Thin-Film Transistors (ZnO TFTs) for AMLCDS,", Journal of the SID, 2007, vol. 15, No. 1, pp. 17-22.

Hosono.H, "68.3:Invited Paper:Transparent Amorphous Oxide Semiconductors for High Performance TFT,", SID Digest '07: SID International Symposium Digest of Technical Papers, 2007, vol. 38, pp. 1830-1833.

Godo.H et al., "P-9:Numerical Analysis on Temperature Dependence of Characteristics of Amorphous In—Ga—Zn—Oxide TFT,", SID Digest of Technical Papers, May 31, 2009, pp. 1110-1112.

Ohara.H et al., "21.3:4.0 In. QVGA AMOLED Display Using In—Ga—Zn—Oxide TFTs With a Novel Passivation Layer,", SID

# (56) References Cited

#### OTHER PUBLICATIONS

Digest '09: SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 284-287.

Miyasaka.M, "SUFTLA Flexible Microelectronics on Their Way to Business,", SID Digest '07: SID International Symposium Digest of Technical Papers, 2007, vol. 38, pp. 1673-1676.

Chern.H et al., "An Analytical Model for the Above-Threshold Characteristics of Polysilicon Thin-Film Transistors,", IEEE Transactions on Electron Devices, Jul. 1, 1995, vol. 42, No. 7, pp. 1240-1246.

Kikuchi.H et al., "39.1:Invited Paper:Optically Isotropic Nano-Structured Liquid Crystal Composites For Display Applications,", SID Digest '09: SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 578-581.

Asaoka.Y et al., "29.1:Polarizer-Free Reflective LCD Combined With Ultra Low-Power Driving Technology,", SID Digest '09: SID International Symposium Digest of Technical Papers, May 31, 2009, pp. 395-398.

Lee.H et al., "Current Status of, Challenges to, and Perspective View of AM-OLED,", IDW '06: Proceedings of the 13th International Display Workshops, Dec. 7, 2006, pp. 663-666.

Kikuchi.H et al., "62.2:Invited Paper:Fast Electro-Optical Switching in Polymer-Stabilized Liquid Crystalline Blue Phases For Display Application,", SID Digest '07: SID International Symposium Digest of Technical Papers, 2007, vol. 38, pp. 1737-1740.

中村真佐樹, "Synthesis of Homologous Compound with New Long-Period Structure,", NIRIM Newsletter, Mar. 1, 1995, vol. 150, pp.1-4. Kikuchi.H et al., "Polymer-Stabilized Liquid Crystal Blue Phases,", Nature Materials, Sep. 1, 2002, vol. 1, pp. 64-68.

Kimizuka.N. et al., "Spinel,YBFE2O4, and YB2FE3O7 Types of Structures for Compounds in the In2O3 and SC2O3—A2O3—BO Systems [A; Fe, Ga, or Al; B: Mg, Mn, Fe, Ni, Cu, or Zn] at Temperatures over 1000° C.,", Journal of Solid State Chemistry, 1985, vol. 60, pp. 382-384.

Kitzerow.H et al., "Observation of Blue Phases in Chiral Networks,", Liquid Crystals, 1993, vol. 14, No. 3, pp. 911-916.

Costello.M et al., "Electron Microscopy of a Cholesteric Liquid Crystal and Its Blue Phase,", Phys. Rev. A (Physical Review. A), May 1, 1984, vol. 29, No. 5, pp. 2957-2959.

Meiboom.S et al., "Theory of the Blue Phase of Cholesteric Liquid Crystals,", Phys. Rev. Lett. (Physical Review Letters), May 4, 1981, vol. 46, No. 18, pp. 1216-1219.

Park.Sang-Hee et al., "42.3: Transparent ZnO Thin Film Transistor for the Application of High Aperture Ratio Bottom Emission AM-OLED Display,", SID DIGEST '08: SID International Symposium Digest of Technical Papers, May 20, 2008, vol. 39, pp. 629-632. Orita.M et al., "Mechanism of Electrical Conductivity of Transparent"

Orita.M et al., "Mechanism of Electrical Conductivity of Transparent InGaZnO4,", Phys. Rev. B (Physical Review. B), Jan. 15, 2000, vol. 61, No. 3, pp. 1811-1816.

Nomura.K et al., "Amorphous Oxide Semiconductors for High-Performance Flexible Thin-Film Transistors,", Jpn. J. Appl. Phys. (Japanese Journal of Applied Physics), 2006, vol. 45, No. 5B, pp. 4303-4308.

Janotti. A et al., "Native Point Defects in ZnO,", Phys. Rev. B (Physical Review. B), 2007, vol. 76, pp. 165202-1-165202-22.

Park.J et al., "Electronic Transport Properties of Amorphous Indium—Gallium—Zinc Oxide Semiconductor Upon Exposure to Water,", Appl. Phys. Lett. Applied Physics Letters), 2008, vol. 92, pp. 072104-1-072104-3.

Hsieh.H et al., "P-29:Modeling of Amorphous Oxide Semiconductor Thin Film Transistors and Subgap Density of States,", SID Digest '08 : SID International Symposium Digest of Technical Papers, 2008, vol. 39, pp. 1277-1280.

Janotti.A et al., "Oxygen Vacancies in ZnO,", Appl. Phys. Lett. (Applied Physics Letters), 2005, vol. 87, pp. 122102-1-122102-3. Oba.F et al., "Defect energetics in ZnO: A hybrid Hartree-Fock density functional study,", Phys. Rev. B (Physical Review. B), 2008, vol. 77, pp. 245202-1-245202-6.

Orita.M et al., "Amorphous transparent conductive oxide InGaO3(ZnO)m (m<4):a Zn4s conductor,", Philosophical Magazine, 2001, vol. 81, No. 5, pp. 501-515.

Hosono. H et al., "Working hypothesis to explore novel wide band gap electrically conducting amorphous oxides and examples,", J. Non-Cryst. Solids (Journal of Non-Crystalline Solids), 1996, vol. 198-200, pp. 165-169.

Mo.Y et al., "Amorphous Oxide TFT Backplanes for Large Size AMOLED Displays,", IDW '08: Proceedings of the 6th International Display Workshops, Dec. 3, 2008, pp. 581-584.

Kim.S et al., "High-Performance oxide thin film transistors passivated by various gas plasmas,", 214th ECS Meeting, 2008, No. 2317.

Clark.S et al., "First Principles Methods Using CASTEP,", Zeitschrift für Kristallographie, 2005, vol. 220, pp. 567-570.

Lany.S et al., "Dopability, Intrinsic Conductivity, and Nonstoichiometry of Transparent Conducting Oxides,", Phys. Rev. Lett. (Physical Review Letters), Jan. 26, 2007, vol. 98, pp. 045501-1-045501-4.

Park.J et al., "Dry etching of ZnO films and plasma-induced damage to optical properties,", J. Vac. Sci. Technol. B (Journal of Vacuum Science & Technology B), Mar. 1, 2003, vol. 21, No. 2, pp. 800-803. Oh.M et al., "Improving the Gate Stability of ZnO Thin-Film Transistors With Aluminum Oxide Dielectric Layers,", J. Electrochem. Soc. (Journal of the Electrochemical Society), 2008, vol. 155, No. 12, pp. H1009-H1014.

Ueno.K et al., "Field-Effect Transistor on SrTiO3 With Sputtered Al2O3 Gate Insulator,", Appl. Phys. Lett. (Applied Physics Letters), Sep. 1, 2003, vol. 83, No. 9, pp. 1755-1757.

\* cited by examiner

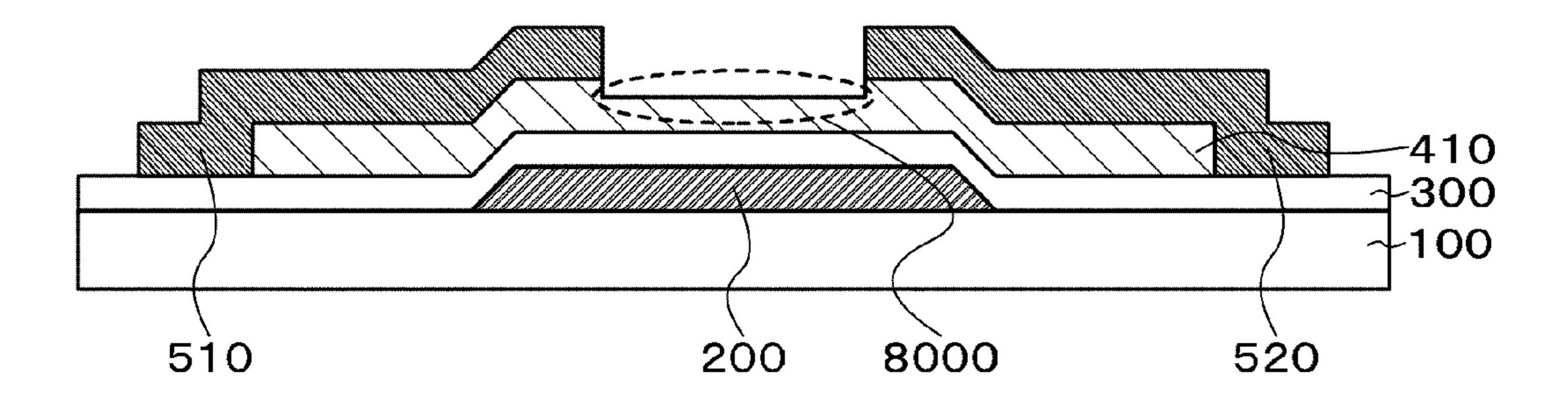

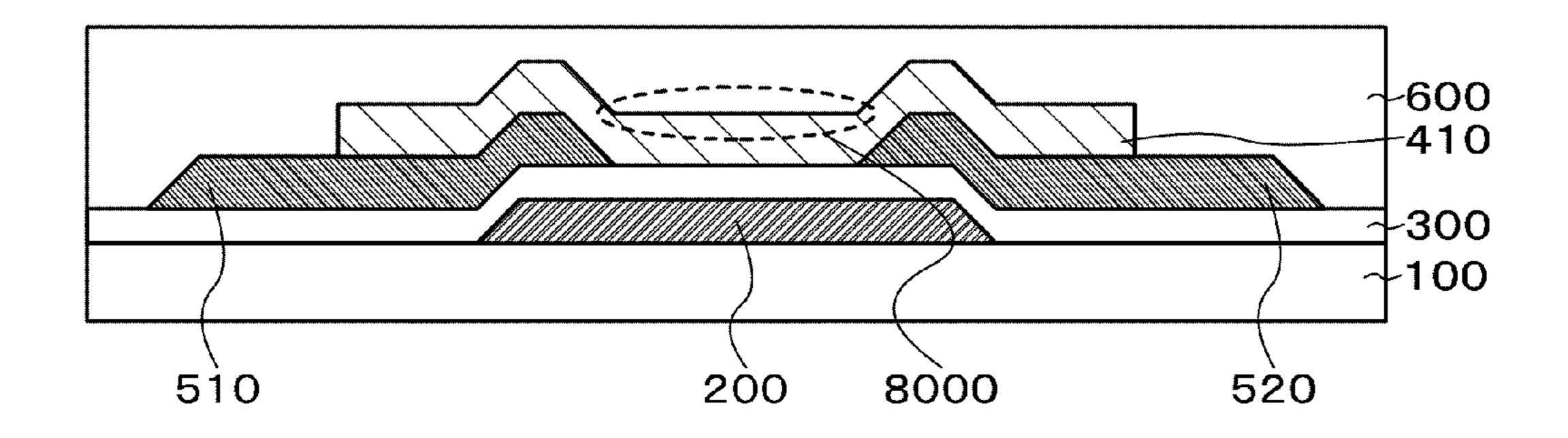

FIG. 1A

FIG. 1B

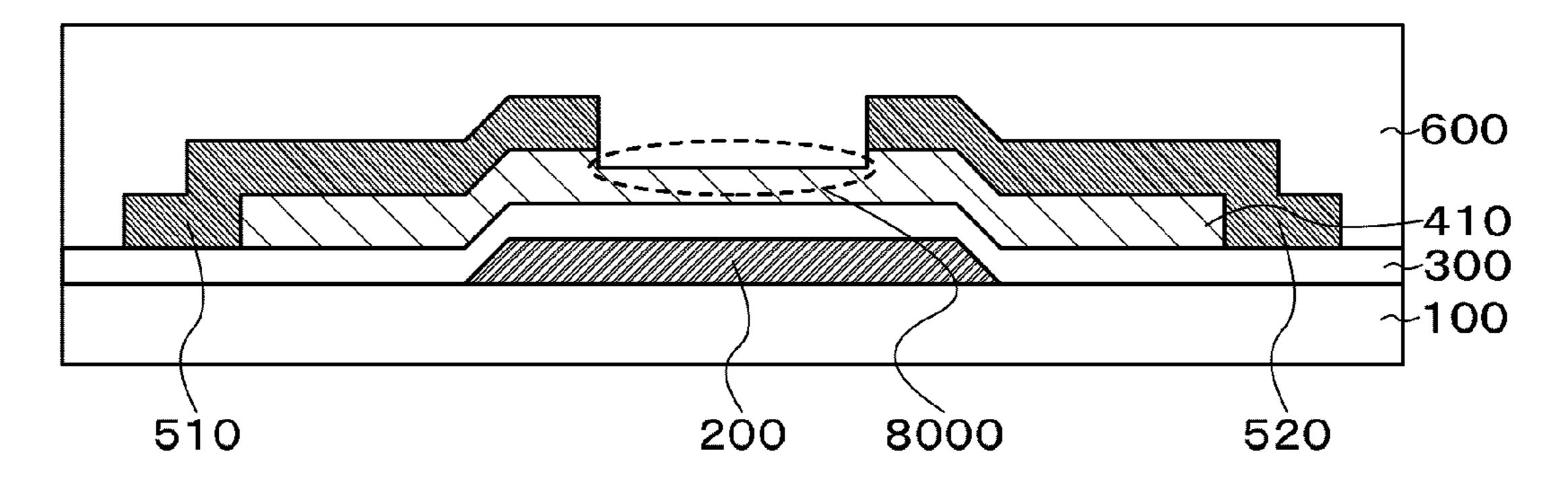

FIG. 1C

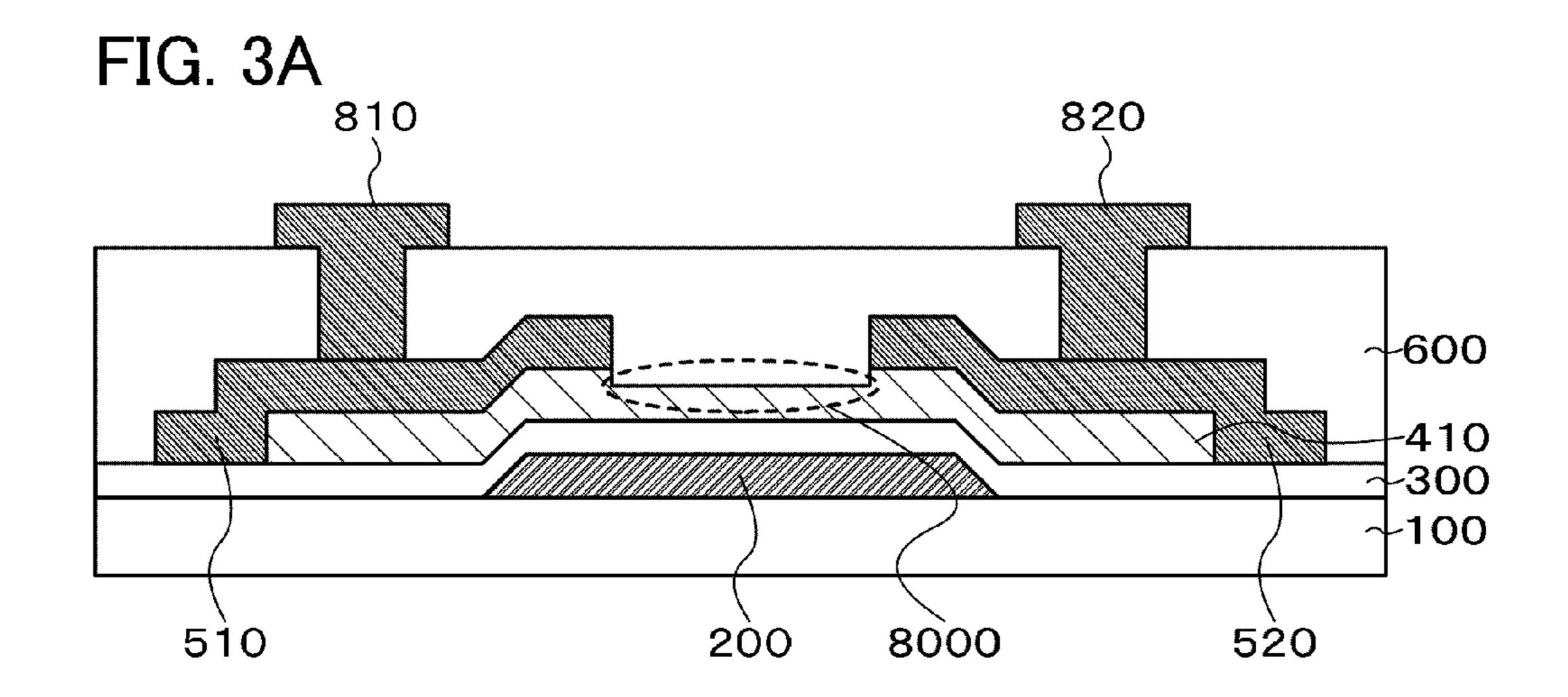

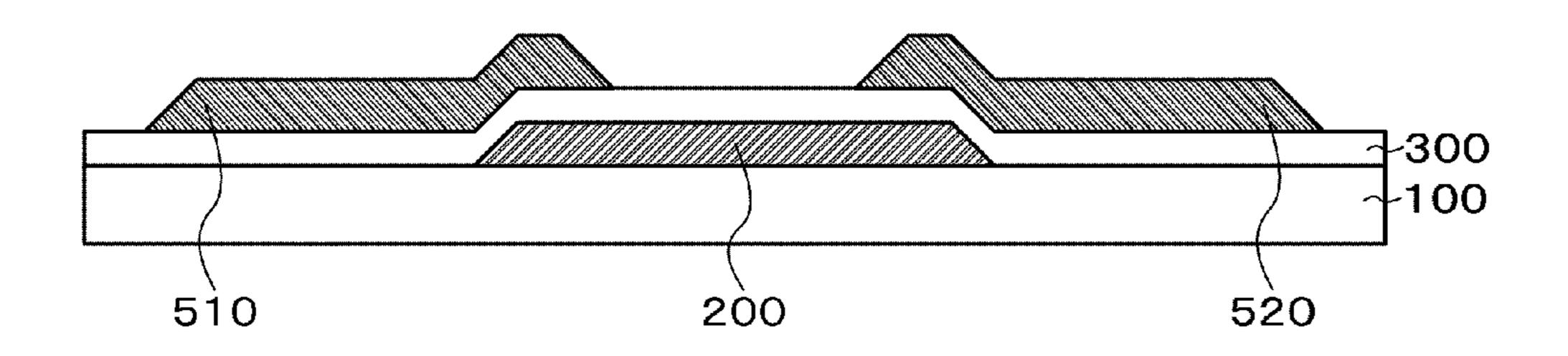

FIG. 2A

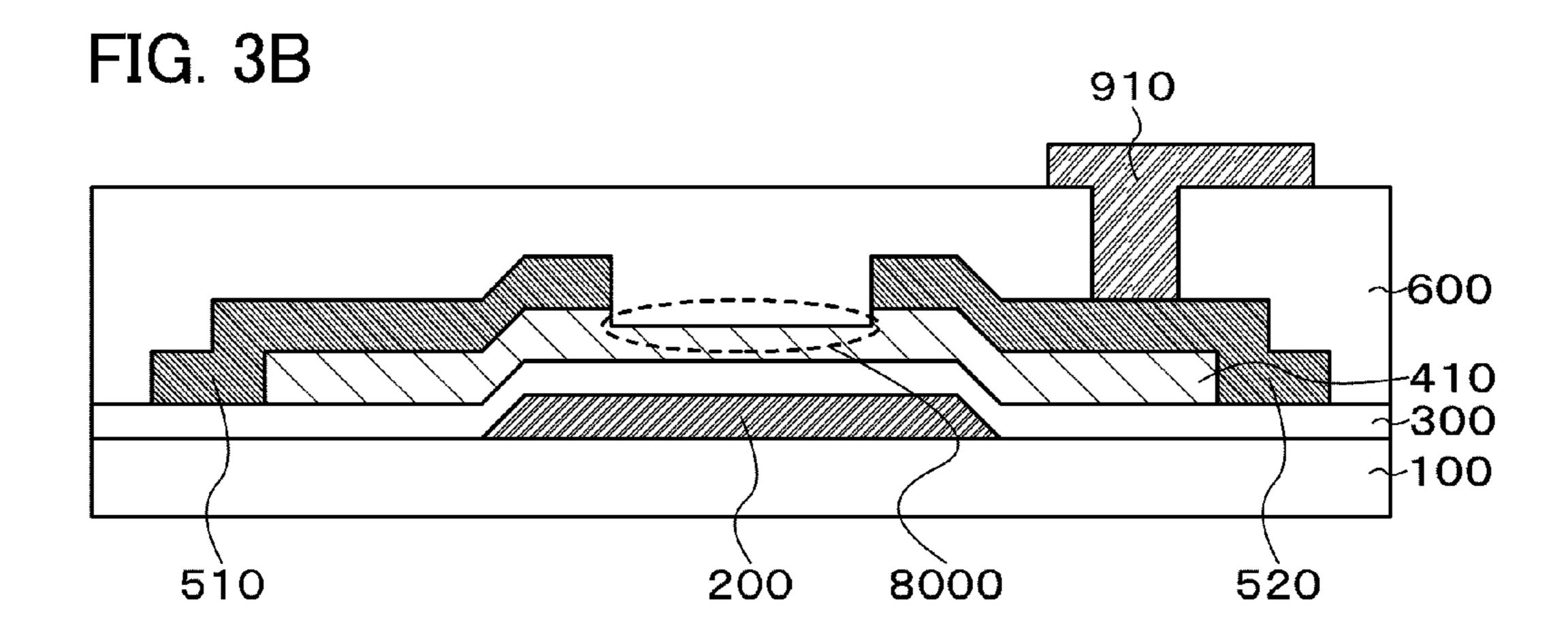

FIG. 2B

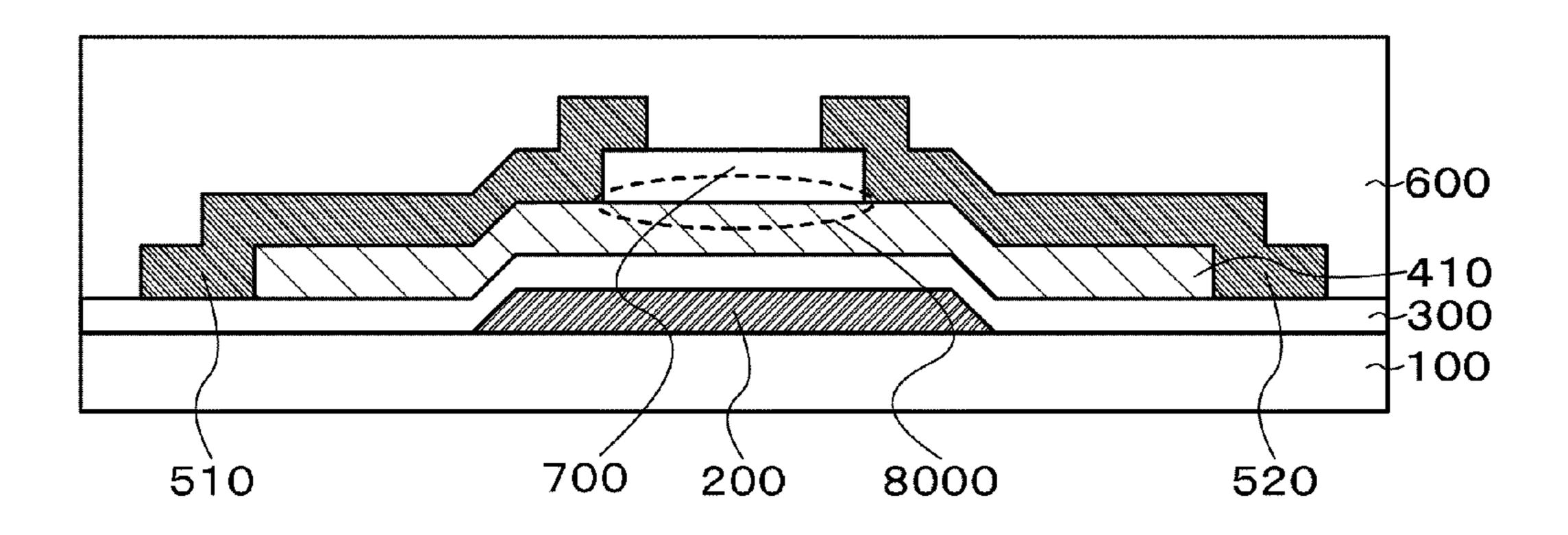

FIG. 4A

FIG. 4B

FIG. 4C

FIG. 5A

FIG. 5B

FIG. 5C

FIG. 6A

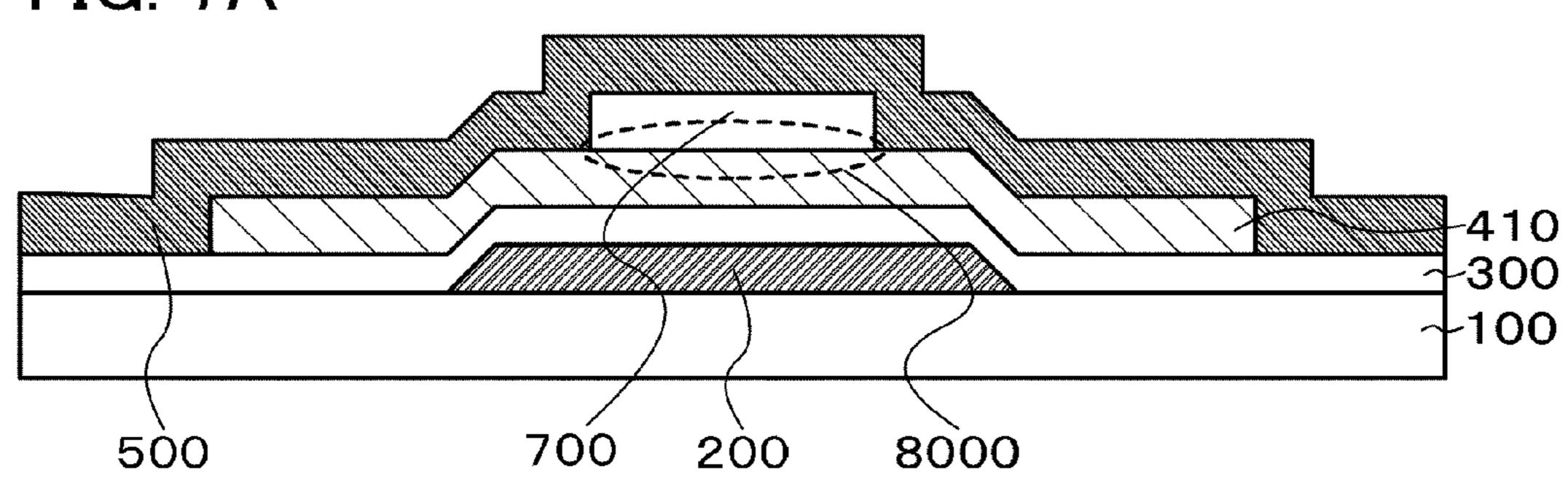

FIG. 7A

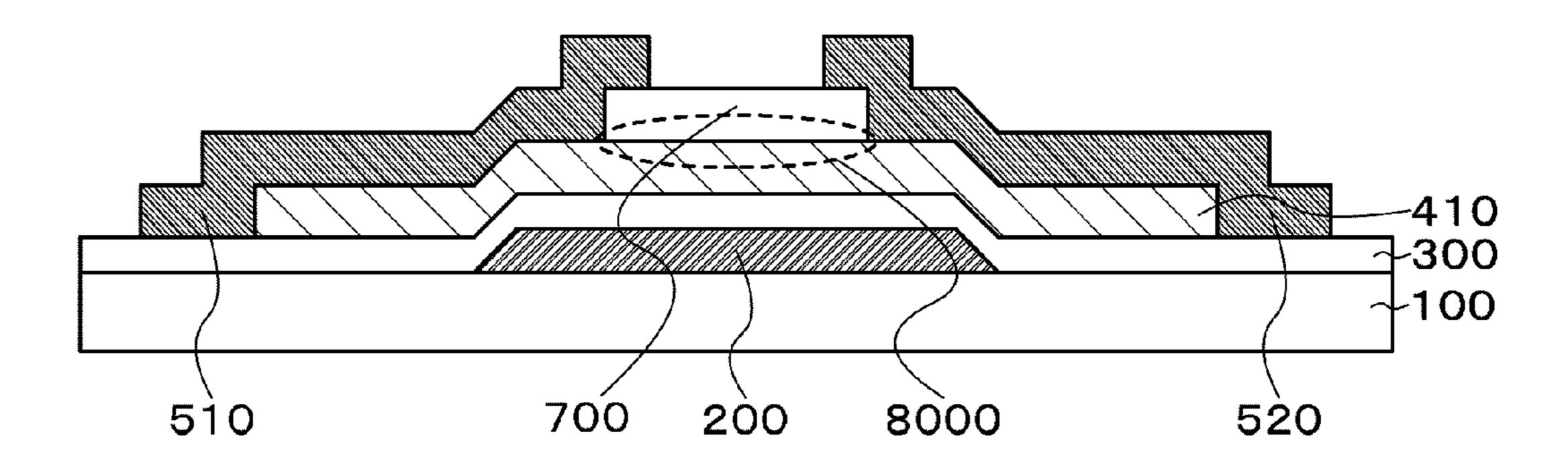

FIG. 7B

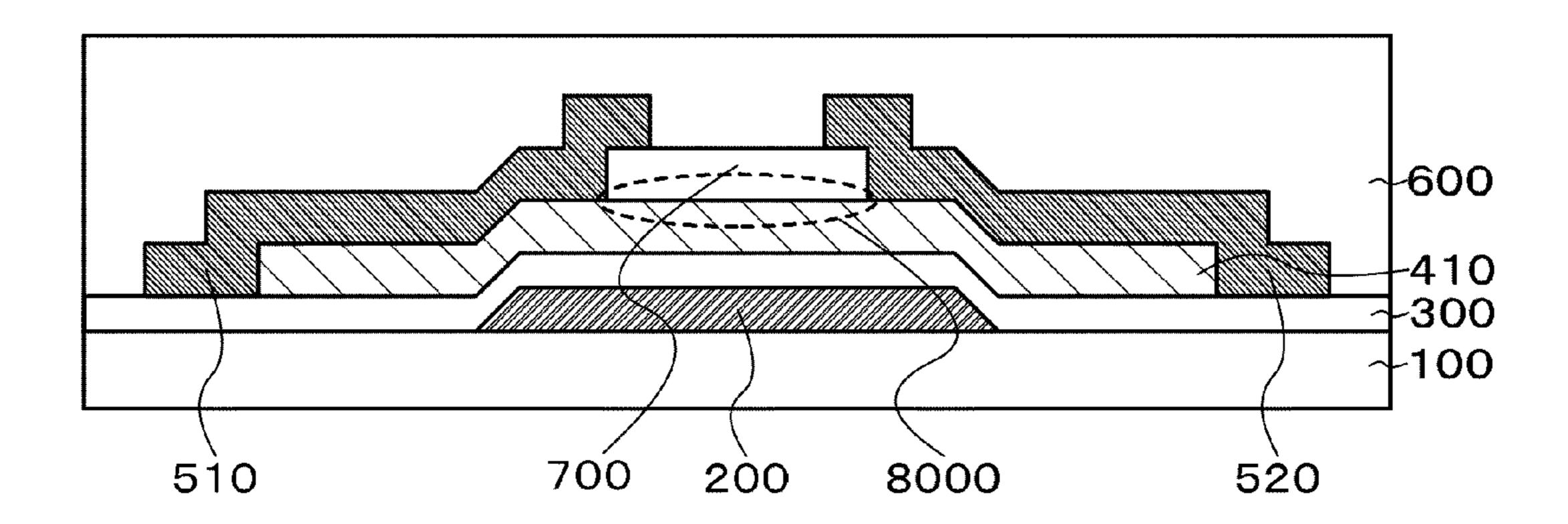

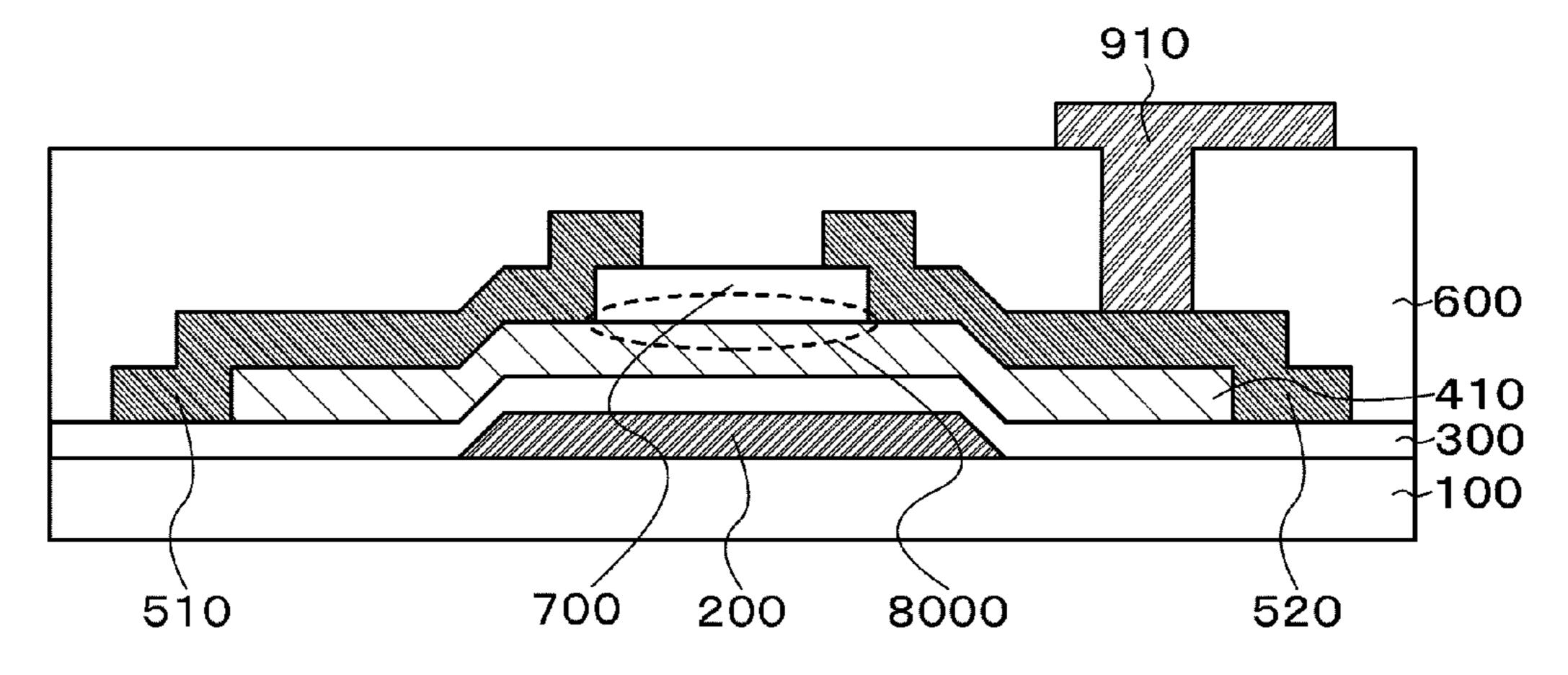

FIG. 7C

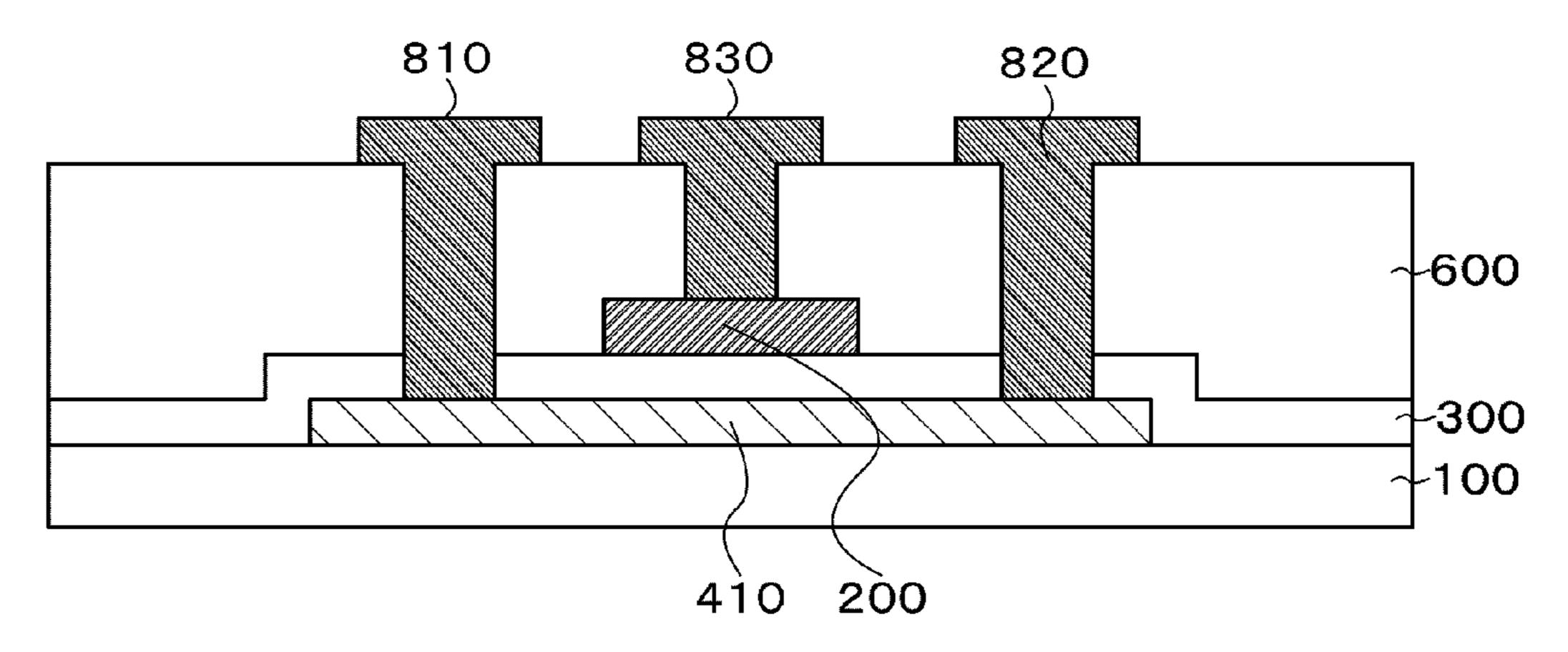

FIG. 8A

810

820

600

410

300

100

FIG. 8B

FIG. 9

FIG. 14A

FIG. 14B

FIG. 15A

FIG. 15B

# SEMICONDUCTOR DEVICE AND METHOD FOR MANUFACTURING THE SAME

#### TECHNICAL FIELD

The present invention relates to an oxide semiconductor.

# BACKGROUND ART

A semiconductor device including an oxide semiconductor <sup>10</sup> is disclosed in Patent Document 1.

#### REFERENCE

#### Patent Document

[Patent Document 1] Japanese Published Patent Application No. 2007-123861

#### DISCLOSURE OF INVENTION

Many of the physical properties of a silicon semiconductor have already been understood, whereas many of the physical properties of an oxide semiconductor have been still unclear.

In particular, an adverse effect of an impurity on an oxide 25 semiconductor has been still unclear.

In view of the above, a structure will be disclosed in which an impurity that influences electrical characteristics of a semiconductor device including an oxide semiconductor layer is prevented or is eliminated.

There are two factors of carriers in an oxide semiconductor layer.

The first factor is oxygen deficiency in an oxide semiconductor layer.

The second factor is a donor element or an acceptor element in an oxide semiconductor layer.

Here, a hydrogen element serves as a carrier (a donor) in an oxide semiconductor layer.

Further, since a hydrogen element has a reducing character, it also serves as an element causing oxygen deficiency.

Therefore, it is said that a substance containing a hydrogen element is an element which prevents an oxide semiconductor layer from being highly purified so that the oxide semiconductor layer is not close to an i-type oxide semiconductor layer because a hydrogen element has two factors of inducing 45 carriers.

Note that as a substance containing a hydrogen element, for example, hydrogen, moisture, hydroxide, hydride, and the like can be given.

As a result of research, the present inventors found that, 50 surprisingly, hydrogen is more likely to enter an oxide semiconductor layer when a large amount of nitrogen is contained in the oxide semiconductor layer.

Conversely, hydrogen is less likely to enter an oxide semiconductor layer in which the nitrogen concentration is 55 reduced.

Specifically, the nitrogen concentration in an oxide semiconductor layer measured by secondary ion mass spectrometry (SIMS) is set to  $1\times10^{20}$  atoms/cm<sup>3</sup> or less (or less than  $1\times10^{20}$  atoms/cm<sup>3</sup>), whereby an oxide semiconductor layer 60 which is difficult for hydrogen to enter can be formed.

That is, a semiconductor device which includes a gate electrode, an oxide semiconductor layer, and a gate insulating layer provided between the gate electrode and the oxide semiconductor layer and in which the nitrogen concentration in 65 the oxide semiconductor layer is  $1 \times 10^{20}$  atoms/cm<sup>3</sup> or less can be provided.

2

A semiconductor device which includes a gate electrode, a gate insulating layer provided over the gate electrode, an oxide semiconductor layer provided over the gate insulating layer, and a pair of contact electrodes provided over the oxide semiconductor layer and in which the nitrogen concentration in the oxide semiconductor layer is  $1 \times 10^{20}$  atoms/cm<sup>3</sup> or less can be provided.

A semiconductor device which includes a gate electrode, a gate insulating layer provided over the gate electrode, a pair of contact electrodes provided over the gate insulating layer, and an oxide semiconductor layer provided over the gate insulating layer and the pair of contact electrodes and in which the nitrogen concentration in the oxide semiconductor layer is  $1 \times 10^{20}$  atoms/cm<sup>3</sup> or less can be provided.

A semiconductor device which includes a gate electrode, a gate insulating layer provided over the gate electrode, an oxide semiconductor layer provided over the gate insulating layer, a channel protective layer provided over the oxide semiconductor layer, and a pair of contact electrodes provided over the oxide semiconductor layer and the channel protective layer and in which the nitrogen concentration in the oxide semiconductor layer is  $1 \times 10^{20}$  atoms/cm<sup>3</sup> or less can be provided.

In addition, the semiconductor device in which the hydrogen concentration in the oxide semiconductor layer is  $6 \times 10^{18}$  atoms/cm<sup>3</sup> or less can be provided.

A method for manufacturing a semiconductor device including a gate electrode, an oxide semiconductor layer, and a gate insulating layer provided between the gate electrode and the oxide semiconductor layer, which includes the step of performing heat treatment on the oxide semiconductor layer having a nitrogen concentration of 1×10<sup>20</sup> atoms/cm<sup>3</sup> or less at 350° C. or higher for 1 hour or longer, can be provided.

A method for manufacturing a semiconductor device including a gate electrode, an oxide semiconductor layer, and a gate insulating layer provided between the gate electrode and the oxide semiconductor layer, which includes the step of performing heat treatment on the oxide semiconductor layer having a nitrogen concentration of 1×10<sup>20</sup> atoms/cm<sup>3</sup> or less at 450° C. or higher for 1 hour or longer, can be provided.

A method for manufacturing a semiconductor device including a gate electrode, an oxide semiconductor layer, and a gate insulating layer provided between the gate electrode and the oxide semiconductor layer, which includes the step of performing heat treatment on the oxide semiconductor layer having a nitrogen concentration of  $1\times10^{20}$  atoms/cm<sup>3</sup> or less at 550° C. or higher for 1 hour or longer, can be provided.

A method for manufacturing a semiconductor device including a gate electrode, an oxide semiconductor layer, and a gate insulating layer provided between the gate electrode and the oxide semiconductor layer, which includes the step of performing heat treatment on the oxide semiconductor layer having a nitrogen concentration of  $1\times10^{20}$  atoms/cm<sup>3</sup> or less at 650° C. or higher for 3 minutes or longer, can be provided.

The nitrogen concentration in an oxide semiconductor layer is reduced, whereby an oxide semiconductor layer which is difficult for hydrogen to enter can be formed.

In other words, the nitrogen concentration in an oxide semiconductor layer is reduced, whereby hydrogen can be prevented from entering the oxide semiconductor layer.

# BRIEF DESCRIPTION OF DRAWINGS

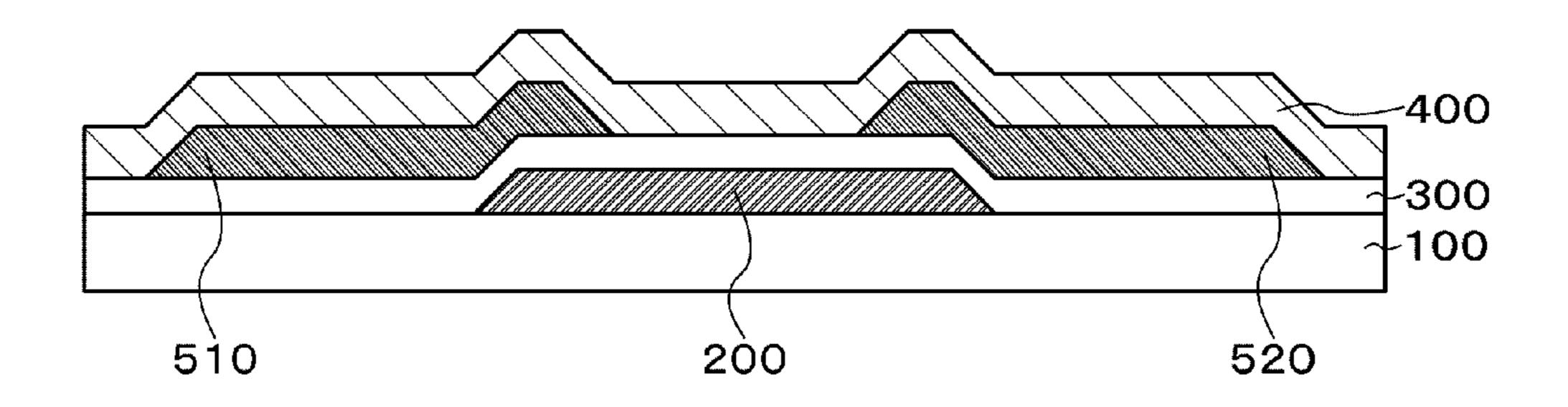

FIGS. 1A to 1C show an example of a method for manufacturing a semiconductor device.

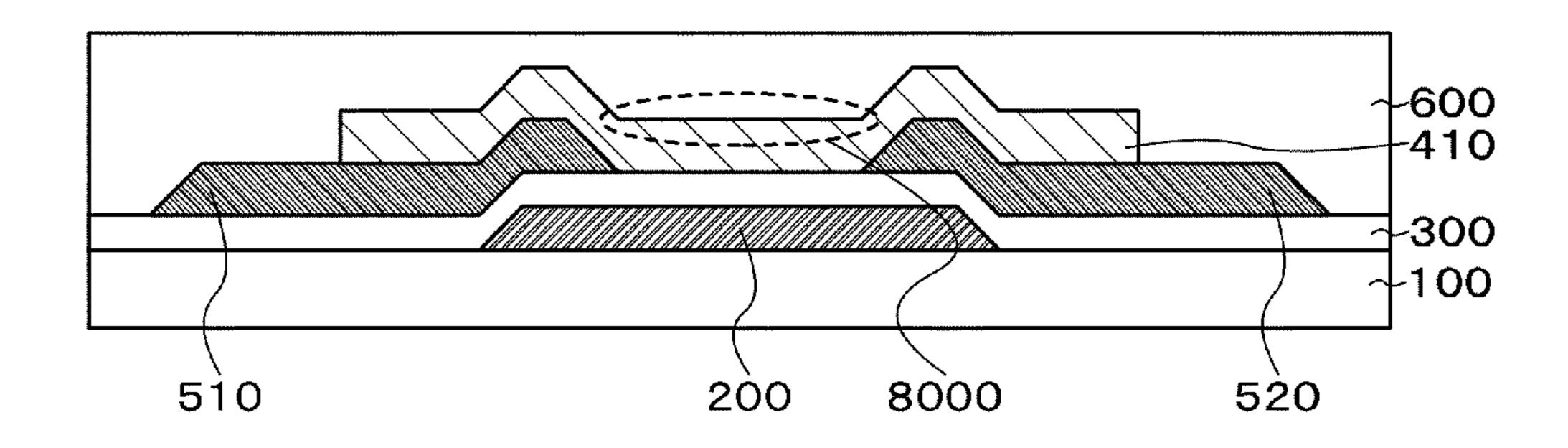

FIGS. 2A and 2B show an example of a method for manufacturing a semiconductor device.

FIGS. 3A and 3B show an example of a method for manufacturing a semiconductor device.

FIGS. 4A to 4C each show an example of a semiconductor device.

FIGS. **5**A to **5**C show an example of a method for manufacturing a semiconductor device.

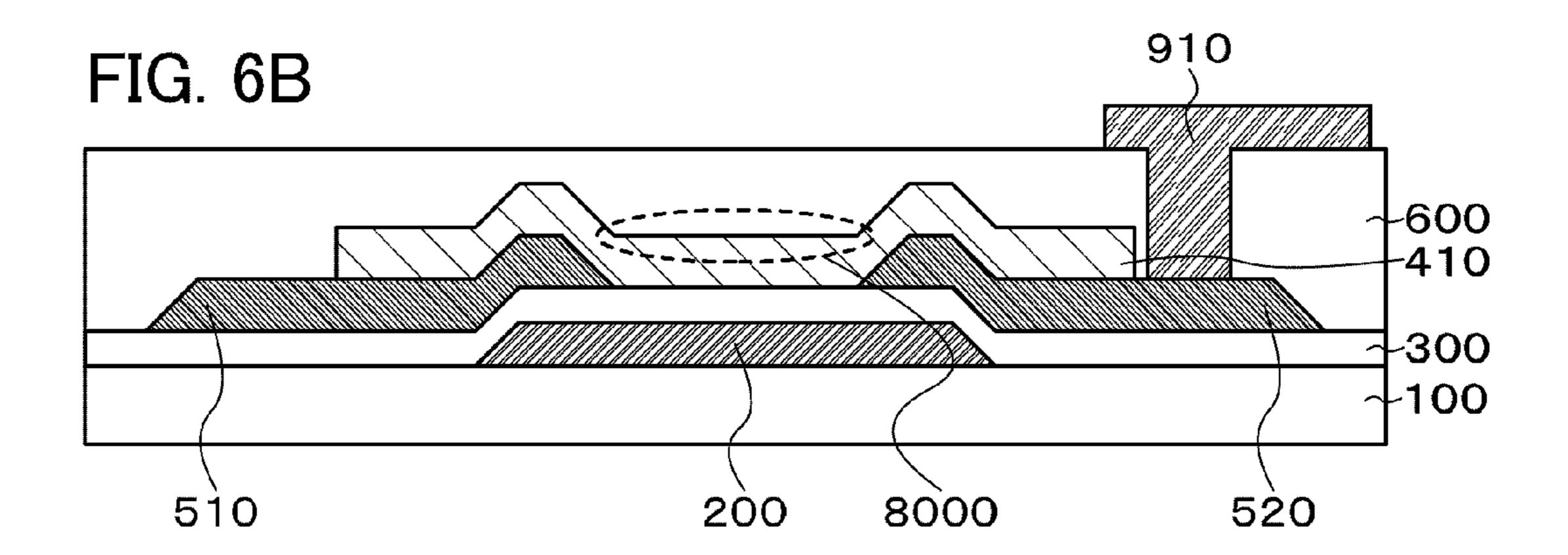

FIGS. 6A and 6B show an example of a method for manufacturing a semiconductor device.

FIGS. 7A to 7C show an example of a method for manufacturing a semiconductor device.

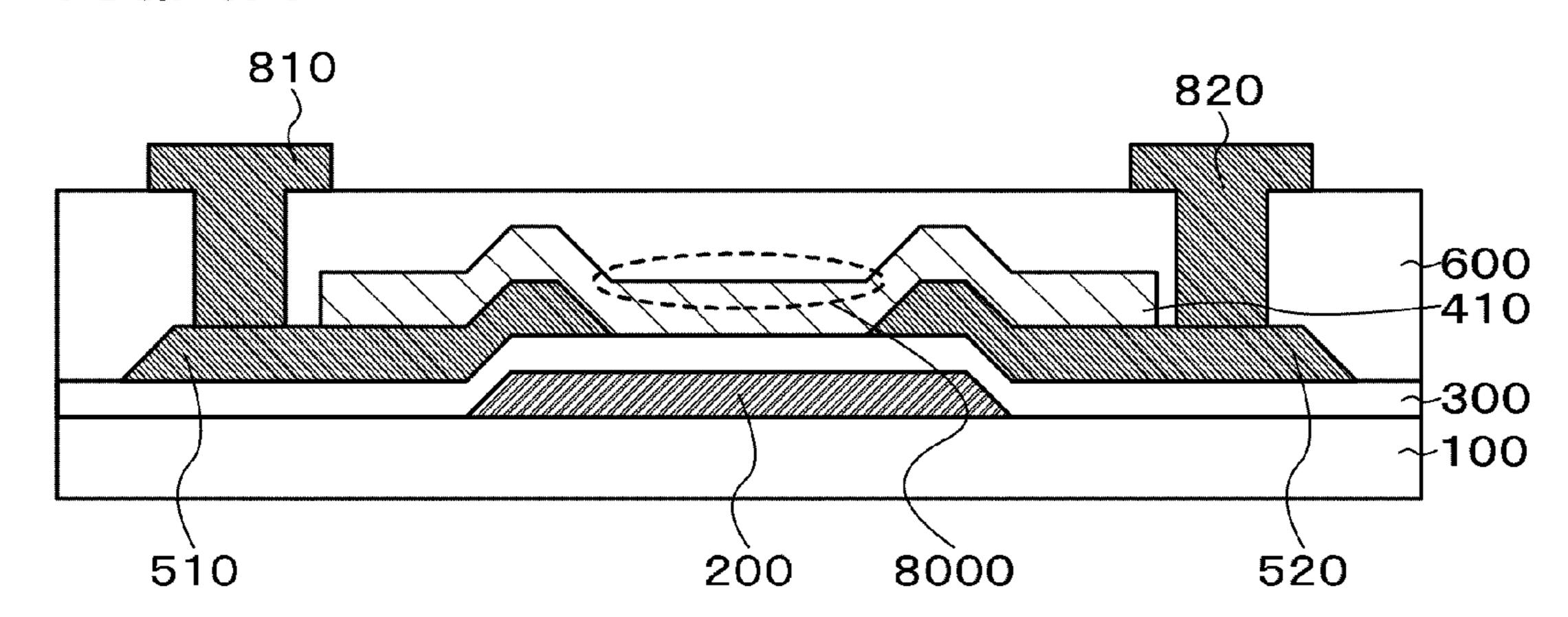

FIGS. 8A and 8B show an example of a method for manufacturing a semiconductor device.

FIG. 9 shows an example of a sputtering apparatus.

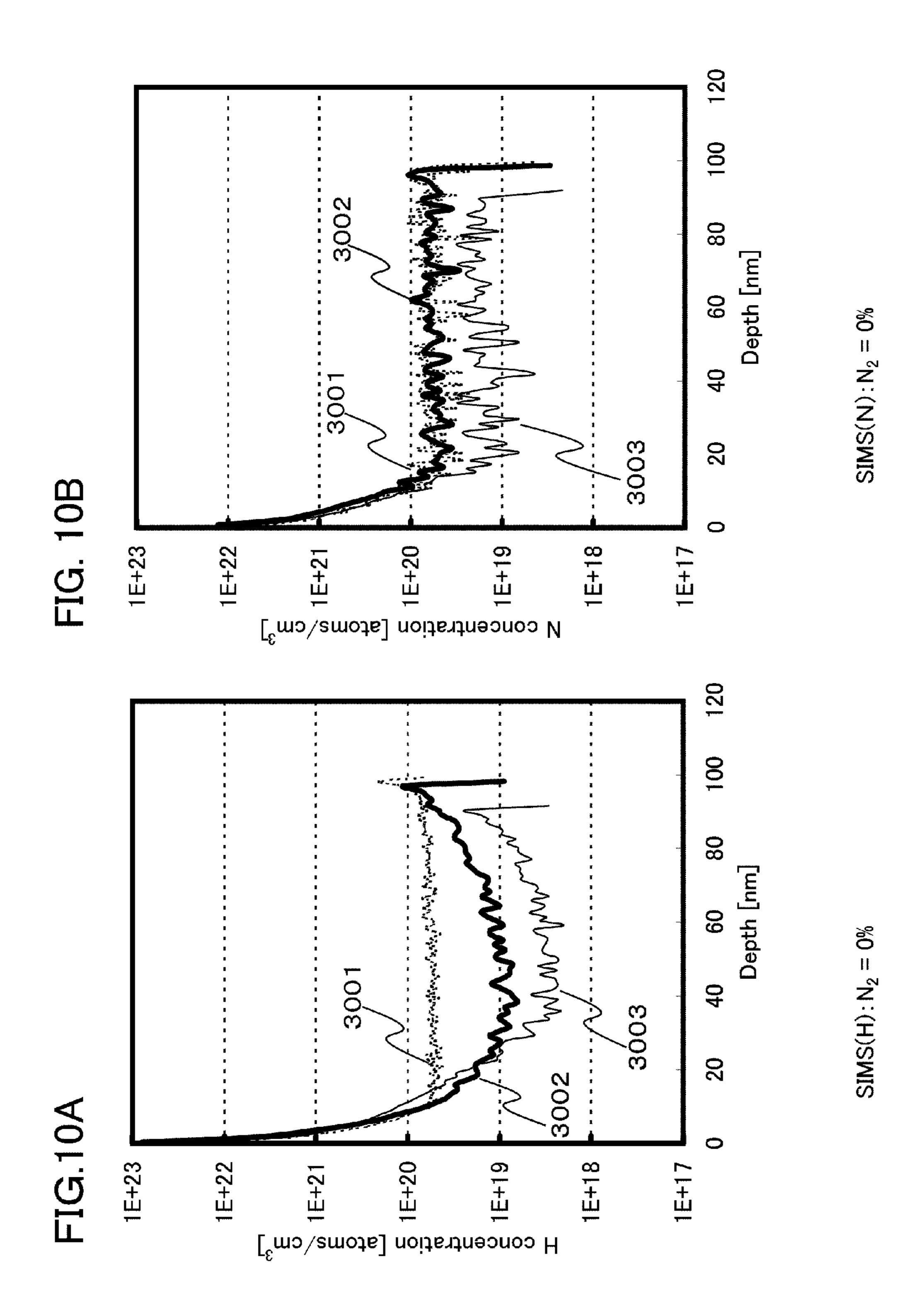

FIGS. 10A and 10B each show SIMS data.

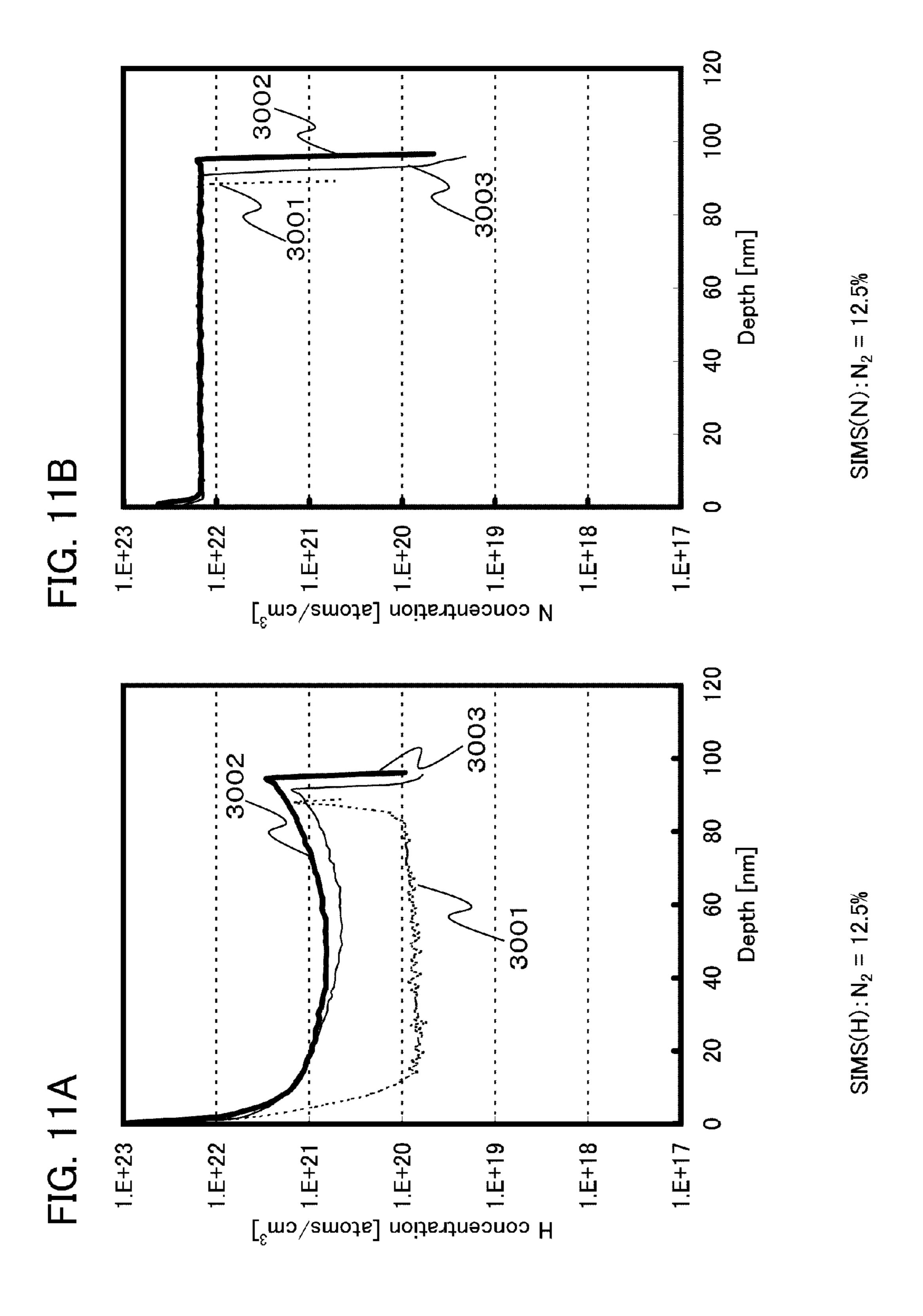

FIGS. 11A and 11B each show SIMS data.

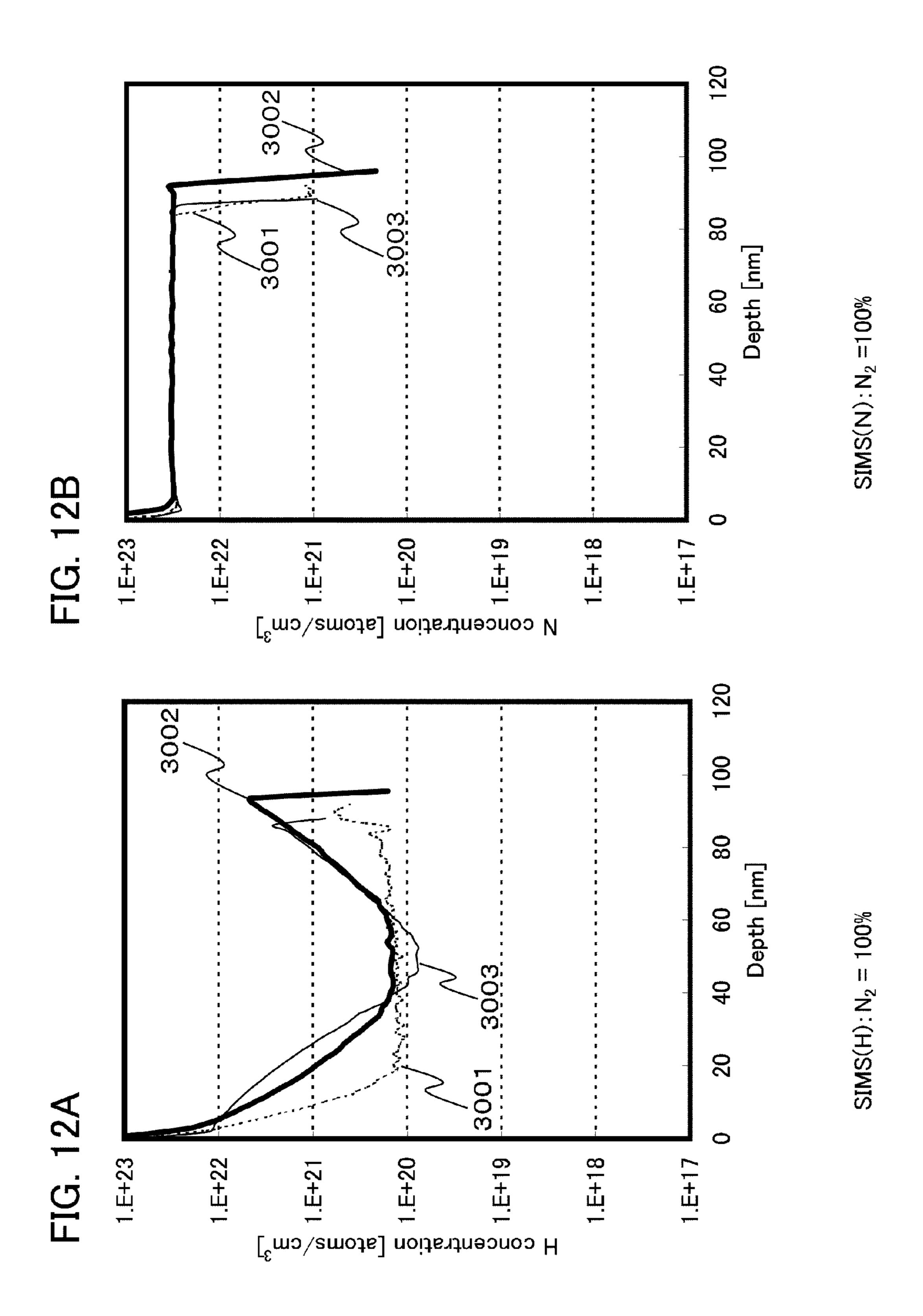

FIGS. 12A and 12B each show SIMS data.

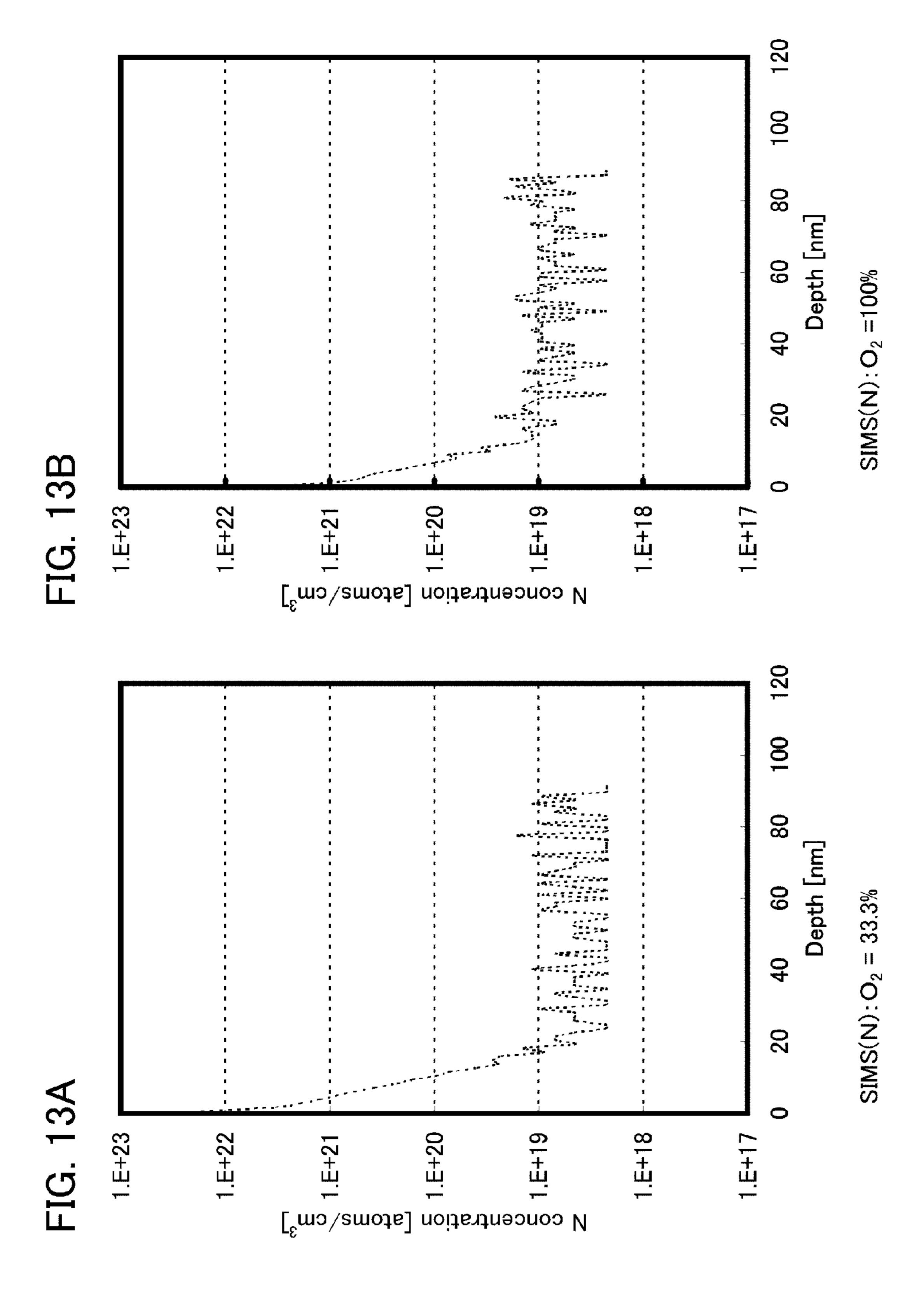

FIGS. 13A and 13B each show SIMS data.

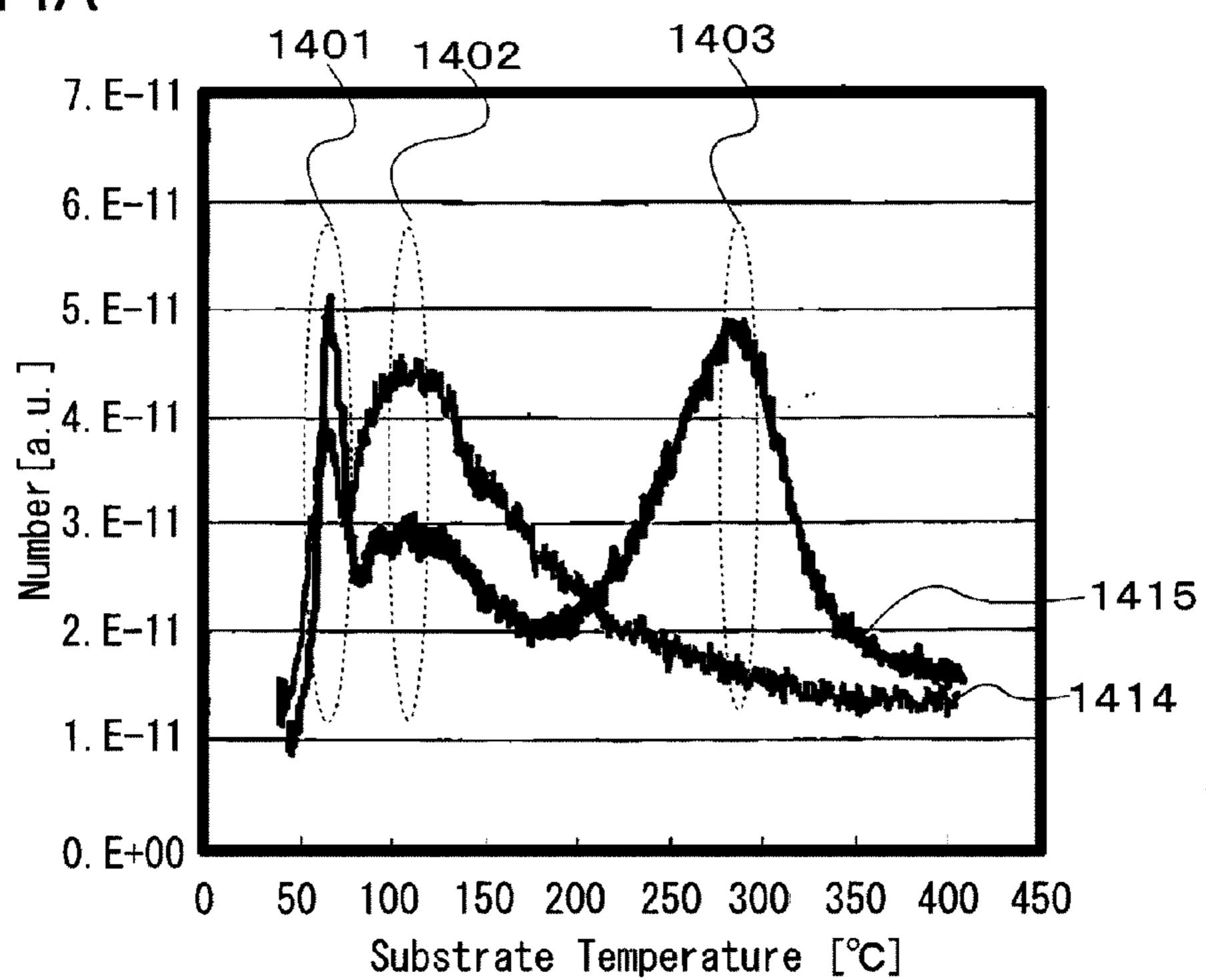

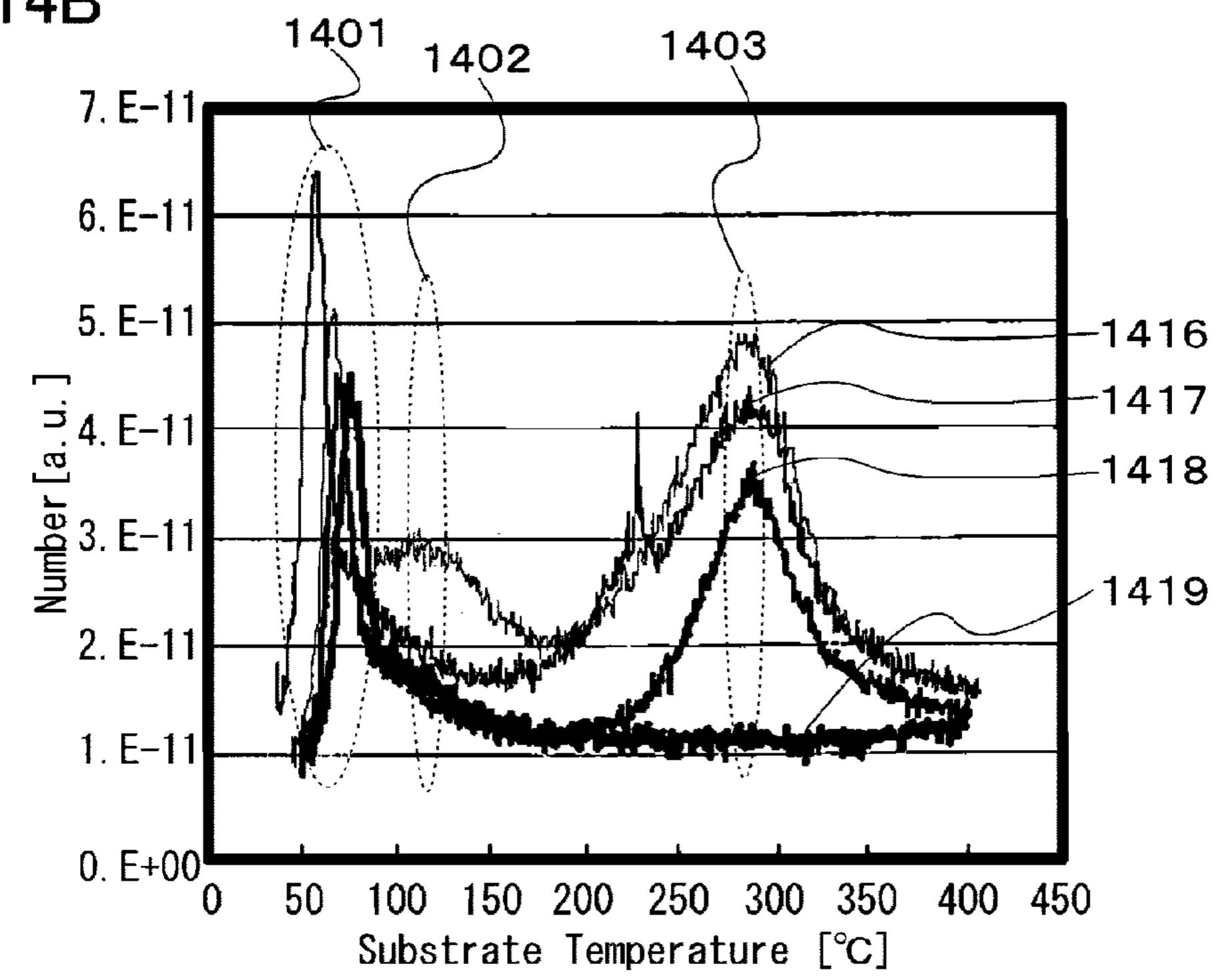

FIGS. 14A and 14B each show TDS data.

FIGS. 15A and 15B each show an example of a semiconductor device.

FIG. **16** shows a TEM photograph.

# BEST MODE FOR CARRYING OUT THE INVENTION

Embodiments and examples will be described in detail with reference to the accompanying drawings.

It is easily understood by those skilled in the art that modes and details of the present invention can be modified in various ways without departing from the spirit of the present inven- 30 tion.

Therefore, the present invention should not be interpreted as being limited to the description of the embodiments and examples below.

Note that in the structures described below, the same por- 35 tions or portions having similar functions are denoted by the same reference numerals in different drawings, and explanation thereof will not be repeated.

The following embodiments and examples can be combined with each other, as appropriate.

# Embodiment 1

An example of a method for manufacturing a semiconductor device will be described.

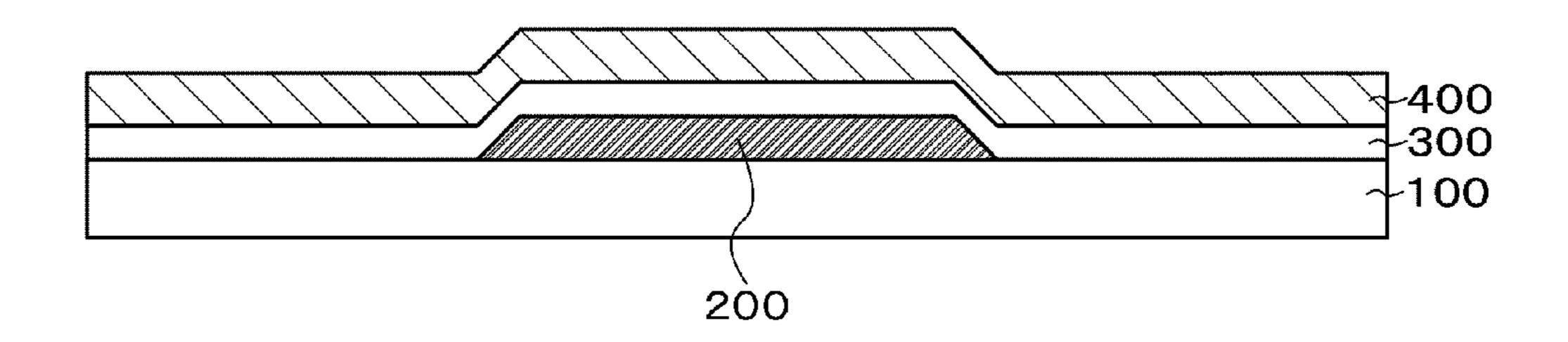

First, a gate electrode 200 is formed over a substrate 100 having an insulating surface. Then, a gate insulating layer 300 is formed over the gate electrode 200, and an oxide semiconductor layer 400 is formed over the gate insulating layer 300 (FIG. 1A).

As the substrate, any material can be used. For example, a glass substrate, a quartz substrate, a metal substrate, a plastic substrate, or a semiconductor substrate can be used, but the substrate is not limited to these examples.

substrate, the substrate has an insulating surface.

On the other hand, in the case where a metal substrate, a semiconductor substrate, or the like is used as the substrate, the substrate can have an insulating surface when a base insulating layer is formed over the substrate.

Note that a base insulating layer may be formed over the substrate also in the case where an insulating substrate is used as the substrate.

As the gate electrode, any material having conductivity can be used. For example, aluminum, titanium, molybdenum, 65 tungsten, gold, silver, copper, silicon, a variety of alloys, or an oxide conductive layer (typically, indium tin oxide and the

like) can be used, but the gate electrode is not limited to these examples. The gate electrode may have a single-layer structure or a stacked-layer structure.

As the gate insulating layer, any material having an insulating property can be used. For example, a silicon oxide film, a silicon nitride film, a silicon oxide film containing nitrogen, a silicon nitride film containing oxygen, an aluminum nitride film, an aluminum oxide film, a hafnium oxide film, or the like can be used, but the gate insulating layer is not limited to these examples. The gate insulating layer may have a single-layer structure or a stacked-layer structure.

Note that the amount of hydrogen and nitrogen in the gate insulating layer is preferably small so that injection of carriers into the oxide semiconductor layer can be prevented.

The gate insulating layer in which the amount of hydrogen is small is preferably formed using a deposition gas which does not contain hydrogen (H) or hydride (e.g., SiH<sub>4</sub>).

The gate insulating layer in which the amount of nitrogen 20 is small is preferably formed using a deposition gas which does not contain nitrogen (N) or nitride (e.g., N<sub>2</sub>O or NH<sub>4</sub>).

Therefore, when attention is focused on the point that the amount of hydrogen is small, a gate insulating film formed by a sputtering method is preferably used because hydride (e.g., 25 SiH₄) is used in a plasma CVD method.

Further, when attention is focused on the point that the amount of nitrogen is small, an oxide film which does not contain nitrogen is preferably used.

Note that a gate insulating layer formed by a plasma CVD method has fewer defects and has higher film quality than a gate insulating layer formed by a sputtering method.

Therefore, in some cases, transistor characteristics become favorable when a gate insulating layer formed by a plasma CVD method is used.

Thus, a plasma CVD method, a sputtering method, or another method may be used as appropriate as needed.

Note that in the case where a gate insulating layer formed by a plasma CVD method is used, a substance containing a hydrogen element is eliminated from the gate insulating layer 40 when heat treatment is performed; therefore, in the case where a plasma CVD method is used, heat treatment (at higher than or equal to 200° C. and lower than or equal to 1000° C. (preferably, higher than or equal to 300° C. and lower than or equal to 800° C.)) is preferably performed after 45 the gate insulating layer is formed.

Note that as a substance containing a hydrogen element, for example, hydrogen, moisture, hydroxide, hydride, and the like can be given.

Examples of the oxide semiconductor layer include, but 50 not limited to, In—Ga—Zn—O-based oxide (containing indium, gallium, zinc, and oxygen as the main components), In—Sn—Zn—O-based oxide (containing indium, tin, zinc, and oxygen as the main components), In—Al—Zn—Obased oxide (containing indium, aluminum, zinc, and oxygen In the case where an insulating substrate is used as the 55 as the main components), Sn—Ga—Zn—O-based oxide (containing tin, gallium, zinc, and oxygen as the main components), Al—Ga—Zn—O-based oxide (containing aluminum, gallium, zinc, and oxygen as the main components), Sn—Al—Zn—O-based oxide (containing tin, aluminum, 60 zinc, and oxygen as the main components), In—Zn—Obased oxide (containing indium, zinc, and oxygen as the main components), Sn—Zn—O-based oxide (containing tin, zinc, and oxygen as the main components), Al—Zn—O-based oxide (containing aluminum, zinc, and oxygen as the main components), In—O-based oxide (oxide of indium (indium oxide)), Sn—O-based oxide (oxide of tin (tin oxide)), Zn—O-based oxide (oxide of zinc (zinc oxide)), and the like.

The oxide semiconductor layer can be formed by a sputtering method, an evaporation method, or the like, for example.

The thickness of the oxide semiconductor layer is preferably 5 nm to 1 µm (more preferably, 20 nm to 80 nm).

In the case where the oxide semiconductor layer is formed, careful attention needs to be paid so that nitrogen is not contained in the oxide semiconductor layer.

Specifically, the oxide semiconductor layer is preferably formed so that the nitrogen concentration in the oxide semiconductor layer measured by secondary ion mass spectrometry (SIMS) is  $1 \times 10^{20}$  atoms/cm<sup>3</sup> or less (or less than  $1 \times 10^{20}$ atoms/cm<sup>3</sup>),  $5 \times 10^{19}$  atoms/cm<sup>3</sup> or less (or less than  $5 \times 10^{19}$ atoms/cm<sup>3</sup>),  $1 \times 10^{19}$  atoms/cm<sup>3</sup> or less (or less than  $1 \times 10^{19}$ atoms/cm<sup>3</sup>),  $5 \times 10^{18}$  atoms/cm<sup>3</sup> or less (or less than  $5 \times 10^{18}$ atoms/cm<sup>3</sup>), or  $1 \times 10^{18}$  atoms/cm<sup>3</sup> or less (or less than  $1 \times 10^{18}$ atoms/cm<sup>3</sup>).

Note that nitrogen is less likely to enter the oxide semiconductor layer even in the case where the oxide semiconductor layer is subjected to heat treatment.

Therefore, the nitrogen concentration in the oxide semiconductor layer after the semiconductor device is completed, which is measured by secondary ion mass spectrometry (SIMS), is also preferably  $1 \times 10^{20}$  atoms/cm<sup>3</sup> or less (or less than  $1\times10^{20}$  atoms/cm<sup>3</sup>),  $5\times10^{19}$  atoms/cm<sup>3</sup> or less (or less 25 than  $5\times10^{19}$  atoms/cm<sup>3</sup>),  $1\times10^{19}$  atoms/cm<sup>3</sup> or less (or less than  $1 \times 10^{19}$  atoms/cm<sup>3</sup>),  $5 \times 10^{18}$  atoms/cm<sup>3</sup> or less (or less than  $5 \times 10^{18}$  atoms/cm<sup>3</sup>), or  $1 \times 10^{18}$  atoms/cm<sup>3</sup> or less (or less than  $1\times10^{18}$  atoms/cm<sup>3</sup>).

Note that as the value of the nitrogen concentration, the 30 average value in the effective range of secondary ion mass spectrometry (SIMS) can be adopted.

Alternatively, as the value of the nitrogen concentration, the maximum value in the effective range of secondary ion mum value in the effective range is smaller than a predetermined value, the average value in the effective range is also smaller than the predetermined value).

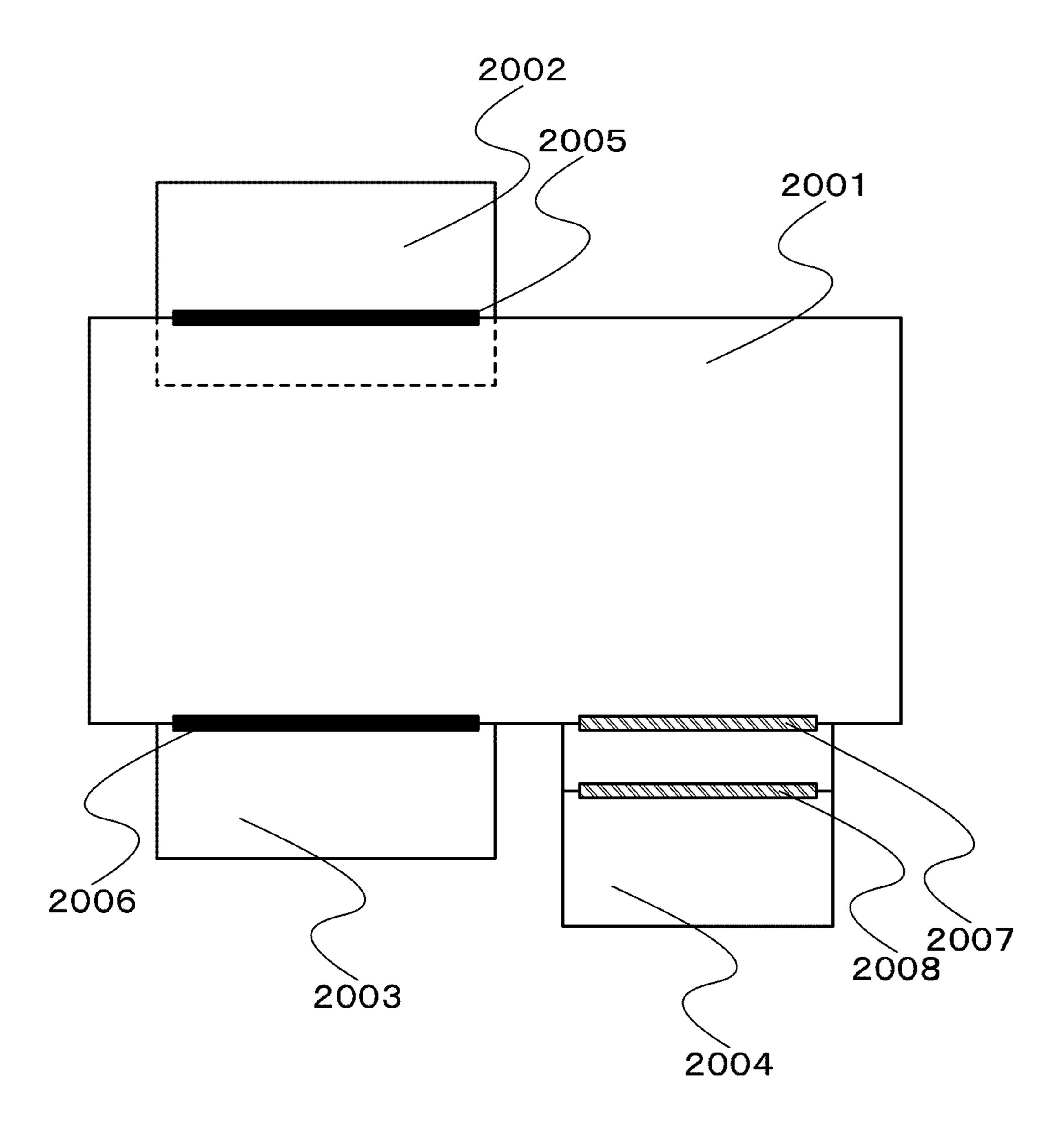

Here, an example of a sputtering apparatus is shown in FIG. **9**.

The sputtering apparatus in FIG. 9 includes a deposition chamber 2001, a cover 2002, a target 2003, and a pump 2004.

Note that a structure is employed in which a substrate is put to be provided for the cover 2002 and the target 2003 is sputtered for deposition.

The deposition chamber 2001 and the cover 2002 are connected to each other, and an O-ring 2005 is provided for a connecting portion.

The deposition chamber 2001 and the target 2003 are connected to each other, and an O-ring 2006 is provided for a 50 connecting portion.

The deposition chamber 2001 and the pump 2004 are connected to each other, and a metal gasket 2007 and a metal gasket 2008 are provided for connecting portions.

Both the O-rings and the metal gaskets are used to prevent 55 leakage from the connecting portion. In other words, by the O-rings and the metal gaskets, air (in particular, nitrogen) is prevented from entering the deposition chamber 2001.

The O-ring is a ring-like packing. A material thereof is, for example, rubber.

The metal gasket is a ring-like fixing sealant. A material thereof is, for example, metal.

The cover 2002 and the target 2003 are frequently opened and closed; therefore, the O-ring is used because it can be easily put on and taken off.

On the other hand, the pump is hardly opened and closed. Although the metal gasket is not easily put on and taken off,

the metal gasket is provided for the pump because it can improve airtightness compared with the O-ring.

In the case where the O-ring or the metal gasket has a chip, a crack, or the like, leakage occurs, so that air outside the deposition chamber 2001 enters the deposition chamber **2001**.

Since air contains a large amount of nitrogen, careful attention needs to be paid so that the O-ring or the metal gasket does not have a chip, a crack, or the like in order to prevent air (in particular, nitrogen) due to the chip, the crack, or the like of the O-ring or the metal gasket from entering the deposition chamber 2001.

Although the maintenance needs to be further done, it is effective to replace all the O-rings with metal gaskets which can improve airtightness because air (in particular, nitrogen) can be prevented from entering the deposition chamber 2001.

On the other hand, in the case where nitrogen is attached to or enters the inner wall of the deposition chamber 2001 or a surface of the target 2003 or in the case where nitrogen floats in the deposition chamber 2001 even when air (in particular, nitrogen) is prevented from entering the deposition chamber 2001, nitrogen might enter an oxide semiconductor layer.

Thus, in order to remove nitrogen which is attached to or enters the inner wall of the deposition chamber, the deposition chamber is heated at higher than or equal to 200° C. and lower than or equal to 500° C.

The deposition chamber is heated, whereby nitrogen which is attached to or enters the inner wall of the deposition chamber is released into the deposition chamber.

Then, nitrogen which is released through heating of the deposition chamber is evacuated with the use of the pump 2004, whereby nitrogen which is attached to or enters the inner wall of the deposition chamber can be removed.

Further, after the heat treatment and the evacuation treatmass spectrometry (SIMS) may be adopted (when the maxi- 35 ment are performed on the deposition chamber and before the oxide semiconductor layer used for a semiconductor device is formed, a step of forming an oxide semiconductor layer over a dummy substrate is preferably performed.

> When the step of forming the oxide semiconductor layer 40 over the dummy substrate is performed, nitrogen which is attached to or enters the surface of the target can be removed.

> Further, since nitrogen which remains in the deposition chamber due to the step of forming the oxide semiconductor layer over the dummy substrate is taken into the oxide semi-45 conductor layer over the dummy substrate, nitrogen which remains in the deposition chamber can be removed before the oxide semiconductor layer used for the semiconductor device is formed.

After that, the dummy substrate is taken out of the deposition chamber, and the oxide semiconductor layer used for the semiconductor device is formed.

Note that it is effective to perform deposition onto the dummy substrate a plurality of times.

As described above, the reduction of leakage from the deposition chamber, the reduction of nitrogen on the inner wall of the deposition chamber, deposition onto the dummy substrate, or the like is sufficiently performed, so that incorporation of nitrogen into the oxide semiconductor layer can be thoroughly prevented.

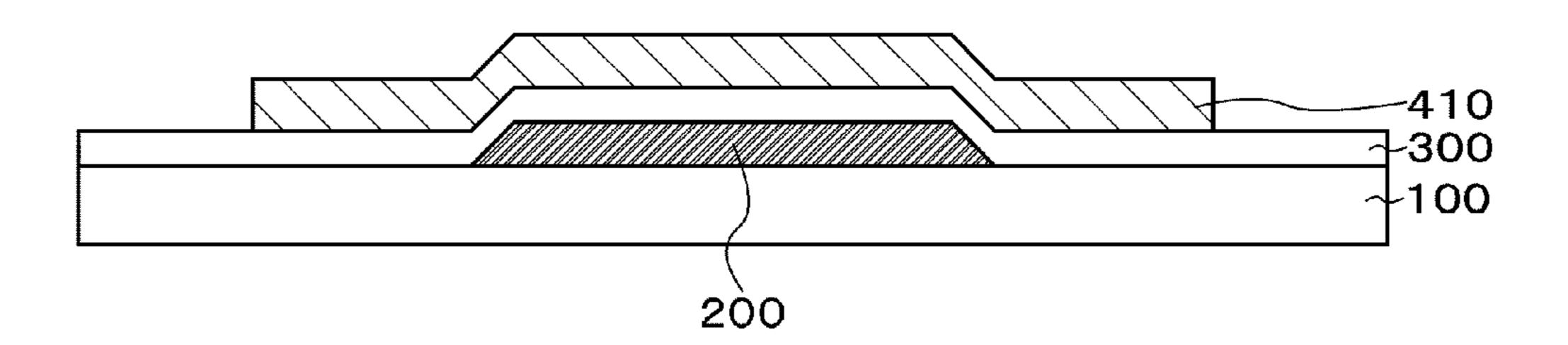

Next, the oxide semiconductor layer 400 is etched into an island shape by a photolithography method, whereby an oxide semiconductor layer 410 is formed (FIG. 1B).

Next, the oxide semiconductor layer is subjected to first heat treatment (at higher than or equal to X° C. and lower than 65 Y° C.).

A nitrogen atmosphere, a rare gas atmosphere, an oxygen atmosphere, an atmosphere containing oxygen and nitrogen,

an atmosphere containing oxygen and a rare gas, an atmosphere containing nitrogen and a rare gas, an atmosphere containing oxygen, nitrogen, and a rare gas, or the like can be selected as appropriate for the atmosphere in which the first heat treatment is performed.

The first heat treatment may be performed before the oxide semiconductor layer 400 is etched into an island shape to form the oxide semiconductor layer 410.

On the other hand, through the step of etching the oxide semiconductor layer 400 into an island shape to form the 10 oxide semiconductor layer 410 by a photolithography method, the oxide semiconductor layer is immersed in moisture of a photoresist and a stripping solution.

Therefore, in order to remove moisture due to the photoresist and the stripping solution, it is more preferable that the 15 first heat treatment be performed after the oxide semiconductor layer 400 is etched into an island shape to form the oxide semiconductor layer 410.

The lower limit (X° C.) of the temperature of the first heat treatment can be set to 350° C. or higher (or higher than 350° 20 C.), 400° C. or higher (or higher than 400° C.), 450° C. or higher (or higher than 450° C.), 500° C. or higher (or higher than 550° C.), 600° C. or higher (or higher than 550° C.), 600° C. or higher (or higher than 650° C.), 700° C. or higher (or higher than 700° 25 C.), or 750° C. or higher (or higher than 750° C.).

The first heat treatment is preferably performed by a heating method with the use of a furnace, an oven, gas RTA, or the like.

Gas RTA refers to a method in which an object is put in a 30 gas heated at high temperature for a short time (several minutes to several tens of minutes) to be rapidly heated.

There is no particular limitation on the upper limit of the temperature of the first heat treatment because the temperature of the first heat treatment is preferably high.

However, the upper limit (Y° C.) of the temperature of the first heat treatment is preferably lower than the allowable temperature limit of the substrate.

Further, the upper limit (Y° C.) of the temperature of the first heat treatment can be set to 1000° C. or lower (or lower 40 than 1000° C.), 900° C. or lower (or lower than 900° C.), 800° C. or lower (or lower than 800° C.), or 700° C. or lower (or lower than 700° C.).

The heating time of the first heat treatment is preferably 1 hour or longer. The upper limit of the heating time is not 45 particularly limited, but can be set to 10 hours or shorter, 9 hours or shorter, or 8 hours or shorter in consideration of reduction in process time.

In the case where the first heat treatment is performed with the use of gas RTA, the heating time of the first heat treatment 50 is preferably 3 minutes or longer. The upper limit of the heating time is not particularly limited, but can be set to 1 hour or shorter, 50 minutes or shorter, or 40 minutes or shorter.

When the measurement is performed by thermal desorption spectroscopy (TDS), a sample on which baking has been 55 performed at 450° C. for 1 hour does not have a peak of moisture at around 300° C. A sample on which baking has been performed at 650° C. for 3 minutes with the use of gas RTA also does not have a peak of moisture at around 300° C. On the other hand, a sample on which baking has been performed at 350° C. for 1 hour has a peak of moisture at around 300° C.

When the measurement is performed by secondary ion mass spectrometry (SIMS), the hydrogen concentration in a sample on which baking has been performed at 550° C. for 1 65 hour is lower than that in a sample on which baking has been performed at 450° C. for 1 hour by almost 1 digit.

8

In other words, the oxide semiconductor layer in which the nitrogen concentration is reduced is subjected to the first heat treatment under a predetermined condition, whereby substances containing a hydrogen element which adversely affect electrical characteristics of a transistor can be drastically reduced.

Note that the higher the energy which is applied to the oxide semiconductor is, the more substances containing a hydrogen element are likely to be eliminated; therefore, the heating temperature is preferably high and the heating time is preferably long.

The hydrogen concentration in the oxide semiconductor layer after the first heat treatment is preferably  $6\times10^{18}$  atoms/cm<sup>3</sup> or less (or less than  $6\times10^{18}$  atoms/cm<sup>3</sup>),  $5\times10^{18}$  atoms/cm<sup>3</sup> or less (or less than  $5\times10^{18}$  atoms/cm<sup>3</sup>),  $4\times10^{18}$  atoms/cm<sup>3</sup> or less (or less than  $4\times10^{18}$  atoms/cm<sup>3</sup>),  $3\times10^{18}$  atoms/cm<sup>3</sup> or less (or less than  $3\times10^{18}$  atoms/cm<sup>3</sup>),  $1\times10^{16}$  atoms/cm<sup>3</sup> or less (or less than  $1\times10^{16}$  atoms/cm<sup>3</sup>),  $1\times10^{14}$  atoms/cm<sup>3</sup> or less (or less than  $1\times10^{14}$  atoms/cm<sup>3</sup>), or  $1\times10^{12}$  atoms/cm<sup>3</sup> or less (or less than  $1\times10^{12}$  atoms/cm<sup>3</sup>).

The oxide semiconductor layer in which the nitrogen concentration is reduced can prevent incorporation of hydrogen in steps after the first heat treatment.

Thus, the hydrogen concentration in the oxide semiconductor layer after the semiconductor device is completed is also preferably  $6\times10^{18}$  atoms/cm<sup>3</sup> or less (or less than  $6\times10^{18}$  atoms/cm<sup>3</sup>),  $5\times10^{18}$  atoms/cm<sup>3</sup> or less (or less than  $5\times10^{18}$  atoms/cm<sup>3</sup>),  $4\times10^{18}$  atoms/cm<sup>3</sup> or less (or less than  $4\times10^{18}$  atoms/cm<sup>3</sup>),  $3\times10^{18}$  atoms/cm<sup>3</sup> or less (or less than  $3\times10^{18}$  atoms/cm<sup>3</sup>),  $1\times10^{16}$  atoms/cm<sup>3</sup> or less (or less than  $1\times10^{16}$  atoms/cm<sup>3</sup>),  $1\times10^{14}$  atoms/cm<sup>3</sup> or less (or less than  $1\times10^{14}$  atoms/cm<sup>3</sup>), or  $1\times10^{12}$  atoms/cm<sup>3</sup> or less (or less than  $1\times10^{12}$  atoms/cm<sup>3</sup>).

Note that as the value of the hydrogen concentration, the average value in the effective range of secondary ion mass spectrometry (SIMS) can be adopted.

Alternatively, as the value of the hydrogen concentration, the maximum value in the effective range of secondary ion mass spectrometry (SIMS) may be adopted (when the maximum value in the effective range is smaller than a predetermined value, the average value in the effective range is also smaller than the predetermined value).

Note that the smaller the quantity of substances containing a hydrogen element in the oxide semiconductor layer is, the more electrical characteristics of the transistor including the oxide semiconductor layer are improved.

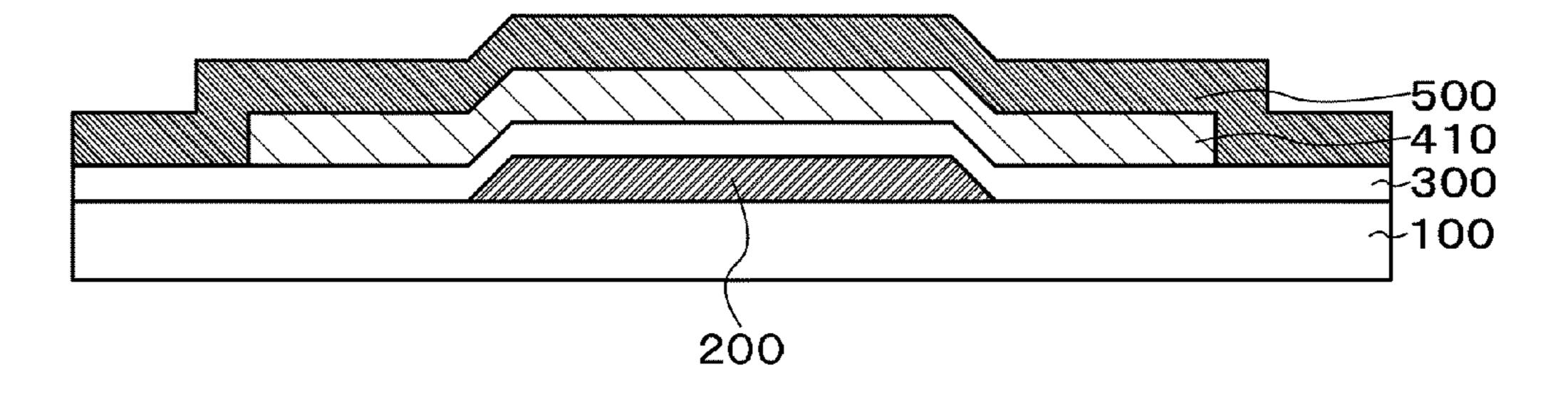

Next, a conductive layer 500 is formed over the oxide semiconductor layer 410 (FIG. 1C).

As the conductive layer, any material having conductivity can be used. For example, aluminum, titanium, molybdenum, tungsten, yttrium, indium, gold, silver, copper, silicon, a variety of alloys containing any of these metals, an oxide conductive layer (typically, indium tin oxide), or the like can be used, but the conductive layer is not limited to these examples. The conductive layer may have a single-layer structure or a stacked-layer structure.

Note that the conductive layer in contact with the oxide semiconductor layer is formed using titanium, indium, yttrium, an indium-zinc alloy, an alloy containing gallium (e.g., gallium nitride), or the like, whereby the contact resistance between the oxide semiconductor layer and an electrode (a wiring) which is formed by etching of the conductive layer can be reduced.

The reason why the contact resistance can be reduced is that the electron affinity of titanium, indium, yttrium, an

indium-zinc alloy, an alloy containing gallium (e.g., gallium nitride), or the like is lower than that of the oxide semiconductor layer.

That is, in the case of a single layer, a metal (or an alloy, a compound) having lower electron affinity than the oxide semiconductor layer is preferable.

On the other hand, in the case of a stacked layer, a metal (or an alloy, a compound) having lower electron affinity than the oxide semiconductor layer is preferably disposed to be in contact with the oxide semiconductor layer.

Since titanium (Ti), indium (In), yttrium (Y), an indiumzinc alloy (an In—Zn alloy), an alloy containing gallium (Ga)

(e.g., gallium nitride), or the like has high resistivity, a material having low resistivity such as aluminum (Al), gold (Au),

silver (Ag), copper (Cu), or a variety of alloys containing any

of these metals is preferably stacked over the conductive layer

which is disposed to be in contact with the oxide semiconductor layer.

channel for

Next, an

interlayer:

As the in

property containing any

of these metals is preferably stacked over the conductive layer

which is disposed to be in contact with the oxide semiconductor layer.

Specifically, the following examples can be given, but not limited to, a structure in which Ti and Al are sequentially stacked, a structure in which Ti and an alloy containing Al are sequentially stacked, a structure in which Y and Al are sequentially stacked, a structure in which Y and an alloy containing Al are sequentially stacked, a structure in which Ti, an alloy containing Al, and Ti are sequentially stacked, a structure in which In, Al, and Mo are sequentially stacked, a structure in which Y, Al, and Ti are sequentially stacked, a structure in which Y, Al, and Ti are sequentially stacked, a structure in which Mo, Al, and Ti are sequentially stacked, and a structure in which Ti, an alloy containing Al, Mo, and Ti are sequentially stacked.

Note that the alloy having low resistivity refers to an alloy containing aluminum, gold, silver, copper, or the like and another substance (e.g., Al—Si, Al—Ti, Al—Nd, Cu—Pb—Fe, or Cu—Ni).

Note that the oxide conductive layer can be formed using a material similar to the material of the oxide semiconductor layer.

There is no particular limitation on the oxide conductive layer as long as the resistivity of the oxide conductive layer is lower than that of the oxide semiconductor layer serving as a channel formation region.

Here, the oxide conductive layer is oxide which is intentionally made to contain a large quantity of substances containing a hydrogen element or a large quantity of oxygen deficiency. Substances containing a hydrogen element and oxygen deficiency induce carriers, so that the conductivity of the oxide can be raised.

The oxide semiconductor layer is oxide which is intentionally made not to contain substances containing a hydrogen element or oxygen deficiency.

That is, the quantity of substances containing a hydrogen element or oxygen deficiency in the oxide semiconductor 55 layer is controlled, whereby the resistivity can be controlled.

Note that in the case where the oxide conductive layer and the oxide semiconductor layer serving as a channel formation region are formed using different materials and the oxide conductive layer has lower resistivity than the oxide semiconductor layer serving as a channel formation region, the resistivity does not need to be controlled by control of the quantity of substances containing a hydrogen element or oxygen deficiency in the oxide semiconductor layer.

Next, the conductive layer **500** is etched to form a plurality of electrodes or a plurality of wirings (a source electrode (a contact electrode), a drain electrode (a contact electrode), a

**10**

wiring, and the like) (FIG. 2A). Note that in FIG. 2A, a contact electrode 510, a contact electrode 520, and the like are shown.

By the step of FIG. 2A, a transistor (a channel-etched transistor) is completed.

Note that a portion surrounded by a dashed line 8000 in FIGS. 2A and 2B is slightly etched at the time of etching the conductive layer 500.

The portion surrounded by the dashed line **8000** is called a back channel because it is disposed on the rear side of the channel formation region.

Next, an insulating layer 600 (a protective layer or an interlayer insulating film) is formed to cover the transistor (FIG. 2B).

As the insulating layer, any material having an insulating property can be used. For example, a silicon oxide film, a silicon nitride film, a silicon oxide film containing nitrogen, a silicon nitride film containing oxygen, an aluminum nitride film, an aluminum oxide film, a siloxane film, an acrylic film, a polyimide film, or the like can be used, but the insulating layer is not limited to these examples. The interlayer insulating film may have a single-layer structure or a stacked-layer structure.

Here, the kind of insulating layer is changed to compare electrical characteristics of transistors. It is found that a film which is formed without using a substance containing a hydrogen element as a sputtering gas is preferably used for the insulating layer in a portion in contact with the back channel (the portion surrounded by the dashed line **8000**).

When a substance containing a hydrogen element is contained in the back channel, the threshold voltage (Vth) of the transistor shifts in a negative direction.

Since a deposition gas containing a hydrogen element (typically, SiH<sub>4</sub> or the like) is used in a plasma CVD method, a substance containing a hydrogen element is added to the back channel when the insulating layer is formed by a plasma CVD method.

A siloxane film, an acrylic film, a polyimide film, or the like contains a large amount of moisture; therefore, a substance containing a hydrogen element is constantly supplied to the back channel if any of these films is employed.

That is, a film in which the quantity of substances containing a hydrogen element is small is preferably used for the insulating layer in contact with the back channel.

Note that the step of FIG. 2B corresponds to a step of forming the insulating layer 600 over the contact electrode 510, the contact electrode 520, and the back channel (the portion surrounded by the dashed line 8000).

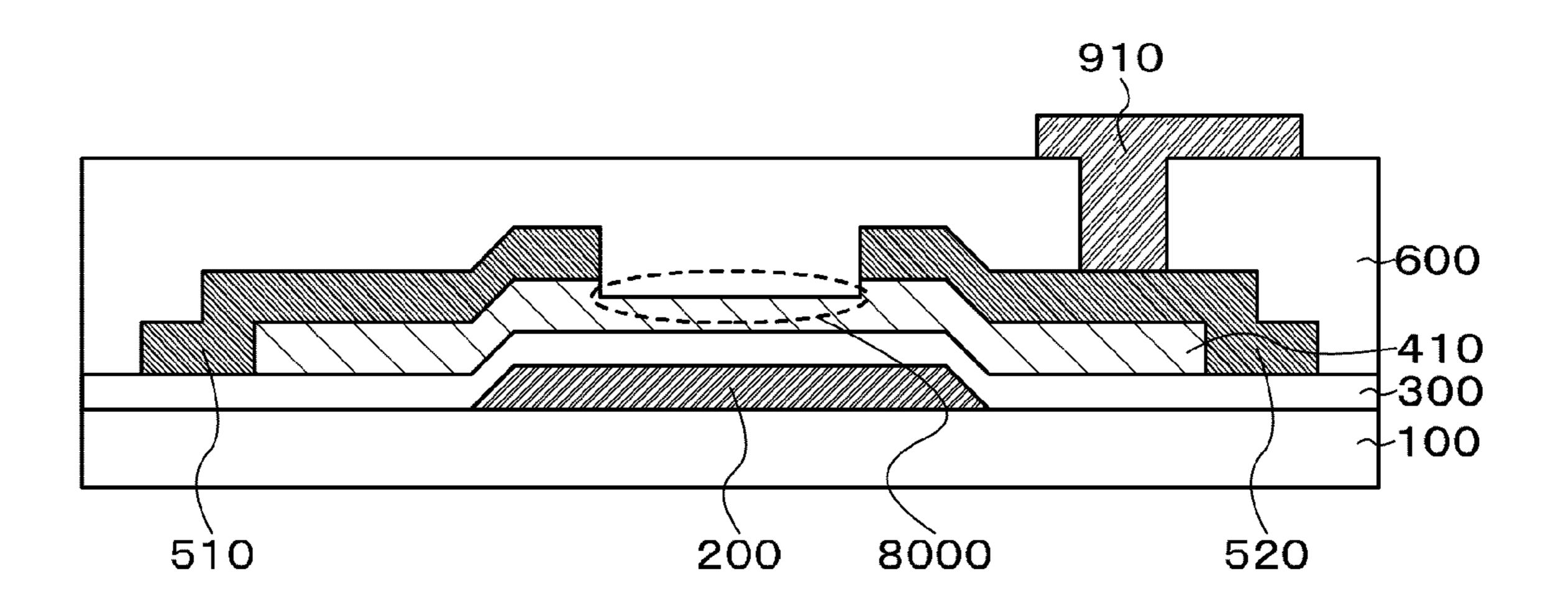

A structure may be employed in which, after the step of FIG. 2B, contact holes are formed in the insulating layer 600 and a wiring 810, a wiring 820, and the like are formed over the insulating layer 600 (FIG. 3A).

Alternatively, a structure may be employed in which, after the step of FIG. 2B, a contact hole is formed in the insulating layer 600 and a pixel electrode 910 is formed over the insulating layer 600 (FIG. 3B).

After the wirings are formed over the insulating layer 600 as illustrated in FIG. 3A, an insulating layer, a wiring, a transistor, a display element, an antenna, or the like may be further formed over the wirings.

After the pixel electrode 910 is formed as illustrated in FIG. 3B, a display element (e.g., an EL element or a liquid crystal element) is formed, whereby a display device can be formed.

After the step of FIG. 3A or FIG. 3B, second heat treatment is preferably performed.

The second heat treatment may be performed between the step of FIG. 2B and the step of FIG. 3A or FIG. 3B.

In other words, the timing of the second heat treatment is not particularly limited as long as it is performed after the insulating layer 600 is formed.

The second heat treatment is preferably performed at higher than or equal to 150° C. and lower than or equal to 500° C. (preferably higher than or equal to 200° C. and lower than or equal to 300° C.).

The heating time of the second heat treatment is preferably longer than or equal to 1 hour and shorter than or equal to 10 hours.

The second heat treatment is preferably performed using a furnace, an oven, gas RTA, or the like.

Note that hydrogen in the oxide semiconductor layer is released and oxygen in the oxide semiconductor layer is also released by the first heat treatment which has been performed previously.

That is, by the first heat treatment, oxygen deficiency is 20 formed in the oxide semiconductor layer.

Thus, when the second heat treatment is performed, the insulating layer is made to be in an oxygen-excess state; therefore, oxygen can be supplied to the oxide semiconductor layer and oxygen deficiency in the oxide semiconductor layer 25 can be reduced.

Examples of the formation method of the insulating layer containing excessive oxygen include, but are not limited to, a method in which, in the case where a non-oxide target (silicon, aluminum, or the like) is used as a sputtering target and oxygen is used as a sputtering gas for reactive sputtering, the flow rate of oxygen is increased; a method in which an oxide target (silicon oxide, aluminum oxide, or the like) is used as a sputtering target and oxygen is used as a sputtering gas (in the case where an oxide target is used, oxygen is not used as a sputtering gas in general); and a method in which an insulating layer is formed and oxygen is introduced into the insulating layer by ion implantation or ion doping (note that in the case where reactive sputtering is performed, a gas such as argon is not preferably used so that a sputtering gas contains oxygen at 100%).

That is, a method in which oxygen is used as a deposition gas for formation of the insulating layer, a method in which oxygen is added to the insulating layer after the insulating 45 layer is formed, or the like may be used. Needless to say, oxygen may be used as a deposition gas for formation of the insulating layer, and in addition, oxygen may be added to the insulating layer after the insulating layer is formed.

Note that in the case where titanium is used for the contact 50 electrode, the second heat treatment is performed after the insulating layer **600** is formed, so that titanium oxide can be formed between the oxide semiconductor layer and titanium.

By formation of titanium oxide, the contact resistance between the oxide semiconductor layer and titanium can be 55 reduced.

Note that when titanium oxide is present between the oxide semiconductor layer and titanium, the contact resistance between the oxide semiconductor layer and titanium can be reduced, so that a structure may be formed in which titanium oxide and titanium are sequentially stacked when the contact electrode is formed.

In this case, titanium oxide can be formed by a sputtering method, an evaporation method, or the like.

The contents of this embodiment or part thereof can be 65 implemented in combination with any of the other embodiments and examples.

12

# Embodiment 2

In this embodiment, a semiconductor device including a transistor which has a structure different from that of the transistor in Embodiment 1 will be described.

Note that materials or the like of the layers are the same as those in Embodiment 1.

A transistor in FIG. 4A is a bottom-gate bottom-contact (BGBC) transistor, and includes the gate electrode 200 provided over the substrate 100 having an insulating surface; the gate insulating layer 300 provided over the gate electrode 200; the contact electrode 510 and the contact electrode 520 provided over the gate insulating layer 300; and the oxide semiconductor layer 410 (island shape) provided over the gate insulating layer 300, the contact electrode 510, and the contact electrode 520.

Note that the insulating layer **600** is provided to cover the transistor.

A portion surrounded by the dashed line **8000** serves as a back channel.

A transistor in FIG. 4B is a top-gate transistor, and includes the oxide semiconductor layer 410 (island shape) provided over the substrate 100 having an insulating surface; the gate insulating layer 300 provided over the oxide semiconductor layer 410; and the gate electrode 200 provided over the gate insulating layer 300.

Note that the insulating layer 600 is provided to cover the transistor, and the wiring 810, the wiring 820, and a wiring 830 are provided through contact holes provided in the insulating layer 600.

A transistor in FIG. 4C is a channel-stop transistor, and includes the gate electrode 200 provided over the substrate 100 having an insulating surface; the gate insulating layer 300 provided over the gate electrode 200; the oxide semiconductor layer 410 (island shape) provided over the gate insulating layer 300; a channel protective layer 700 provided over the oxide semiconductor layer 410; and the contact electrode 510 and the contact electrode 520 provided over the oxide semiconductor layer 410 and the channel protective layer 700.

Note that the insulating layer 600 is provided to cover the transistor.

A portion surrounded by the dashed line **8000** serves as a back channel.

Here, the channel protective layer 700 can be formed using a material similar to the material of the insulating layer 600 described in Embodiment 1. The channel protective layer 700 and the insulating layer 600 may be formed using either the same material or different materials.

In the channel-stop transistor, a portion in contact with the back channel is not the insulating layer 600 but the channel protective layer 700.

That is, a film in which the quantity of substances containing a hydrogen element is small is preferably used for the channel protective layer 700.

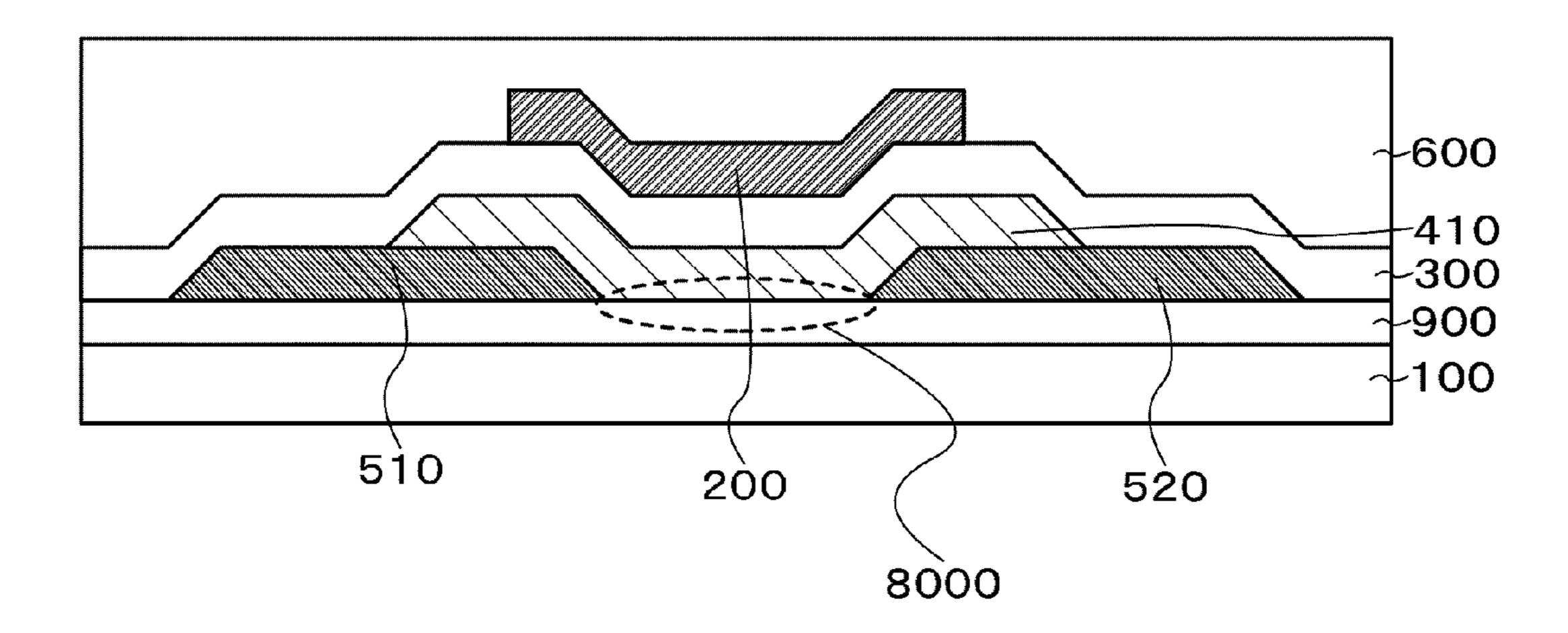

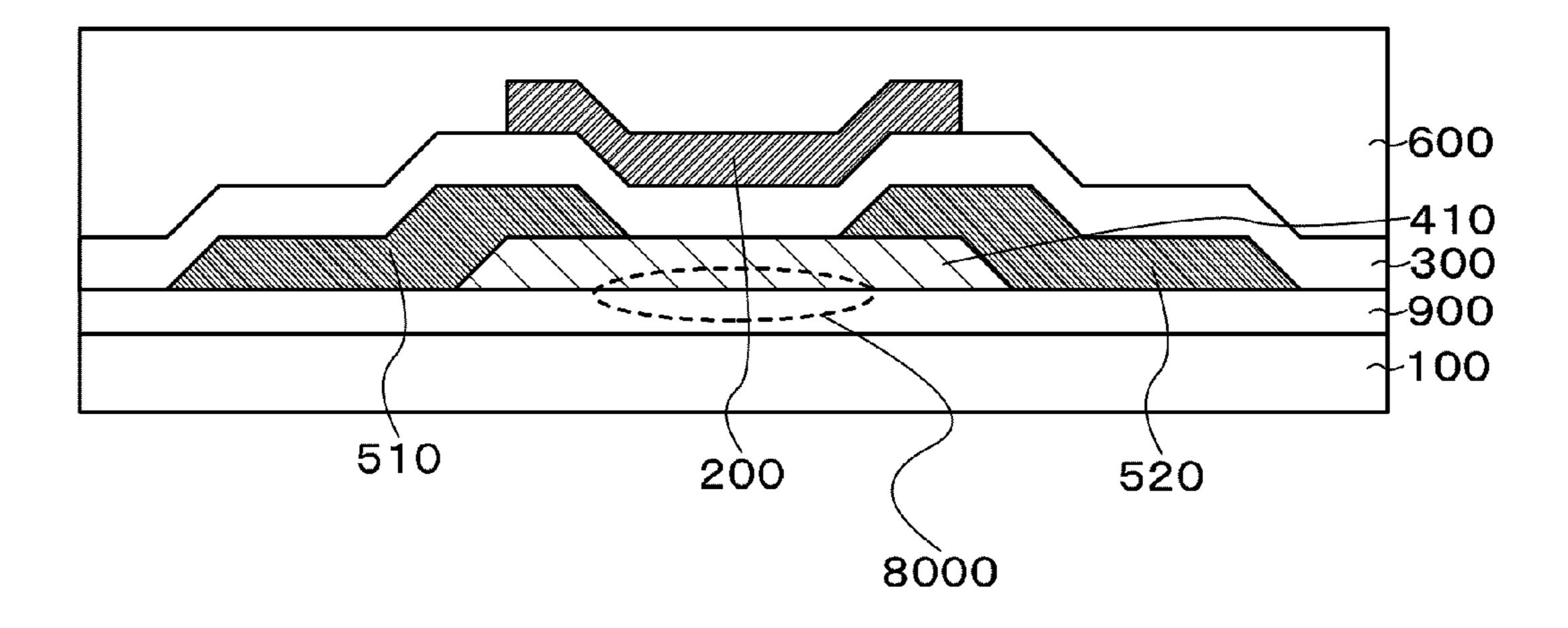

A transistor in FIG. 15A is a top-gate bottom-contact (TGBC) transistor, and includes the contact electrode 510 and the contact electrode 520 provided over a base insulating layer 900; the oxide semiconductor layer 410 (island shape) provided over the base insulating layer 900, the contact electrode 510, and the contact electrode 520; the gate insulating layer 300 provided over the oxide semiconductor layer 410; and the gate electrode 200 provided over the gate insulating layer 300.

Note that the base insulating layer 900 is provided over the substrate 100.

The insulating layer 600 is provided to cover the transistor.

A portion surrounded by the dashed line **8000** serves as a back channel.

Here, the base insulating layer 900 can be formed using a material similar to the material of the insulating layer 600 described in Embodiment 1. The base insulating layer 900 5 and the insulating layer 600 may be formed using either the same material or different materials.

In the top-gate bottom-contact transistor, a portion in contact with the back channel is not the insulating layer 600 but the base insulating layer 900.

That is, a film in which the quantity of substances containing a hydrogen element is small is preferably used for the base insulating layer 900.

The base insulating layer 900 is preferably formed using an insulating layer containing excessive oxygen by a method 15 similar to the method described in Embodiment 1. In this case, when first heat treatment is performed, oxygen is released from the oxide semiconductor layer and oxygen is supplied to the oxide semiconductor layer from the base insulating layer at the same time.

A transistor in FIG. 15B is a top-gate top-contact (TGTC) transistor, and includes the oxide semiconductor layer 410 (island shape) provided over the base insulating layer 900; the contact electrode 510 and the contact electrode 520 provided over the oxide semiconductor layer 410 and the base insulating layer 900; the gate insulating layer 300 provided over the oxide semiconductor layer 410, the contact electrode 510, and the contact electrode 520; and the gate electrode 200 provided over the gate insulating layer 300.

Note that the base insulating layer 900 is provided over the 30 substrate 100.

The insulating layer 600 is provided to cover the transistor. A portion surrounded by the dashed line 8000 serves as a back channel.

Here, the base insulating layer 900 can be formed using a material similar to the material of the insulating layer 600 described in Embodiment 1. The base insulating layer 900 and the insulating layer 600 may be formed using either the same material or different materials.

In the top-gate top-contact transistor, a portion in contact 40 with the back channel is not the insulating layer 600 but the base insulating layer 900.

That is, a film in which the quantity of substances containing a hydrogen element is small is preferably used for the base insulating layer 900.

Note that in the transistor in FIG. 4B, an off-set region having a width of several micrometers is formed between a channel formation region (a region where the gate electrode and the oxide semiconductor layer overlap with each other) and each of contact regions (regions where the wirings and 50 the oxide semiconductor layer are in contact with each other).

The off-set region has an advantage of reducing off current of the transistor, but it has a disadvantage of reducing also on current of the transistor.

On the other hand, unlike in FIG. 4B, an off-set region is 55 lating layer 600 (FIG. 6B). not present in FIGS. 15A and 15B; thus, unlike the transistor in FIG. 4B, the transistors in FIGS. 15A and 15B have an advantage of improving on current.

I ating layer 600 (FIG. 6B). After the wirings are form as illustrated in FIG. 6A, transistor, a display element.

As described above, the transistor may employ any structure.

In other words, the transistor may employ any structure as long as the transistor includes at least the gate electrode, the oxide semiconductor layer, and the gate insulating layer provided between the gate electrode and the oxide semiconductor layer.

A dual-gate transistor may be employed in which a first gate electrode, a first gate insulating layer over the first gate

14

electrode, an oxide semiconductor layer over the first gate insulating layer, a second gate insulating layer over the oxide semiconductor layer, and a second gate electrode over the second gate insulating layer are provided.

Therefore, the structure of the transistor is not limited to any of the structures described in Embodiment 1 and 2.

The contents of this embodiment or part thereof can be implemented in combination with any of the other embodiments and examples.

#### Embodiment 3

An example of a method for manufacturing the semiconductor device in FIG. 4A will be described.

Note that materials, conditions of heat treatment, and the like are the same as those in another embodiment.

The gate electrode 200 is formed over the substrate 100 having an insulating surface. Then, the gate insulating layer 300 is formed over the gate electrode 200, and the contact electrode 510 and the contact electrode 520 are formed over the gate insulating layer 300 (FIG. 5A).

Next, the oxide semiconductor layer 400 is formed over the gate insulating layer 300, the contact electrode 510, and the contact electrode 520 (FIG. 5B).

Next, the oxide semiconductor layer is subjected to first heat treatment.

The conditions of the first heat treatment are the same as those in Embodiment 1.

The first heat treatment may be performed after the oxide semiconductor layer 400 is etched into an island shape to form the oxide semiconductor layer 410.

However, after the oxide semiconductor layer 400 is etched into an island shape to form the oxide semiconductor layer 410, the contact electrodes are exposed.

When the first heat treatment is performed in the state where the contact electrodes are exposed, surfaces of the contact electrodes are oxidized and the conductivity of the surfaces are reduced.

Therefore, the first heat treatment is preferably performed in the state where the contact electrodes are covered with the oxide semiconductor layer 400.

Next, the oxide semiconductor layer 400 is etched into an island shape to form the oxide semiconductor layer 410, and the insulating layer 600 is formed to cover a transistor (FIG. 5C).

Note that a portion surrounded by the dashed line **8000** serves as a back channel.

A structure may be employed in which, after the step of FIG. 5C, contact holes are formed in the insulating layer 600 and the wiring 810, the wiring 820, and the like are formed over the insulating layer 600 (FIG. 6A).

Alternatively, a structure may be employed in which, after the step of FIG. 5C, a contact hole is formed in the insulating layer 600 and a pixel electrode 910 is formed over the insulating layer 600 (FIG. 6B).

After the wirings are formed over the insulating layer 600 as illustrated in FIG. 6A, an insulating layer, a wiring, a transistor, a display element, an antenna, or the like may be further formed over the wirings.

After the pixel electrode **910** is formed as illustrated in FIG. **6**B, a display element (e.g., an EL element or a liquid crystal element) is formed, whereby a display device can be formed.

After the step of FIG. **6**A or FIG. **6**B, second heat treatment is preferably performed.