#### US009099334B2

# (12) United States Patent Ishii et al.

## (10) Patent No.: US 9,099,334 B2 (45) Date of Patent: \*Aug. 4, 2015

## (54) METHOD OF MANUFACTURING SEMICONDUCTOR DEVICE AND SEMICONDUCTOR DEVICE

#### (71) Applicant: Renesas Electronics Corporation, Kawasaki-shi, Kanagawa (JP)

## (72) Inventors: **Yasushi Ishii**, Kanagawa (JP); **Hiraku Chakihara**, Kanagawa (JP); **Kentaro**

Saito, Kanagawa (JP)

## (73) Assignee: RENESAS ELECTRONICS CORPORATION, Kawasaki-shi (JP)

### (\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal disclaimer.

(21) Appl. No.: 14/089,959

(22) Filed: Nov. 26, 2013

#### (65) Prior Publication Data

US 2014/0077310 A1 Mar. 20, 2014

#### Related U.S. Application Data

(63) Continuation of application No. 13/662,509, filed on Oct. 28, 2012, now Pat. No. 8,617,974.

#### (30) Foreign Application Priority Data

(51) Int. Cl.

H01L 21/3205

H01L 27/088

(2006.01) (2006.01)

(Continued)

(52) **U.S. Cl.**

...... H01L 27/088 (2013.01); H01L 21/28008 (2013.01); H01L 21/82 (2013.01); H01L

21/82385 (2013.01); H01L 21/823425 (2013.01); H01L 21/823814 (2013.01); (Continued)

#### (58) Field of Classification Search

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| / /         |  | Sakai et al<br>Ema et al |  |  |  |

|-------------|--|--------------------------|--|--|--|

| (Continued) |  |                          |  |  |  |

#### FOREIGN PATENT DOCUMENTS

JP 05-326513 A 12/1993 JP 2005-005508 A 1/2005

Primary Examiner — Brook Kebede

(74) Attorney, Agent, or Firm — Miles & Stockbridge P.C.

#### (57) ABSTRACT

An improvement is achieved in the manufacturing yield of a semiconductor device including a plurality of field effect transistors having different characteristics over the same substrate. By combining anisotropic dry etching with isotropic wet etching or isotropic dry etching, three types of sidewalls having different sidewall lengths are formed. By reducing the number of anisotropic dry etching steps, in a third n-type MISFET region and a third p-type MISFET region where layout densities are high, it is possible to prevent a semiconductor substrate from being partially cut between n-type gate electrodes adjacent to each other, between the n-type gate electrode and a p-type gate electrode adjacent to each other, and the p-type gate electrodes adjacent to each other.

#### 6 Claims, 49 Drawing Sheets

# US 9,099,334 B2 Page 2

| (51) | Int. Cl.                                                            |                        | (56)                | References Cited       |

|------|---------------------------------------------------------------------|------------------------|---------------------|------------------------|

|      | H01L 21/82<br>H01L 21/8234                                          | (2006.01)<br>(2006.01) | U.S. I              | PATENT DOCUMENTS       |

| (52) | H01L 21/8238<br>H01L 21/28<br>U.S. Cl.                              | (2006.01)<br>(2006.01) | 2005/0101076 A1*    | 8/2003 Taniguchi et al |

|      | CPC <i>H01L21/823857</i> (2013.01); <i>H01L 21/823864</i> (2013.01) |                        | * cited by examiner |                        |

Aug. 4, 2015

Aug. 4, 2015

Aug. 4, 2015

Aug. 4, 2015

Aug. 4, 2015

F/G. 48

F/G. 49

F/G. 50

F/G. 51

# METHOD OF MANUFACTURING SEMICONDUCTOR DEVICE AND SEMICONDUCTOR DEVICE

# CROSS-REFERENCE TO RELATED APPLICATIONS

The disclosure of Japanese Patent Application No. 2011-236675 filed on Oct. 28, 2011 including the specification, drawings and abstract is incorporated herein by reference in its entirety.

#### **BACKGROUND**

The present invention relates to a method of manufacturing a semiconductor device and the semiconductor device, and particularly to a technology which is effective when applied to a semiconductor device in which a plurality of field effect transistors different in gate length and layout density are produced in the same substrate.

For example, Japanese Unexamined Patent Publication No. Hei 5 (1993)-326513 (Patent Document 1) discloses a technique which forms a SiO<sub>2</sub> spacer layer by dry etching and then removes a thermal oxidation SiO<sub>2</sub> film remaining over a 25 substrate surface by wet etching to thereby inhibit damage to the substrate surface.

Also, Japanese Unexamined Patent Publication No. 2005-5508 (Patent Document 2) discloses a technique which dryetches a sidewall spacer formation layer to form sidewall spacers and then removes the sidewall spacers in a low-voltage-transistor formation region by wet etching.

### RELATED ART DOCUMENTS

## Patent Documents

[Patent Document 1]

Japanese Unexamined Patent Publication No. Hei 5 (1993)326513

[Patent Document 2]

Japanese Unexamined Patent Publication No. 2005-5508

#### **SUMMARY**

recent years, to meet finely differentiated use applications, a plurality of MISFETs (Metal Insulator Semiconductor Field Effect Transistors) designed for individual required characteristics (such as breakdown voltage, leakage current, and 50 operating speed) are formed over the same substrate. Accordingly, if the individual required characteristics are to be obtained, a plurality of MISFETS which are different in, e.g., the thickness of a gate insulating film, gate length, the thicknesses of sidewalls, layout density, or the like may be formed 55 over the same substrate. However, when the plurality of MIS-FETs designed for the individual required characteristics are to be formed over the same substrate, it is difficult to control processing conditions in each of manufacturing steps, or a manufacturing process may be complicated. Therefore, a 60 technique for manufacturing the plurality of MISFETs which satisfy the individual required characteristics with an improved yield or a technique for manufacturing the plurality of MISFETs in a simpler and easier manufacturing process is in demand.

An object of the present invention is to provide a technique which allows an improvement in the manufacturing yield of a

2

semiconductor device having a plurality of field effect transistors having different characteristics over the same substrate.

The above and other objects and novel features of the present invention will become apparent from a statement in the present specification and the accompanying drawings.

The following is a brief description of an embodiment of a representative aspect of the invention disclosed in the present application.

The embodiment provides a method of manufacturing a semiconductor device including high-voltage MISFETs in a first region, low-leakage low-voltage MISFETs in a second region, and high-speed-operation low-voltage MISFETs in a third region. The method of manufacturing the semiconduc-15 tor device includes the step of forming first gate electrodes in the first region each via a first gate insulating film, forming second gate electrodes in the second region each via a second gate insulating film, and forming third gate electrodes in the third region each via a third gate insulating film, the step of forming a first insulating film over a main surface of a semiconductor substrate so as to cover the first gate electrodes, the second gate electrodes, and the third gate electrodes therewith, the step of forming a second insulating film over the first insulating film, the step of processing the second insulating film by anisotropic dry etching to leave the second insulating film over each of the side surfaces of the first gate electrodes, the second gate electrodes, and the third gate electrodes, the step of processing the second insulating film left over each of the side surfaces of the second gate electrodes and the third gate electrodes by isotropic dry etching or isotropic wet etching, the step of removing the second insulating film left over each of the side surfaces of the third gate electrodes by isotropic dry etching or isotropic wet etching, the step of forming a third insulating film over the main surface of the semicon-35 ductor substrate so as to cover the first gate electrodes, the second insulating film left over each of the side surfaces of the first gate electrodes, the second gate electrodes, the second insulating film left over each of the side surfaces of the second gate electrodes, and the third gate electrodes, the step of 40 processing the third insulating film by anisotropic dry etching to leave the third insulating film over each of the side surfaces of the first gate electrodes via the first insulating film and the second insulating film, each of the side surfaces of the second gate electrodes via the first insulating film and the second 45 insulating film, and each of the side surfaces of the third gate electrodes via the first insulating film, and the step of removing the exposed first insulating film. First sidewalls are each formed of the first insulating film, the second insulating film, and the third insulating film which are formed over each of the side surfaces of the first gate electrodes. Second sidewalls are each formed of the first insulating film, the second insulating film, and the third insulating film which are formed over each of the side surfaces of the second gate electrodes. Third sidewalls are each formed of the first insulating film and the third insulating film which are formed over each of the side surfaces of the third gate electrodes.

Alternatively, the embodiment provides a method of manufacturing a semiconductor device including high-voltage MISFETs in a first region, low-leakage low-voltage MIS-60 FETs in a second region, and high-speed-operation low-voltage MISFETs in a third region. The method of manufacturing the semiconductor device includes the step of forming first gate electrodes in the first region each via a first gate insulating film, forming second gate electrodes in the second region each via a second gate insulating film, and forming third gate electrodes in the third region each via a third gate insulating film, the step of forming a first insulating film over a main

surface of a semiconductor substrate so as to cover the first gate electrodes, the second gate electrodes, and the third gate electrodes therewith, the step of forming a second insulating film over the first insulating film, the step of processing the second insulating film by anisotropic dry etching to leave the 5 second insulating film over each of the side surfaces of the first gate electrodes, the second gate electrodes, and the third gate electrodes, the step of processing the second insulating film left over each of the side surfaces of the second gate electrodes and the third gate electrodes by isotropic dry etching or isotropic wet etching, the step of processing the second insulating film left over each of the side surfaces of the third gate electrodes by isotropic dry etching or isotropic wet etching, and the step removing the exposed first insulating film. 15 First sidewalls are each formed of the first insulating film and the second insulating film which are formed over each of the side surfaces of the first gate electrodes. Second sidewalls are each formed of the first insulating film and the second insulating film which are formed over each of the side surfaces of 20 the second gate electrodes. Third sidewalls are each formed of the first insulating film and the second insulating film which are formed over each of the side surfaces of the third gate electrodes.

The embodiment also provides a semiconductor device <sup>25</sup> including high-voltage MISFETs in a first region, low-leakage low-voltage MISFETs in a second region, high-speedoperation low-voltage MISFETs in a third region, first sidewalls each having a first sidewall length and provided over side surfaces of first gate electrodes each having a first gate 30 length in the high-voltage MISFETs, second sidewalls each having a second sidewall length and provided over side surfaces of second gate electrodes each having a second gate length in the low-leakage low-voltage MISFETs, and third 35 sidewalls each having a third sidewall length and provided over side surfaces of third gate electrodes each having a third gate length in the high-speed-operation low-voltage MIS-FETs. The second sidewall length is shorter than the first the second sidewall length. The height of each of the second sidewalls from a main surface of a semiconductor substrate is shorter than a height of each of the first sidewalls from the main surface of the semiconductor substrate, and the height of each of the third sidewalls from the main surface of the 45 semiconductor substrate is shorter than the height of each of the second sidewalls from the main surface of the semiconductor substrate.

The following is a brief description of effects achievable by the embodiment of the representative aspect of the invention 50 disclosed in the present application.

An improvement can be achieved in the manufacturing yield of a semiconductor device including a plurality of field effect transistors having mutually different characteristics 55 over the same substrate.

# BRIEF DESCRIPTION OF THE DRAWINGS

- FIG. 1 is a main-portion cross-sectional view of a semiconductor device according to Embodiment 1 of the present invention, which illustrates a manufacturing step of the semiconductor device;

- FIG. 2 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a 65 manufacturing step of the semiconductor device, which is subsequent to FIG. 1;

- FIG. 3 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 2;

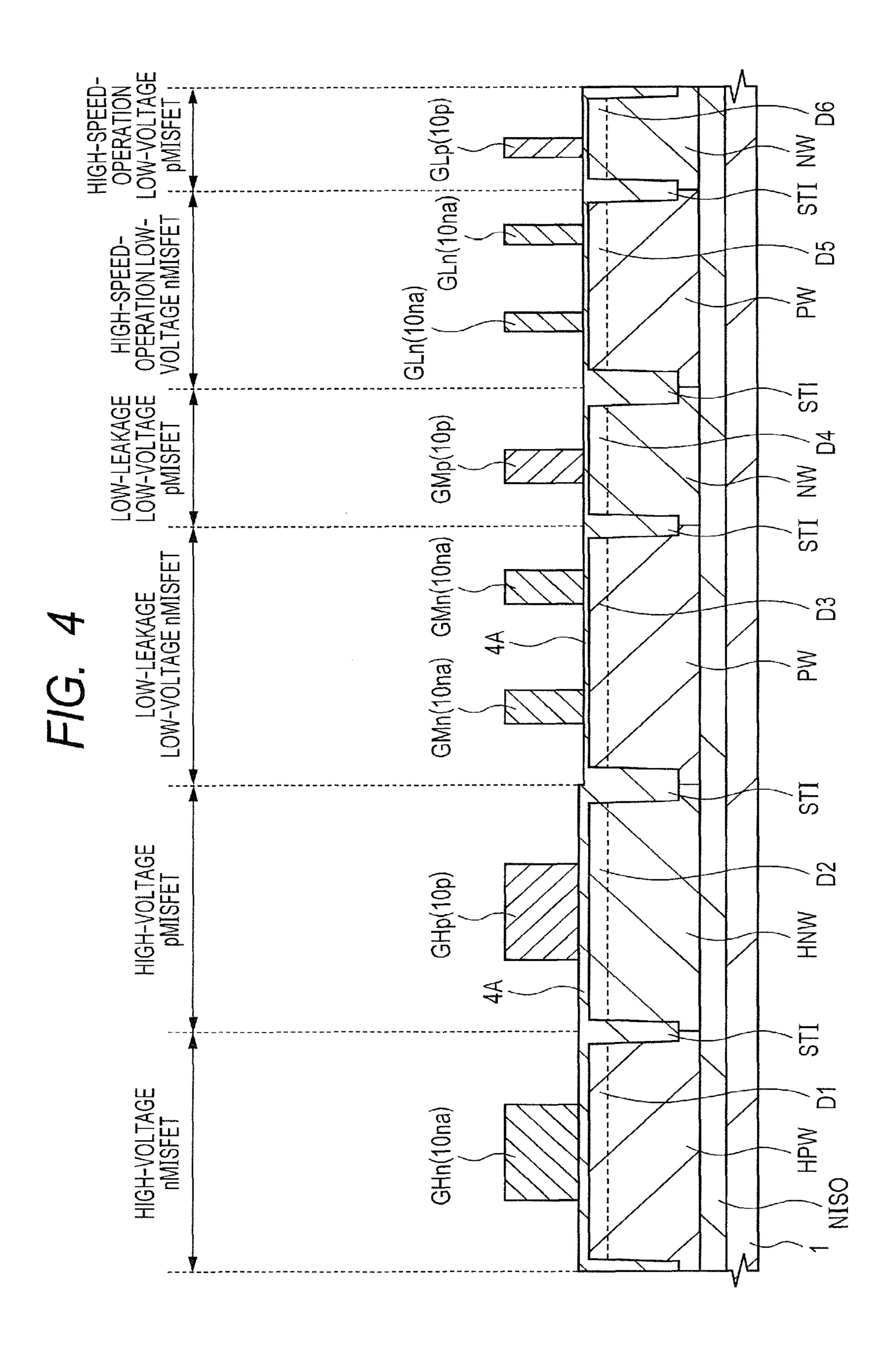

- FIG. 4 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 3;

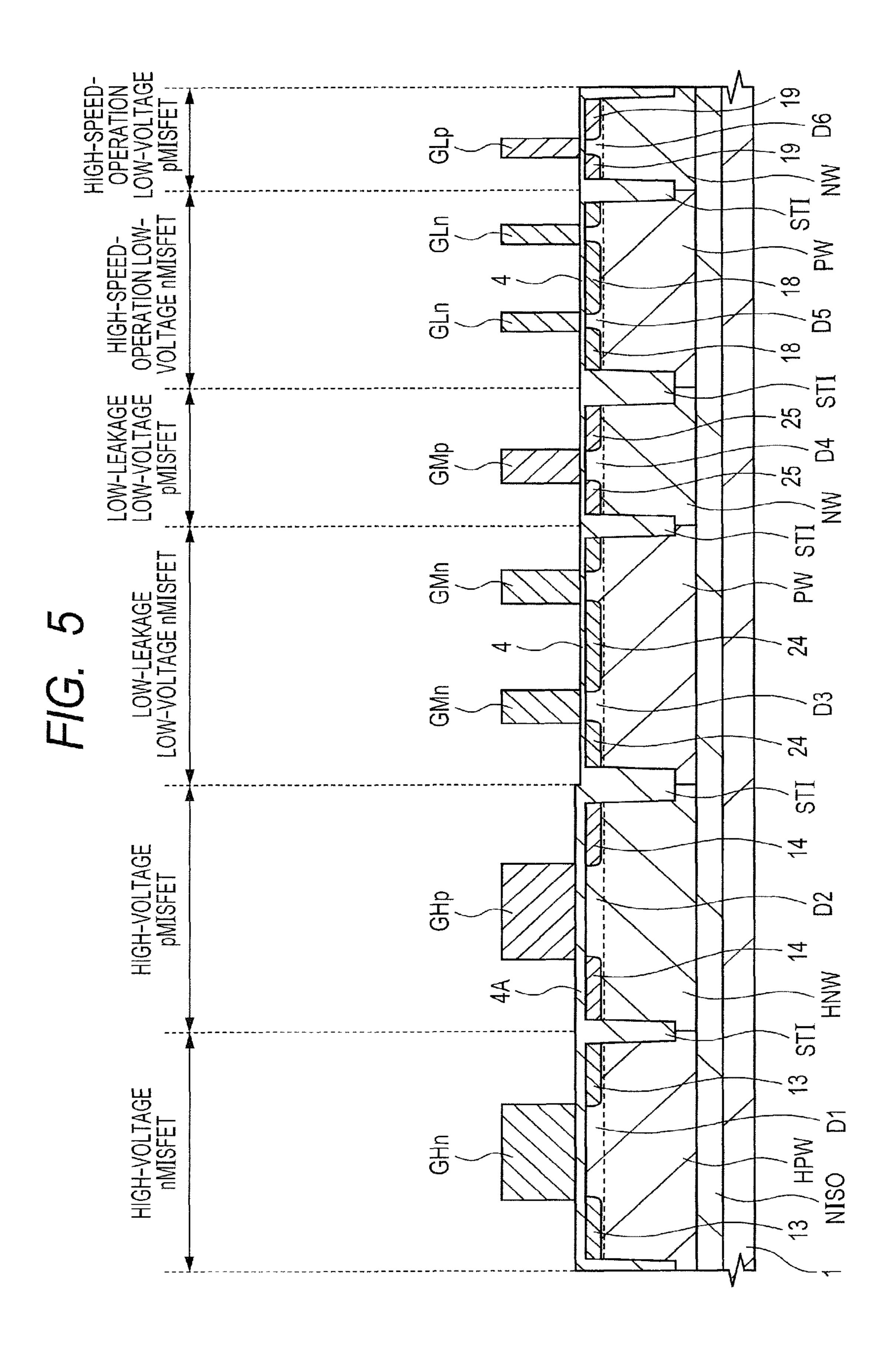

- FIG. 5 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 4;

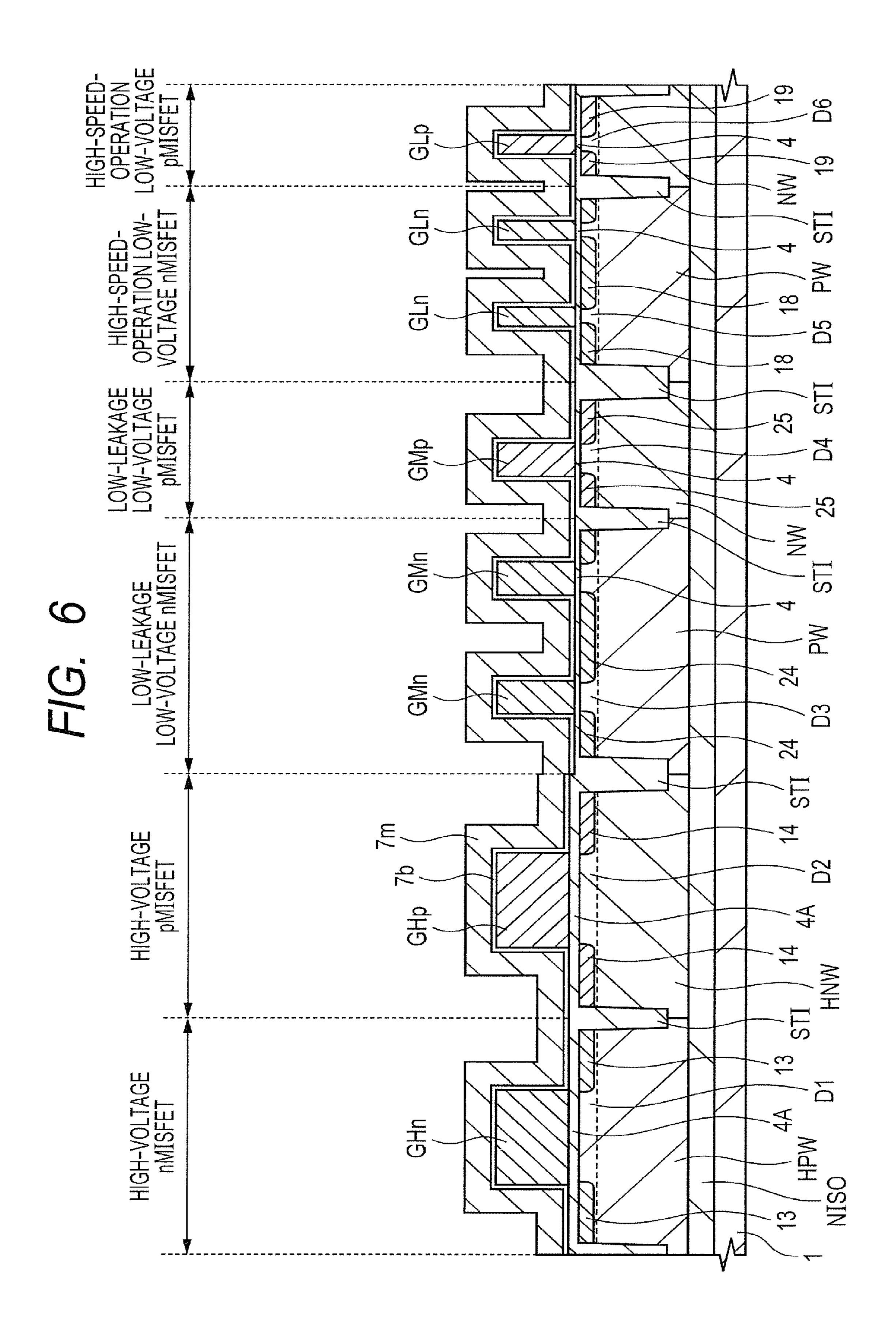

- FIG. 6 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 5;

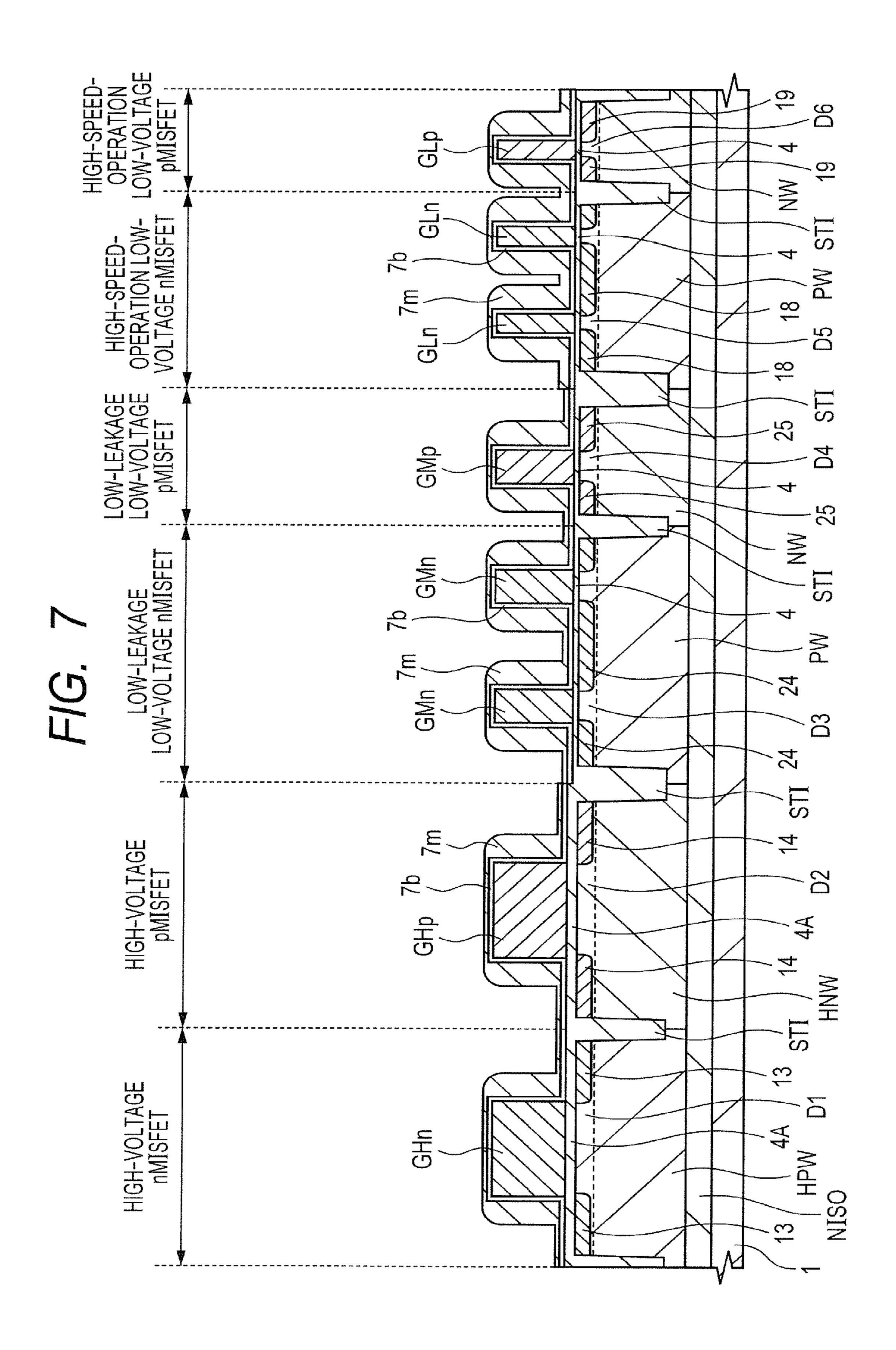

- FIG. 7 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 6;

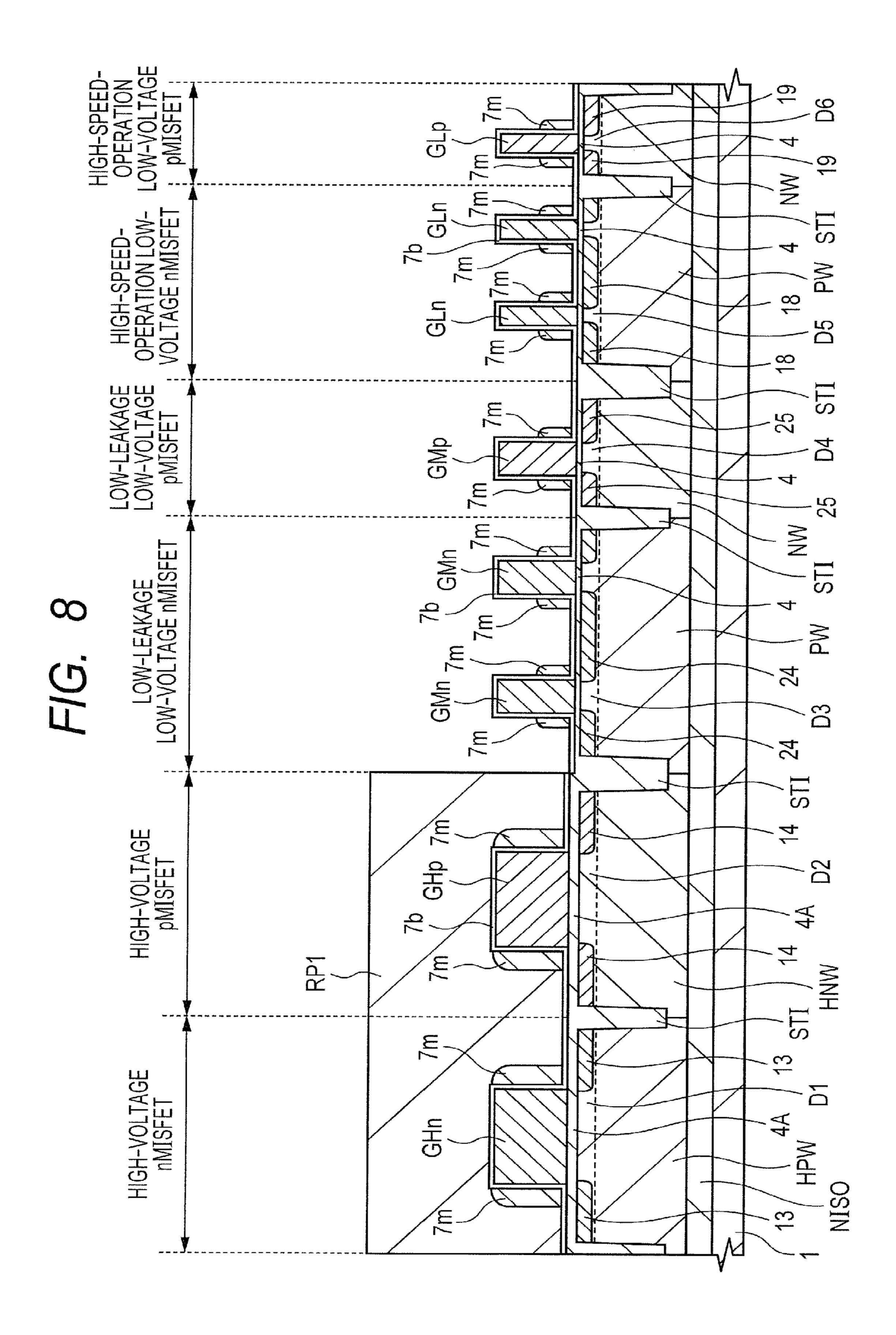

- FIG. 8 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 7;

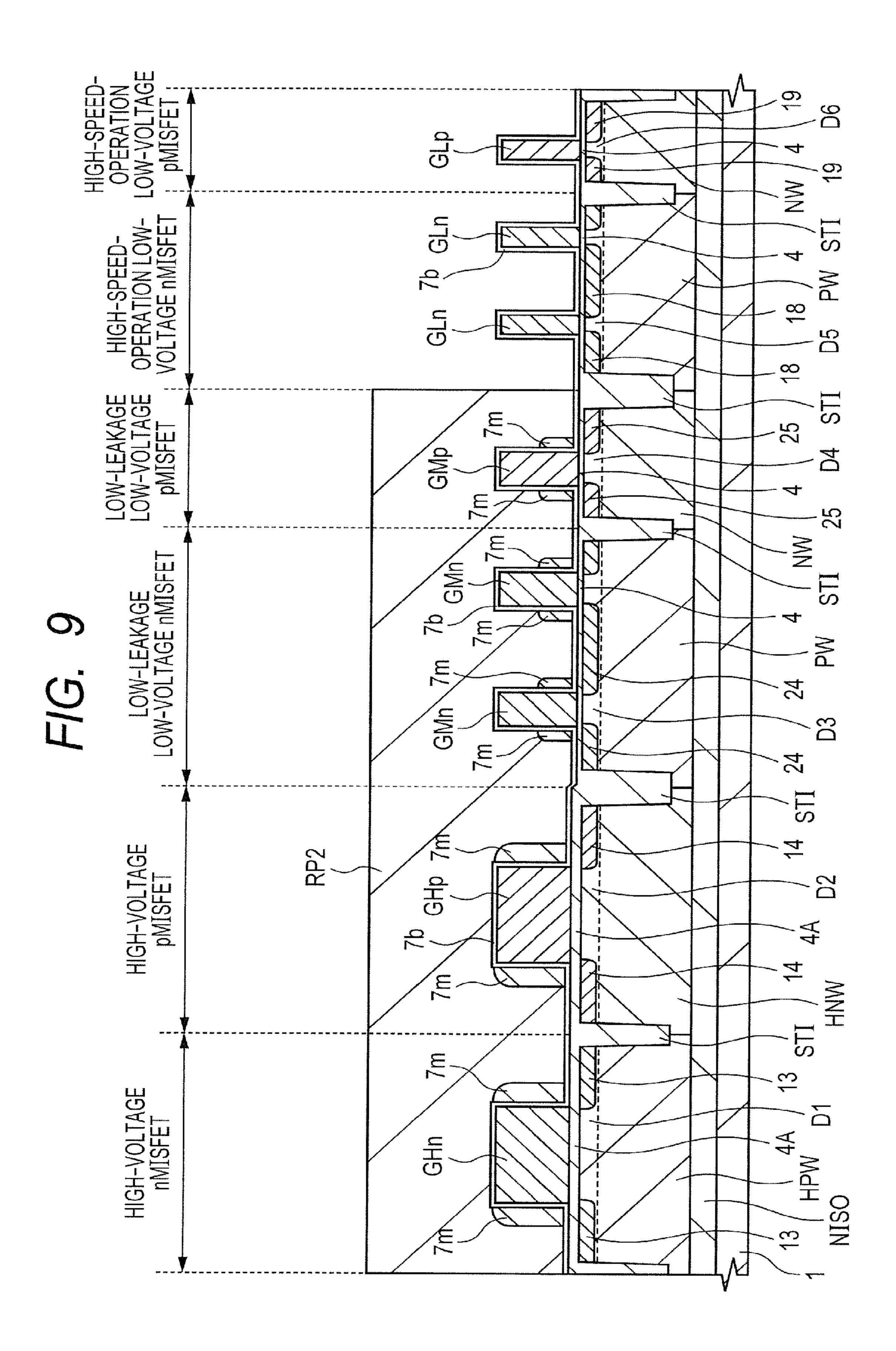

- FIG. 9 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 8;

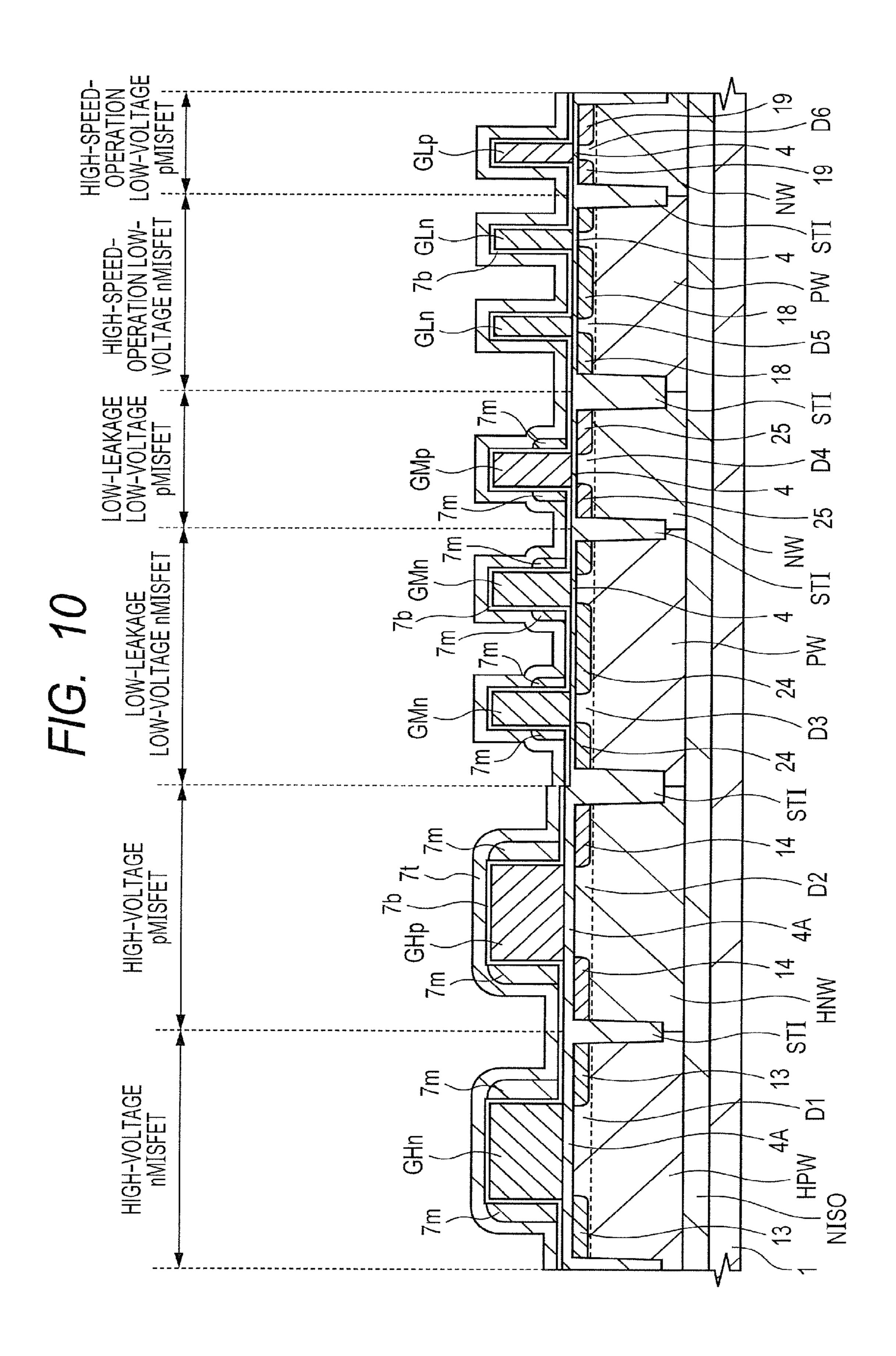

- FIG. 10 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 9;

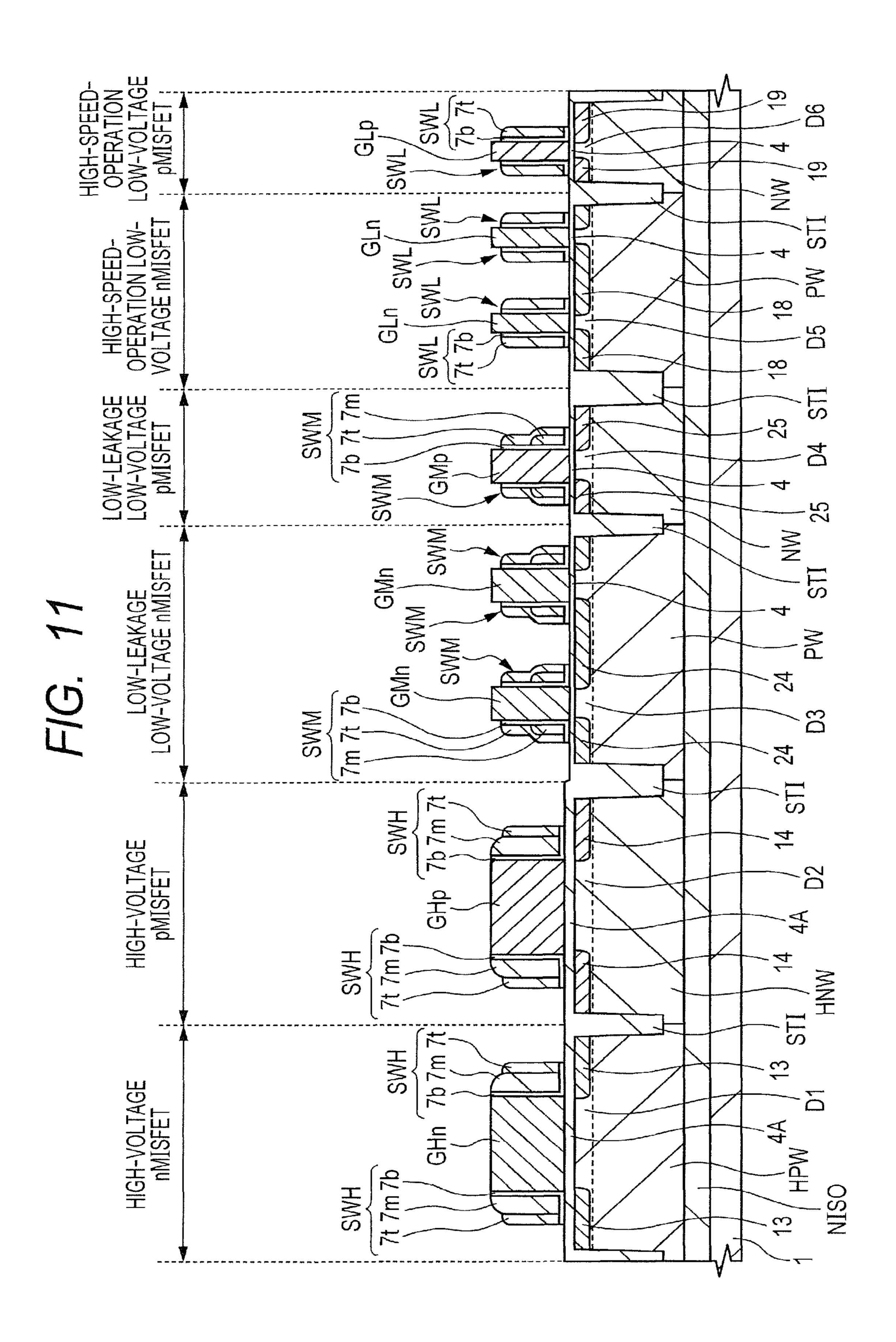

- FIG. 11 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 10;

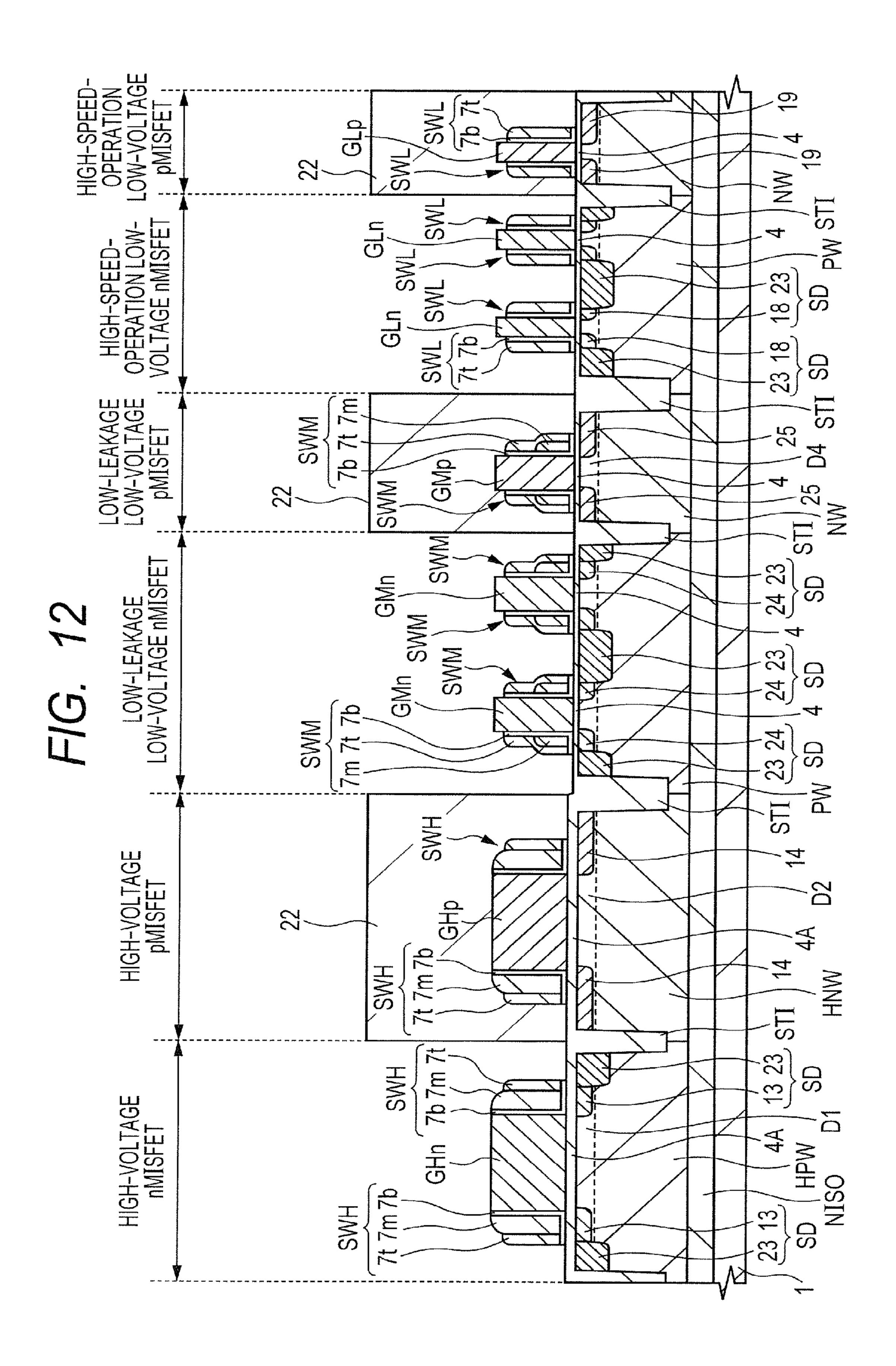

- FIG. 12 is a main-portion cross-sectional view of the same sidewall length, and the third sidewall length is shorter than 40 portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 11;

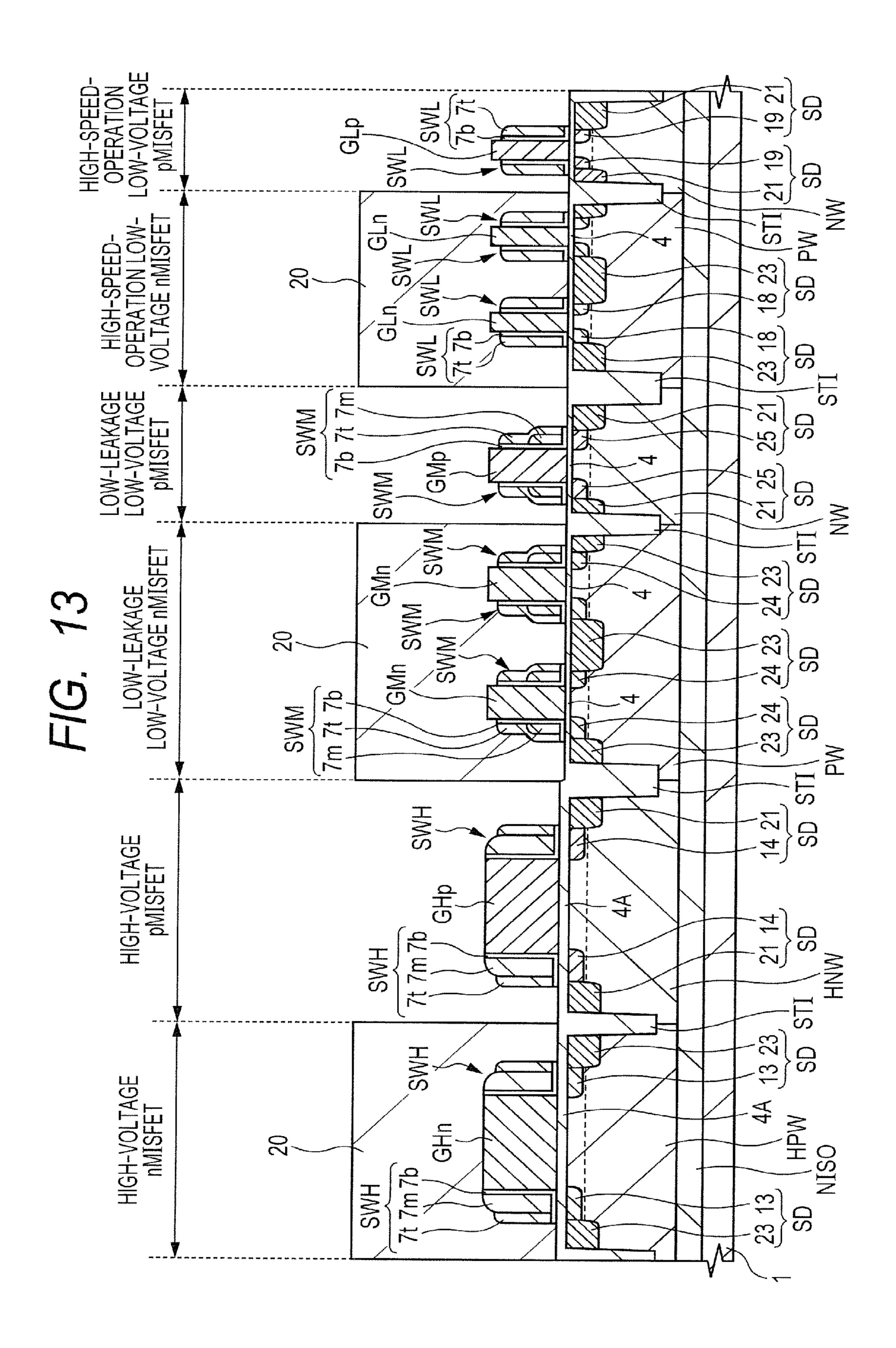

- FIG. 13 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 12;

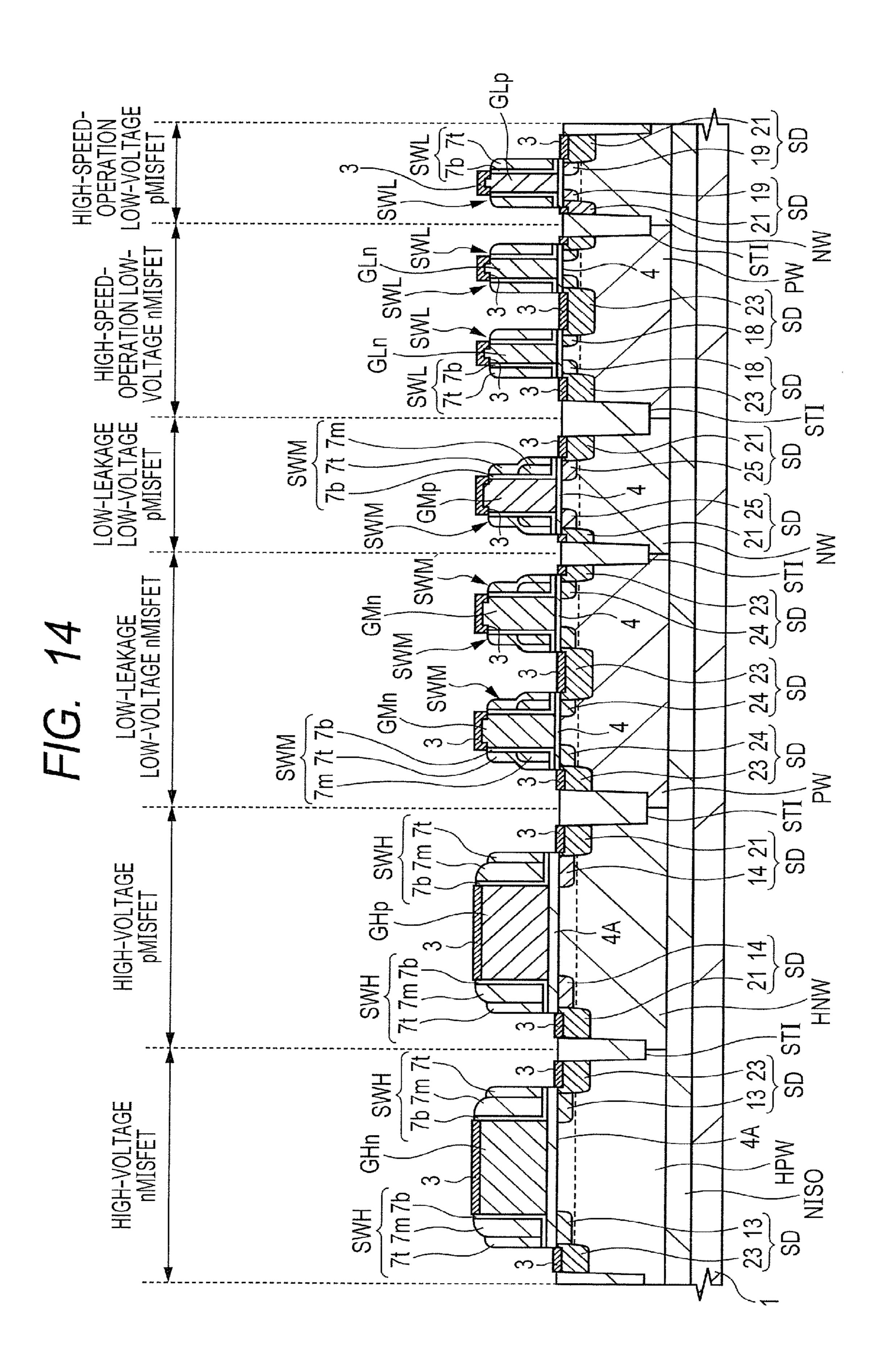

- FIG. 14 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 13;

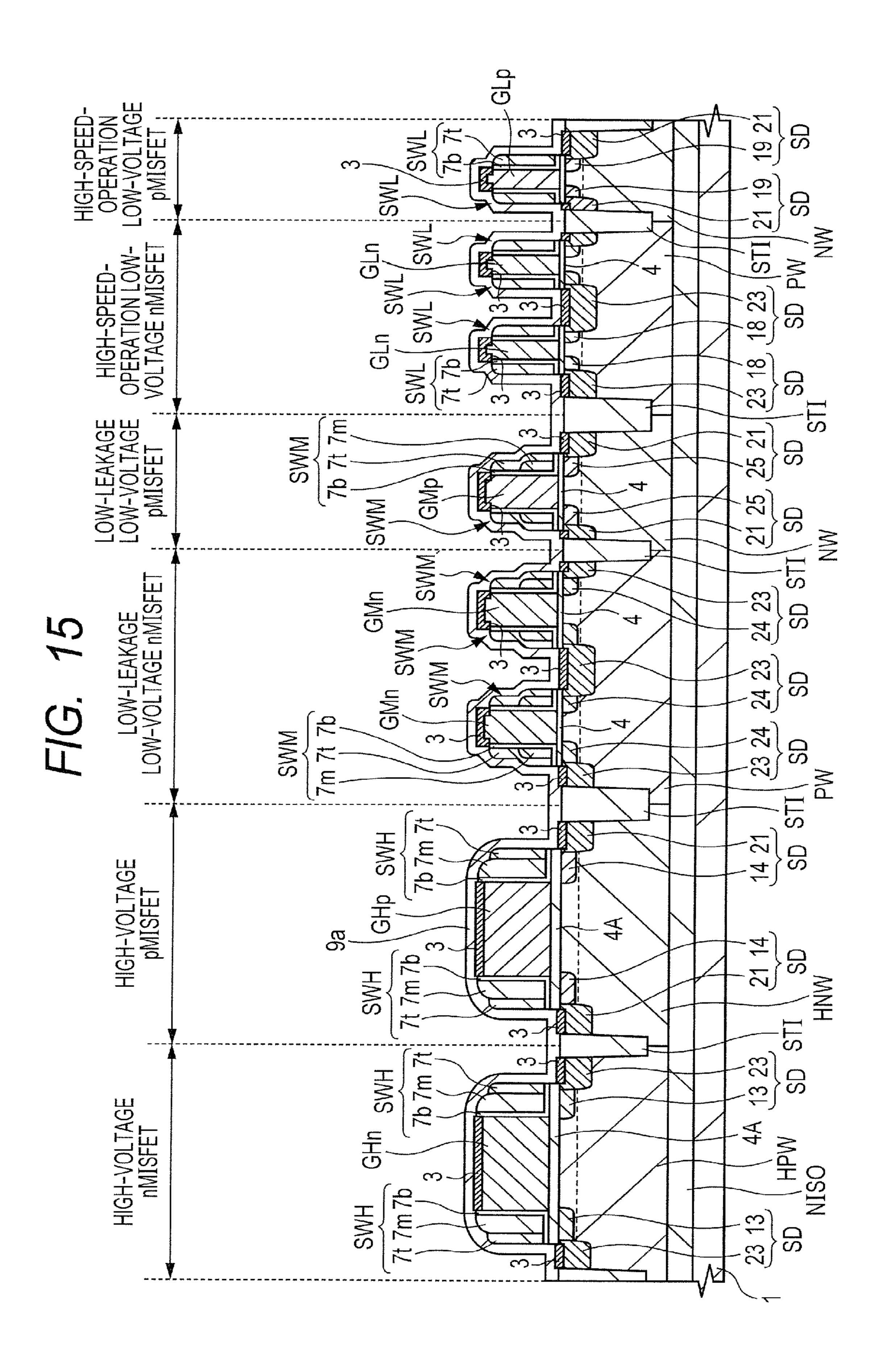

- FIG. 15 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 14;

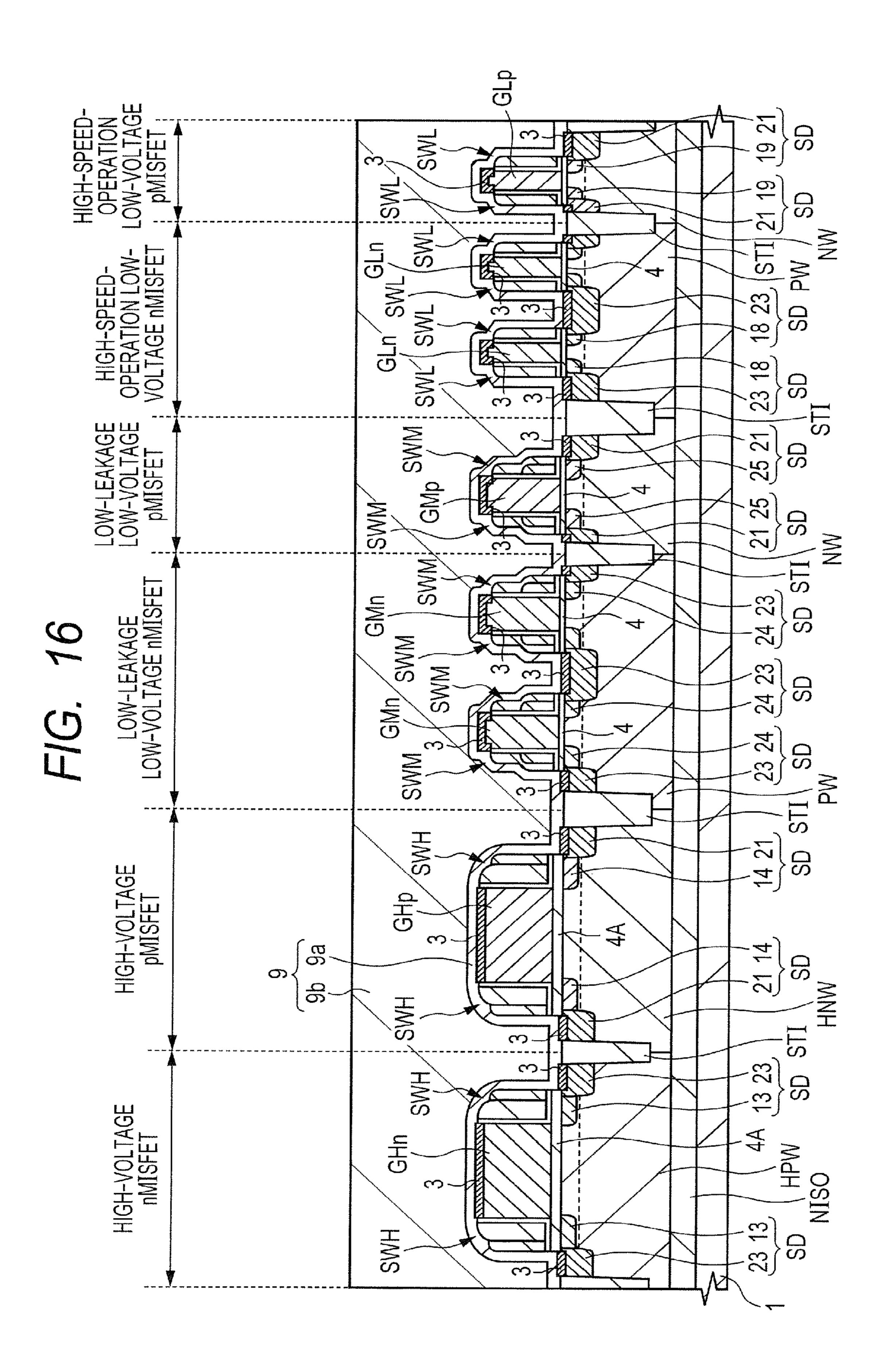

- FIG. 16 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 15;

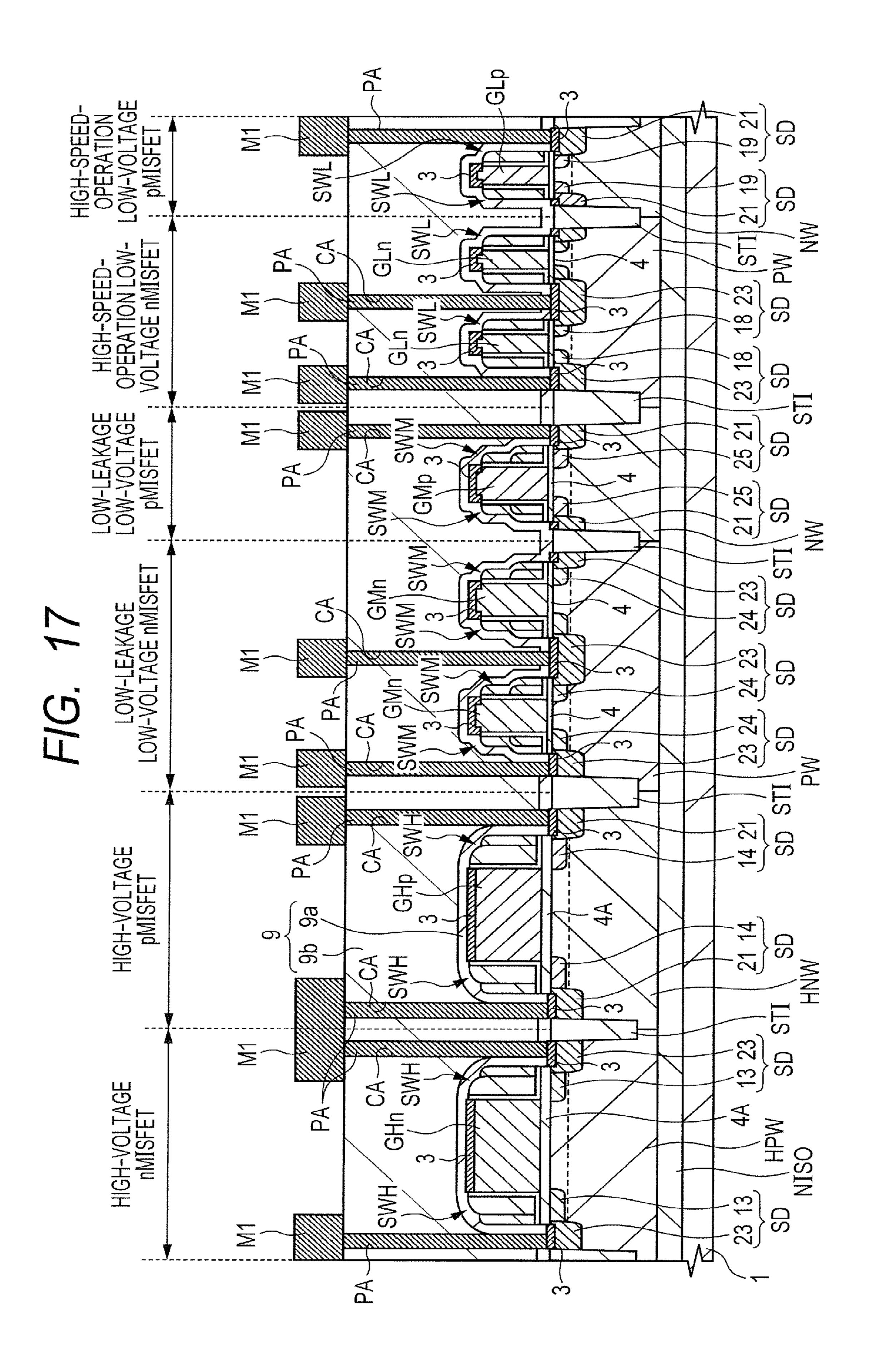

- FIG. 17 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 1 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 16;

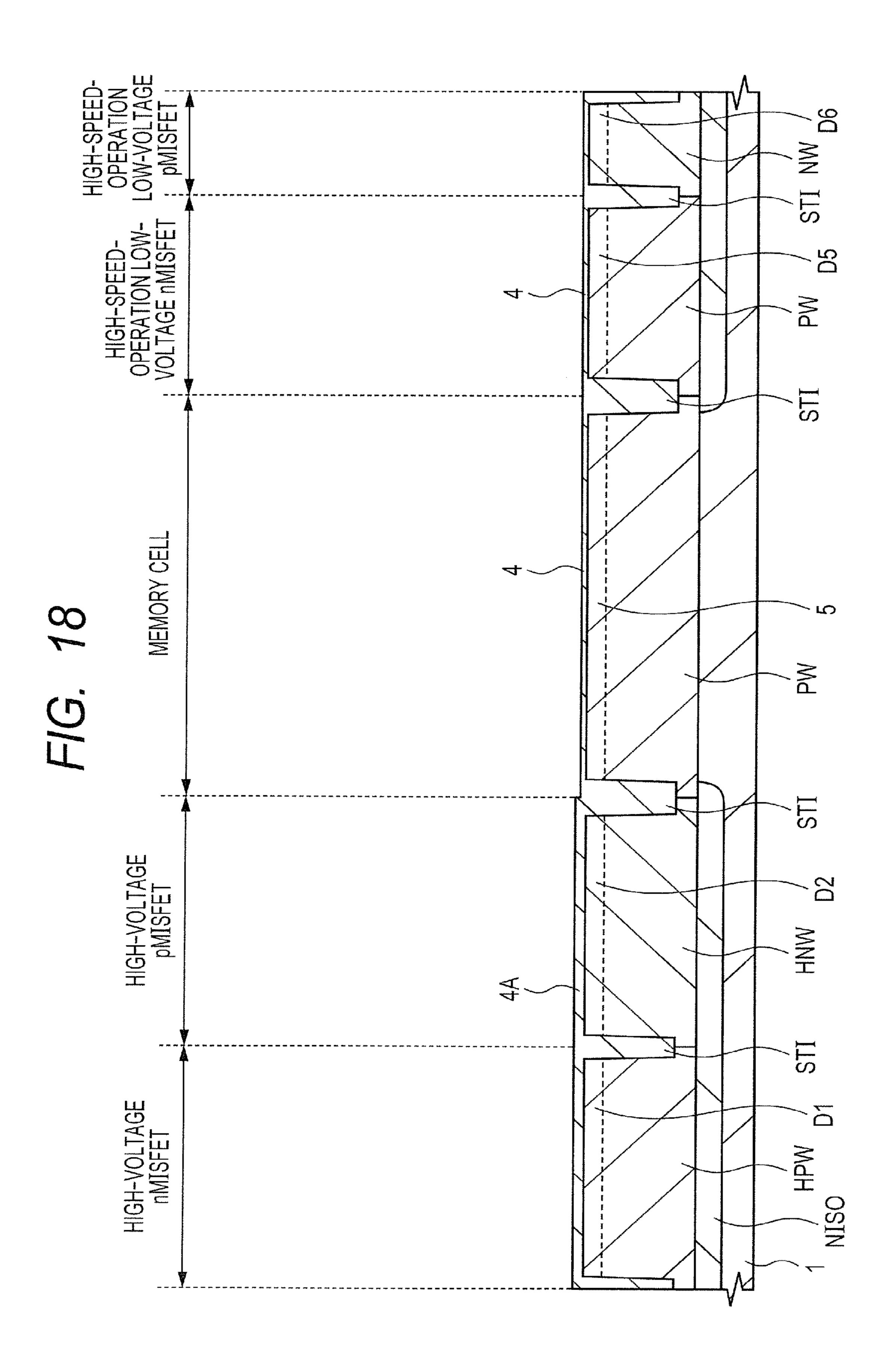

- FIG. 18 is a main-portion cross-sectional view of the semiconductor device according to Embodiment 1 of the present invention, which illustrates another example of a manufacturing step of the semiconductor device;

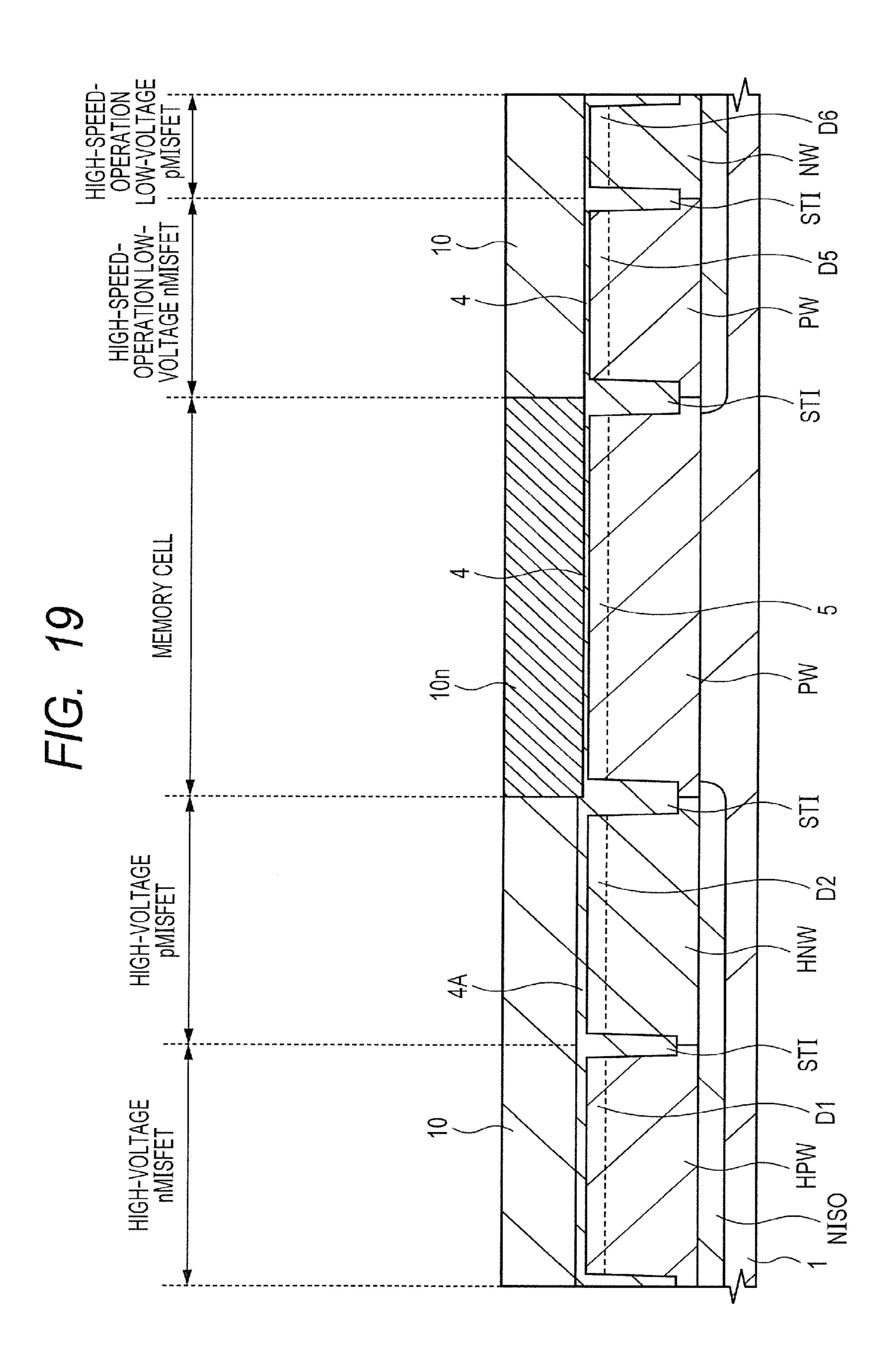

- FIG. 19 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 18;

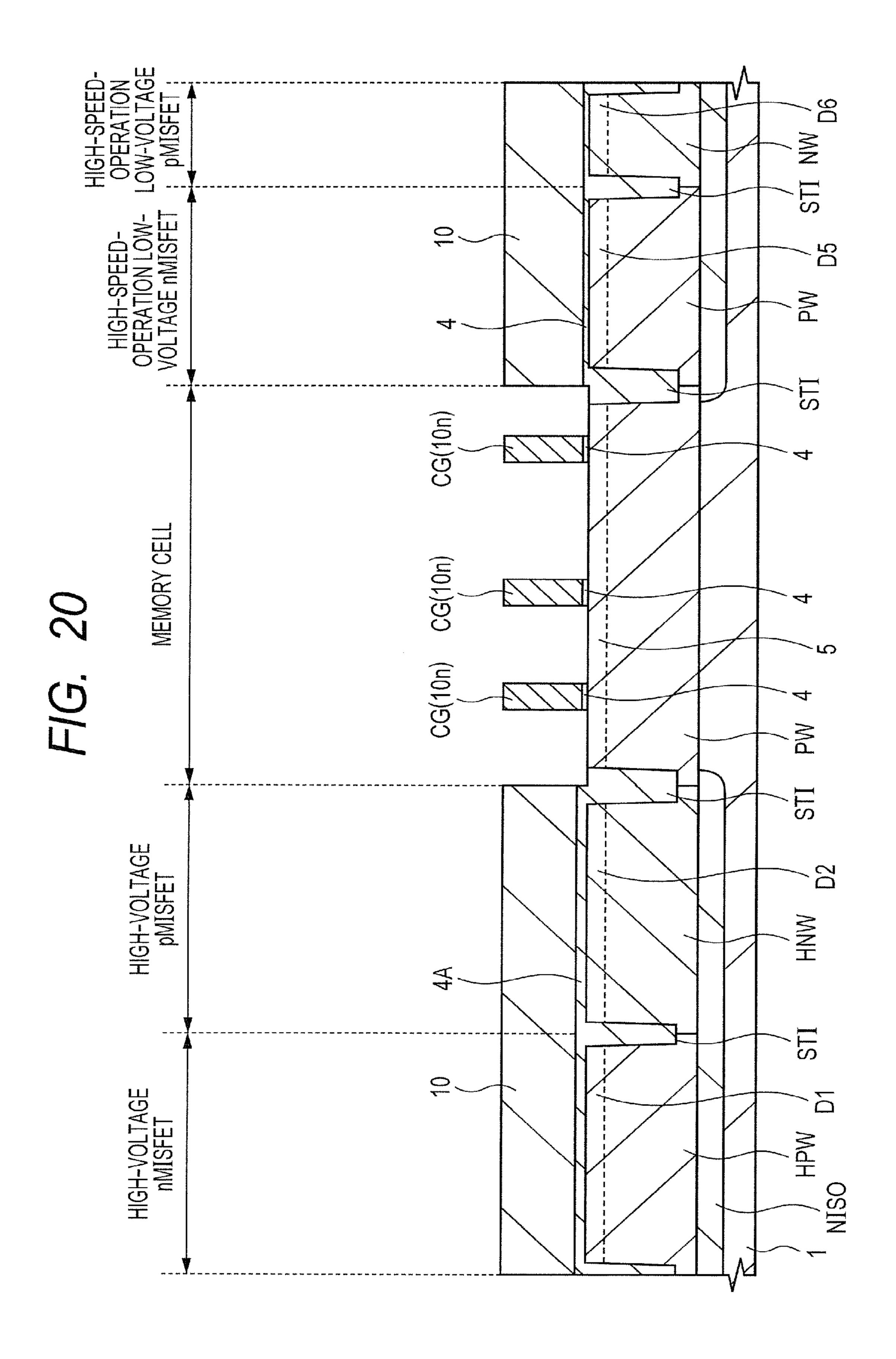

- FIG. 20 is a main-portion cross-sectional view of the same 5 portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 19;

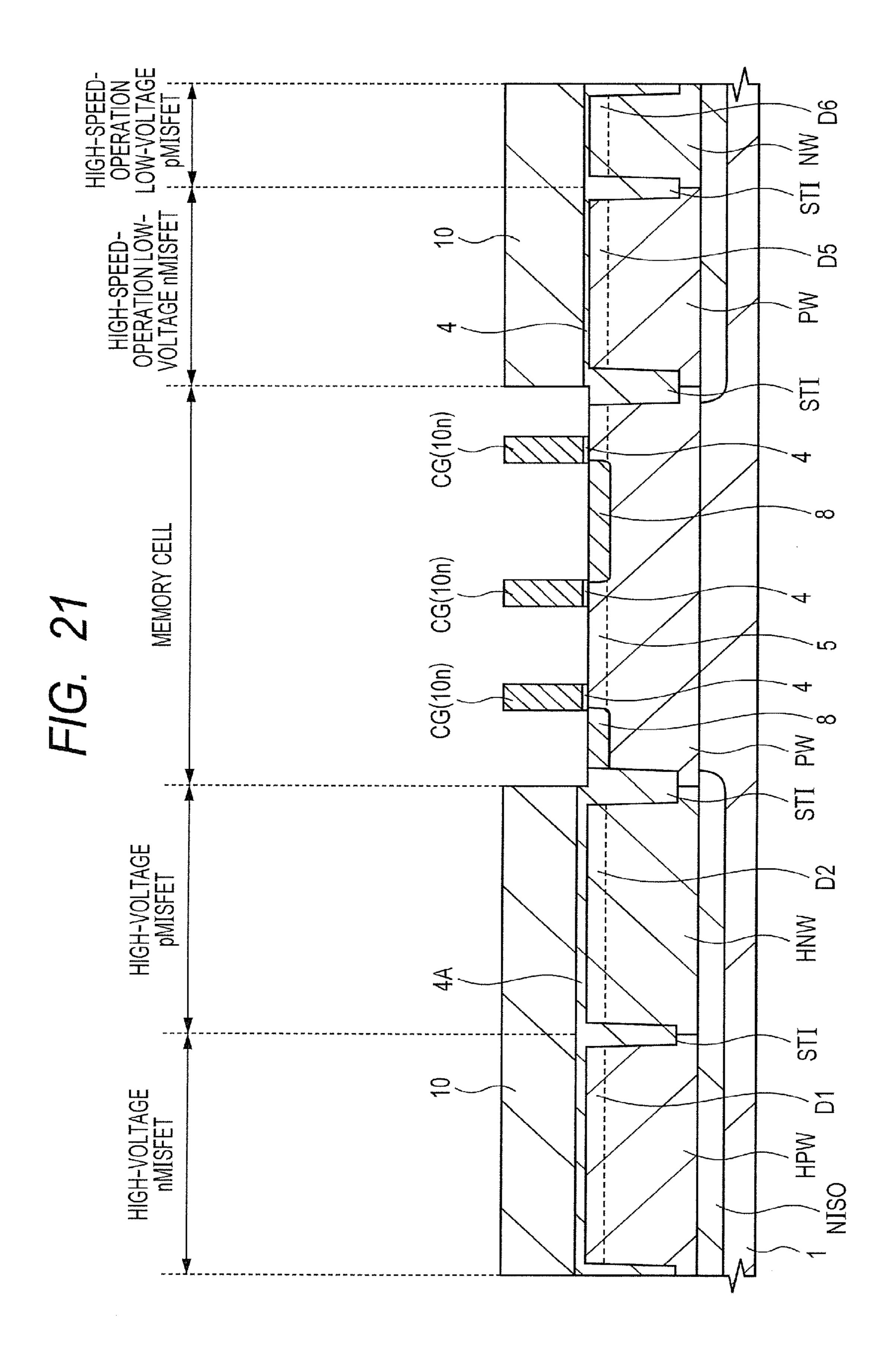

- FIG. 21 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 20;

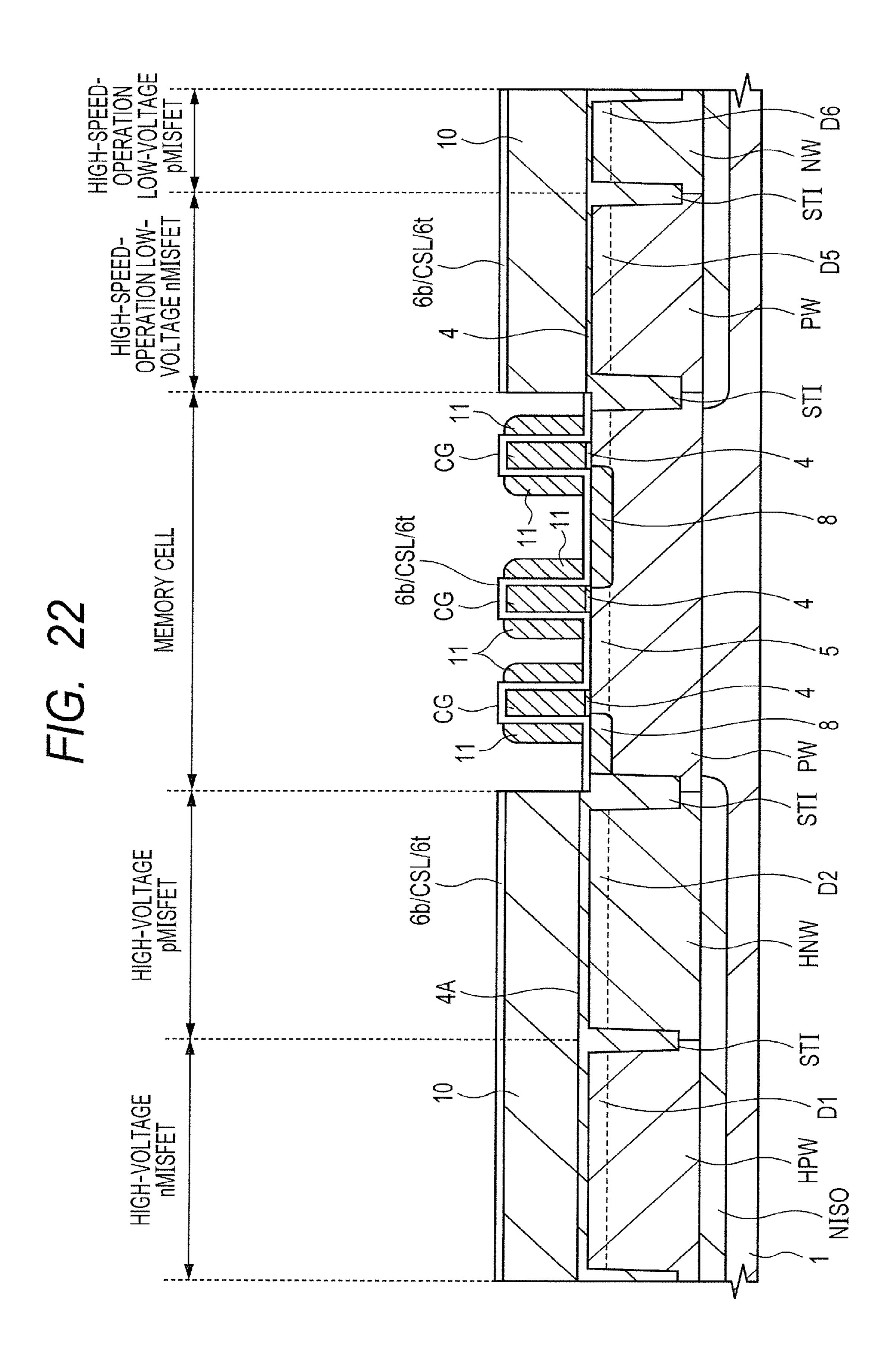

- FIG. 22 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 21;

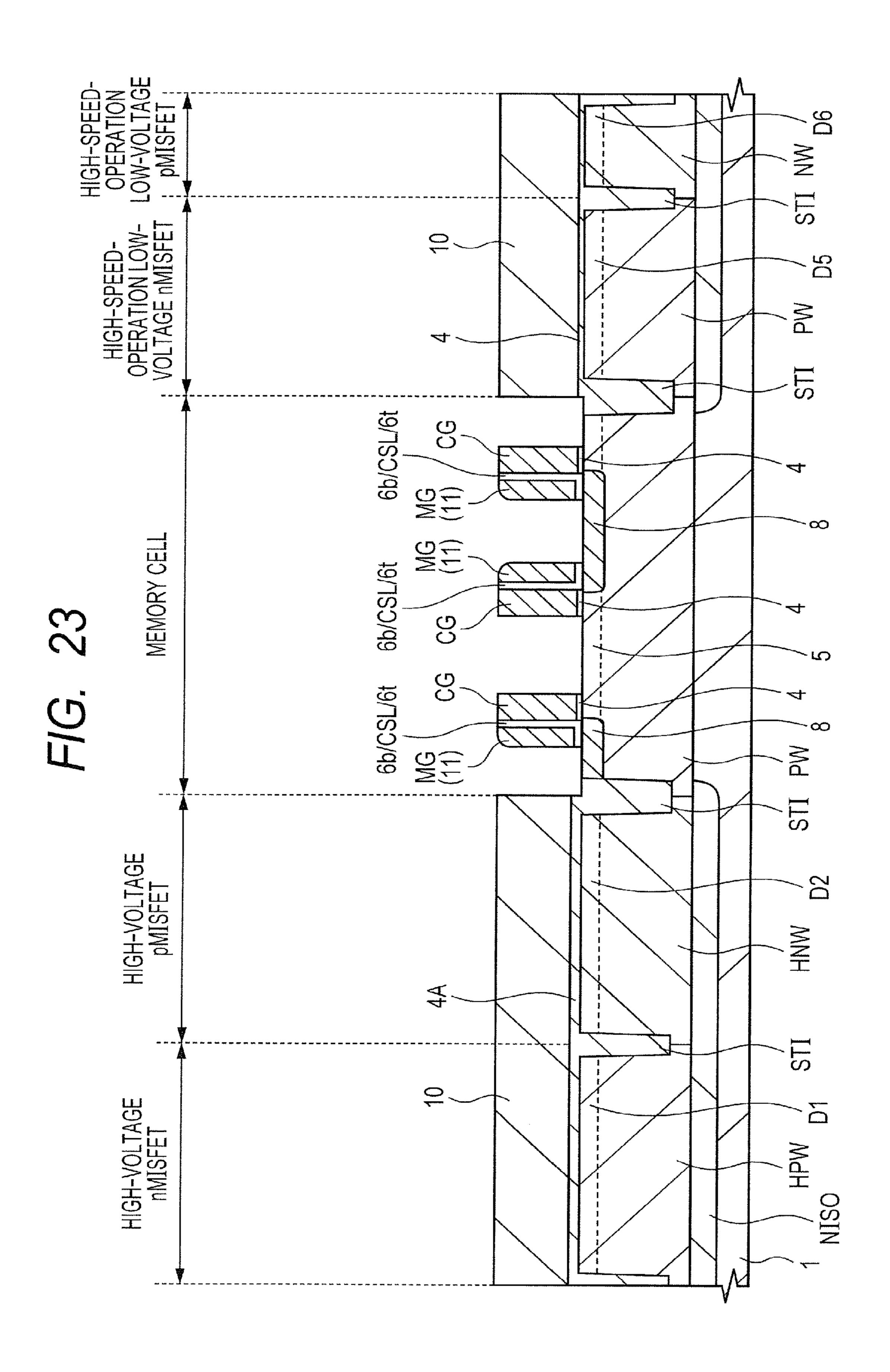

- FIG. 23 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is 20 subsequent to FIG. 22;

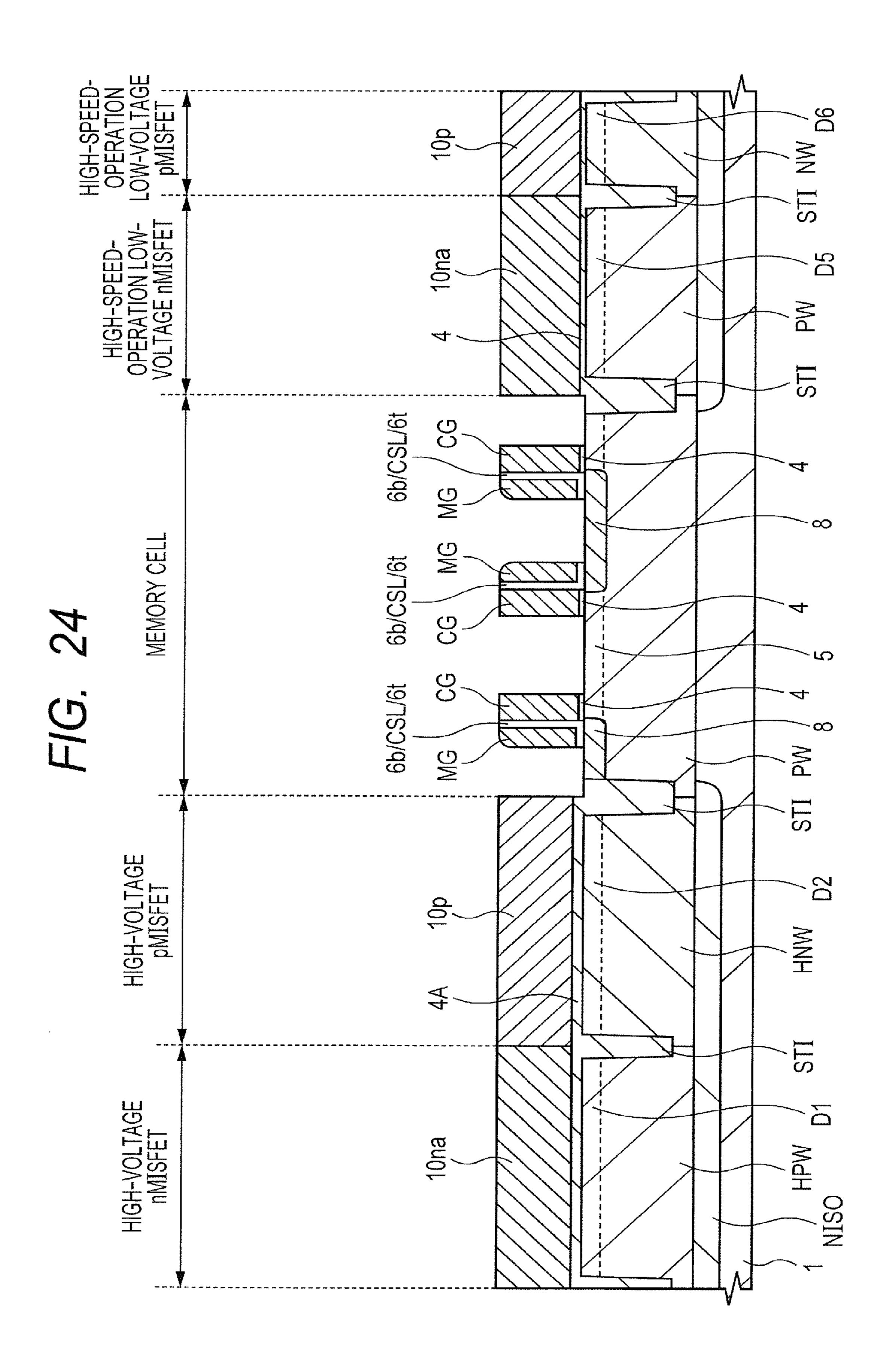

- FIG. 24 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 23;

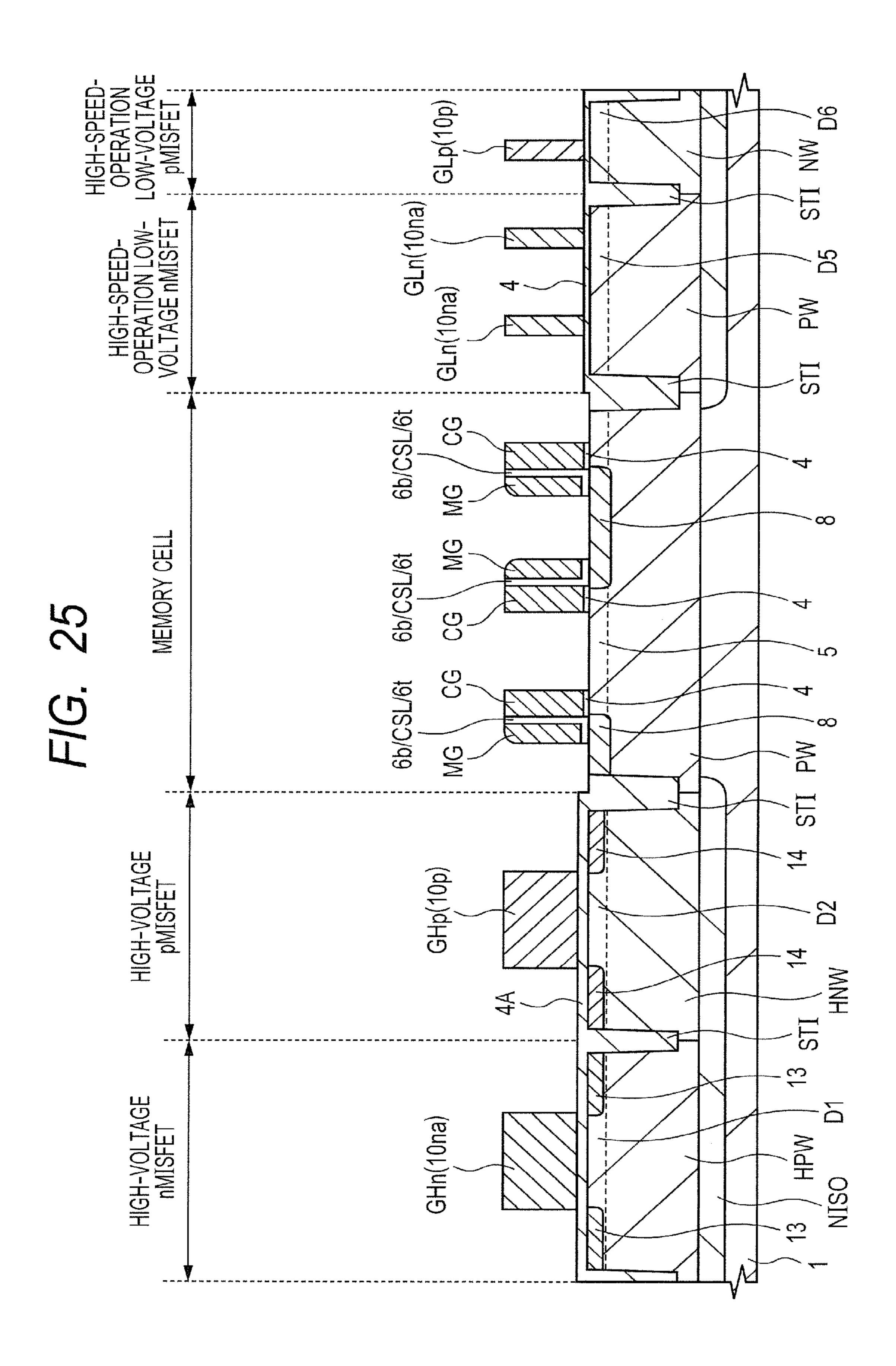

- FIG. 25 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 24;

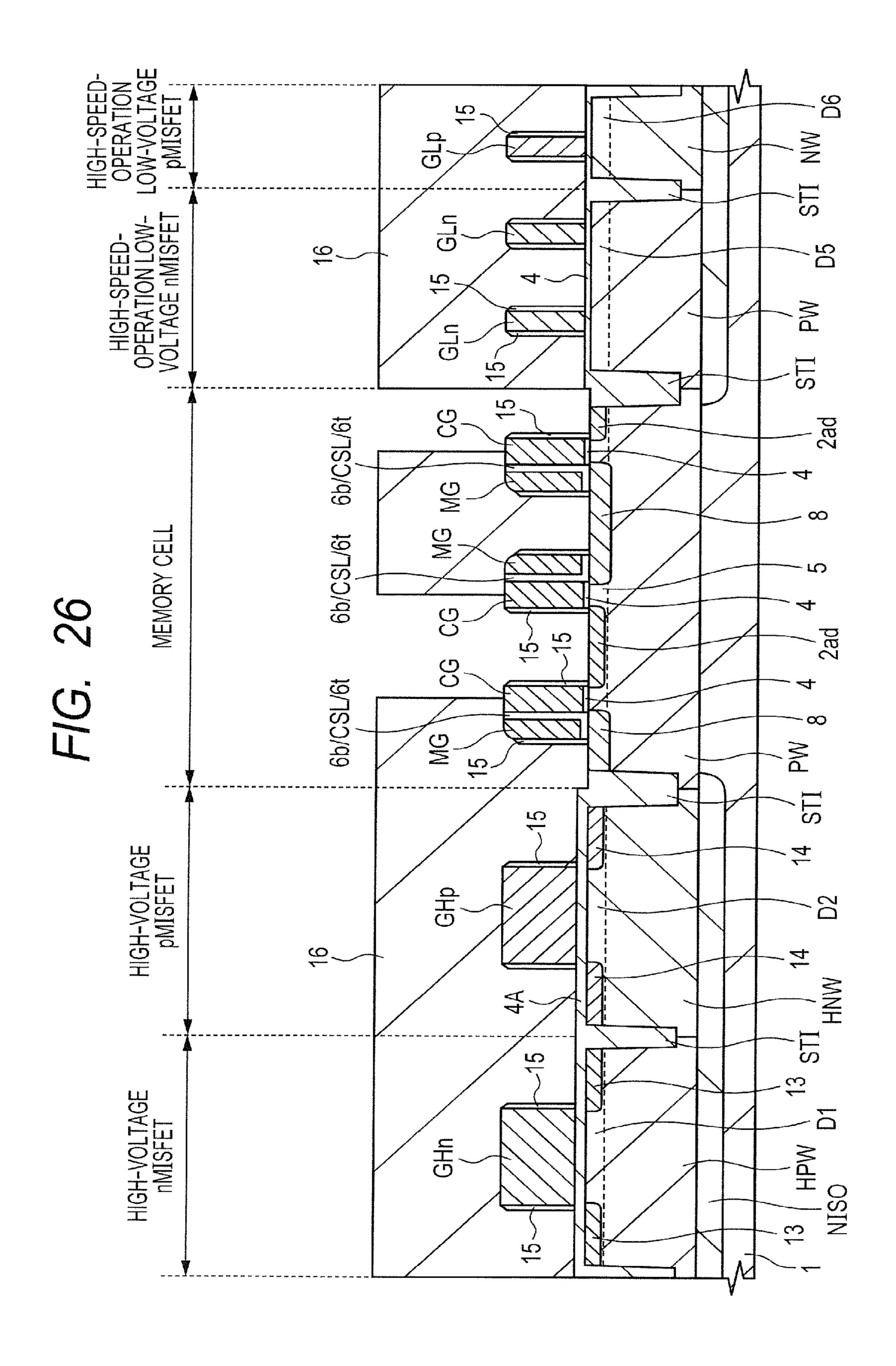

- FIG. 26 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 25;

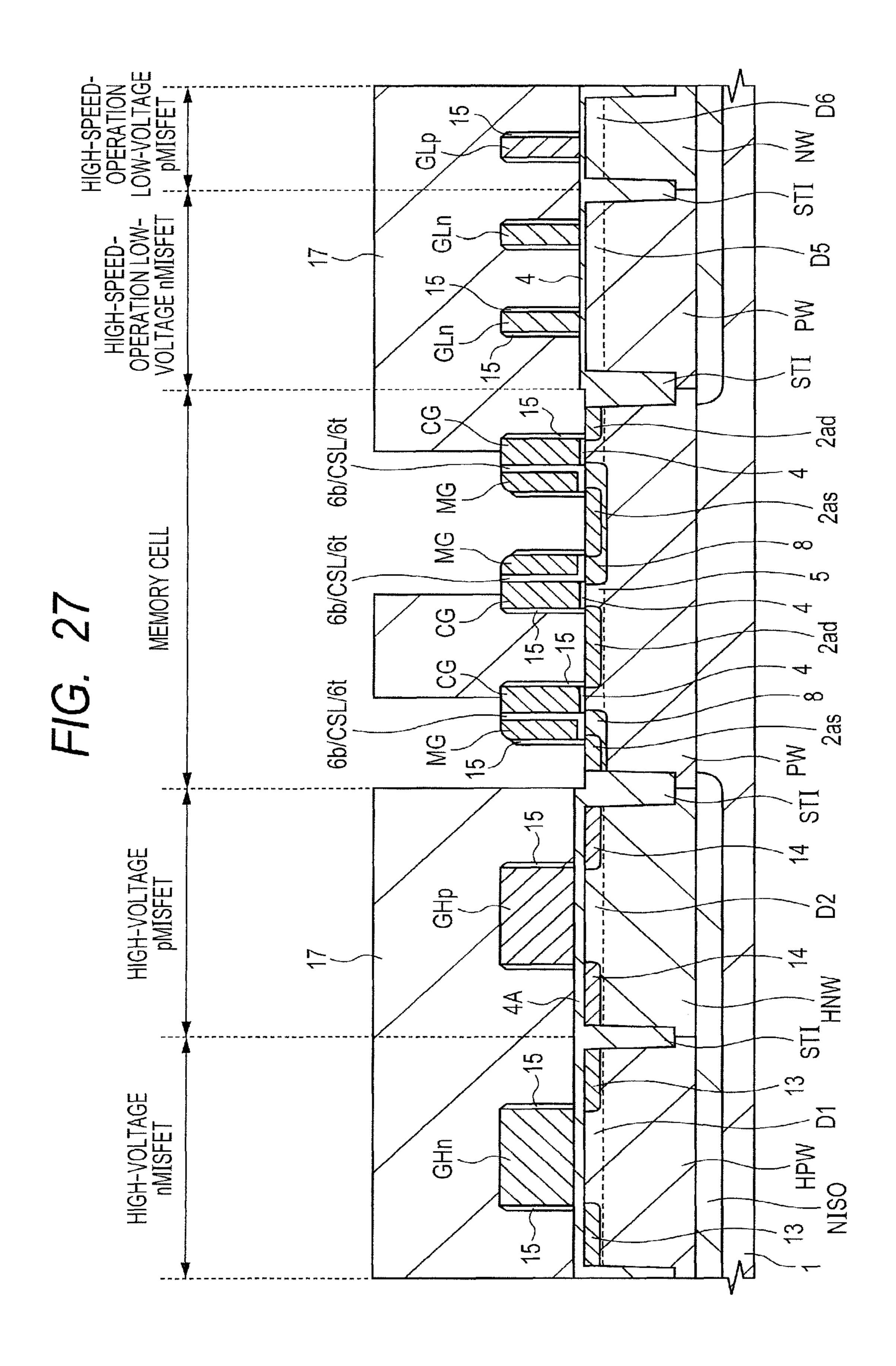

- FIG. 27 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 26;

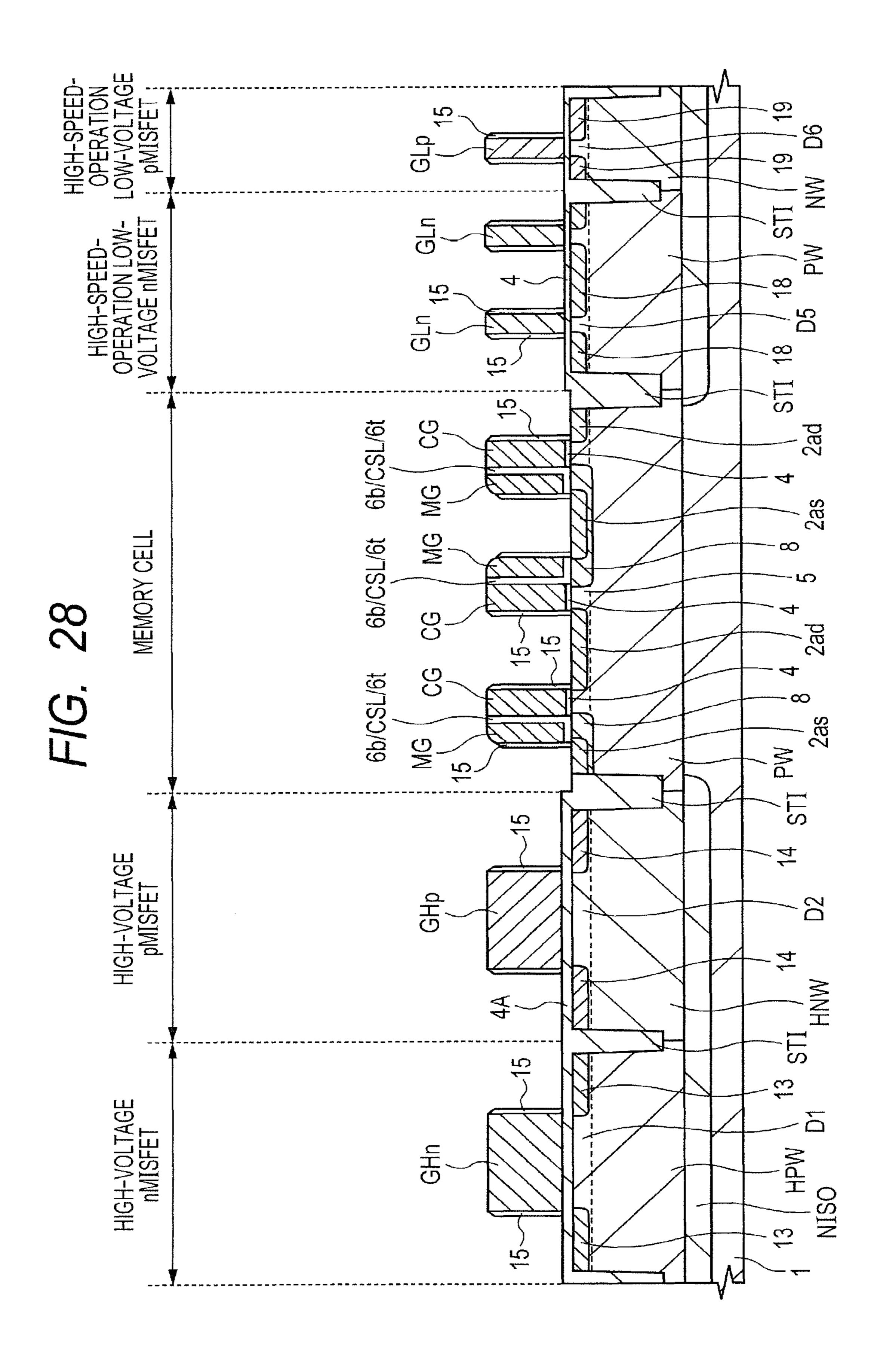

- FIG. 28 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a 40 manufacturing step of the semiconductor device, which is subsequent to FIG. 27;

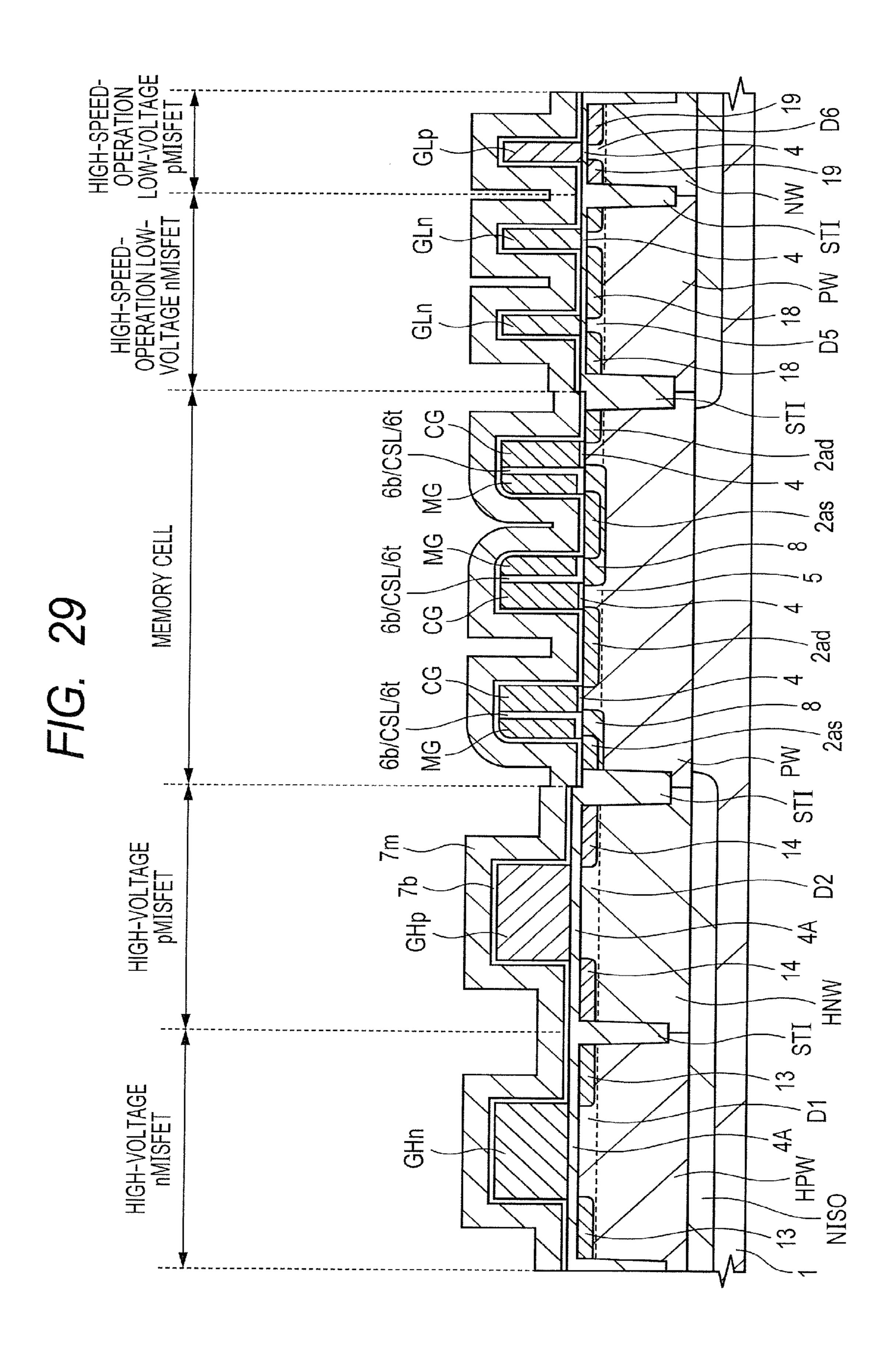

- FIG. 29 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is 45 subsequent to FIG. 28;

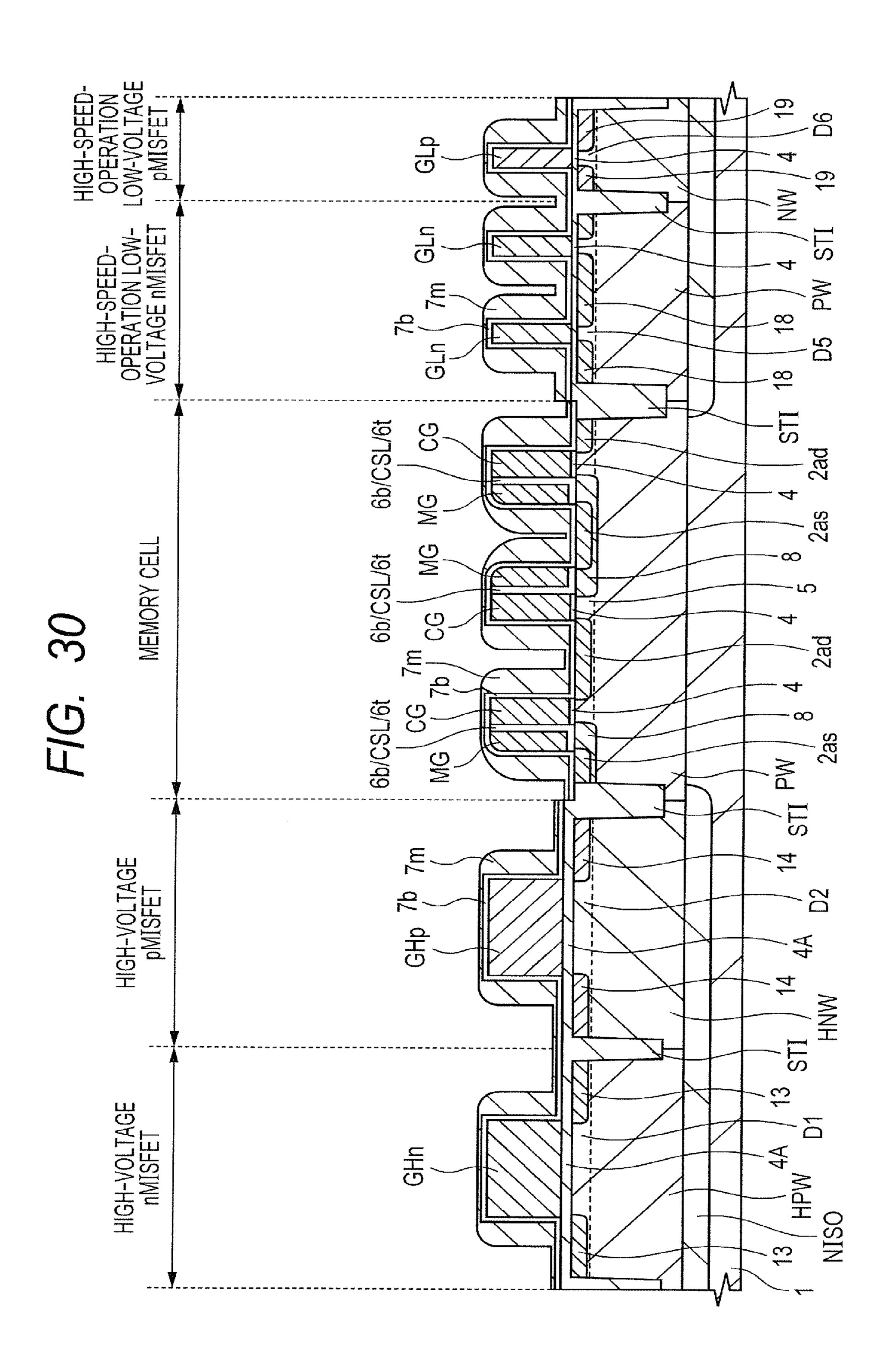

- FIG. 30 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 29;

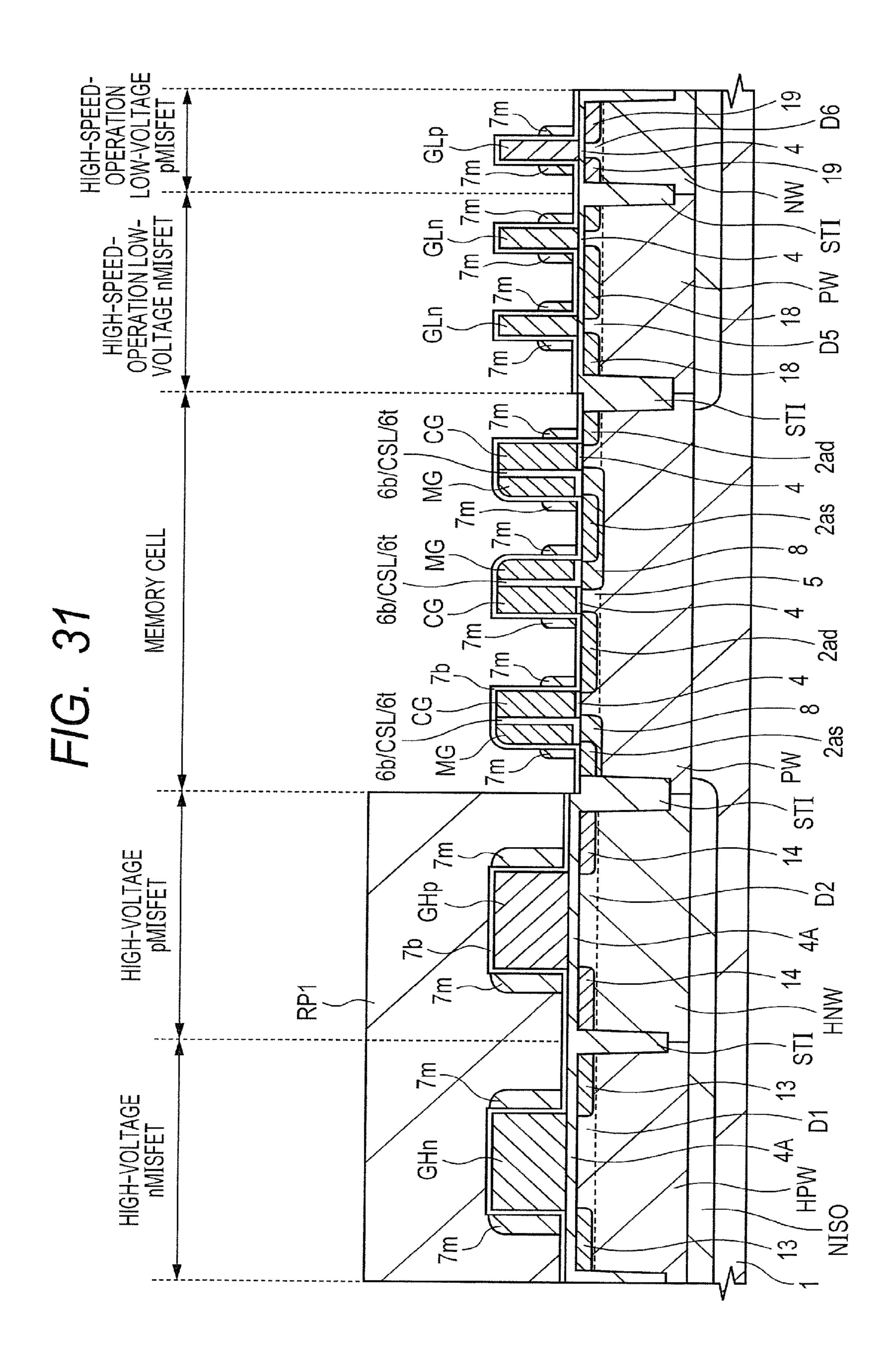

- FIG. 31 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 30;

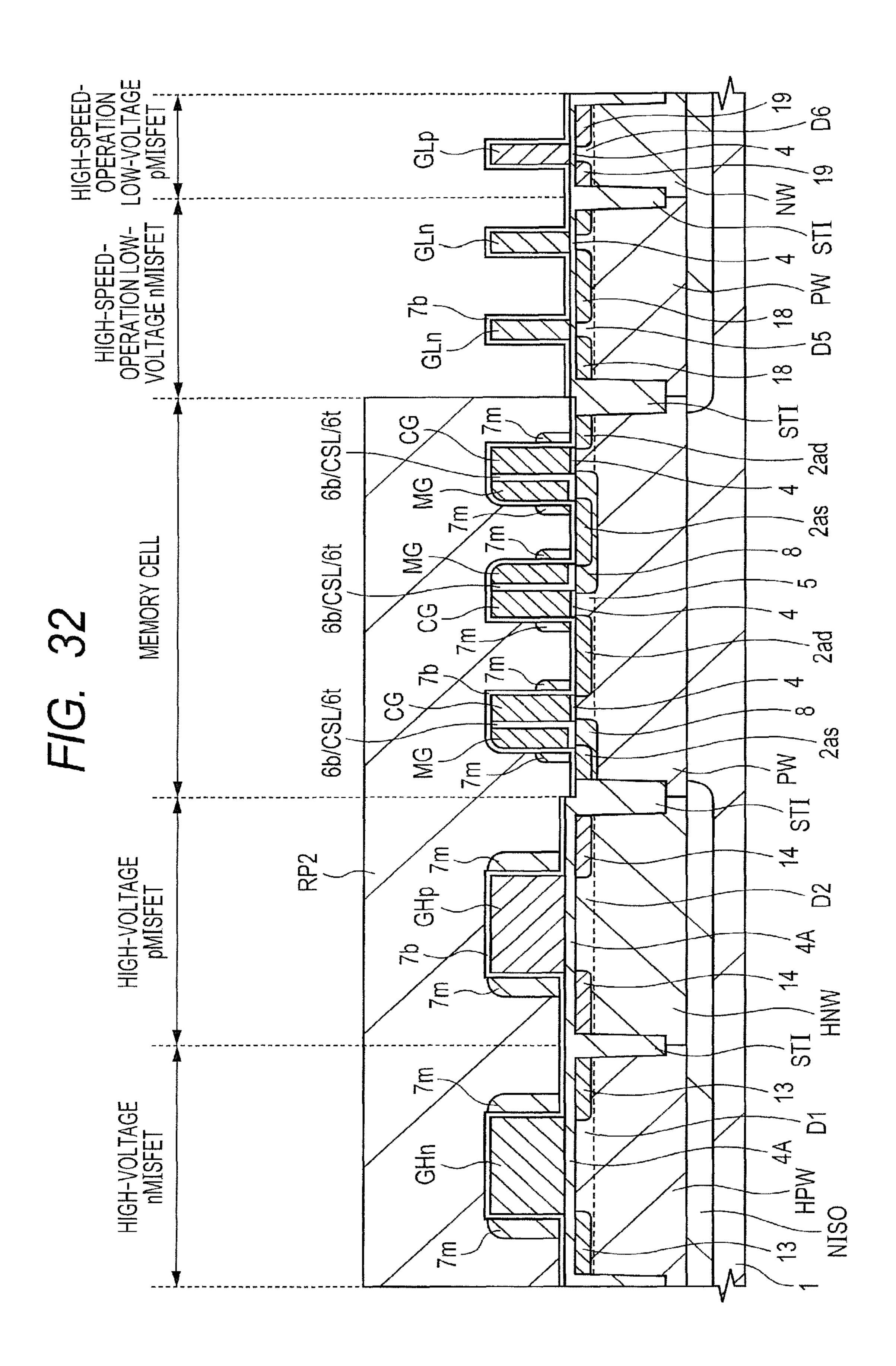

- FIG. 32 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 31;

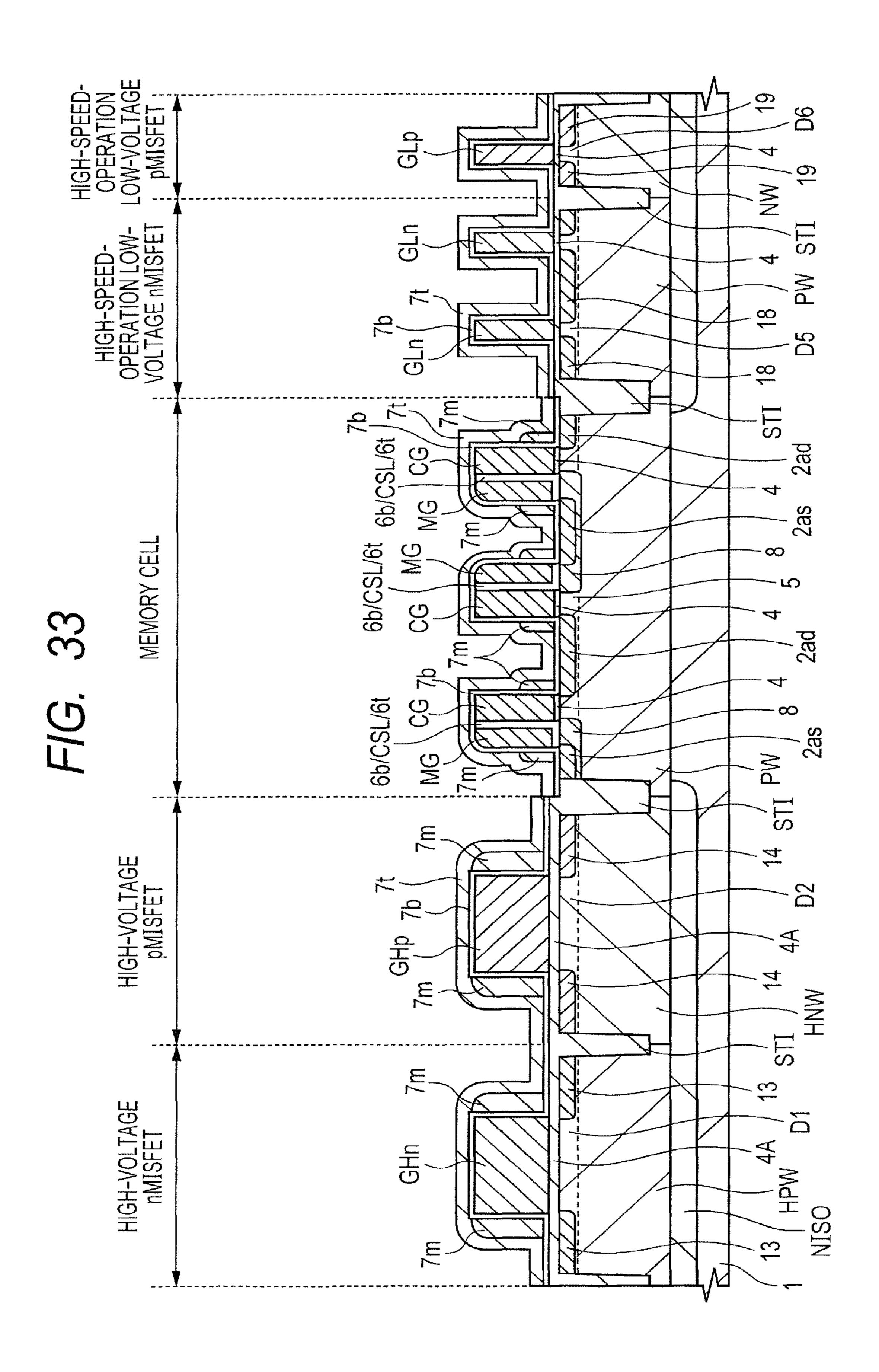

- FIG. 33 is a main-portion cross-sectional view of the same 60 portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 32;

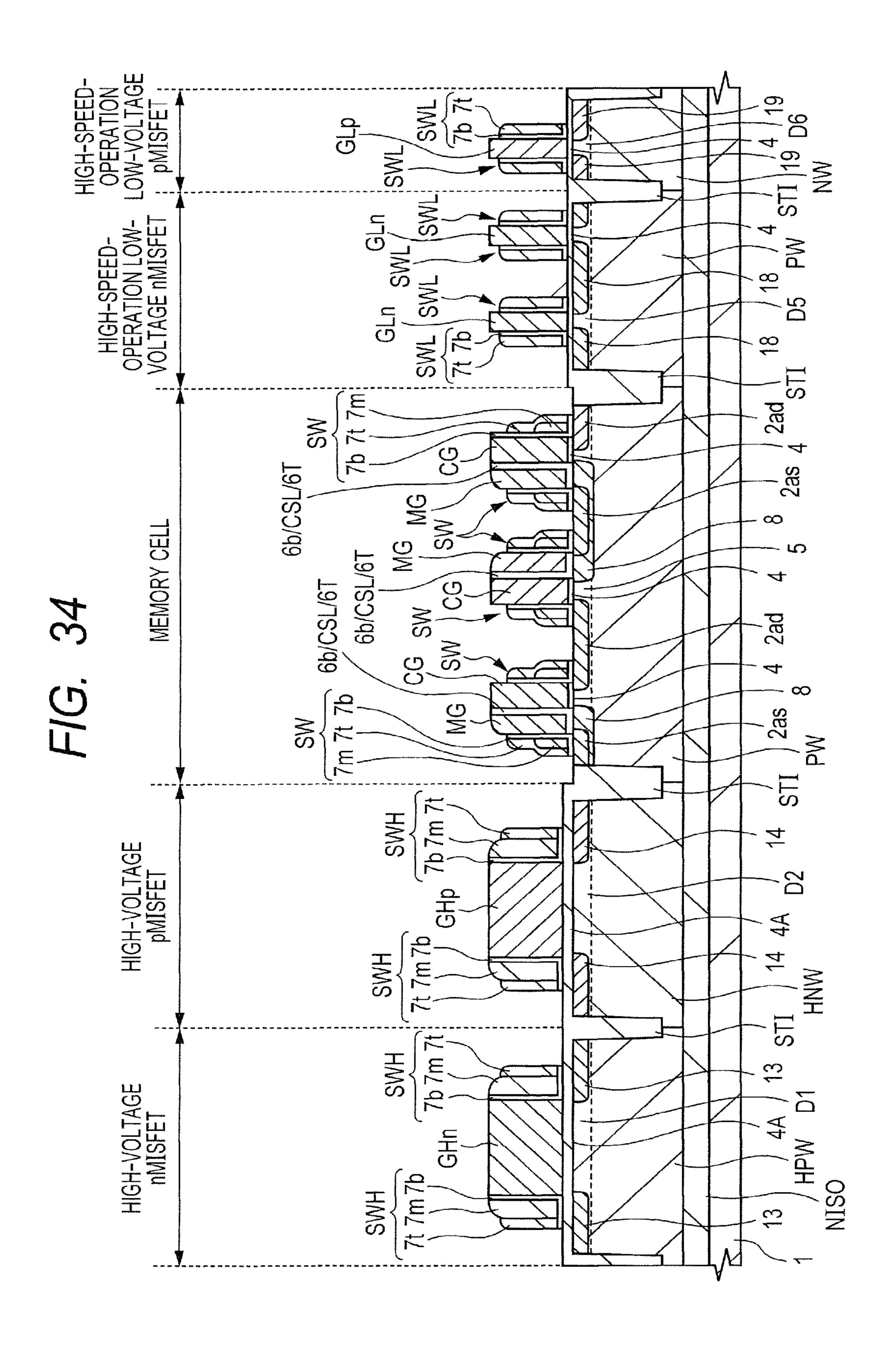

- FIG. 34 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a 65 manufacturing step of the semiconductor device, which is subsequent to FIG. 33;

6

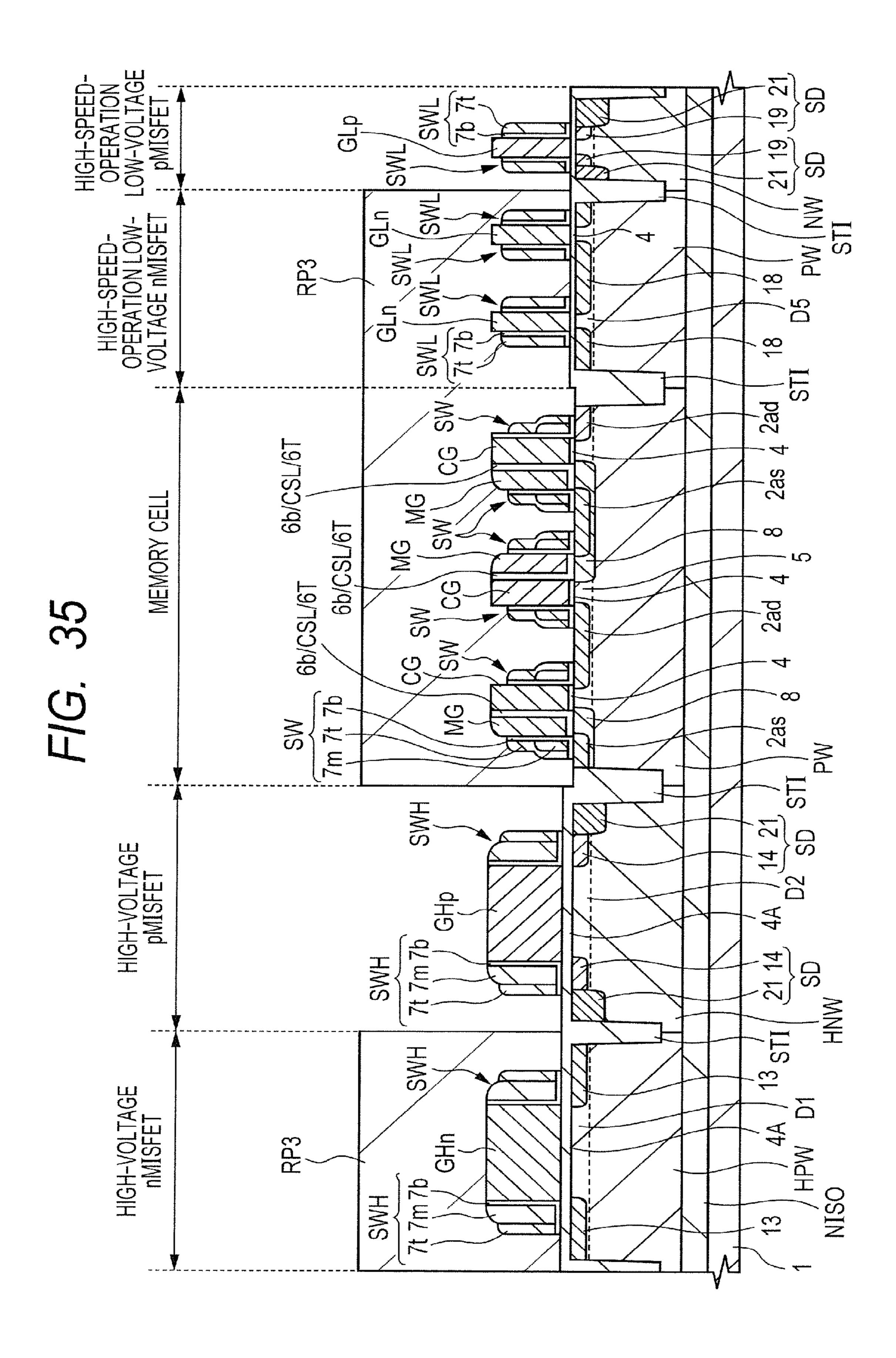

- FIG. 35 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 34;

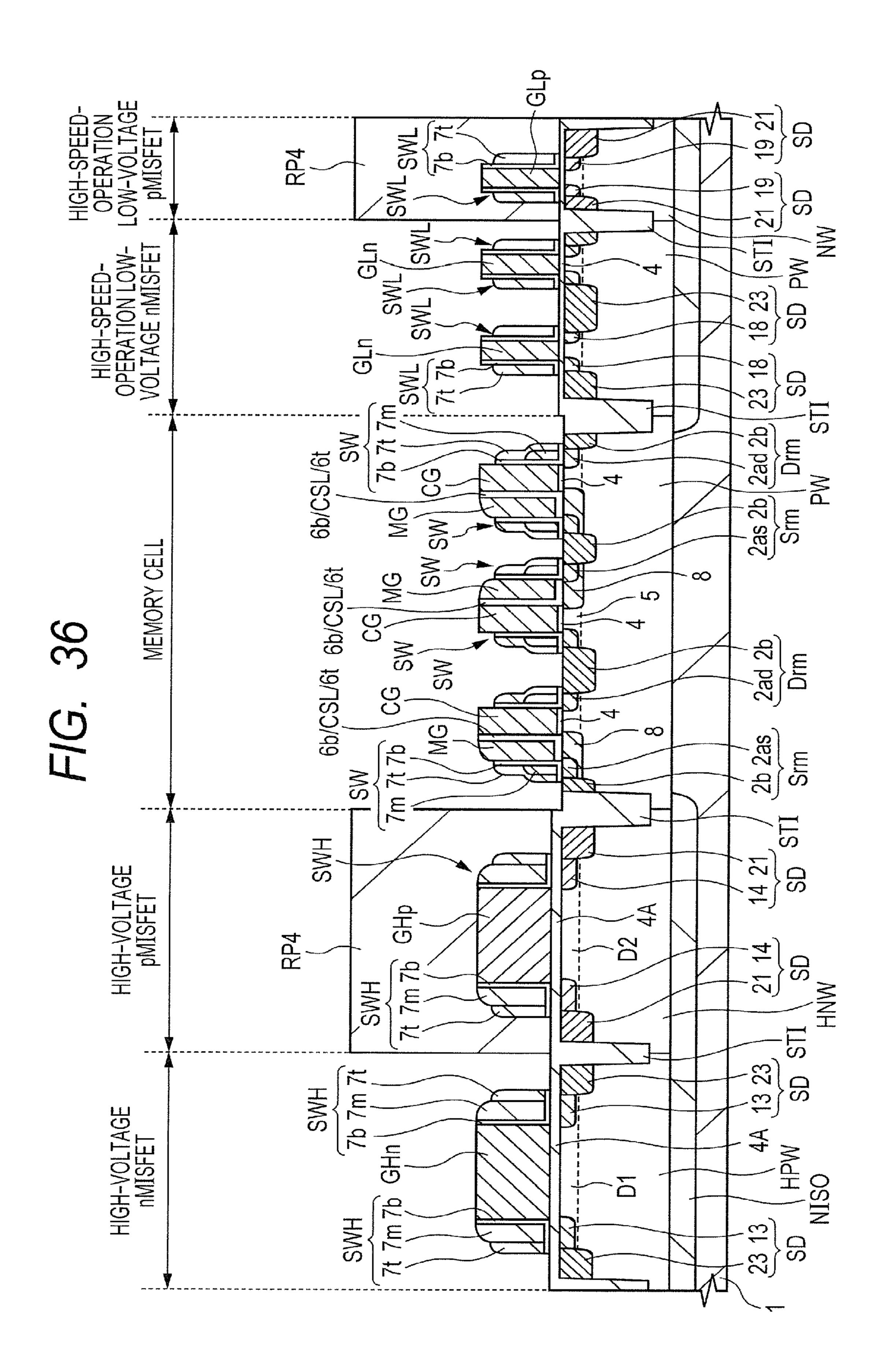

- FIG. 36 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 35;

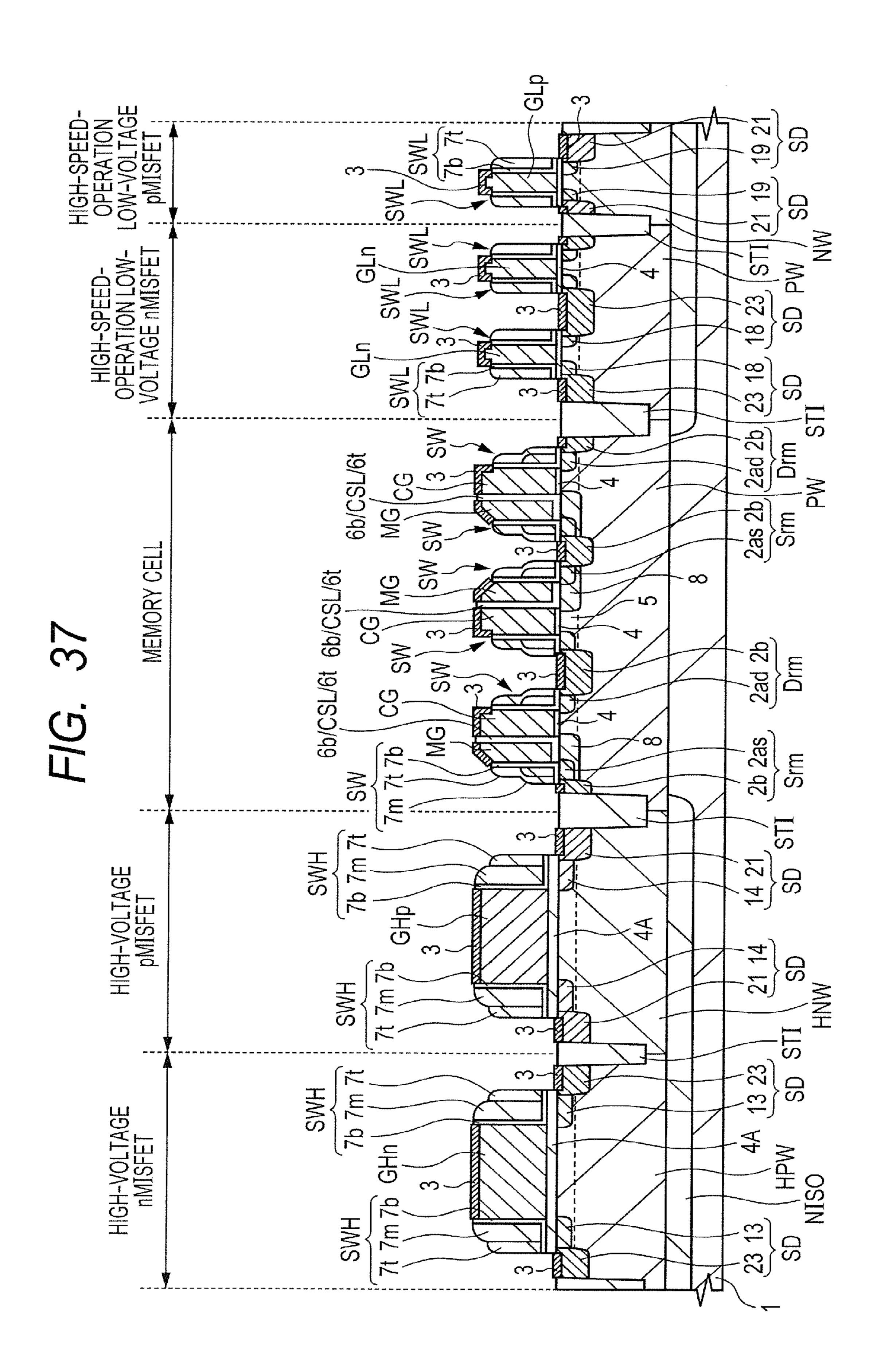

- FIG. 37 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 18 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 36;

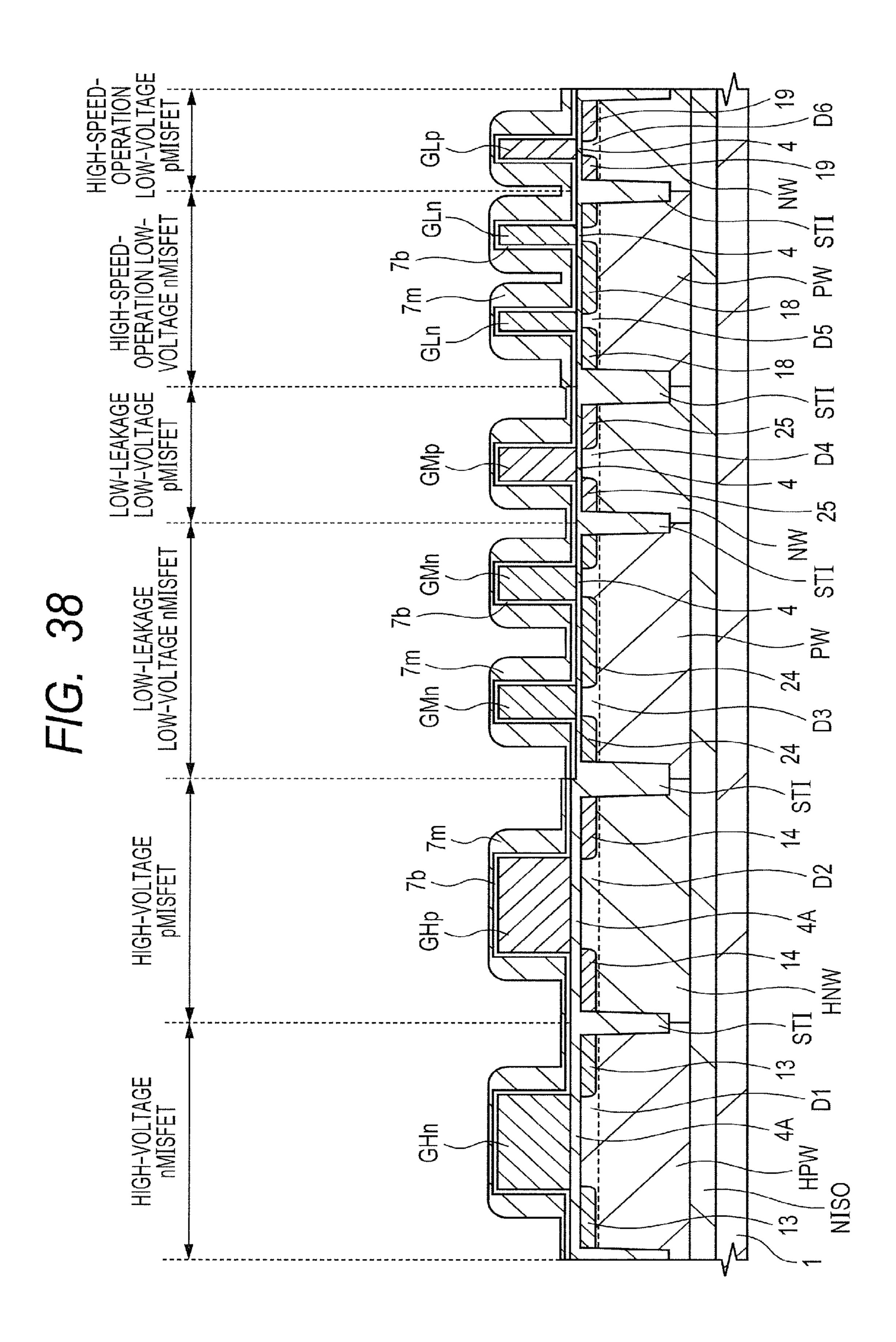

- FIG. 38 is a main-portion cross-sectional view of a semiconductor device according to Embodiment 2 of the present invention, which illustrates a manufacturing step of the semiconductor device;

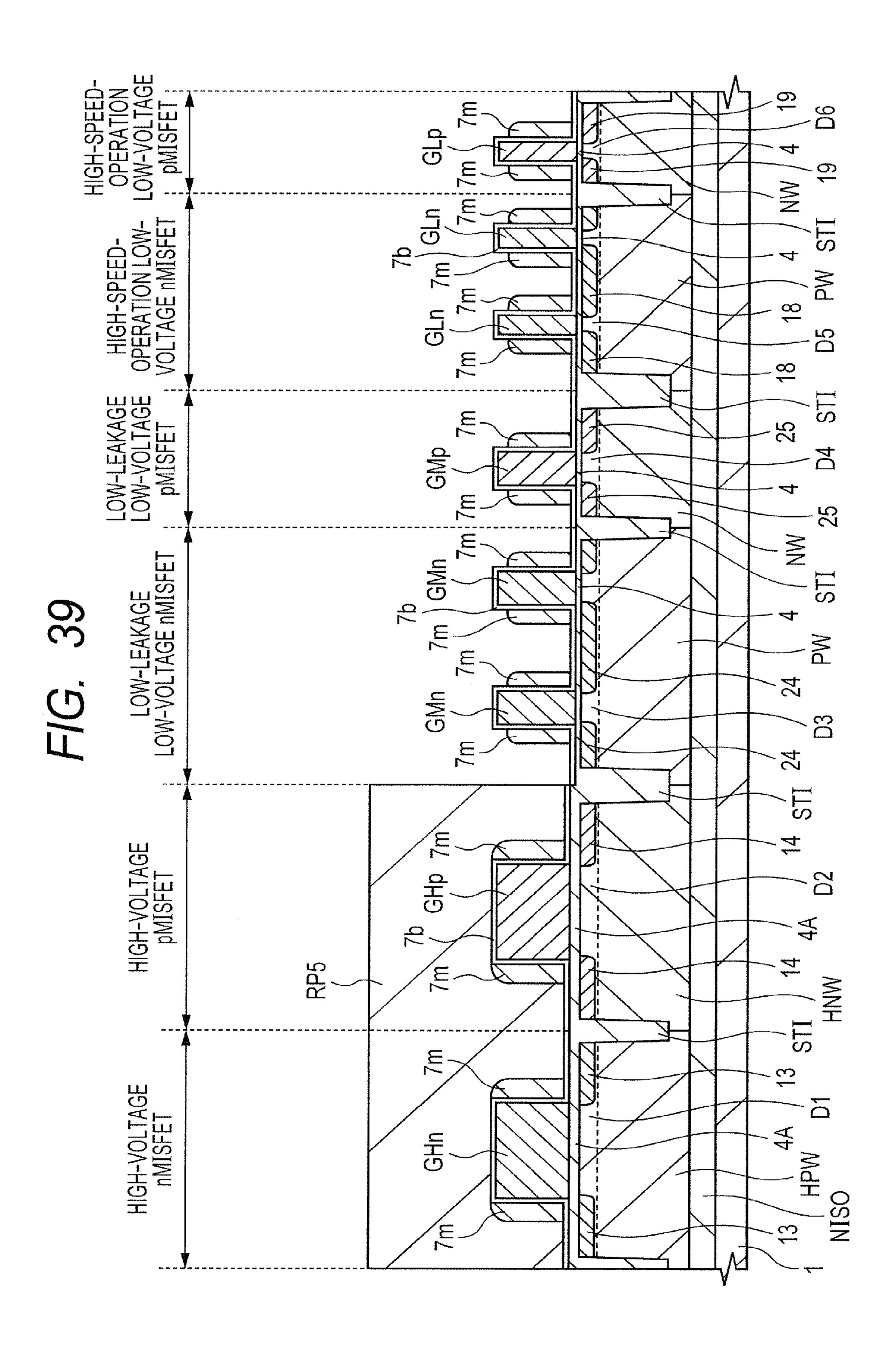

- FIG. 39 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 38 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 38;

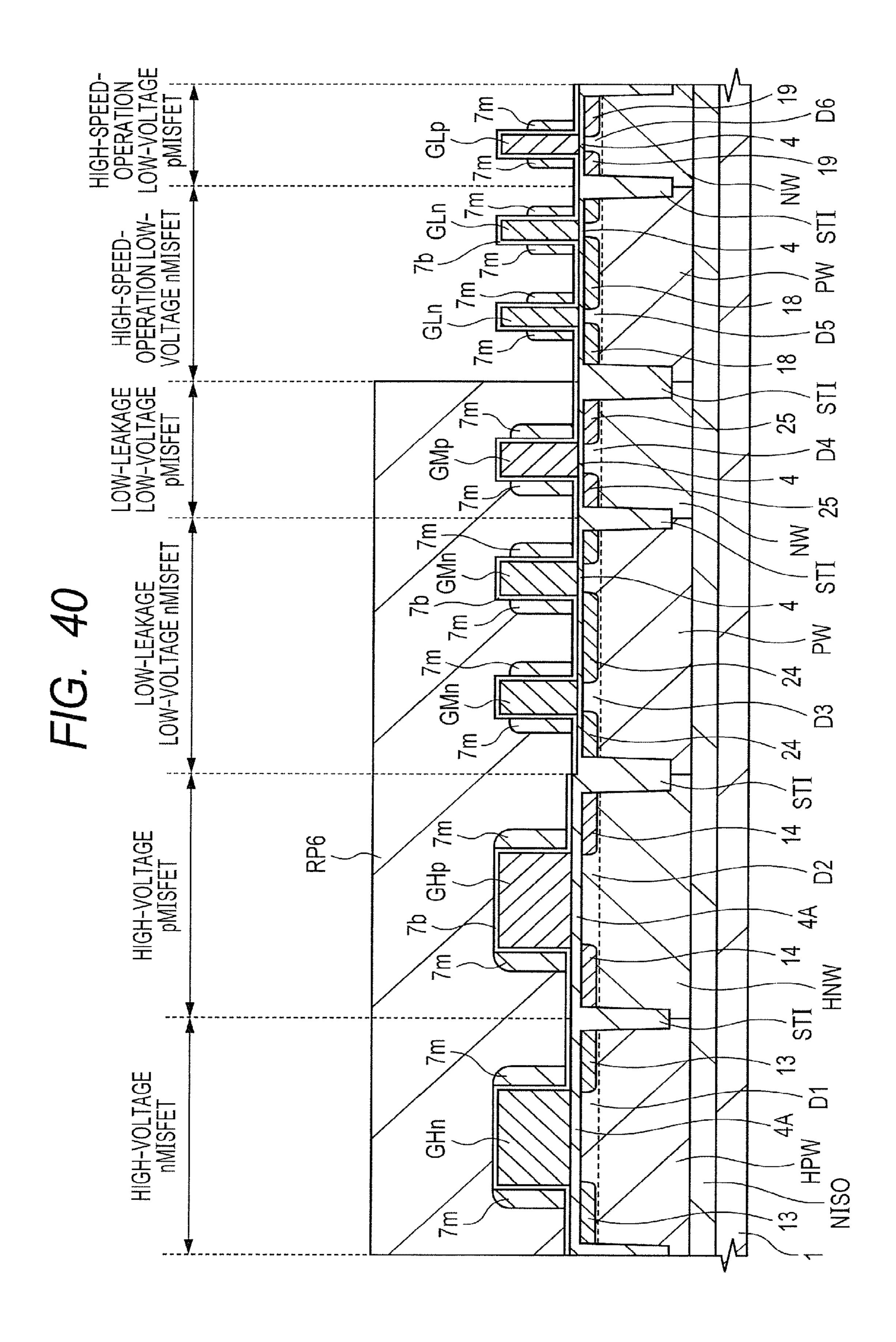

- FIG. 40 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 38 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 39;

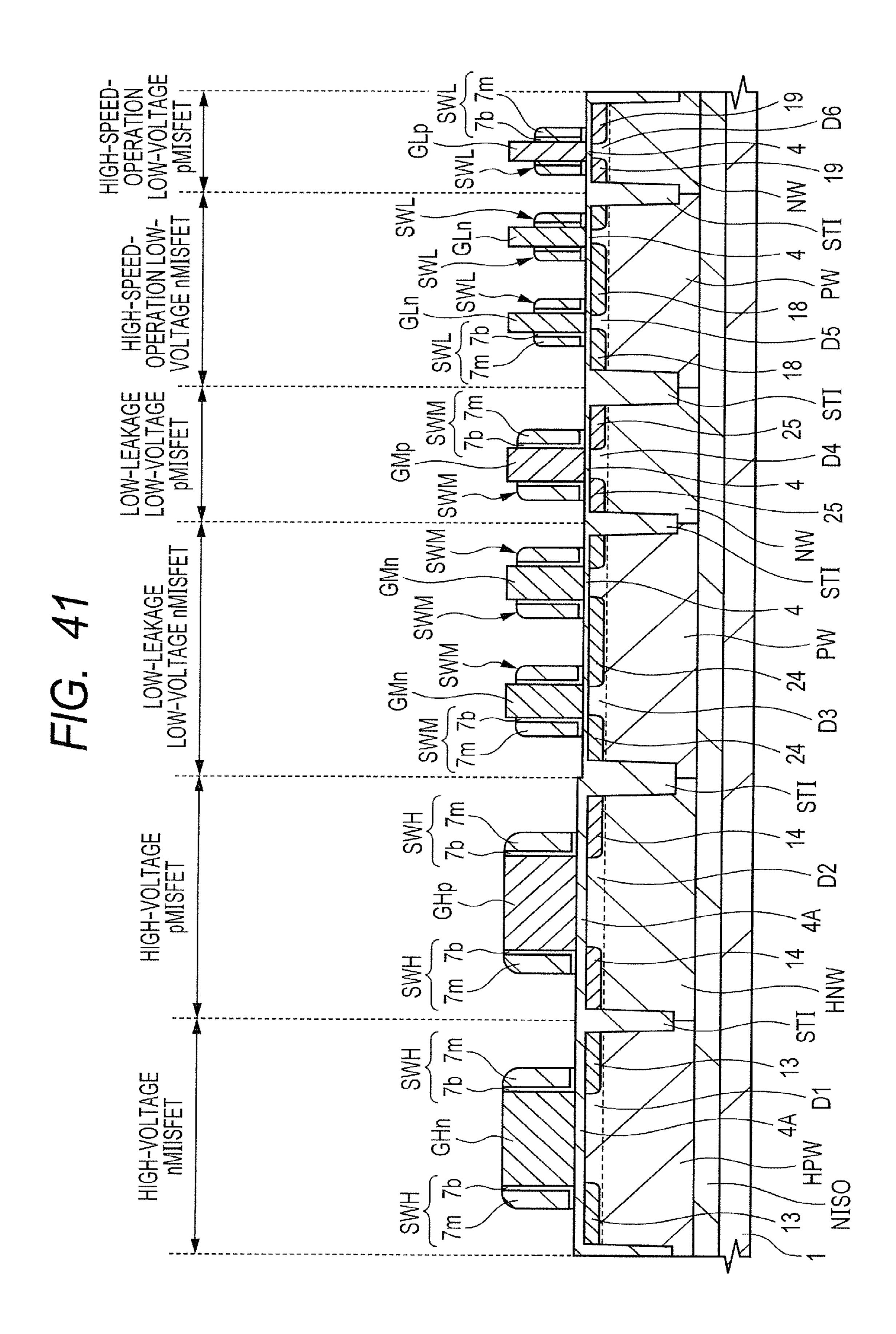

- FIG. 41 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 38 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 40;

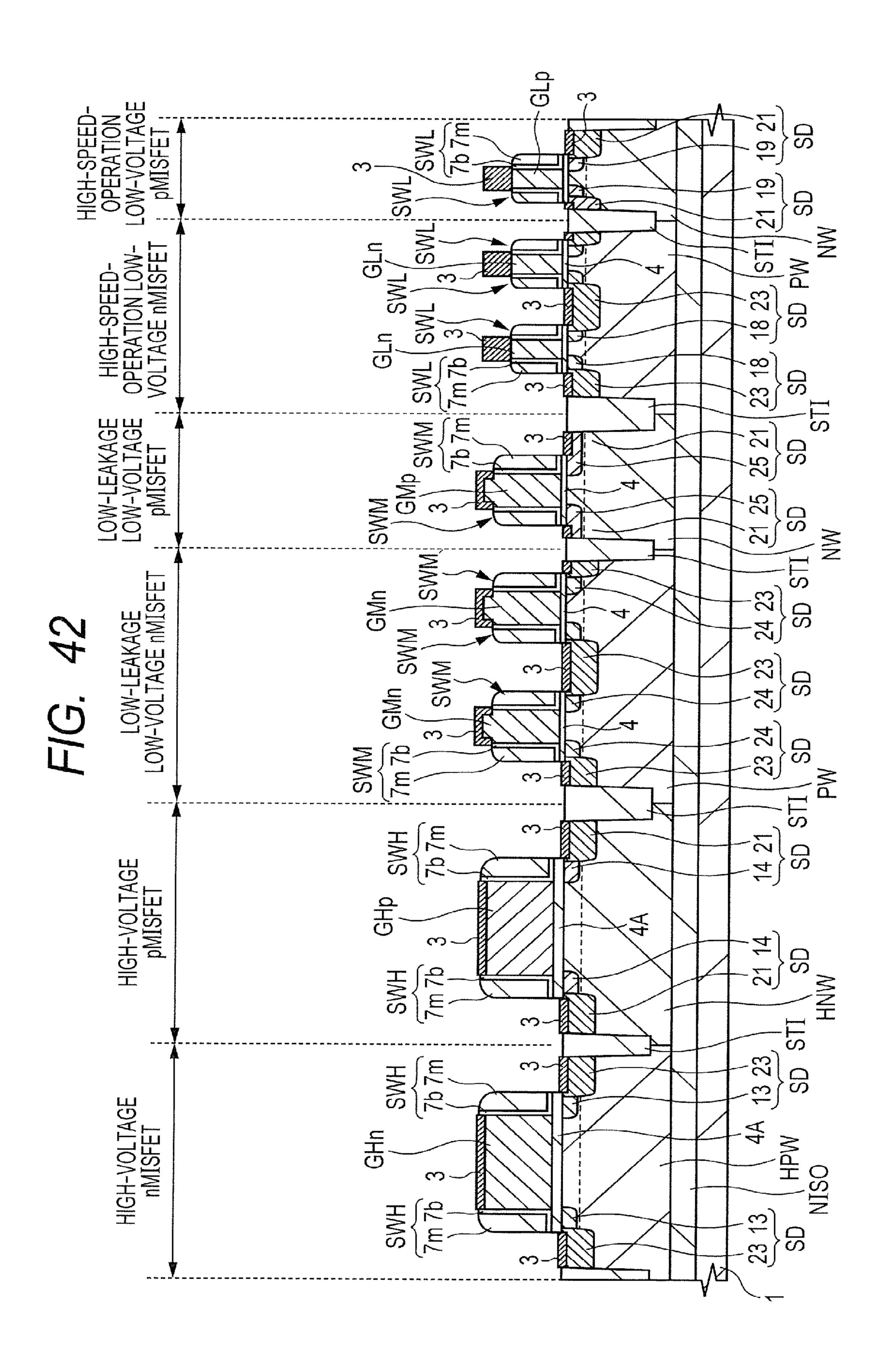

- FIG. **42** is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. **38** in a manufacturing step of the semiconductor device, which is subsequent to FIG. **41**;

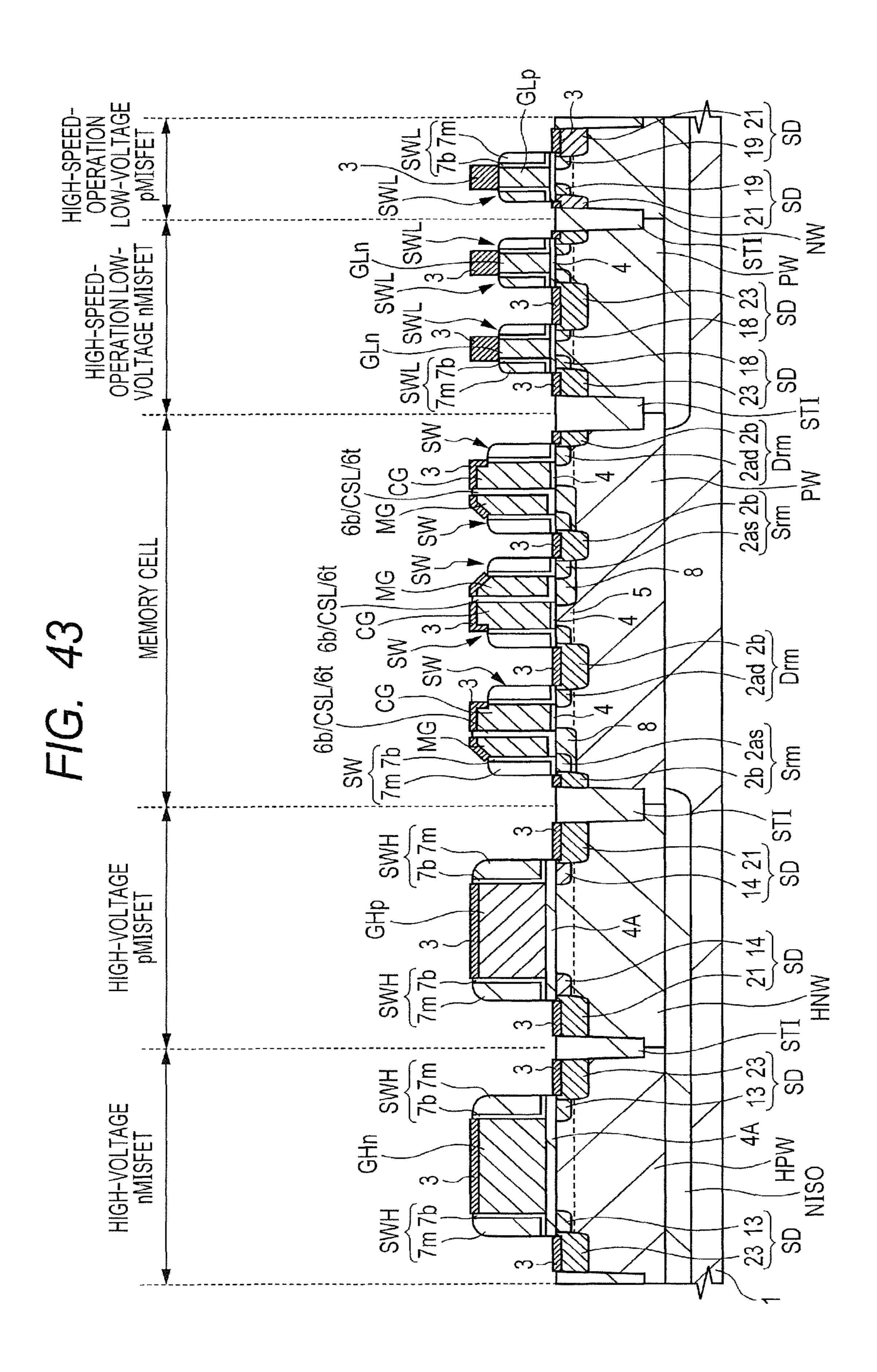

- FIG. **43** is a main-portion cross-sectional view of the semiconductor device according to Embodiment 2 of the present invention, which illustrates another example of a manufacturing step of the semiconductor device;

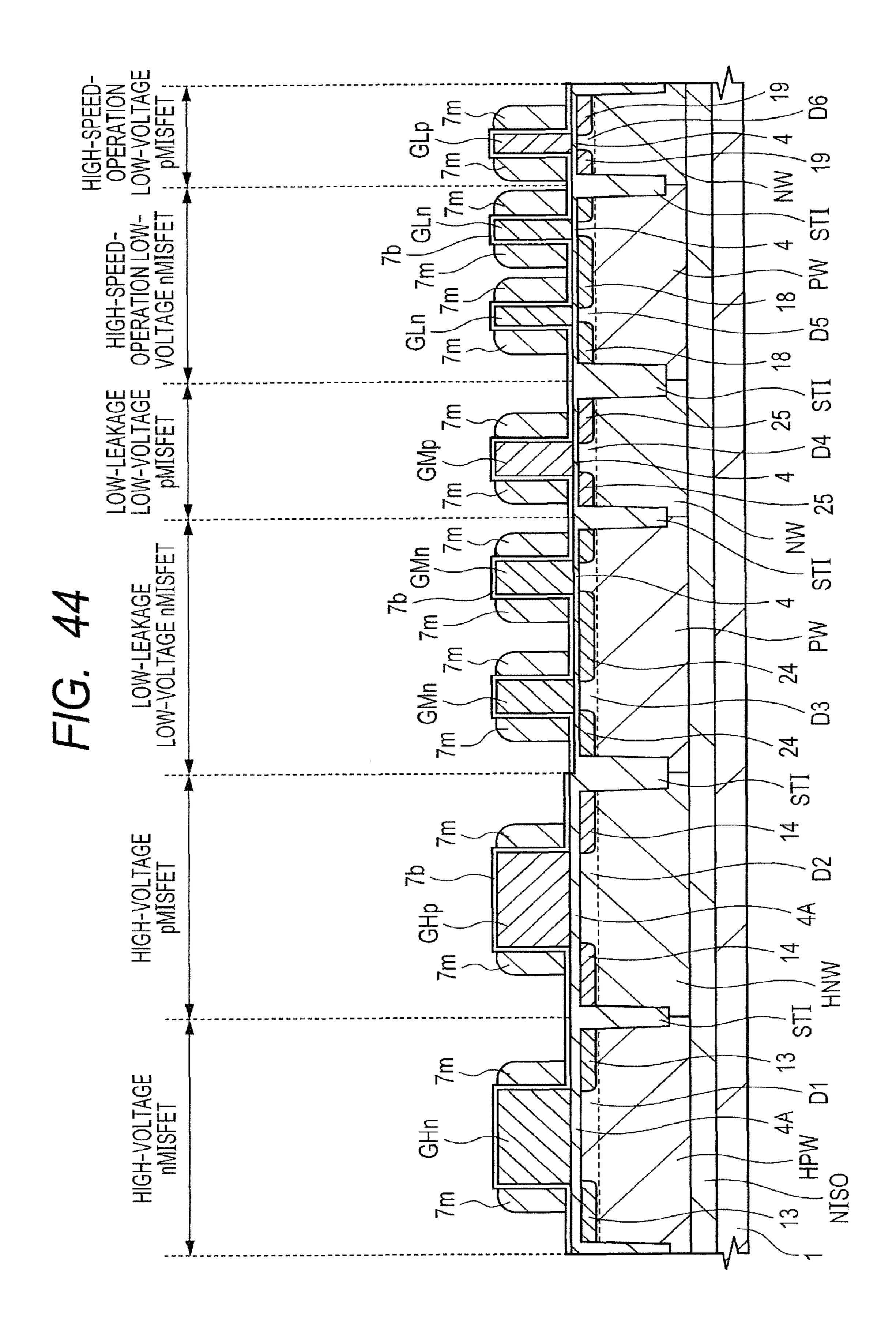

- FIG. 44 is a main-portion cross-sectional view of a semiconductor device according to Embodiment 3 of the present invention, which illustrates a manufacturing step of the semiconductor device;

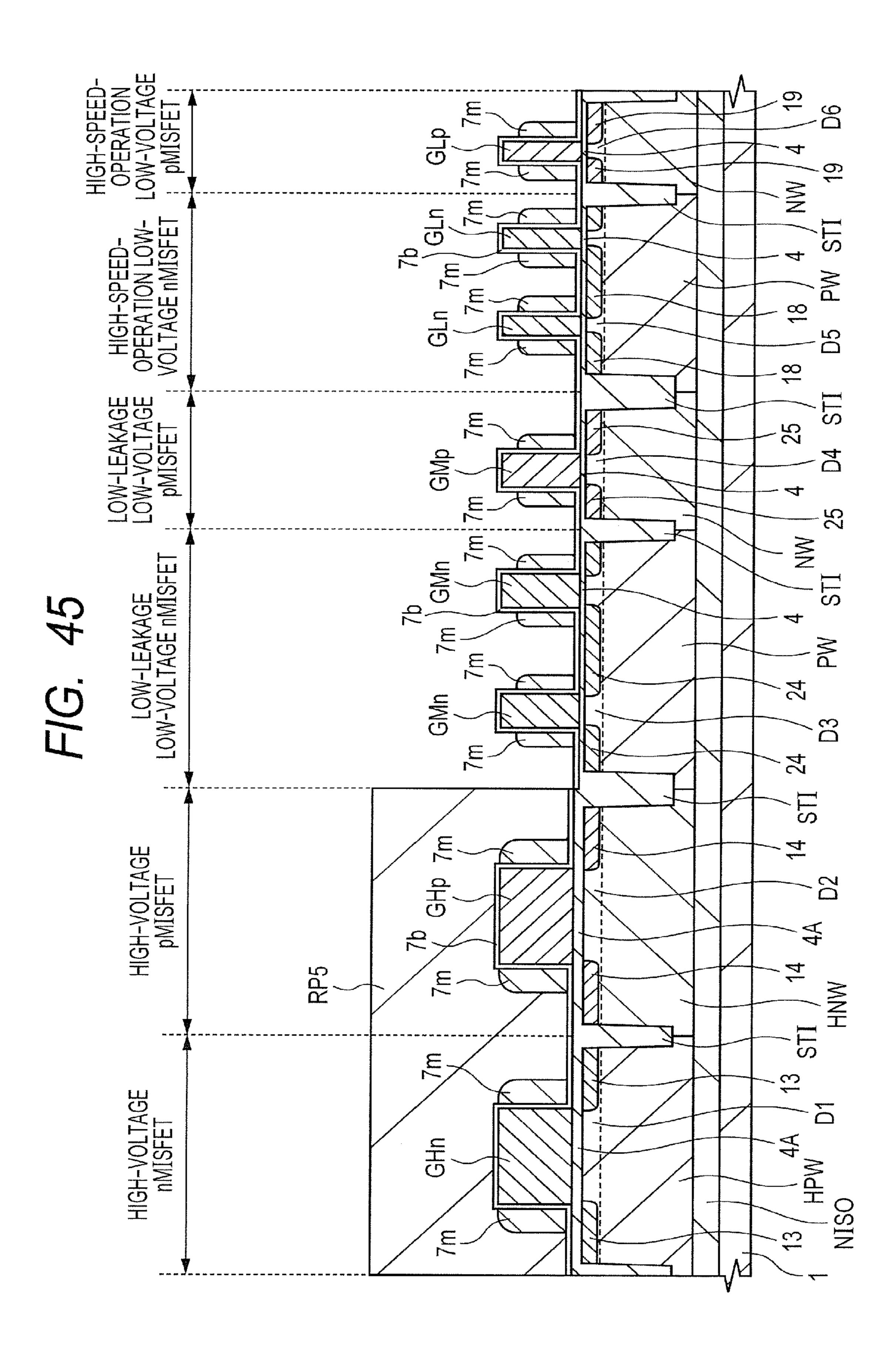

- FIG. **45** is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. **44** in a manufacturing step of the semiconductor device, which is subsequent to FIG. **44**;

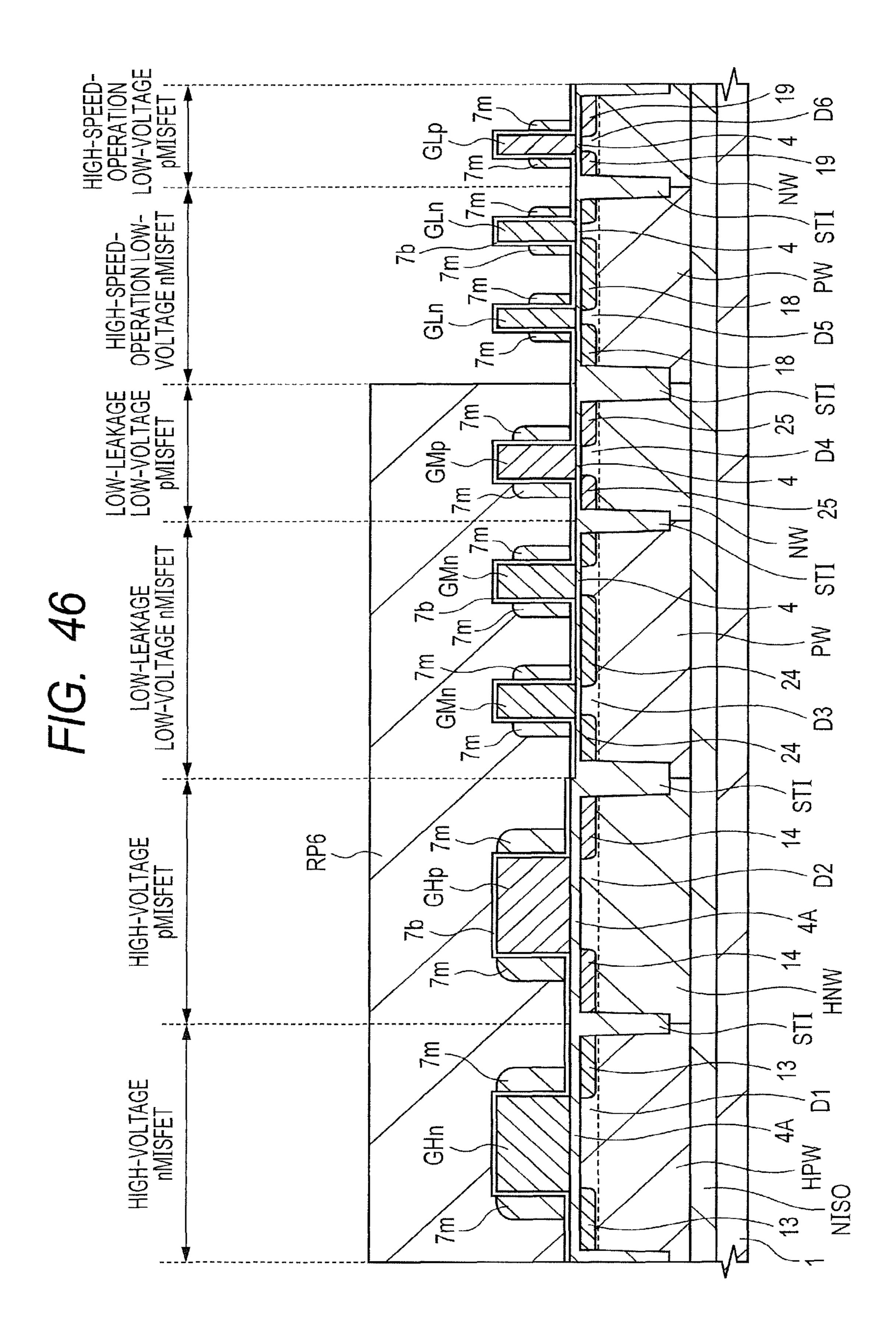

- FIG. **46** is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. **44** in a manufacturing step of the semiconductor device, which is subsequent to FIG. **45**;

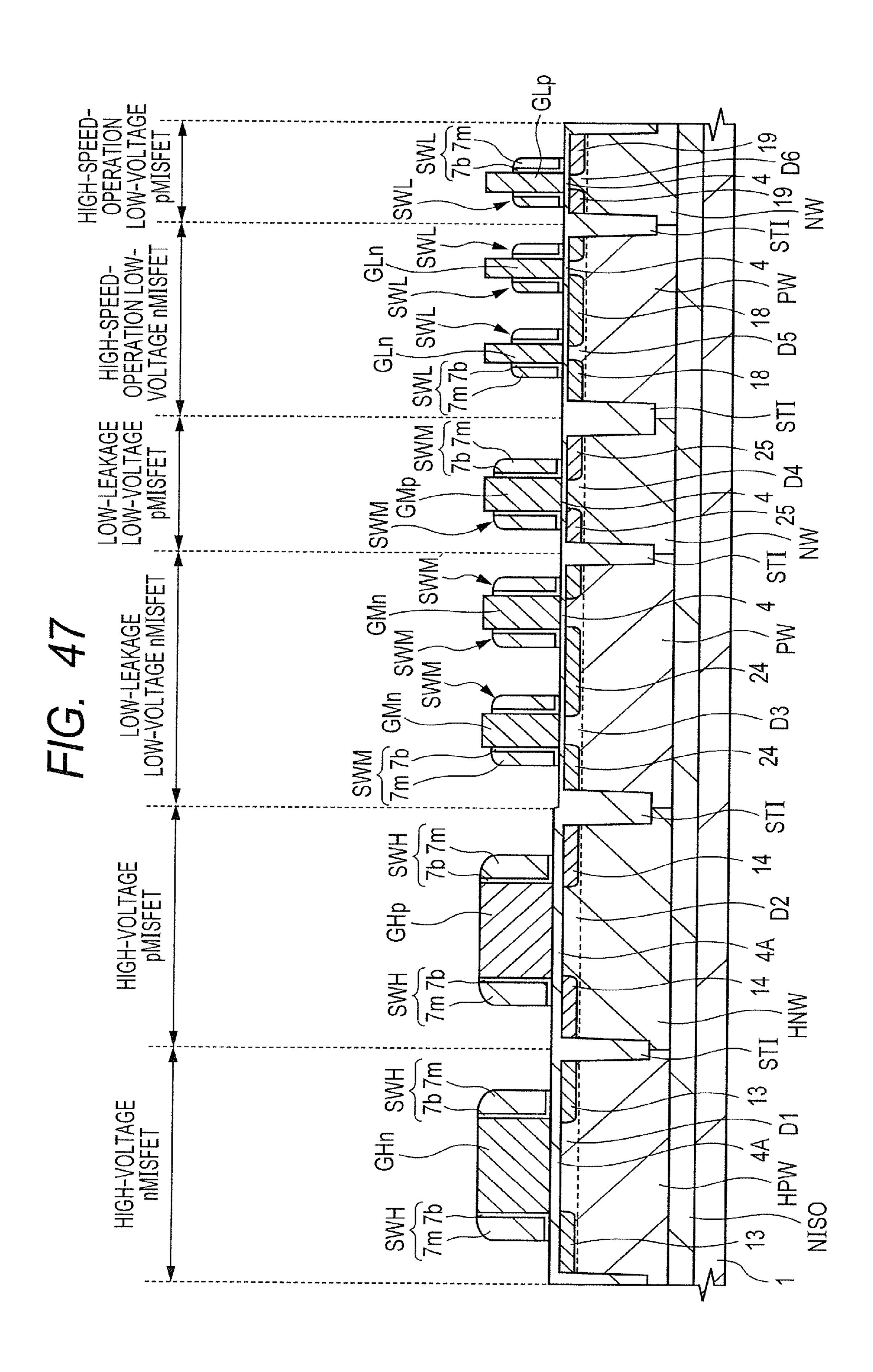

- FIG. 47 is a main-portion cross-sectional view of the same portion of the semiconductor device as shown in FIG. 44 in a manufacturing step of the semiconductor device, which is subsequent to FIG. 46;

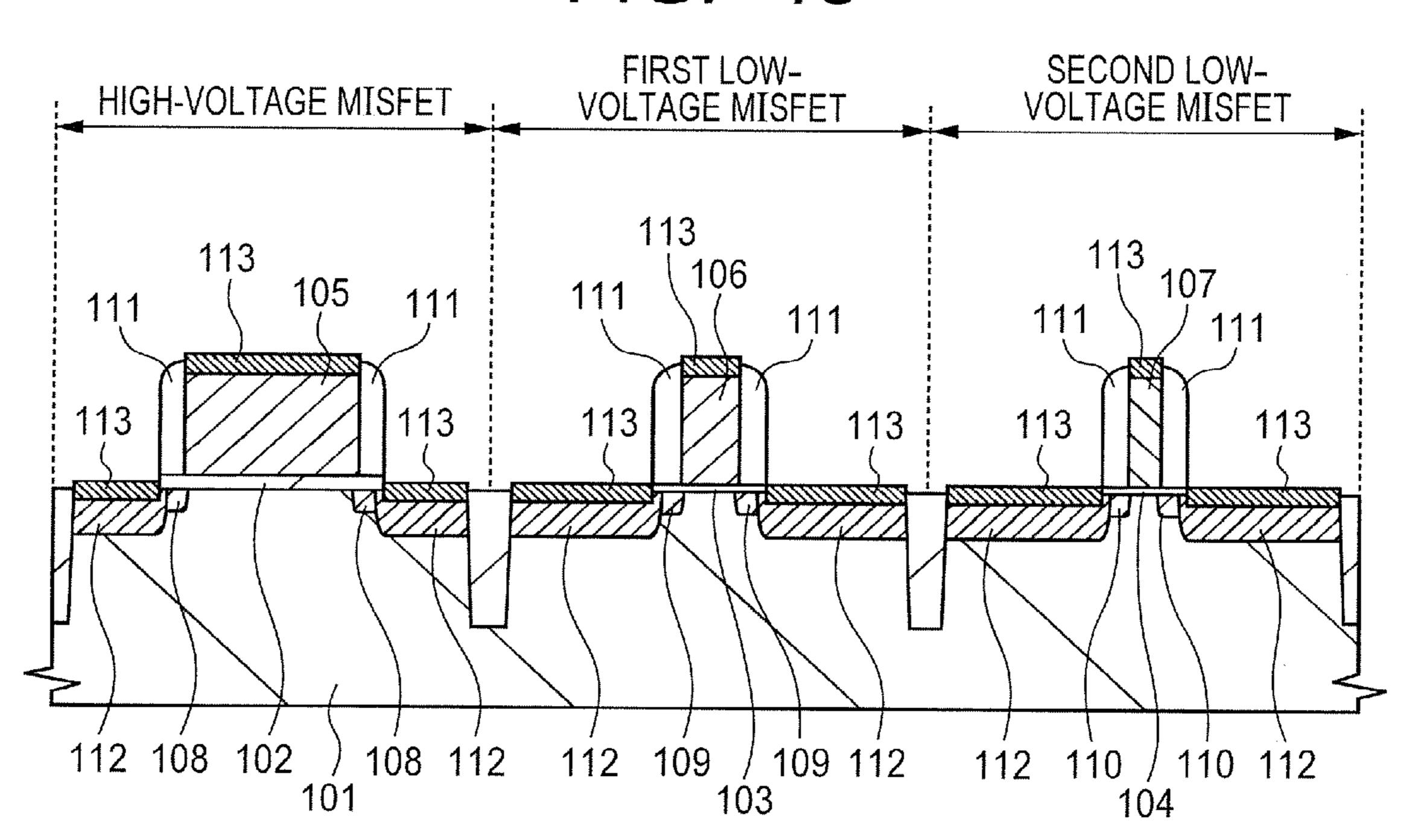

- FIG. 48 is a main-portion cross-sectional view of a semiconductor device (high-voltage MISFETs and low-voltage 55 MISFETs) studied by the present inventors, which illustrates a first example of a method of manufacturing the semiconductor device;

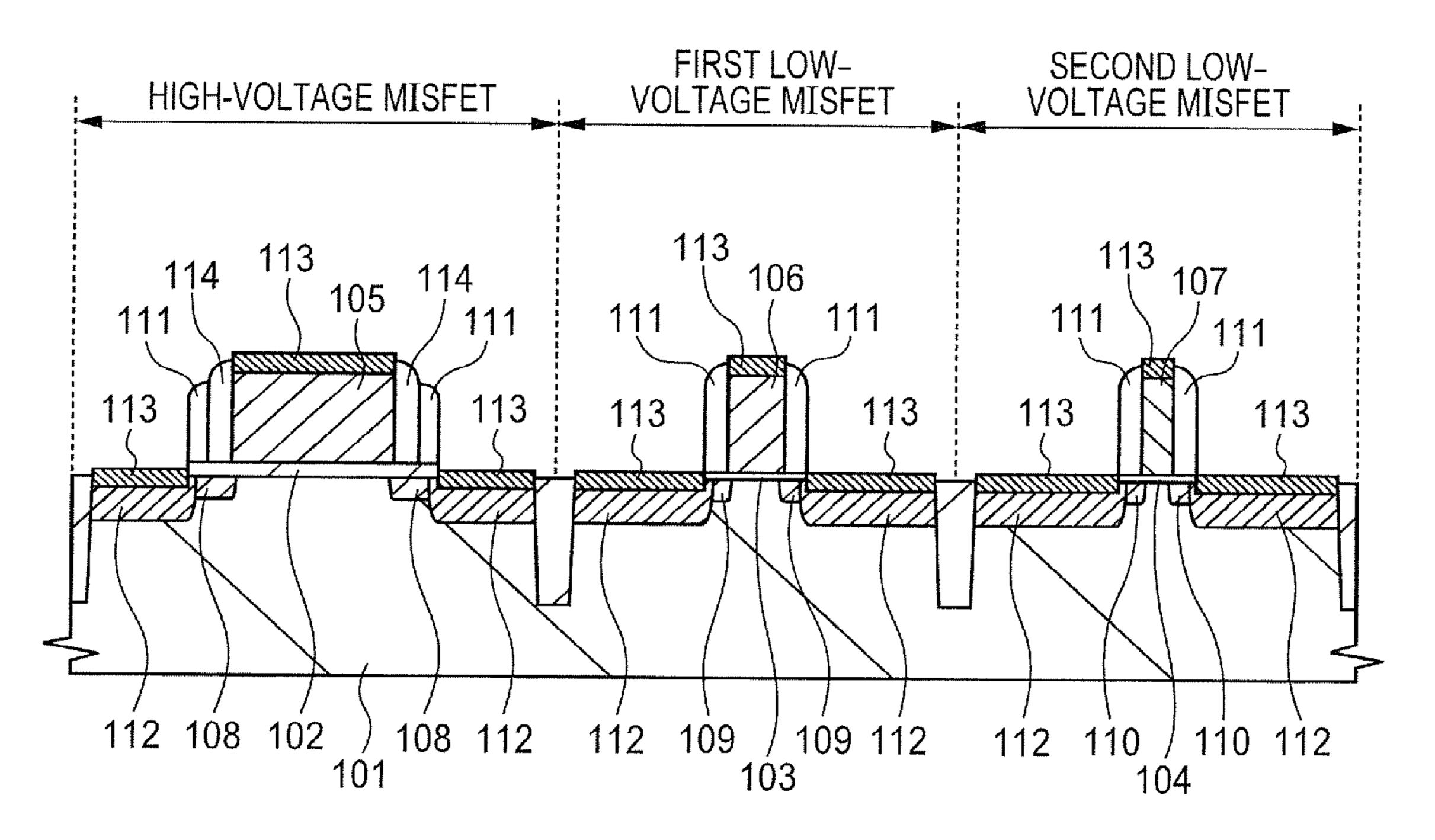

- FIG. 49 is a main-portion cross-sectional view of the semiconductor device (high-voltage MISFETs and low-voltage MISFETs) studied by the present inventors, which illustrates a second example of the method of manufacturing the semiconductor device;

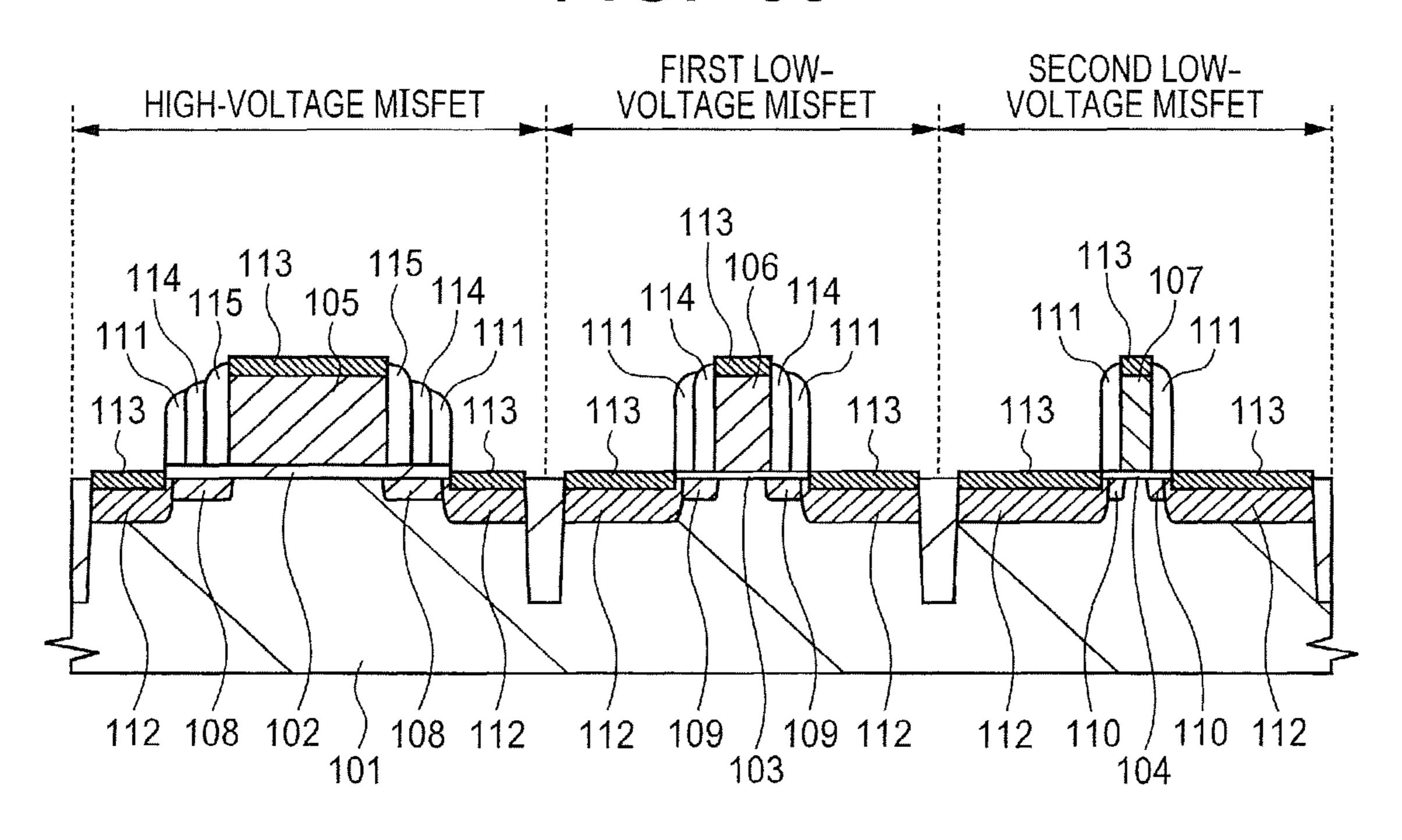

- FIG. **50** is a main-portion cross-sectional view of the semi-conductor device (high-voltage MISFETs and low-voltage MISFETs) studied by the present inventors, which illustrates a third example of the method of manufacturing the semiconductor device; and

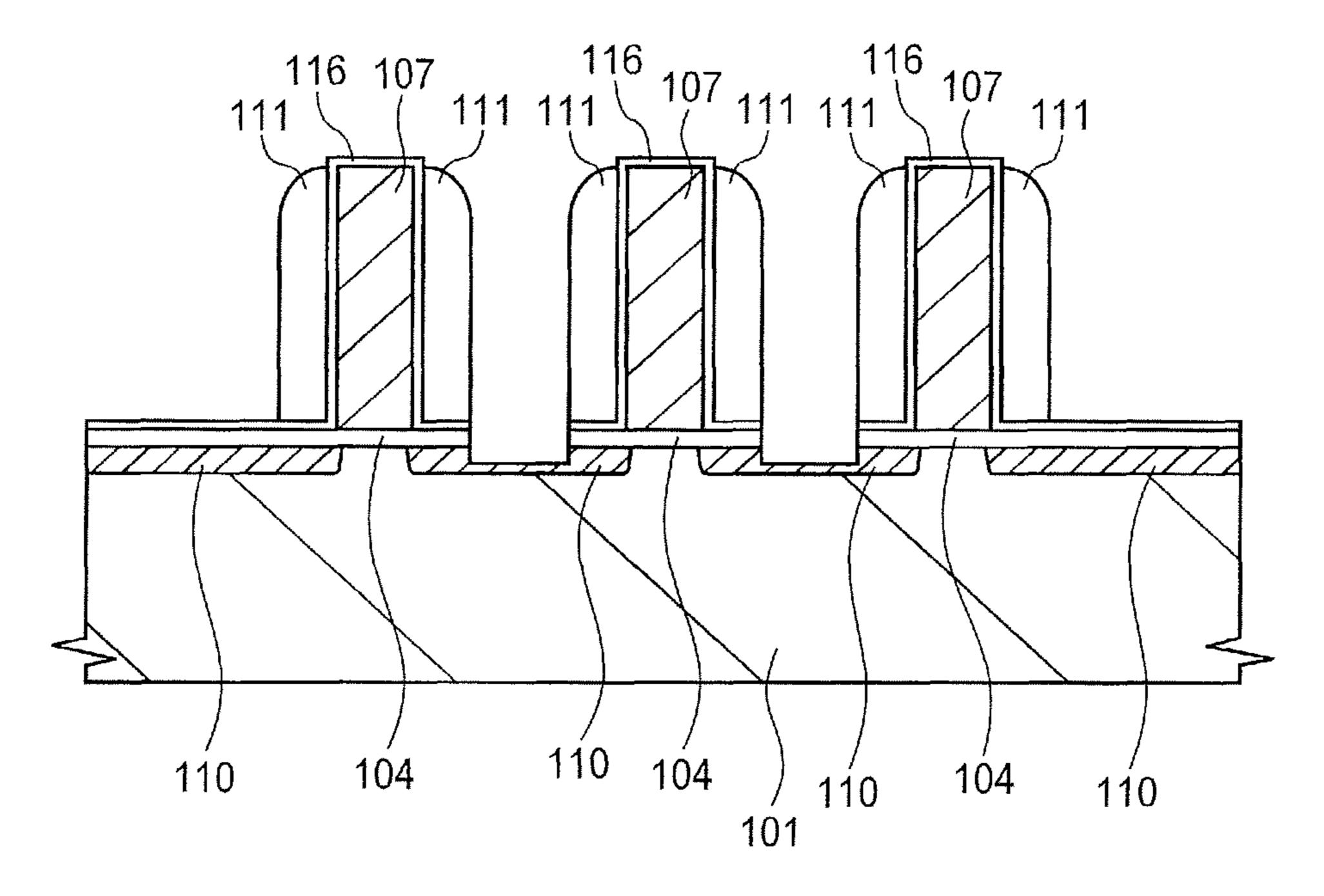

FIG. **51** is a main-portion cross-sectional view of the semiconductor device, which illustrates a processing defect in the process of manufacturing the semiconductor device found by the present inventors.

#### DETAILED DESCRIPTION

In the following embodiments, if necessary for the sake of convenience, the embodiments will be each described by being divided into a plurality of sections or embodiments. However, they are by no means irrelevant to each other unless particularly explicitly described otherwise, and one of the sections or embodiments is modifications, details, supplementary explanation, and so forth of part or the whole of the others.

When the number and the like (including the number, numerical value, amount, range, and the like thereof) of elements are referred to in the following embodiments, they are not limited to specific numbers unless particularly explicitly described otherwise or unless they are obviously limited to 20 specific numbers in principle. The number and the like of the elements may be not less than or not more than specific numbers. It will be appreciated that, in the present embodiments, the components thereof (including also elements, steps, and the like) are not necessarily indispensable unless 25 particularly explicitly described otherwise or unless the components are considered to be obviously indispensable in principle. Likewise, if the shapes, positional relationships, and the like of the components and the like are referred to in the following embodiments, the shapes and the like are assumed 30 to include those substantially proximate or similar thereto and the like unless particularly explicitly described otherwise or unless it can be considered that they obviously do not in principle. The same shall apply in regard to the foregoing numerical value and range.

In the following embodiments, a MISFET representative of a field effect transistor is shortened as a MIS, a p-channel MISFET is shortened as a pMISFET, and an n-channel MIS-FET is shortened as an nMISFET. It will be appreciated that a MONOS nonvolatile memory cell described in the follow- 40 ing embodiments is also included in the subordinate concept of the foregoing MIS. In the following embodiments, when silicon nitride is mentioned, it naturally includes Si<sub>3</sub>N<sub>4</sub>, but is not limited thereto. It is assumed that silicon nitride includes not only Si<sub>3</sub>N<sub>4</sub>, but also an insulating film of a nitride of 45 silicon having a similar composition. Also in the following embodiments, when a wafer is mentioned, it mainly refers to a Si (Silicon) single-crystal wafer, but is not limited thereto. It is assumed that a wafer refers to not only the Si single-crystal wafer, but also a SOI (Silicon On Insulator) wafer, an insu- 50 lating film substrate for forming an integrated circuit thereover, or the like. It is also assumed that the shape thereof includes not only a circular or approximately circular shape, but also a square, a rectangle, and the like.

Note that, throughout all the drawings for illustrating the following embodiments, members having the same functions are designated by the same reference numerals, and a repeated description thereof is omitted. Hereinbelow, the embodiments of the present invention will be described in detail based on the drawings.

First, a method of manufacturing high-voltage MISFETs and low-voltage MISFETs each studied by the present inventors prior to the present invention will be described below conceivably because, by doing so, a method of manufacturing a semiconductor device according to the embodiments of the present invention will become clearer. The gate insulating film of each of the high-voltage MISFETs is formed thicker

8

than the gate insulating film of each of the low-voltage MIS-FETs. Also, each of the high-voltage MISFETs is formed to have a gate length longer than that of each of the low-voltage MISFETs. Accordingly, even when a relatively high voltage is applied thereto, the high-voltage MISFETs can operate without breaking down. In addition, due to different breakdown voltages, the layout density of the high-voltage MISFETs is lower than that of the low-voltage MISFETs.

A first example of the method of manufacturing the high-voltage MISFETs and the low-voltage MISFETs each studied by the present inventors will be described below using FIG. **48**. FIG. **48** shows a main-portion cross-sectional view of each of the high-voltage MISFETs which is driven with an applied voltage of, e.g., 3.3 to 5 V, a main-portion cross-sectional view of each of first low-voltage MISFETs (low-leakage MISFETs) which is driven with an applied voltage of, e.g., 1.2 V, and a main-portion cross-sectional view of each of second low-voltage MISFETs (high-speed-operation MISFETs) which is driven with an applied voltage of, e.g., 1.2 V.

The leakage current between the gate and drain of the first low-voltage MISFET can be controlled to be lower than that of the second low-voltage MISFET, and the second low-voltage MISFET can perform a higher-speed operation than performed by the first low-voltage MISFET. That is, the first low-voltage MISFET and the second low-voltage MISFET are different in gate length and layout density. The gate length of the first low-voltage MISFET is longer than the gate length of the second low-voltage MISFET, and the layout density of the first low-voltage MISFETs is lower than the layout density of the second low-voltage MISFETs. Note that, here, the n-channel high-voltage MISFET, the n-channel first low-voltage MISFET, and the n-channel second low-voltage MISFET are shown by way of example.

First, over the main surface of a p-type semiconductor 35 substrate 101 in which the high-voltage MISFETs are formed, a gate insulating film 102 having a thickness of, e.g., about nm is formed and, over the main surface of the semiconductor substrate 101 in which the first and second lowvoltage MISFETs are formed, gate insulating films 103 and 104 each having a thickness of, e.g., about 3 nm are formed. Then, gate electrodes 105 of the high-voltage MISFETs are formed over the gate insulating film 102, gate electrodes 106 of the first low-voltage MISFETs are formed over the gate insulating film 103, and gate electrodes 107 of the second low-voltage MISFETs are formed over the gate insulating film 104. The gate lengths of the high-voltage MISFETs are, e.g., about 800 nm, the gate lengths of the first low-voltage MISFETs are, e.g., about 55 nm, and the gate lengths of the second low-voltage MISFETs are, e.g., about 44 nm. The gate electrodes 105, 106, and 107 are each made of, e.g., polysilicon.

Next, using the gate electrodes 105 of the high-voltage MISFETs as a mask, an n-type impurity is introduced into the semiconductor substrate 101 by an ion implantation method to form lightly doped diffusion layers 108 of the high-voltage MISFETs. Likewise, lightly doped diffusion layers 109 of the first low-voltage MISFETs are formed, and lightly doped diffusion layers 110 of the second low-voltage MISFETs are formed

Next, over the respective side surfaces of the gate electrodes 105 of the high-voltage MISFETs, the gate electrodes 106 of the first low-voltage MISFETs, and the gate electrodes 107 of the second low-voltage MISFETs, sidewalls 111 are formed. Then, using the gate electrodes 105 of the high-voltage MISFETs, the gate electrodes 106 of the first low-voltage MISFETs, the gate electrodes 107 of the second low-voltage MISFETs, and the sidewalls 111 as a mask, an n-type

impurity is introduced into the semiconductor substrate 101 by an ion implantation method to form heavily doped diffusion layers 112.

Next, by a self alignment method, over the gate electrodes 105, 106, and 107 and in the upper surfaces of the heavily 5 doped diffusion layers 112, silicide layers 113 are formed. Then, an interlayer insulating film which covers the high-voltage MISFETs, the first low-voltage MISFETs, and the second low-voltage MISFETs, interconnect wires, and the like are formed.

Note that the sidewall lengths of the sidewalls 111 formed over the respective surfaces of the gate electrodes 105 of the high-voltage MISFETs, the gate electrodes 106 of the first low-voltage MISFETs, and the gate electrodes 107 of the second low-voltage MISFETs are determined by perfor- 15 mance required of the second low-voltage MISFETs which are the shortest in gate length and the highest in layout density. Therefore, by performing ion implantation in forming the lightly doped diffusion layers 108 of the high-voltage MISFETs, the lightly doped diffusion layers 109 of the first 20 low-voltage. MISFETs, and the lightly doped diffusion layers 110 of the second low-voltage MISFETs in different process steps and appropriately using optimum ion implantation conditions (such as implantation energy and dose), performances required of the high-voltage MISFETs, the first low-voltage 25 MISFETs, and the second low-voltage MISFETs are satisfied.

However, the problem has arisen that, in each of the high-voltage MISFETs, an electric field between the gate electrode 105 and each of the silicide layers 113 formed in the upper 30 surfaces of the heavily doped diffusion layers 112 becomes intense to increase leakage currents between the gate electrode 105 and the heavily doped diffusion layers 112 and between the heavily doped diffusion layers 112 and the semiconductor substrate 101.

To solve the problem, the present inventors have studied the approach of setting the sidewall lengths of the sidewalls of the high-voltage MISFETs longer than, the sidewall lengths of the sidewalls of the first and second low-voltage MISFETs.

A second example of the method of manufacturing the 40 high-voltage MISFETs and the low-voltage MISFETs each studied by the present inventors will be described below using FIG. 49. The structures of the first and second low-voltage MISFETs are substantially the same as the structures shown in FIG. 48 described above. By contrast, in each of the highvoltage MISFETs, the two-layer sidewalls 111 and 114 are formed over the side surfaces of the gate electrode 105. Accordingly, in the high-voltage MISFET, the distance between the gate electrode 105 and each of the silicide layers 113 formed in the upper surfaces of the heavily doped diffusion layers **112** is increased to weaken the electric field. This has allowed reductions in the leakage currents between the gate electrode 105 and the heavily doped diffusion layers 112 and between the heavily doped diffusion layers 112 and the semiconductor substrate 101.

However, as semiconductor devices have been more highly integrated, in each of the first low-voltage MISFETs also, a demand for particularly reducing leakage currents between the gate electrode 106 and the heavily doped diffusion layers 112 has become stronger.

Accordingly, the present inventors have further studied the approach of setting the sidewall lengths of the sidewalls of the first low-voltage MISFETs longer than the sidewall lengths of the sidewalls of the second low-voltage MISFETs.

A third example of the method of manufacturing the high- 65 voltage MISFETs and the low-voltage MISFETs each studied by the present inventors will be described below using FIG.

**10**

50. The structure of each of the second low-voltage MISFETs is substantially the same as the structure shown in FIG. 48 described above. By contrast, in each of the first low-voltage MISFETs, the two-layer sidewalls 111 and 114 are formed over the side surfaces of the gate electrode 106 and, in each of the high-voltage MISFETs, the three-layer sidewalls 111, 114, and 115 are formed over the side surfaces of the gate electrode 105. Accordingly, in the first low-voltage MISFET, the electric field between the gate electrode 106 and each of the heavily doped diffusion layers 112 is weakened and, in the high-voltage MISFET, the electric field between the gate electrode 105 and each of the heavily doped diffusion layers 112 is further weakened to allow reductions in the respective leakage currents.

However, as shown in FIG. **51**, the problem has arisen that, in the second low-voltage MISFET, a part of the semiconductor substrate **101** between the adjacent gate electrodes **107** is cut. The following is a conceivable reason for this.

When the foregoing two-layer sidewalls 111 and 114 and the foregoing three-layer sidewalls 111, 114, and 115 are formed, it is necessary to repeat the step of depositing an upper-layer insulating film (e.g., a silicon oxide film) for covering the gate electrodes 105 of the high-voltage MIS-FETs, the gate electrodes 106 of the first low-voltage MIS-FETs, and the gate electrodes 107 of the second low-voltage MISFETs over the main surface of the semiconductor substrate 101, and the step of etching back the upper-layer insulating film. Under the upper-layer insulating film, a lower-layer insulating film (e.g., a silicon nitride film) 116 which functions as an etching stopper is formed.

When the space between the adjacent gate electrodes 105 or between the adjacent gate electrodes 106 is relatively wide as in the high-voltage MISFET or the first low-voltage MIS-FET, the composition ratio of an etching gas when the upperlayer insulating film is etched back remains unchanged so that the etching selectivity of the upper-layer insulating film to the lower-layer insulating film 116 remains unchanged. Therefore, the etching of the upper-layer insulating film can be stopped by the lower-layer insulating film 116. By contrast, when the space between the adjacent gate electrodes 107 is relatively narrow as in the second low-voltage MISFET, various gases forming an etching gas do not equally enter the spaces between the adjacent gate electrodes 107 so that the composition ratio of the etching gas when the upper-layer insulating film is etched back is undesirably changed. Accordingly, the etching selectivity of the upper-layer insulating film to the lower-layer insulating film 116 gradually changes. As a result, it becomes difficult for the lower-layer insulating film 116 to stop the etching of the upper-layer insulating film so that the semiconductor substrate 101 is partially cut.

# Embodiment 1

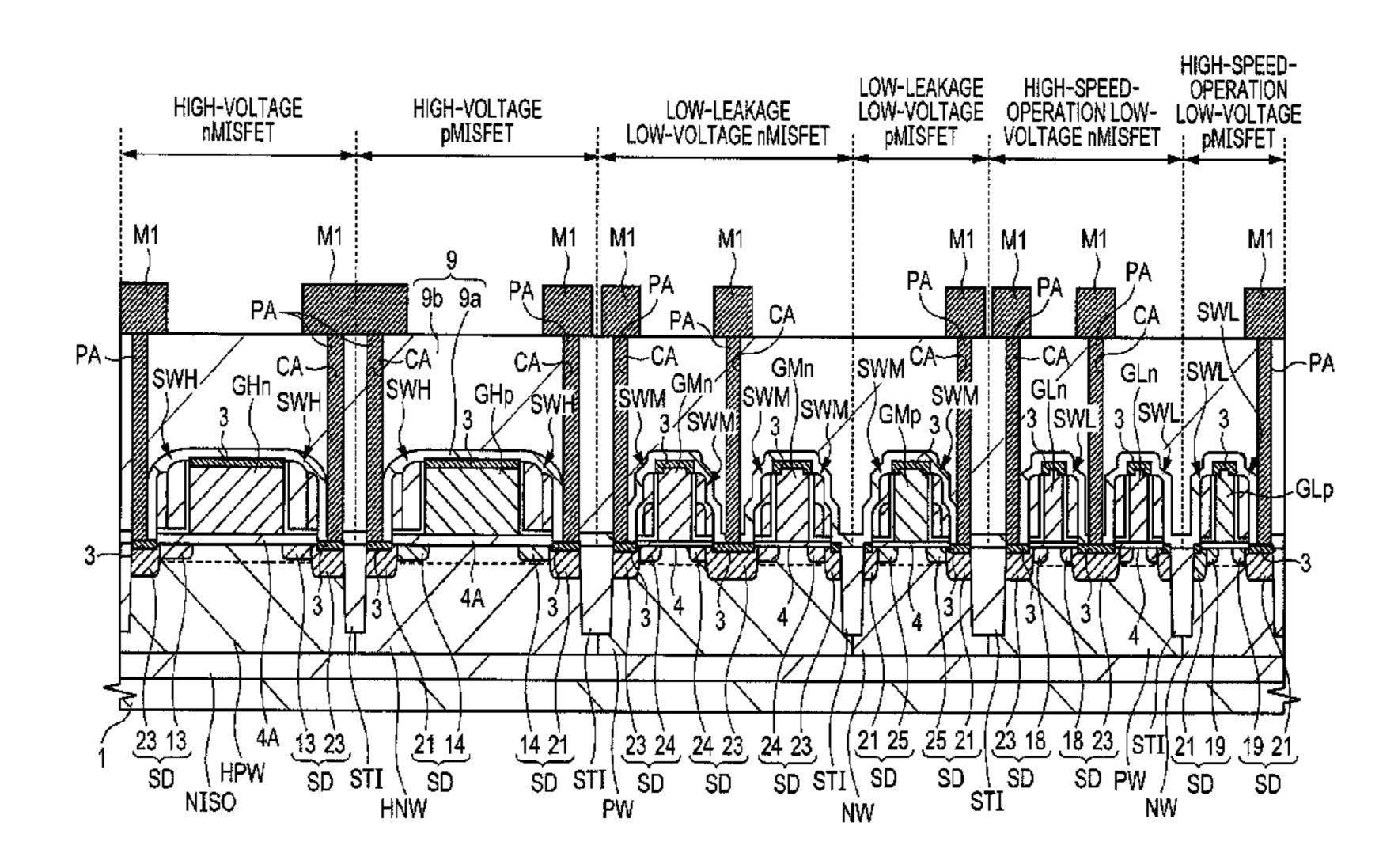

A method of producing a semiconductor device including first nMISFETs, first pMISFETs, second nMISFETs, second pMISFETs, third nMISFETs, and third pMISFETs which form a peripheral circuit according to Embodiment 1 will be described in the order of process steps using FIGS. 1 to 17.

FIGS. 1 to 17 are main-portion cross-sectional views of an example of the first nMISFETs, the first pMISFETs, the second nMISFETs, the second pMISFETs, the third nMISFETs, and the third pMISFETs which are formed in the peripheral circuit region in the manufacturing steps of the semiconductor device. Each of the drawings shows a main-portion cross section in which channels are cut along the gate length directions of gate electrodes. In Embodiment 1, the first nMIS-

FETs and the first pMISFETs are formed as, e.g., high-voltage MISFETs, the second nMISFETs and the second pMISFETs are formed as, e.g., low-leakage low-voltage MISFETs, and the third nMISFETs and the third pMISFETs are formed as, e.g., high-speed-operation low-voltage MIS- 5 FETs.

Each of the high-voltage MISFETs forms, e.g., an input/ output (I/O) circuit. Each of the low-voltage MISFETs forms a logic circuit such as, e.g., a PLL (Phase Locked Loop), a CPU (Central Processing Unit), or a processor. For the low- 10 voltage MISFETs, various structures which are different in gate material, gate length, impurity concentrations in the source/drain regions thereof, layout density, or the like are used appropriately depending on operation characteristics FETs of each of which a low-leakage operation is required (in each of which higher priority is given to a low-leakage operation than to a high-speed operation) and the high-speed-operation low-voltage MISFETs of each of which a high-speed operation is required (in each of which higher priority is given 20 to a high-speed operation than to a low-leakage operation) are shown by way of example.

Each of the high-voltage MISFETs is driven with an applied voltage of, e.g., 3.3 to 5 V. The gate length of the gate electrode thereof is, e.g., 800 nm, and the sidewall lengths of 25 sidewalls formed over the side surfaces of the gate electrode are, e.g., about 80 to 90 nm. Each of the low-leakage lowvoltage MISFETs is driven with an applied voltage of, e.g., 1.2 V. The gate length of the gate electrode thereof is, e.g., about 55 nm, and the sidewall lengths of sidewalls formed 30 over the side surfaces of the gate electrode are, e.g., about 40 to 50 nm. Each of the high-speed-operation low-voltage MIS-FETs is driven with an applied voltage of, e.g., 1.2 V. The gate length of the gate electrode thereof is, e.g., about 44 nm, and the sidewall lengths of sidewalls formed over the side sur- 35 faces of the gate electrode are, e.g., about 30 nm.

That is, the high-voltage MISFETs, the low-leakage lowvoltage MISFETs, and the high-speed-operation low-voltage MISFETs are different in terms of structure, mainly gate length and layout density. The gate lengths of the high-voltage MISFETs are the longest, and the gate lengths of the low-leakage low-voltage MISFETs and the high-speed-operation low-voltage MISFETs are progressively shorter in this order. Also, the layout density of the high-voltage MIS-FETs is the lowest, and the layout densities of the low-leakage 45 low-voltage MISFETs and the high-speed-operation lowvoltage MISFETs are progressively higher in this order.

First, as shown in FIG. 1, in the main surface of a semiconductor substrate (which is a thin plate of a semiconductor having a generally circular plan view shape and called a 50 semiconductor wafer at this stage) 1, e.g., a trench-shaped isolation portion STI, active regions located so as to be surrounded thereby, and the like are formed. That is, after an isolation trench is formed in a predetermined portion of the semiconductor substrate 1, an insulating film made of, e.g., a 55 silicon oxide or the like is deposited over the main surface of the semiconductor substrate 1. The insulating film is further polished by a CMP (Chemical Mechanical Polishing) method or the like so as to remain only in the isolation trench and thus embedded in the isolation trench. In this manner, the isolation 60 portion STI is formed.

Next, an n-type impurity is ion-implanted into the semiconductor substrate 1 to form an n-type embedded well NISO. Subsequently, a p-type impurity is selectively ionimplanted into the semiconductor substrate 1 in a first nMIS- 65 FET region to form a p-type well HPW, while an n-type impurity is selectively ion-implanted into the semiconductor

substrate 1 in a first pMISFET region to form an n-type well HNW. Likewise, a p-type impurity is selectively ion-implanted into the semiconductor substrate 1 in a second nMIS-FET region and a third nMISFET region to form p-type wells PW, while an n-type impurity is selectively ion-implanted into the semiconductor substrate 1 in a second pMISFET region and a third pMISFET region to form n-type wells NW.

Next, into the semiconductor substrate 1 in the first nMIS-FET region, the first pMISFET region, the second nMISFET region, the second pMISFET region, the third nMISFET region, and the third pMISFET region, predetermined impurities are respectively ion-implanted. Thus, in the semiconductor substrate 1 in the first nMISFET region, the first pMIS-FET region, the second nMISFET region, the second required thereof. Here, the low-leakage low-voltage MIS- 15 pMISFET region, the third nMISFET region, and the third pMISFET region, channel-formation semiconductor regions D1, D2, D3, D4, D5, and D6 are respectively formed.

> Next, by performing oxidation treatment on the semiconductor substrate 1, a gate insulating film 4A made of, e.g., a silicon oxide and having a thickness of about 10 to 20 nm is formed over the main surface of the semiconductor substrate 1. Subsequently, the gate insulating film 4A in the second nMISFET region, the second pMISFET region, the third nMISFET region, and the third pMISFET region is removed therefrom. Thereafter, oxidation treatment is performed on the semiconductor substrate 1. Thus, over the main surface of the semiconductor substrate 1 in the second nMISFET region, the second pMISFET region, the third nMISFET region, and the third pMISFET region, a gate insulating film 4 made of, e.g., a silicon oxide and having a thickness of about 1 to 5 nm is formed. The gate insulating film 4 is not limited to a silicon oxide film. The gate insulating film 4 may also be formed of a high-dielectric-constant film of a hafnium oxide (HfSiON) or the like.

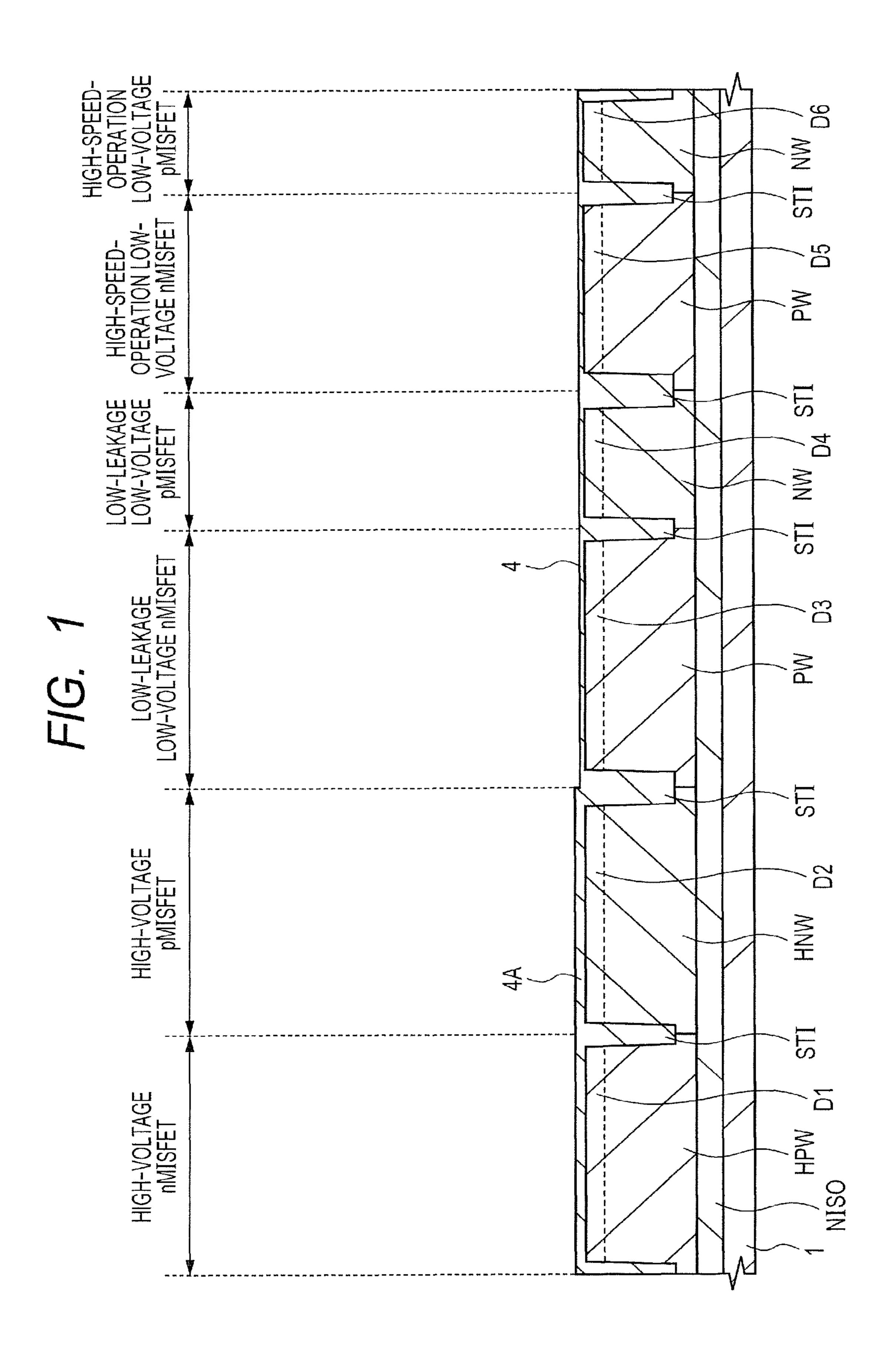

> Next, as shown in FIG. 2, over the main surface of the semiconductor substrate 1, a conductive film 10 made of, e.g., amorphous silicon is deposited by a CVD (Chemical Vapor Deposition) method. The thickness of the conductive film 10 is, e.g., about 100 nm.

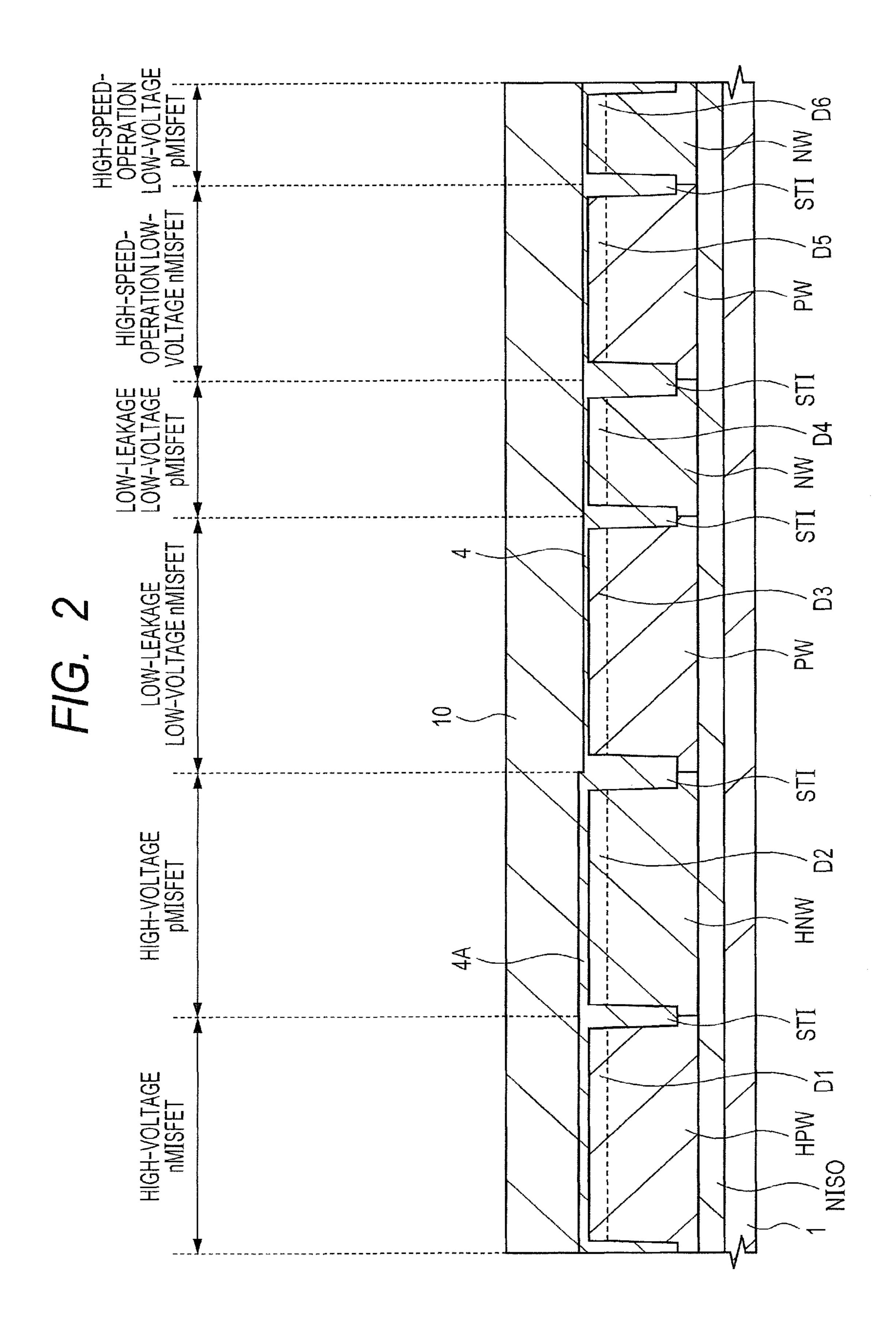

> Next, as shown in FIG. 3, an n-type impurity is introduced into the conductive film 10 in the first nMISFET region, the second nMISFET region, and the third nMISFET region by an ion implantation method or the like to form n-type conductive films 10na. On the other hand, a p-type impurity is introduced into the conductive film 10 in the first pMISFET region, the second pMISFET region, and the third pMISFET region by an ion implantation method or the like to form p-type conductive films 10p.

> Next, as shown in FIG. 4, the conductive films 10na and 10p are patterned using photolithography and dry etching to form gate electrodes GHn of the first nMISFETs each made of the conductive film 10na, gate electrodes GHp of the first pMISFETs each made of the conductive film 10p, gate electrodes GMn of the second nMISFETs each made of the conductive film 10na, gate electrodes GMp of the second pMIS-FETs each made of the conductive film 10p, gate electrodes GLn of the third nMISFETs each made of the conductive film 10na, and gate electrodes GLp of the third pMISFETs each made of the conductive film 10p.

> In the active region, the gate lengths of the gate electrodes GHn of the first nMISFETs and the gate electrodes GHp of the first pMISFETs are, e.g., about 800 nm. In the active region, the gate lengths of the gate electrodes GMn of the second nMISFETs and the gate electrodes GMp of the second pMISFETs are, e.g., about 55 nm, and the minimum spacing between the adjacent gate electrodes GMn, between the adjacent gate electrodes GMn and GMp, and between the adjacent

gate electrodes GMp is, e.g., about 110 nm. In the active region, the gate lengths of the gate electrodes GLn of the third nMISFETs and the gate electrodes GLp of the third pMISFETs are, e.g., about 44 nm, and the minimum spacing between the adjacent gate electrodes GLn, between the adjacent gate electrodes GLn and GLp, and between the adjacent gate electrodes GLp is, e.g., about 88 nm.

Next, as shown in FIG. **5**, into the main surface of the semiconductor substrate **1** in the first nMISFET region, an n-type impurity, e.g., arsenic is ion-implanted to form n<sup>-</sup>-type 10 semiconductor regions **13** in the main surface of the semiconductor substrate **1** in the first nMISFET region by self-alignment with respect to the gate electrodes GHn. Likewise, into the main surface of the semiconductor substrate **1** in the first pMISFET region, a p-type impurity, e.g., a boron fluoride is 15 ion-implanted to form p<sup>-</sup>-type semiconductor regions **14** in the main surface of the semiconductor substrate **1** in the first pMISFET region by self-alignment with respect to the gate electrodes GHp.

Next, into the main surface of the semiconductor substrate 1 in the second nMISFET region, an n-type impurity, e.g., arsenic is ion-implanted to form n<sup>-</sup>-type semiconductor and GI regions 24 in the main surface of the semiconductor substrate 1 in the second nMISFET region by self-alignment with respect to the gate electrodes GMn. Likewise, into the main 25 speed.

In second pMISFET region, a p-type impurity, e.g., a boron fluoride is ion-implanted to form p<sup>-</sup>-type semiconductor regions 25 in the main surface of the semiconductor substrate 1 in the second pMISFET region by self-alignment with respect to the gate 30 electrodes GMp.

Next, into the main surface of the semiconductor substrate 1 in the third nMISFET region, an n-type impurity, e.g., arsenic is ion-implanted to form n<sup>-</sup>-type semiconductor regions 18 in the main surface of the semiconductor substrate 35 1 in the third nMISFET region by self-alignment with respect to the gate electrodes GLn. Likewise, into the main surface of the semiconductor substrate 1 in the third pMISFET region, a p-type impurity such as, e.g., a boron fluoride is ion-implanted to form p<sup>-</sup>-type semiconductor regions 19 in the main 40 surface of the semiconductor substrate 1 in the third pMIS-FET region by self-alignment with respect to the gate electrodes GLp.

Next, as shown in FIG. 6, over the main surface of the semiconductor substrate 1, a first insulating film (e.g., silicon 45 nitride film) 7b is deposited by a CVD method. The thickness of the first insulating film 7b is, e.g., about 10 nm. Subsequently, over the first insulating film 7b, a second insulating film (e.g., silicon oxide film) 7*m* is formed by a CVD method. The thickness of the second insulating film 7m is, e.g., about 50 50 to 60 nm. Here, a material for the first insulating film 7b and a material for the second insulating film 7m are selectively determined to provide a high dry etching selectivity and a high wet etching selectivity (ratios between the etching speeds of the first insulating film 7b and the etching speeds of 55the second insulating film 7m). The respective thicknesses of the first insulating film 7b and the second insulating film 7mare set so as to approach the sidewall lengths (e.g., about 80 to 90 nm) of the sidewalls formed over the respective side surfaces of the gate electrodes GHn of the first nMISFETs and 60 the gate electrodes GHp of the first pMISFETs as target values.

Next, as shown in FIG. 7, the second insulating film 7*m* is etched back by anisotropic dry etching. Thus, the second insulating film 7*m* over the respective upper surfaces of the 65 gate electrodes GHn of the first nMISFETs, the gate electrodes GMn

**14**

of the second nMISFETs, the gate electrodes GMp of the second pMISFETs, the gate electrodes GLn of the third nMISFETs, and the gate electrodes GLp of the third pMISFETs and over the main surface of the semiconductor substrate 1 where the gate electrodes GHn, GHp, GMn, GMp, GLn, and GLp are not formed is removed completely or such that a part thereof (corresponding to e.g., about 1 to 3 nm) remains.

At this time, even when the second insulating film 7*m* over the upper surfaces of the gate electrodes GHn and GHp and over the main surface of the semiconductor substrate 1 where the gate electrodes GHn and GHp are not formed is removed completely in the first nMISFET region and the first pMISFET region, the second insulating film 7*m* may remain over the main surface of the semiconductor substrate 1 where the gate electrodes GLn and GLp are not formed in the third nMISFET region and the third pMISFET region. The conceivable reasons for this include the second insulating film 7*m* which is embedded in the spaces between the adjacent gate electrodes GLn and GLp, and between the adjacent gate electrodes GLn and GLp, and between the adjacent gate electrodes GLp, and the composition ratio of an etching gas used for the anisotropic dry etching which gradually changes to reduce the etching speed.

In such a case, it may also be possible to perform wet etching after performing the anisotropic dry etching and remove the second insulating film 7m remaining over the main surface of the semiconductor substrate 1 where the gate electrodes GLn and GLp are not formed. Even when the second insulating film 7m is embedded in the spaces between the adjacent gate electrodes GLn and GLp, and between the adjacent gate electrodes GLn and GLp, and between the adjacent gate electrodes GLp, an etchant can enter the second insulating film 7m from an interfacial surface in contact with the surface of the second insulating film 7m due to capillary and remove the second insulating film 7m remaining over the main surface of the semiconductor substrate 1 where the gate electrodes GLn and GLp are not formed.

Next, as shown in FIG. 8, the first nMISFET region and the first pMISFET region are covered with a photoresist pattern RP1, and the second insulating film 7m in the second nMISFET region, the second pMISFET region, the third nMISFET region, and the third pMISFET region is processed by isotropic wet etching or isotropic dry etching. Since isotropic etching is used, the second insulating film 7m is etched from above in a vertical direction and in a lateral direction.

Thus, over each of the side surfaces of the gate electrodes GMn of the second nMISFETs, the gate electrodes GMp of the second pMISFETs, the gate electrodes GLn of the third nMISFETs, and the gate electrodes GLp of the third pMISFETs, the second insulating film 7m having a width of about 20 to 30 nm in the lateral direction (gate length direction) is left. Since the etching selectivity between the first insulating film 7b and the second insulating film 7m is high, the first insulating film 7b is unlikely to be etched, and therefore the main surface of the semiconductor substrate 1 is not partially cut.

Next, as shown in FIG. 9, after the photoresist pattern RP1 is removed, the first nMISFET region, the first pMISFET region, the second nMISFET region, and the second pMISFET region are covered with a photoresist pattern RP2, and the second insulating film 7m in the third nMISFET region and the third pMISFET region is removed by isotropic wet etching. In the same manner as in the previous step, the etching selectivity between the first insulating film 7b and the second insulating film 7m is high so that the first insulating

film 7b is unlikely to be etched, and therefore the main surface of the semiconductor substrate 1 is not partially cut.

Next, as shown in FIG. 10, after the photoresist pattern RP2 is removed, a third insulating film (e.g., silicon oxide film) 7t is deposited over the main surface of the semiconductor substrate 1 by a CVD method. The thickness of the third insulating film 7t is, e.g., about 20 to 30 nm. The thickness of the third insulating film 7t is set so as to approach the sidewall lengths (e.g., about 30 nm) of the sidewalls formed over the respective side surfaces of the gate electrodes GLn of the third 10 nMISFETs and the gate electrodes GLp of the third pMISFETs as target values.

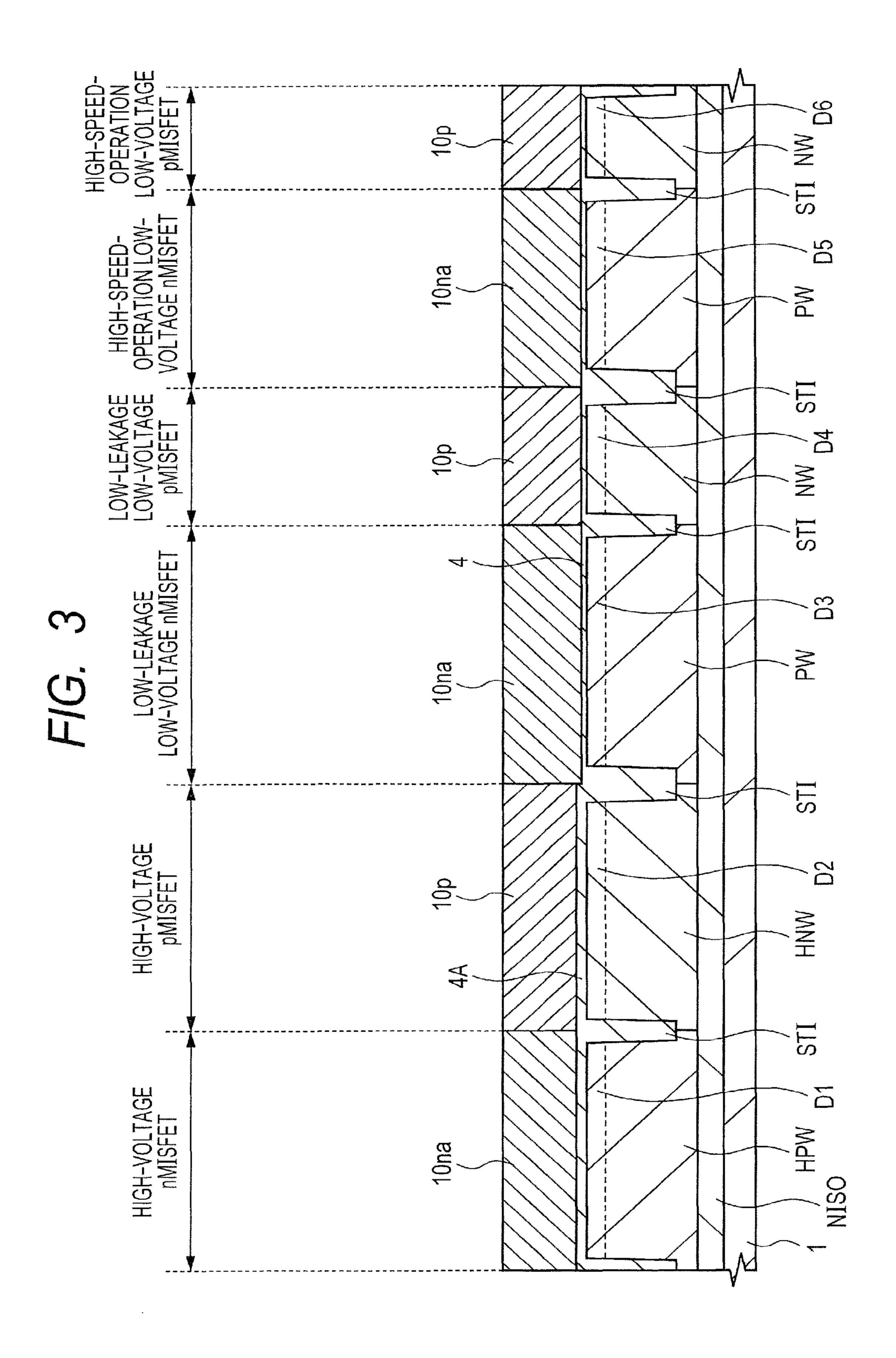

Next, as shown in FIG. 11, after the third insulating film 7t is etched back by anisotropic dry etching, the exposed first insulating film 7b is removed by dry etching or wet etching. 15 Thus, in the first nMISFETs and the first pMISFETs, sidewalls SWH each including the first insulating film 7b, the second insulating film 7m, and the third insulating film 7t are formed over the side surfaces of the gate electrodes GHn and GHp. Also, in the second nMISFETs and the second pMIS- 20 FETs, sidewalls SWM each including the first insulating film 7b, the second insulating film 7m, and the third insulating film 7t are formed over the side surfaces of the gate electrodes GMn and GMp. On the other hand, in the third nMISFETs and the third pMISFETs, sidewalls SWL each including the 25 first insulating film 7b and the third insulating film 7t are formed over the side surfaces of the gate electrodes GLn and GLp. The sidewall lengths of the foregoing sidewalls SWH are, e.g., about 80 to 90 nm. The sidewall lengths of the foregoing sidewalls SWM are, e.g., about 40 to 50 nm. The 30 sidewall lengths of the foregoing sidewalls SWL are, e.g., about 30 nm.

By thus reducing the number of anisotropic etching steps in the manufacturing processes (of three kinds in Embodiment 1) for forming the plurality of sidewalls SWL, SWM, and 35 SWH having different sidewall lengths and combining anisotropic dry etching with isotropic wet etching or isotropic dry etching, the foregoing sidewalls SWL, SWM, and SWH are formed. As a result, particularly in the third nMISFET region and the third pMISFET region where layout densities are 40 high, the semiconductor substrate 1 can be prevented from being partially cut between the adjacent gate electrodes GLn, between the adjacent gate electrodes GLn and GLp, and between the adjacent gate electrodes GLp.

The heights of the sidewalls SWM formed over the side surfaces of the gate electrodes GMn and GMp of the second nMISFETs and the second pMISFETs from the main surface of the semiconductor substrate 1 are lower than the heights of the gate electrodes GMn and GMp from the main surface of the semiconductor substrate 1. Likewise, the heights of the sidewalls SWL formed over the side surfaces of the gate electrodes GLn and GLp of the third nMISFETs and the third pMISFETs from the main surface of the semiconductor substrate 1 are lower than the heights of the gate electrodes GLn and GLp from the main surface of the semiconductor substrate 1. The heights of the foregoing sidewalls SWM from the main surface of the semiconductor substrate 1 are the same as the heights of the foregoing sidewalls SWL from the main surface of the semiconductor substrate 1.

Thus, in the regions where the spacings between the adjacent gate electrodes are relative small, the heights of the foregoing sidewalls SWM and SWL from the main surface of the semiconductor substrate 1 are reduced to allow an improvement in the coverage (embeddedness) of an interlayer insulating film formed over the main surface of the 65 semiconductor substrate 1 in the step described later. When the coverage (embeddedness) of the interlayer insulating film

**16**

is improved, in the third nMISFET region and the third pMISFET region, the interlayer insulating film is more likely to enter the spaces between the adjacent gate electrodes GLn, between the adjacent gate electrodes GLn and GLp, and between the adjacent gate electrodes GLp, and a void (cavity) is less likely to be formed. If the void is formed, when contact holes are formed in the interlayer insulating film in the step described later, the contact holes suffer shape defects, which may cause a short-circuit between the adjacent contact holes.

On the other hand, the heights of the sidewalls SWH formed over the side surfaces of the gate electrodes GHn and GHp of the first nMISFETs and the first pMISFETs from the main surface of the semiconductor substrate 1 are substantially the same as the heights of the gate electrodes GHn and GHp from the main surface of the semiconductor substrate 1. In addition, the heights of the foregoing sidewalls SWH from the main surface of the semiconductor substrate 1 are higher than the heights of the foregoing sidewalls SWM and SWL from the main surface of the semiconductor substrate 1. Thus, the heights of the foregoing sidewalls SWH from the main surface of the semiconductor substrate 1 are not set as low as those of the other foregoing sidewalls SWM and SWL from the main surface of the semiconductor substrate 1 for the following reason. That is, since the layout densities of the first nMISFETs and the first pMISFETs are lower than the layout densities of the second nMISFETs, the second pMISFETs, the third nMISFETs, and the third pMISFETs, the coverage (embeddedness) of the interlayer insulating film formed over the main surface of the semiconductor substrate 1 in the step described later is excellent. Accordingly, there is no need to reduce the heights of the foregoing sidewalls SWH from the main surface of the semiconductor substrate 1.

Also, in the third nMISFETs and the third pMISFETs, the sidewall lengths of the sidewalls SWL formed over the side surfaces of the gate electrodes GLn and GLp are determined by the thickness of the third insulating film 7t, and etching conditions for the anisotropic dry etching of the third insulating film 7t. This leads to high layout densities and easy control of the operation characteristics of the third nMISFETs and the third pMISFETs which are each required to perform a high-speed operation.

Next, as shown in FIG. 12, into the main surface of the semiconductor substrate 1 in the first nMISFET region, the second nMISFET region, and the third nMISFET region, n-type impurities, e.g., arsenic and phosphorus are ion implanted using a photoresist pattern 22 as a mask to form n<sup>+</sup>-type semiconductor regions 23 by self-alignment with respect to the gate electrodes GHn of the first nMISFETs, the gate electrodes GMn of the second nMISFETs, and the gate electrodes GLn of the third nMISFETs.

Thus, source/drain regions SD of the first nMISFETs including the n<sup>-</sup>-type semiconductor regions 13 and the n<sup>+</sup>-type semiconductor regions 23 are formed, the source/drain regions SD of the second nMISFETs including the n<sup>-</sup>-type semiconductor regions 24 and the n<sup>+</sup>-type semiconductor regions 23 are formed, and the source/drain regions SD of the third nMISFETs including the n<sup>-</sup>-type semiconductor regions 18 and the n<sup>+</sup>-type semiconductor regions 23 are formed.

Next, as shown in FIG. 13, into the main surface of the semiconductor substrate 1 in the first pMISFET region, the second pMISFET region, and the third pMISFET region, a p-type impurity, e.g., boron or a boron fluoride is ion-implanted using a photoresist pattern 20 as a mask to form p<sup>+</sup>-type semiconductor regions 21 by self-alignment with respect to the gate electrodes GHp of the first pMISFETs, the

gate electrodes GMp of the second pMISFETs, and the gate electrodes GLp of the third pMISFETs.

Thus, the source/drain regions SD of the first pMISFETs including the p<sup>-</sup>-type semiconductor regions **14** and the p<sup>+</sup>-type semiconductor regions **21** are formed, the source/drain regions SD of the second pMISFETs including the p<sup>-</sup>-type semiconductor regions **25** and the p<sup>+</sup>-type semiconductor regions **21** are formed, and the source/drain regions SD of the third pMISFETs including the p<sup>-</sup>-type semiconductor regions **19** and the p<sup>+</sup>-type semiconductor region **21** are formed.

Next, as shown in FIG. 14, over the gate electrodes GHn of the first nMISFETs, in the upper surfaces of the n<sup>+</sup>-type semiconductor regions 23, over the gate electrodes GHp of the first pMISFETs, in the upper surfaces of the p<sup>+</sup>-type semiconductor regions 21, over the gate electrodes GMn of the second nMISFETs, in the upper surfaces of the n<sup>+</sup>-type semiconductor regions 23, over the gate electrodes GMp of the second pMISFETs, in the upper surfaces of the p<sup>+</sup>-type semiconductor regions 21, over the gate electrodes GLn of the third nMISFETs, in the upper surfaces of the n<sup>+</sup>-type semiconductor regions 23, over the gate electrodes GLp of the third pMISFETs, and in the upper surfaces of the p<sup>+</sup>-type semiconductor regions 21, silicide layers 3 are formed by a 25 Salicide (Self-Align silicide) process. For the silicide layers 3, e.g., nickel silicide, cobalt silicide, or the like is used.

By forming the silicide layers 3, coupling resistance between the silicide layers 3 and plugs or the like formed thereover in the step described later can be reduced. In addition, it is possible to reduce the resistances of the gate electrodes GHn of the first nMISFETs, the gate electrodes GHp of the first pMISFETs, the gate electrodes GMn of the second nMISFETs, the gate electrodes GMp of the second pMISFETs, the gate electrodes GLn of the third nMISFETs, and the gate electrodes GLp of the third pMISFETs as well as the resistances of the source/drain regions SD.

Here, in the first nMISFETs and the first pMISFETs, a silicide reaction proceeds from each of the exposed upper surfaces of the gate electrodes GHn and GHp. On the other 40 hand, in the second nMISFETs and the second pMISFETs, a silicide reaction proceeds from each of the exposed upper surfaces and both side surfaces of the gate electrodes GMn and GMp. Likewise, in the third nMISFETs and the third pMISFETs, a silicide reaction proceeds from each of the 45 exposed upper surfaces and both side surfaces of the gate electrodes GLn and GLp. As a result, the silicide layers 3 are formed also over the both side surfaces of the upper portions of the gate electrodes GMn, GMp, GLn, and GLp. Therefore, it is possible to further reduce the resistances of the gate 50 electrodes GMn, GMp, GLn, and GLp.

If the portions of the silicide layer 3 formed by the silicide reaction which proceeds from the both side surfaces of the upper portion of each of the gate electrodes GMn and GMp of the second nMISFETs and the second pMISFETs and the 55 gate electrodes GLn and GLp of the third nMISFETs and the third pMISFETs are united, the film thickness of the entire silicide layer 3 equals the total film thickness of the film thickness of the portion of the silicide layer 3 formed from the upper surface and the film thicknesses of the portions of 60 thereof formed from the both side surfaces of the upper portion, though not shown. As a result, a case may also be considered where the film thicknesses of the silicide layers 3 formed over the gate electrodes GMn and GMp of the second nMISFETs and the second pMISFETs and the gate electrodes 65 GLn and GLp of the third nMISFETs and the third pMISFETs are larger than the film thicknesses of the silicide layers 3

18

formed over the gate electrodes GHn and GHp of the first nMISFETs and the first pMISFETs.

Next, as shown in FIG. 15, over the main surface of the semiconductor substrate 1, a silicon nitride film 9a is deposited as an insulating film by a CVD method. The silicon nitride film 9a functions as an etching stopper when contact holes are formed in the step described later.

Next, as shown in FIG. 16, a silicon oxide film 9b is deposited as an insulating film by a CVD method and, by polishing the surface of the silicon oxide film 9b by a CMP method, an interlayer insulating film 9 including the silicon nitride film 9a and the silicon oxide film 9b is formed. As described above, in the third nMISFETs and the third p-type MISFETs, the sidewalls SWL are formed to have heights 15 from the main surface of the semiconductor substrate 1 which are lower than the heights of the gate electrodes GLn and GLp from the main surface of the semiconductor substrate 1. Therefore, the interlayer insulating film 9 can be formed to show excellent coverage (embeddedness). The improved coverage (embeddedness) of the interlayer insulating film 9 can prevent the contact holes formed in the interlayer insulating film 9 in the step described later from suffering shape defects.

Next, as shown in FIG. 17, in the first nMISFETs, the first pMISFETs, the second nMISFETs, the second pMISFETs, the third nMISFET, and the third pMISFETs, contact holes CA are formed to reach the silicide layers 3 formed over the gate electrodes GHn, GHp, GMn, GMp, GLn, and GLp and in the respective upper surfaces of the source/drain regions SD. In FIG. 17, for simpler illustration, only the contact holes CA reaching the source/drain regions SD of the first nMISFET, the first pMISFET, the second nMISFET, the second pMISFET, the third nMISFET, and the third pMISFET are shown by way of example.

Next, in the contact holes CA, plugs PA are formed. The plugs PA are each formed of a laminate film including a relatively thin barrier film in which, e.g., titanium and a titanium nitride are stacked and a relatively thick conductive film made of tungsten, aluminum, or the like and formed so as to be wrapped with the barrier film. Thereafter, over the interlayer insulating film **9**, a first-layer interconnect wire M1 containing, e.g., copper or aluminum as a main component is formed.

By the manufacturing process described above, in the peripheral circuit region, the first nMISFETs, the first pMISFETs, the second nMISFETs, the second pMISFETs, the third nMISFETs, and the third pMISFETs are substantially completed. Thereafter, by performing typical manufacturing steps of a semiconductor device, further upper-layer interconnect wires are formed, whereby the semiconductor device having the nonvolatile memory is manufactured.

Note that, in Embodiment 1 described above, as the MIS-FETs including the gate electrodes having gate lengths shorter than the gate lengths of the gate electrodes GHn and GHp of the first nMISFETs and the first pMISFETs and longer than the gate lengths of the gate electrodes GLn and GLp of the third nMISFETs and the third pMISFETs, the second nMISFETs and the second pMISFETs are shown by way of example, but they are not limited thereto. For examples, MISFETs forming nonvolatile memory cells formed in a memory region can also be shown by way of example.

In recent years, as an electrically rewritable nonvolatile memory cell, a MONOS (Metal Oxide Nitride Oxide Silicon) nonvolatile memory cell using an insulating film having a trap level, such as a nitride film, as a charge storing layer has drawn attention. In this case, charges contributing to data

storage are stored in a discrete trap in the nitride film which is an insulator. Accordingly, even if a defect occurs in any part of an oxide film surrounding a storage node to cause an abnormal leakage, not all the charges in the charge storing layer come off. Therefore, it is possible to improve the reliability of 5 data retention.

However, a semiconductor device including a nonvolatile memory in which the MONOS nonvolatile memory cells are arranged as an array have various technical problems to be solved, which will be described below.

To achieve a nonvolatile memory having high reliability, high reliability is required also of the peripheral circuit of the nonvolatile memory. For example, the peripheral circuit needs a voltage boosting circuit for generating a voltage higher than a power source voltage given from the outside, a 15 circuit for applying the generated high voltage to any of the nonvolatile memory cells, and the like. Accordingly, when the nonvolatile memory is to be operated, semiconductor elements each having breakdown voltage performance higher than that of each of the nonvolatile memory cells are required 20 for the peripheral circuit.

Accordingly, the present inventors have formed the low-voltage MISFETs each operating at a relatively low voltage (e.g., the same voltage as the power source voltage) and the high-voltage MISFETs each operating at a voltage higher 25 than the voltage at which each of the low-voltage MISFETs operates in the peripheral circuit to thereby implement desired operation performance and breakdown voltage performance.

The method of manufacturing the semiconductor device 30 having the nonvolatile memory cells, first nMISFETs, first pMISFETs, third nMISFETs, and third pMISFETs according to Embodiment 1 will be described in the order of process steps using FIGS. 18 to 37. FIGS. 18 to 37 are main-portion cross-sectional views of the nonvolatile memory cells which 35 are formed in the memory region, the first nMISFETs, the first pMISFETs, the third nMISFETs, and the third pMISFETs which are formed in the peripheral circuit region in the manufacturing steps of the semiconductor device. Each of the drawings shows a main-portion cross section in which the 40 channels are cut along the gate length directions of the gate electrodes. The first nMISFETs and the first pMISFETs are formed as, e.g., the high-voltage MISFETs, while the third nMISFETs and the third pMISFETs are formed as, e.g., the high-speed-operation low-voltage MISFETs.

As the nonvolatile memory cells, MONOS nonvolatile memory cells each having a split-gate structure in which the memory gate electrode of a memory nMISFET in the form of a sidewall is formed on one side surface of the selection gate electrode of a selection nMISFET is shown by way of 50 example. The sidewall lengths of the sidewalls formed over the side surfaces of the selection gate electrodes opposite to the memory gate electrodes and over the side surfaces of the memory gate electrodes are about 40 to 50 nm.

The first nMISFETs and the first pMISFETs forming the peripheral circuit are the same as described above, and each driven with an applied voltage of, e.g., 3.3 to 5 V. The sidewall lengths of the sidewalls formed over the side surfaces of the gate electrodes thereof are, e.g., about 80 to 90 nm. The third nMISFETs and the third pMISFETs forming the peripheral circuit are the same as described above, and each driven with an applied voltage of, e.g., 1.2 V. The sidewall lengths of the sidewalls formed over the side surfaces of the gate electrodes thereof are, e.g., about 30 nm.

That is, the first nMISFETs and the first pMISFETs formed 65 in the peripheral circuit region, the third nMISFETs and the third pMISFETs formed in the peripheral circuit region, and

**20**

the nonvolatile memory cells formed in the memory region are different in terms of gate length and layout density. The gate lengths of the first nMISFETs and first pMISFETs are the longest, and the gate lengths of the nonvolatile memory cells and the third nMISFETs and third pMISFETs are progressively shorter in this order. The layout density of the first nMISFETs and first pMISFETs is the lowest, and the layout densities of the nonvolatile memory cells and the third nMISFETs and third pMISFETs are progressively higher in this order.

First, as shown in FIG. 18, in the same manner as described above using FIG. 1, the isolation portion STI is formed in the main surface of the semiconductor substrate 1, and an n-type embedded well NISO, a p-type well HPW, an n-type well HNW, a p-type well PW, and an n-type well NW are formed. Then, into the semiconductor substrate 1 in the memory region, a p-type impurity is selectively ion-implanted. Thus, in the semiconductor substrate 1 in the memory region, a p-type semiconductor region 5 for forming the channels of the selection nMISFETs is formed. Likewise, into the semiconductor substrate 1 in the first nMISFET region, the first pMIS-FET region, the third nMISFET region, and the third pMIS-FET region, predetermined impurities are ion-implanted. Thus, in the semiconductor substrate 1 in the first nMISFET region, the first pMISFET region, the third nMISFET region, and the third pMISFET region, the channel-formation semiconductor regions D1, D2, D5, and D6 are formed.

Next, over the main surface of the semiconductor substrate 1 in the first nMISFET region and the first pMISFET region, a gate insulating film 4A made of, e.g., a silicon oxide and having a thickness of about 10 to 20 nm is formed and, over the main surface of the semiconductor substrate 1 in the memory region, the third nMISFET region, and the third pMISFET region, a gate insulating film 4 made of, e.g., a silicon oxide and having a thickness of about 1 to 5 nm is formed

Next, as shown in FIG. 19, over the main surface of the semiconductor substrate 1, the conductive film 10 made of, e.g., amorphous silicon is deposited by a CVD method. Then, into the conductive film 10 in the memory region, an n-type impurity is introduced by an ion implantation method or the like to form an n-type conductive film 10n. The thicknesses of the conductive films 10 and 10n are, e.g., about 100 nm.

Next, as shown in FIG. **20**, the n-type conductive film **10***n* in the memory region is patterned using photolithography and dry etching. In this manner, in the memory region, selection gate electrodes CG of the selection nMISFETs each made of the n-type conductive film **10***n* are formed. The gate lengths of the selection gate electrodes CG in the memory region are, e.g., about 100 nm.

Next, as shown in FIG. 21, using the selection gate electrodes CG and a photoresist pattern as a mask, into the main surface of the semiconductor substrate 1 in the memory region, an n-type impurity, e.g., arsenic or phosphorus is ion implanted to form n-type semiconductor regions 8 for forming the channels of the memory nMISFETs.

Next, as shown in FIG. 22, over the main surface of the semiconductor substrate 1, insulating films 6b each made of, e.g., a silicon oxide, charge storing layers CSL each as an insulating film having a trap level made of, e.g., a silicon nitride, and insulating films 6t each made of, e.g., a silicon oxide are successively formed. The insulating films 6b are formed by, e.g., a thermal oxidation method, an ISSG (In-Situ Steam Generation) oxidation method, or the like. The charge storing layers CSL are formed by, e.g., a CVD method or the like. The insulating films 6t are formed by, e.g., a CVD method, an ISSG oxidation method, or the like. As the thick-

nesses of laminate films (hereinafter referred to as the insulating films 6b and 6t and the charge storing layers CSL) including the insulating films 6b, the charge storing layers SCL, and the insulating films 6t, about 20 nm can be shown by way of example. Each of the insulating films 6b and 6t may 5 also be formed of, e.g., a silicon oxide containing nitrogen. Each of the charge storing layers CSL may also be formed of a high-dielectric-constant film having a dielectric constant higher than that of a silicon nitride such as, e.g., an aluminum oxide (alumina), a hafnium oxide, or a tantalum oxide. Note 10 that, in the drawings, the insulating films 6b and 6t and the charge storing layers CSL are denoted by 6b/CSL/6t.

Next, over the main surface of the semiconductor substrate 1, a conductive film made of low-resistance polysilicon is deposited. The conductive film is formed by a CVD method. 15 The thickness of the conductive film is, e.g., about 50 nm. Subsequently, using photolithography and anisotropic dry etching, the conductive film is processed. Thus, in the memory region, over the both side surfaces of the selection gate electrodes CG, the sidewalls 11 are formed via the insu-20 lating films 6*b* and 6*t* and the charge storing layers CSL.

Next, as shown in FIG. 23, using a photoresist pattern as a mask, the sidewalls 1 exposed therefrom are etched. Thus, in the memory region, memory gate electrodes MG of the memory nMISFETs are formed only over one side surfaces of 25 the selection gate electrodes CG. The gate lengths of the memory gate electrodes MG are, e.g., about 65 nm.