### US008863378B2

# (12) United States Patent

# Muramatsu et al.

# (10) Patent No.:

US 8,863,378 B2

# (45) **Date of Patent:**

Oct. 21, 2014

#### (54)METHOD FOR MANUFACTURING A WIRING **BOARD**

Inventors: Masaki Muramatsu, Komaki (JP);

Shinji Yuri, Kasugai (JP); Makoto Origuchi, Komaki (JP); Kazuhiro

**Urashima**, Konan (JP)

Assignee: NGK Spark Plug Co., Ltd., Aichi (JP)

Subject to any disclaimer, the term of this Notice:

patent is extended or adjusted under 35

U.S.C. 154(b) by 1128 days.

Appl. No.: 12/706,695

Feb. 16, 2010 (22)Filed:

#### (65)**Prior Publication Data**

US 2010/0139090 A1 Jun. 10, 2010

# Related U.S. Application Data

Division of application No. 11/445,288, filed on Jun. 2, (62)2006, now Pat. No. 7,696,442.

#### (30)Foreign Application Priority Data

| Jun. 3, 2005  | (JP) | 2005-163673 |

|---------------|------|-------------|

| Oct. 6, 2005  | (JP) | 2005-293806 |

| Mar. 28, 2006 | (JP) | 2006-087569 |

(51)Int. Cl.

H01K 3/10 (2006.01)H01L 23/50 (2006.01)

(Continued)

U.S. Cl. (52)

CPC ...... *H01L 21/6835* (2013.01); *H01L 23/50* (2013.01); *H01L 2924/01047* (2013.01); *H05K 1/0231* (2013.01); *H01L 2924/19041* (2013.01); **H01L 24/97** (2013.01); H05K 2201/096 (2013.01); *H01L 2924/01027* (2013.01);

(Continued)

Field of Classification Search (58)

> 174/E23.062, E23.067, E23.079; 361/763,

361/764

See application file for complete search history.

#### (56)**References Cited**

### U.S. PATENT DOCUMENTS

4/2004 Naito et al. 6,721,153 B2 4/2004 Inagaki et al. 6,724,638 B1

(Continued)

# FOREIGN PATENT DOCUMENTS

EP 1 041 631 A2 10/2000 EP 1 139 705 A1 10/2001

(Continued)

Primary Examiner — Thiem Phan

(74) Attorney, Agent, or Firm — Sughrue Mion, PLLC

#### (57)ABSTRACT

A method for manufacturing a wiring board including, as steps executed in written order: a sub-core accommodation step of accommodating the ceramic sub-core in the sub-core accommodation space through the first-major-surface-side opening of the sub-core accommodation space; and a film formation and charging step of forming a lowest resin insulating layer of the first-major-surface-side wiring laminate by sticking a resin material to the core body and the ceramic sub-core from the first major surface side, and forming a groove-filling portion that is continuous with the lowest resin insulating layer by charging the resin material into a gap between the core body and the ceramic sub-core.

# 3 Claims, 23 Drawing Sheets

| (54)  | T                     |                                             | 2002/0   | 101260 |               | 10/20/             | 2.2      | T .              |

|-------|-----------------------|---------------------------------------------|----------|--------|---------------|--------------------|----------|------------------|

| (51)  | Int. Cl.              |                                             |          | 191368 |               | 12/200             |          | Li               |

|       | H05K 1/02             | (2006.01)                                   |          | 009335 |               |                    |          | Kojima et al.    |

|       | H01L 23/00            | (2006.01)                                   |          | 014317 |               | 1/200              |          | Sakamoto et al.  |

|       | H05K 1/18             | (2006.01)                                   |          | 140553 |               |                    |          | Naito et al.     |

|       |                       |                                             |          | 160751 |               |                    |          | Inagaki et al.   |

|       | H01L 21/48            | (2006.01)                                   |          | 157478 |               |                    |          | Inagaki et al.   |

|       | H01L 21/56            | (2006.01)                                   |          | 207091 |               |                    |          | Kambe et al.     |

|       | H01L 21/683           | (2006.01)                                   |          | 281008 |               |                    |          | He et al.        |

|       | H01L 23/498           | (2006.01)                                   |          | 137902 |               |                    |          | Kubota et al.    |

|       | H05K 1/11             | (2006.01)                                   |          | 209831 |               | 9/200              |          | Sakamoto et al.  |

|       |                       |                                             |          | 258225 |               | 11/200             |          | Inagaki et al.   |

|       | H05K 1/16             | (2006.01)                                   |          | 055872 |               |                    |          | Inagaki et al.   |

|       | $H05K\ 1/14$          | (2006.01)                                   |          | 142255 |               |                    |          | Inagaki et al.   |

|       | H05K 3/46             | (2006.01)                                   |          | 144298 |               |                    |          | Inagaki et al.   |

| (52)  | U.S. Cl.              |                                             | 2008/0   | 148563 | A1            | 6/200              | 98       | Sakamoto et al.  |

| (32)  |                       | <b>85</b> (2013.01); <i>H01L 2924/01013</i> | 2008/0   | 151522 | <b>A</b> 1    | 6/200              | 98       | Sakamoto et al.  |

|       |                       |                                             | 2008/0   | 158838 | $\mathbf{A}1$ | 7/200              | 98       | Inagaki et al.   |

|       | · //                  | L 2924/01059 (2013.01); H01L                | 2008/0   | 158841 | A1            | 7/200              | 98       | Inagaki et al.   |

|       | <i>2924/30107</i> (20 | 013.01); <i>H05K 1/112</i> (2013.01);       | 2008/0   | 169120 | A1            | 7/200              | 80       | Inagaki et al.   |

|       | H01L                  | 21/4857 (2013.01); H01L 24/81               | 2008/0   | 169123 | <b>A</b> 1    | 7/200              | 98       | Sakamoto et al.  |

|       |                       | L 2924/01029 (2013.01); H01L                | 2008/0   | 206926 | <b>A</b> 1    | 8/200              | 80       | Sakamoto et al.  |

|       | · / /                 | 01 (2013.01); H01L 2924/01078               |          | 230914 |               | 9/200              | 98       | Sakamoto et al.  |

|       |                       |                                             |          | 077796 |               | 3/200              |          | Sakamoto et al.  |

|       |                       | H01L 21/568 (2013.01); H01L                 |          | 263939 |               | 10/200             |          | Sakamoto et al.  |

|       | 2924/0101             | 19 (2013.01); H01L 2924/01055               |          | 014261 |               |                    |          | Inagaki et al.   |

|       | (2013.01); I          | H01L 2924/14 (2013.01); H05K                |          | 118502 |               |                    |          | Inagaki et al.   |

|       | 1/162 (201)           | 3.01); <i>H01L 2224/97</i> (2013.01);       |          | 140803 |               |                    |          | Sakamoto et al.  |

|       | `                     | 0712 (2013.01); <b>H01L 23/49822</b>        |          | 226108 |               |                    |          | Inagaki et al.   |

|       |                       |                                             |          | 328915 |               |                    |          | Inagaki et al.   |

|       | · //                  | L 2924/01075 (2013.01); H01L                | 2010/0   | 320713 | 711           | 12/201             | 10       | magaki et ai.    |

|       |                       | 81801 (2013.01); H01L 2224/16               |          | EC     | DEI           | TNI DAT            | CEN      | AT DOCLIMENTS    |

|       | · //                  | L 2924/01033 (2013.01); H01L                |          | гO     | KEN           | JN PAI             |          | NT DOCUMENTS     |

|       | <i>2924/01082</i> (20 | 013.01); <i>H05K 1/142</i> (2013.01);       | ID       |        | 626           |                    |          | 9/1994           |

|       | H01L 2924/0           | 014 (2013.01); H01L 2924/0103               | JP<br>JP |        |               | 58098 A<br>3540 A  |          | 10/1995          |

|       | (2013.01): <i>H01</i> | L 2924/01005 (2013.01); H01L                | JP       | 20     |               | 3837 A             |          | 8/2000           |

|       | · //                  | 46 (2013.01); H01L 2924/15311               | JP       |        |               | .3637 A<br>19225 A |          | 12/2000          |

|       |                       | × //                                        | JP       |        |               | 9227 A             |          | 12/2000          |

|       | · //                  | L 2924/01006 (2013.01); H05K                | JP       |        |               | 4034 A             |          | 10/2001          |

|       | •                     | ); H01L 2924/01051 (2013.01);               | JP       |        |               | 2437 A             |          | 11/2001          |

|       | H01L 2924/010         | 024 (2013.01); H01L 2924/0105               | JP       |        |               | 00875              |          | 4/2002           |

|       | (2013.01); H01        | L 2224/13111 (2013.01); H05K                | JP       |        |               | 8365 A             |          | 4/2002           |

|       |                       | 74 (2013.01); <i>H</i> 01L 2924/01041       | JP       |        |               | 8367 A             |          | 4/2002           |

|       |                       | 1); <i>H01L 2924/01079</i> (2013.01)        | JP       | 20     | 02-20         | 4045               |          | 7/2002           |

|       | `                     | · · · · · · · · · · · · · · · · · · ·       | JP       | 20     | 02-20         | 4071 A             |          | 7/2002           |

|       | USPC                  | <b>29/852</b> ; 29/825; 29/829; 29/846      | JP       | 20     | 02-23         | 7683               |          | 8/2002           |

| (5.6) | T                     |                                             | JP       | 20     | 02-24         | 6757 A             |          | 8/2002           |

| (56)  | Refere                | nces Cited                                  | JP       | 20     | 02-27         | '0991 A            |          | 9/2002           |

|       |                       |                                             | JP       | 20     | 02-27         | '1025 A            |          | 9/2002           |

|       | U.S. PATENT           | ΓDOCUMENTS                                  | JP       |        |               | '1033 A            |          | 9/2002           |

|       |                       |                                             | JP       |        |               | 4071 A             |          | 12/2002          |

|       |                       | Inagaki et al.                              | JP       |        |               | 1010 A             |          | 12/2003          |

|       |                       | Ogawa et al.                                | JP       |        |               | 1812               |          | 1/2004           |

|       |                       | Kambe et al.                                | JP       |        |               | 00201 A            | <b>L</b> | 7/2004           |

|       |                       | Kambe et al.                                | JP       |        |               | 9672               |          | 12/2004          |

|       |                       | Ogawa et al.                                | JP<br>ID |        |               | 9217               |          | 2/2005           |

|       |                       | Inagaki et al.                              | JP<br>ID |        |               | 19243<br>12627 A   |          | 2/2005           |

|       |                       | Inagaki et al.  McCormack et al.            | JP<br>ID |        |               | '2627 A<br> 3850 A |          | 3/2005<br>9/2005 |

|       |                       | McCormack et al. McCormack et al.           | JP<br>JP |        |               | 13830 A<br>19762 A |          | 9/2005<br>2/2006 |

| 2002  | 10113402 A1 11/2002   | , wiccommack of al.                         | JI       | 20     | 00-04         | DIUL A             |          | 2/2000           |

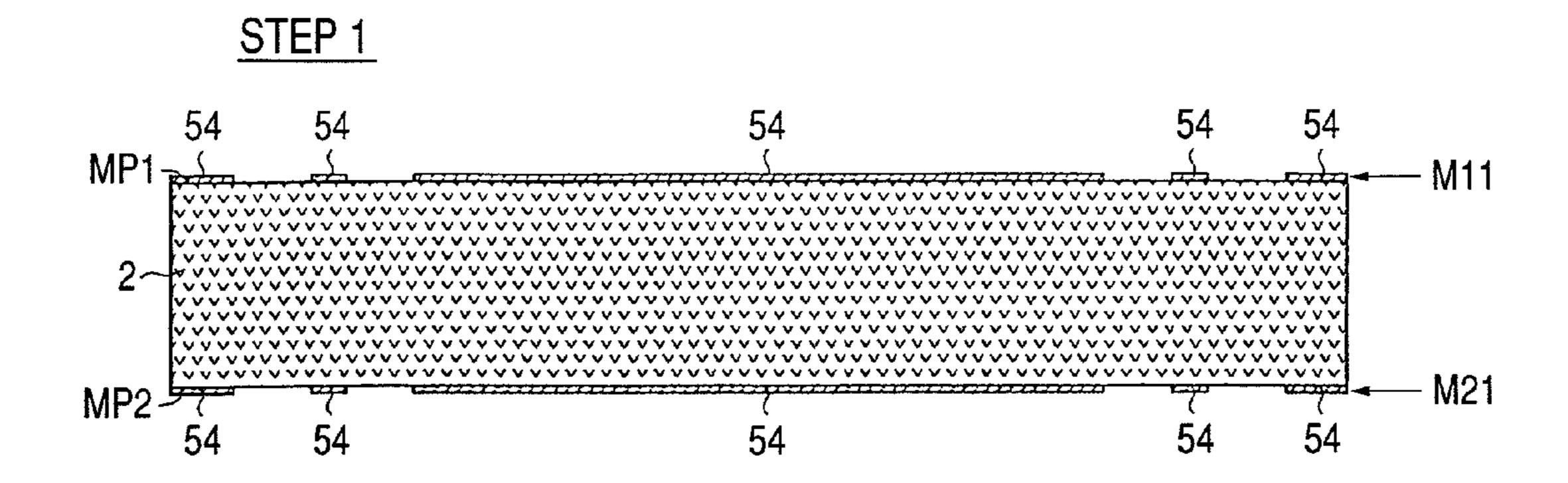

FIG. 2

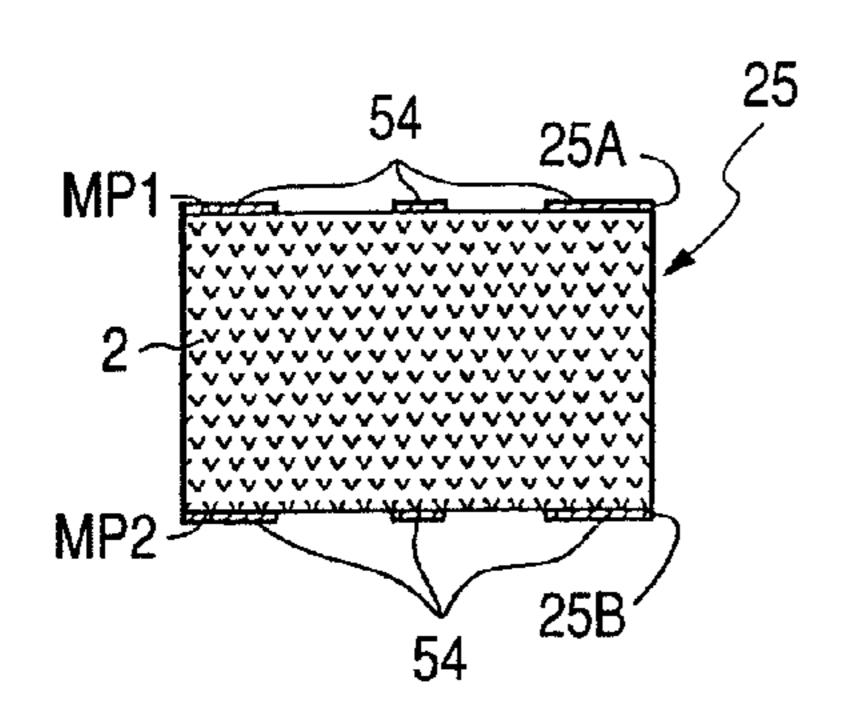

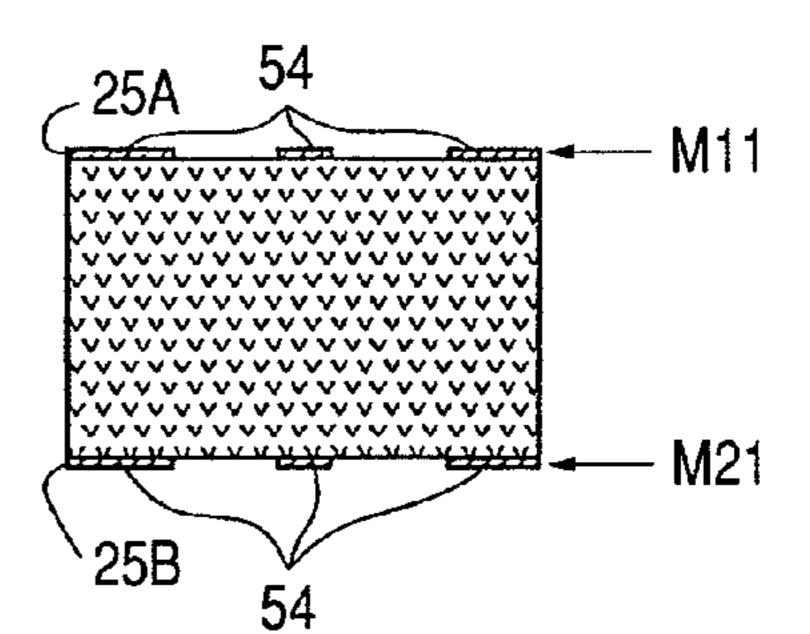

FIG. 3

FIG. 4

STEP 2

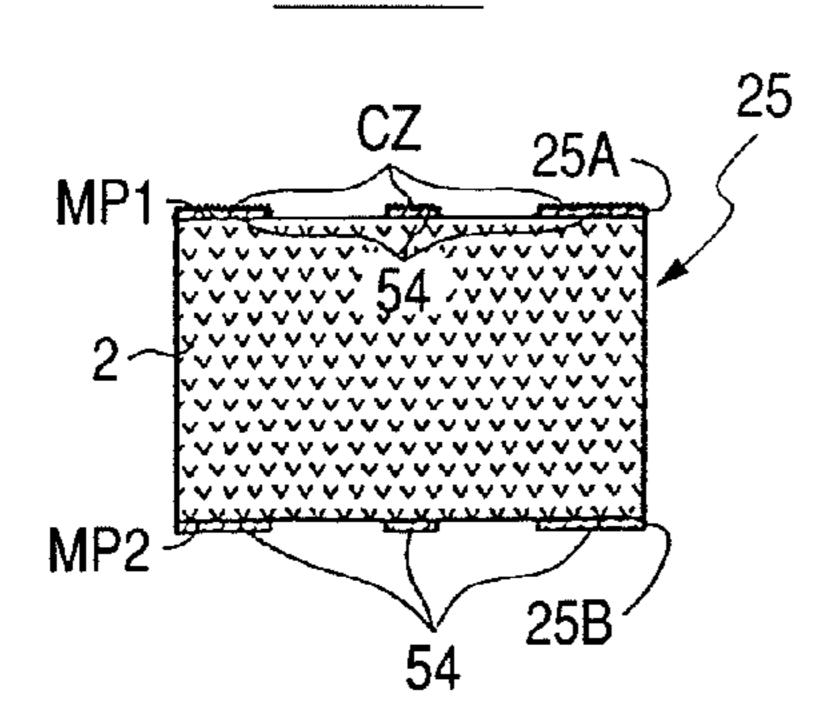

STEP 3

FIG. 5

FIG. 6

STEP 6

FIG. 7

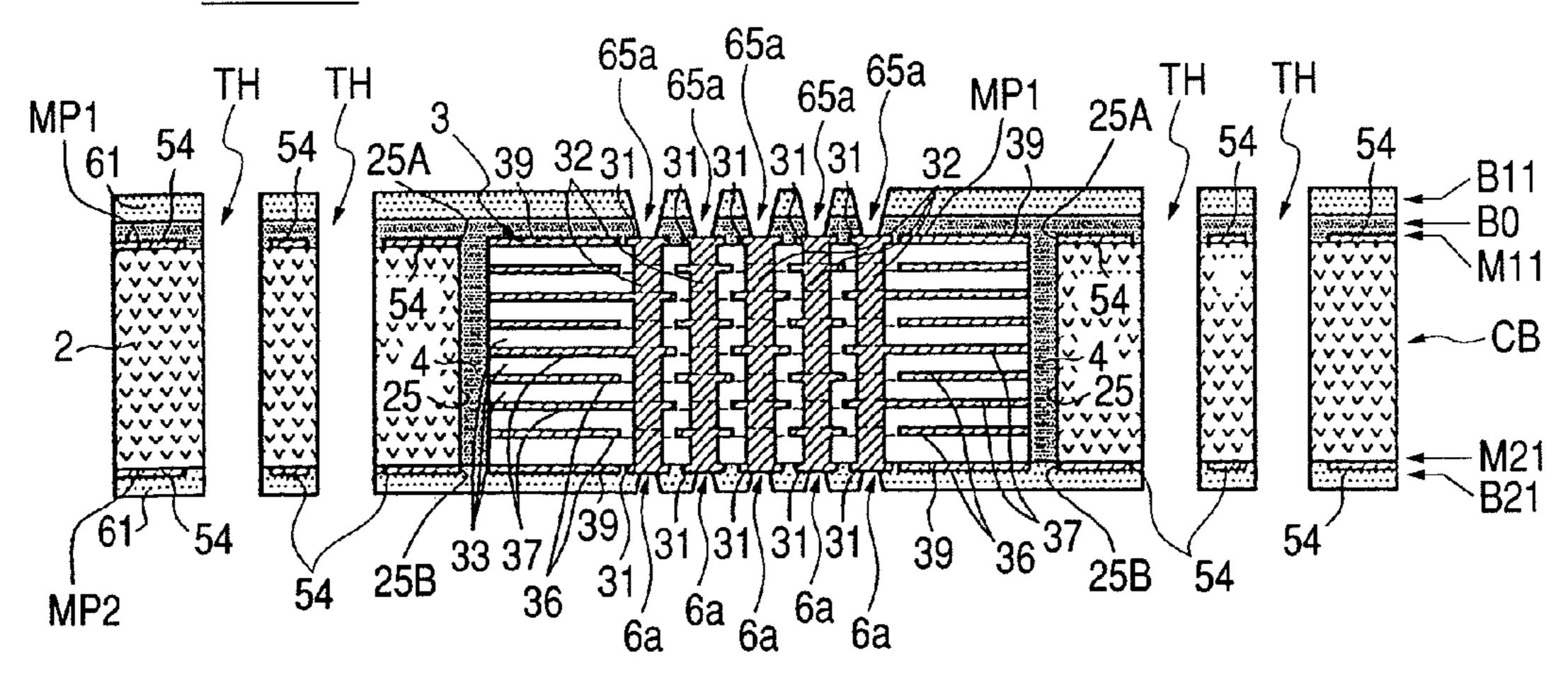

STEP 9

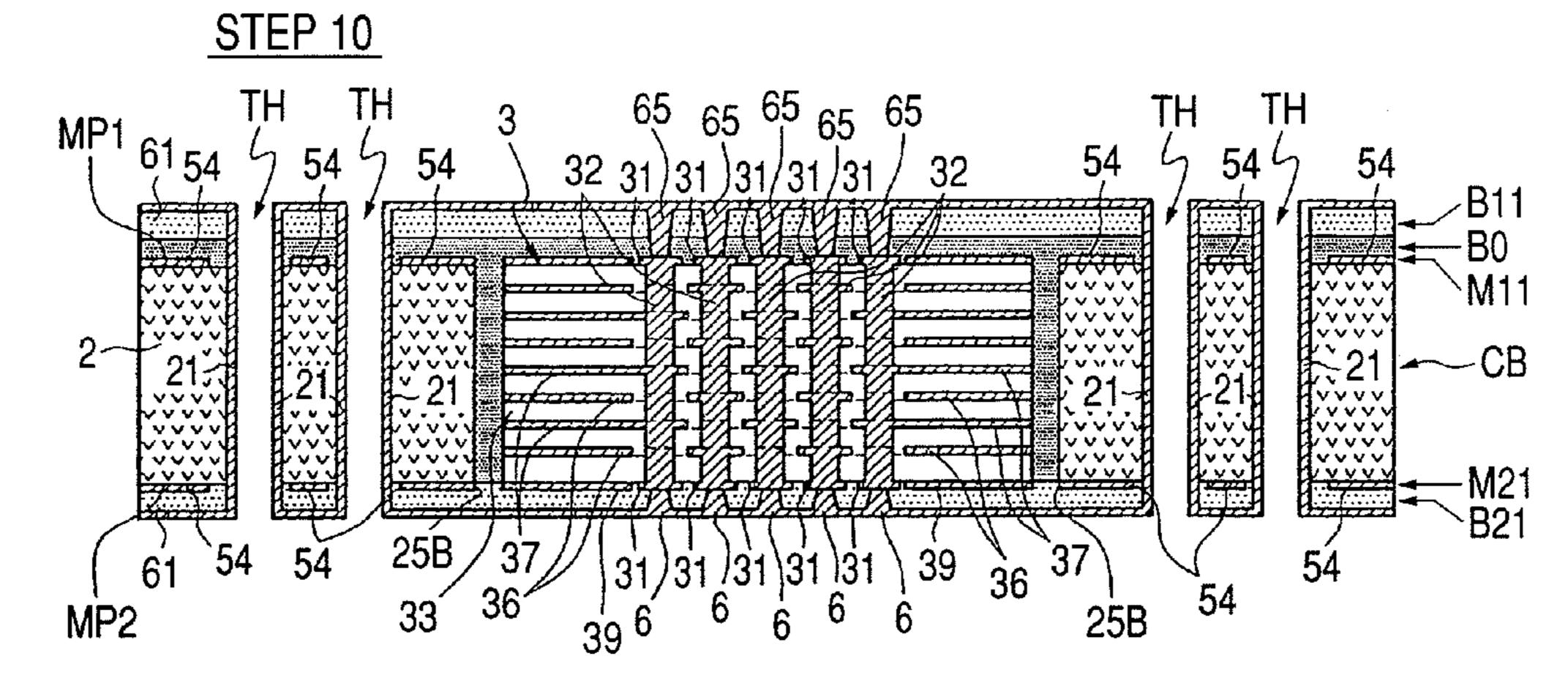

FIG. 8

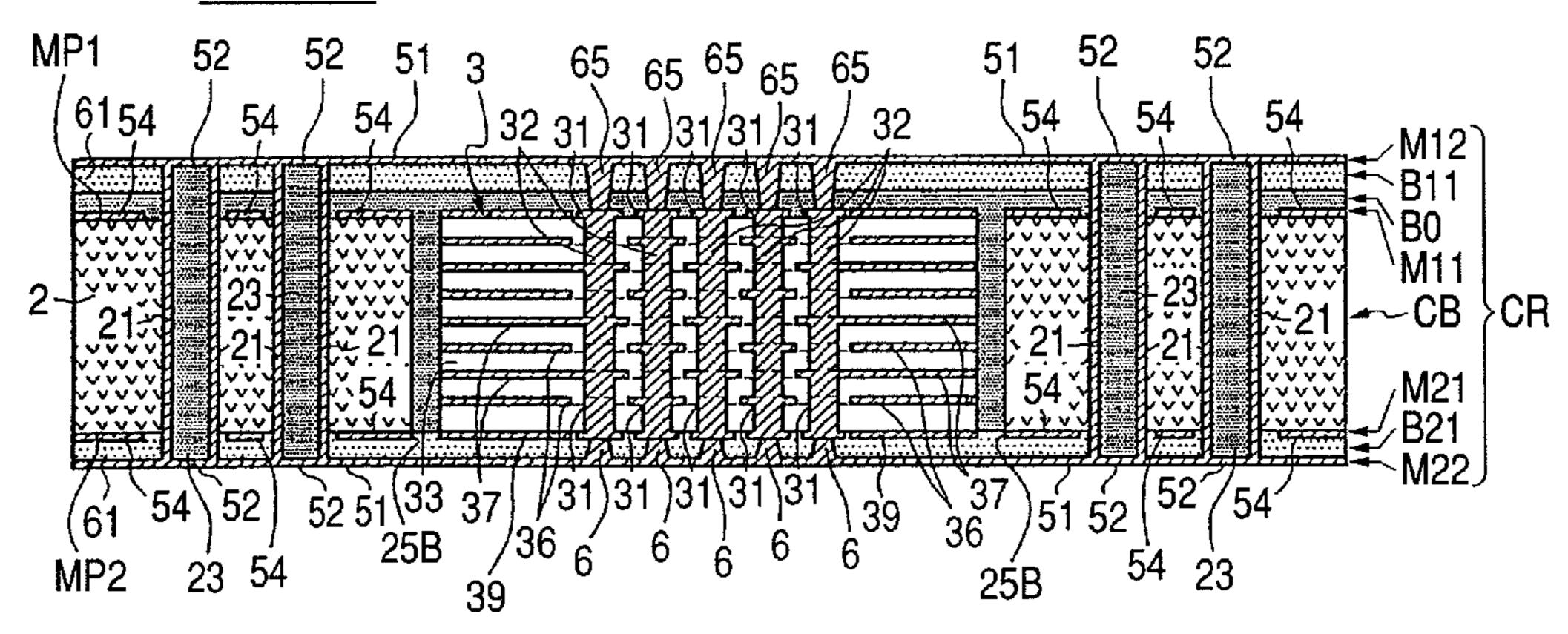

# STEP 11

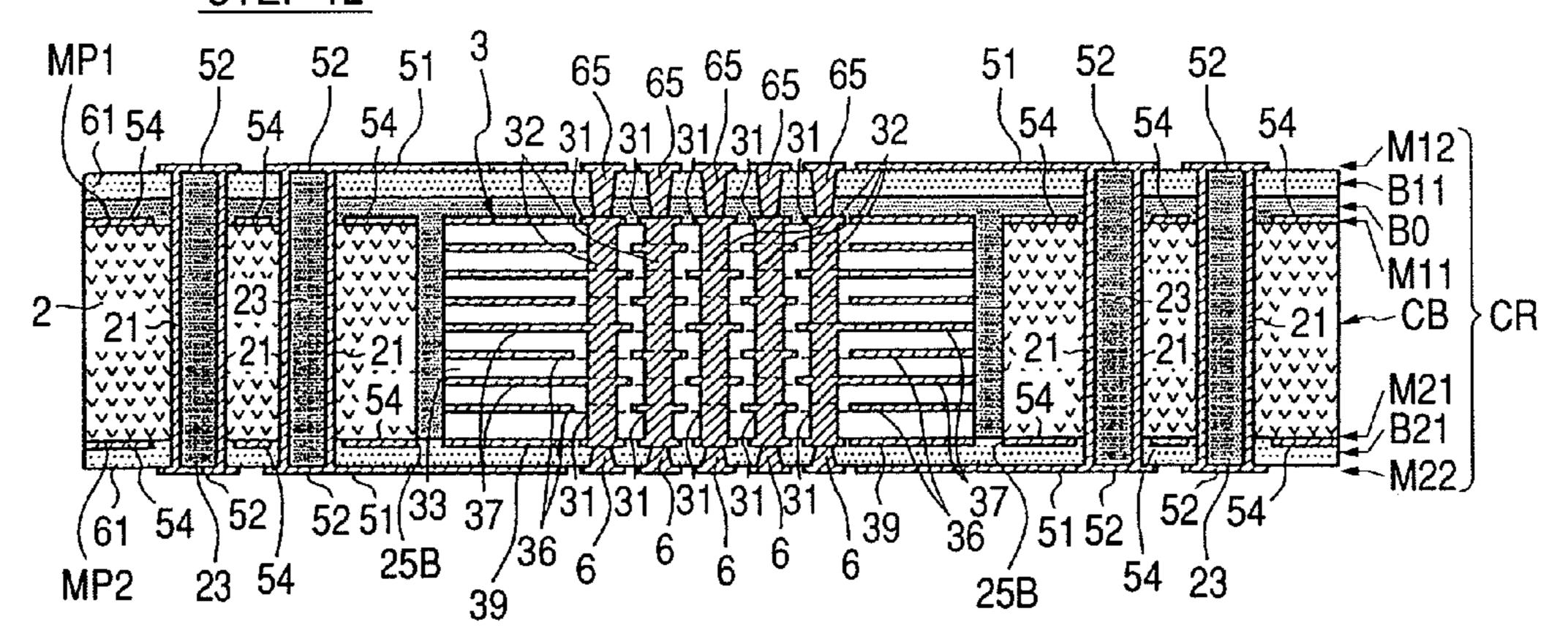

# STEP 12

FIG. 9A

FIG. 9B

FIG. 10

F/G. 11

FIG. 13A

FIG. 13B

FIG. 14A

FIG. 14B

F/G. 15

FIG. 16

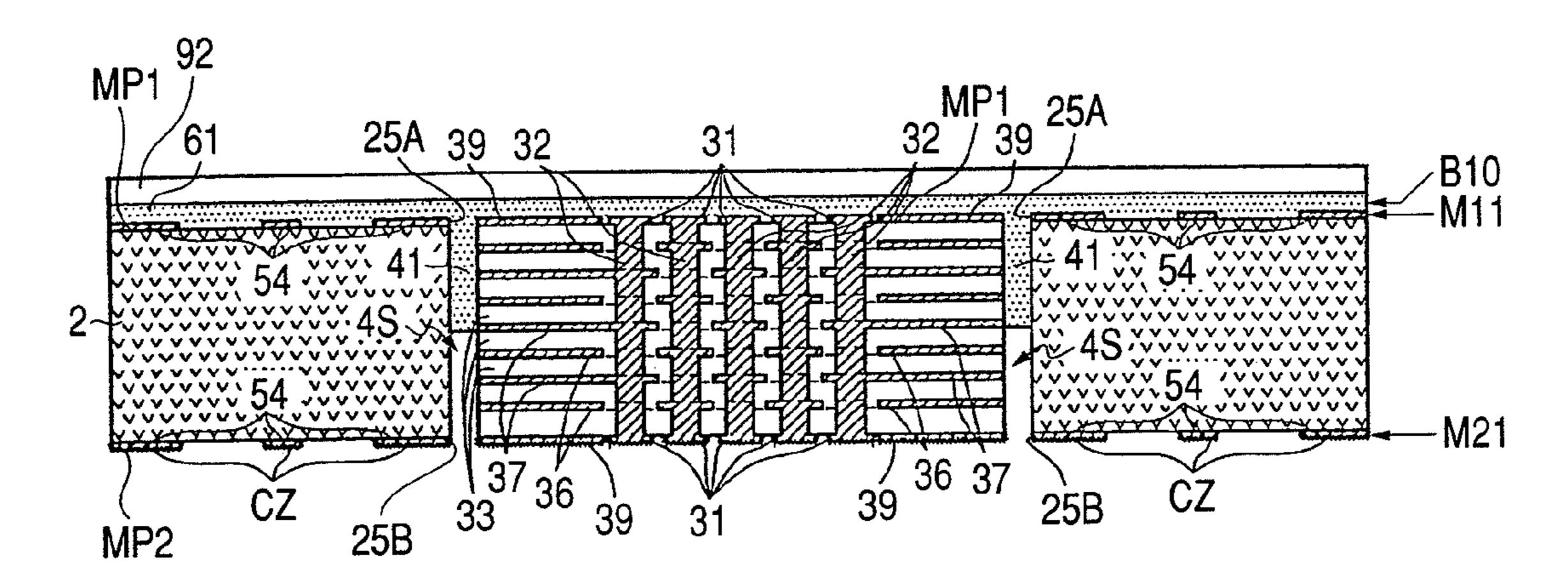

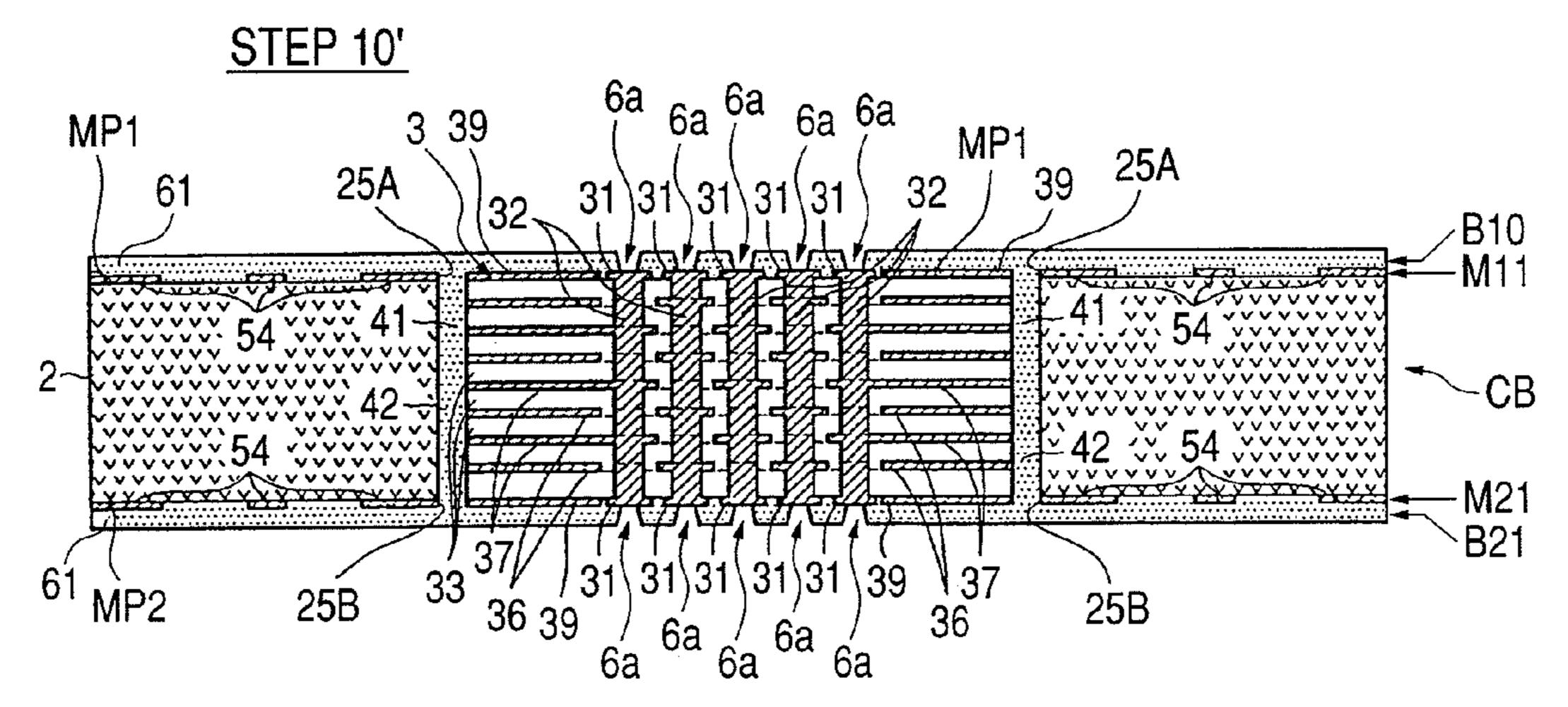

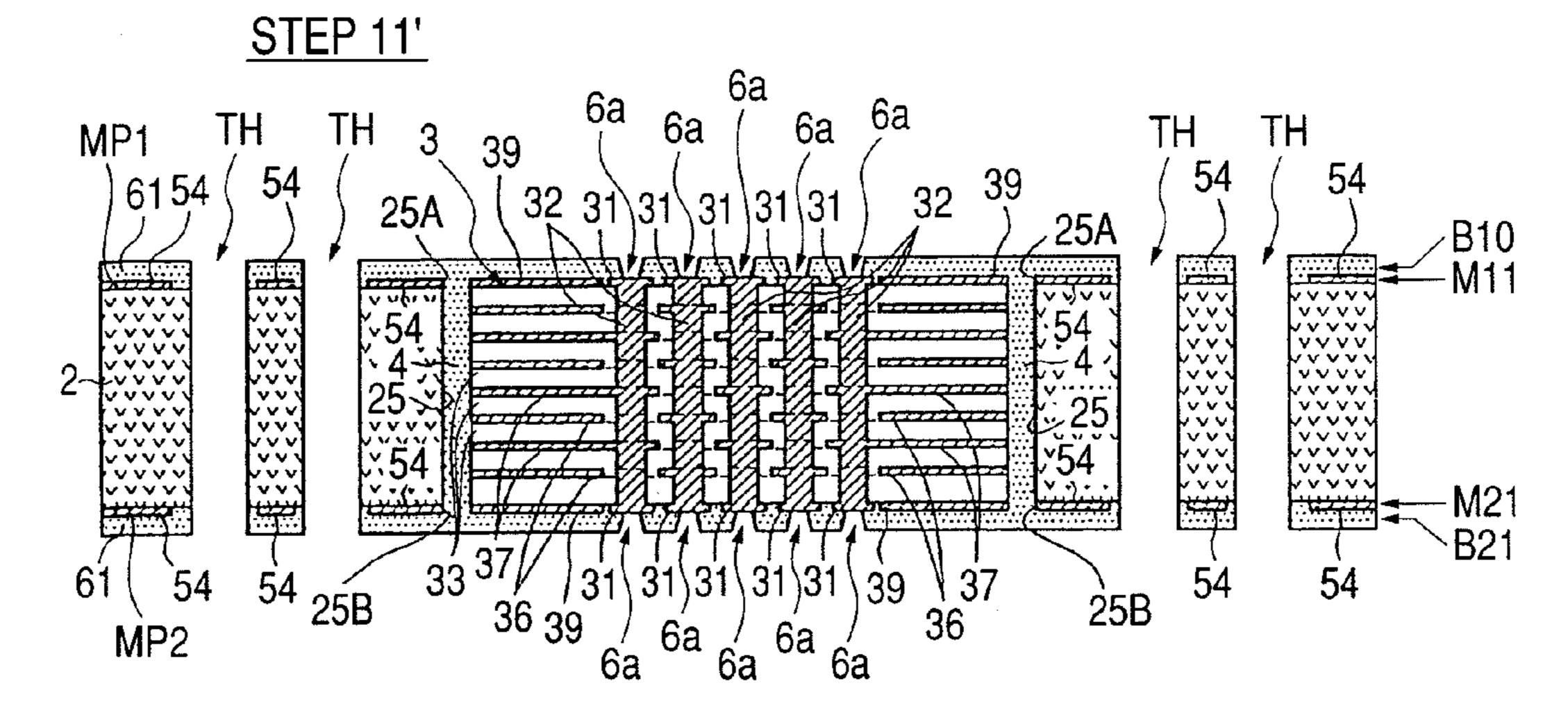

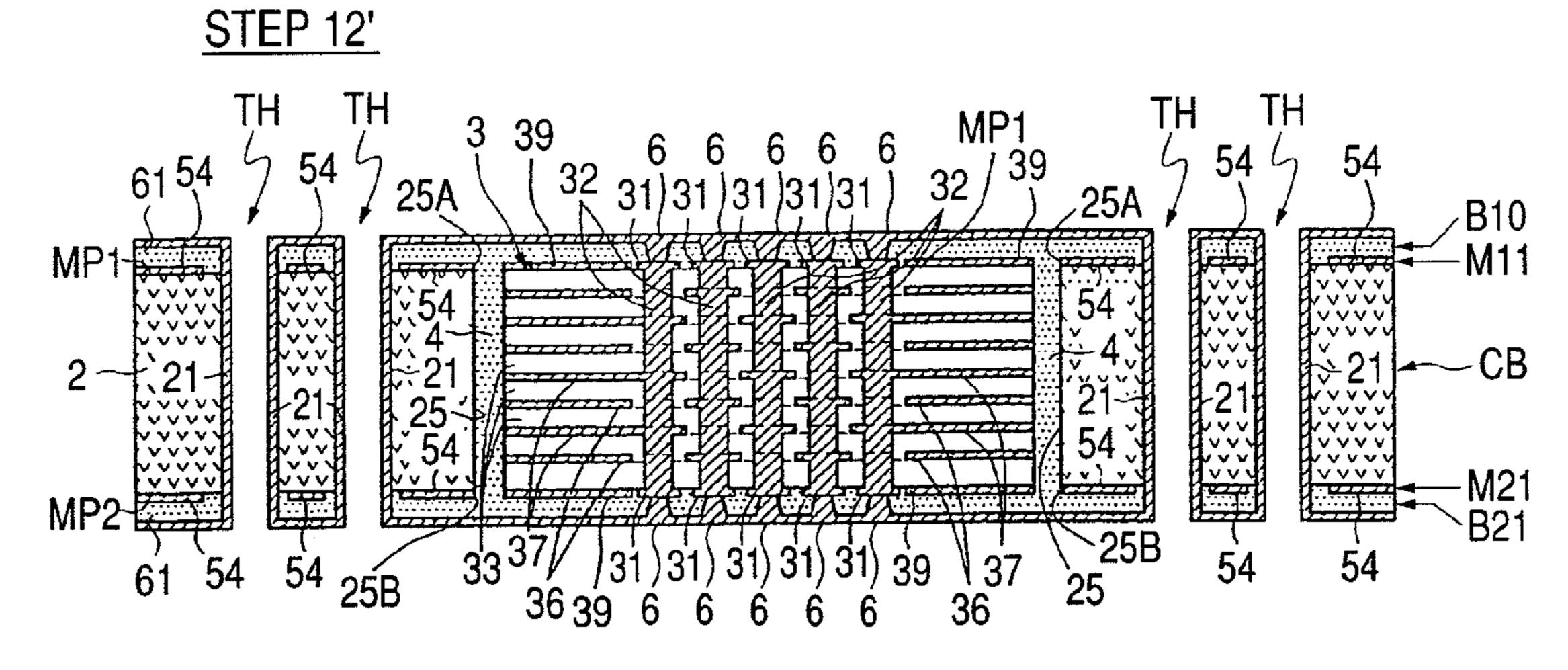

STEP 7'

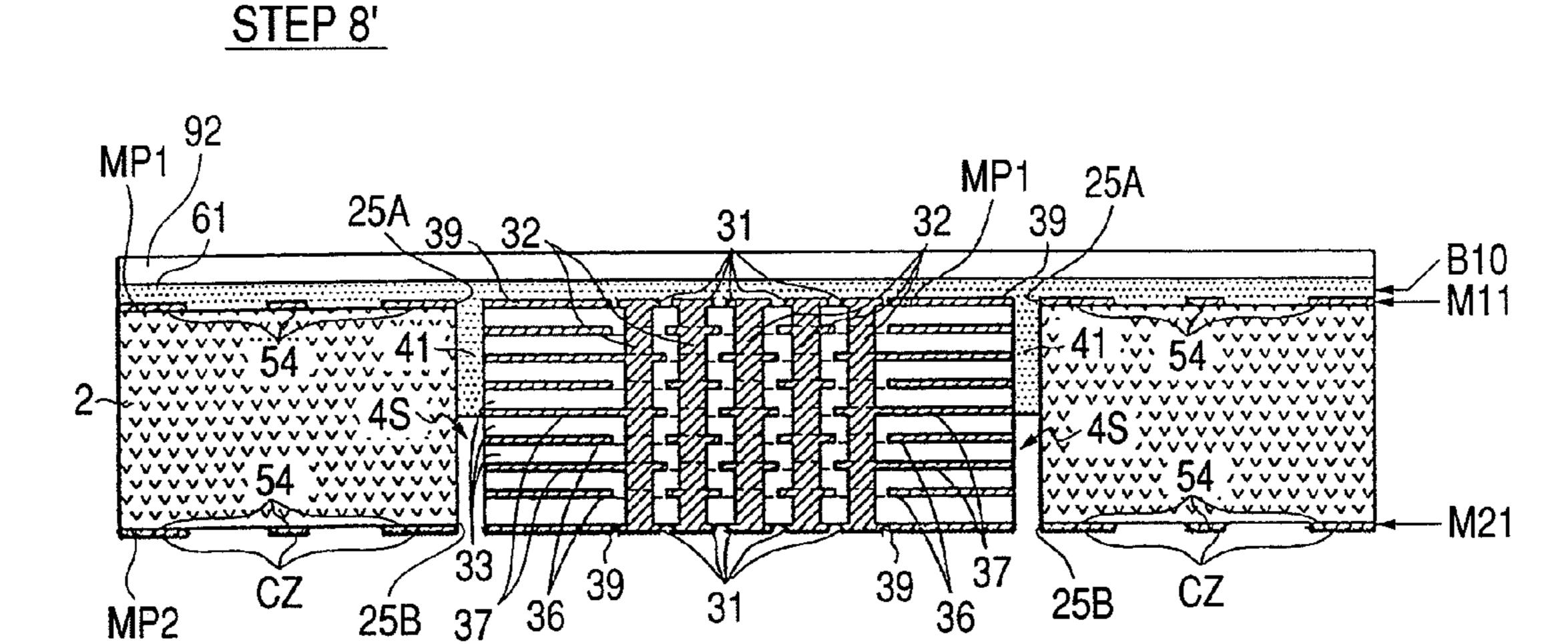

FIG. 17

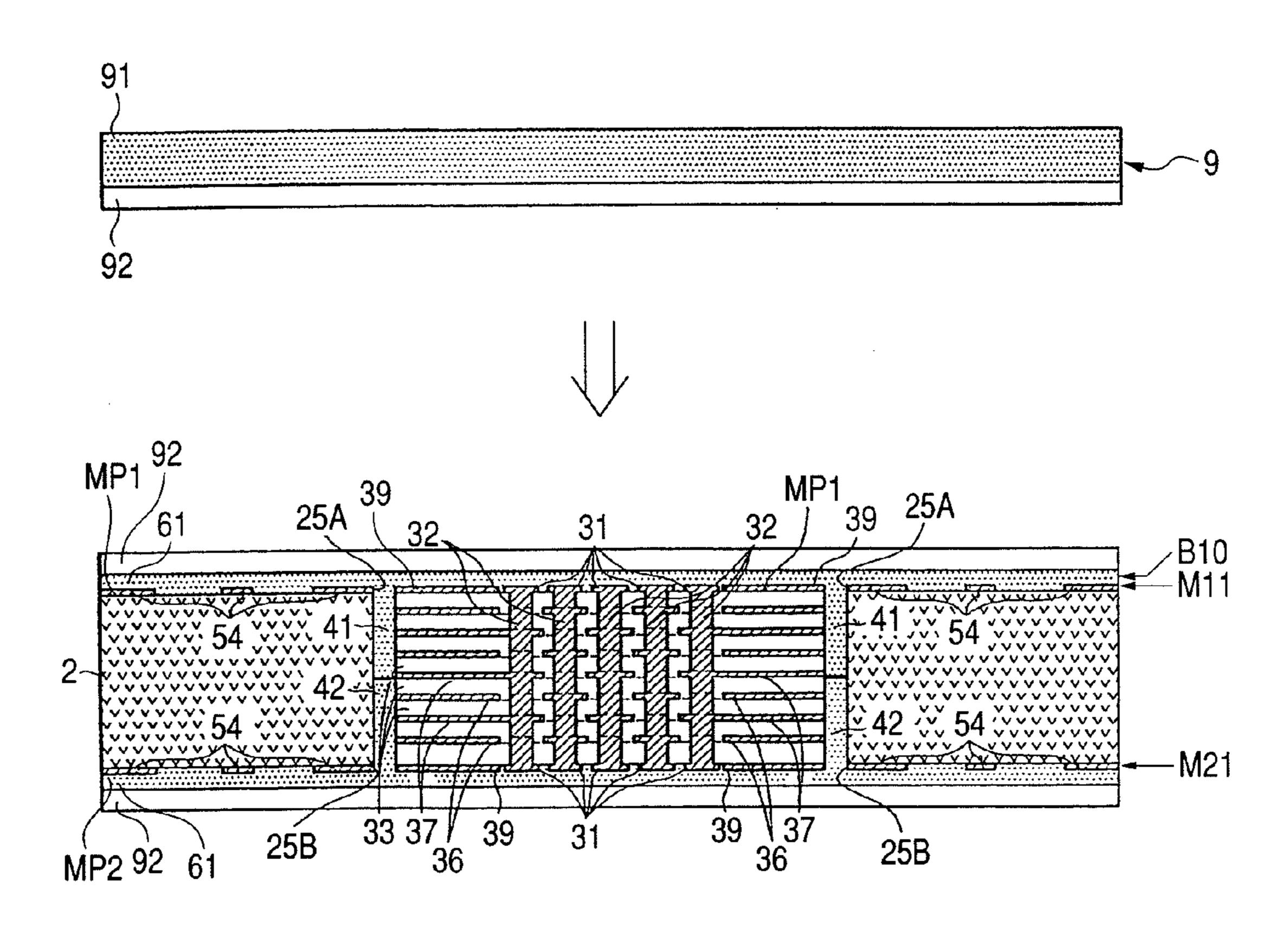

FIG. 18

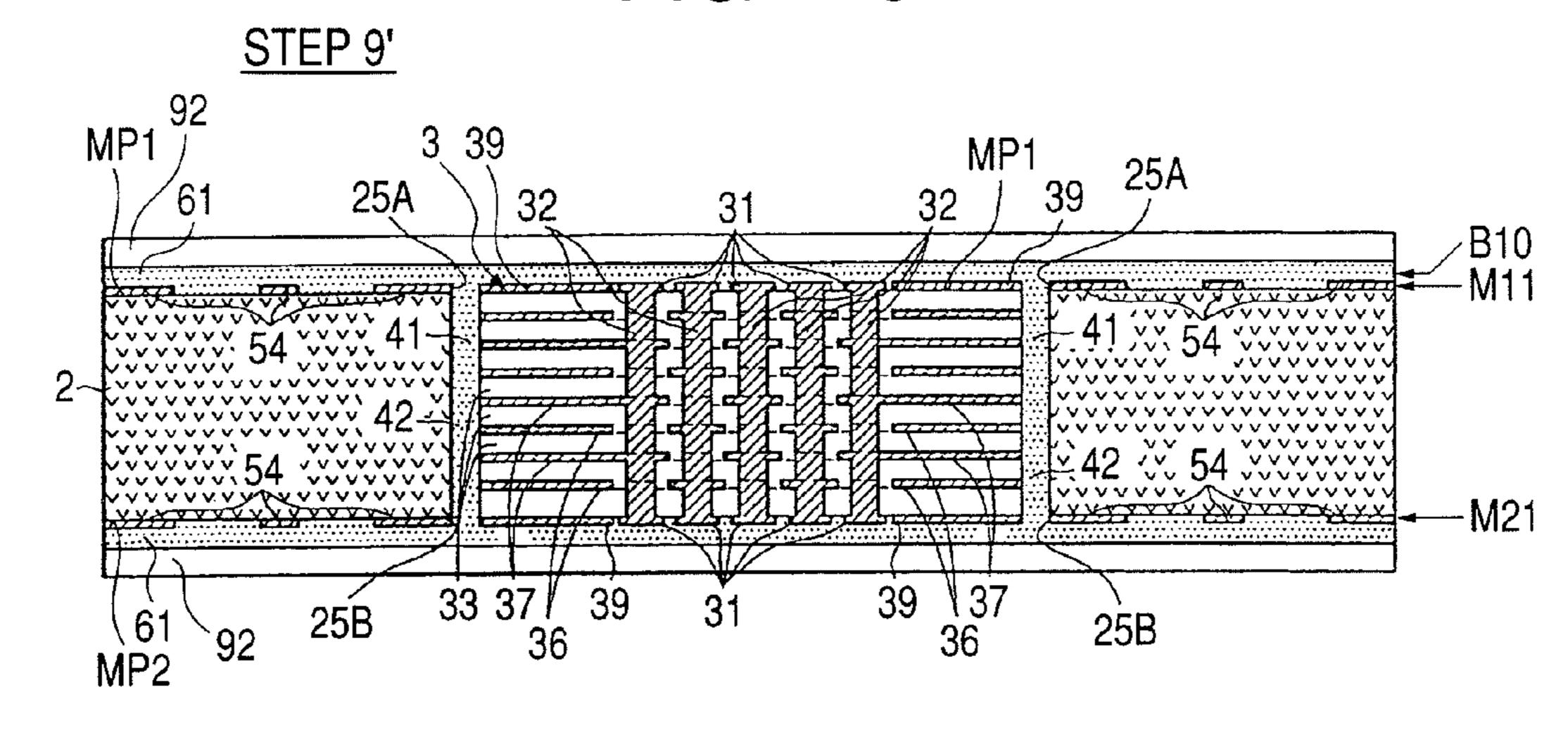

FIG. 19

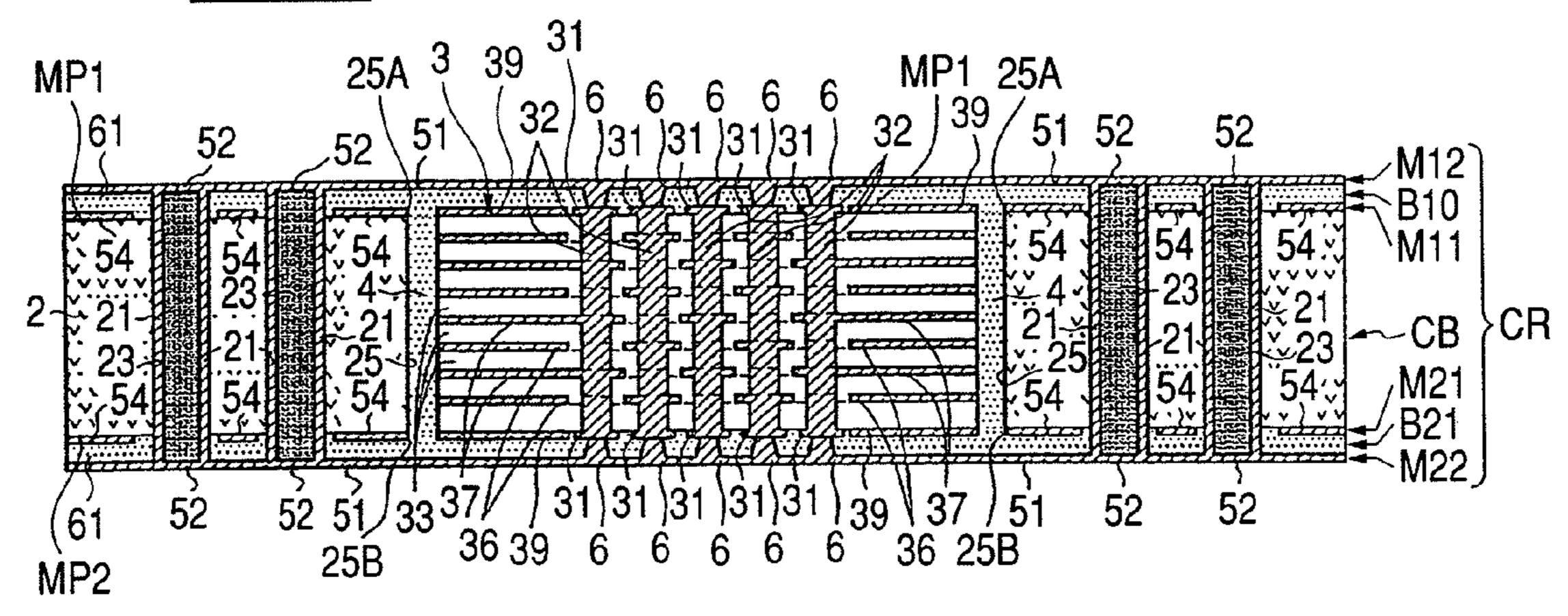

# STEP 13'

# **STEP 14'**

FIG. 22

FIG. 23

FIG. 24A

FIG. 24B

# METHOD FOR MANUFACTURING A WIRING **BOARD**

# CROSS REFERENCE TO RELATED APPLICATIONS

This application is a Rule 53(b) Divisional of U.S. patent application Ser. No. 11/445,288 filed Jun. 2, 2006, incorporated herein by reference in its entirety.

### FIELD OF THE INVENTION

The present invention relates to a wiring board having a core board that accommodates a ceramic sub-core mainly made of ceramics.

### BACKGROUND OF THE INVENTION

Conventionally, to reduce the switching noise of a semiconductor integrate circuit device (hereinafter referred to as 20 "IC chip") and stabilize its operation power supply voltage, a capacitor is provided in a wiring board that is mounted with the IC chip. As for the manner of mounting the capacitor on the wiring board, as the lengths of interconnections between the IC chip and the capacitor increase, the inductance com- 25 ponents of the interconnections increase and it becomes more difficult to attain the above effects sufficiently. It is therefore desirable that the capacitor be disposed as close to the IC chip as possible. JP-A-2005-39243 proposes a wiring board in which a core board located right under an IC chip accommodates a ceramic sub-core that incorporates a capacitor.

# SUMMARY OF THE INVENTION

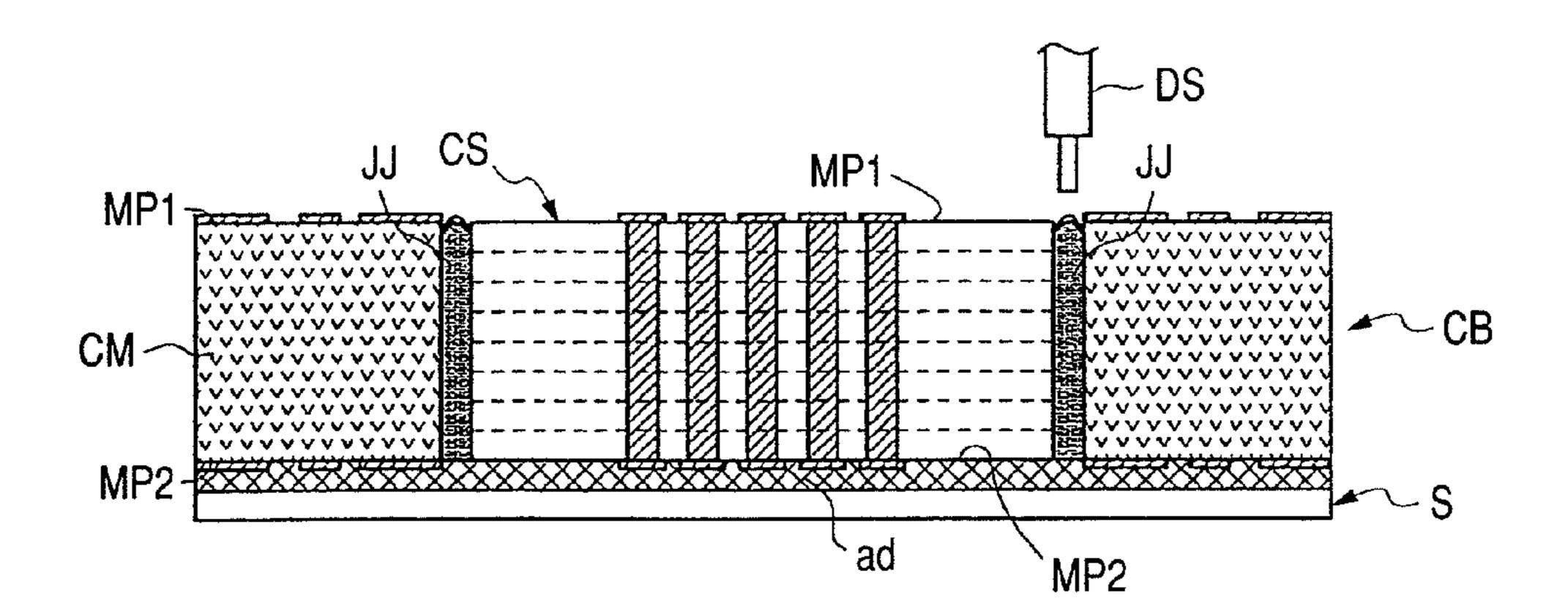

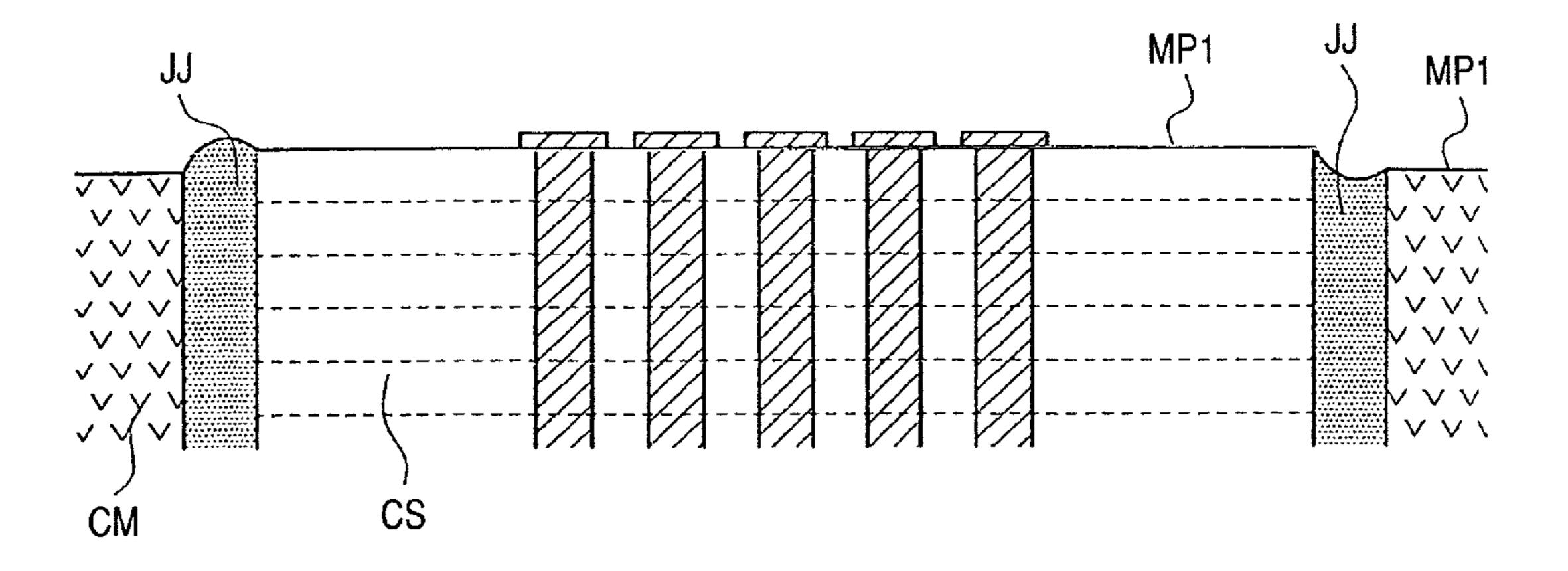

is produced in the following manner. As shown in FIG. 14A, a second major surface MP2 of a core body CM in which a sub-core accommodation space (through-hole) is formed is covered with an adhesive sheet S having an adhesive ad. A ceramic sub-core CS is accommodated in the core body CM 40 by inserting the ceramic sub-core CS through the opening in a first major surface MP1 and fixing it to the adhesive ad. Then, a filling resin JJ containing an inorganic filler such as a silica filler is injected into the gap between the core body CM and the ceramic sub-core CS by means of a known dispenser 45 DS.

However, where as mentioned above the filling resin JJ is injected using the dispenser DS, the following problem arises on the first major surface MP1 side of the ceramic sub-core CS. The shape of the sub-core accommodation space and the 50 size and positional accuracy of the ceramic sub-core CS have certain variations. Therefore, even if the dispenser DS injects a constant amount of filling resin JJ, as shown in FIG. 14B the filling resin JJ injected in the gap between the core body CM and the ceramic sub-core CS is projected or recessed to cause 55 asperities on the surface. In this case, it is difficult to form flat insulating resin layers thereon because they reflect those asperities.

The present invention has been made in view of the above problem, and an object of the present invention is therefore to 60 provide a wiring board which has a core board accommodating a ceramic sub-core and in which flat insulting resin layers are formed on the core board.

To attain the above object, the invention provides a wiring board provided with a core board having a plate-like core 65 body and a ceramic sub-core which is accommodated in a sub-core accommodation space that is a through-hole that

communicates with major surfaces of the core body or a recess having an opening in a first major surface of the core body; and wiring laminates each formed by resin insulating layers and conductor layers laminated on each of major sur-5 faces of the core board, characterized in:

that a groove-filling portion which fills a gap between the core body and the ceramic sub-core is integral with a lowest resin insulating layer of the first-major-surface-side wiring laminate; and

that via conductors that are connected to respective conductor patterns formed on a first major surface of the ceramic sub-core penetrate through the lowest resin insulating layer.

And, preferably, a surface, located over the gap between the core body and the ceramic sub-core, of the lowest resin insulating layer is smaller than a surface connecting a top end of an inner side surface of the core body and a top end of an outer side surface of the ceramic sub-core in an inclination from the first major surface of the core body.

With the above configuration, since the groove-filling portion which fills the gap between the core body and the ceramic sub-core is integral with the lowest resin insulating layer of the first-major-surface-side wiring laminate, the surface of the lowest resin insulating layer is flat and hence the entire wiring laminate is made flat.

As for the flatness of the lowest resin insulating layer, it is preferable that that surface of the lowest resin insulating layer which is located over the gap between the core body and the ceramic sub-core, where largest asperities would otherwise occur, be higher in parallelism with (i.e., smaller in the inclination from) the first major surface of the core body than the surface connecting the top end of the inner side surface of the core body and the top end of the outer side surface of the ceramic sub-core.

The lowest resin insulating layer may be provided on the Incidentally, for example, a core board as described above 35 gap between the core body and the ceramic sub-core, the ceramic sub-core, and the core body, and an inclination of the surface of the lowest resin insulating layer may be smaller than an inclination of the surface connecting the top end of the inner side surface of the core body and the top end of the outer side surface of the ceramic sub-core, said inclinations being defined with respect to the first major surface of the core body.

> That is, from the viewpoint of making the entire lowest resin insulating layer flat, it is preferable that not only that surface of the lowest resin insulating layer which is located over the gap between the core body and the ceramic sub-core but also those surfaces of the lowest resin insulating layer which are located over the ceramic sub-core and the core body be higher in parallelism with the first major surface of the core body than the surface connecting the top end of the inner side surface of the core body and the top end of the outer side surface of the ceramic sub-core.

> For example, the lowest resin insulating layer which is integral with the groove-filling portion can be produced by printing a resin paste on the first major surfaces of the ceramic sub-core and the core body using a squeegee or the like in a state that the ceramic sub-core is accommodated in the subcore accommodation space.

> A first specific form of the wiring board according to the invention is such that in the first-major-surface-side wiring laminate, the via conductors which penetrate through the lowest resin insulating layer are parts of respective multilayer penetration via conductors that penetrate through plural layers that are the lowest resin insulating layer and a resin insulating layer adjacent to the lowest resin insulating layer, and connect the conductor patterns formed on the first major surface of the ceramic sub-core to the conductor layer formed on the adjacent resin insulating layer.

This configuration makes it possible to form the lowest resin insulating layer with a material that is smaller than the adjacent resin insulating layer in the linear expansion coefficient. In particular, the lowest resin insulating layer can be made of a material whose linear expansion coefficient lies 5 halfway between the linear expansion coefficients of the adjacent resin insulating layer and the ceramic sub-core, which provides an effect of absorbing a difference in the linear expansion coefficient in the thickness direction. More specifically, the lowest resin insulating layer may be made of a 10 material whose average linear expansion coefficient in a range of room temperature to 200° C. (hereinafter referred to simply as "linear expansion coefficient") is smaller than or equal to 35 ppm/° C. (preferably, smaller than or equal to 33 ppm/° C.). If the linear expansion coefficient of the lowest 15 resin insulating layer exceeds this upper limit, it is on the same level as that of the wiring laminate which is mainly made of a polymeric material and hence the above effect may not be attained satisfactorily. To attain such a linear expansion coefficient, the lowest resin insulating layer may be made of 20 a material that is higher in filler content than the adjacent resin insulating layer. More specifically, the filler content of the lowest resin insulating layer may be set at 50 to 80 wt %.

A second specific form of the wiring board according to the invention is such that in the first-major-surface-side wiring 25 laminate, the via conductors which penetrate through the lowest resin insulating layer connect the conductor patterns formed on the first major surface of the ceramic sub-core to the conductor layer formed on the lowest resin insulating layer. This configuration makes it possible to form good via 30 holes that are free of steps, which in turn enables connections by good via conductors.

Furthermore, the invention provides a wiring board provided with a core board having a plate-like core body and a ceramic sub-core which is accommodated in a sub-core 35 accommodation space that is a through-hole that communicates with major surfaces of the core body or a recess having an opening in a first major surface of the core body; and wiring laminates each formed by resin insulating layers and conductor layers laminated on each of major surfaces of the 40 core board, characterized in:

that a groove-filling portion which fills a gap between the core body and the ceramic sub-core is integral with a lowest resin insulating layer of the first-major-surface-side wiring laminate; and

that via conductors that are connected to respective conductor patterns formed on a first major surface of the ceramic sub-core penetrate through the lowest resin insulating layer.

And, preferably, a surface, located over the gap between the core body and the ceramic sub-core and the ceramic 50 sub-core, of the lowest resin insulating layer is substantially parallel with the first major surface of the core body.

With the above configuration, since the groove-filling portion which fills the gap between the core body and the ceramic sub-core is integral with the lowest resin insulating layer of the first-major-surface-side wiring laminate, the surface of the lowest resin insulating layer is substantially parallel with the first major surface of the core body and is flat following the flat first major surface of the core body. The entire wiring laminate is thus made flat.

The invention provides a first manufacturing method of a wiring board provided with a core board in which a sub-core accommodation space that is a through-hole that communicates with major surfaces of a plate-like core body or a recess having an opening in a first major surface of the core body is formed in the core body and a ceramic sub-core is accommodated in the sub-core accommodation space; and wiring lami-

4

nates each formed by resin insulating layers and conductor layers laminated alternately on each of major surfaces of the core board, characterized by comprising, as steps executed in written order:

a sub-core accommodation step of accommodating the ceramic sub-core in the sub-core accommodation space through the first-major-surface-side opening of the sub-core accommodation space; and

a pressure printing step of charging a resin paste into a gap between the core body and the ceramic sub-core by pressureprinting the resin paste from the side of the first major surface of the core body and a first major surface of the ceramic sub-core.

According to the first manufacturing method of a wiring board according to the invention, a charged resin portion for filling the gap between the ceramic sub-core and the core body and fixing them to each other can be formed satisfactorily without formation of voids by pressure-printing (charging) a resin paste into the gap between the ceramic sub-core and the core body.

It is preferable that the viscosity of the resin paste be 3 to 60 Pa·s in a temperature range of room temperature (e.g., 25° C.) to 120° C. (it is even preferable that the viscosity be 5 to 58 Pa·s). To perform pressure printing, it is preferable that the viscosity be higher than the lower limit. On the other hand, if the viscosity is higher than the upper limit, the resin paste may not be charged satisfactorily even by pressure printing because its flowability becomes too low. To obtain such viscosity, it is preferable that the filler content of the resin paste be 50 to 80 wt % (it is even preferable that the filler content be 52 to 78 wt %).

In the first manufacturing method of a wiring board according to the invention, it is preferable that in the pressure printing step, the resin paste be charged into the gap between the core body and the ceramic sub-core by pressure-printing the resin paste at least on the first major surface of the ceramic sub-core directly without intervention of a mask and a layer that is continuous with the resin paste charged in the gap be formed as a continuous-with-charged-resin layer so as to cover at least the first major surface of the ceramic sub-core. This manufacturing method can simplify the process because pressure printing is performed at least on the first major surface of the ceramic sub-core without using a mask. Furthermore, the continuous-with-charged-resin layer can be formed at the same time as the resin paste is charged into the space between the core body and the ceramic sub-core.

In the first manufacturing method of a wiring board according to the invention, in the pressure printing step, the resin paste may be charged into the gap between the core body and the ceramic sub-core by pressure-printing the resin paste on the first major surfaces of the ceramic sub-core and the core body directly without intervention of a mask and a layer that is continuous with the resin paste charged in the gap may be formed as a continuous-with-charged-resin layer so as to entirely cover the first major surfaces of the ceramic sub-core and the core body. This manufacturing method can simplify the process because pressure printing is performed without using a mask. Furthermore, since the continuous-with-charged-resin layer is formed so as to cover the entire first major surface of the core board, this manufacturing method contributes to flattening of a wiring board produced.

The first manufacturing method of a wiring board according to the invention may further comprise, as a step executed before the sub-core accommodation step, a closing step of closing a second-major-surface-side opening of the sub-core accommodation space that is the through-hole that communicates with the major surfaces of the core body with a sheet

having an adhesive on one surface in such a manner that the adhesive is exposed inside the sub-core accommodation space; and in the sub-core accommodation step, the ceramic sub-core may be accommodated through the first-major-surface-side opening of the sub-core accommodation space and fixed to the adhesive. The pressure printing step is executed in this state. Where the sub-core accommodation space is a through-hole, this manufacturing method makes it possible to execute the pressure printing step in a state that the ceramic sub-core is fixed by means of the adhesive on the sheet surface.

The first manufacturing method of a wiring board according to the invention may further comprise, as steps executed mation step of forming a lowest resin insulating layer of the first-major-surface-side wiring laminate on the continuouswith-charged-resin layer; a multi-layer penetration via hole formation step of forming multi-layer penetration via holes that penetrate through the lowest resin insulating layer and the 20 continuous-with-charged-resin layer and thereby exposing, inside the multi-layer penetration via holes, conductor pads formed on the first major surface of the ceramic sub-core; and a multi-layer penetration via conductor formation step of forming multi-layer penetration via conductors in the respec- 25 tive multi-layer penetration via holes by charging. Even if the continuous-with-charged-resin layer exists between the ceramic sub-core and the wiring laminate that is formed on the first major surface of the ceramic sub-core, this manufacturing method enables conduction between the conductor 30 pads on the ceramic sub-core and interconnections in the wiring laminate by forming the multi-layer penetration via conductors.

A wiring board according to the invention which is produced by the above manufacturing method is a wiring board 35 provided with a core board in which a sub-core accommodation space that is a through-hole that communicates with major surfaces of a plate-like core body made of a polymeric material or a recess having an opening in one major surface of the core body is formed in the core body and a plate-like 40 ceramic sub-core made of ceramics is accommodated in the sub-core accommodation space; and wiring laminates each formed by dielectric layers made of a polymeric material and conductor layers laminated alternately on each of major surfaces of the core board, characterized in:

that a continuous-with-charged-resin layer that is continuous with a charged resin portion that fills a gap between the core body and the ceramic sub-core is interposed between the ceramic sub-core and the wiring laminate formed on its major surface; and

that multi-layer penetration via conductors that penetrate through a lowest dielectric layer of the wiring laminate and the continuous-with-charged-resin layer are connected to conductor pads formed on the major surface of the ceramic sub-core.

According to this manufacturing method of a wiring board according to the invention, since the continuous-withcharged-resin layer which is continuous with the charged resin portion is formed between the ceramic sub-core and the wiring laminate formed on its major surface, the difference 60 between the linear expansion coefficient (in the thickness direction) of the ceramic sub-core and that of the wiring laminate (and an IC chip mounted thereon) can be absorbed by elastic deformation of the continuous-with-charged-resin layer. This prevents such trouble as disconnection of inter- 65 connections around the ceramic sub-core. The continuouswith-charged-resin layer may cover the entire major surface

of the core board, which not only provides the above effect but also contributes to flattening of the wiring board.

The continuous-with-charged-resin layer may be made of a material that is smaller than the dielectric layers in the linear expansion coefficient. In particular, the linear expansion coefficient of the continuous-with-charged-resin layer may lie halfway between the linear expansion coefficients of the ceramic sub-core and the dielectric layers. This allows the above-described effect of absorbing the difference between the linear expansion coefficients in the thickness direction to be attained satisfactorily. More specifically, the continuouswith-charged-resin layer may be made of a material whose average linear expansion coefficient in a range of room temperature (e.g., 25° C.) to 200° C. (hereinafter referred to after the pressure printing step a lowest dielectric layer forequal to 35 ppm/° C. (preferably, smaller than or equal to 33 ppm/° C. excluding 0). If the linear expansion coefficient of the continuous-with-charged-resin layer exceeds this upper limit, it is on the same level as that of the wiring laminate which is mainly made of a polymeric material and hence the above effect may not be attained satisfactorily. To attain such a linear expansion coefficient, the continuous-with-chargedresin layer may be made of a material that is higher in filler content than the dielectric layers. More specifically, the filler content of the continuous-with-charged-resin layer may be set at 50 to 80 wt %.

The invention provides a second manufacturing method of a wiring board provided with a core board in which a sub-core accommodation space that is a through-hole that communicates with major surfaces of a plate-like core body or a recess having an opening in a first major surface of the core body is formed in the core body and a plate-like ceramic sub-core mainly made of ceramics is accommodated in the sub-core accommodation space; and wiring laminates each formed by resin insulating layers and conductor layers laminated alternately on each of major surfaces of the core board, characterized by comprising, as steps executed in written order:

- a sub-core accommodation step of accommodating the ceramic sub-core in the sub-core accommodation space through the first-major-surface-side opening of the sub-core accommodation space; and

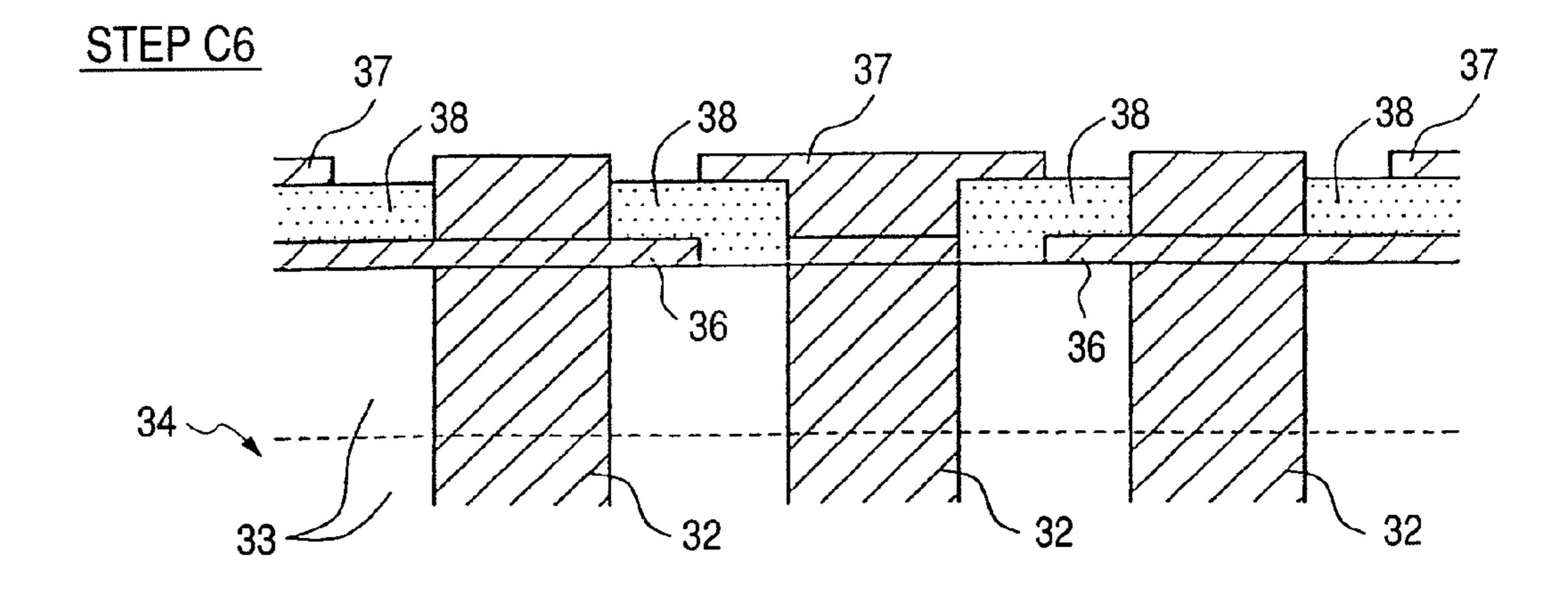

- a film formation and charging step of forming a lowest resin insulating layer of the first-major-surface-side wiring laminate by sticking a resin material to the core body and the 45 ceramic sub-core from the first major surface side, and forming a groove-filling portion that is continuous with the lowest resin insulating layer by charging the resin material into a gap between the core body and the ceramic sub-core.

A wiring board according to the invention produced by the above manufacturing method is a wiring board provided with a core board in which a sub-core accommodation space that is a through-hole that communicates with major surfaces of a plate-like core body or a recess having an opening in a first major surface of the core body is formed in the core body and 55 a plate-like ceramic sub-core mainly made of ceramics is accommodated in the sub-core accommodation space; and wiring laminates each formed by resin insulating layers and conductor layers laminated alternately on each of major surfaces of the core board, characterized in:

that a groove-filling portion which fills a gap between the core body and the ceramic sub-core is continuous with a lowest resin insulating layer of the first-major-surface-side wiring laminate; and

that via conductors for conduction between conductor patterns formed on the first major surface of the core body or the ceramic sub-core under the single-layer, lowest resin insulating layer of the first-major-surface-side wiring laminate and a

conductor layer formed on the lowest resin insulating layer are formed in the lowest resin insulating layer.

According to this manufacturing method of a wiring board according to the invention, the lowest resin insulating layer of the first-major-surface-side wiring laminate and the groovefilling portion which fills the gap between the core body and the ceramic sub-core are formed together so as to be continuous and integral with each other. Therefore, the above-described charged resin portion is not necessary. Since two layers having different characteristics are not formed in 10 superimposition on the ceramic sub-core, via holes can be formed satisfactorily. Since the lowest resin insulating layer and the groove-filling portion are formed together, the lowest resin insulating layer formed on the core board is given a uniform thickness distribution. Further, since the step of 15 injecting a filling resin in the conventional process is omitted, the manufacturing process can be simplified. Still further, the lowest resin insulating layer and the groove-filling portion of a wiring board produced are continuous and integral with each other, the adhesion between the core board and the 20 wiring laminate is increased. Since the ceramic sub-core is surrounded by the groove-filling portion, the adhesion between the core body and the ceramic sub-core is increased.

The invention provides a third manufacturing method of a wiring board provided with a core board in which a sub-core accommodation space that is a through-hole that communicates with major surfaces of a plate-like core body is formed in the core body and a plate-like ceramic sub-core mainly made of ceramics is accommodated in the sub-core accommodation space; and wiring laminates each formed by resin 30 insulating layers and conductor layers laminated alternately on each of major surfaces of the core board, characterized by comprising, as steps executed in written order:

a sub-core accommodation step of accommodating the ceramic sub-core in the sub-core accommodation space; and 35

a film formation and charging step of forming lowest resin insulating layers of the wiring laminates of the two respective major surface sides by sticking a resin material sequentially to the core body and the ceramic sub-core from the sides of the two major surfaces, and forming a groove-filling portion that 40 is continuous with the lowest resin insulating layers of the two major surface sides by charging the resin material into a gap between the core body and the ceramic sub-core.

A wiring board according to the invention produced by the above manufacturing method is a wiring board provided with 45 a core board in which a sub-core accommodation space that is a through-hole that communicates with major surfaces of a plate-like core body is formed in the core body and a plate-like ceramic sub-core mainly made of ceramics is accommodated in the sub-core accommodation space; and wiring laminates each formed by resin insulating layers and conductor layers laminated alternately on each of major surfaces of the core board, characterized in:

that a groove-filling portion which fills a gap between the core body and the ceramic sub-core is continuous with lowest 55 resin insulating layers of the respective wiring laminates; and

that via conductors for conduction between conductor patterns formed on each major surface of the core body or the ceramic sub-core under the single-layer, lowest resin insulating layer of the wiring laminate of each of the two major 60 surface sides and a conductor layer formed on the lowest resin insulating layer are formed in the lowest resin insulating layer.

According to this manufacturing method of a wiring board according to the invention, the lowest resin insulating layer of 65 the wiring laminate of each of the two major surface sides and the groove-filling portion which fills the gap between the core

8

body and the ceramic sub-core are formed so as to be continuous and integral with each other. Therefore, the abovedescribed charged resin portion is not necessary. Since two layers having different characteristics are not formed in superimposition on the ceramic sub-core, via holes can be formed satisfactorily. Since the groove-filling portion is formed together with at least one lowest resin insulating layer, the lowest resin insulating layer(s) formed on the core board is given a uniform thickness distribution. Further, since the step of injecting a filling resin in the conventional process is omitted, the manufacturing process can be simplified. Still further, the lowest resin insulating layer of each major surface side and the groove-filling portion of a wiring board produced are continuous and integral with each other, the adhesion between the core board and the wiring laminates is increased. Since the ceramic sub-core is surrounded by the groovefilling portion, the adhesion between the core body and the ceramic sub-core is increased.

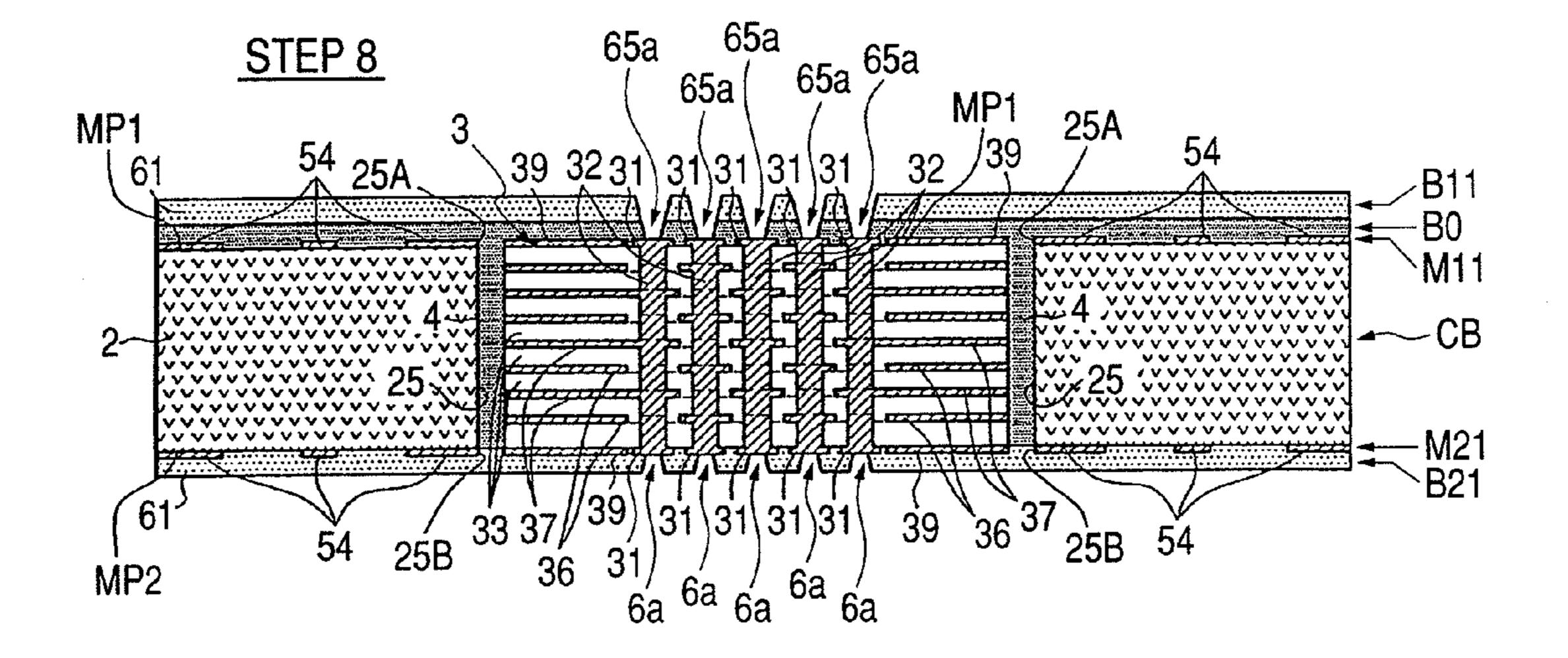

The second or third manufacturing method of a wiring board according to the invention may further comprise, as a step executed after the film formation and charging step, the step of forming via conductors for conduction between conductor patterns formed on the/each major surface of the core body or the ceramic sub-core under the single-layer, lowest resin insulating layer of the/each wiring laminate and a conductor layer formed on the lowest resin insulating layer are formed in the lowest resin insulating layer.

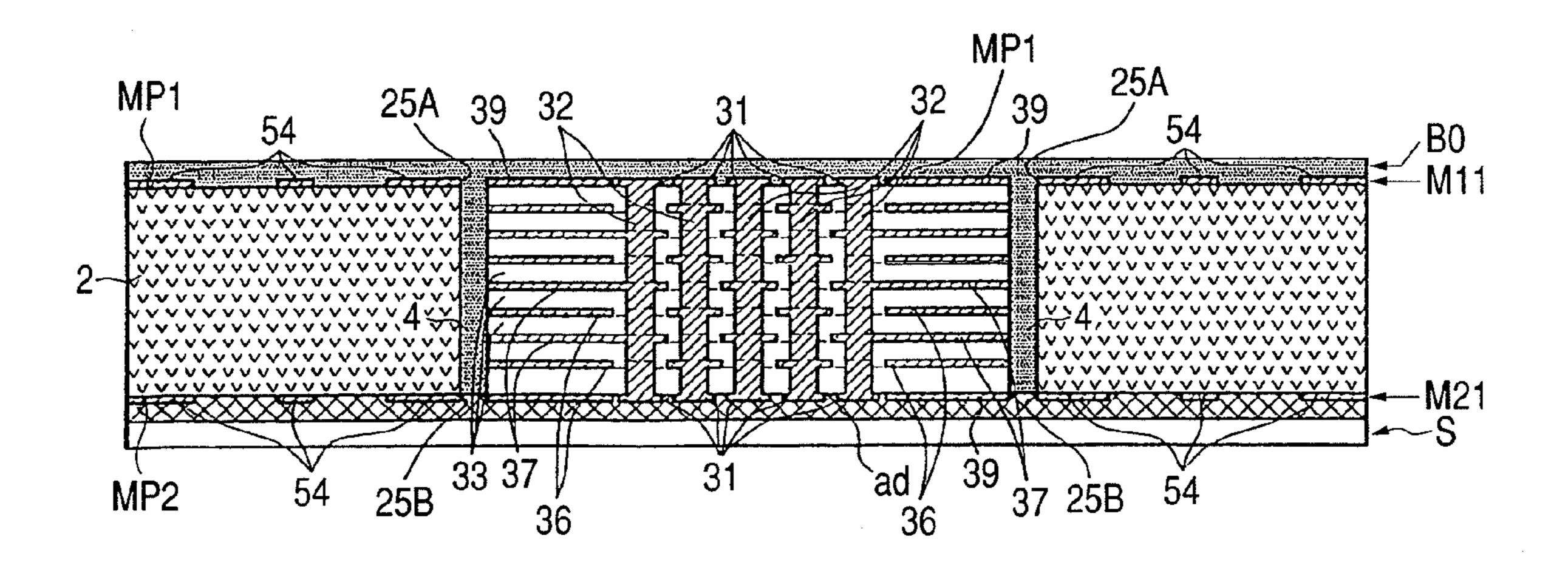

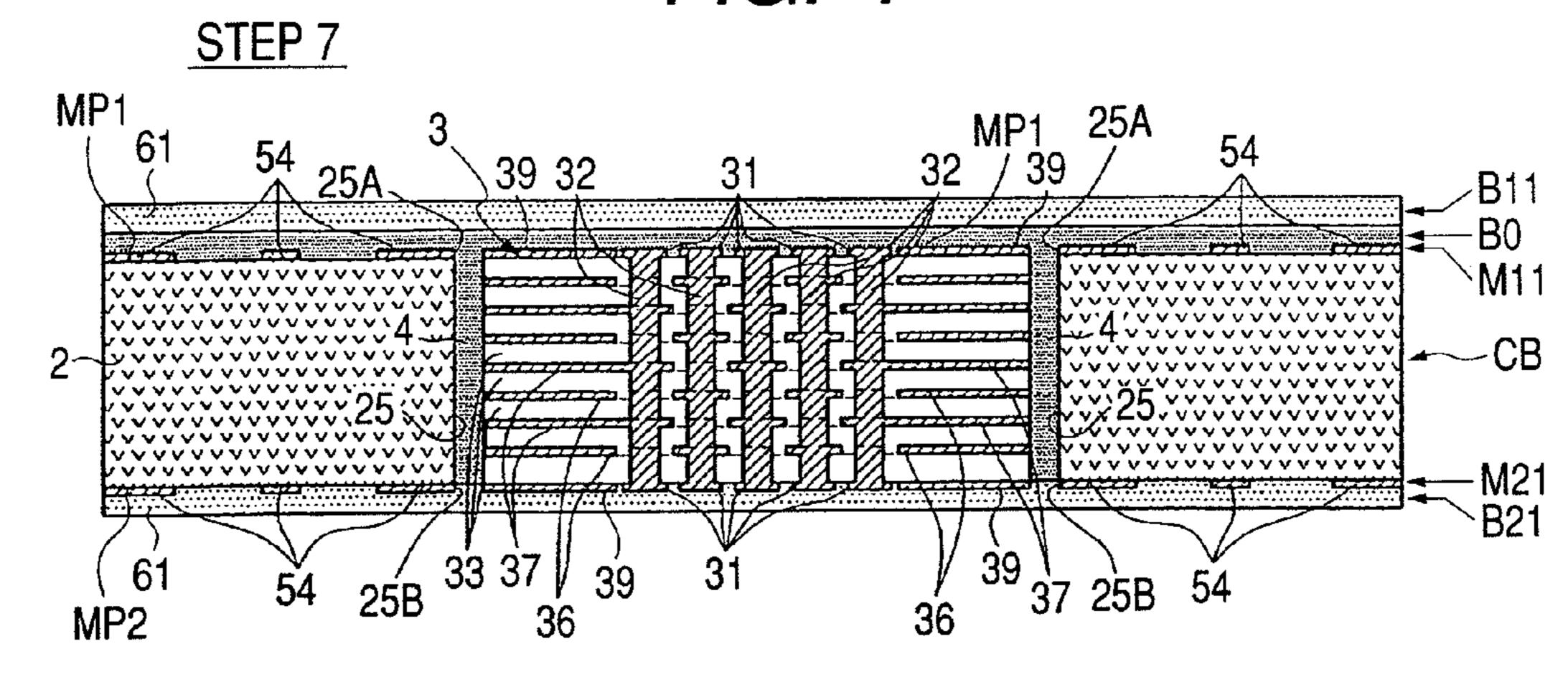

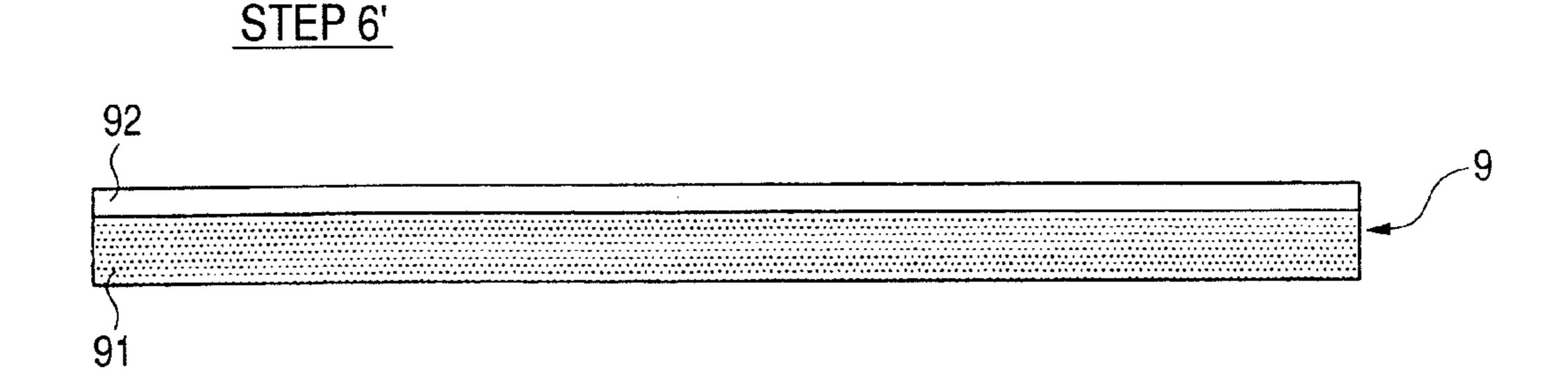

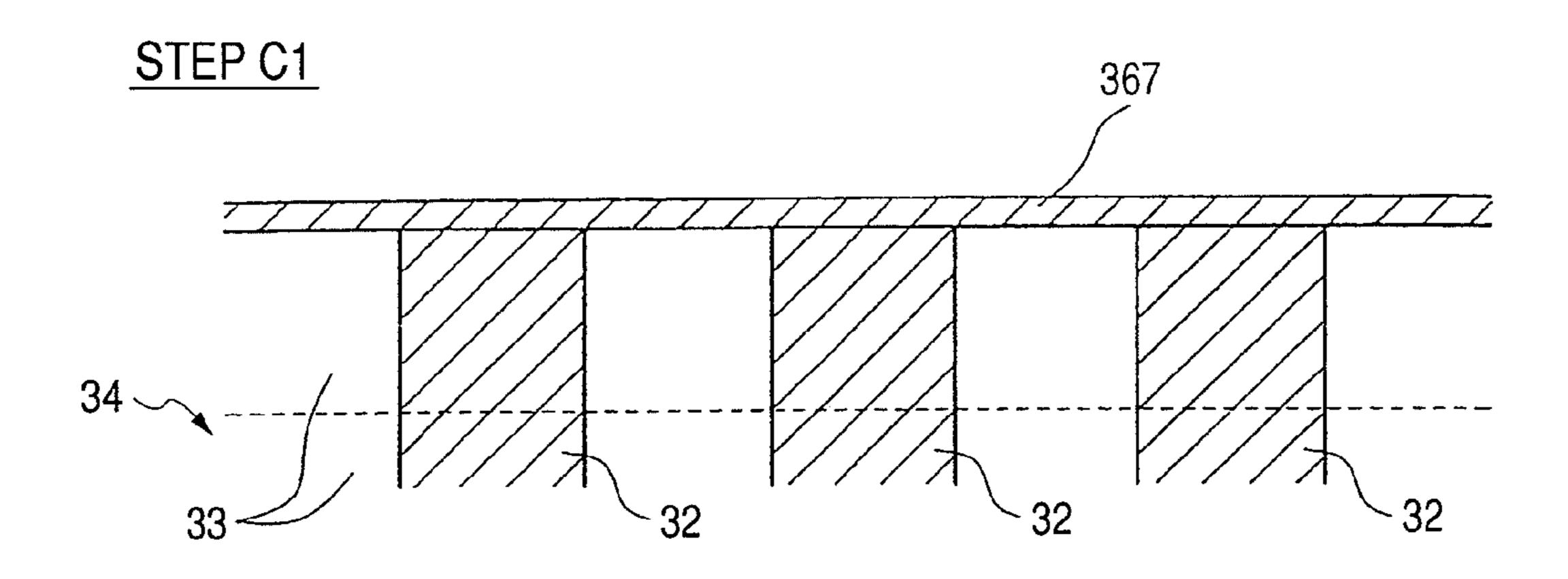

In the second or third manufacturing method of a wiring board according to the invention, the film formation and charging step may comprise the steps of

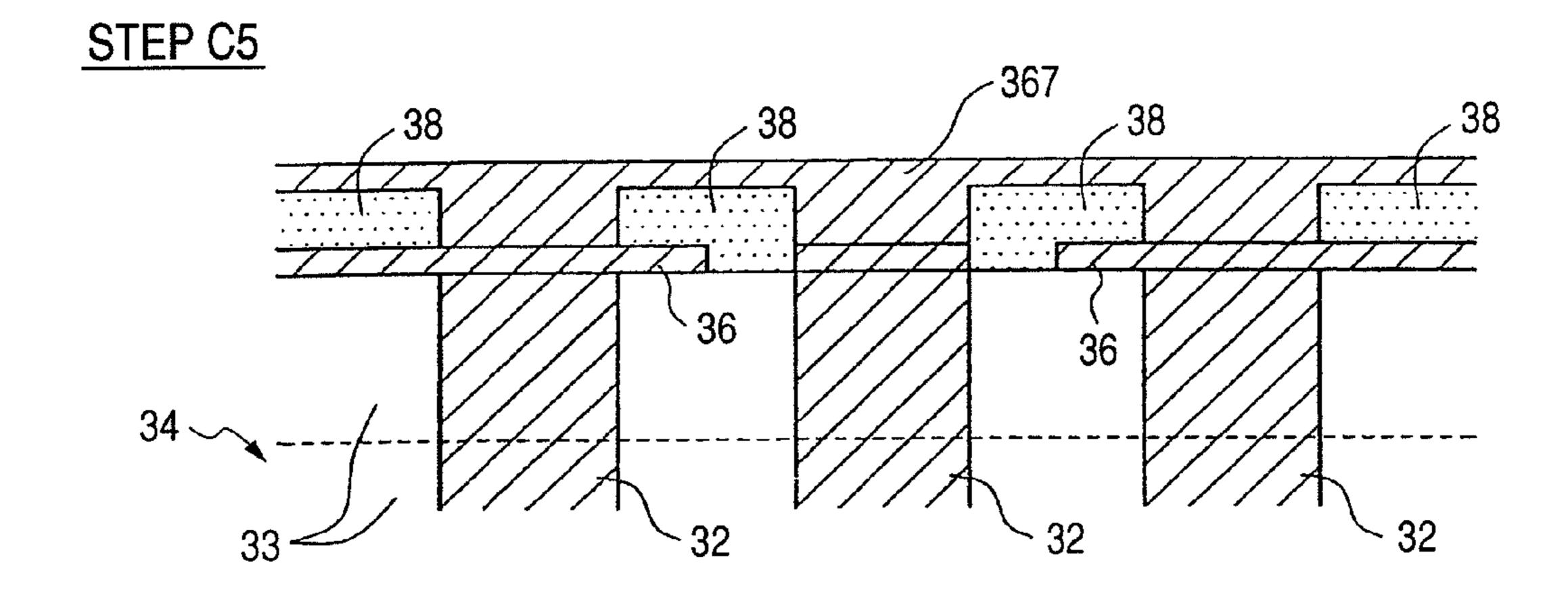

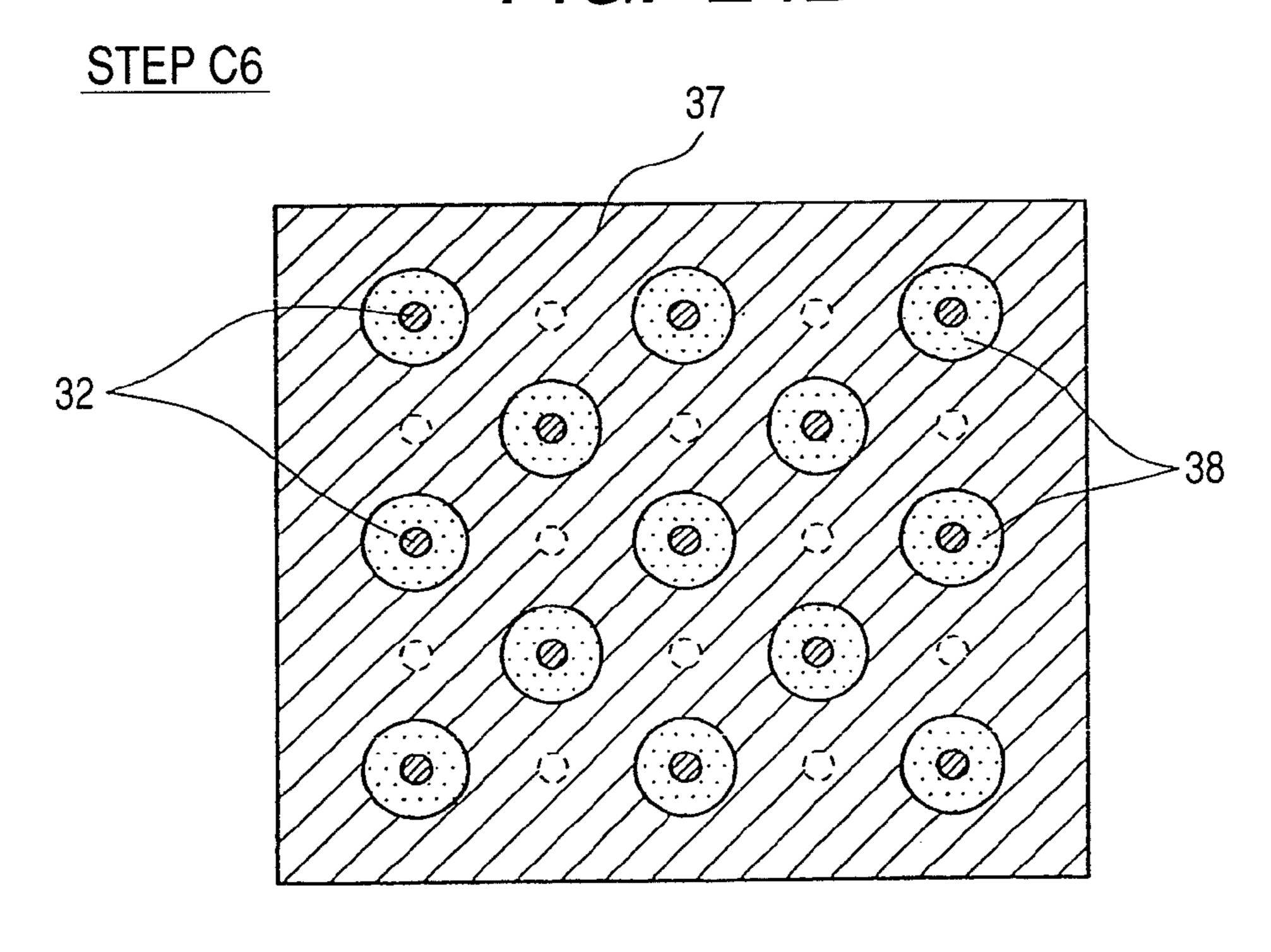

forming a first lowest resin insulating layer as the lowest resin insulating layer of the first-major-surface-side wiring laminate and forming a first groove-filling portion that is continuous with the first lowest resin insulating layer in such a manner that at least a first-major-surface-side portion of the gap between the core body and the ceramic sub-core is filled with the first groove-filling portion by compression-bonding a resin film to the core body and the ceramic sub-core from the first major surface side in a state that ceramic sub-core is supported from a second major surface side in the sub-core accommodation space that is the through-hole that communicates with the major surfaces of the core body; and

forming a second lowest resin insulating layer as the lowest resin insulating layer of the second-major-surface-side wiring laminate and forming a second groove-filling portion that is continuous with the second lowest resin insulating layer in such a manner that a residual portion, not filled with the first groove-filling portion, of the gap between the core body and the ceramic sub-core is filled with the second groove-filling portion by compression-bonding a resin film to the core body and the ceramic sub-core from the second major surface side in a state that ceramic sub-core is supported from the first major surface side by the first lowest resin insulating layer and the first groove-filling portion.

According to this manufacturing method of the invention, the first lowest resin insulating layer and the first groove-filling portion are formed together so as to be continuous and integral with each other by compression-bonding a resin film from the first major surface side. Then, the second lowest resin insulating layer and the second groove-filling portion are formed together so as to be continuous and integral with each other by compression-bonding a resin film from the second major surface side. The first groove-filling portion and the second groove-filling portion are combined together into the above-mentioned groove-filling portion. Compression-bonding a resin film in the above-described manner makes it possible to form the first or second lowest resin insulating

layer having a uniform thickness distribution together with the first or second groove-filling portion in such a manner that they are continuous and integral with each other. Furthermore, combining the first groove-filling portion and the second groove-filling portion together into the groove-filling portion can increase the adhesion of the ceramic sub-core on both of the first and second major surface sides.

In the second or third manufacturing method of a wiring board according to the invention, in the film formation and charging step, the second lowest resin insulating layer and the second groove-filling portion may be formed by compression-bonding the resin film from the second major surface side in a state that the first lowest resin insulating film and the first groove-filling portion are not fully cured (are half set).

According to this manufacturing method of the invention, since the second lowest resin insulating layer and the second groove-filling portion may be formed by compression-bonding the resin film from the second major surface side in a state that the first lowest resin insulating film and the first groove-filling portion are not fully cured (are half set), the first groove-filling portion and the second groove-filling portion are rendered continuous and integral with each other and thus become the groove-filling portion. Therefore, the adhesion between the core board and the wiring laminates is increased further.

In the second or third manufacturing method of a wiring board according to the invention, the manufacturing method may further comprise, as a step executed before the sub-core accommodation step, the step of closing a second-major-surface-side opening of the sub-core accommodation space 30 that is the through-hole that communicates with the major surfaces of the core body with a sheet having an adhesive on one surface in such a manner that the adhesive is exposed inside the sub-core accommodation space; and in the sub-core accommodation step, the ceramic sub-core may be supported from the second major surface side by accommodating the ceramic sub-core through the first-major-surface-side opening of the sub-core accommodation space and fixing the ceramic sub-core to the adhesive.

According to this manufacturing method of the invention, 40 since the ceramic sub-core is accommodated in the sub-core accommodation space by fixing the former to the sheet bearing the adhesive, the ceramic sub-core can be positioned easily and accurately before formation of the lowest resin insulating layer and the (first) groove-filling portion.

The second or third manufacturing method of a wiring board according to the invention may further comprise, as steps executed before the sub-core accommodation step, the step of performing surface chemical treatment for increasing adhesion to a resin material only on first-major-surface-side 50 conductor patterns among conductor patterns formed on the two major surfaces of the core body, and the step of covering second-major-surface-side conductor patterns that have not been subjected to the surface chemical treatment with an adhesive by closing a second-major-surface-side opening of 55 the sub-core accommodation space by a sheet, and the manufacturing method may be such that:

in the sub-core accommodation step, the ceramic sub-core in which surface chemical treatment has been performed only on first-major-surface-side conductor patterns among conductor patterns formed on the two major surfaces of the ceramic sub-core is accommodated in the sub-core accommodation space; and

in the film formation and charging step, the step of forming the first lowest resin insulating layer and the first groove- 65 filling portion by compression-bonding the resin film to the core body and the ceramic sub-core from the first major **10**

surface side, the step of peeling the sheet off the second major surfaces of the core body and the ceramic sub-core and performing surface chemical treatment simultaneously on the second-major-surface-side conductor patterns formed on the core body and second-major-surface-side conductor patterns formed on the ceramic sub-core, and the step of forming the second lowest resin insulating layer and the second groove-filling portion by compression-bonding the resin film on the core body and the ceramic sub-core from the second major surface side are executed in the above order.

Where a sealing member is stuck to the core body or the ceramic sub-core by bringing an adhesive into contact with conductor patterns on the core body or the ceramic sub-core that have been subjected to surface chemical treatment for increasing adhesion to a resin material (e.g., roughening treatment), the sticking of the sealing member may cause an event that the conductor patterns lose the effect of the surface chemical treatment after the sealing member is peeled off (e.g., the asperities of the roughened surfaces are smoothed out by the adhesive). Such an event can be avoided by performing the surface chemical treatment on the conductor patterns on the core body and the ceramic sub-core in the order of the above manufacturing method according to the invention.

### BRIEF DESCRIPTION OF THE DRAWINGS

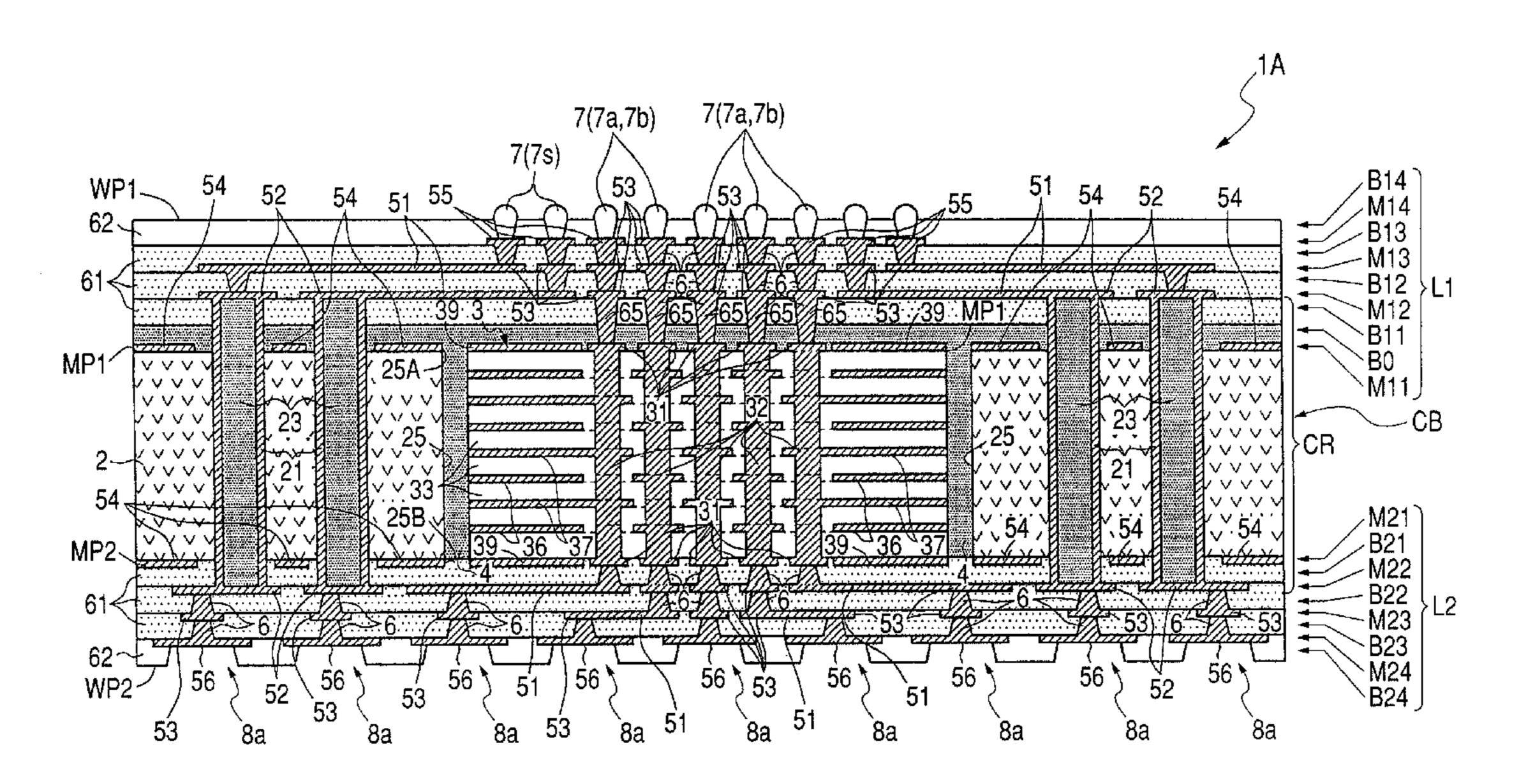

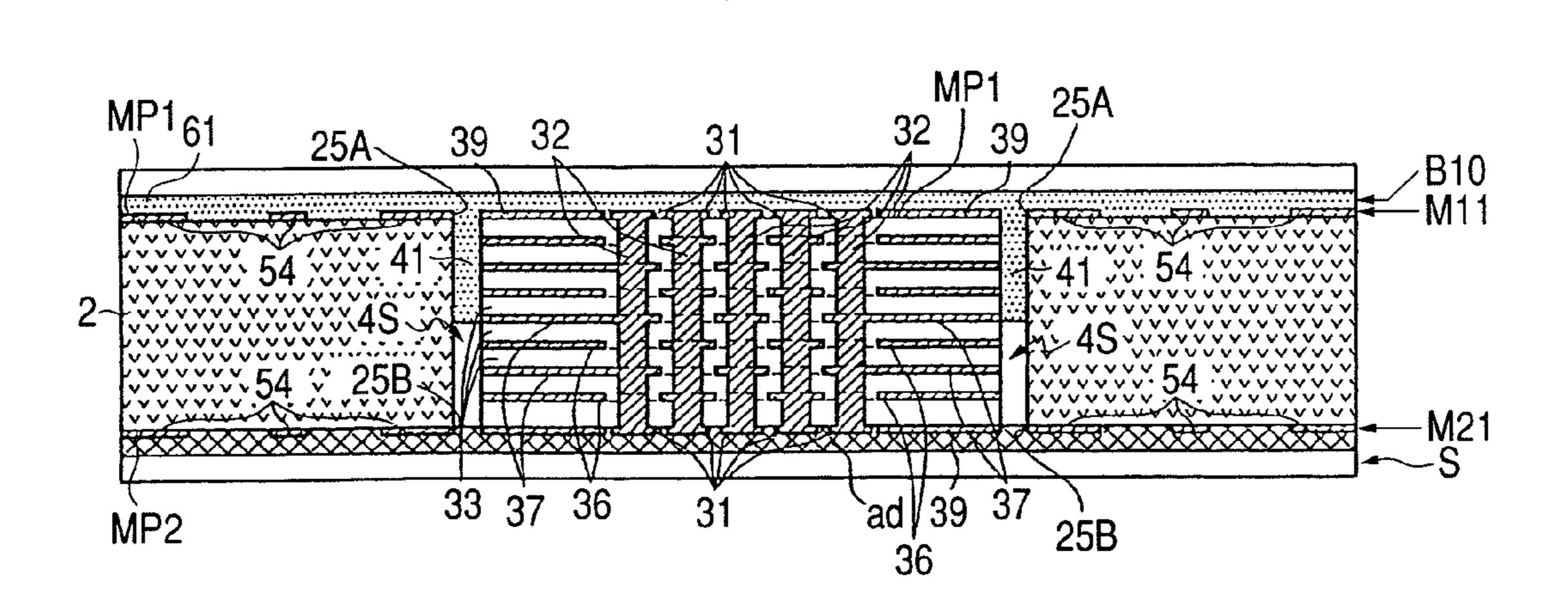

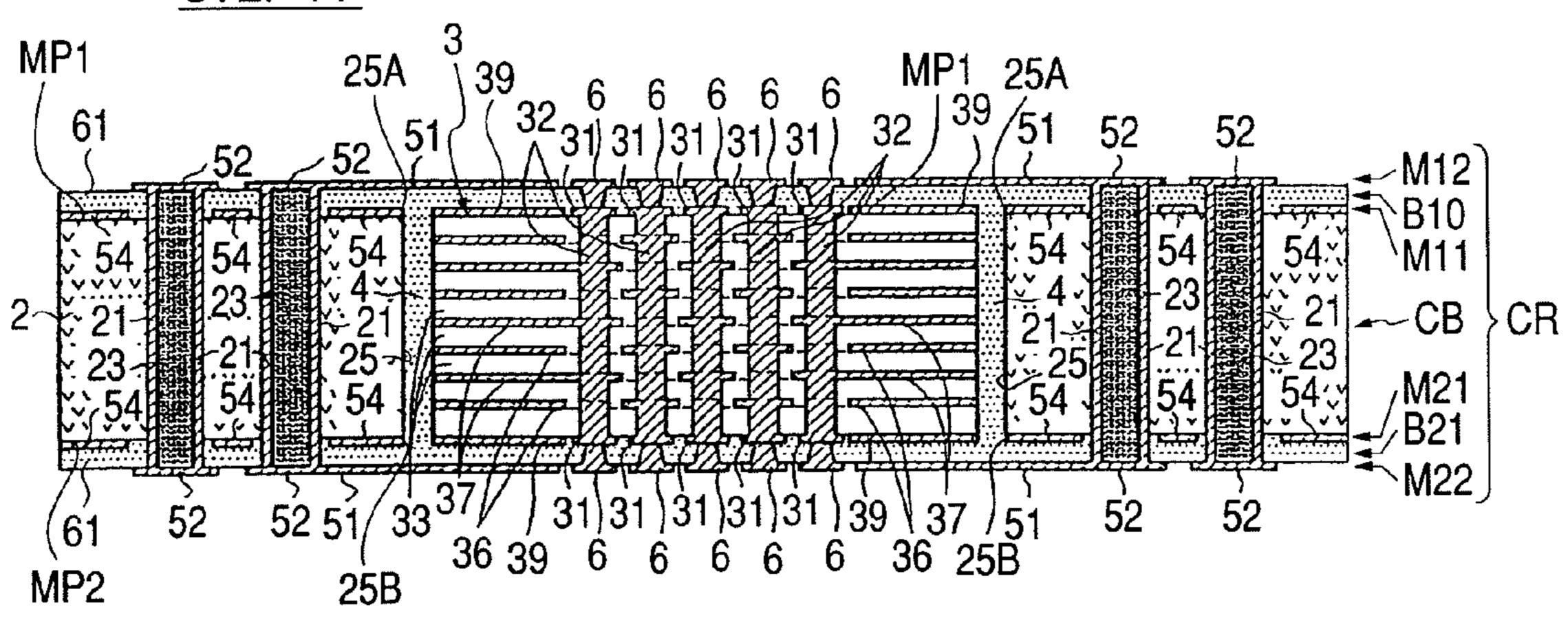

FIG. 1 is a schematic sectional view showing the configuration of a wiring board according to a first embodiment of the present invention.

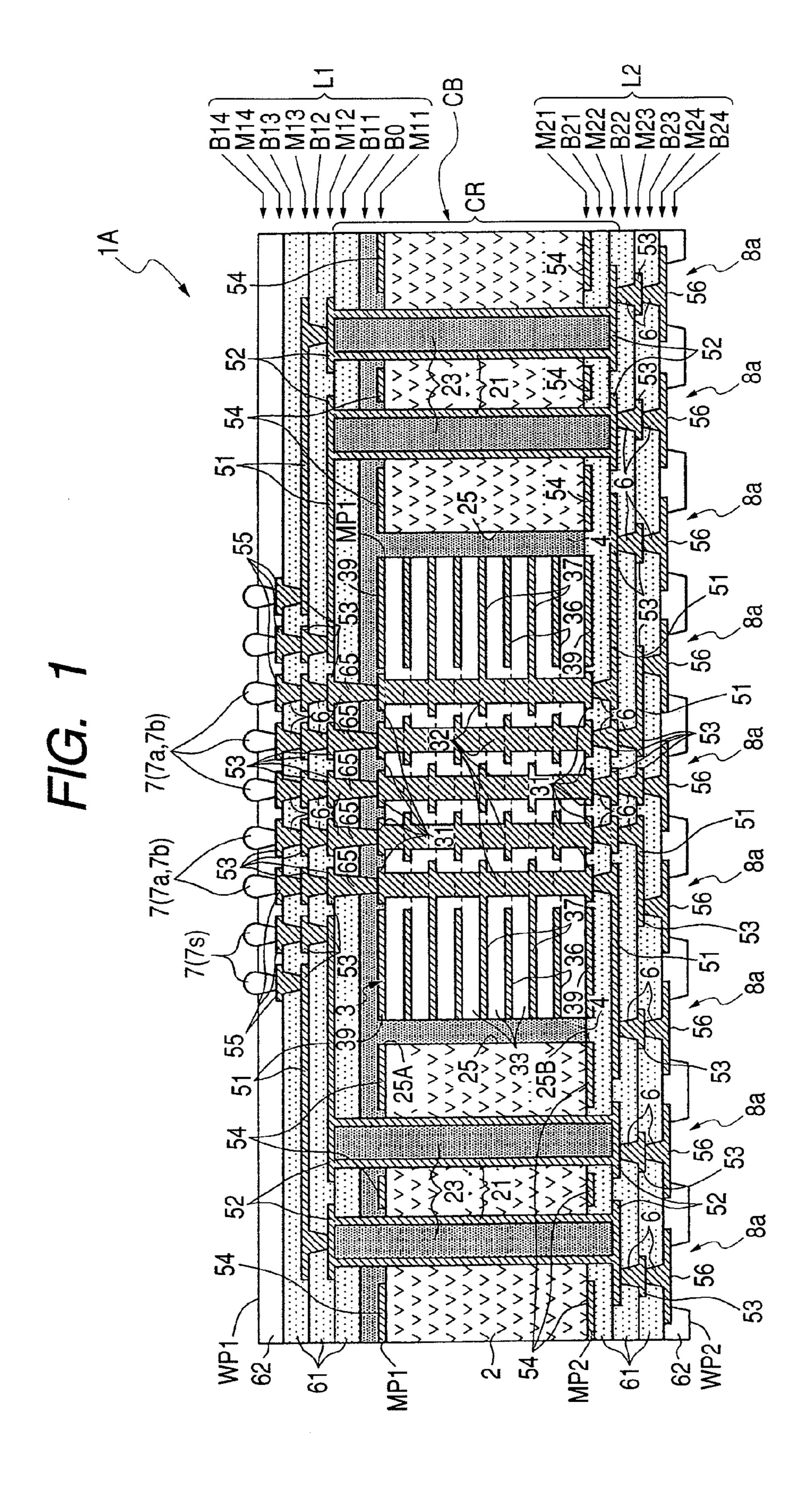

FIG. 2 shows the wiring board that is disposed between a semiconductor integrated circuit device (IC chip) and a main board (e.g., mother board).

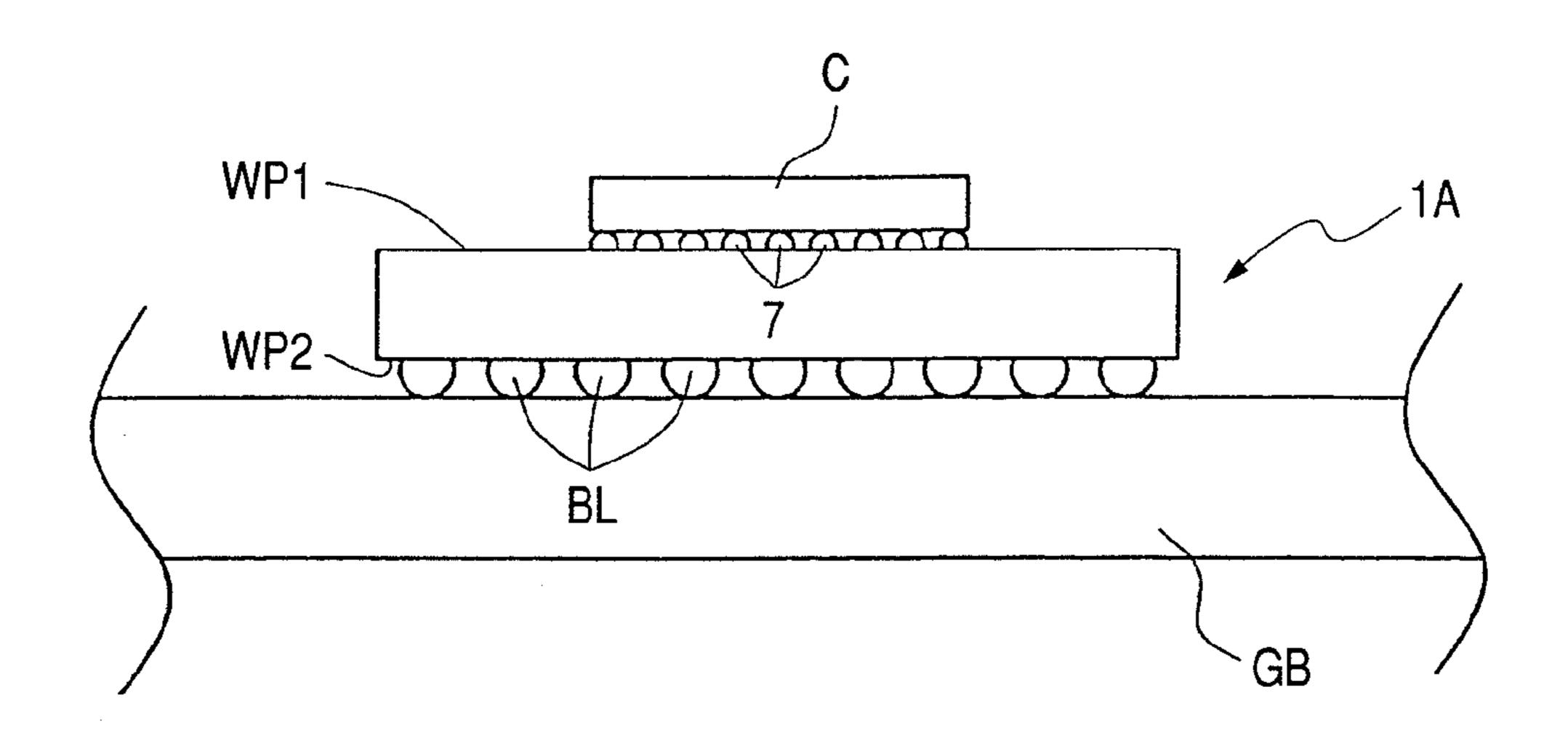

FIG. 3 shows a first major surface of the wiring board.

FIG. 4 shows manufacturing steps of a wiring board.

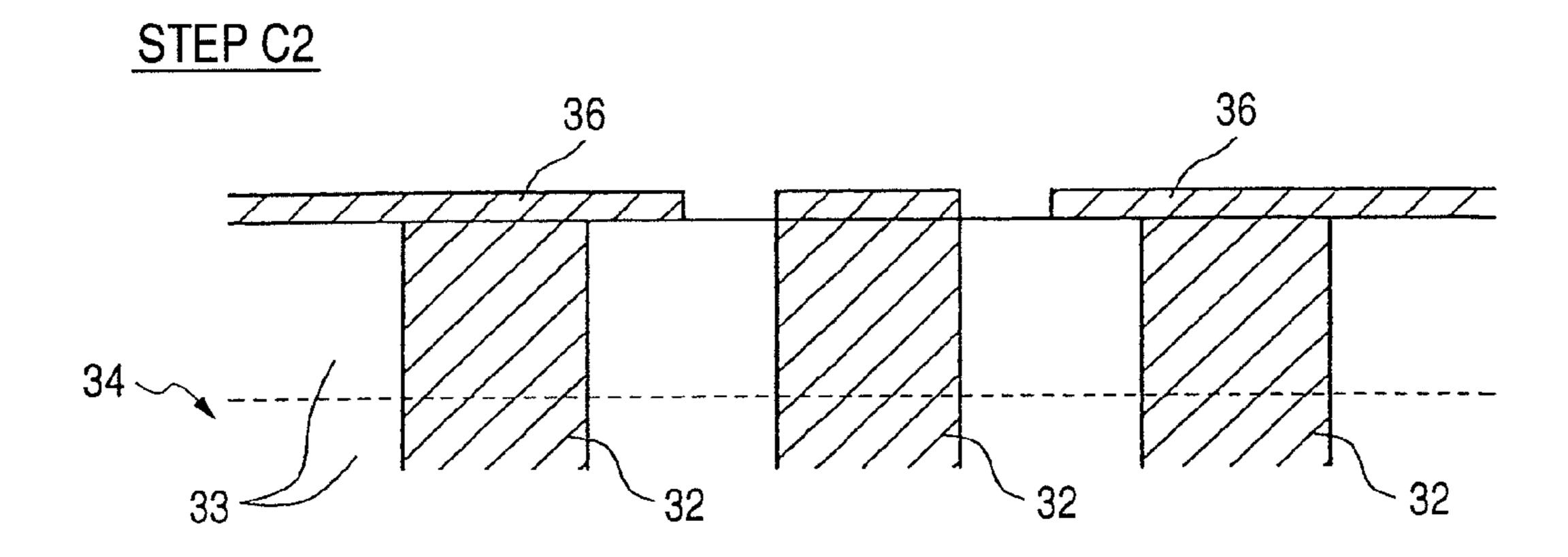

FIG. **5** shows manufacturing steps following the manufacturing steps of FIG. **4**.

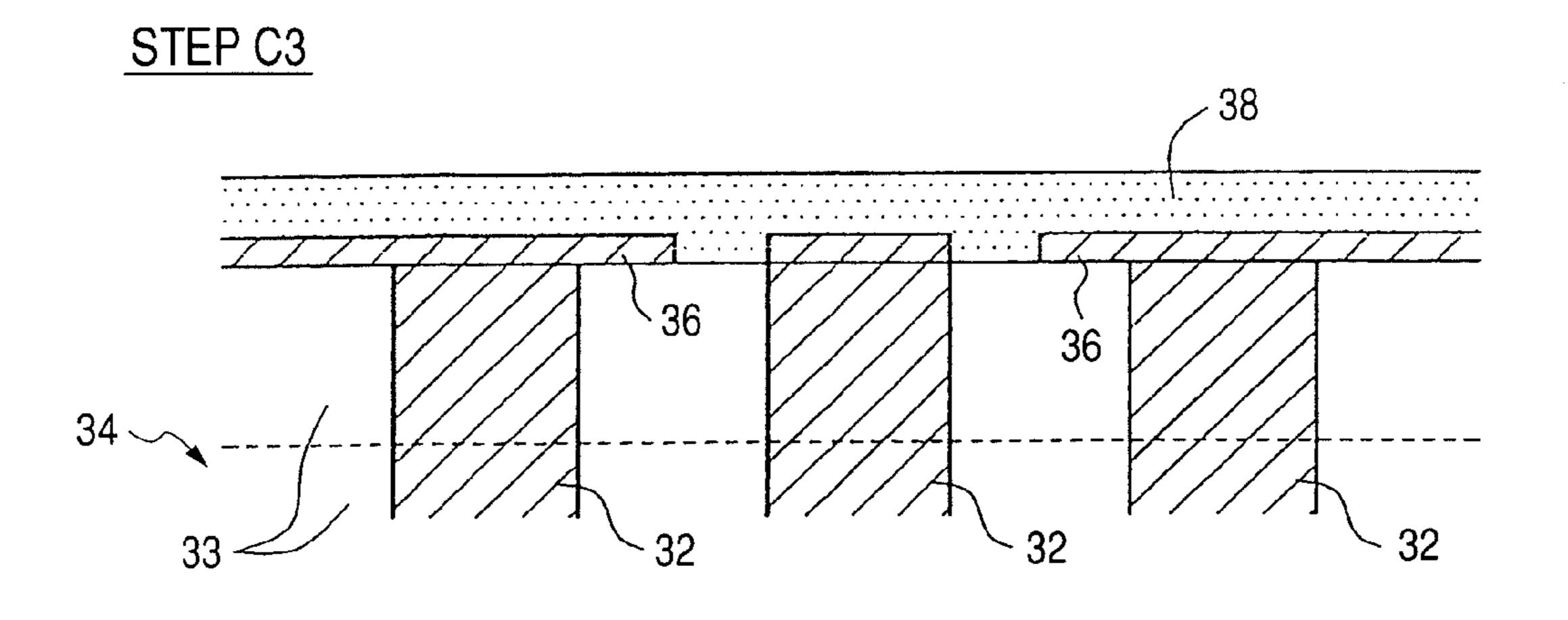

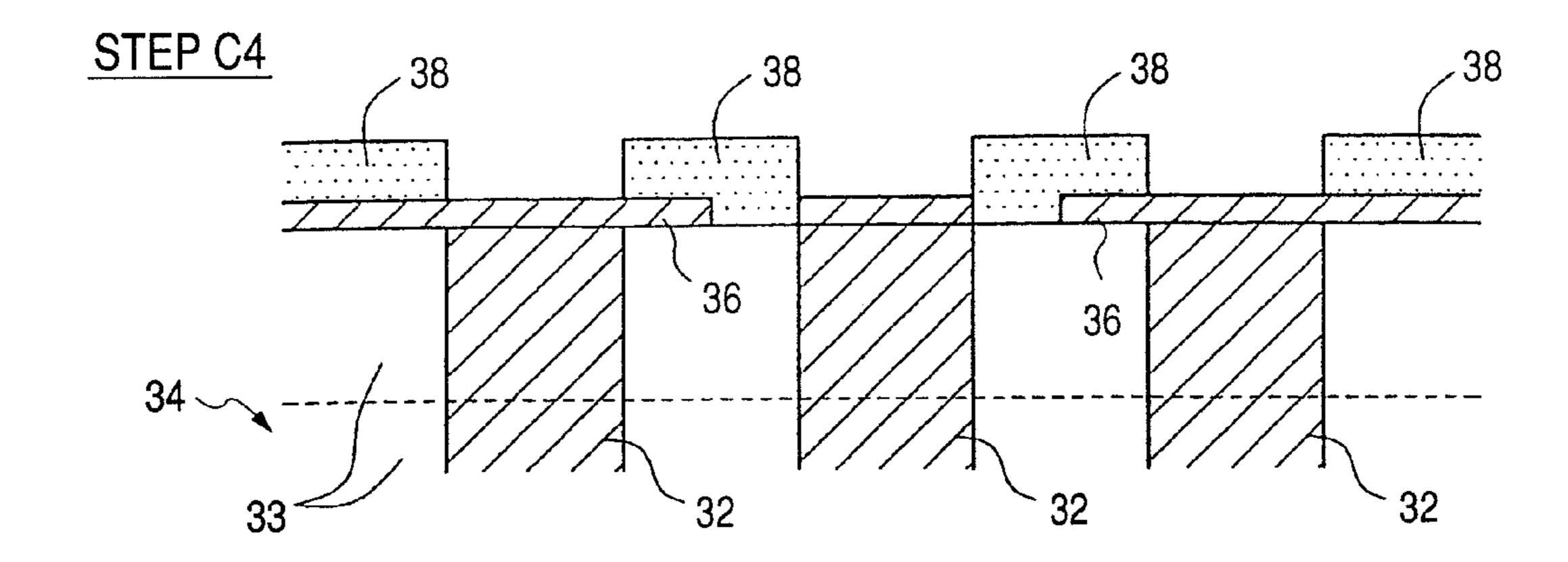

FIG. **6** shows a manufacturing step following the manufacturing steps of FIG. **5**.

FIG. 7 shows manufacturing steps following the manufacturing step of FIG. 6.

FIG. 8 shows manufacturing steps following the manufacturing steps of FIG. 7.

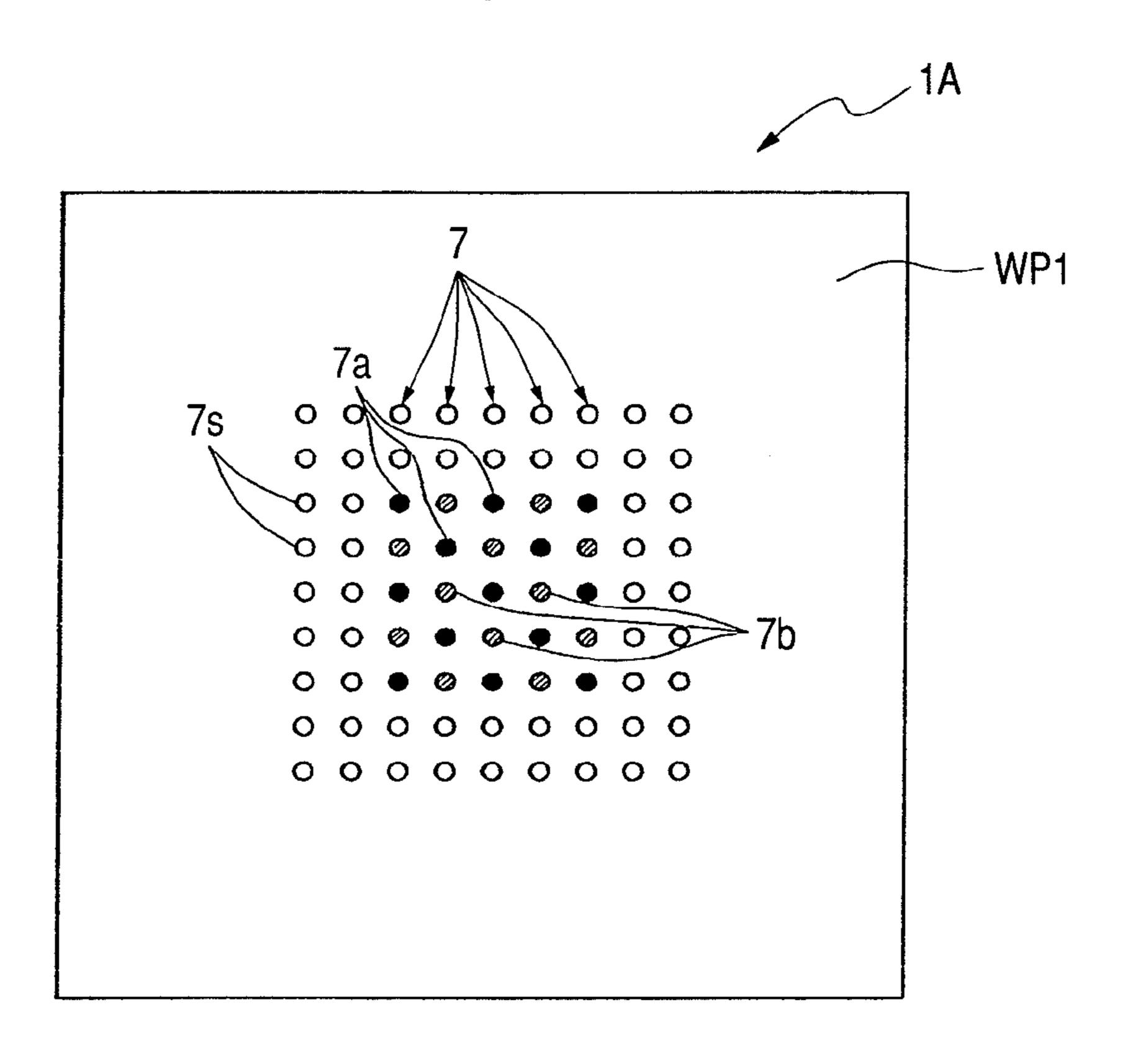

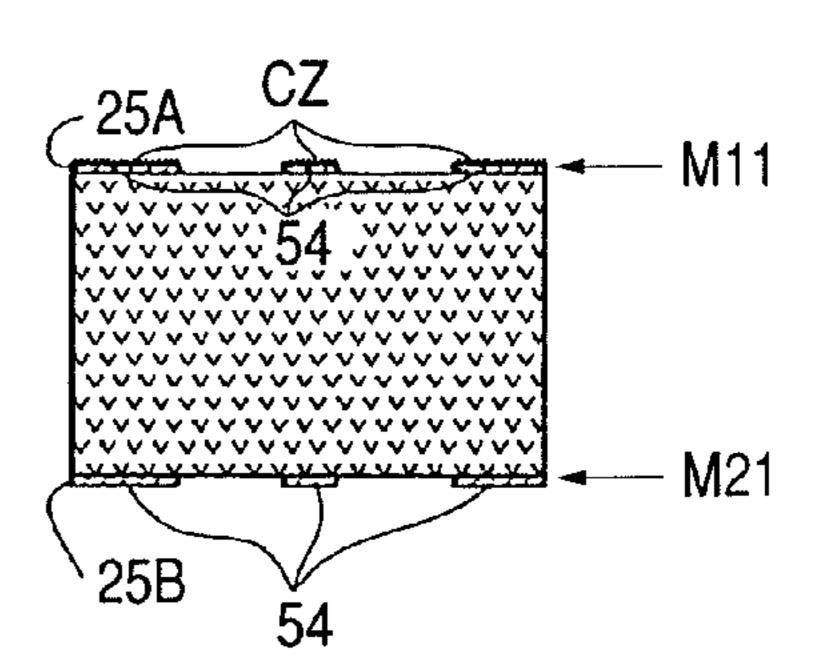

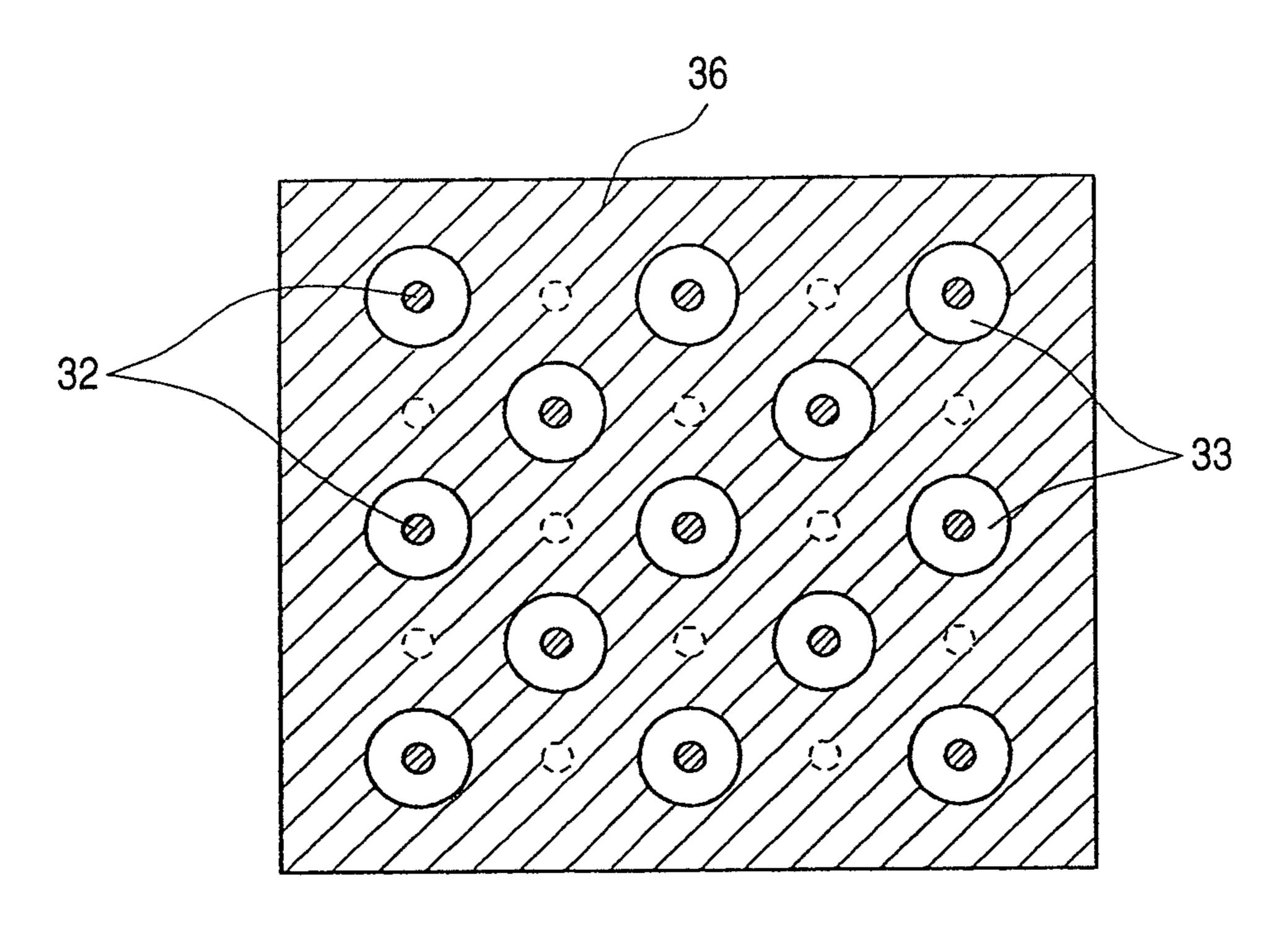

FIG. 9 (FIGS. 9A and 9B) is horizontal sectional views of a ceramic sub-core (laminated ceramic capacitor).

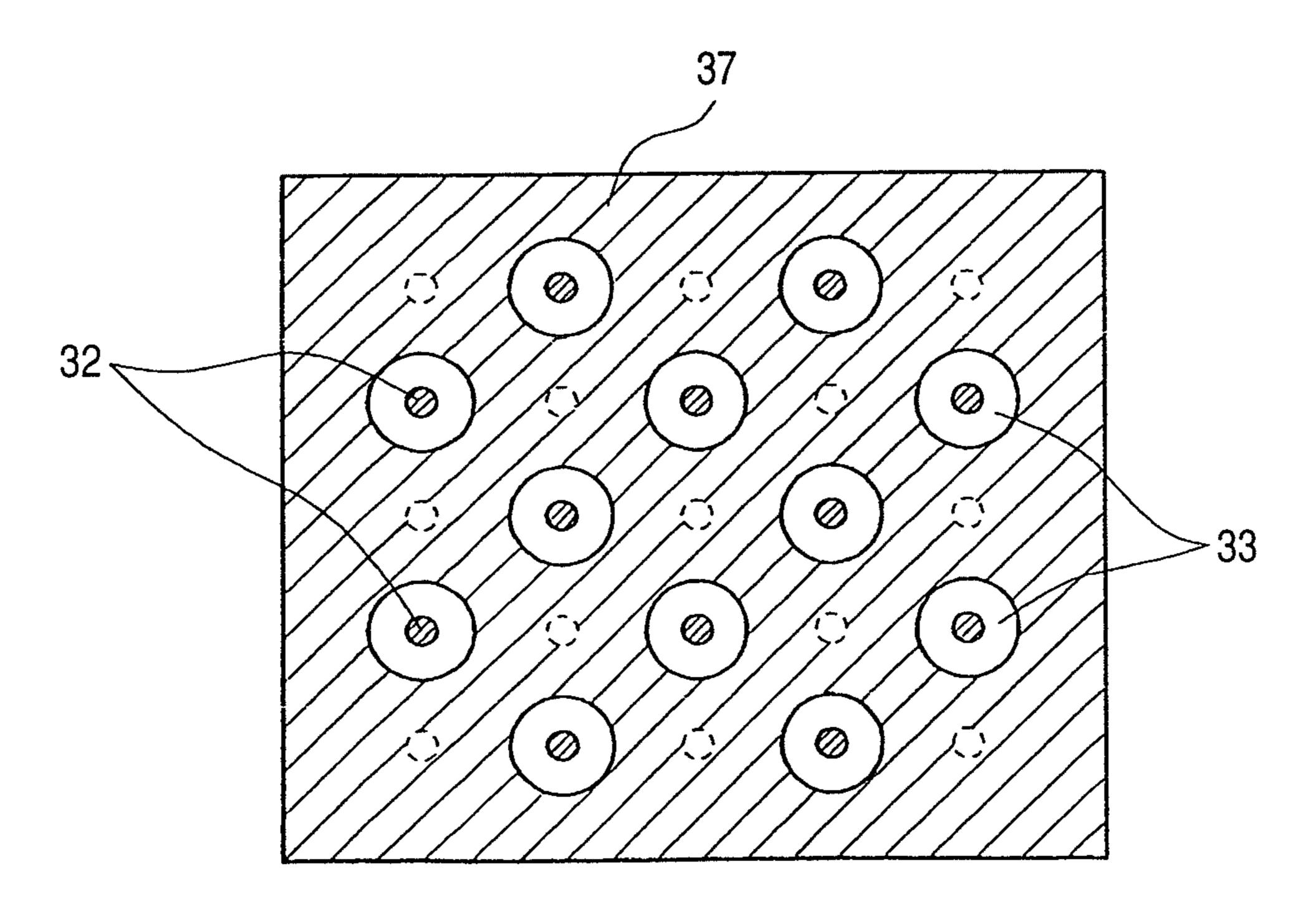

FIG. 10 shows a manufacturing process of the ceramic sub-core (laminated ceramic capacitor).

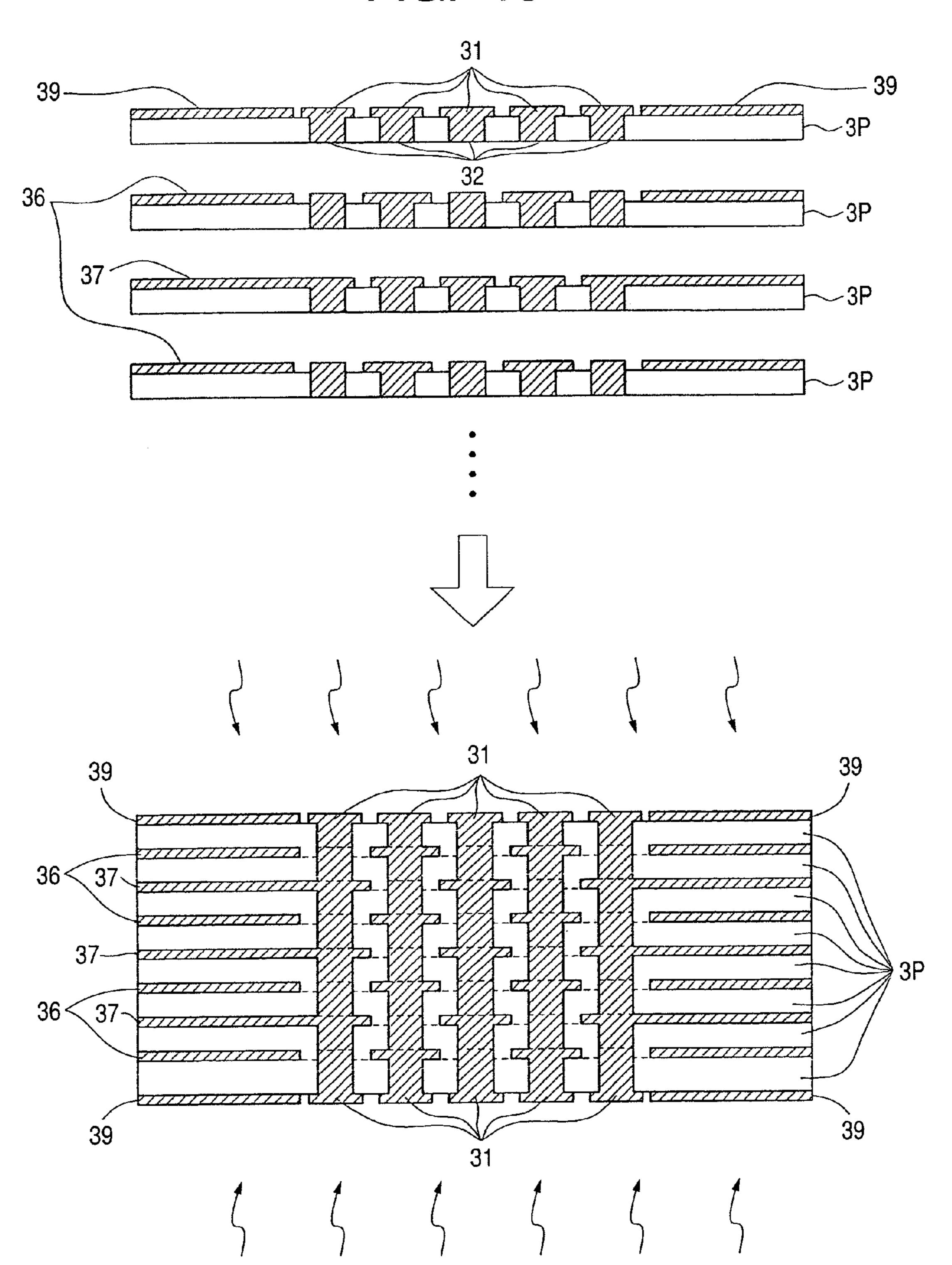

FIG. 11 is a top view of a board in a state that step 5 (sub-core accommodation step) has just completed.

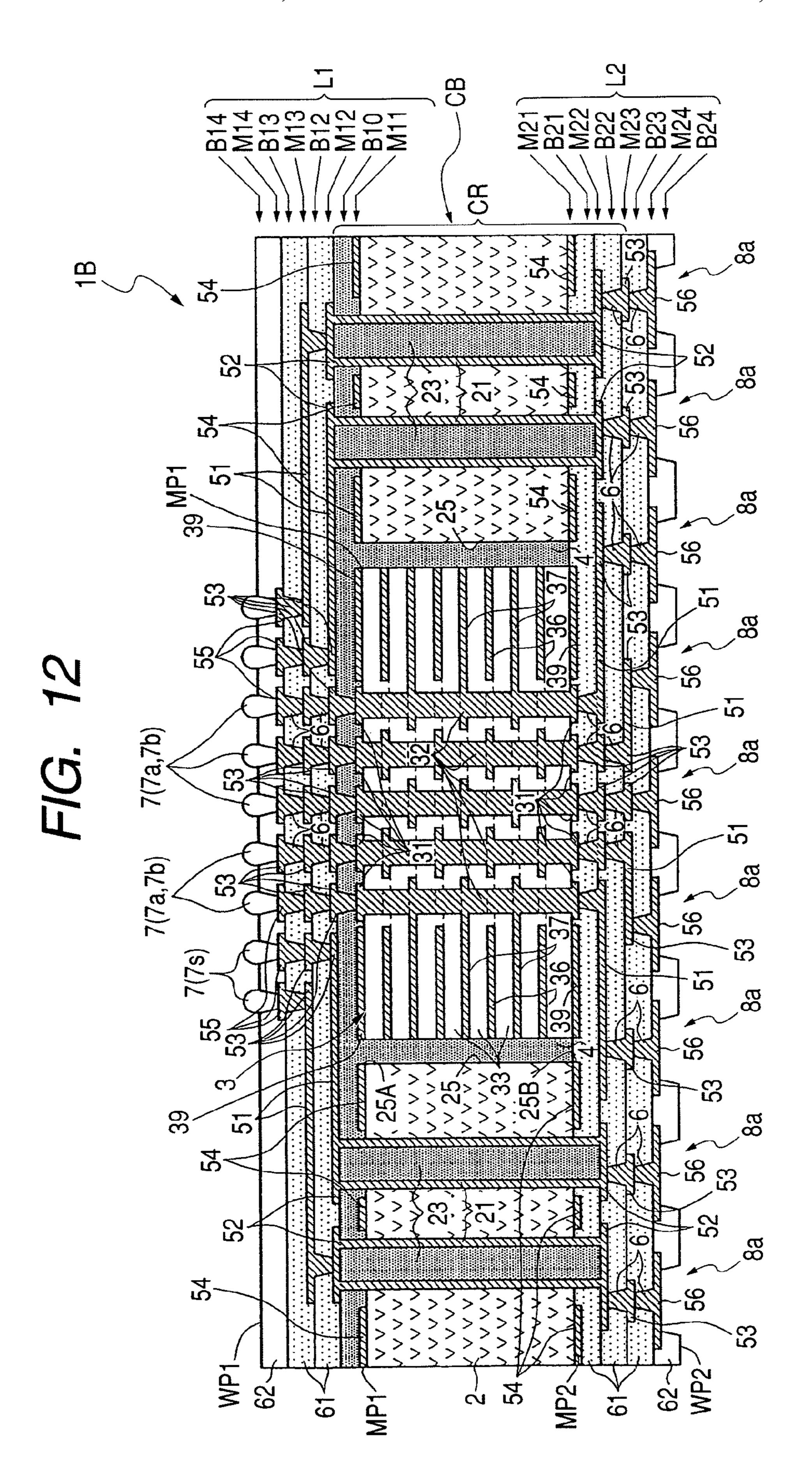

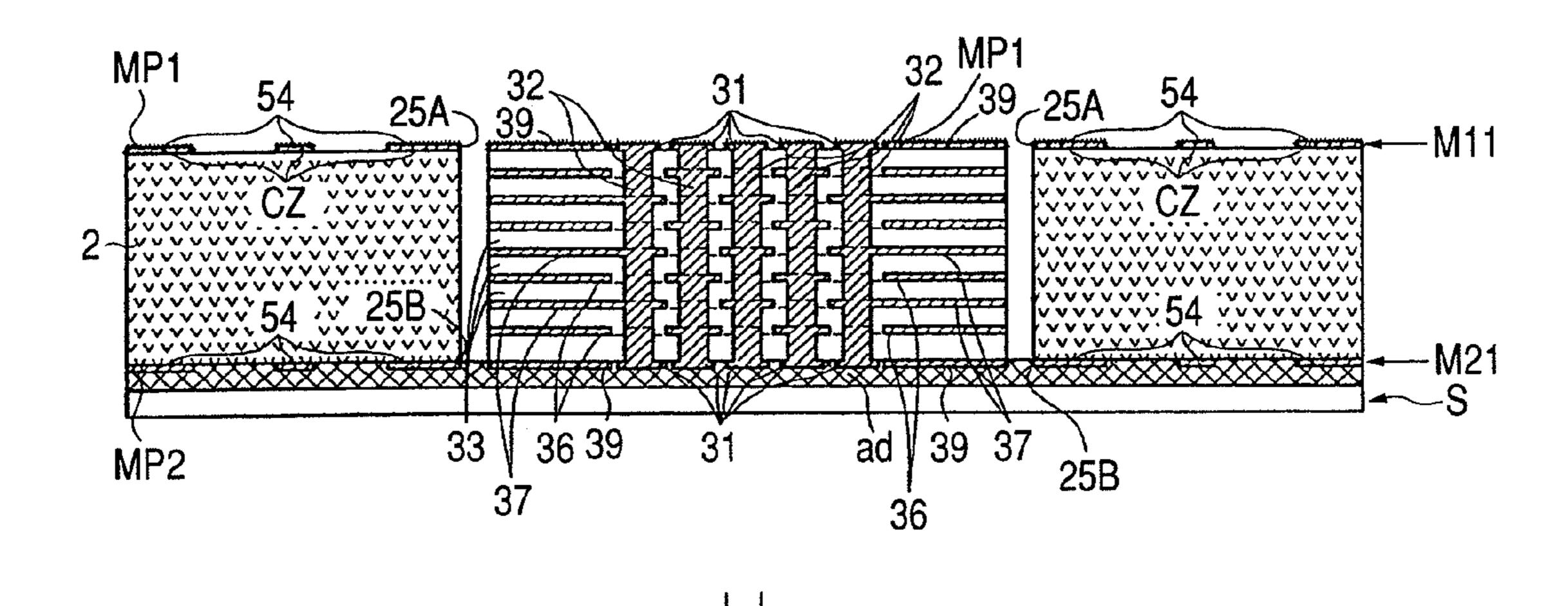

FIG. 12 is a schematic sectional view showing the configuration of a wiring board according to a second embodiment of the present invention.

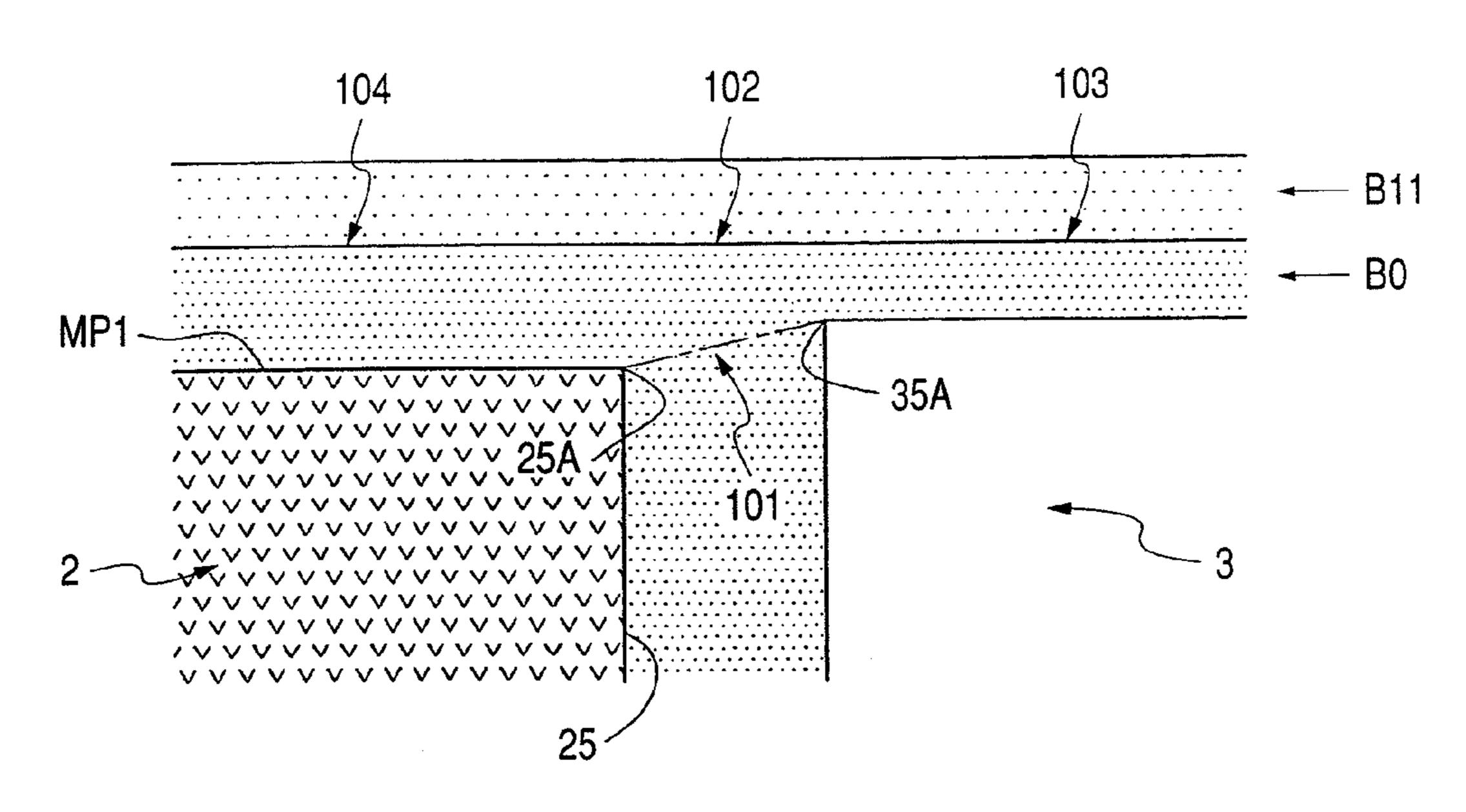

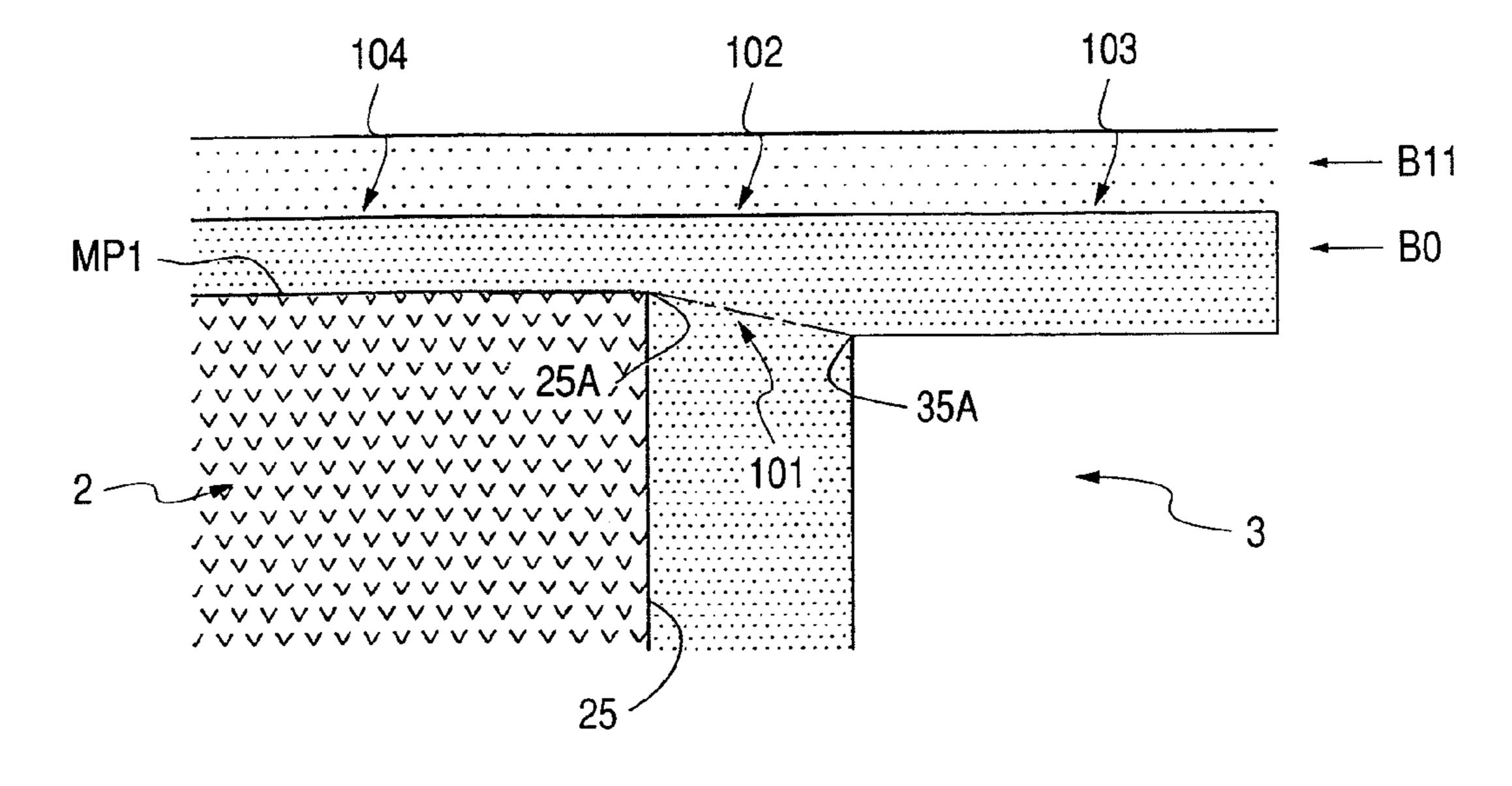

FIG. 13 (FIGS. 13A and 13B) is enlarged views of an important part of the wiring board according to the invention.

FIG. 14 (FIGS. 14A and 14B) shows a manufacturing process of a conventional wiring board.

FIG. 15 shows a manufacturing step of another manufacturing process of a wiring board.

FIG. 16 shows a manufacturing step following the manufacturing step of FIG. 15.

FIG. 17 shows a manufacturing step following the manufacturing step of FIG. 16.

FIG. 18 shows manufacturing steps following the manufacturing step of FIG. 17.

FIG. 19 shows manufacturing steps following the manufacturing steps of FIG. 18.

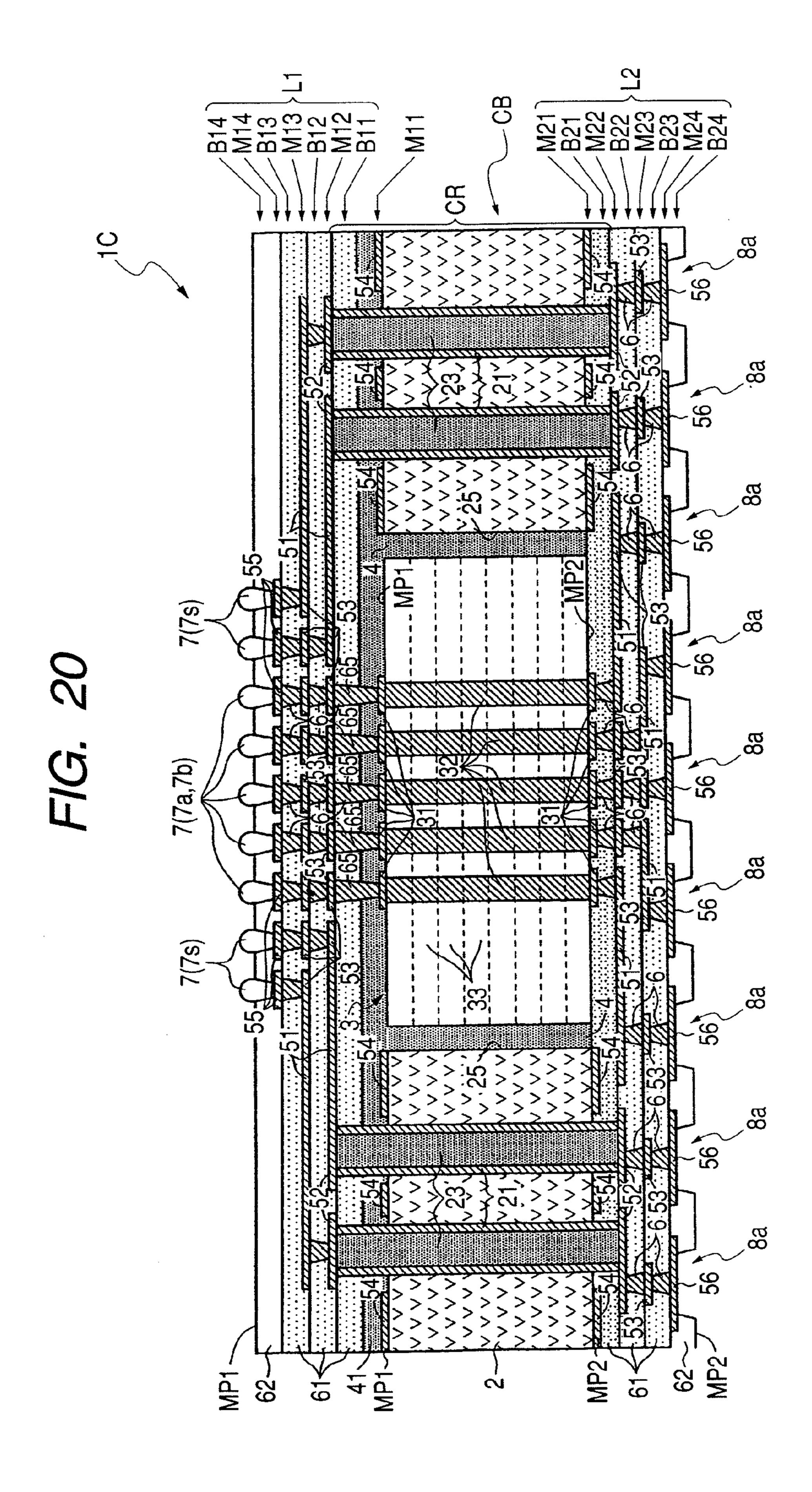

FIG. 20 shows a modification of the first embodiment in which no laminated ceramic capacitor is provided in the ceramic sub-core.

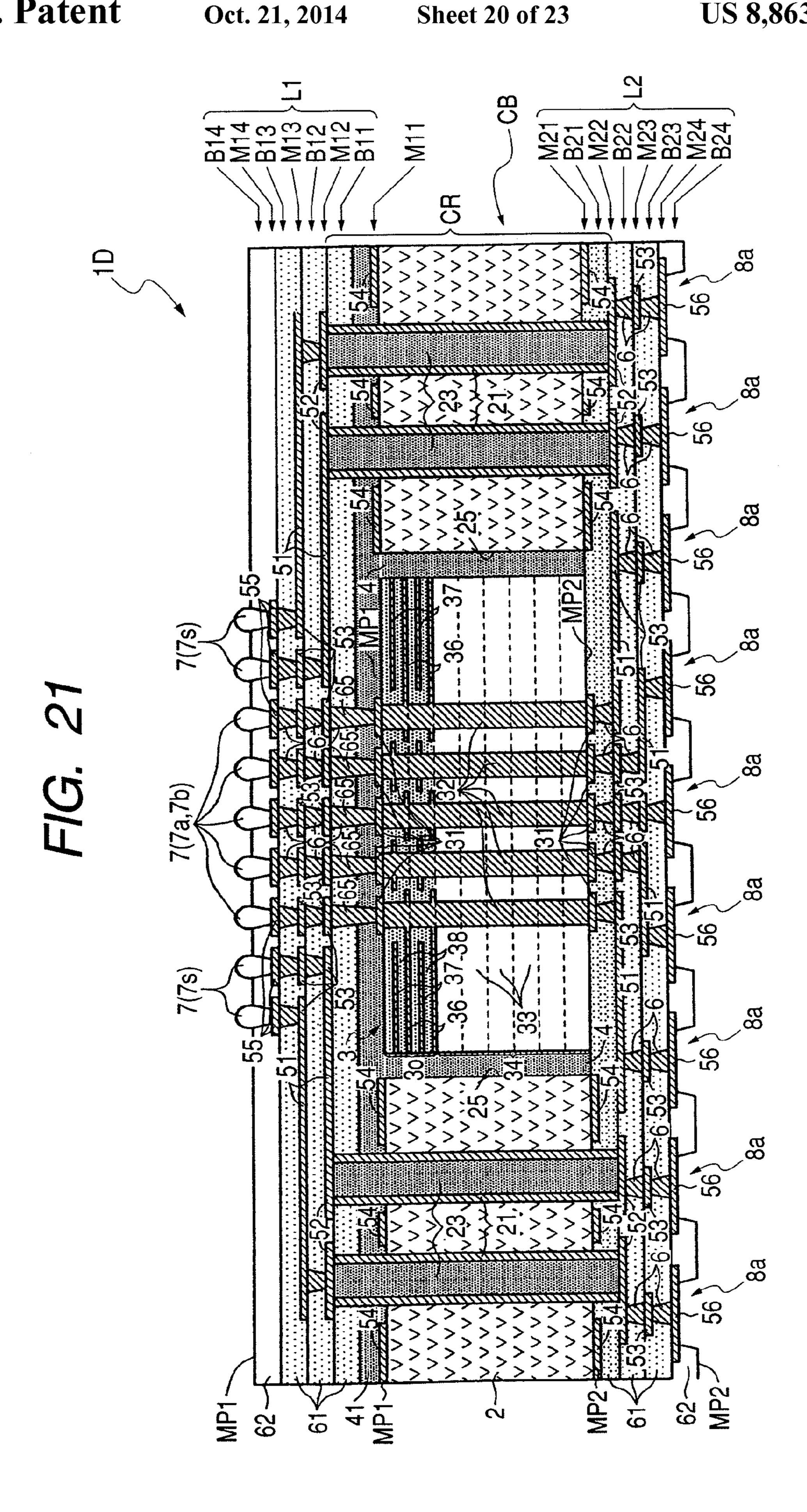

FIG. 21 shows a modification of the second embodiment in which a laminated ceramic capacitor is provided only on the side of a first major surface of the ceramic sub-core.

FIG. 22 shows manufacturing steps of a thin-film capacitor portion.

FIG. 23 shows manufacturing steps following the manufacturing steps of FIG. 22.

FIG. 24 (FIGS. 24A and 24B) is top views of in-process thin-film capacitor portions.

# DESCRIPTION OF SYMBOLS

1A, 1B, 1C, 1D: Wiring board

2: Core body

25: Sub-core accommodation space (through-hole)

25A: First-major-surface-side opening

25B: Second-major-surface-side opening

3: Ceramic sub-core (laminated ceramic capacitor)

31: Conductor pad

**32**: Penetration conductor

**33**: Ceramic layer

36, 37: Electrode conductor layer

4: Groove-filling portion

6, 65: Via conductor

7: Solder bump (power terminal 7a, ground terminal 7b, signal terminal 7s)

CB: Core board

CR: Core portion

L (L1, L2): Wiring laminate

B: Resin insulating layer

B0, B10: Lowest resin insulating layer of first-major-surfaceside wiring laminate

B11: Resin insulating layer adjacent to lowest resin insulating layer (adjacent resin insulating layer)

M: Conductor layer

M11: Conductor patterns formed on first major surfaces of core body and ceramic sub-core

M12: Conductor layer formed on lowest resin insulating layer (or adjacent resin insulating layer)

C: Semiconductor integrated circuit device (IC chip)

GB: Main board (e.g., mother board)

S: Adhesive sheet

101: Plane connecting top end of inner side surface of core body and top end of outer side surface of ceramic sub-core

102: Layer surface located over gap between core body and ceramic sub-core

103: Layer surface located over ceramic sub-core

104: Layer surface located over core body

## DETAILED DESCRIPTION OF THE INVENTION

# First Embodiment

A wiring board according to a first embodiment of the present invention will be described below with reference to the drawings. FIG. 1 is a schematic sectional view showing the configuration of a wiring board 1A according to the first 60 embodiment. In the following description, as for a plate-like member, a surface shown above in a figure will be called a first major surface WP1, MP1 and a surface shown below will be called a second major surface WP2, MP2. The wiring board 1A has a ceramic sub-core (laminated ceramic capacitor) 3 65 under solder bumps 7 in a core board CB. The use of the ceramic sub-core 3 shorten the lengths of interconnections

12

between a semiconductor integrated circuit device (IC chip) C and the ceramic sub-core 3 contributes to reduction of the inductance components of the interconnections, which is important in reducing the switching noise of the IC chip C and stabilizing its operation power supply voltage. Since the ceramic sub-core 3 which is made of ceramics and hence has a smaller linear expansion coefficient than that of a core body 2 which is made of an insulative material is located under the solder bumps 7 in the core board CB, the difference of the linear expansion coefficient of the wiring board 1A from that of the IC chip C is reduced and hence the wiring board 1A is not prone to line disconnections or the like due to thermal stress. A detailed description will follow.

FIG. 2 shows the wiring board 1A that is disposed between

15 an IC chip C and a main board (e.g., mother board) GB. The

1C chip C has signal terminals, power terminals, and ground

terminals on a second major surface and is flip-chip-connected to the solder bumps 7 (Pb—Sn, Sn—Ag, Sn—Sb, or

Sn—Zn solder) that are formed on a first major surface WP1

20 of the wiring board 1A. To elongate the thermal fatigue life of

the solder bumps 7, the space between the IC chip C and the

first major surface WP1 of the wiring board 1A is filled with

an under fill material that is a thermosetting resin. On the

other hand, the main board (e.g., mother board) GB is mainly

25 made of a resin material that is reinforced by a filler that is

ceramic particles or fiber, and is connected to terminal pads

56 (see FIG. 1) via solder balls BL formed on a second major

surface WP2 of the wiring board 1A.

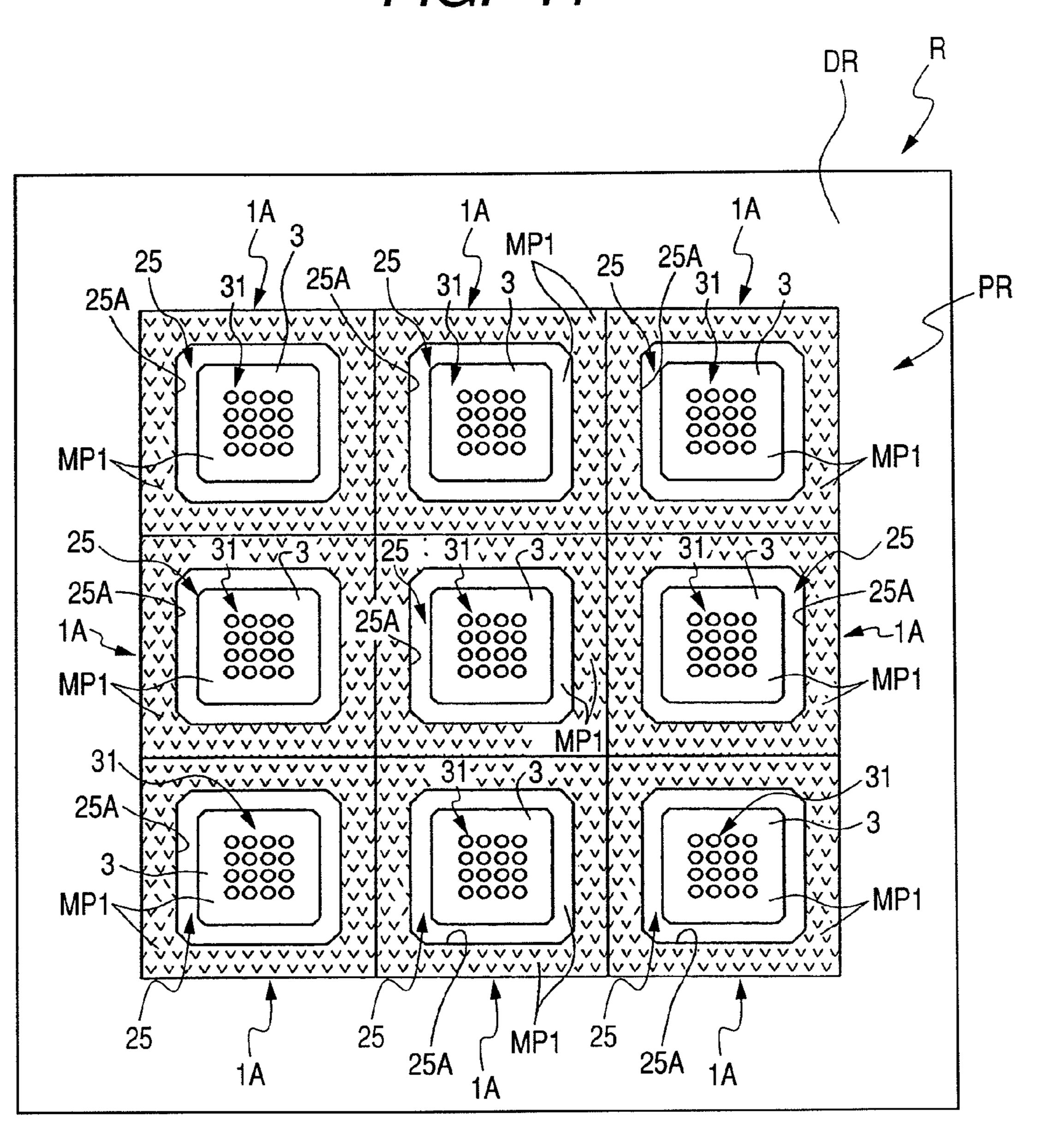

FIG. 3 shows the first major surface WP1 of the wiring board 1A. The solder bumps 7 are arranged in lattice form (or in a staggered manner). Among the solder bumps 7, power terminals 7a and ground terminals 7b are arranged in checkered form in a central region and signal terminals 7s are arranged around them. The solder bumps 7 correspond to the respective terminals of the IC chip C.

A core body 2 is a plate-like member of a heat resistant resin plate (e.g., bismaleimide triazine resin plate) or a fiber-reinforced resin plate (e.g., glass-fiber-reinforced epoxy resin plate). Wiring patterns (inner layer patterns) may be formed inside the core body 2, in which case the wiring board 1A can even be enhanced in functionality. Furthermore, the core body 2 may be formed by laminating thin insulating layers on a core. A sub-core accommodation space (through-hole) 25 is formed in a region including the region under the solder bumps 7 so as to communicate with major surfaces MP1 and MP2. A plate-like ceramic sub-core 3 is accommodated in the sub-core accommodation space 25. The core board CB is thus formed.

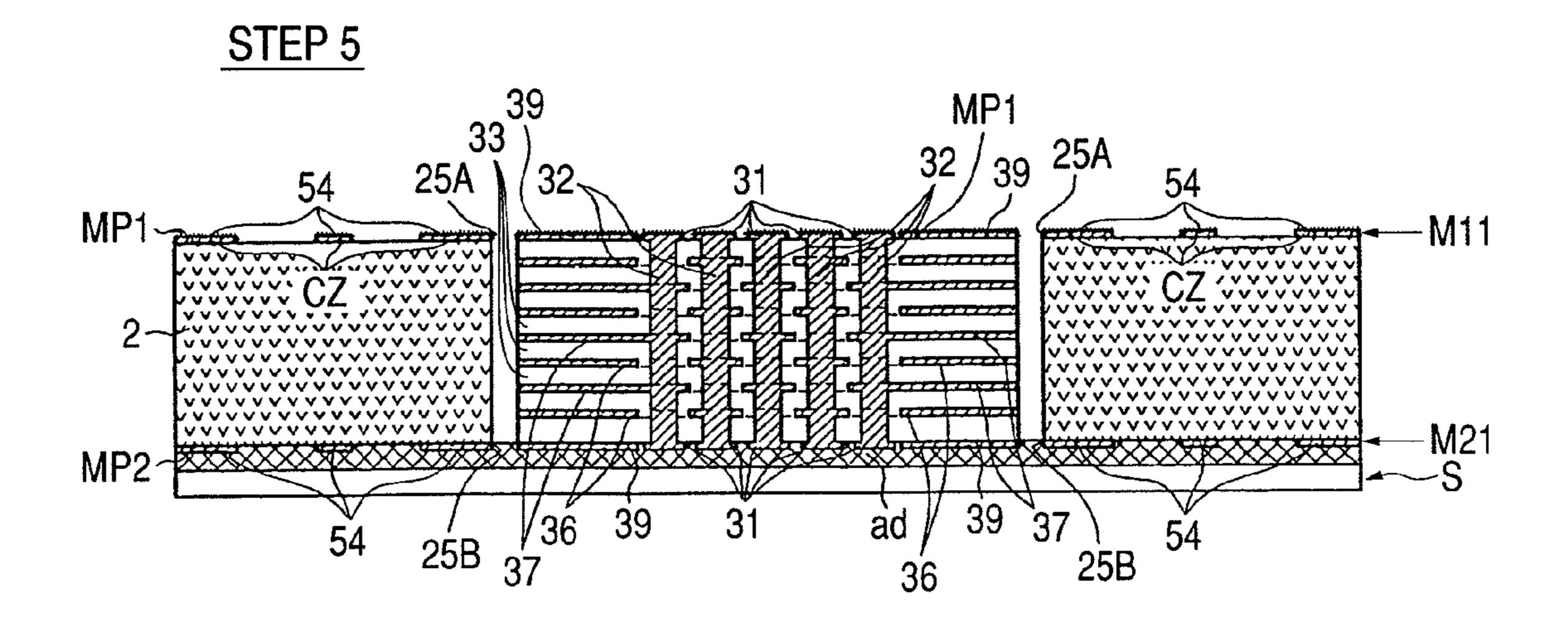

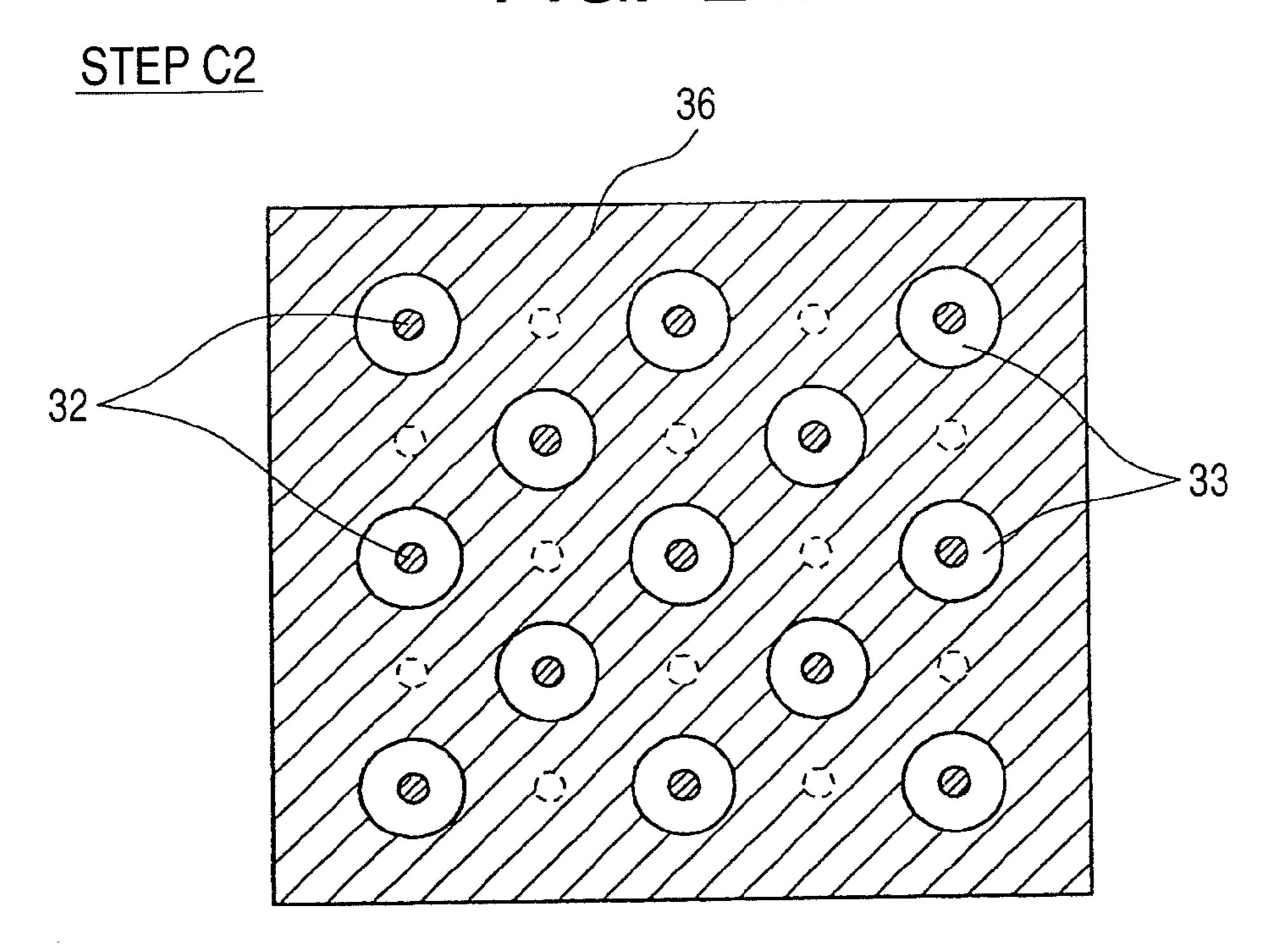

The ceramic sub-core 3 is a laminated ceramic capacitor in 50 which plural ceramic layers 33 and plural electrode conductor layers 36 or 37 are laminated alternately. One of the set of electrode conductor layers 36 and the set of electrode conductor layers 37 is power-side electrode conductor layers corresponding to the power terminals 7a and the other is 55 ground-side electrode conductor layers corresponding to the ground terminals 7b. As such, the electrode conductor layers 36 and the electrode conductor layers 37 are arranged alternately in the lamination direction so as to be separated from each other by the ceramic layers 33 and hence isolated from each other in a DC sense. Metallization pads 31 connected to the power-side electrode conductor layers or the ground-side electrode conductor layers and a dam metallization layer 39 surrounding the metallization pads 31 are formed in each of the major surfaces MP1 and MP2 of the ceramic sub-core 3.

More specifically, as shown in a horizontal sectional view of FIG. 9A, in a layer in which the electrode conductor layer 36 extends in a horizontal plane, the electrode conductor layer

36 is isolated from penetration conductors 32 that are connected to the electrode conductor layers 37 located immediately over and under the electrode conductor layer 36 with ceramic layers 33 interposed in between and the gaps are filled with connecting portions of the ceramic layers 33. On 5 the other hand, as shown in FIG. 9B, in a layer in which an electrode conductor layer 37 extends in a horizontal plane, the electrode conductor layer 37 is isolated from penetration conductors 32 that are connected to the electrode conductor layers 36 located immediately over and under the electrode conductor layer 37 with ceramic layers 33 interposed in between and the gaps are filled with connecting portions of the ceramic layers 33. Having the above structure, the ceramic sub-core 3 functions as a laminated ceramic capacitor.

The above laminated ceramic capacitor can be produced by firing a ceramic material and a metal material simultaneously as described below. As shown in FIG. 10, through-holes are formed in a ceramic green sheet containing a ceramic material 20 powder (to become a ceramic layer 33) by punching, laser hole formation, or the like. The through-holes are filled (to form portions of penetration conductors 32) and patterns to become an electrode conductor layer 36 or 37 or metallization pads 31 and a dam metallization layer 39 are formed on one 25 major surface of the ceramic green sheet by applying a metal paste containing a metal material powder by printing. Ceramic plate units 3P thus obtained are laminated together and a resulting laminated body is fired, whereby a laminated ceramic capacitor is obtained. The electrode conductor layers 30 36 or 37, which are finally connected to each other in the lamination direction by the penetration conductors 32, are formed separately in forming their patterns by applying the metal paste by printing.

are alumina, silicon nitride, aluminum nitride, and glass ceramics produced by adding an inorganic filler such as borosilicate glass or borosilicate lead glass by 40 to 60 parts by weight. Examples of the metal material of the metallization pads 31, the penetration conductors 32, the electrode conductor layers 36 and 37, and the dam metallization layers 39 are Ni or Ag-based metals. The surfaces of the metallization pads 31 and the dam metallization layers 39 are plated with Cu.

The ceramic sub-core 3 is a square flat plate measuring 12.0 mm×12.0 mm×0.8 mm (thickness). It is preferable that 45 the thickness of the ceramic sub-core 3 be 0.2 mm to 1.0 mm. If the thickness were smaller than 0.2 mm, the ceramic subcore 3 could not reliably support the IC chip C when it is mounted on the top solder bumps 7. On the other hand, if the thickness were greater than 1.0 mm, the wiring board 1A 50 would be too thick. The ceramic sub-core 3 is chamfered along the four vertical edges.

Returning to FIG. 1, the gap between the ceramic sub-core 3 and the core body 2, which is part of the sub-core accommodation space 25, is filled with a groove-filling portion 4 55 made of a resin material. The groove-filling portion 4 is continuous and integral with a lowest resin insulating layer B0 of a wiring laminate L1 which is formed on the side of the first major surface MP1. As such, the groove-filling portion 4 serves to fix the ceramic sub-core 3 to the core body 2 and to 60 absorb the differences between the linear expansion coefficients in the horizontal directions and the thickness direction of the ceramic sub-core 3 and those of the core body 2 by its own elastic deformation. Being continuous and integral with the lowest resin insulating layer B0, the groove-filling portion 65 4 is high in the adhesion to the core board CB and the wiring laminate L1.

14

The wiring laminate L1 which is provided on the major surface MP1 of the core board CB has a lamination structure consisting of resin insulating layers B0 and B11-B14 and conductor layers M11-M14. A wiring laminate L2 which is provided on the major surface MP2 of the core board CB has a lamination structure consisting of resin insulating layers B21-B24 and conductor layers M21-M24.

The lowest resin insulating layer B0 which is continuous and integral with the groove-filling portion 4 is formed on the first major surface MP1 of the core board CB. The lowest resin insulating layer B0 is made of the same resin material as the groove-filling portion 4. Covering the core board CB with the lowest resin insulating layer B0 makes it possible to absorb the difference between the linear expansion coefficient (in the thickness direction) of the ceramic sub-core 3 and that of the IC chip C mounted on the wiring laminate L1 by elastic deformation of the lowest resin insulating layer B0. This prevents such trouble as a disconnection of interconnections around the ceramic sub-core 3. The groove-filling portion 4 and the lowest resin insulating layer B0 may be made of a resin produced by adding acid anhydride to an epoxy resin or such a resin as amine.

The resin insulating layers B11-B14 and B21-B24 are basically made of a resin material such as an epoxy resin and contain an appropriate amount of inorganic filler such as a silica powder for adjustment of the dielectric constant or the dielectric breakdown voltage. Among the resin insulating layers B11-B14 and B21-B24, the resin insulating layers B11-B13 and B21-B23 are called build-up layers or via layers and serve for insulation between the conductor layers M11-M13 or M21-M23. Via conductors 6 and multi-layer penetration via conductors 65 for inter-layer connection are formed through the resin insulating layers B11-B14 and B21-B24. On the other hand, the resin insulating layers B14 and B24 are Examples of the ceramic material of the ceramic layers 33 35 solder resist layers and are formed with holes for exposing the pads **55** or **56**.

> Although the groove-filling portion 4 and the lowest resin insulating layer B0 are basically made of the same epoxy resin as the resin insulating layers B11-B14 and B21-B24, their linear expansion coefficients are adjusted by changing the contents of the inorganic filler. That is, the groove-filling portion 4 and the lowest resin insulating layer B0 are higher in filler content and hence have a smaller linear expansion coefficient than the resin insulating layers B11-B14 and B21-B24.

> The linear expansion coefficient of the lowest resin insulating layer B0 lies halfway between the linear expansion coefficients of the ceramic sub-core 3 and the resin insulating layers B11-B14 and B21-B24. More specifically, whereas the linear expansion coefficients of the ceramic sub-core 3 and the resin insulating layers B11-B14 and B21-B24 are 3 to 13 ppm/° C. and 40 to 50 ppm/° C., respectively, the linear expansion coefficient of the lowest resin insulating layer B0 is smaller than or equal to 32 ppm/° C. (excluding 0). (In particular, it is preferable that the linear expansion coefficient of the lowest resin insulating layer B0 be smaller than or equal to 25 ppm/° C. in the case where it is intended to match the lowest resin insulating layer B0 with the ceramic sub-core 3 in the linear expansion coefficient.) To obtain such a linear expansion coefficient, the filler content of the lowest resin insulating layer B0 may be set at 53 to 80 wt \%. (In particular, it is preferable that the filler content of the lowest resin insulating layer B0 be higher than or equal to 70 wt % in the case where it is intended to match the lowest resin insulating layer B0 with the ceramic sub-core 3 in the linear expansion coefficient.)

> It is rare the core body 2 and the ceramic sub-core 3 are completely the same in height. Usually, either is high as

shown in FIGS. 13A and 13B and hence a plane 101 connecting the top end 25A of the inner side surface of the core body 2 (i.e., the opening on the side of the first major surface MP1) and the top end 35A of the outer side surface of the ceramic sub-core 3 is inclined from the first major surface MP1 of the core body 2. On the other hand, since the lowest resin insulating layer B0 is formed by printing with a resin paste (described later in detail), the lowest resin insulating layer B0 is flattened so that the inclination, from the first major surface MP1 of the core body 2, of its surface 102 located over the gap 10 between the core body 2 and the ceramic sub-core 3 is made close to zero. Since the lowest resin insulating layer B0 is so flattened, the overlying resin insulating layers B11-B14 can also be flattened. Likewise, those surfaces 103 and 104 of the 15 is called "core portion CR." lowest resin insulating layer B0 which are located over the ceramic sub-core 3 and the core body 2, respectively, are also made substantially parallel with the first major surface MP1 of the core body 2 (i.e., the inclinations of the surfaces 103 and 104 are made close to zero).

The inclinations can be defined with respect to the first major surface MP1 of the core body 2. That is, the inclinations of the surface 102 located over the gap between the core body 2 and the ceramic sub-core 3, the surface 103 located over the ceramic sub-core 3, and the surface 104 located over the core 25 body 2 are defined as angles formed by straight lines as the surfaces 102-104 appearing in a cross section taken parallel with the thickness direction of the wiring board 1A and a straight line as the first major surface MP1 of the core body 2 appearing in the same cross section. Likewise, the inclination 30 of the plane 101 connecting the top end 25A of the inner side surface of the core body 2 and the top end 35A of the outer side surface of the ceramic sub-core 3 is defined as an angle formed by a straight line as the plane 101 appearing in a cross section taken parallel with the thickness direction of the wiring board 1A and a straight line as the first major surface MP1 of the core body 2 appearing in the same cross section.

A plane is defined by a passing point and a normal vector (i.e., a vector perpendicular to the plane). Therefore, by determining prescribed reference positions, the inclinations (from the first major surface MP1 of the core body 2) of the planes of the surface 102 located over the gap between the core body 2 and the ceramic sub-core 3, the surface 103 located over the ceramic sub-core 3, the surface 104 located over the core body 2, and the plane 101 connecting the top end 25A of the inner side surface of the core body 2 and the top end 35A of the outer side surface of the ceramic sub-core 3 are defined as angles formed by the normal vectors of the surfaces 102-104 and the plane 101 and the normal vector of the first major surface MP1 of the core body 2, respectively.

The conductor layers M11-M14 and M21-M24 consist of Cu-plating-formed interconnections 51 and 53, pads 55 and 56, etc. The via conductors 6 and 65 serve for inter-layer connections between the conductor layers M11-M14 and M21-M24, whereby conduction paths (for signal transmission, power supply, and grounding) from the pads 55 to the pads 56 are formed. The pads 55 and 56 are provided for formation of the solder bumps 7 or the solder balls BL, and their surfaces are Ni—Au-plated.

In particular, the via conductors **65** are multi-layer penetration via conductors that penetrate through the two layers, that is, the lowest resin insulating layer B**0** and the adjacent resin insulating layer B**11**. As such, the via conductors **65** connect the conductor pads **31** (conductor layer M**11**) formed on the first major surface MP**1** of the ceramic sub-core **3** to the 65 conductor layer M**12** formed on the adjacent resin insulating layer B**11**.

**16**

Through-holes are formed through the core body 2 of the bore board CB and the resin insulating layers B0, B11, and B21, and through-hole conductors 21 for conduction between the wiring laminates L1 and L2 are formed on the inner surfaces of the through-holes. The through-hole conductors 21 correspond to the respective signal terminals 7s. The inside spaces of the through-hole conductors 21 are filled with a resin hole-filling material 23 that is an epoxy resin containing an inorganic filler such as a silica filler, and Cu-plating-formed lid conductors 52 are provided at both ends of each through-hole conductor 21. That portion of the wiring board 1A which extends from the conductor layer M12 to the conductor layer M22 and has the core substrate CB as a main part is called "core portion CR."

Next, a manufacturing method of a wiring board according to the embodiment of the invention will be described with reference to the drawings. FIGS. **4-8** show a manufacturing method of the wiring board **1**A.

At step 1, conductor patterns 54 (conductor layers M11 and M12) are formed on the two major surfaces MP1 and MP2 of a core body 2. For this purpose, a copper-clad laminate is used in which 35-µm-thick copper foil is stuck to both major surfaces of a heat resistant resin plate (e.g., bismaleimide triazine resin plate) or a fiber-reinforced resin plate (e.g., glass-fiber-reinforced epoxy resin plate) measuring 400 mm×400 mm×0.8 mm (thickness). The copper foil is etched into the conductor patterns 54 by using masks.

At step 2, a through-hole as a sub-core accommodation space 25 that communicates with the major surfaces MP1 and MP2 is formed by a router. The through-hole as the sub-core accommodation space 25 is a hole having an substantially square cross section each side of which measures 14.0 mm. The walls of the sub-core accommodation space (through-hole) 25 is formed with fillets along the four wall-connecting lines. The adhesion to a later-charged groove-filling portion 4 can be increased by subjecting the side surfaces of the sub-core accommodation space 25 to roughening treatment using potassium permanganate or the like. Furthermore, an organic compound (coupling agent) may be applied to the side surfaces.

At step 3 (roughening step), surface chemical treatment for increasing the adhesion to a resin material is performed only on the conductor patterns **54** formed on the first major surface MP1 among the conductor patterns **54** formed on the two major surfaces MP1 and MP2 of the core body 2. An example of this surface chemical treatment is Cu roughening treatment to be used for roughening a copper surface (e.g., known micro-etching treatment or blackening treatment). Roughen-50 ing the copper surfaces increases the adhesion to the lowest resin insulating layer B0 of the wiring laminate L1 by the anchor effect. To attain this effect sufficiently, it is preferable that the Cu roughening treatment be performed so that the JIS-B-0601 10-point average roughness (Rz) becomes about 0.3 to 20 μm. Cleaning treatment is performed after the Cu roughening treatment. If necessary, coupling treatment may be performed by using a silane coupling agent.

Another example of the surface chemical treatment is treatment of forming a very thin adhesion layer of an alloy including Cu and Sn on the copper surfaces. This treatment can attain sufficient adhesion to the lowest resin insulating layer B0 of the wiring laminate L1 without the need for roughening the copper surfaces. More specifically, the adhesion layer includes an alloy of Cu, Sn, and a third metal (at least one metal selected from Ag, Zn, Al, Ti, Bi, Cr, Fe, Co, Ni, Pd, Au, and Pt). For example, the adhesion layer includes Cu at about 1 to 50 at. %, Sn at about 20 to 98 at. %, and the third metal at

about 1 to 50 at. %. To attain a sufficient adhesion effect, it is preferable that the thickness of the adhesion layer be 0.001 to 1  $\mu m$ .

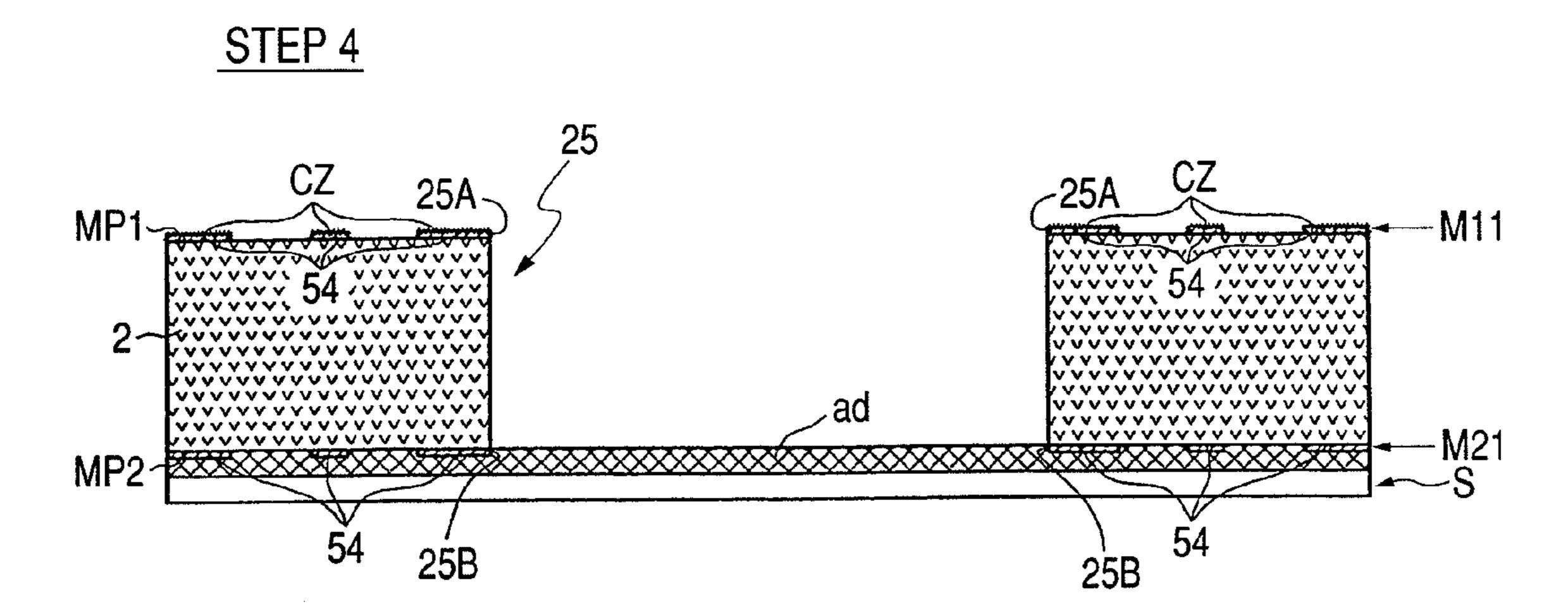

At step 4 (closing step), a second-major-surface-MP2-side opening 25B of the sub-core accommodation space 25 is 5 closed by an adhesive sheet S having an adhesive ad on one surface in such a manner that the adhesive ad is exposed to the inside of the sub-core accommodation space 25. It is preferable that the adhesive ad of the adhesive sheet S have adhesive strength that is higher than or equal to 8.0 N/25 mm (measured by the 180° peeling method (JIS Z 0237)). The unit "N/25 mm" means force obtained by a measurement on a 25-mm-wide adhesive sheet sample. The adhesive sheet S (base) may be a resin sheet of polyester, polyimide, PET, or the like. For example, the adhesive ad that is provided on one 15 surface of the adhesive sheet S may be a silicone adhesive, an acrylic adhesive, a thermoplastic rubber adhesive, or the like.

At step 5 (sub-core accommodation step), a ceramic sub-core 3 is inserted into the sub-core accommodation space 25 through its first-major-surface-MP1-side opening 25A and is 20 fixed to the adhesive ad. As a result, the ceramic sub-core 3 is supported from the second major surface MP2 side. The ceramic sub-core 3 can be accommodated accurately by using a mounting apparatus.

The ceramic sub-core 3 that is accommodated at this step is such that only the metallization pads 31 and the conductor pattern 39 provided on its first major surface MP1 have been subjected to Cu roughening treatment in advance. As shown in FIG. 5, the adhesive ad of the adhesion sheet S is adhered to the conductor patterns 54 provided on the second major surface MP2 of the core body 2 and the metallization pads 31 and the conductor pattern 39 provided on the second major surface MP2 of the ceramic sub-core 3. However, since these pads and patterns have not been subjected to Cu roughening treatment, there does not occur an even that the adhesive ad is 35 buried in the asperities of roughened surfaces.

As shown in FIG. 11 (top view), the manufacturing process of the wiring board 1A is executed on a multi-product manufacturing board R that consists of a product region PR in which plural product portions to become wiring boards 1A 40 are arranged and a margin region DR around the product region PR. FIG. 11 shows a state after completion of step 5, that is, a state that the ceramic sub-core 3 has just been accommodated in the sub-core accommodation space 25. A gap is formed between the core body 2 and the ceramic 45 sub-core 3. In the next step, the gap will be filled with a resin material in forming a lowest resin insulating layer B0 and a groove-filling portion 4 will thereby be formed. The sub-core accommodation space 25 and the ceramic sub-core 3 have square shapes. To prevent an event that cracks will develop in 50 a groove-filling portion 4 when it is formed in the gap, the walls of the sub-core accommodation space 25 are formed with fillets along the wall-connecting lines and the corresponding edges of the ceramic sub-core 3 are chamfered.

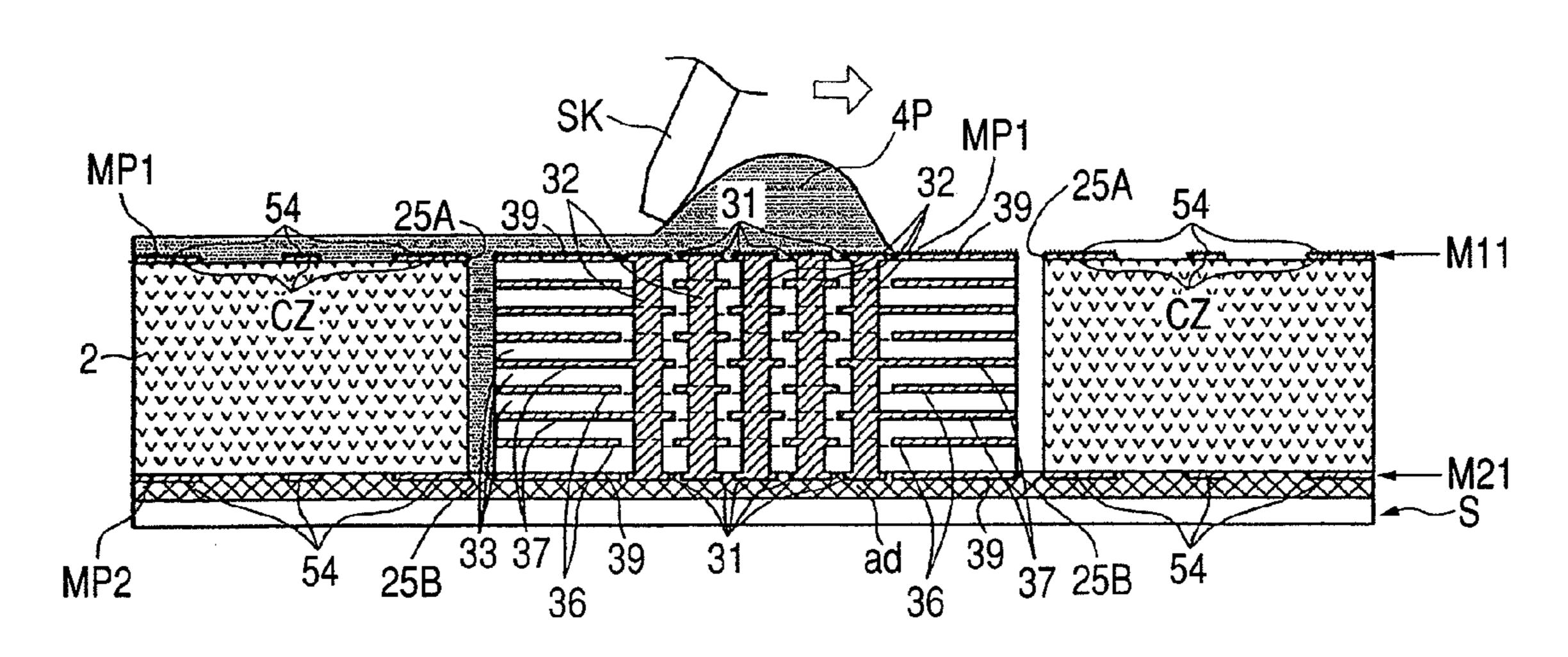

At step 6 (printing step), a resin paste 4P is charged into the gap between the ceramic sub-core 3 and the core body 2 (a charged resin portion is formed) by pressure-printing the resin paste 4P from the side of the first major surfaces MP1 of the ceramic sub-core 3 and the core body 2 using a rubber squeegee SK. The pressure printing using the rubber squeegee SK allows the resin paste 4P to be charged into the gap between the ceramic sub-core 3 and the core body 2 without formation of voids. In this pressure printing, the resin paste 4P is directly printed on the first major surfaces MP1 of the ceramic sub-core 3 and the core body 2 without intervention of any mask. Therefore, at the same time as the gap between the ceramic sub-core 3 and the core body 2 is filled with the

**18**

resin paste 4P, the first major surfaces MP1 of the ceramic sub-core 3 and the core body 2 are entirely covered with a layer that is continuous and integral with the charged resin portion (i.e., a layer to become a lowest resin insulating layer B0 is formed). The thus-formed charged portion and covering layer of the resin paste 4P are set (cured) by heating and drying them, whereby a groove-filling portion 4 and a lowest resin insulating layer B0 are formed.

Referring to FIG. 11, at step 6, a resin paste 4P is deposited on a portion, located on one side of the ceramic sub-core 3, of the margin region DR and is moved by the squeegee SK (see FIG. 6) toward another portion, located on the other side of the ceramic sub-core 3, of the margin region DR, whereby the resin paste 4P is charged into the gap between the ceramic sub-core 3 and the core body 2 and a layer entirely covering the first major surfaces MP1 of the ceramic sub-core 3 and the core body 2 is formed.

For example, the viscosity of the resin paste 4P is set at about 6 (preferably 30) to 57 Pa·s in a temperature range of room temperature (e.g., 25° C.) to 120° C. To obtain such viscosity, the filler content of the resin paste 4P may be set at 53 (preferably 70) to 80 wt %. The resin paste 4P may be a resin produced by adding acid anhydride to an epoxy resin or such a resin as amine.

The adhesion to later-formed resin insulating layers B11 and B21 can be increased by performing roughening treatment using potassium permanganate or the like after the groove-filling portion 4 and the lowest resin insulating layer B0 have been formed by setting (curing) the resin paste 4P by heating and drying it.