#### US008860494B2

# (12) United States Patent

Mazzola et al.

# (54) HALF-BRIDGE CIRCUITS EMPLOYING NORMALLY ON SWITCHES AND METHODS OF PREVENTING UNINTENDED CURRENT FLOW THEREIN

(71) Applicant: **Power Integrations, Inc.**, San Jose, CA (US)

(72) Inventors: **Michael S. Mazzola**, Starkville, MS (US); **Robin Schrader**, Columbus, MS (US)

(73) Assignee: **Power Integrations, Inc.**, San Jose, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 13/908,956

(22) Filed: **Jun. 3, 2013**

# (65) Prior Publication Data

US 2013/0265095 A1 Oct. 10, 2013

#### Related U.S. Application Data

- (60) Continuation of application No. 13/021,132, filed on Feb. 4, 2011, now Pat. No. 8,456,218, which is a continuation of application No. 12/557,199, filed on Sep. 10, 2009, now Pat. No. 7,907,001, which is a division of application No. 11/802,388, filed on May 22, 2007, now Pat. No. 7,602,228.

- (51) Int. Cl.

H03K 17/56 (2006.01)

H02M 1/08 (2006.01)

H03K 17/687 (2006.01)

H03K 17/0812 (2006.01)

H03K 17/16 (2006.01)

(10) Patent No.: US 8,860,494 B2 (45) Date of Patent: Oct. 14, 2014

*H03K 2017/6875* (2013.01); *H03K 17/162* (2013.01); *H03K 2217/0036* (2013.01); *H03K 17/08122* (2013.01)

(58) Field of Classification Search

None

See application file for complete search history.

# (56) References Cited

### U.S. PATENT DOCUMENTS

4,002,931 A 1/1977 Tsang et al. 4,125,814 A 11/1978 Baker (Continued)

### OTHER PUBLICATIONS

Akagi, et al., "130 kHz 7.5 kW Current Source Inventers Using Static Induction Transistors for Induction Heating Applications", IEEE Transactions on Power Electronics, vol. 3, No. 3, 1988, pp. 303-309.

(Continued)

Primary Examiner — Long Nguyen

# (57) ABSTRACT

A method for rendering a half-bridge circuit containing normally on switches such as junction field effect transistors (JFETs) inherently safe from uncontrolled current flow is described. The switches can be made from silicon carbide or from silicon. The methods described herein allow for the use of better performing normally on switches in place of normally off switches in integrated power modules thereby improving the efficiency, size, weight, and cost of the integrated power modules. As described herein, a power supply can be added to the gate driver circuitry. The power supply can be self starting and self oscillating while being capable of deriving all of its source energy from the terminals supplying electrical potential to the normally on switch through the gate driver. The terminal characteristics of the normally on switch can then be coordinated to the input-to-output characteristics of the power supply.

# 19 Claims, 6 Drawing Sheets

# (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,191,899 | A            | 3/1980  | Tomczak et al.        |

|-----------|--------------|---------|-----------------------|

| 4,393,337 | $\mathbf{A}$ | 7/1983  | Nagai et al.          |

| 5,218,523 | $\mathbf{A}$ | 6/1993  | Sugishima             |

| 5,747,943 | $\mathbf{A}$ | 5/1998  | Houk et al.           |

| 5,801,557 | $\mathbf{A}$ | 9/1998  | Dubhashi et al.       |

| 5,969,964 | $\mathbf{A}$ | 10/1999 | Mangtani              |

| 6,215,329 | B1           | 4/2001  | Campardo et al.       |

| 6,353,345 | B1           | 3/2002  | Yushan et al.         |

| 7,046,040 | B2           | 5/2006  | Guedon                |

| 7,248,093 | B2 *         | 7/2007  | West 327/390          |

| 7,602,228 | B2 *         | 10/2009 | Mazzola et al 327/423 |

| 7,907,001 | B2 *         | 3/2011  | Mazzola et al 327/423 |

| 8,456,218 | B2 *         | 6/2013  | Mazzola et al 327/423 |

#### OTHER PUBLICATIONS

Batarseh, Issa, "Power Electronic Circuits:Buck-Derived Isolated Converters 5.2.2 Half-Bridge Converter", Wiley, ISBN 0-471-12662-4, 2004, pp. 224-225.

Batarseh, Issa, "Power Electronic Circuits:Basic Half-Bridge Inverter Circuits 9.2.1 Restrictive Load", Wiley, ISBN 0-471-12662-4, 2004, pp. 426-427.

Kelley, Robin, "High Side Gate Driver for Providing Inherent Safety to Normally on SiC JFETs in Motor Drive Applications", ECE 7000, Scalable SiC Devices, DIS, Dec. 9, 2005, pp. 1-6.

Kelley, et al., "Inherently Safe DC/DC Converter using a Normally-on SiC JFET", Applied Power Electronics Conference and Exposition, APEC, Twentieth Annual IEEE, vol. 3, Mar. 6-10, 2005, pp. 1561-1565.

Kelley, et al., "Inherently Safe Resonant Reset Forward Converter Using a Bias-Enhanced SiC JFET", ICSCRM Sep. 2005, 4 pages.

Kelley, et al., "Inherently Safe Resonant Reset Forward Converter Using a Bias-Enhanced SiC JFET", Materials Science Forum, vol. 527-529, 2006, pp. 1211-1214.

Mazzola et al., "Scalable SiC Power Switches for Applications in More Electric Vehicles" Pro. of 6.sup.th Int. All Electric Combat Vehicle Conference, AECV, Jun. 13-16, 2005, 7 pages.

Mohan, et al., "Power Electronics:Converters, Applications and Design:Three-Phase Inverters", 2nd ed., 8-4 Figure 8-21, John Wiley and Sons, ISBN 0-471-58408-8, 1995, p. 225.

Mohan, et al., "Power Electronics: Converters, Applications and Design:Switch-Mode Converters" CUK dc-dc Converter, Figure 7.25, John Wiley and Sons, Inc. XP002500632, 2003, pp. 184-188. Orellana, et al., "Fast Gate Drive for SiC-JFET Using a Conventional Driver for MOSFETs and Additional Protections", Industrial Electronics Society, vol. 1, Nov. 2-6, 2004, pp. 938-943.

Ossmann, M., "Small DC-DC converters; DC-DC converters under the magnifying glass," Elektor Electronics, vol. 29, No. 317, 2003, pp. 54-58.

International Preliminary Report on Patentability received for PCT Application No. PCT/US2008/064339, issued on Nov. 24, 2009, 21 pages.

International Search Report and Written Opinion received for PCT Patent Application No. PCT/US2008/064339, mailed on Nov. 14, 2008, 26 pages.

Rashid, Muhammad H., "Insulated Gate Bipolar Transistor", Power Electronics Handbook, ed. M. Rashid, Academic Press, ISBN 0-12-581650-2, 2001, pp. 109-110.

Rebbereh, et al., "First inverter using silicon carbide power switches only", 10th European Conference on Power Electronics and Applications, XP008097914, ISBN 90-75815-07-7, Section "Inverter Topology," figure 2, 2003, 10 pages.

\* cited by examiner

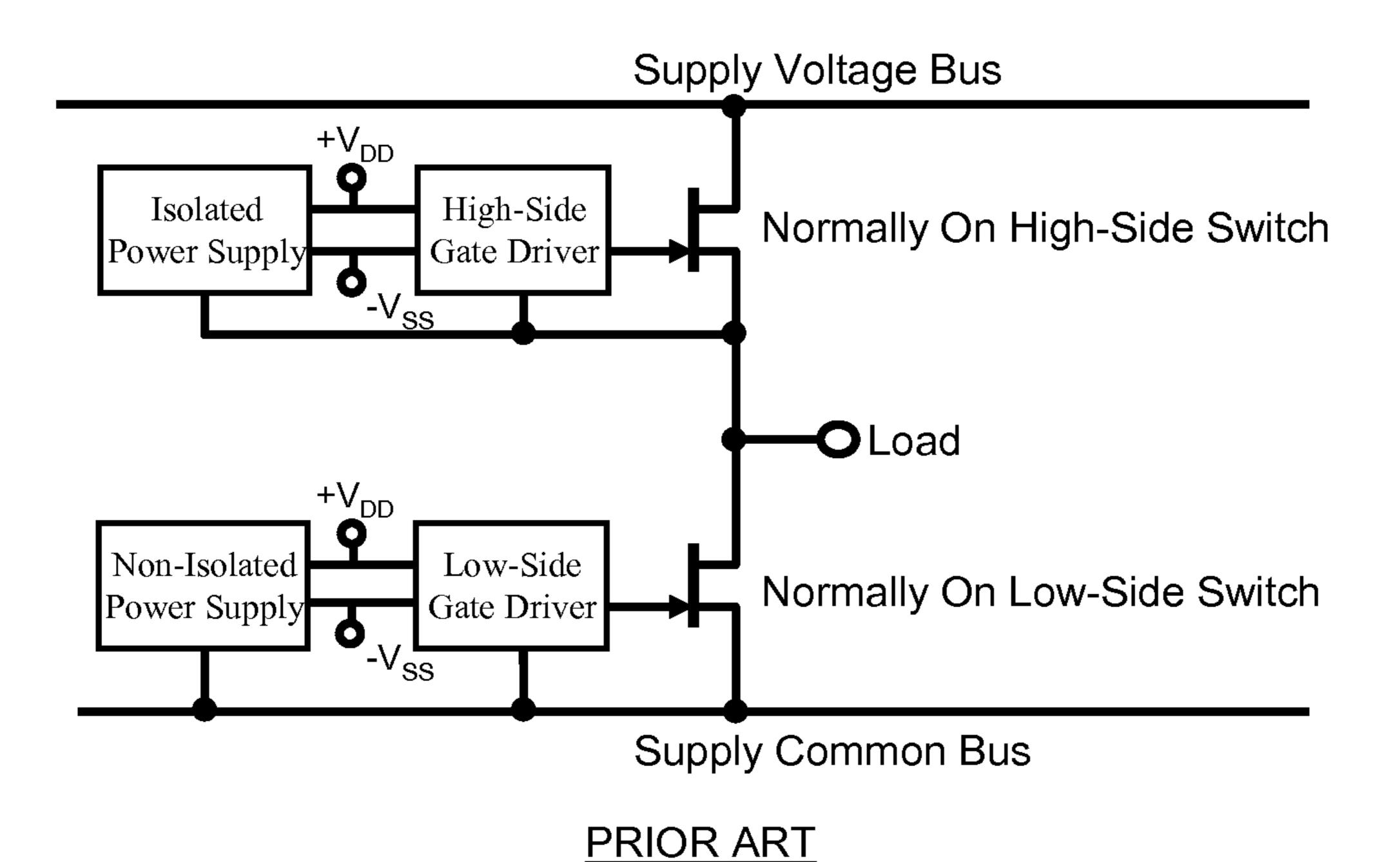

PRIOR ART

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 11

# HALF-BRIDGE CIRCUITS EMPLOYING NORMALLY ON SWITCHES AND METHODS OF PREVENTING UNINTENDED CURRENT FLOW THEREIN

This application is a continuation of U.S. patent application Ser. No. 13/021,132, filed on Feb. 4, 2011, now U.S. Pat. No. 8,456,218, which is a continuation of U.S. patent application Ser. No. 12/557,199, filed on Sep. 10, 2009, now U.S. Pat. No. 7,907,001, which is a divisional application of U.S. patent application Ser. No. 11/802,388, filed on May 22, 2007, now U.S. Pat. No. 7,602,288. Each of the above applications is hereby incorporated by reference in its entirety.

#### **BACKGROUND**

## 1. Technical Field

This application relates generally to half-bridge circuits employing normally on switches and to electrical devices 20 which include one or more such circuits.

# 2. Background of the Technology

Silicon Carbide (SiC), a wide band-gap semiconductor material, is very attractive for use in high-power, high-temperature, and/or radiation resistant electronics. SiC power 25 switches are logical candidates for these applications due to their excellent material physical properties such as wide energy band-gap, high breakdown field strength, high saturated electron drift velocity and high thermal conductivity compared to the conventional silicon counter part. In addition 30 to the above advantages, SiC power devices can operate with much lower specific on-resistance than conventional silicon power devices [1]. Because of these properties, SiC unipolar devices are expected to displace silicon bipolar switches (such as the insulated gate bipolar transistor or IGBT) and 35 rectifiers in the 600-3000 V range.

A necessary component to the value proposition that the market demands to adopt the new SiC switch technology is found in the lower specific on resistance of SiC switches. A factor of ten or more reduction is inherent to SiC devices, but 40 only in the form most likely to produce these specific onresistance reductions. The SiC junction field effect transistor (JFET) has demonstrated the lowest specific on-resistance of any SiC switch. In particular, the normally on version of this device will minimize the specific on-resistance at any voltage 45 rating. The market place, however, tends to prefer normally off devices because they are perceived as being inherently safe when imbedded in an application.

An independent trend in the market place is to package powerful switches into modules that typically consist of two, 50 four, or six switches arranged in parallel half-bridge configurations. These modules are particularly useful for the control of rotating machinery in devices known as motor drives, the operating principals of which are well known [2, 3]. FIG. 1 illustrates a single half-bridge module containing two silicon 55 IGBT switches. Typical ratings for the switches in the modules are 600-V or 1200-V blocking potential and hundreds of amperes of conduction (e.g., 300-A, 400-A, or 600-A) but the voltages and currents can be higher or lower. The half-bridge interconnection and the constituent IGBT both have weak- 60 nesses. The former requires the added complication of an isolated gate driver for the high-side switch. The latter has a gate terminal that can be easily damaged by incorrect or excessively stressful control potentials. The market has responded by including imbedded gate driver circuitry into 65 the switch modules so that the application external to the module does not actually apply potentials to the gate termi2

nals of the IGBTs. This additional level of safety has dramatically increased the reliability of IGBTs used in the field.

There still exists a need, however, for improved circuits and devices which modulate the flow of electrical current from one or more electrical sources to one or more electrical loads.

### **SUMMARY**

According to a first embodiment, a circuit is provided which comprises:

- a first normally-on switch having a source, a drain and a gate, the source of the first normally-on switch electrically connected to a load and the drain of the first normally-on switch electrically connected to a supply voltage;

- a second normally-on switch having a source, a drain, and a gate, the source of the second normally-on switch electrically connected to a common voltage and the drain of the second normally-on switch electrically connected to the load;

- a first gate driver electrically connected between the gate and the source of the first normally-on switch;

- a second gate driver electrically connected between the gate and the source of the second normally-on switch; and

- a first oscillating power supply electrically connected in parallel across the drain and the source of the first switch, the first power supply configured to power the first gate driver such that, for a given voltage applied to the input to the first power supply, the first power supply generates an output voltage which can be supplied to the gate of the first switch by the first gate driver;

- a second oscillating power supply electrically connected in parallel across the drain and the source of the second switch, the second power supply configured to power the second gate driver such that, for a given voltage applied to the input to the second power supply, the second power supply generates an output voltage which can be supplied to the gate of the second switch by the second gate driver.

The input-output characteristics of the first power supply can be coordinated with the characteristics of the first switch such that the first switch is in active current limiting mode over at least 50 percent of a voltage range of 0 to the breakdown voltage of the first switch applied to the power supply and wherein the input-output characteristics of the second power supply are coordinated with the characteristics of the second switch such that the second switch is in active current limiting mode over at least 50 percent of a voltage range of 0 to the breakdown voltage of the second switch applied to the second power supply.

The input-output characteristics of the first power supply can be coordinated with the characteristics of the first switch such that the first switch is in active current limiting mode over at least 75 percent of a voltage range of 0 to the breakdown voltage of the first switch applied to the power supply and wherein the input-output characteristics of the second power supply are coordinated with the characteristics of the second switch such that the second switch is in active current limiting mode over at least 75 percent of a voltage range of 0 to the breakdown voltage of the second switch applied to the second power supply.

The input-output characteristics of the first oscillating power supply can be coordinated with the characteristics of the first switch such that the first switch does not overheat when in passive current limiting mode and wherein the inputoutput characteristics of the second oscillating power supply

are coordinated with the characteristics of the second switch such that the second switch does not overheat when in passive current limiting mode.

The first gate driver and the second gate driver can each comprise a totem pole driver.

A device is also provided comprising three circuits as set forth above arranged in parallel, wherein the device is a three-phase motor drive.

The circuit can further comprise an external controller which is adapted to bias the first switch to minimum on-  $^{10}$  resistance via the first gate driver. The first gate driver can be adapted to apply a bias voltage to the gate of the first switch  $(V_{GS})$  which is equal to the output from the first power supply  $(-V_{SS})$  when the external controller is not biasing the first switch to minimum on resistance.

According to a second embodiment, a circuit is provided which comprises:

- a first normally-on switch having a source, a drain and a gate, the source of the first normally-on switch electrically connected to a load and the drain of the first normally-on switch electrically connected to a supply voltage;

- a second normally-on switch having a source, a drain, and a gate, the source of the second normally-on switch electrically connected to a common voltage and the <sup>25</sup> drain of the second normally-on switch electrically connected to the load;

- a first gate driver electrically connected between the gate and the source of the first normally-on switch;

- a second gate driver electrically connected between the <sup>30</sup> gate and the source of the second normally-on switch; and

- an oscillating power supply electrically connected across the voltage source and the common voltage, wherein the power supply is configured to power the first and second 35 gate drivers such that, for a given voltage applied to the input of the power supply, the power supply generates a first output voltage which can be supplied to the gate of the first switch by the first gate driver and a second output voltage which can be supplied to the gate of the 40 second switch by the second gate driver.

According to a third embodiment, an electrical device comprising at least one circuit as set forth above is also provided.

According to a fourth embodiment, an electrical device 45 comprising three circuits as set forth above arranged in parallel wherein the device is a three-phase motor drive is also provided.

# BRIEF DESCRIPTION OF THE DRAWINGS

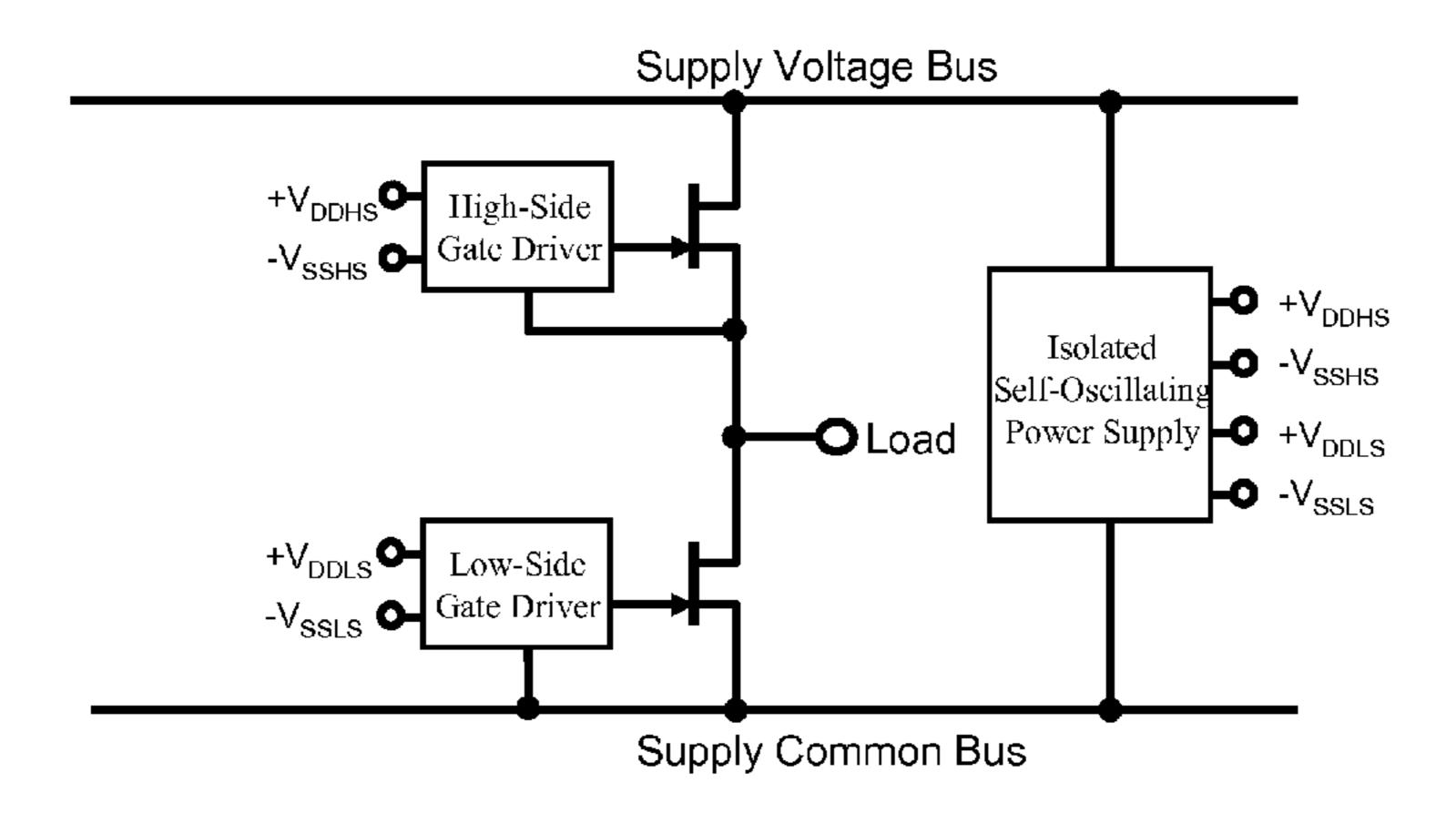

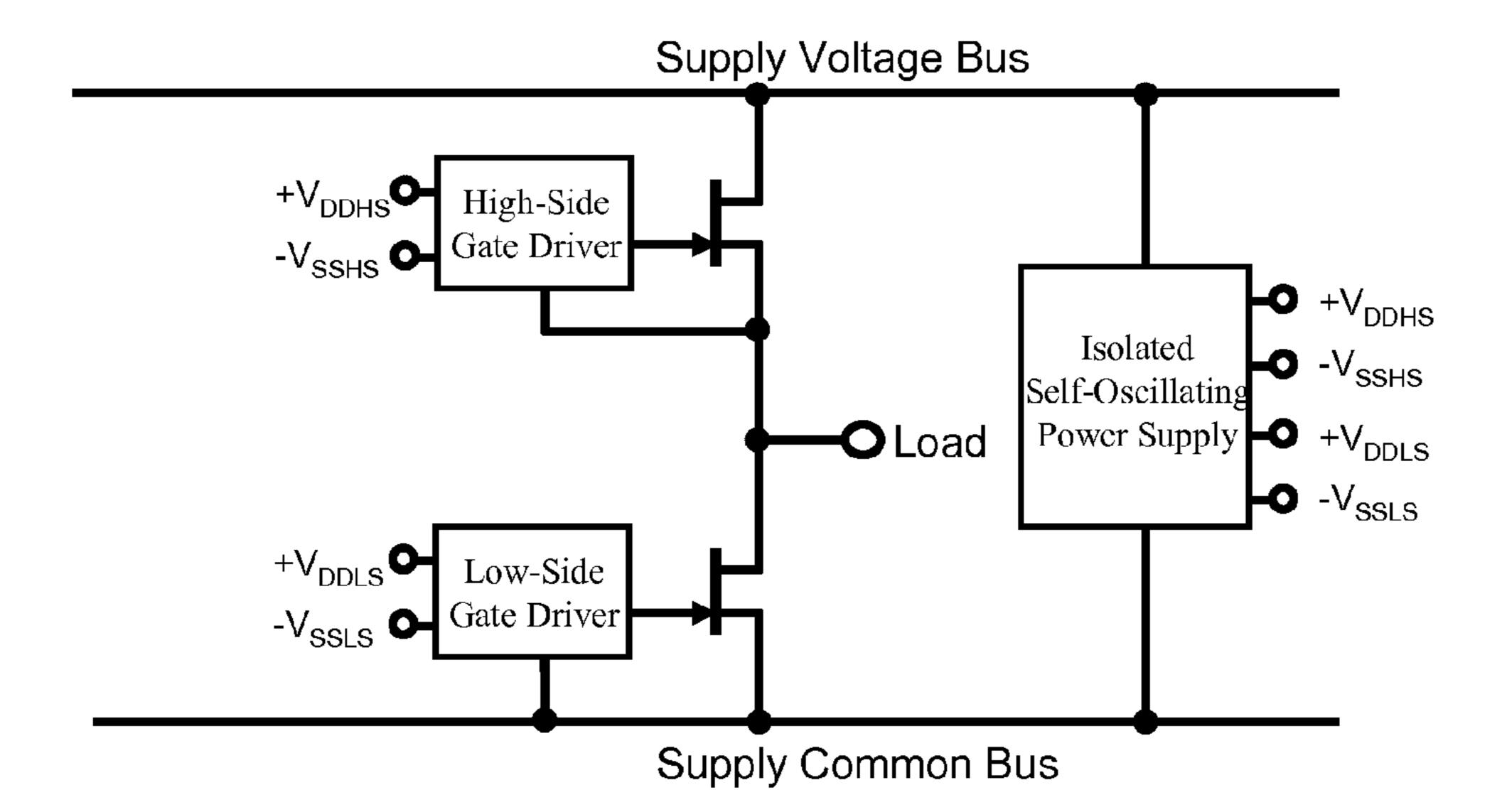

FIG. 1 is an example of a half-bridge switch module consisting of a silicon IGBT (normally off high-side switch) in series with a second IGBT (normally off low-side switch). The module shown in FIG. 1 can also include an anti-parallel diode rectifier (not shown). Isolated power supplies can be used to derive negative and positive potentials to drive the insulated gate of the switch.

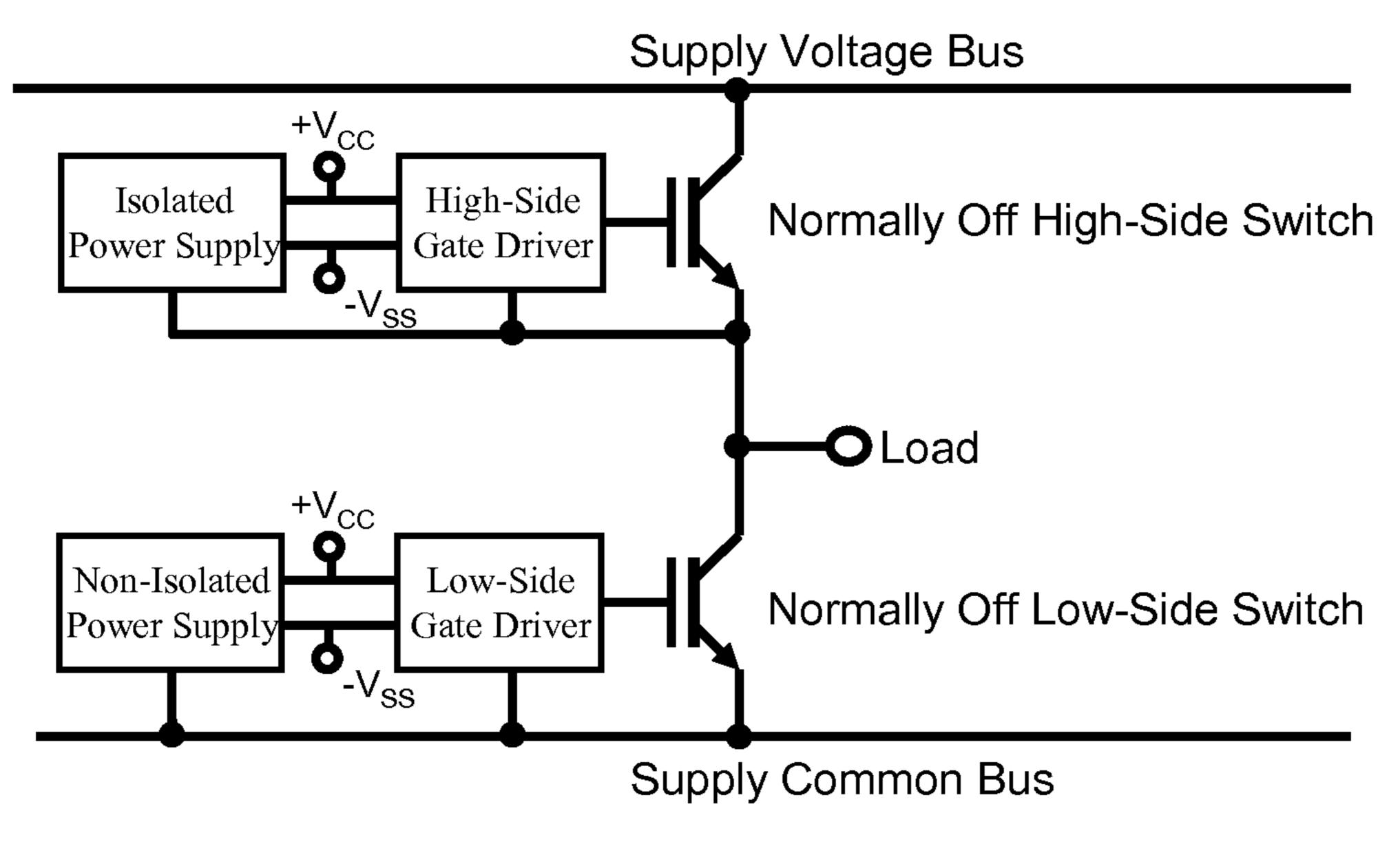

FIG. 2 is an example of a half-bridge switch module comprising a normally on switch such as a junction field effect fransistor (JFET) in series with a second normally on switch. The module shown in FIG. 2 can also include an anti-parallel diode rectifier (not shown). Isolated power supplies can be used to derive negative and positive potentials to drive the insulated gate of the switch.

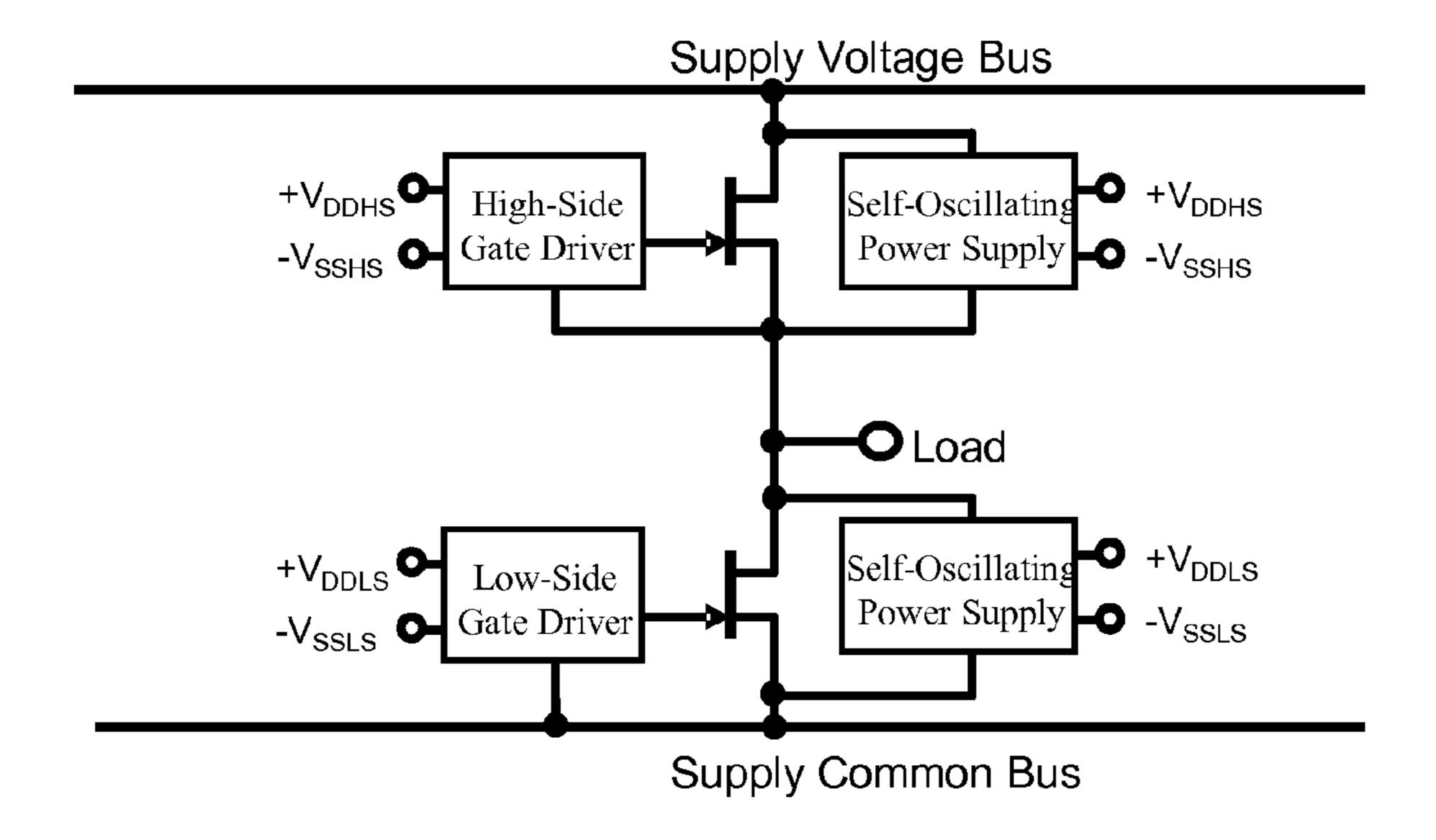

FIG. 3 is a schematic diagram of a power half-bridge circuit comprising a normally on junction field effect transistor

4

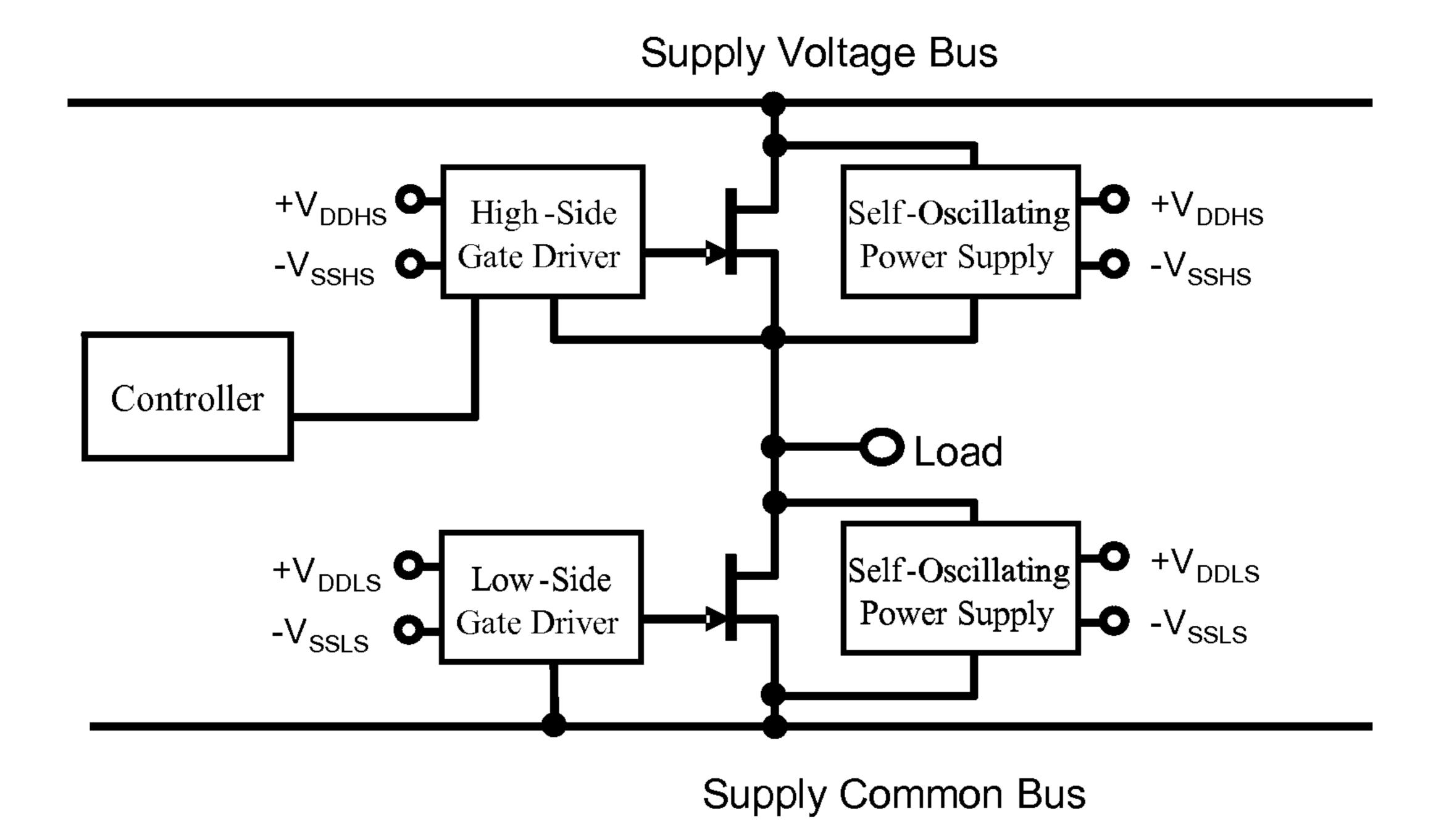

(JFET) made from silicon carbide in the high and low side switch positions. As shown in FIG. 3, a power supply is connected across the input to the drain and source terminals of each JFET. The input-to-output characteristics of the power supply can be coordinated with the blocking characteristics of the JFET.

FIG. 4 is a schematic diagram of a power half-bridge circuit wherein the input to a single power supply is connected from the upper bus to the lower bus of the half-bridge module. This power supply derives two isolated outputs, one for the high-side JFET and one for the low-side JFET. The input-to-output characteristics of the power supply can be coordinated with the blocking characteristics of the JFET.

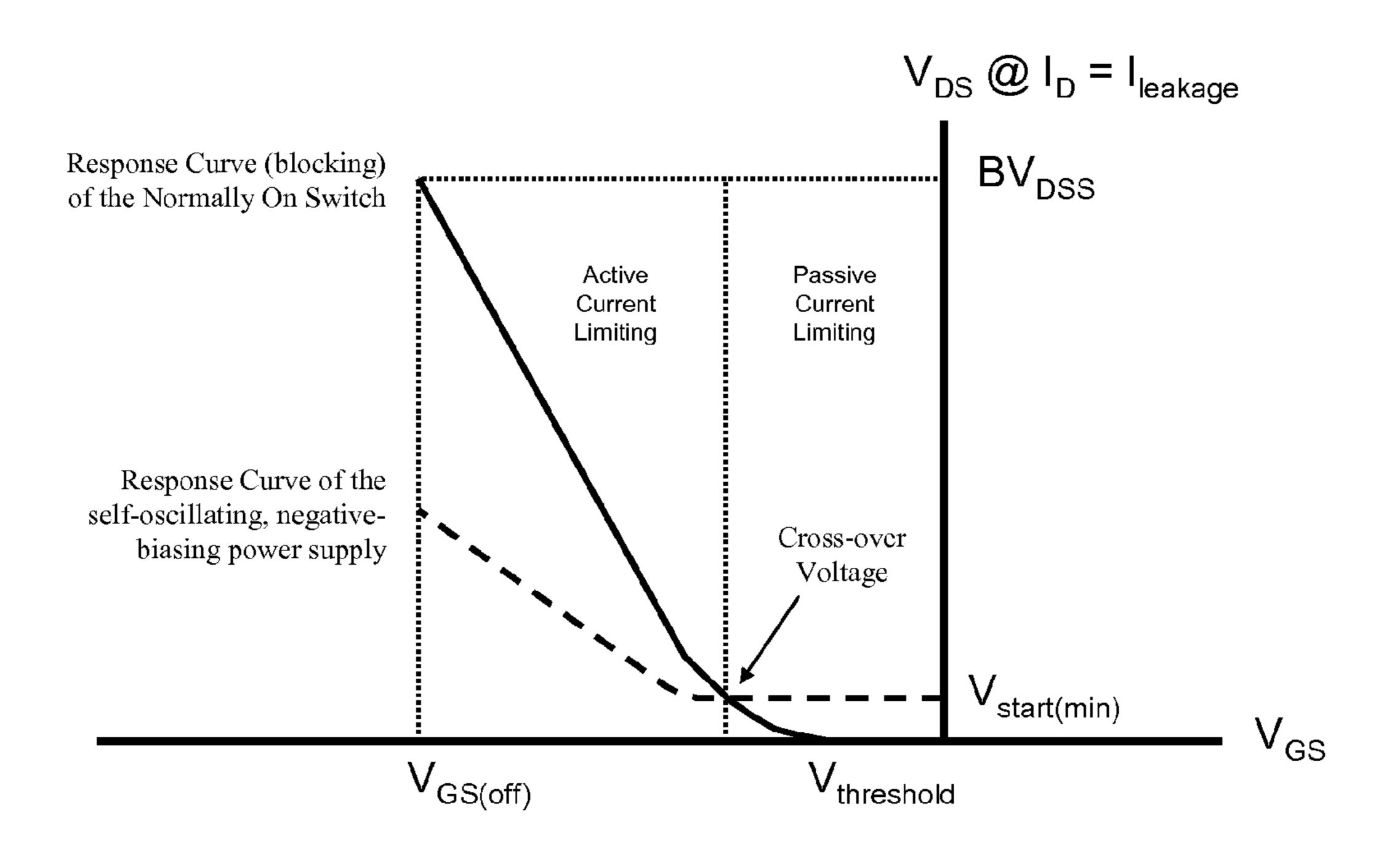

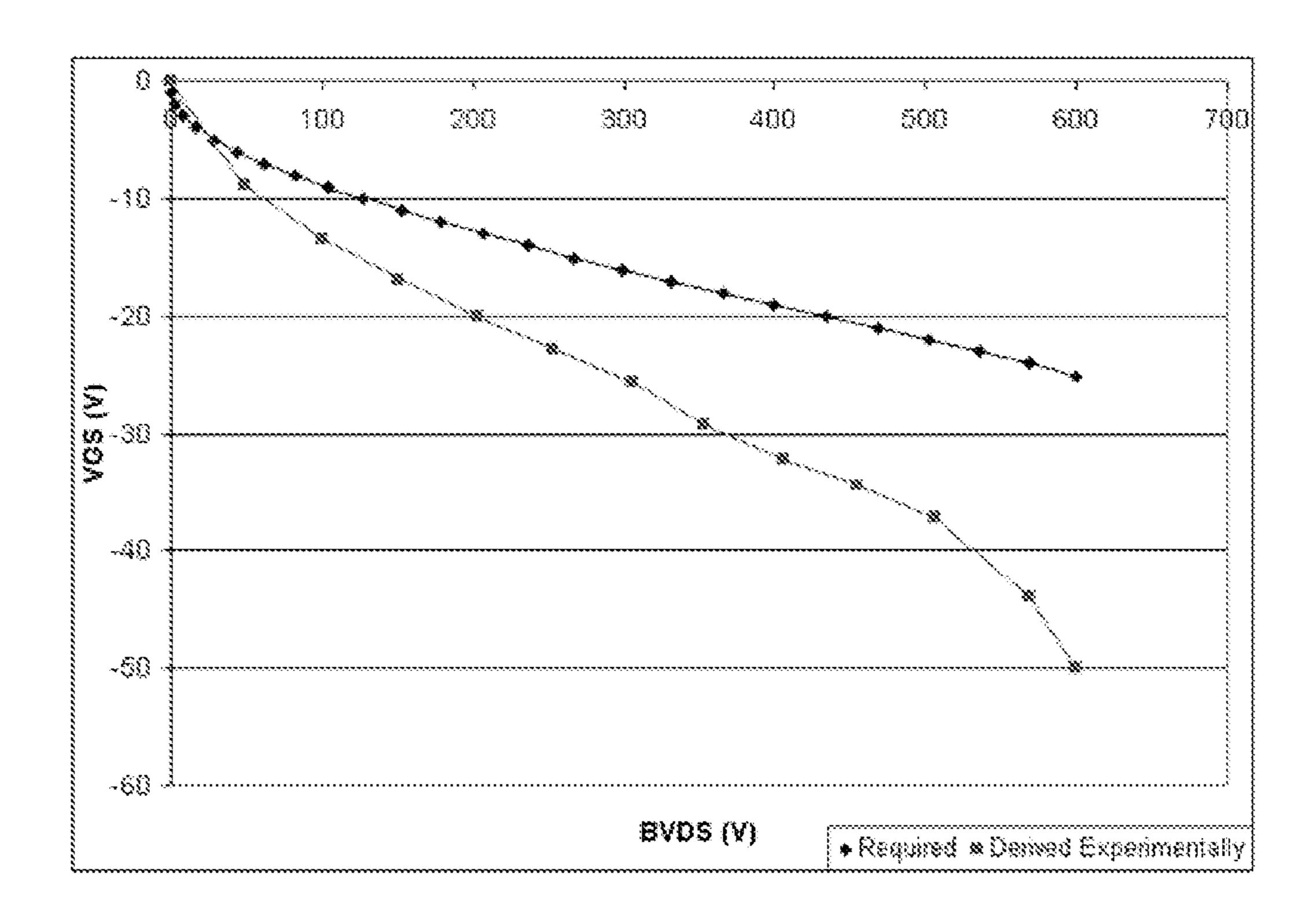

FIG. **5** is a graph showing coordination between the inputoutput characteristic of the power supply and the blocking characteristic of the corresponding normally on switch (e.g., JFET) protected by the power supply.

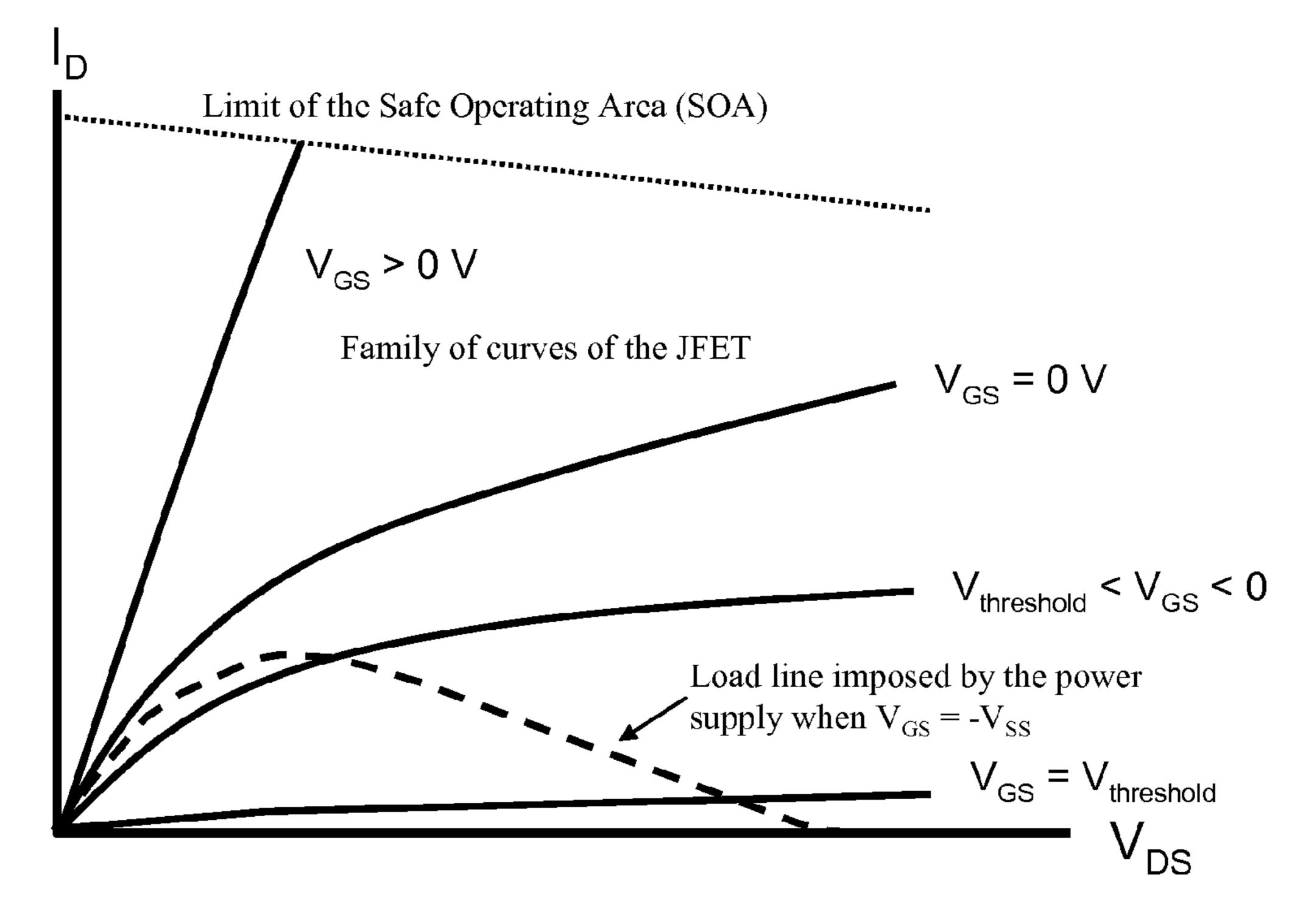

FIG. 6 is a further illustration of the coordination between the input-to-output characteristic of the power supply and the family of curves of the normally on JFET while the JFET is in the passive current limiting mode.

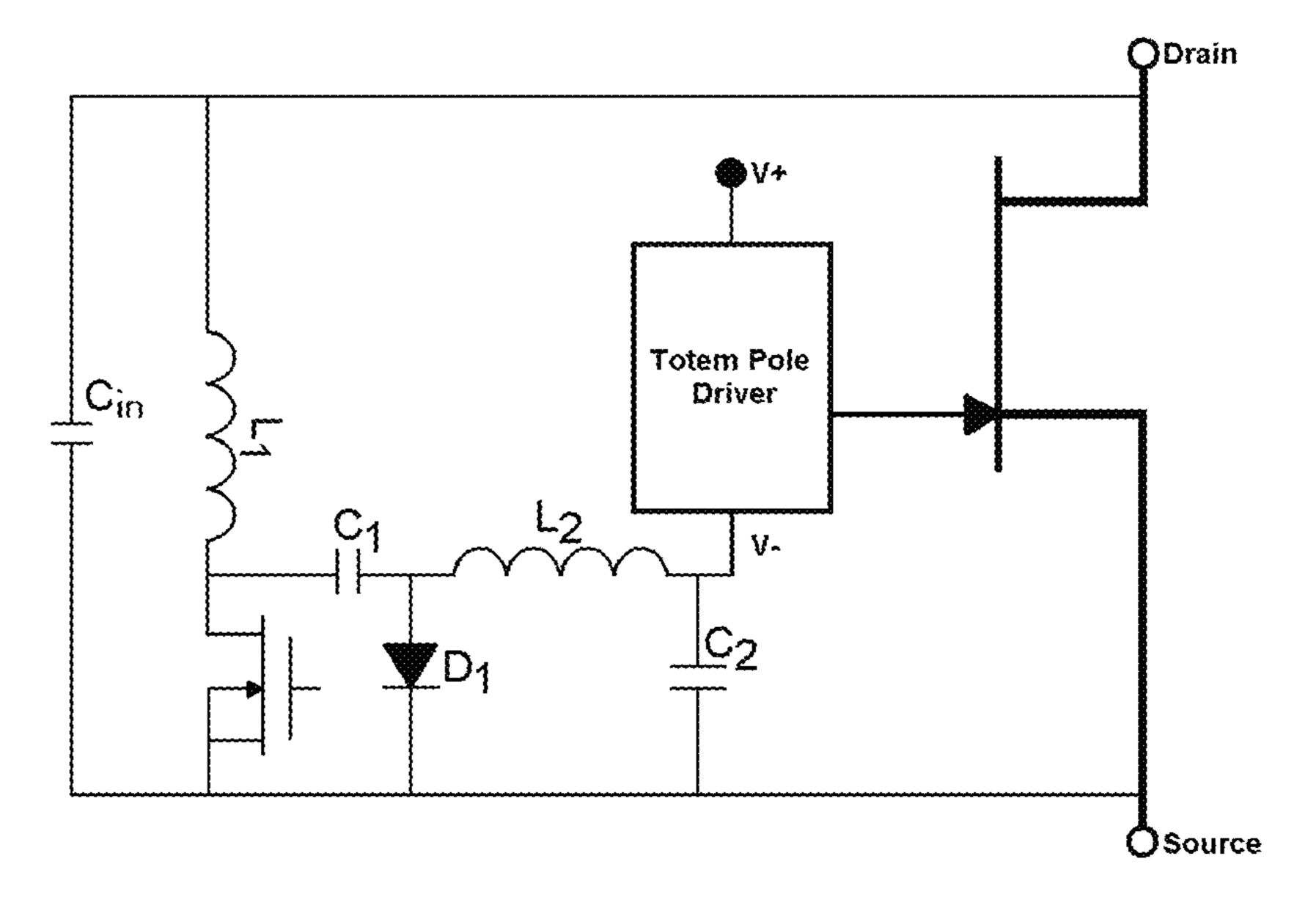

FIG. 7 is a schematic diagram of one physical implementation of the power supply based on a non-isolated Cuk converter that is connected across the drain-to-source terminals of the protected JFET.

FIG. 8 is a plot of the experimental data measured using the physical implementation shown in FIG. 7. In the figure the data marked "required" refers to the experimental blocking characteristic curve of the SiC JFET being controlled by the gate drive. The data marked "derived experimentally" is the input-to-output characteristic of the power supply shown in FIG. 7.

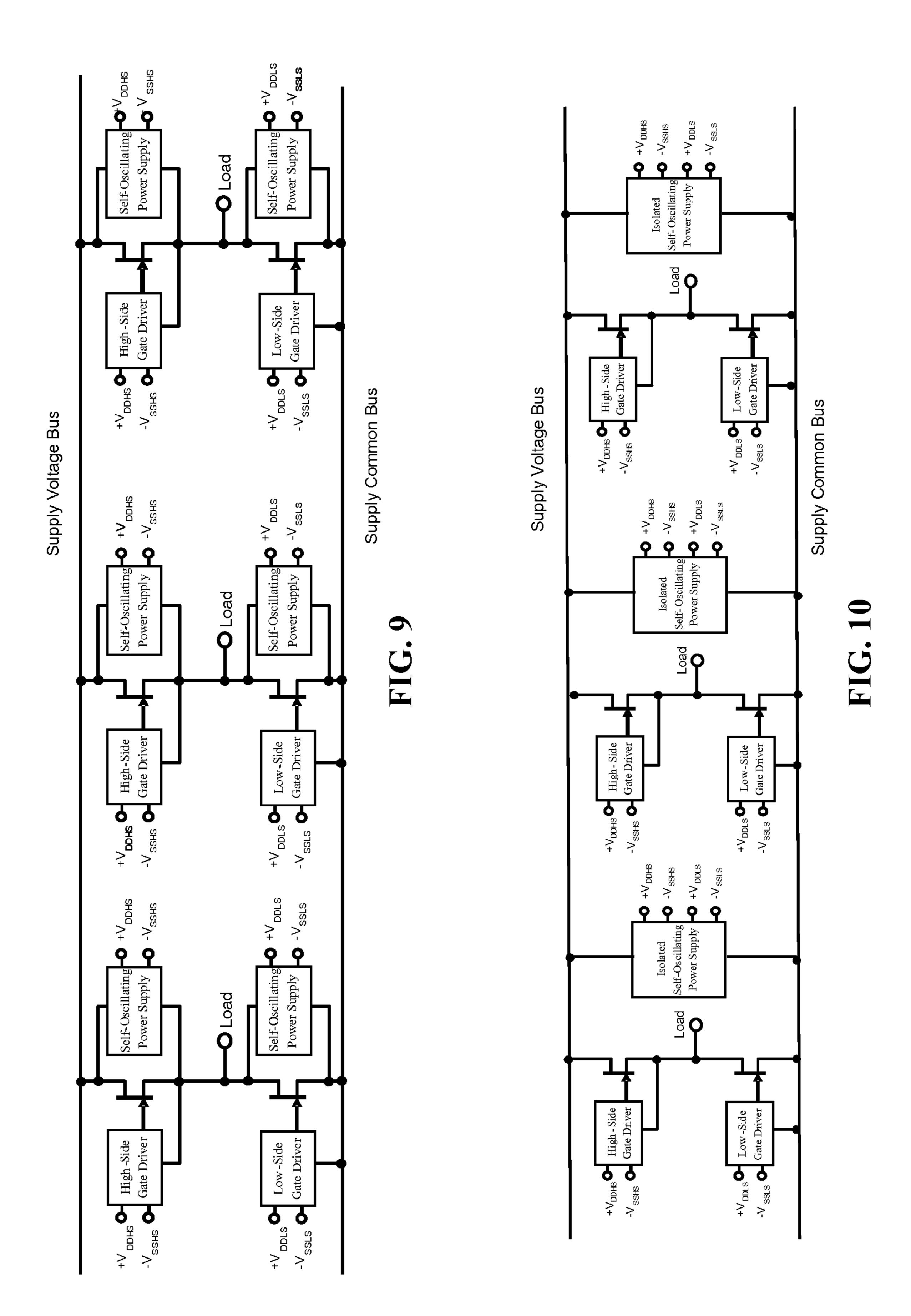

FIG. 9 is a schematic diagram of an electrical device comprising three circuits as shown in FIG. 3, arranged in parallel.

FIG. 10 is a schematic diagram of an electrical device comprising three circuits as shown in FIG. 4, arranged in parallel.

FIG. 11 shows schematically a diagram of a power half-bridge circuit having an external controller adapted to bias the first switch to minimum on-resistance via the first gate driver.

# DETAILED DESCRIPTION

A method for rendering the use of normally on switches inherently safe when packaged in a module consisting of one or more switches that are in turn arranged and controlled so as to modulate the flow of electrical current from one or more electrical sources to one or more electrical loads is described. The switches can be made from a semiconductor material such as silicon or silicon carbide. The normally on switch can be a junction field effect transistor (JFET), but the methods are not limited to such switches. Any normally on switch that exhibits a proportional relationship between the potential applied across the control terminals of the device and the potential that the device can block across the controlled terminals of the device without the flow of excessive leakage current can be rendered safe by the methods described herein.

A described herein, a circuit can be added to the gate drive circuitry of each switch in the module such that a normally on switch can have the same inherent safety, from the point of view of the external terminals of the module, that is usually available only from a normally off switch. In this way, better performing normally on switches can be used in the module without compromising the safety, or the perception of safety, in the eyes of the application designer. Furthermore, the circuitry can be coordinated with the physical properties of the switch to ensure a safe (i.e., non-damaging) response to any

potential applied to the switch. An exemplary, non-limiting example of the normally on switch is a silicon carbide power JFET.

As set forth above, a method for rendering a half-bridge circuit containing normally on switches, such as junction field effect transistors (JFETs) made, for example, from silicon carbide or from silicon, inherently safe from uncontrolled current flow (i.e., "shoot through") is provided. The methods described herein allow for the use of better performing normally on switches in place of normally off switches in integrated power modules thereby improving the efficiency, size, weight, and cost of such integrated power modules.

As set forth herein, a power supply may be added to the gate driver circuitry. The power supply may be self starting and self oscillating while being capable of deriving all of its source energy from the terminals supplying electrical potential to the normally on switch. Such a configuration is common to a wide class of devices known as integrated power modules. The methods described herein, however, are not 20 limited to integrated power modules. Rather, these methods are applicable to any system consisting of one or more halfbridge circuits. A common example is the three-phase electric motor drive, which uses three half-bridge circuits in parallel.

As also described herein, the terminal characteristics of the normally on switch can be coordinated to the input-to-output characteristics of the power supply. The details of the coordination and the results from a working model are described below.

An object of the present invention is to illustrate a means 30 for rendering normally on power semiconductor switches with the same inherent safety against potentially damaging unintended flow of electrical current that is provided by the normally off switches.

connection of additional circuitry in the gate driver portion of the typical power switch module that provides one aspect of the means for rendering normally on switches inherently safe.

A further object of the invention is to describe the coordination between the properties of the additional circuitry and 40 the properties of the normally on power switch that results in the inherently safe design.

A further object of the invention is to describe the constraints that define the "crossover" between active current limiting, which is provided by the additional circuitry men- 45 tioned above, and passive current limiting, which is provided by the normally on power switch itself.

As described herein, the result of these various objects is a means of rendering the normally on power switch inherently safe that is robust, technically feasible, and consistent with 50 current and future design practice in power modules.

The benefits of the current invention are considerable. For example, better performing normally on power switches can be used in power modules, especially when the switches are made from silicon carbide, which will shrink the size and 55 weight of these modules and make them more efficient. In addition, it is likely that more applications for power modules will become possible because of the faster switching performance typical of unipolar devices over bipolar devices.

The present invention will be described in greater detail 60 hereafter with reference to the accompanying drawings, in which a preferred embodiment of the invention is described with silicon carbide (SiC) normally on Junction Field Effect Transistors (JFETs).

By "normally on" it is meant a transistor switch that will 65 conduct significant current when no voltage or current bias is applied to the gating terminal of the transistor.

Silicon carbide crystallizes in more than 200 different poly-types. The most important are: 3C-SiC (cubic unit cell, zincblende); 2H-SiC; 4H-SiC; 6H-SiC (hexagonal unit cell, wurtzile); and 15R-SiC (rhombohedral unit cell). However, the 4H-polytype is more attractive for power devices thanks to its larger bandgap and higher electron mobility. Although 4H-SiC is preferred, it is to be understood that the present invention is applicable to devices made of other poly-types of silicon carbide or made from elemental silicon, by way of 10 example.

Referring to FIG. 1, an example schematic of a two-switch half bridge commonly used by itself as a power processor in numerous power electronic applications (e.g., dc-dc converter [1] and dc-ac inverters [2]) or as a building block for three-phase inverters which typically requires three halfbridge circuits in parallel [3]. The switches illustrated in FIG. 1 are normally off insulated gate bipolar transistors (IGBT). In modules spanning the range of voltage ratings from 600 V to thousands of volts and spanning the range of current ratings from 50 A to thousands of amperes, the silicon IGBT is most common. While a negative gate potential is not generally required to cause the IGBT switch to be in the non-conducting state, FIG. 1 includes the possibility of a negative potential  $(-V_{SS})$  in FIG. 1) because this is known to improve the efficiency of switching certain types of IGBTs in applications [4].

New switch technology in the form of normally on SiC JFETs have exhibited the lowest specific on-resistance and the lowest gate charge figures of merit among power semiconductor devices with voltage ratings substantially above 300 V, and thus have the potential to displace silicon IGBTs in many of their current and future applications [5]. The advantages of using a unipolar device, like the SiC JFET, over a bipolar device, like the Si IGBT, can accrue benefits such as A further object of the invention is to describe the inter- 35 better switching response, lower forward conduction loss, and relaxed thermal management. In contrast, traditional silicon unipolar devices such as the MOSFET simply cannot deliver low enough forward conduction loss to compete with the silicon IGBT, especially at voltages above 600-V. Nontraditional normally on silicon and silicon carbide unipolar devices are competitive, the latter extremely so.

As illustrated in FIG. 2, a normally on silicon JFET (also known as the static induction transistor or SIT) has been used to make power inverters [6]. However, for these devices the negative potential required to pinch-off a normally on switch and thus render it in the non-conducting state is derived from the power supply powering the gate driver in a manner similar to that commonly provided for normally off switches. The disadvantage of this approach is that if the source of isolated power is removed (e.g., by accident or by failure) then the means for supplying the necessary negative potential is also removed. This can leave the half bridge made from normally on switches in an uncontrolled conducting state which can severely damage the semiconductor switches and/or the external load or source by permitting uncontrolled and excessive electrical current flow (sometimes referred to as "shoot through"). This concern, above all, has favored the silicon IGBT over the silicon JFET in virtually all practical applications.

Referring now to FIG. 3, a schematic block diagram is shown for a power half-bridge circuit comprising a normally on junction field effect transistor (JFET) made from silicon carbide in the high and low side switch positions. The provision of negative gate potential is no longer dependent on an isolated power source, although one can still be provided as a means of redundancy. Instead, or in addition, a power supply is connected across the drain and the source terminals of the

normally on switch (e.g., a JFET as depicted in FIG. 3). This power supply can have input-to-output characteristics which are coordinated with the electrical characteristics of the JFET in a manner described below. This coordination can be used to ensure that, for any combination of electrical potentials applied across the drain and source terminals of the JFET, an uncontrolled electrical current cannot flow through the JFET. In FIG. 3, two power supplies are shown, one for each switch of the half bridge. This arrangement provides maximum protection to each JFET. In one embodiment, as shown in FIG. 10 11, the power half-bridge circuit includes an external controller that is configured to bias the first switch to minimum on-resistance via the first gate driver.

FIG. 4 illustrates an alternative embodiment in which a single power supply with appropriately coordinated input-to-output characteristics is used to derive the negative potential for both JFETs in the half bridge. The power supply in the device shown in FIG. 4 is isolated. The device depicted in FIG. 4 can be used in applications where the source of potential that can be applied to the JFETs in the half bridge is 20 limited to the upper and the lower bus connections spanned by the half bridge. The configuration shown in FIG. 3 can be used in all power module applications. The device shown in FIG. 4 is suitable for many common applications and has the advantage of requiring only one power supply which may reduce 25 cost and part count.

The power supply illustrated in FIG. 3 and FIG. 4 derives power to operate from the source of potential applied to either the drain-source terminals (FIG. 3) or the upper and lower buses (FIG. 4). In addition, the power supply depicted in 30 FIGS. 3 and 4 will start oscillating automatically upon application of a voltage to its input.

In addition, the input-to-output characteristics of the power supply can be coordinated with the semiconductor device or devices being protected. For example, the voltage that a ver- 35 tical power JFET will block can be represented on a graph as illustrated in FIG. 5. On the horizontal axis or abscissa is plotted the potential applied across the gate to the source of the JFET. On the vertical axis or ordinate is plotted the potential applied across the drain to the source of the JFET when 40 the specified leakage current flows into the drain. The solid curve on the graph traces the blocking characteristics of the JFET. The gate-source voltage can be positive or negative, but  $V_{DS}@I_D=I_{leakage}$  increases monotonically as the gatesource voltage decreases. If  $V_{GS} > V_{threshold}$  and  $I_D$  is limited 45 to  $\leq I_{leakage}$ , then no appreciable  $V_{DS}$  can be blocked. The maximum voltage that the JFET can block is given by  $BV_{DSS}$ which occurs when  $V_{GS}=V_{GS(off)}$ . A "normally on device" is generally one in which  $V_{threshold} < 0$ . Even though it is a normally on device, it may not reach its full ability to conduct 50 (i.e., exhibiting the minimum resistance to electrical current) until  $V_{GS} > 0$ .

Superimposed on the graph in FIG. **5** is a dashed line which represents the input-to-output characteristics of the self-oscillating power supply. When a certain  $V_{DS}$  is applied to the 55 input of the power supply, it will generate an output that is applied to  $V_{GS}$  by the gate driver circuit. The locus of ordered pairs of  $V_{GS}$  and  $V_{DS}$  is represented by the dashed line. According to some embodiments, coordination can be used to ensure that the dashed line falls below the solid line for the 60 majority of applied  $V_{DS}$ . For the region where this is true, labeled "active current limiting" on the graph, it is certain that the applied  $V_{DS}$  will produce a leakage current through the JFET that is less than  $I_{leakage}$ . In other words, over the range of  $V_{GS}$  corresponding to active current limiting the JFET is 65 safely in its non-conducting state, which means the current flowing through the JFET will be very small and inconse-

8

quential. The cross over voltage is defined as the boundary value of  $V_{GS}$  separating the active current limiting mode from the passive current limiting mode.

When  $V_{GS}$  is greater than the cross over voltage, the JFET is at least partly passively limiting the current. If the gate driver is not actively commanded by an external controller to bias the JFET to minimum on-resistance, then the gate driver design will inherently cause  $V_{GS} = -V_{SS} \le 0$ . The design of gate drive circuits satisfying this requirement is simple and reliable, and known to those skilled in the art. When the JFET is passively limiting the current, it is dissipating more energy that when it is actively limiting the current. The locus of  $V_{GS}$  vs.  $V_{DS}$  produced by the power supply can be such that, when  $V_{GS}$  is greater than the cross over voltage, the JFET will not overheat. To those skilled in the art, this means that the JFET remains within its safe operating area at all times.

FIG. 6 illustrates the general condition under which safe passive current limiting will be achieved. The graph plots the JFET's drain current  $(I_D)$  on the ordinate and the drain-source voltage  $(V_{DS})$  on the abscissa. A family of curves is drawn on the graph by graphing the ordered pairs of  $I_D$  vs.  $V_{DS}$  for a constant  $V_{GS}$ , and then incrementing  $V_{GS}$  and redrawing the  $I_D$  vs.  $V_{DS}$  curve. In FIG. 6 it is assumed that  $V_{GS}$  ranges from positive values to negative values. The last curve plotted is that for  $V_{GS} = V_{threshold}$ .  $V_{GS} = 0$  V is another curve indicated on the graph. An example of a family of curves for a SiC JFET might cover  $-4 \text{ V} \leq \text{V}_{GS} \leq +3 \text{ V}$ . The more negative that  $\text{V}_{GS} \leq +3 \text{ V}$ becomes, the more resistive the JFET becomes, which reduces  $I_D$  at any given  $V_{DS}$ . As long as the gate driver is preventing uncontrolled current from flowing through the JFET, then  $V_{GS}$  will be clamped to  $-V_{SS}$  (i.e.,  $V_{GS} = -V_{SS}$ ). Since the maximum value of  $-V_{SS}=0$ , then it is not possible for  $I_D$  to fall on a line above the  $V_{GS}=0$  V curve. In practice, even a modest  $V_{DS}$  will cause  $-V_{SS}$ <0, thus  $I_D$  must always fall on a line below that bounded by the  $V_{GS}=0$  V curve. This limiting load line is plotted on the graph in FIG. 6 as a dashed line. By definition, the safe operating area (SOA) of the JFET will be bounded at low  $V_{DS}$  by the rated maximum allowable current of the JFET. In turn, the maximum allowable current will fall on the minimum resistance curve. In the case of a typical SiC JFET, the minimum resistance curve will occur well above the  $V_{GS}=0$  V curve. For example, in the range 0  $V < V_{GS} \le +3 V$ , as is illustrated in FIG. 6. As a result it is not possible while the gate driver clamps  $V_{GS} = -V_{SS}$  for the drain current through the JFET to exceed that permitted by the SOA. In other words, while in the passive current limiting mode the current flowing through the JFET may not be very small, but it will be inconsequential from the standpoint of damaging the JFET.

Referring now to FIG. 7, a schematic diagram of a circuit including an exemplary and non-limiting embodiment of a self oscillating power supply is illustrated. This circuit is the Cuk converter useful for converting an input voltage into an output voltage that is smaller in magnitude and opposite in polarity. The circuit shown in FIG. 7 includes a normally-on switch having a gate, a source and a drain, and a Totem pole driver electrically coupled to the gate of the switch. The Totem pole driver has a positive supply voltage, V+, and a negative supply voltage, V-. The circuit also includes a first capacitor,  $C_1$ , a second capacitor,  $C_2$ , a first inductor,  $L_1$ , a second inductor  $L_2$ , and a diode,  $D_1$ . The first inductor,  $L_1$  is electrically connected between the drain of the switch and one terminal of the first capacitor  $C_1$ , where its other terminal is electrically connected to the anode of the diode  $D_1$ . The cathode of the diode  $D_1$  is electrically connected to the source of the switch. The second inductor  $L_2$  is electrically connected between the anode of the diode  $D_1$  and the negative

supply voltage V- of the Totem pole driver. The second capacitor,  $C_2$  is electrically connected between the negative supply voltage V- of the Totem pole driver and the source of the switch. Additionally, the circuit further includes a third capacitor,  $C_{in}$ , electrically connected between the drain and 5 source of the switch. The power supply shown in FIG. 7 is non-isolated. It is therefore suitable for use in the circuit illustrated in FIG. 3.

As illustrated in FIG. **8**, the power supply shown in FIG. **7** accepts a positive input voltage ranging from 0 to 600 V and 10 converts it into a negative output voltage ranging from 0 to -50 V. The cross over voltage for this power supply occurs at approximately  $V_{GS}$ =-5 V which easily satisfies the safe operating area criteria for a SiC power JFET paired with the power supply.

FIG. 9 is a schematic of an electrical device comprising three circuits as depicted in FIG. 3 arranged in parallel according to one embodiment. The device depicted in FIG. 9 can be a three-phase motor drive.

FIG. 10 is a schematic of an electrical device comprising 20 three circuits as depicted in FIG. 4 arranged in parallel according to one embodiment. The device depicted in FIG. 10 can be a three-phase motor drive.

While the foregoing specification teaches the principles of the present invention, with examples provided for the purpose 25 of illustration, it will be appreciated by one skilled in the art from reading this disclosure that various changes in form and detail can be made without departing from the true scope of the invention.

### **REFERENCES**

- [1] Issa Batarseh, *Power Electronic Circuits*. Wiley, ISBN 0-471-12662-4, 2004, pp. 224-225.

- [2] Issa Batarseh, *Power Electronic Circuits*. Wiley, ISBN 35 0-471-12662-4, 2004, pp. 426-427.

- [3] N. Mohan, T. M. Undeland, and W. P. Robbins, *Power Electronics*. Wiley, ISBN 0-471-58408-8, 1995, p. 225.

- [4] S. Abedinpour and K. Shenai, "Insulated Gate Bipolar Transistor," *Power Electronics Handbook*, ed. M. Rashid. 40 Academic Press, ISBN 0-12-581650-2, 2001, pp. 109-110.

- [5] M. S. Mazzola, L. Cheng, J. Casady, D. Seale, V. Bondarenko, R. Kelley, and J. Casady, "Scalable SiC Power Switches for Applications in More Electric Vehicles," *Proc. of 6<sup>th</sup> Int. All Electric Combat Vehicle Conf.*, AECV 45 2005, Bath, England 13-16 June, 2005.

- [6] H. Akagi, T. Sawae, and A. Nabae, "130 kHz 7.5 kW current source inverters using static induction transistors for induction heating applications," *IEEE Trans. Power Electronics*, vol. 3, no. 3, pp. 303-309, 1988.

What is claimed is:

1. A device comprising:

a half bridge configuration of multiple switches arranged in series, the multiple switches of the half bridge configuration comprising a normally-on semiconductor switch having a source, a drain, and a gate, wherein the normally-on semiconductor switch is able to block an electric potential difference between the drain and the source without an excessive leakage current, wherein the blockable electric potential difference varies with an electric potential difference across the gate and the source, wherein the half bridge configuration further comprises an oscillating power supply electrically coupled in parallel across the drain and the source and supplied with power by the electric potential difference between the drain and the source to generate an output voltage, and

**10**

a gate driver coupled between the gate and the source to apply the electric potential difference across the gate and the source and thereby switch the normally-on semiconductor switch between an on state and an off state, wherein the gate driver is powered by the output voltage generated by the oscillating power supply,

wherein the oscillating power supply and the normally-on semiconductor switch are coordinated so that, for any electric potential difference between the drain and the source of the normally-on semiconductor switch, the excessive leakage current cannot flow through the normally-on semiconductor switch.

- 2. The device of claim 1, wherein the oscillating power supply and the normally-on semiconductor switch are coordinated so that, for an active current limiting range of the electric potential difference across the gate and the source, the output voltage generated by the oscillating power supply for a given electric potential difference between the drain and the source suffices to ensure that, upon application of the output voltage across the gate and the source, the blockable electric potential difference remains above the electric potential difference between the drain and the source.

- 3. The device of claim 2, wherein the active current limiting range encompasses a majority of the electric potential differences between the drain and the source.

- 4. The device of claim 2, wherein the oscillating power supply and the normally-on semiconductor switch are coordinated so that, for a passive current limiting range of the electric potential difference across the gate and the source, the electric potential difference between the drain and the source is so low that the normally-on semiconductor switch itself passively limits current flow between the source and the drain to be below the excessive leakage current.

- 5. The device of claim 1, wherein the gate driver is to apply the output voltage generated by the oscillating power supply between the gate and the source to bias the gate negatively with respect to the source in response to an absence of a control signal to turn on the normally-on semiconductor switch.

- 6. The device of claim 1, wherein the output voltage generated by the oscillating power supply is smaller in magnitude and opposite in polarity to the electric potential difference between the drain and the source.

7. The device of claim 1, wherein:

50

the multiple switches of the half bridge configuration further comprise a second normally-on semiconductor switch having a second source, a second drain, and a second gate, wherein the second normally-on semiconductor switch is able to block an electric potential difference between the second drain and the second source without a second excessive leakage current, wherein the blockable second electric potential difference varies with an electric potential difference across the second gate and the second source; and

the half bridge configuration further comprises

- a second oscillating power supply electrically coupled in parallel across the second drain and the second source and supplied with power by the electric potential difference between the second drain and the second source to generate a second output voltage, and

- a second gate driver coupled between the second gate and the second source to apply the electric potential difference across the second gate and the second source and thereby switch the second normally-on semiconductor switch between an on state and an off

state, wherein the second gate driver is powered by the second output voltage generated by the second oscillating power supply,

- wherein the second oscillating power supply and the second normally-on semiconductor switch are coordinated so that, for any electric potential difference between the second drain and the second source of the second normally-on semiconductor switch, the second excessive leakage current cannot flow through the second normally-on semiconductor switch.

- 8. The device of claim 1, wherein the normally-on semiconductor switch is a high-side switch in the half bridge configuration.

- 9. The device of claim 1, wherein the output voltage generated by the oscillating power supply varies with the electric potential difference between the drain and the source.

- 10. A device comprising:

- a half bridge configuration of multiple switches arranged in series, the multiple switches of the half bridge configuration comprising a normally-on semiconductor switch 20 having a source, a drain, and a gate, wherein the half bridge configuration further comprises:

- an oscillating power supply electrically coupled in parallel across the drain and the source of the normallyon switch and supplied with power by a potential 25

difference between the drain and the source, the oscillating power supply to convert the potential difference

between the drain and the source into an output voltage, and

- a gate driver coupled between the gate and the source of the normally-on switch to switch the normally-on semiconductor switch between an on state and an off state, wherein the gate driver is to apply the output voltage between the gate and the source to bias the gate negatively with respect to the source in response 35 to an absence of a control signal to turn on the normally-on semiconductor switch.

- 11. The device of claim 10, wherein the oscillating power supply and the normally-on semiconductor switch are coordinated so that, for any electric potential difference between 40 the drain and the source of the normally-on semiconductor switch, the excessive leakage current cannot flow through the normally-on semiconductor switch.

- 12. The device of claim 11, wherein the oscillating power supply and the normally-on semiconductor switch are coordinated so that, for an active current limiting range of the electric potential difference across the gate and the source, the output voltage generated by the oscillating power supply for a given electric potential difference between the drain and the source suffices to ensure that, upon application of the output voltage across the gate and the source, the blockable electric potential difference remains above the electric potential difference between the drain and the source.

12

- 13. The device of claim 12, wherein the active current limiting range encompasses a majority of the electric potential differences between the drain and the source.

- 14. The device of claim 12, wherein the oscillating power supply and the normally-on semiconductor switch are coordinated so that, for a passive current limiting range of the electric potential difference across the gate and the source, the electric potential difference between the drain and the source is so low that the normally-on semiconductor switch itself passively limits current flow between the source and the drain to be below the excessive leakage current.

- 15. The device of claim 10, wherein the gate driver is to apply the output voltage generated by the oscillating power supply between the gate and the source to bias the gate negatively with respect to the source in response to an absence of a control signal to turn on the normally-on semiconductor switch.

- 16. The device of claim 10, wherein the output voltage generated by the oscillating power supply is smaller in magnitude and opposite in polarity to the electric potential difference between the drain and the source.

- 17. The device of claim 10, wherein:

- the multiple switches of the half bridge configuration further comprise a second normally-on semiconductor switch having a second source, a second drain, and a second gate; and

the half bridge configuration further comprises:

- a second oscillating power supply electrically coupled in parallel across the second drain and the second source of the second normally-on switch and supplied with power by a potential difference between the second drain and the second source, the second oscillating power supply to convert the potential difference between the second drain and the second source into a second output voltage, and

- a second gate driver coupled between the second gate and the second source of the second normally-on switch to switch the second normally-on semiconductor switch between an on state and an off state, wherein the second gate driver is to apply the second output voltage between the second gate and the second source to bias the second gate negatively with respect to the second source in response to an absence of a control signal to turn on the second normally-on semiconductor switch.

- 18. The device of claim 10, wherein the normally-on semiconductor switch is a high-side switch in the half bridge configuration.

- 19. The device of claim 10, wherein the output voltage generated by the oscillating power supply varies with the electric potential difference between the drain and the source.

\* \* \* \* \*