#### US008773562B1

# (12) United States Patent

#### Fan

(10) Patent No.:

# US 8,773,562 B1

# (45) **Date of Patent:** Jul. 8, 2014

## (54) VERTICALLY STACKED IMAGE SENSOR

(71) Applicant: Apple Inc., Cupertino, CA (US)

(72) Inventor: **Xiaofeng Fan**, San Jose, CA (US)

(73) Assignee: Apple Inc., Cupertino, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 13/756,459

(22) Filed: Jan. 31, 2013

(51) **Int. Cl.**

H04N 5/335 (2011.01) H04N 3/14 (2006.01) H01L 27/00 (2006.01)

(52) **U.S. Cl.**

USPC ...... **348/308**; 257/E27.135; 257/E25.006; 250/208.1

(58) Field of Classification Search

See application file for complete search history.

# (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,506,429    | A    | 4/1996  | Tanaka et al.        |

|--------------|------|---------|----------------------|

| 7,561,390    | B2 * | 7/2009  | Furuta 361/56        |

| 7,671,435    | B2   | 3/2010  | Ahn                  |

| 7,858,915    | B2   | 12/2010 | McCarten             |

| 8,049,256    | B2   | 11/2011 | Guidash              |

| 8,310,003    | B2   | 11/2012 | Kohyama              |

| 8,478,123    | B2   | 7/2013  | Cao et al.           |

| 8,531,567    | B2   | 9/2013  | Roy et al.           |

| 2003/0049925 | A1*  | 3/2003  | Layman et al 438/614 |

| 2009/0159944 | A1*  | 6/2009  | Oh 257/292           |

| 2010/0019130 | A1*        | 1/2010  | Lee 250/208.1            |

|--------------|------------|---------|--------------------------|

| 2010/0258890 | A1*        | 10/2010 | Ahn 257/432              |

| 2010/0276572 |            |         | Iwabuchi et al 250/208.1 |

| 2011/0042552 | <b>A</b> 1 | 2/2011  | Furuya et al.            |

| 2011/0157445 | A1*        | 6/2011  | Itonaga et al 348/308    |

| 2011/0315854 | A1*        | 12/2011 | Janesick                 |

| 2012/0086845 | <b>A</b> 1 | 4/2012  | Enomoto et al.           |

| 2012/0217374 | A1*        | 8/2012  | Nishizawa 250/208.1      |

| 2013/0062504 | A1*        | 3/2013  | Sukegawa et al           |

#### FOREIGN PATENT DOCUMENTS

| EP | 1562233        | 8/2005 |

|----|----------------|--------|

| WO | WO 2013/118646 | 8/2013 |

#### OTHER PUBLICATIONS

Invitation to Pay Additional Fees dated Apr. 1, 2014, PCT/US2014/011682, 5 pages.

\* cited by examiner

Schreck, LLP

Primary Examiner — Sinh Tran

Assistant Examiner — Shahbaz Nazrul

(74) Attorney, Agent, or Firm — Brownstein Hyatt Farber

### (57) ABSTRACT

A vertically stacked image sensor having a photodiode chip and a transistor array chip. The photodiode chip includes at least one photodiode and a transfer gate extends vertically from a top surface of the photodiode chip. The image sensor further includes a transistor array chip stacked on top of the photodiode chip. The transistor array chip includes the control circuitry and storage nodes. The image sensor further includes a logic chip vertically stacked on the transistor array chip. The transfer gate communicates data from the at least one photodiode to the transistor array chip and the logic chip selectively activates the vertical transfer gate, the reset gate, the source follower gate, and the row select gate.

# 14 Claims, 35 Drawing Sheets

FIG.1A

FIG.1B

FIG.2

FIG.3

FIG.5

FIG.7

FIG.8

FIG.9A

FIG.11

FIG.12A

FIG.12B

FIG.12C

FIG.12D

FIG.12E

FIG.13

FIG.14

FIG.15A

FIG.15B

FIG.15C

FIG.16A

FIG.16B

FIG.18

FIG.19A

FIG.19B

FIG.19C

FIG.26C

FIG.28

## VERTICALLY STACKED IMAGE SENSOR

#### TECHNICAL FIELD

The present invention relates generally to electronic <sup>5</sup> devices, and more specifically, to image sensors for electronic devices.

#### **BACKGROUND**

Cameras and other image recording devices often use one or more image sensors, such as a charged-coupled device (CCD) sensor or a complementary metal-oxide-semiconductor (CMOS) image sensor. A typical CMOS image sensor may include a two-dimensional array of pixels, where each pixel may include a photo detector, such as a photodiode, and one or more transistors to activate each pixel. An image sensor may be implemented in a rolling shutter configuration or a global shutter configuration.

In a rolling shutter, each of the pixels within the image 20 sensor capture light row by row, and the captured light is then read out to a processor row by row. In this configuration, there may be a time delay between when the first pixel row captures light from the scene and when the last pixel row captures light from the scene. Accordingly, if there is movement in the scene 25 between the first and last pixel rows, the movement may be captured as blurred lines or other motion artifacts. In a global shutter, each of the pixels capture light at the same time (i.e., has the same integration period) and then the pixels transfer the light to a storage component until the pixels can be read 30 out by a processor. In a global shutter configuration, motion is captured and reproduced in an image better than a rolling shutter, as each of the pixels capture light at the exact same time. However, in this configuration, the image sensor generally must include storage space for each pixel, which may 35 of FIG. 1A. require a reduction in resolution or an increase in size for the image sensor.

For example, the resolution of an image sensor typically depends on the number of pixels, that the higher the number of pixels, the higher the resolution of the image sensor. However, as the resolution increases, often the size of the image sensor die also increases. The increase in size is especially true of image sensors in a global shutter configuration, where each pixel includes a light capturing element (e.g., photodiode) and a storage component. Accordingly, image shutters incorporating a global shutter implementation generally have lower resolution than a rolling shutter image sensor of the same size.

Additionally, many image sensors may sacrifice an increased resolution to have a smaller size. For example, 50 many portable electronic devices, such as cell phones, tablet computers, and the like, may include a camera, but the image sensor of the camera may be designed to be as small as possible. Therefore, many cameras for portable devices may have image sensors with decreased resolutions so that they 55 may be as small as possible.

#### **SUMMARY**

Examples of the disclosure may an image sensor for an 60 chip. electronic device. The image sensor includes a pixel array split between a photodiode chip and a transistor array chip. The photodiode chip including at least one photodiode or photogate for receiving light. In some embodiments, a transfer gate extends vertically from a top surface of the photodiode chip. The image sensor further includes a transistor array chip in communication with the photodiode chip. The

2

transistor array chip includes a floating diffusion node in communication with the at least one photodiode, a reset gate in communication with the at least one photodiode, a source follower gate in communication with the floating diffusion node, and a row select gate in communication with the source follower gate and the floating diffusion node. The image sensor further includes a logic chip operably connected to the transistor array chip and in communication therewith. The transfer gate communicates data from the at least one photodiode to the transistor array chip and the logic chip selectively activates the vertical transfer gate, the reset gate, the source follower gate, and the row select gate.

Other examples of the disclosure may a mobile electronic device. The mobile electronic device includes a processor, a display screen in communication with the processor and the display screen and at least one camera in communication with the processor. The at least one camera includes a lens and at least one image sensor optical communication with the lens, the image sensor comprising a three chip vertical stack including a control circuitry chip, a photodiode chip, and a logic chip.

Yet other examples of the disclosure include an image sensor including a vertical and/or lateral transfer gate. In these embodiments, the image sensor may include one or more shared pixels, different doping for the one or more gates within the pixel architecture and varying charge transfers throughout integration.

#### BRIEF DESCRIPTION OF THE DRAWINGS

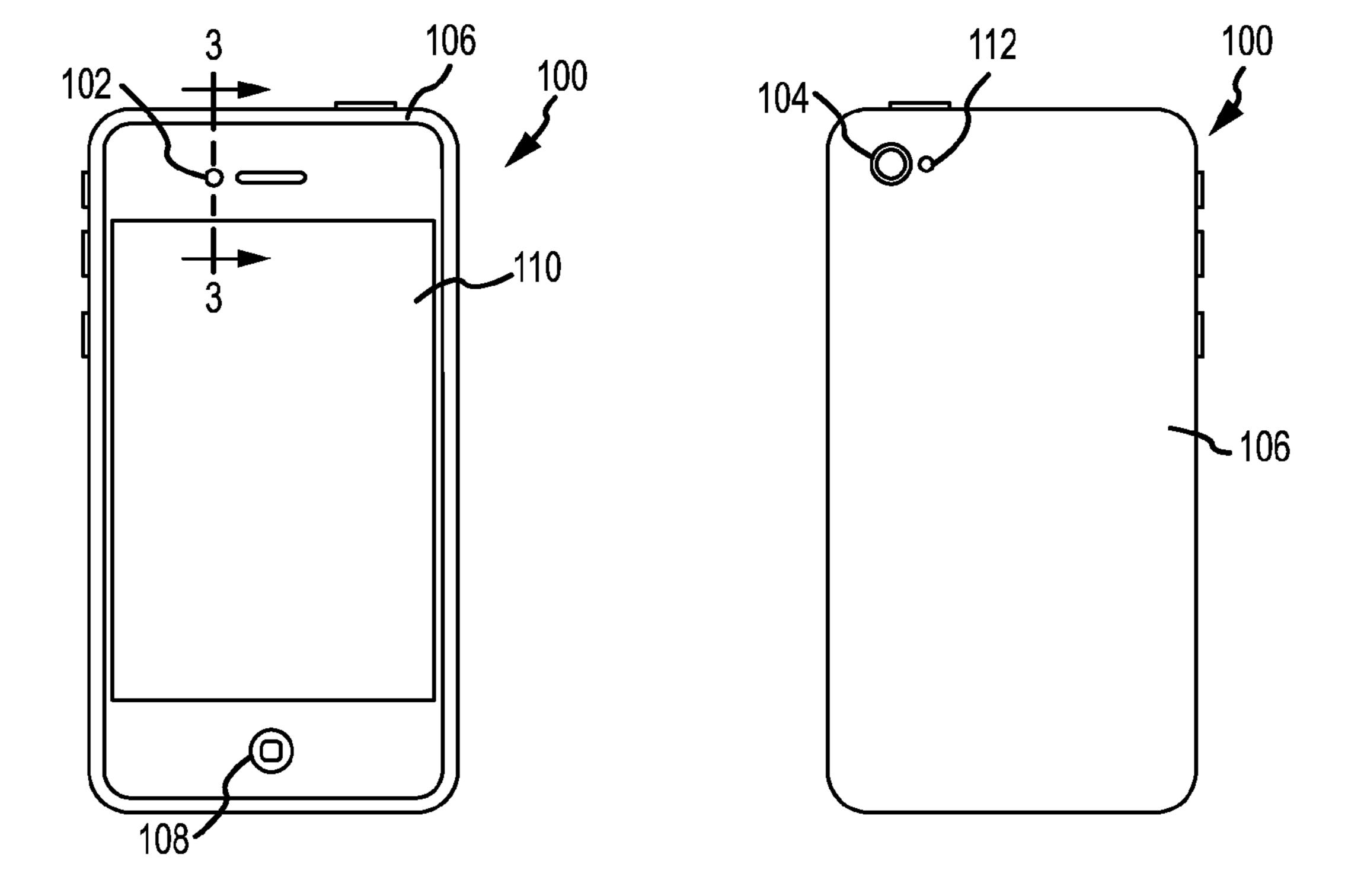

FIG. 1A is a front perspective view of an electronic device including one or more cameras.

FIG. 1B is a rear perspective view of the electronic device of FIG. 1A.

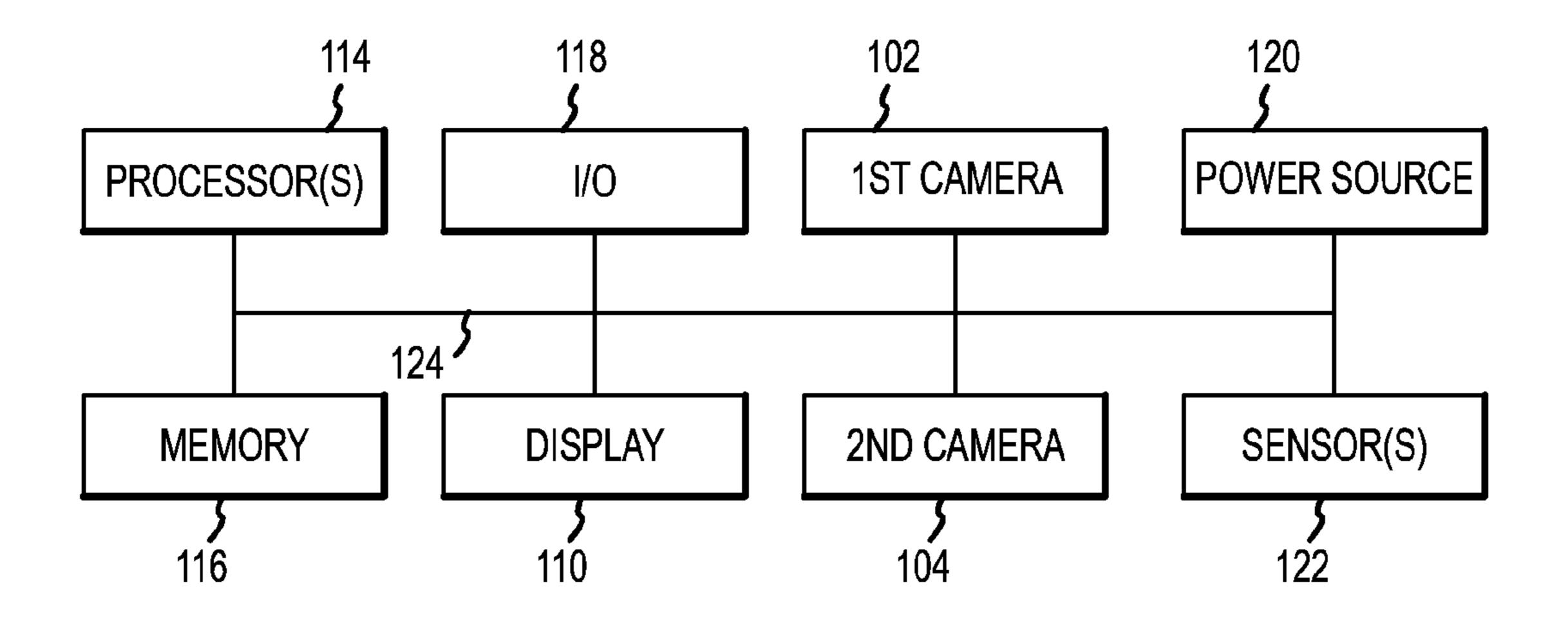

FIG. 2 is a simplified block diagram of the electronic device of FIG. 1A.

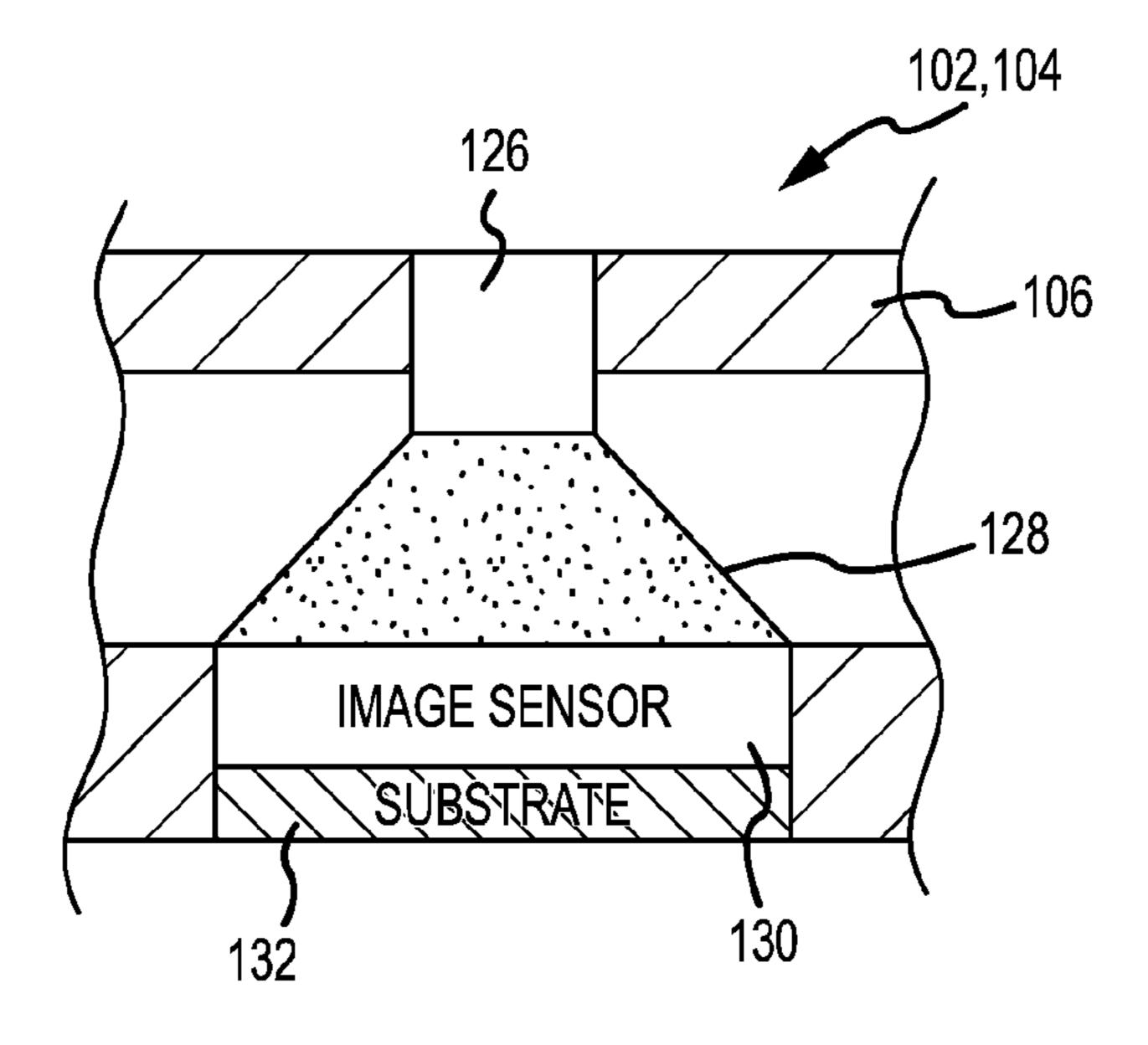

FIG. 3 is a cross-section view of the electronic device of FIG. 1A taken along line 3-3 in FIG. 1A.

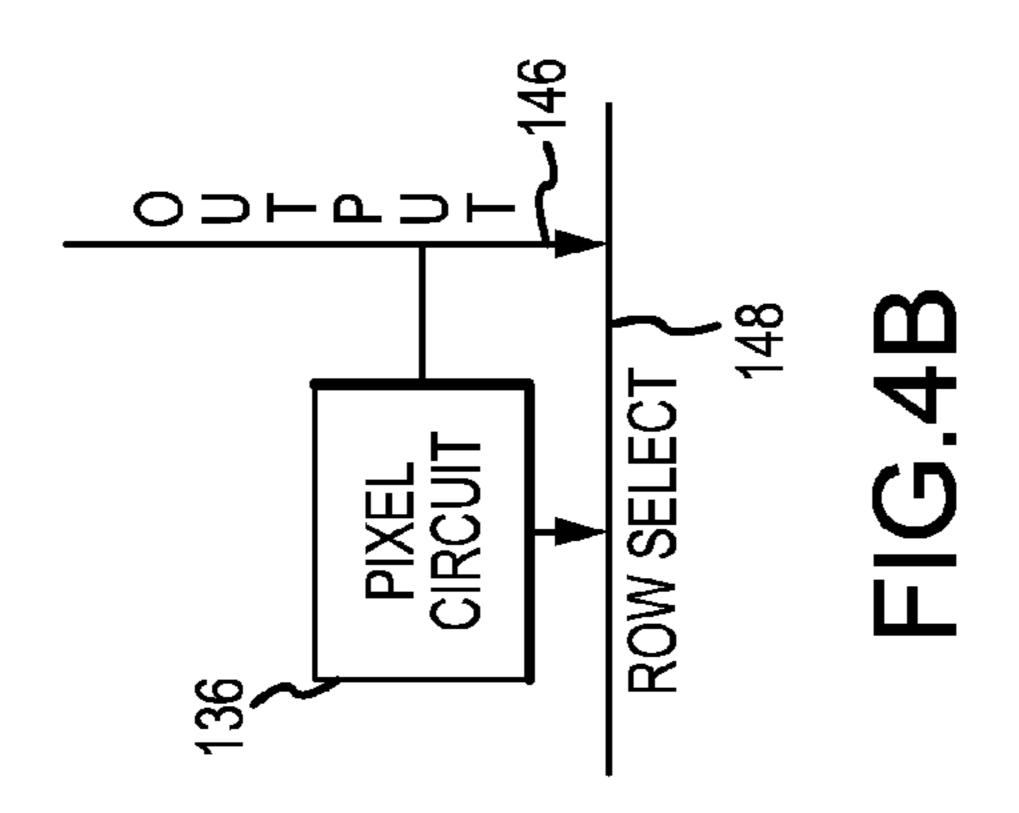

FIG. 4A is a simplified diagram of an image sensor architecture for a camera of the electronic device.

FIG. 4B is an enlarged view of the pixel architecture of FIG. 4A illustrating a single pixel.

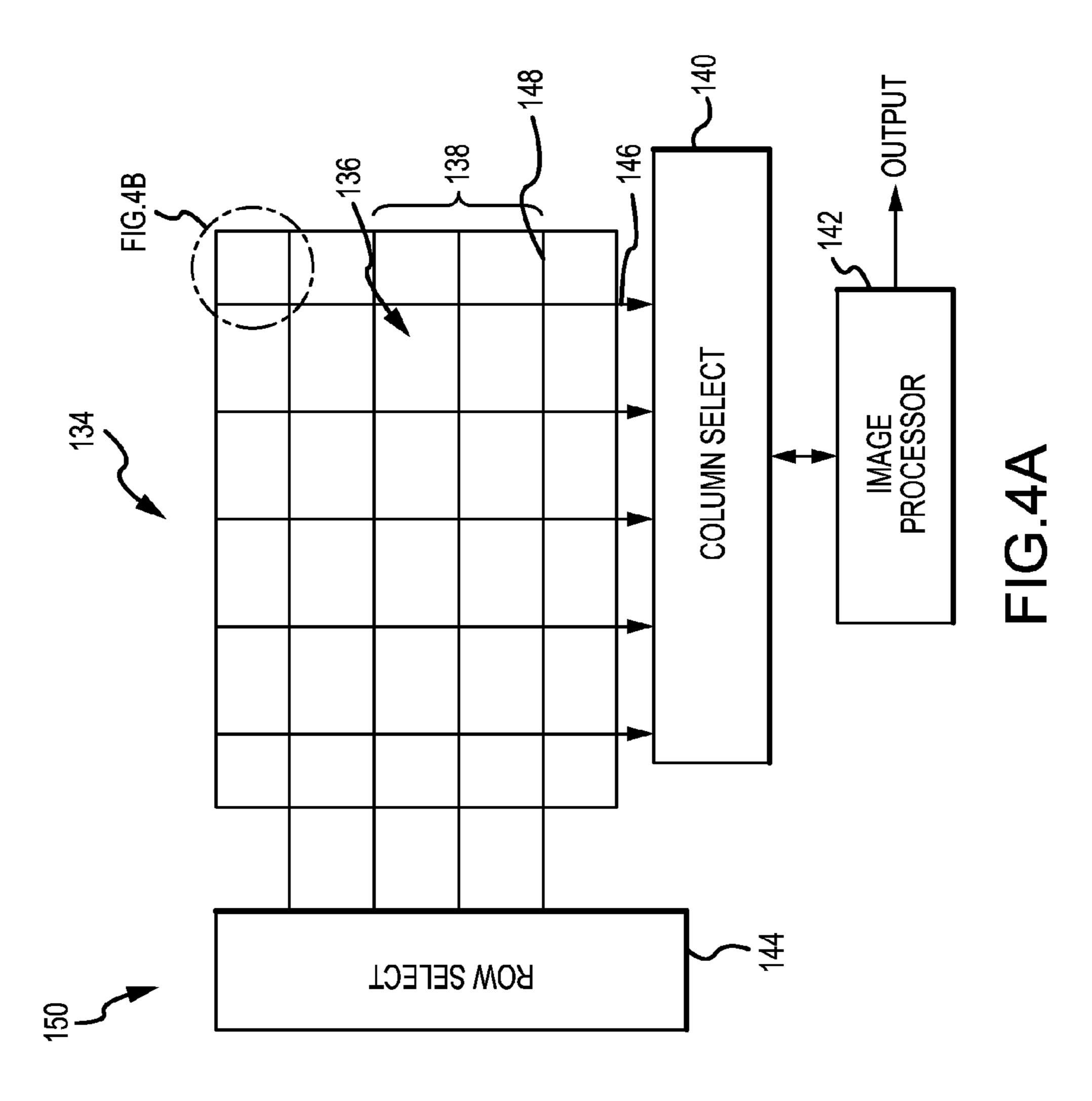

FIG. **5** is a simplified schematic view of the pixel of FIG. **4**A.

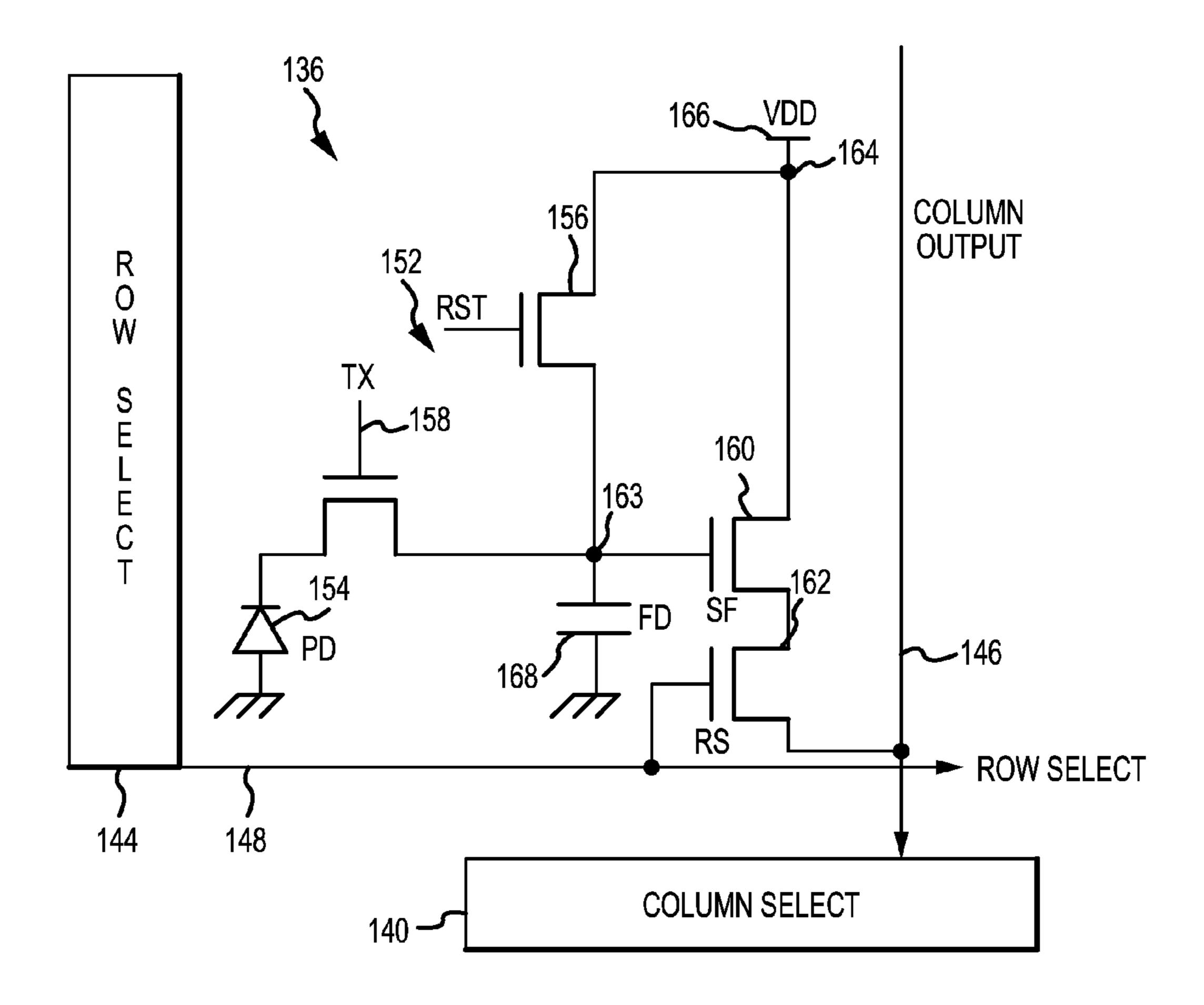

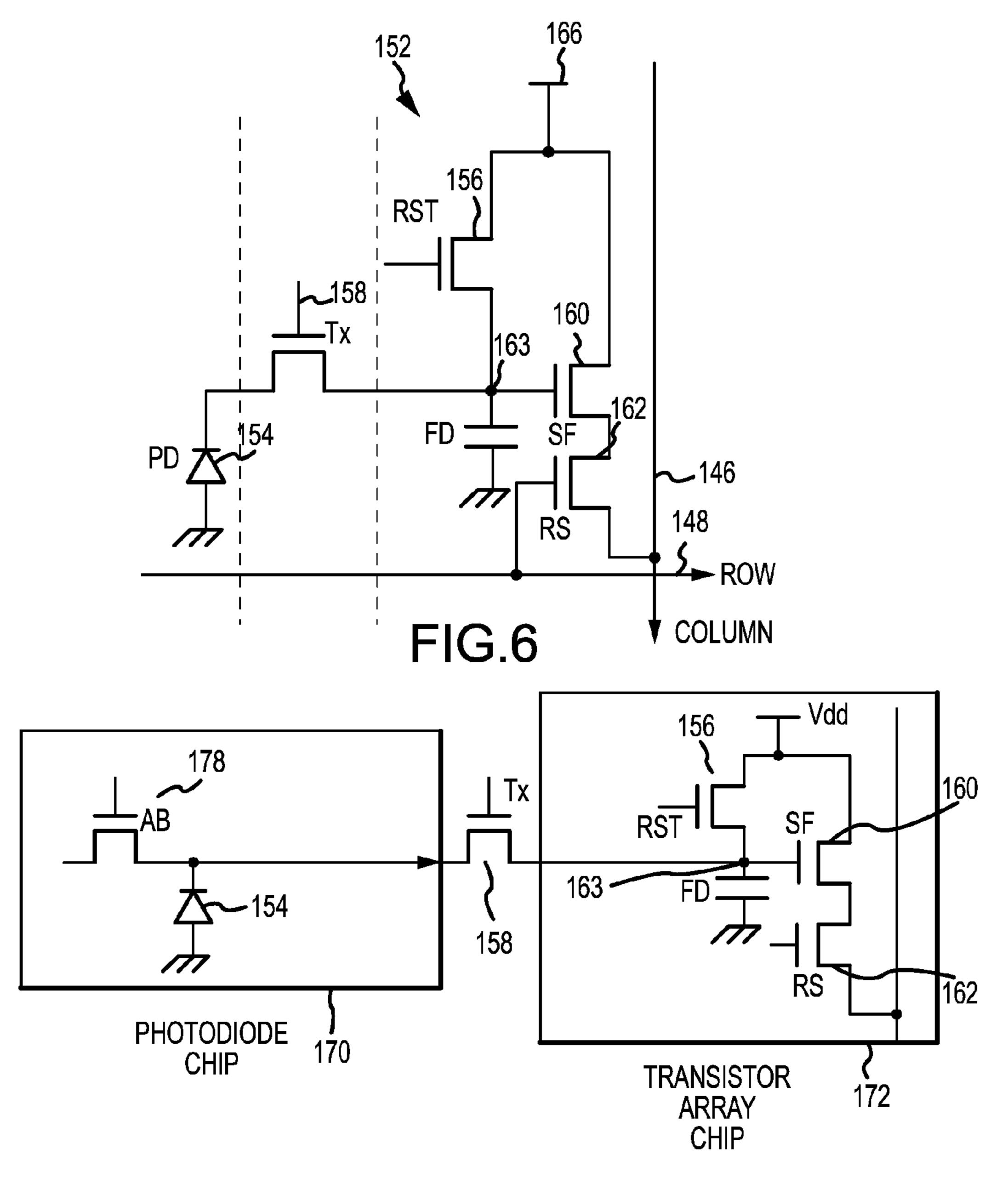

FIG. 6 is a schematic view of the pixel of FIG. 5 illustrating a vertical transfer gate.

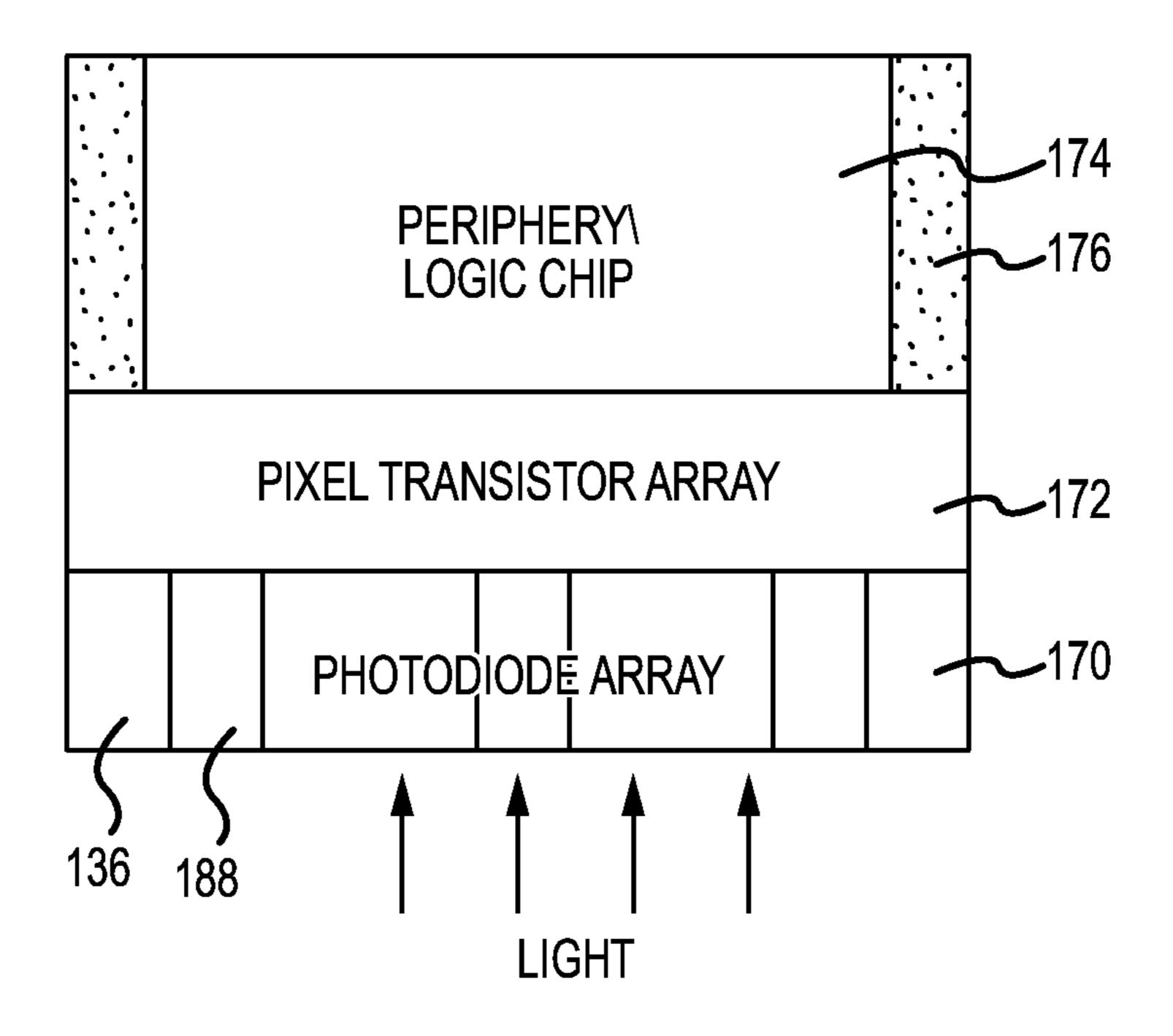

FIG. 7 is a block diagram of the schematic of FIG. 6 illustrating the vertical transfer gate extending between a photodiode chip and a transistor array chip.

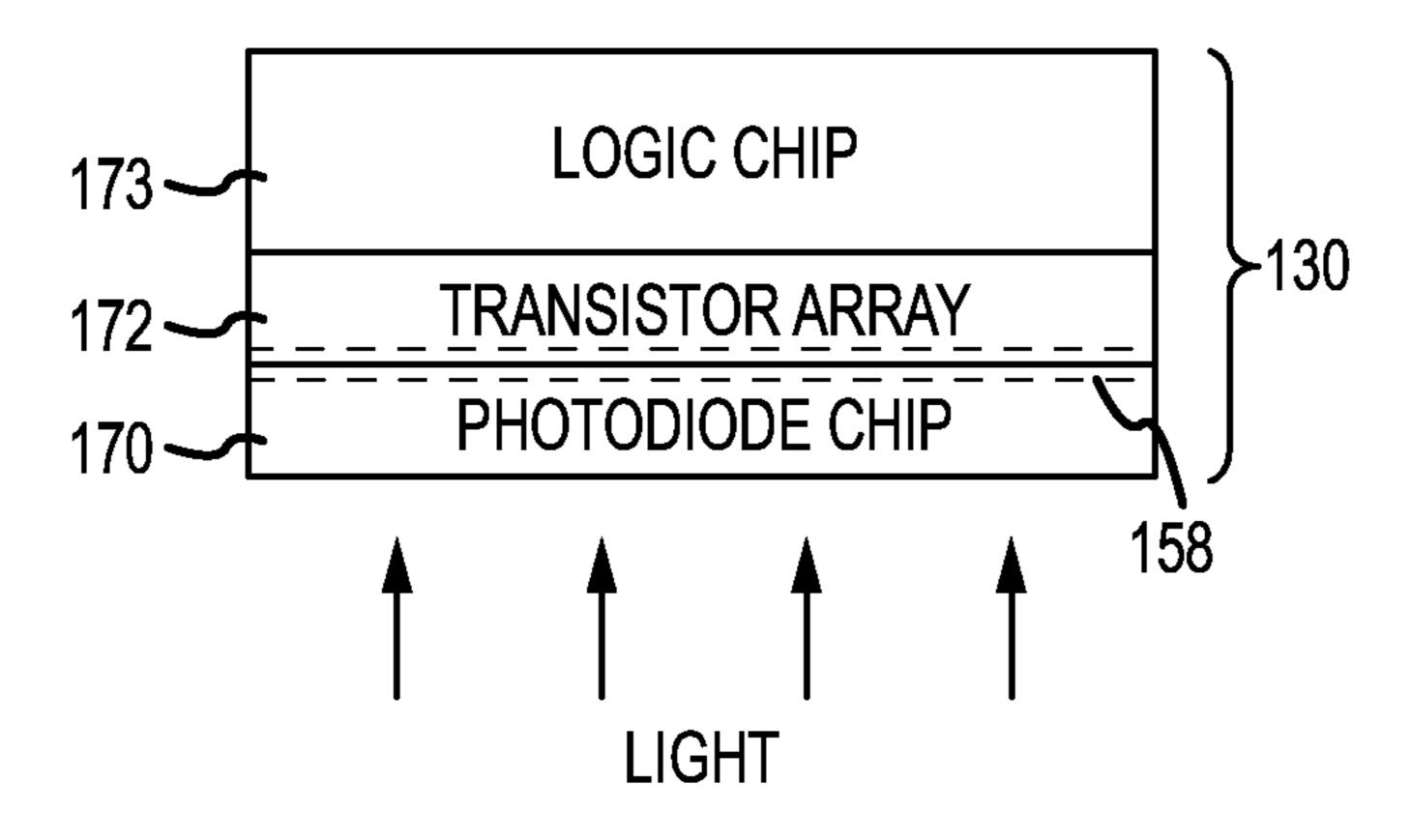

FIG. 8 is a simplified block diagram of the image sensor illustrating the chip stack including the photodiode chip, the transistor array chip, and a logic chip.

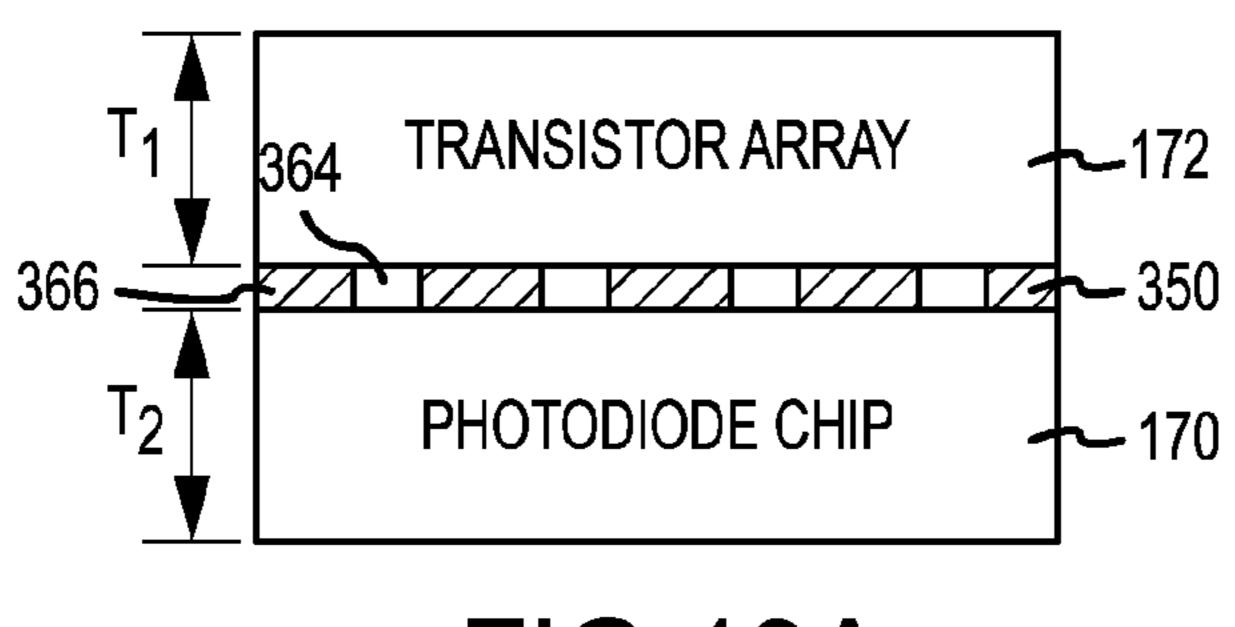

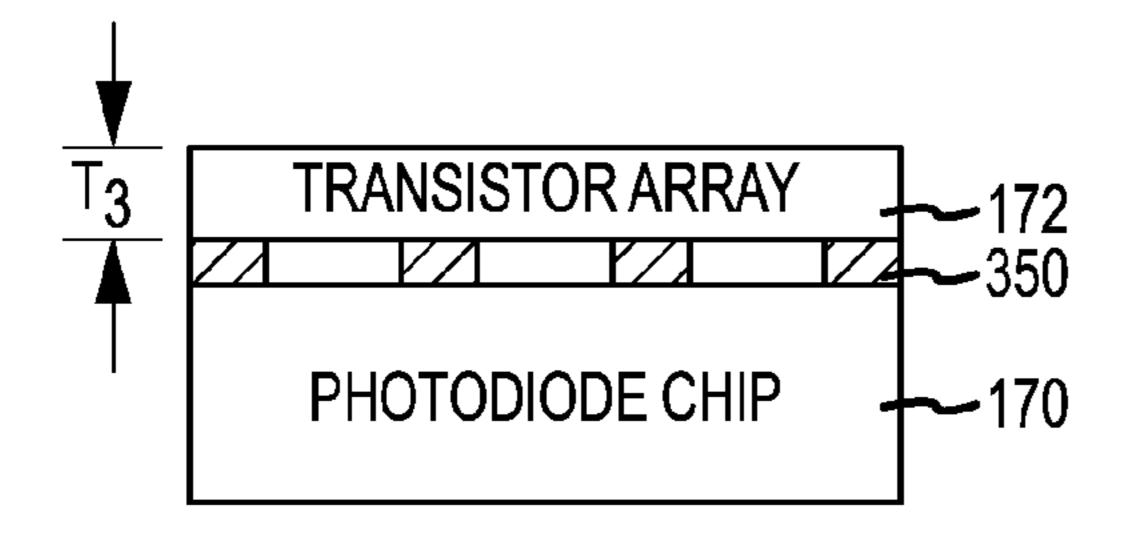

FIG. 9A is a block diagram illustrating a simplified structure of the image sensor and particularly the transfer gate between the photodiode chip and the transistor array chip.

FIG. 9B is a block diagram illustrating a simplified structure for a pixel cell having four pixels illustrating the transfer gate between the photodiode chip and the transistor array chip

FIG. 10 is a cross-section view of the transfer gate take along line 10-10 in FIG. 9A.

FIG. 11 is a simplified diagram of a pixel on the photodiode chip and the transistor array chip including a storage gate on the photodiode chip.

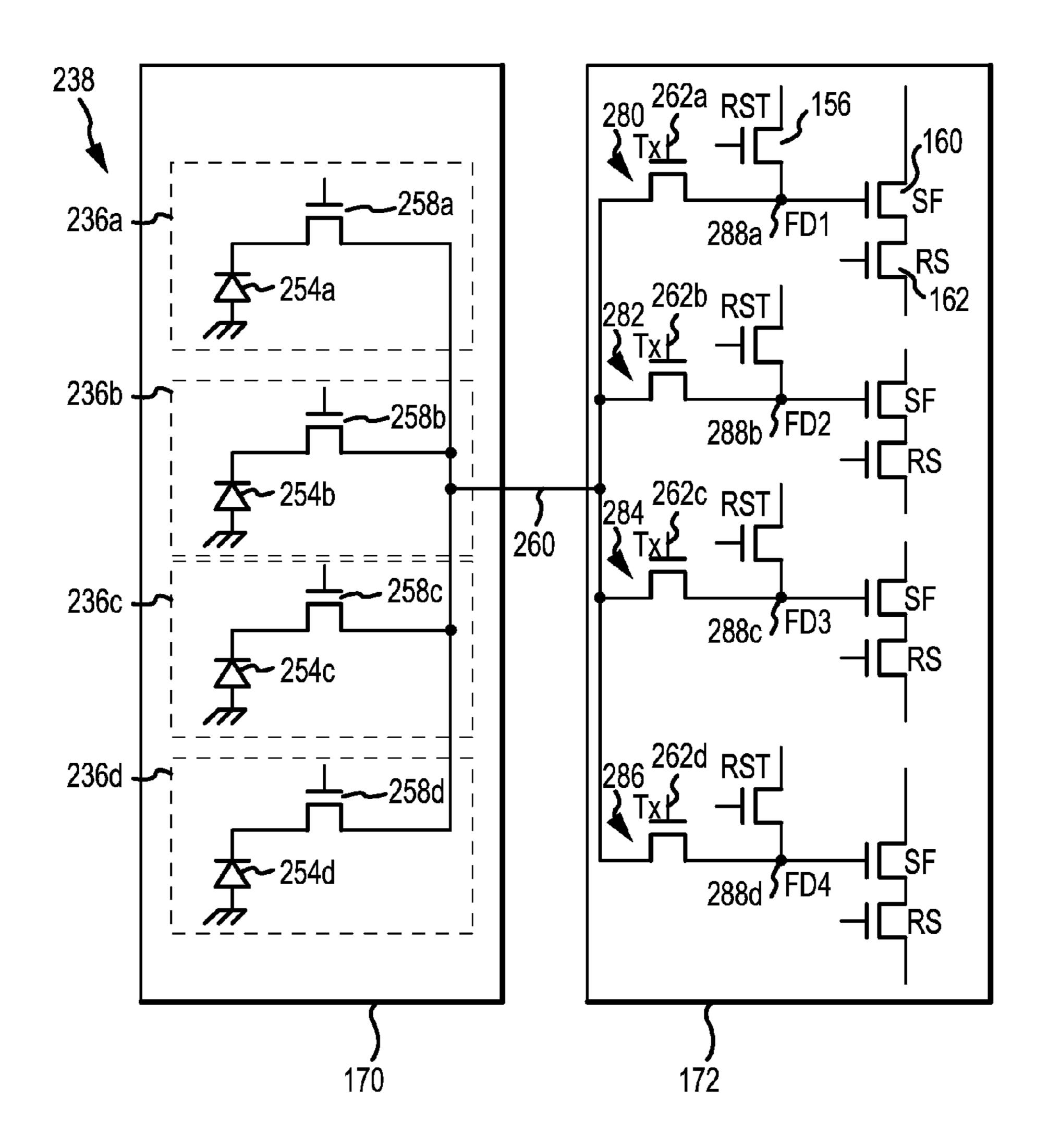

FIG. 12A is a simplified schematic view of a pixel cell having a shared control circuitry.

- FIG. 12B is a simplified cross-section of the image sensor including the shared architecture of FIG. 12A.

- FIG. 12C is a simplified schematic view of a pixel sharing architecture for a monochrome mode image sensor including four pixels sharing a floating diffusion node

- FIG. 12D is a simplified schematic view of a pixel sharing architecture for implementing a global shutter monochrome mode image sensor.

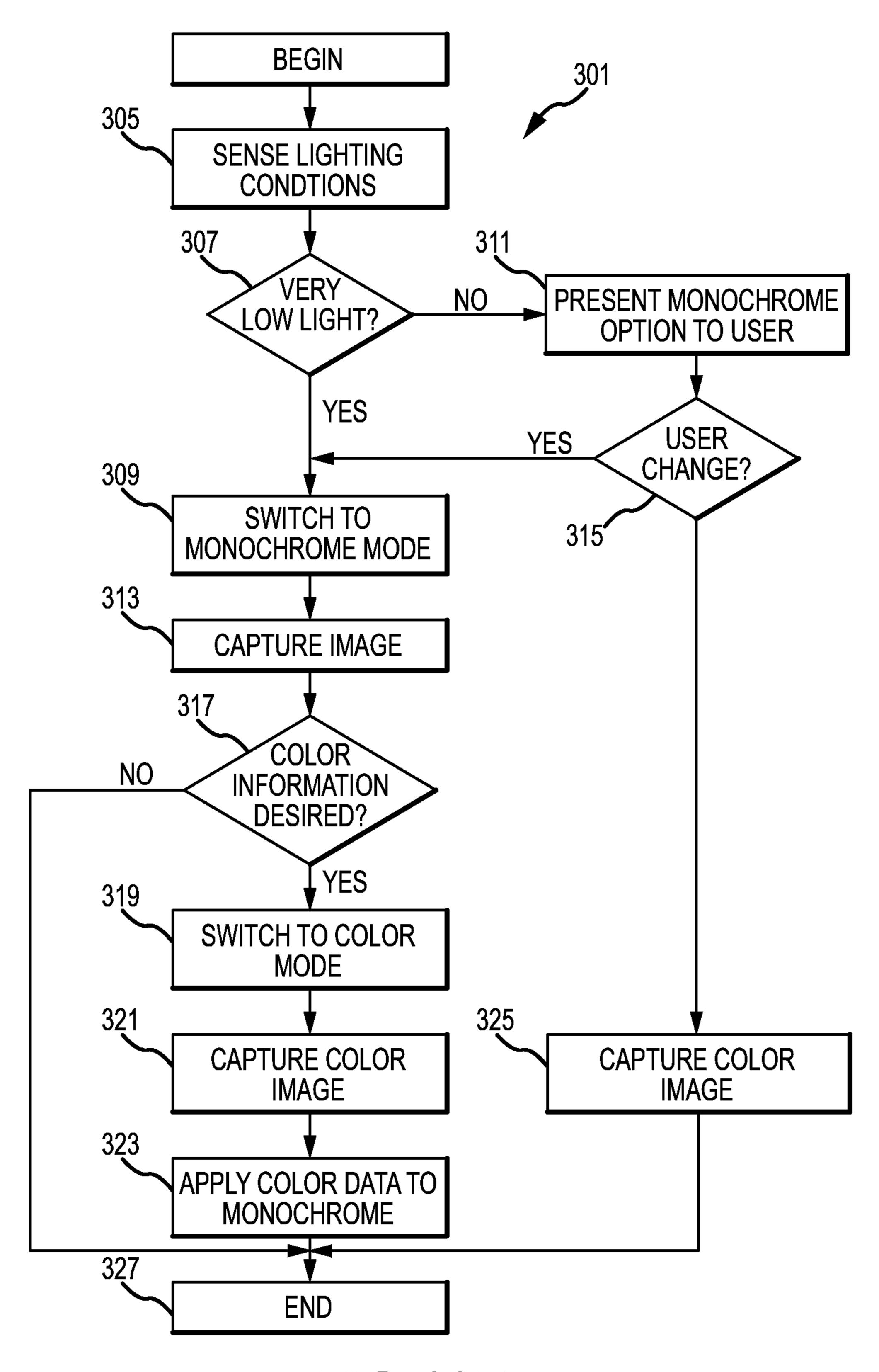

- FIG. 12E is a flow chart illustrating a method of operating a dual mode image sensor.

- FIG. 13 is a simplified schematic view of another example of a shared pixel architecture including multiple control pathways.

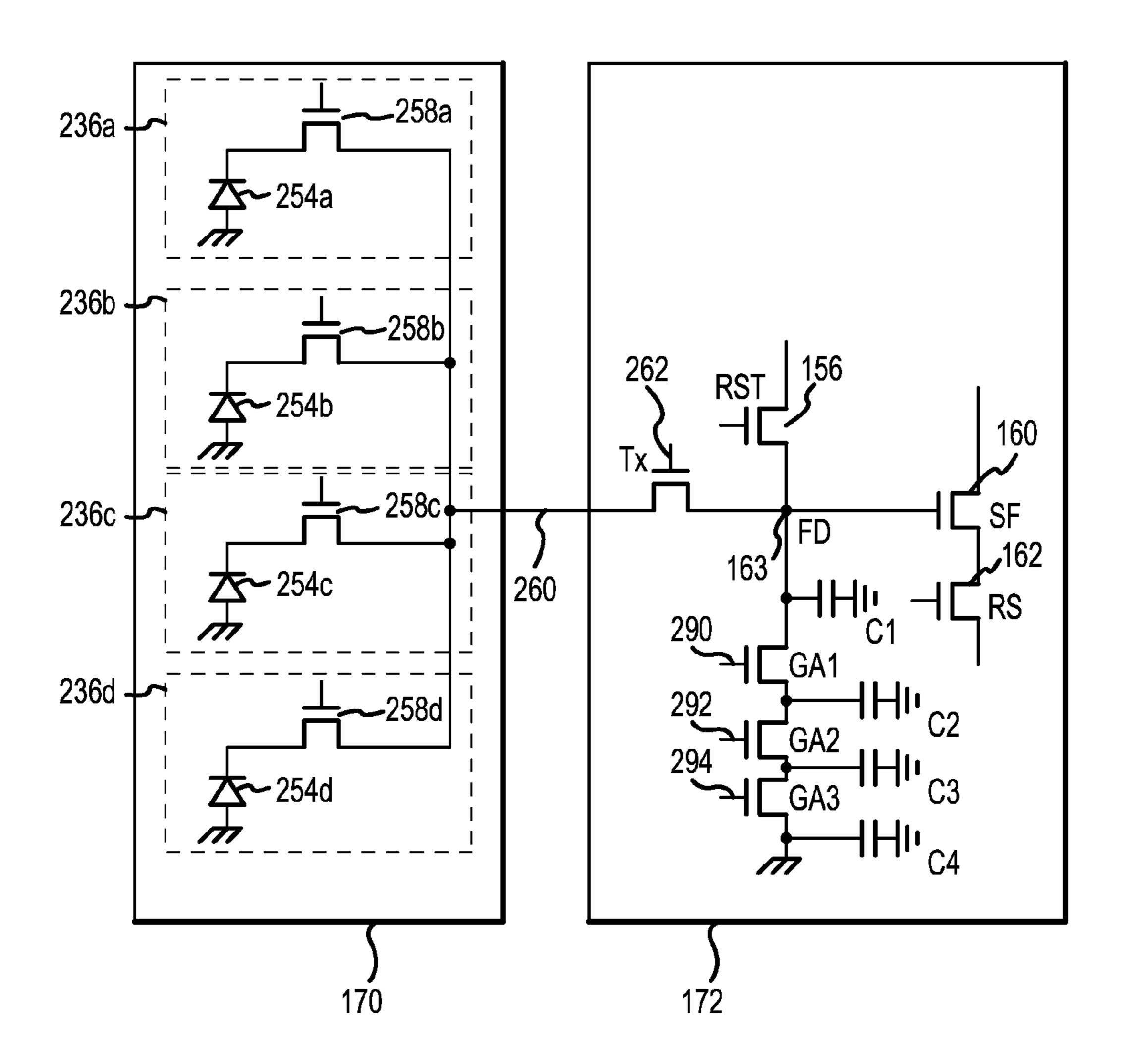

- FIG. 14 is a simplified schematic view of an image sensor having a shared architecture including a floating diffusion node having an adjustable conversion gain.

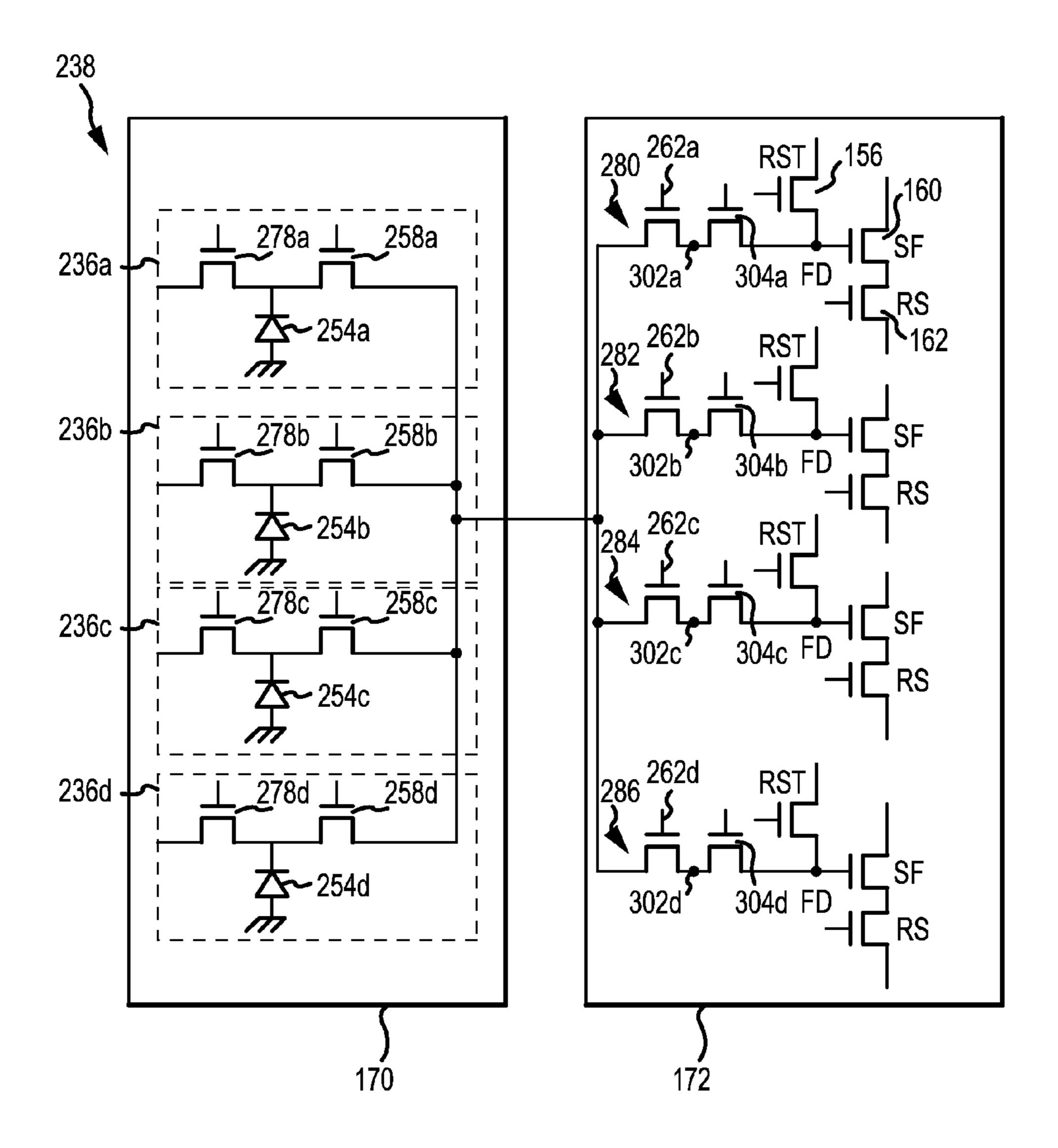

- FIG. 15A is a simplified schematic view of a pixel cell having a shared control circuitry and global shutter configuration.

- FIG. 15B is a simplified schematic of a global shutter shared architecture configuration.

- FIG. 15C illustrates another example of a shared pixel architecture including storage nodes for each pixel and an adjustable conversion gain.

- FIG. 16A is a simplified schematic view of a four pixel cell including an effective global shutter configuration.

- FIG. **16**B is a timing diagram for the schematic of FIG. **16**A.

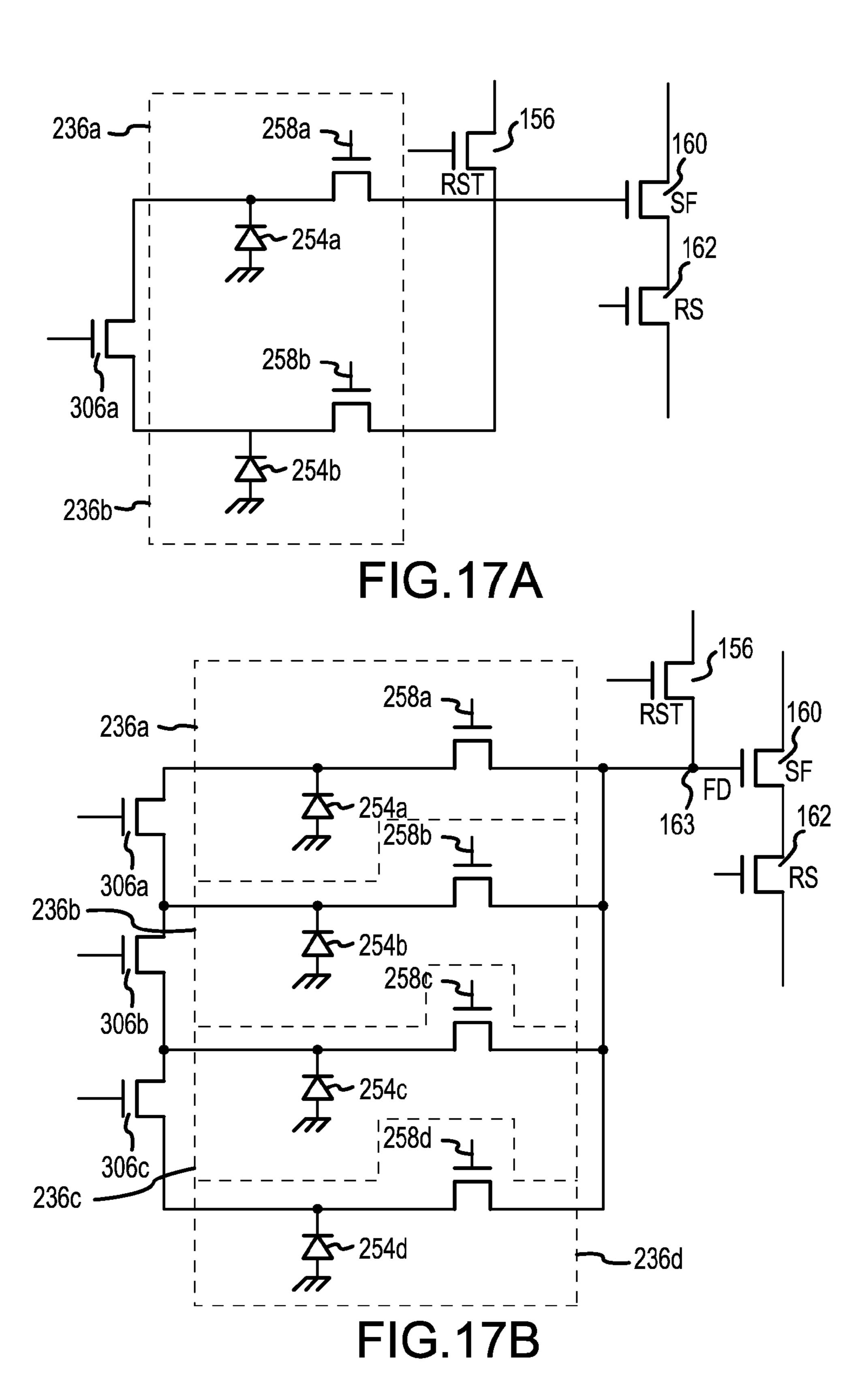

- FIG. 17A is a simplified schematic of the image sensor 30 including a two pixel mixing configuration.

- FIG. 17B is a simplified schematic of a four or quadra pixel mixing configuration.

- FIG. 18 is a simplified diagram illustrating the image sensor including a three chip stacked array.

- FIG. 19A is a simplified block diagram illustrating the transistor array chip and the photodiode chip after initially being connected together.

- FIG. 19B is a simplified block diagram of the transistor array chip and the photodiode chip, after the transistor array 40 chip has been thinned.

- FIG. 19C is a simplified block diagram of the transistor array chip and the photodiode chip operably connected to a logic chip.

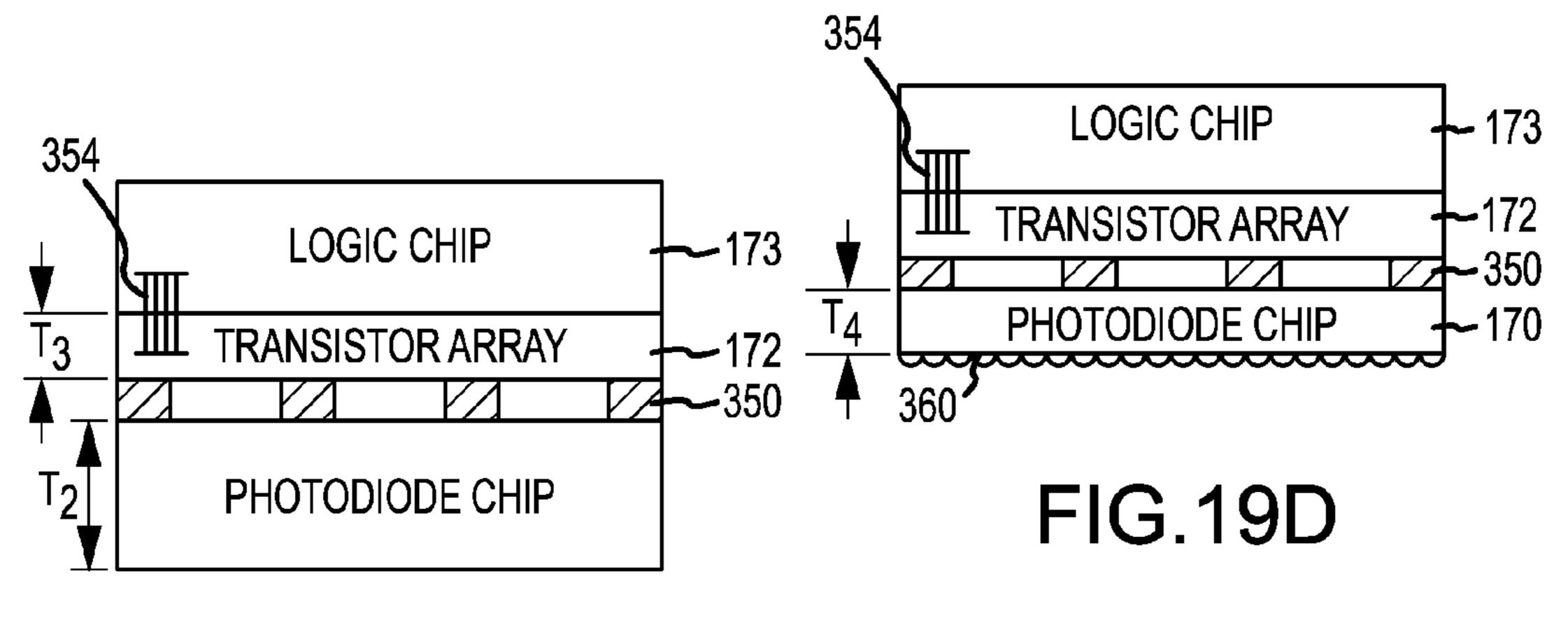

- FIG. 19D is simplified block diagram of the transistor array 45 chip, the logic chip, and the photodiode chip operably connected together after the photodiode chip has been thinned.

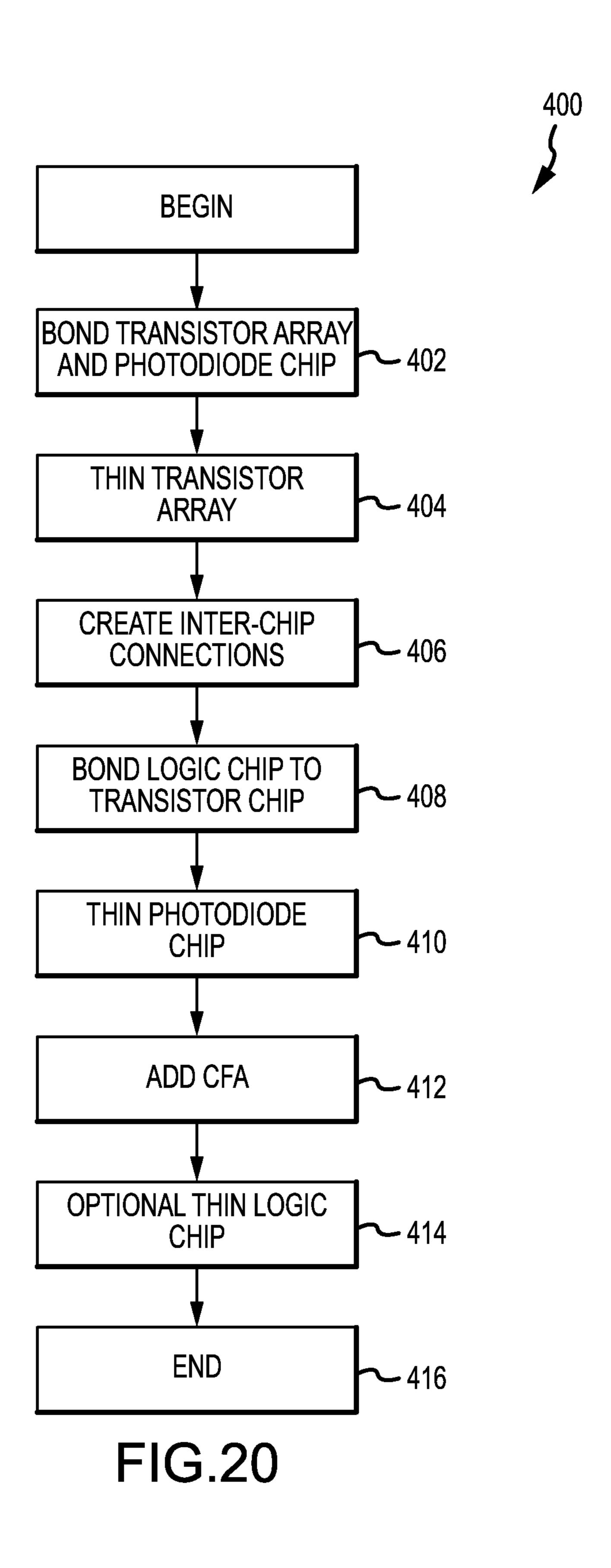

- FIG. 20 is a flow chart illustrating a first example of a manufacturing process for the image sensor.

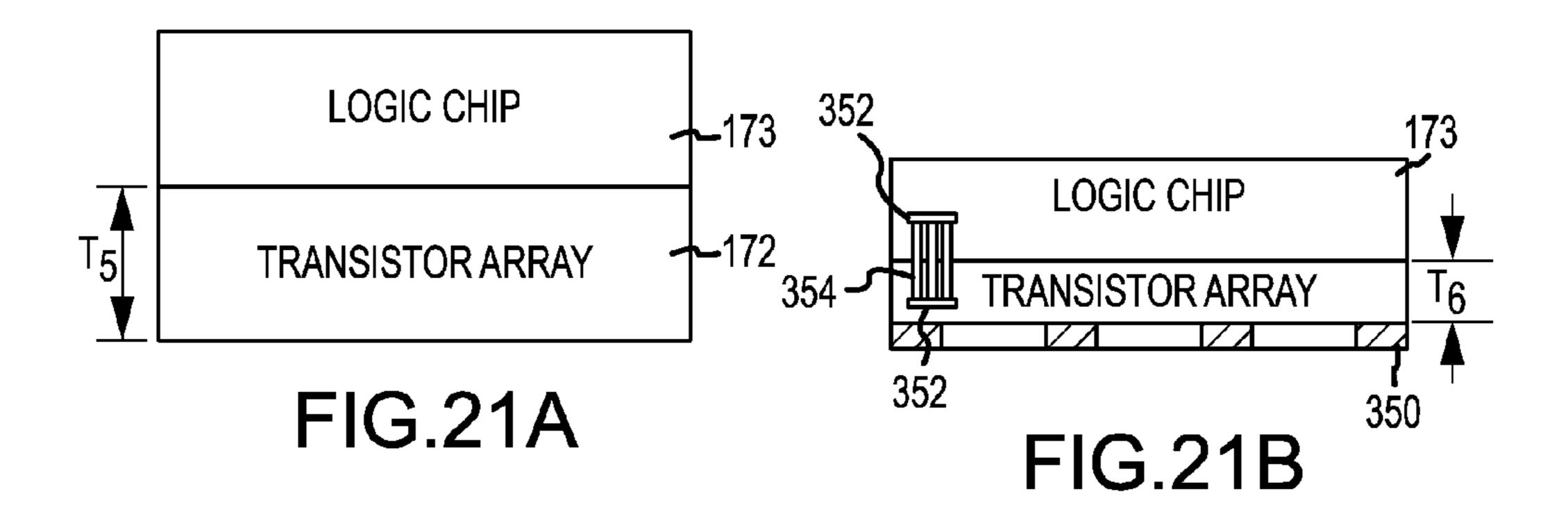

- FIG. 21A is a simplified block diagram illustrating the 50 transistor array chip and the logic chip after being operably connected together.

- FIG. 21B is a simplified block diagram illustrating the logic chip and the transistor array chip operably connected together with the transistor array chip thinned down.

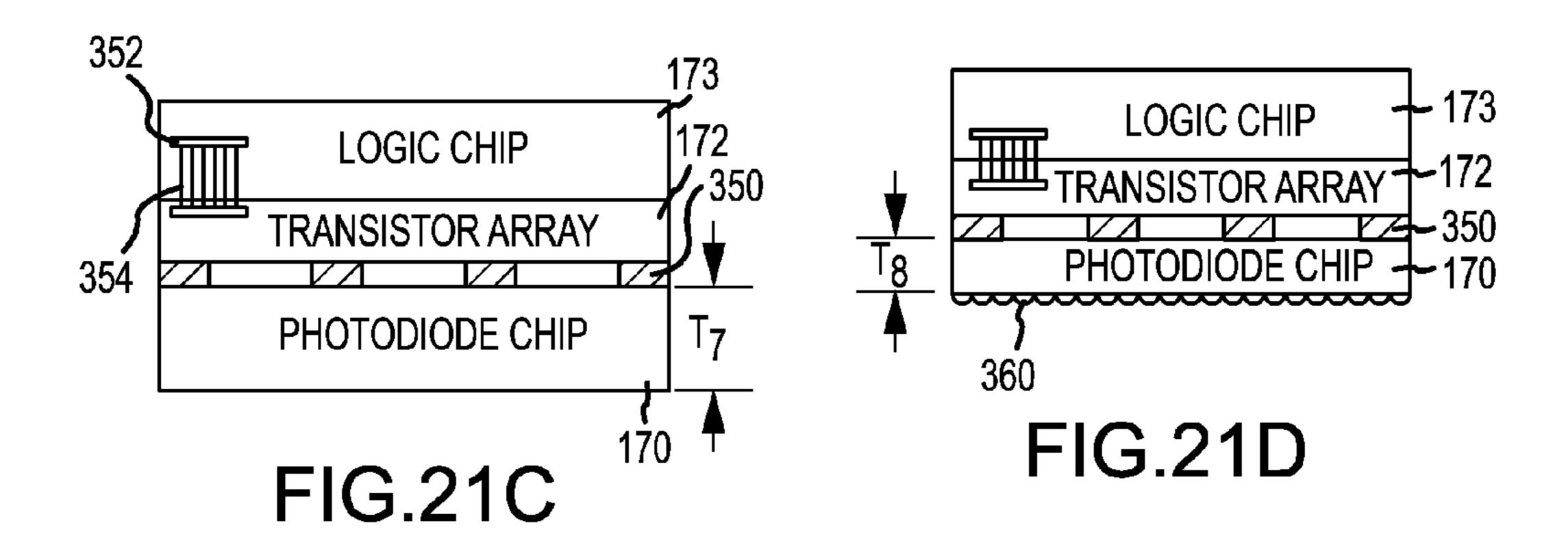

- FIG. 21C is a simplified block diagram illustrating the logic chip and the transistor array chip operably connected to the photodiode chip.

- FIG. 21D is a simplified block diagram illustrating the logic chip, the transistor array chip, and the photodiode chip operably connected together with the photodiode chip thinned down.

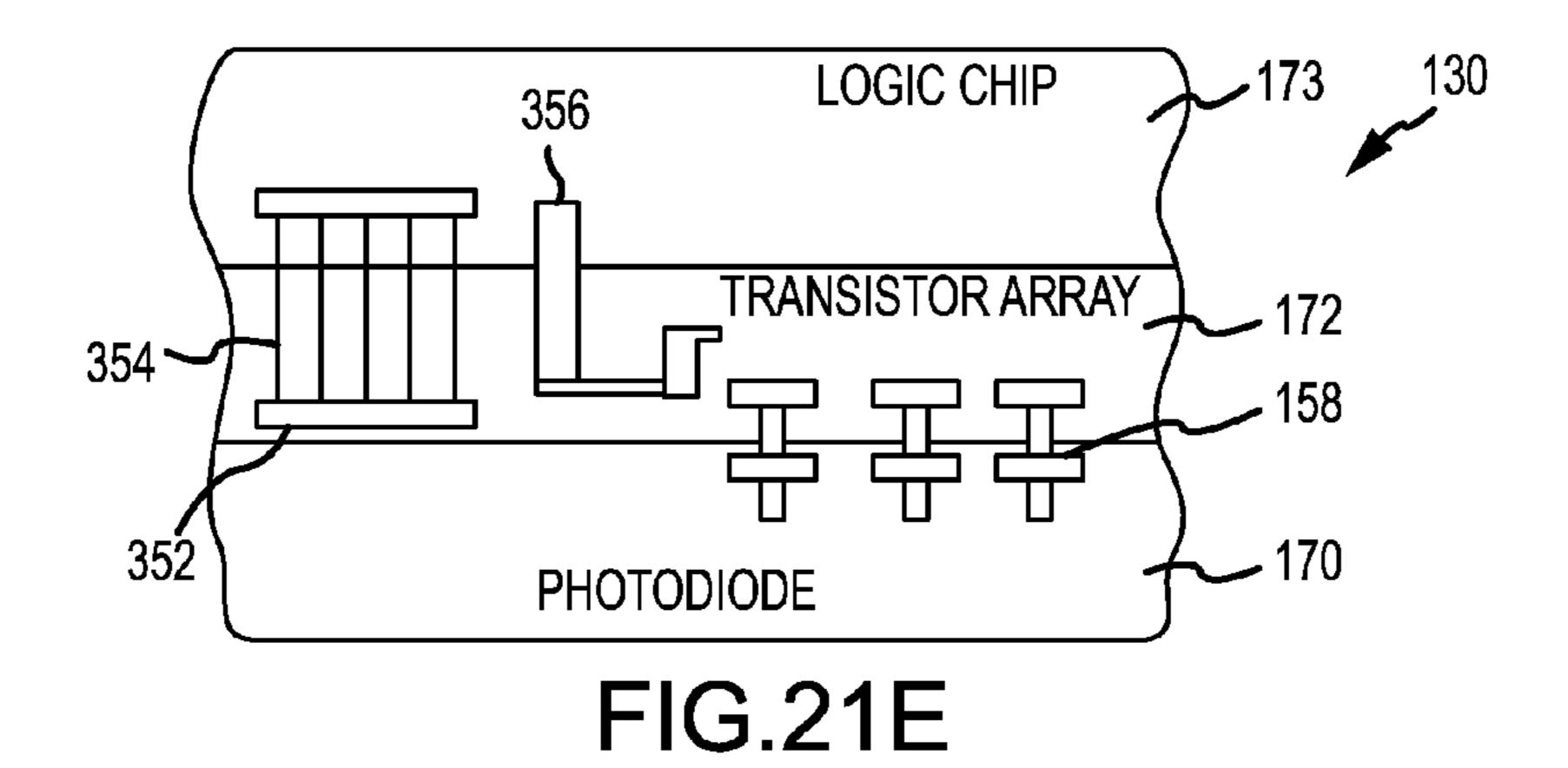

- FIG. 21E is a simplified block diagram of the image sensor stack including the photodiode chip, the transistor array chip, and the logic chip.

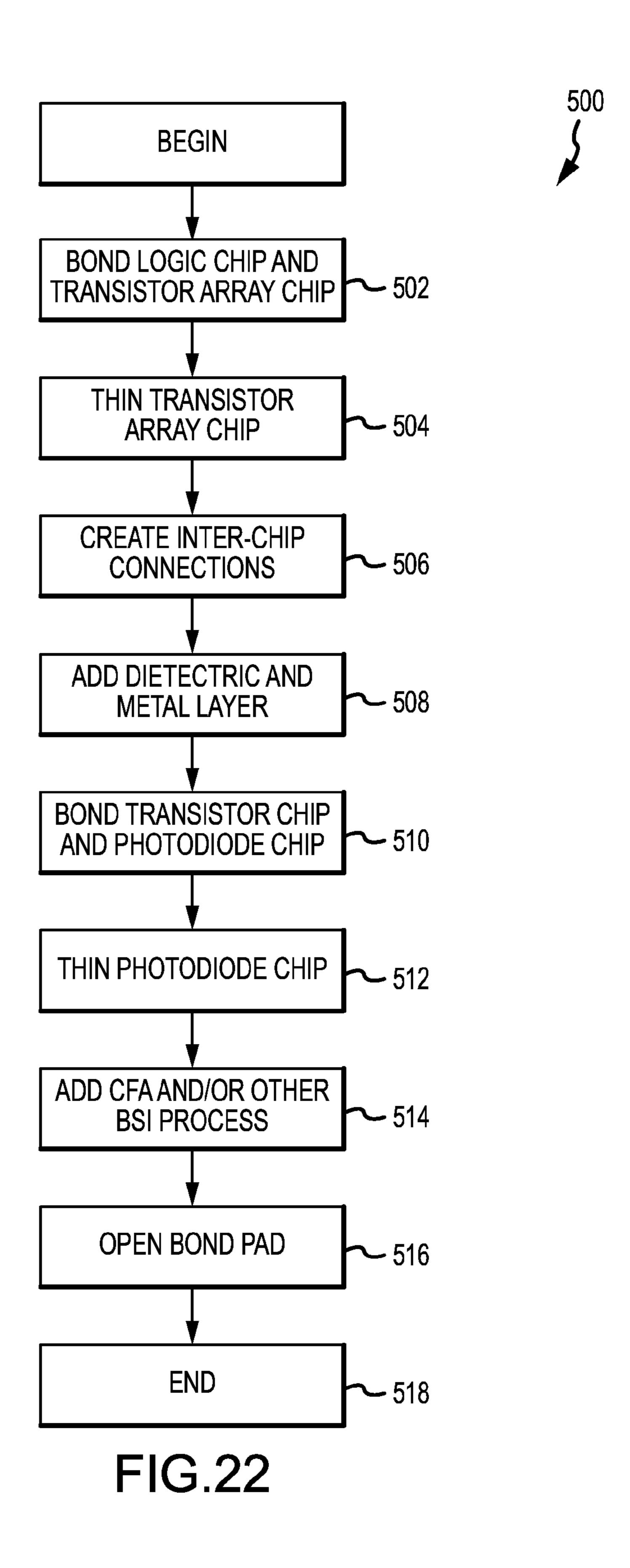

- FIG. 22 is a flow chart illustrating a second example of a manufacturing process for the image sensor.

4

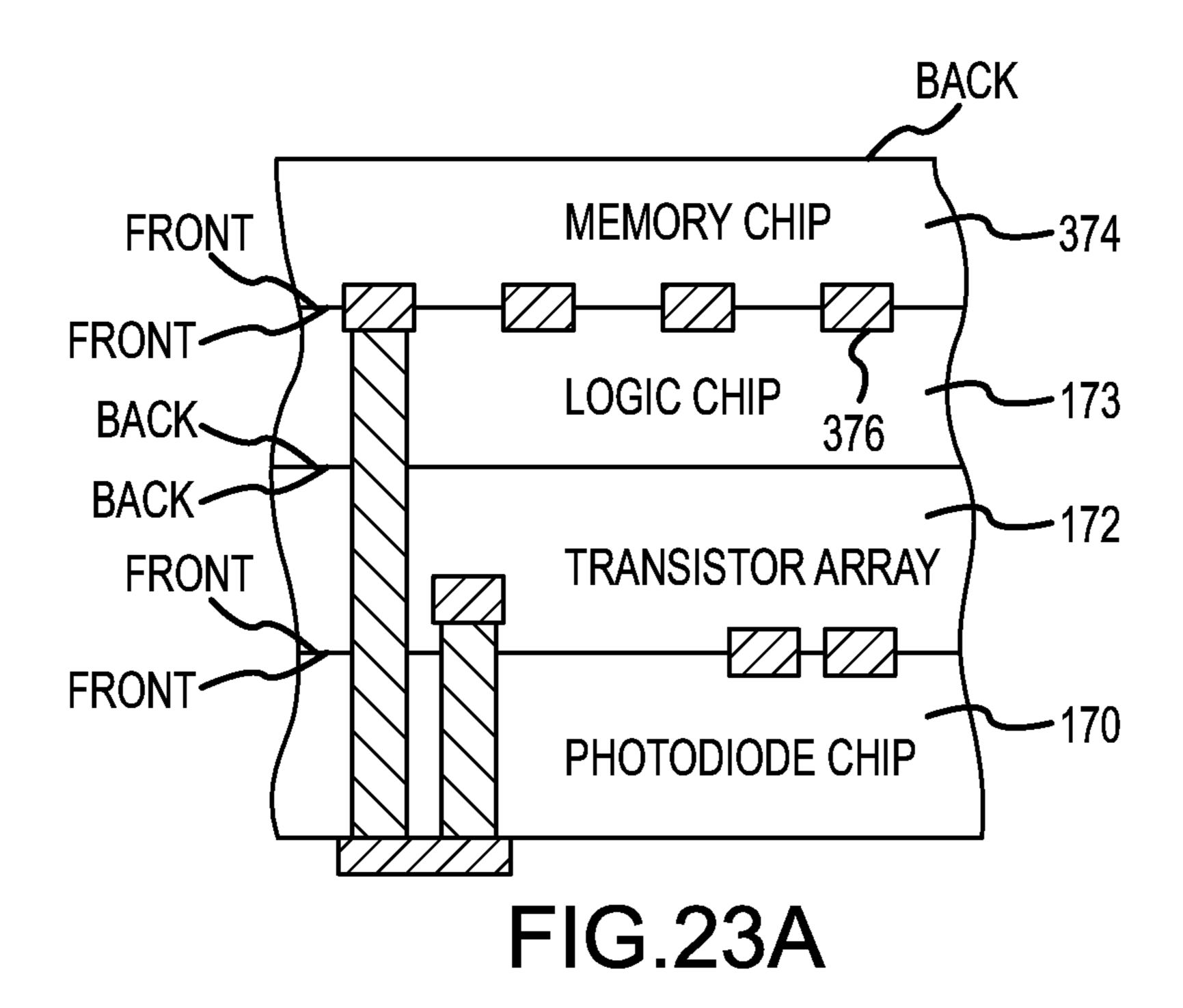

- FIG. 23A is a simplified block diagram illustrating an image sensor including a four-chip stack.

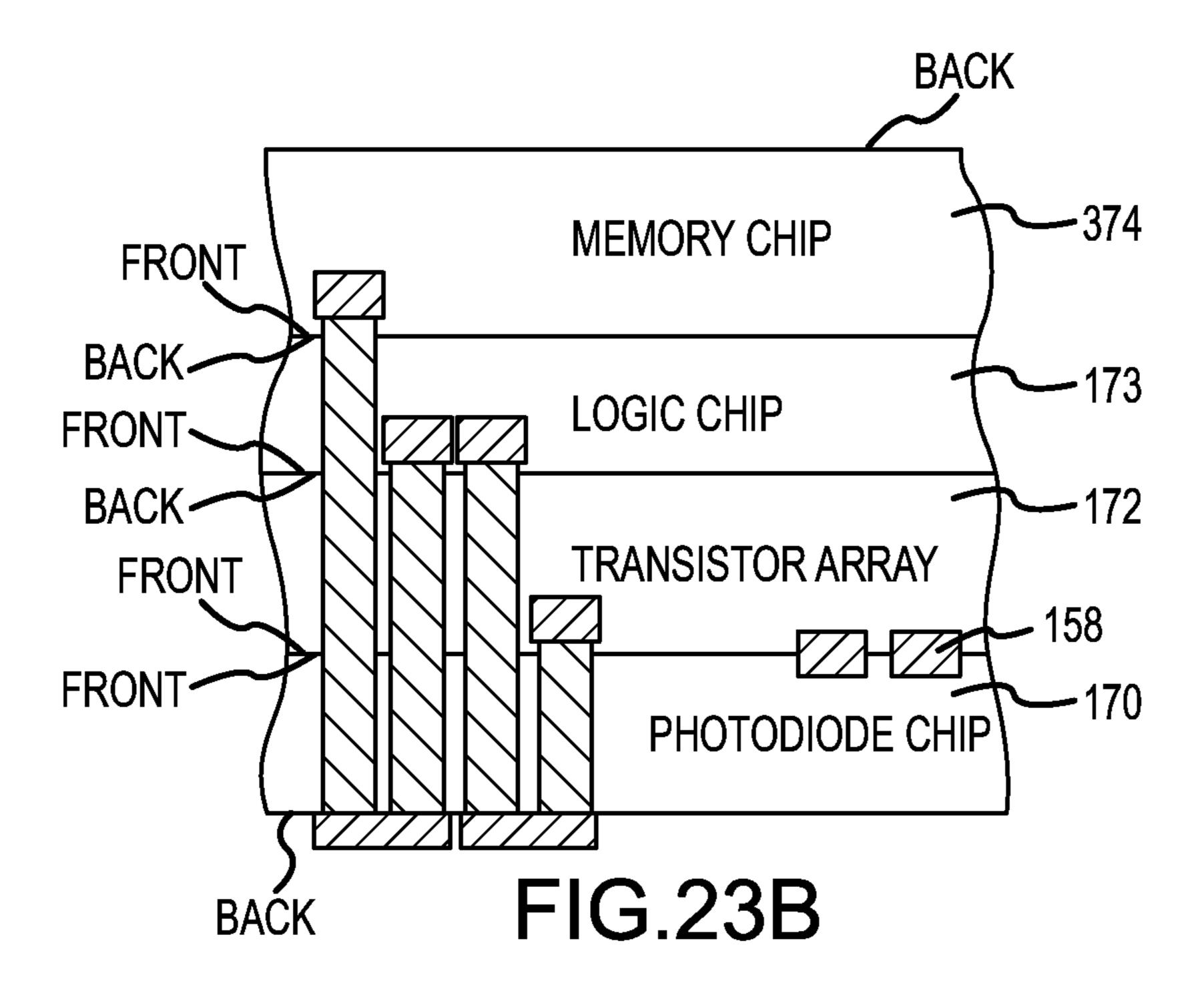

- FIG. 23B is a simplified block diagram illustrating another example of an image sensor including a four-chip stack.

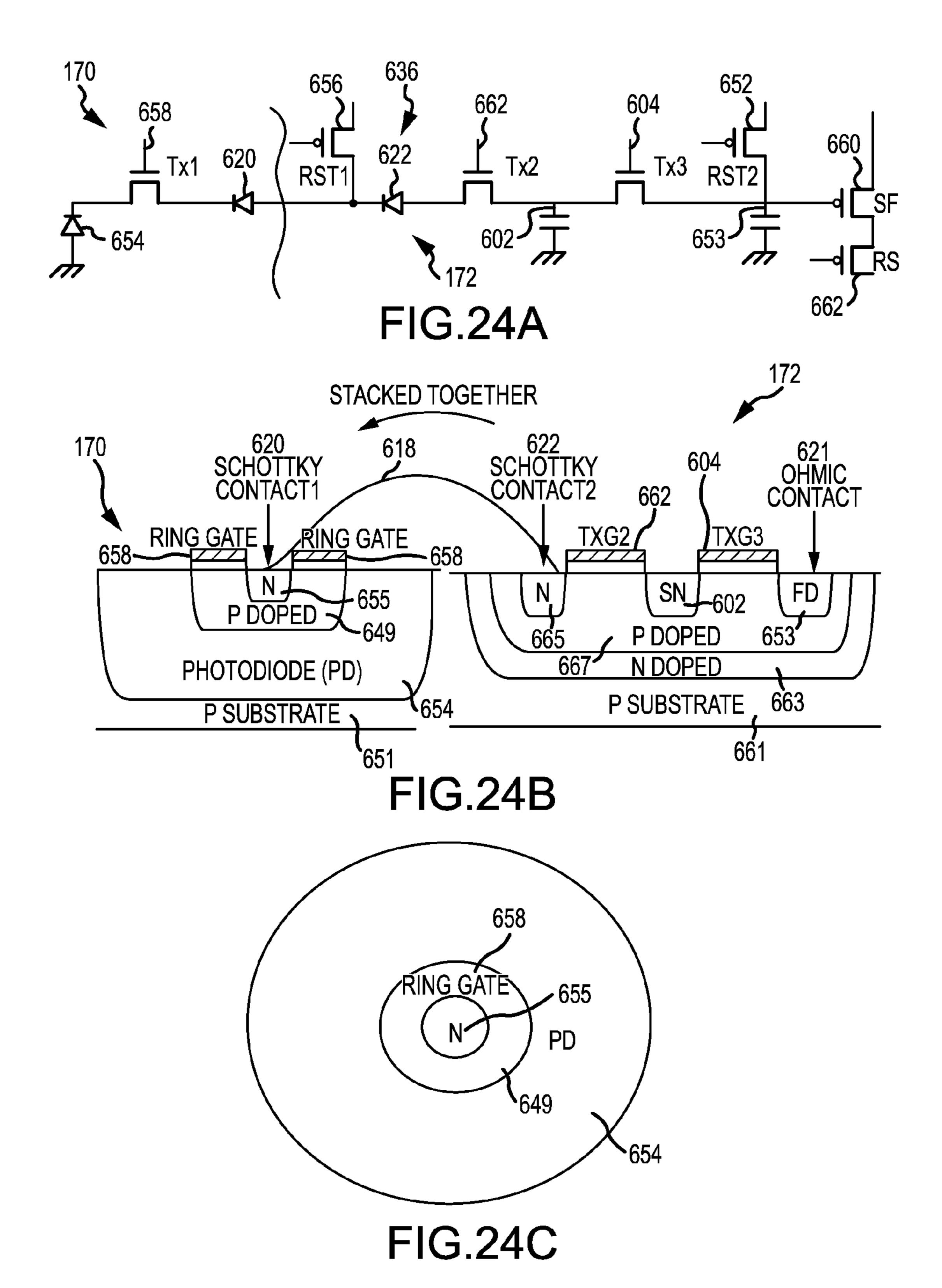

- FIG. 24A is a simplified schematic view of a pixel circuitry including differently doped contacts for inter-chip connections.

- FIG. 24B is a simplified cross section of the photodiode chip and the transistor array chip of FIG. 24A illustrating first and second Schottky contacts and a ring gate structure.

- FIG. 24C is a top view of the photodiode chip of FIG. 24B.

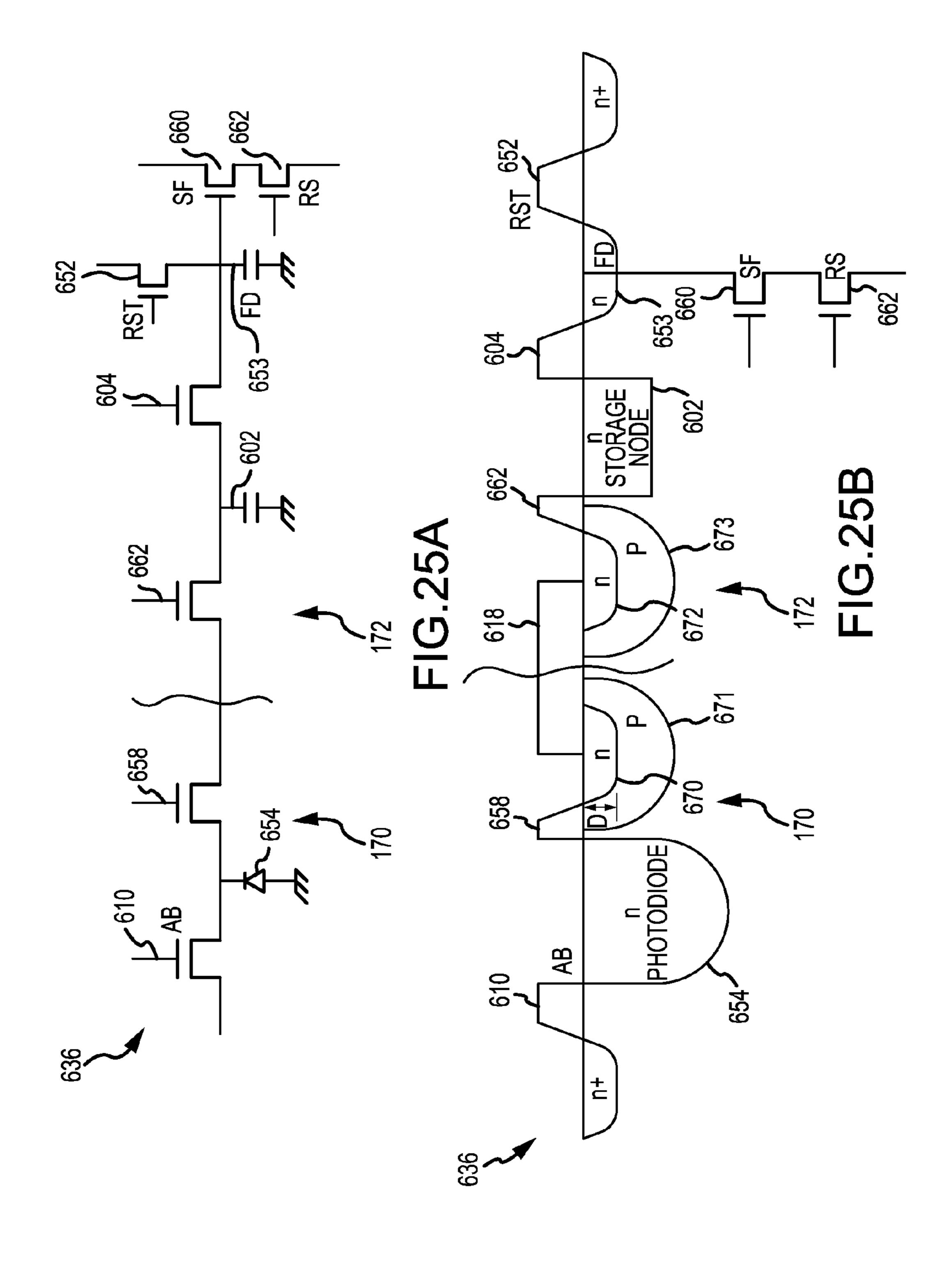

- FIG. 25A is a simplified schematic of a pixel circuitry including shallow doped regions for the inter-chip contacts.

- FIG. **25**B is a simplified block diagram illustrating the doping scheme for the circuitry of FIG. **25**A.

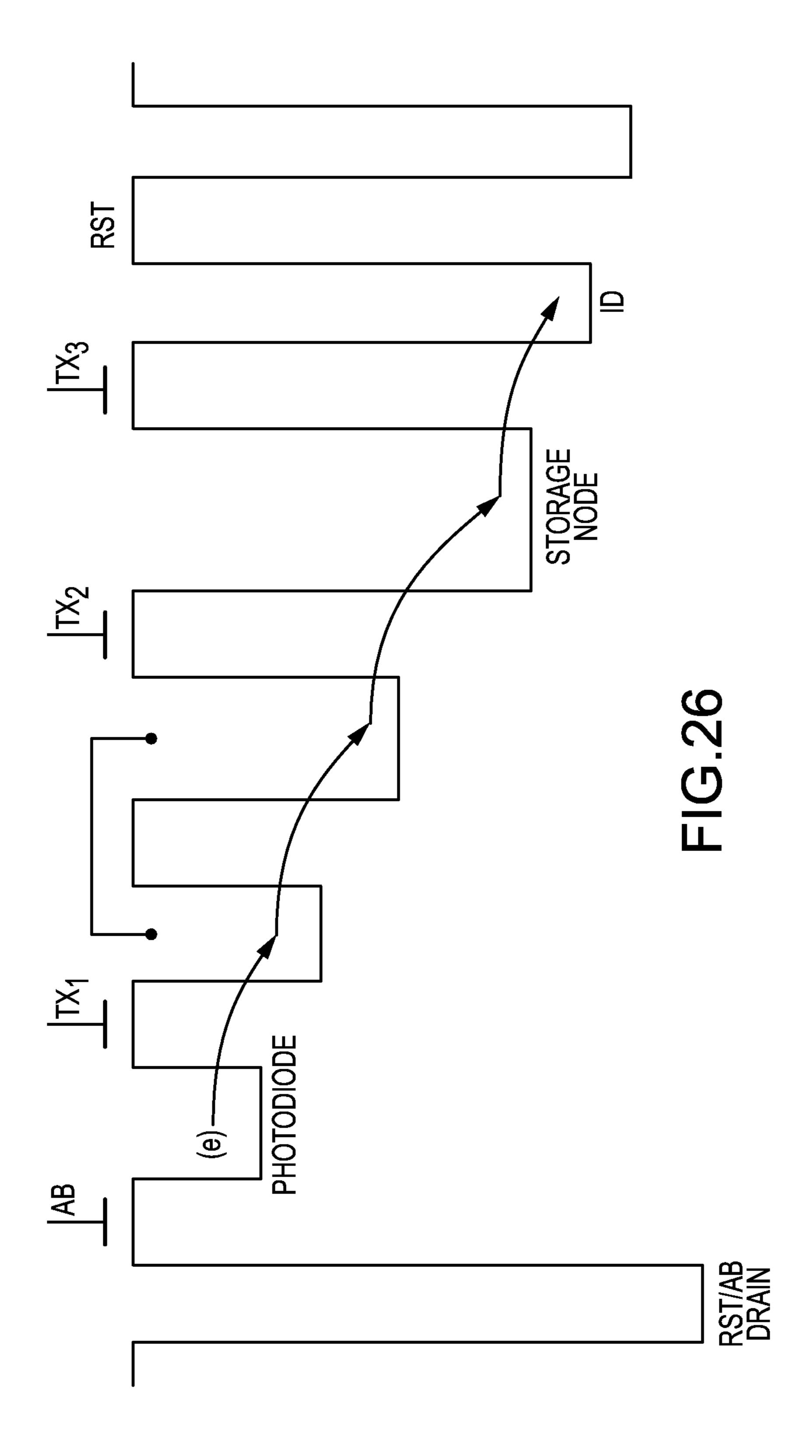

- FIG. 26 is a potential diagram illustrating the potential increases across the pixel circuitry from the photodiode towards the floating diffusion node.

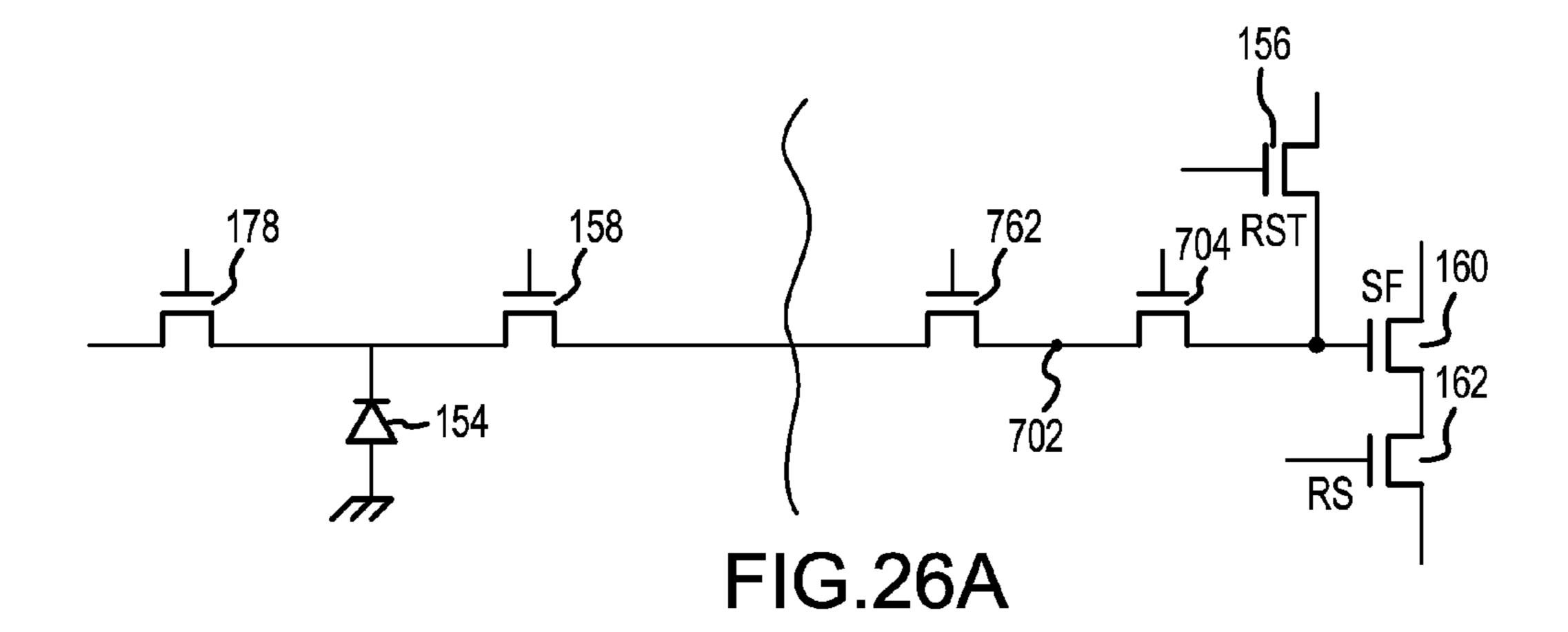

- FIG. **26**A is a simplified schematic view of a pixel circuitry including a storage node positioned on the transistor array chip.

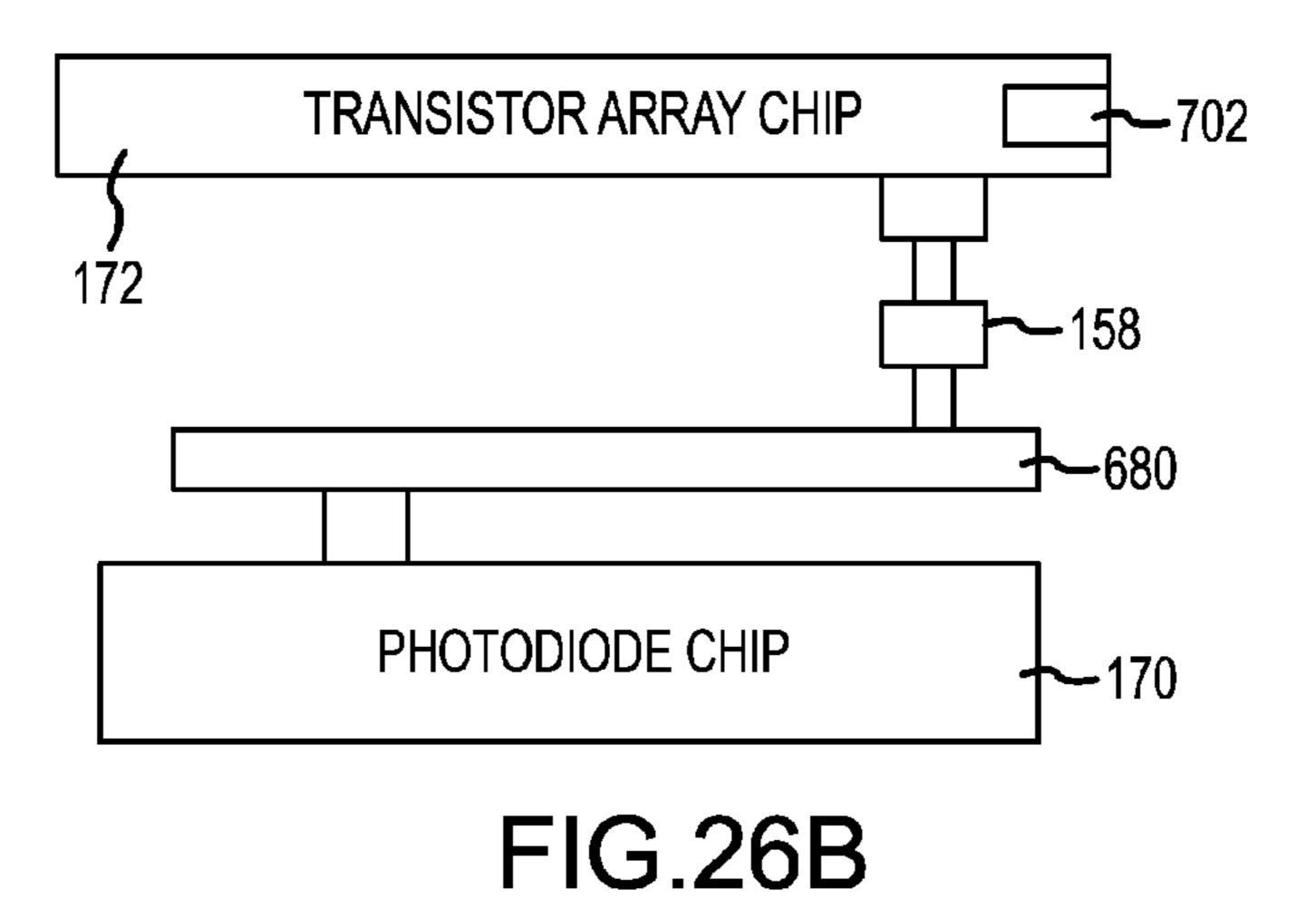

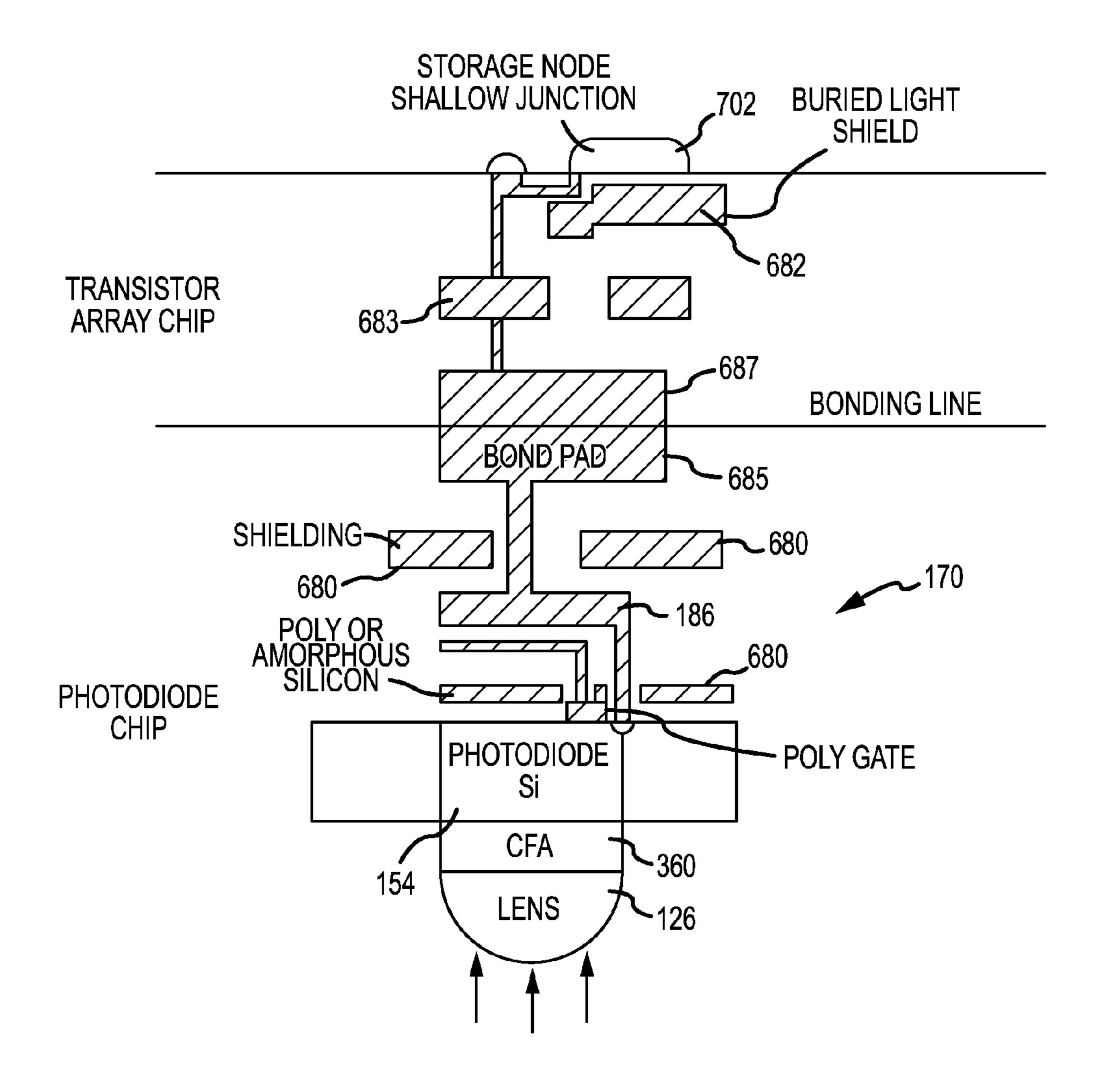

- FIG. **26**B is a diagram illustrating the photodiode chip stacked with the transistor array chip including a light shield.

- FIG. **26**C is a diagram illustrating the photodiode chip stacked with the transistor array chip including a plurality of light shielding layers.

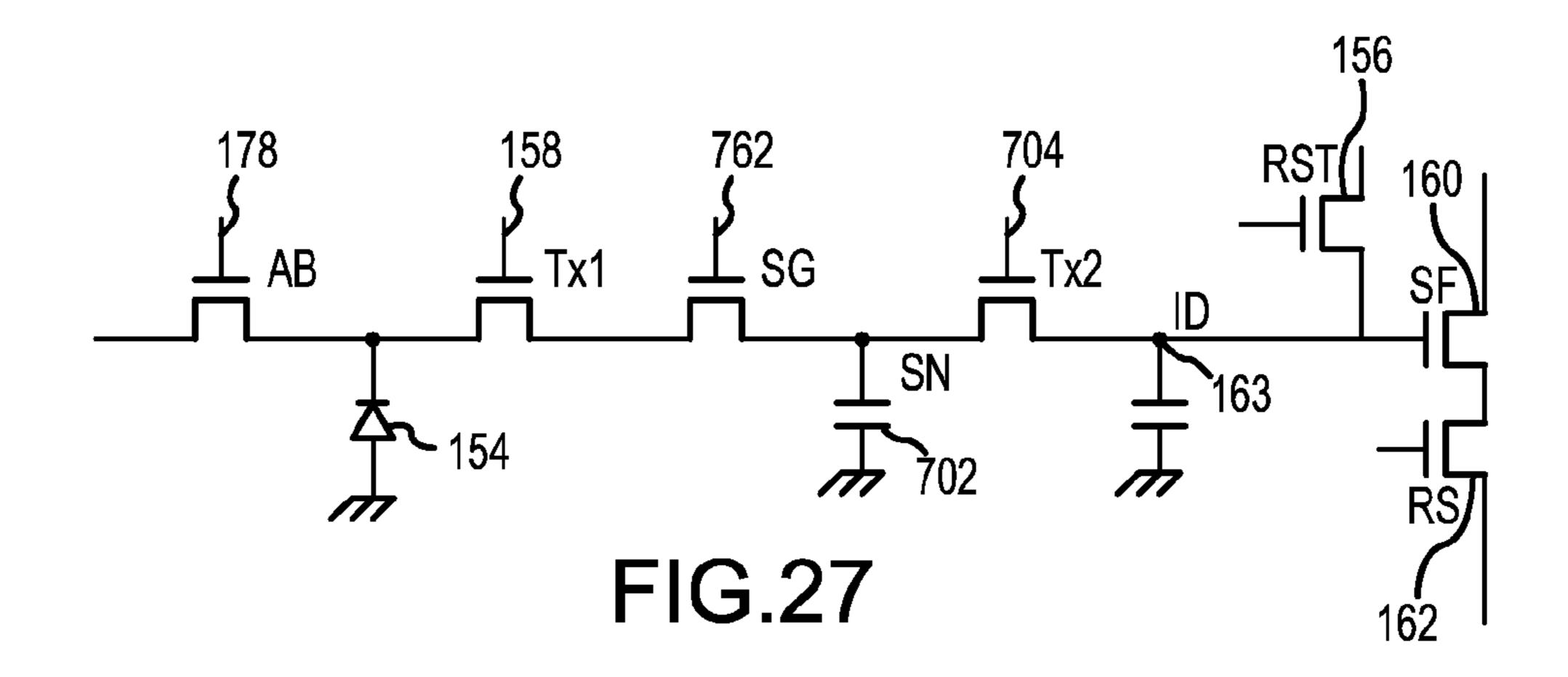

- FIG. 27 illustrates an example schematic for a pixel of the image sensor having a dynamically adjustable full well capacity.

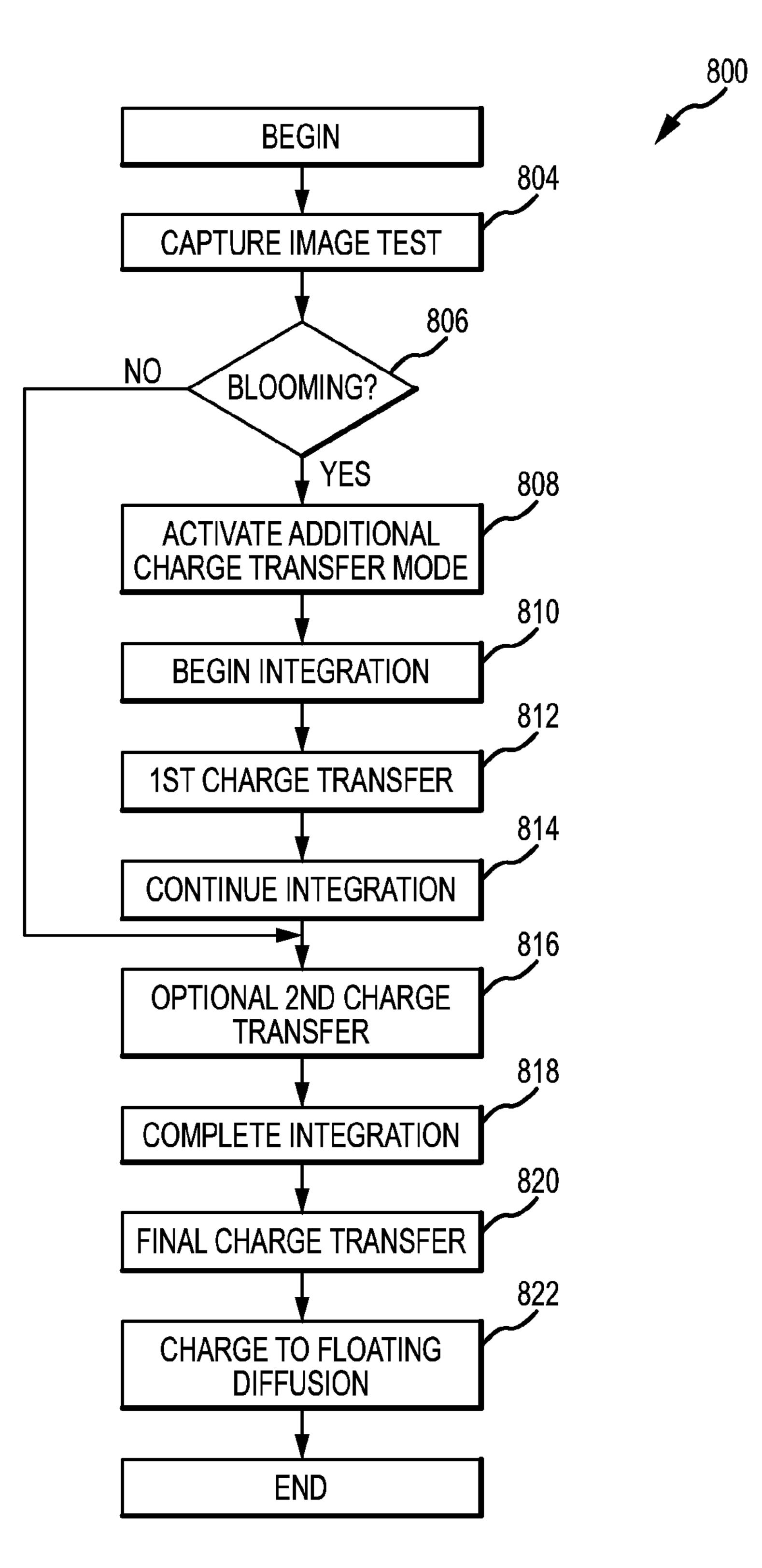

- FIG. 28 is a flow chart illustrating a method for adjusting the full well capacity for one or more photodiodes of the image sensor.

## SPECIFICATION

Overview

The disclosure may take the form of an image sensor for cameras and other electronic devices. Many embodiments of the present disclosure include an image sensor having a transfer gate to communicate between the photodiodes in the image sensor and the readout circuitry for those photodiodes. In some embodiments, the transfer gate may be vertically oriented (as discussed in more detail below), and in other embodiments, the transfer gate may be laterally oriented. The orientation of the transfer gate may be selected based on the desired embodiment to be implemented and the desired size, shape, and functionality of the image sensor.

In some embodiments, the image sensor may include a pixel array having two or more chips stacked together and interconnected with a vertical gate structure. In other words, the pixel array may be split into two chips, e.g., one chip having the photodiodes and another chip having the readout circuitry and transistor array. For example, a first chip may first include the photodiode and a second chip, which may be vertically stacked on the first chip, may include the transistor array. A vertical transfer gate may communicatively couple the two chips together. By including the transistor array on a separate chip, the photodiode exposure area may be maximized, as the first chip may not have to include space for the transistor array. This saved space may be used for additional pixels or to increase the well size for each of photodiode.

In some embodiments, the image sensor may further include a third chip, such as a logic chip, stacked on top of the transistor array chip. The transistor array chip, photodiode chip, and the logic chip may be in communication through one or more vertical transfer gates, metal to metal (or other conductive material) contacts, and/or through silicon vias. In

some instances, two chips, such as the transistor array chip and the logic chip, may be in communication through one communication connection (e.g., through silicon via) and the third chip (e.g., the photodiode chip) may be in communication with one of the other two chips through another connection (e.g., vertical transfer gate). Additionally, in some embodiments, the image sensor may include a fourth chip stacked on the logic chip. For example, the image sensor may include a memory chip stacked on the logic chip.

In other embodiments, the photodiode chip and the tran- 10 sistor array chip may be in communication through a ring gate structure. The ring gate structure may be formed on the photodiode chip and an inter-chip connection (such as a conductive wire) may extend vertically to connect with the transistor array chip. In this example, the photodiode chip and the 15 transistor array chip may each include one or more Schottky contacts connected together through an inter-chip connection. Each of the Schottky contacts may be formed in a triple well structure, to reduce leakage current. For example, each contact may be surrounded by a well having a doping material 20 opposite of the contact (e.g., n-doped contact surrounded by a p-doped well). The Schottky contacts allow the inter-chip connection between the photodiode chip and the transistor array chip to be pinned, which may control the depletion voltage and charge storage amounts for the photodiode. Addi- 25 tionally, while under forward bias the Schottky contacts may be fully depleted as the active area size and doping for the image sensor may be optimized for the bias needed to fully deplete the active regions. In other words, the doping amount and area may be determined to correspond to the anticipated 30 charge transfer from the photodiode. The doping type of the contacts between the photodiode chip and the transistor array chip may be varied based on the desired pixel architecture of the image sensor.

In another example, the doping concentration, doping 35 depth, and node active area of the nodes forming and in communication with the transfer gate may be controlled so that the charge transfer nodes may have substantially the same state between reset and post transfer. For example, the image sensor may include shallow doped regions forming 40 charge storage nodes, where the doping concentration may be relatively high. In other words, each of the shallow doped regions may be highly doped but have a thin thickness or depth. The small size, but high doping concentration may allow the charge to be completely transferred from the storage 45 node, reducing noise and error within a captured image.

In some embodiments, the pinning potentials for each node of the image sensor may increase from the photodiode towards a floating diffusion node. In other words, the doping concentration for each node may increase from the photodiode towards the floating diffusion node. In these embodiments the voltage depletion level increases from the photodiode towards the floating diffusion node, which may allow a charge to more easily be transferred between the photodiode to the floating diffusion node (where it may be eventually read 55 out).

In some embodiments, the stacked image sensor may also provide for a global shutter with a smaller pixel size. This is possible as the storage node that stores the charge from the photodiode can be positioned above the photodiode exposure 60 area, thus maintaining the size of the photodiode area, although an additional component is included in the image sensor. Additionally, in some global shutter operations additional transistors may be needed to operate the pixel. For example, the storage gate may include one or more transistors 65 that control the entry and exit of charge into the storage node. In these embodiments, the image sensor may allow these

6

additional transistors to be positioned above the photodiode and thus not reduce the surface area or space on the first chip allowed for the photodiode.

Additionally, the stacked image sensor may include one or more shields may be used to optically and/or electrically isolate the storage component (which may be used to implement a global shutter). For example, the image sensor may illuminated on its back side and the storage component may be positioned on the transistor array chip and metal shielding may be positioned between the photodiode chip and the transistor array chip. In this example, the storage component or node may be optically isolated from the light source exposed to the photodiode, which may reduce artifacts that could be introduced into images captured by the image sensor due to the storage component being exposed to light. The metal shielding may prevent light pollution (e.g., light not captured by the photodiode during integration) from entering into the storage node and corrupting the data stored therein. This may reduce errors due light reflected within the photodiode chip or light that enters into the photodiode chip after integration.

In other embodiments, the image sensor may include one or more components that may be shared by neighboring pixels. For example, one or more storage nodes or transistors may be shared by groups of pixels. Continuing with this example, in a global shutter implementation, the charge for each of the shared pixels within a group of pixels may be transferred sequentially to the storage node and each group of pixels (e.g., pixel cells) may be accessed globally. As another example, pixels within a select pixel cell may be summed together to produce a maximum signal, such as during low light.

In some embodiments including a shared pixel architecture, the charge for a cell of pixels may be rebalanced by sharing the charge of some pixels with other pixels. For example, select pixels within a pixel cell may be reset and charge stored in the photodiodes of the other pixels within the cell may be distributed (at least in part) to the reset pixel or pixels. Rebalancing the charge among pixels may allow the sensitivity of the image sensor to be dynamically adjusted without the requirement for an aperture control within the camera.

The present disclosure may also include examples of methods of manufacturing the image sensor. In embodiments including a vertical transfer gate, the stacked image sensor may be manufactured in some instances so that each of the chips may have substantially the same die size and may be stacked at the wafer level. Stacking the chips at the wafer level may reduce the overall die/module size as compared to conventional image sensors, as well as enhance the pixel/sensor functions. Additionally, because certain functions of the image sensor, e.g., the photodiode and the transistor logic, may be separated into discrete chips, each chip may be optimized to the particular function.

In some embodiments, the image sensor may be configured to vary the conversion gain to optimize or enhance a pixel signal based on lighting and other operating conditions. For example, because the photodiode has been separated from the transistor array, the amount of silicon available for each pixel is increased, which allows for further components to be used. In some instances, different floating diffusion nodes may be selected (e.g., through a multiplexing process) based on the pixel charge level or the floating diffusion area may be connected to capacitors or similar components through convert ion gain control gates.

### DETAILED DESCRIPTION

Turning now to the figures, the image sensor and an illustrative electronic device for incorporating the image sensor

will be discussed in more detail. FIG. 1A is a front elevation view of an electronic device 100 including the image sensor. FIG. 1B is a rear elevation view of the electronic device 100. The electronic device 100 may include a first camera 102, a second camera 104, an enclosure 106, a display 110, and an input/output button 108. The electronic device 100 may be substantially any type of electronic or computing device, such as, but not limited to, a computer, a laptop, a tablet, a smart phone, a digital camera, a printer, a scanner, a copier, or the like. The electronic device 100 may also include one or more 10 internal components (not shown) typical of a computing or electronic device, such as, but not limited to, one or more processors, memory components, network interfaces, and so

As shown in FIG. 1, the enclosure 106 may form an outer 15 data from a WiFi or other network. surface or partial outer surface and protective case for the internal components of the electronic device 100 and may at least partially surround the display 110. The enclosure 106 may be formed of one or more components operably connected together, such as a front piece and a back piece, or may 20 be formed of a single piece operably connected to the display **110**.

The input member 108 (which may be a switch, button, capacitive sensor, or other input mechanism) allows a user to interact with the electronic device 100. For example, the input 25 member 108 may be a button or switch to alter the volume, return to a home screen, and the like. The electronic device 100 may include one or more input members 108 and/or output members, and each member may have a single input or output function or multiple input/output functions.

The display 110 may be operably connected to the electronic device 100 or may be communicatively coupled thereto. The display 110 may provide a visual output for the electronic device 100 and/or may function to receive user inputs to the electronic device 100. For example, the display 35 110 may be a multi-touch capacitive sensing screen that may detect one or more user inputs.

The electronic device 100 may also include a number of internal components. FIG. 2 is a simplified block diagram of the electronic device 100. The electronic device 100 may also 40 include one or more processors 114, a storage or memory component 116, an input/output interface 118, a power source 120, and one or more sensors 122, each will be discussed in turn below.

The processor 114 may control operation of the electronic 45 device 100. The processor 114 may be in communication, either directly or indirectly, with substantially all of the components of the electronic device 100. For example, one or more system buses 124 or other communication mechanisms may provide communication between the processor 114, the 50 cameras 102, 104, the display 110, the input member 108, the sensors 122, and so on. The processor 114 may be any electronic device cable of processing, receiving, and/or transmitting instructions. For example, the processor 114 may be a microprocessor or a microcomputer. As described herein, the term "processor" is meant to encompass a single processor or processing unit, multiple processors, or multiple processing units, or other suitably configured computing element.

The memory 116 may store electronic data that may be utilized by the electronic device 100. For example, the 60 memory 116 may store electrical data or content e.g., audio files, video files, document files, and so on, corresponding to various applications. The memory 116 may be, for example, non-volatile storage, a magnetic storage medium, optical storage medium, magneto-optical storage medium, read only 65 memory, random access memory, erasable programmable memory, or flash memory.

The input/output interface 118 may receive data from a user or one or more other electronic devices. Additionally, the input/output interface 118 may facilitate transmission of data to a user or to other electronic devices. For example, in embodiments where the electronic device 100 is a phone, the input/output interface 118 may be used to receive data from a network, or may be used to send and transmit electronic signals via a wireless or wired connection (Internet, WiFi, Bluetooth, and Ethernet being a few examples). In some embodiments, the input/output interface 118 may support multiple network or communication mechanisms. For example, the network/communication interface 118 may pair with another device over a Bluetooth network to transfer signals to the other device, while simultaneously receiving

The power source 120 may be substantially any device capable of providing energy to the electronic device 100. For example, the power source 120 may be a battery, a connection cable that may be configured to connect the electronic device 100 to another power source such as a wall outlet, or the like.

The sensors 122 may include substantially any type of sensor. For example, the electronic device 100 may include one or more audio sensors (e.g., microphones), light sensors (e.g., ambient light sensors), gyroscopes, accelerometers, or the like. The sensors 122 may be used to provide data to the processor 114, which may be used to enhance or vary functions of the electronic device 100.

With reference again to FIGS. 1A and 1B, the electronic device 100 may also include one or more cameras 102, 104 and optionally a flash 112 or light source for the cameras. FIG. 3 is a simplified cross-section view of one camera 102, taken along line 3-3 in FIG. 1A. Although FIG. 3 illustrates the first camera 102, it should be noted that the second camera 104 may be substantially similar to the first camera 102. In some embodiments one camera may include a global shutter configured image sensor and one camera may include a rolling shutter configured image sensor. In other examples, one camera may have an image sensor with a higher resolution than the image sensor in the other camera. With reference to FIG. 3, the cameras 102, 104 may include a lens 126 in optical communication with an image sensor 130. The lens 126 may be operably connected to the enclosure 106 and positioned above the image sensor 130. The lens 126 may direct or transmit light 128 within its field of view on to a photodiode layer (discussed in more detail below) of the image sensor **130**.

The image sensor 130 may be supported beneath the lens **126** by a substrate **132** or other support structure. The image sensor 130 may convert light 128 into electrical signals that may represent the light from the captured scene. In other words, the image sensor 130 captures the light 128 optically transmitted via the lens 126 into electrical signals. Image Sensor Architecture

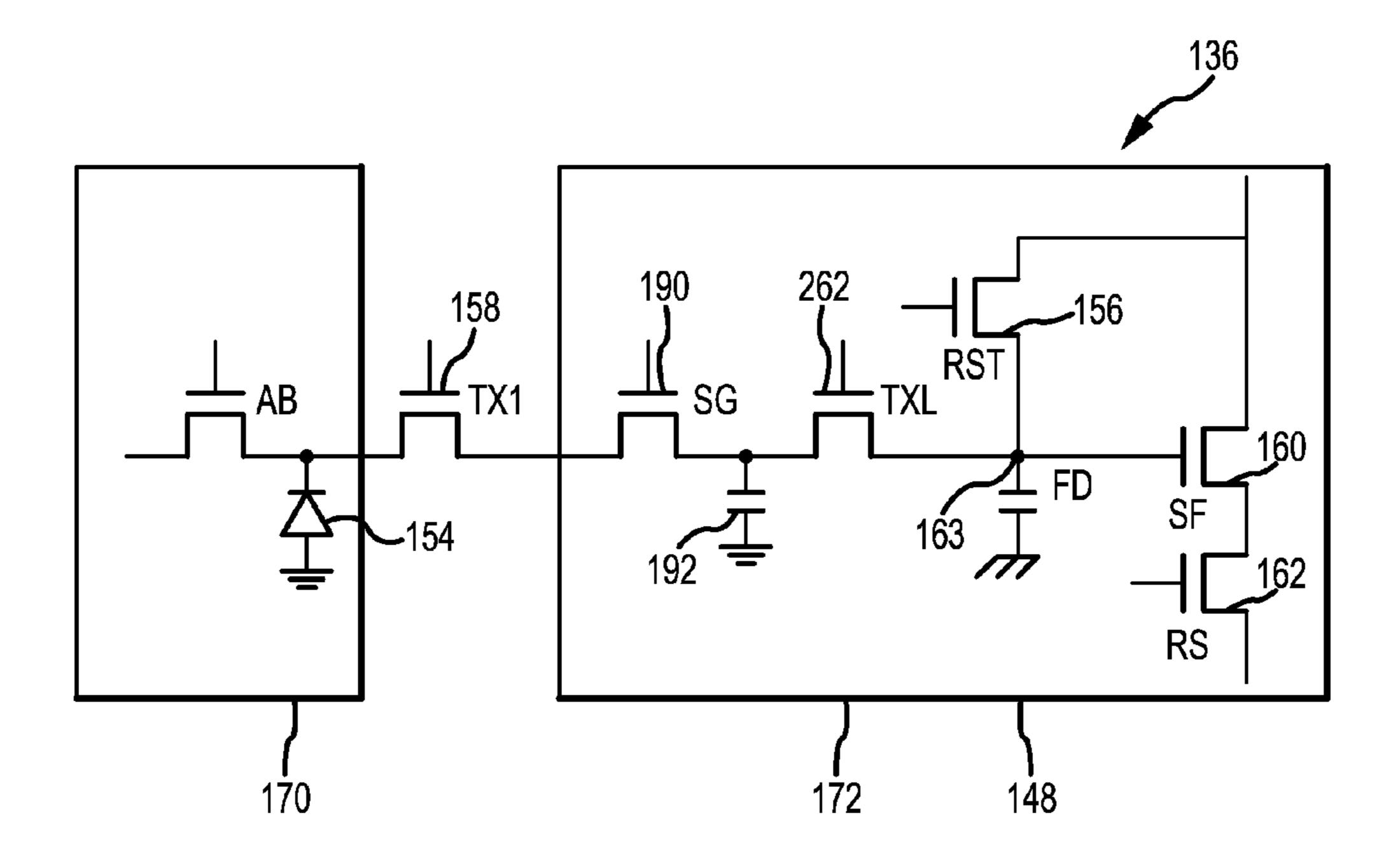

An illustrative architecture for the image sensor 130 will now be discussed in more detail. FIG. 4A is a simplified schematic of an architecture for the image sensor 130. FIG. 4B is an enlarged view of a pixel of the pixel architecture of FIG. 4A. FIG. 5 is a simplified schematic view of the pixel of FIG. 4A. With reference to FIGS. 4A-5, the image sensor may include an image processing component 150 and a pixel architecture 134 or pixel array. This architecture defines one or more pixels 136 and/or groups of pixel cells 138 (e.g., groups of pixels 136 grouped together to form a Bayer pixel or other set of pixels). The pixel architecture 134 may be in communication with a column select 140 through one or more column output lines 146 and a row select 144 through one or more row select lines 148.

The row select 144 and/or the column select 140 may be in communication with an image processor 142. The image processor 142 may process data from the pixels 136 and provide that data to the processor 114 and/or other components of the electronic device 100. It should be noted that in 5 some embodiments, the image processor 142 may be incorporated into the processor 114 or separate therefrom. The row select 144 may selectively activate a particular pixel 136 or group of pixels, such as all of the pixels 136 on a certain row. The column select 140 may selectively receive the data output 10 from select pixels 136 or groups of pixels 136 (e.g., all of the pixels with a particular column).

With reference to FIG. 5, each pixel 136 may include a transistor array 152 or control circuitry and a photodiode 154. The photodiode 154 may be in optical communication with 15 the lens 126 to receive light transmitted therethrough. The photodiode 154 may absorb light and convert the absorbed light into an electrical signal. The photodiode 154 may be an electron-based photodiode or a hole based photodiode. Additionally, it should be noted that the term photodiode as used 20 herein is meant to encompass substantially any type of photon or light detecting component, such as a photogate or other photon sensitive region. The photodiode 154 is coupled to a transfer gate 158, the transfer gate 158 selectively connects the photodiode 154 to the remaining control circuitry 152 of 25 the pixel 136.

The transfer gate 158 is coupled to a reset gate 156 and a source follower (SF) gate 160. The reset gate 156 and the SF gate 160 are coupled to a reference voltage node 164 which connects the two gates to a reference voltage source (Vdd) 30 166. The row select gate 162 is coupled to a row select line 148 for the pixel 136. A floating diffusion node 163 including a charge storage component 168 may be coupled between the transfer gate 158 and the reset gate 156 and SF gate 160. The control circuitry 152 (or transistor array) may include additional gates other than those shown in FIG. 5. For example, an anti-blooming gate may be in communication with the photodiode 154 to drain charge in excess of saturation level from the photodiode.

Generally, in operation, when one of the cameras 102, 104 40 is actuated to take a picture by a user, the reference voltage 166 is applied to the reset gate 156 and the transfer gate 158. When the transfer gate 158 is open, the charge within the photodiode 154 is drained to deplete the photodiode. In some embodiments, the cameras 102, 104 may not include a shutter 45 over the lens 126, and so the image sensor 130 may be constantly exposed to light. In these embodiments, the photodiode 154 may have to be reset or depleted before a desired image is to be captured. Once the charge from the photodiode **154** has been depleted, the transfer gate **158**, and the reset gate 50 156 may be turned off, isolating the photodiode 154. The photodiode 154 may then begin integration and collecting light 128 transmitted to the image sensor 130 from the lens 126. As the photodiode 154 receives light, it starts to collect charge (e.g., a depletion region reduces as electrons from the 55 light are received). However, the charge within the photodiode 154 may remain within a well of the photodiode 154 because the transfer gate 158 (connecting the photodiode 154) to the control circuitry 150 and other gates is off.

Once integration is complete and the photodiode 154 has 60 collected light 128 from the lens 126, the reset gate 152 may be turned on to reset the floating diffusion node 163. Once the floating diffusion 163 has been reset, the reset gate 156 may be turned off and the transfer gate 158 may be turned on. The charge from the photodiode 154 can then be transferred to the 65 floating diffusion node 163 and be stored in the storage component 168. To read out the charge from the photodiode 154

**10**

(here, via the floating diffusion 163), the row select gate 152 and the SF gate 160 may be activated, and the SF gate 160 amplifies the charge within the floating diffusion 163 and through the row select gate 162, the signal or charge is provide to the column output line 146.

In a rolling shutter operation, photodiodes 154 in different rows may be exposed at different times. Accordingly, if one or more objects within a scene are moving, a first row may capture a different position of the image than a second row as they are exposed sequentially, which may cause motion artifacts in the sensed image. In a global shutter operation, additional storage nodes may be added to store charge from the photodiode 154. In the global shutter operation, each row within the pixel architecture 134 may be reset and exposed at substantially the same time. Each pixel may also simultaneously transfer the charge from the photodiode 154 to a storage node, and then each pixel 136 may be read out row by row.

#### Vertical Transfer Gate

In some embodiments, the image sensor 130 may include a pixel array including a two-chip stacked structure with the transfer gate 158 extending between the two chips. In this example, the components of each pixel may be split into two separate chips. In some embodiments, the image sensor may further include a third chip, a logic chip, within the stacked structure. FIG. 6 is a schematic view of a pixel of the image sensor 130 illustrating the division of chips for the image sensor. FIG. 7 is a simplified block diagram of the pixel illustrated in FIG. 6, including an optional anti-blooming gate. FIG. 8 is a simplified side elevation view of the image sensor 130 including the transfer gate structure of the FIG. 6. With reference to FIGS. 6-8, the image sensor 130 may include a photodiode chip 170 and a transistor array chip 172, where the two chips 170, 172 are vertically stacked. In this configuration, the transfer gate 158 may extend vertically between the two chips 170, 172 to communicatively couple them together.

Each of the chips may include a top and bottom surface and a thickness. In some instances, the dimensions of the thicknesses may be less than the dimension of the surfaces or faces for each respective chip. As used herein, the term "vertically stacked" is meant to encompass embodiments where the photodiode chip, the transistor array chip, and/or the logic chip may be stacked so that their faces or surfaces abut one another and are generally aligned across the thickness dimension.

In some embodiments, the photodiode chip 170 may include the photodiode 154 and optionally an anti-blooming gate 178 and the transistor array chip 172 may include the control circuitry 150 or transistor array. The transfer gate 158 may be defined through the connection between the photodiode chip 170 and the transistor array chip 172. In some embodiments, the drain or charge storage node of the transfer gate 158 (i.e., the end of the gate that connects to the floating diffusion node 163) may be located on the transistor array chip 172. This may allow more space on the photodiode chip 170 to be dedicated to the photodiodes for each pixel. Thus, the number of photodiodes **154** and/or their well size may be increased, without causing a subsequent increase in the surface area of the image sensor 130. Additionally, as will be discussed in more detail below, the two chips 170, 172 may be manufactured in light of their specialized functions, e.g., the photodiode chips 170 may be manufactured to increase performance of the photodiode function, which may allow the chips to be optimized for their desired performance.

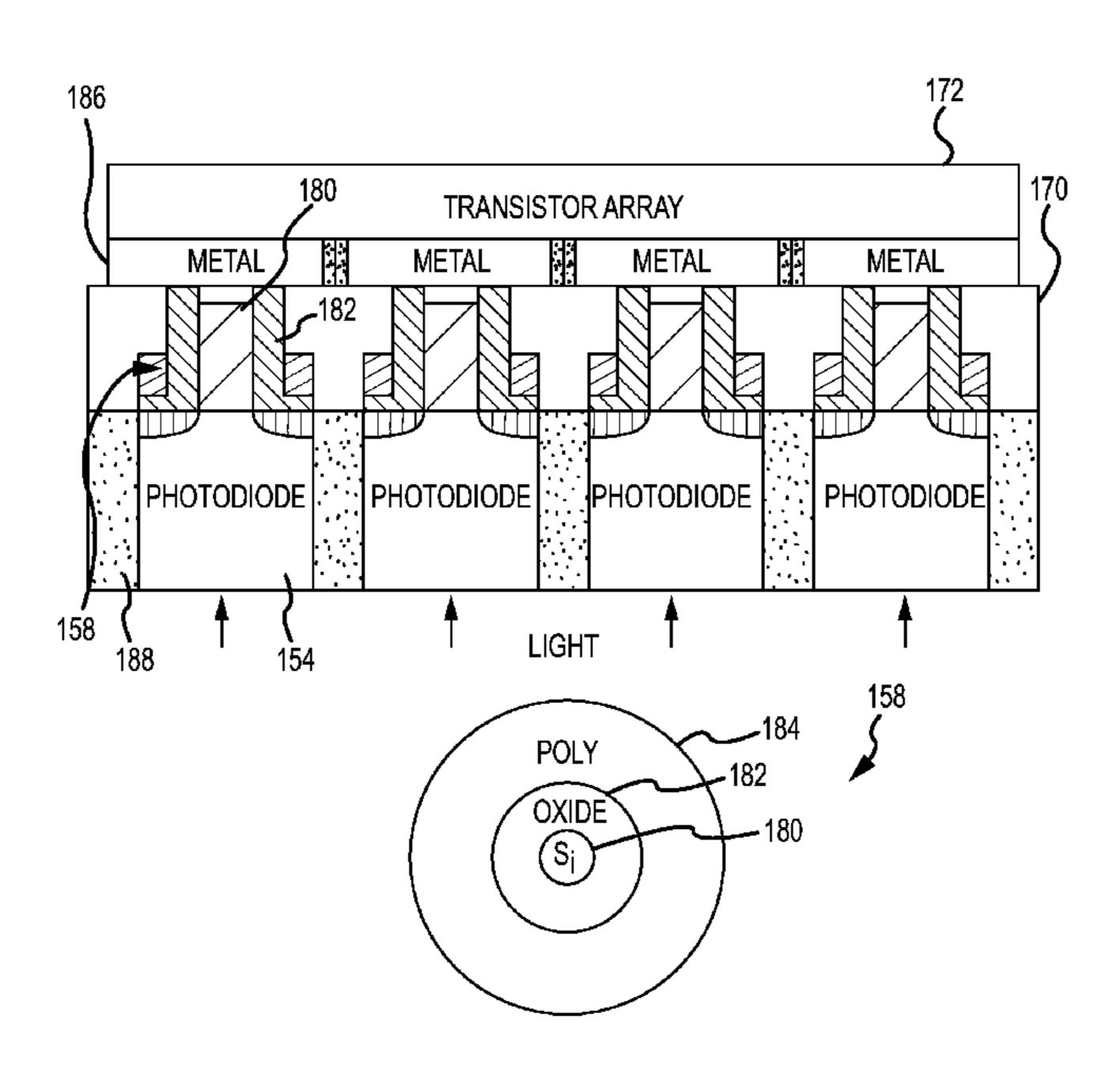

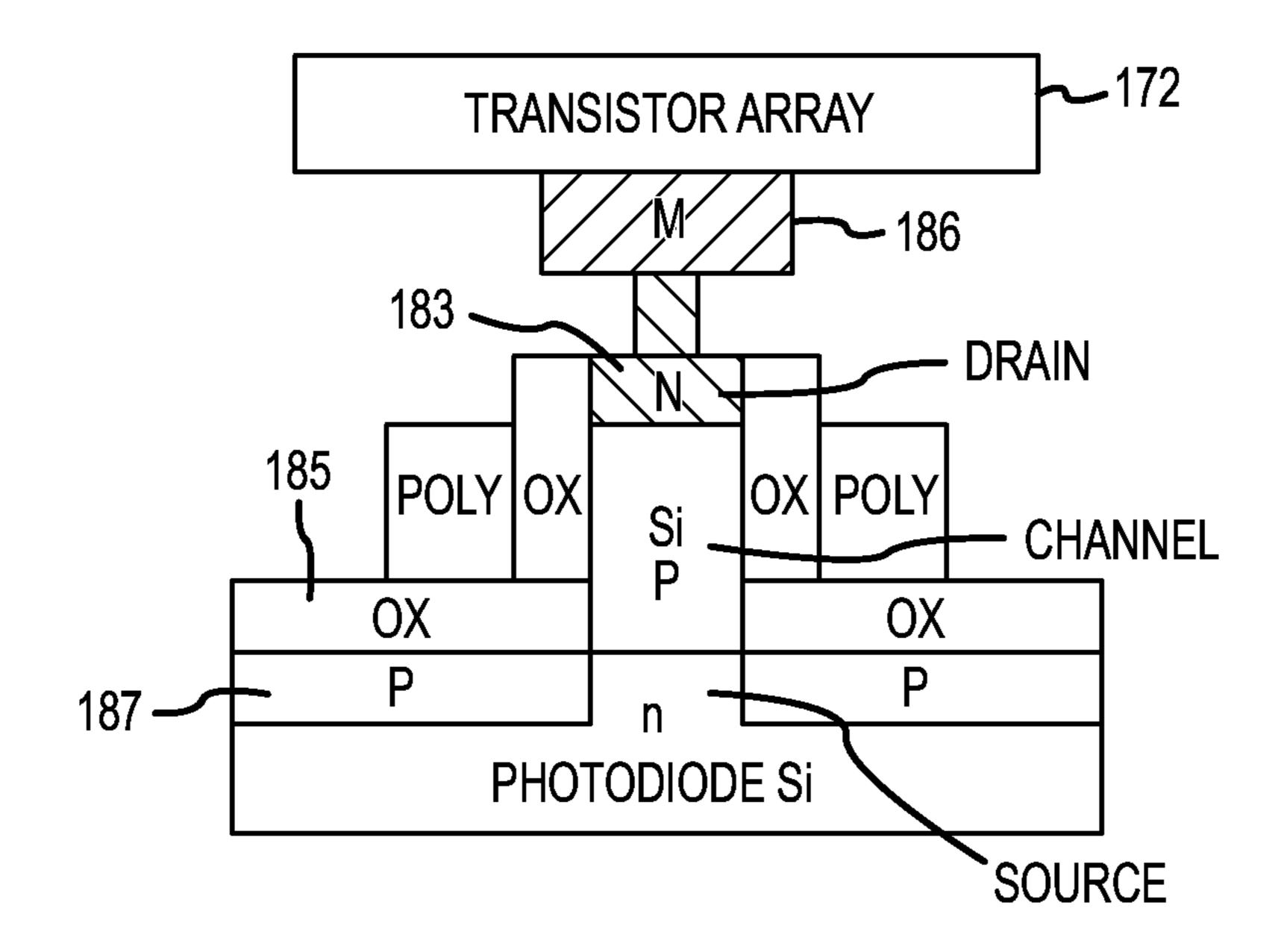

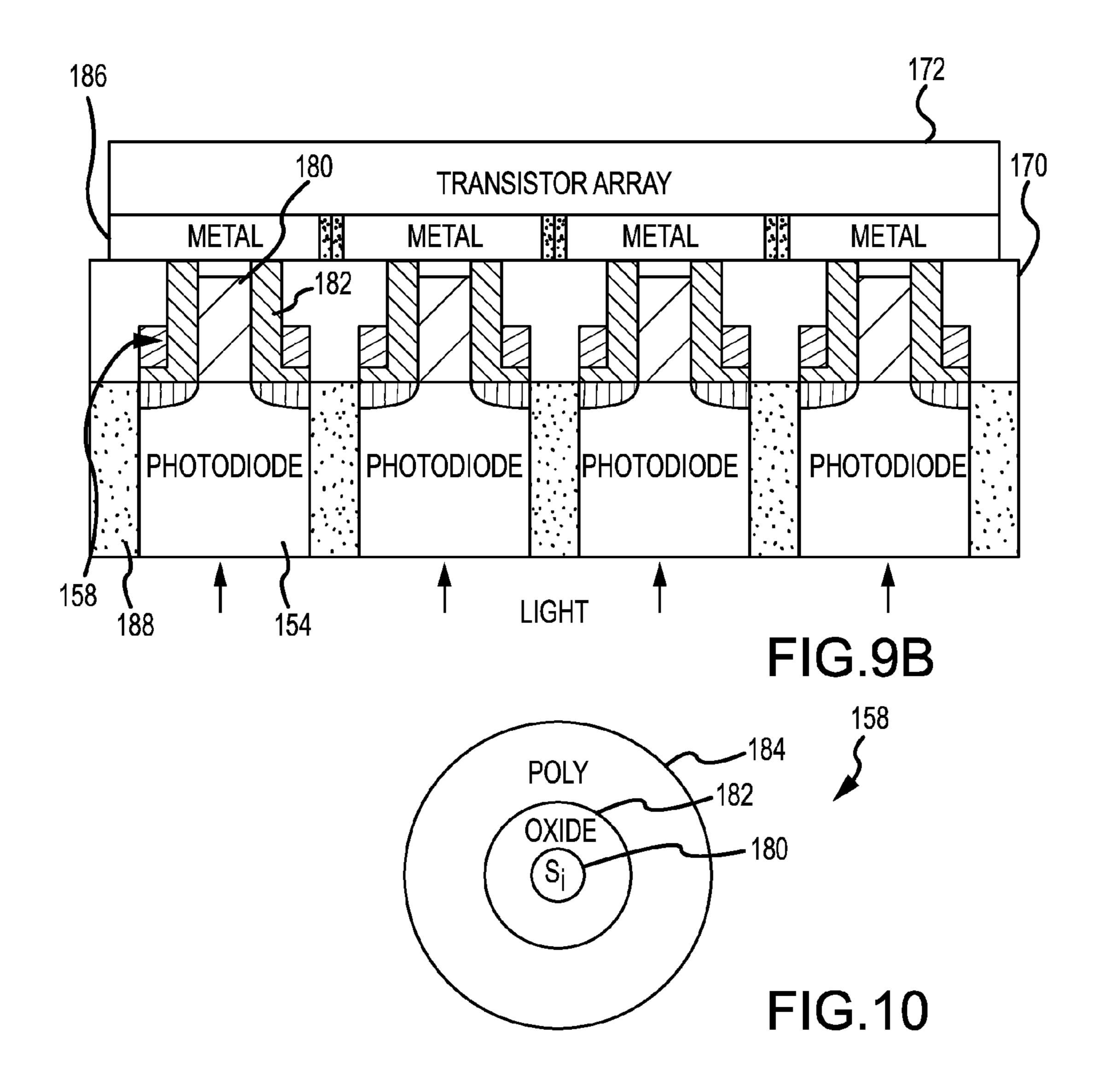

A simplified structure of the image sensor 130 and particularly the transfer gate 158 is illustrated in FIG. 9A. A simplified structure for a pixel cell 138 is illustrated in FIG. 9B. With

reference to FIGS. 9A and 9B, the transfer gate 158 may extend from the photodiode chip 170 (which may include a silicon substrate). The transfer gate 158 may include a semiconductor transfer channel 180 that may be surrounded by a oxide layer 182 (e.g., silicon oxide) and a polysilicon layer 5184. FIG. 10 is a cross-section view of the transfer gate 158 taken along line 10-10 in FIG. 9A. As shown in FIG. 10, the transfer channel 180 may be surrounded by the oxide layer 182, which may be surrounded (at least in part) by the polysilicon layer 184.

With reference to FIGS. 9A-10, a metal layer 186 may connect the transfer channel 180 to the transistor array chip 172. The metal layer 186 may include one or more isolations 181 (see FIG. 9B) or insulating barriers positioned between the connections for each pixel. The isolations 181 may help to 15 ensure that the signals from one photodiode 154 are not inadvertently transferred or combined with the signals from adjacent photodiodes during transfer to the transistors.

A top of the semiconductor transfer channel 180 may include a drain region 183 positioned on a top thereof. In this 20 embodiment, the semiconductor transfer channel 180 may be p-doped and the drain region 183 may be n-doped; however, other variations are envisioned. With continued reference to FIG. 9A, a bottom oxide layer 185 may be positioned between the photodiode 154 and the polysilicon layer 184. In this 25 embodiment, base doped region 187 may be positioned between the bottom oxide layer 185 and the photodiode 154.

When the transfer gate 158 is activated, e.g., turned on, the metal layer 186 may encourage electrons to flow from the photodiode 154 through the transfer channel 180. The silicon 30 base forming the photodiode 154 forms the source for the transfer gate 158, with the silicon transfer channel 180 acting as the channel or pathway for electrons, and the drain region 183 forms the drain for the transfer gate 158. This structure allows electrons to be transmitted from the photodiode to the 35 transistor array 172 (via the channel and the metal 186 contact.

The transfer gate **158** structure may be formed through a selective epitaxy (EPI) process. For example, the gate oxide layer 182 may be formed by thermal oxidation of the EPI. In 40 this example, the threshold voltage of the transfer gate 158 may be varied by adjusting EPI doping or ion implantation. In other embodiments, the transfer gate 158 may be formed through other processes. As one example, amorphous or polysilicon may form the transfer channel **180** and/or the polysili-45 con layer 182 may be formed through metal materials or other semiconductor materials, such as, but not limited to amorphous silicon, tantalum, or tungsten. The metal contacts between the photodiode chip 170 and the transistor array chip 172 may be used in place of a through silicon via (TSV) 50 between the photodiode chip 170 and the transistor array chip 172. By using connections that do not require a TSV, the image sensor 130 may be used to create smaller sized pixel architectures as the photodiode array 170 substrate (e.g., silicon) may not have to be large enough to accommodate the 55 additional size of the vias. In other words, substantially all of the space on the photodiode chip 170 may be used to collect light. It should be noted that in some embodiments, one or more TSVs may also be used in addition to or instead of the vertical transfer gates.

With reference again to FIGS. 8 and 9B, in some embodiments, the photodiode array chip 170 may include a plurality of photodiodes for each pixel 136 defined therein. For example, a substrate forming the photodiode chip 170 may include implants of pixel separators 188 between the photodiode 154 for each pixel 136. The pixel separators 188 may separate each pixel well from adjacent pixel wells, and may

12

define each photodiode **154** area. As one example, the pixel separators 188 may be implants of silicon. In these embodiments, the transfer gate 158 for each pixel 136 may be formed on a top surface of the photodiode chip 170, but separated from adjacent transfer gates by a distance substantially equal to a length of the separating material 188. For each photodiode 154, the photodiode chip 170 may include an inter-chip connection to the transistor array chip 170 through a separate vertical transfer gate 158. For example, the number of connections between the two chips 170, 172 may be determined by the number of pixels. That is, for every photodiode 154, the photodiode chip and the transistor array may include a communication pathway or interconnect for the data sensed by each photodiode 154. Using through silicon vias to provide a connection for every pixel to its control circuitry would be difficult, and require the size of the image sensor to be increased. With the vertical transfer gate, each pixel may have its own connection to the control circuitry. However, in other embodiments (see, for example, FIG. 16A) the number of inter-chip connections may be reduced as the circuitry for a set of pixels may be shared.

The image sensor 130 structure illustrated in FIGS. 8-10 may provide for an increased photon sensing area. This is because the surface area of the image sensor 130 exposed to light may include photodiodes 154 only and may not need additional control circuitry, such as one or more storage nodes or switching transistors. Thus, the exposed surface may be maximized for light collection, while the control circuitry may be positioned behind the light collection area. This may allow for the pixel architecture 134 to have substantially the same exposure area as conventional pixels, but include an increased number of pixels 136. This may provide for an increased sensitivity and resolution as compared to conventional pixels having the same surface area. Additionally or alternatively, the well size for each photodiode 154 may be increased to receive more light before reaching a saturation level, without reducing the number of pixels that can be positioned on the photodiode chip.

In some embodiments, the photodiode chip 170 may be illuminated from the backside, i.e., a bottom of the photodiode chip 170 may be in optical communication with the lens 126. The back illumination may allow the entire back surface of the photodiode chip 170 including the photodiodes 154 to be exposed to light, without the light being blocked by the transfer gate 158 or components of the transistor array.

In some embodiments, the image sensor 130 may be further configured for a global shutter mode. FIG. 11 is a simplified diagram of the photodiode chip 170 and the transistor array 172 chip including a storage gate. With reference to FIG. 11, each pixel 136 may include a storage gate 190 that defines a storage node **192**. The storage gate **190** may store a charge from the photodiode 154 in the storage node 192 region to allow a global shutter operation. For example, in a global shutter operation, each of the pixels 136 of image sensor 130 may begin charge integration at the same time. During the integration period, each of the photodiodes 154 may accumulate charge corresponding to light transmitted through the lens 126 that encounters each photodiode 154. After integration, the storage gate 190 may be activated and the charge from the photodiode 154 may be transmitted to the storage node 192 (which in some embodiments may be formed as a n-doped region beneath the storage gate 190). The data from the photodiode 154 may be held at the storage node 192 until the particular pixel 136 is ready to be read out.

When the pixel 136 is to be read out, the transfer gate 158 may be activated to transfer the charge from the storage node 192 to the floating diffusion 163 node. Once the data is stored

in the floating diffusion 163, the pixel 136 may be operated in substantially the same manner as described above with respect to FIG. 6, i.e., every pixel may be read out sequentially. During a global shutter operation, all of the pixels 136 may capture light at substantially the same time, which may decrease artifacts in an image due to an object moving. For example, during a rolling shutter operation where each pixel is sequentially integrated and read out, if an object moves between a first pixel row integration and a last row integration, the image may have blurred or distorted lines. In the 10 image sensor 130 of FIG. 11, the pixels capture light at the same time, the light is then stored, which allows for the pixels to be read out sequentially, but capture light simultaneously.

It should be noted that the vertically stacked pixel structure may allow the image sensor 130 to implement a global shutter 15 mode without requiring a significant reduction in resolution. For example, conventional image sensors having a global shutter mode may have to use a reduced number of pixels as each pixel may have to be increased in size to accommodate the additional transistor and storage node for global shutter 20 operation. The increased pixel size may result in a reduced number of pixels that fit onto a particular image sensor substrate. On the contrary, the image sensor 130 of FIG. 11 may allow a storage node 192 at each pixel 136, without sacrificing photodiode space. This is because the transfer gate **158** is 25 formed vertically and may not require space on the photodiode chip 170. Thus, the image sensor 130 may be used to capture moving objects without requiring a reduction in pixel resolution as compared to a conventional image sensor having the same light exposure surface area.

## Shared Pixel Architecture

In some embodiments, one or more components for each pixel may be shared across a group or cell of pixels. Using a stacked chip configuration, specifically, the vertical transfer gate structure illustrated above, may require small pitch inter- 35 chip connections between the photodiode chip and the transistor array chip. For example, in instances where the pixel size is small, an inter-chip connection under 2 µm may be required. However, by having groups of pixels share one or more components, the number of inter-chip connections may 40 be reduced, which may allow the size of each inter-chip connection to be increased. For example, pixel transistor sharing (e.g., sharing one or more of the source follower gate, reset gate, and/or row select gate) reduces the number of transistors per pixels. This reduction allows for smaller pixel 45 sizes and/or pixel binning functions. Having multiple pixels sharing the same inter-chip connection may also reduce the number of interchip connections and allow an increased size of the interchip connection, which reduces the complexity of the interchip connection process. It should be noted that the 50 image sensor may implement these sharing architectures without or without a vertical transfer gate (e.g., the image sensor may include a lateral transfer gate).

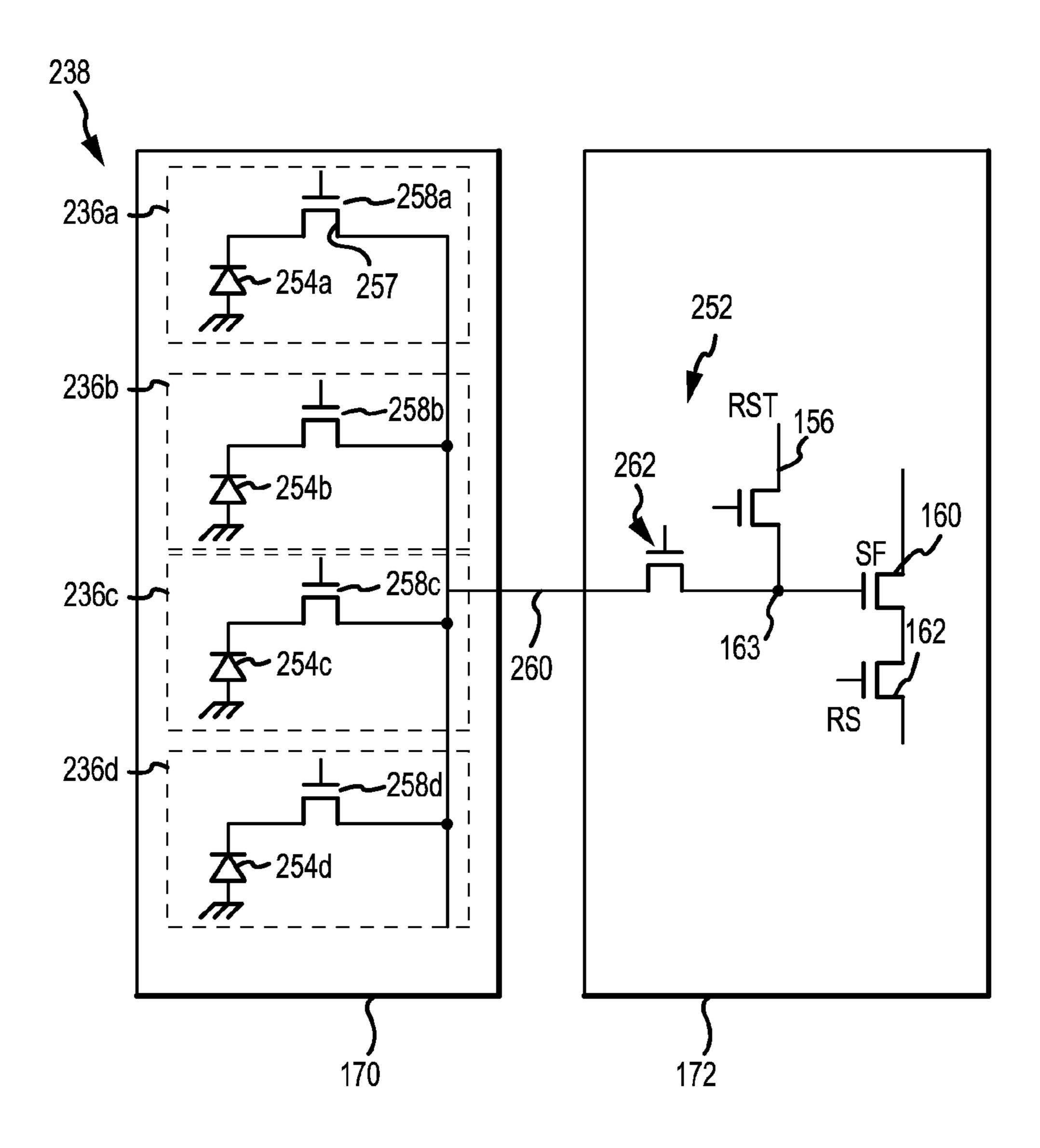

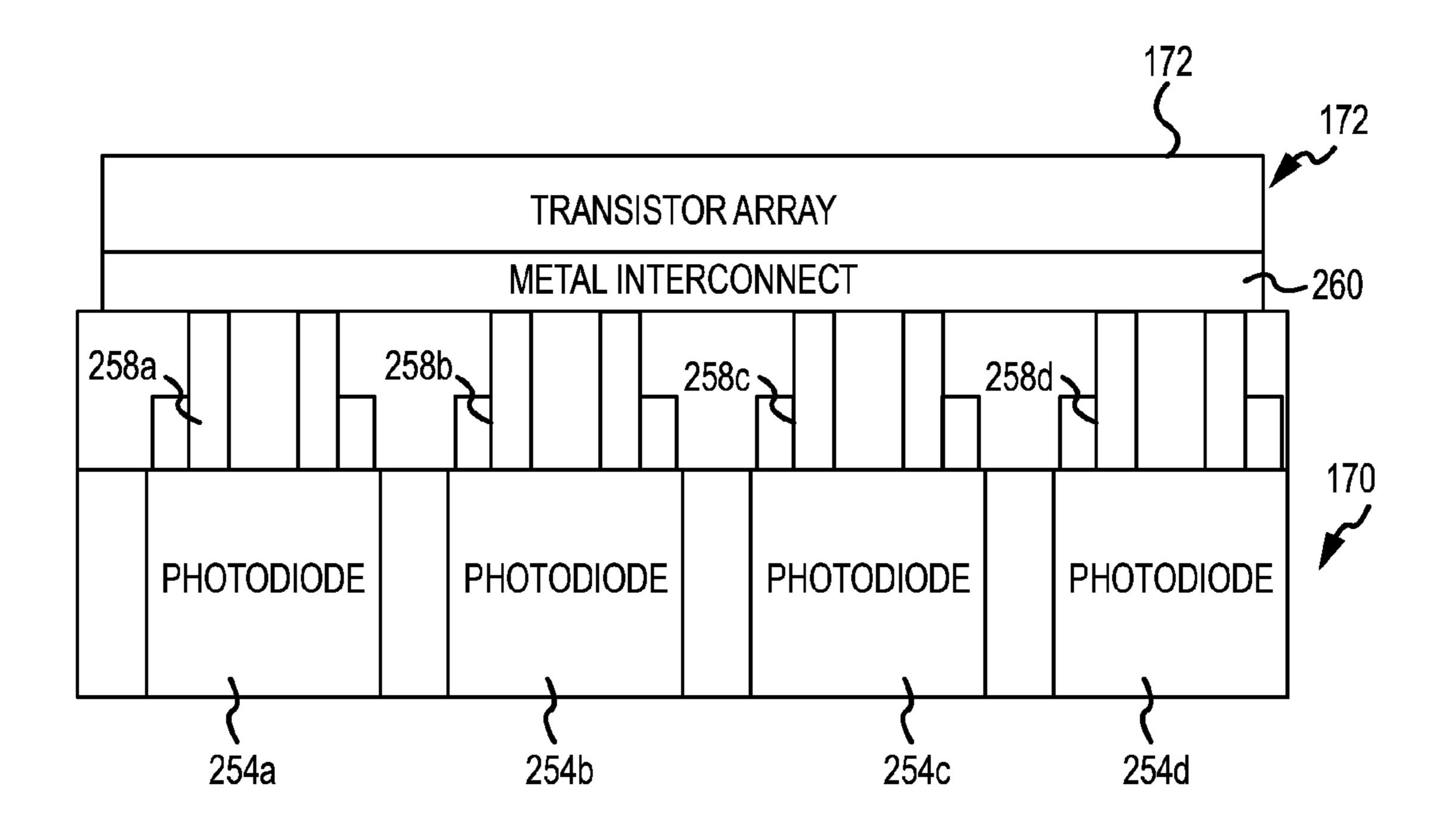

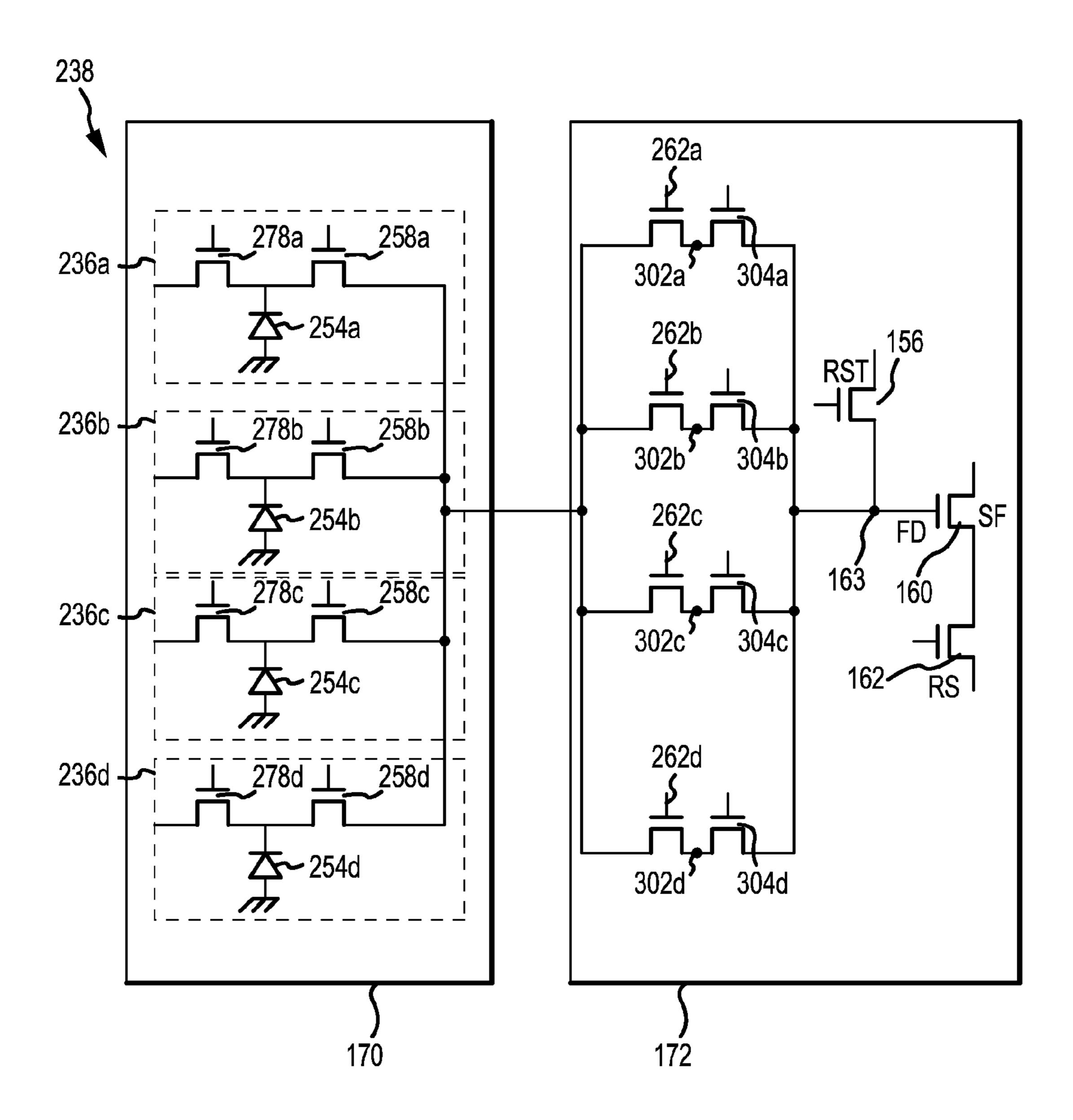

FIG. 12A is a simplified schematic view of a pixel cell having a shared control circuitry. FIG. 12B is a simplified 55 cross-section of the image sensor including the shared architecture of FIG. 12A. With reference to FIGS. 12A and 12B, a group of pixels 236a, 236b, 236c, 236d may form a pixel cell 238. In the pixel cell 238, each of the pixels 236a, 236b, 236c, 236d may include a different color filter, such as, red, green, 60 blue. For example, each pixel cell 238 may form a Bayer pixel array. In other embodiments, each of the pixels 236a, 236b, 236c, 236d may have the same color filters, no color filters, or may be otherwise varied. In the embodiment illustrated in FIGS. 12A and 12B, each of the pixels 236a, 236b, 236c, 65 236d within the pixel cell 238 may share a control circuitry 252 or transistor array. For example, each photodiode 254a,

14

254b, 254c, 254d may be connected through one or more activating or trigger transistors 258a, 258b, 258c, 258d to an interconnect 260. The interconnect 260 may connect the photodiodes 254a, 254b, 254c, 254d to the control circuitry 252.

In some embodiments, each trigger transfer gate 258a, 258b, 258c, 258d may be in communication with the interconnect 260. In this example, a drain 257 for each transfer gate may be in communication with the transistor array chip 172. Alternatively, each of the transfer gates may be interconnected or otherwise in communication at a particular node on the photodiode chip 170 and a single vertical transfer gate may extend to communicatively connect the photodiode chip 170 and the transistor array chip 172. For maximum resolution, each pixel may have its own transfer gate 158 (which may either be a vertical transfer gate as shown in FIGS. 9A-10 or may be a lateral transfer gate). In some embodiments, a transfer gate may in communication with the interconnect 260 and may be in communication with all four pixels. In other words, the transfer gate may transfer the signal from four or more pixels to the transistor array to reduce the complexity of the pixel circuitry.

With reference to FIG. 12A, the control circuitry 252 on the transistor array 272 may include a second transfer transistor 262, in addition to the rest gate 156, the SF gate 160, and the row select gate 162. The second transfer gate 262 may communicate the charge or data from each photodiode 254a, 254b, 254c, 254d to the floating diffusion node 163, the SF gate 160, and the row select gate 162.

With reference to FIGS. 12A and 12B, in operation, the lens 126 may direct light onto the image sensor 130, and specifically, onto the photodiode diodes 254a, 254b, 254c, 254d of the pixel chip 170. The photodiodes 254a, 254b, 254c, 254d may, in turn, accumulate a charge. As the charge is accumulating or after a set integration time, the trigger transfer gates 258a, 258b, 258c, 258d of each pixel 236a-236b may be selectively activated. For example, the first trigger gate 258a may be selectively activated (e.g., an activating voltage may be applied to the gate 258a) while the other trigger gates 258b, 258c, 258d of the remaining pixels 236b, 236c, 236d remain deactivated or off. In this configuration, the first photodiode **254***a* is communicatively coupled to the floating diffusion node 163 (when the second transfer transistor **262** is activated). The floating diffusion **163** may then selectively provide the charge to the SF 160 and row select 162. Once the charge from the first pixel 236a has been read out, the first trigger transistor 258a may be deselected or deactivated and the second trigger transistor 258b may be activated while the other trigger transistors remain off. The image sensor 130 may continue to read out each pixel by activating the respective trigger transistor until each of the pixels 236*a*, 236*b*, 236*c*, 236*d* within the pixel cell 238 have been read out. It should be noted that in some embodiments, each of the pixels 236a, 236b, 236c, 236d may include one more storage nodes or storage gates on the photodiode chip 170. In these implementations, the charge from the photodiodes 254a, 254b, 254c, 254d may be transferred to the storage nodes which may hold the charge until the trigger transistor is activated.

In the shared architecture of FIGS. 12A and 12B, the number of transistors required for a select pixel cell 238 may be reduced as compared to conventional image sensors. This may decrease the expense and/or complexity of the image sensor of FIGS. 12A and 12B as compared to conventional image sensors. In some embodiments, each of the transfer gates of the pixels may be connected to the metal interconnect layer. Alternatively, in other embodiments, the transfer gates

may be interconnected together at the pixel chip 170 and a single vertical transfer gate may be interconnected with the transistor array chip.

Dual Mode—Color and Monochrome

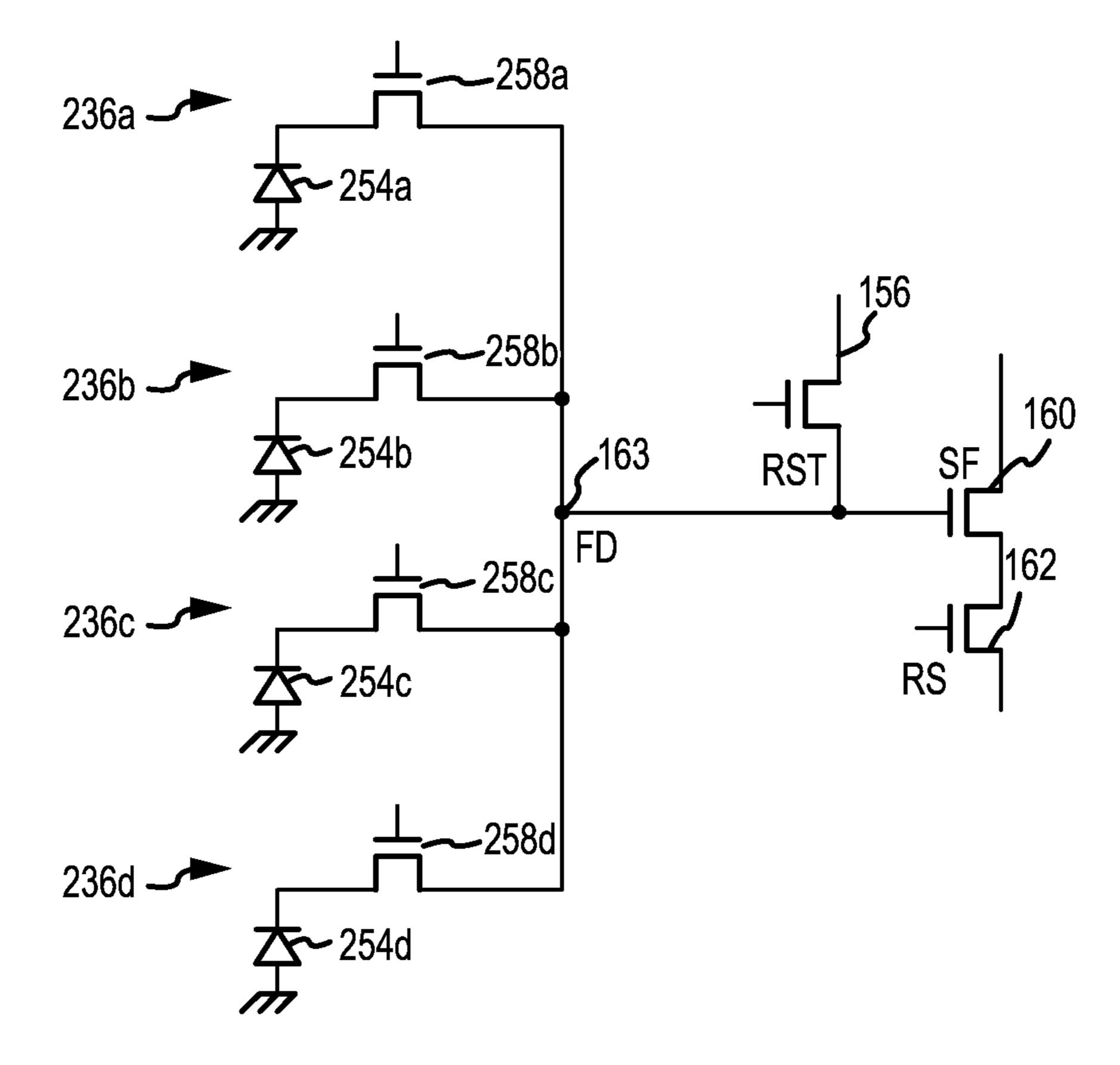

In some embodiments, the image sensor may have two or more modes. For example, the image sensor may have a monochrome mode and a color mode. In monochrome mode two or more of the pixels may be summed together, which may enhance the sensitivity of the image sensor in low light environments. In color mode, each of the pixels may be read out individually. FIGS. 12C and 12D illustrate a sharing architecture for an image sensor with a monochrome mode. In the architectures illustrated in FIGS. 12C and 12D, two or more of the photodiodes may be summed together to enhance the sensitivity of the image sensor. FIG. 12C illustrates a 15 sample architecture for a rolling shutter implementation and FIG. 12D illustrates a sample architecture for a global shutter implementation.

With reference to FIG. 12C, in a rolling shutter implementation, each pixel 236a, 236b, 236c, 236d may share the 20 floating diffusion node 163 such that if each transfer gate 258a, 258b, 258c, 258d is activated at the same time, the charge from each of the photodiodes 254a, 254b, 254c, 254d may each be transferred to the floating diffusion node 163 to then be read out.

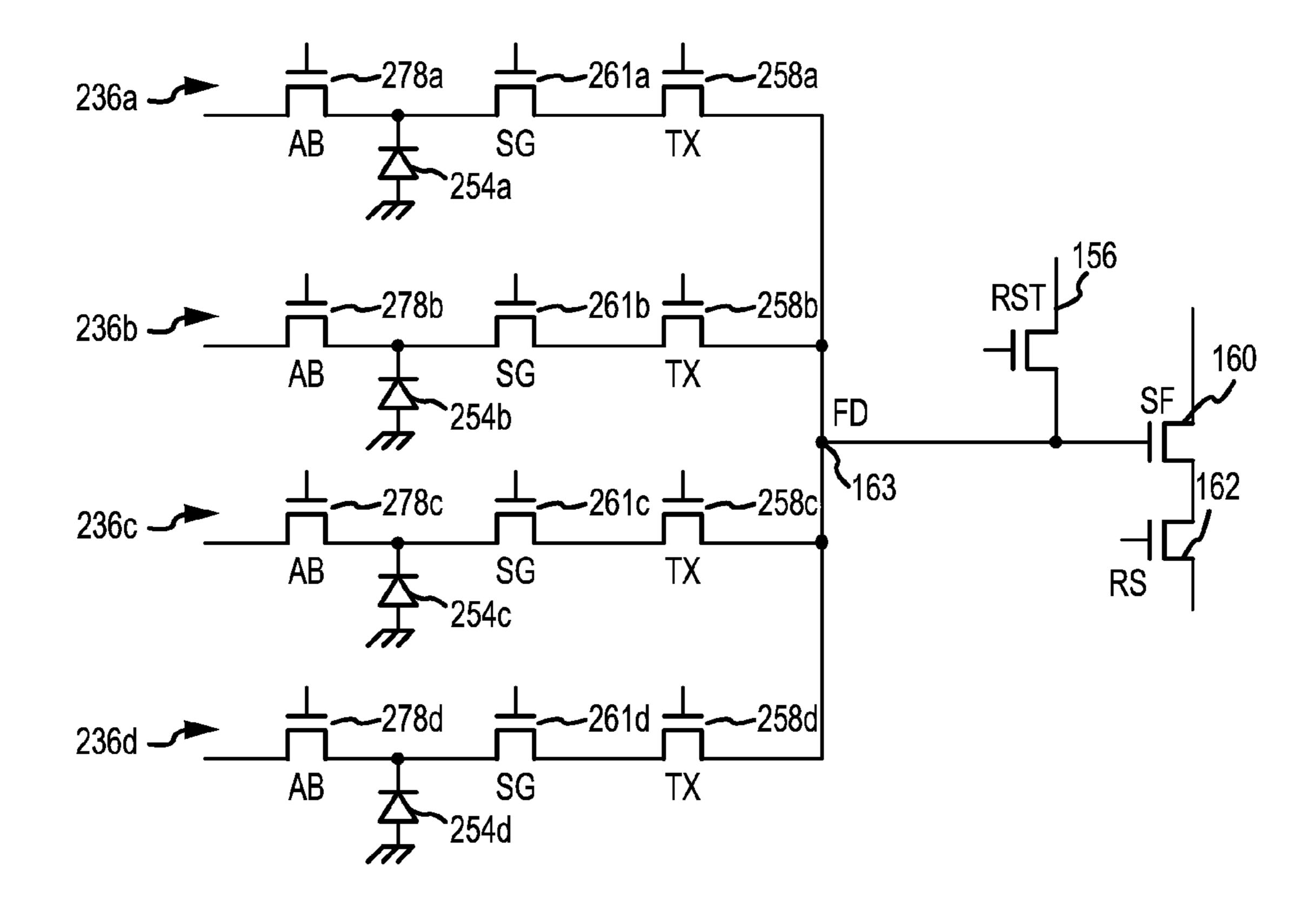

With reference to FIG. 12D, in a global shutter implementation, each pixel **236***a*, **236***b*, **236***c*, **236***d* may further include a storage gate 261a, 261b, 261c, 261d between the transfer gate 258a, 258b, 258c, 258d and the photodiode 254a, 254b, **254**c, **254**d. The storage gate **261**a, **261**b, **261**c, **261**d may 30 store the charge from the photodiodes 254a, 254b, 254c, 254d prior to the charge being transferred through the transfer gates to the floating diffusion 163. In the embodiments illustrated in FIGS. 12C and 12D, four pixels may each share a single floating diffusion node. However, in other embodiments, 35 fewer or more pixels may share the floating diffusion node or may otherwise be shared together. Alternatively, it should be noted that the shared architectures disclosed herein (e.g., FIGS. 12A-17B) may also be used to implement a monochrome mode and/or share charge from one or more of the 40 pixels. Moreover, although the below embodiments are discussed with response to a monochrome mode, in some embodiments, the image sensor may include subsets of shared pixels, which each subset having the same color filter, so that color information may not be lost.

FIG. 12E is a flow chart illustrating a method of operating a dual mode or monochrome image sensor. The method **301** may begin with operation 305 and the image sensor 130 or an ambient light sensor or other sensor may sense the light conditions. For example, the image sensor 130 may capture a 50 test image that may be analyzed to determine the lighting conditions of the object to be photographed. Once the test image has been captured or the light conditions have otherwise been sensed, the method 301 may proceed to operation **307**. In operation **307** the processor **114** may analyze the test 55 image (or signals from the one or more pixels) to determine if the light is very low light. For example, the device 100 may include a setting for determining a low threshold in which a low light mode may be activated. Alternatively, the user may analyze the test image to determine if the light is sufficiently 60 low to activate a "low light" mode.

If the light is determined to be sufficiently low, the method 301 may proceed to operation 309. In operation 309, the image sensor 130 may be switched into monochrome or low light mode. For example, during operation 309, two or more 65 pixels or groups of pixels may be communicatively coupled to share a common floating diffusion node 163 (or the pixels

**16**

may otherwise be summed together). For example, one or more sharing or grouping transistors or gates may be activated so that one or more pixels may be summed together.

However, if the light is not sufficiently low to activate monochrome or low light mode, the method 301 may proceed to optional operation 311. In operation 311, the device 100 may present an option to the user to allow an override and switch the image sensor 130 into monochrome mode. For example, the display 110 may present a "switch to monochrome mode" and allow the user to provide input to the device 100 that may override the automatic analysis of the processor regarding low light mode. After operation 311, the method 301 may proceed to operation 315 and the processor 114 may analyze a received user input. In operation 315, the processor 114 may determine whether the user provided input to change the image sensor 130 to monochrome mode.

If the user did not change the image sensor 130 into monochrome mode, the method 301 may proceed to operation 325. In operation 325, the image sensor 130 may capture an image with each individual pixel being read out individually, and optionally including one or more color filters. In this operation, the captured image may have an increased resolution and color data as compared to the monochrome mode. However, if the user did provide input to change the image sensor 130 to monochrome mode, the method 301 may proceed to operation 309.

After operation 309 and the image sensor has been switched to monochrome mode, the method 301 may proceed to operation 313. In operation 313, the image sensor 130 may capture an image. For example, the image sensor 130 may begin integration for the pixel array and each of the pixels may receive light through the lens 126. After integration, the signals for select groups of pixels may be summed together. In low light, the pixels may not exceed the full well capacity of the floating diffusion node although the signals from two or more pixels are combined. This is because due to the low level of the light signals captures, the pixels (even when combined) may not receive enough light to exceed the capacity of the floating diffusion 163. Additionally, the image captured during monochrome mode may have reduced noise, as the "cross-talk" between pixels may be eliminated. This is because each of pixels are summed together and thus color noise due to one colored pixel receiving more light than another color pixel may be rendered moot when the pixels are 45 summed together.

It should be noted that summing the pixels together may allow a monochrome mode to the activated without changing or removing any color filters that may be positioned on the pixel array 134. For example, although each of the pixels may include a color filter, when summed together, the image sensor 130 may capture images that are grayscale or monochrome. In addition to allowing the image sensor to increase it's sensitivity during low light, the monochrome option may provide a user with an option to capture black and white or grayscale images without requiring a user to change or modify the image sensor. Additionally, the monochrome mode may be implemented to capture black and white images directly, without removing the color data after the image has been captured.

After operation 313, the method 301 may proceed to operation 317. In operation 317, the processor 114 may determine whether color information for the captured image is desired. For example, the device may receive a user input that the user wishes to have color data in the captured image. If colored information is desired, the method 301 may proceed to operation 319. However, if colored information is not desired, the method 301 may proceed to an end state 327 and terminate.

In instances where colored information is desired, the method 301 may proceed to operation 319. In operation 319, the image sensor 130 may switch into color mode. In color mode, the one more groups of pixels that were shared together may be decoupled and/or one the groups of pixels having 5 similar colors may be shared together.

After operation 319, the method 301 may proceed to operation 321. In operation 321, the image sensor 130 may capture a second image, this image may include color data from the captured object or scene. Once the color image has been 10 captured, the method 301 may proceed to operation 323 and the color data from the color image may be applied to the monochrome image. In other words, the color image may capture luminance which may be "painted" onto the originally captured monochrome image. The monochrome image 15 may have an increased sensitivity as compared to the color image as the light may be sufficiently low that the sum of two or more pixels may produce more light data than the single colored pixels in the color image. By using the color data from the color image, the final image may have an increased sen- 20 sitivity, along with some color data transposed onto it. After operation 323, the method 301 may proceed to the end state **327**.

Implementing a shared pixel architecture allows the image sensor to be dual-mode, providing both color and monochrome images. Using the monochrome mode, the image sensor 130 may maximize the signal to noise ratio during low light and allow images that may be not be visible during color mode to be visible. It should be noted that this type of dual-mode operation may be implemented with substantially any of the shared pixel architectures discussed herein, and that although the discussion of the monochrome has been made with respect to FIGS. 12C-12E, other shared architectures, such as those shown in FIGS. 12A and 13-17B may be used to implement the same or similar functionality.

Additionally, it should be noted that in some embodiments, the pixels summed together may be selected that have the same color filter, which may reduce the loss of color data. However, in instances where the light may be significantly low, summing pixels of multiple color planes together, or 40 otherwise summing more pixels together may produce greater sensitivity. In some instances, the method **301** shown in FIGS. 12C and 12D may be done by sharing one floating diffusion. In this case, once the transfer gates are activated, the charge from each of the pixels may be deposited into the 45 floating diffusion node 163 at substantially the same time. Using summing, the signal may be increased without increasing the noise and summing may be done during pixel integration. Alternatively, a binning operation may be used. In this operation, pixels may be read out individually and the signals 50 may be averaged together for a select group of pixels. Using binning, the noise ratio may increases by a square root of two. Using binning, the averaging may be done after integration and may allow the user to view an image and then sum the signals together to enhance resolution.

Programmable Conversion Gain

In other embodiments, the pixel cell **238** may include a number of control circuitry pathways which may be used to vary the conversion gain for each pixel. FIG. **13** is a simplified schematic view of another example of a shared pixel architecture including multiple control pathways. With reference to FIG. **13**, the pixel group **238** may be in selective communication with a plurality of communication paths **280**, **282**, **284**, **286**. Each communication pathway may include a transfer transistors **262***a*, **262***b*, **262***c*, **262***d*, a floating diffusion 65 **288***a*, **288***b*, **288***c*, **288***d*, a reset gate **156**, a SF gate **160**, and a row select gate **162**. The reset, SF, and row select gates **156**,

**18**

160, 162 may be substantially the same for each communication pathway 280, 282, 284, 286. However, in some embodiments, each of the floating diffusion nodes 288a, 288b, 288c, 288d may be differently doped or otherwise configured to have varying properties, as will be discussed in more detail below.

In some embodiments, the floating diffusion nodes 288a, 288b, 288c, 288d may be regions formed in the transistor array chip 172 silicon that are electrically isolated from other nodes. The floating diffusion nodes 288a, 288b, 288c, 288d may each have a capacitance value. The capacitance value for each of the floating diffusion nodes may determine the conversion gain of each node, i.e., the change of the potential or voltage of the node with the addition of one electron. Because each of the floating diffusion nodes 288a, 288b, 288c, 288d, or subset thereof, may have different capacitance values, the transistor array in this example may have multiple conversion gains. In other words, each of the communication paths 280, 282, 284, 286 may have a different conversion gain from the other communication pathways.

In these embodiments, the communication pathway 280, 282, 284, 286 may be dynamically selected for each pixel based on the desired conversion gain. In other words, the particular communication pathway 280, 282, 284, 286 that is selected (e.g., by activating a select transfer transistor 262*a*-262*d*) may be activated based on a desired conversion gain. In this manner the conversion gain for each of the floating diffusions 288*a*-288*d* may be used to determine which communication pathway is activated for any of the pixels. Adjusting the conversion gain may vary the change in the output voltage due to the absorption of one charge, which may vary the sensitivity of the image sensor, speed of saturation, or the like.

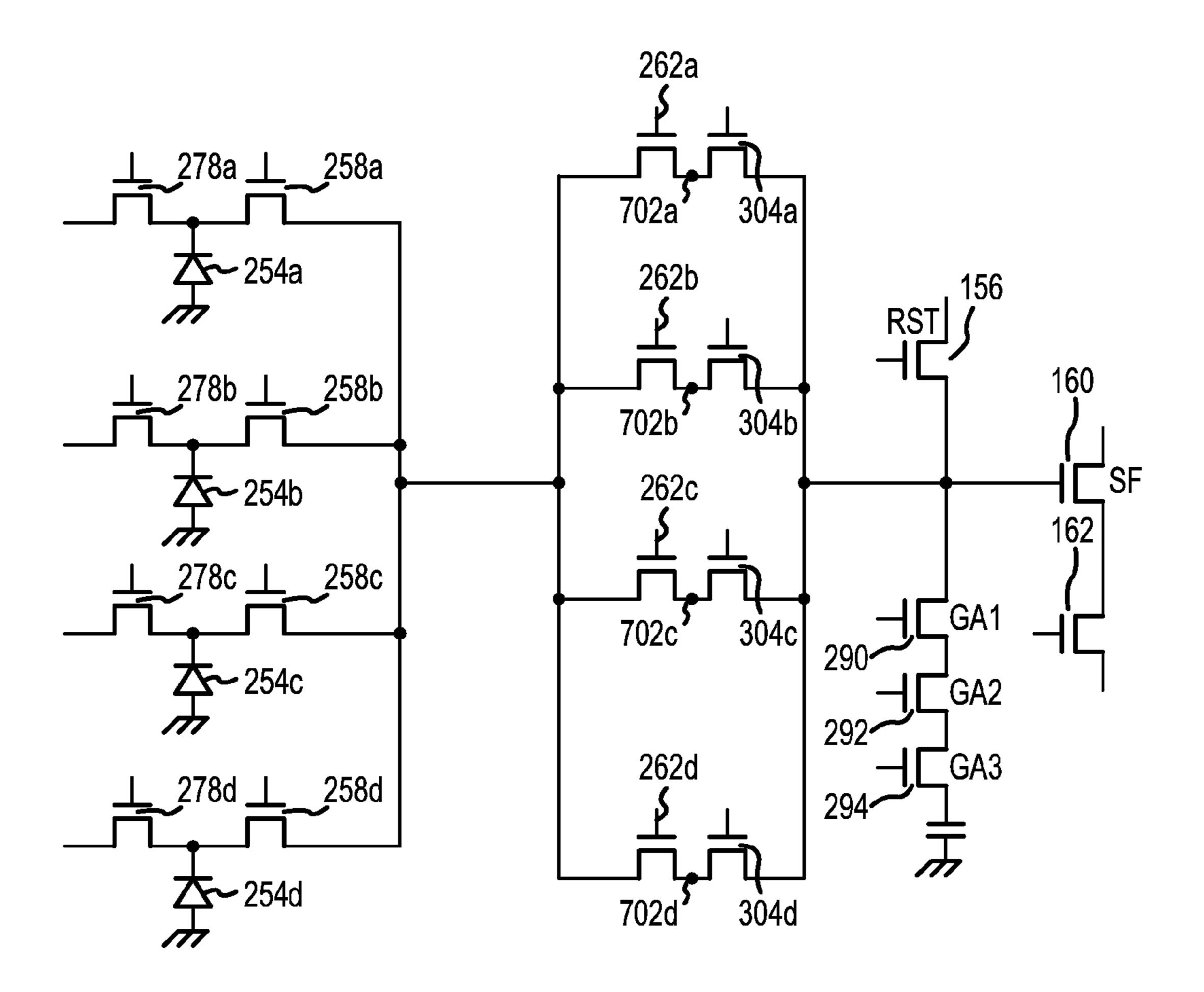

In yet another embodiment, the floating diffusion node may be dynamically adjusted for each of the pixels by adjusting the conversion gain of one or more floating diffusion nodes. FIG. 14 is a simplified schematic view of an image sensor having a shared architecture including an adjustable floating diffusion node. With reference to FIG. 14, the transistor array and control circuitry may include one transfer transistor 262, a floating diffusion node 263, and one or more conversion gain adjustment gates 290, 292, 294. The gain adjustment gates 290, 292, 294 may be operably connected to the floating diffusion node 263 between the transfer gate 262 and the SF 160.

The gain adjustment gates 290, 292, 294 may be one or more transistors coupled to one or more capacitors, the transistors may be selectively activated to vary the conversion gain at the floating diffusion node 263. For example, when the first gain adjustment gate 290 is activated, the capacitance value of the floating diffusion node 263 may be varied. Generally, the conversion gain of the floating diffusion node 263 may be inversely related to the capacitance at the node 263. By selectively activating one or more of the gain adjustment gates 290, 292, 294 (which may have the same or different capacitive values), the capacitance at the floating diffusion node 263 is varied.

For example, when all of the gain adjustment gates 290, 292, 294 are deactivated or in the off position, the floating diffusion node 163 may have a capacitance equal to the capacitive value of capacitor C1. When the first gain adjustment gates 290 is on, but the remaining gain adjustment gates 292, 294 are off, the floating diffusion node 163 has a capacitance that is equal to sum of the capacitive values of C1 and C2 (e.g., C1+C2). When the first two gain adjustment gates are on, the floating diffusion node 163 has a capacitive value equal to capacitive values C1, C2, and C3 summed together. Finally, when all of the gain adjustment gates are activated,

the floating diffusion may have the maximum capacitive value which is equal C1, C2, C3, and C4 summed together.

As demonstrated by the above example, in some embodiments, the gain adjustment gates may be activated in select groups to additively vary the capacitance at the floating diffusion node. In this example, each gain adjustment gate may provide an incremental change to the capacitive value of the floating diffusion node and, as such, a user may tailor the number of gain adjustment gates to be activated to select the conversion gain of the floating diffusion node. It should be noted that the gain adjustment gates 290, 292, 294 may be communicatively coupled to the row drivers to be selectively activated as desired. Additionally, the "on" voltage for each of the gain adjustment gates may be selected to be sufficiently high to avoid voltage drops across each gain adjustment gate. It should be noted that the capacitive values of the capacitors C1, C2, C3, and C4 may be the same or may be different from each other. In some embodiments, each of the capacitors may have a different value, which may be progressively smaller, so 20 that the value of the capacitance at the floating diffusion node may adjust in smaller increments as each additional gain adjustment gate is activated.

Using either a dynamically changing floating diffusion node (e.g., FIG. 14) or multiple floating diffusion nodes having different conversion gain values, the conversion gain for one or more pixels may be adjusted. Adjusting the conversion gain may allow the image sensor to maximize the pixel properties based on different lighting conditions and/or exposure times. For example, the image sensor may be configured to maximize the conversion gain at low light to increase the pixel output signals. Conversely, the image sensor may be configured to reduce the conversion gain during high light conditions to accommodate the increased signal charge amount from each photodiode. It should be noted that other 35 changes may be implemented as desired by the user.

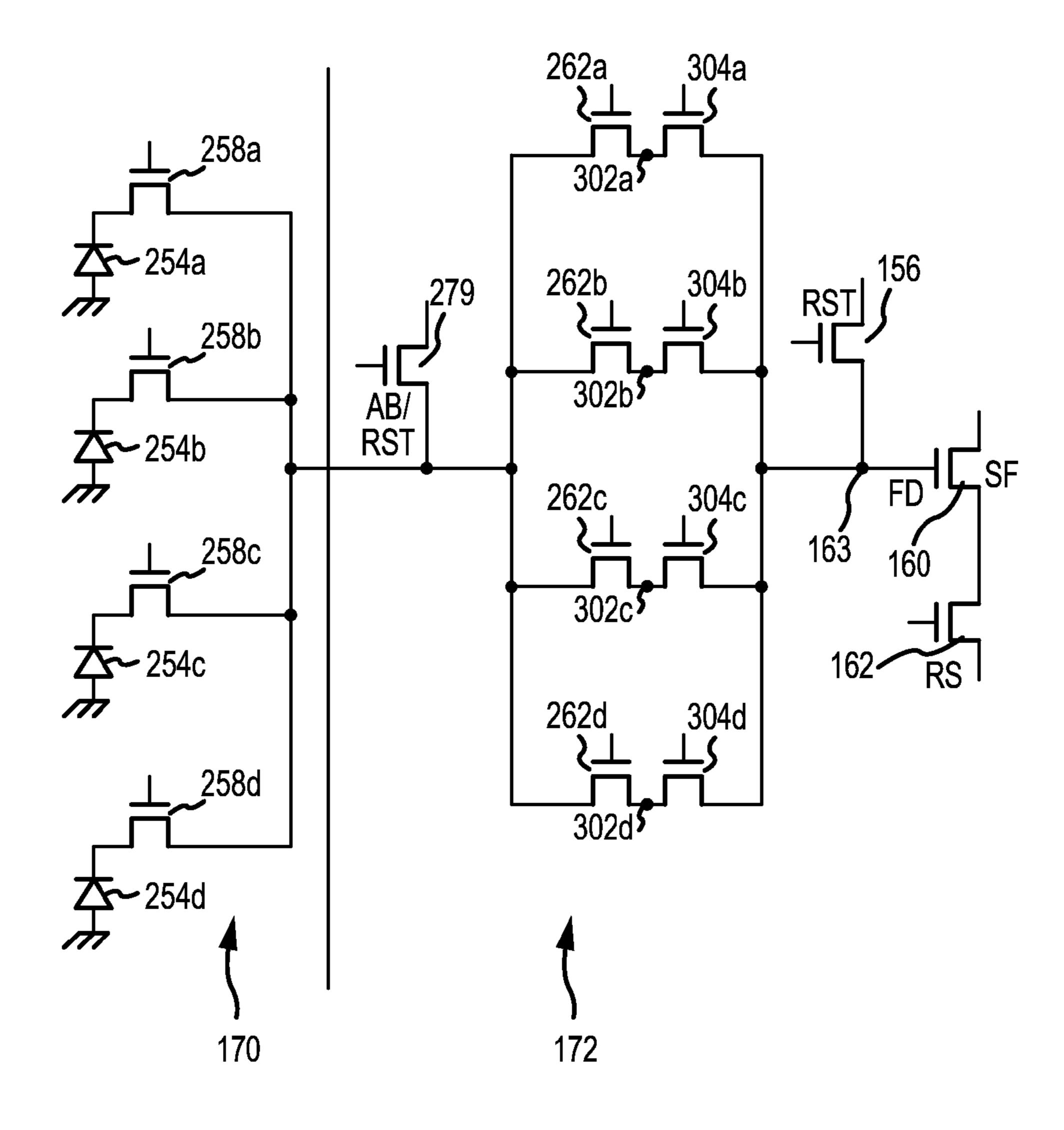

The shared pixel architecture as described above with respect to FIGS. 12-14 may be also be used in a global shutter configuration. FIG. 15A is a simplified schematic view of a pixel cell having a shared control circuitry and global shutter 40 configuration. With reference to FIG. 15A, the image sensor may include one or more anti-blooming gates 278a, 278b, 278c, 278d in communication with each photodiode 254a, 254b, 254c, 254d. It should be noted that although the antiblooming gates **278***a*, **278***b*, **278***c*, **278***d* are illustrated in FIG. 45 15A with respect to a global shutter configuration, in other embodiments, the anti-blooming gates may be incorporated into a rolling shutter configuration such as those shown in FIGS. 12-14. As described above with respect to FIG. 7, the anti-blooming gates 278a, 278b, 278c, 278d may drain excess 50 charge from the photodiodes 254a, 254b, 254c, 254d after the photodiodes have been saturated.

With continued reference to FIG. 15A, the transistor array chip 172 may include an additional transfer gate defining a storage node between the transfer gate and the floating diffusion 263. For example, the transistor array chip 170 may include a storage transfer gate 304a, 304b, 304c, 304d positioned between the transfer gates 262a, 262b, 262c, 262d and the SF 160 for each communication pathway. A storage node 302a, 302b, 302c, 302d may be defined between the transfer gates 262a, 262b, 262c, 262d and the storage transfer gates 304a, 304b, 304c, 304d. The storage nodes 302a, 302b, 302c, 302d store the charge transferred from the photodiode chip 172, that is, the charge from each of the photodiodes 254a, 254b, 254c, 254d prior to the charge being read out. In this manner, each of the photodiodes 254a, 254b, 254c, 254d may integrate at substantially the same time, but once the data has

**20**

been transferred to the storage nodes 302a, 302b, 302c, 302d, the data from each pixel may be read out sequentially.

As is explained in more detail below, the shared architecture illustrated in FIG. 15A may provide for an "effective" global shutter. In these embodiments, pixels in each group may be read out within the pixel cell individually, but the values for each pixel cell or group may be read out collectively. In this implementation, as the "rolling shutter" occurs only in the individual pixels within each cell and the "rolling" 10 time for the image sensor may only be the time to read out four pixel rows (or the number of pixels within the pixel cell). Each pixel cell is read out globally and therefore the only time difference between the readout between the first pixel row in the image sensor and the last pixel row in the image sensor is the time to read out each of the four pixel rows in each pixel cell. This time difference is a substantially smaller time difference as compared to a conventional rolling shutter where time difference between the readout of the first pixel row and the last pixel row is determined by the entire number of rows in the pixel array. Thus, in these effective global shutter configurations, the final image is very close to those of an actual global shutter.

In some embodiments, the global shutter configuration illustrated in FIG. 15A may be modified to allow a pixel group or cell to share a SF gate, a reset gate, and/or a row select gate. FIG. 15B is a simplified schematic of a global shutter shared architecture configuration. With reference to FIG. 15B, each of the pixels 236a-236d may be in communication with the reset gate 156, the SF gate 160, and the row select gate 162. In this manner, the number of transistors on the transistor array chip 172 may be reduced, as there may only be a single set of control gates 156, 160, 162 for a group of four or more pixels. The circuit may operate in substantially the same manner as described above with respect to FIG. 15A. However, in this example, the data from each of the photodiodes 254a-254d may remain within the storage nodes 302a-302d until the storage transfer gates 254*a*-254*d* are activated to provide the data to the SF 160 and eventually to the read out circuitry (e.g., column select 142).

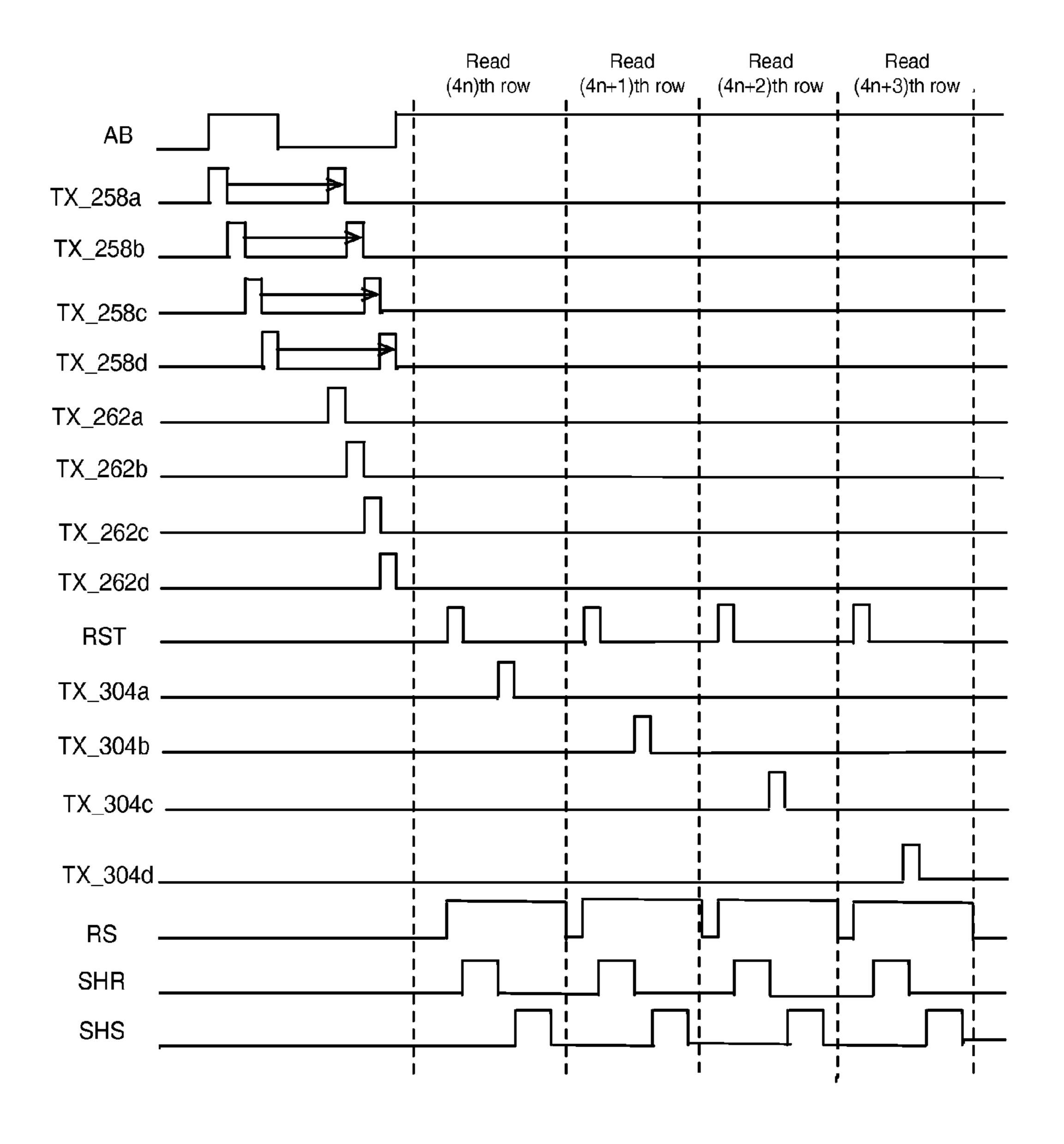

Effective Global Shutter Using Rolling Shutter Configuration As briefly explained above, in embodiments, the shared architecture may be configured to provide a hybrid between a global shutter and rolling shutter implementation. In this example, select pixels may be read out sequentially, but the pixels may be grouped into cells, and each of the cells may be read out globally. FIG. 16A is a simplified schematic view of a four pixel cell. FIG. 16B is a timing diagram for the schematic of FIG. 16A. With reference to FIG. 16A, the pixel cell 138 may include four pixels 136, which may each share an anti-blooming/reset gate 279. In some embodiments, the antiblooming/reset gate 279 may be a vertical gate extending between the photodiode chip 170 and the transistor array chip 172. This may allow the two chips 170, 172 to have a single inter-chip connection between the two chips. By reducing the number of inter-chip connections, the pitch between the two chips may be increased, and the complexity in creating the connection may be reduced.