#### US008598675B2

# (12) United States Patent Wang

# I E EOD

# US 8,598,675 B2

### (45) Date of Patent:

## Dec. 3, 2013

# (54) ISOLATION STRUCTURE PROFILE FOR GAP FILLING

(75) Inventor: Shiang-Bau Wang, Pingzchen (TW)

(73) Assignee: Taiwan Semiconductor Manufacturing

Company, Ltd., Hsin-Chu (TW)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 13/024,577

(22) Filed: Feb. 10, 2011

### (65) Prior Publication Data

US 2012/0205774 A1 Aug. 16, 2012

(51) Int. Cl. *H01L 21/70*

(2006.01)

(52) **U.S. Cl.**

(58) Field of Classification Search

#### (56) References Cited

(10) Patent No.:

#### U.S. PATENT DOCUMENTS

| 2009/0072355 A1 3/2009 Cheng et al. | 2007/0072389 A1*<br>2007/0194402 A1<br>2008/0318392 A1<br>2009/0045482 A1 | 3/2007<br>8/2007<br>12/2008<br>2/2009 | Lee |  |

|-------------------------------------|---------------------------------------------------------------------------|---------------------------------------|-----|--|

|-------------------------------------|---------------------------------------------------------------------------|---------------------------------------|-----|--|

<sup>\*</sup> cited by examiner

Primary Examiner — Douglas Menz

(74) Attorney, Agent, or Firm — Haynes and Boone, LLP

#### (57) ABSTRACT

An trench isolation structure and method for manufacturing the trench isolation structure are disclosed. An exemplary trench isolation structure includes a first portion and a second portion. The first portion extends from a surface of a semiconductor substrate to a first depth in the semiconductor substrate, and has a width that tapers from a first width at the surface of the semiconductor substrate to a second width at the first depth, the first width being greater than the second width. The second portion extends from the first depth to a second depth in the semiconductor substrate, and has substantially the second width from the first depth to the second depth.

#### 20 Claims, 6 Drawing Sheets

**100**

FIG.

FIG. 2

FIG.

# ISOLATION STRUCTURE PROFILE FOR GAP FILLING

#### BACKGROUND

The semiconductor integrated circuit (IC) industry has experienced rapid growth. In the course of IC evolution, functional density (i.e., the number of interconnected devices per chip area) has generally increased while geometry size (i.e., the smallest component (or line) that can be created 10 using a fabrication process) has decreased. This scaling down process generally provides benefits by increasing production efficiency and lowering associated costs. Such scaling down has also increased the complexity of processing and manufacturing ICs and, for these advances to be realized, similar 15 developments in IC manufacturing are needed. For example, because a trench isolation structure's aspect ratio increases as device technology nodes scale down, filling the trench isolation structure, such as a shallow trench isolation (STI) structure, has become complex and costly. Conventional trench 20 isolation structure profiles and processes for filling the trench isolation structures implement complex and costly combinations of etching, deposition, annealing, and curing processes to achieve adequate filling. Accordingly, although existing trench isolation structure profiles and methods for filling <sup>25</sup> these trench isolation structures have been generally adequate for their intended purposes, they have not been entirely satisfactory in all respects.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The present disclosure is best understood from the following detailed description when read with the accompanying figures. It is emphasized that, in accordance with the standard practice in the industry, various features are not drawn to scale 35 and are used for illustration purposes only. In fact, the dimensions of the various features may be arbitrarily increased or reduced for clarity of discussion.

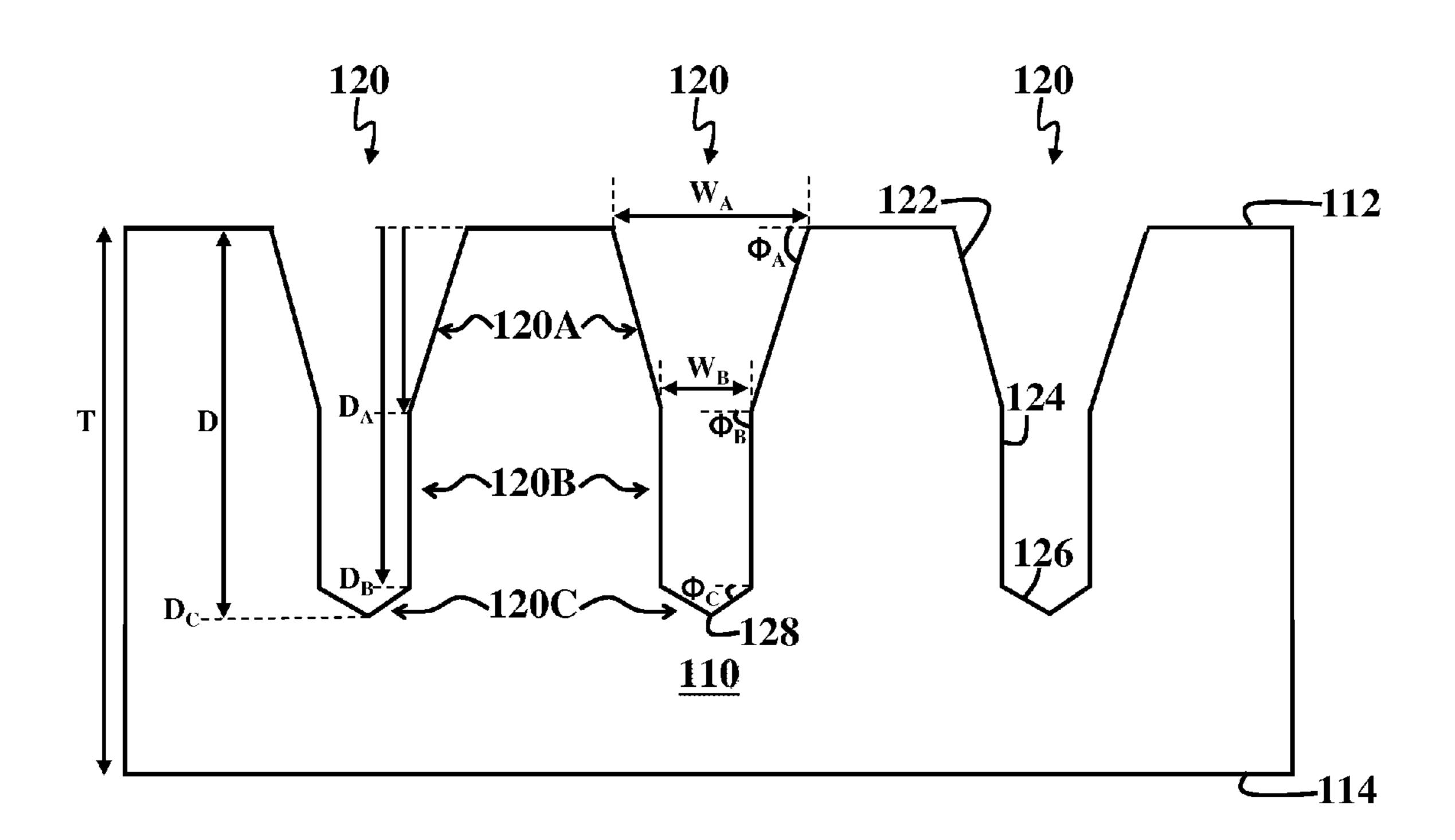

FIG. 1 is a diagrammatic cross-sectional view of an embodiment of a device that includes a trench isolation struc- 40 ture according to various aspects of the present disclosure.

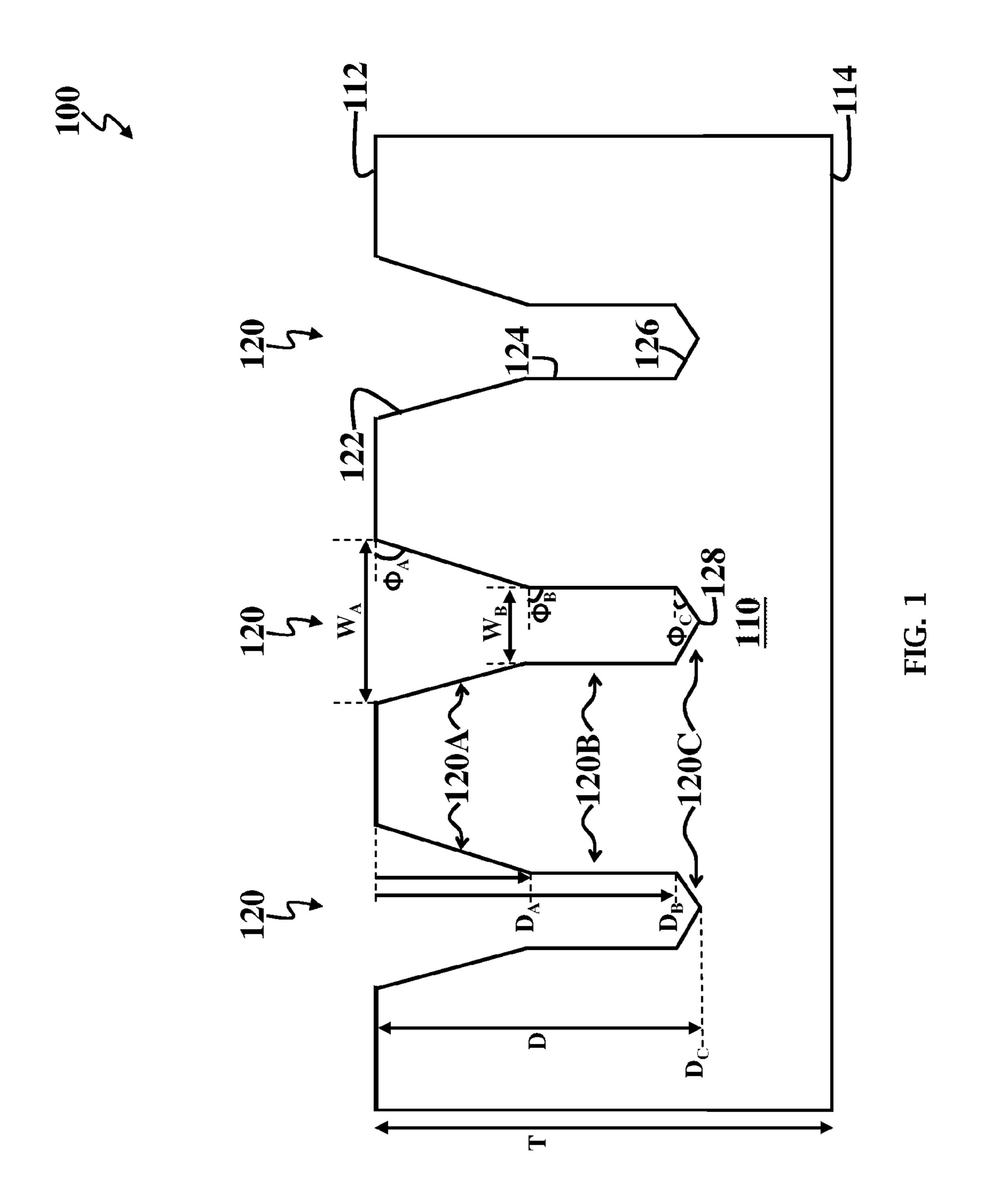

FIGS. 2A and 2B are diagrammatic cross-sectional views of the device of FIG. 1 according to various aspects of the present disclosure.

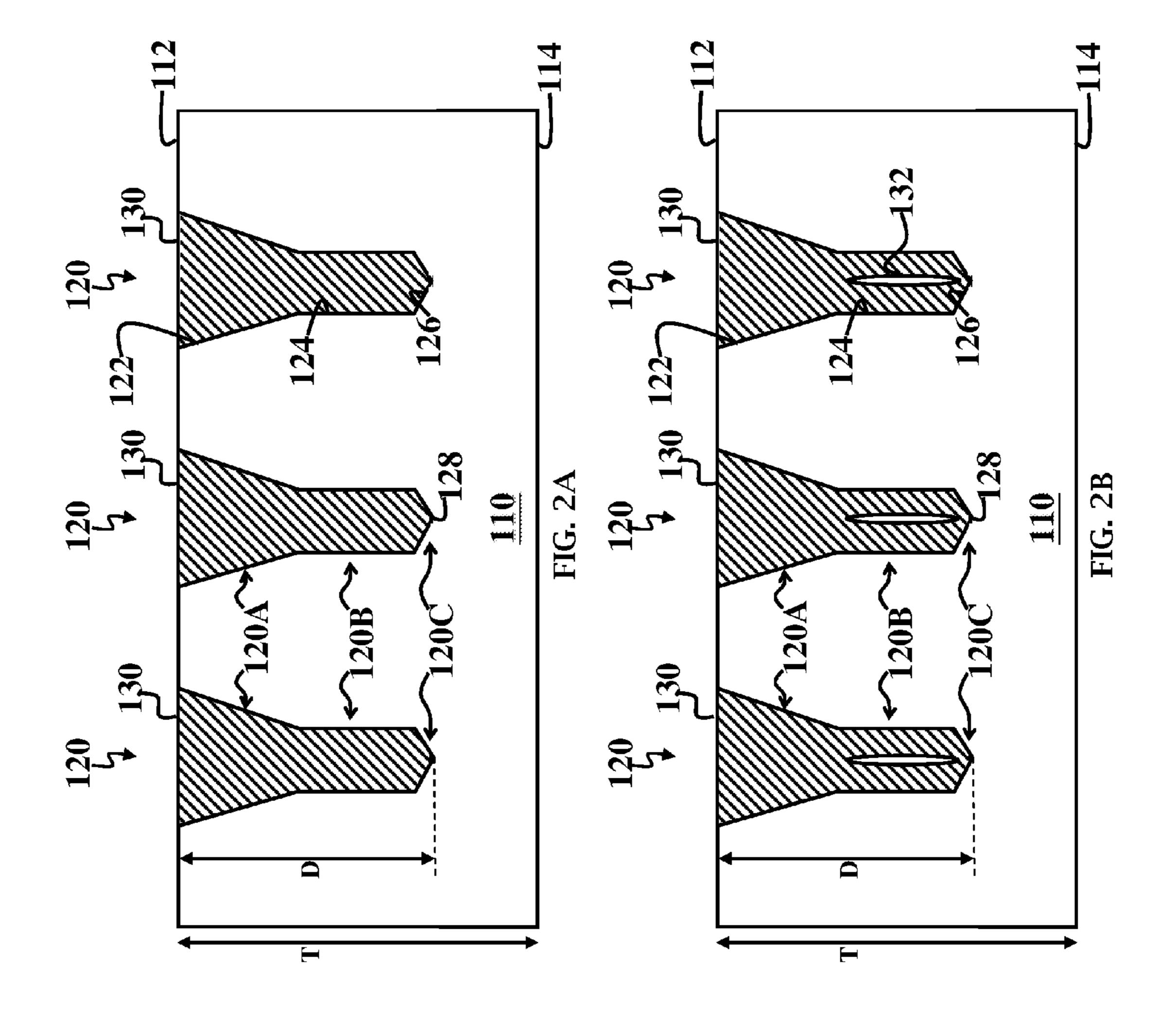

FIG. 3 is a flow chart of a method for fabricating a trench isolation structure according to various aspects of the present disclosure.

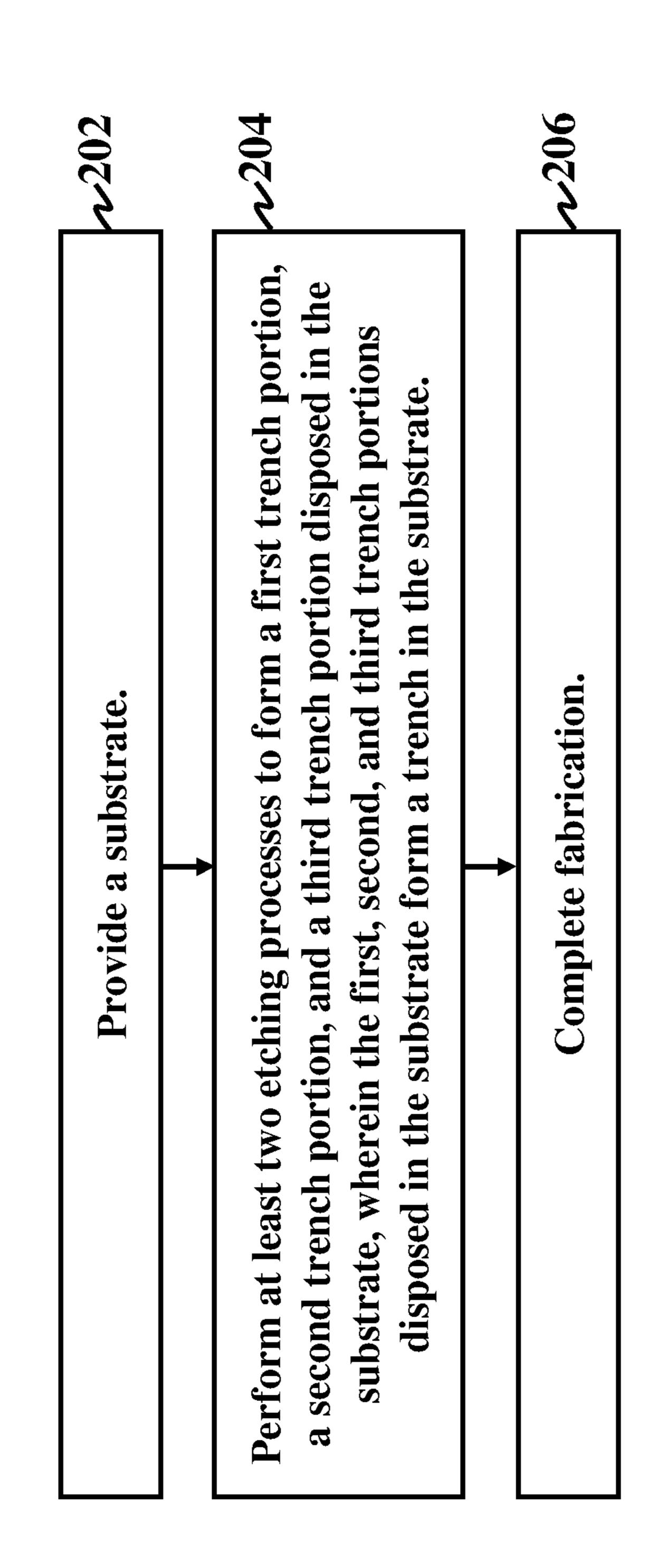

FIGS. **4-6** are various diagrammatic cross-sectional views of an embodiment of a device that includes a trench isolation structure during various fabrication stages according to the 50 method of FIG. **3**.

#### DETAILED DESCRIPTION

The following disclosure provides many different embodiments, or examples, for implementing different features of the invention. Specific examples of components and arrangements are described below to simplify the present disclosure. These are, of course, merely examples and are not intended to be limiting. For example, the formation of a first feature over or on a second feature in the description that follows may include embodiments in which the first and second features are formed in direct contact, and may also include embodiments in which additional features may be formed between the first and second features, such that the first and second features may not be in direct contact. In addition, the present disclosure may repeat reference numerals and/or letters in the

2

various examples. This repetition is for the purpose of simplicity and clarity and does not in itself dictate a relationship between the various embodiments and/or configurations discussed.

Further, spatially relative terms, such as "beneath," "below," "lower," "above," "upper" and the like, may be used herein for ease of description to describe one element or feature's relationship to another element(s) or feature(s) as illustrated in the figures. The spatially relative terms are intended to encompass different orientations of the device in use or operation in addition to the orientation depicted in the figures. For example, if the device in the figures is turned over, elements described as being "below" or "beneath" other elements or features would then be oriented "above" the other elements or features. Thus, the exemplary term "below" can encompass both an orientation of above and below. The apparatus may be otherwise oriented (rotated 90 degrees or at other orientations) and the spatially relative descriptors used herein may likewise be interpreted accordingly.

FIG. 1 is a diagrammatic cross-sectional view of an embodiment of a device 100 that includes a trench isolation structure according to various aspects of the present disclosure. FIG. 1 has been simplified for the sake of clarity to better understand the inventive concepts of the present disclosure. Additional features can be added in the trench isolation structure 100, and some of the features described below can be replaced or eliminated for additional embodiments of the trench isolation structure 100.

In FIG. 1, the device 100 includes a substrate 110. The 30 substrate may be doped p-type or n-type. In the depicted embodiment, the substrate 110 is a semiconductor substrate including silicon. Alternatively or additionally, the substrate 110 includes another elementary semiconductor, such as germanium and/or diamond; a compound semiconductor including silicon carbide, gallium arsenic, gallium phosphide, indium phosphide, indium arsenide, and/or indium antimonide; an alloy semiconductor including SiGe, GaAsP, AlInAs, AlGaAs, GaInAs, GaInP, and/or GaInAsP; or combinations thereof. The substrate 110 may be a semiconductor on insulator (SOI). The substrate 110 may include a doped epi layer, a gradient semiconductor layer, and/or a semiconductor layer overlying another semiconductor layer of a different type, such as a silicon layer on a silicon germanium layer. The substrate 110 has a surface 112 and a surface 114 that is opposite the surface 112. A thickness, T, of the substrate 110 is measured between the surfaces 112 and 114.

The device 100 includes a trench isolation structure having trenches 120 disposed in the substrate 110. In the depicted embodiment, the trench isolation structure includes three trenches 120 disposed in the substrate 110. The trench isolation structure may include less trenches, for example only one, or more trenches, depending on design requirements of the device 100. For ease of discussion, the following will limit discussion to a single trench 120. In the depicted embodiment, the trench 120 extends from the substrate surface 112 to a depth, D, in the substrate 110. D is less than the thickness, T, of the substrate 110. In an example, the trench 120 has a depth, D, from about 1,000 Å to about 3,000 Å. As discussed further below, the trench 120 has a profile that enhances filling of the trench 120 with a material, such as a dielectric material. More specifically, the trench 120 has a profile that includes a first portion 120A, a second portion 120B, and a third portion **120**C.

The first portion 120A extends from the substrate surface 112 to a depth,  $D_A$ , in the substrate 110. In the depicted embodiment, the depth,  $D_A$ , is from about 100 Å to about 2,500 Å. A width of the first portion 120A tapers from the

substrate surface 112 to the depth,  $D_A$ . For example, the first portion 120A has a width,  $W_A$ , at the substrate surface 112; a width,  $W_B$ , at the depth,  $D_A$ ; and a width that ranges between  $W_A$  and  $W_B$  between the substrate surface 112 and the depth,  $D_A$ . In an example,  $W_A$  is from about 15 nm to about 45 nm, and  $W_B$  is about 5 nm to about 25 nm. The first portion 120A includes a sidewall 122 that extends at an angle,  $\Phi_A$ , from the substrate surface 112 to the depth,  $D_A$ . In the depicted embodiment,  $\Phi_A$  between the substrate surface 112 and the sidewall 122 is less than about 85°. In another example,  $\Phi_A$  between the substrate surface 112 and the sidewall 122 is less than or equal to about 83°.

The second portion 120B is disposed below the first portion 120A. The second portion 120B extends from the depth,  $D_A$ ,  $_{15}$ in the substrate 110 to a depth,  $D_B$ , in the substrate 110. In the depicted embodiment, the depth,  $D_B$ , is from about 1,000 Å to about 3,000 Å. A width of the second portion 120B is substantially the same from depth,  $D_A$ , to depth,  $D_B$ . For example, the second portion 120B has a width of about  $W_B$  from depth, 20  $D_A$ , to depth,  $D_B$ . In an example, as noted above,  $W_B$  is about 5 nm to about 25 nm. The second portion 120B includes a sidewall 124 that extends from the sidewall 122 of the first portion 120A to the depth,  $D_B$ . The sidewall 124 is substantially perpendicular to the substrate surface 112. For example, 25 an angle,  $\Phi_B$ , between the substrate surface 112 and the sidewall **124** is less than about 120°. In the depicted embodiment, the angle,  $\Phi_B$ , between the substrate surface 112 and the sidewall **124** is about 90°.

The third portion 120C is disposed below the second portion 120B. The third portion 120C extends from the depth,  $D_R$ , in the substrate 110 to a depth,  $D_C$ , in the substrate 110. In the depicted embodiment, the depth,  $D_C$ , is equal to the depth, D, of the trench 120, and thus, the depth,  $D_C$ , is from about 1,000 Å to about 3,500 Å. A width of the third portion 120C 35 tapers from the depth,  $D_B$ , to the depth,  $D_C$ . For example, the third portion 120C has the width,  $W_B$ , at the depth,  $D_B$ ; a width that is about 0 at the depth,  $D_C$ ; and a width that ranges between  $W_B$  and 0 between the depth,  $D_B$ , and the depth,  $D_C$ . In an example, as noted above,  $W_B$  is about 5 nm to about 25 40 FIG. 3. nm. The third portion 120C includes a sidewall 126 that extends from the sidewall 124 to the depth,  $D_C$ . In the depicted embodiment, since the width of the third portion **120**C tapers to about 0, the sidewall **128** tapers to a point **128**. The point 128 may be rounded point or other suitable shaped 45 point. Further, in the depicted embodiment, an angle,  $\Phi_C$ , between the substrate surface 112 and the sidewall 128 is less than or equal to about 45°.

Referring to FIGS. 2A and 2B, the trenches 120 may be filled with an insulating material **130**. The insulating material 50 130 includes a dielectric material, such as silicon oxide, silicon nitride, silicon oxynitride, other suitable materials, or combinations thereof. In the depicted embodiment, the insulating material 130 includes a high density plasma (HDP) oxide, a high aspect ratio process (HARP) oxide, a flowable 55 chemical vapor deposition (CVD) oxide, or combinations thereof. The insulating material 130 that fills the trenches 120 may have a multi-layer structure, such as a thermal oxide liner layer formed on the sidewalls of the trenches 120 and a silicon nitride or silicon oxide layer formed over the thermal oxide 60 liner layer. In the depicted embodiment, the filled trenches 120 isolate various regions of the substrate 110. For example, the filled trenches 120 may isolate various devices (not shown) of the device 100. In the depicted embodiment, the filled trenches 120 are shallow trench isolation (STI) struc- 65 tures that define and electrically isolate various regions of the device 100.

4

The disclosed trench profile facilitates complete filling of the trenches 120 as depicted in FIG. 2A, or the trench profile limits any void 132 formed in the trenches 120 to the second portion 120B and/or third portion 120C of the trenches 120. Confining any void 132 to the bottom portion of the trench, particularly the second portion 120B and/or third portion **120**C, ensures that the void will not degrade device performance. For example, if the void 132 were to form in the first portion 130A, the void 132 would likely be filled with a 10 conductive material during subsequent processing, which would degrade device performance. The disclosed trench profile thus facilitates filling of the trench 120 in a way that eliminates the void 132 or confines the void 132 to a portion of the trench 120 that will not interfere with device integrity. As discussed further below, since the disclosed trench profile promotes improved filling of the trench 120 using HDP oxide and HARP oxide deposition processes, the disclosed trench profile reduces manufacturing costs by requiring fewer and less costly processing steps than conventional trench profiles.

FIG. 3 is a flow chart of an embodiment of a method 200 for fabricating a trench isolation structure according to various aspects of the present disclosure. The method 200 begins at block 202 where a substrate is provided. At block 204, at least two etching processes are performed to form a first trench portion, a second trench portion, and a third trench portion disposed in the substrate. The first, second, and third trench portions disposed in the substrate form a trench in the substrate. The method **200** continues with block **206** where fabrication of the trench isolation structure is completed. For example, the trench may be filled with a dielectric material. In an example, the trench is filled with an oxide material formed by a HDP deposition process, a HARP deposition process, a flowable CVD process, other suitable deposition process, or combinations thereof. Additional steps can be provided before, during, and after the method 200, and some of the steps described can be replaced or eliminated for additional embodiments of the method. The discussion that follows illustrates various embodiments of the trench isolation structure that can be fabricated according to the method 200 of

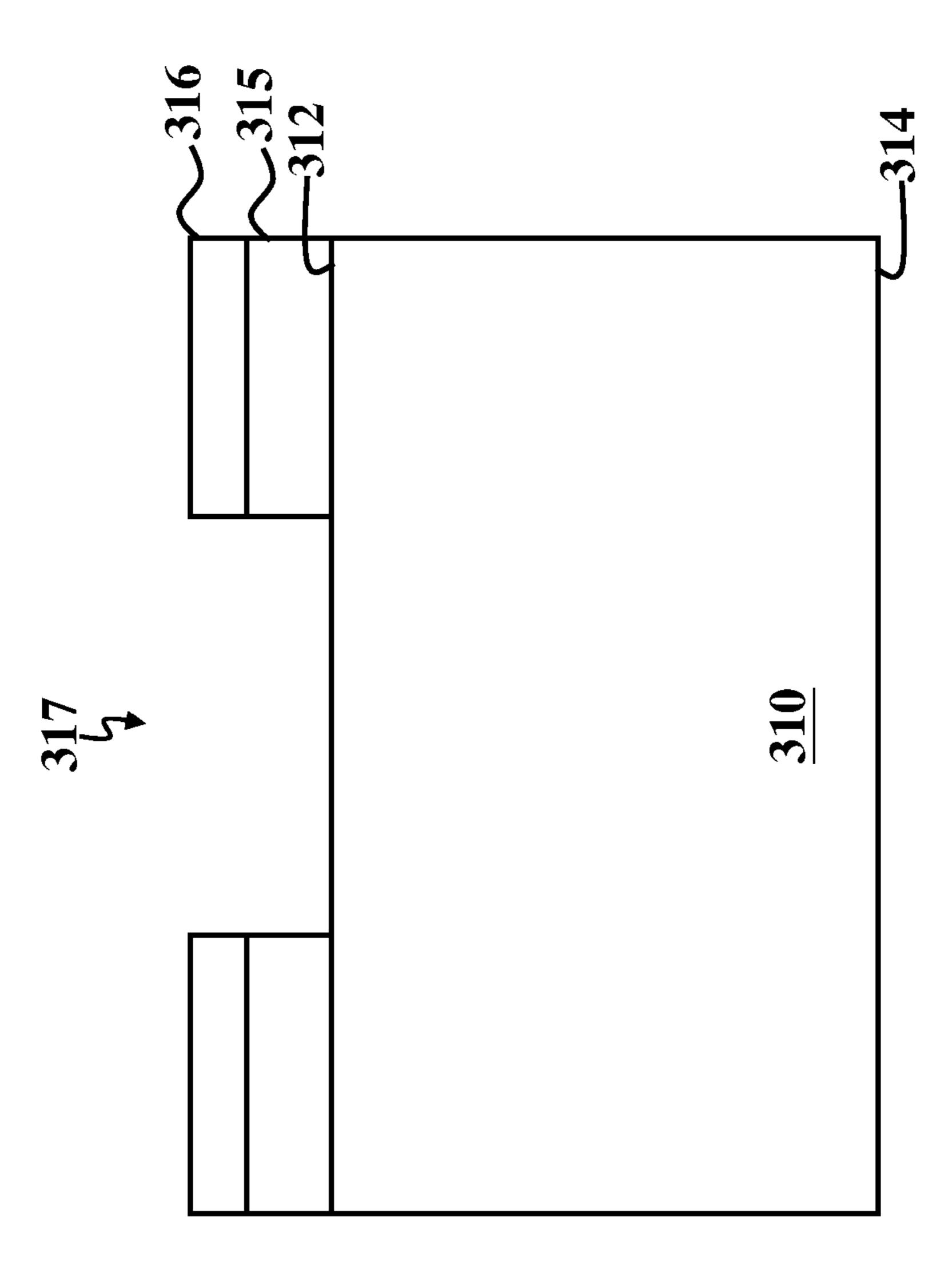

FIGS. **4-6** are various diagrammatic cross-sectional views of an embodiment of an integrated circuit device 300 during various fabrication stages according to the method 200 of FIG. 3. In the depicted embodiment, the integrated circuit device 300 includes a trench isolation structure. The integrated circuit device 300 may include an integrated circuit (IC) chip, system on chip (SoC), or portion thereof, that includes various passive and active microelectronic components, such as resistors, capacitors, inductors, diodes, metaloxide-semiconductor field effect transistors (MOSFET), complementary MOS (CMOS) transistors, bipolar junction transistors (BJT), laterally diffused MOS (LDMOS) transistors, high power MOS transistors, fin-like field effect transistors (FinFET), other suitable components, or combinations thereof. The trench isolation structure may isolate the various devices of the integrated circuit device 300. FIGS. 4-6 have been simplified for the sake of clarity to better understand the inventive concepts of the present disclosure. Additional features can be added in the integrated circuit device 300, and some of the features described below can be replaced or eliminated for additional embodiments of the integrated circuit device 300.

In FIG. 4, a substrate 310 is provided. In the depicted embodiment, the substrate 310 is a semiconductor substrate including silicon. The substrate may be doped p-type or n-type. Alternatively or additionally, the substrate 310 includes another elementary semiconductor, such as germa-

nium and/or diamond; a compound semiconductor including silicon carbide, gallium arsenic, gallium phosphide, indium phosphide, indium arsenide, and/or indium antimonide; an alloy semiconductor including SiGe, GaAsP, AlInAs, AlGaAs, GaInAs, GaInP, and/or GaInAsP; or combinations thereof. The substrate 310 may be a semiconductor on insulator (SOI). The substrate 310 may include a doped epi layer, a gradient semiconductor layer, and/or a semiconductor layer overlying another semiconductor layer of a different type, such as a silicon layer on a silicon germanium layer.

In the depicted embodiment, the substrate 310 has a surface 312 and a surface 314 that is opposite the surface 312. A thickness of the substrate 310 is measured between the surfaces 312 and 314. The substrate may be a p-type or an n-type substrate depending on design requirements of the integrated circuit device 300. P-type dopants that the substrate 310 are doped with include boron, gallium, indium, other suitable p-type dopants, or combinations thereof. N-type dopants that the substrate 310 can be doped with include phosphorus, arsenic, other suitable n-type dopants, or combinations 20 thereof. The substrate 310 may include various p-type doped regions and/or n-type doped regions. Doping may be implemented using a process such as ion implantation or diffusion in various steps and techniques.

A patterning layer 315 is disposed over the substrate sur- 25 face 312, and a patterning layer 316 is disposed over the patterning layer 316. In the depicted embodiment, patterning layers 315 and 316 include a dielectric material, such as silicon oxide, silicon nitride, silicon oxynitride, other suitable dielectric material, or combinations thereof. For example, the 30 patterning layer 315 is a silicon nitride layer, and the patterning layer 316 is an oxide layer. Alternatively, the patterning layer 315 and/or patterning layer 316 may be a resist, such as a photoresist. The patterning layers 315 and 316 include an opening 317 that exposes a portion of the substrate surface 35 312. The opening 317 may be formed by a lithography and etching process. The lithography process may include photoresist coating (e.g., spin-on coating), soft baking, mask aligning, exposure, post-exposure baking, developing the photoresist, rinsing, drying (e.g., hard baking), other suitable 40 processes, or combinations thereof. Alternatively, the lithography exposing process may be include maskless photolithography, electron-beam writing, or ion-beam writing. The etching processes include dry etching, wet etching, other etching methods, or combinations thereof. In an example, 45 forming the opening 317 may include forming the patterning layers 315 and 316 over the substrate surface 312, forming a photoresist layer over the patterning layer 316, exposing and developing the photoresist layer to have an opening therein that exposes the patterning layer **316**, and etching the exposed 50 patterning layer 316 and underlying patterning layer 315 until the portion of the substrate surface **312** is exposed.

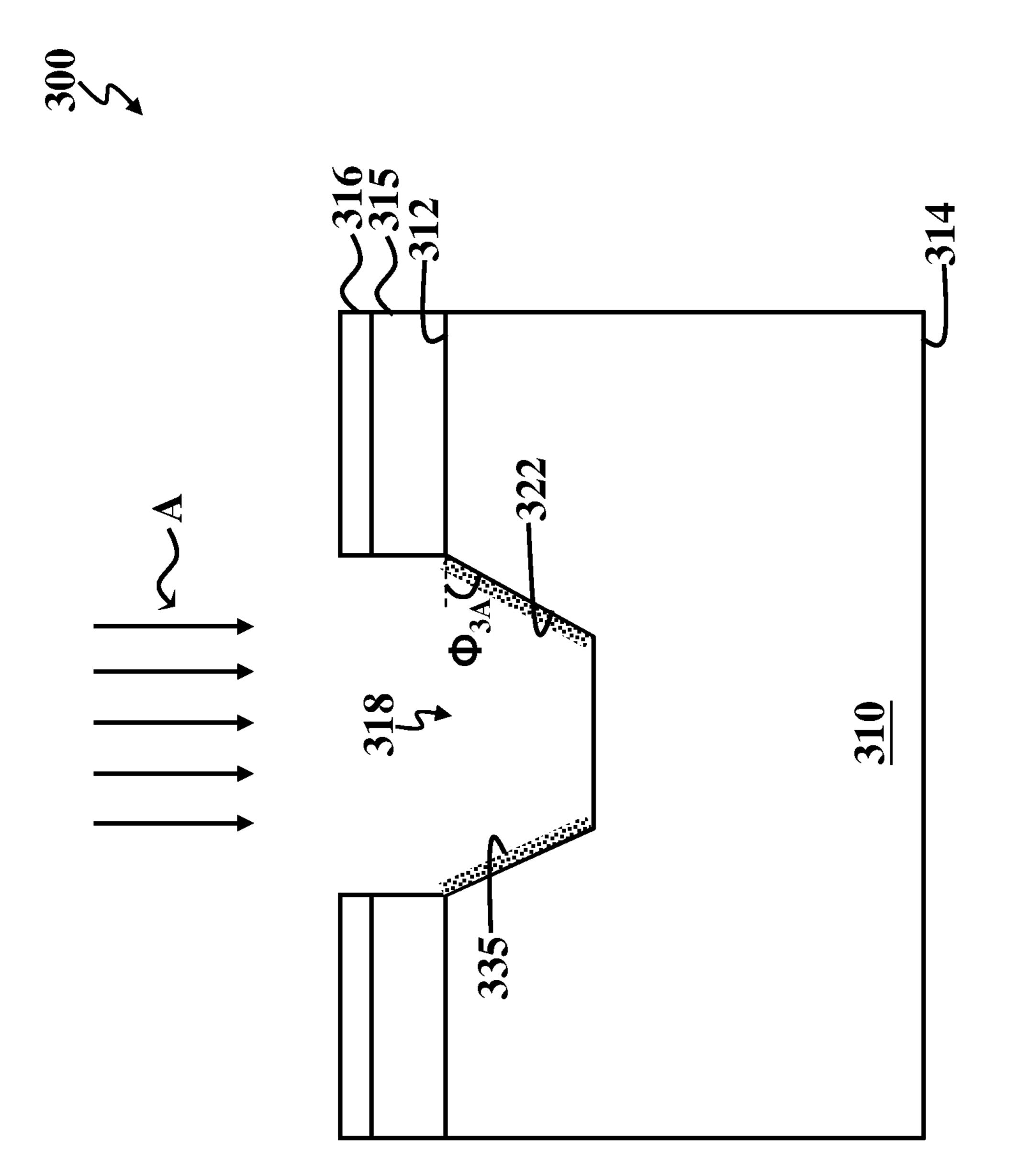

In FIG. 5, an etching process A removes exposed portions of the substrate 310 to form trench 318 in the substrate 310. The etching process A is controlled to achieve a desired 55 profile of the trench 318. More specifically, the etching process A uses a polymer rich gas that is tuned to achieve a first trench portion (such as first trench portion 120A described with reference to FIGS. 1 and 2A-2B) having a tapered profile, such as that illustrated in FIG. 5. The trench 318 has a sidewall 322 that extends from the substrate surface 312 into the substrate 310. An angle,  $\Phi_{3,4}$ , between the substrate surface 312 and the sidewall 322 is less than about 85°. In the depicted embodiment, the etching process A is a dry etching process. The dry etching process has etching parameters that can be tuned, such as etchants used, etching pressure, source power, radio-frequency (RF) bias voltage, RF bias power,

6

etchant flow rate, and other suitable parameters. For example, an etching pressure of about 1 mT (milli-Torr) to about 50 mT may be used, a source power of about 500 W (Watts) to about 2,000 W, and an etchant that includes a carbon fluoride containing gas (such as CH<sub>2</sub>F<sub>2</sub>, CH<sub>3</sub>F, C<sub>2</sub>F<sub>6</sub>, C<sub>3</sub>F<sub>8</sub>, C<sub>4</sub>F<sub>6</sub>, C<sub>4</sub>F<sub>8</sub>, or combinations thereof), a chlorine containing gas (such as Cl<sub>2</sub>), an oxygen containing gas (such as O<sub>2</sub>), a hydrogen containing gas (such as HBr, CH<sub>4</sub>, or combinations thereof), other suitable gases, or combinations thereof may be used. In an example, the etching process A uses an etching pressure of about 1 mT to about 50 mT, a source power of about 500 W to about 2,000 W, an RF bias voltage of about 50 V (Volts) to about 300 V, a CH<sub>2</sub>F<sub>2</sub> gas flow of about 15 secm (standard cubic centimeters per minute) to about 45 sccm, a Cl<sub>2</sub> gas flow of about 40 seem to about 120 seem, an O<sub>2</sub> gas flow of about 5 secm to about 20 secm, and an HBr gas flow of about 200 sccm to about 500 sccm. The etching profile of the trench 318 has a suitable depth. During the etching process, a polymer layer 335 forms on sidewalls 322 of the trench 318. The polymer layer 335 will prevent subsequent etching processes from affecting the tapered profile of the trench 318, thereby ensuring that the angle,  $\Phi_{3A}$ , between the substrate surface **312** and the sidewall remains less than about 85°.

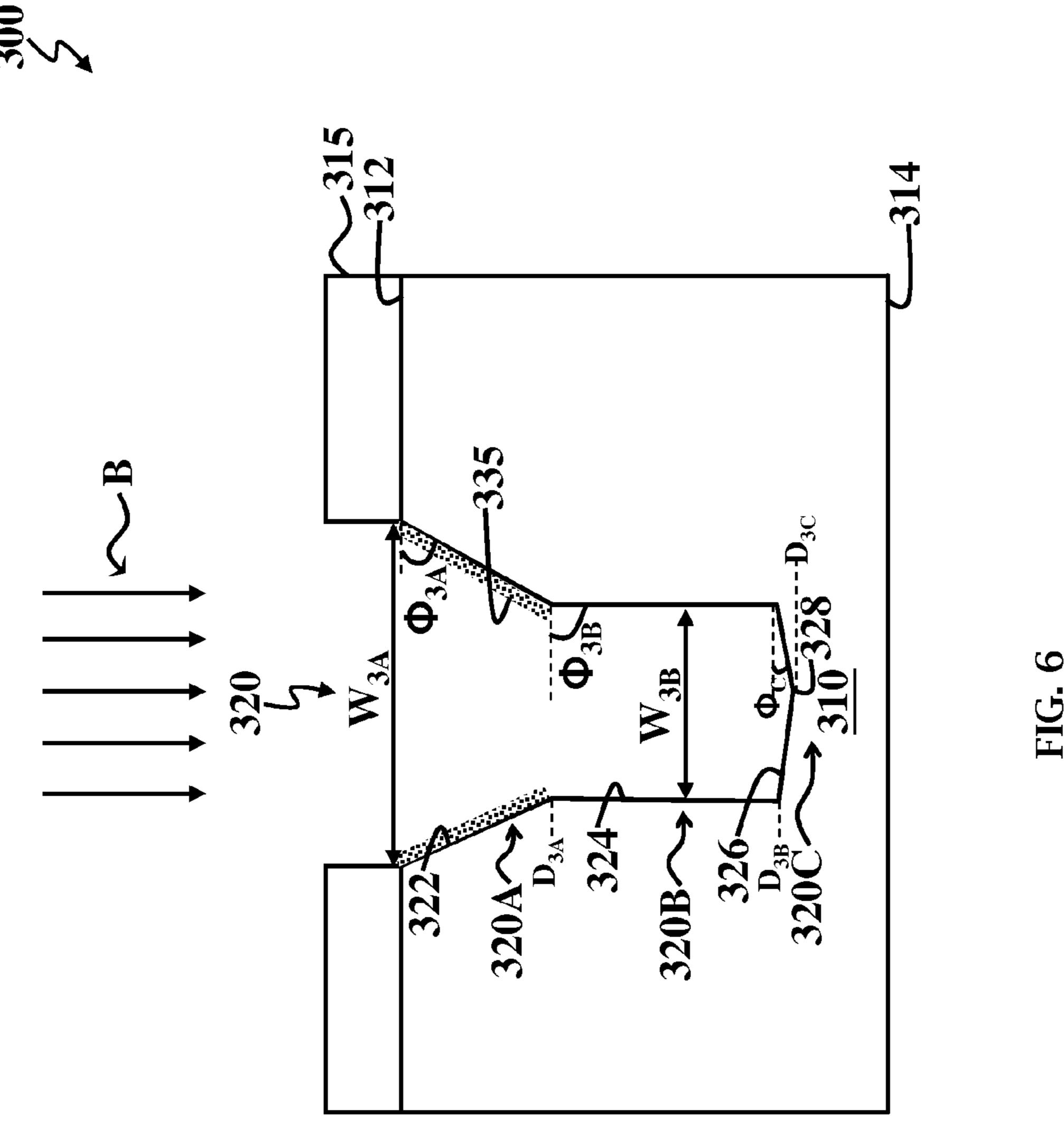

After the etching process A, portions of the substrate 310 remain exposed in the trench 318. In FIG. 6, an etching process B removes exposed portions of the substrate 310 to form trench 320 in the substrate 310. The etching process B uses a leaner chemistry than etching process A that is controlled to achieve a desired trench profile for the trench 320. More specifically, the etching process B is tuned to achieve a first trench portion 320A, a second trench portion 320B, and a third trench portion **320**C. During the etching process B, the leaner chemistry can form a slight passivation layer that facilitates forming the second trench portion 320B with a vertical profile. Because etching process B uses a leaner chemistry, the etching process B (particularly gases used in the etching process) will generate less of a passivation layer on the trench sidewalls when compared to etching process A. In the depicted embodiment, the etching process B is a dry etching process. The dry etching process has etching parameters that can be tuned, such as etchants used, etching pressure, source power, radio-frequency (RF) bias voltage, RF bias power, etchant flow rate, and other suitable parameters. Particularly, the etching process may be tuned to achieve a vertical profile of second trench portion 320B of the trench **320**. For example, an etching pressure of about 1 mT (milli-Torr) to about 50 mT may be used, a source power of about 200 W (Watts) to about 1,000 W, and an etchant that includes a fluorine containing gas (such as SF<sub>6</sub>, CH<sub>2</sub>F<sub>2</sub>, CF<sub>4</sub>, CH<sub>3</sub>F, C<sub>2</sub>F<sub>6</sub>, C<sub>3</sub>F<sub>8</sub>, C<sub>4</sub>F<sub>6</sub>, C<sub>4</sub>F<sub>8</sub>, NF<sub>3</sub>, or combinations thereof), a chlorine containing gas (such as Cl<sub>2</sub>), a nitrogen containing gas (such as  $N_2$ ), an oxygen containing gas (such as  $O_2$ ), a hydrogen containing gas (such as HBr, CH<sub>4</sub>, or combinations thereof), a helium containing gas (such as He), other suitable gasses, or combinations thereof may be used. In an example, the etching process B uses an etching pressure of about 1 mT to about 50 mT, a source power of about 200 W to about 1,000 W, an RF bias voltage of about 20 V (Volts) to about 200 V, an SF<sub>6</sub> gas flow of about 20 sccm to about 100 sccm, a CH<sub>2</sub>F<sub>2</sub> gas flow of about 30 secm to about 100 secm, a N<sub>2</sub> gas flow of about 30 sccm to about 150 sccm, an He gas flow of about 50 seem to about 300 seem.

In FIGS. 5 and 6, the etching processes A and B achieve a trench profile that enhances subsequent filling of the trench 320. The first portion 320A, second portion 320B, and third portion 320C form a funnel-shaped trench profile that has a vertical portion positioned between two tapered portions. The

first portion 320A extends from the substrate surface 312 to a depth,  $D_{34}$ , in the substrate 310. In the depicted embodiment, the depth,  $D_{34}$ , is from about 100 Å to about 2,500 Å. A width of the first portion 320A tapers from the substrate surface 312 to the depth,  $D_{34}$ . For example, the first portion 320A has a 5 width,  $W_{3A}$ , at the substrate surface 312; a width,  $W_{3B}$ , at the depth,  $D_{3A}$ ; and a width that ranges between  $W_{3A}$  and  $W_{3B}$ between the substrate surface 312 and the depth,  $D_{34}$ . In an example,  $W_{3A}$  is from about 15 nm to about 45 nm, and  $W_{3B}$ is about 5 nm to about 25 nm. The first portion 320A includes the sidewall 322 that extends at the angle,  $\Phi_{34}$ , from the substrate surface 312 to the depth,  $D_{34}$ . As noted above, in the depicted embodiment,  $\Phi_{3A}$  between the substrate surface 312 and the sidewall 322 is less than about 85°. In another example,  $\Phi_{3A}$  between the substrate surface 312 and the sidewall **322** is less than or equal to about 83°.

The second portion 320B is disposed below the first portion 320A. The second portion 320B extends from the depth,  $D_{34}$ , in the substrate 310 to a depth,  $D_{3B}$ , in the substrate 310. In the 20depicted embodiment, the depth,  $D_{3B}$ , is from about 100 Å to about 3,000 Å. A width of the second portion 320B is substantially the same from depth,  $D_{3A}$ , to depth,  $D_{3B}$ . For example, the second portion 320B has a width of about  $W_{3R}$ from depth,  $D_{3A}$ , to depth,  $D_{3B}$ . In an example, as noted 25 above,  $W_{3B}$  is about 5 nm to about 25 nm. The second portion **320**B includes a sidewall **324** that extends from the sidewall 322 of the first portion 320A to the depth,  $D_{3B}$ . The sidewall **324** is substantially perpendicular to the substrate surface **312**. For example, an angle,  $\Phi_{3B}$ , between the substrate sur- 30 face 312 and the sidewall 324 is less than about 120°. In the depicted embodiment, the angle,  $\Phi_{3B}$ , between the substrate surface 312 and the sidewall 324 is about 90°.

The third portion 320C is disposed below the second portion 320B. The third portion 320C extends from the depth, 35  $D_{3B}$ , in the substrate 310 to a depth,  $D_{3C}$ , in the substrate 310. In the depicted embodiment, the depth,  $D_{3C}$ , is a depth of the trench 320. In an example, the depth,  $D_{3C}$ , is from about 1,000 Å to about 3,500 Å. A width of the third portion 320C tapers from the depth,  $D_{3B}$ , to the depth,  $D_{3C}$ . For example, the third 40 portion 320C has the width,  $W_{3B}$ , at the depth,  $D_{3B}$ ; a width that is about 0 at the depth,  $D_{3C}$ ; and a width that ranges between  $W_{3B}$  and 0 between the depth,  $D_{3B}$ , and the depth,  $D_{3C}$ . In an example, as noted above,  $W_{3B}$  is about 5 nm to about 25 nm. The third portion 320C includes a sidewall 326 45 that extends from the sidewall 324 to the depth,  $D_{3C}$ . In the depicted embodiment, since the width of the third portion **320**C tapers to about 0, the sidewall **328** tapers to a point **328**. The point 328 may be rounded point or other suitable shaped point. Further, in the depicted embodiment, an angle,  $\Phi_{3C}$ , 50 between the substrate surface 312 and the sidewall 328 is less than or equal to about 45°.

The disclosed trench profile of the trench 320, which is achieved by the etching processes A and B, facilitates adequate filling of the trench 320 using conventional insulating materials, such as a dielectric material. For example, the trench 320 may be filled with silicon oxide, silicon nitride, silicon oxynitride, other suitable materials, or combinations thereof. In an example, the insulating material filling the trench 320 includes a HDP oxide, a HARP oxide, a flowable 60 CVD oxide, or combinations thereof. The insulating material that fills the trench 320 may have a multi-layer structure, such as a thermal oxide liner layer formed on the sidewalls of the trenches 320 and a silicon nitride or silicon oxide layer formed over the thermal oxide liner layer. The filled trench 65 320 isolates various regions of the substrate 310. In an example, the filled trench 320 may be a shallow trench isola-

8

tion (STI) structure that defines and electrically isolates various regions of an integrated circuit device.

The disclosed trench profile of the trench 320 facilitates complete filling of the trench, or confines any void formed in the insulating material to the second portion 320B and/or third portion 320C of the trench 320. Confining voids to the bottom portion of the trench, particularly the second portion 320B and/or third portion 320C, ensures that the void will not degrade device performance. The disclosed trench profile thus facilitates filling of the trench 320 in a way that eliminates voids or confines voids to a portion of the trench 320 that will not interfere with device integrity. Since the disclosed trench profile promotes improved filling of the trench 320 using HDP oxide and HARP oxide deposition processes, the disclosed trench profile eliminates the need for more complex and costly processes used to fill trenches at smaller technology nodes, such as 20 nm technology nodes and below. Instead, the disclosed trench profile is formed and filled with reduced manufacturing costs. It is understood that different embodiments may have different advantages, and that no particular advantage is necessarily required of any embodiment.

The present disclosure provides for many different embodiments. For example, a trench isolation structure includes a first trench isolation portion, a second trench isolation portion, and third trench isolation portion. The first trench isolation portion has a first sidewall that extends from a surface of a semiconductor substrate to a first depth in the semiconductor substrate, where a first angle between the first sidewall and the surface of the semiconductor substrate is less than or equal to about 85°. The second trench isolation portion has a second sidewall that extends from the first sidewall at the first depth to a second depth in the semiconductor substrate, where a second angle between the second sidewall and the surface of the semiconductor substrate is about 90°. The third trench isolation portion has a third sidewall that extends from the second sidewall at the second depth to a third depth in the semiconductor substrate, where a third angle between the third sidewall and the surface of the semiconductor substrate is less than 90°, for example, less than or equal to about 45°.

The first trench isolation portion may have a width that tapers from a first width at the surface of the semiconductor substrate to a second width at the first depth, the first width being greater than the second width. The second trench isolation portion may have a width that is substantially equal to the second width from the first depth to the second depth. The third trench isolation portion may have a width that tapers from the second width at the second depth to a third width at the third depth, the second width being greater than the third width. A bottom portion of the third isolation portion may be a rounded point. The first, second, and third trench isolation portions may be filled with an insulating material. Any void in the insulating material may be confined within the second trench isolation portion, third trench isolation portion, or both the second and third trench isolation portions.

In another example, a device includes a semiconductor substrate and a trench in the semiconductor substrate. The trench includes a first portion, a second portion, and a third portion. The first portion extends from a surface of a semiconductor substrate to a first depth in the semiconductor substrate, and has a width that tapers from a first width at the surface of the semiconductor substrate to a second width at the first depth, the first width being greater than the second width. The second portion extends from the first depth to a second depth in the semiconductor substrate, and has substantially the second width from the first depth to the second

depth. The third portion extends from the second depth to a third depth in the semiconductor substrate, and has a width that tapers from the second width at the second depth to a third width at the third depth, the second width being greater than the third width.

The first portion may include a tapered sidewall, where an angle between the surface of the semiconductor substrate and the tapered sidewall is less than about 85°. The second portion may include a sidewall, where an angle between the surface of the semiconductor substrate and the sidewall is less than about 120°. The third portion may include a tapered sidewall, where an angle between the surface of the semiconductor substrate and the tapered sidewall is less than 90°, for example, less than or equal to about 45°. The first depth may be from about 100 Å to about 2,500 Å, and the third depth may be from about 1000 Å to about 3,000 Å. The third width may be about 0, such that a bottom portion of the trench is a point. The device may further include a dielectric material disposed in the trench. The trench may be a shallow trench isolation 20 (STI) structure.

In yet another example, a method includes providing a semiconductor substrate, performing at least two etching processes to form a trench in the semiconductor substrate, and filling the trench with a material. Performing the at least two 25 etching processes includes performing a first etching process to form a first trench portion, and performing a second etching process to form a second trench portion and a third trench portion. The first trench portion extends from a surface of the semiconductor substrate to a first depth in the semiconductor substrate, wherein the first portion has a width that tapers from a first width at the surface of the semiconductor substrate to a second width at the first depth, the first width being greater than the second width. The second trench portion extends from the first depth to a second depth in the semiconductor substrate, wherein the second portion has substantially the second width from the first depth to the second depth. The third portion extends from the second depth to a third depth in the semiconductor substrate, wherein the third portion has a 40 width that tapers from the second width at the second depth to a third width at the third depth, the second width being greater than the third width. Performing the first etching process and the second etching process may include using a carbon fluoride gas. In an example, performing the first etching process 45 includes using an etching recipe that includes a CH<sub>2</sub>F<sub>2</sub> gas, a Cl<sub>2</sub> gas, a O<sub>2</sub> gas, and a HBr gas. In an example, performing the second etching process includes using an etching recipe that includes a  $CH_2F_2$  gas, a  $SF_6$  gas, a  $N_2$  gas, and a He gas. Filling the trench with the material may include depositing a 50 high aspect ratio process (HARP) oxide or a high density plasma (HDP) oxide in the trench. In an example, before depositing the HARP oxide or HDP oxide, a flowable chemical vapor deposition (CVD) process is performed to form a flowable CVD oxide in the trench.

The foregoing outlines features of several embodiments so that those skilled in the art may better understand the aspects of the present disclosure. Those skilled in the art should appreciate that they may readily use the present disclosure as a basis for designing or modifying other processes and structures for carrying out the same purposes and/or achieving the same advantages of the embodiments introduced herein. Those skilled in the art should also realize that such equivalent constructions do not depart from the spirit and scope of the present disclosure, and that they may make various 65 changes, substitutions, and alterations herein without departing from the spirit and scope of the present disclosure.

**10**

What is claimed is:

- 1. A device comprising:

- a semiconductor substrate; and

- a trench in the semiconductor substrate that includes:

- a first portion extending from a surface of the semiconductor substrate to a first depth in the semiconductor substrate, wherein the first portion has a width that tapers from a first width at the surface of the semiconductor substrate to a second width at the first depth, the first width being greater than the second width,

- a second portion extending from the first depth to a second depth in the semiconductor substrate, wherein the second portion has substantially the second width from the first depth to the second depth, and

- a third portion extending from the second depth to a third depth in the semiconductor substrate,

- wherein the third portion includes a first substantially linear sidewall and a second substantially linear sidewall,

- wherein the first substantially linear sidewall has a first length and the second substantially linear sidewall has a second length, wherein the first and second length extend from the second depth to the third depth,

- wherein the first substantially linear sidewall and the second substantially linear sidewalls physically contact at the third depth, and

- wherein the first length is transverse to a top surface of the semiconductor substrate and the second length is transverse to the top surface of the semiconductor substrate.

- 2. The device of claim 1 wherein the first portion includes a tapered sidewall, an angle between the surface of the semiconductor substrate and the tapered sidewall being less than about 85°.

- 3. The device of claim 1 wherein the second portion includes a sidewall, an angle between the surface of the semiconductor substrate and the sidewall being less than about 120°.

- 4. The device of claim 1 further including a high density plasma oxide material that fills the trench.

- 5. The device of claim 1 wherein an angle between the surface of the semiconductor substrate and the first substantially linear sidewall of the third portion is greater than 0° and less than or equal to about 45°.

- 6. The device of claim 1 wherein:

- a first angle between a sidewall of the first portion and the surface of the semiconductor substrate is about 83° to about 85°;

- a second angle between a sidewall of the second portion and the surface of the semiconductor substrate is about 90°; and

- a third angle between the first substantially linear sidewall of the third portion and the surface of the semiconductor substrate is greater than 0° and less than or equal to about 45°.

- 7. The device of claim 1 further including a high aspect ratio process oxide material that fills the trench.

- 8. The device of claim 1 wherein the trench is a shallow trench isolation (STI) structure.

- 9. A device comprising:

- a semiconductor substrate; and

- a trench isolation structure in the semiconductor substrate, wherein the trench isolation structure has a third depth in the semiconductor substrate and includes:

- a first trench isolation portion having a first sidewall that extends from a surface of the semiconductor substrate to a first depth in the semiconductor substrate, a first angle being between the first sidewall and the surface of the semiconductor substrate;

- a second trench isolation portion having a second sidewall that extends from the first sidewall at the first depth to a second depth in the semiconductor substrate, a second angle being between the second sidewall and the surface of the semiconductor substrate, wherein the first angle is less than the second angle; and

- a third trench isolation portion having a third sidewall that extends from the second sidewall at the second depth to the third depth in the semiconductor substrate, wherein an entire length of the third sidewall is disposed at a third angle, the third angle being defined between the third sidewall and the surface of the semiconductor substrate, and wherein the third angle is greater than zero and less than the first angle and the second angle.

- 10. The device of claim 9 wherein the first trench isolation portion has a width that tapers from a first width at the surface of the semiconductor substrate to a second width at the first depth, the first width being greater than the second width.

- 11. The device of claim 10 wherein the second trench isolation portion has a width that is substantially equal to the <sup>20</sup> second width from the first depth to the second depth.

- 12. The device of claim 9 wherein the first, second, and third trench isolation portions are filled with an insulating material.

- 13. The device of claim 11 wherein the third trench isolation portion has a width that tapers from the second width at the second depth to a point at the third depth.

- 14. The device of claim 9 wherein the first angle is less than or equal to about 85°, the second angle is about 90°, and the third angle is about 45°.

- 15. The device of claim 12 wherein the insulating material in the second trench isolation portion includes a void and the insulating material in the first trench isolation portion is free of the void.

- 16. A device comprising:

- a semiconductor substrate; and

- a trench in the semiconductor substrate, comprising:

- a first trench portion extending from a surface of the semiconductor substrate to a first depth in the semi-

12

- conductor substrate, wherein the first trench portion has a width that tapers from a first width at the surface of the semiconductor substrate to a second width at the first depth, the first width being greater than the second width,

- a second trench portion, the second trench portion extending from the first depth to a second depth in the semiconductor substrate, wherein the second trench portion has substantially the second width from the first depth to the second depth;

- a third trench portion extending from the second depth to a third depth in the semiconductor substrate, wherein the third trench portion has a width that tapers from the second width at the second depth to a third width at the third depth, the second width being greater than the third width, and wherein the third trench portion includes a substantially linear sidewall extending from the second depth to the third depth; and

- a material in the trench, wherein the material in the second trench portion includes a void therein and the material in the first trench portion is free of the void.

- 17. The device of claim 16 wherein the void is further disposed in the material in the third trench portion.

- 18. The device of claim 16 wherein the material is one of a high aspect ratio process oxide material and a high density plasma oxide material.

- 19. The device of claim 16 wherein:

- a first angle between a sidewall of the first trench portion and the surface of the semiconductor substrate is about 83° to about 85°;

- a second angle between a sidewall of the second trench portion and the surface of the semiconductor substrate is about 90°; and

- a third angle between the substantially linear sidewall of the third trench portion and the surface of the semiconductor substrate is about 45°.

- 20. The device of claim 16 wherein the width of the third trench portion tapers to a point at the third depth.

\* \* \* \* \*