#### US008482136B2

# (12) United States Patent

# Gulpen et al.

# (10) Patent No.:

# US 8,482,136 B2

# (45) **Date of Patent:**

Jul. 9, 2013

#### (54) FAN-OUT CHIP SCALE PACKAGE

(75) Inventors: Jan Gulpen, Nijmegen (NL); Tonny

Kamphuis, Lent (NL); Pieter

Hochstenbach, Nijmegen (NL); Leo van Gemert, Nijmegen (NL); Eric van Grunsven, Someren (NL); Marc de

Samber, Lommel (BE)

(73) Assignee: **NXP B.V.**, Eindhoven (NL)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 699 days.

(21) Appl. No.: 12/648,634

(22) Filed: **Dec. 29, 2009**

## (65) Prior Publication Data

US 2011/0156237 A1 Jun. 30, 2011

(51) Int. Cl.

H01L 23/48 (2006.01) H01L 23/52 (2006.01) H01L 29/40 (2006.01)

Field of Classification Search

(52) **U.S. Cl.**

(58)

USPC ...... **257/784**; 257/786

257/784, 786

See application file for complete search history.

# (56) References Cited

#### U.S. PATENT DOCUMENTS

|     | 5,386,623 | A             |   | 2/1995  | Okamoto et al. |         |

|-----|-----------|---------------|---|---------|----------------|---------|

|     | 5,668,405 | A             | * | 9/1997  | Yamashita      | 257/668 |

|     | 5,751,060 | $\mathbf{A}$  | * | 5/1998  | Laine et al    | 257/702 |

|     | 5,990,546 | $\mathbf{A}$  | * | 11/1999 | Igarashi et al | 257/700 |

| (   | 6,011,694 | A             | * | 1/2000  | Hirakawa       | 361/774 |

| (   | 6,051,450 | A             | * | 4/2000  | Ohsawa et al   | 438/123 |

| (   | 6,586,836 | B1            | * | 7/2003  | Ma et al       | 257/723 |

| ,   | 7,189,596 | B1            | * | 3/2007  | Mu et al       | 438/110 |

| 006 | 5/0157847 | A1            |   | 7/2006  | Hsu            |         |

| 006 | 5/0158804 | $\mathbf{A}1$ |   | 7/2006  | Usui et al.    |         |

|     |           |               |   |         |                |         |

#### OTHER PUBLICATIONS

International Search Report and Written Opinion in Application No. PCT/IB2010/056012 dated Jun. 29, 2012.

Primary Examiner — S. V. Clark

# (57) ABSTRACT

A chip scale package has a semiconductor die having an array of die bond pads arranged with a bond pad density per unit area, embedded in a molded die support body having a surface supporting an array of conducting contacts, each of the contacts connected by an electrical lead to a corresponding one of the die bond pads.

# 23 Claims, 4 Drawing Sheets

<sup>\*</sup> cited by examiner

FIG. 1

FIG. 2

FIG. 5

FIG. 7

FIG. 8

# FAN-OUT CHIP SCALE PACKAGE

#### TECHNICAL FIELD

Embodiments relate generally to chip scale packages <sup>5</sup> manufactured from semiconductor chips with an array of densely spaced bond pads.

#### **BACKGROUND**

Semiconductor dies or chips are frequently embedded in a molding composition to produce packages. In modern uses, small packages, commonly known as Chip Scale Packages, are frequently preferred. Chip Scale Packages, or CSPs, based on the IPC/JEDEC J-STD-012 definition, are singledie, direct surface mountable packages with an area no more than 20% greater than the original die area. The IPC/JEDEC definition does not specify a particular design or construction of a chip scale package, so any package that meets the surface mountability and dimensional requirements of the definition 20 may be viewed as a CSP.

The advantages offered by chip scale packages include small size, reduced weight, and improvement in electrical performance. The small size of a CSP makes it useful in portable devices, such as cell phones, laptops, palmtops, and 25 digital cameras.

Wafer-level Chip Scale Packages (WL-CSPs) may be made by extending wafer fabrication processes to include device interconnection and device protection processes. Redistribution Layer and Bump technology, the most widelyused WL-CSP technology, extends the conventional fabrication process with an additional step that deposits a thin-film metal rerouting and interconnection system on the surface of the wafer by photolithography and thin film deposition techniques. This metal rerouting and interconnection system 35 redistributes the bonding pads from the periphery of the upper surface of each chip to an array of metal bonding pads that are evenly deployed over the chip's surface. The solder balls or bumps used in connecting the device to the application circuit board are subsequently placed over these evenly deployed 40 bonding pads. This redistribution technique improves chip reliability by allowing the use of larger and more robust balls for interconnection between the bonding pads and the leadframe.

However, the WL-CSP technology described has inherent limitations because it arranges solder balls directly on a surface of the die and, since the solder balls must have greater than a certain minimum spacing to avoid contact between adjacent solder balls, the larger the number of solder balls that are required means the larger the required chip area. This requirement for a large area on which to arrange the solder bumps may still persist even after deposition of a redistribution layer with an array of metal bonding pads that are evenly deployed over the chip's surface.

#### SUMMARY

In light of the long-felt need for improvements in structure and function of electrical connections to spaced arrays of die bond pads, a brief summary of various embodiments is presented. Some simplifications and omissions may be made in the following summary, as this is intended to highlight and introduce illustrative aspects of the various examples, but not to limit the scope of the invention.

One or more various exemplary embodiments includes a 65 semiconductor die embedded in a die support body formed of a molding composition, the semiconductor die having a die

2

surface having a first area and having a plurality of first bond pads disposed in a first spaced arrangement on the first area, the first spaced arrangement having a first minimum center-to-center bond pad spacing, and includes a bond pad spacing interface structure supported, at least in part, by a layer support surface of the die support body, the bond pad spacing interface structure supporting a plurality of second bond pads in a second spaced arrangement over a second area, the second spaced arrangement having a second minimum center-to-center spacing that can be larger than the first minimum center-to-center spacing, and the bond pad spacing interface structure having a plurality of electrical conductors, each of the electrical conductors connecting a corresponding one of the first pads to a corresponding one or more of the second pads.

According to one aspect of various exemplary embodiments, the bond pad spacing interface structure includes a dielectric layer disposed on at least a portion of the first area of the semiconductor die, having a plurality of bond pad clearance openings, each bond pad clearance opening being aligned with a corresponding one of the second bond pads.

According to one aspect of various exemplary embodiments, the bond pad spacing interface structure includes a dielectric layer disposed on at least a portion of the first area of the semiconductor die, and disposed on at least a portion of the second area of the molding composition, the dielectric layer having a plurality of bond pad clearance openings, each bond pad clearance opening being aligned with a corresponding one of the second bond pads.

According to one aspect of various exemplary embodiments, the bond pad spacing interface structure includes a patterned conductive layer overlaying at least a portion of the dielectric layer and forming the electrical conductors.

According to one aspect of various exemplary embodiments, the bond pad spacing interface structure includes a solder mask disposed over at least a portion of the patterned conductive layer.

According to one aspect of various exemplary embodiments the bond pad density interface structure includes a solder bump disposed within a clearance opening of the solder mask, the solder bump having a bottom surface contacting one of the second bond pads and a top surface projecting outward beyond a surface plane of the solder mask.

According to one aspect of various exemplary embodiments, at least some of the second bond pads are disposed on the die support body so that, viewed substantially perpendicular to the plane in which the second bond pads lie, the second bond pads are located outside a projection of the perimeter of the semiconductor die.

According to one aspect of various exemplary embodiments, at least one first bond pad is electrically connected to another first bond pad.

Example methods of making a chip scale package according to one or more various exemplary embodiments include providing a semiconductor die having a first area supporting a plurality of first bond pads arranged in a first arrangement, and arranging a dielectric layer over at least a portion of the first area, embedding the semiconductor in a die support body formed of a molding material, in an orientation and position exposing at least a portion of the dielectric layer above the first area, and then opening holes in the dielectric layer to expose at least two of the first bond pads. Such example methods further include forming electrical leads on the dielectric layer, each of the electrical leads forming at least one second bond pad and extending from the at least one

second bond to a corresponding one of the first bond pads, and then forming a conducting bump pad on at least one of the second bond pads.

According to one aspect of example methods having one or more various exemplary embodiments, an outer perimeter of 5 the semiconductor die surrounds the first area, the dielectric layer is a self-supporting dielectric layer, the arranging of the dielectric layer over at least a portion of the first area arranges the self-supporting dielectric layer to have portions extending beyond the outer perimeter, and the embedding of the semiconductor in a die support body forms a layer support surface of the die support body at the extending portions of the dielectric layer.

According to one aspect of example methods having one or more various exemplary embodiments, the first bond pads are 1 arranged in a first arrangement having a first minimum centerto-center bond pad spacing, and the forming a plurality of electrical leads on the dielectric layer forms the second bond pads in a second arrangement having a second minimum center-to-center bond pad spacing that can be larger than the 20 first minimum center-to-center bond pad spacing.

According to one aspect of example methods having one or more various exemplary embodiments, at least some of the second bond pads are disposed on the die support body so that, viewed substantially perpendicular to the plane in which 25 the second bond pads lie, the second bond pads are located outside a projection of the perimeter of the semiconductor die.

According to one aspect of example methods having one or more various exemplary embodiments, at least one first bond 30 pad is electrically connected to another first bond pad.

## BRIEF DESCRIPTION OF THE DRAWINGS

concepts sufficient to practice according to various exemplary embodiments, reference is made to the accompanying drawings, wherein:

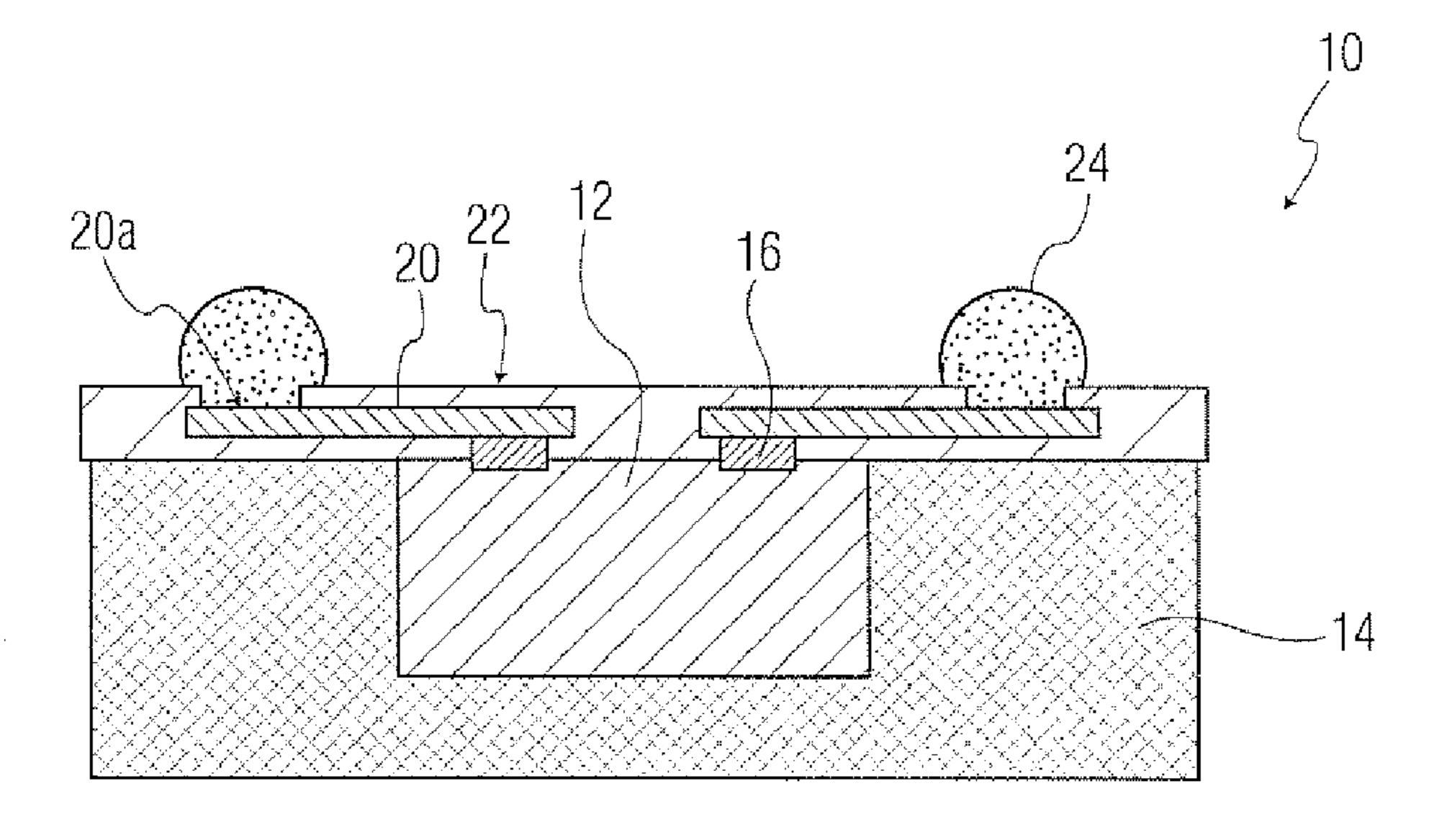

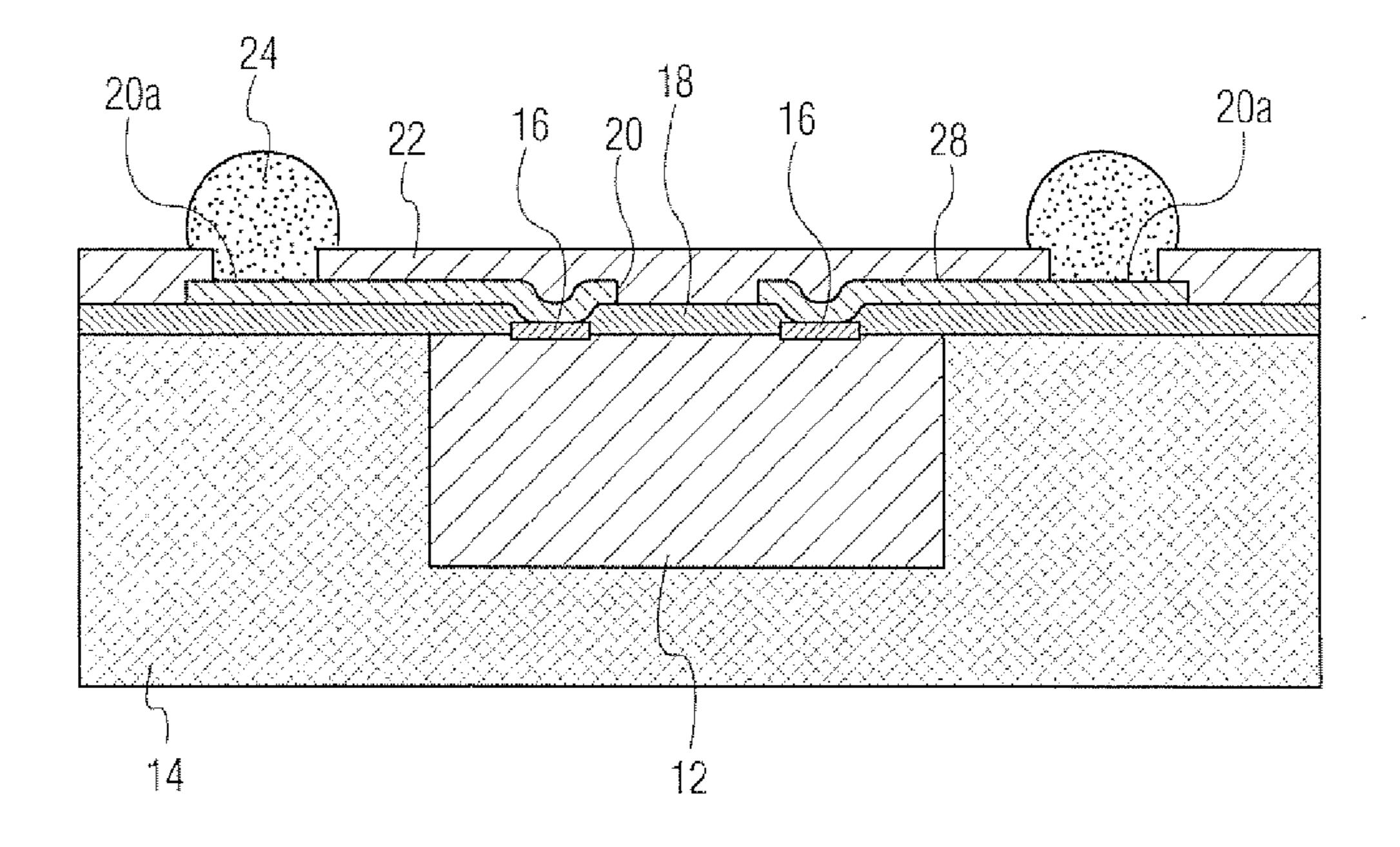

FIG. 1 shows an illustrative example chip scale package according to various embodiments; and

FIGS. 2-8 show various illustrative examples of a manufacture, and steps of a manufacture of a chip scale package according to one or more various embodiments, including an embodiment as illustrated at FIG. 1, wherein:

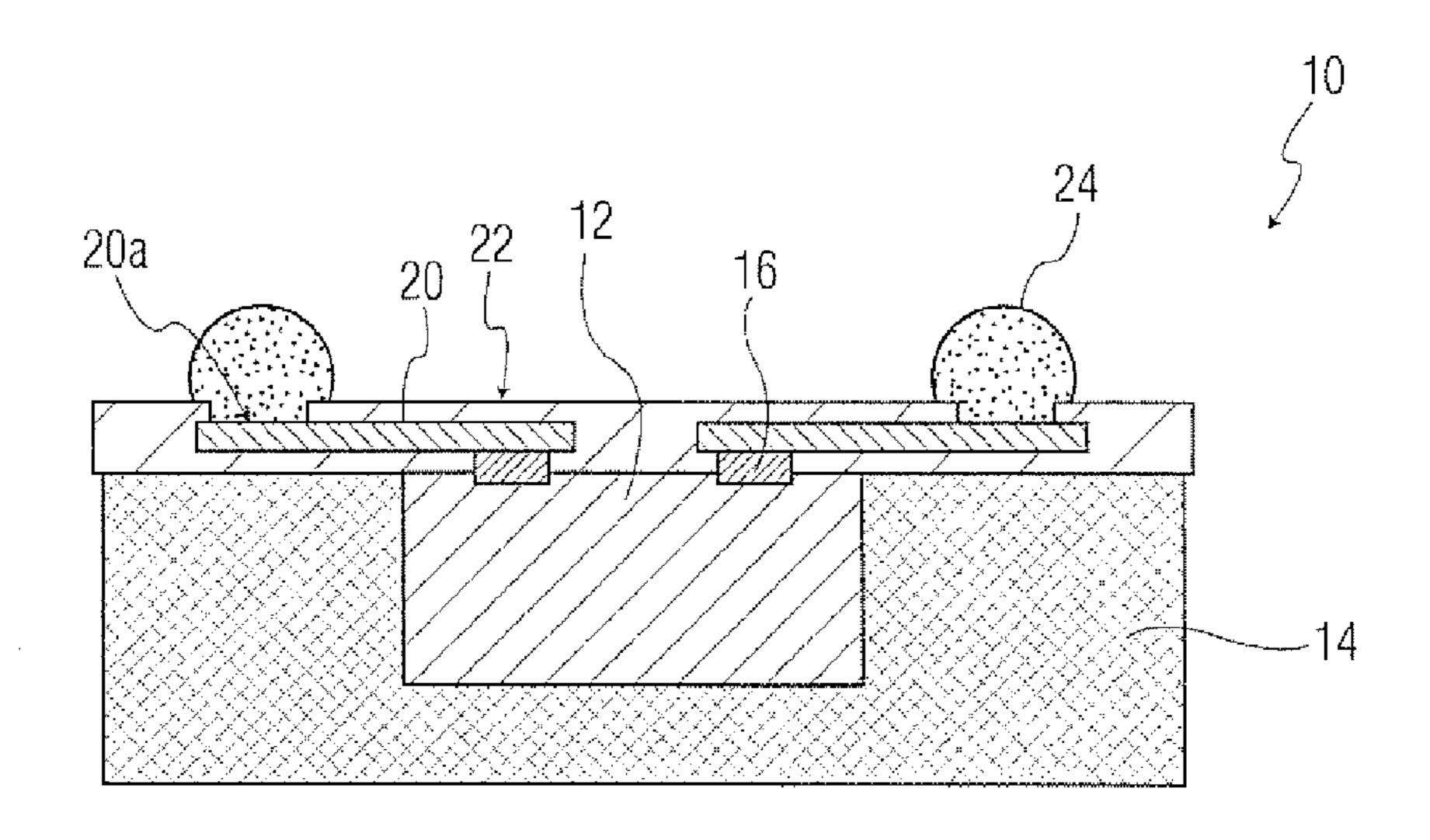

FIG. 2 shows one example of a semiconductor chip or die 45 mounted on one example sacrificial substrate through an example intervening dielectric layer, as used in one example preparation of a chip scale package according to one or more of the various embodiments, including the example described in reference to FIG. 1 of the present disclosure;

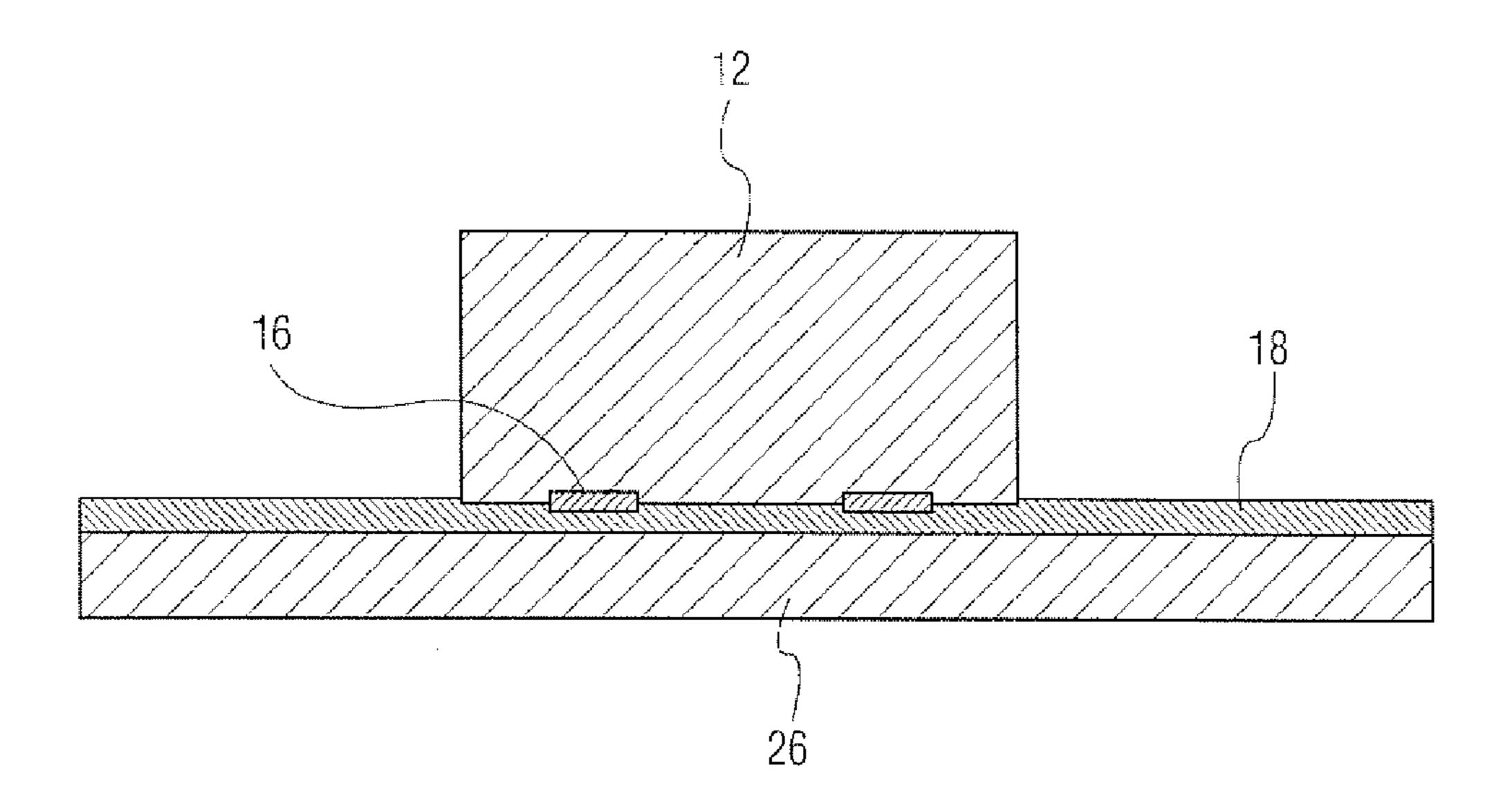

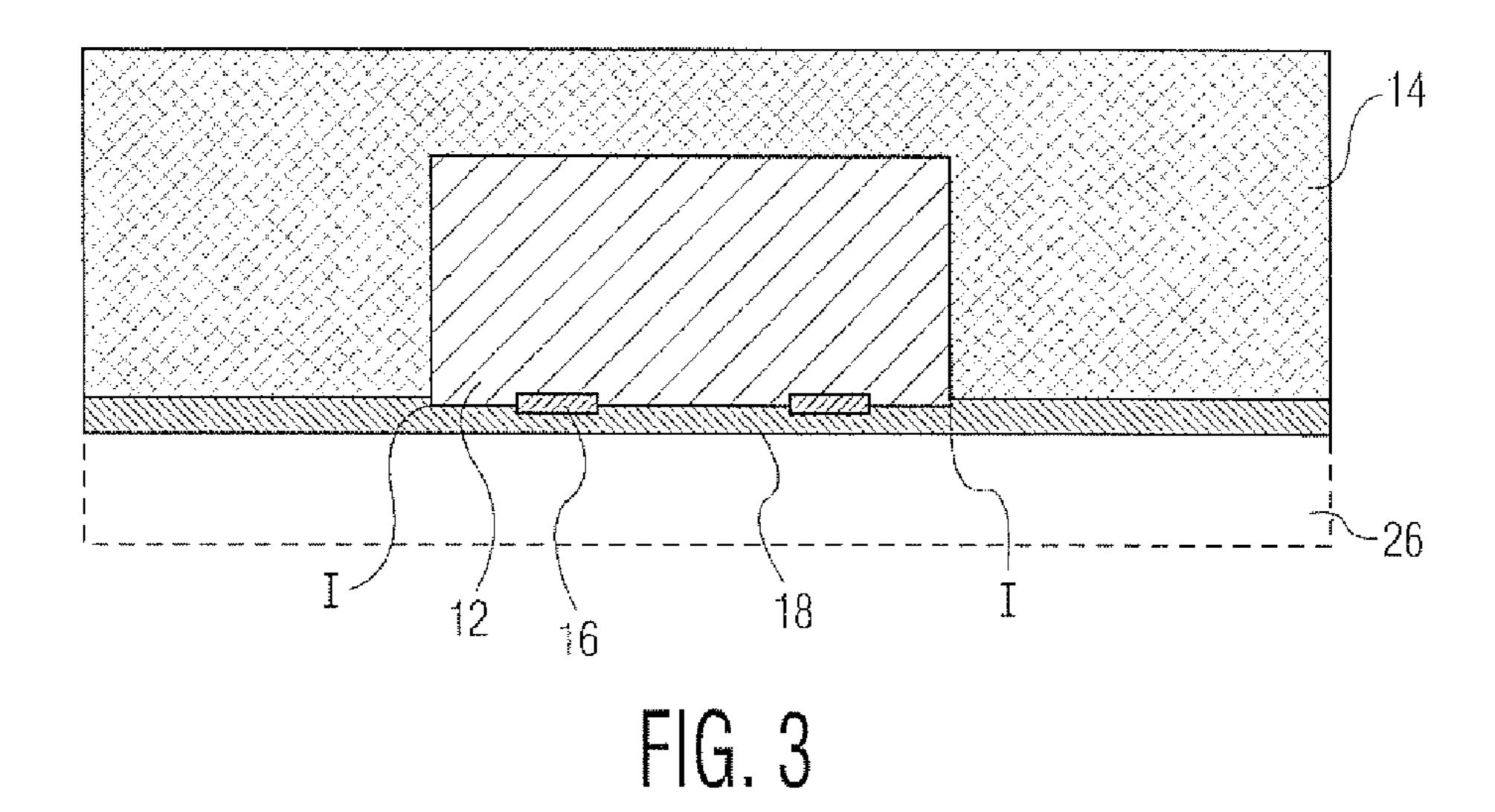

FIG. 3 shows one illustrative example of a deposition of a molding composition over an example intervening dielectric layer, such as the example intervening layer depicted at FIG. 2, with a removal of an example sacrificial substrate;

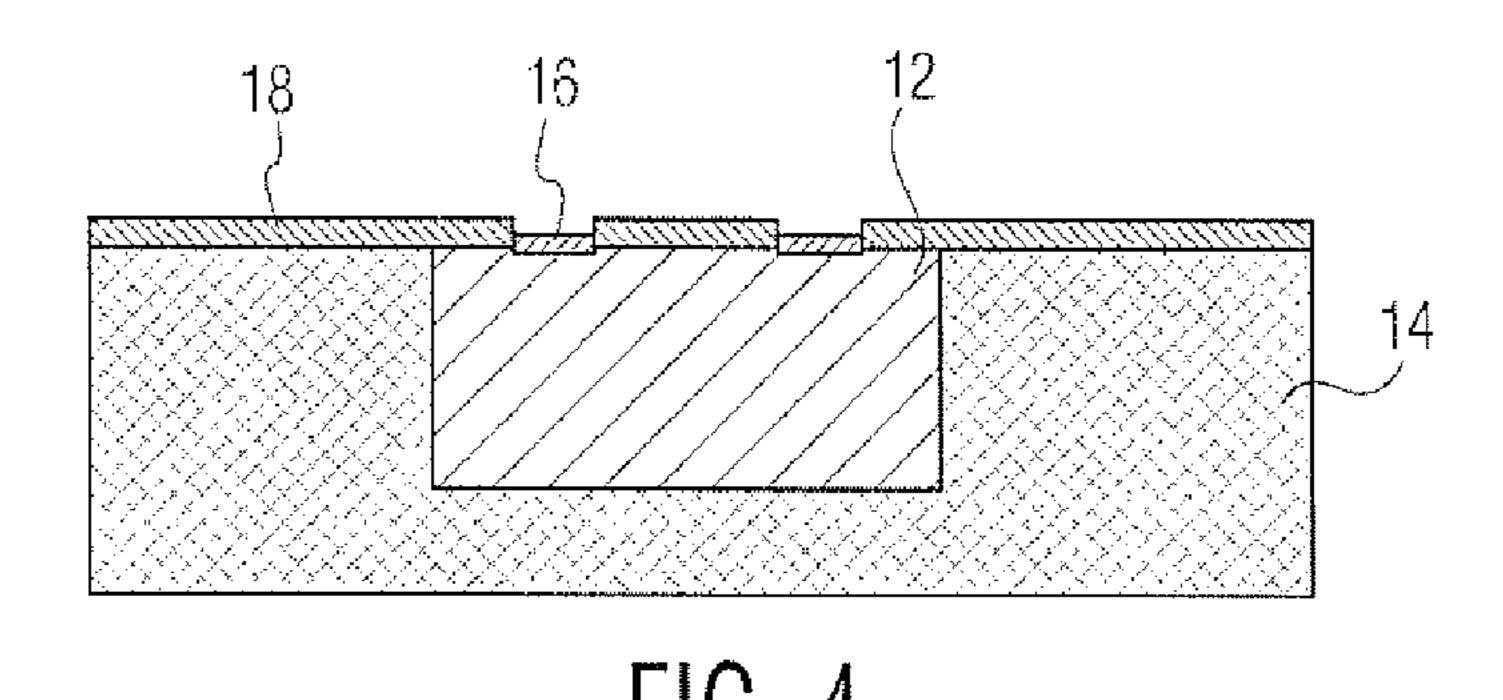

FIG. 4 shows one illustrative example of a patterning of one 55 example dielectric layer, such as the example dielectric layer depicted at FIG. 3;

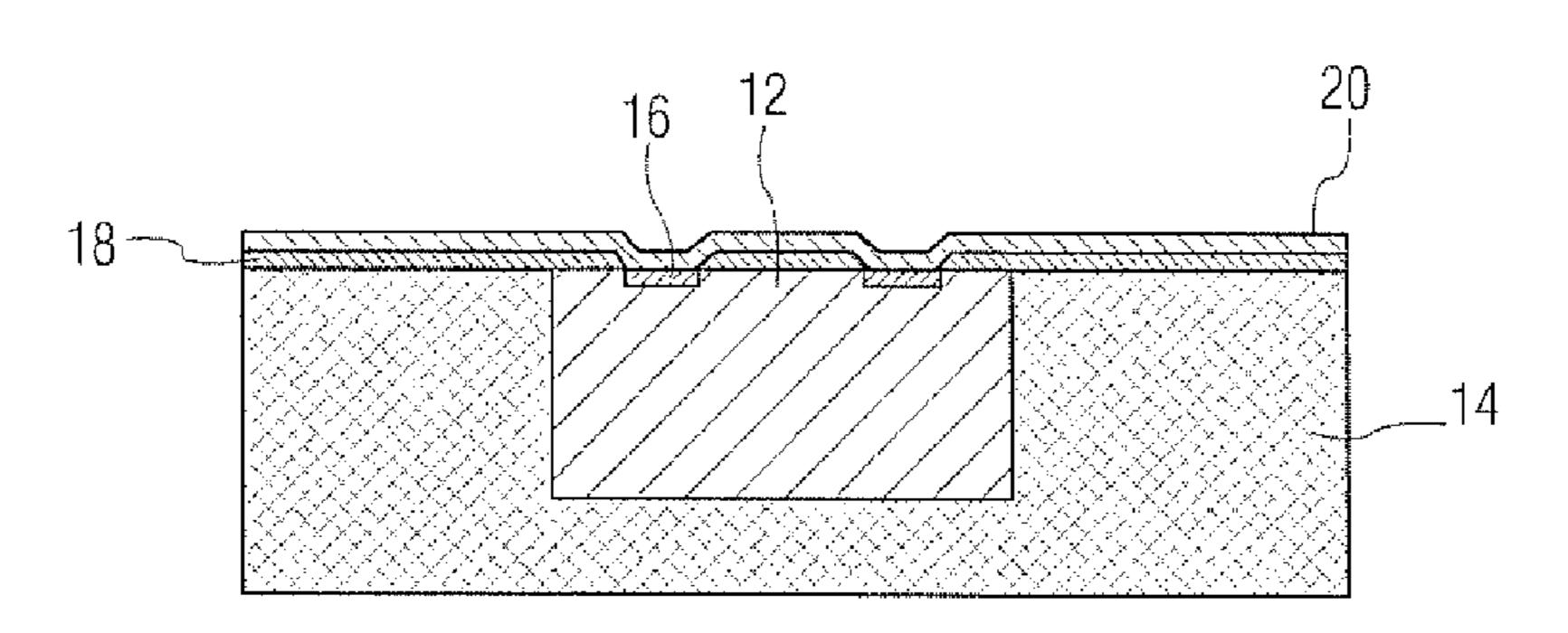

FIG. 5 shows one illustrative example of a deposition of a conductive layer over one example patterned dielectric layer, such as the patterned dielectric layer of FIG. 4;

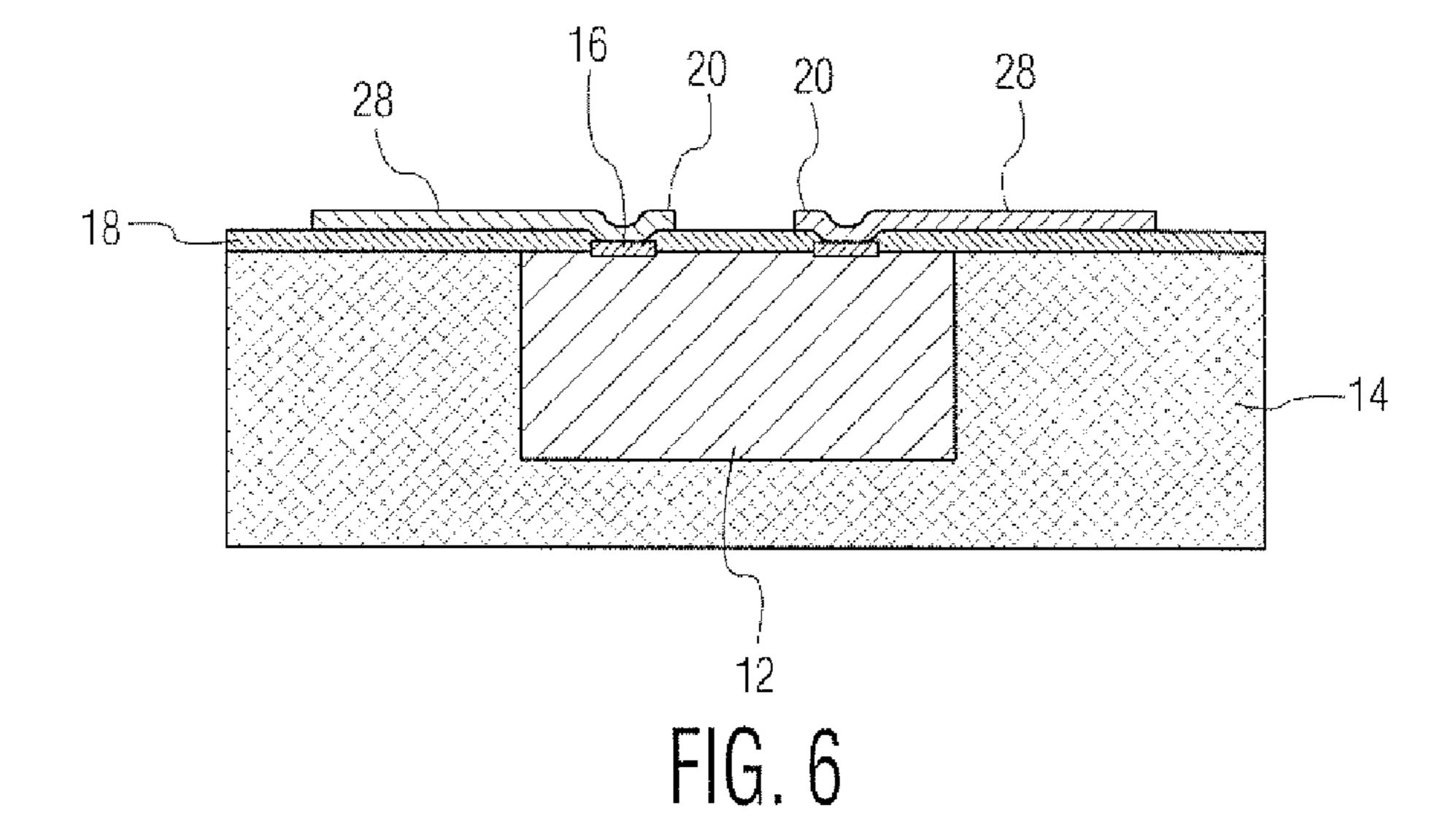

FIG. 6 shows one illustrative example of a patterning of one example of a conductive layer, such as the conductive layer of FIG. **5**;

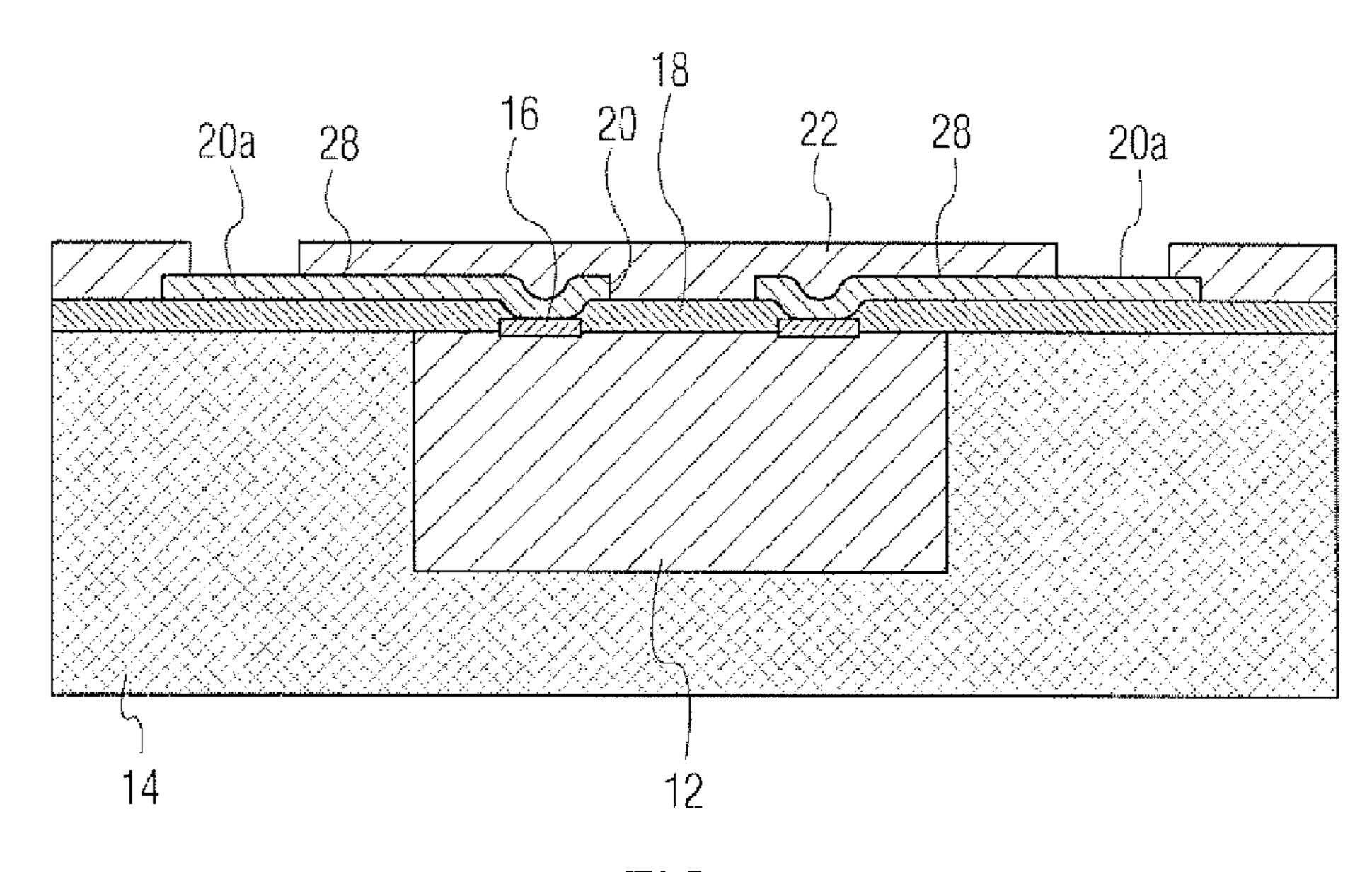

FIG. 7 shows one illustrative example of a deposition of a patterned solder mask over one example patterned conductive 65 layer, such as the example patterned conductive layer illustrated at FIG. 6; and

FIG. 8 shows one illustrative example of a deposition of solder bumps on one example patterned conductive layer through example openings in a patterned solder mask, such as the example patterned solder mask illustrated at FIG. 7.

## DETAILED DESCRIPTION

Referring now to the drawings, in which like numerals refer to like components or steps, there are disclosed broad aspects of various example embodiments. FIG. 1 shows one example of a chip scale package 10 according to one or more example embodiments. The FIG. 1 example 10 chip scale package includes a semiconductor chip or die such as, for example, the depicted example 12, embedded in a composition 14 such as, for example, a polymeric molding composition or equivalent. One example composition 14 may be, but is not necessarily, an epoxy resin. Conducting bond pads 16 which may, for example, be metallic, may be deposited in an arrangement, such as the FIG. 1 depicted arrangement, this arrangement being arbitrarily termed in this description as a "first array," spaced array, on an exposed surface of chip or die 12. The first array of conducting bond pads 16 may be formed by bond pads positioned along a peripheral edge of the chip or die 12; or the first array of bond pads 16 may be formed by bond pads evenly distributed over an exposed surface of the chip or die 12. It will be understood that "array" does not limit the arrangement of the conducting bond pads 16 to an evenly spaced column row arrangement along perpendicular axes, and uneven arrays of bond pads also are contemplated. The first array of bond pads 16 has a corresponding first density, in terms of bond-pads per unit area, and a first minimum centerto-center spacing between neighboring bonding pads 16.

With continuing reference to FIG. 1, a dielectric layer 18 may be deposited over an area of, or over all the exposed In order to facilitate a ready understanding of inventive 35 surface of embedded chip or die 12. According to one aspect, at least a portion of the conducting bond pads 16 may be exposed through openings in the dielectric layer 18. A patterned conductive layer 20 may be deposited over the dielectric layer 18 so as to make electrical contact with the conduct-40 ing bond pads 16 exposed through openings in the dielectric layer 18. Patterned conductive layer 20 may define a plurality of electrical leads, each of the leads extending from one of the exposed surface of the bond pads 16. Preferably, at least one of the electrical leads extends from a bond pad 16 across an interface between die or chip 12 and molding composition 14 onto the molding composition 14. Each electrical lead is preferably electrically isolated from all other electrical leads. A solder mask 22 may be deposited on the patterned conductive layer 20 and patterned to define openings which expose 50 bond pads 20a, where each bond pad 20a is located at the end of an electrical lead defined by patterned conductive layer 20. Preferably, each bond pad 20a is located at the end of an electrical lead which is remote from a bond pad 16 and which is in electrical communication with that bond pad 16.

Solder bumps 24 may be deposited on bond pads 20a, where each solder bump makes electrical contact with a bond pad 16 through an electrical lead defined by conductive layer 20 and running from a bond pad 16 to an associated bond pad 20a. Bond pads 20a may be arranged to define what will be arbitrarily labeled in this description as a "second array" of bond pads, and such a second array of bond pads 20a preferably may be much less densely spaced than the first array of bond pads 16. This is by way of example only, and all spacing arrangements, whether more or less dense, and uniform or non-uniform, are contemplated. As will be readily understood by a person of ordinary skill in the art of chip packaging from this disclosure, when less dense spacing is used, because of

the less dense spacing provided by these and other embodiments, solder balls deposited on bond pads 20a are much less likely to cause unwanted short circuits through direct contact between solder balls on different bond pads 20a than are solder balls deposited directly on closely spaced bond pads 16 as in the known art.

Illustrative examples of steps and processes of making a chip package having one or embodiments will now be described. In one illustrative example, a construction of one example chip package having one or more of the various exemplary embodiments may begin with an assembly such as shown in FIG. 2. In one example, at least one semiconductor die or chip 12 may be deposited on a dielectric layer 18, with bond pads 16 on die or chip 12 making contact with the dielectric layer 18. The dielectric layer 18 may be, but is not 15 necessarily, a dielectric polymeric film (not separately shown) supported on a sacrificial substrate. The sacrificial substrate 26 may be a metal foil such as a copper foil, an aluminum foil, or a chromium foil. The sacrificial substrate 26 may be a flexible polymeric foil bonded to the dielectric 20 layer 18 directly or through an optional release layer (not shown in the figures). According to one embodiment, the dielectric layer 26 may be a self-supporting polymeric film. The use of other materials also is contemplated.

In example embodiments forming the dielectric layer 18 as 25 a dielectric polymeric film supported on a sacrificial substrate 26, the dielectric layer 18 may be a continuous layer covering an entire face of sacrificial substrate 26, as seen in FIG. 2. Alternatively, the dielectric layer 18 may be a discontinuous layer covering defined patches (not explicitly depicted), for 30 example, evenly spaced square or rectangular patches, on a face of sacrificial substrate 26. Uneven arrangements also are contemplated. Each die or chip 12 may be deposited on a defined patch of a discontinuous dielectric layer 18 so that dielectric layer 18 prevents at least bond pads 16 on die or 35 chip 12, and preferably the entire surface of die or chip 12, from contacting the sacrificial substrate 26, among other features and benefits.

In various exemplary embodiments, the semiconductor chip or die 12 may be a single crystal or polycrystalline 40 semiconductor. The semiconductor chip or die 12 may be made from, for example, silicon; germanium; silicon carbide; silicon-germanium alloys ( $Si_xG_{e_{1-x}}$ ); antimonides, arsenides, nitrides, or phosphides of a Group III element selected from the group consisting of aluminum, gallium, indium, boron, or 45 mixtures thereof; and oxides, sulfides, selenides or tellurides of a Group II element selected from the group consisting of zinc, cadmium, mercury, and mixtures thereof. Other useful semiconductors include Lead selenide (PbSe), Lead sulfide (PbS), Lead telluride (PbTe), Tin sulfide (SnS), Tin telluride 50 (SnTe), Bismuth telluride ( $B_{i2}T_{e3}$ ), Cadmium phosphide  $(C_{d3P2})$ , Cadmium arsenide  $(C_{d3}A_{s2})$ , Cadmium antimonide  $(C_{d3}S_{b2})$  Zinc phosphide  $(Z_{n3P2})$ , Zinc arsenide  $(Z_{n3}A_{s2})$ , Zinc antimonide  $(Z_{n3}S_{b2})$ , Copper oxides, and Uranium oxides. Other compositions are also contemplated.

The dielectric layer **18** may be made from, for example, benzocyclobutene resin, a polyamide, a benzocyclobutene-modified polyamide, a benzocyclobutene-modified silicone, a silicone resin, a polyolefin resin, a diene resin, poly(methyl methacrylate), polysulfones, polyetherimides and/or styrene for resins. According to one aspect of one or more various example embodiments, the polymeric dielectric layer **18** may be from about 0.1 to 50 microns thick, and preferably from about 1 to 10 microns thick. According to one aspect, the dielectric layer **18** may be a stress buffer material with a low for moisture uptake and an elongation of from about 10% to 300%, preferably from about 20% to 50%. It also is desirable

6

that the dielectric layer 18 be made from material which is strong enough to withstand the forces which may be applied during fabrication and assembly. One of the benefits and features of examples according to this aspect is that if the dielectric layer 18 and the semiconductor die 12 have a mismatched coefficient of thermal expansion so that the dielectric layer 18 and die 12 undergo different dimensional changes as a result of temperature changes, the dielectric layer can elongate as required to compensate for the differing size changes of the two materials. Among other further benefits and advantages, this feature provides a substantially reduced likelihood that the effects of a mismatched coefficient of thermal expansion will stretch or tear electrical leads formed from patterned conductive layer 20. The dielectric layer 18 may be deposited by, for example, spin coating/ lamination on either the Si wafer or on the sacrificial substrate. Thus, the dielectric layer 18 serves as a stress buffer material which can decouple the patterned conductive layer 20 and the solder bumps 24 from the molding composition 14, and the transition from the semiconductor die 12 to the molding material 14.

The bond pads 16 on the silicon die may be formed from a metal having excellent conductivity such as, for example, copper, aluminum, gold, silver, or alloys thereof. The bond pads 16 may be formed by, for example, chemical vapor deposition, physical vapor deposition, electroplating, electroless plating, or sputtering, or any other suitable technique.

As shown in FIG. 3, a polymeric resin 14 may be deposited on the polymeric dielectric layer 18 to cover the polymeric dielectric layer and substantially embed the semiconductor die or chip 12 in the polymeric resin 14. Polymeric resin 14 may be, for example, a thermoset polymeric resin or a liquid crystal resin. Useful thermoset polymeric resins include, as illustrative examples without limiting the choice of resins to only these examples, phenol-formaldehyde resins; epoxy resins, or polyimide resins. Illustrative examples of useful liquid crystal resins include, without limiting the choice of liquid crystal resins to these examples, polyesters containing p-hydroxybenzoic acid, p-(4-hydroxyphenyl)benzoic acid, or related monomers. If the polymeric resin layer 14 is supported on an optional sacrificial substrate 26 (shown in dashed lines in FIG. 3), the sacrificial substrate 26 is then removed. If the sacrificial substrate 26 is a metal foil, the sacrificial substrate may be removed by etching. If the sacrificial substrate 26 is a flexible polymeric foil bonded to the dielectric layer directly or through an optional release layer, the sacrificial substrate 26 may be removed by peeling the flexible polymeric foil away from the dielectric layer 18. After removal of the sacrificial layer 26 (if present), the resulting structure includes a semiconductor die or chip 12 embedded in polymeric resin 14 so as to expose one surface of die or chip 12.

The dielectric polymeric layer 18, which may be continuous or discontinuous, covers at least bond pads 16 on die or chip 12, and preferably the entire exposed face of die or chip 12. If dielectric polymeric layer 18 is continuous, it covers the exposed face of die or chip 12 and the surface of polymeric resin 14, as seen in FIG. 3. If dielectric polymeric layer 18 is discontinuous, it covers at least the exposed face of die or chip 12, preferably the exposed face of die or chip 12 and an interface I between die or chip 12 and polymeric resin 14.

In the next step of making an example chip scale package according to one or more of the exemplary embodiments, at least two selected bond pads 16 in the array of bond pads 16 on the semiconductor die or chip 12 are exposed by defining holes in polymeric dielectric layer 18 over the selected bond pads 16, as seen in FIG. 4. Holes in polymeric layer 18 may be

defined by depositing a patterned etch mask which completely covers layer 18, except for defined regions of layer 18 over selected bond pads 16 which are exposed through the etch mask. The exposed regions of layer 18 may be removed by dry etching or by wet etching. For example, an exposed 5 portion of polymeric layer 18 formed from benzocyclobutene resin may be removed by dry etching using CF<sub>4</sub>/O<sub>2</sub> and SF<sub>6</sub>/ O<sub>2</sub> plasmas. A polymeric layer **18** formed from polyamide resin may undergo wet etching using 3N hydrochloric acid or a mixed solution of hydrochloric acid and stannic chloride. Additionally, holes in polymeric layer 18 over the selected bond pads 16 may be defined by burning or ablating holes through the polymeric resin layer over the selected bond pads 16 with a laser. Use of a laser to define holes in polymeric layer 18 over the selected bond pads 16 has the advantage that 15 the step of depositing an etch mask is unnecessary. Other techniques for selectively removing portions of polymeric layer are also contemplated.

After holes are defined in polymeric layer 18 over the selected bond pads 16, a metal layer 20 is deposited over 20 polymeric dielectric layer 18 so that the metal layer 20 is electrically insulated from semiconductor die or chip 12, except where holes have been defined in polymeric dielectric layer 18 over the selected bond pads 16, as seen in FIG. 5. These holes in layer 18 allow metal layer 20 to make electrical 25 contact with the selected bond pads 16. The metal layer 20 may be formed from a metal having excellent conductivity, such as copper, aluminum, gold, chromium, silver, or alloys thereof. The high conductivity metal layer 20 may be positioned on top of an optional metal-based barrier layer line of 30 a material such as, for example, titanium/titanium nitride (Ti/TiN), nickel (Ni) and/or chromium (Cr) (not shown in the drawings). The optional barrier layer line, if present, may be formed by chemical vapor deposition on the dielectric polymeric layer by physical vapor deposition, electroplating, 35 electroless plating processes, or sputtering or a combination of these techniques, or any other suitable techniques, alone or in combination. The metal layer 20 may be formed by chemical vapor deposition on the dielectric polymeric layer or, if present, on the optional barrier layer line by physical vapor 40 deposition, electroplating, electroless plating processes, or sputtering or a combination of these techniques, or any other suitable techniques, alone or in combination.

As seen in FIG. 6, the next step in fabrication of a chip scale package according to the exemplary embodiments involves 45 patterning layer 20 to define a plurality of electrical leads 28 which each extend from one of the selected bond pads 16. Preferably, leads 28 do not make electrical contact with each other. In various embodiments, the metal layer 20 is patterned with a laser to define a plurality of leads 28. In certain embodi- 50 ments, the metal layer 20 is patterned by etching. The metal layer 20 may be etched by depositing a photoresist composition on layer 20, patterning the photoresist to define soluble regions and insoluble regions, and dissolving the soluble portion of the photoresist to expose portions of the metal layer 55 20. The insoluble portion of the photoresist protects the portions of the metal layer 20 which will define leads 28. The exposed portions of metal layer 20 are then removed by etching. For example, an aluminum layer 20 may be etched with a mixture of 80% phosphoric acid (H<sub>3</sub>PO<sub>4</sub>), 5% acetic 60 acid, 5% nitric acid (HNO<sub>3</sub>), and 10% water. A chromium layer 20 may be etched with a solution of ceric ammonium nitrate and nitric acid, or with hydrochloric acid. A copper layer 20 or aluminum layer 20 may be etched with a ferric chloride solution, while a silver layer 20 may be etched with 65 ferric nitrate solutions. After etching, the photoresist layer is removed.

8

As seen in FIG. 7, the next step in fabrication of the chip scale package according to the exemplary embodiments is deposition of a solder mask 22 over patterned conductive layer 20. The solder mask is patterned to expose bond pads 20a and to protect other structures. In various embodiments, each bond pad 20a is an exposed portion of patterned conductive layer 20, located at an end of an electrical lead 28 defined by patterned conductive layer 20 and covered by solder mask 22. In various embodiments, the solder mask 22 may be made from a lacquer like layer of polymer that provides a permanent protective coating for the electrical leads 28 defined by conductive layer 20. The solder mask prevents solder from bridging between conductors, thereby preventing short circuits. In various embodiments, the solder mask is formed from a UV-curable epoxy liquid that is silkscreened through a woven mesh on to the dielectric layer 18 and the patterned conductive layer 20, where an ink-blocking stencil prevents transfer of the epoxy liquid onto at least some of bond pads 20a. The applied epoxy solder mask is then cured. Other types of solder mask which can be used include photoimageable solder masks, including liquid photoimageable solder mask (LPSM) inks and dry film photoimageable solder masks (DFSM). LPSM can be silkscreened or sprayed on the dielectric layer 18 and the patterned conductive layer 5. DFSM is vacuum laminated onto the dielectric layer 4 and the patterned conductive layer 20. The LPSM or DFSM solder mask layer is then imaged through a photomask with UV radiation to provide a partially cured patterned layer having unexposed and uncured portions over at least some of bond pads 20a. The LPSM or DFSM layer is then developed by removing the uncured portions of the solder mask layer to provide openings in the solder mask layer for parts to be soldered to the bond pads 20a. After the unexposed portion of the solder mask layer is removed, the remaining solder mask layer is fully cured with UV radiation and/or heat.

Solder 24 is then deposited on exposed bond pads 20a, as seen in FIG. 8. The solder may be deposited by screen printing or by depositing preformed solder bumps 24 onto bond pads 20a. Solders which may be used to form solder bumps 24 or printed onto bond pads 20a include, for example, lead-free solders.

As may be seen in FIG. 8, patterned metal layer 20 serves as a redistribution layer, where the metal leads 28 defined by patterned layer 20 allow electrical contacts to the densely spaced bond pads 16 on the semiconductor die or chip 12 to be made by making electrical contacts to the less densely spaced bond pads 20a through solder bumps 24. Each electrical lead 28 defined by the patterned metal redistribution layer 20 "fans out" from the semiconductor die or chip 12, so as to electrically connect a bond pad 16 to a bond pad 20a; thus, metal leads 28 enable redistribution of the exposed bond pads for making electrical contact to die or chip 12 so that the less densely spaced bond pads 20a are used in place of the densely spaced bond pads 16.

Solder balls 24 may now be used to solder the semiconductor die or chip 12 to a printed circuit board (not shown).

Although the various exemplary embodiments have been described in detail with particular reference to certain exemplary aspects thereof, it should be understood that the invention is capable of other embodiments and its details are capable of modifications in various obvious respects. As is readily apparent to those skilled in the art, variations and modifications can be affected while remaining within the spirit and scope of the invention. More specifically, this invention is applicable to any suitable semiconductor die or chip construction, including, but not limited to, those in conformance with the standards described in this specification. Ele-

ments and compositions described herein are exemplary and not limiting. Accordingly, the foregoing disclosure, description, and figures are for illustrative purposes only and do not in any way limit the invention, which is defined only by the claims.

What is claimed is:

- 1. A chip scale package, comprising:

- a semiconductor die embedded in a die support body formed of a molding composition, the semiconductor 10 die having a die surface with a first area, the die support body having a layer support surface proximal the first area, the die having a plurality of first bond pads disposed in a first spaced arrangement on the first area, the first spaced arrangement having a first minimum center- 15 to-center bond pad spacing;

- a bond pad spacing interface structure supported, at least in part, by the layer support surface of the die support body, the bond pad spacing interface structure having a plurality of second bond pads in a second spaced arrangement over a second area, the second spaced arrangement having a second minimum center-to-center bond pad spacing, and a plurality of electrical conductors, each of the electrical conductors connecting a corresponding one of the first bond pads to a corresponding one or more of the second bond pads, wherein the first bond pads are arranged with a first average density of bond pads per unit area and the second bond pads are arranged with a second average density value of bond pads per unit area that is lower than said first density.

- 2. The chip scale package of claim 1, wherein the semiconductor die includes a dielectric layer disposed on at least a portion of the first area of the semiconductor die, the dielectric layer having a plurality of bond pad clearance openings, each bond pad clearance opening aligned with a corresponding one of the first bond pads.

- 3. The chip scale package of claim 1, wherein the bond pad spacing interface structure includes a dielectric layer disposed on at least a portion of the first area of the semiconductor die and at least a portion of the layer support surface of the 40 die support body, the dielectric layer having a plurality of bond pad clearance openings, each bond pad clearance opening aligned with a corresponding one of the first bond pads.

- 4. The chip scale package of claim 2, wherein the bond pad density interface structure includes a patterned conductive 45 layer overlaying at least a portion of the dielectric layer, the patterned conductive layer forming the electrical conductors.

- 5. The chip scale package of claim 3, wherein the bond pad density interface structure includes a patterned conductive layer overlaying at least a portion of the dielectric layer, the 50 patterned conductive layer forming the electrical conductors.

- 6. The chip scale package of claim 4, wherein the bond pad density interface structure includes a solder mask disposed over at least a portion of the patterned conductive layer, the solder mask having clearance openings respectively aligned 55 with the second bond pads.

- 7. The chip scale package of claim 5, wherein the bond pad density interface structure includes a solder mask disposed over at least a portion of the patterned conductive layer, the solder mask having clearance openings respectively aligned 60 with the second bond pads.

- 8. The chip scale package of claim 6, wherein the bond pad density interface structure includes a solder bump disposed within a clearance opening of the solder mask, the solder bump having a bottom surface contacting one of the second 65 bond pads and a top surface projecting outward beyond a surface plane of the solder mask.

**10**

- 9. The chip scale package of claim 7, wherein the bond pad density interface structure includes a solder bump disposed within a clearance opening of the solder mask, the solder bump having a bottom surface contacting one of the second bond pads and a top surface projecting outward beyond a surface plane of the solder mask.

- 10. The chip scale package of claim 1, wherein the first minimum center-to-center spacing is smaller than the second minimum center-to-center spacing.

- 11. The chip scale package of claim 1, wherein the first area of the die surface is substantially coplanar with the second area of the die support body.

- 12. The chip scale package of claim 2, wherein the dielectric layer is a polymeric dielectric buffer material with a low moisture uptake and an elongation of from approximately 10% to 300%.

- 13. The chip scale package of claim 3, wherein the dielectric layer is a polymeric dielectric buffer material with a low moisture uptake and an elongation of from approximately 10% to 300%.

- 14. A chip scale package, comprising:

- a semiconductor die embedded in a die support body formed of a molding composition, the semiconductor die having a die surface with a first area, the die support body having a layer support surface proximal the first area, the die having a plurality of first bond pads disposed in a first spaced arrangement on the first area, the first spaced arrangement having a first minimum centerto-center bond pad spacing;

- a bond pad spacing interface structure supported, at least in part, by the layer support surface of the die support body, the bond pad spacing interface structure having a plurality of second bond pads in a second spaced arrangement over a second area, the second spaced arrangement having a second minimum center-to-center bond pad spacing, and a plurality of electrical conductors, each of the electrical conductors connecting a corresponding one of the first bond pads to a corresponding one or more of the second bond pads wherein the semiconductor die includes a dielectric layer disposed on at least a portion of the first area of the semiconductor die, the dielectric layer having a plurality of bond pad clearance openings, each bond pad clearance opening aligned with a corresponding one of the first bond pads, and the dielectric layer is a polymeric dielectric buffer material with a low moisture uptake and an elongation of from approximately 20% to 100%.

- 15. The chip scale package of claim 3, wherein the dielectric layer is a polymeric dielectric buffer material with a low moisture uptake and an elongation of from approximately 20% to 50%.

- 16. The chip scale package of claim 2, wherein the dielectric layer is selected from the group consisting of an epoxy, a benzocyclobutene resin, a polyamide, a benzocyclobutene-modified polyamide, a benzocyclobutene-modified silicone, a silicone resin, a polyolefin resin, a diene resin, poly(methyl methacrylate), polysulfones, polyetherimides and styrene resins.

- 17. The chip scale package of claim 3, wherein the dielectric layer is selected from the group consisting of an epoxy, a benzocyclobutene resin, a polyamide, a benzocyclobutene-modified polyamide, a benzocyclobutene-modified silicone, a silicone resin, a polyolefin resin, a diene resin, poly(methyl methacrylate), polysulfones, polyetherimides and styrene resins.

- 18. The chip scale package of claim 2, wherein the dielectric layer is from approximately 0.1 to approximately 50 microns thick.

- 19. The chip scale package of claim 3, wherein the dielectric layer is from approximately 0.1 to approximately 50 5 microns thick.

- 20. A chip scale package, comprising:

- a semiconductor die embedded in a die support body formed of a molding composition, the semiconductor die having a die surface with a first area, the die support 10 body having a layer support surface proximal the first area, the die having a plurality of first bond pads disposed in a first spaced arrangement on the first area, the first spaced arrangement having a first minimum centerto-center bond pad spacing;

- a bond pad spacing interface structure supported, at least in part, by the layer support surface of the die support body, the bond pad spacing interface structure having a plurality of second bond pads in a second spaced arrangement over a second area, the second spaced arrangement having a second minimum center-to-center bond pad spacing, and a plurality of electrical conductors, each of the electrical conductors connecting a corresponding one of

12

the first bond pads to a corresponding one or more of the second bond pads wherein the semiconductor die includes a dielectric layer disposed on at least a portion of the first area of the semiconductor die, the dielectric layer having a plurality of bond pad clearance openings, each bond pad clearance opening aligned with a corresponding one of the first bond pads, wherein the dielectric layer is from approximately 1 to approximately 10 microns thick.

- 21. The chip scale package of claim 3, wherein the dielectric layer is from approximately 1 to approximately 10 microns thick.

- 22. The chip scale package of claim 1, wherein at least some of the second bond pads are disposed on the die support body so that, viewed in a direction substantially perpendicular to a plane in which the second bond pads lie, the second bond pads are located beyond a projection of a perimeter of the semiconductor die.

- 23. The chip scale package of claim 1, wherein at least one first bond pad is electrically connected to another first bond pad.

\* \* \* \*