#### US008380884B2

### (12) United States Patent

#### Ramchandran

## (10) Patent No.: US 8,380,884 B2 (45) Date of Patent: \*Feb. 19, 2013

### (54) ADAPTABLE DATAPATH FOR A DIGITAL PROCESSING SYSTEM

(75) Inventor: Amit Ramchandran, San Jose, CA (US)

(73) Assignee: Altera Corporation, San Jose, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 13/042,391

(22) Filed: Mar. 7, 2011

#### (65) Prior Publication Data

US 2011/0161535 A1 Jun. 30, 2011

#### Related U.S. Application Data

- (63) Continuation of application No. 12/556,894, filed on Sep. 10, 2009, now Pat. No. 7,904,603, which is a continuation of application No. 11/800,577, filed on May 3, 2007, now Pat. No. 7,606,943, which is a continuation of application No. 10/626,833, filed on Jul. 23, 2003, now abandoned.

- (60) Provisional application No. 60/422,063, filed on Oct. 28, 2002.

- (51) **Int. Cl.**

G06F 3/00 (2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

3,409,175 A 11/1968 Byrne 3,666,143 A 5/1972 Weston 3,938,639 A 2/1976 Birrell 3,949,903 A 4/1976 Benasutti et al.

| 3,960,298 | $\mathbf{A}$ | 6/1976  | Birrell         |

|-----------|--------------|---------|-----------------|

| 3,967,062 | $\mathbf{A}$ | 6/1976  | Dobias          |

| 3,991,911 | $\mathbf{A}$ | 11/1976 | Shannon et al.  |

| 3,995,441 | $\mathbf{A}$ | 12/1976 | McMillin        |

| 4,076,145 | $\mathbf{A}$ | 2/1978  | Zygiel          |

| 4,143,793 | A            | 3/1979  | McMillin et al. |

| 4,172,669 | A            | 10/1979 | Edelbach        |

| 4,174,872 | $\mathbf{A}$ | 11/1979 | Fessler         |

| 4,181,242 | A            | 1/1980  | Zygiel et al.   |

| RE30,301  | E            | 6/1980  | Zygiel          |

| 4,218,014 | $\mathbf{A}$ | 8/1980  | Tracy           |

| 4,222,972 | $\mathbf{A}$ | 9/1980  | Caldwell        |

| 4,237,536 | $\mathbf{A}$ | 12/1980 | Enelow et al.   |

|           |              | (Cont   | tinued)         |

|           |              |         |                 |

#### FOREIGN PATENT DOCUMENTS

DE 100 18 374 A1 10/2001 EP 0 301 169 A1 2/1989

#### (Continued)

#### OTHER PUBLICATIONS

Abnous et al., "Ultra-Low-Power Domain-Specific Multimedia Processors," VLSI Signal Processing, IX, 1998, IEEE Workshop in San Francisco, CA, USA, Oct. 30-Nov. 1, 1998, pp. 461-470 (Oct. 30, 1998).

#### (Continued)

Primary Examiner — Chun-Kuan Lee

Assistant Examiner — Dayton Lewis-Taylor

(74) Attorney Agent or Firm — Nivon Poobody

(74) Attorney, Agent, or Firm — Nixon Peabody LLP

#### (57) ABSTRACT

The present invention includes an adaptable high-performance node (RXN) with several features that enable it to provide high performance along with adaptability. A preferred embodiment of the RXN includes a run-time configurable data path and control path. The RXN supports multiprecision arithmetic including 8, 16, 24, and 32 bit codes. Data flow can be reconfigured to minimize register accesses for different operations. For example, multiply-accumulate operations can be performed with minimal, or no, register stores by reconfiguration of the data path. Predetermined kernels can be configured during a setup phase so that the RXN can efficiently execute, e.g., Discrete Cosine Transform (DCT), Fast-Fourier Transform (FFT) and other operations. Other features are provided.

#### 33 Claims, 3 Drawing Sheets

## US 8,380,884 B2 Page 2

| HC DATENT                                 | ΓDOCUMENTS                         | 5,368,198 A                | 11/1994          | Goulet                                 |

|-------------------------------------------|------------------------------------|----------------------------|------------------|----------------------------------------|

|                                           |                                    | 5,379,343 A                |                  | Grube et al.                           |

| , , , , , , , , , , , , , , , , , , , ,   | Shannon                            | 5,381,546 A                |                  | Servi et al.                           |

|                                           | Widergren et al.<br>Fessler et al. | 5,381,550 A                |                  | Jourdenais et al.                      |

|                                           | Desai et al.                       | 5,388,212 A                |                  | Grube et al.                           |

| , ,                                       | McMillin et al.                    | 5,392,960 A                |                  | Kendt et al.                           |

| 4,393,468 A 7/1983                        |                                    | 5,437,395 A<br>5,450,557 A |                  | Bull et al.<br>Kopp et al.             |

| 4,413,752 A 11/1983                       | McMillin et al.                    | 5,454,406 A                |                  | Rejret et al.                          |

| * *                                       | Annese et al.                      | 5,465,368 A                |                  | Davidson et al.                        |

|                                           | Basile et al.                      | 5,479,055 A                | 12/1995          |                                        |

| , , ,                                     | Shoaf et al. Austin et al.         |                            |                  | Blakeney, II et al.                    |

|                                           | Jeans                              | 5,491,823 A                |                  | Ruttenberg                             |

|                                           | Austin                             | 5,507,009 A<br>5,515,519 A |                  | Grube et al.<br>Yoshioka et al.        |

| 4,553,573 A 11/1985                       | McGarrah                           | 5,515,519 A<br>5,517,600 A |                  | Shimokawa                              |

|                                           | McMillin et al.                    | 5,519,694 A                |                  | Brewer et al.                          |

|                                           | Fessler Scholl et al               | 5,522,070 A                | 5/1996           | Sumimoto                               |

|                                           | Scholl et al.<br>Sedam et al.      | 5,530,964 A                |                  | Alpert et al.                          |

| ,                                         | Terepin et al.                     | 5,534,796 A                |                  | Edwards                                |

|                                           | Hassell                            | 5,542,265 A                |                  | Rutland Parayyald at al                |

| 4,694,416 A 9/1987                        | Wheeler et al.                     | 5,553,755 A<br>5,555,417 A |                  | Bonewald et al.<br>Odnert et al.       |

|                                           | Gaunt et al.                       | 5,560,028 A                |                  | Sachs et al.                           |

|                                           | Worley, Jr. et al.                 | 5,560,038 A                |                  | Haddock                                |

|                                           | Scott<br>Scott                     | 5,570,587 A                | 11/1996          | Kim                                    |

|                                           | Baker                              | 5,572,572 A                |                  | Kawan et al.                           |

| , ,                                       | Chiarulli et al.                   | 5,590,353 A                |                  | Sakakibara et al.                      |

| , , , , , , , , , , , , , , , , , , ,     | Webb                               | 5,594,657 A<br>5,600,810 A |                  | Cantone et al.<br>Ohkami               |

| , ,                                       | Lamb                               | 5,600,844 A                |                  | Shaw et al.                            |

|                                           | McMillin et al.                    | 5,602,833 A                | 2/1997           |                                        |

| , ,                                       | Cedrone et al.                     | 5,603,043 A                |                  | Taylor et al.                          |

|                                           | Vogel<br>Johnson et al.            | 5,607,083 A                |                  | Vogel et al.                           |

|                                           | Nosenchuck et al.                  | 5,608,643 A                |                  | Wichter et al.                         |

|                                           | Holzboog                           | 5,611,867 A<br>5,623,545 A |                  | Cooper et al.<br>Childs et al.         |

| 4,827,426 A 5/1989                        | Patton et al.                      | 5,625,669 A                |                  | McGregor et al.                        |

| , , ,                                     | Hancock et al.                     | 5,626,407 A                |                  | Westcott                               |

|                                           | Gerstung                           | 5,630,206 A                |                  | Urban et al.                           |

| * *                                       | Burton<br>Metcalfe et al.          | 5,635,940 A                | 6/1997           | Hickman et al.                         |

|                                           | Rudick                             | 5,646,544 A                | 7/1997           | Iadanza                                |

|                                           | Austin et al.                      | 5,646,545 A                |                  | Trimberger et al.<br>Assis Mascarenhas |

| 4,936,488 A 6/1990                        | Austin                             | 5,647,512 A                | //1997           | de Oliveira et al.                     |

| , , , ,                                   | Scott                              | 5,667,110 A                | 9/1997           |                                        |

|                                           | Scott et al.                       | 5,684,793 A                |                  | Kiema et al.                           |

|                                           | Teller et al.<br>Dawes             | 5,684,980 A                | 11/1997          | Casselman                              |

| , ,                                       | Bennett et al.                     | 5,687,236 A                |                  | Moskowitz et al.                       |

|                                           | Scott                              | 5,694,613 A                | 12/1997          | _                                      |

| 4,993,604 A 2/1991                        | Gaunt et al.                       | 5,694,794 A<br>5,699,328 A | 12/1997          | Jerg et al.<br>Ishizaki et al.         |

| , ,                                       | Sassak                             | 5,701,482 A                |                  | Harrison et al.                        |

|                                           | Campbell et al.                    | 5,704,053 A                |                  | Santhanam                              |

|                                           | Maag<br>Farkas                     | 5,706,191 A                | 1/1998           | Bassett et al.                         |

|                                           | Dabbish et al.                     | 5,706,976 A                |                  | Purkey                                 |

|                                           | Austin                             | 5,712,996 A                |                  | Schepers                               |

|                                           | Scott                              | 5,720,002 A<br>5,721,693 A | 2/1998<br>2/1998 | •                                      |

|                                           | Hassell et al.                     | 5,721,854 A                |                  | Ebcioglu et al.                        |

|                                           | Goulet et al.                      | 5,732,563 A                |                  | Bethuy et al.                          |

| 5,165,575 A 11/1992<br>5,190,083 A 3/1993 | Gupta et al.                       | 5,734,808 A                | 3/1998           | Takeda                                 |

| , ,                                       | Zimmer et al.                      | 5,737,631 A                |                  | Trimberger                             |

| 5,193,151 A 3/1993                        | _                                  | 5,742,180 A                |                  | DeHon et al.                           |

| 5,193,718 A 3/1993                        | Hassell et al.                     | 5,742,821 A<br>5,745,366 A |                  | Prasanna<br>Higham et al.              |

|                                           | Tarsy et al.                       | RE35,780 E                 |                  | Hassell et al.                         |

|                                           | Haynes                             | 5,751,295 A                |                  | Becklund et al.                        |

|                                           | Feldman<br>Bigo et al.             | 5,754,227 A                | 5/1998           | Fukuoka                                |

|                                           | Cherry et al.                      | 5,758,261 A                | 5/1998           | Wiedeman                               |

| · · · · · · · · · · · · · · · · · · ·     | Vogel                              | 5,768,561 A                | 6/1998           |                                        |

|                                           | Motta et al.                       | 5,778,439 A                |                  | Trimberger et al.                      |

| , ,                                       | Benton et al.                      | 5,784,636 A                | 7/1998           |                                        |

|                                           | Wagner                             | 5,787,237 A<br>5,790,817 A | 7/1998<br>8/1998 | Asghar et al.                          |

| , , , , , , , , , , , , , , , , , , ,     | Shannon Thompson et al.            | 5,790,817 A<br>5,791,517 A | 8/1998           |                                        |

| •                                         | Burmeister et al.                  | 5,791,517 A<br>5,791,523 A | 8/1998           |                                        |

| , ,                                       | Swanson et al.                     | 5,794,062 A                | 8/1998           |                                        |

| 5,361,362 A 11/1994                       |                                    | 5,794,067 A                |                  | Kadowaki                               |

|                                           |                                    |                            |                  |                                        |

# US 8,380,884 B2 Page 3

| 5,802,055 |                   | 9/1998  | Krein et al.          | 6,091,765 A                           |         | Pietzold, III et al.                  |

|-----------|-------------------|---------|-----------------------|---------------------------------------|---------|---------------------------------------|

| 5,818,603 | $\mathbf{A}$      | 10/1998 | Motoyama              | 6,094,065 A                           | 7/2000  | Tavana et al.                         |

| 5,822,308 | $\mathbf{A}$      | 10/1998 | Weigand et al.        | 6,094,726 A                           | 7/2000  | Gonion et al.                         |

| 5,822,313 | Α                 |         | Malek et al.          | 6,111,893 A                           |         | Volftsun et al.                       |

| 5,822,360 |                   |         | Lee et al.            | 6,111,935 A                           |         | Hughes-Hartogs                        |

| / /       |                   |         |                       | , ,                                   |         | •                                     |

| 5,828,858 |                   |         | Athanas et al.        | 6,115,751 A                           |         | Tam et al.                            |

| 5,829,085 |                   |         | Jerg et al.           | 6,120,551 A                           |         | Law et al.                            |

| 5,835,753 | $\mathbf{A}$      | 11/1998 | Witt                  | 6,122,670 A                           | 9/2000  | Bennett et al.                        |

| 5,838,165 | $\mathbf{A}$      | 11/1998 | Chatter               | 6,138,693 A                           | 10/2000 | Matz                                  |

| 5,845,815 |                   | 12/1998 | Vogel                 | 6,141,283 A                           |         | Bogin et al.                          |

| 5,860,021 |                   |         | Klingman              | 6,150,838 A                           |         | Wittig et al.                         |

| / /       |                   |         |                       | , ,                                   |         | · · · · · · · · · · · · · · · · · · · |

| 5,862,961 |                   |         | Motta et al.          | 6,154,494 A                           |         | Sugahara et al.                       |

| 5,870,427 | Α                 | 2/1999  | Tiedemann, Jr. et al. | 6,157,997 A                           | 12/2000 | Oowaki et al.                         |

| 5,873,045 | $\mathbf{A}$      | 2/1999  | Lee et al.            | 6,175,854 B1                          | 1/2001  | Bretscher                             |

| 5,881,106 | Α                 | 3/1999  | Cartier               | 6,175,892 B1                          | 1/2001  | Sazzad et al.                         |

| 5,884,284 |                   |         | Peters et al.         | 6,181,981 B1                          |         | Varga et al.                          |

|           |                   |         |                       |                                       |         | •                                     |

| 5,886,537 |                   |         | Macias et al.         | 6,185,418 B1                          |         | MacLellan et al.                      |

| 5,887,174 |                   |         | Simons et al.         | 6,192,070 B1                          |         | Poon et al.                           |

| 5,889,816 | $\mathbf{A}$      | 3/1999  | Agrawal et al.        | 6,192,255 B1                          | 2/2001  | Lewis et al.                          |

| 5,890,014 | $\mathbf{A}$      | 3/1999  | Long                  | 6,192,388 B1                          | 2/2001  | Cajolet                               |

| 5,892,900 | Α                 |         | Ginter et al.         | 6,195,788 B1                          |         | Leaver et al.                         |

| 5,892,961 |                   |         | Trimberger            | 6,198,924 B1                          |         | Ishii et al.                          |

| / /       |                   |         | <u> </u>              | , ,                                   |         |                                       |

| 5,894,473 |                   | 4/1999  |                       | 6,199,181 B1                          |         | Rechef et al.                         |

| 5,901,884 | A                 |         | Goulet et al.         | 6,202,130 B1                          |         | Scales, III et al.                    |

| 5,903,886 | $\mathbf{A}$      | 5/1999  | Heimlich et al.       | 6,219,697 B1                          | 4/2001  | Lawande et al.                        |

| 5,907,285 | $\mathbf{A}$      | 5/1999  | Toms et al.           | 6,219,756 B1                          | 4/2001  | Kasamizugami                          |

| 5,907,580 |                   | 5/1999  | Cummings              | 6,219,780 B1                          |         | Lipasti                               |

| 5,910,733 |                   |         | Bertolet et al.       | 6,223,222 B1                          |         | Fijolek et al.                        |

| / /       |                   |         | _                     | , ,                                   |         | •                                     |

| 5,912,572 |                   |         | Graf, III             | 6,226,387 B1                          |         | Tewfik et al.                         |

| 5,913,172 | Α                 | 6/1999  | McCabe et al.         | 6,230,307 B1                          | 5/2001  | Davis et al.                          |

| 5,917,852 | $\mathbf{A}$      | 6/1999  | Butterfield et al.    | 6,237,029 B1                          | 5/2001  | Master et al.                         |

| 5,920,801 | Α                 | 7/1999  | Thomas et al.         | 6,246,883 B1                          | 6/2001  | Lee                                   |

| 5,931,918 |                   |         | Row et al.            | 6,247,125 B1                          |         | Noel-Baron et al.                     |

| 5,933,642 |                   |         | Greenbaum et al.      | , , ,                                 |         |                                       |

| , ,       |                   |         |                       | 6,249,251 B1                          |         | Chang et al.                          |

| 5,933,855 |                   |         | Rubinstein            | 6,258,725 B1                          |         | Lee et al.                            |

| 5,940,438 | Α                 | 8/1999  | Poon et al.           | 6,263,057 B1                          | 7/2001  | Silverman                             |

| 5,949,415 | $\mathbf{A}$      | 9/1999  | Lin et al.            | 6,266,760 B1                          | 7/2001  | DeHon et al.                          |

| 5,950,011 | Α                 | 9/1999  | Albrecht et al.       | 6,272,579 B1                          | 8/2001  | Lentz et al.                          |

| 5,950,131 |                   | 9/1999  |                       | 6,281,703 B1                          |         | Furuta et al.                         |

| , ,       |                   |         |                       | · · · · · · · · · · · · · · · · · · · |         |                                       |

| 5,951,674 |                   |         | Moreno                | 6,282,627 B1                          |         | Wong et al.                           |

| 5,953,322 |                   |         | Kimball               | 6,289,375 B1                          |         | Knight et al.                         |

| 5,956,518 | $\mathbf{A}$      | 9/1999  | DeHon et al.          | 6,289,434 B1                          | 9/2001  | Roy                                   |

| 5,956,967 | $\mathbf{A}$      | 9/1999  | Kim                   | 6,289,488 B1                          | 9/2001  | Dave et al.                           |

| 5,959,811 | Α                 | 9/1999  | Richardson            | 6,292,822 B1                          |         | Hardwick                              |

| 5,959,881 |                   |         | Trimberger et al.     | 6,292,827 B1                          |         |                                       |

| , ,       |                   |         |                       | / /                                   |         |                                       |

| 5,963,048 |                   |         | Harrison et al.       | 6,292,830 B1                          |         | Taylor et al.                         |

| 5,966,534 |                   |         | Cooke et al.          | 6,301,653 B1                          |         | Mohamed et al.                        |

| 5,970,254 | $\mathbf{A}$      | 10/1999 | Cooke et al.          | 6,305,014 B1                          | 10/2001 | Roediger et al.                       |

| 5,987,105 | $\mathbf{A}$      | 11/1999 | Jenkins et al.        | 6,311,149 B1                          | 10/2001 | Ryan et al.                           |

| 5,987,611 | Α                 | 11/1999 | Freund                | 6,321,985 B1                          |         | •                                     |

| 5,991,302 |                   |         | Berl et al.           | 6,346,824 B1                          |         |                                       |

| / /       |                   |         |                       | , ,                                   |         |                                       |

| 5,991,308 |                   |         | Fuhrmann et al.       | 6,347,346 B1                          |         |                                       |

| 5,993,739 |                   |         |                       | 6,349,394 B1                          |         | Brock et al.                          |

| 5,999,734 | Α                 | 12/1999 | Willis et al.         | 6,353,841 B1                          | 3/2002  | Marshall et al.                       |

| 6,005,943 | A                 | 12/1999 | Cohen et al.          | 6,356,994 B1                          | 3/2002  | Barry et al.                          |

| 6,006,249 | $\mathbf{A}$      | 12/1999 |                       | 6,359,248 B1                          |         | <u> </u>                              |

| 6,016,395 |                   |         | Mohamed               | 6,360,256 B1                          |         |                                       |

| 6,021,186 |                   |         | Suzuki et al.         | 6,360,259 B1                          |         | Bradley                               |

| / /       |                   |         |                       | //                                    |         |                                       |

| 6,021,492 |                   | 2/2000  |                       | 6,360,263 B1                          |         | Kurtzberg et al.                      |

| 6,023,742 |                   |         | Ebeling et al.        | 6,363,411 B1                          |         | Dugan et al.                          |

| 6,023,755 | A                 | 2/2000  | Casselman             | 6,366,999 B1                          | 4/2002  | Drabenstott et al.                    |

| 6,028,610 | $\mathbf{A}$      | 2/2000  | Deering               | 6,377,983 B1                          | 4/2002  | Cohen et al.                          |

| 6,036,166 |                   | 3/2000  |                       | 6,378,072 B1                          |         | Collins et al.                        |

| 6,039,219 |                   |         | Bach et al.           | 6,381,735 B1                          |         |                                       |

| 6,041,322 |                   |         | Meng et al.           | 6,385,751 B1                          |         |                                       |

| , ,       |                   |         | $\mathcal{L}$         | , ,                                   |         |                                       |

| 6,041,970 |                   | 3/2000  | S                     | 6,405,214 B1                          |         | Meade, II                             |

| 6,046,603 |                   | 4/2000  |                       | 6,408,039 B1                          |         |                                       |

| 6,047,115 | A                 | 4/2000  | Mohan et al.          | 6,410,941 B1                          | 6/2002  | Taylor et al.                         |

| 6,052,600 | $\mathbf{A}$      | 4/2000  | Fette et al.          | 6,411,612 B1                          | 6/2002  | Halford et al.                        |

| 6,055,314 |                   |         | Spies et al.          | 6,421,372 B1                          |         | Bierly et al.                         |

| , ,       |                   |         | 1                     | , ,                                   |         | •                                     |

| 6,056,194 |                   | 5/2000  |                       | 6,421,809 B1                          |         | Wuytack et al.                        |

| 6,059,840 | A                 | 5/2000  | Click, Jr.            | 6,430,624 B1                          | 8/2002  | Jamtgaard et al.                      |

| 6,061,580 | A                 | 5/2000  | Altschul et al.       | 6,433,578 B1                          | 8/2002  | Wasson                                |

| 6,073,132 |                   |         | Gehman                | 6,434,590 B1                          |         | Blelloch et al.                       |

| , ,       |                   |         |                       | , ,                                   |         |                                       |

| 6,076,174 |                   | 6/2000  |                       | 6,438,737 B1                          |         | Morelli et al.                        |

| 6,078,736 |                   |         | Guccione              | 6,456,996 B1                          |         | Crawford, Jr. et al.                  |

| 6,085,740 | $\mathbf{A}$      | 7/2000  | Ivri et al.           | 6,459,883 B2                          | 10/2002 | Subramanian et al.                    |

| 6,088,043 |                   |         | Kelleher et al.       | 6,473,609 B1                          |         | Schwartz et al.                       |

| 6,091,263 |                   |         | New et al.            | 6,507,947 B1                          |         | Schreiber et al.                      |

| 0,071,203 | $\Gamma$ <b>1</b> | 112000  | TIOW OF AI.           | 0,507, <b>54</b> 7 <b>D</b> 1         | 1/2003  | Semenous et al.                       |

|           |                   |         |                       |                                       |         |                                       |

# US 8,380,884 B2 Page 4

|                                    |         |                                      |              |                   | ,     |                        |

|------------------------------------|---------|--------------------------------------|--------------|-------------------|-------|------------------------|

| 6,510,138 B1                       |         | Pannell                              | 2002/0083423 |                   |       | Ostanevich et al.      |

| 6,510,510 B1                       | 1/2003  |                                      | 2002/0087829 |                   |       | Snyder et al.          |

| 6,538,470 B1                       |         | Langhammer et al.                    | 2002/0089348 |                   |       | Langhammer             |

| 6,556,044 B2                       |         | Langhammer et al.                    | 2002/0101909 |                   | /2002 | Chen et al.            |

| 6,563,891 B1                       |         | Eriksson et al.                      | 2002/0107905 |                   |       | Roe et al.             |

| 6,570,877 B1                       |         | Kloth et al.                         | 2002/0107962 |                   |       | Richter et al.         |

| 6,577,678 B2                       | 6/2003  | Scheuermann                          | 2002/0119803 |                   | /2002 | Bitterlich et al.      |

| 6,587,684 B1                       | 7/2003  | Hsu et al.                           | 2002/0120672 | A1 8              | /2002 | Butt et al.            |

| 6,590,415 B2                       | 7/2003  | Agrawal et al.                       | 2002/0138716 | $A1 \qquad 9$     | /2002 | Master et al.          |

| 6,601,086 B1                       | 7/2003  | Howard et al.                        | 2002/0141489 | A1 = 10           | /2002 | Imaizumi               |

| 6,601,158 B1                       | 7/2003  | Abbott et al.                        | 2002/0147845 | A1 = 10           | /2002 | Sanchez-Herrero et al. |

| 6,604,085 B1                       | 8/2003  | Kolls                                | 2002/0159503 | A1 = 10           | /2002 | Ramachandran           |

| 6,606,529 B1                       | 8/2003  | Crowder, Jr. et al.                  | 2002/0162026 | A1 = 10           | /2002 | Neuman et al.          |

| 6,615,333 B1                       | 9/2003  | Hoogerbrugge et al.                  | 2002/0168018 | A1 = 11           | /2002 | Scheuermann            |

| 6,618,434 B2                       | 9/2003  | Heidari-Bateni et al.                | 2002/0181559 | A1 12             | /2002 | Heidari-Bateni et al.  |

| 6,640,304 B2                       | 10/2003 | Ginter et al.                        | 2002/0184291 | A1 12             | /2002 | Hogenauer              |

| 6,653,859 B2                       | 11/2003 | Sihlbom et al.                       | 2002/0184498 | A1 = 12           | /2002 | Qi                     |

| 6,662,260 B1                       | 12/2003 | Wertheim et al.                      | 2002/0191790 | A1 12/            | 2002  | Anand et al.           |

| 6,675,265 B2                       | 1/2004  | Barroso et al.                       | 2002/0199090 | A1  12            | 2002  | Wilson                 |

| 6,691,148 B1                       | 2/2004  | Loyall et al.                        | 2003/0007606 | A1 = 1            | 2003  | Suder et al.           |

| 6,711,617 B1                       | 3/2004  | Bantz et al.                         | 2003/0012270 | A1 = 1            | 2003  | Zhou et al.            |

| 6,718,182 B1                       | 4/2004  | Kung                                 | 2003/0018446 | $\mathbf{A}1$     | /2003 | Makowski et al.        |

| 6,721,286 B1                       |         | Williams et al.                      | 2003/0018700 | <b>A</b> 1 1/     | /2003 | Giroti et al.          |

| 6,721,884 B1                       |         | De Oliveira Kastrup Pereira et al.   | 2003/0023830 | $\mathbf{A}1$ $1$ | /2003 | Hogenauer              |

| 6,732,354 B2                       |         | Ebeling et al.                       | 2003/0026242 |                   |       | Jokinen et al.         |

| 6,735,621 B1                       |         | Yoakum et al.                        | 2003/0030004 |                   |       | Dixon et al.           |

| 6,738,744 B2                       |         | Kirovski et al.                      | 2003/0046421 |                   |       | Horvitz et al.         |

| 6,748,360 B2                       |         | Pitman et al.                        | 2003/0061260 |                   |       | Rajkumar               |

| 6,754,470 B2                       |         | Hendrickson et al.                   | 2003/0061311 |                   | /2003 |                        |

| 6,760,587 B2                       |         | Holtzman et al.                      | 2003/0063656 |                   |       | Rao et al.             |

| 6,766,165 B2                       |         | Sharma et al.                        | 2003/0076815 |                   |       | Miller et al.          |

| 6,778,212 B1                       |         | Deng et al.                          | 2003/0099223 |                   |       | Chang et al.           |

| 6,785,341 B2                       |         | Walton et al.                        | 2003/0102889 |                   |       | Master et al.          |

| 6,819,140 B2                       |         | Yamanaka et al.                      | 2003/0102009 |                   |       | Master et al.          |

| 6,823,448 B2                       |         | Roth et al.                          | 2003/0110485 |                   |       | Lu et al.              |

| 6,829,633 B2                       |         | Gelfer et al.                        | 2003/0142818 |                   |       | Raghunathan et al.     |

| 6,832,250 B1                       |         | _                                    | 2003/0154357 |                   |       | Master et al.          |

| 6,836,839 B2                       |         |                                      | 2003/0154337 |                   |       | Kozuch et al.          |

| 6,865,664 B2                       |         | Budrovic et al.                      | 2003/0103723 |                   |       | McCormack et al.       |

| 6,871,236 B2                       |         | Fishman et al.                       | 2003/0172130 |                   |       | Srinivasan et al.      |

| 6,883,084 B1                       |         | Donohoe                              | 2003/01/2133 |                   |       | Ebeling et al.         |

| 6,894,996 B2                       | 5/2005  |                                      | 2003/0200338 |                   |       | Meyer et al.           |

| 6,901,440 B1                       |         | Bimm et al.                          | 2003/0212084 |                   |       | Vandeweerd             |

| 6,912,515 B2                       |         | Jackson et al.                       | 2004/0010645 |                   |       | Scheuermann et al.     |

| 6,985,517 B2                       |         | Matsumoto et al.                     | 2004/0015970 |                   |       | Scheuermann            |

| 6,986,021 B2                       |         | Master et al.                        | 2004/0013970 |                   |       | Scheuermann et al.     |

| 6,988,139 B1                       |         | Jervis et al.                        | 2004/0023139 |                   |       | Valio                  |

| 7,032,229 B1                       |         | Flores et al.                        | 2004/0057303 |                   |       | McDonough et al.       |

| 7,032,229 B1<br>7,044,741 B2       | 5/2006  |                                      | 2004/0002300 |                   |       | Parolari               |

| 7,044,741 B2<br>7,082,456 B2       |         | Mani-Meitav et al.                   | 2004/0093479 |                   |       | Ramchandran            |

| , ,                                |         | Ainsworth et al.                     |              |                   |       |                        |

| 7,139,910 B1<br>7,142,731 B1       | 11/2006 |                                      | 2004/0168044 |                   |       | Ramchandran            |

| 7,142,731 B1<br>7,249,242 B2       |         | Ramchandran                          | 2005/0166038 |                   |       | Wang et al.            |

| 2001/0003191 A1                    |         | Kamenandran<br>Kovacs et al.         | 2005/0198199 |                   |       | Dowling                |

| 2001/0003191 A1<br>2001/0023482 A1 |         |                                      | 2006/0031660 | $\mathbf{A}1$ 2   | /2006 | Master et al.          |

| 2001/0023482 A1<br>2001/0029515 A1 | 9/2001  | _ · · · · ·                          | EC           | DEICNI            | DATE  | NIT DOCLIMENITS        |

| 2001/0029313 A1<br>2001/0034795 A1 | 10/2001 | Moulton et al.                       | ЪТ           | MEIUN I           | LAIE  | NT DOCUMENTS           |

| 2001/0034793 A1<br>2001/0039654 A1 |         | Miyamoto                             | EP           | 0 166 586         | 5 B1  | 1/1991                 |

| 2001/0039034 A1<br>2001/0048713 A1 |         | Medlock et al.                       | EP           | 0 236 633         | 3 B1  | 5/1991                 |

| 2001/0048713 A1<br>2001/0048714 A1 | 12/2001 | -                                    | EP           | 0 478 624         | 4 B1  | 4/1992                 |

| 2001/0048/14 A1<br>2001/0050948 A1 |         | Ramberg et al.                       | EP           | 0 479 102         | 2 A2  | 4/1992                 |

| 2001/0030948 A1                    |         | Kamano et al.                        | EP           | 0 661 83          | 1 A2  | 7/1995                 |

| 2002/0010348 A1<br>2002/0013799 A1 |         | Blaker                               | EP           | 0 668 659         | 9 A2  | 8/1995                 |

| 2002/0013799 A1<br>2002/0013937 A1 |         | Ostanevich et al.                    | EP           | 0 690 588         | 3 A2  | 1/1996                 |

| 2002/0015937 A1<br>2002/0015435 A1 |         | Rieken                               | EP           | 0 691 754         | 4 A2  | 1/1996                 |

| 2002/0015435 A1<br>2002/0015439 A1 |         | Kohli et al.                         | EP           | 0 768 602         | 2 A2  | 4/1997                 |

| 2002/0013439 A1<br>2002/0023210 A1 |         | Tuomenoksa et al.                    | EP           | 0 817 006         | 5 A2  | 1/1998                 |

|                                    |         |                                      | EP           | 0 821 495         | 5 A2  | 1/1998                 |

| 2002/0024942 A1<br>2002/0024993 A1 |         | Tsuneki et al.<br>Subramanian et al. | EP           | 0 866 210         | ) A2  | 9/1998                 |

|                                    |         |                                      | EP           | 0 923 247         | 7 A2  | 6/1999                 |

| 2002/0031166 A1                    |         | Subramanian et al.                   | EP           | 0 926 596         |       | 6/1999                 |

| 2002/0032551 A1                    |         | Zakiya                               | EP           | 1 056 217         |       | 11/2000                |

| 2002/0035623 A1                    |         | Lawande et al.                       | EP           | 1 061 437         |       | 12/2000                |

| 2002/0041581 A1                    |         | Aramaki                              | EP           | 1 061 443         |       | 12/2000                |

| 2002/0042907 A1                    |         | Yamanaka et al.                      | EP           | 1 126 368         |       | 8/2001                 |

| 2002/0061741 A1                    | 5/2002  | Leung et al.                         | EP           | 1 150 506         |       | 10/2001                |

| 2002/0069282 A1                    | 6/2002  | Reisman                              | EP           | 1 189 358         |       | 3/2002                 |

| 2002/0072830 A1                    | 6/2002  | Hunt                                 | GB           | 2 067 800         |       | 7/1981                 |

| 2002/0078337 A1                    | 6/2002  | Moreau et al.                        | GB           | 2 237 908         |       | 5/1991                 |

| 2002/0083305 A1                    | 6/2002  | Renard et al.                        |              | 62-249456         |       | 10/1987                |

|                                    | -       |                                      |              |                   |       |                        |

| JP | 63-147258      | 6/1988  |

|----|----------------|---------|

| JP | 4-51546        | 2/1992  |

| JP | 7-064789       | 3/1995  |

| JP | 7066718        | 3/1995  |

| JP | 10233676       | 9/1998  |

| JP | 10254696       | 9/1998  |

| JP | 11296345       | 10/1999 |

| JP | 2000315731     | 11/2000 |

| JP | 2001-053703    | 2/2001  |

| WO | WO 89/05029 A1 | 6/1989  |

| WO | WO 89/11443 A2 | 11/1989 |

| WO | WO 91/00238 A1 | 1/1991  |

| WO | WO 93/13603 A1 | 7/1993  |

| WO | WO 95/11855 A1 | 5/1995  |

| WO | WO 96/33558 A1 | 10/1996 |

| WO | WO 98/32071 A3 | 7/1998  |

| WO | WO 99/03776 A1 | 1/1999  |

| WO | WO 99/21094 A2 | 4/1999  |

| WO | WO 99/26860 A1 | 6/1999  |

| WO | WO 99/65818 A1 | 12/1999 |

| WO | WO 00/19311 A1 | 4/2000  |

| WO | WO 00/65855 A1 | 11/2000 |

| WO | WO 00/69073 A1 | 11/2000 |

| WO | WO 01/11281 A1 | 2/2001  |

| WO | WO 01/22235 A1 | 3/2001  |

| WO | WO 01/76129 A2 | 10/2001 |

| WO | WO 02/12978 A2 | 2/2002  |

|    |                |         |

#### OTHER PUBLICATIONS

Aggarwal et al.., "Efficient Huffman Decoding," International Conference on Image Processing IEEE 1:936-939 (Sep. 10-13, 2000). Allan et al., "Software Pipelining," ACM Computing Surveys, 27(3):1-78 (Sep. 1995).

Alsolaim et al., "Architecture and Application of a Dynamically Reconfigurable Hardware Array for Future Mobile Communication Systems," Field Programmable Custom Computing Machines, 2000 IEEE Symposium, Napa Valley, Los Alamitos, CA. IEEE Comput. Soc. pp. 205-214 (Apr. 17-19, 2000).

Ashenden et al., "The VHDL Cookbook," Dept. Computer Science, University of Adelaide, South Australia. Downloaded from http://tams-www.informatik.uni-hamburg.de/vhdl/doc/cookbook/VHDL-Cookbook.pdf on Dec. 7, 2006 (Jul. 1990).

Bacon et al., "Compiler Transformations for High-Performance Computing," ACM Computing Surveys 26(4):368-373 (Dec. 1994). Balasubramonian et al., "Reducing the Complexity of the Register File in Dynamic Superscalar Processors," Proceedings of the 34th Annual ACM/IEEE International Symposium on Microarchitecture, pp. 237-248 (Dec. 1, 2001).

Banerjee et al., "A Matlab Compiler for Distributed, Heterogeneous, Reconfigurable Computing Systems," 2000 IEEE Symposium, pp. 39-48, (Apr. 17-19, 2000).

Bapte et al., "Uniform Execution Environment for Dynamic Reconfiguration," Darpa Adaptive Computing Systems, http://isis.vanderbilt.edu/publications/archive/babty\_T\_#\_0\_1999\_Uniform\_Ex.pdf, pp. 1-7 (1999).

Baumgarte et al., "PACT XPP—A Self-Reconfigurable Data Processing Architecture," NN www.pactcorp.com/sneu/download/ersa01.pdf; retrieved on Nov. 25, 2005 (Jun. 25, 2001).

Becker et al., "An Application-Tailored Dynamically Reconfigurable Hardware Architecture for Digital Baseband Processing," IEEE Conference Proceedings Article pp. 341-346 (Sep. 18, 2000).

Becker et al., "Design and Implementation of a Coarse-Grained Dynamically Reconfigurable Hardware Architecture," VLSI 2001, Proceedings IEEE Computer Soc. Workshop, Piscataway, NJ, USA, pp. 41-46 (Apr. 19-20, 2001).

Bevstar, BevStar Bottled Water Model Advertisement *Automatic Merchandiser* at www.AMonline.com (2005).

Bevstar, BevStar Point of Use Water Model Advertisement *Automatic Merchandiser* at www.AMonline.com (2005).

Bishop & Loucks, "A Heterogeneous Environment for Hardware/ Software Cosimulation," Proceedings of the 30th Annual Simulation Symposium, pp. 14-22 (Apr. 7-9, 1997).

Brakensiek et al., "Re-Configurable Multi-Standard Terminal for Heterogeneous Networks," Radio and Wireless Conference, Rawcon 2002 IEEE. pp. 27-30 (2002).

Brown et al., "Quick PDA Data Exchange," PC Magazine pp. 1-3 (May 22, 2001).

Buck et al., "Ptolemy: A Framework for Simulating and Prototyping Heterogeneous Systems," International Journal of Computer Simulation 4:155-182 (Apr. 1994).

Burns et al., "A Dynamic Reconfiguration Run-Time System," Proceedings of the 5th Annual Symposium on Field-Programmable Custom Computing Machines, pp. 1 66-1 75 (Apr. 16, 1997).

Business Wire, "Whirlpool Internet-Enabled Appliances to Use Beeline Shopper Software Features," http://www.whirlpoocorp.com/news/releases/release.asp?rid =90 (Feb. 16, 2001).

Buttazzo et al., "Optimal Deadline Assignment for Scheduling Soft Aperiodic Tasks in Hard Real-Time Environments," Engineering of Complex Computer Systems, Proceedings of the Third IEEE International Conference on Como, pp. 39-48 (Sep. 8, 1997).

Callahan et al., "Adapting Software Pipelining for Reconfigurable Computing," in Proceedings of the International Conference on Compilers, Architectrue and Synthesis for Embedded Systems p. 8, ACM (Cases '00, San Jose, CA) (Nov. 17-18, 2000).

Chapman & Mehrotra, "OpenMP and HPF: Integrating Two Paradigms," Proceedings of the 4th International Euro-Par Conference (Euro-Par'98), Springer-Verlag Heidelberg, Lecture Notes in Computer Science 1470:650-658 (1998).

Chen et al., "A Reconfigurable Multiprocessor IC for Rapid Prototyping of Algorithmic-Specific High-Speed DSP Data Paths," IEEE Journal of Solid-State Circuits, IEEE 35:74-75 (Feb. 1, 2001).

Clarke, "Embedded Solutions Enters Development Pact with Marconi," EETimes Online (Jan. 26, 2000).

Compton & Hauck, "Reconfigurable Computing: A Survey of Systems and Software," ACM Press, ACM Computing Surveys (CSUR) 34(2):171-210 (Jun. 2002).

Compton et al., "Configuration Relocation and Defragmentation for Run-Time Reconfigurable Computing," Northwestern University, http://citeseer.nj.nec.com/compton00configuration.html, pp. 1-17 (2000).

Conte et al., "Dynamic Rescheduling: A Technique for Object Code Compatibility in VLIW Architectures," Proceedings of the 28th Annulal International Symposium on Microarchitecture pp. 208-218 (Nov. 29, 1995).

Conte et al., "Instruction Fetch Mechanisms for VLIW Architectures with Compressed Encodings," Proceedings of the Annual IEEE/ACM International Symposium on Microarchitecture (MICRO) 29:201-211 (Dec. 2, 1996).

Cray Research Inc., "Cray T3E Fortran Optimization Guide," Ver. 004-2518-002, Section 4.5 (Jan. 1999).

Cummings et al., "FPGA in the Software Radio," IEEE Communications Magazine . 37(2):108-112 (Feb. 1999).

Dandalis et al., "An Adaptive Cryptograhic Engine for IPSec Architectures," IEEE pp. 132-141 (Jan. 2000).

David et al., "DART: A Dynamically Reconfigurable Architecture Dealing with Future Mobile Telecommunication Constraints," Proceedings of the International Parallel and Distributed Processing Symposium pp. 156-163 (Apr. 15, 2002).

Deepakumara et al., "FPGA Implementation of MD5 has Algorithm," Canadian Conference on Electrical and Computer Engineering, IEEE (2001).

Dehon et al., "Reconfigurable Computing: What, Why and Implications for Design Automation," Design Automation Conference Proceedings pp. 610-615 (1999).

Dipert, "Figuring Out Reconfigurable Logic," EDN 44(16):107-114 (Aug. 5, 1999).

Dominikus, "A Hardware Implementation of MD4-Family Hash Algorithms," 9th International Conference on Electronics, Circuits and Systems IEEE (2002).

Dorband, "aCe C Language Reference Guide," Online (Archived Mar. 2001), http://web.archive.org/web/20000616053819/http://newton.gsfc.nasa.gov/aCe/aCe\_dir/aCe\_cc\_Ref.html (Mar. 2001). Drozdowski, "Scheduling Multiprocessor Tasks—An Overview," Instytut Informatyki Politechnika, pp. 1-31 (Jan. 31, 1996).

Ebeling et al., "RaPiD Reconfigurable Pipelined Datapath," Springer-Verlag, 6th International Workshop on Field-Programmable Logic and Applications pp. 126-135 (1996).

Fawer et al., "A Multiprocessor Approach for Implementing a Time-Diversity Spread Specturm Receiver," Proceeding sof the 1990 International Zurich Seminal on Digital Communications, pp. 173-180 (Mar. 5-8, 1990).

Fisher, "Gone Flat," Forbes pp. 76-79 (Oct. 2001).

Fleischmann et al., "Prototyping Networked Embedded Systems," Integrated Engineering, pp. 116-119 (Feb. 1999).

Forbes "Best of the Web—Computer Networking/Consumer Durables," *The Forbes Magnetic* 40 p. 80 (May 2001).

Gibson, "Fresh Technologies Will Create Myriad Functions," FT Information Technology Review; World Wide Web at http://technews.acm.org/articles/2000-2/0301w.

html?searchterm=%22fresh+technologies%22 (Mar. 1, 2000).

Gluth, "Tntegrierte Signalprozessoren," Elektronik 35(18):112-118 Francis Verlag GMBH, Munich, Germany (Sep. 5, 1986).

Gokhale & Schlesinger, "A Data Parallel C and Its Platforms," Proceedings of the Fifth Symposium on the Frontiers of Massively Parallel Computation pp. 194-202 (Frontiers '95) (Feb. 1995).

Grimm et al., "A System Architecture for Pervasive Computing," Washington University, pp. 1-6 (Sep. 2000).

Halbwachs et al., "The Synchronous Data Flow Programming Language LUSTRE," Proceedings of the IEEE 79(9):1305-1319 (Sep. 1991).

Hammes et al., "Cameron: High Level Language Compilation for Reconfigurable Systems," Proc. of the Intl. Conf. on Parallel Architectures and Compilation Techniques, pp. 236-244 (Oct. 1999).

Hartenstein, "Coarse Grain Reconfigurable Architectures," Design Automation Conference, 2001. Proceedings of the ASP-DAC 2001, Asian and South Pacific Jan. 30, 2001-Feb. 2, 2001, Piscataway, NJ, US, IEEE, pp. 564-569 (Jan. 30, 2001).

Heinz, "An Efficiently Compilabic Extension of {M}odula-3 for Problem-Oriented Explicitly Parallel Programming," Proceedings of the Joint Symposium on Parallel Processing (May 1993).

Hinden et al., "The DARPA Internet: Interconnecting Heterogeneous Computer Networks with Gateways," IEEE Computer Magazine pp. 38-48 (1983).

Horton, "Beginning Java 2: JDK 1.3 Edition," Wrox Press, Chapter 8, pp. 313-316 (Feb. 2001).

Huff et al., "Lifetime-Sensitive Modulo Scheduling," 6th Conference on Programming Language, Design and Implementation, pp. 258-267, ACM (1993).

IBM, "Multisequencing a Single Instruction Stream Scheduling with Space-time Tradeoffs," IBM Technical Disclosure Bulletin 36(2):105-108 (Feb. 1, 1993).

IEEE, "IEEE Standard Verilog Hardware Description Language," downloaded from http://insteecs.berkeley.edu/~cs150/fa06/Labs/verilog-ieee.pdf on Dec. 7, 2006.(Sep. 2001).

Internet Wire, Sunbeam Joins Microsoft in University Plug and Play Forum to Establish A "Universal" Smart Appliance Technology Standard (Mar. 23, 2000).

Ishii et al., "Parallel Variable Length Decoding with Inverse Quantization for Software MPEG-2 Decoders," Workshop on Signal Processing Systems, Design and Implementation, IEEE pp. 500-509 (Nov. 3-5, 1997).

Isoworth, "Isoworth Beverage Dispensing Technology Worldwide Company," Brochure (May 22, 2000).

Jain et al., "An Alternative Approach Towards the Design of Control Units," Microelectronics and Reliability 24(6):1009-1012 (1984).

Jain, "Parallel Processing with the TMS320C40 Parallel Digital Signal Processor," Sonitech International Inc., pp. 13-46. Retrieved from: http://www-s.ti.com/sc/psheets/spra031/spra031.pdf retrieved on Apr. 14, 2004 (Feb. 1994).

Janssen et al., "Partitioned Register File for TTAs," Proceedings of the 28th Annual International Symposium on Microarchitecture, pp. 303-312 (Nov. 1995).

Jong-Pyng et al., "Real-Time Virtual Channel Flow Control," Proceedings of the Annual International Phoenix Conference on Computers and Communications, Conf. 13, pp. 97-103 (Apr. 12, 1994). Jung et al., "Efficient Hardware Controller Synthesis for Synchronous Dataflow Graph in System Level Design," Proceedings of the 13th International Symposium on System Synthesis pp. 79-84 (ISSS'00) (Sep. 2000).

Kaufmann et al., "Digital Spread-Spectrum Multipath-Diversity Receiver for Indoor Communication," from Pioneers to the 21st Century; Denver, Proceedings of the Vehicular Technology Socity [sic] Conference, NY, IEEE, US 2(Conf. 42):1038-1041 (May 10-13, 1992).

Kneip et al., "An Algorithm Adapted Autonomous Controlling Concept for a Parallel Single-Chip Digital Signal Processor," Journal of VLSI Signal Processing Systems for Signal, Image, an dVideo Technology 16(1):31-40 (May 1, 1997).

Lee & Messerschmitt, "Pipeline Interleaved Programmable DSP's: Synchronous Data Flow Programming," IEEE Transactions on Acoustics, Speech, and Signal Processing ASSP-35(9):1334-1345 (Sep. 1987).

Lee & Messerschmitt, "Synchronous Data Flow," Proceedings of the IEEE 75(9):1235-1245 (Sep. 1987).

Lee & Parks, "Dataflow Process Networks," Proceedings of the IEEE 83(5):773-799 (May 1995).

Liu et al., "Scheduling Algorithms for Multiprogramming in a Hard-Real-Time Environment," *Journal of the Association for Computing* 20(1):46-61 (1973).

Llosa et al., "Lifetime-Sensitive Modulo Scheduling in a Production Environment," IEEE Trans. on Comps. 50(3):234-249 (Mar. 2001). Lu et al., "The Morphosys Dynamically Reconfigurable System-On-Chip," Proceedings of the First NASA/DOD Workshop on Evolvable Hardware, pp. 152-160 (Jul. 19, 1999).

Mangione-Smith et al., "Seeking Solutions in Configurable Computing," *Computer* 30(12):38-43 (Dec. 1997).

Manion, "Network CPU Adds Spice," Electronic Engineering Times, Issue 1126 (Aug. 14, 2000).

Mascia & Ishii., "Neural Net Implementation on Single-Chip Digital Signal Processor," IEEE (1989).

McGraw, "Parallel Functional Programming in Sisal: Fictions, Facts, and Future," Lawrence Livermore National Laboratory pp. 1-40 (Jul. 1993).

Najjar et al., "High-Level Language Abstraction for Reconfigurable Computing," *Computer* 36(8):63-69 (Aug. 2003).

Nichols et al., "Data Management and Control-Flow Constructs in a SIMD/SPMD Parallel Language/ Compiler," Proceedings of the 3rd Symposium on the Frontiers of Massively Parallel Computation pp. 397-406 (Oct. 1990).

OPENMP Architecture Review Board, "OpenMP C and C++ Application Program Interface," pp. 7-16 (Oct. 1998).

Oracle Corporation, "Oracle8i JDBC Developer's Guide and Reference," Release 3, 8.1.7, pp. 10-8-10-10 (Jul. 2000).

Pauer et al., "Algorithm Analysis and Mapping Environment for Adaptive Computing Systems: Further Results," Proc. IEEE Symposium on FPGA's for Custom Computing Machines (FCCM), Napa CA (1999).

Pauer et al., "Algorithm Analysis and Mapping Environment for Adaptive Computing Systems," Presentation slides, Third Bi-annual Ptolemy Miniconference (1999).

Ramamritham et al., "On Scheduling Algorithms for Real-Time Multiprocessor Systems," Algorithms and Applications, Proceedings of the International conference on Parallel Processing 3:143-152 (Aug. 8, 1989).

Schneider, "A Parallel/Serial Trade-Off Methodology for Look-Up Table Based Decoders," Proceedings of the Design Automation Conference 34:498-503 (Jun. 9-13, 1997).

Sidhu et al., "A Self-Reconfigurable Gate Array Architecture," 10 International Workshop on Field Programmable Logic and Applications http://coblitz.codeen.org:3125/citeseer.ist.psu.edu/cache/papers/cs/17524/http:zSzzSzmaarcii.usc.

eduzSzPublicationsZSzsidhu\_fp100.pdf/

sidhu00selfreconfigurable.pdf retrieved on Jun. 21, 2006 (Sep. 1, 2001).

Smith, "Intro to ASICs: ASIC Cell Libraries," at http://iroi.seu.edu.cn/books/asics/Book2/CH01/CH01.5.htm, printed on Feb. 4, 2005 (Jun. 1997).

Souza, "Computing's New Face—Reconfigurable Devices Could Rattle Supply Chain," Electronic Buyers' News Issue 1205, p. P.1 (Apr. 3, 2000).

Souza, "Quicksilver Buys White Eagle," Electronic Buyers News, Issue 1220 (Jul. 17, 2000).

Sriram et al., "MPEG-2 Video Decoding on the TMS320C6X DSP Architecture," Conference Record of the 32nd Asilomar Conference on Signals, Systems, and Computers, IEEE pp. 1735-1739 (Nov. 1-4, 1998).

Steiner, "Coke Chief's Latest Daft Idea—A Cola Tap in Every House," Sunday Times (Mar. 2001).

Sun Microsystems, "FORTRAN 3.0.1 User's Guide, Revision A," pp. 57-68 (Aug. 1994).

Svensson, "Co's Join on Home Web Wiring Network," Associated Press Online printed on Apr. 30, 2008 (Jun. 2000).

Tang et al., "Thread Partitioning and Scheduling Based on Cost Model," Proceedings of the Ninth Annual ACM Symposium on Parallel Algorithms and Architectures, pp. 272-281 Retrieved from: htp://doi.acm.org/10.1145/258492.2585 retrieved on Aug. 25, 2004 (1997).

Vaya, "VITURBO: A Reconfigurable Architecture for Ubiquitous Wireless Networks," A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree Master of Science; Rice University (Aug. 2002).

Wang et al., "Cell Search in W-CDMA," IEEE Journal on Selected Areas in Communications 18(8):1470-1482 (Aug. 2000).

Wardell, "Help for Hurried Cooks?," Popular Science, p. 32 (May 2000).

Whiting & Pascoe, "A History of Data-Flow Languages," IEEE Annals of the History of Computing 16(4):38-59 (1994).

Williamson & Lee, "Synthesis of Parallel Hardware Implementations from Synchronous Dataflow Graph Specifications," Conference Record of the Thirtieth Asilomar Conference on Signals, Systems and Computers 1340-1343 (Nov. 1996).

Wirtilin et al., "A Dynamic Instruction Set Computer," Proceedings of the IEEE Symposium on FPGA's for Custom Computing Machines, pp. 99-107 (Apr. 21, 1995).

www.appliancemagazine.com, World Wide Web at http://web.archive.org/web/20000511085402/http://www.appliancemagazine.com/printed on Apr. 30, 2008.

www.Bestrom.com, BreakMateTM from www.bestrom.com printed on Apr. 29, 2008.

www.Beverageexpress.com, Beverage Express from.www. beverageexpress.com printed on Apr. 30, 2008.

www.Bevstar.com, Tsoworth Beverage Dispensing Technology Worldwide from www.bevstar.com printed on Apr. 30, 2008.

WWW.BONATOR.COM, from the World Wide Web at http://web.archive.org/web/20000510102440/http://www.bonator.com/printed on Apr. 30, 2008.

www.Ecommerce.Dewpointinc.com, Swiss Mountain Coffees from www.ccommerce.dewpointinc.com printed on Apr. 30, 2008.

www.Gateway.com, World Wide Web, http://web.archive.org/web/20000229192734/www.gateway.com/productpages/9300splash/index.shtml Available on Mar. 3, 2000, 1 page (Mar. 3, 2000).

www.Icl.com, from the World Wide Web at http://www.icl.com printed on Apr. 30, 2008.

www.Maegherita2000.com; from Margherita2000.com printed Apr. 30, 2008 (Jan. 26, 2001).

www.Sodaclubenterprises.com, Soda-Club Enterprises from www. sodaclubenterprises.com printed on Apr. 30, 2008.

www.Symbol.com, Symbol from www.symbol.com printed on Apr. 30, 2008.

www.Wunderbar.com, Wunder-Bar Dispensing Systems from www. wunderbar.com printed on Apr. 30, 2008.

Xilinx, "Virtex-II Pro Platform FPGAs: Functional Description DS083-2 (v2.5)," Product Specification, pp. 13-46 (Jan. 20, 2003). Young, "Architecture Powers up IPSec, SSL," EETimes, Los Gatos, CA, pp. 1-4 http://www.eetimes.com/story/OEG20011102S0065 (Nov. 2, 2001).

Yuan et al., "A Decomposition Approach to Non-Preemptive Real-Time Scheduling," Real Time Systems 6(1):7-35 (1994).

Zaino et al., "Algorithm Analysis and Mapping Environment for Adaptive Computing Systems," Final Technical Report, DARPA Contract F33615-97-C-1174 (Sep. 2001).

Zhang et al., "A 1V Heterogeneous Reconfigurable Processor IC for Baseband Wireless Applications," 2000 IEEE Solid.

International Search Report for PCT/US03/34046 dated Mar. 23, 2005.

International Search Report for PCT/US03/34049 dated Feb. 18, 2005.

U.S. Appl. No. 10/626,833 Office Action Mailed Dec. 8, 2005.

U.S. Appl. No. 10/626,833 Office Action Mailed Jun. 23, 2006.

U.S. Appl. No. 11/800,577 Office Action Mailed May 28, 2008.

U.S. Appl. No. 11/800,577 Office Action Mailed Feb. 23, 2009.

FIG. 1

PRIOR ART

### ADAPTABLE DATAPATH FOR A DIGITAL PROCESSING SYSTEM

### CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a continuation of U.S. application Ser. No. 12/556,894, filed Sep. 10, 2009, which is a continuation of U.S. application Ser. No. 11/800,577, filed May 3, 2007, which is a continuation of U.S. application Ser. No. 10/626, 833, filed Jul. 23, 2003, which claims the benefit of U.S. Provisional Application No. 60/422,063, filed Oct. 28, 2002, each of the aforementioned applications are incorporated by reference herein.

This application is related to the following co-pending U.S. Patent Applications that Are each incorporated by reference as if set fourth in full in this application: "Input Pipeline Registers For A Node In An Adaptive Computing Engine," Ser. No. 10/626,479, filed Jul. 23, 2003; "Cache For Instruc- 20 tion Set Architecture Using Indexes to Achieve Compression", Ser. No. 11/628,083, filed Jul. 24, 2003; "Method For Ordering Operations For Scheduling By A Modulo Scheduler For Processors With A Large Number Of Function Units And Reconfigurable Data Paths", Ser. No. 10/146,857, filed on 25 May 15, 2002; "Uniform interface For A Functional Node In An Adaptive Computing Engine", Ser. No. 10/443,554, filed on May 21, 2003; "Hardware Task Manager For Adaptive Computing ", Ser. No. 10/443,501, filed on May 21, 2003; and "Adaptive Integrated circuitry With heterogeneous And 30 Reconfigurable Matrices Of Diverse And Adaptive Computational Units Having fixed, Application Specific Computational Element", Ser. No. 09/815,122, filed on Mar. 22, 2001.

#### BACKGROUND OF THE INVENTION

This invention is related in general to digital processing architectures and more specifically to the use of an adaptable data path using register files to efficiently implement digital signal processing operations.

Digital Signal Processing (DSP) calculations require many iterations of fast multiply-accumulate and other operations. Typically, the actual operations are accomplished by "functional units" such as multipliers, adders, accumulators, shifters, etc. The functional units obtain values, or operands, 45 from a fast main memory such as Random Access Memory (RAM). The DSP system can be included within a chip that resides in a device such as a consumer electronic device, computer, etc.

The design of a DSP chip can be targeted for specific DSP 50 includes applications. For example, in a cellular telephone, a DSP chip may be optimized for Time-Division Multiple Access (TDMA) processing. A Voice-Over-Internet Protocol (VOIP) application may require vocoding operations, and so on. It is desirable for a chip manufacturer to provide a single chip 55 (DAG). design that can be adapted to different DSP applications. Such a chip is often described as an adaptable, or configurable, design.

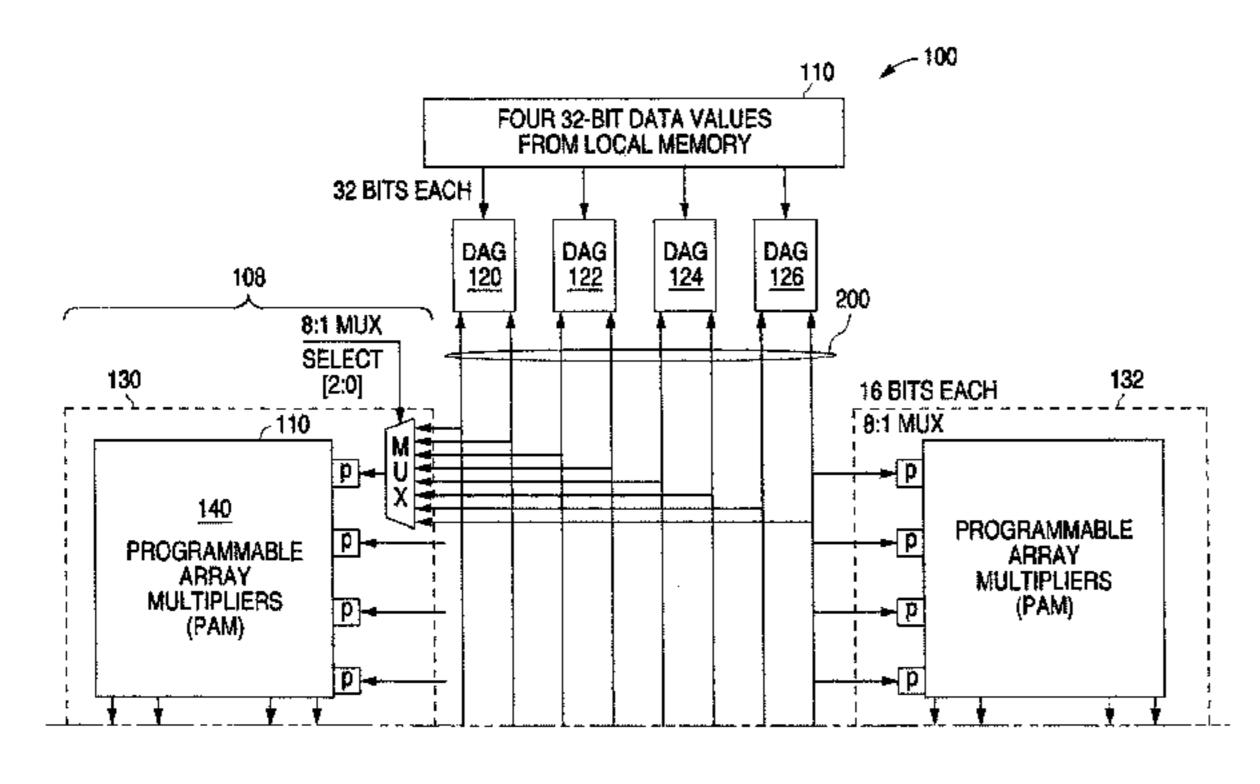

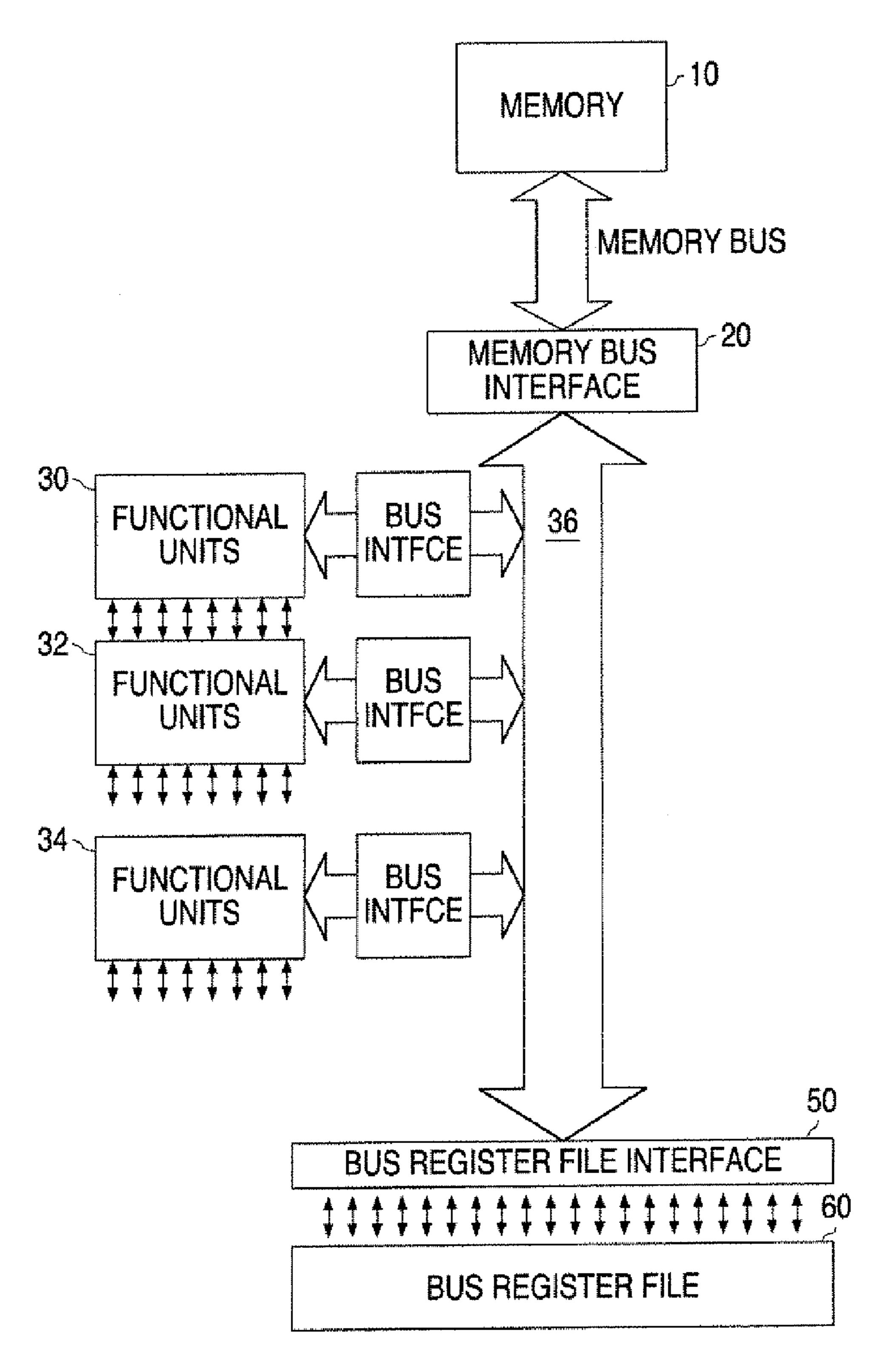

One aspect of an adaptable design for a DSP chip includes allowing flexible and configurable routing between the different functional units, memory and other components such as registers, input/output and other resources on the chip. A traditional approach to providing flexible routing uses a data bus. Such an approach is shown in FIG. 1.

In FIG. 1, memory bus 10 interfaces with a memory (not 65 data fetch. shown) to provide values from the memory to processing In one components such as functional unit blocks 30, 32 and 34.

2

Values from memory bus 10 are selected and routed through memory bus interface 20 to data path bus 36. The functional unit blocks are able to obtain values from data path bus 36 by using traditional bus arbitration logic (e.g., address lines, bus busy, etc.). Within a block, such as functional unit block 30 of FIG. 1, there may be many different components, such as a bank of multipliers, to which the data from data path bus 36 can be transferred. In this manner, any arbitrary value from memory can be provided to any functional unit block, and to components within blocks of functional units.

Values can also be provided between functional unit blocks by using the data path bus. Another resource is register file 60 provided on data path bus 36 by register file interface 50. Register file 60 includes a bank of fast registers, or fast RAM. Register file interface 50 allows values from data path bus 36 to be exchanged with the register file. Typically, any register or memory location within register file 60 can be placed on data path bus 36 within the same amount of time (e.g., a single cycle). One way to do this is to provide an address to a location in the register file, either on the data path bus, itself, or by using a separate set of address lines. This approach is very flexible in that any value in a component of a functional unit block can be transferred to any location within the register file and vice versa.

However, a drawback with the approach of FIG. 1, is that such a design is rather expensive to create, slow and does not scale well. A bus approach requires considerable overhead in control circuitry and arbitration logic. This takes up real estate on the silicon chip and increases power consumption. The use of a large, randomly addressable register file also is quite costly and requires inclusion of tens of thousands of additional transistors. The use of such complicated logic often requires bus cycle times to be slower to accommodate all of the switching activity. Finally, such an approach does not scale well since, e.g., adding more and more functional unit blocks will require additional addressing capability that may mean more lines and logic. Additional register file space may also be required. The data path bus would also need to be routed to connect to the added components. Each functional unit block also requires the bus control and arbitration cir-40 cuitry.

Thus, it is desirable to provide an interconnection scheme for digital processor applications that improves over one or more of the above, or other, shortcomings in the prior art.

#### SUMMARY OF THE INVENTION

The present invention uses dedicated groups of configurable data path lines to transfer data values from a main memory to functional units. Each group of data path lines includes a register file dedicated for storage for each group of lines. Functional units can obtain values from, and store values to, main memory and can transfer values among the registers and among other functional units by using the dedicated groups of data path lines and a data address generator (DAG)

DAG circuitry interfaces each group of datapath lines to a main memory bus. Each DAG is controllable to select a value of varying bit width from the memory bus, or to select a value from another group of data path lines. In a preferred embodiment, eight groups of 16 data path lines are used. Each group includes a register file of eight 16-bit words on each group of 16 data path lines. Registers can hold a value onto their associated group of data path lines so that the value is available at a later time on the lines without the need to do a later data fetch.

In one embodiment the invention provides a data path circuit in a digital processing device, wherein the data path

circuit is coupled to a memory bus for obtaining values from a memory, the data path circuit comprising a first plurality of data lines; a first data address generator for coupling the first plurality of data lines to the memory bus so that a value from the memory transferred by the memory bus can be placed 5 onto the first plurality of data lines; one or more functional units for performing a digital operation coupled to the plurality of data lines; and a register coupled to the first plurality of data lines, wherein the register selectively stores a value from the first plurality of data lines so that the value is selectively 10 available on the first plurality of data lines.

Another aspect of the invention provides both general and direct data paths between array multipliers and accumulators. Banks of accumulators are coupled to the groups of config- 15 urable data path lines and are also provided with direct lines to the multipliers. An embodiment of the invention provides a digital processing system comprising a multiplier; an accumulator; a configurable data path coupled to the multiplier and the accumulator; and a direct data path coupled between 20 the multiplier and the accumulator.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 shows a prior art approach using a data path bus;

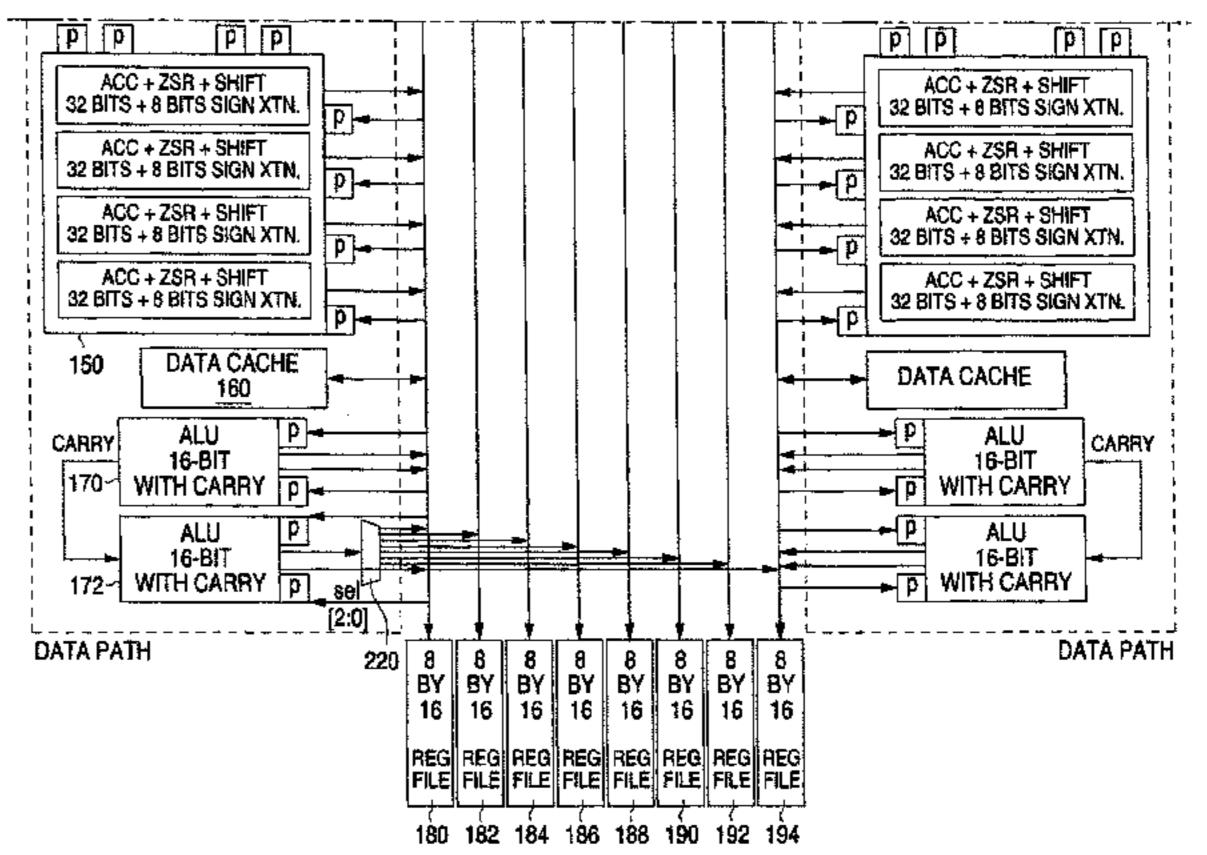

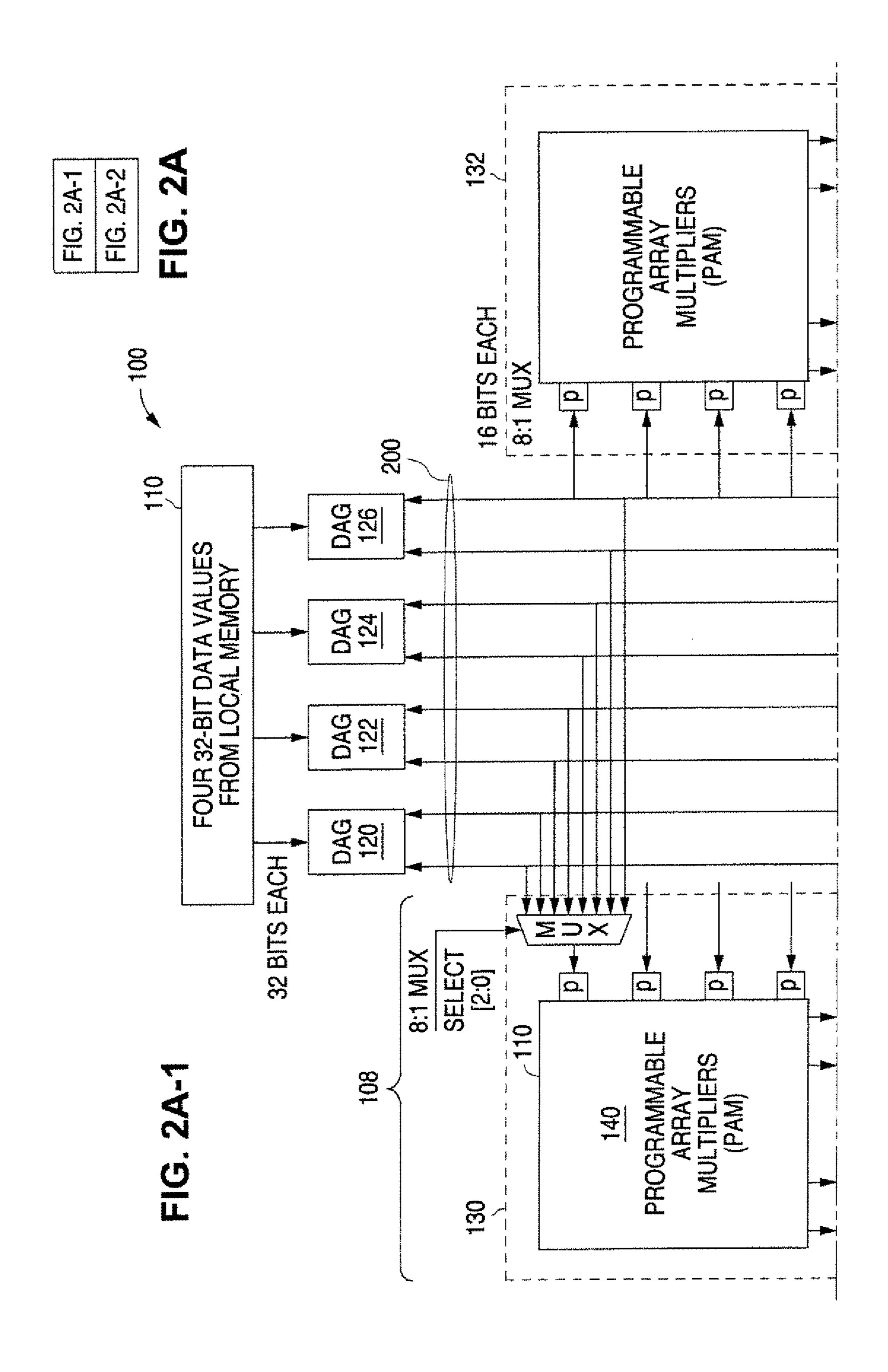

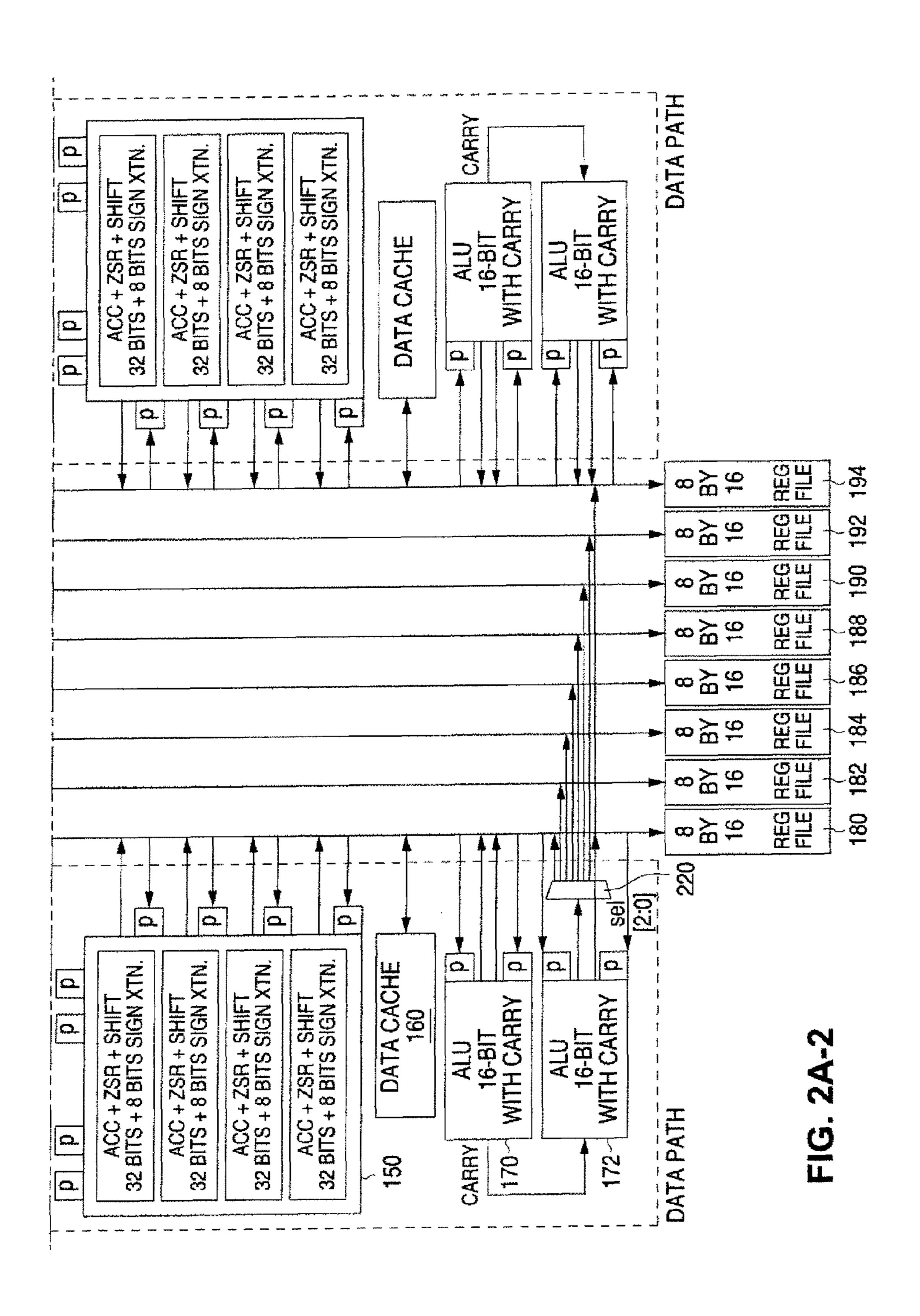

FIG. 2A comprising FIG. 2A-1 and FIG. 2A-2 illustrates the configurable data path arrangement of a preferred embodiment of the present invention;

#### DETAILED DESCRIPTION OF THE INVENTION

A preferred embodiment of the invention is incorporated 35 into a node referred to as a Adaptable Node (RXN) in a adaptive computing engine (ACE) manufactured by Quicksilver, Inc., of San Jose, Calif. Details of the ACE engine and RXN node can be found in the priority and related patent applications reference above. Aspects of the invention 40 described herein are adaptable for use with any generalized digital processing system, such as a system adapted for digital signal processing or other types of processing.

FIG. 2A comprising FIG. 2A-1 and FIG. 2A-2 illustrates the configurable data path arrangement according to a preferred embodiment of the present invention.

In FIG. 2A, digital processing system 100 is designed for fast DSP-type processing such as in discrete cosine transformation (DCT), fast fourier transformation (FFT), etc. Digital 50 processing system 100 includes four 32-bit data path address generators (DAG) to interface between four groups of configurable data path lines 200 and a main memory bus 110. Main memory bus 110 is an arbitrated high-speed bus as is known in the art. Other types of main memory accessing can 55 be used.

Each group of 32 lines includes two subgroups of 16 lines each. Each subgroup is connected to a register file of eight files 180 and 182. DAG 122 is connected to register files 184 and 186. Similarly, DAGs 124 and 126 are connected to register files 188, 190 and 192, 194, respectively. Naturally, other embodiments can use any number of DAGs, groups, and subgroups register files. Although specific bit widths, num- 65 bers of lines, components, etc., and specific connectivity are described, many variations are possible and are within the

scope of the invention. Although the DAGs play a major role in the preferred embodiment, other embodiments can use other types of interfacing to the main memory bus. Although the DAGs provide a high degree of configurable routing options (as discussed below), other embodiments can vary in the degree of configurability, and in the specific configuration options and control methods. In some cases, simple registers, register files, multiplexers or other components might be used in place of the DAGs of the present invention.

The use of register files on each of the discrete subgroup lines simplifies the interconnection architecture from that of the more generalized bus and multiport register file shown in FIG. 1 of the prior art. This approach can also provide benefits in reduced transistor count, power consumption, improved scalability, efficient data access and other advantages. Although configuring the data path of the present invention may be more complex than with generalized approaches, in practice, a compiler is able to automatically handle the configuration transparently to a human programmer. This allows creation of faster-executing code for a variety of DSP applications by using the same hardware architecture without placing any undue burden on the programmer. If desired, a programmer can customize the data path configuration in order to further optimize processing execution.

Groups of data path lines 200 are used to transfer data from memory bus 110 to functional units within blocks 130 and 132, and also to transfer data among the functional units, themselves. The functional unit blocks are essentially the same so only block 130 is discussed in detail. Functional units include Programmable Array Multipliers (PAMs) 140, accumulators (and shift registers) 150, data cache 160 and Arithmetic/Logic Units (ALUs) 170 and 172. Naturally, the functional units used in any specific embodiment can vary in number and type from that shown in FIG. 2A.

Functional units are connected to the data path line groups via multiplexers and demultiplexers such as 210 and 220, respectively. Inputs and Outputs (I/Os) from the functional units can, optionally, use multiplexing to more than one subgroup of data path lines; or an I/O can be connected directly to one subgroup. A preferred embodiment uses pipeline registers between I/O ports and data path lines, as shown by boxes labeled "p" in FIG. 2A. Pipeline registers allow holding data at I/O ports, onto data lines, or for other purposes. The pipeline registers also allow obtaining a zero, 1, or other desired binary values and provide other advantages. Pipeline registers are described in more detail in the co-pending patent application "Input Pipeline Registers For A Node In An Adaptive Computing Engine" referenced above.

Table I, below, shows DAG operations. The configuration of the data path from cycle to cycle is set by a control word, or words obtained from the main memory bus in accordance with controller modules such as a hardware task manager, scheduler and other processes and components not shown in 16-bit words. For example, DAG 120 is connected to register 60 FIG. 2A but discussed in related patent applications. Part of the configuration information includes fields for DAG operations. A DAG operation can change from cycle to cycle and includes reading data of various widths from memory or from another DAG. DAG operations other than those shown in Table I can be used. Each DAG has one 5-bit 'dag-op' field and one 4-bit 'address' field. There is a single 'pred' field that defines non-sequencing operations.

| Dag-op        | Mnemonic    | Description                                                                             | Cycles      |

|---------------|-------------|-----------------------------------------------------------------------------------------|-------------|