#### US008326938B1

## (12) United States Patent

## Chiang et al.

# (54) PACKET BUFFER APPARATUS AND METHOD

(75) Inventors: John M. Chiang, San Jose, CA (US);

Cesar A. Johnston, Sunnyvale, CA (US)

(73) Assignee: Marvell International Ltd., Hamilton

(BM)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 13/228,936

(22) Filed: Sep. 9, 2011

### Related U.S. Application Data

- (63) Continuation of application No. 12/898,343, filed on Oct. 5, 2010, now Pat. No. 8,019,825, which is a continuation of application No. 11/948,753, filed on Nov. 30, 2007, now Pat. No. 7,818,389.

- (60) Provisional application No. 60/868,216, filed on Dec. 1, 2006.

- (51) Int. Cl. G06F 15/167 (2006.01)

- (52) **U.S. Cl.** ....... **709/212**; 709/213; 709/214; 709/216

- (58) Field of Classification Search ............ 709/212–216 See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,804,257 | B1 * | 10/2004 | Benayoun et al | 370/471 |

|-----------|------|---------|----------------|---------|

| 6,941,391 | B2   | 9/2005  | Kasper         |         |

| 7,079,481 | B2   | 7/2006  | Kramer         |         |

| 7,571,216 | B1   | 8/2009  | McRae et al.   |         |

| 7,849,274 | B2   | 12/2010 | Pittman        |         |

| 8,069,279 | B2 * | 11/2011 | Go et al.      | 710/22  |

# (10) Patent No.: US 8,326,938 B1 (45) Date of Patent: Dec. 4, 2012

|                  |        | Wolrich et al         |

|------------------|--------|-----------------------|

| 2006/0067228 A1* | 3/2006 | Ronciak et al 370/235 |

| 2006/0075142 A1* | 4/2006 | Cornett et al 709/246 |

| 2010/0161750 A1* | 6/2010 | Pandva 709/212        |

#### OTHER PUBLICATIONS

ITU-T Telecommunication Standardization Sector of ITU—G.984. 4—Series G: Transmission Systems and Media, Digital Systems and Networks, Digital sections and digital line system—Optical line systems for local and access networks—Gigabit-capable Passive Optical Networks (G-PON): ONT management and control interface specification (2004).

ITU-T Telecommunication Standardization Sector of ITU—G.984.4 Amendment 1, Series G: Transmission Systems and Media, Digital Systems and Networks, Digital sections and digital line system—Optical line systems for local and access networks—Gigabit-capable Passive Optical Networks (G-PON): ONT management and control interface specification (2005).

(Continued)

Primary Examiner — Abdullahi Salad

#### (57) ABSTRACT

An apparatus including a first memory, a second memory, and a direct memory access engine. The first memory stores one or more packet descriptors. The second memory stores one or more packets for transmission via a communication link. The direct memory access engine is configured to i) determine when the one or more packet descriptors have been written, by a host, to the first memory, ii) read the one or more packet descriptors from the first memory in response to determining that the one or more packet descriptors have been written to the first memory by the host, iii) determine, using the one or more packet descriptors, one or more respective locations of one or more packets in a host memory, and iv) initiate a direct memory access transfer of the one or more packets from the one or more respective locations in the host memory to the second memory.

#### 10 Claims, 13 Drawing Sheets

#### OTHER PUBLICATIONS

ITU-T Telecommunication Standardization Sector of ITU—0.984.4 Amendment 2—Series G: Transmission Systems and Media, Digital Systems and Networks, Digital sections and digital line system—Optical line systems for local and access networks—Gigabit-capable Passive Optical Networks (G-PON): ONT management and control interface specification (2006).

ITU-T Telecommunication Standardization Sector of ITU G.984.3—Series G: Transmission Systems and Media, Digital Systems and Networks, Digital sections and digital line system—Optical line systems for local and access networks—Gigabit-capable Passive Optical Networks (G-PON): Transmission convergence layer specification (2004).

ITU-T Telecommunication Standardization Sector of ITU G.984.4, Series G: Transmission Systems and Media, Digital Systems and Networks, Digital sections and digital line system—Optical line systems for local and access networks, Gigabit-capable Passive Optical Networks (G-PON): ONT management and control interface specification (2004).

ITU-T Telecommunication Standardization Sector of ITU G.984.4 Amendment 1, Series G: Transmission Systems and Media, Digital Systems and Networks—Digital sections and digital line system—Optical line systems for local and access networks, Gigabit-capable Passive Optical Networks (G-PON): ONT management and control interface specification (2005).

ITU-T Telecommunication Standardization Sector of ITU G.984.4 Amendment 2, Series G: Transmission Systems and Media, Digital Systems and Networks—Digital sections and digital line system—Optical line systems for local and access networks, Gigabit-capable Passive Optical Networks (G-PON): ONT management and control interface specification (2006).

\* cited by examiner

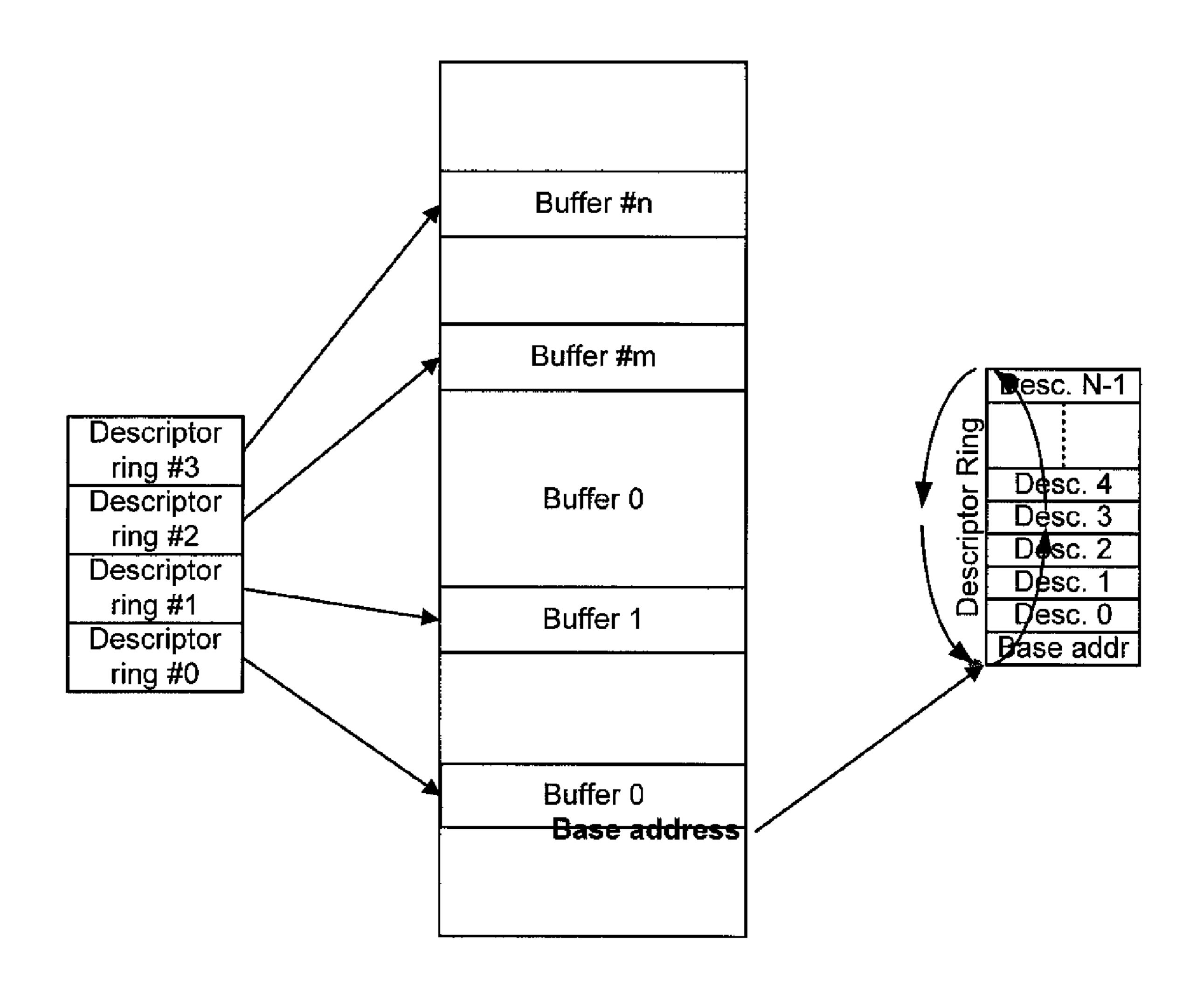

F16. 2

Dec. 4, 2012

US 8,326,938 B1

FIG. 8

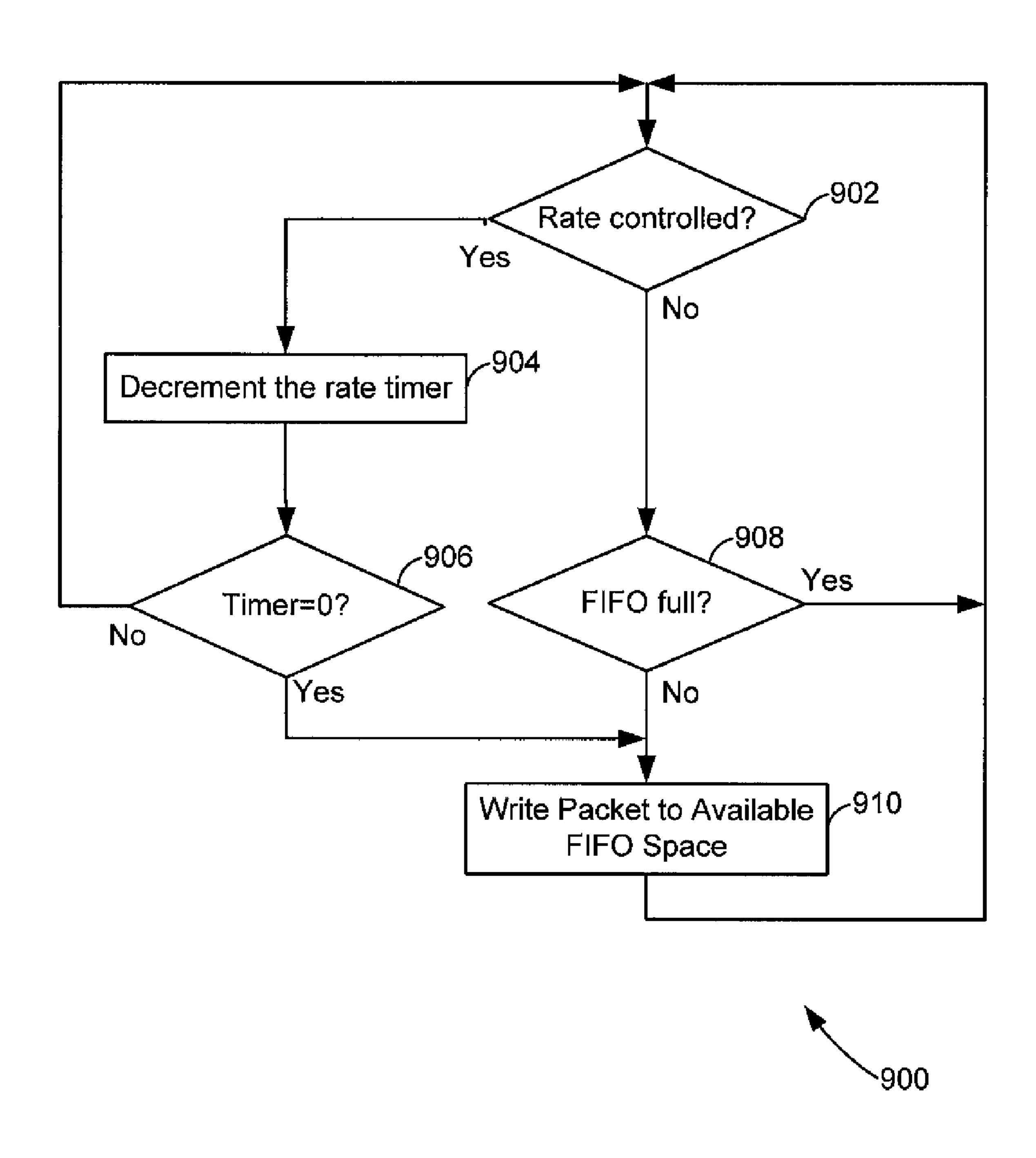

FIG. 9

# PACKET BUFFER APPARATUS AND METHOD

## CROSS-REFERENCES TO RELATED APPLICATIONS

The present disclosure is a continuation of U.S. application Ser. No. 12/898,343, filed on Oct. 5, 2010, which is a continuation of U.S. application Ser. No. 11/948,753 (now U.S. Pat. No. 7,818,389), filed on Nov. 30, 2007, which claims priority under 35 U.S.C. §119(e) to U.S. Provisional Application No. 60/868,216, filed on Dec. 1, 2006.

#### FIELD OF TECHNOLOGY

The present disclosure relates generally to packet buffering <sup>15</sup> and handling, and more particularly, to packet buffering and handling within a gigabit passive optical network.

#### DESCRIPTION OF THE RELATED ART

The traditional descriptor ring architecture has been used widely in the communication world. A traditional descriptor ring architecture set up a descriptor ring in the host memory, which, in combination with related Direct Memory Access (DMA) hardware, controlled the packet buffering. Firmware or software configured the set of descriptor rings. The hardware polled into the host constantly to see if the descriptor was ready for use by the hardware.

Previous data packet buffering and handling methods involved many read operations, for example reading data descriptors from the host memory by polling the hardware. As 30 a result, the host memory read operations took a long time as compared to the host memory write operations. Read operations therefore took a lot of overhead, which is undesirable when buffering time-sensitive data packets (low latency), such as audio, video, etc. Even when using a fast bus for 35 time-sensitive data packets, the bus was often unable to get a read done in one transaction. Instead, the bus tried the read operation in several tries, each time having to reschedule each read which was controlled by a bus arbiter. This caused even a single read to be time consuming. Read operations also 40 caused the host to have to stop and wait for a data return, thereby creating slow and inefficient processing, and thus lost bandwidth due to unnecessary overhead traffic. Polling the ownership bits further caused lost bandwidth and unnecessary traffic. For example, every time a hardware DMA engine unit device, respectively; finished transmitting or receiving, the DMA engine went into the host memory descriptor ring and changed the ownership bits to the host. This constant changing of ownership bits were therefore an inefficient and wasteful use of bus bandwidth. On the other hand, direct writes to memory are much faster. In a multi-processor and/or multi-thread system, service inter- 50 rupts to the host caused all processors or threads to be activated to determine which interrupts had been enabled, which tended to increase processor overhead and reduce the efficient use of the processors or threads.

However, there are few implementations that try to solve 55 issues such as slow response time, high processor overhead, host/hardware polling, long latency due to double or even triple layers of lookup and translation, and the utilization of a large cache to store the descriptor table and caching. At the same time, these few implementations include control logic 60 which may be quite complicated and cause the die size of the chip to be large and increase verification time.

### SUMMARY OF THE DISCLOSURE

In one embodiment, this specification discloses an apparatus including a first memory, a second memory, and a direct

2

memory access engine. The first memory stores one or more packet descriptors. The second memory stores one or more packets for transmission via a communication link. The direct memory access engine is configured to i) determine when the one or more packet descriptors have been written, by a host, to the first memory, ii) read the one or more packet descriptors from the first memory in response to determining that the one or more packet descriptors have been written to the first memory by the host, iii) determine, using the one or more packet descriptors, one or more respective locations of one or more packets in a host memory, and iv) initiate a direct memory access transfer of the one or more packets from the one or more respective locations in the host memory to the second memory.

In another embodiment, this specification discloses an apparatus including a first memory, a second memory and a direct memory access engine. The first memory is configured to store one or more packet descriptors, and the second memory to store one or more packets received via a communication link. The direct memory access engine is configured to i) read the one or more packet descriptors from the first memory, ii) determine, using the one or more packet descriptors, one or more respective locations in a host memory for storing the one or more packets, and iii) initiate a direct memory access transfer of the one or more packets from the second memory to the one or more respective locations in the host memory.

#### BRIEF DESCRIPTION OF THE DRAWINGS

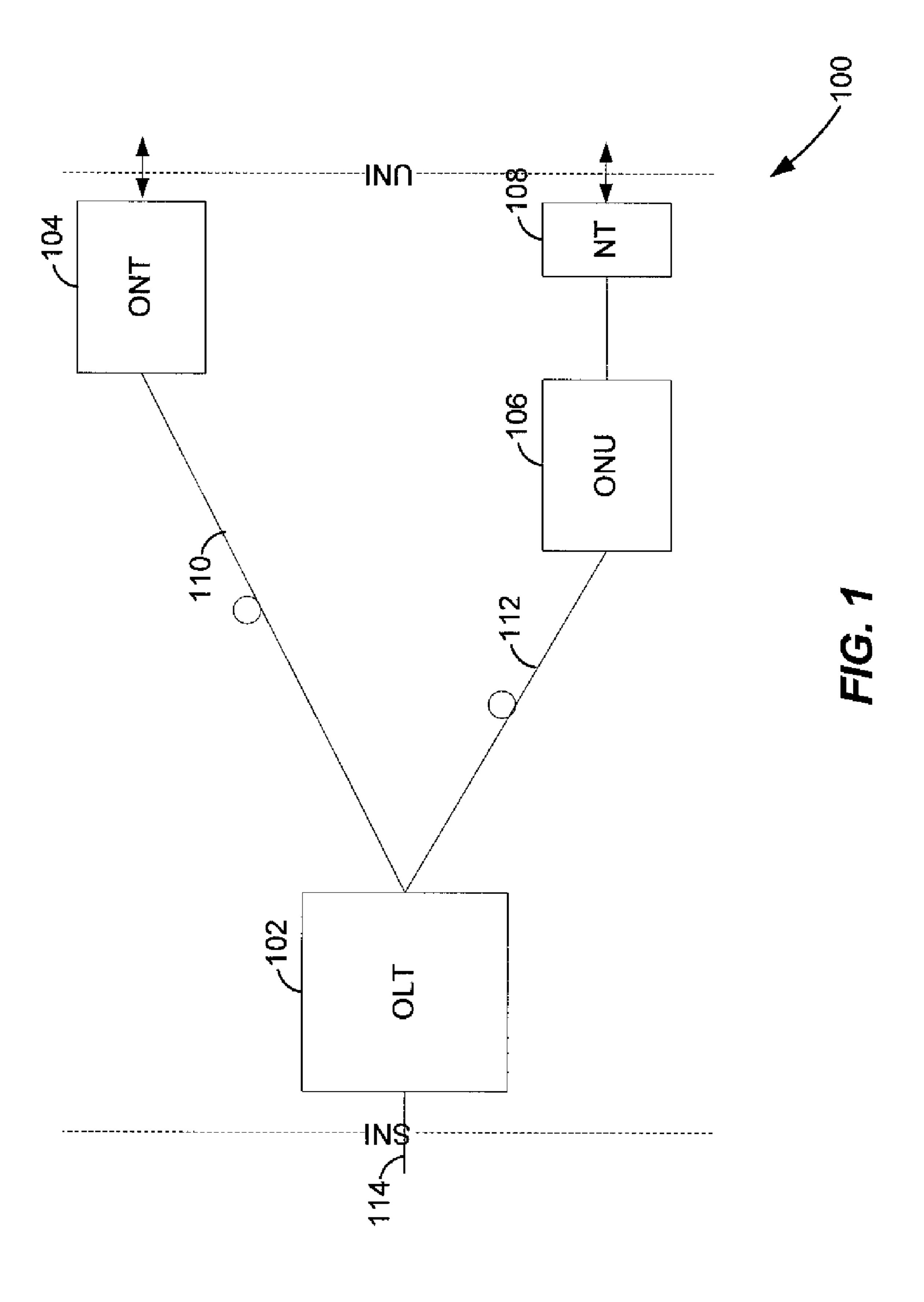

FIG. 1 a block diagram of a passive optical network;

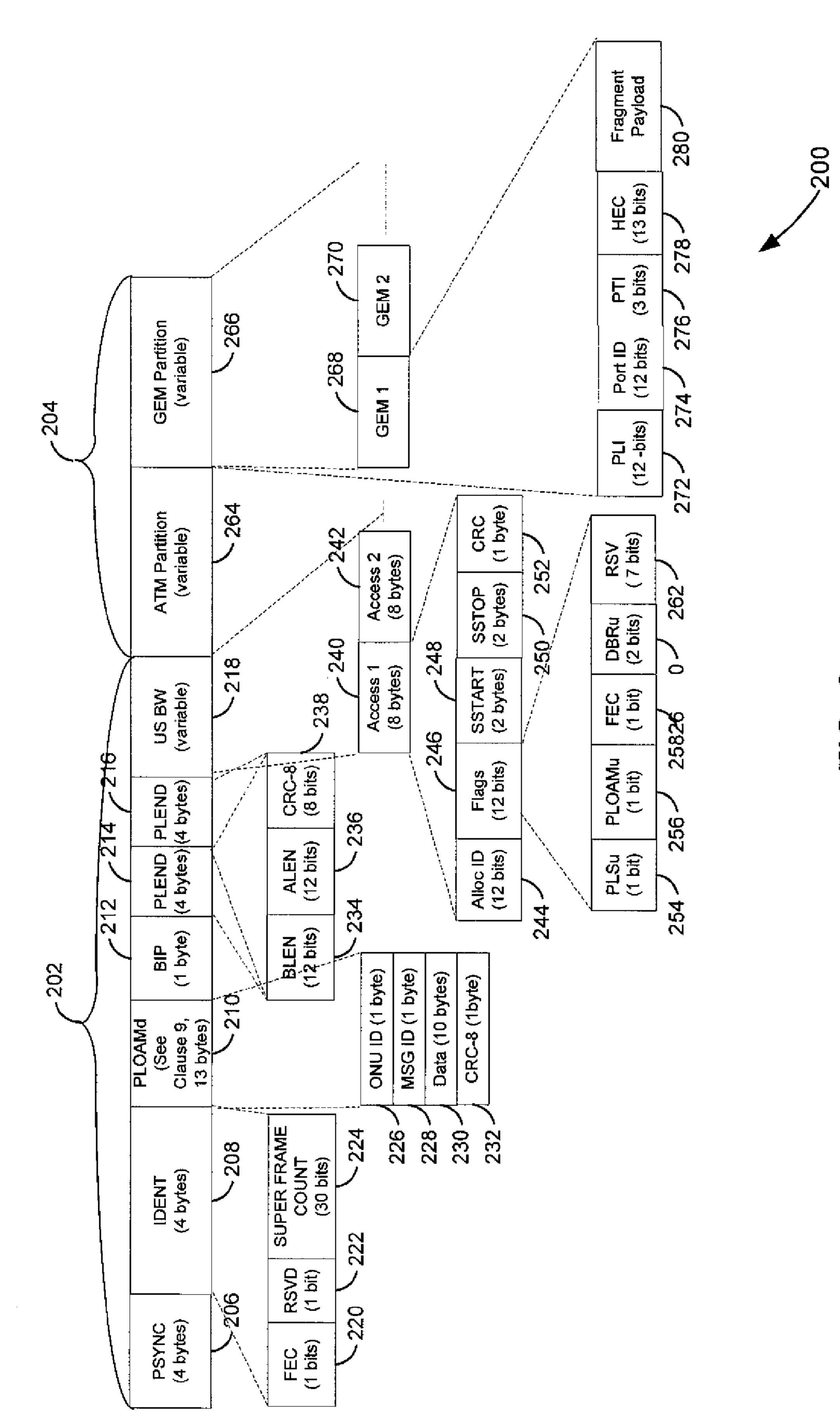

FIG. 2 is a schematic diagram of a downstream gigabit passive optical network transmission convergence frame format;

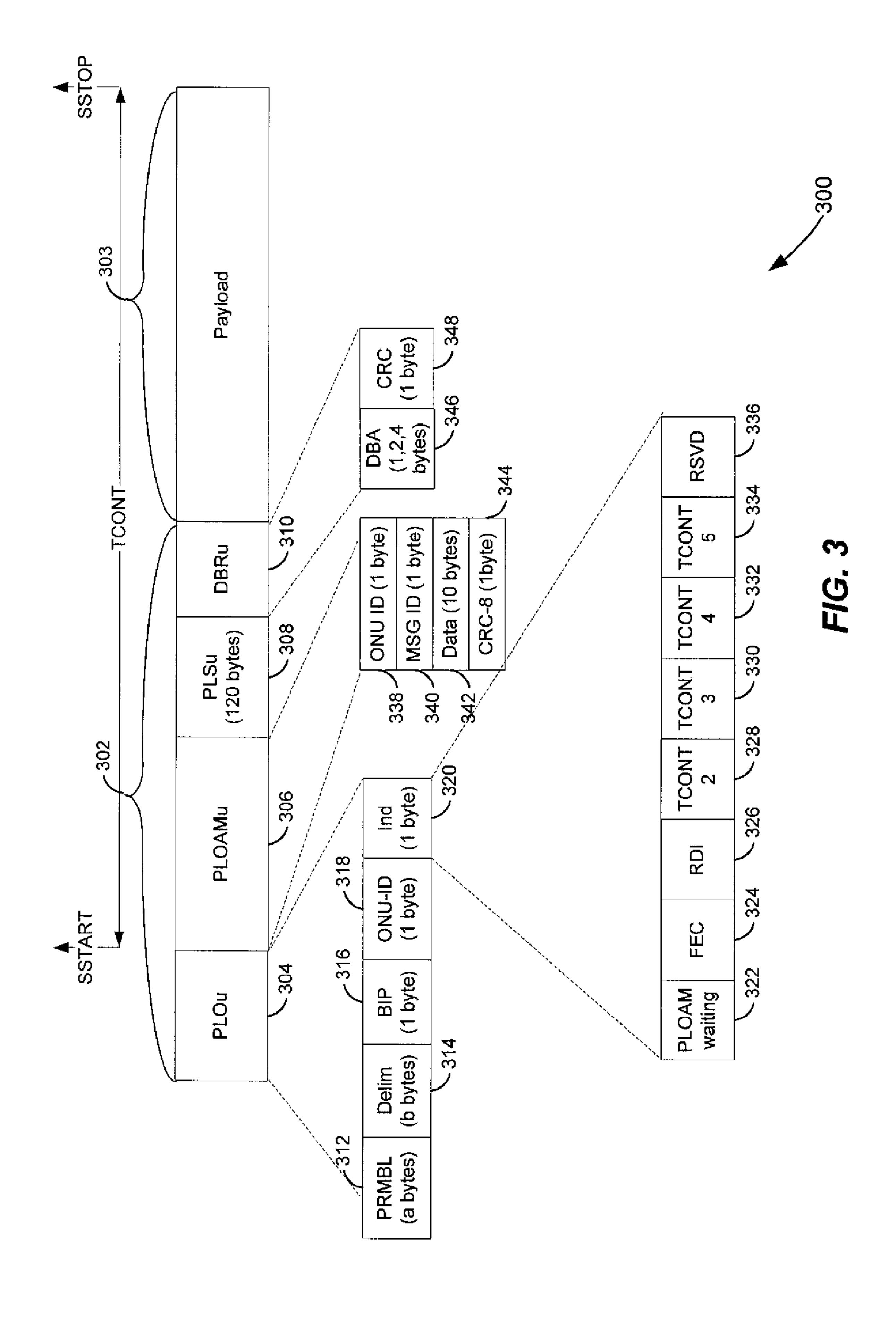

FIG. 3 is a schematic diagram of an upstream gigabit passive optical network transmission convergence frame format;

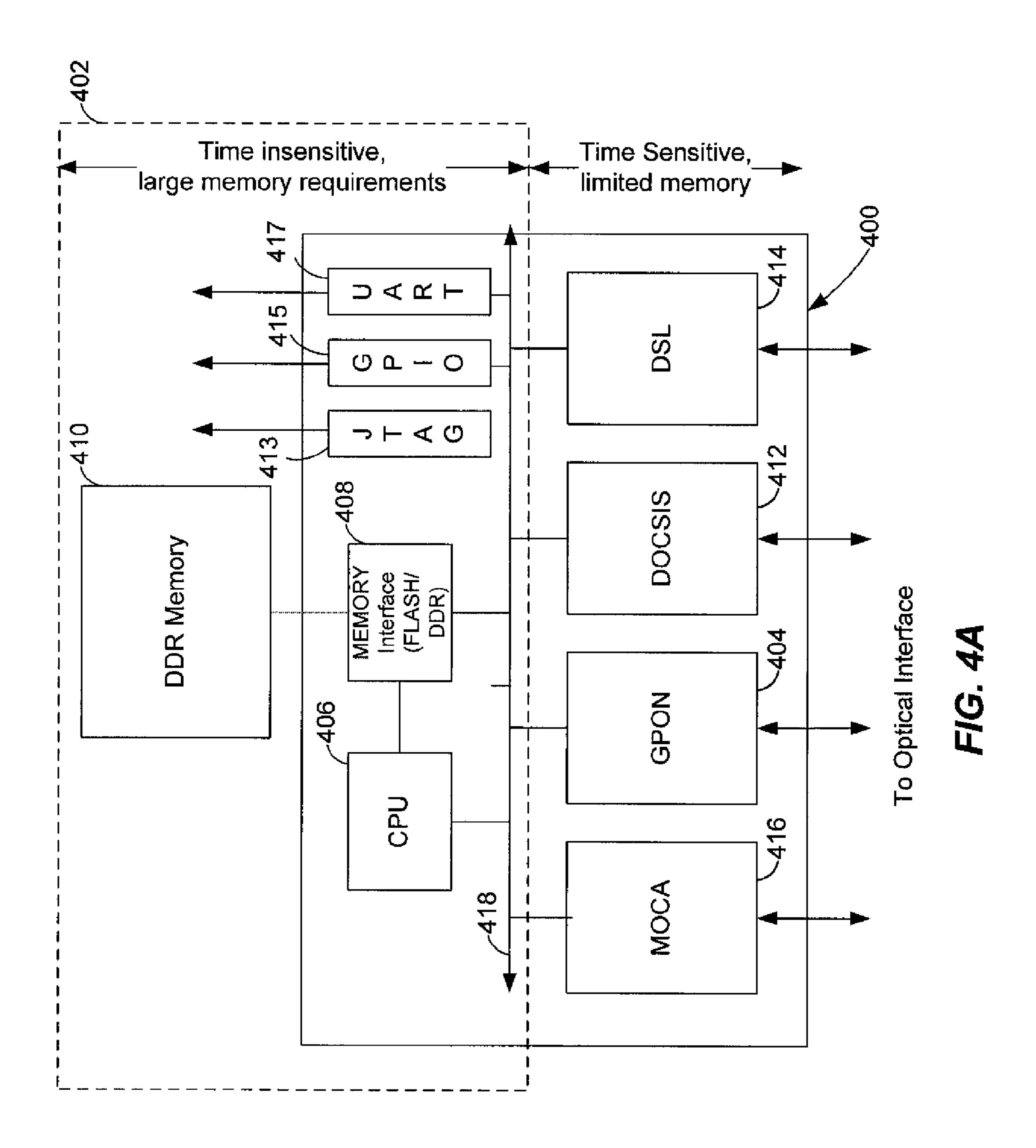

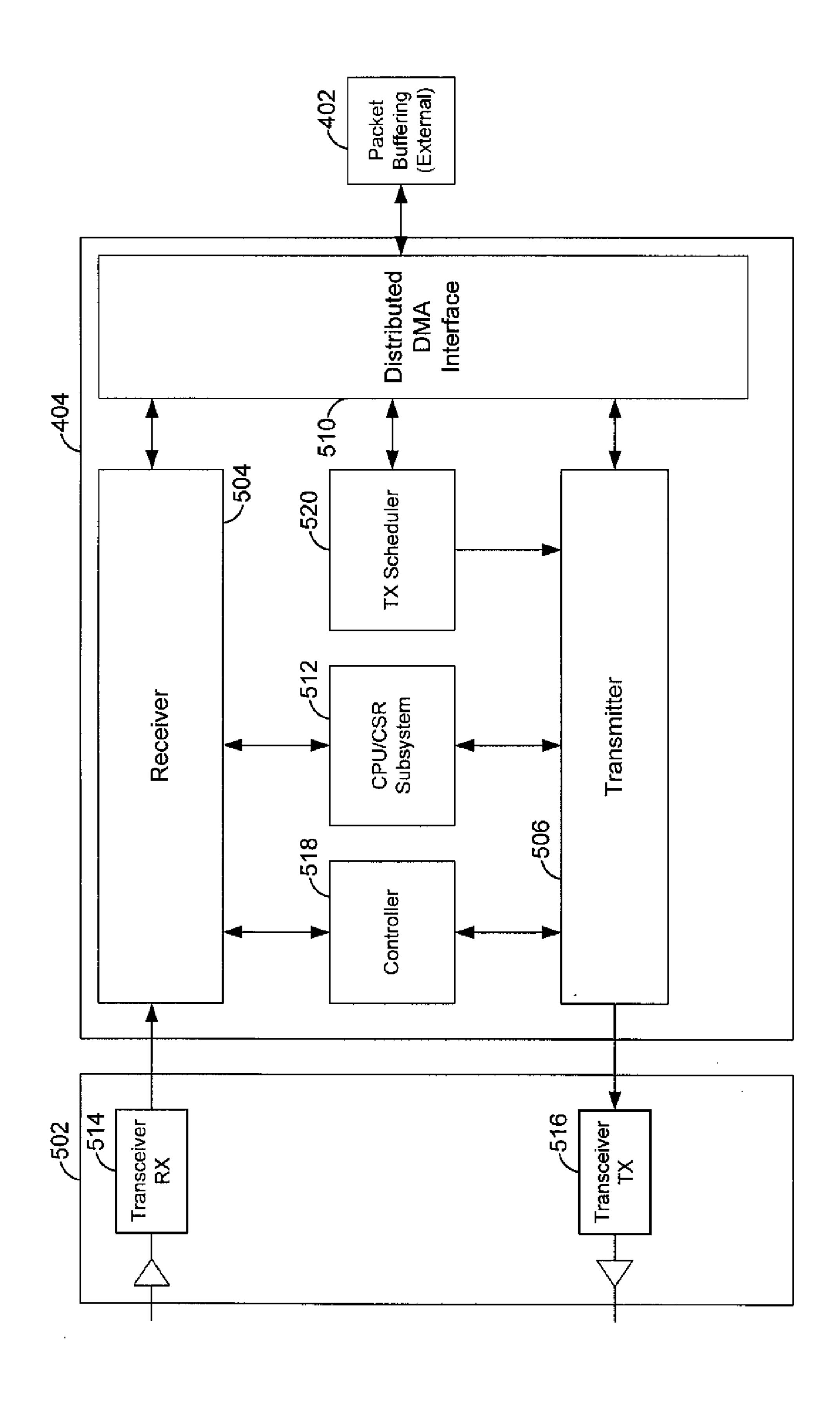

FIG. 4A is a block diagram of an example architecture of an integrated circuit within a passive optical network line termination unit;

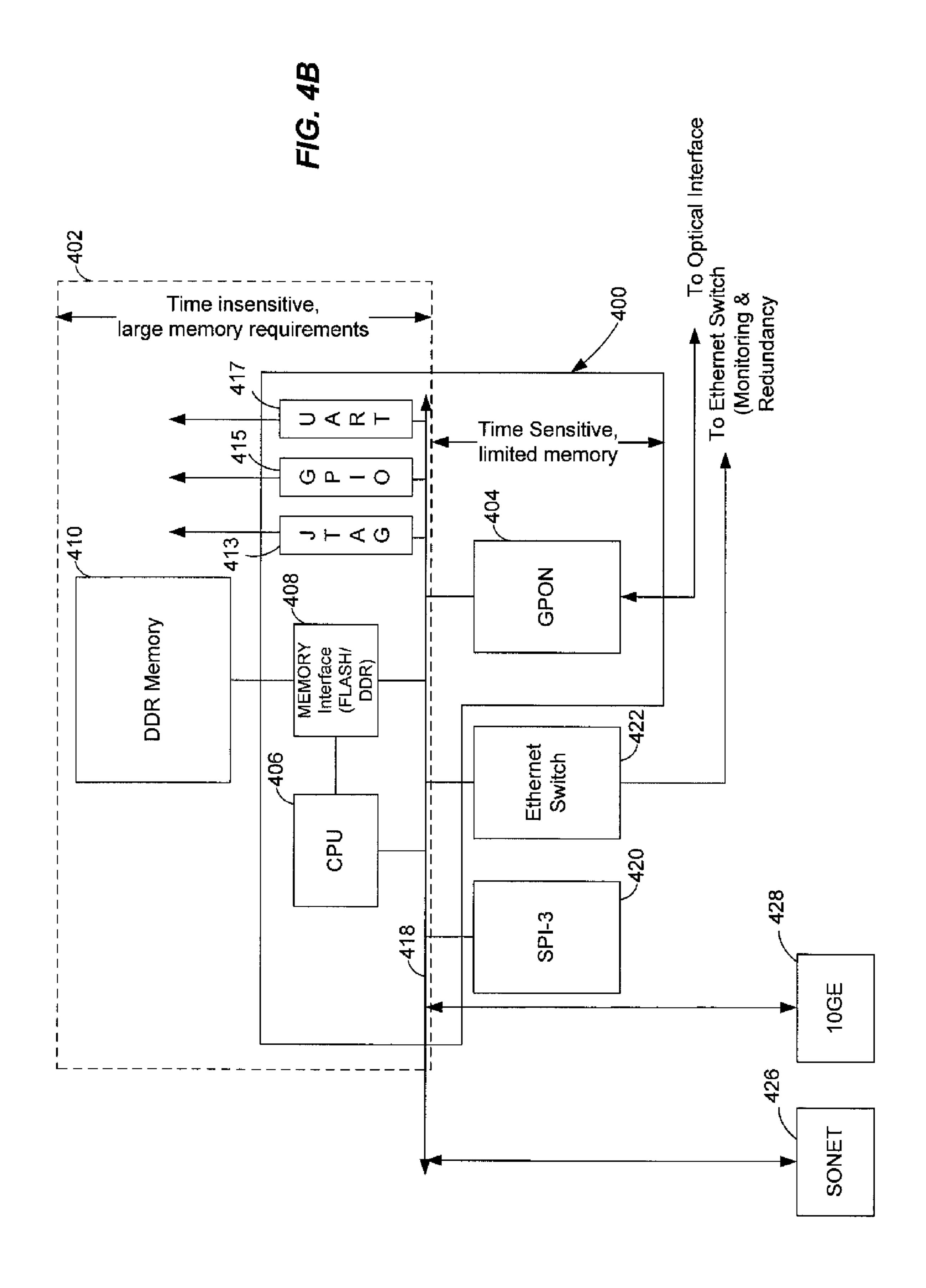

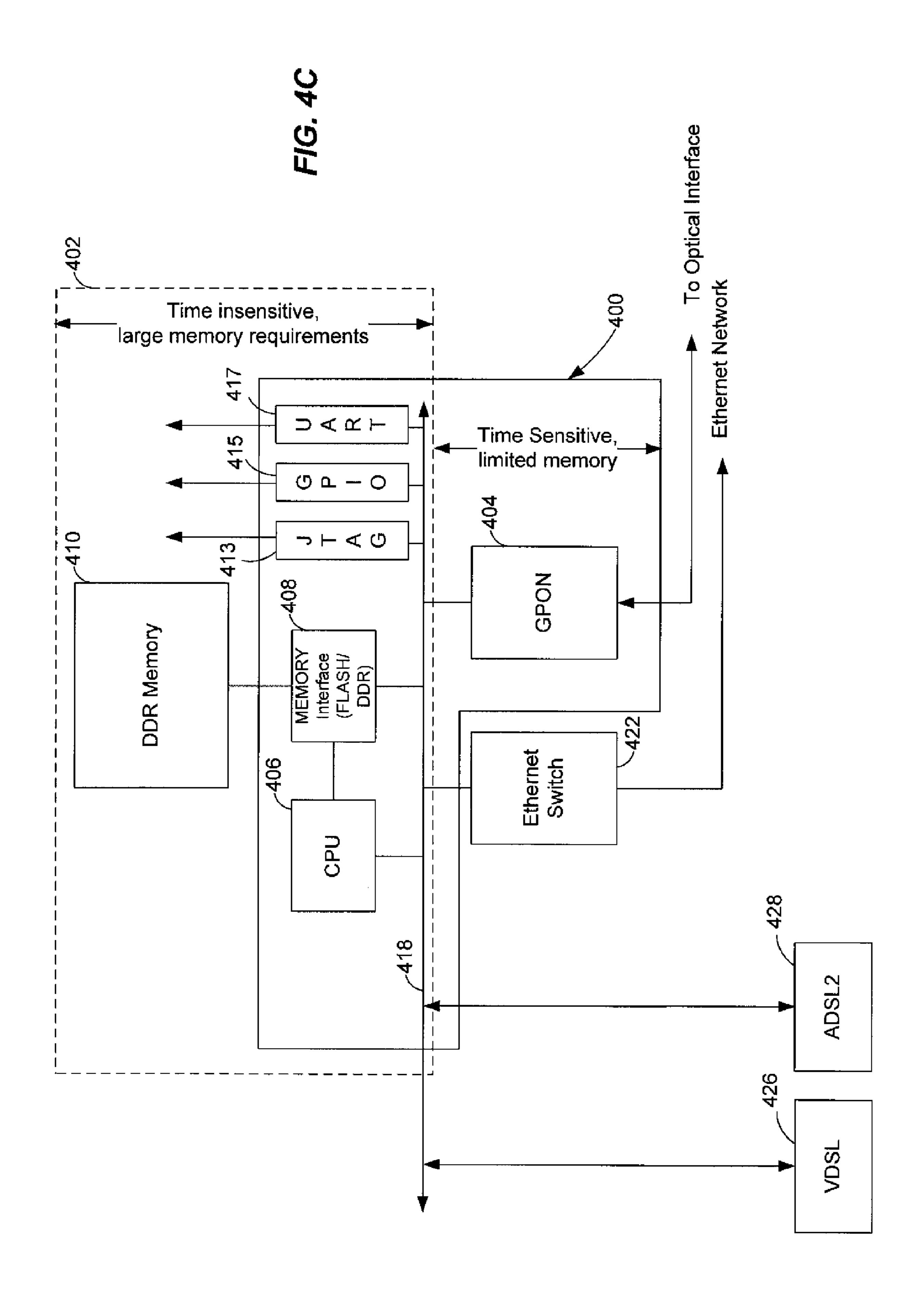

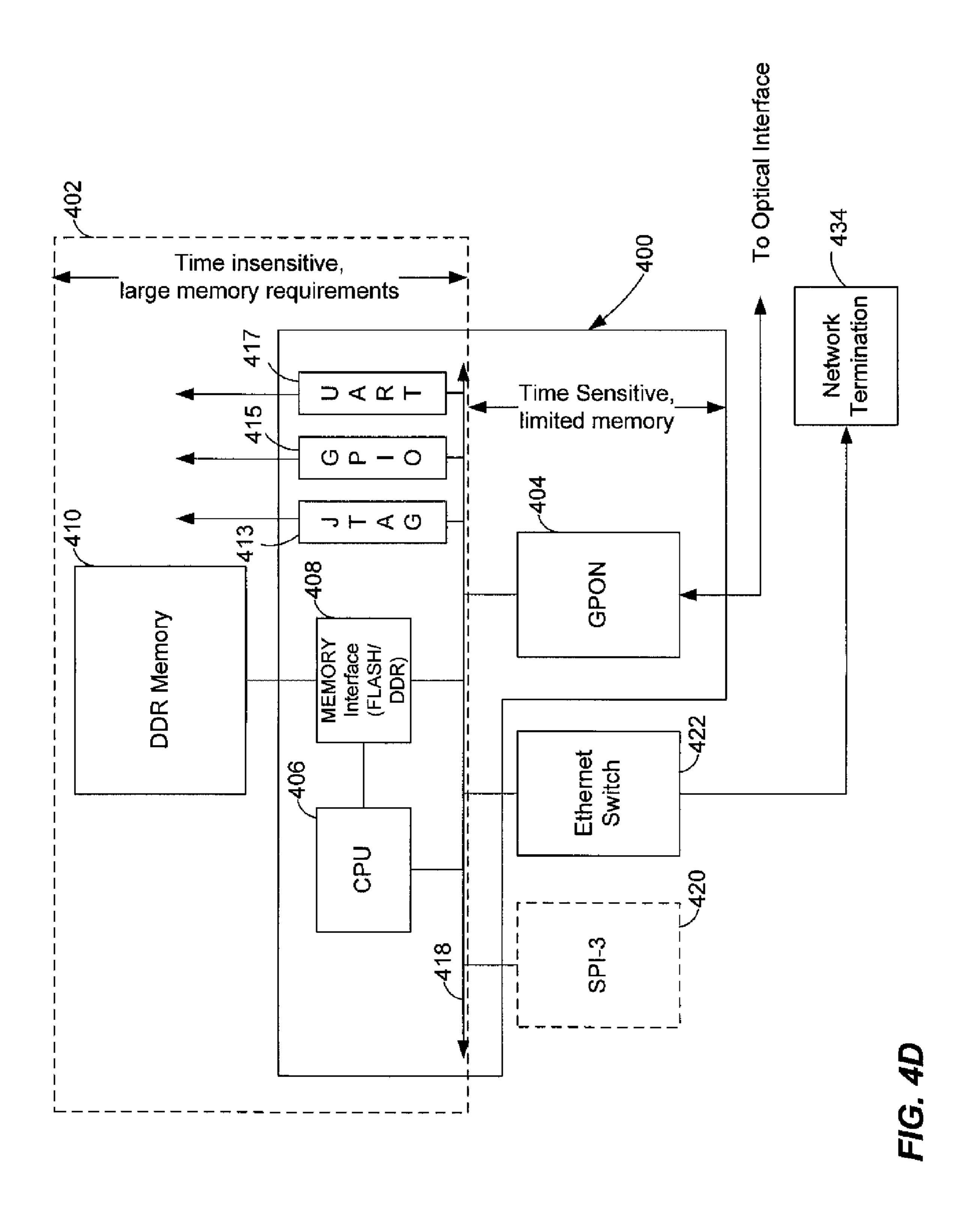

FIGS. 4B-4D are block diagrams of example architecture implementations of the integrated circuit configuration of FIG. 4A, and in the form of an optical line termination device, optical network termination device, and an optical network unit device, respectively;

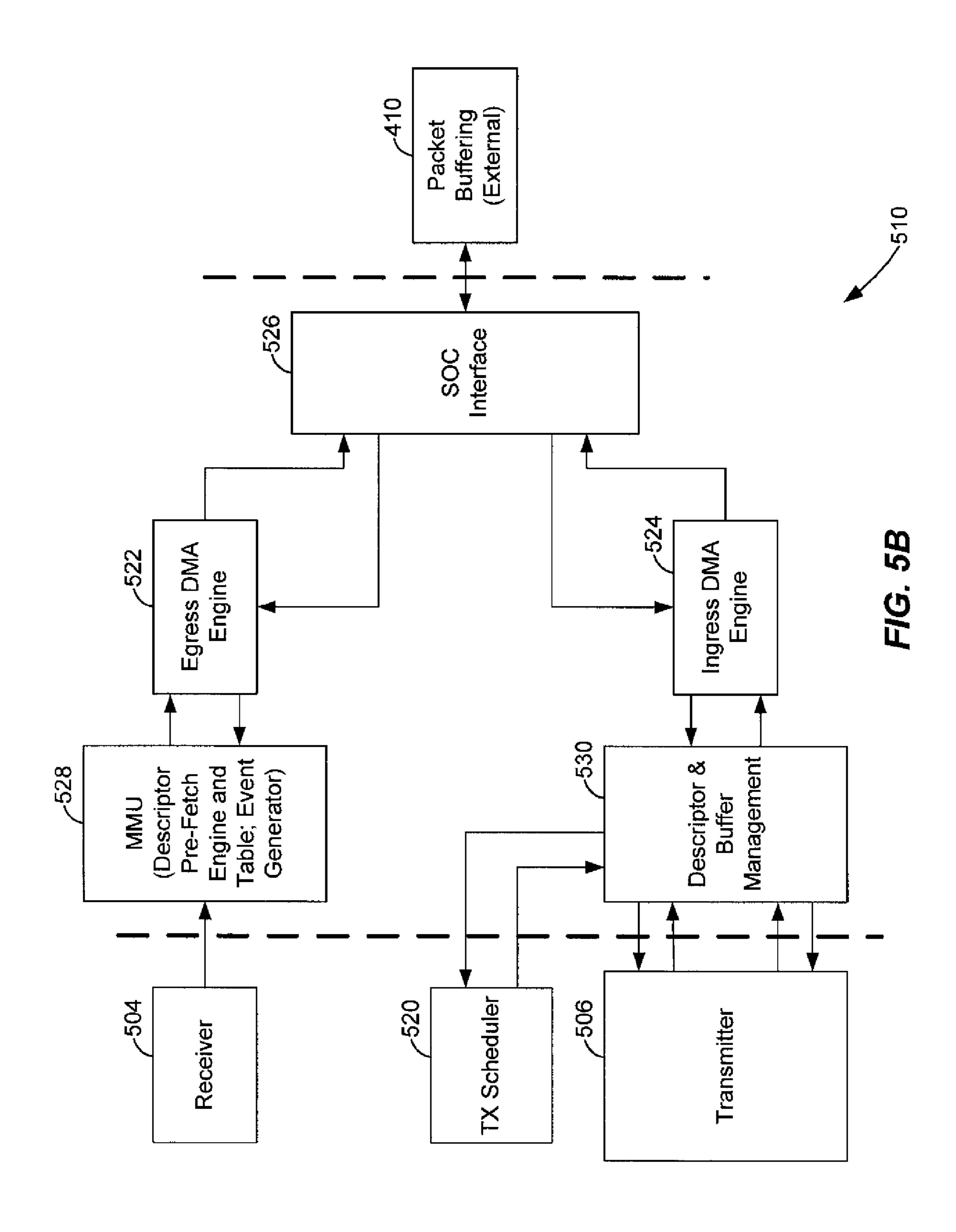

FIGS. 5A-5B are block diagrams of an example gigabit passive optical network chip of the integrated circuit within the passive optical network line termination unit, such as the example shown in FIG. 4A;

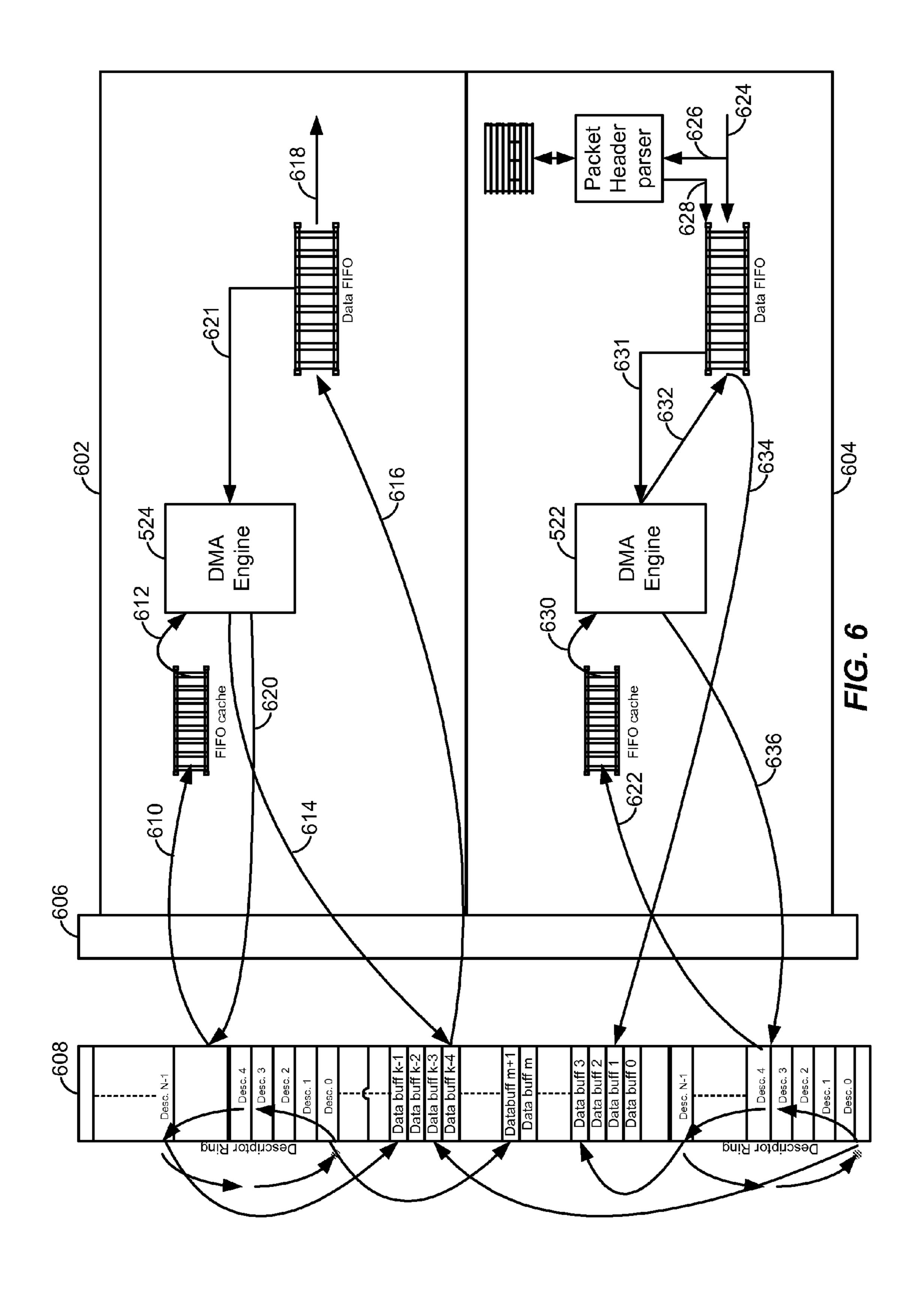

FIG. 6 is a block diagram of an example of buffer management and handling of data packets between a receiver or transmitter and a host;

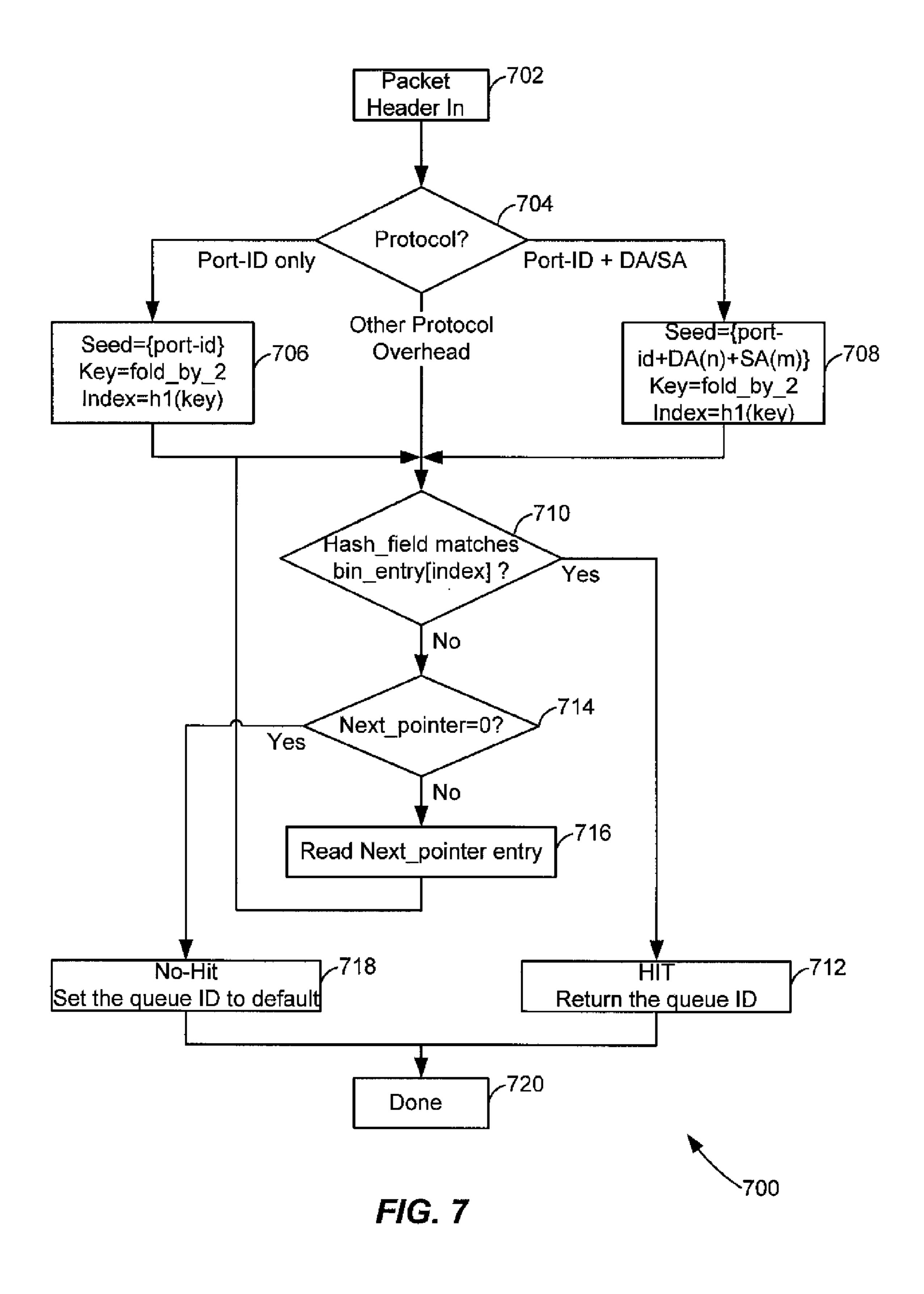

FIG. 7 is a flow diagram of an example of a routine for parsing a header of a data packet to determine a destination in the host memory;

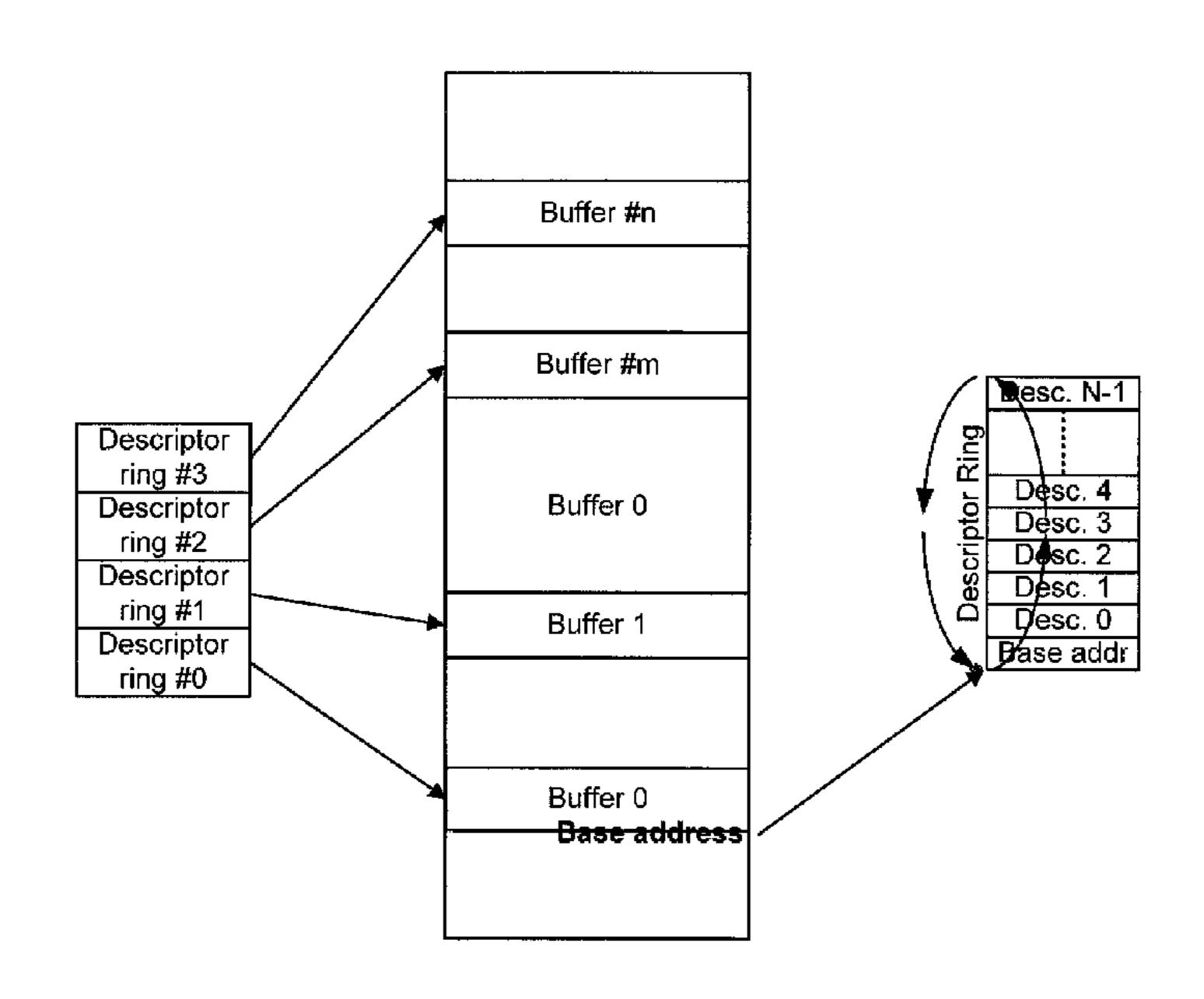

FIG. 8 is a schematic diagram of descriptor queues and descriptor ring structure in a host memory; and

FIG. 9 is a flow diagram of a rate control routine for transmitting data packets.

## DETAILED DESCRIPTION

FIG. 1 is a block diagram of an example passive optical network 100 that includes an optical line termination (OLT) 102 coupled to an optical network terminal (ONT) 104 and an optical network unit (ONU) 106. Generally, the passive optical network 100 is a point-to-multipoint network, where the

OLT **102** is provided as a service node interface, for example at a server or service provider, such as an internet service provider, television service provider, telephony service provider or other provider of network services. The ONT **104** and/or ONU **106** are each provided as an user node interface, for example at or near an end user. While the OLT **102** may be provided at the service provider site, the OLT **102** may also be provided as one of several OLTs within a distributed network, where each OLT is associated with corresponding ONUs **106** and/or ONTs **104**.

As shown in FIG. 1, the OLT 102 is communicatively coupled to the ONT 104 via an optical fiber 110, and communicatively coupled to the ONU 106 via an optical fiber 112. The optical fibers 110, 112 may be part of an optical distribution network (ODN). Although only one ONT **104** and one 15 ONU **106** are shown to be communicatively coupled to the OLT **102**, it should be understood that in a point-to-multipoint optical network, optical fibers may be each be run, one-to-one from the OLT 102 to an ONT 104 and/or an ONU 106, where there may be multiple ONTs 104 and/or ONUs 106 in the 20 passive optical network 100 each of which may, in turn, service multiple end users. As such, a single OLT 102 may service multiple end users on the same or a few optical fibers. As is understood, both the ONT 104 and the ONU 106 operate to terminate the passive optical network 100. An ONT 104 25 may refer to an integrated unit for an end user that presents the services of the service provider to the end user (e.g., video, data, telephony, etc.). An ONU 106 may be an optoelectronic interface to network termination (NT) equipment 108, where the ONU 106 terminates the passive optical network and the 30 NT equipment 108 provides the services to the end user. The ONU 106 handles data packet conversion between the passive optical network 100 and the NT equipment 108, and the NT equipment 108 may provide an interface to the end user. While this disclosure references both ONTs 104 and ONUs 35 **106**, it should be understood that in the context of this disclosure, ONTs 104 and ONUs 106 may be treated similarly and these terms may be used interchangeably with optical network terminal generally referring to both ONTs 104 and ONUs **106**.

Generally, the OLT **102** provides downstream broadcasts to each of the ONTs 104 and each of the ONUs 106 on different dedicated one-to-one fibers, where each ONT 104 and/or ONU 106 individually reads only the content of the transmissions intended for the particular ONT 104 and/or 45 ONU 106. The ONTs 104 and the ONUs 106 provide upstream transmissions to the OLT 102 via their virtual fibers via time division multiplexed (TDM) bursting. Communications between the OLT 102 and the ONT 104 or ONU 106 generally utilize wavelength division multiplexing with the 50 downstream broadcasts utilizing one wavelength and upstream transmissions utilizing another wavelength. Although the passive optical network 100 is described as having one-to-one fibers between the OLT **102** and the ONTs/ ONUs **104**, **106**, it should be understood that multiple fibers 55 may be utilized in the one-to-one correspondence between the OLT 102 and each corresponding ONT/ONU 104, 106. In one example, each connection between the OLT 102 and the ONTs/ONUs 104, 106 may utilize two fibers, with one for upstream transmissions and one for downstream transmis- 60 sion, rather than wavelength division multiplexing signals that share the same fiber.

The OLT 102 provides a variety of functions within the passive optical network 100. At one level, the OLT 102 provides the interface 114 between the passive optical network 65 100 and a backbone network of the service provider network, which may include supporting time division multiplexed

4

(TDM) protocols at different rates of speed, internet protocol (IP) traffic, asynchronous transfer mode (ATM) protocols, etc. The OLT **102** further facilitates both upstream and downstream communication between the service provider and the ONTs 104 and ONUs 106, and between ONTs 104 and ONUs 106. For example, the OLT 102 allocates upstream bandwidth to the ONTs 104 and ONUs 106 by granting intervals of time (e.g., time slot assignments) to each of the ONTs 104 and ONUs 106 to transmit upstream communications without 10 collisions on the fiber. Upstream bandwidth allocation may be fixed for ONTs 104 or ONUs 106 requiring continuous (e.g., guaranteed) bandwidth availability. For ONTs 104 or ONUs 106 that do not require continuous bandwidth availability (e.g., burst transmissions), the OLT 102 may utilize dynamic bandwidth allocation (DBA) based on either polling bandwidth information from the ONTs 104 and ONUs 106 or based on the occurrence of idle gigabit passive optical network (GPON) encapsulation method (GEM) frames from the ONTs 104 or ONUs 106. In addition, the ONTs 104 and ONUs are typically provided at different distances from the OLT 102, and the OLT 102 utilizes a ranging protocol to equalize the optical path length and equalize the transmission delay between the OLT 102 and the various ONTs 104 and ONUs 106. For example, the OLT 102 may measure the transmission delay for each ONT 104 and ONU 106, and transmits a physical layer operations and maintenance (PLOAM) message to set the transmission delay in the ONT 104 or ONU 106. The OLT 102 further provides centralized media access control (MAC) for the passive optical network 100 for purposes of upstream bandwidth allocation.

Upstream and downstream transmissions between the OLT 102 and the ONTs 104 or ONUs 106 may be performed in a transmission convergence frame format, whereby the transmission data, regardless of the services being provided, is encapsulated in the same type of data packet for transmission over the passive optical network 100. In particular, the transmissions between the OLT 102 and the ONTs 104 or ONUs 106 may take advantage of the gigabit passive optical network (GPON) standard developed by the International Telecommunications Union (ITU). The GPON standard is also known as ITU-T G.984. As is known, the GPON standard generally provides greater security as compared to previous standards, greater bandwidth, larger variable-width data packets, higher data rates and supports various Layer 2 protocols including ATM and GPON encapsulation method (GEM).

Although the disclosure generally refers to a gigabit passive optical network (GPON), it should be understood that all or part of this disclosure may be equally applicable to, or supportive of, previous-generation passive optical network standards, such as asynchronous transfer mode (ATM) passive optical network (APON) and broadband passive optical network (BPON), current passive optical network standards, such as Ethernet passive optical network (EPON), and future passive optical network standards, such as wavelength division multiplex passive optical network (WDM-PON). The disclosure may also be equally applicable to variations on the GPON standard.

FIG. 2 is an example of a downstream transmission convergence layer (TC-Layer) frame format 200 using the GPON standard and which may be utilized for downstream transmissions from the OLT 102 to the ONTs 104 and ONUs 106. The downstream frame format 200 generally includes an overhead field 202 and a payload field 204, where the overhead field 202 includes several sub-fields to be assembled by the OLT 102 and the payload field 204 includes the information being sent to the ONT 104 or ONU 106 (e.g., service data). As indicated above, the data for the payload field 204 may be

provided in one or more transport formats, such as ATM or GEM, and as a variable length data packet. As also indicated above, while the following disclosure involves an example of the downstream transmission convergence layer (TC-Layer) frame format 200, as well as the subsequent upstream trans- 5 mission convergence layer (TC-Layer) frame format discussed further below, it should be understood that variations of the downstream and upstream formats may occur and the disclosure is not limited to the particulars examples given herein. Generally, the downstream frame provides a common 10 time reference for the passive optical network 100, and provides common control signaling for the upstream.

The overhead field **202** for the downstream transmission frame is generally broadcast by the OLT 102 to all ONTs/ ONUs **104**, **106**. Each ONT/ONU **104**, **106** is then able to act 15 upon relevant information contained in the overhead field **202**. The overhead field **202** for the downstream transmission frame may be referred to as the physical control block downstream (PCBd), and may include a physical synchronization (PSYNC) field 206, an identification (Ident) field 208, a 20 physical layer operations and maintenance downstream (PLOAMd) field 210, a bit interleaved parity (BIP) field 212, two payload length downstream (PLEND) fields 214, 216 and an upstream bandwidth map (US BWmap) field 218. The PSYNC field **206** is a fixed pattern that generally begins the 25 overhead field 202, such that an ONT 104 or ONU 106 may use the PSYNC field 206 to identify the beginning of the frame 200 and establish synchronization with the downstream transmission. When the ONT **104** or ONU **106** finds the P SYNC field **206** within a frame of a downstream transmission from the OLT 102, the ONT/ONU 104, 106 may utilize a synchronization state machine, or other synchronization method, and search for other PSYNC fields 206 within subsequent frames to establish and monitor the synchronization state with the transmission. In one example, a counter 35 may be set upon identifying a unique value in the PSYNC field 206, with the counter being incremented for each valid PSYNC field 206 read by the ONT/ONU 104, 106. Once the counter reaches a predetermined threshold of consecutive PSYNC fields, the ONT/ONU 104, 106 is able to enter into a 40 synchronization state whereby the ONT/ONU 104, 106 is in synchronization with the downstream transmission rate. The ONT/ONU 104, 106 may thereby determine it has discovered the downstream frame structure and begin to process the overhead information. The ONT/ONU 104, 106 may also 45 maintain a count for invalid or incorrect PSYNC fields 206, and if the incorrect count reaches a predetermined threshold of consecutive PSYNC fields, the ONT/ONU 104, 106 may determine that it has lost the downstream frame structure and repeat the search for a valid or correct P SYNC field **206**. 50 However, it should be understood that different state machines or different manners of establishing and monitoring synchronization with the transmission may be utilized.

The Ident field 208 may be used to indicate large frame structures (superframes) within the downstream transmission 55 frame, and which may be used to control data encryption. Generally, the Ident field 208 includes an FEC field 220, a reserved field 222 and a superframe counter 224. The FEC field 220 indicates whether forward error correction (FEC) is being enabled on the present downstream frame and may be 60 begin using a new encryption key. used for FEC control. As is known, forward error correction is a method of error control for transmissions, where the OLT 102 may add redundant data to the downstream transmission frame, and the ONT/ONU 104, 106 may detect and correct errors using the redundant data, thereby avoiding retransmis- 65 sion of the downstream transmission frame from the OLT 102. The reserved field 222 is reserved for other purposes, and

the superframe counter 224 provides error checking for potential dropped frames. The ONT/ONU 104, 106 loads the superframe counter value and compares its local expected value with the superframe counter value, whereby a match indicates correct synchronization and a mismatch indicates a transmission error or desynchronization.

The PLOAMd field **210** contains a downstream PLOAM message from the OLT 102 for the ONT/ONU 104, 106. A PLOAM message is generally a control message that may relate to a variety of information or instructions for the ONT/ ONU 104, 106, including, but not limited to, alerts, activation-related messages, instructions, etc. For example, an Upstream\_Overhead PLOAM message may instruct the ONT/ONU 104, 106 to use a particular preassigned equalization delay during ranging and number of preamble bytes for upstream transmissions, define the transmission power of the ONT/ONU 104, 106. A Serial\_number\_mask PLOAM message may provide a serial number and a mask for part of the serial number. An Assign\_ONU-ID PLOAM message may assign an identification with the serial number of the ONT/ ONU 104, 106. A Ranging\_Time PLOAM message may provide a value for an equalization delay register of the ONT/ ONU 104, 106. A Deactivate\_ONU-ID PLOAM message may provide a deactivation/reset instruction to stop sending upstream transmissions. A Disable\_serial\_number PLOAM message may provide a disable/enable instruction to an ONT/ ONU 104, 106. A Configure\_VP/VC PLOAM message may activate or deactivate a virtual channel or a virtual path at the ATM layer. An Encrypted\_Port-ID/VPI PLOAM message may indicate encrypted and unencrypted channels to the ONT/ONU 104, 106. A Request\_password PLOAM message may request a password from the ONT/ONU 104, 106 for verification. An Assign\_Alloc-ID PLOAM message may assign an allocation identification to an ONT/ONU 104, 106. A POPUP PLOAM message may instruct the ONT/ONU 104, 106 to move to a ranging state or an operation state. A Request\_Key PLOAM message may trigger the ONT/ONU 104, 106 to generate a new encryption key. A Configure Port-ID PLOAM message may link a management and control interface of the ONT/ONU 104, 106 (OMCI) with a Port-ID which may be appended to an overhead of GEM encapsulated payload to be used as an addressing mechanism to route the OMCI over the GEM channel. A PEE-Physical Equipment Error PLOAM message to indicate that the OLT is unable to sent both ATM cells, GEM frames and ONT/ONU 104, 106 Management and Control Channel (OMCC). A Change-Power-Level PLOAM message may trigger the ONT/ONU 104, 106 to increase or decrease it transmission power level. A PST (PON Section Trace) PLOAM message may be provided to check the connectivity between the ONT/ ONU **104**, **106** and the OLT, and to perform Automatic Protective Switching (APS). A BER interval PLOAM message may be provided to define the accumulation interval per ONT/ONU 104, 106 expressed as a number of downstream frames for the ONT/ONU 104, 106 counting the number of downstream bit errors. A Key Switching Time PLOAM message may indicate when the ONT/ONU 104, 106 when to

As seen in FIG. 2, the PLOAMd field 210 is formatted to include an ONU ID 226, a Message-ID 228, the message Data 230 and a cyclic redundancy check (CRC) 232. The ONU ID 226 identifies the ONT/ONU 104, 106 to receive the PLOAM message. The Message-ID **228** identifies the type of PLOAM message, example of which are provided above. The message Data 230 are used for the payload of the PLOAM message.

The CRC 232 is a frame check sequence, such that the PLOAM message may be discarded upon receipt if the CRC is incorrect.

The BIP field **212** contains the bit interleaved parity of the bytes that have been transmitted since the previous BIP. The 5 ONT/ONU **104**, **106** independently determined the BIP and compares the result to the BIP field **212** to measure the number of errors in the transmission.

The Plend field **214**, **216** specifies the length of the bandwidth map (BWmap) (also referred to as the bandwidth allo- 10 future use. cation) and any ATM partition in the payload 204. The BWmap length is provided in a Blen field 234, and the ATM partition length related information is provided in a Alen field 236. As seen in FIG. 2, the Plend field 214, 216 is a redundant field for error robustness. The Plend field **214**, **216** may be 15 protected by CRC (e.g., CRC-8) for error detection and correction as provide in a CRC field 238. In particular, the length of the bandwidth map provides the limit of the number of allocation IDs that may be granted in any particular duration in any 125 microsecond duration up to 4095. The actual 20 length of the BWmap field 218 is then 8 times the Blen value. The Alen field 236 may allow up to a particular number of ATM cells in a frame (e.g., a 12-bit Alen field allows 4095 ATM cells), up to a particular data rate (e.g., 10 Gbits/s). The length of the ATM partition is then 53 times Alen. The ONT/ ONU 104, 106 implements the error detection and correcting functions of the CRC field 238, decodes both copies of the Plend field 214, 216, and uses the copy based upon the result of the CRC detection process (e.g., the copy that is error free or that has a correctible error).

The US BWmap field **218** provides an upstream bandwidth allocation as processed by the OLT acting as the main or central controller for the ONTs **104** and ONUs **106**. The BWmap field is provided as an array of allocation structures **240**, **242** (Access1, Access2, etc.), where each entry in the 35 array represents a single bandwidth allocation to a particular transmission container (T-CON). The number of entries in the BW map is provided in the Plend field **214**, **216**. The access fields are distributed to the ONT/ONU **104**, **106** which become slaves to the OLT and are required to follow the 40 provided format.

As shown in FIG. 2, each allocation structure 240, 242 includes an Alloc ID field 244, a Flags field 246, a SSTART field 248, a SSTOP field 250 and a CRC field 252. The Alloc ID field 244 indicated the particular T-CONT that is being 45 granted time on the upstream, and includes an address of the ONT/ONU 104, 106 receiving the T-CONT.

The Flags field **246** contains five separate indications on how the allocation should be used by the ONT/ONU 104, **106**, including information to be sent back to the OLT during 50 the bandwidth allocation provided to the ONT/ONU 104, 106. The Flags field 246 includes a PLSu field 254, a PLOAMu field 256, an FEC field 258, a DBRu field 260 and an RSV field **262**. The PLSu field **254** is a power leveling sequence used for power control measurements by the ONT/ ONU 104, 106 which, if set, directs the ONT/ONU 104, 106 to send its PLSu information during the bandwidth associated allocation. If the PLSu bit is not set, the ONT/ONU 104, 106 does not send its PLSu information for the associated bandwidth allocation. The power control measurements function 60 allows for adjustment of the power levels of the ONT/ONU 104, 106 to reduce the optical dynamic range as seen by the OLT, and is useful in initial power set-up of the ONT/ONU 104, 106 (e.g., during activation), and power mode change of the ONT/ONU 104, 106 transmitter (e.g., during activation or 65 operation). The PLOAMu field 256 directs the ONT/ONU 104, 106 to send its PLOAMu information during the associ8

ated bandwidth allocation, if the bit is set. Examples of the PLOAM messages are discussed above. The FEC field **258** causes the ONT/ONU **104**, **106** to compute and insert an FEC parity during the associated bandwidth allocation, if the bit is set. The DBRu field **260** causes the ONT/ONU **104**, **106** to send an upstream Dynamic Bandwidth Report indicating the number of cells or blocks in the T-CONT buffer of the ONT/ONU **104**, **106**, whereby the OLT may determine the congestion status of each T-CONT. The RSV field **262** is reserved for future use

The SSTART field **248** is the start time field indicating the starting time for upstream transmission (i.e., the starting time of the bandwidth allocation). The SSTOP field **250** is the stop time field indication the stop time for the upstream transmission. Each ONT/ONU 104, 106 uses the SSTART and SSTOP fields 248, 250 to determine when to start and stop its upstream transmission. Each ONT/ONU 104, 106 identifies which particular information among the allocation structures is for its own use as filtered through the Allocation ID **244** bits within the access portion of the frame. The CRC field 252 is a cyclic redundancy check (e.g., CRC-8) that protects each allocation structure, where the ONTs/ONUs 104, 106 BWmap field 218 processing implements error detecting and correcting functions of the CRC. If an uncorrectable error occurs as indicated by the CRC function, the allocation structure is discarded.

The transmission convergence payload field 204 may include both an ATM payload field **264** or partition, and a GEM payload field **266** or partition. As such, a variety of user data type may be carried in the GPON transmission convergence payload. The ATM partition 264 may contain a number of ATM cells, the length of which is provided in the Plend/ Alen fields 214/236, 216/236. The OLT 102 may allocate as many cell durations as needed in the downstream, including almost all of the downstream frame. Generally, the ATM partition 264 is an integer multiple of 53 bytes long based upon the Plend/Alen fields 214/236, 216/236, and the ATM cells are aligned to the partition. The downstream cell stream is filtered at the ONT/ONU 104, 106 based upon a virtual path identifier (VPI) or virtual channel identifier (VCI). In particular, each ONT/ONU 104, 106 is configured to recognize which VPI belongs to it, and ATM cells that belong to the ONT/ONU 104, 106 are passed on to the ATM client process.

The GEM partition 266 contains a variable number of GEM frame-mode delineated frames 268, 270 (GEM1, GEM2, etc.). The length of the GEM partition 266 is determined based on whatever remains after the overhead 202 and ATM partitions 264 are subtracted from the overall frame length. The GEM protocol provides delineation of the user data frame (either going to or coming from a user) and provides port identification for multiplexing. Delineation and port identification are accomplished by the GEM header discussed below. The delineation process uses the GEM header at the beginning of every downstream GEM partition and every upstream GEM payload. As such, in a downstream transmission the ONT/ONU 104, 106 is assured of finding the first header and may find subsequent headers using the payload length identifier (PLI) as a pointer.

As seen in FIG. 2, each GEM frame 268, 270 includes a header containing a PLI field 272, a Port-ID field 274, a PTI field 276, HEC field 278, and a fragment payload 280. The PLI field 272 indicates the length of the fragment payload 280 following the header, and is used to identify the next header in the GEM stream to provide delineation. The size of the PLI field 272 (e.g., 12-bits) determines the size of the GEM fragments (e.g., up to 4095 bytes), where data frames larger than the GEM fragment payload size are fragmented into smaller

sizes to accommodate the GEM fragment payload size. The Port-ID field **274** is a unique traffic identifier on the passive optical network **100** to provide traffic multiplexing. The PTI field **276** indicates the content type of the fragment payload **280** and how the fragment payload **280** should be treated (e.g., user data fragment; congestion has or has not occurred; end or not end of a frame). The PTI field **276** may be similar to that used in the ATM header. The PTI field **276** indicates which fragment contains the end of the user data frame. The downstream frame transmission is filtered at the ONT/ONU **104**, **106** based upon the Port-ID field **274** contained in each GEM fragment. Frames belonging to the ONT/ONU **104**, **106**, each of which are configured to recognize which Port-IDs belong to it, are passed on to the GEM client process.

The HEC field 278 is header error control which provides error detection and correction functions for the GEM header. The GEM header may be provided at the beginning of each downstream GEM payload and the ONT/ONU 104, 106 uses the PLI field **272** to find the first header, and finds subsequent 20 headers using the PLI as a pointer. The ONT/ONU 104, 106 may thereby transition to the "sync" state at the beginning of each partition and payload. If uncorrectable errors occur in the header as determined based on the HEC field 278, delineation of the GEM partition may lose synchronization with 25 the data stream, and the ONT/ONU 104, 106 attempts to reacquire synchronization. The ONT/ONU 104, 106 searches for a GEM header HEC field 278, and when one is found, the ONT/ONU 104, 106 transitions to a pre-synchronized state, where it looks for the HEC field **278** at the location indicated 30 in the previously found header. If the HEC matches, then the transition is made to the synchronized state. If it does not match, then the transition is made to the search for another HEC.

gence layer (TC-Layer) frame format 300 using the GPON standard and which may be utilized for upstream transmissions from the ONTs 104 and/or ONUS 106 to the OLT 102. The upstream frame format 300 generally includes an overhead field 302 and a payload field 303. The overhead field 302 includes several sub-fields to be assembled by the ONT/ONU 104, 106 and processed by the OLT 102 and the payload field 303 includes the information being sent to the OLT 102 or to the service provider network. As indicated above, the data for the payload field 303 may be provided in one or more trans- 45 port formats, such as ATM or GEM, and as a variable length data packet. The frame length of the upstream transmission convergence layer (TC-Layer) frame format 300 may be the same as that of the downstream transmission convergence layer (TC-Layer) frame format 200 for all transmission rates. 50 Each frame may contain a number of transmissions from one or more ONT/ONU 104, 106, where the BWmap defines the arrangement of the transmissions. As seen in FIG. 3, the T-CONT of the upstream message is defined by the start and stop transmission times (SSTART and SSTOP) as determined 55 by the OLT 102 during the downstream transmission, but does not include the PLOu field which is sent immediately prior to the start time pointer SSTART.

The overhead field 302 for the upstream transmission frame may include various types of overheads, including 60 physical layer overhead (PLOu) 304, physical layer operations and management upstream (PLOAMu) 306, power leveling sequence upstream (PLSu) 308 and dynamic bandwidth report upstream (DBRu) 310. As discussed above, the Flag field 246 in the downstream transmission assembled by the 65 OLT 102 indicates whether PLOAMu, PLSu or DBRu information should be sent from the ONT/ONU 104, 106 on each

**10**

bandwidth allocation. The upstream frame is generally scrambled, and may be scrambled using a frame-synchronous scrambling polynomial.

The PLOu field **304** includes the physical layer overhead, which is provided as a preamble (PRMBL) field 312 and a delimiter (Delim) field 314. Three additional fields of data corresponding to the ONT/ONU 104, 106 as a whole are also provided: a bit interleaved parity (BIP) field 316, a ONT/ ONU 104, 106 identification (ONU-ID) field 318 and an indication (Ind) field **320**. The above data is generally provided at the beginning on any transmission burst from an ONT/ONU 104, 106. The status of the PLOu information is given by the arrangement of the bandwidth allocations. Every time an ONT/ONU 104, 106 takes over the passive optical 15 network 100 from another ONT/ONU 104, 106, the ONT/ ONU 104, 106 sends a new copy of the PLOu data. The GPON transmission convergence layer sources the PLOu 304. The preamble field 312 is used to synchronize the OLT 102 to the incoming message, and the delimiter field 314 is used by the OLT 102 to identify where the first bit of information in the frame begins. The preamble field 312 and the delimiter field 314 are formed as determined by the OLT in the Upstream\_Overhead PLOAM message discussed above. As seen in FIG. 3, the preamble and delimiter fields 312, 314 are transmitted before the allocation start time SSTART pointer, as previously dictated by the OLT.

The BIP field 316 contains the bit interleaved parity of the bytes transmitted since the last BIP from the transmitting ONT/ONU 104, 106 transitions to a pre-synchronized state, here it looks for the HEC field 278 at the location indicated the previously found header. If the HEC matches, then the ansition is made to the synchronized state. If it does not atch, then the transition is made to the search for another EC.

FIG. 3 is an example of an upstream transmission conversence layer (TC-Layer) frame format 300 using the GPON

The BIP field 316 contains the bit interleaved parity of the bytes transmitted since the last BIP from the transmitting ONT/ONU 104, 106, excluding those of the preamble and delimiter fields 312, 314. The OLT 102 computes the bit-interleaved parity for each ONT/ONU 104, 106 burst, and compares the result to the BIP of the BIP field 316 to measure the number of errors in the link. The ONU-ID field 318 contains the bit interleaved parity of the bytes transmitted since the last BIP from the transmitting ONT/ONU 104, 106, excluding those of the preamble and delimiter fields 312, 314. The OLT 102 computes the bit-interleaved parity for each ONT/ONU 104, 106 burst, and compares the result to the BIP of the BIP field 316 to measure the number of errors in the link. The ONU-ID field 318 contains the bit interleaved parity of the bytes transmitted since the last BIP from the transmitting ONT/ONU 104, 106, excluding those of the preamble and delimiter fields 312, 314. The OLT 102 computes the interleaved parity for each ONT/ONU 104, 106 burst, and compares the result to the BIP of the BIP field 316 to measure the number of errors in the link. The ONU-ID is generally assigned to the ONT/ONU 104, 106 during the ranging process.

The Ind field 320 provide a real-time ONT/ONU 104, 106 status report to the OLT. As shown in FIG. 3, the format of the Ind field 320 is provided as a PLOAM waiting field 322 indicating if one or more PLOAM messages are waiting, an FEC field 324 indicating if forward error correction is enabled or not, a remote defect indication (RDI) field 326 indicating if a defect occurred or not, traffic waiting indicator fields for type 2 T-CONTs 328, type 3 T-CONTs 330, type 4 T-CONTs 332 and type 5 T-CONTs 334, as well as reserved bits 336. If the PLOAM waiting field 322 indicated an urgent PLOAM message is waiting, the OLT 102 may issue an upstream allocation that allows the ONT/ONU 104, 106 to send the PLOAM message in a timely manner. Further uses of the Ind field 320, and in particular the T-CONT fields 328, 330, 332, 334, are discussed below in relation to the DBRu field 310.

Examples of the PLOAM messages as provided in the PLOAMu field 306 are discussed above, and may be provided by the transmitting ONT/ONU 104, 106 in response to a corresponding request from the OLT 102. In particular, the PLOAMu field 306 may only be sent when indicated by the Flags field 246. The PLOAMu field 306 may have a similar structure as the PLOAMu field 210, including an ONU ID 338 of the transmitting ONT/ONU 104, 106, a Message-ID 340 identifying the type of PLOAM message, the message Data 342 for the payload of the message, and a cyclic redundancy check (CRC) 344 to detect and correct errors in the header fields 338, 340, 342.

The PLSu field 308 is used for power control measurements by the ONT/ONU 104, 106 and adjusts the ONT/ONU 104, 106 power levels to reduce the optical dynamic range seen by the OLT. The content of the PLSu field 308 is gener-

ally set by the ONT/ONU 104, 106, and is sent by the ONT/ONU 104, 106 when indicated in the Flags field 246 of a downstream transmission from the OLT 102. For example, the OLT 102 may set the PLSu bit on broadcast allocation to allow the ONT/ONU 104, 106 to set up its transmitter during 5 the activation process. If the ONT/ONU 104, 106 does not use the PLSu field 308, the ONT/ONU 104, 106 may deactivate its transmitter for that time. During operation of the ONT/ONU 104, 106, the ONT/ONU 104, 106 generally transmits following the PLSu field 308 such that the ONT/ONU 104, 10 106 sends the PLSu field 308 when it is requested by the OLT regardless of any need to perform transmitter adjustment.

The DBRu field 310 includes information that is associated with the T-CONT entity, rather than the ONT/ONU 104, 106. The DBRu field 310 is sent when requested by the OLT in the 15 Flags field 246 of a downstream transmission. The DBRu field 310 includes a dynamic bandwidth allocation (DBA) field 346 and a CRC field 348. The DBA field 346 contains the traffic status of the particular T-CONT, and may be used by the OLT 102 for bandwidth allocation for the ONT/ONU 104, 20 106. The DBA field 346 may be supported via status reporting and OLT traffic monitoring for those ONT/ONU 104, 106 that do not report status. Status reporting DBA field 346 may be provided as status indications in the PLOu, in the DBRu as shown in FIG. 3, or in an ONU report in a DBA payload.

Status indications may be carried as four bits in the PLOu Ind field **320**, and provide a report for each type of T-CONT 328, 330, 332, 334. Each bit may correspond to a different T-CONT type. If a bit is set for a particular T-CONT type 328, **330**, **332**, **334**, the OLT **102** may assume there is some data 30 waiting in one of the T-CONT buffers of that type. It is noted that T-CONT types 2, 3 and 4 328, 330, 332 may not have a fixed bandwidth component and any data waiting in those T-CONTs 328, 330, 332 causes the corresponding indicator to be set, whereas a T-CONT type 5 field **334** buffer may 35 contain data belonging to a fixed bandwidth such that the presence of non-fixed bandwidth sets the corresponding indicator. The status indications provide an early warning to the OLT **102** that data is waiting, though it is not required that the OLT **102** DBA algorithm wait for such indications before 40 allocating bandwidth to the ONT/ONU 104, 106 in order to avoid unnecessary delays. The OLT **102** may use the status indications for a fast alert that DBA supervision may be needed at the ONT/ONU 104, 106 without identifying the T-CONT 328, 330, 332, 334 or bandwidth detail.

Status reporting DBA in the DBRu field 310, shown in FIG. 3 as the DBA field 346, provides a continuous update of the traffic status of a particular T-CONT and is carried in the DBRu field **310** associated with the T-CONT. The status report in the DBA field **346** specifies the amount of data 50 waiting in the T-CONT buffer corresponding to the allocation identification (Alloy-ID) that triggered the DBRu transmission. The OLT **102** may trigger the transmission of the DBRu by setting the DBRu field 260 in the Flags field 246 of a downstream transmission. The CRC field 348 protects the 55 report in the DBA field **346** and DBRu structure with error correction and detection. The OLT may implement the error detecting and correcting functions associated with the CRC field 348 (e.g., CRC-8). If the CRC function indicates an uncorrectable error, the information in the DBRu field 310 60 may be discarded.

An ONU report in a DBA payload allows for the ONT/ONU 104, 106 to send a DBA report on any T-CONT in the transmission, and is carried in a dedicated DBA payload partition allocated by the OLT in the upstream. The ONT/ 65 ONU 104, 106 may select the T-CONT that is the subject of the report, and allows the OLT 102 to schedule a DBA pay-

12

load which is generally smaller that that required to report on all the T-CONTs in the ONT/ONU 104, 106.

The upstream payload field 303 may be used to carry ATM cells, GEM-delineated frames or DBA reports. The ATM upstream payload includes a number of ATM cells from the ONT/ONU 104, 106 to the OLT 102, and the length of the payload is given by the duration of the allocation minus the size of any requested overhead. The ONT/ONU 104, 106 may buffer the ATM cells as they are provided by the OLT 102 and send them in burst during the allocated time. The OLT 102 receives the ATM cells, and may multiplex them with other bursts from other ONT/ONU 104, 106 and pass them to the OLT ATM client. The GEM payload contains any number of GEM frame-mode delineated frames, and the length of the payload is also given by the duration of the allocation minus the size of any requested overhead. The GEM protocol provides delineation of the user data frame (either going to or coming from a user) and provides port identification for multiplexing. As discussed above, delineation and port identification are accomplished by a GEM header, where the delineation process uses the GEM header at the beginning of every upstream GEM payload. As such, in an upstream transmission the OLT 102 is assured of finding the first header and may find subsequent headers using the PLI as a pointer. The DBA 25 payload is discussed above, and contains a group of dynamic bandwidth allocation reports from the ONT/ONU 104, 106.

FIG. 4A is a block diagram indicating an example of a general architecture 400 that may be implemented in the OLT **102** or the ONT/ONU to divide and execute time sensitive functions from non-time sensitive functions. Generally, the architecture 400 includes a sub-system 402 which may be used to execute non-time sensitive functions, such as those that require large memory requirements or low latency, and integrated circuits 404 having an embedded processor for performing time-sensitive functions, such as those that may only need limited memory. Time-sensitive versus non-time sensitive functions may be determined based on time threshold or response threshold requirements for processing the functions. For example, some functions, such as Media Access Control (MAC), may require immediate response (i.e., fast response threshold, time sensitive), whereas other functions, such as TCP/IP routing or packet processing, may not require an immediate response (i.e., non-time sensitive). It is recognized that in practice the actual response time for 45 some non-time sensitive functions may be comparable to the response time threshold of time-sensitive functions. However, it should be understood that it is the response time requirements (e.g., time threshold requirements) that establish whether a function is time-sensitive or not, rather than the actual response time seen in practice. As such, the time threshold requirements delineating between time-sensitive and non-time sensitive are not necessarily predetermined or static, but are rather based on the allowable response time for executing the function.

As will be apparent from the discussions below in regards to FIGS. 5A and 5B, the integrated circuit 404 may perform a variety of time-sensitive functions depending on the information received at a receiver end of the circuit 404 and the information to be transmitted from a transmitter end thereof. In a GPON context, for example, these functions may include processing of various subfields in overhead data in a received transmission. The integrated circuit may pre-process these subfields prior to offloading payload information to the subassembly 402. The integrated circuit 404 may identify the corresponding incoming upstream transmission for the OLT and the location, length and value of the various subfields contained in the overhead field. On the transmitter side, the

integrated circuit **404** may create the transmitted data overheads based on information from the receiver side as well as information (such as payload information) from the subassembly **402**. In fact, one aspect of the architecture **400** is that in some examples information obtained from processing the received data may be used to directly control processing of transmitter data without resorting to offloading all such data retrieval and reconstruction to the subassembly **402**. In this way, internal delays in a processing unit of a PON (e.g., an OLT) may be reduced. Further, because clock data recovery may be performed within the integrated circuit **404** and communicated directly with the transmitter within the integrated circuit **404**, the architecture **400** may be used to more accurately correct for internal delays.

The subassembly **402** may be provided as part of a systems-on-a-chip (SoC) which may be re-usable for a variety of different implementations, including implementation of different integrated circuits as discussed below. As such, the subassembly **402** provides a "snap-and-run" architecture in which a variety of chips may be coupled to the subassembly **402**, and the subassembly **402** is not limited to OLTs **102**, ONTs **104** or ONUs **106**, much less the example provided herein. The subassembly **402** may therefore be used to reduce the time-to-market chip assembly, as it can be used among a variety of chip designs and to build different chips.

Generally, the subassembly 402 includes an SoC processor 406 for processing the non-time sensitive functions and a memory interface 408 coupled to the SoC processor 406. A memory 410 is further provided and coupled to the memory interface 408 for buffering data from the integrated circuits 30 404 (e.g., packet buffering) and may include embedded memory management. The memory 410 thereby stores data for execution of non-time sensitive functions to be processed by the SoC processor 406. The SoC processor 406 controls the memory 410 and movement of data packets in and out of 35 the memory 410 as needed.

The SoC processor 406 and the memory 410 are provided external to the integrated circuit 404 to support the processing of non-time sensitive functions while the processing of timesensitive functions is handled by the integrated circuit 404. Accordingly, the SoC processor 404 and memory 410 may be used to minimize the amount of processing required at the chip level (e.g., packet level). That is, non-time sensitive functions that require additional processing complexity may be passed from the integrated circuits **404** to the subassembly 45 402. Different types of memories may be used for the memory 410, including double data rate (DDR) memory, flash memory, etc. The memory interface 408 may be provided as an interface corresponding to the memory **410** (e.g., a DDR) memory interface, flash memory interface, etc.). The subas- 50 sembly 402 may further include additional components, such as a debugging port (e.g., a joint task action group (JTAG) port 413), an input/output interface (e.g., a general purpose input/output (GPIO) 415), or a receiver and/or transmitter (e.g., a universal asynchronous receiver/transmitter (UART) 55 417), or other peripheral interfaces in different SoC embodiments. The devices 413, 415, 417, the memory 408 and the processor 406 are all coupled to a backplane bus 418 of the SoC subassembly 402.

As shown in FIG. 4A, the integrated circuit 404 may be a 60 GPON chip 404 coupled to the subassembly 402, thus forming an SoC. The integrated circuit 404, which may be a GPON chip 404, communicates with the SoC subassembly 402 through an interface coupled to the backplane bus 418. Further disclosure of the GPON chip 404 is provided by way of 65 example below. Generally, the GPON chip 404 includes an internal processor, and an SoC interface to the SoC subas-

14

sembly 402 which interfaces with the SoC processor 406 and with the memory 410 via the memory interface 408. It should be understood that while the architecture 400 is described with reference to particular components, integrated circuits and particular transmission standards, the architecture 400 may be readily applied to different components and standards where time-sensitive and non-time sensitive functions may be applicable, including, but not limited to, wireless and wireline technologies.

While the architecture 400 may include only a passive optical network communicatively coupled to the SoC subassembly 402, the SoC subassembly 402 may be coupled to other types of networks or layers. For example, although the architecture 400 is shown to include a GPON 404 chip which interfaces with the passive optical network 100, it should be understood that different integrated circuits may be utilized in the architecture 400. As seen in FIG. 4A, additional or alternative technologies, such as Data Over Cable Service Interface Specifications (DOCSIS) 412, Digital Subscriber Line (DSL) 414 or Multimedia Over Coax Alliance (MOCA) 416 may be implemented and interfaced with wireline networks.

As further examples, the architecture may include an Ethernet switch interface circuit coupled to an Ethernet switch for monitoring and redundancy, a system packet interface layer 3 (SPI-3) circuit to interface with the backplane bus 418 of the SoC subassembly, a synchronous optical network (SONET), Ethernet (e.g., 10 gigabit Ethernet or 10GE), etc. Other layers may also be supported by the architecture. As seen in FIGS. 4B-4D, the SoC subassembly 402 may be coupled to a system packet interface level 3 (SPI-3) circuit 420 for chipto-chip packet communications through a backplane. In some other examples, the SoC subassembly 402 may be coupled to an Ethernet switch 422, for example for monitoring and redundancy or for connecting to an Ethernet distribution network or network termination device.

FIGS. 4B-4D show example implementations of the architecture 400 used in an OLT, ONT, and ONU application, respectively. FIG. 4B, for example, shows an OLT application in which the SPI-3 circuit **420** is coupled to the backplane bus 418 as are a synchronous optical network (SONET) 426 and a 10 Gigabit Ethernet network **428**. FIG. **4**C shows an ONT application in which the backplane bus 418 couples the SPI-3 interface 420 to a very high density digital subscriber line (e.g., VDSL or VDSL2) distribution network 430 and an asymmetric digital subscriber line (e.g., ADSL or ADSL2) distribution network 432. FIG. 4D shows an ONU application, in which the SPI-3 interface 420 is optional and the Ethernet interface 422 is coupled to an Ethernet network termination 434, like the NT 108 shown in FIG. 1. Other layers may also be supported by the architecture 400. Generally, whenever a division of the time sensitive versus non-time sensitive functions is desired, each integrated circuit included in the architecture 400 may include an internal processor for execution of the time sensitive functions and an SoC interface to forward data packets for non-time sensitive functions to the sub-assembly 402 for execution therein.

Although many of the above examples have been described with reference to various wireline technologies, it should be understood that various wireless technologies may be utilized with wireless integrated circuits utilized in the architecture 400, such wireless technologies including, but not limited to, the Institute of Electrical and Electronics Engineers wireless local area network IEEE 802.11 standard, Worldwide Interoperability for Microwave Access (WiMAX), Ultrawideband (UWB) radio technology, and cellular technology. Generally, whenever a division of the time sensitive versus non-time sensitive functions is desired, each integrated cir-

cuit included in the architecture 400 may include an internal processor for execution of the time sensitive functions and an SoC interface to forward data packets for non-time sensitive functions to the sub-assembly 402 for execution therein.

In the context of an OLT 102, the GPON chip 404 further 5 includes a receiver for receiving upstream burst transmissions from an ONT/ONU 104, 106, a transmitter for assembling and transmitting downstream transmissions to the ONT/ONU 104, 106 and an optoelectronic interface to the passive optical network 100. The internal processor of the OLT 102 may 10 therefore be used to perform time-sensitive functions associated with the OLT 102, such as assembling the overhead field 202 of a downstream transmission along with functions associated therewith, and processing the overhead field 302 of an upstream transmission along with the functions associated 15 therewith. In the example provided below, the GPON chip **404** is described with reference to the upstream and downstream GPON transmission convergence frame formats discussed above. However, it is noted that the inclusion of an internal processor in the GPON chip **404** not only allows for 20 execution of time sensitive functions, but also provides the flexibility to adapt the GPON chip 404 to changes in the GTC frame formats and other related GPON functions including MAC, etc.

FIGS. 5A and 5B are block diagrams of an example of a 25 general GPON chip 404 for an OLT 102, an ONT 104 or an ONU 106 shown in FIG. 4A, and will be described in the context of the GTC frame formats discussed above. In particular, the GPON chip 404 is coupled to the passive optical network 100 via an optoelectronic transceiver interface 502, 30 and includes a receiver 504 for receiving upstream burst transmissions from an ONT/ONU 104, 106, a transmitter 506 for assembling and transmitting downstream transmissions to the ONT/ONU 104, 106 receiving transmissions over the passive optical network 100, a transmitter 508 for assembling 35 and transmitting transmissions over the passive optical network 100, a distributed direct memory access (DMA) interface 510 to interconnect with the subsystem 402, and an internal processor 512 for processing time-sensitive functions associated with the transmission, such as processing the 40 overhead of a transmission and assembling the frame of a transmission.

The optoelectronic interface 502 generally includes an optoelectronic transceiver receiver 514 coupled to the receiver 504, and an optoelectronic transceiver transmitter 45 516 coupled to the transmitter 506, though it should be understood that different optoelectronic interfaces may be used. The receiver 504 and transmitter 506 generally conform to the transmission format used by the OLT **102**, the ONT **104** and the ONU **106**, such as the upstream and downstream GTC 50 frame formats provided above. In the case of an OLT 102, upstream GTC frame formatted data is transmitted from the ONT/ONU 104, 106 over the fiber 110, 112 into the transceiver receiver 514 and is provided to the receiver 504, and downstream GTC frame formatted data is transmitted from 55 the transmitter 516 to the transceiver transmitter 516 for transmission over the fiber 110, 112 to the ONT/ONU 104, 106. Likewise, in the case of an ONT 104, or an ONU 106, downstream GTC frame formatted data is transmitted from the OLT 102 over the fiber 110, 112 into the transceiver 514 60 and is provided to the receiver **504**, and upstream GTC frame formatted data is transmitted from the transmitter **516** to the transceiver 516 for transmission over the fiber 110, 112 to the OLT **102**.

In particular, the GPON chip **404** further includes a controller **518**, which may be a downstream bandwidth (DSBW) controller for an OLT **102** or a transmission framing control-

**16**

ler for an ONT/ONU 104, 106, which interacts with the transmitter 506 and the internal processor 512 to control the transmissions of the transmitter 506. Generally, the controller 518 and the internal processor 512 enable various functions of the receiver 504 and the transmitter 506. For example, the internal processor 512 may be used to determine errors in the communication link between the OLT 102 and the ONT/ONU 104, 106, process or provide instructions related to PLOAM messages, perform functions related to PLOAM messages, allocate bandwidth, dynamic ranging and power transmission levels adjustment.

As further seen in FIG. 5A, the transmitter 506 is coupled to a scheduler 520, the controller 518 and the internal processor 512. The scheduler 520 may be a downstream transmission scheduler for an OLT 102 or an upstream transmission scheduler for an ONT/ONU 104, 106. Generally, the schedule 520 may be used for traffic shaping, bandwidth allocation and head-of-line (HOL) arbitration.

The distributed DMA interface 510 provides distributed management of the packet buffer (e.g., external memory 410). In particular, the distributed DMA interface 510 provides an interface to the sub-assembly 402, and may be implemented in any integrated circuit 404. Referring to FIG. 5B, the distributed DMA interface 510 includes an egress DMA engine **522** and an ingress DMA engine **524**. The egress DMA engine 522 and ingress DMA engine 524 are coupled to an SoC interface **526**. The egress DMA engine **522** is able to write data directly to the external memory 410 via the SoC interface **526**. The ingress DMA engine **524** is able to read data directly from the external memory 410 via the SoC interface **526**. As discussed above, the SoC processor **406** is responsible for non-time sensitive functions, the data of which is moved in and out of the memory 410 for processing by the SoC processor 406, and which may be provided from or provided to the integrated circuit **404** as needed. The DMA engines **522**, **524** thereby provide DMA processing via CPU 406 control of the sub-assembly 402.

In the context of the GPON chip 404 of FIGS. 5A-5B, data written by the egress DMA engine 522 is provided by the receiver 504 via a memory management unit (MMU) 528. The MMU 528 and egress DMA 522 are provided with the responsibility of moving the information to the external memory 410. As discussed in greater detail below, the MMU 528 performs descriptor pre-fetching for incoming data packets, maintains a lookup table to determine the destination location of a data packet in the memory 410 and generates events for reporting to the subassembly 402. Generally, the egress DMA engine 522 notifies the MMU 528 when it is ready to read data, and the MMU 528 manages access of the egress DMA engine 522 to the external memory 410 and provides the data to be written to the external memory 410.

Data read by the ingress DMA engine **524** is provided to the transmitter **506** via a descriptor and buffer management unit **530**. The descriptor and buffer management unit **530** may provide frame status data to the scheduler **520**, and may be controlled by the scheduler **520**. Generally, the descriptor and buffer management unit **530** manages access of the ingress DMA engine **524** to the external memory **410**. In particular, ingress DMA engine **524** notifies the descriptor and buffer management unit **530** when it is ready to receive data for transmission, and the descriptor and buffer management unit **530** notifies the ingress DMA engine **524** it is ready to receive the data.

The distributed DMA interface 510 is provided with sufficient memory within the GPON chip 404 to pass information in and out of the GPON chip to a larger external memory by virtue of the MMU 528 and the descriptor and buffer man-

agement unit **530**. In particular, the GPON chip **404** is able to pass data associated with memory-intensive and/or processor-intensive functions that have low time sensitive requirements (e.g., client payload data) to the external SoC processor **406** and memory **410**, and reserve the internal processor **512** for time-sensitive functions, such as processing upstream transmission frame and assembling downstream transmission frames.

FIG. 6 is a block diagram depicting an example of buffer management and handling of data packets between a receiver 10 504/transmitter 506 and a host, such as the subassembly 402. Although the following discusses buffer management and data packet handling in the context of passive optical network and in particular in the context of gigabit passive optical networks, the disclosure is not limited thereto and the buffer 15 management and data packet handling may be applicable to any situation in which descriptors are used to move data in and out of memory.

Referring to FIG. 6, an example of a transmit data path 602, a receive data path 604 and a control plane 606 are shown. 20 Generally, the transmit data path 602 and the receive data path 604 are described in the context of a hardware implementation, such as the distributed DMA interface 510, whereas the host is described in the context of a host memory, such as the external memory 410, one or more processors, such as the 25 SoC processor 406, and software associated therewith, such as a software driver. As discussed below, the buffer management and handling of data packets is performed as a series of writes, as opposed to a series of reads, between the host and the hardware in order to reduce latency for both transmission 30 and receiving operations. The control plane 606 may include many of the components shown in FIGS. 4A-4D, with the exception of the integrated circuit 404.

The transmit data path 602 may include function blocks including transmit queuing, transmit data, transmit cache and 35 transmit events. The transmit queuing includes data transmission caches (e.g. data FIFOs) and descriptor cache (e.g., FIFO cache). The transmit data block may manage data writing into the caches, and may include a DMA controller, data multiplexing and cache write controllers. The transmit cache block 40 may include a cache for each DMA engine with a different DMA engine for each type of data packet (e.g. each type of T-CON), although it is noted that only one DMA engine is shown in the transmit data path 602. The transmit of the block may include a transmit event generator.

The receive data path **604** may include function blocks including receive packet processor, receive filter, receive cache, and receive data control. The received packet processor block may classify and process received data packets based on the data packet Port-ID, as discussed further below. 50 The receive packet processor block may further generate events if the data packet contains errors, as also discussed further below. The receive filter block may receive the Port-ID filtering and lookup, and may contain a filter/lookup table and perform hashing and searching to identify the destination 55 associated with the Port-ID. The receive cache block may include a data reception cache (e.g. receive data FIFO) with control word. The receive data control block may include a receive data controller and manages descriptor caches and buffers (e.g., FIFO cache).

Referring to the transmit data path 602, a host software driver is aware of the number of data packets to be transmitted, and the host memory includes a descriptor ring having a descriptor for each data packet to be transmitted. In the case of large data packets, the data packet may be fragmented with 65 a descriptor associated with each data packet fragment. The host software is able to access the blocks shown in the trans-

**18**

mit and receive data paths **602**, **604** through a Gigabit bus or other bus interface, through an SoC bus (not shown) and to/from the blocks.

Knowing the number of data packets to be transmitted, the host 608 writes the descriptors of the corresponding data packets for transmission to a descriptor ring cache, shown in the transmit data path as a Fast In Fast Out (FIFO) cache. In particular, the host 608 pushes in the descriptors into the descriptor ring cache (see path 610). In one example, the host 608 may push in the entire descriptor ring, including all descriptors therein, associated with a particular data transmission queue, as discussed further below.

The DMA engine **524** reads the descriptors from the descriptor ring cache (see path **612**) and deciphers the location of the associated data packet in the host memory, the size of the data packet and any transmission priority associated with the data packet. For example, data packets that may require transmission in real-time, such as audio or video data packets, may receive a higher transmission priority than Internet data packets. Thereafter, the DMA engine **524** activates direct memory access to the host memory where the packet resides (see path **614**) and initiates a buffer transfer from the host **608** to a transmission data buffer, shown in FIG. **6** as a data FIFO.

The DMA **524** writes the requested data packet(s) to the transmission data buffer (see path **616**). The transition data buffer caches the data packet written from the host memory and processes (e.g. transmits) the cached data packet out of the data transmission buffer (see path **618**). In the event a data packet is received having a higher priority than a previous data packet being cached in the data transmission buffer, the hardware may interrupt transmission of the previous data packet, for example by implementing DMA arbitration. Alternatively, the data transmission buffer may be provided as multiple data transmission buffers, each associated with a particular priority such that a data packet is written to the appropriate data transmission buffer according to its transmission priority.

as to the status of the buffer (see path 621). In particular, after a data packet has been processed (e.g. transmitted) the DMA engine generates return pointers that are written to the host memory (see path 620). The return pointers indicate that the descriptor has been read from the descriptor ring cache and the corresponding data packet has been transmitted.

In order to reduce traffic between the hardware and the host 608, the return pointer may refer to the last descriptor read from the descriptor ring cache. Because descriptors within a descriptor ring are consecutive, and because the host 608 writes the descriptors to the descriptor ring cache, the host 608 is aware of the last descriptor that may be read from the descriptor ring cache. As a result, the host 608 is able to read the return pointer referring to the last descriptor read from the descriptor ring cache and understand that all descriptors have been read from the descriptor ring cache, and the host understand exactly how many data packets have been processed as a result. Accordingly, the host 608 may push new descriptors into the descriptor ring cache. Alternatively, a return pointer may refer to a batch of descriptors or return pointers for each descriptor may be batched and returned to the host 608. As discussed further below, events may be generated by the hardware, including an event to write the return pointers to the host **608**.

Referring to the receive data path 604, the host pushes descriptors of a descriptor ring from the host memory into a descriptor ring cache (see path 622), shown in the received data path as a FIFO cache. In one example, the receive data

path 604 may include several descriptor ring caches, each corresponding to a different transmission rate (e.g., different bandwidths), in order to accommodate data packets having different transmission requirements (e.g., priorities). Each descriptor ring cache may then correspond to a receive queue 5 within the host memory.

Upon receiving a data packet (see path **624**), the hardware parses the header of the data packet (see path 626) in order to determine a destination within the host memory for the data packet (e.g., a data reception queue). In the case of multiple 10 descriptor ring caches, the hardware may also determine the appropriate descriptor ring cache for the data packet based upon its destination within the host memory. In particular, a Port identification (e.g., Port ID 274) may be read from the header and a lookup table may be utilized to match the Port 15 identification with the data packet's destination (e.g., Queue ID), based on the assumption the destination is able to receive the data packet. Once the destination has been determined, the destination data along with the header are cached in the data reception buffer (see path 628). In one example, the destination data and the header are cached in the data reception buffer simultaneously with the data packet received along path 624.

The data reception cache periodically updates the DMA engine 522 with its status (see path 631). The DMA engine 522 will read a descriptor from the descriptor ring cache (see path 630). According to the descriptor, the DMA engine 522 reads the data from the data reception buffer (see path 632), and the data packet is written to the host memory according to its destination via control of the DMA engine 522 direct memory access (see path 634). Once the data has been written to the host memory, the DMA engine 522 triggers an event to writes a return pointer to the host 608 indicating that the data packet has been written to the host memory (see path 636). As a result, the host 608 does not need to read the data from the data reception buffer, but may be notified once the data has been written to the host memory.

At the same time the data packet is written to the host memory, the DMA engine 522 may check the integrity of the packet by including a CRC block reading a checksum value (e.g. CRC) from the header of the packet (see path 631). If the DMA engine 522 determines that there is anything wrong with the data packet, an event may be generated and sent to the host 608. Accordingly, the host 608 may be informed of any problems associated with the data packet as the data packet is received and they process the data packet accordingly without 45 being burdened with the processing requirements associated with evaluating the integrity of the data packet.

As is known, GPON utilizes different bandwidth requirements. A standardized system generally includes a normal line rates (downstream/upstream) according to the following 50 table:

| Downstream      | Upstream      |

|-----------------|---------------|

| 1244.16 Mbits/s | 155.52 bit/s  |

| 1244.16 Mbits/s | 622.08 bit/s  |

| 1244.16 Mbits/s | 1244.16 bit/s |

| 2488.32 Mbits/s | 155.52 bit/s  |

| 2488.32 Mbits/s | 622.08 bit/s  |

| 2488.32 Mbits/s | 1244.16 bit/s |

| 2488.32 Mbits/s | 2488.32 bit/s |

At a 2.448G data rate, back-to-back 64-byte packets arrive every 221.83 ns, as shown in the following equation:

With host logic running at 155.5 MHz, there are 34 cycles for each packet to be processed at 16-bit bus width. In order to match an SoC configuration, 32-bit bus, the data packets may be packed into 32-bit before storing in the data reception cache. As a result, regardless the bus width, there are plenty of cycles for the packet header parser show in FIG. 6 to do filtering and lookup and then write back to data reception cache's control word. For upstream burst transmissions, the same bandwidth may be met with a 32-bit cache running at 155.5 MHz.