### US008310044B2

# (12) United States Patent

## **Takahashi**

# (10) Patent No.: US 8,310,044 B2

# (45) Date of Patent:

# Nov. 13, 2012

# (54) SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME

(75) Inventor: Noriyuki Takahashi, Nanae (JP)

(73) Assignee: Renesas Electronics Corporation,

Kawasaki-shi (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 12/962,625

(22) Filed: **Dec. 7, 2010**

## (65) Prior Publication Data

US 2011/0133329 A1 Jun. 9, 2011

### (30) Foreign Application Priority Data

(51) **Int. Cl.**

**H01L 23/34** (2006.01) **H01L 21/60** (2006.01)

See application file for complete search history.

### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,583,377 A * | 12/1996 | Higgins, III | 257/707 |

|---------------|---------|--------------|---------|

| 5,991,156 A * | 11/1999 | Bond et al   | 361/707 |

| 6,683,795 B1* | 1/2004  | Yoo          | 361/816 |

#### FOREIGN PATENT DOCUMENTS

JP 11-163230 A 6/1999

\* cited by examiner

Primary Examiner — Peniel M Gumedzoe

(74) Attorney, Agent, or Firm — Miles & Stockbridge P.C.

### (57) ABSTRACT

The heat-release properties of semiconductor device are to be improved and the reliability thereof is to be improved.

The semiconductor device has a wiring substrate, a heatreleasing plate having a convex part inserted into a throughhole of the wiring substrate, a semiconductor chip mounted over the convex part of the heat-releasing plate, and a bonding wire coupling an electrode pad of the semiconductor chip with a bonding lead of the wiring substrate, and further has a sealing portion covering a portion of an upper surface of the wiring substrate, a sealing portion covering a portion of a lower surface of the wiring substrate including the semiconductor chip and the bonding wire, and a solder ball placed over a lower surface of the wiring substrate. In manufacturing the semiconductor device, the heat-releasing plate is positioned at the upper surface side of the wiring substrate such that the convex part is positioned in the through-hole, and a groove in the main surface of the convex part is forcibly widened to swage the convex part and to be fixed to the wiring substrate.

# 19 Claims, 64 Drawing Sheets

2 2b

$\mathcal{C}$

2

F/G. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 8

F/G. 9

FIG. 10

FIG. 11

F/G. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 16

F/G. 17

F/G. 18

28

FIG. 22

FIG. 23

FIG. 24

FIG. 25

FIG. 26

FIG. 27

FIG. 28

FIG. 29

FIG. 30

FIG. 31

FIG. 32

FIG. 33

FIG. 34

FIG. 35

FIG. 36

FIG. 37

FIG. 38

FIG. 39

FIG. 40

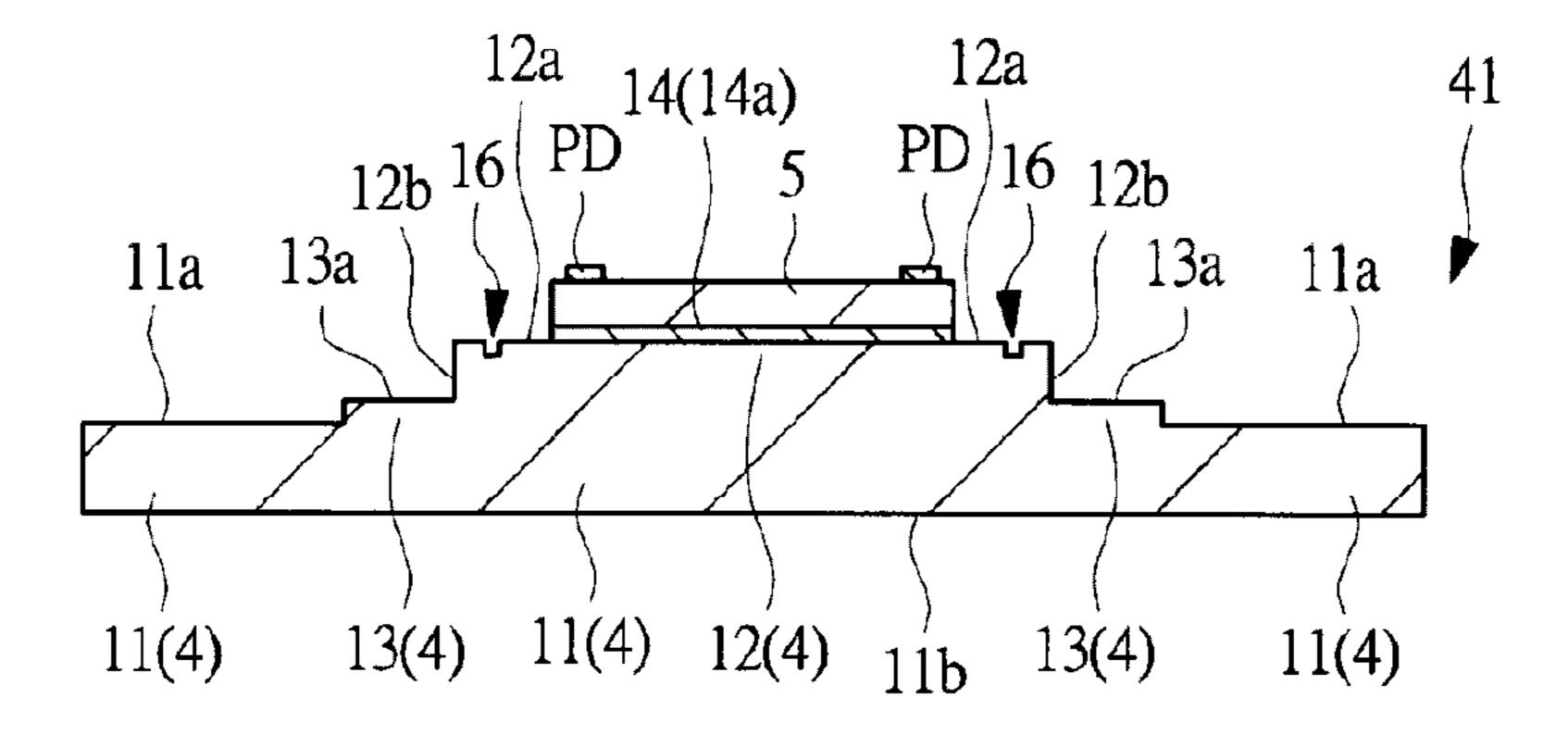

FIG. 41

FIG. 42

FIG. 43

FIG. 44

FIG. 45

FIG. 46

FIG. 47

Nov. 13, 2012

FIG. 48

FIG. 49

FIG. 50

FIG. 51

FIG. 52

FIG. 53

FIG. 54

Nov. 13, 2012

FIG. 55

31a 31b 31 4 31 4 31 4 --31 4 31 31

57

FIG. 58

FIG. 59

F/G. 60

FIG. 61

FIG. 62

FIG. 63

FIG. 64

FIG. 65

Nov. 13, 2012

FIG. 66

FIG. 67

FIG. 68

FIG. 69

FIG. 70

FIG. 71

FIG. 72

FIG. 73

FIG. 74

FIG. 75

F/G. 76

FIG. 77

F/G. 78

FIG. 79

FIG. 80

FIG 81

FIG. 83

FIG. 84

Nov. 13, 2012

FIG. 85

F/G. 86

F/G. 87

F/G. 88

FIG. 89

# SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME

## CROSS-REFERENCE TO RELATED APPLICATION

The disclosure of Japanese Patent Application No. 2009-278214 filed on Dec. 8, 2009 including the specification, drawings and abstract is incorporated herein by reference in its entirety.

#### BACKGROUND OF THE INVENTION

The present invention relates to a semiconductor device and a method of manufacturing thereof, and in particular, to a technology effective for a highly heat-releasing semiconductor package and a method of manufacturing thereof.

A BGA package type semiconductor device is manufactured by mounting a semiconductor chip over a wiring substrate, by coupling electrically an electrode of the semiconductor chip with a coupling terminal of the wiring substrate through the use of a bonding wire, by sealing the semiconductor chip and the bonding wire with a resin, and then by connecting a solder ball with the rear surface of the wiring 25 substrate.

Japanese Patent Laid-Open No. 1999-163230 (Patent Document 1) describes the technology of semiconductor device in which a semiconductor chip is placed in a facedown position within an opening of the package substrate, the rear surface of the semiconductor chip and the rear surface of the package substrate are brought into contact with a thermal-conducting member, and the bonding pad over the semiconductor chip is coupled with an external terminal of the package substrate.

#### SUMMARY OF THE INVENTION

The study of the inventor of the present invention derived the following findings.

A semiconductor device which uses a wiring substrate having an insulation layer and mounts a semiconductor chip over the wiring substrate has lower heat-release properties than that of a semiconductor device which uses a lead frame made of metal and mounts a semiconductor chip over the lead 45 frame.

Accordingly, as a measure against heat release from a semiconductor device using a wiring substrate, there can be considered a method of locating an external terminal (solder bump) for heat release over the mounting surface of the wir- 50 ing substrate, and of releasing the heat from the semiconductor device to the mounting substrate (mounting substrate on which the semiconductor device is mounted) via the heat-releasing external terminal.

In the case of that type of semiconductor device, however, 55 there is required, also at the side of the mounting substrate, placing a bump land (electrode pad) coupled with the heat-releasing external terminal directly thereon, which lowers the freedom of wiring layout over the mounting substrate.

Consequently, the inventor of the present invention has 60 studied the fixing of a heat-releasing plate made of metal as the thermal-conducting member to the wiring substrate, as described in Patent Document 1, and the mounting of the semiconductor chip over the heat-releasing plate. The structure of Patent Document 1 would allow not only the improvement of the heat-release properties, but also the additional improvement of the heat-release properties by connecting

2

other heat-releasing member (heat sink) with the heat-releasing plate after mounting the semiconductor device over the mounting substrate.

However, according to the method of attaching the heatreleasing plate to the wiring substrate as described in Patent Document 1, it was found that the heat-releasing plate is separated from the wiring substrate in some cases owing to the heat generated in mounting the semiconductor chip over the heat-releasing plate or to the effect of load. A cause of the phenomenon is the difference in the thermal expansion coefficient between the wiring substrate and the heat-releasing plate. Thermal effect causes expansion and shrinkage in each of the wiring substrate and the heat-releasing plate. Since the magnitude of expansion and of shrinkage differ in each of the 15 wiring substrate and the heat-releasing plate, the stress is focused on the adhesion layer to cause fracture at the adhesion layer. In inserting the protruded chip-mounting part (the chipmounting part of the heat-releasing plate) into the throughhole of the wiring substrate, a gap is preliminarily formed between the side surface of the chip-mounting part and the inside wall of the through-hole of the wiring substrate for the convenience of insertion of the heat-releasing plate into the wiring substrate, which weakens the holding force of heatreleasing plate.

The present invention has been made in view of the above circumstances and provides a technology capable of improving the heat-releasing characteristics of semiconductor device.

Furthermore, the present invention has been made in view of the above circumstances and provides a technology capable of improving the reliability of semiconductor device capable of improving the reliability of semiconductor device.

The other purposes and the new feature of the present invention will become clear from the description of the present specification and the accompanying drawings.

The following explains briefly the outline of a typical invention among the inventions disclosed in the present application.

According to a method of manufacturing semiconductor device in a typical embodiment, the heat-releasing plate is positioned over the first main surface of the wiring substrate so that the side surface of the convex part of the heat-releasing plate faces the inside wall of the through-hole of the wiring substrate, and then the groove formed in the main surface of the convex part of the heat-releasing plate is forcibly widened to bring a portion of the side surface of the convex part of the heat-releasing plate to contact with the inside wall of the through-hole of the wiring substrate, and to thereby fix the heat-releasing plate to the wiring substrate.

The following explains briefly the effect acquired by the typical invention among the inventions disclosed in the present application.

The typical embodiments can improve the heat-release properties of semiconductor device.

Furthermore, the typical embodiments can improve the reliability of semiconductor device.

#### BRIEF DESCRIPTION OF THE DRAWINGS

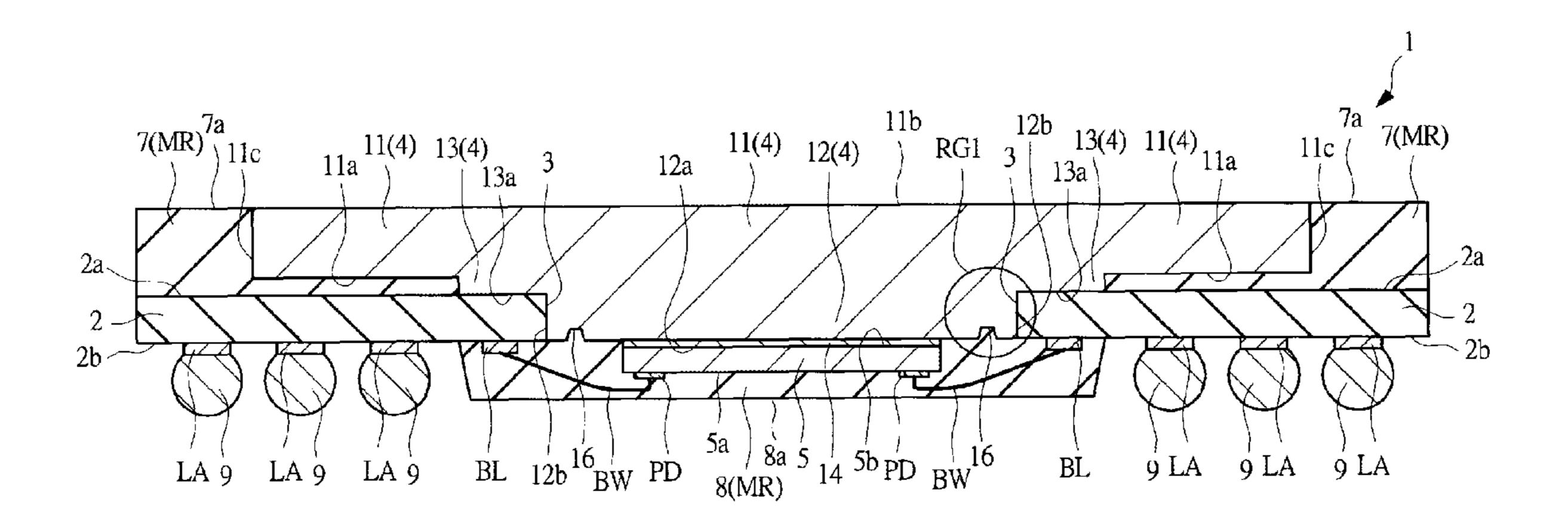

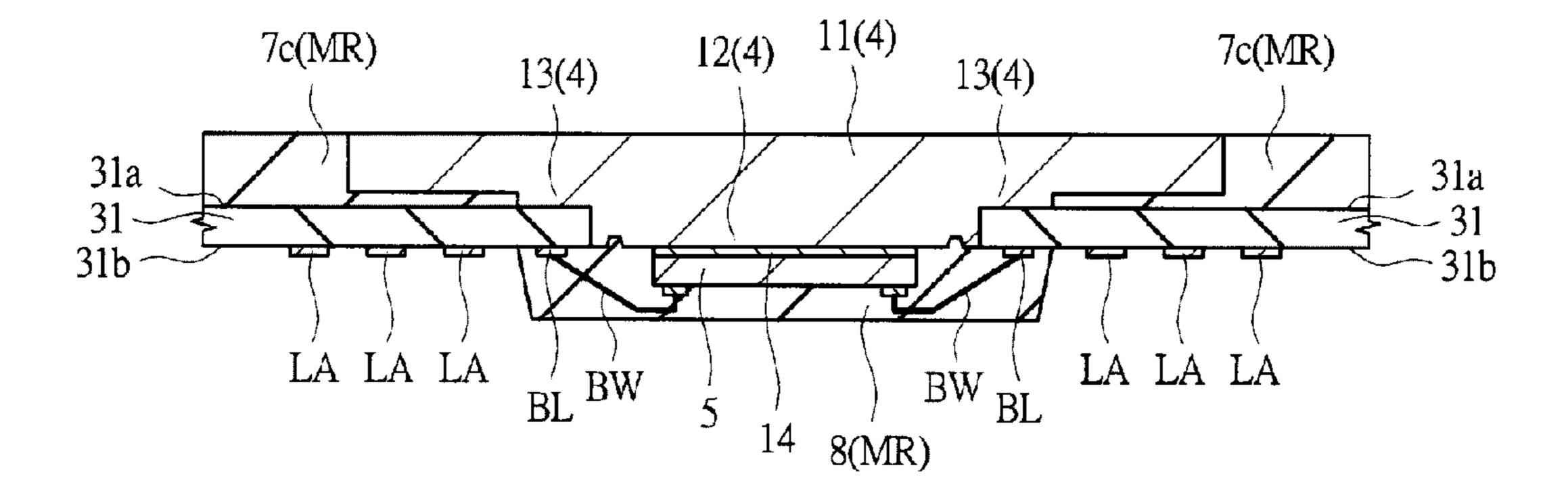

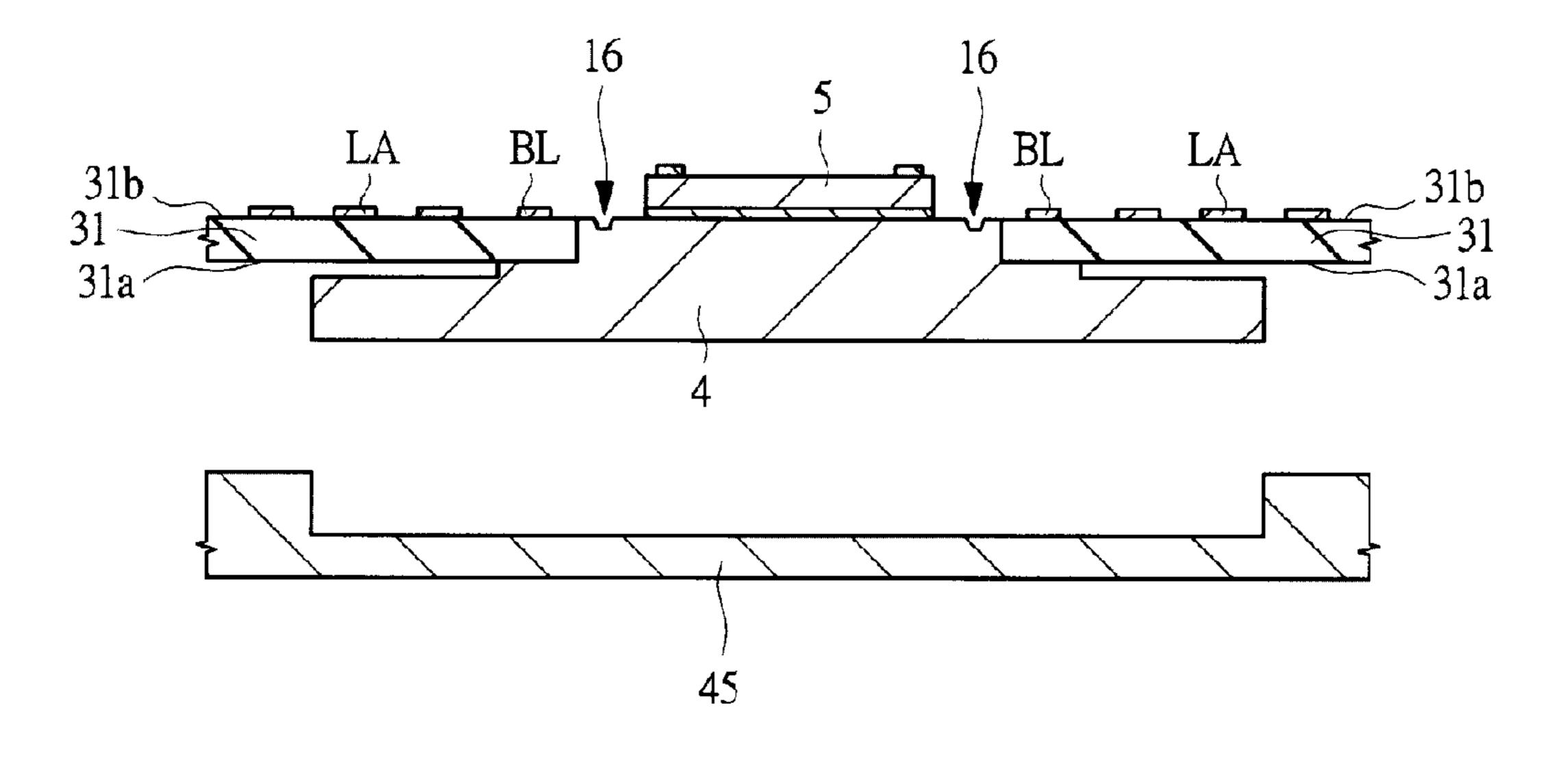

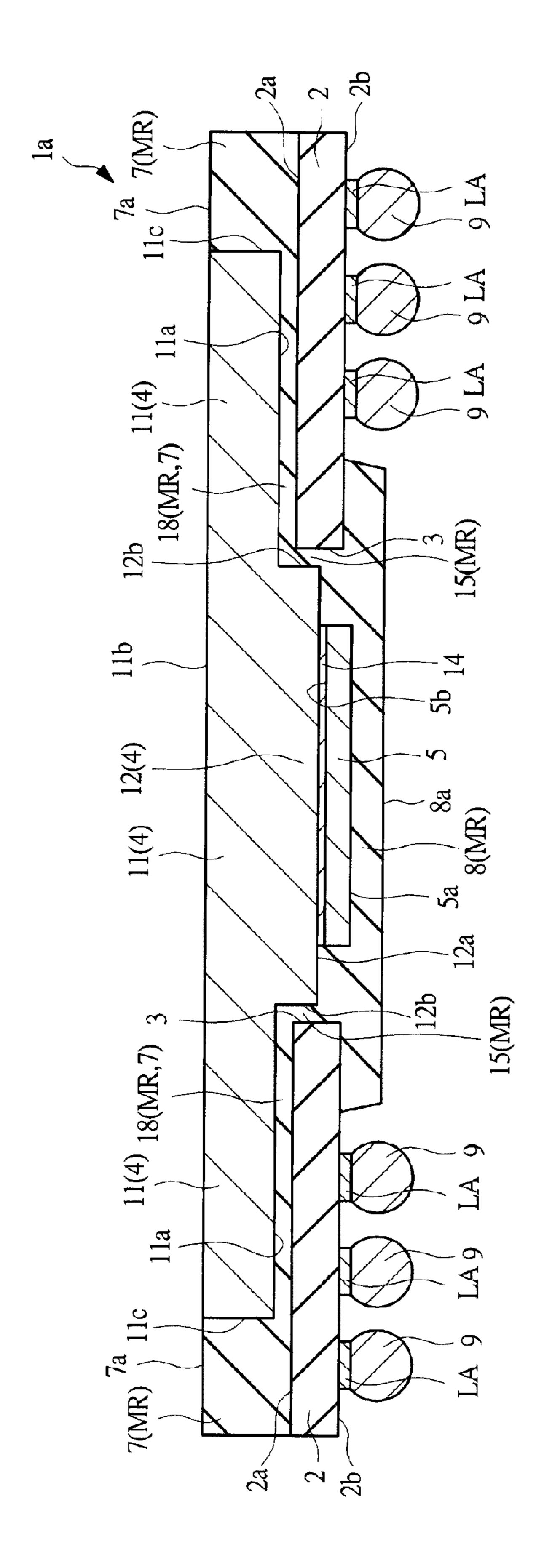

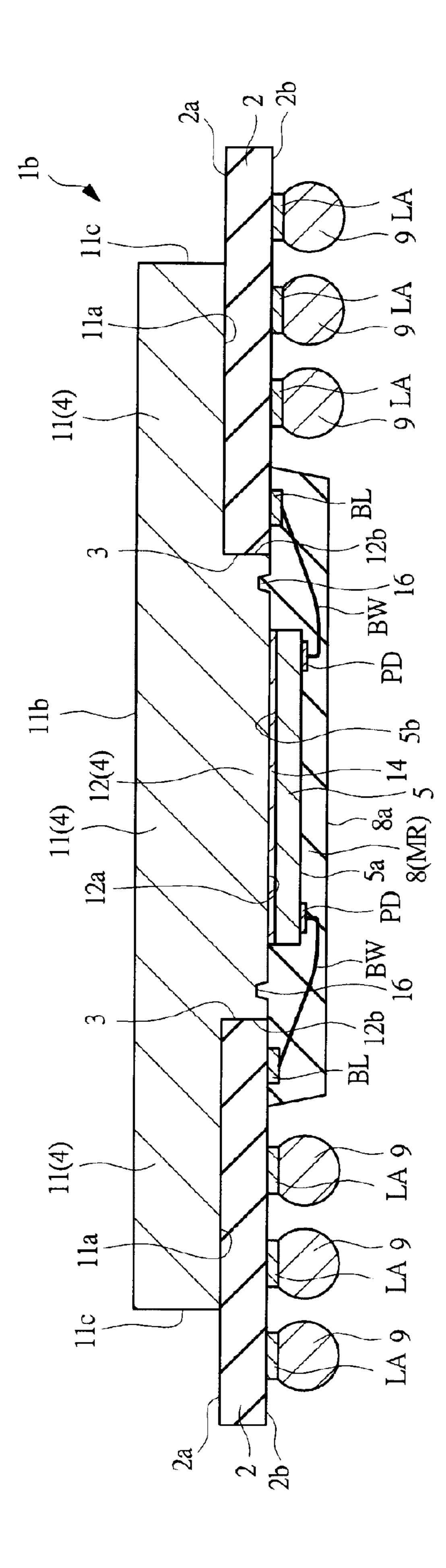

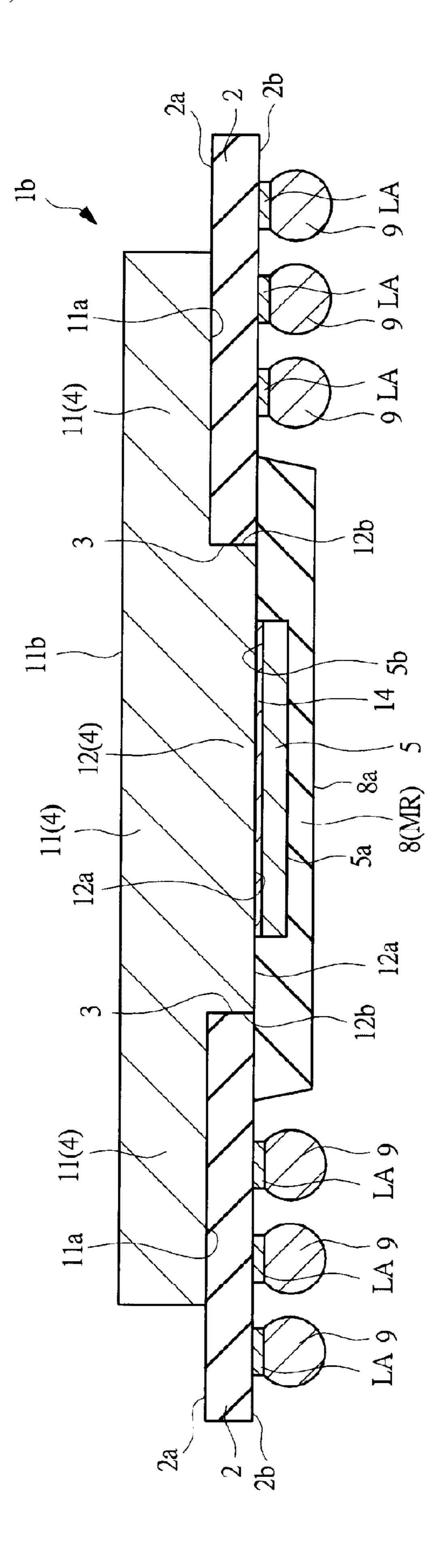

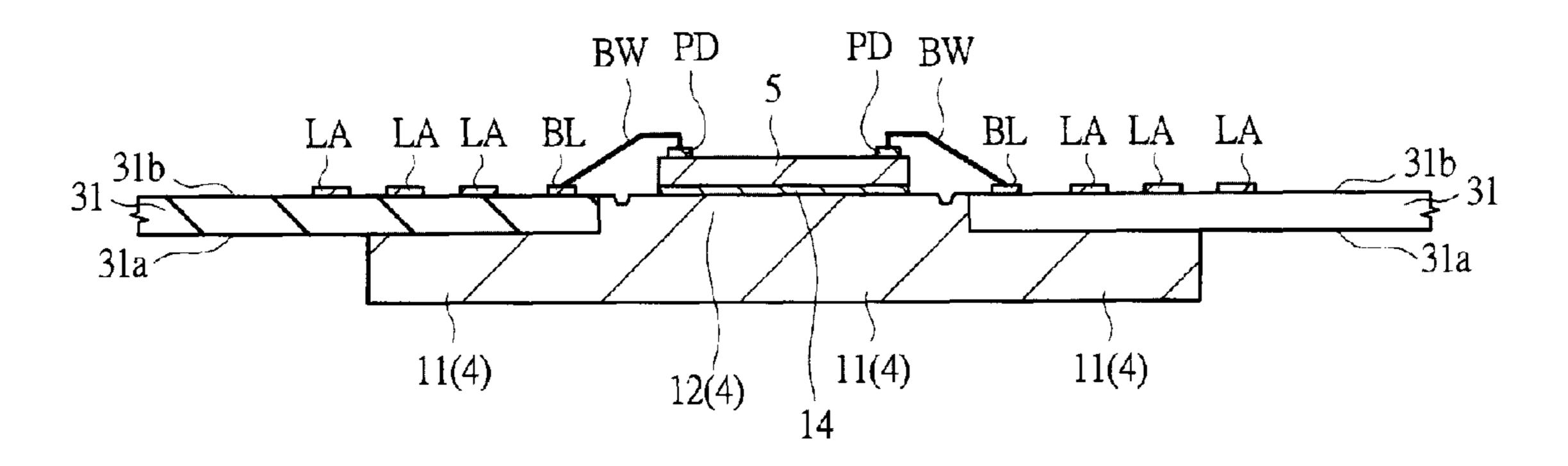

FIG. 1 is a cross-sectional view of a semiconductor device in an embodiment of the present invention;

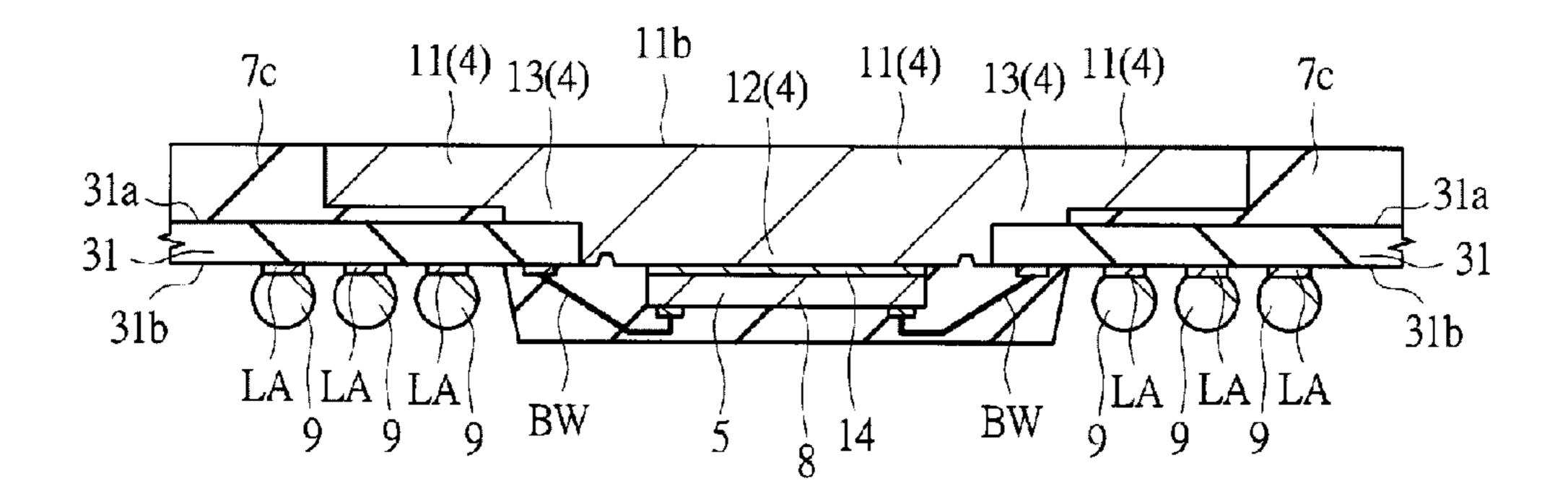

FIG. 2 is a cross-sectional view of a semiconductor device in an embodiment of the present invention;

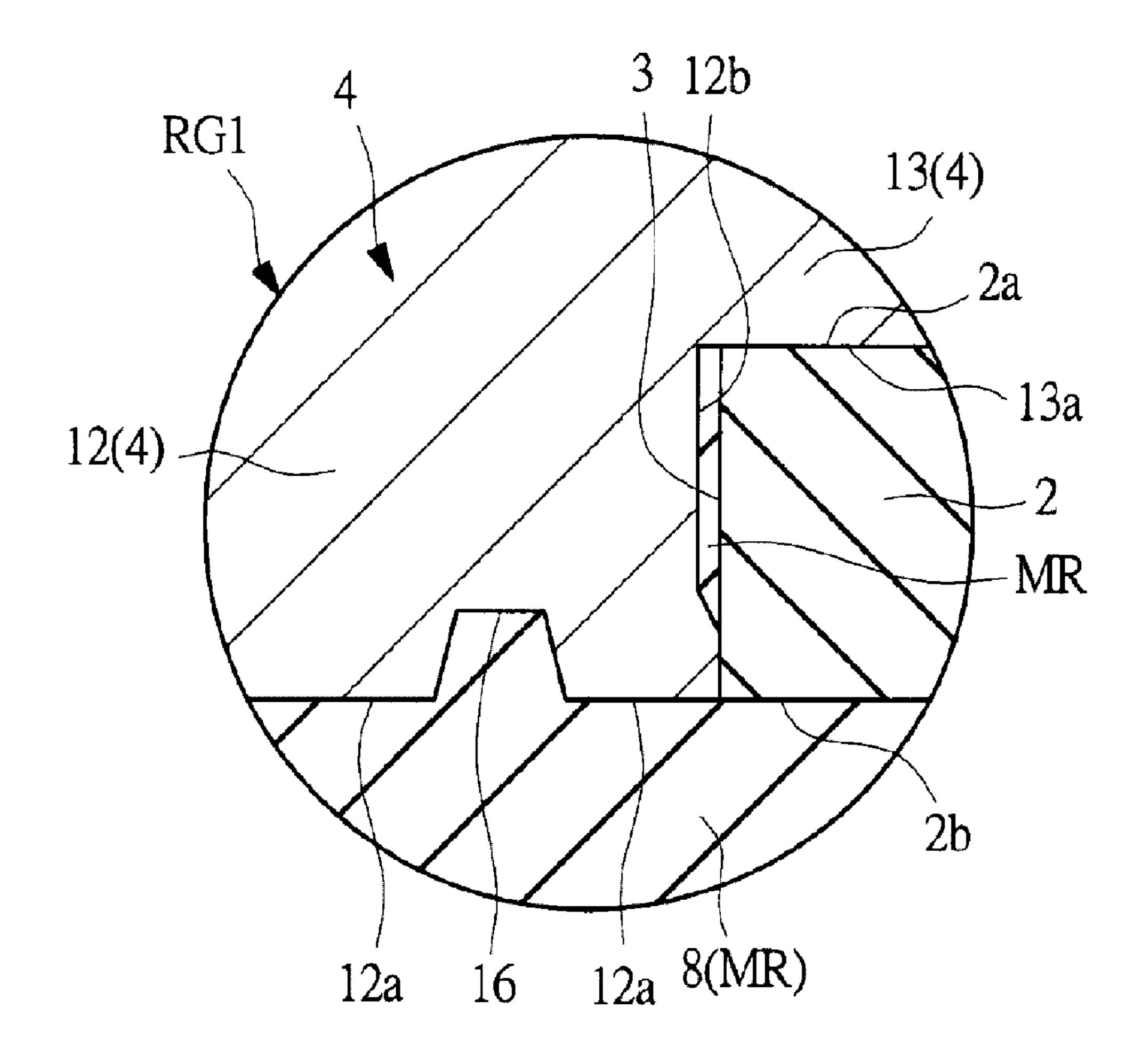

FIG. 3 is a main-part cross-sectional view of a semiconductor device in an embodiment of the present invention;

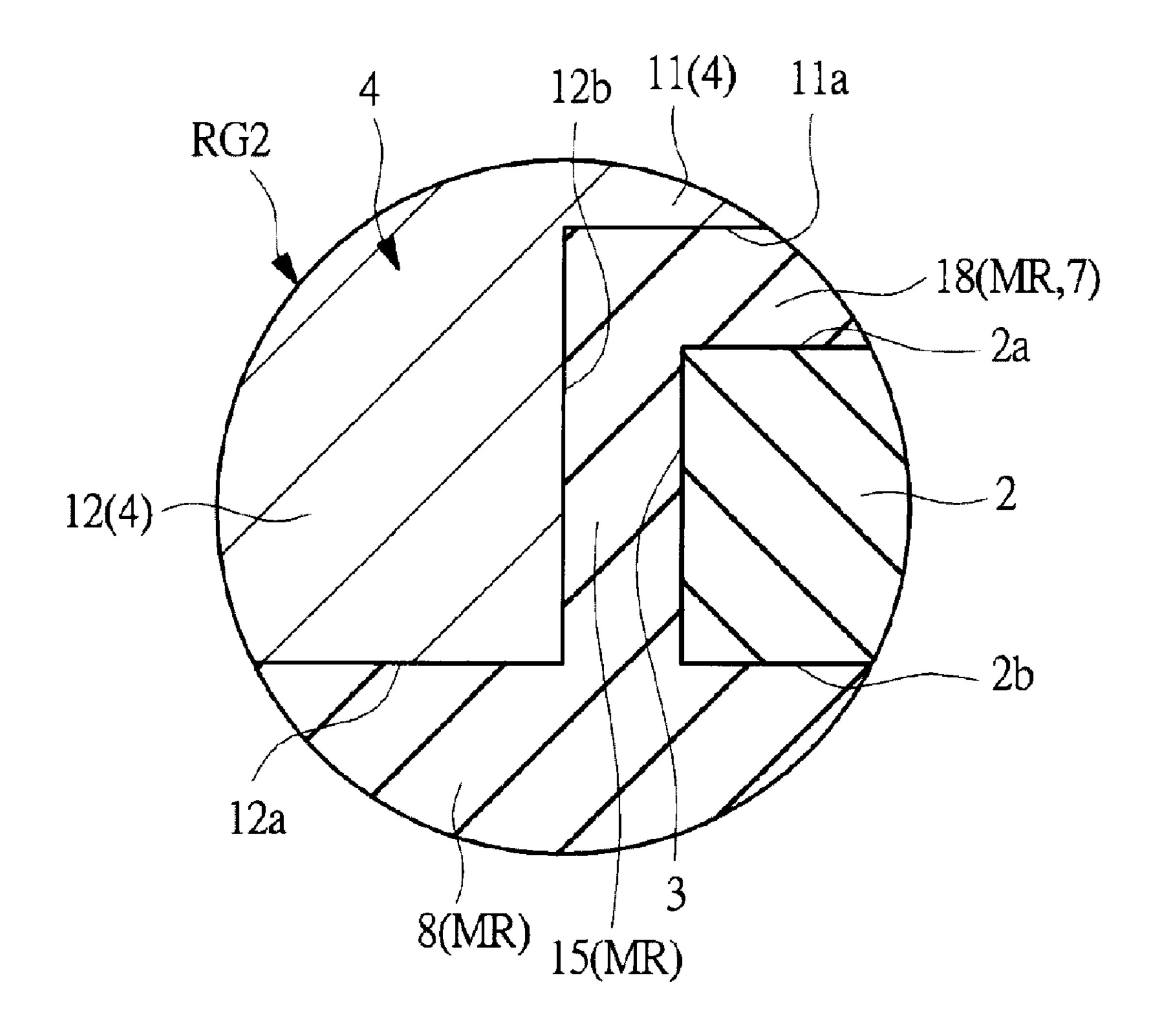

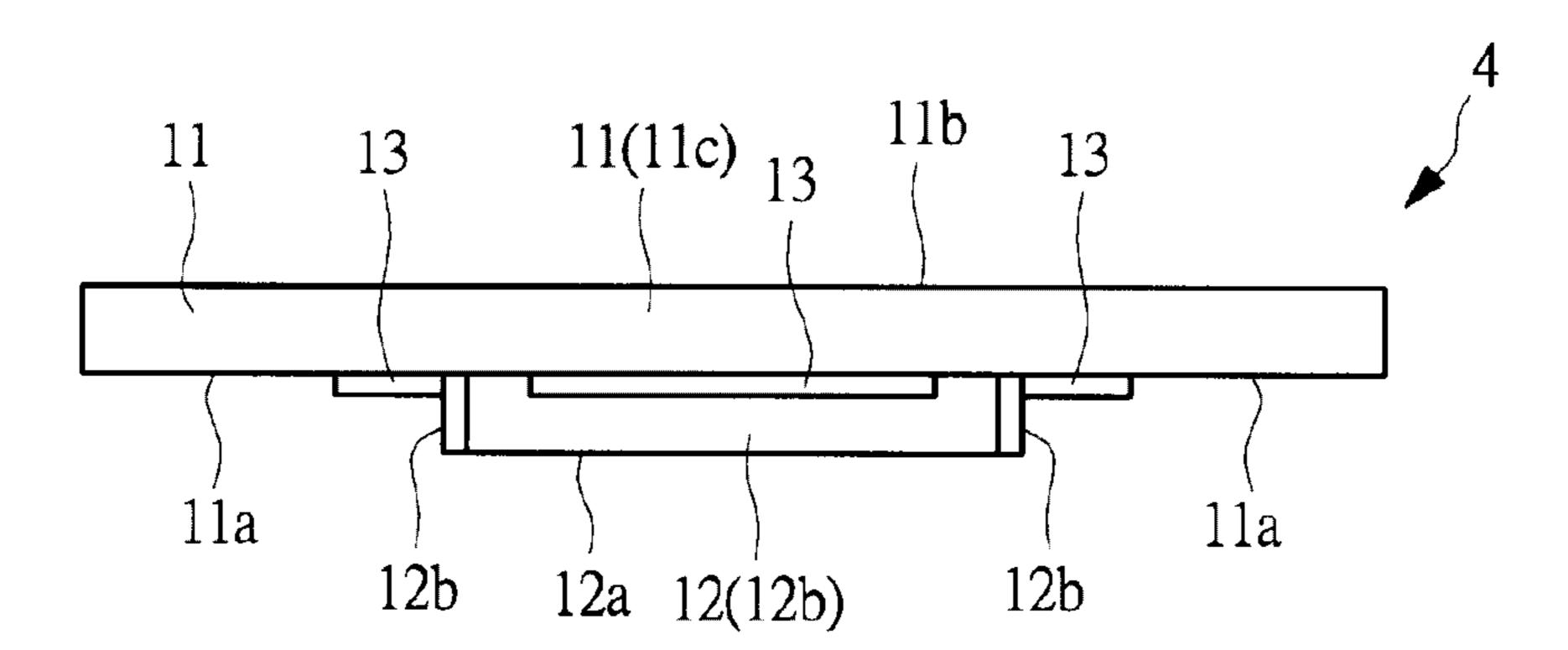

FIG. 4 is a main-part cross-sectional view of a semiconductor device in an embodiment of the present invention;

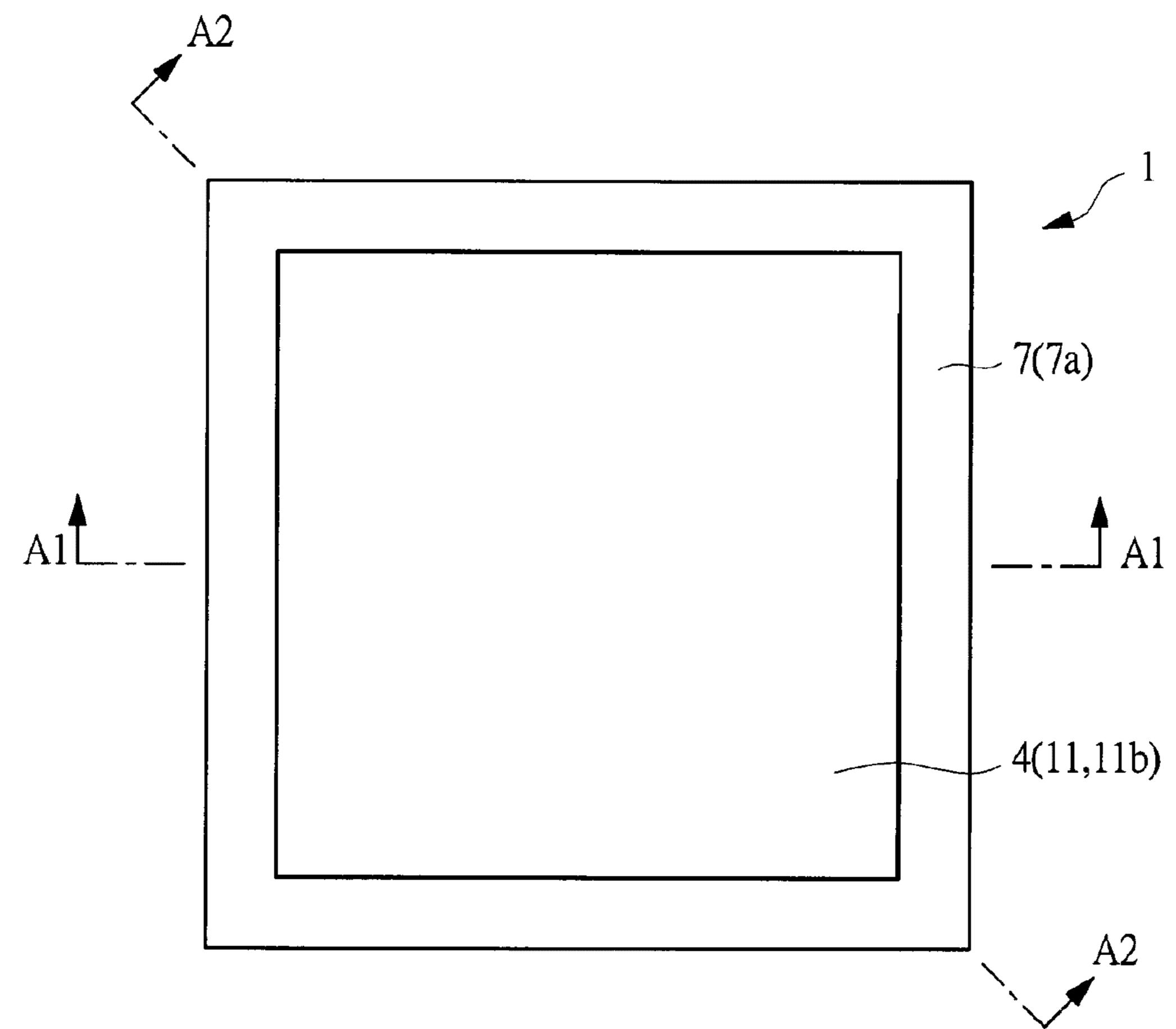

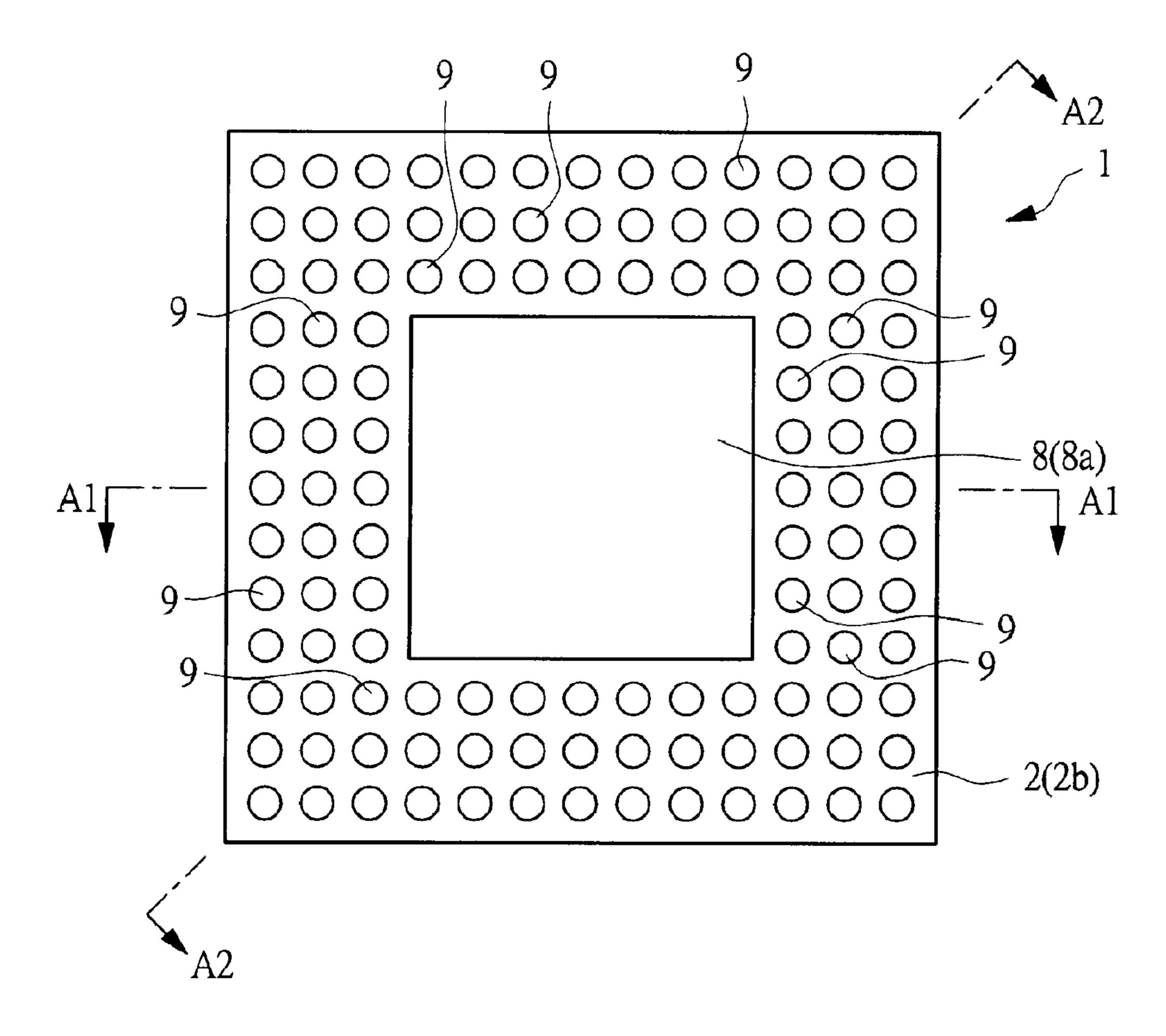

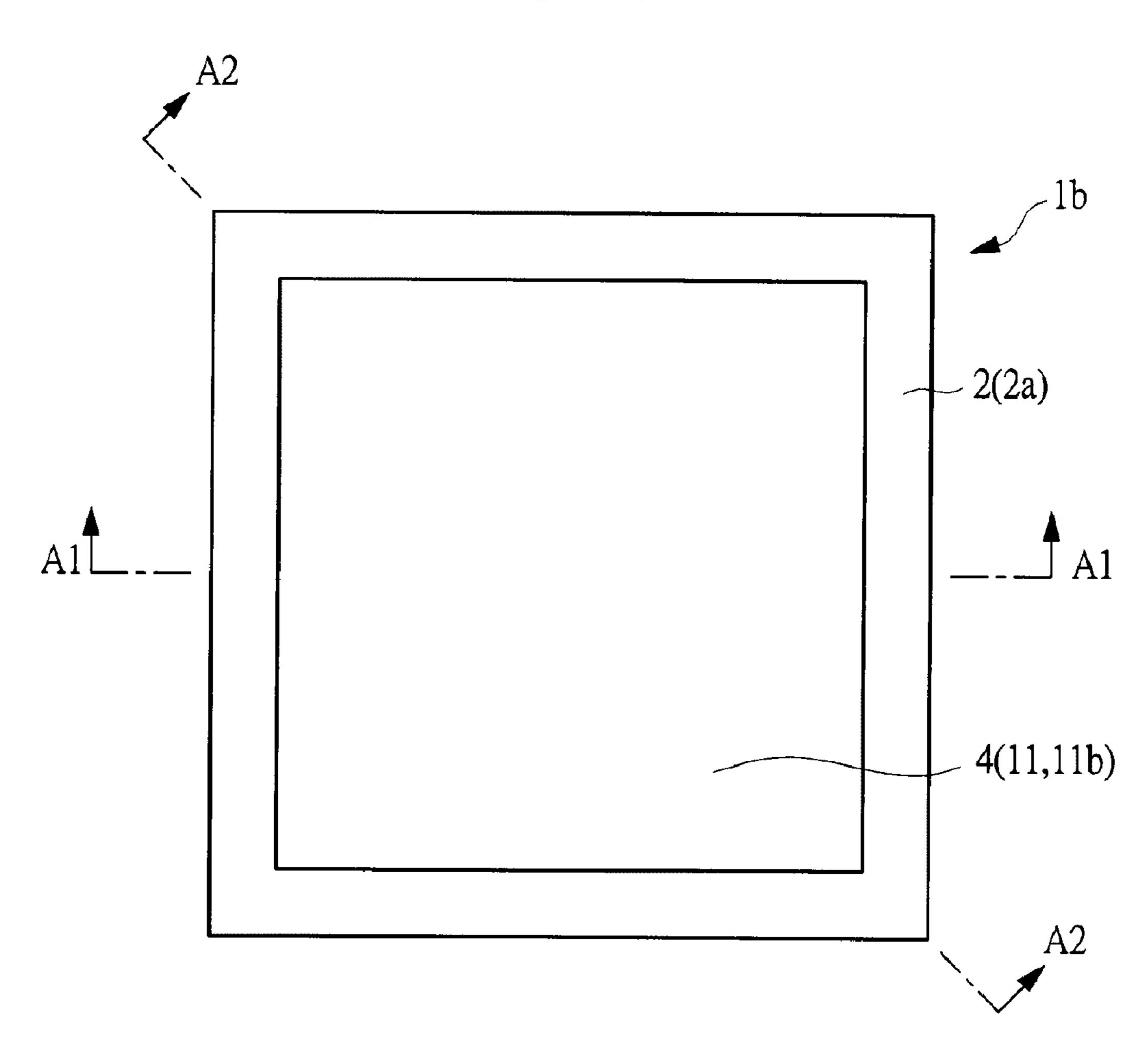

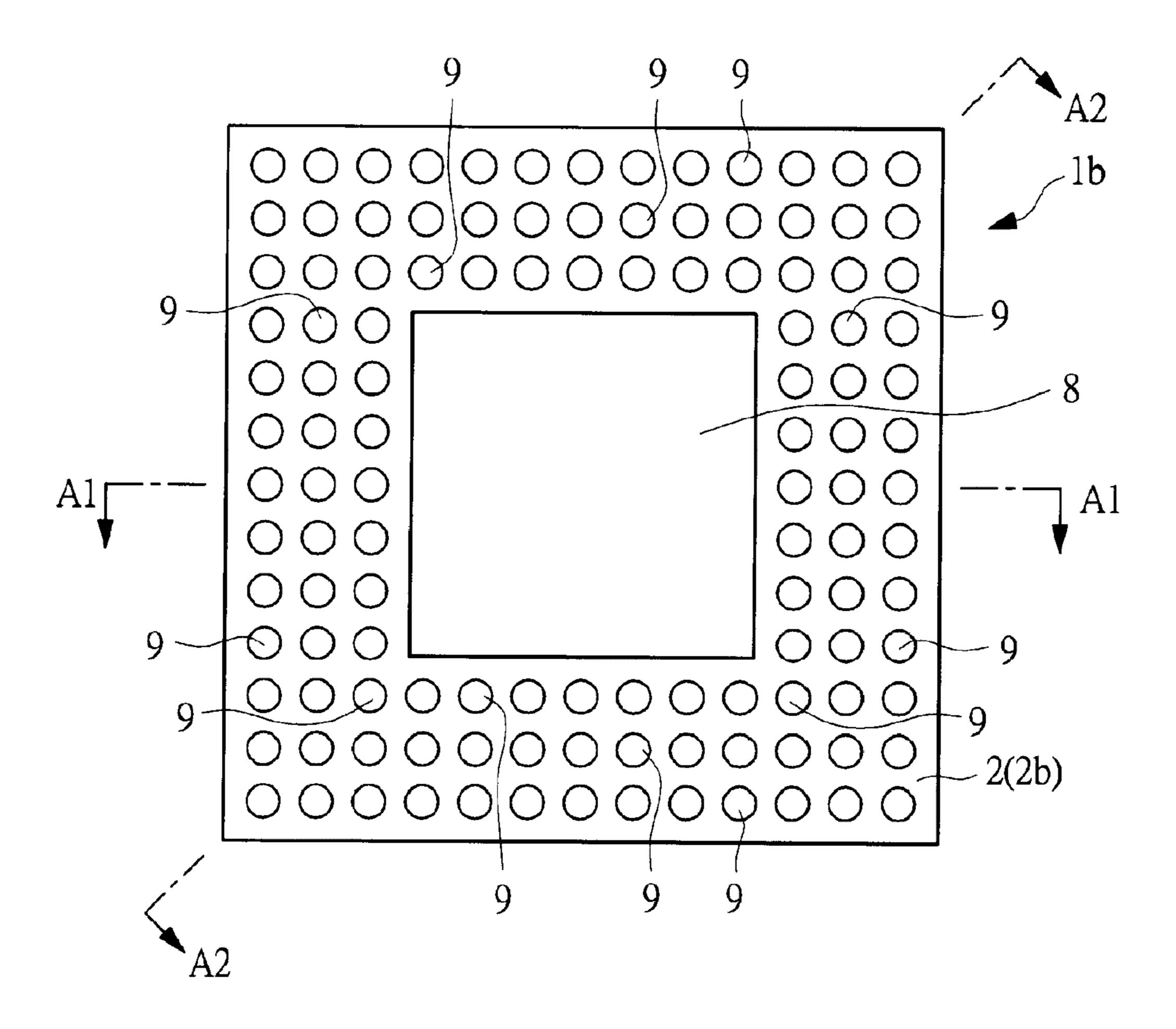

- FIG. 5 is a top view of a semiconductor device in an embodiment of the present invention;

- FIG. **6** is a bottom view of a semiconductor device in an embodiment of the present invention;

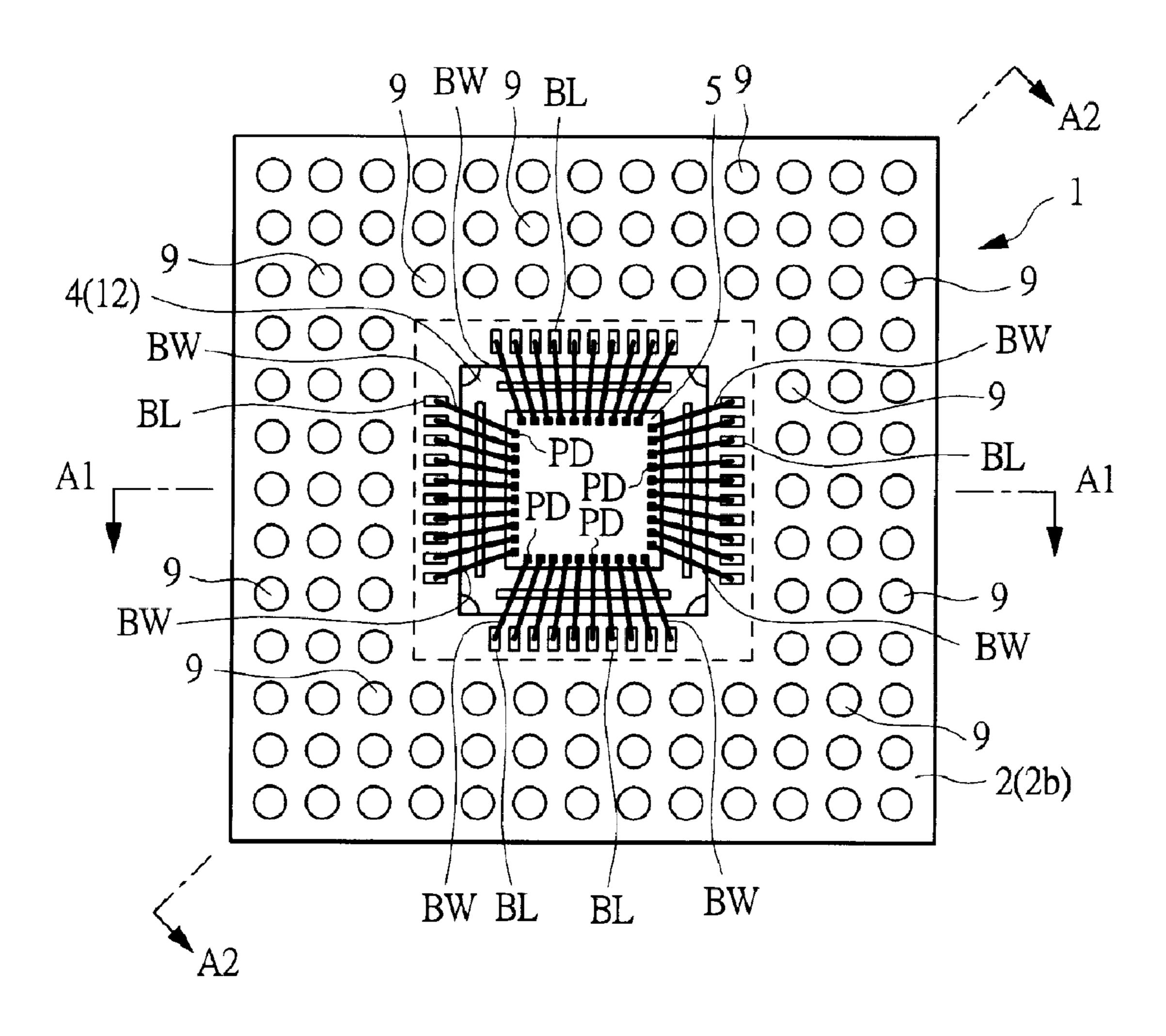

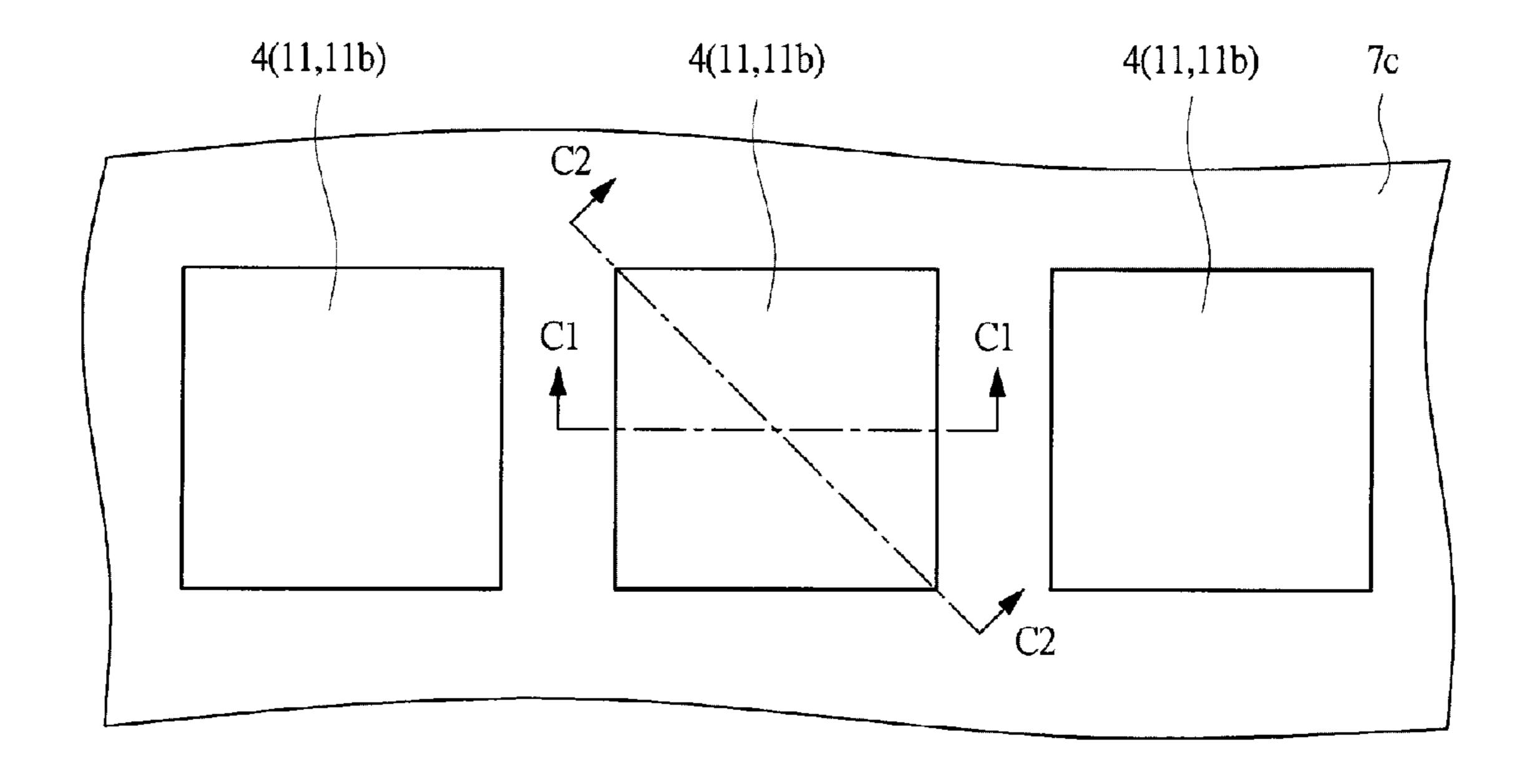

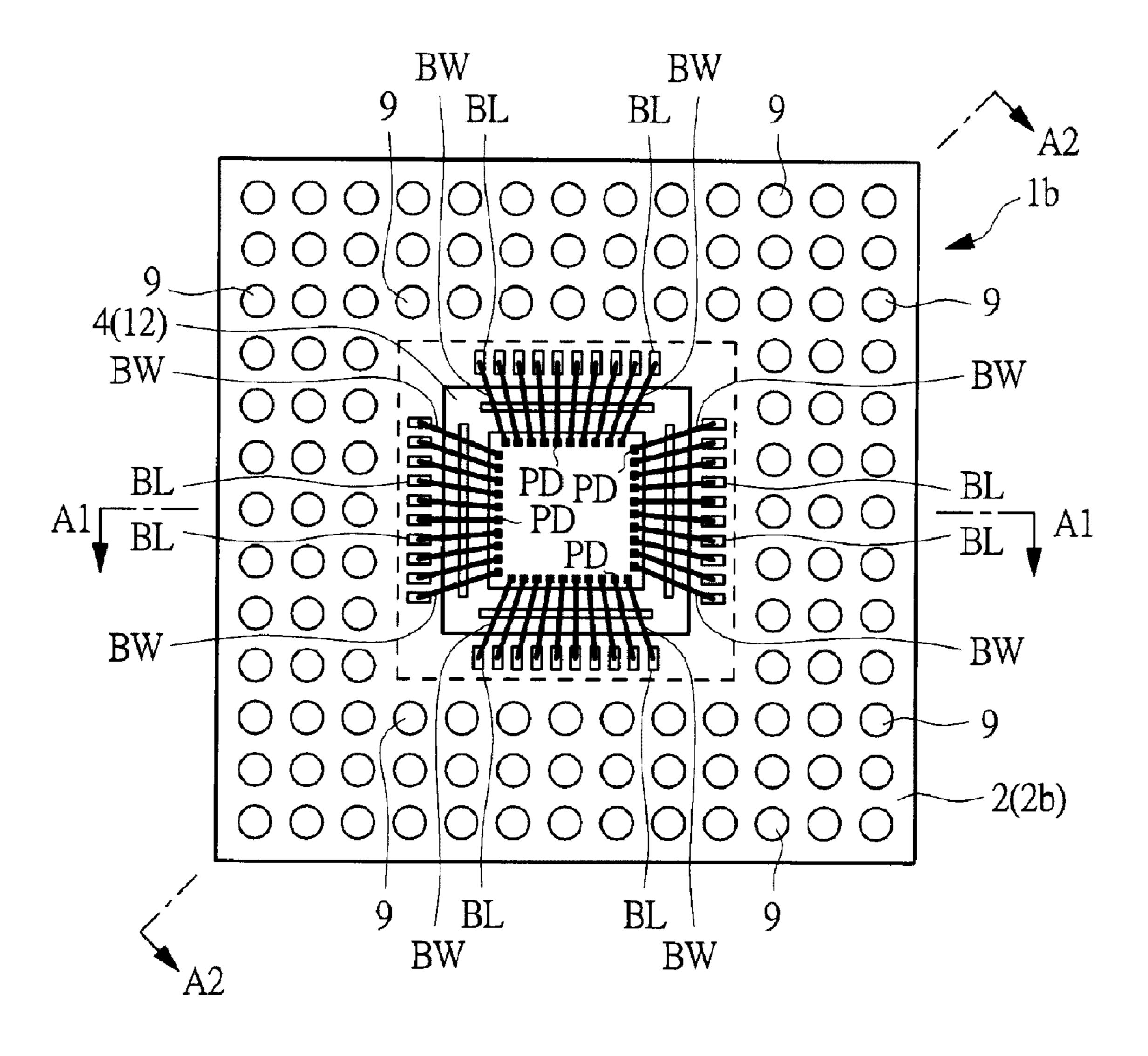

- FIG. 7 is a plane perspective view (top view) of a semicon- 5 ductor device in an embodiment of the present invention;

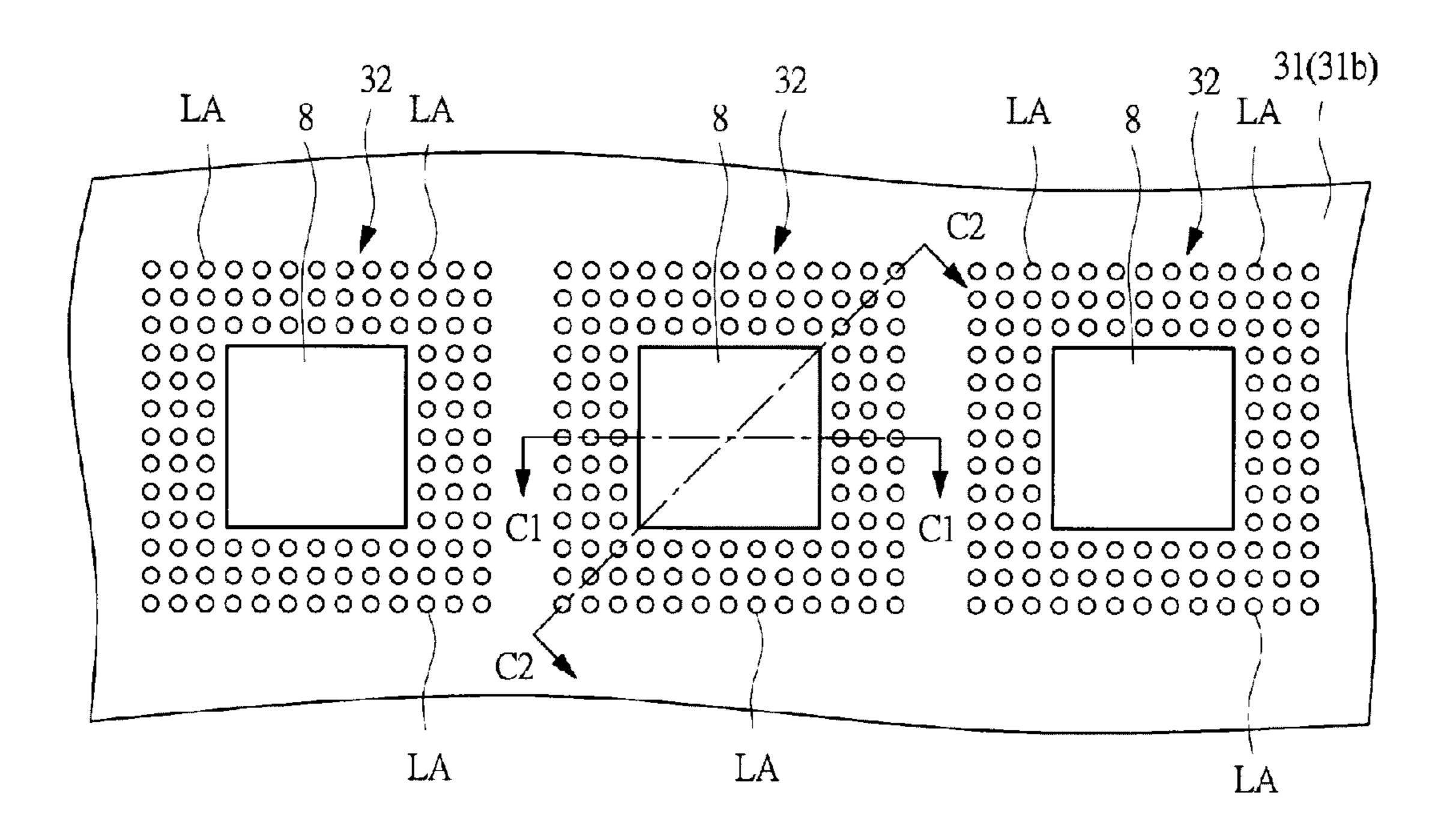

- FIG. 8 is a plane perspective view (bottom view) of a semiconductor device in an embodiment of the present invention;

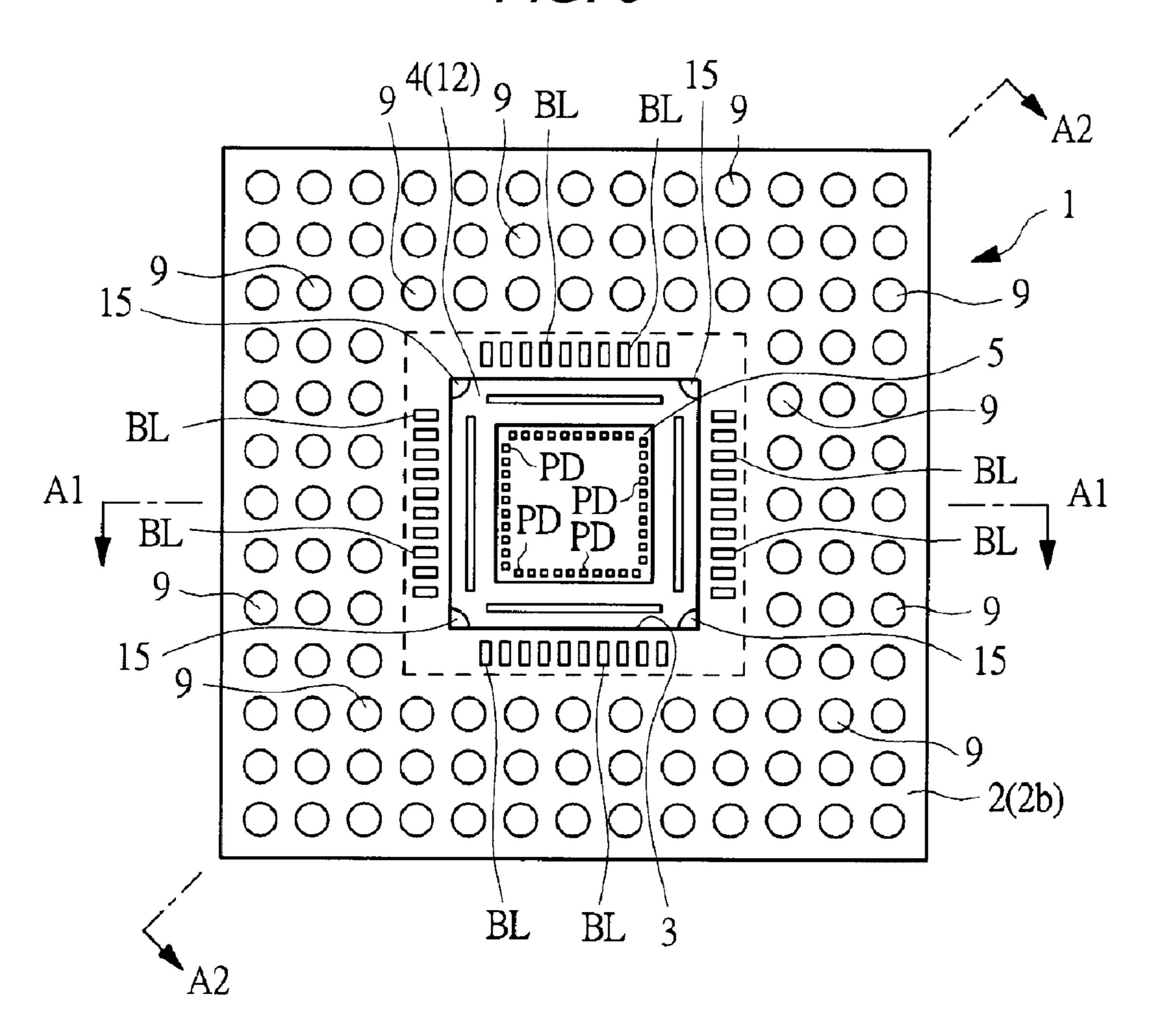

- FIG. 9 is a plane perspective view (bottom view) of a 10 semiconductor device in an embodiment of the present invention;

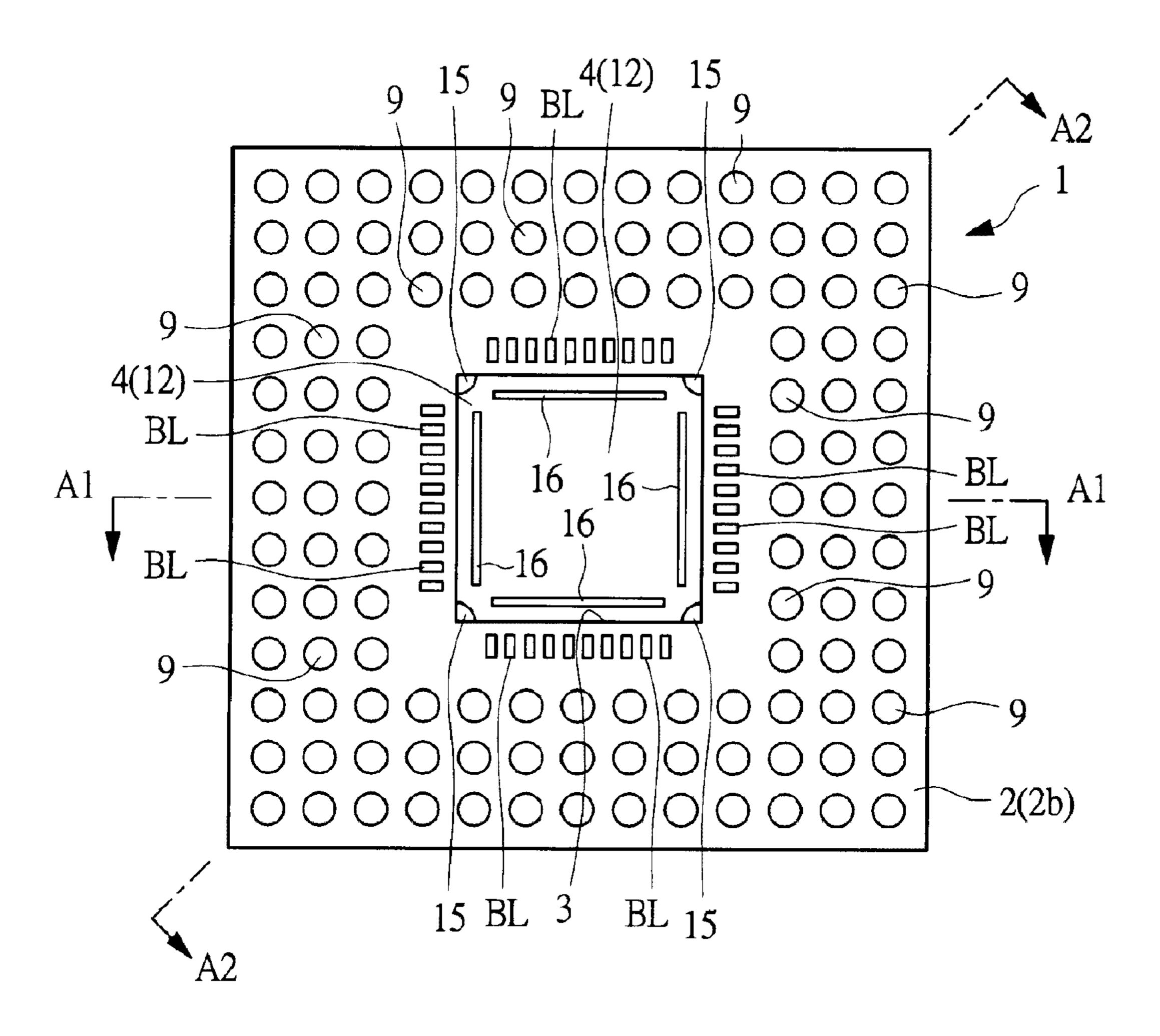

- FIG. 10 is a plane perspective view (bottom view) of a semiconductor device in an embodiment of the present invention;

- FIG. 11 is a top view of a wiring substrate used in semiconductor device in an embodiment of the present invention;

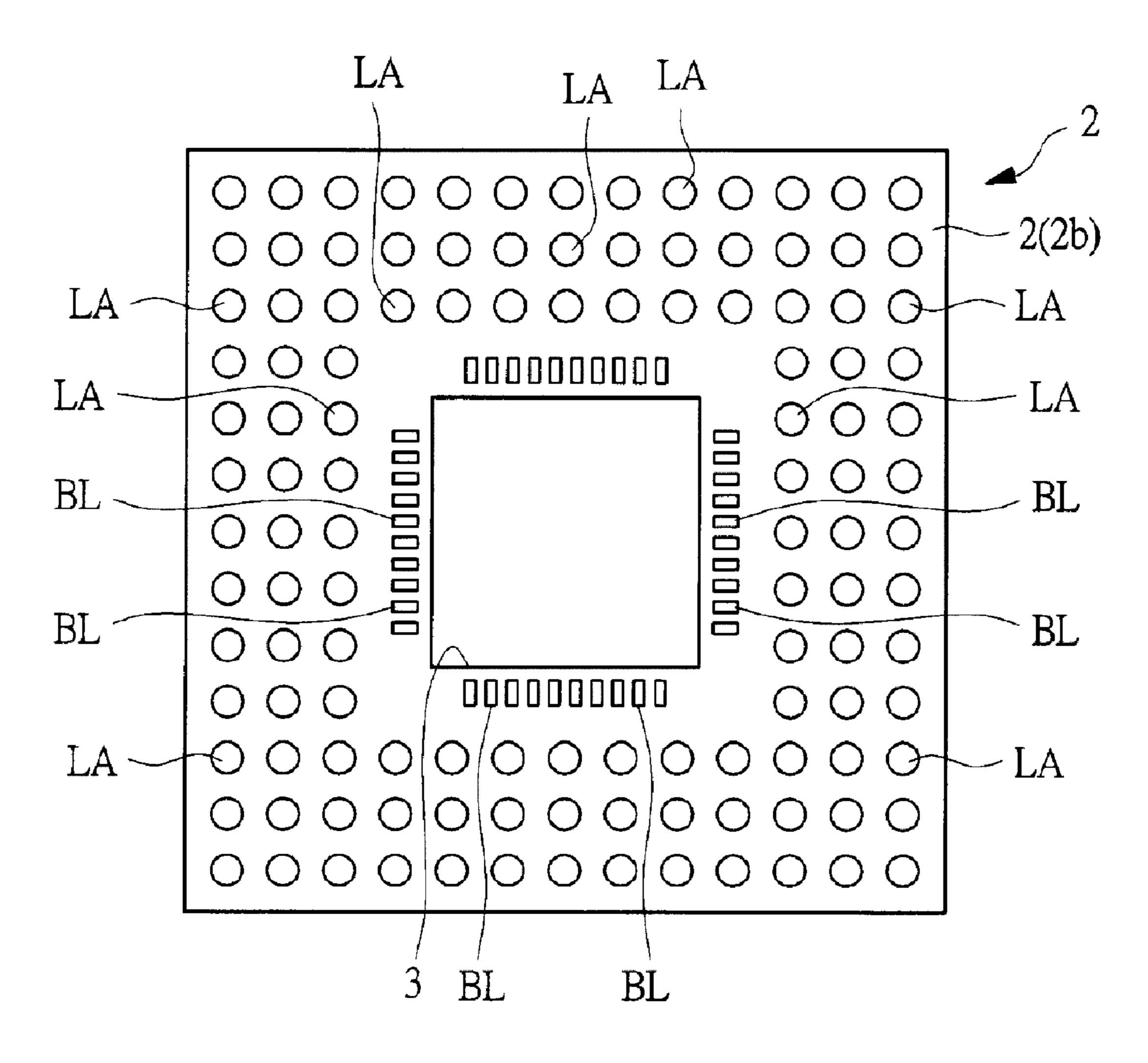

- FIG. 12 is a bottom view of a wiring substrate used in semiconductor device in an embodiment of the present invention;

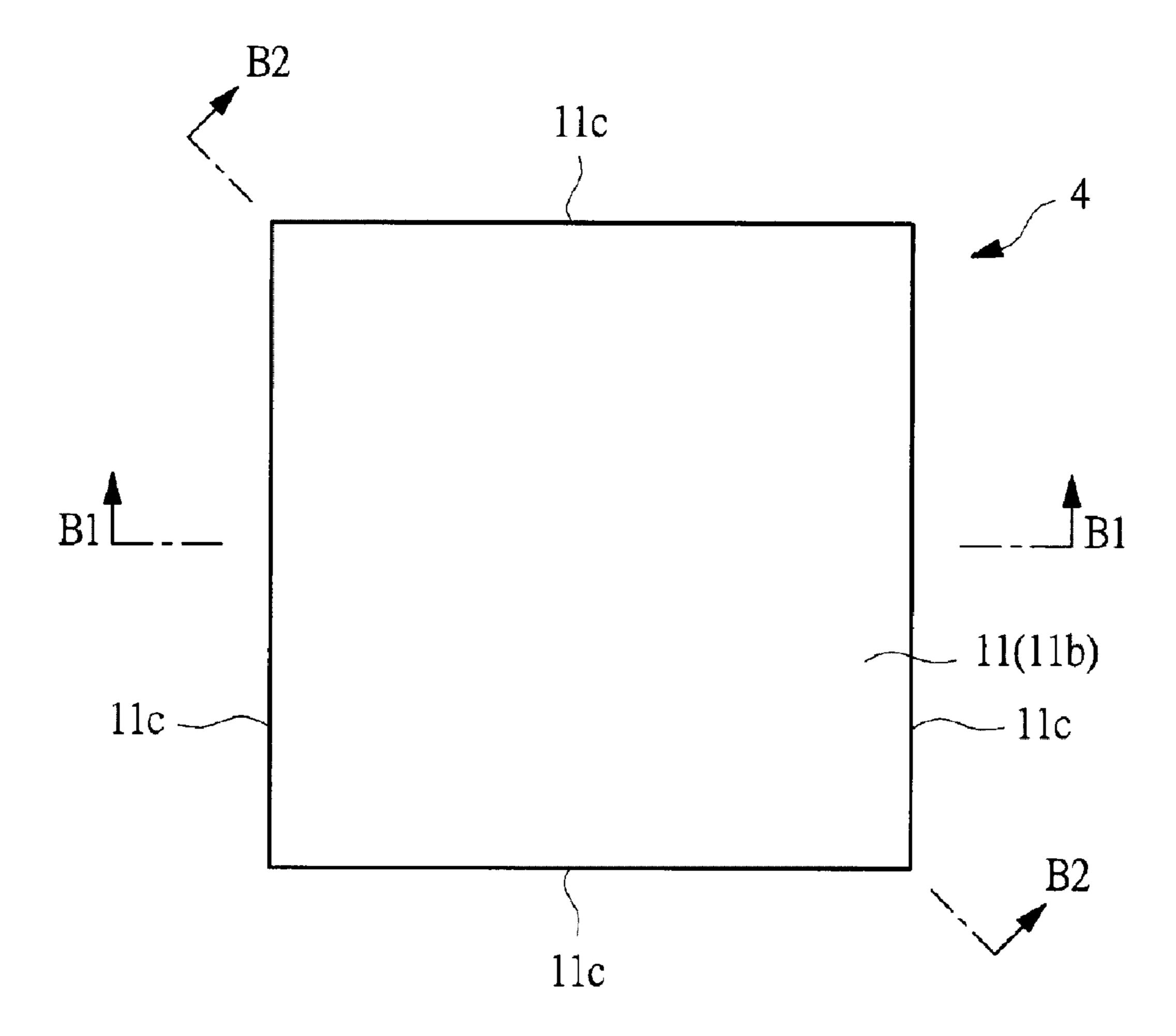

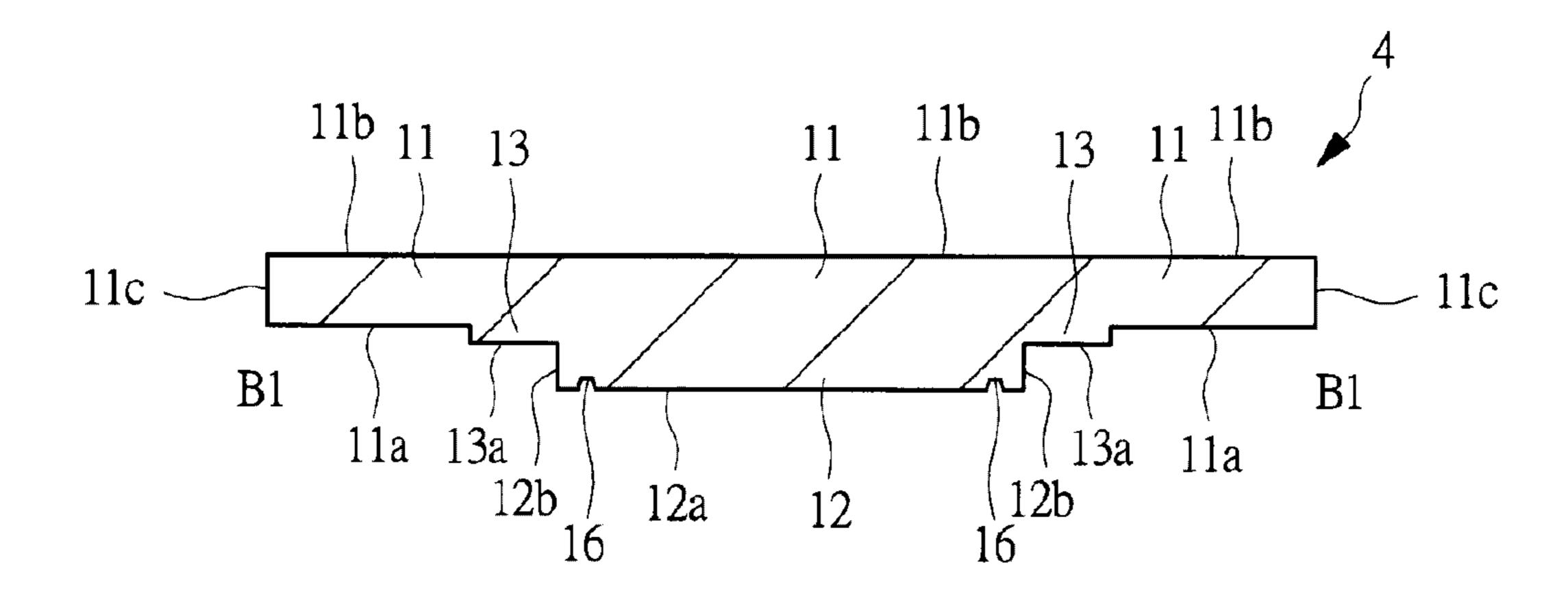

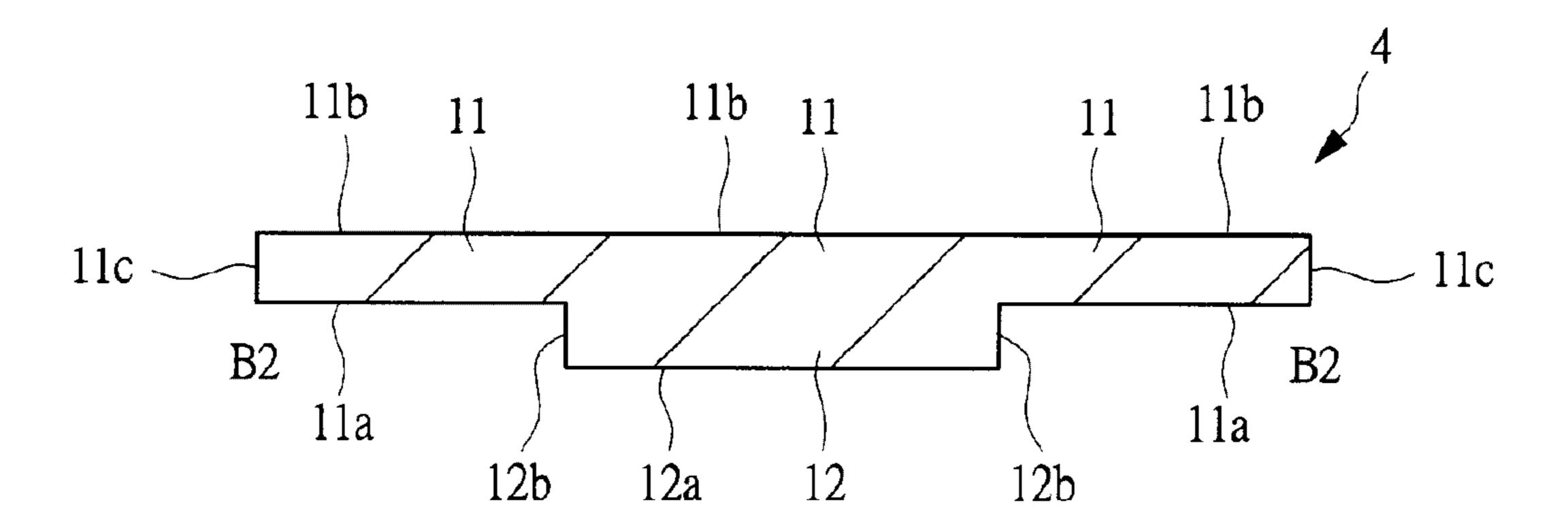

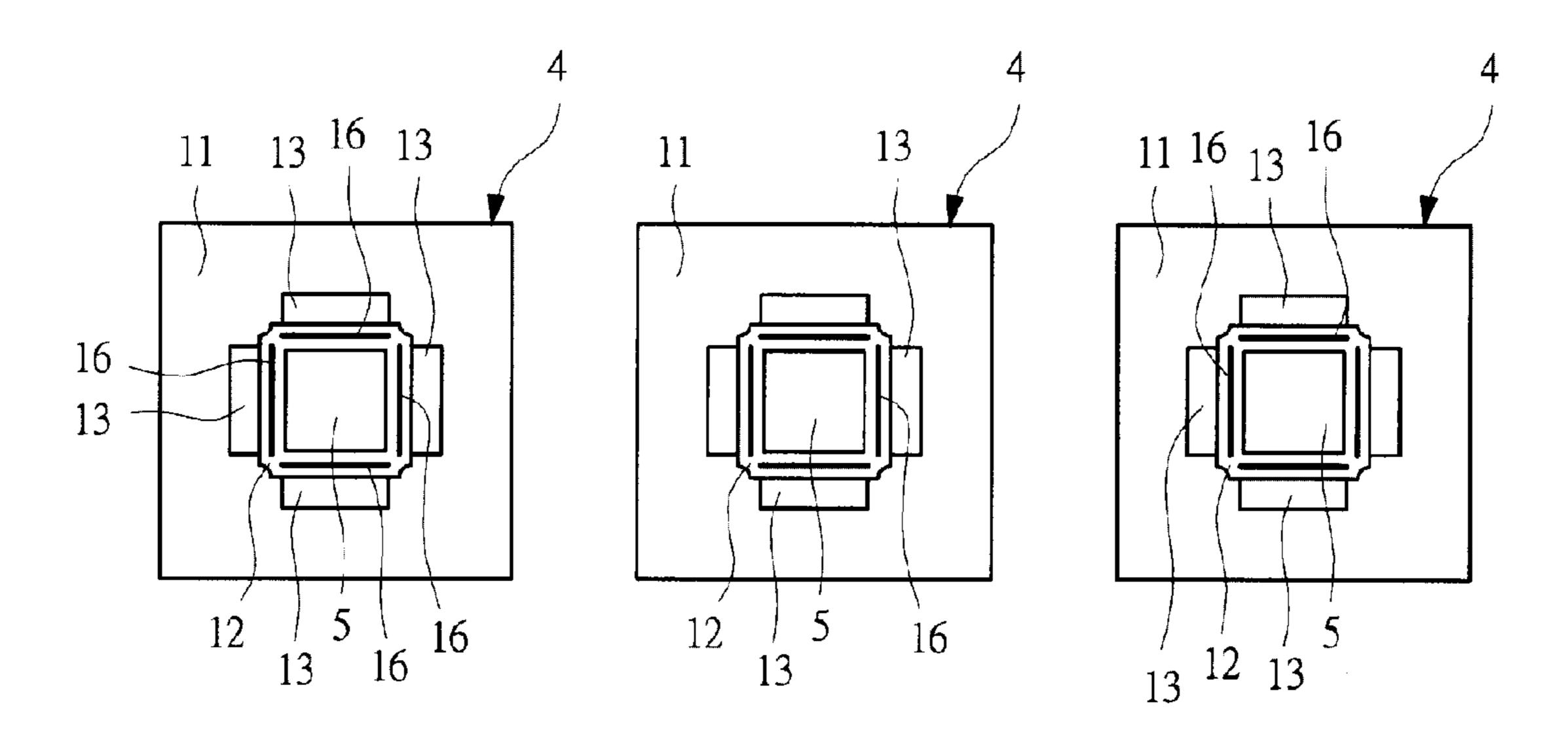

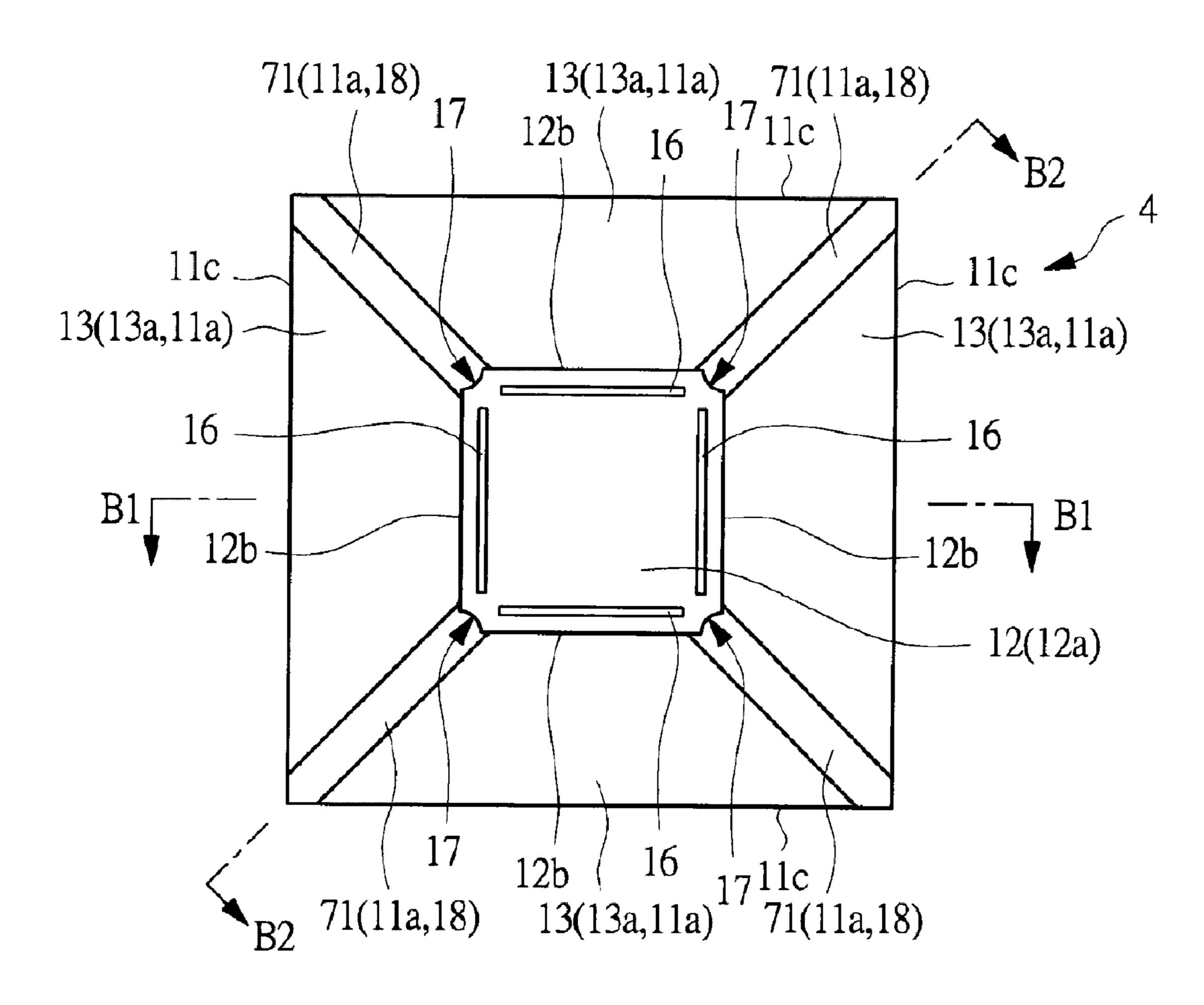

- FIG. 13 is a top view of a heat-releasing plate used in semiconductor device in an embodiment of the present invention;

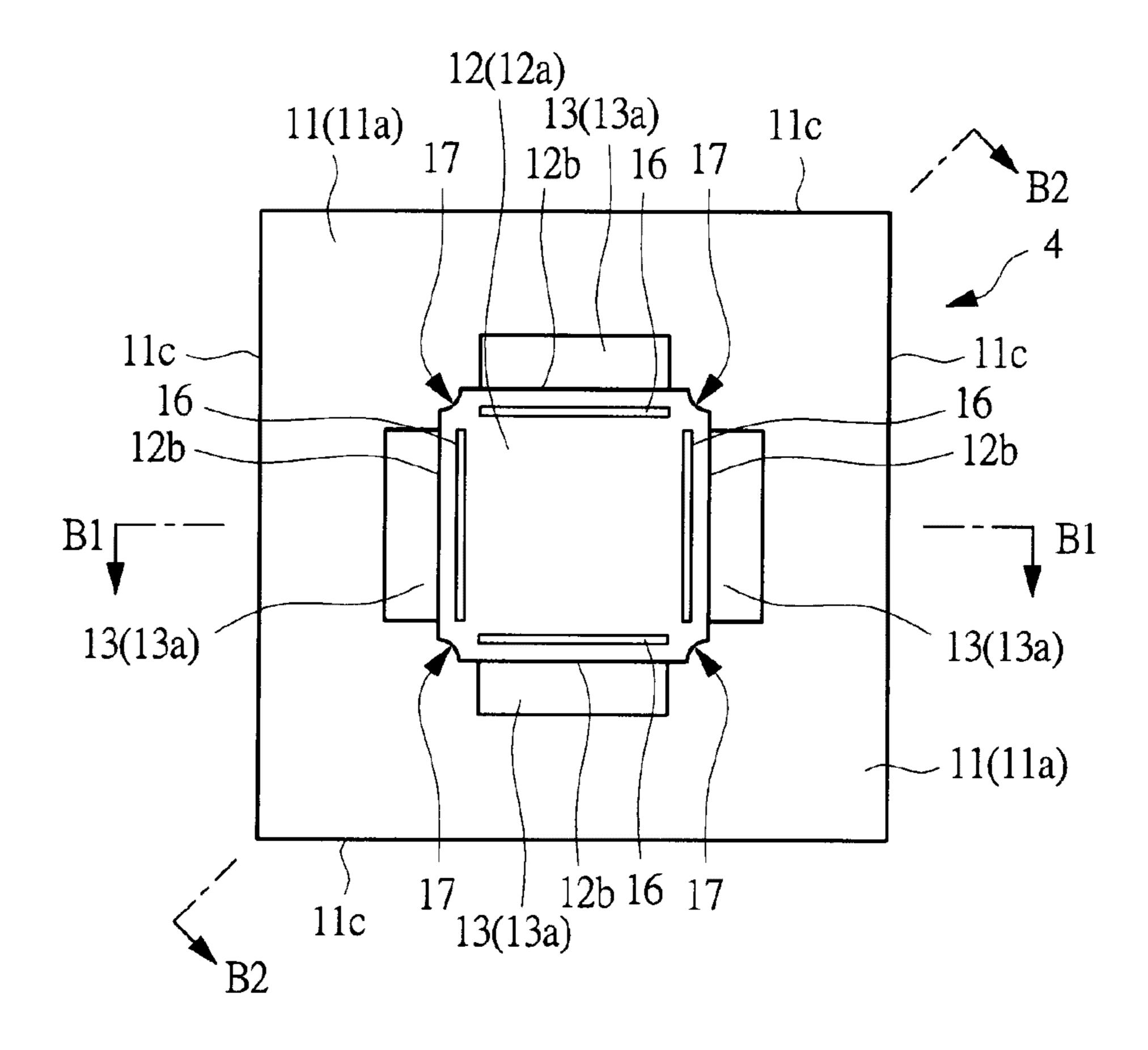

- FIG. 14 is a bottom view of a heat-releasing plate used in semiconductor device in an embodiment of the present invention;

- FIG. 15 is a side view of a heat-releasing plate used in semiconductor device in an embodiment of the present invention;

- FIG. 16 is a cross-sectional view of a heat-releasing plate 30 used in semiconductor device in an embodiment of the present invention;

- FIG. 17 is a cross-sectional view of a heat-releasing plate used in semiconductor device in an embodiment of the present invention;

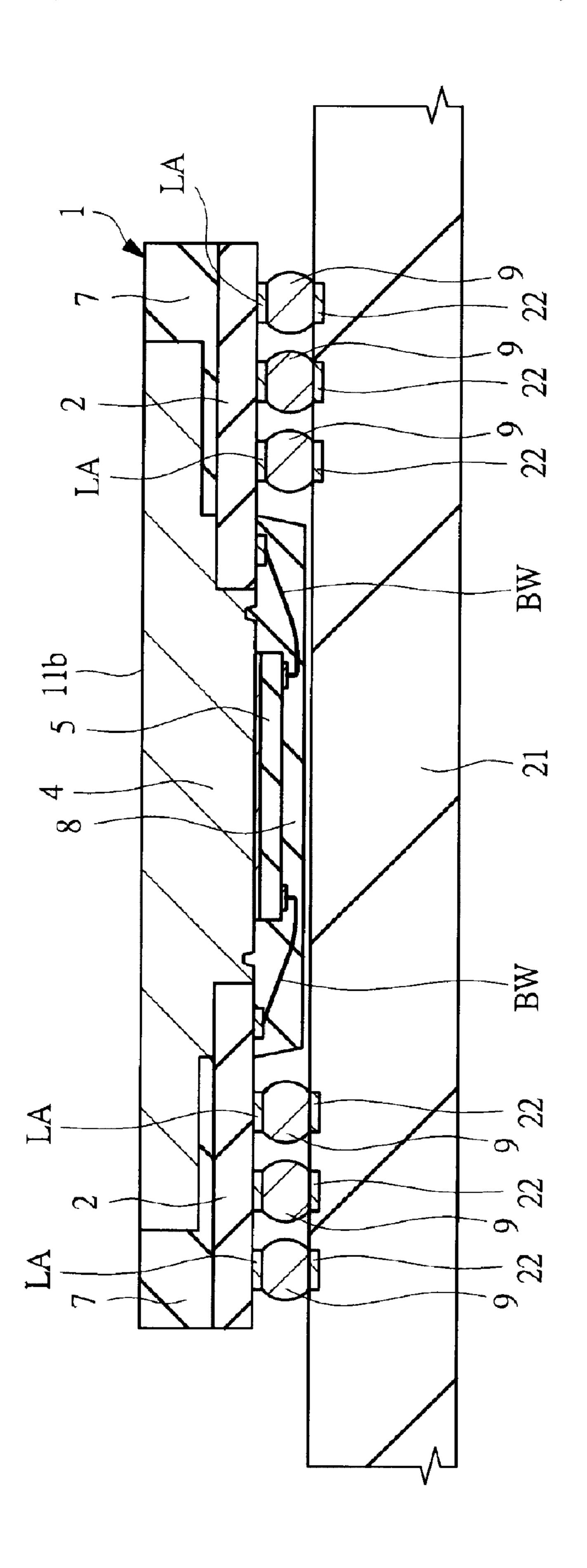

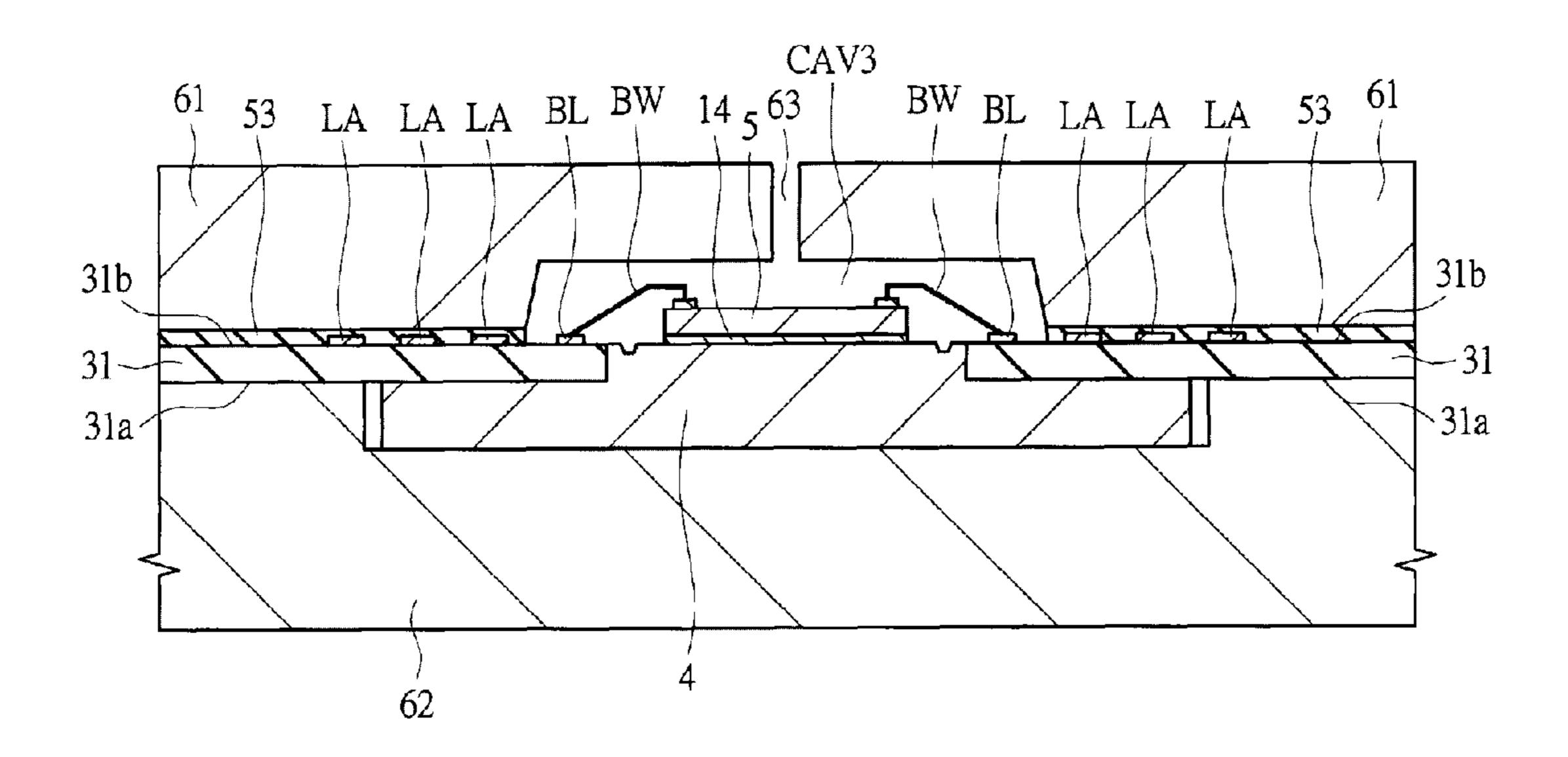

- FIG. 18 illustrates amounting example of a semiconductor device, in cross-sectional view, in an embodiment of the present invention;

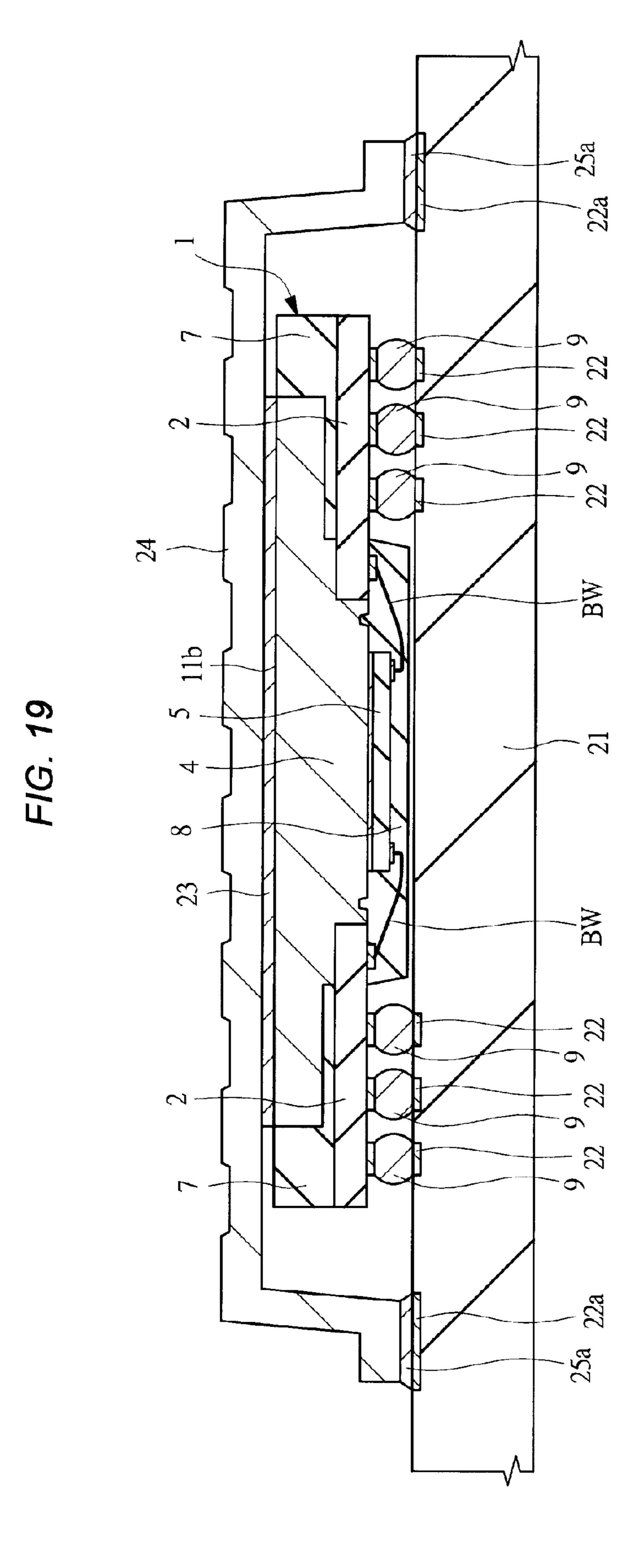

- FIG. 19 illustrates another mounting example of a semiconductor device, in cross-sectional view, in an embodiment 40 of the present invention;

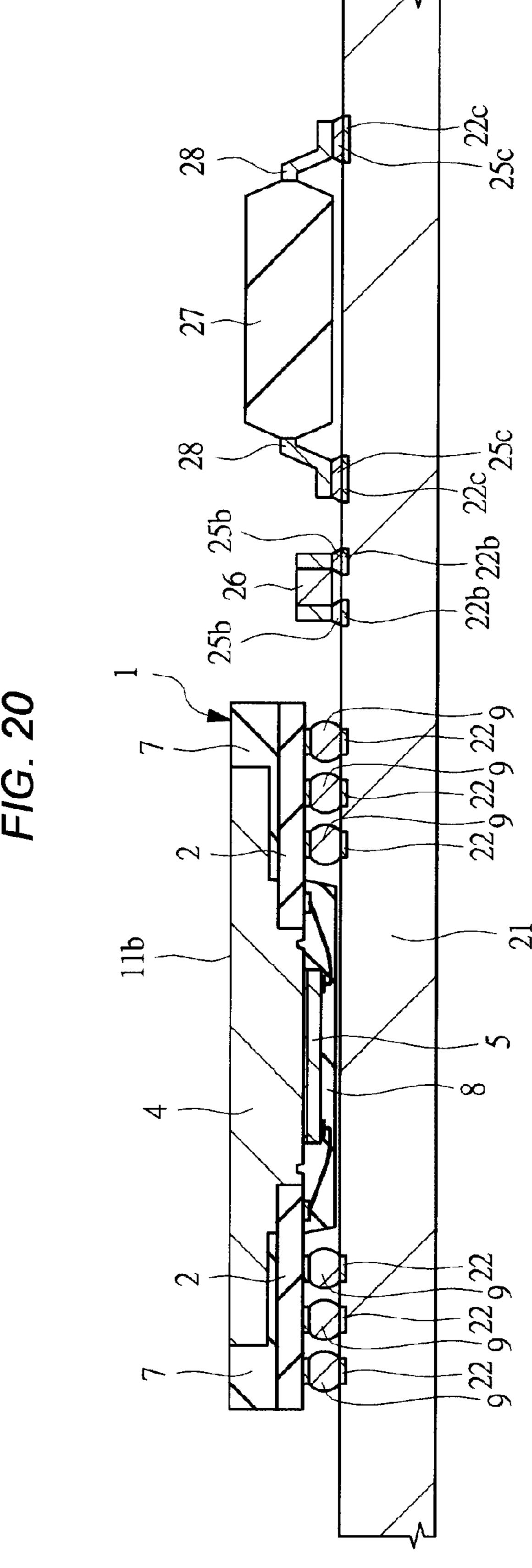

- FIG. 20 illustrates a further mounting example of a semiconductor device, in cross-sectional view, in an embodiment of the present invention;

- FIG. 21 illustrates a still another mounting example of a 45 semiconductor device, in cross-sectional view, in an embodiment of the present invention;

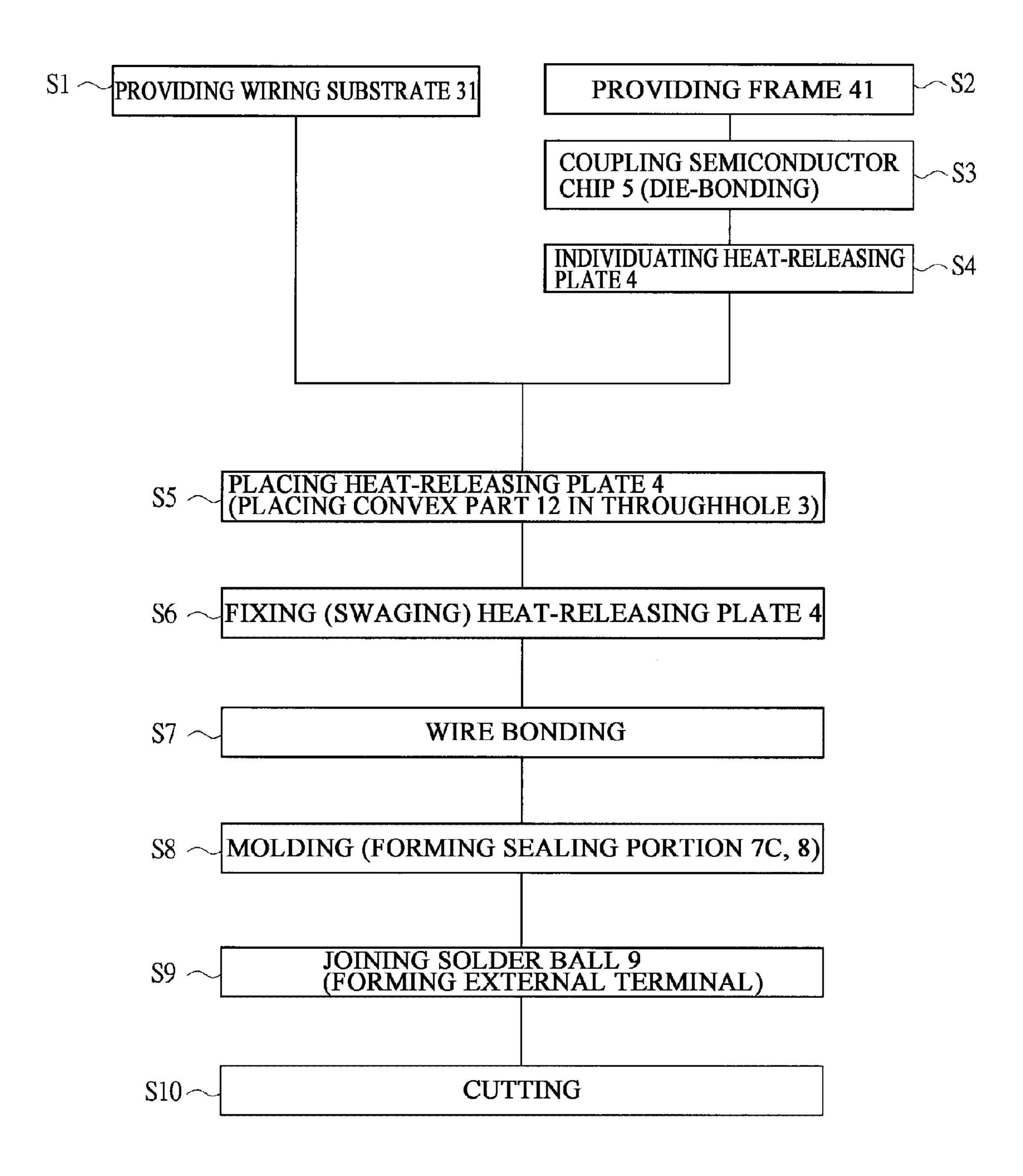

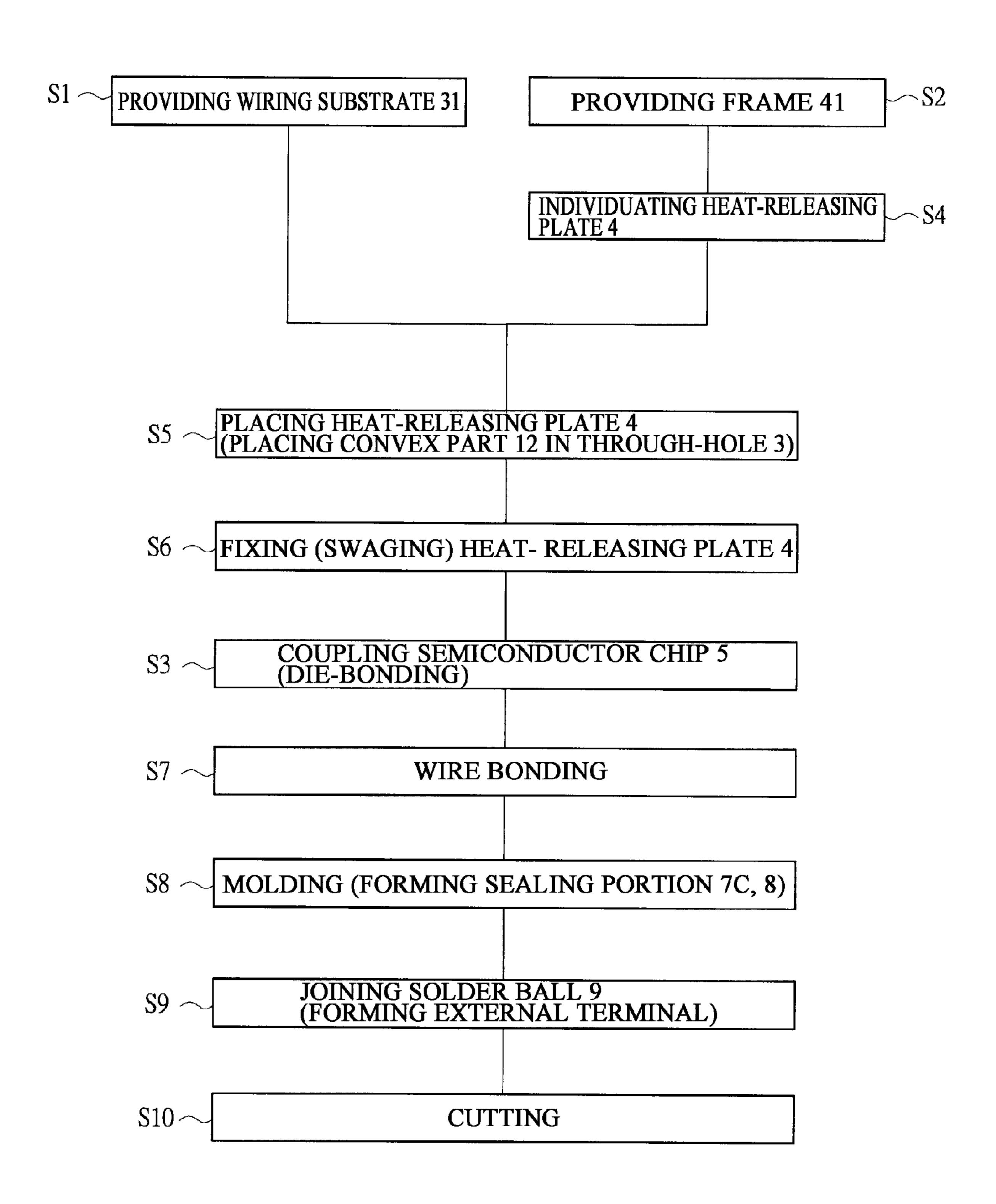

- FIG. 22 illustrates a flow diagram of manufacturing process of semiconductor device in an embodiment of the present invention;

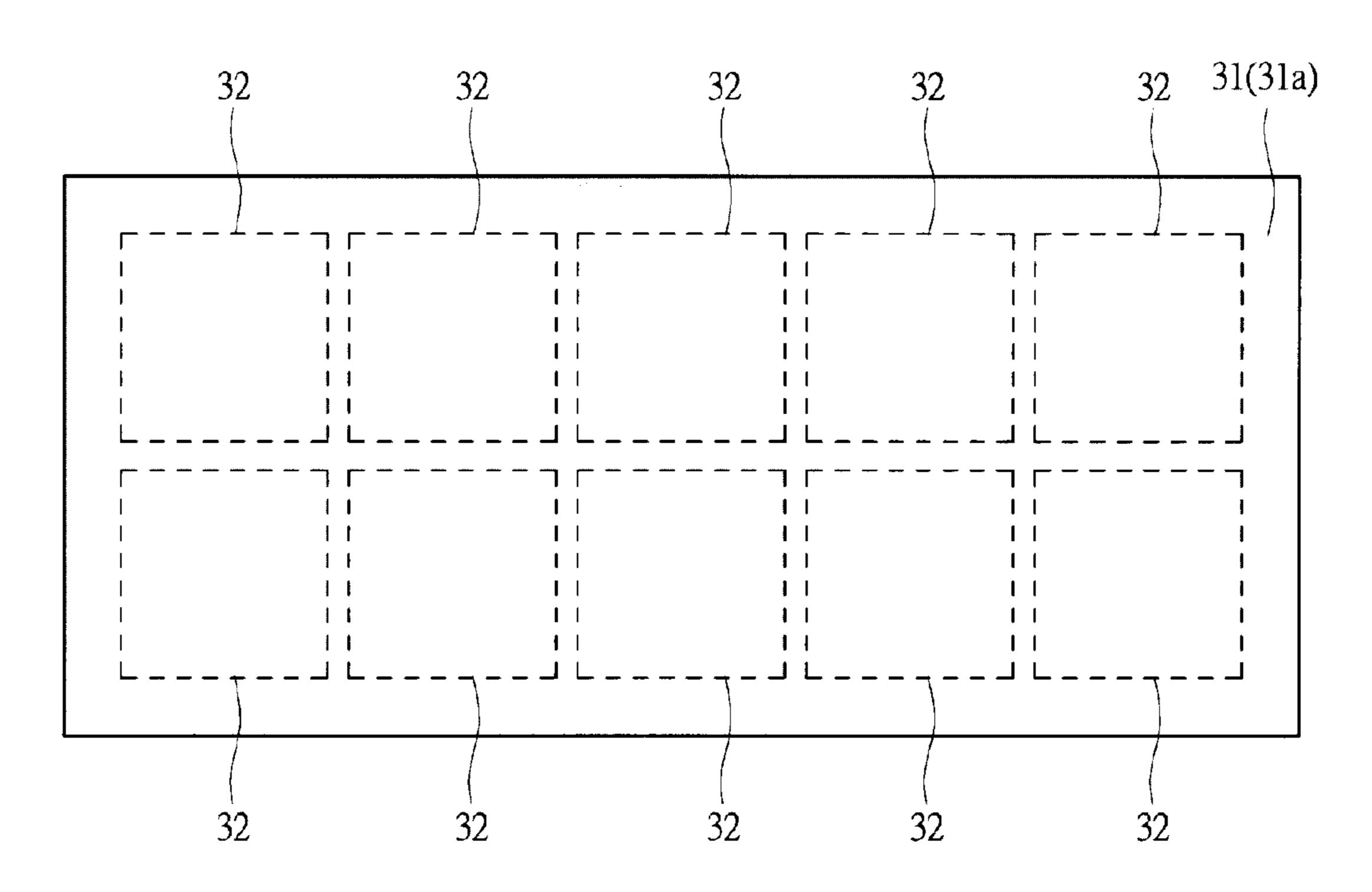

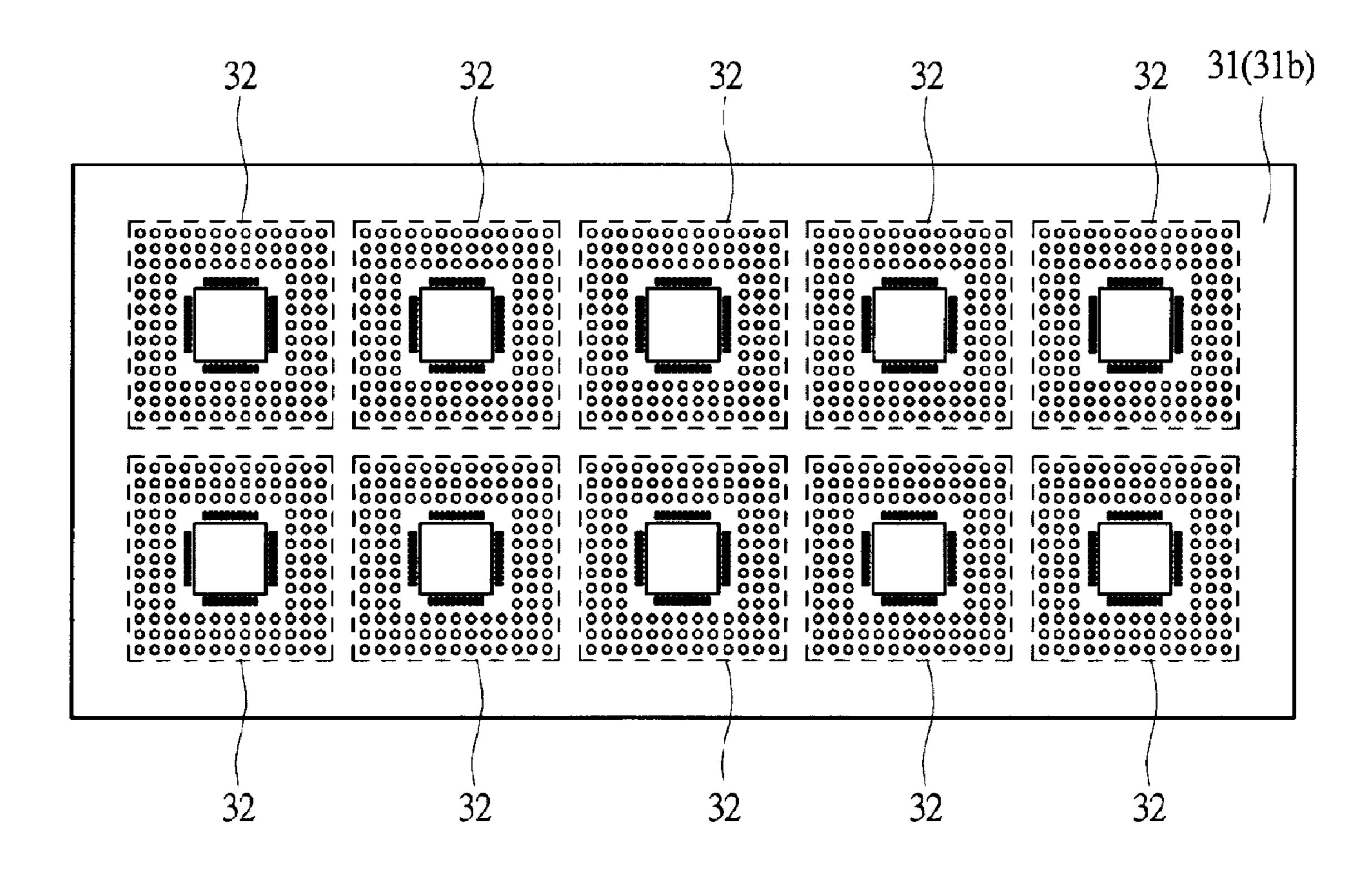

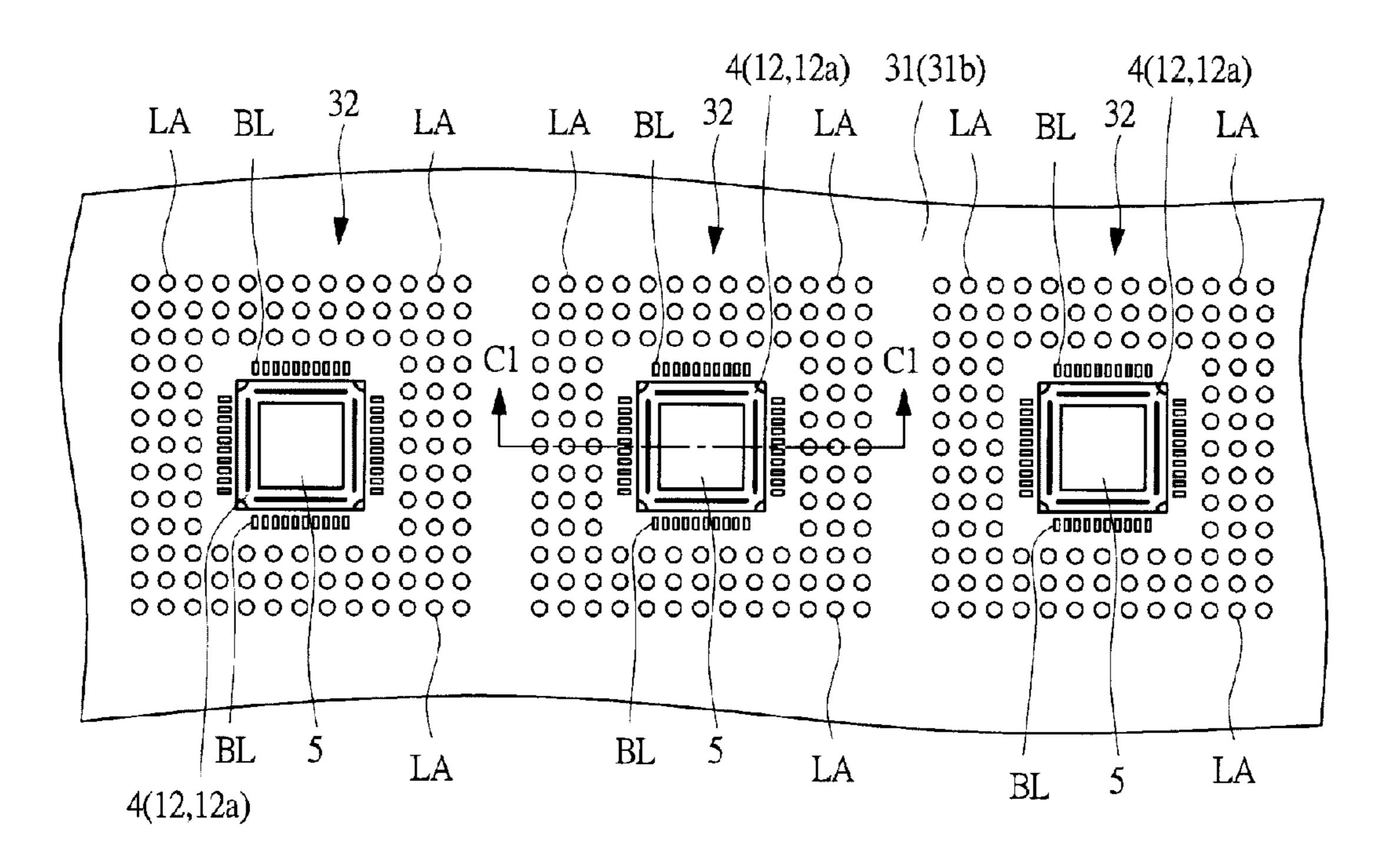

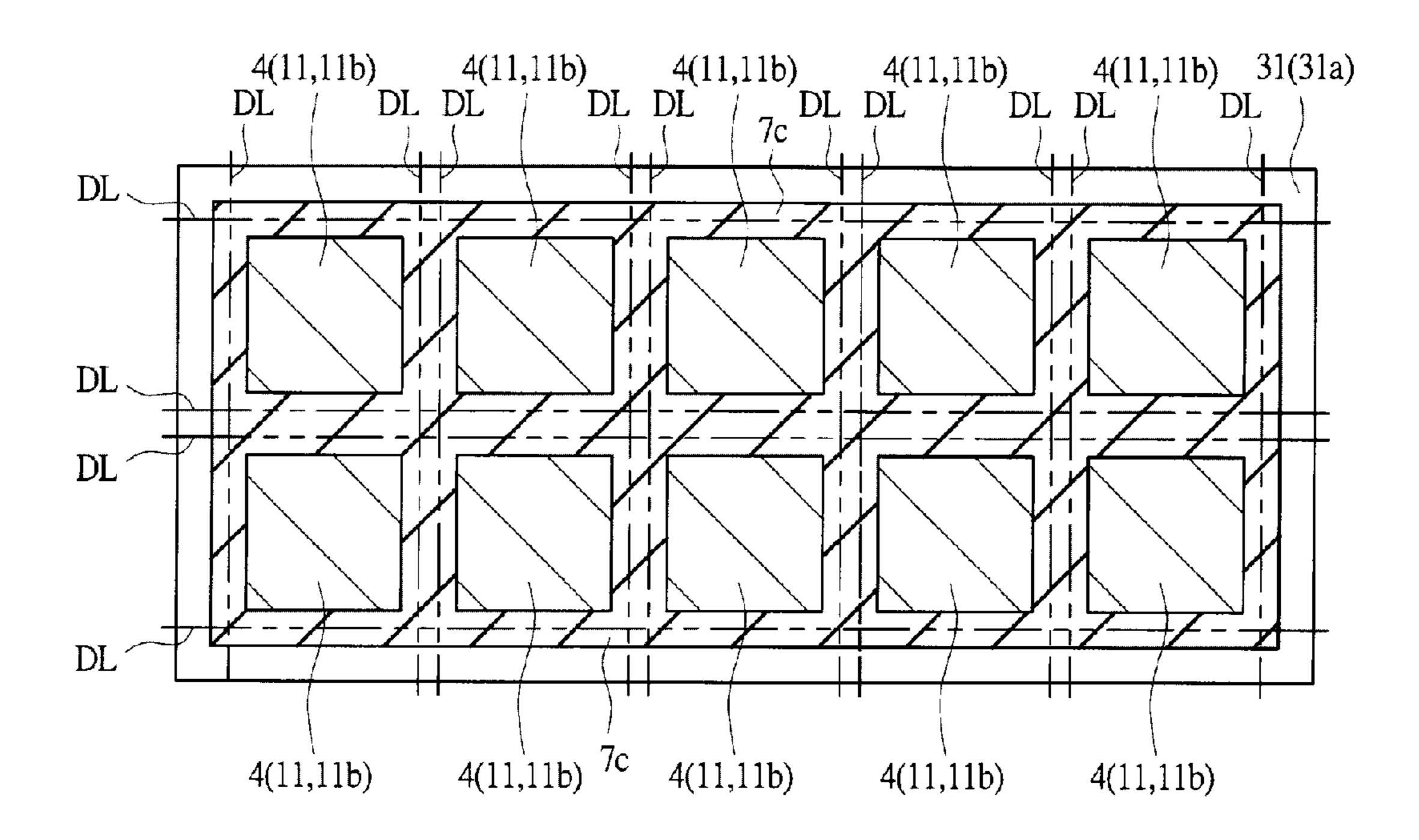

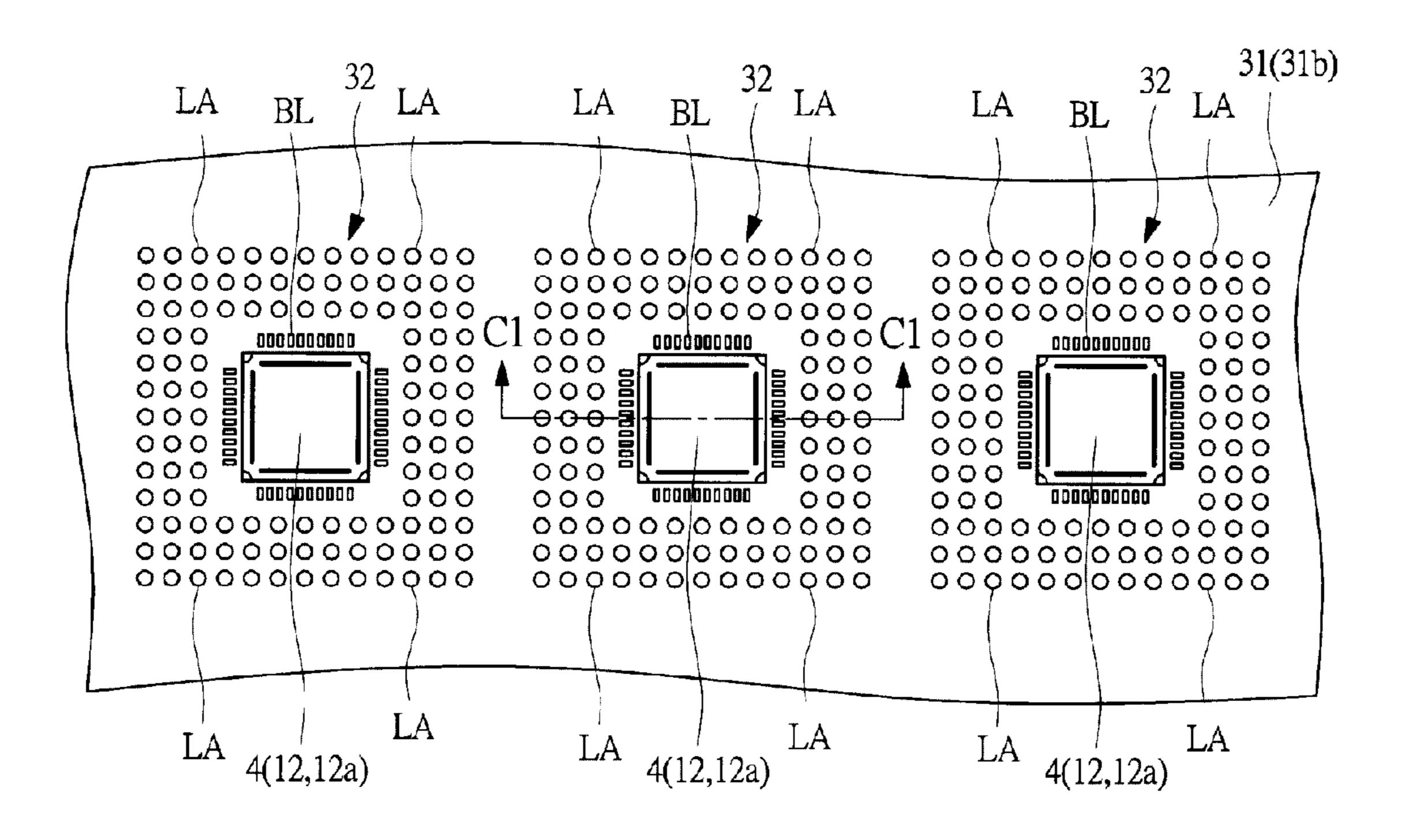

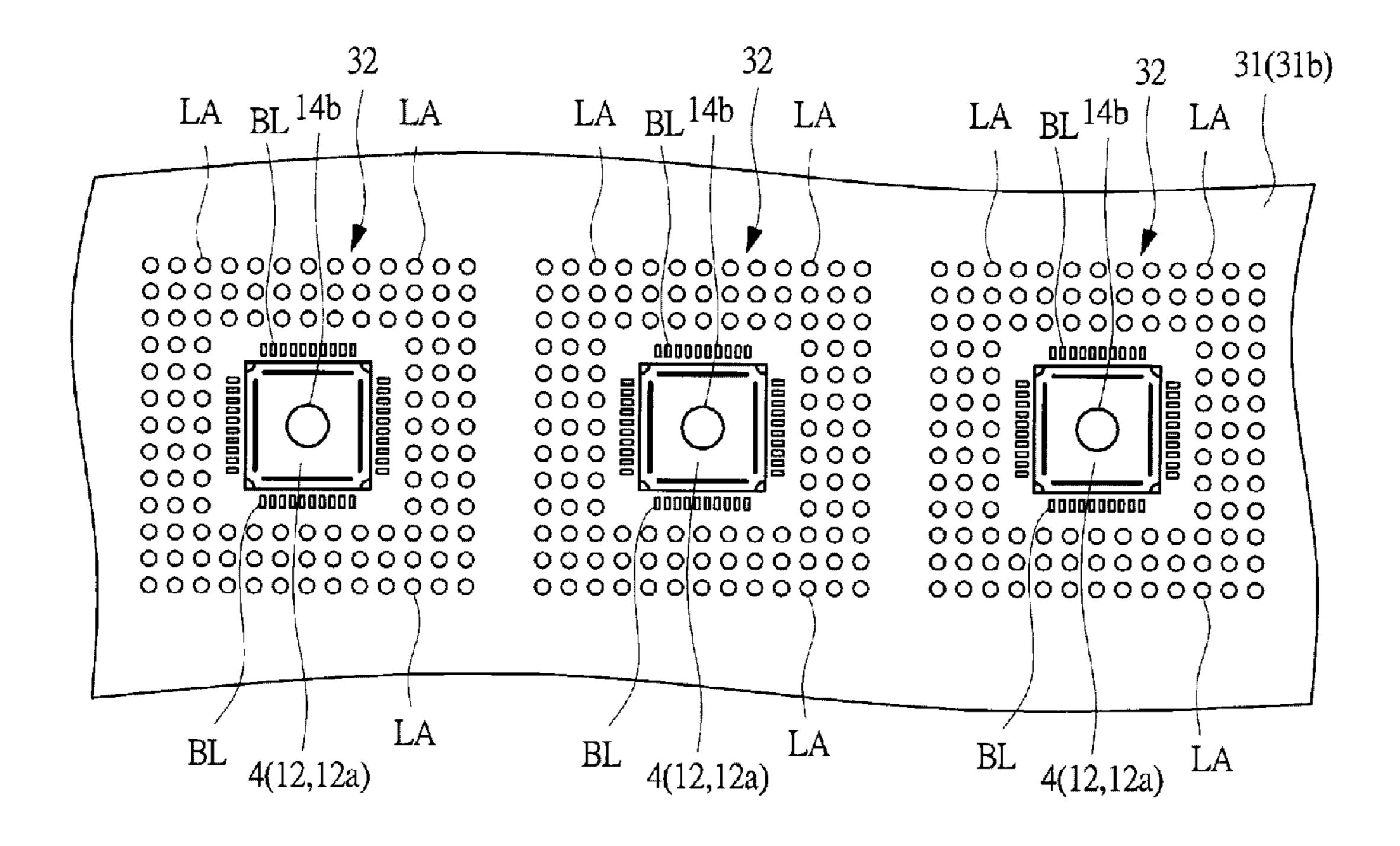

- FIG. 23 is a top view (entire plan view) of a wiring substrate used in the manufacturing process of semiconductor device in an embodiment of the present invention;

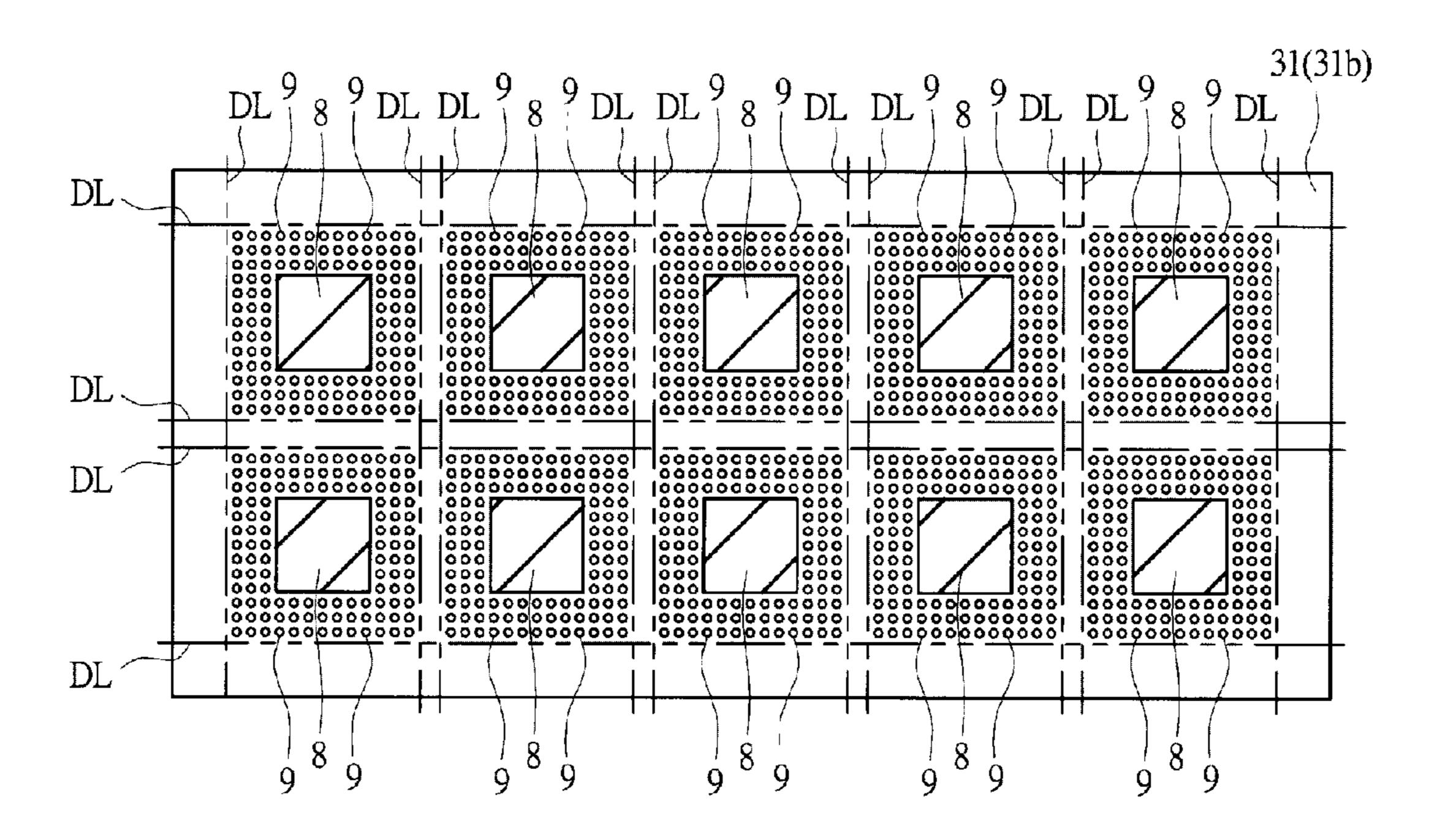

- FIG. 24 is a bottom view (entire plan view) of a wiring substrate used in the manufacturing process of semiconductor 55 device in an embodiment of the present invention;

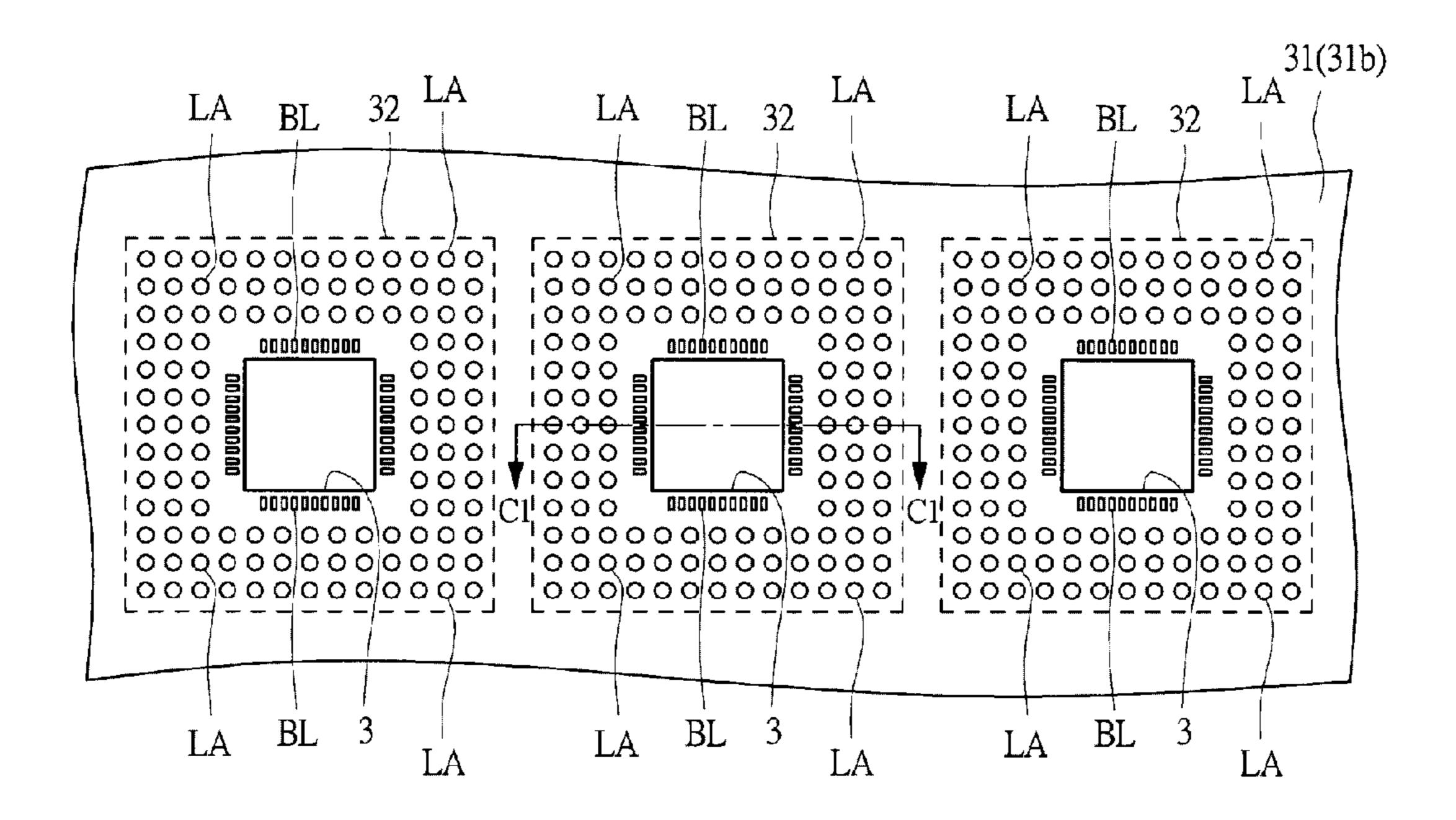

- FIG. **25** is a part-enlarged plan view (bottom view) of FIG. **24**;

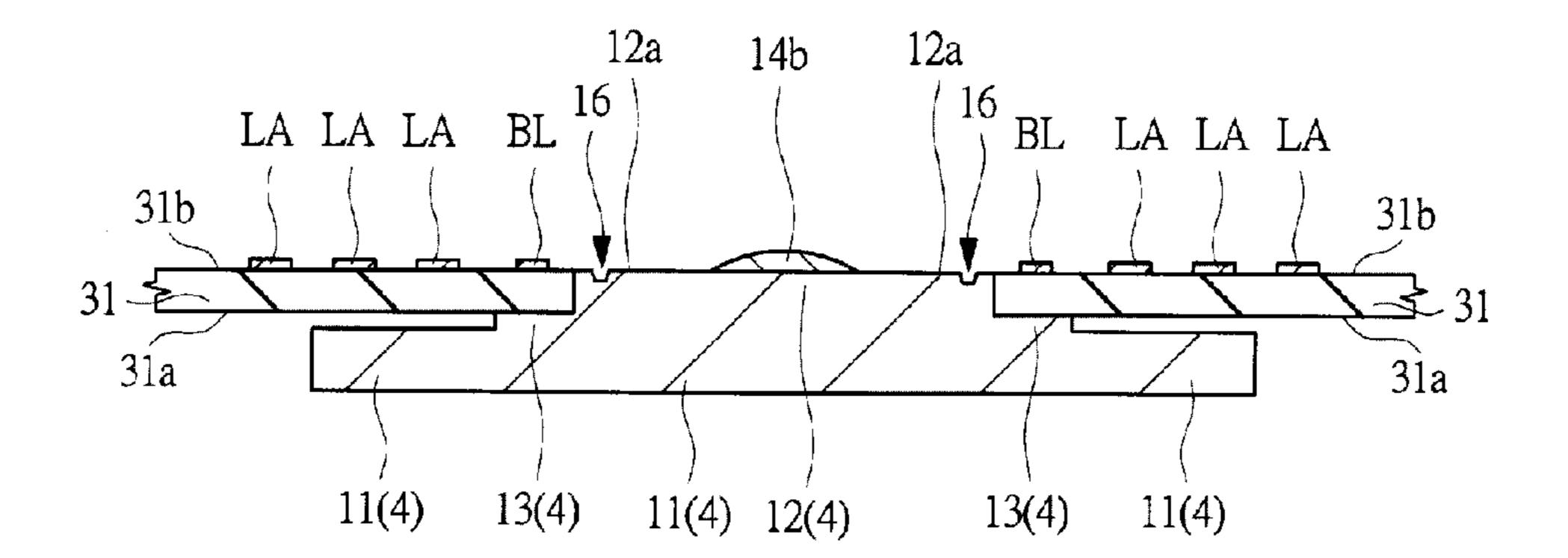

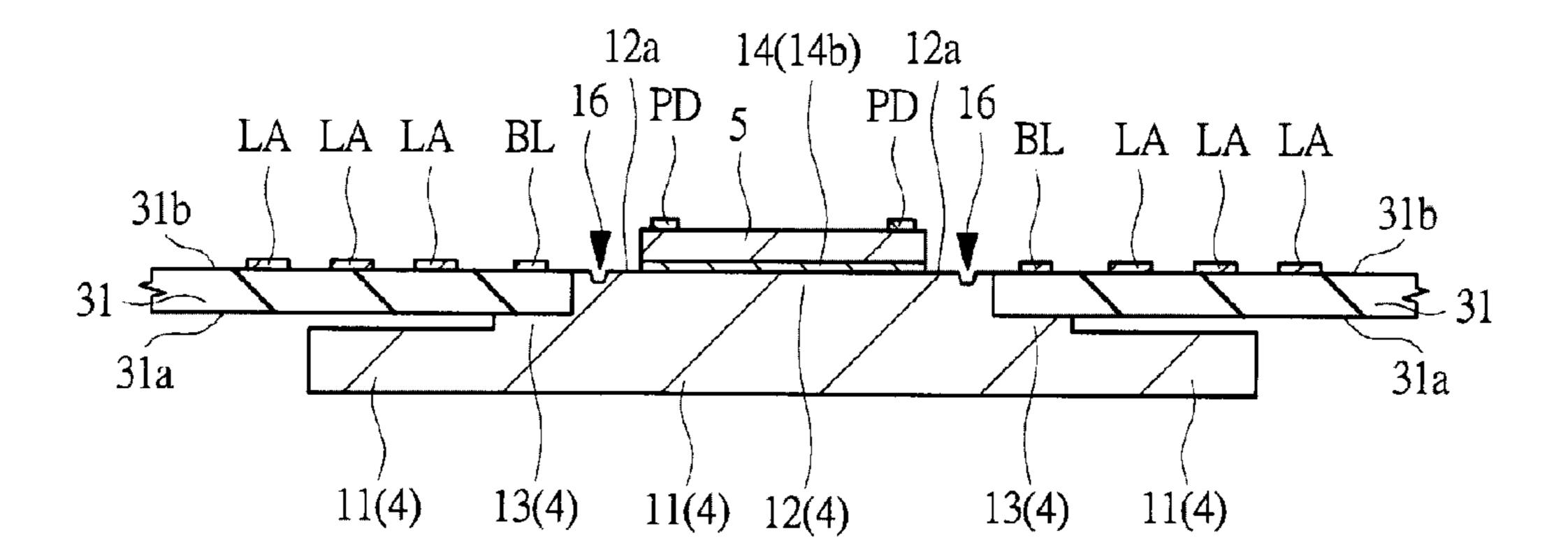

- FIG. **26** is a cross-sectional view of the wiring substrate of FIG. **25**;

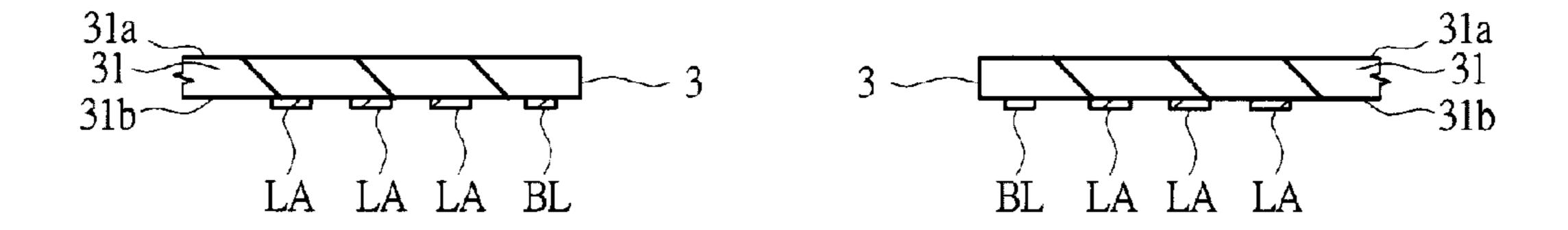

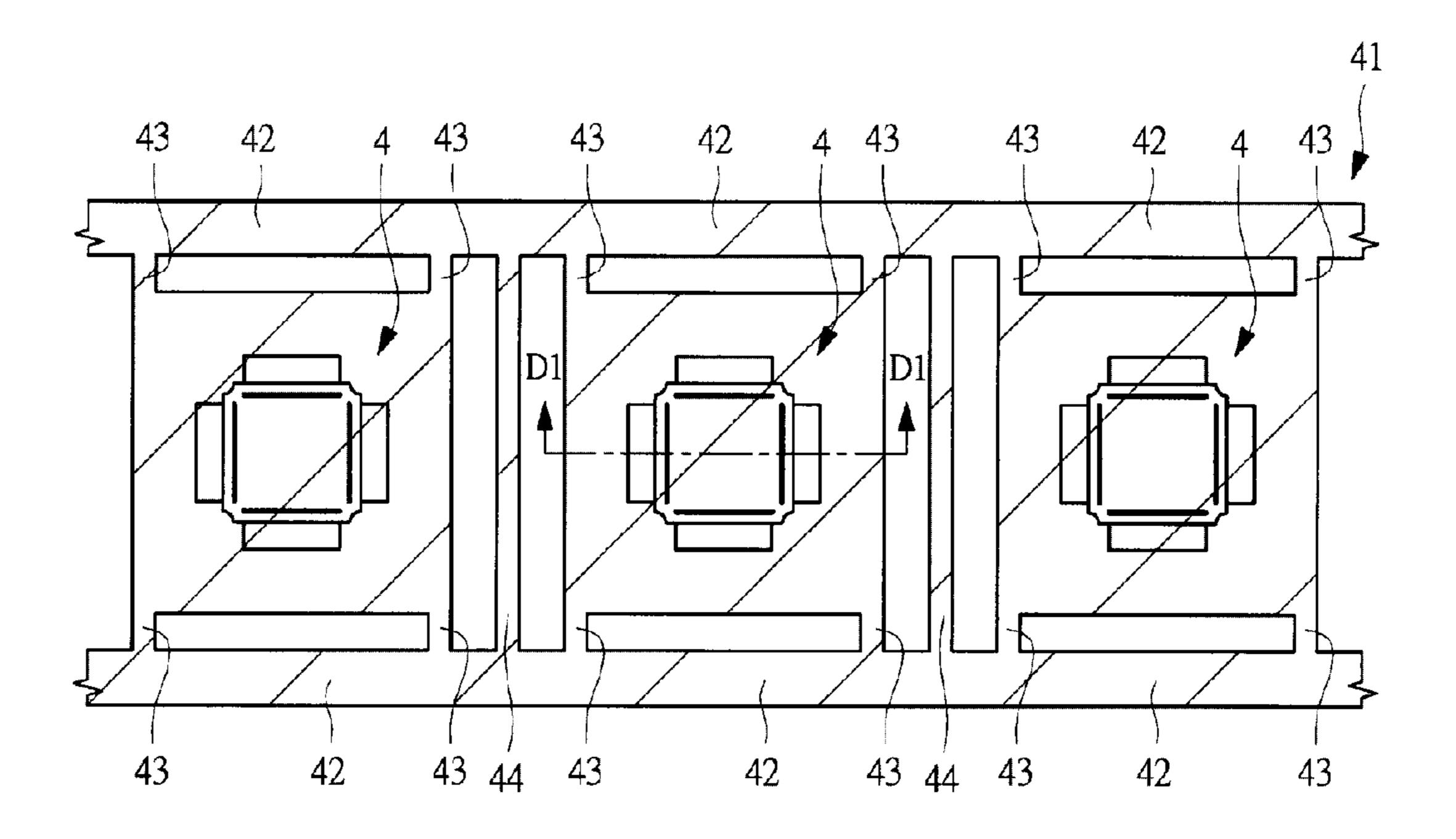

- FIG. 27 is a plan view of a frame used in the process of manufacturing semiconductor device in an embodiment of the present invention;

- FIG. 28 is a cross-sectional view of the frame of FIG. 27;

- FIG. 29 is a plan view of a semiconductor device during 65 manufacturing process in an embodiment of the present invention;

4

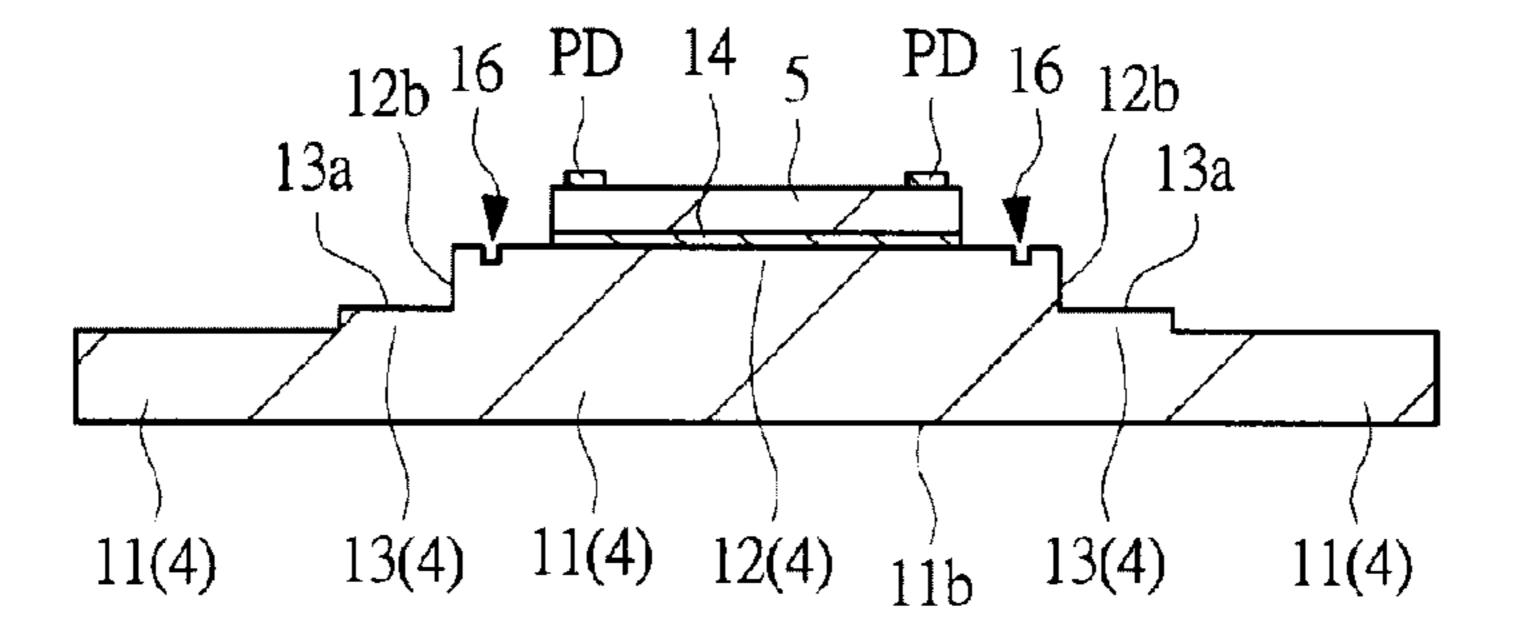

- FIG. 30 is a cross-sectional view of the semiconductor device, which is the same as in FIG. 29, during manufacturing process;

- FIG. 31 is a plan view of the semiconductor device in the next step of FIG. 29, during manufacturing process;

- FIG. 32 is a cross-sectional view of the semiconductor device, which is the same as in FIG. 31, during manufacturing process;

- FIG. 33 is a plan view of the semiconductor device in the next step of FIG. 31, during manufacturing process;

- FIG. 34 is a cross-sectional view of the semiconductor device, which is the same as in FIG. 33, during manufacturing process;

- FIG. 35 is a plan view of the semiconductor device in the next step of FIG. 33, during manufacturing process;

- FIG. 36 is a plan view of the semiconductor device, the same as that in FIG. 35, during manufacturing process;

- FIG. 37 is a cross-sectional view of the semiconductor device, which is the same as in FIG. 35, during manufacturing process;

- FIG. 38 is a plan view of the semiconductor device in the next step of FIG. 35, during manufacturing process;

- FIG. 39 is a cross-sectional view of the semiconductor device, which is the same as in FIG. 38, during manufacturing process;

- FIG. 40 is a plan view of the semiconductor device in the next step of FIG. 38, during manufacturing process;

- FIG. 41 is a plan view of the semiconductor device, the same as that in FIG. 40, during manufacturing process;

- FIG. **42** is a cross-sectional view of the semiconductor device, which is the same as in FIG. **40**, during manufacturing process;

- FIG. **43** is a cross-sectional view of the semiconductor device in the next step of FIG. **42**, during manufacturing process;

- FIG. 44 illustrates a state immediately before the cutting step;

- FIG. **45** illustrates a state immediately before the cutting step;

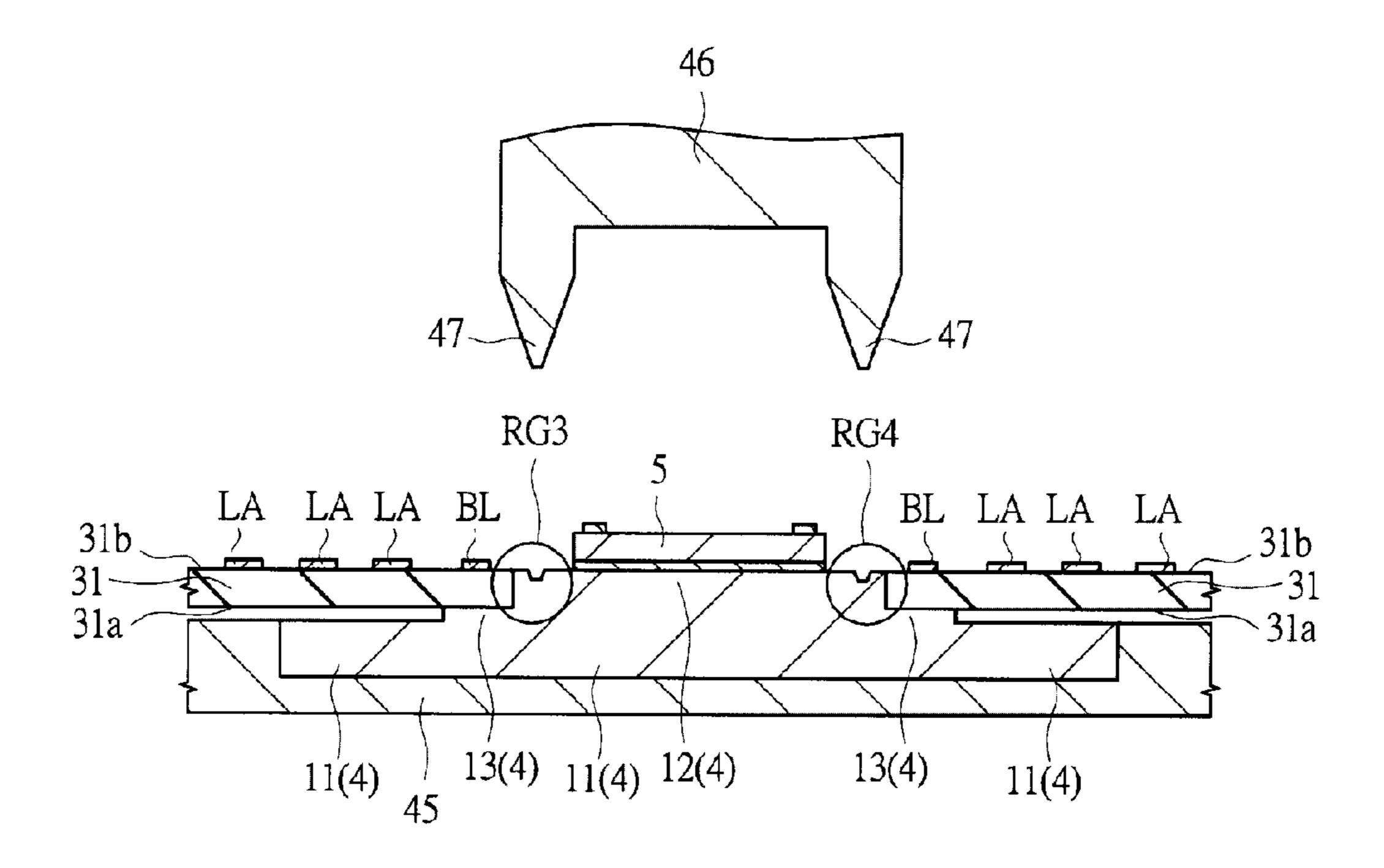

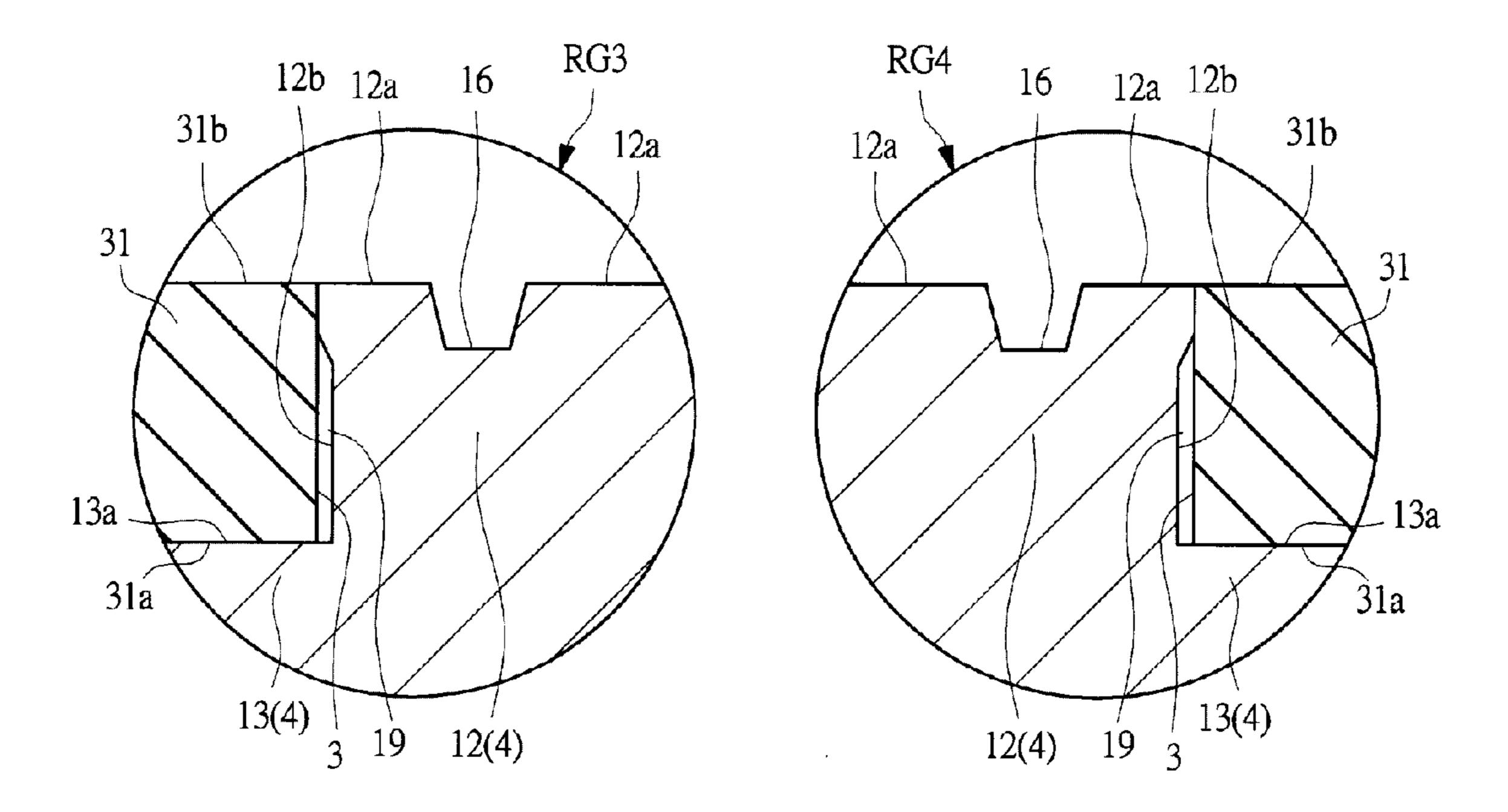

- FIG. 46 is a cross-sectional view of the semiconductor device in the next step of FIG. 43, during manufacturing process;

- FIG. 47 illustrates the step of positioning heat-releasing plate 4 and the step of fixing (swaging) thereof in the steps S5 and S6, respectively;

- FIG. 48 illustrates the step of positioning heat-releasing plate 4 and the step of fixing (swaging) thereof in the steps S5 and S6, respectively;

- FIG. 49 illustrates the step of positioning heat-releasing plate 4 and the step of fixing (swaging) thereof in the steps S5 and S6, respectively;

- FIG. **50** illustrates the step of positioning heat-releasing plate **4** and the step of fixing (swaging) thereof in the steps S**5** and S**6**, respectively;

- FIG. **51** illustrates the step of positioning heat-releasing plate **4** and the step of fixing (swaging) thereof in the steps S**5** and S**6**, respectively;

- FIG. **52** illustrates the step of positioning heat-releasing plate **4** and the step of fixing (swaging) thereof in the steps S**5** and S**6**, respectively;

- FIG. 53 illustrates the step of positioning heat-releasing plate 4 and the step of fixing (swaging) thereof in the steps S5 and S6, respectively;

- FIG. **54** illustrates the step of positioning heat-releasing plate **4** and the step of fixing (swaging) thereof in the steps S**5** and S**6**, respectively;

- FIG. 55 illustrates the step of positioning heat-releasing plate 4 and the step of fixing (swaging) thereof in the steps S5 and S6, respectively;

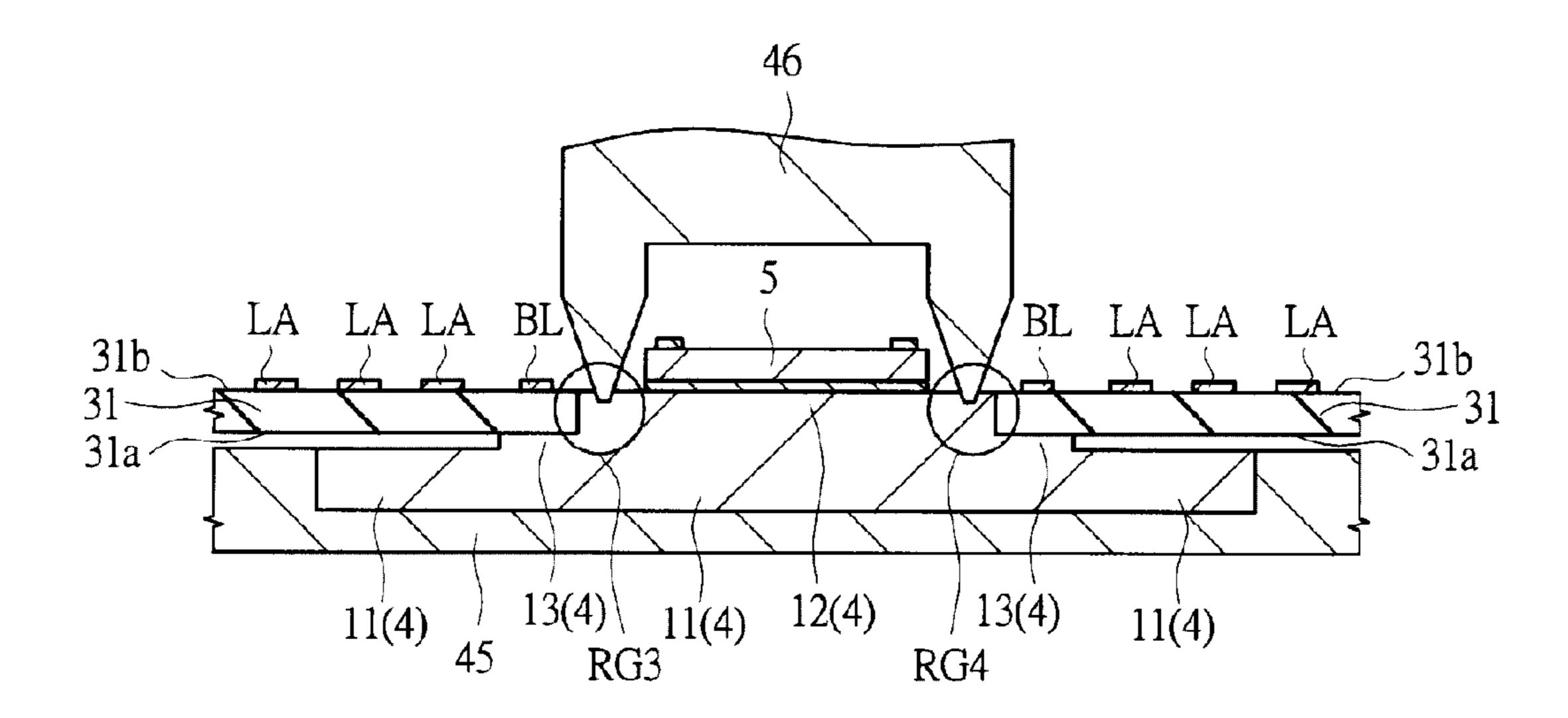

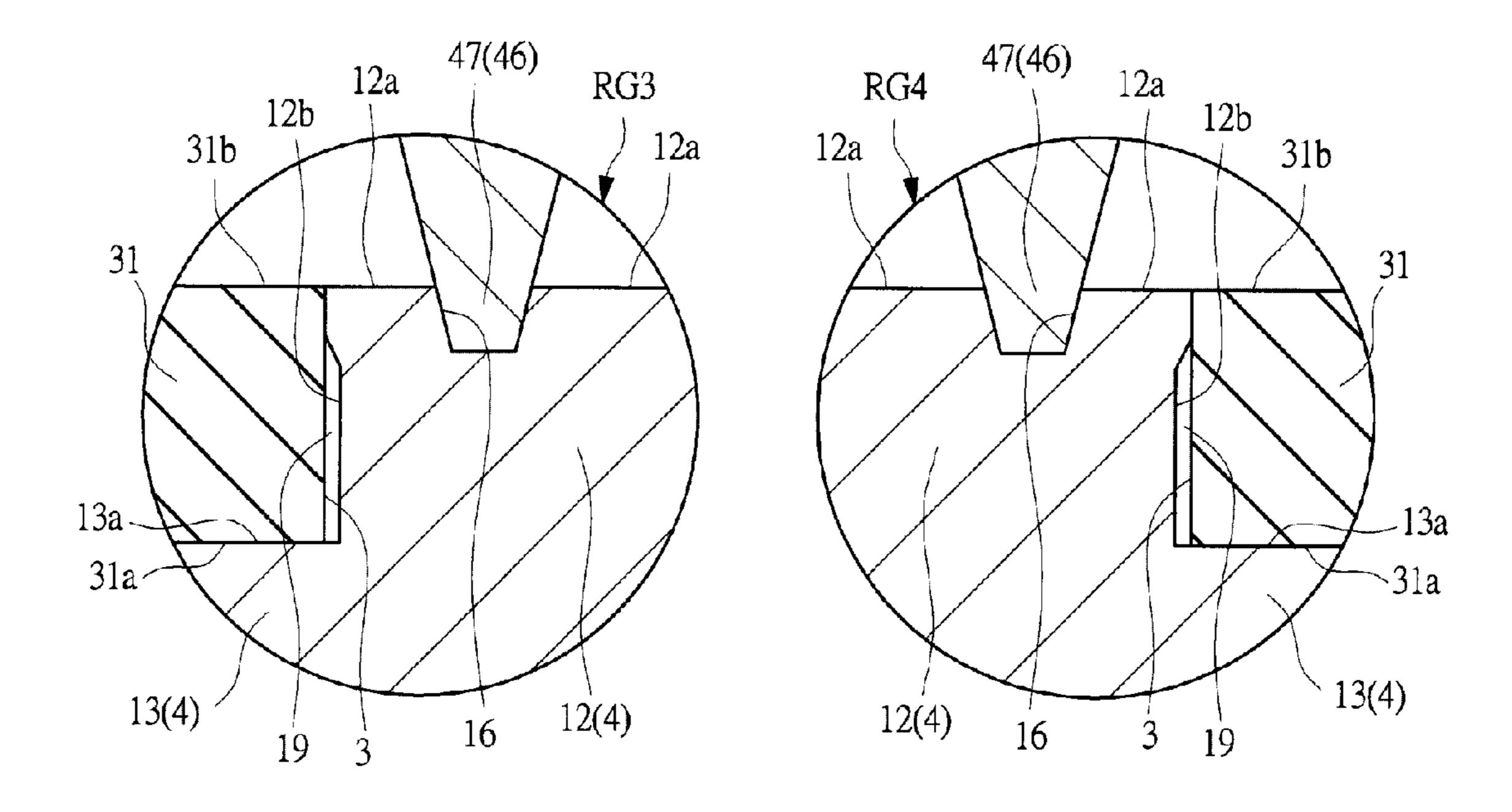

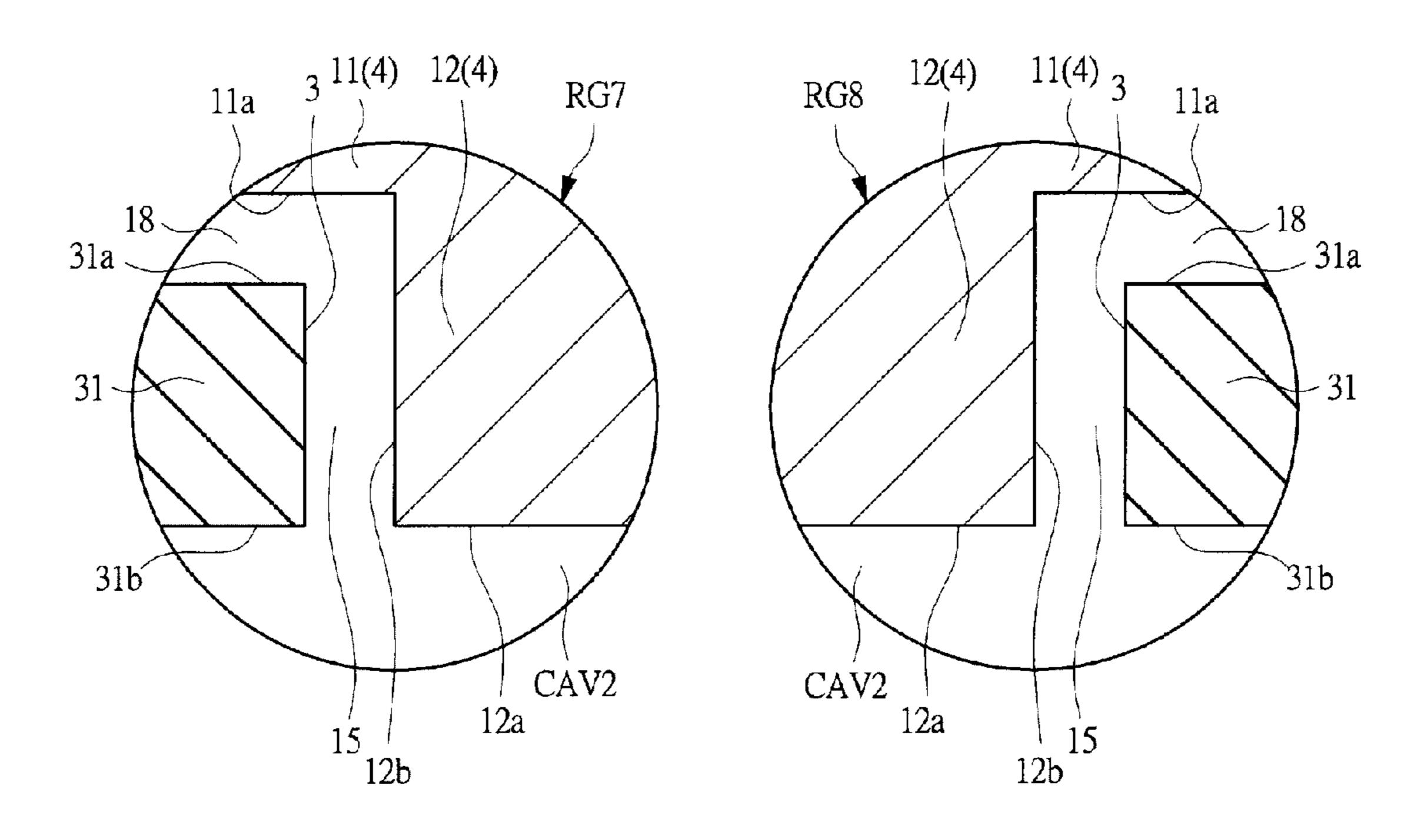

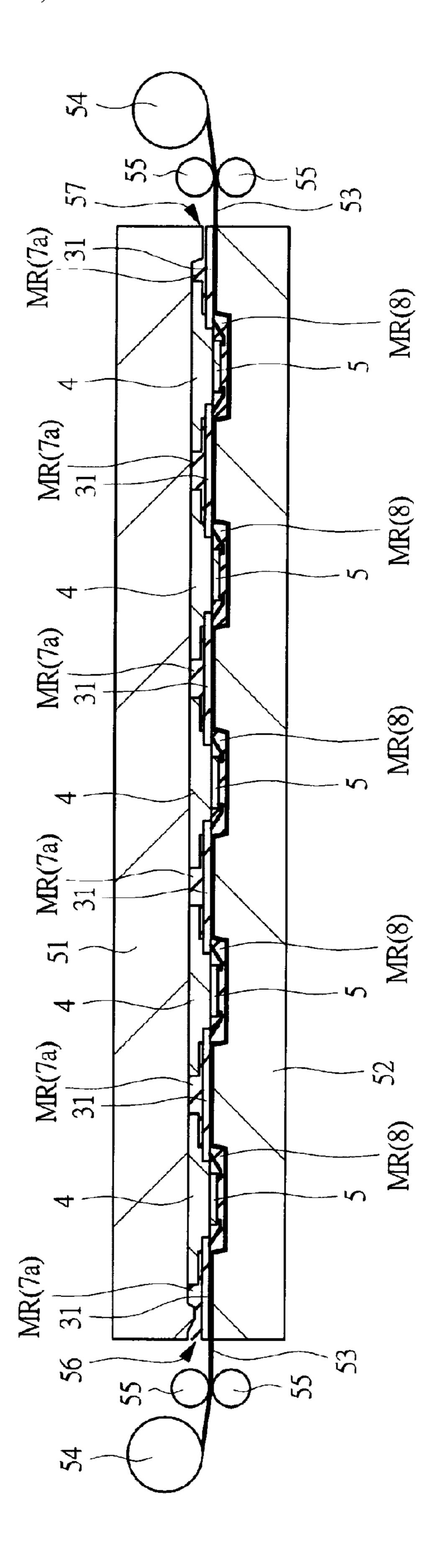

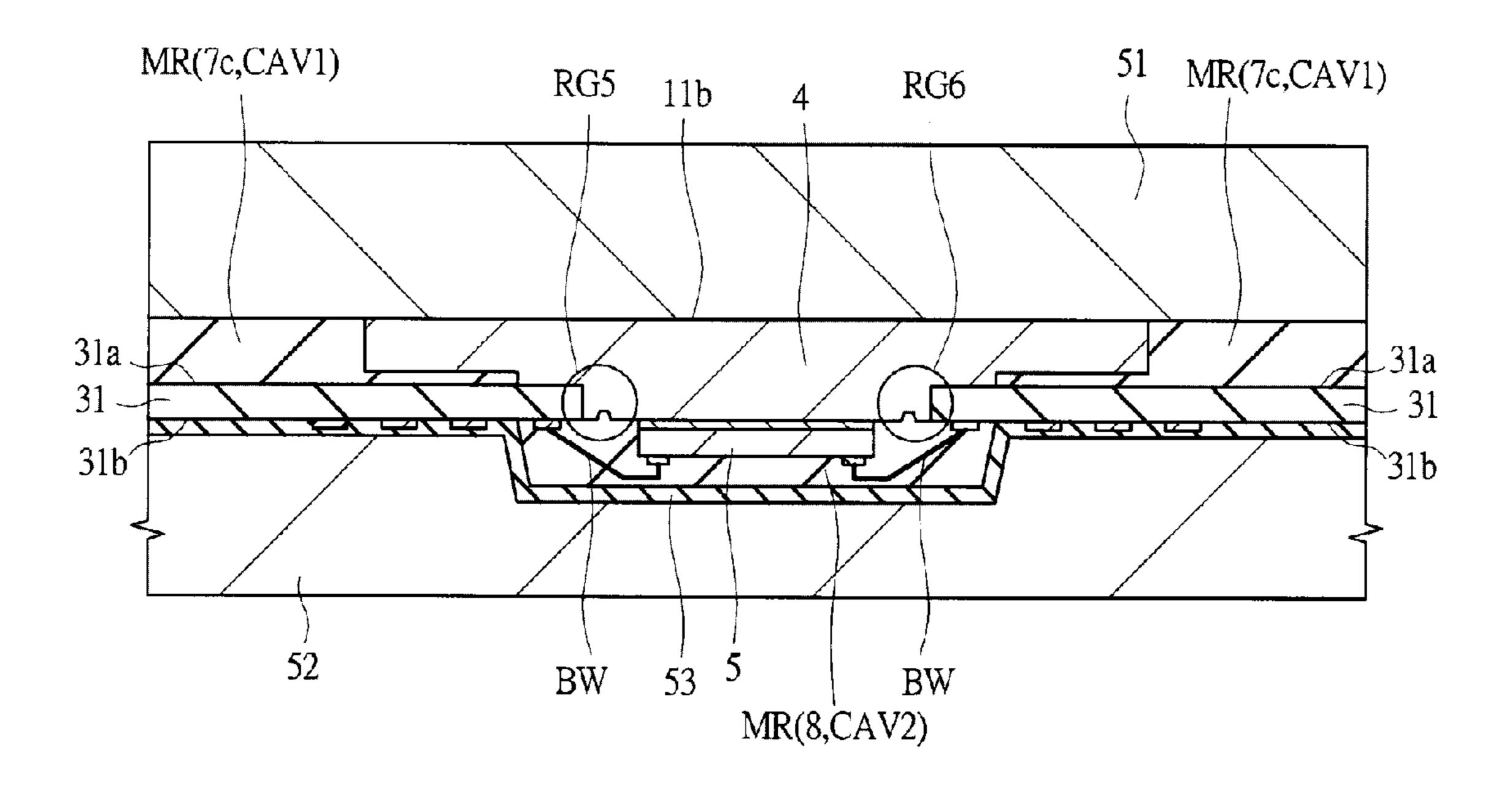

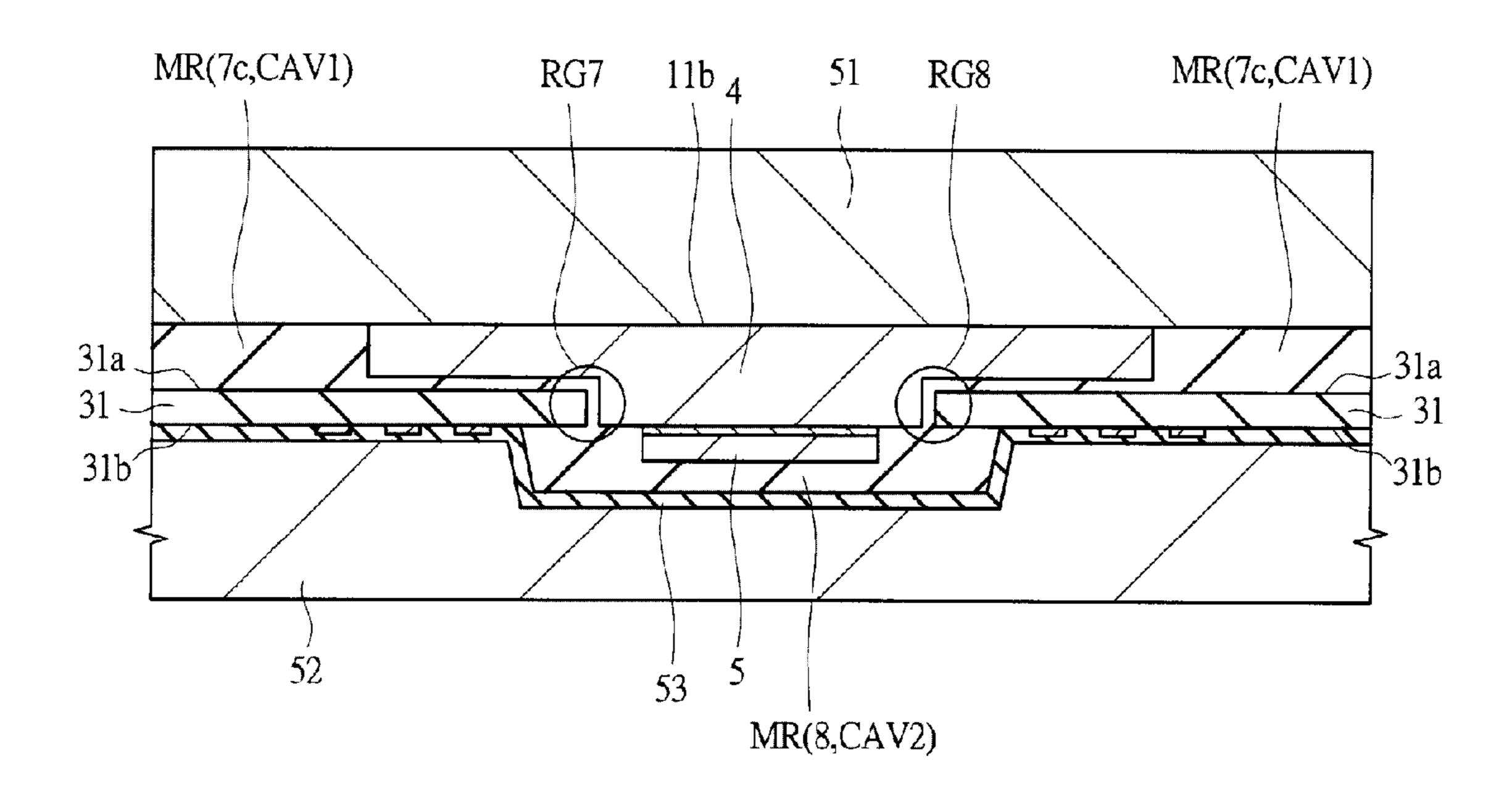

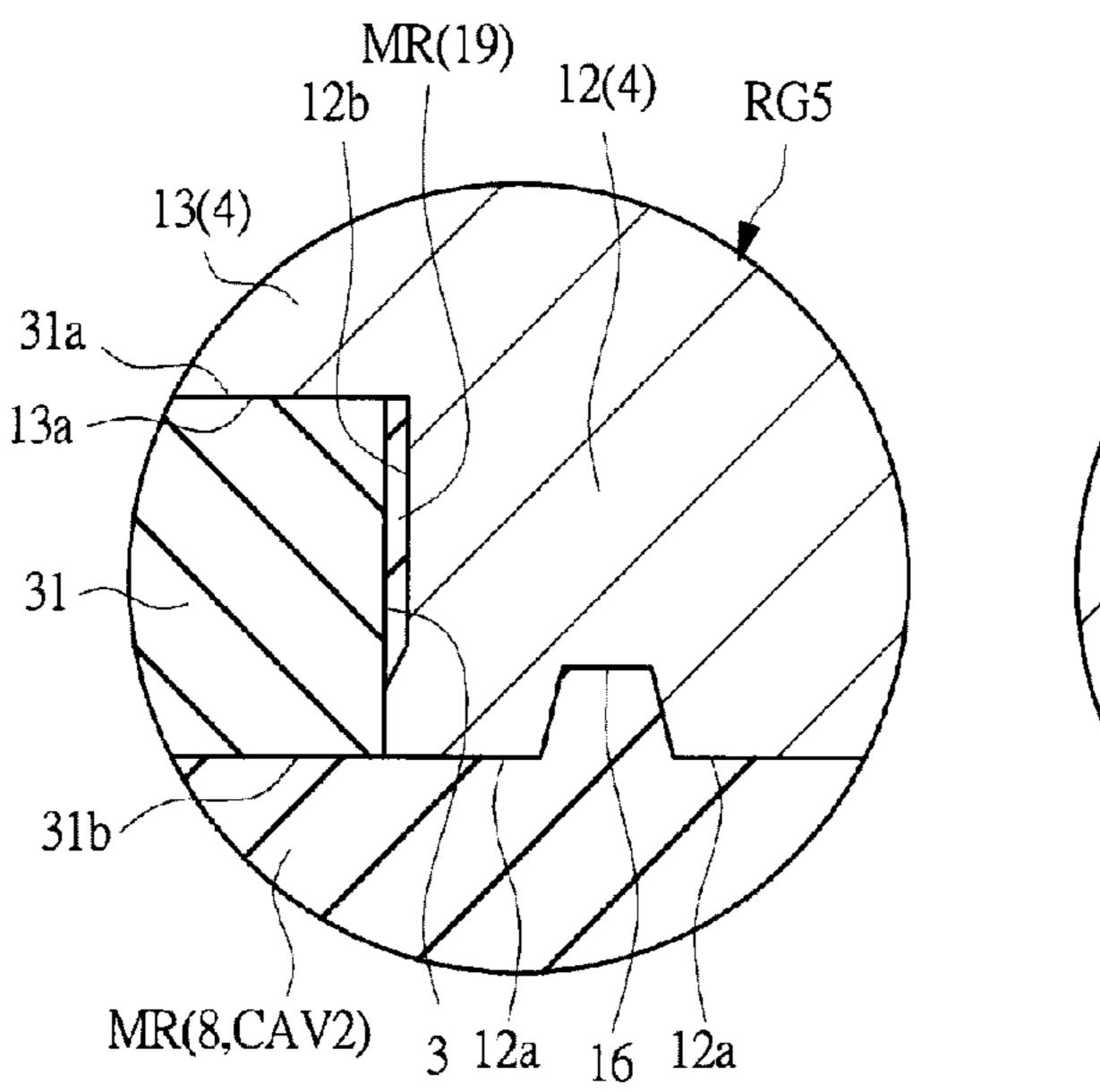

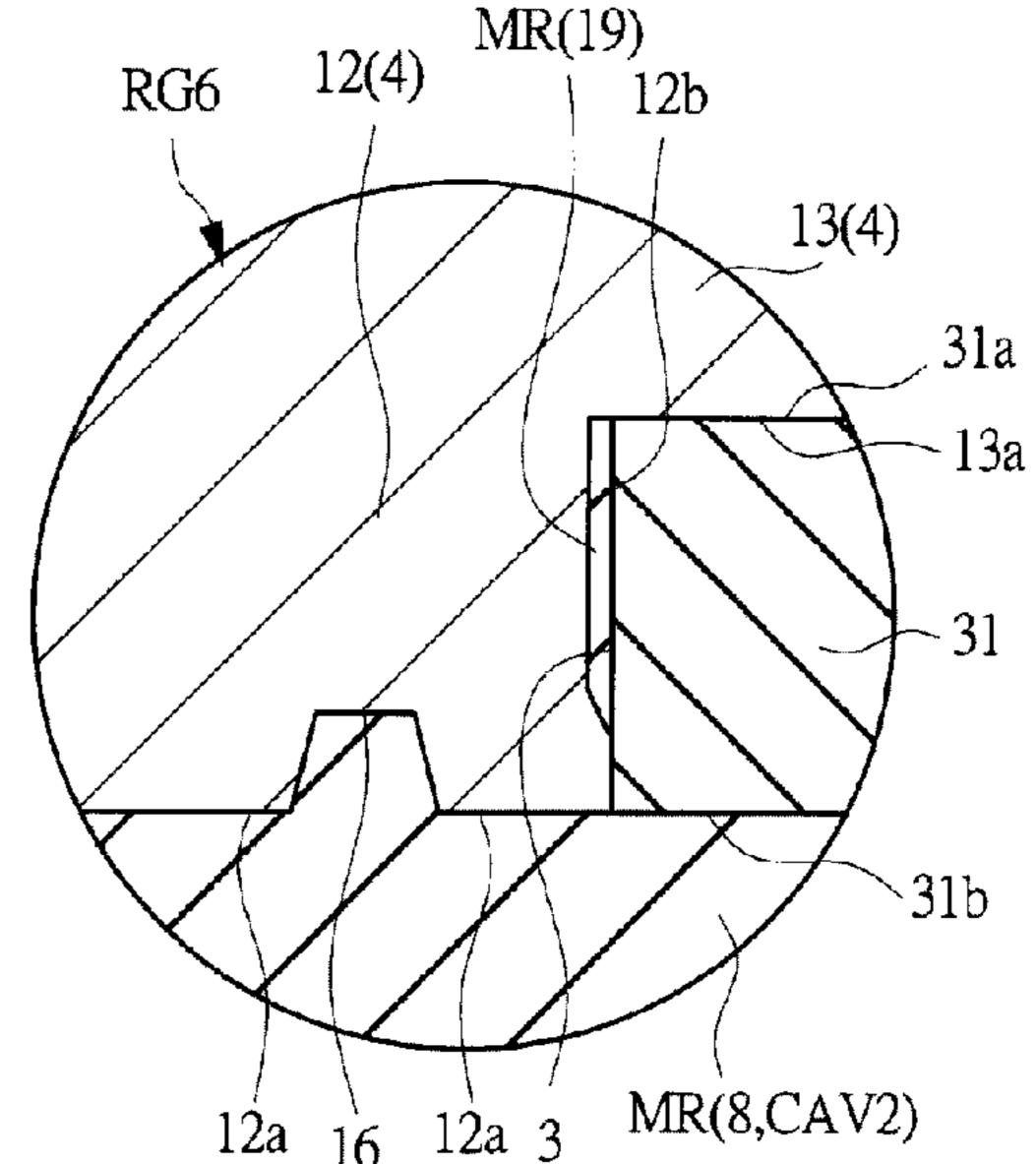

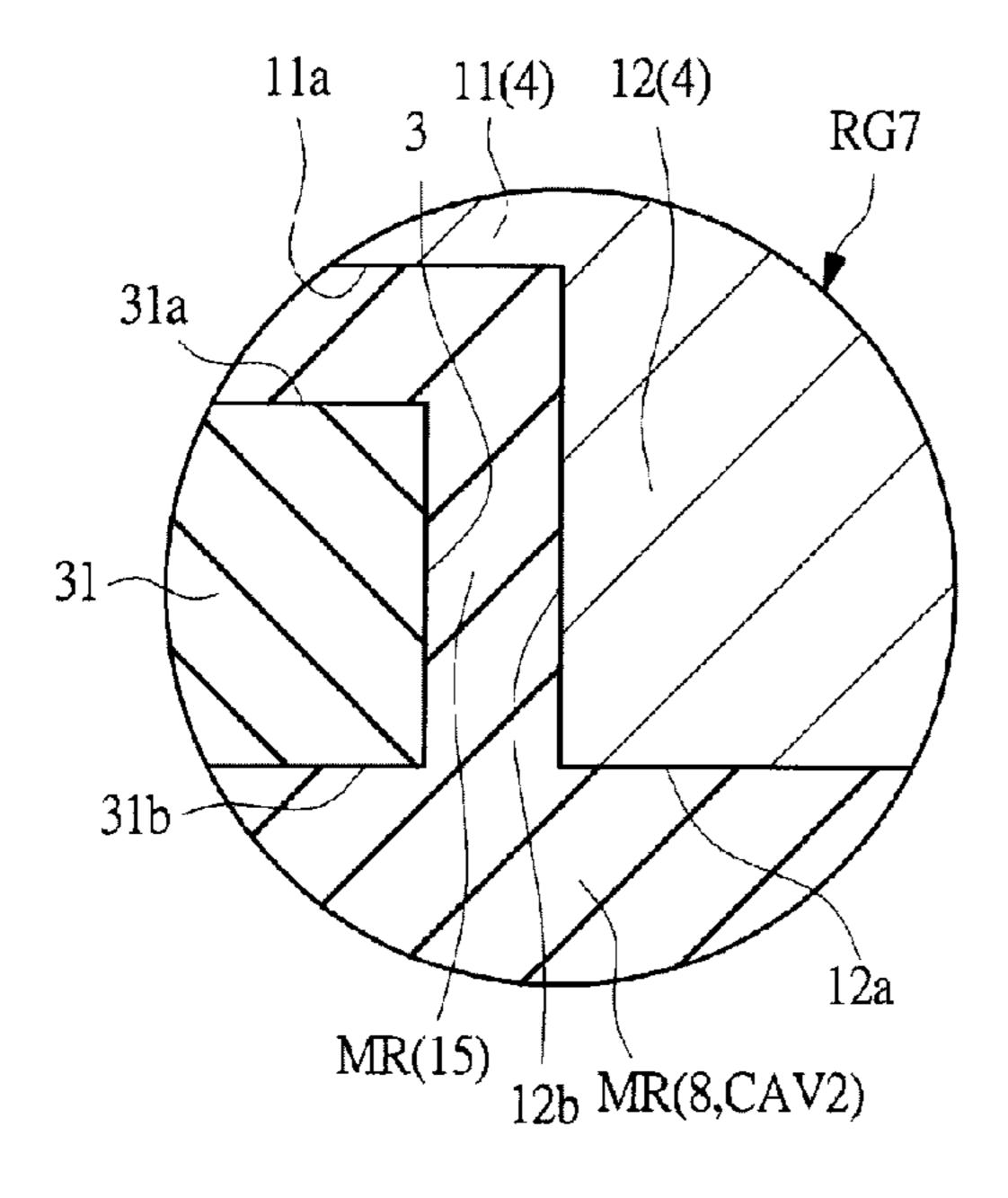

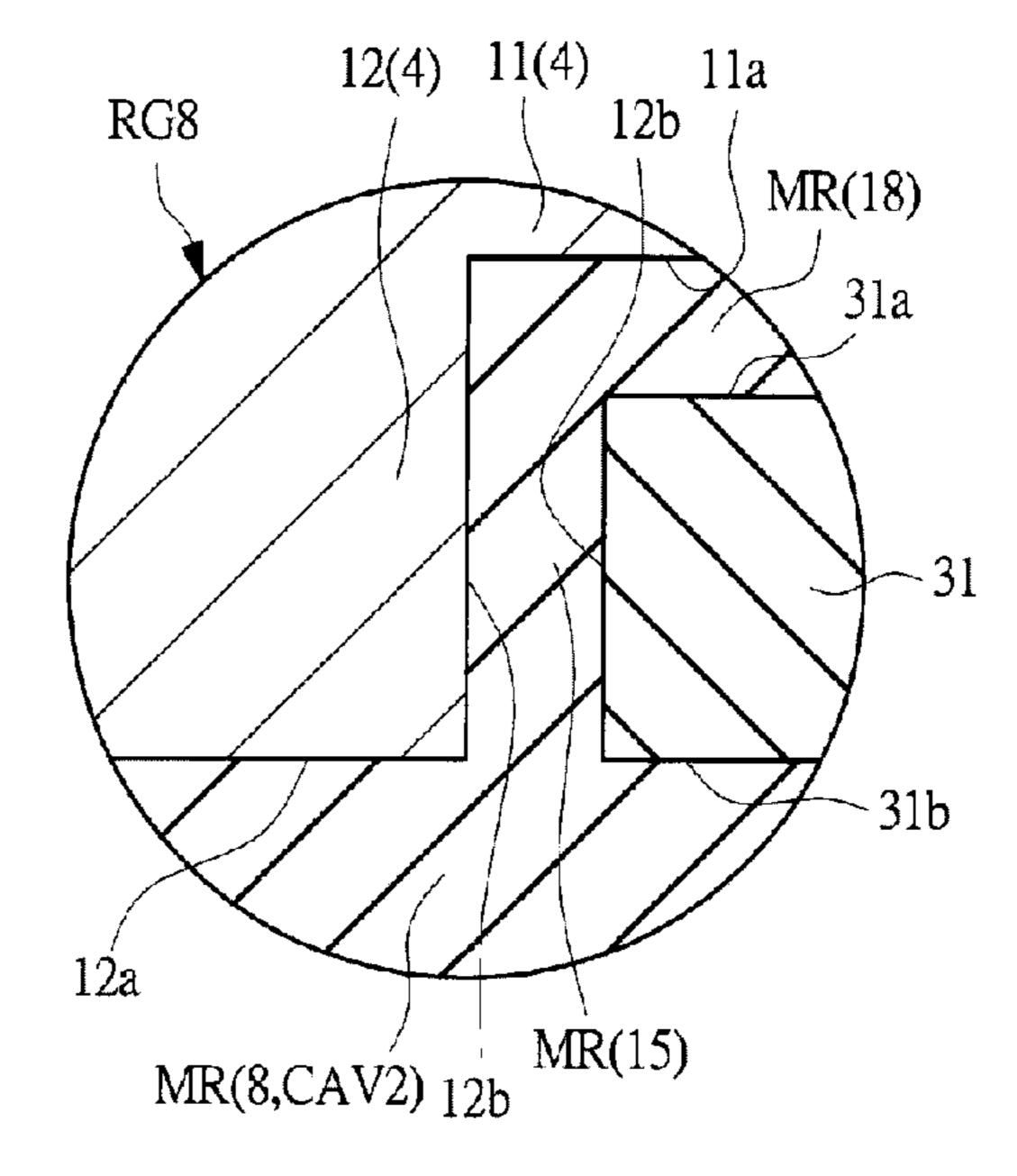

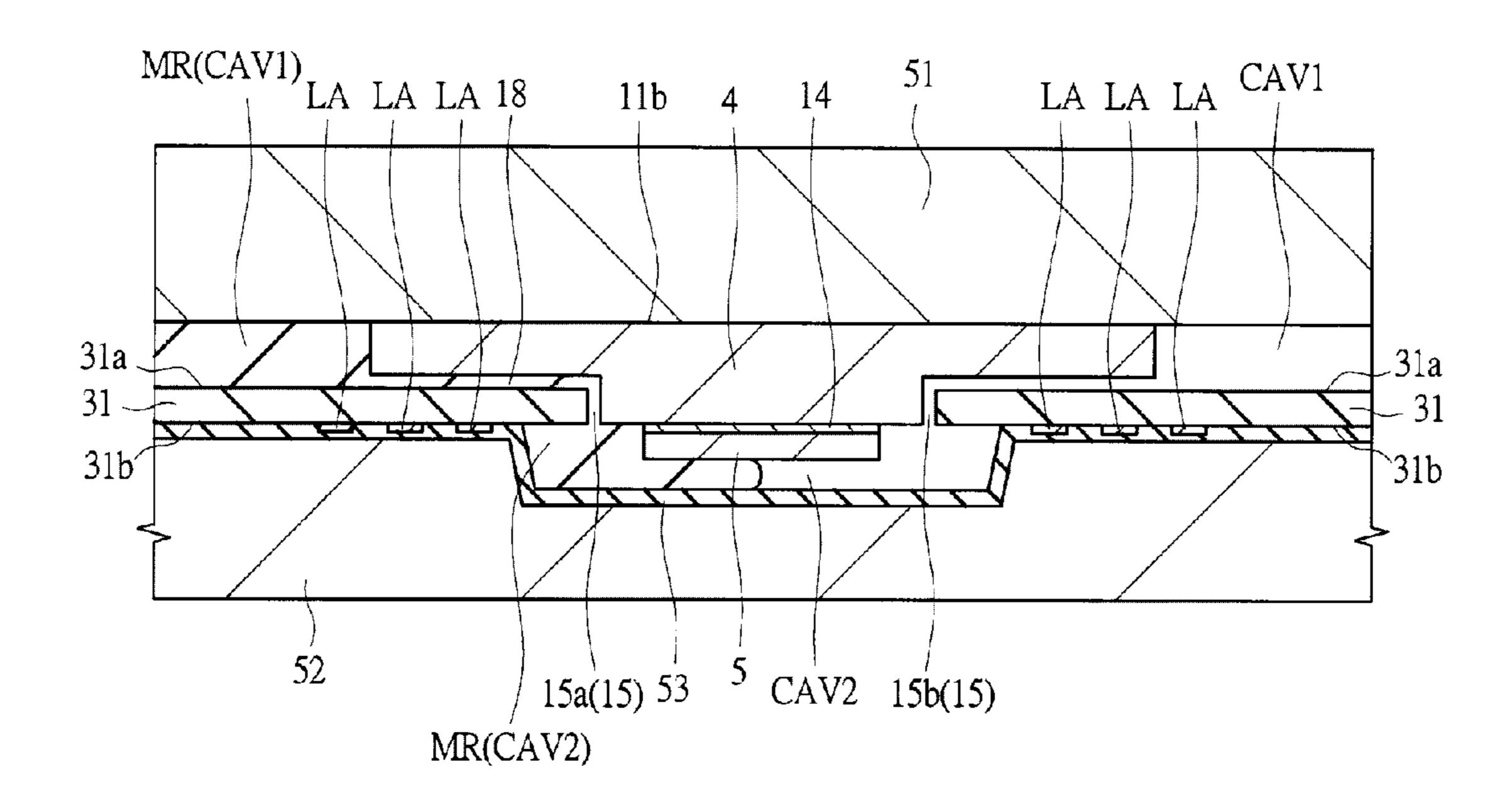

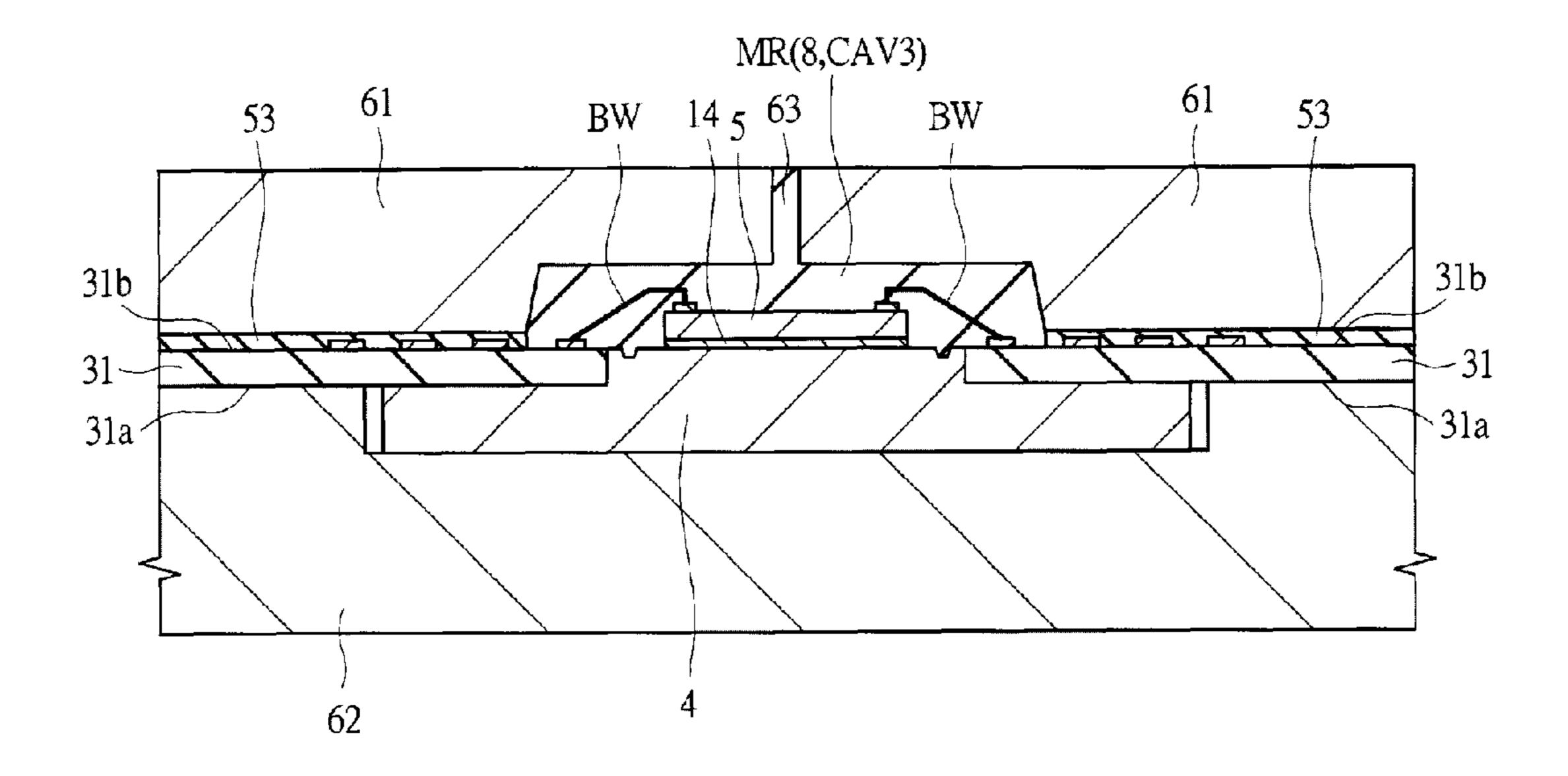

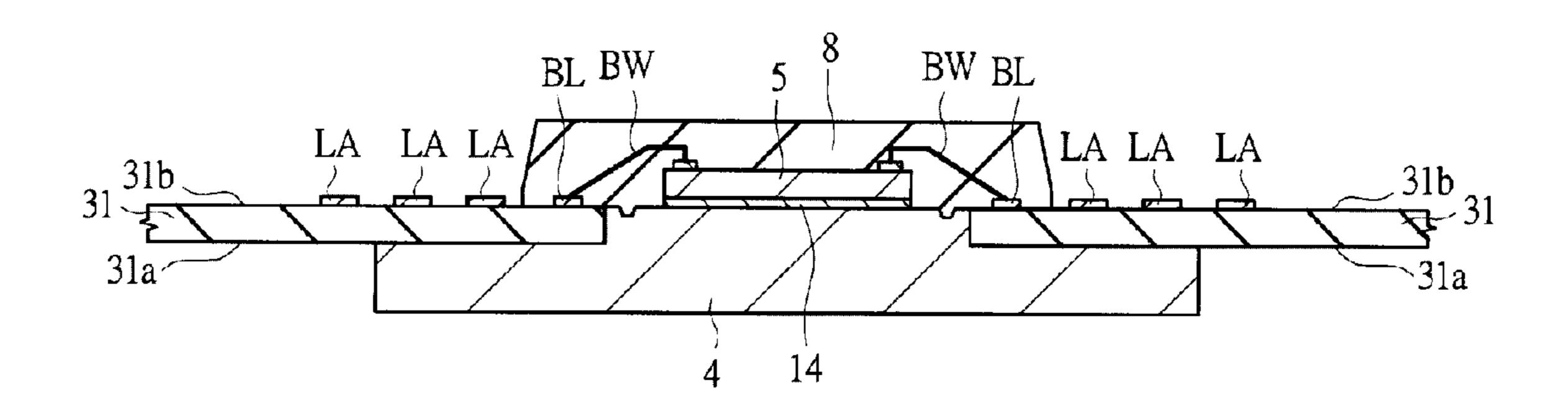

- FIG. **56** illustrates the step of molding;

- FIG. 57 illustrates the step of molding;

- FIG. **58** illustrates the step of molding;

- FIG. **59** illustrates the step of molding;

- FIG. **60** illustrates the step of molding;

- FIG. **61** illustrates the step of molding;

- FIG. **62** illustrates the step of molding;

- FIG. 63 illustrates the step of molding;

- FIG. **64** illustrates the step of molding;

- FIG. **65** illustrates the step of molding;

- FIG. 66 illustrates the step of molding;

- FIG. 67 illustrates the step of molding;

- FIG. 68 illustrates a flow diagram of manufacturing process of semiconductor device in other embodiments of the present invention;

- FIG. **69** is a plan view of semiconductor device during manufacturing process in other embodiments of the present 20 invention;

- FIG. 70 is a cross-sectional view of the semiconductor device, which is the same as in FIG. **69**, during manufacturing process;

- FIG. **71** is a plan view of the semiconductor device in the 25 next step of FIG. 69, during manufacturing process;

- FIG. 72 is a cross-sectional view of the semiconductor device, which is the same as in FIG. 71, during manufacturing process;

- FIG. **73** is a plan view of the semiconductor device in the next step of FIG. 71, during manufacturing process;

- FIG. 74 is a cross-sectional view of the semiconductor device, which is the same as in FIG. 73, during manufacturing process;

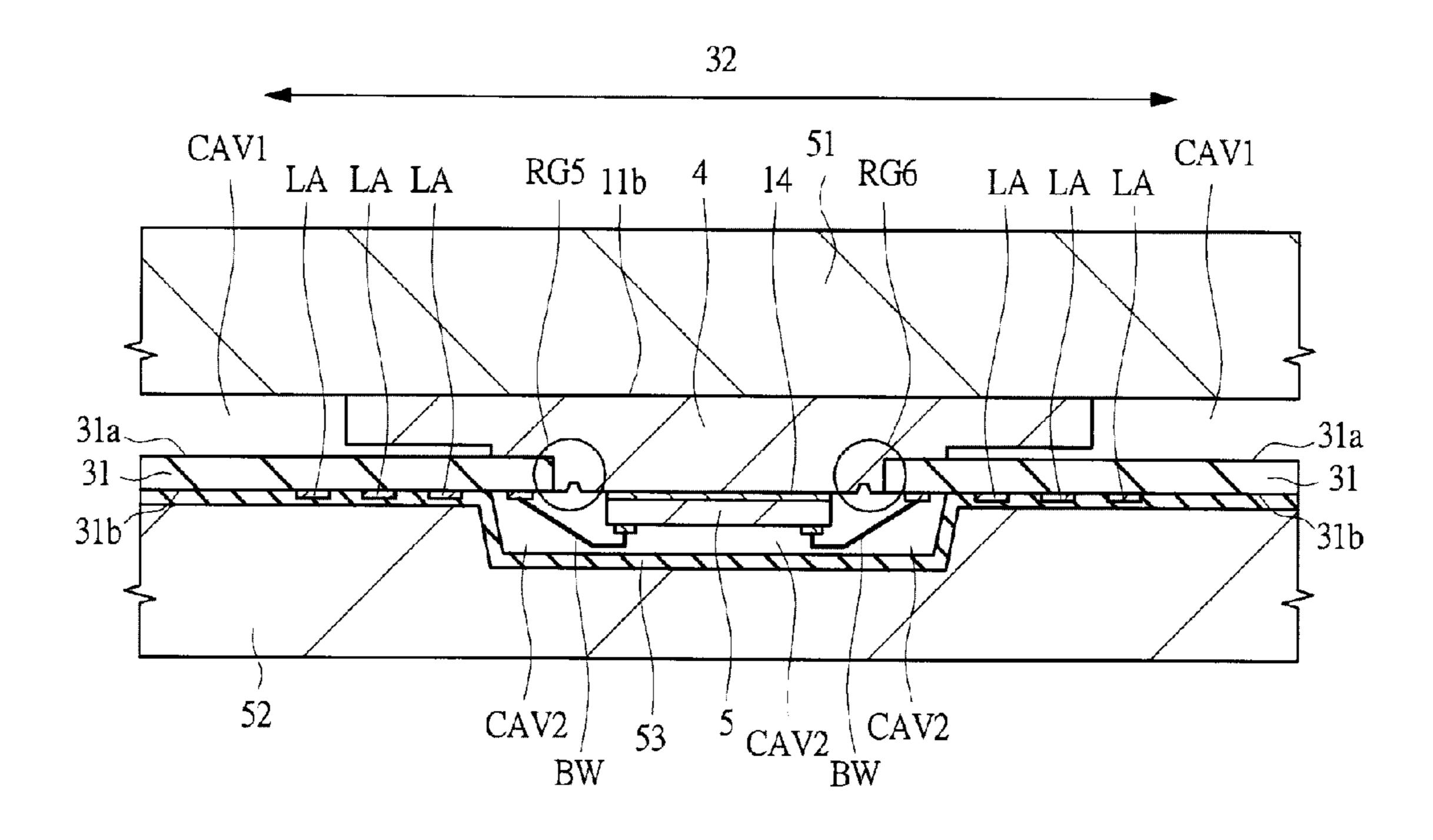

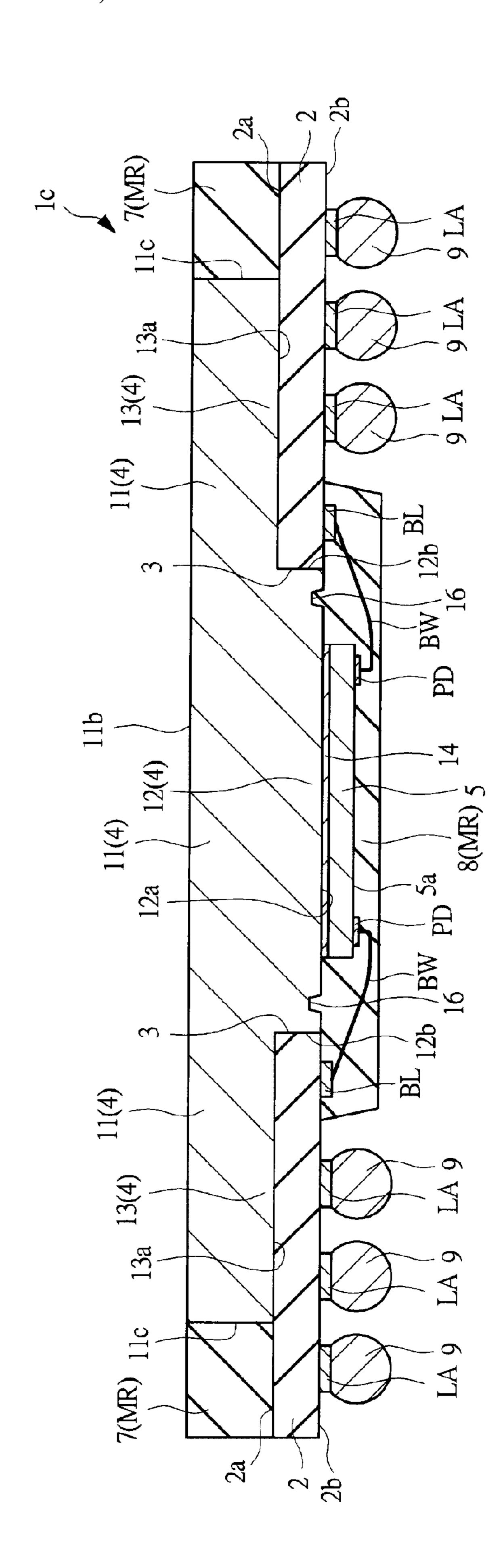

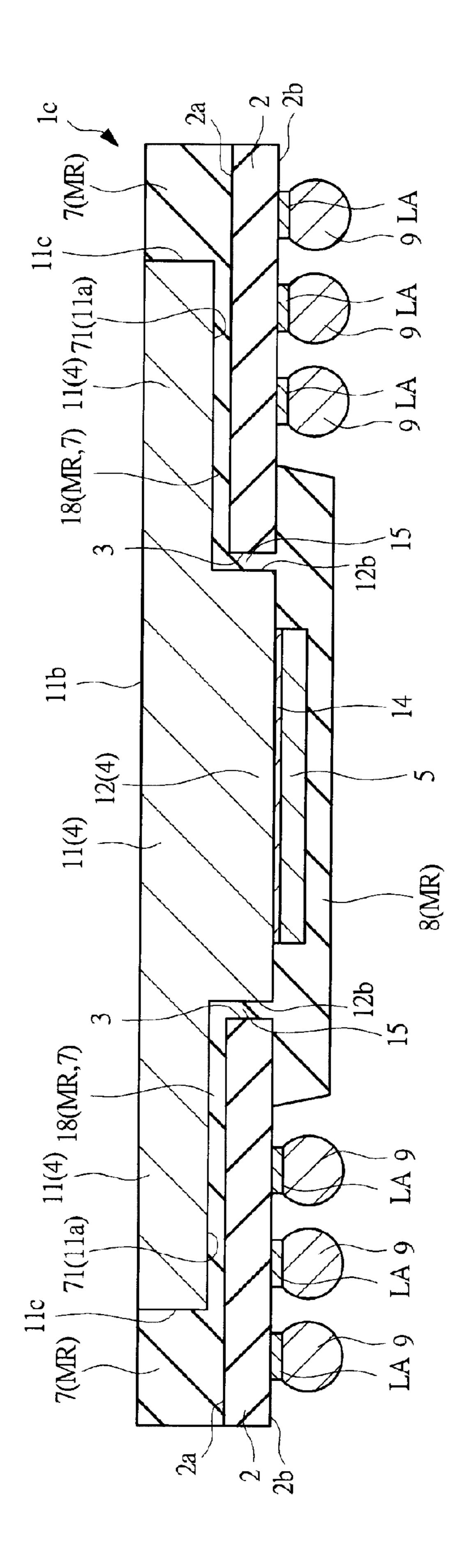

- FIG. 75 is a cross-sectional view of a semiconductor device 35 in further embodiment of the present invention;

- FIG. 76 is another cross-sectional view of the semiconductor device of FIG. 75;

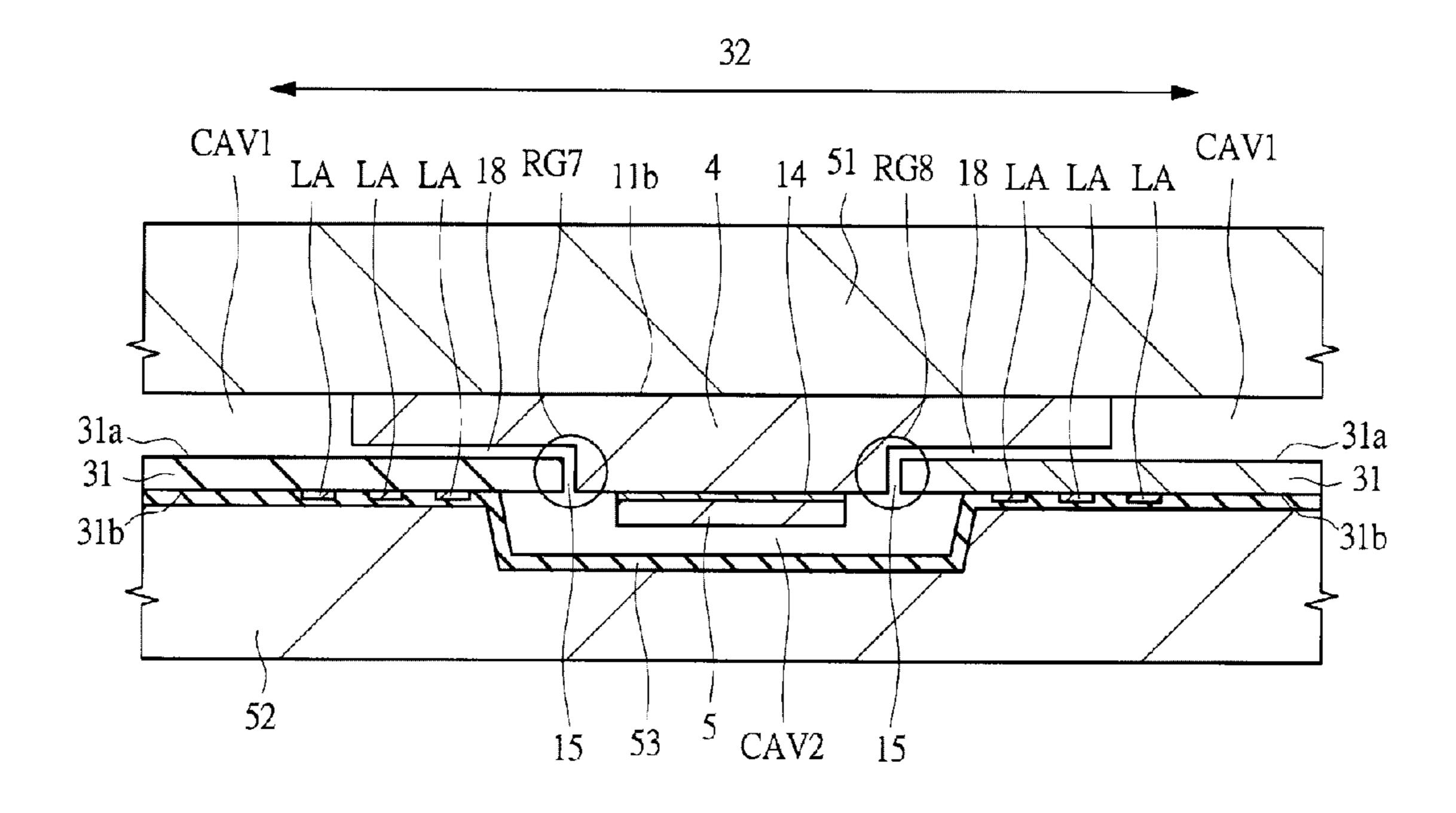

- FIG. 77 is a cross-sectional view of a semiconductor device in other embodiment of the present invention;

- FIG. 78 is another cross-sectional view of the semiconductor of FIG. 77,

- FIG. 79 is an upper surface view of the semiconductor device of FIG. 77;

- FIG. 80 is a lower surface view of the semiconductor 45 device of FIG. 77;

- FIG. 81 is a plane perspective view (lower surface view) of the semiconductor device of FIG. 77;

- FIG. 82 is a plane perspective view (lower surface view) of the semiconductor device of FIG. 77;

- FIG. 83 illustrates the process of manufacturing semiconductor device in further embodiment of the present invention;

- FIG. **84** illustrates the process of manufacturing semiconductor device in the further embodiment of the present invention;

- FIG. 85 illustrates the process of manufacturing semiconductor device in the further embodiment of the present invention;

- FIG. **86** illustrates the process of manufacturing semiconductor device in the further embodiment of the present invention;

- FIG. 87 is across sectional view of semiconductor device in still further embodiment of the present invention;

- FIG. 88 is another cross-sectional view of the semiconductor device of FIG. 87; and

- FIG. 89 is a plan view of the heat-releasing plate used in the semiconductor device of FIG. 87.

### DETAILED DESCRIPTION OF THE PREFERRED **EMBODIMENTS**

The following embodiments will be explained, divided 5 into plural sections or embodiments, if necessary for convenience. Except for the case where it shows clearly in particular, they are not mutually unrelated and one has relationships such as a modification, details, and supplementary explanation of some or entire of another. In the following embodiments, when referring to the number of elements, etc. (including the number, a numeric value, an amount, a range, etc.), they may be not restricted to the specific number but may be greater or smaller than the specific number, except for the case where they are clearly specified in particular and where 15 they are clearly restricted to a specific number theoretically. Furthermore, in the following embodiments, it is needless to say that an element (including an element step etc.) is not necessarily indispensable, except for the case where it is clearly specified in particular and where it is considered to be clearly indispensable from a theoretical point of view, etc. Similarly, in the following embodiments, when shape, position relationship, etc. of an element etc. is referred to, what resembles or is similar to the shape substantially shall be included, except for the case where it is clearly specified in particular and where it is considered to be clearly not right from a theoretical point of view. This statement also applies to the numeric value and range described above.

The embodiments of the present invention will be described below in detail referring to the drawings. In all the drawings for explaining embodiments, the same symbol is attached to the same member, as a principle, and the repeated explanation thereof is omitted. In the following embodiments, description about the same or similar part is not repeated, in principle, other than the case specifically required.

In order to make a drawing intelligible, hatching may not be attached even if it is a cross-sectional view, and hatching may be attached even if it is a plan view.

#### Embodiment 1

The semiconductor device and the method of manufacturing thereof (manufacturing process) according to an embodiment of the present invention are described below referring to the drawings.

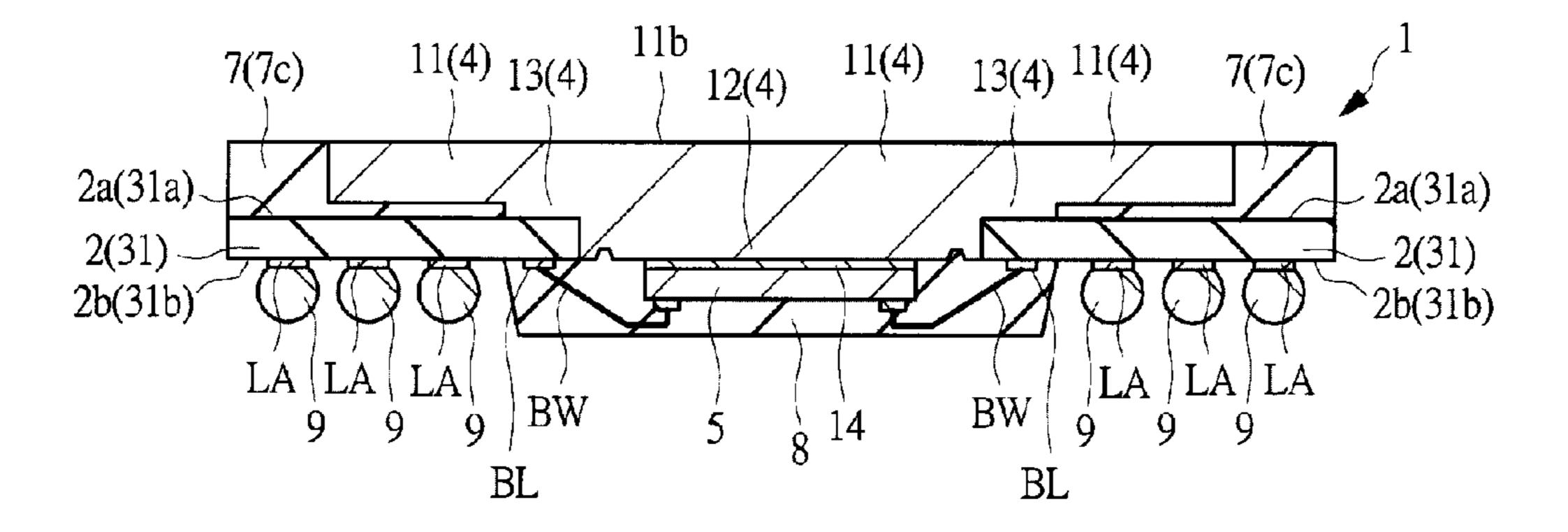

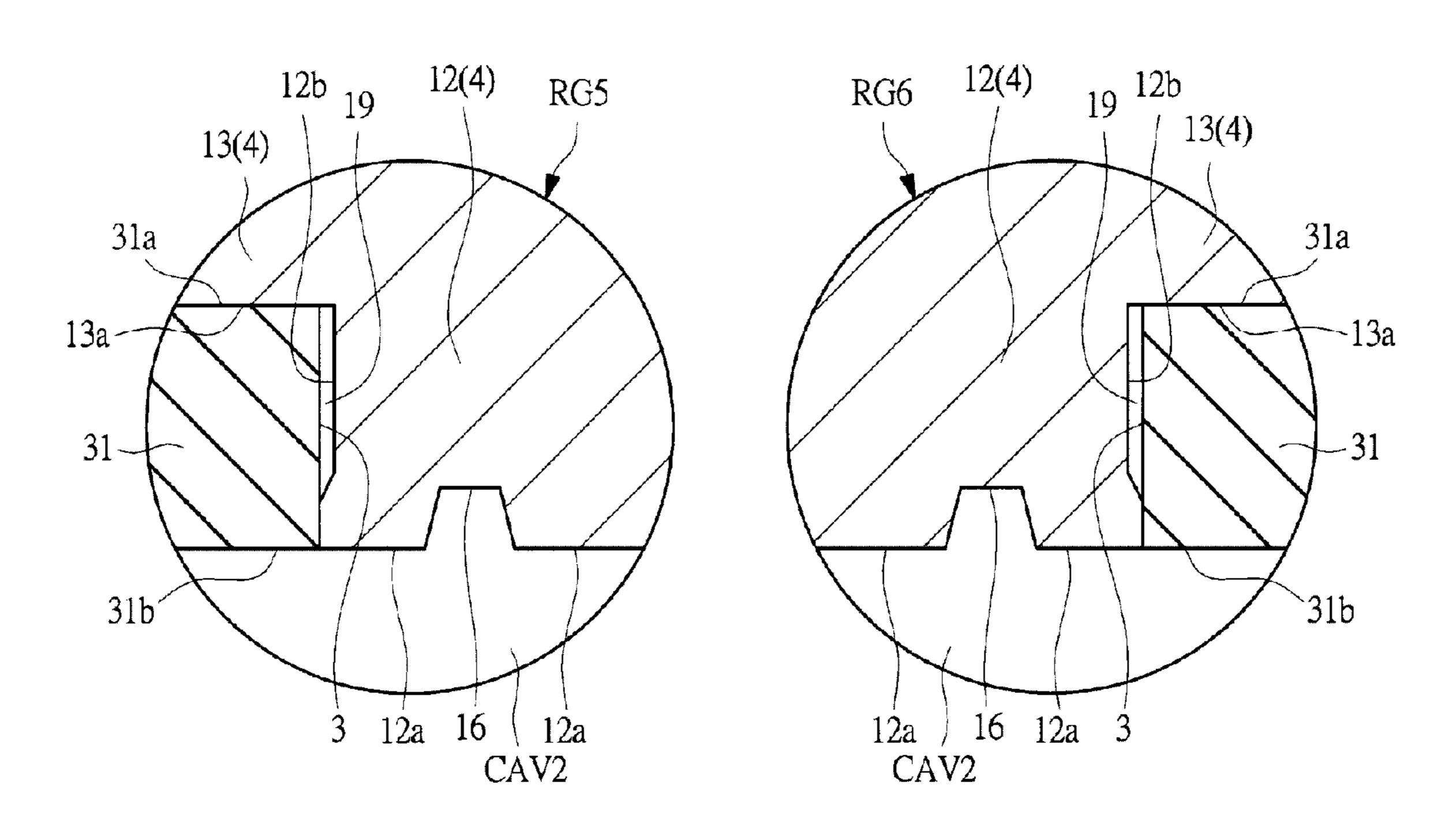

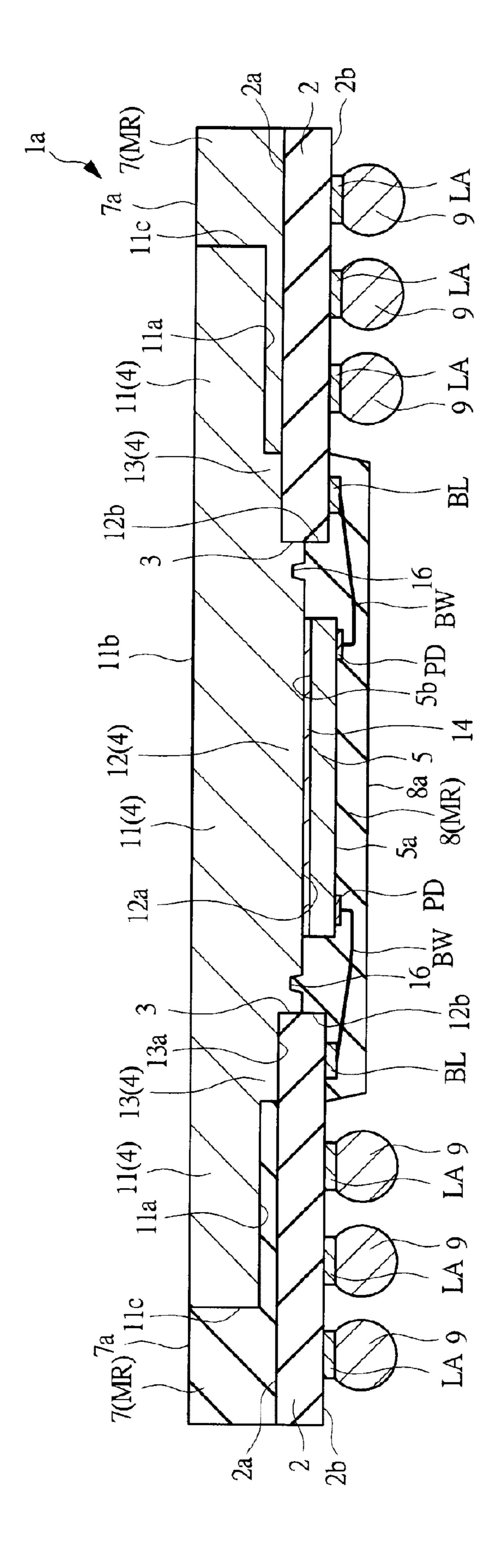

<Structure of Semiconductor Device> FIG. 1 and FIG. 2 show cross-sectional views (side surface cross-sectional views) of a semiconductor device 1 according to an embodiment of the present invention. FIG. 3 and FIG. 4 50 show main-part cross-sectional views (part-enlarged cross sectional views) of the semiconductor device 1. FIG. 5 is an upper surface view (plan view) of the semiconductor device 1. FIG. 6 is a lower surface view (bottom face view, rear surface view, plan view) of the semiconductor device 1. FIG. 55 7 is a plane perspective view (upper surface view) of the semiconductor device 1, illustrating the upper surface side of the semiconductor device 1 when seen through a sealing portion 7. FIG. 8 is a plane perspective view (lower surface view) of the semiconductor device 1, illustrating the lower side view of the semiconductor device 1 when seen through a sealing portion 8. FIG. 9 is a plane perspective view (lower surface view) of the semiconductor device 1 in a state in which, in FIG. 8, the bonding wire BW is further removed (seen through). FIG. 10 is a plane perspective view (lower 65 surface view) of the semiconductor device 1 in a state in which, in FIG. 9, a semiconductor chip 5 is further removed (seen through). The cross section along the A1-A1 line in

FIGS. 5 to 10 almost corresponds to FIG. 1. The cross section along the A2-A2 line in FIGS. 5 to 10 almost corresponds to FIG. 2. FIG. 3 corresponds to the part-enlarged view of a region RG1 (circled) in FIG. 1. FIG. 4 corresponds to the part-enlarged view of a region RG2 (circled) in FIG. 2. FIG. 5 11 is an upper surface view (plan view) of a wiring substrate 2 used in the semiconductor device 1 in the embodiment 1 of the present invention. FIG. 12 is a lower surface view (plan view) of the wiring substrate 2 used in the semiconductor device 1 in the embodiment 1. FIG. 13 is an upper surface view (plan view) of a hear-releasing plate 4 used in semiconductor device 1 in the embodiment 1. FIG. 14 is a lower surface view (plan view) of the heat-releasing plate 4 used in side surface view of the heat-releasing plate 4 used in the semiconductor device in the embodiment 1. FIG. 16 and FIG. 17 are each a cross-sectional view (side surface cross-sectional view) of the heat-releasing plate 4 used in the semiconductor device 1 in the embodiment 1. The cross section along 20 the B1-B1 line in FIGS. 13 and 14 almost corresponds to FIG. 16. The cross section along the B2-B2 line in FIGS. 13 and 14 almost corresponds to FIG. 17. However, the position of B1-B1 line in FIGS. 13 and 14 corresponds to the position of A1-A1 line in FIGS. 5 to 10, and the position of B2-B2 line in 25 FIG. 13 and FIG. 14 corresponds to the position of A2-A2 line in FIGS. 5 to 10. Therefore FIG. 16 shows the same cross section as that of FIG. 1, and FIG. 17 shows the same cross section as that of FIG. 2. For convenience of understanding, FIG. 7 shows the position of a through-hole 3 by a broken line, 30 which through-hole 3 is invisible behind the heat-releasing plate 4 even looking through the sealing portion 7. Similarly FIG. 8 shows the position of outer shape of the sealing portion 8 seen through, by a broken line.

1, given in FIGS. 1 to 10, is a semiconductor device of resin-seal type semiconductor package structure.

The semiconductor device 1 of the embodiment 1 comprises the wiring substrate 2, the heat-releasing plate 4 being inserted in a part thereof (a convex part 12) into the throughhole 3 of the wiring substrate 2, the semiconductor chip 5 being mounted over the convex part 12 of the heat-releasing plate 4, and a plurality of bonding wires BW each coupling electrically the respective electrode pads PD of the semiconductor chip 5 with the respective bonding leads BL of the 45 wiring substrate 2. The semiconductor device 1 further comprises the sealing portion 7 covering a portion of an upper surface 2a of the wiring substrate 2, the sealing portion 8 covering a portion of a lower surface 2b of the wiring substrate 2 including the semiconductor chip 5 and the bonding 50 wires BW, and a plurality of solder balls 9 positioned directly on the lower surface 2b of the wiring substrate 2.

The wiring substrate 2 (substrate, package substrate, wiring substrate for packaging) illustrated in FIGS. 1 to 12 has the upper surface (top surface) 2a as a main surface at one side 55 and the lower surface (rear surface) as a main surface at opposite side to the upper surface 2a. In mounting the semiconductor device 1 over a mounting substrate 21 (described later) or the like, since the lower surface 2b side of the wiring substrate 2 becomes the mounting surface (facing the mount- 60 ing substrate 21 described later), the lower surface 2b of the wiring substrate 2 can be considered as the mounting surface. The upper surface 2a and the lower surface 2b of the wiring substrate 2 are nearly in parallel each other. Near the central part of the wiring substrate 2, the through-hole 3 (hole part, 65 opening) penetrating from the upper surface 2a to the lower surface 2b of the wiring substrate 2 is located.

The heat-releasing plate 4 (heat-releasing member, thermal-conducting member, heat-spreader) illustrated in FIGS. 1 to 10 and FIGS. 13 to 17 has an integral structure of: a base material part 11 having a main surface 11a facing the upper surface 2a of the wiring substrate 2; the convex part 12 being located at central part of the main surface 11a of the base material part 11 and protruding from the base material part 11; and a supporting part 13 being formed in the main surface 11a of the base material part 11 and contacting with the upper surface 2a of the wiring substrate 2. The heat-releasing plate 4 is positioned directly on and fixed to the upper surface 2a of the wiring substrate 2 so that the convex part 12 is positioned in the through-hole 3.

The base material part 11 (base part, flat plate part, heatthe semiconductor device 1 in the embodiment 1. FIG. 15 is a 15 releasing part) of the heat-releasing plate 4 is in a flat plate shape, and has the main surface 11a facing the upper surface 2a of the wiring substrate 2 and a rear surface 11b which is a main surface at opposite side to the main surface 11a. The rear surface 11b of the base material part 11 is exposed from the sealing portion 7 (an upper surface 7a of the sealing portion 7) to form an exposure surface (heat-releasing surface, heatreleasing part) of the heat-releasing plate 4. The rear surface 11b of the base material part 11 can be set to be almost flat. A side surface 11c of the base material part 11 is covered with the sealing portion 7. Larger size of the base material part 11 of the heat-releasing plate 4 further increases the heat-releasing performance.

The convex part 12 (protruding part, chip-mounting part) protruding almost vertical to the main surface 11a is formed near the center of the main surface 11a of the base material part 11. The convex part 12 is positioned (inserted) in the through-hole 3 of the wiring substrate 2. Furthermore, the semiconductor chip 5 is mounted over a main surface (top surface) 12a of the convex part 12. Accordingly, the convex The semiconductor device 1 according to the embodiment 35 part 12 of the heat-releasing plate 4 can be considered as the chip-mounting part. That is, at the lower surface 2b side of the wiring substrate 2, the semiconductor chip 5 is mounted (die-bonded) over the convex part 12 of the heat-releasing plate 4 positioned in the through-hole 3 of the wiring substrate 2, and thus the semiconductor chip 5 is in a state of being located at the lower surface 2b side of the wiring substrate 2.

> Since the convex part 12 is positioned in the through-hole 3 of the wiring substrate 2, the convex part 12 is located in the main surface 11a of the base material part 11 at a position overlapped in a planar view with (included) the through-hole 3 of the wiring substrate 2. On the other hand, since the supporting part 13 is positioned outside the through-hole 3 of the wiring substrate 2 to contact with the upper surface 2a of the wiring substrate 2, the supporting part 13 is located at a position not overlapped in a planar view with the throughhole 3 of the wiring substrate 2 in the main surface 11a of the base material part 11. The term "overlapped in a planar view", "not overlapped in a planar view", or "viewed planarly" refers to herein the case of being viewed (or viewed in projection) in a plane parallel to the upper surface 2a or the lower surface 2bof the wiring substrate 2.

> In the semiconductor device 1, the main surface 11a of the base material part 11 of the heat-releasing plate 4 and the upper surface 2a of the wiring substrate 2 are almost parallel to each other. The convex part 12 of the heat-releasing plate 4 has the main surface 12a (chip-mounting surface) and the side surface 12b (side wall), and the main surface 12a of the convex part 12 is surrounded by the side surface 12b of the convex part 12. In other words, the side surface 12b of the convex part 12 is positioned between the main surface 12a of the convex part 12 and the main surface 11a of the base material part 11. Since the main surface 12a of the convex part

12 of the heat-releasing plate 4 is almost parallel to the main surface 11a of the base material part 11, the main surface 12a is also almost parallel to the lower surface 2b of the wiring substrate 2. Furthermore, when viewed planarly, the convex part 12 is included in a planar view in the base material part 11. The semiconductor chip 5 is adhered to be fixed to the main surface 12a of the convex part 12 via a connecting material 14 (adhesive, die-bonding material). The side surface 12b of the convex part 12 faces the inside wall of the through-hole 3 of the wiring substrate 2.

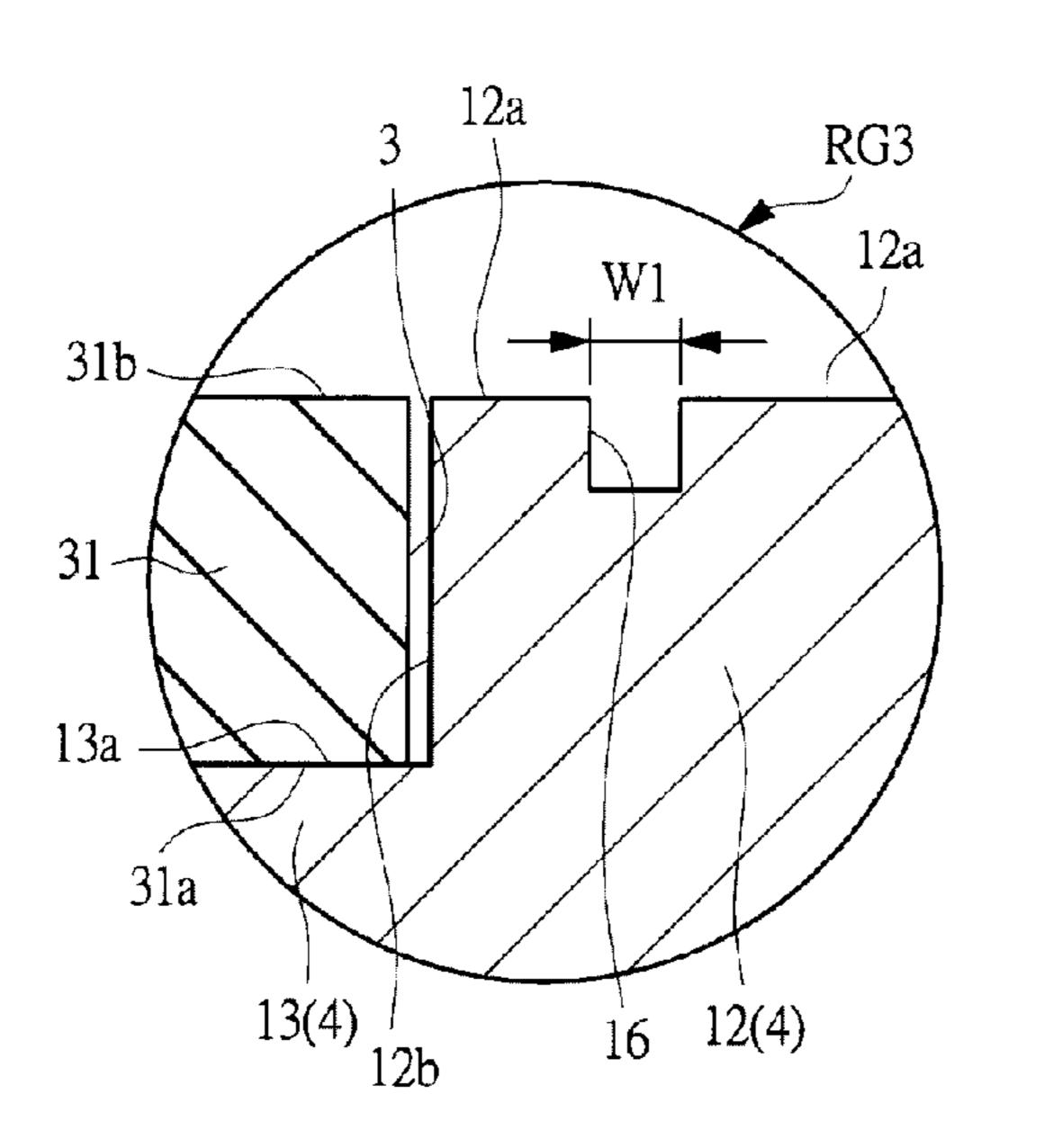

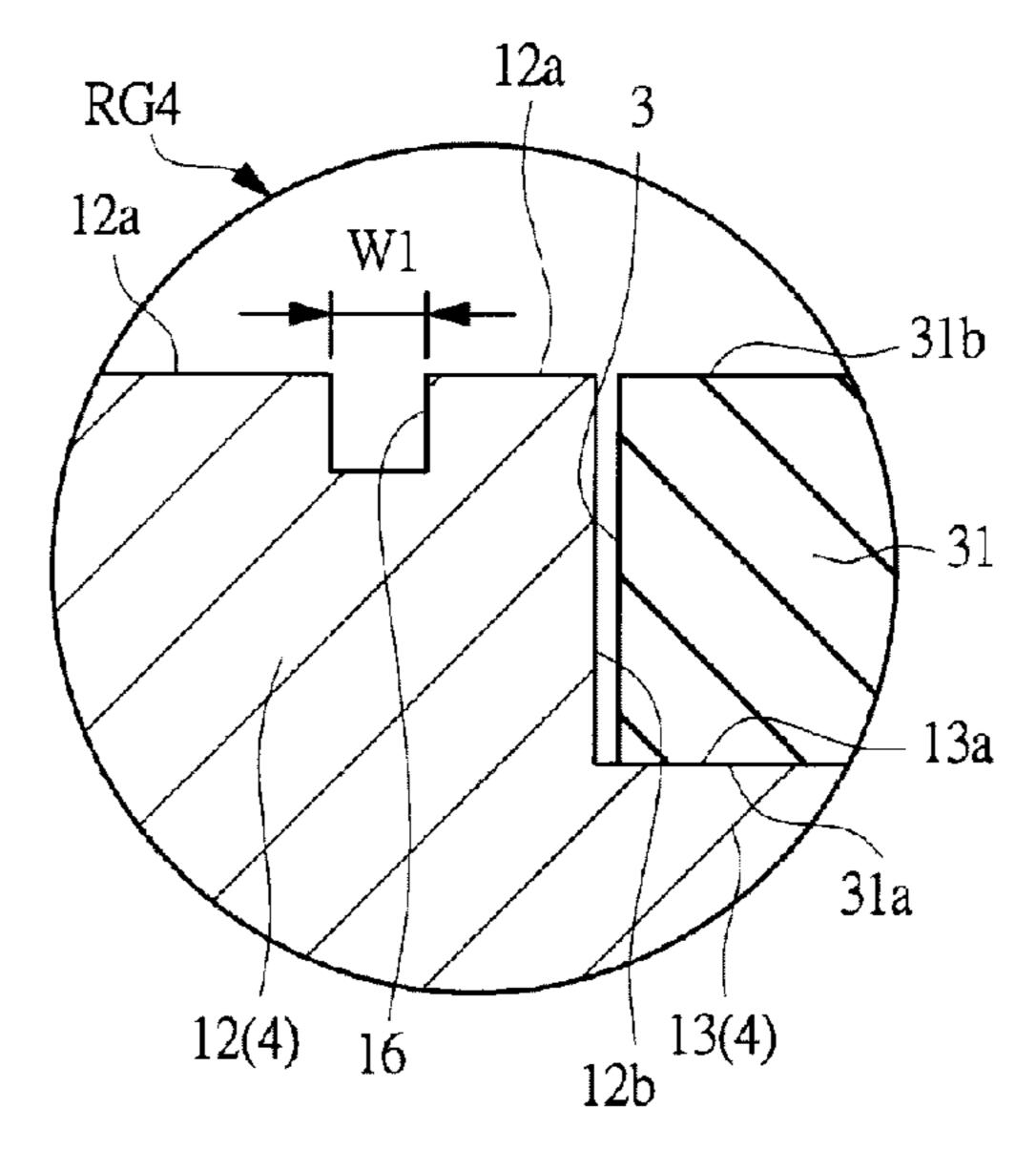

The side surface 12b of the convex part 12 is almost vertical to the main surface 11a of the base material part 11. As described later, however, the manufacturing process of the semiconductor device 1, (the process corresponding to the step S6 described later), widens forcibly a groove 16 in the 15 convex part 12 to swage the heat-releasing plate 4 (the convex part 12 of the heat-releasing plate 4) to the wiring substrate 2 (specifically, a wiring substrate 31 described later). Consequently, as schematically illustrated in FIG. 3, a region close to the main surface 11a in the side surface 12b of the convex 20 part 12 is deformed (inclined) toward the inside wall of the through-hole 3 of the wiring substrate 2, thus contacting with the inside wall of the through-hole 3 of the wiring substrate 2. As a result, in the stage before the step S6 of swaging described later, the entire side surface 12b of the convex part 25 12 of the heat-releasing plate 14 becomes almost vertical to the main surface 11a of the base material part 11, and also a region close to the main surface 11a in the side surface 12b of the convex part 12 is not deformed (not inclined), (refer to FIG. **49** described later).

The supporting part 13 located in the main surface 11a of the base material part 11 has a supporting surface 13a contacting with the upper surface 2a of the wiring substrate 2. The supporting surface 13a can be set as a flat surface. The main surface 11a of the base material part 11, the supporting 35 surface 13a of the supporting part 13, and the main surface 12a of the convex part 12 have different height from each other. On the basis of the main surface 11a of the base material part 11, the supporting surface 13a of the supporting part 13 is at a higher position than the main surface 11a of the base 40 material part 11, and the main surface 12a of the convex part 12 is at a much higher position than the main surface 11a of the base material part 11 and the supporting surface 13a of the supporting part 13, (herein the direction of higher height is defined as the side of the main surface 12a of the convex part 45 12 from the main surface 11a of the base material part 11). In other words, the supporting part 13 (the supporting surface 13a of the supporting part 13) is at a lower position than the convex part 12 (the main surface 12a of the convex part 12), and the main surface 11a of the base material part 11 (the 50 region in which both of the convex part 12 and the supporting part 13 are not formed) is at a lower position than the supporting part 13 (the supporting surface 13a of the supporting part **13**).

Consequently, the region, where the convex part 12 is positioned (inserted) in the through-hole 3 of the wiring substrate 2, the supporting surface 13a of the supporting part 13 contacts with the upper surface 2a of the wiring substrate 2, and no convex part 12 and no supporting part 13 in the main surface 11a of the base material part 11 are provided, is in a 60 state of being apart from the upper surface 2a of the wiring substrate 2. Therefore, a gap 18 (gap part) is formed between the upper surface 2a of the wiring substrate 2 and the region having no convex part 12 and no supporting part 13 in the main surface 11a of the base material part 11, and the gap 18 is filled with a portion of the sealing portion 7 (namely, a resin material MR for the sealing portion 7).

10

As described above, the heat-releasing plate 4 is structured by forming integrally: the base material part 11 being positioned outside the through-hole 3 at the side of upper surface 2a of the wiring substrate 2; the convex part 12 being positioned (inserted) in the through-hole 3 of the wiring substrate 2; and the supporting part 13 contacting with the upper surface 2a of the wiring substrate 2 to separate the main surface 11a of the base material part 11 from the upper surface 2a of the wiring substrate 2, (namely, to form the gap 18 between the main surface 11a of the base material part 11 and the upper surface 2a of the wiring substrate 2).

The main surface 12a of the convex part 12 is the chipmounting surface (the face on which the semiconductor chip 5 is mounted), and the chip-mounting surface of the heatreleasing plate 4 (in the main surface 12a of the convex part 12) is positioned in almost the same plane as the lower surface 2b of the wiring substrate 2. The structure is attained by setting the difference in elevation (the height difference) between the supporting surface 13a of the supporting part 13 and the main surface 12a of the convex part 12 to be nearly equal to the thickness of the wiring substrate 2 (or the height difference between the upper surface 2a and the lower surface 2b of the wiring substrate 2).

The heat-releasing plate 4 plays a role of conductor part (metal part) for chip-mounting and also a role of conductor part (metal part) for heat-releasing. By placing the heat-releasing plate 4 to the upper surface 2a side of the wiring substrate 2 so that the convex part 12 is positioned in the through-hole 3 of the wiring substrate 2, and by placing the semiconductor chip 5 over the convex part 12 of the heat-releasing plate 4, the heat generated from the semiconductor chip 5 during the use of the semiconductor device 1 is allowed to be transferred to the heat-releasing plate 4, and then the heat is released outside the semiconductor device 1 from the exposure part (the rear surface 11b of the base material part 11) of the heat-releasing plate 4.

Since the heat-releasing plate 4 is a member for releasing the heat generated from the semiconductor chip 5, the heatreleasing plate 4 preferably has high thermal conductivity, and the heat conduction property (thermal conductivity) of the heat-releasing plate 4 is required to be higher than each of the heat conduction properties (thermal conductivities) of at least the wiring substrate 2 and the sealing portions 7 and 8. Since the conductive material (specifically metallic material) has high thermal conductivity, the heat-releasing plate 4 is preferably made of a conductive material, and more preferably made of a metallic material. The use of metallic material such as copper (Cu) and the one composed mainly of copper (Cu) alloy for the heat-releasing plate 4 is further preferable because the heat-releasing plate 4 is provided with high thermal conductivity and is easy to be processed (formation of the heat-releasing plate 4).

The through-hole 3 of the wiring substrate 2 and the convex part 12 positioned in the through-hole 3 have almost equal cross sectional shape at a position parallel to the upper surface 2a of the wiring substrate 2, and a portion of the side surface 12b of the convex part 12 directly contacts with (adheres to) the inside wall (side wall, side surface) of the through-hole 3 of the wiring substrate 2. However, not the entire surface of the side surface 12b of the chip-mounting part 12 directly contacts with (adheres to) the inside wall of the through-hole 3 of the wiring substrate 2.

That is, there is the gap part 15 at least one position (preferably several positions) between the inside wall of the through-hole 3 of the wiring substrate 2 and the side surface 12b of the convex part 12, which gap part separates the inside wall of the through-hole 3 from the side surface 12b of the

convex part 12, and penetrates (connects, passes through) from the upper surface 2a to the lower surface 2b of the wiring substrate 2. The gap part 15 is filled (fully) with a resin material which is integrally formed with the sealing portions 7 and 8.

The plane of the convex part 12 and the through-hole 3 can be set as various shapes, and a rectangular shape (near rectangle) is preferred. FIGS. 1 to 17 illustrate the case in which the planar shape of the convex part 12 and the through-hole 3 is set as a rectangle. To allow the formation of the gap part 15 described above, however, the planar shape of the convex part 12 and the planar shape of the through-hole 3 are not caused to be completely the same as each other, and the planar shape of the through-hole 3 is caused to be large in a limited region compared with the planar shape of the convex part 12, or the planar shape of the convex part 12 is caused to be small in a limited region compared with the planar shape of the through-hole 3.

For example, as illustrated in FIG. 11 and FIG. 12, the 20 planar shape of the through-hole 3 of the wiring substrate 2 is set as a rectangle having nearly right angles at each of four corners, and in contrast, as illustrated in FIG. 14, the planar shape of the convex part 12 is set as a rectangle in which the four corners are not at right angles but to be chamfered. 25 Alternatively, the planar shape of the through-hole 3 of the wiring substrate 2 may be set as a rectangle in which the four corners are not at right angles but to be locally widened in the angle while the planar shape of the convex part 12 may be set as a rectangle in which the four corners are nearly at right 30 angles. The planar shape of the through-hole 3 is a shape in a plane parallel to the upper surface 2a or the lower surface 2bof the wiring substrate 2, and the planar shape of the convex part 12 corresponds to a shape in a plane parallel to the main surface 11a of the base material part 11 or the main surface 35 12a of the convex part 12. Structural example of FIG. 14 is described more specifically in the following. At each of the four corners given by the reference symbol 17 in FIG. 14, (four corners of the rectangle structuring the planar shape of the convex part 12), the planar shape (the shape in a plane 40 parallel to the main surface of the convex part 12) is, for example, about a quarter of circle, and has a groove which extends from the main surface 12a of the convex part 12 to the main surface 11a of the base material part 11 along the side surface 12b of the convex part 12.

With that structure, when the convex part 12 of the heat-releasing plate 4 is positioned (inserted) in the through-hole 3 of the wiring substrate 2, the side surface 12b of the convex part 12 and the inside wall of the through-hole 3 of the wiring substrate 2 come close to each other at regions other than the regions near the four corners of the rectangle (rectangle structuring the planar shape of the convex part 12 and the through-hole 3). To the contrary, in the regions near the four corners, the side surface 12b of the convex part 12 and the inside wall of the through-hole 3 of the wiring substrate 2 are separated 55 from each other, which creates the gap part 15 near each of the four corners of the rectangle.

The gap part 15 is formed between the side surface 12b of the convex part 12 and the inside wall of the through-hole 3 in the stage in which the convex part 12 of the heat-releasing 60 plate 4 is placed (inserted) in the through-hole 3 for fixing (swaging) in the steps S5 and S6 described later. Before forming the sealing portions 7 and 8, the gap part 15 is empty, and is in a state of not being filled with the resin material MR. In forming the sealing portions 7 and 8, the gap part 15 65 functions as the flow passage of the resin material MR, and thus is filled with the resin material MR.

12

That is, although the detail is described later, on forming the sealing portions 7 and 8, (corresponding to the step S8 of molding described later), the resin material MR for forming the sealing portions 7 and 8 is supplied to the upper surface 2aside of the wiring substrate 2, and the resin material MR is supplied also to the lower surface 2b side of the wiring substrate 2 through the gap 8 and the gap part 15, and thus the sealing portion 7 and the sealing portion 8 are formed over the upper surface 2a and the lower surface 2b of the wiring substrate 2, respectively. To do this, each gap part 15 is formed to have a size allowing the resin material MR for forming the sealing portions 7 and 8 to flow therethrough in forming the sealing portions 7 and 8, and the gap part 15 extends continuously (penetrates) from the upper surface 2ato the lower surface 2b of the wiring substrate 2. As a result, at the upper surface 2a side of the wiring substrate 2, each gap part 15 connects with the gap 18 between the main surface 11a of the base material part 11 and the upper surface 2a of the wiring substrate 2, while at the lower surface 2b side of the wiring substrate 2, each gap part 15 connects with the sealing portion 8. Both of the sealing portion 7 and the sealing portion 8 are formed by the same resin material MR, and the same resin material MR fills (fully) the gap 18 and the gap part 15. That is, the sealing portion 7 and the sealing portion 8 are connected integrally via the resin material MR filling the gap part **15**.

The groove 16 (concave part, concavity) is formed in the main surface 12a of the convex part 12 of the heat-releasing plate 4. The groove 16 is formed in peripheral area (outer peripheral area) of the main surface 12a of the convex part 12. The semiconductor chip 5 is mounted over the main surface 12a of the convex part 12 at a position closer to the center of the principal case 12a than the region in which the groove 16 is formed. That is, in the main surface 12a of the convex part 12, the groove 16 is formed at a more outer periphery side than the region in which the semiconductor chip 5 is mounted. In the main surface 12a of the convex part 12, the groove 16 is preferably formed along each side of the main surface 12a. As illustrated in FIG. 14, when the main surface 12a has a rectangular shape, the groove 16 is preferably formed along the four sides of the main surface 12a except the area near to the four corners.

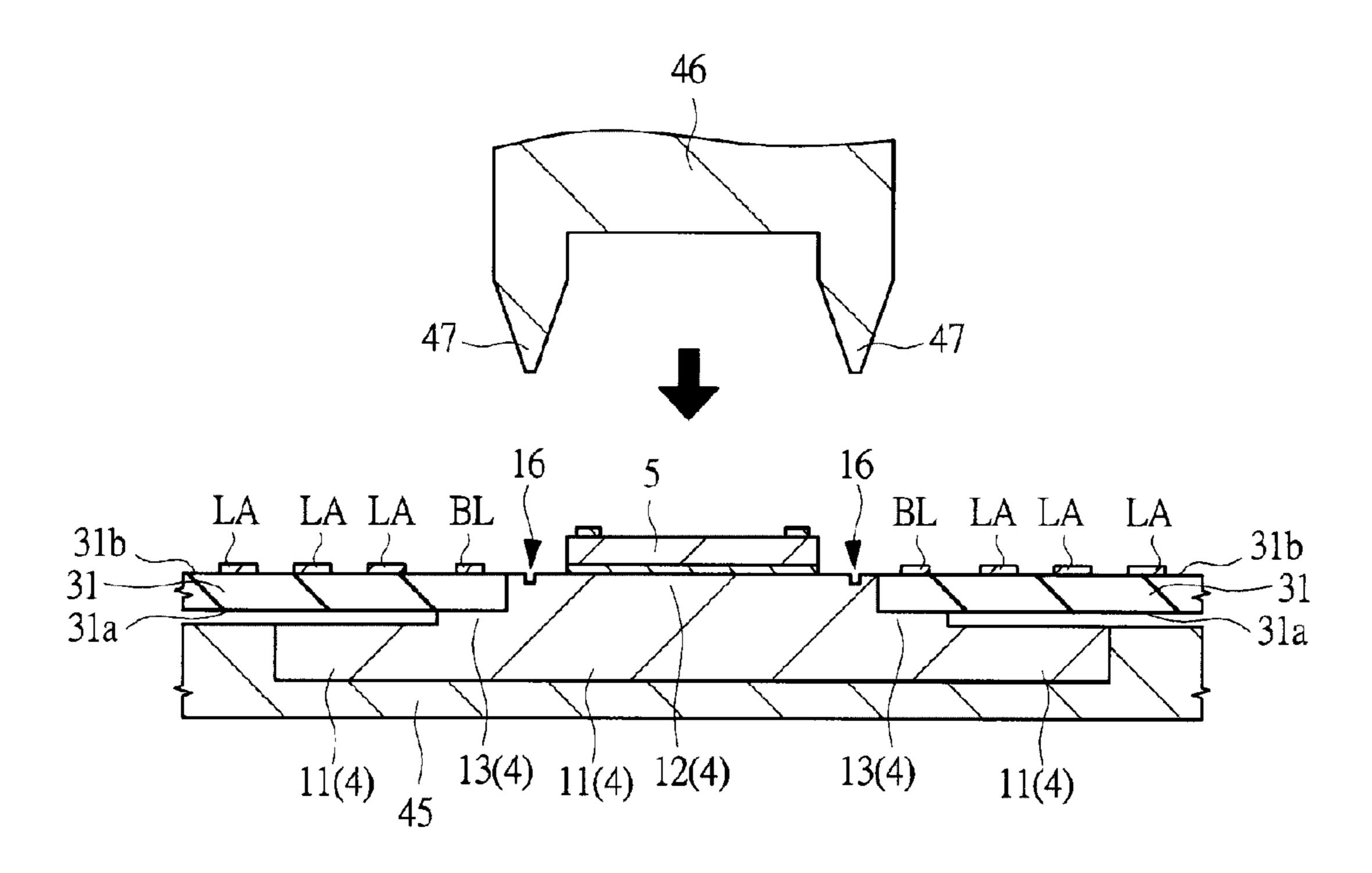

At the time of manufacturing the semiconductor device 1, the groove 16 is used to swage and fix the heat-releasing plate 45 4 (the convex part 12 of the heat-releasing plate 4) to the wiring substrate 2. That is, at the time of manufacturing the semiconductor device 1, the convex part 12 of the heat-releasing plate 4 is inserted into the through-hole 3 of the wiring substrate 2, and then the groove 16 in the main surface 2a of the convex part 12 is widened forcibly by a jig 46 or the like (described later), and thus the heat-releasing plate 4 (the convex part 12 of the heat-releasing plate 4) and the wiring substrate 2 are swaged and fixed together. When the groove 16 in the main surface 12a of the convex part 12 is widened forcibly, a portion of the convex part 12 is widened in the horizontal direction by an amount of the volume of widened groove 16, which allows a portion of the side surface 12b of the convex part 12 to contact with (adhere to) the inside wall of the through-hole 3 of the wiring substrate 2. By the reaction force, there is generated a force to cause the inside wall of the through-hole 3 of the wiring substrate 2 to closely contact with and press a portion of the side surface 12b of the convex part 12, which thus allows swaging the heat-releasing plate 4 (the convex part 12 of the heat-releasing plate 4) and the wiring substrate 2, and allows the heat-releasing plate 4 to be fixed to the wiring substrate 2. As a result, the heat-releasing plate 4 can be fixed to the wiring substrate 2 until the sealing

portions 7 and 8 are formed, which makes the manufacturing of semiconductor device 1 easy.

The semiconductor chip 5 has a planar rectangular shape (quadrangle) which crosses the thickness thereof. For example, the semiconductor chip 5 is manufactured by the 5 steps of: forming various kinds of semiconductor elements or semiconductor integral circuits over the main surface of the semiconductor substrate (semiconductor wafer) composed of single crystal silicon and the like; performing back-grinding of the semiconductor substrate, as necessary; and then sepa- 10 rating the semiconductor substrate into individual semiconductor chips 5 by using dicing and the like. The semiconductor chip 5 has a top surface 5a (main surface at the side of forming the semiconductor element, upper surface) and a rear surface 5b (main surface opposite to the top surface, lower 15 surface) as the two main surfaces at opposite positions to each other. In the top surface 5a of the semiconductor chip 5, there are formed a plurality of electrode pads PD (electrodes, bonding pads, pad electrodes). Each electrode pad PD is coupled with the semiconductor element or the semiconductor inte- 20 gral circuit being formed inside of or in the surface layer portion of the semiconductor chip 5.

The semiconductor chip 5 is face-up-bonded to the convex part 12 of the heat-releasing part 4. The rear surface 5b of the semiconductor chip 5 is adhered and fixed to the main surface 25 12a of the convex part 12 of the heat-releasing plate 4 via a joining material 14 (adhesive, die-bonding material). The plane size of the through-hole 3 of the wiring substrate 2 and of the convex part 12 of the heat-releasing plate 4 is larger than the plane size of the semiconductor chip 5. The semiconductor chip 5 mounted over the convex part 12 of the heat-releasing plate 4 is positioned so as to be included horizontally of the through-hole 3 of the wiring substrate 2 and of the convex part 12 of the heat-releasing plate 4. The joining material 14 is preferably an adhesive having high thermal 35 conductivity, and applicable ones include solder and conductive paste material (silver paste is preferred as the conductive paste material).

The wiring substrate 2 has an insulating base material layer (insulating substrate, core material) and a conductor layer 40 (conductor pattern, conductor film pattern, wiring layer) formed directly on upper surface and lower surface of the base material layer. The wiring substrate 2 may be a substrate having a conductor layer at top and bottom of a single insulating layer (base material layer) or may be a multilayer 45 wiring substrate (multilayer substrate) in which a plurality of insulating layers (base material layers) and a plurality of conductor layers (wiring layers) are alternately formed (laminated) and integrated across many layers. For the convenience of wiring, however, the multilayer wiring substrate is 50 preferred. FIGS. 1 to 4 do not show the wiring layer inside (between base material layers) of the wiring substrate 2. An example of the base material layer of the wiring substrate 2 is a resin material (such as glass-epoxy resin).

According to the semiconductor device 1 of the embodiment 1, the semiconductor chip 5 is positioned at the lower surface 2b side (above the convex part 12) of the wiring substrate 2, and the external terminals (solder balls 9 in this embodiment) at the lower surface 2b side of the wiring substrate 2. Because of this structure, the upper surface 2a side of the wiring substrate 2 does not need to have the conductor layer constituting the terminals (bonding leads, bump lands) and wiring. On the other hand, at the lower surface 2b side of the wiring substrate 2, there are formed a plurality of bonding leads BL (electrode pads, coupling terminals, electrodes, 65 bonding pads, pad electrodes) for coupling the bonding wire BW, and a plurality of bump lands LA (electrode pads, con-

**14**

ductive lands, electrodes, land electrodes, pads, terminals) for coupling the solder balls 9 as the bump electrodes. The bonding leads BL and the bump lands LA are made up of apart of the conductor layer, which can be formed by a conductive material such as, in the embodiment 1, copper thin film prepared by plating method.

As illustrated in FIG. 12, the bonding leads BL are arranged (formed) around the through-hole 3 in the lower surface 2b of the wiring substrate 2, and the bump lands LA are arranged (formed) around the region in which the bonding leads BL are arranged in the lower surface 2b of the wiring substrate 2.

In the wiring substrate 2, the bonding leads BL and the bump lands LA are coupled with each other via the respective wiring lines of the wiring substrate 2. The type of the wiring line for coupling electrically the bonding lead BL with the bump land LA is used responding to the requirements, including the wiring layer of the lower surface 2b of the wiring substrate 2, the wiring layer of the upper surface 2a of the wiring substrate 2, the wiring layer inside the wiring substrate 2, and via-wiring line for coupling different wiring layers of the wiring substrate 2. In the same way as the bonding lead BL and the bump land LA, these wiring lines are made up of a part of the conductor layer of the wiring substrate 2. Although not shown in the drawings, there can be formed a solder resist layer (insulating layer, insulating film), as necessary, directly on the upper surface 2a and the lower surface 2b of the wiring substrate 2. In this case, in the lower surface 2b of the wiring substrate 2, the bonding lead BL and the bump land LA are exposed from the solder resist layer (opening of the solder resist layer), while the wiring line (wiring line coupling the bonding lead BL with the bump land LA) in the lower surface 2b of the wiring substrate 2 is covered by the solder resist layer. When the solder resist layer (insulating layer, insulating film) is formed directly on the upper surface 2a (31a) of the wiring substrate 2 (31), the surface of the solder resist layer (insulating layer, insulating film) can be considered as the upper surface 2a (31a) of the wiring substrate 2 (31a). The supporting surface 13a of the supporting part 13 of the heatreleasing plate 4 comes into contact with the surface of the solder resist layer (insulating layer, insulating film). When the solder resist layer (insulating layer, insulating film) is formed directly on the lower surface 2b (31b) of the wiring substrate 2, the surface of the solder resist layer (insulating layer, insulating film) can be considered as the lower surface 2b (31b) of the wiring substrate 2 (31).

Consequently, the electrode pads PD of the semiconductor chip 5 are coupled with the bonding leads BL, placed directly on the lower surface 2b of the wiring substrate 2, via the bonding wires BW, and further are coupled with the bump lands LA (and the solder balls 9 coupled with the bump lands LA), placed directly on the lower surface 2b of the wiring substrate 2, via the wiring lines of the wiring substrate 2 and the like. Each bonding wire BW (conductive wire, conductive coupling member) functions as the conductive coupling member for electrically coupling each electrode pad PD of the semiconductor chip 5 with each bonding lead BL of the wiring substrate 2. Preferably the bonding wire BW is made of a conductive wire (coupling member) such as metal thin wire including gold wire.

The bump lands LA are arranged in an array pattern directly on the lower surface 2b of the wiring substrate 2 within a region in which the sealing portions 8 are not arranged. Each bump land LA is coupled with the solder ball 9 (ball electrode, solder bump, bump electrode, protruded electrode). As a result, in the lower surface 2b of the wiring

substrate 2, the solder balls 9 as the external terminals are arranged in an array pattern in the region in which the sealing portions 8 are not arranged.

The lower surface 2b of the wiring substrate 2 on which the solder balls 9 are arranged becomes the lower surface of the 5 semiconductor device 1 and becomes the mounting surface (main surface of the side being mounted to the mounting substrate) of the semiconductor device 1. Consequently, the semiconductor device 1 of the embodiment 1 is a semiconductor of BGA (Ball Grid Array package) type. The solder 10 ball 9 is made of a solder material and functions as the bump electrode (protruded electrode, solder bump) of the semiconductor device 1, and can function as the external terminal (terminal for external coupling) of the semiconductor device 1. Therefore, it can be said that the respective external terminals (solder balls 9 in the embodiment 1) are formed directly on the bump lands LA of the wiring substrate 2.

The sealing portions 7 and 8 (sealing resin portion, resin sealing portion, sealing resin, sealing body) are made of a resin material such as thermosetting resin material, and can 20 contain a filler. For example, the sealing portions 7 and 8 can be prepared by using an epoxy resin containing a filler.

The sealing portion 7 is formed at the upper surface 2a side of the wiring substrate 2, while the sealing portion 8 is formed at the lower surface 2b side of the wiring substrate 2. However, the main surface 8a (the main surface distant from the lower surface 2b of the wiring substrate 2) of the sealing portion 8 is positioned at closer side to the lower surface 2b of the wiring substrate 2 than the position of the lower end of the solder ball 9 (or the end part opposite to the side coupling the 30 bump land LA, or the front end of the solder ball 9). That is, when the semiconductor device 1 is placed directly on a flat plane, the flat plane contacts with the lower end of the solder ball 9, and does not contact with the sealing portion 8 (the main surface 8a of the sealing portion 8). The structure prevents the sealing portion 8 from interfering with the mounting of the semiconductor device 1 over the mounting substrate.

The sealing portion **8** is formed above the lower surface **2**b of the wiring substrate **2** and above the main surface **12**a of the convex part **12** of the heat-releasing plate **4** so that the semiconductor chip **5** and the bonding wires BW are covered. Thus the sealing portion **8** seals the semiconductor chip **5** and the bonding wires BW to protect them. In the lower surface **2**b of the wiring substrate **2**, the bonding leads BL are covered with the sealing portion **8**. However, the bump lands LA and 45 the solder balls **9** coupling the bump lands LA are not covered with the sealing portion **8**. That is, in the lower surface **2**b of the wiring substrate **2**, the solder balls **9** are exposed and function as the external terminals of the semiconductor device **1**.

The sealing portion 7 is formed to seal a portion of the heat-releasing plate 4 and to cover the side surface of the base material part 11 of the heat-releasing plate 4 over the upper surface 2a of the wiring substrate 2. However, the rear surface 11b of the base material part 11 of the heat-releasing plate 4 is exposed from the sealing portion 7 (the upper surface 7a of the sealing portion 7). The upper surface 7a of the sealing portion 7 and the rear surface 11b of the base material part 11 of the heat-releasing plate 4, exposed from the upper surface 7a of the sealing portion 7, can be formed in nearly flat plane. 60 Nevertheless, it is preferable that the rear surface 11b of the base material part 11 of the heat-releasing plate 4, exposed from the upper surface 7a of the sealing portion 7, is in nearly the same plane as the upper surface 7a of the sealing portion 7, or is protruded to some extent from the upper surface 7a of 65 the sealing portion 7. A part of the sealing portion 7 is formed in the gap 18.

**16**

As described above, the sealing portion 7 and the sealing portion 8 are integrally connected each other via the resin material MR which fills the gap part 15 between the side surface 12b of the convex part 12 of the heat-releasing plate 4 and the inside wall of the through-hole 3. Consequently, the sealing portion 7 (the sealing portion 7 includes the resin material MR in the gap 18), the sealing portion 8, and the resin in the gap part 15 are integrally formed, and they are formed by the same resin material MR.

As described above, the semiconductor device 1 of the present embodiment is a semiconductor device (semiconductor package) which mounts the semiconductor chip 5 over the convex part 12 of the heat-releasing plate 4 positioned in the through-hole 3 of the wiring substrate 2. To the lower surface 2b of the wiring substrate 2, the solder balls 9 as the external terminals are joined, and the heat-releasing plate 4 (the base material part 11 of the heat-releasing plate 4) is exposed from the sealing portion 7 of the upper surface 2a of the wiring substrate 2. The heat generated from the semiconductor chip 5 is transferred by conduction to the heat-releasing plate 4 (the convex part 12 of the heat-releasing plate 4) via the joining material 14, and the heat is released to the outside of the semiconductor device 1 from the exposed portion (the rear surface 11b of the base material part 11 of the heat-releasing plate 4) at the upper surface side (the upper surface 2a of the wiring substrate 2) of the semiconductor device 1. Owing to the structure, the embodiment 1 can improve the heat-release performance (heat-release properties) of the semiconductor device. The semiconductor device 1 of the embodiment 1 is a high-heat-releasing type semiconductor device (semiconductor package). The solder ball 9 can also contribute to the heat-release to the outside of the semiconductor device 1, though the heat-releasing effect is smaller than that of the heat-releasing plate 4.

By the close contact (adhesion) of the sealing portions 7 and 8 with (to) the wiring substrate 2 and the heat-releasing plate 4, respectively, the wiring substrate 2, the heat-releasing plate 4, and the sealing portions 7 and 8 couple together, and by filling a resin into the gap part 15 and the gap 18 integrally with the sealing portions 7 and 8, the coupling of the wiring substrate 2, the heat-releasing plate 4, and the sealing portions 7 and 8 is further strengthened.

<Mounting the Semiconductor Device>

The mounting of the semiconductor device 1 is described below.

FIG. 18 is a cross-sectional view (side surface cross sectional view) of semiconductor device 1 in the present embodiment, illustrating an example of mounting. FIG. 18 shows the semiconductor device 1 mounted over the mounting substrate 21 (wiring substrate).

The mounting substrate 21 given in FIG. 18 is a wiring substrate (mounting substrate) for mounting the semiconductor device 1 thereon. To the upper surface as the mounting surface for mounting the semiconductor device 1 thereon, a plurality of substrate-side terminals 22 (terminals, electrodes, pad electrodes, conductive lands) for coupling the respective solder balls of the semiconductor device 1 are provided. Although FIG. 18 gives a simplified illustration of the crosssectional structure of the mounting substrate 21, the mounting substrate 21 is preferably a multilayer wiring substrate being formed by laminating integrally a plurality of insulator layers (dielectric layers, insulating base material layers) and a plurality of wiring layers (conductor layers, conductor pattern layers). The substrate-side terminal 22 is a terminal for coupling the solder ball 9 (bump electrode) as the external terminal of the semiconductor device 1. The substrate-side termi-

nal 22 is positioned so as to face the solder ball 9 when the semiconductor device 1 is mounted over the upper surface of the mounting substrate 21.

Mounting of the semiconductor device 1 over the mounting substrate 21 is done by supplying a solder paste (the solder paste is unified with the solder ball 9 by the solder reflow treatment) directly onto the substrate-side terminals 22 of the mounting substrate 21 by using printing method and the like, and by mounting (placing) the semiconductor device 1 over the mounting substrate 21 so that the position of the solder ball 9 of the semiconductor device 1 and the position of the substrate-side terminal 22 of the mounting substrate 21 are aligned, and then by applying solder reflow treatment.

By the above procedure, as illustrated in FIG. 18, the semiconductor device 1 is mounted (solder-mounted) over the mounting substrate 21, the semiconductor device 1 is fixed to the mounting substrate 21, and the solder balls 9 as the external terminals of the semiconductor device 1 are coupled with the substrate-side terminals 22 of the mounting substrate 21, 20 respectively.

For the mounting case of FIG. 18, the heat generated from the semiconductor chip 5 is transferred to the heat-releasing plate 4 (the convex part 12 of the heat-releasing plate 4), and the heat is released to the outside (to air in this case) of the 25 semiconductor device 1 from the exposed portion of the upper surface side of the semiconductor device 1 in the heat-releasing plate 4, (from the rear surface 11b of the base material part 11 of the heat-releasing plate 4). There may be the heat-release generated from the solder ball 9 to the mounting 30 substrate 21, though the heat-releasing effect is smaller than that of the heat-releasing plate 4.

FIG. 19 is a cross-sectional view (side surface cross-sectional view) of the semiconductor device 1 in the present embodiment, illustrating another example of mounting. FIG. 35 18 shows the semiconductor device 1 mounted over the mounting substrate 21 (wiring substrate).

The example of mounting of FIG. 19 differs from that of FIG. 18 in the following respects.

In the same way as the case of FIG. 18, the semiconductor 40 device 1 is mounted over the mounting substrate 21, and the solder balls 9 of the semiconductor substrate 1 are coupled with the substrate-side terminals 22 of the mounting substrate 21, respectively. In FIG. 19, however, the semiconductor device 1 mounted over the mounting substrate 21 is covered 45 with a casing 24, (or contained in the casing 24). The heatreleasing plate 4 (the rear surface 11b of the base material part 11 of the heat-releasing plate 4) being exposed at upper surface side of the semiconductor device 1 is coupled with the casing 24 via a conductive sheet 23 (adhesive). The casing 24 is a heat-releasing casing, has electric conductivity, and is preferably formed by a metallic material. A portion of the casing 24 (lead part) is coupled and fixed to a substrate-side terminal 22a of the mounting substrate 21 via a solder 25a and the like.

For the mounting example of FIG. 19, the heat generated from the semiconductor chip 5 is transferred to the heat-releasing plate 4 (the convex part 12 of the heat-releasing plate 4), and is released (conducted) to the casing 24 from the heat-releasing plate 4 via the conductive sheet 23. The heat 60 transferred (released) from the heat-releasing plate 4 to the casing 24 is released via a passage from the casing 24 to the mounting substrate 21 via the solder 25a. Connecting the heat-releasing plate 4 of the semiconductor device 1 with the casing 24 further 65 improves the heat-release properties of the semiconductor device 1.

**18**

FIG. 20 is a cross-sectional view (side surface cross-sectional view) of the semiconductor device 1 in the embodiment 1, illustrating further example of mounting. FIG. 20 shows the semiconductor device 1 mounted over the mounting substrate 21 (wiring substrate).

The mounting example of FIG. 20 differs from that of FIG. 18 in the following points.

In the same way as the case of FIG. 18, the semiconductor device 1 is mounted over the mounting substrate 21, and the solder balls 9 of the semiconductor device 1 are coupled with the substrate-side terminals 22 of the mounting substrate 21, respectively. In FIG. 20, however, components other than the semiconductor device 1, such as a chip component 26 and a semiconductor device 27 (semiconductor package), are mounted over the mounting substrate 21. The chip component 26 is structured by passive components such as a chip capacitor and a chip inductor, and the like. The electrode of the chip component 26 is coupled and fixed to a substrate-side terminal 22b of the mounting substrate 21 via a solder 25b and the like. An outer lead part 28 of the semiconductor device 27 (semiconductor package) is coupled and fixed to a substrateside terminal 22c of the mounting substrate 21 via a solder 25c and the like. The type and the number of the components to be mounted over the mounting substrate 21 can be adequately selected as necessary.

FIG. 21 is a cross-sectional view (side surface cross-sectional view) of the semiconductor device 1 in the embodiment 1, illustrating an example of mounting. FIG. 21 shows the semiconductor device 1 mounted over the mounting substrate 21 (wiring substrate).

The mounting example of FIG. 21 differs from that of FIG. 20 in the following respects.

In the same way as the case of FIG. 20, the semiconductor device 1, the chip component 26, and the semiconductor device 27 are mounted over the mounting substrate 21. In FIG. 21, however, the semiconductor device 1, the chip component 26, and the semiconductor device 27 mounted over the mounting substrate 21 are covered with the casing 24, (or are contained in the casing 24). The heat-releasing plate 4 (the rear surface 11b of the base material part 11 of the heat-releasing plate 4) being exposed at the upper surface side of the semiconductor device 1 is coupled with the casing 24 via the conductive sheet 23. The casing 24 is a heat-releasing casing, has electric conductivity, and is preferably formed by a metallic material. A portion of the casing 24 (lead part) is coupled and fixed to the substrate-side terminal 22a of the mounting substrate 21 via the solder 25a and the like.

For the mounting example of FIG. 21, the heat generated from the semiconductor chip 5 is transferred to the heat-releasing plate 4 (the convex part 12 of the heat-releasing plate 4), and is released (transferred) to the casing 24 from the heat-releasing plate 4 via the conductive sheet 23. The heat transferred (released) from the heat-releasing plate 4 to the casing 24 is released via a passage from the casing 24 into the air and via a passage from the casing 24 to the mounting substrate 21 via the solder 25a. Connecting the heat-releasing plate 4 of the semiconductor device 1 with the casing 24 further improves the heat-release properties of the semiconductor device 1.

<Manufacturing Process of Semiconductor Device>

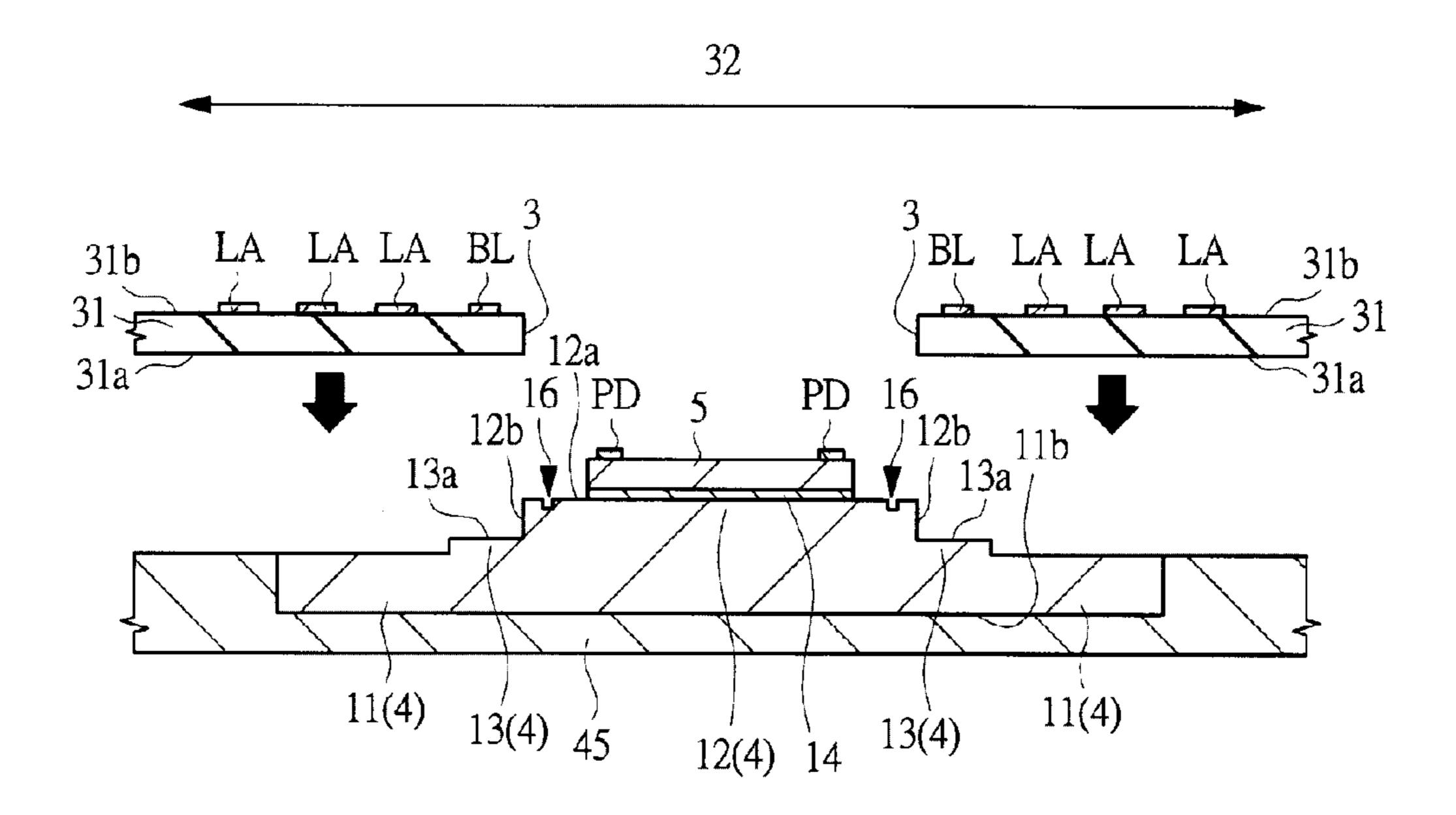

The method of manufacturing the semiconductor device 1 of the embodiment 1 is described in the following referring to the drawings. FIG. 22 illustrates the flow diagram of manufacturing process of semiconductor device 1 in the embodiment 1. FIGS. 23 to 46 are plan views or cross-sectional views of the semiconductor device 1 of the embodiment 1 during the manufacturing process.

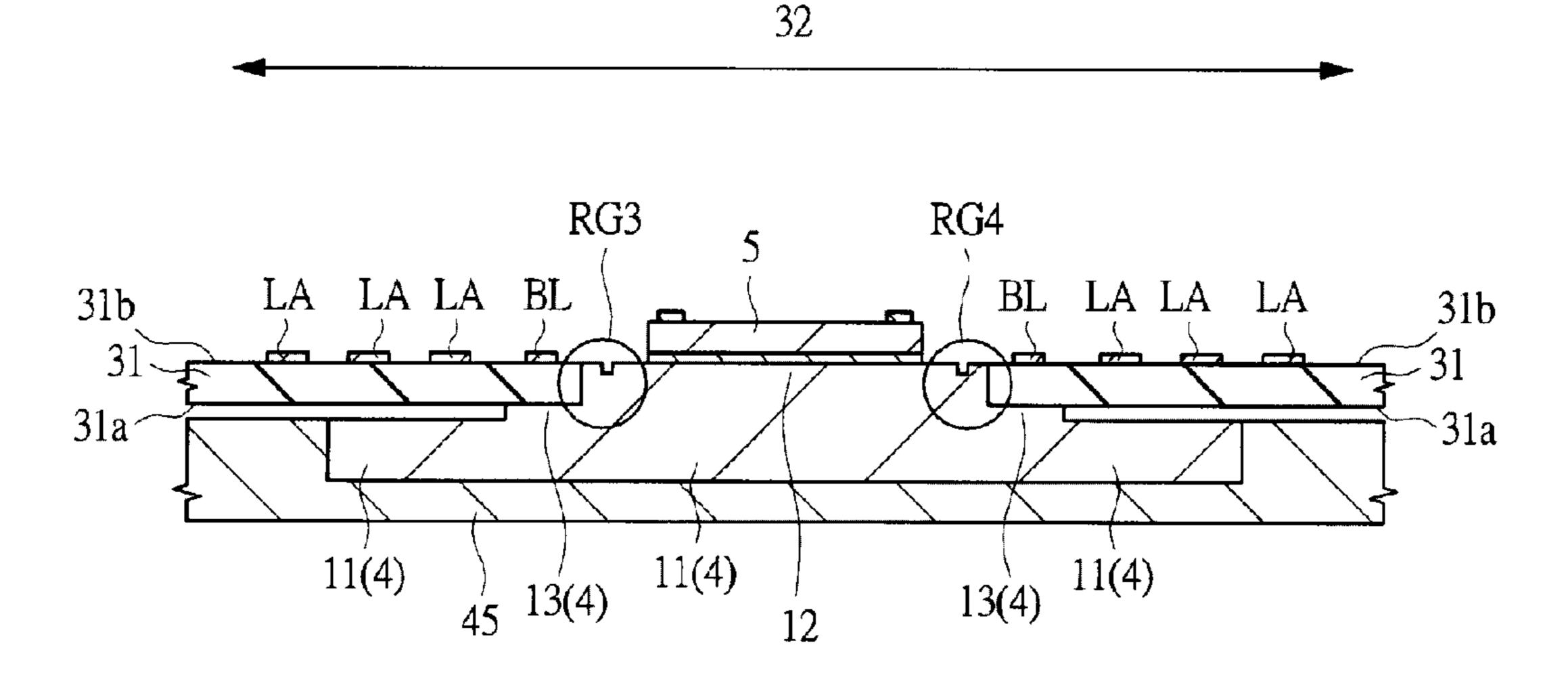

The embodiment 1 describes the case of manufacturing the individual semiconductor device 1 by using a wiring substrate 31 (wiring substrate base body) for family molding, (or using the wiring substrate 31 directly on which a plurality of wiring substrates 2 is formed in a row or in an array pattern).

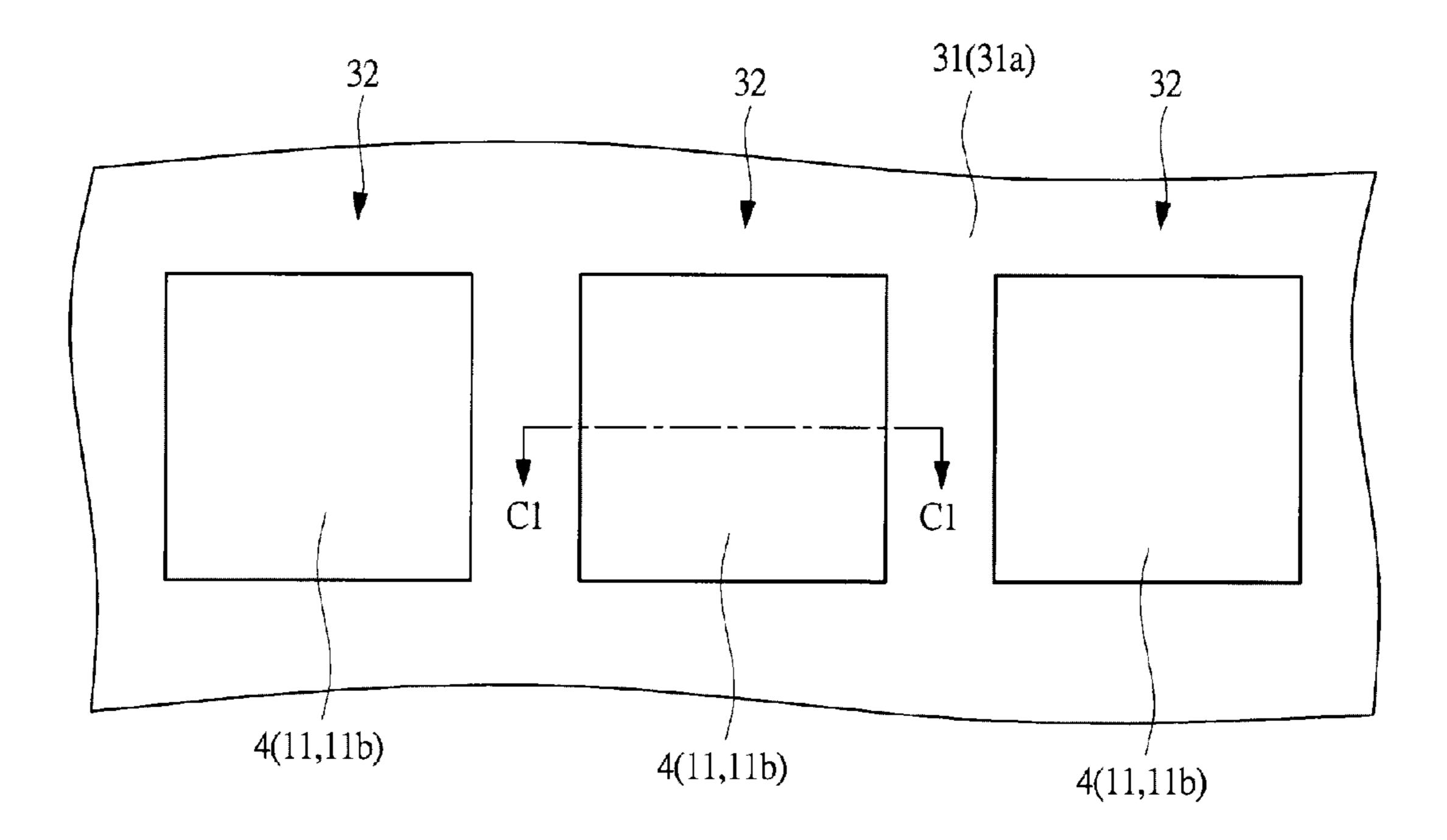

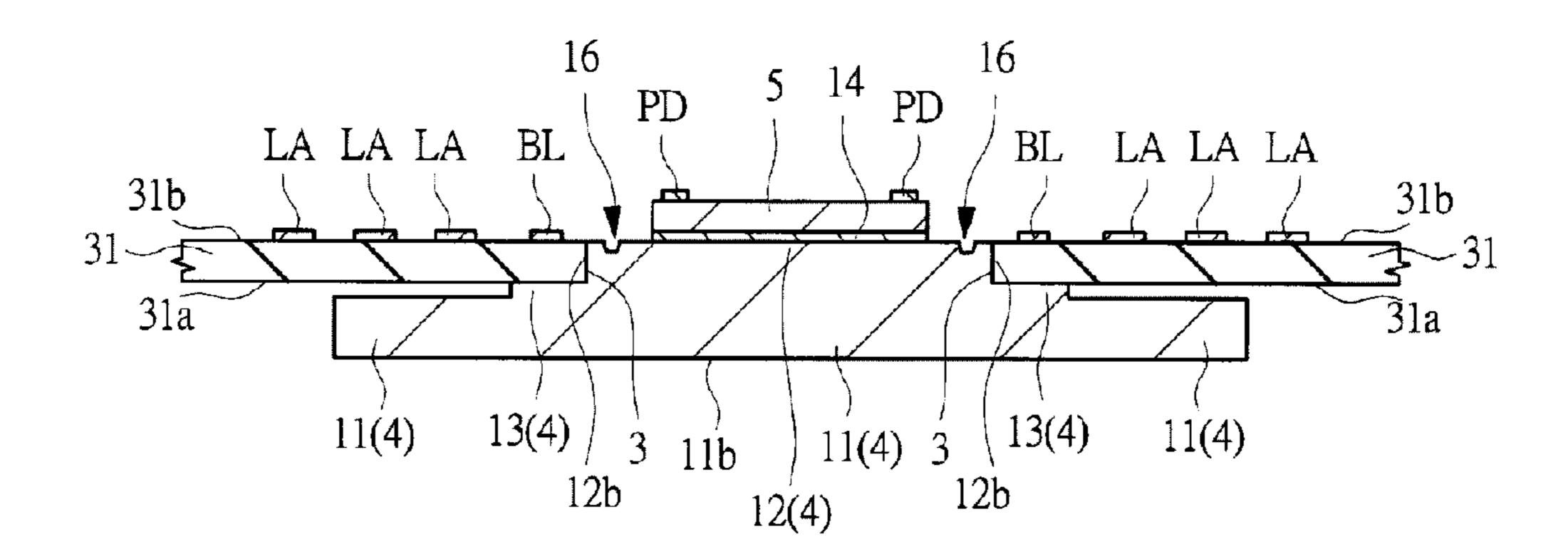

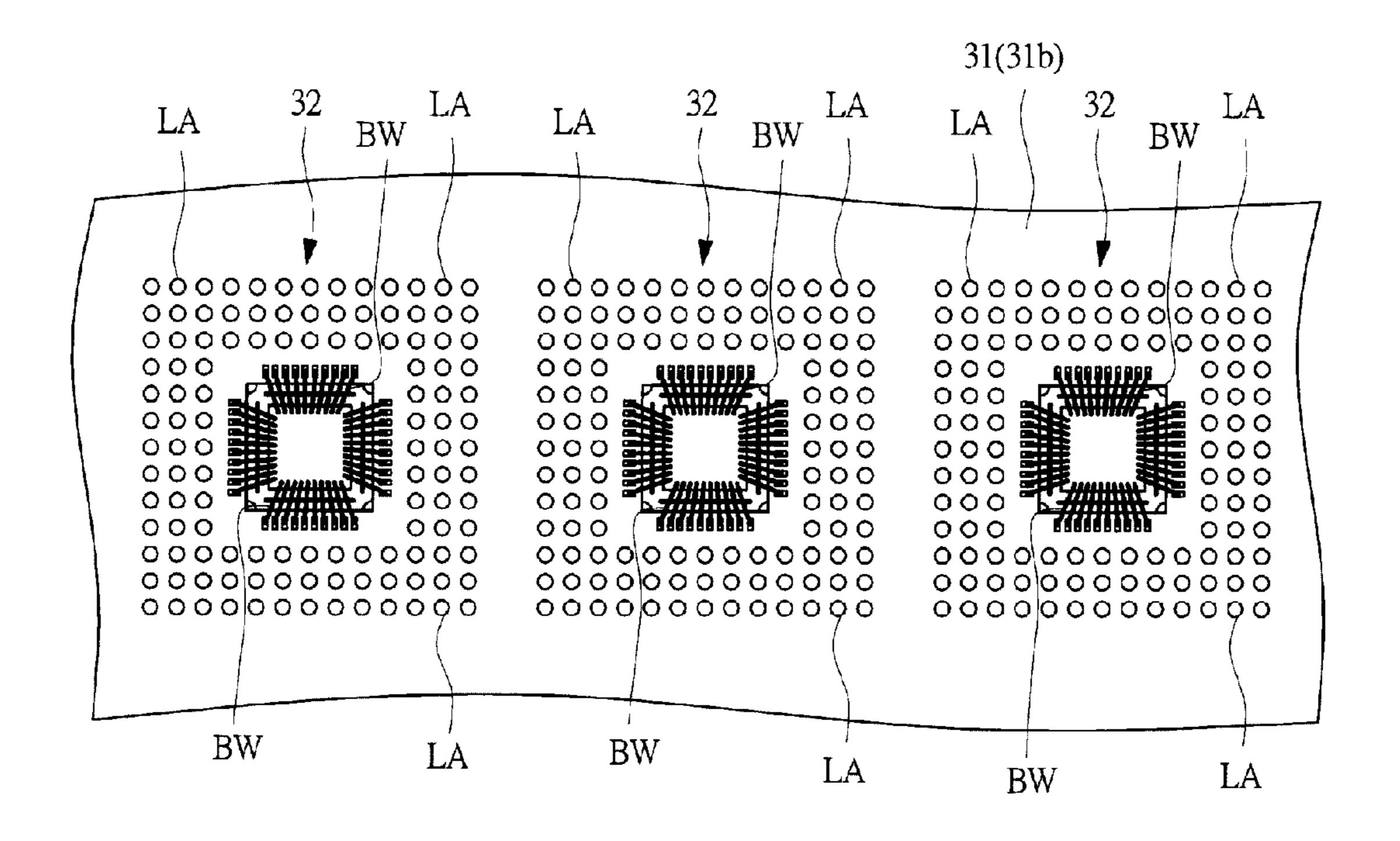

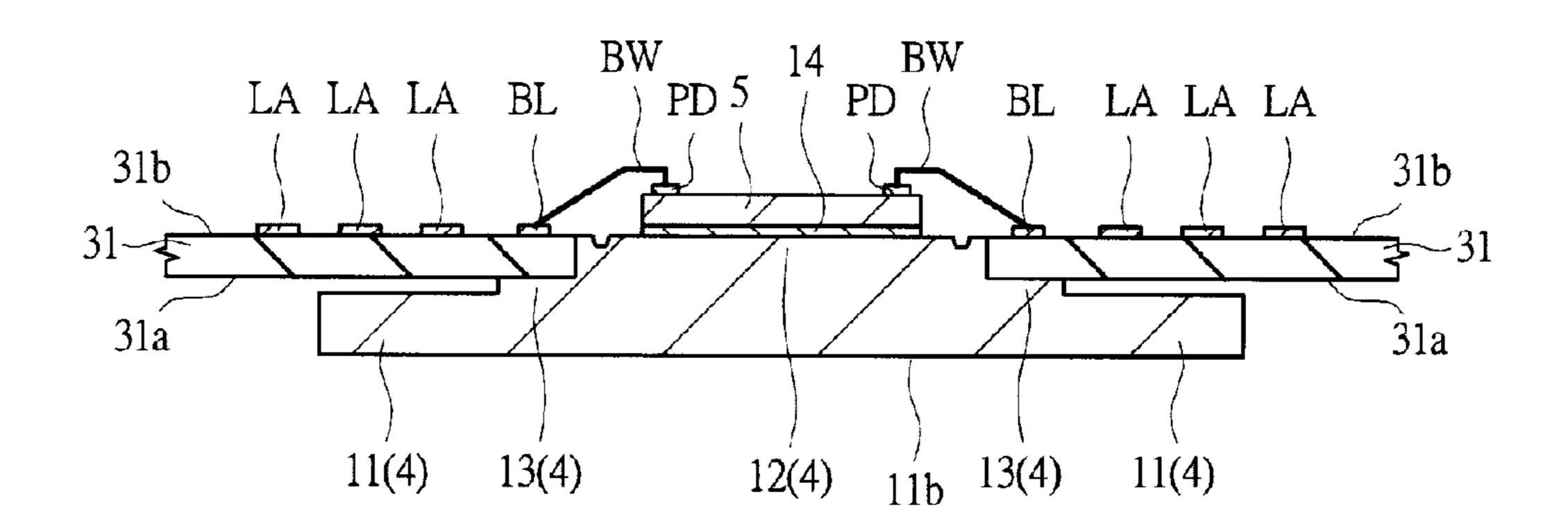

As illustrated in FIGS. 23 to 26, the wiring substrate 31 is provided (step S1 of FIG. 22). FIG. 23 is the upper surface view of the wiring substrate 31, and FIG. 24 and FIG. 25 are the lower surface views of the wiring substrate 31. FIG. 23 shows the entire upper surface 31a of the wiring substrate 31, and FIG. 24 shows the entire lower surface 31b of the wiring substrate 31. FIG. 25 is a part-enlarged view of FIG. 24, (or three semiconductor device regions 32 in the lower surface 31b of the wiring substrate 31). FIG. 26 is a cross-sectional view (main-part cross sectional view) of the wiring substrate 31, giving the cross section along the C1-C1 line of FIG. 25. The position of C1-C1 line of FIG. 25 corresponds to the position of A1-A1 l line of FIGS. 5 to 10. Accordingly, FIG. 26 gives the same cross section as that of FIG. 1.

The wiring substrate 31 is the mother body of the wiring substrate 2. The wiring substrate 31 is cut in the step of cutting (described later) into individual semiconductor device regions 32 (substrate region, unit substrate region) which correspond to the wiring substrates 2 of the semiconductor device 1. The wiring substrate 31 has a structure of a row or a matrix of arranged semiconductor device regions 32, each of the semiconductor regions 32 forms each semiconductor device 1 thereon. Accordingly, the structure of each semiconductor device region 32 in the wiring substrate 31 is similar to 30 that of the wiring substrate 2. Consequently, when the upper surface (main surface) 31a and the lower surface (rear surface) 31b of each semiconductor device region 32 of the wiring substrate 31 are enlarged, 31a and 31b are the same as FIG. 11 and FIG. 12, respectively.

Thus, the wiring substrate 31 has the upper surface (main surface) 31a as the main surface at one side and the lower surface (rear surface) 31b as the main surface at opposite side. The upper surface 31a of the wiring substrate 31 becomes the upper surface 2a of the wiring substrate 2 in succeeding step, and the lower surface 31b of the wiring substrate 31 becomes the lower surface 2b of the wiring substrate 2 in succeeding step. In each semiconductor device region 32 of the wiring substrate 31, the through-hole 3 which penetrates from the upper surface 31a to the lower surface 31b of the wiring 45 substrate 31 is formed, and in each semiconductor device region 32 of the lower surface 31b of the wiring substrate 31, the bonding leads BL and the bump lands LA are formed.

In each semiconductor device region 32 of the lower surface 31b of the wiring substrate 31, the bonding leads BL are 50 formed at periphery of the through-hole 3. In each semiconductor device region 32 of the lower surface 31b of the wiring substrate 31, the bump lands LA are formed in peripheral area of the region in which the bonding leads BL are arranged. The bonding leads BL and the bump lands LA in each semiconductor device region 32 of the lower surface 31b of the wiring substrate 31 are coupled with each other via wring lines of each semiconductor device region 32 of the wiring substrate 31.

In FIGS. 23 to 25, each semiconductor device region 32 is 60 encircled by a broken line. FIG. 23 and FIG. 24 (entire plan view of the wiring substrate 31) give an example in which ten semiconductor device regions 32 in five rows and two columns is arranged to form the wiring substrate 31. The arrangement is not limited to the example, and the number of 65 rows and columns of the semiconductor device regions 32 can be varied as necessary.

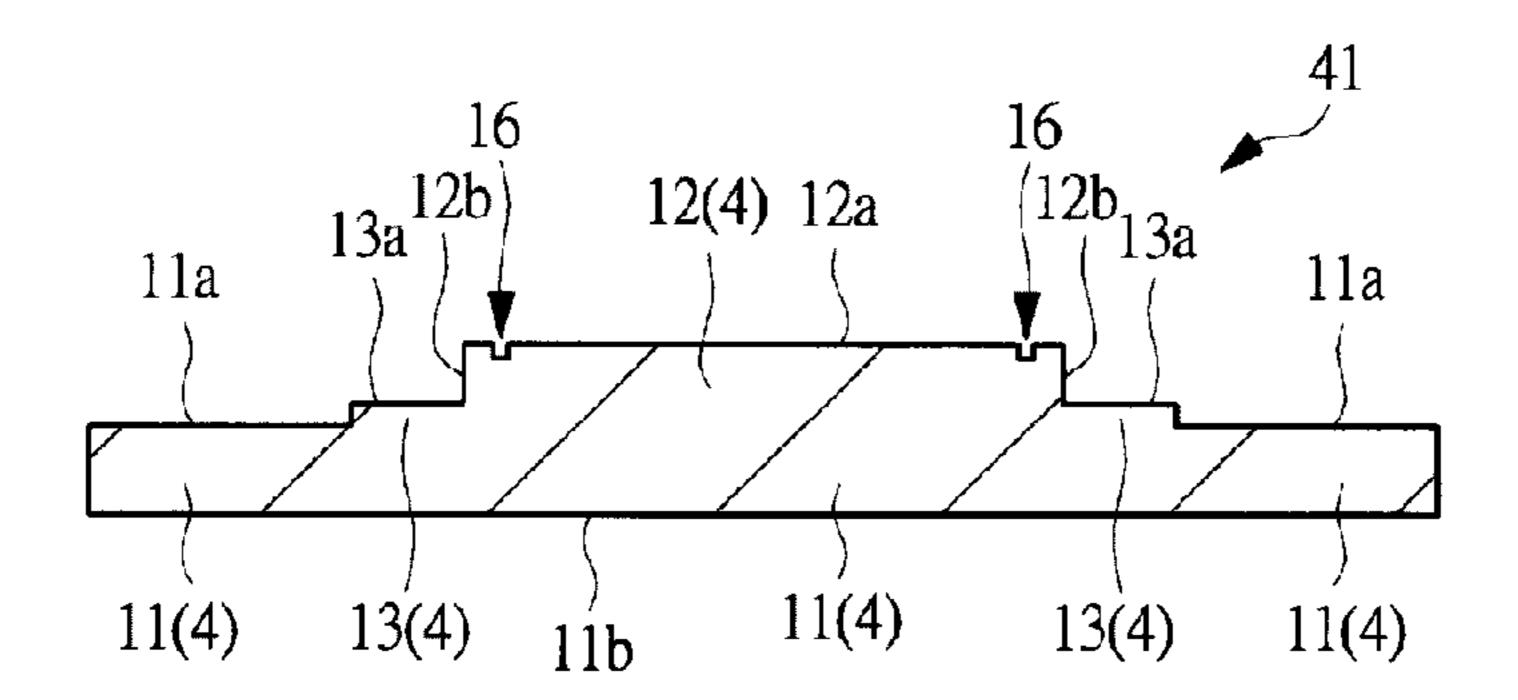

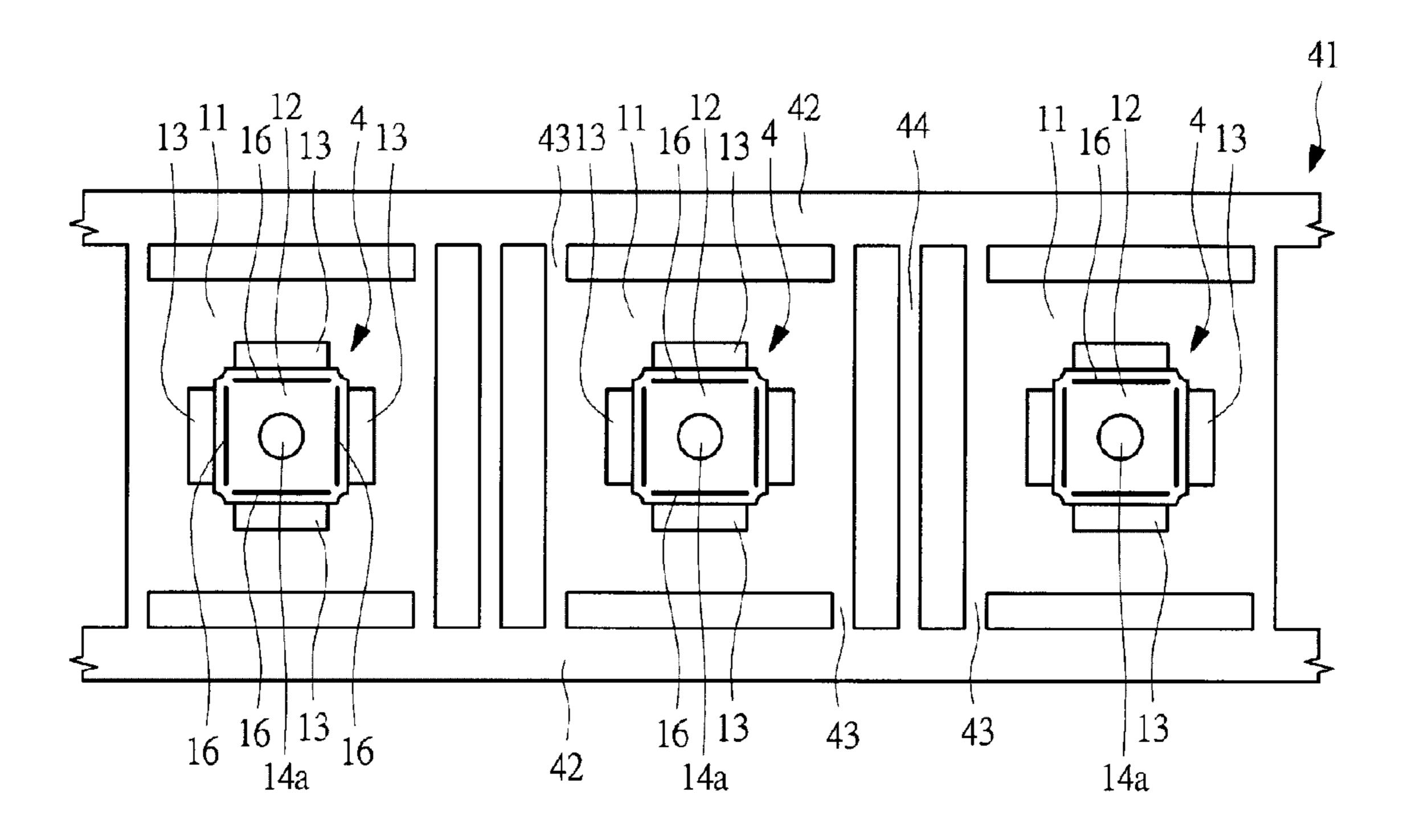

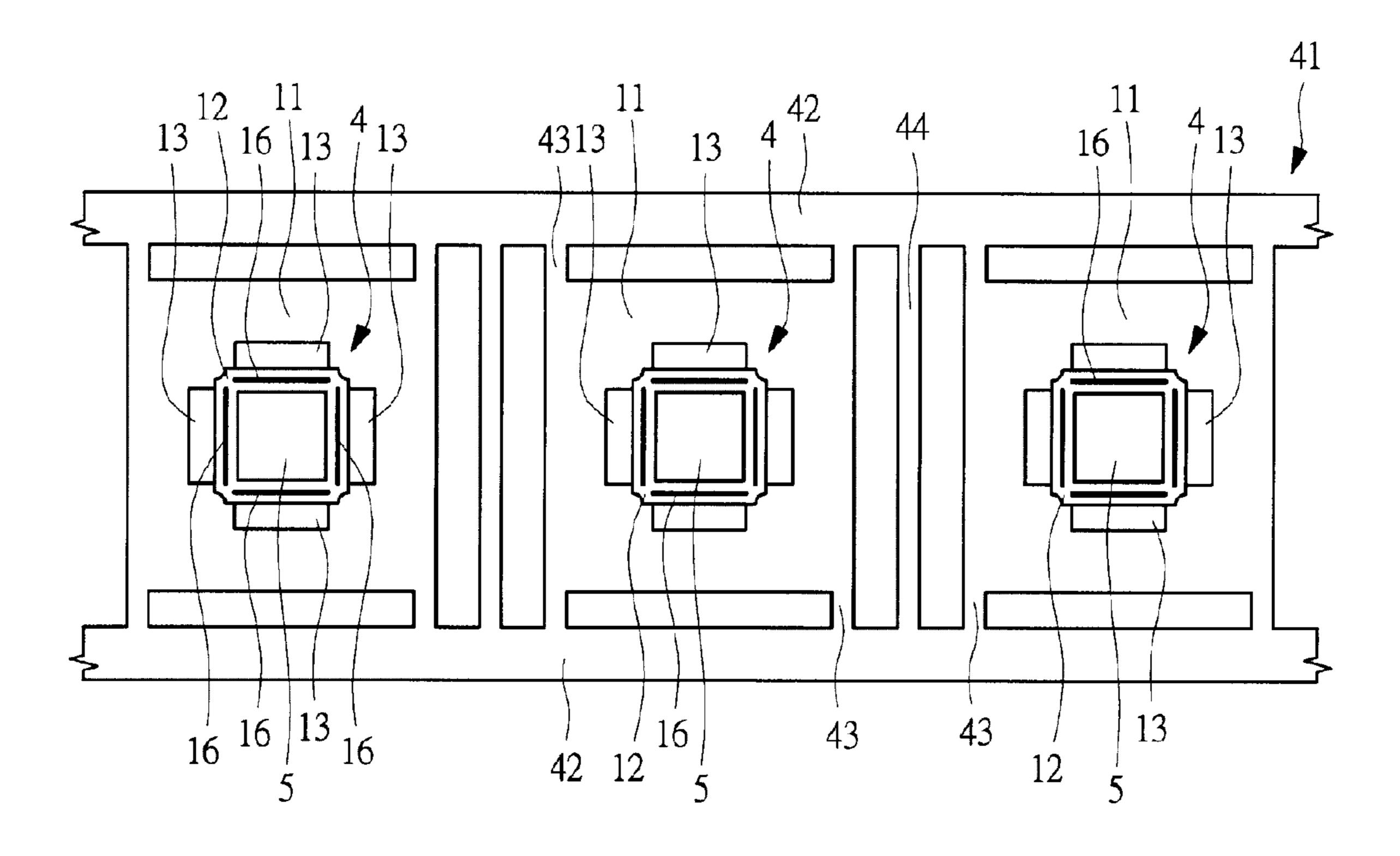

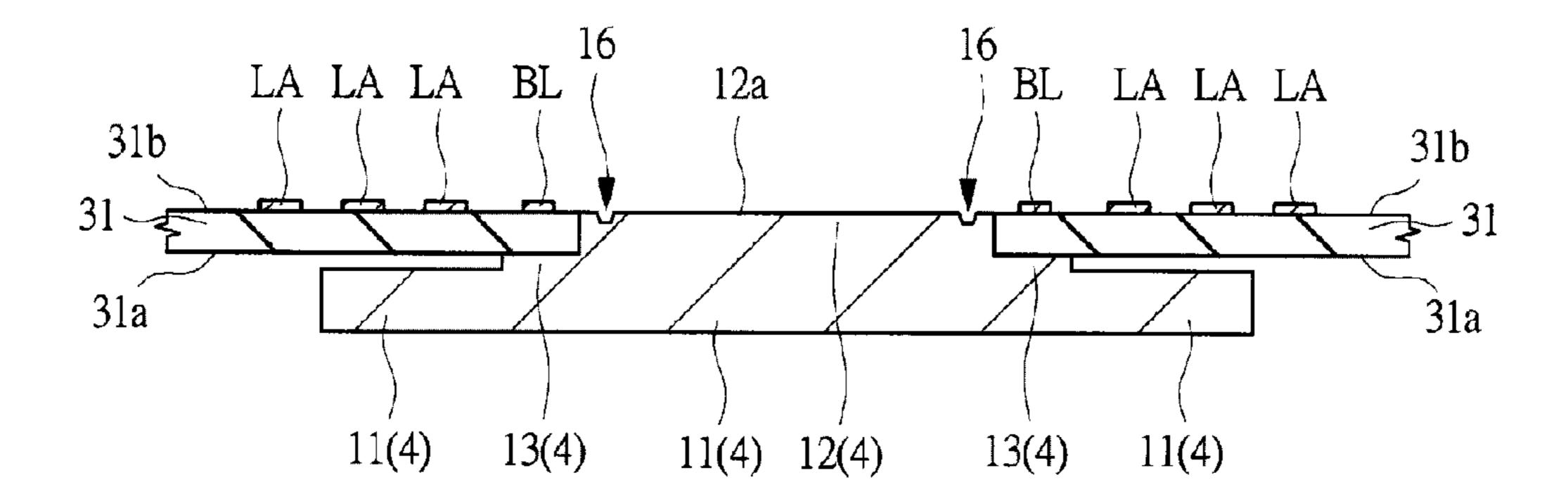

Next, as illustrated in FIG. 27 and FIG. 28, a frame 41 for the heat-releasing plate 4 is provided, (step S2 of FIG. 22). FIG. 27 is the plan view of the frame 41 at the side of forming the convex part 12 of the heat-releasing plate 4. FIG. 28 corresponds to the cross-sectional view along the D1D1 line in FIG. 27. FIG. 27 is a plan view, which is emphasized with hatching for the convenience of recognition of the frame 41. The position of D1-D1 line in FIG. 27 corresponds to the position of A1-A1 line of FIGS. 5 to 10 and to the position of B1-B1 line of FIG. 13. FIG. 28 and FIG. 16 are upside down from each other, though FIG. 28 shows the same cross section as that of FIG. 16.

The frame 41 is configured such that a plurality of heatreleasing plates 4 is integrally joined with a frame rim 42 (rim

part). That is, the heat-releasing plates 4 are arranged at a

specified spacing between two frame rims 42 extending in the

same direction, and the position near each of the four corners

of the base material part 11 of each heat-releasing plate 4 is

joined with the frame rim 42 via a joining part 43. The frame

41 can be formed by working a copper plate, for example, in

a die. In the frame 41, a joining part 44 for joining the frame

rims 42 together is located between adjacent heat-releasing

plates 4 in order to reinforce the frame 41. If not required, the

joining part 43 can be omitted. For the frame 41, the heatreleasing plate 4, the frame rim 42, the joining part 43, and the

joining part 44 are integrally formed by the same material.

As described above, each heat-releasing plate 4 is composed integrally of: the base material part having the main surface 11a and the rear surface 11b at opposite side to the main surface 11a; the convex part 12 being located at central part of the main surface 11a of the base material part 11, and protruding from the main surface 11a; and the supporting part 13 being formed in the main surface 11a of the base material part 11 and being positioned at lower level than the level of the convex part 12. In the main surface 12a of the convex part 12, the groove 16 (concave part, concavity) is formed.

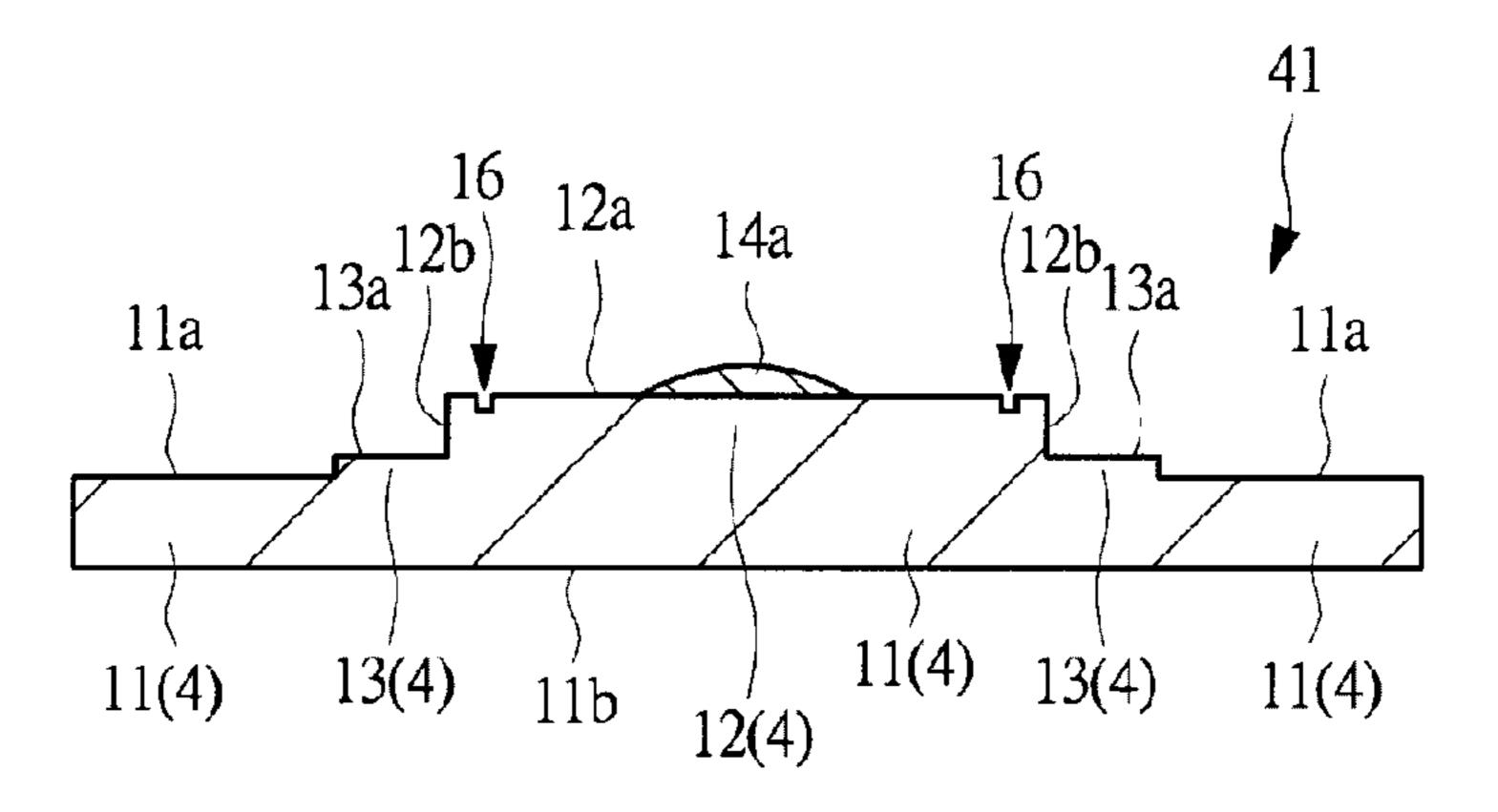

Next is the die-bonding step, where the semiconductor chip 5 is mounted to join the main surface 12a of the convex part 12 of each heat-releasing plate 4 of the frame 41 via the joining material 14 (step S3 of FIG. 22). The joining step (or die-bonding step) for the semiconductor chip 5 in the step S3 can be conducted by the following procedure.

As illustrated in FIG. 29 (plan view of the region same as FIG. 27) and FIG. 30 (cross-sectional view corresponding to FIG. 28), the lower surface of the frame 41 is faced upward so that the main surface 12a of the convex part 12 of each heat-releasing plate 4 of the frame 41 faces upward. Then a solder 14a is applied (placed) directly on the main surface 12a of the convex part 12 of each heat-releasing plate 4 of the frame 41. After that, as necessary, the solder 14a directly on the main surface 12a of the convex part 12 of each heatreleasing plate 4 of the frame 41 is agitated, and then the semiconductor chip 5 is mounted (placed) over the main surface 12a of the convex part 12 of each heat-releasing plate 4 of the frame 41 via the solder 14a as illustrated in FIG. 31 (plan view of the region the same as that of FIG. 27 and FIG. 29) and FIG. 32 (cross sectional view corresponding to FIG. 28 and FIG. 30). These steps, or the step of applying the solder 14a to the convex part 12 of each heat-releasing plate 4 of the frame 41, the step of agitating the solder 14a, and the step of mounting the semiconductor chip 5 over the convex part 12 of the heat-releasing plate 4 are executed while heating entire frame 41 including the heat-releasing plate 4, and after completing the step of mounting the semiconductor chip 5 over the convex part 12 of the heat-releasing plate 4, the frame 41 is cooled near room temperature. By the above procedure, the solder 14a which was in a molten state on mounting the

semiconductor chip 5 is solidified. Thus solidified solder 14a is joined to fix the semiconductor chip 5 to the convex part 12 (main surface 12a of the convex part 12) of the heat-releasing plate 4. The solidified solder 14a becomes the joining material 14.