### US008285230B2

### (12) United States Patent

### Komori

## (10) Patent No.: US 8,285,230 B2 (45) Date of Patent: Oct. 9, 2012

# (54) AMPLIFYING CIRCUIT, SEMICONDUCTOR INTEGRATED CIRCUIT, WIRELESS TRANSMISSION SYSTEM, AND COMMUNICATION APPARATUS

(75) Inventor: Kenji Komori, Kanagawa (JP)

(73) Assignee: Sony Corporation, Tokyo (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 275 days.

(21) Appl. No.: 12/805,088

(22) Filed: **Jul. 12, 2010**

### (65) Prior Publication Data

US 2011/0028089 A1 Feb. 3, 2011

### (30) Foreign Application Priority Data

(51) **Int. Cl.**

**H04B 1/04** (2006.01) **H03F 3/04** (2006.01)

330

See application file for complete search history.

### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,006,815 A * | 4/1991  | Klumperink et al | 330/253 |

|---------------|---------|------------------|---------|

|               |         | Koskowich        |         |

| 5,959,491 A * | 9/1999  | Kang             | 327/359 |

| 5,973,563 A * | 10/1999 | Seven            | 330/265 |

| 6,784,741 B1* | 8/2004  | Redman-White     | 330/283 |

#### FOREIGN PATENT DOCUMENTS

| JP | 2007-195189 | 8/2007 |

|----|-------------|--------|

| JP | 2009-005137 | 1/2009 |

<sup>\*</sup> cited by examiner

Primary Examiner — Sonny Trinh

(74) Attorney, Agent, or Firm — Rader Fishman & Grauer, PLLC

### (57) ABSTRACT

An amplifying circuit includes: an amplifying cell portion configured by cascade-connecting a plurality stage of amplifying cells each including a pair of N-type transistors differentially connected to each other, load resistors and a current source for generating an operating current, and each having a function of amplifying differential signals; a feedback portion configured to feed differential output signals from the amplifying cell in a rear stage side of the amplifying cell portion back to differential input terminals of the amplifying cell on a front stage side; and an input portion configured to supply differential input signals to input terminals in a first stage of the amplifying cell portion.

### 20 Claims, 9 Drawing Sheets

F I G . 2

312 302 160 44 2 ppn N31 184 182 300

### FIG.6B

## FIG.6C

FIG.6D

| COMP_1 | COMP_2 | VOLTAGE<br>RELATIONSHIP                                     | OPERATION OF VOLTAGE JUDGING PORTION |

|--------|--------|-------------------------------------------------------------|--------------------------------------|

| Н      | Н      | Th_2≦Vadj4                                                  | TURN ON ONLY 506_3                   |

| H      | L      | Th_1≦Vadj4 <th_2< td=""><td>TURN ON ONLY 506_2</td></th_2<> | TURN ON ONLY 506_2                   |

| L      | L      | Vadj4 <th_1< td=""><td>TURN ON ONLY 506_1</td></th_1<>      | TURN ON ONLY 506_1                   |

1200F (202)

FIG.8A AMPLITUDE S\_TX S\_RX **FREQUENCY** F\_TX F\_RX TRANSMISSION RECEPTION SYSTEM SYSTEM FIG.8B MPLITUDE S\_1 S\_2 S\_N **FREQUENCY** F\_N F\_1 F\_2 FIG.8C 1113 1108 1115\_1 \ 1116\_1 1117\_1 ~ 1114\_1 1009 PARALLEL-SERIAL HIGH-FREQUENCY FREQUENCY MODULATING CONVERTING AMPLIFYING

PORTION CONVERTING SION PATH PORTION PORTION PORTION PORTION 1116\_2 1115\_2~ 1114 2-HIGH-FREQUENCY FREQUENCY PARALLEL-SERIAL MODULATING CONVERTING AMPLIFYING CONVERTING PORTION PORTION PORTION PORTION TRANSMI S. WAVE 1117\_N 1115\_N 1116\_N 1114\_N HIGH-FREQUENCY FREQUENCY PARALLEL-SERIAL MODULATING SCONVERTING AMPLIFYING PORTION Σα∣ CONVERTING S\_N PORTION PORTION PORTION 1228 1208 1225\_1 1224\_1 ~ 1227\_1 \ 1226\_1 WIRELESS ÉLECTROM/ FREQUENCY HIGH-FREQUENCY SERIAL-PARALLEL DE-MODULATING CONVERTING AMPLIFYING CONVERTING TRANSMISSION PATH COUPLING PORTION PORTION PORTION PORTION PORTION 1225\_2 1224\_2 1226\_2 > FREQUENCY HIGH-FREQUENCY SERIAL-PARALLEL DE-MODULATING CONVERTING AMPLIFYING CONVERTING PORTION PORTION PORTION PORTION UNIFIC 1224\_N 1225\_N√ 1227\_N-1226\_N HIGH-FREQUENCY FREQUENCY DE-SERIAL-PARALLEL MODULATING CONVERTING AMPLIFYING CONVERTING PORTION PORTION PORTION PORTION FIG.8D  $S_N S_1 S_2$ S\_N S\_1 S\_2 FREQUENCY F\_1 F\_2 F\_2 F\_N F\_N

TRANSMISSION SYSTEM

RECEPTION SYSTEM

# AMPLIFYING CIRCUIT, SEMICONDUCTOR INTEGRATED CIRCUIT, WIRELESS TRANSMISSION SYSTEM, AND COMMUNICATION APPARATUS

### BACKGROUND OF THE INVENTION

### 1. Field of the Invention

The present invention relates to an amplifying circuit, a semiconductor integrated circuit having the same mounted thereto, a wireless transmission system having the same mounted thereto, and a communication apparatus having the same mounted thereto. For example, the present invention relates to a high-frequency amplifying circuit which is applied to each of a communication apparatus on a transmis- 15 sion side and a communication apparatus on a reception side each of which operates in an Ultra Wide Band (UWB) or in a millimeter waveband.

### 2. Description of the Related Art

A broadband amplifying circuit which has flat amplifica- 20 tion characteristics in a wide frequency range, for example, is proposed in Japanese Patent Laid-Open Nos. 2009-005137 and 2007-195189 (hereinafter referred to as Patent Documents 1 and 2) as an amplifying circuit which can respond to both requests for a broadband and a large gain.

For example, Patent Document 1 proposes a high-frequency circuit. This high-frequency circuit is configured as follows. That is to say, the high-frequency circuit includes a transistor, a load, a connection point, and a series circuit. In this case, the transistor has a source terminal a potential at 30 which is fixed, and a gate terminal at which an input signal is received. The load is connected to a drain terminal of the transistor. The drain terminal of the transistor, and the load are connected to each other at the connection point. Also, in the series circuit, an inductor and a capacitor are connected in 35 series with an output terminal of the high-frequency circuit. In addition, a band-pass filter having predetermined characteristics is composed of an output equivalent circuit expressing an output impedance of the transistor, the load, and the series circuit. In a word, a broadband amplifying circuit hav- 40 ing a broadband of GHz or more is realized in the form of a load circuit using the inductor.

Patent Document 2 proposes a differential transimpedance amplifying circuit including a first operational amplifier, a second operational amplifier, a first feedback element, a sec- 45 ond feedback element, a third feedback element, and a fourth feedback element. In this case, the first operational amplifier has a first inverting input terminal, a first non-inverting input terminal, a first inverting input terminal, and a first noninverting output terminal. The second operational amplifier 50 has a second inverting input terminal, a second non-inverting input terminal, a second inverting input terminal, and a second non-inverting output terminal. The second non-inverting output terminal is connected to the first inverting input terminal. The second non-inverting output terminal is connected to 55 the first inverting input terminal. The first feedback element is connected to each of the first non-inverting input terminal and the first inverting input terminal. The second feedback element is connected to each of the first inverting input terminal and the first non-inverting input terminal. The third feedback 60 element is connected to each of the second inverting input terminal and the first inverting output terminal. Also, the fourth feedback element is connected to each of the first non-inverting input terminal and the first non-inverting output terminal. In a word, a broadband amplifying circuit having a 65 broadband of GHz or more is realized in the form of a resistance feedback type circuit.

2

### SUMMARY OF THE INVENTION

However, the configuration of the high-frequency circuit described in Patent Document 1 involves a drawback due to the fact that the inductor is used in the load circuit (the details thereof will be described in a chapter of "DETAILED DESCRIPTION OF THE PREFERRED EMBODI-MENTS"). In addition, in the configuration of the differential transimpedance amplifier circuit described in Patent Document 2, a circuit using a PMOS transistor is described, for example, with reference to FIGS. 26 to 29. Moreover, "this figure shows a first-order nested TIA700 of FIG. 7, and the TIA700 includes a first embodiment of an operational amplifier 710" is described in a paragraph 81. However, the differential transimpedance amplifier circuit is configured by using a plurality of transimpedance amplifiers using P-type transistors (such as a PMOS transistor or a PNP transistor) which is inferior in the frequency characteristics to an N-type transistor. Therefore, the differential transimpedance amplifier circuit involves a drawback in a widening of the broadband.

The present invention has been made in order to solve the problems described above, and it is therefore desirable to provide an amplifying circuit in which a satisfactory gain can be obtained over a broadband without using any of an inductor and a P-type transistor in a load, a semiconductor integrated circuit having the same mounted thereto, a wireless transmission system having the same mounted thereto, and a communication apparatus having the same mounted thereto.

In order to attain the desire described above, according to an embodiment of the present invention, there is provided an amplifying circuit including: an amplifying cell portion configured by cascade-connecting a plurality stage of amplifying cells each including a pair of N-type transistors differentially connected to each other, load resistors and a current source for generating an operating current, and each having a function of amplifying differential signals; a feedback portion configured to feed differential output signals from the amplifying cell in a rear stage side of the amplifying cell portion back to differential input terminals of the amplifying cell on a front stage side; and an input portion configured to supply differential input signals to input terminals in a first stage of the amplifying cell portion.

In a word, none of the inductor and the P-type transistor is used, but the load resistors are used as the load of the pair of N-type transistors which are differentially connected to each other in the amplifying cell. In addition thereto, the plurality stage of amplifying cells are cascade-connected to one another, thereby obtaining the large gain, and the differential output signals are fed from the output terminals of the amplifying cell on the rear stage side back to the input terminals of the amplifying cell on the front stage side, thereby configuring the negative feedback amplifying circuit.

According to another embodiment of the present invention, there is provided a semiconductor integrated circuit including: an amplifying cell portion configured by cascade-connecting a plurality stage of amplifying cells each including a pair of N-type transistors differentially connected to each other, load resistors and a current source for generating an operating current, and each having a function of amplifying differential signals; a feedback portion configured to feed differential output signals from the amplifying cell in a rear stage side of the amplifying cell portion back to differential input terminals of the amplifying cell on a front stage side; an input portion configured to supply differential input signals to input terminals in a first stage of the amplifying cell portion;

and a semiconductor substrate in which the amplifying cell portion, the feedback portion, and the input portion are formed.

In addition, each of the amplifying circuit and the semiconductor integrated circuit having the respective configurations as described above, for example, is applied as an amplifying portion (high-frequency amplifying circuit) in each of a communication apparatus on a transmission side and a communication apparatus on a reception side of a wireless transmission system for carrying out wireless transmission in a UWB or a millimeter waveband.

According to still another embodiment of the present invention, there is provided a wireless transmission system including: a first communication apparatus; a second communication apparatus; and a millimeter wave signal transmis- 15 sion path through which information is adapted to be transmitted between the first communication apparatus and the second communication apparatus in a millimeter waveband. Each of the first communication apparatus and the second communication apparatus has an amplifying circuit includ- 20 ing: an amplifying cell portion configured by cascade-connecting a plurality stage of amplifying cells each including a pair of N-type transistors differentially connected to each other, load resistors and a current source for generating an operating current, and each having a function of amplifying 25 differential signals; a feedback portion configured to feed differential output signals from the amplifying cell in a rear stage side of the amplifying cell portion back to differential input terminals of the amplifying cell on a front stage side; and an input portion configured to supply differential input 30 signals to input terminals in a first stage of the amplifying cell portion. In the wireless transmission system, the first communication apparatus converts a signal as an object of transmission into a millimeter wave signal and amplifies the resulting millimeter wave signal in the amplifying circuit, and 35 transmits the resulting millimeter wave signal thus amplified to the second communication apparatus through the millimeter wave signal transmission path, or the second communication apparatus receives the millimeter wave signal from the first communication apparatus through the millimeter wave 40 signal transmission path and amplifies the millimeter wave signal in the amplifying circuit, and demodulates the millimeter wave signal thus amplified into the signal as the object of the transmission.

According to yet another embodiment of the present inven- 45 tion, there is provided a communication apparatus on a transmission side including: a signal generating portion on the transmission side configured to signal-process a signal as an object of transmission to generate a millimeter wave signal; an amplifying portion configured to amplify the millimeter 50 wave signal generated in the signal generating portion on the transmission side; and a signal coupling portion on the transmission side configured to couple the millimeter wave signal amplified in the amplifying portion to a millimeter wave signal transmission path through which a millimeter wave 55 signal is transmitted. The amplifying portion includes: an amplifying cell portion configured by cascade-connecting a plurality stage of amplifying cells each including a pair of N-type transistors differentially connected to each other, load resistors and a current source for generating an operating 60 current, and each having a function of amplifying differential signals; a feedback portion configured to feed differential output signals from the amplifying cell in a rear stage side of the amplifying cell portion back to differential input terminals of the amplifying cell on a front stage side; and an input 65 portion configured to supply the differential millimeter wave signal generated in the signal generating portion on the trans4

mission side as an input signal to input terminals in a first stage of the amplifying cell portion.

According to a further embodiment of the present invention, there is provided a communication apparatus on a reception side including: a signal coupling portion on the reception side configured to receive a millimeter wave signal transmitted through a millimeter wave signal transmission path; an amplifying portion configured to amplify the millimeter wave signal received in the signal coupling portion on the reception side; and a signal generating portion on the reception side configured to signal-process the millimeter wave signal amplified in the amplifying portion to generate a signal as an object of transmission. The amplifying portion includes: an amplifying cell portion configured by cascade-connecting a plurality stage of amplifying cells each including a pair of N-type transistors differentially connected to each other, load resistors and a current source for generating an operating current, and each having a function of amplifying differential signals; a feedback portion configured to feed differential output signals from the amplifying cell in a rear stage side of the amplifying cell portion back to differential input terminals of the amplifying cell on a front stage side; and an input portion configured to supply the millimeter wave signal received in the signal coupling portion on the reception side as an input signal to input terminals in a first stage of the amplifying cell portion.

According to an even further embodiment of the present invention, there is provided a communication apparatus including: a transmission portion including a signal generating portion on a transmission side configured to signal-process a signal as an object of transmission to generate a transmission signal, and an amplifying portion on the transmission side configured to amplify the transmission signal generated in the signal generating portion on the transmission side; and/or a reception portion including an amplifying portion on a reception side configured to amplify a received signal, and a signal generating portion on the reception side configured to signal-process the received signal amplified in the amplifying portion on the reception side to generate the signal as the object of the transmission. The amplifying portion includes: an amplifying cell portion configured by cascade-connecting a plurality stage of amplifying cells each including a pair of N-type transistors differentially connected to each other, load resistors and a current source for generating an operating current, and each having a function of amplifying differential signals; a feedback portion configured to feed differential output signals from the amplifying cell in a rear stage side of the amplifying cell portion back to differential input terminals of the amplifying cell on a front stage side; and an input portion configured to supplying the differential millimeter wave signal generated in the signal generating portion on the transmission side as an input signal to input terminals in a first stage of the amplifying cell portion.

As set forth hereinabove, according to the present invention, it is possible to realize the amplifying circuit in which the large gain is realized in the broadband without using any of the inductor and the P-type transistor inferior in the frequency characteristics to the N-type transistor, the semiconductor integrated circuit having the same mounted thereto, the wireless transmission system having the same mounted thereto, and the communication apparatus having the same mounted thereto.

### BRIEF DESCRIPTION OF THE DRAWINGS

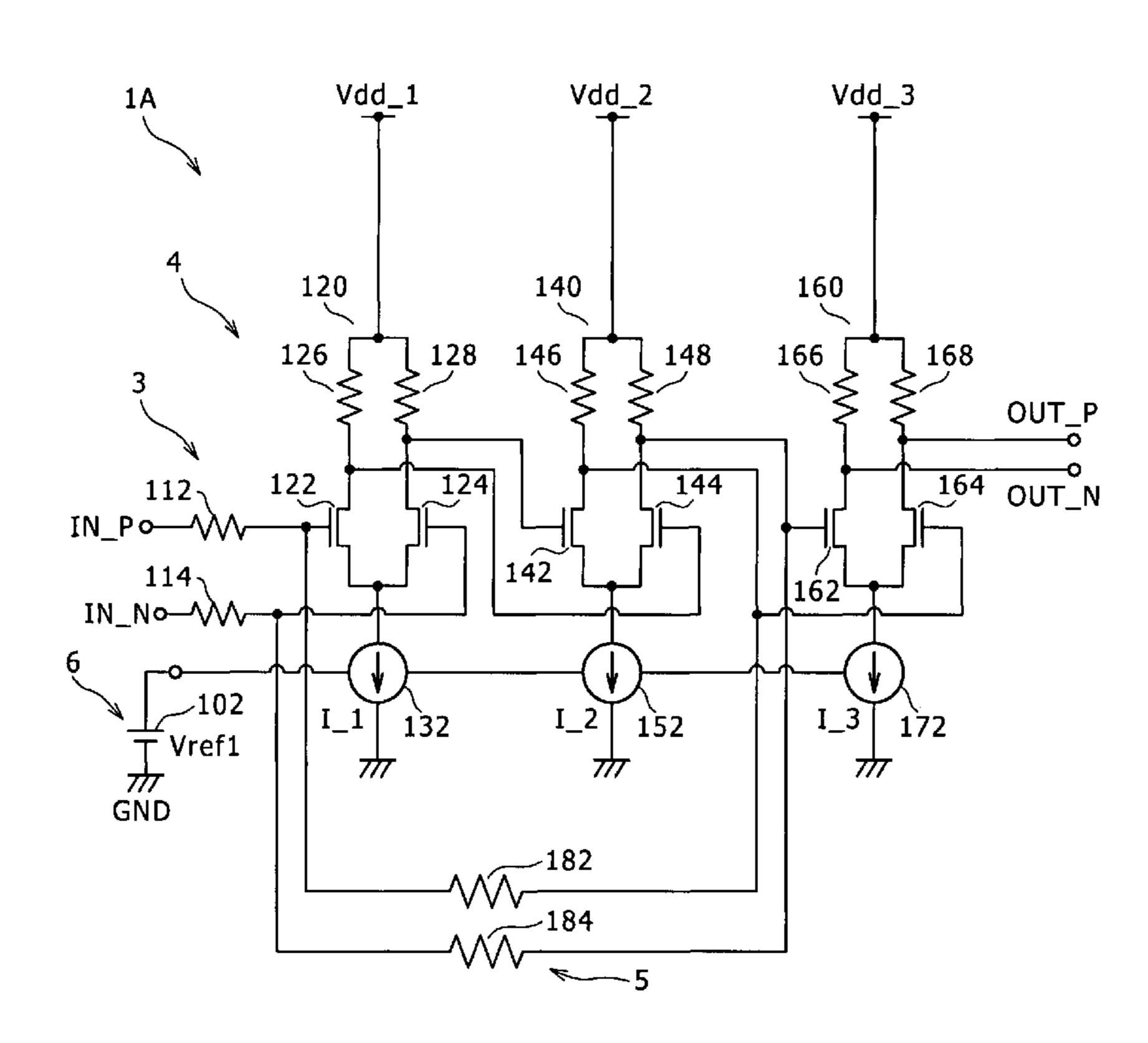

FIG. 1 is a circuit diagram showing a configuration of an amplifying circuit according to a first embodiment of the present invention;

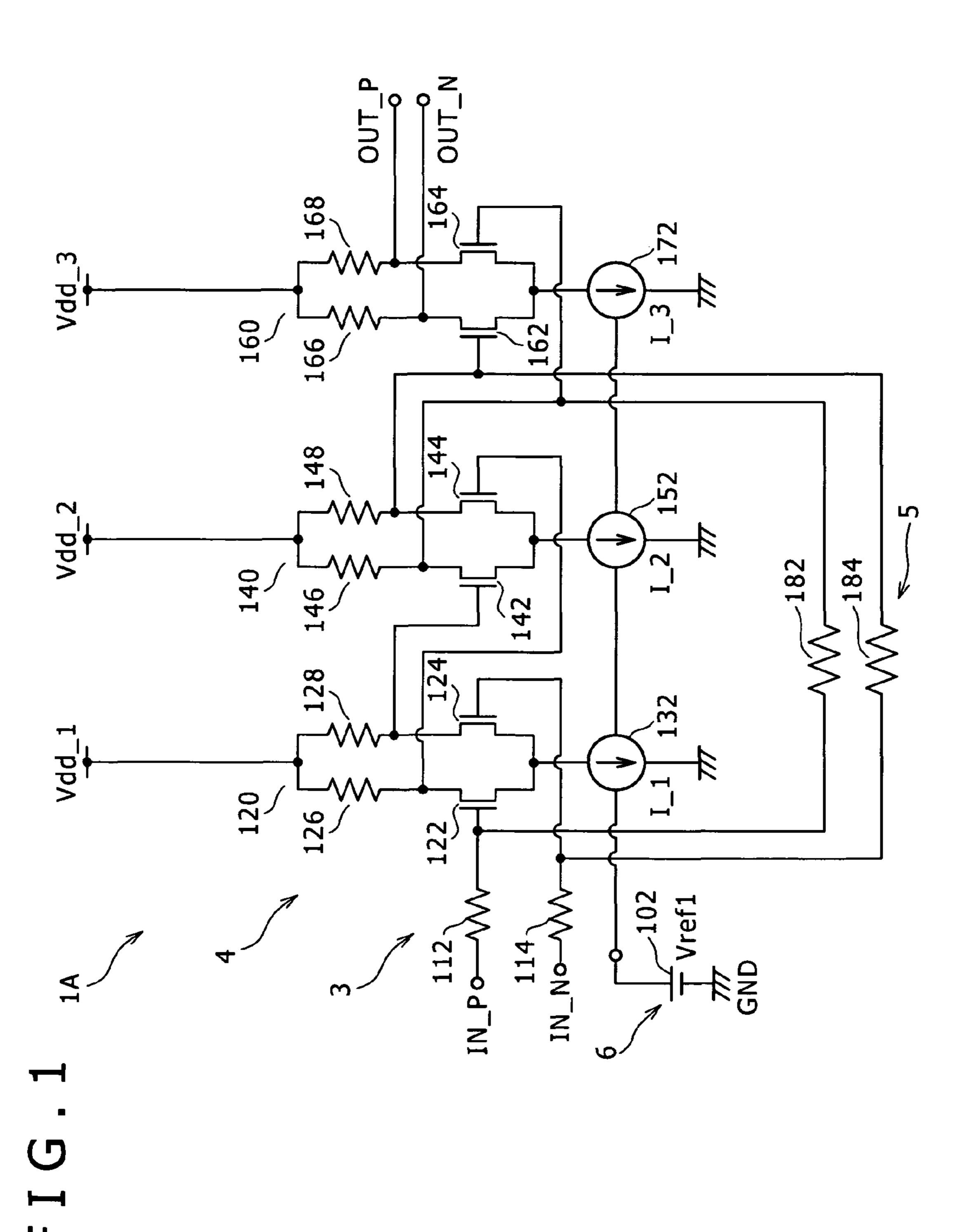

FIG. 2 is a graphical representation explaining a frequency band of the amplifying circuit according to the first embodiment of the present invention;

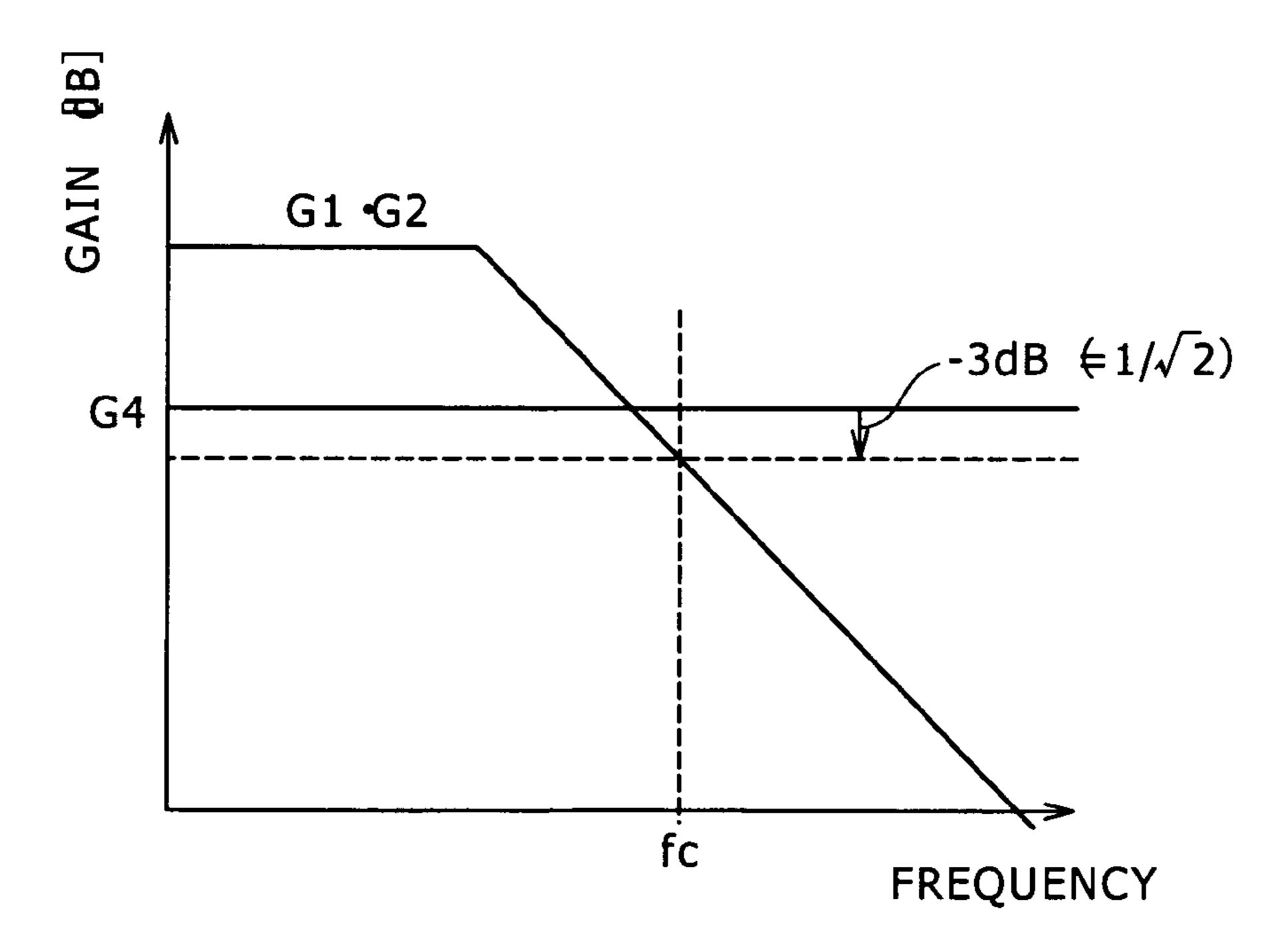

FIG. 3 is a circuit diagram showing a configuration of an amplifying circuit according to a second embodiment of the present invention;

FIGS. 4A and 4B are respectively a circuit diagram showing a configuration of an amplifying circuit according to a third embodiment of the present invention, and a circuit diagram showing a configuration of a negative capacitance circuit in the amplifying circuit shown in FIG. 4A;

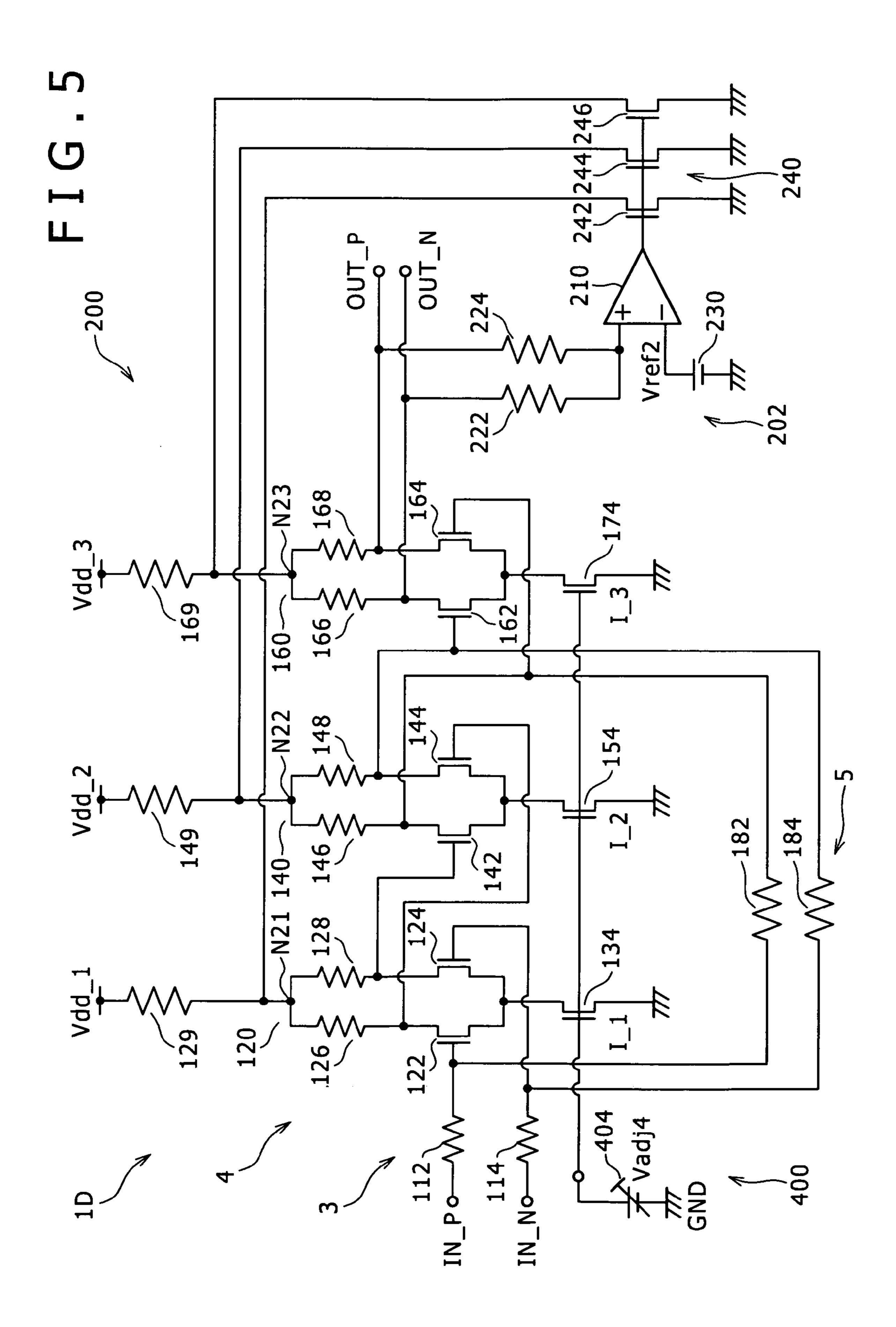

FIG. 5 is a circuit diagram showing a configuration of an amplifying circuit according to a fourth embodiment of the present invention;

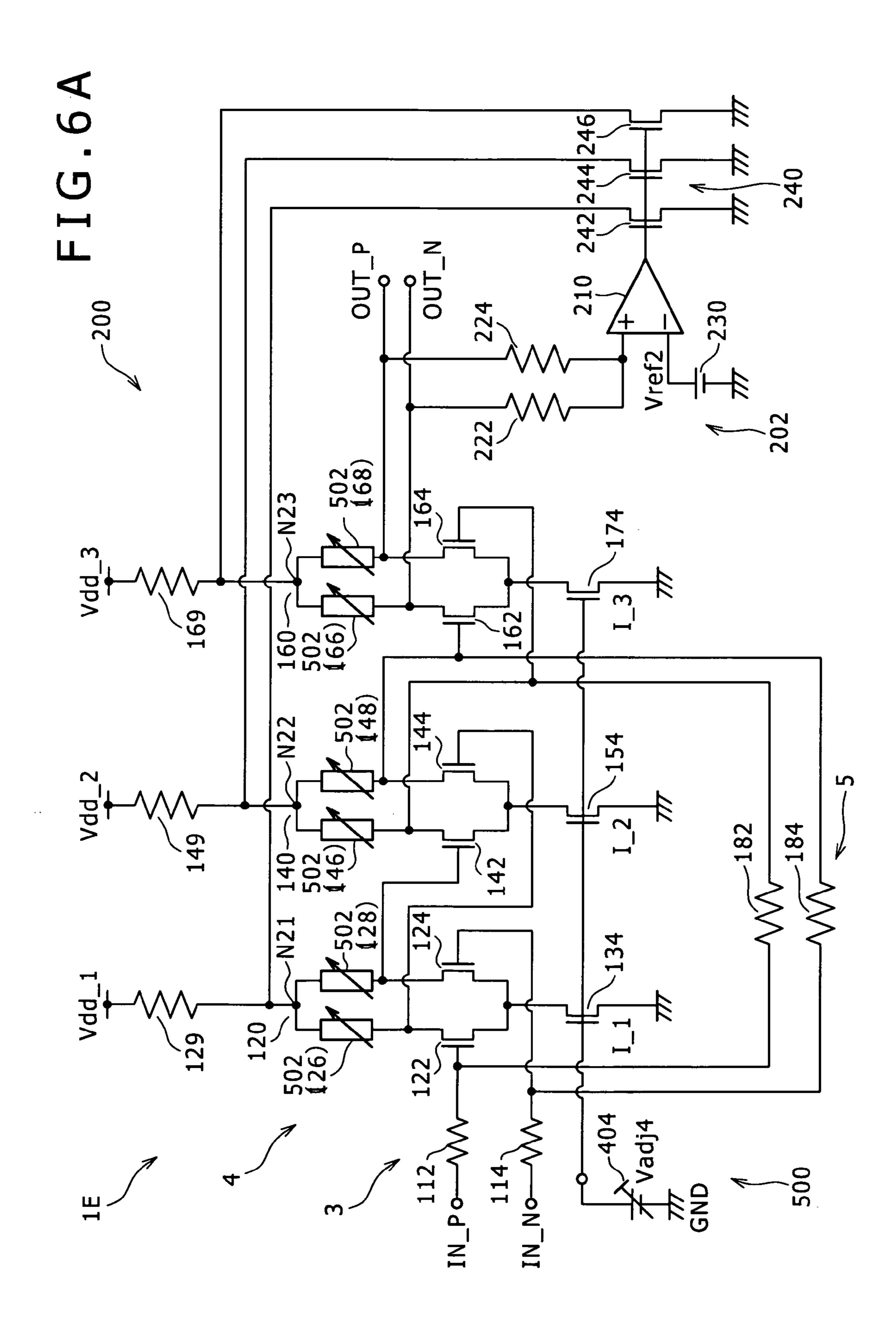

FIG. **6**A is a circuit diagram showing a configuration of an amplifying circuit according to a fifth embodiment of the present invention;

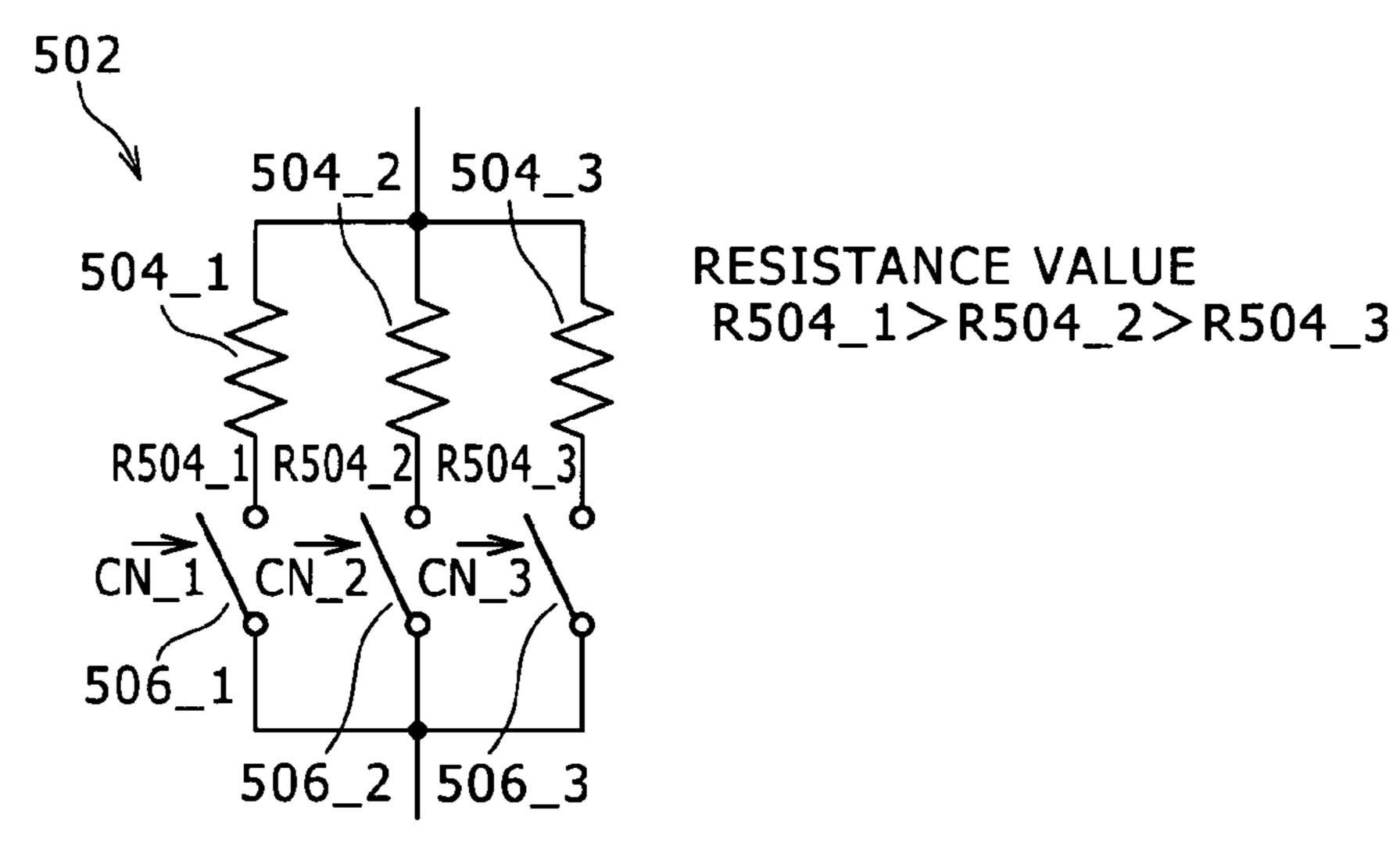

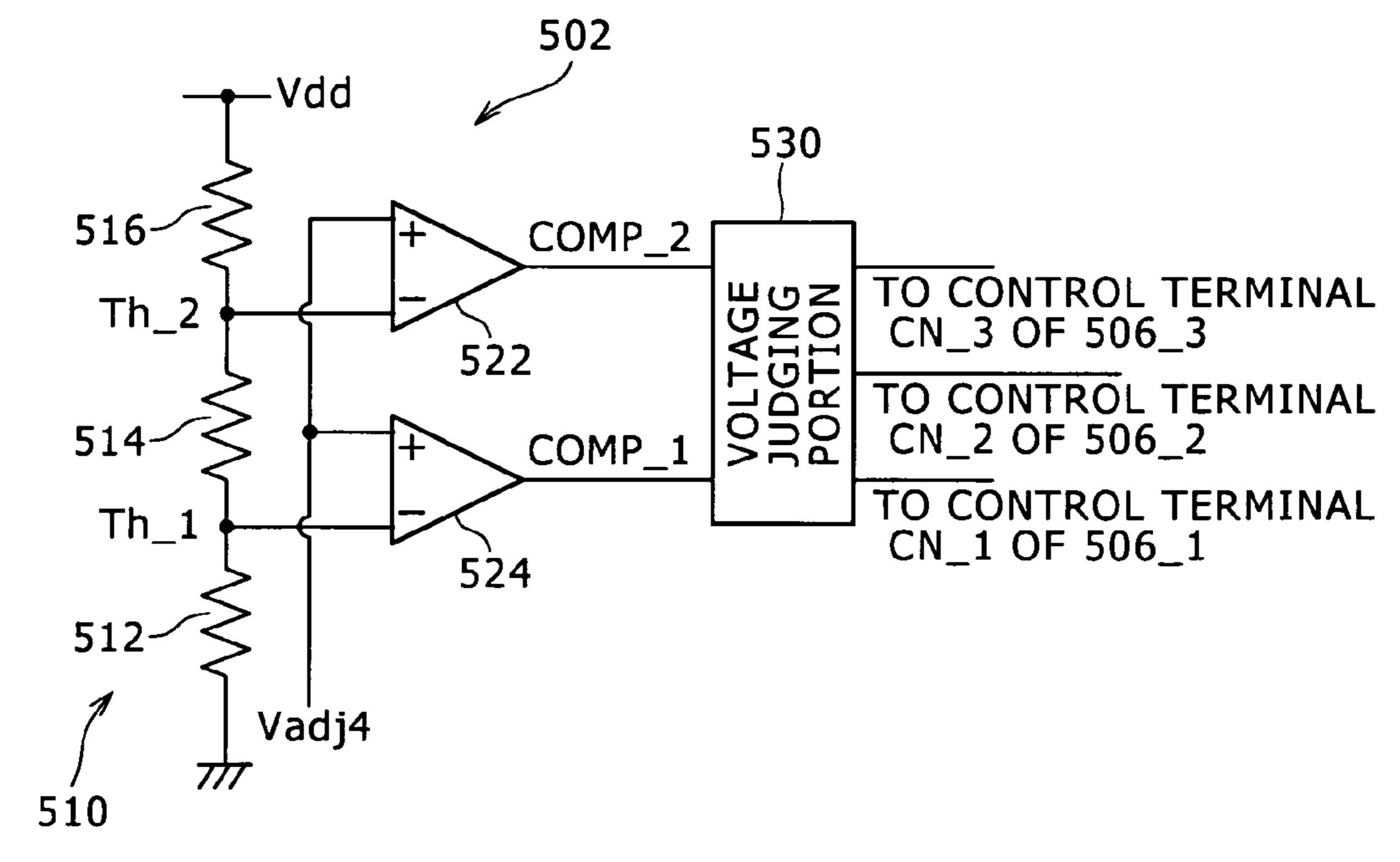

FIGS. 6B to 6D are respectively a circuit diagram showing a configuration of a functional portion on a variable resistor circuit side, a circuit diagram showing a configuration of a 20 functional portion on a control circuit side, and a diagram explaining a relationship between a voltage relation and an operation of a voltage judging portion;

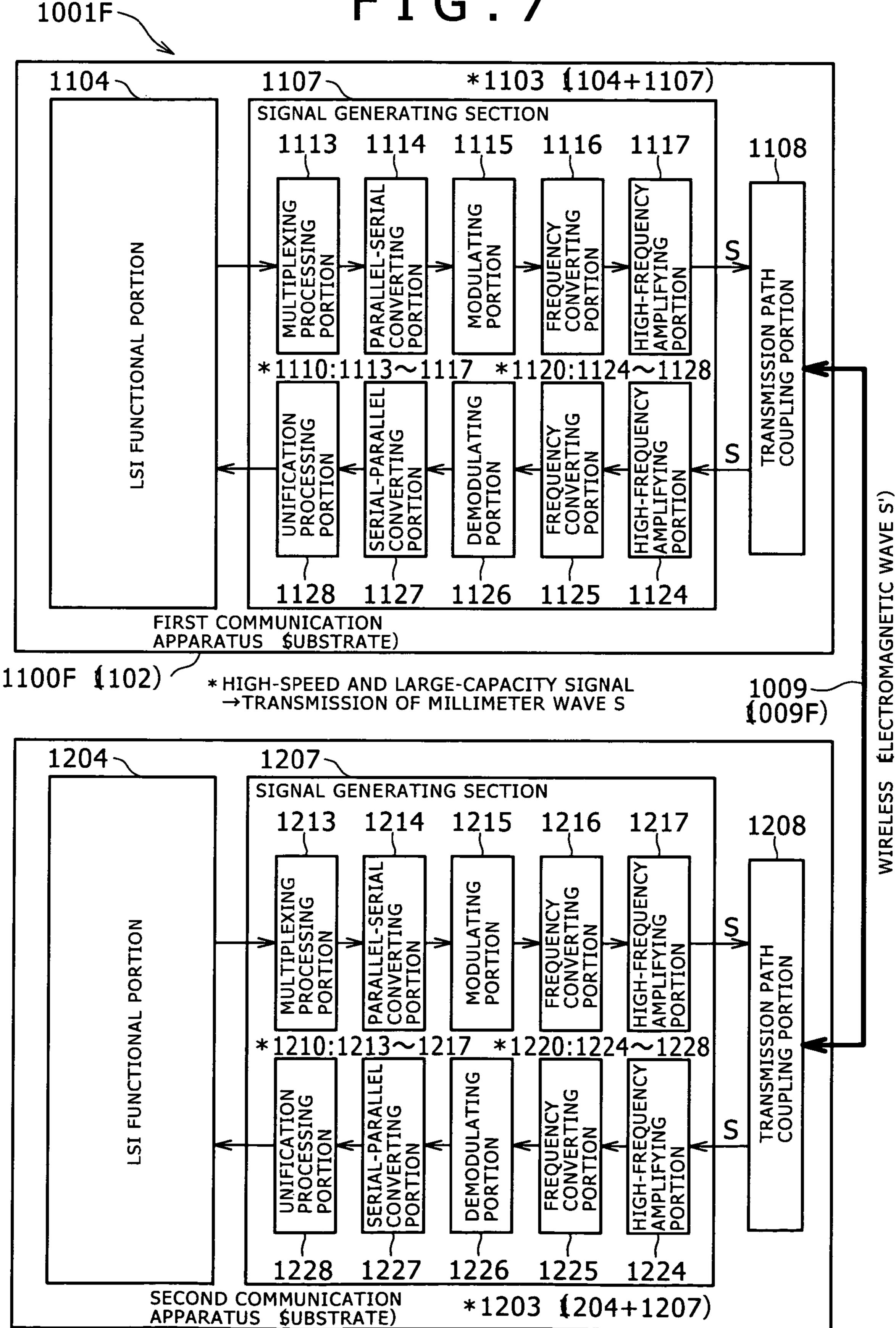

FIG. 7 is a block diagram explaining a signal interface in a wireless transmission system, to which the amplifying circuit 25 is mounted, from a functional configuration side according to a seventh embodiment of the present invention; and

FIGS. 8A and 8B, 8C, and 8D are respectively graphical representations, a block diagram, and a graphical representation explaining multiplexing of signals in the wireless trans- <sup>30</sup> mission system of the seventh embodiment shown in FIG. 7.

### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

The preferred embodiments of the present invention will be described in detail hereinafter with reference to the accompanying drawings. When functional constituent elements are distinguished among embodiments, the functional constituent elements are described by adding reference symbols of 40 upper case alphabetic characters such as A, B, C, . . . to original reference numerals, respectively. On the other hand, when the description is given without the especial distinction, the functional constituent elements are described with these reference symbols being omitted. This also applies to the 45 drawings.

It is noted that the description will be given below in accordance with the following order.

- 1. Amplifying Circuit (First to Fifth Embodiments)

- 2. Semiconductor Integrated Circuit (Sixth Embodiment)

- 3. Wireless Transmission System (Seventh Embodiment)

- 4. Communication Apparatus on Transmission Side (Eighth Embodiment)

- 5. Communication Apparatus on Reception Side (Ninth Embodiment)

- 6. Communication Apparatus (Tenth Embodiment)

- 1. Amplifying Circuit

First Embodiment (Plurality Stage of Amplifying Cells+Feedback Circuit)

FIGS. 1 and 2 are respectively a circuit diagram and a 60 graphical representation explaining an amplifying circuit according to a first embodiment of the present invention. Here, FIG. 1 is the circuit diagram showing a configuration of the amplifying circuit according to the first embodiment of the present invention, and FIG. 2 is the graphical representation explaining a frequency band of the amplifying circuit according to the first embodiment of the present invention.

6

The amplifying circuit 1A of the first embodiment includes an input portion 3, an amplifying cell portion 4, a D.C. feedback path 5, and a reference power source portion 6. In this case, in the amplifying cell portion 4, a plurality stage of amplifying cells AS each having a function of amplifying a signal are cascade-connected to one another. Also, the reference power source portion 6 generates a reference voltage in accordance with which an operating current is regulated. The input portion 3, the amplifying cell portion 4, the D.C. feedback path 5, and the reference power source portion 6 (functional portions) are configured on the same semiconductor substrate, and are provided in the form of a semiconductor Integrated Circuit (IC).

In this case, the amplifying cell portion 4 is configured by cascade-connecting three stages of amplifying cells AS (120, 140 and 160) each configured as a differential amplifier to one another. The amplifying cell 160 in a final stage functions as an output amplifier as well. A plurality stage of amplifying cells AS are cascade-connected to one another, thereby obtaining a large gain, and thus a D.C. operating point is stably maintained in a certain degree of a range due to a D.C. negative feedback operation by the D.C. feedback portion 5. The wording "in a certain degree of a range" is stated in consideration of a point different from such a negative feedback circuit that an operating point of a certain portion agrees with a reference point. When only an A.C. gain is considered, the feedback may be carried out through capacitive coupling.

Here, for configuring each of the amplifying cells AS as the differential amplifier, the feature of the first embodiment is that the differential pair is configured by using N-type transistors, and none of an active load and an inductance cell is used as a load, but resistors are used as the load instead. Although any of an N-channel transistor (NMOS transistor) and an N-type bipolar junction transistor (NPN transistor) may be used as the N-type transistor, in the following description, the NMOS transistor is used as the N-type transistor.

It is expected that the P-type transistor (such as the P-channel transistor (PMOS transistor) or the PNP transistor) is used either in the differential pair or in the active load. However, the P-type transistor is not adopted herein because the P-type transistor is inferior in the high-frequency characteristics to the N-type transistor.

For example, it is expected that an amplifier is configured by using a plurality of transimpedance amplifiers each using the transistor inferior in the frequency characteristics. In this case, however, the amplifier thus configured is not suitable for an amplifier for a base-band signal corresponding to a broadband.

In addition, the use of the inductor involves a drawback that a band width is narrowed due to a Q value of the inductor to show band-pass (BPF) characteristics. Although it is expected that when the band of the BPF characteristics is equal to or wider than that in the original use application, there is no problem. However, there is a drawback that the performance is deteriorated due to the constant dispersion. In addition, when the amplifying circuit 1A is mounted in the form of the semiconductor Integrated Circuit (IC), the use of the inductor causes a drawback that a chip size becomes large. When the chip size is prioritized, it is also necessary to dispose the inductor outside the chip in some cases. On the other hand, the resistor is more easily formed in the semiconductor IC than the inductor, and the constant dispersion is less in the resistors.

Each of the amplifying cells AS (120, 140 and 160) includes a differential pair of NMOS transistors, resistors as a load, and a current source for generating an operating current for corresponding one of the amplifying cells 120, 140 and

160. For example, the amplifying cell 120 in an initial stage (in a first stage) includes a differential pair of NMOS transistors 122 and 124, load resistors 126 and 128 having one terminals which are connected to drain terminals of the NMOS transistors 122 and 124, respectively, and a current 5 source 132 having one terminal which is commonly connected to source terminals of the NMOS transistors 122 and 124. The other terminals of the load resistors 126 and 128 are each connected to a power source Vdd\_1 on a high potential side. The other terminal of the current source 132 is connected to the ground (GND). It is noted that a power source voltage Vss\_1 on a low potential side may be used instead of using the ground.

The amplifying cell 140 in a second stage includes a differential pair of NMOS transistors 142 and 144, load resistors 146 and 148 having one terminals which are connected to drain terminals of the NMOS transistors 142 and 144, respectively, and a current source 152 having one terminal which is commonly connected to source terminals of the NMOS transistors 142 and 144. The other terminals of the load terminals 20 146 and 148 are each connected to a power source Vdd\_2 on the high potential side. The other terminal of the current source 152 is connected to the ground (GND). It is noted that a power source voltage Vss\_2 (preferably, Vss\_1=Vss\_2) on the low potential side may be used instead of using the ground 25 (GND).

The amplifying cell **160** in the final stage (in a third stage) includes a differential pair of NMOS transistors **162** and **164**, load resistors **166** and **168** having one terminals which are connected to drain terminals of the NMOS transistors **162** and 30 **164**, respectively, and a current source **172** having one terminal which is commonly connected to source terminals of the NMOS transistors **162** and **164**. The other terminals of the load terminals **166** and **168** are each connected to a power source Vdd\_3 on the high potential side. The other terminal of 35 the current source **172** is connected to the ground (GND). It is noted that a power source voltage Vss\_3 (preferably, Vss\_1=Vss\_2=Vss\_3) on the low potential side may be used instead of using the ground (GND).

When the power source voltages Vss\_1, Vss\_2 and Vss\_3 on the low potential side are used as the references on the low potential sides of the amplifying cells 120, 140 and 160, respectively, instead of using the ground, a power source voltage Vss on a lower potential side is also used as a reference on a lower potential side for each of portions in the 45 second to fifth embodiments which will be described later instead of using the ground.

A reference power source portion 6 includes one reference voltage source 102 which is common to a plurality stage of amplifying cells AS (120, 140 and 160). Each of the current sources 132, 152 and 172 is connected to the reference voltage source 102, so that a reference potential Vref1 for setting of a current value is commonly supplied to the current sources 132, 152 and 172. The current sources 132, 152 and 172, supply D.C. bias currents I\_1, I\_2 and I\_3 (operating currents) each corresponding to the reference potential Vref1 to the differential pair of NMOS transistors 122 and 124, the differential pair of NMOS transistors 142 and 144, and the differential pair of NMOS transistors 162 and 164, respectively. For the purpose of optimizing the operating points and the mutual conductances of the first to third stages, the D.C. bias current value is set every amplifying cell AS.

In this connection, the D.C. bias current value is divided into two parts every amplifying cell AS to be caused to flow through the two load resistors, thereby determining the operating point of the output signal. In addition thereto, the mutual conductance of the differential pair increases or decreases in

8

accordance with the D.C. bias current. That is to say, the gain of the amplifying cell AS is determined in accordance with the set value of the D.C. bias current. In the case of this configuration, the operating point and the mutual conductance (that is, the gain) are not set independently of each other, but are set in conjunction with each other. In other words, when the operating point is optimized (for example, in a midpoint between the power source Vdd and the ground), the mutual conductance (gain) is determined in accordance with the D.C. bias current at that time. Contrary to this, when the D.C. bias current is set so as to obtain the necessary mutual conductance (gain), it cannot be said that the operating point is not necessarily optimal. When the operating point becomes improper, the distortion performance is necessarily determined. In particular, since the output amplitude is large in the final stage, a problem about a relationship between the operating point and the distortion performance remarkably appears.

The input portion 3 is provided on the input side (in a gate side) of the amplifying cell 120 in the initial stage. The input portion 3 has such a configuration as to have the resistors corresponding to the differential signals on the signal paths, respectively. That is to say, in the input portion 3, one terminals of input resistors 112 and 114 are connected to the gate terminals of the NMOS transistors 122 and 124 for the differential inputs in the amplifying cell 120, respectively. The other terminals of the input resistors 112 and 114 are connected to signal input terminals, that is, an input terminal IN\_P for a clockwise signal, and an input terminal IN\_N for an inversion signal of the amplifying circuit 1A, respectively, thereby supplying the differential signals, that is, a normalphase input signal SP and a reverse-phase input signal SN to the gate terminals of the NMOS transistors 122 and 124 in the differential pair, respectively.

Differential output signals from the amplifying cell 120 in the initial stage become differential input signals to the amplifying cell 140 in the second stage, respectively. In this case, an output terminal (drain terminal) of the NMOS transistor 122 is connected to a gate terminal of the NMOS transistor 144, and an output terminal (drain terminal) of the NMOS transistor 124 is connected to a gate terminal of the NMOS transistor 142.

Likewise, differential output signals from the amplifying cell 140 in the second stage become differential input signals to the amplifying cell 160 in the third stages, respectively. In this case, an output terminal (drain terminal) of the NMOS transistor 142 is connected to a gate terminal of the NMOS transistor 164, and an output terminal (drain terminal) of the NMOS transistor 144 is connected to a gate terminal of the NMOS transistor **162**. An output terminal (drain terminal) of the NMOS transistor 162 of the amplifying cell 160 in the third stage is connected to an output terminal (clockwise signal output terminal OUT\_P) for a signal in phase with a signal inputted to an input terminal IN\_P (clockwise signal input terminal) of the amplifying circuit 1A. An output terminal (drain terminal) of the NMOS transistor 164 of the amplifying cell 160 in the third stage is connected to an output terminal (inversion signal output terminal OUT\_N) for a signal in phase with a signal inputted to an input terminal IN\_N (inversion signal input terminal) of the amplifying circuit 1A.

The D.C. feedback portion 5 adopts such a configuration as to feed the output signals on the rear stage side back to the front stage side through D.C. coupling, thereby functioning so as to maintain the operating D.C. level in the amplifying cells AS between the front stage side and the rear stage side at a constant value. D.C. components are extracted from the output signals on the rear stage side to be D.C. fed back to the

input terminals on the front stage side, thereby optimizing a D.C. bias for the output signals from the amplifying cell AS on the rear stage side. Thus, even when the output amplitude is increased, the distortion performance is improved.

For example, the D.C. feedback portion **5** adopts such a configuration as to have resistors corresponding to the differential signals, respectively, on the signal path. In the first embodiment, the D.C. feedback portion **5** adopts such a configuration that the differential output signals from the amplifying cell **140** in the second stage (the differential input signals to the amplifying cell **160** in the third stage) are fed back to the gate terminals of the NMOS transistors **122** and **124** of the amplifying cell **120** in the initial stage through feedback resistors **182** and **184**, respectively.

It is noted that although in the first embodiment, the differential output signals from the amplifying cell 140 in the second stage are fed back to the amplifying cell 120 in the initial stage, the present invention is by no means limited thereto, and, for example, the differential outputs from the 20 amplifying cell 160 in the final stage may be fed back to the amplifying cell 120 in the initial stage. However, in this case, the degree of freedom of setting for an output impedance of the amplifying circuit 1A is reduced. For example, although it is important for an output amplifier used either with the UWB 25 or with the millimeter waveband to have a large gain and a high output power, it is also important for the output amplifier used either with the UWB or with the millimeter waveband to meet output matching in the band used. When the output matching is insufficiently met, for example, unnecessary 30 reflection is caused in an external circuit in an antenna or the like, and thus the abnormal oscillation of a circuit may be generated. Therefore, it is necessary for the output amplifier used in a communication system in an ultra-broad band such as the UWB or the millimeter waveband to meet the output <sup>35</sup> matching over the entire band.

In consideration of this respect, the first embodiment adopts such a configuration that when the D.C. feedback portion 5 is provided, the differential output signals from the amplifying cell in the stage (the second stage in the first embodiment) just before the final stage are fed back to the amplifying cell in the initial stage through the D.C. coupling, thereby making the final stage independent from the feedback loop.

Here, an amplification gain G1 of the amplifying cell 120 in the first stage is expressed by Expression (1):

$$G1 = \frac{gm1 \cdot R1}{1 + j2\pi f \cdot C1 \cdot R1} \tag{1}$$

where gm1 is a mutual conductance of each of the NMOS transistors 122 and 124, R1 is a resistance value of each of the load resistors 126 and 128, and C1 is a capacitance of each of the load capacitors. It is noted that the capacitance C1 of each of the load capacitors is represented in consideration of, for example, a wiring capacitance, and input capacitances of the NMOS transistors 142 and 144 which are connected in the form of impedances of the next stage (second stage) (a composite value of gate capacitances, gate-to-drain capacitances, gate-to-source capacitances, and the like). The amplification gain G1 becomes a function of a frequency because not only the pure resistances, but also the load capacitances C1 exist as the load impedance.

An amplification gain G2 of the amplifying cell 140 in the second stage is expressed by Expression (2):

$$G2 = \frac{gm2 \cdot R2}{1 + j2\pi f \cdot C2 \cdot R2} \tag{2}$$

where gm2 is a mutual conductance of each of the NMOS transistors 142 and 144, R2 is a resistance value of each of the load resistors 146 and 148, and C2 is a capacitance of each of the load capacitors. It is noted that the load capacitances C2 is represented in consideration of, for example, a wiring capacitance, and input capacitances of the NMOS transistors 162 and 164 which are connected in the form of impedances of the next stage (third stage) (a composite value of gate capacitances, gate-to-drain capacitances, gate-to-source capacitances, and the like). The amplification gain G2 becomes a function of the frequency because not only the pure resistances, but also the load capacitances C2 exist as the load impedance.

An amplification gain G3 of the amplifying cell 160 in the third stage is expressed by Expression (3):

$$G3 = \frac{gm3R3Zo}{R3 + Zo} \tag{3}$$

where gm3 is a mutual conductance of each of the NMOS transistors 162 and 164, R2 is a resistance value of each of the load resistors 146 and 148, and Zo is a load impedance.

An open gain of the amplifying circuit 1A of the first embodiment is expressed by a product of the amplification gains G1, G2 and G3 in the first to third stages. Since the amplifying circuit 1A of the first embodiment is provided with the D.C. feedback portion 5 for feeding the differential output signals from the amplifying cell 140 in the second stage back to the amplifying cell 120 in the first stage, the actual amplification gain does not become the open gain, but becomes a closed loop gain.

That is to say, the differential output signals from the amplifying cell 140 in the second stage are negatively fed back to the amplifying cell 120 in the first stage, and thus the negative feedback amplifying circuit is composed of all of the input portion 3, the amplifying cells 120 and 140 in the first and second stages, and the D.C. feedback portion 5. Here, an amplification gain G4 (closed loop gain) of the negative feedback amplifying circuit is expressed by Expression (4):

$$G4 = \frac{R5}{R4} \cdot \frac{G1 \cdot G2}{1 + G1 \cdot G2} \cong \frac{R5}{R4}$$

$$\therefore G1 \cdot G2 >> 1$$

(4)

where R4 is a resistance value of each of the input resistors 112 and 114, and R5 is a resistance value of each of the feedback resistors 182 and 184.

When the amplification gains G1 and G2 in the first and second stages are each sufficiently large, the amplification gain G4 is determined in accordance with a ratio of the resistance value R5 of each of the feedback resistors 182 and 184 to the resistance value R4 of each of the input resistors 112 and 114.

Since not only the pure resistances, but also the load capacitors C1 and C2 exist as the load impedance in the amplifying cells 120 and 140, respectively, as previously stated, each of the amplification gains G1 and G2 becomes the

function of the frequency, f. Thus, the closed loop gain G4 of the negative feedback amplifying circuit also has the frequency characteristics.

For example, if a frequency band when no feedback is carried out for each of the amplifying cells **120** and **140** <sup>5</sup> (referred to as a single amplifiers) is regulated by a cut-off frequency, f1 (a frequency of a 3 dB-down value), the cut-off frequency, f1, when C1=C2, R1=R2, and gm1=gm2 is expressed by Expression (5):

$$f1 = \frac{1}{2\pi \cdot C1 \cdot R1} \tag{5}$$

On the other hand, if a frequency band of the negative feedback amplifying circuit is regulated by a cut-off frequency, fc (a frequency of a 3 dB-down value), the cut-off frequency, fc, when C1=C2, R1=R2, and gm1=gm2 is expressed by Expression (6) because of  $(1/\sqrt{2})\times G4=G1\times G2$ : 20

$$\frac{1}{\sqrt{2}} \frac{R5}{R4} = \frac{(gm1 \cdot R1)^2}{1 + (2\pi fc \cdot C1 \cdot R1)^2}$$

$$\therefore fc = \frac{1}{2\pi \cdot C1 \cdot R1} \sqrt{\sqrt{2} \frac{R4}{R5} (gm1 \cdot R1)^2 - 1} = \frac{1}{2\pi \cdot C1 \cdot R1} \sqrt{\sqrt{2} \frac{(G1 \cdot G2)}{G4} - 1}$$

As understood from Expressions (1) to (6), the amplification gains G1 and G2 of the amplifying cells 120 and 140 in the first and second stages are each increased with respect to the closed loop gain G4, whereby the frequency band (the cut-off frequency fc) of the negative feedback amplifying circuit can be widened with respect to the frequency band (the cut-off frequency f1) in the single amplifier expressed by Expression (5). Although being dependent on the set values of the capacitance values C1 and C2 of the load capacitors, the resistance values R1 and R2 of the load resistors, and the mutual conductances gm1 and gm2, for example, the cut-off frequency fc can also be set at about several gigahertz.

Although in the first embodiment, the negative feedback 45 amplifying circuit is composed of the two stages of the amplifying cells AS, when the number of stages is further increased, the gain which can be realized in the same frequency band can be increased, and when the gain is held at the same level, the frequency band can be widened.

As described above, the amplifying circuit 1A of the first embodiment is configured in such a way that a plurality of amplifying cells AS each including a pair of NMOS transistors differentially connected to each other and the two load resistors are cascade-connected to one another, and the differential output signals from the amplifying cell in the rear stage side are D.C.-fed back to the amplifying cell in the front stage side. As a result, the large gain can be realized in the wide band of Direct Current (D.C.) to several gigahertz without using any of the inductance cell and the PMOS transistor 60 inferior in the frequency characteristics to the NMOS transistor. By configuring the amplifying circuit 1A without using the inductance cell, the chip area can be reduced as compared with the case where the inductance cell is used. Since all the circuit elements can be configured on the chip, including the 65 current sources 132, 152 and 172, any of peripheral elements is unnecessary, and thus the cost can also be reduced.

12

Although it is expected to adopt a complementary amplifying circuit in which the NMOS transistor is replaced with the PMOS transistor, the PMOS transistor is inferior in the frequency characteristics to the NMOS transistor in the first place, and thus the cut-off frequency thereof is reduced. The amplifying circuit 1A is configured without using the PMOS transistor inferior in the frequency characteristics to the NMOS transistor, whereby the band can be widened as compared with the amplifying circuit using the PMOS transistor.

In addition, in the amplifying circuit 1A, in the D.C. feedback portion 5, the differential output signals from the amplifying cell in the stage right before the final stage are fed back to the amplifying cell in the first stage through the D.C. coupling, thereby making the amplifying cell in the final stage independent of the feedback loop. As a result, the output impedance of the amplifying circuit 1A can be set independently of the feedback loop, and thus the degree of freedom of the design for a relationship with the load connected to the subsequent stage can be increased.

Second Embodiment (First Embodiment+D.C. Operating Point Stabilizing Circuit)

FIG. 3 is a circuit diagram showing a configuration of an amplifying circuit according to a second embodiment of the present invention. The feature of the amplifying circuit 1B according to the second embodiment of the present invention is to include an operating point voltage stabilizing circuit 200 (in other words, a D.C. operating point change suppressing circuit) based on the amplifying circuit 1A of the first embodiment. The operating point voltage stabilizing circuit 200 monitors an operating point voltages of the differential output signals from the amplifying cell AS, and carries out control in such a way that the operating point voltages of the amplifying cells AS are each held constant based on the monitoring result. Hereinafter, the amplifying circuit 1B of the second embodiment will be described by focusing on a difference between the first embodiment and the second embodiment.

In the amplifying circuit 1B of the second embodiment, firstly, in each of the amplifying cells AS (120, 140 and 160) in the first to third stages, the load resistors are not directly connected to the power sources Vdd, respectively, but are connected to the power sources Vdd through D.C. operating point adjusting elements, respectively. In the second embodiment, a resistor is used as the D.C. operating point adjusting element. For example, the amplifying cell 120 in the first stage includes the D.C. operating point adjusting element 129 composed of the resistor disposed between a connection point (a node N21) between the resistors 126 and 128, and the power source Vdd\_1. The amplifying cell 140 in the second stage includes the D.C. operating point adjusting element 149 50 composed of the resistor disposed between a connection point (a node N22) between the resistors 146 and 148, and the power source Vdd\_2. Also, the amplifying cell 160 in the final stage includes the D.C. operating point adjusting element 169 composed of the resistor disposed between a connection point (a node N23) between the resistors 166 and 168, and the power source Vdd\_3.

In addition, the amplifying circuit 1B of the second embodiment includes a D.C. operating point controlling portion 202 and a current driving portion 240 in a stage next to the final stage. The functional portions including the D.C. operating point controlling portion 202 and the current driving portion 240 are configured on the same semiconductor substrate and are provided in the form of a semiconductor Integrated Circuit (IC).

The D.C. operating point controlling portion 202 includes a differential amplifying circuit 210 (which may also be a comparator), monitoring elements 222 and 224, and a refer-

ence voltage source 230 for generating a reference potential Vref2. In the second embodiment, resistors are used as the monitoring elements 222 and 224, respectively. The differential amplifying circuit 210 compares each of the operating point voltages of the differential output signals, from the 5 amplifying cell AS (the amplifying cell 160 in the second embodiment), which are monitored by the mounting elements 222 and 224, respectively, with the reference potential Vref2 generated by the reference voltage source 230.

The current driving portion 240 causes D.C. currents to 10 flow through the D.C. operating point adjusting elements 129, 149 and 169 of the amplifying cells 120, 140 and 160 in the first to third stages, respectively, in accordance with an output signal from the differential amplifying circuit 210. From this reason, the current driving portion 240 includes driving transistors 242, 244 and 246 corresponding to the D.C. operating point adjusting elements 129, 149 and 169 of the amplifying cells 120, 140 and 160 in the first to third stages, respectively.

The D.C. operating point adjusting elements 129, 149 and 169 of the amplifying cells 120, 140 and 160 in the first to third stages, the D.C. operating point controlling portion 202, and the current driving portion 240 monitor the operating point voltages of the differential output signals from the amplifying cells 120, 140 and 160 in the first to third stages, respectively. Also, the operating point voltage stabilizing circuit 200 is configured which carries out the control in such a way that the operating point voltages are each held constant in accordance with the monitoring results.

It is noted that it is expected that the D.C. operating point controlling portions 202 for monitoring the D.C. potential 30 levels (operating point voltages) are provided so as to correspond to the differential output signals from the amplifying cells AS (120, 140 and 160) in the first to third stages, respectively. In this case, however, the circuit is scaled up. In order to cope with such a situation, the second embodiment adopts 35 a configuration that the D.C. opening point controlling portion 202 is provided only in the stage next to the final stage so that each of the differential output signals from the final stage having a less margin for the D.C. bias change of the output signals is made a monitoring point, and the negative feedback 40 control is carried out in such a way that not only the D.C. levels of the differential output signals from the amplifying cell in the final stage, but also the D.C. levels of the differential output signals from the amplifying cells in the remaining stages are each held constant in accordance with a control 45 signal based on the monitoring results.

One terminal of the monitoring element 222 is connected to the drain terminal (that is, the clockwise signal output terminal OUT\_P) of the NMOS transistor 162 in the amplifying cell 160 in the final stage. One terminal of the monitoring element 224 is connected to the drain terminal (that is, the inversion signal output terminal OUT\_N) of the NMOS transistor 164 in the amplifying cell 160 in the final stage. The reason that each of the monitoring elements 222 and 224 is connected to the node N23 of the amplifying cell 160 in the 55 final stage is because a respect that the output amplitude is large in the amplifying cell 160 in the final stage, and thus a problem about a relationship between the operating point and the distortion performance remarkably appears is taken into consideration.

The other terminals of the monitoring elements 222 and 224 are commonly connected to one input terminal (a non-inverting input terminal (+) in this embodiment) of the differential amplifying circuit 210. The other input terminal (an inverting input terminal (–) in this embodiment) of the differential amplifying circuit 210 is connected to the reference voltage source 230, and thus a reference potential Vref2 is

**14**

supplied to the inverting input terminal (-) of the differential amplifying circuit 210. The reference potential Vref2 shows one-to-one correspondence with each of the operating point potentials Vo of the output signals, and, for example, has the same value as a midpoint potential between the power source Vdd and the ground (or the power source voltage Vss on the low potential side).

NMOS transistors are used as the driving transistors 242, 244 and 246 in the second embodiment, respectively. Gate terminals of the driving transistors 242, 244 and 246 in the second embodiment composed of the NMOS transistors, respectively, are commonly connected to an output terminal of the differential amplifier 210, and source terminals of the driving transistors 242, 244 and 246 are each grounded. A drain terminal of the driving transistor 242 is connected to the node N21 of the amplifying cell 120 in the first stage. A drain terminal of the driving transistor 244 is connected to the node N22 of the amplifying cell 140 in the second stage. Also, a drain terminal of the driving transistor 246 is connected to the node N23 of the amplifying cell 160 in the final stage.

The differential amplifying circuit 210 compares each of the D.C. levels (in a word, each of the operating point potentials Vo in the final stage) at the node N23, of the amplifying cell 160 in the final stage, which are detected through the monitoring elements 222 and 224, respectively, with the reference potential Vref2 set by the reference voltage source 230. Thus, the differential amplifying circuit 210 carries out the negative feedback control through the driving transistors 242, 244 and 246 so that each of the operating point potentials Vo and the reference potential Vref2 agree with each other.

For example, when a relationship of each of the operating point potentials Vo>the reference potential Vref2 is established, an output voltage from the differential amplifying circuit 210 increases and drain currents of the driving transistors 242, 244 and 246 each increase. Therefore, currents caused to flow through the D.C. operating point adjusting elements 129, 149 and 169, respectively, each increase. As a result, voltages developed at the nodes N21, N22 and N23, respectively, each drop, and each of the operating point potentials Vo (in a word, the voltage at the clockwise signal output terminal OUT\_P and the voltage at the inversion signal output terminal OUT\_N) of the amplifying cell 160 in the final stage each drop. Thus, each of the operating point potentials Vo is controlled so as to approach the reference potential Vref2.

Contrary to this, when a relationship of each of the operating point potentials Vo<the reference potential Vref2 is established, the output voltage from the differential amplifying circuit 210 decreases and the drain currents of the driving transistors 242, 244 and 246 each decrease. Therefore, the currents caused to flow through the D.C. operating point adjusting elements 129, 149 and 169, respectively, each decrease. As a result, the voltages developed at the nodes N21, N22 and N23, respectively, each rise, and each of the operating point potentials Vo (in a word, the voltage at the clockwise signal output terminal OUT\_P and the voltage at the inversion signal output terminal OUT\_N) of the amplifying cell 160 in the final stage each rise. Thus, each of the operating point potentials Vo is controlled so as to approach the reference potential Vref2.

In a word, the D.C. operating point controlling portion 202 carries out the control in such a way that each of the operating point potentials Vo agrees with the reference potential Vref2. Therefore, with the amplifying circuit 1B of the second embodiment, each of the operating points, and the mutual conductance (in a word, the gain) can be set independently of each other. For example, when the D.C. bias current is set by the reference voltage source 102 so as to obtain the necessary

mutual conductance (gain), the potentials at the nodes N21, N22 and N23 are set in accordance with the setting for the D.C. bias current. In this case, it cannot be necessarily said that each of the opening point potentials Vo is optimal. However, the D.C. operating point controlling portion 202 detects 5 the potentials at the nodes N21, N22 and N23, and carries out the control in such a way that each of the operating point potentials Vo agrees with the reference potential Vref2.

The amplifying circuit 1B extracts the D.C. components from the output signals and feeds the D.C. components thus 10 extracted in the form of the currents to the connection points (the nodes N21, N22 and N23) of the load resistors 126 and 128, the load resistors 146 and 148, and the load resistors 166 and 168, respectively. Thus, the negative feedback control is carried out in such a way that each of the operating points Vo 15 is held at a constant value (an optimal value: a value agreeing with the reference potential Vref2 in the second embodiment). For this reason, it is possible to realize the amplifier in which the distortion performance can be improved even when the D.C. biases for the output signals are optimized to 20 increase the output amplitude while the frequency characteristics are held at the same level as that in the frequency characteristics of the amplifying circuit 1A of the first embodiment.

It is noted that although the NMOS transistors are used as 25 the driving transistors 242, 244 and 246, respectively, in the second embodiment, PMOS transistors may be used as the driving transistors 242, 244 and 246, respectively, instead because the D.C. operating point stabilizing processing does not require the high-frequency characteristics such as the signal amplification. In this case, however, the amplifying circuit 1B is configured in consideration of a respect that the use of the PMOS transistors results in an operation which is complementary to that of the NMOS transistor.

242, 244 and 246 composed of the PMOS transistors are connected to the power sources Vdd, respectively, and the drain terminals thereof are connected to the nodes N21, N22 and N23, respectively. When the output voltage from the differential amplifying circuit **210** is reduced, the drain currents of the driving transistors 242, 244 and 246 are each increased, while when the output voltage from the differential amplifying circuit 210 is increased, the drain currents of the driving transistors 242, 244 and 246 are each decreased. Therefore, one terminals of the monitoring elements **222** and 45 224 are each connected to the inverting input terminal of the differential amplifying circuit 210, and the reference voltage source 230 is connected to the non-inverting input terminal of the differential amplifying circuit **210**.

Third Embodiment (First Embodiment+Load Parasitic 50 Capacitance Correcting Circuit)

FIGS. 4A and 4B are respectively a circuit diagram showing a configuration of an amplifying circuit according to a third embodiment of the present invention, and a circuit diagram showing a configuration of a negative capacitance cir- 55 cuit in the amplifying circuit shown in FIG. 4A. The feature of the amplifying circuit 1C of the third embodiment is to include parasitic capacitance correcting circuits for correcting (canceling) load capacitances which occur parasitically on the output sides of the amplifying cells AS based on the 60 amplifying circuit 1A of the first embodiment. Hereinafter, a description will be given by focusing on a difference from the amplifying circuit 1A of the first embodiment.

As shown in FIG. 4A, the amplifying circuit 1C of the third embodiment includes negative capacitance circuits 300 each 65 functioning as the parasitic capacitance correcting circuit on the output sides of the amplifying cells AS (the amplifying

**16**

cells 120, 140 and 160) in the first to third stages, respectively. The functional portions including the negative capacitance circuits 300 are configured on the same semiconductor substrate and are provided in the form of the semiconductor IC.

Each of the negative capacitance circuits 300 has a function of carrying out an operation for equivalently canceling a parasitic capacitance (including a transistor capacitance and a wiring capacitance in the next stage) equivalently connected in parallel with the load resistors of the corresponding one of the amplifying cells AS (120, 140 and 160) in the first to third stages, thereby widening the frequency band of the corresponding one of the amplifying cells AS.

In the negative capacitance circuit 300\_1 connected to the output side of the amplifying cell 120 in the first stage, a first output node 301 is connected to the drain terminal of the NMOS transistor 122, and a second output node 311 is connected to the drain terminal of the NMOS transistor 122. In the negative capacitance circuit 300\_2 connected to the output side of the amplifying cell 140 in the second stage, the first output node 301 is connected to the drain terminal of the NMOS transistor 142, and the second output node 311 is connected to the drain terminal of the NMOS transistor 144. Also, in the negative capacitance circuit 300\_3 connected to the output side of the amplifying cell 160 in the third stage, the first output node 301 is connected to the drain terminal of the NMOS transistor 162, and the second output node 311 is connected to the drain terminal of the NMOS transistor 164.

As shown in FIG. 4B, the negative capacitance circuit 300 includes a pair of NMOS transistors 302 and 312, current sources 304 and 314 for generating operating currents for the NMOS transistors 302 and 312, and correcting capacitors 306 and 316. One terminals of the current sources 304 and 314, and one terminals of the correcting capacitors 306 and 316 are For example, the source terminals of the driving transistors 35 connected to the source terminals (the other terminals) of the cross-coupled NMOS transistors 302 and 312, respectively. In this case, in the cross-coupled NMOS transistors **302** and **312**, the gate terminal (control input terminal) of the NMOS transistor 302 is connected to the drain terminal (one terminal) of the NMOS transistor 312, and the drain terminal of the NMOS transistor 302 is connected to the gate terminal of the NMOS transistor 312. The other terminals of the current sources 304 and 314, and the other terminals of the correcting capacitors 306 and 316 are all grounded.

> Capacitance value of each of the correcting capacitors 306 and 316 is set as such a value as to correspond to the parasitic capacitance of the amplifying cell AS. Each of the correcting capacitors 306 and 316 may be made in the form of a capacitor between a metal and a metal in which electrodes are disposed so as to be opposite to each other, or may be made by utilizing a parasitic capacitance (for example, a capacitance between a gate and a drain/source) of a MOS transistor.

> The negative capacitance circuit 300 causes a current Io (=Vin×jωCo) to flow into each of the correcting capacitors 306 and 316 (each of capacitance values is taken to be Co) by using a signal voltage Vin supplied to each of the NMOS transistors 302 and 312. The negative capacitance circuit 300 feeds the currents generated on the drain sides of the NMOS transistors 302 and 312 in accordance with the current. Io back to the reverse polarity sides, thereby operating as if the negative capacitance seemingly exists in the output terminal of the amplifying cell AS. As a result, the influences of the parasitic capacitances equivalently connected in parallel with the respective negative resistors of the amplifying cells AS (120, 140 and 160) in the respective stages are canceled, thereby widening the frequency bands of the amplifying cells AS (120, 140 and 160).

It should be noted that although in the amplifying circuit 1C of the third embodiment, the description, has been given with respect to the configuration in which the negative capacitance circuits 300 are added to the amplifying circuit 1A of the first embodiment, the present invention is by no means limited thereto, and thus the negative capacitance circuits 300 can also be applied to the second embodiment or to fourth and fifth embodiments which will be described later.

Fourth Embodiment (Second Embodiment+Gain Adjusting Circuit)

FIG. 5 is a circuit diagram showing a configuration of an amplifying circuit according to a fourth embodiment of the present invention. The feature of the amplifying circuit 1D of the fourth embodiment is to add a gain adjusting function based on the amplifying circuit 1B of the second embodinent. Hereinafter, the amplifying circuit 1D of the fourth embodiment will be described by focusing on a difference from the amplifying circuit 1B of the second embodiment.

As shown in FIG. 5, in the amplifying circuit 1D of the fourth embodiment, the current sources 132, 152 and 172 of 20 the amplifying circuit 1B are replaced with NMOS transistors 134, 154 and 174, respectively, and the reference voltage source 102 of the reference power source portion 6 of the amplifying circuit 1B is replaced with a variable voltage source 404. In a word, the reference power source portion 6 25 has one variable voltage source 404 which is common to a plurality stage of amplifying cells AS (120, 140 and 160). A gain adjusting circuit 400 is composed of the NMOS transistors 134, 154 and 174, and the variable voltage source 404.

Gate terminals of the NMOS transistors 134, 154 and 174 are each connected to a positive side one terminal of the variable voltage source 404, and thus an adjustment potential Vadj4 for adjustment of a current value is commonly supplied to the gate terminals of the NMOS transistors 134, 154 and 174. The NMOS transistors 134, 154 and 174 supply D.C. 35 bias currents I\_1, I\_2 and I\_3 (operating currents) each corresponding to the adjustment potential Vadj4 to the differential pairs, respectively. As understood from this, the NMOS transistors 134, 154 and 174 function as current source transistors for generating the operating currents for the amplifying cells AS (120, 140 and 160), respectively. For the purpose of optimizing the operating points and the mutual conductances in the respective stages, the D.C. bias current value is set every amplifying cell AS.

As estimated from the description given with respect to the 45 setting of the reference potential Vref1 by the reference voltage source 102 in the amplifying circuit 1A of the first embodiment, when the adjustment potential Vadj4 is adjusted by the variable voltage source 404, the D.C. bias currents I\_1, I\_2 and I\_3 for the respective differential pairs are adjusted, and thus the mutual conductances of the amplifying circuits 120, 140 and 160 are increased or decreased depending on the D.C. bias currents I\_1, I\_2 and I\_3, respectively. In a word, the gains of the amplifying cells AS (120, 140 and 160) are determined depending on the set value of the adjustment 55 potential Vadj4. Since each of the gains G1 and G2 of the amplifying circuits 120 and 140 in the first and second stages follows Expression (4) due to the presence of the D.C. feedback portion 5, even when the gains G1 and G2 of the amplifying cells AS (120, 140 and 160) are changed, no gain is 60 substantially changed in terms of the respective feedback amplifying circuit. However, when the adjustment potential Vadj4 is adjusted by the variable voltage source 404, the amplification gain G3 of the amplifying cell 160 in the final stage is increased or decreased depending on the D.C. bias 65 current I\_3. Therefore, the gain of the amplifying circuit 1D can be controlled.

**18**

At this time, as estimated from the description given with respect to the setting of the D.C. bias current by the reference voltage source 102 in the amplifying circuit 1A of the first embodiment, when the D.C. bias currents are changed by adjusting the adjustment potential Vadj4 so as to obtain the necessary mutual conductances, amounts of voltage drop across the load resistors are changed in accordance with the increase or decrease of the D.C. bias currents, so that the operating points (bias voltages) of the differential output signals are attempting to be changed. In a word, if this goes on, an output D.C. offset may be caused along with the gain adjustment.

However, the amplifying circuit 1D of the fourth embodiment includes the D.C. operating point controlling portion 202 in the stage next to the final stage based on the amplifying circuit 1B of the second embodiment. For this reason, the D.C. operating point controlling, portion 202 functions so as to cancel the output D.C. offset following the gain adjustment by the variable voltage source 404, whereby the negative feedback control is carried out in such a way that each of the operating point potentials Vo of the amplifying cell 160 in the final stage agrees with the reference potential Vref2. Even when the gain adjusting function obtained by adjusting the operating currents of the amplifying cells AS (120, 140 and 160) is used in combination, each of the operating points of the amplifying cells AS (120, 140 and 160) can be maintained constant.

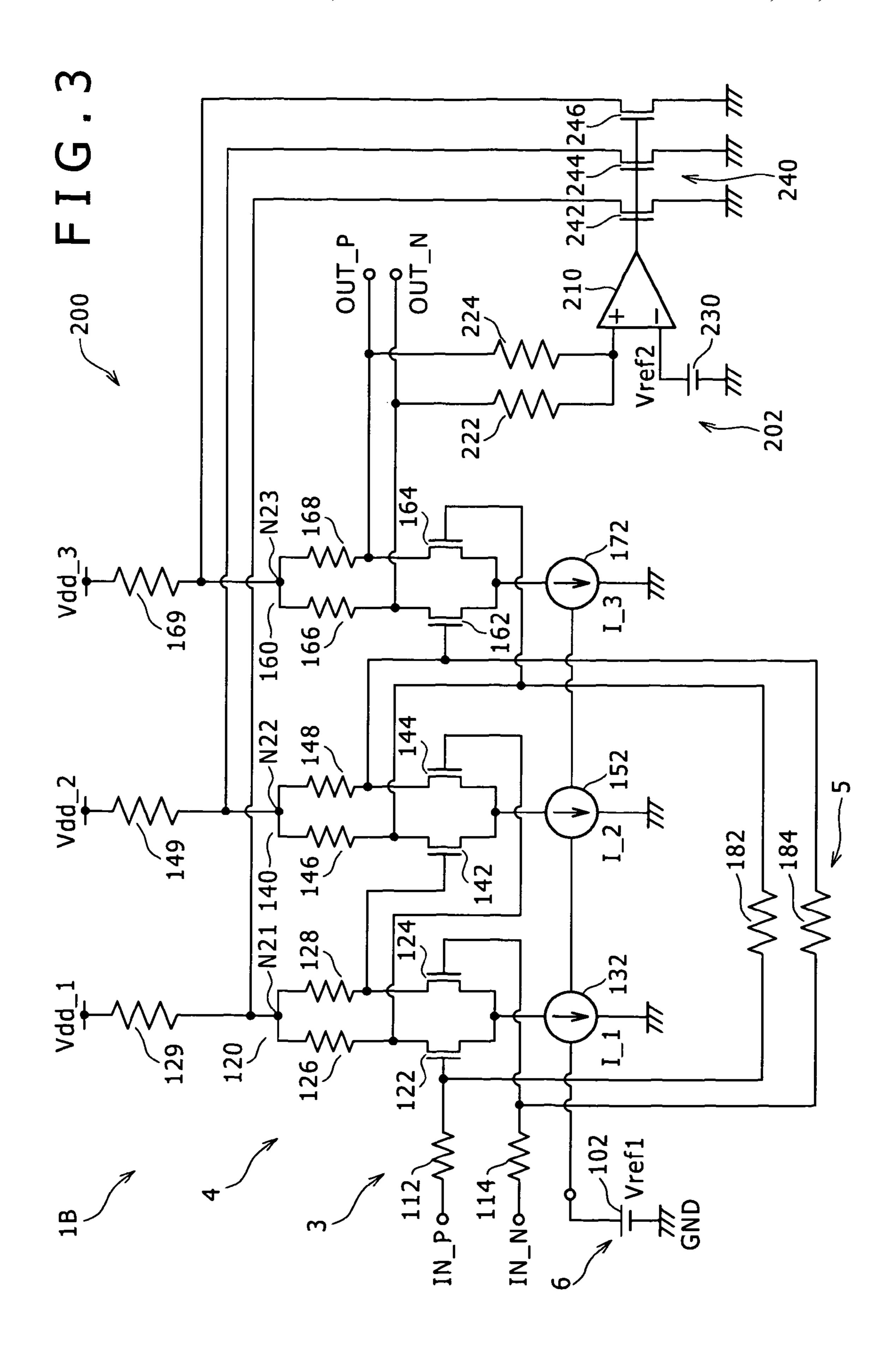

Fifth Embodiment (Fourth Embodiment+Operating Current Setting Corresponding to Necessary Frequency Band)

FIGS. 6A to 6C, and 6D are respectively circuit diagrams, and a diagram explaining an amplifying circuit according to a fifth embodiment of the present invention. Here, FIG. 6A is a circuit diagram showing a configuration of the amplifying circuit of the fifth embodiment. FIGS. 6B and 6C are respectively a circuit diagram showing a configuration of an operating point voltage change correcting portion (a functional portion on a variable resistor circuit side) used in the amplifying circuit of the fifth embodiment, and a circuit diagram showing a configuration of the operating point voltage change correcting portion (a functional portion on a control circuit side) used in the amplifying circuit of the fifth embodiment. Also, FIG. 6D is a block diagram explaining an operation of the operating point voltage change correcting portion (the functional portion on the control circuit side).

The feature of the amplifying circuit IE of the fifth embodiment is to add a function of switching the operating current over to another one in accordance with the necessary frequency band based on the amplifying circuit 1D of the fourth embodiment. Hereinafter, the amplifying circuit 1D of the fourth embodiment will be described by focusing on a difference from the amplifying circuit 1D of the fourth embodiment.

In the amplifying circuit 1E of the fifth embodiment, resistors 126 and 128, the resistors 146 and 148, and the resistors 166 and 168 on the load side of the amplifying cells AS (the amplifying cells 120, 140 and 160) in the first to third stages of the fourth embodiment are replaced with variable resistors 502 and 502, variable resistors 502 and 502, and variable resistors 502 and 502 in the first to third stages, respectively. In this configuration, these variable resistors 502 in the first to third stages can be changed in resistance values thereof in accordance with the necessary frequency band. In the case of the fifth embodiment, an operating current adjusting circuit 500 is composed of the NMOS transistors 134, 154 and 174, and the variable voltage source 404.

In addition, the amplifying circuit 1E of the fifth embodiment includes the operating point voltage change correcting

portion **502**. In this case, the operating point voltage change correcting portion **502** functions so as to correct (cancel) a change, of the output D.C. level (operating point voltage) of the amplifying cell AS, caused by a change of the operating current (D.C. bias current) adjusted by the operating current 5 adjusting circuit **500**.

The amplifying circuit 1E of the fifth embodiment is configured by changing the amplifying circuit 1D of the fourth embodiment. Thus, in principle, the load resistors 126, 128, **146**, **148**, **166**, and **168**, and the D.C. operating point adjusting 10 elements 129, 149 and 169 in the amplifying circuit 1D of the fourth embodiment can become an object of the resistors on the load side. In the fifth embodiment, as shown in FIG. 6A, of the load resistors 126, 128, 146, 148, 166, and 168, and the D.C. operating point adjusting elements 129, 149 and 169, the 15 load resistors 126, 128, 146, 148, 166, and 168 are changed into the variable resistor circuits. For example, when the operating current adjusting circuit 500 adjusts the operating current to the smaller values, the functional portion on the variable resistor circuit side of the operating point voltage 20 change correcting portion 502 increases each of the values of the load resistors of the amplifying cell AS. On the other hand, when the operating current adjusting circuit 500 adjusts the operating current to the larger values, the functional portion on the variable resistor circuit side of the operating point 25 voltage change correcting portion 502 decreases each of the values of the load resistors of the amplifying cell AS.

For realizing this operation, the functional portion on the variable resistor circuit side of the operating point voltage change correcting portion 502 adopts such a configuration 30 that a plurality of series circuits each composed of a resistor 504 functioning as the load resistor, and a switching element 506 are connected in parallel with one another. Therefore, the resistance value of the operating point voltage change correcting portion 502 is changed in a phased manner so as to 35 correspond to the frequency band. For example, as shown in FIG. 6B, three systems of series circuits are provided, and resistance values R504\_1, R504\_2 and R504\_3 of resistors 504\_1,504\_2 and 504\_3 are set so as to meet a relationship of R504\_1>R504\_2>R504\_3.

It is expected that a transistor switch of any one of the NMOS transistor or the PMOS transistor is used as the switching element **506**. Or, it is also expected that the switching element **506** is configured in the form of a switch having a so-called transfer gate configuration in which the NMOS 45 transistor and the PMOS transistor are connected in parallel with each other. Note that, the configuration of the operating point voltage change correcting portion **502** shown in FIG. **6B** is merely an example. Thus, various kinds of change configurations such that in one system in FIG. **6B**, the switching 50 element **506** is removed away, and so forth may be adopted for the operating point voltage change correcting portion **502**.

For changing the resistance values of the load resistors by the operating point voltage change correcting portion **502**, it is considered that the changing of the resistance values of the load resistors is made to correspond to the adjustment for the D.C. bias currents I\_1, I\_2 and I\_3 by the variable voltage source **404**. By the way, with the configuration of the operating point voltage change correcting portion **502** shown in FIG. **6**B, the resistance value is changed in a phased manner (in the three stages in the fifth embodiment), which actually copes with that consideration.

Basically, the changing of the resistance values of the load resistors is made to correspond to the adjustment for the adjustment potential Vadj4 by the variable voltage source 65 **404**, in a word, the adjustment for the D.C. bias currents I\_1, I\_2 and I\_3. Thus, when the signal to be amplified has the

**20**

narrow band, the resistance values of the load resistors 502 are increased to reduce the operating currents to be used. Contrary to this, when the signal to be amplified has the wide band, the resistance values of the load resistors 502 are reduced to increase the operating currents to be used. In addition, similarly, an input impedance Zo of the circuit connected to the next stage is made variable, thereby making it possible to control the operating currents in the manner following Expression (3).

For example, the functional portion on the control circuit side of the operating point voltage change correcting portion 502, as shown in FIG. 6C, includes a resistor ladder circuit 510, a voltage comparing portion 520, and a voltage judging portion 530. The resistor ladder circuit 510 has such a configuration that resistors 512, 514 and 516 are connected in series between a power source Vdd and the ground. Thus, a threshold value Th\_1 is set at a connection point between the resistors 512 and 514, and a threshold value Th\_2 (Th\_1<Th\_2) is set at a connection point between the resistors 514 and 516. The voltage comparing portion 520 includes a comparator 522 for comparing the adjustment potential Vadj4 with the threshold value Th\_1, and a comparator 524 for comparing the adjustment potential Vadj4 with the threshold value Th\_2 (Th\_1<Th\_2).

The voltage judging portion 530 includes a plurality of judgment output terminals (three judgment output terminals in the fifth embodiment) corresponding to a plurality of switching elements 506 (the three switching elements 506\_1, 506\_2 and 506\_3 in the fifth embodiment), respectively. In this case, the three judgment output terminals are connected to control terminals CN\_1, CN\_2 and CN\_3 of the three switching elements 506\_1, 506\_2 and 506\_3 corresponding to the three judgment output terminals, respectively. The voltage judging portion 530 judges based on comparison results COMP\_1 and COMP\_2 which of Vadj4<Th\_1, Th\_1 Vadj4<Th\_2, and Th\_2≤Vadj4 is met, and turn ON only one of a plurality of switching elements (the three switching elements 506\_1, 506\_2 and 506\_3 in the fifth embodiment).