### US008223469B2

# (12) United States Patent

# Barber

# (10) Patent No.: US 8,223,469 B2 (45) Date of Patent: US 17, 2012

# (54) POWER NODE SWITCHING CENTER WITH ACTIVE FEEDBACK CONTROL OF POWER SWITCHES

(75) Inventor: **John P. Barber**, Kettering, OH (US)

(73) Assignee: SPD Electrical Systems, Kettering, OH

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 283 days.

(21) Appl. No.: 12/652,383

(22) Filed: **Jan. 5, 2010**

# (65) Prior Publication Data

US 2011/0007432 A1 Jan. 13, 2011

## Related U.S. Application Data

- (63) Continuation-in-part of application No. 11/959,055, filed on Dec. 18, 2007, now Pat. No. 7,667,938.

- (51) Int. Cl. H01H 51/22 (2006.01)

- (58) **Field of Classification Search** ...... 361/93.7–93.9, 361/139, 160

See application file for complete search history.

## (56) References Cited

## U.S. PATENT DOCUMENTS

4,025,820 A 5/1977 Penrod 5,559,656 A 9/1996 Chokhawala

| 5,650,906 A *   | 7/1997  | Marquardt et al 361/88 |

|-----------------|---------|------------------------|

| 5,933,304 A     |         | Irissou                |

| 5,970,964 A *   | 10/1999 | Furuhata et al 123/644 |

| 6,097,582 A     | 8/2000  | John et al.            |

| 6,336,448 B1*   | 1/2002  | Furuhata et al 123/644 |

| 6,407,413 B1*   | 6/2002  | Kawamoto 257/133       |

| 7,315,439 B2*   | 1/2008  | Muenzer et al 361/91.1 |

| 2008/0143462 A1 | 6/2008  | Belisle et al.         |

| 2009/0154047 A1 | 6/2009  | Ykema et al.           |

| 2009/0289691 A1 | 11/2009 | Fuller et al.          |

|                 |         |                        |

<sup>\*</sup> cited by examiner

Primary Examiner — Danny Nguyen

(74) Attorney, Agent, or Firm—Fox Rothschild LLP; Dennis M. Carleton

# (57) ABSTRACT

A circuit fault detector and interrupter which consists of parallel current conduction paths, including a path through a mechanical contactor and a path through a power electronics switch having active feedback control. A fault can be detected by a fault detection circuit within 50 microseconds of the occurrence of the fault, causing the mechanical contactor to be opened and the fault current to be commutated via a laminated, low-inductance bus through the power electronics switch. The power electronics switch is thereafter turned off as soon as possible, interrupting the fault current and absorbing the inductive energy in the circuit. The fault current can be interrupted within 200 microseconds of the occurrence of the fault, and the device reduces or eliminates arcing when the mechanical contactor is opened.

# 16 Claims, 15 Drawing Sheets

# PNSC TOPOLOGY

# 20 kArms Available Fault

Jul. 17, 2012

Legacy 28 kA let thru 35 ms interruption

PNSC 0.3 kA let thru 40 micro sec interruption

Figure 12

# POWER NODE SWITCHING CENTER WITH ACTIVE FEEDBACK CONTROL OF POWER SWITCHES

# RELATED APPLICATION

This application is a continuation-in-part of and claims priority to co-pending U.S. application Ser. No. 11/959,055, filed Dec. 18, 2007 and entitled "Power Node Switching Center".

#### BACKGROUND OF THE INVENTION

An electrical power delivery system is a complex system consisting of one or more generators with power flowing 15 through cables to nodes, and then to loads. The functions required of the high-powered nodes are distribution, switching and power management. The functions of conversion and power conditioning are most appropriately handled at the branch level nodes. The node level functions are performed at 20 high-power nodes in prior art legacy systems by circuit breakers and switch gear.

In the event of a fault, a prior art system may permit a high fault current, which has a potential for catastrophic collateral damage and which may also deprive other loads on the same 25 or upwardly connected nodes of energy. When a fault occurs in the prior art system, a circuit breaker upstream from the fault opens. The prior art electromechanical circuit breaker may take up to 50 milliseconds to open for a high fault and 100 or more milliseconds for an intermediate fault. During 30 these transient time periods, the systems upstream of the fault are perturbed. This perturbation is usually exhibited by a significant drop in voltage, particularly in close proximity to the fault, which may result in the voltage dropping to near zero for the period of time between the occurrence of the fault 35 and the opening of the circuit breaker. This means that all loads being supplied by other circuits emanating from a node with a fault will experience a very low or zero voltage condition during the time of the fault. Sensitive loads may malfunction and some loads may become disconnected or may 40 need to be reset or rebooted, causing them to be offline for a period of time significantly longer than the actual fault. This is obviously undesirable for sensitive and critical loads. Other loads may be transferred to alternate sources, which may cause further disturbances to the electrical system. In addi- 45 tion, there may be substantial arcing at the point of fault while the electromechanical circuit breaker is opening.

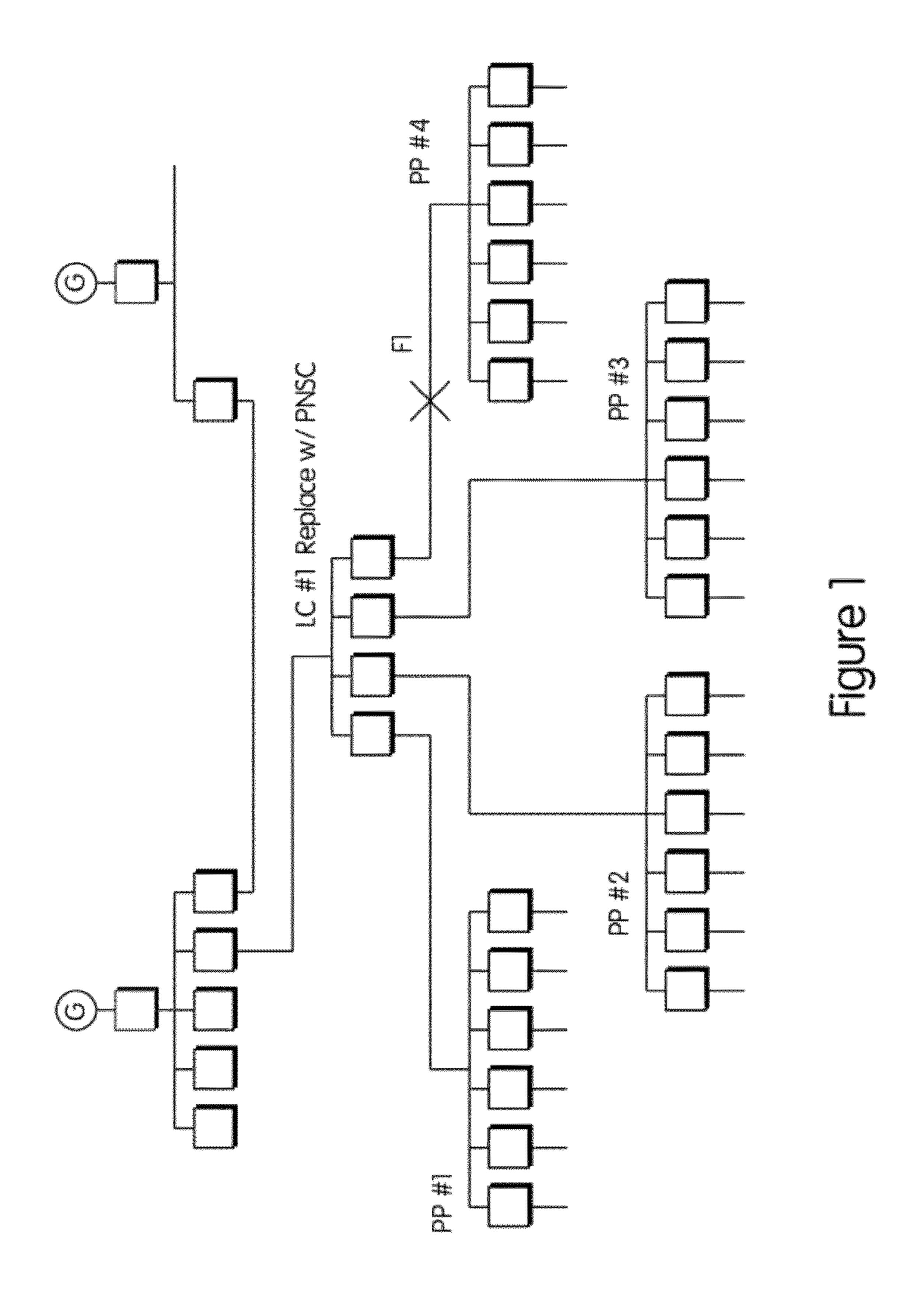

Such a scenario is shown in FIG. 1. In this example, there are 4 power panels (PP), each with six loads, fed from a load center node (LC). If a fault occurs at F1, with legacy equip- 50 ment, the 18 loads in power panels #1, #2, and #3 will be deprived of power until the fault is cleared, which may take a minimum of 50 milliseconds and which could take as long as 400 milliseconds. The 6 loads in power panel #4 will be lost because the cable feeding them is faulted.

The parent to this application proposed a replacement for the electromechanical circuit breakers that currently detect and switch off faulted circuits which consisted of a device having two parallel current paths for each line (or phase). One path consisted of power electronic devices which could be 60 gated to switch current on and off very quickly and the second, parallel path consisted of a mechanical contactor device which carries current very efficiently and which can open sufficiently quickly to commutate the current to the power electronic path in less than 25 microseconds. When a fault is 65 detected, the mechanical contactor is tripped and the fault current is commuted to the power electronics path until the

2

power electronics can be switched off. Using this configuration, it was possible to detect a high fault current within about 50 microseconds and to interrupt a high fault current in less than 400 microseconds. This innovation provided an approximate thousand-fold increase in speed over prior art legacy systems. In addition, it also was able to minimize or eliminate the arcing that traditionally occurs when an electromechanical circuit breaker is opened.

Once the fault current has been detected and commuted to the power electronics path, the flow of current from the source to the load can be interrupted by opening, or switching off, the power electronics path. The switch in the power electronics path typically consists of an IGBT which can be gated to interrupt the current flow.

One problem with this configuration is that the inductive energy stored in the source and load inductances must be dissipated in the interrupting switch in order to bring the circuit current to zero. The voltage that can be developed during interruption is the sum of the open circuit voltage of the source and the back EMF developed by the source and load inductances. As the interruption time decreases, dI/dt increases and the inductive voltage increases. As interruption time increases, the inductive voltage decreases, but the switch is forced to carry current while dropping the source voltage and so dissipates more energy. The switch can be destroyed either by excessive voltage or excessive dissipation (heating). There is an optimum opening time which limits voltage to a safe value, while dissipating the minimum energy.

In the current art, the switch is protected by employing a parallel snubber circuit. The role of the snubber circuit is to limit the voltage across the switch and absorb the energy from the circuit. Therefore, the switch can be opened as quickly as possible, while commutating current to the snubber circuit. The switch thereby dissipates minimum energy while the snubber circuit limits the voltage and absorbs the energy. The snubber circuit can be constructed with passive or active components or a combination of both.

One of the most common snubber circuits is the resistorcapacitor-diode (RCD) configuration in which a series resistor-capacitor with a diode across the resistor is attached in parallel with the switch. When the switch is opened, current flows through the diode into the capacitor, providing a low impedance path for the commutated current. The capacitor is sized such that the peak voltage, which is reached when the circuit energy has all been absorbed in the capacitor, is below the maximum allowable for the switch. When the switch is closed the diode then blocks voltage and forces the capacitor to discharge through the resistor. The resistor thus ends up dissipating the circuit energy. There are many variations on this approach which can include inductors, capacitors, resistors and diodes. One problem with this configuration, however, is that, in high power circuits, the size, weight and cost of these components is significant and therefore poses an important impediment to market acceptance.

An alternative approach to voltage and energy management is to use active components such as varistors with or without a series switch as the parallel snubber. A varistor is a nonlinear resistive element that displays high resistance at low voltage and low resistance above some threshold voltage. By selecting a varistor that has a threshold voltage above the circuit voltage, but below the safe limit of the switch, the voltage can be limited during rapid switch turn off, while the varistor is forced to absorb the circuit energy. Varistors do not have a sharp threshold voltage cutoff so adequate control of voltage sometimes requires selection of a low threshold voltage device which then leaks current and dissipates power during normal voltage operation. A series switch is then used

to isolate the varistor during normal operation, and then connect it during interruption. Varistors are generally smaller than passive snubbers, but repeated operation deteriorates performance and the limited, and somewhat unpredictable, life of the device is a major impediment to broad application. The addition of a series switch improves life and reliability but with the penalty of another active component together with all the controls and auxiliaries necessary to operate it.

Therefore, it would be desirable to provide a circuit configuration which provides the same features as the snubber circuits of the prior art, but without the disadvantages and drawbacks associated therewith.

#### SUMMARY OF THE INVENTION

The power node switching center (PNSC) of the present invention replaces existing upstream circuit breakers with ultra-fast circuit interrupters capable of detecting faults within 50 microseconds and interrupting faults within 400 microseconds.

The criteria regarding the time to interrupt the current are dependent upon two conditions. First, that the interruption time is so short that the loss of voltage during the fault will not jeopardize the operation of loads on adjacent circuits and, 25 second, that the magnitude of the fault current will not jeopardize the integrity of the power electronics. This enhances the survivability of loads being fed by adjacent circuits and effectuates a tremendous reduction in collateral damage caused by a fault.

The electromechanical switch consists of a very low resistance contact structure that can open in less then 25 microseconds which consists of coaxial stationary poles, each having multiple contacts, and a lightweight conductive disk that makes electrical contact between the poles of the switch. 35 Upon fault detection, a rapidly acting magnetic system launches the disk away from the poles, thereby opening the circuit. This magnetic system consists essentially of a capacitor, a fast switch and a magnetic pancake coil. The disk has low mass to allow a high acceleration and rapid contact separation.

A low inductance, laminated bus structure between the contactor and the solid state power electronics enables non-arcing commutation of the current from the contactor to the solid state power electronics within 25 microseconds.

This concept eliminates the losses that would be experienced with prior art, electromechanical circuit breakers. The system therefore has an efficiency equal to or better than the electro-mechanical circuit breaker.

One innovative aspect of the invention is the fault detection 50 circuitry, which is able to detect fault conditions within about 30 microseconds. This is accomplished with a narrow bandwidth, high gain integrator operating on the output of a Rogowski coil current detector.

Another innovative aspect of the invention is in the opening 55 mechanism of the mechanical contactor, which relies on a traditional Thompson drive, combined with very low inductance achieved via the integration of the low mass mechanical contactor and the power electronics switch. The low mass allows the movement of the mechanical contactor at a very 60 high speed and commutation of the current to the power electronics. The current is thus interrupted before it reaches high values, which eliminates the magnetic stress on upstream circuits between the generator and the point of fault. In addition, the voltage on the upstream node is lost for such 65 a short period of time that all loads being fed from the node having the fault or upstream of the node having the fault

4

survive the event and continue to operate normally, and may not even be aware of the occurrence of the fault event.

Yet another innovative aspect of the invention is the energy absorbing feature of the power electronics path, which allows the controlled absorption of the energy stored in the source and load inductances. In this aspect of the invention, the power electronics are turned on under active feedback control to limit the voltage developed during turn off, allowing the power electronics to absorb the energy of the source and load inductances, thereby eliminating the need for a snubber circuit to protect the power electronics.

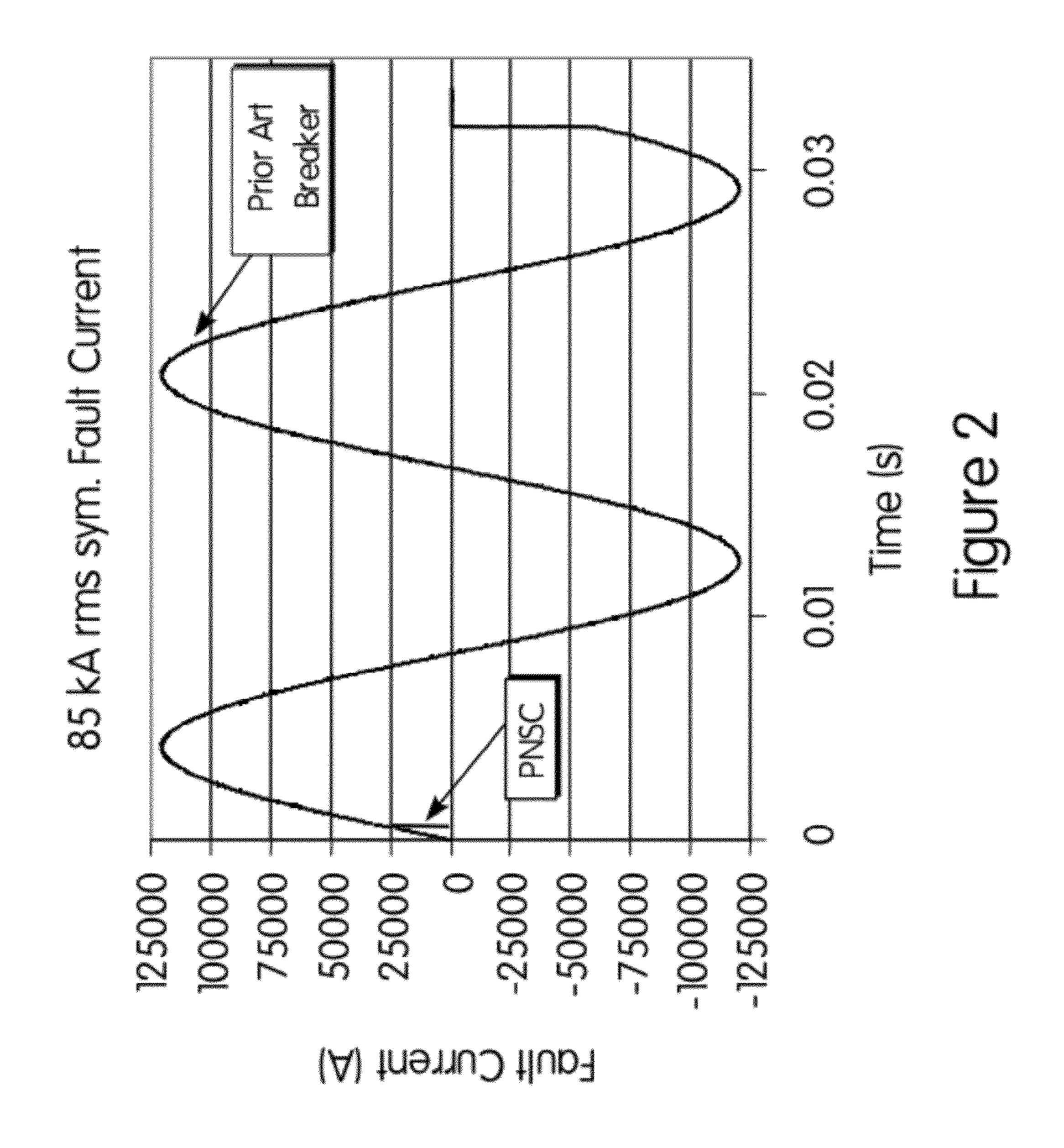

FIG. 2 shows a comparison between the fault detection and interruption of legacy systems and the power node switching center. As can be seen, for an 85 kA rms fault current, a legacy system will take between 1 and 2 full cycles (30 milliseconds) to detect and interrupt the current. During this time, the fault current could reach 40-50 times the rated load current. The power node switching center can interrupt the current in about 200 microseconds, thereby limiting the current to the load to approximately 2 times the rated load current.

The power node switching center is a device which will distribute, switch and control power at electrical power nodes whose power handling capacity ranges from 0.5 MW to 50 MW, while accurately detecting downstream system faults and stopping the current flow in less then 400 microseconds.

### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a schematic representation of an electrical power system, showing a fault at F1

FIG. 2 is a graph showing the response time to fault current interruption with legacy electro-mechanical circuit breaker and the Power Node Switching Center of the present invention

FIG. 3 is a schematic representation of the topology of the switching module of the power node switching center of the present invention.

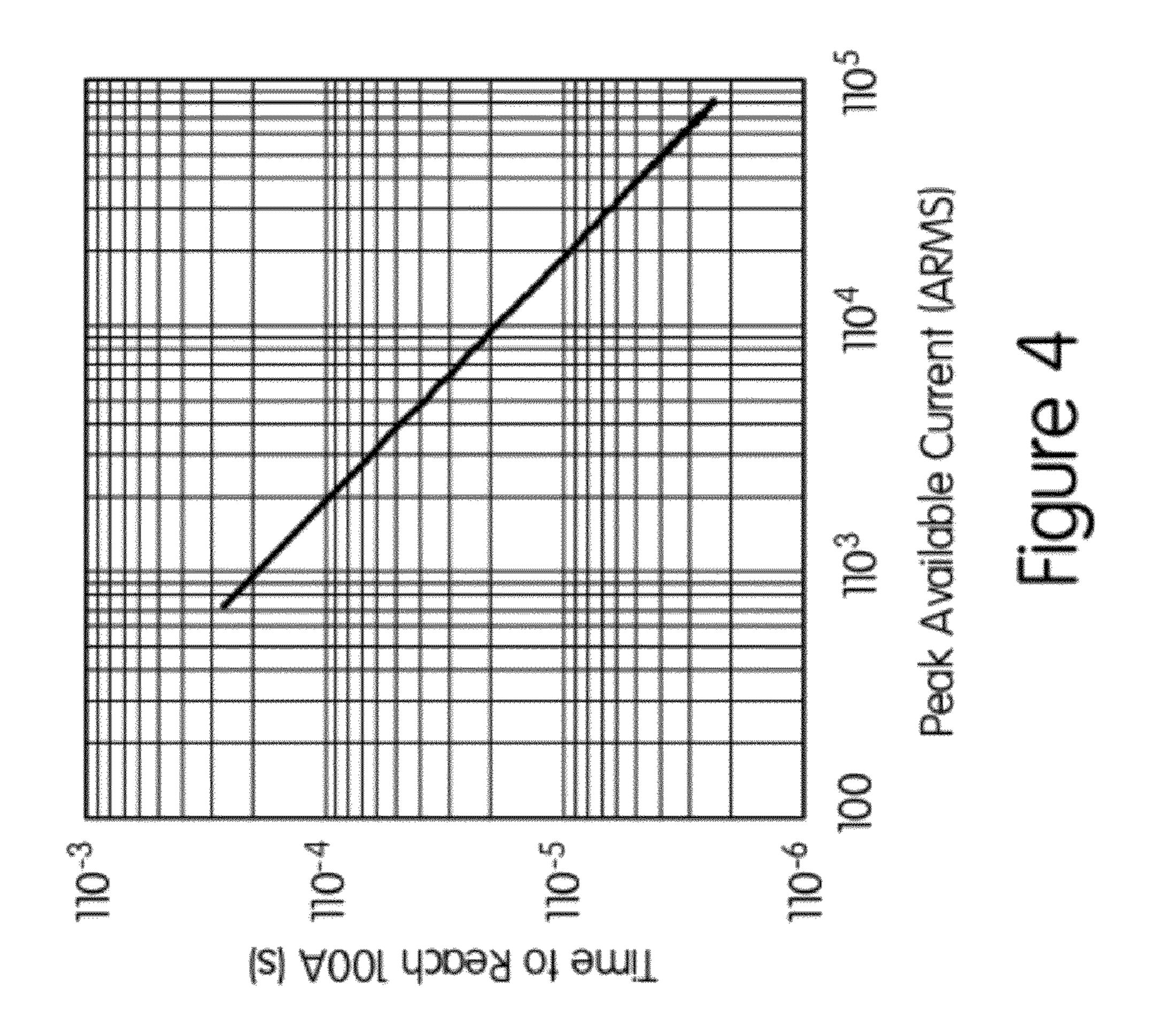

FIG. 4 is a graph showing time to detect a ~100 A change in current versus the peak available current. This graph shows that the higher the peak available current, the less time it will take to detect a ~100 A change.

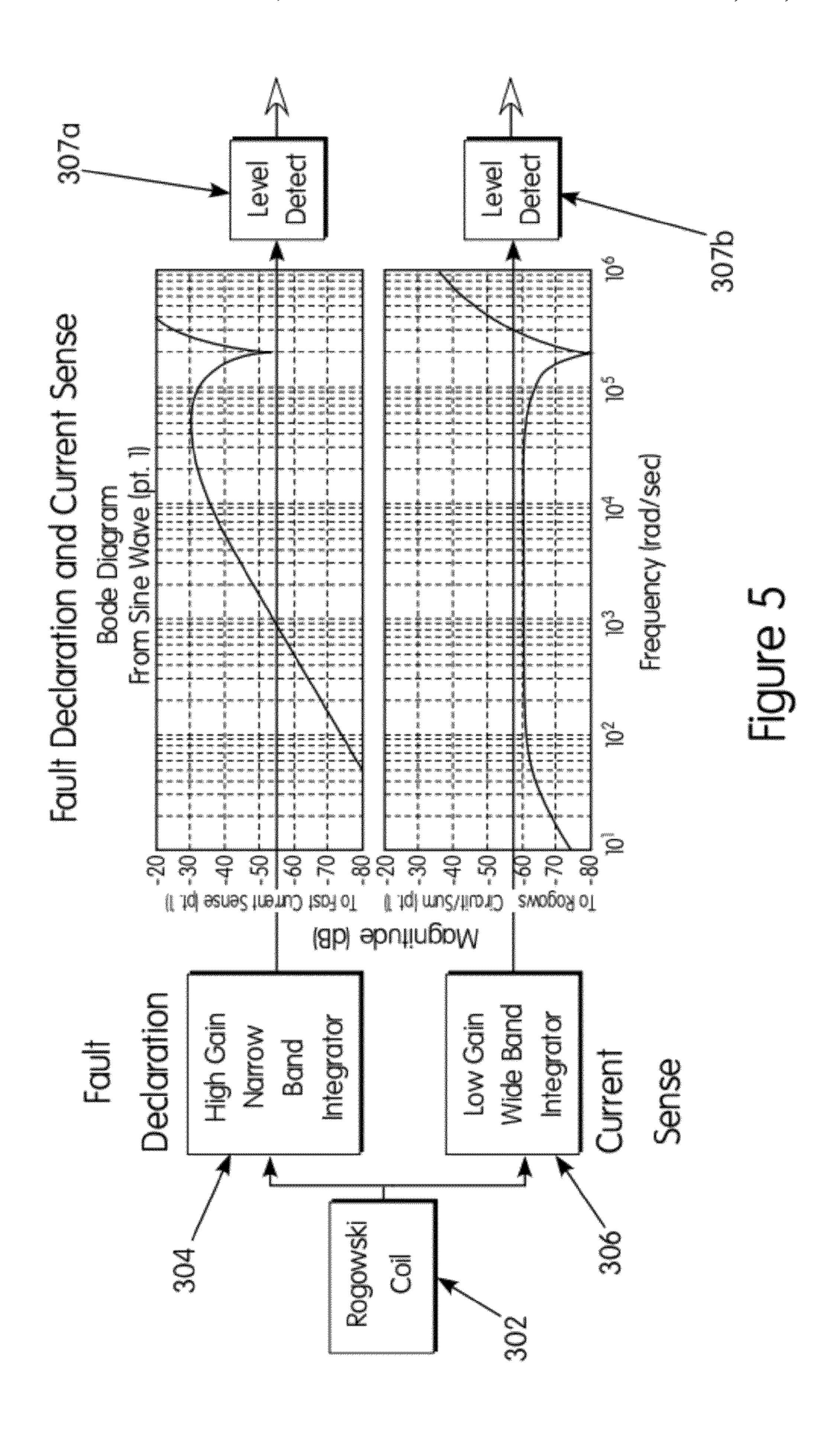

FIG. **5** is a block diagram of the fault detection portion of the invention, showing the frequency response of the integrators.

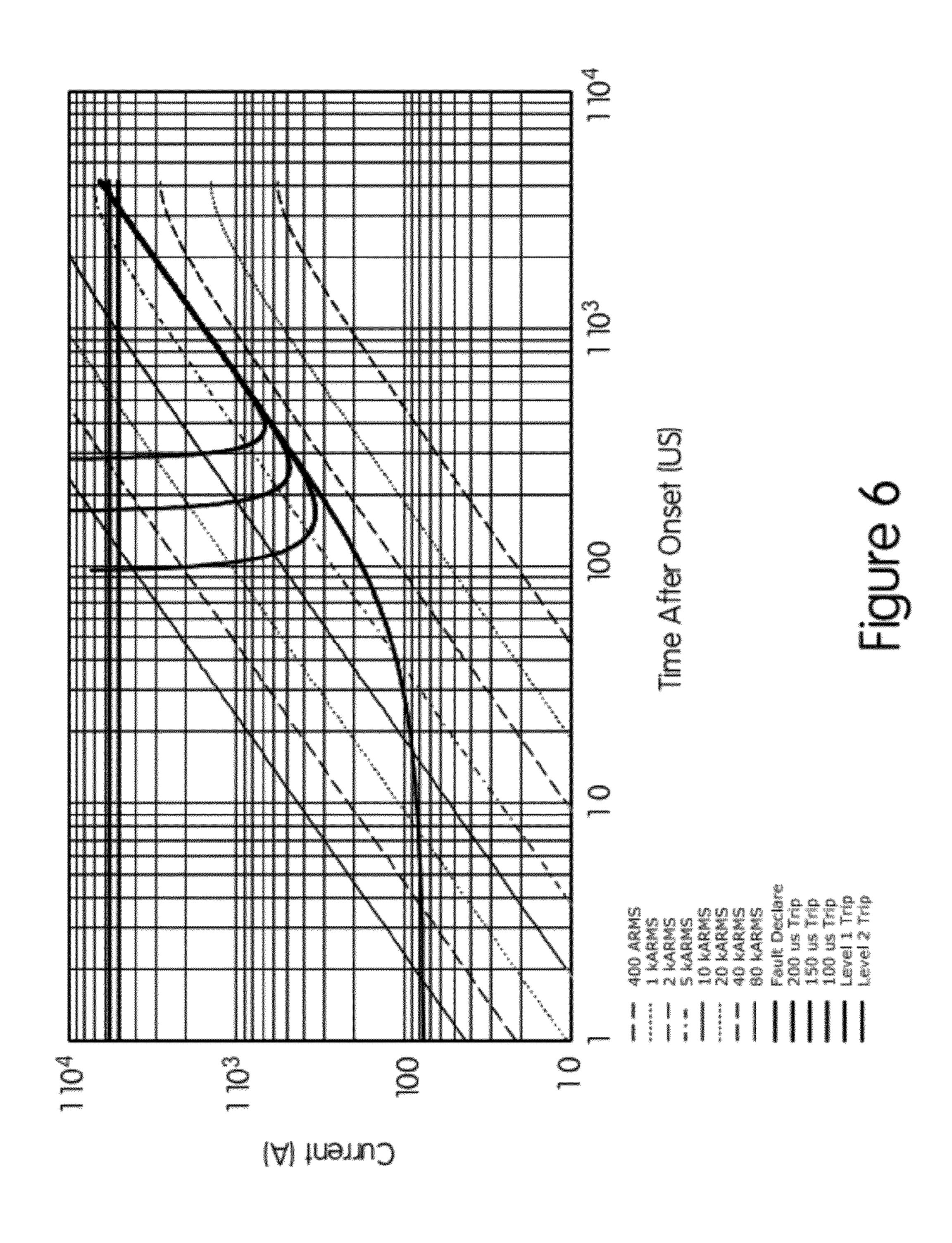

FIG. 6 is graph showing the response of the fault detection circuit for various magnitudes of fault current.

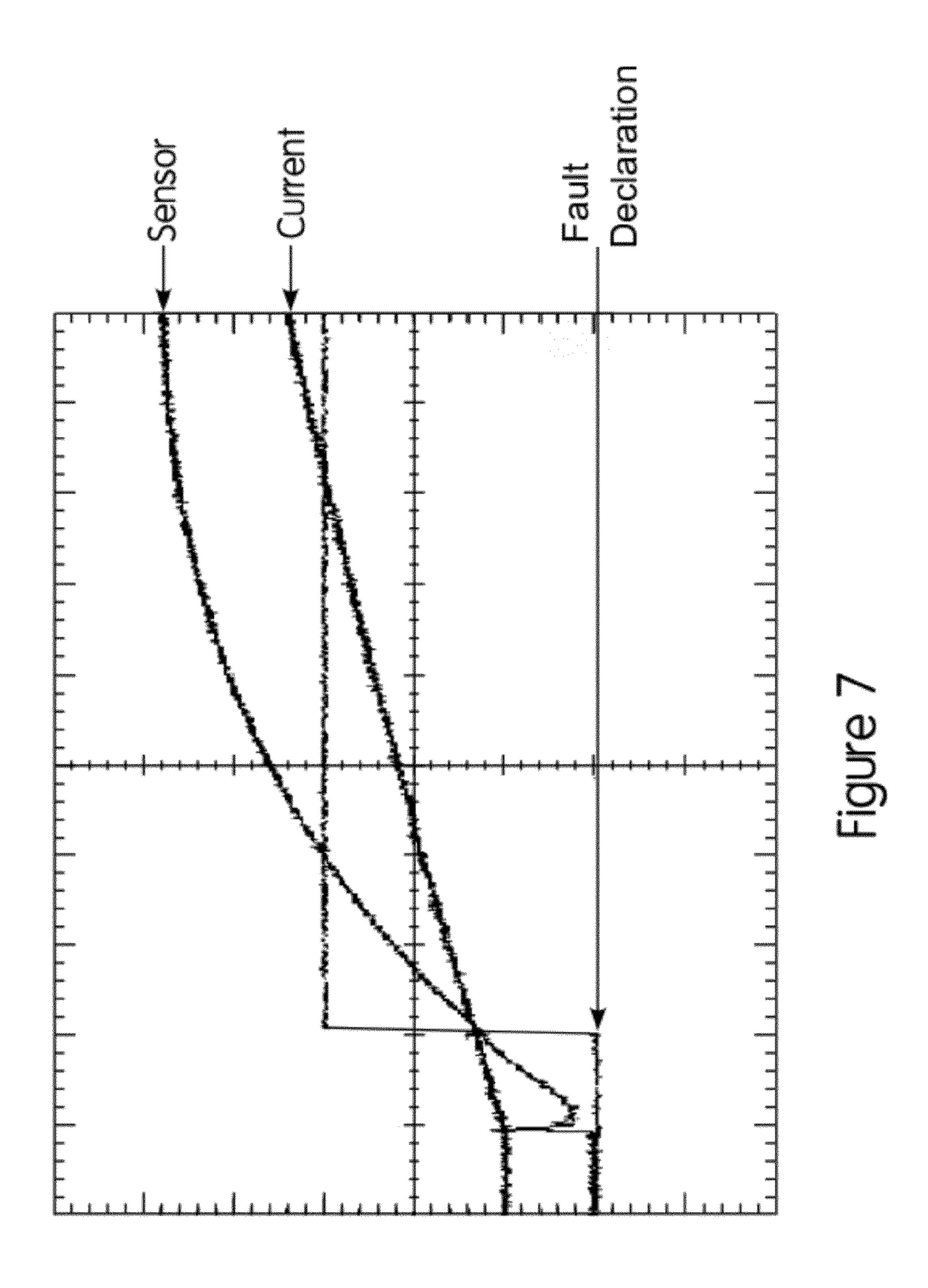

FIG. 7 is a graph showing the point of fault declaration as current rises.

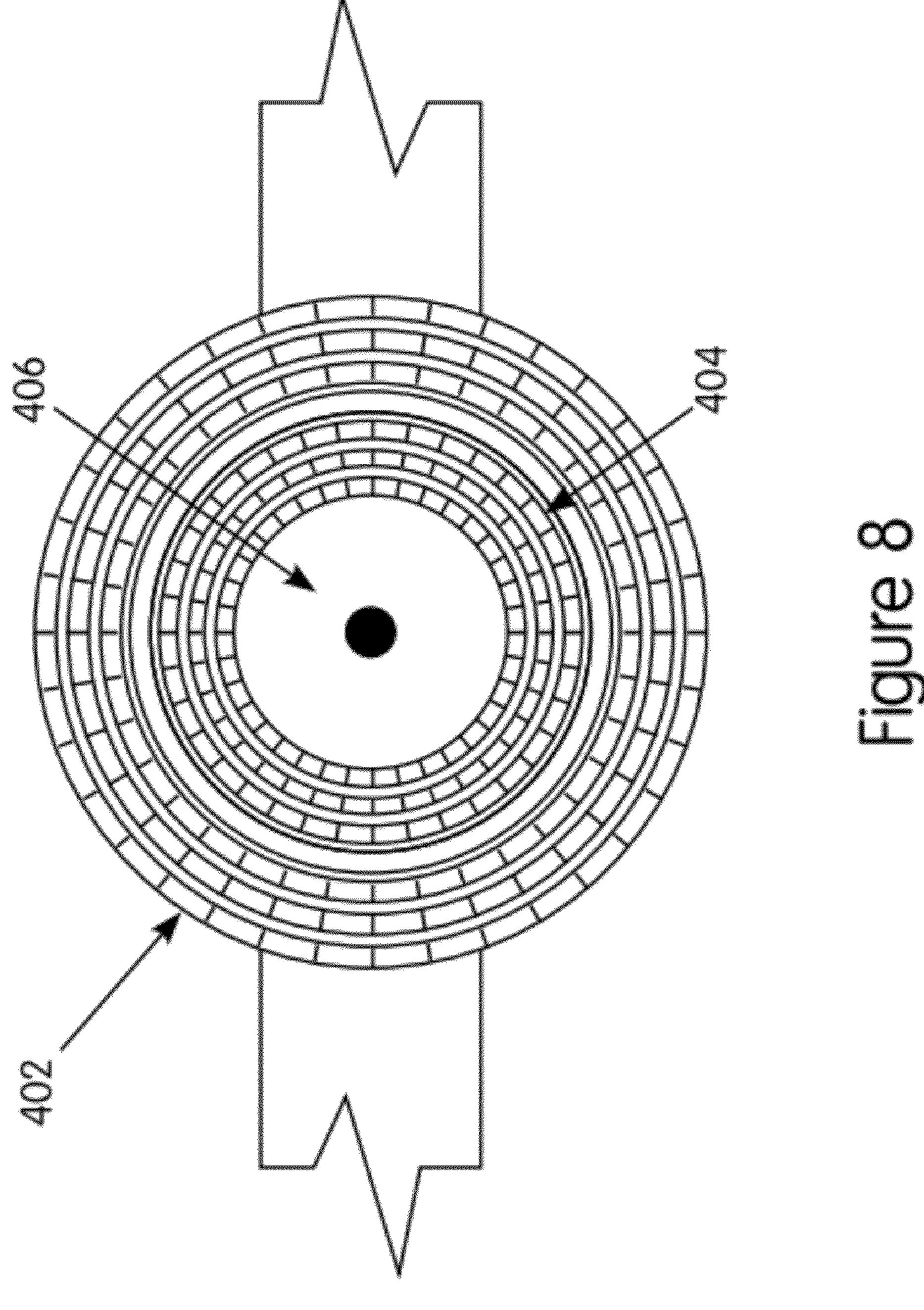

FIG. 8 is a photograph of the stationary contacts and pancake coil of the mechanical contactor of the present invention.

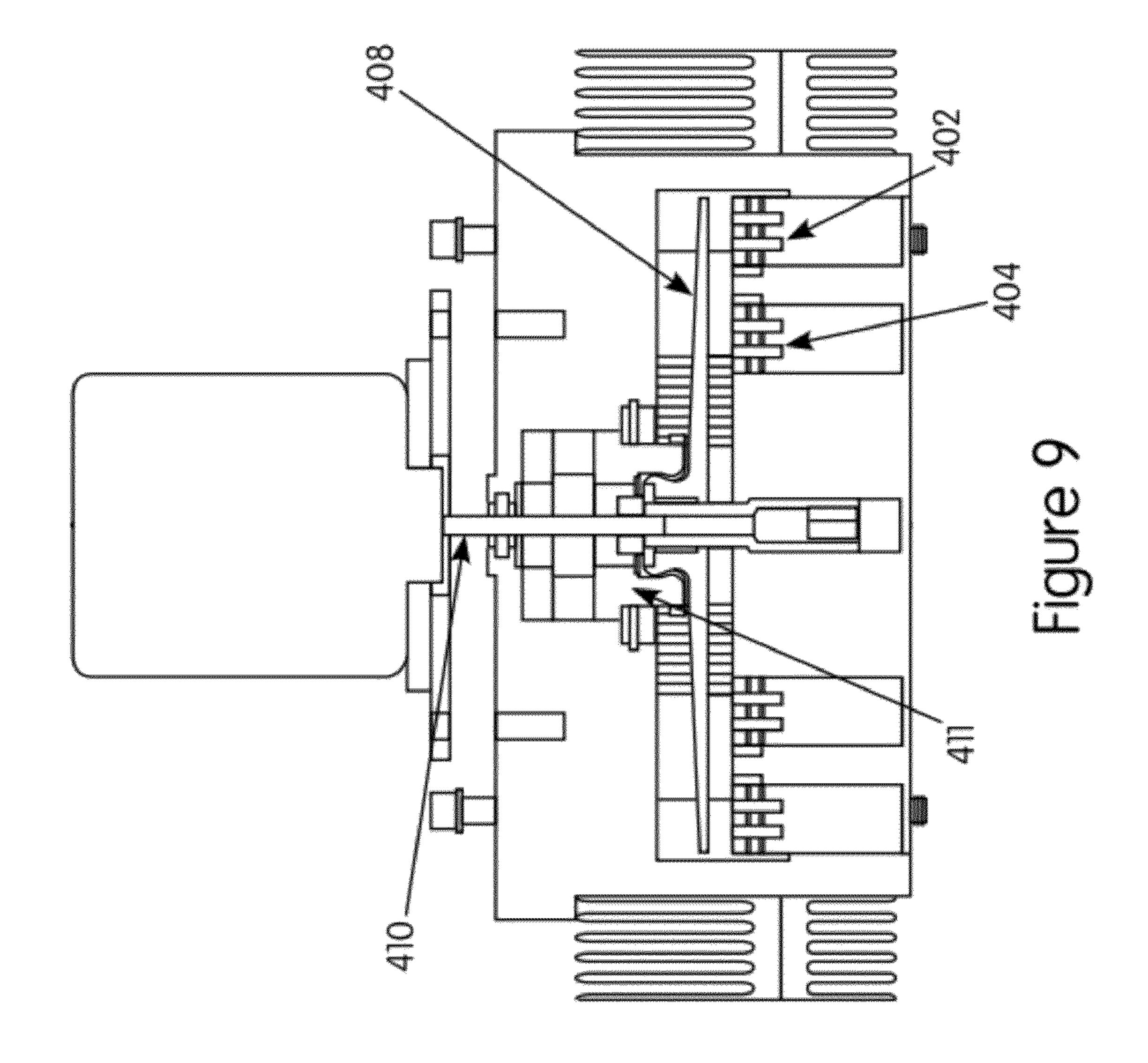

FIG. 9 is a cross sectional view of the mechanical contactor mechanism.

FIG. 10 shows a series of time-lapsed photographs showing the disk of the mechanical contactor moving away from the contacts.

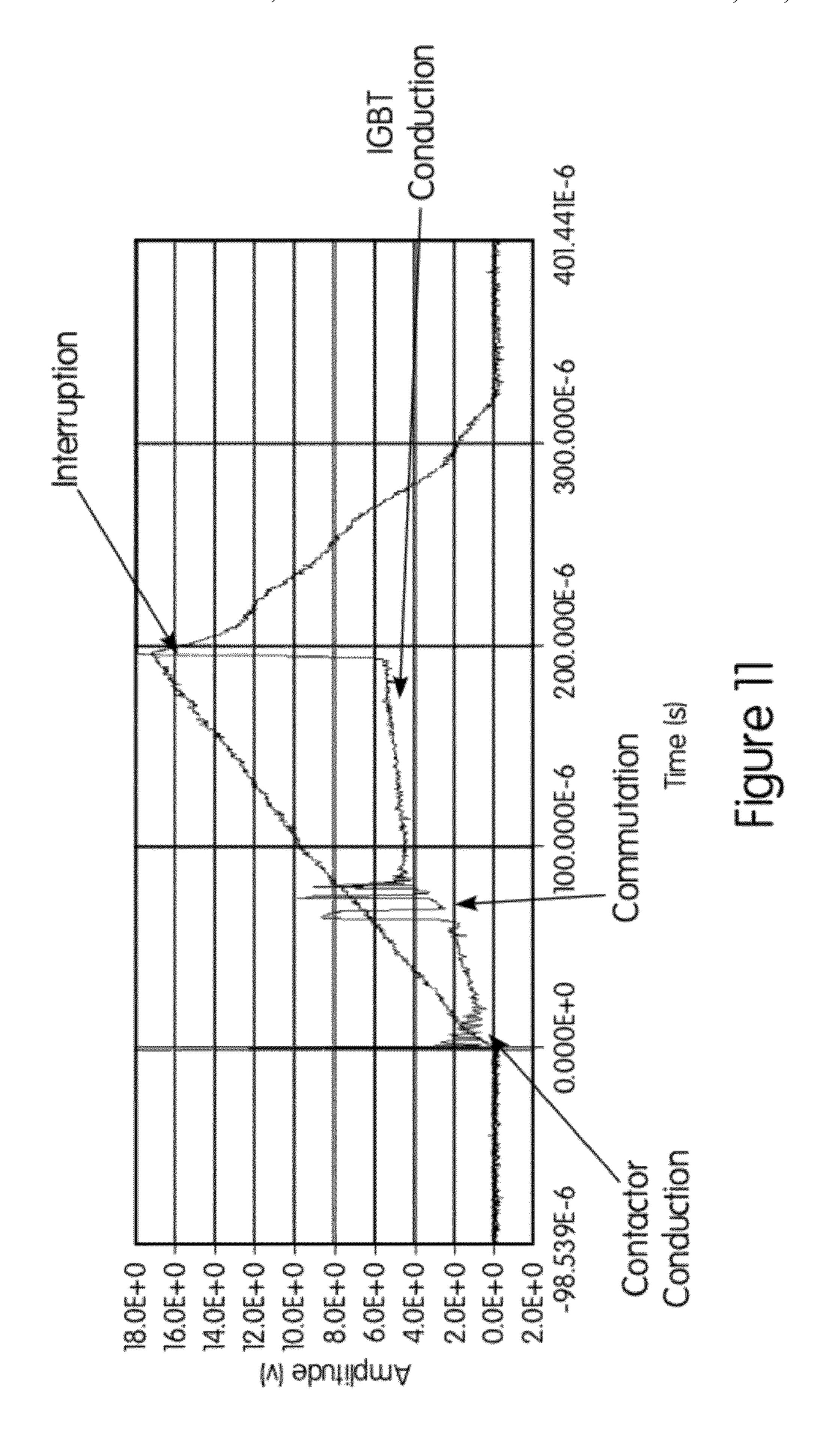

FIG. 11 is a graph of voltage and current versus time, showing the various stages of the fault interruption process.

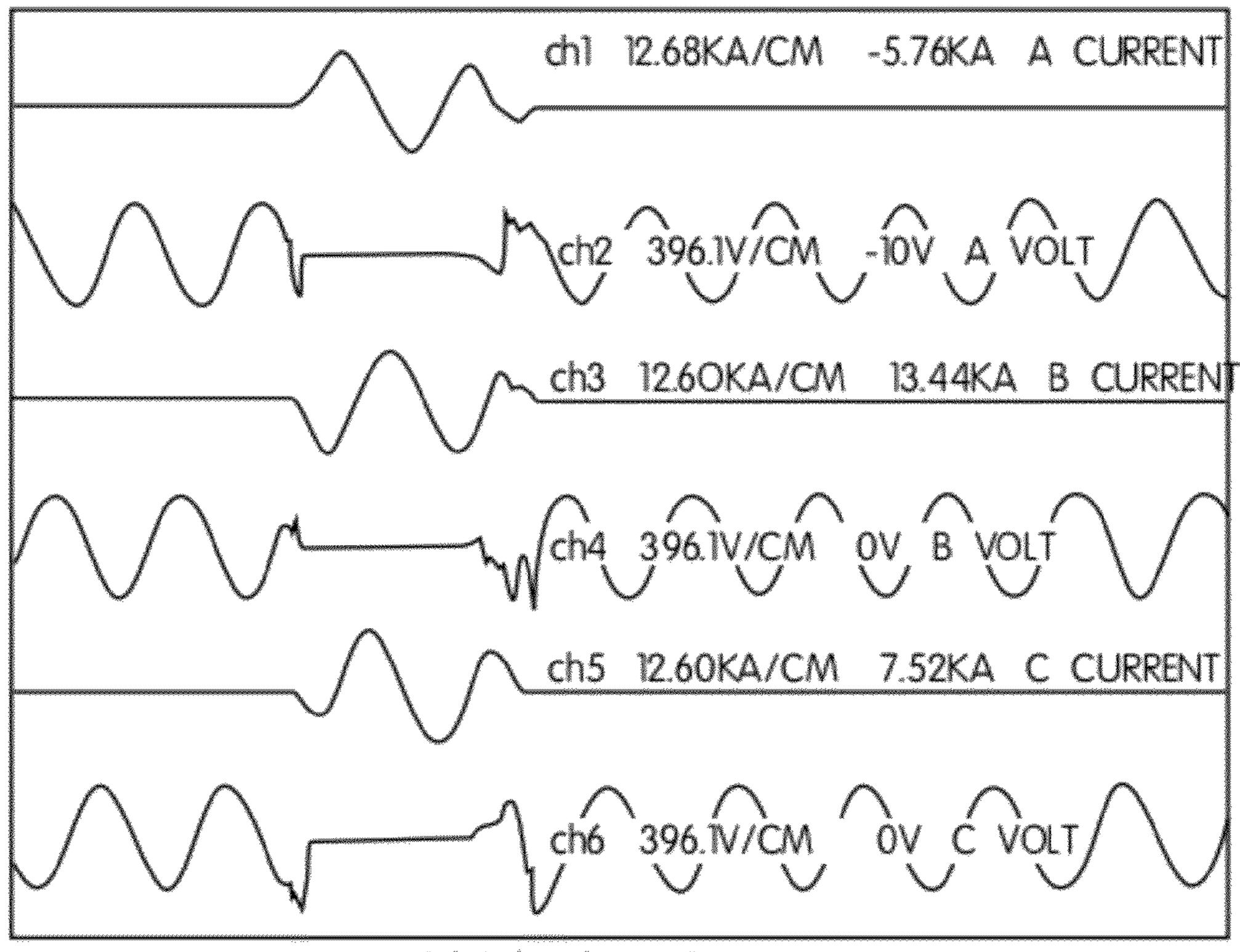

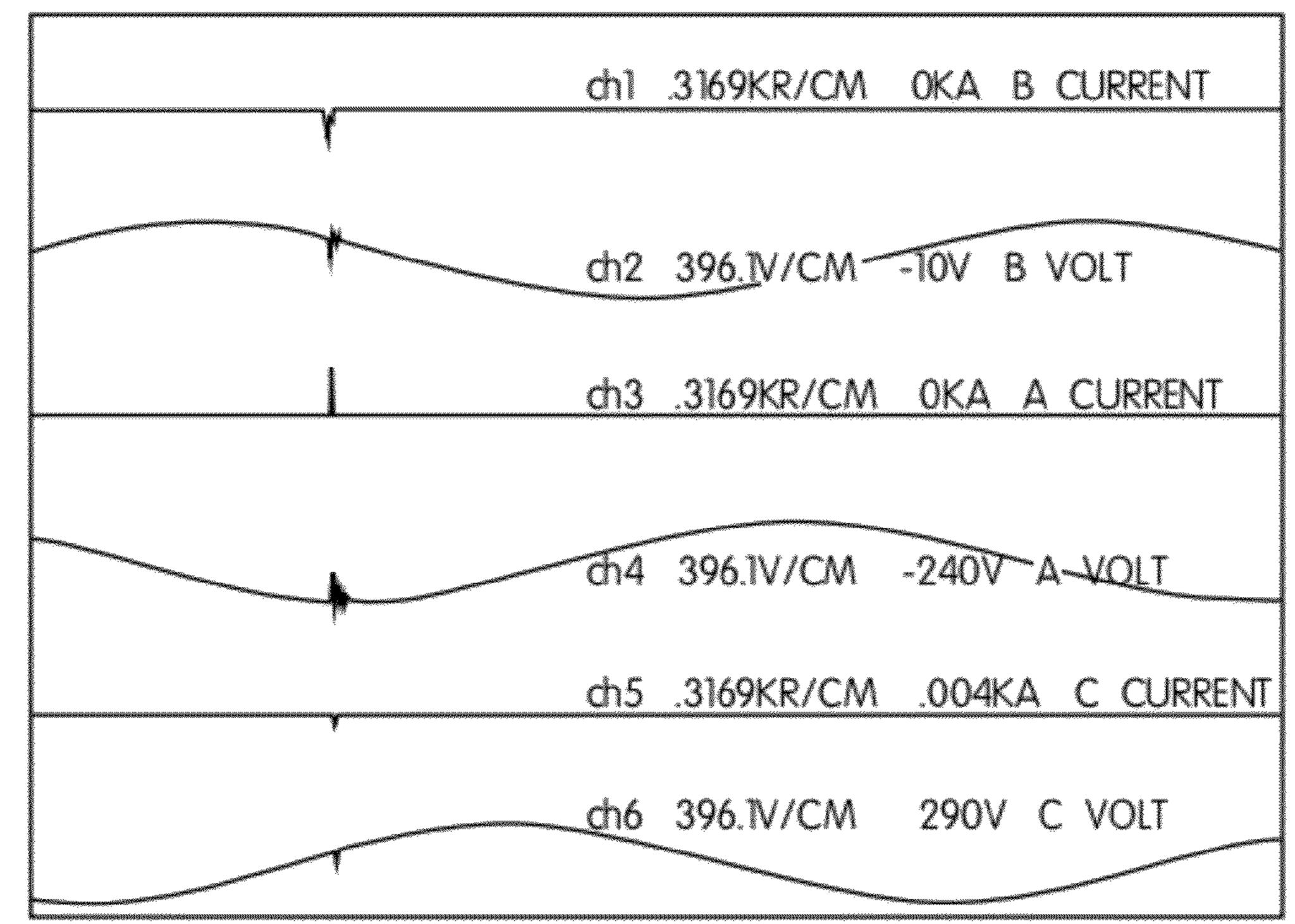

FIG. 12 is a graph showing the voltage and current during a fault for both legacy systems and for the device of the present invention.

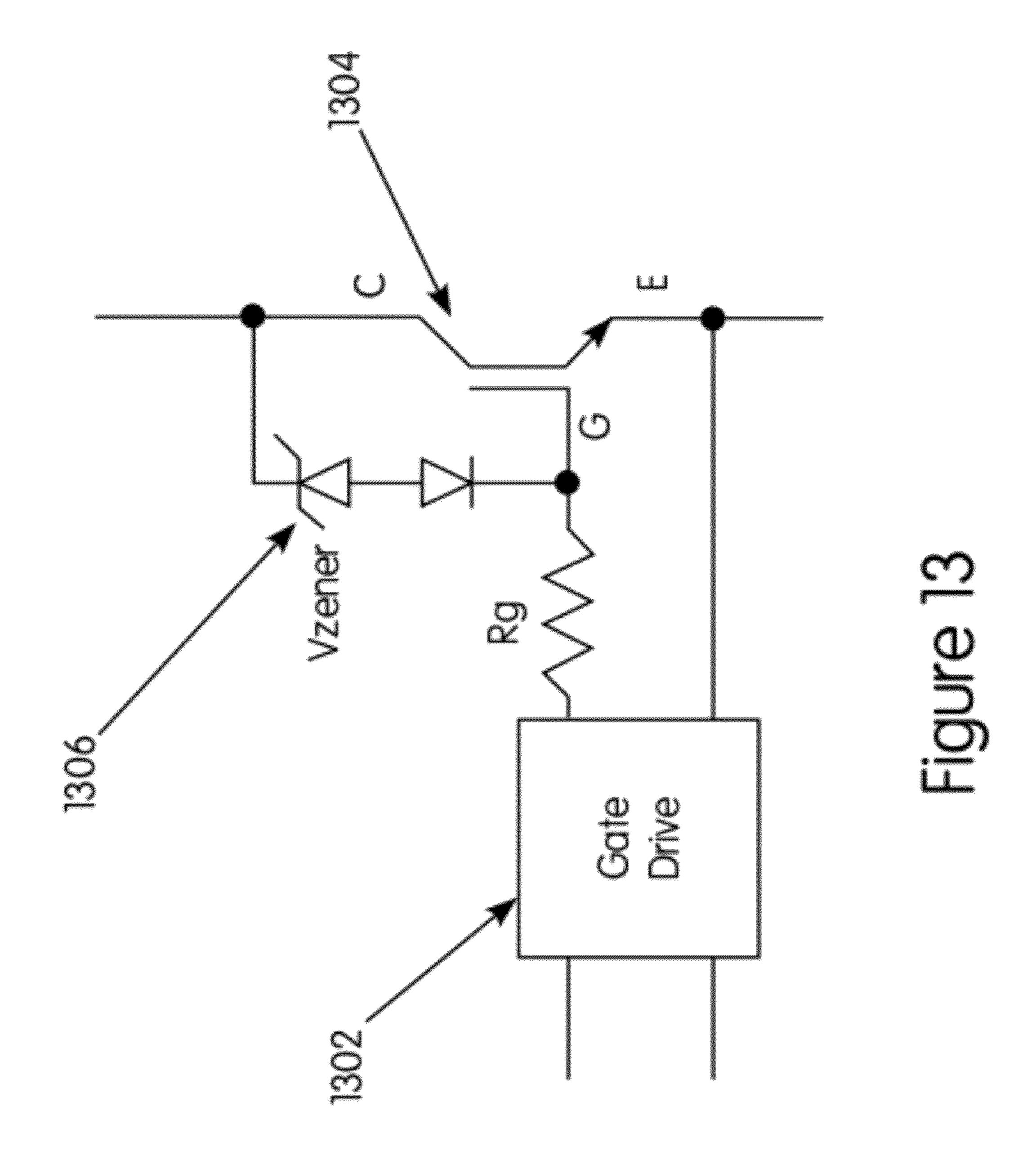

FIG. 13 is a circuit diagram of the active feedback control for the power electronics.

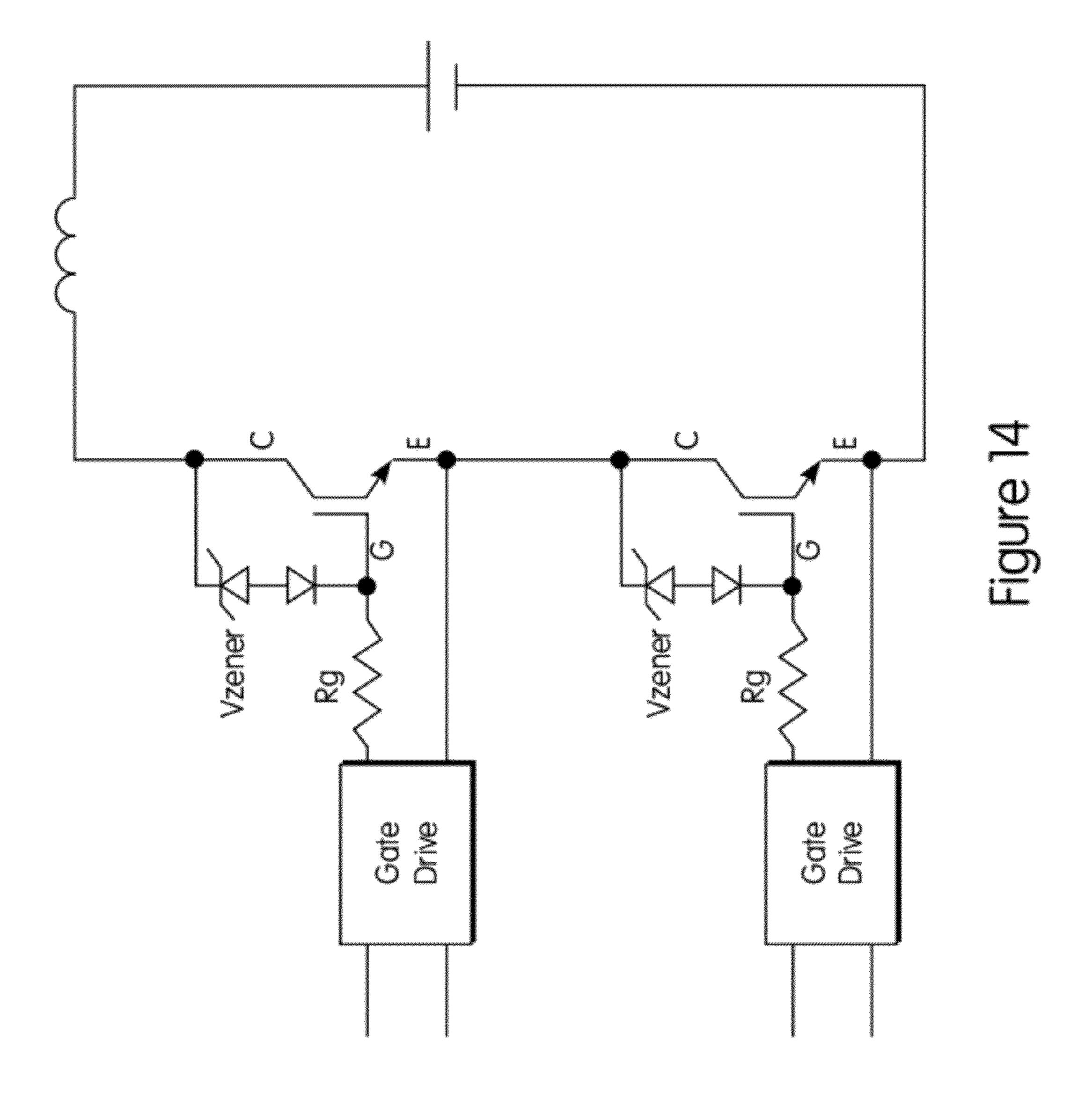

FIG. 14 is a circuit diagram showing multiple IGBTs in series using the active feedback control feature.

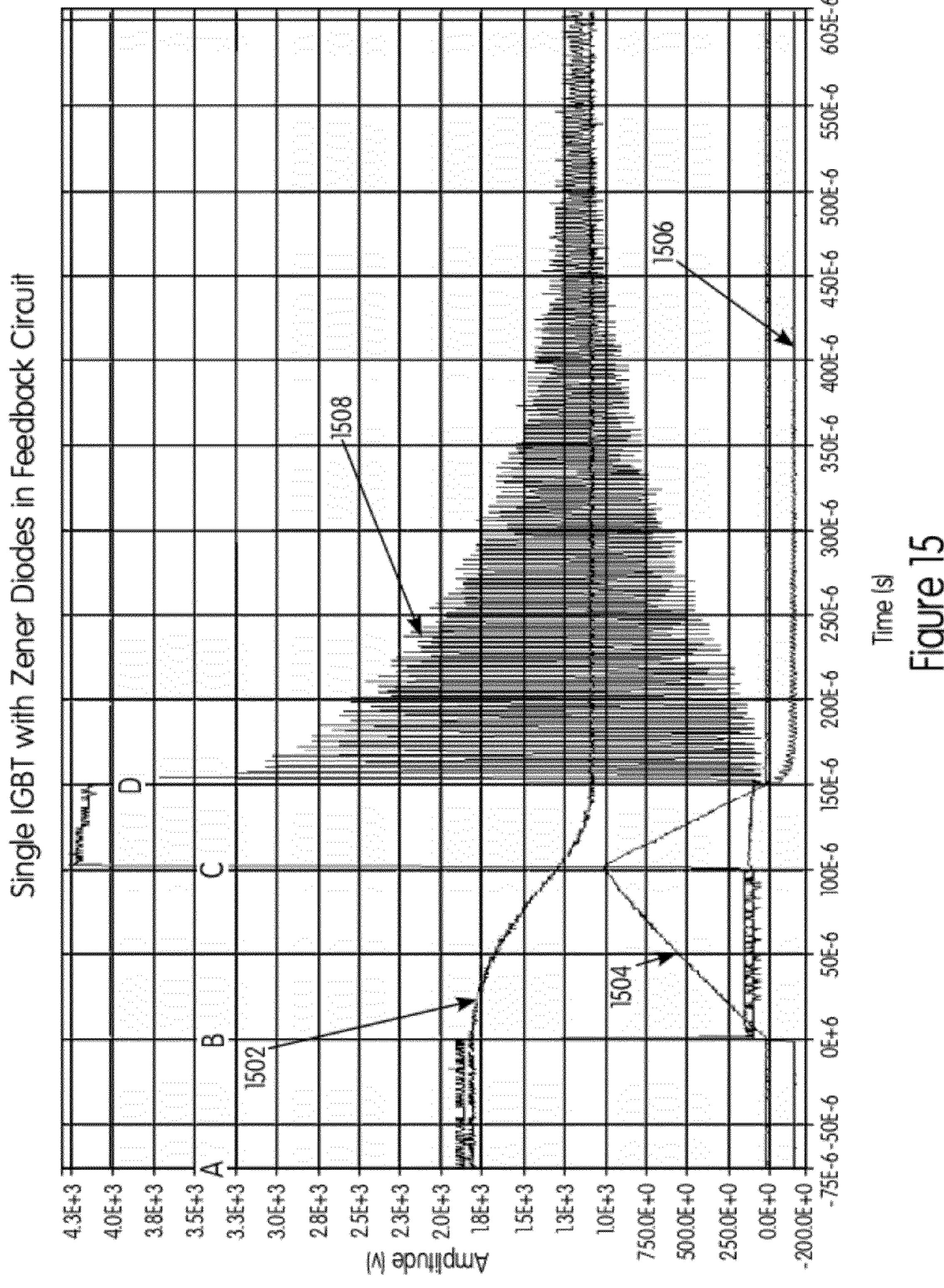

FIG. **15** is a graph showing various voltages in an circuit using the active feedback control during a shutdown procedure.

#### DETAILED DESCRIPTION OF THE INVENTION

The operation of the switching module of the power node switching center PNSC consists of three main functions. These are: (1) detection of a fault current; (2) commutation of the current from a path traversing a mechanical contactor to a path through a power electronics switch; and (3) interruption of the fault current by opening the power electronics switch.

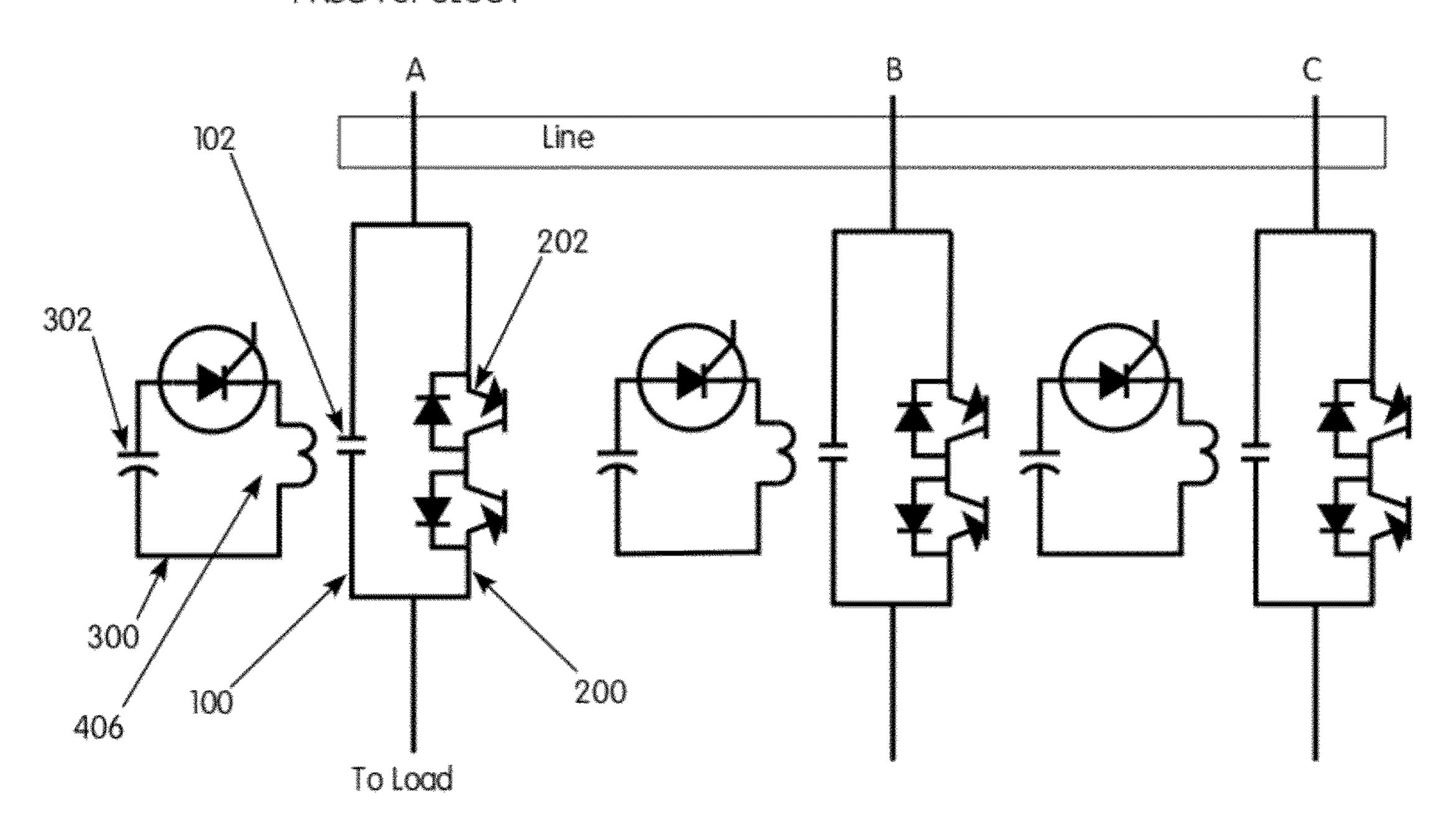

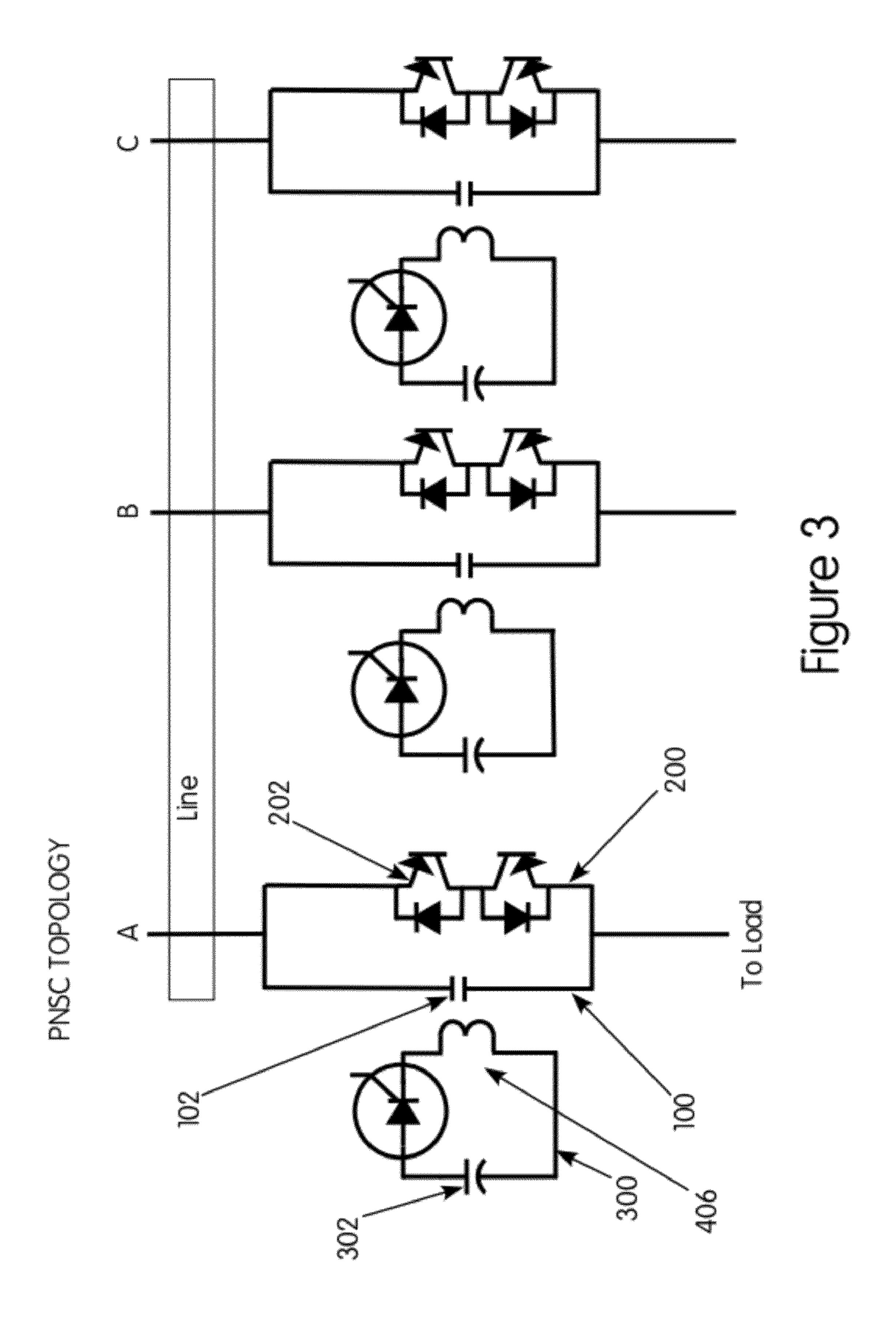

The basic topology of the PNSC switching module is shown in FIG. 3. FIG. 3 shows the switching module in three phase configuration, in which separate circuits for all three 15 phases would be housed in a single enclosure. This is not meant to be a limitation of the invention, however, as any number of phases could be housed together and still be within the spirit of the invention.

The preferred embodiment of the PNSC switching module 20 consists essentially of two parallel current carrying paths 100 and 200 for each phase. Path 100 includes mechanical contactor 102, and is the primary current carrying path during normal (non-fault) operations. When a fault is detected, discharge circuit 300 is gated, causing mechanical contactor 102 25 to open by dumping the charge stored in capacitor 302 through pancake coil 406, thereby inducing a repulsive magnetic force between pancake coil 406 and disk 408 (See FIG. 9). As mechanical contactor 102 opens, current is commutated from mechanical path 100 to electronic path 200, and is 30 then conducted via power electronics 202, which may consist of a pair of IGBTs or other power electronic devices. Power electronics 202, in the preferred embodiment, are continuously gated, even during non-fault operation, but in alternate embodiments may be turned off and gated only when a fault 35 is detected.

The connection between mechanical path 100 and power electronic path 200 consists primarily of a laminated bus, which provides a low-inductance connection between paths 100 and 200. This allows for fast commutation of the current 40 from path 100 to path 200. Because of the speed of the commutation, the voltage between the line end and the load end of path 100 does not have time to rise to a level which would result in the ionization of the air in the gap between disk 407 and contacts 402 and 404. This will reduce or elimi-45 nate arcing when mechanical contactor 102 is opened.

One novel aspect of the invention is the ability to detect a fault current within a few microseconds of the onset of the fault condition. During a fault condition, the current will rise rapidly. To detect a fault, the detection circuitry looks for an approximate 100 A change in current within a few microseconds. The detector, however, must not confuse a fault current with the normal operating current, which may consist of thousands of amps, normally at 60 Hz. Therefore, the detector must have a narrow bandwidth to detect the fault current, 55 which typically has a high frequency content. The bandwidth for the detector will therefore typically be in the 10 kHz-100 kHz range, allowing the detection of the rise in current within a time range of 1-100 microseconds (1/F), depending upon the magnitude of the fault current.

FIG. 4 shows a graph of the time it takes to detect a 100 A change in current as a function of the peak available fault current. It can be seen that the higher the peak available currents, the shorter the time that is required to detect the change in the current necessary to declare a fault condition. 65

The current detector of the present invention is shown diagrammatically in FIG. 5. A Rogoswki coil 302 of a type

6

well known in the art will produce a voltage which is proportional to the rate of change of the current flowing through a conductor (dI/dt). This signal is integrated for the purposes of fault detection using a high gain, narrow bandwidth integrator 304, with a passband in the range of 10 kHz-100 kHz. The response of the fault sensor is shown in the top half of FIG. 5. The sensor has a relatively flat response of about –30 dB (32 mV/A) between 20 kHz and 100 kz. At the line frequency of 60 Hz, the integrator is ineffective and the Rogowski output is passed through without being integrated. The gain is 30 dB below the high frequency integrated response, showing that the system is relatively insensitive to line frequency current. The output of the sensor is connected to a level detect circuit 307a. If the output voltage of the sensor exceeds the set level, a fault is considered to be present.

The output of the Rogowski coil is also integrated by a low gain, wide bandwidth integrator 306 for line frequency current sensing purposes. The response of this sensor is shown in the bottom half of FIG. 5. The response is flat from about 50 Hz to 100 kHz with a gain of about -60 dB (1 mV/A). This system senses line current over a wide bandwidth, down to line current frequency, but is over 30 times less sensitive than the fault current sensor at high frequencies. The output from this sensor is fed to level detect circuit 307b. When the sensor signal exceeds the set level an overload fault is considered to be present. Preferably, the level at which a fault is determined to have occurred will be adjustable.

FIG. 6 is a graph showing current versus time after the onset of a fault. The time required for the detection of the fault occurrence is shown where the straight line for the various current levels crosses the "Fault Declare" line. Note that this graph also shows that the time for a fault to be detected is a function of the magnitude of the current. This graph, for example, shows that an available fault current level of 80 kA is able to be detected in less than 2 microseconds, while a fault current of 5 kA is detected within 13 microseconds. FIG. 7 shows the declaration of a fault occurring when the current exceeds the sensor threshold level.

Prior to the detection of the fault, the primary path for current was path 100, through mechanical contactor 102. Once the fault has been detected, mechanical contactor 102 is opened and the current is then commutated to and conducted through path 200 until power electronics 102 can be shut down, thereby stopping the flow of all current.

Mechanical contactor 102 is a novel improvement to prior art contactors based on a Thompson Drive. FIG. 8 shows the stationary contacts of mechanical contactor 102. The poles of the contactor are represented by concentric rings of finger-like protrusions labeled in FIG. 8 as outer stationary contacts 402 and inner stationary contacts 404, representing the two poles of the switch. Pancake coil 406 is disposed concentrically in the center of the outer and inner stationary contacts, 402 and 404 respectively, and is used for quickly moving the low mass disk 408 away from the contacts, thus opening current path 100.

Contactor 102 is shown in cross-sectional view in FIG. 9. In normal operation, disk 408 is in contact with both sets of stationary contacts 402 and 404. Once a fault has been detected, pancake coil 406 is energized by dumping the charge stored in capacitor 302 into pancake coil 406, thereby driving disk 408 away from contacts 402 and 404, breaking the electrical connection between them. Disk 408 slides along rod 410 and is caught by a mechanical catch mechanism 411, which serves to hold disk 408 away from contacts 402 and 404. To engage the contact, mechanical catch mechanism 411 is released and disk 408 is driven into contact with contacts

402 and 404 via a solenoid acting on rod 410. Disk 408 is held in place during normal operation by a mechanical spring force, not shown in FIG. 9.

The novel aspects of the contactor mechanism 102 include the concentric configuration of stationary contacts 402 and 5 404 and pancake coil 406, and the low mass of moveable disk 408 which allows the disk to be driven away from contacts 402 and 404 in a very short period of time. Prior art mechanical contactors utilizing a Thompson drive typically have the contactor disk attached to a piston, such that the pancake coil 10 must drive the mass of both the piston and the disk. In the contactor of the present invention, disk 408 slides along rod 410. As such pancake coil 406 is only required to drive the mass of disk 408 when it is energized.

FIG. 10 shows a series of time-lapsed photographs showing the movement of disk 408 away from the contacts as a function of time. (Note that, in FIG. 10, only outer contacts 402 can be seen.) As can be seen, disk 408 is completely separated from the contacts at the 100 microsecond mark. Therefore, once a fault has been detected by the detection 20 circuitry, the current can be interrupted by the power electronics 202 within 100 microseconds.

FIG. 11 is a graph showing both voltage and current over time throughout the entire fault interruption process. (Note that the scale for the current in this graph is 100 times the scale 25 for the voltage shown on the left side of the graph). The fault in FIG. 11 starts at time zero and mechanical contactor 102 is conducting the current. At around the 50 microsecond mark, commutation starts. Within that 50 microseconds, the fault was detected and the Thompson drive coil was energized to 30 launch disk 408 away from contacts 402 and 404 of mechanical contactor 102. By about the 80 microsecond mark, the current is completely commutated and is being conducted by power electronics 202. The entire commutation process takes approximately 30 microseconds. The voltage during that time 35 never exceeds about 10 volts, which is not large enough to cause arcing in the gap between stationary contacts 402 and **404** and moveable disk **408**. It is estimated that at least 15v would be needed for arcing to occur. Note that the normal voltage drop between the supply side and the load side 40 through mechanical contactor 102 is about 2v. As a result, there is no arcing during the commutation process.

During the period between about 80 microseconds and 195 microseconds, power electronics **202** are conducting the fault current. At a little after the 195 microsecond mark, the power 45 electronics are switched off and the current is interrupted. Thus, the entire process from start of the fault to interruption of the current has taken less than 200 microseconds.

FIG. 12 shows a graph of both current and voltage for three phases of a system for both legacy prior art systems and for 50 the power node switching center of the present invention when closing on a faulted circuit. As can be seen in the legacy system, for a 20 kA rms available fault current, the interruption process takes about 2 cycles or about 35 milliseconds. During this time period, the voltage has dropped to zero and 55 the upstream system has been subjected to a 28 kA fault current. Using the present invention, the fault current is limited to about 0.3 kA and the interruption of the voltage to other loads has been limited to about 40 microseconds. This represents an approximate thousand fold improvement over the 60 prior art systems.

In another aspect of the invention an active feedback control is provided to control the opening and closing of the IGBT during a shutdown procedure. The basic circuit diagram is shown in FIG. 13. This circuit configuration 65 addresses the shortcomings of both passive and active snubbing while completely eliminating parallel snubbing compo-

8

nents. The interrupting switch is used to control the voltage and absorb the energy. This is accomplished by turning off the switch under active feedback control to limit the voltage developed during turnoff. The switch then absorbs the circuit energy eliminating the need for any additional energy absorbing components. The feedback control is accomplished with minimal, low cost components without adding significant size, weight, and cost to the system.

The interruption should be conducted at the constant, maximum voltage which is safe and which will minimize interruption time and energy dissipation. An ideal interrupter would have a low on-state voltage drop, then when commanded to turn off, it would develop a preset, maximum safe voltage, and maintain that voltage until the current is forced to zero and all the energy from the circuit is absorbed in the switch. Of necessity, the maximum safe voltage must be higher than the source voltage to drive current in the circuit to zero.

A linear solid state device, such as a transistor (IGBT, FET, BJT, etc.) 1304, can be used to achieve near ideal interrupter performance. Gate drive 1302 determines when the switch should be turned on or off, responsive to the input signals which would typically indicate a fault in the circuit. Feedback from the power terminals (e.g. drain to source voltage on a FET) is provided to the gate such that, when gated off, the device linearly regulates to a predetermined set voltage. As shown in FIG. 13, this can be accomplished by connecting zener diode 1306 with a limit voltage equal to the desired preset voltage level between the collector and gate of IGBT 1304. The set voltage must be below the safe voltage for the device and above the source voltage. When gated off the device will then develop a constant voltage that is greater than the source voltage due to the circuit inductance, which will drive the circuit current to zero. FIG. 14 also illustrates that devices can be connected in series to achieve higher interruption voltage capability. Devices can also be connected in parallel to achieve higher current interruption and energy absorption capability (not shown).

The basic operation of the circuit is as follows. The gate of switch 1304 is tied to the high voltage side of the switch via zener diode 1304. As long as the voltage across switch 1304 is below the turn-on voltage of zener diode 1306, the gate of switch 1304 is pulled down by gate drive circuit 1302 and switch 1304 is off. Initially, during a fault condition, switch 1304 is commanded on to conduct the current which previously flowed through the normal current path, in the case of the PNSC, the previously-described mechanical contactor. When switch 1304 is thereafter commanded off, the voltage across it will rise due to the inductive energy stored in the circuit components, and, when the voltage exceeds the threshold voltage of zener diode 1306, zener diode 1306 is turned on and the gate voltage is thereby raised to turn on switch 1304 just enough to keep the voltage across switch 1304 at the threshold voltage of zener diode 1306.

FIG. 15 shows the parameters of the circuit in operation. For purposes of example, this circuit has a single IGBT with 10 zener diodes in series, each having a turn-on voltage of 400v, raising the maximum voltage drop across the IGBT to 4000v. The IGBT must be properly sized to handle the maximum potential voltage drop. Additionally, this graph shows the operation of the circuit under test conditions, not as in-use in an actual PNSC, that is, the IGBT is not in parallel with a mechanical contactor for purposes of this graph.

The graph in FIG. 15 begins as the IGBT is initially turned off at time A. Line 1502 is the source voltage and starts at 1800V. Line 1508 is the voltage across the IGBT, and, as the device is not in parallel with a mechanical contactor, is ini-

tially at the source voltage (under actual use, in parallel with a mechanical contactor, this voltage would be near zero). At time B, the fault is simulated, the switch is turned on and the voltage across it collapses to a very low value. Line **1504** is the current, which is initially zero when the switch is turned off. At time B, when the switch is turned on, the current begins to rise and reaches 1000 A, when the IGBT is turned off at time C. The 100 millisecond delay between time B and time C is the approximate time that it takes for a mechanical contractor as described herein to open and stop conducting current. Thus, the rising current between times B and C represent current that would normally be conducted by the mechanical contactor prior to its opening.

At time C the IGBT is commanded off by the gate drive and the gate voltage dips slightly, causing the voltage across the IGBT to rise to about 4200V, representing the source voltage and the voltage across the inductance in the circuit. This voltage remains nearly constant until the current is driven to zero. This shows the voltage regulation action of the zener diodes. The IGBT absorbs all the energy in the circuit during the time the current falls to zero at time D. Once the current is driven to zero, the voltage across the IGBT can no longer be maintained and begins to fall. Once the voltage falls below the threshold voltage of the zener diode, the gate voltage is drawn down to -15V by the gate drive and the IGBT is turned off. 25 The voltage drop across the IGBT settles at the same voltage as the voltage source.

Line **1506** is the gate voltage (multiplied by 100 to make it visible on the plot). At time A, when the IGBT is turned off, the gate voltage is at –15V, holding the IGBT off. At time B, 30 the gate voltage is commanded by the gate drive to +15V, to turn the IGBT on. At time C, the gate drive commands the gate voltage back to –15V to turn the IGBT off. As the gate voltage falls at time C, the voltage across the IGBT immediately jumps high and the zener diode turns on and maintains the 35 gate voltage at about 12V, thus keeping the IGBT on. The gate voltage then falls slightly as the zener diode maintains just enough voltage on the gate to maintain the voltage across the IGBT above 4000V, until time D.

This graph shows that the zener feedback loop can regulate 40 the voltage across the IGBT as it turns off. The voltage at which it regulates is almost exactly equal to the zener threshold voltage, so by adjusting the number and value of the zener diodes the voltage which the IGBT will develop can be easily selected. The IGBT must absorb the inductive energy in the 45 circuit, as is apparent from the graph, which shows the voltage across the IGBT at 4000V while it is carrying the (falling) current.

While the general concepts of the power node switching center have been outlined herein, the specific implementation 50 details are meant to be exemplary only and not part of the invention. It should be readily realizable to one of ordinary skill in the art that many different implementations are possible and still remain within in the spirit of the invention. This entire scope of the invention is defined by the claims which 55 follow.

## I claim:

- 1. A circuit interrupting device comprising:

- a. a first current path, traversing a mechanical contactor;

- b. a second current path, parallel to said first current path, traversing a switch having active feedback control, said switch including:

- a power transistor device having a collector, an emitter and a gate; and

- a zener diode connected between said collector and said gate of said transistor device;

**10**

- wherein a voltage drop between the collector and the emitter of said transistor device equal to or greater than the threshold voltage of said zener diode will cause said zener diode to be turned on and a voltage to be applied to said gate sufficient to turn said transistor device on and to hold said voltage drop at or near said threshold voltage until current flowing through said transistor device is reduced to zero; and

- c. fault detection circuitry, for detecting a fault condition; wherein a fault current is commutated from said first current path to said second current path upon detection of said fault current by said fault detection circuitry.

- 2. The switch of claim 1 further comprising gate control circuitry, responsive to outside signals and coupled to said gate of said transistor device, to turn said transistor device on or off, and wherein said voltage applied to said gate when said zener diode is turned on will turn on said transistor device independent of said gate control circuitry.

- 3. The circuit interrupting device of claim 1 wherein said fault detection circuitry comprises:

- a current detector;

- a high gain, narrow bandwidth integrator, coupled to the output of said current detector; and

- a first level detection circuit, coupled to the output of said narrow bandwidth integrator,

- for producing a fault signal when a fault condition is detected.

- 4. The device of claim 1 wherein:

- said mechanical contactor is opened when said fault detection circuitry detects a fault condition; and

- said active feedback control switch is shut down as soon as possible after said commutation of said fault current.

- 5. The device of claim 3 wherein the bandwidth of said narrow bandwidth integrator is in the range of 10 kHz to 100 kHz.

- 6. The device of claim 5 wherein a fault signal is produced when the response of said narrow bandwidth integrator exceeds a predetermined level.

- 7. The device of claim 1 wherein said narrow bandwidth integrator produces a response to line frequency current that is below said predetermined level.

- 8. The device of claim 6 wherein said predetermined level of said first level detection circuit is adjustable.

- 9. The device of claim 1 further comprising:

- a low gain, wide bandwidth integrator for sensing line frequency current; and

- a second level detection circuit, coupled to the output of said wide bandwidth integrator, for sensing line frequency current and for producing a fault signal when a fault condition is detected.

- 10. The device of claim 9 wherein a fault signal is produced when the response of said wide bandwidth integrator exceeds a predetermined level.

- 11. The device of claim 9 wherein said predetermined level of said second level detection circuit is adjustable.

- 12. The device of claim 9 wherein said current detector is a high frequency, narrow bandwidth current detector that can detect current components with frequencies between 10 kHz and 100 kHz and which is insensitive to line frequency current.

- 13. The device of claim 11 wherein said current detector is a Rogowski Coil.

- 14. The device of claim 1 wherein said switch having active feedback control comprises two or more switches having active feedback control arranged in series.

- 15. The device of claim 1 wherein said switch having active feedback control comprises two or more switches having active feedback control arranged in parallel.

- 16. A circuit interrupting device comprising:

- a. fault detection circuitry, for detecting a fault condition; 5

- b. a first current path, traversing a mechanical contactor;

- c. a second current path, parallel to said first current path, traversing a switch having active feedback control, said switch comprising:

- a transistor device having a collector, an emitter and a gate;

- a zener diode connected between said collector and said gate of said transistor device; and

12

gate control circuitry, responsive to signals from said fault detection circuitry and coupled to said gate of said transistor device, to turn said transistor device on or off;

wherein a voltage drop between the collector and the emitter of said transistor device equal to or greater than the threshold voltage of said zener diode will cause a voltage to be applied to said gate sufficient to turn on said transistor device independent of said gate control circuitry and to hold said voltage drop at or near said threshold voltage until current flowing through said transistor device is reduced to zero.

\* \* \* \* \*