#### US008213751B1

## (12) United States Patent Ho et al.

### (10) Patent No.: US 8,213,751 B1 (45) Date of Patent: Jul. 3, 2012

# (54) ELECTRONIC-INTEGRATION COMPATIBLE PHOTONIC INTEGRATED CIRCUIT AND METHOD FOR FABRICATING ELECTRONIC-INTEGRATION COMPATIBLE PHOTONIC INTEGRATED CIRCUIT

- (75) Inventors: **Seng-Tiong Ho**, Wheeling, IL (US); **Yingyan Huang**, Wilmette, IL (US)

- (73) Assignee: Optonet Inc., Evanston, IL (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 372 days.

- (21) Appl. No.: 12/626,178

- (22) Filed: Nov. 25, 2009

#### Related U.S. Application Data

- (60) Provisional application No. 61/200,315, filed on Nov. 26, 2008.

- (51) Int. Cl.

G02B 6/00 (2006.01)

H01L 21/00 (2006.01)

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

|                   | 4,750,799 A<br>6,393,185 B<br>6,922,508 B | *<br>1 *<br>2 * | 6/1988<br>5/2002<br>7/2005 | Kawachi et al. Kawachi et al. Deacon Glebov et al. Glebov et al. | 385/14<br>385/50<br>385/43 |

|-------------------|-------------------------------------------|-----------------|----------------------------|------------------------------------------------------------------|----------------------------|

| 2002, 0022022 111 | 2003/0035632 A                            | 1*              | 2/2003                     | Glebov et al                                                     | 385/43                     |

\* cited by examiner

Primary Examiner — Brian Healy

(74) Attorney, Agent, or Firm — William L. Botjer

#### (57) ABSTRACT

An electronic-integration compatible photonic integrated circuit (EIC-PIC) for achieving high-performance computing and signal processing is provided. The electronic-integration compatible photonic integrated circuit comprises a plurality of electronic circuit structures and a plurality of photonic circuit structures. The electronic and photonic circuit structures are integrated by a process referred to as monolithic integration. An electronic circuit structure includes one or more electronic devices and a photonic circuit structure includes one or more photonic devices. The integration steps of electronic and photonic devices are further inserted into standard CMOS process. The photonic circuit structures and the electronic circuit structures are integrated to form the electronic-integration compatible photonic integrated circuit device.

#### 22 Claims, 56 Drawing Sheets

Jul. 3, 2012

# ELECTRONIC-INTEGRATION COMPATIBLE PHOTONIC INTEGRATED CIRCUIT AND METHOD FOR FABRICATING ELECTRONIC-INTEGRATION COMPATIBLE PHOTONIC INTEGRATED CIRCUIT

### REFERENCE TO RELATED APPLICATION

This application claims the priority of U.S. provisional patent application, Ser. No. 61/200,315, filed Nov. 26, 2008, titled, 'ELECTRONIC-INTEGRATION COMPATIBLE PHOTONIC INTEGRATED CIRCUIT AND METHOD FOR FABRICATING ELECTRONIC-INTEGRATION COMPATIBLE PHOTONIC INTEGRATED CIRCUIT', the contents of which are herein incorporated by reference.

#### FIELD OF THE INVENTION

This invention relates generally to the field of Integrated Circuits and more specifically to Photonic Integrated Circuits 20 that are compatible with Electronic Device Integration.

#### BACKGROUND OF THE INVENTION

An electronic Integrated Circuit (IC) is a device having 25 integration of electronic circuits and components onto the surface of a substrate of a semiconductor material by processes of fabrication. The substrate materials include, but are not limited to, silicon (Si), Silicon on insulator (SOI), germanium (Ge), indium phosphide (InP), gallium arsenide 30 (GaAs), gallium nitride (GaN) etc. Majority of the electronic integrated circuits; however, are fabricated on silicon due to their low cost of fabrication and the high reliability of silicon electronics. GaAs, InP, and GaN are used only occasionally. For example, GaAs and InP are used when high speed is 35 required and GaN is used when high power is required. In electronics, an integrated circuit can also be referred to as a microcircuit, a microchip, a silicon chip, or simply a chip. Integrated circuits include a combination of active electronic devices with passive components onto a single semiconductor crystal. The examples of active electronic devices include, but are not limited to, transistors, diodes etc. The examples of passive components include, but are not limited to, resistors, capacitors, inductor etc. The processes involved in the fabrication of integrated circuits can include, but are not limited to, 45 vapor-phase deposition of semiconductors and insulators, oxidation, solid-state diffusion, ion implantation, vacuum deposition and sputtering etc.

Electronic Integrated Circuits (ICs) have demonstrated a combination of low cost, high reliability, low power require- 50 ments, and high processing speeds compared to the previously existing techniques of vacuum tubes and discrete transistors. Applications of Integrated circuits include, but are not limited to, computing, communications, manufacturing and transport systems, the Internet, computers, cellular phones, 55 and other digital appliances.

A Photonic Integrated Circuit (PIC) is a device that integrates multiple photonic functions. The difference between the PIC and an IC is that the PIC process signals are imposed on optical beams while IC process signals are imposed on electrical currents or voltages. These optical beams typically have wavelengths ranging from the UV/visible spectrum (200-750 nm) to near Infrared spectrum (750 nm-1650 nm). The Photonic Integrated Circuit can also be interchangeably referred to as an Integrated Optical Circuit. The materials 65 used for the fabrication of PICs include, but are not limited to, silica (SiO<sub>2</sub>) on silicon, silicon on insulator (SOI), various

polymers and compound semiconductor materials such as GaAs, InP, and GaN. Integrated photonic devices can also be classified into "passive photonic devices" that do not consume or exchange energy; "emissive/absorptive photonic devices" that involve light emission, optical gain, and absorption, or electronic energy level transitions that give rise to the spontaneous emission, stimulated emission, or absorption of photons; "electro-optic devices" that require an applied electrical voltage or current but do not require optical emission/ absorption for their main functionalities; and nonlinear optical devices that involve nonlinear-optical properties of materials. Passive devices include, but are not limited to, optical beam splitters, optical wavelength filters, optical resonators, optical waveguides, optical wavelength multiplexers, optical couplers, optical polarizers, optical isolators, polarization rotators etc. Emissive devices include, but are not limited to, optical amplifiers, lasers, and light-emitting devices. Absorptive devices include photodetectors etc. Electro-optic devices include, but are not limited to, electro-optic modulators, electro-optic phase shifters, electro-optic switches, etc. Nonlinear-optical devices include second harmonic generators, photonic transistor, and all-optical switches etc. Emissive/absorptive, electro-optic, and nonlinear optical devices together are part of "active devices" that are devices that consume or exchange energy. Beside the above, there are other active devices such as opto-mechanical devices that involve mechanical power but the above are the main classes of active photonic devices of interest here. These active devices of interest are sometimes classified into optoelectronic devices (those that involve applied electrical power) and all optical devices that do not involve applied electrical power. All optical devices are typically devices that involve direct interaction of light with light. These nomenclatures are not always precise in usage and are defined above specifically for their application here.

The fabrication techniques for PIC are typically similar to the fabrication techniques used in ICs. In the fabrication process, the PIC devices that can be mounted on a PIC chip include, but are not limited to, the above mentioned passive, active, and electro-optic devices, with applications ranging from the field of fiber-optic communication, computing, sensing, to biomedical.

Typically photonic integrations are of two types; namely, Hybrid and Monolithic integrations. Monolithic integration involves "wafer-level" processes that result in many devices on a single substrate. Hybrid integration involves fabrication of individual devices separately before placing them together to form a subsystem in a packaged module. Monolithic integration can take advantage of the economy of scale much better than hybrid integration, as the production cost per wafer in monolithic integration does not vary too much with wafer size. However, larger wafer size provides integration of many devices on the wafer, resulting in much lower cost of manufacturing per device. The production of monolithic photonic integrated circuits involves construction of the PIC devices on a common substrate using wafer-level processes.

The most common function of the PIC device is to optically transmit data. Optical Data Transmission requires various steps such as sending light by using lasers, splitting the light into different wavelengths by using wavelength multiplexers or optical filters or optical resonators, encoding data by using modulators or direct current modulation of semiconductor lasers, and receiving data by using photo detectors, as are known to those skilled in the art. Further, the optical data transmission also requires low loss interconnect waveguides. As is known to those skilled in the art, the Optical Data Transmission using photonic circuit typically is capable of

substantially higher data transfer rates than Electrical Data Transmission using electronic circuit, and at the same time eliminates problems resulting from electromagnetic interference. PICs can allow optical systems to be more compact and perform higher functionally as compared to discrete optical components.

A main challenge in photonic device integration is that photonic devices are typically large in size as compared to the electronic devices. They have typical sizes of hundreds of micrometers to millimeters or centimeters. As known to those 10 skilled in the art, to address the challenge, photonic devices that are much smaller in size have been realized recently by utilizing photonic device waveguide structures that have high refractive index contrast between the waveguide core and waveguide cladding. These photonic devices are referred to as 15 dielectric 'nanophotonic devices'. As is known to those skilled in the art, dielectric nanophotonic devices include, but are not limited to, photonic bandgap devices, photonic crystal devices, microring resonators, microdisk resonators, superprisms, photonic crystal based slow or fast wave devices, 20 photonic-wire waveguides, and nano-lasers. There are also small photonic devices realized with photonic device structures that involve electron plasma in metals, which are referred to as plasmonic nanophotonic devices. The dielectric and plasmonic nanophotonic devices below will be referred 25 to as nanophotonic devices. As is known to those skilled in the art, plasmonic nanophotonic devices include, but are not limited to, plasmonic waveguides, plasmonic lasers, plasmonic ring and disk resonators, plasmonic photonic crystals, surface plasmon devices, plasmonic slow-wave devices, plasmonic 30 fast-wave devices, and negative dielectric or negative refractive index devices. The optoelectronic or all-optical versions of such devices will be referred to as nano-optoelectronic devices and nano all-optical devices, respectively. Nanophotonic devices have typical device sizes of nanometers to hundreds of micrometers at the optical wavelength of about one micrometer and are substantially smaller than conventional photonic devices. As is known to those skilled in the art, the physical size of the device scales somewhat proportionally to the electromagnetic wavelength of operation. Hence, the 40 physical size examples given here are not absolute but shall scale somewhat proportionally to the electromagnetic wavelength of operation.

Photonic integrated circuits and electronic integrated circuits complement each other in fulfilling the demanding performance requirements of high-speed communications and high-performance computing etc. However, at present photonics and electronics are still handled by different materials platforms and technologies. While ultra-large-scale integration of electronics has become a reality, the large-scale monolithic integration of high-performance photonic circuits on a chip is still largely unaccomplished. It is expected that if photonic devices and electronic devices can be integrated in large scale on a same chip, new functionalities can be brought that will combine the high data transport rate of photonics with the high data processing speed of electronics, resulting in an integrated Electronic-Photonic Integrated Circuit (EPIC) that will be much faster than IC or PIC alone.

In light of the foregoing, there exists a need for a technology that could realize integration of photonic devices on a 60 chip in a way that is compatible with electronic device integration.

At present, majority of the large-scale electronic integrated circuits are fabricated with silicon material and majority of the active photonic or nanophotonic devices are fabricated 65 with compound semiconductor materials such as InP, GaAs, or GaN. The fabrication process of electronic devices for

4

silicon electronics such as those used in fabricating CMOS (Complementary Metal Oxide Semiconductor) transistors involve temperatures around 1000° C. Most compound semiconductors cannot withstand such high temperatures without suffering from chemical decomposition. A method that will address such incompatibility and enable the fabrication of photonic or nanophotonic devices in a way that will be compatible with electronic devices will be of interest.

Furthermore, current photonic integrated circuit technology is not favorable due to various issues, including the difficulty in achieving low-loss and cost-effective coupling of light from optical fiber into the photonic chip, the cost of integration of compatible optoelectronic and all-optical devices on the chip, the integration of optoelectronic devices on the chip, the integration of the newer generation of nanophotonic and nano-optoelectronic devices on the chip, and the integration of passive photonic devices on the chip.

In light of the foregoing, there exists a need for a technology that could achieve large scale integration of photonic devices on a chip with efficient and cost-effective optical coupling to optical fiber, and that could achieve low fabrication cost in the integration of compatible optoelectronic and all optical devices on the chip, the integration of optoelectronic devices on the chip, the integration of the newer generation of nanophotonic and nano-optoelectronic devices on the chip, and the integration of passive photonic devices on the chip, and preferably do so in a way that is compatible with electronic device integration.

## **SUMMARY**

An object of the present invention is to provide a method and system for monolithic integration of active and/or passive photonic and/or nanophotonic devices in a way that is compatible with electronic integration, resulting in an electronic integration-compatible photonic-integrated circuit (EIC-PIC).

Another object of the invention is to provide a system for integration of photonic and/or nanophotonic and electronic devices on a single substrate.

Yet another object of the present invention is to provide a method and system for monolithic integration of active and/or passive photonic and/or nanophotonic devices in a way that is compatible with electronic integration resulting in an electronic-integration-compatible photonic-integrated circuit (EIC-PIC) with a single optical waveguiding layer known as Single-Optical-Layer EIC-PIC.

Yet another object of the present invention is to provide a method and system for monolithic integration of active and/or passive photonic and/or nanophotonic devices in a way that is compatible with electronic integration resulting in an electronic-integration-compatible photonic-integrated circuit (EIC-PIC) with an optical waveguiding core layer and another active optical layer put on the waveguiding core layer known as Direct Double-Optical-Layer EIC-PIC (DDOL-EIC-PIC).

Yet another object of the present invention is to provide a method and system for monolithic integration of active and/or passive photonic and/or nanophotonic devices in a way that is compatible with electronic integration resulting in an electronic-integration-compatible photonic-integrated circuit (EIC-PIC) with an optical waveguiding core layer and another active optical layer put on the waveguiding core layer inter-spaced with a dielectric layer known as Indirect Double-Optical-Layer EIC-PIC (IDDOL-EIC-PIC).

Yet another object of the present invention are to couple light beam up and down between the waveguiding core layer

and the active optical layer in Indirect Double-Optical-Layer EIC-PIC (IDDOL-EIC-PIC) using an optical tapered waveguide.

Yet another object of the present invention is to provide a method and system for monolithic integration of active and/or passive photonic and/or nanophotonic devices and their process insertion into the electronic device fabrication process (e.g. CMOS process).

Yet another object of the present invention is to provide a method and system for the monolithic integration of semi- 10 conductor or compound semiconductor active/passive devices and their process insertion into the electronic device fabrication process (e.g. CMOS process).

Yet another object of the invention is to provide a method and system for integration of photonic and/or nanophotonic 15 integrated circuits on a single substrate with a means to couple light from one or more optical fibers into the photonic integrated circuits and/or from the photonic integrated circuits into one or more optical fibers. The means of coupling light involves an integrated Super-high-numerical-aperture 20 GRIN lens (Super lens).

Yet another object of the invention is to provide a method and system for integration of photonic and/or nanophotonic and electronic integrated circuits on a single substrate with electronic device fabrication compatible process (e.g. CMOS 25 compatible process) based on local-area wafer bonding.

Yet another object of the invention is to provide an electronic device fabrication compatible process (e.g. CMOS compatible process) that requires local-area wafer bonding be done after the high-temperature processes for fabricating 30 transistors.

Yet another object of the invention is to provide an electronic device fabrication compatible process (e.g. CMOS compatible process) that involves local-area wafer bonding process bonding small areas of photonic gain and/or absorp- 35 tive materials on different areas of the substrate.

Yet another object of the invention is to provide a method and system for integration of active/passive photonic and/or nanophotonic integrated circuits on a single substrate using Quantum-Well Intermixing.

Yet another object of the invention is to provide an EIC-PIC chip with high-data-rate signal input-output provided by one or more optical fibers to the chip. Each optical fiber carries one or more optical beams. Each optical beam is lightwave at an optical wavelength carrying a wavelength channel. The 45 optical beam for each wavelength channel is modulated in amplitude and/or phase to transmit signals.

Yet another object of the invention is to provide an EIC-PIC chip with integrated photonic devices on the chip to enable separation of beams carrying different wavelength channels 50 to different photodectectors. A device that separates the wavelength channels is referred to as wavelength demultiplexing device.

Yet another object of the invention is to provide an EIC-PIC chip with integrated photonic devices on the chip to enable 55 combining of beams from different on-chip lasers emitting different wavelength channels to a single waveguide and then coupled out to a single optical fiber. A device that combines the wavelength channels is referred to as wavelength multiplexing device.

Yet another object of the invention is to provide an EIC-PIC chip with the wavelength multiplexing and/or demultiplexing device realized by a curved grating with high spectral resolution and compact physical size known as compact curved grating (CCG) or super-compact grating (SCG).

Yet another object of the invention is to provide an EIC-PIC chip with one or more all-optical devices on the chip.

6

Yet another object of the invention is to provide an EIC-PIC chip with the all optical device being an efficient all-optical device known as photon transistor based on Gain and Absorption Manipulation of Coupler Interference (GAMCI).

Yet another object of the invention is to provide an EIC-PIC chip with the active photonic devices whose electrodes for n and/or p contact is made up of transparent conducting oxide (TCO) to enable effective electrical contact to the active photonic and/or nanophotonic devices without inducing too much optical loss like a metal contact will. This facilitates the integration of compact active photonic devices on the electronic-photonic chip.

Yet another object of the invention is to provide the active photonic devices with TCO as the contact electrodes that are optical modulators.

Yet another object of the present invention is to provide a method and system for fabricating a photonic integrated circuit capable of high-speed communications, control, RF photonics, high-performance computing, bio-sensing, gas-sensing, and high bandwidth signal processing.

The various embodiments of the invention provide a method for monolithic integration of a plurality of electronic circuit structures and a plurality of photonic circuit structures on a single substrate. Each electronic circuit structure includes one or more electronic devices. Each photonic circuit structure includes one or more photonic devices. The method includes inserting integration steps of the photonic devices into electronic device fabrication process (e.g. CMOS process). The method further includes integrating the photonic devices by monolithic integration process. Further, the method includes inserting integration steps of the electronic devices into electronic device fabrication process (e.g. CMOS process). The method further includes integrating the electronic devices by using a monolithic integration process.

# BRIEF DESCRIPTION OF THE DRAWINGS

The preferred embodiments of the invention will hereinafter be described in conjunction with the appended drawings, provided to illustrate and not to limit the invention, wherein like designations denote like elements, and in which:

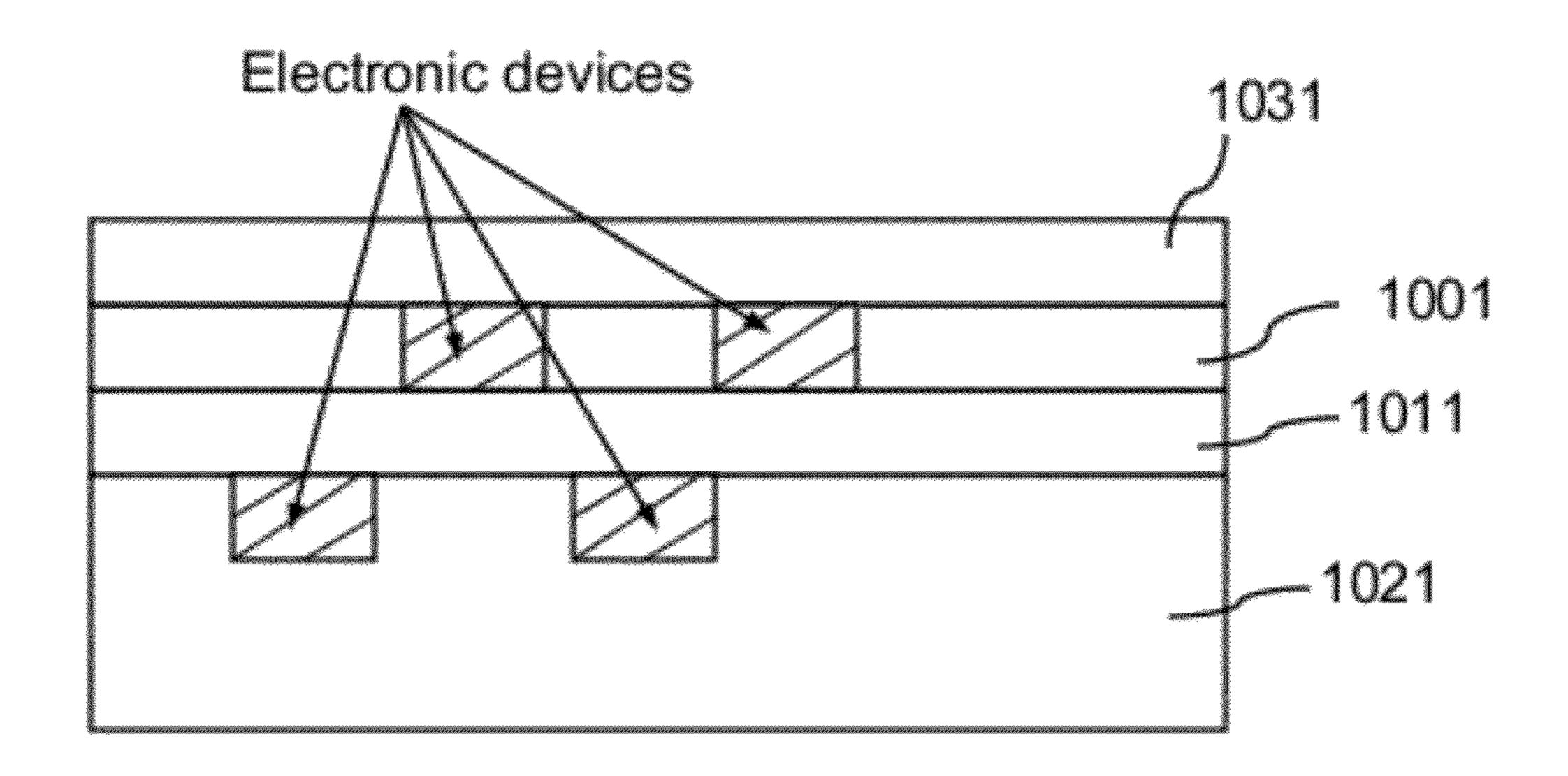

FIG. 1 illustrates a basic wafer structure for an Electronic-Integration Compatible Photonic/Nanophotonic Integrated Circuit in accordance with an embodiment of the invention;

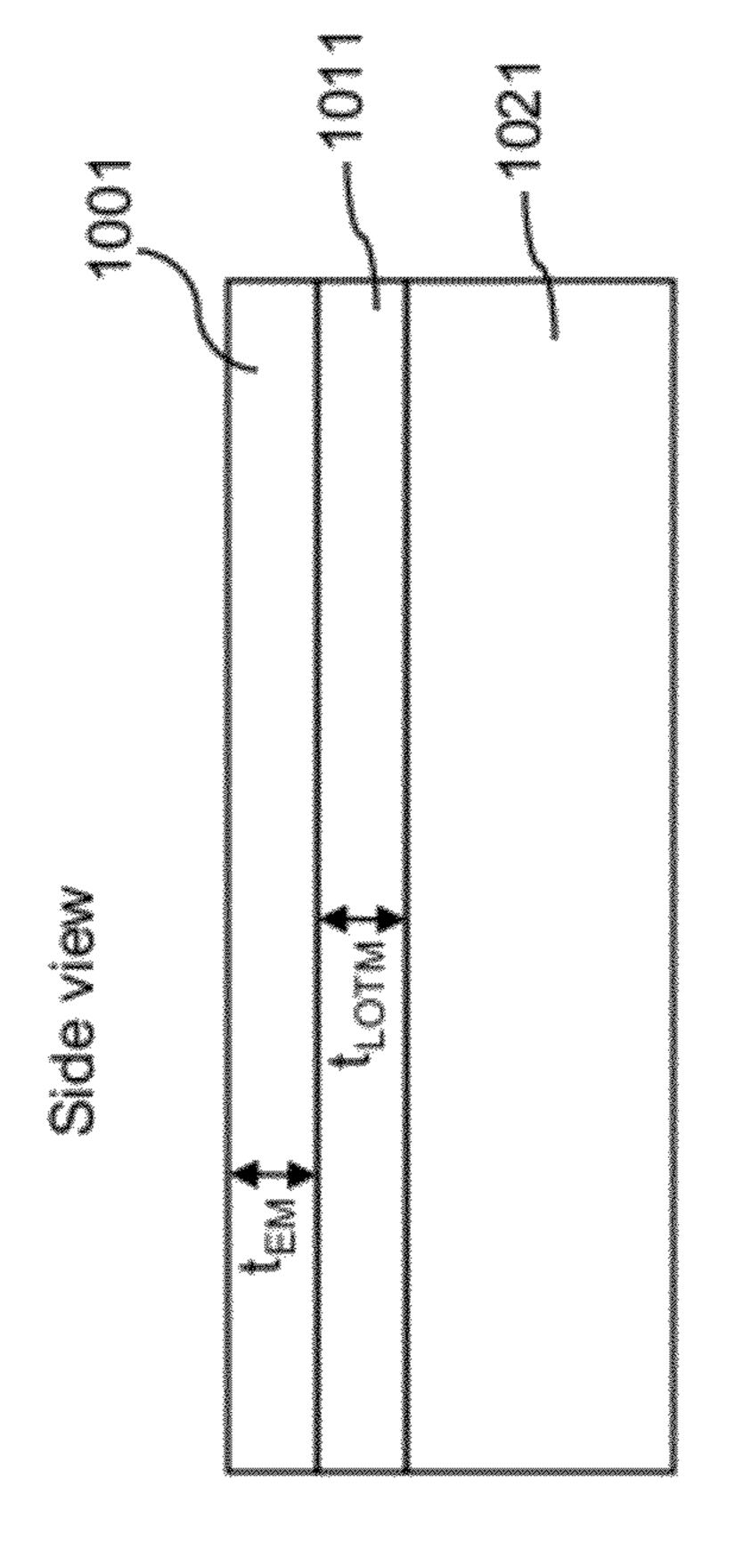

FIG. 2 illustrates a basic wafer structure for an Electronic-Integration Compatible Photonic/Nanophotonic Integrated Circuit in accordance with an embodiment of the invention;

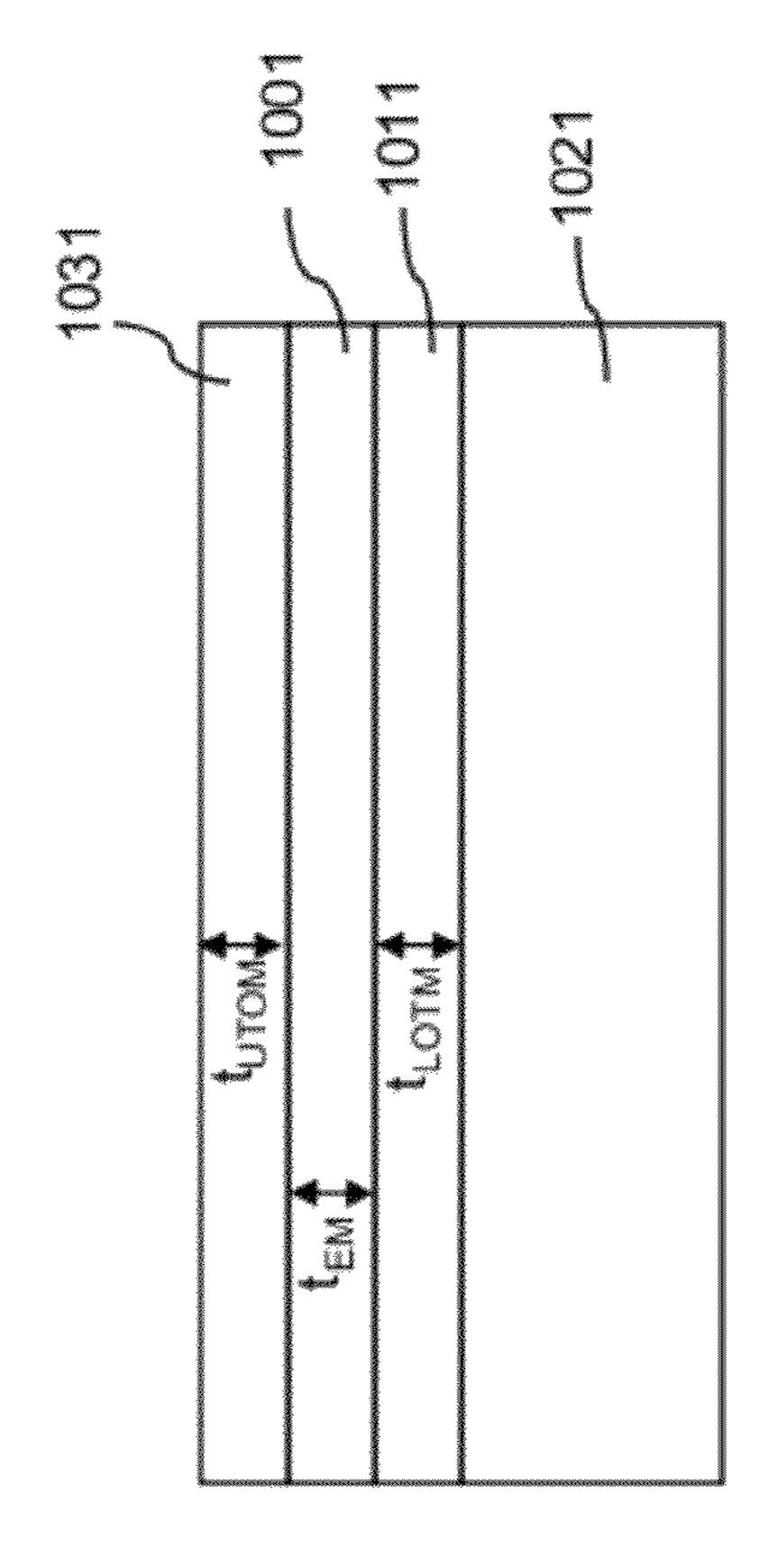

FIG. 3 illustrates a basic wafer structure for an Electronic-Integration Compatible Photonic/Nanophotonic Integrated Circuit in accordance with an embodiment of the invention;

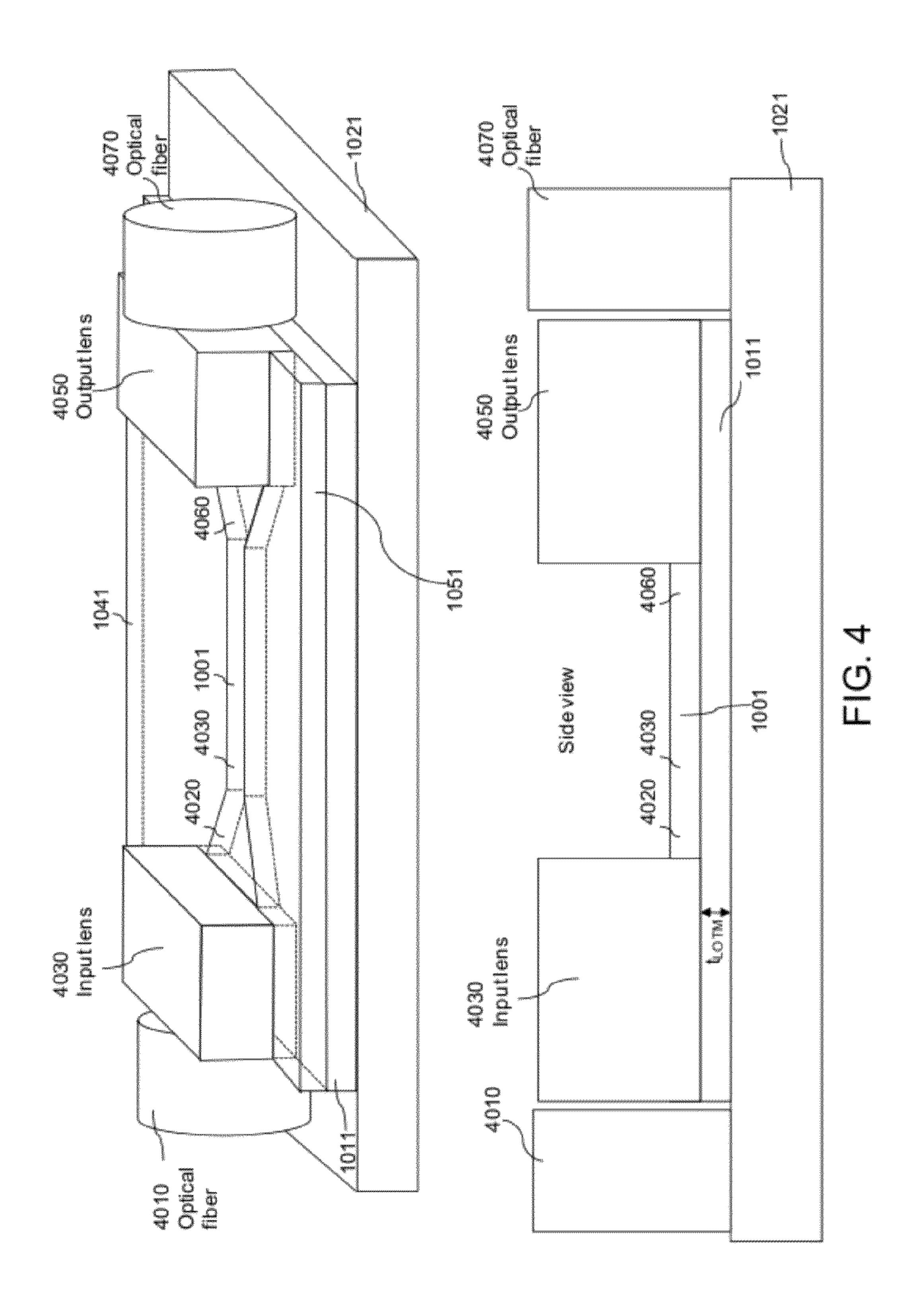

FIG. 4 illustrates a Single-Optical-Layer an Electronic-Integration Compatible Photonic/Nanophotonic Integrated Circuit (SOL-EIC-PIC) in accordance with an embodiment of the invention;

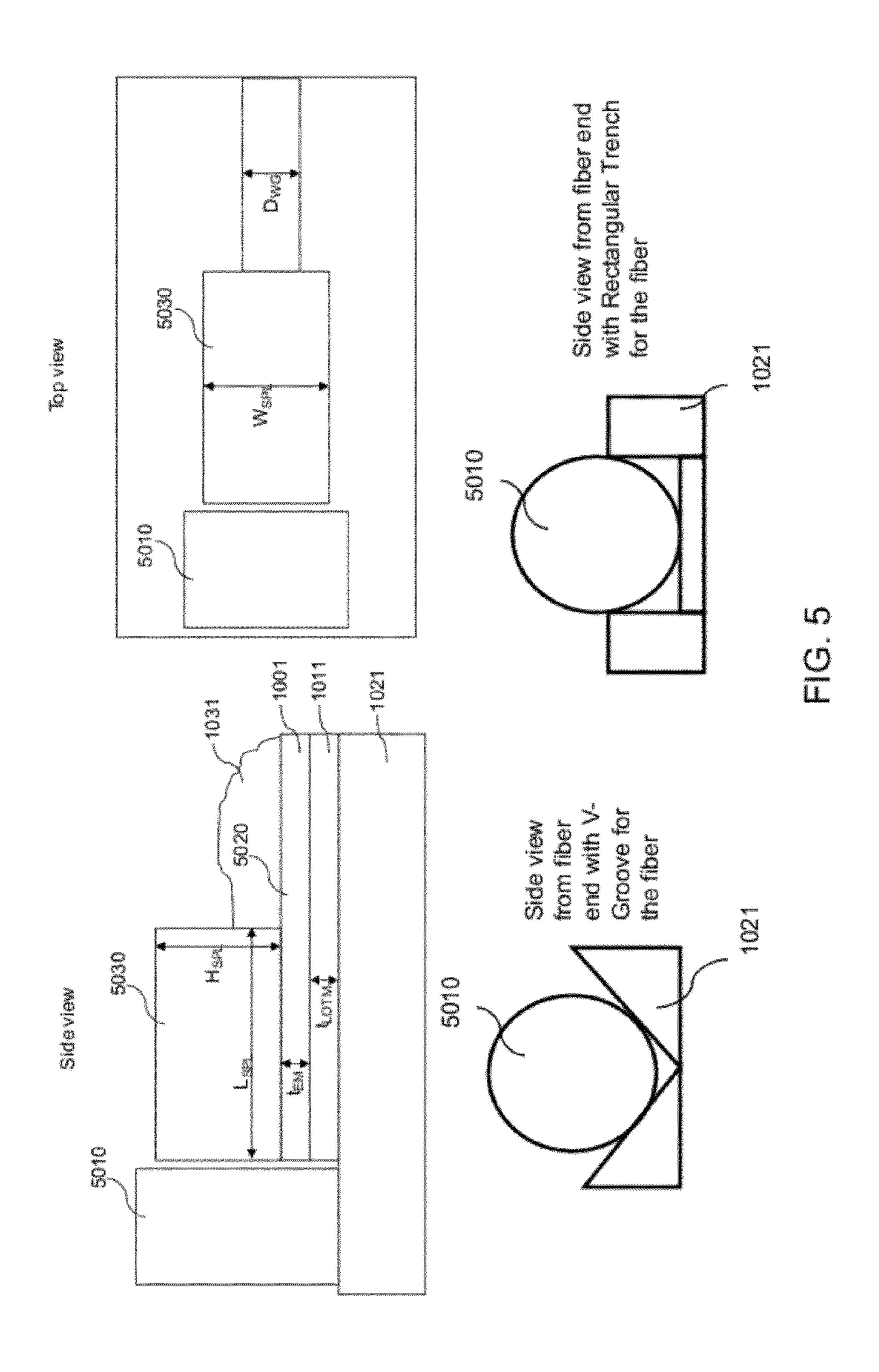

FIG. 5 illustrates a Superlens coupling optics, integrated on an Electronic-Integration Compatible Photonic/Nanophotonic Integrated Circuit chip, in accordance with an embodi-60 ment of the invention;

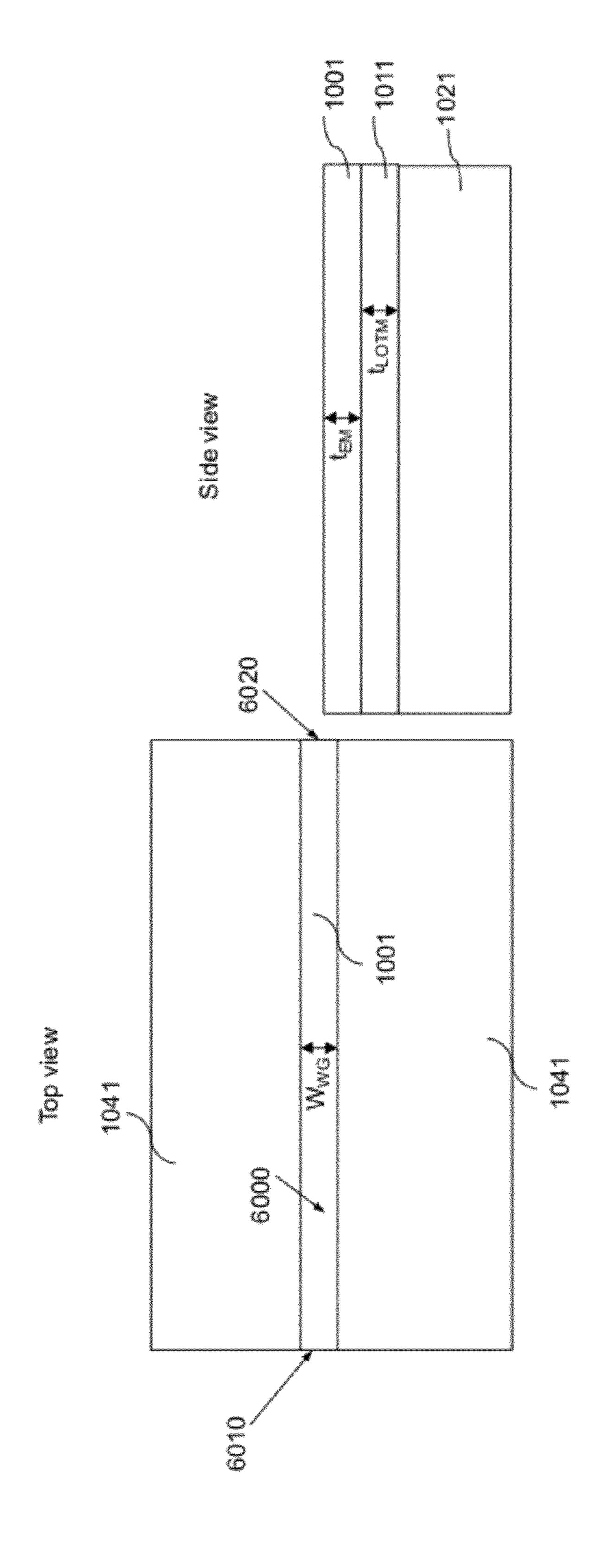

FIG. 6 illustrates an optical waveguide, integrated on an Electronic-Integration Compatible Photonic/Nanophotonic Integrated Circuit chip;

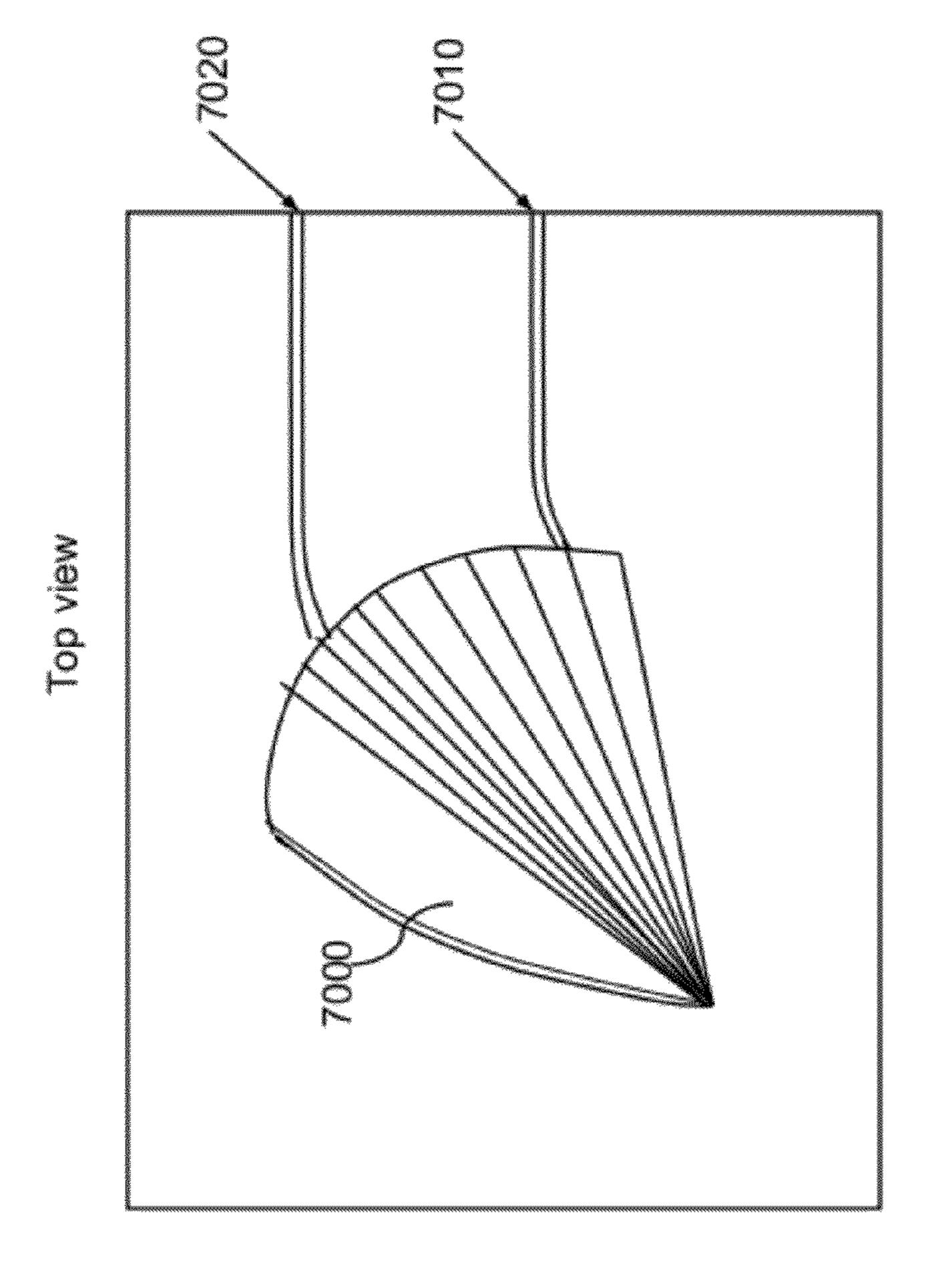

FIG. 7 illustrates an ultra-compact wavelength multi-65 plexer/demultiplexer, also called Super-Compact Grating or Compact Curved Grating integrated on an EIC-PIC chip, in accordance with an embodiment of the invention;

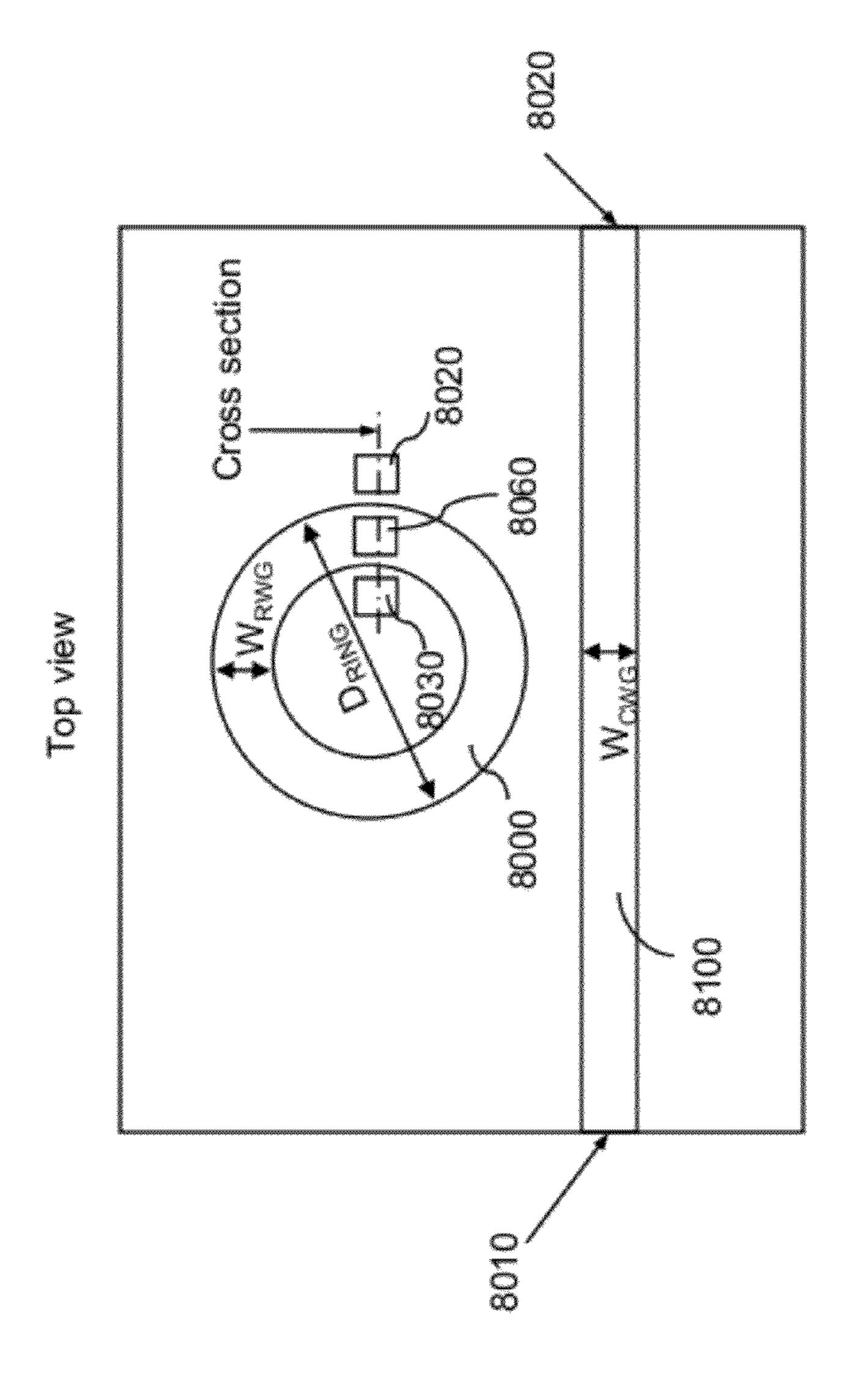

- FIG. **8**A illustrates a tunable optical ring resonator integrated on an Electronic-Integration Compatible Photonic/Nanophotonic Integrated Circuit chip, in accordance with an embodiment of the invention;

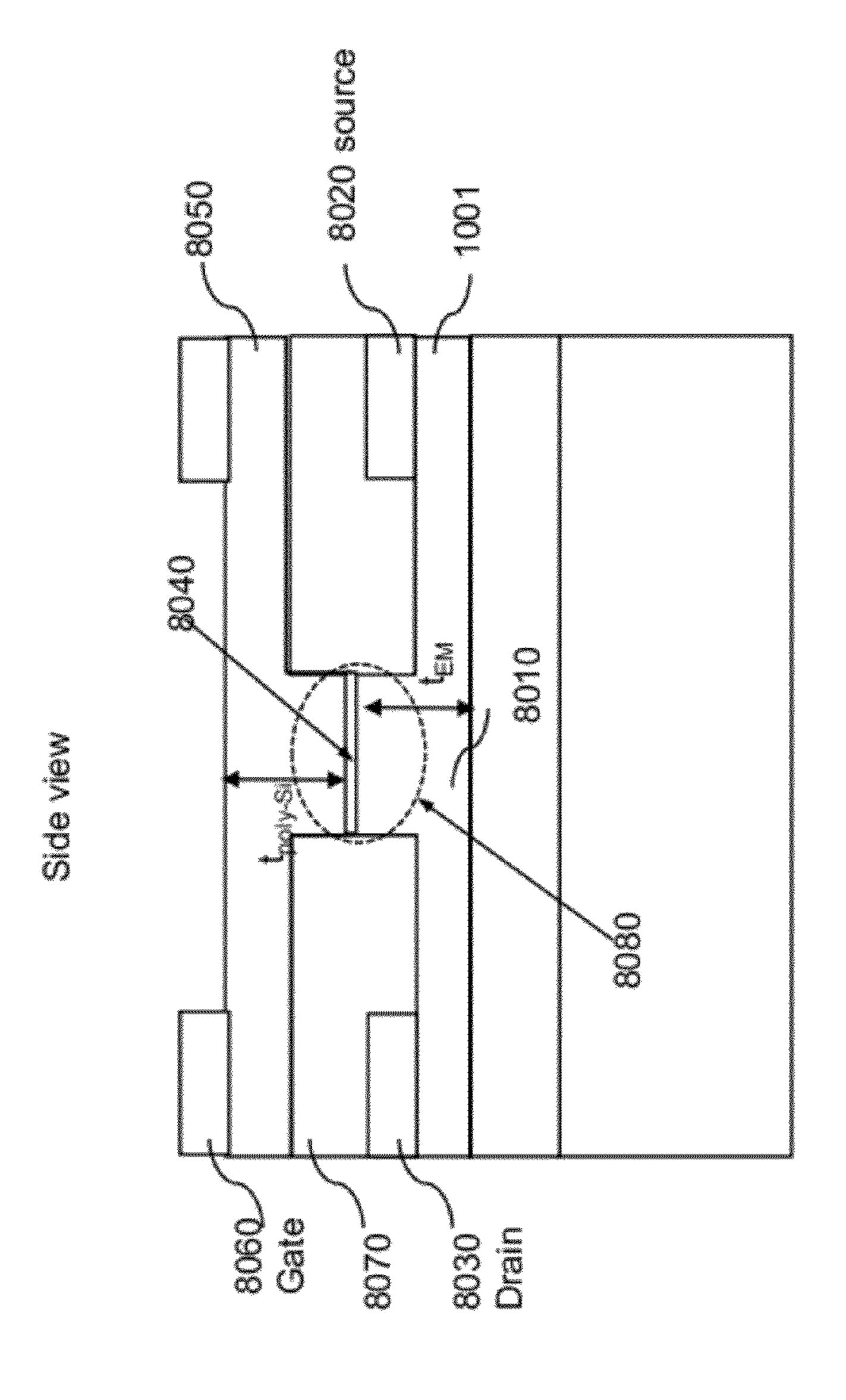

- FIG. 8B illustrates the cross-sectional view of a tunable 5 optical ring reonstor with poly-silicon as the top electrode integrated on an Electronic-Integration Compatible Photonic/Nanophotonic Integrated Circuit chip, in accordance with an embodiment of the invention;

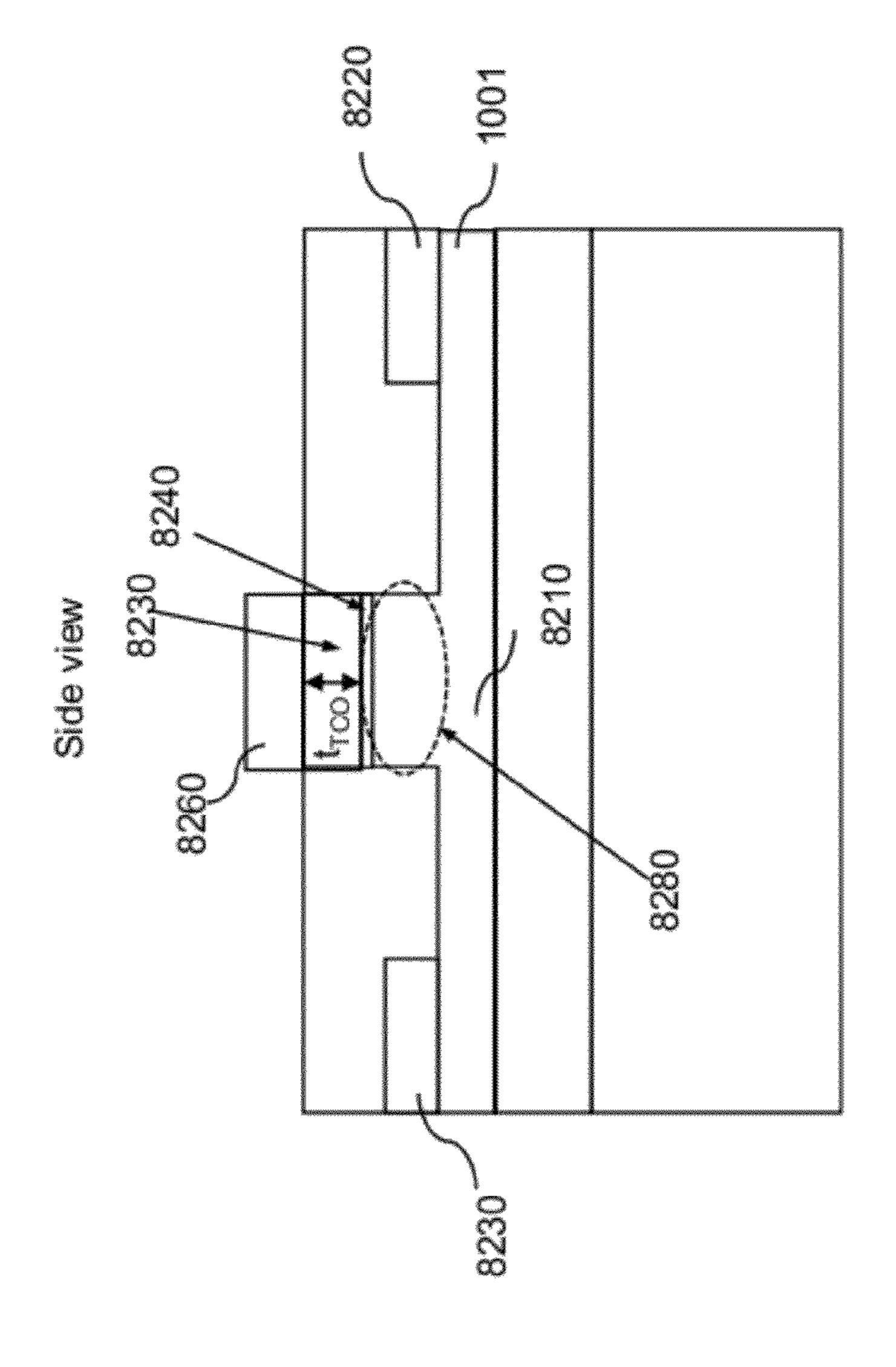

- FIG. 8C illustrates the cross-sectional view of a tunable optical ring reonstor with transparent conducting oxide (TCO) as the top electrode integrated on an EIC-PIC chip, in accordance with an embodiment of the invention;

- FIG. 9 illustrates electromagnetic simulation of light energy coupling from a lower silicon waveguide on SOI 15 with an active and a passive photonic with an embodiment of the invention; FIG. 14B illustrates the cross-section bouble-Optical-Layer EIC-PIC (DDO accordance with an embodiment of the invention; tiple electronic device areas integrated to the invention;

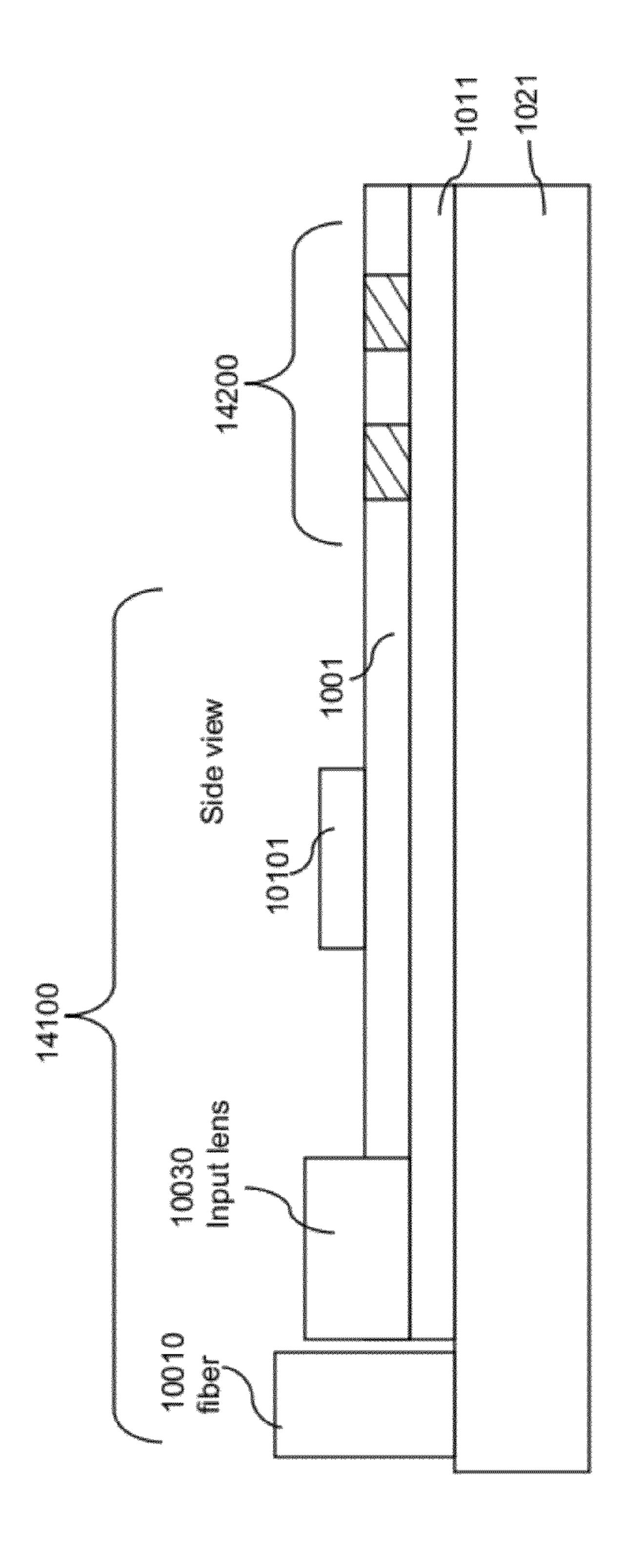

- FIG. **10**A illustrates a Direct Double-Optical-Layer EIC-PIC (DDOL-EIC-PIC), in accordance with an embodiment of 20 the invention;

- FIG. 10B illustrates a Direct Double-Optical-Layer EIC-PIC (DDOL-EIC-PIC) with multiple active photonic areas, in accordance with an embodiment of the invention;

- FIG. **10**C illustrates a Direct Double-Optical-Layer EIC- 25 PIC (DDOL-EIC-PIC), in accordance with an embodiment of the invention;

- FIG. 10D illustrates a Direct Double-Optical-Layer EIC-PIC (DDOL-EIC-PIC) with a tapered waveguide structure to squeeze the mode in and out of the region with active photonic material, in accordance with an embodiment of the invention;

- FIG. 10E illustrates a Direct Double-Optical-Layer EIC-PIC (DDOL-EIC-PIC) with a tapered waveguide structure to squeeze the mode in and out of the region with active photonic material, in accordance with an embodiment of the invention; 35

- FIG. 11A illustrates an Indirect Double-Optical-Layer EIC-PIC (IDDOL-EIC-PIC), in accordance with an embodiment of the invention;

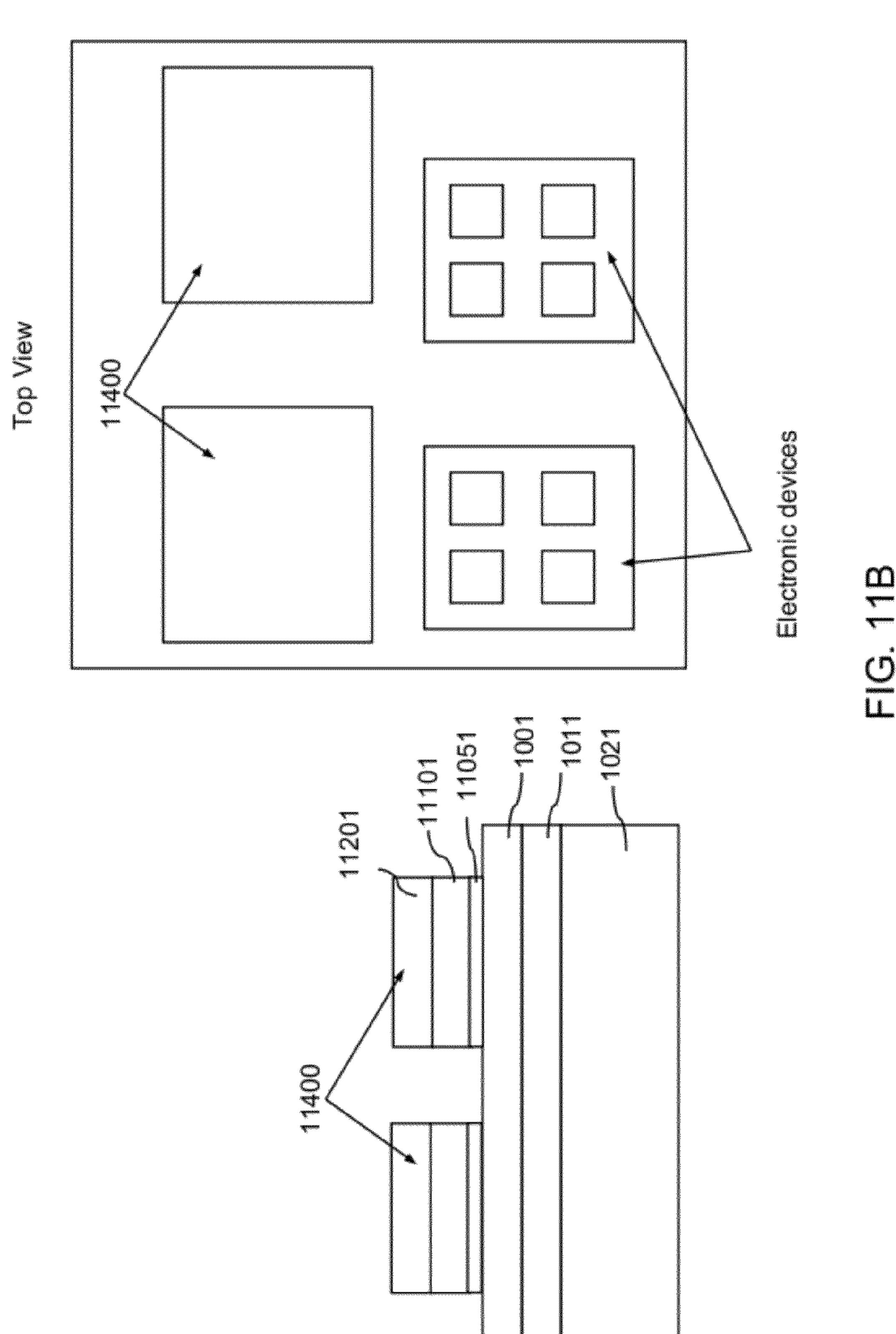

- FIG. 11B illustrates an Indirect Double-Optical-Layer EIC-PIC (IDDOL-EIC-PIC) with multiple active photonic 40 areas, in accordance with an embodiment of the invention;

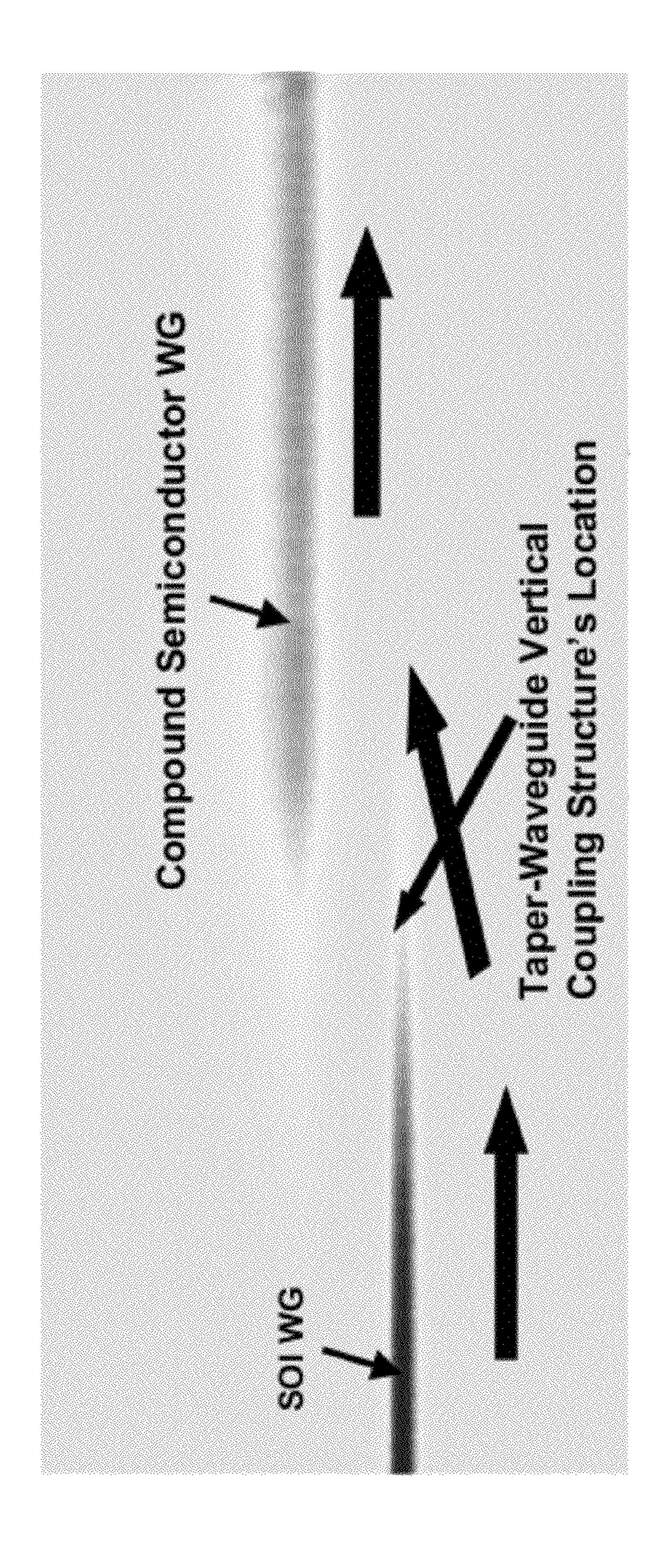

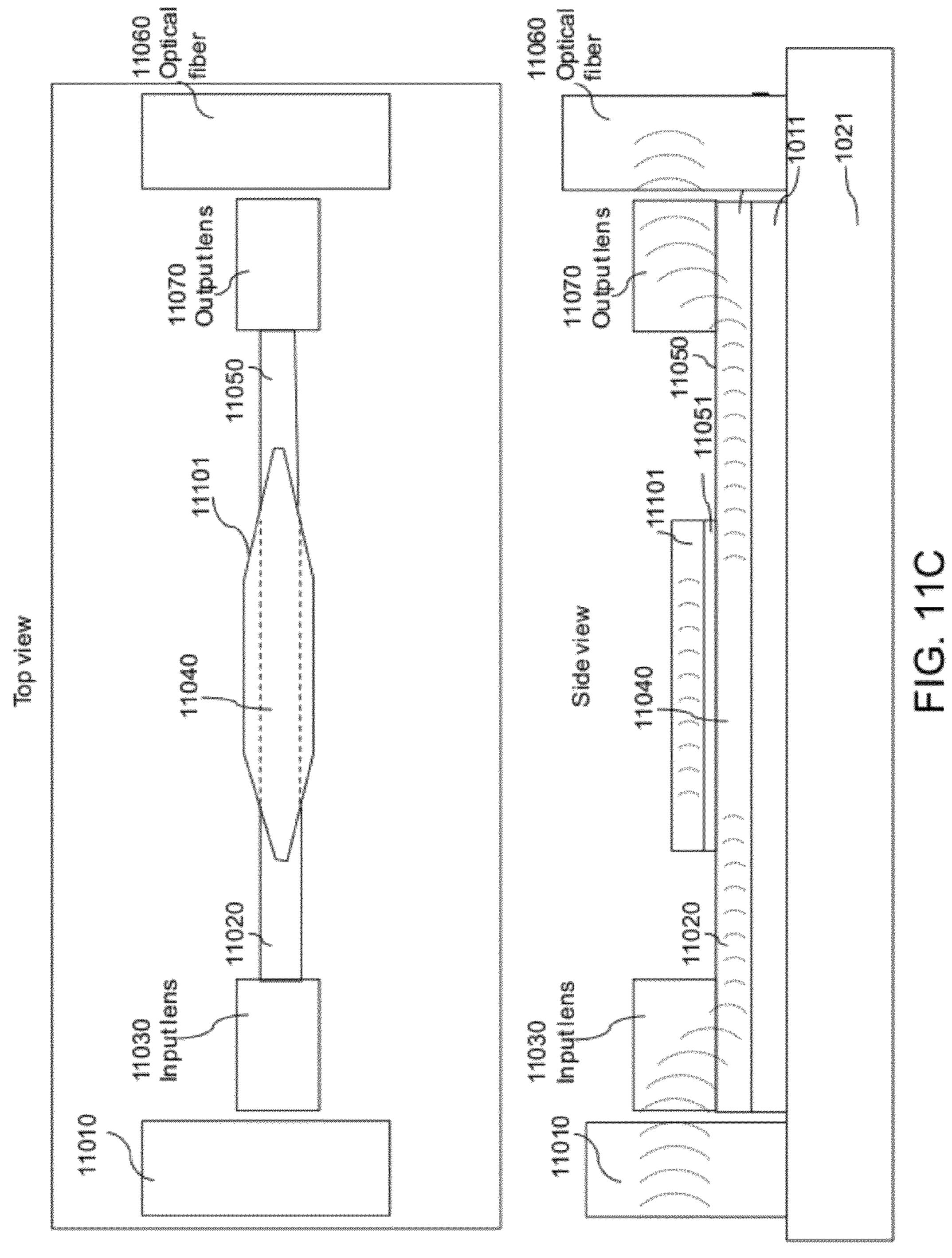

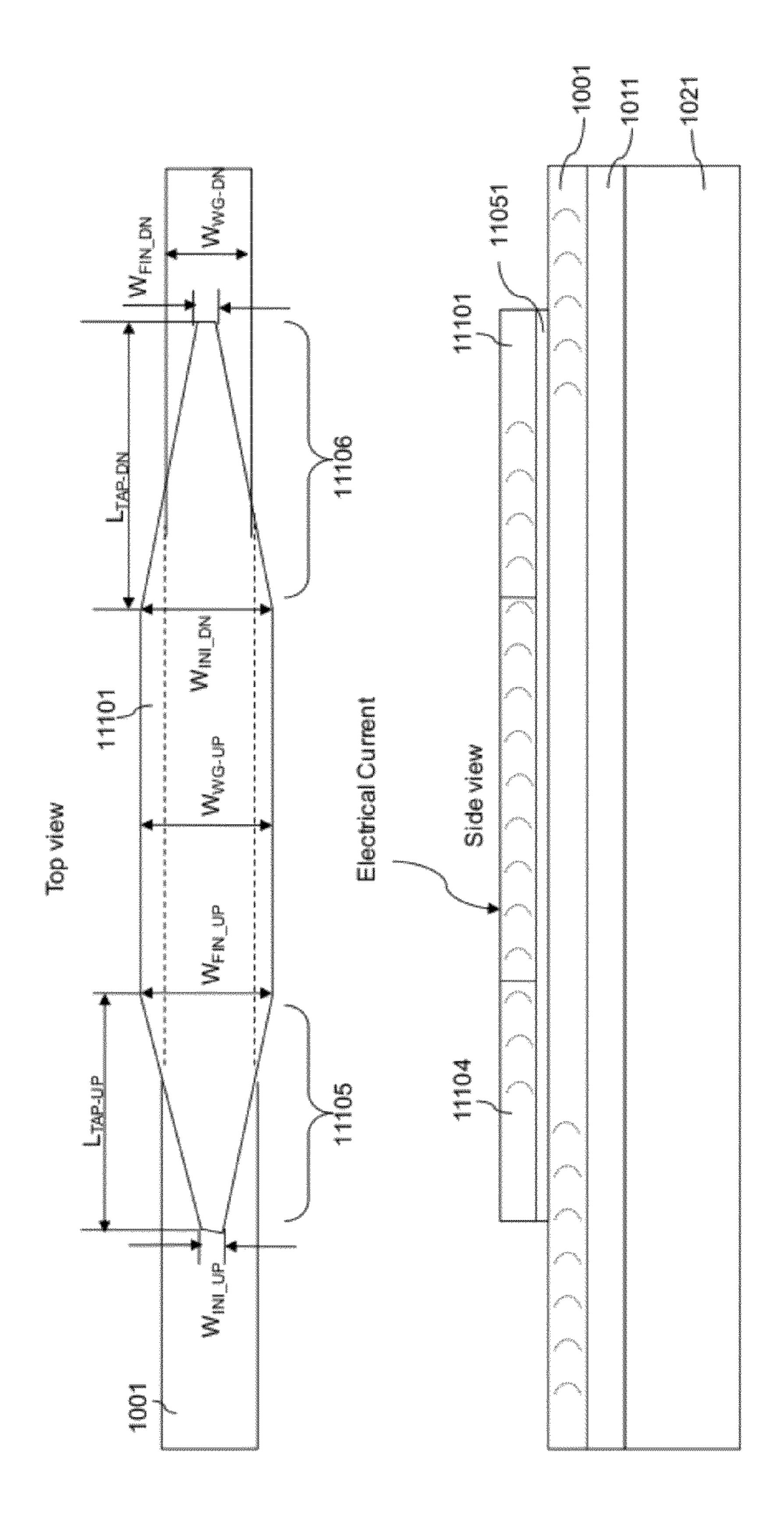

- FIG. 11C illustrates an Indirect Double-Optical-Layer EIC-PIC (IDDOL-EIC-PIC) with tapered waveguide vertical coupling structures to couple light beam energy between a bottom waveguide core and a top waveguide core, in accor- 45 dance with an embodiment of the invention;

- FIG. 11D illustrates a tapered waveguide vertical coupling structured to couple light beam energy between a bottom waveguide core and a top waveguide core, in accordance with an embodiment of the invention;

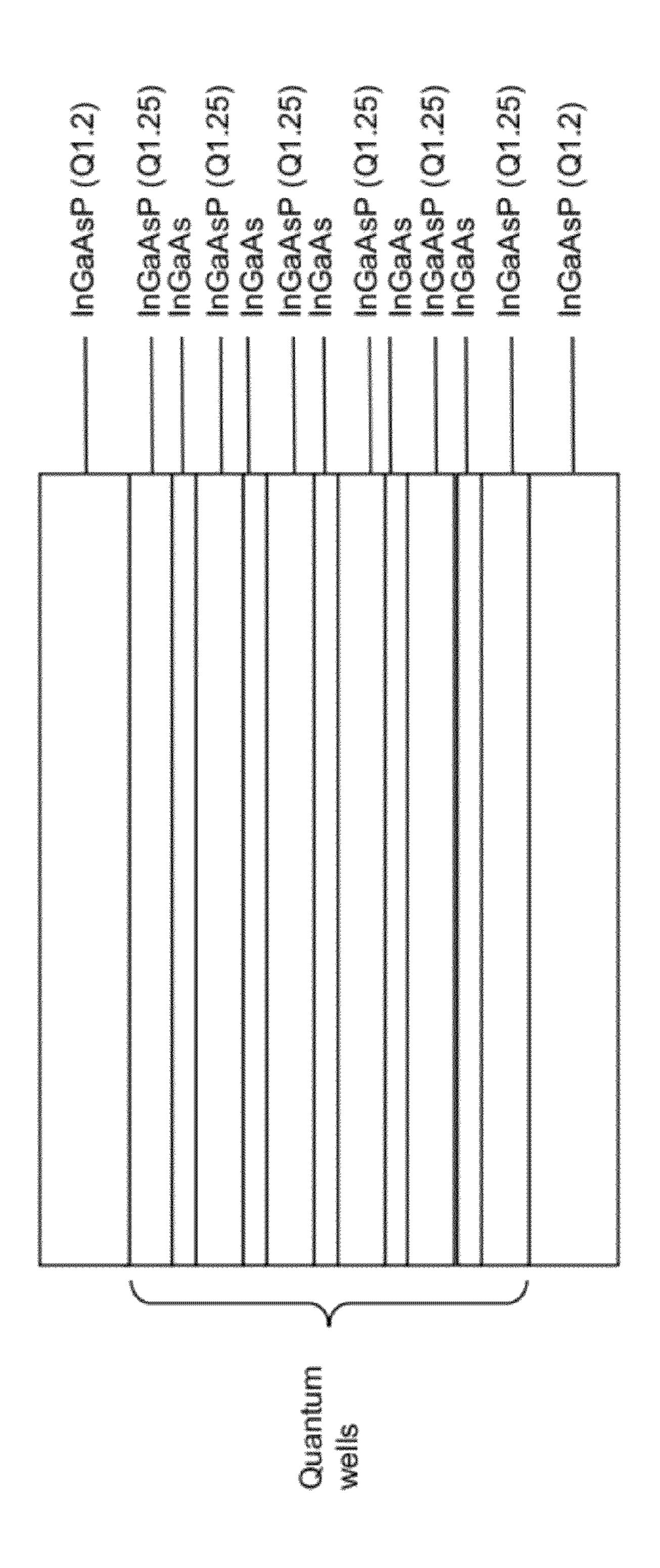

- FIG. 11E illustrates the layer structure of a tapered waveguide vertical coupling in accordance with an embodiment of the invention;

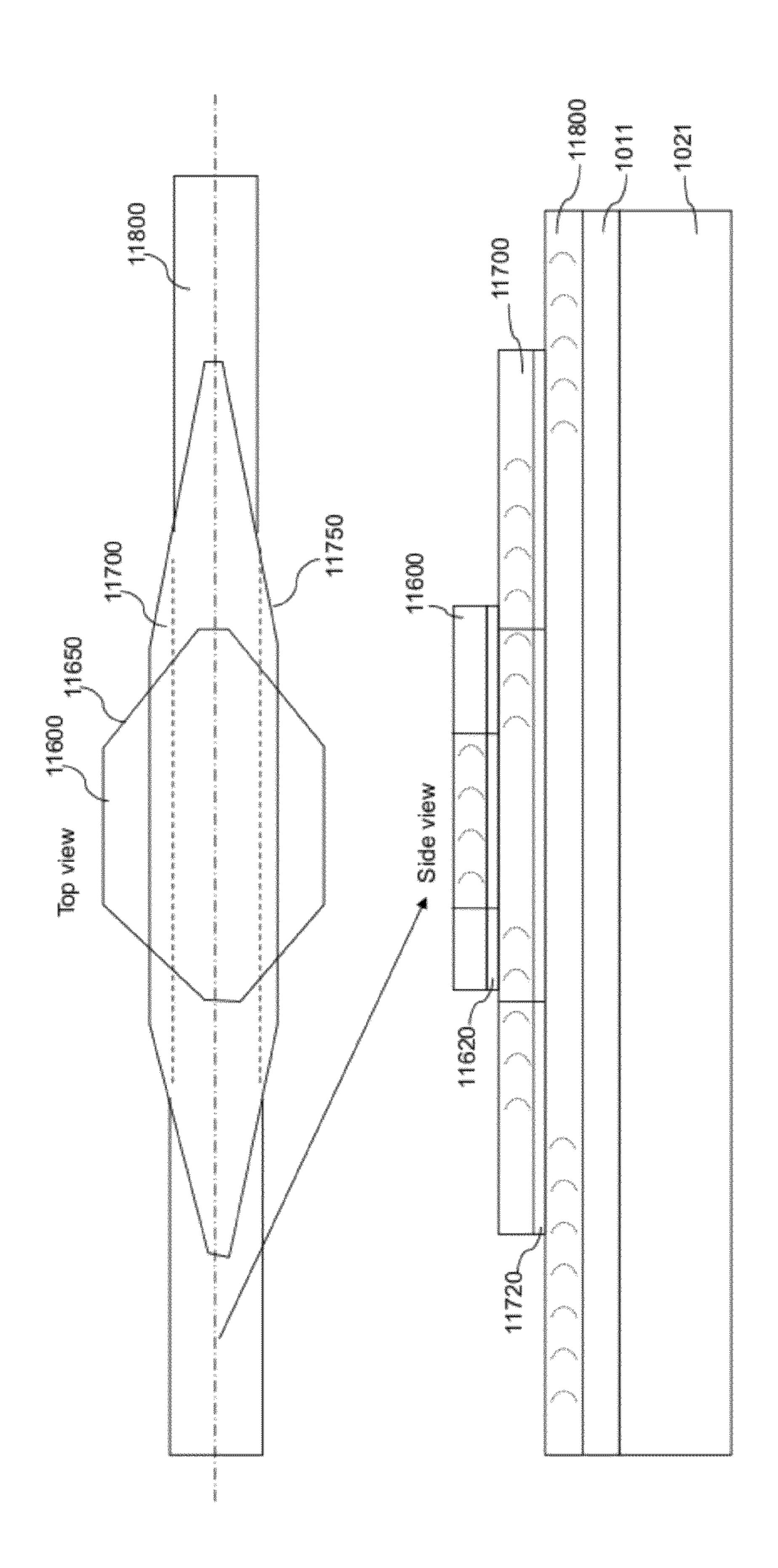

- FIG. 11F illustrates a tapered waveguide vertical coupling structured to couple light beam energy between a bottom 55 tion; waveguide core and a top waveguide core, in accordance with an embodiment of the invention; patib

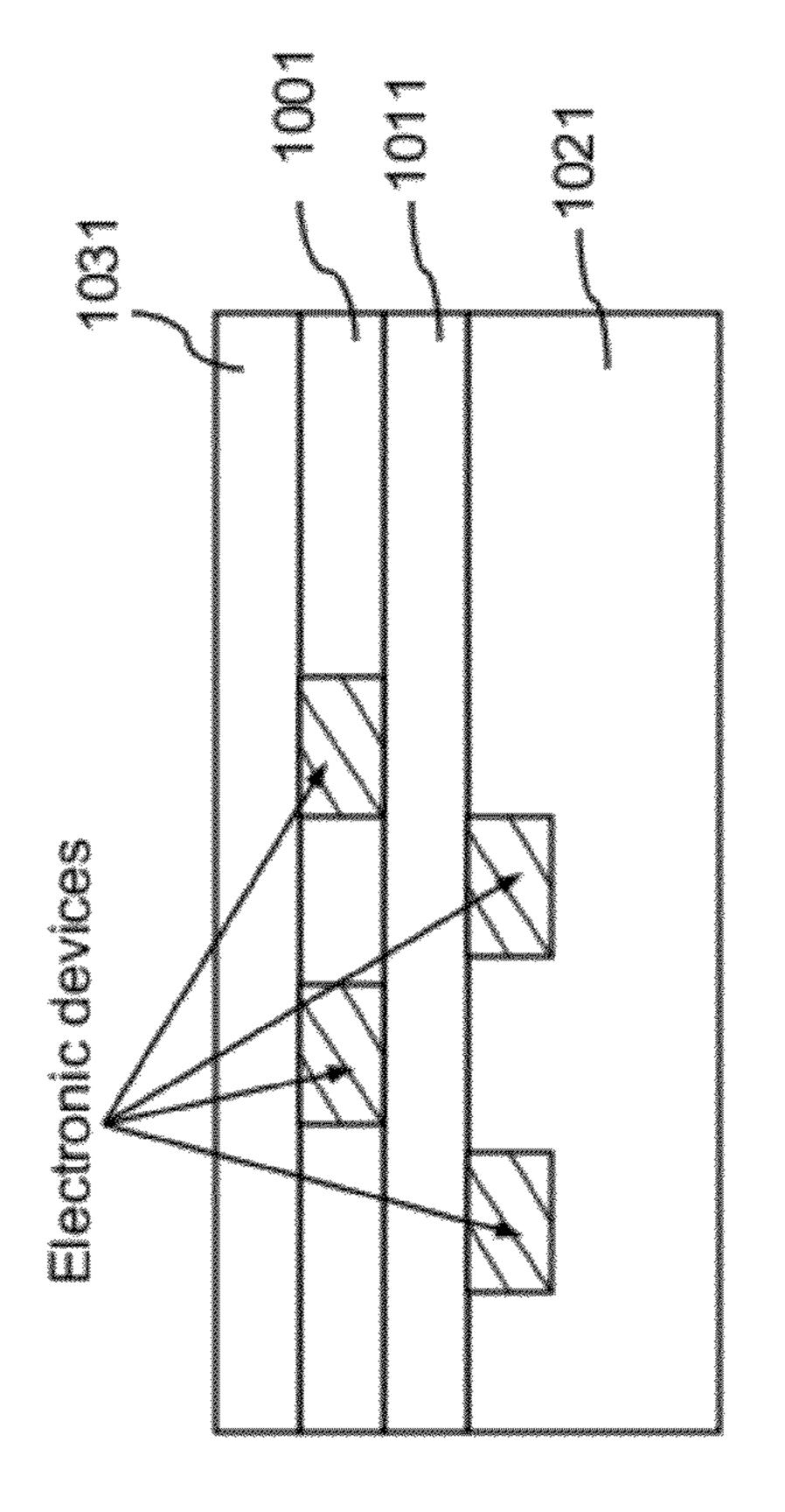

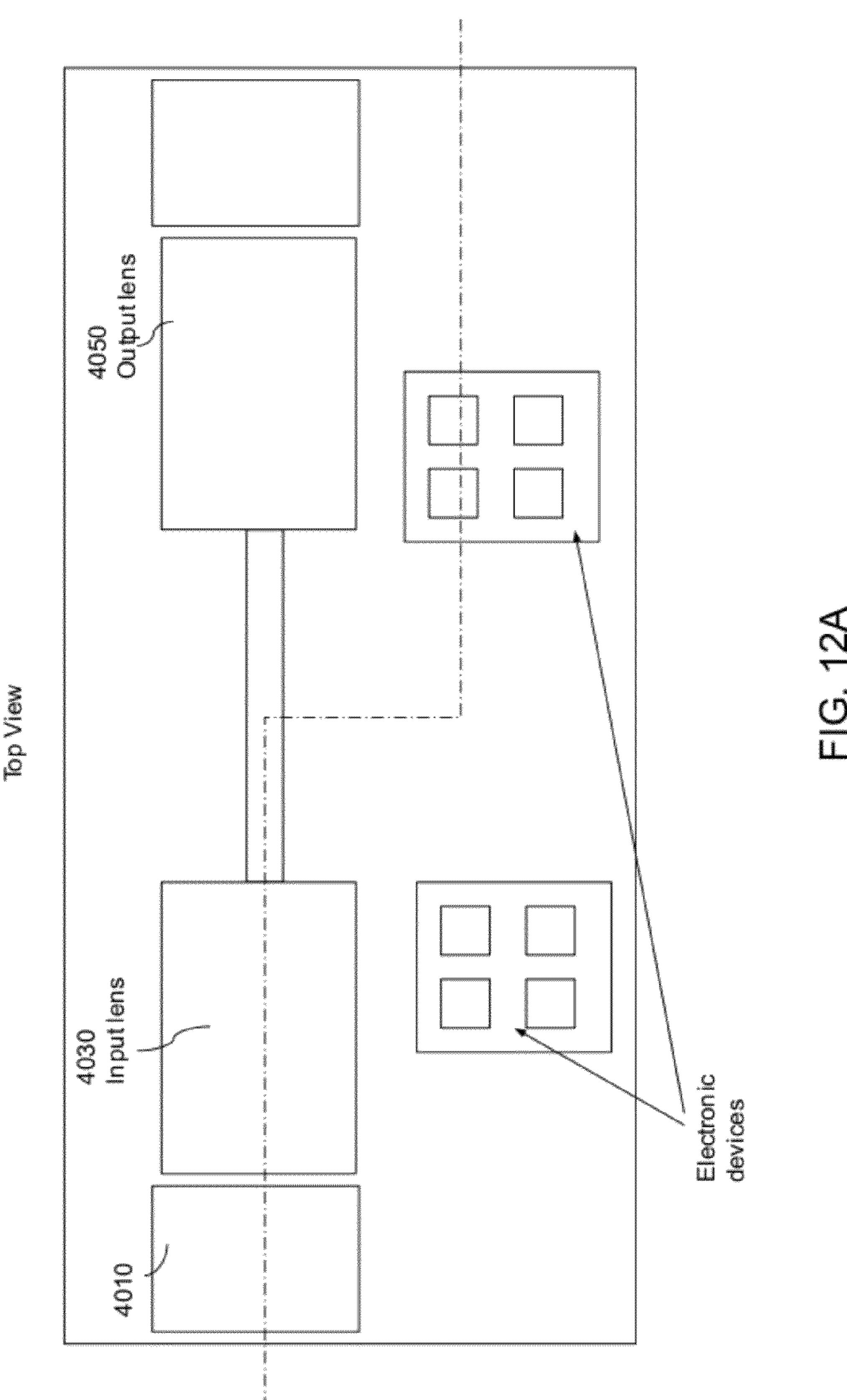

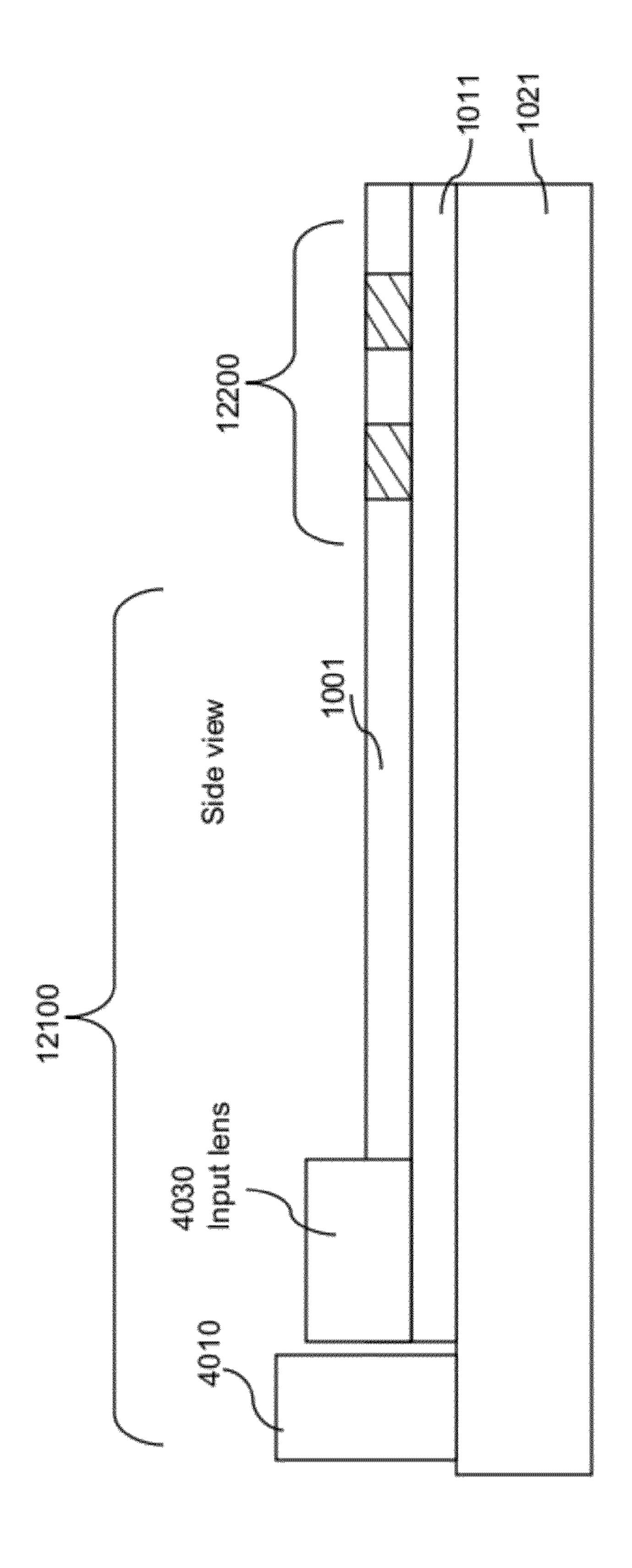

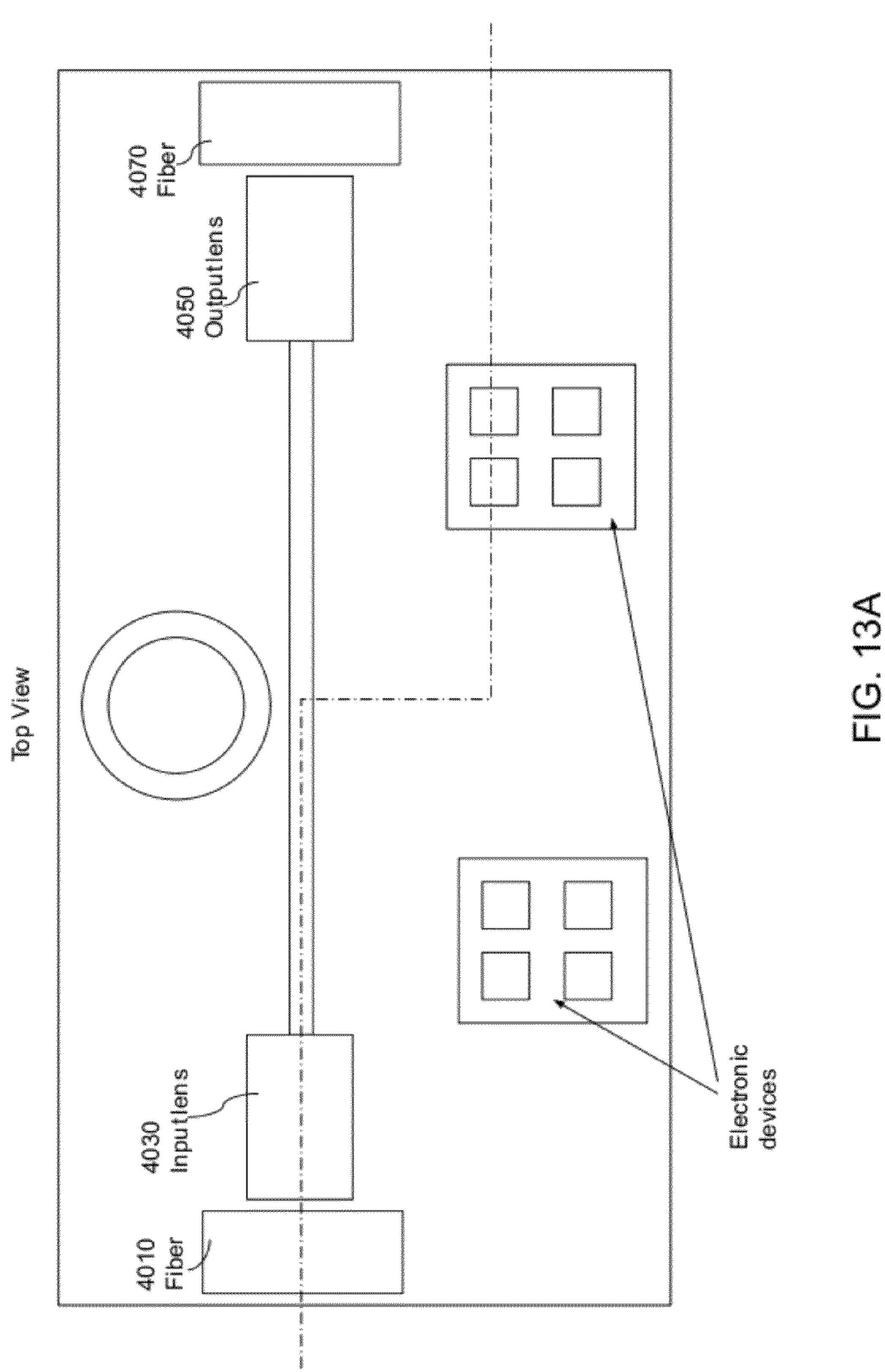

- FIG. 12A illustrates the top view of a Single-Optical-Layer EIC-PIC (SOL-EIC-PIC) with multiple electronic device areas integrated with a photonic device area with a passive 60 photonic device, in accordance with an embodiment of the invention;

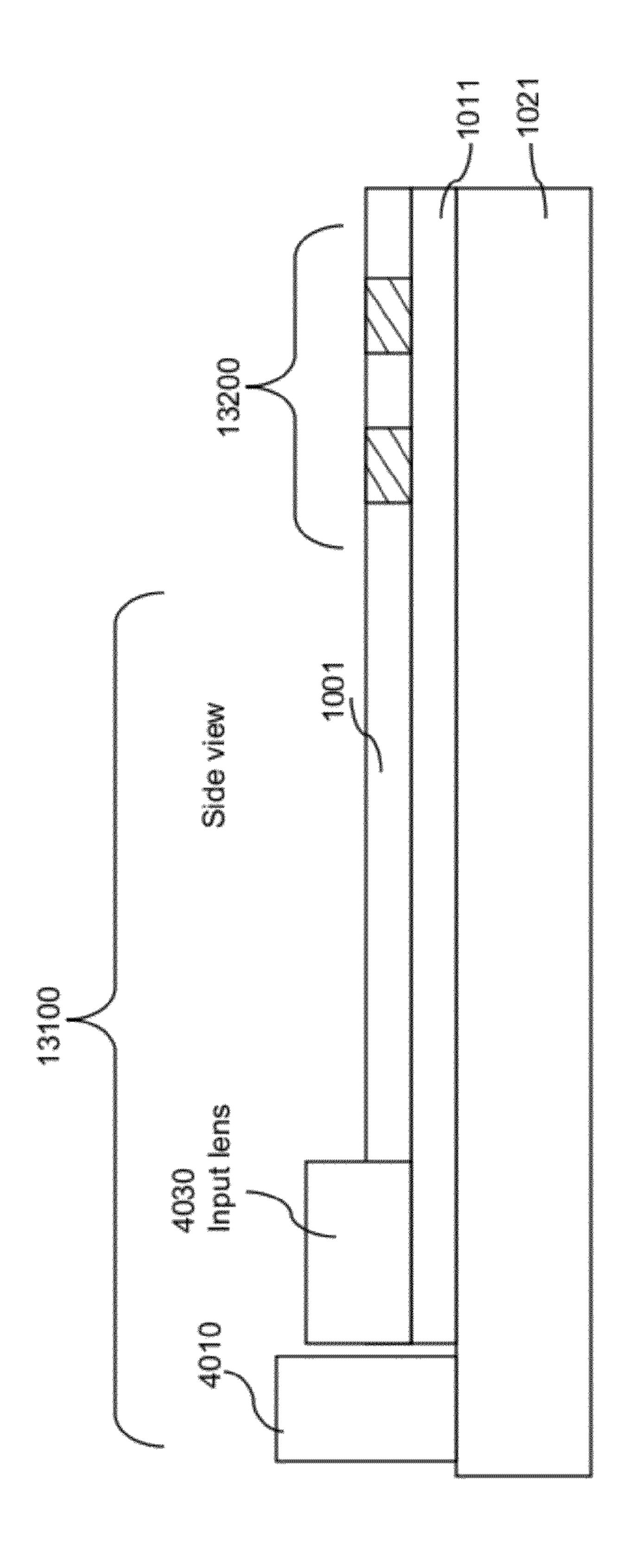

- FIG. 12B illustrates the cross-sectional view of a Single-Optical-Layer EIC-PIC (SOL-EIC-PIC) with multiple electronic device areas integrated with a photonic device area 65 with a passive photonic device, in accordance with an embodiment of the invention;

8

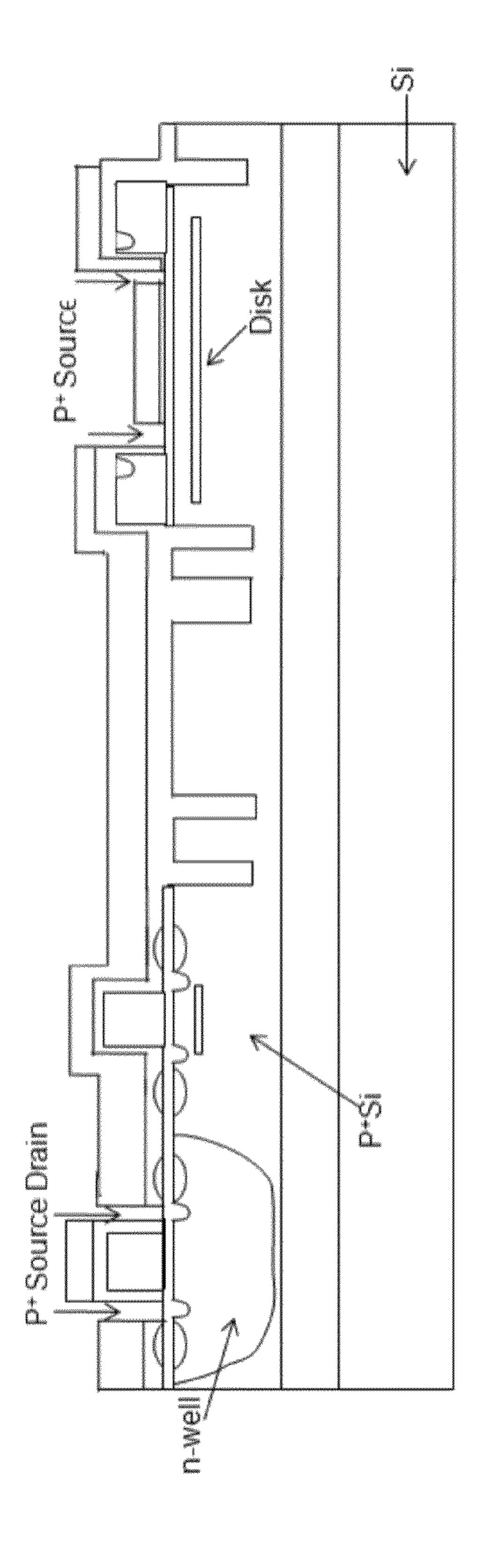

- FIG. 13A illustrates the top view of a Single-Optical-Layer EIC-PIC (SOL-EIC-PIC) with multiple electronic device areas integrated with a photonic device area with an active and a passive photonic device, in accordance with an embodiment of the invention;

- FIG. 13B illustrates the cross-sectional view of a Single-Optical-Layer EIC-PIC (SOL-EIC-PIC) with multiple electronic device areas integrated with a photonic device area with an active and a passive photonic device, in accordance with an embodiment of the invention;

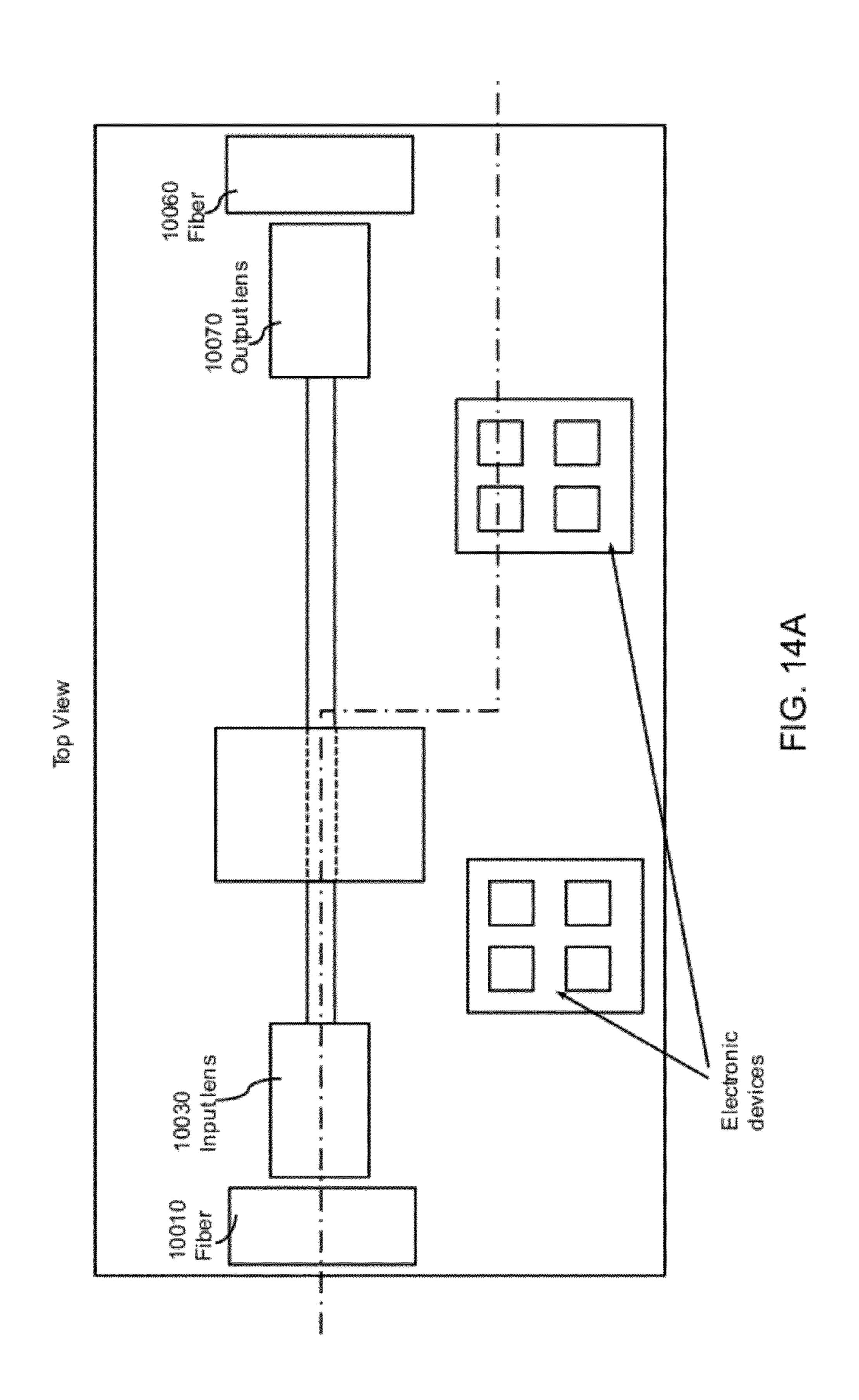

- FIG. 14A illustrates the top view of a Direct Double-Optical-Layer EIC-PIC (DDOL-EIC-PIC) with multiple electronic device areas integrated with a photonic device area with an active and a passive photonic device, in accordance with an embodiment of the invention:

- FIG. 14B illustrates the cross-sectional view of a Direct Double-Optical-Layer EIC-PIC (DDOL-EIC-PIC) with multiple electronic device areas integrated with a photonic device area with an active and a passive photonic device, in accordance with an embodiment of the invention;

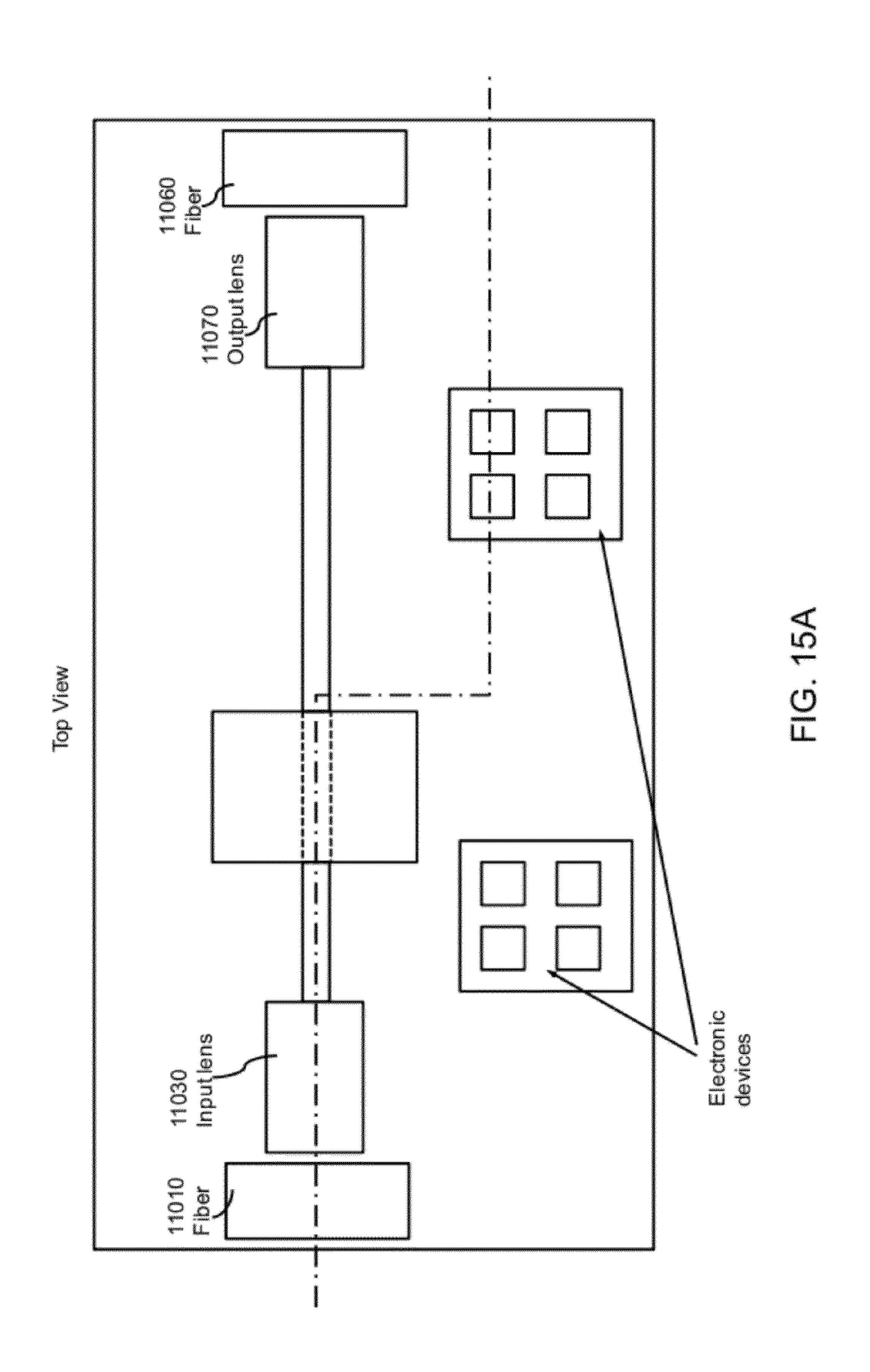

- FIG. 15A illustrates the top view of an Indirect Double-Optical-Layer EIC-PIC (IDDOL-EIC-PIC) with multiple electronic device areas integrated with a photonic device area with an active and a passive photonic device, in accordance with an embodiment of the invention;

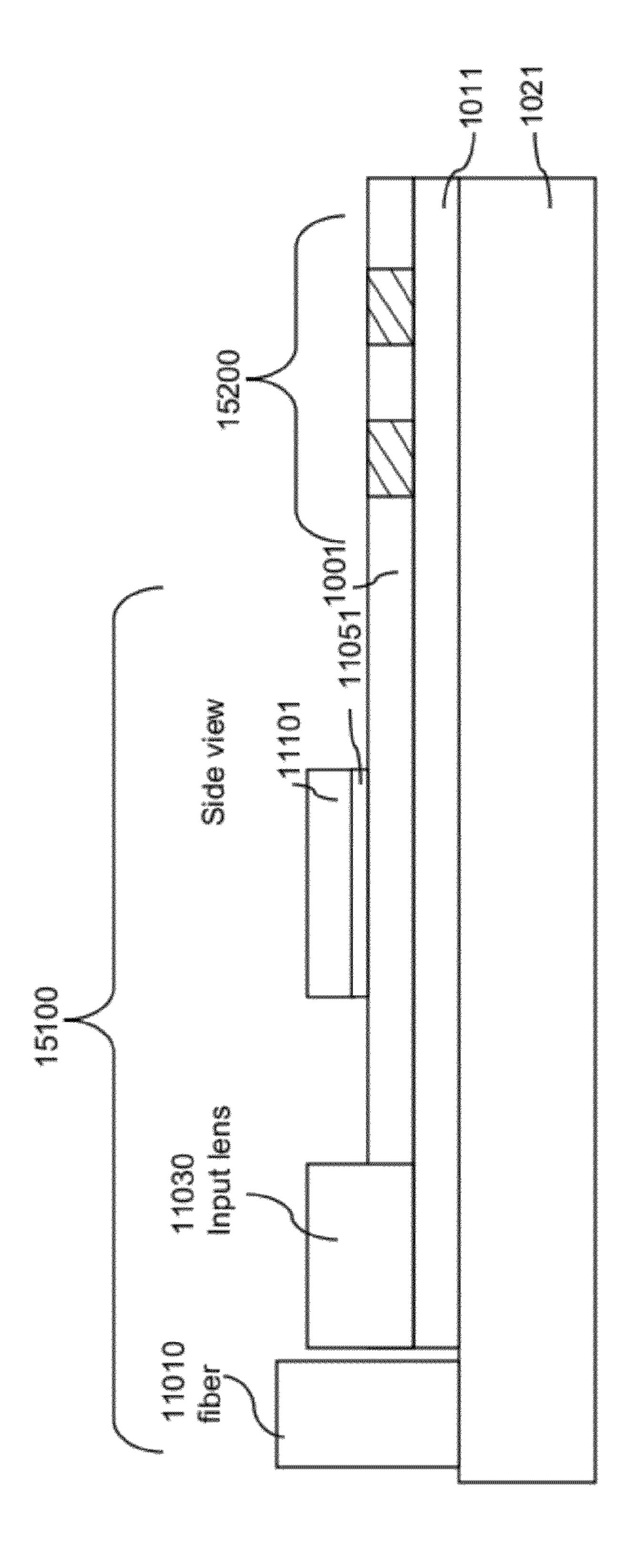

- FIG. 15B illustrates the cross-sectional view of an Indirect Double-Optical-Layer EIC-PIC (IDDOL-EIC-PIC) with multiple electronic device areas integrated with a photonic device area with an active and a passive photonic device, in accordance with an embodiment of the invention;

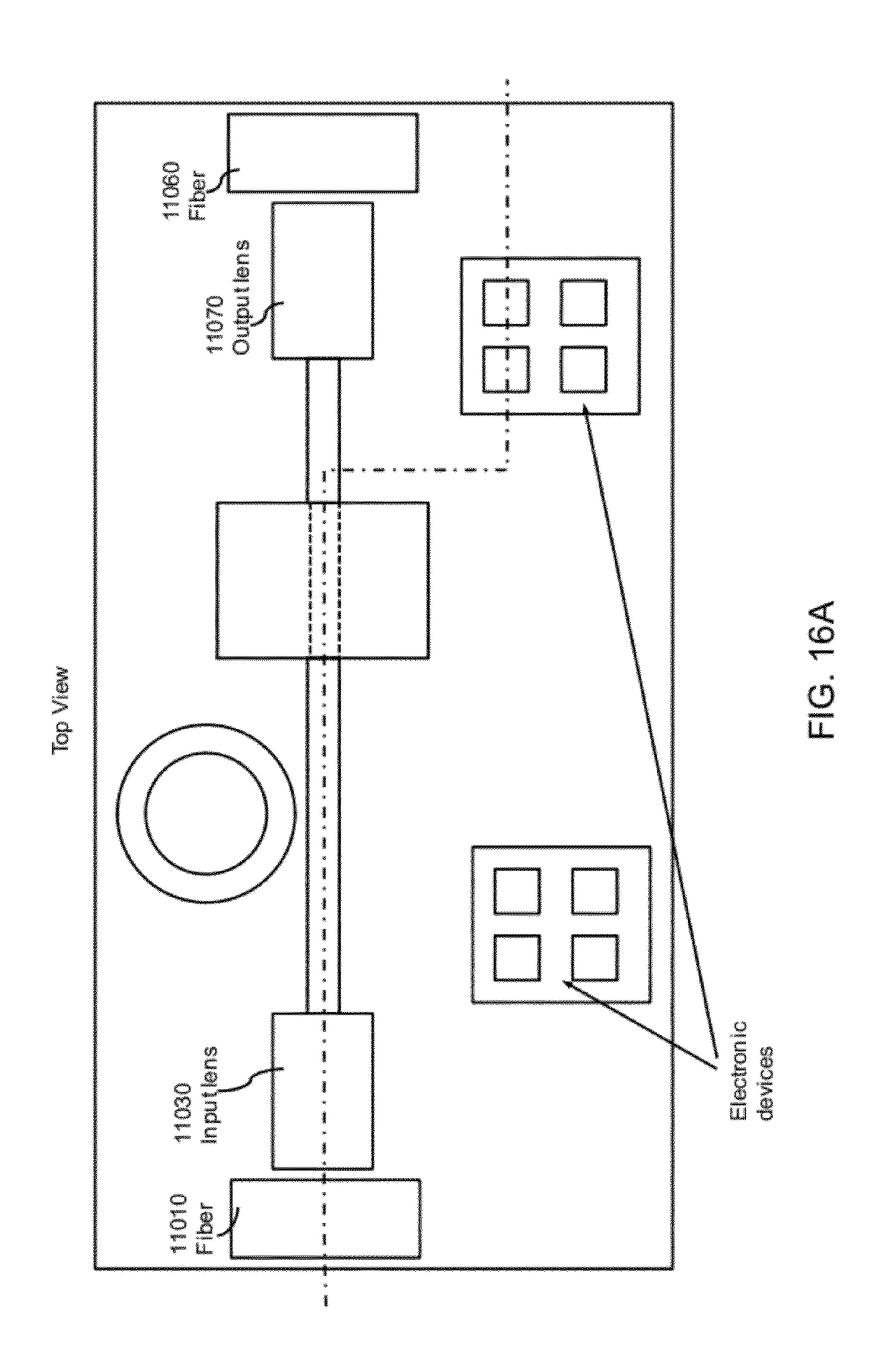

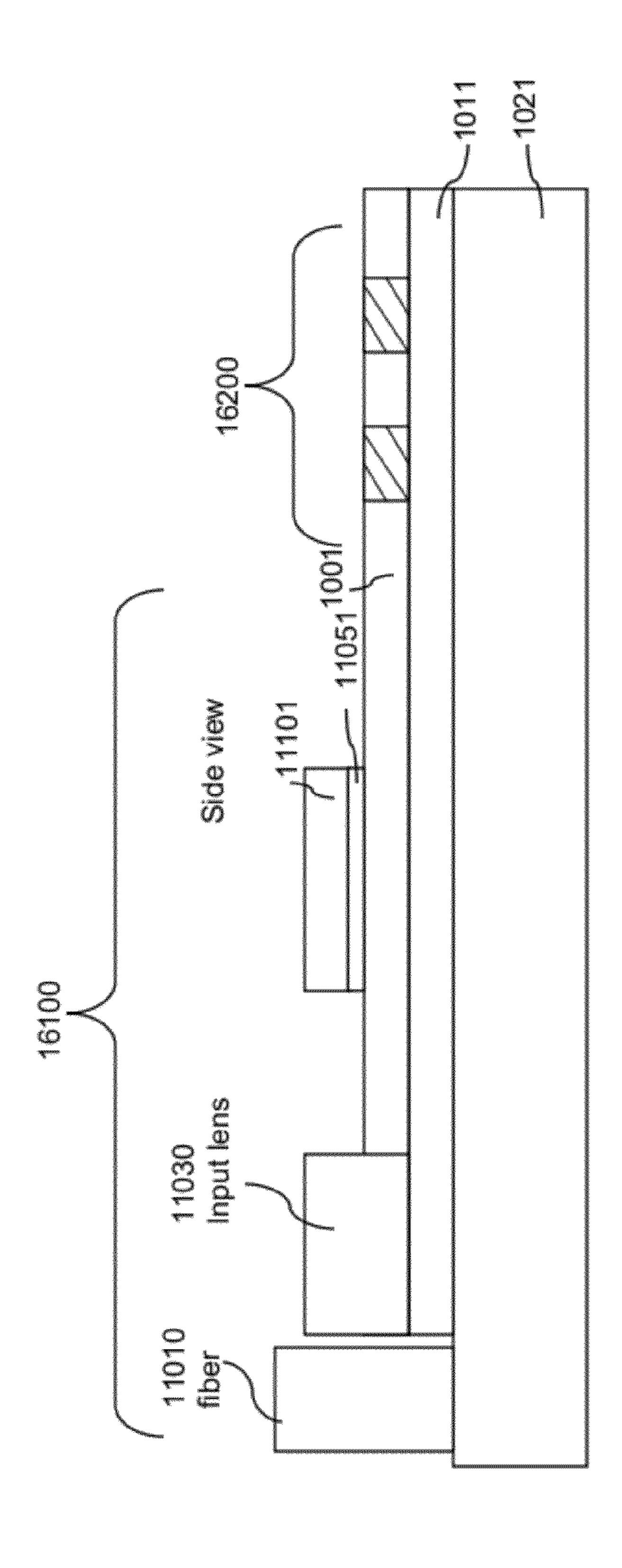

- FIG. 16A illustrate the top view of an Indirect Double-Optical-Layer EIC-PIC (IDDOL-EIC-PIC) with multiple electronic device areas integrated with a photonic device area with multiple active and passive photonic devices, in accordance with an embodiment of the invention;

- FIG. 16B illustrates the cross-sectional view of an Indirect Double-Optical-Layer EIC-PIC (IDDOL-EIC-PIC) with multiple electronic device areas integrated with a photonic device area with multiple active and passive photonic devices, in accordance with an embodiment of the invention;

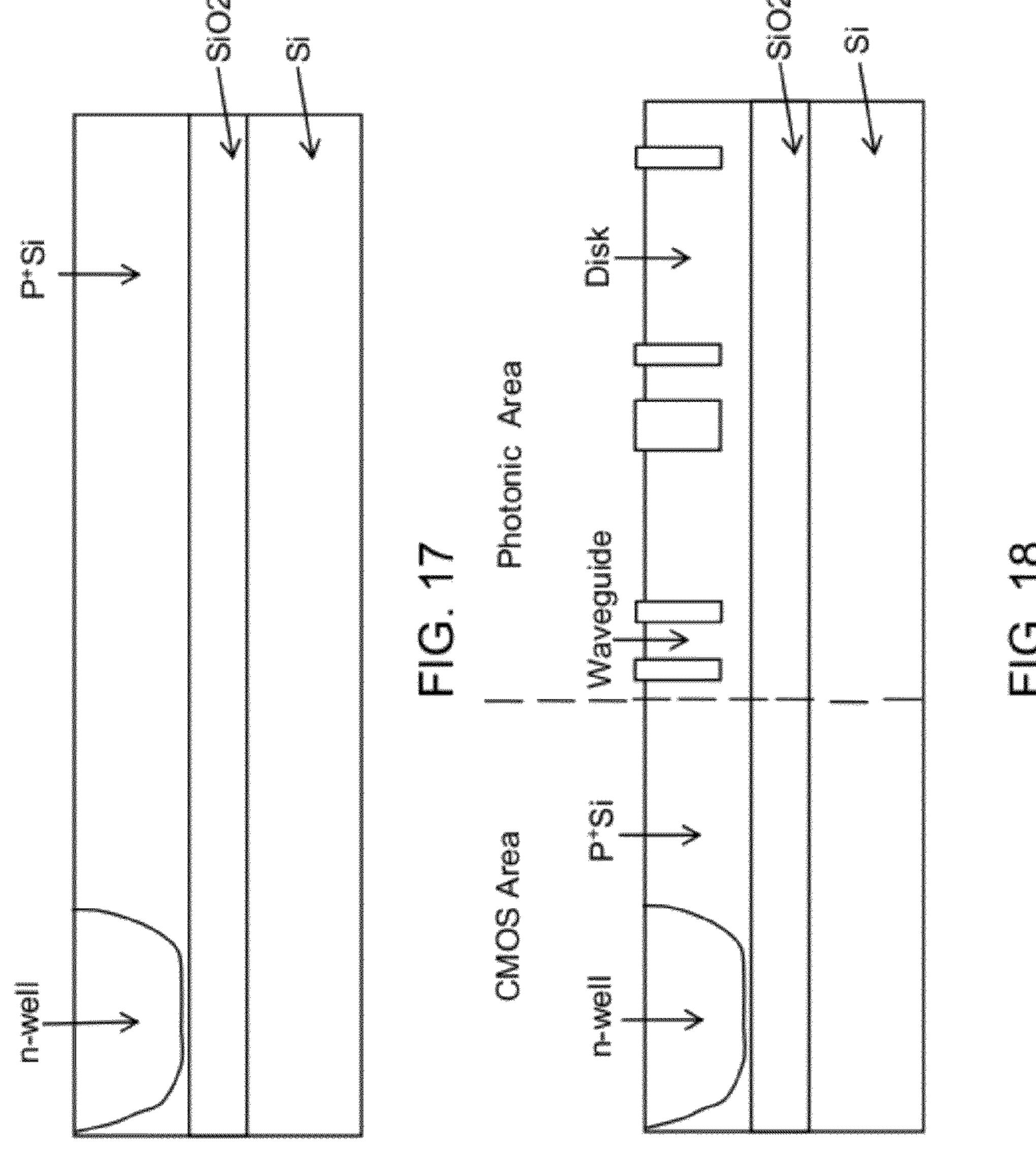

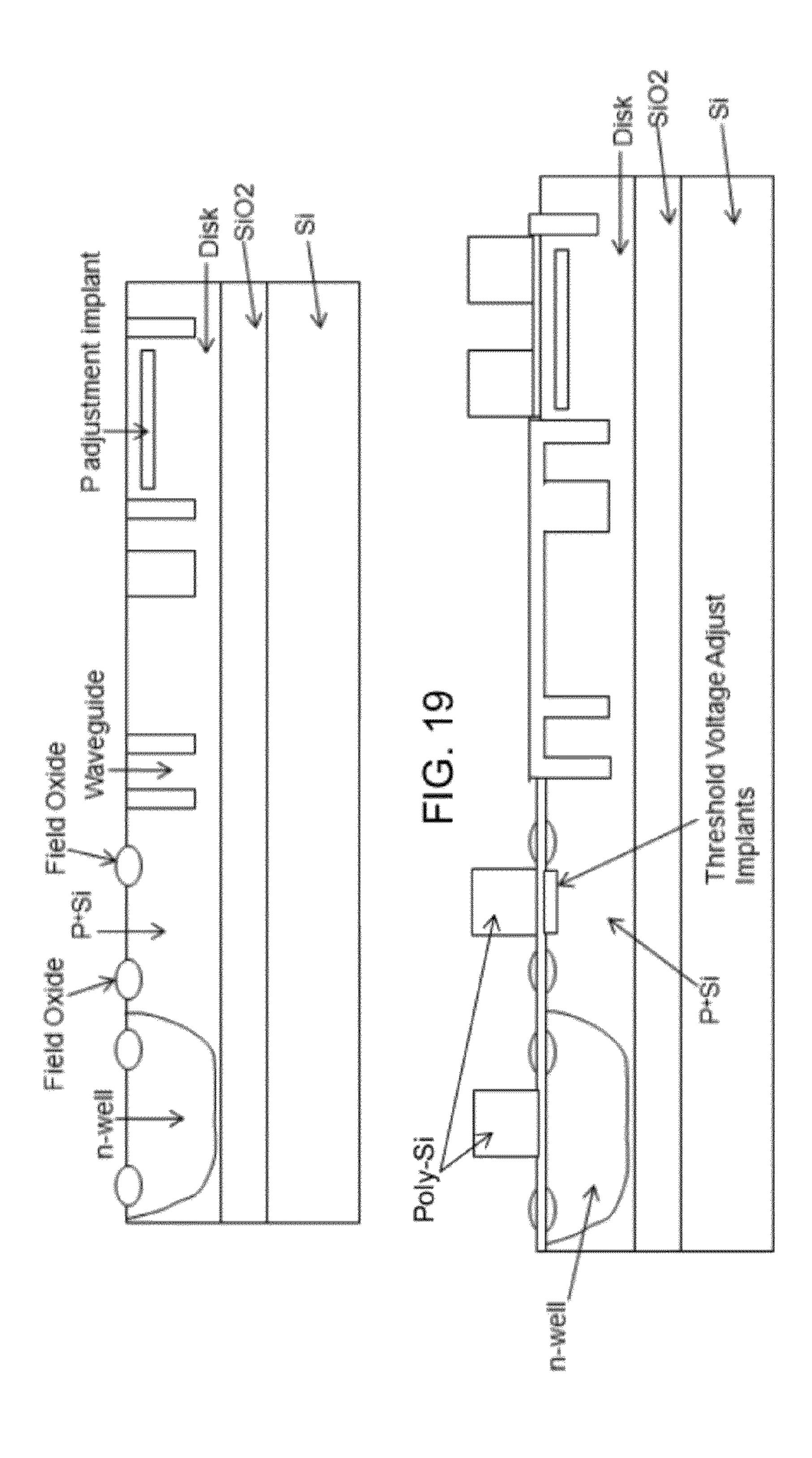

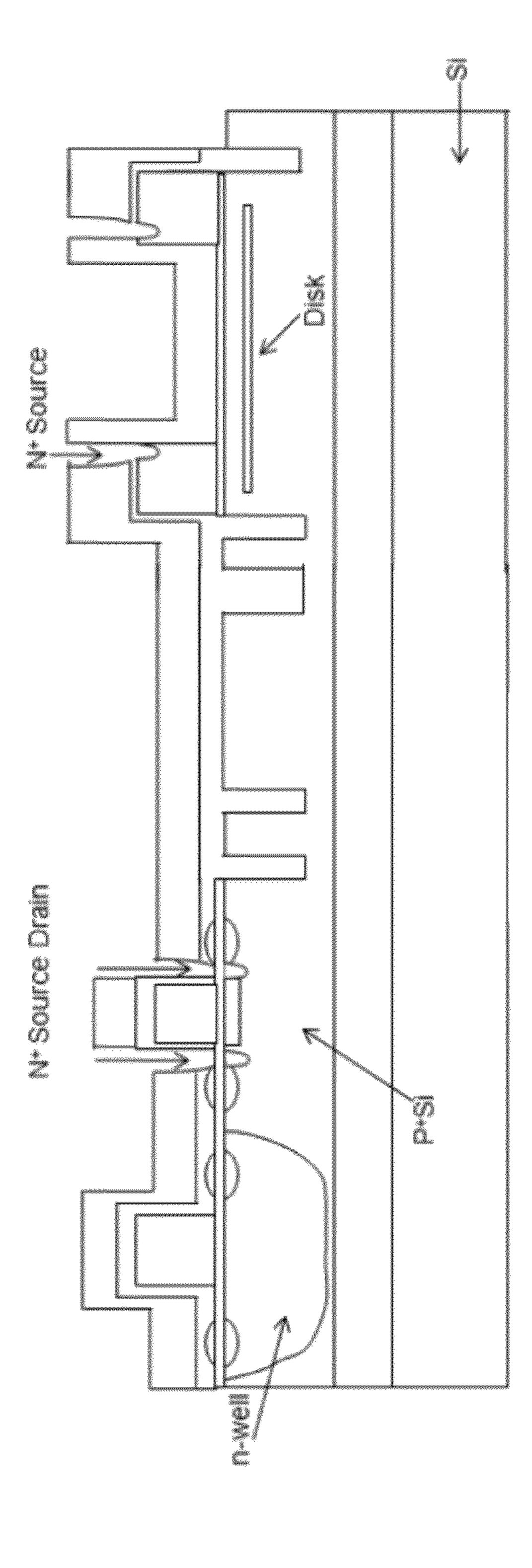

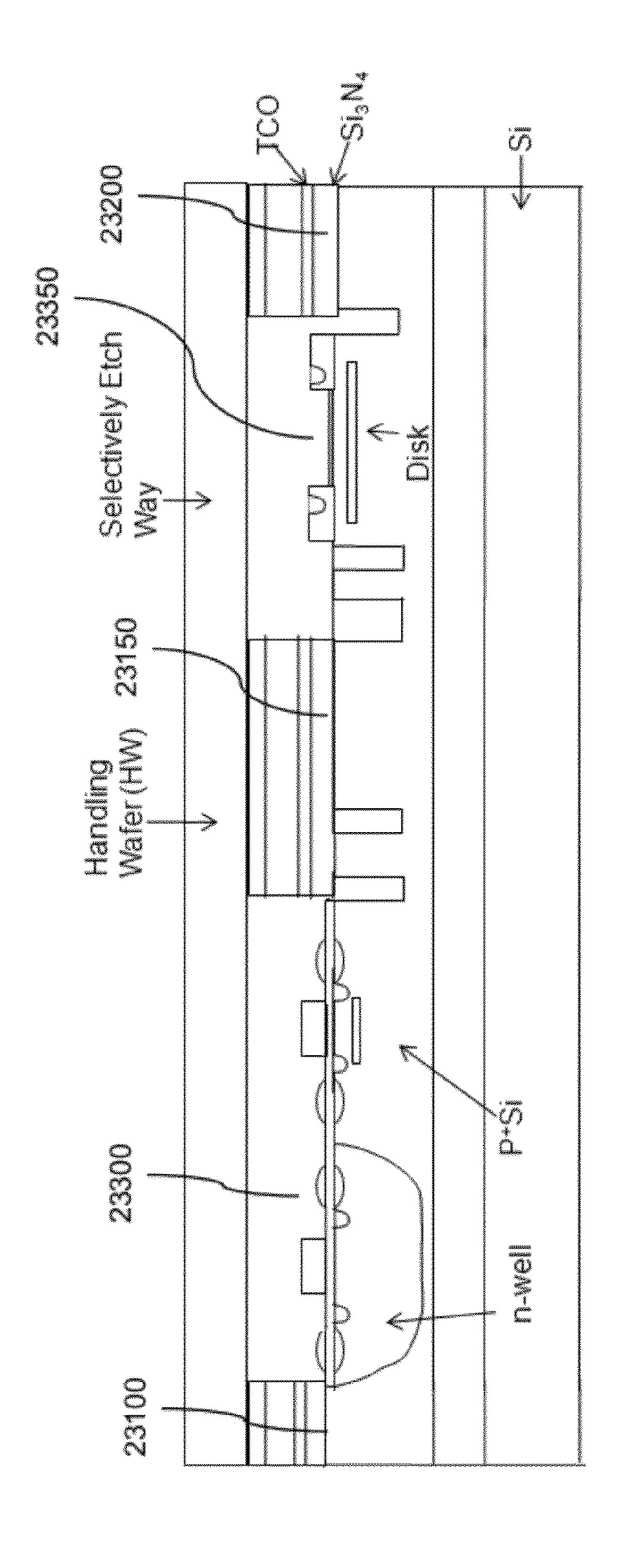

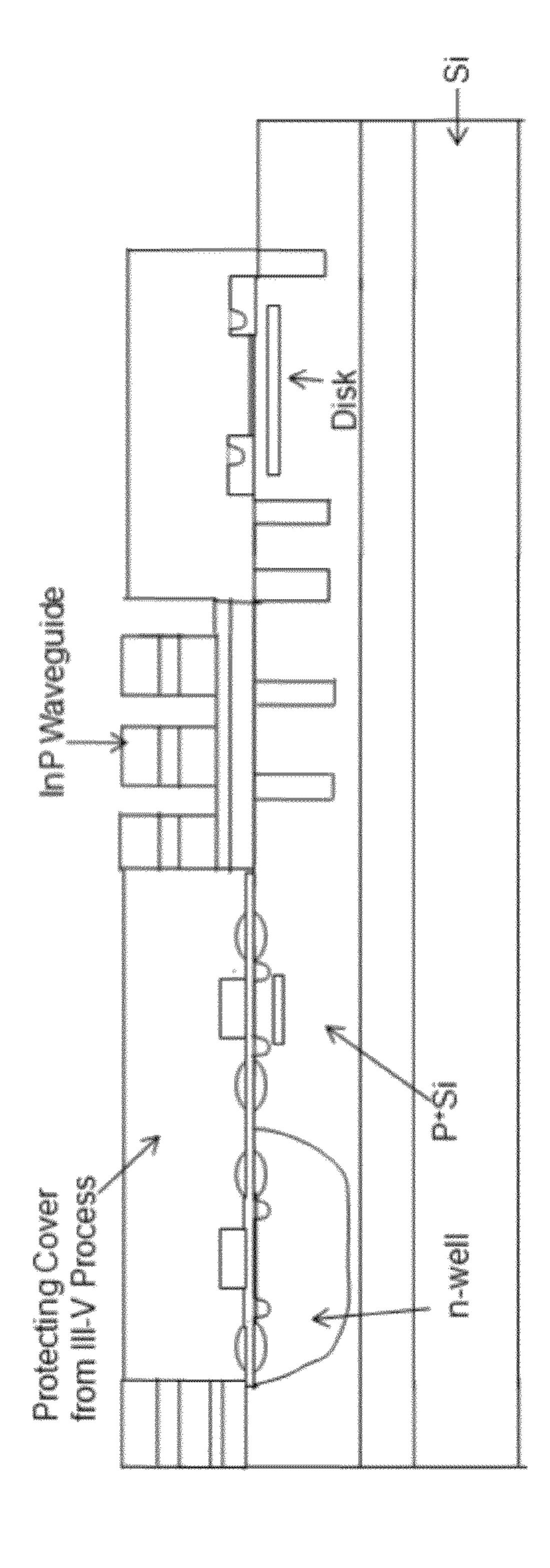

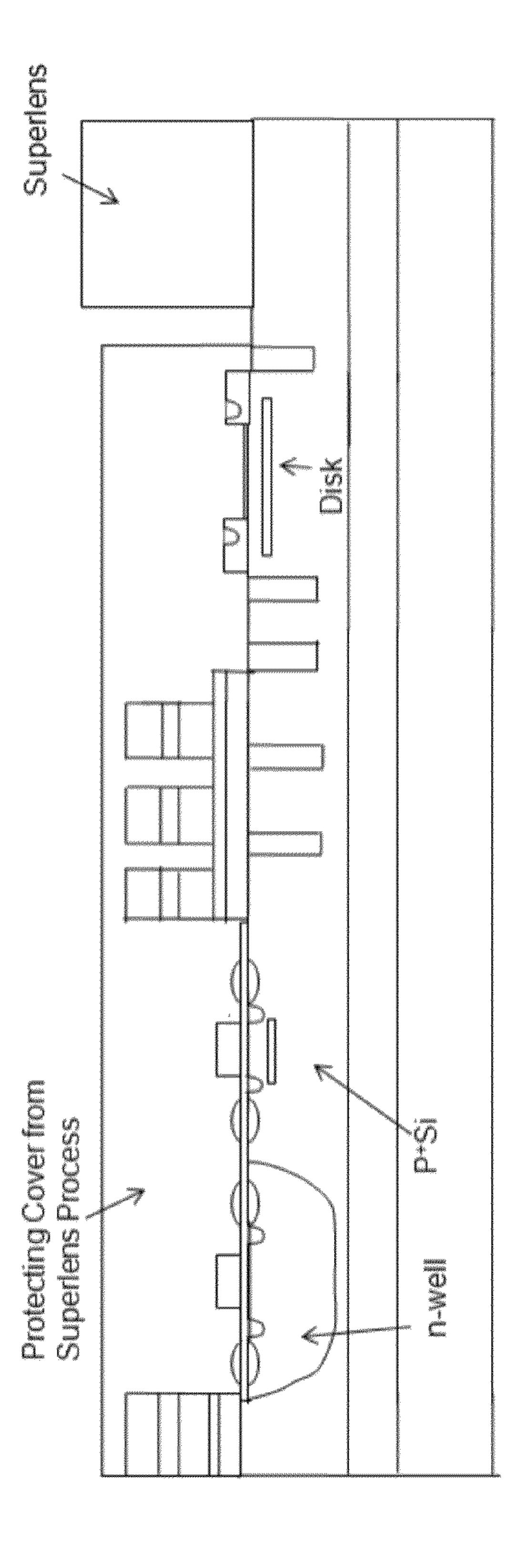

- FIGS. 17-26 illustrate the steps involved in the fabrication process of an electronic-photonic device, in accordance with various embodiments of the invention;

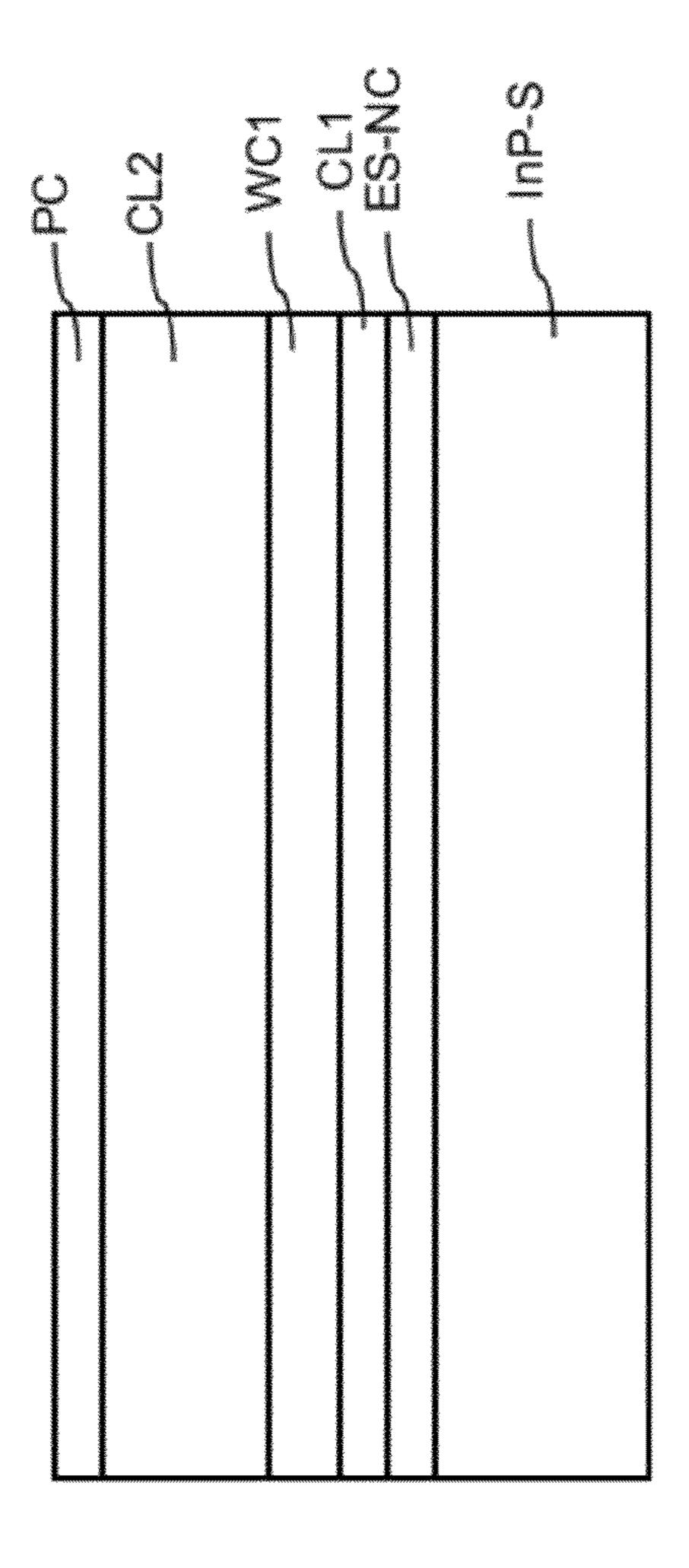

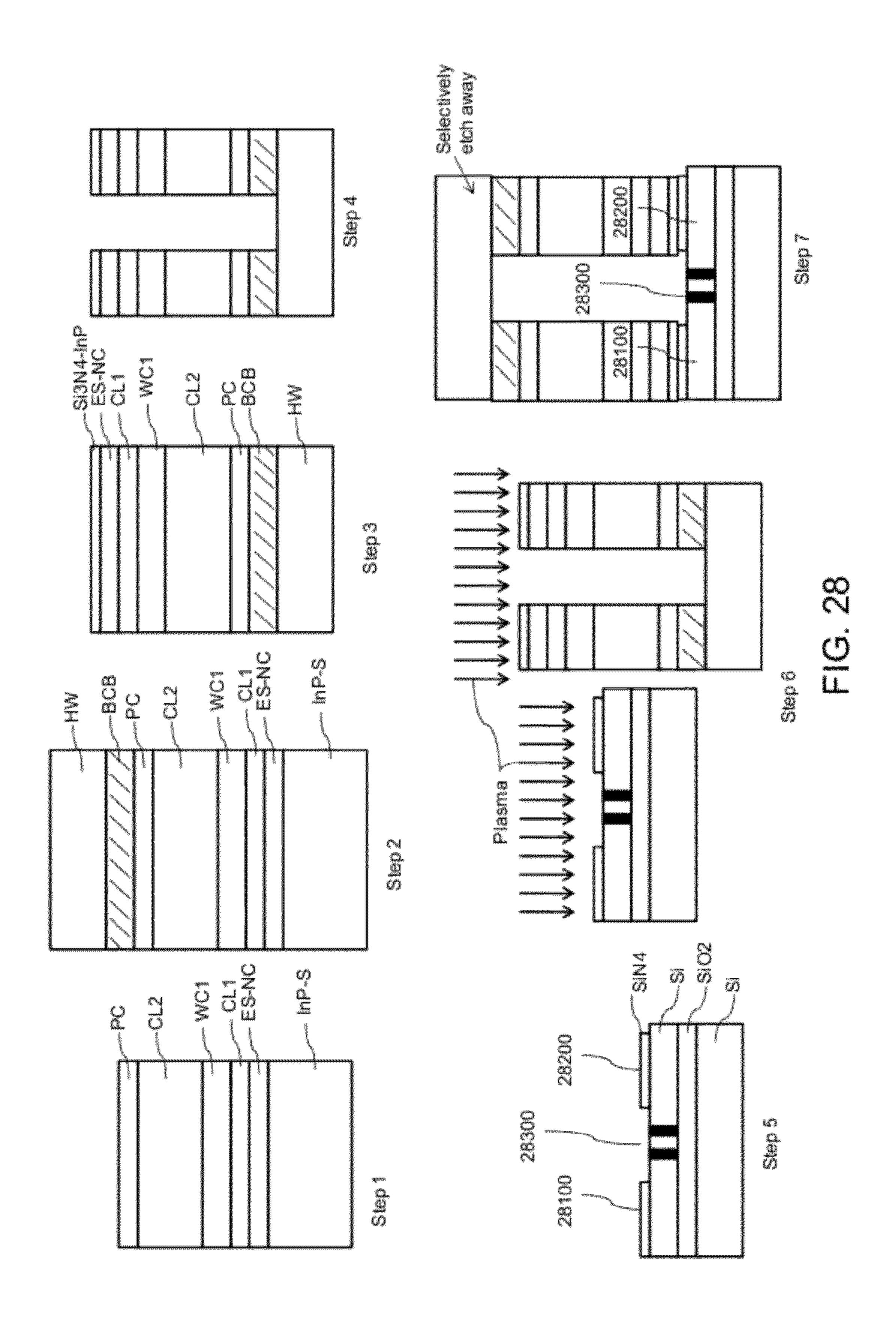

- FIG. 27 illustrates an epitaxial layer structure for the localarea wafer bonding process shown in FIG. 28, in accordance with an embodiment of the invention;

- FIG. 28 illustrates an exemplary embodiment of the localarea wafer bonding process, in accordance with an embodiment of the invention;

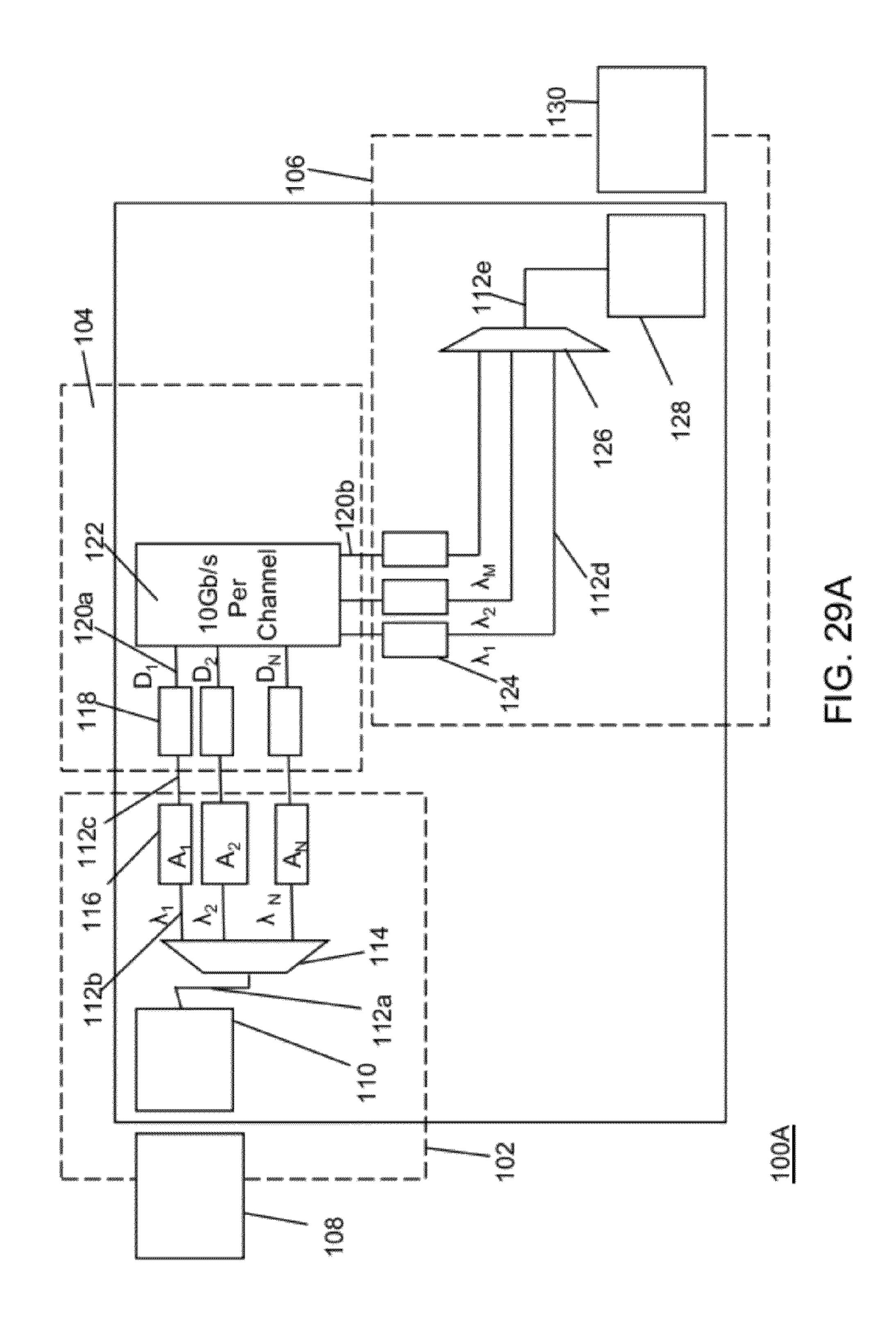

- FIG. **29**A illustrates a schematic for the connections between various devices in a first exemplary electronic-integration compatible photonic/nanophotonic integrated circuit with integrated chip-level optical network (EIC-PIC+ICON) device in accordance with various embodiments of the invention;

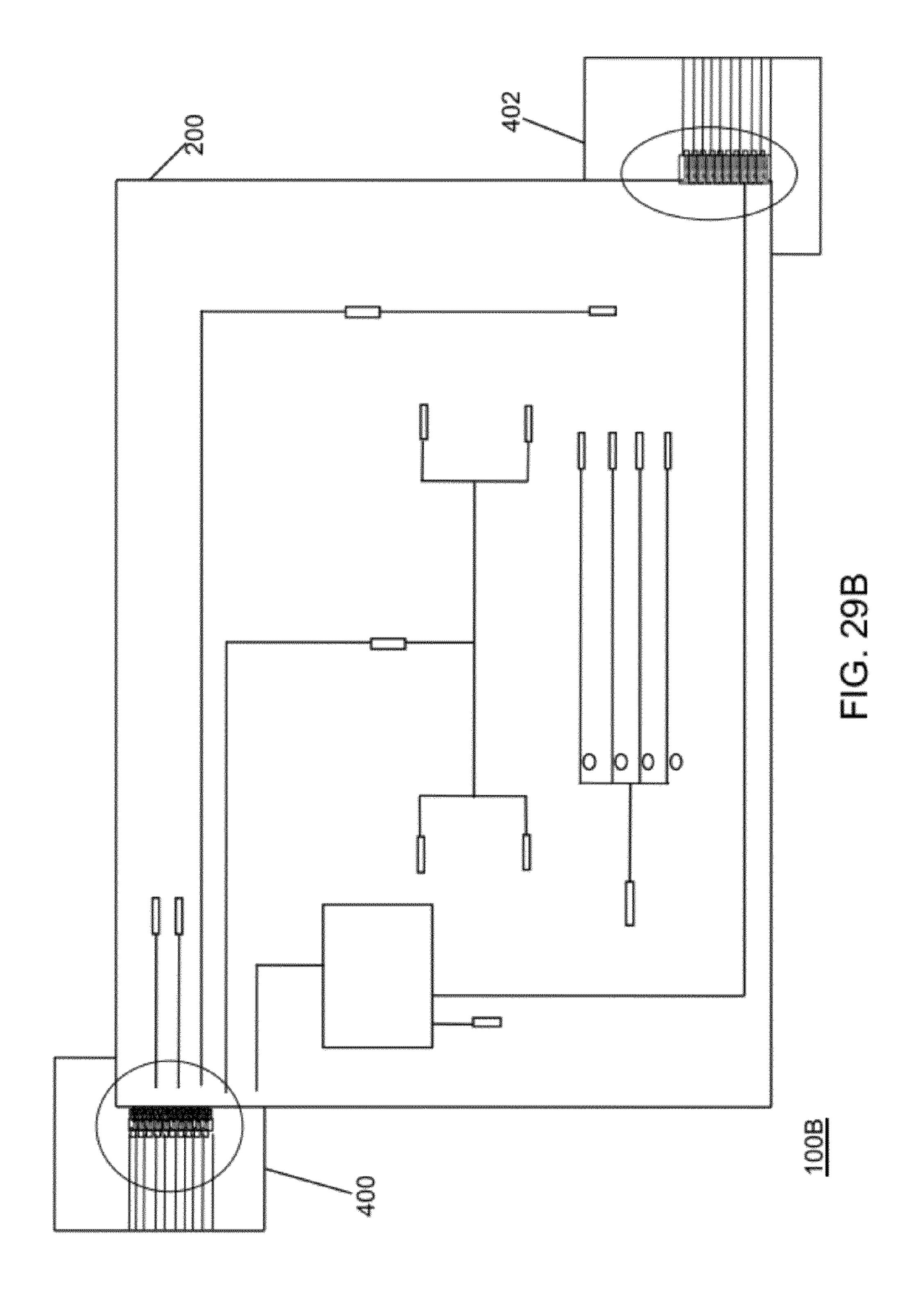

- FIG. 29B illustrates a second electronic-integration compatible photonic/nanophotonic integrated circuit with integrated chip-level optical network EIC-PIC+ICON device in accordance with an embodiment of the invention;

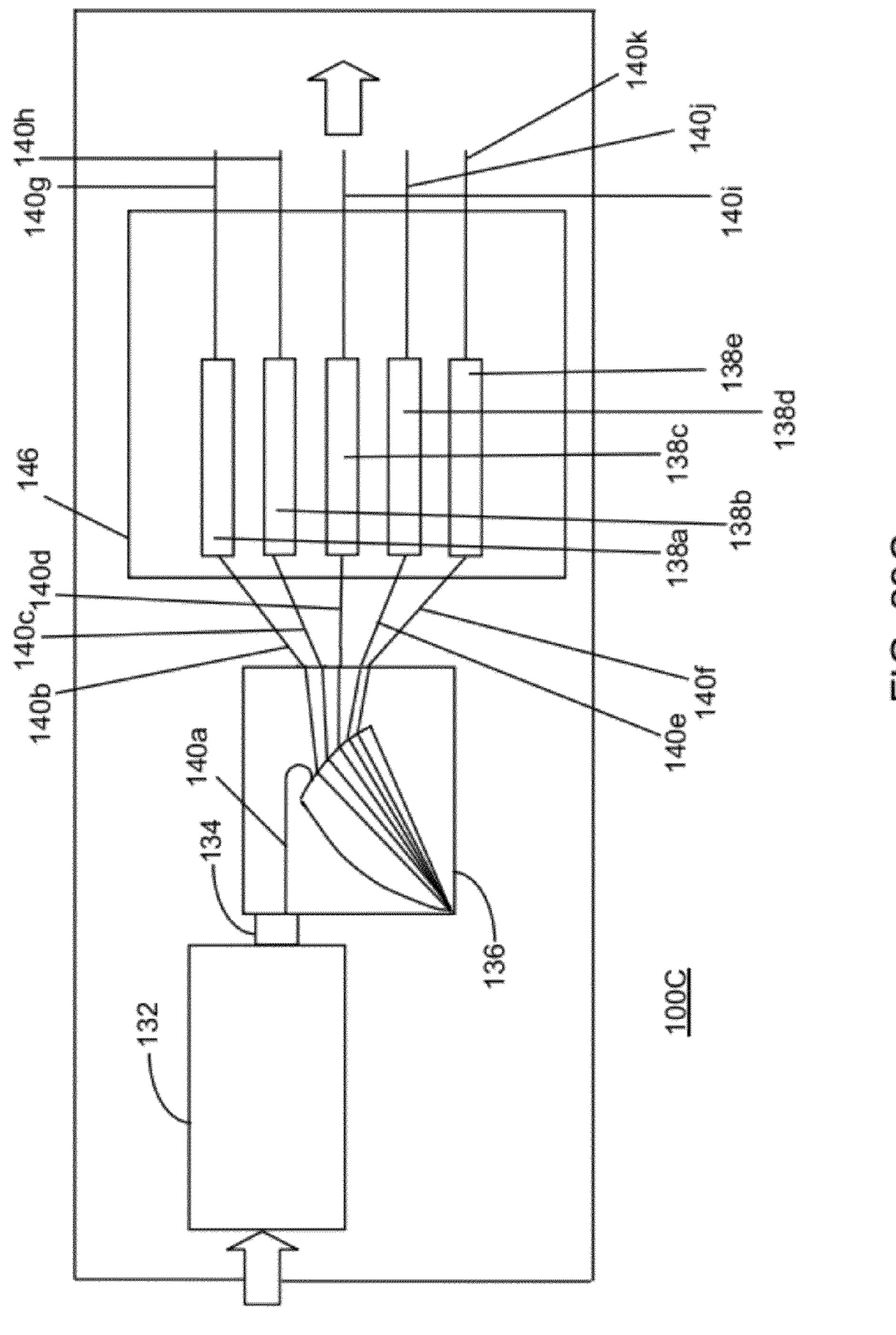

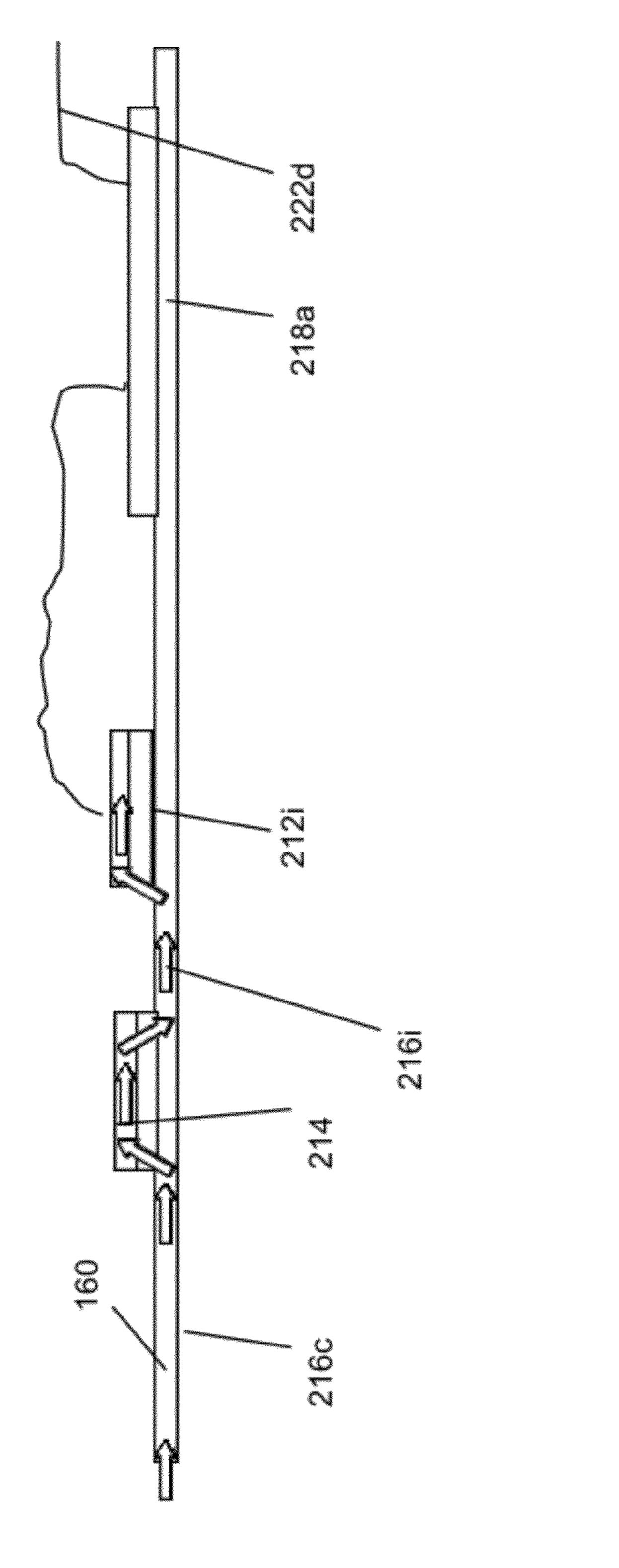

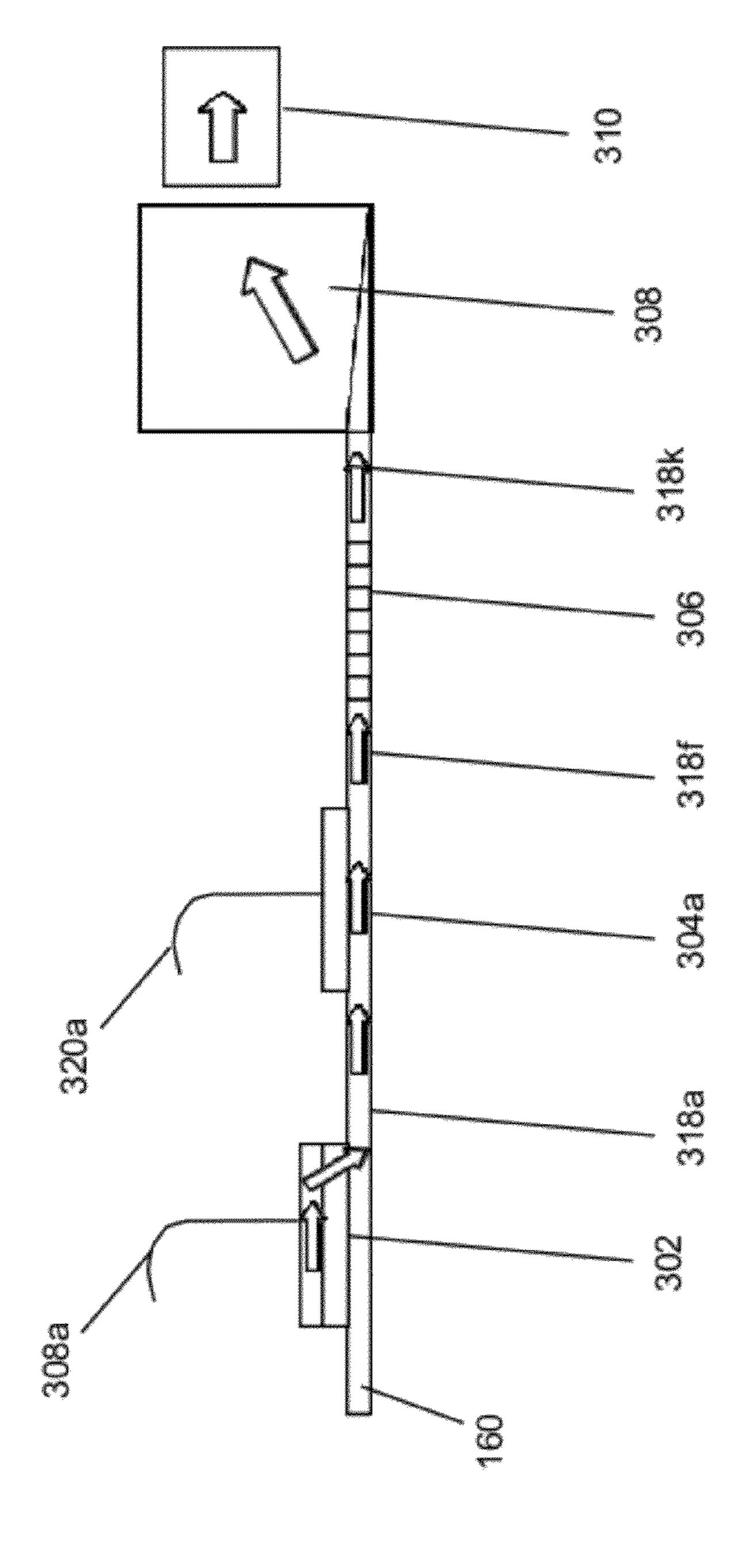

- FIG. **29**C illustrates a set-up for input part of electronic-photonic device, in accordance with an embodiment of the invention;

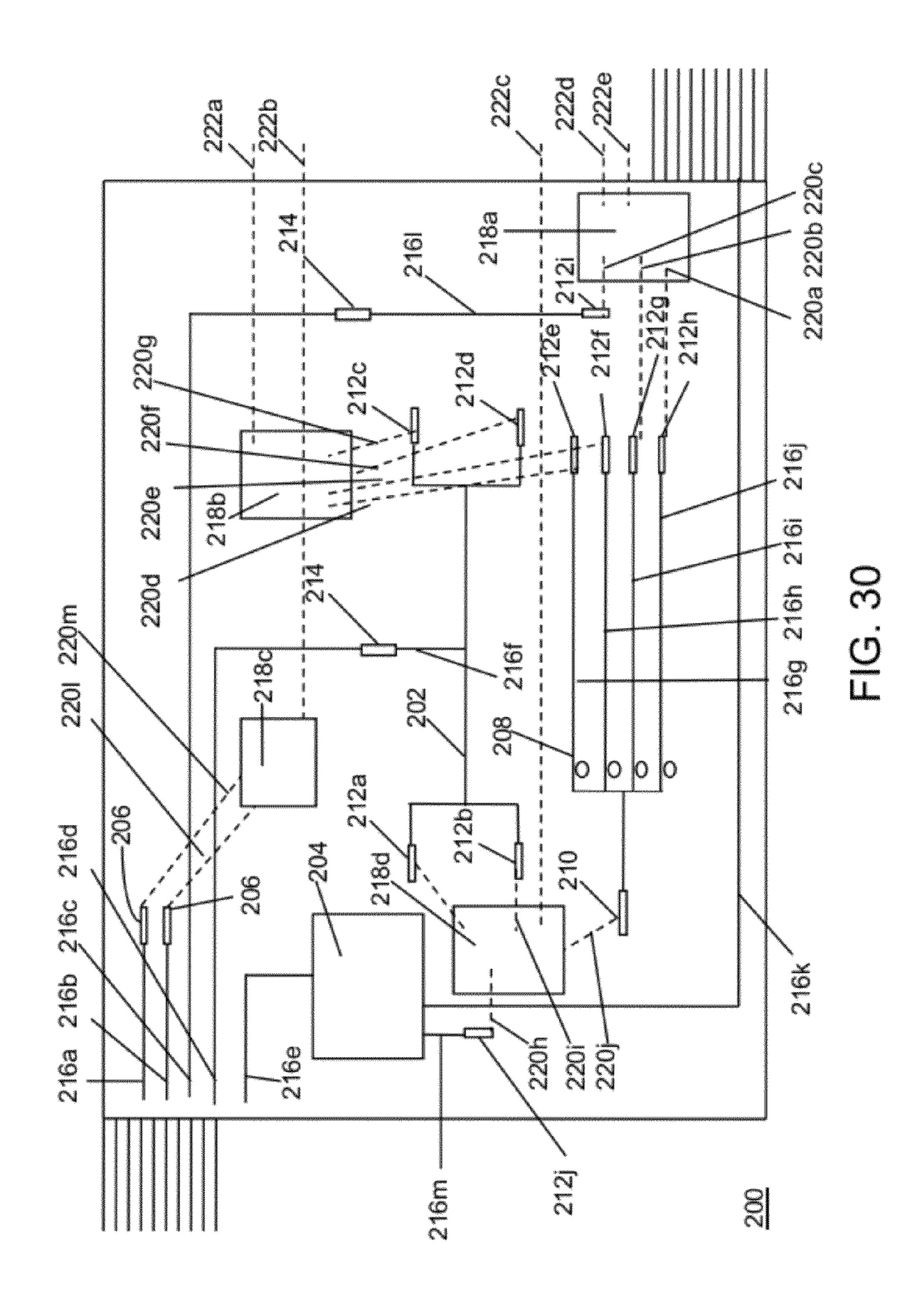

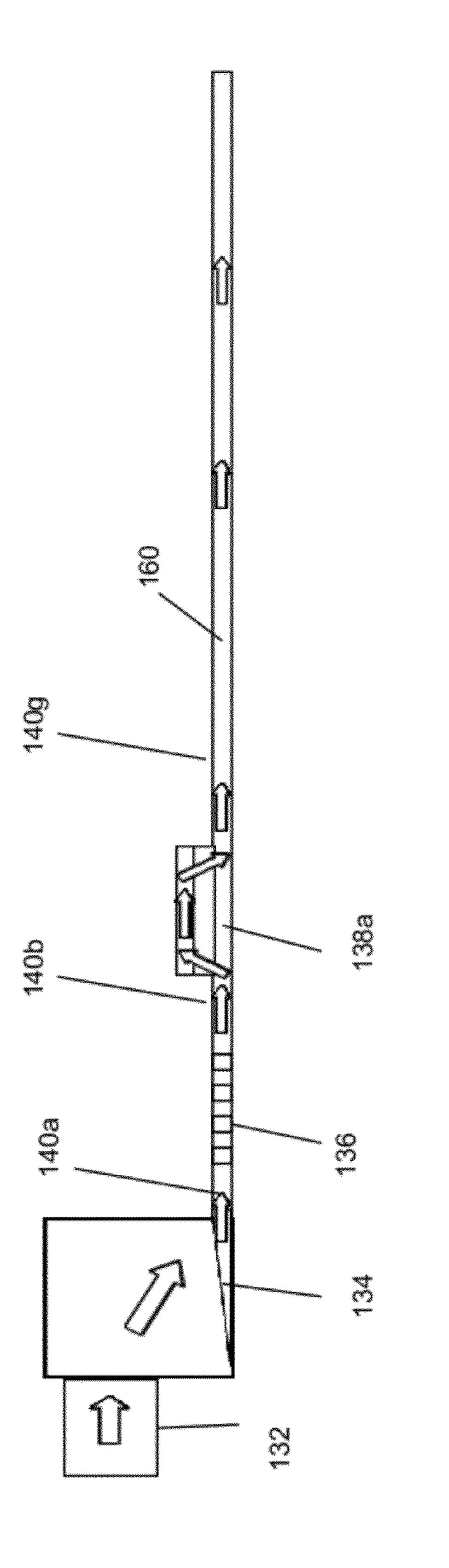

- FIG. 30 illustrates an electronic-photonic device set-up, in accordance with various embodiments of the invention;

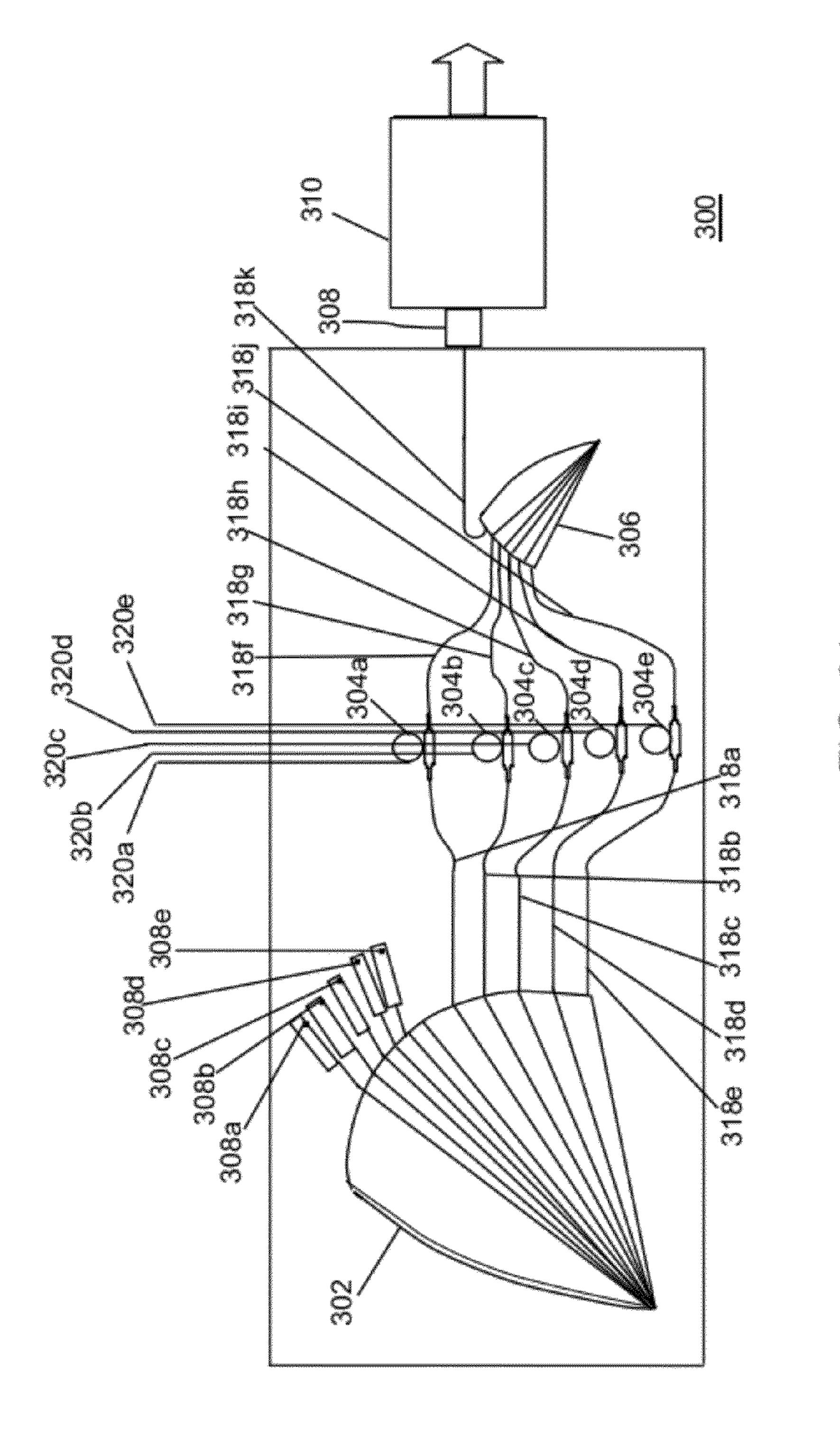

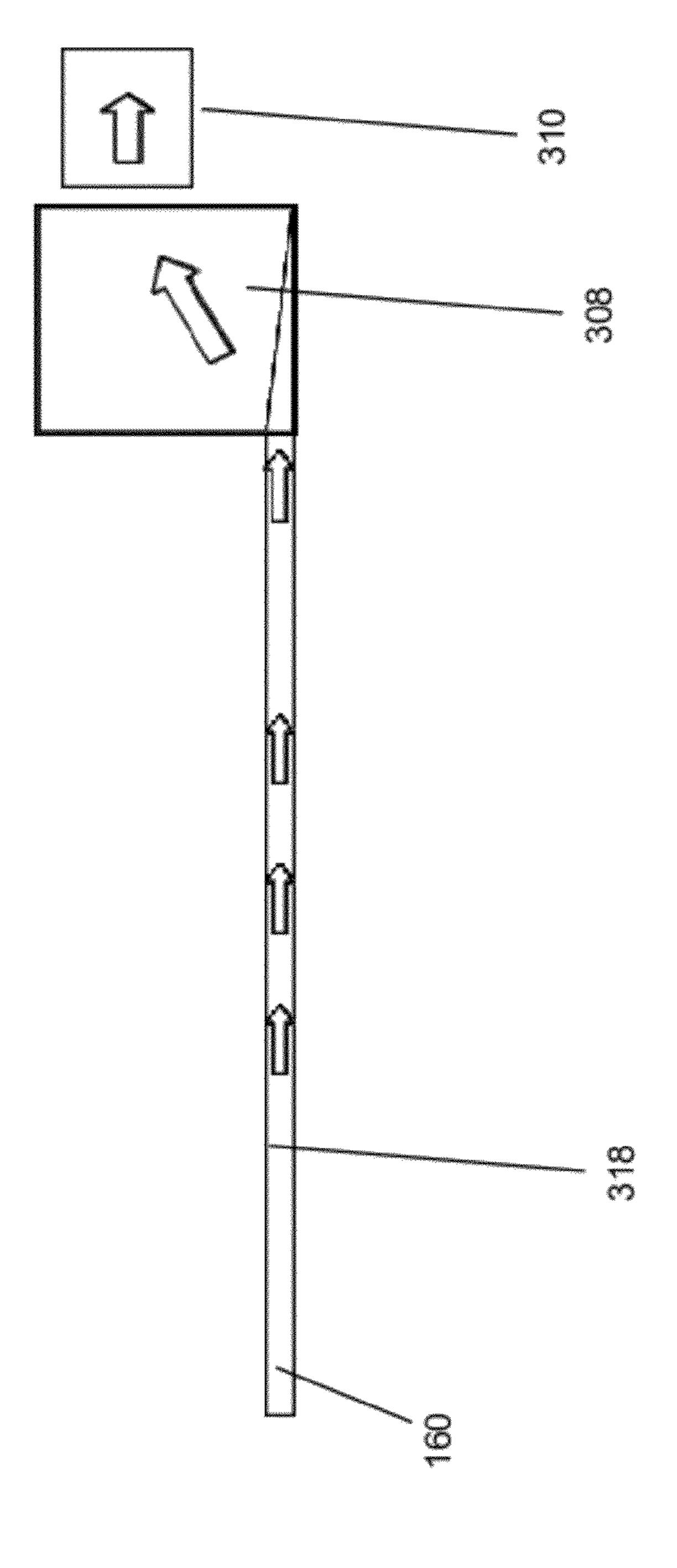

- FIG. 31 illustrates a set-up for output part of electronicphotonic device, in accordance with an embodiment of the invention;

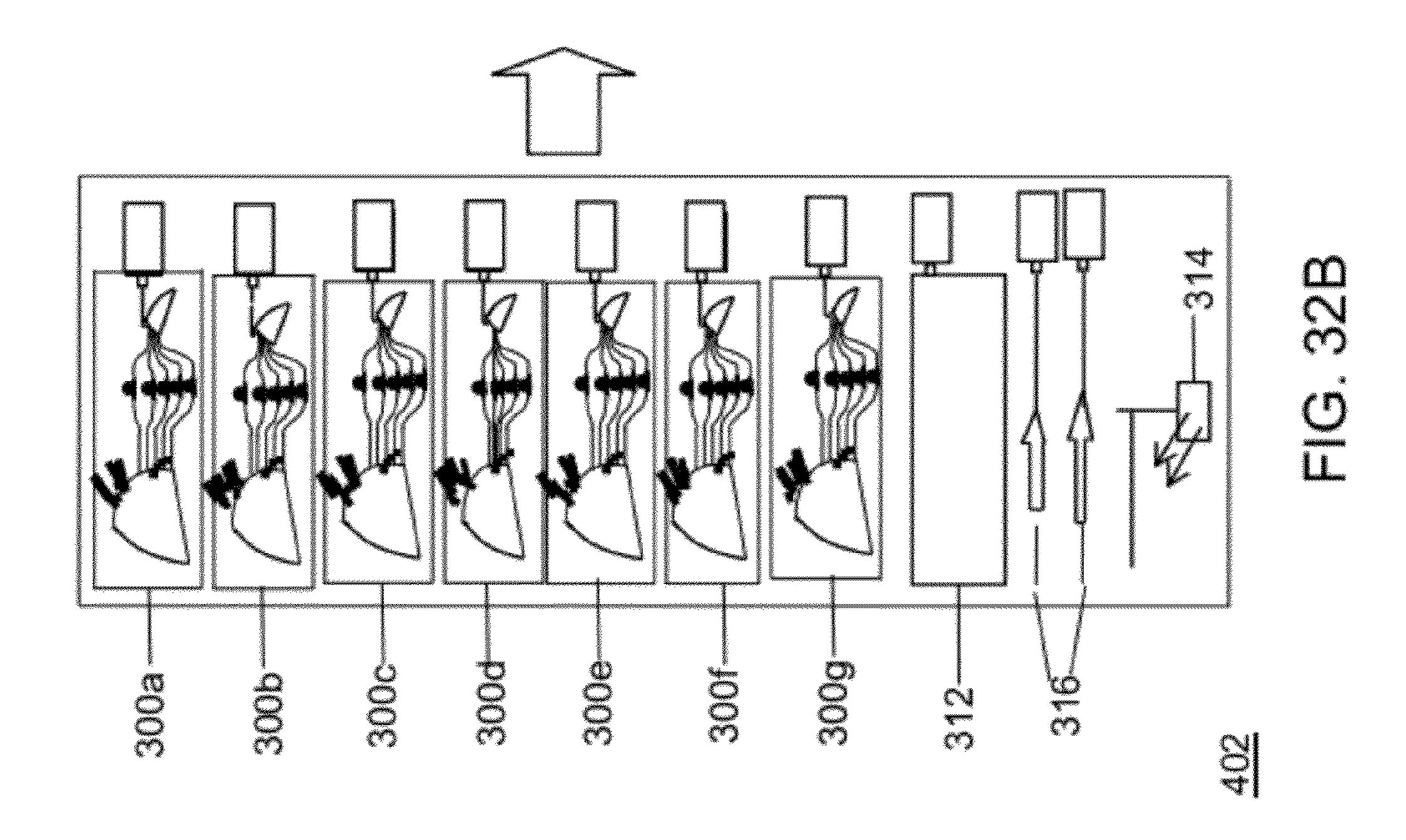

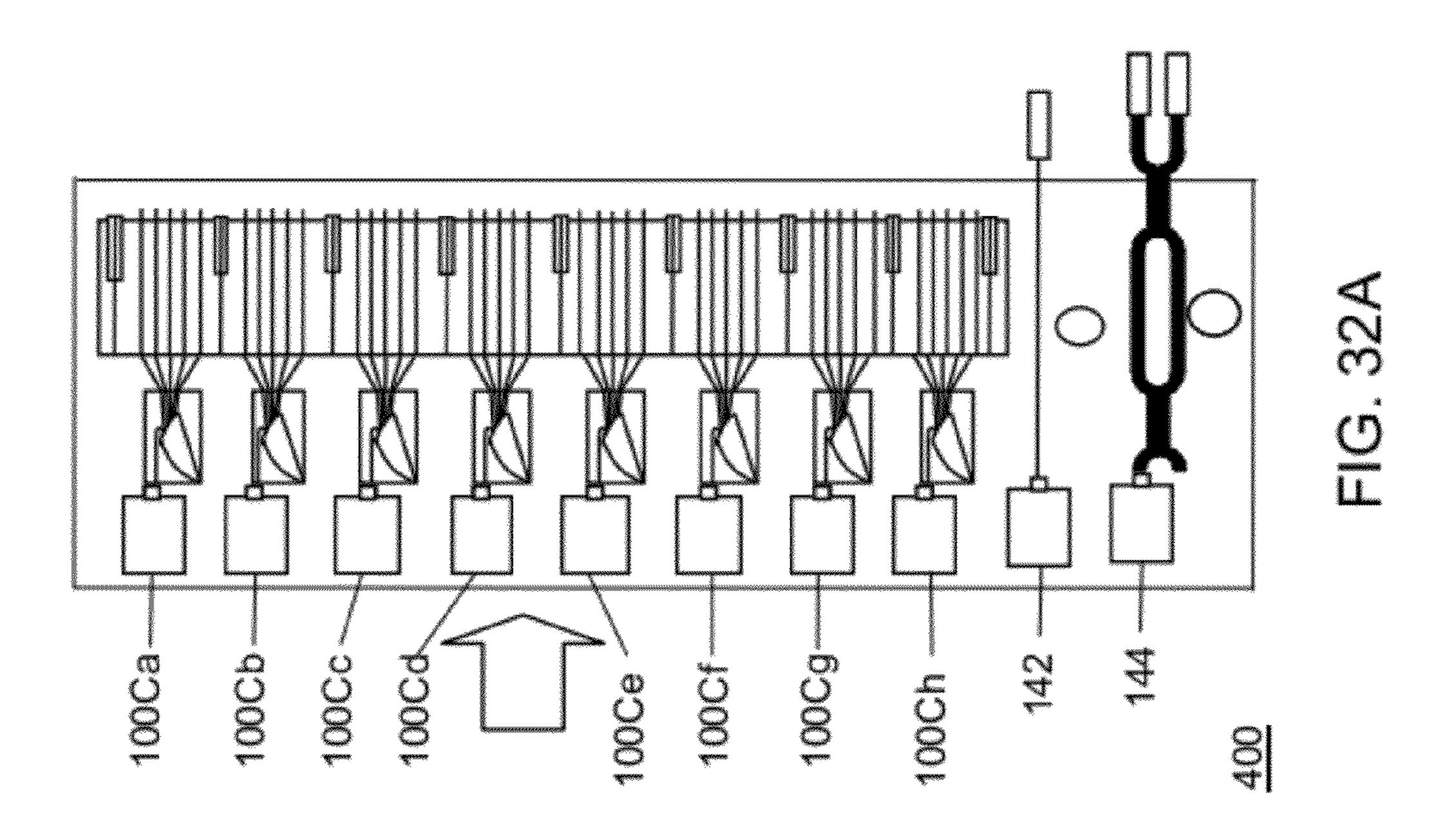

FIG. 32A illustrates a multiple optics fiber input port, in accordance with an embodiment of the invention;

FIG. 32B illustrates a multiple optics fiber output port, in accordance with an embodiment of the invention;

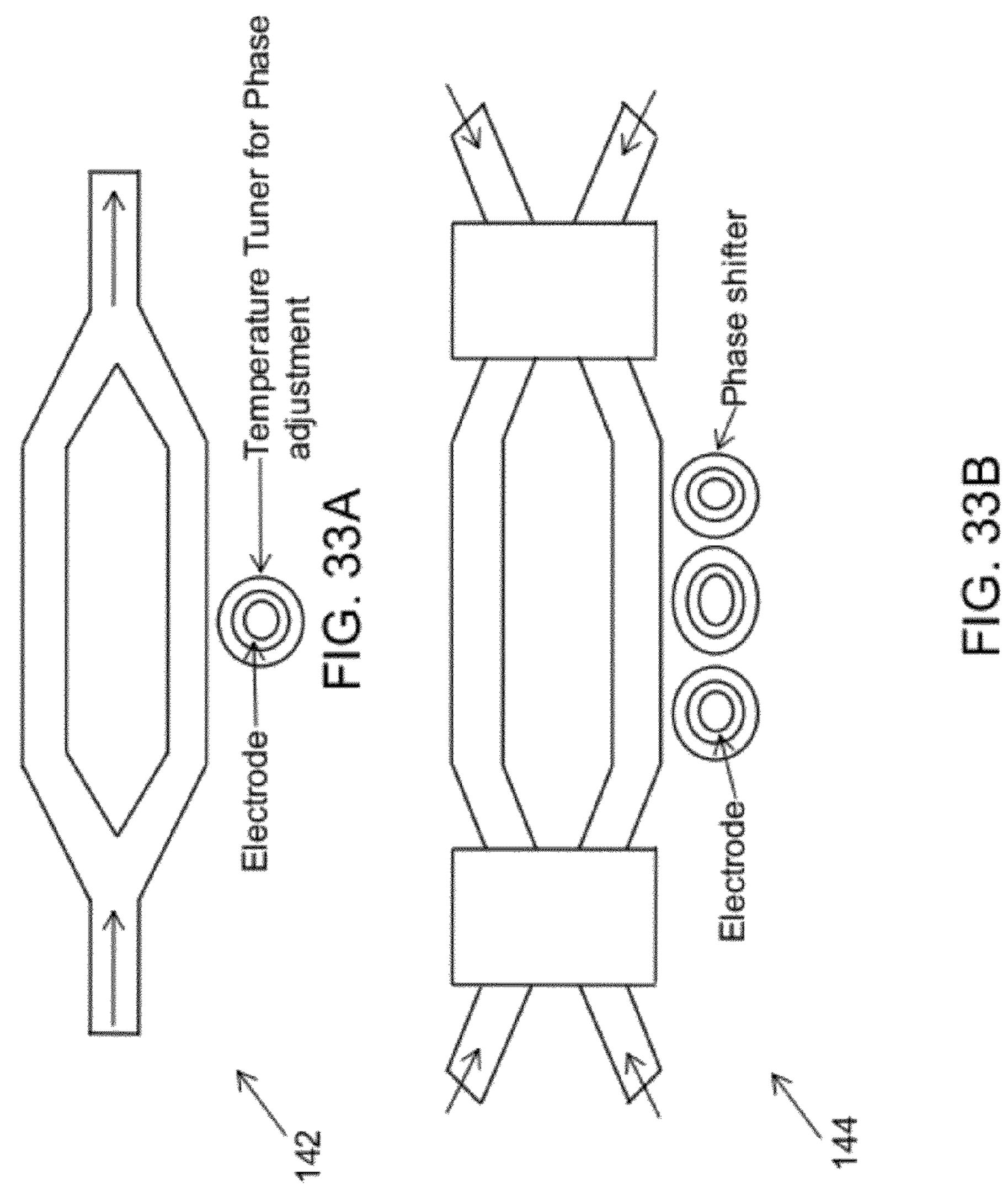

FIG. 33A illustrates a silicon ring-resonator tunable wavelength filter (Si-R-TWF) to be used in electronic-photonic device, in accordance with an embodiment of the invention;

FIG. 33B illustrates a silicon high-speed optical switch (Si-HS-OS) to be used in an electronic-photonic device, in accordance with another embodiment of the invention;

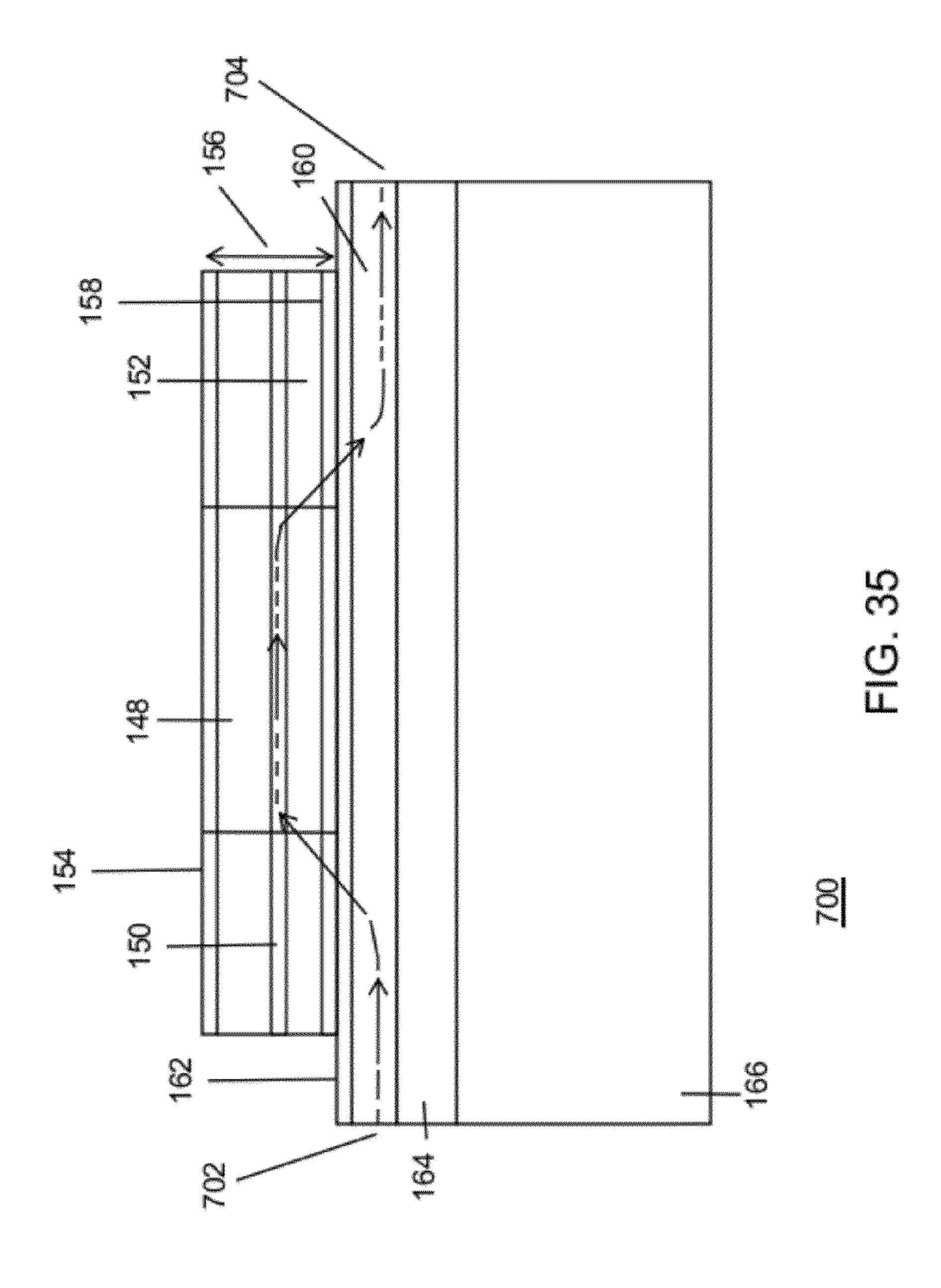

FIG. 34 illustrates a view of device structure for the evanescence coupling between compound semiconductor (e.g. III-V semiconductor) and Si waveguide and metal contact configuration in accordance with another embodiment of the invention;

FIG. 35 illustrates another view of device structure for the evanescence coupling between compound semiconductor and Si waveguide and metal contact configuration in accordance with another embodiment of the invention;

FIG. **36** illustrates a vertical structure for Input Port of an <sup>20</sup> electronic-integration compatible photonic/nanophotonic integrated circuit with integrated chip-level optical network EIC-PIC+ICON device, in accordance with an embodiment of the invention;

FIG. 37 illustrates a vertical structure for Interior Part of 25 electronic-integration compatible photonic/nanophotonic integrated circuit with integrated chip-level optical network EIC-PIC+ICON device in accordance with an embodiment of the invention;

FIG. **38** illustrates a vertical structure for Output Port of an <sup>30</sup> electronic-integration compatible photonic/nanophotonic integrated circuit with integrated chip-level optical network EIC-PIC+ICON device in accordance with an embodiment of the invention;

electronic-integration compatible photonic/nanophotonic integrated circuit with integrated chip-level optical network EIC-PIC+ICON device in accordance with another embodiment of the invention; and

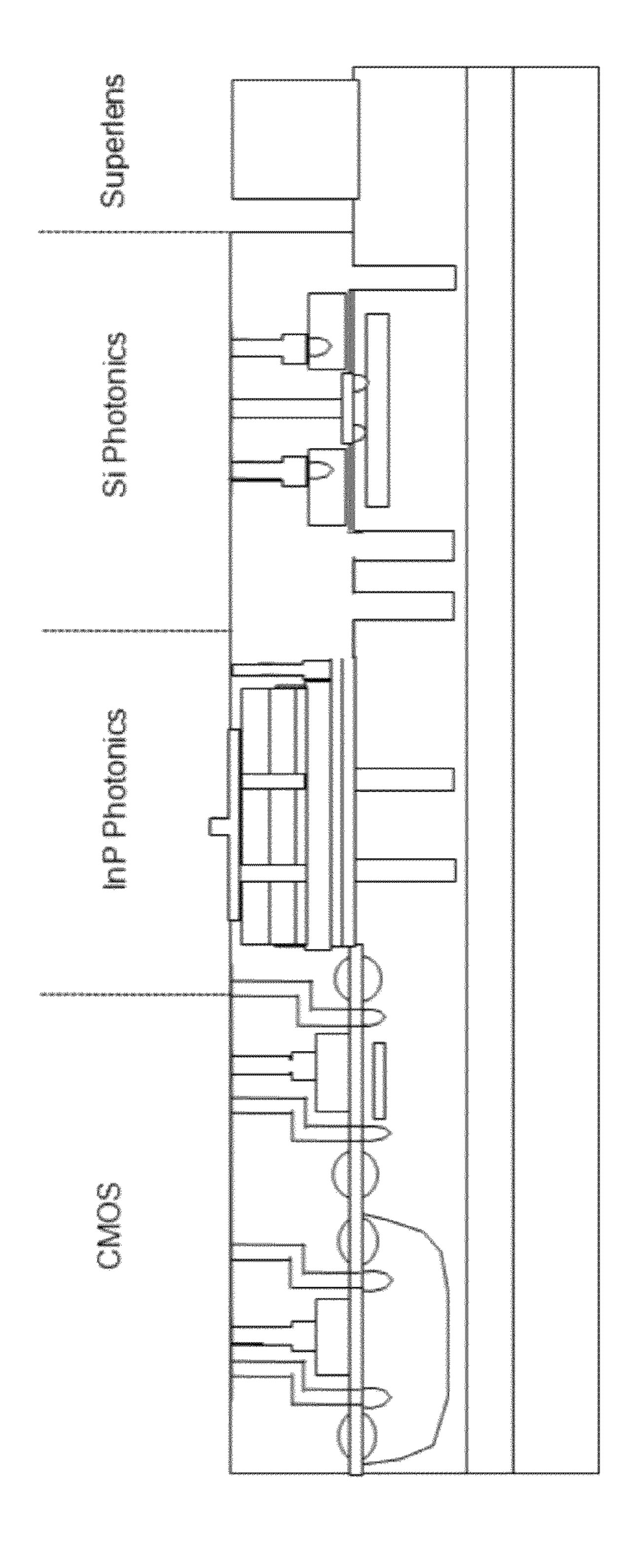

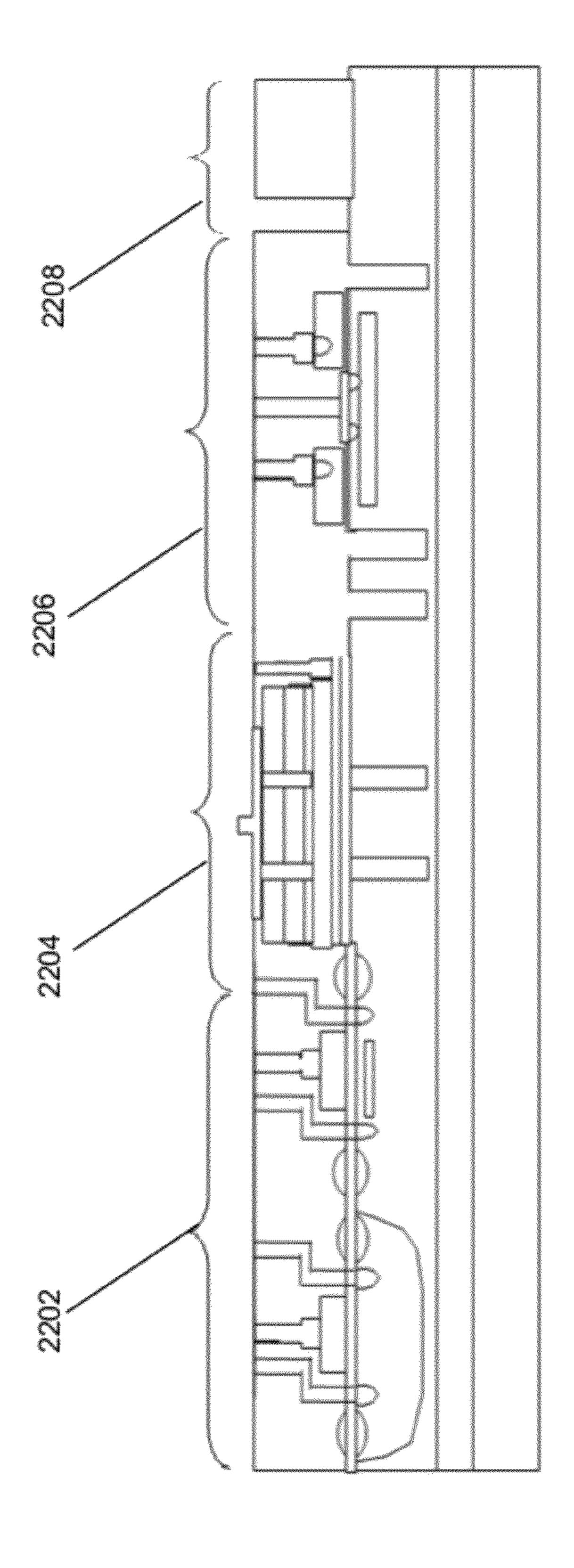

FIG. 40 illustrates general cross section of an electronic- 40 integration compatible photonic/nanophotonic integrated circuit EIC-PIC device according to an embodiment of the invention.

# DESCRIPTION OF EMBODIMENTS

Overview of EIC-PIC:

The present invention provides a method for the realization of Photonic/Nanophotonic Integrated Circuits that are compatible with electronic integration, referred to as electronic- 50 integration compatible Photonic/Nanophotonic integrated circuit that will be referred to as EIC-PIC. An EIC-PIC shall have photonic devices integrated on a substrate using fabrication processes that are compatible with electronic integration processes.

Electronic Device Materials:

Electronic devices are typically fabricated on a layer of semiconductor material made up of silicon, GaAs, InP, or GaN substrate. The most commonly used material is Silicon. For illustration but not limitation, we will focus our discus- 60 sion on the case of Silicon electronics integrated with photonic devices. Generalization to the utilization of other materials for electronics other than Silicon will be obvious to those skilled in the art.

Photonic Device Materials and Optical Wavelength:

For illustration but not limitation, the photonic/nanophotonic devices are illustrated for operations at  $\lambda_{opt}$ =1550 nm

wavelength range. Generalization of the photonic devices for operation at other wavelength range will be obvious to those skilled in the art by scaling the device dimensions somewhat proportional to the wavelength of operation, by utilizing passive optical materials transparent at the wavelength of operation, and by utilizing active optical material that can provide optical gain at the wavelength of operation.

Basic EIC-PIC Structure:

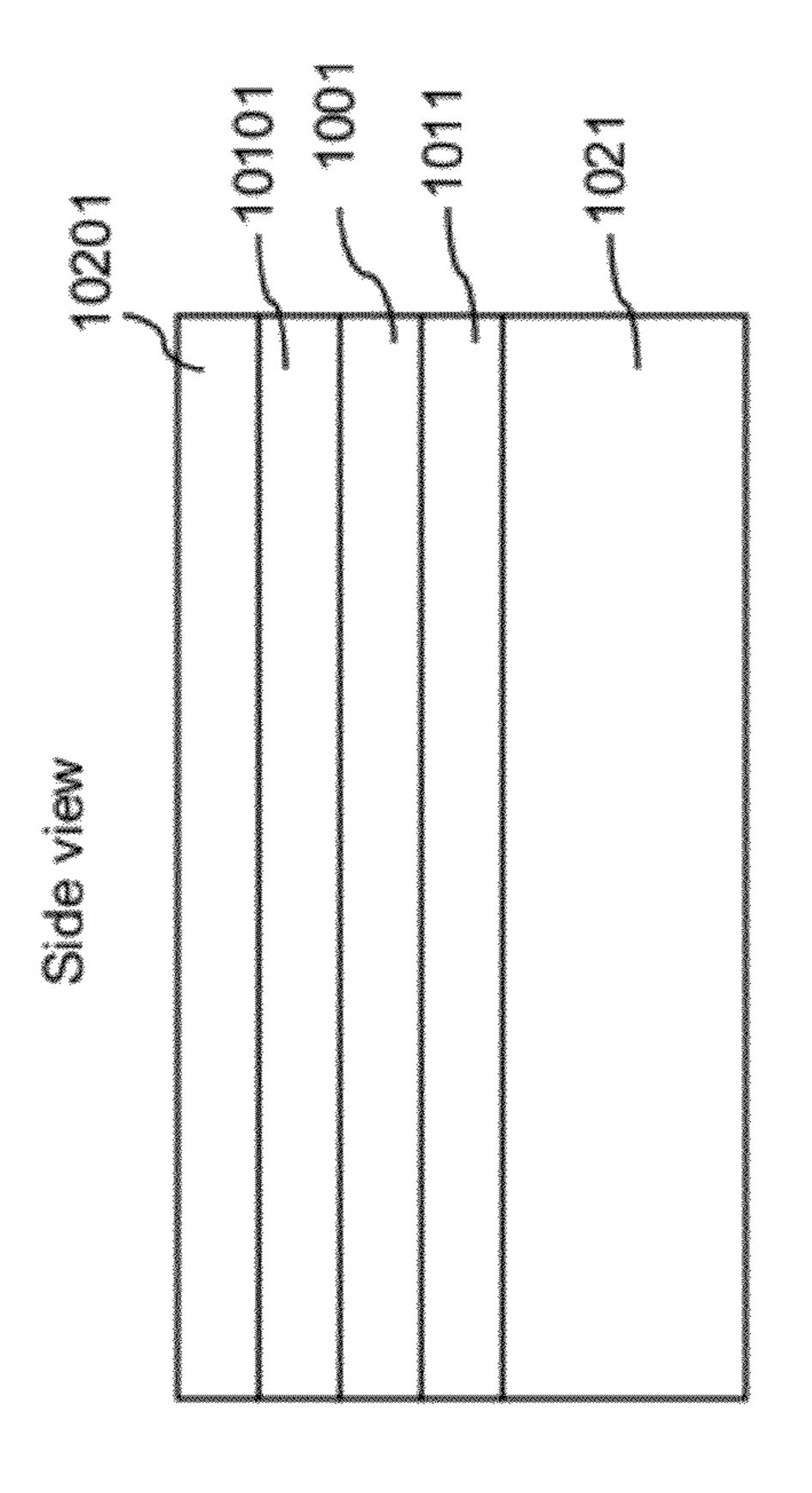

A basic wafer structure for an EIC-PIC provided by the present invention is illustrated in FIG. 1 showing its crosssectional view. A thin layer of electronic material 1001 with thickness  $t_{EM}$  is placed on top of a thin layer of (lower) optically transparent dielectric material 1011 with thickness  $t_{LOTM}$ . The thin layer of dielectric material 1011 is placed on 15 top of a substrate 1021. For illustration but not limitation, common dielectric materials for layer 1011 are silicon dioxide, silicon nitrides, titanium dioxide, zinc oxide, tantalum pentaoxide, and various polymer materials with optical transparency at the optical wavelength of operation  $\lambda_{opt}$ . In an exemplary embodiment of the invention, 1001 and 1021 are Silicon, and **1011** is silicon dioxide, forming a wafer structure commonly referred to as Silicon-On-Insulator (SOI). In another embodiment of the invention,  $\lambda_{opt}$  is 1550 nm,  $t_{EM}$  is 300 nm thick silicon, and  $t_{LOTM}$  is 1 µm thick silicon dioxide.

In an exemplary embodiment, the thin layer of electronic material 1001 is also transparent to the optical wavelength of operation  $\lambda_{opt}$  forming the first optical core layer and the dielectric layer 1011 has a refractive index that is lower than the refractive index of first optical core layer 1001, enabling layer 1001 to be used as a transparent optical waveguide core surrounded below by lower waveguide cladding 1011 and above by air as the upper waveguide "cladding", both the upper and lower waveguide claddings have lower refractive index than waveguide core layer 1001. As shown in FIG. 2, in FIG. 39 illustrates a vertical structure for Output Port of an 35 another exemplary embodiment, at least another thin layer of (upper) dielectric material layer 1031 with thickness  $t_{UTOM}$  is placed on top of layer 1001. Layer 1031 has a refractive index lower than that of layer 1001 and forms an upper waveguide cladding for waveguide core 1001. For illustration but not limitation, common dielectric material for layer 1031 is silicon dioxide, or silicon nitrides, or titanium dioxide, or zinc oxide, or tantalum pentaoxide, or air, or various metal oxide or polymer materials with optical transparency at the optical wavelength of operation  $\lambda_{opt}$ . In an exemplary embodiment of 45 the invention, 1031 is silicon dioxide with thickness  $t_{UTOM}$ =300 nm.

Single-Optical-Layer EIC-PIC: For the purpose of illustration but not limitation, as shown in FIG. 3, in an exemplary embodiment, electronic devices are fabricated in a first optical core layer 1001 and/or on a first substrate 1021. An EIC-PIC can be realized with this structure by fabricating photonic/nanophotonic devices utilizing first optical core layer 1001 to propagate optical beam. The first optical core layer 1001 with thickness  $t_{EM}$  is on top of a first lower optical cladding layer 1011 with thickness  $t_{LOTM}$ . The first lower optical cladding layer 1011 is on top of the first substrate 1021. The refractive index  $n_{EM}$  of the first optical core layer is higher than the refractive index  $n_{LCL}$  of the first lower optical cladding layer. In the case of Silicon, layer 1001 cannot provide optical gain but can be used to fabricate various passive photonic devices and active electro-optic devices or active all-optical devices. In another exemplary embodiment, at least one dielectric layer (first upper optical cladding layer) 1031 with thickness  $t_{UOTM}$  and refractive index  $n_{UCL}$  is 65 further placed on top of layer 1001. EIC-PIC based on this embodiment will be referred to as Single-Optical-Layer EIC-PIC (SOL-EIC-PIC).

In an exemplary embodiment, the first substrate layer 1021 is the silicon substrate of a silicon-on-insulator (SOI) wafer, the first lower optical cladding layer 1011 is the silicon dioxide layer on top of the silicon substrate in the SOI wafer, the first optical core layer 1001 is the top silicon layer of the SOI wafer, and the first upper optical cladding layer 1031 is a silicon dioxide layer.

Input and Output Lens:

In an exemplary embodiment of the invention, the SOL-EIC-PIC consists of at least one input or output optical-fiber 10 coupling optics (i.e. it can have only one or more input coupling optics without any output coupling optics or only one or more output coupling optics without any input coupling optics. It can also have both input coupling optics and output coupling optics)

FIG. 4 illustrates the case with one input optical-fiber coupling optics and one output optical-fiber coupling optics, in accordance with an embodiment of the invention. At the input end, FIG. 4 shows the Single-Optical-Layer EIC-PIC consists of one input optical-fiber coupling optics 4030 coupling light 20 from the optical fiber 4010 into first optical layer 1001 forming an optical waveguide 4020 utilizing an integrated lens 4030 on layer 1011. In an exemplary embodiment of the invention, the input optical-fiber coupling optics 4030 is a Superlens. At the output end, FIG. 4 shows that the Single-Optical-Layer EIC-PIC includes one output optical-fiber coupling optics; coupling light from first optical core layer 1001 of an output waveguide 4060 to an output optical fiber 4070 utilizing an integrated lens 4050 on layer 1011. In an exemplary embodiment of the invention, the output coupling optics 30 4050 is a Superlens 4050. In an exemplary embodiment, the Superlens 4030 and 4050 are made up of two alternating thin dielectric layers that have different refractive indices. In another exemplary embodiment, the alternating layer is made up of silicon and silicon dioxide. (The general design of superlens is disclosed in US patents "Varying refractive index optical medium using at least two materials with thickness less than a wavelength, U.S. Pat. No. 7,426,328" and "Superlens and a method for making the same, U.S. Pat. No. 7,643, 719", the contents of which are herein incorporated by refer- 40 ence.)

The superlens 4030 or 4050 is further shown in FIG. 5 as lens 5030. The side and top view of a superlens 5030 coupling between an optical fiber 5010 and a nano waveguide 5020 are shown in FIG. 5. In an exemplary embodiment, the input 45 waveguide 5020 may be an optical waveguide with a step refractive index with Silicon as the waveguiding core 1001 with refractive index  $n_{Si}=3.5$  and thickness  $t_{EM}$ , air as the upper cladding 1031 with refractive index  $n_{Air}=1$ , and silicon dioxide as the lower cladding 1021 with refractive index 50  $n_{SiO2}$ =1.5 and thickness  $t_{LOTM}$ . The waveguide **5020** has a width  $D_{WG}$  fabricated by vertically etching down the silicon material to the bottom of the waveguide core 1001 using etching technique well known to those skilled in the art. An example of such etching technique is dry etching using Induc- 55 tively Coupled Plasma (ICP) etcher with Chlorine or Fluorine chemistry. In an exemplary embodiment, the width  $D_{WG}$  is 10  $\mu$ m, and the thickness  $t_{EM}$  is 300 nm. The thickness of lower cladding  $t_{LOTM}$  is 1 µm. The superlens **5030** has a width  $W_{SPL}$ , height  $H_{SPL}$  and length  $L_{SPL}$  fabricated on top of the 60 waveguide 5020 by depositing multi-layers of alternating dual materials.

In an exemplary embodiment, the dual materials are Silicon (Si) and Silicon Dioxide (SiO<sub>2</sub>). The superlens **5030** dimensions are  $W_{SPL}$ =20 µm,  $H_{SPL}$ =15 µm, and length 65  $L_{SPL}$ =20 µm. The thickness ratio of Silicon and Silicon Dioxide is varied such that the effective index of the superlens is

12

close to n=3.5 at the bottom of the lens near the surface of waveguide 5020 and will be mainly of silicon (i.e. it will have thicker layers of silicon versus silicon dioxide). The effective index of the superlens is close to n=1.5 near the top of the superlens and will be mainly of silicon dioxide (i.e. it will have thicker layers of silicon dioxide versus silicon). The optical fiber 5010 is an optical fiber with a full-width-half maximum (FWHM) mode size diameter of about 8 µm. The optical wavelength of operation  $\lambda_{OPT}$  is 1550 nm. The index variation of the superlens 5030 with the design algorithm shown in U.S. Pat. No. 7,643,719 will be such that the mode from the nano waveguide 5020 will expand in the lens such that the strong lensing effect in the superlens results in an output beam of about 8 µm in diameter over less the 20 µm of propagation through the superlens, and the wavefront is a flat wavefront at the output surface of the superlens. The 8 µm optical beam diameter at the output surface of the superlens with flat beam wavefront matches the fiber beam diameter of 8 μm. Thus, the superlens **5030** enables efficient coupling of the light from the nano waveguide 5020 to the optical fiber 5010 or from the optical fiber 5010 to nano waveguide 5020 due to the reciprocity of light propagation as is known to those skilled in the art.

In an exemplary embodiment, the input or output optical fiber is held from below by a V-groove or a trench structure fabricated on the substrate 1021 to match the size of the fiber and hold it at the right height with respect to the lens optical center to achieve maximum coupling of light beam energy between the optical fiber and the waveguide on chip. This is illustrated in FIG. 5 showing optical fiber 5010 held from below by substrate 1021. The trench can be of rectangular shape or arbitrary shape designed to hold the fiber in steady position. There can be additional materials between substrate 1021 and fiber 5010 to help hold the fiber. Such variations are contemplated and are within the scope of the present invention.

Photonic or Nanophotonic Device:

In an exemplary embodiment of the invention, as shown in FIG. 4, the Single-Optical-Layer EIC-PIC consists of at least one photonic/nanophotonic device 4030, that can be an optical waveguide, an optical wavelength multiplexer, an optical wavelength demultiplexer, an optical grating, an optical beam splitter, a polarization beam splitter, an optical isolator, a polarization rotator, an optical interferometer, an optical modulator, an optical ring resonator, an optical disk resonator, an optical curved reflector or an optical mirror, an optical amplifier, a laser, a light-emitting device, an optical detector, a nonlinear-optical device, a photonic transistor, an optical harmonic frequency generator, an all-optical device, or other photonic/nanophotonic devices well known to those skilled in the art. Each of these devices has at least an input or output waveguide port for an optical beam. When there is more than one device, light propagates from one device to another by connecting the output port of an earlier device to the input port of a latter device.

The vertical optical mode confinement of photonic/nano-photonic device is due to the high refractive index core layer 1001 that confines the light energy to propagate mainly in core layer 1001. The horizontal confinement and propagation geometry of the optical beam or beams will depend on the device as described below. The horizontal geometry is defined by lithography (photolithography or E-Beam lithography etc) and by vertically etching down the core layer 1001, as is well know to those skilled in the art.

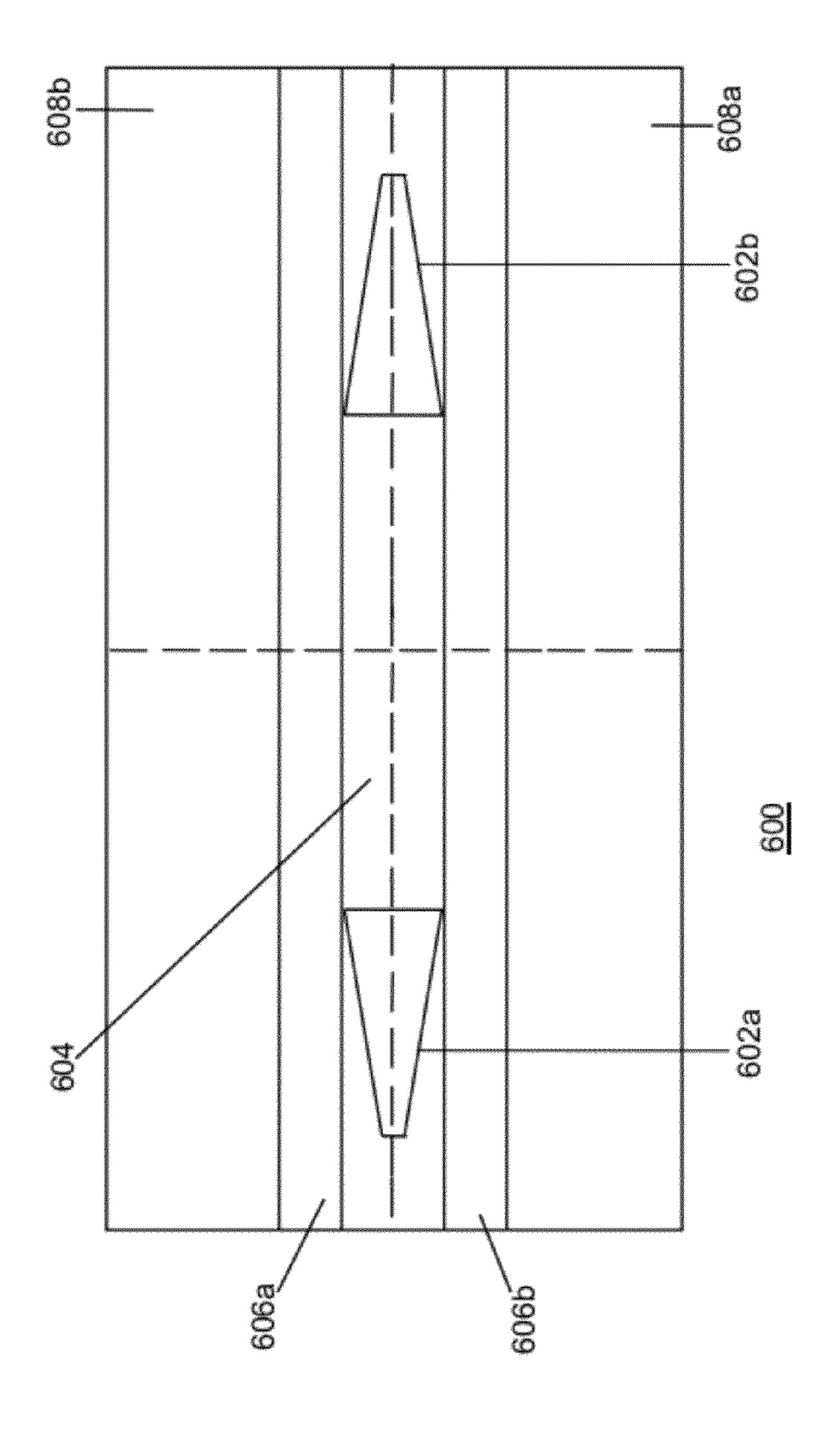

An exemplary embodiment of an optical waveguide is a straight or curved waveguide 6000 shown in FIG. 6, guiding optical beam confined vertically by the high-refractive index

core 1001. This waveguide is fabricated by horizontally patterning the planar pattern of the waveguide by using lithography (e.g. photolithography or E-Beam lithography) and then etching down the silicon layer 1001 to form the waveguide of a certain width  $W_{WG}$  to provide the horizontal optical confinement surrounded by air or by low refractive index material 1041 and 1051 on both side of the waveguide as shown in FIG. 6, The waveguide has an optical beam input port 6010 and an output port 6020 as shown in FIG. 6. In an exemplary embodiment, waveguide 6000 has width  $W_{WG}$ =400 nm for an optical operation wavelength  $\lambda_{OPT}$  of 1550 nm.

An exemplary embodiment of an optical wavelength multiplexer or an optical grating is an ultra-compact wavelength multiplexer/demultiplexer, also called the Super-Compact Grating or the Compact Curved Grating (hereinafter referred to as UCλDeMux 7000 as shown in FIG. 7. The general design of ultra-compact wavelength multiplexer/demultiplexer is given in patents "Curved grating spectrometer, U.S. Pat. No. 7,283,233" and "Integrated signal manipulator for manipulating optical signals, application Ser. No. 11/451, 797," contents of which are herein incorporated by reference. UCλDeMux 7000 could also be referred to as Ultra-Compact Wavelength Multiplexer/DeMultiplexer, based on Ultra- 25 Large-Angle-Grating for High Bandwidth Data Communications through WDM. The wavelength multiplexer 7000 has an optical beam input port 7010 and an output port 7020 as shown in FIG. 7.

FIG. 8A illustrates a Ring-Resonator 8000 that can be used 30 as Tunable Wavelength Filter (R-TWF), in accordance with an embodiment of the invention. The Tunable Ring Resonator 8000 is coupled to an adjacent waveguide 8100. The Tunable Ring Resonator 8000 has an optical beam input port 8010 and an output port **8020** operated with an optical beam at optical 35 wavelength  $\lambda_{OPT}$  as shown in FIG. 8A. The waveguide 8100 has a width  $W_{CWG}$ . The ring resonator is made up of a waveguide of width  $W_{RWG}$  formed into a ring with a ring diameter of  $D_{RING}$ . The resonance frequency of the ring resonator is tuned by capacitative effect that brings the electrical 40 charges across a thin layer of gate oxide. The electrical charges cause a change in the refractive index at the gate region and hence the propagating refractive index of the waveguiding ring. This change in the propagating index then shifts the resonance frequency of the ring as is known to those 45 skilled in the art. In an exemplary embodiment,  $W_{CWG} = W_{RWG} = 400 \text{ nm}, D_{RWG} = 20 \mu\text{m}.$

In one exemplary embodiment based on poly-silicon gate, the vertical cross section of Tunable Ring Resonator **8000** is shown in FIG. 8B in which the Silicon waveguide core layer 50 1001 with thickness  $t_{EM}$  is doped by ion implantation at spatial region 8010. A source electrode 8020 and a drain electrode 8030 are deposited on two ends of 8010, each on an n+ well or p+ well region. A gate oxide 8040 with thickness of tens of nanometers or thinner is deposited on the central 55 region of **8010**. A doped poly-silicon **8050** with thickness  $t_{POLY-Si}$  is deposited on top of the gate oxide 8040. A gate electrode 8060 is deposited on the side of poly-silicon structure 8050 that is placed on a low refractive index oxide layer **8070**. The waveguiding region **8080** is shown in the figure. 60 The optical mode goes across from the lower silicon layer **8010** to the top poly-silicon layer **8050**. Applying a voltage across the gate and the source electrode will drive charges to reside just across the gate oxide layer 8040, resulting in a refractive index change at the center of the optical beam mode 65 **8080**. In an exemplary embodiment  $t_{POLY-Si}$ =200 nm and  $t_{EM} = 300 \text{ nm}.$

14

In another exemplary embodiment based on transparent conducting oxide (TCO) gate, the vertical cross section of Tunable Ring Resonator **8000** is shown in FIG. **8**C in which the Silicon waveguide core layer 1001 is doped by ion implantation at spatial region 8210. A source electrode 8220 and a drain electrode 8230 are deposited on two ends of 8210. A gate oxide 8240 with thickness of tens of nanometers or thinner is deposited on the central region of **8210**. A transparent conducting oxide (TCO) layer 8230 with thickness  $t_{TCO}$  is deposited on top of the gate oxide **8240**. A gate electrode **8260** is deposited on top of the TCO layer structure 8230. The waveguiding region 8280 is shown in the figure. The TCO has low refractive index of typically  $n_{TCO}=1.7$  to 2. This enables the optical mode to reside mainly in the lower silicon layer 15 **8210** with much higher refractive index of  $n_{Si}=3.5$ , which provides a tighter optical mode confinement than the polysilicon case described above in FIG. 8B. Applying a voltage across the gate and the source electrode will drive charges to reside just across the gate oxide layer, resulting in a refractive index change. The tighter optical mode confinement to within the bottom Silicon layer and the higher conductivity of TCO enables lower switching voltage and higher switching speed.

Optical beam splitter, optical polarization beam splitter, optical isolator, polarization rotator, optical interferometer, optical phase shifter, optical modulator, optical ring resonator, optical disk resonator, optical curved reflector, optical mirror, nonlinear-optical device, photonic transistor, optical harmonic frequency generator, all-optical device, are some of the examples of common integrated optical devices that are well known to those skilled in the art. For example, an optical interferometer can be a Mach Zehnder interferometer with an input beam splitter splitting the wave into two waveguiding arms and recombine them at another beam splitter. They can be fabricated in a way similar to the case of the optical waveguide by patterning the planar pattern of the two beam splitters/combiners and two waveguide arms using lithography and then etch down the silicon layer 1001 to form the required pattern on the chip. Optical phase shifting or modulation can make use of the refractive index change of silicon with temperature by fabricating a heating element to shift the refractive index of the waveguide in the device involved. Optical phase shifting or modulation can also make use of the refractive index change of silicon with electron or hole carrier density by fabricating an electrical structure as is known to those skilled in the art to inject electrons or holes into the silicon to shift the refractive index of the waveguide in the device involved. All-optical device can be realized utilizing the nonlinear optical absorption in silicon to change the phase or absorption of an optical beam by another optical beam as is known to those skilled in the art.

Optical amplifier, laser, light-emitting device, and Optical detector are more specialized devices. In the case of silicon as layer 1001, optical amplifier and optical detector cannot be easily realized on layer 1001 and will require the Double-Optical-Layer EIC-PIC (DOL-EIC-PIC) technique to be described below. In the case of GaAs, GaN, InP, as layer 1001, these materials can provide optical gain and absorption and can be used to realize detectors or amplifiers in layer 1001.

Fabrication:

The Single-Optical-Layer EIC-PIC can be fabricated by using an electronic device fabrication compatible process (e.g. CMOS compatible process) to be described below to realize at least one coupling lens and at least one optical device on the chip.

Direct Double-Optical-Layer EIC-PIC:

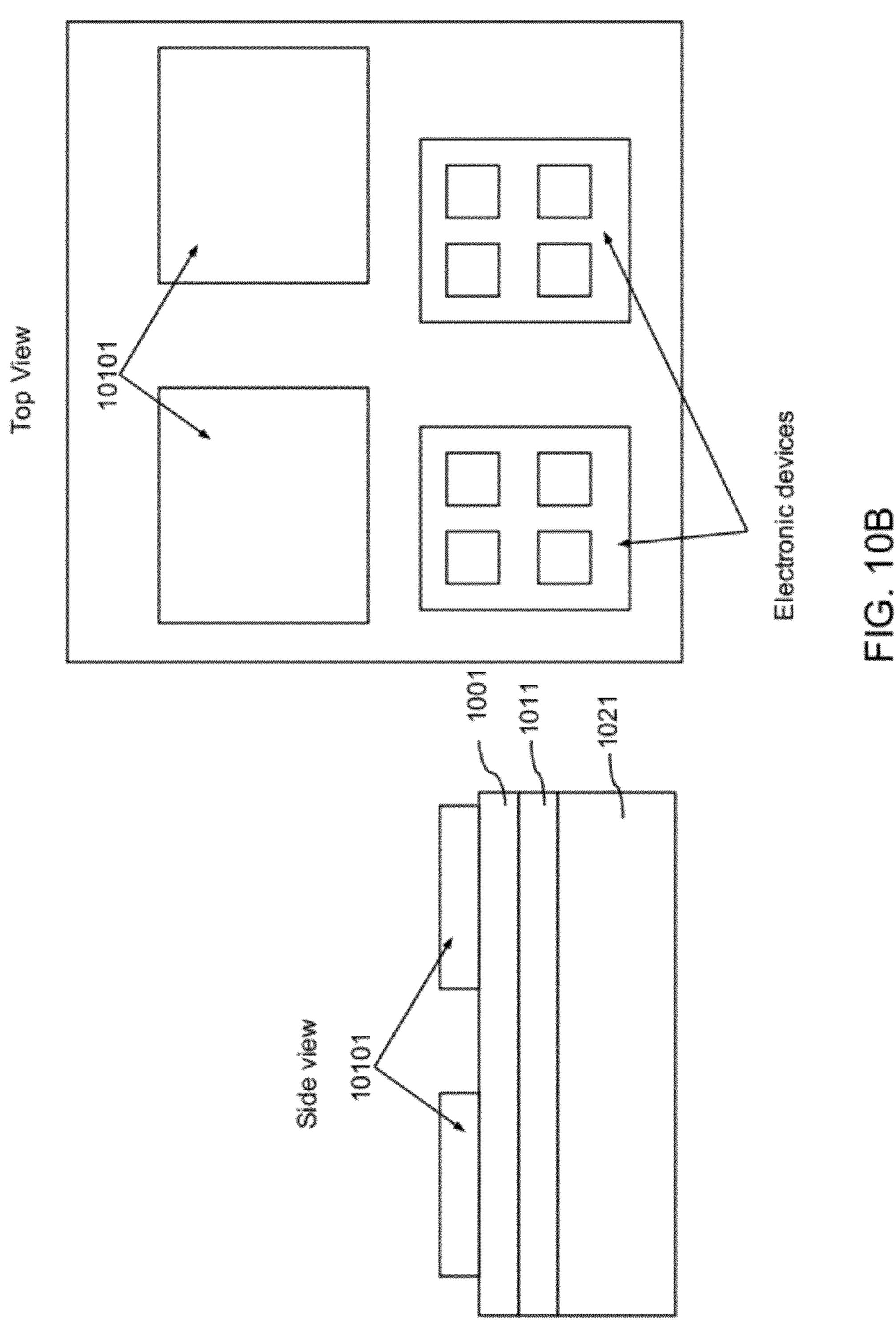

For the purpose of illustration but not limitation, as shown in FIG. 10A, in an exemplary embodiment, an adjacent opti-

cal layer 10101 is further put directly on top of first optical core layer 1001 resulting in Direct Double-Optical-Layer EIC-PIC (DDOL-EIC-PIC). The first optical core layer 1001 with thickness  $t_{EM}$  is on top of a first lower optical cladding layer 1011 with thickness  $t_{LOTM}$ . The first lower optical clad- 5 ding layer 1011 is on top of the first substrate 1021. The refractive index  $n_{EM}$  of the first optical core layer is higher than the refractive index  $n_{LCL}$  of the first lower optical cladding layer. In one embodiment, the refractive index  $n_{AOL}$  of the adjacent optical layer 10101 with thickness  $tt_{Ph}$  is near the refractive index  $n_{EM}$  of the first optical core layer. In one embodiment, the adjacent optical layer 10101 is an optical gain or absorptive material. In one embodiment, the adjacent optical layer 10101 is InGaAs quantum well structure with InGaAsP barrier material to provide optical gain for the wave propagating in layer 1001 with optical field penetrating into the adjacent optical layer 10101. As is well known to those skilled in the art, there are other gain material structures one can use to achieve optical gain. In another exemplary embodiment, at least one dielectric layer (first upper optical cladding layer) 10201 with thickness  $t_{UOTM}$  and refractive index  $n_{UCL}$ is further placed on top of layer 10101.

In an exemplary embodiment, the first substrate layer 1021 is the silicon substrate of a silicon-on-insulator (SOI) wafer, 25 the first lower optical cladding layer 1011 is the silicon dioxide layer on top of the silicon substrate in the SOI wafer, the first optical core layer 1001 is the top silicon layer of the SOI wafer, the adjacent optical layer 10101 is made of III-V semiconductor materials (e.g. InGaAs/InGaAsP/InP or 30 GaAs/AlGaAs material systems), and the first upper optical cladding layer 10201 is a silicon dioxide layer.

Multiple Active Areas:

In one embodiment, the adjacent optical layer 10101 is placed on multiple sub-areas on the chip as illustrated by the 35 side and top views in FIG. 10B In one embodiment, these gain-material areas are placed using local-area-bonding technique to be described below.

Input or Output Lens:

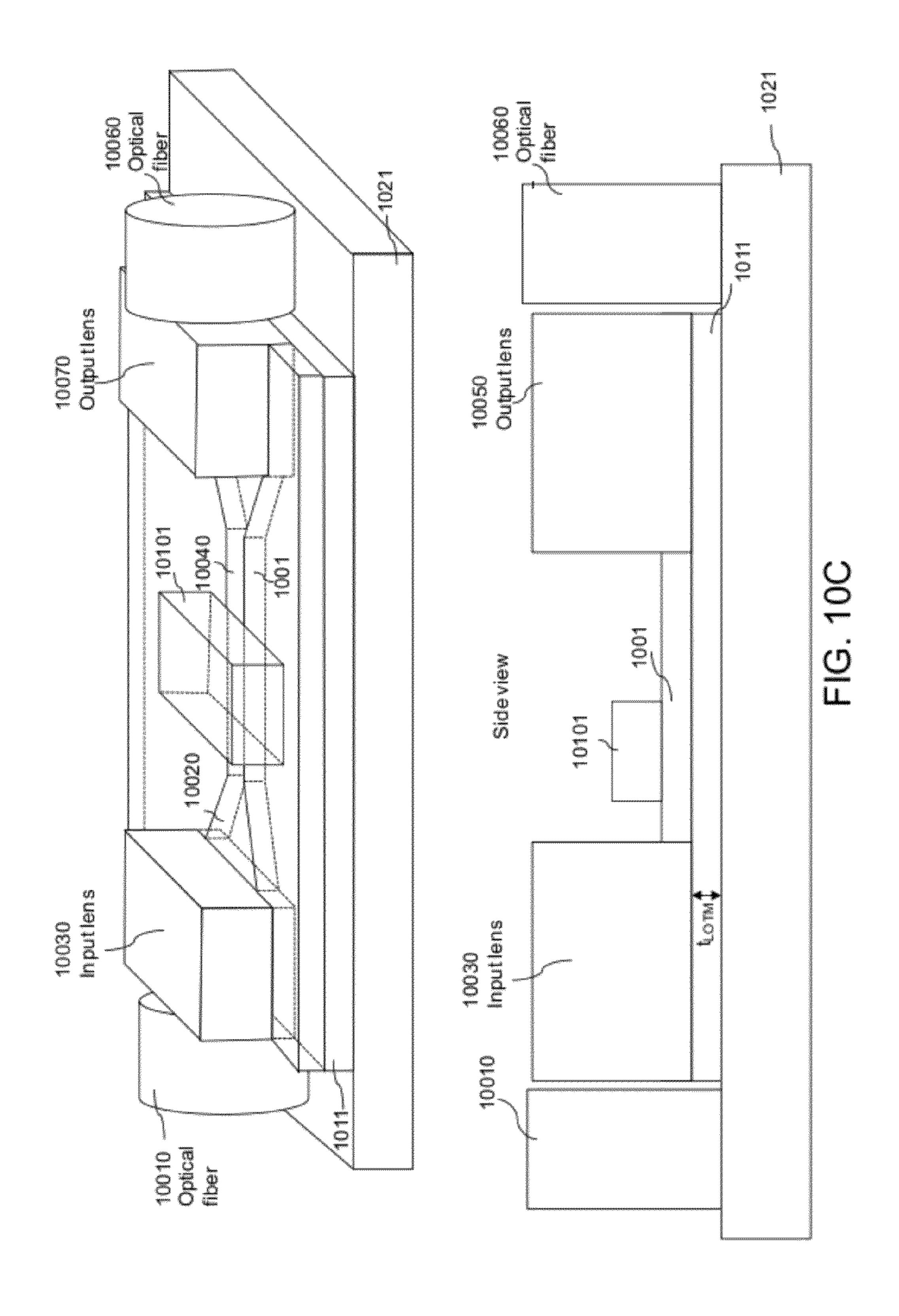

In an exemplary embodiment of the invention, the DDOL- 40 EIC-PIC consists of at least one input or output optical-fiber coupling optics (i.e. it can have only one or more input coupling optics without any output coupling optics or only one or more output coupling optics without any input coupling optics. It can also have both input coupling optics and output 45 coupling optics). FIG. 10C illustrates the case with one input optical-fiber coupling optics and one output optical-fiber coupling optics. At the input end, FIG. 10C shows the input optical-fiber coupling optics couples light from the optical fiber 10010 into layer 1001 that formed a channel waveguide 50 10020 utilizing an integrated lens on layer 10030. In an exemplary embodiment of the invention, the input coupling optics 10030 is a Superlens. At the output end, FIG. 10C shows the output optical-fiber coupling optics 10070 couples light from layer 1001 formed into a channel waveguide 10050 to an 55 output optical fiber 10060 utilizing an integrated lens 10070 on layer 1001. In an exemplary embodiment of the invention, the output coupling optics is a Superlens 10070. In an exemplary embodiment, the Superlens 10030 and Superlens 10070 are made up of two alternating thin dielectric layers that have 60 different refractive indices. In an exemplary embodiment, the alternating layer is made up of silicon and silicon dioxide with a structure similar to the superlens **5030** illustrated in FIG. **5**. In another exemplary embodiment, the input optical fiber 10010 or output optical fiber 10060 is held from below by a 65 V-groove or a trench structure fabricated on the substrate 1021 to match the size of the fiber and hold it at the right

**16**

height with respect to the lens optical center to achieve maximum coupling of light beam energy between the optical fiber and the waveguide on chip.

Photonic or Nanophotonic Device:

In an exemplary embodiment of the invention, as shown in FIG. 10C, the DDOL-EIC-PIC consists of at least one photonic/nanophotonic device 10040, that can be an optical waveguide, an optical wavelength multiplexer, an optical wavelength demultiplxer, an optical grating, an optical beam splitter, a polarization beam splitter, an optical isolator, a polarization rotator, an optical interferometer, an optical modulator, an optical ring resonator, an optical disk resonator, an optical curved reflector, an optical mirror, an optical amplifier, an optical detector, a laser, a light-emitting device, a one or more InGaAs quantum wells inter-spaced with 15 nonlinear-optical device, a photonic transistor, an optical harmonic frequency generator, an all-optical device, or other photonic/nanophotonic device well known to those skilled in the art.

> In an embodiment of the invention, the first optical core layer 1001 is silicon which silicon cannot provide optical gain. Thus in the case of active optical devices such as optical amplifiers, lasers, or light-emitting devices, the adjacent optical layer 10101 can then be made of an optical material with gain such as compound semiconductor material. Thus the direct Double-Optical-Layer structure can be used to achieve a wide range of active integrated optical devices that involve optical gain.

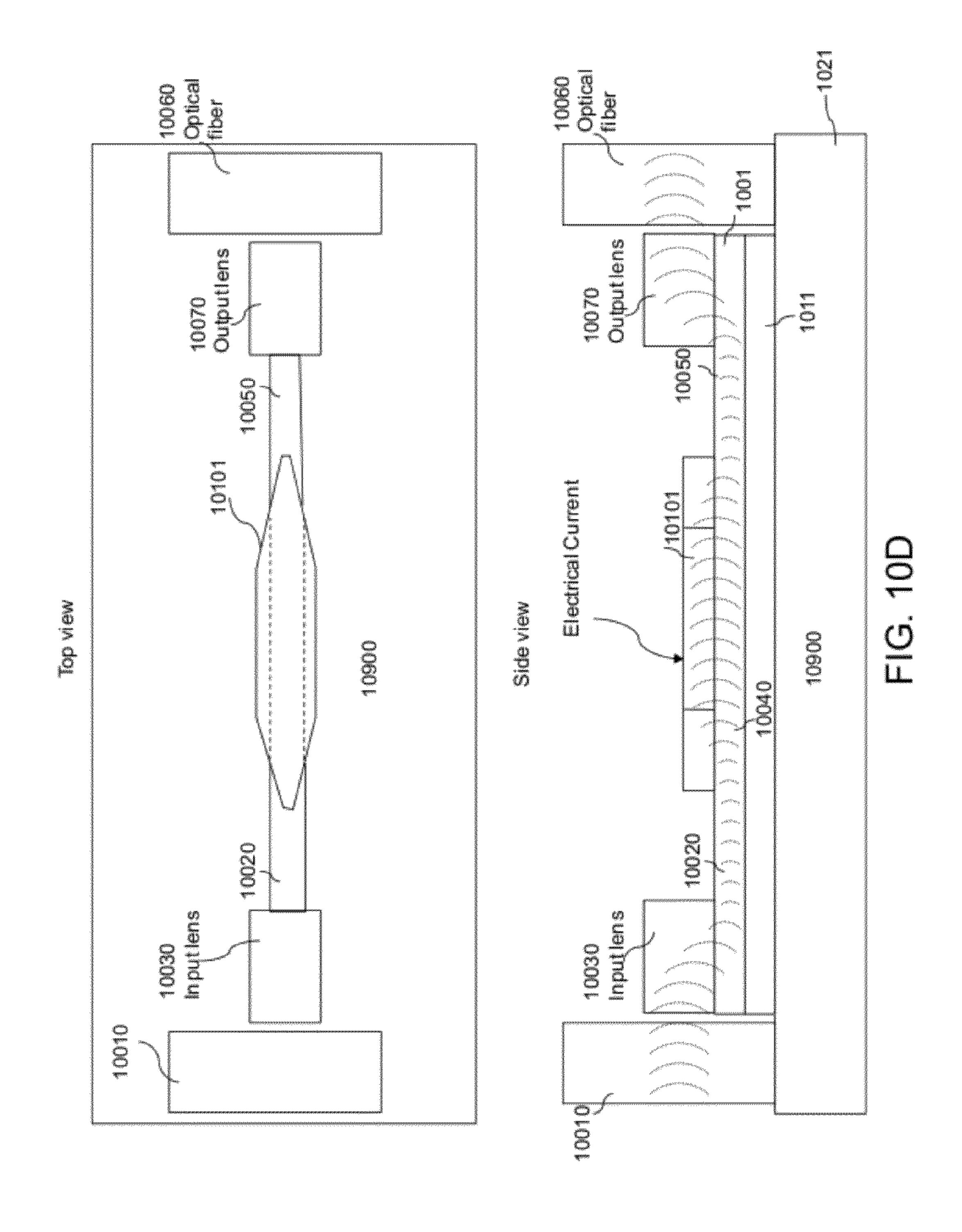

> In an exemplary embodiment of device 10900 shown in FIG. 10D, layer 1001 is silicon and the adjacent optical layer 10101 contains InGaAs quantum well structure with one or more InGaAs quantum wells inter-spaced with InGaAsP barrier material. Silicon cannot provide optical power gain. However, as is well known to those skilled in the art, InGaAs quantum wells can provide optical gain under current injection. Optical beam at a wavelength of  $\lambda_{OPT}$ =1550 nm propagating in layer 1001 enters the waveguiding section that is bonded with layer 10101 and propagates through the waveguiding section with optical gain layer 10101 to achieve optical power gain. In this exemplary embodiment, device 10900 acts as an optical amplifier.

Fabrication:

The DDOL-EIC-PIC can be fabricated using an electronic device fabrication compatible process (e.g. CMOS compatible process) to be described below to realize at least one coupling lens and at least one optical device on the chip.

Tapered Waveguide Structure:

FIG. 10D illustrates a tapered waveguide structure that can be used for the Direct Double-Optical-Layer EIC-PIC to push energy from the bottom waveguiding core layer 1001 to the top thin film layer 10101 with optical gain or vice versa, in accordance with an embodiment of the invention. The taper helps to squeeze the energy up to the adjacent optical layer 10101 or down to layer 1001 more gradually. Such gradual process reduces optical reflection at the edges or end regions where the adjacent optical layer 10101 is introduced, and increases optical power propagating through the device region with the adjacent optical layer 10101. The actual dimensional variation for the waveguide tapers is not be very important as long as the tapered waveguide width goes from a width large compared to half the wavelength in the waveguiding core 1001 to a width small compared to half the wavelength in the waveguiding core 1001. In an exemplary embodiment, device region with the adjacent optical layer 10101 shown in FIG. 10D is electrically excited via an injection current and acts as an optical power amplifier.

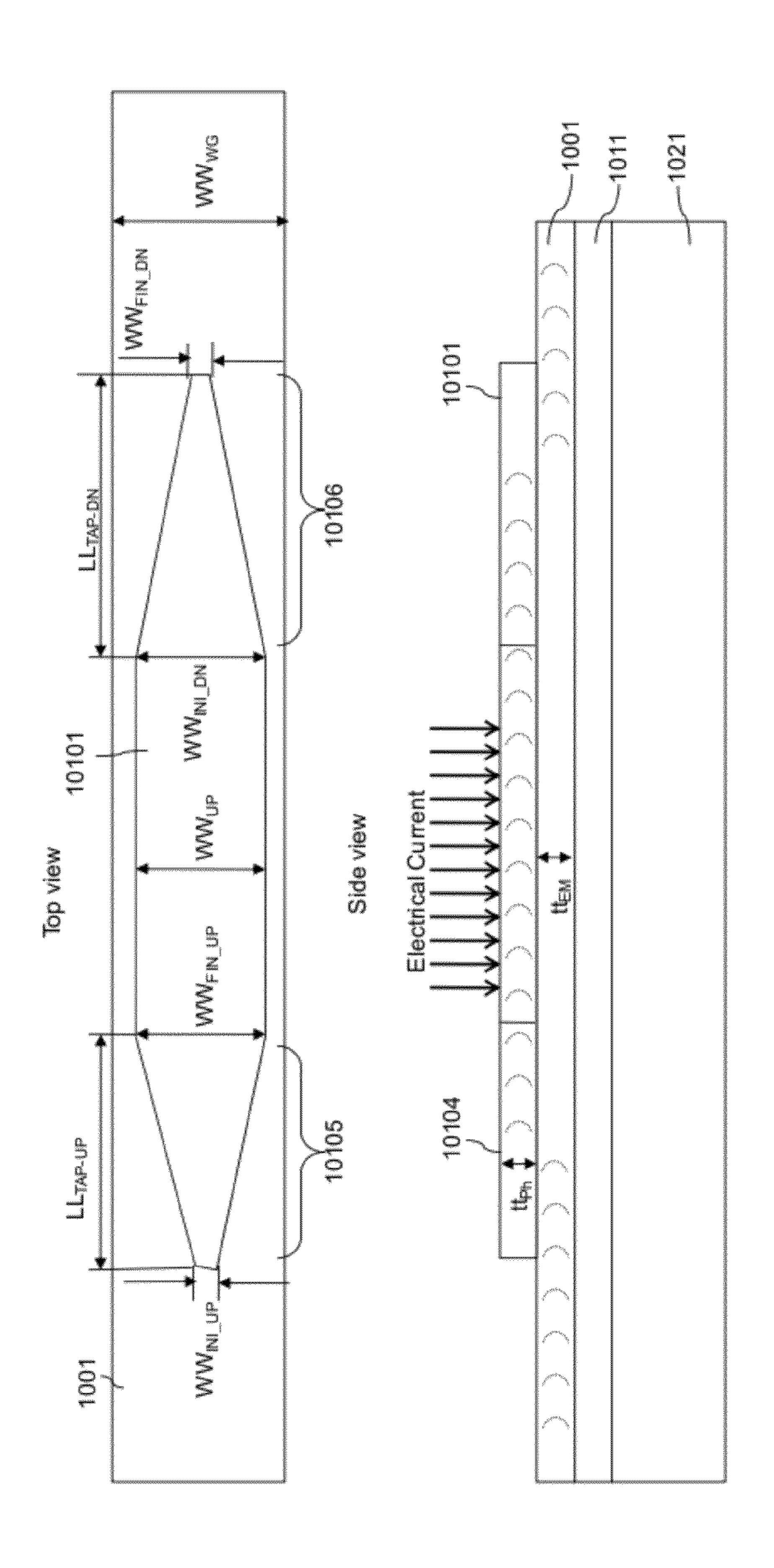

In an embodiment of the invention, as shown in FIG. 10E, the beam from the first waveguide core layer 1001 enters the

adjacent optical layer **10101** region with a tapered waveguide **10105**. **10105** is a tapering waveguide section in layer **10101** tapering from an initial width  $WW_{INI-UP}$  to a final width  $WW_{FIN-UP}$  in a taper length  $LL_{TAP-UP}$ . The width of layer **10101**  $WW_{UP}$  and waveguide width of layer **10101**  $WW_{WG}$  can 5 be equal or different.

In another embodiment of the invention, as shown in FIG. 10E, the beam from the waveguide with the adjacent optical layer 10101 enters the first waveguide core layer 1001 region with a tapered waveguide 10106. 10106 is a tapering waveguide section in layer 10101 tapering from an initial width  $WW_{INI-DN}$  to a final width  $WW_{FIN-DN}$  in a taper length  $LL_{TAP-DN}$ . The width of layer 10101  $WW_{UP}$  and waveguide width of layer 1001  $WW_{UG}$  can be equal or different.

The height of layer 1001 is  $t_{EM}$ , and the height of layer 15 coupling structure as discussed below. 10101 is  $t_{Ph}$ .

In an exemplary embodiment, waveguide core **1001** is silicon with thickness  $t_{EM}$ =300 nm, and top waveguide layer **10101** is InGaAs quantum well structure with three InGaAs quantum wells interspaced with InGaAsP barrier layers and 20 adjacent optical layer **10101** has a refractive index around  $n_{AOL}$ =3.4 and a total thickness  $tt_{Ph}$ =150 nm. The taper dimensions are  $WW_{INI-UP}$ = $WW_{FIN-DN}$ =100 nm,  $WW_{INI-DN}$ = $WW_{FIN-UP}$ =400 nm,  $V_{INI-UP}$ = $V_{INI-UP$

The various methods and systems described above for monolithic integration of active and/or passive photonic (and/or nanophotonic) devices in a way that is compatible with electronic integration will become clear with detailed descriptions of the methods and systems for the various 30 exemplary EIC-PICs described below.

Indirect Double-Optical-Layer EIC-PIC:

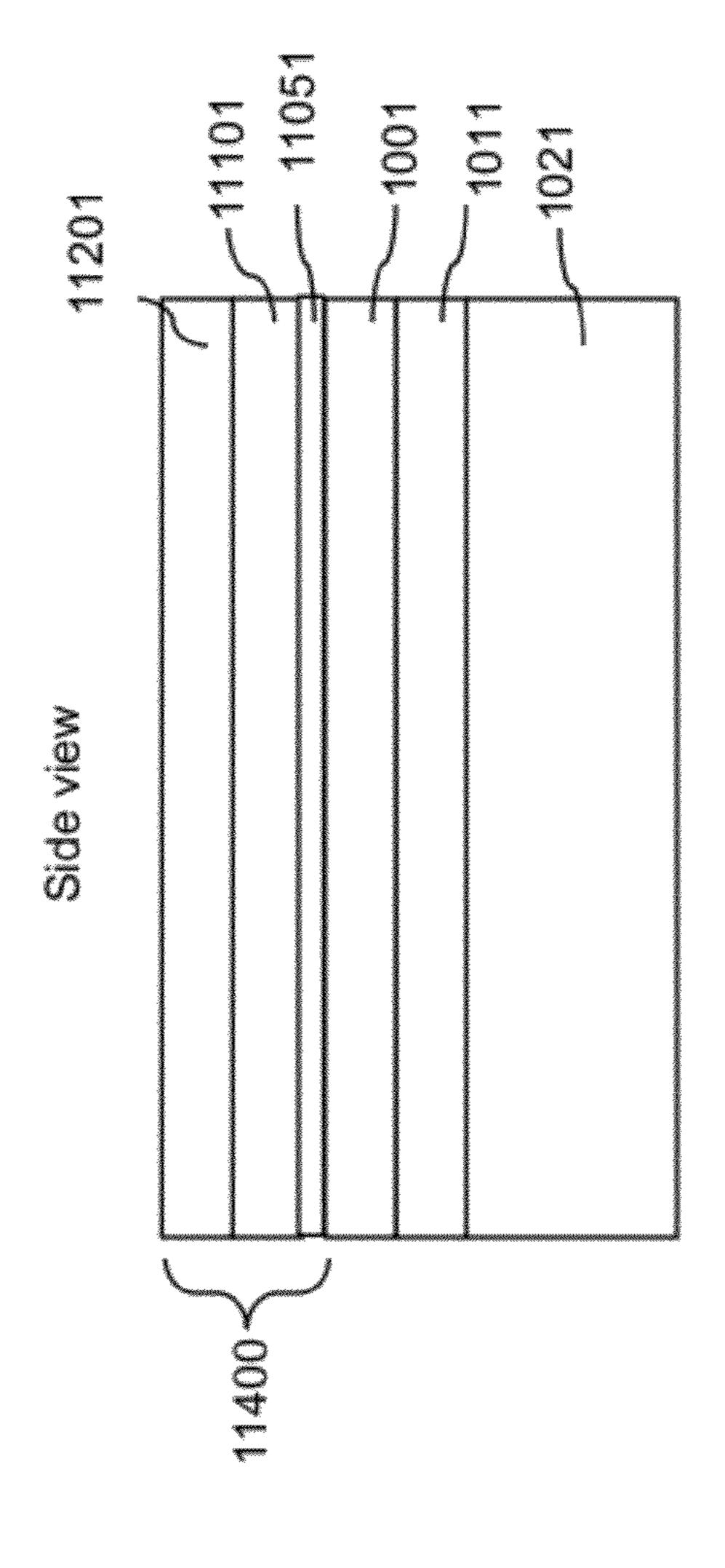

For the purpose of illustration but not limitation, as shown in FIG. 11A, in an exemplary embodiment, a thin first interspaced dielectric structure layer 11051 with thickness  $t_{DIE}$  35 and refractive index  $n_{DIE}$  is placed on the first optical core layer 1001 and a second optical core layer 11101 is further put directly on top of layer 11051 resulting in Indirect Double-Optical-Layer EIC-PIC (IDDOL-EIC-PIC). The first optical core layer 1001 with thickness  $t_{EM}$  is on top of a first lower 40 optical cladding layer 1011 with thickness  $t_{LOTM}$ . The first lower optical cladding layer 1011 with thickness is on top of the first substrate 1021. The refractive index  $n_{EM}$  of the first optical core layer is higher than the refractive index  $n_{LCL}$  of the first lower optical cladding layer. The first interspaced 45 dielectric structure layer 11051 may be made up of one or more further-divided layers of different dielectric materials. The refractive index  $n_{2QC}$  of the second optical core layer 11101 and the refractive index  $n_{EM}$  of the first optical core layer 1001 are both higher than the refractive index of the first 50 interspaced dielectric structure layer 11051, In one embodiment, the second optical core layer 11101 is an optical gain or absorptive material layer.

In another exemplary embodiment, at least one dielectric layer (first upper optical cladding layer) 11201 with thickness 55  $t_{UOTM}$  and refractive index  $n_{UCL}$  is further placed on top of layer 11101. Layer 11051 and layer 11101 with optional layer 11201 together is referred to as "active-layer structure" 11400. In one embodiment, layer 11051 is Silicon Nitride and layer 11101 is InGaAs quantum well structure with one or 60 more InGaAs quantum wells inter-spaced with InGaAsP barrier material to provide optical gain for the wave coupling from layer 1001 to layer 11101. As is well known to those skilled in the art, there are other gain material structures one can use to achieve optical gain.

In an exemplary embodiment, the first substrate 1021 layer is the silicon substrate of a silicon-on-insulator (SOI) wafer,

18

the first lower optical cladding layer 1011 is the silicon dioxide layer on top of the silicon substrate in the SOI wafer, the first optical core layer 1001 is the top silicon layer of the SOI wafer, the first interspaced dielectric structure layer 11051 is a silicon nitride layer, the second optical core layer 11101 is made of III-V semiconductor materials (e.g. InGaAs/In-GaAsP/InP or GaAs/AlGaAs material systems), and the first upper optical cladding layer 11201 is a silicon dioxide layer.

Up/Down Coupling Tapered Waveguide in Indirect Double-Optical-Layer EIC-PIC:

In an embodiment of the invention, the coupling between optical beam propagating in the second waveguide core layer 11101 and optical beam propagating in the first waveguide core layer 1001 is achieved using tapered waveguide vertical coupling structure as discussed below.

FIG. 11D illustrates the coupling of optical beam from propagating in layer 1001 up to propagating in layer 11101 which is achieved by using a tapered waveguide vertical up-coupling structure 11105. 11105 is a tapering waveguide section in layer 11101 tapering from an initial with  $W_{INI-UP}$  to a final width  $W_{FIN-UP}$  in a taper length  $L_{TAP-UP}$ . The waveguide width of layer 1101  $W_{WG-UP}$  and waveguide width of layer 1001  $W_{WG-DN}$  can be equal or different.

In another embodiment, the coupling of optical beam from propagating in layer 11101 down to propagating in layer 1001 is achieved by using an optical vertical down-coupling tapered waveguide structure 11106. 11106 is a tapering waveguide section in layer 11101 tapering from an initial with  $W_{INI-DN}$  to a final width  $W_{FIN-DN}$  in a taper length  $L_{TAP-DN}$ . The waveguide width of layer 1101  $W_{WG-UP}$  and waveguide width of layer 1001  $W_{WG-DN}$  can be equal or different.

The height of layer 1001 is  $t_{EM}$ , the height of layer 11101 is  $t_{Ph}$ , and the height of layer 11105 is  $t_{DIE}$ .

Tapered Waveguide Coupling Structure Design:

As is well known to those skilled in the art, if the first waveguide core layer 1001 has a propagating refractive index  $n_E$ , lower than the propagating refractive index  $n_{Ph}$  of the second waveguiding core layer 11101 with width W=W(Z) at location Z, where Z is spatial displacement along the direction of propagation as shown in FIG. 11D. The propagating refractive index  $n_{Ph}$  is a function of W and hence Z so that  $n_{Ph}=n_{Ph}(W)=n_{Ph}(W(Z))$ . A person skilled in the art will appreciate that the wider the W, the higher the  $n_{Ph}$ .

By tapering the waveguide 11105 so that W(Z) changes with Z in layer 11101, one can change the propagating index  $n_{Ph}$  so that it matches the value of  $n_{El}$ . At the region 11104 in FIG. 11D when  $n_{Ph}$  is approximately equal to  $n_{El}$ , there will be resonant waveguide coupling so that the wave will couple from the bottom waveguiding core 1001 to the top waveguiding core 11101. Similarly for the tapered waveguide coupler 11106, by tapering 11106, again at the region when  $n_{Ph}=n_{El}$ , there will be resonant waveguide coupling so that the wave will couple from the top waveguiding core 11101 to the bottom waveguiding core 1001.

As is well known to those skilled in the art, the exact shape of the taper is not so important as to have one substantial length of the tapering section where  $n_{Ph}=n_{EI}$ . Hence the taper can have arbitrary curvilinear shape the way it changes its horizontal width W(Z) as a function of spatial coordinate distance Z along the direction of wave propagation. As is well known to those skilled in the art, when this substantial length is equal about one coupling length, there will be efficient transfer of light energy between the top and the bottom waveguiding core layers 11101 and 1001 (typically >90%). Thus, the taper's width typically will go from a width approximately equal to or larger than half the wavelength in

the top waveguiding core 11101 to a width smaller than half the wavelength in the top waveguiding core 11101. The tapering length  $L_{TAP-UP}$  or  $L_{TAP-DN}$  is chosen so that a substantial length of the taper achieves near-resonant waveguide energy coupling as described above.

Once the optical beam energy is transferred from the lower waveguide core 1001 to the upper waveguide core 11101 and propagates into a straight waveguiding section with constant width, the energy will stay in 11101. This is because  $n_{Ph}(W)$ will become higher than  $n_{EI}$  (due to the increased width at the taper end connecting to the straight waveguiding section of 11101) so light energy will only guide in the upper waveguiding core 11101 until it meet with the down-coupling tapered waveguide.

In one exemplary embodiment, lower waveguide core 15 layer 1001 is silicon with thickness  $t_{EM}$ =200 nm, upper waveguide core layer 11101 is InGaAs quantum well structure with five InGaAs quantum wells interspaced with InGaAsP barrier layers with the respective material bandgap energies and thicknesses shown in FIG. 11E and layer 11101 has a refractive index around  $n_{2OL} = n_{InGaAsP} = 3.3$  and a total thickness  $t_{Ph}$ =350 nm, layer 1001 has a refractive index around  $n_{EM} = n_{Si} = 3.5$ , and dielectric layer 11051 is Silicon Nitride with a refractive index around  $n_{SiN}$ =2.0 and a thickness  $t_{DIE}$ =200 nm. The taper dimensions are  $W_{INI-UP}$ = 25  $W_{FIN-DN}=100$  nm,  $W_{INI-DN}=W_{FIN-UP}=400$  $L_{TAP-UP} = L_{TAP-DN} = 30 \mu m, W_{WG-UP} = 400 nm, W_{WG-DN} = 400 nm$ nm.  $n_{FI}=2.2$ ,  $n_{Ph}(400 \text{ nm})=2.383$ .

FIG. 9 shows an electromagnetic simulation of energy coupling from the bottom waveguiding core **1001** to the top 30 waveguiding core 11101 through a taper-waveguide vertical coupling structure, in accordance with an embodiment of the invention.

Multiple Active Areas:

placed on multiple sub-areas on the chip as illustrated by the top view and cross-sectional view in FIG. 11B. In one embodiment, these active-layer structure areas are placed using local-area-bonding technique to be described below.

Input or Output Lens:

In an exemplary embodiment of the invention, the IDDOL-EIC-PIC consists of at least one input or output optical-fiber coupling optics (i.e. it can have only one or more input coupling optics without any output coupling optics or only one or more output coupling optics without any input coupling 45 optics. It can also have both input coupling optics and output coupling optics) FIG. 11C illustrates the case with one input optical-fiber coupling optics and one output optical-fiber coupling optics. At the input end, FIG. 11C shows the input optical-fiber coupling optics coupling light from the optical 50 fiber 11010 into layer 1001 that forms a channel waveguide 11020 utilizing an integrated lens on layer 11030. In an exemplary embodiment of the invention, the input coupling optics 11030 is a Superlens. FIG. 11C shows the output optical-fiber coupling optics 11070 coupling light from layer 1001 formed 55 into a channel waveguide 11050 to an output optical fiber 10060 utilizing an integrated lens 11070 on layer 1001. In an exemplary embodiment of the invention, the output coupling optics is a Superlens 11070. In an exemplary embodiment, the Superlens 11030 and Superlens 11070 are made up of two 60 alternating thin dielectric layers that have different refractive indices. In an exemplary embodiment, the alternating layer is made up of silicon and silicon dioxide with a structure similar to the superlens **5030** illustrated in FIG. **5**. In another exemplary embodiment, the input optical fiber 11010 or output 65 optical fiber 11060 is held from below by a V-groove or a trench structure fabricated on the substrate 1021 to match the

**20**

size of the fiber and hold it at the right height with respect to the lens optical center to achieve maximum coupling of light beam energy between the optical fiber and the waveguide on chip.

Photonic/Nanophotonic Device:

In an exemplary embodiment of the invention, the IDDOL-EIC-PIC consists of at least one photonic/nanophotonic device 11040, that can be an optical waveguide, an optical wavelength multiplexer, an optical wavelength demultiplxer, an optical grating, an optical beam splitter, a polarization beam splitter, an optical isolator, a polarization rotator, an optical interferometer, an optical modulator, an optical ring resonator, an optical disk resonator, an optical curved reflector, an optical mirror, an optical amplifier, a laser, a lightemitting device, an optical detector, a nonlinear-optical device, a photonic transistor, an optical harmonic frequency generator, an all-optical device, or other photonic/nanophotonic devices well known to those skilled in the art.

In an embodiment, layer 1001 is silicon which silicon cannot provide optical gain. Thus in the case of active optical devices such as optical amplifier, laser, or light-emitting device, up-down vertical coupling structure is used to transport beam from layer 1001 to layer 11101. Layer 11101 can then be made of an optical material with gain such as compound semiconductor material. Thus the Indirect Double-Optical-Layer structure can be used to achieve a wide range of active integrated optical devices that involve optical gain.

In an exemplary embodiment of device 11900 shown in FIG. 11D, layer 1001 is silicon and layer 11101 contains InGaAs quantum well structure with one or more InGaAs quantum wells inter-spaced with InGaAsP barrier material. Silicon cannot provide optical power gain. However, as is well known to those skilled in the art, InGaAs quantum wells can provide optical gain under current injection. Optical In one embodiment, the "active-layer structure" 11400 is 35 beam at a wavelength of  $\lambda_{OPT}$ =1550 nm propagating in layer 1001 is coupled up to layer 11101 using vertical up-coupling tapered waveguide 11105 and propagates through the optical gain layer 11101 to achieve optical power gain. The beam is then coupled from layer 11101 down to layer 1001 using vertical down-coupling tapered waveguide 11106. In this exemplary embodiment, device 11900 acts as an optical amplifier.

Fabrication:

The IDDOL-EIC-PIC can be fabricated using an electronic device fabrication compatible process (e.g. CMOS compatible process) to realize at least one coupling lens and at least one optical device on the chip to be described below.

The various methods and systems described above for monolithic integration of active and/or passive photonic (and/ or nanophotonic) devices in a way that is compatible with electronic integration will become clear with detailed descriptions of the methods and systems for the various exemplary EIC-PICs described below.

Indirect Triple-Optical-Layer EIC-PIC:

For the purpose of illustration but not limitation, as shown in FIG. 11F, the structure can be extended from doubleoptical layer to triple optical layer via the use of tapered waveguide coupler 11650 to vertically couple light from the top optical layer 11600 to the middle optical layer 11700 and similar tapered waveguide coupler to couple light from the middle optical layer 11700 to the top optical layer 11600, and the use of tapered waveguide coupler 11750 to vertically couple light from the middle optical layer 11700 to the bottom optical layer 11800 and similar tapered waveguide coupler to couple light from the bottom optical layer 11800 to the middle optical layer 11700. In FIG. 11D, the top optical layer 11600 is compound semiconductor (e.g. III-V semiconductor) layer