#### US008188583B2

## (12) United States Patent

#### Arita et al.

# (10) Patent No.: US 8,188,583 B2 (45) Date of Patent: May 29, 2012

### (54) SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING SAME

(75) Inventors: Junichi Arita, Tokyo (JP); Kazuko

Hanawa, Tokyo (JP); Makoto Nishimura, Tokyo (JP)

(73) Assignee: Renesas Electronics Corporation,

Kawasaki-shi (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 180 days.

(21) Appl. No.: 12/731,201

(22) Filed: Mar. 25, 2010

(65) Prior Publication Data

US 2010/0244214 A1 Sep. 30, 2010

#### (30) Foreign Application Priority Data

Mar. 31, 2009 (JP) ...... 2009-086427

(51) **Int. Cl.**

$H01L\ 23/495$  (2006.01)

(52) **U.S. Cl.** ...... **257/676**; 257/E23.039; 257/669; 257/670; 257/674; 438/123

(58) **Field of Classification Search** ....................... 257/E23.039, 257/E23.031, E21.506, 676, 666, 669, 670, 257/667, 674; 438/123, 124, 112, 127

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,942,454 A | * | 7/1990 | Mori et al 257/676     |

|-------------|---|--------|------------------------|

| 5,150,193 A | * | 9/1992 | Yasuhara et al 257/669 |

| 5,378,656 A | * | 1/1995 | Kajihara et al 29/827  |

| 5,712,507 A | * | 1/1998 | Eguchi et al 257/666   |

| 5,874,773 A * 5,942,794 A * 5,986,333 A * 6,020,625 A * | 2/1999<br>8/1999<br>11/1999<br>2/2000  | Terada et al.       257/676         Okumura et al.       257/666         Nakamura       257/667         Qin et al.       257/666   |

|---------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 6,087,715 A * 6,114,752 A * 6,137,160 A * 6,306,687 B1* | 7/2000<br>9/2000<br>10/2000<br>10/2001 | Sawada et al.       257/666         Huang et al.       257/666         Ishikawa       257/676         Corisis et al.       438/123 |

| 6,454,158 B1 * 6,642,609 B1 * 6,828,659 B2 *            | 9/2002<br>11/2003<br>12/2004           | Takahashi       228/180.5         Minamio et al.       257/666         Iwakiri       257/666                                       |

| 6,828,661 B2*                                           | 12/2004<br>(Con                        | Araki et al 257/676 tinued)                                                                                                        |

#### FOREIGN PATENT DOCUMENTS

JP 6-216303 A 8/1994 (Continued)

Primary Examiner — Chris Chu

(74) Attorney, Agent, or Firm — Miles & Stockbridge P.C.

#### (57) ABSTRACT

To improve the heat dissipation characteristics of a semiconductor device.

The semiconductor device has a die pad, a heat dissipating plate in the form of a frame arranged between the die pad and a plurality of leads so as to surround the die pad, a plurality of members that connect the die pad and the inner edge of the heat dissipating plate, and a suspension lead linked to the outer extension of the heat dissipating plate, wherein a semiconductor chip the outer shape of which is larger than the die pad is mounted over the die pad and the members. The top surface of the die pad and the top surface of the members at the part in opposition to the back surface of the semiconductor chip are bonded to the back surface of the semiconductor chip in their entire surfaces with a silver paste. Heat in the semiconductor chip is conducted from the back surface of the semiconductor chip to the heat dissipating plate via the silver paste, the die pad, and the member, and dissipated to the outside of the semiconductor device therefrom via the lead.

#### 19 Claims, 49 Drawing Sheets

### US 8,188,583 B2

Page 2

### U.S. PATENT DOCUMENTS FOREIGN PATENT DOCUMENTS

| 6,943,456 B2*    | 9/2005  | Miyaki et al 257/784   | JP        | 8-78605 A     | 3/1996  |

|------------------|---------|------------------------|-----------|---------------|---------|

| 7,834,429 B2*    | 11/2010 | Uematsu                | JP        | 11-168169 A   | 6/1999  |

| 7,952,177 B2*    | 5/2011  | Kawasaki et al 257/678 | JP        | 2001-345412 A | 12/2001 |

| 2006/0033185 A1* | 2/2006  | Kummerl et al 257/666  | JP        | 2005-183492 A | 7/2005  |

| 2007/0007634 A1* | 1/2007  | Youn et al 257/676     | * cited 1 | by examiner   |         |

FIG. 1 4(4b) 4(4b) SD4 4(4b) 4(4b) \_B1\_ <u>B1</u> \_\_\_ -7(7a) $\sim$  4(4b) 4(4b) \_\_\_\_ Al/ SD2 / 4(4b) 4(4b) 4(4b)

FIG. 2 4(4b) 4(4b)4(4b) SD2 A1` 13~4(4b) 4(4b) \_\_\_\_ SD3 — \_\_ SD1 \_\_B1 **♦ ▼**B1 - 7(7b) 13-4(4b) 4(4b) Al` SD4 4(4b) 4(4b) 4(4b)

FIG. 3 4(4b) 4(4a) \_ 4(4b) 4(4b) 4(4a) 4(4a) B1 • **≜** B1 4(4a) 4(4a) 4(4b) \_ 4(4a) 4(4a) 4(4b) 4(4b)

FIG. 4

FIG. 5

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15 H4

FIG. 17

FIG. 19

FIG. 20

FIG. 24

FIG. 25

F/G. 26

FIG. 27

FIG. 28

FIG. 29

F/G. 33

FIG. 38

FIG. 41

FIG. 48

FIG. 52

FIG. 53

FIG. 54

F/G. 55

F/G. 56

FIG. 57

FIG. 58

FIG. 59 4(4b) 4(4b) SD2 \_ 4(4b) 4(4b) \_\_\_\_ \_ 4(4b) 4(4b) \_\_\_\_ 6(6b) 7(7b) SD3 ~ — SD1 -4(4b)7(7b)SD4 4(4b) 4(4b)4(4b)

FIG. 60

FIG. 64

FIG. 65 1d 4(4d)4(4d) 4(4d) 7(7b) 4(4d) 4(4d) — - 7(7b) 4(4d) - 6(6b) 4(4d) 4(4d) -4(4d) 4(4d) 4(4d)

F/G. 66

F/G. 67

FIG. 70 A4 4(4a)4(4a) **≜** B4

# SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING SAME

## CROSS-REFERENCE TO RELATED APPLICATION

The disclosure of Japanese Patent Application No. 2009-86427 filed on Mar. 31, 2009 including the specification, drawings and abstract is incorporated herein by reference in its entirety.

#### BACKGROUND OF THE INVENTION

The present invention relates to a semiconductor device and a method of manufacturing the same, in particular, to 15 technology which is effective when applied to a resin-sealed semiconductor package and a method of manufacturing the same.

A QFP semiconductor device is manufactured by mounting a semiconductor chip over a chip mounting part of a lead 20 frame, coupling a plurality of leads of the lead frame and a plurality of electrodes of the semiconductor chip with a bonding wire, forming a sealing resin part that seals the chip mounting part, the semiconductor chip, the bonding wire, and the inner lead part of the leads, cutting the lead from the lead 25 frame, and bending the outer lead part of the lead.

Japanese Patent Laid-Open No. Hei 6-216303 (Patent Document 1) describes a technique to make the outer dimensions of a die pad smaller than the outer dimensions of a semiconductor chip to be mounted thereon.

Japanese Patent Laid-Open No. Hei 11-168169 (Patent Document 2) describes a technique to provide a ground coupling part electrically coupled to a tab suspension lead and supported thereby.

Japanese Patent Laid-Open No. Hei 8-78605 (Patent Document 3) describes a technique to provide a slit in the center of a die pad part and at the same time, to provide a plurality of slits that surround the slit around the outer circumference of the die pad part.

Japanese Patent Laid-Open No. 2001-345412 (Patent 40 Document 4) describes a semiconductor device having a configuration in which a die pad support that supports a die pad has a stress relaxing part in a region located between the die pad and the tip end of an inner lead.

Japanese Patent Laid-Open No. 2005-183492 (Patent 45 Document 5) describes that a die pad has a bonded part in the center, an opened slit part, and a circumferential edge part, the circumferential edge part is formed around the outside of the bonded part, the slit part is formed so as to surround the bonded part and to be located between the bonded part and the 50 circumferential edge part, the four corners of a semiconductor chip bonded to the bonded part are supported while overlapping the circumferential edge part, and part of the slit part bulges out to the outside of the semiconductor chip.

### SUMMARY OF THE INVENTION

The examination of the inventors of the present invention has found the following.

A semiconductor package (semiconductor device) used in 60 an automobile etc. is placed in a high temperature environment when on board, and therefore, an LSI formed in a semiconductor chip in the package is operated in a high temperature environment as a result. Further, as the functions of an LSI are improved or its operation speed is increased, 65 power consumption of a semiconductor chip in a package tends to increase and the amount of generated heat also tends

2

to increase. Because of this, the temperature of a semiconductor element in operation, which constitutes the LSI in the semiconductor chip, is the sum of the high temperature in the environment and an increase in temperature due to heat generation, and therefore, the temperature becomes higher and higher.

However, the higher the temperature of a semiconductor element (MISFET element etc.) in operation, which constitutes an LSI in a semiconductor chip, the more likely the deterioration of a gate insulating film etc. occurs, and therefore, its lifetime is reduced. Further, in an operation at high temperatures, the leak current tends to increase and therefore a malfunction becomes more likely to occur. Because of this, it is desired to suppress an increase in temperature of a semiconductor chip in a package by improving the heat dissipation characteristics of the semiconductor package. For example, for a semiconductor package used as a microcomputer for controlling an engine and a transmission of an automobile, it is demanded to suppress the temperature of a semiconductor element formed in a semiconductor chip in the package to 150° C. or less under the conditions that power consumption is 0.7 W and the temperature of the environment when in operation is 125° C.

Because of this, a semiconductor package is desired, which has high reliability and has improved the heat dissipation characteristics (that is, the thermal resistance is low).

The present invention has been made in view of the above circumstances and provides a technique capable of improving the heat dissipation characteristics of a semiconductor device.

The other purposes and the new feature of the present invention will become clear from the description of the present specification and the accompanying drawings.

The following explains briefly the outline of a typical invention among the inventions disclosed in the present application

A semiconductor device according to a typical embodiment has a semiconductor chip, a plurality of leads arranged around the semiconductor chip, a bonding wire that electrically couples the lead and an electrode, respectively, a chip mounting part on which the semiconductor chip is mounted, a frame body part arranged between the chip mounting part and the lead so as to surround the chip mounting part, and a plurality of suspension leads linked to the outer edge of the frame body part. Further, the semiconductor device comprises a sealing body that seals the semiconductor chip, the bonding wire, the chip mounting part, the frame body part, the suspension lead, and part of the lead. Then, the chip mounting part is located immediately under the semiconductor chip and has a first part smaller than the outer shape of the semiconductor chip and a plurality of second parts that connect the first part and the inner edge of the frame body part, and the main surface of the first part and the main surface of the part of the second part in opposition to the back surface of the semiconductor chip are bonded to the back surface of the 55 semiconductor chip in their entire surfaces with an adhesive.

A semiconductor device according to another typical embodiment has a semiconductor chip, a plurality of leads arranged around the semiconductor chip, a bonding wire that electrically couples the lead and the electrode, respectively, a chip mounting part on which the semiconductor chip is mounted, a frame body part arranged between the chip mounting part and the lead so as to surround the chip mounting part, and a plurality of suspension leads linked to the outer edge of the frame body part. Further, the semiconductor device comprises a sealing body that seals the semiconductor chip, the bonding wire, the chip mounting part, the frame body part, the suspension lead, and part of the lead. Then, the

chip mounting part is located immediately under the semiconductor chip and has a first part smaller than the outer shape of the semiconductor chip and a plurality of second parts that connect the first part and the inner edge of the frame body part, the main surface of the first part and the main surface of the part of the second part in opposition to the back surface of the semiconductor chip are bonded to the back surface of the semiconductor chip in their entire surfaces with an adhesive, and the thermal conductivity of the adhesive is higher than the thermal conductivity of the sealing body.

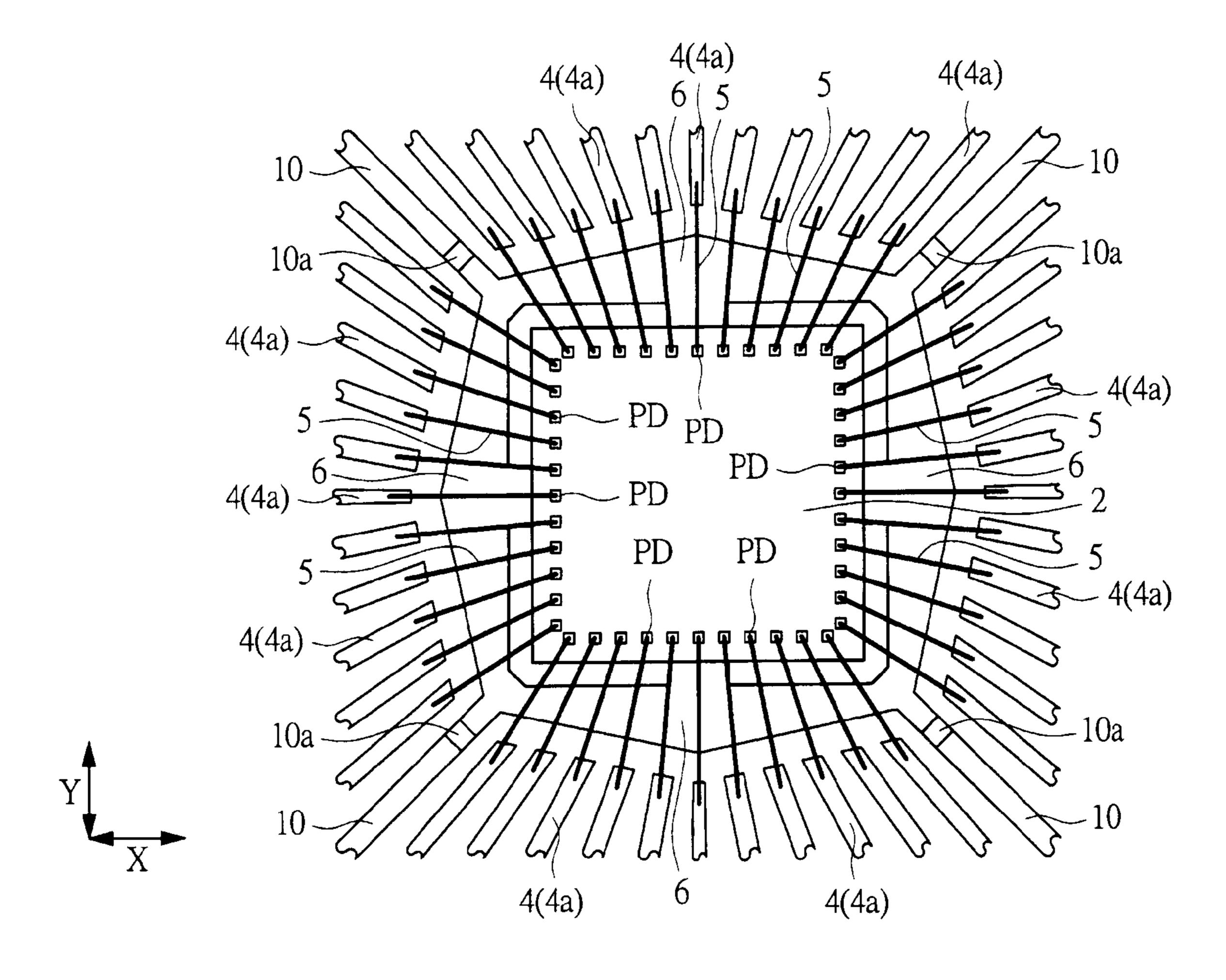

A semiconductor device according to still another typical embodiment has a semiconductor chip, a plurality of leads arranged around the semiconductor chip, a bonding wire that electrically couples the lead and the electrode, respectively, a chip mounting part on which the semiconductor chip is 15 mounted, and a plurality of suspension leads linked to the chip mounting part. Further, the semiconductor device comprises a sealing body that seals the semiconductor chip, the bonding wire, the chip mounting part, the suspension lead, and part of the lead. Then, the outer edge of the chip mounting 20 part is located outside the outer circumference of the semiconductor chip, a plurality of openings that penetrate through from the main surface to the back surface is formed in the chip mounting part, and the respective openings have a part that overlaps the semiconductor chip in a planar manner and a part 25 that does not. Then, the main surface of the chip mounting part in the region in opposition to the back surface of the semiconductor chip and in the region where the openings are not formed is bonded to the back surface of the semiconductor chip in its entire surface with an adhesive.

A method of manufacturing a semiconductor device according to still another typical embodiment has the steps of (a) preparing a lead frame having a chip mounting part having a frame body part, a first part located in the center of a region surrounded by the frame body part, and a plurality of second 35 parts that connect the first part and the inner edge of the frame body part, and a plurality of leads arranged around the frame body part, and (b) applying an adhesive over the main surface of the chip mounting part of the lead frame. Further, the method has the steps of (c) after the step (b), arranging the 40 semiconductor chip via the adhesive over the main surface of the chip mounting part of the lead frame so that the back surface of the semiconductor chip is in opposition to the main surface of the chip mounting part, and spreading the adhesive on the entire surface of the part where the main surface of the 45 chip mounting part and the back surface of the semiconductor chip are in opposition to each other by applying a load to the semiconductor chip, and (d) after the step (c), curing the adhesive.

The following explains briefly the effect acquired by the 50 typical invention among the inventions disclosed in the present application.

According to a typical embodiment, it is possible to improve the heat dissipation characteristics of a semiconductor device.

## BRIEF DESCRIPTION OF THE DRAWINGS

- FIG. 1 is a top view of a semiconductor device in a first embodiment of the present invention;

- FIG. 2 is a bottom view of the semiconductor device in the first embodiment of the present invention;

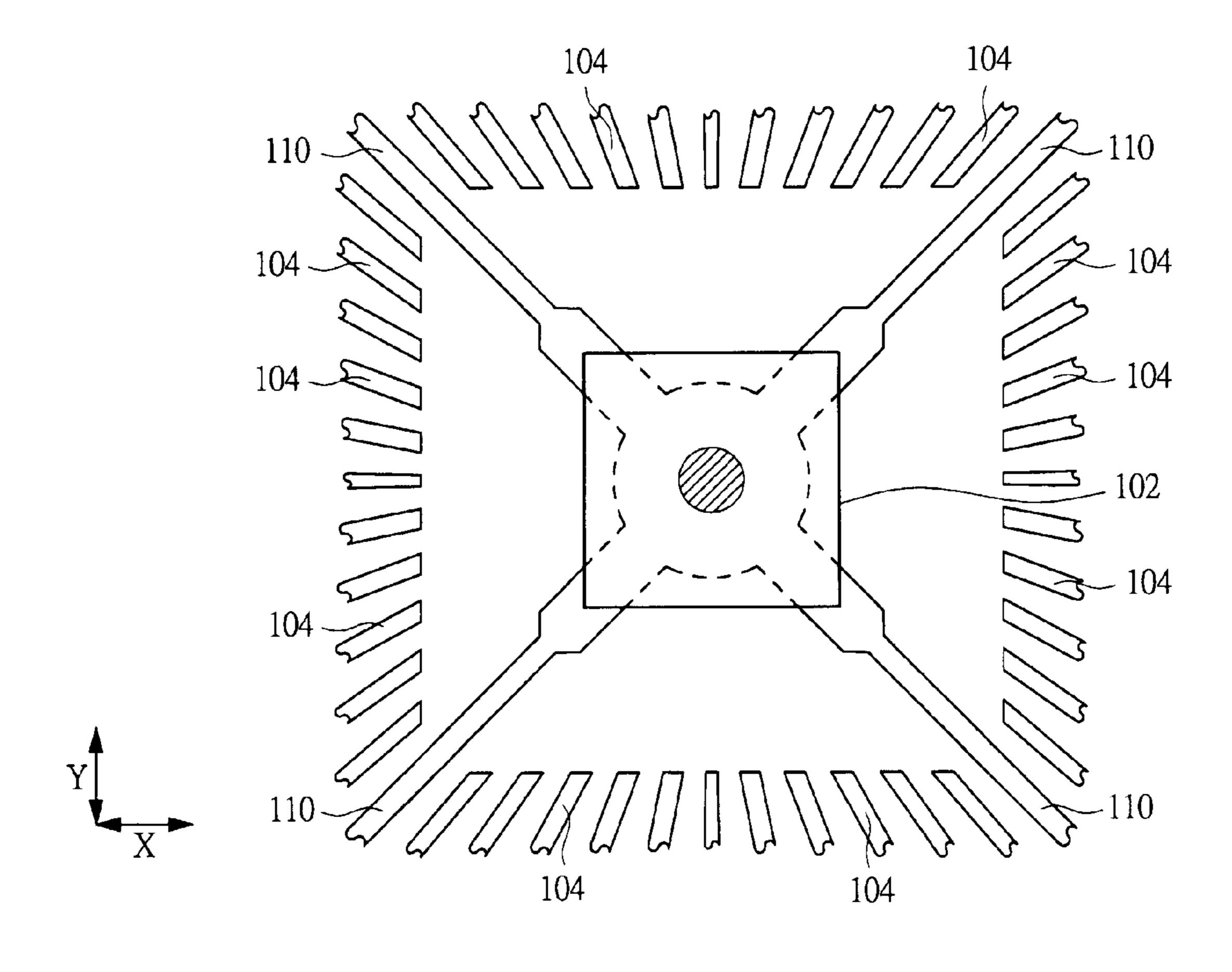

- FIG. 3 is a plan perspective view of the semiconductor device in the first embodiment of the present invention;

- FIG. 4 is a partially enlarged plan perspective view of the 65 semiconductor device in the first embodiment of the present invention;

4

- FIG. **5** is a partially enlarged plan perspective view of the semiconductor device in the first embodiment of the present invention;

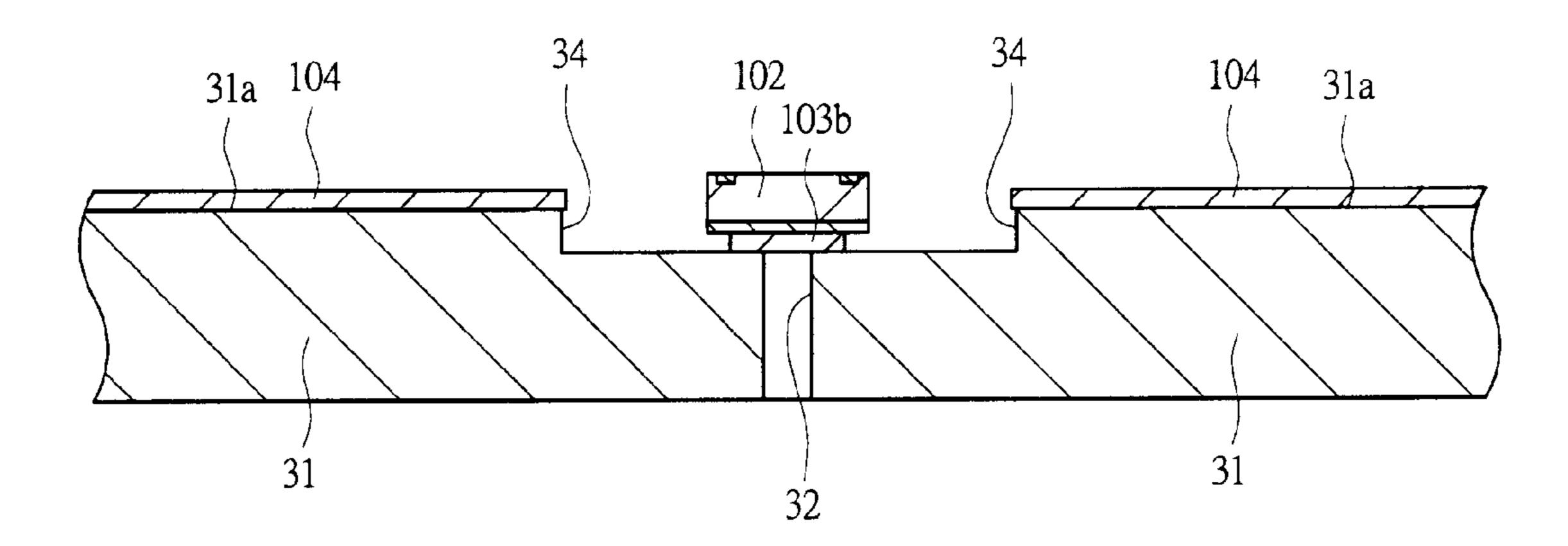

- FIG. **6** is a section view of the semiconductor device in the first embodiment of the present invention;

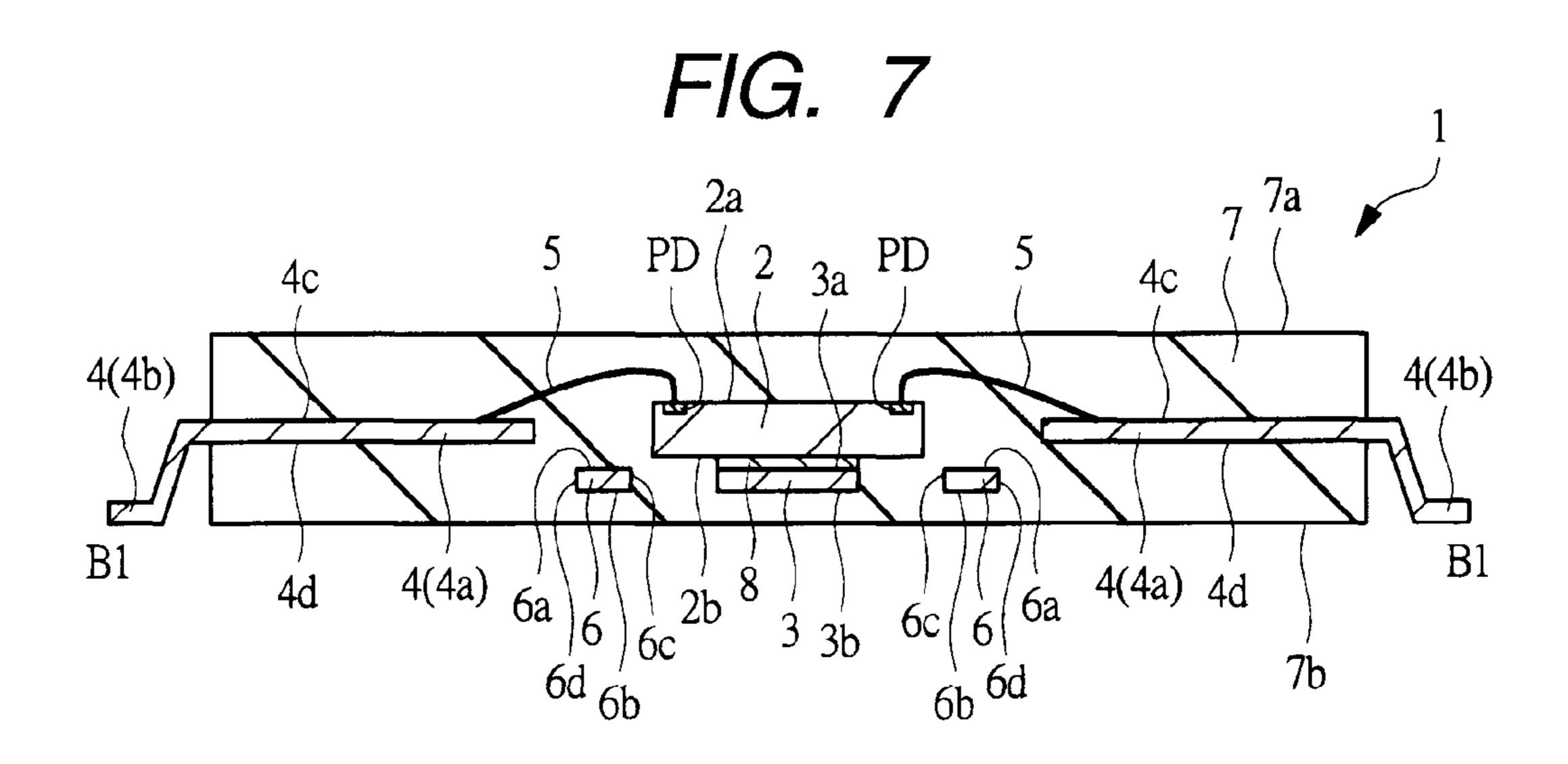

- FIG. 7 is a section view of the semiconductor device in the first embodiment of the present invention;

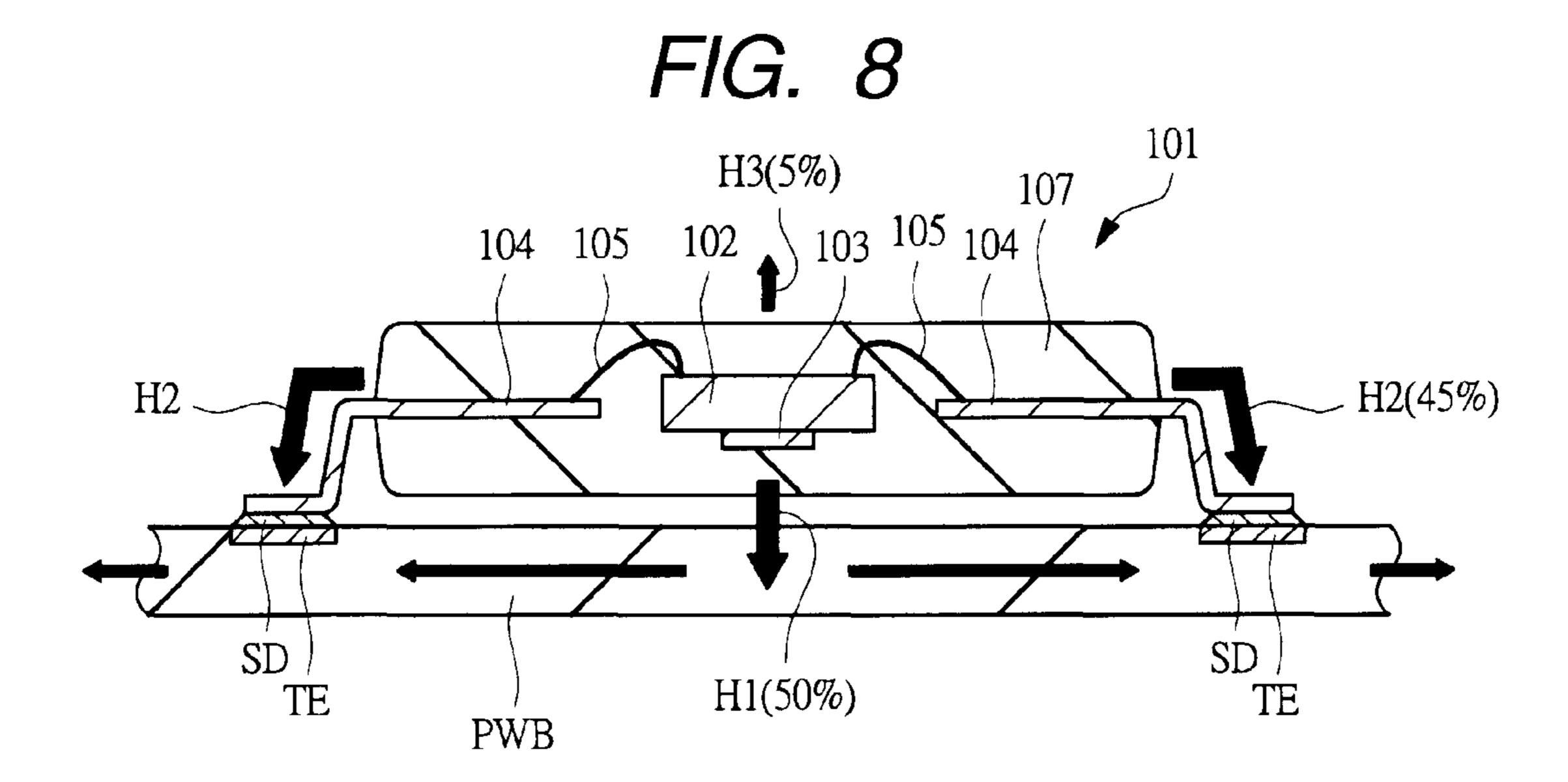

- FIG. 8 an explanatory diagram of a heat dissipation path of a QFP semiconductor device;

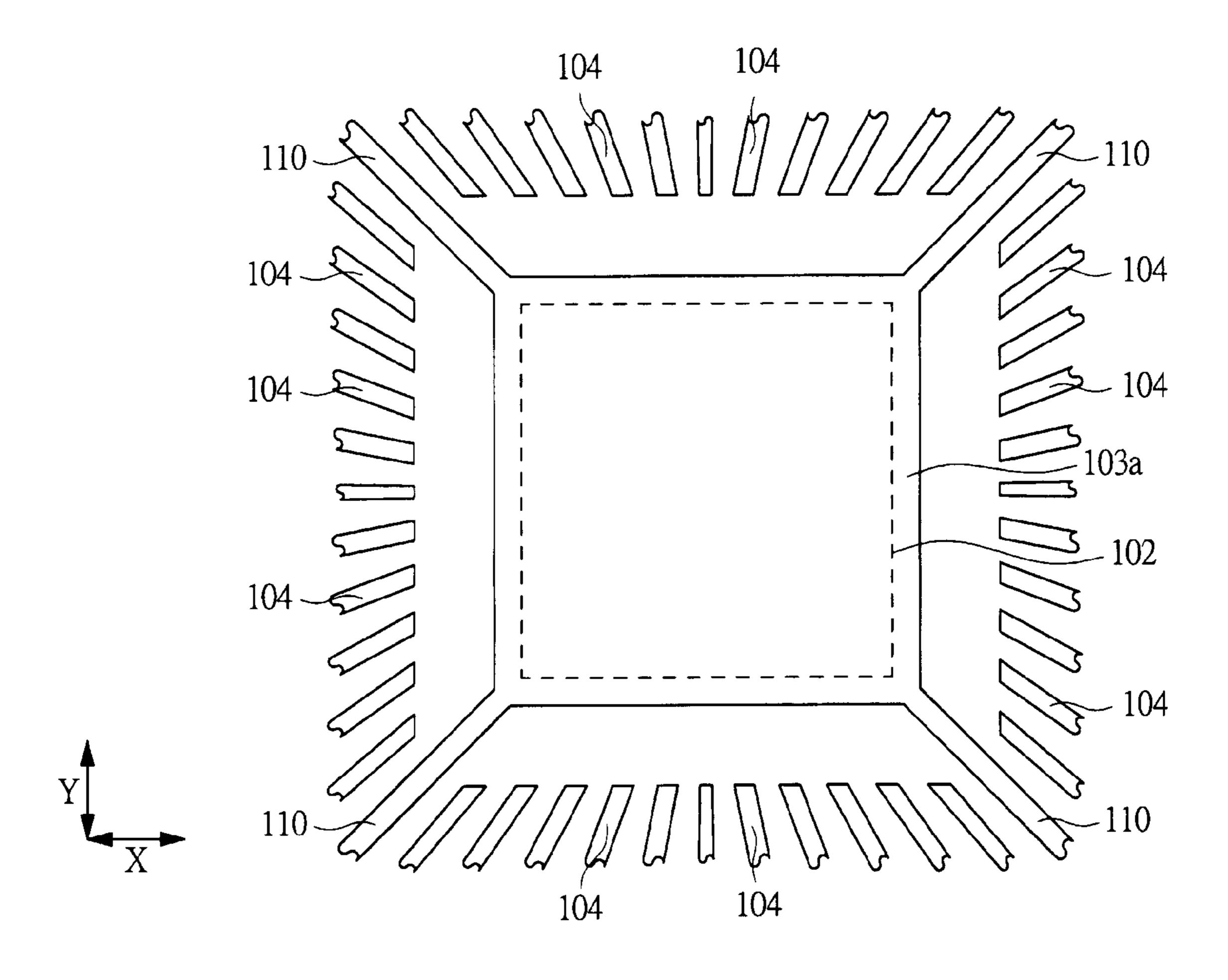

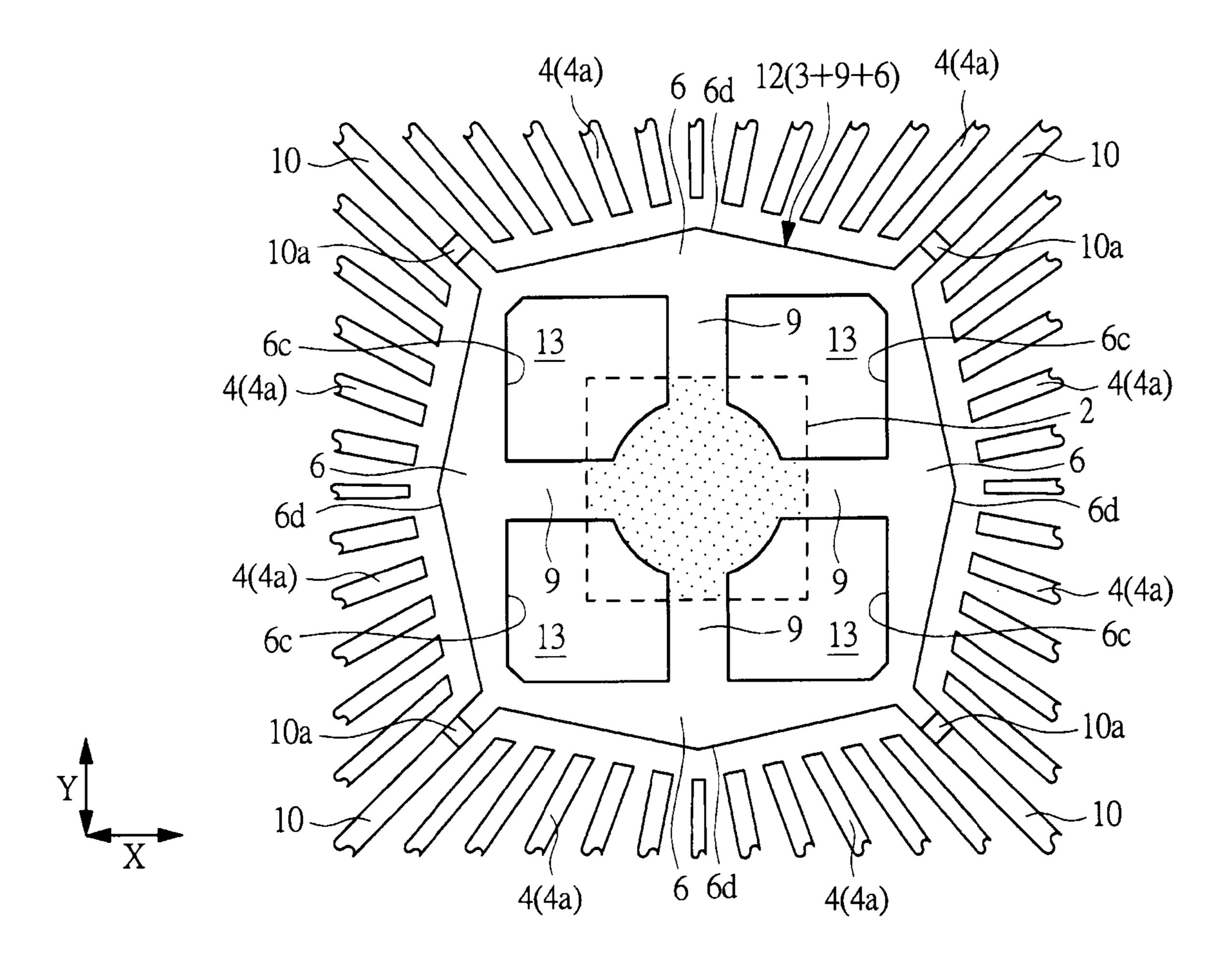

- FIG. 9 is a plan perspective view of essential parts of a semiconductor device when a die pad in a first comparative example is applied;

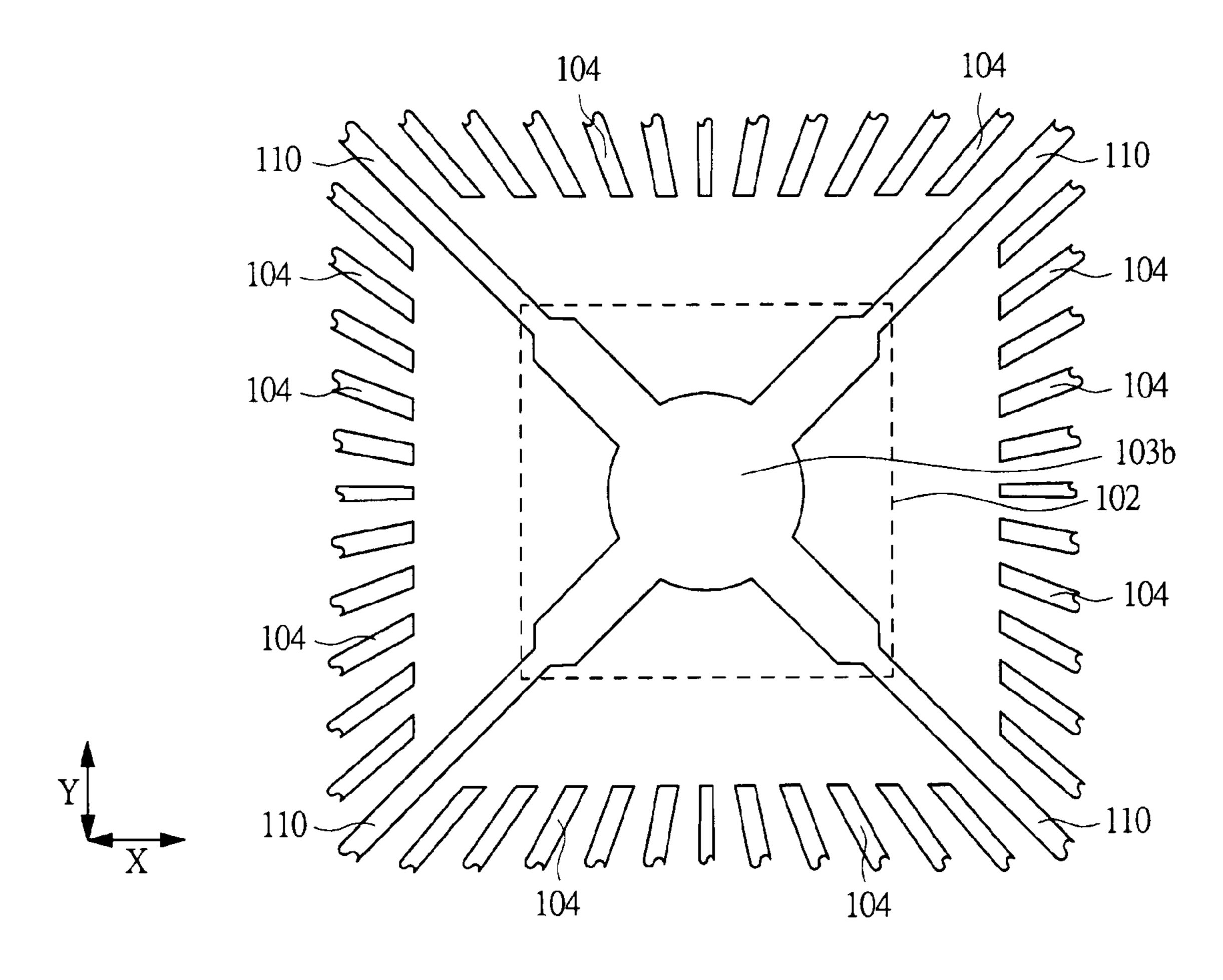

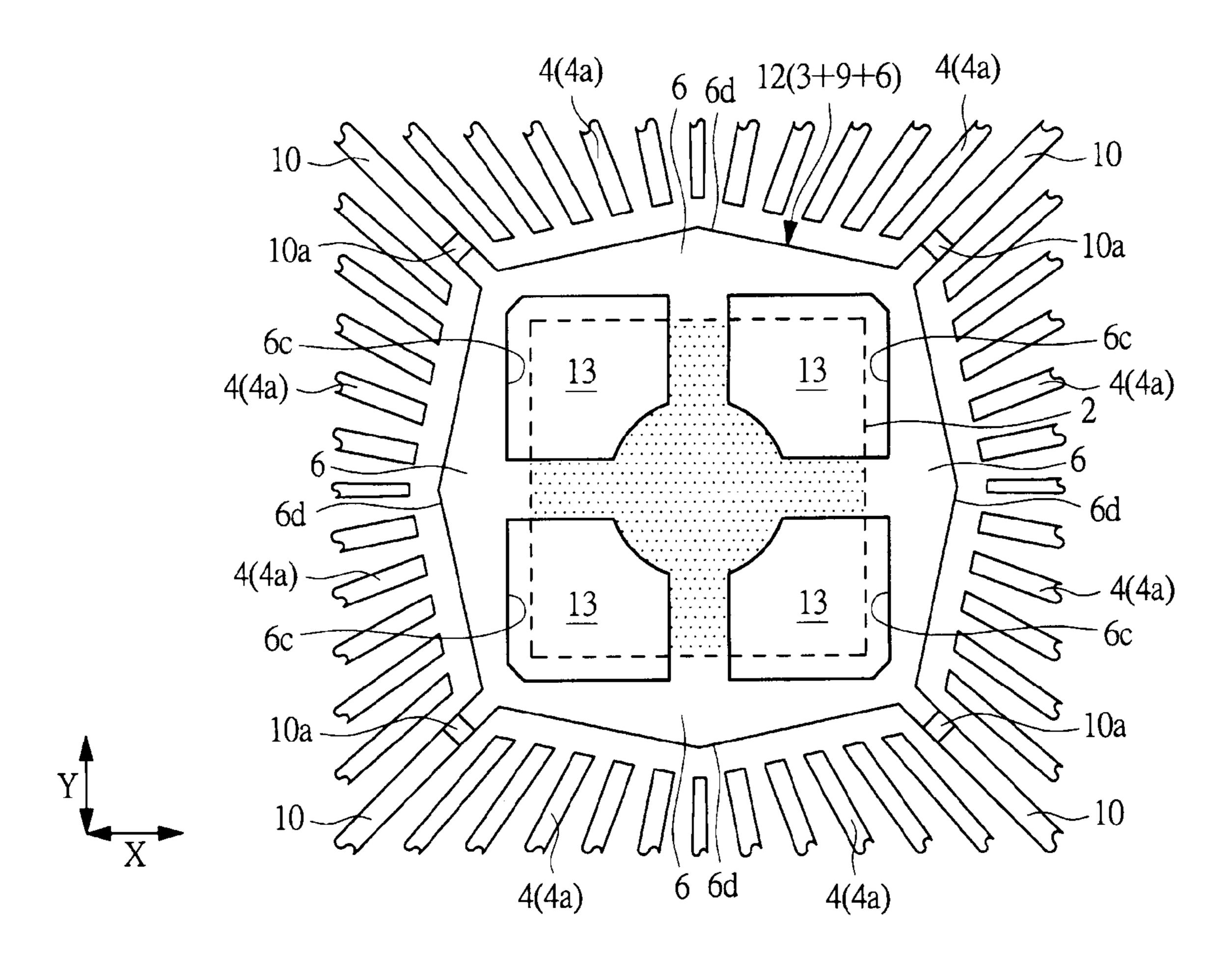

- FIG. 10 is a plan perspective view of essential parts of a semiconductor device when a die pad in a second comparative example is applied;

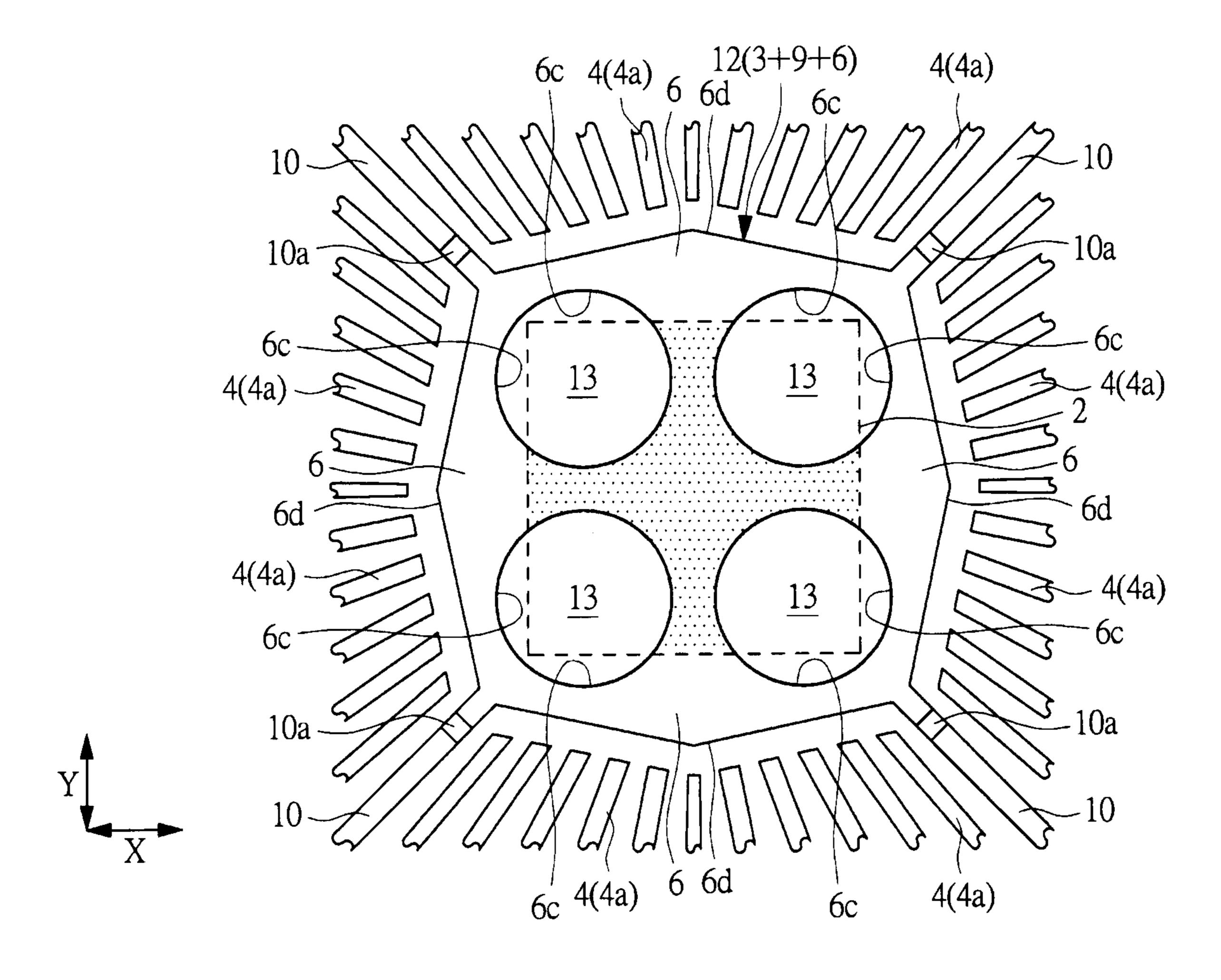

- FIG. 11 is a plan perspective view of essential parts of a semiconductor device when a die pad in a third comparative example is applied;

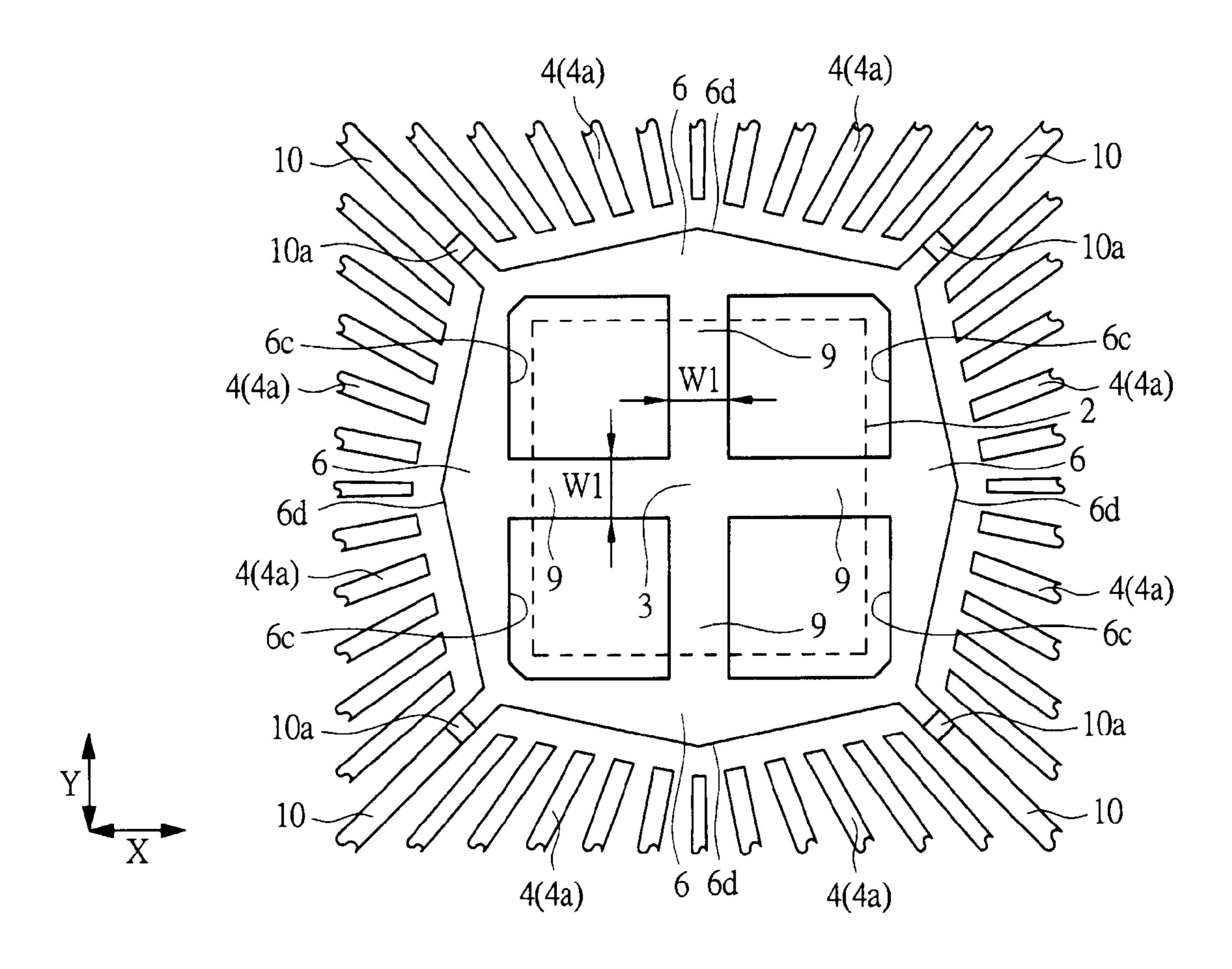

- FIG. 12 is a plan perspective view of essential parts of a semiconductor device when a die pad in a fourth comparative example is applied;

- FIG. 13 is a partially enlarged plan perspective view of the semiconductor device in the first embodiment of the present invention;

- FIG. 14 is a partially enlarged plan perspective view of the semiconductor device in the first embodiment of the present invention;

- FIG. **15** is an explanatory diagram of heat dissipation of the semiconductor device in the first embodiment of the present invention;

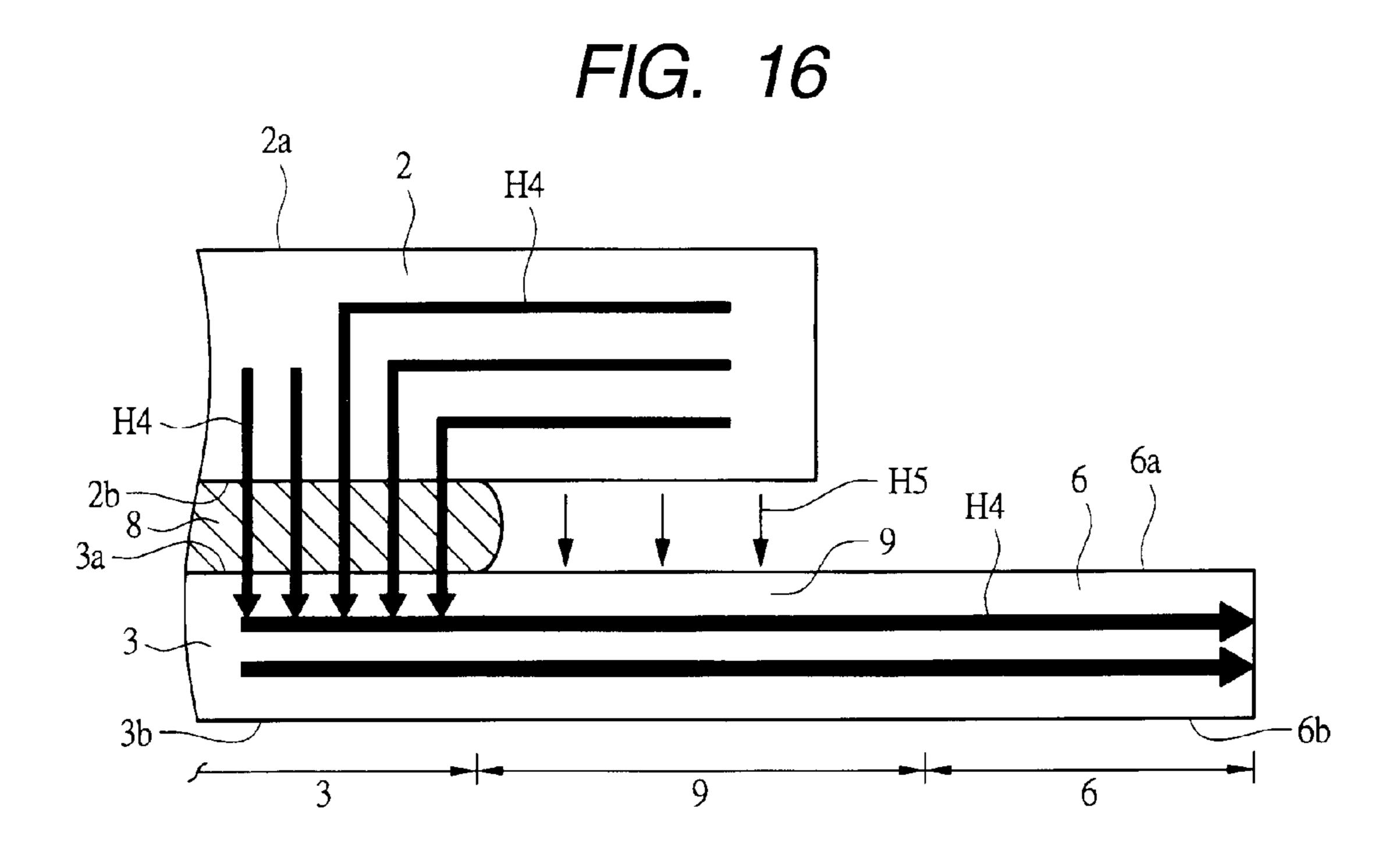

- FIG. 16 an explanatory diagram of heat dissipation;

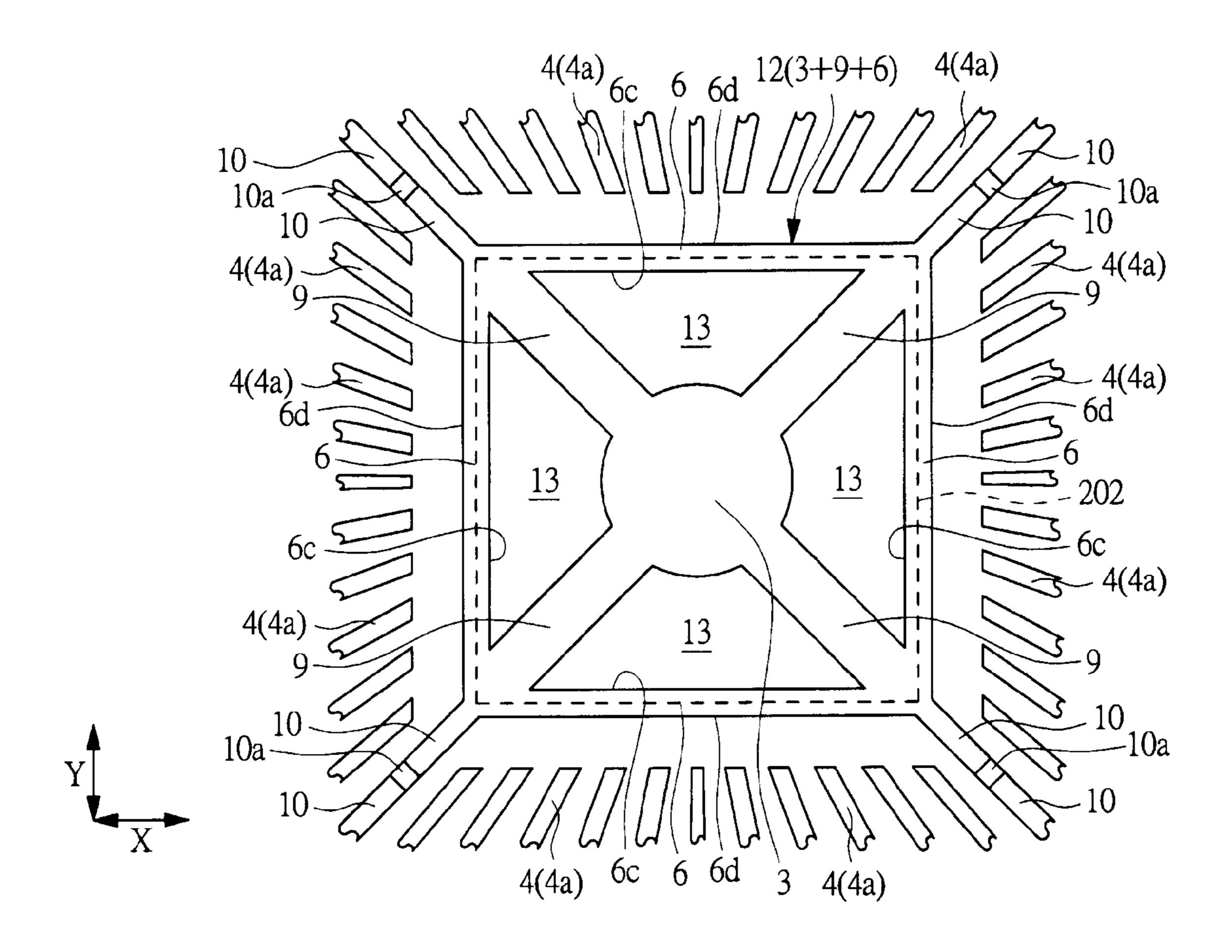

- FIG. 17 is a plan perspective view of essential parts of a semiconductor device when a large semiconductor chip is mounted;

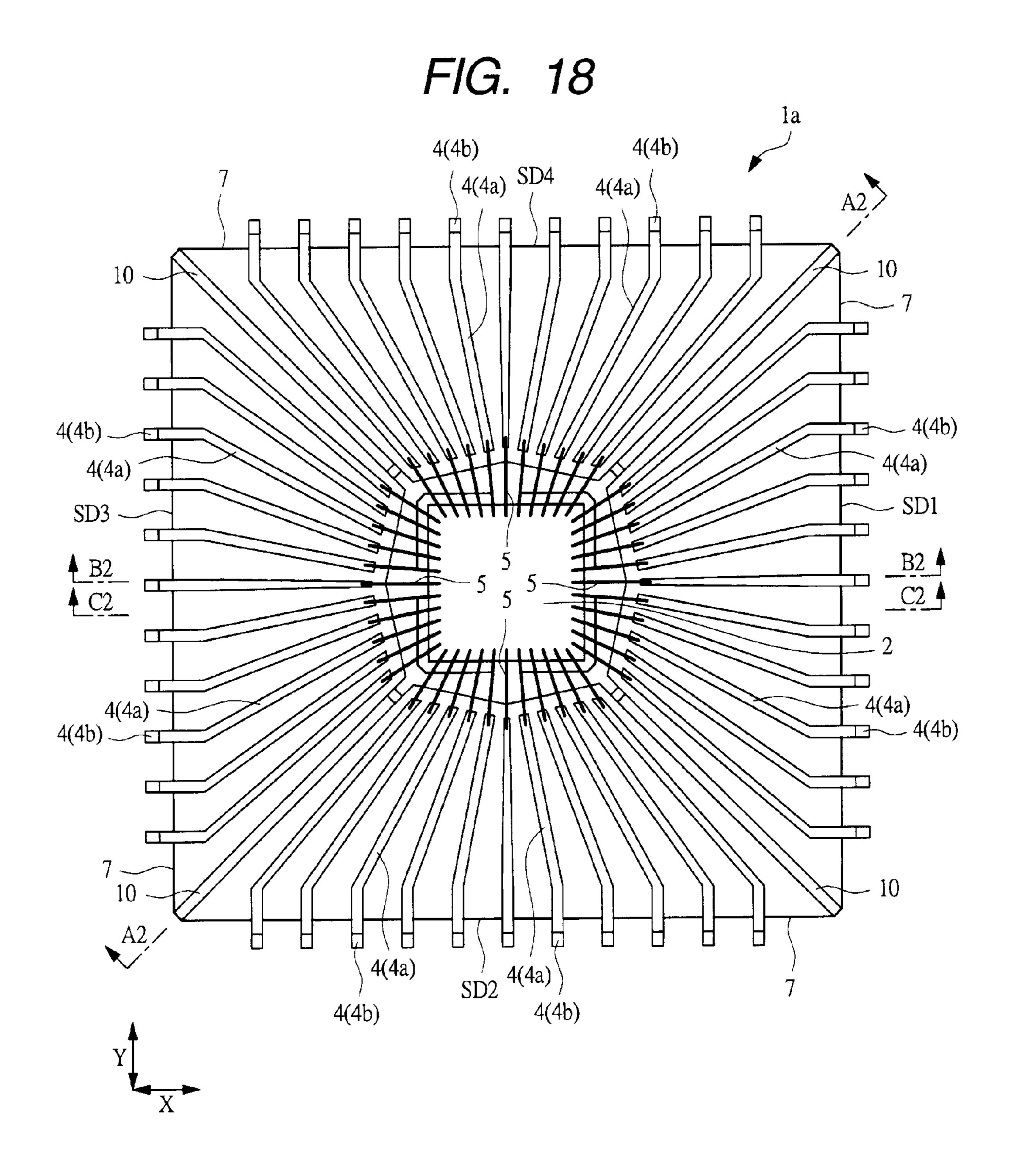

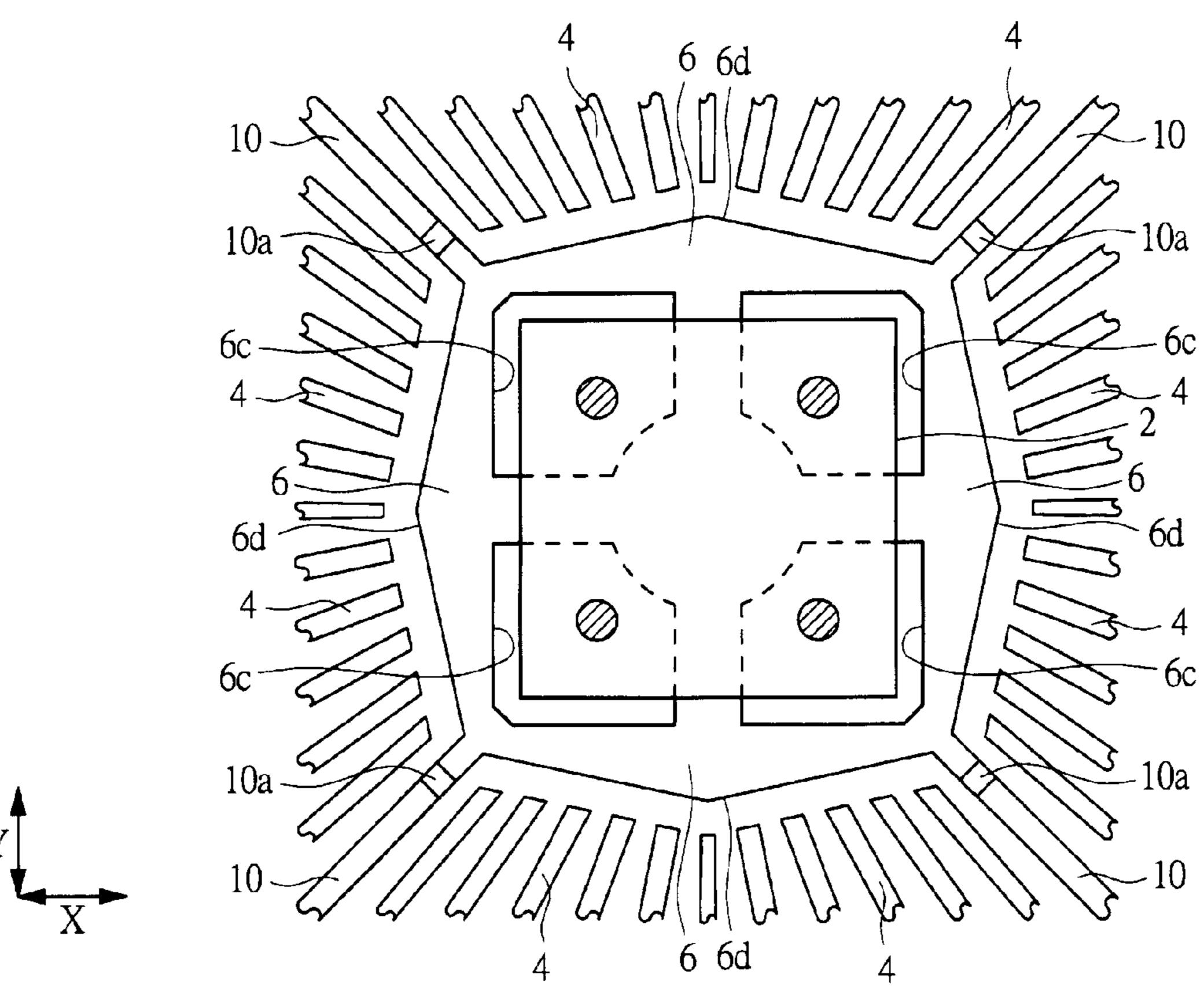

- FIG. 18 is a plan perspective view of a semiconductor device in a second embodiment of the present invention;

- FIG. 19 is a partially enlarged plan perspective view of the semiconductor device in the second embodiment of the present invention;

- FIG. 20 is a partially enlarged plan perspective view of the semiconductor device in the second embodiment of the present invention;

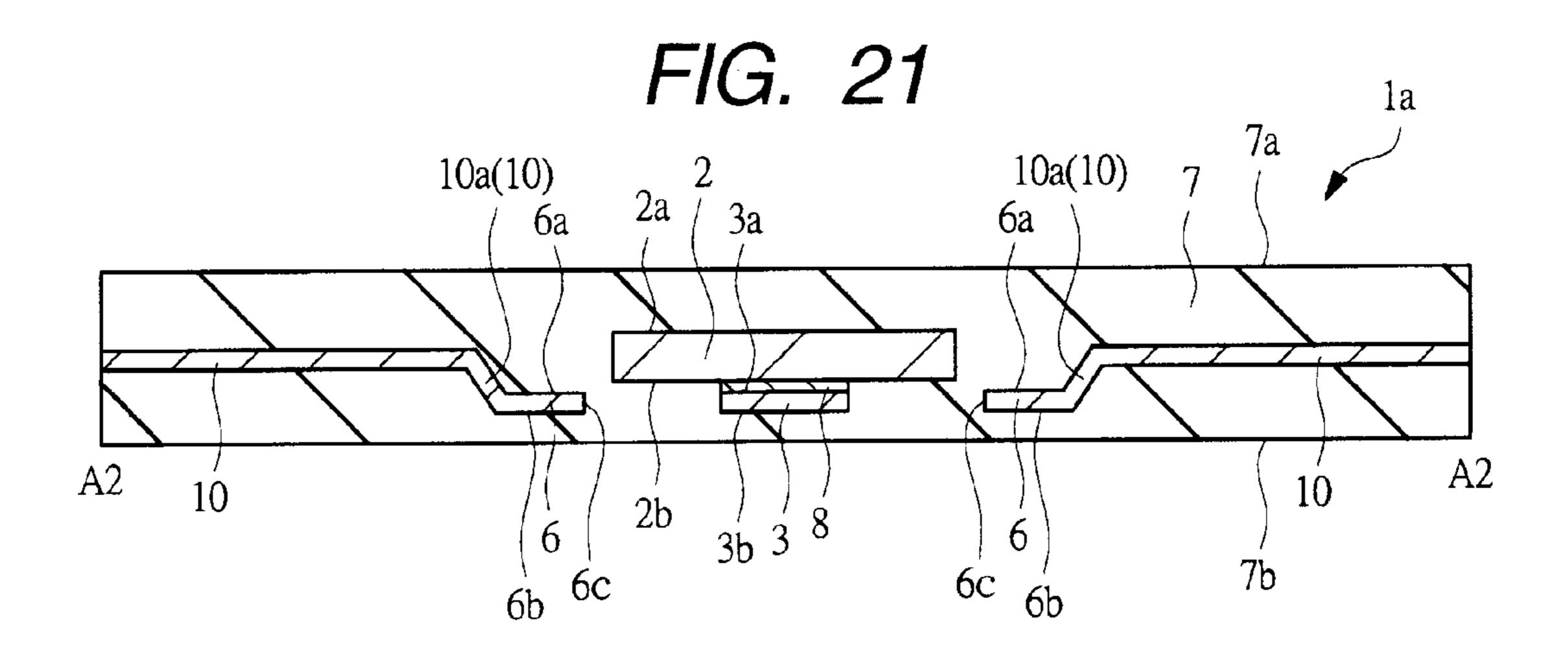

- FIG. 21 is a section view of the semiconductor device in the second embodiment of the present invention;

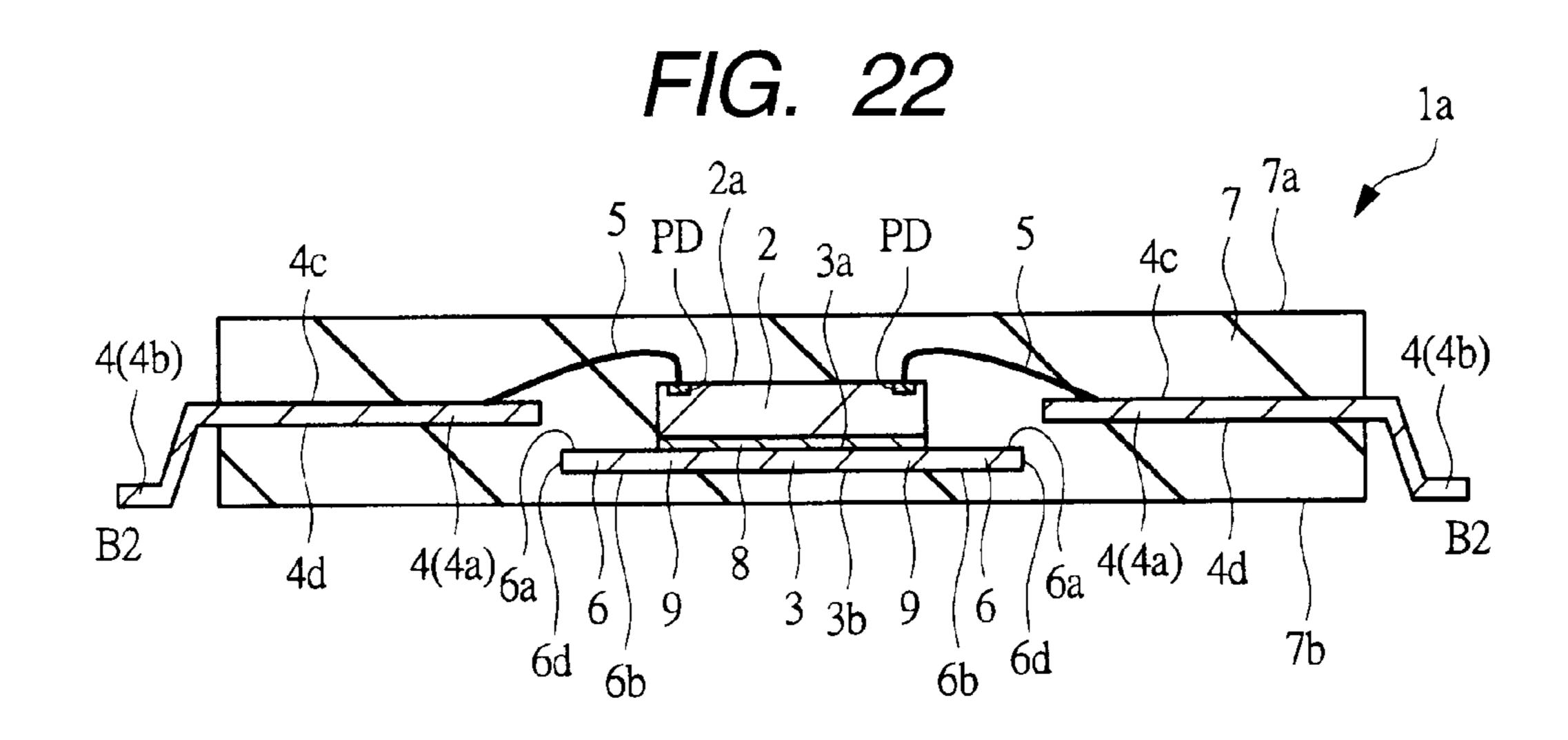

- FIG. 22 is a section view of the semiconductor device in the second embodiment of the present invention;

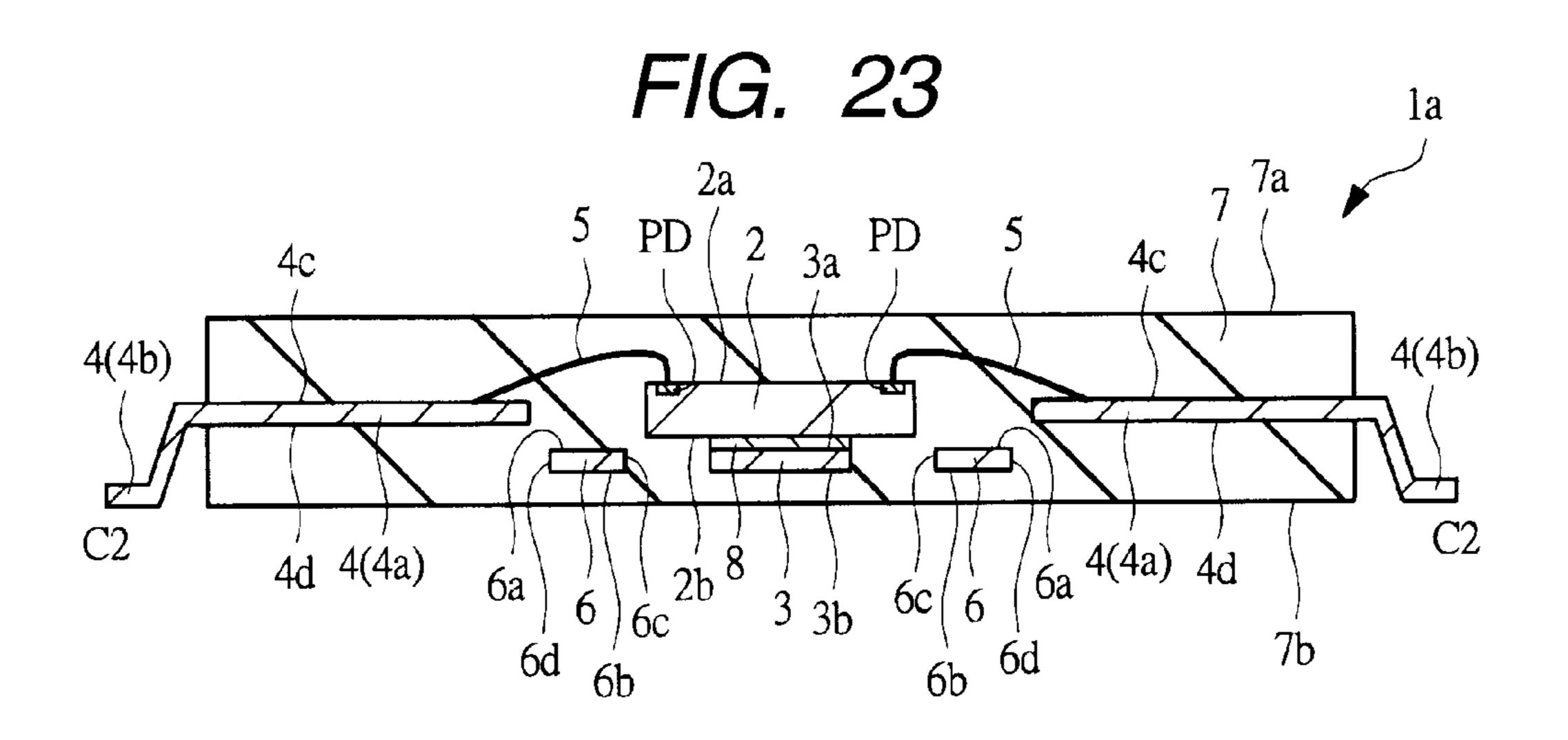

- FIG. 23 is a section view of the semiconductor device in the second embodiment of the present invention;

- FIG. 24 is a partially enlarged plan perspective view of the semiconductor device in the second embodiment of the present invention;

- FIG. **25** is a partially enlarged plan perspective view of the semiconductor device in the second embodiment of the present invention;

- FIG. 26 is a partially enlarged plan perspective view showing a modified example of the semiconductor device in the second embodiment of the present invention;

- FIG. 27 is a plan perspective view of essential parts of a semiconductor device in a third embodiment of the present invention;

- FIG. 28 is a plan perspective view of essential parts of a semiconductor device in a fourth embodiment of the present invention;

- FIG. 29 is a plan perspective view of essential parts of a semiconductor device in a fifth embodiment of the present invention;

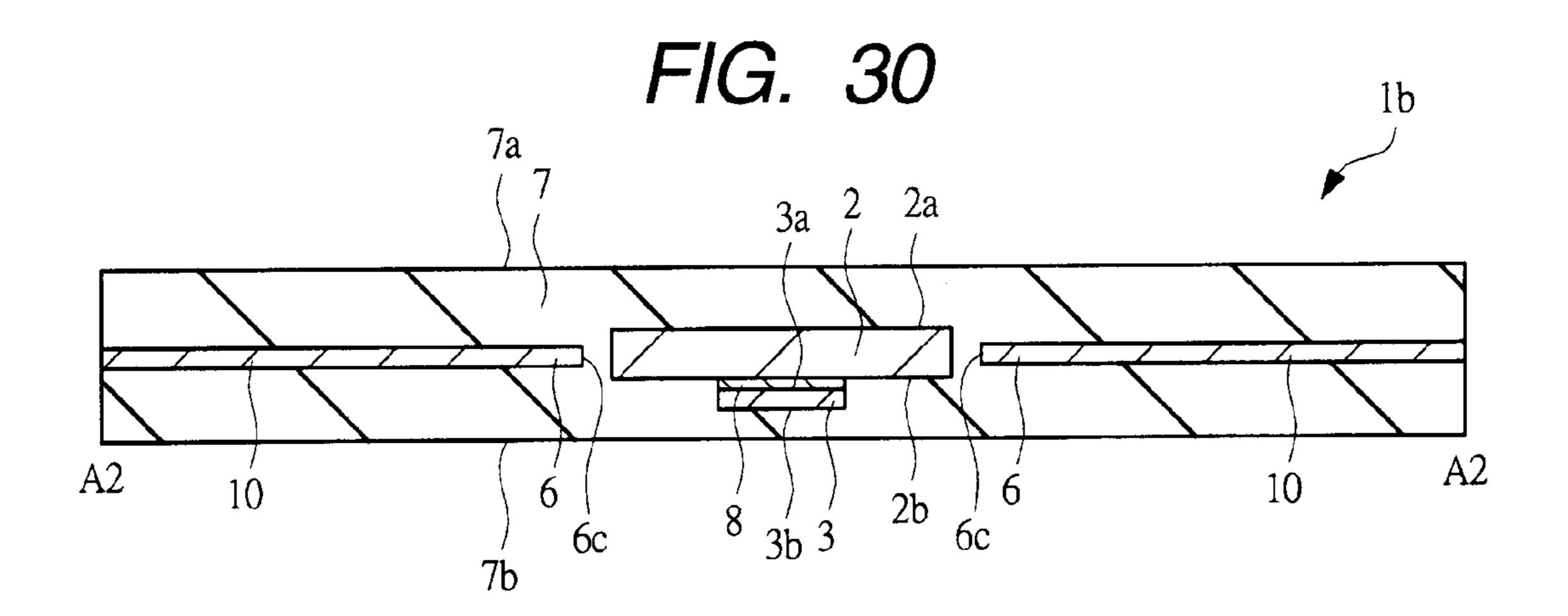

- FIG. 30 is a section view of the semiconductor device in the fifth embodiment of the present invention;

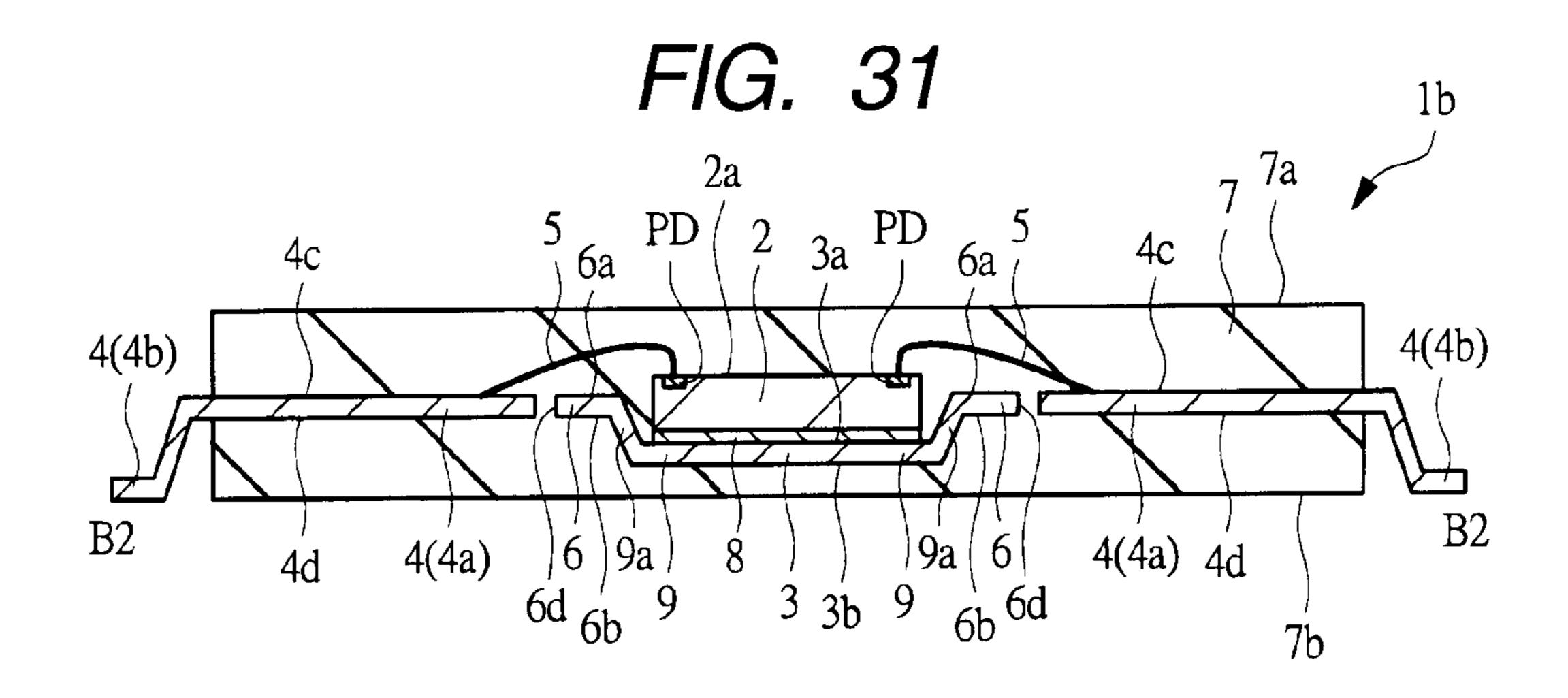

- FIG. 31 is a section view of the semiconductor device in the fifth embodiment of the present invention;

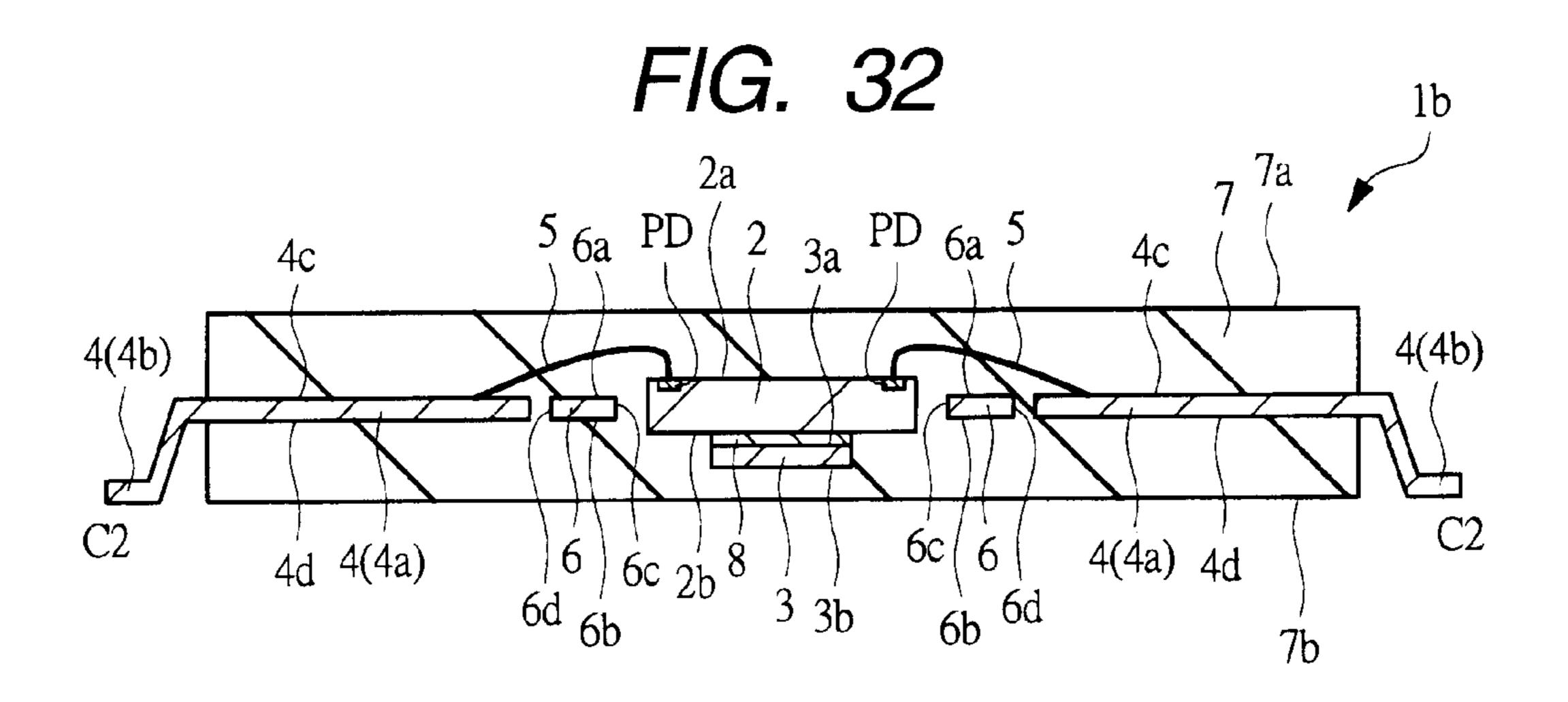

- FIG. 32 is a section view of the semiconductor device in the fifth embodiment of the present invention;

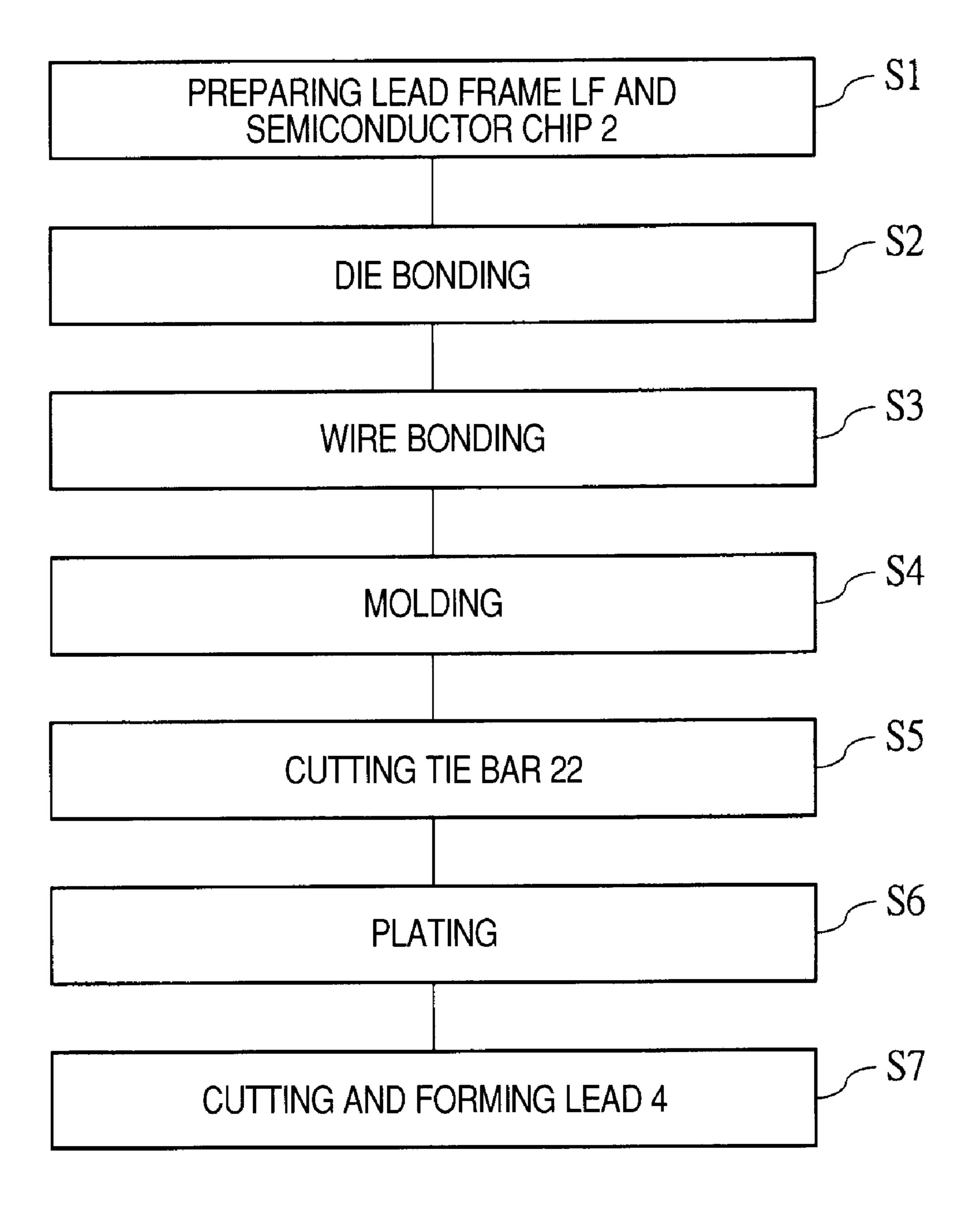

- FIG. 33 is a manufacturing process flowchart showing manufacturing steps of the semiconductor device in the second embodiment of the present invention;

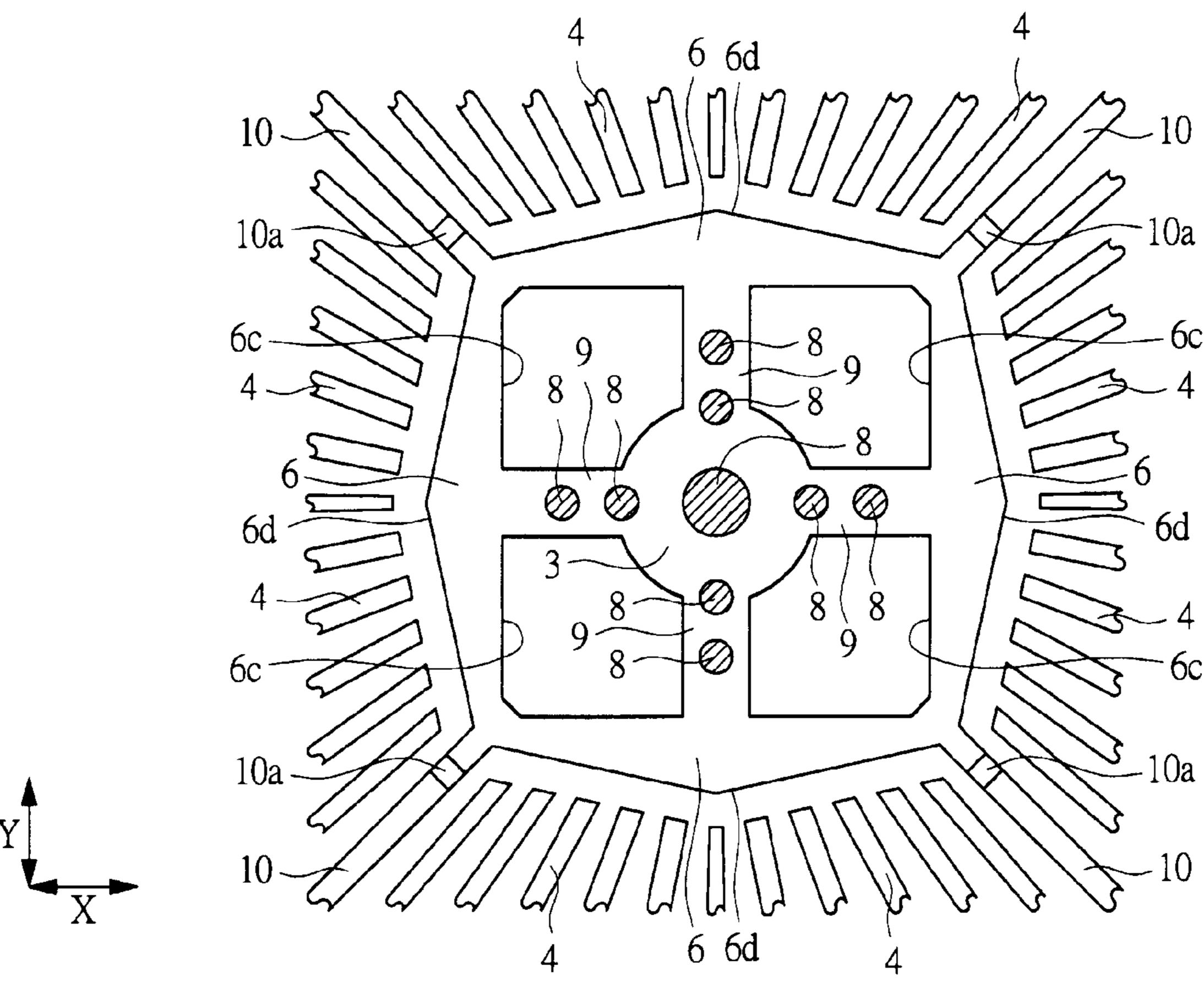

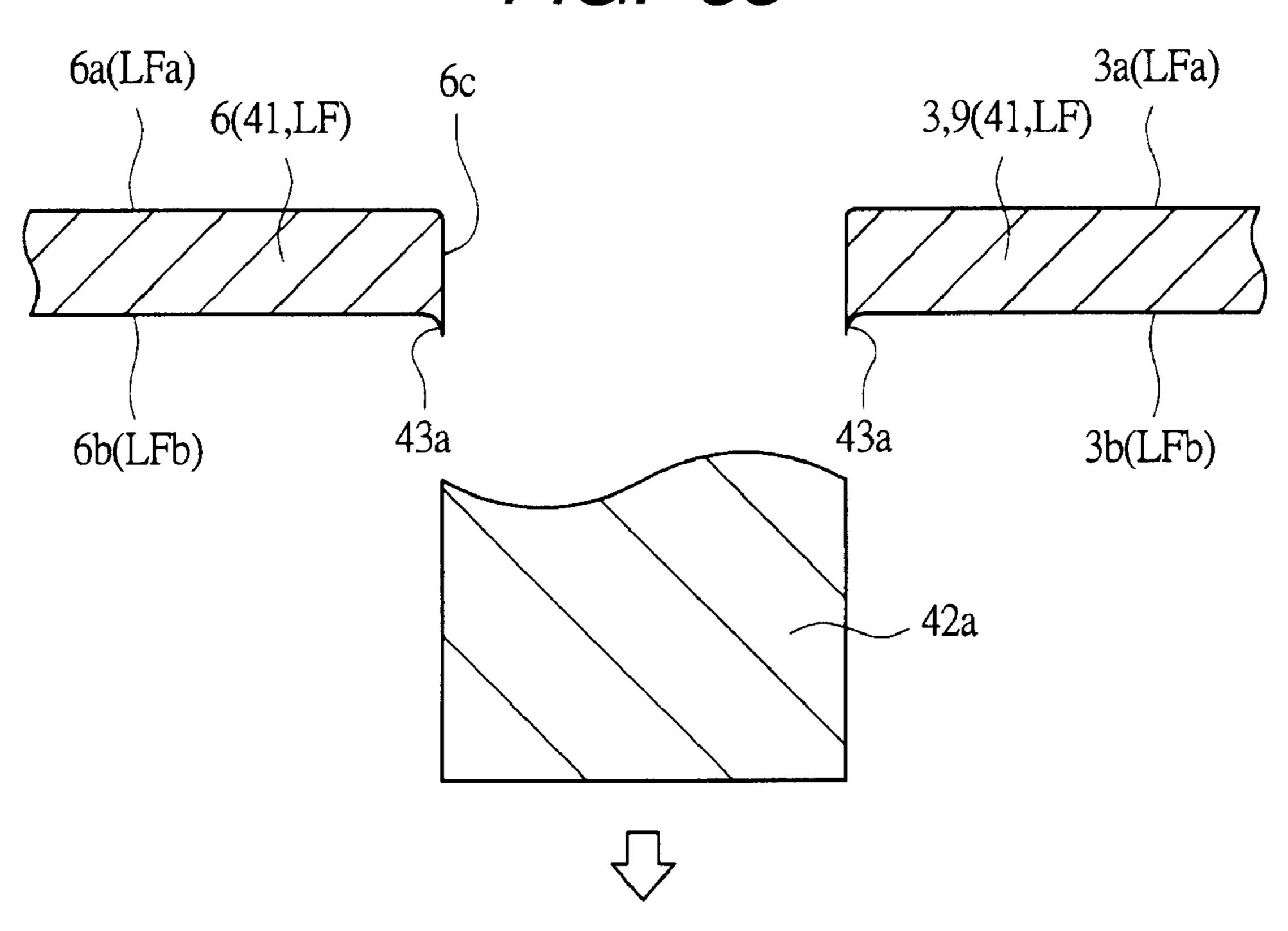

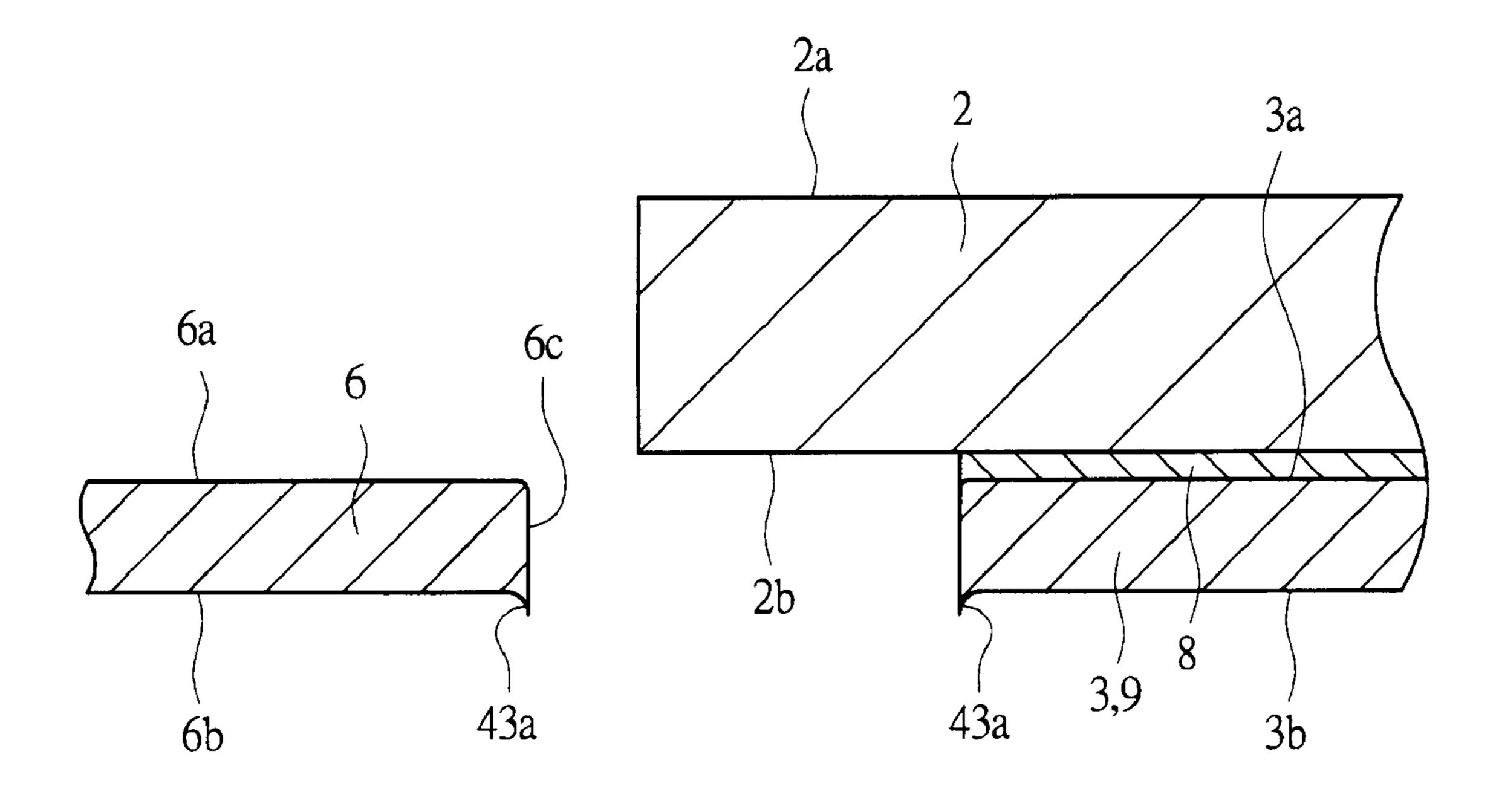

- FIG. **34** is a plan view of a lead frame used to manufacture the semiconductor device in the second embodiment of the present invention;

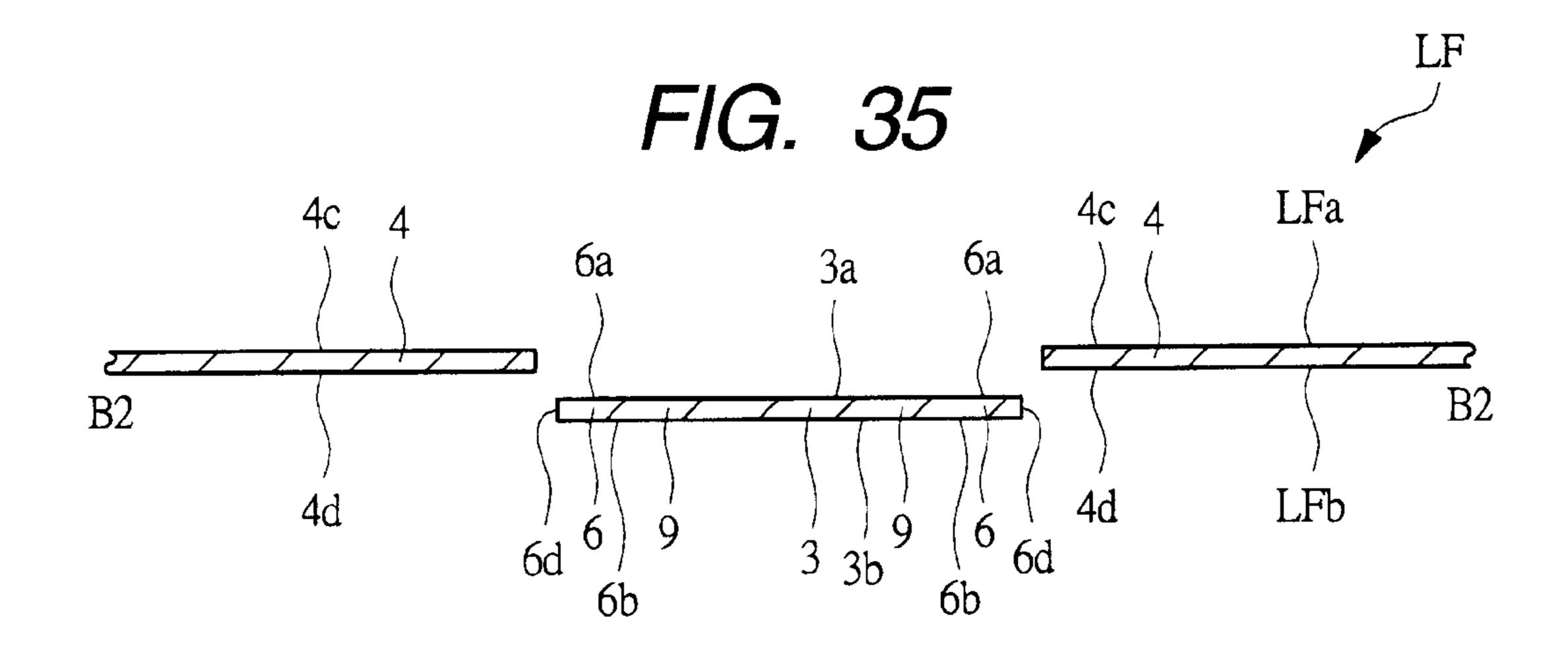

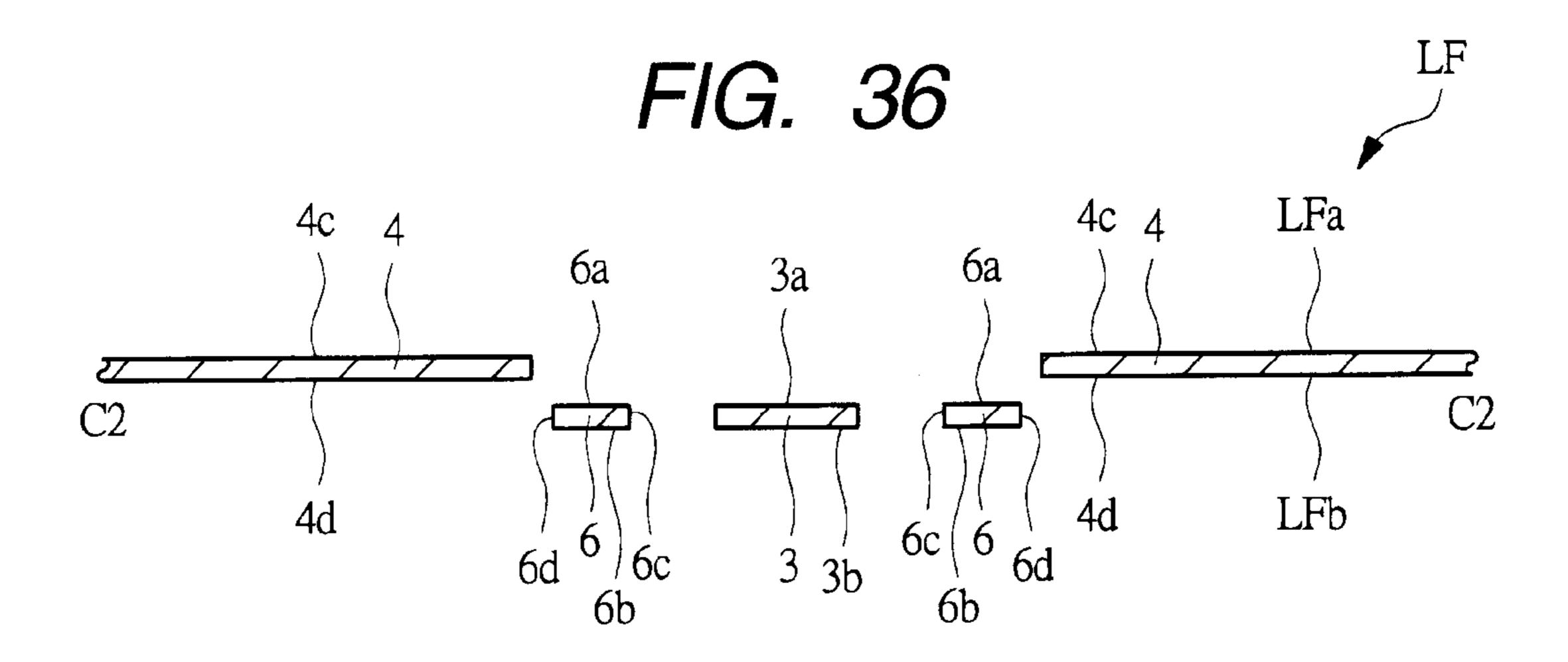

- FIG. 35 is a section view of the lead frame in FIG. 34;

- FIG. 36 is a section view of the lead frame in FIG. 34;

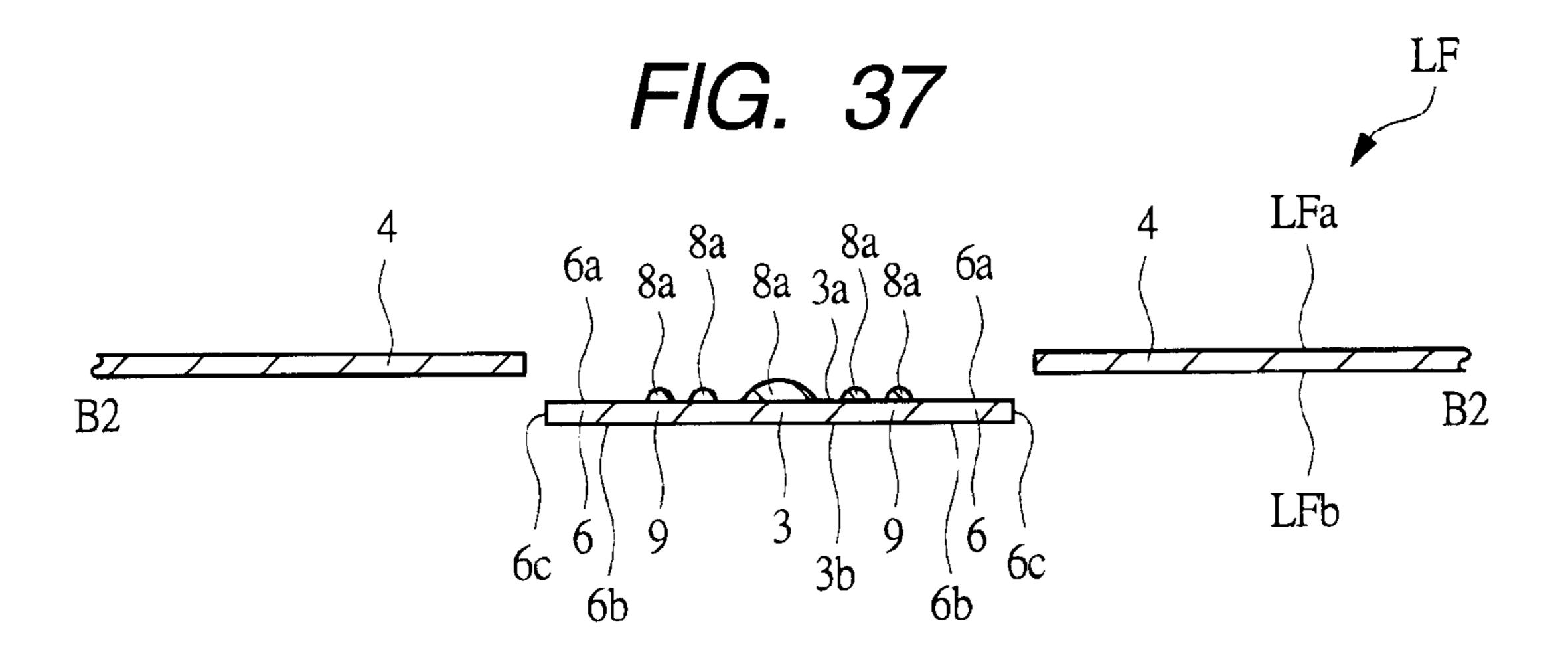

- FIG. 37 is a section view during a manufacturing step of the semiconductor device in the second embodiment of the present invention;

- FIG. 38 is a plan view of essential parts during the manufacturing step of the semiconductor device, similar to FIG. 20 37;

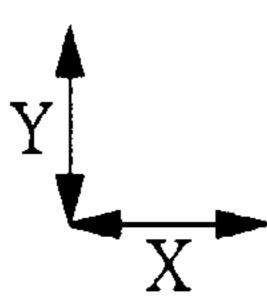

- FIG. 39 is a section view during the manufacturing step of the semiconductor device, following FIG. 37;

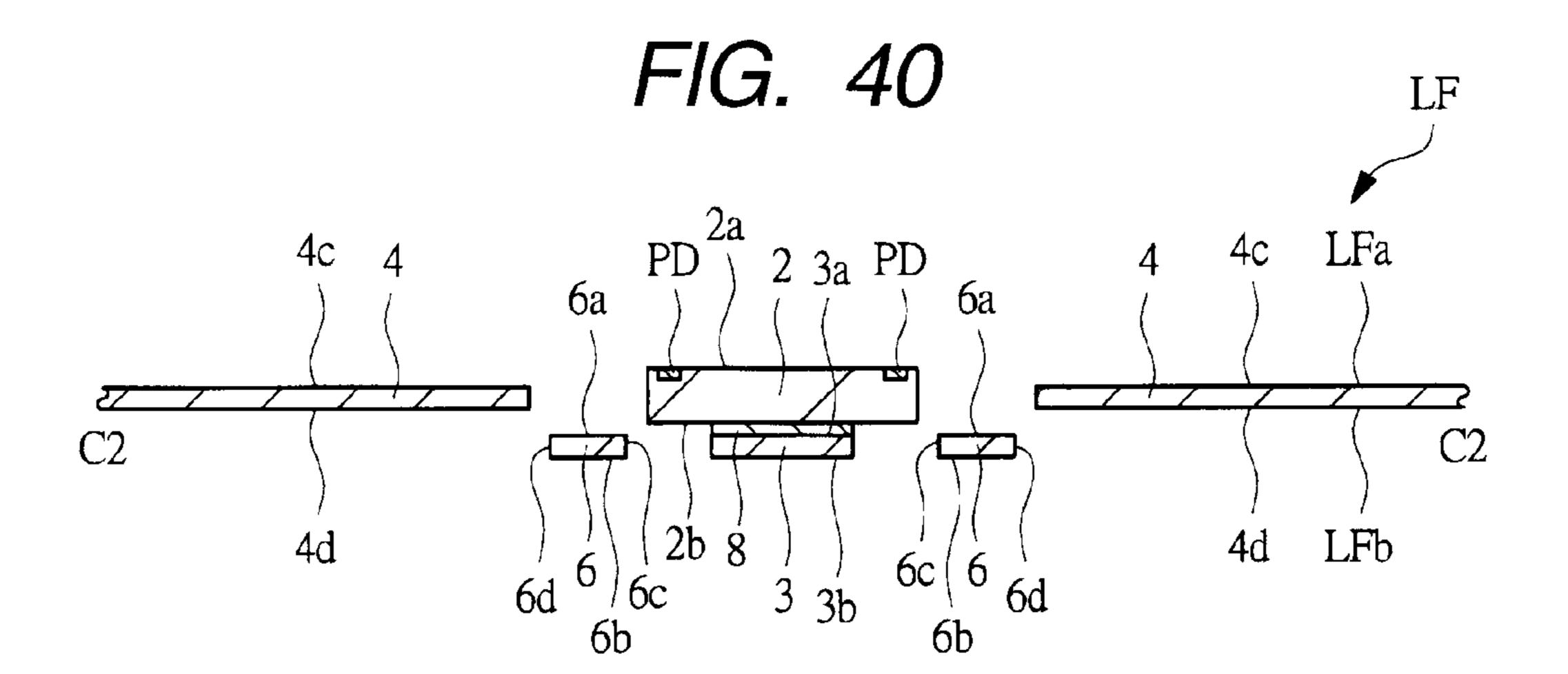

- FIG. 40 is a section view during the manufacturing step of the semiconductor device, similar to FIG. 39;

- FIG. 41 is a plan view of essential parts during the manufacturing step of the semiconductor device, similar to FIG. 39;

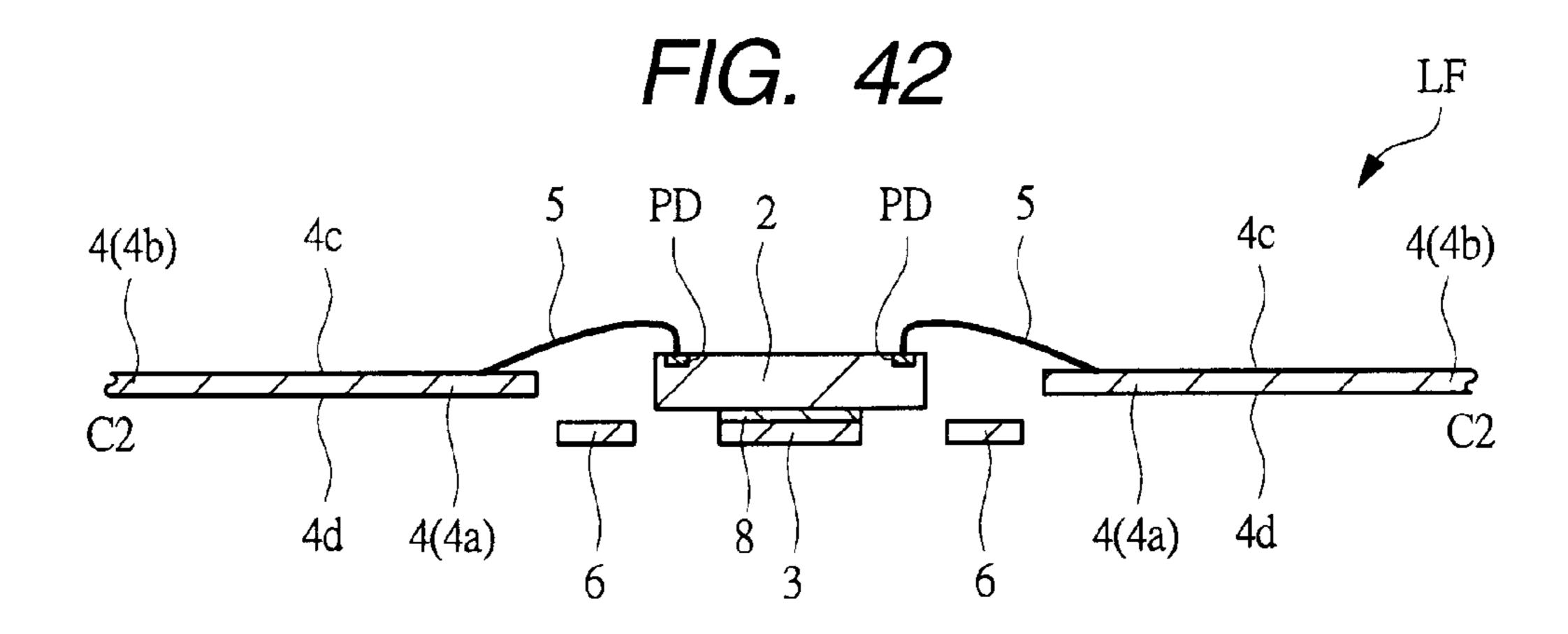

- FIG. 42 is a section view during the manufacturing step of the semiconductor device, following FIG. 39;

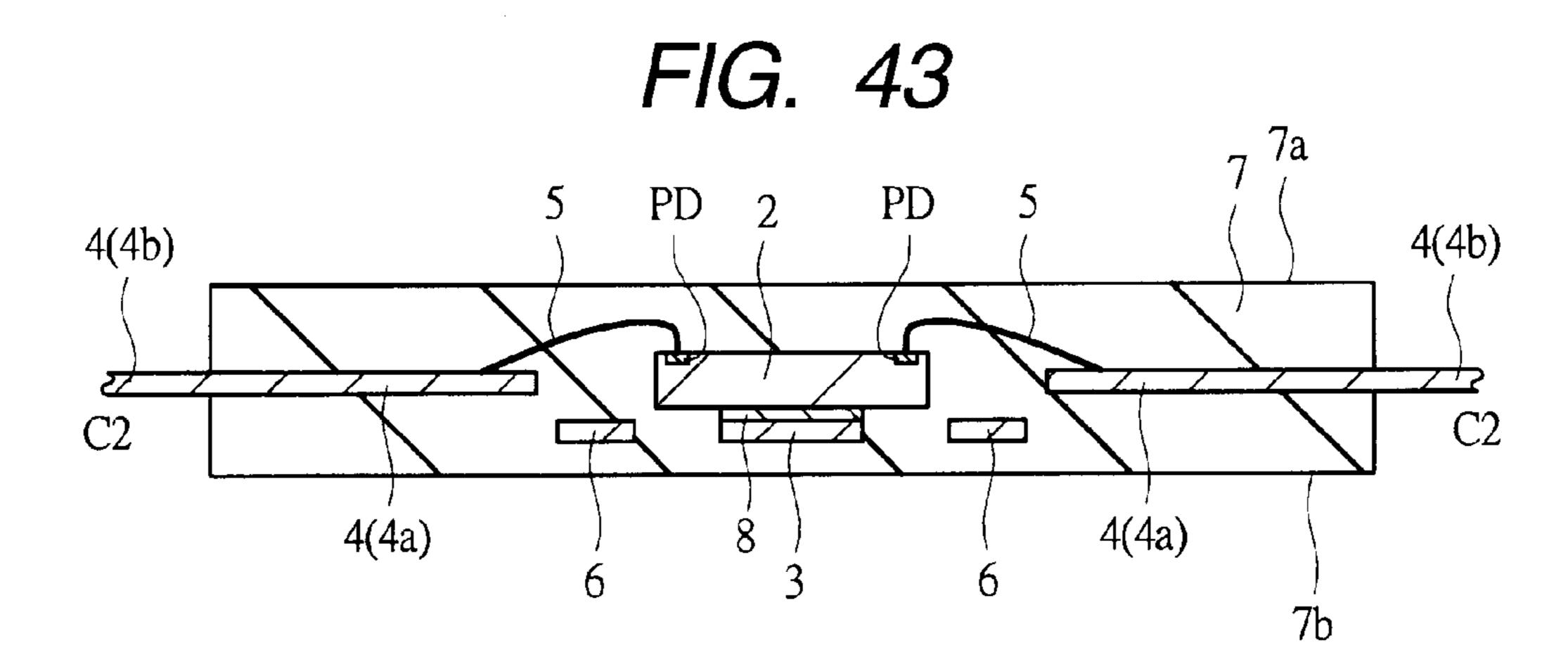

- FIG. 43 is a section view during the manufacturing step of the semiconductor device, following FIG. 42;

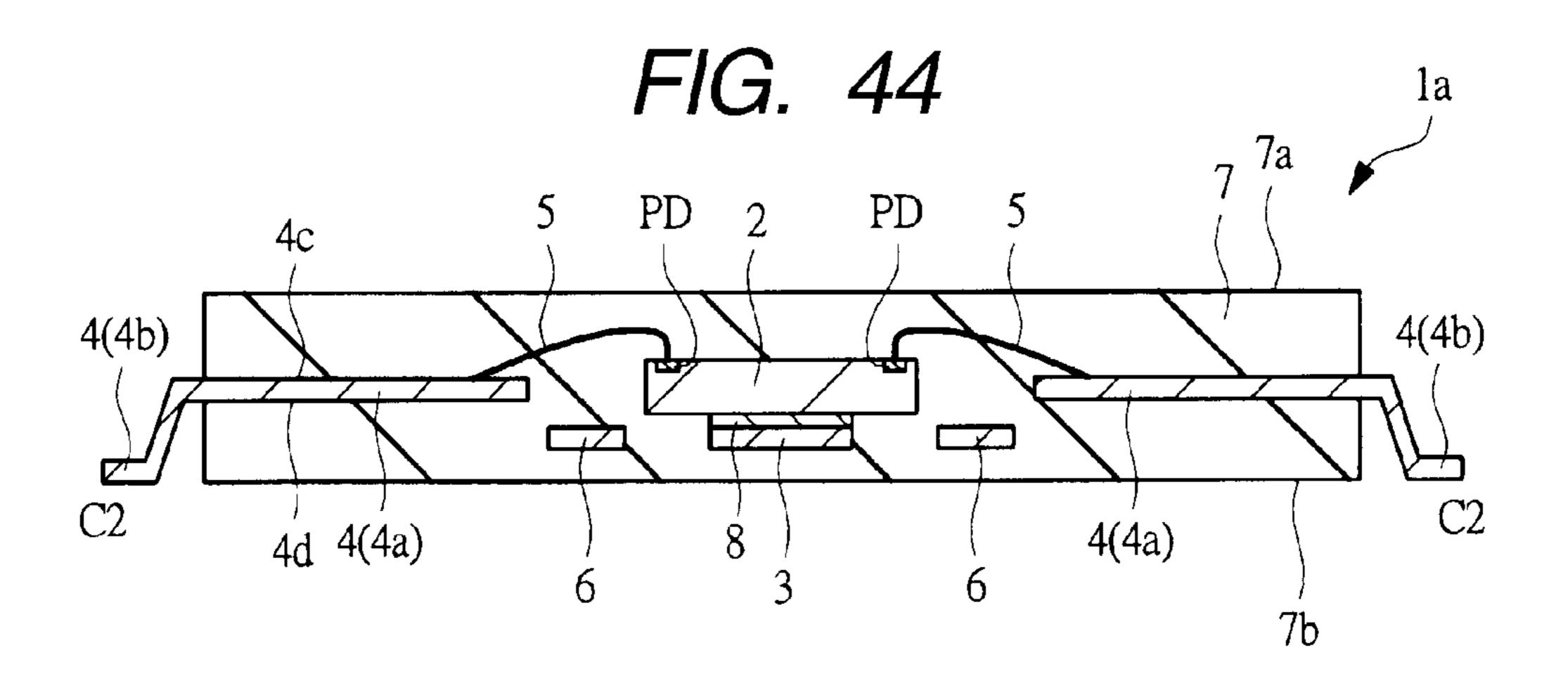

- FIG. 44 is a section view during the manufacturing step of the semiconductor device, following FIG. 43;

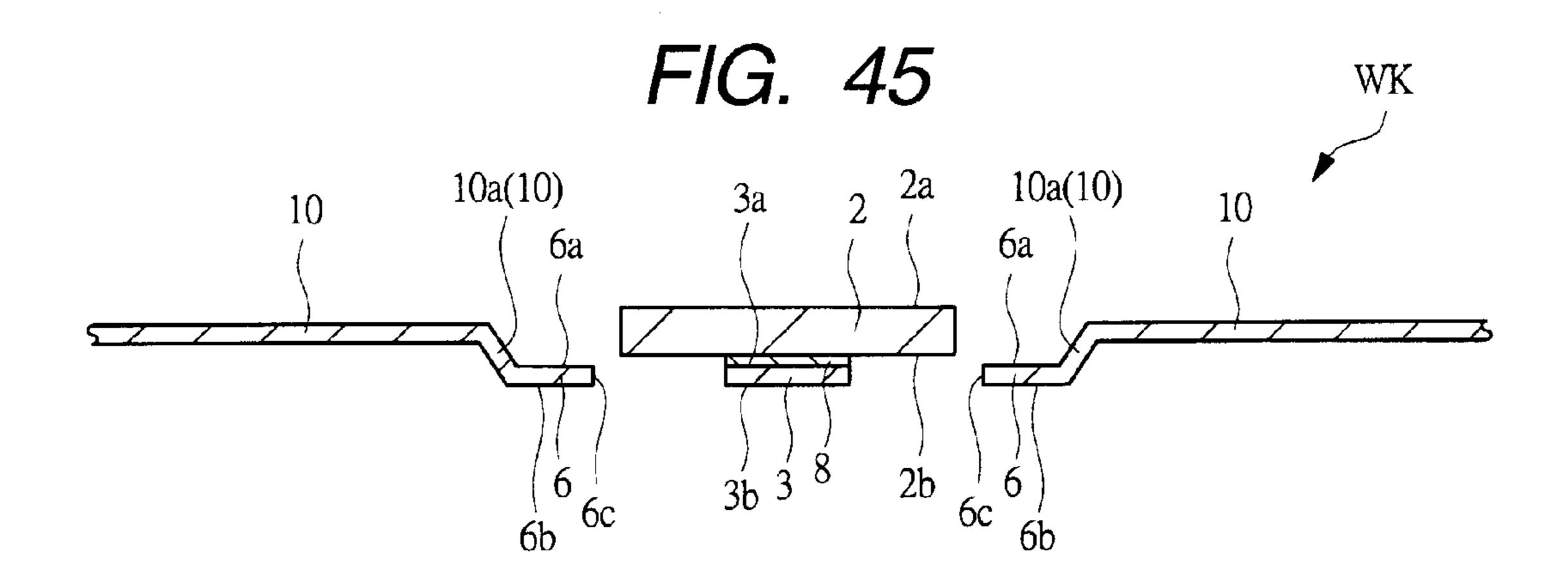

- FIG. 45 is an explanatory diagram of a wire bonding step; 35

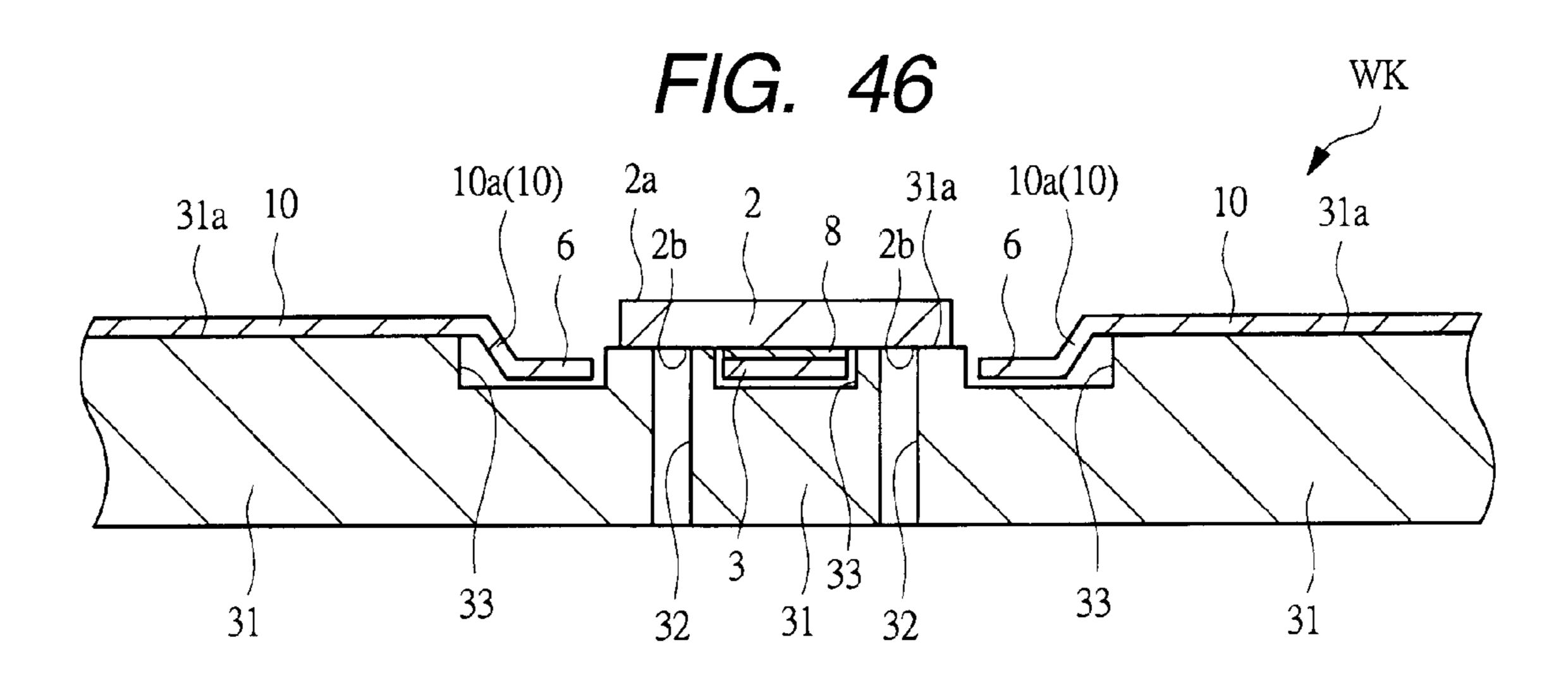

- FIG. 46 is an explanatory diagram of the wire bonding step;

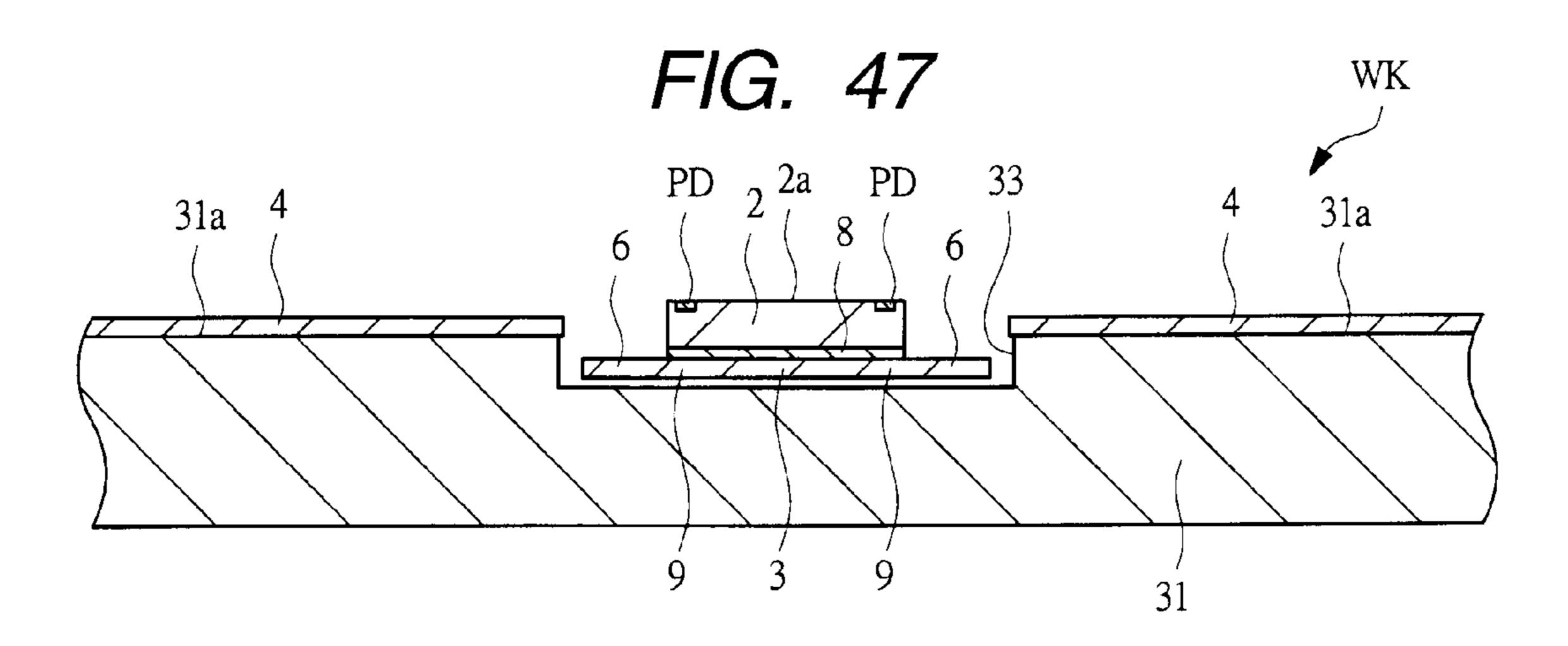

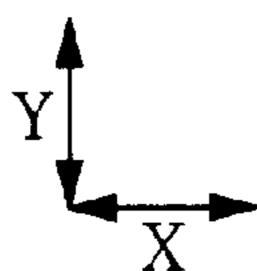

- FIG. 47 is an explanatory diagram of the wire bonding step;

- FIG. 48 is an explanatory diagram of the wire bonding step;

- FIG. 49 is an explanatory diagram of the wire bonding step;

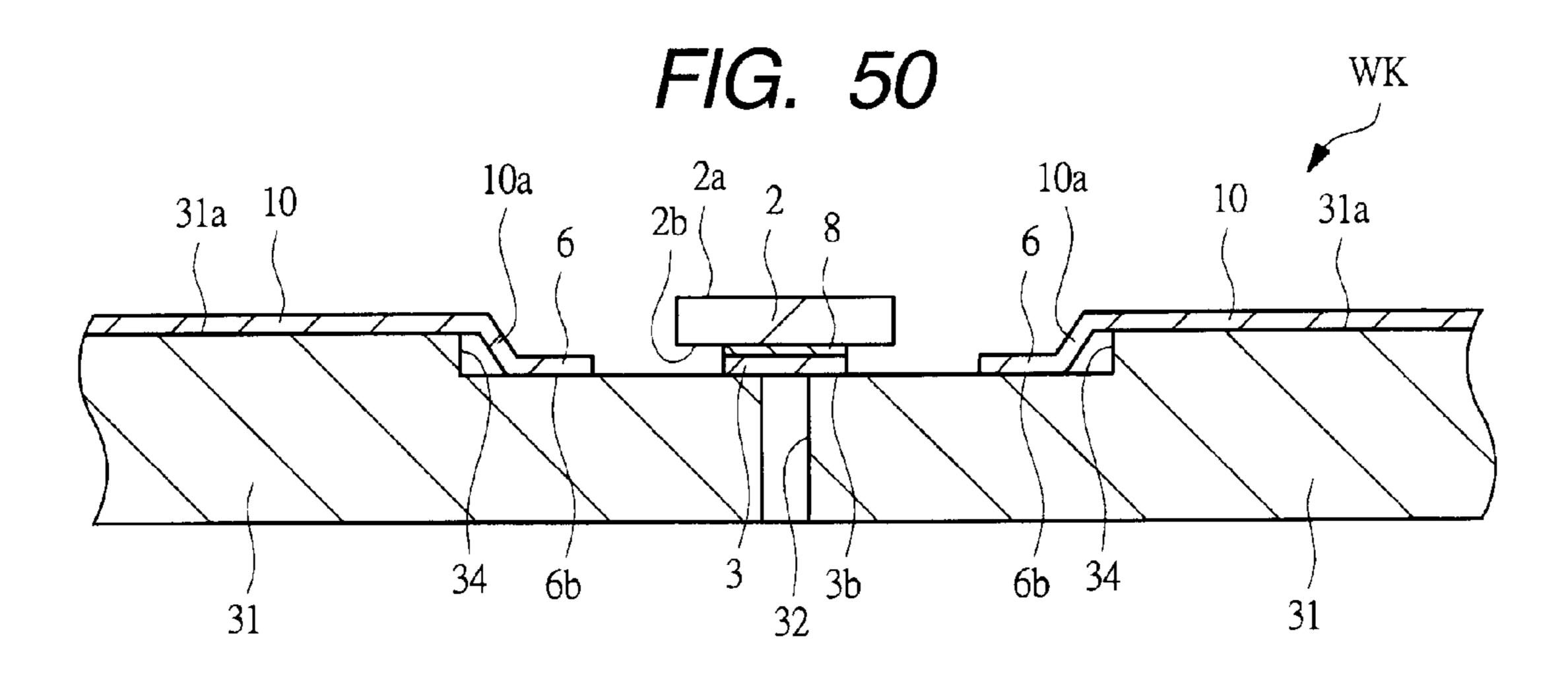

- FIG. 50 is an explanatory diagram of the wire bonding step; 40

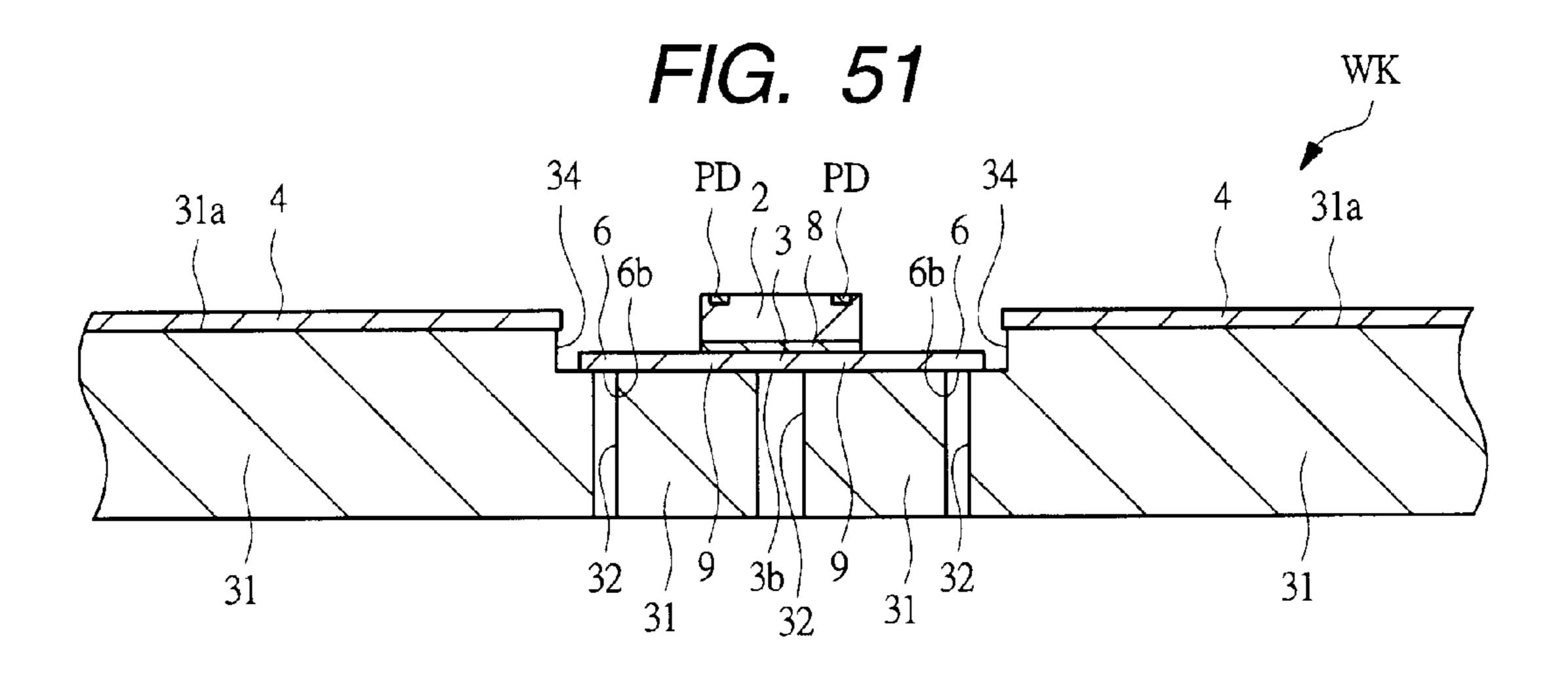

- FIG. 51 is an explanatory diagram of the wire bonding step;

- FIG. 52 is an explanatory diagram of the wire bonding step;

- FIG. **53** is an explanatory diagram of a wire bonding step when the die pad in the second comparative example is applied;

- FIG. **54** is an explanatory diagram of the wire bonding step when the die pad in the second comparative example is applied;

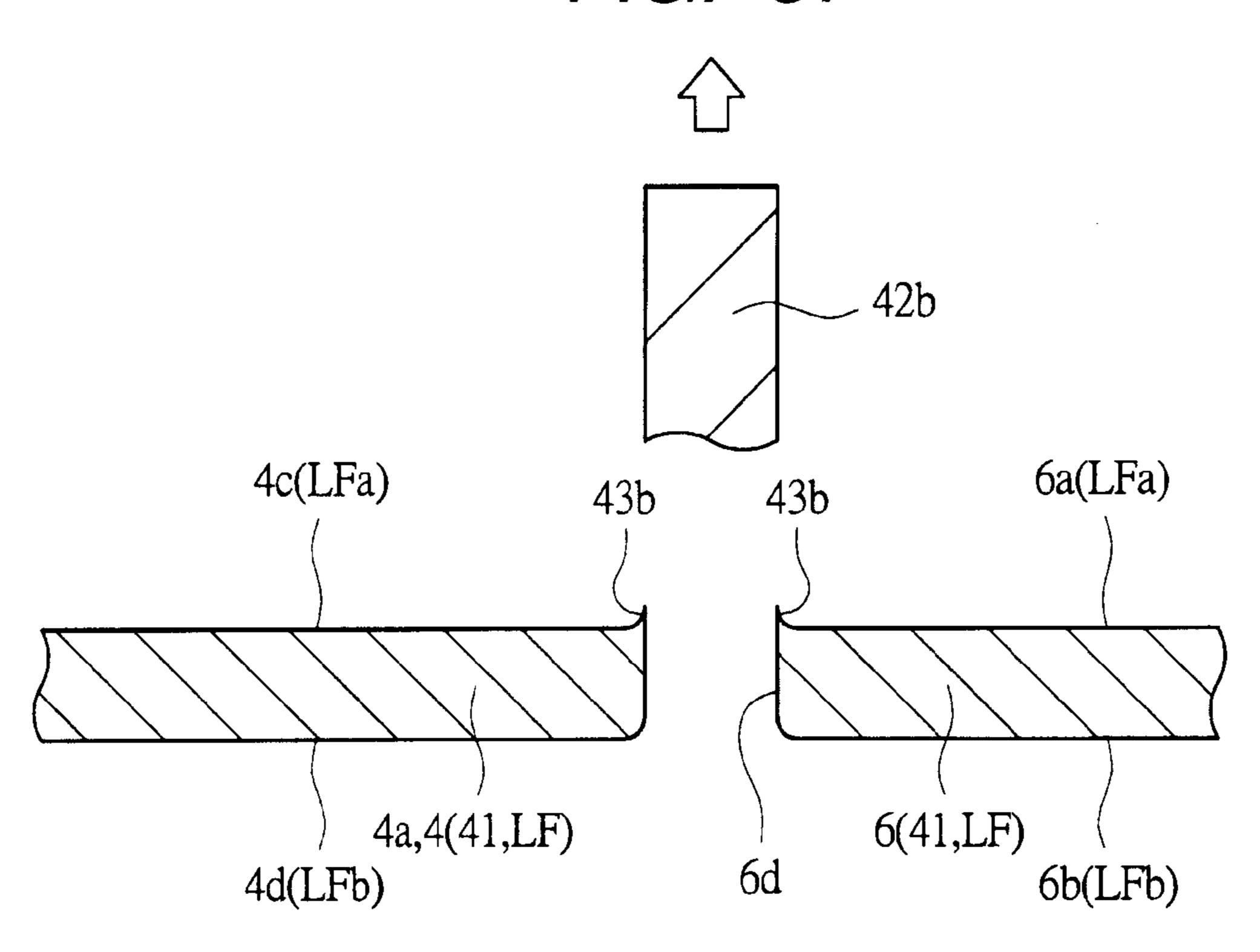

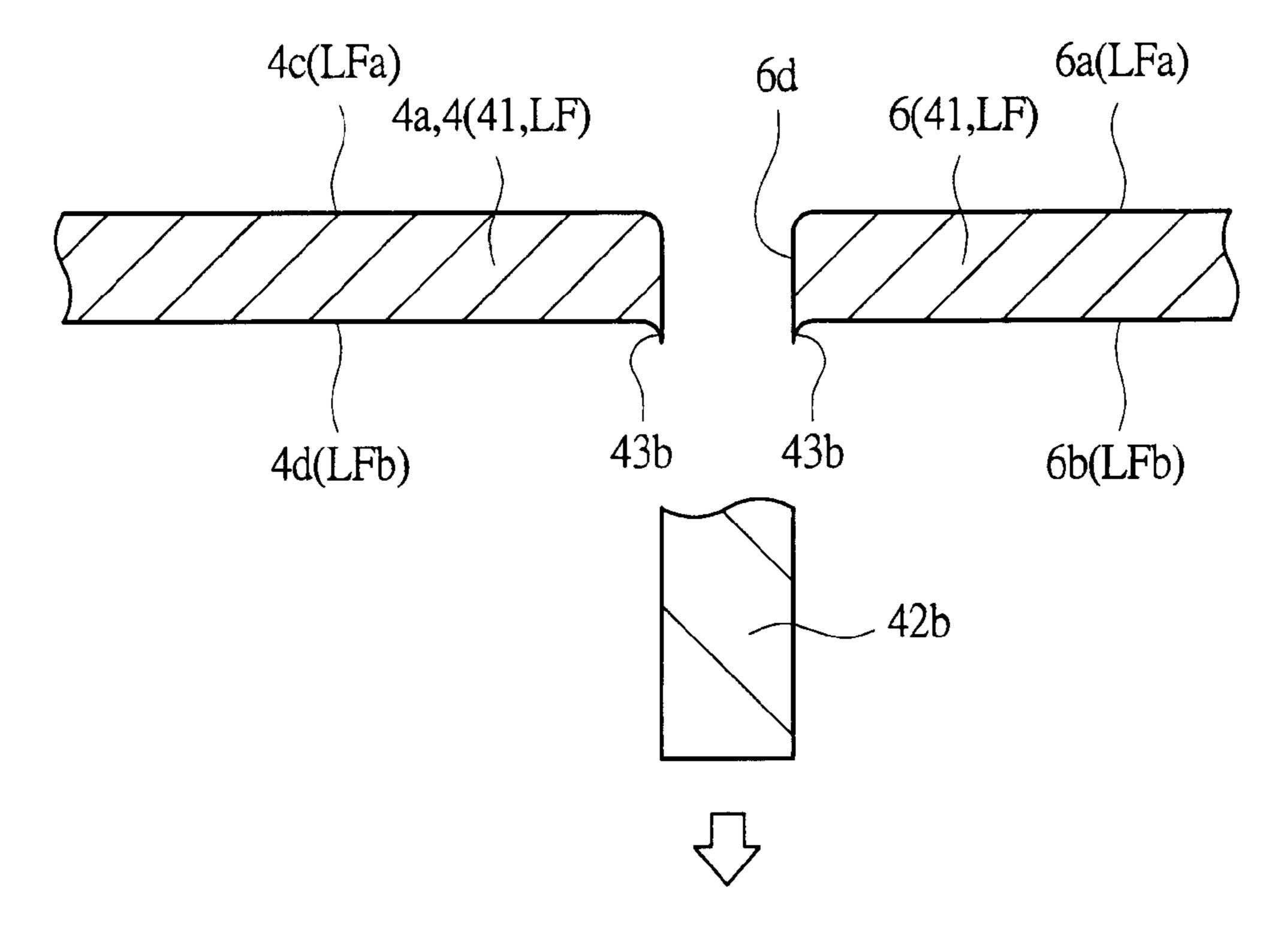

- FIG. **55** is an explanatory diagram of a technique to form a lead frame;

- FIG. **56** is an explanatory diagram of the technique to form the lead frame;

- FIG. **57** is an explanatory diagram of the technique to form the lead frame;

- FIG. **58** is an explanatory diagram of the technique to form 55 the lead frame;

- FIG. **59** is a bottom view of a semiconductor device in a seventh embodiment of the present invention;

- FIG. **60** is a partially enlarged plan perspective view of the semiconductor in the seventh embodiment of the present 60 invention;

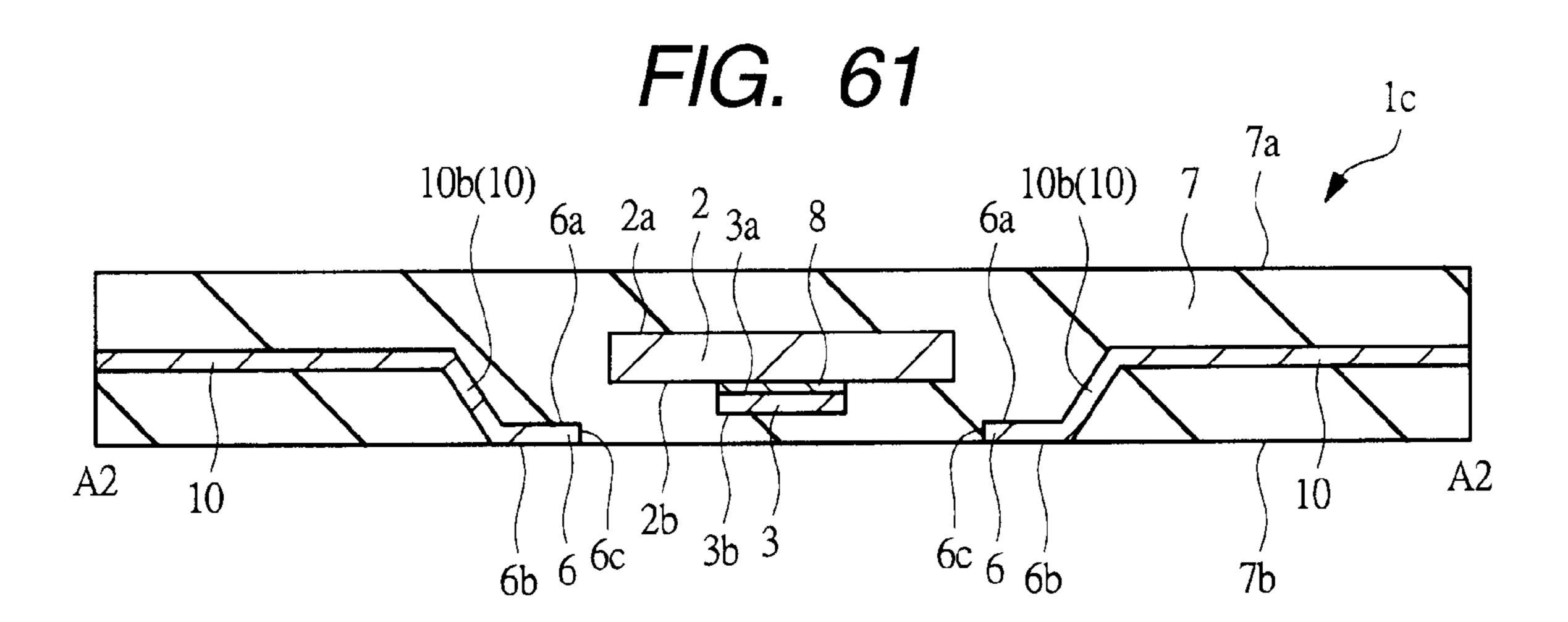

- FIG. **61** is a section view of the semiconductor device in the seventh embodiment of the present invention;

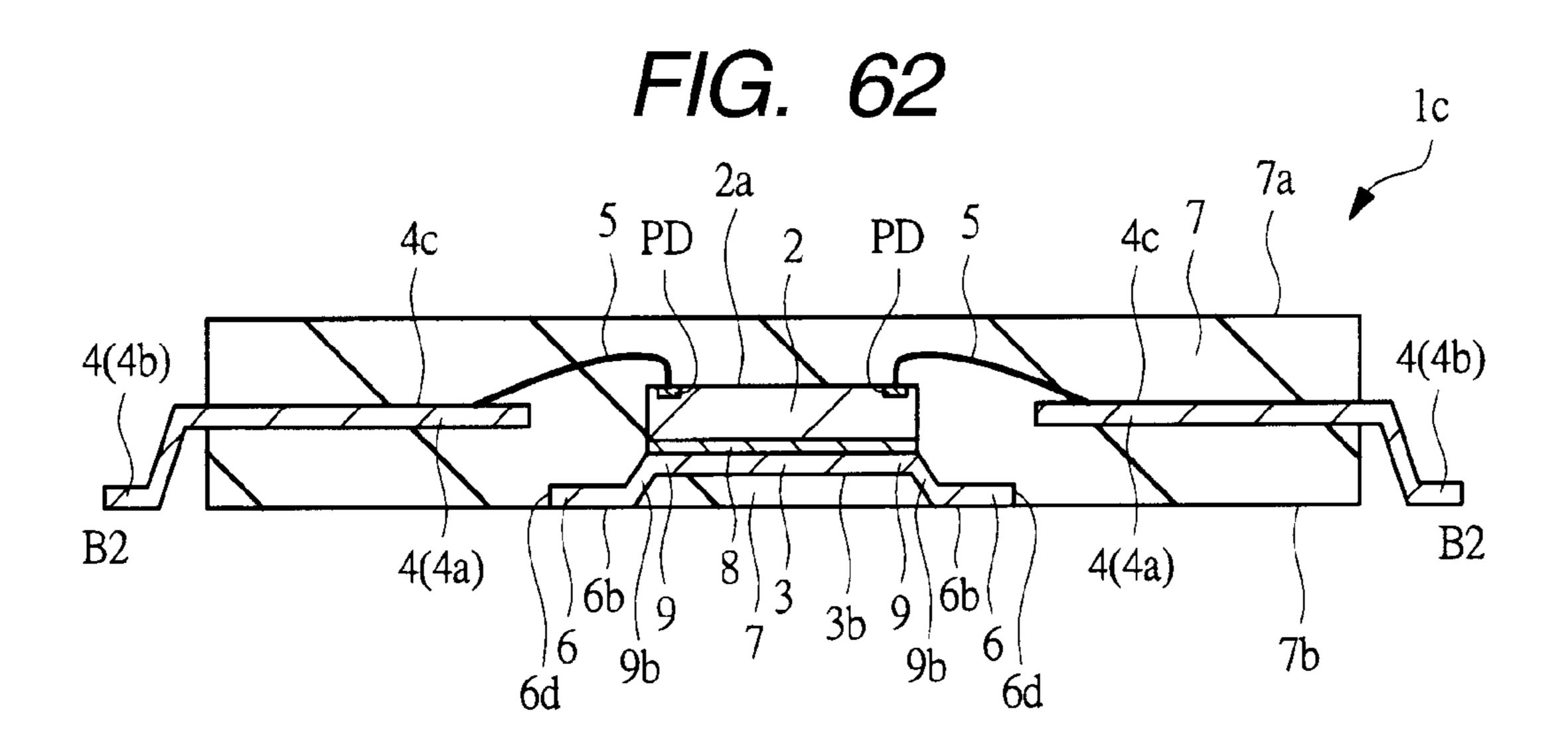

- FIG. **62** is a section view of the semiconductor device in the seventh embodiment of the present invention;

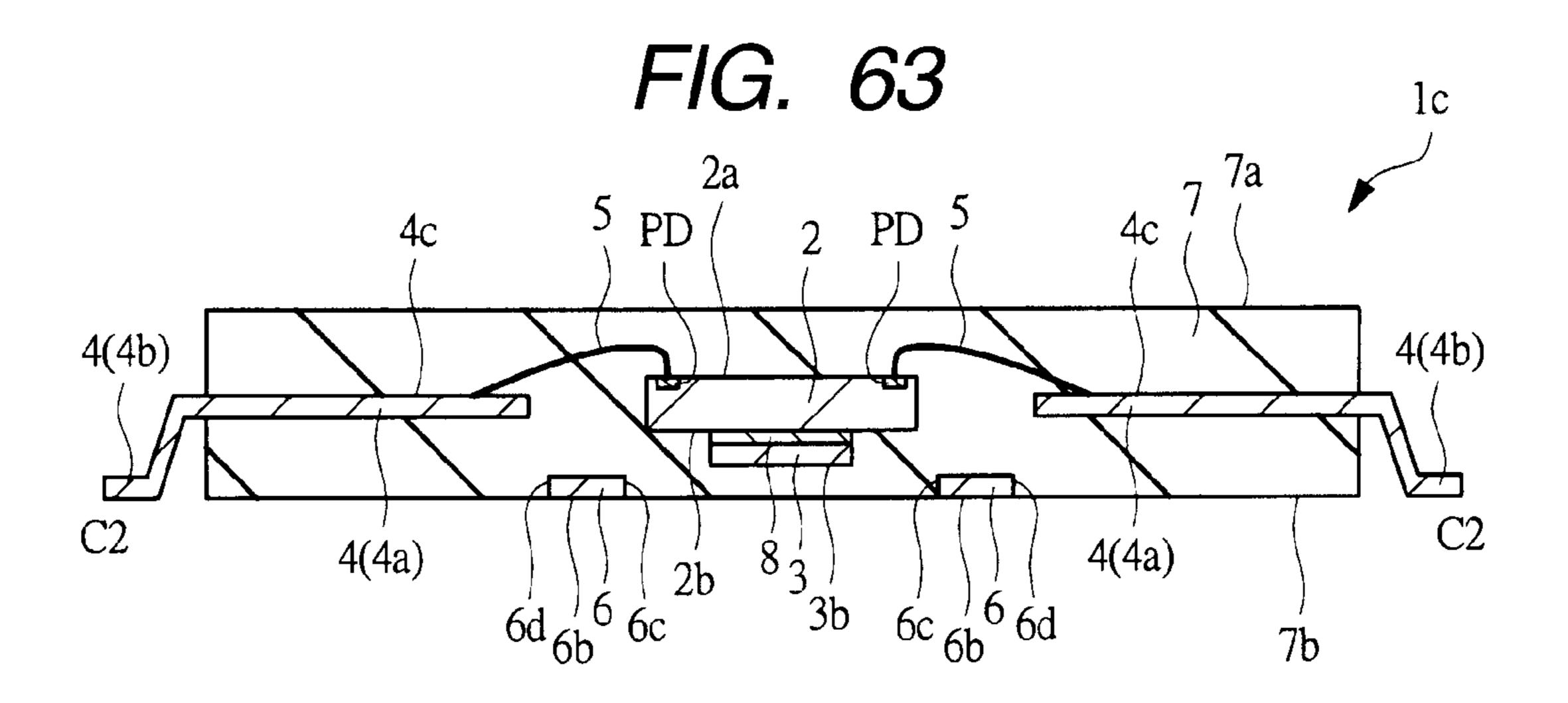

- FIG. 63 is a section view of the semiconductor device in the seventh embodiment of the present invention;

6

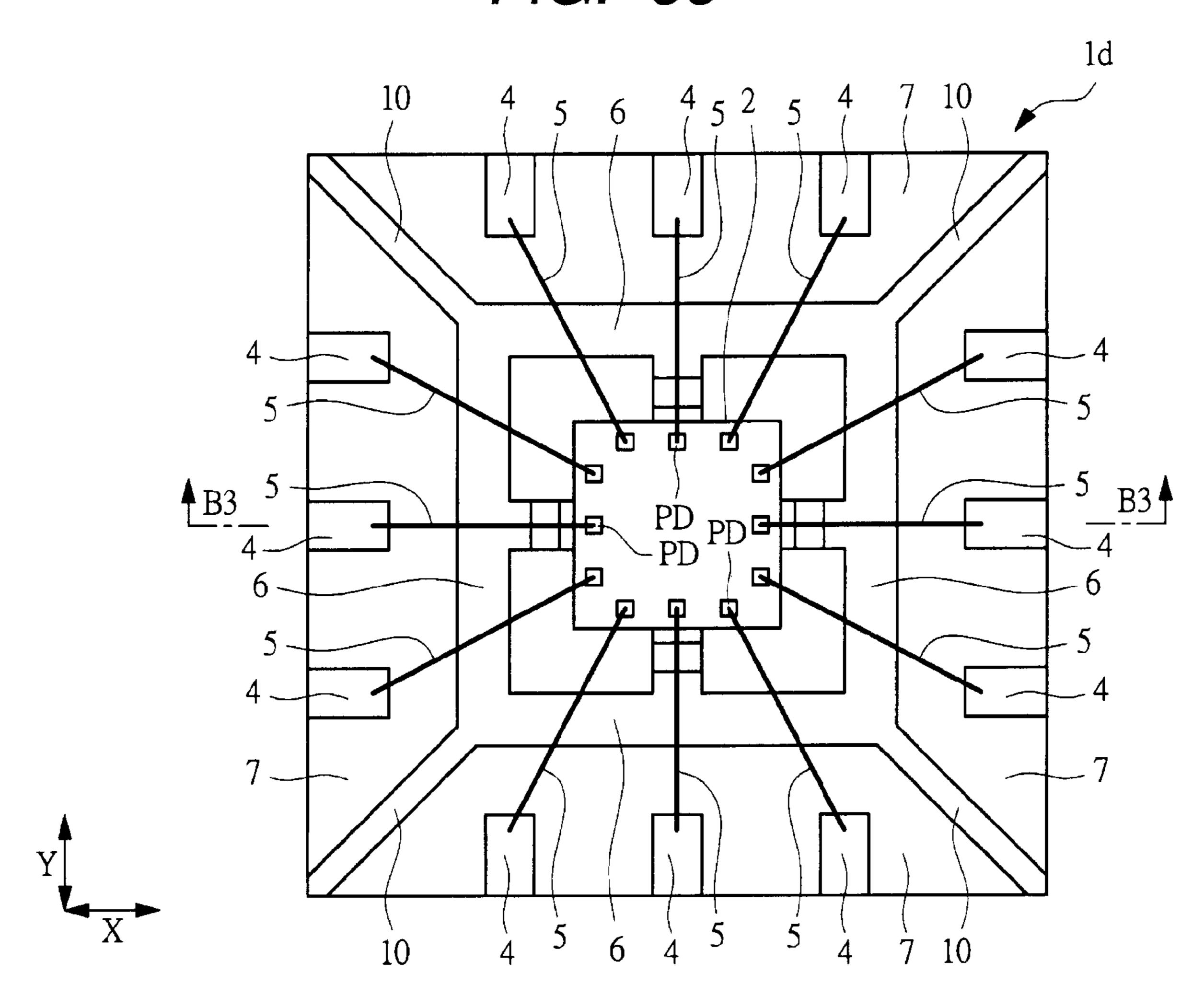

- FIG. **64** is a top view of a semiconductor device in an eighth embodiment of the present invention;

- FIG. **65** is a bottom view of the semiconductor device in the eighth embodiment of the present invention;

- FIG. **66** is a plan perspective view of the semiconductor device in the eighth embodiment of the present invention;

- FIG. 67 is a plan perspective view of the semiconductor device in the eighth embodiment of the present invention;

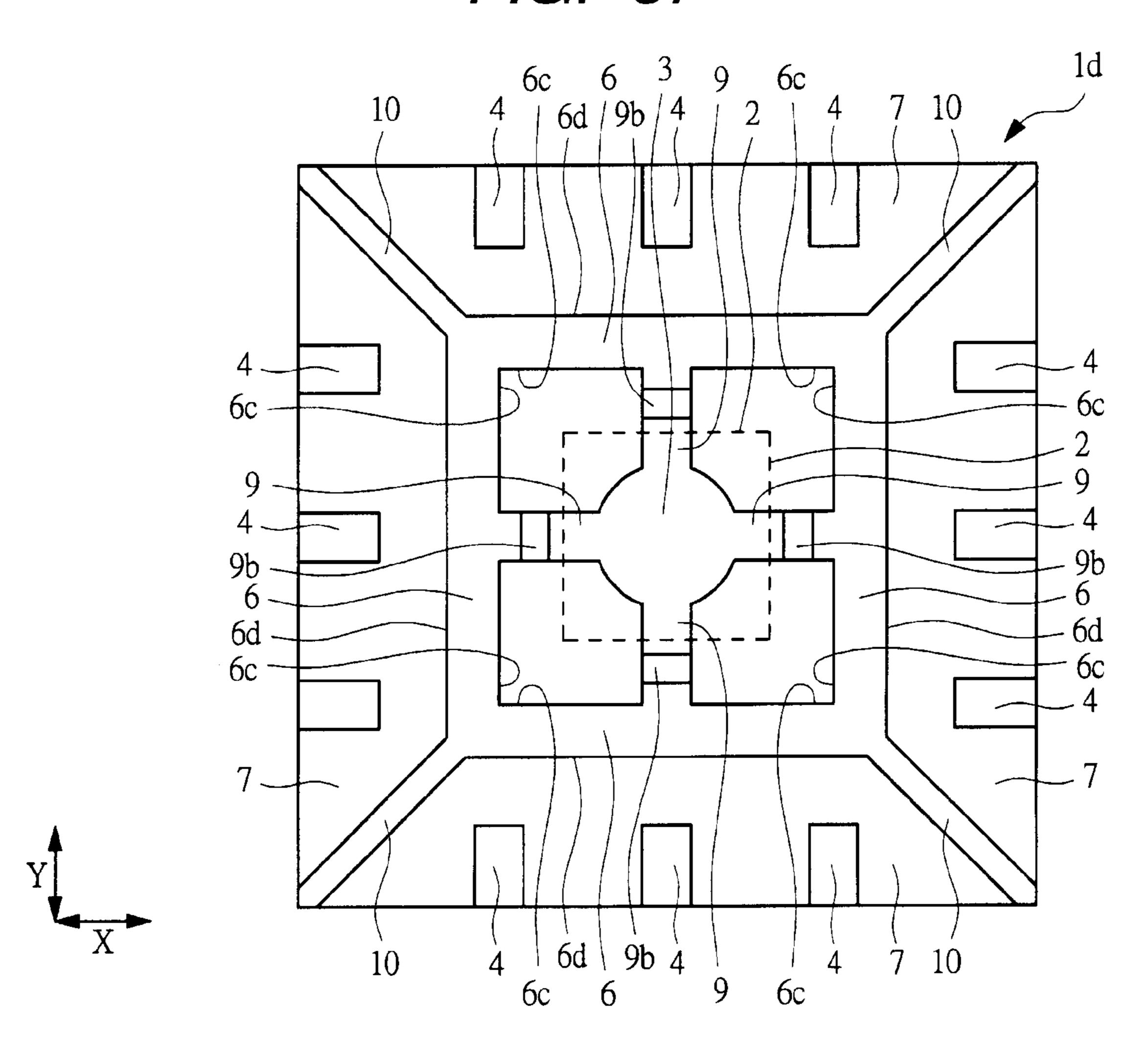

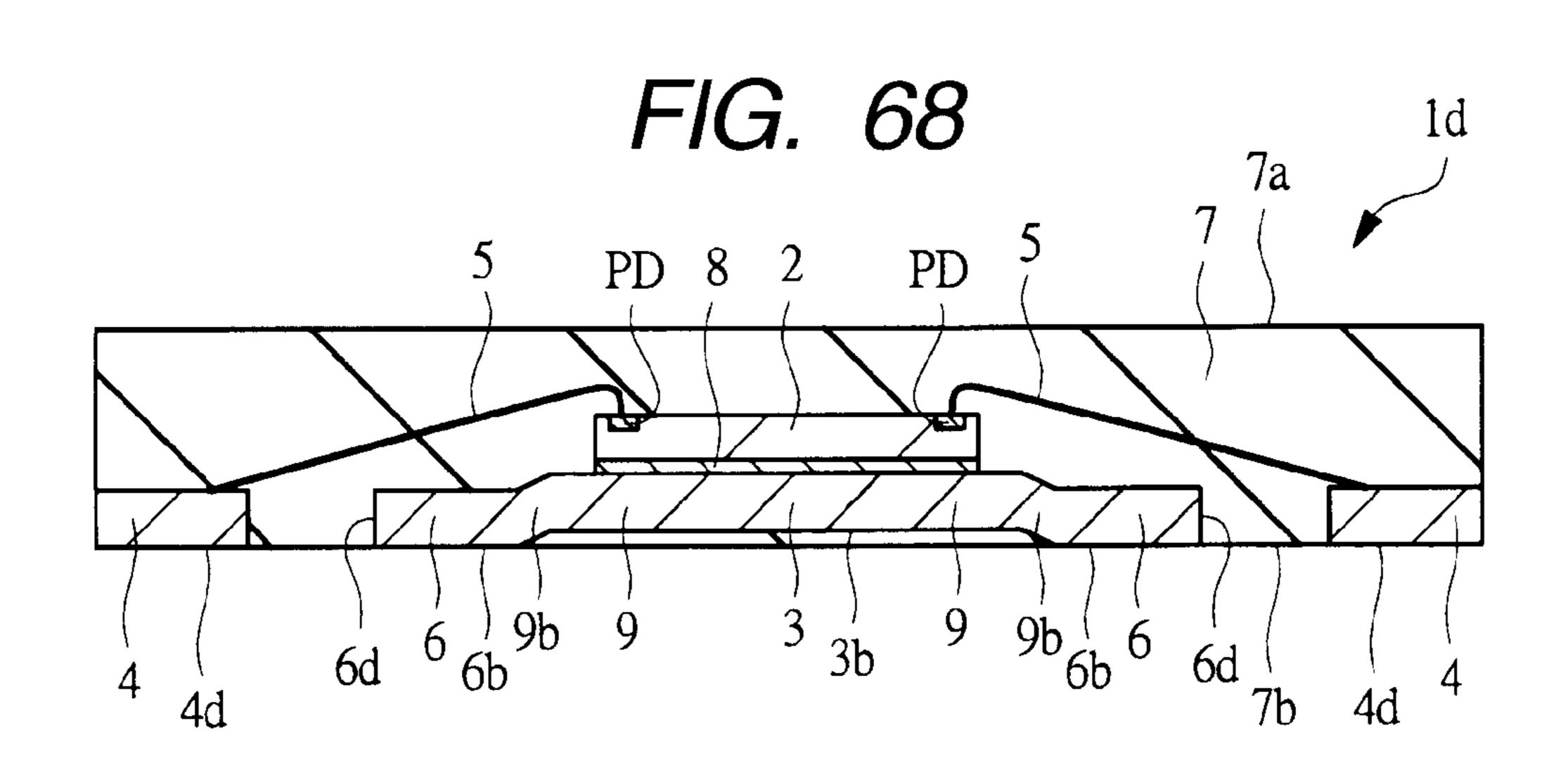

- FIG. **68** is a section view of the semiconductor device in the eighth embodiment of the present invention;

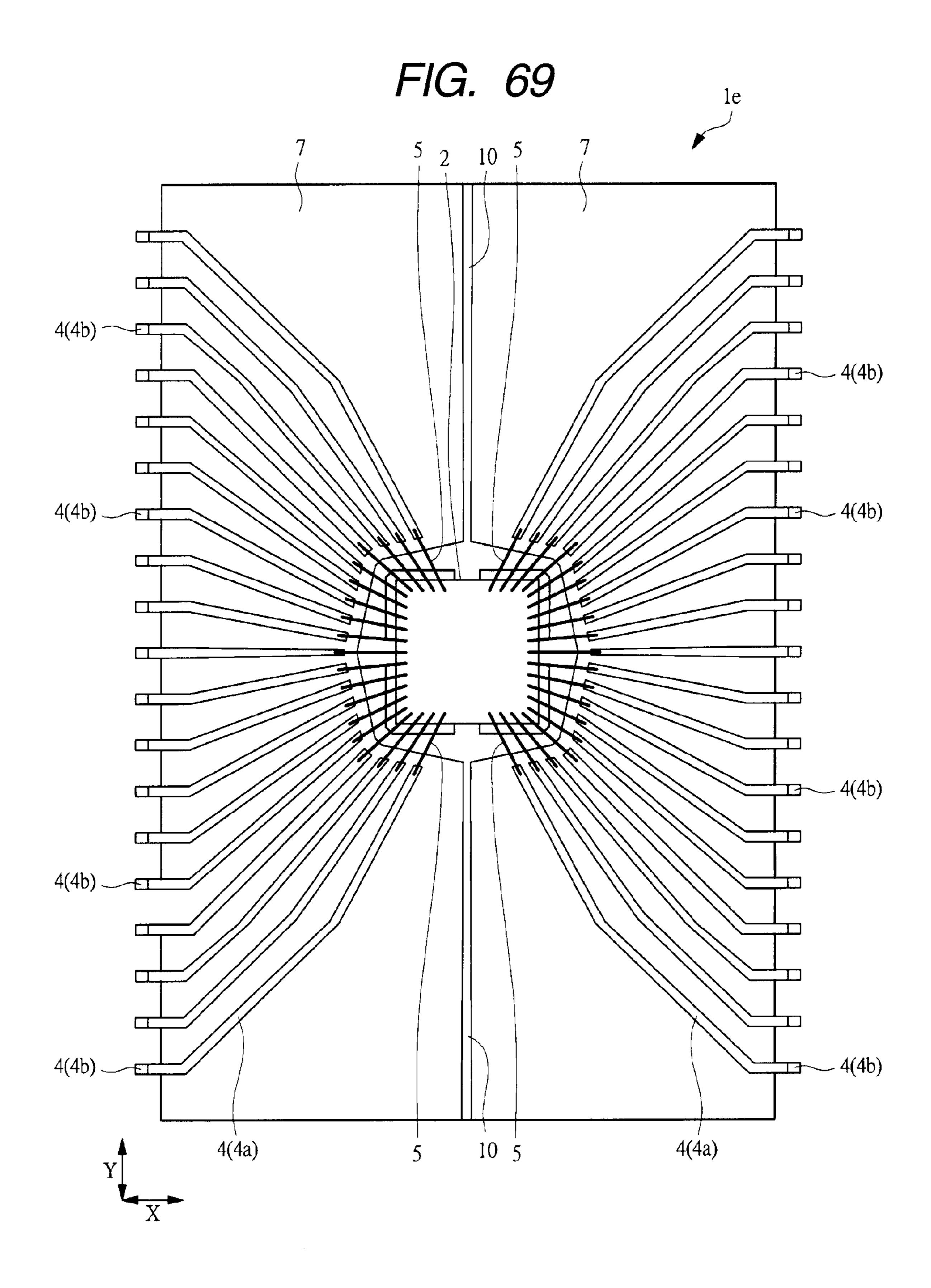

- FIG. **69** is a plan perspective view of a semiconductor device in a ninth embodiment of the present invention;

- FIG. 70 is a plan perspective view of the semiconductor device in the ninth embodiment of the present invention;

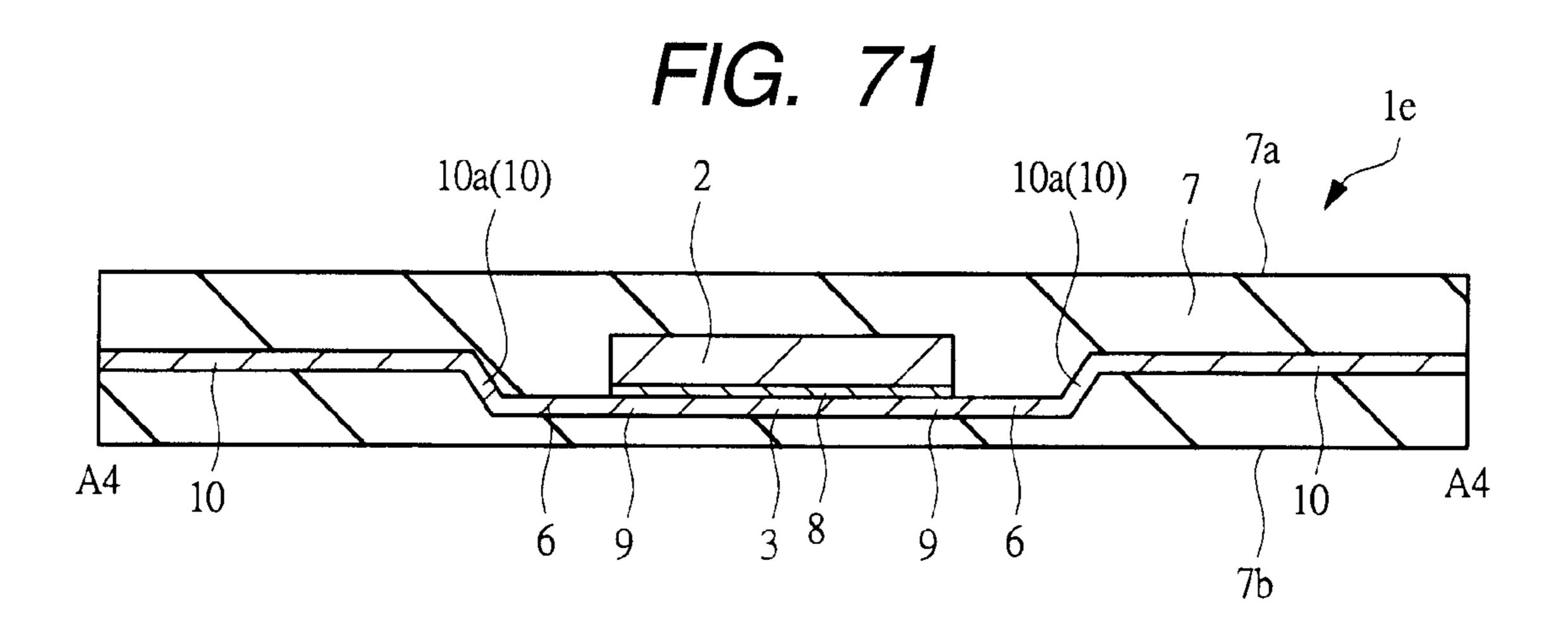

- FIG. 71 is a section view of the semiconductor device in the ninth embodiment of the present invention;

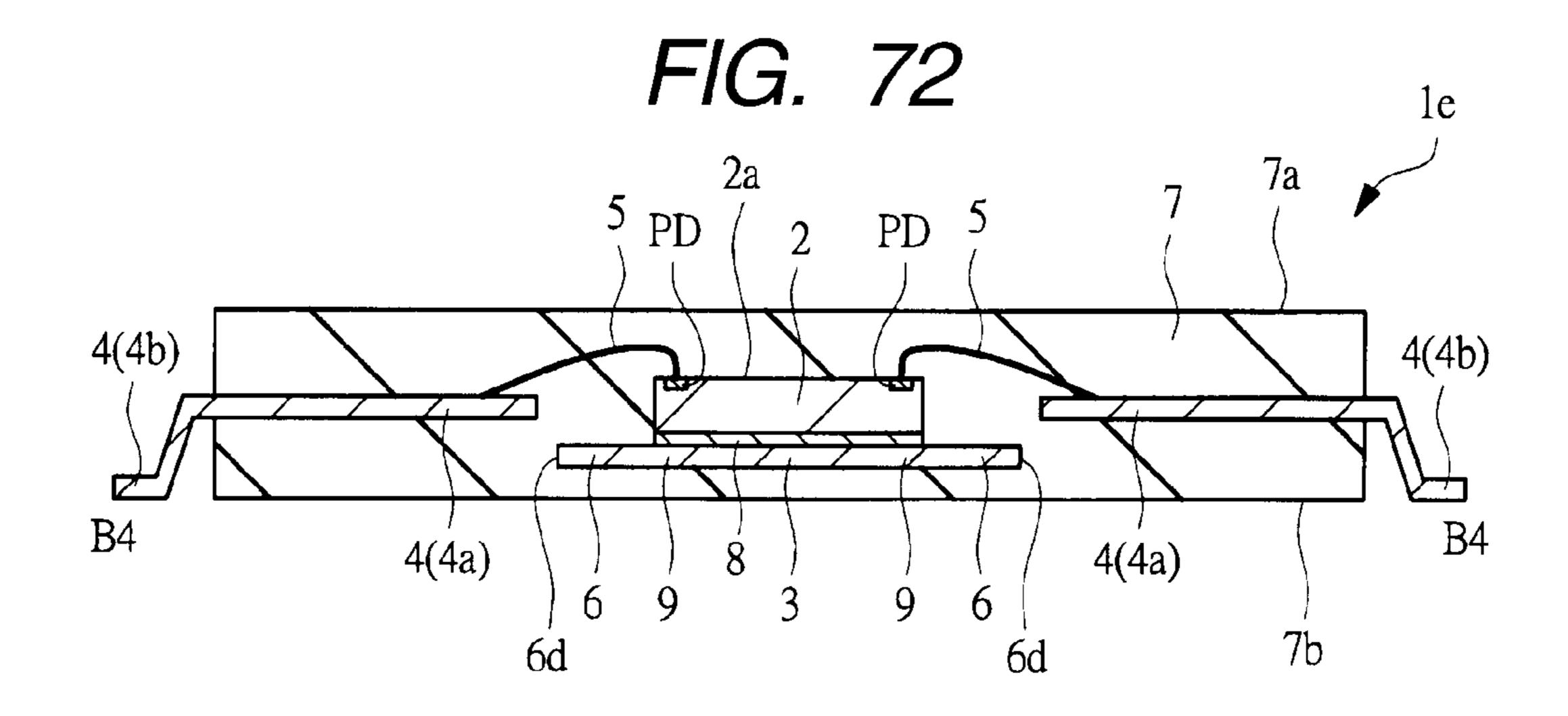

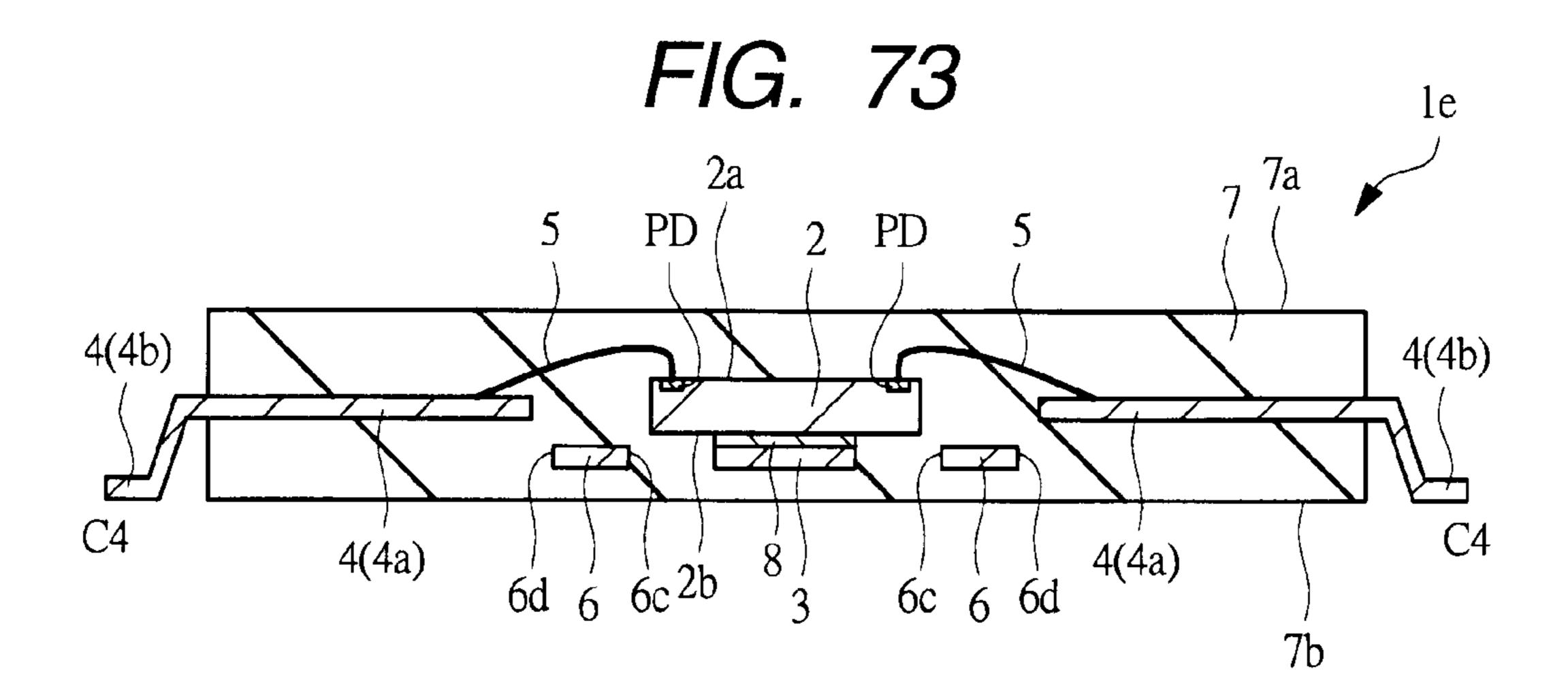

- FIG. 72 is a section view of the semiconductor device in the ninth embodiment of the present invention; and

- FIG. 73 is a section view of the semiconductor device in the ninth embodiment of the present invention.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

The following embodiments will be explained, divided into plural sections or embodiments, if necessary for convenience. Except for the case where it shows clearly in particular, they are not mutually unrelated and one has relationships such as a modification, details, and supplementary explanation of some or entire of another. In the following embodiments, when referring to the number of elements, etc. (including the number, a numeric value, an amount, a range, etc.), they may be not restricted to the specific number but may be greater or smaller than the specific number, except for the case where they are clearly specified in particular and where they are clearly restricted to a specific number theoretically. Furthermore, in the following embodiments, it is needless to say that an element (including an element step etc.) is not necessarily indispensable, except for the case where it is clearly specified in particular and where it is considered to be clearly indispensable from a theoretical point of view, etc. Similarly, in the following embodiments, when shape, position relationship, etc. of an element etc. is referred to, what resembles or is similar to the shape substantially shall be included, except for the case where it is clearly specified in particular and where it is considered to be clearly not right from a theoretical point of view. This statement also applies to the numeric value and range described above.

Embodiments of the present invention are explained in detail below based on the drawings. In all the drawings for explaining embodiments, the same symbol is attached to the same member having the same function, as a principle, and the repeated explanation thereof is omitted. In the following embodiments the explanation of the same or similar parts is not given unless it is necessary in particular.

In the drawings used in the embodiments, in order to make a drawing intelligible, hatching may be omitted even if it is a section view. In order to make a drawing intelligible, hatching may be attached even if it is a plan view.

#### First Embodiment

#### About Structure of Semiconductor Device

A semiconductor device in an embodiment of the present 5 invention is explained with reference to the drawings.

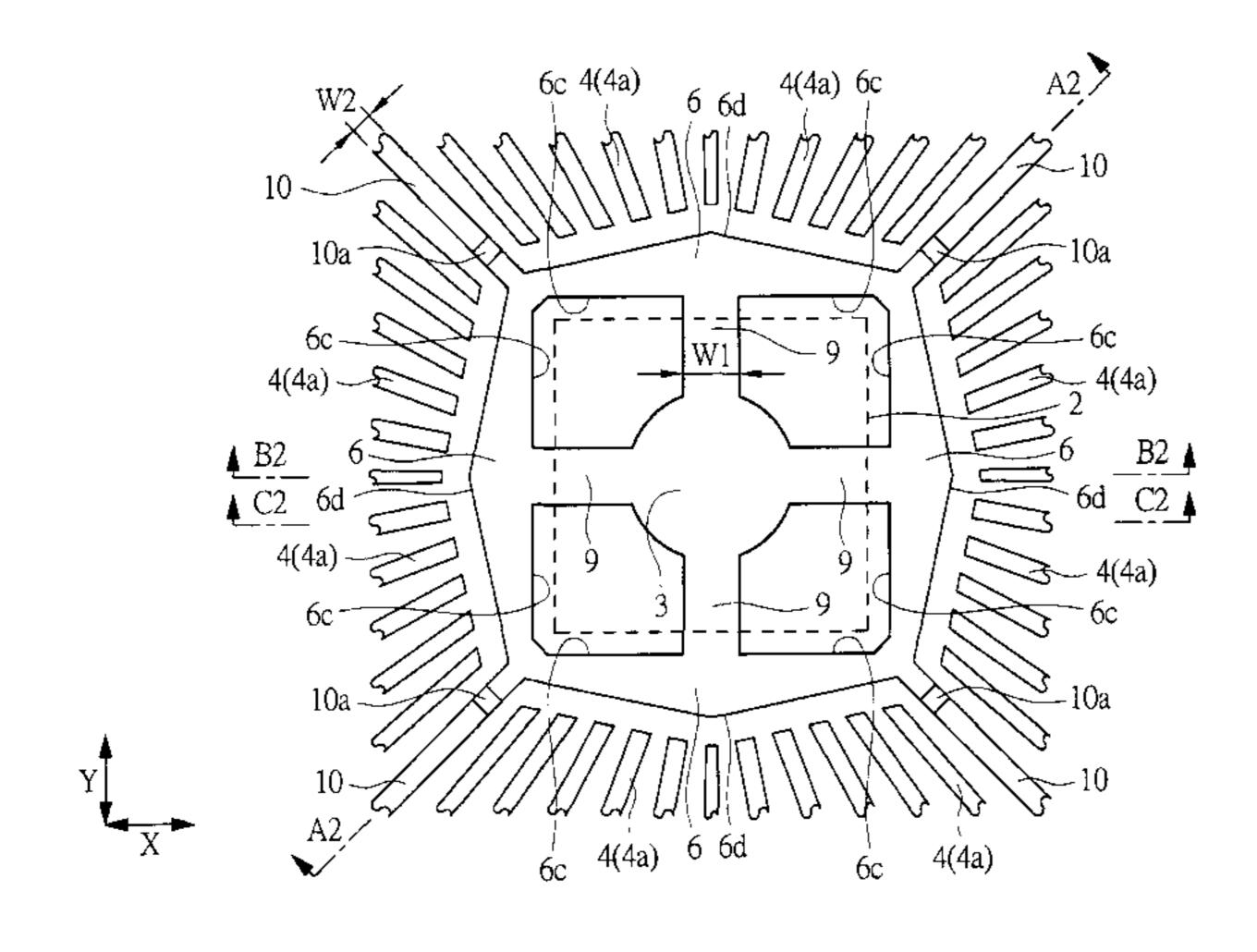

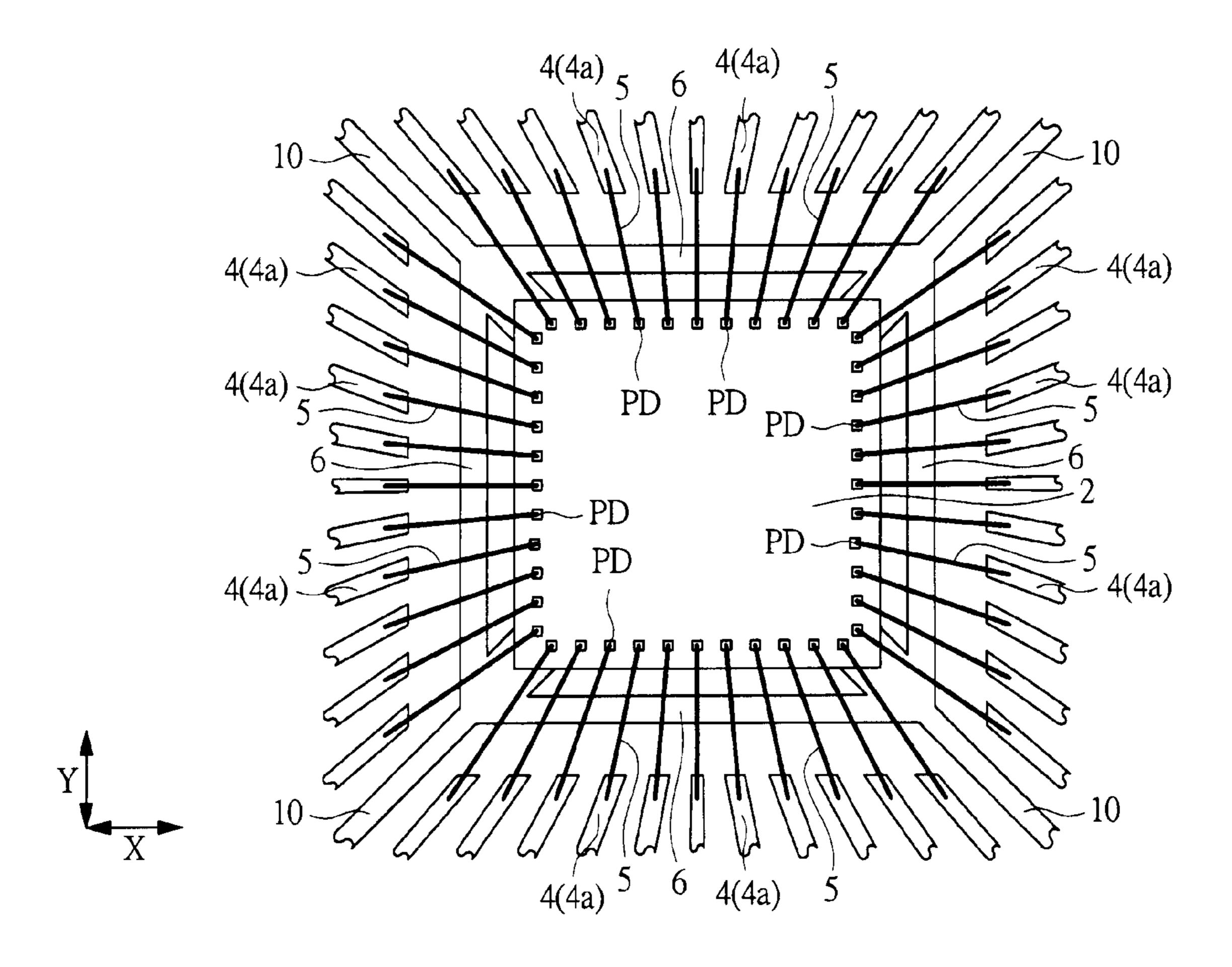

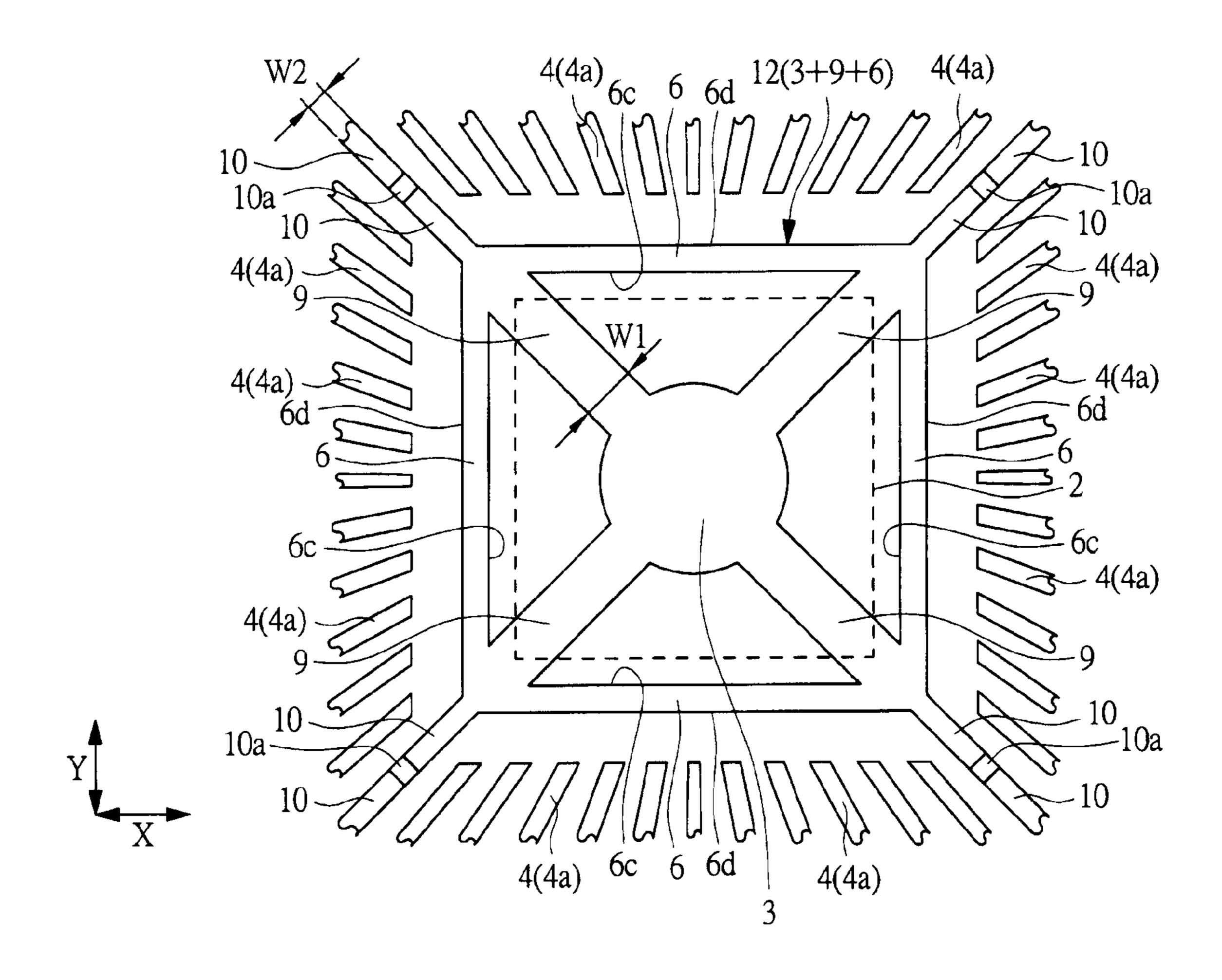

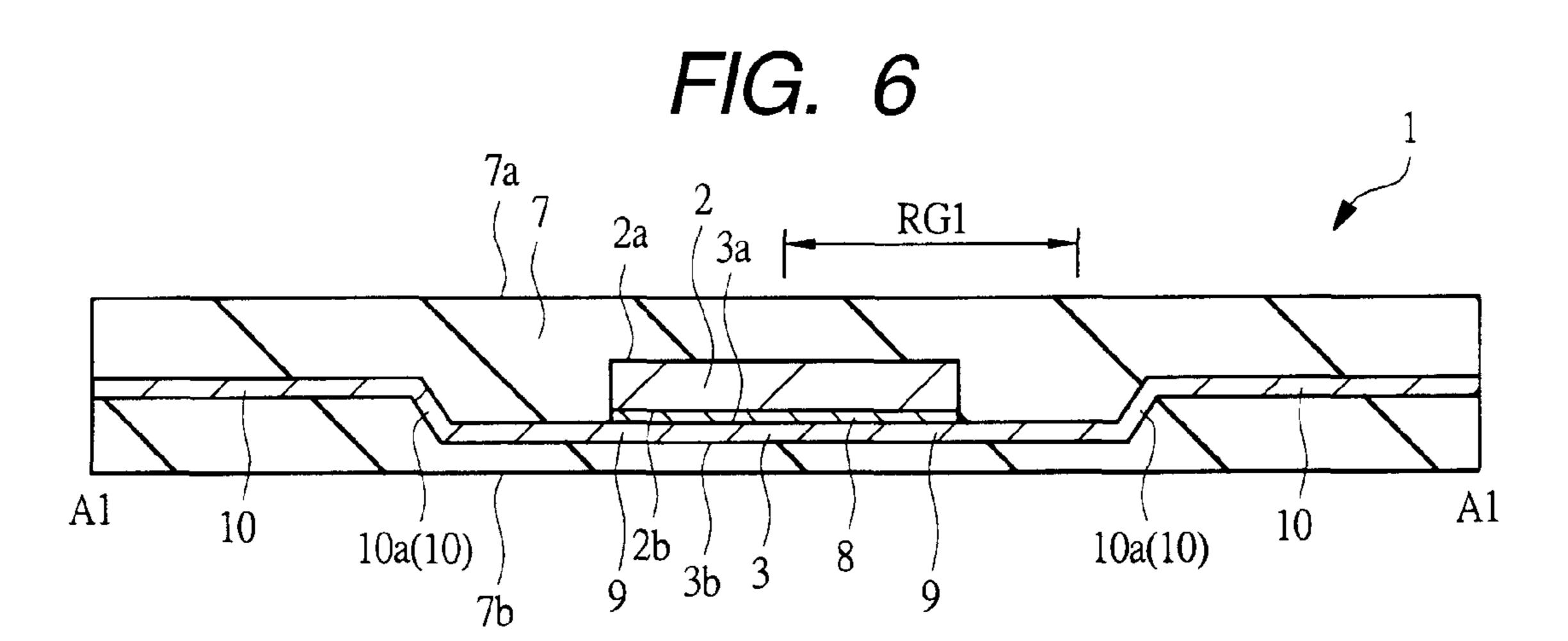

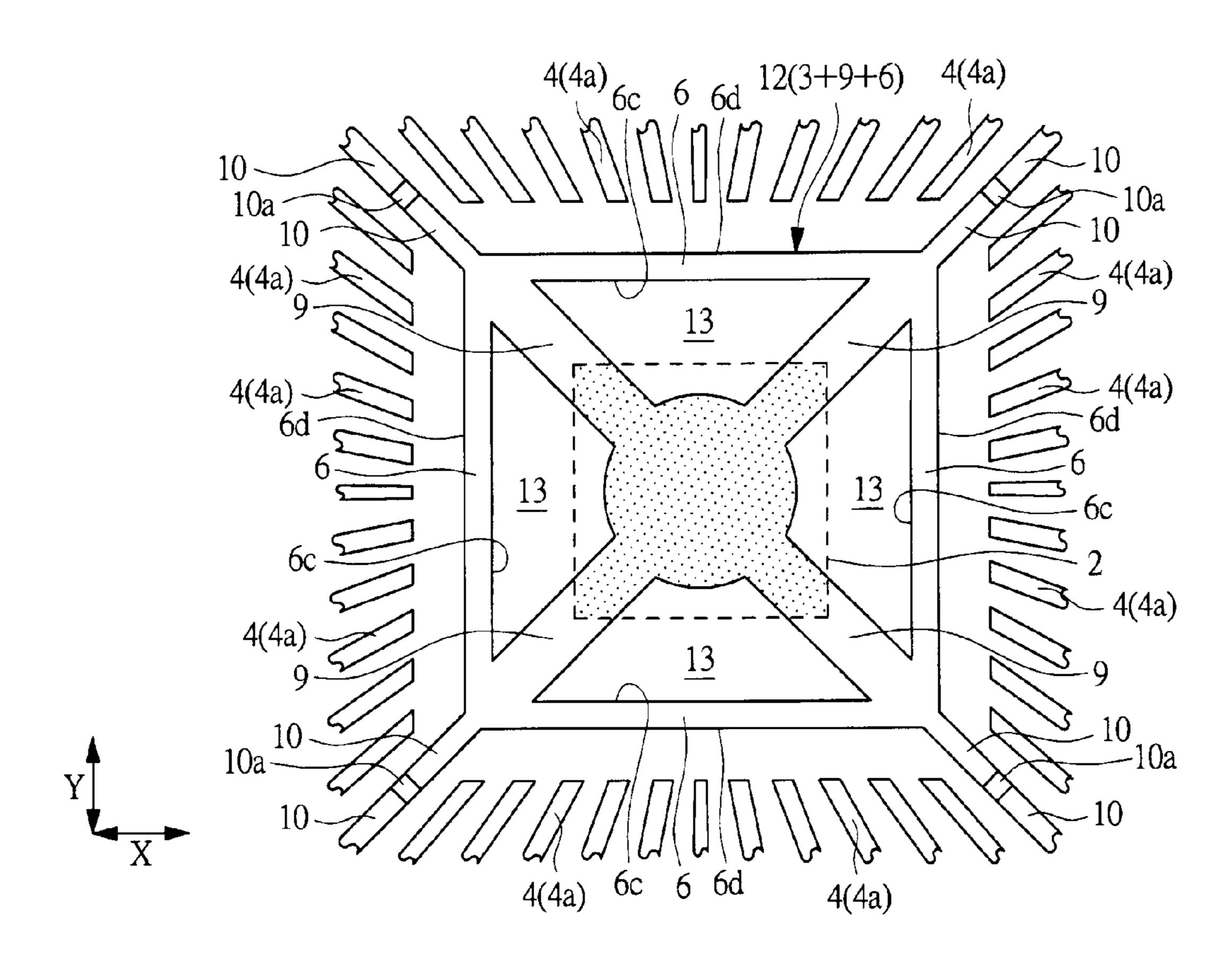

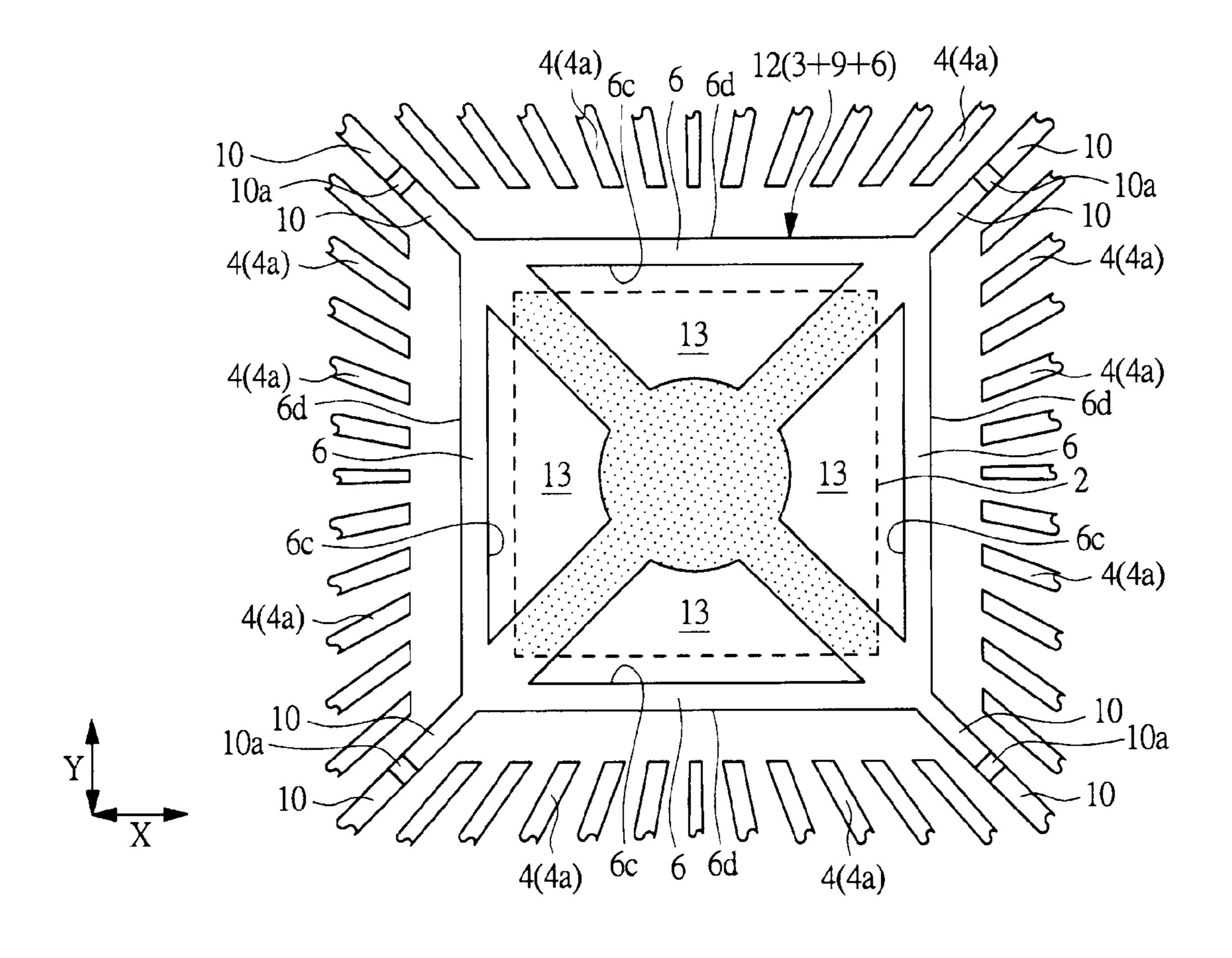

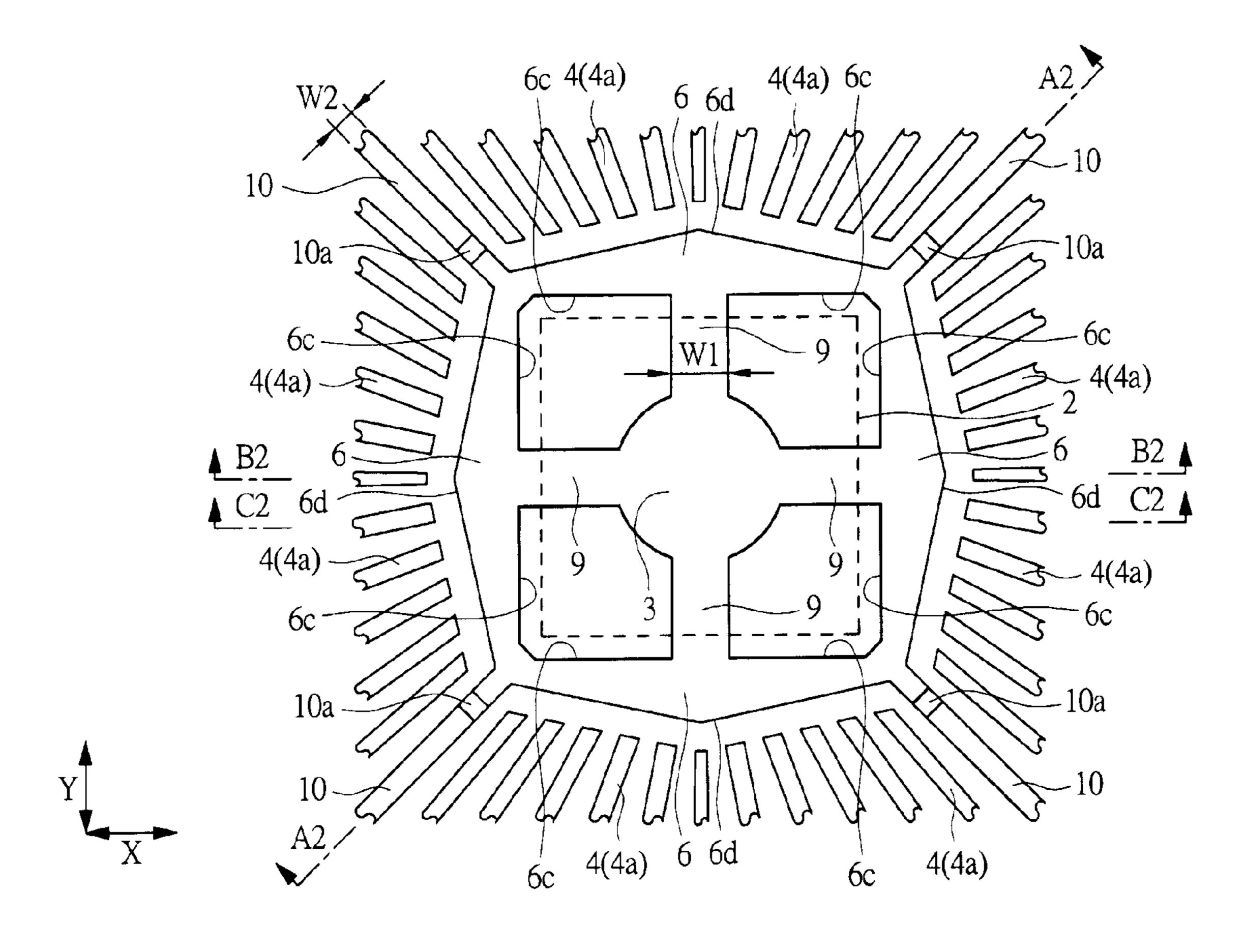

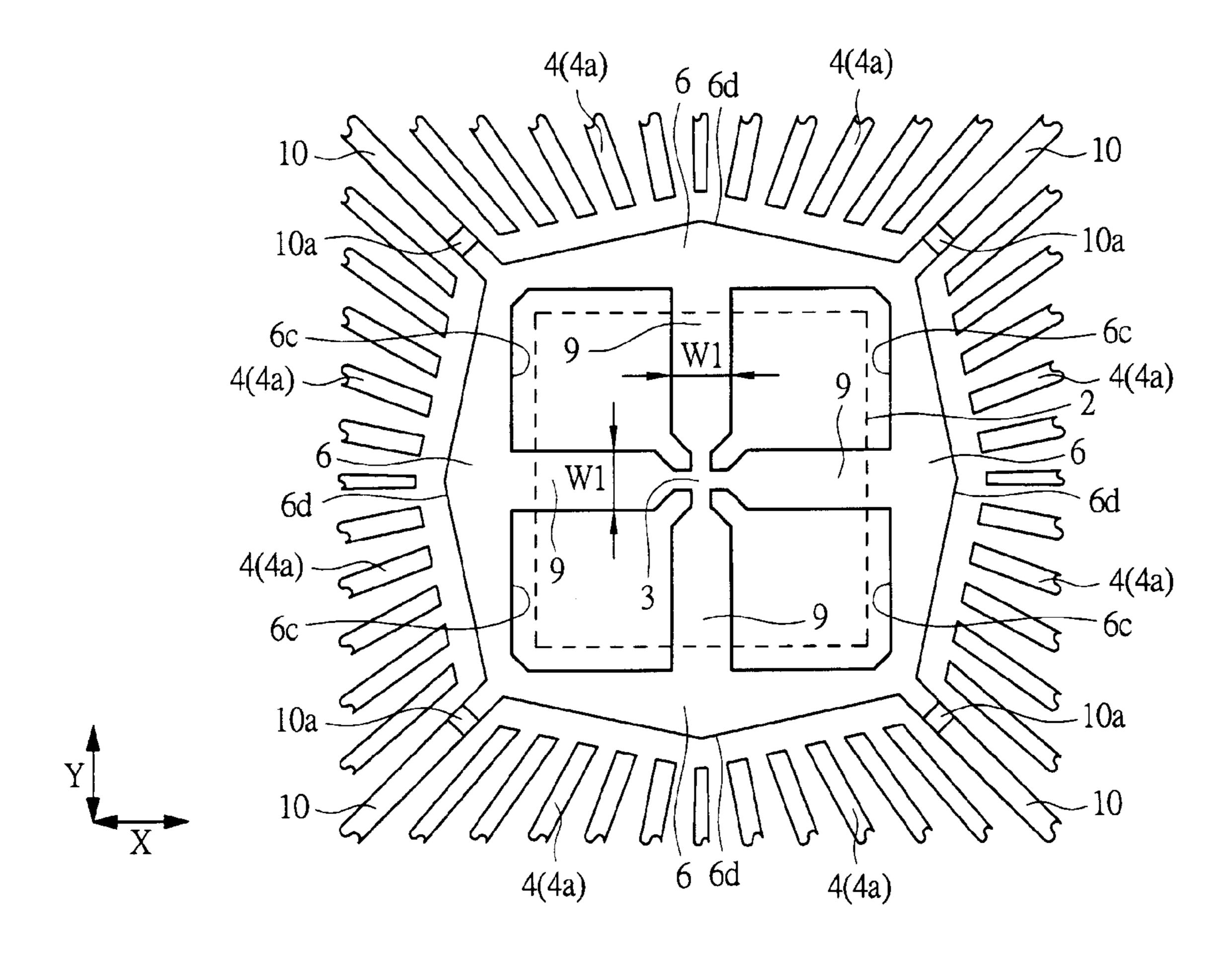

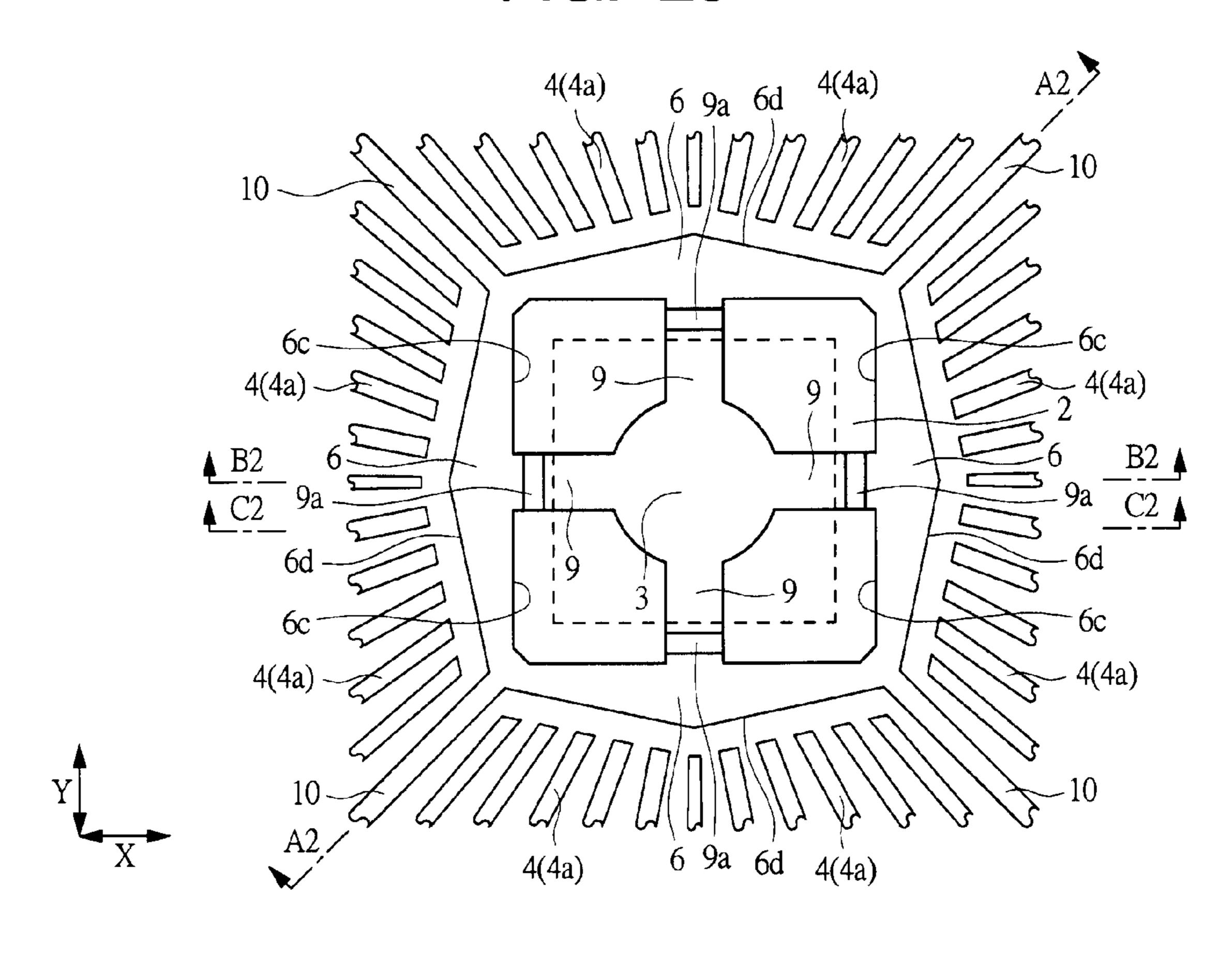

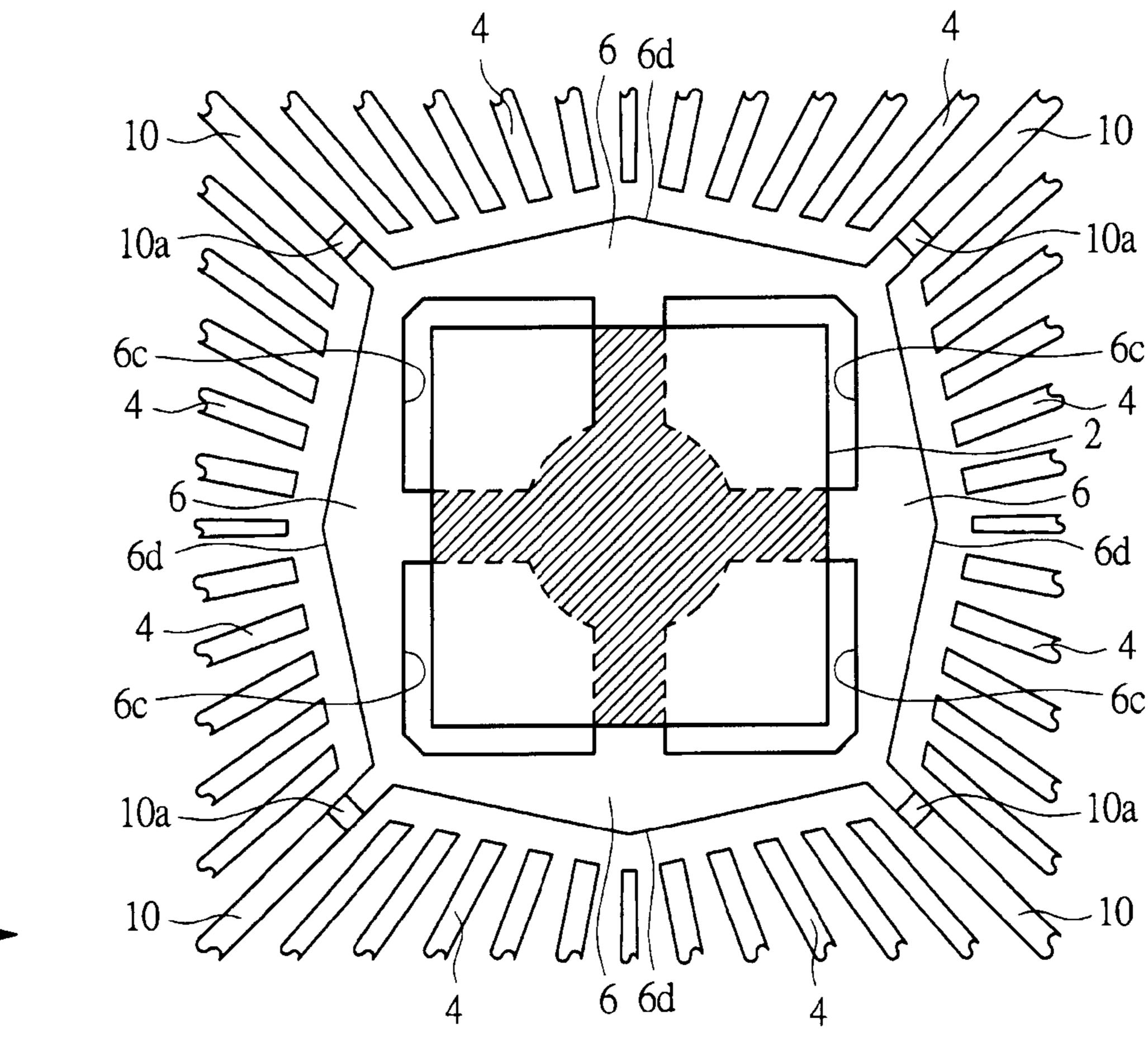

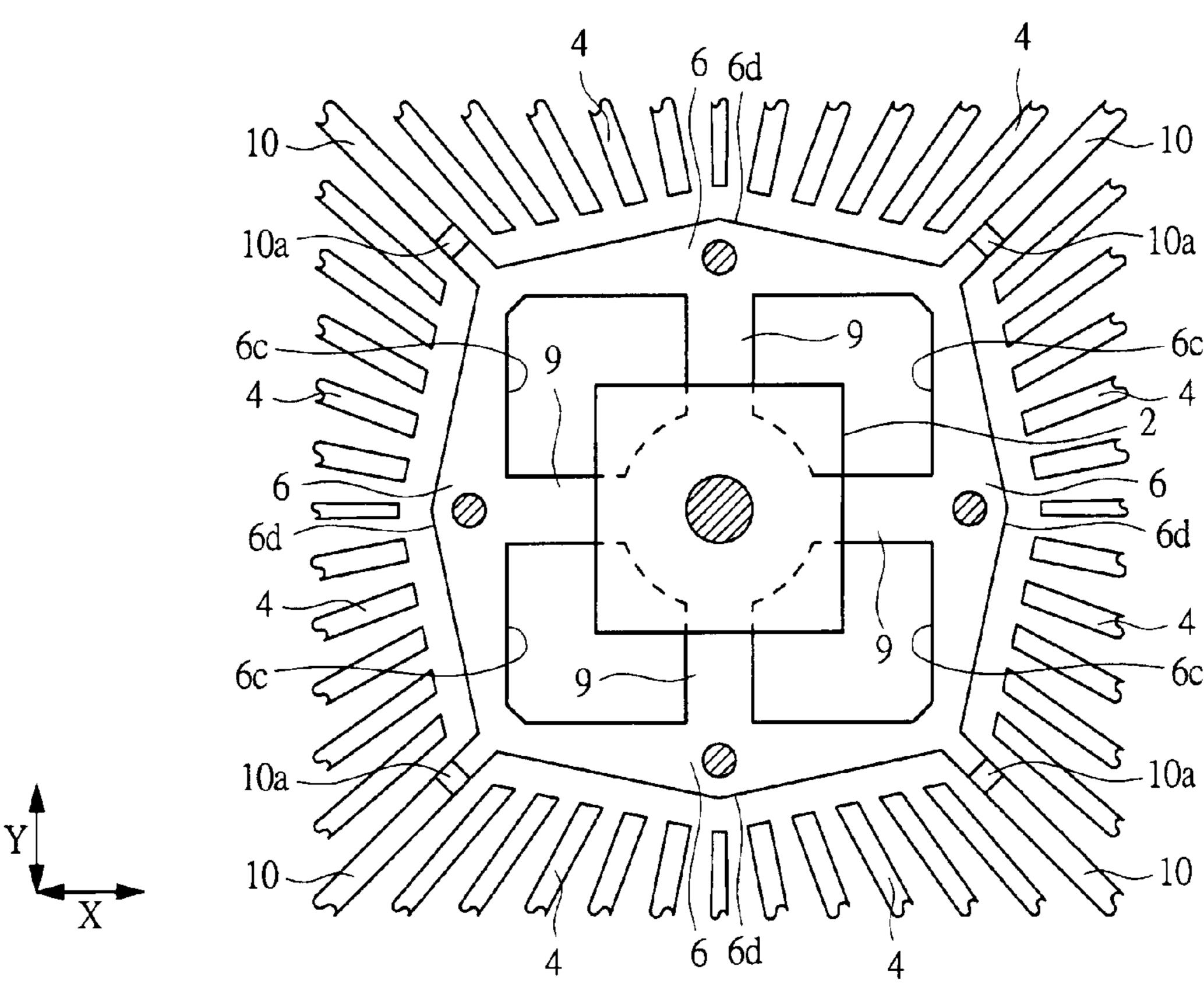

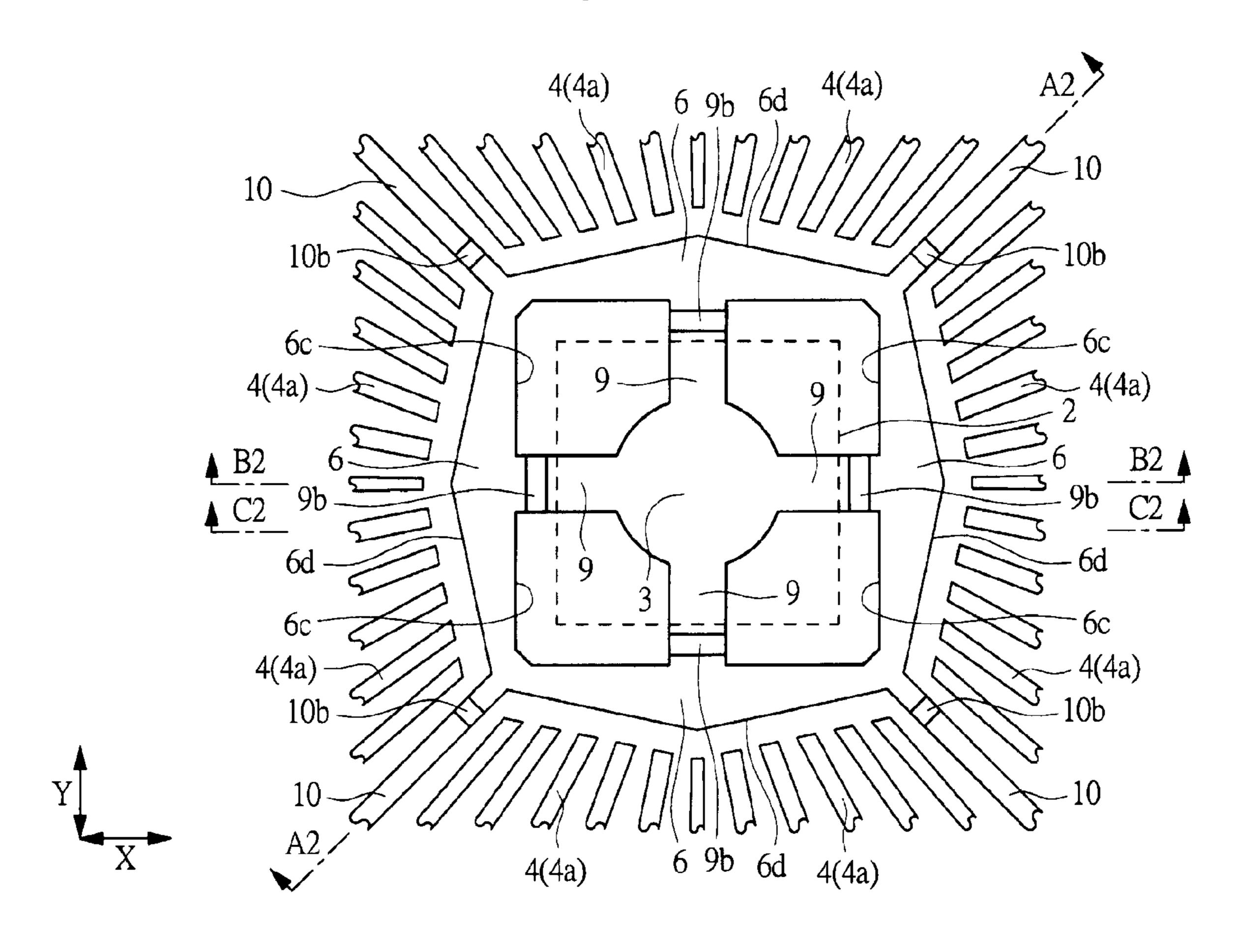

FIG. 1 is a top view (plan view) of a semiconductor device 1, which is an embodiment of the present invention, FIG. 2 is a bottom view (back view) of the semiconductor device 1, and FIG. 3 is a plan perspective view (top view) of the semiconductor device 1 when a sealing resin part 7 is viewed perspectively. FIG. 4 is a partially enlarged view (partially enlarged) plan perspective view) of FIG. 3, showing an enlarged view of the part in the vicinity of the center (a semiconductor chip 2 and a region in the vicinity thereof) in FIG. 3. FIG. 5 is a plan 15 perspective view (partially enlarged plan perspective view) of the semiconductor device 1 when the semiconductor chip 2 and a bonding wire 5 are removed (when viewed perspectively). For easier understanding, the position at which the semiconductor chip 2 is mounted (arranged) is shown by a 20 dotted line in FIG. 5. FIG. 6 and FIG. 7 are each a section view (side section view) of the semiconductor device 1 and the section view at the position along A1-A1 line in FIG. 1 to FIG. 3 substantially corresponds to FIG. 6 and the section view at the position along B1-B1 line in FIG. 1 to FIG. 3 substantially 25 corresponds to FIG. 7. Symbol X shown in each plan view (plan views in the first embodiment and in second to ninth embodiments to be described later) indicates a first direction (X direction) and symbol Y indicates a second direction (Y direction) perpendicular to the first direction X.

The semiconductor device 1 in the present embodiment shown in FIG. 1 to FIG. 7 is a semiconductor device in the form of a resin-sealed semiconductor package, that is, a QFP (Quad Flat Package) semiconductor device.

the semiconductor chip 2, a die pad 3 that supports or mounts the semiconductor chip 2, a plurality of leads 4 formed by a conductor, a plurality of the bonding wires 5 that electrically couple the leads 4 and a plurality of electrodes PD on a surface 2a of the semiconductor chip 2, respectively, a heat dissipating plate 6 arranged between the semiconductor chip 2 and the leads 4, and the sealing resin part 7 that seals these parts.

The sealing resin part (sealing part, sealing resin, sealing body) 7 includes, for example, a resin material, such as a thermosetting resin material, and may include a filler etc. By 45 the sealing resin part 7, the semiconductor chip 2, the lead 4, the bonding wire 5, and the heat dissipating plate 6 are sealed and protected both electrically and mechanically. The sealing resin part 7 has a top surface 7a, which is one of the main surfaces, and a bottom surface (back surface, bottom surface) 50 7b, which is the main surface on the opposite side of the top surface 7a. The plane figure (outer shape) of the sealing resin part 7 that intersects its width is a rectangle and each of sides SD1, SD2, SD3, SD4 of the plane rectangle of the sealing resin part 7 is parallel with the X direction or Y direction. That 55 is, the side SD1 and the side SD3 in opposition to each other of the sealing resin part 7 are parallel with the Y direction and the side SD2 and the side SD4 in opposition to each other of the sealing resin part 7 are parallel with the X direction perpendicular to the Y direction.

The plane figure of the semiconductor chip 2 that intersects its width is a rectangle, and the semiconductor chip 2 is manufactured by, for example, after forming various semiconductor elements or semiconductor integrated circuits on the main surface of a semiconductor substrate (semiconduc- 65 tor wafer) including single crystal silicon etc., separating the semiconductor substrate into each semiconductor chip by

dicing etc. The semiconductor element formed in the semiconductor chip 2 includes a MISFET (Metal Insulator Semiconductor Field Effect Transistor) element etc. Hereinafter, when the plane figure is a rectangle, it may sometimes be referred to as a plane rectangle.

On the surface (main surface, top surface) 2a, which is one of the main surfaces of the semiconductor chip 2 and at the same time, is the main surface on the semiconductor element formation side, a plurality of the electrodes (pad electrodes, bonding pads) PD is formed. Each electrode PD of the semiconductor chip 2 is electrically coupled to a semiconductor element or semiconductor integrated circuit formed inside the semiconductor chip 2 or in the surface layer part. It is assumed that the main surface of the semiconductor chip 2 on the side on which the electrode PD is formed is referred to as the surface 2a and the main surface on the opposite side of the main surface (that is, the surface 2a) on which the electrode PD is formed is referred to as a back surface 2b of the semiconductor chip 2. The electrodes PD are arranged along the periphery of the surface 2a of the semiconductor chip 2.

The semiconductor chip 2 is mounted (arranged) over a top surface 3a of the die pad 3 so that the surface 2a of the semiconductor chip 2 faces upward, and the back surface 2b of the semiconductor chip 2 is bonded (joined) to and fixed on the top surface 3a of the die pad 3 via an adhesive (die bond material, joint material) 8. As the adhesive 8, an adhesive having a high thermal conductivity is used. In particular, it is recommended to use a silver paste containing a filler of silver (Ag) in an epoxy resin as the adhesive 8. The thermal conductivity of the adhesive 8 is higher than the thermal conductivity of the sealing resin part 7. For example, when the sealing resin part 7 is an epoxy resin containing a silica filler, its thermal conductivity is about 1 W/m·K and when the adhesive 8 is an epoxy resin containing a silver filler, its The semiconductor device 1 in the present embodiment has 35 thermal conductivity is about 3 to 6 W/m·K. The semiconductor chip 2 is sealed in the sealing resin part 7 and not exposed from the sealing resin part 7. The semiconductor chip 2 is arranged in the sealing resin part 7 so that each side (each of the four sides of the plane rectangular semiconductor chip 2) of the semiconductor chip 2 is parallel with the X direction or the Y direction.

> The lead (lead part) 4 includes a conductor, and preferably, is made of a metal material, such as copper (Cu) or copper alloy. Each lead 4 includes an inner lead part 4a, which is a part of the lead 4 located inside the sealing resin part 7, and an outer lead part 4b, which is a part of the lead 4 located outside the sealing resin part 7, and the outer lead part 4b projects from the side surface of the sealing resin part 7 to the outside of the sealing resin part 7.

> The leads 4 are arranged around the semiconductor chip 2 so that one end part of each lead 4 (tip end part of the inner lead part 4a) is in opposition to the semiconductor chip 2. Hereinafter, the end part of the lead 4 on the side in opposition to the semiconductor chip 2 is referred to as the tip end part of the inner lead part 4a.

A material that constitutes the sealing resin part 7 is filled between the inner lead parts 4a of the neighboring leads 4. Each electrode PD on the surface 2a of the semiconductor chip 2 is electrically coupled to the inner lead part 4a of each lead 4 via the bonding wire 5, which is a conductive coupling member. That is, one end part of both ends of each bonding wire 5 is coupled to each electrode PD of the semiconductor chip 2 and the other end part is coupled to a top surface 4c of the inner lead part 4a of each lead 4. The bonding wire 5 is a conductive coupling member for electrically coupling the electrode PD of the semiconductor chip 2 and the lead 4, and more specifically, it is a conductive wire and preferably, made

of a thin metal wire, such as a gold (Au) wire or copper (Cu) wire. The bonding wire 5 is sealed in the sealing resin part 7 and not exposed from the sealing resin part 7.

The outer lead part 4b of each lead 4 is bent and worked so that the bottom surface of the outer lead part 4b in the vicinity of the end part is located somewhat below the bottom surface 7b of the sealing resin part 7. The outer lead part 4b of the lead 4 functions as an external coupling terminal part (external terminal) of the semiconductor device 1.

The heat dissipating plate (frame body, frame body part) 6 10 is arranged so as to be located between the semiconductor chip 2 and the leads 4 and to surround the semiconductor chip 2 in a planar view. The heat dissipating plate 6 is a member in the form of a frame (that is, a frame body part) that surrounds the semiconductor chip 2 in a planar manner, and preferably, 15 is arranged at a position and in a form that do not overlap the semiconductor chip 2 in a planar manner. That is, preferably, the semiconductor chip 2 is arranged inside an inner edge (inner circumference) 6c of the heat dissipating plate 6 in the form of a frame so that the outer circumference of the semi- 20 conductor chip 2 is located inside (that is, toward the side nearer to the die pad 3) the inner edge 6c of the heat dissipating plate 6 in the form of a frame in a planar view. The inner lead parts 4a of the leads 4 are arranged so as to surround an outer edge (outer circumference) 6d of the heat dissipating plate 6 in the form of a frame along the outer edge 6d of the heat dissipating plate 6 in the form of a frame in a planar view. Preferably, the heat dissipating plate 6 and the leads 4 do not overlap in a planar manner, and if so, it becomes easy to work the die pad 3 and the heat dissipating plate 6 so as to be 30 lowered.

In the present application, the wording "in a planar manner" or "in a planar view" means that something is viewed in a plane parallel with the top surface 2a or the back surface 2b of the semiconductor chip 2. Further, in the present application, the wording "to surround in a planar manner" or just "to surround" means that something is surrounded when viewed in a plane parallel with the top surface 2a or the back surface 2b of the semiconductor chip 2 and the case is also included, where the height of what surrounds differs from the height of 40 what is to be surrounded.

The die pad 3 is surrounded by the heat dissipating plate 6 in the form of a frame in a planar manner, and the die pad (first part of a chip mounting part) 3 is arranged in the center of the region surrounded by the heat dissipating plate 6 in the form 45 of a frame, and the heat dissipating plate 6 and the die pad 3 are linked with a plurality of members (second parts of the chip mounting part) 9. The heat dissipating plate 6, the die pad 3, and the member 9 are formed integrally by the same material, and the member 9 is a linking part that connects (links) an 50 inner edge 6b of the heat dissipating plate 6 and the die pad 3.

In the die pad 3, the inner lead part 4a, the heat dissipating plate 6, and the member 9, respectively, the main surface facing the side of the top surface 7a of the sealing resin part 7 is referred to as a top surface and the main surface facing the 55 side of the bottom surface 7b of the sealing resin part 7 is referred to as a bottom surface (or back surface), and the top surface and the bottom surface are the main surfaces on the opposite sides. The top surfaces of die pad 3, the inner lead part 4a, the heat dissipating plate 6, and the member 9, respec- 60 tively, face in the same direction (toward the side of the top surface 7a of the sealing resin part 7) and the bottom surfaces of the die pad 3, the inner lead part 4a, the heat dissipating plate 6, and the member 9, respectively, face in the same direction (toward the side of the bottom surface 7b of the 65 sealing resin part 7). Consequently, the heat dissipating plate 6 has a top surface (main surface) 6a facing the side of the top

**10**

surface 7a of the sealing resin part 7, the bottom surface (back surface) 6b on the opposite side of the top surface 6a and facing the side of the bottom surface 7b of the sealing resin part 7, the inner edge 6c facing the side of the die pad 3, and an outer edge 6d on the opposite side of the inner edge 6c. The top surface of the die pad 3 and the top surface of the member 9 are continuous and flat. Because of this, the top surface of the die pad 3 and the top surface of the member 9 are both assigned symbol 3a and referred to as the top surface (main surface) 3a, and the bottom surface of the die pad 3 and the bottom surface of the member 9 are both assigned symbol 3b and referred to as a bottom surface (back surface) 3b.

One end of each member 9 is formed (linked, coupled) integrally to the inner edge 6c of the heat dissipating plate 6 and the other end is formed (linked, coupled) integrally to the die pad 3. A plurality of the members 9 is formed and preferably, the four members 9 are formed. In the present embodiment, the four members 9 are formed so that the four corners of the heat dissipating plate 6 are connected (linked) to the die pad 3. The plane figure of the die pad 3 is, for example, a circle, and the plane dimensions (outer shape, outer dimensions) of the die pad 3 are less than the plane dimensions (outer shape, outer dimensions and the die pad 3 is included in a planar manner by the semiconductor chip 2 mounted thereon.

The die pad 3 is arranged immediately under the semiconductor chip 2 and preferably, is arranged immediately under the center part of the semiconductor chip 2 (center part of the back surface 2b). However, the plane dimensions of the die pad 3 are less than the plane dimensions (outer dimensions) of the semiconductor chip 2, and therefore, the entire top surface of the die pad 3 overlaps the semiconductor chip 2 in a planar manner, however, the back surface 2b of the semiconductor chip 2 includes a region that overlaps the die pad 3 in a planar manner, a region that overlaps the member 9 in a planar manner, and a region that overlaps none of the die pad 3, the member 9, and the heat dissipating plate 6.

The region of the back surface 2b of the semiconductor chip 2, which overlaps the die pad 3 in a planar manner and which is in opposition to the top surface 3a of the die pad 3, is bonded to the top surface 3a of the die pad 3 in its entire region via the adhesive 8. Then, the region of the back surface 2b of the semiconductor chip 2, which overlaps the member 9 in a planar manner and which is in opposition to the top surface 3a of the member 9 in its entire region via the adhesive 8. On the other hand, to the region of the back surface 2b of the semiconductor chip 2, which overlaps none of the die pad 3, the member 9, and the heat dissipating plate 6 in a planar manner and which is in opposition to neither the top surface 3a of the die pad 3 nor the top surface 3a of the member 9, the sealing resin part 7 is bonded.

In other words, the whole of the top surface 3a of the die pad 3 and part of the top surface 3a of each member 9 overlap the semiconductor chip 2 in a planar manner and are in opposition to the back surface 2b of the semiconductor chip 2, and in the region that overlaps the semiconductor chip 2 in a planar manner and which is in opposition to the back surface 2b of the semiconductor chip 2, the whole of the top surface 3a of the die pad 3 and the member 9 is bonded to the back surface 2b of the semiconductor chip 2 with the adhesive 8. Because the heat dissipating plate 6 in the form of a frame and the semiconductor chip 2 do not overlap in a planar manner, the part of the top surface 3a of each member 9 in the vicinity of the part linked to the heat dissipating plate 6 may not overlap the semiconductor chip 2 in a planar manner. Because of this, in the region that does not overlap the semiconductor

chip 2 in a planar manner and which is not in opposition to the back surface 2b of the semiconductor chip 2, the sealing resin part 7 is bonded over the top surface 6a of the heat dissipating plate 6 and over the top surface 3a of each member 9. That is, all of the regions of the top surface 3a of the die pad 3 and each member 9, which are in opposition to the back surface 2b of the semiconductor chip 2, are bonded to the back surface 2b of the semiconductor chip 2 via the adhesive 8.

In the present embodiment, the semiconductor chip 2 is bonded not only to the die pad 3 but also to the member 9 with 10 the adhesive 8, and therefore, it is possible to regard the combination of both the die pad 3 and the member 9 as a chip mounting part. Because of this, the top surface 3a of the die pad 3 and the member 9 is a chip mounting surface (surface on which the semiconductor chip 2 is mounted). The member 9 15 further has a function as a heat conduction path (heat dissipation path) that conducts heat produced in the semiconductor chip 2 to the heat dissipating plate 6 via the member 9, in addition to the function to hold the die pad 3 to the heat dissipating plate 6 and the function to mount the semiconductor chip 2.

On the outer edge (outer circumference) 6d of the heat dissipating plate 6, a plurality of suspension leads 10 is formed integrally. The suspension lead 10 is provided in order to hold the die pad 3, the member 9, and the heat dissipating plate 6 to (the frame of) the lead frame for manufacturing the semiconductor device 1 when manufacturing the semiconductor device 1.

Each suspension lead 10 is formed integrally with the heat dissipating plate 6 by the same material as that of the heat 30 dissipating plate 6, and one end is formed (linked, coupled) integrally to the heat dissipating plate 6 and extends outwardly (in the direction of departing from the heat dissipating plate 6 and the die pad 3 in a planar manner), and extends in the sealing resin part 7 until the end part on the opposite side 35 of the side linked to the heat dissipating plate 6 reaches the side surface of the sealing resin part 7. Preferably, to the respective four corners of the outer edge 6d of the heat dissipating plate 6, the suspension lead 10 is formed integrally and extends in the sealing resin part 7 until the end part on the 40 opposite side of the side coupled to the heat dissipating plate 6 of each suspension lead 10 reaches the side surface of the four corners (corner parts) of the sealing resin part 7 in the form of a plane rectangle. In other words, each suspension lead 10 extends in the sealing resin part 7 in the direction from 45 the center of the sealing resin part 7 toward the corner parts (four corners) of the sealing resin part 7 in a planar view.

The part of the suspension lead 10 that projects from the sealing resin part 7 is cut after the sealing resin part 7 is formed, and the cut surface (end surface) produced by the 50 cutting of the suspension lead 10 is exposed at the side surface (here, the side surface of the four corners) of the sealing resin part 7. The cut surface of the suspension lead 10 exposed at the side surface (here, the side surface of the four corners) of the sealing resin part 7 is the end part on the opposite side of 55 the end part on the side coupled to the heat dissipating plate 6 of the suspension lead 10. Each of the (four, here) suspension leads 4 is bent at a bending part (flexing part) 10a so that the top surface 3a of the die pad 3 and the member 9 and the top surface 6a of the heat dissipating plate 6 are lower than the top surface 4c of the inner lead part 4a of the leads 4.

The die pad 3, the (four, here) members 9, the heat dissipating plate 6, and the (four, here) suspension leads 10 are formed integrally by the same material. The heat dissipating plate 6 is arranged in order to promote the dissipation of heat 65 produced in the semiconductor chip 2 to the lead 4. Because of this, it is preferable to use a metal material having a high

12

thermal conductivity as a material to constitute the die pad 3, the member 9, the heat dissipating plate 6, and the suspension lead 10.

Further, it is preferable to form the suspension lead 10 into a thin shape so as not to block the array of the leads 4 as long as it has rigidity capable of holding the die pad 3, the member 9, and the heat dissipating plate 6 to the lead frame when manufacturing the semiconductor device 1. On the other hand, the member 9 has the function to conduct (transmit) heat produced in the semiconductor chip 2 to the heat dissipating plate 6, and therefore, if it is formed into too thin a shape, the heat dissipating characteristics are degraded. Because of this, preferably, a width (width in the direction perpendicular to the direction in which the member 9 extends from the die pad 3 toward the heat dissipating plate 6) W1 of the member 9 is greater than a width (width in the direction perpendicular to the direction in which the suspension lead 10 extends) W2 (that is, W1>W2). As a result, it is possible to cause both the improvement in the thermal conductivity from the semiconductor chip 2 to the heat dissipating plate 6 via the member 9 and the easiness of arraying the leads 4 to coexist.

The lead 4 is separated from the die pad 3, the member 9, the heat dissipating plate 6, and the suspension lead 10 and not formed integrally therewith. However, it is made easy to manufacture the semiconductor device 1 by providing the lead 4, the die pad 3, the member 9, the heat dissipating plate 6, and the suspension lead 10 in the same lead frame. Because of this, it is preferable that the lead 4, the die pad 3, the member 9, the heat dissipating plate 6, and the suspension lead 10 be formed by the same material and due to this, it is possible to manufacture the semiconductor device 1 by providing the lead 4, the die pad 3, the member 9, the heat dissipating plate 6, and the suspension lead 10 in the same lead frame and thereby the manufacture of the semiconductor device 1 is made easy. Because the lead 4 has the function to lead the circuit within the semiconductor chip 2 to the outside of the semiconductor device, and therefore, it is preferable to use a material having a high electric conductivity and because a metal material has a high electric conductivity, it is preferable to use a metal material as a material to constitute the lead 4. Because of this, it is preferable for the die pad 3, the lead 4, the heat dissipating plate 6, the member 9, and the suspension lead 10 to be formed by the same metal material from the standpoint of the high thermal conductivity of the heat dissipating plate 6 and the high electric conductivity of the lead 4. It is particularly preferable for the die pad 3, the lead 4, the heat dissipating plate 6, the member 9, and the suspension lead 10 to be formed by a metal material that contains copper (Cu) as its principal component, such as copper (Cu) and copper alloy, from the standpoint of the high thermal conductivity, high electric conductivity, cost, and easiness of working.

The semiconductor chip 2, the die pad 3, the bonding wire 5, the heat dissipating plate 6, and the member 9 are sealed in the sealing resin part 7 and not exposed from the sealing resin part 7. On the other hand, as to the lead 4, the inner lead part 4a is sealed in the sealing resin part 7 and the outer lead part 4b is exposed from the sealing resin part 7 as described above. The end surface of the suspension lead 10 on the opposite side of the side coupled to the heat dissipating plate 6 is exposed at the corner part side surface of the sealing resin part 7 and other parts are sealed in the sealing resin part 7.

<About Heat Dissipation Path of QFP>

Next, a heat dissipation path of a QFP semiconductor device is explained. FIG. 8 is an explanatory diagram heat dissipation path of a QFP semiconductor device 101.

In the semiconductor device 101, a semiconductor chip 102 is mounted over a die pad 103 of a lead frame, a lead 104 of the lead frame and the electrode of the semiconductor chip 102 are coupled with a bonding wire 105, the die pad 103, the semiconductor chip 102, the bonding wire 105, and the inner lead part of the lead 104 are sealed by a sealing resin part 107, the lead 104 is cut from the lead frame, and the outer lead part of the lead **104** is bent and worked. The semiconductor device 101 is packaged (by solder) over a packaging substrate (wiring substrate) PWB. At this time, the outer lead part of the 10 lead **104** of the semiconductor device **101** and a terminal TE on the top surface of the packaging substrate PWB are joined and electrically coupled via a solder SD. The method of packaging the semiconductor device 1 described above in the present embodiment on the packaging substrate PWB is the 15 same as that of the semiconductor device **101**. That is, when packaging the above-mentioned semiconductor device 1 on the packaging substrate PWB, (the bottom surface 4c of) the outer lead part 4b of the lead 4 of the semiconductor device 1 is joined and electrically coupled to the terminal TE on the top 20 surface of the packaging substrate PWV via the solder SD. When the above-mentioned semiconductor device 1 is packaged on the packaging substrate PWB, it is only required to read the semiconductor device 101, the semiconductor chip **102**, the die pad **103**, the lead **104**, the bonding wire **105**, and 25 the sealing resin part 107 as the semiconductor device 1, the semiconductor chip 2, the die pad 3, the lead 4, the bonding wire 5, and the sealing resin part 7, respectively.

In the case of a general packaging method as shown in FIG. **8**, in which a heat dissipating fin etc. is not provided over the top surface of the sealing resin part 107 of the semiconductor device 101, most of the heat produced in the semiconductor chip 2 in the semiconductor device 101 is dissipated through the following three paths (first heat dissipation path, second heat dissipation path, third heat dissipation path).

The first heat dissipation path is a heat dissipation path schematically shown by an arrow H1 in FIG. 8, and heat produced in the semiconductor chip 2 flows directly downward from the semiconductor chip 2 and flows through the die pad 103 and the sealing resin part 107, and then, flows into the packaging substrate PWB through the air from the bottom surface of the sealing resin part 107. Then the heat that has flowed into the packaging substrate PWB is further dissipated in the planar direction within the packaging substrate PWB and dissipated into the air from the packaging substrate PWB.

The second heat dissipation path is a heat dissipation path schematically shown by an arrow H2 in FIG. 8, and heat produced in the semiconductor chip 2 flows from the peripheral part of the semiconductor chip 2 into the inner lead part of the lead 104 via the bonding wire 105 and the sealing resin 50 part 107, and then flows into the packaging substrate PWB along the outer lead part of the lead 104. Then, the heat that has flowed into the packaging substrate PWB is further dissipated in the planar direction within the packaging substrate PWB and dissipates into the air from the packaging substrate 55 PWB.

The third heat dissipation path is a heat dissipation path schematically shown by an arrow H3 in FIG. 8, and heat produced in the semiconductor chip 2 flows directly upward from the semiconductor chip 2 and is dissipated into the air 60 from the top surface of the sealing resin part 107 via the sealing resin part 107.

In the case where the general QFP type semiconductor device 101 is packaged in a general manner, such as one in which a heat dissipating fin etc. is not provide on the top 65 surface thereof, as shown in FIG. 8, heat dissipation through the first and second heat dissipation paths is predominant. For

14

example, in the QFP in which one side of the sealing resin part 107 has a length of 20 mm, the above-mentioned first heat dissipation path (heat dissipation path shown by the arrow H1 in FIG. 8) accounts for about 50% of the total amount of heat dissipation, the above-mentioned second heat dissipation path (heat dissipation path shown by the arrow H2 in FIG. 8) about 45% of the total amount of heat dissipation, and the above-mentioned third heat dissipation path (heat dissipation path shown by the arrow H3 in FIG. 8) about 5% of the total amount of heat dissipation.

< Heat Dissipation Characteristics >

As the functions of an LSI are improved and its operation speed is increased, the power consumption of the semiconductor chip in the package increases and for a recent semiconductor package whose amount of produced heat tends to increase, it is demanded to improve the heat dissipation characteristics to dissipate heat produced in the semiconductor chip in the package to the outside of the semiconductor package. In order to improve the heat dissipation characteristics, it can be conceived to expose the bottom surface of the die pad 103 that mounts the semiconductor chip 102 from the bottom surface of the sealing resin part 107, and thereby, the heat dissipation through the first heat dissipation path is improved and thus the heat dissipation characteristics of the semiconductor device **101** can be improved. However, when the bottom surface of the die pad 103 is exposed from the bottom surface of the sealing resin part 107, there is a possibility that moisture (water) etc. may reach the semiconductor chip 102 through the boundary surface between the die pad 103 exposed at the bottom surface of the sealing resin part 107 and the sealing resin part 107 in a high-temperature and highhumidity load test and there is a risk that the reliability (moisture resistance) of a semiconductor device is degraded. Because of this, it is desirable that the die pad 103 be not 35 exposed at the bottom surface of the sealing resin part 107 from the standpoint of improvement of the reliability (moisture resistance) of a semiconductor device.

Because of the above, in the present embodiment, the heat dissipating plate 6 is provided inside the sealing resin part 7 in order to improve the heat dissipation characteristics without exposing the back surface of the die pad 103. Its working for the first heat dissipation path is to improve the heat dissipation characteristics by increasing the sectional area of the heat dissipation path by causing heat produced in the semiconductor chip 2 to flow downward after once spreading the heat in the heat dissipating plate 6.

For the second heat dissipation path, the heat dissipation characteristics are improved by providing the heat dissipating plate 6 between the chip 2 and the tip end of the inner lead 4 to reduce the resistance of heat flow from the side of the semiconductor chip 2 to the inner lead 4a. This will be explained later in detail.

<a href="#"><About Structure of Die Pad in Comparative Example></a>

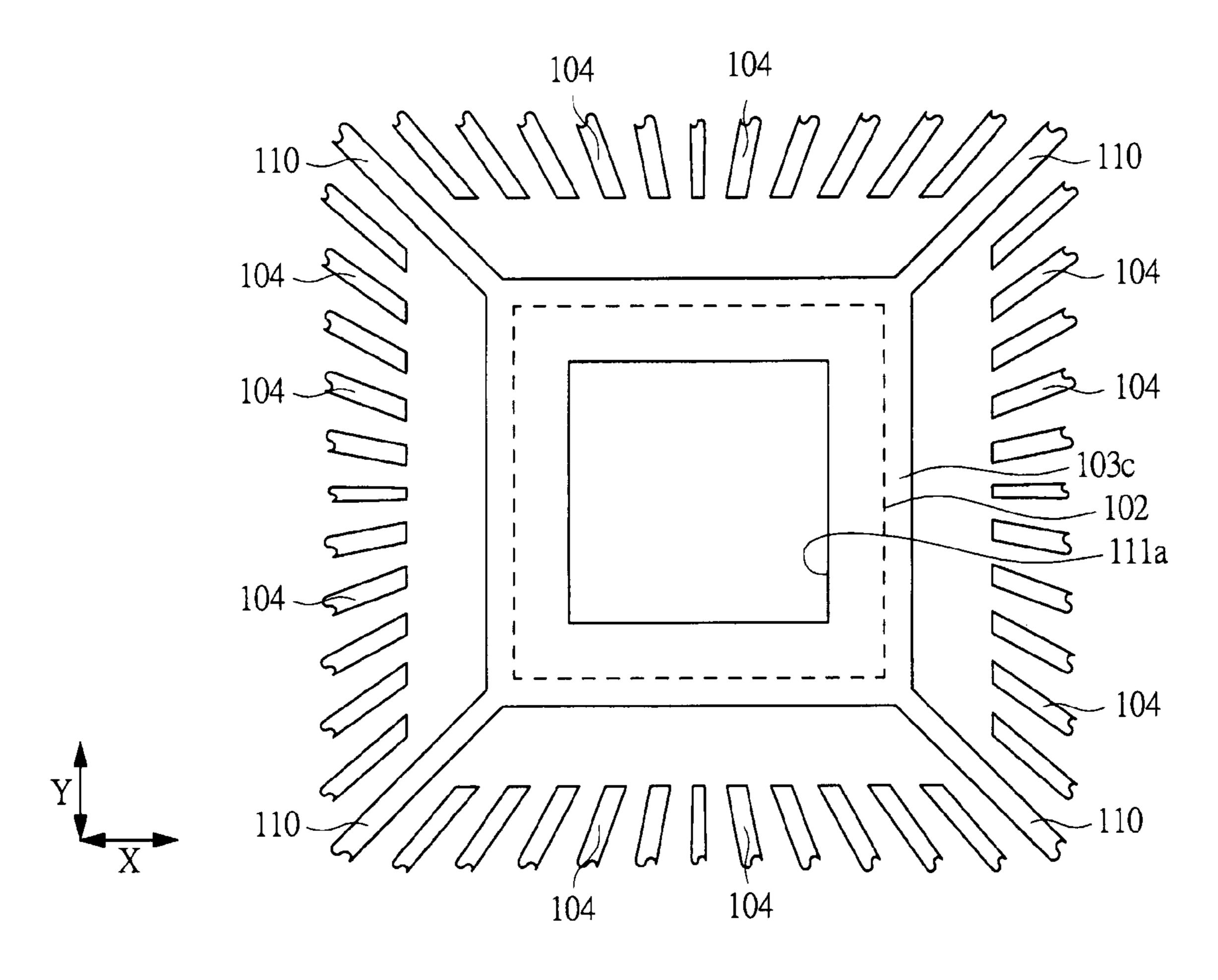

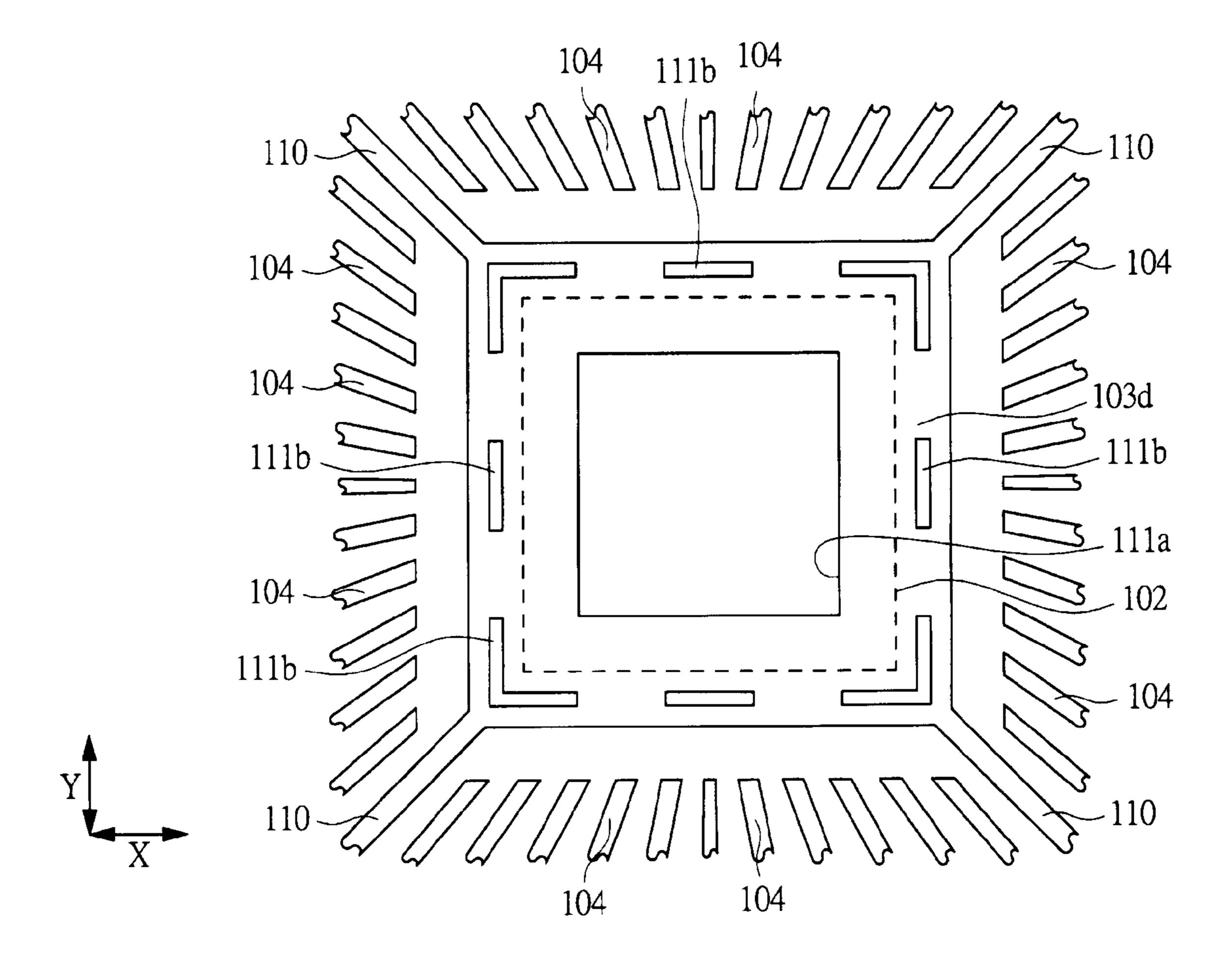

FIG. 9 is a plan perspective view of essential parts when a die pad 103a in a first comparative example the inventors of the present invention have examined is applied as the die pad 103 in the semiconductor device 101. FIG. 10 is a plan perspective view of essential parts when a die pad 103b in a second comparative example the inventors of the present invention have examined is applied, FIG. 11 is that when a die pad 103c in a third comparative example the inventors of the present invention have examined is applied, and FIG. 12 is that when a die pad 103d in a fourth comparative example the inventors of the present invention have examined is applied. FIG. 9 to FIG. 12 correspond to FIG. 5 in the present embodiment. As in FIG. 5, the position where the semiconductor chip 102 is mounted (arranged) is indicated by a dotted line also in

FIG. 9 to FIG. 12. In FIG. 9 to FIG. 12, symbol 110 denotes a suspension lead, provided in order to hold the die pads 103a to 103d to the lead frame when manufacturing the semiconductor device 101.

FIG. 9 to FIG. 12 are each a plan perspective view when the sealing resin part 107, the semiconductor chip 102, and the bonding wire 105 are viewed perspectively, and therefore, the sealing resin part 107 or the bonding wire 105 is not shown schematically in FIG. 9 to FIG. 12. However, in the semiconductor device, as can also be seen from FIG. 8, the die pads 103a to 103d, the semiconductor chip 102, the suspension lead 110, and the lead 4 (also including the bonding wire 105 that couples the electrode of the semiconductor chip 102 and the lead 104) shown in FIG. 9 to FIG. 12 are sealed by the sealing resin part 107.

As shown in FIG. 9, the die pad 103a in the first comparative example has plane dimensions greater than the plane dimensions of the semiconductor chip 102. Because of this, the entire back surface of the semiconductor chip 102 is bonded to the top surface of the die pad 103a with a die bond 20 material (adhesive).

However, when the entire back surface of the semiconductor chip 102 is bonded to the top surface of the die pad 103a with a die bond material, the semiconductor chip 102 becomes more likely to be peeled off from the die pad 103a at 25 the time of solder reflow when packaging the semiconductor device 101 on the packaging substrate PWB, and therefore, the reliability (solder reflow resistance) of the semiconductor device is degraded. This results mainly from that the strength of the die bond material itself is low and that the strength of 30 adhesion between the sealing resin part 107 and the die pad 103a is low.

The plane dimensions of the die pad 103b in the second comparative example shown in FIG. 10 are less than the plane dimensions of the semiconductor chip 102. Because of this, if 35 the semiconductor chip 102 is mounted over the die pad 103b, the center part of the back surface of the semiconductor chip **102** is bonded to the top surface of the die pad **103**b with a die bond material (adhesive), however, to the region of the back surface of the semiconductor chip 102, which is not in oppo-40 sition to the die pad 103, the sealing resin part 107 is bonded as a result. The strength of adhesion between the back surface of the semiconductor chip 102 and the sealing resin part 107 is far higher than the strength of adhesion between the sealing resin part 107 and the die pad 103b. Because of this, com- 45 pared to the case where the die pad 103a in the first comparative example in FIG. 9 is used, in the case where the die pad 103b in the second comparative example in FIG. 10 is used, it is possible to prevent the semiconductor chip 102 from peeling off from the die pad 103b at the time of solder reflow when 50 packaging the semiconductor device 101 on the packaging substrate PWB by the firm adhesion of the part of the back surface of the semiconductor chip 102 to the sealing resin part 107. Consequently, it is possible to improve the reliability (solder reflow resistance) of the semiconductor device 101.

The plane figure of the die pad 103c in the third comparative example shown in FIG. 11 is a frame and an opening 111a is formed in the center part. Because of this, if the semiconductor chip 102 is mounted over the die pad 103c, the peripheral part of the back surface of the semiconductor chip 102 is bonded to the top surface of the die pad 103c with a die bond material (adhesive), however, the center part of the back surface of the semiconductor chip 102 is exposed from the opening 111a of the die pad 103c and the sealing resin part 107 is bonded thereto. Because of this, as in the case where the die 65 pad 103b in the second comparative example in FIG. 10 is used, in the case also where the die pad 103c in the third

**16**

comparative example in FIG. 11 is used, it is possible to prevent the semiconductor chip 102 from peeling off from the die pad 103b at the time of solder reflow when packaging the semiconductor device 101 on the packaging substrate PWB by the firm adhesion of the part of the back surface of the semiconductor chip 102 to the sealing resin part 107, and therefore, it is possible to improve the reliability of the semiconductor device 101.

However, over the die pad 103c in the third comparative example, only the semiconductor chip 102 can be mounted, the plane dimensions of which are greater than the plane dimensions of the opening 111a. This is because if the semiconductor chip 102 is smaller than the opening 111a of the die pad 103c, it will drop from the opening 111a. Because of this, when the die pad 103c in the third comparative example is used, there are limitations to the plane dimensions of the semiconductor chip 102 that can be mounted and it is no longer possible to use a common lead frame for the semiconductor chip 102 of different plane dimensions. That is, it is necessary to change the plane dimensions of the die pad 103c for each of the semiconductor chips 102 of different plane dimensions, resulting in a disadvantage in reducing the cost of the semiconductor device.

On the other hand, in the case of the die pad 103b in the second comparative example shown in FIG. 10, the semiconductor chips 102 of various dimensions can be mounted over the die pad 103b, and therefore, it is possible to use a common lead frame for the semiconductor chips 102 of different plane dimensions, and therefore, an attempt can be made to reduce the cost of the semiconductor device. However, in the case of the die pad 103b in the second comparative example shown in FIG. 10, when the plane dimensions of the semiconductor chip 102 to be mounted are reduced, the space between the semiconductor chip 102 and the lead 104 increases, resulting in a disadvantage in dissipating heat through the second heat dissipation path (heat dissipation path shown by the arrow H2 in FIG. 8). Then, the die pad 103b in the second comparative example shown in FIG. 10 has a large space between the die pad 103b and the lead 104 and a structure in which heat is hard to conduct from the die pad 103b to the lead 104 because the die pad 103b is small in size, and therefore, the die pad 103can hardly contribute in heat dissipation through the second heat dissipation path (heat dissipation path shown by the arrow H2 in FIG. 8).

Like the die pad 103c in the third comparative example shown in FIG. 11, the plane figure of the die pad 103d in the fourth comparative example shown in FIG. 12 is a frame and the opening 111a is provided in the center part, however, compared to the die pad 103c in the third comparative example, the outer edge side of the die pad 103d is widened so as to come close to the lead part 104. In the die pad 103d in the fourth comparative example in FIG. 12, a slit 111b is provided at a position where it does not overlap the semiconductor chip **102**. As described above, there is a risk that the boundary surface peels off at the time of solder reflow because of the low adhesion strength between the top surface of the die pad 103d and the sealing resin part 107. In the fourth comparative example, the width of the die pad 103d is greater than that in the third comparative example, and therefore, if a peeling occurs, it develops into a crack of the sealing resin part 107 and there is a risk that the wire is cut. Because of this, the slit 111b is provided to confine a peeling to a small area even if it occurs and to prevent it from developing into a crack.

Compared to the case where the die pad 103c in the third comparative example in FIG. 11 is used, in the case where the die pad 103d in the fourth comparative example in FIG. 12 is used, the distance from the outer edge of the die pad 103d to

the tip end of the inner lead part of the lead 104 is reduced, and therefore, heat produced in the semiconductor chip 102 can be easily conducted to the inner lead part of the lead 104 via the die pad 103d. Consequently, this is an advantage in heat dissipation through the second heat dissipation path (heat 5 dissipation path shown by the arrow H2 in FIG. 8). However, like the die pad 103c in the third comparative example in FIG. 11, also in the case of the die pad 103d in the fourth comparative example in FIG. 12, there are limitations to the plane dimensions of the semiconductor chip 102 that can be 10 mounted, and it is no longer possible to use a common lead frame for the semiconductor chips 102 of different plane dimensions. That is, it is necessary to change the plane dimensions of the die pad 103d for each of the semiconductor chips 102 of different plane dimensions, resulting in a disadvantage 15 in reducing the cost of the semiconductor device.

The characteristics of the die pad structure in the comparative examples shown in FIG. 9 to FIG. 12 are explained as above. In contrast to these comparative examples, in the semiconductor device 1 in the present embodiment, the die pad 3 is arranged immediately under the center part of the back surface 2b of the semiconductor chip 2. That is, the center part of the semiconductor chip 2 overlaps the die pad 3 in a planar manner. In other words, the center part of the back surface 2b of the semiconductor chip 2 is located immediately over the die pad 3.

<Characteristics of Semiconductor Device>

Because of this, it is possible to mount the semiconductor chips 2 of various dimensions over the die pad 3. FIG. 13 and FIG. 14 are each a partially enlarged plan perspective view of 30 the semiconductor device 1 in the present embodiment, corresponding to FIG. 5 described above, and FIG. 13 corresponds to the case where the semiconductor chip 2 to be mounted is small and FIG. 14 corresponds to the case where the semiconductor chip 2 to be mounted is large. Like FIG. 5 35 described above, in FIG. 13 and FIG. 14 also, the position where the semiconductor chip 2 is mounted (arranged) is shown by a dotted line, however, unlike FIG. 5, in FIG. 13 and FIG. 14, the region in which the adhesive 8 is arranged (applied) is hatched. A difference between FIG. 5 and FIG. 14 40 lies only in that the region in which the adhesive 8 is arranged (applied) is hatched in FIG. 14 and the size of the semiconductor chip 2 is the same in both FIG. 5 and FIG. 14. A difference between FIG. 13 and FIG. 14 lies in the plane dimensions (outer size) of the semiconductor chip 2 and the 45 plane dimensions of the semiconductor chip 2 in FIG. 14 are greater than those in FIG. 13.

As can also be seen from FIG. 13 and FIG. 14, it is possible to hold (support) the semiconductor chip 2 by the die pad 3 (and the member 9) even if the plane dimensions of the 50 semiconductor chip 2 are different. This is because it is possible to mount the semiconductor chip 2 so that the die pad 3 is arranged immediately under the center part of the back surface 2b of the semiconductor chip 2 when the semiconductor chip 2 is small as shown in FIG. 13 and when the 55 semiconductor chip 2 is large as shown in FIG. 14. Because of this, it is possible to mount the semiconductor chips 2 of various plane dimensions over the die pad 3. Consequently, it is possible to make an attempt to reduce the cost of a semiconductor device because a common lead frame can be used 60 for the semiconductor chips 2 of various plane dimensions.

Further, in the present embodiment, the plane dimensions of the die pad 3 are made smaller than the plane dimensions of the semiconductor chip 2. Because of this, the part of the back surface 2b of the semiconductor chip 2 mounted over the die 65 pad 3, which is in opposition to the die pad 3 and the member 9, is bonded to the die pad 3 and the member 9 via the adhesive

**18**

8, however, there is a part of the back surface 2b of the semiconductor chip 2, which is in opposition to neither the die pad 3 nor the member 9, and the sealing resin part 7 is bonded thereto. That is, at least part of the back surface 2b of the semiconductor chip 2 is in opposition to neither the die pad 3 nor the member 9 and the sealing resin part 7 is bonded thereto in opposition to the sealing resin part 7, and this also applies to second to ninth embodiments to be described later, not only to the present embodiment. Because of this, compared to the case where the die pad 103a in the first comparative example in FIG. 9 is used, in the present embodiment, it is possible to prevent the semiconductor chip 102 from peeling off from the die pad 103b and the member 9 at the time of solder reflow when packaging the semiconductor device 1 on the packaging substrate PWB by the firm adhesion of (the part of the back surface 2b in opposition to neither the die pad 3 nor the member 9) the back surface 2b of the semiconductor chip 2 to the sealing resin part 107. Consequently, it is possible to improve the reliability (solder reflow resistance) of the semiconductor device 1.

Further, in the present embodiment, the heat dissipating plate 6 is provided in order to improve the heat dissipation characteristics of the semiconductor device 1. As a result, it is possible to improve the heat dissipation characteristics through the first heat dissipation path (heat dissipation path shown by the arrow H1 in FIG. 8) by once diffusing the heat produced in the semiconductor chip 2 to the heat dissipation plate 6. It is also possible to improve the heat dissipation characteristics through the second heat dissipation path (heat dissipation path shown by the arrow H2 in FIG. 8) by conducting the heat in the semiconductor chip 2 to the inner lead part 4a of the lead 4. This is explained with reference to FIG. 15 and FIG. 16.

FIG. 15 is an explanatory diagram of heat dissipation of the semiconductor device 1 in the present embodiment and an enlarged view of the region corresponding to the region shown by symbol RG1 in FIG. 6 is shown. In FIG. 15, a sealing resin part 16 is not shown schematically. FIG. 16 is an explanatory diagram of heat dissipation when the back surface 2b of the semiconductor chip 2 is bonded to the die pad 3 with the adhesive 8 but not bonded to the member 9 with the adhesive 8, unlike the present embodiment, and the same region as that in FIG. 15 is shown. In FIG. 15 and FIG. 16, how heat produced in the semiconductor chip 2 flows to the heat dissipating plate 6 is schematically shown by an arrow H4.

In the present embodiment, as can also be seen from FIG. 6, FIG. 7, and FIG. 13 to FIG. 15, the semiconductor chip 2 is mounted over the die pad 3 and the member 9 and the entire surface of the part of the back surface 2b of the semiconductor chip 2, which is in opposition to (the top surface 3a of) the die pad 3 and the member 9, is bonded to the die pad 3 and the member 9 with the adhesive 8. Because of this, as shown schematically in FIG. 15, heat produced in the semiconductor chip 2 is conducted mainly from the back surface 2b of the semiconductor chip 2 to the die pad 3 and the member 9 through the adhesive 8 and is further conducted to the heat dissipating plate 6 via the member 9. Heat conducted from the member 9 to the heat dissipating plate 6 spreads over the entire heat dissipating plate 6 in the form of a frame. Because the heat conduction path from the back surface 2b of the semiconductor chip 2 to the heat dissipating plate 6 does not pass byway of the sealing resin part 7 the thermal conductivity of which is low, it is possible to efficiently conduct heat produced in the semiconductor chip 2 to the heat dissipating plate 6. Part of heat having spread over the entire heat dissipating plate 6 is conducted downward from the bottom sur-

face 6b of the heat dissipating plate 6 and flows into the packaging substrate (PWB) (the packaging substrate PWB that has packaged the semiconductor device 1) from the bottom surface 7b of the sealing resin part 7 via a thin air layer thereunder. Because of this, as to the first heat dissipation path, its sectional area is the sum of the area of the semiconductor chip 2, the area of the heat dissipating plate 6, and the area of the part of the member 9, which does not overlap the semiconductor chip 2 in a planar manner. Further, part of heat having spread over the entire heat dissipating plate 6 is con- 10 ducted to the inner lead part 4a of the lead 4 via the sealing resin part 7 interposed between the heat dissipating plate 6 and the inner lead part 4a. Heat conducted from the heat dissipating plate 6 to the inner lead part 4a flows into the packaging substrate PWB (the packaging substrate PWB that 15 has packaged the semiconductor device 1) through the outer lead part 4a of the lead 4.

Unlike the present embodiment, in the second comparative example in FIG. 10 described above, in which nothing corresponding to the heat dissipating plate 6 is provided, there is 20 nothing corresponding to the heat dissipating plate 6, and therefore, the sectional area of the first heat dissipation path is limited approximately only to the area of the semiconductor chip 2 and the heat dissipation performance is low. As the second heat dissipation path described above (heat dissipa- 25 tion path shown by the arrow H2 in FIG. 8), there are only a path through which heat is dissipated from the side surface of the semiconductor chip 2 to the inner lead part of the lead 104 via the sealing resin part 107 and a path through which heat is dissipated from the electrode PD over the semiconductor chip 30 2 to the inner lead part of the lead 104 via the bonding wire 5, and therefore, the heat dissipation characteristics are low and if the semiconductor chip 2 is reduced in size, the heat dissipation characteristics are further deteriorated.

sectional area of the first heat dissipation path described above (heat dissipation path shown by the arrow H1 in FIG. 8) is the sum of the area of the semiconductor chip 2, the area of the heat dissipating plate 6, and the area of the part of the member 9, which does not overlap the semiconductor chip 2 40 in a planar manner. As the second heat dissipation path described above (heat dissipation path shown by the arrow H2 in FIG. 8), in addition to a path through which heat is dissipated from the side surface of the semiconductor chip 2 to the inner lead part 4a via the sealing resin part 7, a path can be 45 used to dissipate heat in the semiconductor chip 2, through which heat is dissipated from the back surface 2b of the semiconductor chip 2 to the heat dissipating plate 6 via the adhesive 8, the die pad 3, and the member 9 and the heat is further dissipated from the heat dissipating plate 6 to the inner 50 lead part 4a via the sealing resin part 7. Because of this, it is possible to improve the heat dissipation characteristics of the semiconductor device 1.

As the plane dimensions of the semiconductor chip 2 become smaller, the sectional area of the first heat dissipation 55 path, that is, the area of the semiconductor chip 2 becomes smaller, and therefore, the heat dissipation performance is deteriorated. Further, as to the second heat dissipation path, the distance from the side surface of the semiconductor chip 2 to the tip end of the inner lead part 4a becomes larger and 60 part 7 is very low. heat dissipation from the side surface of the semiconductor chip 2 to the inner lead part 4a via the sealing resin part 7 becomes less efficient. However, in the present embodiment, the heat dissipating plate 6 is provided and the sectional area of the first heat dissipation path is the sum of the area of the 65 semiconductor chip 2, the area of the heat dissipating plate 6, and the area of the part of the member 9, which does not

**20**

overlap the semiconductor chip 2 in a planar manner, and therefore, it is possible to suppress the deterioration of the heat dissipation characteristics. As to the second heat dissipation path, even if the semiconductor chip 2 to be mounted becomes smaller, the distance between the heat dissipating plate 6 and the inner lead part 4a remains unchanged. Because of this, as shown in FIG. 13, even when the plane dimensions of the semiconductor chip 2 to be mounted are small, heat can be dissipated from the back surface 2b of the semiconductor chip 2 to the heat dissipating plate 6 via the adhesive 8, the die pad 3, and the member 9, and the heat can be further dissipated from the heat dissipating plate 6 to the inner lead part 4a via the sealing resin part 7, and therefore, it is possible to suppress the deterioration of the heat dissipation characteristics accompanying the downsizing of the semiconductor chip 2 to be mounted.