US008089821B2

# (12) United States Patent

#### Schmitt et al.

### (10) Patent No.:

## US 8,089,821 B2

#### (45) **Date of Patent:**

\*Jan. 3, 2012

#### (54) MEMORY DEVICE USING ANTIFUSES

(75) Inventors: Jonathan Alois Schmitt, Eden Prairie,

MN (US); Laurentiu Vasiliu, San Diego, CA (US); Myron Buer, Gilbert,

AZ (US)

(73) Assignee: Broadcom Corporation, Irvine, CA

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 12/689,122

(22) Filed: **Jan. 18, 2010**

#### (65) Prior Publication Data

US 2010/0118584 A1 May 13, 2010

#### Related U.S. Application Data

- (63) Continuation of application No. 11/505,744, filed on Aug. 17, 2006, now Pat. No. 7,649,798.

- (51) Int. Cl. G11C 17/16 (2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,622,886 A | 4/1997 | Allum et al. |

|-------------|--------|--------------|

| 5,767,734 A | 6/1998 | Vest et al.  |

| 5,793,246 A | 8/1998 | Vest et al.  |

| 5,880,502 A | 3/1999 | Lee et al.   |

| 5,886,392 A | 3/1999 | Schuegraf    |

| 5,976,960       | A          | 11/1999 | Cheffings                |

|-----------------|------------|---------|--------------------------|

| 6,044,012       | A          | 3/2000  | Rao et al.               |

| 6,096,589       | A          | 8/2000  | Lee et al.               |

| 6,320,235       | B1         | 11/2001 | Cheffings                |

| 6,417,550       | B1*        | 7/2002  | Madurawe et al 257/408   |

| 6,841,846       | B1*        | 1/2005  | Chen et al 257/530       |

| 6,865,382       | B2 *       | 3/2005  | Behzad 455/323           |

| 6,903,993       | B2         | 6/2005  | Smith et al.             |

| 7,146,585       | B2 *       | 12/2006 | Blodgett 703/15          |

| 7,206,247       | B2         | 4/2007  | Jenne                    |

| 7,250,665       | B1         | 7/2007  | Toros et al.             |

| 7,279,406       | B2         | 10/2007 | Koontz                   |

| 2003/0176033    | <b>A</b> 1 | 9/2003  | Grider et al.            |

| 2004/0058117    | A1*        | 3/2004  | Nishihara et al 428/64.2 |

| 2005/0101280    | A1         | 5/2005  | Behzad                   |

| 2006/0092742    | A1*        | 5/2006  | Paillet et al 365/225.7  |

| 2006/0097345    | <b>A</b> 1 | 5/2006  | Marr                     |

| 2006/0146158    | <b>A</b> 1 | 7/2006  | Toros et al.             |

| 2006/0291267    | <b>A</b> 1 | 12/2006 | Jenne et al.             |

| 2006/0291316    | <b>A</b> 1 | 12/2006 | Jenne                    |

| 2007/0008800    | <b>A</b> 1 | 1/2007  | Jenne                    |

| 2007/0285965    | A1*        | 12/2007 | Toda et al 365/148       |

| 2009/0003113    | A1         | 1/2009  | Terzioglu et al.         |

| * cited by avan | ainar      |         |                          |

<sup>\*</sup> cited by examiner

Primary Examiner — Michael Tran

(74) Attorney, Agent, or Firm — McAndrews, Held & Malloy, Ltd.

#### (57) ABSTRACT

Herein described is a method of implementing one or more native NMOS antifuses in an integrated circuit. Also described is a method for programming one or more native NMOS antifuses used within a memory device. The method further comprises verifying one or more states of the one or more native NMOS antifuses after the programming has been performed. In a representative embodiment, the one or more native NMOS antifuses are implemented by blocking the implantation of a dopant into a substrate of an integrated circuit. In a representative embodiment, an integrated circuit incorporates the use of one or more native NMOS antifuses. In a representative embodiment, the integrated circuit comprises a memory device, such as a one time programmable memory.

#### 36 Claims, 3 Drawing Sheets

FIGURE 1

FIGURE 2

FIGURE 3

1

#### MEMORY DEVICE USING ANTIFUSES

This Application is a continuation of U.S. patent application Ser. No. 11/505,744, filed on Aug. 17, 2006, the complete subject matter of which is incorporated herein by reference in its entirety.

## FEDERALLY SPONSORED RESEARCH OR DEVELOPMENT

[Not Applicable]

#### MICROFICHE/COPYRIGHT REFERENCE

[Not Applicable]

#### BACKGROUND OF THE INVENTION

Improvements in integrated circuit technology have produced smaller devices with higher performance and reduced 20 power consumption. These improvements may be employed in the fabrication of integrated circuits such as integrated circuit memories. One such memory comprises a one time programmable memories (OTPs). When designing or fabricating a one time programmable memory (OTP), the supply 25 voltages that are used to power the OTP may be large because of internal design requirements. Such internal design requirements may be related to the voltage level requirements of the individual components that are used to implement the OTP. These voltage levels may be related to proper biasing of the 30 electronic components in the OTP. When an OTP is implemented using NMOS (n channel MOSFET) logic, proper forward biasing of an n channel MOSFET may result in a voltage drop, VT, across the gate to the drain of such a transistor, for example. Unfortunately, such voltage drops may relate to increases in power consumption when operating a one time programmable memory (OTP).

The limitations and disadvantages of conventional and traditional approaches will become apparent to one of skill in the art, through comparison of such systems with some aspects of the present invention as set forth in the remainder of the present application with reference to the drawings.

#### BRIEF SUMMARY OF THE INVENTION

Aspects of the invention provide at least a method of implementing an antifuse in an integrated circuit. Aspects of the invention provide at least an integrated circuit that incorporates the use of one or more native NMOS antifuses. The various aspects of the invention are substantially shown in 50 and/or described in connection with at least one of the following figures, as set forth more completely in the claims.

These and other advantages, aspects, and novel features of the present invention, as well as details of illustrated embodiments, thereof, will be more fully understood from the following description and drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

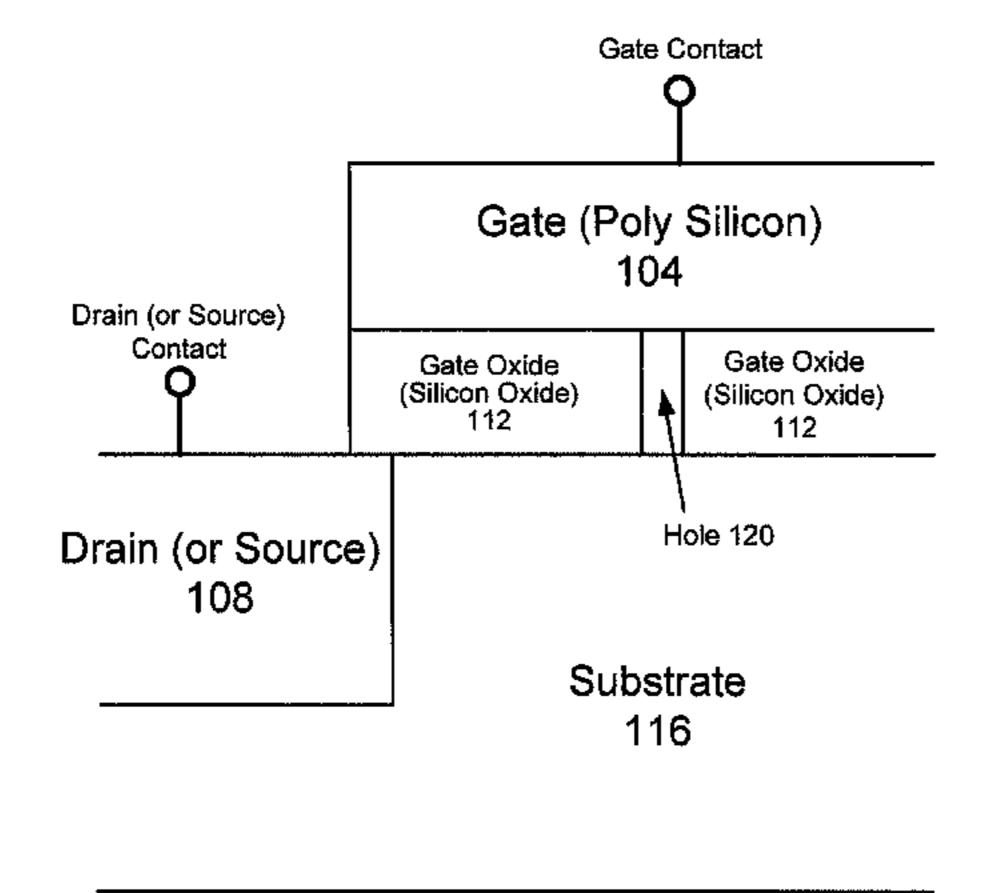

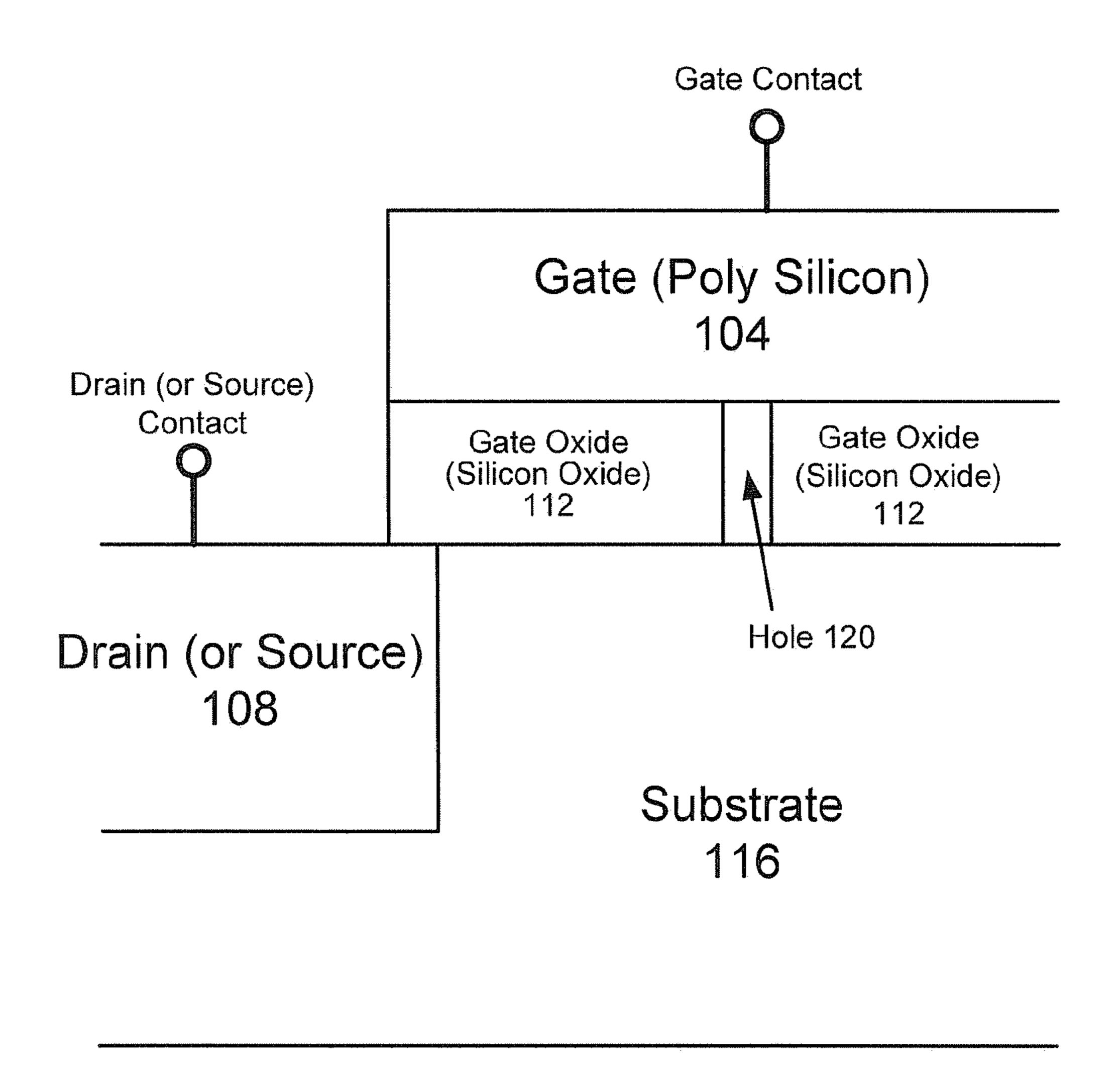

FIG. 1 is a block diagram of a crossectional view of a native 60 NMOS antifuse as fabricated in an integrated circuit in accordance with an embodiment of the invention.

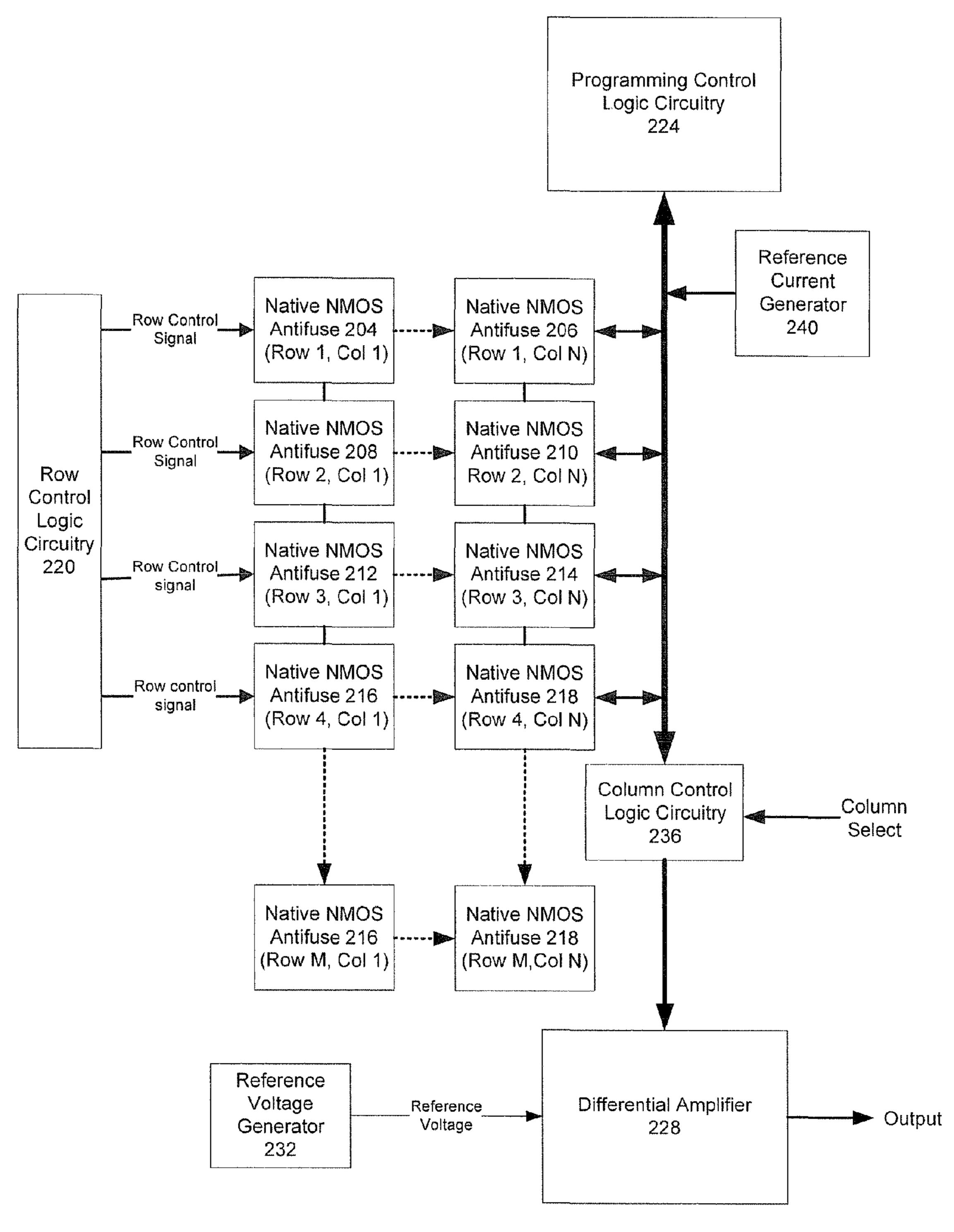

FIG. 2 is a block diagram of a memory device illustrating a number of native NMOS antifuses along with supporting circuitry in accordance with an embodiment of the invention. 65

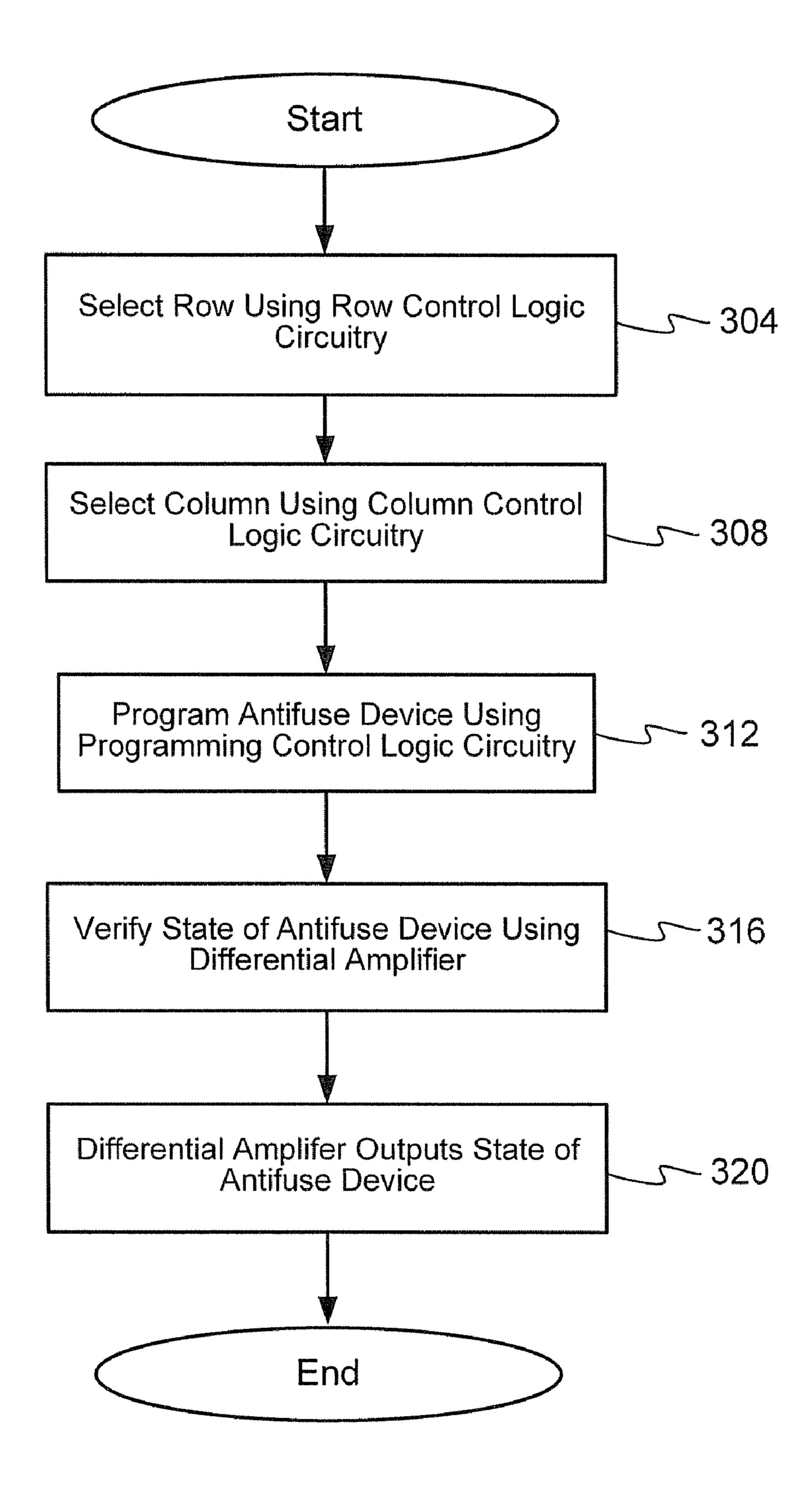

FIG. 3 is an operational flow diagram describing the programming of a native NMOS antifuse and subsequent verifi-

2

cation of a state of a native NMOS antifuse for the memory device illustrated in FIG. 2, in accordance with an embodiment of the invention.

#### DETAILED DESCRIPTION OF THE INVENTION

Various aspects of the invention provide for a method of fabricating a native NMOS antifuse. Furthermore, the various aspects of the invention provide for at least an integrated 10 circuit that is implemented using one or more native NMOS antifuses. In a representative embodiment, the integrated circuit comprises a memory device. In accordance with the various aspects of the invention, the native NMOS antifuse may be fabricated by way of blocking a threshold implant that 15 is typically used during a NMOS fabrication process. By blocking the threshold implant, occurrence of a threshold voltage between a gate and a drain of an antifuse may be minimized or reliably eliminated when the antifuse is programmed. In a NMOS process, for example, a parasitic transistor diode may be created between a gate and a drain of an antifuse when the antifuse is programmed, for example. The parasitic transistor diode creates a typical diode characteristic having a threshold voltage, VT. Unfortunately, an existence of such a threshold voltage may inhibit or interfere with a subsequent verification test that may be used to properly read the state of the antifuse. Furthermore, the existence of the threshold voltage also makes it difficult to further program the antifuse.

By using a native NMOS process, a memory device may be implemented using one or more antifuses. In a representative embodiment, the memory device comprises a one time programmable memory (OTP). The OTP may be fabricated as a high speed digital integrated circuit, for example.

FIG. 1 is a block diagram of a crossectional view of a native 35 NMOS antifuse as fabricated in an integrated circuit in accordance with an embodiment of the invention. The native NMOS antifuse comprises a poly silicon gate 104, a drain (or source) 108, a gate oxide (silicon oxide) layer 112, a hole 120 within the gate oxide layer 112, and a substrate 116. In a representative embodiment, the native NMOS antifuse may be fabricated using either a drain or source 108 of an NMOS transistor. In contrast to a non-native NMOS antifuse, the substrate 116 of the native NMOS antifuse is not doped or implanted with any dopant. For example, implantation of a dopant, such as boron or phosphorus, into the substrate 116 of an NMOS antifuse is not allowed in a native NMOS process. The hole 120 comprises a semiconductor material that provides a path in which current may travel from the gate 104 to the drain 108. However, the current flows only when the voltage at the gate is higher than a threshold voltage, VT, for a non-native NMOS antifuse. When an antifuse is fabricated using a native NMOS process, the voltage threshold is eliminated, such that the path between the hole 120 and the drain 108 is purely resistive. The native NMOS antifuse delineated in FIG. 1 may represent one cell in an integrated circuit. This cell may be used any number of times in the design and creation of an integrated circuit memory. The representative embodiment of FIG. 1 also depicts a gate contact connected to the gate and a drain (or source) contact connected to the drain (or source) of the native NMOS antifuse. The integrated circuit memory may comprise a one time programmable memory (OTP), for example.

FIG. 2 is a block diagram of a memory device illustrating a number of native NMOS antifuses along with supporting circuitry in accordance with an embodiment of the invention. In a preferred representative embodiment, one or more native NMOS antifuses are used to implement an integrated circuit

memory, such as a one time programmable memory (OTP). Absence of a threshold voltage in the one or more native NMOS antifuses facilitates the use of lower supply voltages in powering the OTP. In a representative embodiment, the absence of a threshold voltage in each of the one or more 5 native NMOS antifuses facilitates the use of a lower supply voltage when powering an associated differential sense amplifier. In this representative embodiment, one or more gates of the native NMOS antifuses are connected to the inputs of the differential sense amplifier. In a representative 10 embodiment, the memory device (or OTP) comprises a number of native NMOS antifuses arranged in rows and columns. In a representative embodiment, the native NMOS antifuses may be arranged as a M×N (i.e., M rows by N columns) array. For the sake of simplicity, only two columns and four rows of 15 native NMOS antifuses 204, 206, 208, 210, 212, 214, 216, 218 (i.e, a total of eight) are shown in the memory device (or OTP) of FIG. 2. The memory device comprises a row control logic circuitry 220, a programming control logic circuitry **224**, a column control logic circuitry **236**, a reference voltage 20 generator 232, a reference current generator 240, and a differential amplifier 228. The column control logic circuitry 236 may comprise a N:1 column multiplexer, where N corresponds to the number of columns of native NMOS antifuse devices in the memory device, for example. The column 25 control logic circuitry 236 may utilize a column select signal as an input for selecting one of N columns in the  $M \times N$  array. The row control logic circuitry 220 may be used to enable a particular row of the M rows represented in the array. The row control logic circuitry 220 may transmit row control signals to 30 each of the native NMOS antifuses in the array. The programming control logic circuitry 224 may comprise a voltage source that may be used for breaking down the gate oxide of each of the native NMOS antifuses in the array. The voltage magnitude to break down the gate oxide reliably. In a representative embodiment, the voltage source comprises a 5 Volt source. The programming control logic circuitry 224 may comprise timing and logic circuitry used in programming one or more the native NMOS antifuses in the array. When one of 40 the one or more native NMOS antifuses are selected and programmed by the programming control logic 224, the gate oxide of the selected antifuse is ruptured or broken down and the gate to drain is electrically connected by way of a low resistance. As a consequence, the gate is essentially shorted to 45 ground (via the drain or source) through the low resistance; and as a consequence, the voltage at the gate is interpreted to be a logical '0' state. If a particular antifuse is not programmed, the gate oxide is left intact, and the gate to drain (or source) is open circuited. The reference current generator 240 50 may be used, for example, to verify the state of a particular antifuse after programming has occurred. The reference current generator 240 may be used to verify whether a particular antifuse was programmed or not. The reference current generator 240 sources current to a selected antifuse. If the antifuse's gate is ruptured or broken, the current passes through the gate to ground; as a consequence, the voltage reading at the gate is a low voltage or interpreted as a logical '0'. If on the other hand, the antifuse's gate is not ruptured, the current cannot pass through the gate, and the voltage reading at the 60 gate is a high voltage or interpreted as a logical '1'. The gate voltage from a particular antifuse may be transmitted to the differential amplifier 228, where it is amplified. The differential amplifier 228 may comprise a differential sense amplifier. The differential amplifier 228 may invert the received 65 gate voltage before it is output. The reference voltage generator 232 provides a reference voltage to power the differential

amplifier 228. The row control logic circuitry 220, the column control logic circuitry 236, and the programming control logic circuitry 224 may comprise any type of digital hardware or electronics.

FIG. 3 is an operational flow diagram describing the programming of a native NMOS antifuse and subsequent verification of a state of a native NMOS antifuse for the memory device illustrated in FIG. 2, in accordance with an embodiment of the invention. At step 304, a particular row is selected in an array of native NMOS antifuses. A row control logic circuitry such as that previously described in reference to FIG. 2 may transmit one or more row control signals to enable the selection of a particular row. For an M×N array, one of M rows may be selected using the row control logic circuitry. At step 308, a particular column may be selected in the array of native NMOS antifuses. A column control logic circuitry such as that previously described in reference to FIG. 2 may be used to select one of N columns in the array. One of N columns in the array may be selected by the column control logic circuitry. After selecting a particular native NMOS antifuse using the row control logic circuitry and column control logic circuitry, the antifuse may be programmed using a programming logic control circuitry, at step 312. The programming control logic circuitry may utilize a supply voltage capable of rupturing or breaking down the gate oxide of the selected native NMOS antifuse. After the gate oxide has been ruptured, the corresponding antifuse is considered to have been programmed. When the gate oxide is ruptured, the gate of the antifuse is considered shorted to ground by way of a small resistance. Next at step 316, the state of the selected antifuse may be verified after programming has been performed. The state of the antifuse may be verified by sourcing a current into the gate of the selected antifuse. A reference current generator, such as that described in reference to FIG. source may be configured to be at a level high enough in 35 2, may be used to source the current. The voltage at the gate may be transmitted to the inputs of a differential amplifier, as previously described in FIG. 2. The differential amplifier may comprise an inverted differential sense amplifier, for example. At step 320, the differential amplifier may output the state of the selected native NMOS antifuse. If the selected native NMOS antifuse was properly programmed, then the output of an inverted differential sense amplifier would be a logical '1', for example.

> However, if the selected native NMOS antifuse was not programmed, then the output of an inverted differential sense amplifier would be a logical '0', for example.

> While the invention has been described with reference to certain embodiments, it will be understood by those skilled in the art that various changes may be made and equivalents may be substituted without departing from the scope of the invention. In addition, many modifications may be made to adapt a particular situation or material to the teachings of the invention without departing from its scope. Therefore, it is intended that the invention not be limited to the particular embodiment disclosed, but that the invention will include all embodiments falling within the scope of the appended claims.

What is claimed is:

- 1. A method for implementing a memory device comprising:

- selecting one or more cells in an array of cells in said memory device, said memory device comprising at least one native NMOS antifuse, said antifuse fabricated using a process that blocks a threshold implant, said selecting performed by a circuitry used for configuring a row selection and a column selection of said array; and applying a voltage source to break down a gate oxide layer of said at least one native NMOS antifuse.

5

- 2. The method of claim 1 wherein said memory device comprises a one time programmable memory (OTP).

- 3. The method of claim 1 wherein using said process eliminates the presence of a threshold voltage between a gate and a drain or said gate and a source of said antifuse.

- 4. The method of claim 1 wherein said circuitry comprises a current source for generating a current used for driving said antifuse and generating a voltage reading at a gate of said antifuse.

- 5. The method of claim 1 wherein said breaking down said gate oxide layer produces a low resistance connection between a gate and a drain of said antifuse.

- 6. The method of claim 1 wherein said breaking down said gate oxide layer produces a low resistance connection between a gate and a source of said antifuse.

- 7. The method of claim 1 wherein said circuitry comprises an antifuse.

- **8**. The method of claim **7** wherein said antifuse comprises a native NMOS antifuse.

- 9. A memory device comprising:

one or more circuits operable for, at least:

selecting one or more cells in an array of cells in said memory device, said memory device comprising at least one NMOS antifuse, said antifuse fabricated 25 using a process that blocks a threshold implant, said selecting performed by configuring a row selection and a column selection of said array; and

applying a voltage source to break down a gate oxide layer of said at least one native NMOS antifuse.

- 10. The memory device of claim 9 wherein said memory device comprises a one time programmable memory (OTP).

- 11. The memory device of claim 9 wherein using said process eliminates the presence of a threshold voltage between a gate and a drain or said gate and a source of said 35 antifuse.

- 12. The memory device of claim 9 wherein said one or more circuits comprises a current source for generating a current used for driving said antifuse and generating a voltage reading at a gate of said antifuse.

- 13. The memory device of claim 9 wherein said breaking down said gate oxide layer produces a low resistance connection between a gate and a drain of said antifuse.

- 14. The memory device of claim 9 wherein said breaking down said gate oxide layer produces a low resistance connection between a gate and a source of said antifuse.

- 15. The memory device of claim 9 wherein said one or more circuits comprises an antifuse.

- 16. The memory device of claim 15 wherein said antifuse comprises a native NMOS antifuse.

- 17. A memory device comprising:

an array of antifuse cells fabricated using a native NMOS process; and one or more circuits operable for, at least: adjusting the selection of a row and a column of said array of native NMOS antifuse cells;

selecting a cell of said array based on said selection; and using a voltage source to break down a gate oxide layer of a native NMOS antifuse of said cell; and using a voltage source to break down a gate oxide layer

18. The memory device of claim 17 wherein said memory device comprises a one time programmable memory (OTP).

of a native NMOS antifuse of said cell.

6

- 19. The memory device of claim 17 wherein using said process eliminates the presence of a threshold voltage between a gate and a drain or said gate and a source of said antifuse.

- 20. The memory device of claim 17 wherein said one or more circuits comprises a current source for generating a current used for driving said antifuse and generating a voltage reading at a gate of said antifuse.

- 21. The memory device of claim 17 wherein said breaking down said gate oxide layer produces a low resistance connection between a gate and a drain of said antifuse.

- 22. The memory device of claim 17 wherein said breaking down said gate oxide layer produces a low resistance connection between a gate and a source of said antifuse.

- 23. The memory device of claim 17 wherein said one or more circuits comprises an antifuse.

- 24. The memory device of claim 23 wherein said antifuse comprises a native NMOS antifuse.

- 25. A memory device comprising one or more antifuses used for configuring said memory device wherein said one or more antifuses are implemented using a native NMOS process.

- 26. The memory device of claim 25 wherein said using a native NMOS process minimizes occurrence of a threshold voltage between a gate and a drain or source of said one or more antifuses.

- 27. The memory device of claim 25 wherein said using a native NMOS process eliminates the presence of a threshold voltage between a gate and a drain or source of said one or more antifuses.

- 28. The memory device of claim 25 wherein said one or more antifuses are used to implement a one time programmable memory (OTP).

- 29. The memory device of claim 25 further comprising a control logic circuitry for selecting a certain antifuse of a plurality of antifuses, said plurality of antifuses arranged in a M by N array, said control logic circuitry comprising:

- a column control logic circuitry for selecting one of N columns in said M by N array; and

- a row control logic circuitry for selecting one of M rows in said M by N array.

- 30. The memory device of claim 29 wherein said column control logic circuitry comprises a multiplexer used to select said one of N columns.

- 31. The memory device of claim 29 further comprising a current source used for driving said certain antifuse when verifying a state of said certain antifuse.

- 32. The memory device of claim 31 wherein a voltage reading is generated from said driving said certain antifuse, said voltage reading transmitted to a differential amplifier.

- 33. The memory device of claim 25 further comprising a voltage source for said programming said memory device.

- 34. The memory device of claim 33 wherein said voltage source is used for rupturing a gate oxide of a certain antifuse of said one or more antifuses.

- 35. The memory device of claim 34 wherein said rupturing said gate oxide produces a low resistance connection between a gate and a drain of said certain antifuse.

- 36. The memory device of claim 34 wherein said rupturing said gate oxide produces a low resistance connection between a gate and a source of said certain antifuse.

\* \* \* \* \*