### US008058845B2

# (12) United States Patent

# Tange et al.

# (10) Patent No.: US 8,058,845 B2 (45) Date of Patent: Nov. 15, 2011

| (54) | BATTERY    | STATE MONITORING CIRCUIT             | 5,825,155        | A *     | 10/1998    |

|------|------------|--------------------------------------|------------------|---------|------------|

| ` /  | AND BAT    | TERY APPARATUS                       | 5,929,593        | A *     | 7/1999     |

|      |            |                                      | 6,340,880        | B1 *    | 1/2002     |

| (75) | Inventors: | Yoshihisa Tange, Chiba (JP); Atsushi |                  |         |            |

|      |            | Sakurai, Chiba (JP); Takakazu Ozawa, | OTHER :          |         | HER PU     |

|      |            | Chiba (JP); Kiyoshi Yoshikawa, Chiba |                  |         |            |

|      |            | (JP)                                 | Patent Abstracts | of Japa | an, public |

(73) Assignee: Seiko Instruments Inc. (JP)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 803 days.

(21) Appl. No.: 12/217,316(22) Filed: Jul. 3, 2008

(65) Prior Publication Data

US 2009/0009133 A1 Jan. 8, 2009

(20) Equation Application Delication Delicat

(30) Foreign Application Priority Data

(51) Int. Cl. H01M 10/46 (2006.01)

See application file for complete search history.

## (56) References Cited

### U.S. PATENT DOCUMENTS

| 5,304,915 A | * | 4/1994 | Sanpei et al   | 320/116 |

|-------------|---|--------|----------------|---------|

| 5,789,900 A | * | 8/1998 | Hasegawa et al | 320/132 |

| 5,808,444 A | * | 9/1998 | Saeki et al    | 320/117 |

| 5,825,155 | A  | * | 10/1998 | Ito et al         | 320/118 |

|-----------|----|---|---------|-------------------|---------|

| 5,929,593 | A  | * | 7/1999  | Eguchi            | 320/139 |

| 6,340,880 | B1 | * | 1/2002  | Higashijima et al | 320/162 |

### OTHER PUBLICATIONS

Patent Abstracts of Japan, publication No. 2005-117780, publication date Apr. 28, 2005.

\* cited by examiner

Primary Examiner — Edward Tso (74) Attorney, Agent, or Firm — Adams & Wilks

### (57) ABSTRACT

Provided is a battery state monitoring circuit which is capable of preventing a discharge leak current from a battery so as to eliminate a load conventionally imposed on a user, including: a battery state detector circuit that detects a state of the battery based on a voltage of the battery; a transmitting terminal that transmits battery state information indicative of the state of the battery to an outside; a receiving terminal that receives battery state information of another battery from the outside; a transistor that is used for transmitting the battery state information, and has any one of two terminals except for a control terminal connected to the transmitting terminal; and a diode that is connected in a direction opposite to a direction of a parasitic diode disposed between the two terminals of the transistor, the diode being disposed between the transmitting terminal and one terminal of the transistor.

### 18 Claims, 15 Drawing Sheets

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 6

FIG. 8

FIG. 10

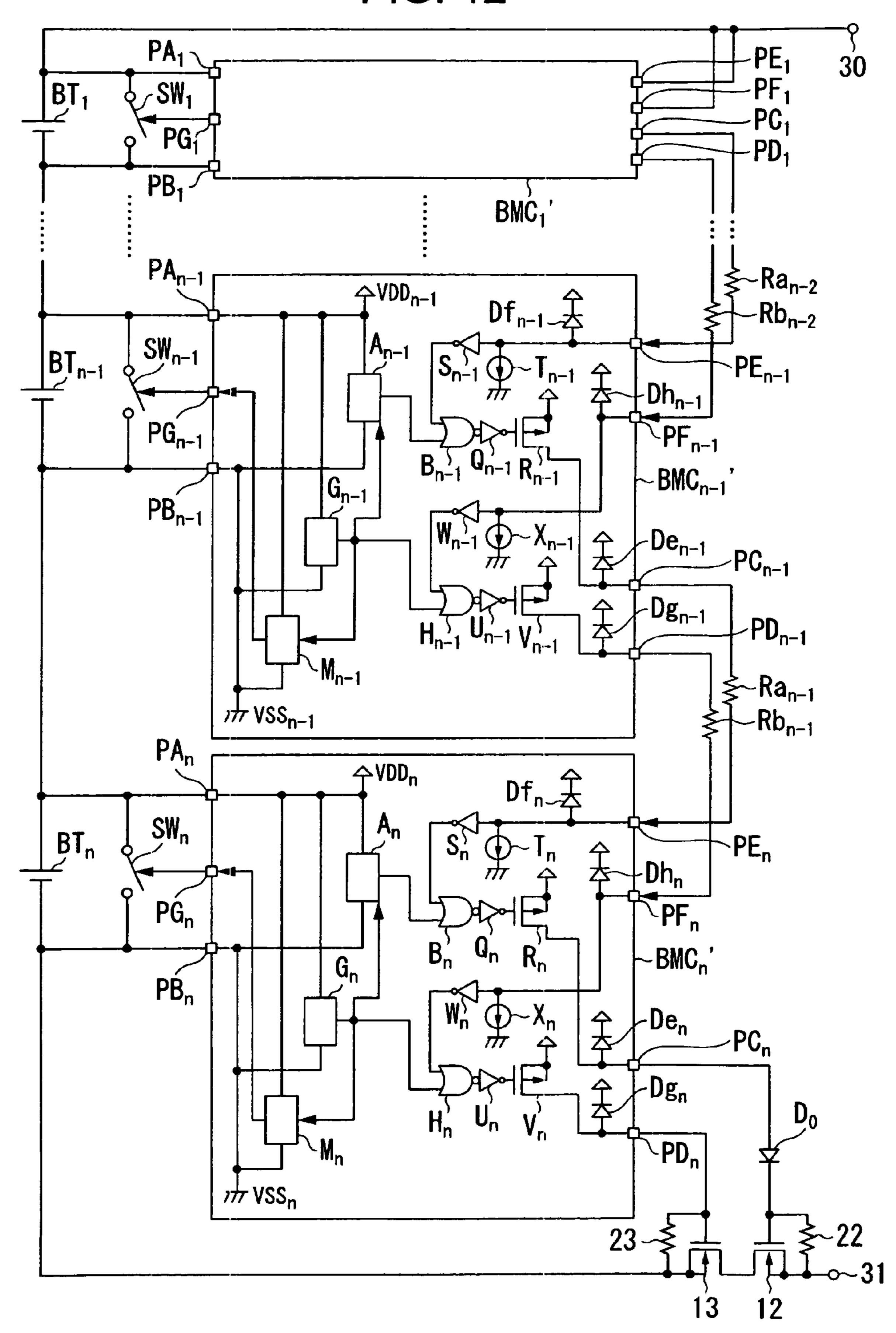

FIG. 12

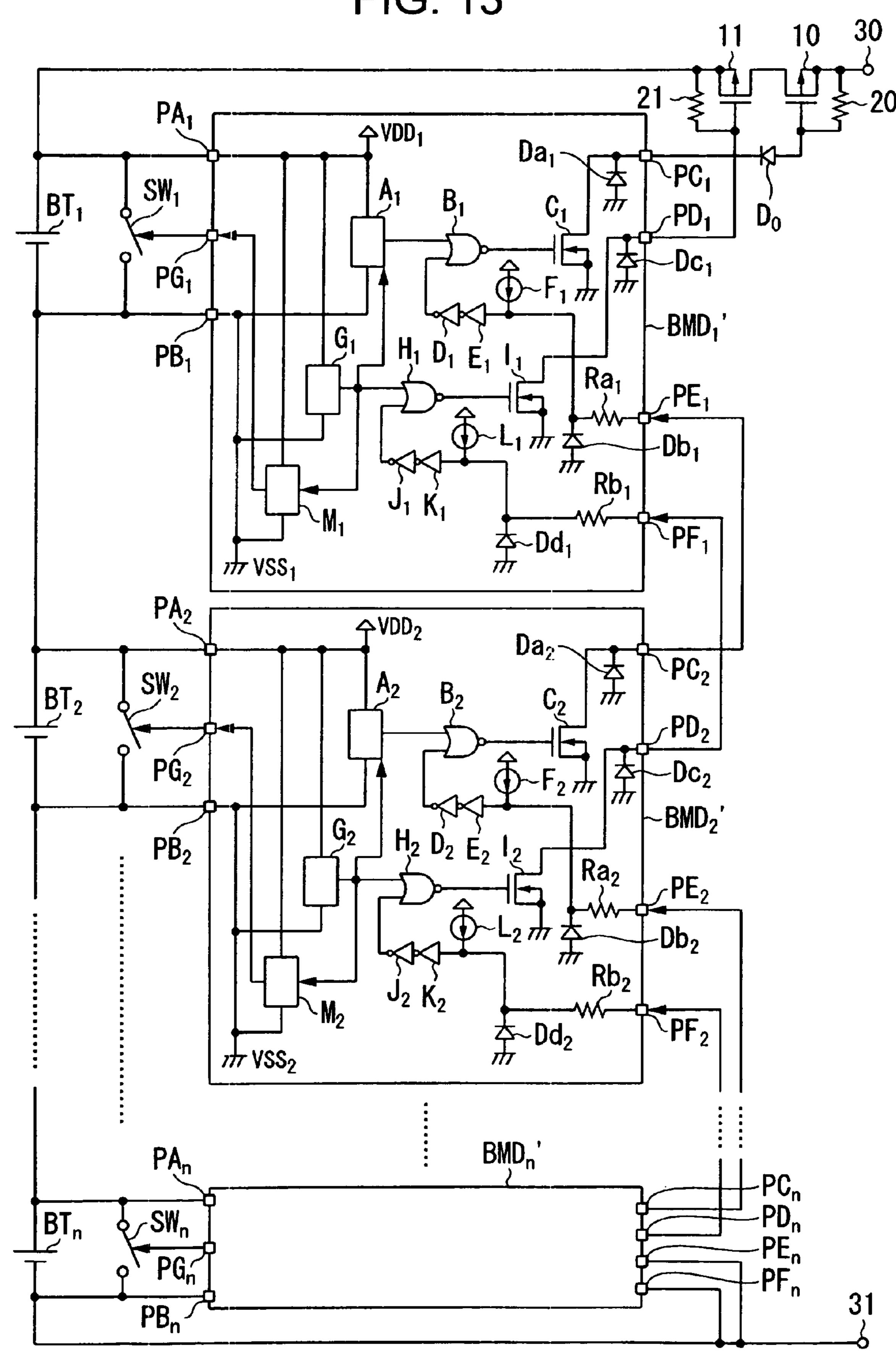

FIG. 13

Nov. 15, 2011

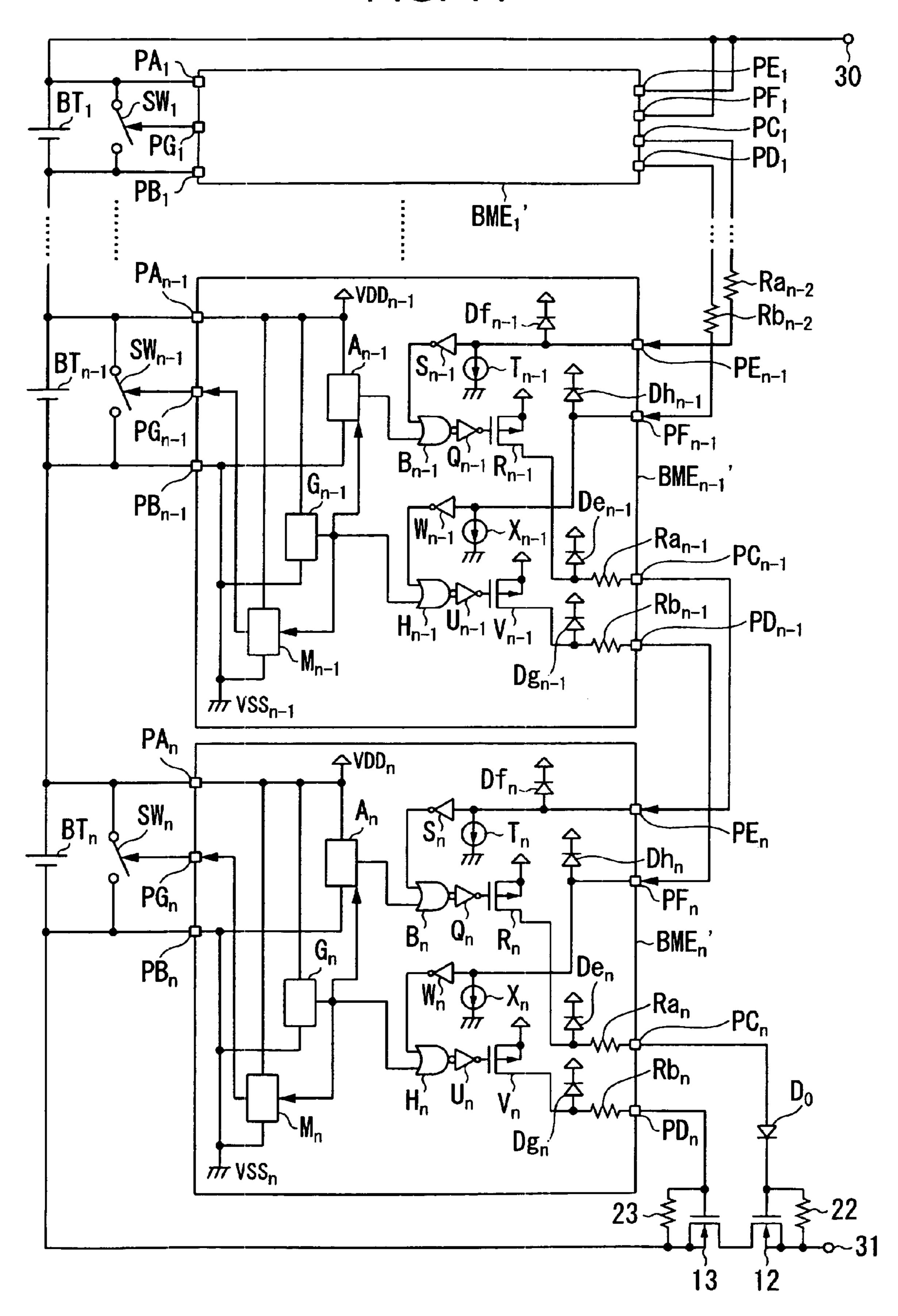

FIG. 14

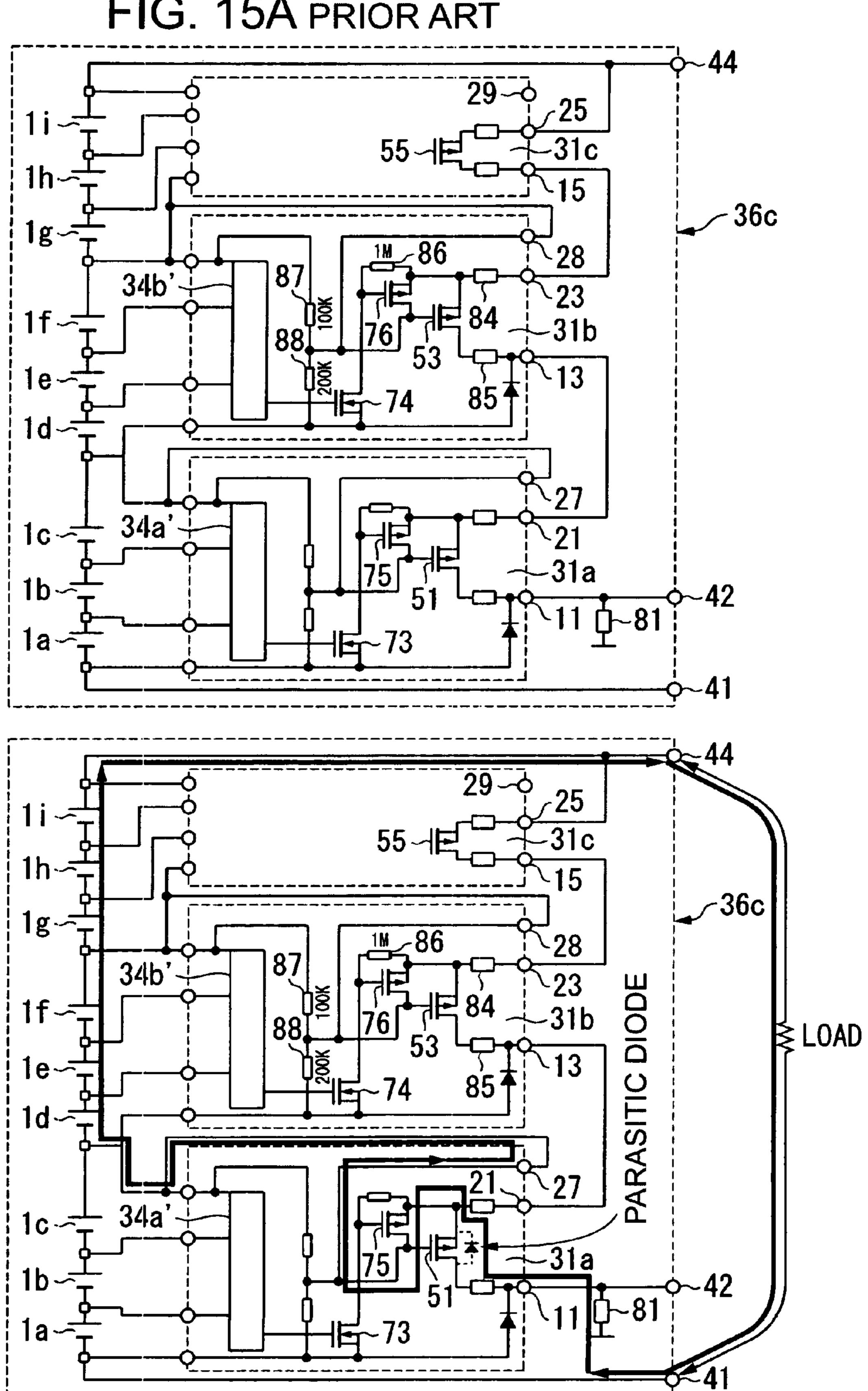

FIG. 15A PRIOR ART

FIG. 15B PRIOR ART

### BATTERY STATE MONITORING CIRCUIT AND BATTERY APPARATUS

#### BACKGROUND OF THE INVENTION

### 1. Field of the Invention

The present invention relates to a battery state monitoring circuit that monitors a state of a battery, and a battery device that is equipped with a plurality of the battery state monitoring circuits.

### 2. Description of the Related Art

For example, JP 2005-117789 A discloses a protective IC that monitors voltages of a plurality of batteries that are connected in series with each other. FIG. 15A shows an example of the protective IC that is disclosed in JP 2005-117780 A. Referring to FIG. 15A, reference numbers 31a, 15 31b, and 31c denote protective ICs, respectively. The protective IC 31a monitors the voltages of batteries 1a to 1c, the protective IC 31b monitors the voltages of batteries 1d to 1f, and the protective IC 31c monitors the voltages of batteries 1g to 1i, respectively. In a normal state, that is, when the voltages 20of the batteries 1a to 1i are not abnormal, because all FETs 51, 53, and 55 of the respective protective ICs 31a, 31b, and 31care on, a current flows through a resistor 81, and a monitor output terminal 42 becomes at high level. On the other hand, for example, when the voltage of any one of the batteries 1a to 25 1c becomes overvoltage (overcharged state), a signal of high level is output from an overvoltage detector circuit 34a' that is disposed in the protective IC 31a with the results that an FET 73 is turned on, and an FET 75 is turned on. In this situation, because the FET 51 is turned off, no current flows in the 30 resistor 81, and the monitor output terminal 42 becomes at low level. The same is applied to overdischarge detection.

As described above, when the voltage of any one of the batteries 1a to 1c becomes overvoltage, the monitor output terminal 42 becomes at low level because the FET 73 is turned on, the FET 75 is turned on, and the FET 51 is turned off. However, a parasitic diode having an anode terminal connected to a drain terminal of the FET 51 and a cathode terminal connected to a source terminal of the FET 51 exists between the drain terminal and a gate terminal of the FET 51. 40 Therefore, when a load is connected between external terminals 41 and 44 in the above state, a current path is formed as shown in FIG. 15B, which leads to such a problem that electricity is discharged from the batteries 1d to 1i to generate discharge leak current.

The voltages of the batteries 1d to 1i are decreased due to an influence of the above discharge leak current, but the other batteries 1a to 1c have the high voltage close to the overvoltage. As a result, the voltage balance of the batteries 1a to 1i is disrupted. A state in which the voltage balance is disrupted is 50 advanced so that the batteries 1a to 1c become voltages close to the overvoltage, and the batteries 1d to 1i become voltages close to overdischarge. As a result, because the overvoltage is detected by small charge, charging cannot be conducted. Also, because the overdischarge is detected by slightly using an application program, the batteries cannot be used. Such batteries are exchanged with fresh batteries. However, because the phenomenon of the discharge leak current is repeated so far as the conventional protective IC is used, the conventional protective IC not only causes inconvenience for 60 a user, but also causes a large load such as costs and time required for battery replacement.

## SUMMARY OF THE INVENTION

The present invention has been made in view of the above circumstances, and therefore an object of the present inven-

2

tion is to provide a battery state monitoring circuit and a battery device which are capable of preventing the discharge leak current from the battery so as to eliminate the load conventionally imposed on the user.

In order to achieve the above-mentioned object, as means for solving the above-mentioned problems, the present invention provides a battery state monitoring circuit, including: a battery state detector circuit that detects a state of a battery based on a voltage of the battery; a transmitting terminal that transmits battery state information indicative of the state of the battery to an outside; a receiving terminal that receives battery state information of another battery from the outside; a transistor that is used for transmitting the battery state information, and has any one of two terminals except for a control terminal connected to the transmitting terminal; and a diode that is connected in a direction opposite to a direction of a parasitic diode disposed between the two terminals of the transistor, the diode being disposed between the transmitting terminal and one terminal of the transistor.

### BRIEF DESCRIPTION OF THE DRAWINGS

In the accompanying drawings:

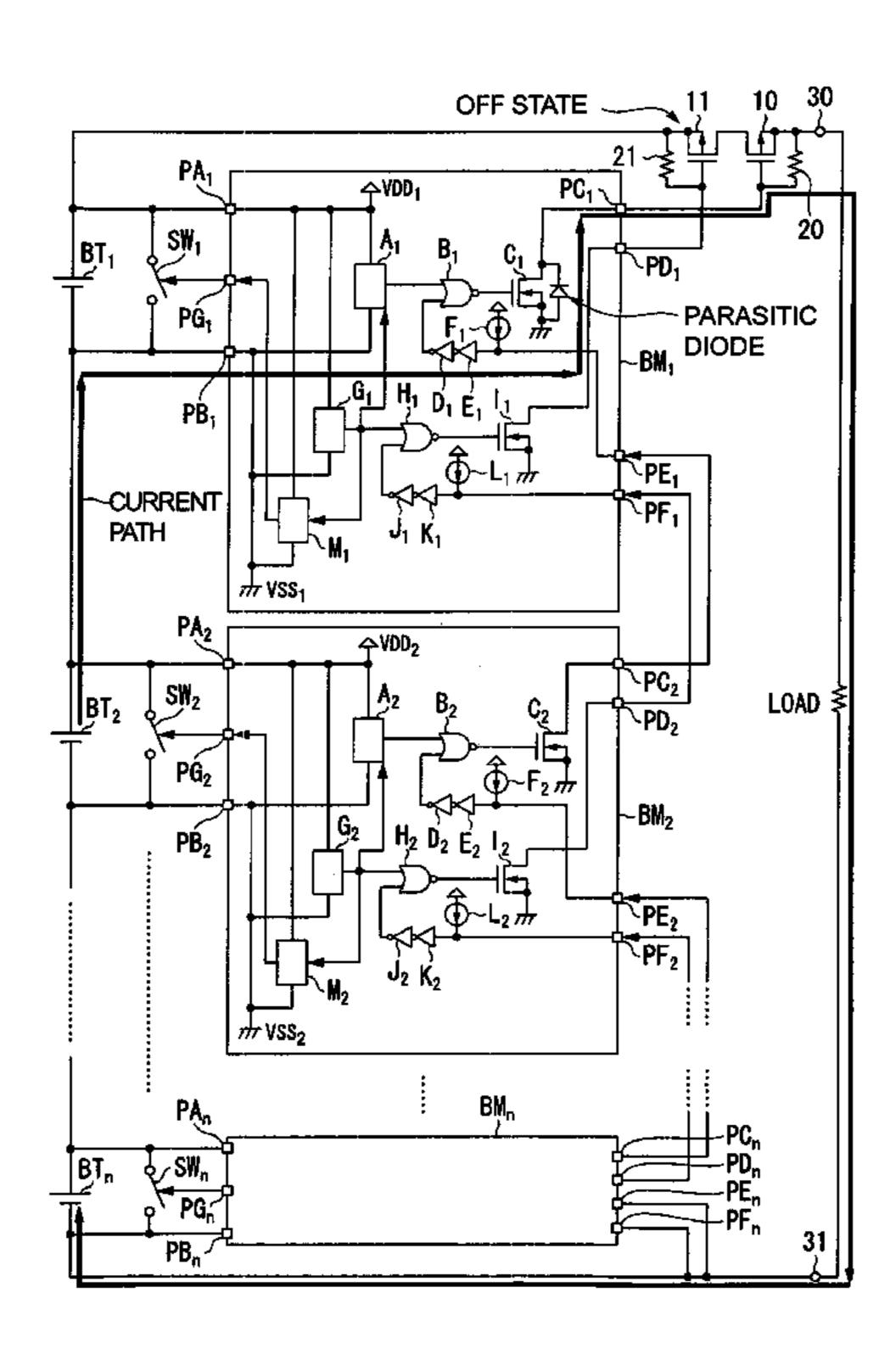

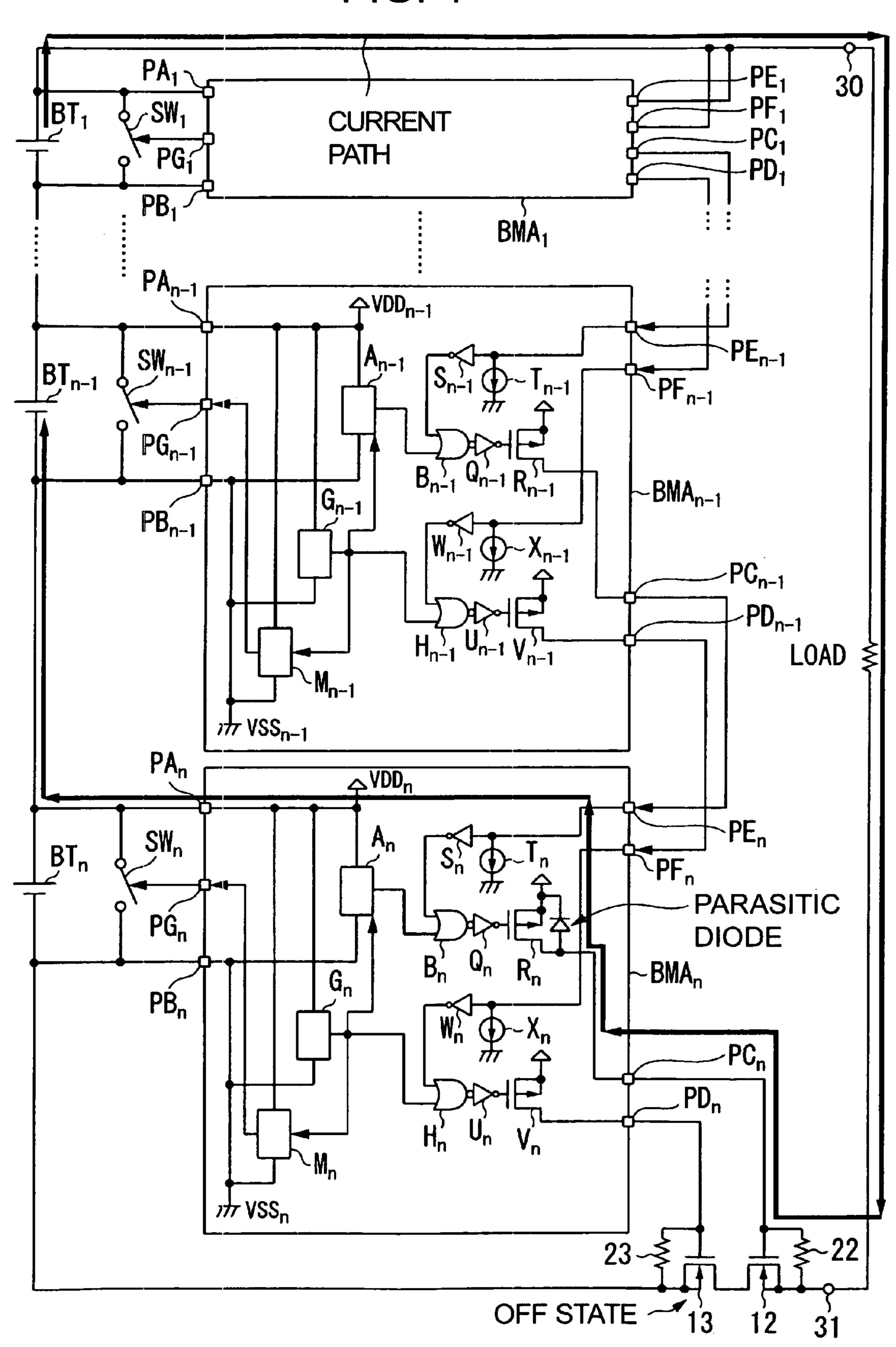

- FIG. 1 is a circuit configuration diagram showing a battery device according to a first embodiment of the present invention;

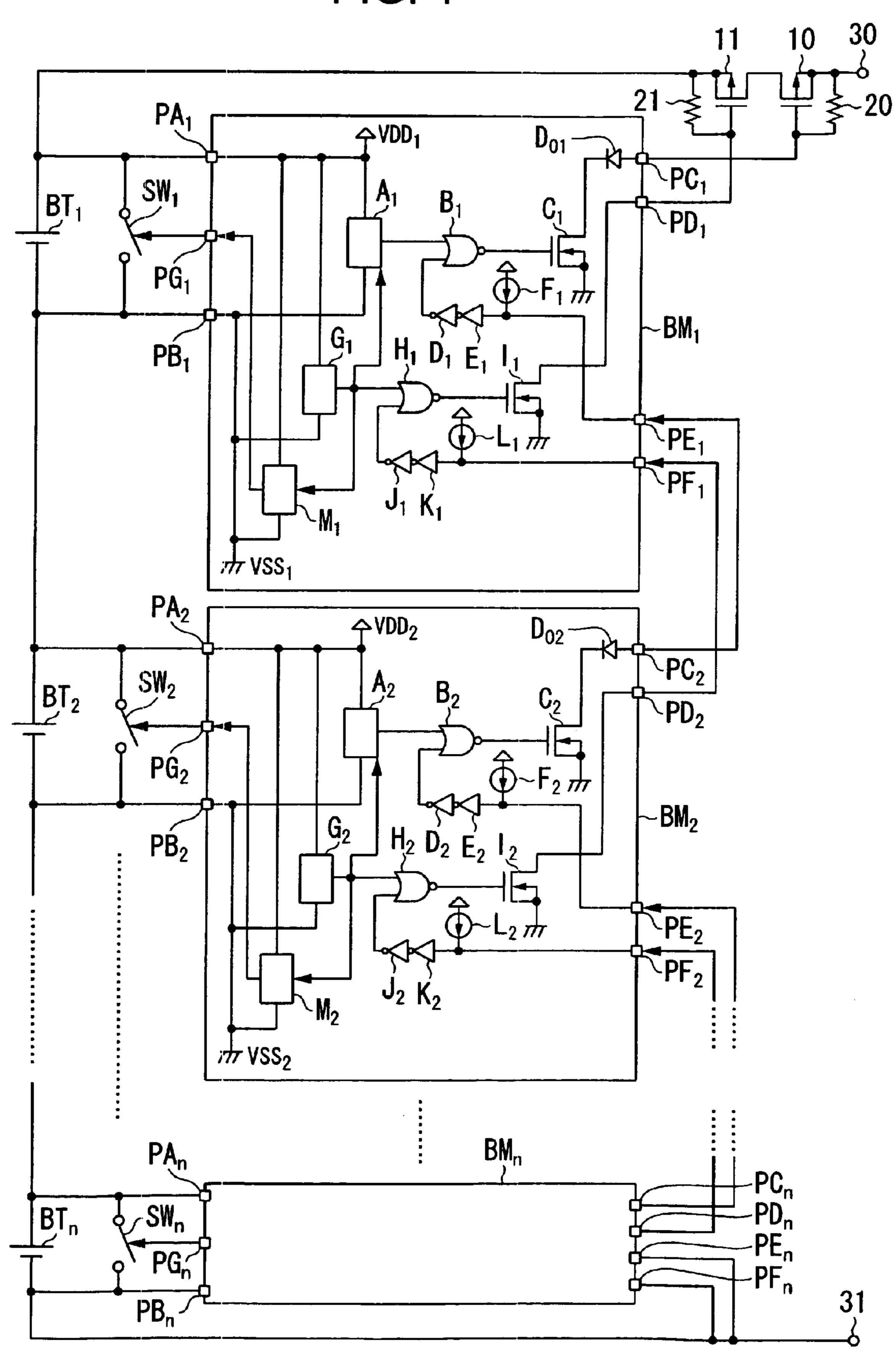

- FIG. 2 is an explanatory diagram showing a discharge leak current preventing principle in the battery device according to the first embodiment of the present invention;

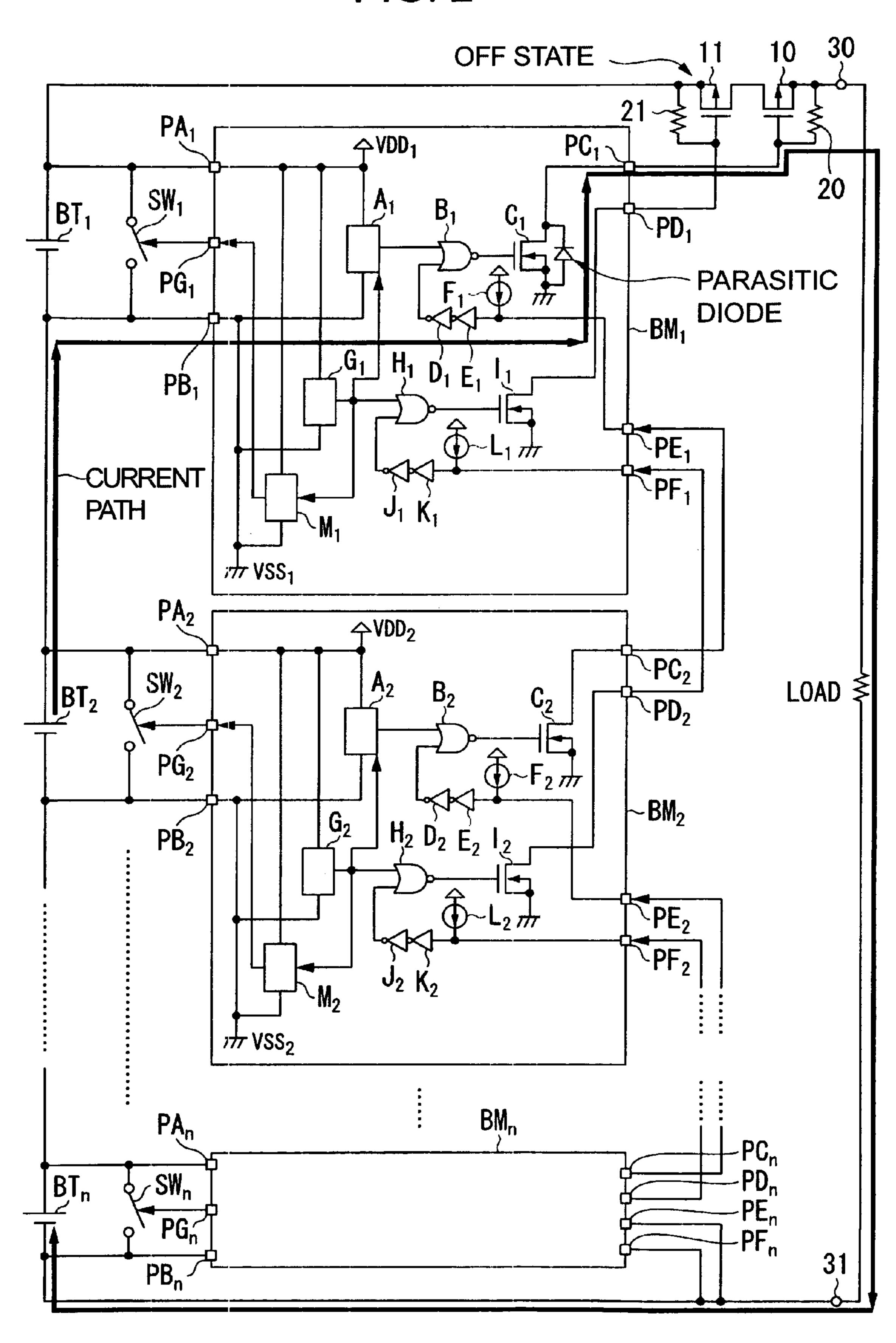

- FIG. 3 is a circuit configuration diagram showing a battery device according to a second embodiment of the present invention;

- FIG. 4 is an explanatory diagram showing a discharge leak current preventing principle in the battery device according to the second embodiment of the present invention;

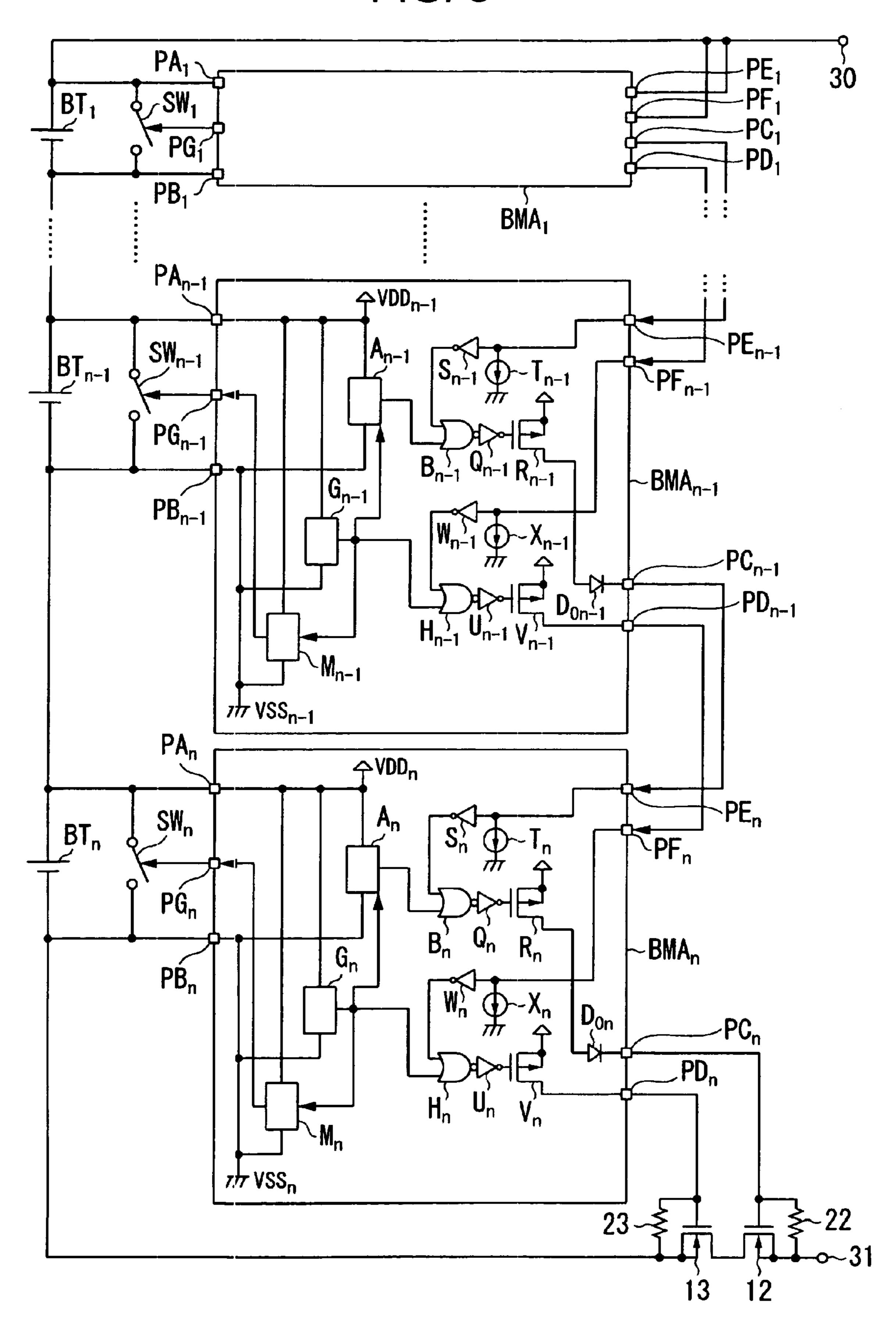

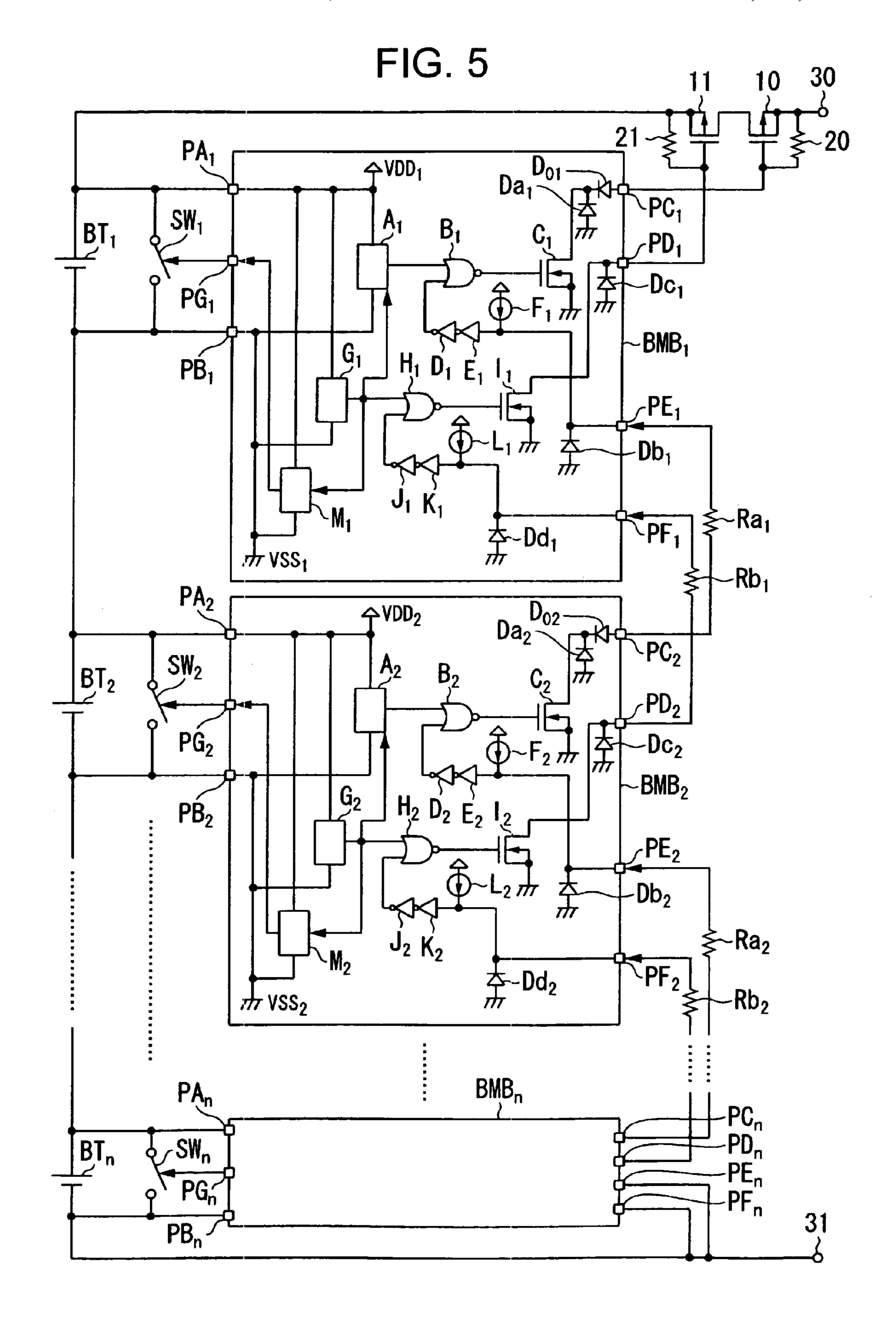

- FIG. **5** is a circuit configuration diagram showing a battery device according to a third embodiment of the present invention;

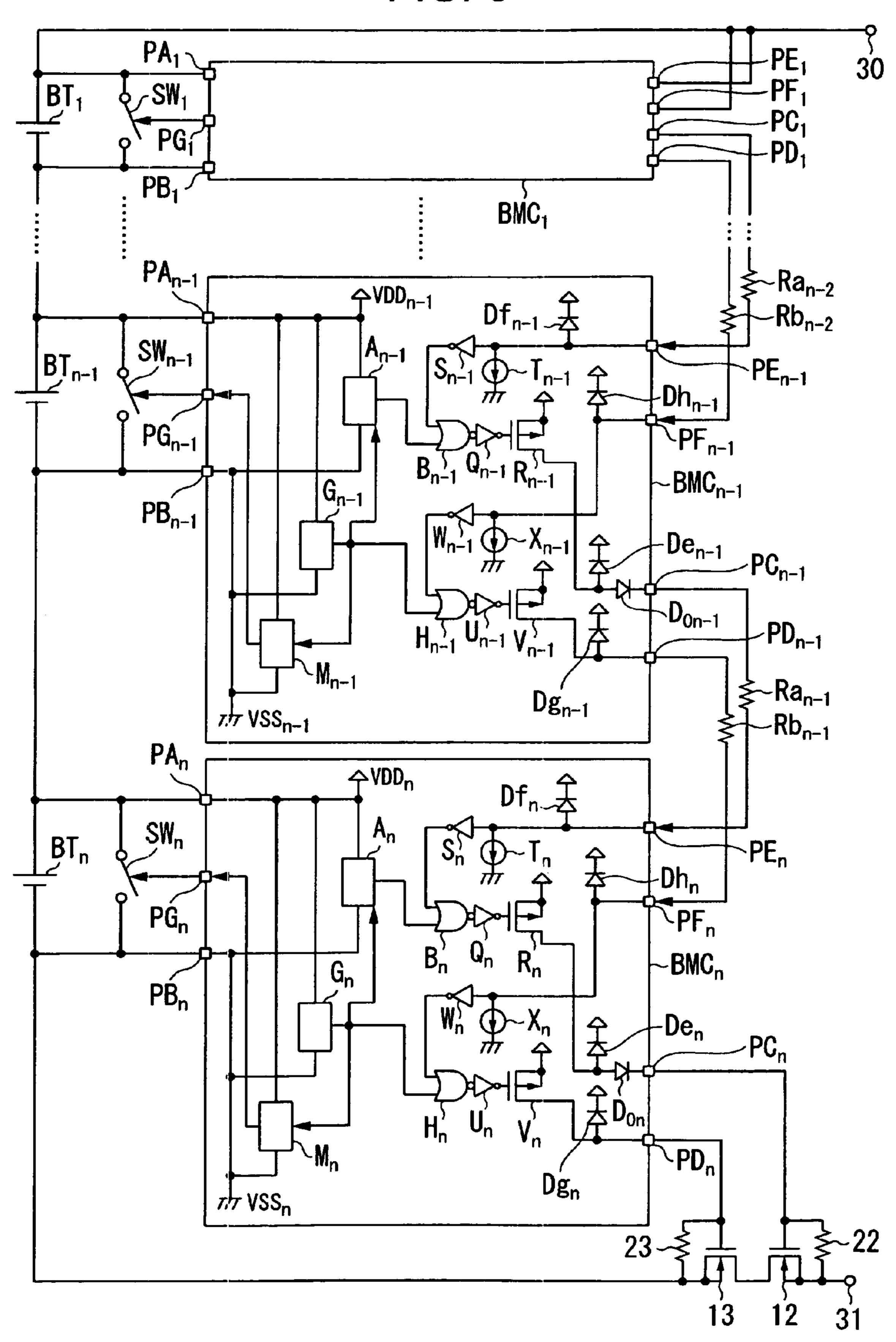

- FIG. 6 is a circuit configuration diagram showing a battery device according to a fourth embodiment of the present invention;

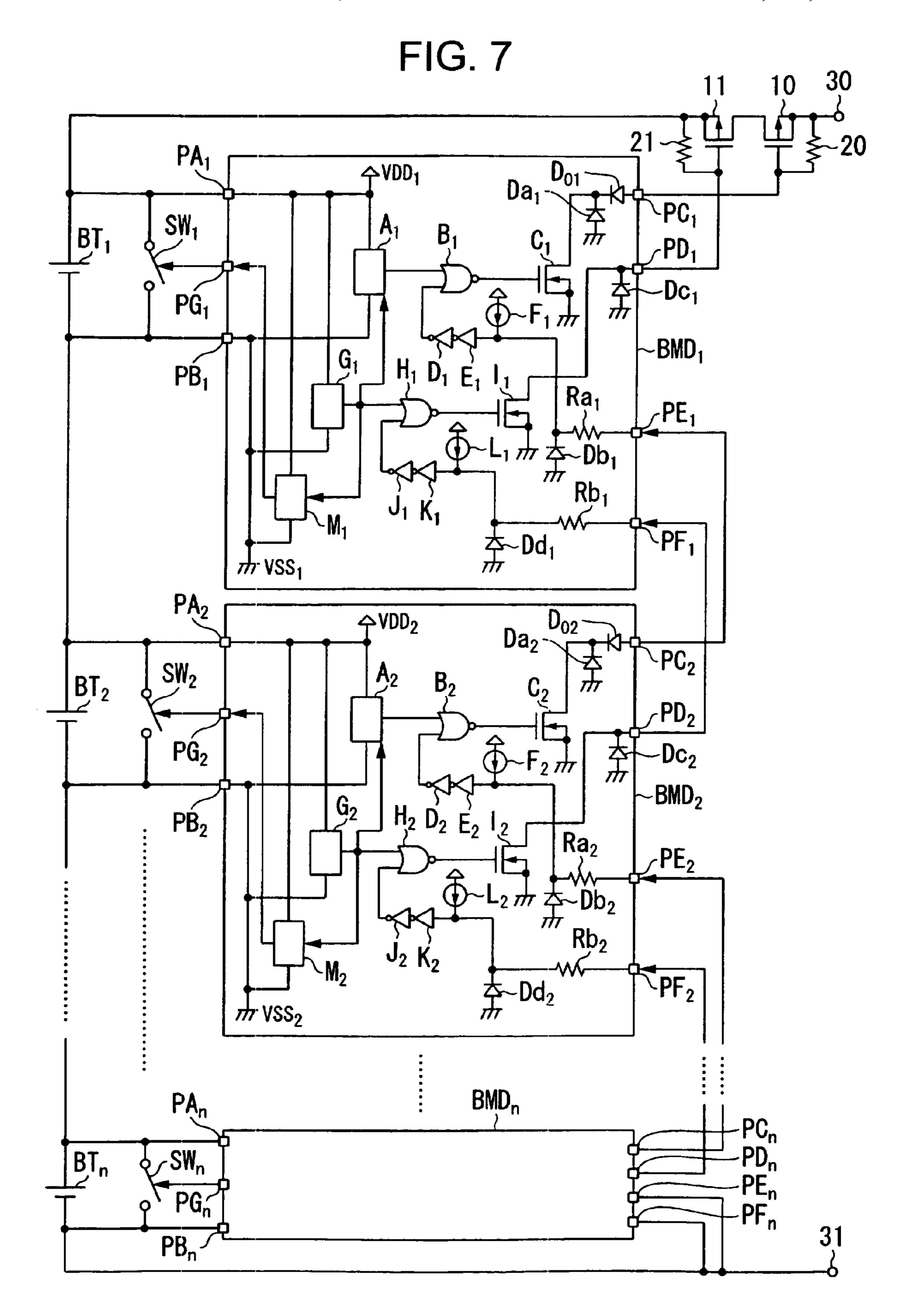

- FIG. 7 is a circuit configuration diagram showing a battery device according to a fifth embodiment of the present invention;

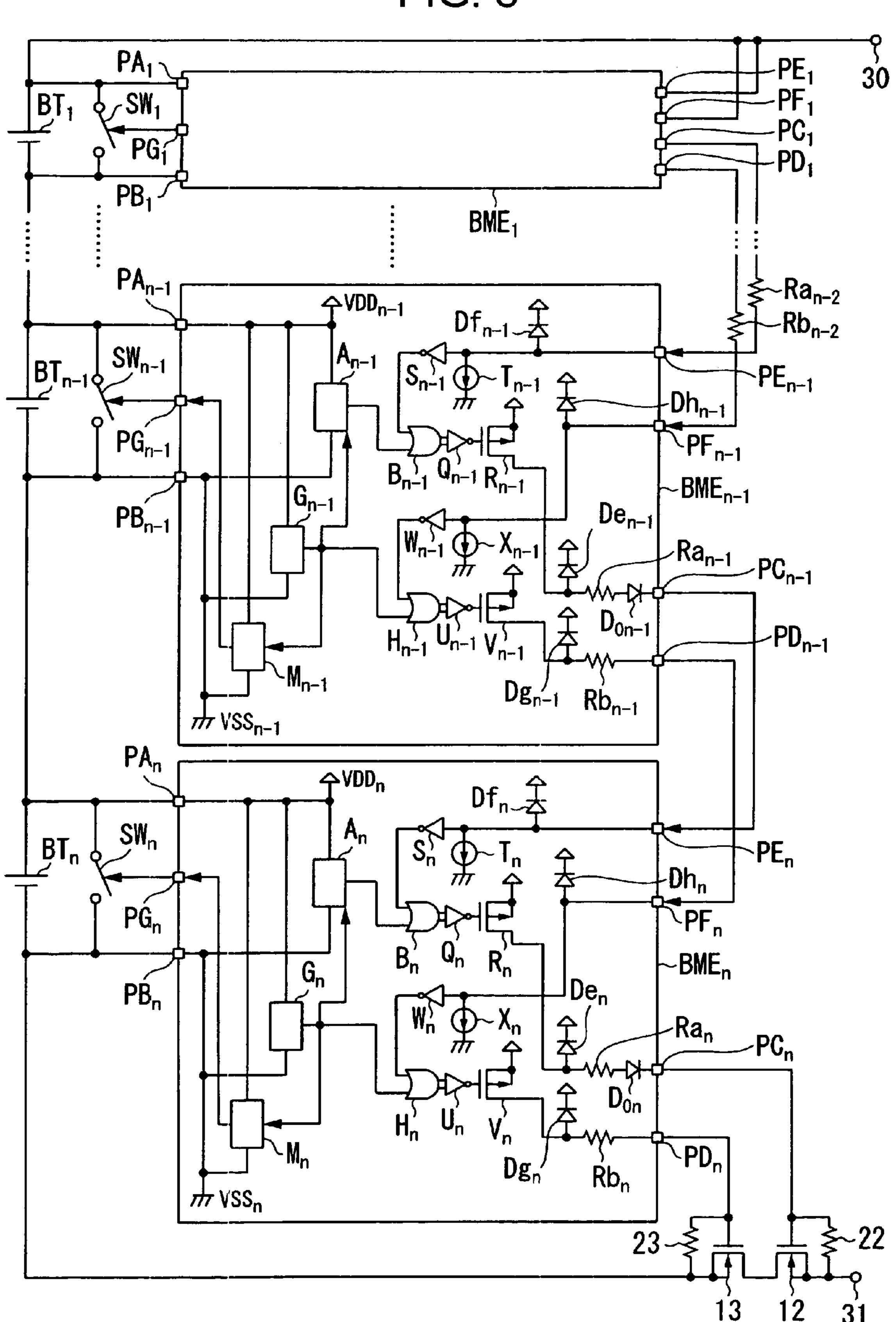

- FIG. **8** is a circuit configuration diagram showing a battery device according to a sixth embodiment of the present invention;

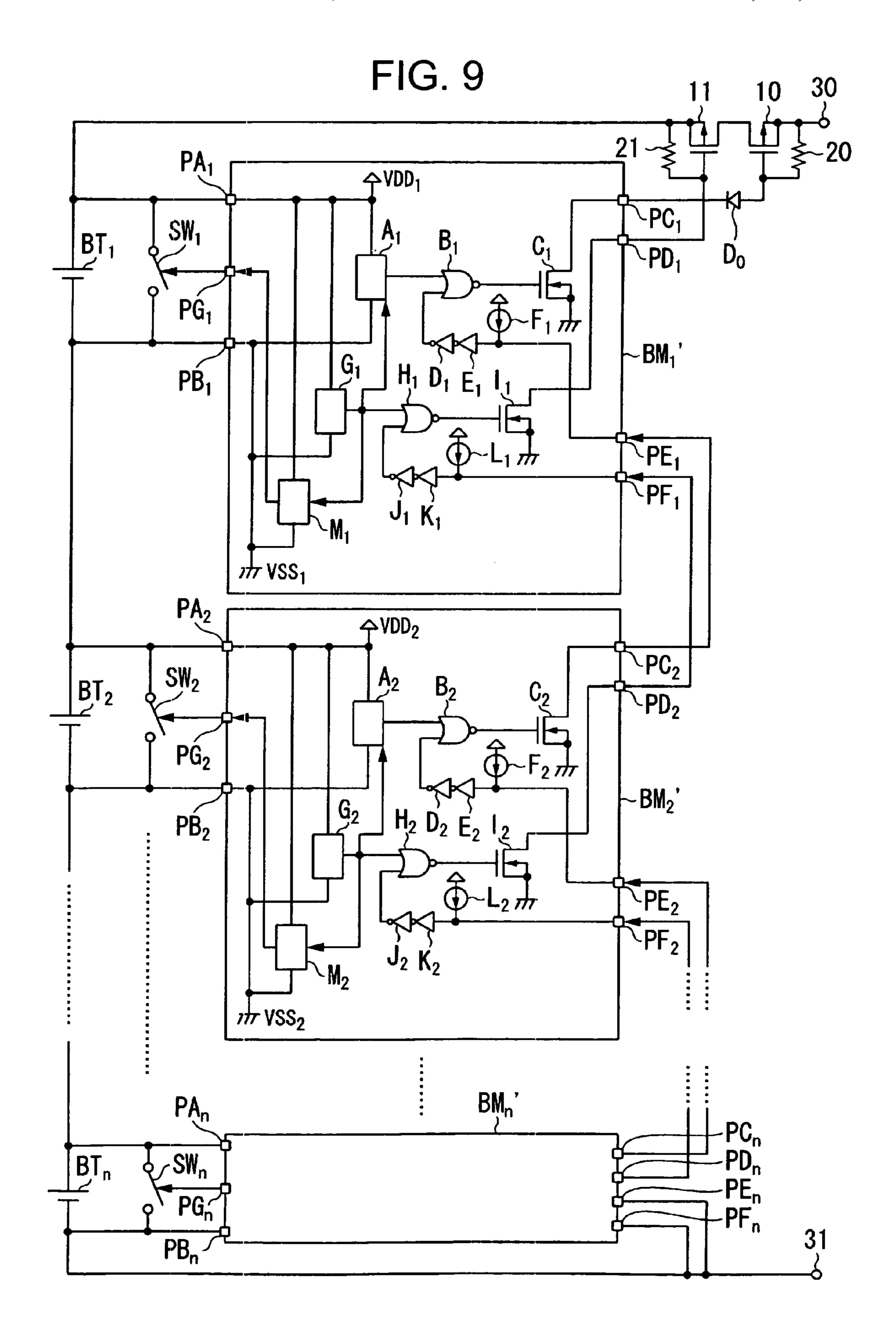

- FIG. 9 is a circuit configuration diagram showing a battery device according to a seventh embodiment of the present invention;

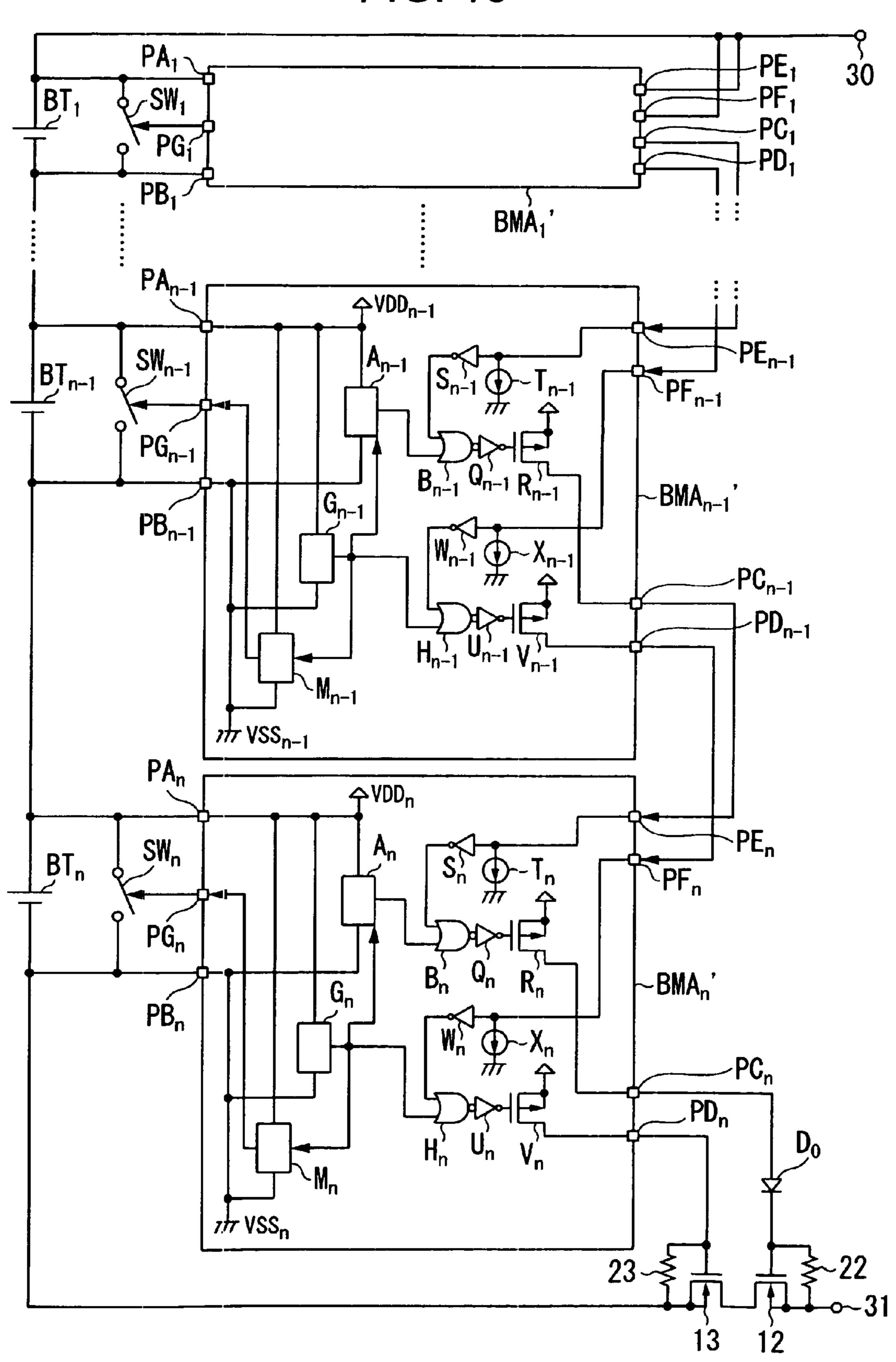

- FIG. 10 is a circuit configuration diagram showing a battery device according to an eighth embodiment of the present invention;

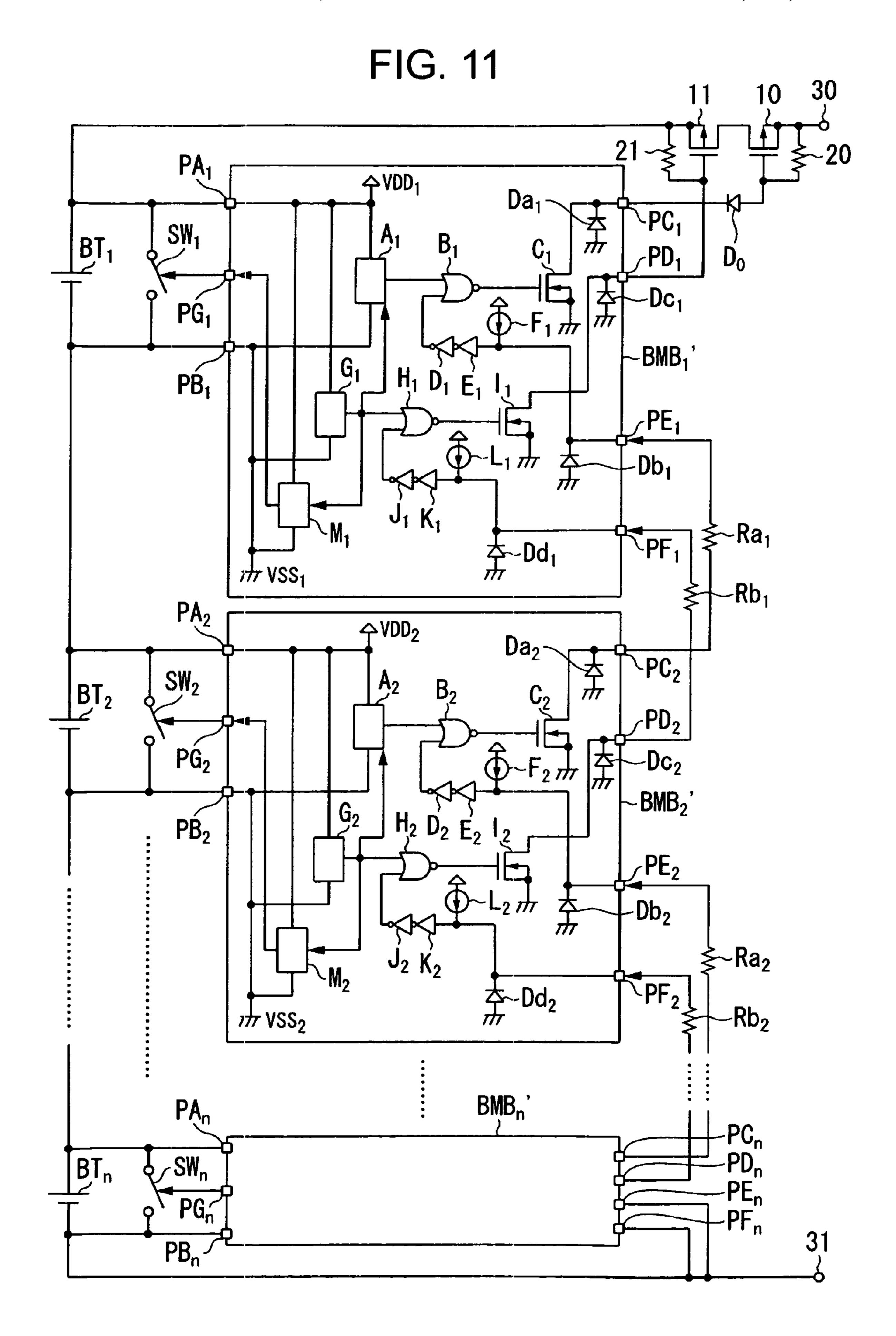

- FIG. 11 is a circuit configuration diagram showing a battery device according to a ninth embodiment of the present invention;

- FIG. 12 is a circuit configuration diagram showing a battery device according to a tenth embodiment of the present invention;

- FIG. 13 is a circuit configuration diagram showing a battery device according to an eleventh embodiment of the present invention;

- FIG. **14** is a circuit configuration diagram showing a battery device according to a twelfth embodiment of the present invention; and

FIG. 15 is an explanatory diagram showing a conventional technology.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Hereinafter, a description will be given of embodiments of the present invention with reference to the accompanying drawings.

#### First Embodiment

FIG. 1 is a circuit configuration diagram showing a battery device according to a first embodiment. As shown in FIG. 1, the battery device according to the first embodiment includes 15 n batteries  $BT_1$  to  $BT_n$ , that are connected in series, n switches (cell balance switch circuits)  $SW_1$  to  $SW_n$  which are connected in parallel with each of the batteries  $Bt_1$  to  $BT_n$ , n battery state monitoring circuits  $BM_1$  to  $BM_n$  that are disposed in correspondence with the respective batteries  $BT_1$  to  $BT_n$ , individually, a first transistor (charging p-channel transistor) 10, a second transistor (discharging p-channel transistor) 11, a first resistive element (first bias resistive element) 20, a second resistive element (second bias resistive element) 21, a first external terminal 30, and a second external terminal 25 31.

The battery state monitoring circuit  $BM_1$  includes an overcharge detector circuit  $A_1$ , a first NOR circuit  $B_1$ , a first output transistor  $C_1$ , a diode  $Do_1$ , a first inverter  $D_1$ , a second inverter  $E_1$ , a first current source  $F_1$ , an overdischarge detector circuit  $G_1$ , a second NOR circuit  $G_1$ , a second output transistor  $G_1$ , a third inverter  $G_1$ , a fourth inverter  $G_1$ , a second current source  $G_1$ , a cell balance circuit  $G_1$ , a first voltage monitor terminal  $G_1$ , a second voltage monitor terminal  $G_1$ , a first transmitting terminal  $G_1$ , a second transmitting terminal  $G_1$ , a first  $G_1$ , a first  $G_2$ , a first  $G_1$ , a first  $G_2$ , a first  $G_2$ , a first  $G_3$ , a first  $G_4$ , a first  $G_1$ , a first  $G_2$ , a first  $G_3$ , a first  $G_4$ , a fir

The other battery state monitoring circuits  $BM_2$  to  $BM_n$  40 have the same components as those of the battery state monitoring circuit  $BM_1$ , and therefore are shown with a change in only symbols. For example, the symbol of the overcharge detector circuit in the battery state monitoring circuit  $BM_2$  is  $A_2$  whereas the symbol of the overcharge detector circuit in 45 the battery state monitoring circuit  $BM_n$  is  $A_n$ . The same is applied to other components.

Since all of the battery state monitoring circuits  $BM_1$  to  $BM_n$  are identical in circuit configuration with each other as described above, the battery state monitoring circuit  $BM_1$  50 corresponding to the battery  $BT_1$  will be representatively described below.

In the battery state monitoring circuit  $BM_1$ , the first voltage monitor terminal  $PA_1$  is connected to a positive terminal of the battery  $BT_1$  and one terminal of the switch  $SW_1$ . Also, the first voltage monitor terminal  $PA_1$  is connected to a positive side common power source wire within the battery state monitoring circuit  $BM_1$ . The second voltage monitor terminal  $PB_1$  is connected to a negative terminal of the battery  $BT_1$  and another terminal of the switch  $SW_1$ . Also, the second voltage monitor terminal  $PB_1$  is connected to a negative side common power source wire within the battery state monitoring circuit  $PS_1$ . In the following description, the positive side common power source wire is  $PS_1$  within the battery state monitoring circuit  $PS_1$  and the negative side common power source wire is  $PS_1$  within the battery state monitoring circuit  $PS_1$  and the positive side common power source wire is  $PS_1$  within the battery state monitoring circuit  $PS_1$  and the positive side common power source wire is  $PS_1$  within the battery state monitoring circuit  $PS_1$  and the negative side common power source wire is  $PS_1$  within the battery state monitoring circuit  $PS_1$  and the negative side common power source wire is  $PS_2$  within the battery state monitoring circuit  $PS_2$  and the negative side common power source wire is  $PS_2$  and the negative side common power source wire is  $PS_2$  and the negative side common power source wire is  $PS_2$  and the negative side common power source wire is  $PS_2$ .

4

$VSS_2$  within the battery state monitoring circuit  $BM_2$ . In the same manner, the positive side common power source wire is  $VDD_n$  and the negative side common power source wire is  $VSS_n$  within the battery state monitoring circuit  $BM_n$ .

The overcharge detector circuit  $A_1$  has one end connected to the first voltage monitor terminal PA<sub>1</sub>, and another end connected to the second voltage monitor terminal PB<sub>1</sub>. The overcharge detector circuit A<sub>1</sub> detects a voltage between the first voltage monitor terminal PA<sub>1</sub> and the second voltage monitor terminal PB<sub>1</sub> (that is, voltage of battery BT<sub>1</sub>). When the voltage of the battery BT<sub>1</sub> is equal to or higher than an overcharge voltage, the overcharge detector circuit  $A_1$  outputs an overcharge detection signal of high level to one input terminal of the first NOR circuit B<sub>1</sub>. Also, when the voltage of the battery BT<sub>1</sub> is lower than the overcharge voltage, the overcharge detector circuit  $A_1$  outputs an overcharge detection signal of low level to the first NOR circuit B<sub>1</sub>. Here, the overcharge voltage is an upper limit chargeable voltage. The overcharge detector circuit  $A_1$  has a function of stopping the operation when the overdischarge detection signal of high level is input to the overcharge detector circuit  $A_1$  from the overdischarge detector circuit  $G_1$ .

To the first NOR circuit  $B_1$ , the above overcharge detection signal and an output signal of the first inverter  $D_1$  are input, and the first NOR circuit  $B_1$  outputs a negative OR signal of both of those signals to a gate terminal of the first output transistor  $C_1$ . The first output transistor  $C_1$  is an n-channel type metal oxide semiconductor (MOS) transistor. The first output transistor  $C_1$  has the gate terminal connected to an output terminal of the first NOR circuit  $B_1$ , a drain terminal connected to a cathode terminal of the diode  $Do_1$ , and a source terminal connected to the VSS<sub>1</sub>. The diode  $Do_1$  has the cathode terminal connected to the drain terminal of the first output transistor  $C_1$ , and an anode terminal connected to the first transmitting terminal  $PC_1$ .

The first inverter  $D_1$  outputs a logical inversion signal of an output signal from the second inverter  $E_1$  to the first NOR circuit  $B_1$ . The second inverter  $E_1$  has an input terminal connected to the first receiving terminal  $PE_1$  and an output terminal of the first current source  $F_1$ , and outputs a logical inversion signal of an input signal to an input terminal to the first inverter  $D_1$ . The first current source  $F_1$  is a current source having an input terminal connected to the  $VDD_1$ , and the output terminal connected to the input terminal of the second inverter  $E_1$  and the first receiving terminal  $PE_1$ .

The overdischarge detector circuit  $G_1$  has one end connected to the first voltage monitor terminal PA<sub>1</sub>, and another end connected to the second voltage monitor terminal PB<sub>1</sub>. The overdischarge detector circuit  $G_1$  detects a voltage between the first voltage monitor terminal PA<sub>1</sub> and the second voltage monitor terminal PB<sub>1</sub> (that is, voltage of battery BT<sub>1</sub>). When the voltage of the battery  $BT_1$  is lower than an overdischarge voltage, the overdischarge detector circuit G<sub>1</sub> outputs an overdischarge detection signal of high level to one input terminal of the second NOR circuit H<sub>1</sub>, the overcharge detector circuit  $A_1$ , and the cell balance circuit  $M_1$ . Also, when the voltage of the battery BT<sub>1</sub> is equal to or higher than the overdischarge voltage, the overdischarge detector circuit G<sub>1</sub> outputs an overdischarge detection signal of low level. Here, the overdischarge voltage is a lower limit dischargeable voltage.

To the second NOR circuit  $H_1$ , the above overdischarge detection signal and an output signal of the third inverter  $J_1$  are input, and the second NOR circuit  $H_1$  outputs a negative OR signal of both of those signals to a gate terminal of the second output transistor  $I_1$ . The second output transistor  $I_1$  is an

n-channel type MOS transistor. The second output transistor  $I_1$  has the gate terminal connected to an output terminal of the second NOR circuit  $H_1$ , a drain terminal connected to the second transmitting terminal  $PD_1$ , and a source terminal connected to the  $VSS_1$ .

The third inverter  $J_1$  outputs a logical inversion signal of an output signal from the fourth inverter  $K_1$  to the second NOR circuit  $H_1$ . The fourth inverter  $K_1$  has an input terminal connected to the second receiving terminal  $PF_1$  and an output terminal of the second current source  $L_1$ , and outputs a logical inversion signal of an input signal to the input terminal to the fourth inverter  $K_1$ . The second current source  $L_1$  is a current source having an input terminal connected to the  $VDD_1$ , and the output terminal connected to the input terminal of the fourth inverter  $L_1$  and the second receiving terminal  $PF_1$ .

The cell balance circuit M<sub>1</sub> has one end connected to the first voltage monitor terminal PA<sub>1</sub>, and another end connected to the second voltage monitor terminal PB<sub>1</sub>. The cell balance circuit M<sub>1</sub> detects a voltage between the first voltage monitor terminal PA<sub>1</sub> and the second voltage monitor terminal PB<sub>1</sub> 20 (that is, voltage of battery BT<sub>1</sub>). When the voltage of the battery BT<sub>1</sub> is equal to or higher than a cell balance voltage, the cell balance circuit M<sub>1</sub> outputs a cell balance signal to the switch SW<sub>1</sub> through the control terminal PG<sub>1</sub>. Also, when the voltage of the battery  $BT_1$  is lower than the cell balance 25 voltage, the cell balance circuit  $M_1$  outputs a cell balance signal of low level to the switch SW<sub>1</sub> through the control terminal PG<sub>1</sub>. Here, the cell balance voltage is a voltage that is equal to or lower than the overcharge voltage in the case in which the battery BT<sub>1</sub> comes to a state close to the over- 30 charged state (voltage in the case in which voltage of battery BT<sub>1</sub> is adjusted to voltages of other batteries to start to balance). The cell balance circuit  $M_1$  has a function of stopping the operation when the overdischarge detection signal of high level is input to the cell balance circuit  $M_1$  from the overdischarge detector circuit  $G_1$ .

The first transmitting terminal  $PC_1$  is connected to a gate terminal of the first transistor  $\mathbf{10}$  and one end of the first resistive element  $\mathbf{20}$ . The second transmitting terminal  $PD_1$  is connected to a gate terminal of the second transistor  $\mathbf{11}$  and one end of the second resistive element  $\mathbf{21}$ . The first receiving terminal  $PE_1$  is connected to a first transmitting terminal  $PC_2$  of the battery state monitoring circuit  $PC_2$ . The second receiving terminal  $PC_1$  is connected to a second transmitting terminal  $PD_2$  of the battery state monitoring circuit  $PC_2$  and  $PC_3$  and  $PC_4$  is connected to a second transmitting terminal  $PD_2$  of the battery state monitoring circuit  $PC_3$ .

Also, a first receiving terminal PE<sub>2</sub> of the battery state monitoring circuit BM<sub>2</sub> is connected to a first transmitting terminal PC<sub>3</sub> of the battery state monitoring circuit BM<sub>3</sub>, and a second receiving terminal PF<sub>2</sub> of the battery state monitoring circuit BM<sub>2</sub> is connected to a second transmitting terminal 50 PD<sub>3</sub> of the battery state monitoring circuit BM<sub>3</sub>. The same is applied to the battery state monitoring circuits  $BM_3$  to  $BM_n$ , and the first receiving terminal of the battery state monitoring circuit on an upstream side (battery BT<sub>1</sub> side) is connected to the first transmitting terminal of the battery state monitoring 55 circuit on a downstream side (battery BT, side). The second receiving terminal of the battery state monitoring circuit on the upstream side is connected to the second transmitting terminal of the battery state monitoring circuit on the downstream side. A first receiving terminal PE, and a second 60 receiving terminal PF<sub>n</sub> of the battery state monitoring circuit BM<sub>n</sub> which is the most downstream side are connected to a negative terminal of the battery  $BT_n$ .

The switch  $SW_1$  is connected in parallel with the battery  $BT_1$ , and changes over between the connection and the disconnection of the two terminals (that is, positive terminal and negative terminal of battery  $BT_1$ ) according to the cell bal-

6

ance signal that is input to the switch  $SW_1$  through the control terminal  $PG_1$ . The switch  $SW_1$  is turned on, that is, changes over the two terminals to the connection state when the cell balance signal is input. The same is applied to the other switches  $SW_2$  to  $SW_n$ .

The first transistor 10 is a p-channel type MOS transistor. The first transistor 10 has the gate terminal connected to the first transmitting terminal PC<sub>1</sub> of the battery state monitoring circuit BM<sub>1</sub> and the one end of the first resistive element 20. The first transistor 10 also has a drain terminal connected to a drain terminal of the second transistor 11, and a source terminal connected to another terminal of the first resistive element 20 and the first external terminal 30. The second transistor 11 is a p-channel type MOS transistor. The second transistor 11 has the gate terminal connected to the second transmitting terminal PD<sub>1</sub> of the battery state monitoring circuit BM<sub>1</sub> and the one end of the second resistive element 21. The second transistor 11 also has the drain terminal connected to the drain terminal of the first transistor 10, and a source terminal connected to another terminal of the second resistive element 21 and the positive terminal of the battery BT<sub>1</sub>. On the other hand, the second external terminal **31** is connected to the negative terminal of the battery BT, on the most downstream side.

In the battery device configured as described above, a load or a charger is connected between the first external terminal 30 and the second external terminal 31 to conduct discharging or charging.

Subsequently, a description will be given of the operation of the battery device according to the first embodiment, which is configured as described above.

(Normal State)

First, a description will be given of a normal state, that is, a case in which all the voltages of the batteries  $BT_1$  to  $BT_n$  are lower than the overcharge voltage, and equal to or higher than the overdischarge voltage. In the normal state thus defined, the overcharge detector circuit  $A_1$  of the battery state monitoring circuit  $BM_1$  outputs the overcharge detection signal of low level to the first NOR circuit  $B_1$ .

In this situation, a first output transistor  $C_2$  of the battery state monitoring circuit  $BM_2$  is on (the reason will be described later). As a result, the input terminal of the second inverter  $E_1$  of the battery state monitoring circuit  $BM_1$  is at low level, and the output signal of low level is output from the first inverter  $D_1$  to the first NOR circuit  $B_1$ . Because, to the first NOR circuit  $B_1$ , the overcharge detection signal of low level and the output signal of low level of the first inverter  $D_1$  are input, the first NOR circuit  $B_1$  outputs the negative OR signal of high level to the gate terminal of the first output transistor  $C_1$ . As a result, because the first output transistor  $C_1$  is turned on, the first transmitting terminal  $PC_1$  becomes at low level, and the first transistor  $\mathbf{10}$  is turned on.

Now, the reason why the first output transistor  $C_2$  of the battery state monitoring circuit  $BM_2$  is on will be described below. Because the first receiving terminal  $PE_n$  of the battery state monitoring circuit  $BM_n$  on the most downstream side is connected to the negative terminal of the battery  $BT_n$ , an input terminal of a second inverter  $E_n$  is always held at low level. Accordingly, a first inverter  $D_n$  always outputs the output signal of low level to a first NOR circuit  $B_n$ , and the overcharge detection signal of low level to the first NOR circuit  $B_n$ . With the above arrangement, the first NOR circuit  $B_n$  outputs the negative OR signal of high level to a gate terminal of a first output transistor  $C_n$ , and the first output transistor  $C_n$  of the battery state monitoring circuit  $BM_n$  is turned on.

As a result, an input terminal of a second inverter  $E_{n-1}$  in the battery state monitoring circuit  $BM_{n-1}$  becomes at low level, and the output signal of low level is output to a first NOR circuit  $B_{n-1}$  from a first inverter  $D_{n-1}$ . On the other hand, since an overcharge detector circuit  $A_{n-1}$  outputs the overcharge detection signal of low level to the first NOR circuit  $B_{n-1}$ , the first NOR circuit  $B_{n-1}$  outputs the negative OR signal of high level to a gate terminal of a first output transistor  $C_{n-1}$ . As a result, the first output transistor  $C_{n-1}$  of the battery state monitoring circuit  $BM_{n-1}$  is turned on.

The above operation is repeated in the upstream side battery state monitoring circuit and the downstream side battery state monitoring circuit, and the first output transistor  $C_2$  of the battery state monitoring circuit  $BM_2$  is turned on.

Also, in the above normal state, the overdischarge detector 15 circuit G<sub>1</sub> of the battery state monitoring circuit BM<sub>1</sub> outputs the overdischarge detection signal of low level to the second NOR circuit H<sub>1</sub>. In this situation, because a second output transistor I<sub>2</sub> of the battery state monitoring circuit BM<sub>2</sub> is also on, the input terminal of the fourth inverter K<sub>1</sub> of the battery 20 state monitoring circuit BM<sub>1</sub> becomes at low level, and the output signal of low level is output to the second NOR circuit  $H_1$  from the third inverter  $J_1$ . Because, to the second NOR circuit H<sub>1</sub>, the overdischarge detection signal of low level and the output signal of low level of the third inverter  $J_1$  are input, 25 the second NOR circuit H<sub>1</sub> outputs the negative OR signal of high level to the gate terminal of the second output transistor  $I_1$ . As a result, because the second output transistor  $I_1$  is turned on, the second transmitting terminal PD<sub>1</sub> becomes at low level, and the second transistor 11 is turned on.

As described above, in the normal state, because the first transistor 10 and the second transistor 11 are turned on, the battery device is chargeable and dischargeable.

(Overcharged State)

Subsequently, a description will be given of an overcharged state, that is, a case in which a charger is connected between the first external terminal  $\mathbf{30}$  and the second external terminal  $\mathbf{31}$  to charge the batteries  $\mathrm{BT}_1$  to  $\mathrm{BT}_n$ , and at least one voltage of those batteries  $\mathrm{BT}_1$  to  $\mathrm{BT}_n$  becomes equal to or higher than the overcharge voltage. In the following description, it is assumed that the voltage of the battery  $\mathrm{BT}_2$  is equal to or higher than the overcharge voltage.

In this case, the overcharge detector circuit  $A_2$  of the battery state monitoring circuit  $BM_2$  outputs the overcharge detection signal of high level to a first NOR circuit  $B_2$ . In this 45 situation, because the output signal of low level is output from a first inverter  $D_2$ , the first NOR circuit  $B_2$  outputs the negative OR signal of low level to a gate terminal of the first output transistor  $C_2$ . As a result, the first output transistor  $C_2$  is turned off.

That is, the input terminal of the second inverter  $E_1$  is pulled up to high level by means of the first current source  $F_1$  and the output signal of high level is output to the first NOR circuit  $B_1$  from the first inverter  $D_1$ . On the other hand, because the overcharge detector circuit  $A_1$  outputs the overcharge detection signal of low level to the first NOR circuit  $B_1$ , the first NOR circuit  $B_1$  outputs the negative OR signal of low level to the gate terminal of the first output transistor  $C_1$ . As a result, the first output transistor  $C_1$  is turned off.

As described above, when the first output transistor  $C_1$  is turned off, the gate terminal of the first transistor 10 becomes at high level by means of the first resistive element 20, and the first transistor 10 is turned off. As a result, the charging from the charger is prohibited.

In the above description, it is assumed that the voltage of  $^{65}$  the battery  $BT_2$  is equal to or higher than the overcharge voltage. The same is applied to a case in which the voltages of

8

the other batteries are equal to or higher than the overcharge voltage. That is, a fact that the overcharged state occurs is communicated from the battery state monitoring circuit corresponding to the battery that has become in the overcharged state to the upstream side battery state monitoring circuit, and the communication reaches the most upstream side battery state monitoring circuit  $BM_1$ . As a result, the first transistor 10 is turned off to prohibit the charging from the charger.

(Overdischarged State)

Subsequently, a description will be given of an overdischarged state, that is, a case in which a load is connected between the first external terminal 30 and the second external terminal 31 to discharge the batteries  $BT_1$  to  $BT_n$ , and at least one voltage of those batteries  $BT_1$  to  $BT_n$  becomes lower than the overdischarge voltage. In the following description, it is assumed that the voltage of the battery  $BT_2$  is lower than the overdischarge voltage.

In this case, an overdischarge detector circuit  $G_2$  of the battery state monitoring circuit  $BM_2$  outputs the overdischarge detection signal of high level to a second NOR circuit  $H_2$ . In this situation, because the output signal of low level is output from a third inverter  $J_2$ , the second NOR circuit  $H_2$  outputs the negative OR signal of low level to a gate terminal of the second output transistor  $I_2$ . As a result, the second output transistor  $I_2$  is turned off.

That is, the input terminal of the fourth inverter  $K_1$  is pulled up to high level by means of the second current source  $L_1$ , and the output signal of high level is output to the second NOR circuit  $H_1$  from the third inverter  $J_1$ . On the other hand, because the overdischarge detector circuit  $G_1$  outputs the overdischarge detection signal of low level to the second NOR circuit  $H_1$ , the second NOR circuit  $H_1$  outputs the negative OR signal of low level to the gate terminal of the second output transistor  $I_1$ . As a result, the second output transistor  $I_1$  is turned off.

As described above, when the second output transistor  $I_1$  is turned off, the gate terminal of the second transistor 11 becomes at high level by means of the second resistive element 21, and the second transistor 11 is turned off. As a result, the discharging to the load is prohibited.

Also, in the above overdischarge state, the overdischarge detector circuit  $G_2$  that has detected the overdischarged state outputs the overdischarge detection signal of high level to the overcharge detector circuit  $A_2$  and a cell balance circuit  $M_2$ .

With the above configuration, because the overcharge detector circuit  $A_2$  and the cell balance circuit  $M_2$  stop the operation, it is possible to reduce the power consumption. Also, a first voltage monitor terminal  $PA_2$  also functions as a VDD power source terminal of the battery state monitoring circuit  $PA_2$  and the power consumption of the battery  $PA_2$  becomes low, and the power consumption of the battery state monitoring circuit  $PA_2$  is reduced as much.

In this example, when the characteristic variation occurs in the respective batteries to decrease the voltage of the battery BT<sub>2</sub> earlier than the voltages of the other batteries during discharging, the overdischarge detector circuit G<sub>2</sub> of the battery state monitoring circuit BM<sub>2</sub> outputs the overdischarge detection signal earlier than other battery state monitoring circuits. Then, the second transistor 11 is turned off to prohibit the discharging. In this situation, in the battery state monitoring circuit BM<sub>2</sub>, the power consumption is reduced more than those of the other battery state monitoring circuits. The battery BT<sub>2</sub> is lower than the other batteries in discharge speed as much as the power consumption is reduced, and the other batteries discharge electricity in the usual manner.

Therefore, since the discharge speed of the overdischarged battery BT<sub>2</sub> becomes low, the battery device is capable of conforming the voltages of the respective batteries to each other (taking cell balance).

In the above description, it is assumed that the voltage of the battery BT<sub>2</sub> is lower than the overdischarge voltage. The same is applied to a case in which the voltages of the other batteries are lower than the overdischarge voltage. That is, a fact that the overdischarged state occurs is communicated from the battery state monitoring circuit corresponding to the battery that has become in the overdischarged state to the upstream side battery state monitoring circuit, and the communication reaches the most upstream side battery state monitoring circuit BM<sub>1</sub>. As a result, the second transistor 11 is turned off to prohibit the discharging to the load.

(Cell Balance State)

Subsequently, a description will be given of a cell balance state, that is, a case in which a charger is connected between the first external terminal 30 and the second external terminal 31 to charge the batteries  $BT_1$  to  $BT_n$ , and at least one voltage of those batteries  $BT_1$  to  $BT_n$  becomes equal to or higher than the cell balance voltage. In the following description, it is assumed that the voltage of the battery  $BT_2$  is equal to or higher than the cell balance voltage.

In this case, the cell balance circuit  $M_2$  of the battery state monitoring circuit  $BM_2$  outputs the cell balance signal to the switch  $SW_2$  through a control terminal  $PG_2$ . With the above configuration, the switch  $SW_2$  is turned on, and the charged battery  $BT_2$  discharges electricity through the switch  $SW_2$ .

In this example, when the characteristic variation occurs in the respective batteries to increase the voltage of the battery BT<sub>2</sub> earlier than the voltages of the other batteries during charging, the battery state monitoring circuit BM<sub>2</sub> outputs the cell balance signal earlier than the other battery state moni- 35 toring circuits. Then, the switch SW<sub>2</sub> is turned on earlier than the other switches, and the battery BT<sub>2</sub> is different from the other batteries in change in amount of charge. For example, the battery BT<sub>2</sub> is lower in charging speed than the other batteries, and the other batteries are charged in the usual 40 manner. Alternatively, the battery BT<sub>2</sub> is discharged, and the other batteries are charged in the usual manner. As a result, since the charging speed of the overcharged battery BT<sub>2</sub> becomes low, or since the overcharged battery BT<sub>2</sub> is discharged, the battery device is capable of taking the cell bal- 45 ance.

Hereinafter, a description will be given of the reason why the discharge leak current can be prevented with the provision of the diode Do<sub>1</sub> in the battery state monitoring circuit BM<sub>1</sub> on the premise of the above operation. FIG. 2 shows the 50 circuit configuration of the battery device in which no diode Do<sub>1</sub> is provided. For example, in FIG. 2, it is assumed that the battery BT<sub>1</sub> is overdischarged during the discharging to the load, and the second transistor 11 is turned off. In this case, the first output transistor  $C_1$  of the most upstream side battery 55 state monitoring circuit BM<sub>1</sub> becomes off. However, because a parasitic diode having a cathode terminal on the drain side and an anode terminal on the source side exists between the drain terminal and the gate terminal of the first output transistor C<sub>1</sub>, a current path is formed as shown in FIG. 2. As a 60 result, the electric discharge of the batteries BT<sub>2</sub> to BT<sub>n</sub> does not stop, thereby causing the discharge leak current to occur. On the other hand, according to the battery state monitoring circuit BM<sub>1</sub> of the first embodiment, because the diode Do<sub>1</sub> of a direction opposite to the parasitic diode of the first output 65 transistor  $C_1$  is provided, it is possible to prevent the discharge leak current shown in FIG. 2 from occurring.

10

As described above, in the battery device according to the first embodiment, the occurrence of the discharge leak current can be prevented, and the disruption of the voltage balance between the batteries as in the conventional technology does not occur. As a result, it is possible to eliminate the load on the user, such as the costs and time required for battery exchange.

### Second Embodiment

Subsequently, a description will be given of a battery device according to a second embodiment. In the above first embodiment, the description is given of a case in which the n-channel type MOS transistors are used as the first output transistor and the second output transistor in the battery state monitoring circuit. In contrast, in the second embodiment, a description will be given of a battery device in the case where p-channel type MOS transistors are used as the first output transistor and the second output transistor.

FIG. 3 is a circuit configuration diagram showing the battery device according to the second embodiment. In FIG. 3, the same components as those of FIG. 1 are denoted by identical symbols, and their description will be omitted. In order to distinguish from FIG. 1, the symbols of the battery state monitoring circuits are BMA<sub>1</sub> to BMA<sub>n</sub>, the symbol of the first transistor is 12, the symbol of the second transistor is 13, the symbol of the first resistive element is 22, and the symbol of the second resistive element is 23. Also, since the circuit configurations of those battery state monitoring circuits BMA<sub>1</sub> to BMA<sub>n</sub> are identical with each other, the most downstream side battery state monitoring circuit BMA<sub>n</sub> will be representatively described below.

The battery state monitoring circuit BMA<sub>n</sub> according to the second embodiment includes the overcharge detector circuit  $A_n$ , the first NOR circuit  $B_n$ , a first inverter  $Q_n$ , a first output transistor  $R_n$ , a diode  $Do_n$ , a second inverter  $S_n$ , a first current source  $T_n$ , an overdischarge detector circuit  $G_n$ , a second NOR circuit  $H_n$ , a third inverter  $U_n$ , a second output transistor  $V_n$ , a fourth inverter  $W_n$ , a second current source  $X_n$ , a cell balance circuit  $M_n$ , a first voltage monitor terminal  $PA_n$ , a second voltage monitor terminal  $PB_n$ , a first transmitting terminal  $PC_n$ , a second transmitting terminal  $PD_n$ , a first receiving terminal  $PE_n$ , a second receiving terminal  $PF_n$ , and a control terminal  $PG_n$ . The battery state monitoring circuit  $PC_n$  and  $PC_n$  having the above components is configured as an  $PC_n$  one chip.

To the first NOR circuit  $B_n$ , an overcharge detection signal that is output from the overcharge detector circuit  $A_n$ , and an output signal of the second inverter S, are input, and the first NOR circuit B, outputs a negative OR signal of those signals to the first inverter  $Q_n$ . The first inverter  $Q_n$  outputs the logical inversion signal of the negative OR signal that is input from the first NOR circuit B, to a gate terminal of the first output transistor  $R_n$ . The first output transistor  $R_n$  is a p-channel type MOS transistor. The first output transistor  $R_n$  has the gate terminal connected to an output terminal of the first inverter Q<sub>n</sub>, a drain terminal connected to an anode terminal of the diode  $Do_n$ , and a source terminal connected to the  $VDD_n$ . The diode Do, is a discharge leak current prevention diode, and has the anode terminal connected to the drain terminal of the first output transistor  $R_n$ , and a cathode terminal connected to the first transmitting terminal  $PC_n$ .

The second inverter  $S_n$  has an input terminal connected to the first receiving terminal  $PE_n$  and an input terminal of the first current source  $T_n$ , and outputs the logical inversion signal of the input signal to the input terminal to the first NOR circuit  $B_n$ . The first current source  $T_n$  is a current source that has the input terminal connected to the first receiving terminal  $PE_n$

and the input terminal of the second inverter  $S_n$ , and an output terminal connected to the  $VSS_n$ .

To the second NOR circuit  $H_n$ , an overdischarge detection signal that is output from the overdischarge detector circuit  $G_n$  and the output signal of the fourth inverter  $W_n$  are input, and the second NOR circuit  $H_n$  outputs a negative OR signal of those signals to the third inverter  $U_n$ . The third inverter  $U_n$  outputs the logical inversion signal of the negative OR signal that is input from the second NOR circuit  $H_n$  to a gate terminal of the second output transistor  $V_n$ . The second output transistor  $V_n$  is a p-channel type MOS transistor, and has the gate terminal connected to an output terminal of the third inverter  $U_n$ , a drain terminal connected to the second transmitting terminal PD<sub>n</sub>, and a source terminal connected to the VDD<sub>n</sub>.

The fourth inverter  $W_n$  has an input terminal connected to the second receiving terminal  $PF_n$  and an input terminal of the second current source  $X_n$ , and outputs the logical inversion signal of the input signal to the input terminal to the second NOR circuit  $H_n$ . The second current source  $X_n$  is a current source that has the input terminal connected to the second receiving terminal  $PF_n$  and the input terminal of the fourth inverter  $W_n$ , and an output terminal connected to the  $VSS_n$ .

The first transmitting terminal PC<sub>n</sub> is connected to a gate terminal of the first transistor 12 and one end of the first 25 resistive element 22. The second transmitting terminal PD<sub>n</sub> is connected to a gate terminal of the second transistor 13 and one end of the second resistive element 23. The first receiving terminal PE<sub>n</sub> is connected to a first transmitting terminal PC<sub>n-1</sub> of the battery state monitoring circuit BMA<sub>n-1</sub>. The 30 second receiving terminal PD<sub>n-1</sub> of the battery state monitoring circuit BMA<sub>n-1</sub>.

The same is applied to the other battery state monitoring circuits, and the first receiving terminal of the battery state 35 monitoring circuit on the downstream side (battery  $BT_n$  side) is connected to the first transmitting terminal of the battery state monitoring circuit on the upstream side (battery  $BT_1$  side). The second receiving terminal of the battery state monitoring circuit on the downstream side is connected to the 40 second transmitting terminal of the battery state monitoring circuit on the upstream side. The first receiving terminal  $PE_1$  and the second receiving terminal  $PF_1$  of the battery state monitoring circuit  $BMA_1$  which is the most upstream side are connected to the positive terminal of the battery  $BT_1$ .

The first transistor 12 is an n-channel type MOS transistor. The first transistor 12 has the gate terminal connected to the first transmitting terminal PC, of the battery state monitoring circuit  $BM_n$  and the one end of the first resistive element 22. The first transistor **12** also has a drain terminal connected to a 50 drain terminal of the second transistor 13, and a source terminal connected to another terminal of the first resistive element 22 and the negative terminal of the battery BT<sub>n</sub>. The second transistor 13 is an n-channel type MOS transistor. The second transistor 13 has the gate terminal connected to the 55 second transmitting terminal PD, of the battery state monitoring circuit BMA, and the one end of the second resistive element 23. The second transistor 13 also has the drain terminal connected to the drain terminal of the second transistor 12, and a source terminal connected to another terminal of the 60 second resistive element 23 and the second external terminal 31. On the other hand, the first external terminal 30 is connected to the positive terminal of the battery BT<sub>1</sub> on the most upstream side.

Subsequently, a description will be given of the operation 65 of the battery device according to the second embodiment, which is configured as described above. The operation in the

12

cell balance state is identical with that in the first embodiment, and therefore its description will be omitted.

(Normal State)

First, a description will be given of a normal state, that is, a case in which the voltages of all the batteries  $BT_1$  to  $BT_n$  are lower than the overcharge voltage, and equal to or higher than the overdischarge voltage. In the normal state thus defined, the overcharge detector circuit  $A_n$  of the battery state monitoring circuit  $BMA_n$  outputs the overcharge detection signal of low level to the first NOR circuit  $B_n$ .

In this situation, a first output transistor  $R_{n-1}$  of the battery state monitoring circuit BMA<sub>n-1</sub> is on (the reason will be described later). As a result, the input terminal of the second inverter  $S_n$  of the battery state monitoring circuit BMA<sub>n</sub> becomes at high level, and the output signal of low level is output from the second inverter  $S_n$  to the first NOR circuit  $B_n$ . The first NOR circuit  $B_n$  outputs the negative OR signal of high level to the first inverter  $Q_n$ , and the first inverter  $Q_n$  outputs the logical inversion signal of low level to the gate terminal of the first output transistor  $R_n$ . As a result, because the first output transistor  $R_n$  is turned on, the first transmitting terminal  $PC_n$  becomes at high level, and the first transistor 12 is turned on.

Now, the reason why the first output transistor  $R_{n-1}$  of the battery state monitoring circuit  $BMA_{n-1}$  is on will be described below. Because the first receiving terminal PE<sub>1</sub> of the battery state monitoring circuit BMA<sub>1</sub> on the most upstream side is connected to the positive terminal of the battery  $BT_1$ , an input terminal of a second inverter  $S_1$  is always held at high level. Accordingly, the second inverter S<sub>1</sub> always outputs the output signal of low level to the first NOR circuit  $B_1$ , and the overcharge detector circuit  $A_1$  outputs the overcharge detection signal of low level to the first NOR circuit B<sub>1</sub>. With the above arrangement, the first NOR circuit B<sub>1</sub> outputs the negative OR signal of high level to a first inverter  $Q_1$ , and the first inverter  $Q_1$  outputs the logical inversion signal of low level to a gate terminal of a first output transistor  $R_1$ . As a result, the first output transistor  $R_1$  of the battery state monitoring circuit BMA<sub>1</sub> is turned on.

In this situation, an input terminal of a second inverter S<sub>2</sub> in the battery state monitoring circuit BMA<sub>2</sub> that is the downstream side of the battery state monitoring circuit BMA<sub>1</sub> becomes at high level, and the output signal of low level is output from the second inverter S<sub>2</sub> to the first NOR circuit B<sub>2</sub>.

Since the overcharge detector circuit A<sub>2</sub> outputs the overcharge detection signal of low level, the first NOR circuit B<sub>2</sub> outputs the negative OR signal of high level to a first inverter Q<sub>2</sub>, and the first inverter Q<sub>2</sub> outputs the logical inversion signal of low level to a gate terminal of a first output transistor R<sub>2</sub>. As a result, the first output transistor R<sub>2</sub> is turned on.

The above operation is repeated in the upstream side battery state monitoring circuit and the downstream side battery state monitoring circuit, and the first output transistor  $R_{n-1}$  of the battery state monitoring circuit BMA<sub>n-1</sub> is turned on.

Also, in the above normal state, the overdischarge detector circuit G of the battery state monitoring circuit  $BM_n$  outputs the overdischarge detection signal of low level to the second NOR circuit  $H_n$ . In this situation, because a second output transistor  $V_{n-1}$  of the battery state monitoring circuit  $BM_{n-1}$  is also on, the input terminal of the fourth inverter  $W_n$  in the battery state monitoring circuit  $BMA_n$  becomes at high level, and the output signal of low level is output to the second NOR circuit  $H_n$  from the fourth inverter  $W_n$ . The second NOR circuit  $H_n$  outputs the negative OR signal of high level to the third inverter  $U_n$ , and the third inverter  $U_n$  outputs the logical inversion signal of low level to the gate terminal of the second output transistor  $V_n$ . As a result, because the second output

transistor  $V_n$  is turned on, the second transmitting terminal  $PD_n$  becomes at high level, and the second transistor 13 is turned on.

As described above, in the normal state, because the first transistor 12 and the second transistor 13 are turned on, the 5 battery device is chargeable and dischargeable.

(Overcharged State)

Subsequently, a description will be given of an over-charged state, that is, a case in which a charger is connected between the first external terminal 30 and the second external terminal 31 to charge the batteries  $BT_1$  to  $BT_n$ , and at least one voltage of those batteries  $BT_1$  to  $BT_n$  becomes equal to or higher than the overcharge voltage. In the following description, it is assumed that the voltage of the battery  $BT_{n-1}$  is equal to or higher than the overcharge voltage.

In this case, the overcharge detector circuit  $A_{n-1}$  of the battery state monitoring circuit BMA<sub>n-1</sub> outputs the overcharge detection signal of high level to the first NOR circuit  $B_{n-1}$ . In this situation, because the output signal of low level is output from a second inverter  $S_{n-1}$ , the first NOR circuit  $B_{n-1}$  20 outputs the negative OR signal of low level to a first inverter  $Q_{n-1}$ , and the first inverter  $Q_{n-1}$  outputs the logical inversion signal of high level to a gate terminal of the first output transistor  $R_{n-1}$ . As a result, the first output transistor  $R_{n-1}$  is turned off.

That is, the input terminal of the second inverter  $S_n$  is pulled down to low level by means of the first current source  $T_n$ , and the output signal of high level is output to the first NOR circuit  $B_n$  from the second inverter  $S_n$ . On the other hand, because the overcharge detector circuit  $A_n$  outputs the overcharge detection signal of low level to the first NOR circuit  $B_n$ , the first NOR circuit  $B_n$  outputs the negative OR signal of low level to the first inverter  $Q_n$ , and the first inverter  $Q_n$  outputs the logical inversion signal of high level to the gate terminal of the first output transistor  $R_n$ . As a result, the first output transistor  $R_n$  is turned off.

As described above, when the first output transistor  $R_n$  is turned off, the gate terminal of the first transistor 12 becomes at low level by means of the first resistive element 22, and the first transistor 12 is turned off. As a result, the charging from 40 the charger is prohibited.

In the above description, it is assumed that the voltage of the battery  $BT_{n-1}$  is equal to or higher than the overcharge voltage. The same is applied to a case in which the voltages of the other batteries are equal to or higher than the overcharge 45 voltage. That is, a fact that the overcharged state occurs is communicated from the battery state monitoring circuit corresponding to the battery that has become in the overcharged state to the downstream side battery state monitoring circuit, and the communication reaches the most downstream side 50 battery state monitoring circuit  $BMA_n$ . As a result, the first transistor 12 is turned off to prohibit the charging from the charger.

(Overdischarged State)

Subsequently, a description will be given of an overdischarged state, that is, a case in which a load is connected between the first external terminal 30 and the second external terminal 31 to discharge the batteries  $BT_1$  to  $BT_n$ , and at least one voltage of those batteries  $BT_1$  to  $BT_n$  becomes lower than the overdischarge voltage. In the following description, it is assumed that the voltage of the battery  $BT_{n-1}$  is lower than the overdischarge voltage.

In this case, an overdischarge detector circuit  $G_{n-1}$  of the battery state monitoring circuit BMA<sub>n-1</sub> outputs the overdischarge detection signal of high level to a second NOR circuit 65  $H_{n-1}$ . In this situation, because the output signal of low level is output from a fourth inverter  $W_{n-1}$ , the second NOR circuit

14

$H_{n-1}$  outputs the negative OR signal of low level to a third inverter  $U_{n-1}$ , and the third inverter  $U_{n-1}$  outputs the logical inversion signal of high level to a gate terminal of the second output transistor  $V_{n-1}$ . As a result, the second output transistor  $V_{n-1}$  is turned off.

That is, the input terminal of the fourth inverter  $W_n$  is pulled down to low level by means of the second current source  $X_n$ , and the output signal of high level is output to the second NOR circuit  $H_n$  from the fourth inverter  $W_n$ . On the other hand, because the overdischarge detector circuit  $G_n$  outputs the overdischarge detection signal of low level to the second NOR circuit  $H_n$ , the second NOR circuit  $H_n$  outputs the negative OR signal of low level to the third inverter  $U_n$ , and the third inverter  $U_n$  outputs the logical inversion signal of high level to the gate terminal of the second output transistor  $V_n$ . As a result, the second output transistor  $V_n$  is turned off.

As described above, when the second output transistor  $V_n$  is turned off, the gate of the second transistor 13 becomes at low level by means of the second resistive element 23, and the second transistor 13 is turned off. As a result, the discharging to the load is prohibited.

In the above description, it is assumed that the voltage of the battery  $BT_{n-1}$  is lower than the overdischarge voltage. The same is applied to a case in which the voltages of the other batteries are lower than the overdischarge voltage. That is, a fact that the overdischarged state occurs is communicated from the battery state monitoring circuit corresponding to the battery that has become in the overdischarged state to the downstream side battery state monitoring circuit, and the communication reaches the most downstream side battery state monitoring circuit  $BMA_n$ . As a result, the second transistor 13 is turned off to prohibit the discharging to the load.

Hereinafter, a description will be given of the reason why the discharge leak current can be prevented with the provision of the diode Do, in the battery state monitoring circuit BMA, on the premise of the above operation. FIG. 4 shows the circuit configuration of the battery device in which no diode Do, is provided. For example, in FIG. 4, it is assumed that the battery BT<sub>n</sub> is overdischarged during the discharging to the load, and the second transistor 13 is turned off. In this case, the first output transistor  $R_{\mu}$  of the battery state monitoring circuit BMA, becomes off. However, because a parasitic diode having a cathode terminal on the source side and an anode terminal on the drain side exists between the drain terminal and the gate terminal of the first output transistor  $R_{n}$ , a current path is formed as shown in FIG. 4. As a result, the electric discharge of the batteries  $BT_1$  to  $BT_{n-1}$  does not stop, thereby causing the discharge leak current to occur. On the other hand, according to the battery state monitoring circuit BMA, of the second embodiment, because the diode Do, of a direction opposite to the parasitic diode of the first output transistor R, is provided, it is possible to prevent the discharge leak current shown in FIG. 4 from occurring.

As described above, in the battery device according to the second embodiment, the occurrence of the discharge leak current can be prevented as in the first embodiment, and the disruption of the voltage balance between the batteries as in the conventional technology does not occur. As a result, it is possible to eliminate the load on the user, such as the costs and time required for battery exchange.

# Third Embodiment

Subsequently, a description will be given of a battery device according to a third embodiment. FIG. 5 is a circuit configuration diagram showing the battery device according to the third embodiment. As shown in the figure, in the third

embodiment, two types of diodes are disposed in the battery state monitoring circuit of the first embodiment. That is, when it is assumed that the symbols of the battery state monitoring circuits are BMB<sub>1</sub> to BMB<sub>n</sub>, the battery state monitoring circuit BMB<sub>1</sub> is newly equipped with a first diode (first clamp diode) Da<sub>1</sub>, a second diode (second clamp diode) Db<sub>1</sub>, a third diode (third clamp diode) Dc<sub>1</sub>, and a fourth diode (fourth clamp diode) Dd<sub>1</sub> in addition to the components of the first embodiment. The same is applied to the other battery state monitoring circuits. In the following description, the battery state monitoring circuit BMB<sub>1</sub> will be representatively described.

The first diode  $Da_1$  has an anode terminal connected to the  $VSS_1$ , and a cathode terminal connected to the drain terminal of the first output transistor  $C_1$ . The first diode  $Da_1$  has such a 15 characteristic as to generate a reverse current when a reverse voltage corresponding to a voltage (for example, 4.5V) that exceeds the withstand voltage of the battery state monitoring circuit is applied between the anode terminal and the cathode terminal. The second diode  $Db_1$  has an anode terminal connected to the input terminal of the second inverter  $E_1$ . It is assumed that the voltage drop of the second diode  $Db_1$  is 0.7 V.

The third diode  $Dc_1$  has an anode terminal connected to the VSS<sub>1</sub>, and a cathode terminal connected to the drain terminal 25 of the second output transistor  $I_1$ . The third diode  $Dc_1$  has such a characteristic as to generate a reverse current when a reverse voltage corresponding to a voltage that exceeds the withstand voltage of the battery state monitoring circuit is applied between the anode terminal and the cathode terminal. 30 The fourth diode  $Dd_1$  has an anode terminal connected to the VSS<sub>1</sub>, and a cathode terminal connected to the input terminal of the fourth inverter  $K_1$ . It is assumed that the voltage drop of the fourth diode  $Dd_1$  is 0.7 V.

Also, resistive elements are connected between the first stransmitting terminal of the downstream side battery state monitoring circuit and the first receiving terminal of the upstream side battery state monitoring circuit, and between the second transmitting terminal of the downstream side battery state monitoring circuit and the second receiving termi-40 nal of the upstream side battery state monitoring circuit, respectively. Specifically, a resistive element Ra<sub>1</sub> is connected between the first transmitting terminal PC<sub>2</sub> of the battery state monitoring circuit BMB<sub>2</sub> and the first receiving terminal PE<sub>1</sub> of the battery state monitoring circuit BMB<sub>1</sub>, 45 and a resistive element Rb<sub>1</sub> is connected between the second transmitting terminal PD<sub>2</sub> of the battery state monitoring circuit BMB<sub>2</sub> and the second receiving terminal PF<sub>1</sub> of the battery state monitoring circuit BMB<sub>1</sub>, respectively.

Subsequently, a description will be given of the operation 50 of the battery device according to the third embodiment, which is configured as described above. The operation in the cell balance state is identical with that in the first embodiment, and therefore its description will be omitted.

(Normal State)

First, a description will be given of a normal state, that is, a case in which all the voltages of the batteries  $BT_1$  to  $BT_n$  are lower than the overcharge voltage, and equal to or higher than the overdischarge voltage. In the normal state thus defined, the overcharge detector circuit  $A_1$  of the battery state monitoring circuit  $BMB_1$  outputs the overcharge detection signal of low level to the first NOR circuit  $B_1$ .

In this situation, the first output transistor  $C_2$  of the battery state monitoring circuit  $BMB_2$  is on. As a result, the input terminal of the second inverter  $E_1$  of the battery state monitoring circuit  $BMB_1$  becomes at low level, and the output signal of low level is output from the first inverter  $D_1$  to the

**16**

first NOR circuit  $B_1$ . The first NOR circuit  $B_1$  outputs the negative OR signal of high level to the gate terminal of the first output transistor  $C_1$ . As a result, because the first output transistor  $C_1$  is turned on, the first transmitting terminal  $PC_1$  becomes at low level, and the first transistor  $\mathbf{10}$  is turned on.

In this situation, when the first output transistor  $C_2$  of the battery state monitoring circuit BMB<sub>2</sub> is on, the first receiving terminal PE<sub>1</sub> of the battery state monitoring circuit BMB<sub>1</sub> is connected to the VSS<sub>2</sub> through the resistive element Ra<sub>1</sub>. However, since the first receiving terminal PE<sub>1</sub> is equipped with the second diode Db<sub>1</sub>, the voltage is clamped to VSS<sub>1</sub>–0.7 V, and does not decrease lower than that value.

Also, in the above normal state, the overdischarge detector circuit  $G_1$  of the battery state monitoring circuit  $BMB_1$  outputs the overdischarge detection signal of low level to the second NOR circuit  $H_1$ . In this situation, the second output transistor  $I_2$  of the battery state monitoring circuit  $BMB_2$  is also on. Therefore, the input terminal of the fourth inverter  $K_1$  in the battery state monitoring circuit  $BMB_1$  becomes at low level, and the output signal of low level is output to the second NOR circuit  $H_1$  from the third inverter  $I_1$ . The second NOR circuit  $I_1$  outputs the negative OR signal of high level to the gate terminal of the second output transistor  $I_1$ . As a result, because the second output transistor  $I_1$  is turned on, the second transmitting terminal  $I_1$  becomes at low level, and the second transistor  $I_1$  is turned on.

Similarly, the voltage of the second receiving terminal  $PF_1$  of the battery state monitoring circuit  $BMB_1$  is clamped to  $VSS_1$ –0.7 V.

As described above, in the normal state, because the first transistor 10 and the second transistor 11 are turned on, the battery device is chargeable and dischargeable.

(Overcharged State)

Subsequently, a description will be given of an overansmitting terminal of the downstream side battery state onitoring circuit and the first receiving terminal of the ostream side battery state monitoring circuit, and between the second transmitting terminal of the downstream side battery state monitoring circuit, and between the first external terminal  $\bf 30$  and the second external terminal  $\bf 31$  to charge the batteries  $\bf BT_1$  to  $\bf BT_n$ , and at least one voltage of those batteries  $\bf BT_1$  to  $\bf BT_n$  becomes equal to or higher than the overcharge voltage. In the following description, it is assumed that the voltage of the battery  $\bf BT_2$  is equal to or higher than the overcharge voltage.

In this case, the overcharge detector circuit  $A_2$  of the battery state monitoring circuit BMB<sub>2</sub> outputs the overcharge detection signal of high level to the first NOR circuit B<sub>2</sub>. In this situation, because the output signal of low level is output from the first inverter D<sub>2</sub>, the first NOR circuit B<sub>2</sub> outputs the negative OR signal of low level to the gate terminal of the first output transistor C<sub>2</sub>. As a result, the first output transistor C<sub>2</sub> is turned off.

That is, the input terminal of the second inverter  $E_1$  is pulled up to high level by means of the first current source  $F_1$ . As a result, a voltage recognized as high level is applied to the input terminal of the second inverter  $E_1$ , and the output signal of high level is output to the first NOR circuit  $B_1$  from the first inverter  $D_1$ . On the other hand, because the overcharge detector circuit  $A_1$  outputs the overcharge detection signal of low level to the first NOR circuit  $B_1$ , the first NOR circuit  $B_1$  outputs the negative OR signal of low level to the gate terminal of the first output transistor  $C_1$ . As a result, the first output transistor  $C_1$  is turned off.

In this situation, the first transmitting terminal PC<sub>2</sub> of the battery state monitoring circuit BMB<sub>2</sub> is pulled up to VDD<sub>1</sub> through the resistive element Ra<sub>1</sub>. However, since the first transmitting terminal PC<sub>2</sub> is equipped with a first diode Da<sub>2</sub>, the terminal voltage is clamped to VSS<sub>2</sub>+4.5 V by a voltage (4.5 V) that causes the reverse current of the first diode Da<sub>2</sub> to be generated. Also, the resistance of the resistive element Ra<sub>1</sub>

is set to a value that allows the voltage of the input terminal of the second inverter  $E_1$  to be pulled up to high level by the first current source  $F_1$ .

As described above, when the first output transistor  $C_1$  is turned off, the gate terminal of the first transistor 10 becomes at high level by means of the first resistive element 20, and the first transistor 10 is turned off. As a result, the charging from the charger is prohibited.

(Overdischarged State)

Subsequently, a description will be given of an overdischarged state, that is, a case in which a load is connected between the first external terminal 30 and the second external terminal 31 to discharge the batteries  $BT_1$  to  $BT_n$ , and at least one voltage of those batteries  $BT_1$  to  $BT_n$  becomes lower than the overdischarge voltage. In the following description, it is assumed that the voltage of the battery  $BT_2$  is lower than the overdischarge voltage.

In this case, the overdischarge detector circuit  $G_2$  of the battery state monitoring circuit  $BMB_2$  outputs the overdischarge detection signal of high level to the second NOR 20 circuit  $H_2$ . In this situation, because the output signal of low level is output from the third inverter  $J_2$ , the second NOR circuit  $H_2$  outputs the negative OR signal of low level to the gate terminal of the second output transistor  $I_2$ . As a result, the second output transistor  $I_2$  is turned off.

That is, the input terminal of the fourth inverter  $K_1$  is pulled up to high level by means of the second current source  $L_1$ . As a result, a voltage is recognized as high level is applied to the input terminal of the fourth inverter  $K_1$ , and the output signal of high level is output to the second NOR circuit  $H_1$  from the 30 third inverter  $J_1$ . On the other hand, because the overdischarge detector circuit  $G_1$  outputs the overdischarge detection signal of low level to the second NOR circuit  $H_1$ , the second NOR circuit  $H_1$  outputs the negative OR signal of low level to the gate terminal of the second output transistor  $I_1$ . As a result, the 35 second output transistor  $I_1$  is turned off.

In this situation, the second transmitting terminal  $PD_2$  of the battery state monitoring circuit  $BMB_2$  is pulled up to  $VDD_1$  through the resistive element  $Rb_1$ . However, since the second transmitting terminal  $PD_2$  is equipped with a third 40 diode  $Dc_2$ , the terminal voltage is clamped to  $VSS_2+4.5 V$  by a voltage (4.5 V) that causes the reverse current of the third diode  $Dc_2$  to be generated. Also, the resistance of the resistive element  $Rb_1$  is set to a value that allows the voltage of the input terminal of the fourth inverter  $K_1$  to be pulled up to high 45 level by the second current source  $L_1$ .

As described above, when the second output transistor  $I_1$  is turned off, the gate terminal of the second transistor 11 becomes at high level, and the second transistor 11 is turned off. As a result, the discharging to the load is prohibited.

In the first embodiment, in the battery state monitoring circuit that has detected the overcharged state or the overdischarged state, the first output transistor or the second output transistor are turned off, and a voltage for two cells (two batteries) is applied to the downstream side first output tran- 5 sistor or second output transistor which has been turned off by the pull-up operation in the upstream side battery state monitoring circuit. That is, the withstand voltage of one battery state monitoring circuit needs to be equal to or higher than the voltage for at least two cells. In contrast, in the third embodiment, in the battery state monitoring circuit that has detected the overcharged state or the overdischarged state, the first output transistor or the second output transistor are turned off, and a voltage for one cell (one battery) is applied to the downstream side first output transistor or second output tran- 65 sistor which has been turned off by the pull-up operation in the upstream side battery state monitoring circuit. That is, the

18

withstand voltage of one battery state monitoring circuit needs to be equal to or higher than the voltage for at least one cell. As a result, according to the third embodiment, the battery state monitoring circuit that is lower in withstand voltage than that of the first embodiment can be fabricated, and a range of the available manufacturing process is further broadened. As in the first embodiment, the occurrence of the discharge leak current can be prevented, and the disruption of the voltage balance between the batteries as in the conventional technology does not occur. As a result, it is possible to eliminate the load on the user such as the costs and time required for battery exchange.

### Fourth Embodiment

Subsequently, a description will be given of a battery device according to a fourth embodiment. FIG. **6** is a circuit configuration diagram showing the battery device according to the fourth embodiment. As shown in the figure, in the fourth embodiment, two types of diodes are disposed in the battery state monitoring circuit of the second embodiment. That is, when it is assumed that the symbols of the battery state monitoring circuits are BMC<sub>1</sub> to BMC<sub>n</sub>, the battery state monitoring circuit BMC<sub>n</sub> is newly equipped with a first diode De<sub>n</sub>, a second diode Df<sub>n</sub>, a third diode Dg<sub>n</sub>, and a fourth diode Dh<sub>n</sub> in addition to the components of the second embodiment. The same is applied to the other battery state monitoring circuits. In the following description, the battery state monitoring circuit BMC<sub>n</sub> will be representatively described.

The first diode  $De_n$  has an anode terminal connected to the drain terminal of the first output transistor  $R_n$ , and a cathode terminal connected to the  $VDD_n$ . The first diode  $De_n$  has such a characteristic as to generate a reverse current when a reverse voltage corresponding to a voltage (for example, 4.5 V) that exceeds the withstand voltage of the battery state monitoring circuit is applied between the anode terminal and the cathode terminal. The second diode  $Df_n$  has an anode terminal connected to the input terminal of the second inverter  $S_n$ , and a cathode terminal connected to the  $VDD_n$ . It is assumed that the voltage drop of the second diode  $Df_n$  is 0.7 V.

The third diode Dg<sub>n</sub> has an anode terminal connected to the drain terminal of the second output transistor V<sub>n</sub>, and a cathode terminal connected to the VDD<sub>n</sub>. The third diode Dg<sub>n</sub> has such a characteristic as to generate a reverse current when a reverse voltage corresponding to a voltage (for example, 4.5 V) that exceeds the withstand voltage of the battery state monitoring circuit is applied between the anode terminal and the cathode terminal. The fourth diode Dh<sub>n</sub> has an anode terminal connected to the input terminal of the fourth inverter W<sub>n</sub>, and a cathode terminal connected to the VDD<sub>n</sub>. It is assumed that the voltage drop of the fourth diode Dh<sub>n</sub> is 0.7 V.

Also, resistive elements are connected between the first transmitting terminal of the upstream side battery state monitoring circuit and the first receiving terminal of the downstream side battery state monitoring circuit, and between the second transmitting terminal of the upstream side battery state monitoring circuit and the second receiving terminal of the downstream side battery state monitoring circuit, respectively. Specifically, a resistive element  $Ra_{n-1}$  is connected between the first transmitting terminal  $PC_{n-1}$  of the battery state monitoring circuit  $PC_{n-1}$  and the first receiving terminal  $PC_{n-1}$  of the battery state monitoring circuit  $PC_{n-1}$  of the battery state monitoring circu

Subsequently, a description will be given of the operation of the battery device according to the fourth embodiment, which is configured as described above. The operation in the cell balance state is identical with that in the first embodiment, and therefore its description will be omitted.

(Normal State)

First, a description will be given of a normal state, that is, a case in which all the voltages of the batteries  $BT_1$  to  $BT_n$  are lower than the overcharge voltage, and equal to or higher than the overdischarge voltage. In the normal state thus defined, the overcharge detector circuit  $A_n$  of the battery state monitoring circuit  $BMC_n$  outputs the overcharge detection signal of low level to the first NOR circuit  $B_n$ .

In this situation, the first output transistor  $R_{n-1}$  of the battery state monitoring circuit  $BMC_{n-1}$  is on. As a result, the 15 input terminal of the second inverter  $S_n$  of the battery state monitoring circuit  $BMC_n$  becomes at high level, and the output signal of low level is output from the second inverter  $S_n$  to the first NOR circuit  $B_n$ . The first NOR circuit  $B_n$  outputs the negative OR signal of high level to the first inverter  $Q_n$ , and 20 the first inverter  $Q_n$  outputs the logical inversion signal of low level to the gate terminal of the first output transistor  $R_n$ . As a result, because the first output transistor  $R_n$  is turned on, the first transmitting terminal  $PC_n$  becomes at high level, and the first transistor 12 is turned on.