#### US008034717B2

## (12) United States Patent

Futase et al.

## (54) MASS PRODUCTION METHOD OF SEMICONDUCTOR INTEGRATED CIRCUIT DEVICE AND MANUFACTURING METHOD OF ELECTRONIC DEVICE

(75) Inventors: **Takuya Futase**, Fussa (JP); **Tomonori Saeki**, Yokohama (JP); **Mieko Kashi**,

Yokohama (JP)

(73) Assignees: Renesas Electronics Corporation,

Kawasaki-shi (JP); Hitachi ULSI Co.,

Ltd., Tokyo (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 435 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 12/207,530

(22) Filed: **Sep. 10, 2008**

(65) Prior Publication Data

US 2009/0011597 A1 Jan. 8, 2009

#### Related U.S. Application Data

(63) Continuation of application No. 12/018,154, filed on Jan. 22, 2008, which is a continuation of application No. 10/795,249, filed on Mar. 9, 2004, now abandoned, which is a continuation of application No. 10/424,854, filed on Apr. 29, 2003, now Pat. No. 6,737,221, which is a continuation of application No. 10/245,503, filed on Sep. 18, 2002, now Pat. No. 6,586,161, which is a continuation of application No. 09/635,569, filed on Aug. 9, 2000, now abandoned.

## (30) Foreign Application Priority Data

| Aug. 31, 1999 | (JP) | 11-245143 |

|---------------|------|-----------|

| Dec. 20, 1999 | (JP) | 11-360349 |

(51) Int. Cl. H01L 21/44 (2006.01) (10) Patent No.: US 8,034,717 B2 (45) Date of Patent: \*Oct. 11, 2011

(52) **U.S. Cl.** ...... **438/686**; 257/E21.009; 257/E21.011; 257/E21.309; 257/E21.476; 257/E27.088

## (56) References Cited

### U.S. PATENT DOCUMENTS

5,409,569 A 4/1995 Seki et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

EP 1 037 261 9/2000 (Continued)

#### OTHER PUBLICATIONS

Chemistry Handbook, Basic Version II, 4<sup>th</sup> Revised Edition, Published on Sep. 30, 1993, Edited by the Chemical Society of Japan, pp. II-464 through II-469.

(Continued)

Primary Examiner — Allan Olsen (74) Attorney, Agent, or Firm — Miles & Stockbridge P.C.

## (57) ABSTRACT

In order to prevent the contamination of wafers made of a transition metal in a semiconductor mass production process, the mass production method of a semiconductor integrated circuit device of the invention comprises the steps of depositing an Ru film on individual wafers passing through a wafer process, removing the Ru film from outer edge portions of a device side and a back side of individual wafers, on which said Ru film has been deposited, by means of an aqueous solution containing orthoperiodic acid and nitric acid, and subjecting said individual wafers, from which said Ru film has been removed, to a lithographic step, an inspection step or a thermal treating step that is in common use relation with a plurality of wafers belonging to lower layer steps (an initial element formation step and a wiring step prior to the formation of a gate insulating film).

### 9 Claims, 22 Drawing Sheets

| U.S. PATENT DOCUMENTS                   |              | FOREIGN P                  | ATENT DOCU        | MENTS                 |

|-----------------------------------------|--------------|----------------------------|-------------------|-----------------------|

| 5,636,401 A 6/1997 Yonemizu et al.      | EP           | 1 055 463                  | 11/2000           |                       |

| 5,897,379 A 4/1999 Ulrich et al.        | JP           | 62-264626                  |                   |                       |

| 5,986,286 A 11/1999 Yamazaki et al.     | JP           | 4-253332                   |                   |                       |

| 6,114,254 A 9/2000 Rolfson              | JP           | 5-3184                     |                   |                       |

| 6,136,708 A 10/2000 Aoki                | JP           | 6-318584                   |                   |                       |

| 6,162,301 A 12/2000 Zhang et al.        | JP           | 7-157832                   |                   |                       |

| 6,165,956 A 12/2000 Zhang et al.        | JP           | 07-157832                  |                   |                       |

| 6,245,678 B1 6/2001 Yamamoto et al.     | JP           | 7-224333                   | 8/1995            |                       |

| 6,287,477 B1 6/2001 Hacker et al.       | JP           | 08-078378                  | A 3/1996          |                       |

| 6,261,849 B1 7/2001 Lee                 | JP           | 9-181026                   | 7/1997            |                       |

| 6,294,027 B1 9/2001 Li et al.           | JP           | 9-246224                   | 9/1997            |                       |

| 6,303,551 B1 10/2001 Li et al.          | JP           | 10-64856                   | 3/1998            |                       |

| 6,322,598 B1 11/2001 Meuris et al.      | JP           | 10-92712                   | 4/1998            |                       |

| 6,331,475 B1 12/2001 Yamazaki et al.    | JP           | 10-312981                  | 11/1998           |                       |

| 6,361,708 B1 3/2002 Kubo et al.         | JP           | 10-313105                  | 11/1998           |                       |

| 6,387,190 B1 5/2002 Aoki et al.         | JP           | 11-154659                  | A 6/1999          |                       |

| 6,413,436 B1 7/2002 Aegerter et al.     | JP           | 11-186218                  | 7/1999            |                       |

| 6,558,478 B1 5/2003 Katakabe et al.     | JP           | 11-312657                  | 11/1999           |                       |

| 6,586,161 B2 * 7/2003 Futase et al      |              | 11-330023                  | 11/1999           |                       |

| 6,615,854 B1 9/2003 Hongo et al.        | JP           | 2000-269178                |                   |                       |

| 6,632,292 B1 * 10/2003 Aegerter et al   | 134/33 JP    | 2000-306877                | 11/2000           |                       |

| 6,635,528 B2 10/2003 Gilbert et al.     | JP           | 2000-331975                |                   |                       |

| 6,683,007 B1 1/2004 Yamasaki et al.     | KR           | 1996-0030318               |                   |                       |

| 6,737,221 B2 * 5/2004 Futase et al      | 430/311 KR   | 1997-0004097               | 1/1997            |                       |

| 6,964,724 B2 11/2005 Yamasaki et al.    |              | OTHED                      | DI IDI ICATIO     | NIC                   |

| 7,399,713 B2 * 7/2008 Aegerter et al    | 438/745      | OTHER                      | L PUBLICATIO      | IN S                  |

| 2001/0029104 A1 10/2001 Aoki            | PO111        | baix, Marcel, Atlas of     | Flectrochemical   | Fauilibria in Aaugous |

| 2003/0017419 A1* 1/2003 Futase et al    | 730/311      |                            |                   | -                     |

| 2003/0207214 A1* 11/2003 Futase et al   |              | tions, Chapter IV, Section | · <b>-</b> -      | ,                     |

| 2004/0023494 A1* 2/2004 Aegerter et al  |              | berg et al., "A Method f   | -                 |                       |

| 2004/0035448 A1* 2/2004 Aegerter et al  |              | ı (VIII) Oxide", Z. Natı   | ,                 |                       |

| 2004/0053508 A1 3/2004 Yamasaki et al.  |              | ım Murarka, et al., "Int   | egrated Process T | Technology for Copper |

| 2004/0259300 A1* 12/2004 Futase et al   | 438/202 ICS' | ', Copper—Fundamen         | tal Mechanisms    | for Microelectronic   |

| 2005/0257889 A1 11/2005 Yamasaki et al. |              | lications, Mar. 10, 2000   |                   |                       |

| 2008/0182414 A1* 7/2008 Futase et al    |              |                            | · • •             | <u> </u>              |

\* cited by examiner

FIG. 1

FIG. 2

FIG. 3

\*\*No. 10

\*\*No. 2

\*\*No. 3

\*\*The state of the st

F/G. 9

## F/G. 10 COMMON DEVICES ELEMENT FORMING DRY ETCHING PHOTOLITHOGRAPHIC STEP STEP INSPECTING DEVICE ANNEALING WIRING STEP DEVICE WASHING STEP FOR NEW AROUND BACK MATERIAL

\* THE DIFFUSION STEP INDICATES THOSE STEPS BEFORE THE FORMATION OF A GATE W FILM, AND THE WIRING STEP INDICATES THE STEPS BEFORE THE FORMATION OF A NEW MATERIAL FILM.

F/G. 11

F/G. 12

F/G. 13

F/G. 14

F/G. 15

## ETCHING RATE OF Ru WITH DIFFERENT TYPES OF CLEANING FLUIDS (40 °C)

| CHEMICALS                                                              | MIXING RATIO | ETCHING RATE (nm/min) |

|------------------------------------------------------------------------|--------------|-----------------------|

| HCI/H2O2/H2O                                                           | 1:1:8        | < 0.1                 |

| NH3/H2O2/H2O                                                           | 1:1:8        | < 0.1                 |

| HF/H2O2/H2O                                                            | 1:1:8        | < 0.1                 |

| HCI/HF/H2O2/H2O                                                        | 1:1:1:7      | < 0.1                 |

| HF/HNO3                                                                | 1:9          | < 0.1                 |

| HCI/HNO3                                                               | 3:1          | < 0.1                 |

| H <sub>2</sub> SO <sub>4</sub> /H <sub>2</sub> O <sub>2</sub> (120 °C) | <b>—</b>     | < 0.1                 |

| OXYGEN AERATED HCI                                                     |              | < 0.1                 |

| O3 AERATED H2SO4 (90°C)                                                |              | < 0.1                 |

| O3 AERATED TMAH (90 °C)                                                |              | < 0.1                 |

| O3 AERATED HCI (90°C)                                                  |              | < 0.1                 |

F/G. 16

|                       |                                              | ACIDITY                                         |                       |

|-----------------------|----------------------------------------------|-------------------------------------------------|-----------------------|

| OXIDIZING AGENT       | OXIDATION-REDUCTION<br>POTENTIAL (pH=0) (V)  | CONCENTRATION OF OXIDIZING<br>AGENT (mol/LITER) | ETCHING RATE (nm/min) |

| PEROXODISULFATE       | 1.96                                         | 1.0                                             | <0.1                  |

| HYDROGEN PEROXIDE     | 1.76                                         | 4.4                                             | <0.1                  |

| SODIUM HYPOCHLORITE   | 1.72                                         | 0.8                                             | < 0.1                 |

| SODIUM META-PERIODATE | 1.65                                         | 0.003                                           | < 0.1                 |

| ORTHO-PERIODIC ACID   | 1.6                                          | 0.1                                             | 13.7                  |

| CHLORIC ACID          | 1.45                                         | 0.7                                             | <0.1                  |

| IODINE                | 0.54                                         | 0.2                                             | <0.1                  |

|                       |                                              | ALKALINITY                                      |                       |

| OXIDIZING AGENT       | OXIDATION-REDUCTION<br>POTENTIAL (PH=14) (V) | CONCENTRATION OF OXIDIZING AGENT (mol/LITER)    | ETCHING RATE (nm/min) |

| PEROXODISULFATE       | 1.96                                         | 9.0                                             | <0.1                  |

| HYDROGEN PEROXIDE     | 0.94                                         | 1.0                                             | <0.1                  |

| SODIUM HYPOCHLORITE   | 0.89                                         | 0.8                                             | 82.4                  |

| SODIUM META-PERIODATE | 0.82                                         | 0.8                                             | 7.5                   |

| ORTHO-PERIODIC ACID   | 1.19                                         | 0.8                                             | 4.8                   |

| CHLORIC ACID          | 0.62                                         |                                                 |                       |

| IODINE                | 0.54                                         | 0.2                                             | <0.1                  |

|                       |                                              |                                                 |                       |

POTENTIAL NECESSARY FOR THE OXIDATION OF RU E=1.13V (pH=0) E=0.30V (pH=14)

F/G. 17

| 50%H5IO6:H2O | H51O6 (wt%) | RATE (nm/min) |

|--------------|-------------|---------------|

| 1:0          | 50.0        | 64.6          |

| 2:1          | 38.1        | 32.3          |

| 1:1          | 30.8        | 20.4          |

| 1:2          | 22.2        | 7.1           |

| 1:6          | 10.5        |               |

F/G. 18

| HNO3 (mol/l) | RATE (nm/min) |

|--------------|---------------|

| 0            | 64.6          |

| 1.0E-6       | 64.6          |

| 1.0E-4       | 62.7          |

| 1.0E-2       | 79.1          |

| 1.0          | 120.5         |

| 2.0          | 148.5         |

## F/G. 19(a)

Oct. 11, 2011

## 50wt%H5lO6

| HNO <sub>3</sub> | H5lO6           | RATE (nm/min) |

|------------------|-----------------|---------------|

| 0                | 10              | 64.6          |

| 1                | 10              | 137.3         |

| 2                | 10              | 155.1         |

| 5                | <sup>-</sup> 10 | 113.8         |

| 10               | 10              | 71.4          |

## F/G. 19(c)

## 30wt%H5lO6

| HNO3 | H5IO6 | RATE (nm/min) |

|------|-------|---------------|

| 0    | 10    | 21.6          |

| 1    | 10    | 42.9          |

| 2    | 10    | 77            |

| 5    | 10    | 92.3          |

| 10   | 10    | 82.2          |

## FIG. 19(b)

## 40wt%H5IO6

| HNO <sub>3</sub> | H51O6 | RATE (nm/min) |

|------------------|-------|---------------|

| 0                | 10    | 40            |

| 1                | 10    | 130.4         |

| 2                | 10    | 136.4         |

| 5                | 10    | 109.1         |

| 10               | 10    | 85.7          |

# F/G. 19(d)

## 20wt%H5lO6

| HNO | H51O6 | RATE (nm/min) |

|-----|-------|---------------|

| 0   | 10    | 9.7           |

| 1   | 10    | 35.5          |

| 2   | 10    | 40            |

| 5   | 10    | 50.4          |

| 10  | 10    | 45.5          |

FIG. 20

FIG. 21

| ACID             | RATE (nm/min) | MAKER                                   |

|------------------|---------------|-----------------------------------------|

| NOT ADDED        | 64.6          |                                         |

| HNO <sub>3</sub> | 155.1         | 69.5% (EL) @SUMITOMO CHEMICAL CO., LTD. |

| CH3COOH          | 138.1         | 98% (EL) @KANTO CHEMICAL CO., INC.      |

| HCI              | NG            | 36% (EL) @KANTO CHEMICAL CO., INC.      |

| H2O2             | NG            | 30% (EL) @KANTO CHEMICAL CO., INC.      |

THE RATE INCREASES BY ADDITION OF NITRIC ACID OR ACETIC ACID, AND DECREASES BY ADDITION OF SULFURIC ACID. HYDROCHLORIC ACID IS NOT GOOD BECAUSE OF THE GENERATION OF CHLORINE, AND HYDROGEN PEROXIDE IS NOT GOOD BECAUSE OF THE PRECIPITATION OF IODINE.

FIG. 22

F/G. 23

F/G. 24

F/G. 25

F/G. 26

F/G. 27

FIG. 28

# FIG. 29(a)

# F/G. 29(b)

F/G. 30

Oct. 11, 2011

## MASS PRODUCTION METHOD OF SEMICONDUCTOR INTEGRATED CIRCUIT DEVICE AND MANUFACTURING METHOD OF ELECTRONIC DEVICE

## CROSS-REFERENCE TO RELATED APPLICATION

This application is a continuation of application Ser. No. 12/018,154 filed Jan. 22, 2008, which is a continuation of application Ser. No. 10/795,249 filed Mar. 9, 2004 (abandoned), which is a continuation of application Ser. No. 10/424,854 filed Apr. 29, 2003 (now U.S. Pat. No. 6,737,221), which is a continuation of application Ser. No. 10/245,503 filed Sep. 18, 2002 (now U.S. Pat. No. 6,586,161), which is a continuation of application Ser. No. 09/635,569 filed Aug. 9, 2000 (abandoned).

### BACKGROUND OF THE INVENTION

This invention relates to a mass production technique of a semiconductor integrated circuit device, and more particularly, to a technique effectively applicable to a semiconductor production process, in which when a large number of wafers are continuously processed over a plurality of steps, the process is carried out in a mass production line wherein the lithographic step of wafers on which a film containing a transition metal such as ruthenium (Ru) is deposited and the lithographic step of wafers belonging to other steps are commonly used.

In the industrial fields other than that of the manufacture of a semiconductor, there is known a technique wherein a platinum group element is dissolved in a dissolution solution and isolated for the purpose of collecting the platinum group element from wastes or the like.

Japanese Laid-Open Patent Publication No. Hei 7-157832 (Ito et al.) discloses a technique of recovering noble metals, such as gold, platinum group elements and the like, from used electronic parts, noble metal-containing, wasted catalysts, and a used jewelry by dissolution thereof in a dissolving solution. For the dissolution of noble metals, there is used a dissolving solution which is obtained by mixing an aqueous 40 solution of an inter-halogen compound (e.g. ClF, BrF, BrCl, ICl, ICl<sub>3</sub>, IBr or the like) and an aqueous solution of a halogenated oxoacid (iodic acid, bromic acid, chloric acid or the like) at a ratio in the range of 1:9 to 9:1. The noble metal dissolved in the solution is first separated as a halogenated 45 complex, to which a solution of a compound (e.g. sodium hydroxide, sodium borohydride, hydrazine or its salt, sulfurous acid or its salt, a bisulfite or the like) is then added, thereby collecting the metal.

Japanese Laid-open Patent Application No. Hei 7-224333 50 (Wada et al) discloses a technique of dissolving out, in the form of an aqueous solution, an alloy formed by nuclear fission and containing noble metals, such as ruthenium (Ru), rhodium (Rh), palladium (Pd) without undergoing such a pretreatment as by liquid metal extraction by immersing the 55 alloy in a dissolving solution of hydroiodic acid (or hydrobromic acid), to which an iodine simple element is added. It is stated that the dissolving solution has a concentration of hydroiodic acid (or hydrobromic acid) ranging from 5 to 57 wt %, and a concentration of the added iodine simple element ranging from 0.01 to 0.5 moles per liter of the former aqueous solution.

## SUMMARY OF THE INVENTION

In order to ensure an accumulated charge quantity of finely divided memory cells, a great capacitance DRAM (Dynamic

2

Random Access Memory) of 1 Gbit or over has a capacitance insulating film of an information storage capacitor constituted of a high dielectric material such as an ABO<sub>3</sub>-type composite oxide having a specific inductive capacity of 100 or over, i.e. a perovskite composite oxide of BST (Ba, Sr) TiO<sub>3</sub>). For use as a capacitance insulating film material of the next generation, studies have been made on ferrodielectric materials having a perovskite crystal structure such as of PZT (PbZr<sub>x</sub>Ti<sub>1-x</sub>O<sub>3</sub>), PLT (PbLa<sub>x</sub>Ti<sub>1-x</sub>O<sub>3</sub>) PLZT, SBT, PbTiO<sub>3</sub>, SrTiO<sub>3</sub> and BaTiO<sub>3</sub>.

Where such a high/ferrodielectric material is used for the capacitance insulating film of a capacitor, it is necessary that conductive films for upper and lower electrodes sandwiching the capacitance insulating film therebetween should be each made mainly of a metal having high affinity for the high/ferrodielectric material, e.g. a platinum group metal (e.g. Ru (ruthenium), Rh (rhodium), Pd (palladium), Os (osmium), Ir (iridium) or Pt (platinum). Especially, ruthenium (Ru) is considered to be full of promise for use as an electrode material of a capacitor wherein the capacitance insulating film is constituted of such a high/ferrodielectric material because of its excellent etching controllability and film stability.

On the other hand, as a countermeasure for preventing an increase in wiring resistance caused by the scale down of a wiring width and the lowering of reliability in the field of high-speed logic LSI's, there has now been introduced copper wirings buried according to a so-called Damascene method. In the method, wiring grooves (and through-holes) are formed in an insulating film deposited on a substrate, and a copper (Cu) film having an electric resistance lower than an Al film is deposited on the insulating film including the inner surfaces of the wiring grooves (and the through-holes), followed by removal of an unnecessary copper film outside of the wiring grooves by a chemical mechanical polishing (CMP) method, the introduction of the buried copper wirings is now under study not only in the field of logic LSD, but also in the field of memories such as DRAM.

However, in order to introduce newcomer transition metals, such as the above-mentioned platinum group metals, perovskite-type high/ferrodielectrics and copper, which have never been in use in known wafer processes, and materials comprising the transition metals, into a semiconductor production process, it is essential to take a measure for preventing wafers from contamination with these transition metals. Especially, a transition metal such as copper has a great coefficient of diffusion in silicon (Si) and readily arrives at a substrate when undergoing an annealing step (thermal treatment step), with the great apprehension that it gives a serious adversely influence on device characteristics even at a very small concentration.

For instance, in the manufacturing process of general-purpose LSI's such as DRAM, a facility investment is suppressed to a minimum to reduce product costs, so that lithographic devices (such as a light exposure device and an EB exposure device), various types of inspection devices, and an annealing (thermal treating) device are commonly used in an initial element-forming step and a wiring step prior to the formation of a gate insulating film. These common devices are employed in the step of forming capacitors by use of such a newcomer material as set out hereinabove. More particularly, after transfer, from the common devices, of a wafer used for carrying out the capacitor-forming step, a fresh wafer used for carrying out the initial element-forming step or used for carrying out the wiring step is, in turn, transferred into the 65 devices. In case where the buried copper wiring formed according to the Damascene method is provided as the wiring formed as an upper layer of the capacitor, a wafer having a

copper film deposited on as an upper layer of the capacitor is transferred to the common devices for annealing (thermal treatment) after or prior to the transfer of another wafer to be subjected to other steps.

A film containing a platinum group metal, a perovskite- 5 type high/ferrodielectric material or a transition metal such as copper, which has been deposited on the device side of a wafer according to a sputtering method or a CVD method, is also deposited on the outer marginal portions (edge portions) or the back side of the wafer. In this condition, when the 10 wafer, from which the transition metal-containing film deposited on the outer edge portions or the back side of the wafer, is transferred to the common devices without removing the film to a satisfactory extent, a wafer stage, a wafer carrier, a conveyor and the like, which has come into contact with the 15 outer edge portion or the back side of the wafer, are deposited on the surface thereof with the transition metal-containing film. This results in the contamination, with the transition metal, of a wafer which will be subsequently transferred to the common devices for performing lower layers steps (such 20 as the step of forming an initial element and the wiring step prior to the formation of a gate insulating film).

Accordingly, in the mass production line for carrying out, by use of the common devices, the lithographic step for the wafer deposited thereon with a transition metal-containing 25 film as stated above and the lithographic step for the wafers belonging to other steps including the lower layers steps, it is essential to provide a cleaning step of removing the transition metal-containing film deposited on the outer edge portions and the back side of a wafer prior to the transfer of the 30 transition metal-containing film-deposited wafer.

However, a solution for dissolving, for example, ruthenium among the afore-indicated transition metals has not been found, so that an effective cleaning method therefor has not been established yet. As having set out before, several types of 35 solutions for dissolving platinum group metals have been proposed in the industrial fields other than that of the manufacture of semiconductor. However, these dissolving solutions are so low in dissolving rate of ruthenium that they cannot be used in the mass production line of semiconductor. 40

Another measure for preventing the contamination of a wafer with a transition metal is to provide an exclusive device for carrying out the lithographic step for the wafer deposited with a transition metal-containing film, separately from the common devices. Nevertheless, this is not of practical value 45 from the standpoint of reduction in production cost.

An object of the invention is to provide a technique of reliably preventing the inconvenience of a wafer being contaminated with a transition metal when the wafer is subjected to an initial element formation step and a wiring step in the semiconductor mass production line wherein an initial element formation step and a wiring step, and a lithographic device, inspection devices, an annealing (thermal treating) device and the like in a transition metal-containing film processing step are commonly used prior to the formation of a 55 gate insulating film.

This and other objects and features of the invention will become apparent from the description of the invention with reference to the accompanying drawings.

of the embodiments disclosed in the invention, typical ones are briefly described or summarized below.

The mass production of a semiconductor integrated circuit device of the invention comprises the steps of:

- (a) depositing a Ru film on individual wafers being in passage of a wafer process;

- (b) removing the Ru film from outer edge portions on a device side of the individual wafers, on which the Ru film has

4

been deposited, and a back side thereof with use of a solution containing an orthoperiodic acid; and

(c) subjecting the individual wafers, from which the Ru film has been removed, to a lithographic step, an inspection step or a thermal treating step which is in common use with plural types of wafers belonging to lower layers steps.

The summary of the invention other than the above-stated one is briefly itemized as numbered below.

- 1. A mass production method of a semiconductor integrated circuit device comprising the steps of:

- (a) depositing a platinum group metal film on a device side of a first wafer among a plurality of wafers passing through a wafer process;

- (b) removing the platinum group metal film from outer edge portions of the device side or a back side of the first wafer, on which the platinum group metal film has been deposited;

- (c) patterning, after the step (b), the platinum group metal film on the device side of the first wafer through an etchingresistant mask pattern formed in a lithographic step;

- (d) depositing a film to be processed different in type from the platinum group metal film on a device side of a second wafer among the plurality of wafers passing through the wafer process; and

- (e) patterning the film to be processed, which has been deposited on the device side of the second wafer, by the lithographic step.

- 2. A mass production method of a semiconductor integrated circuit device as recited in 1 above, characterized in that the platinum group metal film is made of a ruthenium film.

- 3. A mass production method of a semiconductor integrated circuit device as recited in 1 or 2 above, characterized in that the step of patterning the film to be processed is a lower layer step in comparison with the step of patterning the platinum group metal film.

- 4. A mass production method of a semiconductor integrated circuit device as recited in any one of 1 to 3 above, characterized in that the platinum group metal film is removed by use of a solution containing an orthoperiodic acid.

- 5. A mass production method of a semiconductor integrated circuit device as recited in any one of 1 to 4 above, characterized in that the platinum group metal film is removed by use of a solution containing an orthoperiodic acid and a second acid.

- 6. A mass production method of a semiconductor integrated circuit device as recited in 5 above, characterized in that the second acid is made of nitric acid.

- 7. A mass production method of a semiconductor integrated circuit device as recited in 6 above, characterized in that the solution has a concentration of orthoperiodic acid of 20 wt % to 40 wt %, and a concentration of nitric acid of 20 to 40 wt %.

- 8. A mass production method of a semiconductor integrated circuit device as recited in 6 above, characterized in that the solution has a concentration of orthoperiodic acid of 25 wt % to 35 wt %, and a concentration of nitric acid of 25 to 35 wt %.

- 9. A mass production method of a semiconductor integrated circuit device as recited in 5 above, characterized in that the second acid is made of acetic acid.

- 10. A mass production method of a semiconductor integrated circuit device as recited in any one of 1 to 9 above, characterized in that the platinum group metal film is removed, at least, from substantially an entire surface of the back side of the individual wafers and the outer edge portions of the device side.

- 11. A mass production method of a semiconductor integrated circuit device comprising the steps of:

- (a) depositing a transition metal-containing film on a device side of a first wafer among a plurality of wafers passing through a wafer process;

- (b) removing the transition metal-containing film from outer edge portions of the device side or a back side of the first wafer, on which the transition metal-containing film has been deposited;

- (c) patterning, after the step (b), the transition metal-containing film on the device side of the first wafer through an etching-resistant mask pattern formed in a lithographic step;

- (d) depositing a film to be processed different in type from the transition metal-containing film on a device side of a 15 second wafer among the plurality of wafers passing through the wafer process; and

- (e) patterning the film to be processed, which has been deposited on the device side of the second wafer, by the lithographic step.

- 12. A mass production method of a semiconductor integrated circuit device as recited in 11 above, characterized in that the transition metal-containing film is made of a perovskite-type high dielectric material or ferrodielectric material.

- 13. A mass production method of a semiconductor integrated circuit device as recited in 12 above, characterized in that the perovskite-type high dielectric material or ferrodielectric material is made of BST.

- 14. A mass production method of a semiconductor integrated 30 circuit device as recited in 11 above, characterized in that the perovskite-type high dielectric material or ferrodielectric material is PZT, PLT, PLZT, SBT, PbTiO<sub>3</sub>, SiTiO<sub>3</sub> or BaTiO<sub>3</sub>.

- circuit device as recited in 11 above, characterized in that the transition metal is made of copper.

- 16. A mass production method of a semiconductor integrated circuit device comprising the steps of:

- (a) depositing a Ru film on a device side of a first wafer 40 among a plurality of wafers passing through a wafer process;

- (b) removing the Ru film from outer edge portions of the device side or a back side of the first wafer, on which the Ru film has been deposited;

- (c) patterning, after the step (b), the Ru film on the device 45 side of the first wafer through an etching-resistant mask pattern formed in a lithographic step, thereby forming a capacitor electrode;

- (d) depositing a film to be processed different in type from the Ru film on a device side of a second wafer among the 50 plurality of wafers passing through the wafer process; and

- (e) patterning the film to be processed, which has been deposited on the device side of the second wafer, by the lithographic step.

- 17. A mass production method of a semiconductor integrated 55 circuit device as recited in 16 above, characterized in that the step of pattering the film to be processed is a lower layer step downstream of or in comparison with the step of patterning the Ru film.

- 18. A mass production method of a semiconductor integrated 60 circuit device as recited in 16 or 17 above, characterized in that the Ru film is removed by use of a solution containing orthoperiodic acid.

- 19. A mass production method of a semiconductor integrated circuit device as recited in 16 or 17 above, characterized in 65 that the Ru film is removed by use of a solution containing an orthoperiodic acid and a second acid.

- 20. A mass production method of a semiconductor integrated circuit device as recited in 19 above, characterized in that the second acid is made of nitric acid.

- 21. A mass production method of a semiconductor integrated circuit device as recited in 20 above, characterized in that the solution has a concentration of orthoperiodic acid of 20 wt % to 40 wt %, and a concentration of nitric acid of 20 to 40 wt %.

- 22. A mass production method of a semiconductor integrated circuit device as recited in 20 above, characterized in that the solution has a concentration of orthoperiodic acid of 25 wt % to 35 wt %, and a concentration of nitric acid of 25 to 35 wt %.

- 23. A mass production method of a semiconductor integrated circuit device comprising the steps of:

- (a) depositing a Ru film on a device side of a first wafer among a plurality of wafers passing through a wafer process;

- (b) removing the Ru film from outer edge portions of the device side or a back side of the first wafer, on which the Ru film has been deposited, by use of a solution containing orthoperiodic acid;

- (c) patterning, after the step (b), the Ru film on the device side of the first wafer through an etching-resistant mask pat-25 tern formed in a lithographic step, thereby forming a capacitor electrode of DRAM;

- (d) depositing a film to be processed different in type from the Ru film on a device side of a second wafer among the plurality of wafers passing through the wafer process; and

- (e) patterning the film to be processed, which has been deposited on the device side of the second wafer, by the lithographic step.

- 24. A mass production method of a semiconductor integrated circuit device as recited in 23 above, characterized in 15. A mass production method of a semiconductor integrated 35 that the step of pattering the film to be processed is a lower layer step downstream of or in comparison with the step of patterning the Ru film.

- 25. A mass production method of a semiconductor integrated circuit device as recited in 24 above, characterized in that the step of patterning the film to be processed is a step of forming a gate electrode or a step of forming a bit line.

- 26. A mass production method of a semiconductor integrated circuit device as recited in any one of 23 to 25 above, characterized in that the Ru film is removed by use of a solution containing orthoperiodic acid and nitric acid.

- 27. A mass production method of a semiconductor integrated circuit device as recited in 26 above, characterized in that the solution has a concentration of orthoperiodic acid of 20 wt % to 40 wt %, and a concentration of nitric acid of 20 to 40 wt %.

- 28. A mass production method of a semiconductor integrated circuit device as recited in 27 above, characterized in that the solution has a concentration of orthoperiodic acid of 25 wt % to 35 wt %, and a concentration of nitric acid of 25 to 35 wt %.

- 29. A mass production method of a semiconductor integrated circuit device comprising the steps of:

- (a) depositing a film containing a transition metal made of a perovskite-type high dielectric material or ferrodielectric material on a device side of a first wafer among a plurality of wafers passing through a wafer process;

- (b) removing the transition metal-containing film from outer edge portions of the device side or a back side of the first wafer, on which the transition metal-containing film has been deposited;

- (c) patterning, after the step (b), the transition metal-containing film on the device side of the first wafer through an

etching-resistant mask pattern formed in a lithographic step, thereby forming a capacitance insulating film of a capacitor of DRAM;

- (d) depositing a film to be processed different in type from the Transition metal-containing film on a device side of a 5 second wafer among the plurality of wafers passing through the wafer process; and

- (e) patterning the film to be processed, which has been deposited on the device side of the second wafer, by the lithographic step.

- 30. A mass production method of a semiconductor integrated circuit device as recited in 29 above, characterized in that the perovskite-type high dielectric material or ferrodielectric material is made of BST.

The general meanings of the terms used in the present 15 invention are illustrated below.

- 1. The term "CMIS integrated circuit" is intended to mean an integrated circuit made of a complementary insulation gate-type FET including, aside from general CMOS integrated circuits, devices having a gate insulating film made, 20 for example, of a dielectric material other than an oxide film such as silicon nitride or tantalum oxide.

- 2. The term "device side" means a main surface of a wafer, on which an integrated circuit pattern corresponding to a plurality of chip regions is formed by photolithography. That 25 is, "device side" is an opposite side of "back side".

- 3. The term "buried wiring" means one wherein a groove is formed in an insulating film as in single Damascene or dual Damascene, and a conductive film such as copper is buried in the groove, followed by removal of an unnecessary 30 conductive film through patterning by a wiring-forming technique.

- 4. The term "semiconductor integrated circuit water" or "semiconductor wafer" is intended to mean a silicon single crystal substrate (usually, substantially in a circular form), a sapphire substrate, a glass substrate, other insulating, anti-insulating and semiconductive substrates, and composite substrates thereof. The term "semiconductor integrated circuit device" (or "electronic device", "electronic circuit device" and the like) means not only a device formed on a single crystal silicon substrate, but also those devices formed on various types of above-mentioned substrates, or other types of substrates including an SOI (silicon on insulator) substrate, a TFT (thin film transistor) liquid crystal-manufacturing substrate, an STN (super 45 twisted nematic) liquid crystal-manufacturing substrate and the like unless otherwise indicated.

- 5. The term "chip-forming portion" means a portion including a plurality of chip regions on the device side of a wafer, indicating an inner region except "an outer edge portion" 50 where it is not intended to make a peripheral chip".

- 6. The term "high dielectric material" means a high dielectric material having a specific inductive capacity of 20 or over, such as Ta<sub>2</sub>O<sub>5</sub>, and a high dielectric material having a specific inductive capacity exceeding 100, such as BST 55 ((Ba, Sr)TiO<sub>3</sub>).

- 7. The term "ferrodielectric material" means PZT, PLT, PLZT, SBT, PbTiO<sub>3</sub>, SrTiO<sub>3</sub> and BaTiO<sub>3</sub>, which, respectively, have a perovskite structure in a ferrodielectric phase at normal temperatures.

- 8. The term "transition metal" generally means elements of group 3, to which yttrium, lanthanum and the like belong, to group 11, to which copper and the like belongs, of the periodic table. The term "transition metal-containing film" means a film which comprises a material containing a 65 transition metal, or a transition metal as a major or minor proportion of an constituent element (e.g. Ru, RuO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>

8

- and the like). The term "transition metal-containing film deposition treatment' means a treatment wherein the above-mentioned transition metal-containing film is attached to or deposited purposely or unintentionally. Accordingly, the treatment includes, aside from the step of depositing an insulating film or a metal film, an etching step. In the practice of the invention, the term "harmful transition metal" means one which is not adequately evidenced with respect to the nature as a contaminant among transition metals employed in a semiconductor process and is selected, for example, from platinum and copper group elements. Moreover, the term "made of copper" used herein is not limited to pure copper alone, but includes copper containing other constituent element, additive, impurity and the like in amounts not impeding the function thereof unless otherwise indicated.

- 9. The term "platinum group element" generally means ruthenium, rhodium, palladium, osmium, iridium and platinum among the elements generally belonging to the groups 8 to 10 of the periodic table.

- 10. The term "lower layers steps" used in a wafer process means a group of a series of steps including the step of formation of a film to be processed, the step of formation of a resist, the steps of exposure, development and patterning of the film, and the like precedent to an intended step when attention is paid to one wafer. For instance, lower wiring steps are a lower layer process or step in comparison with upper wiring steps. The reverse is called "upper layer steps". It will be noted that these definitions do not always mean a physical upstream or downstream relationship.

- 11. The term "lithographic step" means that with the case of light exposure, for example, the step covers from the step of coating a photoresist onto a wafer after the step of formation of a given film to the step of exposing the photoresist to light and developing the exposed photoresist (including the baking step, if necessary). The common use relation in the lithographic step means the relation where wafers belonging to different steps pass through a lithographic step made of the same arrangement. In this case, the same arrangement does not include all devices in common use. One of devices, e.g. an exposure device (e.g. a light exposure device, an EB exposure device or the like), may be in common use.

- 12. The term "mass production" in a wafer line generally means a throughput of approximately 1000 wafers/day. In the practice of the invention, taking the tendency toward a large-sized wafer into account, a throughput of approximately 100 wafers/day is included for the mass production. In this case, it is as a matter of course that the same type of wafer is used for the purpose.

- 13. The term "chemical mechanical polishing (CMP)" generally means one wherein while a surface to be polished is in contact with a polishing pad made of a relatively soft cloth-like sheet material under which a slurry is supplied, they are relatively moved along the surface. Beside, CML (chemical mechanical lapping), in which a surface to be polished is moved relative to the surface of a hard grind stone, may be included in the practice of the invention.

### BRIEF DESCRIPTION OF THE DRAWINGS

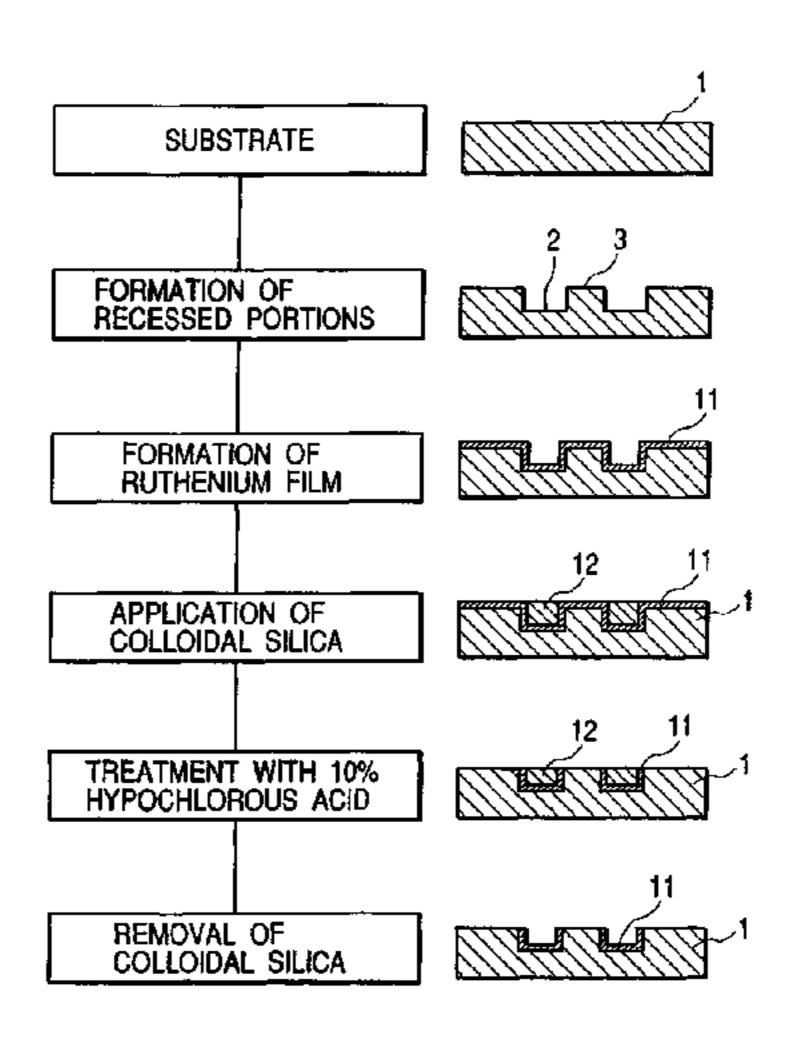

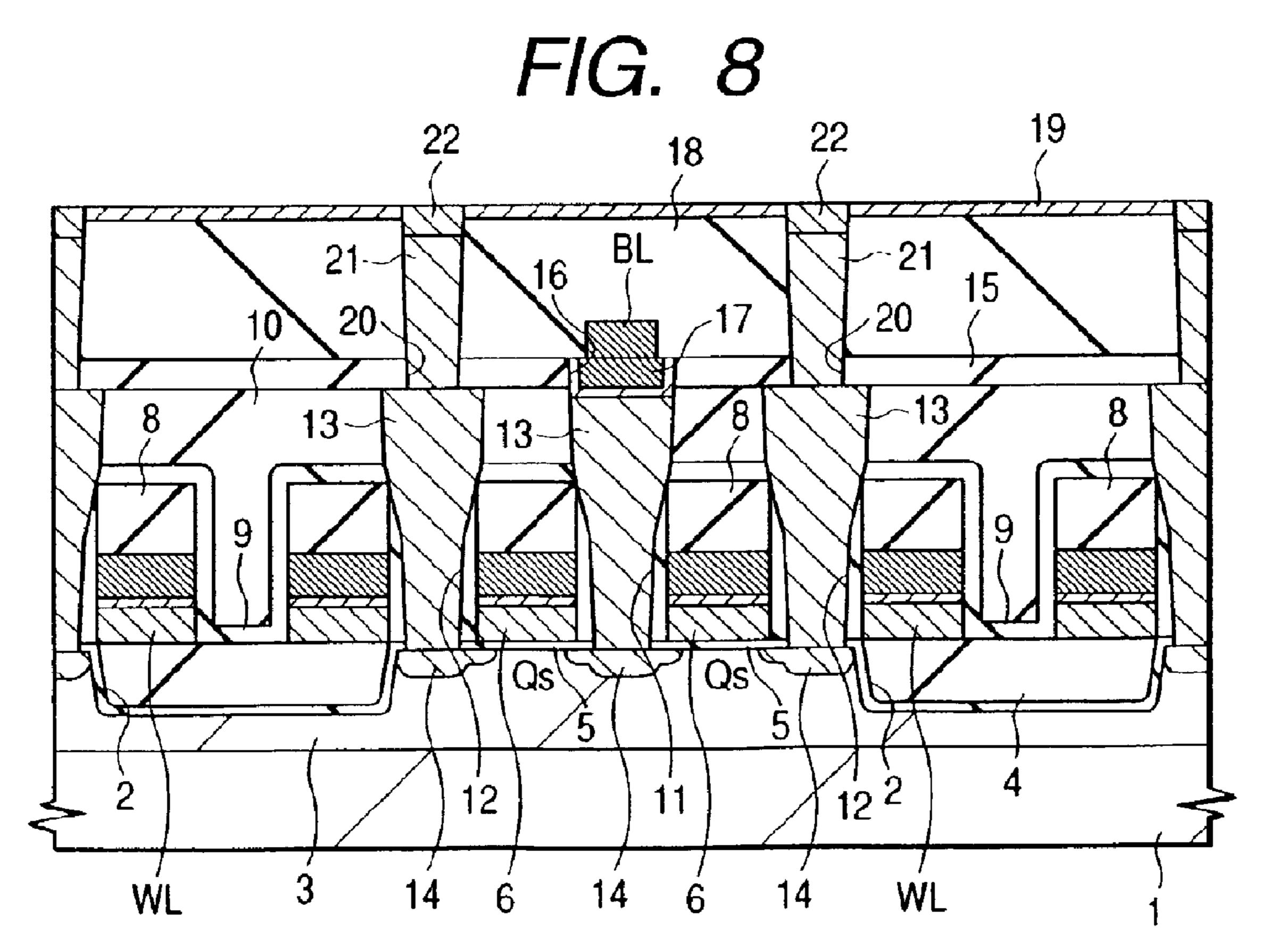

FIG. 1 is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to one embodiment of the invention;

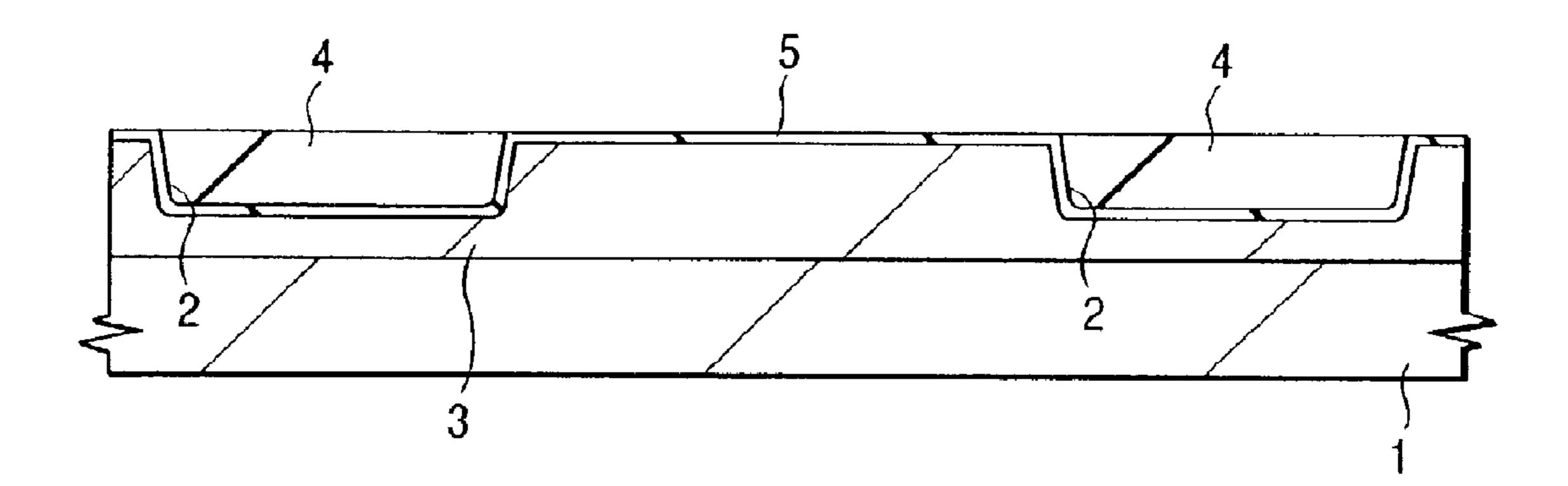

- FIG. 2 is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one embodiment of the invention;

- FIG. 3 is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one embodiment of the invention;

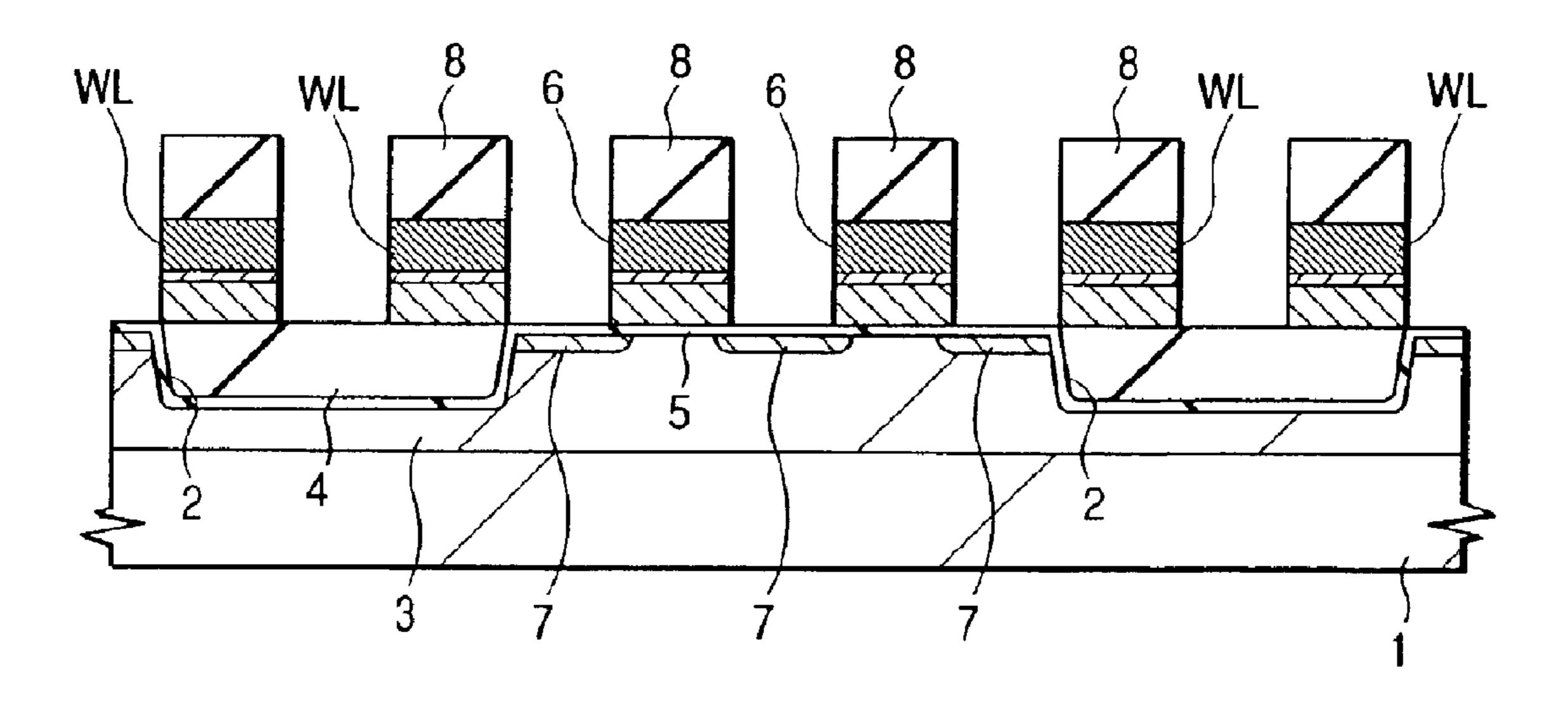

- FIG. 4 is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one embodiment of the invention;

- FIG. **5** is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one embodiment of the invention;

- FIG. **6** is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one 20 embodiment of the invention;

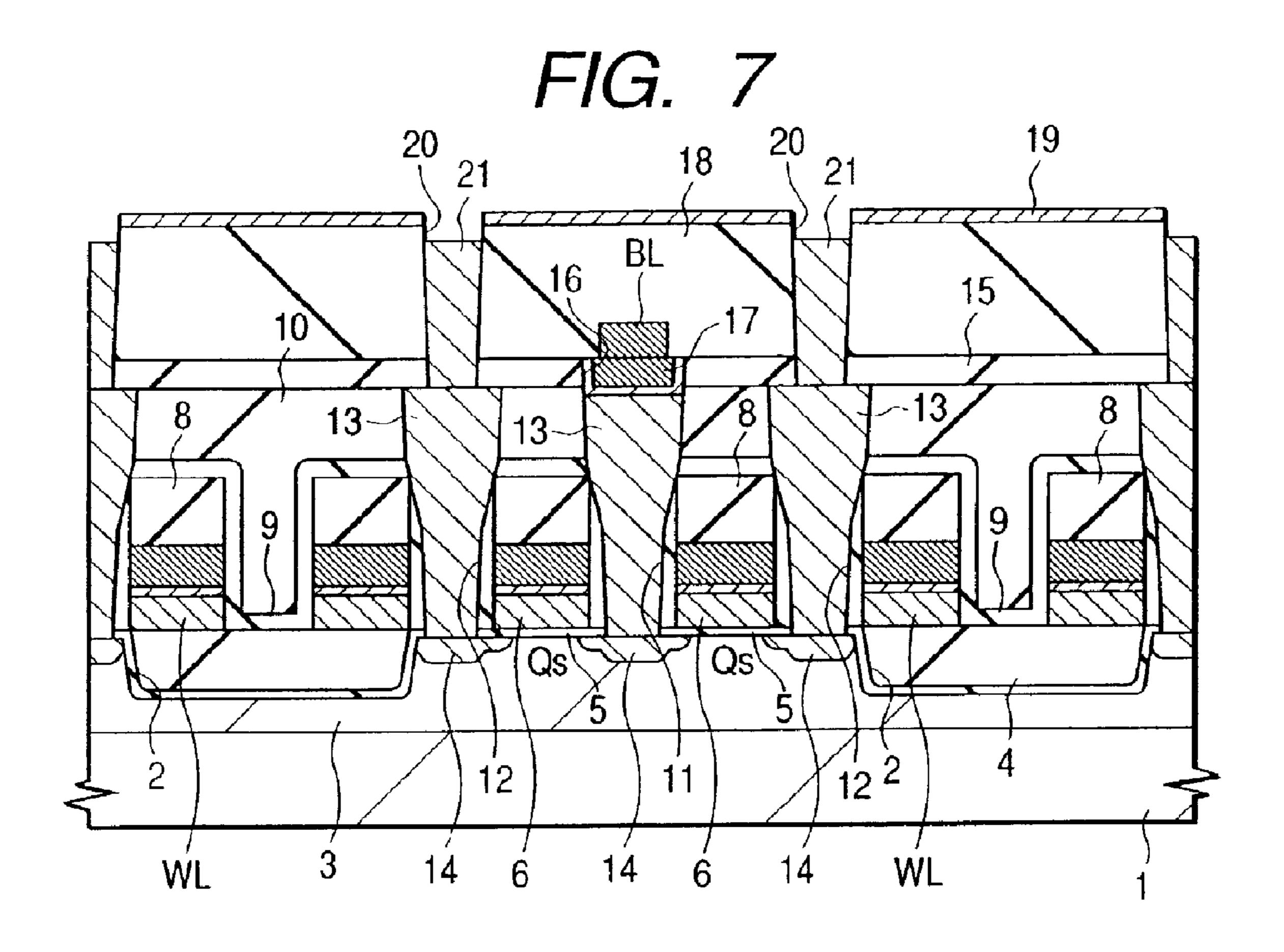

- FIG. 7 is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one embodiment of the invention;

- FIG. 8 is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one embodiment of the invention;

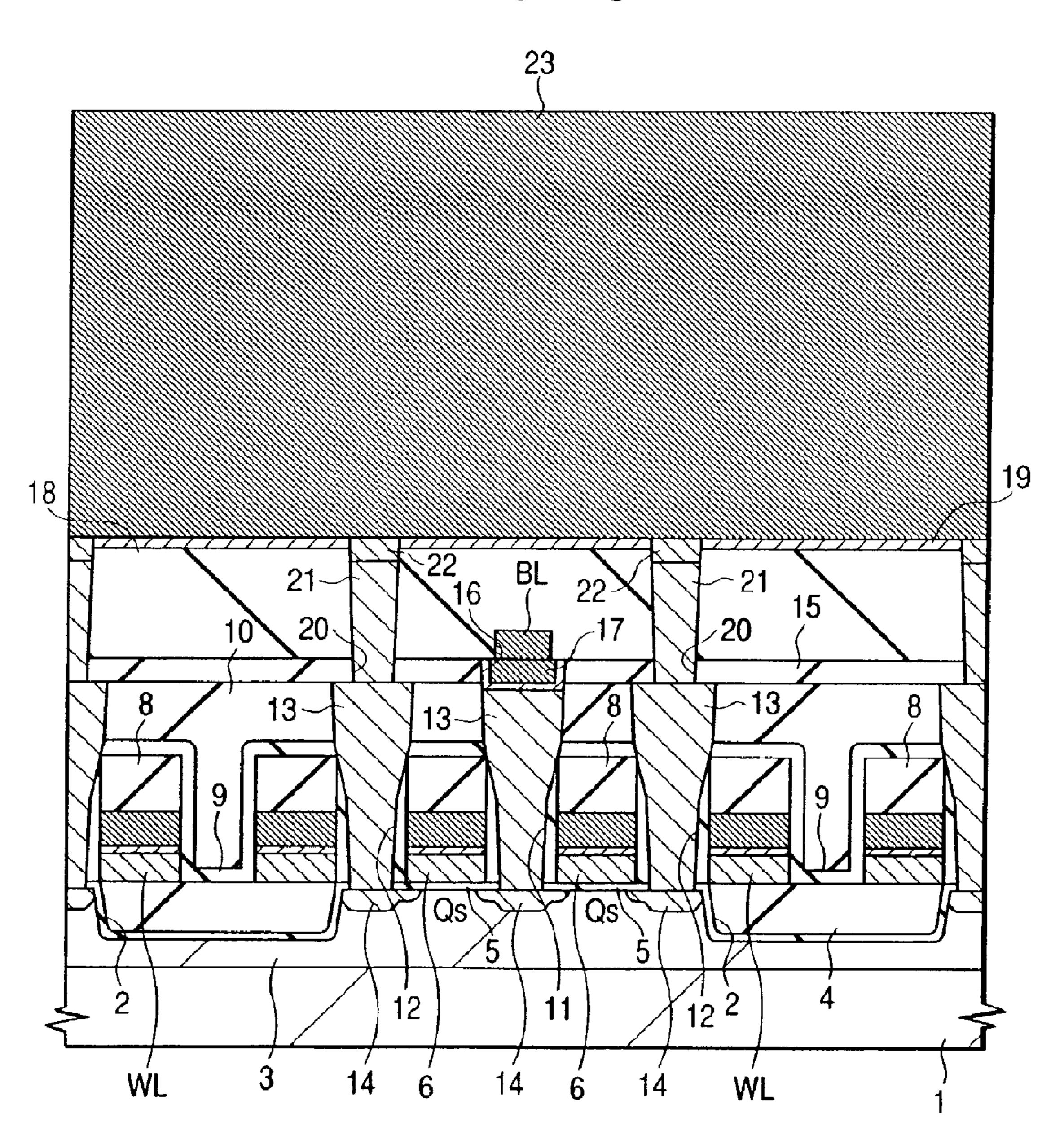

- FIG. 9 is a sectional view of an essential part of a semicon- 30 ductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one embodiment of the invention;

- FIG. 10 is a view illustrating a concept of common use of a lithographic step in a mass production process of a semi- 35 conductor integrated circuit device;

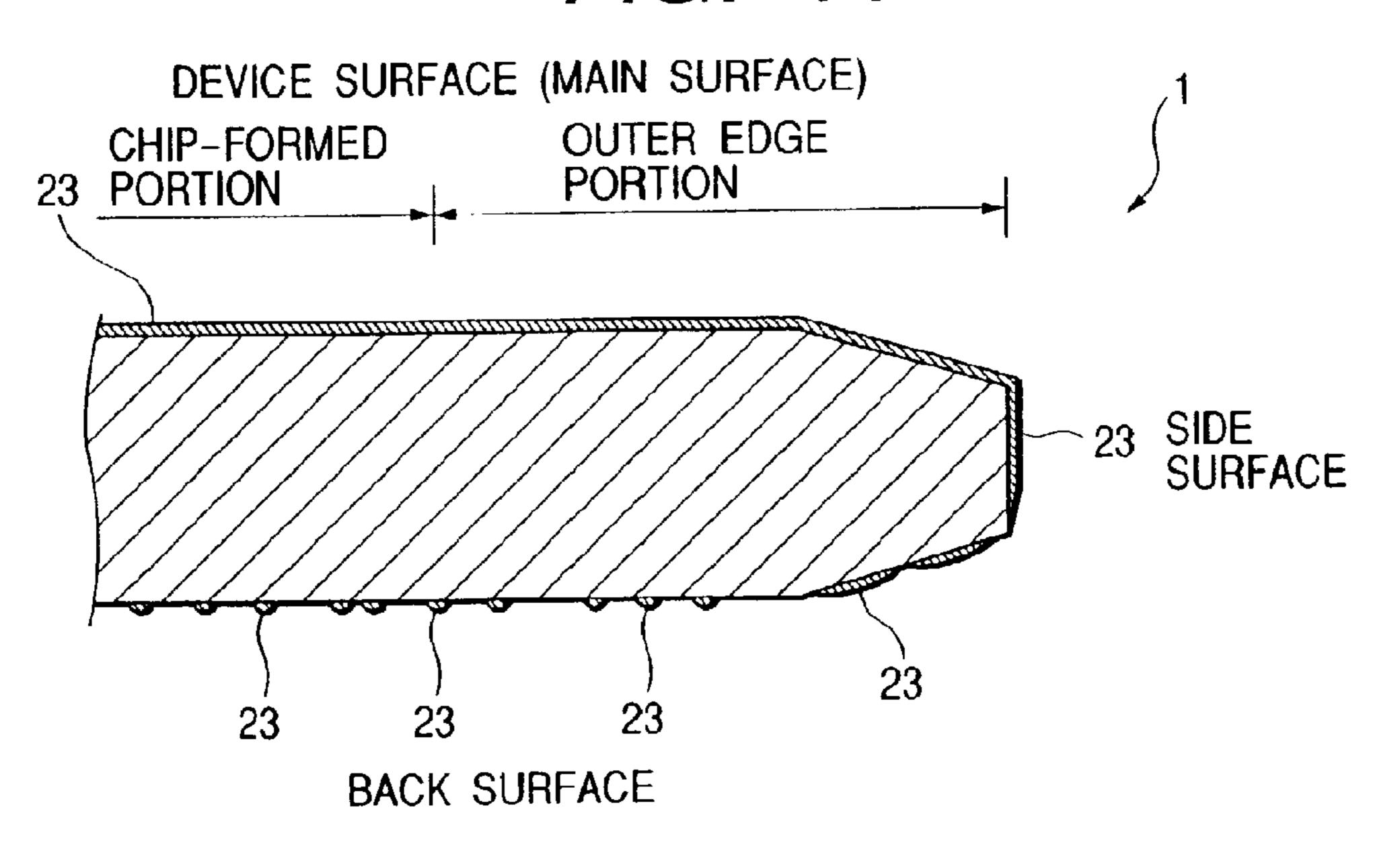

- FIG. 11 is a sectional view showing a peripheral portion of a wafer on which an Ru film is deposited;

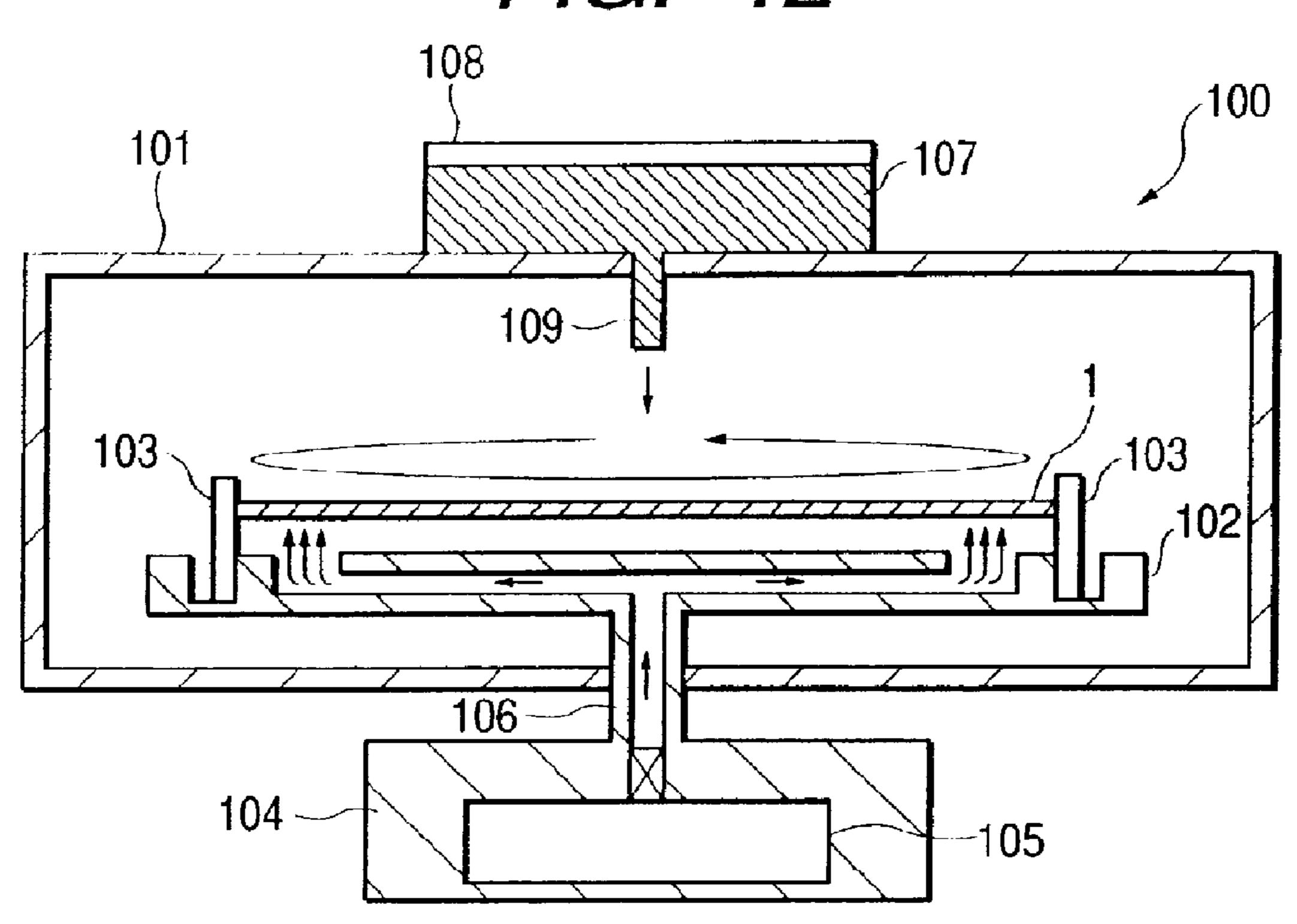

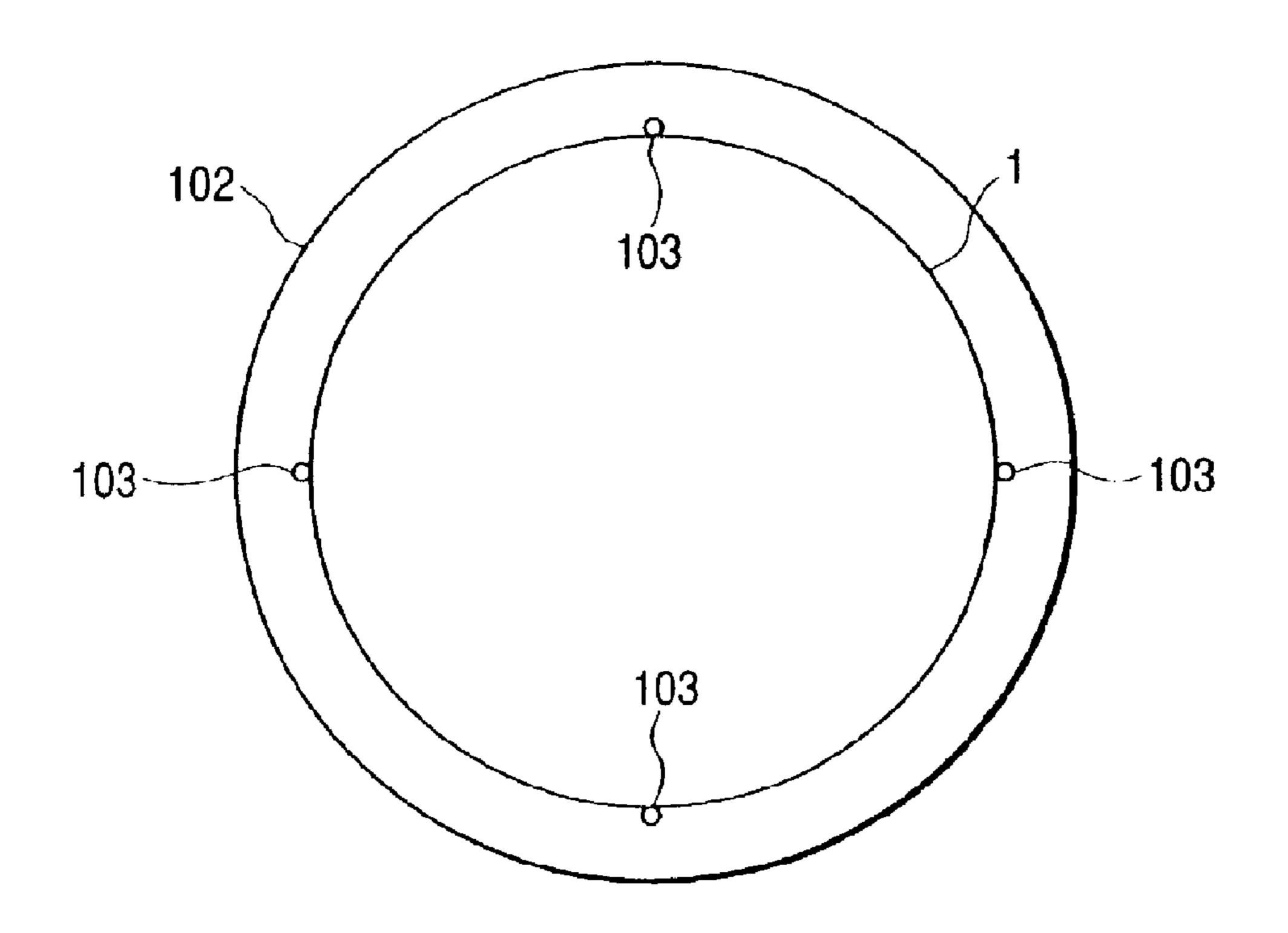

- FIG. 12 is a schematic sectional view showing an example of a cleaning device used in the one embodiment of the 40 invention;

- FIG. 13 is a plan view showing the stage of the cleaning device shown in FIG. 12;

- FIG. 14 is a schematic sectional view showing a method of holding a wafer in the cleaning device shown in FIG. 12;

- FIG. 15 is a table showing the etching rate of Ru depending on different types of cleaning solutions used in a semiconductor production process;

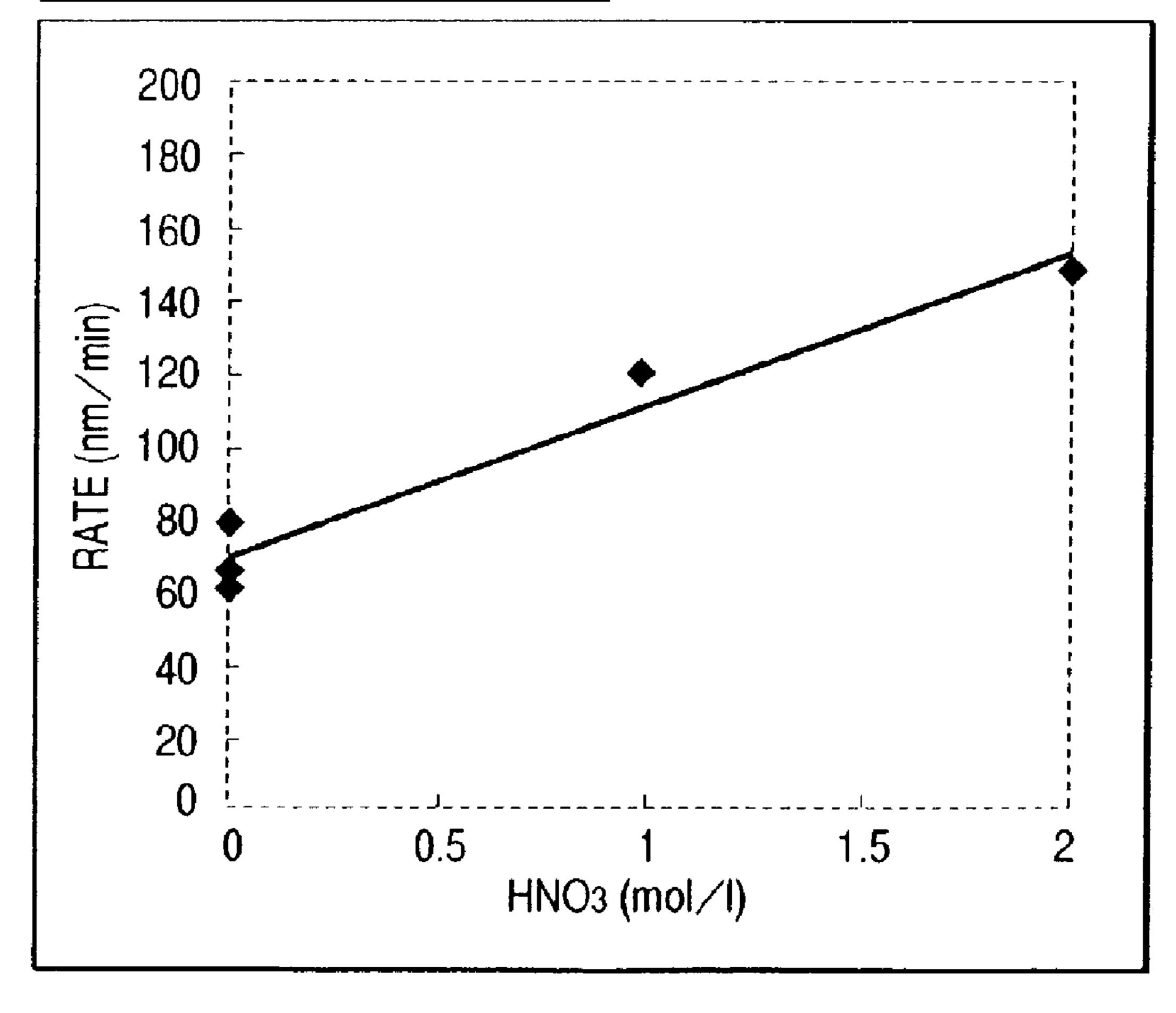

- FIG. 16 is a table showing the etching rate of Ru depending on different types of oxidizing agents;

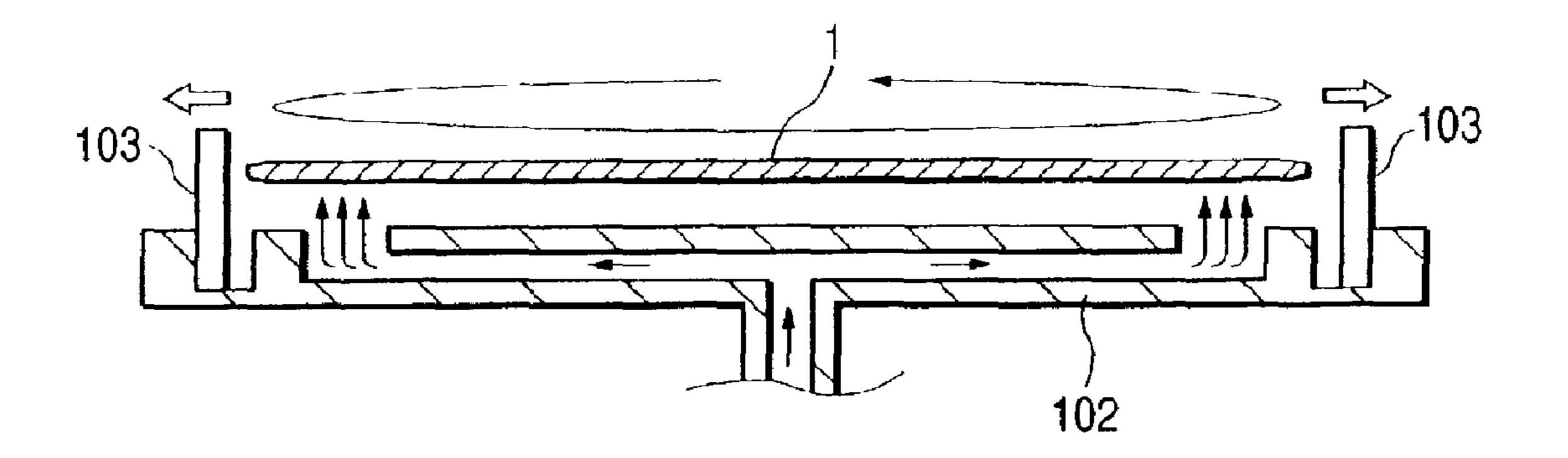

- FIG. 17 is a table and a graph showing the relation between the concentration of an orthoperiodic acid aqueous solution and the etching rate of Ru;

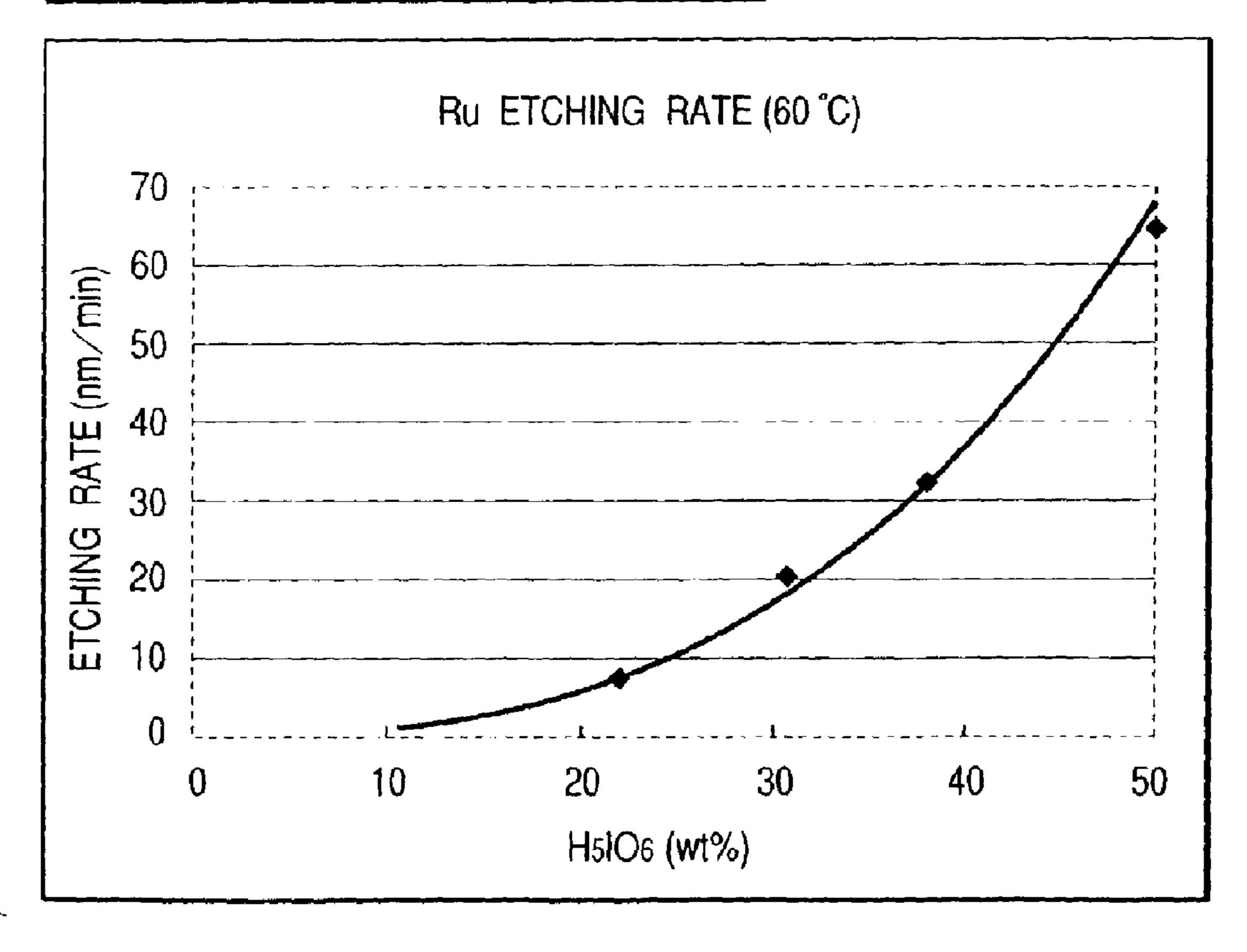

- FIG. 18 is a table and a graph showing the relation between the concentration of nitric acid and the etching rate when Ru 55 is etched by use of an orthoperiodic acid aqueous solution to which nitric acid is added;

- FIGS. 19(a) to 19(d) are, respectively, a table showing the relation between the mixing ratio of nitric acid and the etching rate when Ru is etched by use of an orthoperiodic acid aque- 60 ous solution, to which a nitric acid aqueous solution is added;

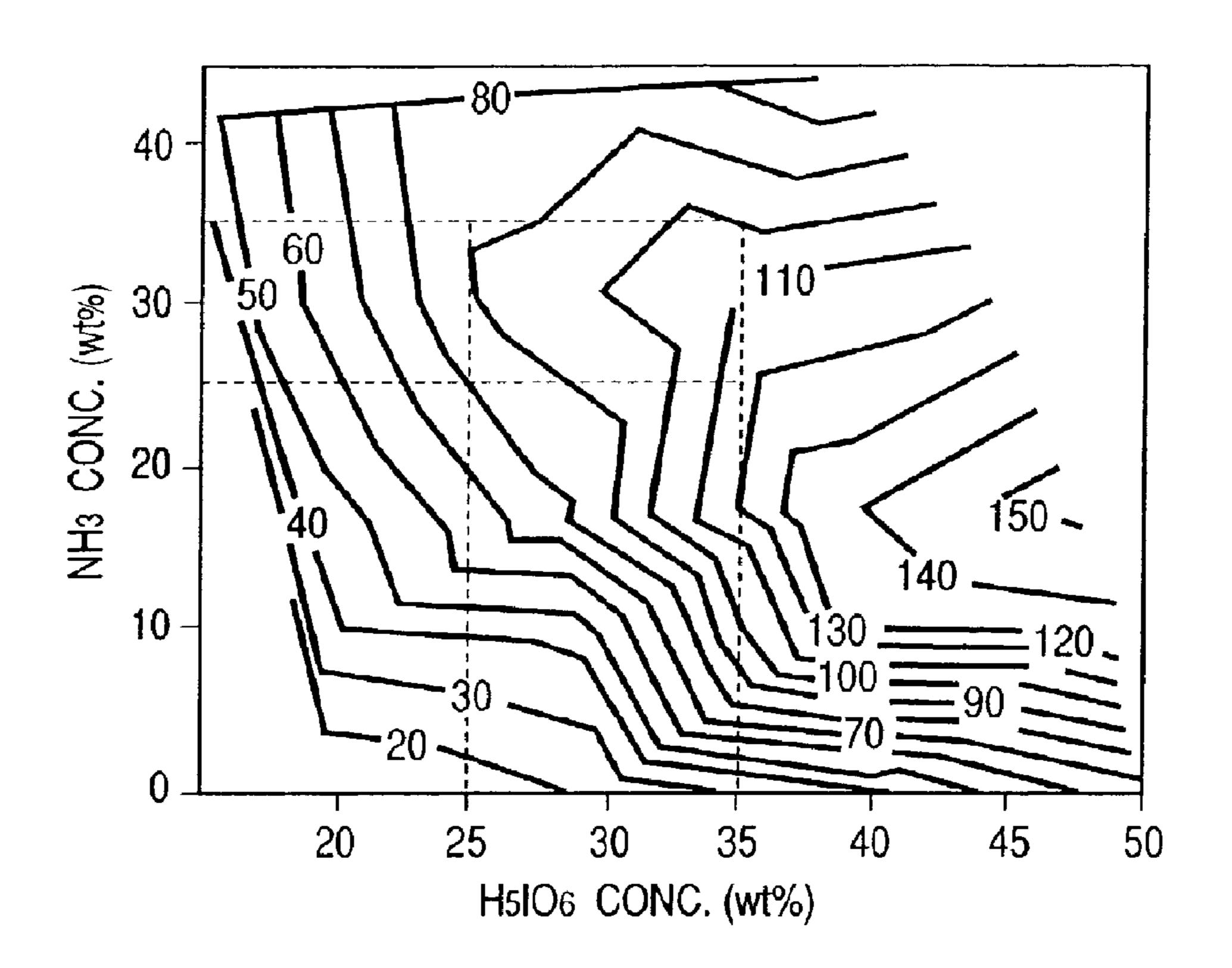

- FIG. 20 is a graph showing, as a contour, the etching rate of Ru with a solution obtained by adding a nitric acid aqueous solution to an orthoperiodic acid aqueous solution;

- FIG. 21 is a table showing the variation in etching rate of Ru when different types of commercially available acids are, respectively, added to an orthoperiodic acid aqueous solution;

**10**

- FIG. 22 is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one embodiment of the invention;

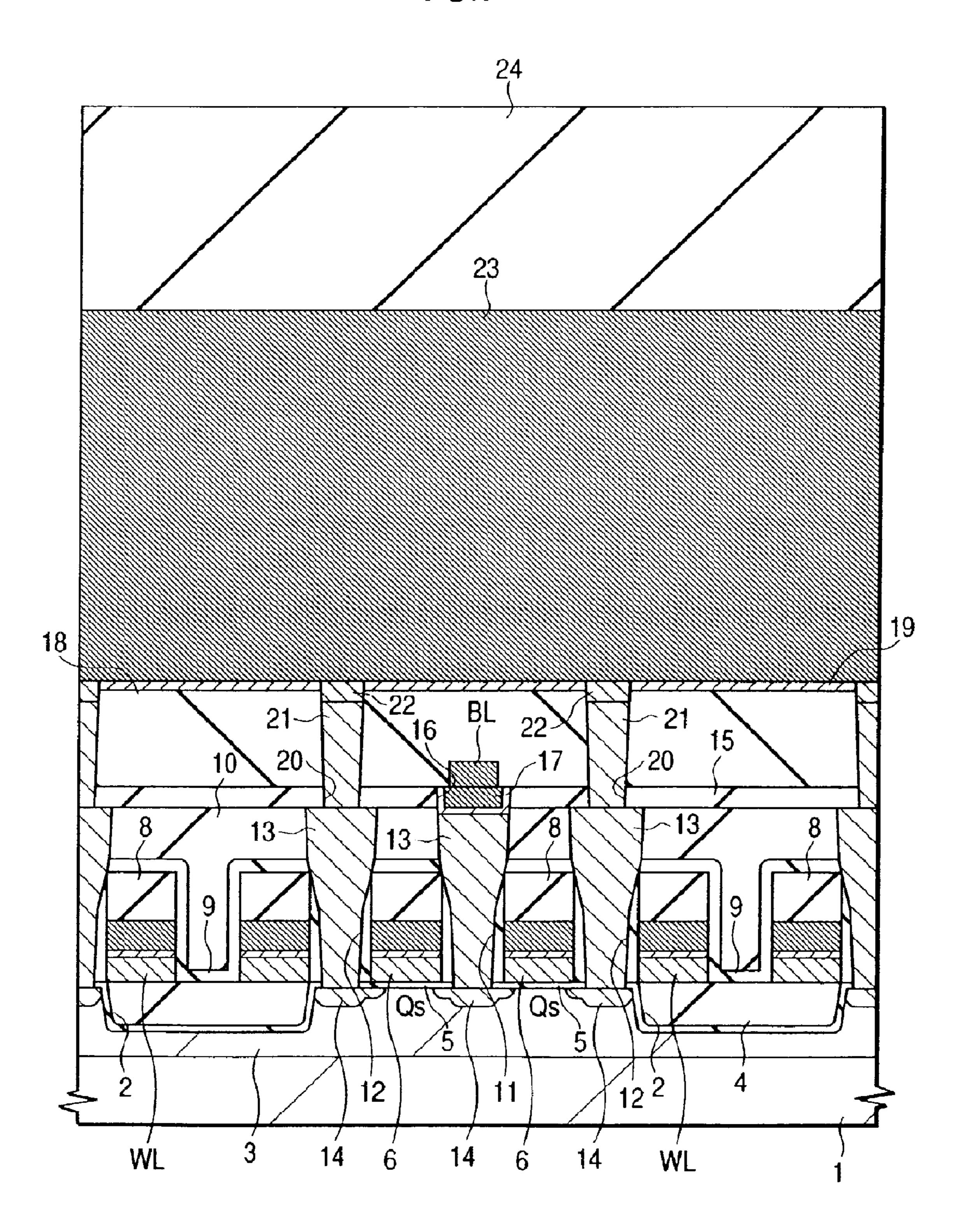

- FIG. 23 is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one embodiment of the invention;

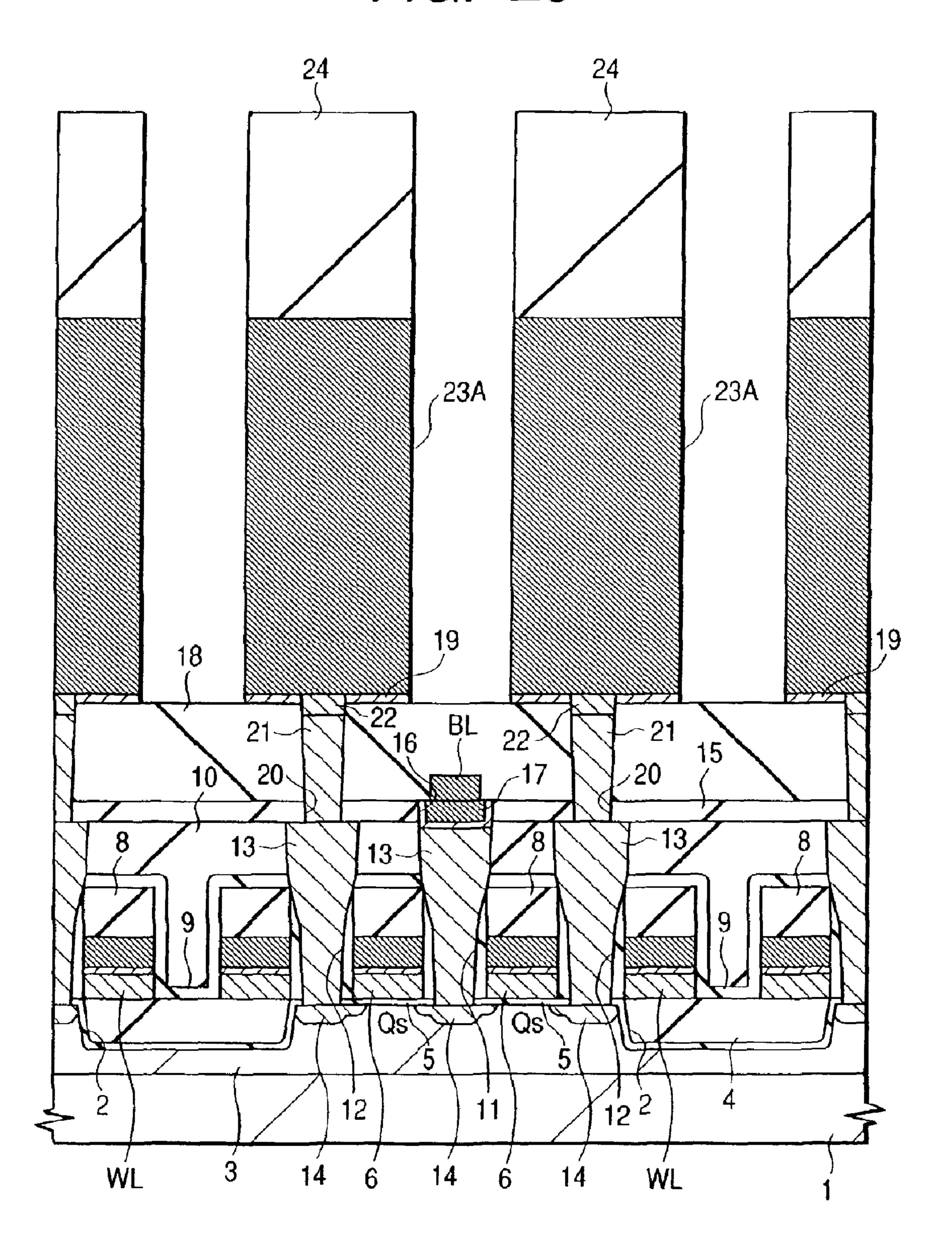

- FIG. 24 is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one embodiment of the invention;

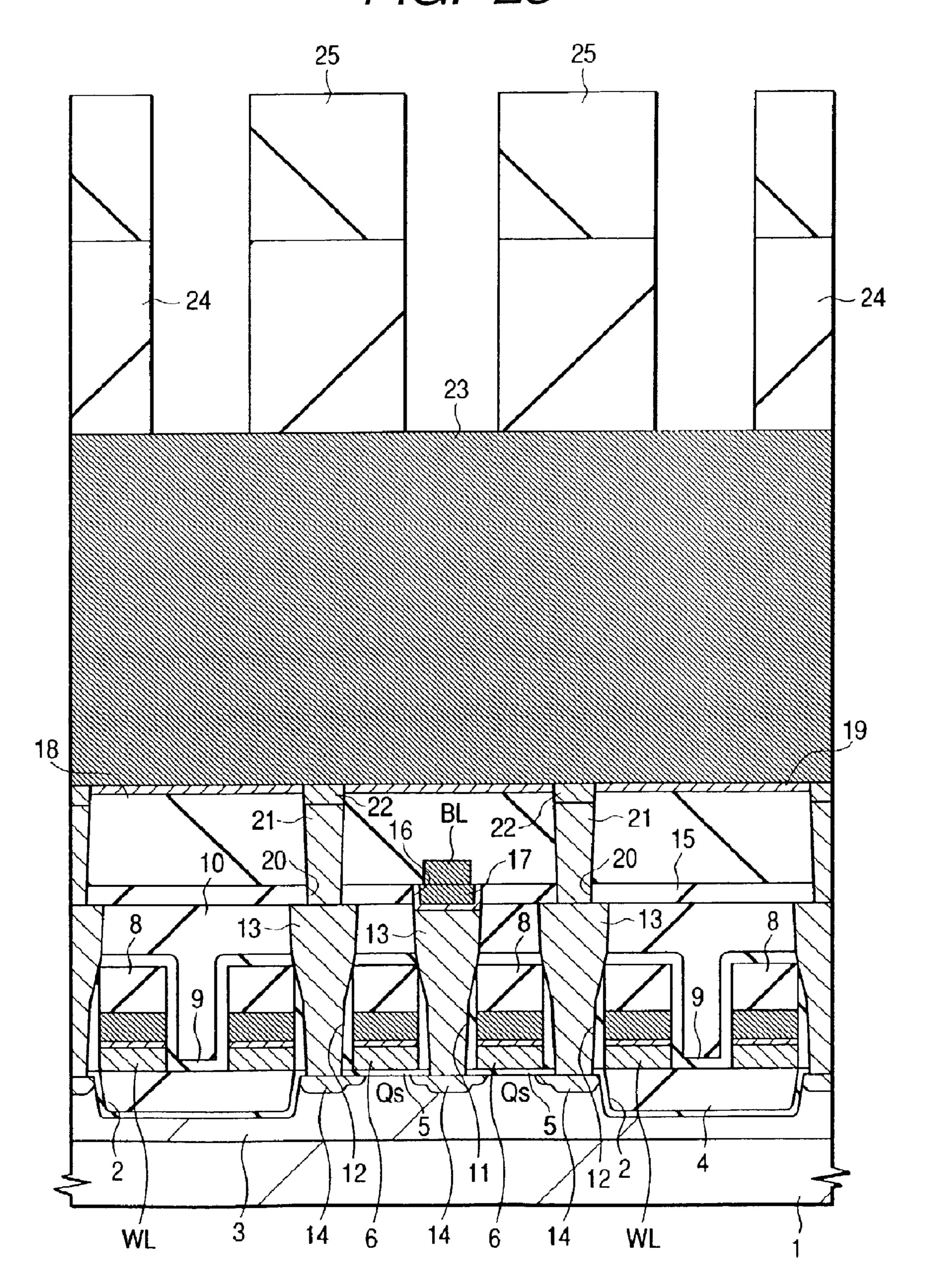

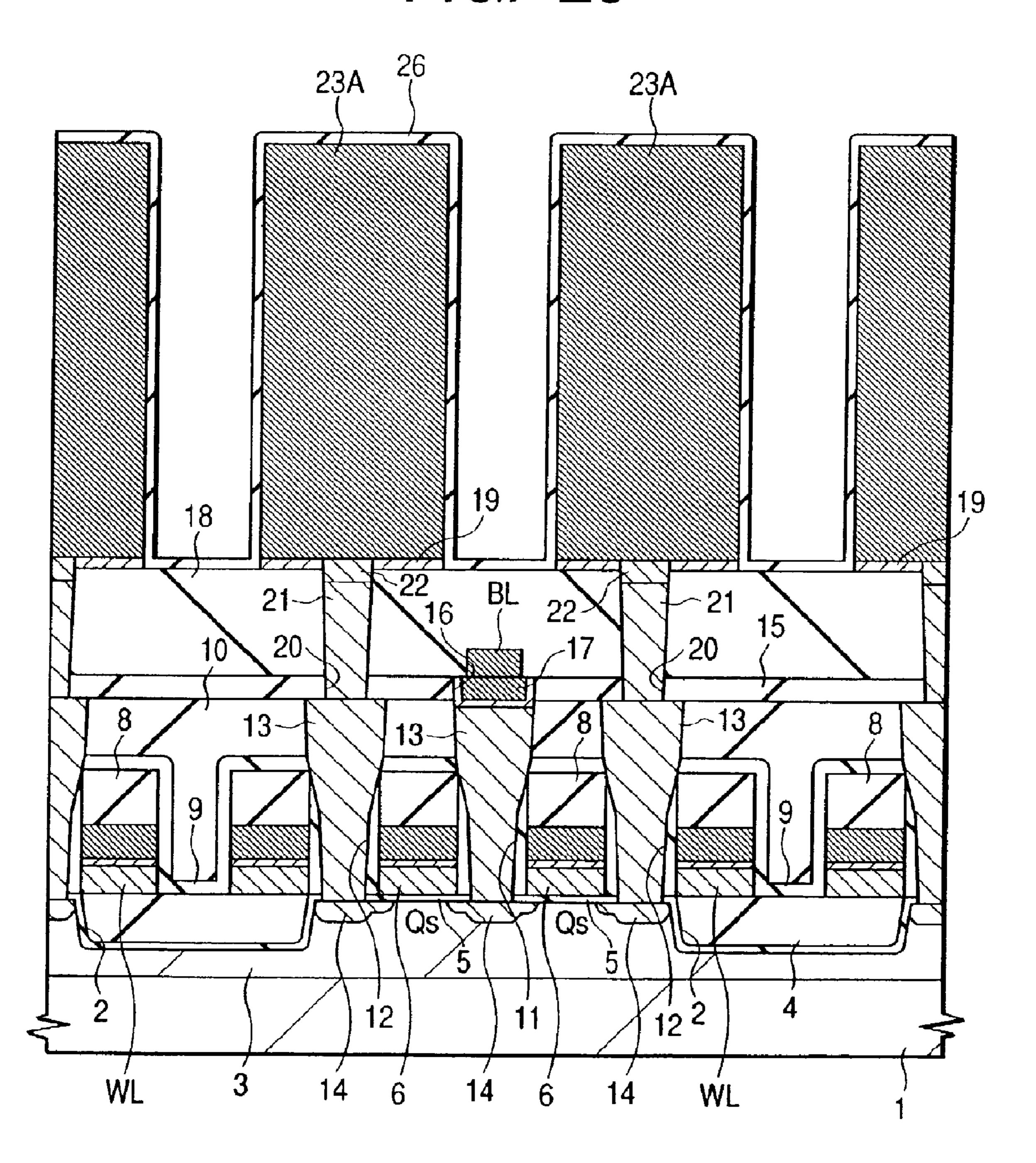

- FIG. 25 is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one embodiment of the invention;

- FIG. 26 is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one embodiment of the invention;

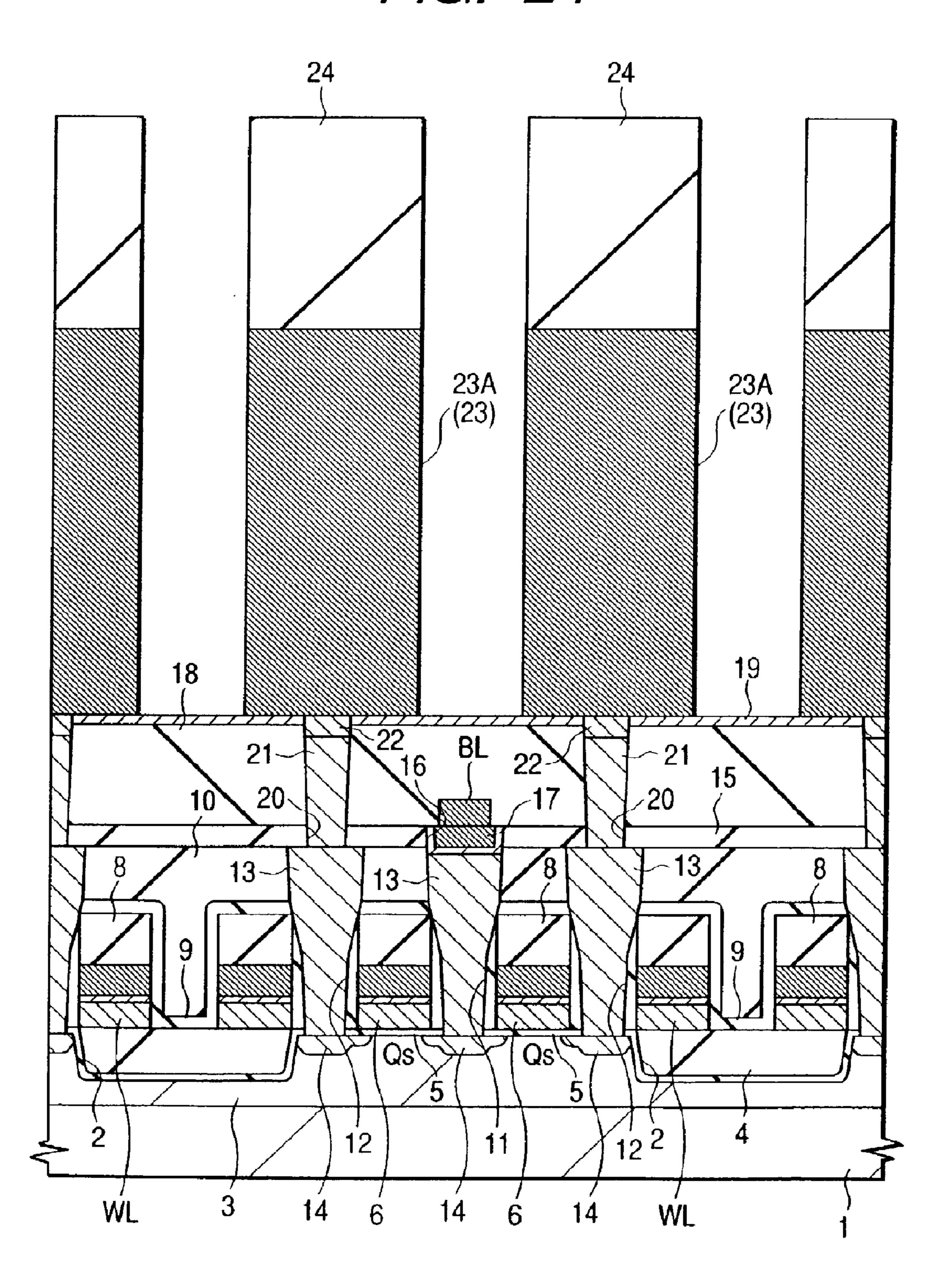

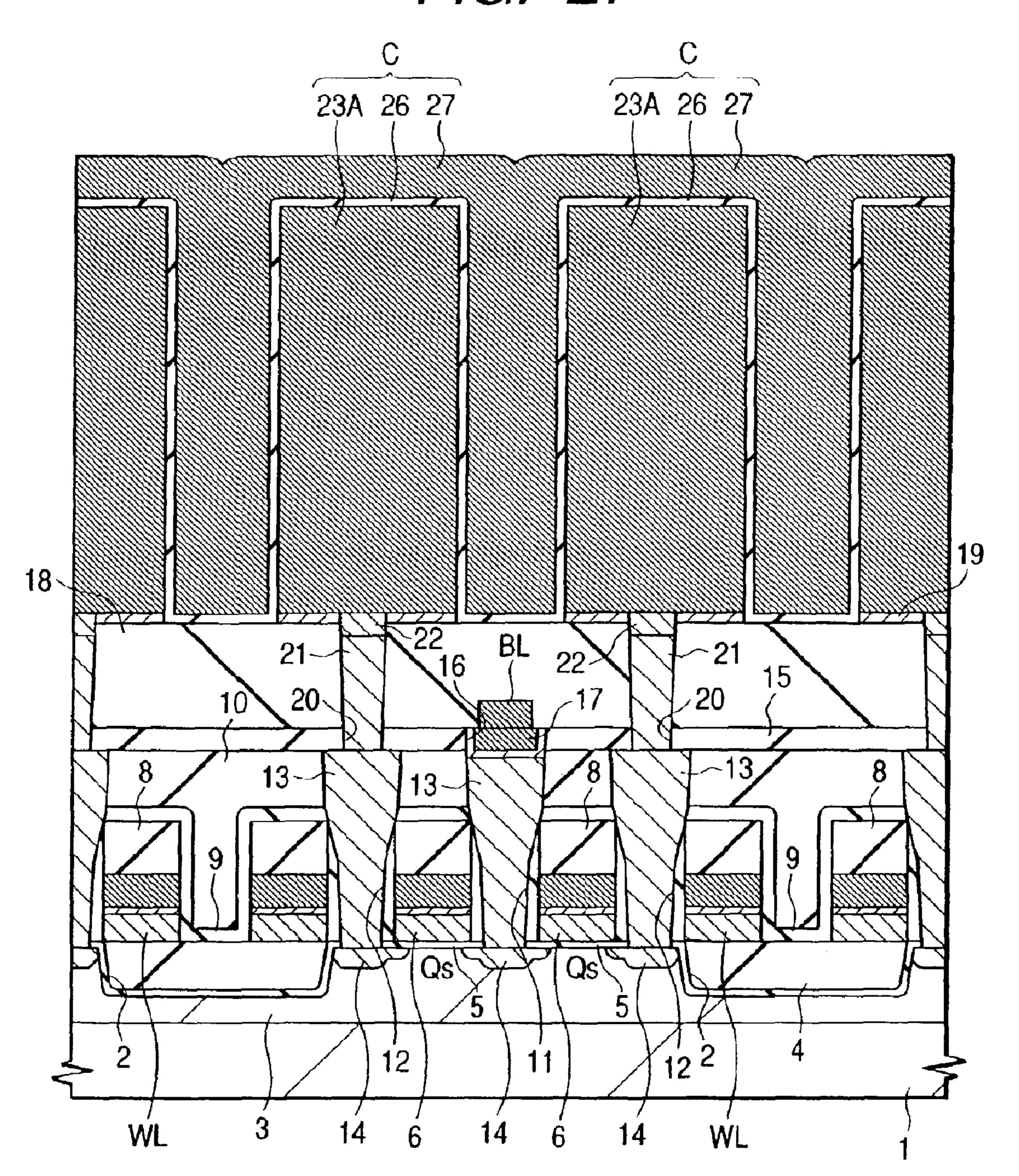

- FIG. 27 is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one embodiment of the invention;

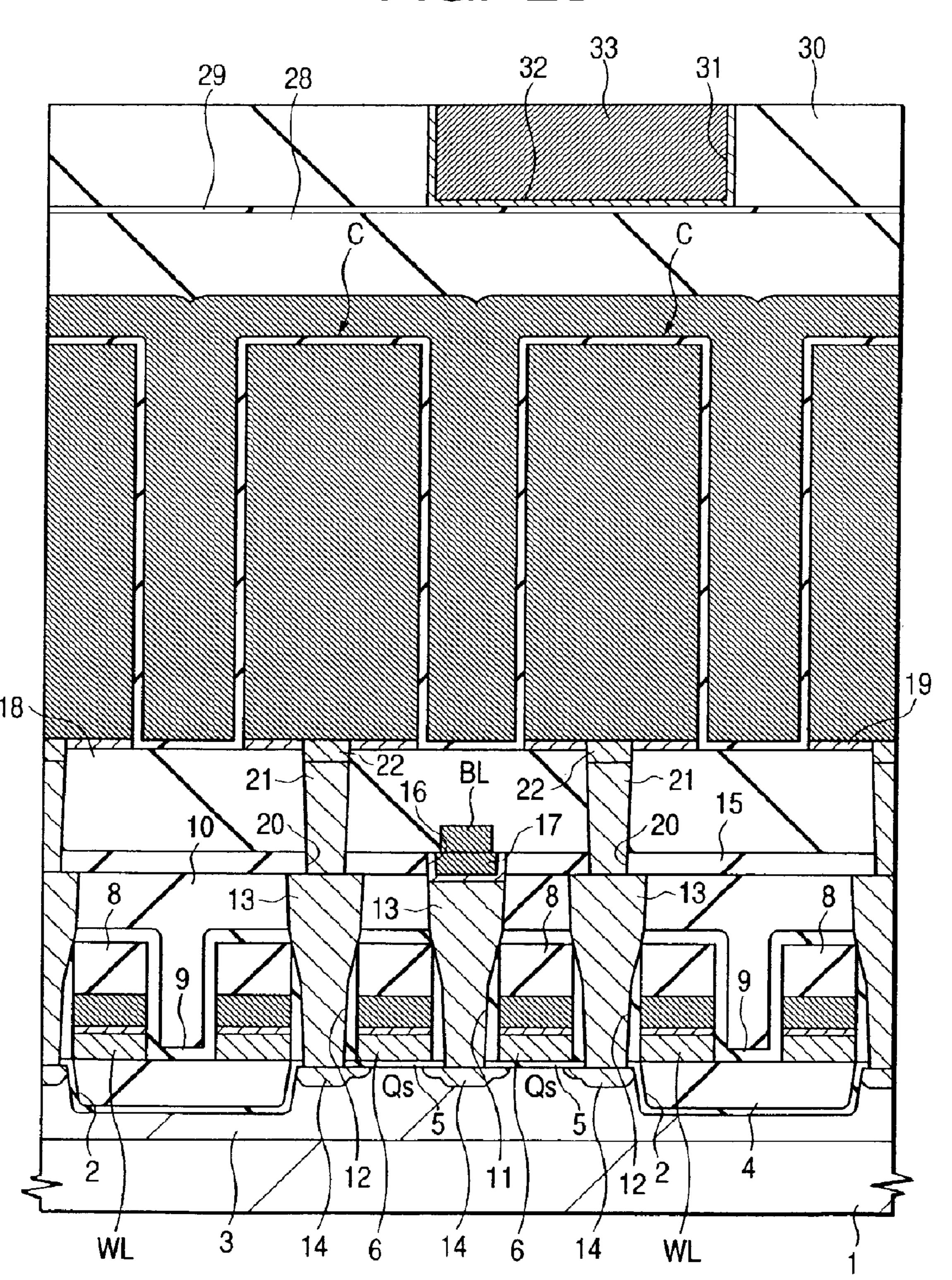

- FIG. 28 is a sectional view of an essential part of a semiconductor substrate showing a mass production method of a semiconductor integrated circuit device according to the one embodiment of the invention;

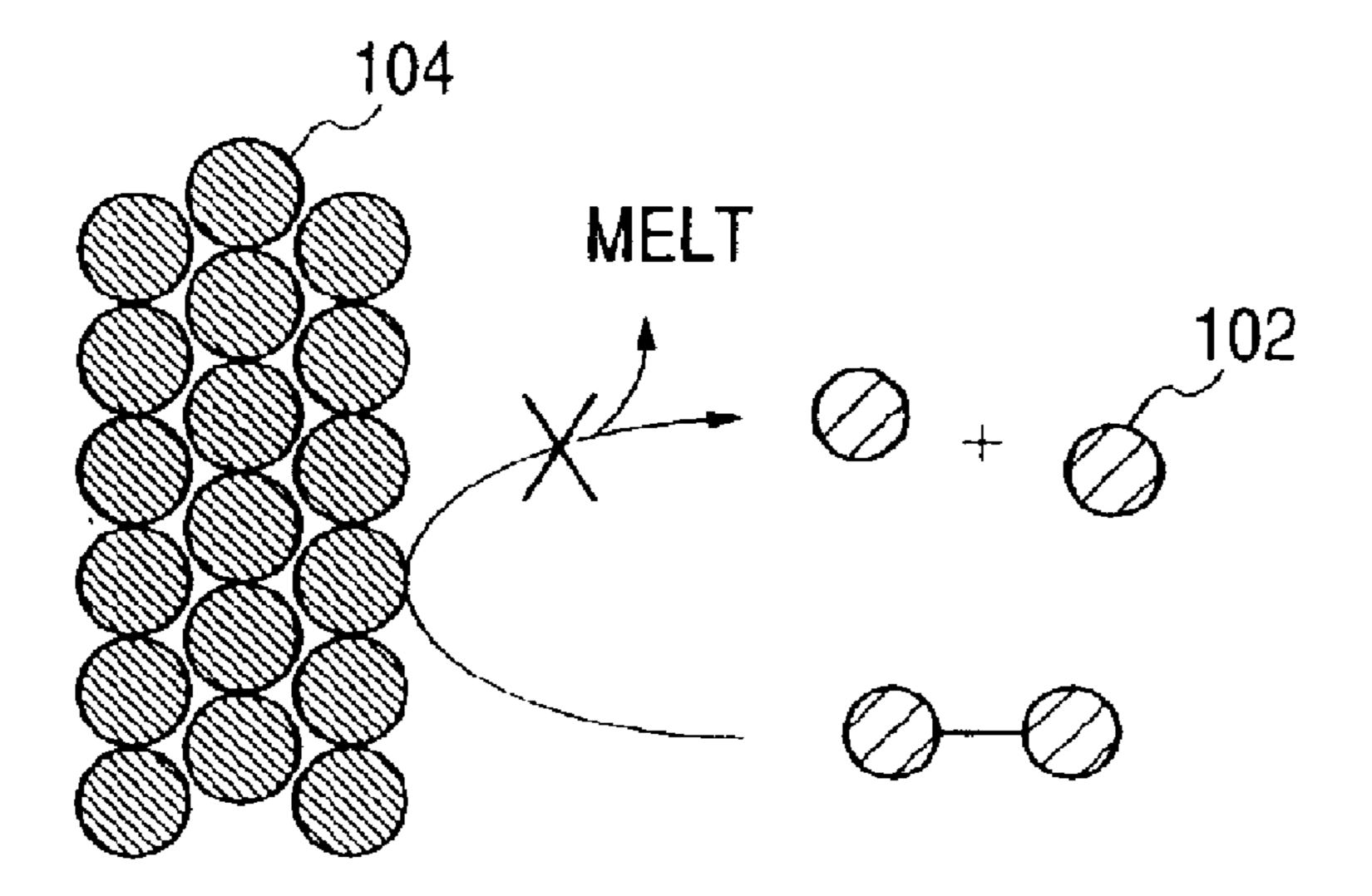

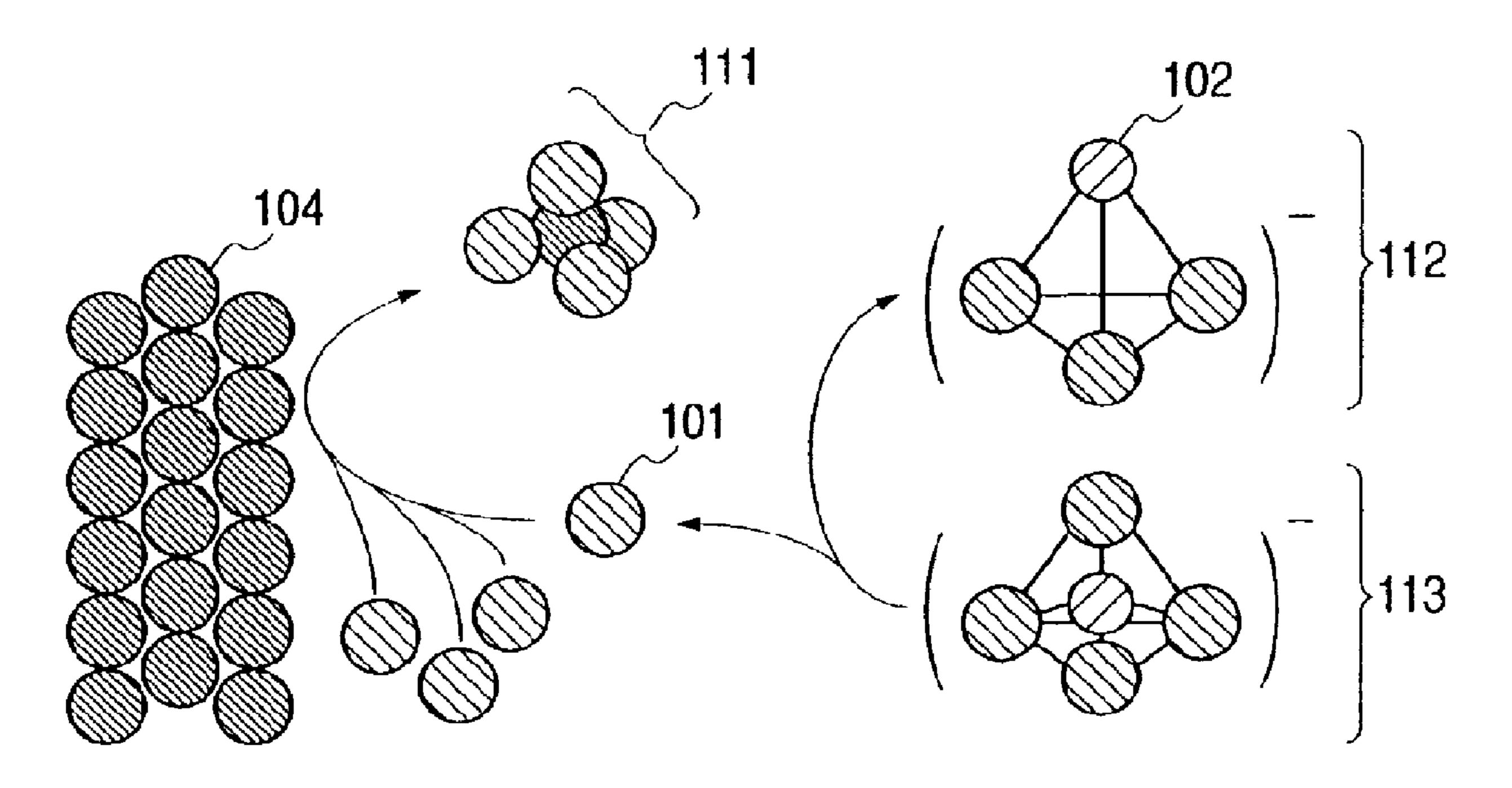

- FIGS. 29(a) and 29(b) are, respectively, a view illustrating the difference in behavior between the oxidizing agent capable of releasing oxygen atoms and the oxidizing agent incapable of releasing oxygen atoms;

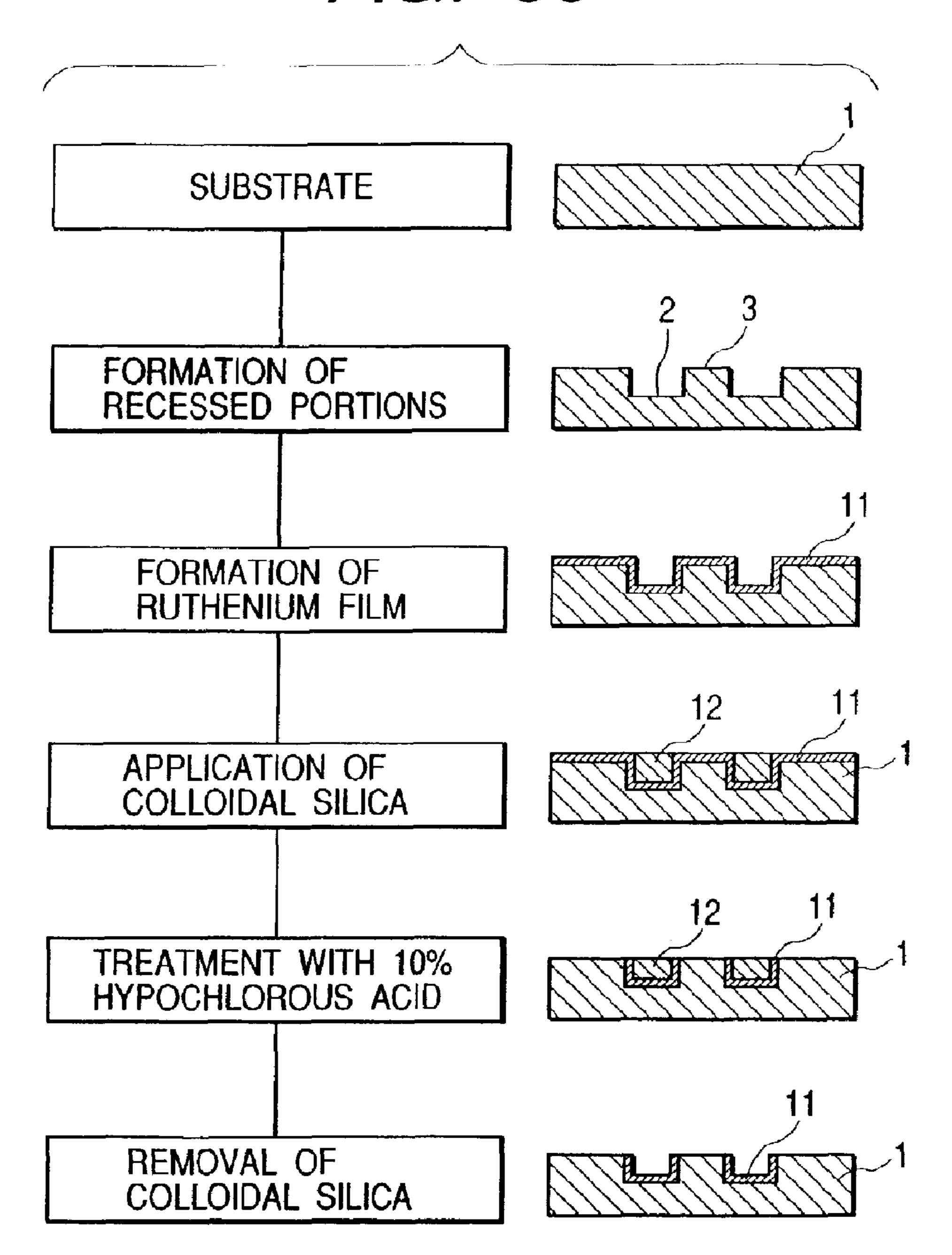

- FIG. 30 is a view illustrating processing steps of a ruthenium thin film according to a second example; and

- FIG. 31 is a view illustrating a cleaning step of ruthenium fine particles according to a third example.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

The embodiments of the invention are described in detail with reference to the accompanying drawings. It should be noted that throughout the drawings illustrating the embodiments, like reference numerals, respectively, indicate like members having the same functions, and are not repeatedly illustrated. In the following embodiments, the same or similar parts or portions are not basically described repeatedly except the case of necessity.

In the following embodiments, if need be for conve-50 nience's sake, a plurality of sections or division into embodiments is illustrated. With the exception of the case indicated specifically, these are not mutually unrelated, and one may be in relation with variations and detailed and supplementary description relative to part or all of others. Moreover, in the following embodiments, where reference is made to the number of elements (including the number, value, amount, range and the like), it should not be construed as limiting to a specified number unless otherwise indicated or except the case where such a number is principally, apparently limited to the specified number. The number over or below the specified number may be within the scope of the invention. In addition, in the following embodiments, the constituting elements (including elemental steps) are not necessarily essential unless otherwise indicated or except the case where such elements are principally, apparently essential.

Likewise, in the following embodiments, where reference is made to the shape and positional relation of a constituting

element, those substantially close or similar to the shape and the like are within the scope of the invention unless otherwise indicated or except the case where such is not a case principally and apparently. This is true of the numerical values and their ranges.

#### EXAMPLE 1

The production process of DRAM according to an embodiment of the invention are described step by step with reference to FIGS. 1 to 28.

As shown in FIG. 1, after formation of an element isolation groove 2 in a main surface of a semiconductor substrate (wafer) 1 made, for example, of p-type single crystal silicon having a specific resistance of approximately 10 Ωcm, a 15 p-type well 3 is formed in the substrate 1. The element isolation groove 2 is formed by forming a groove by dry etching of the substrate 1 at an element isolation region thereof, depositing a silicon oxide film 4 over the substrate 1 including the inside of the groove according to a CVD method and polishing the silicon oxide film 4 by a chemical mechanical polishing (CMP) method to leave it in the groove. The p-type well 3 is formed by ion implanting an r-type impurity, e.g. P (phosphorus) into the substrate 1 and annealing (thermally treating) the substrate 1 to permit the n-type impurity to be 25 diffused.

Next, the p-type well 3 is cleaned on the surface thereof with a hydrofluoric acid-based (HF) cleaning solution, after which the substrate 1 is wet oxidized to form a clean gate oxide film 5 on the surface of the p-type well 3.

As shown in FIG. 2, a gate electrode 6 (word line WL) is formed on the top of the gate oxide film 5, followed by formation of an n-type semiconductive region 7 of a low impurity concentration on the p type well 3 at the opposite side of the gate electrode 6.

The gate electrode 6 (word line WL) is formed by depositing, on the substrate 1, a polysilicon film doped with an n-type impurity such as, for example, P according to a CVD method, depositing, on the top thereof, a WN (tungsten nitride) film and a W (tungsten) film by a sputtering method, 40 further depositing a silicon nitride film B thereover by the CVD method, and dry etching these films by the mask of a photoresist film. The n-type semiconductive region 7 is formed by ion implantation of an n-type impurity such as, for example, arsenic (As).

Thereafter, as shown in FIG. 3, a silicon nitride film 9 and a silicon oxide film 10 are successively deposited over the substrate 1 by a CVD method, followed by planarization of the silicon oxide 10 on the surface thereof by a chemical mechanical polishing method.

Next, as shown in FIG. 4, using a photoresist film (not shown) as a mask, the silicon oxide film 10 and the silicon nitride film 9 above the semiconductive region 7 are dry etched to form contact holes 11, 12. Subsequently, as shown in FIG. 5, a plug 13 made of a polysilicon is formed inside the 55 contact holes 11, 12. The plug 13 is formed by depositing, for example, inside the contact holes 11, 12 and over the silicon oxide film 10, a polysilicon film doped with an n-type impurity such as P by a CVD method, after which the polysilicon film is removed from the top of the silicon oxide film 10 by a 60 chemical mechanical polishing (or etching-back) method, and left inside the contact holes 11, 12.

Thereafter, the substrate is annealed (thermally treated) so that the n-type impurity in the polysilicon film serving as the plug 13 is diffused into the substrate 1 (n-type semiconduc- 65 tive region 7), thereby forming n-type semiconductive regions (source, drain) of a high impurity concentration.

**12**

According to the steps set out hereinabove, MISFEQs of the n-channel type for memory cell selection, which constitute part of a memory cell of DRAM are completed.

Next, as shown in FIG. 6, a silicon oxide film 15 is deposited over the silicon oxide film 10 according to a CVD method, and the silicon oxide film 15 is subsequently dry etched to form a through-hole 16 above the contact hole 11, followed by forming a plug 17 inside the through-hole and further forming a bit line BL over the plug 17.

The plug 17 is formed by depositing a TiN (tungsten nitride) film and a W film, for example, inside the throughhole 16 and above the silicon oxide film 15 by a CVD method or sputtering method, followed by removing the TiN film and W film on the silicon oxide film 15 by a chemical mechanical polishing method to leave them inside the through-hole 16. The bit line BL is formed, for example, by depositing a W film on the silicon oxide film 15 by a sputtering method and dry etching the W film through the mask of a photoresist film. The bit line BL is electrically connected to either (the n-type semiconductive region 14) of the source and drain of MIS-FETQs for memory selection through the plug 17 within the through-hole 16 and the plug 13 within the contact hole 11.

Next, as shown in FIG. 7, a silicon oxide film 18 is deposited on the silicon oxide film 15 by a CVD method, and a TiN film 19 is further formed on the silicon oxide film 18 by a sputtering method, followed by dry etching of the TiN film 19 and the silicon oxide film 18 to form a through-hole 20 over the contact hole 12, followed by formation of a plug inside the through-hole 20. The plug 21 is formed, for example, by depositing a polysilicon film doped with an n-type impurity, such as P, inside the through-hole 20 and on the TiN film 19 by a CVD method, and the polysilicon film on the TiN film 19 is removed by an etching-back method to leave it inside the through-hole 20. At this time, the polysilicon film constituting the plug 21 is over-etched so that the surface of the plug 21 is recessed relative to the surface of the TiN film.

Next, as shown in FIG. 8, a barrier metal 22 is formed on the plug 21. The barrier metal 22 is formed, for example, by depositing A WN film inside the through-hole 20 and on the TiN film 10 by a sputtering method, and the WN film on the TiN film is removed by a chemical mechanical polishing (or etching-back) method to leave the W film inside the through-hole 20.

The barrier metal on the plug 21 is formed for the purposes of preventing the reaction between a lower electrode material (Ru) of an information storage capacitor element deposited on the TiN film 19 in a subsequent step and the plug 21 (polysilicon film) and preventing oxidation of the plug 21 (polysilicon film) with oxygen present in a capacitance insulating film material (BST). The barrier metal 22 may be constituted, aside from WN, of TiN, TaN (tantalum nitride), TaSiN, WSiN, TiSiN or the like.

As shown in FIG. 9, a Ru film serving as a lower electrode of an information storage capacitor element is deposited on the TiN film by a sputtering method.

In the production process of general-purpose LSI such as DRAM, lithographic devices (a light exposure device and an EB exposure device), various inspection devices, an annealing (thermal treating) device and the like are commonly used for the initial element formation step and wiring step prior to the formation of a gate insulating film in order to suppress a facility investment to a minimum and reduce the production cost, as is particularly shown in FIG. 10. In the formation of an information storage capacitor element wherein transition metals or material containing the metals, such as the Ru film 23 and a BST film described hereinafter, which have never been used in prior art wafer processes, there common use

devices are employed Accordingly, the wafer (substrate) 1, on which the Ru film 23 or the BST film has been deposited, is transferred from a device, after which the wafer 1 is transferred to the common use devices for carrying out an initial element formation step or wiring step. The term "wiring step" 5 used herein means the step of forming the gate electrode 6 and the bit line BL shown in FIGS. 2 to 8, and the step of forming wirings on an information storage capacitor element described hereinafter.

FIG. 11 is a sectional view showing a peripheral portion of 10 the wafer 1 on which the Ru film is deposited. As shown, the Ru film 23 is deposited on the device side (main surface) of the wafer (substrate) 1 by a sputtering method, whereupon the Ru film 23 is deposited not only on a chip formation portion on the device side and an outer edge portion, but also on a side 15 surface (edge portion). Part of the film is deposited on the back side of the wafer 1. In this condition, when the wafer 1 is transferred to the common use devices without satisfactory removal of the Ru film from the side surface and the back side thereof, a wafer stage, wafer carrier, conveyor and the like, 20 which come into contact with the side surface and the back side, are attached with the Ru film 23 on the surfaces thereof. This results in the contamination, with Ru, of the wafers 1 of the lower layers steps (including the initial element formation step and wiring step prior to the gate insulating film formation 25 step, which are subsequently fed to the common use devices).

In this embodiment, prior to the step of forming a lower electrode after transfer of the wafer, on which the Ru film 23 is deposited, to the common use devices, the unnecessary Ru film 23 deposited on the side surface and the backside of the 30 wafer 1 is removed in the following way.

FIG. 12 is a schematic sectional view showing an example of a cleaning device used to remove the Ru film 23 deposited on the side surface and the back side of the wafer 1, and FIG. 13 is a plan view showing the stage of the cleaning device.

A cleaning device 100 includes a treating chamber 101

having a stage 102, on which the wafer 1 is mounted, at a central portion thereof. The stage 102 has, on the upper surface thereof, four pins 103 which are in contact with the side surfaces of the wafer 1 and are located at equal intervals.

These pins 103 are arranged to be rotated thereabout within a horizontal plane. The wafer 1 is horizontally held in such a state that its back side is turned upwardly by urging the pins 103 against the wafer. The wafer 1 supported with the pins 103 is in a non-contact state with the stage 102 except for the four side surfaces in contact with the individual pins 103.

Centration iodine) has identified and the readout within a horizontal plane. The wafer 1 is horizontally held in such a in an acid the other and alkaliance. The wafer 1 supported with the pins an alkaliance hypochlosure is a stage 102 except for the 45 hypochlosure.

There are provided, below the treating chamber 101, a drive unit 104 capable of rotating the stage 102 within the horizontal plane and a gas feed unit 105 filled with an inert gas such as nitrogen. The nitrogen gas in the gas feed unit 105 is 50 supplied to the upper surface of the stage 102 through a pipe 106 below the stage 102.

As shown in FIG. 14, the four pins 103 arranged above the stage 102 can be, respectively, moved horizontally in a direction kept away from the wafer. When the wafer 1 is held with 55 the four pins 104, these pins 103 have been preliminarily moved at positions remote from the wafer 1, under which the nitrogen gas is fed against the lower surface of the wafer 1 to permit the wafer to be floated. In this state, the pins 103 are urged against the side surfaces of the wafer 1.

A cleaning vessel 108 is provided above the stage 102. A cleaning solution 107 is charged into the cleaning vessel 103 for removing the Ru film 23 deposited on the side surface and the back side of the wafer 1. The cleaning solution is applied to the upper surface (back side) of the wafer 1 through a 65 nozzle 109, so that the back side and the side surface of the wafer 1, which is rotated while holding with the pins 103, are

**14**

cleaned. When the rotation speed of the stage 102 is appropriately controlled, the cleaning solution 107 can be spread toward the outer edge portion at the lower surface (device side) of the wafer 1.

Next, the composition of the cleaning solution 107 is illustrated. First, the etching rates of Ru with different types of cleaning solutions used in a semiconductor production process are shown in FIG. 15. A sample used was a 3 cm×4 cm square silicon chip on which a 100 nm thick Ru film has been deposited, and the thickness of the Ru film etched per unit minute was measured. As shown in the figure, the etching rate of Ru was 0.1 nm/minute or below for all the cleaning solutions. It will be noted that the rate of 0.1 nm/minute is a limit value of the measurement of the device used. From the results, it will be seen that the known cleaning solutions used in the semiconductor production process do not enable Ru to be removed.

Then, the dissolving mechanism of Ru is described. In order to remove the Ru film 23, it is necessary to use chemicals capable of dissolving Ru. For the dissolution of Ru, it is also necessary to oxidize Ru. The oxidation reaction of Ru proceeds according to the following formulas:

$$Ru+4H_2O \rightarrow RuO_4+8H^++8e^-(pH=0)$$

$$Ru+8OH^{-} \rightarrow RuO_4 + 4H_2O + 8e^{-}(pH=14)$$

The oxidation reduction potential (E) necessary for the reaction is at 1.13 V for an acidic aqueous solution (pH=0) and at 0.30 V for an alkaline aqueous solution (pH=14). Accordingly, for the oxidation of Ru, it is necessary to use an oxidizing agent whose oxidation reduction potential is at a level of 1.13 V or over in an acidic aqueous solution and is at 0.30 V or over in an alkaline aqueous solution.

FIG. 16 shows etching rates of Ru at predetermined concentrations of different types of oxidizing agents (except iodine) having oxidation reduction potentials larger than the above-mentioned values. It will be noted that the sample used and the measurement of the etching rate are the same as in FIG. 15.

As shown, an oxidizing agent showing a great etching rate in an acidic condition is only orthoperiodic acid ( $H_5IO_6$ ). On the other hand, oxidizing agents having a great etching rate in an alkaline condition include three compounds such as hypochlorous acid, metaperiodic acid and orthoperiodic acid. However, among the oxidizing-agents showing a great etching rate in an alkaline condition, hypochlorous acid and metaperiodic acid are available in the form of a salt with an alkali metal such as sodium (Na). Thus, these cannot be employed in the semiconductor production process wherein contamination with an alkali metal is not favored. Accordingly, the oxidizing agent, which can be used as the cleaning solution 107 for the Ru film among these oxidizing agents, is substantially orthoperiodic acid alone. The advantage of the oxidizing agent used in an acidic condition is that any salt with a solute is not formed, unlike an oxidizing agent used in an alkaline condition.

FIG. 17 is a graph showing the relation between the concentration of an orthoperiodic acid aqueous solution (60° C.) and the etching rate (nm/minute) of Ru. As shown, it will be seen that when the concentration of orthoperiodic acid in the aqueous solution is at about 10 wt % or over, the etching rate of Ru increases approximately in proportion to the concentration of orthoperiodic acid. Accordingly, where an orthoperiodic acid aqueous solution is used as the cleaning solution 107 of the Ru film 23, the concentration of orthoperiodic acid may be within a range of about 10 wt % to a saturation.

Further, we have found that when nitric acid is mixed with the orthoperiodic acid aqueous solution, the etching rate of Ru further increases.

FIG. 18 is a graph showing the relation between the concentration of nitric acid and the etching rate when Ru is etched 5 by use of an aqueous solution (temperature of 60° C.) obtained by adding nitric acid to an orthoperiodic acid aqueous solution having a concentration of 47 wt % (wherein a sample is the same as used in FIG. 15). As shown, when the concentration of nitric acid is within a range of up to 2 mols/l, 10 the etching rate increases substantially in proportion to the amount of nitric acid.

FIGS. 19(a) to 19(d) are, respectively, tables showing the relation between the mixing ratio of nitric acid and the etching rate when etching Ru with aqueous solutions (temperature of  $60^{\circ}$  C.) obtained by adding a nitric acid aqueous solution with a concentration of 69 wt % at ratios of 0 (not added), 1, 2, 5 and 10 relative to 10 of orthoperiodic acid aqueous solutions having four concentrations (of 20 wt %, 30 wt %, 40 wt % and 50 wt %) (the sample is the same as that used in FIG. 15). In 20 all the cases, the addition of nitric acid results in a significant increase in etching rate of Ru in comparison with the case using orthoperiodic acid singly.

FIG. 20 is a graph showing the etching rate of Ru as a contour wherein the concentrations of orthoperiodic acid and 25 nitric acid in FIG. 19 are recalculated as percent by weight. As shown, the aqueous solutions having a concentration of orthoperiodic acid of 20 wt % to 40 wt % and a concentration of nitric acid of 20 wt % to 40 wt % exhibit a reduced variation in the etching rate of Ru. Especially, it will be seen that the 30 aqueous solutions having a concentration of orthoperiodic acid of 25 wt % to 35 wt % and a concentration of nitric acid of 25 wt % to 35 wt %, indicated by broken lines in the figure, have a variation in the etching rate of Ru as small as about 10%.

From the above, where an aqueous solution containing orthoperiodic acid and nitric acid is used as the cleaning solution 107 of the Ru film 23, the concentrations of orthoperiodic acid and nitric acid are, respectively, within a range of 20 wt % to 40 wt %, preferably 25 wt % to 35 wt %, within 40 which the variation in etching rate of Ru depending on the variation in concentration of the cleaning solution 107 can be suppressed, thus enabling one to take a wide process margin. More particularly, a mixed aqueous solution of orthoperiodic acid+nitric acid within the above-defined concentration 45 ranges is used as a cleaning solution suitable for the mass production process wherein a large number of wafers are continuously processed.

The reason why mixing of nitric acid with an orthoperiodic acid aqueous solution results in the increase of the etching 50 rate of Ru is assumed as follows. More particularly, orthoperiodic acid ( $H_5IO_6$ ) is in an ionization equilibrium in an aqueous solution as shown by the following formulas.

$$H_{5}IO_{6} \Leftrightarrow H_{4}IO_{6}^{-} + H^{+}$$

$H_{4}IO_{6}^{-} \Leftrightarrow H_{3}IO_{6}^{2-} + H^{+}$

$H_{3}IO_{6}^{2-} \Leftrightarrow H_{2}IO_{6}^{3-} + H^{+}$

$H_{4}IO_{6}^{-} \Leftrightarrow IO_{4}^{-} + H_{2}O$

$2H_{3}IO_{6}^{2-} \Leftrightarrow H_{2}I_{2}O_{10}^{4-} + 2H_{2}O$

Of these molecules and ionic species contained in the aqueous solution, one that has the capability of oxidizing Ru is only orthoperiodic acid ( $H_5IO_6$ ) alone. When nitric acid is 65 added to the orthoperiodic acid aqueous solution, the concentration of the proton ( $H^+$ ) derived from nitric acid increases in wafer 1 using the solution of the proton ( $H^+$ ) derived from nitric acid increases in

**16**

the aqueous solution, so that the above equilibrium proceeds toward the left side. Eventually, the concentration of orthoperiodic acid (H<sub>5</sub>IO<sub>6</sub>) capable of oxidizing Ru becomes high, from which it is assumed that the etching rate of Ru increases.

Accordingly, the addition of an acid other than nitric acid and capable of permitting the equilibrium to proceed to the left side enables the etching rate of Ru to be increased. For instance, FIG. 21 shows the variation in etching rate of Ru when different types of commercially available acids are, respectively, added to an orthoperiodic acid aqueous solution. As shown, the etching rate of Ru increases when adding, aside from nitric acid, acetic acid.

Examples of the acid capable of increasing the etching rate of Ru includes: carboxylic acids, typical of which are the above-indicated acetic acid and HCOOH (formic acid);

hydrohalogenic acids such as HF (hydrofluoric acid), HBr (hydrobromic acid), HI (hydroiodic acid) and the like;

halogenated oxo acids such as HClO<sub>3</sub> (chloric acid), HClO<sub>4</sub> (perchloric acid), HBrO<sub>3</sub> (bromic acid), HBrO<sub>4</sub> (perbromic acid) and the like;

H<sub>2</sub>S (hydrogen sulfide), hydrogen polysulfides such as H<sub>2</sub>S<sub>3</sub>, H<sub>2</sub>S<sub>4</sub> and the like, hydrides of elements of group 6 such as H<sub>2</sub>Se (hydrogen selenide), H<sub>2</sub>Te (hydrogen telluride) and the like;

oxo acids of sulfur such as  $H_2S_2O_3$  (thiosulfuric acid),  $H_2S_2O_7$  (disulfuric acid),  $H_2SO_6$  (polythionic acid),  $H_2SO_5$  (peroxosulfuric acid),  $H_2S_2O_8$  (peroxodisulfuric acid) and the like;

H<sub>2</sub>SeO<sub>4</sub> (selenic acid), H<sub>6</sub>TeO<sub>6</sub> (telluric acid) and the like; polyphosphoric acids such as H<sub>3</sub>PO<sub>4</sub> (orthophosphoric acid), H<sub>4</sub>P<sub>2</sub>O<sub>7</sub> (pyrophosphoric acid), H<sub>5</sub>P<sub>3</sub>O<sub>10</sub> (triphosphoric acid), H<sub>6</sub>P<sub>4</sub>O<sub>13</sub> (tetraphosphoric acid) and the like, and oxoacids of phosphorus, typical of which is (HPO<sub>3</sub>)<sub>n</sub> (cyclophosphoric acid); and

H<sub>3</sub>AsO<sub>4</sub> (arsenic acid), HN<sub>3</sub> (hydrogen azide), H<sub>2</sub>CO<sub>3</sub> (carbonic acid), H<sub>3</sub>BO<sub>3</sub> (boric acid) and the like.

Next, the cleaning method using the cleaning solution 107 made of an orthoperiodic acid aqueous solution or aqueous solutions mixed with different types of acids indicated above is described with reference to FIGS. 12 to 14.

Initially, the wafer 1 deposited thereon with the Ru film 23 is transferred into the treating chamber of the cleaning device 100 wherein nitrogen gas is fed toward the upper surface of the stage 102 from the gas feed unit 105 thereby causing the wafer to be floated (FIG. 14). Next, the pins 103 are pressed against the side surfaces of the wafer 1 to hold the wafer 1 horizontally (FIGS. 12, 13).

Subsequently, while rotating the stage 102, the cleaning solution 107 is supplied from the cleaning vessel 108 through a nozzle 109 toward the upper surface (back side) of the wafer 1, thereby cleaning the back side and the side surface of the wafer 1. If necessary, the outer edge portion at the lower surface (device side) of the wafer 1 is also cleaned. The cleaning solution 107 used may be a mixed aqueous solution made, for example, of orthoperiodic acid (concentration of 30 wt %) and nitric acid (concentration of 30 wt %), both heated to 60° C.

During the course of the cleaning, the pins 103 in contact with the wafer 1 are each rotated within a horizontal plane. In this way, the wafer 1 is rotated by the frictional force with the pins 103, so that the side portions in contact with the pins 103 are changed to clean the entire side surfaces of the wafer 1. It will be noted that the cleaning device used herein is described in detail in our Japanese Patent Application No. Hei

The cleaning of the back side and the side surface of the wafer 1 using the cleaning solution 107 of this embodiment

may be carried out by use of a device other than the abovestated cleaning device 100, e.g. the known Bernoulli chucktype pin etching device. Prior to the cleaning of this embodiment, the back side of the wafer 1 may be subjected to brush cleaning.

The etching rate of the Ru film 23 with the above-mentioned mixed aqueous solution of orthoperiodic acid+nitric acid (60° C.) was found to be 2.244×10<sup>-3</sup> g/minute on the weight basis. In contrast, the etching rate of Ru with a solution (100° C.) of 33% HIO<sub>3</sub>: 20% ICI=1:1 in the case of the 10 afore-referenced Japanese Laid-open Patent Application No. Hei 7-157832 was at  $1.567 \times 10^{-6}$  g/minute, or the etching rate of Ru with a solution (70° C.) of 37% HI+0.01 mol/liter of I<sub>2</sub> in the case of the afore-referenced Japanese Laid-open Patent Application No. Hei 7-224333 was at  $0.9625 \times 10^{-6}$  g/minute, 15 thus both being very small. Quantitatively, it may be said that Ru is not substantially dissolved. More particularly, according to the method of the invention, Ru can be dissolved at an etching rate as high as not less than 1000 times that of these prior art techniques. In addition, the method of the invention 20 is advantageous in that Ru can be dissolved at a temperature lower than in solutions of the prior art techniques.

Next, the method of forming a lower electrode using the Ru film 23 as an electrode material is described. First, the wafer 1, obtained after completion of the cleaning treatment, is 25 transferred to an inspection device for common use shown in FIG. 10, in which the degree of contamination at the back side and the side surface is checked. Thereafter, the wafer 1 is annealed (thermally treated) in an atmosphere of nitrogen at about 700° C. by use of a common use annealing (thermal 30 treating) device, thereby causing the stress of the Ru film 23 to be released.

Thereafter, the wafer 1 is transferred to a CVD device (not shown), and a silicon oxide film 24 is deposited on the Ru film 23 as shown in FIG. 22. For the dry etching of the Ru film 23, an oxygen-based gas is used, so that an oxidation-resistant material, such as the silicon oxide film 24, is used as an etching mask.

Next, the wafer 1 is subjected to a lithographic step using the common use devices shown in FIG. 10. More particularly, 40 as shown in FIG. 23, the silicon oxide film 24 is dry etched through the mask of a photoresist film 24 deposited on the silicon oxide film 24, thereby forming a hard mask for dry etching the Ru film 23.