### US007956629B2

## (12) United States Patent Root

## (45) **Date of Patent:**

(10) Patent No.:

US 7,956,629 B2

\*Jun. 7, 2011

### PROBE TILE FOR PROBING SEMICONDUCTOR WAFER

Inventor: **Bryan J. Root**, Apple Valley, MN (US)

(73)Assignee: Celadon Systems, Inc., Apple Valley,

MN (US)

Subject to any disclaimer, the term of this Notice:

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

Appl. No.: 12/841,584

Jul. 22, 2010 (22)Filed:

### (65)**Prior Publication Data**

US 2010/0283494 A1 Nov. 11, 2010

### Related U.S. Application Data

- Continuation of application No. 11/928,469, filed on (63)Oct. 30, 2007, now Pat. No. 7,786,743, which is a continuation of application No. 11/484,868, filed on Jul. 11, 2006, now Pat. No. 7,345,494, which is a continuation of application No. 11/074,533, filed on Mar. 8, 2005, now Pat. No. 7,148,710, which is a continuation of application No. 10/601,764, filed on Jun. 23, 2003, now Pat. No. 6,882,168, which is a continuation of application No. 09/730,130, filed on Dec. 4, 2000, now Pat. No. 6,586,954, which is a continuation-in-part of application No. 09/021,631, filed on Feb. 10, 1998, now Pat. No. 6,201,402.

- Provisional application No. 60/042,812, filed on Apr. 7, 1997.

- (51)Int. Cl. G01R 31/067 (2006.01)G01R 31/00 (2006.01)

**U.S. Cl.** ....... **324/755.01**; 324/755.07; 324/756.01; 324/756.04

Field of Classification Search ...... None (58)See application file for complete search history.

### **References Cited** (56)

### U.S. PATENT DOCUMENTS

| 2,589,368 | A | 3/1952      | Graham et al.   |  |  |  |

|-----------|---|-------------|-----------------|--|--|--|

| 3,560,907 | A | 2/1971      | Heller          |  |  |  |

| 3,597,528 | A | 8/1971      | Penfield et al. |  |  |  |

| 3,787,768 | A | 1/1974      | Kubota et al.   |  |  |  |

| 3,963,986 | A | 6/1976      | Morton et al.   |  |  |  |

| 4,001,685 | A | 1/1977      | Roch            |  |  |  |

| 4,365,109 | A | 12/1982     | O'Loughlin      |  |  |  |

|           |   | (Continued) |                 |  |  |  |

### FOREIGN PATENT DOCUMENTS

EP 0177809 4/1986 (Continued)

Primary Examiner — Vinh P Nguyen (74) Attorney, Agent, or Firm — Hamre, Schumann, Mueller & Larson, P.C.

### ABSTRACT (57)

A tile used to hold one or more probes for testing a semiconductor wafer is disclosed. The tile has one or more sites for inserting one or more probes to test the semiconductor wafer. Each site has one or more holes. Each hole is coupled with a slot forming an angle. A probe is inserted into the tile from a top of the tile through the hole and seated on the slot. The probe has a probe tip. The probe top is in contact with the semiconductor wafer at one end of the slot at a bottom of the tile. The probe tip is aligned with an X and Y coordinate of a bond pad on the semiconductor wafer.

### 12 Claims, 19 Drawing Sheets

# US 7,956,629 B2 Page 2

| U.S. PATENT DOCUMENTS                                            | 6,137,302            | Δ      | 10/2000              | Schwindt         |

|------------------------------------------------------------------|----------------------|--------|----------------------|------------------|

| U.S. TATENT DOCUMENTS                                            | 6,201,402            |        |                      | Root 324/754     |

| 4,480,223 A 10/1984 Aigo                                         | 6,275,051            |        |                      | Bachelder et al. |

| 4,491,686 A 1/1985 Caviar                                        | 6,276,956            |        | 8/2001               | -                |

| 4,626,775 A 12/1986 Cho et al.                                   | 6,377,062            |        |                      | Ramos et al.     |

| 4,667,523 A 5/1987 Becker et al.                                 | 6,420,888            |        |                      | Griffin et al.   |

| 4,731,577 A 3/1988 Logan                                         | 6,429,673            |        |                      | Obata et al.     |

| 4,768,973 A 9/1988 Bakermans                                     | 6,586,954            |        |                      | Root 324/754     |

| 4,814,028 A 3/1989 Sawaki et al.                                 | 6,603,322            |        |                      | Boll et al.      |

| 4,845,426 A 7/1989 Nolan et al.                                  | 6,608,496            |        |                      | Strid et al.     |

| 4,849,689 A 7/1989 Gleason et al.                                | 6,690,185            |        |                      | Khandros et al.  |

| 5,003,254 A 3/1991 Hunt et al.                                   | 6,696,849            |        |                      | Ban et al.       |

| 5,015,947 A 5/1991 Chism                                         | 6,710,608            |        |                      | Yoshida et al.   |

| 5,148,103 A 9/1992 Pasiecznik, Jr.                               | 6,727,726            |        | 4/2004               |                  |

| 5,150,040 A 9/1992 Byrnes et al.                                 | 6,744,267            |        |                      | Sauk et al.      |

| 5,151,653 A 9/1992 Yutori et al.                                 | 6,747,467            |        | 6/2004               |                  |

| 5,168,218 A 12/1992 Rich                                         | 6,798,227            |        | 9/2004               |                  |

| 5,192,907 A 3/1993 Bonaria                                       | 6,815,961            |        |                      | Mok et al.       |

| 5,196,789 A 3/1993 Golden et al.                                 | , ,                  |        |                      | Lesher et al.    |

| 5,214,243 A 5/1993 Johnson                                       | , ,                  |        |                      | Root 324/754     |

| 5,325,052 A 6/1994 Yamashita                                     | 6,958,449            |        |                      | Ziebart et al.   |

| 5,345,170 A 9/1994 Schwindt et al.                               | 6,963,207            |        |                      | Root et al.      |

| 5,397,996 A 3/1995 Keezer                                        | , ,                  |        |                      | Root et al.      |

| 5,431,758 A 7/1995 Delalle                                       | 7,148,710            |        | 12/2006              |                  |

| 5,449,017 A 9/1995 Collins et al.                                | , ,                  |        |                      | Root 324/754     |

| 5,473,254 A 12/1995 Asar                                         | , ,                  |        |                      | Root             |

| 5,477,160 A 12/1995 Love                                         | 2001/0011902         |        |                      | Schwindt         |

| 5,486,770 A 1/1996 Johnson                                       |                      |        |                      |                  |

| 5,488,292 A 1/1996 Tsuta                                         | 2002/0084794         |        | 7/2002               |                  |

| 5,517,126 A 5/1996 Yamaguchi                                     | 2004/000920          |        |                      | Root et al.      |

| 5,525,911 A 6/1996 Marumo et al.                                 | 2004/0051541         |        |                      | Zhou et al.      |

| 5,729,150 A 3/1998 Schwindt                                      | 2004/0056676         |        | 3/2004               |                  |

| 5,742,174 A 4/1998 Kister et al.                                 | 2005/0206395         |        | 9/2005               |                  |

| 5,821,764 A 10/1998 Slocum et al.                                | 2007/0069747         | Al     | 3/2007               | Root             |

| 5,952,843 A 9/1999 Vinh                                          | EC                   | DEIG   | N DATE               | NT DOCUMENTS     |

| 6,014,032 A 1/2000 Maddix et al.                                 | rc                   | /IXIXI | JIN I <i>P</i> XIII. | INT DOCUMENTS    |

| 6,020,750 A 2/2000 Berger et al.                                 | JP                   | 6088   | 8906                 | 3/1994           |

| 6,037,785 A 3/2000 Higgins<br>6,050,829 A 4/2000 Eldridge et al. | WO                   | 99/04  | 4273                 | 1/1999           |

| 6,075,376 A 6/2000 Endringe et al.                               | WO 20                | 04/08  | 1980                 | 9/2004           |

| 6,124,723 A * 9/2000 Costello                                    | * cited by example * | niner  |                      |                  |

| 0,127,723 A                                                      | ched by chai         | milei  |                      |                  |

Fig. 3

Fig. 4A

Fig. 4B

Fig. 4C

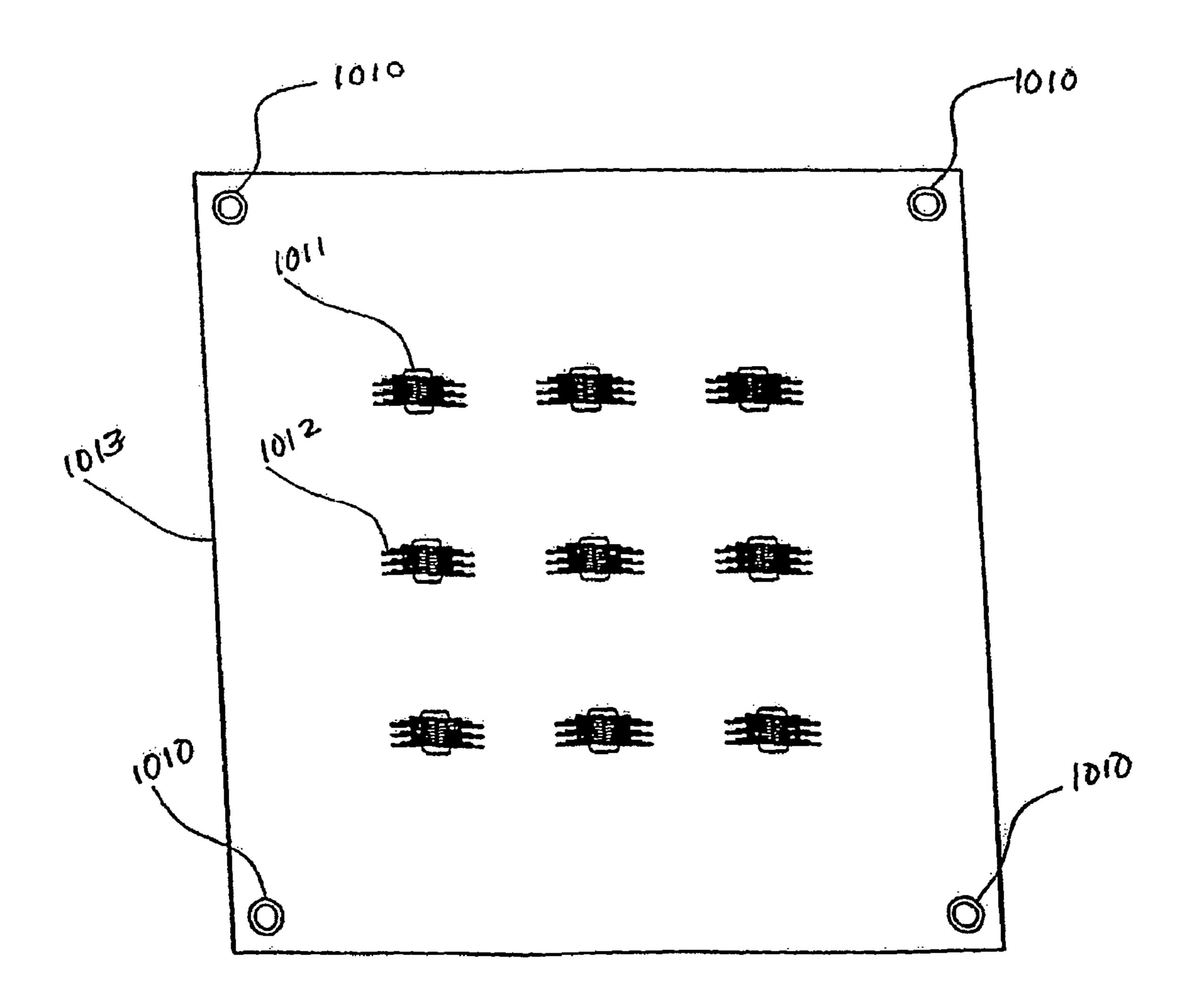

# FIGURE 10A

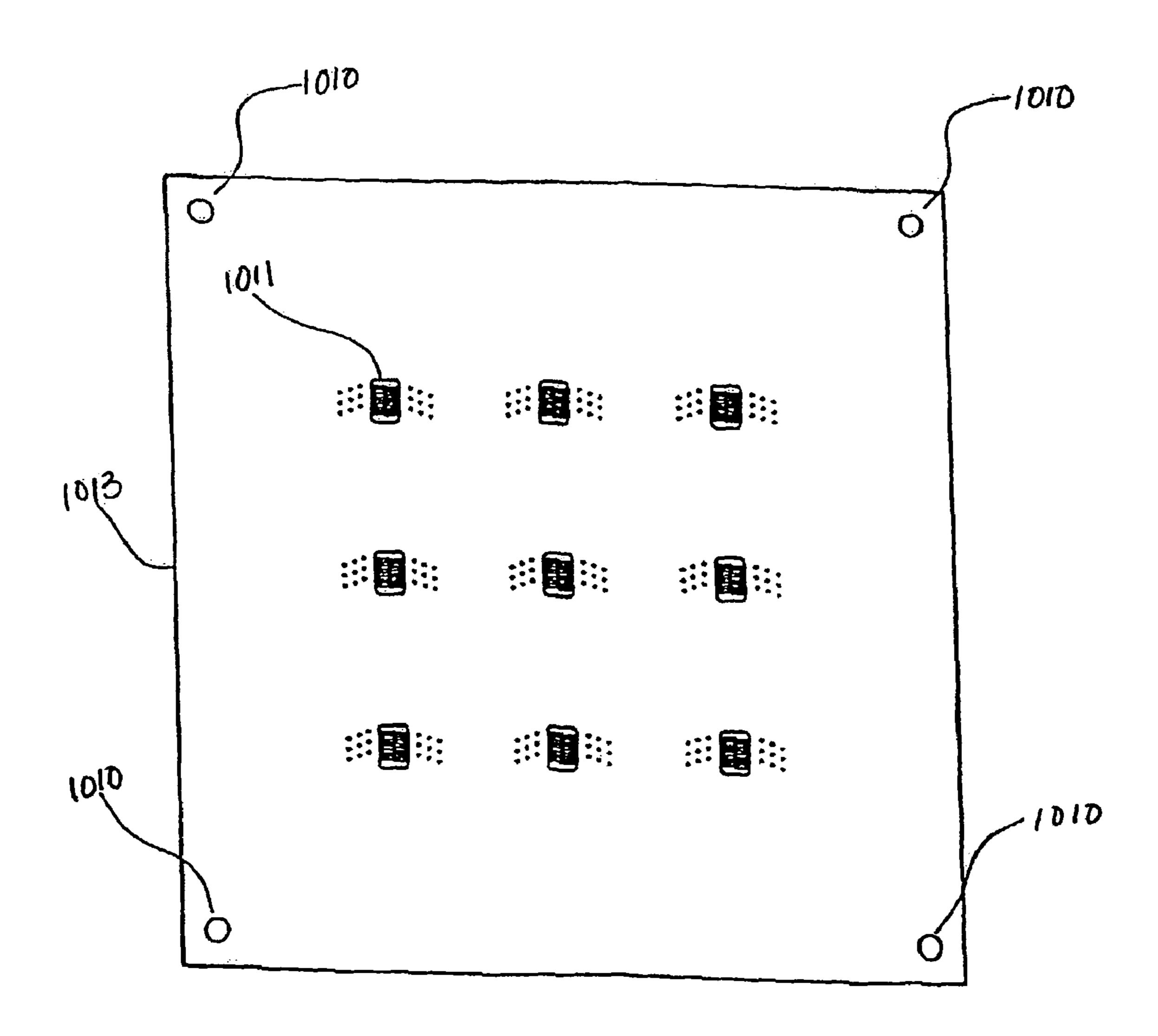

# FIGURE 10B

Jun. 7, 2011

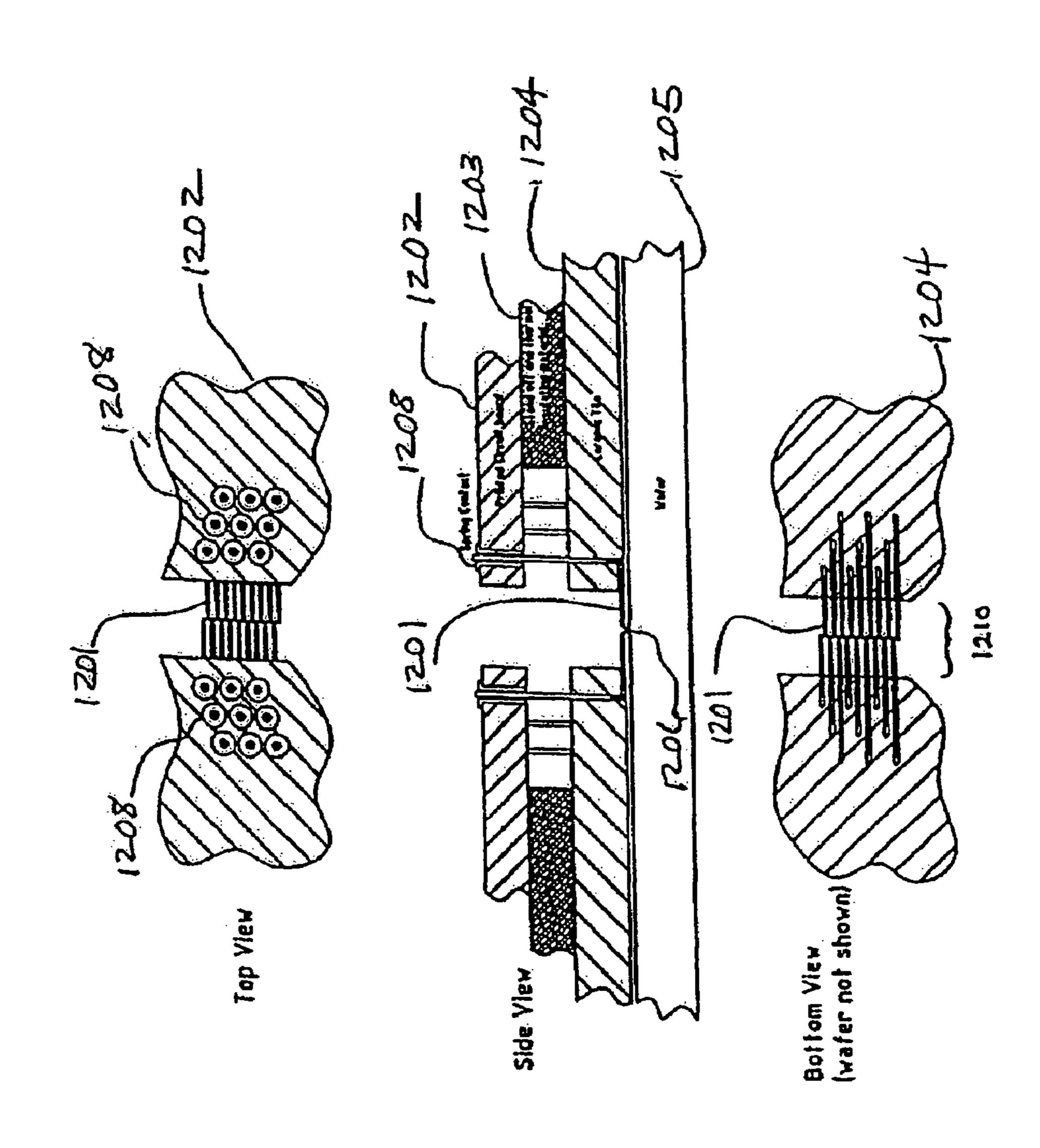

FIGURE 14

# PROBE TILE FOR PROBING SEMICONDUCTOR WAFER

This application is a continuation of U.S. application Ser. No. 11/928,469 filed on Oct. 30, 2007, now U.S. Pat. No. 5,786,743, which is a continuation of U.S. application Ser. No. 11/484,868 filed on Jul. 11, 2006, now U.S. Pat. No. 7,345,494, which is a continuation of U.S. application Ser. No. 11/074,533 filed on Mar. 8, 2005, now U.S. Pat. No. 7,148,710, which is a continuation of U.S. application Ser. No. 10/601,764 filed on Jun. 23, 2003, now U.S. Pat. No. 6,882,168, which is a continuation of U.S. application Ser. No. 09/730,130 filed on Dec. 4, 2000, now U.S. Pat. No. 6,586,954, which is a continuation-in-part of U.S. application No. 09/021,631 filed on Feb. 10, 1998, now U.S. Pat. No. 6,201,402, which claims the benefit of U.S. Provisional application Ser. No. 60/042,812 filed on Apr. 7, 1997.

### FIELD OF THE INVENTION

This invention relates generally to semiconductor test equipment, and more particularly, to a system and method for using a plurality of probe tiles and probes for electrically probing a semiconductor wafer.

### BACKGROUND OF THE INVENTION

The semiconductor industry has a need to access many electronic devices on a semiconductor wafer. As the semiconductor industry grows and devices become more complex, engineers and scientists require tools to access devices quickly and easily on a semiconductor wafer. Many wafer tests take hours, days, or weeks to perform, and would more efficiently be performed in parallel. Probe cards have been developed to probe long rows or areas of the wafer. However, these developments are still geared to a short-term electrical tests and a limited temperature range.

Semiconductor wafer probing is typically performed with probe cards built using FR-4, polyamide or a similar material. Such cards typically use an epoxy ring to hold tungsten 40 proves in place. These types of probe cards are generally designed for probing one device at a time on the wafer in a narrow temperature range. The larger vendors of these types of probe cards are Cerprobe, Probe Technology, MJC Japan, and others. Probers, built by companies such as Electraglass 45 and TEL, step the probe card across the wafer so the devices on the wafer can be electrically probed.

Ceramic versions of a typical probe card have been developed, however these are limited to, and designed for, probing a single device. Other ceramic probe cards have been 50 designed for probing a confined area of a wafer at a narrow temperature range. These probe cards can be permanently damaged and broken if driven into the wafer.

No method is currently known to probe multiple locations over a broad area on a semiconductor wafer. The need to 55 access several locations on a semiconductor wafer will increase as design rules shrink device features, the speed of devices increases, and device shipments continue to grow at high rates. Therefore, there is a need for a way to probe multiple locations on a semiconductor wafer. Further, there is 60 a need for a robust probe card which may probe a wafer at a wide temperature range without breaking.

## SUMMARY OF THE INVENTION

In one embodiment of the present invention, a tile used to hold one or more probes for testing a semiconductor wafer is 2

disclosed. The tile has one or more sites for inserting one or more probes to test the semiconductor wafer. Each site has one or more holes. Each hole is coupled with a slot forming an angle. A probe is inserted into the tile from a top of the tile through the hole and seated on the slot. The probe has a probe tip. The probe top is in contact with the semiconductor wafer at one end of the slot at a bottom of the tile. The probe tip is aligned with an X and Y coordinate of a bond pad on the semiconductor wafer.

### BRIEF DESCRIPTION OF THE DRAWINGS

The present invention is illustrated by way of example by the accompanying drawings, in which like references indicate similar elements and in which:

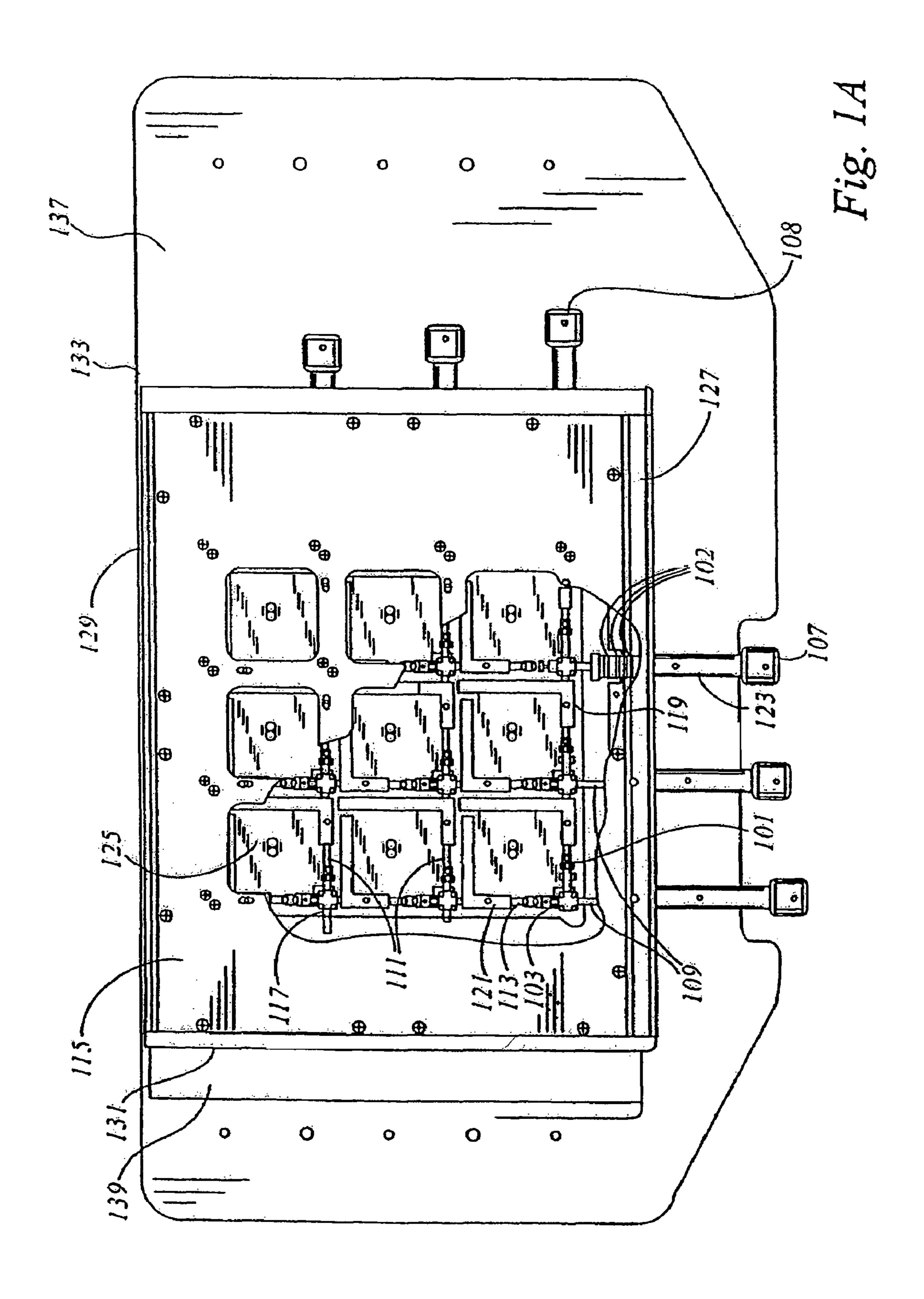

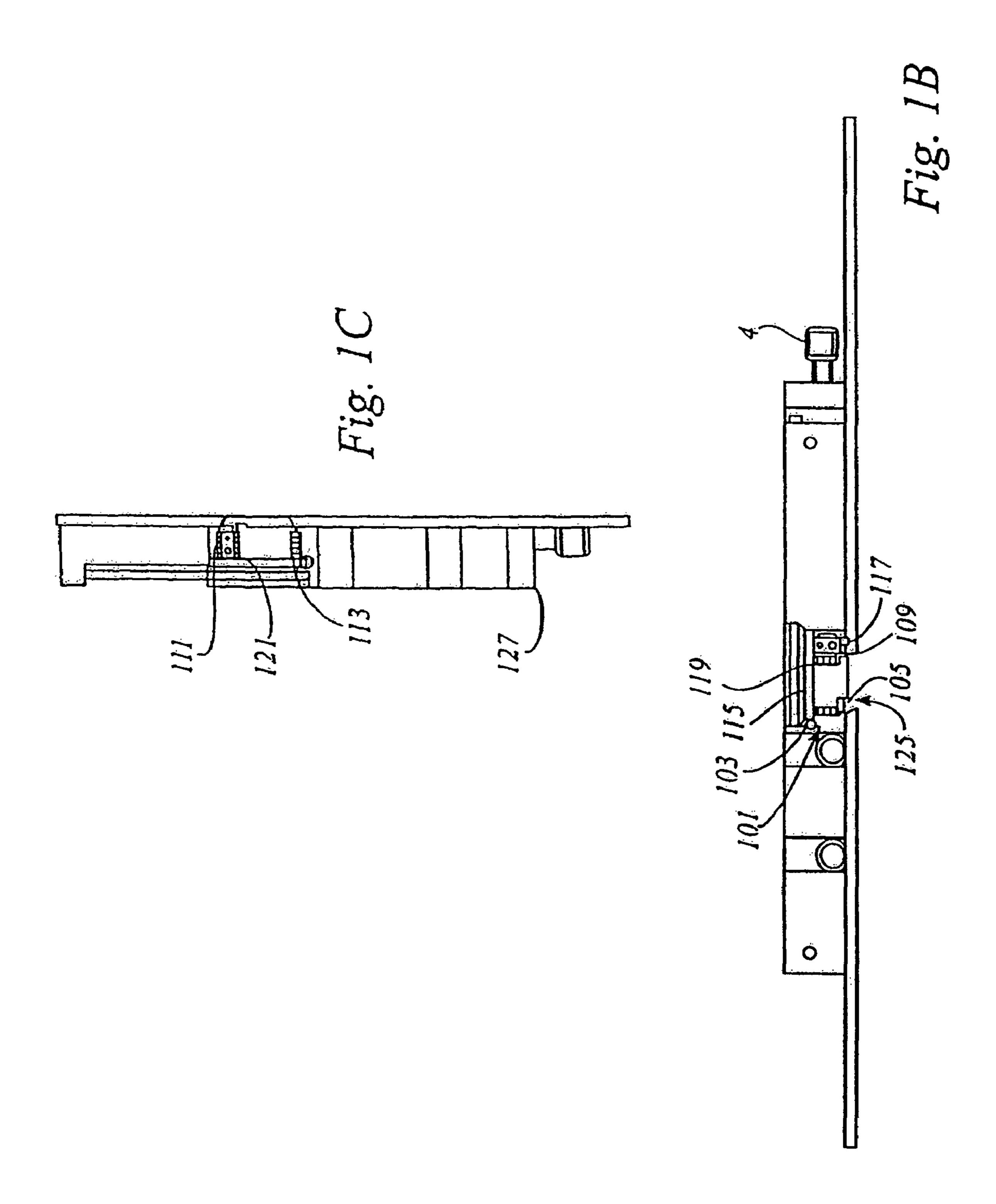

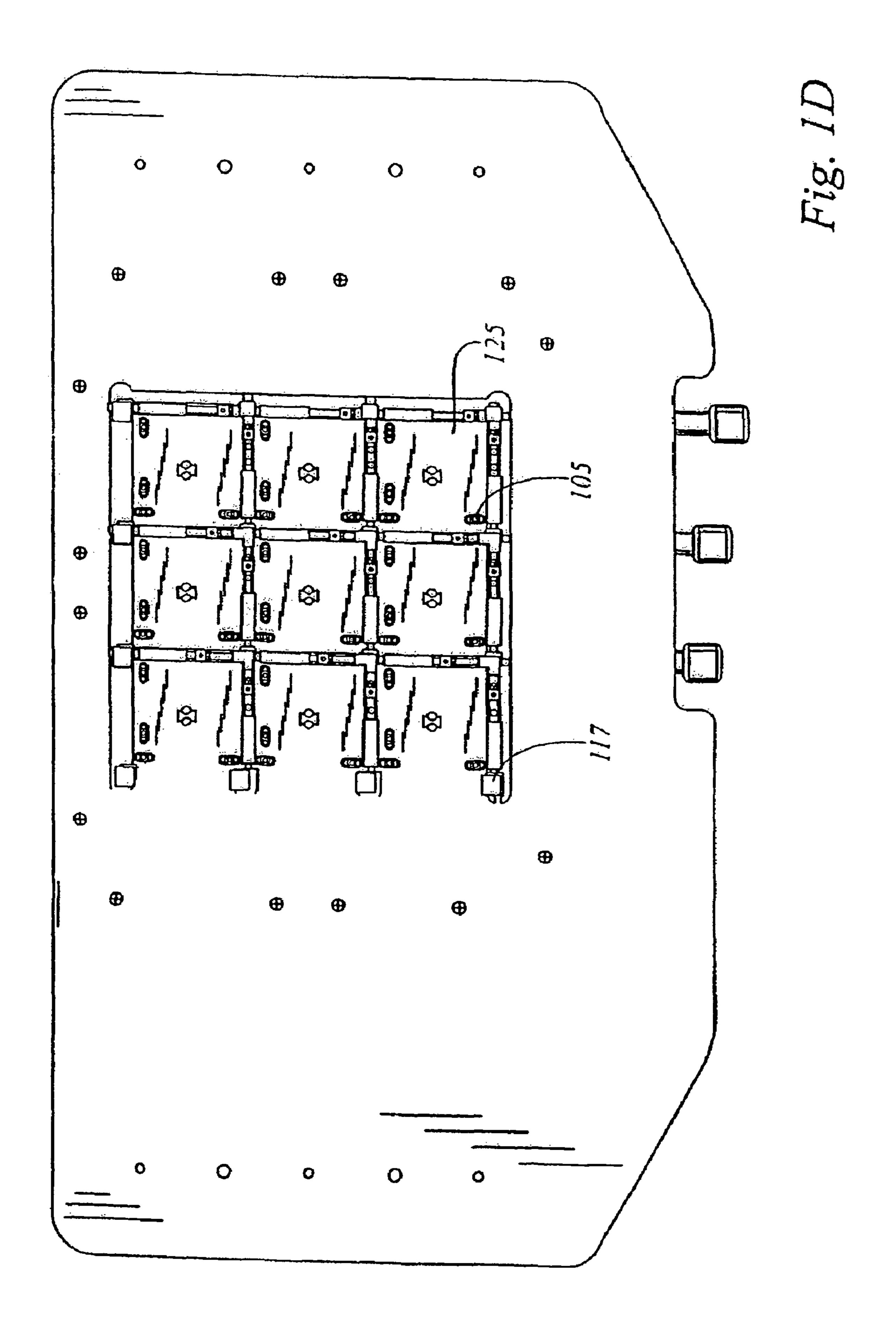

FIGS. 1A, 1B, 1C, 1D show a top, front, and side view, and bottom view of a probe tile and probe platform compatible with the present invention;

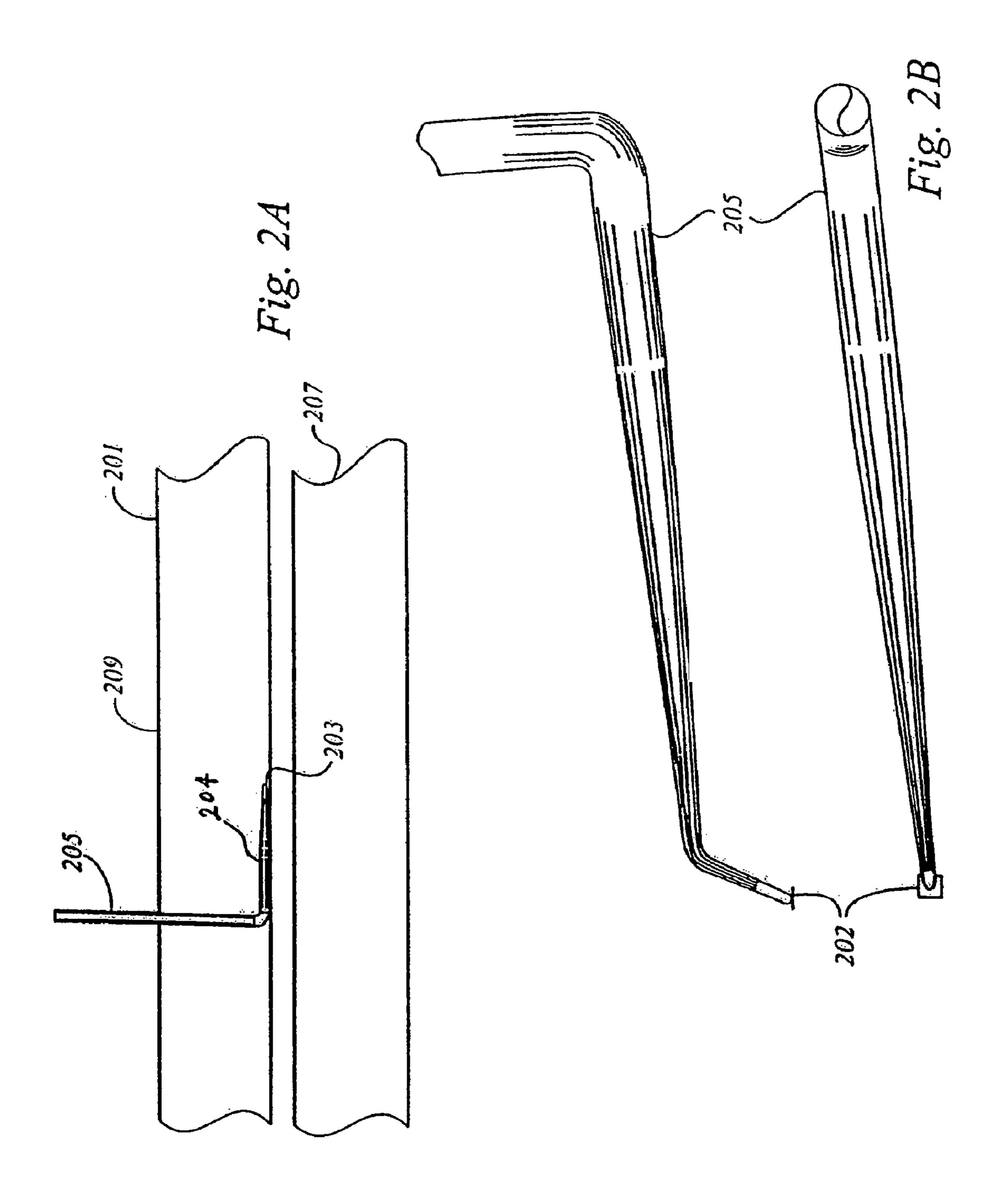

FIG. 2A shows a ceramic tile, probe wire, and a semiconductor wafer detail compatible with the present invention;

FIG. 2B shows an exemplary probe and bond pad compatible with the present invention;

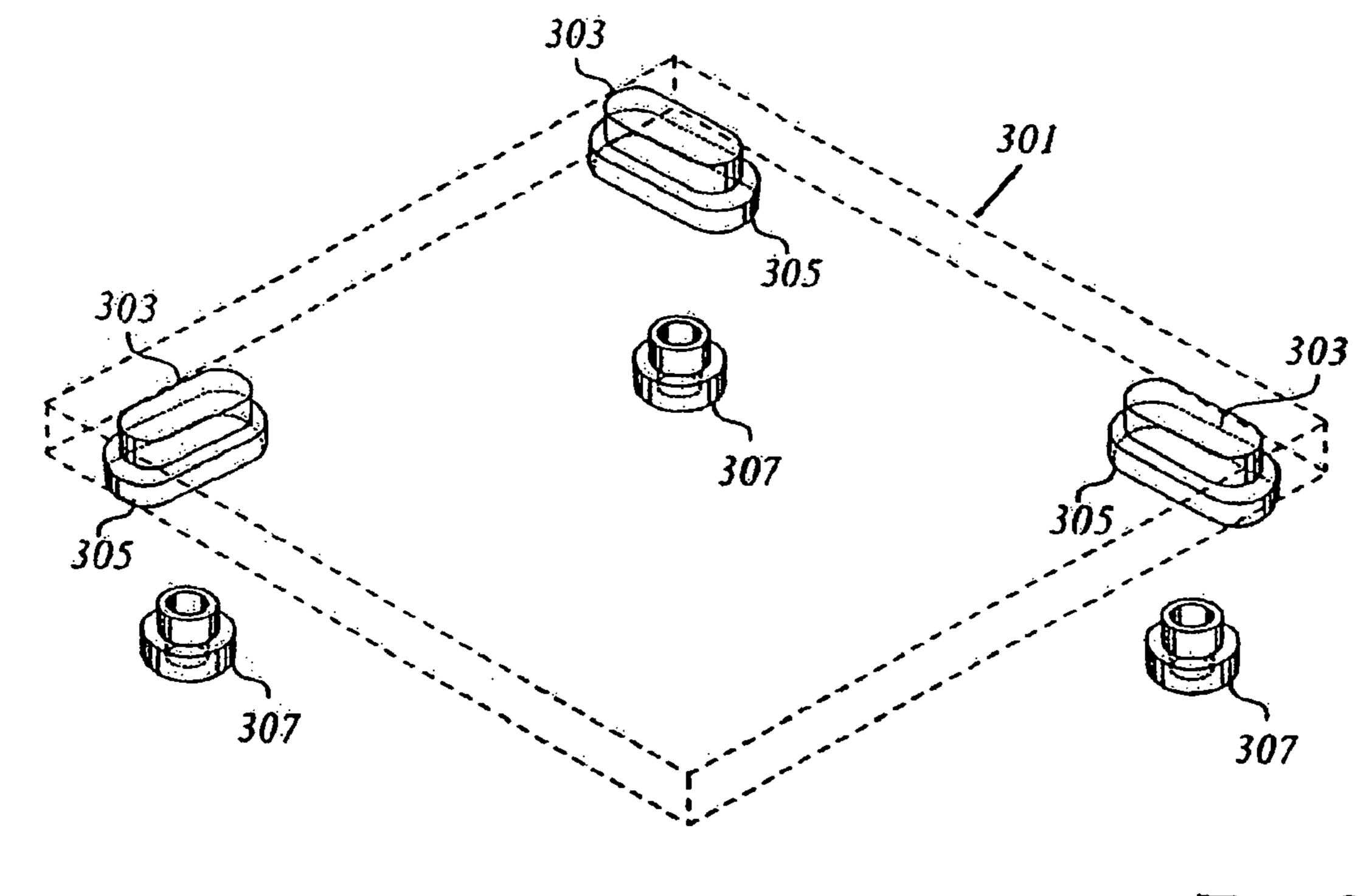

FIG. 3 shows an exploded view of a ceramic tile with tile bushing compatible with the present invention;

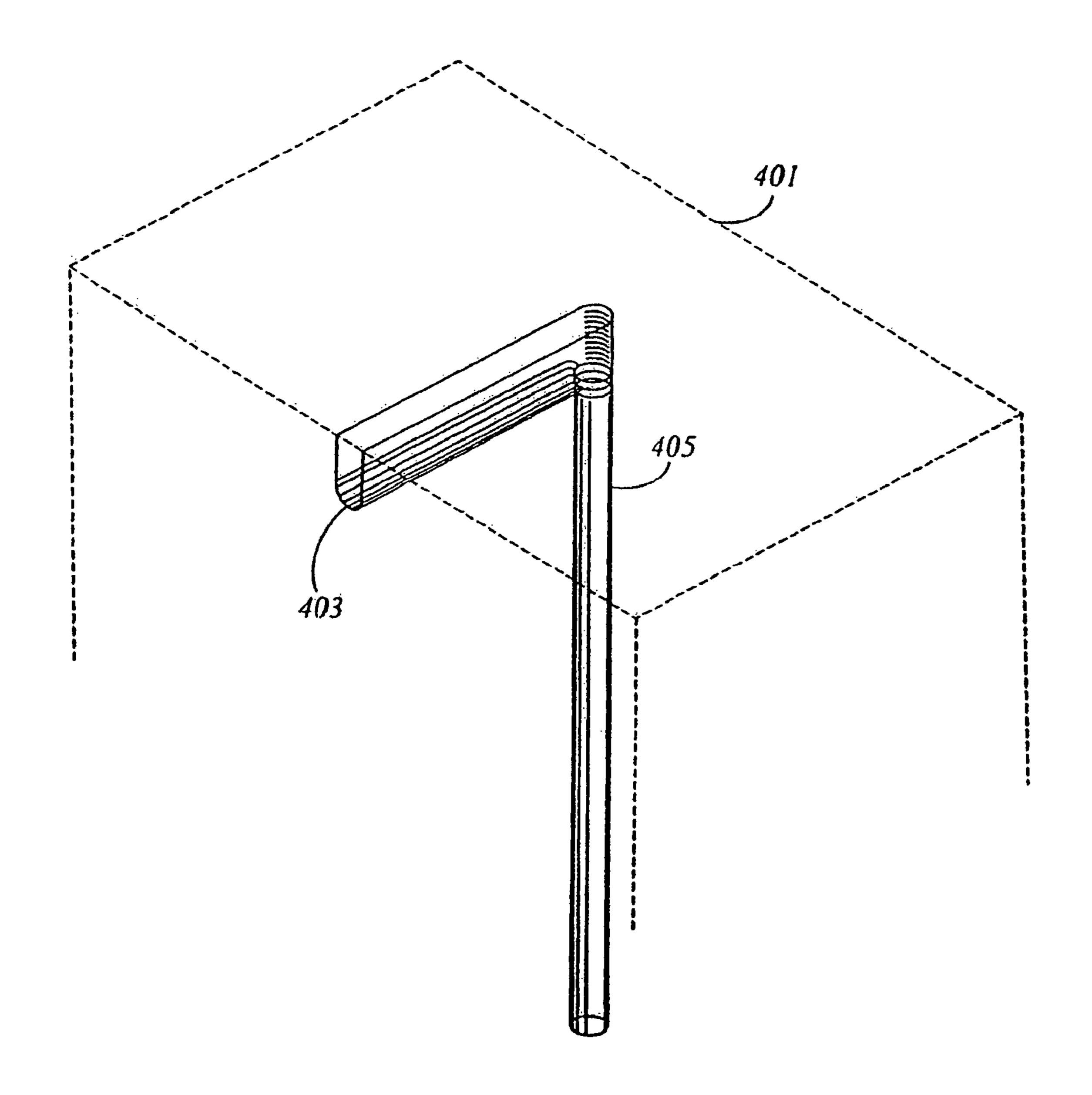

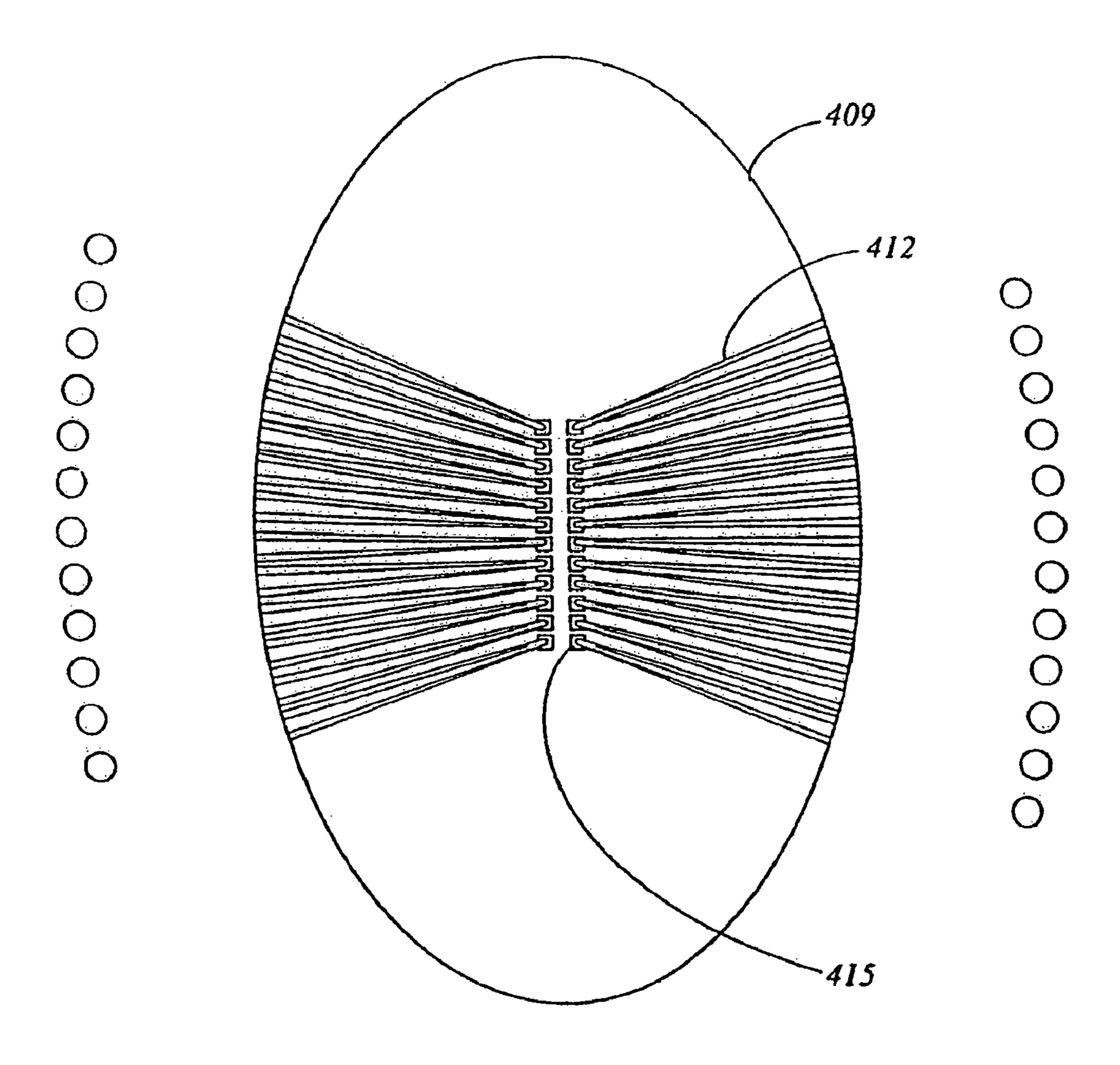

FIG. 4A shows a milled self-aligning hole compatible with the present invention;

FIG. 4B illustrates an exemplary drawing of a plurality of drill holes, machined guides, and view hole compatible with the present invention;

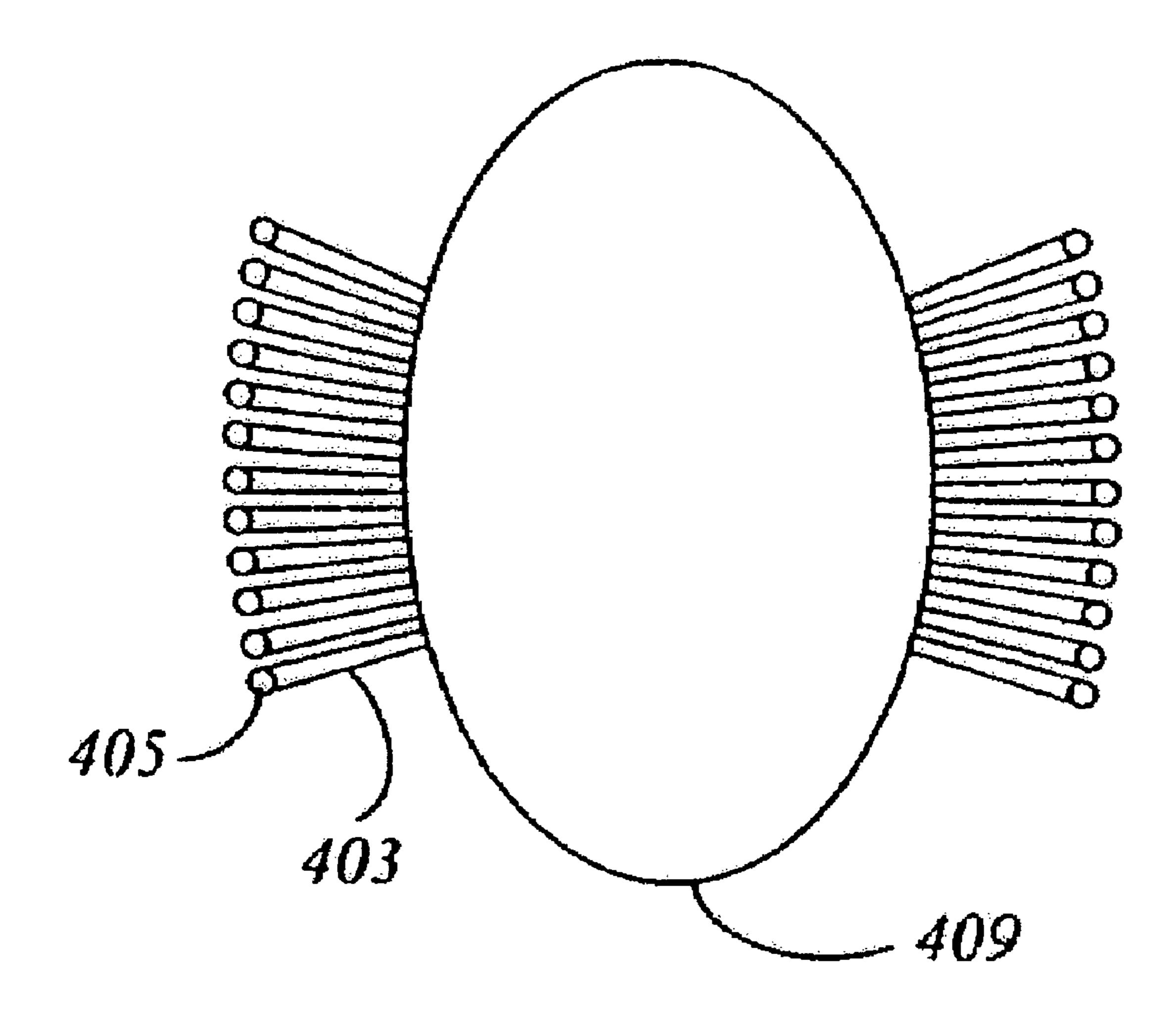

FIG. 4C illustrates an exemplary close up top down view of the view hole showing the plurality of probes.

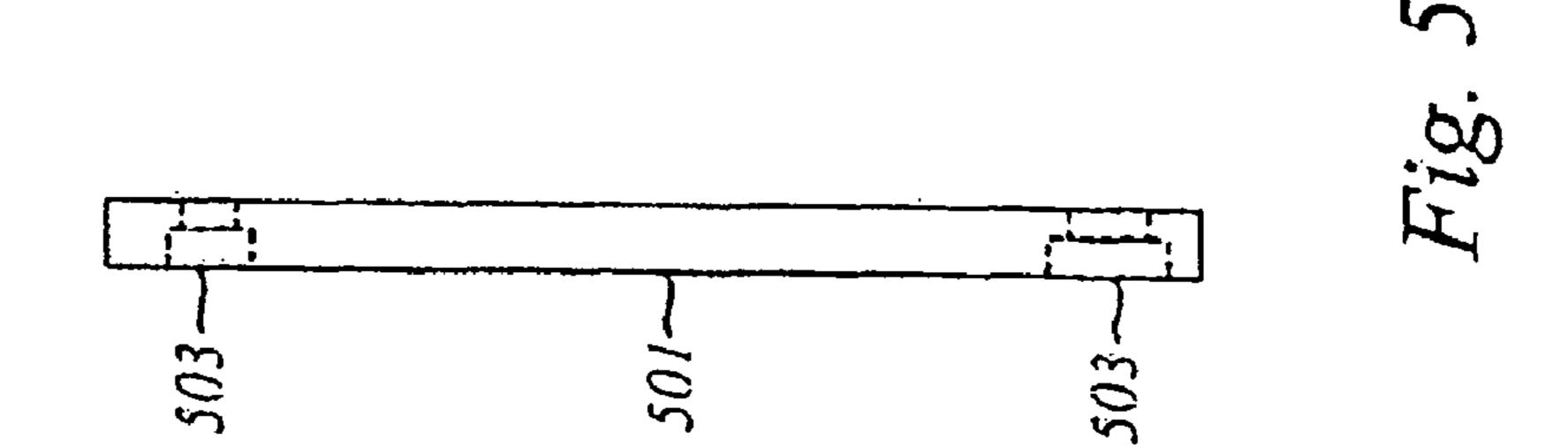

FIG. 5 shows a small square ceramic tile compatible with the present invention;

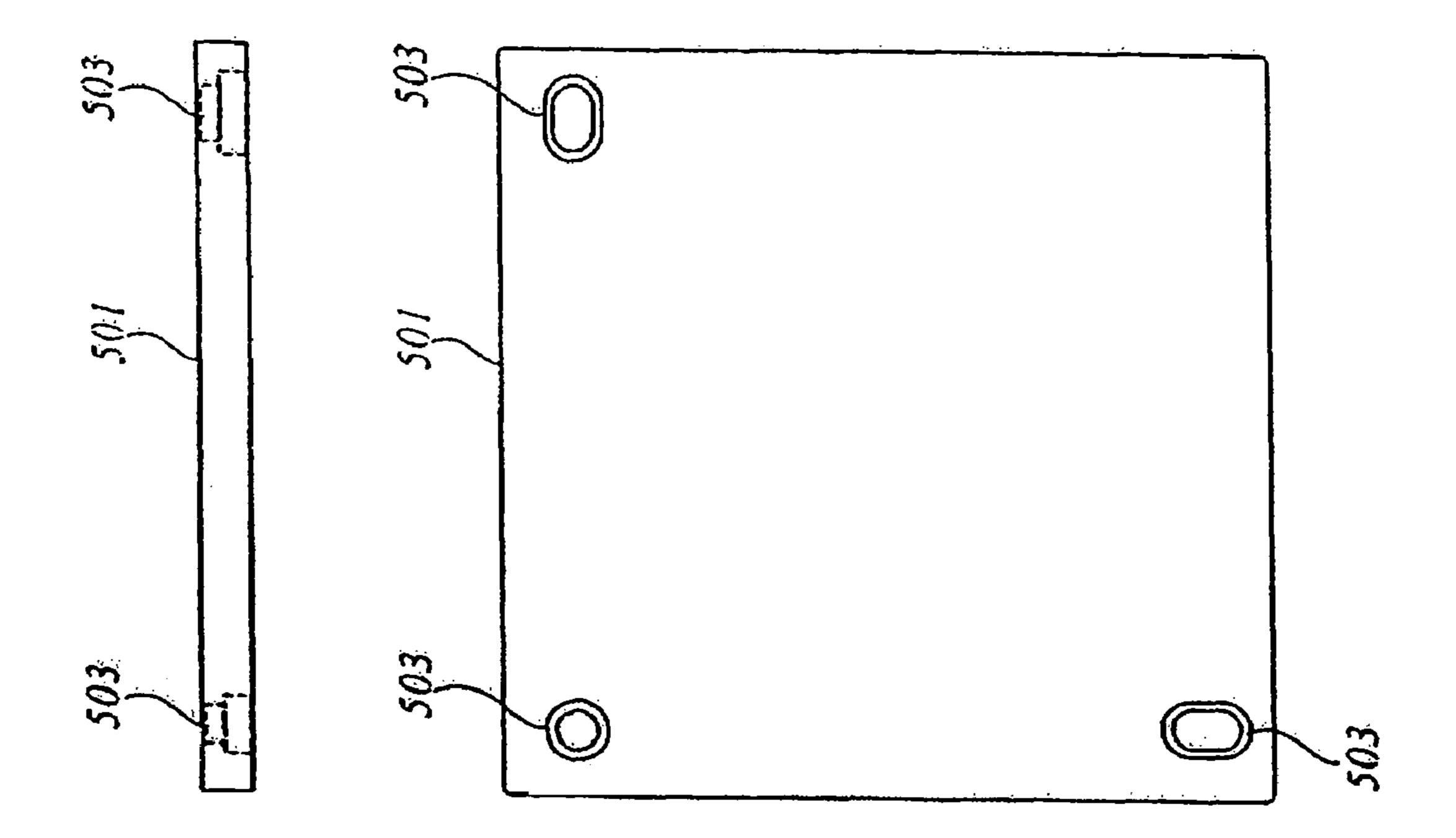

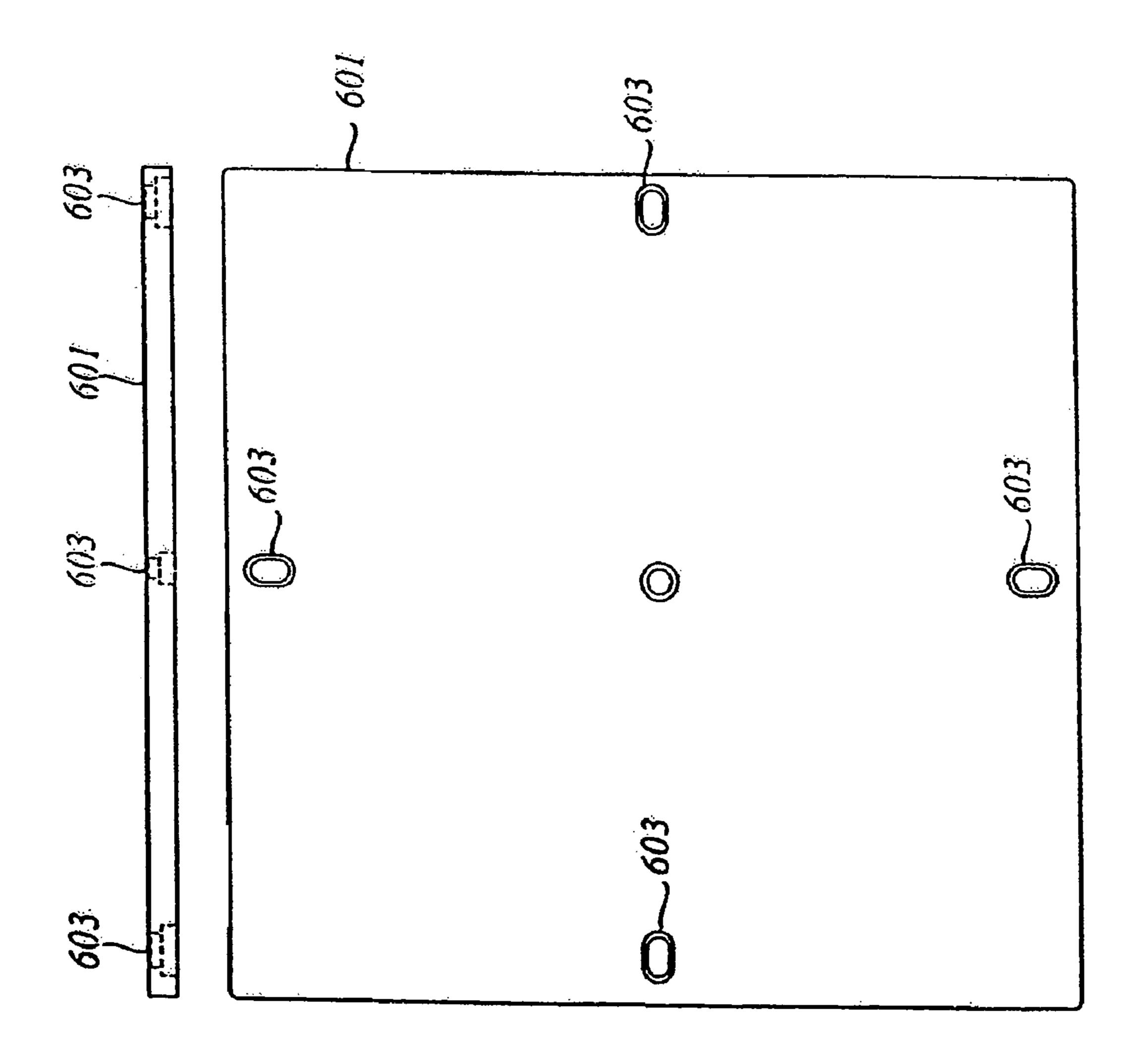

FIG. 6 shows a square ceramic tile compatible with the present invention;

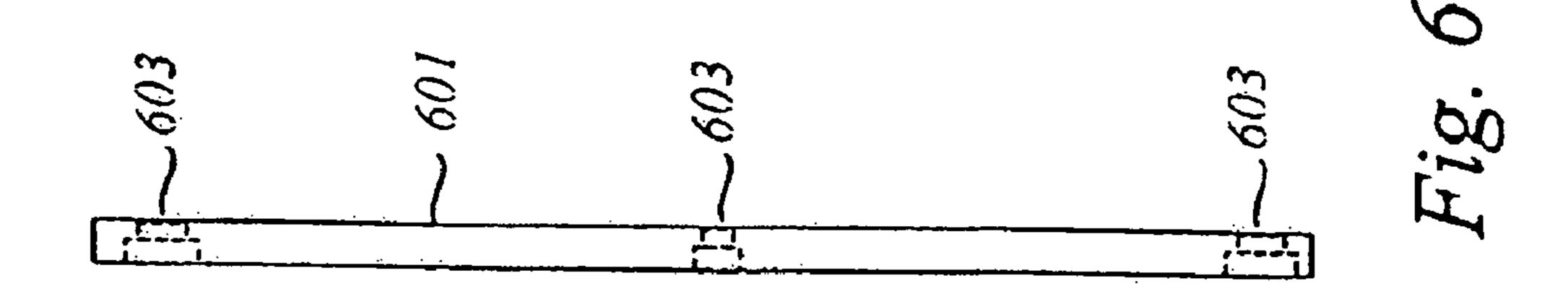

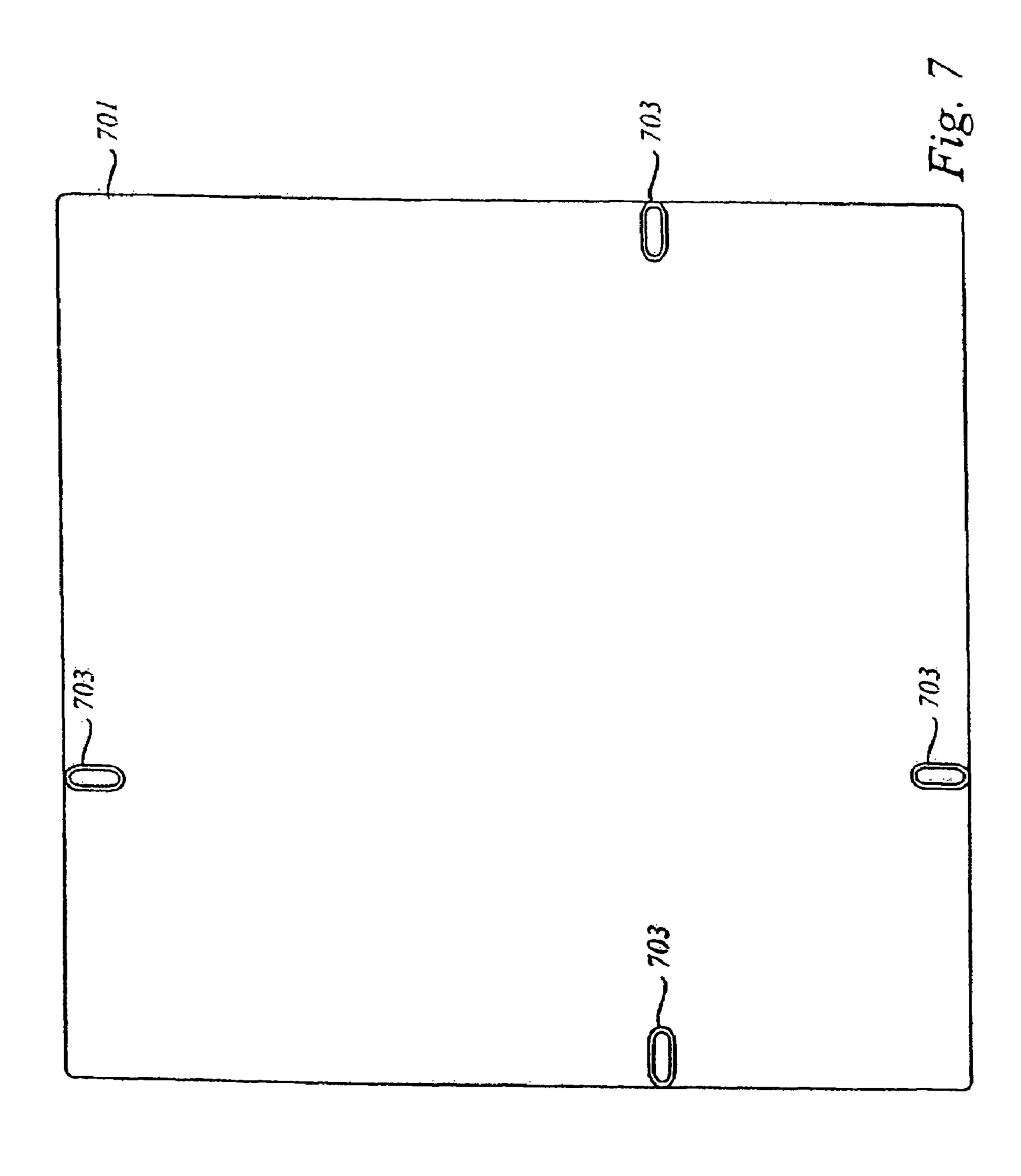

FIG. 7 shows a large square ceramic tile compatible with the present invention;

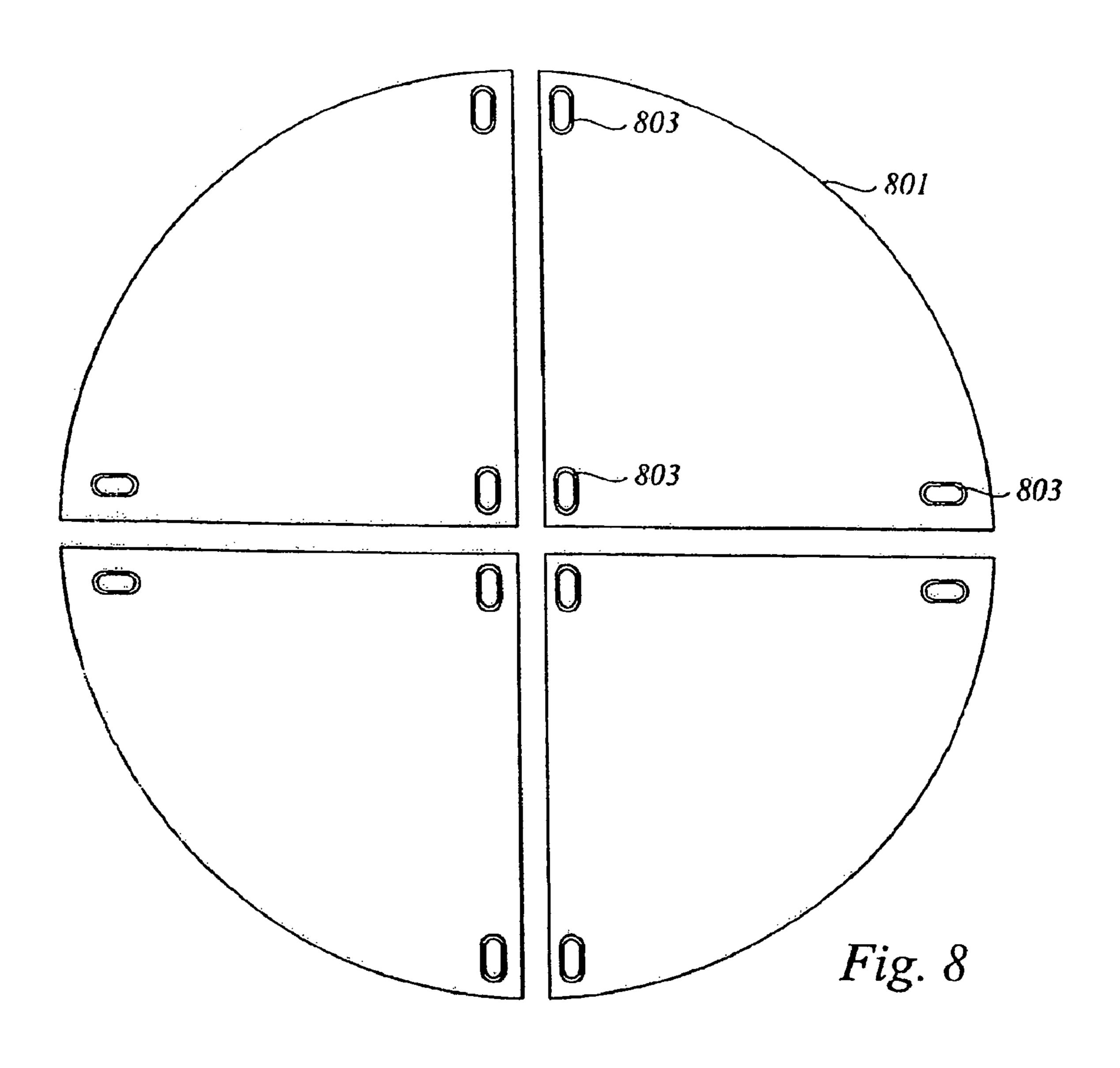

FIG. 8 shows pie shaped ceramic tiles compatible with the present invention;

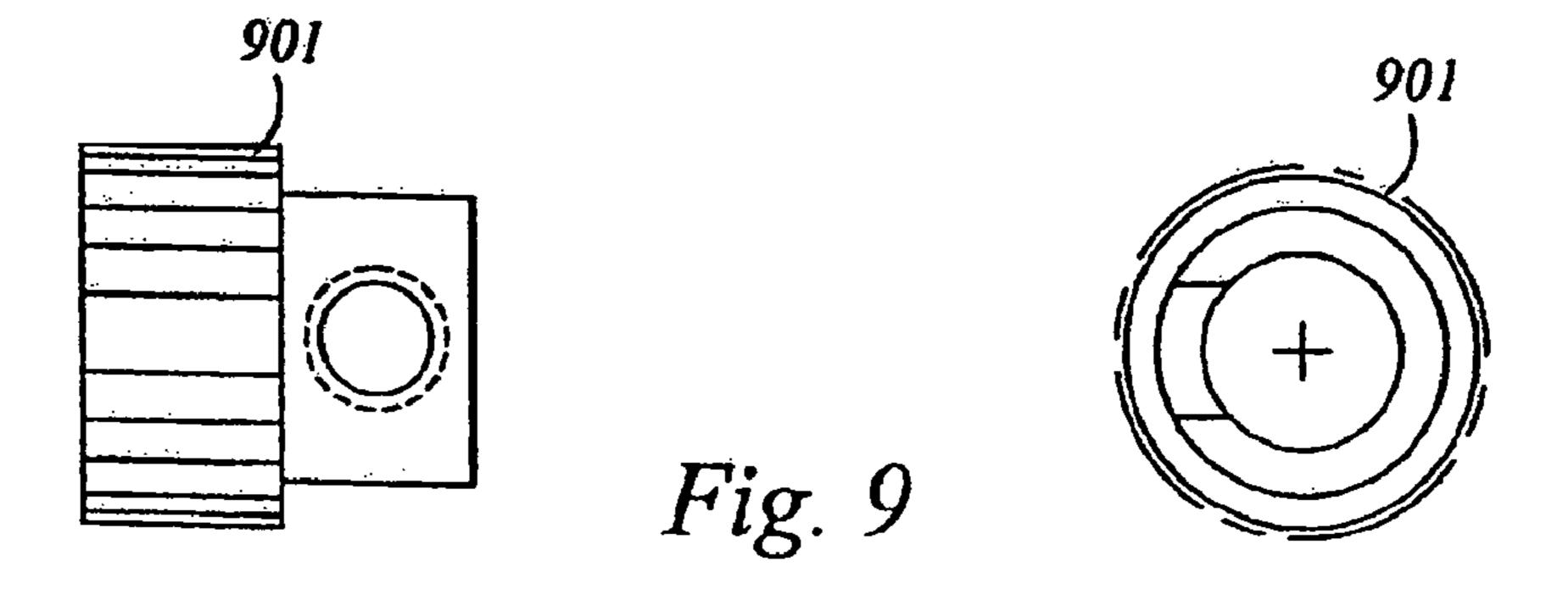

FIG. 9 shows a gear wheel compatible with the present invention.

FIG. 10A is an exemplary illustration of a bottom-up view of a tile with multiple probes.

FIG. 10B is an exemplary illustration of a top-down view of the tile illustrated in FIG. 10A.

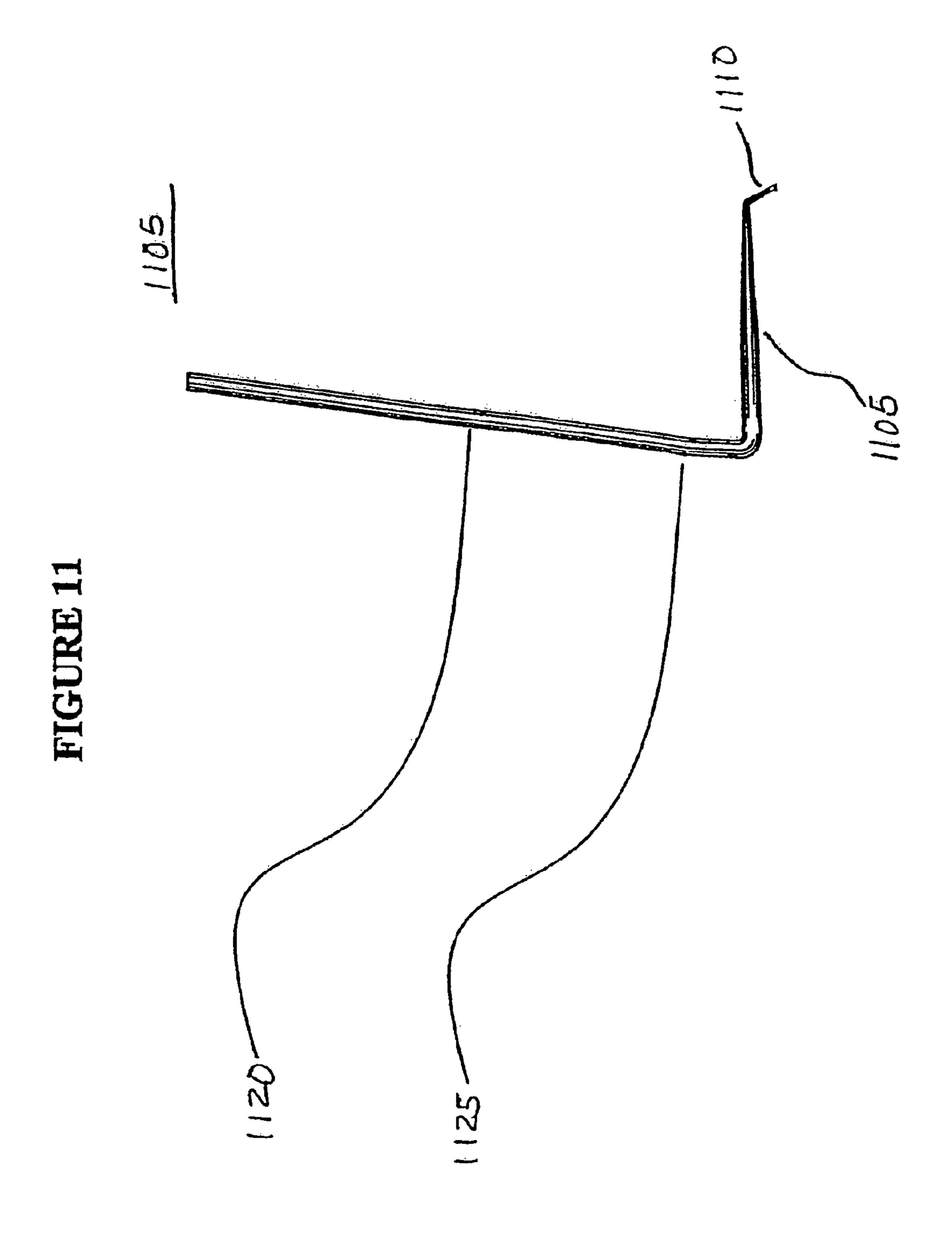

FIG. 11 is an exemplary illustration of one embodiment of a probe in the present invention.

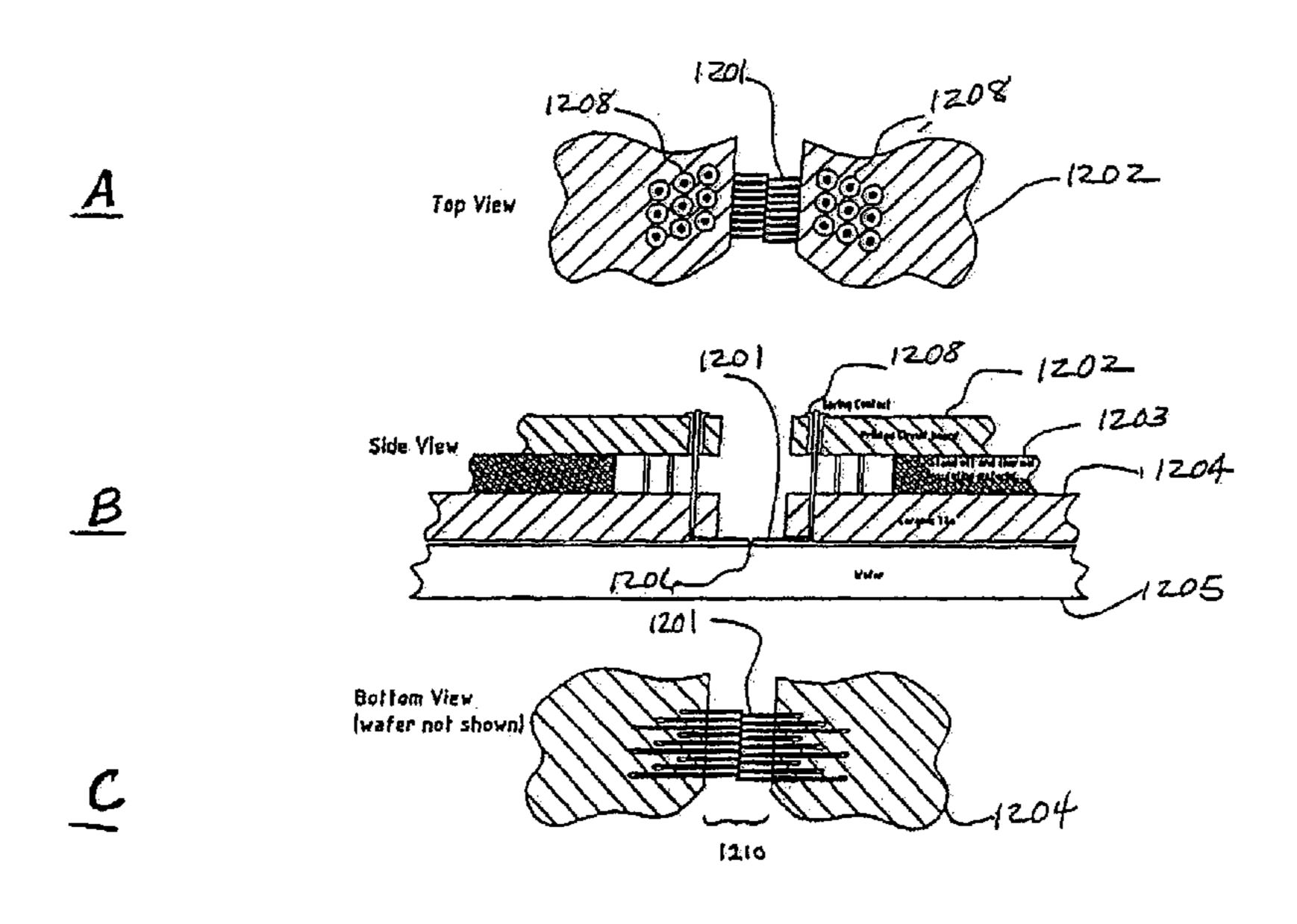

FIGS. 12A, 12B and 12C illustrated one exemplary embodiment of a tile mounted on a PCB configuration used in a high temperature environment.

FIGS. 13A, 13B and 13C illustrate one exemplary embodiment of a tile configuration used in an environment where high temperature is not required.

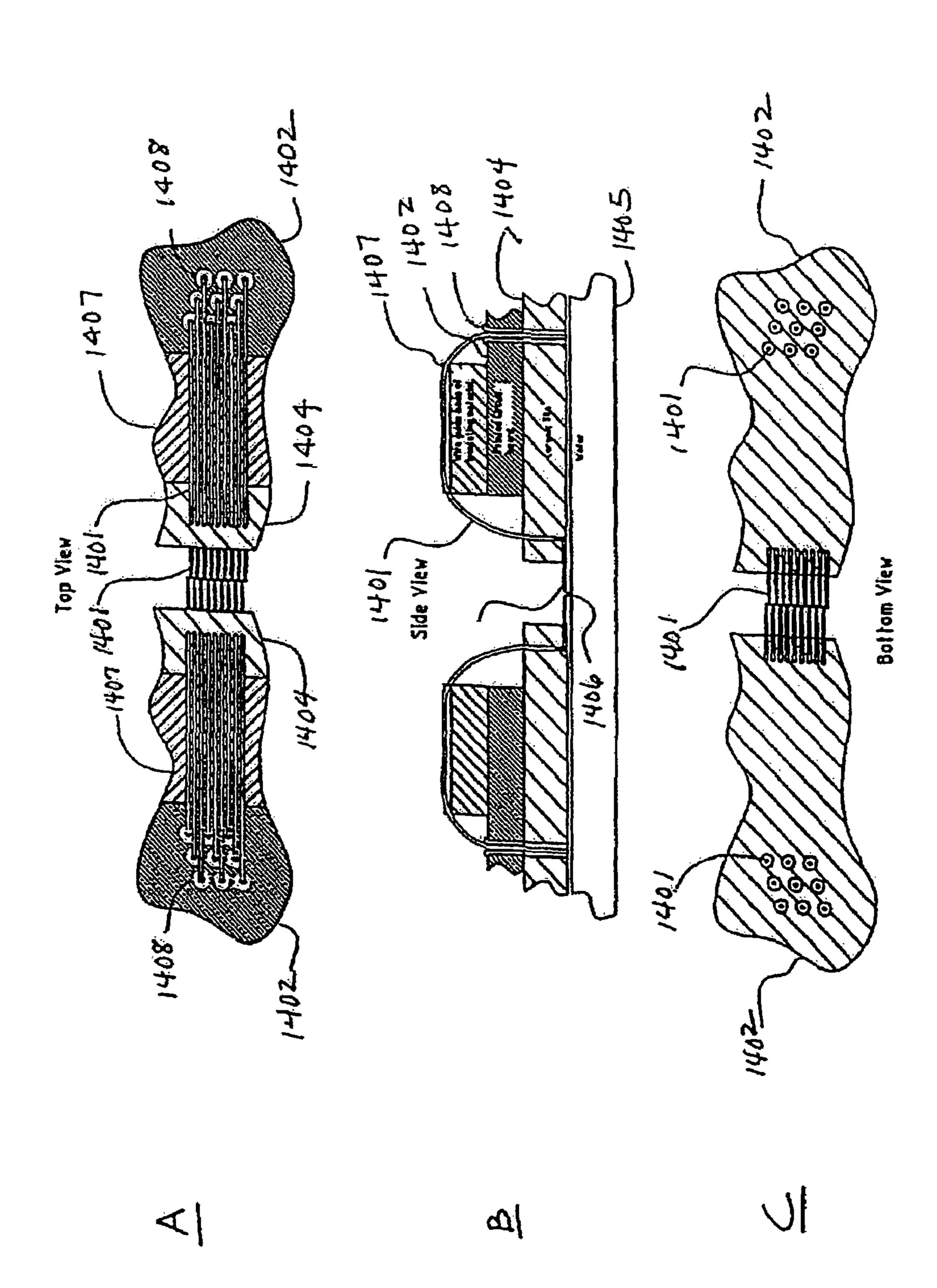

FIGS. 14A, 14B and 14C illustrate one exemplary embodiment of a tile configuration used in an environment where high temperature is not required.

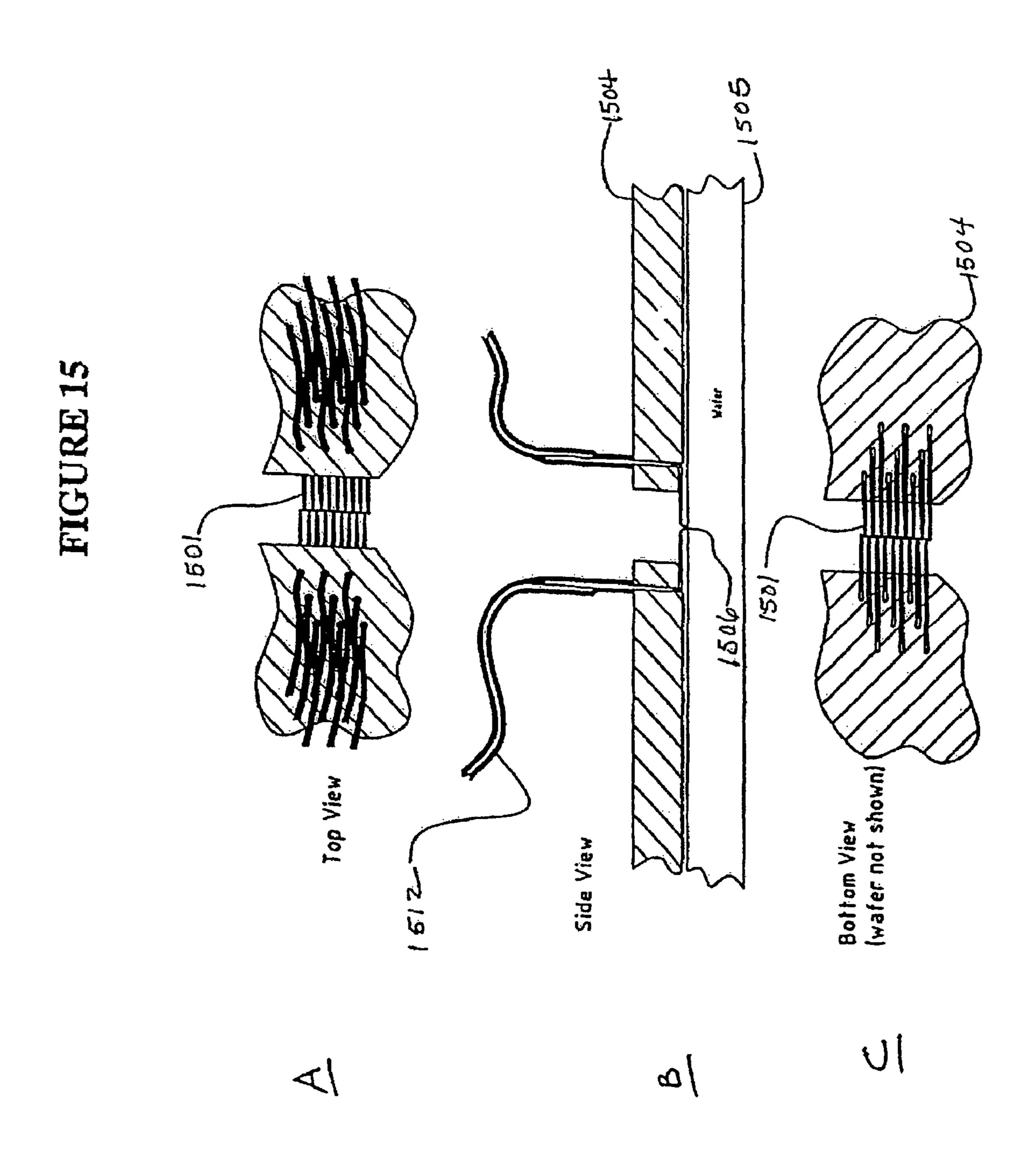

FIGS. 15A, 15B and 15C illustrate one exemplary embodiment of a tile configuration used in an environment where high temperature is not required.

## DETAILED DESCRIPTION

In the following description of a preferred embodiment, reference is made to the accompanying drawings, which form a part hereof, and in which is shown by way of illustration a specific embodiment in which the invention may be practiced. It is to be understood that other embodiments may be utilized

and structural changes may be made without departing from the scope of the present invention.

For purposes of explanation, numerous specific details are set forth in the following description in order to provide a thorough understanding of the present invention. However, it 5 will be evident to one of ordinary skill in the art that the present invention may be practiced without some of these specific details. In other instances, well-known structures and devices are shown in block diagram form in order to facilitate description.

The present invention significantly decreases the amount of time required to probe multiple dies on a semiconductor wafer. The present invention is useful in assisting the determination of semiconductor reliability, and assisting device manufacturers with device development, research and development, process development, yield enhancement, device failure analysis and device testing.

The present invention provides a probe tile and probe platform for electrically probing many semiconductor wafer bond pads over a broad areas of the semiconductor wafer. 20 Nine ceramic tiles are configured in a flat three by three matrix, and are held in a place by a probing platform. The tiles preferably have the dimensions of 1.8 inches (45.7 mm) long, by 1.8 inches (45.7 mm) wide, by 0.125 inches (3.2 mm) high, but it will be recognized by one of ordinary skill in the art that 25 other tile dimensions, for example four inch tiles or six inch tiles, may be used without loss of generality. Each tile may be moved independently in an X and Y direction. FIG. 1A illustrated one embodiment of the probe platform having three side control knobs 108 to move a tile in the X direction and 30 three front controls knobs 107 to move a tile in the Y direction. The front control knobs 107 are attached to front transmission shafts 109, and the side control knobs 108 are attached to side transmission shafts 111. The front and side transmission shafts 109 and 111 slide back and forth into three ball detent 35 positions 102. The ball detent positions 102 determine which tile is engaged and can be manipulated. The front and side control knobs 107 and 108 and ball detent positions 102 are preferably operated by hand, but may also be attached to a motor or other movement mechanism for automatic position- 40 ing and selecting of the semiconductor wafers and dies during testing. It will be recognized by one of ordinary skill in the art that the number of ceramic tiles, control knobs, and transmission shafts may be increased or decreased without loss of generality. For example, the present invention could be con- 45 figured with sixteen tiles having four control knobs and transmission shafts on the side of the platform and four control knobs and transmission shafts on the front of the platform.

A preferred embodiment of the present invention is shown in FIGS. 1A, 1B, and 1C. A round front control knob 107 is 50 connected to a front transmission shaft 109, and a round side control knob 108 is connected to a side transmission shaft 111. The front control knob 107 or the side control knob 108 permits the user to transmit rotational power to a transmission shaft. There are three side control knobs 108 and three side 55 transmission shafts 111 on the right side of the probing platform, and there are three front control knobs 107 and three front transmission shafts 109 on the front of the probing platform.

A front transmission shaft 109 or a side transmission shaft 111 is connected to three gears 101. The front transmission shaft 109 or the side transmission shaft 111 transmits rotational power to the connected gears 101. Each round front control knob 107 and front transmission shaft 109 or each round side control knob 108 and side transmission shaft 111 65 is connected to a round detent strike 123. The detent strike 123, together with a ball plunger 135, permits the user to

4

engage only one gear at a time by sliding it back and forth in three detent positions 102. A gear 101 is connected to a front transmission shaft 109 or a side transmission shaft 109 or the side transmission shaft 111 to a stub shaft gear 103.

The stub shaft gear 103 is connected to a stub shaft 113. The stub shaft gear 103 transmits rotational input from the gears to the stub shaft 113. As the stub shaft 113 rotates, threads move the X-transfer block 119 back and forth in the X direction, or the Y-transfer block 121 back and forth in the Y direction.

The stub shaft 113 and the front transmission shaft 109 or the side transmission shaft 111 are held in place by a square bearing 117. There are preferably sixteen square bearings 117, one located at each corner of the three by three matrix.

A ceramic tile 125 is fastened to the X-transfer block 119 and the Y-transfer block 121 by a round tile bushing 105, and a flag head screw. There are preferably three bushings 105 and three screws used on each tile 125. FIG. 1D illustrates an exemplary bottom view of the platform, showing the square bearings 117, the bushing 105, and the tile 125. The square bearings 117 are preferably held in place by a mounting plate 115. The mounting plate 115 is held in place by front standoff 127, back standoff 129, left standoff 131, and right standoff 133. The standoffs attach to a base plate 137.

A removable clear glass plate 139 is present on the platform. Not shown is a removable opaque cover, roughly conforming to the shape of the mounting plate 115, that may be placed over the glass plate 139 during light sensitive experiments. Also not shown are vacuum couplings, attached to base plate 137, which provide a vacuum to retain the base plate 137 to a probe station.

The base plate 137, as well as certain other portions of the platform, are preferably constructed from stainless steel throughout to permit testing in high temperatures and to provide a thermal coefficient of expansion equal in all parts of the platform.

As shown in FIG. 2A, a ceramic tile 201 holds electrochemically etched tungsten probe tips 203 to permit semiconductor wafer testing over a wide temperature range. The probes 205 are self-aligning and preferably have a high density of 0.020 inch linear pitch. As shown in FIG. 2, the probes configured to fit the tile pattern of the probe platform. The tungsten probes 205 are preferably set into drilled holes in each ceramic tile with high temperature ceramic epoxy, but it will be recognized by one of ordinary skill in the art that the probes may be attached in other ways and by other means without loss of generality. It will also be recognized that while the probes 205 may be made of tungsten, they may also be made of electrically conductive material, such as beryllium copper (BeCu), which does not substantially deform and remains electrically conductive over a wide range of temperatures. FIG. 2B illustrates an exemplary drawing of the probe 205 and the bonding pad 202. As shown in FIG. 3, a ceramic tile 301 includes special mounting holes 303 and guides 305 to allow their connection to the probe platform. Bushings 307 are used to attach the tile to the probe platform.

As shown in FIG. 4A, the tungsten probes are typically placed in precision machined guides 403 and drill holes 405 in the ceramic tile 401 to self align the probes with bond pads on the semiconductor wafer. FIG. 4B illustrates an exemplary drawing of a plurality of drill holes 405, machined guides 403, and view hold 409. The number of probes on a semiconductor wafer is primarily depending upon the semiconductor wafer type and the number of electrical contacts. There may be as little as one probe, or else there may be many probes per semiconductor wafer. Drilled holes 405 and machined guides 403 in the ceramic tiles 401 are provided to accommodate the

tungsten probes. FIG. 4C illustrates an exemplary close up top down view of the view hole showing the plurality of probes. Through the view hole 409, the plurality of probes 412 and the bond pads 415 can be seen. Referring back to FIG. 2A, the semiconductor wafer 207 rests on a semiconductor wafer chuck below the ceramic tile 201 which enables the tungsten probes 205 to then make electrical contact with the bond pad of the semiconductor wafer 207.

View holes **209** may optionally be created through some or all of the ceramic tiles to permit viewing of the semiconductor wafer **207** if required by certain applications. The low profile of the ceramic tiles **201** enables a dry nitrogen environment near the semiconductor wafer **207**, and the optionally present view holes **209** enable the ability to view a device under test (DUT) without breaking the nitrogen environment. To maintain a dry nitrogen environment, a clear glass plate is placed in the platform, forming a seal with the platform. The seal may be a loose seal if a positive pressure nitrogen environment is maintained. Alternatively, the seal may be gas-tight if a non-positive pressure nitrogen environment is used.

Alternative embodiments of ceramic tiles which may be used with the present invention are shown in FIGS. 5, 6, 7, and 8. As shown in FIG. 5, a preferred embodiment of the tile may be a 62 mm×62 mm square tile **501** having three retainer slots **503**, one each of the retainer slots **503** being located in three 25 of the four corners of the tile. As shown in FIG. 6, an alternative embodiment of the tile may be a 110 mm×110 mm square tile 601 having four retainer slots 603, one each of the retainer slots 603 being located along each edge of the tile and substantially centered along each side. As shown in FIG. 7, an 30 alternative embodiment of the tile may be a 160 mm×160 mm square tile 701 having four retainer slots 703, one each of the retainer slots 703 being located along each edge of the tile and substantially off-centered along each side. As shown in FIG. 8, another alternative embodiment of the tile may be pie 35 shaped tiled 801 with a combined radius of 200 mm square, each tile having three retainer slots 803, one each of the retainer slots 803 being located in each of the three corners of a tile 801. It will be recognized by one of ordinary skill in the art that the dimensions of a tile, and the number and place- 40 ment of retainer slots on a tile may vary from the embodiments described about without loss of generality.

A preferred gear wheel **901** is shown in FIG. **9**, showing a side view and a front view. A gear wheel **901** is attached to the front transmission shafts **109** and to the side transmission 45 shafts **111**, as shown by gears **101** in FIG. **1**. The gear wheels engage each other and transmit rotational power from a front transmission shaft **109** or a side transmission shaft **111** to move a probe tile in the direction of either the X direction or Y direction.

The tile and probe platform discussed above together form the probe card to electrically probe many semiconductor wafer bond pads over a broad area of a semiconductor wafer. The platform positions the tile over the semiconductor wafer. The tile can be replaced without replacing the platform. Fur- 55 thermore, tiles of different sizes can be used with the platform to accommodate change in devices and wafer requirements. This is advantageous over the existing probe card technology (e.g., epoxy ring probe cards, ceramic blade probe cards, etc.). For example, the probes on the epoxy ring probe card 60 are epoxyed in place on a substrate, and the ceramic blades on the ceramic probe cards are soldered in place. The tiles in the present invention are constructed of a rigid ceramic to provide thermal, mechanical and electrical characteristics to allow the tiles to perform in high temperature over a long period of 65 time. The tiles and the stainless steel probe platform allow the probe card to operate in a wide temperature range (e.g., -65

6

degrees Celsius to 300 degrees Celsius) or at low current leakages at one site or at multiple sites. This is advantageous over the existing probe card technology, which normally operates in a narrower temperature range.

In one embodiment, the tile described above may be mounted on a printed circuit board (PCB) to test the wafer. In this case, the tile is held in place by the PCB instead of by the platform. The tile can be in different sizes and thickness. For example, when mounted on the PCB, the tile can be round, square, rectangular or hexagonal, from 30 mm in diameter to 210 mm in diameter. The thickness varies (e.g., 3 mm to 9 mm) depending on the stiffness required. One or more probes are mounted on the tile. The probes are used to electrically probe multiple devices or multiple sites depending on the layout of the semiconductor wafer to be probed.

The probes are placed into the tile according to the bond pad pattern. As discussed above, the tile is designed with slots (or grooves) and drilled holes to accommodate the probes. The slot and drilled holes are fabricated into the tile in a manner that allows the seated probe to be aligned with the X and Y coordinates of the bond pad on the semiconductor wafer. The slot forces a specific X, Y and Z orientation of the probe. In one embodiment, the slot and the drilled hole form a 90 degree angle (e.g., "L" shape) to help the probe self align with the bond pad. Each probe is inserted into the drilled hole and seats itself into the slot.

FIG. 10A is an exemplary illustration of a bottom-up view of a tile with multiple probes. In this example, the probes are mounted in nine sites across the tile 1013. Also illustrated in FIG. 10A are the retainer slots 1010, the probes 1012 at each of the nine locations and the view hole 1011. Each of the probes 1012 can be removed from its slot and drilled hole without disturbing adjacent probes. The number of sites on the tile, the number of probes accommodated by the tile, the positions of the probes, and the size of the tile vary depending on the area of coverage and the number of sites to be probed.

The probes may be connected to wires to interface with a test system. The probes may also be connected to the PCB using a permanent solder connection or a spring contact pin receptacle. The spring contact permits quick replacement of any damaged probes. FIG. 10B is an exemplary illustration of a top-down view of the tile illustrated in FIG. 10A. The tile is shown without the PCB or the wire interface.

FIG. 11 is an exemplary illustration of one embodiment of a probe in the present invention. The probe 1105 is FIG. 11 comprises a probe tip 1110, a beam or cantilever 1115, and the vertical shank 1120 that goes through the tile. The probe tip 1110 is the bent down end of the probe 1105 that touches the bond pad. When the probe tip 1110 is damaged or worn out the entire probe 1105 is replaced. The probe 1105 is different from the probe 205 in FIG. 2A and FIG. 2B. The vertical shank of the probe 205 in FIG. 2A and FIG. 2B is straight, whereas the vertical shank 1120 of the probe 1105 in FIG. 11 has a kink at location 1125. The kink is advantageous because it provides a spring action to the probe 1105 to firmly retain the probe 1105 in the drilled hole and slot of the tile.

FIGS. 12A, 12B and 12C illustrate on exemplary embodiment of a tile mounted on a PCB configuration used in a high temperature environment. FIG. 12A illustrates a top view, FIG. 12B illustrates a side view, and FIG. 12C illustrates a bottom view. The tile 1204 is mounted onto the PCB 1202. A stand off and thermal insulating material 1203 allows the tile 1204 from the PCB 1202. The insulating material 1203 allows the tile 1204 to be used at high temperatures without causing deterioration of the PCB 1202 that has a lower operating temperature. The probe 1201 is attached to the PCB 1202 using a spring contact pin receptacle 1208. The probe tip of

the probe 1201 is in contact with the semiconductor wafer bond pad 1206 to probe the semiconductor wafer 1205. The space 1210 represents the opening in the view hole.

FIGS. 13A, 13B and 13C illustrate one exemplary embodiment of a tile configuration used in an environment where high temperature is not required. FIG. 13A illustrates a top view, FIG. 13B illustrates a side view, and FIG. 13C illustrates a bottom view. The tile 1304 is mounted onto the PCB 1302. There is no stand off thermal insulating material between the tile 1304 and the PCB 1302 because this embodiment is not used in high temperature environments. The probe 1301 is attached to the PCB 1302 using a spring contact pin receptacle 1308. The probe tip of the probe 1301 is in contact with the semiconductor wafer bond pad 1306 to probe the semiconductor wafer 1305.

FIGS. 14A, 14B and 14C illustrate one exemplary embodiment of a tile configuration used in an environment where high temperature is not required. FIG. 14A illustrates a top view, FIG. 14B illustrates a side view, and FIG. 14C illustrates a bottom view. The tile 1404 is mounted onto the PCB 1402. In this embodiment, a wire guide is used to provide various probe patterns by swapping the tiles on one PCB. There is no stand off thermal insulating material between the tile 1504 and the PCB 1502 because this embodiment is not used in high temperature environments. The probe 1401 is attached to the PCB 1402 using a spring contact pin receptacle 1408. The probe tip of the probe 1401 is in contact with the semiconductor wafer bond pad 1406 to probe the semiconductor wafer 1405. The wire guide 1407 is made of an 30 insulating material.

FIGS. 15A, 15B and 15C illustrate one exemplary embodiment of a tile configuration used in an environment where high temperature is not required. FIG. 15A illustrates a top view, FIG. 15B illustrates a side view, and FIG. 15C illustrates a bottom view. In this embodiment, each probe 1501 is attached to an insulated wire 1512. There is no spring contact pin receptacle when quick removal and replacement of the probe 1501 is not required. Furthermore, there is no stand off thermal insulating material used with the tile 1504 because 40 this embodiment is not used in high temperature environments. The probe 1501 is attached to the tile 1504 semi permanently with epoxy. The probe tip of the probe 1501 is in contact with the semiconductor wafer bond pad 1506 to probe the semiconductor wafer 1505.

Thus what has been described is a tile and a probe used for electrically conductive probing of semiconductor wafer. The tile is specifically designed with slots and drilled holes to accommodate a probe. The probe can be inserted into any drilled holes in the tile. Each probe may be designed with a 50 kink to help keep the probe seated in the tile. When quick removal is necessary, the probe can be held in place by using spring contact pin receptable. The probe is fabricated in an angle including a kink to act as a spring to retain the probe in the drilled hole of the tile. Typically, the probe described 55 above is made of tungsten. However, the probe can also be fabricated using other conductive alloy or similar materials. In addition, although the invention describes probing the semiconductor wafer, one skilled in the art would recognize that the invention may also be used to test a multi-chip module 60 and other substrates.

8

From the above description and drawings, it will be understood by those of ordinary skill in the art that the particular embodiments shown and described are for purposes of illustration only and are not intended to limit the scope of the invention. Those of ordinary skill in the art will recognize that the invention may be embodied in other specific forms without departing from its spirit or essential characteristics. References to details of particular embodiments are not intended to limit the scope of the claims.

What is claimed is:

- 1. In a semiconductor wafer testing system where one or more probes are used to test a semiconductor wafer, a tile is used to hold the one or more probes for making contact with the semiconductor wafer, the tile comprising:

- one or more holes, each hole coupled with a slot forming an angle,

- the hole is receivable of a probe through a top of the tile, and

- the slot has an end at a bottom of the tile, the slot is receivable of a probe tip of the probe so as to allow contact with a semiconductor wafer at the end of the slot at the bottom of the tile, the hole and slot are configured so as to allow the probe tip to align with an X and Y coordinates of a bond pad on the semiconductor wafer.

- 2. The tile of claim 1, wherein the angle formed by the hole and the slot is 90 degrees.

- 3. The tile of claim 1 further comprising a view hole view the probe tip.

- 4. In a semiconductor wafer testing system where one or more probes are used to test a semiconductor wafer and where a tile is used to hold the one or more probes for making contacts with the semiconductor wafer, the probe comprising: a probe tip;

- a cantilever coupled with the probe tip; and

- a vertical shank coupled with the cantilever, the vertical shank forming an angle with the cantilever, the vertical shank and cantilever are configured to align the probe tip with an X and Y coordinates of a bond pad on a semiconductor wafer,

- wherein the probe is insertable into a tile through a hole in the tile, and the vertical shank has a kink, the kink is configured to retain the probe in the tile.

- 5. The probe of claim 4, wherein the angle formed by the vertical shank and the cantilever is 90 degrees.

- 6. The probe of claim 4, wherein the kink in the vertical shank is configured to spring against a wall of the hole in the tile to hold the probe in place.

- 7. The probe of claim 4, wherein the probe tip includes a bent down end.

- 8. The probe of claim 4, wherein the probe is removable from the tile without affecting other remaining probes.

- 9. The probe of claim 4, wherein the probe is attached to the tile with epoxy.

- 10. The probe of claim 4, wherein the probe is attached to an insulated wire.

- 11. The probe of claim 4, further comprising a wire guide attached to the probe, the wire guide is made of an insulating material.

- 12. The probe of claim 11, wherein the wire guide is configured to provide a probe pattern.

\* \* \* \* \*