### US007902660B1

### (12) United States Patent

### Lee et al.

## (10) Patent No.: US 7,902,660 B1 (45) Date of Patent: Mar. 8, 2011

### (54) SUBSTRATE FOR SEMICONDUCTOR DEVICE AND MANUFACTURING METHOD THEREOF

(75) Inventors: **Kyu Won Lee**, Seoul (KR); **Doo Hyun**

Park, Gyeonggi-do (KR); Dong Hee

Kang, Gyeonggi-do (KR)

(73) Assignee: Amkor Technology, Inc., Chandler, AZ

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 241 days.

- (21) Appl. No.: 11/440,548

- (22) Filed: May 24, 2006

- (51) **Int. Cl.**

$H01L\ 23/04$  (2006.01)

- (52) **U.S. Cl.** ...... **257/698**; 257/700; 257/E21.507

### (56) References Cited

### U.S. PATENT DOCUMENTS

| 2,596,993 A   | 5/1952  | Gookin                |

|---------------|---------|-----------------------|

| 3,435,815 A   | 4/1969  | Forcier 125/16        |

| 3,734,660 A   | 5/1973  | Davies et al 425/123  |

| 3,781,596 A * | 12/1973 | Galli et al 361/751   |

| 3,838,984 A   | 10/1974 | Crane et al 29/193.5  |

| 4,054,238 A   | 10/1977 | Lloyd et al           |

| 4,189,342 A   | 2/1980  | Kock 156/656          |

| 4,258,381 A   | 3/1981  | Inaba 357/70          |

| 4,289,922 A   | 9/1981  | Devlin                |

| 4,301,464 A   | 11/1981 | Otsuki et al 357/70   |

| 4,332,537 A   | 6/1982  | Slepcevic 425/121     |

| 4,417,266 A   |         | Grabbe                |

| 4,451,224 A   | 5/1984  | Harding 425/548       |

| 4,530,152 A   | 7/1985  | Roche et al 29/588    |

| 4,541,003 A   | 9/1985  | Otsuka et al 357/74   |

| 4,646,710 A   | 3/1987  | Schmid et al 125/16 R |

| 4,707,724 A   | 11/1987 | Suzuki et al 357/71   |

|               |         |                       |

| 4,727,633 A | 3/1988 | Herrick 228/122         |

|-------------|--------|-------------------------|

| 4,729,061 A | 3/1988 | Brown                   |

| 4,737,839 A | 4/1988 | Burt 357/67             |

| 4,756,080 A | 7/1988 | Thorp, Jr. et al 29/827 |

| 4,812,896 A | 3/1989 | Rothgery et al 357/70   |

| 4,862,245 A | 8/1989 | Pashby et al 357/70     |

| 4,862,246 A | 8/1989 | Masuda et al 357/70     |

| 4,907,067 A | 3/1990 | Derryberry 357/74       |

| 4.920.074 A | 4/1990 | Shimizu et al.          |

#### (Continued)

### FOREIGN PATENT DOCUMENTS

DE 197 34 794 7/1998

(Continued)

### OTHER PUBLICATIONS

Sheridan et al., U.S. Appl. No. 10/868,244, filed Jun. 15, 2004, entitled "Embedded Leadframe Semiconductior Package".

(Continued)

Primary Examiner — Charles D Garber

Assistant Examiner — Pape Sene

(74) Attorney, Agent, or Firm — Gunnison, McKay & Hodgson, L.L.P.; Serge J. Hodgson

### (57) ABSTRACT

A substrate for a semiconductor device and a manufacturing thereof, and a semiconductor device using the same and a manufacturing method thereof are disclosed. For example, in the substrate according to the present invention, a core is eliminated, so that the substrate has a very thin thickness, as well, the length of electrically conductive patterns becomes shorter, whereby the electrical efficiency thereof is improved. Moreover, since a carrier having a stiffness of a predetermined strength is bonded on the substrate, it can prevent a warpage phenomenon during the manufacturing process of the semiconductor device. Furthermore, the carrier is removed from the substrate, whereby a solder ball fusing process or an electrical connecting process of the semiconductor die can be easily performed.

### 15 Claims, 24 Drawing Sheets

# US 7,902,660 B1 Page 2

| U.S. PATENT                             | DOCUMENTS                                         | 5,578,525 A                | 11/1996          | Mizukoshi                       |

|-----------------------------------------|---------------------------------------------------|----------------------------|------------------|---------------------------------|

|                                         | Kalfus et al 357/68                               | 5,581,122 A                | 12/1996          | Chao et al 257/691              |

|                                         | Mori et al 357/08                                 | 5,592,019 A                |                  | Ueda et al                      |

|                                         | Schlesinger et al 357/70                          | 5,592,025 A                |                  | Clark et al                     |

|                                         | Yasunaga et al 357/72                             | 5,594,274 A<br>5,595,934 A | 1/1997<br>1/1997 | Suetaki                         |

|                                         | Chao et al 29/827                                 | 5,604,376 A                |                  | Hamburgen et al 257/676         |

| , , , , , , , , , , , , , , , , , , , , | McShane 357/79                                    | 5,608,265 A                |                  | Kitano et al 257/738            |

| , ,                                     | Yamazaki 357/70                                   | 5,608,267 A                | 3/1997           | Mahulikar et al 257/796         |

|                                         | Tsutsumi et al 264/272.14<br>Matsuki et al 357/68 | 5,619,068 A                |                  | Benzoni                         |

|                                         | Johnson et al.                                    | 5,625,222 A                |                  | Yoneda et al 257/687            |

| , , ,                                   | Long et al 357/69                                 | 5,633,528 A                |                  | Abbott et al                    |

|                                         | Asada et al.                                      | 5,639,990 A<br>5,640,047 A |                  | Nishihara et al                 |

| , , , , , , , , , , , , , , , , , , ,   | Hobson                                            | 5,641,997 A                |                  | Ohta et al                      |

| ·                                       | Murphy 439/68                                     | 5,643,433 A                |                  | Fukase et al 205/78             |

|                                         | Kikuchi et al                                     | 5,644,169 A                | 7/1997           | Chun 257/787                    |

|                                         | Murphy 439/70                                     | 5,646,831 A                |                  | Manteghi 361/813                |

|                                         | Yamaguchi                                         | 5,650,663 A                |                  | Parthasarathi                   |

|                                         | McShane et al 357/74                              | 5,661,088 A<br>5,665,996 A |                  | Tessier et al                   |

|                                         | Gow, 3rd et al 257/666                            | 5,673,479 A                |                  | Hawthorne                       |

|                                         | Zimmerman                                         | 5,683,806 A                |                  | Sakumoto et al 428/343          |

|                                         | Casto                                             | 5,689,135 A                | 11/1997          | Ball 257/676                    |

| , ,                                     | Enomoto et al 428/620<br>Lin et al.               | , ,                        |                  | Miles et al 361/764             |

|                                         | Kwon 257/707                                      | 5,701,034 A                |                  | Marrs                           |

|                                         | King et al                                        | 5,703,407 A                |                  | Hori                            |

|                                         | Lin et al 257/688                                 | 5,710,064 A<br>5,723,899 A |                  | Song et al. Shin                |

|                                         | Kudo 257/735                                      | 5,724,233 A                |                  | Honda et al 361/813             |

| , ,                                     | Burns                                             | 5,726,493 A                |                  | Yamashita et al 257/698         |

|                                         | Sloan et al                                       | 5,736,432 A                | 4/1998           | Mackessy 438/123                |

|                                         | Eichelberger<br>Michii 257/666                    | 5,736,448 A *              |                  | Saia et al 438/393              |

|                                         | Furui et al                                       | 5,745,984 A                |                  | Cole, Jr. et al                 |

|                                         | Nishi et al 257/706                               | 5,753,532 A<br>5,753,977 A | 5/1998           | Sim<br>Kusaka et al 257/787     |

|                                         | Goodrich et al 437/15                             | 5,766,972 A                |                  | Takahashi et al 438/127         |

| , ,                                     | Lin et al.                                        | 5,769,989 A                |                  | Hoffmeyer et al 156/94          |

|                                         | Sakumoto et al                                    | 5,770,888 A                |                  | Song et al                      |

|                                         | Nagaraj et al                                     | 5,776,798 A                |                  | Quan et al 438/112              |

| , ,                                     | Singh Deo et al 257/666                           | 5,783,861 A                |                  | Son                             |

|                                         | Notani et al 333/33                               | 5,786,238 A                |                  | Pai et al                       |

| 5,327,008 A 7/1994                      | Djennas et al 257/666                             | 5,801,440 A<br>5,814,877 A |                  | Chu et al                       |

|                                         | Liang et al 174/52.4                              | 5,814,881 A                |                  | Alagaratnam et al 257/686       |

|                                         | Murphy                                            | 5,814,883 A                |                  | Sawai et al 257/712             |

|                                         | Juskey et al                                      | 5,814,884 A                |                  | Davis et al                     |

| ·                                       | Fillion et al                                     | 5,817,540 A                |                  | Wark                            |

| 5,358,905 A 10/1994                     |                                                   | 5,818,105 A                |                  | Kouda                           |

| 5,365,106 A 11/1994                     | Watanabe 257/669                                  | 5,821,457 A<br>5,821,615 A |                  | Mosley et al                    |

|                                         | Lerner et al                                      | , ,                        |                  | Cho                             |

| , ,                                     | Tomita et al                                      | •                          |                  | Ishii                           |

| ·                                       | Yamaji 361/749<br>Morita et al 257/783            | ·                          |                  | Eichelberger 257/723            |

|                                         | Fujii et al                                       |                            |                  | Fujita et al                    |

|                                         | Wang et al 257/702                                | 5,856,911 A<br>5,859,471 A |                  | Riley                           |

| 5,417,905 A 5/1995                      | Lemaire et al 264/139                             | 5,859,471 A<br>5,859,475 A |                  | Freyman et al.                  |

|                                         | Djennas et al 257/666                             | 5,866,939 A                |                  | Shin et al                      |

|                                         | Cha 257/676                                       | 5,871,782 A                |                  | Choi 425/116                    |

|                                         | Mowatt et al. Bindra et al 29/830                 | 5,874,770 A                |                  | Saia et al                      |

|                                         | Song et al                                        | 5,874,784 A                |                  | Aoki et al                      |

|                                         | Chang                                             | 5,877,043 A<br>5,886,397 A |                  | Alcoe et al                     |

| 5,454,904 A * 10/1995                   | Ghezzo et al 216/13                               | 5,886,398 A                |                  | Ewer                            |

|                                         | Fogelson 156/651.1                                | 5,894,108 A                |                  | Mostafazadeh et al 174/52.4     |

| , ,                                     | Djennas et al.                                    | 5,897,339 A                |                  | Song et al 438/118              |

|                                         | Neu                                               | 5,900,676 A                | 5/1999           | Kweon et al 257/787             |

|                                         | Fillion et al.                                    | 5,903,049 A                |                  | Mori                            |

| , ,                                     | Lin 257/691                                       | 5,903,050 A                |                  | Thurairajaratnam et al. 257/695 |

| · · · · · · · · · · · · · · · · · · ·   | Bigler et al 257/666                              | 5,909,053 A                |                  | Fukase et al                    |

|                                         | Aono et al                                        | 5,915,998 A<br>5,917,242 A |                  | Stidham et al                   |

|                                         | Pavio                                             | 5,917,242 A<br>5,937,324 A |                  | Abercrombie et al 438/648       |

| , ,                                     | Rostoker<br>Iverson et al 257/670                 | 5,939,779 A                |                  | Kim 257/692                     |

|                                         | Diffenderfer et al 257/670                        | 5,942,794 A                |                  | Okumura et al 257/666           |

|                                         | Romero et al 29/832                               | 5,951,305 A                |                  | Haba                            |

| , , , , , , , , , , , , , , , , , , ,   | Barber 257/691                                    | 5,959,356 A                | 9/1999           | Oh 257/738                      |

| 5,576,517 A 11/1996                     | Wojnarowski et al 174/262                         | 5,969,426 A                | 10/1999          | Baba et al                      |

|                                         |                                                   |                            |                  |                                 |

# US 7,902,660 B1 Page 3

| 5 072 200 A                  | 10/1000      | C14 -1               | 257/676     | 6 205 077              | D1         | 10/2001 | Dinn an at a1          | 125/16 02 |

|------------------------------|--------------|----------------------|-------------|------------------------|------------|---------|------------------------|-----------|

| 5,973,388 A                  |              | Chew et al           |             | 6,295,977              |            |         | Ripper et al           |           |

| 5,976,912 A                  |              | Fukutomi et al       |             | 6,297,548              |            |         | Moden et al            |           |

| 5,977,613 A                  | 11/1999      | Takata et al         | 257/666     | 6,303,984              | В1         | 10/2001 | Corisis                | . 257/670 |

| 5,977,615 A                  | 11/1999      | Yamaguchi et al      | 257/666     | 6,303,997              | B1         | 10/2001 | Lee                    | . 257/778 |

| 5,977,630 A                  |              | Woodworth et al      |             | 6,307,272              | B1         | 10/2001 | Takahashi et al        | . 257/787 |

| 5,981,314 A                  |              | Glenn et al          |             | 6,309,909              |            |         | Ohgiyama               |           |

| 5,982,632 A                  |              |                      |             | 6,316,822              |            |         | ~ ·                    |           |

| , ,                          |              | Mosley et al         |             | , ,                    |            |         | Venkateshwaran et al   |           |

| 5,986,333 A                  |              | Nakamura             |             | 6,316,838              |            |         | Ozawa et al            |           |

| 5,986,885 A                  | 11/1999      | Wyland               | 361/704     | 6,323,550              | B1         | 11/2001 | Martin et al           | . 257/704 |

| 6,001,671 A                  | 12/1999      | Fjelstad             | 438/112     | 6,326,243              | B1         | 12/2001 | Suzuya et al           | . 438/124 |

| 6,013,947 A                  |              | Lim                  |             | 6,326,244              |            |         | Brooks et al           |           |

| 6,018,189 A                  |              | Mizuno               |             | 6,326,678              |            |         | Karnezos et al         |           |

| , ,                          |              |                      |             | , ,                    |            |         |                        |           |

| 6,020,625 A                  |              | Qin et al            |             | 6,335,564              |            |         | Pour                   |           |

| 6,025,640 A                  | 2/2000       | Yagi et al           | 257/666     | 6,337,510              | В1         | 1/2002  | Chun-Jen et al         | . 257/666 |

| 6,031,279 A                  | 2/2000       | Lenz                 | 257/686     | 6,339,255              | B1         | 1/2002  | Shin                   | . 257/686 |

| RE36,613 E                   |              | Ball                 |             | 6,348,726              | B1         |         | Bayan et al            |           |

| 6,034,423 A                  |              | Mostafazadeh et al   |             | 6,355,502              |            |         | Kang et al             |           |

| , ,                          |              |                      |             | , ,                    |            |         | •                      |           |

| 6,040,626 A                  |              | Cheah et al          |             | 6,365,974              |            |         | Abbott et al           |           |

| 6,043,430 A                  |              | Chun                 |             | 6,369,447              |            |         | Mori                   |           |

| 6,060,768 A                  | 5/2000       | Hayashida et al      | 257/666     | 6,369,454              | B1         | 4/2002  | Chung                  | . 257/787 |

| 6,060,769 A                  | 5/2000       | Wark                 | 257/666     | 6,373,127              | B1         | 4/2002  | Baudouin et al         | . 257/676 |

| 6,072,228 A                  |              | Hinkle et al         |             | 6,380,048              | B1         |         | Boon et al             |           |

| 6,075,284 A                  |              | Choi et al           |             | 6,384,472              |            |         | Huang                  |           |

| , ,                          |              |                      |             | , ,                    |            |         | _                      |           |

| 6,081,029 A                  |              | Yamaguchi            |             | 6,388,336              |            |         | Venkateshwaran et al   |           |

| 6,084,310 A                  |              | Mizuno et al         |             | 6,395,578              |            |         | Shin et al             |           |

| 6,087,715 A                  | 7/2000       | Sawada et al         | 257/666     | 6,396,148              | B1 *       | 5/2002  | Eichelberger et al     | . 257/758 |

| 6,087,722 A                  | 7/2000       | Lee et al            | 257/723     | 6,396,153              | B2         | 5/2002  | Fillion et al          | . 257/774 |

| 6,097,089 A *                |              | Gaku et al           |             | 6,400,004              |            |         | Fan et al.             |           |

| , , , ,                      |              |                      |             | , ,                    |            |         |                        |           |

| 6,100,594 A                  |              | Fukui et al          |             | 6,410,979              |            |         | Abe                    |           |

| 6,113,474 A                  |              | Shih et al           |             | 6,414,385              |            |         | Huang et al            |           |

| 6,114,752 A                  | 9/2000       | Huang et al          | 257/666     | 6,418,615              | B1 *       | 7/2002  | Rokugawa et al         | 29/852    |

| 6,118,174 A                  | 9/2000       | Kim                  | 257/676     | 6,420,779              | B1         | 7/2002  | Sharma et al           | . 257/666 |

| 6,118,184 A                  | 9/2000       | Ishio et al          | 2.57/787    | 6,429,508              | B1         |         | Gang                   |           |

| RE36,907 E                   |              | Templeton, Jr. et al |             | 6,437,429              |            |         | Su et al.              |           |

| /                            |              | · ,                  |             | , ,                    |            |         |                        |           |

| 6,130,115 A                  |              | Okumura et al        |             | 6,444,499              |            |         | Swiss et al            |           |

| 6,130,473 A                  |              | Mostafazadeh et al   |             | 6,448,633              |            |         | Yee et al              |           |

| 6,133,623 A                  | 10/2000      | Otsuki et al         | 257/666     | 6,452,279              | B2         | 9/2002  | Shimoda                | . 257/777 |

| 6,140,154 A                  | 10/2000      | Hinkle et al         | 438/123     | 6,459,148              | B1         | 10/2002 | Chun-Jen et al         | . 257/692 |

| , ,                          |              | Glenn                |             | 6,464,121              |            |         | Reijnders              |           |

| ,                            |              |                      | 17 17 5 2.1 | , ,                    |            |         | 3                      |           |

| , ,                          |              | <del>-</del>         |             | ·                      |            |         | Hung et al             |           |

| 6,169,329 B1                 |              | Farnworth et al      |             | 6,476,474              |            |         | Hung                   |           |

| 6,177,718 B1                 | 1/2001       | Kozono               | 257/666     | 6,482,680              | В1         | 11/2002 | Khor et al             | . 438/123 |

| 6,181,002 B1                 | 1/2001       | Juso et al           | 257/686     | 6,486,005              | B1         | 11/2002 | Kim                    |           |

| 6,184,465 B1                 | 2/2001       | Corisis              | 174/52.4    | 6,498,099              | B1         | 12/2002 | McLellan et al         | . 438/689 |

| 6,184,573 B1                 |              | Pu                   |             | 6,498,392              |            |         | Azuma                  |           |

| , ,                          |              |                      |             | , ,                    |            |         |                        |           |

| 6,194,250 B1                 |              | Melton et al.        |             | 6,507,096              |            |         | Gang                   |           |

| 6,194,777 B1                 | 2/2001       | Abbott et al         | 257/666     | 6,507,120              | B2         |         | Lo et al               |           |

| 6,197,615 B1                 | 3/2001       | Song et al           | 438/111     | 6,521,530              | B2         | 2/2003  | Peters et al           | . 438/667 |

| 6,198,171 B1                 | 3/2001       | Huang et al          | 257/787     | 6,524,885              | B2         | 2/2003  | Pierce                 | . 438/106 |

| 6,201,186 B1                 |              | Daniels et al        |             | 6,534,849              | B1         |         | Gang                   |           |

| 6,201,292 B1                 |              | Yagi et al           |             | 6,545,332              |            |         | Huang                  |           |

| , ,                          |              | $\mathbf{c}$         |             | , ,                    |            |         | _                      |           |

| 6,204,554 B1                 |              | Ewer et al           |             | 6,545,345              |            |         | Glenn et al.           |           |

| 6,208,020 B1                 |              | Minamio et al        |             | 6,548,898              |            |         | Matsuki et al          |           |

| 6,208,021 B1                 | 3/2001       | Ohuchi et al         | 257/690     | 6,549,891              | B1 *       | 4/2003  | Rauber et al           | 705/28    |

| 6,208,023 B1                 | 3/2001       | Nakayama et al       | 257/696     | 6,559,525              | B2         | 5/2003  | Huang                  | . 257/675 |

| 6,211,462 B1                 |              | Carter, Jr. et al    |             | 6,566,168              | B2         |         | Gang                   |           |

| 6,214,525 B1                 |              | Boyko et al.         |             | 6,583,503              |            |         | Akram et al            |           |

| 6,217,987 B1 *               |              | Ono et al            |             | 6,593,645              |            |         | Shih et al.            |           |

| , ,                          |              |                      |             | , ,                    |            |         | _                      |           |

| 6,218,731 B1                 |              | Huang et al          |             | 6,603,196              |            |         | Lee et al              |           |

| 6,222,258 B1                 |              | Asano et al          |             | 6,624,005              |            |         | DiCaprio et al         |           |

| 6,222,259 B1                 |              | Park et al           |             | 6,667,546              | B2         |         | Huang et al            |           |

| 6,225,146 B1                 | 5/2001       | Yamaguchi et al      | 438/123     | 6,671,398              | B2         | 12/2003 | Reinhorn et al         | . 382/145 |

| 6,229,200 B1                 |              | Mclellan et al       |             | 6,727,576              | B2         |         | Hedler et al           |           |

| 6,229,205 B1                 |              | Jeong et al.         |             | 6,730,857              |            |         | Konrad et al.          |           |

| , ,                          |              | •                    |             | , ,                    |            |         |                        |           |

| 6,239,367 B1                 |              | Hsuan et al          |             | 6,740,964              |            | 5/2004  |                        | 0.55/550  |

| 6,239,384 B1                 |              | Smith et al          |             | 6,831,371              |            |         | Huemoeller et al       |           |

| 6,242,281 B1                 | 6/2001       | Mclellan et al       | 438/106     | 6,838,776              |            |         | Leal et al             |           |

| 6,256,200 B1                 | 7/2001       | Lam et al            | 361/704     | 6,845,554              | B2         | 1/2005  | Frankowsky et al       | 29/832    |

| 6,258,192 B1                 |              | Natarajan 1          |             | 6,853,060              |            |         | Seok et al             |           |

| 6,258,629 B1                 |              | Niones et al         |             | 6,905,914              |            |         | Huemoeller et al       |           |

| , ,                          |              |                      |             | , ,                    |            |         |                        |           |

| 6,261,918 B1                 |              | So                   |             | 6,919,514              |            |         | Konrad et al.          |           |

| 6,281,566 B1                 | 8/2001       | Magni                | 257/666     | 6,921,975              | B2         | 7/2005  | Leal et al             | . 257/723 |

| 6,281,568 B1                 | 8/2001       | Glenn et al          | 257/684     | 6,930,256              | B1         | 8/2005  | Huemoeller et al       | . 174/260 |

| 6,282,095 B1                 |              | Houghton et al       |             | 7,015,075              |            |         | Fay et al.             |           |

| , ,                          |              | •                    |             | , ,                    |            |         | -                      |           |

| 6,285,075 B1                 |              | Combs et al          |             | 7,041,534              |            |         | Chao et al             | . 438/114 |

| 6,291,271 B1                 |              | Lee et al            |             | 7,129,158              |            | 10/2006 | Nakai                  |           |

| 6,291,273 B1                 | 9/2001       | Miyaki et al         | 438/123     | 7,196,408              | B2         | 3/2007  | Yang et al.            |           |

| 0,201,270                    | <del>-</del> | _                    |             | , , , -                |            | _       |                        |           |

| , ,                          | 9/2001       | Fan et al            | 216/14      | 7.202 107              | <b>B</b> 2 | 4/2007  | •                      |           |

| 6,294,100 B1<br>6,294,830 B1 |              | Fan et alFjelstad    |             | 7,202,107<br>7,238,602 |            |         | Fuergut et al.<br>Yang |           |

| 7,242,081                    | B1 7                 | 7/2007           | Lee                              |          | JP                                                                                            | 63-033854                                     | 2/1988             |                      |  |

|------------------------------|----------------------|------------------|----------------------------------|----------|-----------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------|----------------------|--|

| 7,262,081                    |                      |                  | Yang et al.                      |          | JP                                                                                            | 63-067762                                     | 3/1988             |                      |  |

| 7,272,444                    |                      |                  | Peterson et al                   | . 607/30 | JP                                                                                            | 63-188964                                     | 8/1988             |                      |  |

| 7,326,592                    |                      |                  | Meyer et al.                     |          | JP<br>ID                                                                                      | 63-205935                                     | 8/1988             |                      |  |

| 7,339,279<br>7,345,361       |                      | 3/2008<br>3/2008 | Yang<br>Mallik et al.            |          | JP<br>JP                                                                                      | 63-233555<br>63-249345                        | 9/1988<br>10/1988  |                      |  |

| 7,343,301                    |                      |                  | Leal et al.                      |          | JP                                                                                            | 63-249951                                     | 11/1988            |                      |  |

| 7,372,151                    |                      |                  | Fan et al.                       |          | JP                                                                                            | 63-316470                                     | 12/1988            |                      |  |

| 7,405,102                    | B2 7                 | 7/2008           | Lee et al.                       |          | JP                                                                                            | 64-054749                                     | 3/1989             |                      |  |

| 7,405,484                    |                      |                  | Usui et al                       |          | JP                                                                                            | 01-106456                                     | 4/1989             |                      |  |

| 7,408,261                    |                      |                  | Yoon et al                       |          | JP                                                                                            | 01-175250                                     | 7/1989             |                      |  |

| 7,459,781<br>7,692,286       |                      |                  | Yang et al.<br>Huemoeller et al. |          | JP<br>JP                                                                                      | 01-205544<br>01-251747                        | 8/1989<br>10/1989  |                      |  |

| 7,714,431                    |                      |                  | Huemoeller et al.                |          | JP                                                                                            | 01-231747                                     | 5/1990             |                      |  |

| 2001/0008305                 |                      |                  | McLellan et al                   |          | JP                                                                                            | 03-069248                                     | 7/1991             |                      |  |

| 2001/0011654                 |                      |                  | Schmidt et al                    |          | JP                                                                                            | 03-177060                                     | 8/1991             |                      |  |

| 2001/0012704                 |                      |                  | Eldridge                         |          | JP                                                                                            | 04-098864                                     | 3/1992             |                      |  |

| 2001/0014538                 |                      |                  | Kwan et al                       |          | JP                                                                                            | 05-129473                                     | 5/1993             |                      |  |

| 2002/0024122                 |                      |                  | Jung et al                       |          | JP<br>ID                                                                                      | 05-166992<br>05-283460                        | 7/1993<br>10/1993  |                      |  |

| 2002/0027297<br>2002/0061642 |                      |                  | Ikenaga et al                    |          | JP<br>JP                                                                                      | 05-283460                                     | 4/1994             |                      |  |

| 2002/0001012                 |                      |                  | Lee                              |          | JP                                                                                            | 06-140563                                     | 5/1994             |                      |  |

| 2002/0140068                 |                      |                  | Lee et al                        |          | JP                                                                                            | 06-260532                                     | 9/1994             |                      |  |

| 2002/0163015                 | A1 11                | /2002            | Lee et al                        | 257/200  | JP                                                                                            | 07-297344                                     | 11/1995            |                      |  |

| 2003/0013232                 |                      |                  | Towle et al                      |          | JP                                                                                            | 07-312405                                     | 11/1995            |                      |  |

| 2003/0030131                 |                      |                  | Lee et al                        | 257/666  | JP                                                                                            | 08-064634                                     | 3/1996             |                      |  |

| 2003/0064548<br>2003/0073265 |                      |                  | Isaak<br>Hu et al                | 439/122  | JP<br>JP                                                                                      | 08-083877<br>08-125066                        | 3/1996<br>5/1996   |                      |  |

| 2003/00/3203                 |                      |                  | Cheng et al                      |          | JP                                                                                            | 08-123000                                     | 3/1990<br>8/1996   |                      |  |

| 2004/0004293                 |                      |                  | Murayama                         |          | JP                                                                                            | 08-306853                                     | 11/1996            |                      |  |

| 2004/0026781                 |                      |                  | Nakai                            |          | JP                                                                                            | 09-008205                                     | 1/1997             |                      |  |

| 2004/0046244                 | A1* 3                | 3/2004           | Nakamura et al                   | 257/700  | JP                                                                                            | 09-008206                                     | 1/1997             |                      |  |

| 2004/0056277                 |                      |                  | Karnezos                         |          | JP                                                                                            | 09-008207                                     | 1/1997             |                      |  |

| 2004/0061212                 |                      |                  | Karnezos                         |          | JP                                                                                            | 09-092775                                     | 4/1997             |                      |  |

| 2004/0061213<br>2004/0063242 |                      |                  | Karnezos                         |          | JP<br>JP                                                                                      | 09-293822<br>10-022447                        | 11/1997<br>1/1998  |                      |  |

| 2004/0063246                 |                      |                  | Karnezos                         |          | JP                                                                                            | 10-022447                                     | 6/1998             |                      |  |

| 2004/0113260                 |                      |                  | Sunohara et al                   |          | JP                                                                                            | 10-199934                                     | 7/1998             |                      |  |

| 2005/0001309                 | _                    |                  | Tanaka et al                     |          | JP                                                                                            | 10-256240                                     | 9/1998             |                      |  |

| 2005/0242425                 |                      |                  | Leal et al                       |          | JP                                                                                            | 2000-150765                                   | 5/2000             |                      |  |

| 2005/0266608                 |                      |                  | Ho et al                         |          | JP                                                                                            | 2000-556398                                   | 10/2000            |                      |  |

| 2005/0282314<br>2006/0145343 |                      |                  | Lo et al                         |          | JP<br>JP                                                                                      | 2001-060648<br>2001-118947                    | 3/2001<br>4/2001   |                      |  |

| 2006/0143343                 | _                    |                  | Lee et alLeal et al.             | 231/131  | JP                                                                                            | 2001-118947                                   | 2/2001             |                      |  |

| 2006/0192301                 |                      |                  | Ooi et al                        | 361/600  | KR                                                                                            | 1994-0001979                                  | 1/1994             |                      |  |

| 2006/0225918                 |                      |                  | Chinda et al                     |          | KR                                                                                            | 10-0220154                                    | 6/1999             |                      |  |

| 2006/0231958                 |                      | /2006            | $\boldsymbol{\mathcal{C}}$       |          | KR                                                                                            | 2002-0049944                                  | 6/2002             |                      |  |

|                              | _                    |                  | Inagaki et al                    |          | KR                                                                                            | 2004-0012028                                  | 2/2004             |                      |  |

| 2006/0284309                 |                      |                  | Park et al                       | 257/731  | WO<br>WO                                                                                      | WO 99/56316<br>WO 99/67821                    | 11/1999<br>12/1999 |                      |  |

| 2007/0059866<br>2007/0273049 |                      |                  | Yang et al.<br>Khan et al.       |          | WO                                                                                            | W O 99/0/021                                  | 12/1999            |                      |  |

| 2007/0273015                 |                      |                  | Zhao et al.                      |          |                                                                                               | OTHER PU                                      | BLICATIONS         |                      |  |

| 2008/0105967                 | A1 5                 | 5/2008           | Yang et al.                      |          | Uu ama alla                                                                                   | rotol IIC Appl N                              | a 11/605 740 fi    | lad Nav. 29, 2006    |  |

| 2008/0128884                 | A1 6                 | 5/2008           | Meyer et al.                     |          |                                                                                               | r et al., U.S. Appl. N<br>lectronic Component | ·                  | ·                    |  |

| 2008/0142960                 |                      |                  | Leal et al.                      |          | Fan-In Trac                                                                                   | -                                             | rackage Compi      | ising ran-Out and    |  |

| 2008/0182363                 |                      |                  | Amrine et al.                    |          |                                                                                               | r et al., U.S. Appl. N                        | No. 11/784 979 f   | filed Apr 9 2007     |  |

| 2008/0230887                 |                      |                  | Sun et al.                       |          |                                                                                               | wo-Sided Wafer Esca                           |                    | med Apr. 9, 2007,    |  |

| 2009/0051025                 | A1 2                 | ./2009           | Yang et al.                      |          |                                                                                               | ., U.S. Appl. No. 11/3                        | _                  | 1. 6, 2006, entitled |  |

| FC                           | DREIGN               | PATE             | NT DOCUMENTS                     |          | •                                                                                             | rite Wafer Level Chip                         | ·                  | ·                    |  |

| EP                           | 0 393 99             | 7                | 10/1990                          |          | Huemoelle                                                                                     | r et al., "Two-Sided Fa                       | an-Out Wafer Esca  | ape Package", U.S.   |  |

| EP                           | 0 459 49             |                  | 12/1991                          |          | Appl. No.                                                                                     | 12/221,797, filed Aug                         | g. 5, 2008.        |                      |  |

| EP                           | 0 720 22             | _                | 7/1996                           |          |                                                                                               | r et al., U.S. Appl. No                       | ,                  |                      |  |

| EP                           | 0 720 23             | 4                | 7/1996                           |          |                                                                                               | /afer Level Package a                         |                    |                      |  |

| EP                           | 0 794 57             |                  | 9/1997                           |          | Huemoeller et al., U.S. Appl. No. 11/297,050, filed on Dec. 7, 2005,                          |                                               |                    |                      |  |

| EP                           | 0 844 66             |                  | 5/1998                           |          | entitled "Stacked Embedded Leadframe".                                                        |                                               |                    |                      |  |

| EP<br>EP                     | 0 936 67<br>0 989 60 |                  | 8/1999<br>3/2000                 |          | Huemoeller et al., "Embedded Electronic Component Package Fab-                                |                                               |                    |                      |  |

| EP                           | 1 032 03             | _                | 8/2000                           |          | rication Method", U.S. Appl. No. 12/459,532, filed Jul. 2, 2009.                              |                                               |                    |                      |  |

| JP                           | 55-16386             |                  | 12/1980                          |          | Berry et al., "Thin Stacked Interposer Package", U.S. Appl. No.                               |                                               |                    |                      |  |

| JP                           | 57-04595             | 9                | 3/1982                           |          | 11/865,617, filed Oct. 1, 2007.  Scanlan, "Package on package (PoP), with Through mold Vinc". |                                               |                    |                      |  |

| JP                           | 59-20875             | 6                | 11/1984                          |          | Scanlan, "Package-on-package (PoP) with Through-mold Vias",                                   |                                               |                    |                      |  |

| JP                           | 59-22714             |                  | 12/1984                          |          | Advanced Packaging, Jan. 2008, 3 pages, vol. 17, Issue 1, PennWell Corporation.               |                                               |                    |                      |  |

| JP<br>ID                     | 60-01075             |                  | 1/1985<br>6/1085                 |          | -                                                                                             | "Application of Thro                          | ough Mold Via (1   | (MV) as PoP base     |  |

| JP<br>JP                     | 60-11623<br>60-19595 |                  | 6/1985<br>10/1985                |          | •                                                                                             | 58 <sup>th</sup> ECTC Proceeding              | •                  | /                    |  |

| JP                           | 60-23134             | •                | 11/1985                          |          | 6 pages, IE                                                                                   |                                               | , , <u>,</u>       | , <b></b> ,          |  |

| JP                           | 61-03955             | _                | 2/1986                           |          |                                                                                               | ., "Direct-Write Wafe                         | er Level Chip Sca  | ale Package", U.S.   |  |

| JP                           | 62-00963             | 9                | 1/1987                           |          | Appl. No.                                                                                     | 11/289,826, filed Nov                         | 7. 29, 2005.       |                      |  |

|                              |                      |                  |                                  |          |                                                                                               |                                               |                    |                      |  |

### US 7,902,660 B1

Page 5

Berry et al., "Direct-Write Wafer Level Chip Scale Package", U.S. Appl. No. 12/661,597, filed Mar. 19, 2010.

Huemoeller et al., "Electronic Component Package Comprising Fan-Out Traces", U.S. Appl. No. 12/661,604, filed Mar. 19, 2010. Huemoeller et al., U.S. Appl. No. 11/047,848, filed Jan. 31, 2005,

entitled "Two-Sided Wafer Escape Package".

Huemoeller et al., U.S. Appl. No. 11/298,016, filed Dec. 8, 2005, entitled "Embedded Electronic Component Package".

Huemoeller et al., U.S. Appl. No. 10/261,868, filed Oct. 1, 2002, entitled "Integrated Circuit Film Substrate Having Embedded Conductive Patterns and Vias".

Huemoeller et al., U.S. Appl. No. 10/297,050, filed Dec. 7, 2005, entitled "Stacked Embedded Leadframe".

\* cited by examiner

FIG.1

FIG.1A

FIG.1B

FIG.1C

FIG.1D

FIG.1E

FIG.1F

FIG.1G

FIG.1H

FIG.11

FIG.1J

FIG.1K

FIG.1L

FIG.1M

FIG.1N

FIG.10

FIG.2

FIG.2A

211 201 210 220

160

161 162

120

120

130

FIG.2B

FIG.2C

FIG.2D

FIG.2E

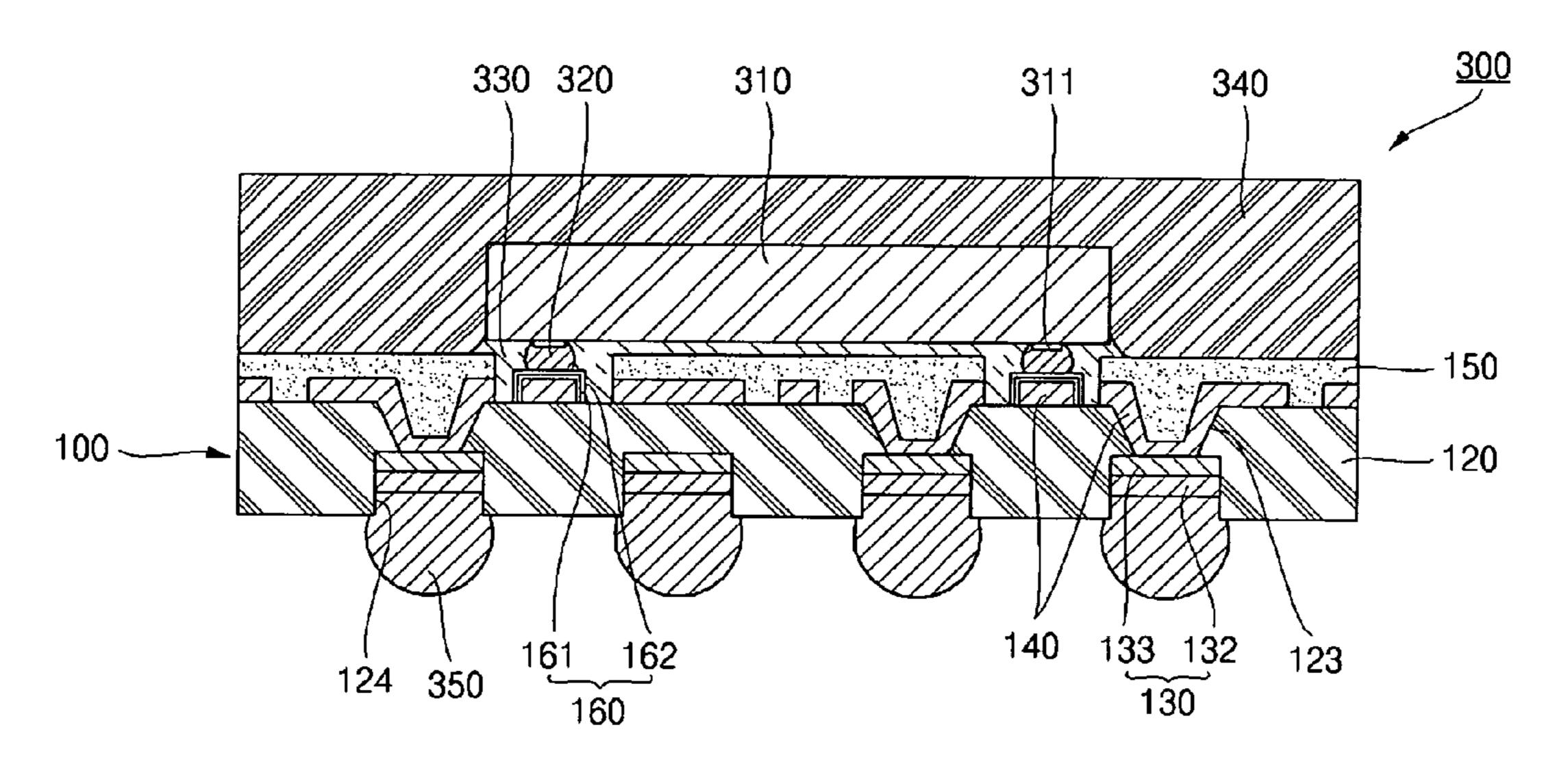

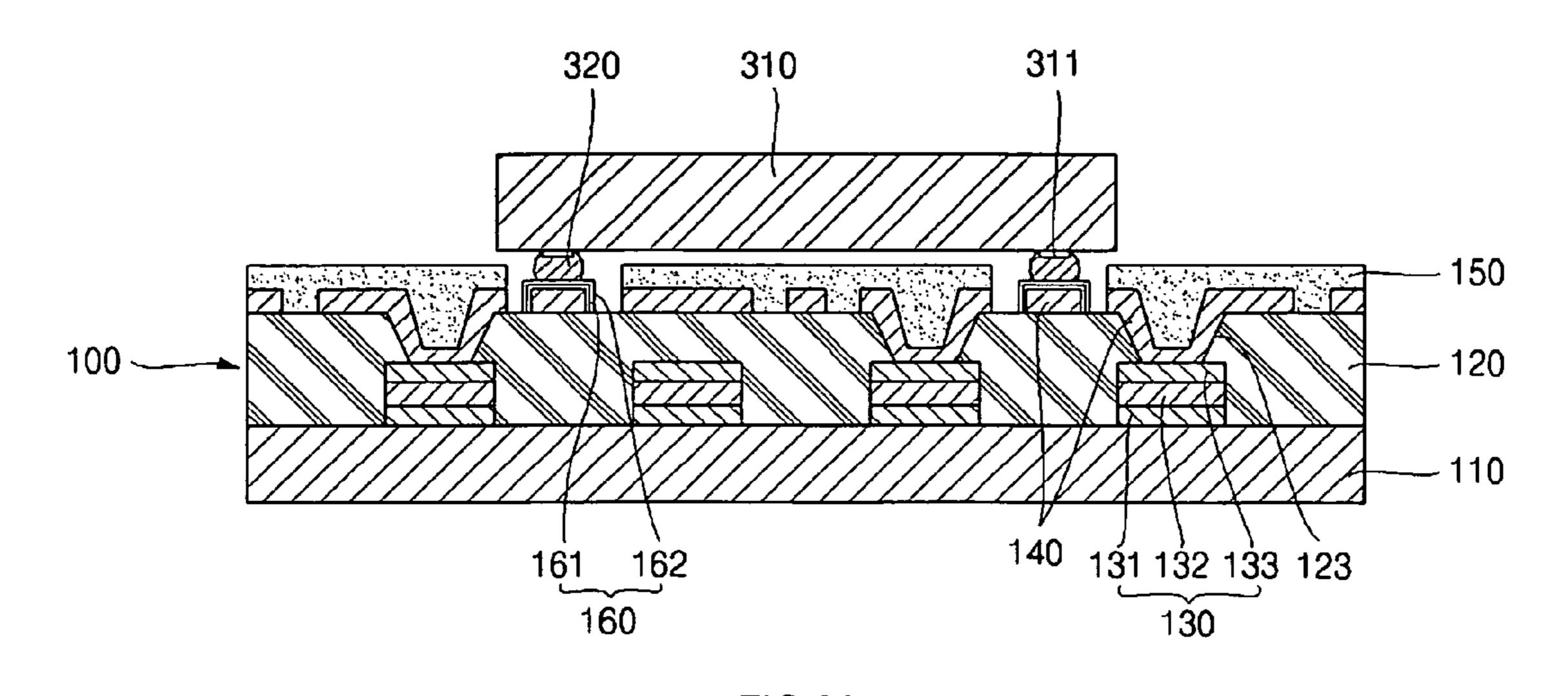

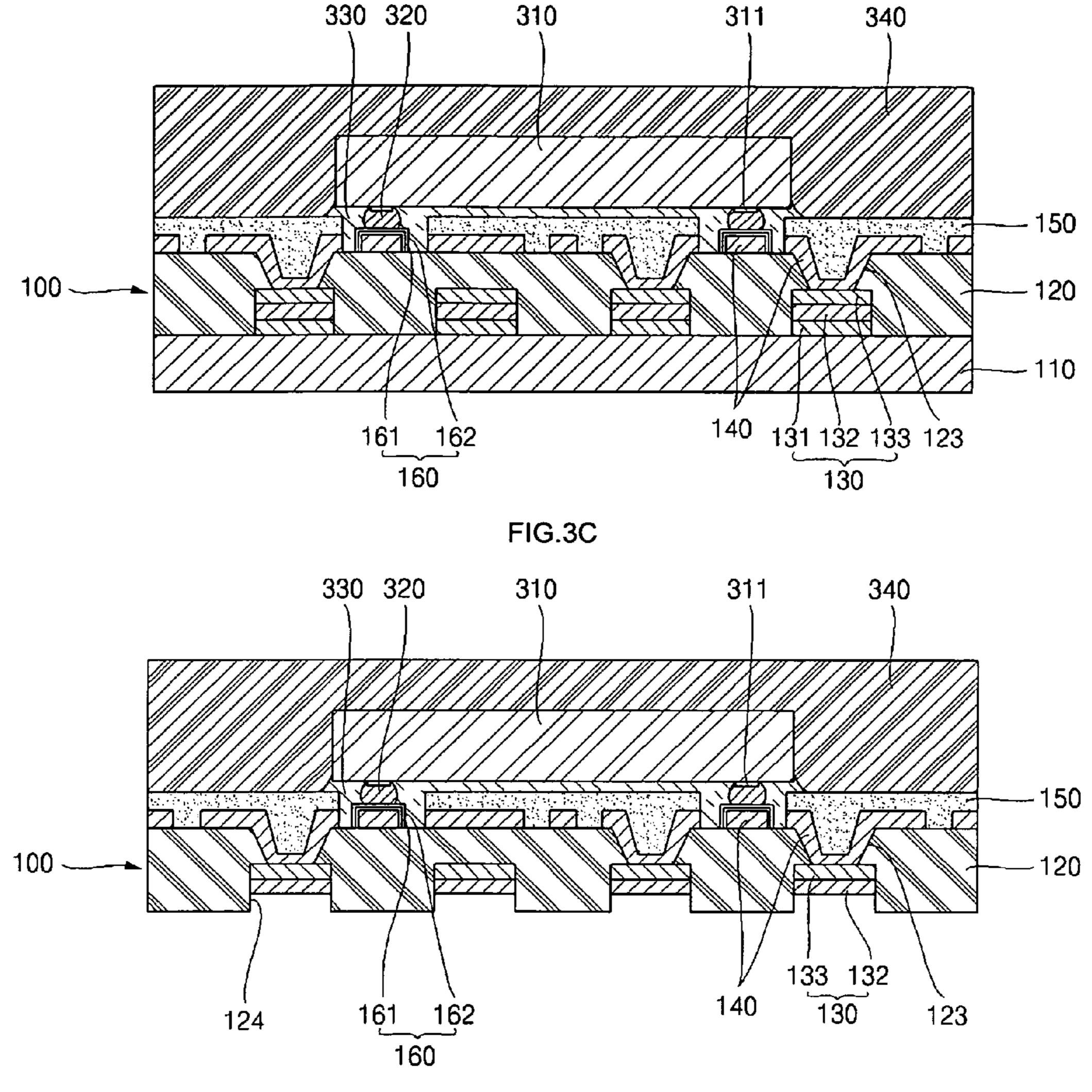

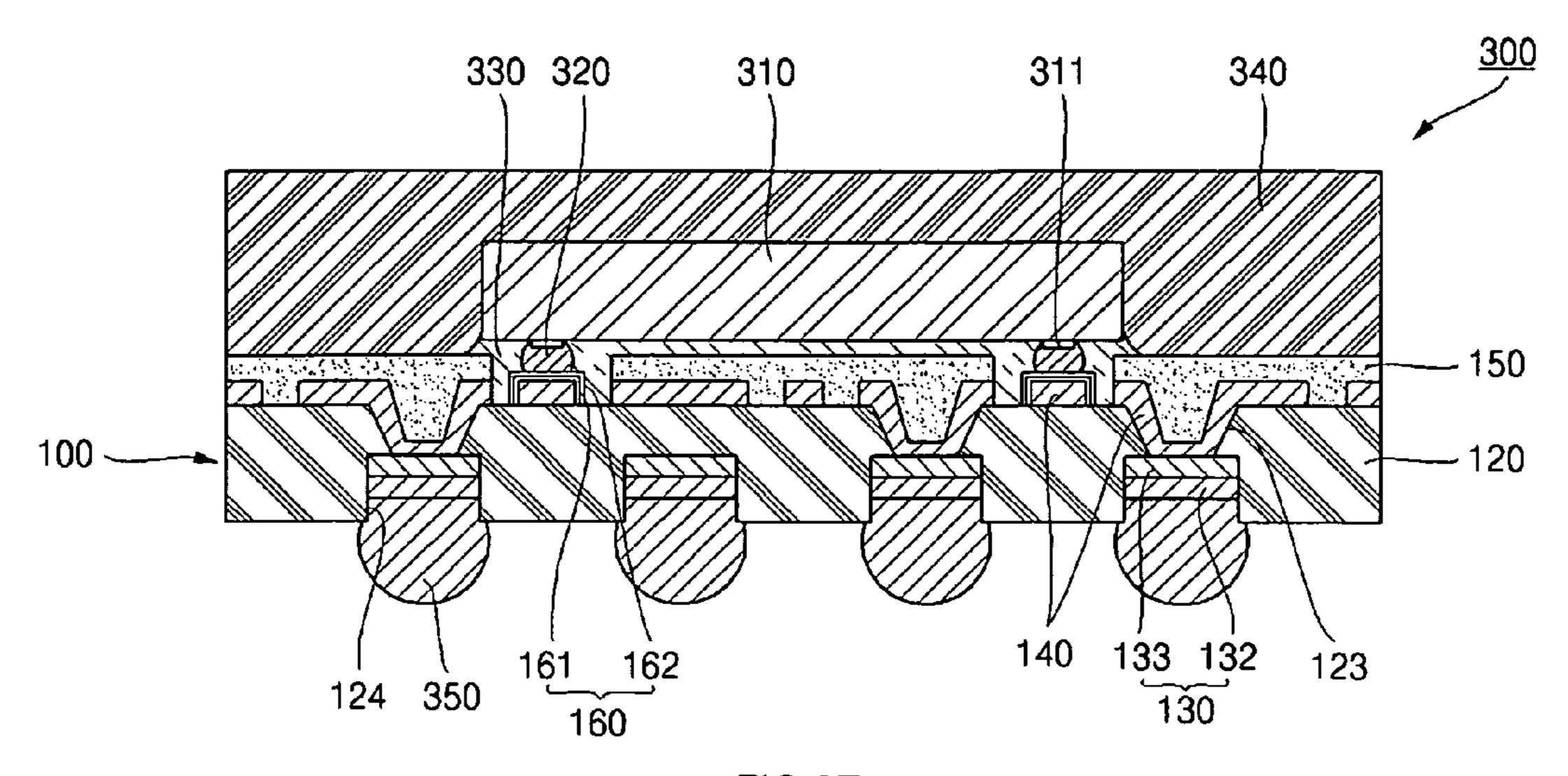

FIG.3

FIG.3A

330 320 310 311

100

161 162 140 131 132 133 123

130

FIG.3B

FIG.3D

FIG.3E

FIG.4

FIG.4A

FIG.4B

FIG.4C

FIG.4D

FIG.4E

FIG.4F

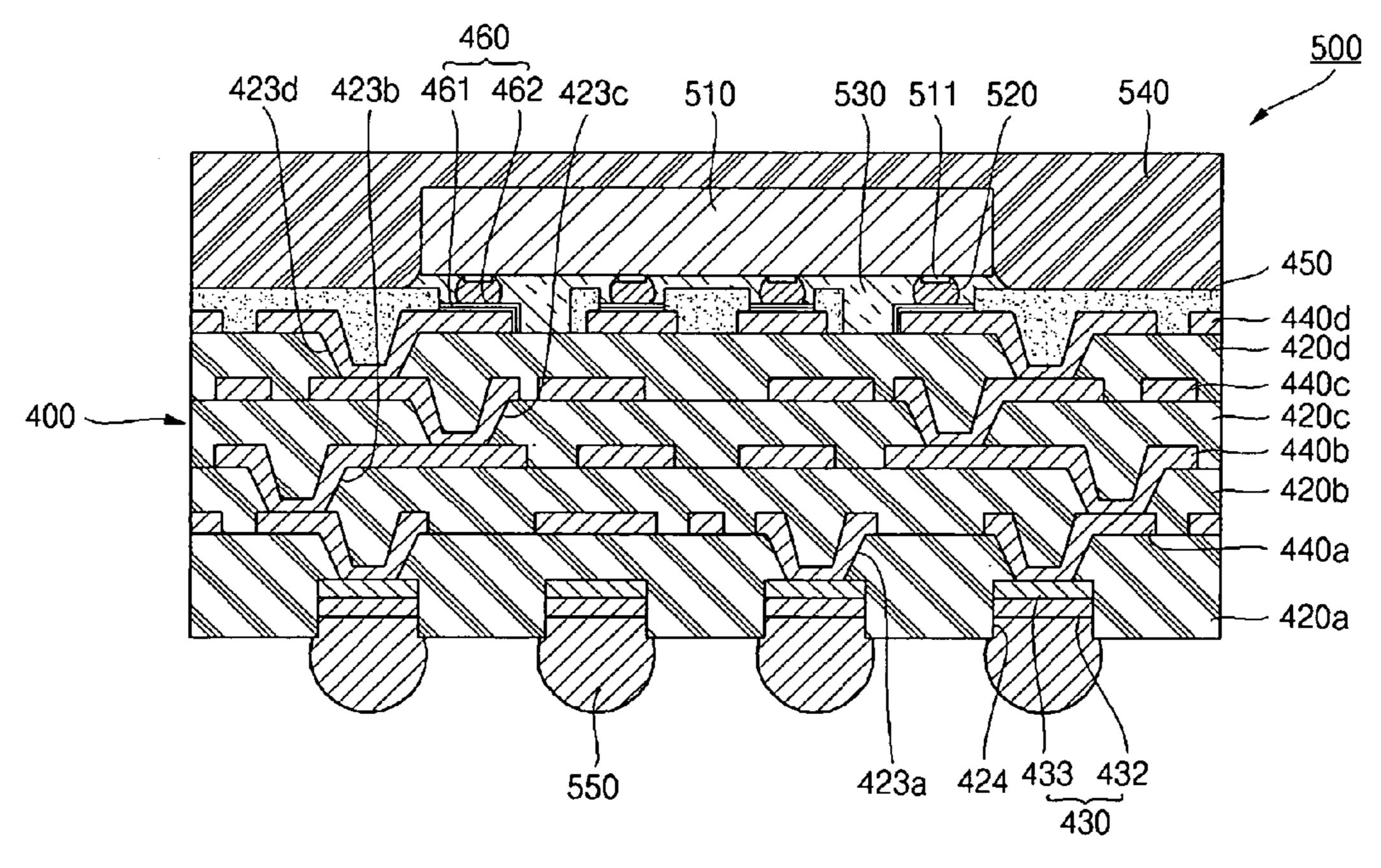

FIG.5

FIG.5A

FIG.5B

FIG.5C

FIG.5D

FIG.5E

FIG.6A

FIG.6B

FIG.6C

FIG.6D

FIG.7B

FIG.7C

460 461 462 451 450 550

FIG.7E

### SUBSTRATE FOR SEMICONDUCTOR DEVICE AND MANUFACTURING METHOD **THEREOF**

### BACKGROUND OF THE INVENTION

### 1. Field of the Invention

The present invention relates to substrate for semiconductor device and manufacturing method thereof, and semiconductor device using the same and manufacturing method thereof.

### 2. Description of the Related Art

Generally, a semiconductor device includes a substrate having a plurality of electrically conductive patterns thereon, 15 a semiconductor die located on the substrate, a plurality of conductive connecting means for electrically connecting the substrate to the semiconductor die, and an encapsulant for encapsulating the semiconductor die and the conductive connecting means. Here, a plurality of solder balls can be further 20 fused to the substrate so as to electrically connect the semiconductor device to an external device.

Meanwhile, a relatively thick core layer is formed at the substrate of the semiconductor device, in order that a warpage is not generated during the manufacturing process of the 25 semiconductor device. That is, the general substrate includes the core layer having a thickness of approximately 800 µm formed at the center thereof and a plurality of relatively thin build-up layers formed at top and bottom surfaces of the core layer. Here, a plurality of electrically conductive patterns is 30 formed at the core layer and the build-up layers. Also, a plurality of via holes passes through the core layer and the build-up layers in order to electrically connect the electrically conductive pattern layers to each other.

However, since such substrate is comparatively thicker, 35 operation; there is a defect in that the thickness of the semiconductor device using the substrate becomes thicker. Also, because each electrically conductive pattern of the substrate is comparatively longer, there is a defect in that the electrical efficiency of the semiconductor device using the electrically 40 conductive patterns is deteriorated. Especially, recent semiconductor devices have been required to have a wide bandwidth, fast data transferring, and higher density structure. However, it is difficult for the general substrate to implement recent trends thereof.

Here, it can solve the problems by eliminating the core layer from the substrate. However, where the core layer is eliminated from the substrate, since the warpage phenomenon is very higher during the manufacturing process of the semiconductor, it is difficult to manufacturer the semiconduc- 50 tor device. Also, it is difficult to manufacture and handle the substrate owing to the low stiffness thereof.

### SUMMARY OF THE INVENTION

A substrate for a semiconductor device and a manufacturing thereof, and a semiconductor device using the same and a manufacturing method thereof are disclosed. For example, in the substrate according to the present invention, a core is eliminated, so that the substrate has a very thin thickness, as 60 well, the length of electrically conductive patterns becomes shorter, whereby the electrical efficiency thereof is improved. Moreover, since a carrier having a stiffness of a predetermined strength is bonded on the substrate, it can prevent a warpage phenomenon during the manufacturing process of 65 the semiconductor device. Furthermore, the carrier is removed from the substrate, whereby a solder ball fusing

process or an electrical connecting process of the semiconductor die can be easily performed.

The present invention is best understood by reference to the following detailed description when read in conjunction with the accompanied drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

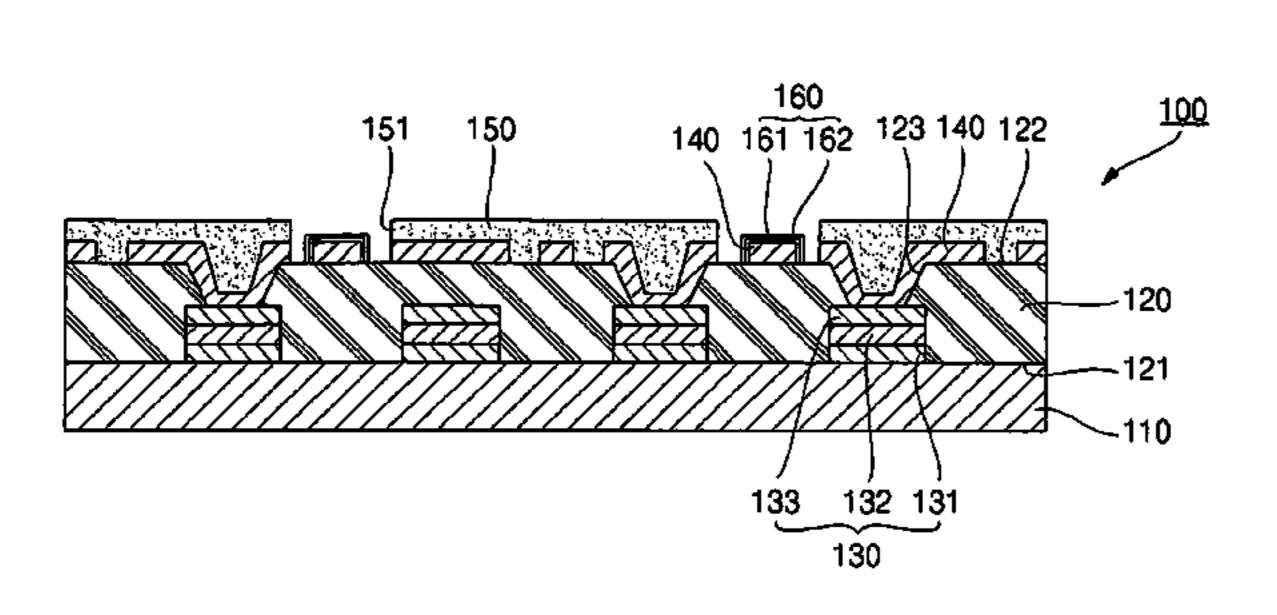

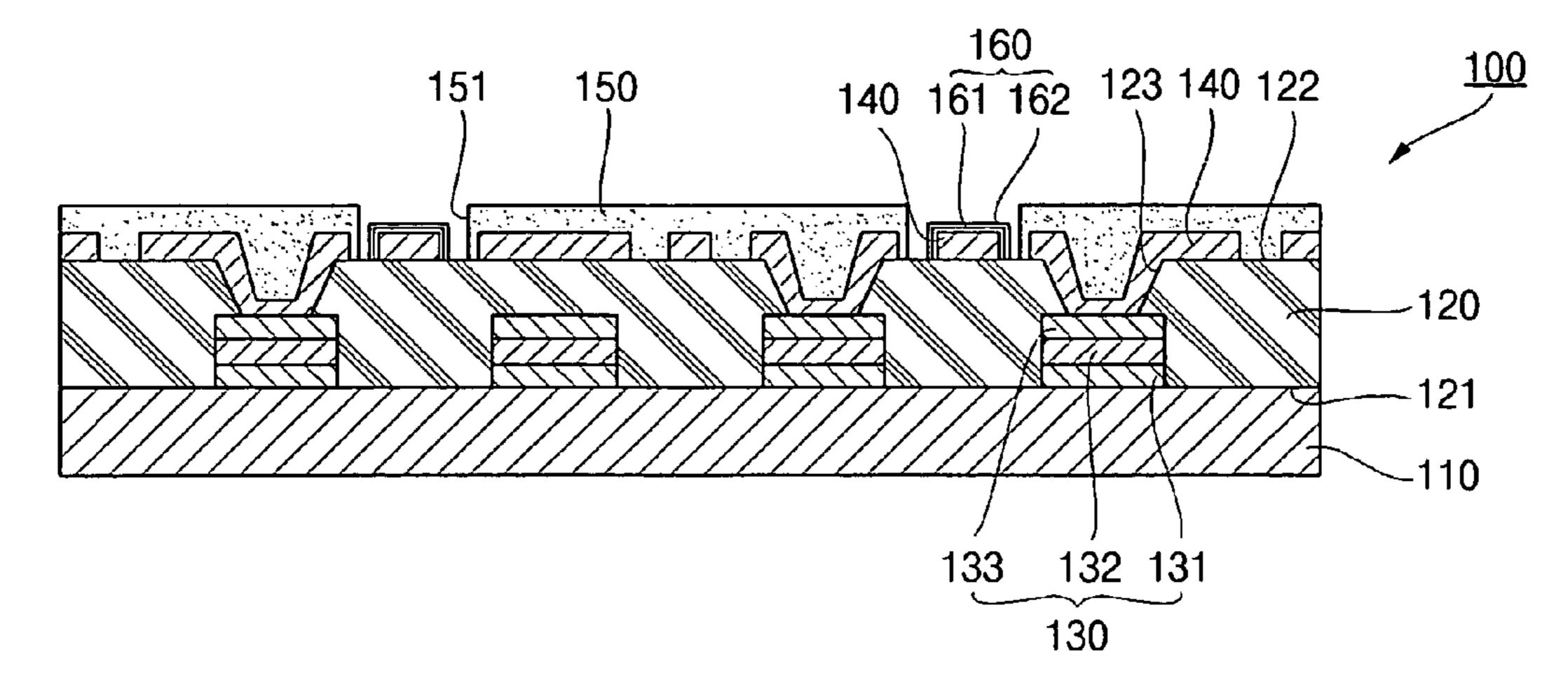

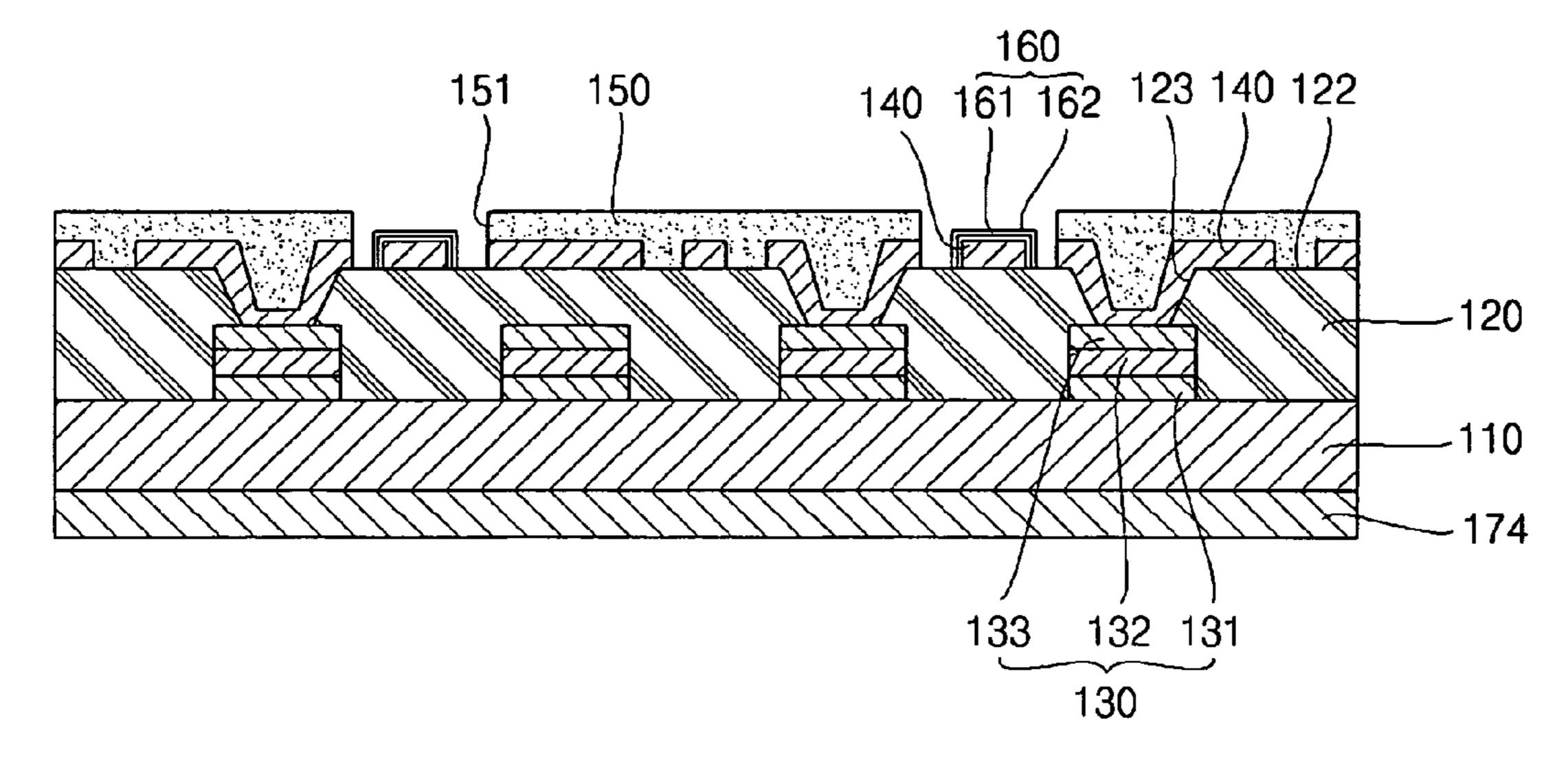

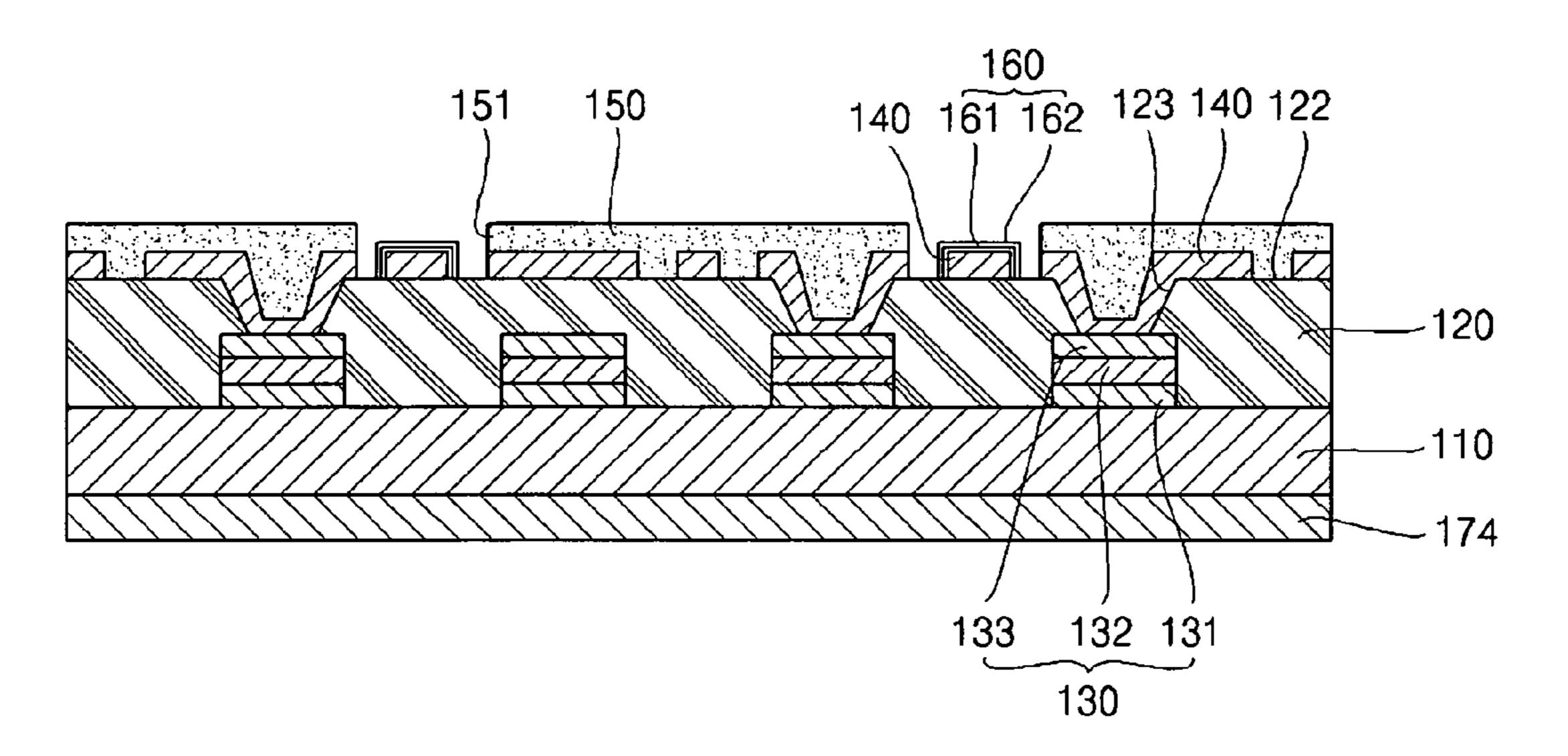

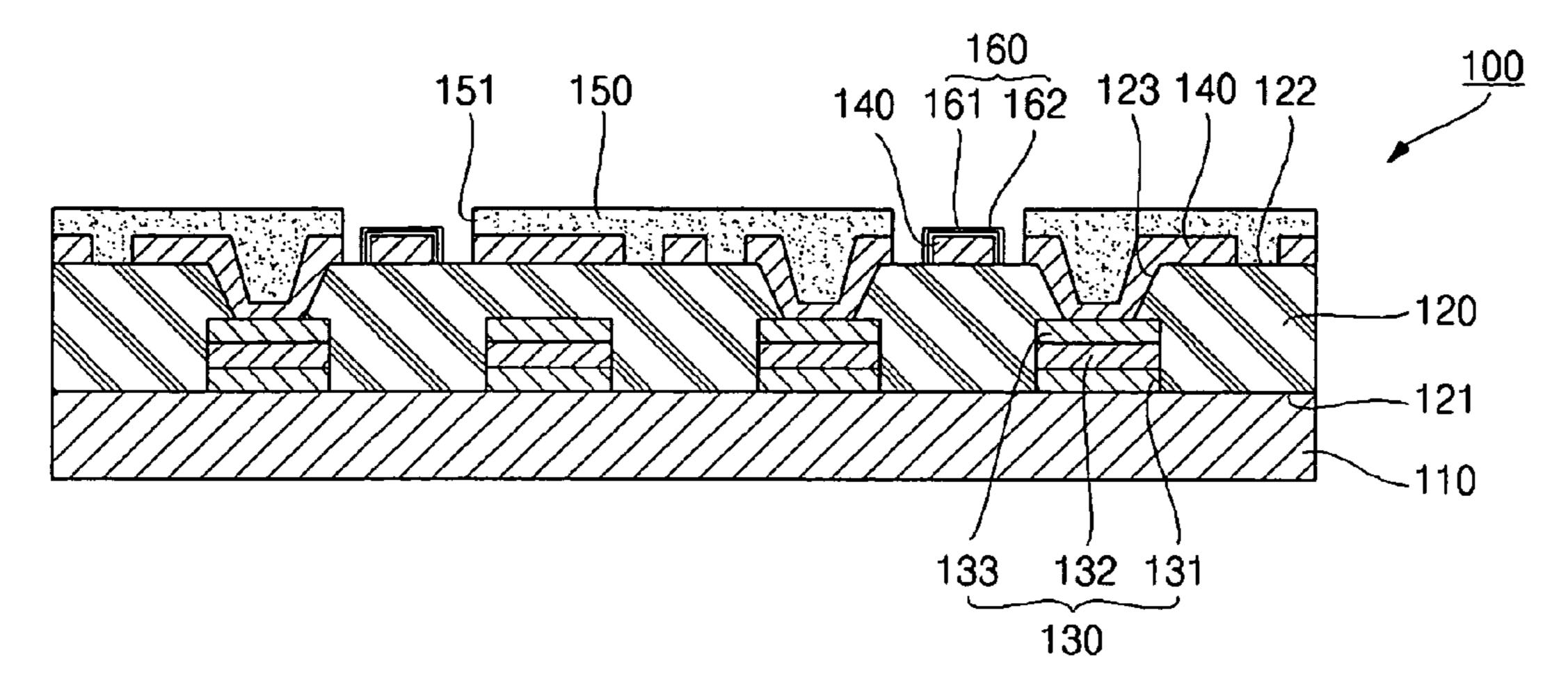

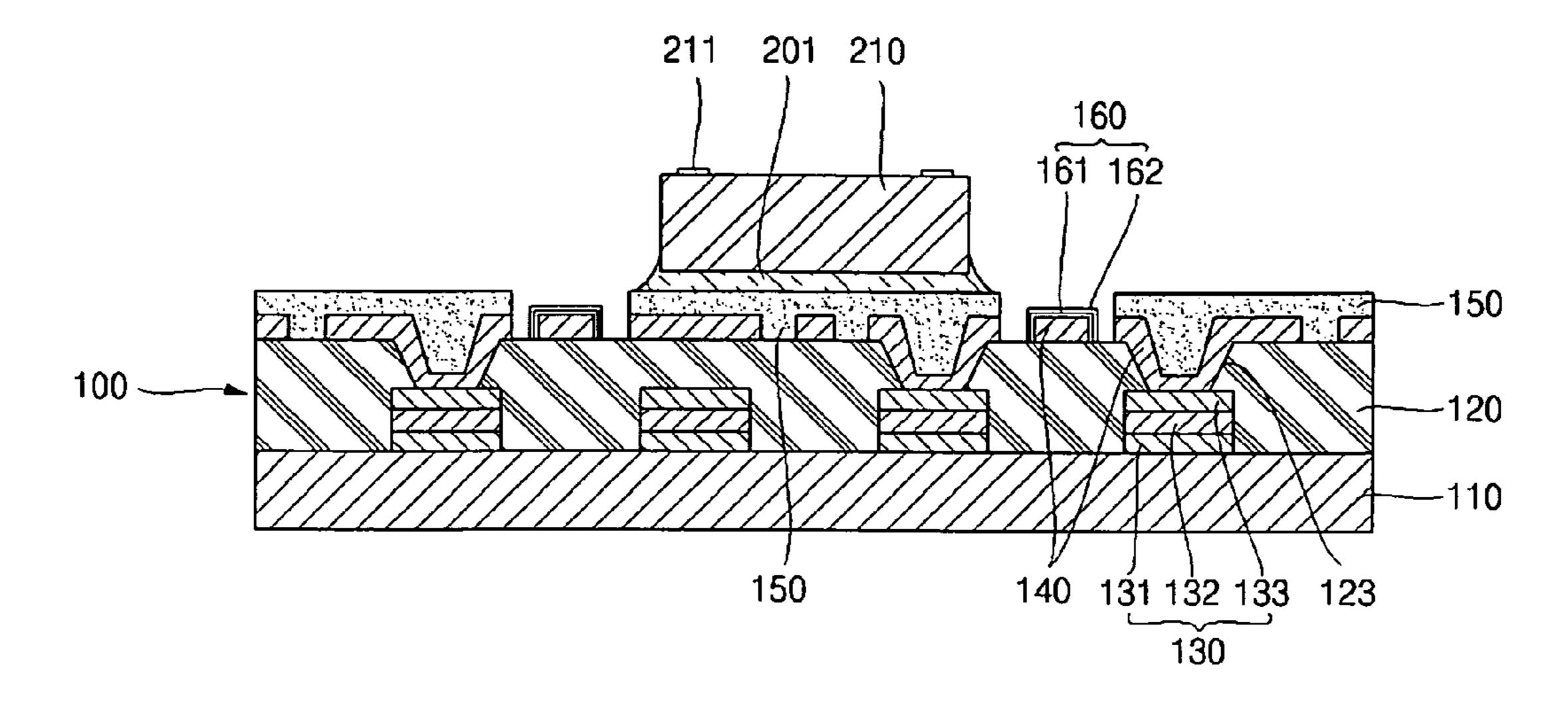

FIG. 1 is a sectional view of a substrate for a semiconductor device according to one embodiment of the present invention;

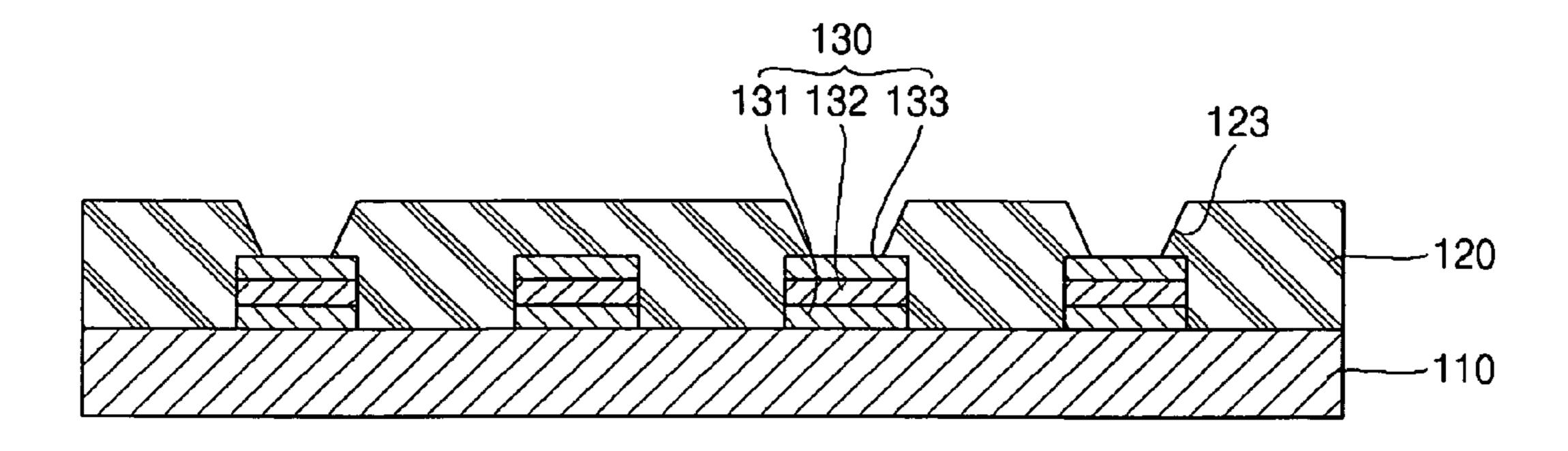

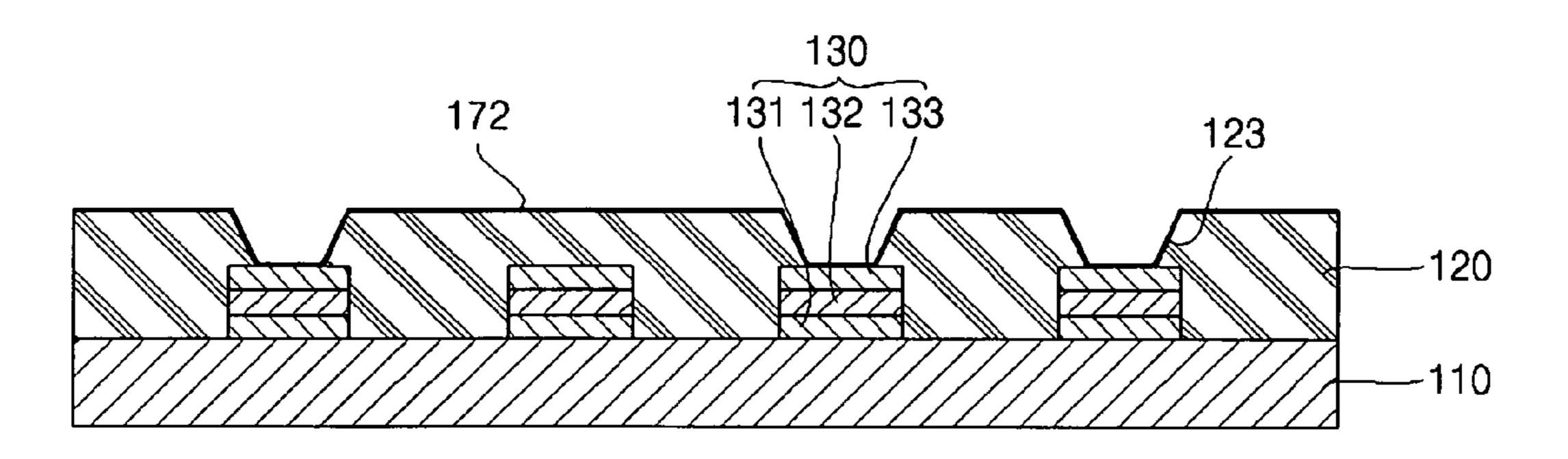

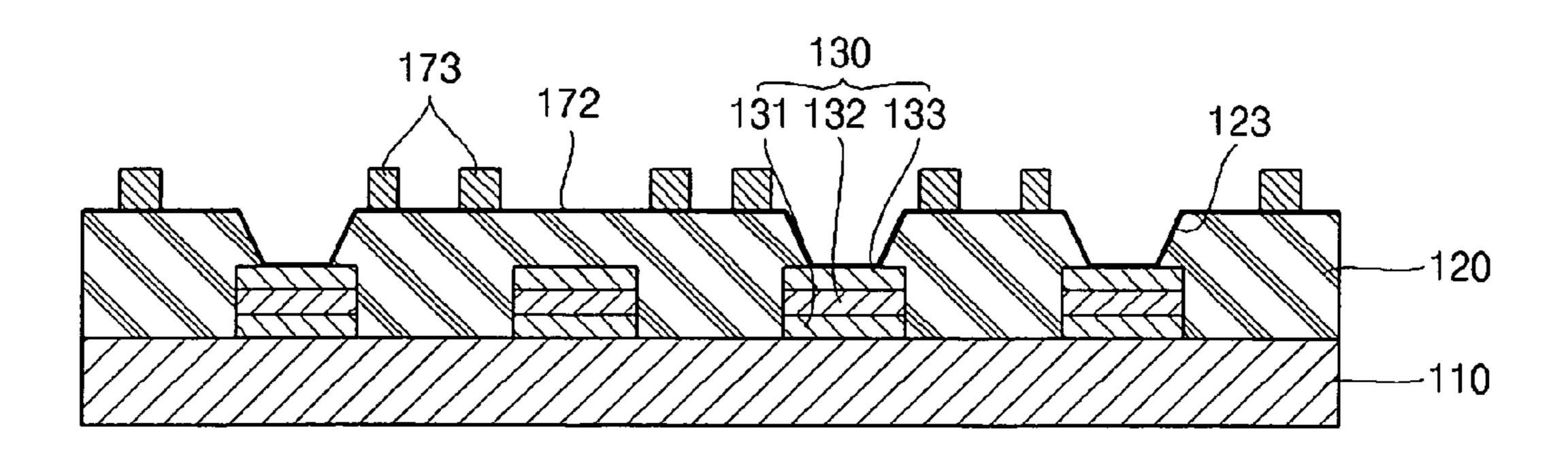

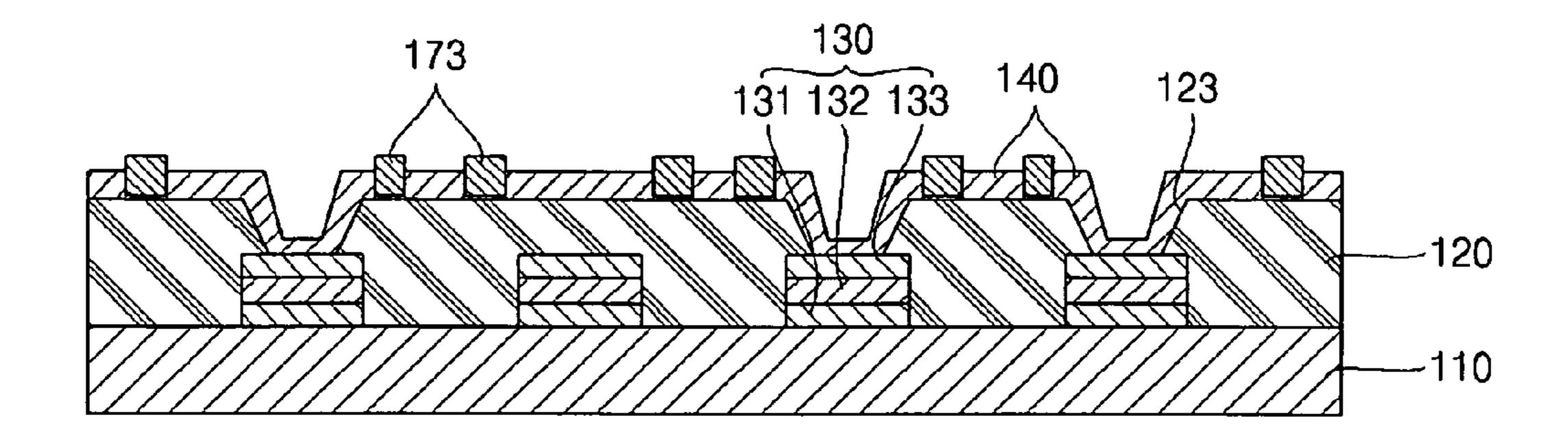

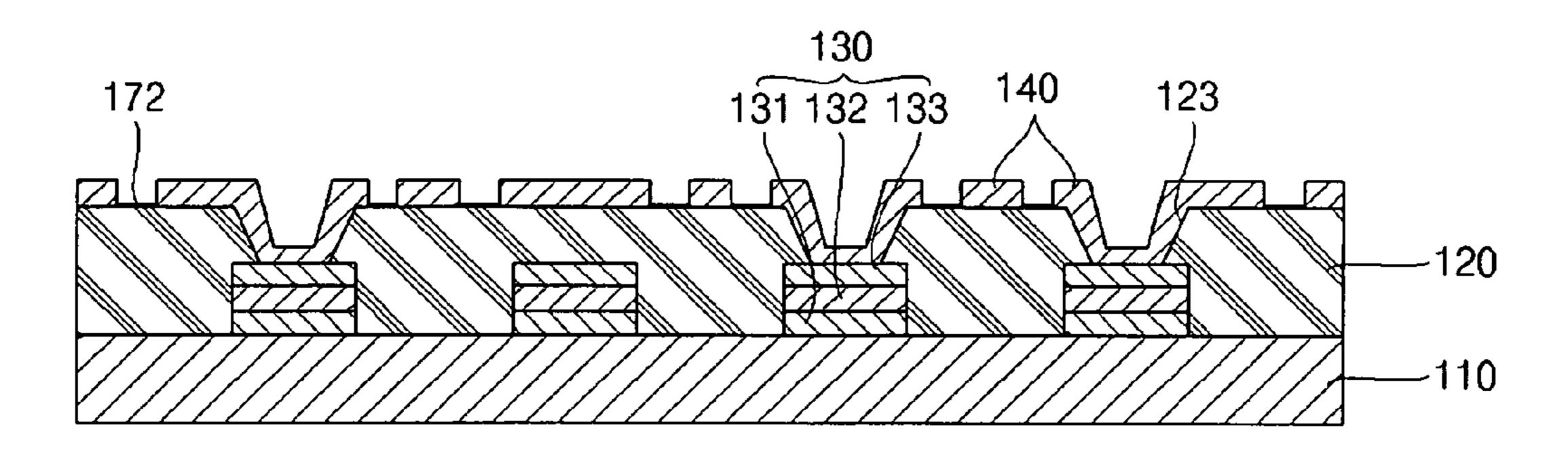

FIG. 1A through FIG. 1P are sectional views showing a fabrication method of the substrate for a semiconductor device according to one embodiment of the present invention where:

FIG. 1A illustrates a carrier providing operation;

FIG. 1B illustrates a first photo sensitive film providing operation;

FIG. 1C illustrates a first plating operation;

FIG. 1D illustrates a first photo sensitive film eliminating operation;

FIG. 1E illustrates a dielectric layer forming operation;

FIG. 1F illustrates a via hole forming operation;

FIG. 1G illustrates a second plating operation;

FIG. 1H illustrates a second photo sensitive film providing operation;

FIG. 1I illustrates a third plating operation;

FIG. 1J illustrates a second photo sensitive film eliminating operation;

FIG. 1K illustrates an etching operation;

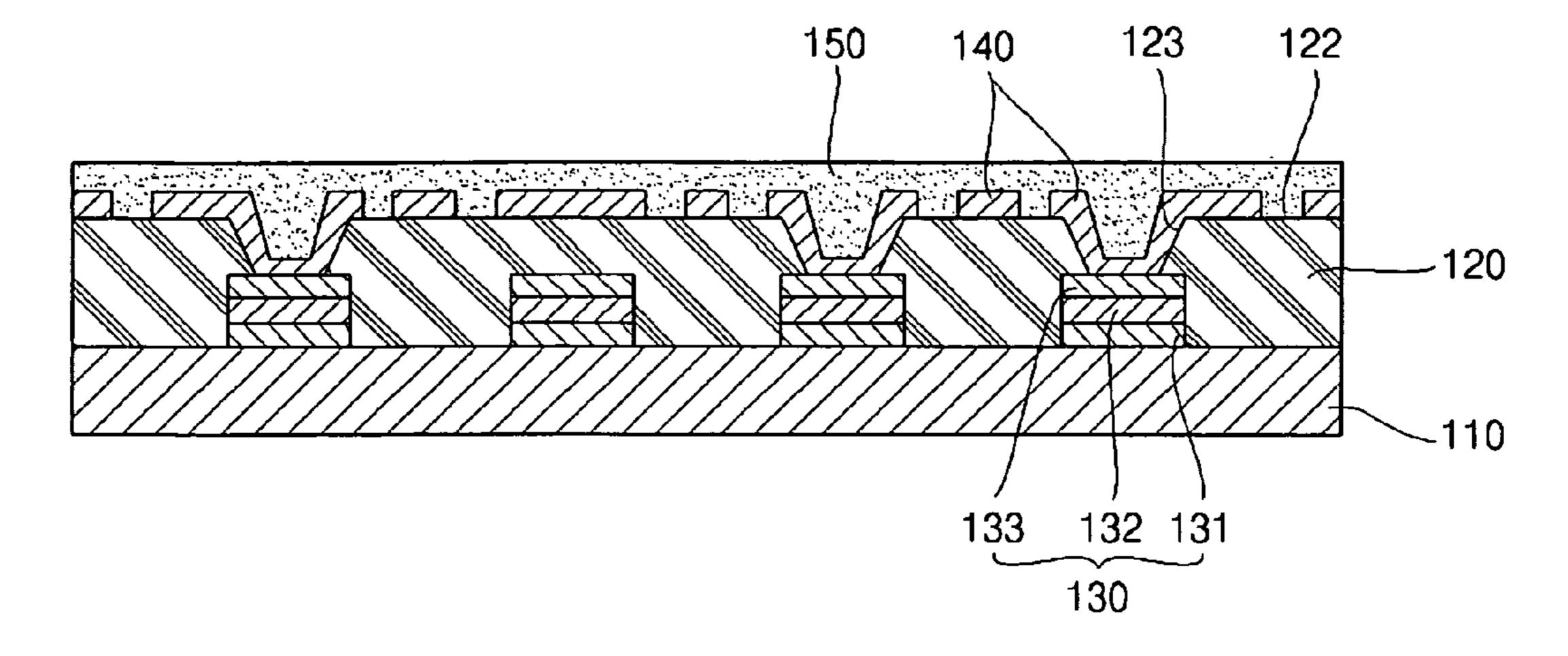

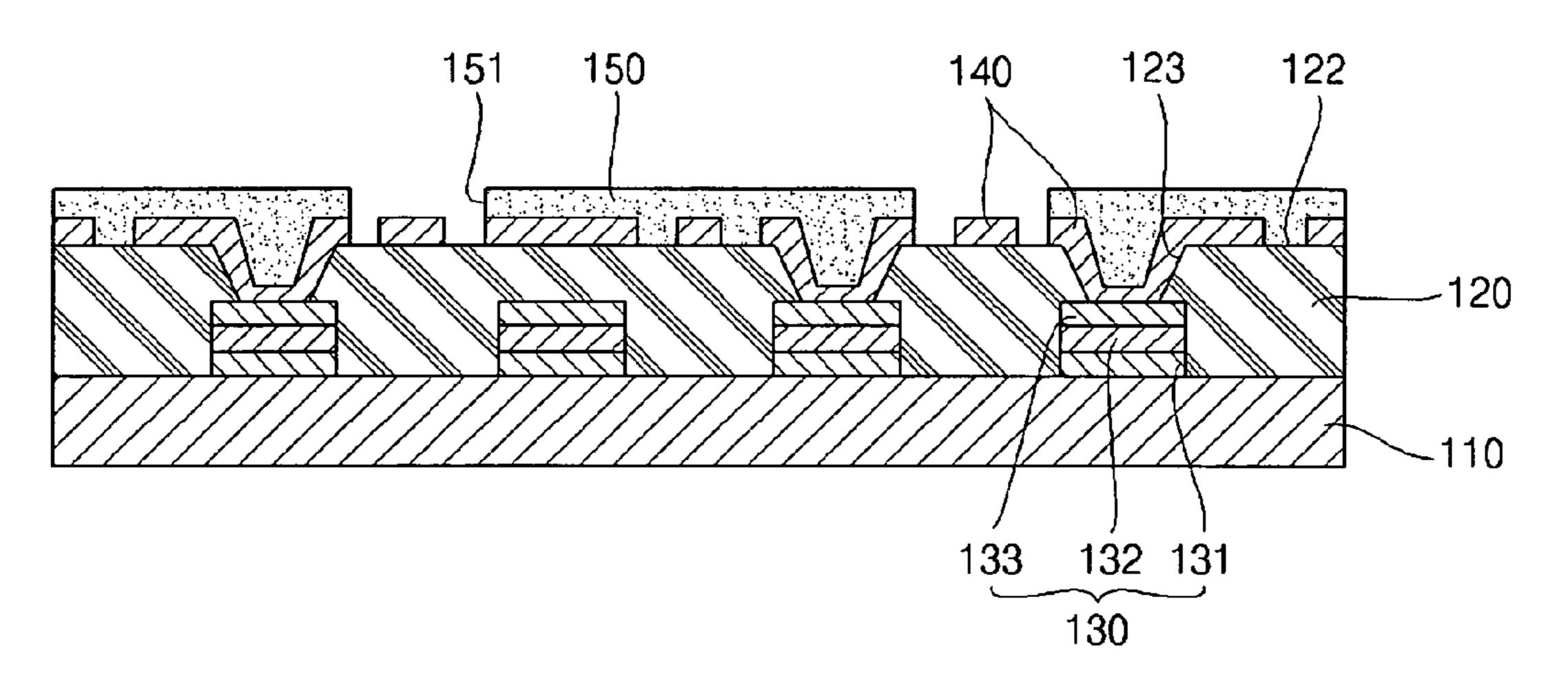

FIG. 1L illustrates a solder mask printing operation;

FIG. 1M illustrates a solder mask exposing/developing operation;

FIG. 1N illustrates a third photo sensitive film providing

FIG. 10 illustrates a fourth plating operation;

FIG. 1P illustrates a third photo sensitive film eliminating operation;

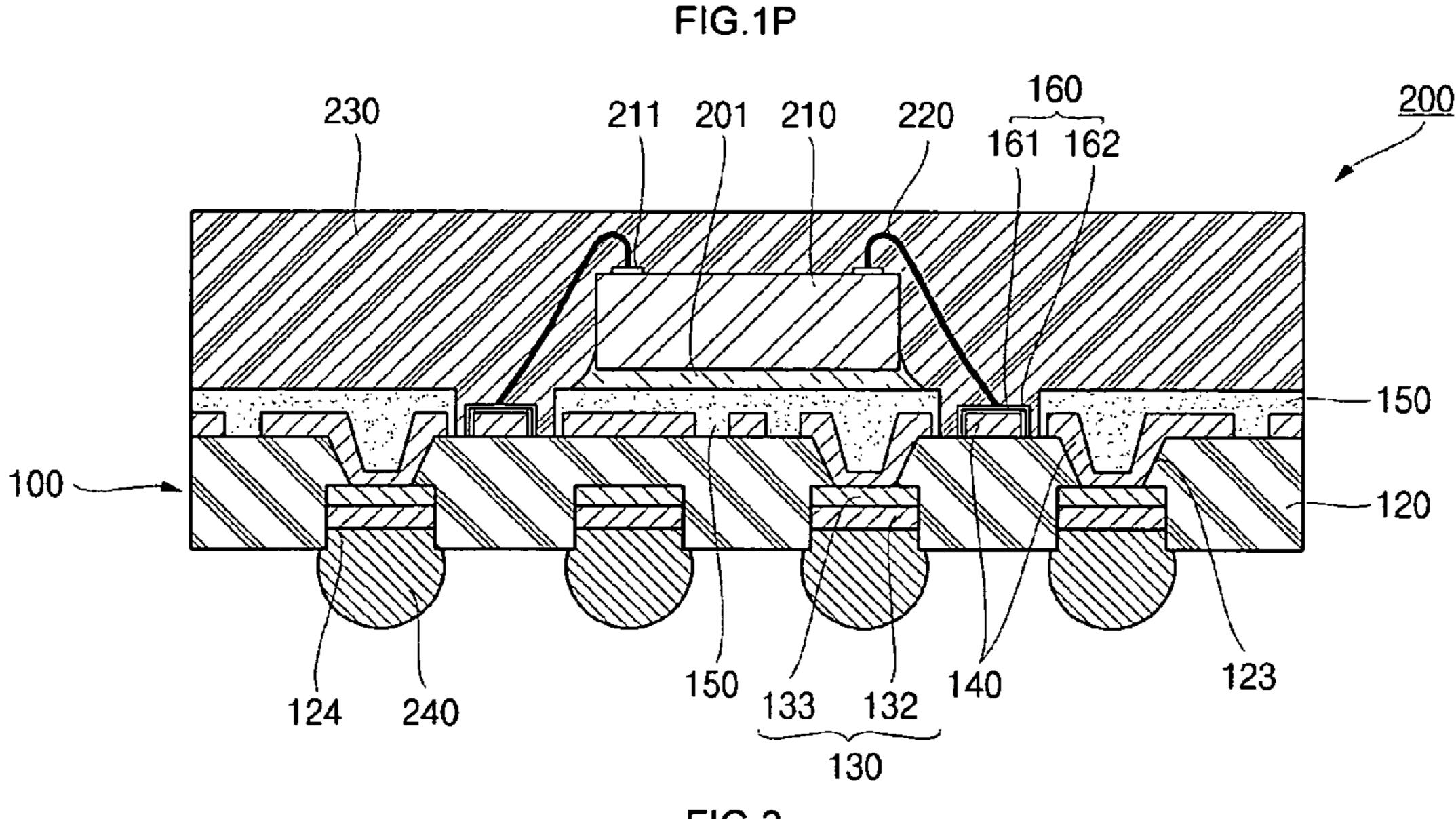

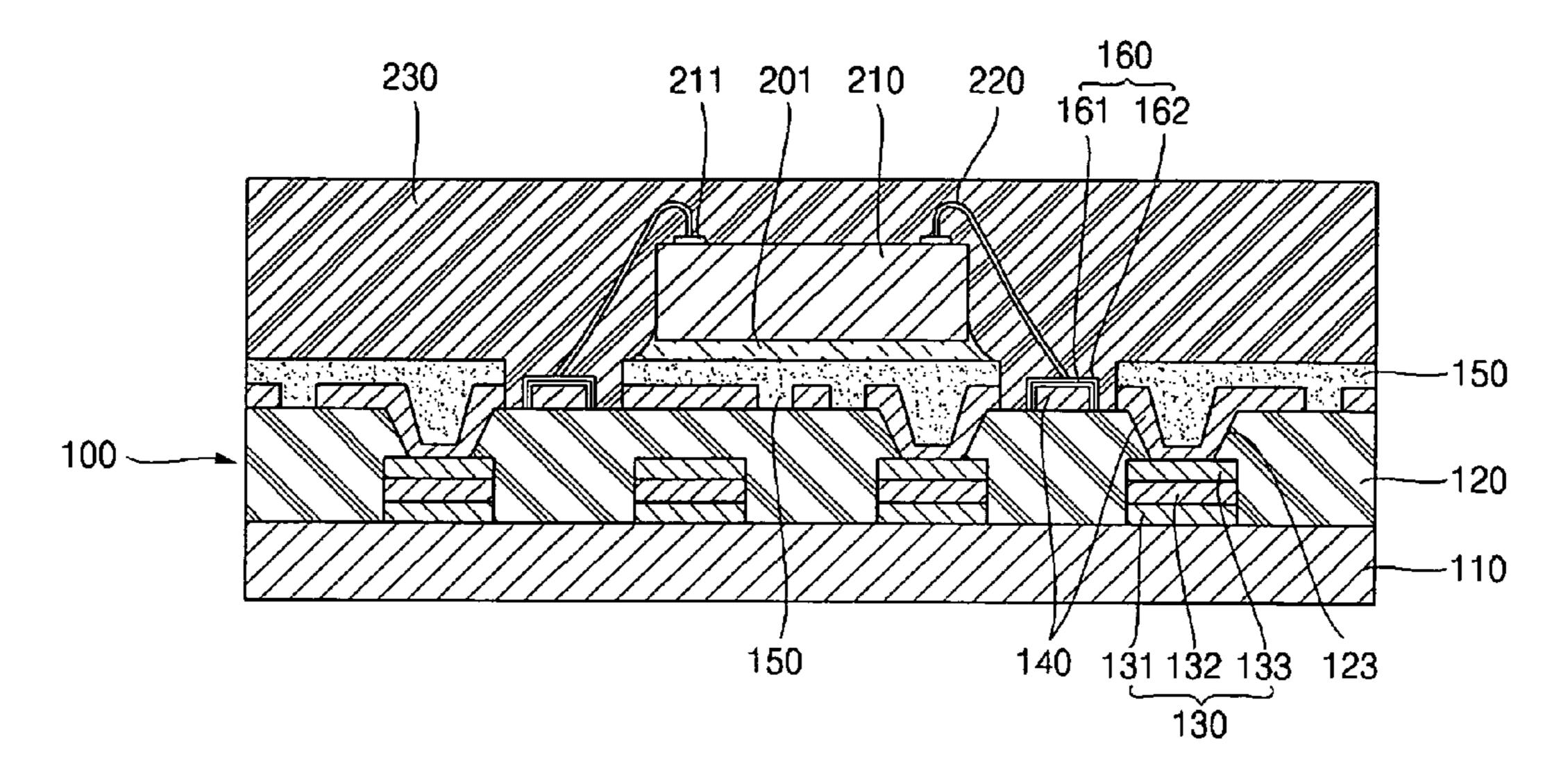

FIG. 2 is a sectional view of a semiconductor device according to one embodiment of the present invention;

FIG. 2A through FIG. 2E are sectional views showing a fabrication method of the semiconductor device according to one embodiment of the present invention where:

FIG. 2A illustrates a semiconductor die attaching opera-45 tion;

FIG. 2B illustrates a wire bonding operation;

FIG. 2C illustrates an encapsulating operation;

FIG. 2D illustrates a carrier eliminating operation;

FIG. 2E illustrates a solder ball fusing operation;

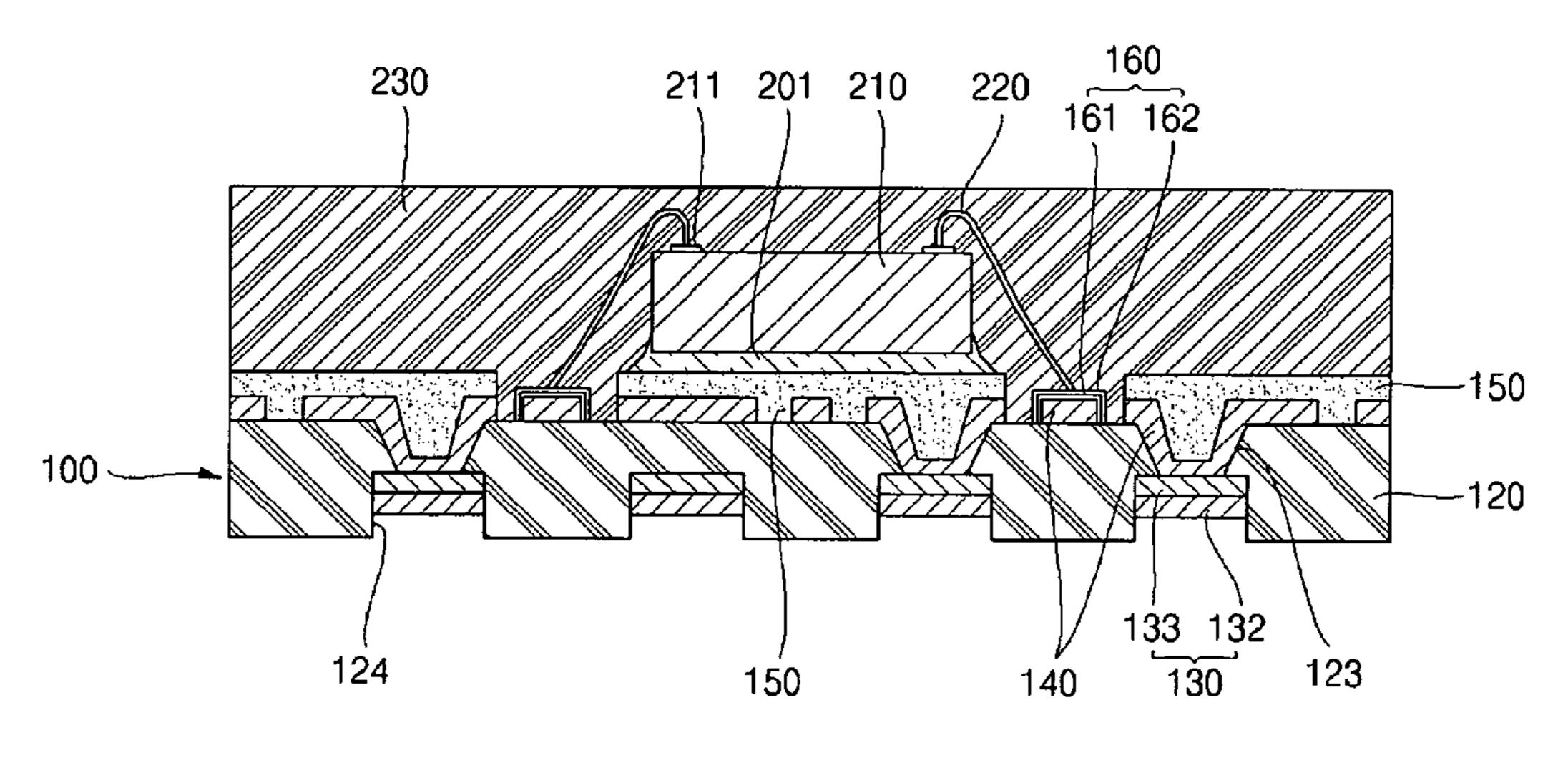

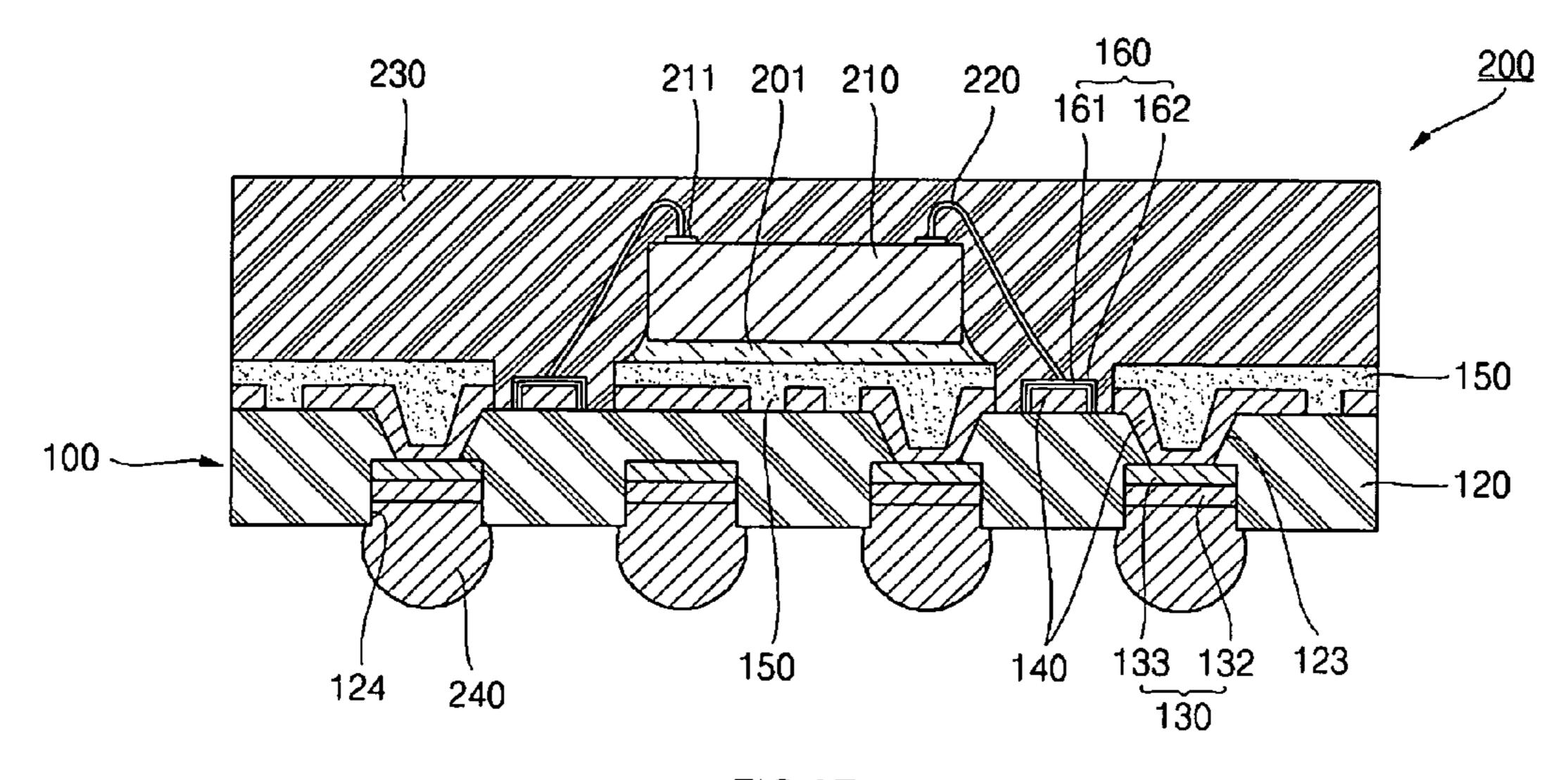

FIG. 3 is a sectional view of a semiconductor device according to another embodiment of the present invention;

FIG. 3A through FIG. 3E are sectional views showing a fabrication method of the semiconductor device according to anther embodiment of the present invention where:

FIG. 3A illustrates a flip chip bonding operation;

FIG. 3B illustrates an underfilling operation;

FIG. 3C illustrates an encapsulating operation;

FIG. 3D illustrates a carrier eliminating operation;

FIG. 3E illustrates a solder ball fusing operation;

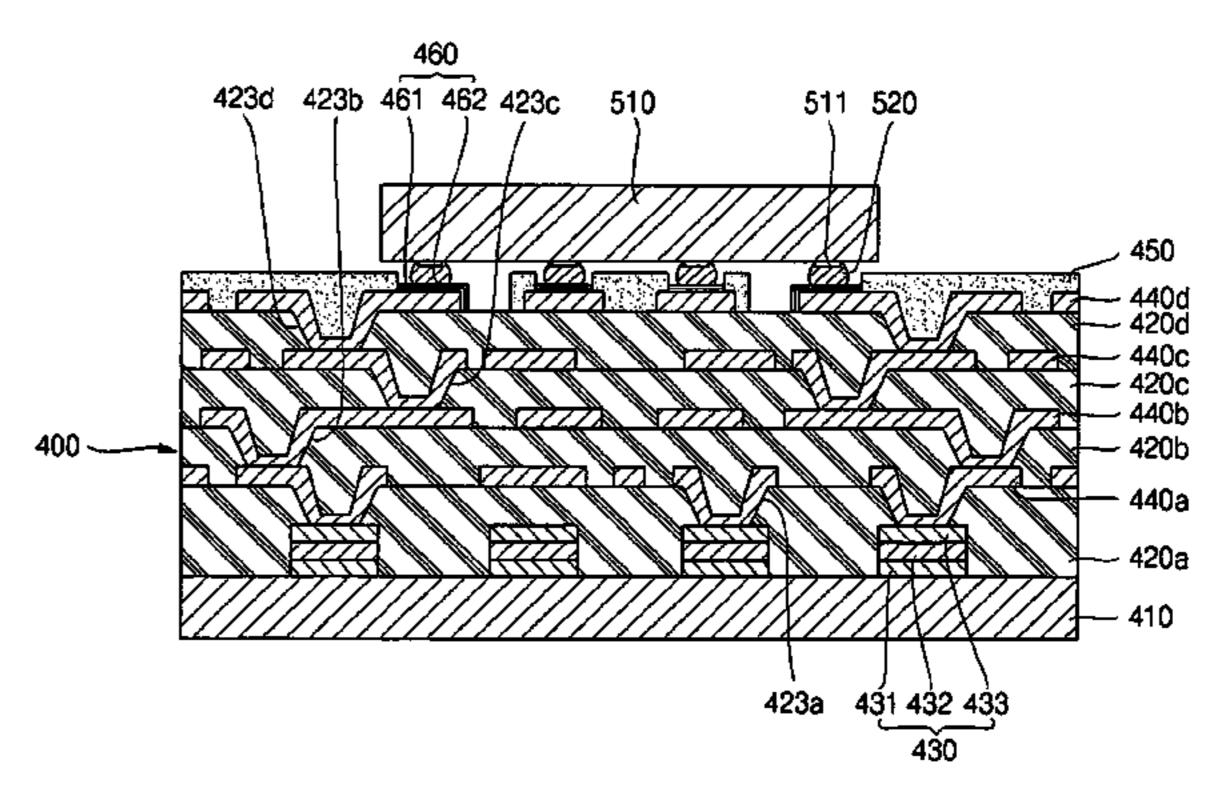

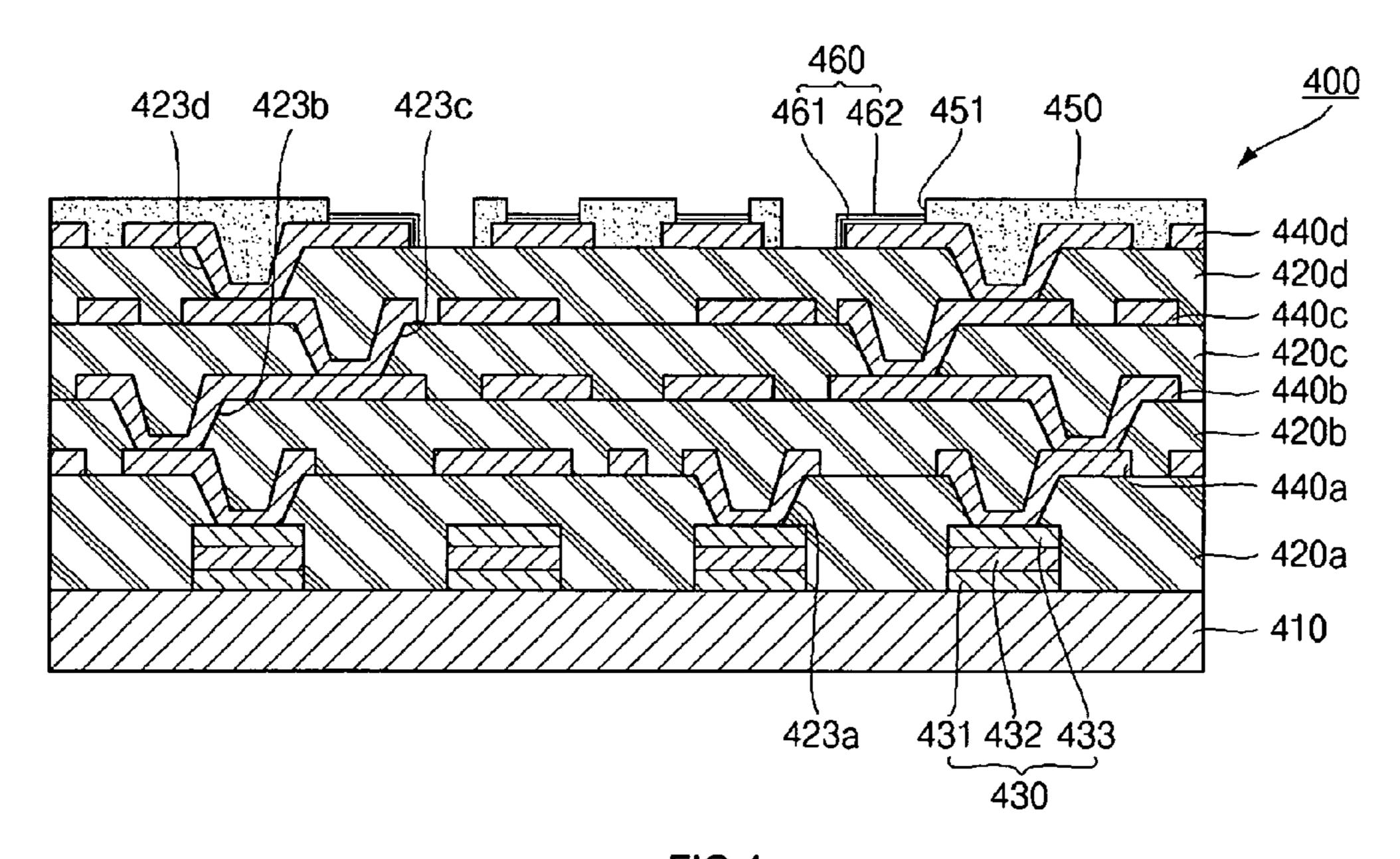

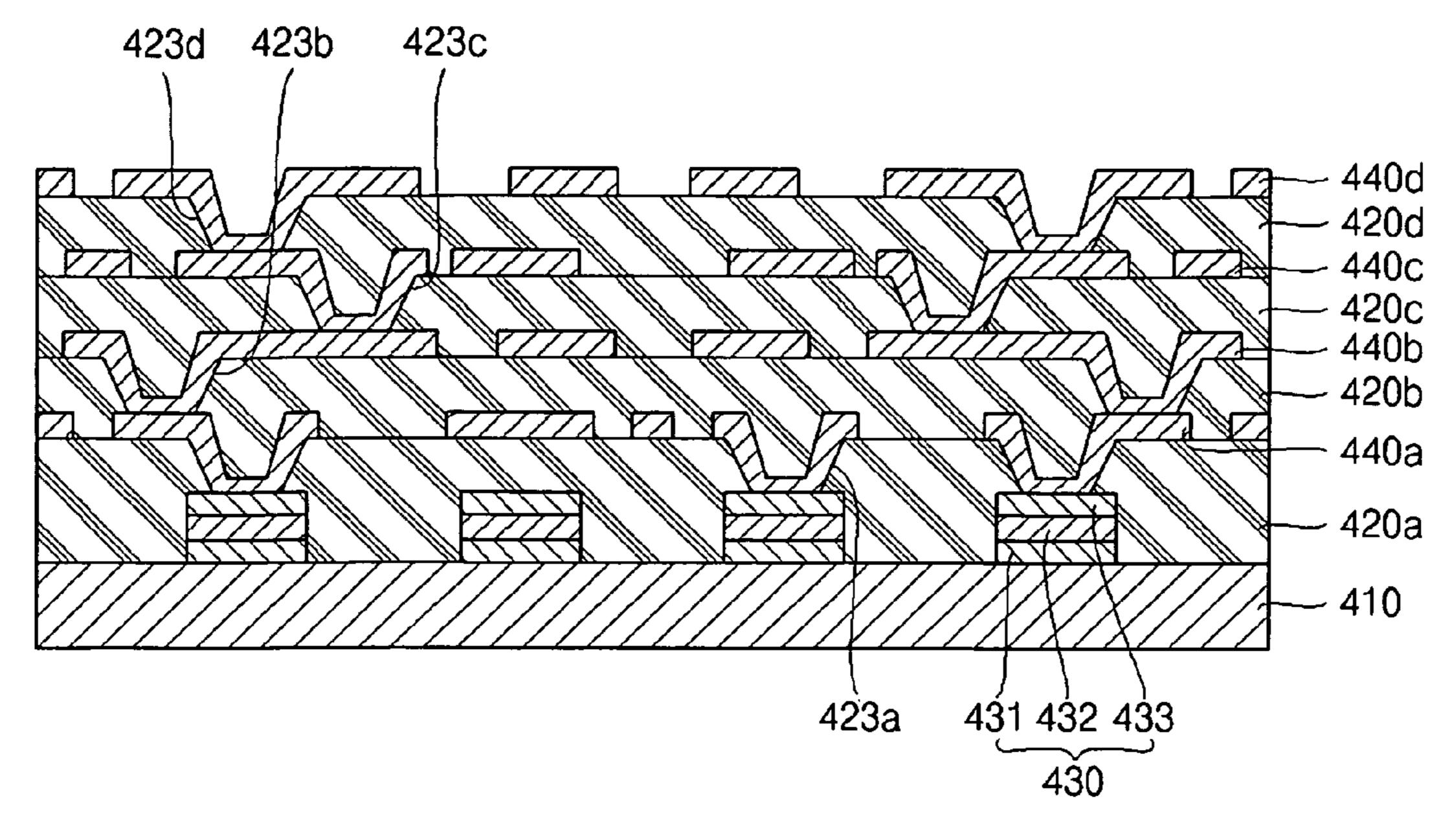

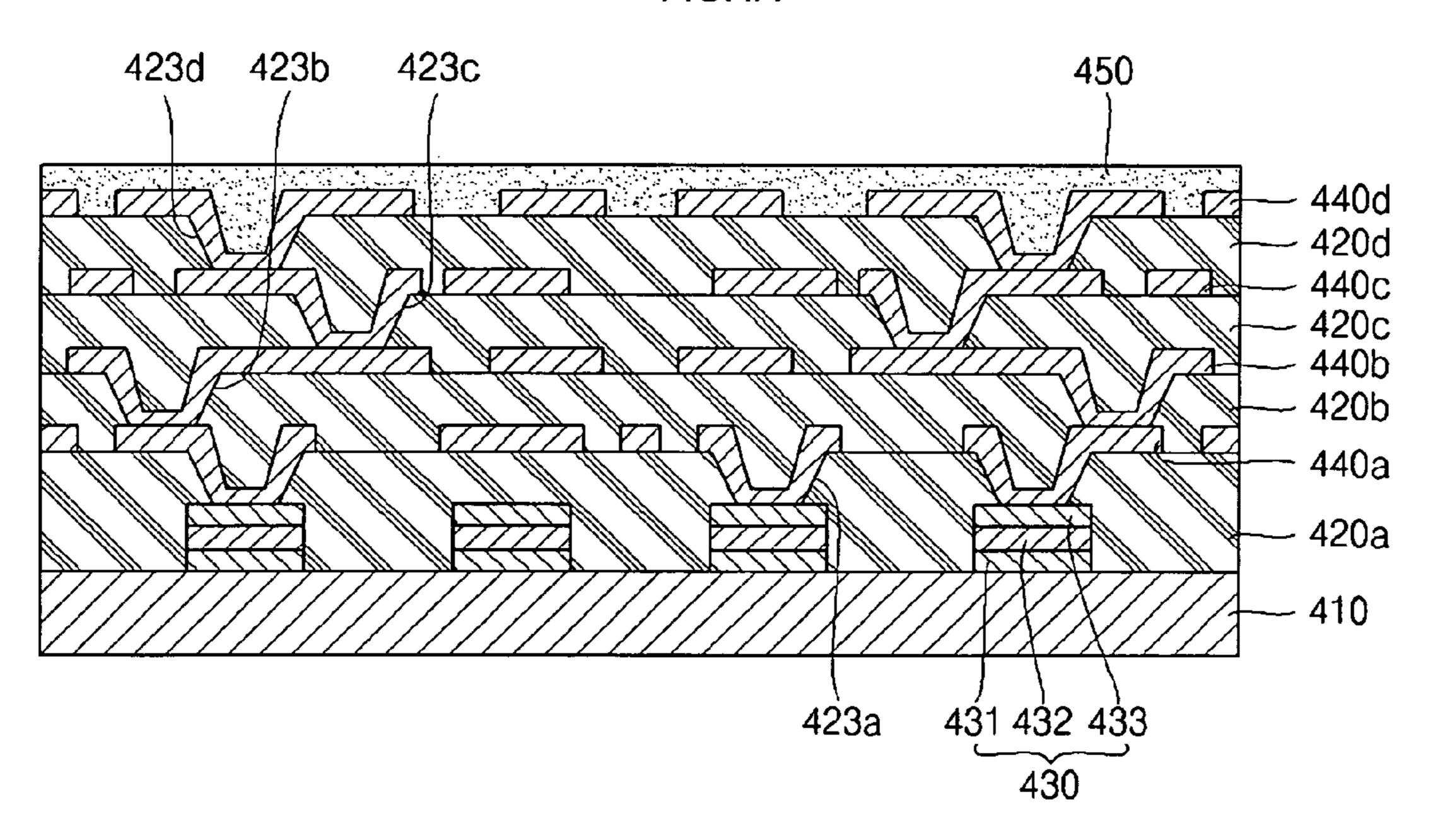

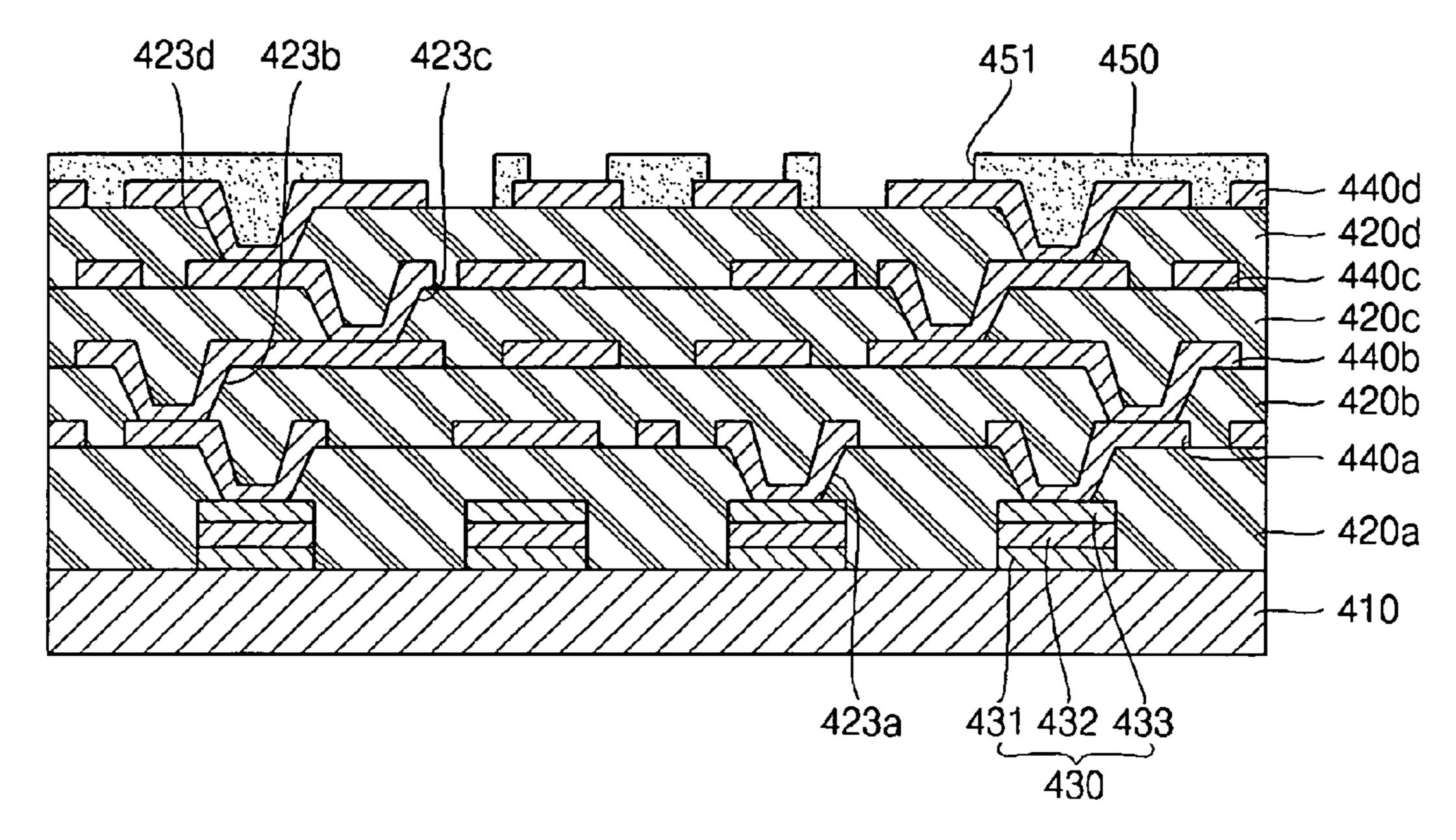

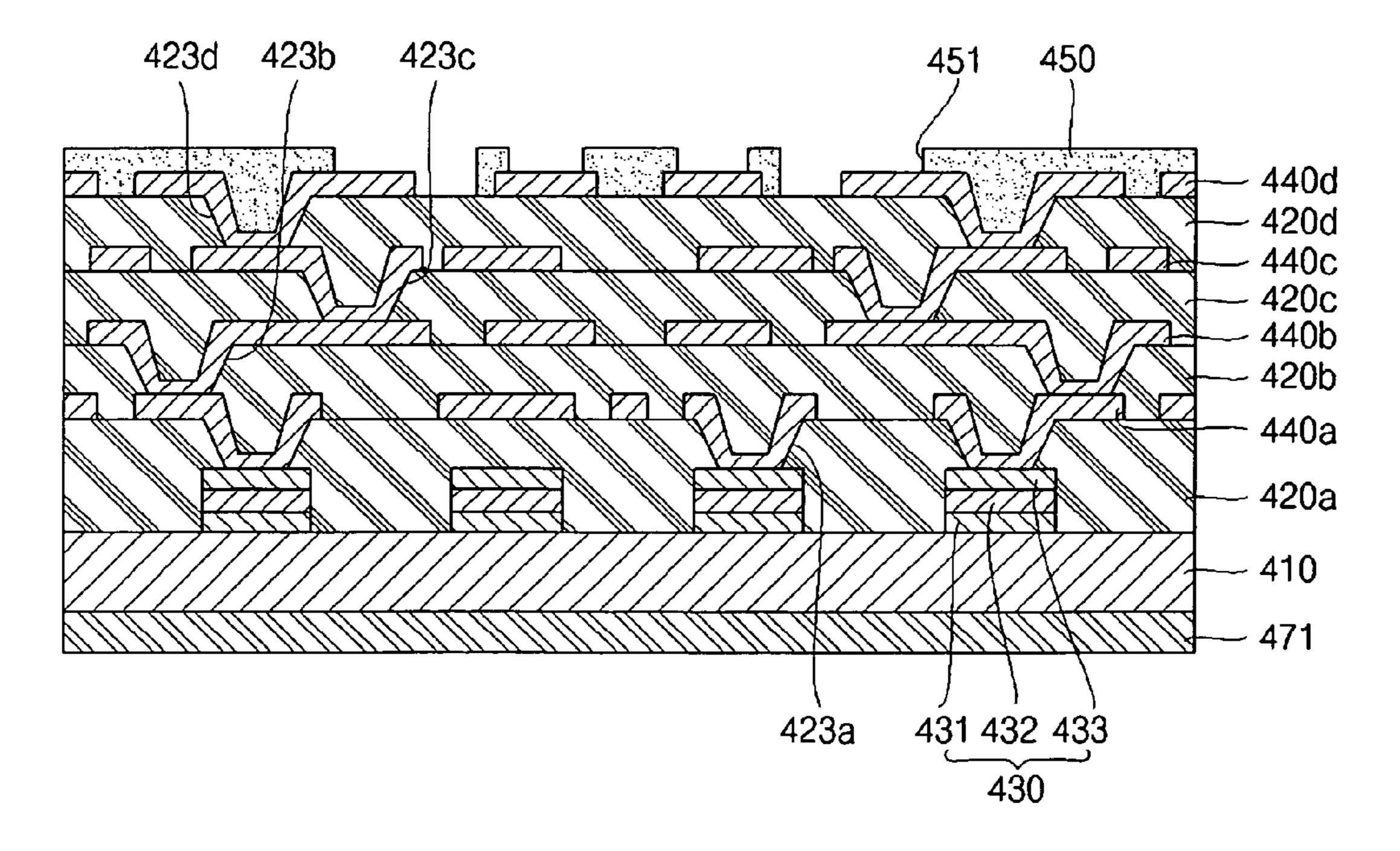

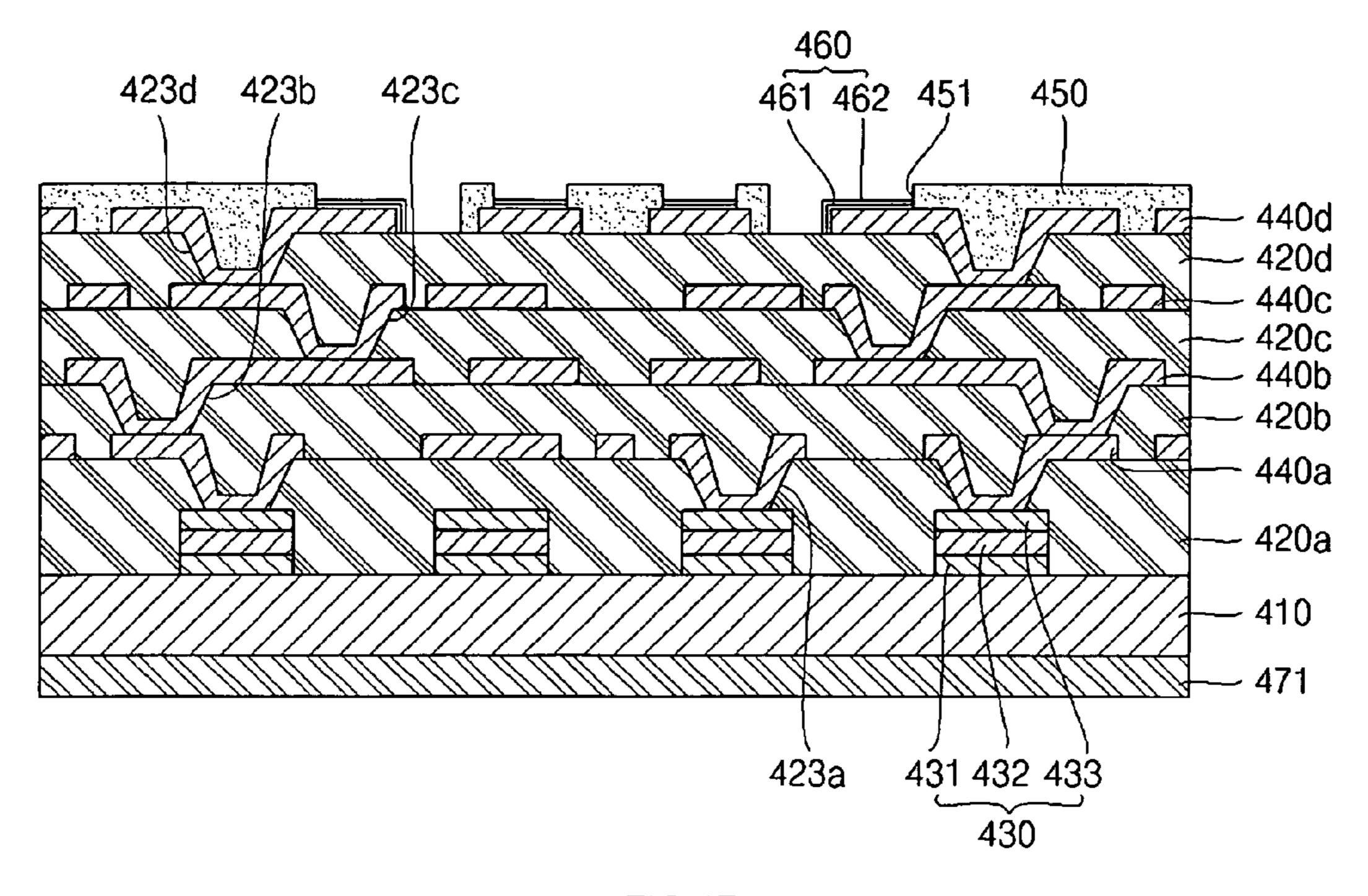

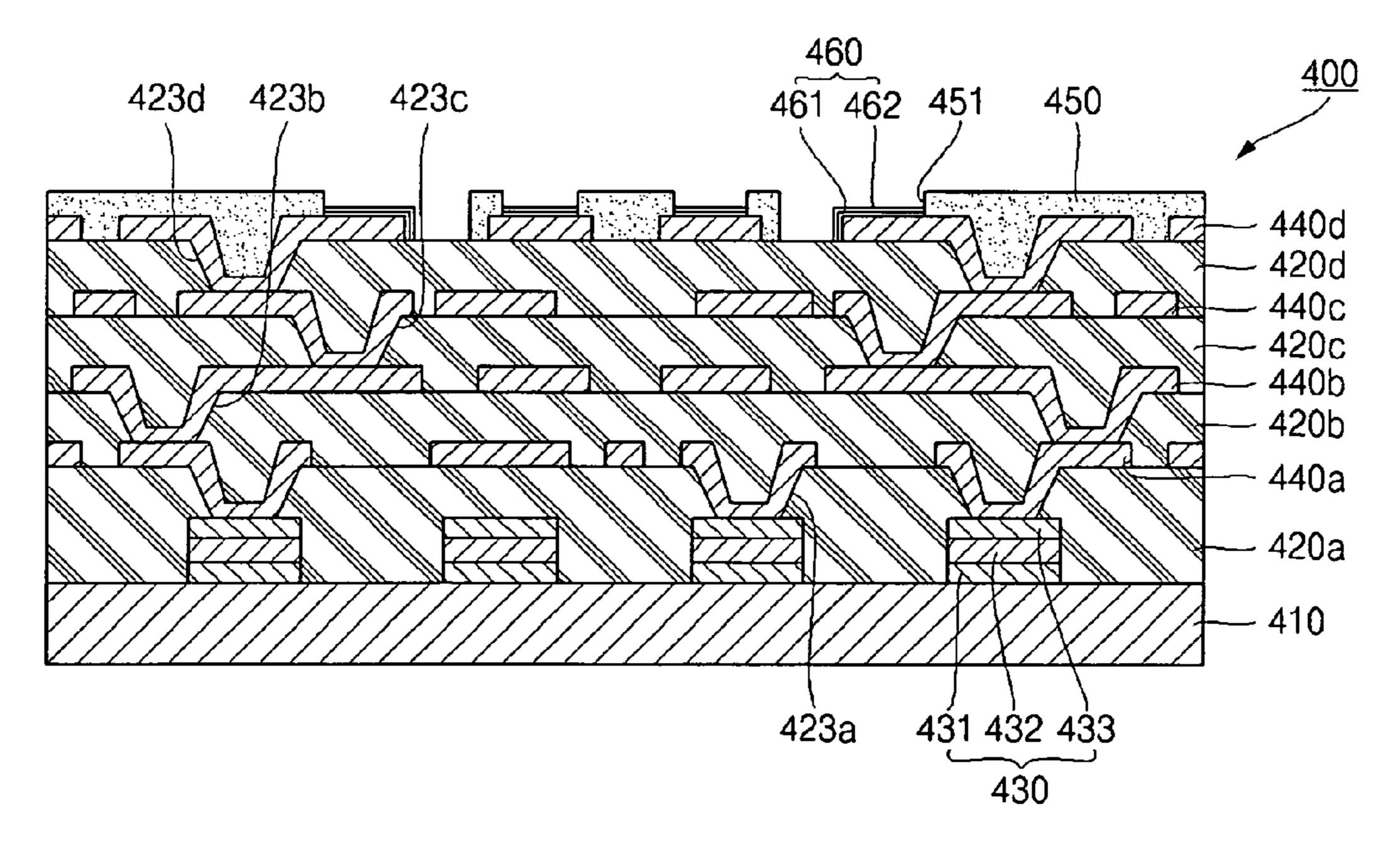

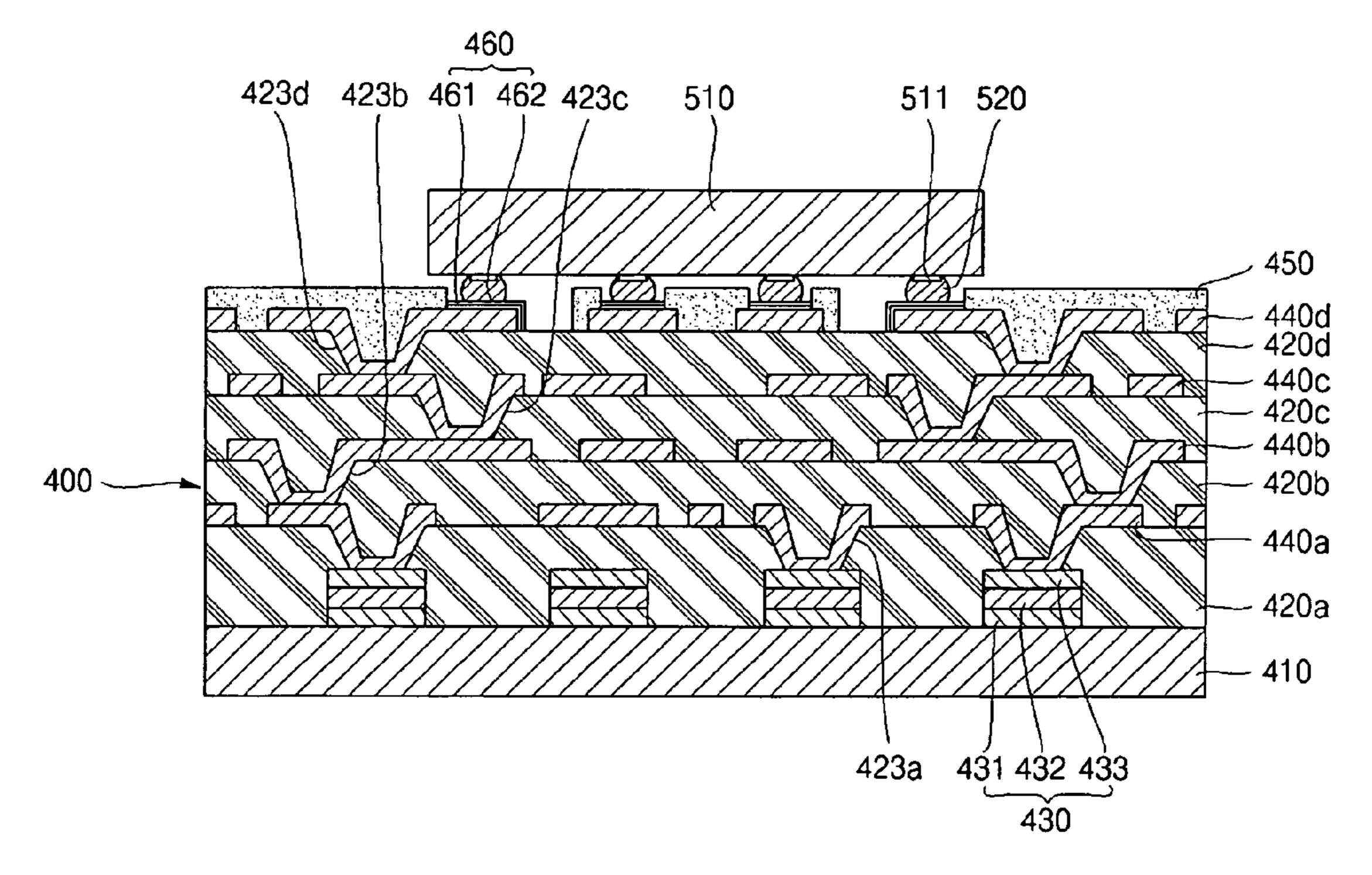

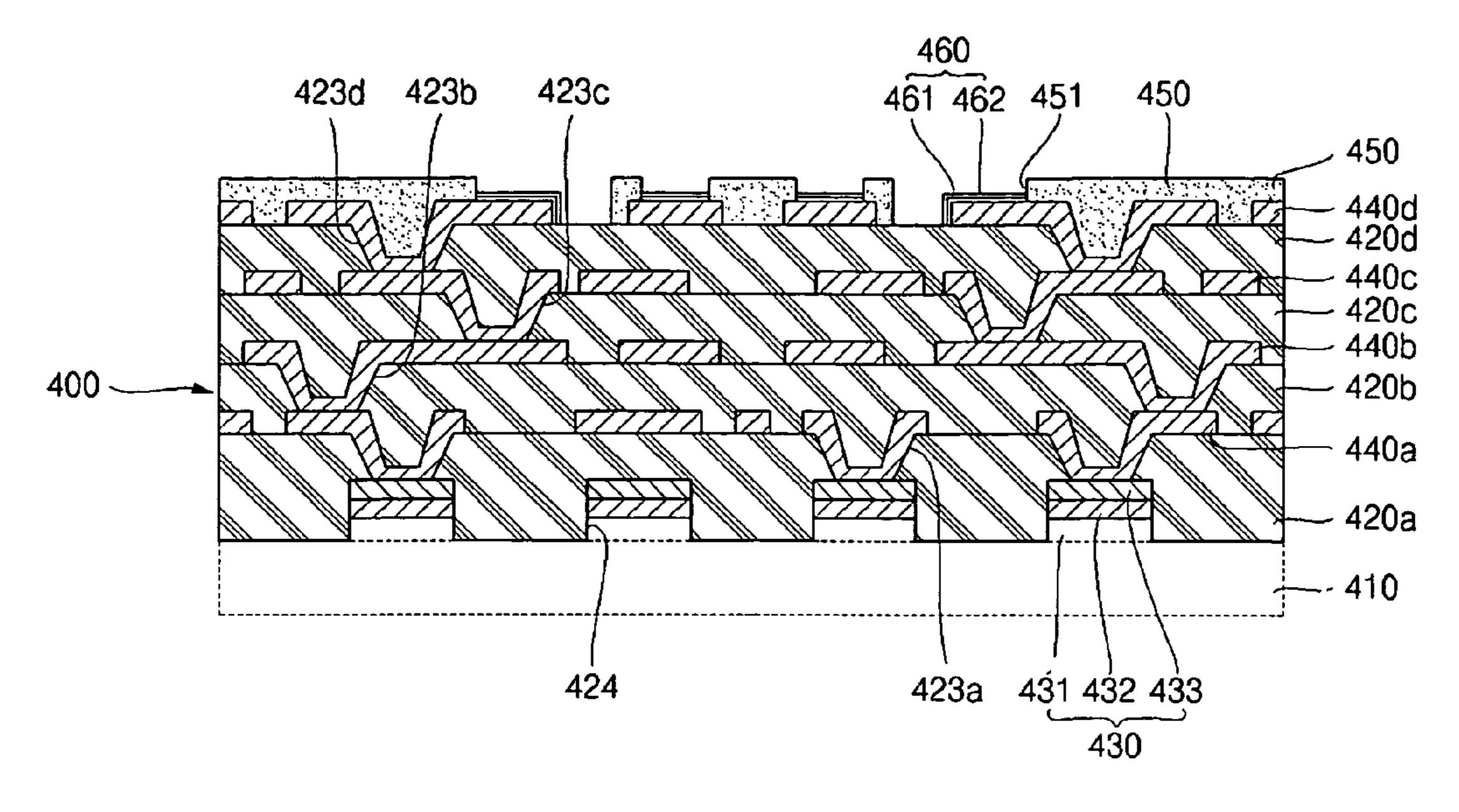

FIG. 4 is a sectional view of a substrate for a semiconductor device according to another embodiment of the present invention;

FIG. 4A through FIG. 4F is a flow chart showing a fabrication method of a semiconductor device according to another embodiment of the present invention;

FIG. 4A illustrates a multi layer forming operation;

FIG. 4B illustrates a solder mask printing operation;

FIG. 4C illustrates a solder mask exposing/developing operation;

FIG. 4D illustrates a photo sensitive film providing operation;

FIG. 4E illustrates a plating operation;

FIG. 4F illustrates a photo sensitive film eliminating operation;

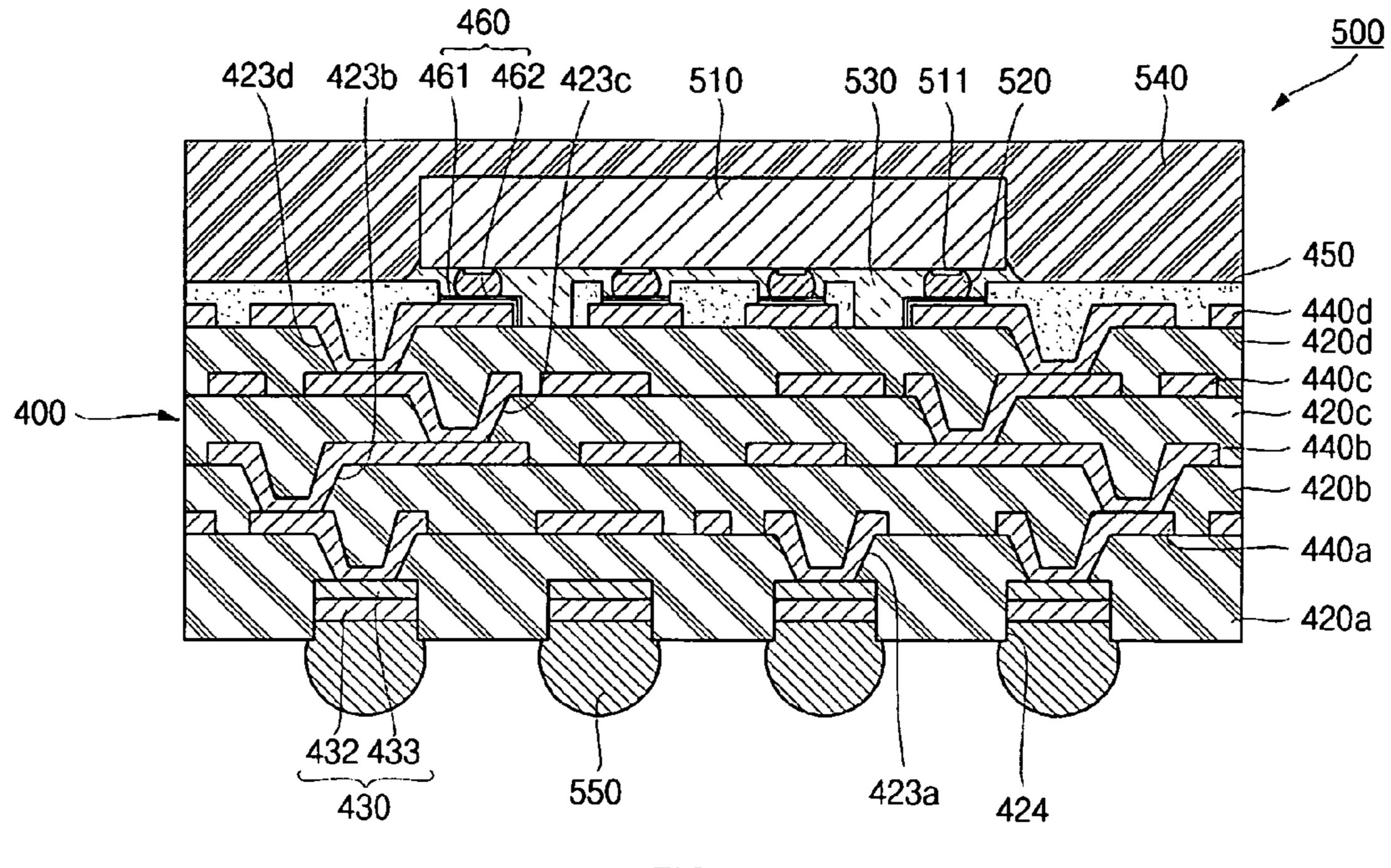

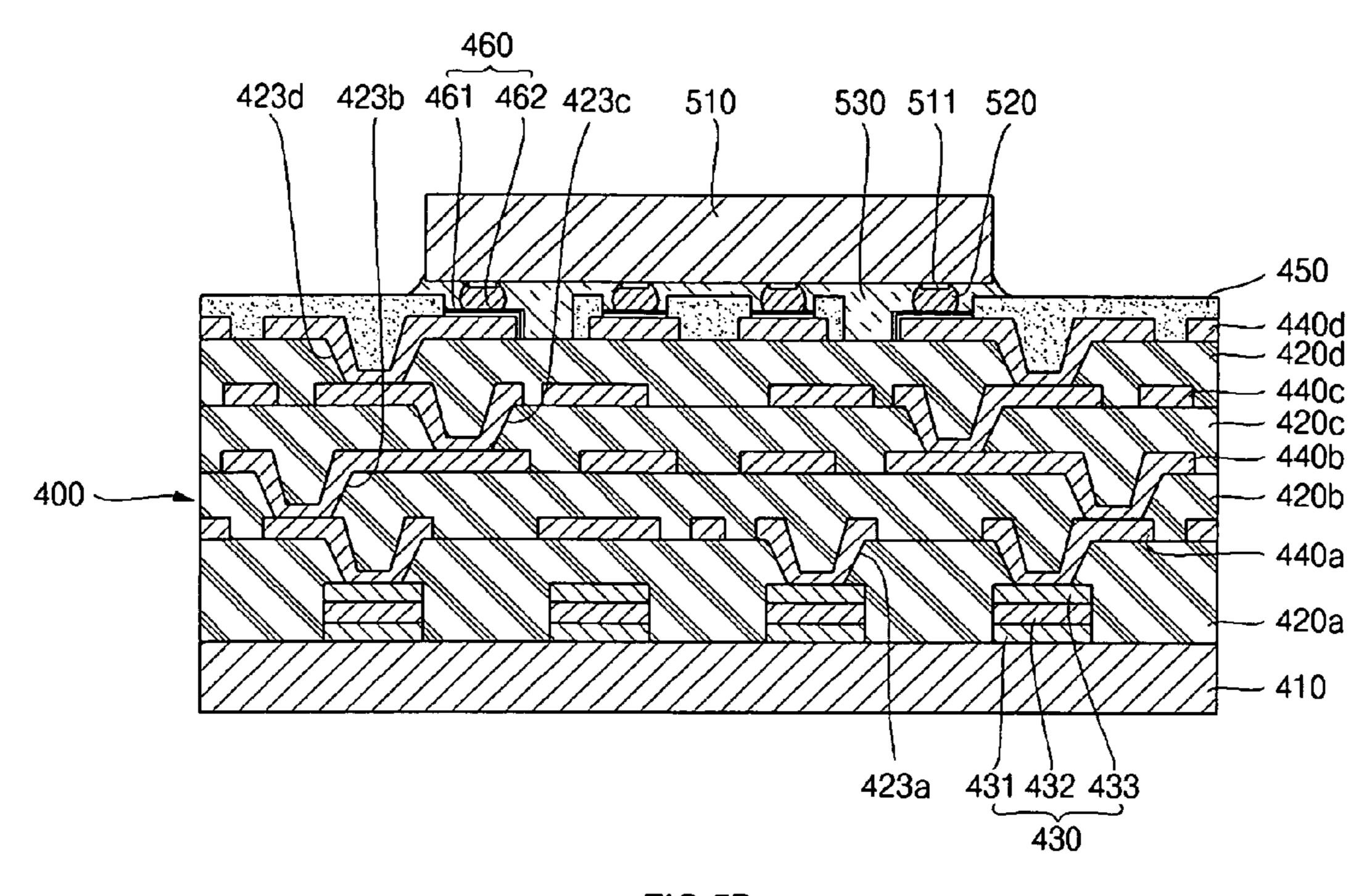

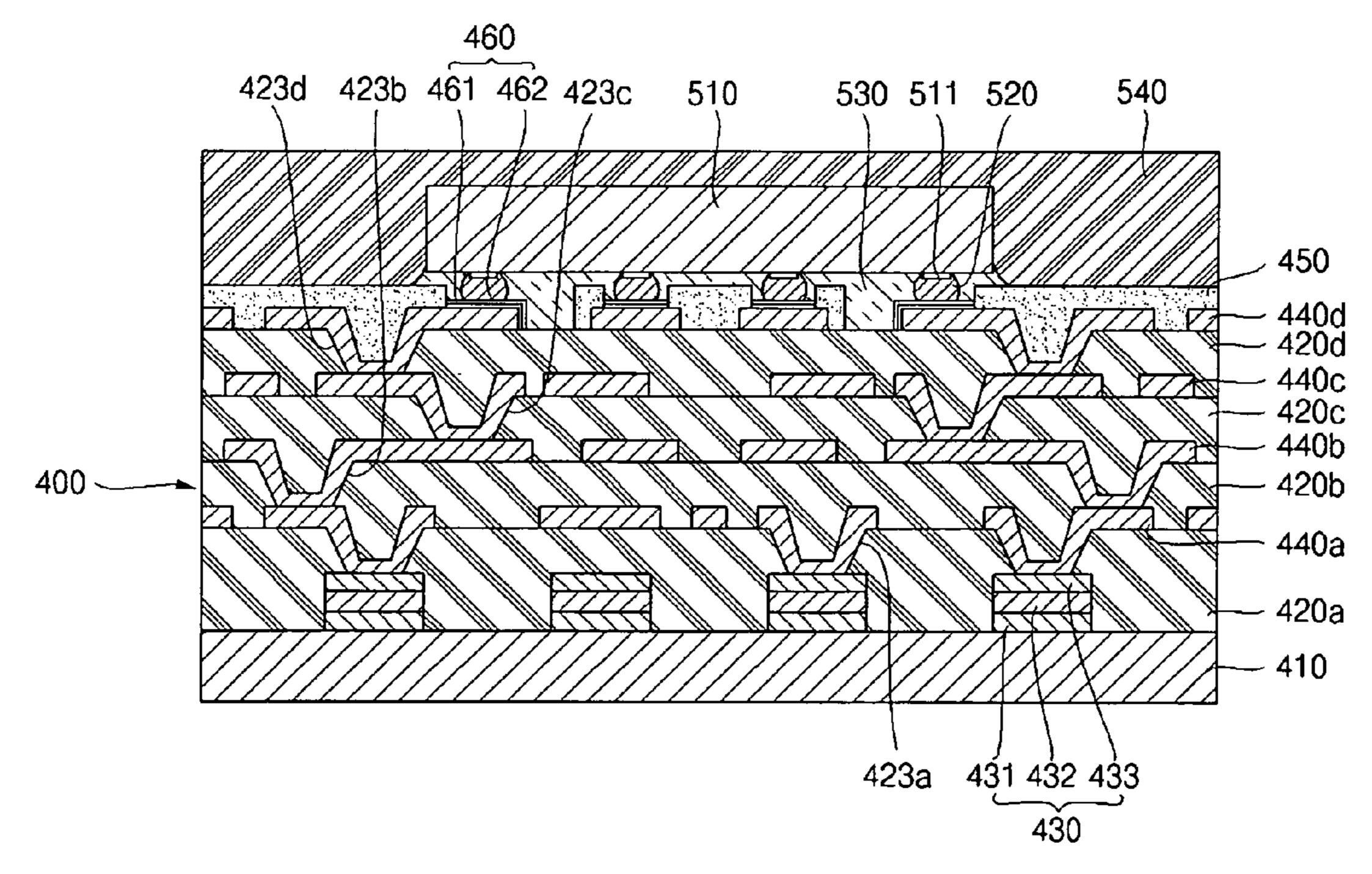

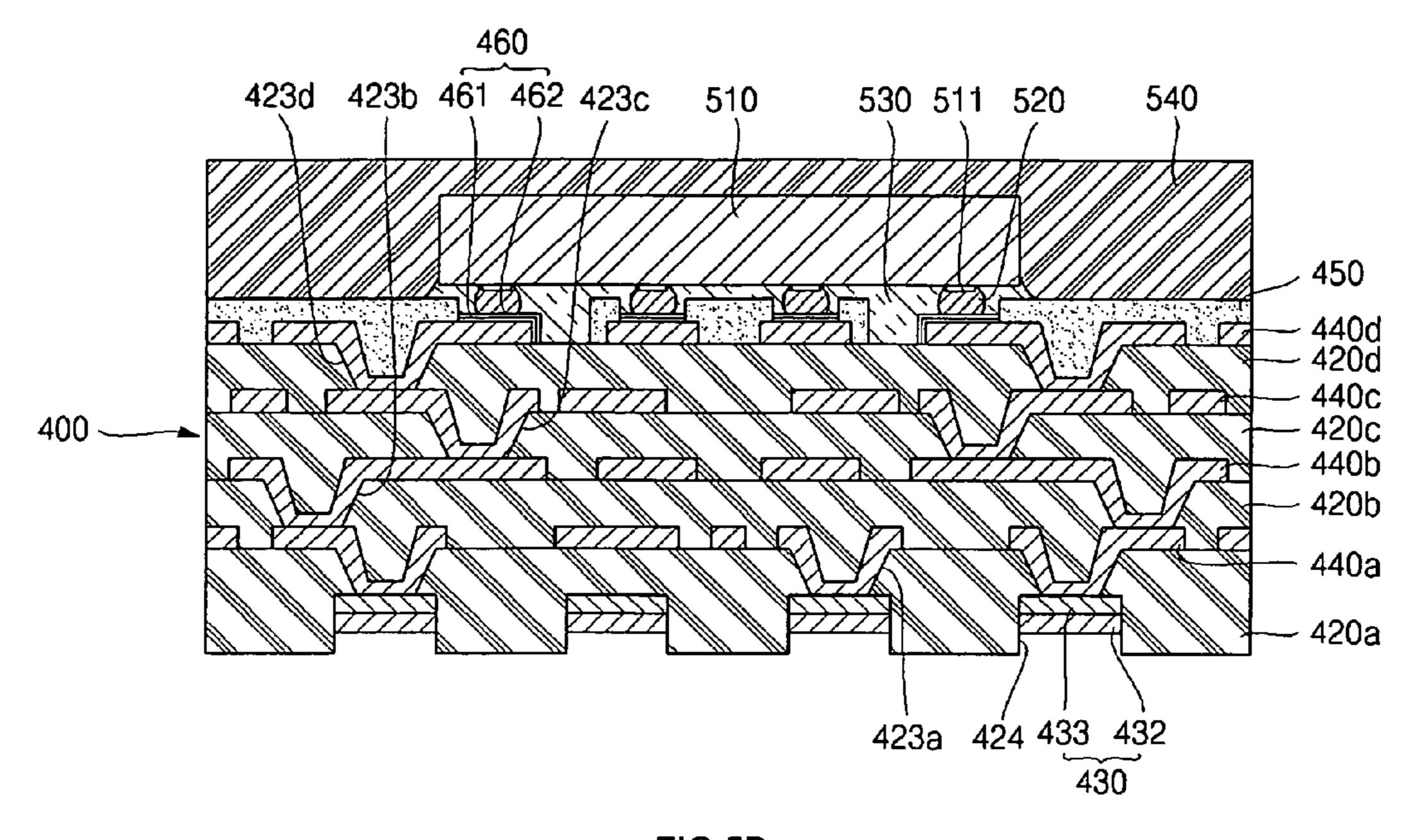

FIG. 5 is a sectional view of a semiconductor device according to another embodiment of the present invention;

FIG. **5**A through FIG. **5**E are sectional views showing a <sup>10</sup> fabrication method of a semiconductor device according to another embodiment of the present invention where:

FIG. 5A illustrates a flip chip bonding operation;

FIG. 5B illustrates an underfilling operation;

FIG. 5C illustrates an encapsulating operation;

FIG. 5D illustrates a carrier eliminating operation;

FIG. **5**E illustrates a solder ball fusing operation;

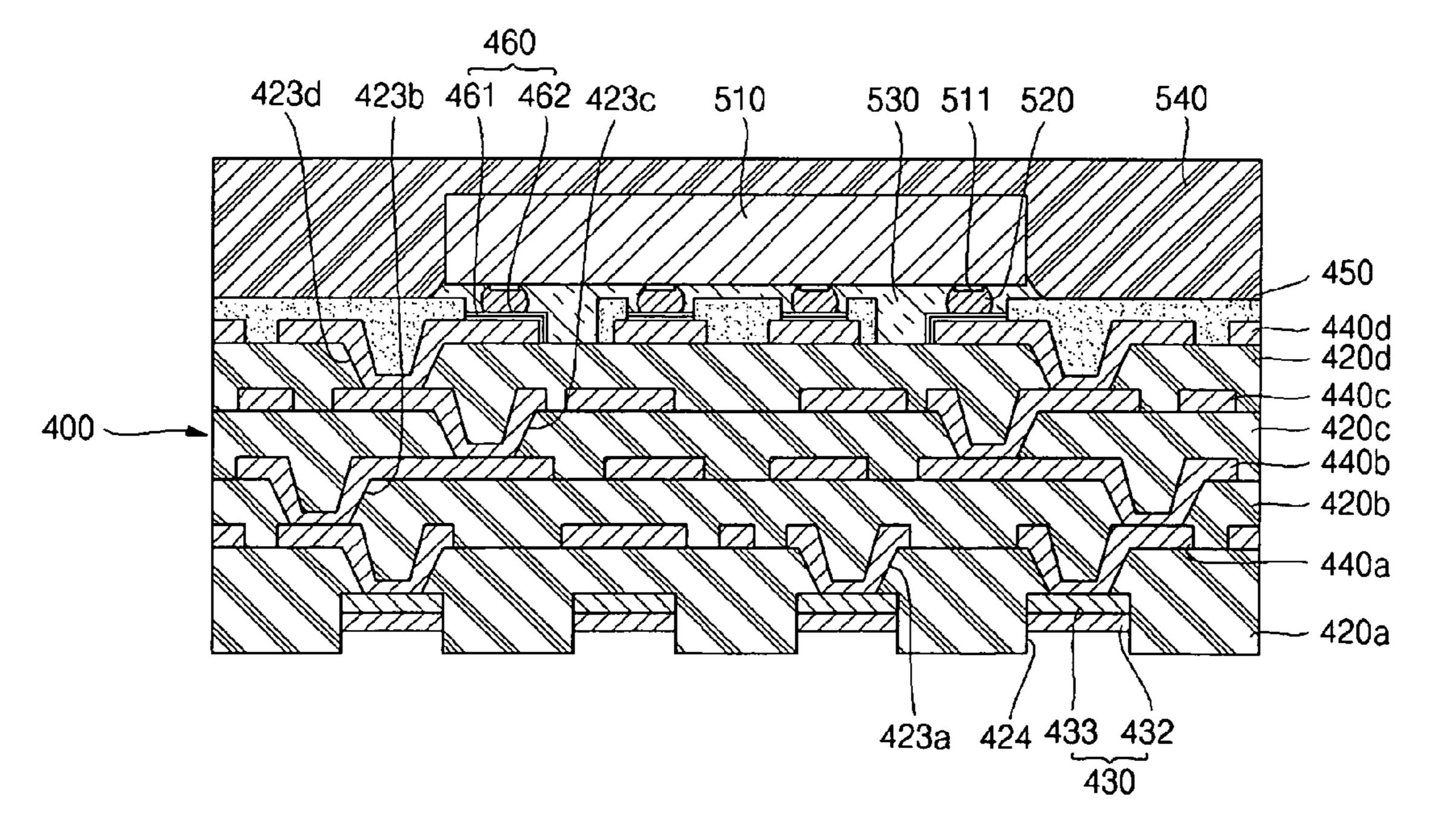

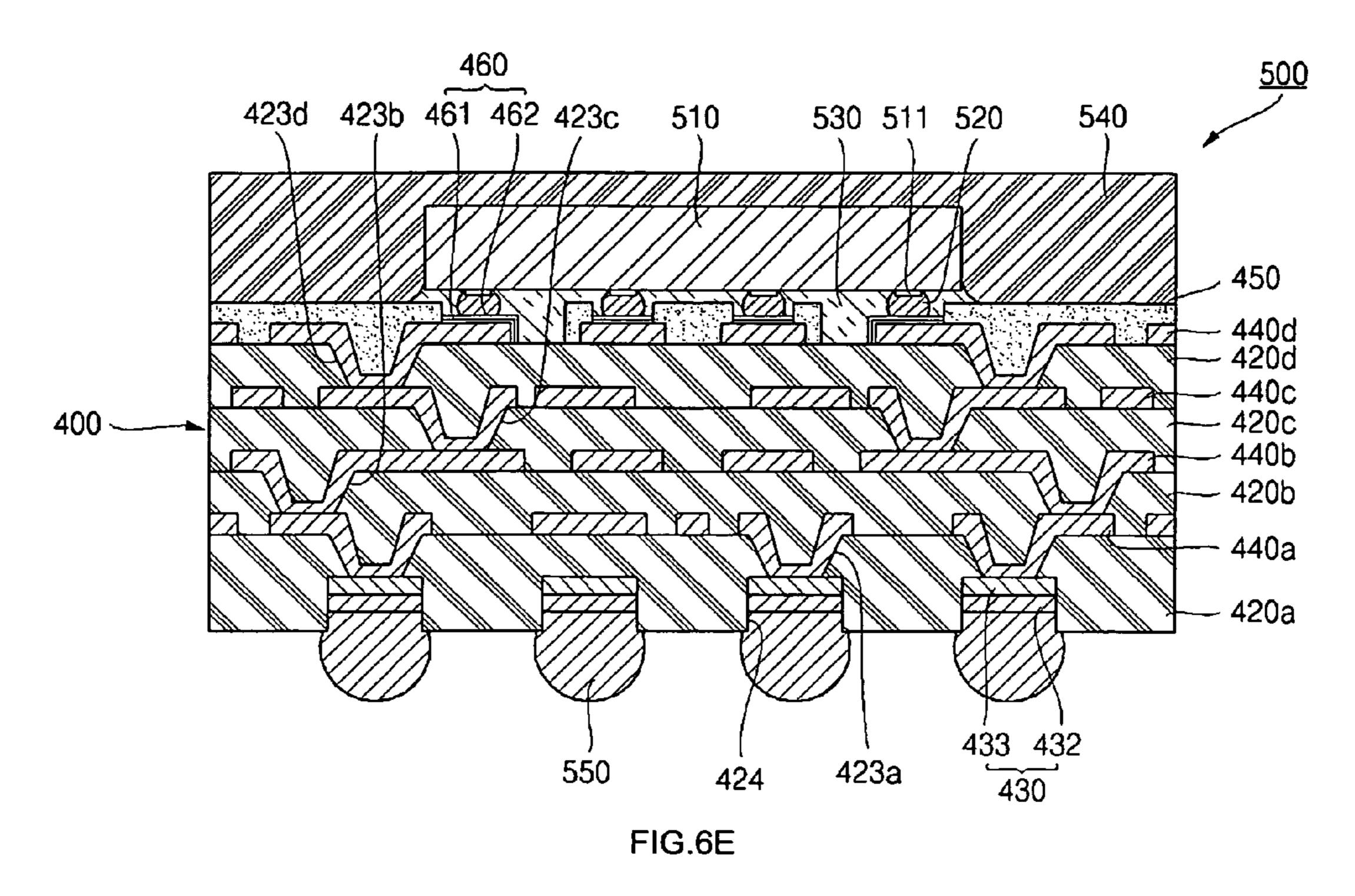

FIG. **6**A through FIG. **6**E are sectional views showing a fabrication method of a semiconductor device according to another embodiment of the present invention where:

FIG. 6A illustrates a carrier eliminating operation;

FIG. 6B illustrates a flip chip bonding operation;

FIG. 6C illustrates an underfilling operation;

FIG. 6D illustrates an encapsulating operation;

FIG. 6E illustrates a solder ball fusing operation;

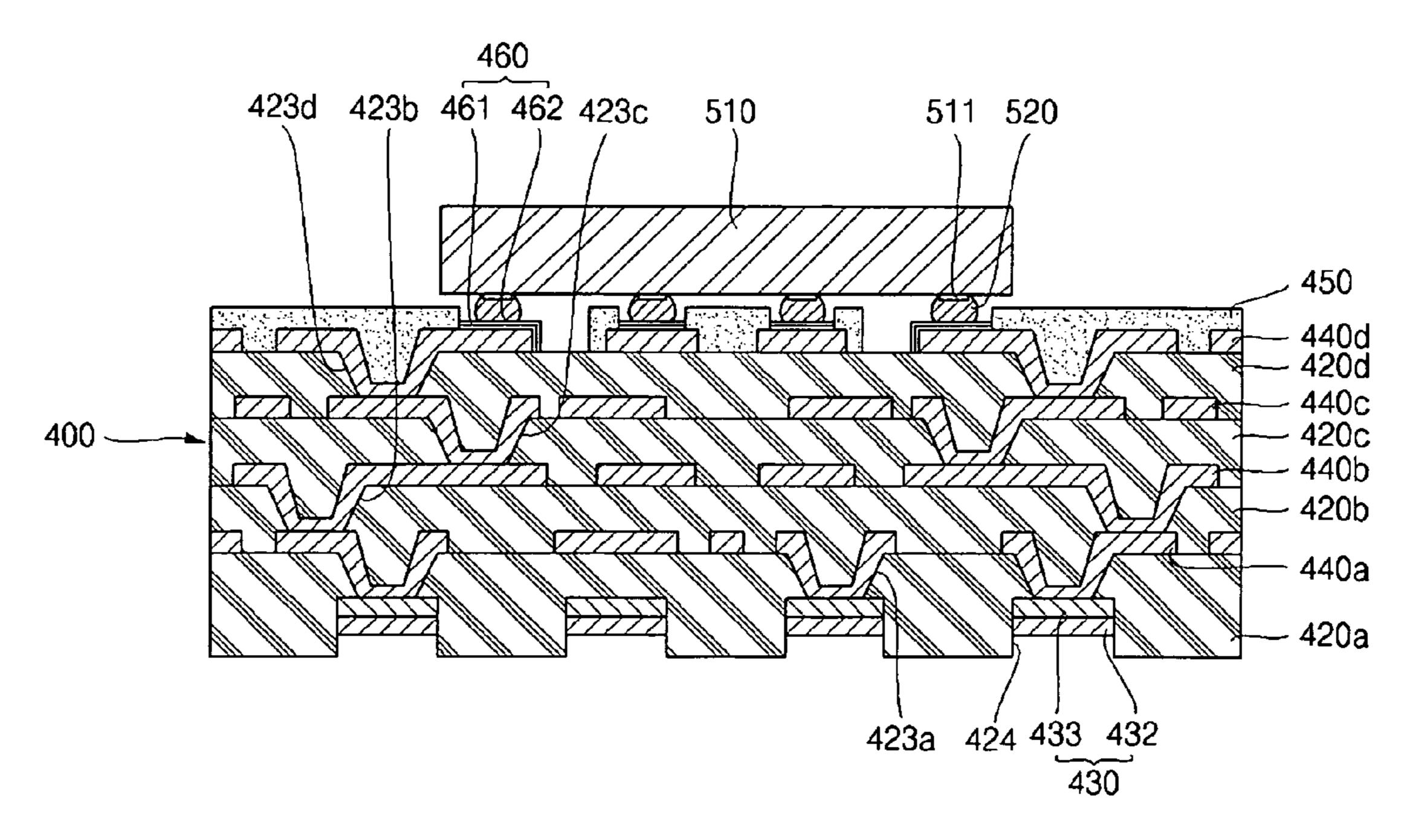

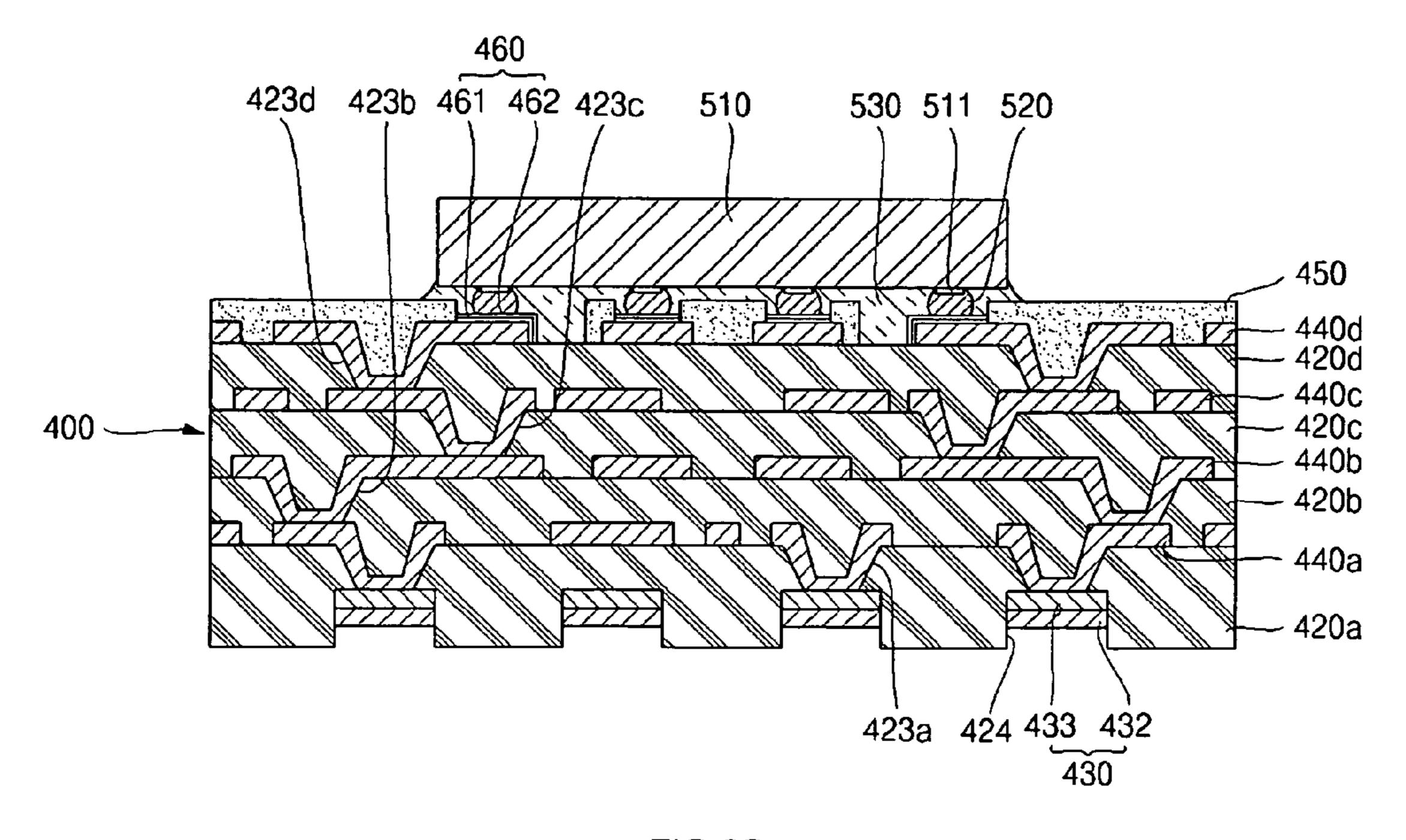

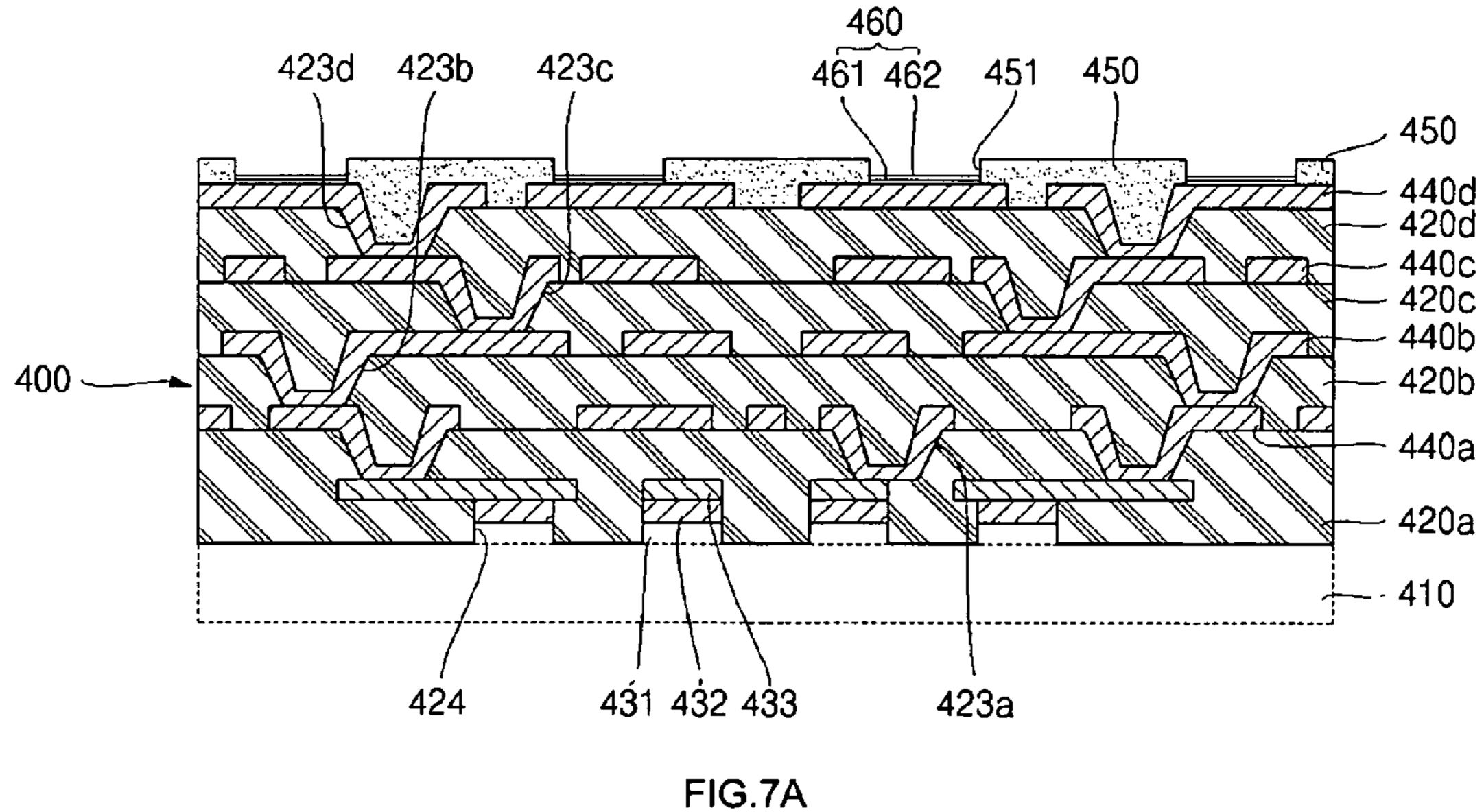

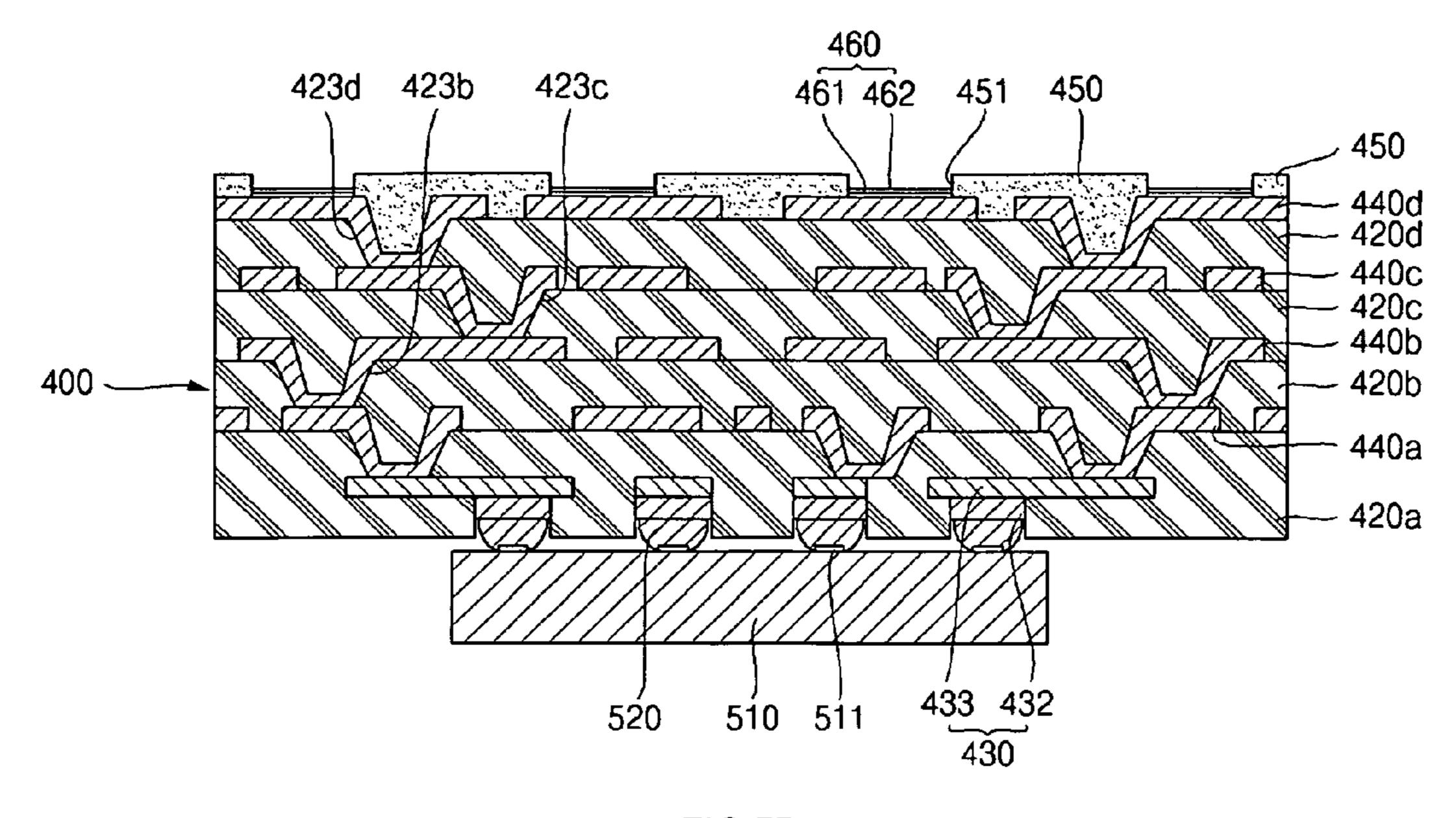

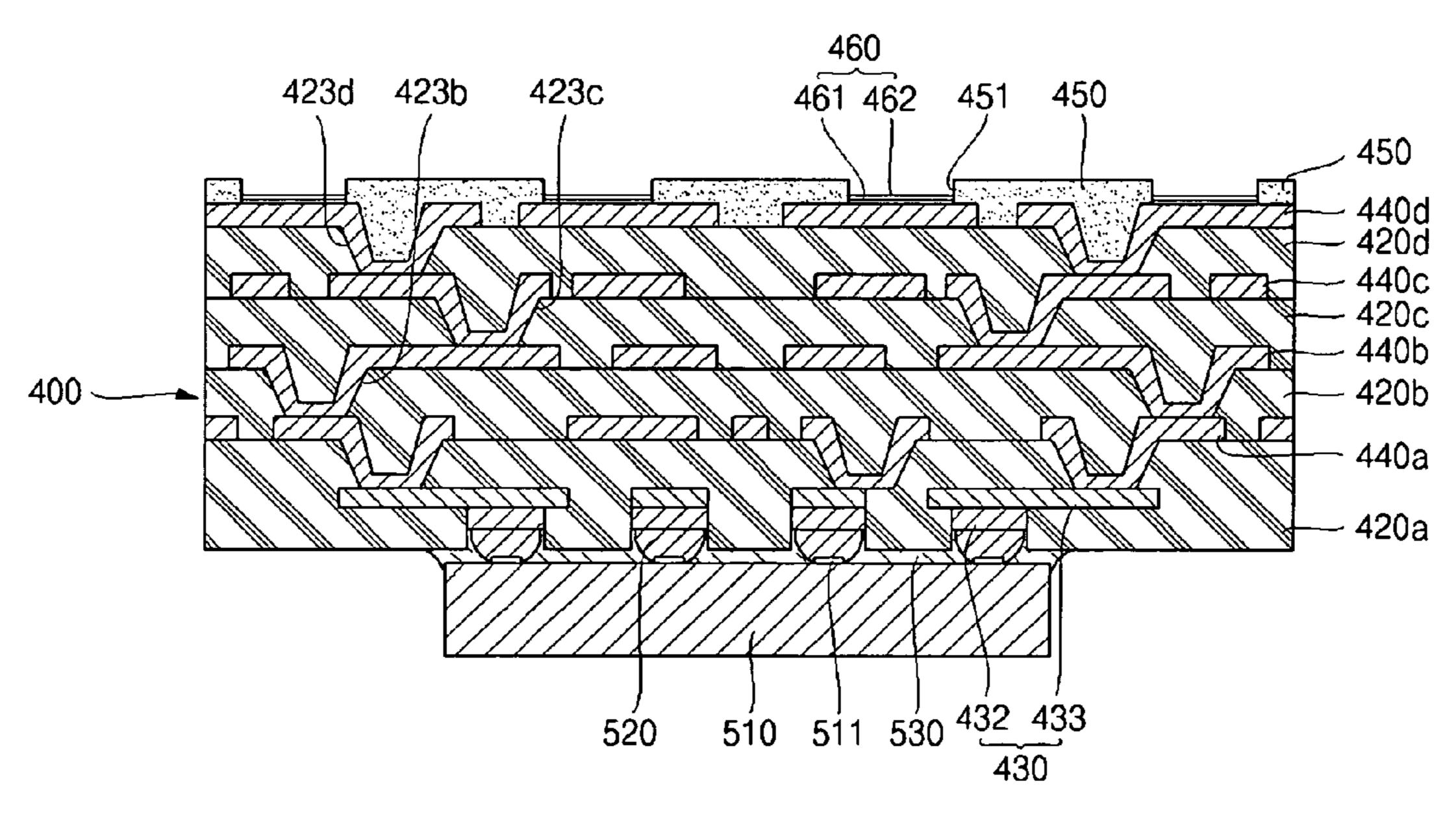

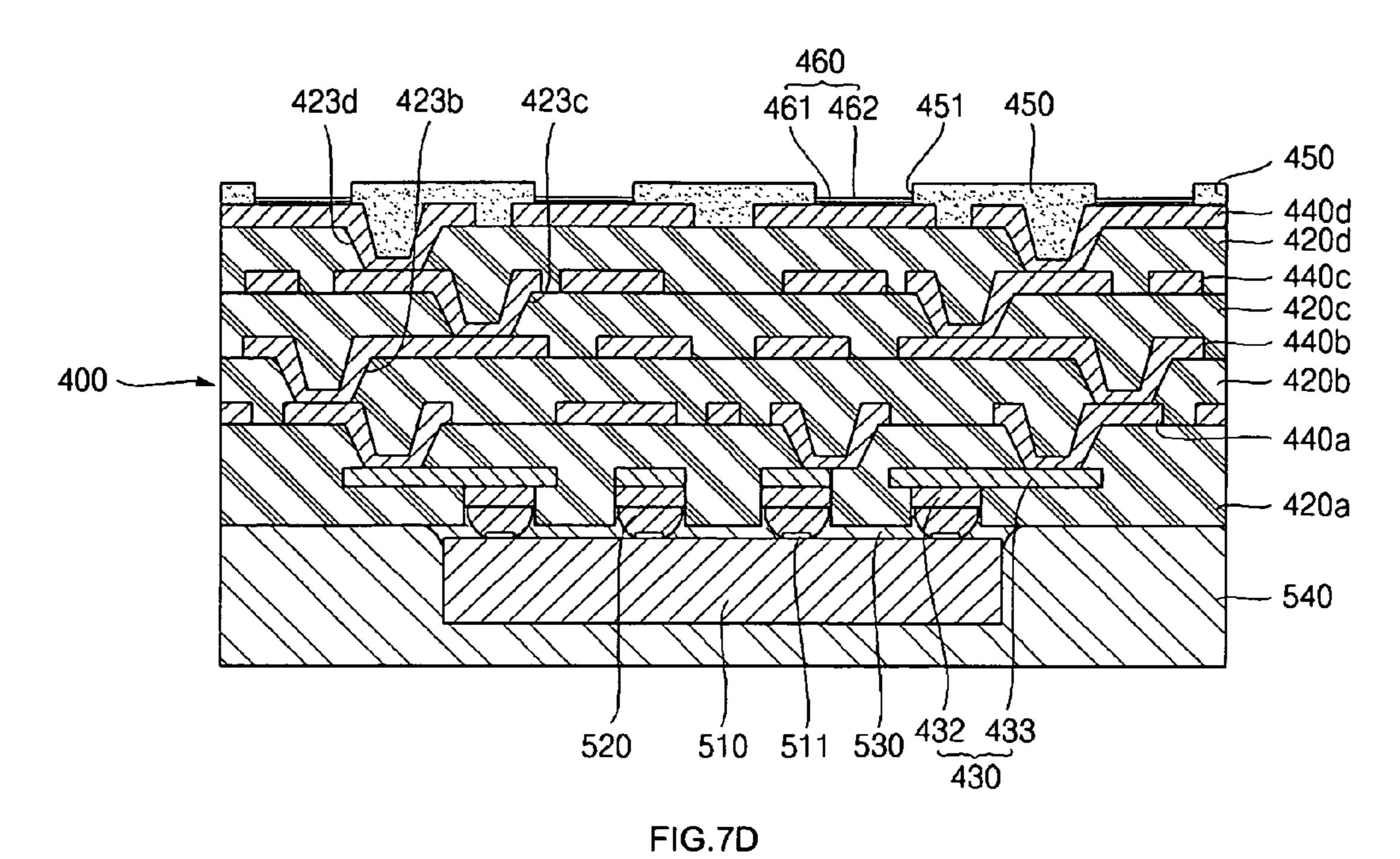

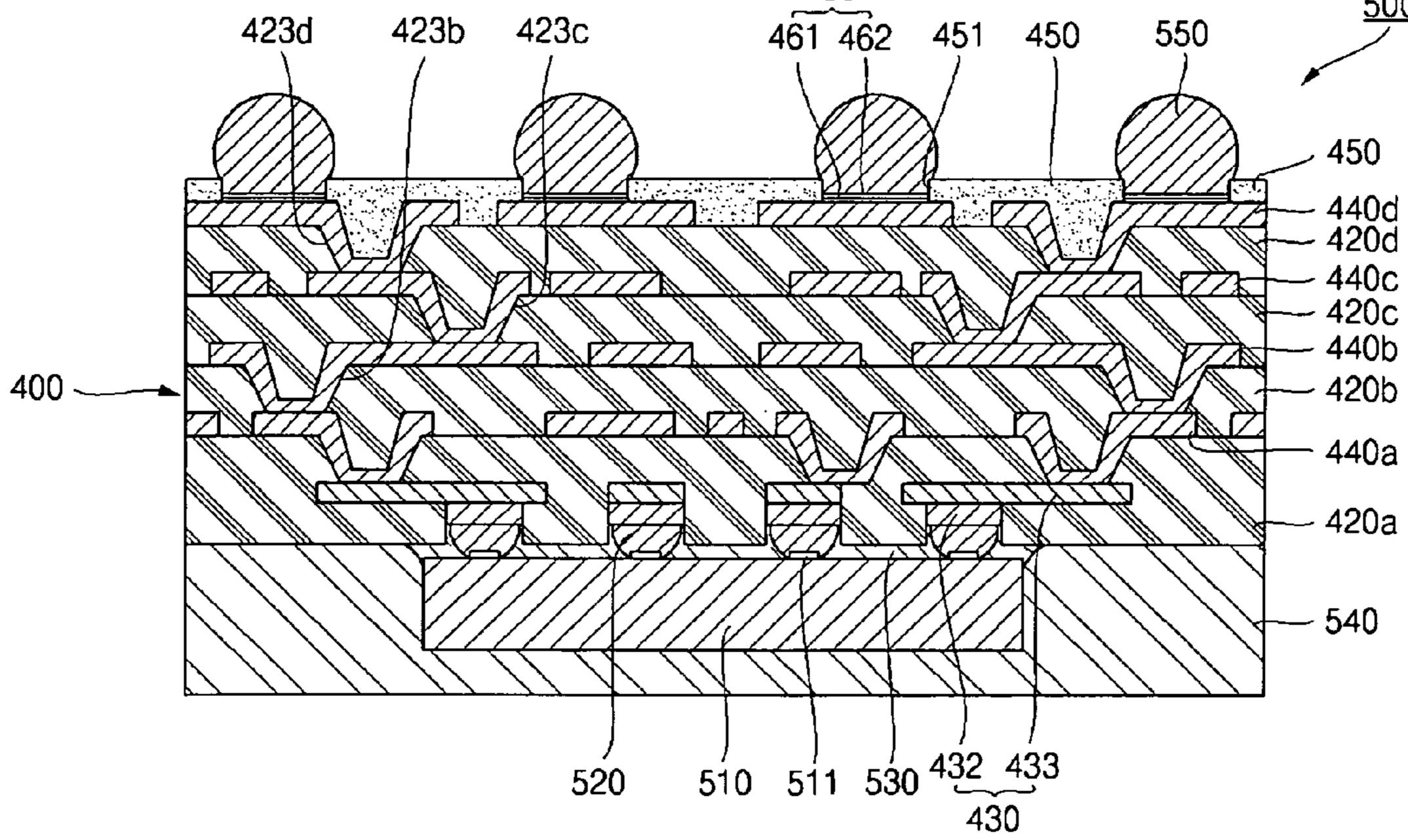

FIG. 7A through FIG. 7E are sectional views showing a fabrication method of a semiconductor device according to another embodiment of the present invention where:

FIG. 7A illustrates a carrier eliminating operation;

FIG. 7B illustrates a flip chip bonding operation;

FIG. 7C illustrates an underfilling operation;

FIG. 7D illustrates an encapsulating operation; and

FIG. 7E illustrates a solder ball fusing operation.

Common reference numerals are used throughout the drawings as well, detailed descriptions are used to indicate 35 like elements.

### DETAILED DESCRIPTION

Referring to FIG. 1, a sectional view of a substrate 100 for 40 a semiconductor device according to one embodiment of the present invention is illustrated.

As shown in FIG. 1, the substrate 100 for a semiconductor device includes a carrier 110 having a predetermined stiffness, a dielectric layer 120 formed on the carrier 110, a 45 plurality of conductive lands 130 electrically connected to the carrier 110 at the inside of the dielectric layer 120, a plurality of electrically conductive patterns 140 electrically connected to the conductive lands 130 at the surface of the dielectric layer 120, and a solder mask 150 for covering the dielectric layer 120 and the electrically conductive patterns 140, a predetermined area of each conductive pattern 140 being exposed to outside.

The carrier 110 is in the form of an approximately planar plate. The material of the carrier 110 may be a metal, a film or 55 its equivalent, in order that a warpage is not generated during the manufacturing process of the semiconductor device. However, the present invention is not limited to any material of the carrier 110. Moreover, in case of the metal as the material of the carrier 110, the material of the carrier 110 may 60 be a copper, an aluminum, a nickel or its equivalent. However, the present invention is not limited to any metal material of the carrier 110.

The dielectric layer 120 of a predetermined thickness is formed on the surface of one side of the carrier 110. The 65 dielectric layer 120 includes a first surface 121 of an approximate planar surface bonded on the carrier 110 and a second

4

surface 122 of an approximate planar surface opposed to the first surface 121. Also, a plurality of via holes 123 of a predetermined depth is further formed at the second surface 122 of the dielectric layer 120, in order to electrically connect the electrically conductive patterns 140 to the conductive lands 130. The material of the dielectric layer 120 may be a prepreg and an ABF (Ajinomoto Buildup Film) of a low dielectric constant or its equivalent, in order to decrease the capacitance of the electrically conductive patterns 140 and so on. However, the present invention is not limited to any material of the dielectric layer 120. Moreover, the thickness of the dielectric layer 120 is approximately 10~150 µm, so that it has a very thin thickness in comparison with the conventional substrate having a core layer.

Each of conductive lands 130 formed at the inside of the dielectric layer 120 have a bottom surface flush (substantially coplanar) with the first surface 121 of the dielectric layer 120. That is, the conductive lands 130 are electrically connected to the carrier 110. Also, the conductive land 130, that is, a copper layer 131, a gold layer 132, another copper layer 133 may be plated on the carrier 110 in order. However, the present invention is not limited to any material of the conductive land 130.

The plurality of electrically conductive patterns 140 are formed at the second surface 122 of the dielectric layer 120.

Here, the plurality of electrically conductive patterns 140 is electrically connected to the conductive lands 130 through the via holes 123 formed at the dielectric layer 120. The material of electrically conductive patterns 140 may be a copper or its equivalent. However, the present invention is not limited to any material of the electrically conductive patterns 140.

The solder mask 150 is coated on the second surface 122 of the dielectric layer 120 in order to cover the electrically conductive patterns 140. Here, a plurality of openings 151 are formed at the solder mask 150, so that a predetermined area of each electrically conductive pattern 140 is exposed to outside. Also, a plurality of bonding pads 160 are formed at the electrically conductive patterns 140 exposed to outside through the openings 151. A semiconductor die will be electrically connected to the bonding pad 160 in future. Also, the bonding pad 160, that is, a nickel layer 161 and a gold layer 162 may be plated on the electrically conductive pattern 140 in order. However, the present invention is not limited to any material of the bonding pad 160.

Referring to FIG. 1A through FIG. 1P, sectional views showing a fabrication method of the substrate 100 for a semiconductor device according to one embodiment of the present invention is illustrated.

As shown in the drawings, the fabrication method of the substrate 100 for a semiconductor device according to the present invention includes a carrier providing operation, a first photo sensitive film providing operation, a first plating operation, a first photo sensitive film eliminating operation, a dielectric layer forming operation, a via hole forming operation, a second plating operation, a second photo sensitive film providing operation, a third plating operation, a second photo sensitive film eliminating operation, an etching operation, a solder mask printing operation, a solder mask exposing/developing operation, a third photo sensitive film providing operation, a fourth plating operation, and a third photo sensitive film eliminating operation.

As shown in FIG. 1A, in the carrier providing operation, the carrier 110 of an approximately planar plate is provided. The material of the carrier 110 may be a metal, a film or its equivalent, in order that a warpage is not generated during the manufacturing process of the semiconductor device, as described above. However, the present invention is not limited to any material of the carrier 110. Moreover, in case of the

metal as the material of the carrier 110, the material of the carrier 110 may be a copper, an aluminum, a nickel or its equivalent. However, the present invention is not limited to any metal material of the carrier 110.

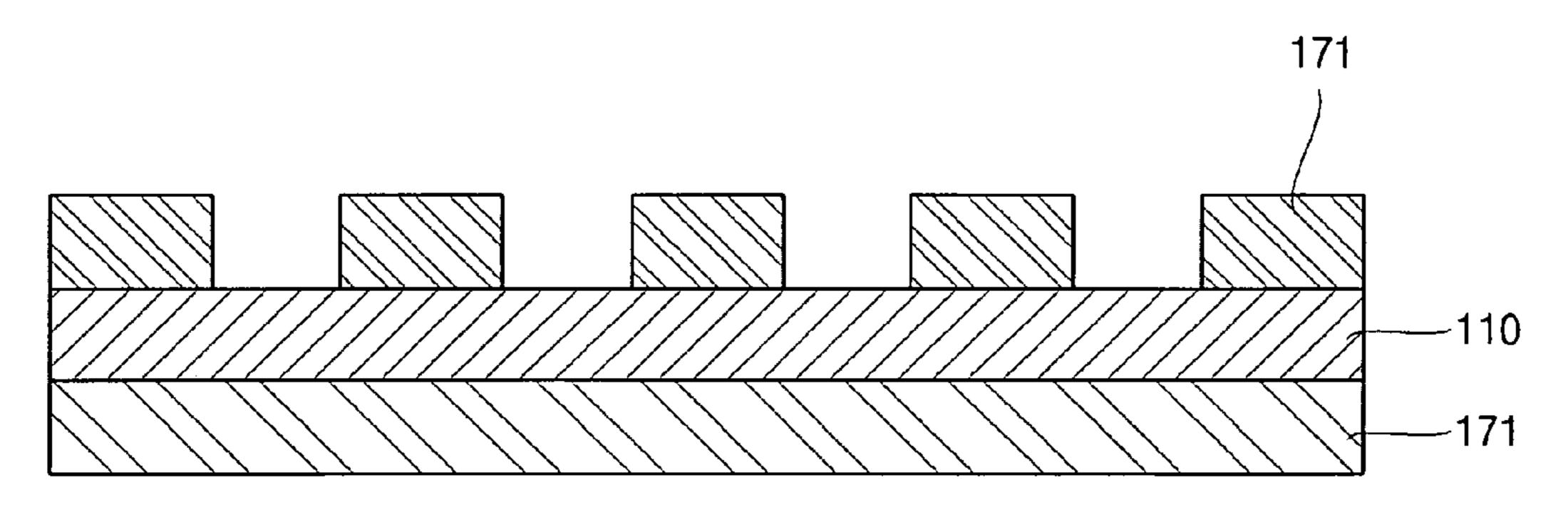

As shown in FIG. 1B, in the first photo sensitive film 5 providing operation, the photo sensitive film 171 of a predetermined pattern is formed at the top surface and the bottom surface of the carrier 110. That is, the photo sensitive film 171, on which any pattern is not formed, is bonded or coated on the top surface and the bottom surface of the carrier 110 and then, only the photo sensitive film 171 having a predetermined pattern is left over the top surface of the carrier 110 through the exposing/developing process. Here, the predetermined region of the carrier 110 is exposed to outside through the photo sensitive film 171.

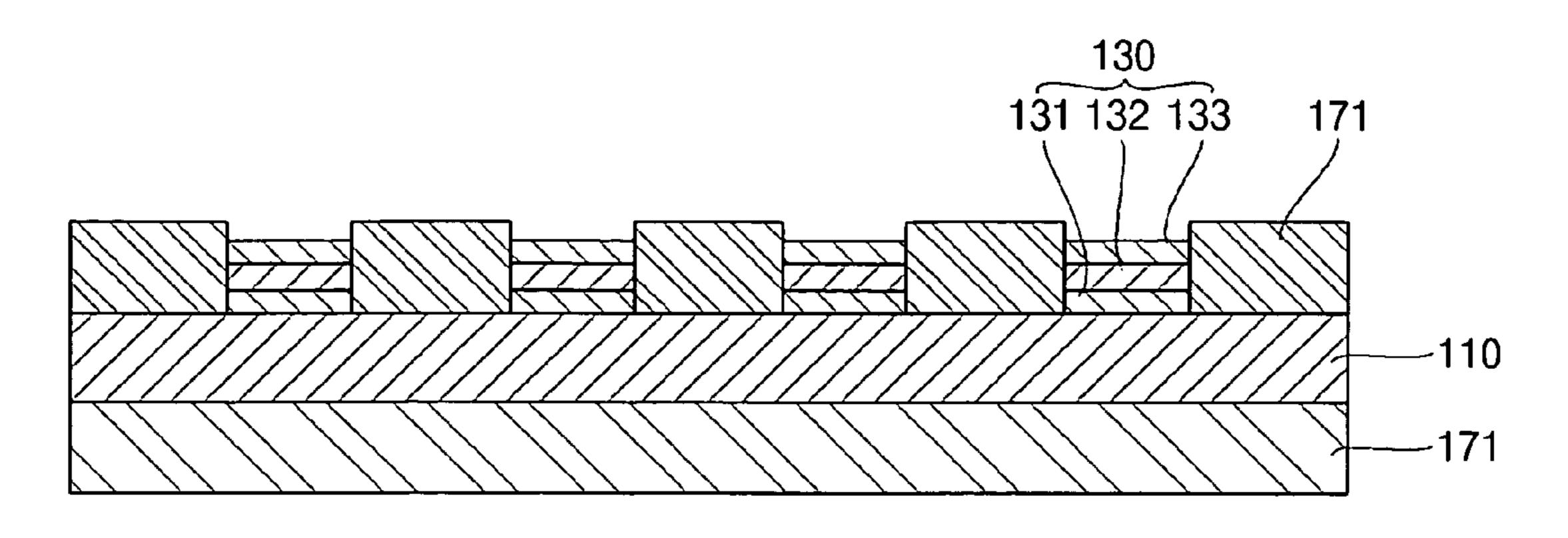

As shown in FIG. 1C, in the first plating operation, the plurality of conductive lands 130 are formed. That is, the copper layer 131, the gold layer 132 and another copper layer 133 are plated on the top surface of the carrier 110 exposed to outside through the photo sensitive film 171 in order, thereby 20 forming the conductive lands 130 of a predetermined thickness.

As shown in FIG. 1D, in the first photo sensitive film eliminating operation, the photo sensitive film 171 left over the carrier 110 is eliminated by a chemical etching and the like. Here, like this, only the plurality of conductive lands 130 is left over the carrier 110. Also, the carrier 110 except for the conductive lands 130 is exposed to outside.

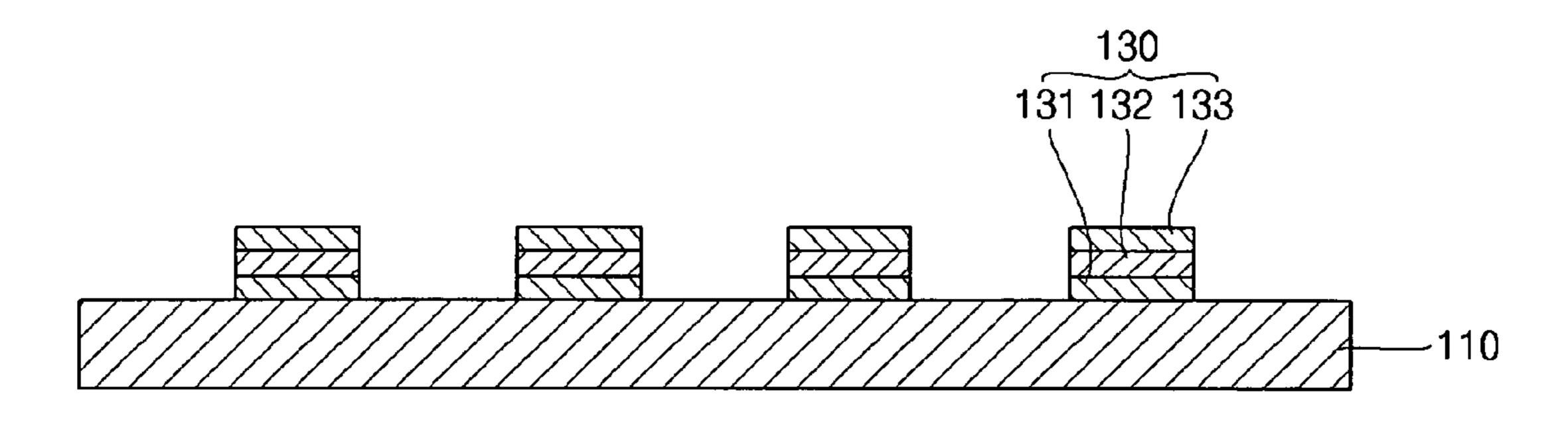

As shown in FIG. 1E, in the dielectric layer forming operation, the dielectric layer 120 of a predetermined thickness is coated and hardened so as to cover the conductive lands 130 formed at the carrier 110 all together. Here, the material of the dielectric layer 120 may be a prepreg and an ABF (Ajinomoto Buildup Film) of a low dielectric constant or its equivalent, in order to decrease the capacitance of the electrically conductive patterns 140 and so on. However, the present invention is not limited to any material of the dielectric layer 120. Moreover, the carrier 110 has an adequate stiffness, so that the warpage is not generated during the manufacturing process of the semiconductor device, thereby the dielectric layer 120 has very thin thickness of 10~150 μm.

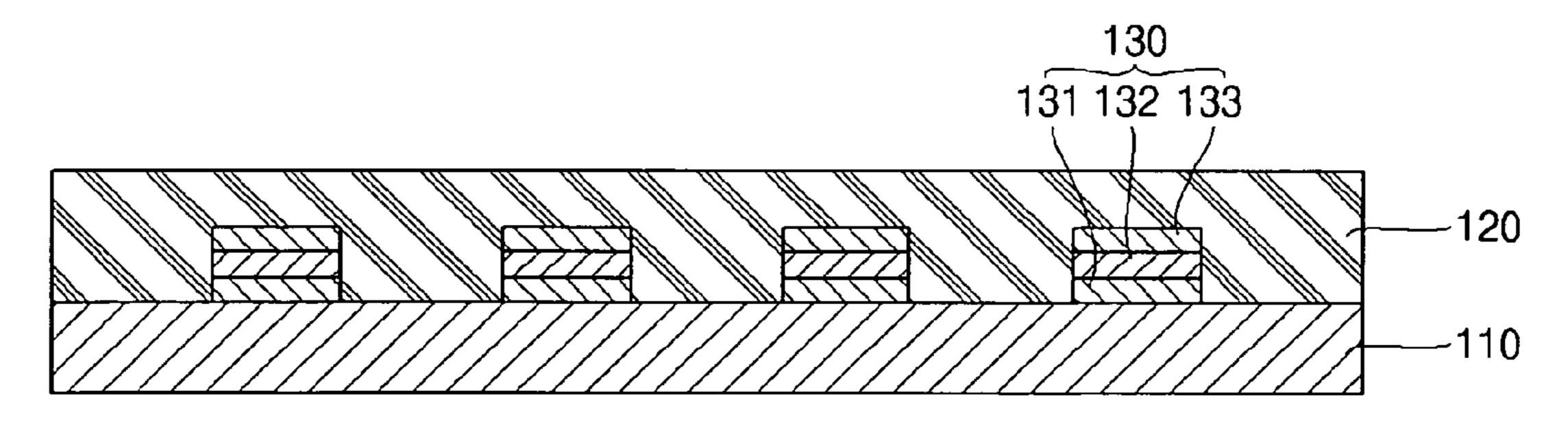

As shown in FIG. 1F, in the via hole forming operation, the via holes 123 of a predetermined depth are formed in such a manner that the conductive lands 130 formed at both the surface of the carrier 110 and the inside of the dielectric layer 45 120 are exposed to outside. That is, the dielectric layer 120 corresponding to the conductive lands 130 is eliminated by a laser drilling, a mechanical drilling or an etching and so on, so that the via holes 123 of a predetermined depth are formed. Here, the predetermined region of each conductive lands 130 50 is exposed to outside through the via holes 123.

As shown in FIG. 1G, in the second plating operation, an electroless plating layer 172, sometimes called a seed layer, of a thin thickness is formed at the surface of the dielectric layer 120 and the surface of the conducive lands 130 exposed 55 to outside through the via holes 123. The electroless plating layer 172 can be formed by means of a conventional electroless plating process. Also, the thickness of the electroless plating layer 172 is in the range of several µm.

As shown in FIG. 1H, in the second photo sensitive film for providing operation, the photo sensitive film 173 of a predetermined pattern is formed at the surface of the electroless plating layer 172 again. Here, it is suited that the photo sensitive film 173 is not formed at the regions corresponding to the via holes 123, so as to electrically connect the electrically conductive patterns 140 and the conductive lands 130 each other. Also, the photo sensitive film 173, on which any pattern

6

is not formed, is bonded or coated on the surface of the electroless plating layer 172 and then, only the photo sensitive film 173 having a predetermined pattern is left over the surface of the electroless plating layer 172 through the exposing/developing process. Here, the predetermined region of the electroless plating layer 172 is exposed to outside through the photo sensitive film 173.

As shown in FIG. 1I, in the third plating operation, an electrolytic plating layer of a predetermined thickness is formed at the electroless plating layer exposed to outside through the photo sensitive film 173. The electrolytic plating layer is the electrically conductive pattern 140 in fact. The electrolytic plating layer can be formed by means of a conventional electrolytic plating process, thereby obtaining the electrically conductive pattern 140 of desiring thickness.

As shown in FIG. 1J, in the second photo sensitive film eliminating operation, the photo sensitive film 173 formed on the electroless plating layer 172 is eliminated by a chemical etching and the like. Here, like this, the electroless plating layer 172 located at the lower portion of the photo sensitive film 173 is exposed to outside. Also, all of the electrically conductive patterns 140 continuously maintain a short status on account of the electroless plating layer 172.

As shown in FIG. 1K, in the etching operation, all electroless plating layers 172 left between the electrically conductive patterns 140 are eliminated by the chemical etching process. Here, since the electroless plating layer 172 has very thin thickness of several  $\mu m$ , it can be easily eliminated through a weak acid.

As shown in FIG. 1L, in the solder mask printing operation, the solder mask 150 of a predetermined thickness is printed on the dielectric layer 120 in order to cover the electrically conductive patterns 140. The material of the solder mask 150 may be photosensitivity or insensitivity. The solder mask 150 serves to prevent the oxidation of the electrically conductive patterns 140 and its damage from the external impact during the manufacturing process of the semiconductor device.

As shown in FIG. 1M, in the solder mask exposing/developing operation, a predetermined region of the solder mask 150 is eliminated by the exposing/developing process. That is, the plurality of openings 151 are formed at the solder mask 150, so that a predetermined area of each electrically conductive pattern 140 is exposed to outside.

As shown in FIG. 1N, in the third photo sensitive film providing operation, the photo sensitive film 174 of a predetermined pattern is formed at the bottom surface of the carrier 110. Here, since the photo sensitive film 174 serves to prevent the plating layer from formed at the bottom surface of the carrier 110 during the plating process, the material of the photo sensitive film 174 may not be photosensitivity.

As shown in FIG. 10, in the fourth plating operation, the plurality of bonding pads 160 is formed at predetermined regions of the electrically conductive patterns 140 exposed to outside through the solder mask 150. The plurality of bonding pads 160 can be formed by means of the electrolytic plating process. That is, the nickel layer 161 and the gold layer 162 may be plated on the electrically conductive pattern 140 of a predetermined region exposed to outside through the solder mask 150, thereby forming the bonding pad 160 of a predetermined thickness. The bonding pad 160 serves to electrically connect with the semiconductor die during manufacturing process of the semiconductor device.

As shown in FIG. 1P, in the third photo sensitive film eliminating operation, the photo sensitive film 174 formed on the bottom surface of the carrier 110 is eliminated by a chemical etching and the like, thereby completing the substrate 100 according to the present invention. Here, the bottom surface