#### US007898891B2

# (12) United States Patent Im

## (10) Patent No.:

US 7,898,891 B2

(45) **Date of Patent:**

Mar. 1, 2011

## (54) SEMICONDUCTOR MEMORY DEVICE

(75) Inventor: Jae-Hyuk Im, Kyoungki-do (KR)

(73) Assignee: Hynix Semiconductor Inc.,

Gyeonggi-do (KR)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 12/562,930

(22) Filed: **Sep. 18, 2009**

(65) Prior Publication Data

US 2010/0008173 A1 Jan. 14, 2010

#### Related U.S. Application Data

(62) Division of application No. 11/819,804, filed on Jun. 29, 2007, now Pat. No. 7,609,566.

## (30) Foreign Application Priority Data

Jan. 3, 2007 (KR) ...... 2007-0000409

(51) **Int. Cl.**

G11C 7/00 (2006.01) G11C 8/00 (2006.01)

See application file for complete search history.

## (56) References Cited

#### U.S. PATENT DOCUMENTS

#### FOREIGN PATENT DOCUMENTS

KR 1020040100439 A 12/2004

#### OTHER PUBLICATIONS

Notice of Allowance issued from Korean Intellectual Property Office on Sep. 26, 2009.

\* cited by examiner

Primary Examiner — Ly D Pham

(74) Attorney, Agent, or Firm — IP & T Group LLP

## (57) ABSTRACT

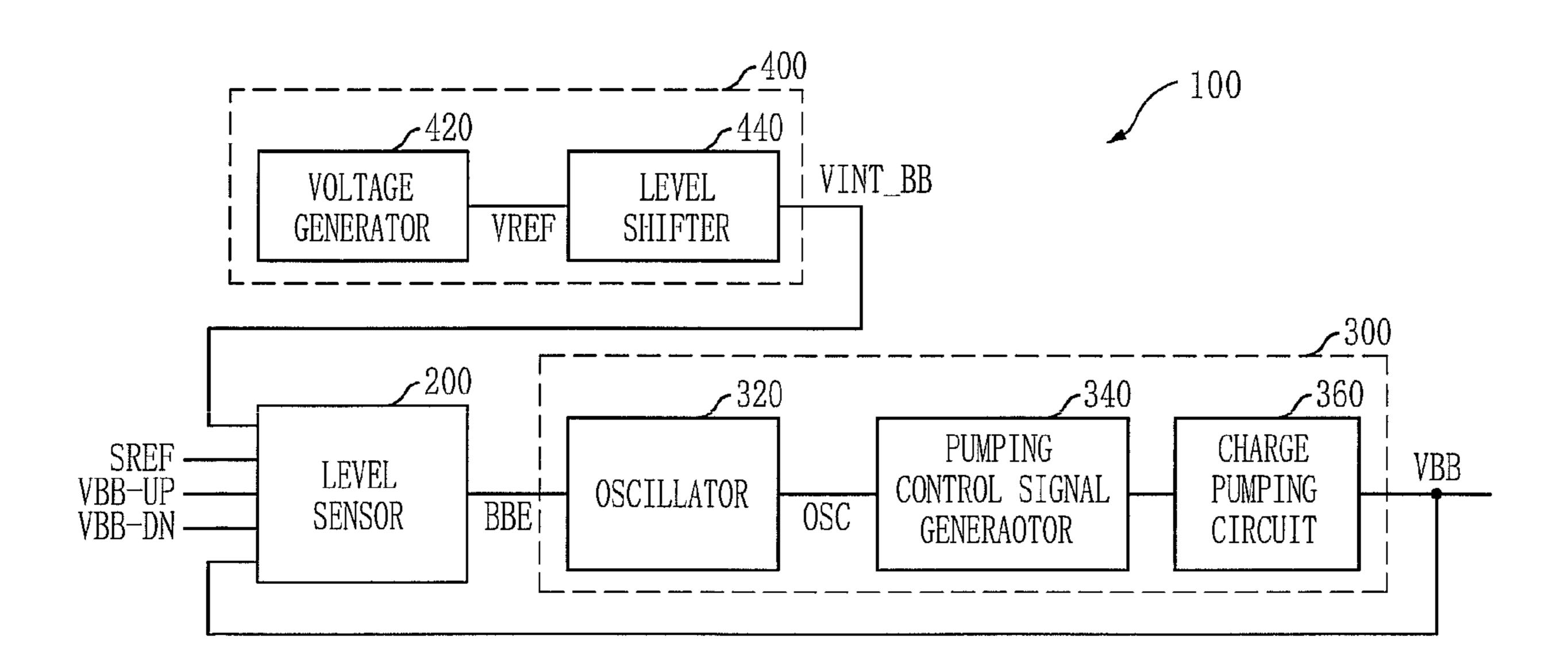

A semiconductor memory device includes a charge pumping circuit, a level sensor, an oscillator, and a pumping control signal generator. The charge pumping circuit performs a negative-pumping operation to an external power in order to generate an internal voltage having a level lower than the external power. The level sensor senses a level of the internal voltage corresponding to a level of an adjusted reference voltage during a refresh mode. The oscillator generates a period signal in response to a sensing signal of the level sensor. The pumping control signal generator controls the operation of the charge pumping circuit in response to the period signal.

## 9 Claims, 9 Drawing Sheets

FIG. 1A

FIG. 1B

FIG. 2

FIG. 3

REFP 90 REFRESH SIGNAL GENERATOR INTERNAL INTERNAL ADDRESS COUNTER AREFP 80 REFRESH PERIOD SIGNAL GENERATOR REFRESH INTERVAL SIGNAL GENERATOR E. AREFP SREF SREF 9 MODE INPUT/OU CONTROL AREF

FIG. 4

FIG.

FIG. 7

FIG. 8

FIG. 9

REFP 500 7000 800 REFRESH SIGNAL GENERATOR INTERNAL ADDRESS COUNTER PERIOD SIGNAL GENERATOR REFRESH SREF VBB VBB 009 -640 INTERVAL SIGNAL GENERATOR AREFP SREF SREF 620 MODE INPUT/OUTPUT CONTROLLER

## SEMICONDUCTOR MEMORY DEVICE

### CROSS-REFERENCE TO RELATED APPLICATION

This application is a division of U.S. patent application Ser. No. 11/819,804 filed on Jun. 29, 2007 now U.S. Pat. No. 7,609,566 which claims priority of Korean patent application number 10-2007-0000409 filed on Jan. 03, 2007. The disclosure of each of the foregoing applications is incorporated 10 herein by reference in its entirety.

#### BACKGROUND OF THE INVENTION

technologies; and, more particularly, to a semiconductor memory device which is provided with an internal power generator capable of increasing a cell retention time during a self refresh mode and a refresh unit capable of minimizing power consumption by adjusting a refresh period depending 20 on a level of an internal power.

Generally, basic operations of a semiconductor memory device include a write operation for storing data provided from outside and a read operation for outputting desired data stored therein upon request from the outside. In order to 25 perform these write and read operations, the semiconductor memory device requires the capability of storing data from the outside.

In particular, since DRAM (Dynamic Random Access Memory) is a nonvolatile memory, data stored therein is lost 30 after a fixed amount of time elapses. Therefore, a refresh operation is needed to fully restore data stored in memory cells before the fixed amount of time in order to prevent the loss of data. This refresh operation has priority over any other operations in DRAM.

Such a refresh operation is done at a fixed period that is closely concerned with a retention time of cell data. More details on this will be given below with reference to a circuit and a cross-sectional view of unit memory cell.

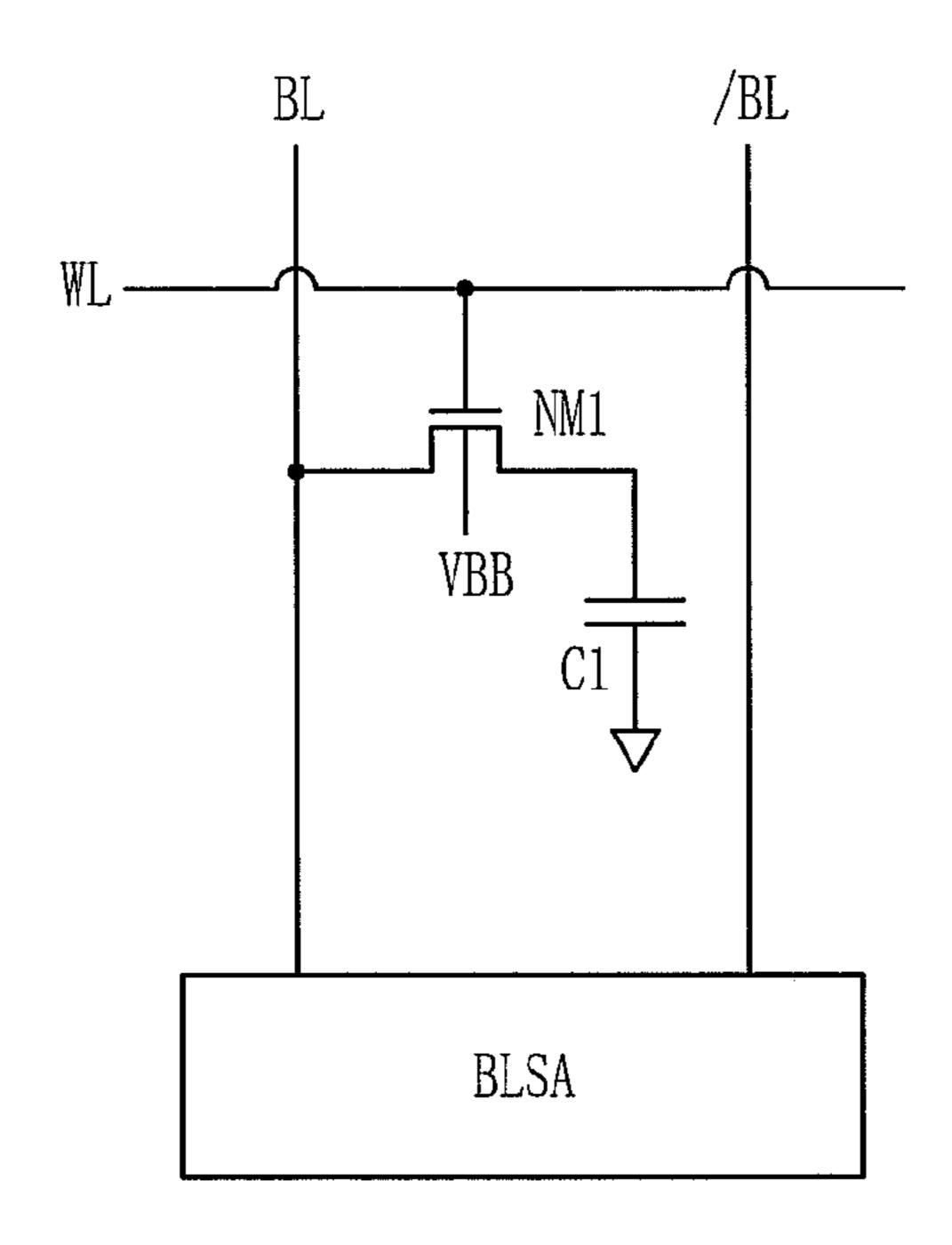

FIG. 1A is a conceptual circuit diagram of unit memory 40 cell of a conventional DRAM. For reference, the unit memory cell denotes a space where 1 bit data is stored.

Referring to FIG. 1A, the unit memory cell is provided with a capacitor C1 for storing data and an NMOS transistor NM1 for accessing the capacitor.

To be more specific, a word line WL is connected to the gate end of the NMOS transistor NM1. And, a bit line BL is connected to one side active region (here, a drain end) of the NMOS transistor NM1 and the cell capacitor to other side active region (here, a source end) thereof.

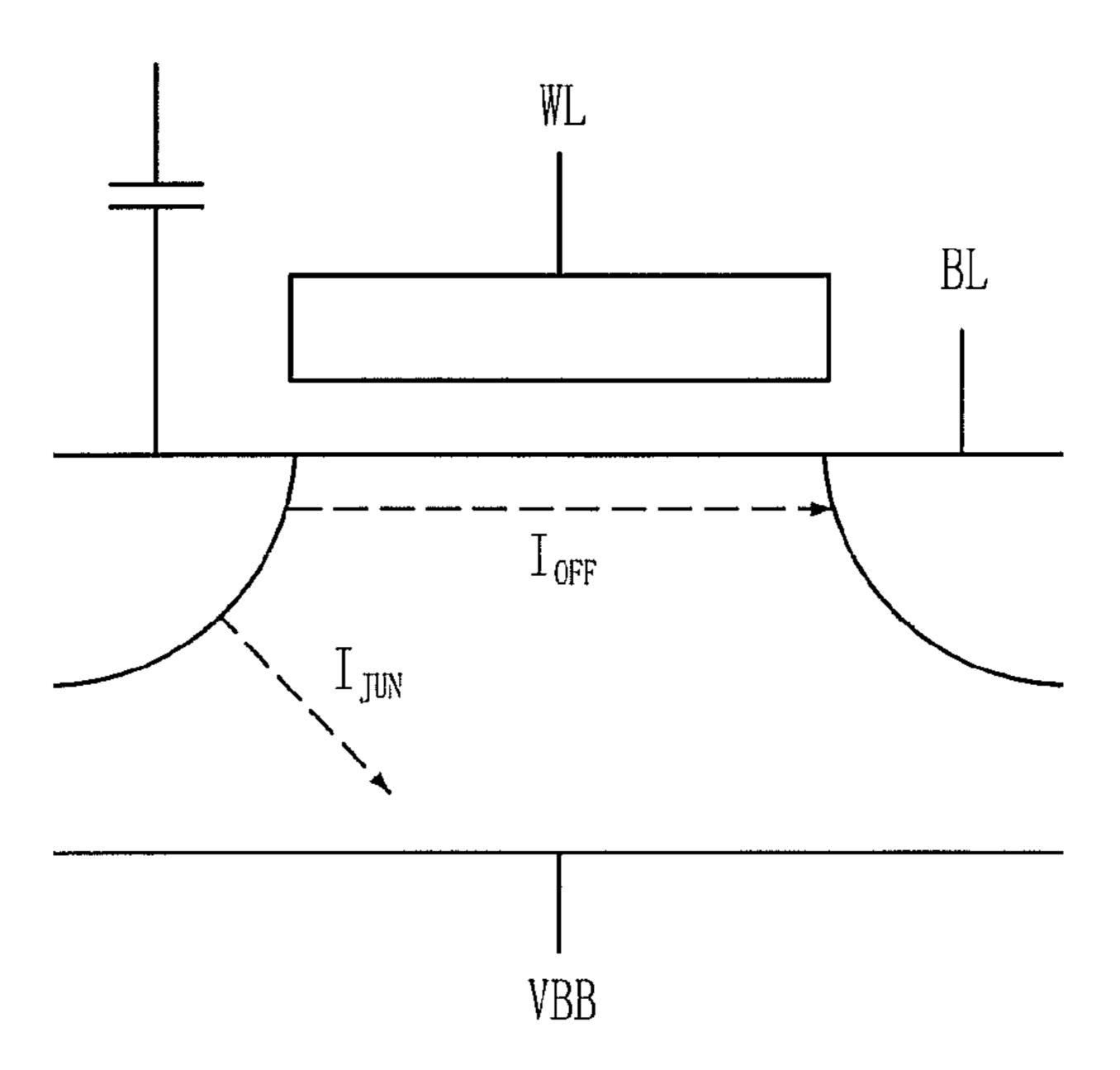

FIG. 1B is a cross-sectional view of the unit memory cell of FIG. 1A, and particularly shows a leakage current generated in the unit memory cell.

As shown in FIG. 1B, although the transistor is turned off, a leakage current occurs in the cell capacitor (here, it is 55 to create the period signal OSC. In response to the period assumed that logic high data is stored in the cell capacitor). Two major factors of the leakage current are an off current  $I_{OFF}$  and a junction current  $I_{JUN}$ .

Meanwhile, an internal power VBB with a negative electric potential lower than a ground voltage is generally connected 60 to a bulk of the NMOS transistor in the unit memory cell shown in FIG. 1A. By keeping the bulk bias low like this, the leakage current as shown in FIG. 1B is reduced by setting a threshold voltage of the transistor higher than that of a general NMOS. But, as the level of the internal power VBB lowers, 65 the threshold voltage becomes higher to decrease off-current, while rather increasing the leakage current by elevation of

junction-current. That is, the off-current and the junctioncurrent constituting the leakage current have a trade-off relationship depending on the level of the internal power VBB. Therefore, in order to extend a retention time of cell data, it is important to find an optimal level of the internal power VBB making both the off-current and the junction-current smaller.

The following is a description for a conventional internal power generator for generating an internal power VBB to be applied to a bulk end of cell and a refresh unit for refreshing cell data.

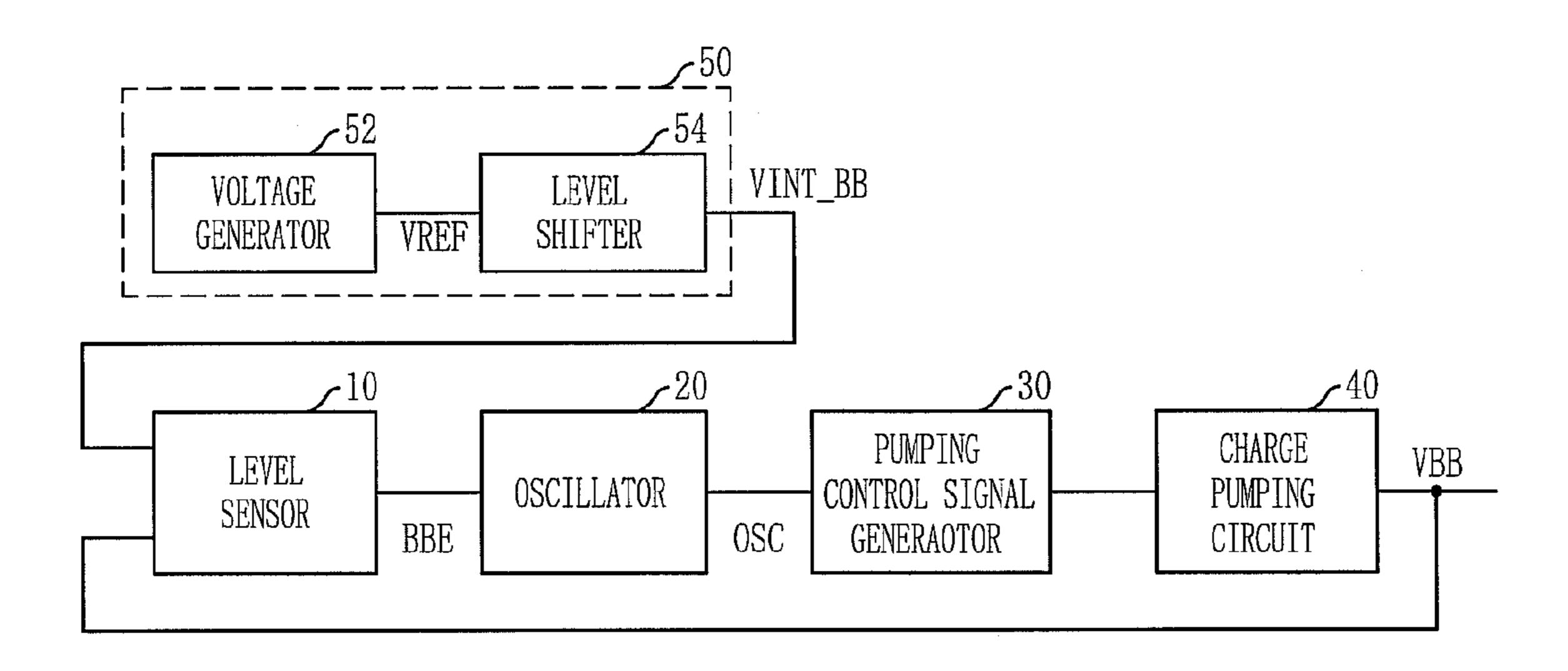

FIG. 2 is a block diagram showing a configuration of a conventional internal power generator.

Referring to FIG. 2, the conventional internal power generator includes a charge pumping circuit 40 for negative-The present invention relates to semiconductor design 15 pumping an external power VDD to generate an internal power VBB with a level lower than the external power VDD, a reference voltage generator 50 for producing a reference voltage VINT\_BB, a level sensor 10 for sensing a level of the internal power VBB on the basis of the reference voltage VINT\_BB, an oscillator 20 for generating a period signal OSC in response to a sensing signal BBE of the level sensor 10, and a pumping control signal generator 30 for controlling the operation of the charge pumping circuit 40 in response to the period signal OSC.

The reference voltage generator **50** is provided with a voltage generator 52 for generating a target voltage of the internal power VBB and a level shifter **54** for level-shifting an output voltage VREF of the voltage generator **52** to generate the reference voltage VINT\_BB having a stable level regardless of the external power VDD (or power supply voltage).

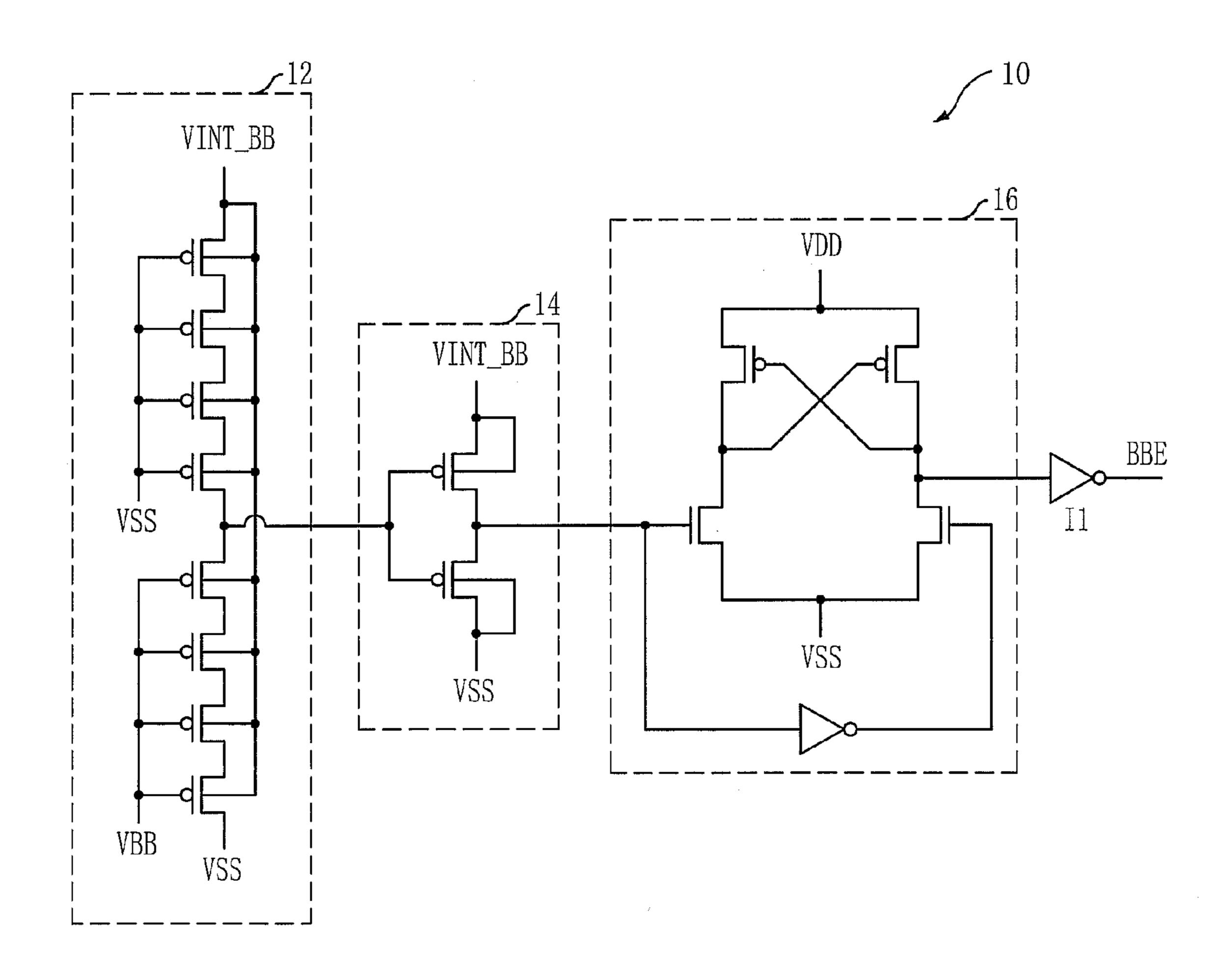

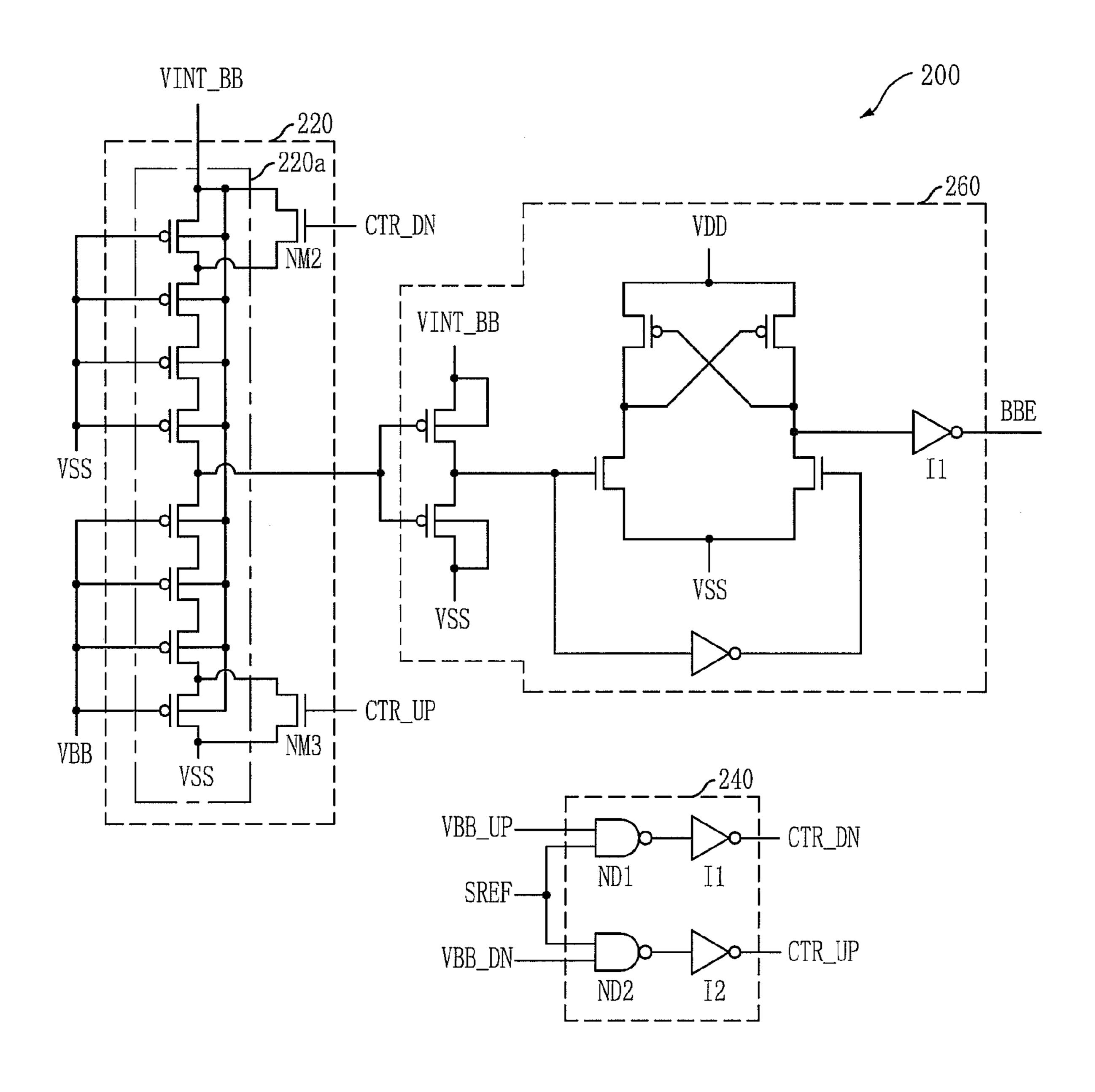

FIG. 3 illustrates an internal circuit diagram of the level sensor 10 of FIG. 2.

Referring to FIG. 3, the level sensor 10 is composed of a voltage divider 12 for voltage-dividing a level difference 35 between the ground voltage VSS and the reference voltage VINT\_BB by a level difference between the ground voltage VSS and the internal power VBB, an inverter 14 for taking the reference voltage VINT\_BB and the ground voltage VSS as driving powers and inverting and outputting an output voltage of the voltage divider 12, a differential amplifier 16 taking an output voltage of the inverter 14 and an inverted voltage of the output of the inverter 14 as differential inputs, and an inverter I1 for inverting an output voltage of the differential amplifier 16 to provide an inverted voltage as the sensing signal BBE.

Hereinafter, the operation of the internal power generator shown in FIGS. 2 and 3 will be briefly described.

First, the level sensor 10 senses a level of a feedbacked internal power VBB on the basis of the reference voltage VINT\_BB. At this time, when the level of the internal power VBB is higher than the reference voltage VINT\_BB and the output voltage of the voltage divider 12 exceeds a logic threshold voltage of the inverter 14, the sensing signal BBE is activated to a logic high level.

Then, the oscillator 20 is active by the sensing signal BBE signal OSC, the pumping control signal generator 30 drives the charge pumping circuit 40, which causes the level of the internal power VBB to drop.

When the level of the internal power VBB drops, the output voltage of the voltage divider 12 becomes lower than the logic threshold voltage of the inverter 14 which makes the sensing signal BBE inactivated to a logic low level.

Thus, the operations of the oscillator 20, the pumping control signal generator 30 and the charge pumping circuit 40 are closed.

As described above, the internal power generator in the conventional semiconductor memory device is driven to

maintain the internal power VBB in a level corresponding to the target level of the reference voltage. Here, as mentioned above, the level of the reference voltage is set such that the operation such as storage of data in write operation or restoration of data in read operation can be made within a designated time, while securing the retention time of data by reduction in leakage current. For reference, in order to secure the retention time of data, it is preferred that the level of the internal power VBB is as low as possible. But, if the level of the internal power VBB becomes lower, the threshold voltage becomes higher, which prolongs the operation time of data storage or restoration.

However, the conventional internal power generator is driven without considering IDD6 circumstance capable of securing a greater margin than an active mode as a driving time for restoration of data. That is, it was impossible to control the retention time of cell data to be extended for the refresh interval.

For reference, the IDD6 circumstance is a mode that is 20 entered when the clock enable signal CLK is transited to a logic low level and again stores all cells by performing 8K number of times of refreshes for 64 ms.

FIG. 4 is a block diagram showing a configuration of a refresh unit included in the conventional semiconductor 25 memory device.

Referring to FIG. 4, the conventional refresh unit includes a mode input/output controller 60 for accepting a clock enable signal CKE and an auto refresh command AREF\_CMD and generating an internal auto refresh signal 30 AREFP, a self refresh entry signal SREF\_EN and a self refresh escape signal SREF\_EXP, a refresh interval signal generator 70 for generating a self refresh interval signal SREF notifying a self refresh interval by using the internal auto refresh signal AREFP, the self refresh entry signal SREF\_EN 35 and the self refresh escape signal SREF\_EXP, a refresh period signal generator 80 for periodically outputting a period-pulse signal PL\_FLG during activation of the self refresh interval signal SREF, an internal refresh signal generator 90 for activating an internal refresh signal REFP in response to the 40 internal auto refresh signal AREFP and the period-pulse signal PL\_FLG, and an internal address counter **95** for increasing a row address by one bit unit in response to the internal refresh signal REFP to output an internal address RCNTI[0: N].

For reference, the clock enable signal CKE is a signal representing whether a clock synchronizing the operation of the semiconductor memory device is valid or not. Thus, if only the clock enable signal CKE is inactivated, the semiconductor memory device enters a power-down mode for mini- 50 mizing its own power consumption.

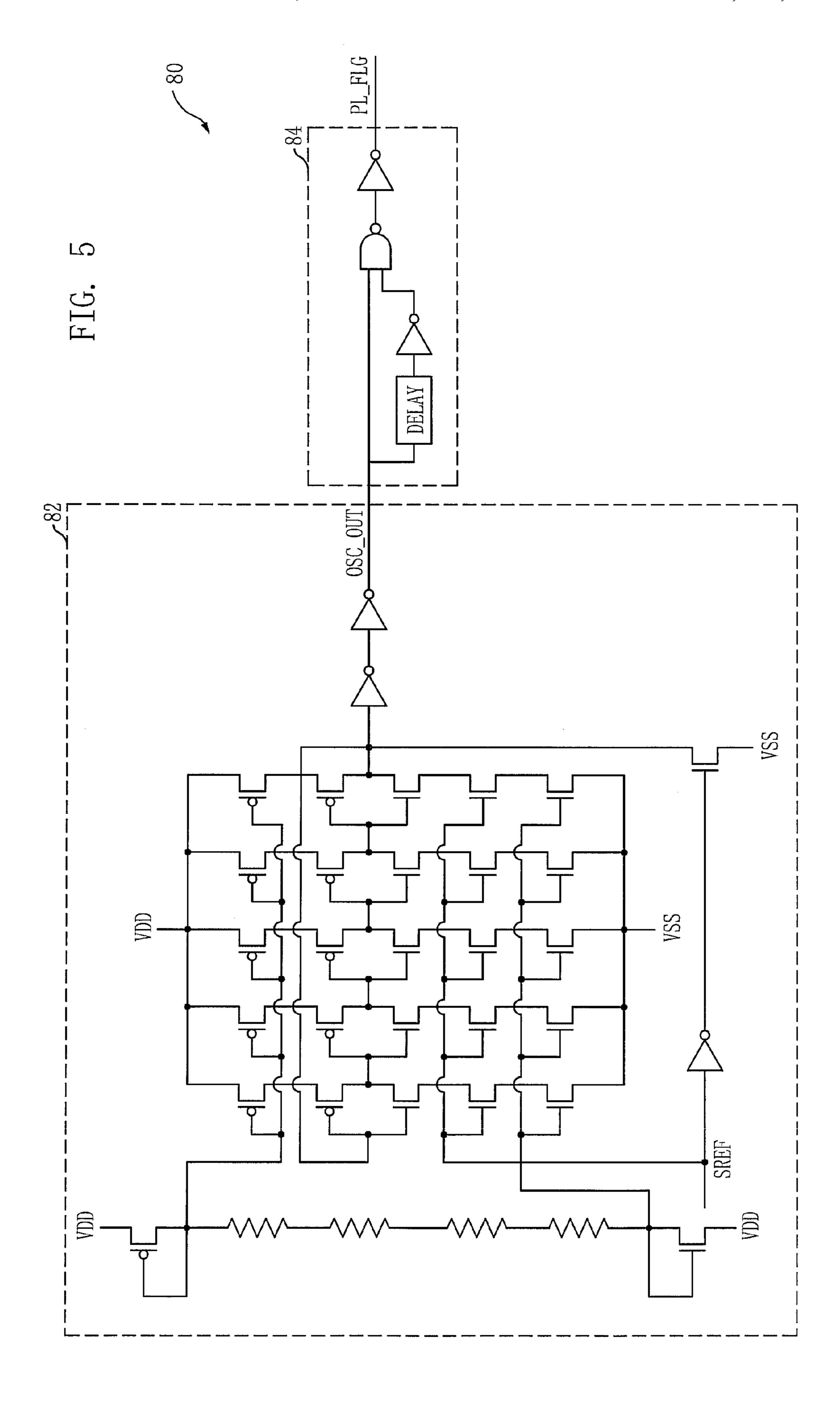

FIG. 5 shows an internal circuit diagram of the refresh period signal generator 80 of FIG. 4.

Referring to FIG. **5**, the refresh period signal generator **80** includes an oscillator **82** which has an inverter chain and is 55 active upon activation of the self refresh interval signal SREF to generate a signal OSC\_OUT at regular intervals, and a pulse generator **84** for producing the period-pulse signal PL\_FLG of pulse type from the output signal OSC\_OUT of the oscillator **82**.

In brief operation, first of all, when the self refresh interval signal SREF is activated to a logic high level, the oscillator **82** generates the signal OSC\_OUT at a regular interval. Here, the regular intervals are determined based on the voltage levels of signals applied to the gate ends of NMOS transistors and 65 PMOS transistors constituting the inverter chain. Next, the pulse generator **84** senses a rising edge of the output signal

4

OSC\_OUT of the oscillator **82**, and generates the period-pulse signal PL\_FLG of pulse type.

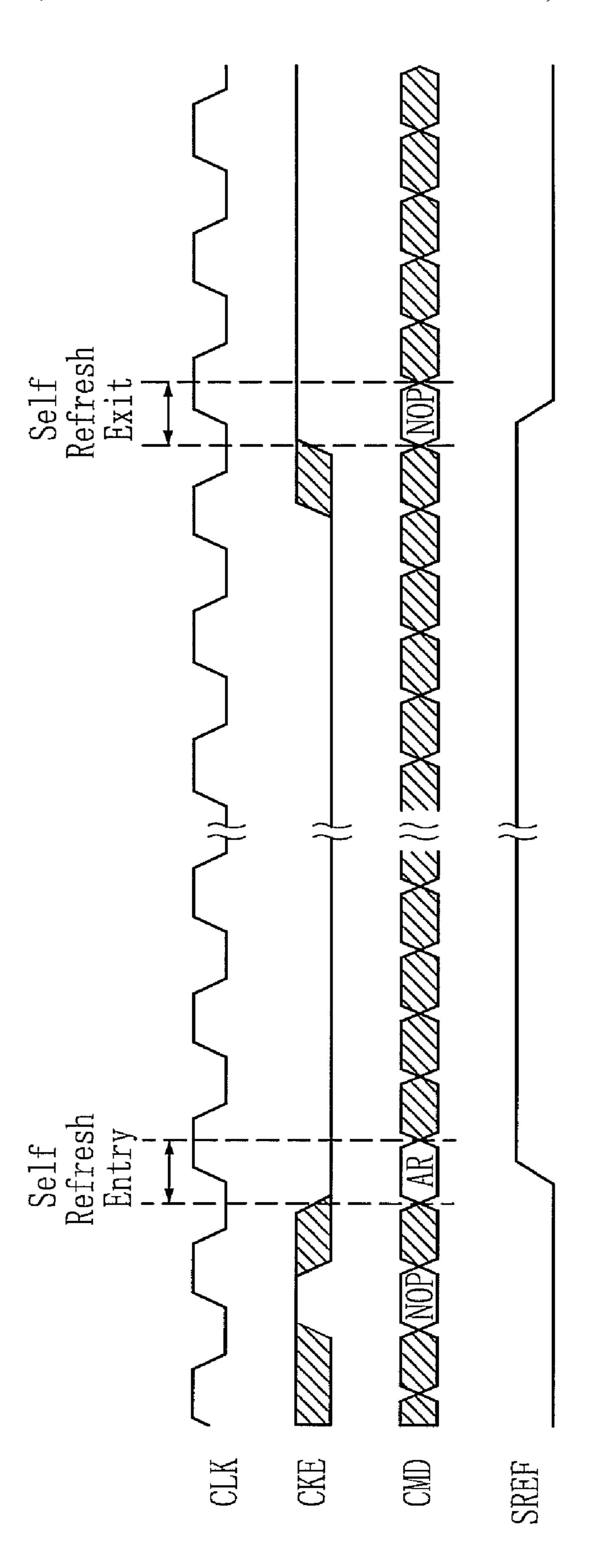

FIG. 6 presents an operational waveform diagram of the refresh unit according to the prior art shown in FIGS. 4 and 5.

As shown in FIG. 6, the clock enable signal CKE is first transited to a logic low level and at the same time the auto refresh command AREF\_CMD is activated. Then, the mode input/output controller 60 activates the self refresh entry signal SREF\_EN in response to the logic level transition of the clock enable signal CKE and activates the internal auto refresh signal AREFP in response to the auto refresh command AR.

Next, the internal refresh signal generator **90** generates the internal refresh signal REFP in response to the internal auto refresh signal AREFP. In succession, the internal address generator **95** increases the row address by one bit unit whenever the internal refresh signal REFP is activated, to output the internal address RCNTI[0:N].

Further, the refresh interval signal generator 70 activates the self refresh interval signal SREF in response to activation of the internal auto refresh signal AREFP and the self refresh entry signal SREF\_EN, wherein this activation is maintained until the self refresh escape signal SREF\_EXP is applied.

Subsequently, the refresh period signal generator **80** periodically activates the period-pulse signal PL\_FLG during the activation of the self refresh interval signal SREF. And then, the internal refresh signal generator **90** activates a new internal refresh signal REFP of pulse type whenever the period-pulse signal PL\_FLG is applied. Lastly, the internal address generator **95** increases the row address by one bit unit whenever the internal refresh signal REFP is activated, to output the internal address RCNTI[0:N].

For reference, the internal refresh signal REFP is applied to each bank, which makes a word line corresponding to the internal address RCNTI[0:N] active to perform self refresh.

Meanwhile, the refresh period by the refresh unit in the conventional semiconductor memory device is determined by the period of the period-pulse signal PL\_FLG. The period-pulse signal PL\_FLG is generated at a regular period, regardless of the level of the internal power VBB. Therefore, although the level of the internal power VBB is optimized so that the retention time is reduced, it is unlikely to reflect the above. This reduces the number of times of refresh and thus cannot decrease power consumption.

Therefore, the conventional semiconductor memory device does not adjust the level of the internal power under the self refresh mode, thereby making it impossible to adjust the retention time of cell data. Also, the refresh unit cannot be driven appropriately according to the retention time.

#### SUMMARY OF THE INVENTION

Embodiments of the present invention are directed to provide a semiconductor memory device for reducing a current consumption by adjusting a refresh period according to a bulk voltage level.

In accordance with an aspect of the present invention, there is provided a semiconductor memory device including a charge pumping circuit, a level sensor, an oscillator, and a pumping control signal generator. The charge pumping circuit performs a negative-pumping operation to an external power in order to generate an internal voltage having a level lower than the external power. The level sensor senses a level of the internal voltage corresponding to a level of an adjusted reference voltage during a refresh mode. The oscillator generates a period signal in response to a sensing signal of the

level sensor. The pumping control signal generator controls the operation of the charge pumping circuit in response to the period signal.

In accordance with another aspect of the present invention, there is provide driving method of a semiconductor memory device including performing a negative-pumping operation to an external power in order to generate a bulk voltage of memory cell; sensing a level of the bulk voltage in response to a reference voltage; and controlling the negative-pumping operation so that the bulk voltage has a level corresponding to the reference voltage. The reference voltage have different voltage levels for a self refresh mode and a normal mode.

In accordance with a further another aspect of the present invention, there is provided a semiconductor memory device including a refresh exit/entry controller and a control signal generator. The refresh exit/entry controller receives a clock enable signal and an auto refresh command and generates a self refresh interval signal notifying that the current operation is in a self refresh mode. The control signal generator periodically generates an internal refresh signal and an internal address for refresh driving during activation of the self refresh interval signal. An activation period of the internal refresh signal is adjusted according to a level of a bulk voltage applied to a memory cell.

In accordance with still another aspect of the present invention, there is provided a driving method of a semiconductor memory device, including operating the semiconductor memory device in a self refresh mode by activating a self refresh interval signal in response to a clock enable signal and an auto refresh command; and generating an internal refresh signal and an internal address for controlling refresh driving at predetermined intervals during an activation of the self refresh interval signal. The self refresh interval signal notifies that a current operation is performed in the self refresh mode. The predetermined intervals are adjusted according to a level of a bulk voltage applied to a memory cell.

In accordance with still another aspect of the present invention, there is provided a semiconductor memory device, 40 including an internal power generator, a refresh unit, a level controller, a period adjustor. The internal power generator performs a negative-pumping operation to an external power in order to generate a bulk voltage to be applied to a bulk end of cell. The refresh unit generates an internal refresh signal for 45 refresh driving at regular intervals during a self refresh mode. The level controller controls a level of the bulk voltage in the self refresh mode. The period adjustor adjusts the regular intervals when the level controller is driven.

## BRIEF DESCRIPTION OF THE DRAWINGS

- FIG. 1A is a conceptual circuit diagram of unit memory cell of a conventional DRAM.

- FIG. 1B is a cross-sectional view of the unit memory cell of 55 power VDD. FIG. 1A, and particularly shows a leakage current generated in the unit memory cell. by the unit memory cell of 55 power VDD. More specification in the unit memory cell.

- FIG. 2 is a block diagram showing a configuration of a conventional internal power generator.

- FIG. 3 is an internal circuit diagram of the level sensor of 60 FIG. 2.

- FIG. 4 is a block diagram showing a configuration of a refresh unit in a conventional semiconductor memory device.

- FIG. 5 is an internal circuit diagram of the refresh period signal generator of FIG. 4.

- FIG. 6 is an operational waveform diagram of the refresh unit according to the prior art shown in FIGS. 4 and 5.

6

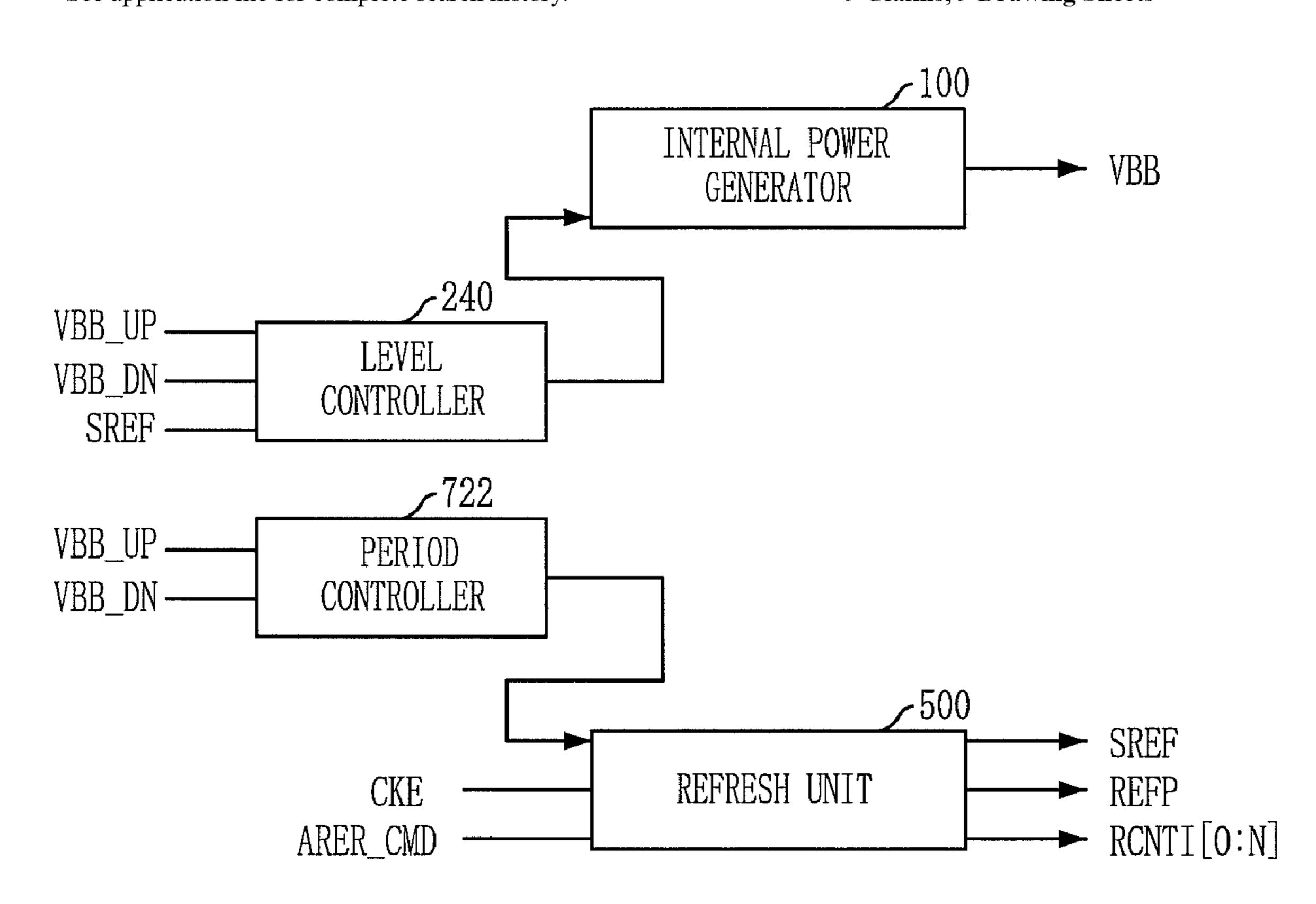

- FIG. 7 is a block diagram illustrating a configuration of a semiconductor memory device in accordance with a preferred embodiment of the present invention.

- FIG. 8 is an internal circuit diagram of the internal voltage generator of FIG. 7.

- FIG. 9 is an internal circuit diagram of the level sensor of FIG. 8.

- FIG. 10 is an internal circuit diagram of the refresh unit of FIG. 7.

- FIG. 11 is an internal circuit diagram of the refresh period signal generator of FIG. 10.

#### DESCRIPTION OF SPECIFIC EMBODIMENTS

Hereinafter, preferred embodiments of the present invention will be described in detail with reference to the accompanying drawings so that the invention can be easily carried out by those skilled in the art.

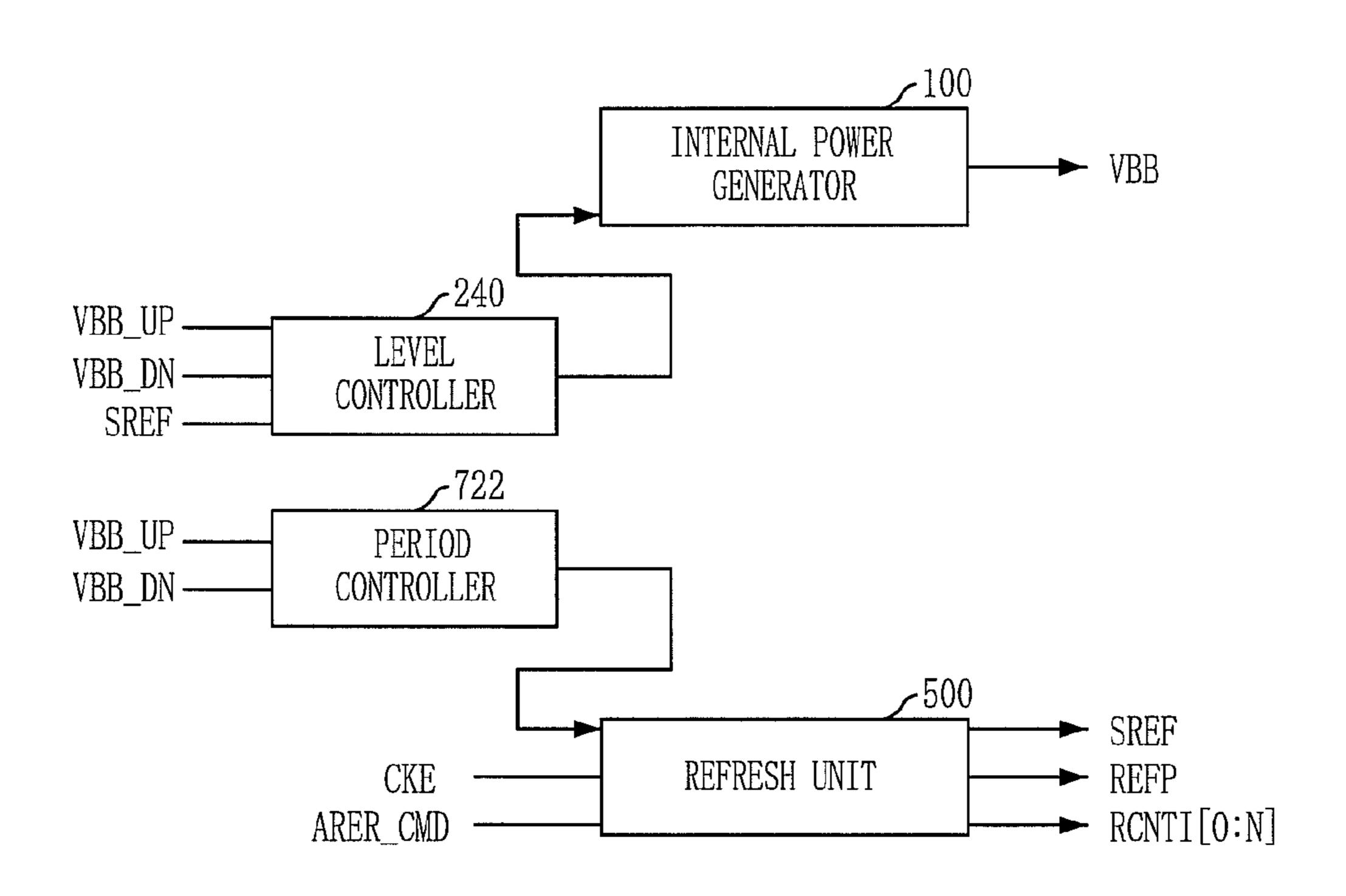

FIG. 7 is a block diagram illustrating a configuration of a semiconductor memory device in accordance with a preferred embodiment of the present invention.

Referring to FIG. 7, the inventive semiconductor memory device includes an internal power generator 100 for negative-pumping an external power to generate an internal power VBB to be applied to a bulk end of cell, a refresh unit 500 for generating an internal refresh signal REFP for refresh driving at regular intervals during a self refresh mode, a level adjustor 240 for adjusting a reference level of the internal power VBB in the self refresh mode, and a period adjustor 722 for adjusting an interval of the internal refresh signal when the level adjustor 240 is driven.

As stated above, the semiconductor memory device of the invention additionally includes the level adjustor **240** adjusts the level of the internal power VBB during the self refresh mode, and adjusts the level of the internal power VBB so that a minimum leakage current is generated from memory cell during the self refresh mode. Further, the semiconductor memory device additionally includes the period adjustor **722** for adjusting an execution interval of refresh by sensing the level adjustment of the internal power VBB, to thereby reduce the number of times of refresh performed during the self refresh mode. Thus, IDD6, that is, power consumed during the self refresh mode can be reduced.

The following is a detailed description for an internal circuit diagram of each block with reference to the drawings.

FIG. 8 is an internal circuit diagram of the internal voltage generator 100 of FIG. 7.

Referring to FIG. **8**, the internal power generator **100** is provided with a level sensor **200** for sensing a level of the internal power VBB corresponding to a level of an adjusted reference voltage VINT\_BB during the refresh mode, and a power supplier **300** for negative-pumping an external power VDD under the control of the level sensor **200** to generate the internal power VBB having a level lower than the external power VDD.

More specifically, the power supplier 300 is composed of a charge pumping circuit 360 for negative-pumping the external power VDD to generate the internal power VBB having a level lower than the external power VDD, an oscillator 320 for generating a period signal OSC in response to a sensing signal BBE of the level sensor 200, and a pumping control signal generator 340 for controlling the operation of the charge pumping circuit 360 in response to the period signal OSC.

For reference, the internal power generator **100** is further provided with a reference voltage generator **400** for generating the reference voltage VINT\_BB having a stable level regardless of the external power VDD. The reference voltage

generator **400** is composed of a voltage generator **420** for producing a target voltage of the internal power VBB and a level shifter **440** for level-shifting an output voltage of the voltage generator **420** to create the reference voltage VINT\_BB having a stable level regardless of the external power (power supply voltage) VDD.

FIG. 9 is an internal circuit diagram of the level sensor 200 of FIG. 8.

Referring to FIG. 9, the level sensor 200 is provided with a feedback circuit 220 for providing a level of the internal power VBB on the basis of the reference voltage VINT\_BB as a feedback voltage, a level controller 40 for controlling a level of the feedback voltage during the self refresh mode, and a differential amplifier 260 for taking the feedback voltage and its inverted feedback voltage as differential inputs to output the sensing signal BBE.

The level controller **240** is composed of an NAND gate ND1 taking a self refresh interval signal SREF notifying that the current operation is in the self refresh mode and a first 20 level adjustment signal VBB\_UPP, an inverter I1 for inverting an output signal of the NAND gate ND1 to provide an upcontrol signal CRT\_UP, an NAND gate ND2 taking the self refresh interval signal SREF and a second level adjustment signal VBB\_DN, and an inverter I2 for inverting an output 25 signal of the NAND gate ND2 to output a down-control signal CRT\_DN.

The feedback circuit **220** is composed of first to fourth PMOS transistors whose each gate takes a ground voltage VSS and which are connected in series between the reference 30 voltage VINT\_BB and an output node, fifth to eighth PMOS transistors whose each gate takes the internal voltage VBB and which are connected in series between the output node and the ground voltage, a first NMOS transistor NM**2** whose gate accepts the down-control signal CRT\_DN and which is 35 connected in parallel with the first PMOS transistor, and a second NMOS transistor NM**3** whose gate receives the upcontrol signal CRT\_UP and which is connected in parallel with the eighth PMOS transistor.

Now, the operation of the level sensor **200** will be briefly 40 described.

First, in the self refresh mode, when the self refresh interval signal SREF notifying that the current operation is in the self refresh mode is activated, the level controller **240** is active to output any activated one of the first and the second level 45 control signals VBB\_UP and VBB\_DN as the up- or down-control signal CTR\_UP or CTR\_DN. Here, if the first level adjustment signal VPP\_UP is assumed to be set, the up-control signal CRT\_UP is activated.

Then, the second NMOS transistor NM3 in the feedback 50 circuit 220 is active by the up-control signal CRT\_UP, and therefore, although the level of the internal power VBB is the same, the level of the feedback voltage taken at the output end drops. Thus, the point of time at which the sensing signal BBE is activated is higher than that in the normal mode, so that the 55 level of the internal power VBB rises.

Meanwhile, when the down-control signal CTR\_DN is activated, the first NMOS transistor NM2 in the feedback circuit 220 is active and the level of the feedback voltage at the output end rises. Thus, the level of the internal power VBB 60 becomes lower than that in the normal mode.

As mentioned above, the internal power generator 100 including the level sensor 200 adjusts the level of the internal power VBB based on the level adjustment signals VBB\_UP and VBB\_DN during the refresh mode, and then outputs an 65 adjusted internal power. That is, leakage current can be minimized by adjusting the level of the internal power VBB.

8

More concretely, in the leakage current generated in the memory cell, an off-current or junction-current has relatively large importance depending on the properties of product. In case an off-current is great, a retention time of cell data can be extended by lowering the level of the internal power VBB through the down-control signal CTR\_DN during the refresh. Similarly, in case a junction-current is great, a retention time of cell data can be prolonged by elevating the level of the internal power VBB through the up-control signal CTR\_UP.

For reference, the level adjustment signals VBB\_UP and VBB\_DN are set in the test step of wafer level so that the leakage current can be minimized. After this test procedure, the level-adjustment signals VBB\_UP and VBB\_DN are set and applied through fuse option or metal option.

As described above, the internal power generator adjusts the level of the internal power VBB during the self refresh mode, thereby decreasing leakage current of cell data. Accordingly, the retention time is prolonged.

Meanwhile, if the retention time of data is increased, the number of times of refresh can be decreased during the self refresh mode, thereby reducing IDD6 power consumption.

The following is a description for the refresh unit 500 capable of adjusting the period of the self refresh on the basis of the adjustment of the internal power VBB. For reference, the period adjustor 722 shown in FIG. 7 may be included in the refresh unit.

FIG. 10 is an internal circuit diagram of the refresh unit 500 depicted in FIG. 7.

Referring to FIG. 10, the refresh unit 500 includes a refresh exit/entry controller 600 for generating the self refresh interval signal SREF notifying that the current operation is in the self refresh mode and the internal auto refresh signal AREFP in response to the clock enable signal CKE and the auto refresh command AREF\_CMD, and a control signal generator 700 and 800 for periodically generating an internal refresh signal REFP and an internal address RCNTI[0:N] during activation of the self refresh interval signal SREF, wherein an activation period of the internal refresh signal REFP is varied upon variation of the level of the internal power VBB applied to a memory cell.

To be more specific, the refresh exit/entry controller 600 is provided with a mode input/output controller 620 for taking the clock enable signal CKE and the auto refresh signal AREF\_CMD and generating the internal auto refresh signal AREFP, a self refresh entry signal SREF\_EN and a self refresh escape signal SREF\_EXP, and a refresh interval signal generator 640 for generating the self refresh interval signal SREF notifying a self refresh interval based on the internal auto refresh signal AREFP, the self refresh entry signal SREF\_EN and the self refresh escape signal SREF\_EXP.

The control signal generator 700 and 800 is provided with a refresh period signal generator 720 for periodically outputting the period pulse signal PL\_FLG during activation of the self refresh interval signal SREF of which period is adjusted depending on the level of the internal power, an internal refresh signal generator 740 for activating the internal refresh signal REFP in response to the internal auto refresh signal AREFP and the period pulse signal PL\_FLG, and an internal address counter 800 for increasing a row address by one bit unit in response to the internal refresh signal REFP to output the internal address RCNTI[0:N].

As mentioned early, in case there is a variation of the level of the internal power VBB determining the retention time of cell data, the refresh unit **500** of the invention reflects the above and adjusts the period of the internal refresh signal REFP. Thus, the period can be delayed by the retention time of cell data, thereby reducing IDD6 power consumption.

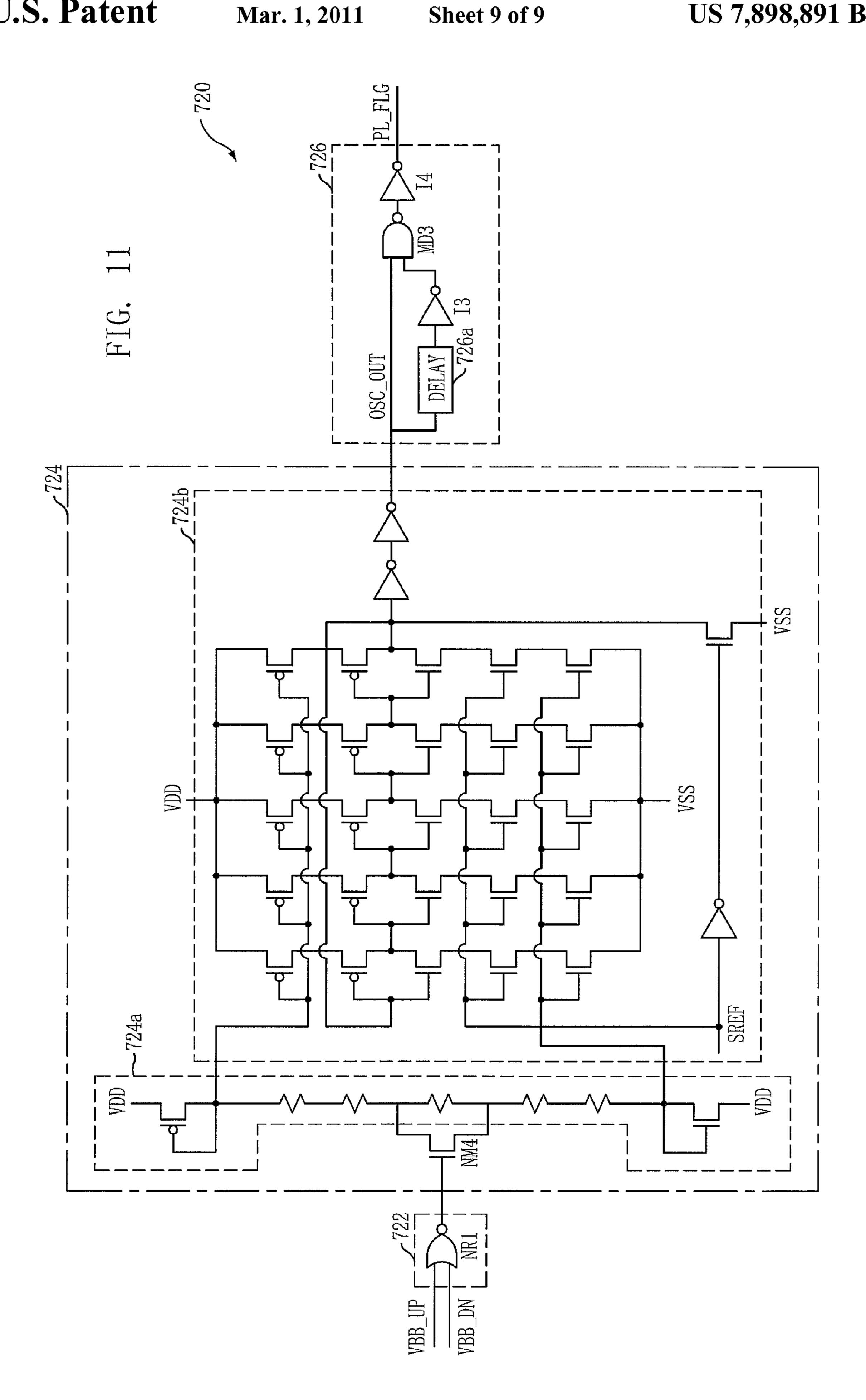

FIG. 11 is an internal circuit diagram of the refresh period signal generator 720 of FIG. 10.

Referring to FIG. 11, the refresh period signal generator 720 is constituted by the period adjustor 722 for generating a period adjustment signal in response to the first and the second level adjustment signals VBB\_UP and VBB\_DN, an oscillator 724 for adjusting the period of the period signal OSC\_OUT during activation of the self refresh interval signal SREF in response to the period adjustment signal, and a pulse generator 726 for generating the period-pulse signal PL\_FLG of pulse type from the period signal OSC\_OUT.

More specifically, the period adjustor 722 has a NOR gate NR1 for taking the first and the second level adjustment signals VBB\_UP and VBB\_DN and outputting the period adjustment signal.

The oscillator **724** is provided with a driving voltage supplier **724***a* for adjusting a level of a driving voltage in response to the period adjustment signal to supply an adjusted driving voltage and an inverter chain **724***b* for producing the period signal OSC\_OUT with a period corresponding to the level of 20 the driving voltage during activation of the self refresh interval signal SREF.

The driving voltage supplier **724***a* is composed of a plurality of resistors coupled in series between the external voltage VDD and the ground voltage VSS and an NMOS transistor 25 NM4 whose gate receives the period adjustment signal and which is coupled in parallel with one of the plurality of resistors, wherein divided voltages are provided as a first and a second driving voltages.

The pulse generator **726** is composed of a delay circuit 30 **726***a* for delaying the period signal OSC\_OUT, an inverter I3 for inverting an output signal of the delay circuit **726***a*, an NAND gate ND3 taking an output signal of the inverter I3 and the period signal OSC\_OUT, and an inverter I4 for inverting an output signal of the NAND gate ND3 to provide the period 35 pulse signal PL\_FLG.

Now, the operation of the refresh period signal generator 720 will be briefly explained.

First, when the first and the second level adjustment signals VBB\_UP and VBB\_DN are all inactivated, the period adjustment signal is inactivated to a logic high level. Thus, the resistor, which is coupled in parallel with the NMOS transistor NM4 that is under the control of the period adjustment signal in the driving voltage supplier 724a, does not affect the total resistance value.

On the other hand, when one of the first and the second level adjustment signals VBB\_UP and VBB\_DN is activated, the period adjustor 722 activates the period adjustment signal to a logic low level. Then, the NMOS transistor NM4 in the driving voltage supplier 724a is turned off, which increases 50 the total resistance value by the resistor coupled in parallel with it. Thus, the amount of current supplied from the driving voltage supplier 724a is decreased and the period of the period signal OSC\_OUT generated by the inverter chain 724b is extended. In succession, the period of the period pulse 55 signal PL\_FLG created by the pulse generator 726 is also prolonged.

As such, the increase in period of the period pulse signal PL\_FLG means an increase in interval of the internal refresh signal REFP generated in response to it, and a small number 60 of times of refresh is performed.

In other words, the level adjustment signals VBB\_UP and VBB\_DN are signals that are set to adjust the level of the internal power VBB so that the retention time of cell data is prolonged. Thus, the refresh unit **500** of the invention including the refresh period signal generator **720** senses the state that the internal power VBB is adjusted by the level adjust-

**10**

ment signals VBB\_UP and VBB\_DOWN and the retention time of cell data is prolonged, and then extends the refresh period. The number of times of refresh executed during the self refresh mode is reduced, which decreases IDD6 power consumption.

Therefore, the semiconductor memory device of the invention set forth above adjusts the level of the internal power VBB so that the retention time of cell data is prolonged during the self refresh mode where only the refresh operation is conducted at regular intervals without any commands from outside. Further, in case the level of the internal power VBB is adjusted, the refresh interval is extended, thereby decreasing IDD6 power consumption.

As a result, the present invention adjusts the level of the internal power VBB (bulk voltage applied to cell) so that the retention time of cell data is prolonged during the self refresh mode and thus extends the refresh interval, thereby decreasing power being consumed during the self refresh mode.

While the present invention has been described with respect to the specific embodiments, it will be apparent to those skilled in the art that various changes and modifications may be made without departing from the spirit and scope of the invention as defined in the following claims.

What is claimed is:

- 1. A semiconductor memory device, comprising:

- a refresh exit/entry controller for taking a clock enable signal and an auto refresh command and generating a self refresh interval signal notifying that the current operation is in a self refresh mode; and

- a control signal generator for periodically generating an internal refresh signal and an internal address for a refresh driving during activation of the self refresh interval signal, wherein an activation period of the internal refresh signal varies upon a variation of a level of a bulk voltage applied to a memory cell.

- 2. The semiconductor memory device as recited in claim 1, wherein the level variation of the bulk voltage is sensed depending on whether level adjustment signals being applied for level control of the bulk voltage are activated.

- 3. The semiconductor memory device as recited in claim 2, wherein the control signal generator includes:

- a refresh period signal generator for periodically outputting a period-pulse signal during activation of the self refresh interval signal, the period of the period-pulse signal being adjusted in response to a level of the bulk voltage;

- an internal refresh signal generator for periodically outputting a period-pulse signal during activation of the self refresh interval signal, the internal refresh signal being activated in response to the period-pulse signal; and

- an internal address counter for increasing a row address by one bit unit in response to the internal refresh signal, to output the internal address.

- 4. The semiconductor memory device as recited in claim 3, wherein the refresh period signal generator includes:

- a period adjustor for producing a period adjustment signal in response to the level adjustment signals;

- an oscillator for generating the period signal during activation of the self refresh interval signal, the period of the period signal being extended upon activation of the period adjustment signal; and

- a pulse generator for generating the period-pulse signal of pulse type whenever the period signal is activated.

- 5. The semiconductor memory device as recited in claim 4, wherein the period adjustor includes a NOR gate for taking a first and a second level adjustment signals to output the period adjustment signal.

- 6. The semiconductor memory device as recited in claim 5, wherein the oscillator includes:

- a driving voltage supplier for adjusting a level of a driving voltage in response to the period adjustment signal to supply an adjusted driving voltage; and

- an inverter chain for generating the period signal having a period corresponding to the level of the driving voltage during activation of the self refresh interval signal.

- 7. The semiconductor memory device as recited in claim 6, wherein the driving voltage supplier includes:

- a plurality of resistors coupled in series between an external voltage and a ground voltage;

- an NMOS transistor whose gate takes the period adjustment signal and which is connected in parallel with one of the plurality of resistors,

- wherein voltages divided by the plurality of resistors are outputted as a first and a second driving voltages.

- **8**. A driving method of a semiconductor memory device, comprising:

12

- operating the semiconductor memory device in a self refresh mode by activating a self refresh interval signal in response to a clock enable signal and an auto refresh command; and

- generating an internal refresh signal and an internal address for controlling a refresh driving at predetermined intervals during an activation of the self refresh interval signal,

- wherein the self refresh interval signal notifies that a current operation is performed in the self refresh mode and the predetermined intervals are adjusted according to a level of a bulk voltage applied to a memory cell.

- 9. The driving method as recited in claim 8, wherein the level variation of the bulk voltage is sensed depending on whether level adjustment signals being applied for level adjustment of the bulk voltage are activated.

\* \* \* \* \*