#### US007872353B2

# (12) United States Patent Ito et al.

# (10) Patent No.: US 7,872,353 B2 (45) Date of Patent: Jan. 18, 2011

#### (54) **SEMICONDUCTOR DEVICE**

(75) Inventors: **Sachiyo Ito**, Yokohama (JP); **Masahiko Hasunuma**, Yokohama (JP)

(73) Assignee: Kabushiki Kaisha Toshiba, Tokyo (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 591 days.

21) Appl. No.: 11/964,336

(22) Filed: Dec. 26, 2007

(65) Prior Publication Data

US 2008/0164614 A1 Jul. 10, 2008

### (30) Foreign Application Priority Data

(51) Int. Cl. H01L 23/52 (2006.01)

See application file for complete search history.

#### (56) References Cited

U.S. PATENT DOCUMENTS

6,958,542 B2 10/2005 Hasunuma et al.

| 7,180,192    | B2         | 2/2007  | Hasunuma et al.        |

|--------------|------------|---------|------------------------|

| 7,285,859    | B2         | 10/2007 | Hasunuma et al.        |

| 2002/0047207 | A1*        | 4/2002  | Sekiguchi              |

| 2005/0167842 | A1*        | 8/2005  | Nakamura et al 257/758 |

| 2006/0145347 | A1*        | 7/2006  | Aida 257/758           |

| 2007/0204243 | <b>A</b> 1 | 8/2007  | Ito et al.             |

#### FOREIGN PATENT DOCUMENTS

JP 2005-150389 6/2005

Primary Examiner—Fernando L Toledo Assistant Examiner—Mamadou Diallo (74) Attorney, Agent, or Firm—Finnegan, Henderson, Farabow, Garrett & Dunner, L.L.P.

#### (57) ABSTRACT

A semiconductor device including at least two layers of interlayer-insulator-films stacked above a substrate and at least partially formed by a low-relative-dielectric-constant-film having a relative-dielectric-constant of 3.4 or less respectively, a plurality of wirings provided at least one within each of the interlayer-insulator-film and at least partially located within the low-relative-dielectric-constant-films, a plurality of plugs provided at least one within each of the interlayerinsulator-film and connected to a lower part of the wirings, and a plurality of reinforcement members provided at least one within each of the interlayer-insulator-film with being separated from the wirings at a predetermined interval, electrically cut from the wirings and the plugs, and at least partially located within the low-relative-dielectric-constantfilms, and wherein, the interlayer-insulator-films, the wirings, the plugs, and the reinforcement members satisfy a predetermined relation for each of the interlayer-insulator-film.

## 20 Claims, 4 Drawing Sheets

<sup>\*</sup> cited by examiner

Jan. 18, 2011

F1G. 2

FIG.3

### SEMICONDUCTOR DEVICE

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application is based upon and claims the benefit of priority from prior Japanese Patent Application No. 2006-352998, filed Dec. 27, 2006, the entire contents of which are incorporated herein by reference.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to an art for improving a quality and a reliability of a semiconductor device, and particularly, the present invention relates to an art for improving a quality and a reliability of a semiconductor device by improving a decay durability in the vicinity of a wiring to be installed in an interlayer-insulator-film formed by stacking a plurality of insulator films including a low-relative-dielectric-constant-film.

#### 2. Description of the Related Art

In recent years, for speed-up of a semiconductor device including an LSI, lowering of wiring resistance and lowering of relative dielectric constant of an interlayer-insulator-film or the like have been promoted. Specifically, a material of wiring is changed from aluminum (Al) into copper (Cu). In addition, as an interlayer-insulator-film, a low-relative-dielectric-constant-film (a low-k film) is also changed from a simple SiO<sub>2</sub> film into a SiO<sub>2</sub> film having fluorine doped 30 thereon, and a SiO<sub>2</sub> film containing an organic constituent.

The low-relative-dielectric-constant-film is formed by lowering a density of a material or eliminating a polarity of the material or the like. For example, in order to lower the density of the material, generally, the material is made 35 porous. Thus, since the low-relative-dielectric-constant-film has a low film density, generally, the low-relative-dielectricconstant-film has a low mechanical property value such as a Young's modulus or the like. In other words, the low-relativedielectric-constant-film has a low strength of the material 40 itself. In addition, the low-relative-dielectric-constant-film has a film structure with low polarity for lowering the dielectric constant in the film. Therefore, an adhesive strength on a stacking boundary face in a stacked insulator film formed by stacking the low-relative-dielectric-constant-film with each 45 other or stacking the low-relative-dielectric-constant-film and other film is low. Specifically, a material of a film changes its nature depending on saturation of gas that is used on machining and forming a via hole and a groove for a wiring or the like on the low-relative-dielectric-constant-film and a 50 machining process. Thereby, there is concern that the mechanical strength of the material itself of the low-relativedielectric-constant-film may be lowered, or the adhesive strength on the boundary face in the stacked insulator film including the low-relative-dielectric-constant-film may be 55 lowered.

A shortage of a strength caused by a weakness of the film strength of this low-relative-dielectric-constant-film is a serious obstacle and particularly, this shortage of the strength becomes a factor of lowering a quality, a reliability, a performance or the like of the entire semiconductor device in a multi-layer process to form a multi-layer structure of the wiring in the interlayer-insulator-film formed by the stacked insulator film including the low-relative-dielectric-constant-film. For example, as one main failure caused by a weakness of the film strength of the low-relative-dielectric-constant-film, separation of an insulator film boundary face in a CMP

2

step may be considered. Specifically, in the case that a region made only of an insulator film having no wiring spreads widely to some extents, separation of a boundary face will easily occur in the interlayer-insulator-film due to a stress generated by a friction between a polishing pad and a surface of a wafer in performing CMP. Therefore, in order to prevent such a separation of a boundary face, an art for introducing a reinforcement member having a high strength such as a metal in the region made only of an insulator film having no wiring 10 has been suggested. For example, in Jpn. Pat. Appln. KOKAI Publication No. 2005-150389, an art for arranging a dummy wiring, a dummy plug or the like that does not configure an actual energizing path in the low-relative-dielectric-constantfilm has been suggested. Thereby, by easing a stress that is generated by a friction between surfaces of the polish pad and the wafer in performing CMP and is applied to the interlayerinsulator-film, a quality, reliability, performance or the like of the entire semiconductor device are intended to be improved.

An effect of easing the stress on the CMP step by this dummy wiring depends not only on a coverage of the dummy wiring but also on a size of the dummy wiring. However, in practice, an art for optimizing the size of the dummy wiring has not been substantially studied yet. Therefore, a stress lowering effect due to the dummy wiring has not been fully achieved, so that a concern that the boundary face is separated in the CMP has not been completely solved yet. In addition, in designing of the dummy wiring, a designing method in consideration of a mechanical property value of the interlayerinsulator-film employing the low-relative-dielectric-constant-film has not been used. Therefore, every time a generation of the semiconductor device and the design rule thereof is changed or a type of the interlayer-insulator-film is changed, it is necessary to decide a dummy wiring structure in which the boundary face is hardly separated by a trial and an error while expending large amounts of masks and lots. As a result, until a desired dummy wiring structure is obtained, many steps, much manpower, much time, and much cost have been expended. Then, even in the case that optimization of the size of the dummy wiring in consideration of a mechanical property value of the interlayer-insulator-film including the low-relative-dielectric-constant-film is not carried out, there was high possibility that a defect of the device is generated due to the boundary face separation in the CMP.

Thus, according to a conventional dummy wiring art, a crucial failure is easily generated in the semiconductor device and the manufacturing method thereof. In other words, a quality, reliability, a performance or the like of the semiconductor device is lowered and the defective semiconductor device is easily manufactured. As a result, a manufacturing yield of the semiconductor device is lowered and a manufacturing efficiency of the semiconductor device is easily lowered. Further, a manufacturing cost of the semiconductor device is difficult to control.

#### BRIEF SUMMARY OF THE INVENTION

According to as an aspect of the invention, there is provided a semiconductor device comprising: at least two layers of interlayer-insulator-films stacked above a substrate and at least partially formed by a low-relative-dielectric-constant-film having a relative-dielectric-constant of 3.4 or less respectively; a plurality of wirings provided at least one within each of the interlayer-insulator-film and at least partially located within the low-relative-dielectric-constant-films; a plurality of plugs provided at least one within each of the interlayer-insulator-film and connected to a lower part of the wirings; and a plurality of reinforcement members provided at least

one within each of the interlayer-insulator-film with being separated from the wirings at a predetermined interval, electrically cut from the wirings and the plugs, and at least partially located within the low-relative-dielectric-constantfilms; and wherein, for each of the reinforcement member, a 5 value obtained by dividing an area of a part that is exposed on an upper face of each of the interlayer-insulator-film by an length of a part contacting each of the interlayer-insulatorfilm of the part that is exposed on the upper face of each of the interlayer-insulator-film is defined to be S; a Young's modu- 10 lus of a respective layer on which the plug is provided among the interlayer-insulator-films is defined to be  $E_P$ ; a Young's modulus of a respective layer on which the wiring is provided among the interlayer-insulator-films is defined to be  $E_w$ ; a Young's modulus of the wirings is defined to be  $E_{\mathcal{M}}$ ; a film 15 thickness of a respective layer on which the plug is provided among the interlayer-insulator-films is defined to be  $d_p$ ; a film thickness of a respective layer on which the wiring is provided among the interlayer-insulator-films are defined to be  $d_w$ ; a coverage of the reinforcement member per unit area in an area 20 in the interlayer-insulator-films where the reinforcement members are provided is defined to be R; and the S, the  $E_P$ , the  $E_{W}$ , the  $E_{M}$ , the  $d_{P}$ , the  $d_{W}$ , and the R satisfy a relation shown in the following formula for each of the interlayer-insulatorfilm:

$$0.025 \times \left(\frac{E_P \times d_P + (E_W \times (1 - R) + E_M \times R) \times d_W}{d_P + d_W}\right)^{0.4} < S < 0.0625 \times \left(\frac{E_P \times d_P + (E_W \times (1 - R) + E_M \times R) \times d_W}{d_P + d_W}\right)^{0.4}$$

# BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING

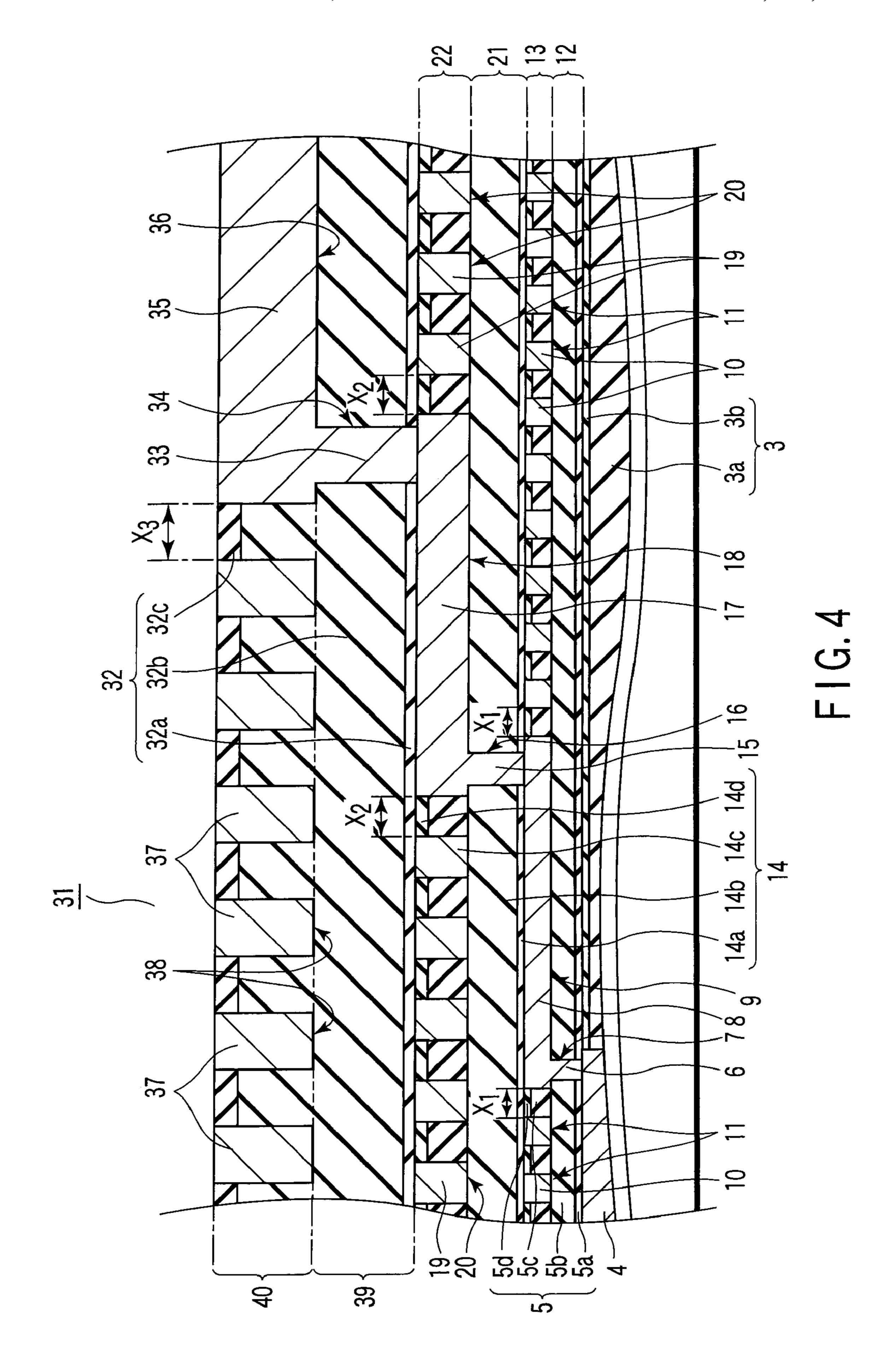

FIG. 1 is a cross sectional view showing a semiconductor device according to a first embodiment;

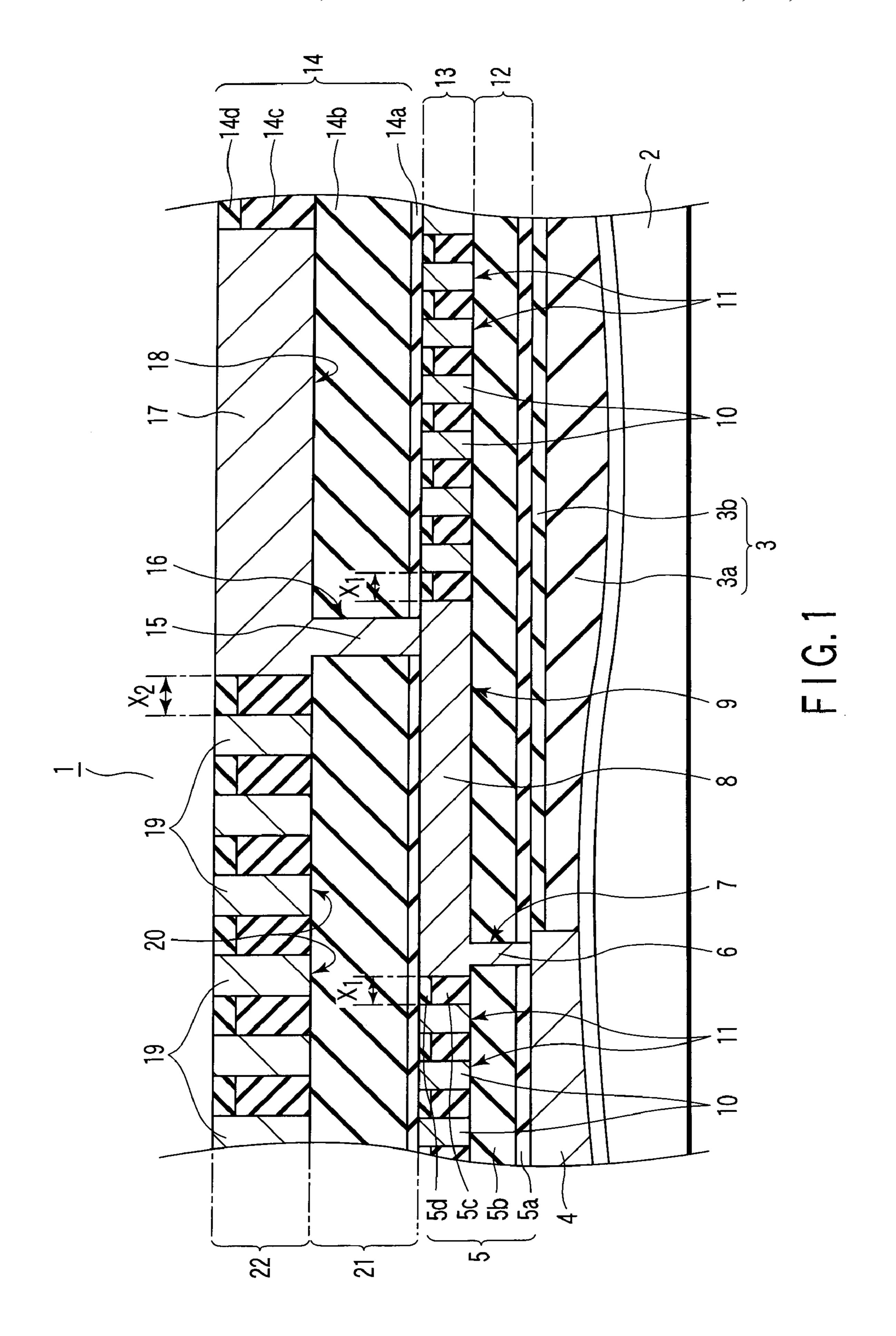

FIG. 2 is a plan view showing the semiconductor device 40 shown in FIG. 1 as seen from above;

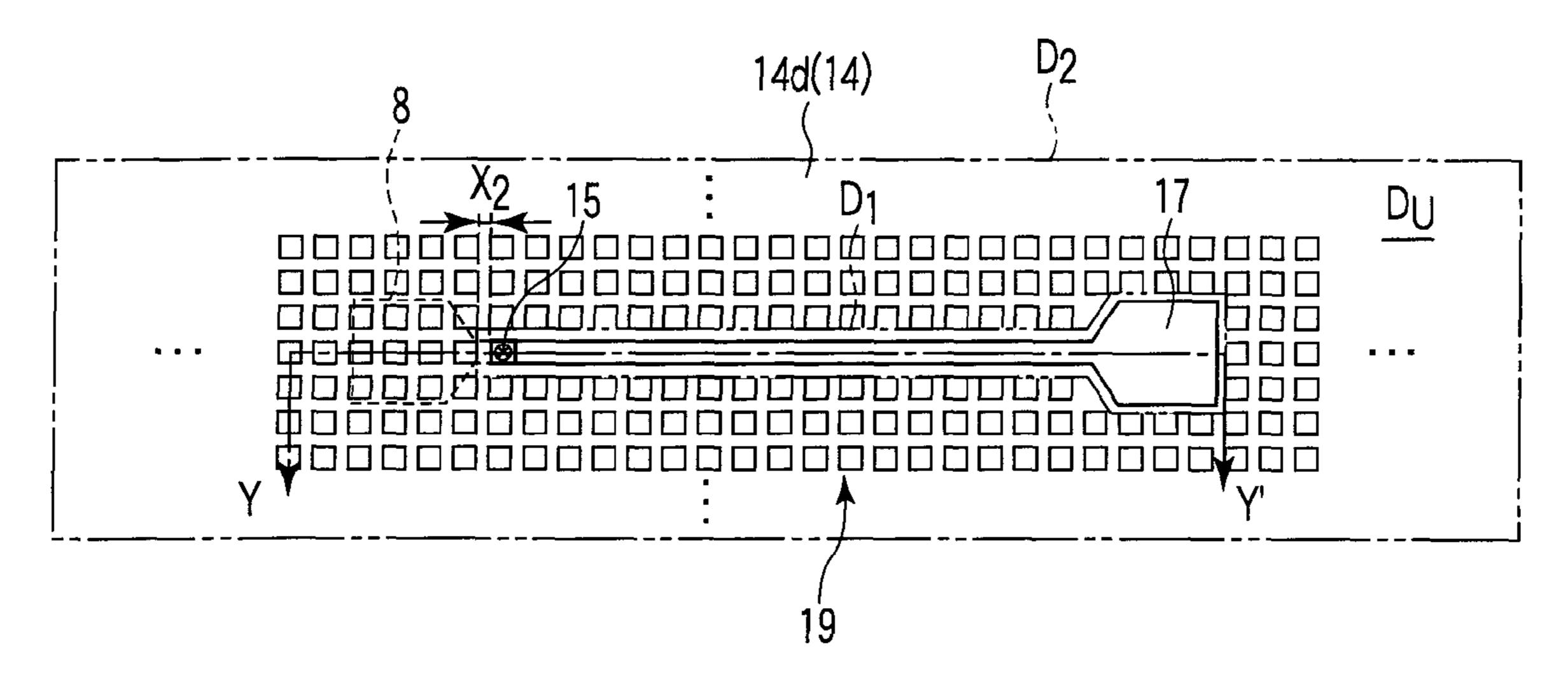

FIG. 3 is a plan view showing a dummy wiring provided to the semiconductor device shown in FIG. 1 as seen from above;

FIG. 4 is a cross sectional view showing a semiconductor 45 device according to a second embodiment; and

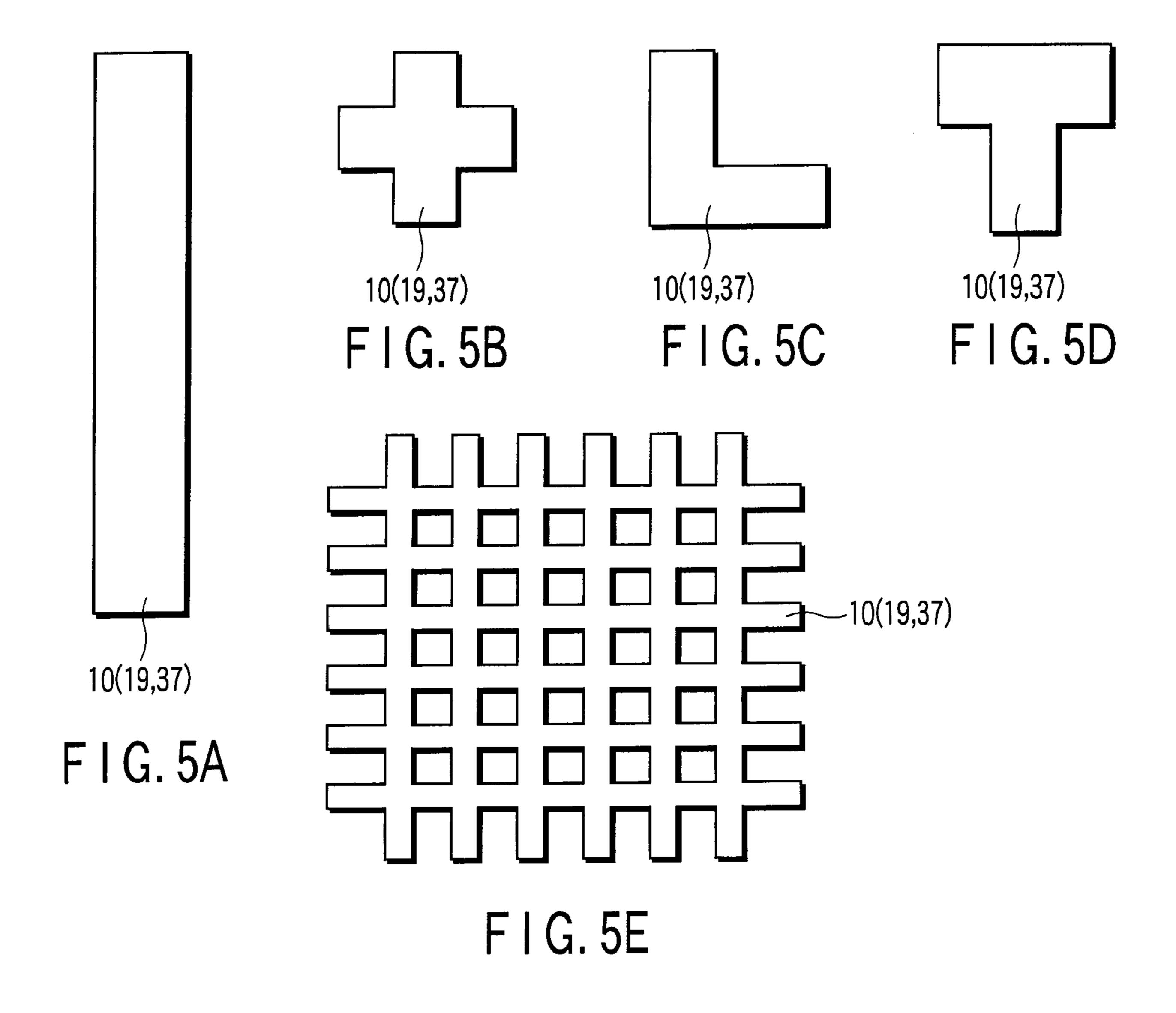

FIGS. **5**A, **5**B, **5**C, **5**D, and **5**E are plan views showing a dummy wiring according to a third embodiment as seen from above.

#### DETAILED DESCRIPTION OF THE INVENTION

The respective embodiments according to the present invention will be described with reference to the drawings below.

#### First Embodiment

First, a first embodiment according to the present invention will be described with reference to FIGS. 1 to 3.

According to the present embodiment, an art for preventing separation of an interlayer-insulator-film in a CMP step in a semiconductor device having a multi-layer structure, in which a plurality of interlayer-insulator-films at least partially including a so-called low-relative-dielectric-constant-film 65 respectively is stacked and a first wiring layer as a lower wiring layer and a second wiring layer as an upper wiring

4

layer are set on predetermined two interlayer-insulator-films among the respective interlayer-insulator-films will be described. Specifically, when providing upper and lower effective wirings to construct an actual energizing path within each of the first and second wiring layers, a dummy wiring that does not construct an actual energizing path is aligned near these effective wirings. In this case, in consideration of a strength and a thickness of a film to configure each interlayerinsulator-film in which the first and second wiring layers are set, the strength of the upper and lower effective wirings, or a coverage of the dummy wiring or the like, the shape and the size or the like of the dummy wiring are defined. Thereby, generation of separation of the interlayer-insulator-film in a CMP step in forming the multi-layer structure is efficiently prevented. Hereinafter, the first embodiment will be specifically described in detail.

First, with reference to FIGS. 1 to 3, a semiconductor device 1 and a manufacturing method thereof according to the present embodiment will be collectively described.

First, a wiring structure of the nth layer (n is a natural number of 1 or larger) of the semiconductor device 1 is formed. Specifically, as shown in FIG. 1, an interlayer-insulator-film 3 of an n-th layer is provided on a semiconductor substrate 2 made of silicon (Si) on which semiconductor device or the like (not illustrated) is formed. Here, the interlayer-insulator-film 3 of the nth layer is formed into a twolayer structure formed by a stacking film including a lowerlayer insulator film 3a and an upper-layer insulator film 3b. First, as a lower insulator film, a porous silicon oxide film (a porous SiO<sub>2</sub> film) 3a is deposited by a CVD method. This porous SiO<sub>2</sub> film 3a has a relative-dielectric-constant of about 2.2. Accordingly, this porous SiO<sub>2</sub> film 3a is a kind of a so-called low-relative-dielectric-constant-film (a low-k film) having a relative dielectric constant of 3.4 or less. In addition, the porous  $SiO_2$  film 3a has a Young's modulus showing its mechanical strength of about 3 GPa. Then, on this porous  $SiO_2$  film 3a, a silicon oxide film (a  $SiO_2$ ) film 3b that is a general insulator film as an upper layer insulator film is accumulated and deposited by a plasma CVD method. This SiO<sub>2</sub> film 3b has a relative dielectric constant of about 4.0 and a Young's modulus of about 55 GPa.

Next, a wiring 4 of the nth layer as wiring of the bottom layer is provided within the interlayer-insulator-film 3 of the nth layer. This wiring 4 of the nth layer is embedded and formed within the interlayer-insulator-film 3 of the nth layer together with a barrier metal film (not illustrated) by a CMP method or the like. In addition, this wiring 4 of the nth layer <sub>50</sub> may be formed by copper (Cu), aluminum (Al), or an alloy containing any of these metal elements. The wiring 4 of the n-th layer constructs an actual energizing path in the semiconductor device 1 together with a wiring 8 of the n+1th layer and a wiring 17 of the (n+2)th layer to be described later or the like. Accordingly, the wiring 4 of the nth layer is also referred to as an effective wiring. In addition, the porous  $SiO_2$  film 3aand the  $SiO_2$  film 3b, on which the effective wiring 4 is formed, are also referred to as a wiring layer of the nth layer collectively. By these steps, the wiring structure of the nth layer of the semiconductor device 1 is formed.

Next, the wiring structure of the (n+1)th layer of the semiconductor device 1 will be formed. Specifically, first, an interlayer-insulator-film 5 of the (n+1)th layer is provided on the interlayer-insulator-film 3 of the nth layer, in which the wiring 4 of the nth layer is embedded and formed. Here, the interlayer-insulator-film 5 of the (n+1)th layer is formed into a four-layer structure including a first interlayer-insulator film

5a, a second insulator film 5b, a third insulator film 5c, and a fourth insulator film 5d from a lower side toward an upper side.

First, on the SiO<sub>2</sub> film 3b, a silicon carbon (SiC) film 5a that is a general insulator film is deposited as a first insulator film 5 with a film thickness of about 35 nm by a plasma CVD method. This SiC film 5a functions as a so-called etching stopper film to prevent the  $SiO_2$  film 3b and the wiring 4 of the n-th layer from being etched when forming a via hole 7 of the (n+1)th layer to be described later within the interlayer-insulator film 5 of the (n+1)th layer. The SiC film 5a has a Young's modulus of about 20 Gpa and has higher strength than that of the low relative-dielectric-constant-film. Therefore, the SiC film 5a may also function as a reinforcement film to prevent a via plug 6 of the (n+1)th layer to be provided within the via 15 hole 7 and be described later from being displaced by the CMP step when embedding the wiring 8 of the (n+1)th layer to be connected to the via plug 6 of the (n+1)th layer and to be described later within the interlayer-insulator film 5 of the (n+1)th layer or from being separated from the wiring 4 of the 20 nth layer by holding the via plug 6 of the (n+1)th layer.

Then, on the SiC film 5a, as the second insulator film, a polymethyl siloxane film 5b is deposited with a film thickness of about 135 mm. Specifically, first, a varnish having a material of the polymethyl siloxane film 5b or polymethyl siloxane 25 as a precursor of the polymethyl siloxane film 5b dissolved in a solvent is spin-coated on a surface of the SiC film 5a by using a coater (not illustrated). Then, after mounting a semiconductor substrate 2 on which a varnish is coated on a hot plate that is kept warm at about 80° C., a heating processing 30° of about one minute is applied. Subsequently, after mounting the semiconductor substrate 2 to which heating processing of about 80° C. is applied on a hot plate that is kept warm at about 200° C., further, a heating processing of about one minute is applied. Then, after mounting the semiconductor substrate 2 35 to which heating processing of about 200° C. is applied on a hot plate that is kept warm at about 450° C., further, a heating processing of about thirty minutes is applied under a nitrogen atmosphere. Thereby, on the SiC film 5a, a polymethyl siloxane film 5b is deposited. This polymethyl siloxane film 5b has 40 a relative-dielectric-constant of about 2.5 and is a kind of a low-relative-dielectric-constant-film. In addition, the polymethyl siloxane film **5**b has a Young's modulus of about 3 GPa similarly to the porous  $SiO_2$  film 3a of the n-th layer that is described above.

Subsequently, on the polymethyl siloxane film 5b, as the third insulator film, a porous  $SiO_2$  film 5c is deposited with a film thickness of about 110 nm by the CVD method. This porous SiO<sub>2</sub> film 5c of the (n+1)th layer has a relative-dielectric-constant of about 2.2 similarly to the above-mentioned 50 porous  $SiO_2$  film 3a of the n-th layer and is a kind of a low-relative-dielectric-constant-film. In addition, the porous SiO<sub>2</sub> film **5**c has a Young's modulus of about 3 GPa similarly to the above-mentioned porous SiO<sub>2</sub> film 3a and the polymethyl siloxane film 5b. Then, as a fourth insulator film, a 55 carbon-containing SiO<sub>2</sub> film (a SiOC film) 5d is formed on this porous SiO<sub>2</sub> film **5**c with a film thickness of about 50 nm by the plasma CVD method. This SiOC film 5d of the (n+1)th layer has a relative-dielectric-constant of about 3.0 and is a kind of a low-relative-dielectric-constant-film. Further, a 60 Young's modulus of this SiOC film **5***d* is about 10 GPa.

By these steps, the interlayer-insulator film 5 of the (n+1)th layer formed by a four-layer complex insulator film including the SiC film 5a, the polymethyl siloxane film 5b, the porous  $SiO_2$  film 5c, and the SiOC film 5d, of which film qualities and 65 film kinds are different from each other, is deposited on the interlayer-insulator film 3 of the n-th layer. In other words, in

6

the interlayer-insulator film **5** of the (n+1)th layer with a four-layer structure, the second layer to the fourth layer from the lower side are formed by a low-relative-dielectric-constant-film and only the first layer as the bottom layer is formed by a general insulator film.

Next, the via hole 7 for providing the via plug 6 of the (n+1)th layer to be connected to the upper part of the wiring 4 of the nth layer and a wiring groove 9 for providing the wiring 8 of the (n+1)th layer to be connected to the upper part of the via plug 6 are formed within the interlayer-insulator film 5 of the (n+1)th layer. Specifically, first, at the position of the upper part of the wiring 4 of the nth layer where the via plug 6 is provided, by eliminating the SiOC film 5d, the porous  $SiO_2$  film 5c, and the polymethyl siloxane film 5balong their film thickness directions until the upper face of the SiC film 5a is exposed by an RIE method, an hole (not illustrated) is formed. Subsequently, at the position of the upper part of this hole where the wiring 8 is provided, by eliminating the SiOC film 5d and the porous SiO<sub>2</sub> film 5calong their film thickness directions by the RIE method, the upper face of the polymethyl siloxane film 5b is exposed. Thereby, the wiring groove 9 to be communicated with the upper part of the hole is formed in the SiOC film 5d and the porous SiO<sub>2</sub> film 5c. After this, by eliminating the SiC film 5alocated on the lower part of the hole by the RIE method, the upper face of the wiring 4 of the nth layer is exposed. Thereby, the via hole 7 to be communicated to the lower part of the wiring groove 9 is formed in the polymethyl siloxane film 5band the SiC film 5a.

In addition, in the interlayer-insulator film 5 of the (n+1)th layer, not only the via plug 6 and the wiring 8 but also a reinforcement member 10 of the (n+1)th layer for preventing generation of an insulator film separation such as a boundary face separation in the interlayer-insulator-film 5 and in the vicinity of the interlayer-insulator-films 5 in the CMP step when embedding and forming the via plug 6 and the wiring 8 in the interlayer-insulator-films 5 are provided. At least one reinforcement member 10 is provided in the interlayer-insulator-film 5 being electrically cut from the wiring 8 and the via plug 6 and being separated from the wiring 8 by at least a predetermined interval. In addition, the reinforcement member 10 is positioned in an inner part of any one of the lowrelative-dielectric-constant-films 5b, 5c, and 5d, at least a part of which forms the interlayer-insulator-film **5**. In this case, as shown in FIG. 1, a plurality of the reinforcement members 10 is provided in the porous  $SiO_2$  film 5c and the SiOC film 5dconstructing a layer in the interlayer-insulator-film 5 where the wiring 8 is provided, being electrically cut from the wiring 8 and the via plug 6 and being separated from the wiring 8 by at least an interval  $X_1$ . In this case, the interval  $X_1$  is determined to be about 2 µm. Then, here, according to the same method as the method for providing the wiring 8, a plurality of the reinforcement members 10 is provided in parallel with providing of the wiring 8 surrounding the periphery of the wiring **8**.

Specifically, first, grooves for a reinforcement member 11 for providing the reinforcement member 10 are formed at plural positions in the interlayer-insulator-film 5 in parallel with forming of the wiring groove 9 by the same step as that for forming the wiring groove 9. These grooves for a reinforcement member 11 are formed at approximately the same height as the wiring groove 9 and at approximately the same depth as the wiring groove 9 in the SiOC film 5d and the porous  $SiO_2$  film 5c. More specifically, these respective grooves for a reinforcement member 11 are formed at plural positions in the SiOC film 5d and the porous  $SiO_2$  film 5c

surrounding the periphery of the wiring groove 9, being separated from the wiring groove 9 by at least about 2 μm.

Next, although the illustration thereof is omitted, a barrier metal layer is provided covering inner faces of the via hole 7, the wiring groove 9, and the grooves for a reinforcement 5 member 11 and the surface of the wiring 4 of the nth layer that is exposed by the via hole 7. This barrier metal layer is deposited on the entire surface of the interlayer-insulator-film **5** of the (n+1)th layer under an atmosphere of about 150° C. by a sputtering method, for example. This barrier metal layer 10 may be formed by using any of a Ta film, a Ti film, a Nb film, and a W film made of an elemental substance of each of tantalum (Ta), titanium (Ti), niobium (Nb) and tungsten (X). Alternatively, this barrier metal layer may be formed by using any of a TaN film, a TiN film, a NbN film, and a WN film made 15 of a nitride of Ta, Ti, Nb, and W. Further, this barrier metal layer may be formed by using a stacked film containing at least two kinds of films among Ta film, Ti film, Nb film, W film, TaN film, TiN film, NbN film, WN film, a ruthenium (Ru) film, and a rhodium (Rh) film.

Next, insides of the via hole 7, the wiring groove 9, and the grooves for a reinforcement member 11 to which the barrier metal layer is provided, a conductive material to be the via plug 6, the wiring 8, and the reinforcement members 10 is arranged. The via plug 6, the wiring 8, and the reinforcement 25 members 10 may be formed by using Cu, Al, or an alloy containing any of the metal elements similarly to the abovedescribed wiring 4 of the nth layer. In this case, all of the via plug 6, the wiring 8, and the reinforcement members 10 are formed by using Cu. Specifically, first, a Cu plating seed layer 30 that is the base of the via plug 6, the wiring 8, and the reinforcement members 10 is deposited on the entire surface of the barrier metal layer by the sputtering method. Then, a Cu plating film that is a main part of the via plug 6, the wiring 8, and the reinforcement members 10 is deposited on the entire 35 surface of the Cu plating seed layer by an electrolytic plating method until insides of the via hole 7, the wiring groove 9, and the grooves for a reinforcement member 11 is filled. This Cu plating film is deposited to be integrated with the Cu plating seed layer. Thereby, a Cu film to be the via plug 6, the wiring 40 8, and the reinforcement members 10 entirely covers the surface of the barrier metal layer to be deposited insides of the via hole 7, the wiring groove 9, and the respective grooves for a reinforcement member 11. A Young's modulus of this Cu film is about 130 GPa.

Next, the Cu film that is arranged in the via hole 7, the wiring groove 9, and the respective grooves for a reinforcement member 11 is annealed. Although the illustration thereof is omitted, this anneal processing will be carried out in a temperature range of about 150° C. to 300° C. by using an 60 electric furnace, a hot plate, or the like and under an atmosphere of a forming gas or a nitrogen gas. In addition, a time required for this anneal processing is about one hour when using the electric furnace and is about one to five minutes when using the hot plate.

Next, unnecessary barrier metal layer and Cu film provided outsides of the via hole 7, the wiring groove 9, and the respective grooves for a reinforcement member 11 are eliminated. Specifically, a barrier metal layer and a Cu film deposited on the surface of the SiOC film 5d that is the insulator film of the 60 top layer of the interlayer-insulator-film 5 of the (n+1)th layer are polished and eliminated by the CMP method. Thereby, the barrier metal layer and the Cu layer are left only insides of the via hole 7, the wiring groove 9, and the respective grooves for a reinforcement member 11. In other words, the via plug 6, the 65 wiring 8, and the reinforcement members 10, of which side parts and bottom parts are covered with the barrier metal

8

layer, are embedded and formed in the interlayer-insulator-film 5 of the (n+1)th layer in parallel.

The via plug 6 is arranged with its upper part located in the polymethyl siloxane film 5b that is a low-relative-dielectric-constant-film and its lower part located in the SiC film 5a having a higher strength than the low-relative-dielectric-constant-film. In addition, the wiring 8 is formed as a so-called dual damascene wiring having a lower part to which the via plug 6 is connected integrally. In addition, the wiring 8 is located in the porous  $SiO_2$  film 5c and the SiOC film 5d that are the low-relative-dielectric-constant-films and its lower face is connected to the polymethyl siloxane film 5b that is also the low-relative-dielectric-constant-film via the barrier metal layer.

In addition, as shown in FIG. 1, the reinforcement members 10 are arranged to be electrically cut from the wiring 8 and the via plug 6. Therewith, a plurality of the reinforcement members 10 is arranged surrounding the periphery of the wiring 8, being separated from the wiring 8 by at least about 2 μm. Similarly to the wiring 8, these respective the reinforcement members 10 are also located in the porous SiO<sub>2</sub> film 5c and the SiOC film 5d with its lower face contacting the polymethyl siloxane film 5b via the barrier metal layer.

According to these steps, the wiring structure of the (n+1) th layer of the semiconductor device 1 is formed. Further, a more specific setting related to the size, the shape, or the arrangement of the reinforcement member 10 of the (n+1)th layer will be described in detail later.

The wiring 8 of the (n+1)th layer configures an actual energizing path of the semiconductor device 1 together with the via plug 6 of the (n+1)th layer that is formed to be integrated with the wiring 8 of the (n+1)th layer and the wiring 4 of the nth layer that is indirectly connected to the wiring 8 of the (n+1)th layer via this via plug 6. On the contrary, the reinforcement members 10 of the (n+1)th layer are not electrically connected to the wiring 8, the via plug 6 or the like, so that they do not configure the actual energizing path of the semiconductor device 1. As a result, in the later descriptions, in order to clearly distinguish the wiring 8 of the (n+1)th layer from the reinforcement members 10 of the (n+1)th layer, the wiring 8 will be referred to as a effective wiring of the (n+1)th layer and the reinforcement members 10 will be referred to as a dummy wiring of the (n+1)th layer. In addition, the lower two layers on which the via plug 6 is formed among the 45 interlayer-insulator film **5** of the (n+1)th layer, namely, the SiC film 5a and the polymethyl siloxane film 5b will be also referred to as a via layer of the (n+1)th layer or a plug layer 12 collectively. Similarly, the upper two layers on which the effective wiring 8 and the respective dummy wirings 10 are formed among the interlayer-insulator film 5 of the (n+1)th layer, namely, the porous  $SiO_2$  film 5c and the SiOC film 5dwill be also referred to as an wiring layer 13 of the (n+1)th layer collectively.

Next, the wiring structure of the (n+2)th layer of the semiconductor device 1 is formed. Specifically, first, an interlayerinsulator-film 14 of the (n+2)th layer is provided on the interlayer-insulator-film 5 of the (n+1)th layer, in which the via plug 6, the effective wiring 8, and the respective dummy wirings 10 of the (n+1)th layer are embedded and formed. Here, similarly to the above-described interlayer-insulatorfilm 5 of the (n+1)th layer, the interlayer-insulator-film 14 of the (n+2)th layer is also formed into a four-layer structure including a first insulator film 14a, a second insulator film 14b, a third insulator film 14c, and a fourth insulator film 14d from a lower side toward an upper side.

First, a silicon carbon nitride film (SiCN film) **14***a* that is general as the first insulator film is deposited with a film

thickness of about 50 nm by the plasma CVD method, covering the surfaces of the SiOC film 5d that is the insulator film on the top layer of the interlayer-insulator-film 5 of the (n+1)th layer, the effective wiring 8, and the respective dummy wirings 10. Similarly to the above-described SiC film 5a of 5 the (n+1)th layer, this SiCN film 14a functions as an etching stopper film to prevent the SiOC film 5d, the effective wiring 8, and the respective dummy wirings 10 from being etched when forming the via hole 16 of the (n+2)th layer to be described later in the interlayer-insulator-film 14 of the (n+2) 10 th layer. In addition, the Young's modulus of the SiCN film **14***a* is about 100 GPa, so that the strength thereof is remarkably higher than that of the SiC film 5a. Therefore, similarly to the SiC film 5a, the SiCN film 14a may also function as a reinforcement film to prevent a via plug 15 of the (n+2)th 15 layer to be provided in the via hole 16 and be described later from being displaced by the CMP step when embedding a wiring 17 of the (n+2)th layer to be connected to the via plug 16 and be described later in the interlayer-insulator-film 14 of the (n+2)th layer or from being separated from the effective 20 wiring 8 of the (n+1)th layer by holding the via plug 15.

Then, on the SiCN film 14a, as the second insulator film, a carbon-containing SiO<sub>2</sub> film (SiOC film) **14**b is formed with a film thickness of about 230 nm by the plasma CVD method. This SiOC film 14b of the (n+2)th layer has a relative dielectric constant of about 3.0 similarly to the above-described SiOC film 5d of the (n+1)th layer and is a kind of a lowrelative-dielectric-constant-film. Further, a Young's modulus of the SiOC film **14**b is about 10 GPa similarly to the SiOC film 5d. Then, on this SiOC film 14b, as the third insulator 30 film, the porous  $SiO_2$  film 14c is formed with a film thickness of about 175 nm by the plasma CVD method. This porous SiO<sub>2</sub> film 14c of the (n+2)th layer also has a relative dielectric constant of about 2.2 similarly to the above-described porous  $SiO_2$  film 3a of the n-th layer and porous  $SiO_2$  film 5c of the 35 (n+1)th layer and is a kind of a low-relative-dielectric-constant-film. Further, a Young's modulus of the porous SiO<sub>2</sub> film **14**c is also about 3 GPa similarly to each of the porous  $SiO_2$  films 3a and 5c. Then, on this porous  $SiO_2$  film 14c, as the fourth insulator film, the  $SiO_2$  film 14d is formed with a 40 film thickness of about 50 nm by the plasma CVD method. This  $SiO_2$  film 14d of the (n+2)th layer also has a relative dielectric constant of about 4.0 similarly to the above-described SiO<sub>2</sub> film 3b of the n-th layer and is a general insulator film. Therewith, a Young's modulus of the SiO<sub>2</sub> film **14***d* is 45 about 55 GPa similarly to the SiO<sub>2</sub> film 3b.

According to these steps, similarly to the above-described interlayer-insulator film **5** of the (n+1)th layer, the interlayer-insulator-film **14** of the (n+2)th layer formed by a four-layer complex insulator film having different film qualities and film 50 kinds of the SiCN film **14**a, the SiOC film **14**b, the porous SiO<sub>2</sub> film **14**c, and the SiO<sub>2</sub> film **14**d is deposited on the interlayer-insulator film **5** of the (n+1)th layer. In other words, in the interlayer-insulator-film **14** of the (n+2)th layer formed in a four-layer structure, the second layer and the third layer, 55 i.e. the two intermediate layers are configured by the low-relative-dielectric-constant-film, and the first layer, i.e. the bottom layer and the fourth layer, i.e. the top layer are configured by a general insulator film.

Next, the via plug 15 of the (n+2)th layer to be connected to the upper part of the effective wiring 8 of the (n+1)th layer and the wiring (effective wiring) 17 of the (n+2)th layer to be connected to the upper part of the via plug 15 are arranged in the interlayer-insulator-film 14 of the (n+2)th layer. Therewith, the reinforcement members (dummy wirings) 19 of the (n+2)th layer are arranged in the interlayer-insulator-film 14 of the (n+2)th layer. These via plug 15, effective wiring 17,

**10**

and dummy wiring **19** of the (n+2)th layer may be formed by the same method as the above-described method for forming the via plug **6**, effective wiring **8**, and dummy wiring **10** of the (n+1)th layer. Hereinafter, this method will be briefly described.

First, at the position of the upper part of the effective wiring  $\bf 8$  of the (n+1)th layer where the via plug  $\bf 15$  is arranged, by eliminating the SiO<sub>2</sub> film  $\bf 14d$ , the porous SiO<sub>2</sub> film  $\bf 14c$ , and the SiOC film  $\bf 14b$  along their film thickness directions by the RIE method until the upper face of the SiCN film  $\bf 14a$  is exposed, a hole is formed (not illustrated). Then, at the position of the upper part of this hole where the effective wiring  $\bf 17$  is arranged, by eliminating the SiO<sub>2</sub> film  $\bf 14d$  and the porous SiO<sub>2</sub> film  $\bf 14c$  along their film thickness directions by the RIE method, the upper face of the SiOC film  $\bf 14b$  is exposed. Thereby, the wiring groove (effective wiring groove)  $\bf 18$  for arranging the effective wiring  $\bf 17$  of the (n+2)th layer is communicated with the upper part of the hole to be formed in the SiO<sub>2</sub> film  $\bf 14d$  and the porous SiO<sub>2</sub> film  $\bf 14c$ .

In addition, in parallel with forming of the effective wiring groove 18, at plural positions surrounding the periphery of the effective wiring groove 18, by eliminating the  $SiO_2$  film 14d and the porous  $SiO_2$  film 14c along their film thickness directions by the RIE method, the upper face of the SiOC film 14b is exposed. Thereby, dummy wiring grooves (grooves for a reinforcement member) 20 for arranging the dummy wiring 19 of the (n+2)th layer are formed at plural positions in the  $SiO_2$  film 14d and the porous  $SiO_2$  film 14c at approximately the same height as that of the effective wiring groove 18 and with approximately the same depth as that of the effective wiring groove 18.

Similarly to the respective dummy wiring grooves 11 of the (n+1)th layer, a plurality of the respective dummy wiring grooves 20 of the (n+2)th layer are separated from the effective wiring groove 18 by at least a predetermined interval  $X_2$ , surrounding the periphery of the effective wiring groove 18. In this case, the interval  $X_2$  is determined to be about 2  $\mu$ m similarly to the interval  $X_1$  between the effective wiring 8 and the dummy wiring 10 of the (n+1)th layer. Further, in FIG. 1, the respective dummy wiring grooves 20 that are formed on the left side of the effective wiring groove 18 among a plurality of the dummy wiring grooves 20 are only illustrated. After this, by eliminating the SiCN film 14a on the lower part of the hole by the RIE method, the upper face of the effective wiring 8 of the (n+1)th layer is exposed. Thereby, the via hole 16 for providing the via plug 15 of the (n+2)th layer is formed in the SiCN film 14a and the SiOC film 14b to be communicated with the lower part of the effective wiring groove 18.

Next, the barrier metal layer of the (n+2)th layer (not illustrated) is entirely deposited on the surface under an atmosphere of about 150° C. by the sputtering method, covering inner faces of the via hole 16 of the (n+2)th layer, the effective wiring groove 18, the respective dummy wiring grooves 20 and the surface of the effective wiring 8 of the (n+1)th layer that is exposed by the via hole 16, and the surface of the SiO<sub>2</sub> film 14d that is a film of the top layer of the interlayerinsulator-film 14 of the (n+2)th layer or the like. Then, while filling insides of the via hole 16, the effective wiring groove 18, and the respective dummy wiring grooves 20 on which the barrier metal layer of the (n+2)th layer is arranged, by the sputtering method and the electrolytic plating method, the Cu film of the (n+2)th layer is deposited on the entire surface of the barrier metal layer of the (n+2)th layer. The Young's modulus of this Cu film of the (n+2)th layer is also about 130 GPa similarly to that of the above-described Cu film of the (n+1)th layer. Then, the anneal processing is applied to the Cu film of the (n+2)th layer under the same condition as the Cu

film of the (n+1)th layer. After this, unnecessary barrier metal layer and Cu film are polished and eliminated by the CMP method, which are arranged outsides of the via hole 16, the effective wiring groove 18, and the respective dummy wiring grooves 20. Thereby, the via plug 15, the effective wiring 17, and the respective dummy wirings 19 of which side part and bottom part are covered with the barrier metal layer, are embedded and formed in the interlayer-insulator-film 14 of the (n+2)th layer in parallel.

The via plug 15 is arranged with its upper part located in the SiOC film 14b that is a low-relative-dielectric-constant-film and its lower part located in the SiCN film 14a having a higher strength than the low-relative-dielectric-constant-film. In addition, similarly to the above-described effective wiring 8 of the (n+1)th layer, the effective wiring 17 is formed as a dual damascene wiring having a lower part to which the via plug 15 is connected integrally. In addition, the effective wiring 17 is arranged with its upper part located in the general SiO<sub>2</sub> film 14d, of which strength is higher than the low-relative-dielectric-constant-film, and its lower part located in the porous SiO<sub>2</sub> film 14c that is the low-relative-dielectric-constant-film. Further, the lower face of the effective wiring 17 contacts the SiOC film 14b that is also the low-relative-dielectric-constant-film via the barrier metal layer.

In addition, as shown in FIG. 1, the respective dummy wirings 19 are provided, being electrically cut from the effective wiring 17 and the via plug 15. In practice, a plurality of the respective dummy wirings 19 is separated from the effective wiring 17 by at least 2 µm, surrounding the periphery of the effective wiring 17. In FIG. 1, the respective dummy wirings 19 provided on the left side of the effective wiring 17 are only illustrated. In addition, similarly to the effective wiring 17, these respective dummy wirings 19 are arranged with their upper parts located in the SiO<sub>2</sub> film 14*d* and their lower parts located in the porous SiO<sub>2</sub> film 14*c*. Further, the lower faces of the respective dummy wirings 19 contact the SiOC film 14*b* via the barrier metal layer.

In addition, the effective wiring 17 of the (n+2)th layer may configure an actual energizing path of the semiconductor device 1 together with the via plug 15 of the (n+2)th layer that is formed to be integrated with the effective wiring 17, the effective wiring 8 and the via plug 6 of the (n+1)th layer that are indirectly connected to the effective wiring 17 via this via plug 15, and the effective wiring 4 of the n-th layer. On the contrary, similarly to the respective dummy wirings 10 of the (n+1)th-layer, the respective dummy wirings 19 of the (n+2) th layer do not configure the actual energizing path of the semiconductor device 1.

According to these steps, the wiring structure of the (n+2)th layer of the semiconductor device 1 is formed. In other words, the semiconductor device 1 according to the present embodiment having a multi-layer wiring structure shown in FIG. 1 is obtained. Further, a more specific setting related to 55 the sizes, the shapes, or the arrangements of the respective dummy wirings 19 of the (n+2)th layer will be also described in detail later together with the setting related to the sizes, the shapes, or the arrangements of the respective dummy wirings 10 of the (n+1)th layer. In addition, the lower two layers on 60 which the via plug 15 is formed among the interlayer-insulator-film 14 of the (n+2)th layer, namely, the SiCN film 14a and the SiOC film 14b will be also referred to as a via layer of the (n+2)th layer or a plug layer 21 collectively. In the same way, the upper two layers on which the effective wiring 17 65 and the respective dummy wirings 19 are formed among the interlayer-insulator-film 14 of the (n+2)th layer, namely, the

12

porous  $SiO_2$  film 14c and the  $SiO_2$  film 14d will be also referred to as a wiring layer 22 of the (n+2)th layer collectively.

FIG. 2 is a plan view showing the semiconductor device 1, on which a wiring structure of an (n+2)th layer is formed, as seen from above. In addition, FIG. 1 is a cross sectional view showing the semiconductor device 1 along a break line Y-Y' in FIG. 2. In FIG. 2, the region extended from a dashed-two dotted line D<sub>1</sub> that is drawn along the effective wiring 17 of the (n+2)th layer to the outside is the region where the dummy wirings 19 are aligned. Then, in FIG. 2, in the region that is surrounded by the dashed-two dotted line D<sub>1</sub> and a dashedtwo dotted line D<sub>2</sub> that is drawn outside of the dashed-two dotted line  $D_1$ , there is a unit area  $D_{IJ}$  for calculating a coverage R by the dummy wiring 19 to be described later. Further, in FIG. 2, in order to facilitate visualization of the drawing, only a part of a plurality of the dummy wirings 19 to be arranged in the dummy wiring forming area of the (n+2)th layer is illustrated and the illustration of the remaining dummy wirings **19** is omitted.

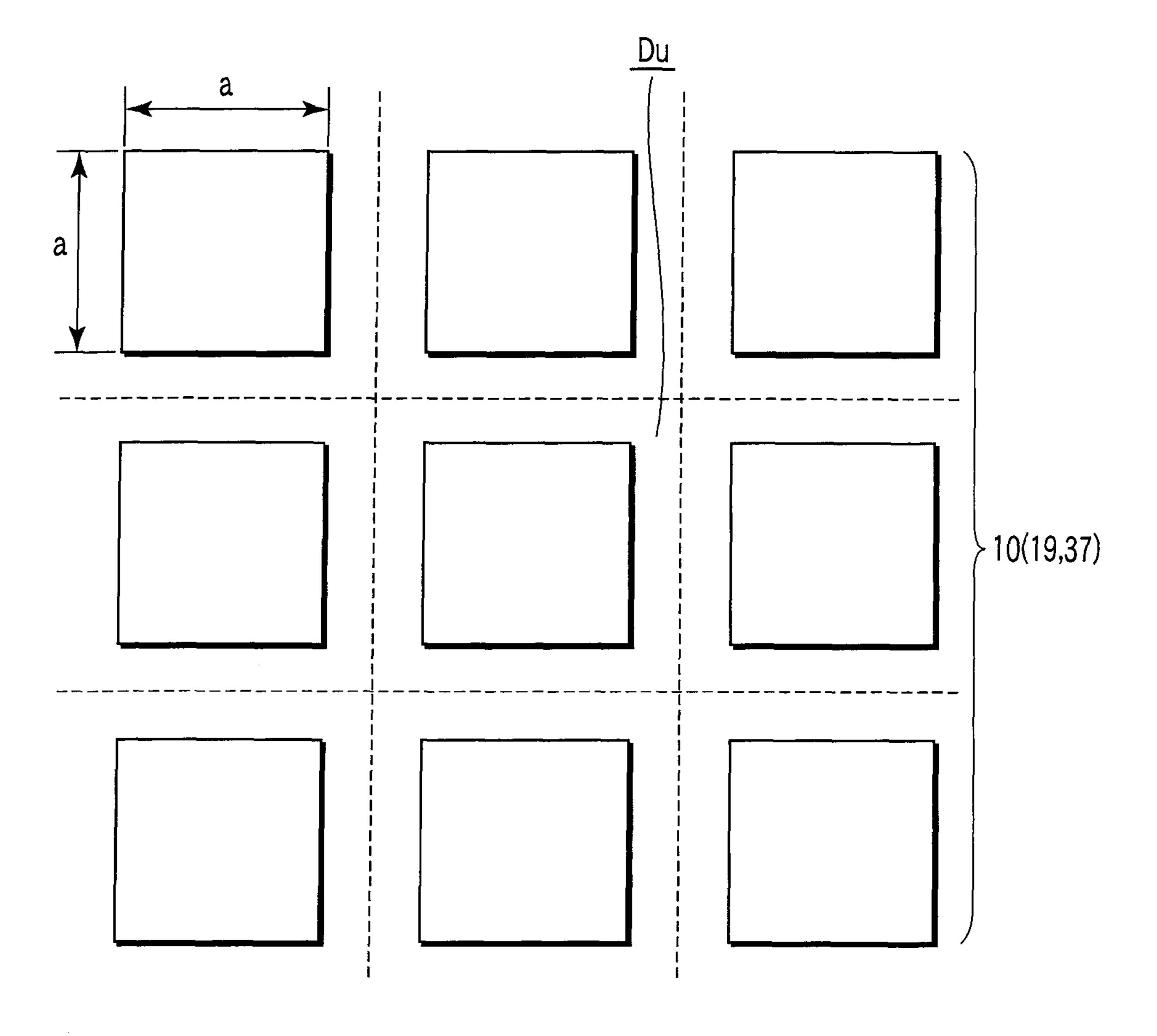

FIG. 3 shows a shape and an arrangement pattern of each of the respective dummy wirings 10 and 19 of the (n+1)th layer and the (n+2)th layer. As shown in FIG. 3, the respective dummy wirings 10 and 19 are formed in a square in which a length of one side is a. According to the present embodiment, the length "a" of one side of the respective dummy wirings 10 and 19 is determined to be about 0.1 to several µm. Then, in the dummy wiring forming areas in the respective interlayerinsulator-film 5 and 14 of the (n+1)th layer and the (n+2)th layer, the respective dummy wirings 10 and 19 shaped in a square are aligned so as to regularly form a dotted pattern in a planar view and surround the respective effective wirings 8 and 17. Thus, in the case that a pattern to regularly form the dummy wirings 10 and 19 of a predetermined shape is aligned within the dummy wiring forming area, as shown in FIG. 3, defining the smallest unit of a shape to be repeated in a planar view as a unit area  $D_{IJ}$ , a coverage of the dummy wirings 10 and 19 can be obtained.

Next, with reference to FIGS. 1 to 3, setting of the size, shape, and arrangement or the like of the respective dummy wirings 10 of the (n+1)th layer and the respective dummy wirings 19 of the (n+2)th layer will be specifically described in detail.

According to the present embodiment, as described above, when arranging the effective wiring 8 of the (n+1)th layer within the interlayer-insulator film 5 of the (n+1)th layer including the polymethyl siloxane film 5b, the porous SiO<sub>2</sub> film 5c, and the SiOC film 5d of the (n+1)th layer that are 50 low-relative-dielectric-constant-films, the respective dummy wirings 10 of the (n+1)th layer are also arranged surrounding the periphery of the effective wiring 8. Thereby, concentration of a stress in the vicinity of the effective wiring 8 is eased, which is generated by a friction between surfaces of a polish pad (not illustrated) and the interlayer-insulator-film 5 (the SiOC film 5d) and the effective wiring 8 when embedding and forming the effective wiring 8 of the (n+1)th layer in the interlayer-insulator film 5 of the (n+1)th layer by the CMP step. Further, a film separation, namely, a so-called boundary face separation is prevented from being generated by a stress generated in the CMP step on each boundary face of the SiC film 5a, the polymethyl siloxane film 5b, the porous SiO<sub>2</sub> film 5c, and the SiOC film 5d to configure the interlayer-insulatorfilm 5. Alternatively, a boundary face separation is prevented from being generated on a boundary face between the interlayer-insulator-film 5 and the interlayer-insulator-film 3 of the n-th layer ( $SiO_2$  film 3b).

In the same way, when arranging the effective wiring 17 of the (n+2)th layer in the interlayer-insulator-film 14 of the (n+2)th layer including the SiOC film 14b and the porous SiO<sub>2</sub> film **14**c that are the low-relative-dielectric-constantfilms, the respective dummy wirings 19 of the (n+2)th layer 5 are also aligned surrounding the periphery of the effective wiring 17. Thereby, concentration of a stress in the vicinity of the effective wiring 17 is eased, which is generated by a friction between surfaces of a polish pad (not illustrated) and the interlayer-insulator-film 14 (the  $SiO_2$  film 14d) and the 10 effective wiring 17 when embedding and forming the effective wiring 17 of the (n+2)th layer in the interlayer-insulatorfilm 14 of the (n+2)th layer by the CMP step. Further, a boundary face separation is prevented from being generated by a stress generated in the CMP step on each boundary face 15 of the SiCN film 14a, the SiOC film 14b, the porous SiOC<sub>2</sub> film 14c, and a SiOC<sub>2</sub> film 14d to configure the interlayerinsulator-film 14. Alternatively, a boundary face separation is prevented from being generated on a boundary face between the interlayer-insulator-film **14** and the interlayer-insulator 20 film 5 of the (n+1)th layer (SiOC film 5d).

According to the present embodiment, in order to efficiently obtain such an effect for easing a stress in the CMP step, the respective dummy wirings 10 of the (n+1)th layer and the respective dummy wirings 19 of the (n+2)th layer will 25 be aligned in accordance with a rule to be described below for each layer.

First, for the wiring structure of the (n+1)th layer, a value obtained by dividing the area of the part that is exposed on the upper face of the interlayer-insulator film 5 of the (n+1)th 30 layer among the respective dummy wirings 10 of the (n+1)th layer by a length of the part contacting the interlayer-insulator-film 5 of the exposed portion is defined to be S (µm). In other words, S is a value obtained by dividing the exposed areas of the respective dummy wirings 10 by a sum of the 35 lengths of boundary faces between the exposed portions and the interlayer-insulator-film 5. In addition, a Young's modulus of the above-described via layer 12 of the (n+1)th layer where the above-described via plug 6 of the (n+1)th layer is arranged in the interlayer-insulator film 5 of the (n+1)th layer 40 is defined to be  $E_{\mathcal{P}}$  (GPa). In addition, a Young's modulus of the wiring layer 13 of the (n+1)th layer where the abovedescribed effective wiring of the (n+1)th layer 8 is arranged in the interlayer-insulator film 5 of the (n+1)th layer is defined to be  $E_W$  (GPa). In addition, a Young's modulus of the effective 45 wiring 8 of the (n+1)th layer is defined to be  $E_{\mathcal{M}}$  (GPa). In addition, a film thickness of the via layer 12 of the (n+1)th layer in the interlayer-insulator film 5 of the (n+1)th layer is defined to be  $d_p$  (nm). In addition, a film thickness of the wiring layer 13 of the (n+1)th layer in the interlayer-insulator 50 film 5 of the (n+1)th layer is defined to be  $d_w(nm)$ . Further, a coverage of each dummy wiring 10 of the (n+1)th layer per unit area  $D_U$  on the upper face of the interlayer-insulator film 5 of the (n+1)th layer excluding the area where the effective wiring 8 of the (n+1)th layer is defined to be R.

In the same way, for the wiring structure of the (n+2)th layer, a value obtained by dividing the area of the part that is exposed on the upper face of the interlayer-insulator-film 14 of the (n+2)th layer among the respective dummy wirings 19 of the (n+2)th layer by a length of the part contacting the 60 interlayer-insulator-film 14 in the exposed portion is defined to be S  $(\mu m)$ . In addition, a Young's modulus of the above-described via layer 21 of the (n+2)th layer where the above-described via plug 15 of the (n+2)th layer is arranged in the interlayer-insulator-film 14 of the (n+2)th layer is defined to 65 be  $E_P$  (GPa). In addition, a Young's modulus of the wiring layer 22 of the (n+2)th layer where the above-described effec-

**14**

tive wiring 17 of the (n+2)th layer is arranged in the interlayer-insulator-film 14 of the (n+2)th layer is defined to be  $E_W$  (GPa). In addition, a Young's modulus of the effective wiring 17 of the (n+2)th layer is defined to be  $E_M$  (GPa). In addition, a film thickness of the via layer 21 of the (n+2)th layer in the interlayer-insulator-film 14 of the (n+2)th layer is defined to be  $d_P$  (nm). In addition, a film thickness of the wiring layer 22 of the (n+2)th layer in the interlayer-insulator-film 5 of the (n+2)th layer is defined to be  $d_W$  (nm). Further, a coverage of each dummy wiring 19 of the (n+2)th layer per unit area  $D_U$  on the upper face of the interlayer-insulator-film 14 of the (n+2)th layer excluding the area where the effective wiring 17 of the (n+2)th layer is defined to be R.

Under such definitions, the shape, the size or the like of the respective dummy wirings 10 and 19 will be determined so that S,  $E_P$ ,  $E_W$ ,  $E_M$ ,  $d_P$ ,  $d_W$ , and R satisfy a relation shown by the following formula (1) for each of the respective interlayer-insulator-film 5 and 14.

$$0.025 \times \left(\frac{E_P \times d_P + (E_W \times (1 - R) + E_M \times R) \times d_W}{d_P + d_W}\right)^{0.4} <$$

$$S < 0.0625 \times \left(\frac{E_P \times d_P + (E_W \times (1 - R) + E_M \times R) \times d_W}{d_P + d_W}\right)^{0.4}$$

(1)

In this formula (1), the following formula (2) shows a complex Young's modulus of the (n+1)th layer, which is a Young's modulus within the dummy wiring forming area of the entire interlayer-insulator film 5 of the (n+1)th layer where the via layer 12 of the (n+1)th layer is added to the wiring layer 13 of the (n+1)th layer. Alternatively, they show the complex Young's modulus of the (n+2)th layer, which is a Young's modulus within the dummy wiring forming area of the entire interlayer-insulator-film 14 of the (n+2)th layer where the via layer 21 of the (n+2)th layer is added to the wiring layer 22 of the (n+2)th layer.

$$\left(\frac{E_P \times d_P + (E_W \times (1 - R) + E_M \times R) \times d_W}{d_P + d_W}\right) \tag{2}$$

Generally, when embedding and forming the wiring in the interlayer-insulator-film it by the CMP method, a relatively large load is given to the upper part of the wiring by a friction between the polish pad and the wiring. Due to this external load, a stress is concentrated on the wiring and the via plug to be connected to the lower part of the wiring. Then, due to this stress concentration, a defect due to a boundary face separation is easily generated inside and outside of the interlayerinsulator-film. Such a phenomenon is generated more easily in the case that at least a part of the interlayer-insulator-film is formed by a low-relative-dielectric-constant-film, of which 55 film structure is scarcer and mechanical strength is lower than a general insulator film. Particularly, in the case that at least a part of the wiring is arranged reaching the inside of the lowrelative-dielectric-constant-film, this phenomenon is more remarkable.

The specific and detailed explanation referring to illustration is omitted; however, in order to resolve a mechanism of generation of a defect of a boundary face separation in such a CMP step, the inventors of the present invention conducted various separation tests and analysis by a stress simulation. As a result of this analysis, it has become clear that the stress to be given to the wiring and the via plug in the CMP step depends on the complex Young's modulus of a material to

form the wiring layer and the via layer, and the coverage and the size of the wiring. Then, it has become clear that, by aligning the respective dummy wirings 10 and 19 so as to satisfy the above-described formula (1), the stress concentration on the respective effective wirings 8 and 17 and the 5 respective via plugs 6 and 15 in the CMP step is efficiently eased so as to efficiently prevent a defect due to separation of an insulator film such as a boundary face separation. In other words, it has been know that, in the semiconductor device 1 having the above-described multi-layer wiring structure, by aligning the respective dummy wirings 10 and 19 so as to satisfy the above-described formula (1) for each of the respective interlayer-insulator-films 5 and 14, it is possible to efficiently prevent separation of the interlayer-insulator-film <sup>15</sup> when embedding the respective effective wirings 8 and 17 in the respective interlayer-insulator-films 5 and 14 by the CMP method to be formed contacting the respective low-relativedielectric-constant-films 5b, 5c, 5d, 14b, and 14c forming a part of the interlayer-insulator-films 5 and 14.

In addition, as described above, the respective via layers 12 and 21 and the respective wiring layers 13 and 22 of the (n+1)th layer and the (n+2)th layer according to the present embodiment are configured by a stacked film of two layers of 25 the insulator film. In such a case, in order to accurately calculate the above-described formula (1), the Young's modulus  $E_P$  of the respective via layers 12 and 21 and the Young's modulus  $E_W$  of the respective wiring layers 13 and 22 are replaced by a complex Young's modulus E<sub>C</sub> that is the Young's modulus of the entire stacking layers to configure the respective via layers 12 and 21 and the respective wiring layers 13 and 22. In the same way, a film thickness  $d_p$  of the respective via layers 12 and 21 and a film thickness  $d_w$  of the  $^{35}$ respective wiring layers 13 and 22 are replaced by a total film thickness  $d_T$  that is the film thickness of the entire stacking layers to configure the respective via layers 12 and 21 and the respective wiring layers 13 and 22.

These complex Young's modulus  $E_C$  and the total film thickness  $d_T$  can be obtained by the following formulas (3) and (4).

$$E_C = \frac{\sum_{i} E_i d_i}{\sum_{i} d_i} \tag{3}$$

(i: Natural number not less than 1)

$$d_T = \sum d_i \tag{4}$$

55

(i: Natural number not less than 1)

In the formula (3),  $E_i$  represents a Young's modulus  $E_i$  of the i-th insulator film from top or bottom in the respective insulator films to configure the respective via layers 12 and 21 and the respective wiring layers 13 and 22. In addition, in the formula (3) and the formula (4),  $d_i$  represents the film thickness of the i-th insulator film from top or bottom in the 65 respective insulator films to configure the respective via layers 12 and 21 and the respective wiring layers 13 and 22.

**16**

Next, a plurality of samples manufactured by the inventors of the present invention on the basis of the above-described present embodiment will be described with reference to Tables 1 to 6. These respective samples according to the present embodiment are manufactured on the basis of the setting to be described next.

First, as shown in FIG. 3, the respective dummy wirings 10 and 19 are formed into a square in which a length of one side is a. In this case, by changing the value of "a" that is an index of sizes of the respective dummy wirings 10 and 19 in increments of about 0.1 μm or about 0.5 μm up to about 0.1 to 2 μm, a plurality of dummy wirings 10 and 19 having different sizes are formed and they are 12 kinds in total. Then, these respective dummy wirings 10 and 19 having various sizes are aligned within the respective interlayer-insulator-films 5 and 14 of the (n+1)th layer and the (n+2)th layer so as to form a dotted pattern as shown in FIG. 3. In this case, these respective dummy wirings 10 and 19 are set so that a coverage R of the respective dummy wirings 10 and 19 takes different three values of about 11%, 25%, and 44% for each layer of the (n+1)th layer and the (n+2)th layer.

Then, for each sample manufactured on the basis of such a setting, presence/absence of the insulator film separation of the interlayer-insulator-film 5 of the (n+1)th layer after the effective wiring 8 of the (n+1)th layer is embedded and formed by the CMP method is observed by using an optical microscope. The observation results for these interlayer-insulator film 5 of the (n+1)th layer are shown in Tables 1 to 3. In the same way, for each sample, presence/absence of the insulator film separation of the interlayer-insulator-film 14 of the (n+2)th layer after the effective wiring 17 of the (n+2)th layer is embedded and formed by the CMP method is observed by using an optical microscope. The observation results for these interlayer-insulator-film 14 of the (n+2)th layer are shown in Tables 4 to 6.

In these Tables 1 to 6, the length a of one side of the respective dummy wirings 10 and 19, S obtained by dividing the areas of the respective dummy wirings 10 and 19 by the perimeters thereof, and the coverages R of the respective dummy wirings 10 and 19 of each sample according to the present embodiment are shown together with the above-described E<sub>P</sub>, E<sub>W</sub>, d<sub>P</sub>, and d<sub>W</sub>. Further, S of the respective dummy wirings 10 and 19 formed by a square, in which the length of one side is a, is represented by a<sup>2</sup>/4a. In addition, in a column of a CMP separation evaluation of Tables 1 to 6, a circle represents a result that there is no separation on the entire surface of a wafer, a triangle represents a result that there is a separation only in the end of the wafer (the edge portion), and a crisscross represents a result that there is a separation on the entire surface of the wafer.

First, as shown in Table 1, in the case that the coverage R of the dummy wiring 10 in the interlayer-insulator-film 5 of the (n+1)th layer is about 11%, assuming that the length a of one side of each dummy wiring 10 is about 0.4  $\mu$ m or about 0.5  $\mu$ m, the insulator film separation was not observed on the entire surface of a wafer 1. In addition, assuming that the length a of one side of each dummy wiring 10 is about 0.3  $\mu$ m or about 0.6  $\mu$ m, the insulator film separation was observed only on the edge portion of the wafer 1. Further, assuming that the length a of one side of each dummy wiring 10 is about 0.2  $\mu$ m or less or about 0.7  $\mu$ m or more, the insulator film separation was observed on the entire surface of the wafer 1.

TABLE 1

| E <sub>P</sub><br>(GPa) | E <sub>W</sub><br>(GPa) | $\begin{array}{c} \operatorname{d}_{P} \\ (\operatorname{nm}) \end{array}$ | d <sub>W</sub> (nm) | R    | a (µm) | S: a <sup>2</sup> /<br>4a (µm) | CMP<br>peeling<br>evalua-<br>tion |

|-------------------------|-------------------------|----------------------------------------------------------------------------|---------------------|------|--------|--------------------------------|-----------------------------------|

| 6.5                     | 5.19                    | 170                                                                        | 160                 | 0.11 | 0.1    | 0.025                          | X                                 |

| - 1                     | 1                       | - 1                                                                        | - 1                 | - 1  | 0.2    | 0.050                          | X                                 |

|                         |                         |                                                                            |                     |      | 0.3    | 0.075                          | Δ                                 |

|                         |                         |                                                                            |                     |      | 0.4    | 0.100                          | $\circ$                           |

|                         |                         |                                                                            |                     |      | 0.5    | 0.125                          | $\circ$                           |

|                         |                         |                                                                            |                     |      | 0.6    | 0.150                          | Δ                                 |

|                         |                         |                                                                            |                     |      | 0.7    | 0.175                          | X                                 |

|                         |                         |                                                                            |                     |      | 0.8    | 0.200                          | X                                 |

|                         |                         |                                                                            |                     |      | 0.9    | 0.225                          | X                                 |

|                         |                         |                                                                            |                     |      | 1.0    | 0.250                          | X                                 |

| <b>\</b>                | <b>\</b>                | \                                                                          | <b>\</b>            | ₩    | 1.5    | 0.375                          | X                                 |

|                         | •                       |                                                                            |                     |      | 2.0    | 0.500                          | X                                 |

Next, as shown in Table 2, in the case that the coverage R of the dummy wiring 10 in the interlayer-insulator-film 5 of the (n+1)th layer is about 25%, assuming that the length a of one side of each dummy wiring 10 is about 0.5 μm or about 0.6 μm, the insulator film separation was not observed on the entire surface of the wafer 1. In addition, assuming that the length a of one side of each dummy wiring 10 is about 0.4 µm or about  $0.7 \mu m$  or about  $0.8 \mu m$ , the insulator film separation was observed only on the edge portion of the wafer 1. Further, 30 assuming that the length a of one side of each dummy wiring 10 is about 0.3  $\mu m$  or less or about 0.9  $\mu m$  or more, the insulator film separation was observed on the entire surface of the wafer 1.

TABLE 2

|                     | (n + 1 | )th lave            | er cove | erage R = | 25%                            |                                   | • |

|---------------------|--------|---------------------|---------|-----------|--------------------------------|-----------------------------------|---|

| $E_P$ $E_W$ $(GPa)$ | $d_P$  | d <sub>W</sub> (nm) | R       | a (µm)    | S: a <sup>2</sup> /<br>4a (µm) | CMP<br>peeling<br>evalua-<br>tion | - |

| 6.5 5.19            | 170    | 160                 | 0.25    | 0.1       | 0.025                          | X                                 | • |

| 1 1                 | - 1    | 1                   | - 1     | 0.2       | 0.050                          | X                                 |   |

|                     |        |                     |         | 0.3       | 0.075                          | X                                 | 4 |

|                     |        |                     |         | 0.4       | 0.100                          | Δ                                 |   |

|                     |        |                     |         | 0.5       | 0.125                          | $\bigcirc$                        |   |

|                     |        |                     |         | 0.6       | 0.150                          | $\circ$                           |   |

|                     |        |                     |         | 0.7       | 0.175                          | Δ                                 |   |

|                     |        |                     |         | 0.8       | 0.200                          | $\Delta$                          |   |

|                     |        |                     |         | 0.9       | 0.225                          | X                                 | 4 |

|                     |        |                     |         | 1.0       | 0.250                          | X                                 |   |

| *                   | *      | *                   | *       | 1.5       | 0.375                          | X                                 |   |

|                     |        |                     |         | 2.0       | 0.500                          | X                                 |   |

Next, as shown in Table 3, in the case that the coverage R of 55 the dummy wiring 10 in the interlayer-insulator-film 5 of the (n+1)th layer is about 44%, assuming that the length a of one side of each dummy wiring 10 is about 0.5 µm to about 0.8 μm, the insulator film separation was not observed on the entire surface of the wafer 1. In addition, assuming that the length a of one side of each dummy wiring 10 is about 0.9 μm or about 1.0 μm, the insulator film separation was observed only on the edge portion of the wafer 1. Further, assuming that the length a of one side of each dummy wiring 10 is about 0.4  $_{65}$ μm or less or about 1.5 μm or more, the insulator film separation was observed on the entire surface of the wafer 1.

TABLE 3

**18**

|    |                        |                         | (n + 1                 | )th laye               | r, cove   | rage R =   | 44%                            |                                   |

|----|------------------------|-------------------------|------------------------|------------------------|-----------|------------|--------------------------------|-----------------------------------|

| 5  | $\mathrm{E}_{P}$ (GPa) | E <sub>W</sub><br>(GPa) | d <sub>P</sub><br>(nm) | d <sub>W</sub><br>(nm) | R         | a (µm)     | S: a <sup>2</sup> /<br>4a (µm) | CMP<br>peeling<br>evalua-<br>tion |

| 10 | 6.5<br>I               | 5.19<br>I               | 170<br>•               | 160<br>I               | 0.44<br>I | 0.1<br>0.2 | 0.025<br>0.050                 | X<br>X                            |

|    |                        |                         |                        |                        |           | 0.3<br>0.4 | 0.075<br>0.100                 | X<br>X                            |

|    |                        |                         |                        |                        |           | 0.5<br>0.6 | 0.125<br>0.150                 | 0                                 |

| 15 |                        |                         |                        |                        |           | 0.7        | 0.175<br>0.200                 | 0                                 |

|    |                        |                         |                        |                        |           | 0.9<br>1.0 | 0.225<br>0.250                 | $\Delta \ \Delta \ \mathbf{v}$    |

|    | <b>T</b>               | <b>T</b>                | <b>V</b>               | <b>T</b>               | *         | 1.5<br>2.0 | 0.375<br>0.500                 | X<br>X                            |

Next, a range of S of the above-described formula (1) in the case that the coverage R of the dummy wiring 10 of the interlayer-insulator film 5 of the (n+1)th layer is about 11% will be obtained. For this purpose, a property value and a film thickness value of each material to configure the wiring structure of the (n+1)th layer are assigned into the above-described formulas (2) to (4).

As described above, the via layer 12 of the interlayerinsulator film 5 of the (n+1)th layer is formed by a two-layer stacked film formed by the SiC film 5a, of which Young's modulus is about 20 GPa and film thickness is about 35 nm, and the polymethyl siloxane film 5b, of which Young's modulus is about 3 GPa and film thickness is about 135 nm. These values are assigned into the above-described formulas (3) and (4). Then, a complex Young's modulus  $E_C$  of the via layer 12 of the (n+1)th layer becomes about 6.5 GPa. In addition, the total film thickness  $d_T$  of the via layer 12 becomes about 170 nm. In addition, the wiring layer 13 of the interlayer-insulator film 5 of the (n+1)th layer is formed by a two-layer stacked film formed by the porous  $SiO_2$  film 5c, of which Young's modulus is about 3 GPa and film thickness is about 110 nm, and the SiOC film 5d, of which Young's modulus is about 10 GPa and film thickness is about 50 nm. These values are assigned into the above-described formulas (3) and (4). Then, the complex Young's modulus  $E_C$  of the wiring layer 13 of the (n+1)th layer becomes about 5.19 GPa. In addition, the total film thickness  $d_T$  of the wiring layer 13 becomes about 160 nm.

These values, the coverage  $R \approx 0.11$ , and the Young's modulus of the Cu film forming the effective wiring 8 of the (n+1)th layer of about 130 GPa are assigned into the above-described formula (2). Thereby, for the range of S in the case that the coverage R of the dummy wiring 10 in the interlayer-insulator-film 5 of the (n+1)th layer is about 11%, a relation of the following formula (5) is obtained.

$$0.069 < S < 0.17$$

(5)

By comparing this formula (5) with the observation result of the insulator film separation shown in Table 1, it is known that the defect due to the insulator film separation on the place other than the end portion of the wafer 1 can be prevented in the case that the size of each dummy wiring 10 is determined

so as to satisfy the relation of the formula (1). In addition, although the specific calculation is omitted, also in the case that the coverage R is about 25% and about 44%, it is known that the defect due to the insulator film separation on the place other than the end portion of the wafer 1 can be prevented in the case that the size of each dummy wiring 10 is determined so as to satisfy the relation of the formula (1).

Further, each value when the previously-obtained coverage R is about 11% is assigned into the following formula (6).

$$0.03 \times \left(\frac{E_P \times d_P + (E_W \times (1 - R) + E_M \times R) \times d_W}{d_P + d_W}\right)^{0.4} < \tag{6}$$

$$S < 0.05 \times \left(\frac{E_P \times d_P + (E_W \times (1 - R) + E_M \times R) \times d_W}{d_P + d_W}\right)^{0.4}$$

Then, for the range of S in the case that the coverage R of the dummy wiring **10** in the interlayer-insulator film **5** of the (n+1)th layer is about 11%, a relation of the following formula (7) is obtained.

$$0.082 < S < 0.14$$

(7)

By comparing this formula (7) with the observation result of the insulator film separation shown in Table 1, it is known that the defect due to the insulator film separation on the entire surface of the wafer 1 can be prevented in the case that the size of each dummy wiring 10 is determined so as to satisfy the relation of the formula (6). In addition, although the specific calculation is omitted, also in the case that the coverage R is about 25% and about 44%, it is known that the defect due to the insulator film separation on the entire surface of the wafer 1 can be prevented in the case that the size of each dummy wiring 10 is determined so as to satisfy the relation of the formula (6).

Next, the respective samples shown in Tables 4 to 6 will be described. In the respective samples shown in these Tables 4 45 to 6, the wiring structure of the (n+2)th layer is formed with respect to a sample in which the defect due to the insulator film separation in the interlayer-insulator-film 5 of the (n+1) th layer is not observed among the respective samples shown 50 in the above-described Tables 1 to 3.

First, as shown in Table 4, in the case that the coverage R of the dummy wiring 19 is about 11% in the interlayer-insulator-film 14 of the (n+2)th layer, assuming that the length of one 55 side of the dummy wiring 19 is about 0.5 to 0.7  $\mu$ m, the insulator film separation was not observed on the entire surface of the wafer 1. In addition, assuming that the length of one side of the dummy wiring 19 is about 0.4  $\mu$ m, about 0.8  $\mu$ m, or about 0.9  $\mu$ m, the insulator film separation was observed only on the end portion of the wafer 1. In addition, assuming that the length a of one side of each dummy wiring 19 is about 0.3  $\mu$ m or less or about 1.0  $\mu$ m or more, the insulator film separation was observed on the entire surface of the wafer 1.

TABLE 4

|                        |                         | (n + 2)                                                            | )th laye               | r, cove | erage R = | 11%                            |                                    |

|------------------------|-------------------------|--------------------------------------------------------------------|------------------------|---------|-----------|--------------------------------|------------------------------------|

| $\mathrm{E}_{P}$ (GPa) | E <sub>W</sub><br>(GPa) | $\begin{array}{c} \operatorname{d}_P \\ (\mathrm{nm}) \end{array}$ | d <sub>W</sub><br>(nm) | R       | a (µm)    | S: a <sup>2</sup> /<br>4a (µm) | CMP<br>peeling<br>evalua-<br>tion  |