#### US007813165B2

## (12) United States Patent

#### Daughton et al.

## (45) Date of Patent:

(10) Patent No.:

US 7,813,165 B2 Oct. 12, 2010

# (54) MAGNETIC MEMORY LAYERS THERMAL PULSE TRANSITIONS

(75) Inventors: James M. Daughton, Eden Prairie, MN (US); Arthur V. Pohm, Ames, IA (US)

(73) Assignee: **NVE Corporation**, Eden Prairie, MN

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 59 days.

(21) Appl. No.: 11/881,097

(22) Filed: Jul. 25, 2007

#### (65) Prior Publication Data

US 2007/0268743 A1 Nov. 22, 2007

#### Related U.S. Application Data

- (62) Division of application No. 11/651,729, filed on Jan. 10, 2007, now Pat. No. 7,266,013, which is a division of application No. 11/292,635, filed on Dec. 2, 2005, now Pat. No. 7,177,178, which is a division of application No. 10/706,613, filed on Nov. 12, 2003, now Pat. No. 7,023,723.

- (60) Provisional application No. 60/425,386, filed on Nov. 12, 2002.

- (51) Int. Cl.

G11C 5/06 (2006.01)

G11C 5/08 (2006.01)

G11C 11/02 (2006.01)

G11C 11/14 (2006.01)

G11C 11/15 (2006.01)

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,771,347 | A  |   | 9/1988  | Horimai et al.  |         |

|-----------|----|---|---------|-----------------|---------|

| 4,780,848 | A  |   | 10/1988 | Daughton et al. |         |

| 5,636,159 | A  |   | 6/1997  | Pohm            |         |

| 5,650,958 | A  | * | 7/1997  | Gallagher et al | 365/173 |

| 5,841,692 | A  |   | 11/1998 | Gallagher       |         |

| 6,072,718 | A  | * | 6/2000  | Abraham et al   | 365/173 |

| 6,351,410 | В1 | * | 2/2002  | Nakao et al     | 365/171 |

| 6,381,171 | В1 | * | 4/2002  | Inomata et al   | 365/173 |

| 6,385,082 | В1 |   | 5/2002  | Abraham et al.  |         |

#### (Continued)

#### OTHER PUBLICATIONS

Beech, R.S. et al. Curie point written magnetoresistive memory; Journal of Applied Physics, vol. 87, No. 9; May 1, 2000; pp. 6403-6405.

Primary Examiner—J. H. Hur (74) Attorney, Agent, or Firm—Kinney & Lange, P.A.

#### (57) ABSTRACT

A ferromagnetic thin-film based digital memory having bit structures therein with a magnetic material film in which a magnetic property thereof is maintained below a critical temperature above which such magnetic property is not maintained, and may also have a plurality of word line structures each with heating sections located across from the magnetic material film in a corresponding one of the bit structures. These bit structures are sufficiently thermally isolated to allow selected currents in the adjacent word lines or in the bit structure, or both, to selectively heat the bit structure to approach the critical temperature. Such bit structures may have three magnetic material layers each with its own critical temperature for maintaining versus not maintaining a magnetic property thereof.

#### 9 Claims, 24 Drawing Sheets

# US 7,813,165 B2 Page 2

| U.S. P        | ATENT  | DOCUMENTS                   | 6,771,534 H     | B2 8/2                   | 2004 | Stipe                 |

|---------------|--------|-----------------------------|-----------------|--------------------------|------|-----------------------|

| 6 525 416 D1  | 2/2002 | T 1 1                       | 6,777,730 H     |                          |      | Daughton et al.       |

| 6,535,416 B1  |        | Daughton et al.             | 6,963,098 H     | B2 11/2                  | 2005 | Daughton et al.       |

| 6,538,919 B1  | 3/2003 | Abraham et al.              | 7,023,723 H     | B2 	 4/2                 | 2006 | Daughton et al.       |

| 6,538,921 B2  | 3/2003 | Daughton et al.             | 7,177,178 H     | $B2 \qquad 2/2$          | 2007 | Daughton et al.       |

| 6,597,049 B1* | 7/2003 | Bhattacharyya et al 257/421 | 2001/0019461 A  | $\mathbf{A1} \qquad 9/2$ | 2001 | Allenspach et al.     |

| 6,603,678 B2  | 8/2003 | Nickel et al.               | 2002/0089874 A  | $\mathbf{A1*}  7/2$      | 2002 | Nickel et al 365/171  |

| 6,704,220 B2  | 3/2004 | Leuschner                   | 2003/0198113 A  | A1* 10/2                 | 2003 | Abraham et al 365/211 |

| 6,724,674 B2  | 4/2004 | Abraham et al.              | 2003/0206434 A  |                          |      | Leuschner             |

| 6,744,086 B2  | 6/2004 | Daughton et al.             | 2004/0057263 A  | A1* 3/2                  | 2004 | Tang 365/33           |

| 6,744,651 B2  | 6/2004 | Tang                        | * cited by exam | iner                     |      |                       |

Fig. 4

Fig. 5

Fig. 614

F19.68

Fig. 12A

Fig. 128

Fig. 13A

Fig. 138

Fig. 16B

Fig. 17B

Fig. 18B

Oct. 12, 2010

Fig. 198

# MAGNETIC MEMORY LAYERS THERMAL PULSE TRANSITIONS

## CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a divisional of U.S. patent application Ser. No. 11/651,729 filed on Jan. 10, 2007, now U.S. Pat. No. 7,266,013 issued on Sep. 4, 2007 for "MAGNETIC MEMORY LAYERS THERMAL PULSE TRANSITIONS", which application is a divisional of U.S. patent application Ser. No. 11/292,635 filed on Dec. 2, 2005, now U.S. Pat. No. 7,177,178 issued on Feb. 13, 2007 for "MAGNETIC MEMORY LAYERS THERMAL PULSE TRANSITIONS", which application is a divisional of U.S. patent application Ser. No. 10/706,613 filed on Nov. 12, 2003, now U.S. Pat. No. 7,023,723 issued on Apr. 4, 2006 for "MAGNETIC MEMORY LAYERS THERMAL PULSE TRANSITIONS", which application claims the benefit of Provisional Application No. 60/425,386 filed Nov. 12, 2002 for "MAGNETIC 20 MEMORY LAYERS THERMAL PULSE TRANSITIONS".

#### BACKGROUND OF THE INVENTION

The present invention relates to ferromagnetic thin-film structures exhibiting relatively large magnetoresistive characteristics and, more particularly, to such structures used for the storage and retrieval of digital data.

Many kinds of electronic systems make use of magnetic devices including both digital systems, such as memories, and analog systems such as magnetic field sensors. Digital data memories are used extensively in digital systems of many kinds including computers and computer systems components, and digital signal processing systems. Such memories can be advantageously based on the storage of digital symbols as alternative states of magnetization in magnetic materials provided in each memory storage cell, the result being memories which use less electrical power and do not lose information upon removals of such electrical power.

Such memory cells, and magnetic field sensors also, can often be advantageously fabricated using ferromagnetic thin-film materials, and are often based on magnetoresistive sensing of magnetic states, or magnetic conditions, therein. Such devices may be provided on a surface of a monolithic integrated circuit to provide convenient electrical interconnections between the device and the operating circuitry therefor.

Ferromagnetic thin-film memory cells, for instance, can be made very small and packed very closely together to achieve a significant density of information storage, particularly when so provided on the surface of a monolithic integrated circuit. In this situation, the magnetic environment can become quite complex with fields in any one memory cell affecting the film portions in neighboring memory cells. Also, small ferromagnetic film portions in a memory cell can lead to substantial demagnetization fields which can cause instabilities in the magnetization state desired in such a cell.

These magnetic effects between neighbors in an array of closely packed ferromagnetic thin-film memory cells can be ameliorated to a considerable extent by providing a memory 60 cell based on an intermediate separating material having two major surfaces on each of which an anisotropic ferromagnetic memory thin-film is provided. Such an arrangement provides significant "flux closure," i.e. a more closely confined magnetic flux path, to thereby confine the magnetic field arising in 65 the cell to affecting primarily just that cell. This result is considerably enhanced by choosing the separating material in

2

the ferromagnetic thin-film memory cells to each be sufficiently thin. Similar "sandwich" structures are also used in magnetic sensors.

In the recent past, reducing the thicknesses of the ferromagnetic thin-films and the intermediate layers in extended "sandwich" structures, and adding possibly alternating ones of such films and layers, i.e. superlattices, have been shown to lead to a "giant magnetoresistive effect" being present in some circumstances. This effect yields a magnetoresistive response which can be in the range of up to an order of magnitude or more greater than that due to the well known anisotropic magnetoresistive response.

In the ordinary anisotropic magnetoresistive response, varying the difference occurring between the direction of the magnetization vector in a ferromagnetic thin-film and the direction of sensing currents passed through that film leads to varying effective electrical resistance in the film in the direction of the current. The maximum electrical resistance occurs when the magnetization vector in the field and the current direction therein are parallel to one another, while the minimum resistance occurs when they are perpendicular to one another. The total electrical resistance in such a magnetoresistive ferromagnetic film can be shown to be given by a constant value, representing the minimum resistance, plus an 25 additional value depending on the angle between the current direction in the film and the magnetization vector therein. This additional resistance has a magnitude characteristic that follows the square of the cosine of that angle.

Operating magnetic fields imposed externally can be used to vary the angle of the magnetization vector in such a film portion with respect to the easy axis of that film. Such an axis comes about in the film because of an anisotropy therein typically resulting from depositing the film during fabrication in the presence of an external magnetic field oriented in the 35 plane of the film along the direction desired for the easy axis in the resulting film. During subsequent operation of the device having this resulting film, such operational magnetic fields imposed externally can be used to vary the angle to such an extent as to cause switching of the film magnetization 40 vector between two stable states which occur for the magnetization being oriented in opposite directions along the film's easy axis. The state of the magnetization vector in such a film can be measured, or sensed, by the change in resistance encountered by current directed through this film portion. This arrangement has provided the basis for a ferromagnetic, magnetoresistive anisotropic thin-film to serve as a memory cell.

In contrast to this arrangement, the resistance in the plane of a ferromagnetic thin-film is isotropic for the giant magnetoresistive effect rather than depending on the direction of the sensing current therethrough as for the anisotropic magnetoresistive effect. The giant magnetoresistive effect involves a change in the electrical resistance of the structure thought to come about from the passage of conduction electrons between the ferromagnetic layers in the "sandwich" structure, or superlattice structure, through the separating nonmagnetic layers with the resulting scattering occurring at the layer interfaces, and in the ferromagnetic layers, being dependent on the electron spins. The magnetization dependant component of the resistance in connection with this effect varies as the sine of the absolute value of half the angle between the magnetization vectors in the ferromagnetic thinfilms provided on either side of an intermediate nonmagnetic layer. The electrical resistance in the giant magnetoresistance effect through the "sandwich" or superlattice structure is lower if the magnetizations in the separated ferromagnetic thin-films are parallel and oriented in the same direction than

it is if these magnetizations are antiparallel, i.e. oriented in opposing or partially opposing directions. Further, the anisotropic magnetoresistive effect in very thin films is considerably reduced from the bulk values therefor in thicker films due to surface scattering, whereas a significant giant magnetoresistive effect is obtained only in very thin films. Nevertheless, the anisotropic magnetoresistive effect remains present in the films used in giant magnetoresistive effect structures.

A memory cell based on the "giant magnetoresistive effect" can be provided by having one of the ferromagnetic 1 layers in the "sandwich" construction being prevented from switching the magnetization direction therein from pointing along the easy axis therein in one to the opposite direction in the presence of suitable externally applied magnetic fields while permitting the remaining ferromagnetic layer to be free 15 to do so in the same externally applied fields. In one such arrangement, a "spin-valve" structure is formed by providing an antiferromagnetic layer on the ferromagnetic layer that is to be prevented from switching in the externally applied fields to "pin" its magnetization direction in a selected direction. In 20 an alternative arrangement often termed a "pseudo-spin valve" structure, the ferromagnetic layer that is to be prevented from switching in the externally applied fields is made sufficiently thicker than the free ferromagnetic layer so that it does not switch in those external fields provided to switch the 25 free layer.

Thus, a digital data memory cell based on the use of structures exhibiting the giant magnetoresistive effect is attractive as compared to structures based on use of an anisotropic magnetoresistive effect because of the larger signals obtainable in information retrieval operations with respect to such cells. Such larger magnitude signals are easier to detect without error in the presence of noise thereby leading to less critical requirements on the retrieval operation circuitry.

An alternative digital data bit storage and retrieval memory 35 cell suited for fabrication with submicron dimensions can be fabricated that provides rapid retrievals of bit data stored therein and low power dissipation memory through use of a cell structure that has a spin dependent tunneling junction (SDTJ), or magnetoresistive tunnel junction (MTJ), device 40 therein based on a pair of ferromagnetic thin-film layers having an electrical insulator layer therebetween of sufficient thinness to allow tunneling currents therethrough. This memory cell can be fabricated using ferromagnetic thin-film materials of similar or different kinds in each of the magnetic 45 memory films present in such a "sandwich" structure on either side of an intermediate nonmagnetic layer where such ferromagnetic films may be composite films, but this intermediate nonmagnetic layer conducts electrical current therethrough based primarily on the quantum electrodynamic 50 effect "tunneling" current mentioned above.

This "tunneling" current has a magnitude dependence on the angle between the magnetization vectors in each of the ferromagnetic layers on either side of the intermediate layer due to the transmission barrier provided by this intermediate 55 layer depending on the degree of matching of the spin polarizations of the electrons tunneling therethrough with the spin polarizations of the conduction electrons in the ferromagnetic layers, the latter being set by the layer magnetization directions to provide a "magnetic valve effect". Such an effect 60 results in an effective resistance or conductance characterizing this intermediate layer with respect to the "tunneling" current therethrough. In addition, an antiferromagnetic layer against one of the ferromagnetic layers is used in such a cell to provide different magnetization switching thresholds 65 between that ferromagnetic layer and the other by fixing, or "pinning", the magnetization direction for the adjacent ferro4

magnetic layer while leaving the other free to respond to externally applied fields. Such devices may be provided on a surface of a monolithic integrated circuit to thereby allow providing convenient electrical connections between each such memory cell device and the operating circuitry therefor.

A "sandwich" structure for such a memory cell, based on having an intermediate thin layer of a nonmagnetic, dielectric separating material with two major surfaces on each of which a anisotropic ferromagnetic thin-film is positioned, exhibits the "magnetic valve effect" if the materials for the ferromagnetic thin-films and the intermediate layers are properly selected and have sufficiently small thicknesses. The resulting "magnetic valve effect" can yield a response which can be several times in magnitude greater than that due to the "giant magnetoresistive effect" in a similar sized cell structure.

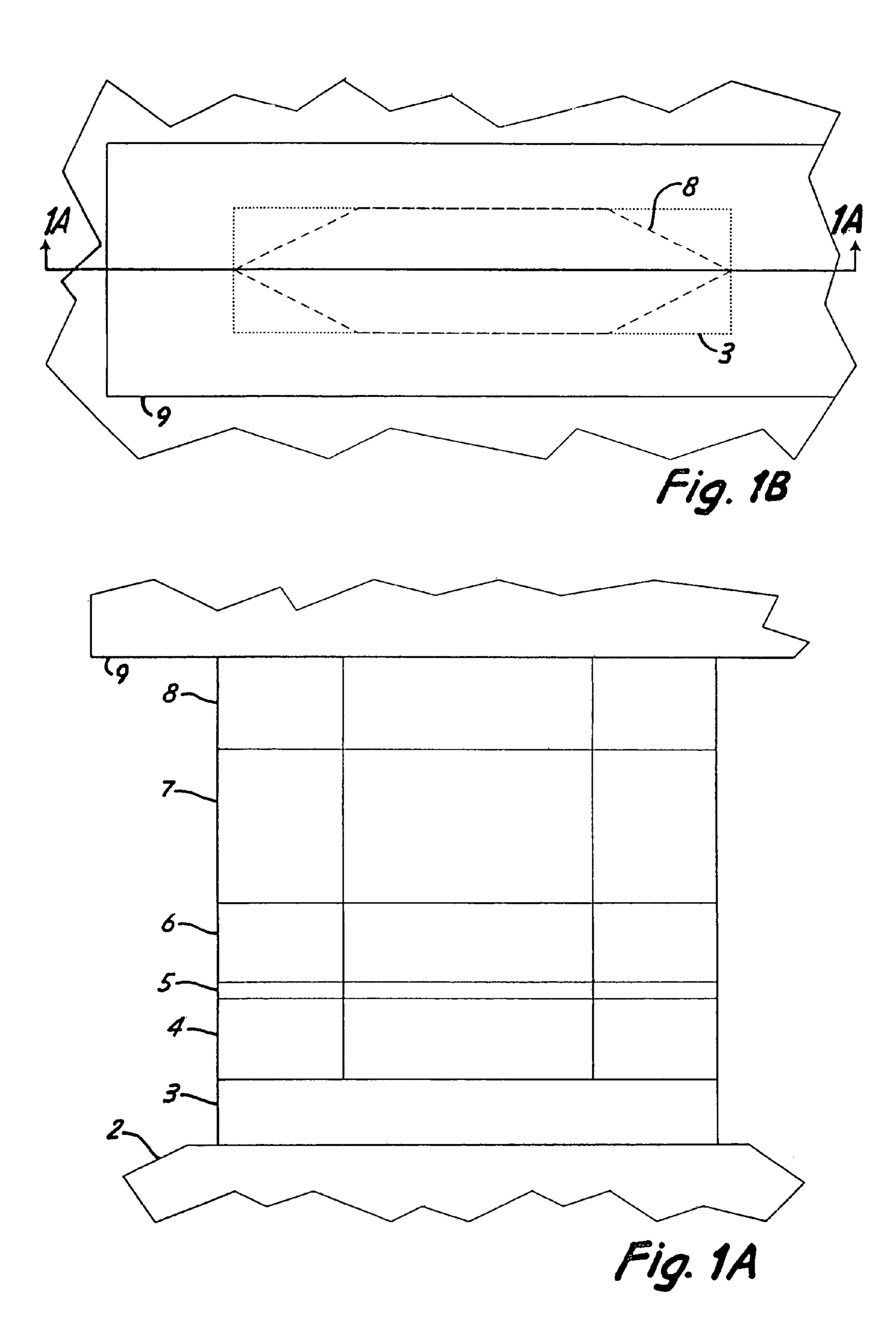

An example of a two state magnetoresistive device structure that is generally common to both of these kinds of memory cells is the "pinned sandwich" structure shown in the layer diagram of FIGS. 1A and 1B where the section line of FIG. 1B defines the view shown in FIG. 1A. This layer diagram gives an indication of the structural layers, but is not a true cross section view in that many dimensions there are exaggerated or reduced relative to one another for purposes of clarity.

A substrate, 2, supports an interconnection structure, 3, as the bottom contact electrode to a magnetic material (ferromagnetic material) free layer, 4, (meaning its magnetization is relatively free to be rotated to an alternative orientation) that is separated by a nonmagnetic material spacer layer, 5, from a magnetic material (ferromagnetic material) relatively fixed layer, 6, (meaning its magnetization is much less free to be rotated to an alternative orientation, i.e. "pinned"). This "pinning" of layer 6 is provided by a further magnetic material layer, 7, the "pinning" layer, that is of an antiferromagnetic material which is magnetically coupled to pinned layer 6 and thereby serves to make this two layer pinned structure relatively resistant to rotation of its initial joint magnetization direction in the presence of moderate external applied magnetic fields. An aluminum cap layer, 8, serves as the device top contact electrode providing a conductive path to a further interconnection, 9.

If spacer layer 5 is an electrical conductor, such as Cu, then the structure will exhibit the giant magnetoresistive (GMR) effect and be termed a "spin valve". If spacer layer 5 is an electrical insulator, such as Al<sub>2</sub>O<sub>3</sub>, that is sufficiently thin, then the device will exhibit the spin dependent tunneling effect and be termed a "magnetic tunnel junction". In either situation, the electrical resistance of the device is typically higher when the magnetizations of the free and fixed layers on either side of the spacer layer are oriented antiparallel to one another, and is lower when these magnetizations are oriented parallel to one another. The electrical resistance versus external applied magnetic field response characteristic for a spin valve that is measured for sense current being established across the magnetic material layers with the conductive layer therebetween is greater in terms of fractional change than that characteristic measured for the sense current established parallel to these layers because the entire collection of spins in the sense current electrons is forced to interact with both magnetic material layers for the sense current being established across these layers but only a fraction of these electrons interact with both layers for sense currents established parallel thereto.

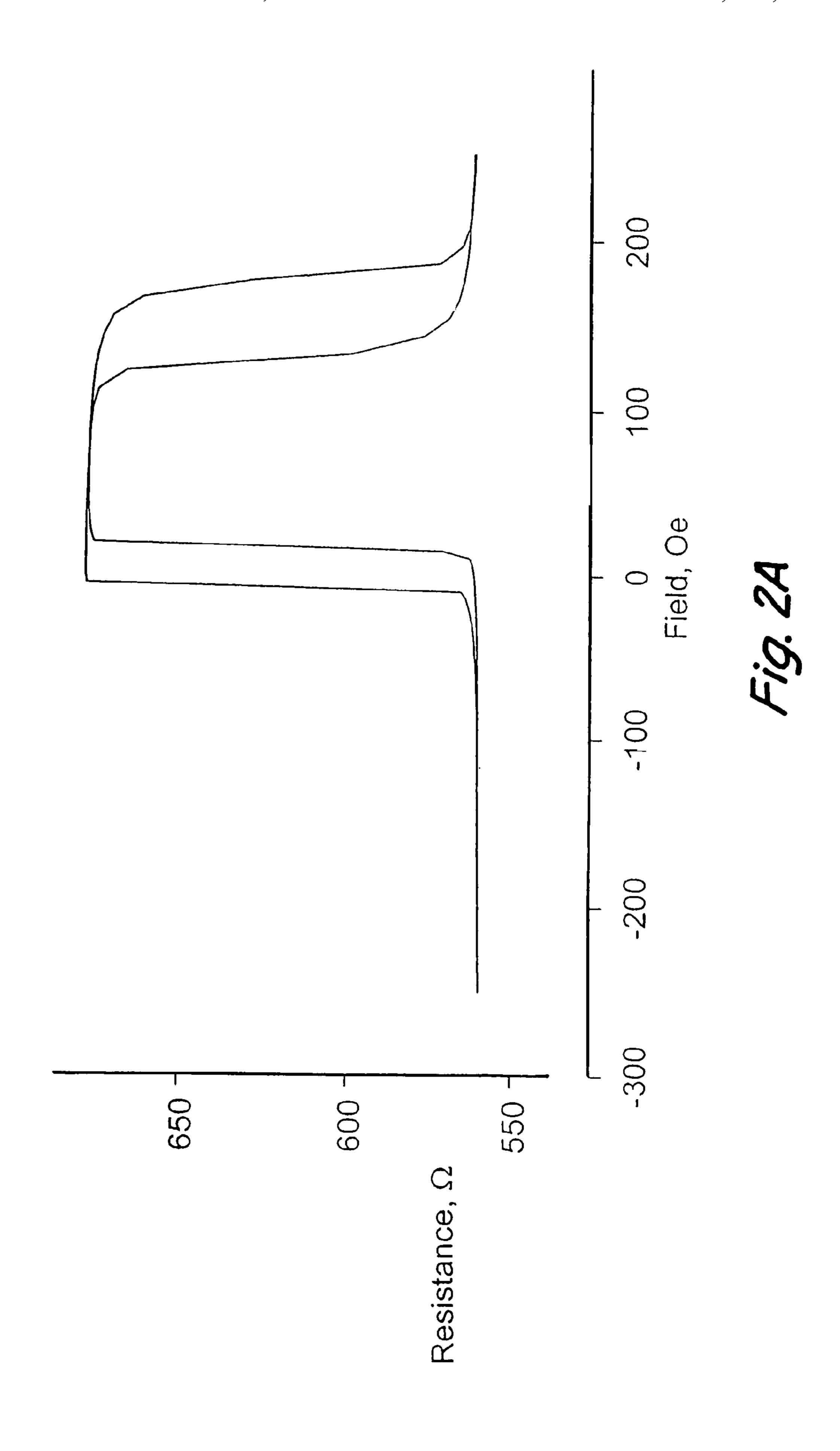

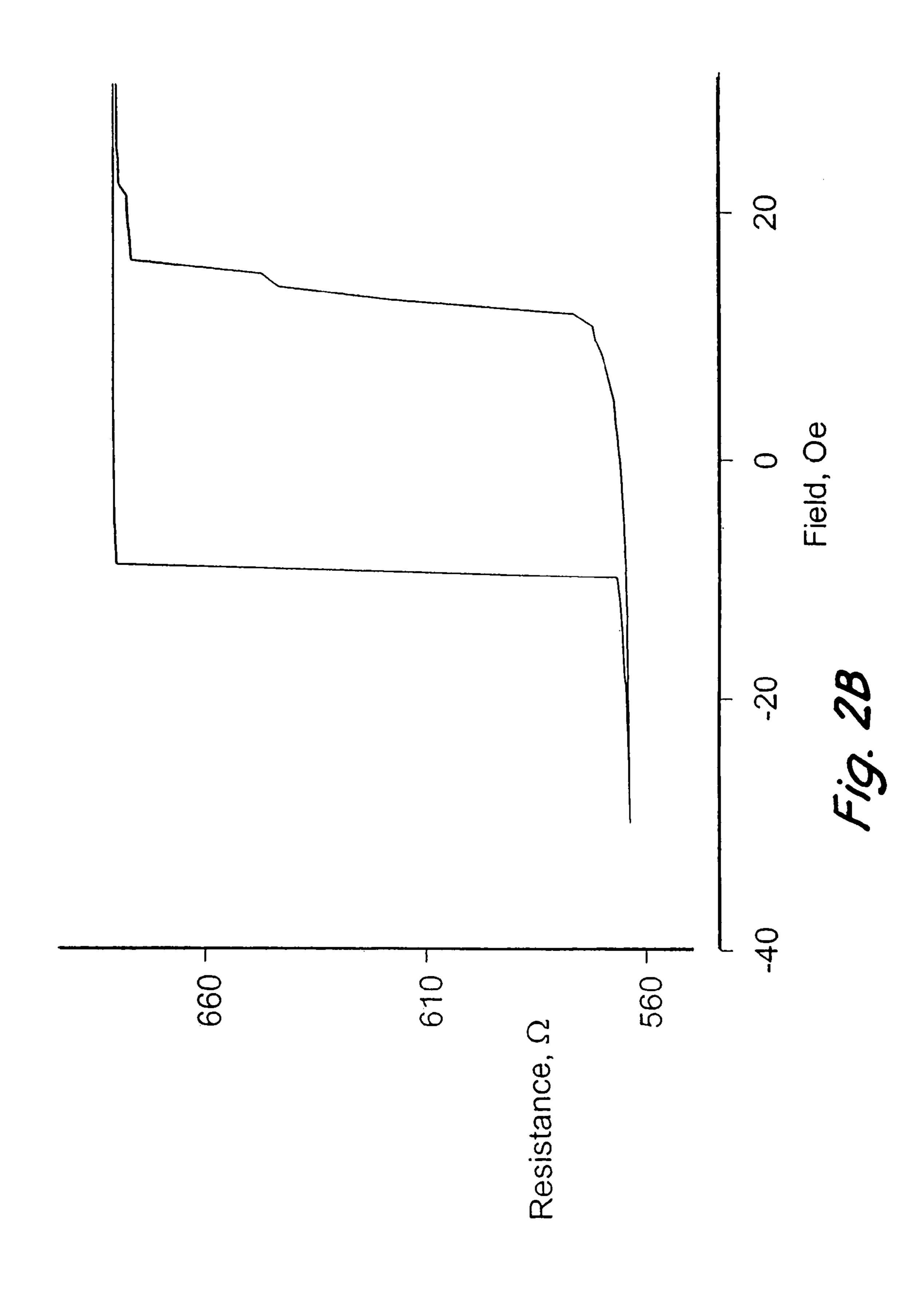

Plots of the high externally applied magnetic field range and the low externally applied magnetic field range response characteristics of a typical spin valve are shown in the graphs of FIGS. 2A and 2B, respectively. The device resistance ver-

sus externally applied magnetic field response characteristics of a magnetic tunnel junction are qualitatively similar. However, the magnitudes of the resistance values and the resistance change values may be quite different. FIG. **2**B shows that at moderately high positive externally applied magnetic fields the device resistance is largest, corresponding to the antiparallel alignment of the magnetizations of free and fixed layers **4** and **6**; and the device resistance is smallest for moderately high negative externally applied magnetic fields, corresponding to the parallel alignment of the magnetizations of free and fixed layers **4** and **6**.

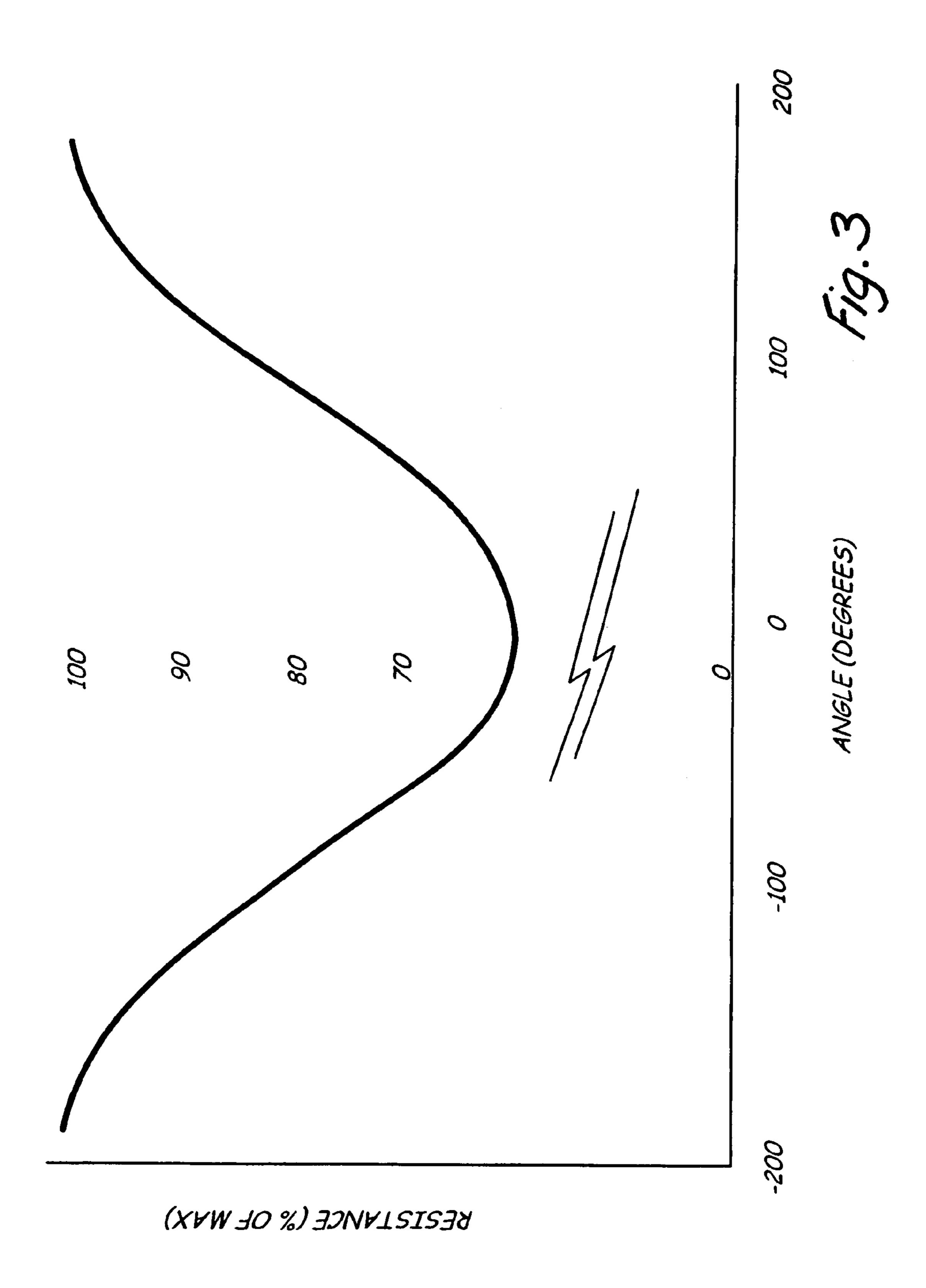

FIG. 3 shows a graph in which the resistance of the device of FIG. 1, either with a conductive or an insulative spacer layer 5, as an approximate fraction of its maximum resistance versus the angle between the magnetizations of free and fixed 15 ferromagnetic layers 4 and 6 on either side of this spacer layer. This relationship is obtained by applying an external magnetic field along the direction indicated by the angle that is larger than the magnetic saturation field of free layer 4 but less than the magnetic saturation field of fixed layer 6.

As stated above, operating magnetic fields imposed externally can be used to vary the angle of the magnetization vector with respect to the easy axis in the ferromagnetic films of these various kinds of memory cell devices, particularly the free layers. Such operational magnetic fields imposed exter- 25 nally can be used to vary the angle to such an extent as to cause switching of the layer magnetization vector between two stable states which occur for the magnetization being oriented in opposite directions along the easy axis of the layer, the state of the cell determining the value of the binary bit being stored 30 therein. One of the difficulties in such memories is the need to provide memory cells therein that have extremely uniform switching thresholds and adequate resistance to unavoidable interjected magnetic field disturbances in the typical memory cell state selection scheme used. This externally applied operating fields scheme is based on selective externally imposed magnetic fields provided by selectively directing electrical currents over or through sequences of such cells thereby giving rise to such magnetic fields so that selection of a cell occurs through coincident presences of such fields at that cell.

In such a coincident current selection arrangement, only that cell in the vicinity of the crossing location, or intersection, of these two paths (one over a sequence of cells and the other through another sequence of cells) experience sufficient magnetic field intensities due to the summing of the fields due 45 to these two currents to cause such a magnetic state change therein. Cells in the array that are located far away from both of these two current paths are not significantly affected by the magnetic fields generated by such currents in the paths because such fields diminish in intensity with distance from 50 the source thereof. Cells, however, located in relatively close proximity to one, but not two, of these two paths do experience more significant magnetic fields thereabout, and those immediately in or adjacent to one such path experience sufficient field intensities to be considered as being "half-se- 55 lected" by the presence of current in that path intended to participate in fully selecting a different cell along that path at the intersection with the other path on which a selection current is present. Half-selection means that a bit is affected by magnetic fields from the current through one path but not 60 another. Such a coincident interjected magnetic fields memory cell state selection scheme is very desirable in that an individual switch, such as that provided by a transistor, is not needed for every memory cell, but the limitations this selection mode imposes on the uniformity of switching thresholds 65 for each memory cell in a memory make the production of high yields difficult.

6

As such magnetic thin-film memory cells are made smaller to thereby increase the cell density over the surface of the substrate on which they are disposed, the resulting cells become more subject to magnetic state, or data, upsets due to thermal fluctuations occurring in the materials therein. The depth of the energy well in the magnetic material of such cells can be approximated as  $H_{weff}^*M_s^*$ Volume, where  $H_{weff}$  is half the effective restoration magnetic field attempting to maintain the current magnetic state following perturbations thereto and so effectively providing the energy well depth, M<sub>s</sub> is the saturation magnetization of the magnetic material in the cell, and Volume is the volume of the magnetic material in the cell. In conventional cells,  $H_{weff}$  is provided by shape anisotropy or anisotropy due to the material properties of the cell magnetic material, or both. Typically, the value of  $H_{weff}$  in these cells is less than 100 Oe.

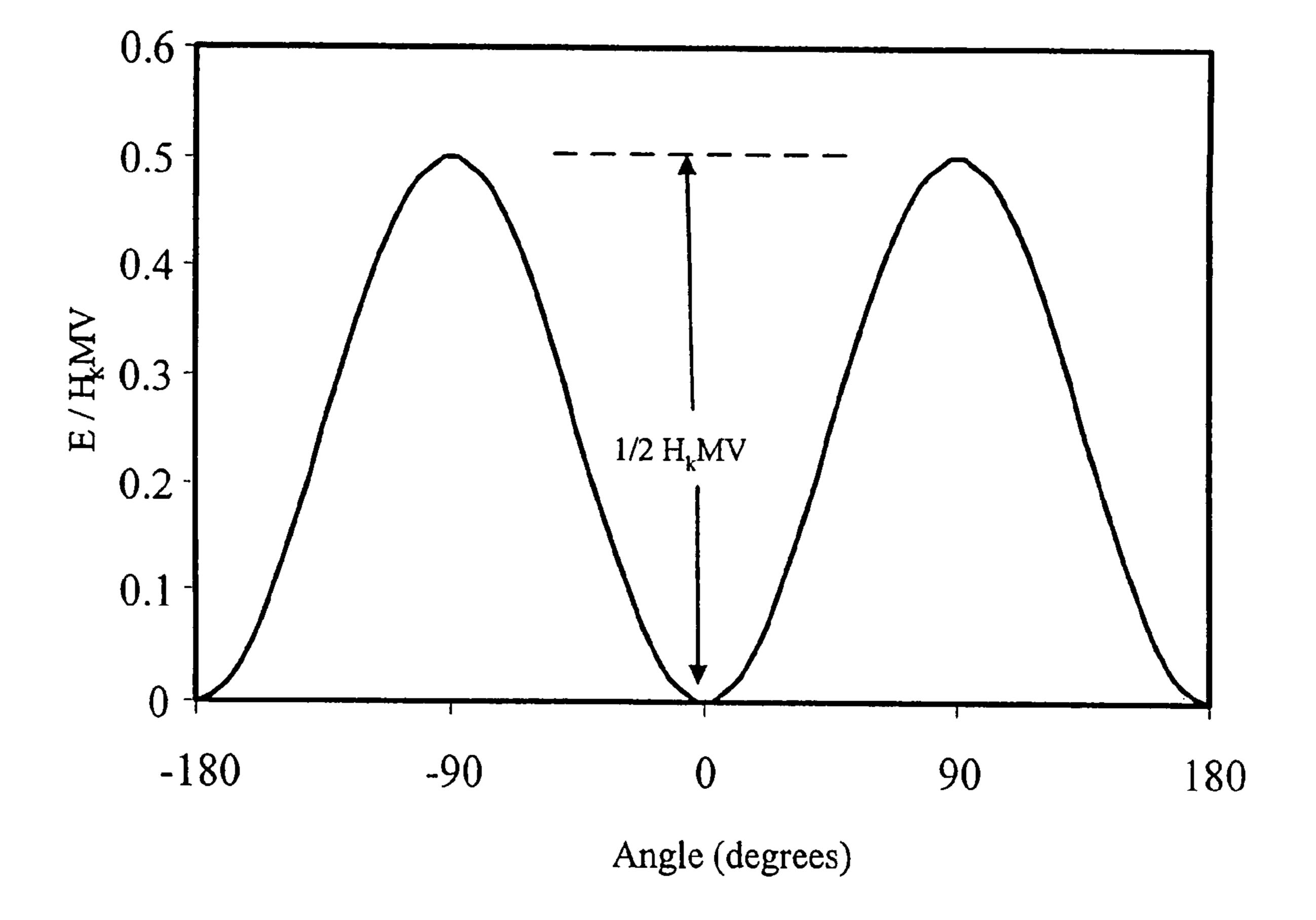

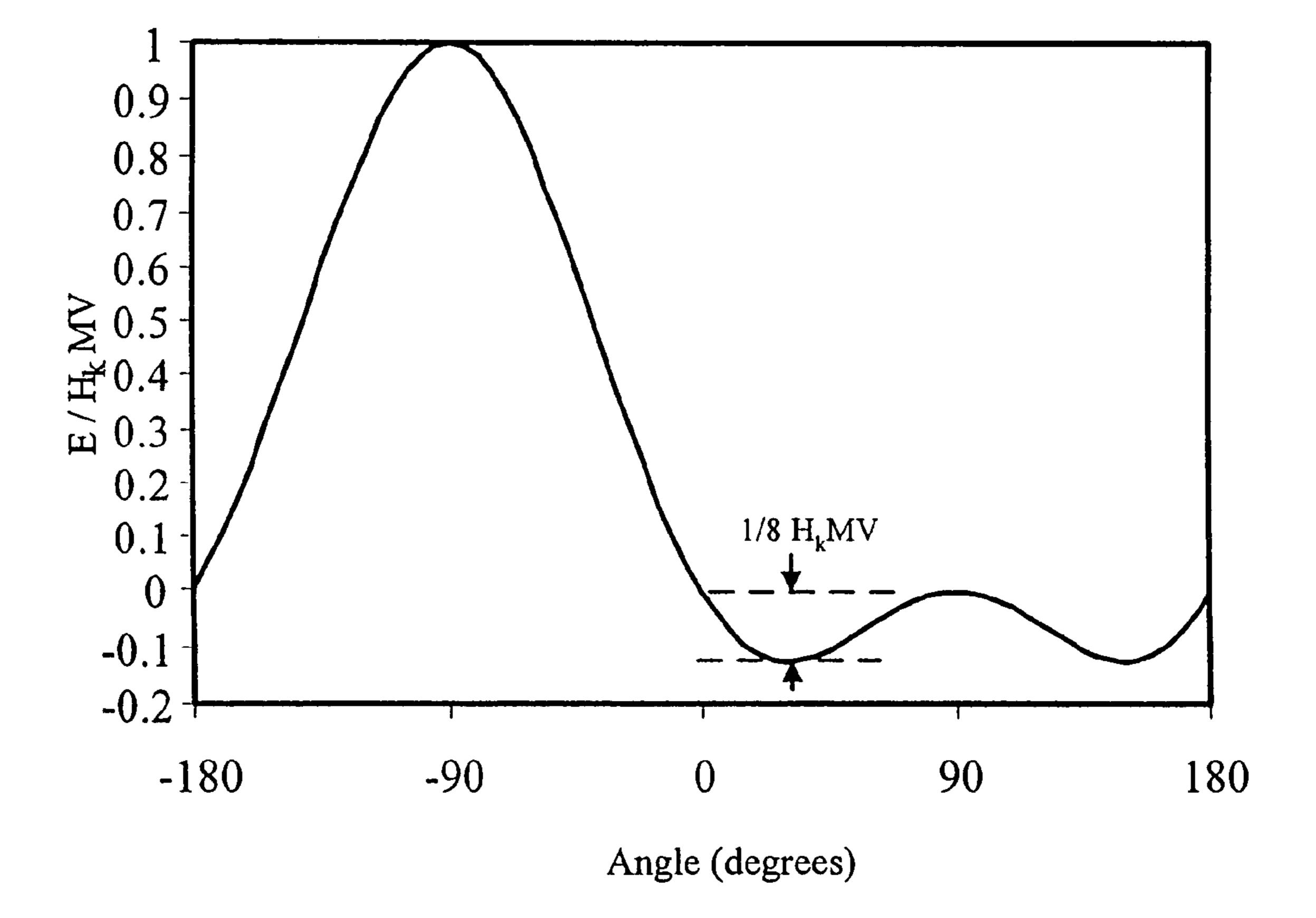

Plotting the magnetostatic energy of a data storage cell magnetic material layer versus the angle between the magnetization and the easy axis of that layer, an energy minimum is seen in the result at the angular value of zero or, with this angle designated as  $\theta$ , at  $\theta$ =0 as shown in the graph of FIG. 4. This minimum, having on either side thereof in this plot an energy maximum, that is energy maxima at  $\theta$ =+90° and  $\theta$ =-90°, is the "energy well". The depth of the energy well when no external magnetic fields are applied is simply the difference between the energy minimum and maxima. The value of this energy well can be calculated from

$$E = \frac{1}{2} \sin^2 \theta | \overrightarrow{M} | H_k V$$

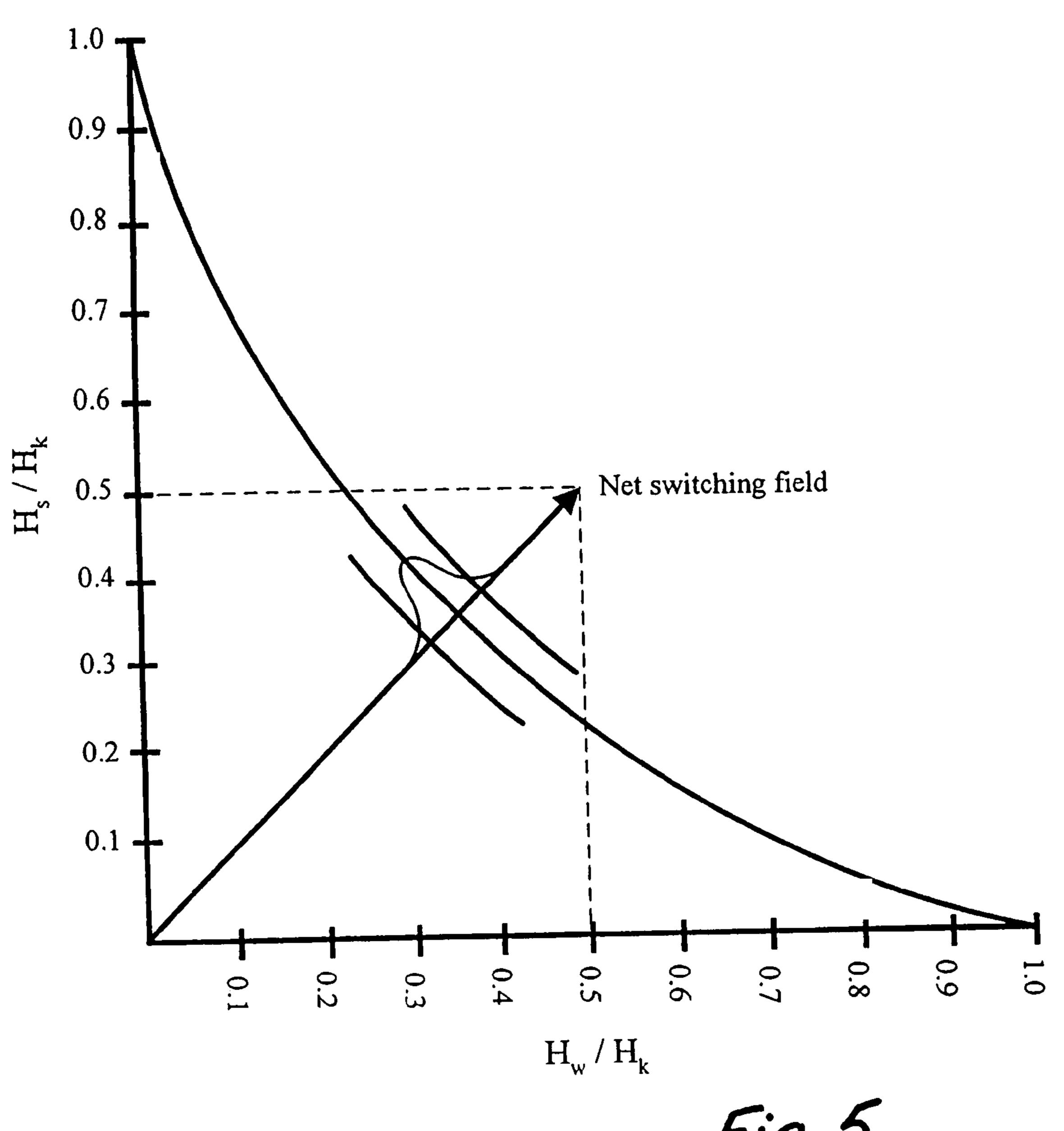

where M is the magnetization,  $H_k$  is the anisotropy field, V is the volume, and  $\theta$  is the angle of M from the easy axis. The magnetization orientation will tend to orient to minimize the magnetostatic energy; i.e.,  $\theta$  will tend toward zero degrees. The graph of FIG. 5 shows a Stoner-Wohlfarth switching threshold plot, a portion of an asteroid, and reasonable values of the word and sense fields to provide adequate margins for a memory employing coincident current selection. The solid curve in the figure represents the total field required to cause a bit magnetization to switch from one to the other of two stable states. The total field is the vector sum of the word magnetic field  $\hat{H}_{w}$  due to current provided in an adjacent word line, and the sense magnetic field H, due to current provided through the cell which currents are typically applied along current paths following the two orthogonal axes in the plane of the cell array. The Gaussian curve portion shown in the middle of the plot is representative of the distribution of cell applied magnetic field switching threshold values in an array of real memory cells. The memory array design, then, must account for the varying cell switching thresholds encountered in view of this distribution. As illustrated in the figure, design values for the word and sense fields are about ½ the value of  $H_k$ . The remaining energy well depth of those cells half-selected is about 1/4 their non-selected depth. This can be shown through calculating the well depth with half selection magnetic fields both present and absent.

The energy expression above, when modified to include the effects of  $\overrightarrow{H}_{w}$  and  $\overrightarrow{H}_{s}$ , becomes

$$E = \frac{1}{2} \sin^2 \theta |\overrightarrow{M}| H_k V - |\overrightarrow{M}| |\overrightarrow{H}_s| V \sin \theta + |\overrightarrow{M}| |\overrightarrow{H}_w| V \cos \theta.$$

Here we assume that  $\overrightarrow{H}_{w}$  is parallel to the effective easy axis while  $\overrightarrow{H}_{s}$  is perpendicular to this axis. The easy axis is parallel to  $H_{k}$ .

If a half-select word field is applied (i.e.  $|\overrightarrow{H}_w| = \frac{1}{2}H_k$  and  $|\overrightarrow{H}_s| = 0$ ), the energy expression becomes:

$$E = \frac{1}{2} \sin^2 \theta |\overrightarrow{M}| H_k V + |\overrightarrow{M}| |\overrightarrow{H}_w| V \cos \theta,$$

where the second term is the energy due to the applied word field. If a half-select sense field is applied (i.e.  $|\overrightarrow{H}_s|^{-1/2}H_k$  and  $|\overrightarrow{H}_w|^{-1/2}$ ), the energy expression becomes:

$$E=\frac{1}{2}\sin^2\theta |\overrightarrow{M}|H_kV-|\overrightarrow{M}||\overrightarrow{H}_s|V\sin\theta,$$

where the second term is the energy due to the applied sense field.

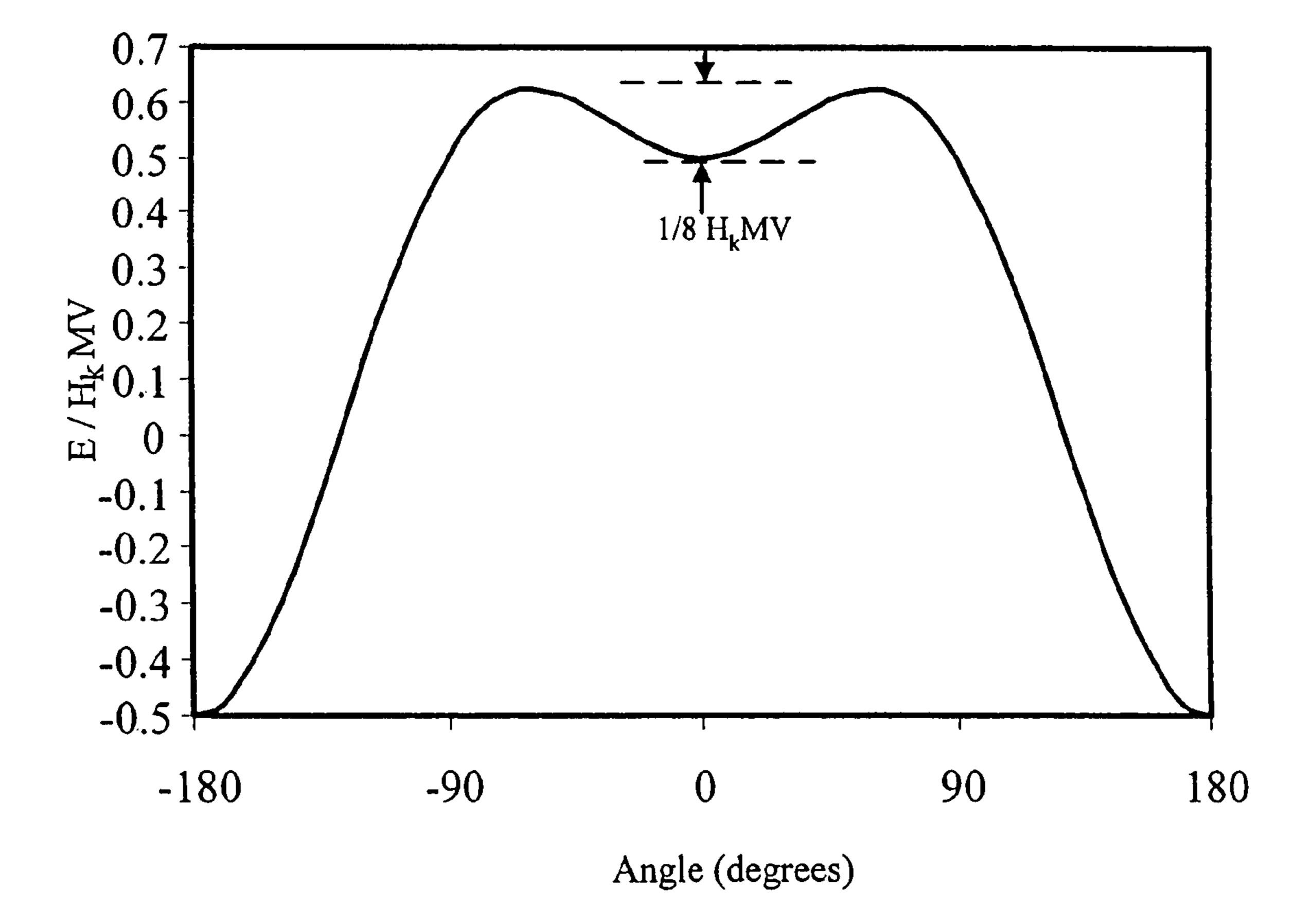

These two equations are plotted in the graphs of FIGS. **6**A and **6**B. In both cases, the well depth has been reduced by a factor of four, from  $\frac{1}{2}$  MH<sub>k</sub>V to  $\frac{1}{8}$  MH<sub>k</sub>V. A physical memory may be designed with slightly different parameters. However, the important factor is the smallest energy well depth for a 25 half-selected cell. The design objective is to ensure that the memory cells are magnetically stable during the data storing, or magnetic state switching, procedure that is repeatedly undertaken with respect to other cells. However, the trade-off between thermal stability and magnetic stability is a serious 30 problem when the total magnetic volume of bits is less than about  $10^5$  nm<sup>3</sup>.

Consider, for instance, a 256 megabit data storage capacity memory cell array provided as part of a monolithic integrated circuit chip organized so as to have 16 byte data blocks (8×17 binary bits) and having implemented therein the well known Hamming single bit error correction code which adds 8 additional bits. A reasonable sub-array to operate would be organized so that the word lines would each be immediately adjacent to 1088 cells to provide magnetic fields thereabout and the sense lines would each connect in series 128 cells for storing and retrieving data binary bits. The data is to be accessed in sequence in two byte groups.

A worst case can be taken to occur if one block had the data therein retrieved continuously for a year. In this case only one block would experience error correction while the remaining 2 million blocks would not. A total of 78 blocks (64-1 +16-1) would be continuously half selected. The unselected blocks with 4 times the well depth can be ignored because their thermally induced failure rate would be negligible.

First, consider the situation without any error correction. For randomly occurring failures in a non-redundant system, reliability theory shows that the total failure rate of the 78 half selected blocks is the sum of the individual failure rates. Also each byte that is present in a block is accessed only ½ of the time. Thus to achieve a desired 10<sup>-5</sup> yearly failure rate for the memory, the failure rate for each cell per ½ year is given by

$$10^{-5}/(78 \text{ blocks*}128 \text{ cells/block})=1.0016\times10^{-9} \text{ failure/(1/8 year)}.$$

Noting that there are  $3.942*10^6$  seconds in ½ year, that the relaxation time for a magnetic element of the type considered is about  $0.5\times10^{-9}$  seconds with the energy state being randomized with respect to each relaxation time ( $t_r$ ) so that there are  $1/t_r$  chances to fail per second, and that if a cell is thermally excited above the barrier, there is a 50% chance it will end in

8

the wrong state, one can compute the required energy barrier height  $(E_b)$  as

$$1.0016 \times 10^{-9} = 0.5 * e^{-(E_b/kT)} * 3.942 * 10^6 * 1/(0.5 * 10^{-9})$$

O

$$E_b = 56.6 \text{ kT}.$$

If there is single bit error correction, then any single bit error in any half-selected block can be corrected and a failure occurs at the end of the year only if two or more errors occur in a block. For small failure probabilities, the failure rate for two or more elements failing in a block is only very slightly more than two elements failing in a block. For convenience, calculations will be based on two bits failing in a block.

Let "f" be the cell failure probability for an element for a year. Using the fact that the number of ways 2 elements can be selected out of 138 is given by 138×137/2, the required value of f can be calculated as follows:

$$10^{-5}/(78*69*137)=f^2; f=0.3683*10^{-6}$$

The required well depth can then be computed directly as follows:

$$0.3683*10^{-6}=0.5*e^{-(E_b/kT)}*3.942*10^6/((0.5*10^{-9}))$$

[half select]  $E_b=50.7$  kT [unselect]  $4*E_b=203$  kT

Incidentally, if the memory has data retrieved from all of the cells therein every 10 hours and corrections made thereto, the required well depth would be reduced by only a relatively a small amount to 47.3 kT.

Taking the more conservative value of  $E_b$ =28 kT for unselected memory cells, and assuming the temperature of a half selected cell rises to 400 K during the writing procedure of another cell, and that the saturation magnetization of the storage layer is about 10,000 emu/cm<sup>3</sup>, and the effective anisotropy of the storage layer is 20 Oe, the minimum volume required to maintain thermal stability is given by the difference between the maximum and the minimum energy values, which occur at  $\theta$ =0 and at  $\theta$ = $\pi$ /2, through the following relationship:

$$^{1}/_{2} \sin^{2}\theta \overrightarrow{M} \overrightarrow{H}_{k} V = 228 \text{ kT};$$

$$V = 2*228(1.381 \times 10^{-23} \text{ Joules/Kelvin})(400 \text{ Kelvin})/(10,000 \text{ emu/cm}^{3})(20 \text{ Oe}) = 12.6*10^{-24} \text{ m}^{3} = 12,600 \text{ nm}^{3}.$$

Because of the exponential nature of the threshold, or energy barrier, unselected cells do not contribute significantly to the error rate. Changing the number of half selected cells by a factor of 10 only changes the energy barrier height requirement by 2.3 kT. Although the required barrier energy can be reduced by use of error correction and periodic retrievals with corresponding corrections of the data stored in the whole memory, such a memory takes additional chip area and increased processing steps thereby increasing costs and reducing operating rapidity.

As an example, consider first a memory cell from FIG. 1 with a 0.2 μm width having ferromagnetic free layer element 4 therein of that same width as depicted in that figure. This cell is to be configured to meet the well depth requirements at a temperature of 85° C., i.e. have the necessary half select energy well in the magnetic material, approximated as H<sub>weff</sub>\*M<sub>s</sub>\*Volume, where again H<sub>weff</sub> is half the effective restoration magnetic field attempting to maintain the current magnetic state following perturbations thereto or H<sub>k</sub>/2. In meeting this requirement, ellipsoid shaped like free layer 4

has outer dimensions chosen to be 0.2  $\mu$ m wide, as indicated above, and to have a length of 0.5  $\mu$ m so as to have a length to width ratio of n=2.5, with the result that it can the requirement by being provided either of a ternary alloy (65% Ni-15% Fe-20% Co, M<sub>s</sub>=1000 emu) with a thickness of 23.5 Å and a total anisotropy field of 130 Oe or alternatively of a permalloy (80% Ni-20% Fe, M<sub>s</sub>=800 emu) with a thickness of 31 Å and an anisotropy field of 124 Oe. In this example, free layer 4 being of such a permalloy is considered in the following.

Assuming that the memory cell is a spin dependent tunnel- 10 ing memory cell, and so having nonmagnetic layer 5 being an electrical insulator to thereby form a magnetic tunnel junction between free layer 4 and pinned layer 6, the cell can be fabricated with free layer 4 directly deposited on a polished, 400 Å thick, copper sense line serving as interconnection 15 structure 3 extending along its length. This sense line is in turn separated by 500 Å of silicon dioxide from a word line therebelow extending along its width. (In a GMR device with nonmagnetic layer 5 being an electrical conductor, the copper sense line would be broken to allow at least free layer 4 to be 20 electrically connected in series with this sense line.) In such a spin dependent tunneling cell structure, the sense current required to generate a 62 Oe half select field is 2.37 mA and the temperature rise from this sense current is 5.3° C. assuming a thermal conductivity for silicon dioxide of 0.014 W/(° 25 C. cm) and a copper sheet resistance of 0.75  $\Omega/\Box$ . For a 0.25 μm thick copper word line clad with 250 Å of permalloy to increase the word field, a current of 3.95 mA is required to generate a 62 Oe word field. With 500 Å of silicon dioxide insulation to the silicon substrate, the temperature rise is less 30 than 0.2° C. for the word line. Current density for the sense line is  $3\times10^7$  A/cm<sup>2</sup> and the current density for the word line is  $3.2 \times 10^6 / \text{cm}^2$ .

Now consider the result of having the dimensions of this cell reduced through dividing them by some scaling factor 35 greater than one to thereby allow increasing the density of cells in the memory chip. Then thermal stability requires that the energy well depth remain constant or that  $H_k M_s V = const.$ Since the same permalloy material will be assumed to be used for the shrunken free layer, M<sub>s</sub> will remain the same and so 40 maintaining  $H_kV$  constant becomes necessary. However,  $H_k$ due to shape anisotropy, which is dominant in small dimension layers, can be written as  $C_1t/w$  where  $C_1$  is a constant, t is the free layer thickness and w is the free layer width, and the volume  $V=C_2(nw)$ wt where  $C_2$  is a constant accounting for 45 the ellipsoidal shape and n, as above, is the cell length to width ratio thus allowing the volume to be written  $C_2$  w<sup>2</sup>t by absorbing the constant n into the constant  $C_2$ . Thus,  $H_kV=(C_1t/w)$  $C_2w^2t=C_1C_2t^2w=C_3$ . Hence, the initial and scaled values of the product  $t^2$ w must equal one another, or  $t_i^2 w_i = t_s^2 w_s$ , so that 50 a scaling of the width and length by a factor k giving w<sub>s</sub>=w<sub>i</sub>/k requires the scaled layer thickness to become  $t_s = \sqrt{k}t_i$ , with the result that the scaled cell anisotropy field  $H_k$  becomes  $C_1k$  $\sqrt{k}t_i/w_i = C_1 k^{3/2}t_i/w_i$ , or alternatively, the thickness t must be varied in any such scaling as  $C_3/\sqrt{w}$  to maintain  $H_kV$  constant. 55

The result, for a scaling factor of two for example, is that the thickness of free layer 4 increases roughly by a factor of the square root of two and the anisotropy field thereof increases roughly by a factor of two times the square root of two. As the external magnetic fields to switch the free layer 60 magnetization are based on providing such fields with magnitudes on the order of  $H_k/2$ , and as the path integral around the conductor carrying the current to supply such a field is proportional to that current, the necessary current I in milliamps can be found from  $H_k/2=(C_1/2)k^{3/2}t_i/w_i=0.4\pi I[(2w_i/65k)+2\sqrt{k}t_i]$  where the terms in the brackets represent the path length around the conductor as a result of the scaling. This

10

expression can be written  $(C_1/2)k^{3/2}=0.4\pi I[(2w_i^2/kt_i)+2\sqrt{k}w_i]$  so that using, from above,  $t_i=C_3/\sqrt{w_i}$  yields  $(C_1/2)k^{3/2}=0.4\pi I[(2w_i^{5/2}/kC_3)+2\sqrt{k}w_i]$ . Thus, the current resulting from scaling is  $I=(C_1/2)k^{3/2}/0.4\pi[(2w_i^{5/2}/kC_3)+2\sqrt{k}w_i]$  showing that the current I increases with the scaling factor as the width becomes correspondingly smaller. Thus, in this example of a scaling factor equaling two, the sense current through the free layer increases roughly by a factor of the square root of two. As a result, the current density in the layer after scaling,  $I/[(w_i/k)(\sqrt{k}t_i)]$ , and the temperature rise in the scaled layer due to  $I^2R$  heating therein,  $I^2\rho nw_i/[(w_i/k)(\sqrt{k}t_i)]$  where  $\rho$  is the layer resistivity, increase roughly by a factor of four times the square root of two.

Thus, to meet the thermal stability requirement of maintaining the same energy well depth, the thickness of the resulting 0.1 micron wide free layer 4 in the scaled down cell must be increased to 45 Å. The total anisotropy field becomes 340 Oe and the required sense line current becomes 3.25 mA and the required word line current becomes 4.75 mA. Current density in the sense line increases to  $1.63 \times 10^8$  Å/cm² and temperature rise in the line increases to  $40^\circ$  C. These results show the very dramatic increase in current density as elements are reduced in width so that electromigration in the current conductors along with heating must be considered.

As indicated above, a ferromagnetic layer and an antiferromagnetic layer can be deposited in succession so they are in contact with one another with the result that relatively large interatomic forces occur aligning electron spins (parallel for ferromagnetism and antiparallel for antiferromagnetism). These coupling forces at the interface between these layers can be such that the magnetization of the ferromagnetic layer is restored to its initial direction prior to being subjected to external magnetic fields even after very large external magnetic fields are subsequently applied thereto. Such external magnetic fields can be 1000 Oe or more, and the magnetization of the ferromagnetic layer will still be restored to its initial direction. Thus, if such an antiferromagnetic layer is provided in contact with a ferromagnetic layer in a memory cell so that relatively large coupling occurs therebetween, the energy well depth for a small memory cell can be greatly increased. Such an arrangement can increase the potential density of memory cells by more than a factor of 10 through permitting the cell dimensions to go from about 0.2 µm minimum dimensions to approximately 0.05 µm dimensions.

A film structure which exhibits even better resistance to the effects of large externally applied magnetic fields is provided by a compound ferromagnetic thin-film layer with an antiferromagnetic layer. This compound ferromagnetic thin-film layer is provided to have a net layer magnetization that, when fixed in orientation in the finally formed structure, will resist rotation of its magnetization so that the magnetization of this compound ferromagnetic thin-film layer will appear fixed in its orientation in the device, i.e. "pinned" in a direction relative to the finally formed structure.

This compound ferromagnetic thin-film layer is formed by depositing a ferromagnetic layer to perhaps a thickness of 40 Å which is deposited in the presence of an easy axis direction determination magnetic field, then a nonmagnetic layer of ruthenium (no orienting magnetic field needed in this instance) to provide a ruthenium antiferromagnetic coupling layer of 9 Å thickness. Thereafter, another ferromagnetic layer is deposited to a thickness of 40 Å again in the presence of an easy axis direction determination magnetic field aligned as was the field for the first ferromagnetic layer. The resulting compound ferromagnetic layer has materials with high spin polarization in its outer layers due to the use of high magnetic induction ferromagnetic material therein, but has little net

magnetic moment because of the ruthenium layer provided therebetween which strongly antiferromagnetically couples these outer layers through primarily exchange coupling (some magnetostatic coupling also present) so that the magnetizations of each are pointed in opposite directions. Thus, 5 this layer is relatively insensitive to externally applied fields and contributes little to the spatial fields thereabout. However, the magnetization direction in this composite layer by itself is not very strongly fixed in any direction because of the relatively weak anisotropy exhibited by the ferromagnetic layers. 10

Thus, a further antiferromagnetic material "pinning" layer exhibiting a substantial magnetic anisotropy must be deposited on the last ferromagnetic layer to strongly set the magnetization direction of the compound layer. Such an antiferromagnetic layer has a strongly fixed magnetization direction which, through exchange coupling to the last ferromagnetic layer on which it is deposited, strongly fixes the direction of magnetization of that layer also, and so that of the first ferromagnetic layer through the ruthenium layer. The result is an antiferromagnetic layer coupled strongly to the compound layer. Hence, an antiferromagnetic pinning layer is deposited on the last ferromagnetic layer to a thickness of 100 Å or more in the presence of a magnetization axis determination magnetic field aligned with the fields used in forming the two ferromagnetic layers.

If this compound ferromagnetic layer with the antiferromagnetic layer thereon is provided across an electrically conductive layer of perhaps 25 Å thickness from a further ferromagnetic layer of again 40 Å thickness, a good "spin-valve" magnetoresistive memory cell is formed in which this last 30 ferromagnetic layer is the "free" layer which can have its magnetization changed to be either parallel or antiparallel to the firmly fixed magnetization direction of the nearest ferromagnetic layer in the compound ferromagnetic layer to select one of the possible the cell magnetization states (the different 35) states resulting in different cell electrical resistances). This can be accomplished through providing a sufficiently large storage electrical current which will flow primarily through the relatively thick conductive layer between the compound ferromagnetic layer and the "free" layer (although some of 40 this current will also pass through these latter two layers also even though being substantially shunted around by the conductive layer). An external magnetic field directed along the storage current path can also be provided through an appropriately positioned current strap to "tip" the magnetization of 45 the "free" layer to reduce the magnitude needed for the storage current to rotate the "free" layer magnetization. A smaller retrieval electrical current can be directed along the cell current path used for the storage current primarily through the conductive layer between the compound ferromagnetic layer 50 and the "free" layer (though again some of this current will also pass through these latter two layers also despite the substantial conductive layer shunting effect).

This common use of the compound ferromagnetic layer with an antiferromagnetic layer thereon is based on its resistance to alteration of its magnetization direction by externally applied magnetic fields. Omitting the antiferromagnetic layer reduces the ability to set the direction of the magnetization in the compound ferromagnetic layer, but whatever magnetization direction results in the compound ferromagnetic layer in 60 the circumstance of no antiferromagnetic layer being present is still, as indicated above, quite insensitive to externally applied magnetic fields if the two ferromagnetic layers therein are well matched in responding to such external fields. This is true since the effect of an external field on one ferromagnetic layer is directly opposed by the effect on the other because of their magnetizations being held strictly antiparal-

12

lel to one another by the Ru layer therebetween. Thus, use of a compound ferromagnetic layer without an antiferromagnetic layer thereon would also result in the energy well depth for a small memory cell based on this structure being substantially increased due to the demagnetization fields in each ferromagnetic layer being maintained in directions to approximately cancel one another.

The magnetic fields necessary to reach the layer switching thresholds to cause switching of the relatively fixed magnetization orientation layers magnetization directions for memory cells of smaller and smaller lengths and widths to thereby change the data stored therein have, of course, magnitudes beyond those of the fields required to switch the magnetization directions in the free layers of those cells which also increase for smaller cells as shown above. Generating such magnetic fields begins to require currents through such cells and associated word lines of magnitudes that result in current densities sufficient to cause significant electromigration of the conductive materials and operating temperature rises of the cell region which will alter device behavior and structure. Such effects thereby lead to a limit of some minimum size for these cells.

One possibility for avoiding such limits has been found through allowing memory cell device operating temperature 25 increases due to heating because of supplying word line currents adjacent to, and sense currents in, memory cells sufficient to approach or exceed the Curie temperature of the ferromagnetic layers in memory cells without a "pinning" layer or layers therein, or to approach or exceed the blocking temperature of the antiferromagnetic "pinning" layer in cells having such a layer. Such word line and sense line current based temperature increases permit storage of information in those cells to be achieved without reaching current magnitudes otherwise necessary to switch the magnetization directions of the ferromagnetic layers. The direction of magnetization of the relatively fixed magnetization orientation layer such as the thicker ferromagnetic layer in a three layer "sandwich" structure can be selected by having a moderate magnetic field present oriented in the selected direction when the layer cools sufficiently below its Curie temperature for cells without a "pinning" layer present, or by a field sufficient to set the direction of the ferromagnetic layer adjacent an antiferromagnetic "pinning" layer when that "pinning" layer cools sufficiently below its blocking temperature for cells using such a "pinning" layer or, alternatively, a "pinning" layer composite. The blocking temperature of an antiferromagnetic layer is the temperature at or above which that layer loses its ability to "pin" the magnetization direction of an adjacent ferromagnetic layer below its Curie temperature which blocking temperature is usually less than the Néel temperature of that layer. Similarly, the Curie temperature may not need to be fully reached to allow relatively easy reorienting of the magnetization direction therein.

Reducing the magnitudes of currents necessary for causing the harder ferromagnetic layer in memory cells without a "pinning" layer to approach or reach its Curie temperature, or the antiferromagnetic layer in memory cells with a "pinning" layer arrangement to approach or reach its blocking temperature, and insulating such memory cells from their neighboring cells to provide good cell selectivity in storing information requires providing some thermal isolation of each cell from its neighbors and the integrated circuit substrate or any other kind of substrate serving as a heat sink. Such thermal isolation can be provided by use of electrical conductive interconnections that are of a relatively low thermal conductivity, and by supporting the memory cell on an electrical insulator of relatively low thermal conductivity. However, as the need for

increased density of magnetoresistance based memory cells supported in and on a monolithic integrated circuit leads to smaller and smaller cell extents, further structural and operational alternatives for such memory cells are desired.

#### BRIEF SUMMARY OF THE INVENTION

The present invention provides a ferromagnetic thin-film based digital memory having bit structures therein with a magnetic material film in which a magnetic property thereof 10 is maintained below a critical temperature above which such magnetic property is not maintained, and may also have a plurality of word line structures each with heating sections located across from the magnetic material film in a corresponding one of the bit structures. These bit structures are 15 sufficiently thermally isolated to allow selected currents in the adjacent word lines or in the bit structure, including those supplied therein through contacts made to the side of the bit structure closest to the substrate supporting it, or both, to selectively heat the bit structure to approach the critical tem- 20 perature. Alternatively, pairs of such word line structures can have the members of each be on opposite sides of corresponding bit structures extending in different directions therefrom to allow selected currents therein to selectively heat the corresponding bit structure to approach the critical temperature. 25 Currents can be selected to be supplied coincidently in the adjacent word line and the bit structure, or instead in a further conductor also adjacent the bit structure rather than in that structure, to cause such a temperature rise, and then selectively be reduced to cool the bit structure while supplying a 30 magnetic field during the cooling to select the direction of magnetization to be maintained thereafter until new data is next stored therein. Such bit structures may have three magnetic material layers each with its own critical temperature for maintaining versus not maintaining a magnetic property 35 thereof.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIGS. 1A and 1B represent a layer diagram of a portion of 40 monolithic integrated circuit structure,

FIGS. 2A and 2B represents graphs of a response for a structure similar to one of those shown in FIGS. 1A and 1B and other structures herein,

FIGS. 3, 4, 5, 6A and 6B, 7, 8A, 8B and 8C, and 9A, 9B and 9C, and 10 represent graphs of conditions and response for structures described herein,

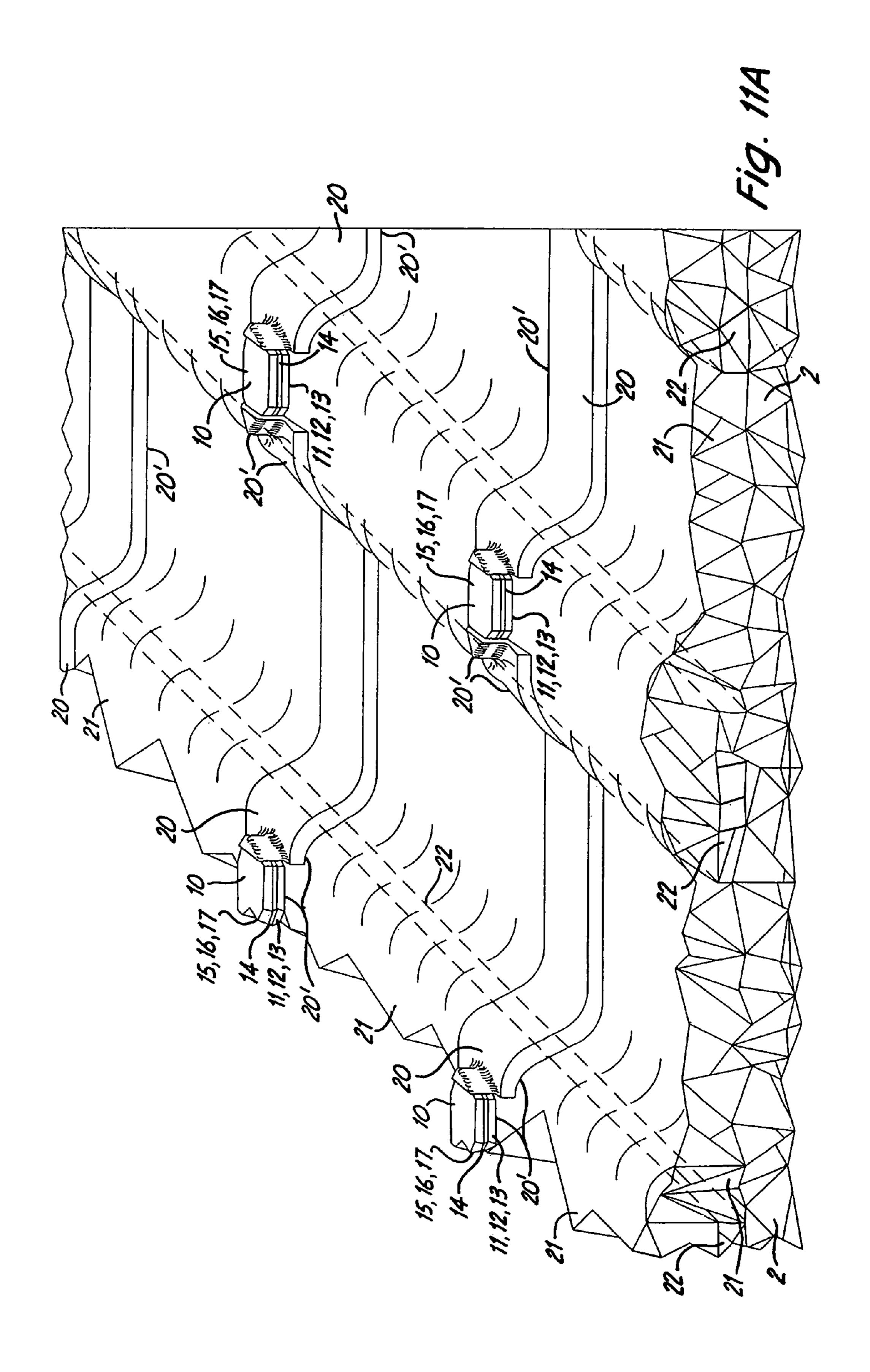

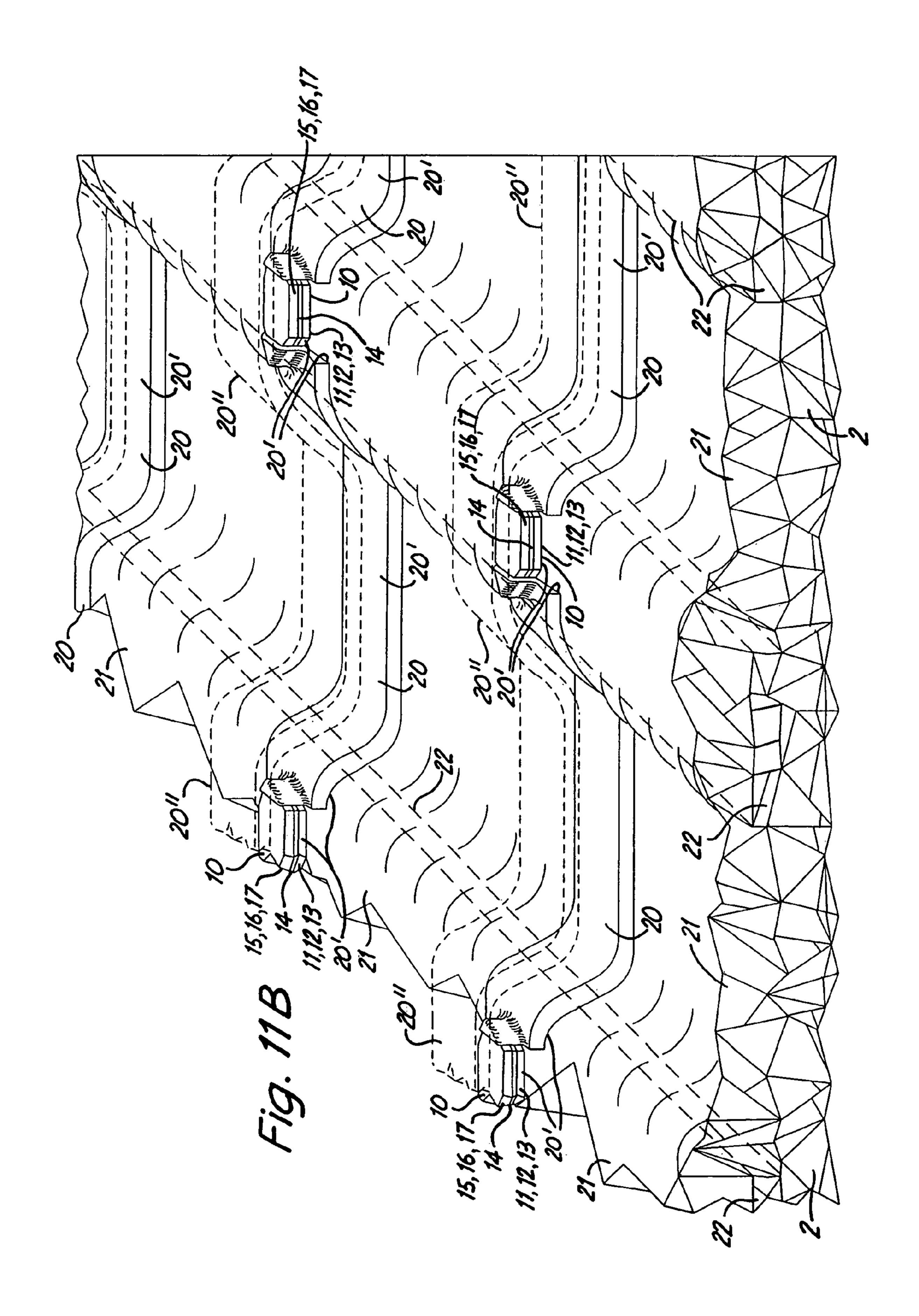

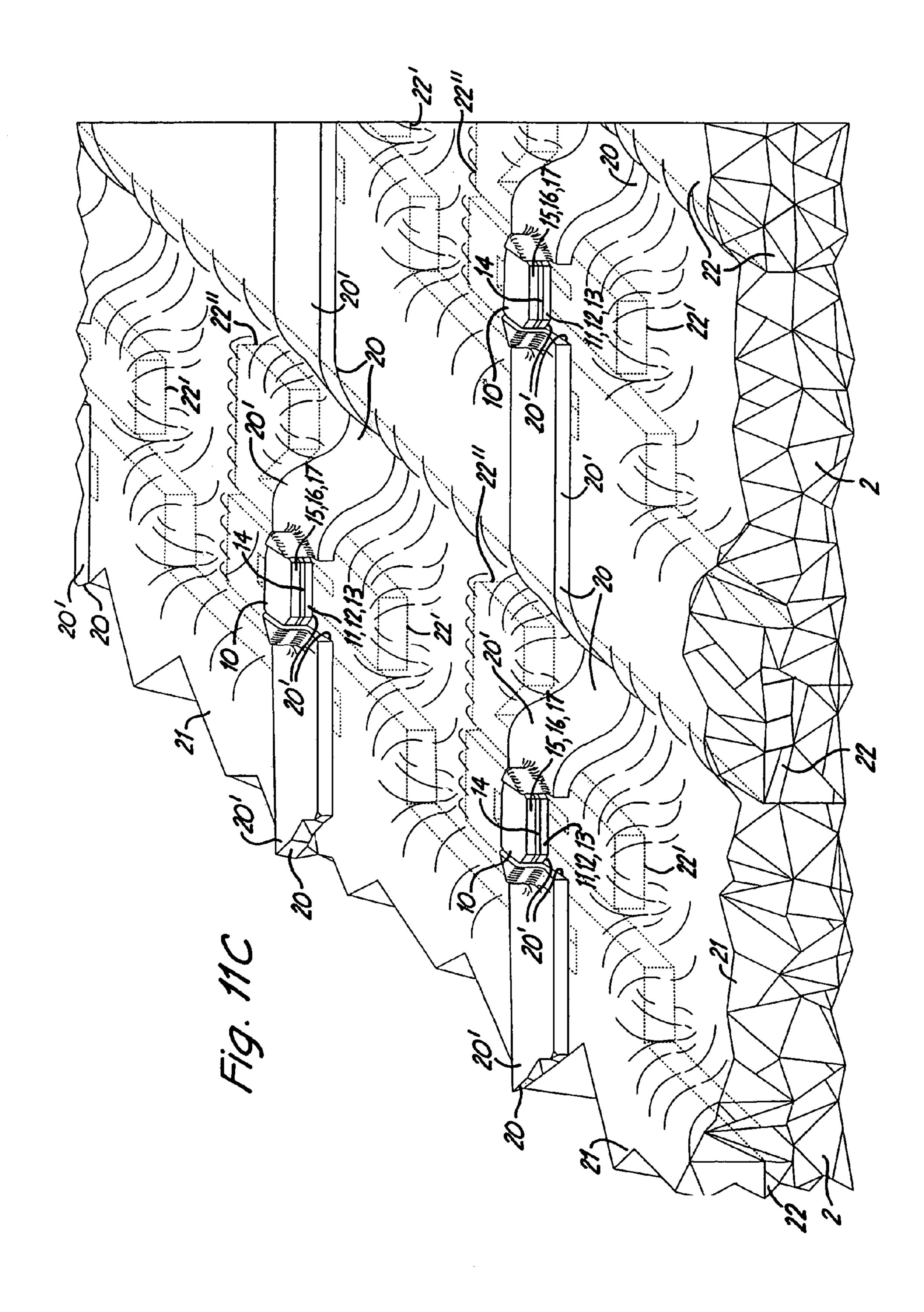

FIGS. 11A, 11B and 11C represent perspective views of portions of monolithic integrated circuit structures embodying the present invention,

FIGS. 12A and 12B represents graphs of a response for a structure similar to that shown in FIG. 11A,

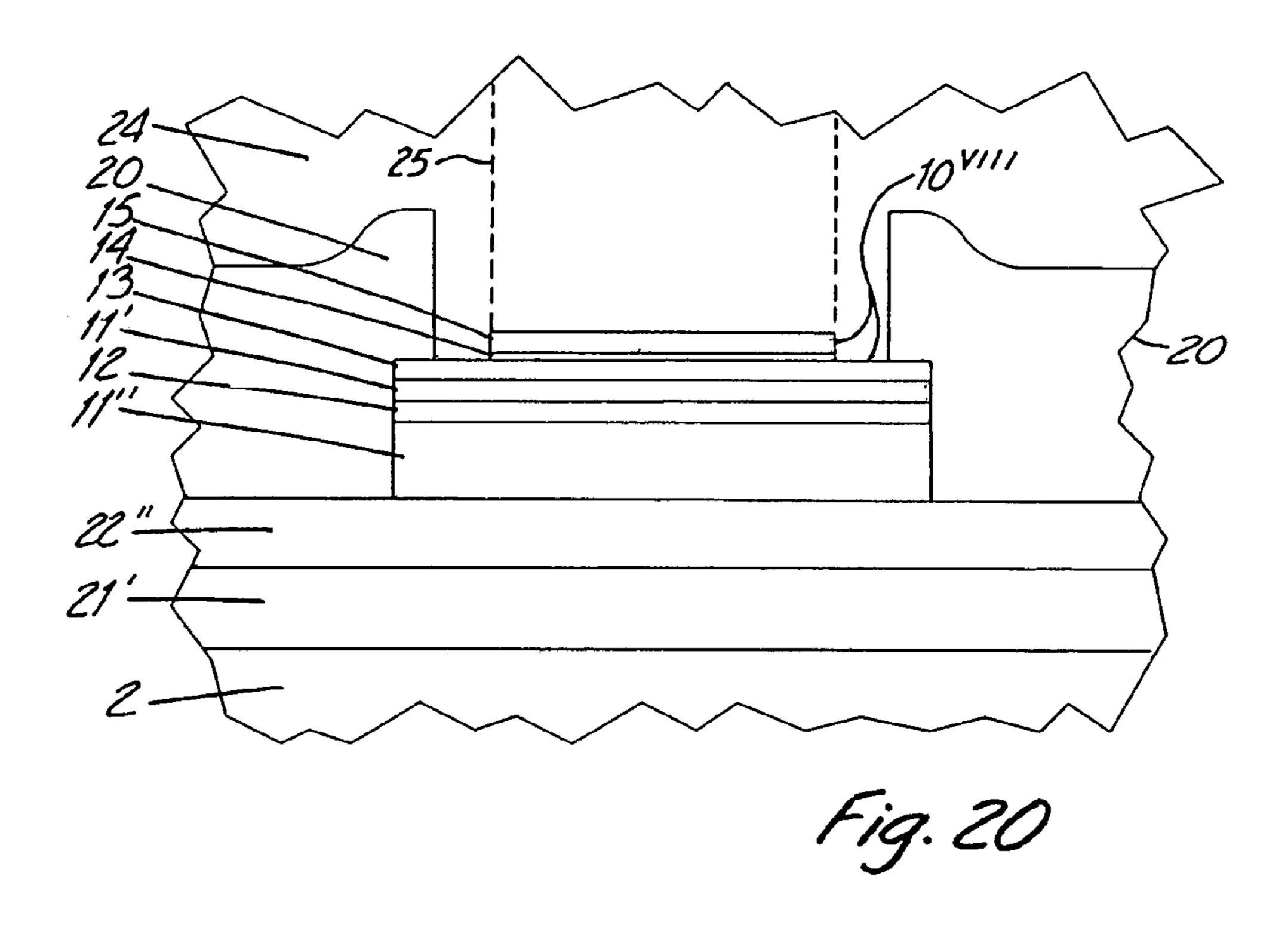

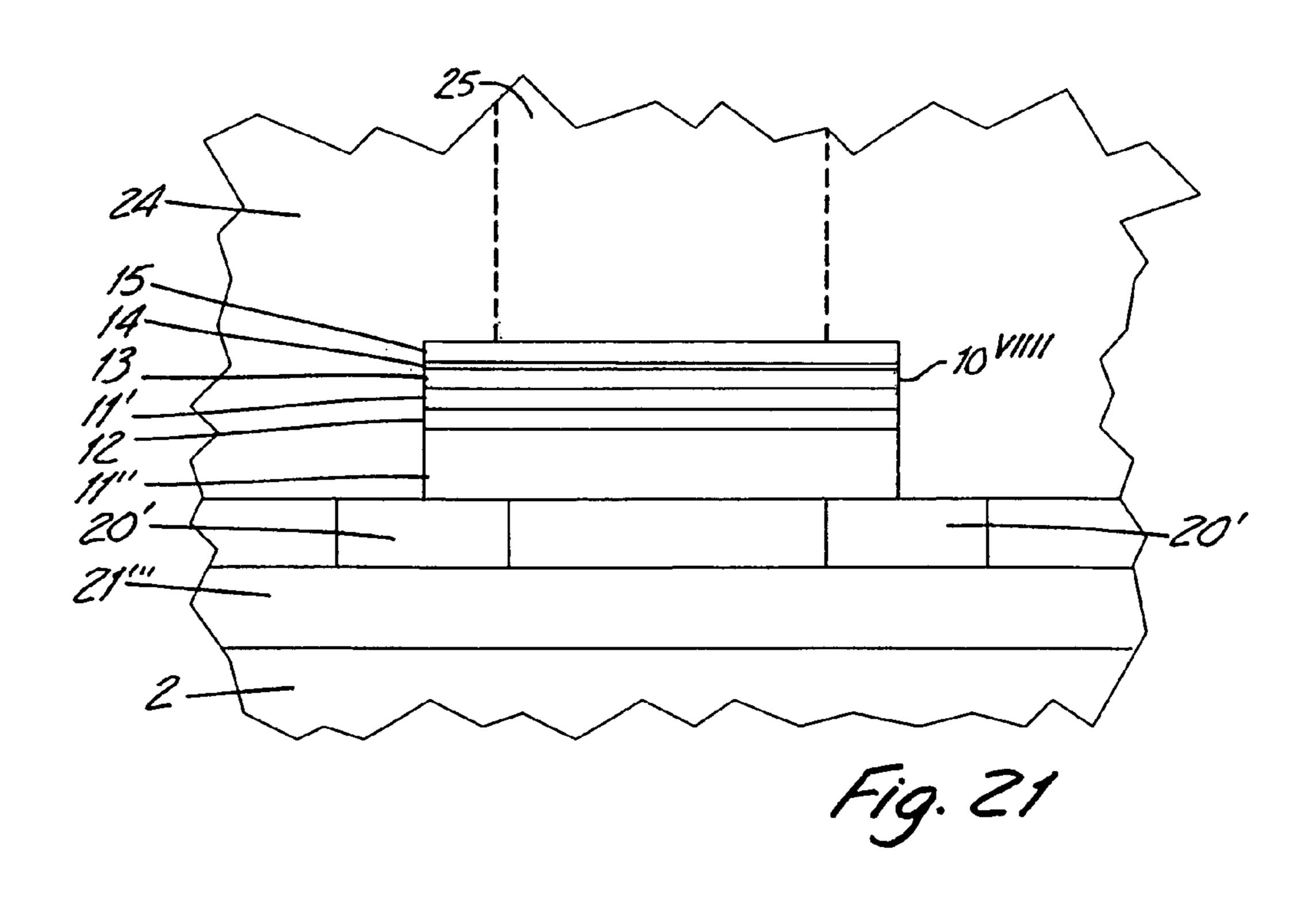

FIGS. 13 through 21 views of portions of monolithic integrated circuit structures embodying the present invention.

#### DETAILED DESCRIPTION

The use of magnetic material layers in the structures of magnetoresistive memory cells either in different arrangements or with different critical temperatures, either Curie 60 point or blocking temperatures as appropriate for each pertinent layer in the cell, or use of both of these structural layer alternatives, can allow memory operation with reduced electrical power or provide other advantages, or some combination thereof. Cell operations are typically initiated using a 65 current pulse through the memory cell, or in an electrical conductor of sufficiently high resistance in the vicinity of the

**14**

memory cell, or both, to generate sufficient heat to raise the temperature of the cell past one or more of these cell layer critical temperatures, and further supplying a suitable magnetizing current at proper times. Such a magnetizing current can be much less than the switching current needed to switch the magnetization direction of a magnetic material layer in an unheated cell.

In such arrangements where memory cell structures have data stored therein in conjunction with selectively heating those structures, the desired rapidity of storage is achieved by using thin isolating layers such as the dielectrics. In thin dielectrics, thermal equilibrium is reached in a very short time. This can be directly calculated by use of the Fourier heat conduction equation and the appropriate material parameters. The temperature rise is given in general by that equation as

$$\frac{\partial T}{\partial t} = \frac{k_{th}}{Cp\rho} \left[ \frac{\partial^2 T}{\partial x^2} + \frac{\partial^2 T}{\partial x^2} + \frac{\partial^2 T}{\partial x^2} \right],$$

where T is the temperature, t is the time,  $k_{th}$  is the thermal conductivity,  $\rho$  is the density,  $C_p$  is the specific heat at constant pressure, and x, y and z are the spatial coordinates. The thermal diffusivity constant is given by

$$k_d = \frac{k_{th}}{Cp\rho}.$$

In one dimension which is a reasonable approximation with a large heat sink directly below the heating sources, the temperature rise is given by

$$\frac{\partial T}{\partial t} = k_d \frac{\partial^2 T}{\partial x^2}.$$

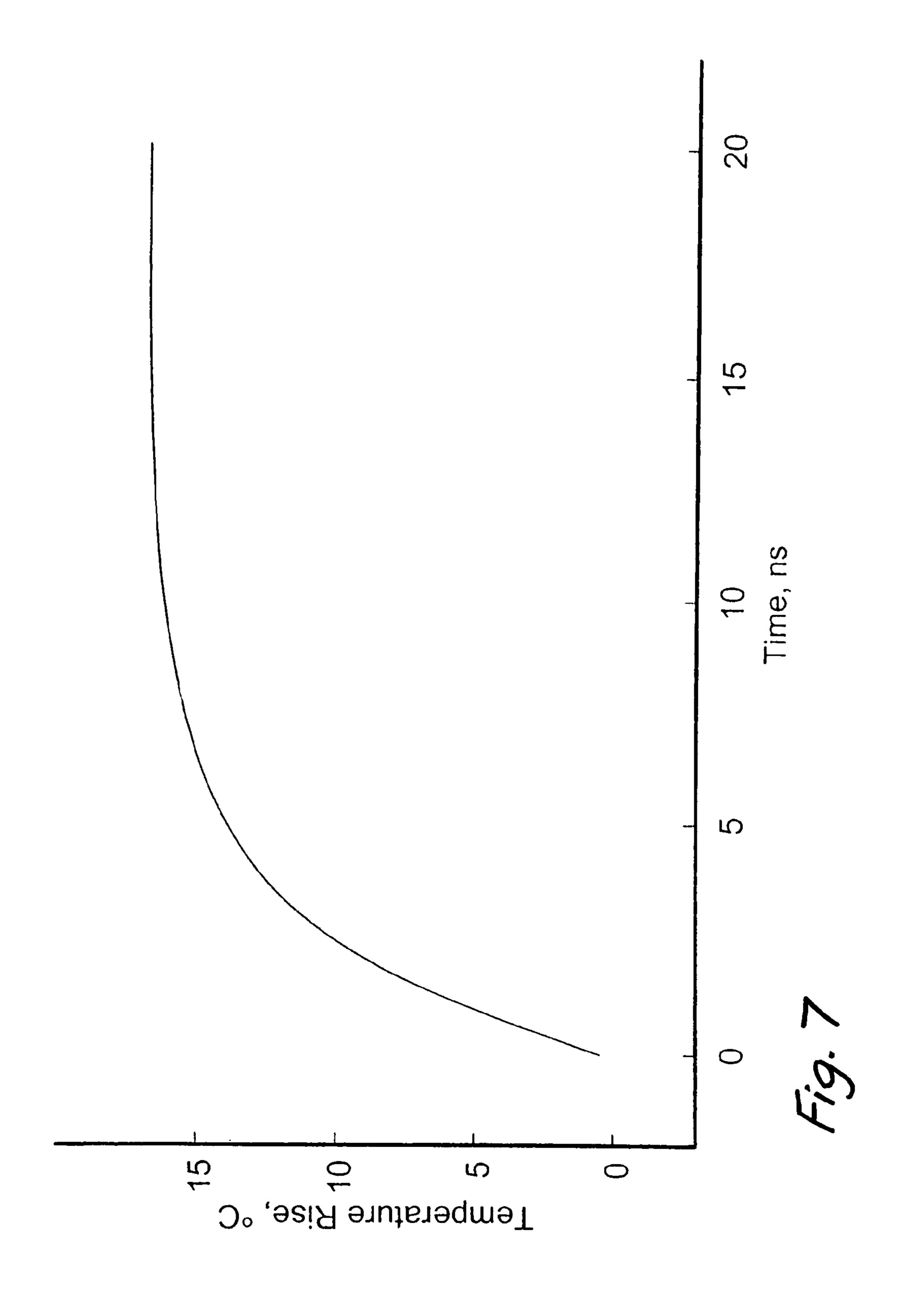

Consider a cell device like that of FIG. 1 but with a one micron wide word line made of 100 Å thick tungsten provided thereover so that such a memory cell located in silicon dioxide 200 Å below this word line, the device positioned over 500 Å of silicon dioxide supported on a substrate therebelow having a silicon integrated circuit therein. The thermal conductivity of silicon dioxide is 0.014 Watts/° C. cm, for tungsten 1.87 watts/° C. cm, and for silicon 1.5 watts/° C. cm. Because the silicon has more than 100 times the thermal conductivity of the silicon dioxide, the silicon in the remaining portions of the substrate can be treated as an infinite heat sink. The volume specific heat for silicon dioxide is 2.27 joules/° C. cm³ and for tungsten is 3.66 joules/° C. cm³. The tungsten line has a resistivity of about 8 Ω/□.

For this example, a 10 mA current was abruptly established in the word line and the temperature transient was determined using the above parameters in a numerical solution of the above on dimension diffusion equation. FIG. 7 shows the 17° C. rise reaching 90% of its final value in 6.5 nanoseconds. Thus, thermal time constants are not a limiting factor in data storage rapidity for sufficiently small versions of the above described memory cells, and will almost always be less, usually much less, than 100 ns.

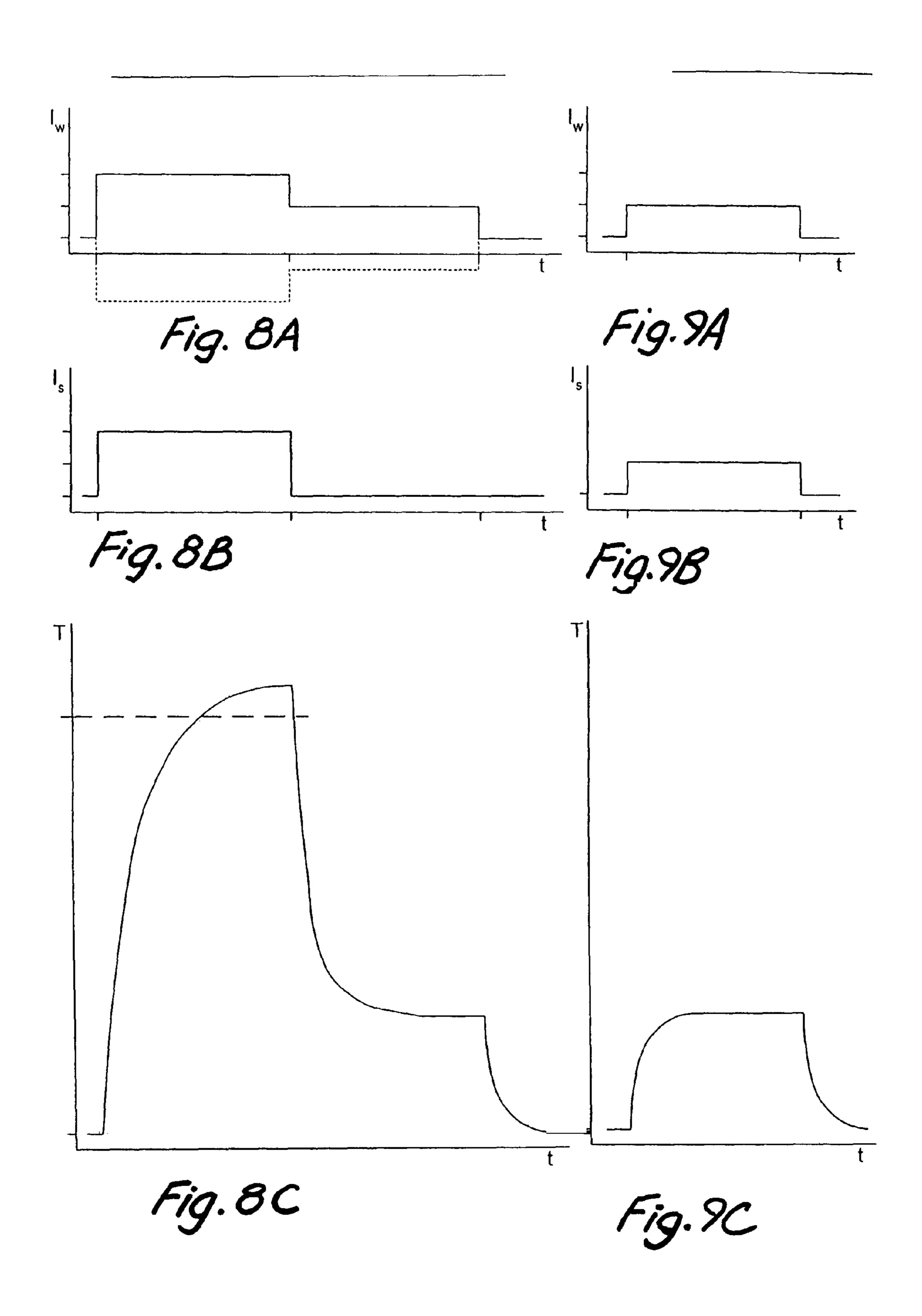

In operation, using coincident pulses in the word current,  $I_{w}$ , and in the sense current,  $I_{s}$ , to store and retrieve information from these kinds of memory cells, there will be typical waveforms of the kinds illustrated in FIG. 8 corresponding to

storage of data based on thermal pulses and FIG. 9 corresponding to data retrieval. In FIG. 8A, a full magnitude current pulse with respect to the initial zero magnitude is applied in the word line adjacent the memory cell in which data is to be stored during the first time period shown. Either a positive current represented by the solid line or, alternatively, a negative current represented by the short dashed line in FIG. 8A can be used depending on the direction of magnetization desired to be stored in the ferromagnetic material associated with the magnetically harder side of the nonmagnetic intermediate layer.

A similar full magnitude current pulse during that first time period is applied through the cell as a sense current as shown in FIG. 8B. Together, the heat generated by these current pulses forces the temperature of the cell up from its ambient value to past either the ferromagnetic material Curie temperature, or the antiferromagnetic material blocking temperature, depending on the kind of cell, as represented by the long dashed line in FIG. 8C. In this situation, the ferromagnetic material associated with the magnetically harder side of the nonmagnetic intermediate layer can relatively easily have the direction of magnetization therein set in the desired direction to hereby store a bit of data therein as described above.

This storage is accomplished by letting the cell cool below the pertinent one of the Curie or blocking temperatures (represented by the long dashed line in FIG. **8**C) while maintaining a magnetization direction setting magnetic field. To do so, the word line current in the second time period shown in FIG. **8**A is reduced in magnitude by one half with the remaining half magnitude current serving to provide the direction selection magnetic field for the ferromagnetic material associated with the magnetically harder side of the nonmagnetic intermediate layer during this cooling. The magnetization direction selected depends on which direction through the adjacent word line the word line current follows in being either the solid line current or the short dashed line current of FIG. **8**A.

The sense current in the second time period shown in FIG. 8B is reduced to zero to speed cooling. As can be seen in FIG. 8C, the temperature of the cell decreases below the dashed line temperature quickly. Following the second time period 40 shown in FIG. 8A, the word line current is reduced to zero and the cell temperature shown in FIG. 8C falls back to ins ambient value thereby completing the storage operation.

Retrieving information from the same cell as to the direction of magnetization of the ferromagnetic material associ- 45 ated with the magnetically harder side of the nonmagnetic intermediate layer is shown in FIG. 9 to be completed in the one time period shown. A half of the full magnitude current pulse is provided in this time period in both the adjacent word line, as shown in FIG. 9A, and through the cell as shown in 50 FIG. 9B. Retrieval circuitry not shown senses any cell resistance value change to make the determination as to the direction of magnetization of the ferromagnetic material associated with the magnetically harder side of the nonmagnetic intermediate layer to thereby retrieve the data represented by 55 this direction. As shown in FIG. 9C, the cell temperature does not rise significantly since in these circumstances only a quarter of the power is dissipated compared to the power dissipated in the first time period involved with the storing of data shown in FIG. **8**A.

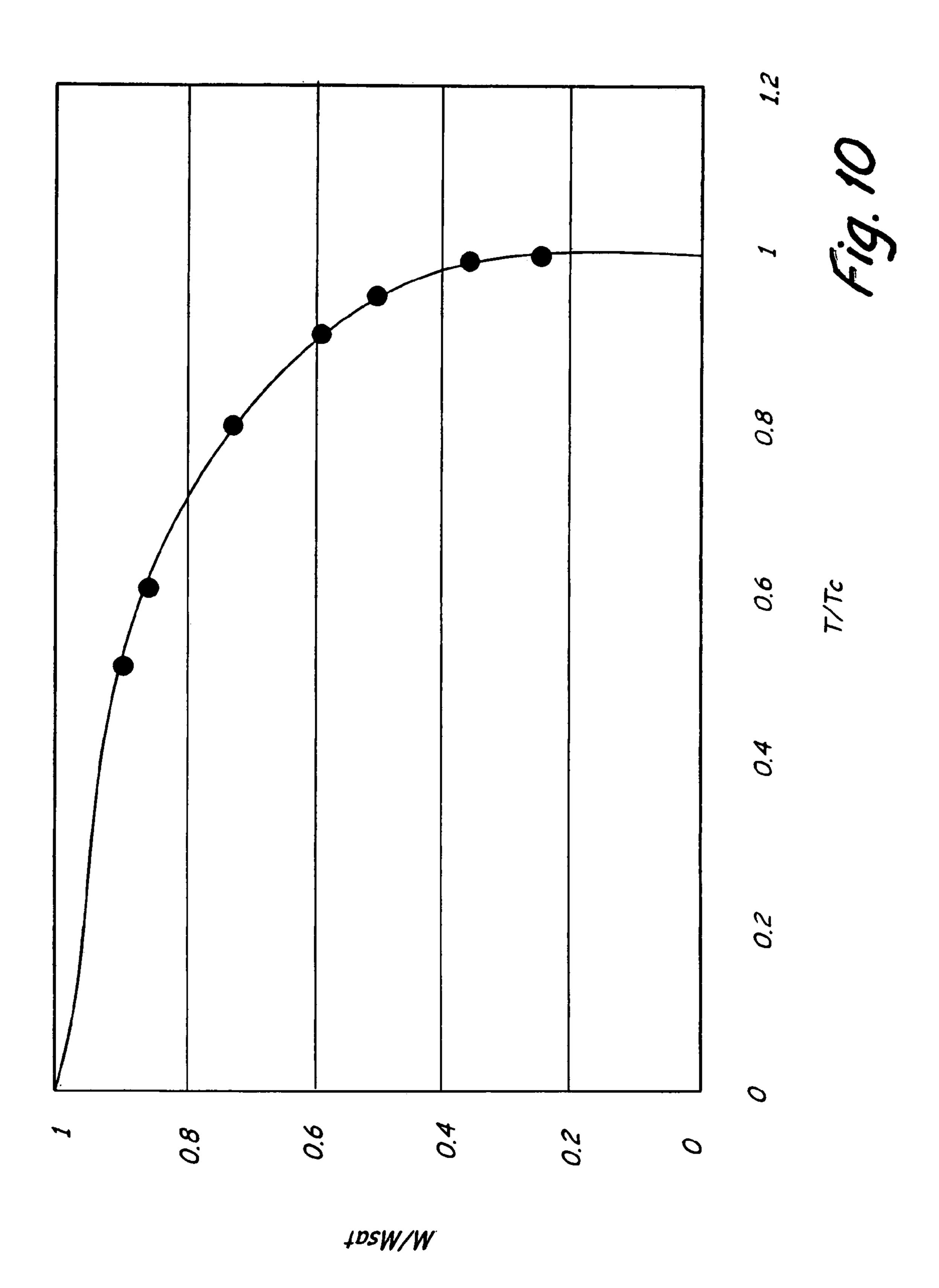

FIG. 10 is a graph in normalized form for a typical ferromagnetic material of the magnetization thereof, normalized through using the material magnetic saturation as the normalizing factor, versus temperature of the material normalized through using the material Curie temperature as the normalizing factor. As the thermal energy increases with temperature, it begins to overwhelm the magnetic anisotropy energy

**16**

of the ferromagnetic material until the summed atomic magnetic moments of the material sample is zero due to the thermal randomization of those magnetic moments.

Returning to FIG. 2A for these circumstances, the graph shows the major resistance versus applied external magnetic field characteristic for a "pinned" layer spin dependent tunneling memory cell having the maintained magnetization direction oriented in one direction along the length of that cell. A mirror image characteristic, i.e. essentially the same characteristic as shown in FIG. 2A rotated about the resistance axis, results for a maintained magnetization direction oriented in the opposite direction along the length of that cell. During the storage of data therein, however, these characteristics are transformed as the blocking temperature for the "pinning" layer is reached by either essentially collapsing if the blocking temperature exceeds the Curie temperature of the adjacent ferromagnetic layer or reverting to the major resistance versus applied field characteristics of just the ferromagnetic layers if it does not.

During retrieval of data from this memory cell, field magnitudes only relatively near zero are applied to these characteristics so that the operating point moves from one to the other of the two resistance lobes shown in FIG. 2A. This behavior effectively results in a minor loop characteristic for retrieval purposes as is shown in FIG. 2B.

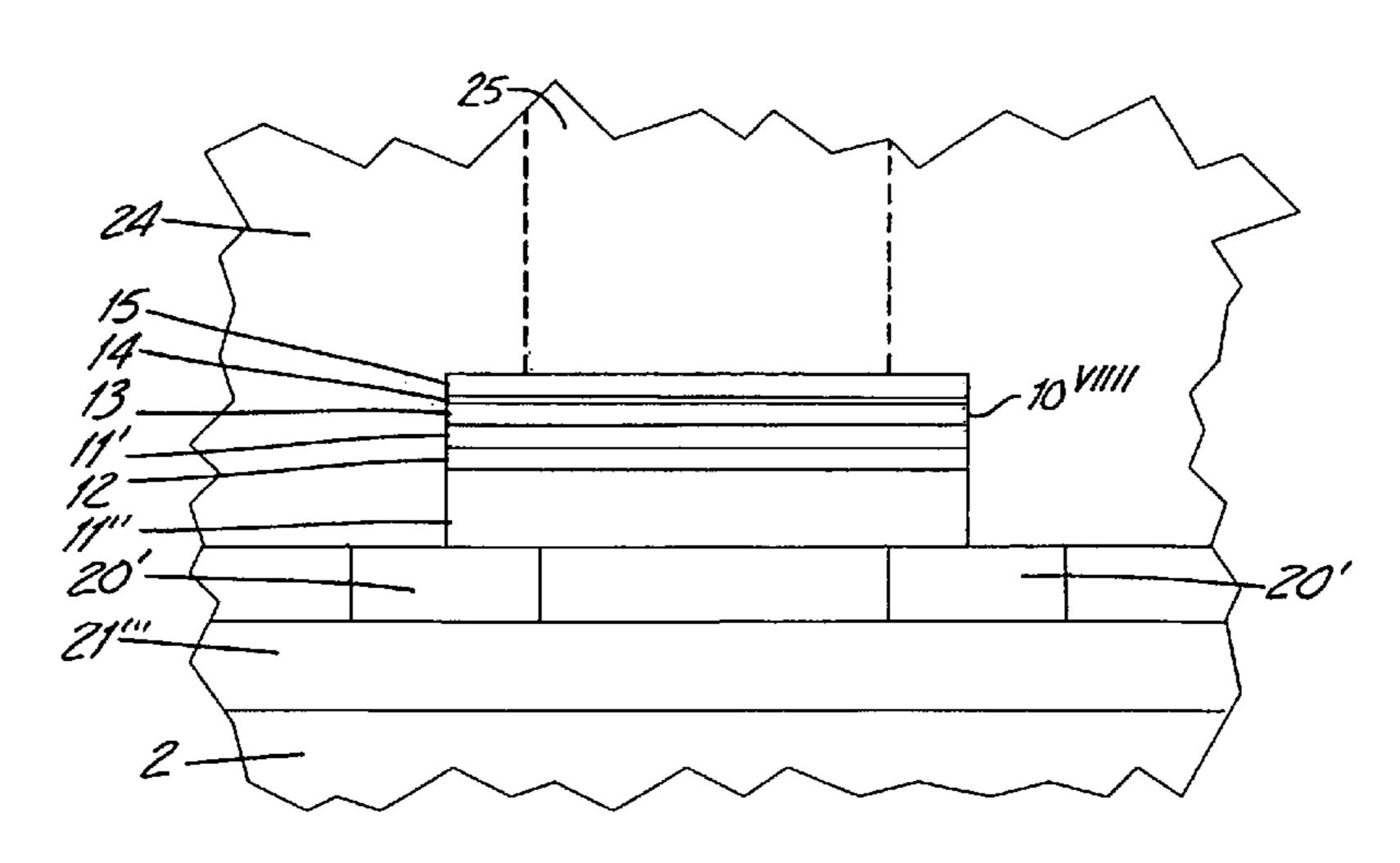

FIG. 11A shows an array of magnetoresistive memory cells, 10, similar in many respects to the cell of FIG. 1 (or that cell with the layers therein provided in inverse order out from the substrate) in and from which data is to be stored and retrieved using thermal methods as indicated above, these cells being provided on substrate 2 containing a monolithic integrated circuit for operating the cells. Cells 10 may each be a GMR effect based cell with a some sort of a "pinning" layer, 11, perhaps an antiferromagnetic material layer, adjacent to a ferromagnetic material layer, 12, perhaps supplemented by another ferromagnetic material layer, 13, to form a "pinned" layer structure, 11, 12, 13, on one side of a nonmagnetic layer, 14, which is electrically conductive in a GMR effect based cell. Provided on nonmagnetic layer 14 is a "free" layer, 15,16,17, of relatively small effective coercivity that is provided to form cell 10 as a spin valve type memory cell. Layer 15,16,17 may be a homogeneous layer of ferromagnetic material, or it may be a layer formed as a composite of other layers of various kinds of materials including plural layers of differing ferromagnetic materials and possibly combined with yet another layer but of a nonmagnetic material.

Memory cells 10 are shown in FIG. 11A interconnected by sense line interconnections, 20, in parallel series strings so that each such string forms a sense line, 20', extending from left to right in the figure (or vice verse). Interconnections 20 and cells 10 in these strings 20' are provided on an electrically insulating material layer, 21, to be separated by portions of that layer from, and positioned over, a set of word lines, 22, shown in dashed line form, that extend parallel to one another and perpendicular to the sense lines so that each of these word lines passes under a corresponding sequential set of cells 10 such that each cell in the set is in a different string.

These sense lines and word lines in FIG. 11A together allow coincident current pulses therein to generate coincident thermal pulses thereabout that combine at selected ones of cells 10 where a current activated sense line and a current activated word line cross one another. Data can be stored in such cells when heated through use of smaller magnitude currents than otherwise required as described above. Data sensing currents for retrieving stored data from cells 10 are established in those cells 10 through sense lines 20' as also described above.

Alternatively, as shown in FIG. 11B, where the same designations are used as in FIG. 11A for similar structures, sense line path heating lines, 20", are provided each parallel to a corresponding sense line on a side thereof opposite the substrate, i.e. word line like structures each paralleling the path of corresponding one of sense lines 21' but on the opposite side of the cell from word lines 22. Heating lines 20" can be of higher resistivity material across from cells 10, or just narrower there, or both, to increase the thermal pulses energies primarily in the vicinity of those cells that result when elec- 10 trical current is established in those heating lines. Thus, the current pulses for heating a selected cell can pass through the adjacent heating line 20" and the adjacent word line 22, and need not pass through such selected ones of cells 10 even though these cells, when selected, are subjected to corre- 15 sponding thermal pulses resulting from those currents. Data sensing currents for retrieving stored data from cells 10 are, as before, established in those cells 10 through sense lines 20'.

In a further alternative, the establishment of heating current pulses for a selected cell 10 can be accomplished through a 20 portion of its sense line 20' and a portion of its corresponding word line 22, as well as through that selected cell, if the cell is electrically connected by a switching transistor to that word line. In the FIG. 11A arrangement, there would be an electrical current conduction via from word line 22 at each of cells 25 10 therealong into substrate 2 to the corresponding switching transistor in the substrate for that cell, and a further conduction via into the substrate to the other side that transistor along the main current flow path therethrough from an adjacent interconnection 20 in contact with that cell. Thus, opening the 30 circuit at one end of a sense line 20' in which a selected cell is connected, and placing the other end at a voltage relatively low or high with respect to the voltage concurrently established on the adjacent one of word lines 22, will allow current word line as well as the cell if the cell switching transistor is switched on to provided a thermal pulse to that cell. Data storage currents are used to store data during such heating in a similar manner to the description above, and sense currents in sense lines 20' again are used to determine the cell resis- 40 tance in retrieving stored data therefrom.

On the other hand, the establishment of heating current pulses for a cell 10 only on a word lines 22, and again not through sense lines 20' and cells 10 therein, can provide sufficient heating pulses for the cells if a corresponding 45 switching transistor is provided for each of cells 10 electrically connected to a corresponding heating structure provided for each of the cells which in turn is connected to an adjacent corresponding word line 22. Such an arrangement is shown in FIG. 11C where again the same designations are used as in 50 FIG. 11A for similar structures. Serpentine heating structures, 22', are provided on the substrate side of insulating material layer 21 each across from a corresponding one of cells 10 and each electrically connected at one end thereof to that word line 22 adjacent to its corresponding cell. A reduced 55 cross section path structure is provided for heating structures 22' between word line 22 and the other end, 22", of each heating structure to increase the electrical resistance thereof but higher resistivity material could used instead of, or together with, the reduced cross sections path structures to 60 raise the electrical resistance value.

The other end 22" of each heating structure is connected to an electrical current conduction via extending into the substrate to electrically connect to a corresponding switching transistor having the other side of that transistor on the main 65 current path therethrough electrically connected to a voltage of a selected value such as at chip ground or at some other

18

chosen value. Thus, a greater or smaller voltage value impressed on a word line 22 will result in an electrical current being established through any heating structure 22' connected to that word line upon having the switching transistor connected to this structure switched on to thereby provide a thermal pulse to that cell 10 corresponding to that heating structure. Again, data storage currents are used to store data during such heating in a similar manner to the description above, and sense currents in sense lines 20' again are used to determine the cell resistance in retrieving stored data therefrom. In an alternative cell construction, cells 10 can instead be spin dependent tunneling memory cells rather than GMR effect based cells if each cell is provided directly on, or at least has its bottom layer connected to, its corresponding word line 22, in which instance sense lines 20' would be continuous and electrically connected to only the top layer of those cells 10 adjacent thereto. There is relatively little change in the cell thermal characteristics since the sense line would be on the opposite side of the cell from the corresponding word line. In this instance, intermediate layer 14 would be of an electrically insulative material. In a further alternative cell construction, cells 10 can instead be spin dependent tunneling bit structure memory cells rather than GMR effect based bit structure memory cells if each cell as shown in FIG. 11B is supplemented as shown by providing a very thin electrically insulative material on layer 15,16,17 and then a ferromagnetic layer on that insulative layer perhaps in connection an antiferromagnetic layer to form a composite "pinning" layer. This "pinning" layer of each such cell is electrically connected to the corresponding one of heating lines 20". At this point in the description, cells 10 will continue to be considered to be GMR effect based cells in accord with the drawing shown in FIG. 11A.

Substrate 2 has a semiconductor base with appropriate to be established through portions of that sense line and that word line as well as the cell if the cell switching transistor is switched on to provided a thermal pulse to that cell. Data storage currents are used to store data during such heating in a similar manner to the description above, and sense currents in sense lines 20' again are used to determine the cell resistance in retrieving stored data therefrom.

On the other hand, the establishment of heating current pulses for a cell 10 only on a word lines 22, and again not through sense lines 20' and cells 10 therein, can provide sufficient heating pulses for the cells if a corresponding switching transistor is provided for each of cells 10 electri-

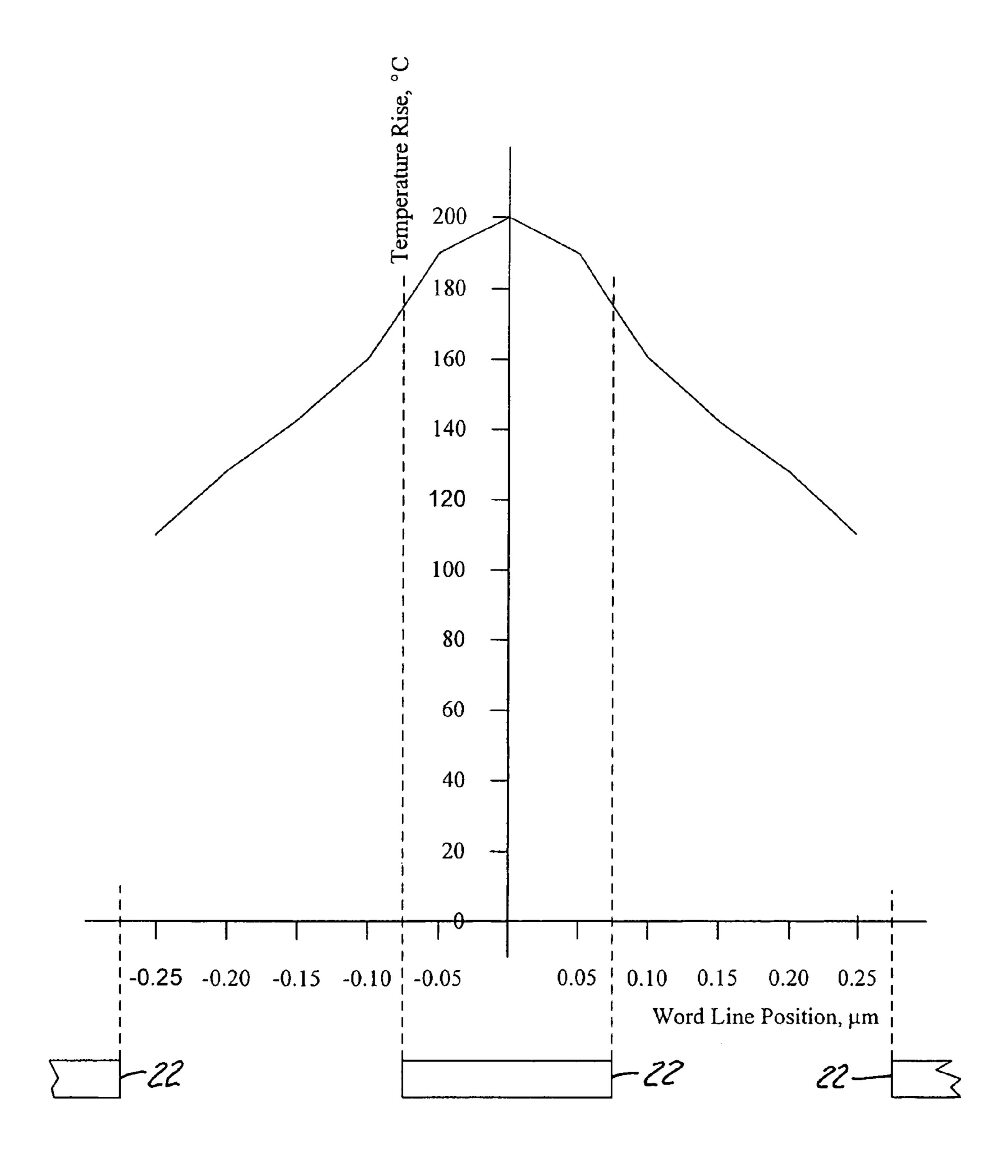

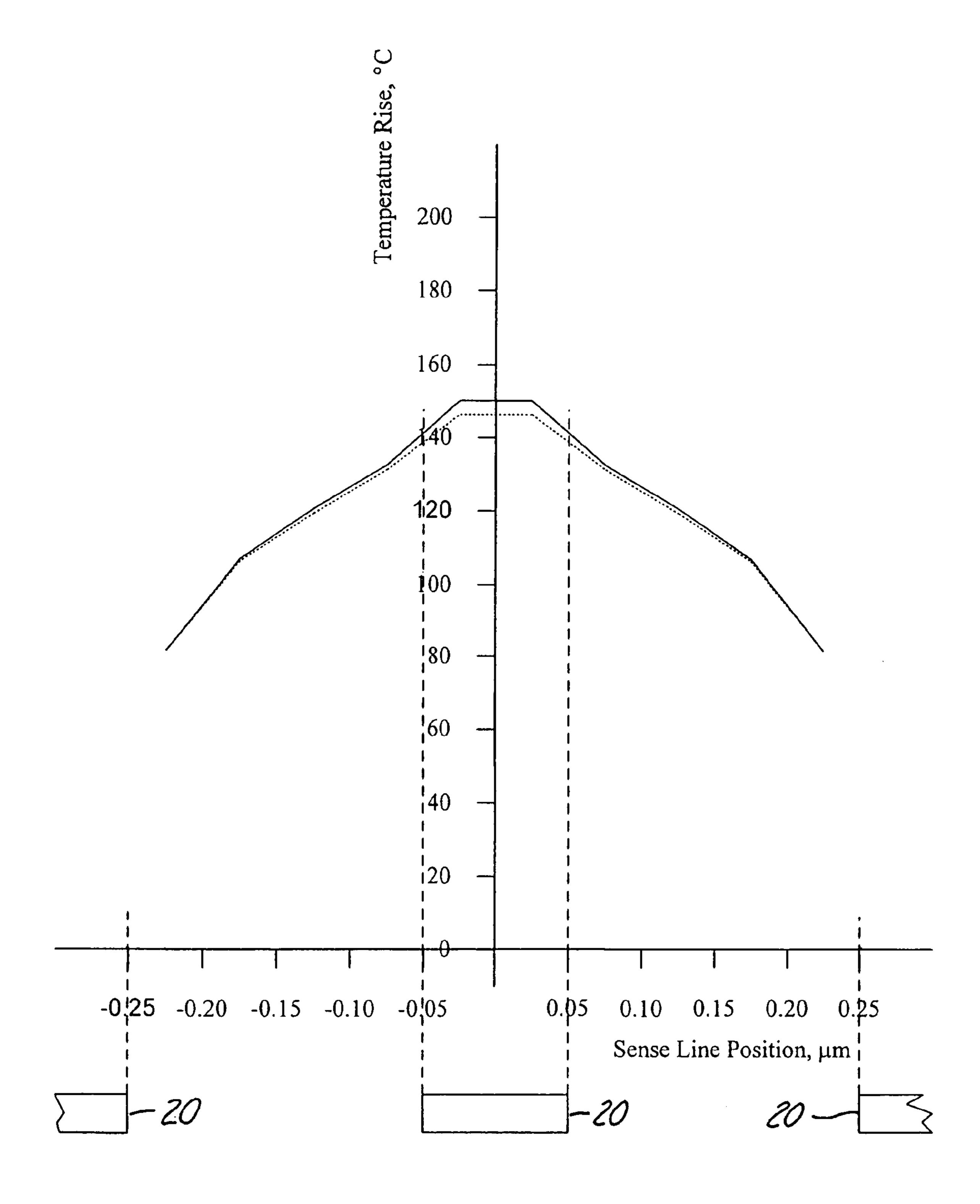

If electrical currents in the device of FIG. 11A are initiated and maintained for a sufficiently long time in a selected one of sense lines 20' and in a selected one of word lines 22, thermal equilibrium will be reached thereabout. A resulting temperature profile calculated for the region about a word line 22 having such a current therein is shown in FIG. 12A and a resulting temperature profile calculated for the region about a sense line 20' having such a current therein is shown in FIG. 12B. The solid line profile represents the result with respect to the center of the word line below which has a higher temperature than at the sides thereof, as seen in FIG. 12A, and the dashed line profile represents the result with respect to the edges of the word line below.

As can be seen, the temperature rise due to these currents in the selected one of word lines 22 and the selected one of sense lines 20' is quite substantial but is, nevertheless, closely confined about the selected lines in there being a much smaller rise at adjacent word lines and sense lines, respectively, so that the magnetizations in these adjacent cells are not disturbed. This occurs because of the sufficient extents of, and the smallness of thermal conductivities of, the interconnec-

tion structures used with the memory cells and because of the sufficient extents of, and the smallness of thermal conductivities of, of those portions of the substrate supporting the memory cells and the materials positioned therebetween.

Such thermal pulses thus can be used to raise the tempera- 5 tures of the layers in a selected magnetoresistive effect based magnetic memory cell in connection with the storage of data therein that is provided in a relatively dense monolithic integrated circuit chip surface array of such cells without adversely affecting the magnetic state of adjacent memory 10 cells. Depending on the structure chosen for such memory cells and the operating methods therefor, one, two, three or even four of the magnetic material layers therein can be involved in thermal pulse data storage operations where these are layers that have a magnetic property that is substantially 15 maintained below a corresponding critical temperature above which such property is not maintained. These critical temperatures can involve the corresponding Curie point temperatures for ferromagnetic material layers or blocking temperatures for antiferromagnetic material layers, or both.

Curie point temperatures can be selected in a range for permalloy ferromagnetic materials by changing the composition thereof to some extent by adding other alloying material such as chromium or vanadium and, of course, different ferromagnetic materials can be substituted for one another to obtain ferromagnetic layer materials with different Curie point temperatures. Similarly, antiferromagnetic materials such as CrPtMn or FeMn can be substituted for one another to obtain antiferromagnetic layer materials with different blocking temperatures or, again, the composition of such a material can be altered to some extent to change blocking temperature values thereof.

As indicated above for very small magnetoresistive effect based memory cells, providing a sufficient energy well depth for a half selected cell to maintain thermal stability is necessary as is keeping the current density within suitable limits in the sense and word lines used with the cells. The use of thermal pulse operating methods with memory cells exploits the heat that is created by currents in these lines rather than accepting such heat generation as a limit to thereby allow the construction of smaller memory cells despite the increased demagnetization fields such smaller cells exhibit below such critical temperatures. Some additional cell structures are described below beyond those already described in the foregoing.

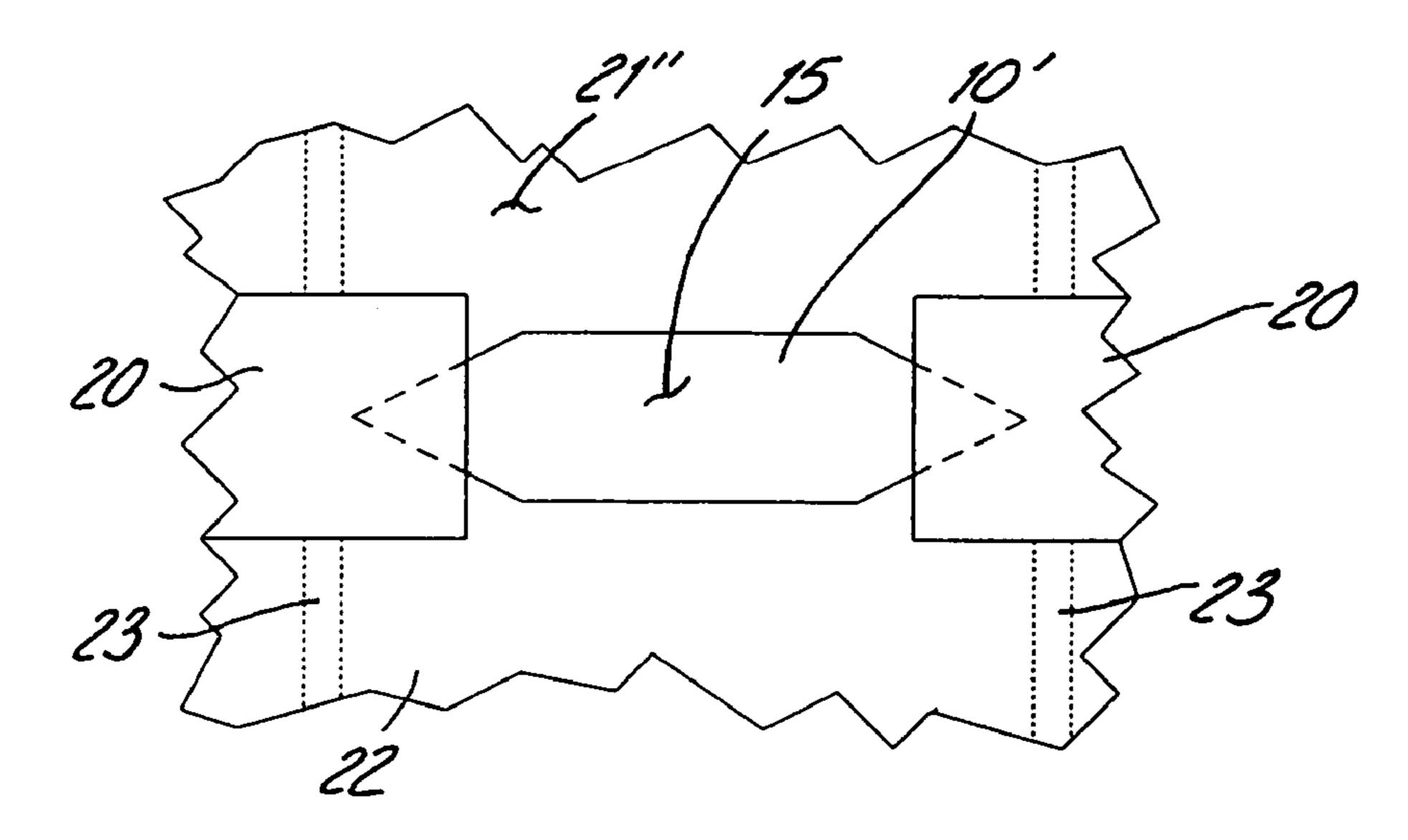

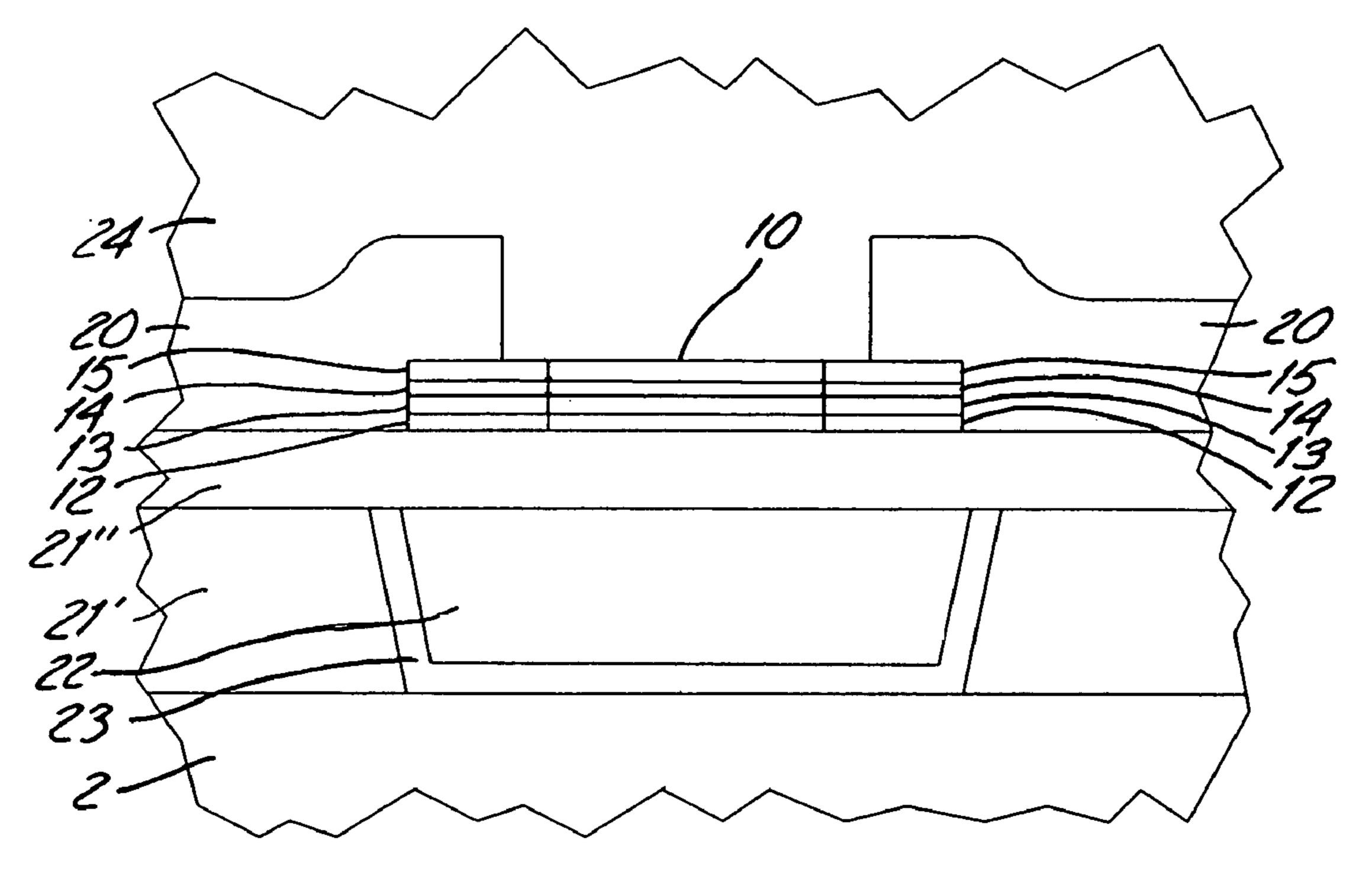

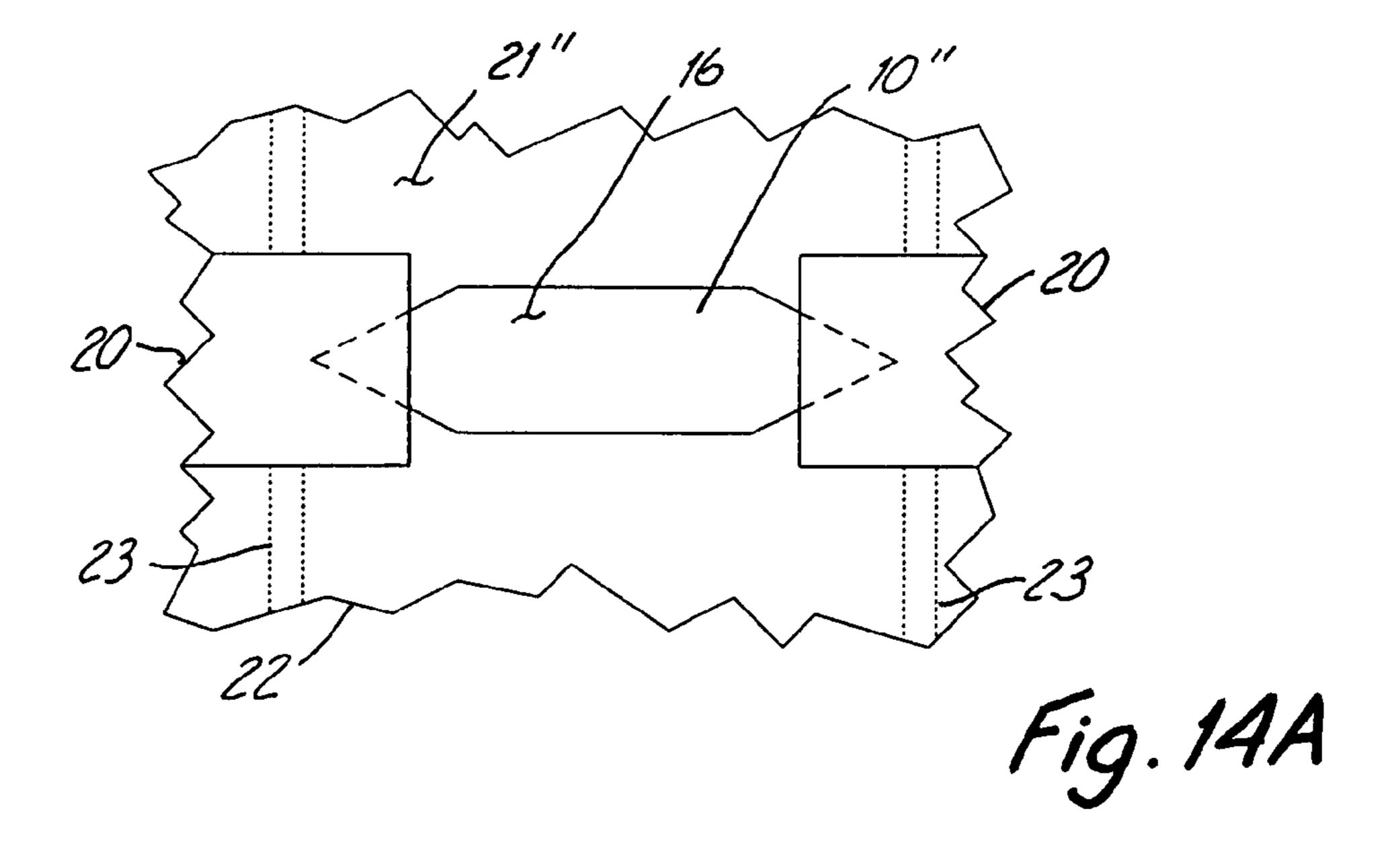

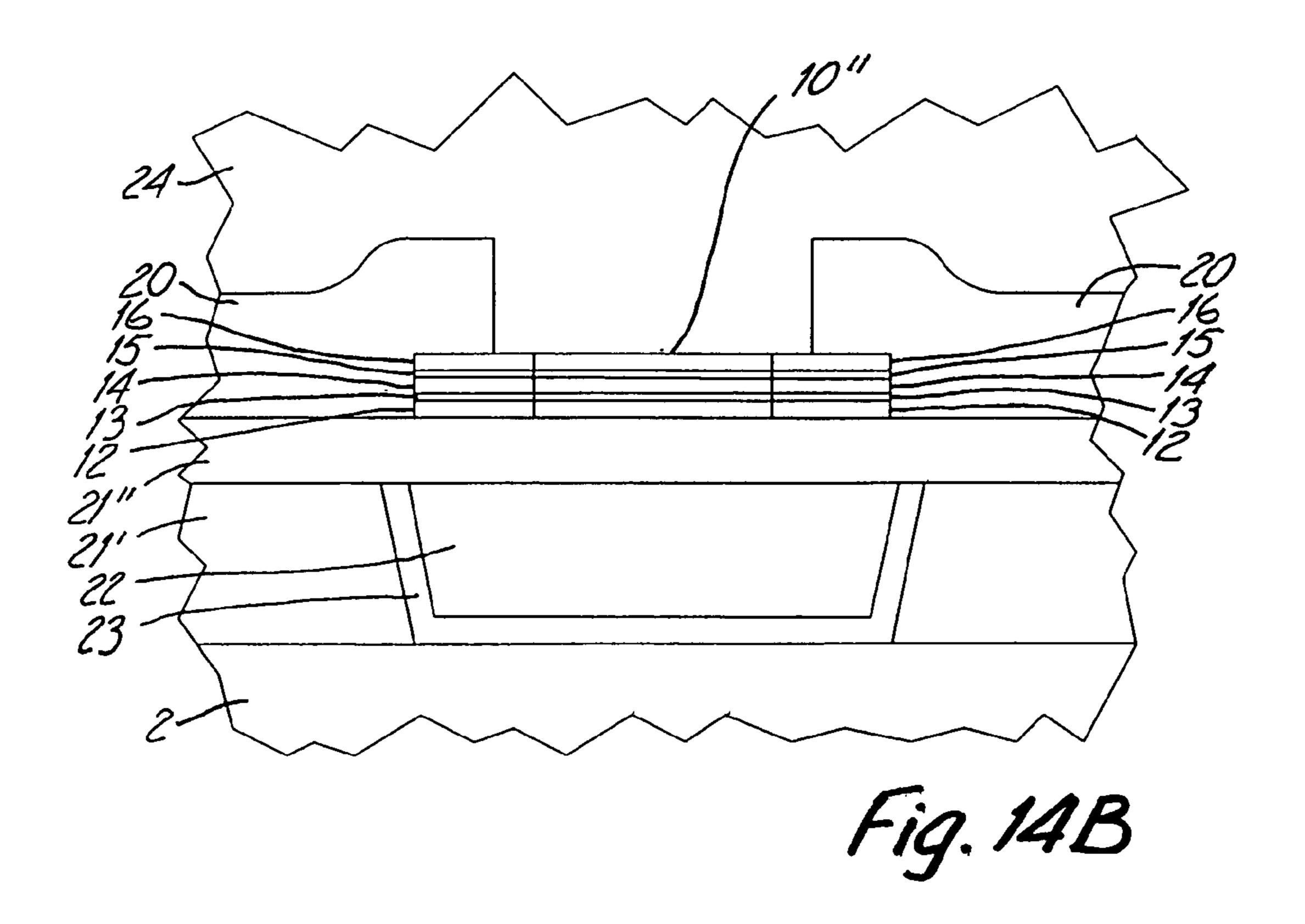

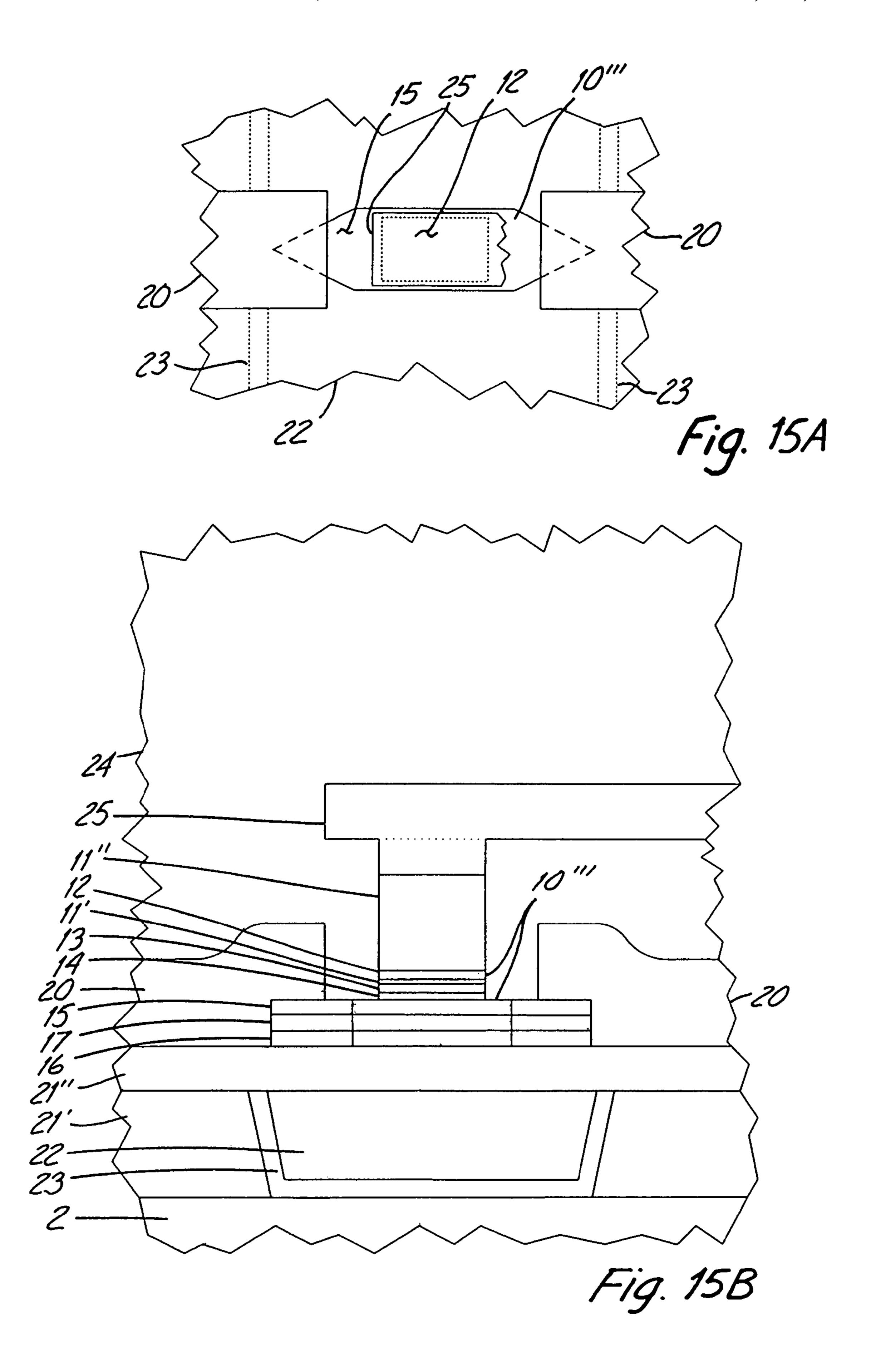

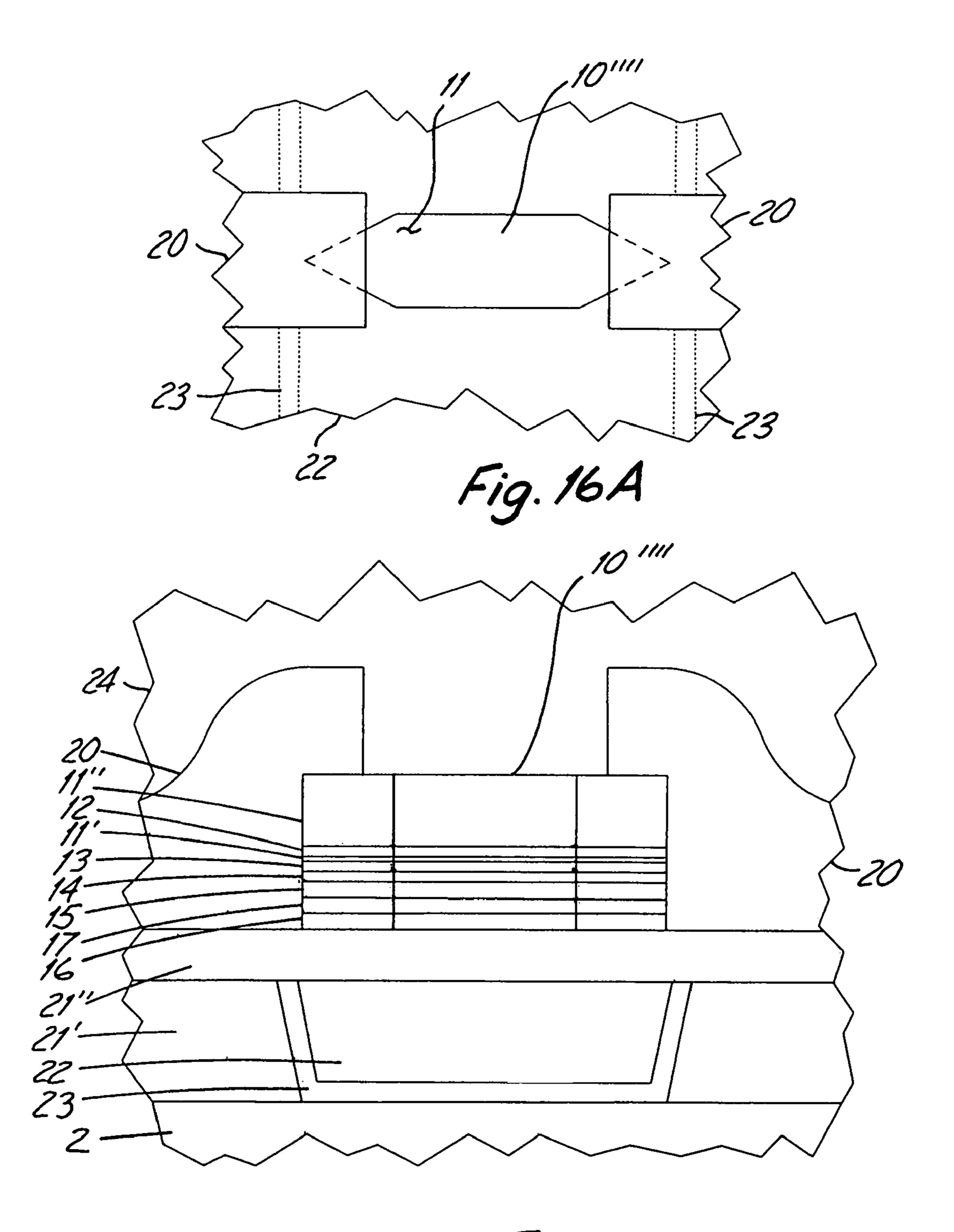

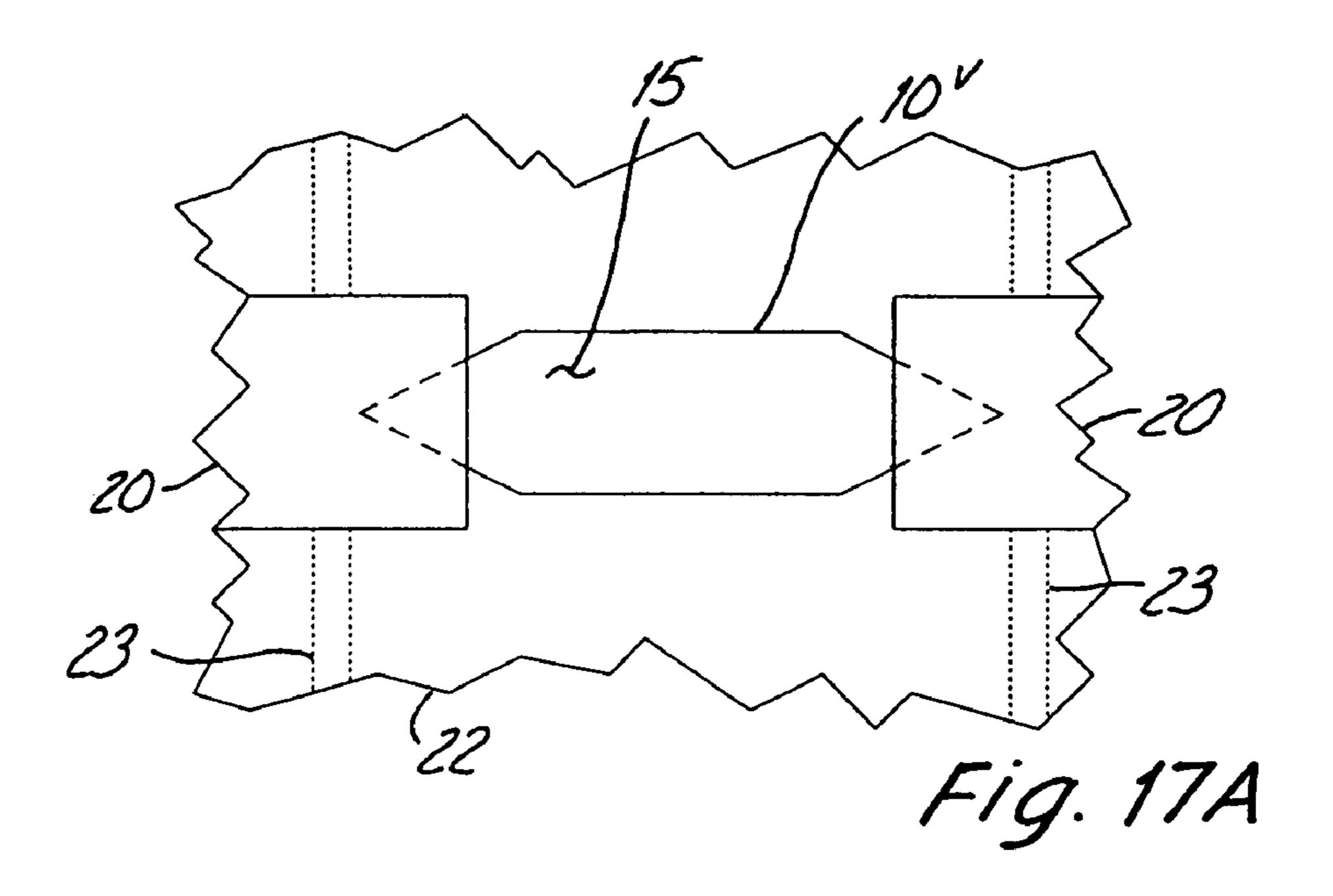

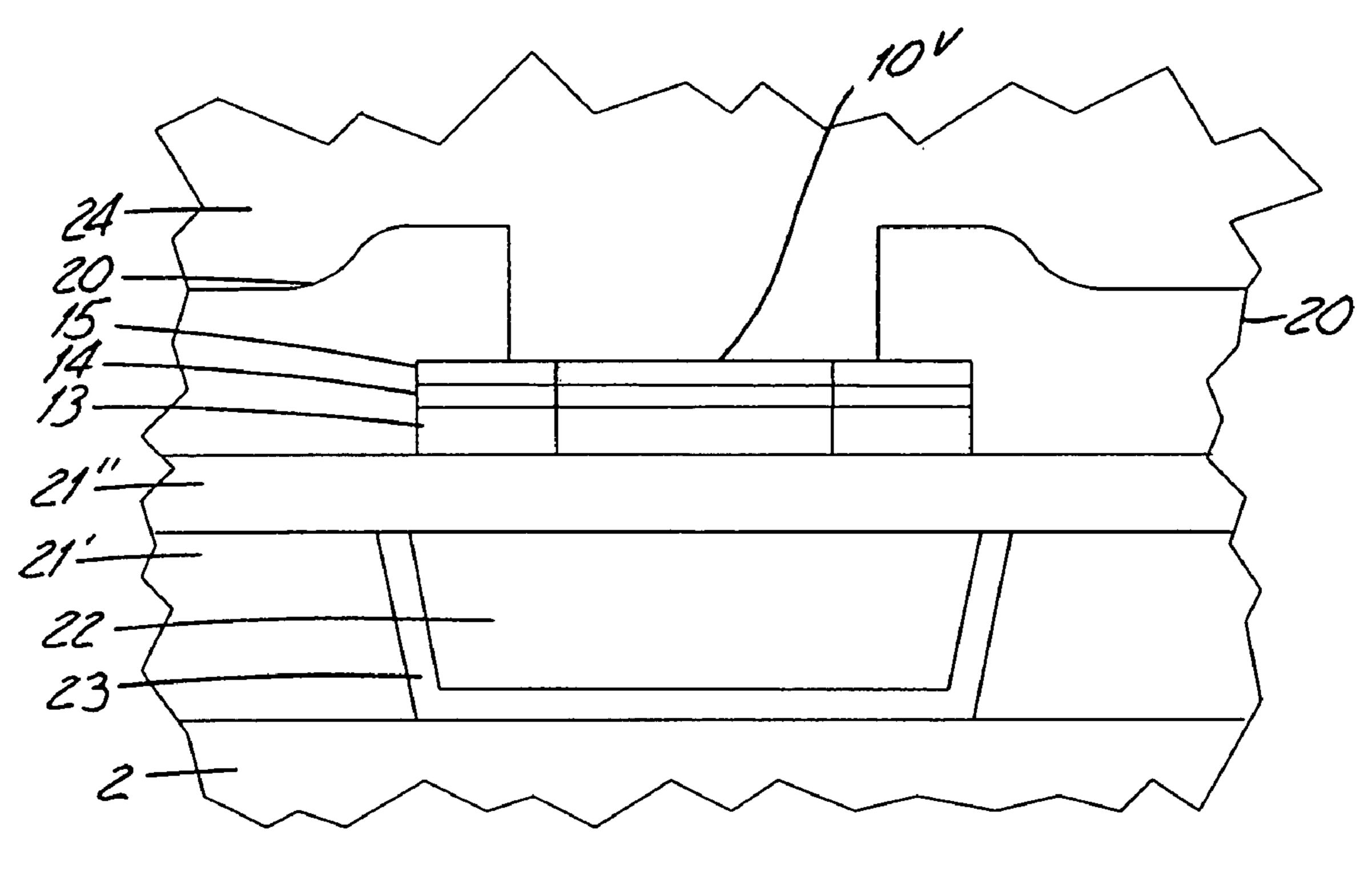

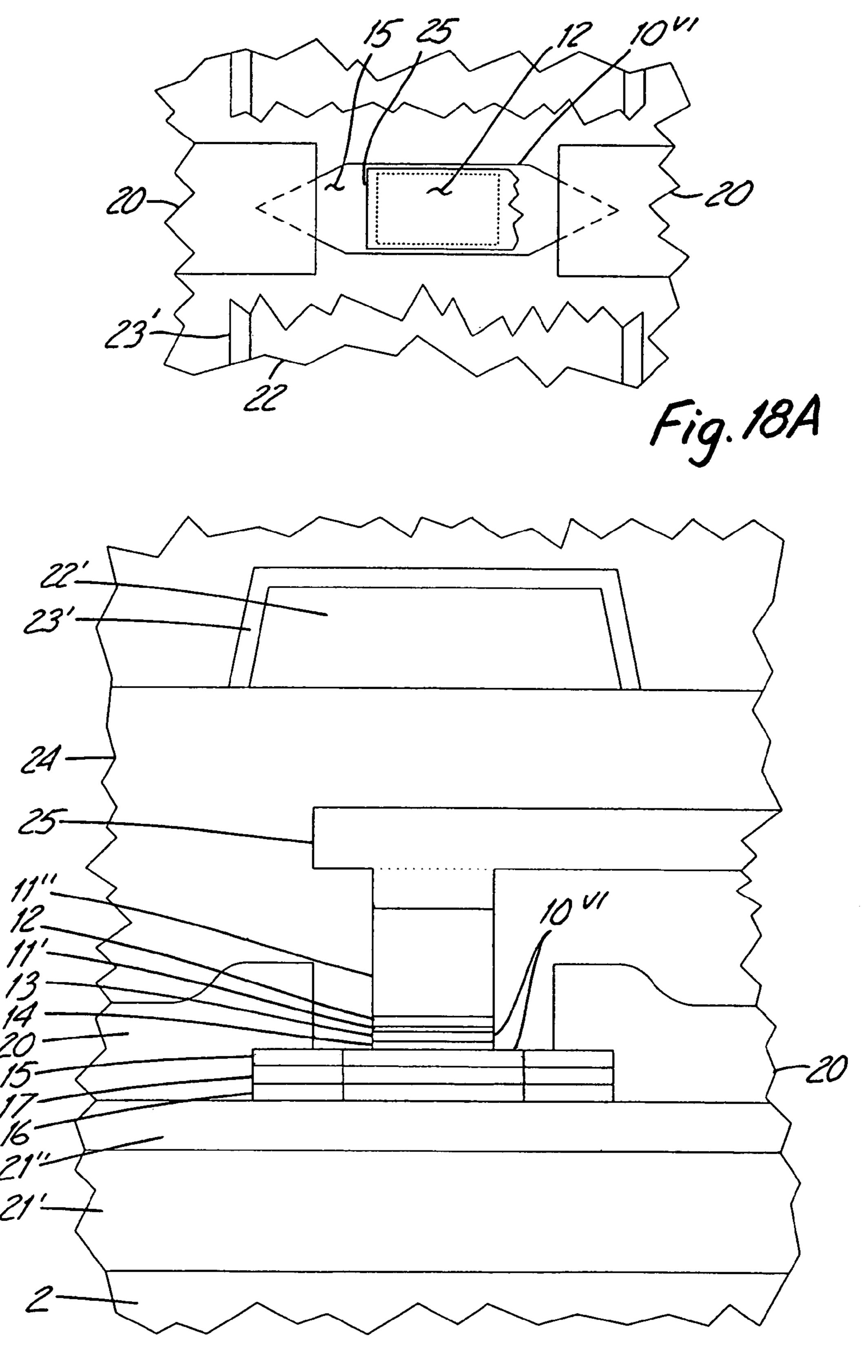

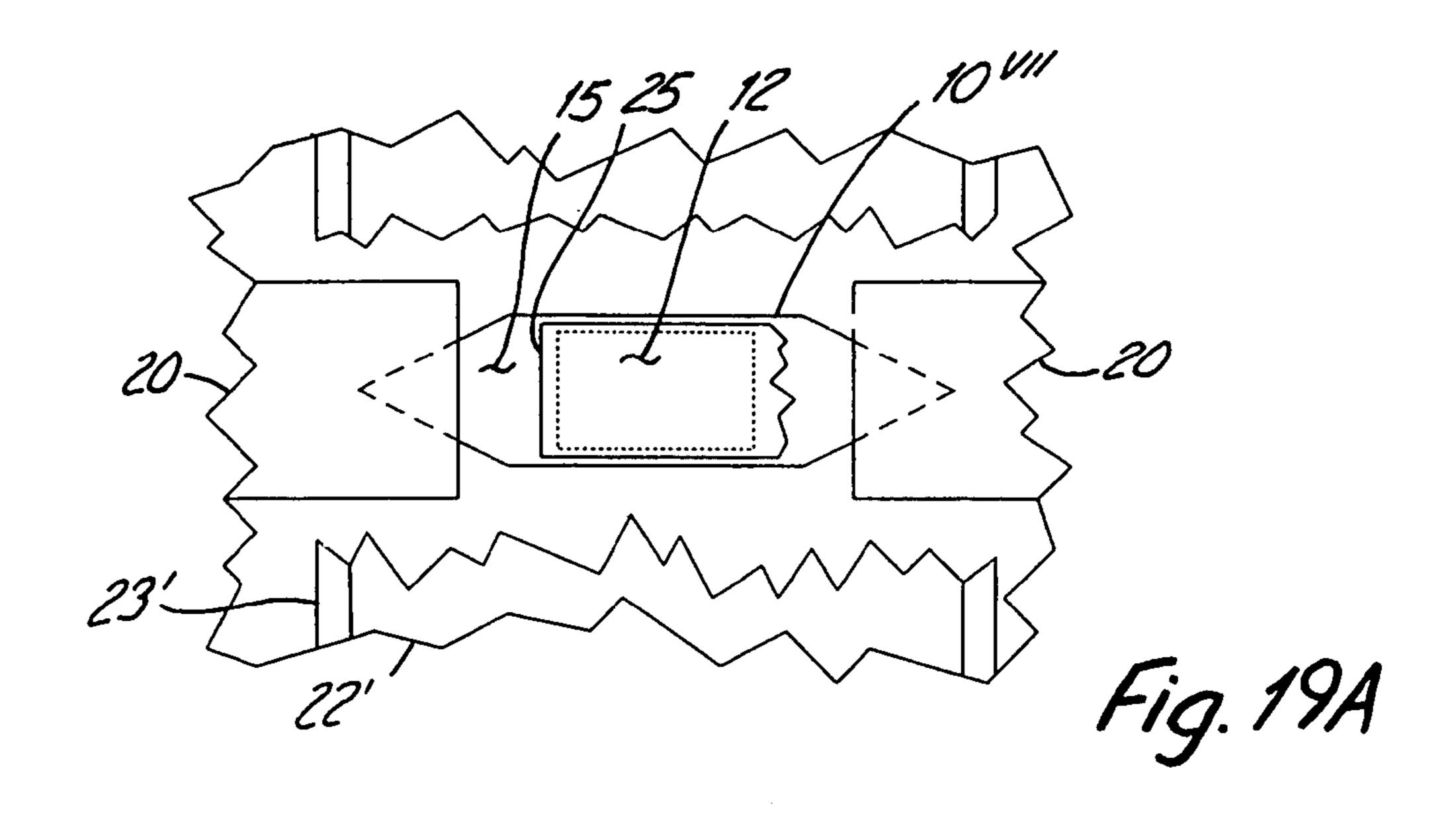

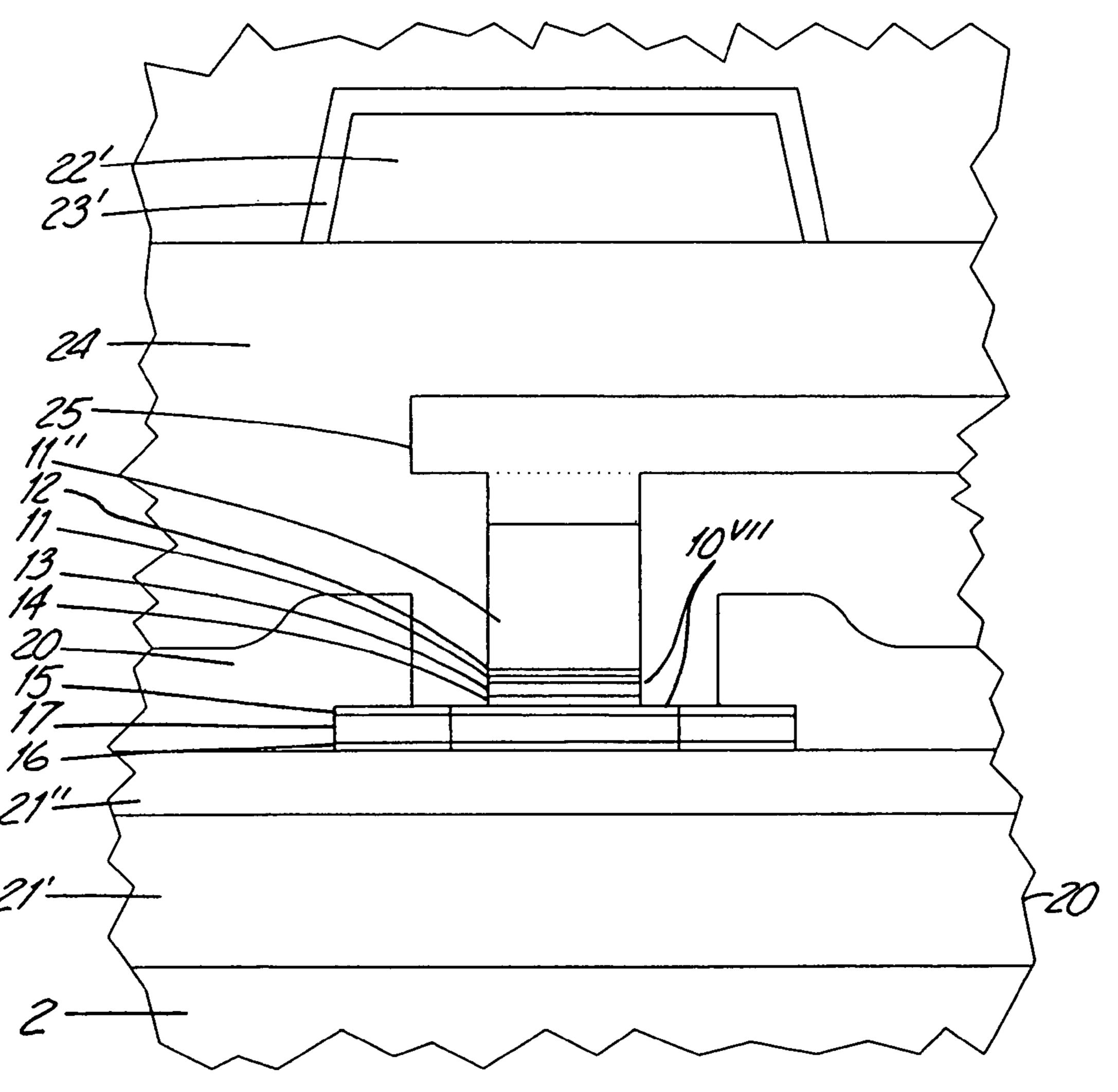

FIG. 13A is a top view, and FIG. 13B is a cross section view, of a thermal pulsed operation magnetoresistive effect based memory cell, 10'. Memory cell 10' is electrically connected to others of the memory cells in the array thereof provided on a surface in the monolithic integrated circuit in 50 which the memory is provided and the operating circuitry therefor through sense lines 20. Word line 22 and ferromagnetic material field keeper cladding, 23, provided about the sides and lower surface of word line 22, are together supported on and separated from the operating integrated circuit 55 portion of substrate 2 by a silicon nitride layer on the interconnection portion of the operating monolithic integrated circuit having a thickness of 500 Å. A further silicon nitride planarization layer, 21', is provided on this last silicon nitride layer in substrate 2 alongside word line 22. Word line 22 is 60 electrically isolated from memory cell, or bit structure, 10' by a further silicon nitride layer, 21", which is 250 Å thick.

Memory cell 10' is a "pseudo" spin valve cell based on the GMR effect in having a relatively high coercivity layer due to the greater thickness of ferromagnetic material on one side of 65 an electrically conductive intermediate layer versus a thinner layer of ferromagnetic material on the opposite side. Hence,

**20**

this latter layer will have the direction of its magnetization switched in the presence of an appropriate externally applied magnetic field of a lower magnitude than that needed to switch the magnetization direction of the thicker ferromagnetic material on the opposite side.