#### US007774493B1

## (12) United States Patent

#### **Damle**

## (10) Patent No.:

US 7,774,493 B1

(45) **Date of Patent:**

\*Aug. 10, 2010

# (54) FRAME STRUCTURE AND METHOD FOR WAVELENGTH CONCATENATED CHANNEL FRAMING

- (75) Inventor: Rajendra R. Damle, Plano, TX (US)

- (73) Assignee: Ceterus Networks, Inc., Richardson,

TX (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 1748 days.

This patent is subject to a terminal disclaimer.

- (21) Appl. No.: 10/927,768

- (22) Filed: Aug. 27, 2004

### Related U.S. Application Data

- (63) Continuation of application No. 10/086,273, filed on Feb. 20, 2002, now Pat. No. 7,237,035, which is a continuation-in-part of application No. 10/074,264, filed on Feb. 12, 2002.

- (51) Int. Cl. G06F 13/00

(2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,383,316 A<br>4,577,312 A<br>4,703,475 A<br>4,775,987 A<br>4,885,738 A<br>4,991,172 A<br>5,065,396 A<br>5,251,210 A<br>5,293,378 A | 5/1983<br>3/1986<br>10/1987<br>10/1988<br>12/1989<br>2/1991<br>11/1991<br>10/1993<br>3/1994 | Nash       370/84         Dretzka et al.       370/60         Miller       375/38         Bowers et al.       370/58.1         Cidon et al.       370/94.1         Castellano et al.       370/84         Mann et al.       370/94.1         Shimizu       370/94.1 |

|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5,065,396 A<br>5,251,210 A                                                                                                          | 11/1991<br>10/1993                                                                          | Castellano et al 370/84<br>Mann et al 370/84                                                                                                                                                                                                                        |

| 5,570,356 A<br>5,754,545 A *<br>6,697,381 B1 *                                                                                      | 10/1996<br>5/1998<br>2/2004                                                                 | Finney et al 370/85.9                                                                                                                                                                                                                                               |

| , ,                                                                                                                                 |                                                                                             | Damle 709/236                                                                                                                                                                                                                                                       |

<sup>\*</sup> cited by examiner

Primary Examiner—Kenneth R Coulter (74) Attorney, Agent, or Firm—Campbell Stephenson LLP

#### (57) ABSTRACT

A method, device, and apparatus that provide a means for generating a network frame that provides information related to one or more super-channels for data transmission, which are comprised of one or more sub-channels for data transmission, over which the network frame is transmitted are disclosed.

### 55 Claims, 23 Drawing Sheets

Fig. 3

Fig. 5

Fig. 6

Fig. 7

Fig. 8

Fig. 9

Fig. 10

Fig. 11

Fig. 12

Fig. 14

Fig. 16A

Fig. 16B

Fig. 16C

Fig. 17

Fig. 18

Fig. 19

Fig. 20

Fig. 21

Fig. 22

Fig. 23

# FRAME STRUCTURE AND METHOD FOR WAVELENGTH CONCATENATED CHANNEL FRAMING

# CROSS-REFERENCES TO RELATED APPLICATIONS

This application is a continuation of U.S. patent application Ser. No. 10/086,273 now U.S. Pat. No. 7,237,035, entitled "FRAME STRUCTURE AND METHOD FOR WAVELENGTH CONCATENATED CHANNEL FRAMING," filed on Feb. 20, 2002, and having Rajendra R. Damle as the inventor, which is a continuation-in-part of patent application Ser. No. 10/074,264, entitled "TRANSPORT OF HIGH-BANDWIDTH DATASTREAMS OVER A NETWORK," filed on Feb. 12, 2002, and having R. Damle, Y. Lee, W. Szeto, R. Butler and H. M. Zadikian as inventors, which, in turn, claims priority from the following provisional patent applications under 35 U.S.C. §119(e):

- 1. Provisional Patent Application Ser. No. 60/268,237, entitled "EVOLUTION OF CARRRIER BACKBONE DATA NETWORK NEW REQUIREMENTS", filed Feb. 12, 2001, and naming R. R. Damle as inventor;

- 2. Provisional Patent Application Ser. No. 60/268,180, entitled "END-TO-END NETWORK ARCHITEC-TURE FOR THE NEXT GENERATION IP NETWORK", filed Feb. 12, 2001, and naming R. K. Butler as inventor;

- 3. Provisional Patent Application Ser. No. 60/287,973, and naming R. K. Butler as inventor; and

- 4. Provisional Patent Application Ser. No. 60/295,645, entitled "TRANSPORT OF HIGH-BANDWIDTH DATASTREAMS OVER A NETWORK", filed Jun. 4, 2001, and naming R. Damle, Y. Lee, W. Szeto, R. Butler and H. M. Zadikian as inventors.

These applications are hereby incorporated by reference herein, in their entirety and for all purposes.

The present application also claims priority from:

1. Provisional Patent Application Ser. No. 60/270,444, entitled "METHOD AND APPARATUS FOR WAVE-LENGTH CONCATENATED CHANNEL FRAM-ING", filed Feb. 20, 2001, and naming R. R. Damle as 45 inventor.

Applicants hereby claim the benefit under 35 U.S.C. §119 (e) of the foregoing-referenced provisional patent application. The foregoing-referenced provisional patent application is hereby incorporated by reference herein, in its entirety and for all purposes.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

This invention relates to the field of information networks, and more particularly relates to a method and system for conveying information over a network.

#### 2. Description of the Related Art

Today's networks carry vast amounts of information. High-bandwidth applications supported by these networks include streaming video, streaming audio, and large aggregations of voice traffic, among other such applications. In the future, these demands are certain to increase. To meet such 65 demands, an increasingly popular alternative is the use of lightwave communications carried over fiber-optic cables.

2

The use of lightwave communications provides several benefits, including high bandwidth, ease of installation, and capacity for future growth.

In this new age of data-centric communication networks, the ability to support terabit rate routing in the network core is becoming a more common requirement. In an effort to make terabit routing a reality, such technology needs to be economical, as well as being efficient in design and integration. Ease of use and serviceability are also important. An efficient design involves framing protocols, integrated hardware and software, and network design as a whole. If addressed, such a solution results in a highly economical and deployable communications system.

Over the next five years, the growth projected by major service providers (e.g., UUNet, AT&T and Sprint) in their data (IP) networks is exponential. The architecture of such high-bandwidthbackbone networks have, among others, at least three important properties:

- 1. Such networks tend to be made up of a relatively small number of switching/routing nodes interconnected by very high bandwidth links. The aggregate capacity of each of such links is projected to go beyond 40 Gbps in the near future, with even higher speeds to follow.

- 2. As the amount of traffic increases, the bandwidth required between these nodes will increase, but the number of nodes is expected to remain relatively constant.

- 3. These switching nodes tend to be widely dispersed, geographically, with large inter-node distances (e.g., typically over 1000 km).

The synchronous optical network (SONET) protocol is among those protocols employed in today's optical infrastructures. SONET is a physical transmission protocol capable of transmission speeds in the multi-gigabit range, and is defined by a set of electrical as well as optical standards.

SONET's ability to use currently-installed fiber-optic cabling, coupled with the fact that SONET significantly reduces complexity and equipment functionality requirements, has given local and interexchange carriers incentive to employ SONET. Also attractive is the immediate savings in operational cost that this reduction in complexity provides. SONET thus allows the realization of high-bandwidth services in a more economical manner than previously existed.

Today, the bandwidth requirements of communications between the core packet switches using SONET have increased from 2.5 Gbps (OC-48 in the SONET standard) to 10 Gbps (OC-192 in the SONET standard) in some cases. Routers with single OC-48- or OC-192-capable port cards and a transport system that can carry such a data rate over a single wavelength have supported these increases.

While the port speeds of routers can (and likely will) be increased beyond 10 Gbps, the transport systems presently in place are unable to transport such high-speed) datastreams (e.g., a 40 Gbps (or greater) datastream) using currently-installed fiber-optic cabling, at least without expensive (and frequent) regeneration. This inability to economically transport such higher-speed datastreams (i.e., beyond 10 Gbps) over long distances using currently-installed fiber-optic cabling is an obstacle to deployment of high-speed transport at the network core.

Moreover, the efficiency (the amount of data versus the overall size of a frame) provided by SONET is somewhat less than desirable. A SONET frame provides an efficiency of about 96.2%. This means that 3.8% of the available bandwidth is consumed by overhead (or is unused). In the case of an OC-192 signal, for example, this equates to wasted bandwidth of about 378 Mbps. Given the costs associated with providing bandwidth at such data rates, this overhead repre-

sents appreciable lost revenues. While 100% efficiency is unlikely, given that some overhead is typically required, it is still desirable to improve the efficiency provided by available communication channels.

One possible alternative to increasing the bandwidth of the connections between core routers is to grow the existing port count and use multiple ports between routers. Although this seems logical from the perspective of the connection, this alternative is not very scalable or economical because the IP forwarding table per port increases linearly and the total 10 memory required for the forwarding table increases as N<sup>2</sup> (where N=number of ports). The large port count also involves larger space and power requirements that add to the cost of this solution.

The definition of a framing protocol and mechanism that support a solution to this predicament are thus required. Such a protocol and mechanism should be efficient and easily implemented in various hardware architectures. Moreover, such a protocol and mechanism should exhibit high functional accuracy that is verifiable via simulations.

#### SUMMARY OF THE INVENTION

The present invention presents a method, device, and apparatus that provide a means for generating a network frame that provides information related to one or more super-channels for data transmission, which are comprised of one or more sub-channels for data transmission, over which the network frame is transmitted.

Accordingly, one aspect of the present invention provides a method for generating a frame, wherein the frame has a frame structure. The frame structure comprises information regarding a super-channel. The super-channel is comprised of one or more sub-channels.

Another aspect of the present invention provides a network device comprising a frame generator. The frame generator is configured to generate a frame having a frame structure. The frame structure comprises information regarding a superchannel. The super-channel is comprised of one or more sub-channels.

Another aspect of the present invention provides a network invention.

FIG. 13

Switching super-channel super-channel is comprised of one or more embodimes.

A further aspect of the present invention provides an apparatus comprising a means for generating a frame. The frame has a frame structure that comprises information about a super-channel. The super-channel is comprised of one or more sub-channels.

The foregoing is a summary and thus contains, by necessity, simplifications, generalizations and omissions of detail; consequently, those skilled in the art will appreciate that the summary is illustrative only and is not intended to be in any way limiting. As will also be apparent to one of skill in the art, the operations disclosed herein may be implemented in a number of ways, and such changes and modifications may be made without departing from this invention and its broader aspects. Other aspects, inventive features, and advantages of the present invention, as defined solely by the claims, will become apparent in the non-limiting detailed description set forth below.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The present invention may be better understood, and its numerous objects, features, and advantages made apparent to those skilled in the art by referencing the accompanying drawings.

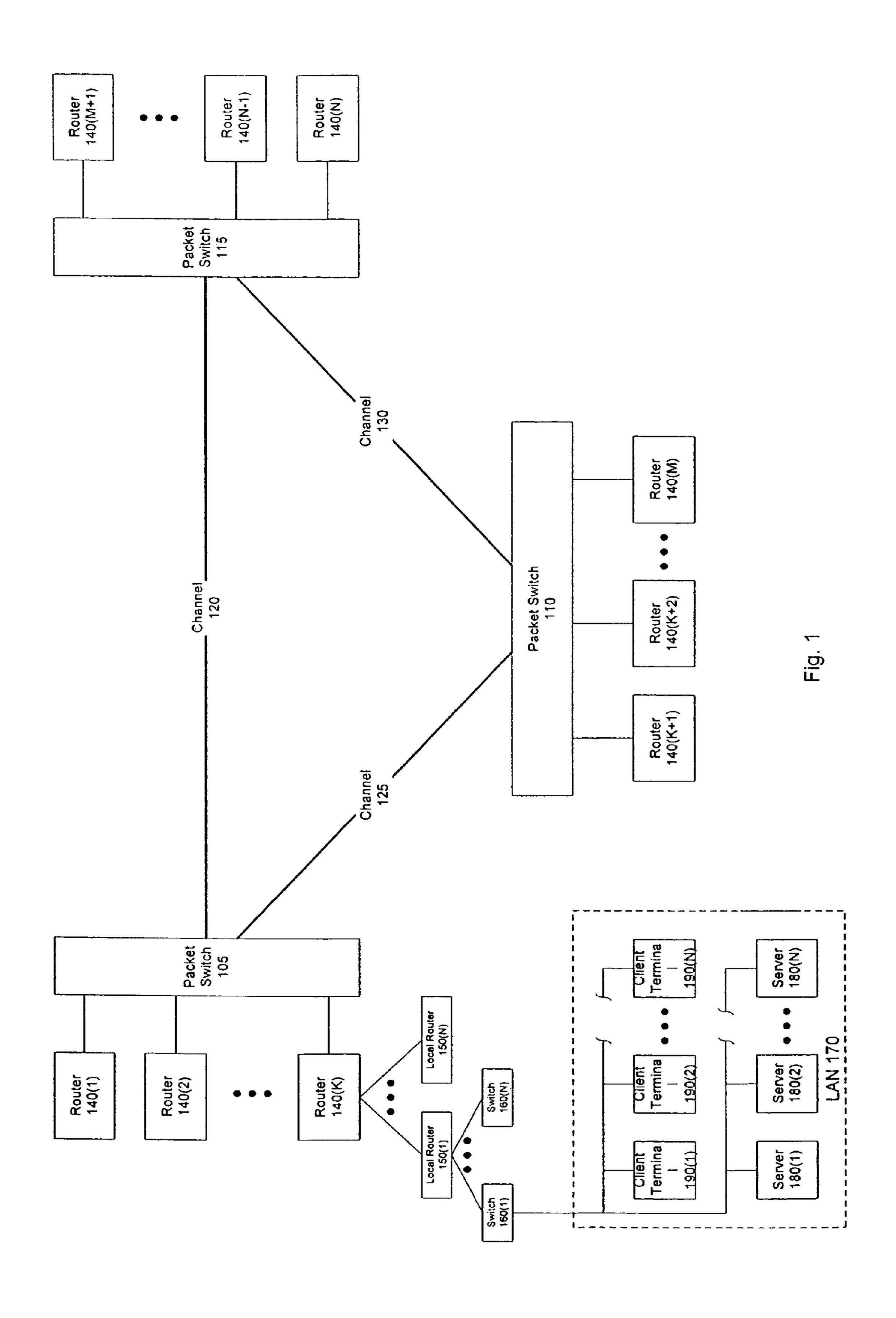

FIG. 1 is a block diagram illustrating a network that sup- 65 ports and employs the use of a framing technology according to embodiments of the present invention.

4

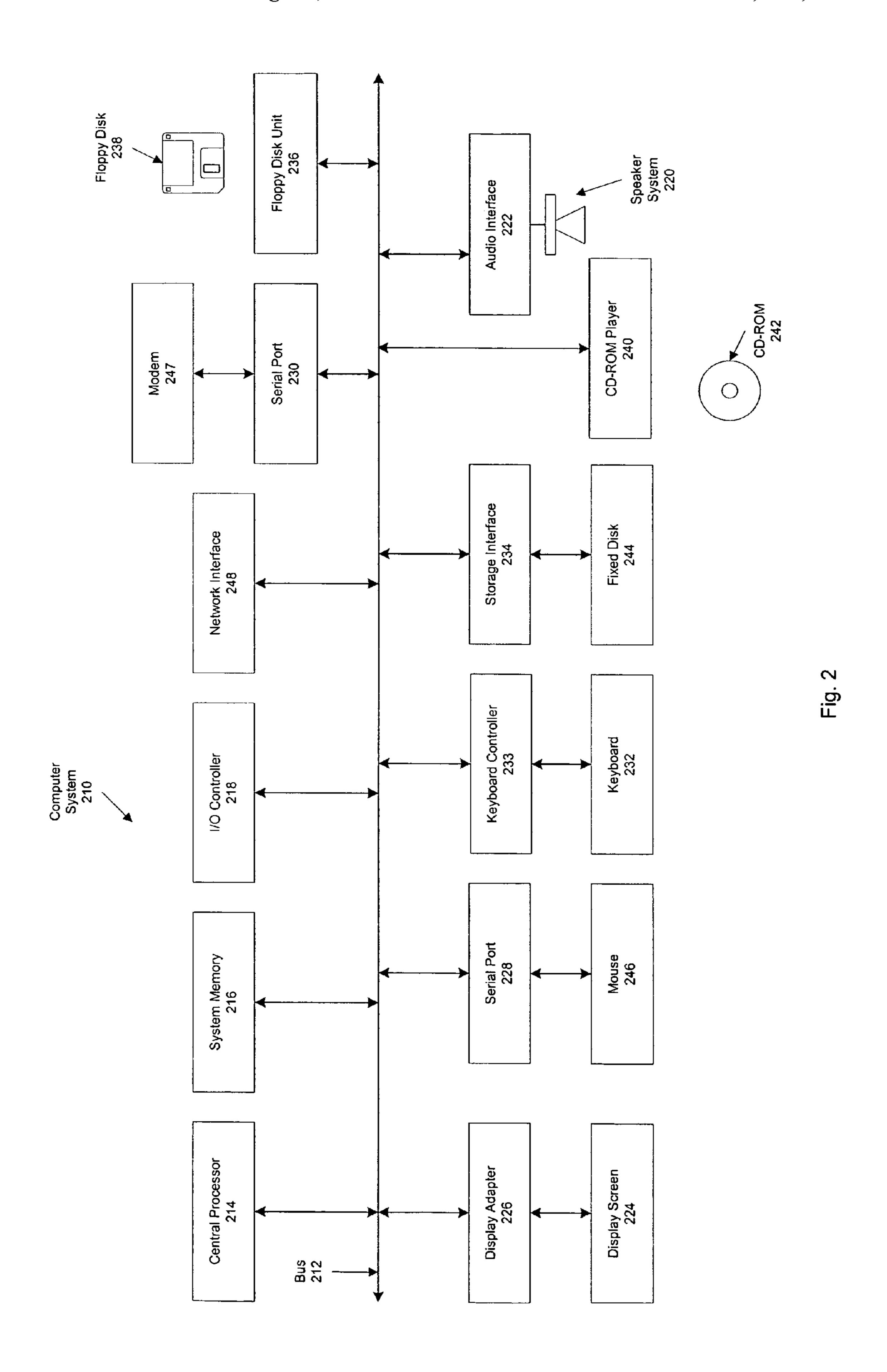

- FIG. 2 depicts a block diagram of a computer system suitable for implementing the present invention.

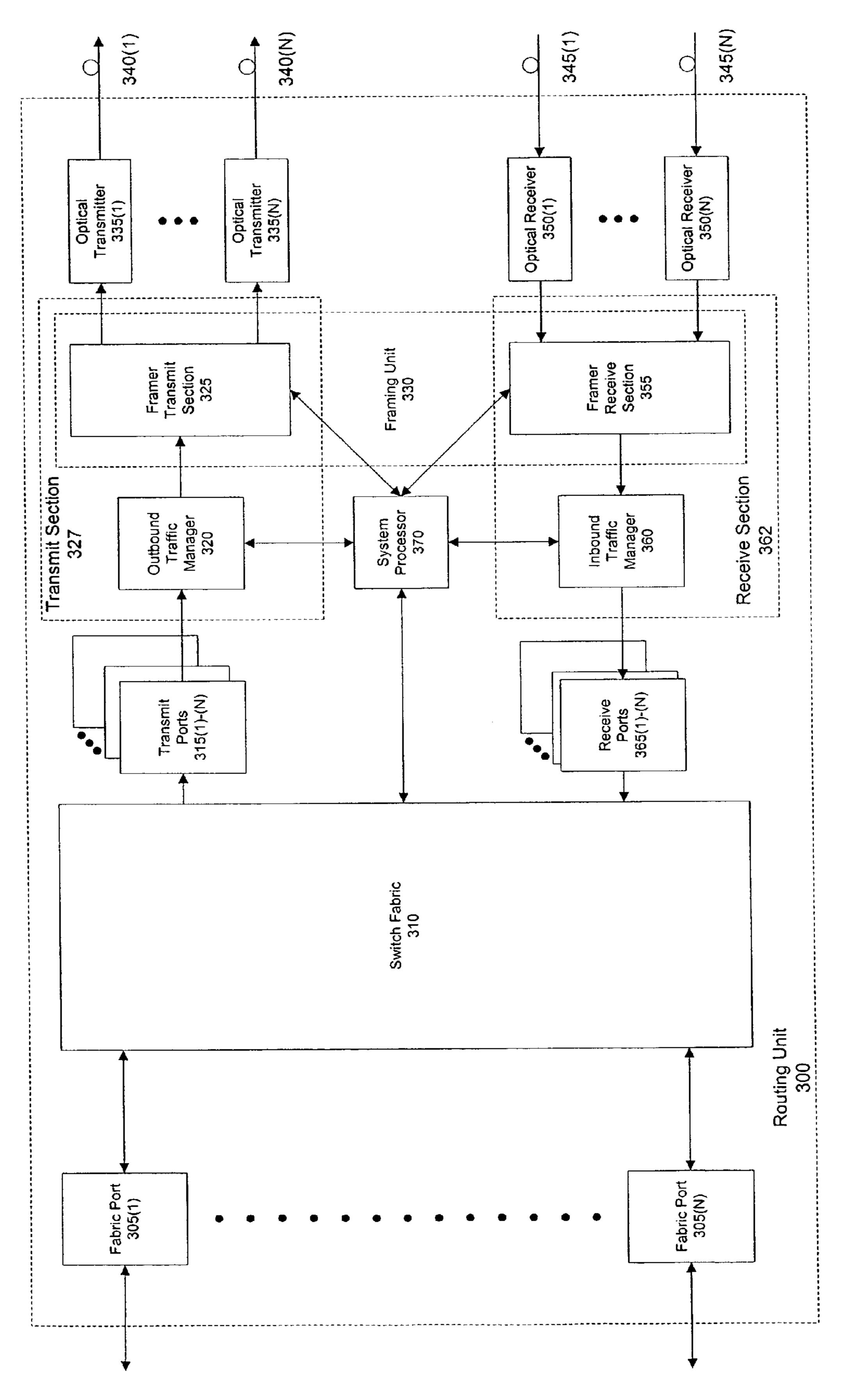

- FIG. 3 is a block diagram illustrating a routing unit according to embodiments of the present invention.

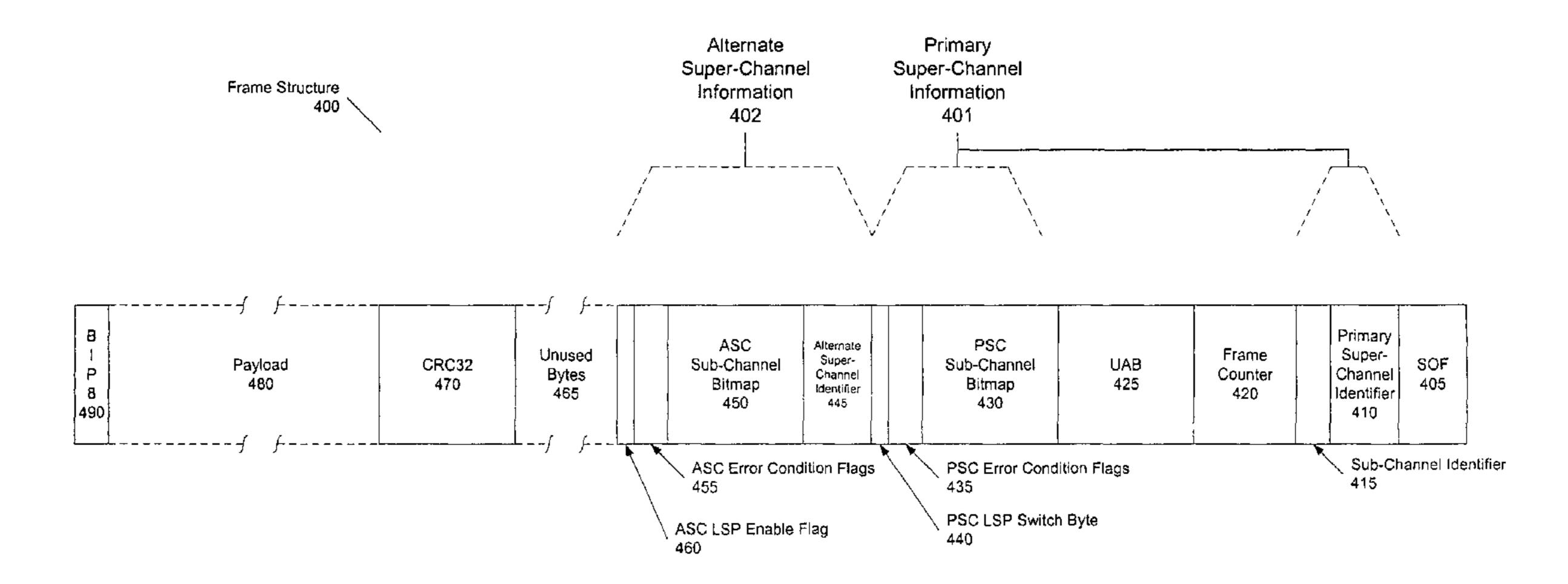

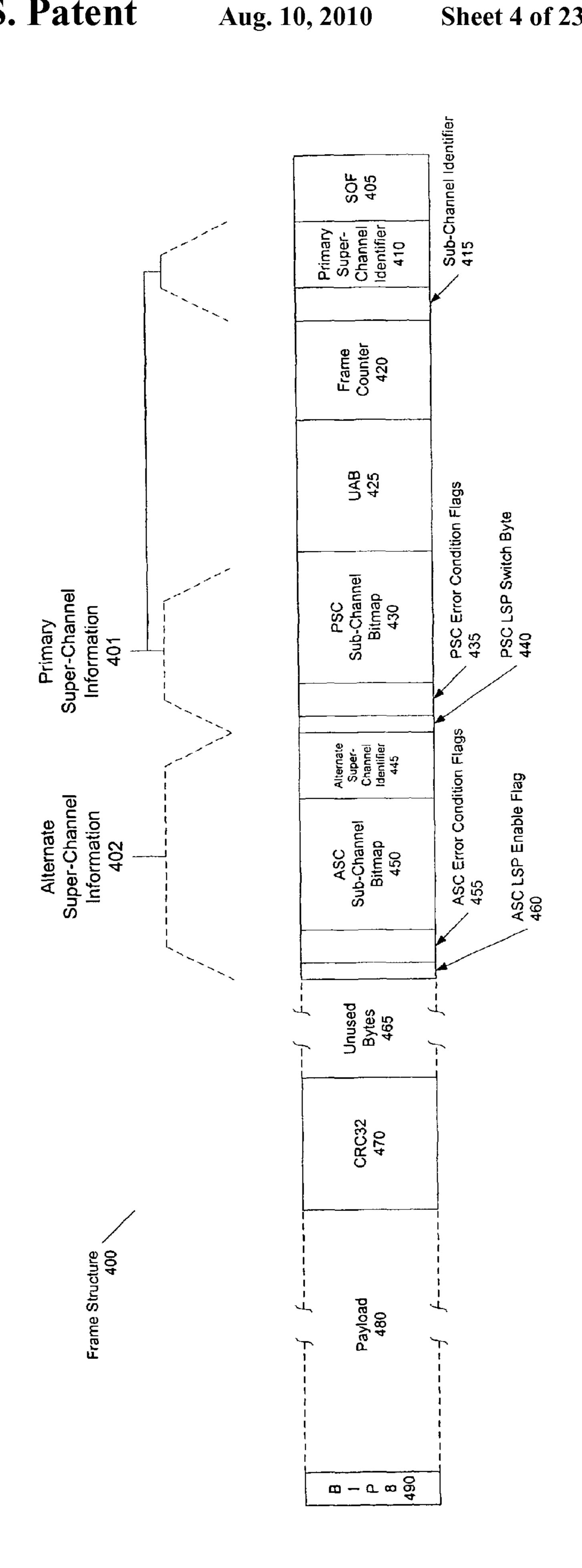

- FIG. 4 is a block diagram of an example layout of the frame structure according to embodiments of the present invention.

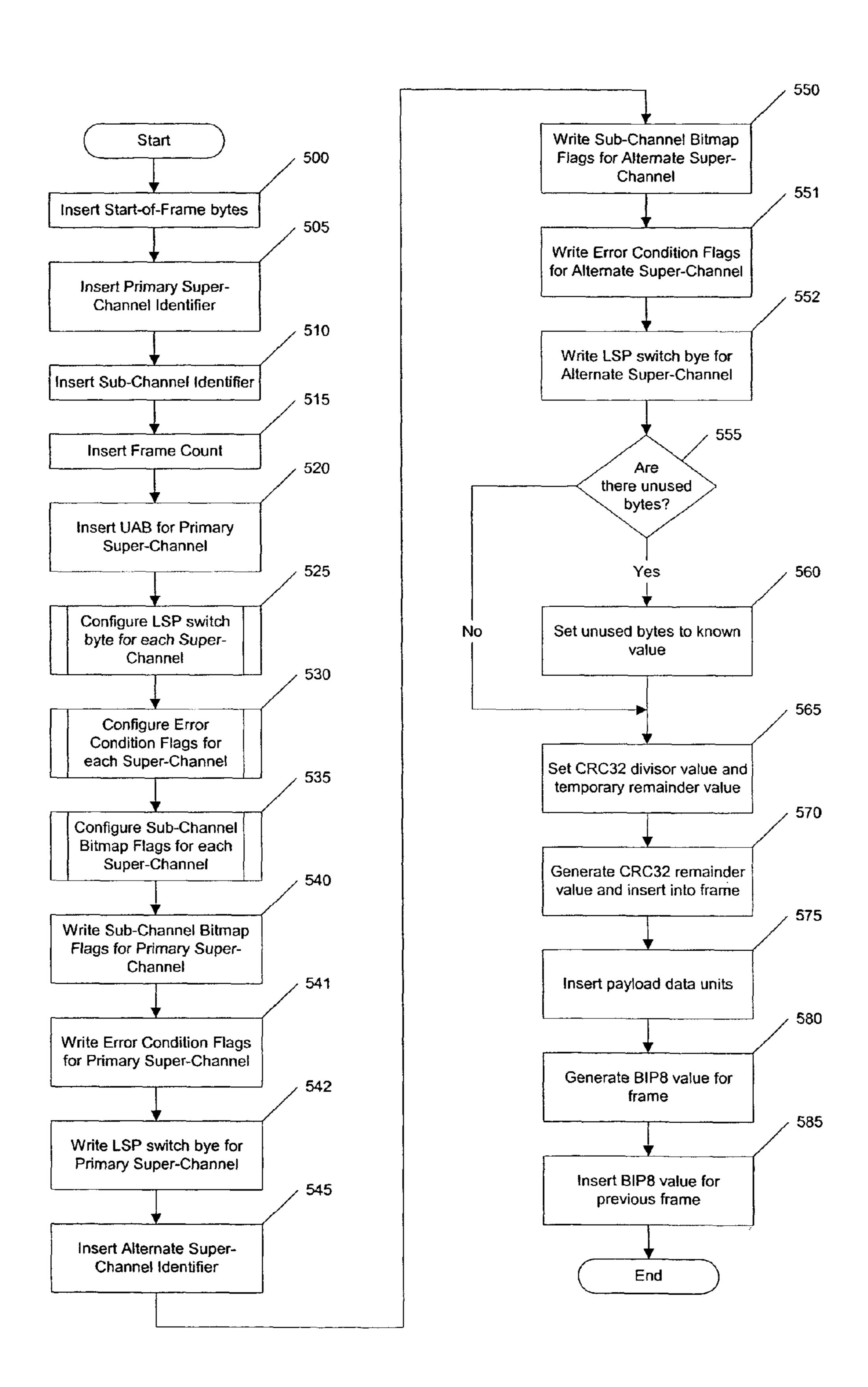

- FIG. **5** is a flow diagram illustrating an example process of generating a frame structure according to embodiments of the present invention.

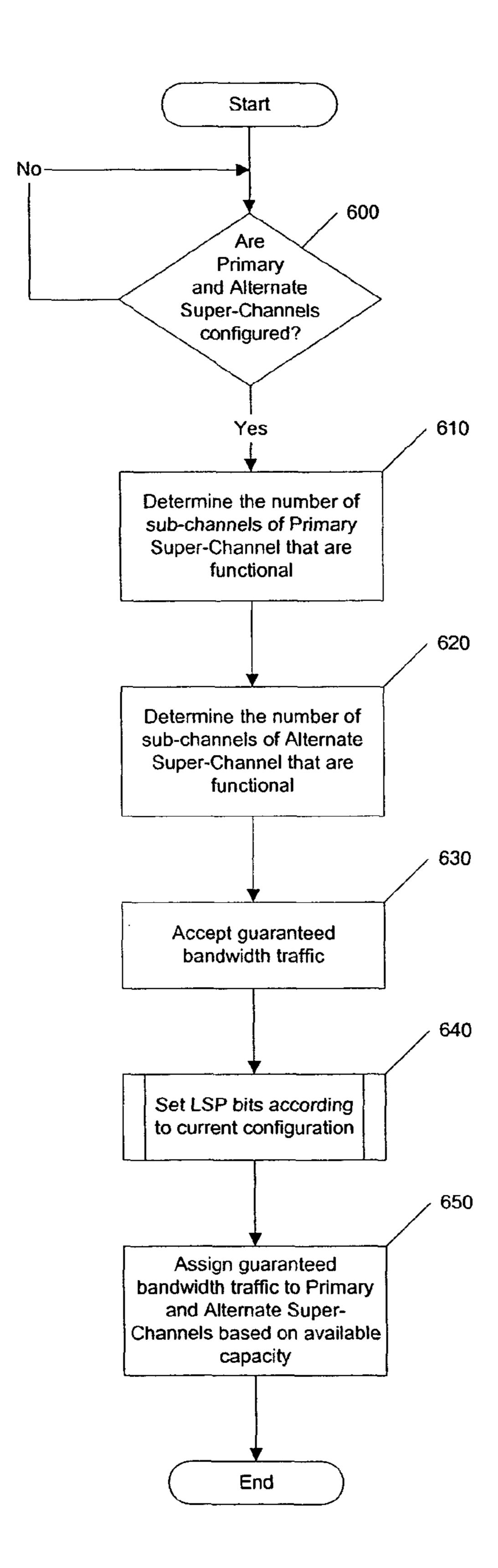

- FIG. 6 is a flow diagram illustrating a process for configuring a label-switched path (LSP) switch byte for primary and alternate super-channels according to embodiments of the present invention.

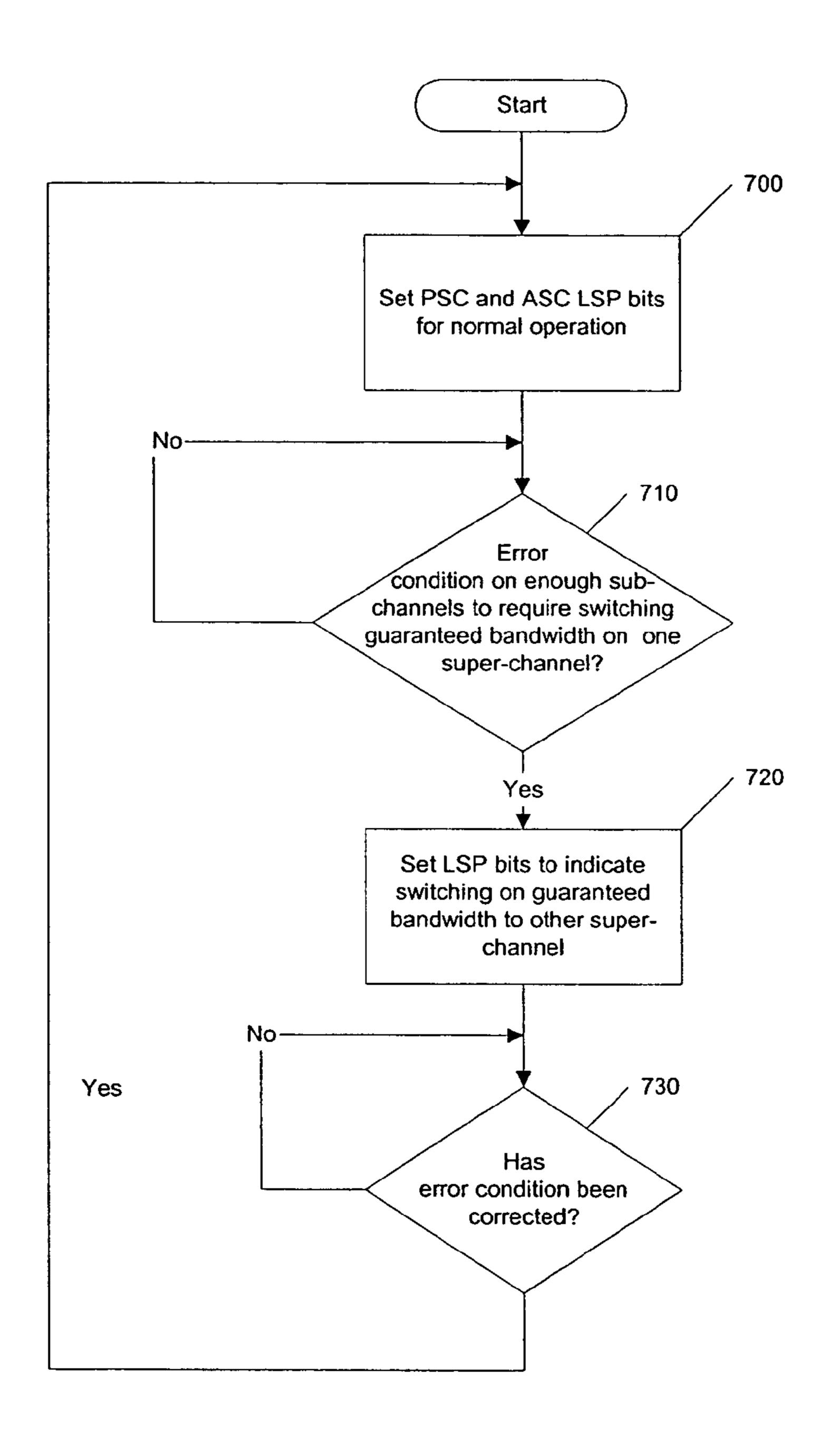

- FIG. 7 is a flow diagram illustrating a process of setting bits of an LSP switch byte according to embodiments of the present invention.

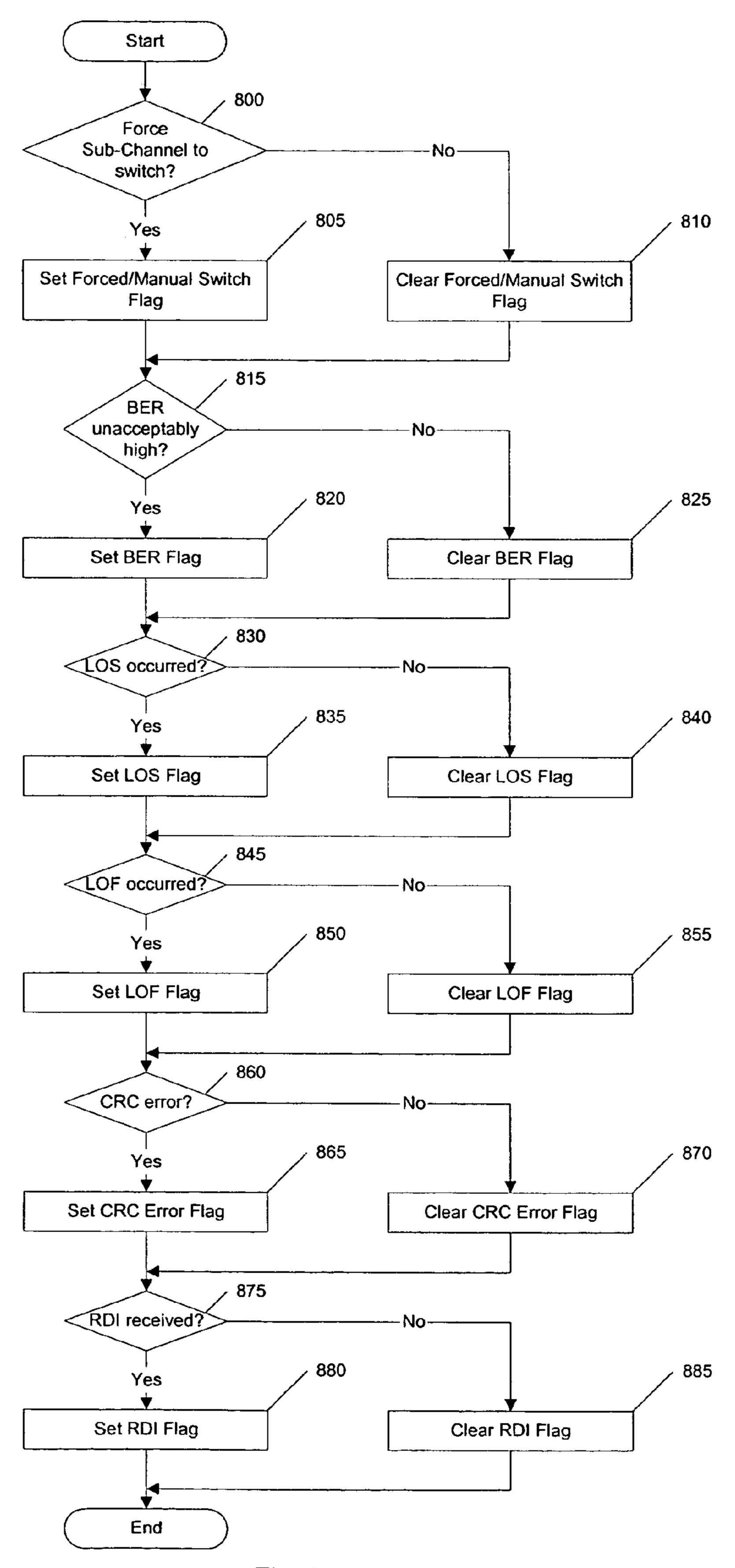

- FIG. 8 is a flow diagram illustrating a process of configuring error condition flags according to embodiments of the present invention.

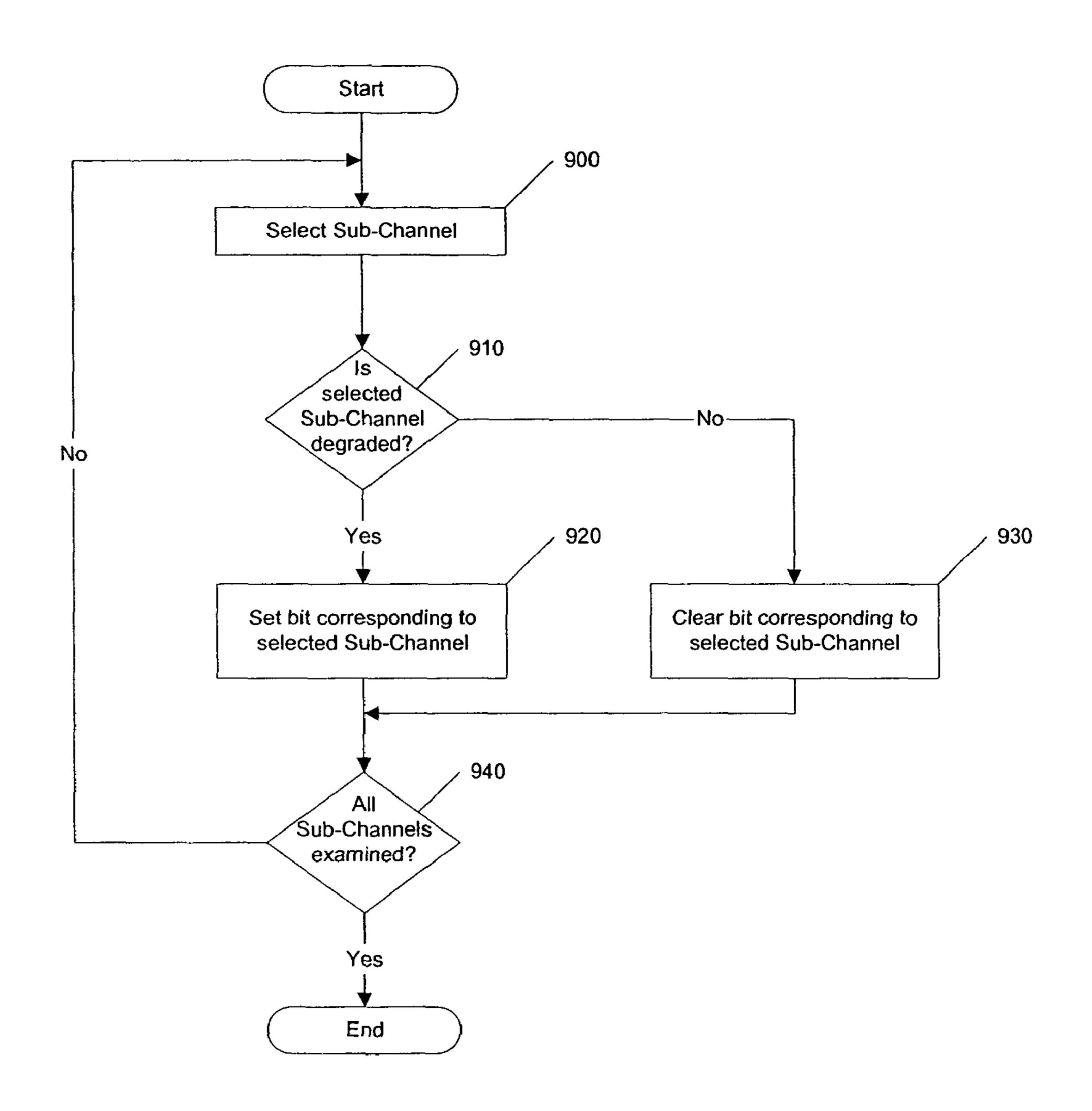

- FIG. 9 is a flow diagram illustrating a process of coarse bitmap generation according to embodiments of the present invention.

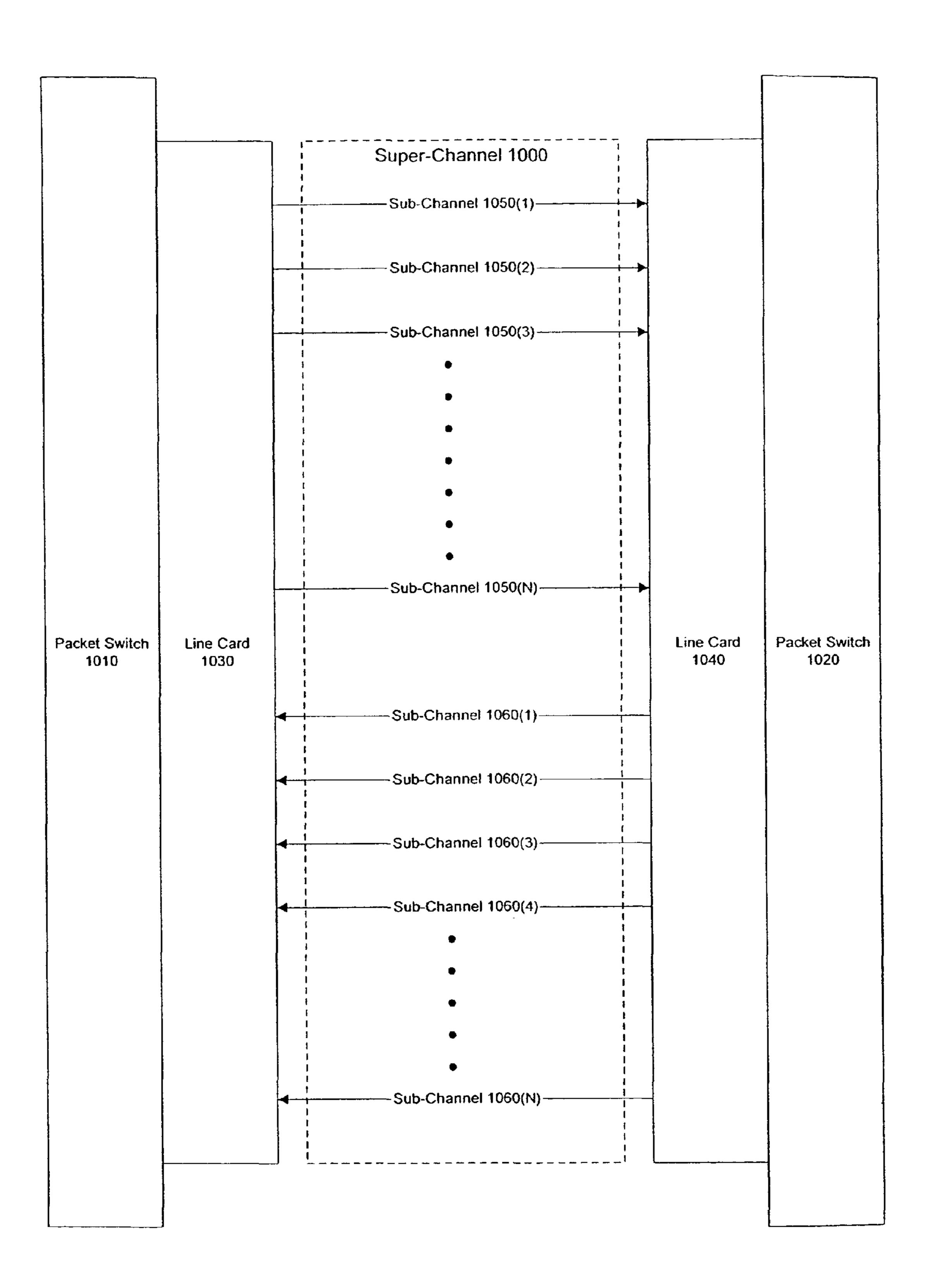

- FIG. 10 is a block diagram illustrating a portion of network in further detail that illustrates structure supporting a subchannel bitmap protection mechanism according to embodiments of the present invention.

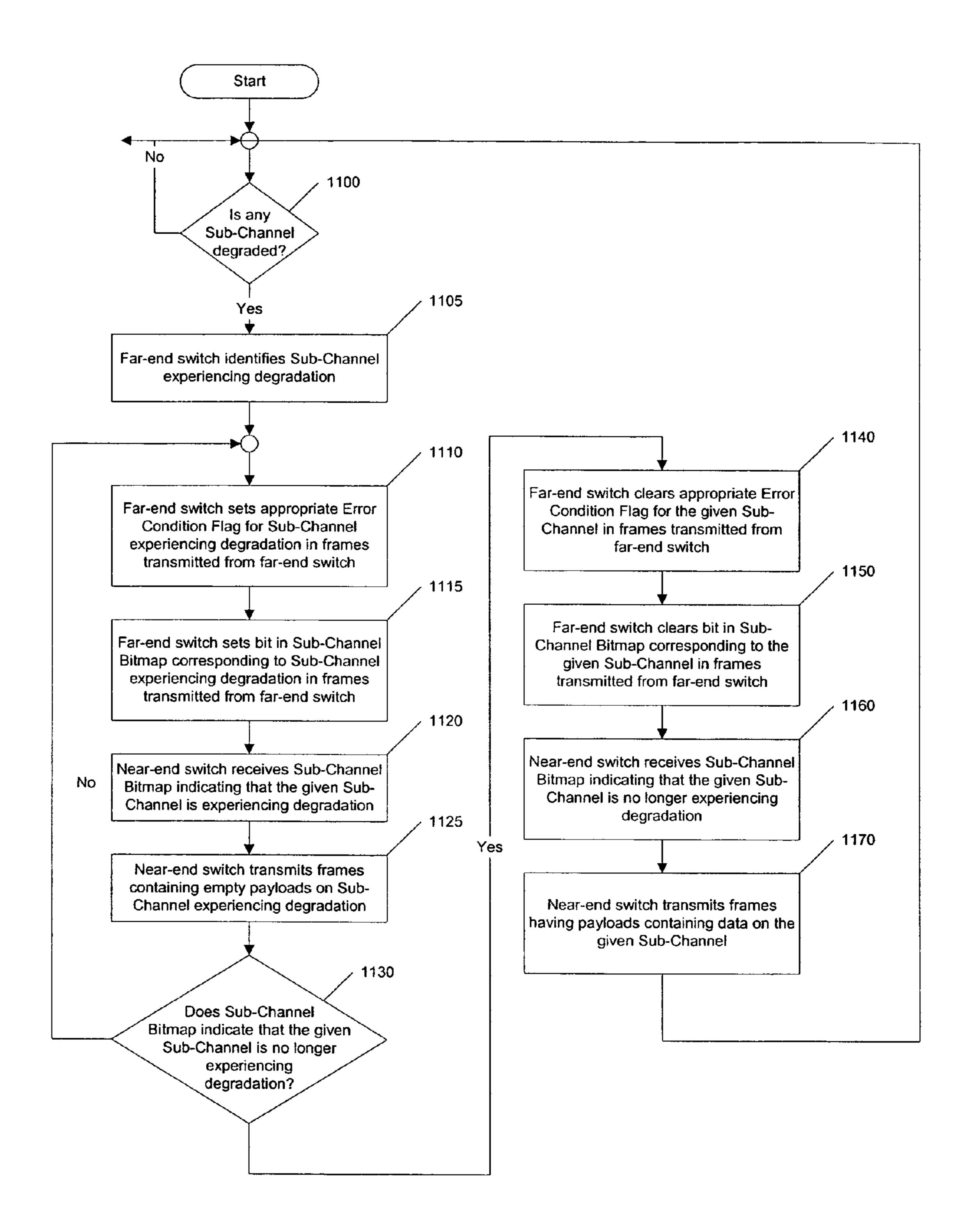

- FIG. 11 is a flow diagram depicting a process of subchannel protection using a sub-channel bitmap protection mechanism according to embodiments of the present invention.

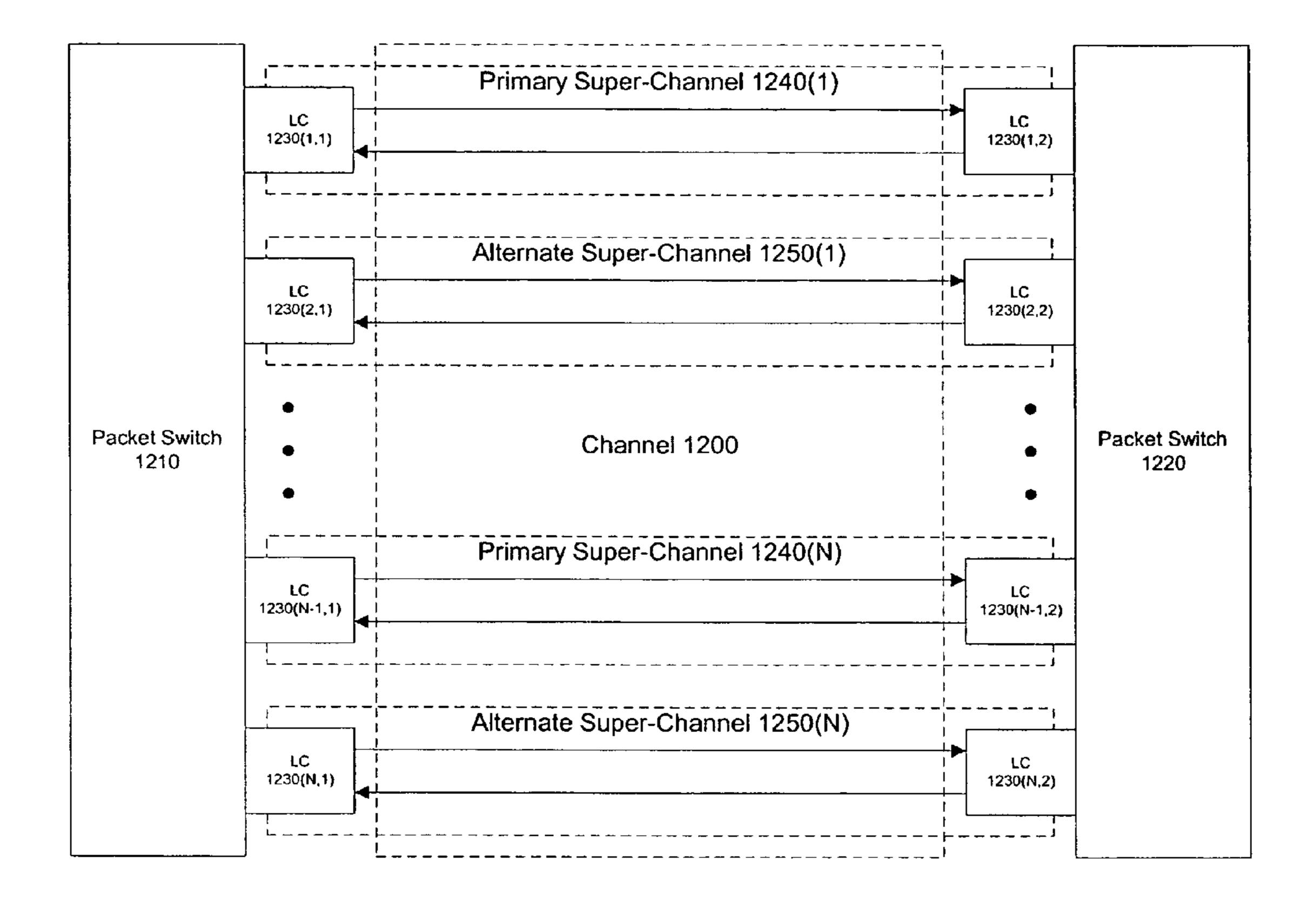

- FIG. 12 is a block diagram illustrating a portion of a network in which a channel supports communications between packet switches according to embodiments of the present invention

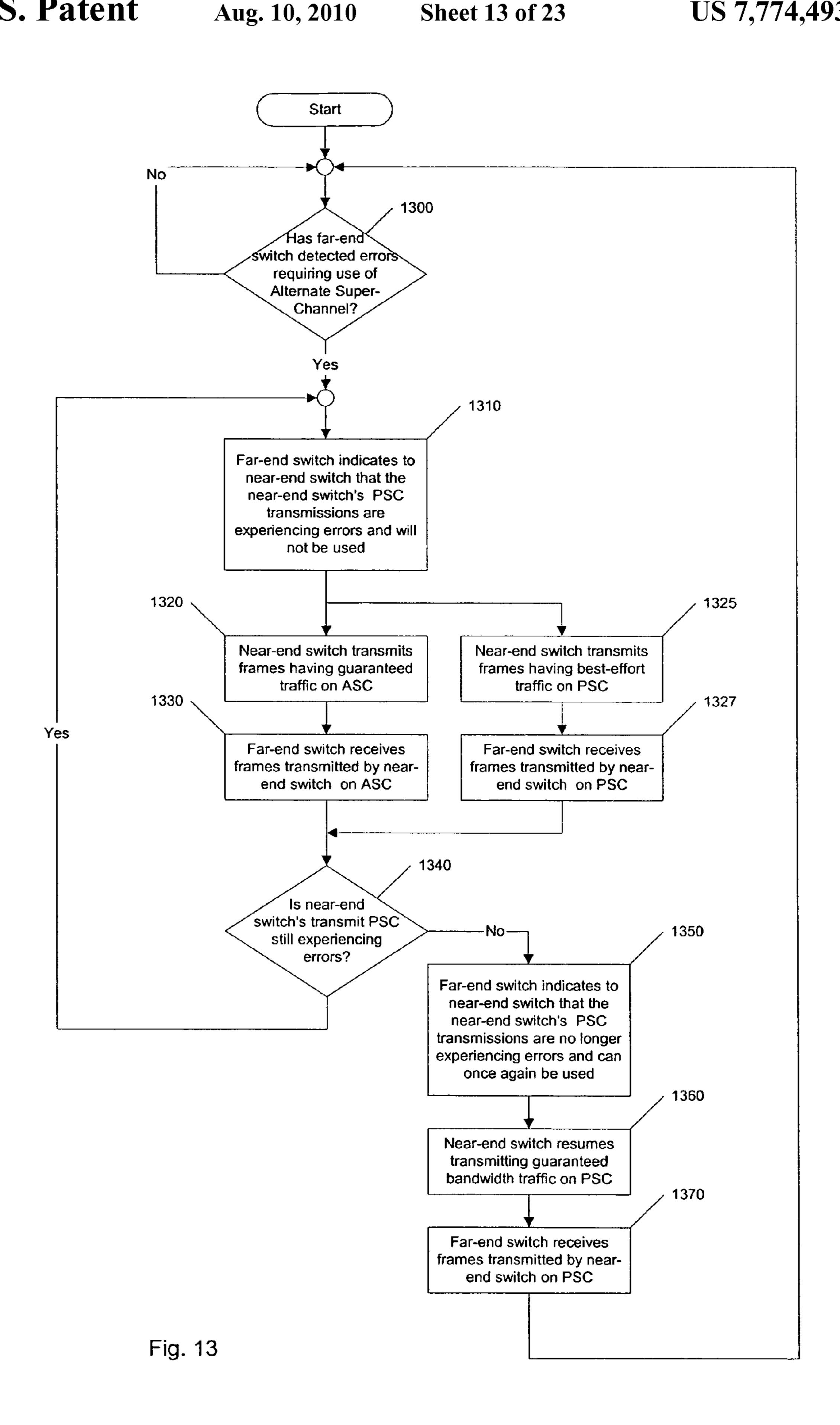

- FIG. 13 is a flow diagram illustrating a procedure for switching guaranteed bandwidth traffic between a primary super-channel and an alternate super-channel according to embodiments of the present invention.

- FIG. 14 is a block diagram illustrating a portion of a network in a more detailed example of elements and processes according to embodiments of the present invention capable of supporting 1+1 protection.

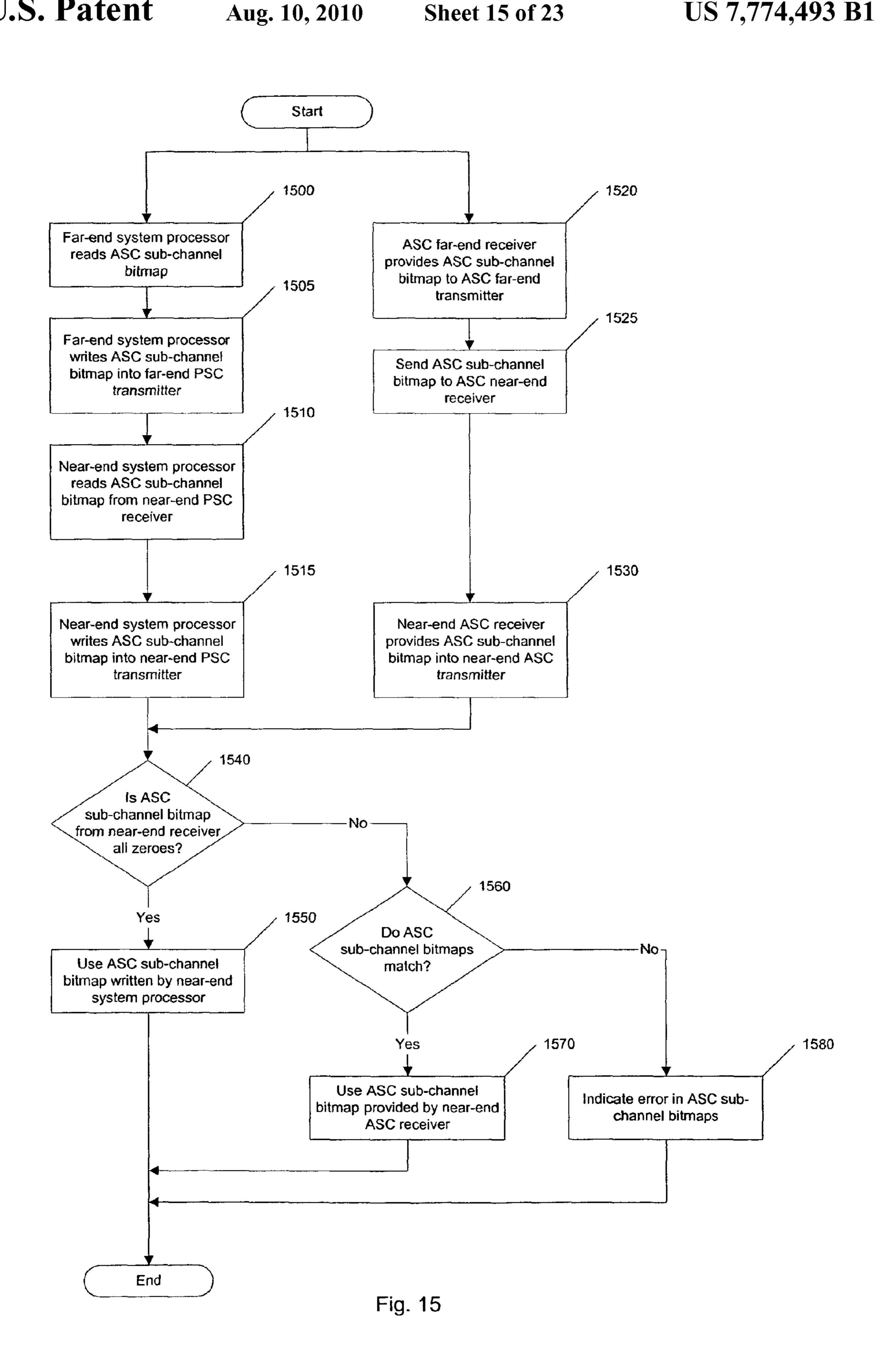

- FIG. **15** is a flow-diagram illustrating an implementation of alternate channel protection using the elements depicted in FIG. **14**.

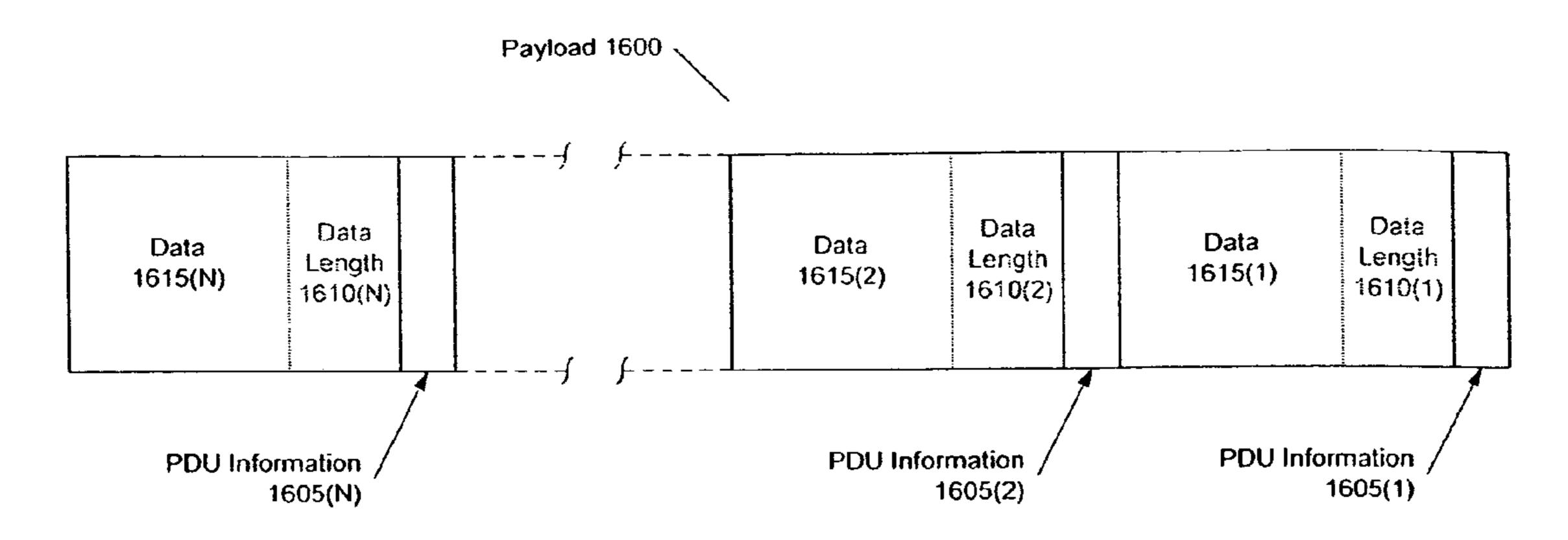

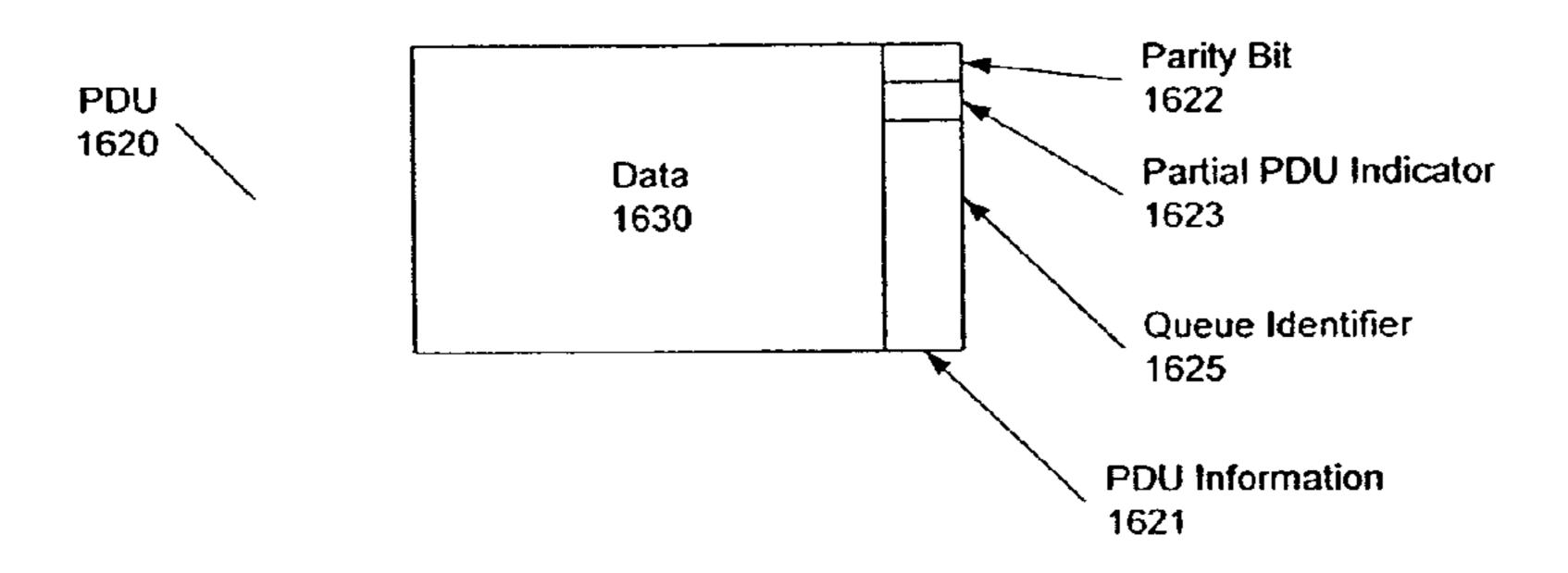

- FIG. **16**A illustrates a payload according to embodiments of the present invention.

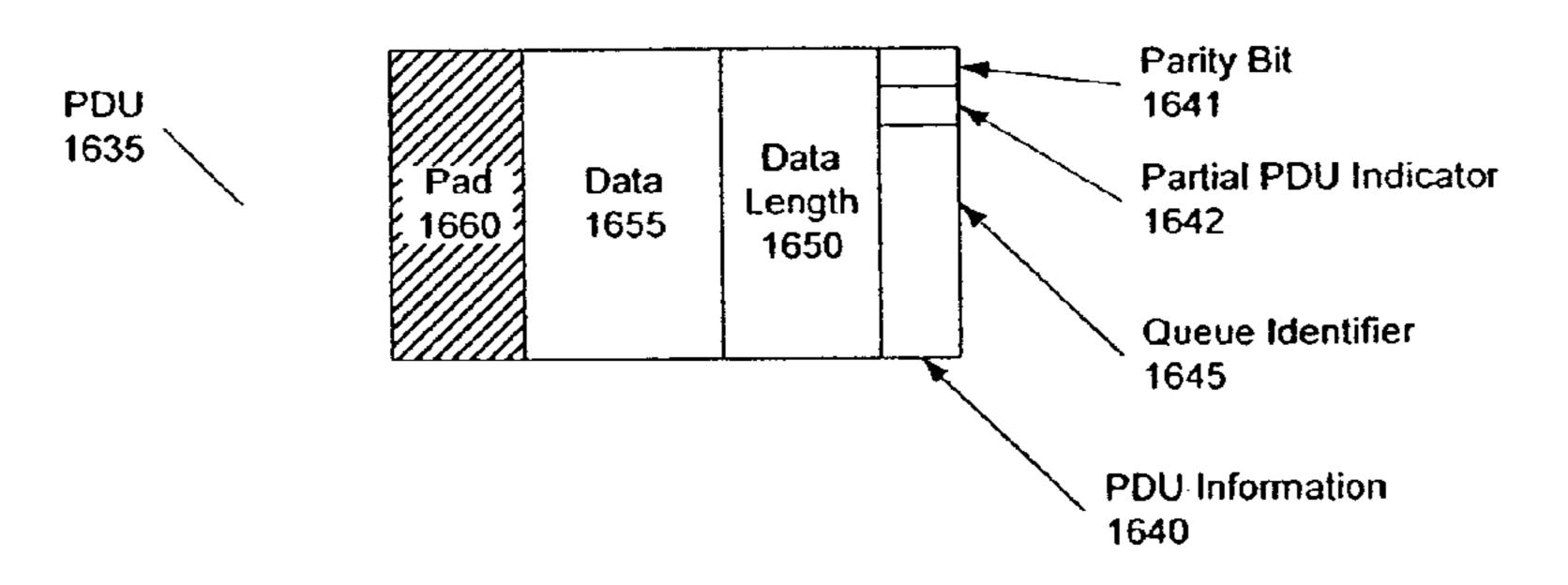

- FIG. 16B is a diagram showing a fully filled payload data unit according to embodiments of the present invention.

- FIG. **16**C is a diagram illustrating a partially-filled payload data unit according to embodiments of the present invention.

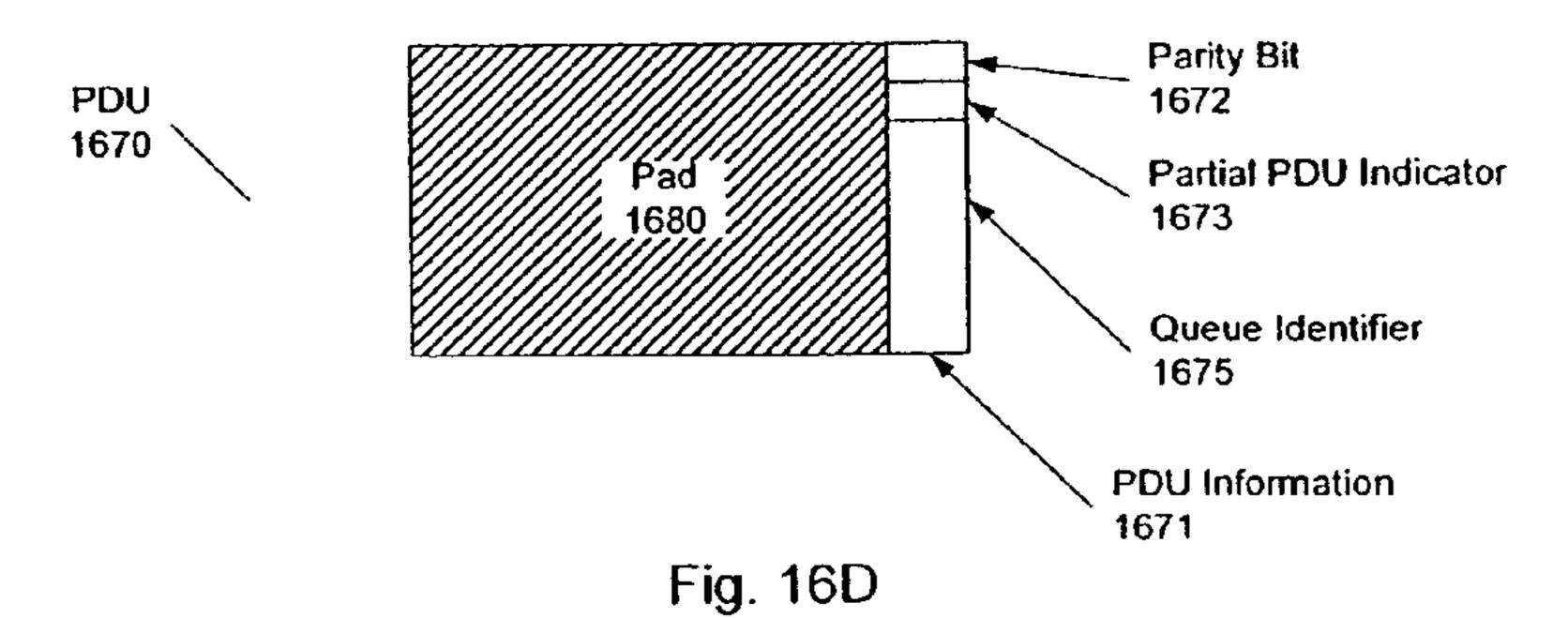

- FIG. 16D is a diagram illustrating what is referred to herein as an "empty" payload data unit according to embodiments of the present invention.

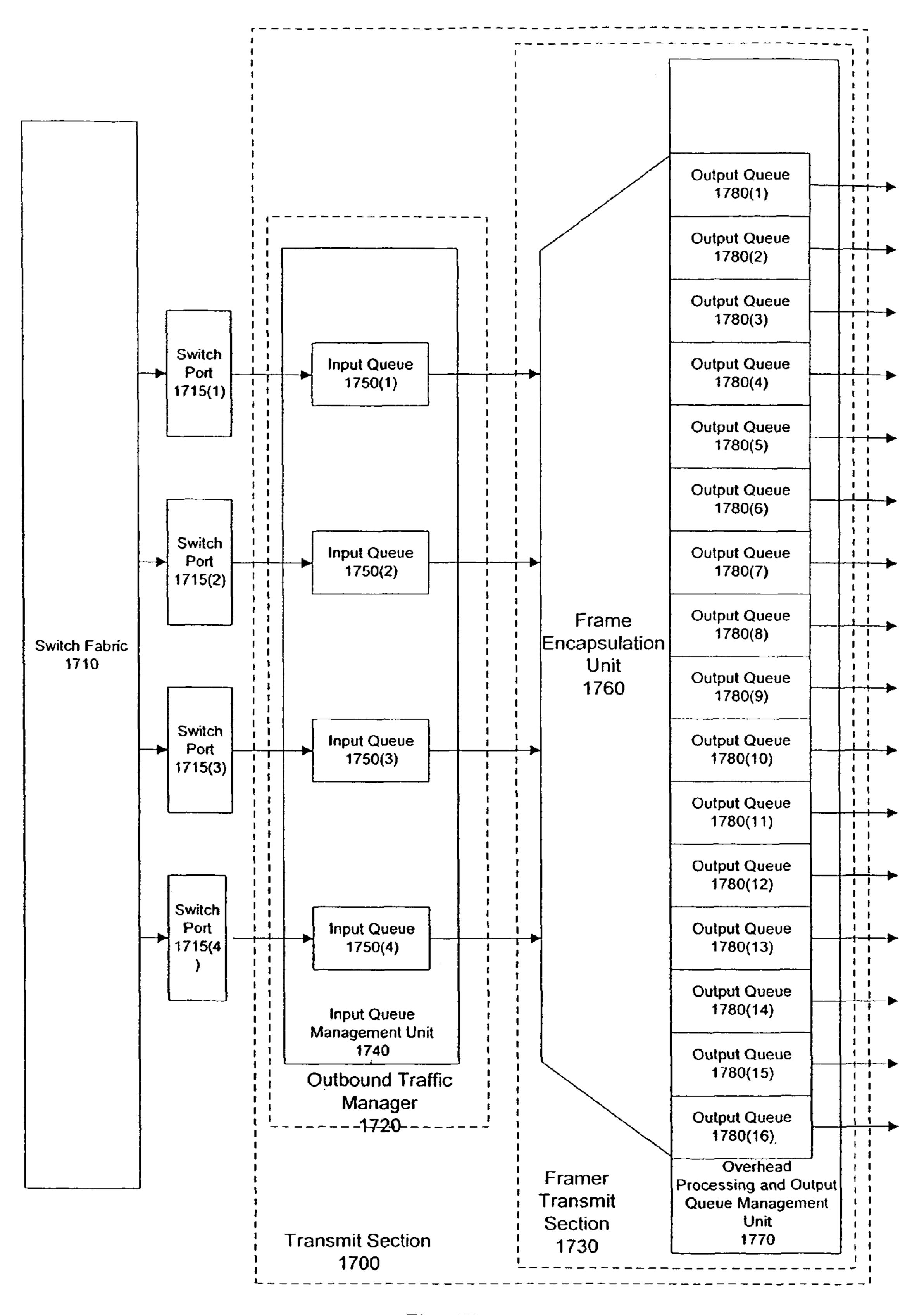

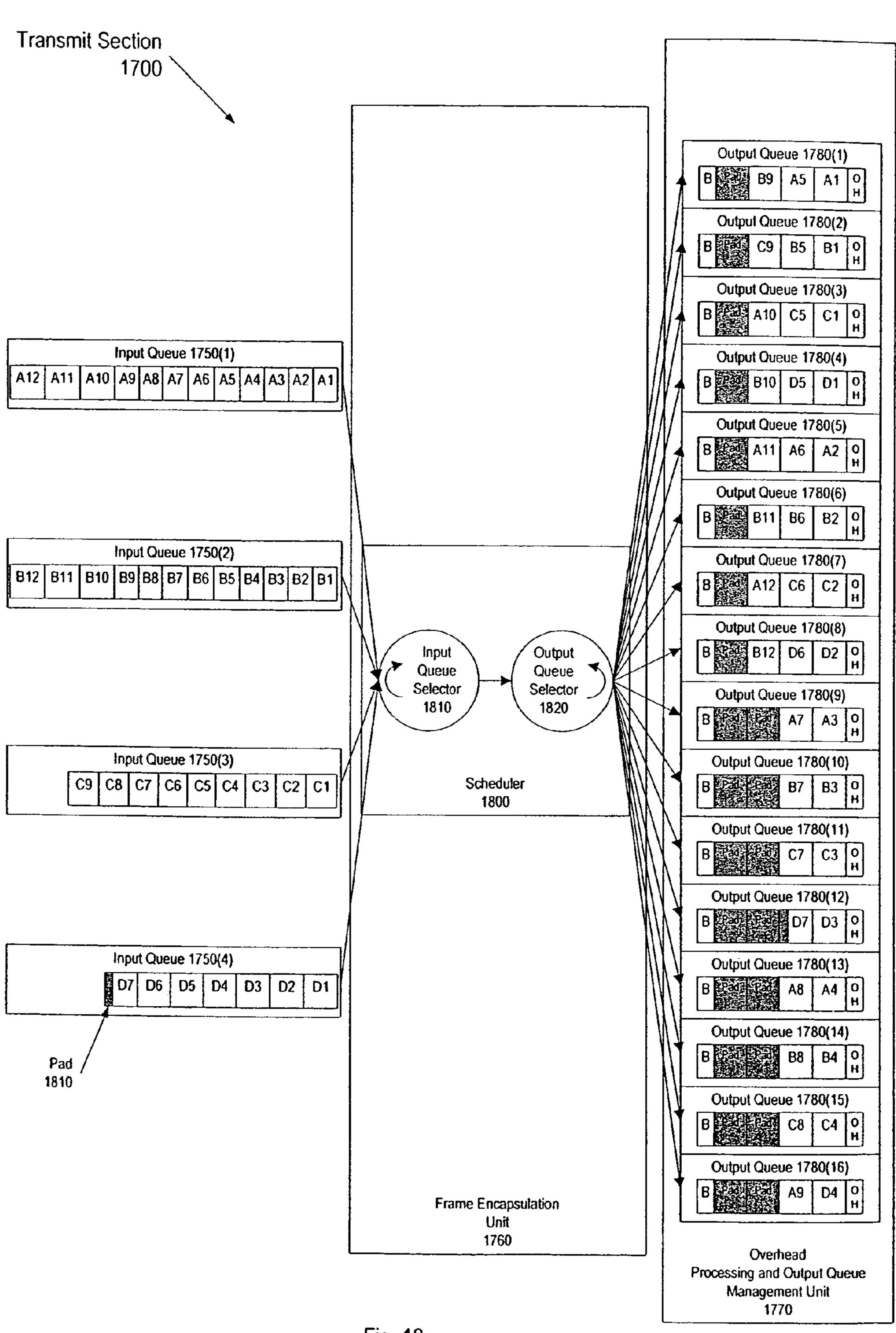

- FIG. 17 is a block diagram showing in further detail a transmit section according to embodiments of the present invention.

- FIG. 18 is a block diagram illustrating an example of the operation of transmit section according to embodiments of the present invention.

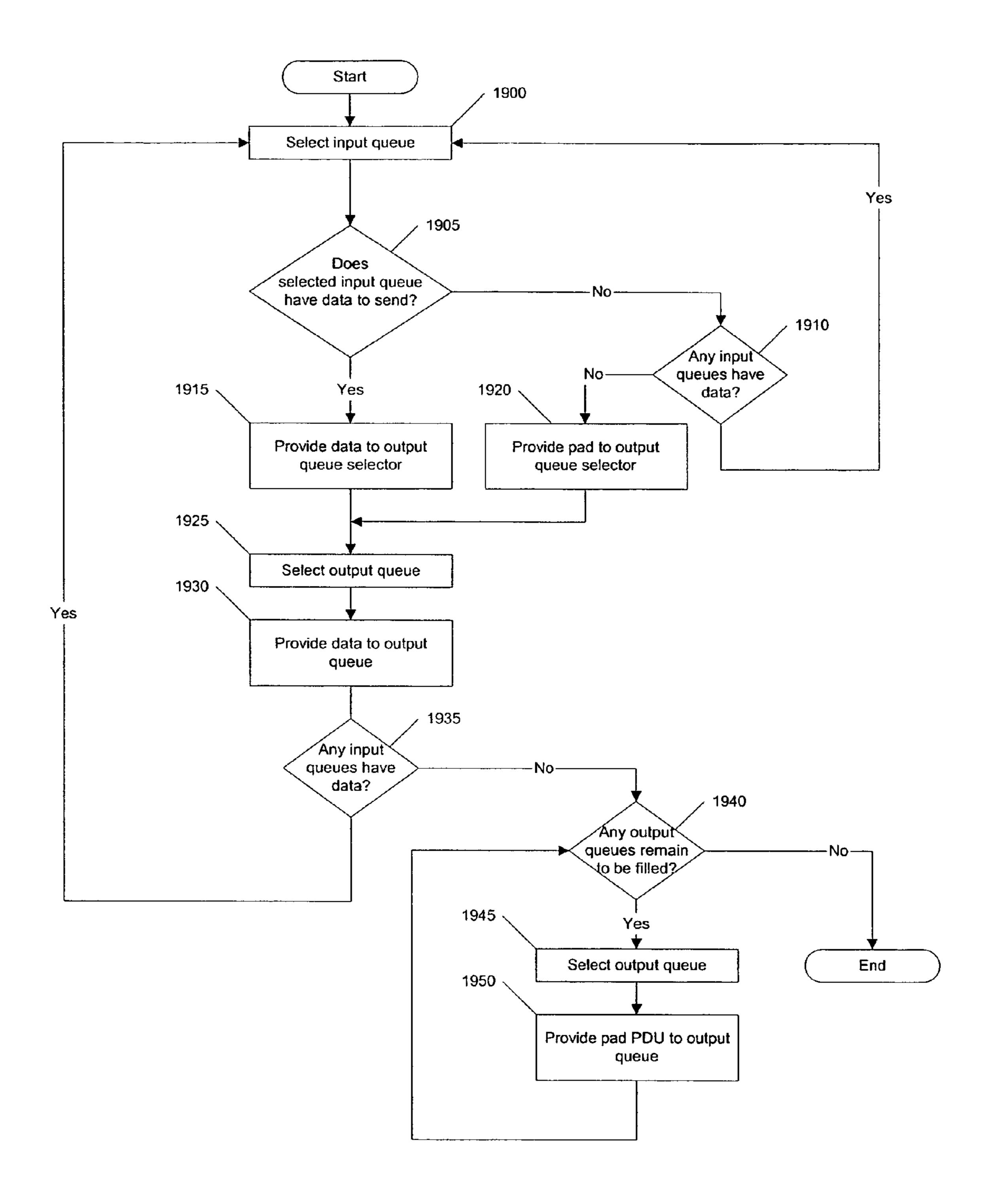

- FIG. 19 is a flow diagram illustrating the process of generating frames according to embodiments of the present invention.

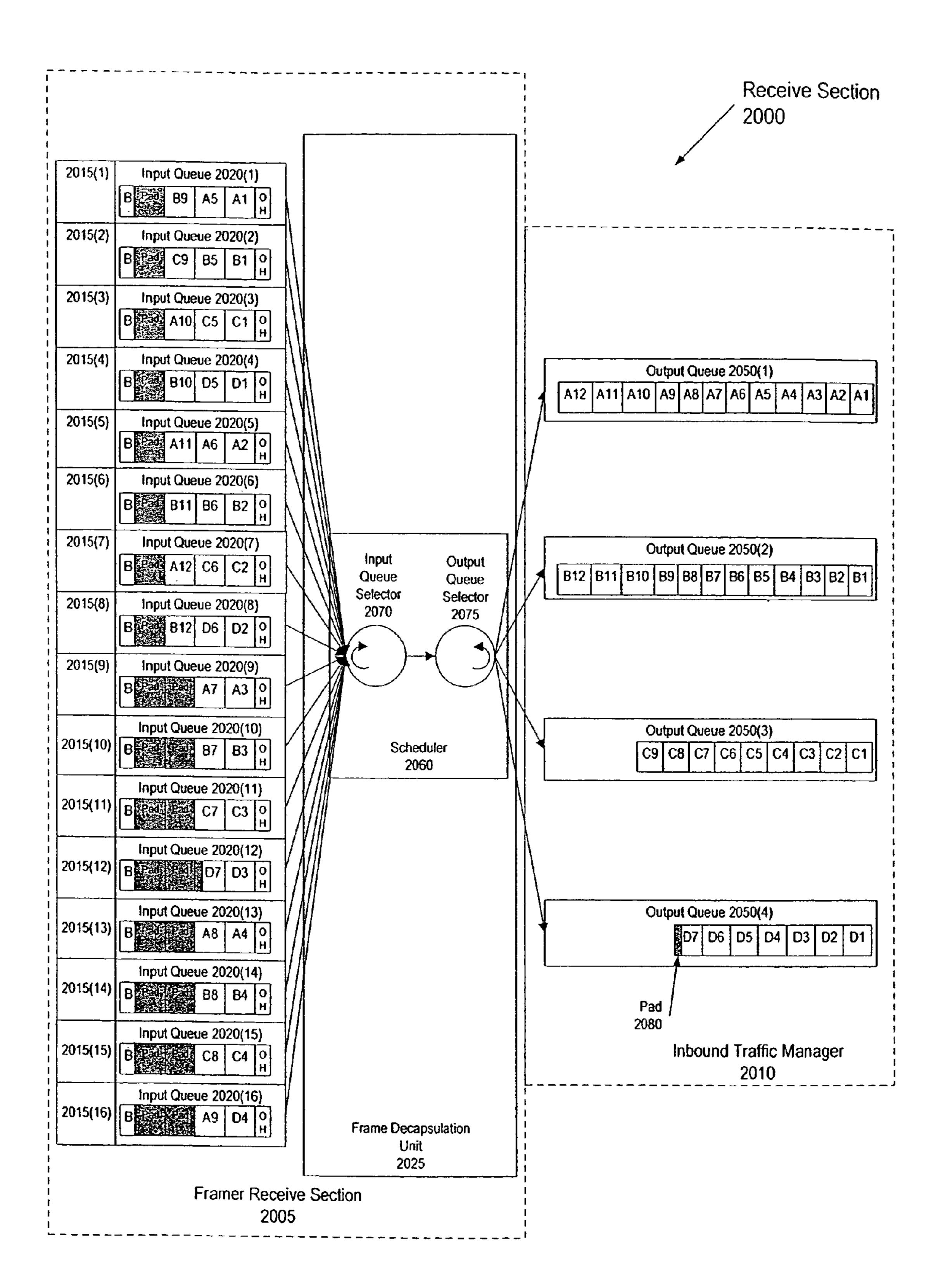

- FIG. 20 is a block diagram illustrating portions of a receive section according to embodiments of the present invention.

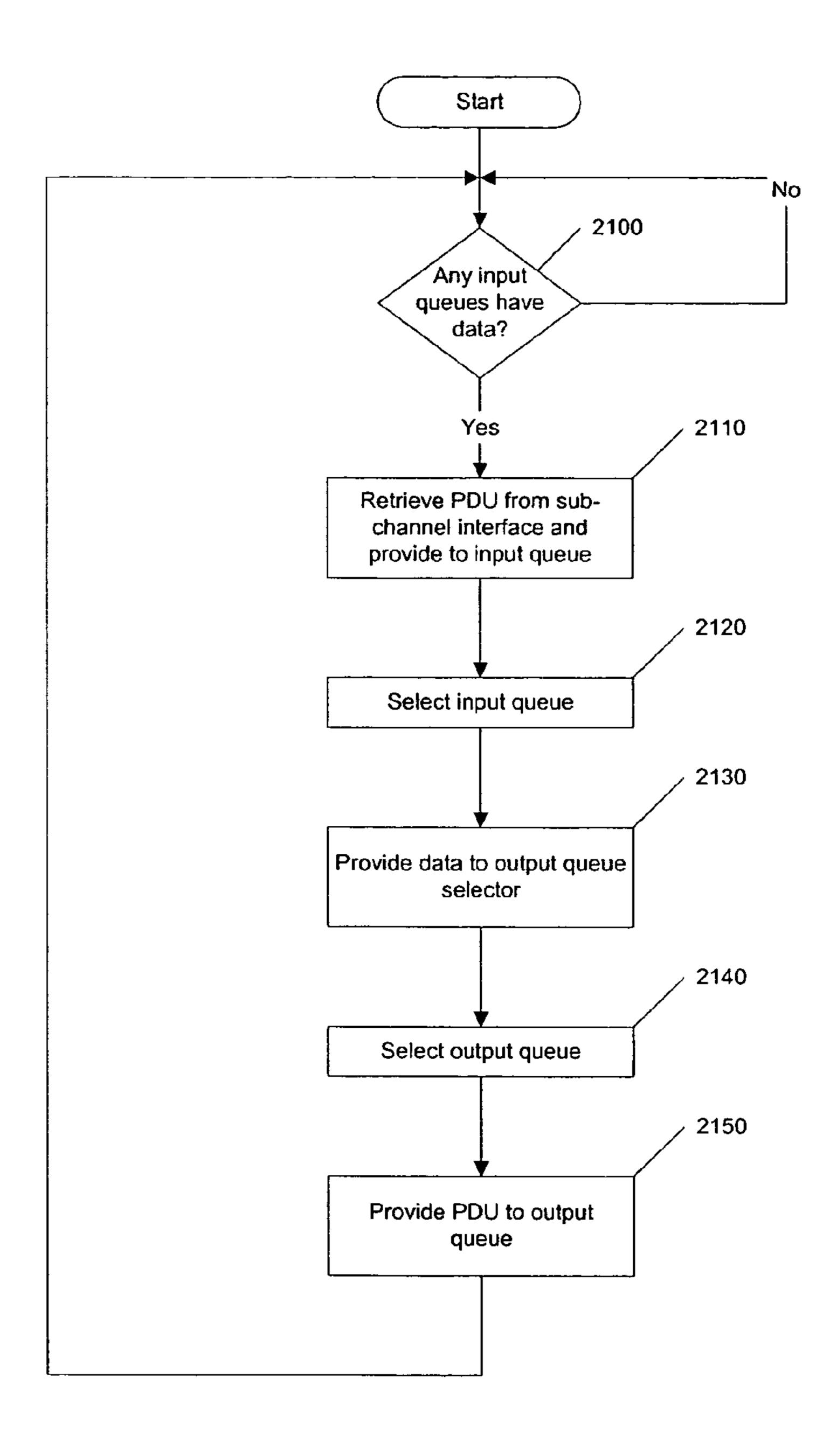

FIG. 21 is a flow diagram illustrating an example of the operation of a receive section according to embodiments of the present invention.

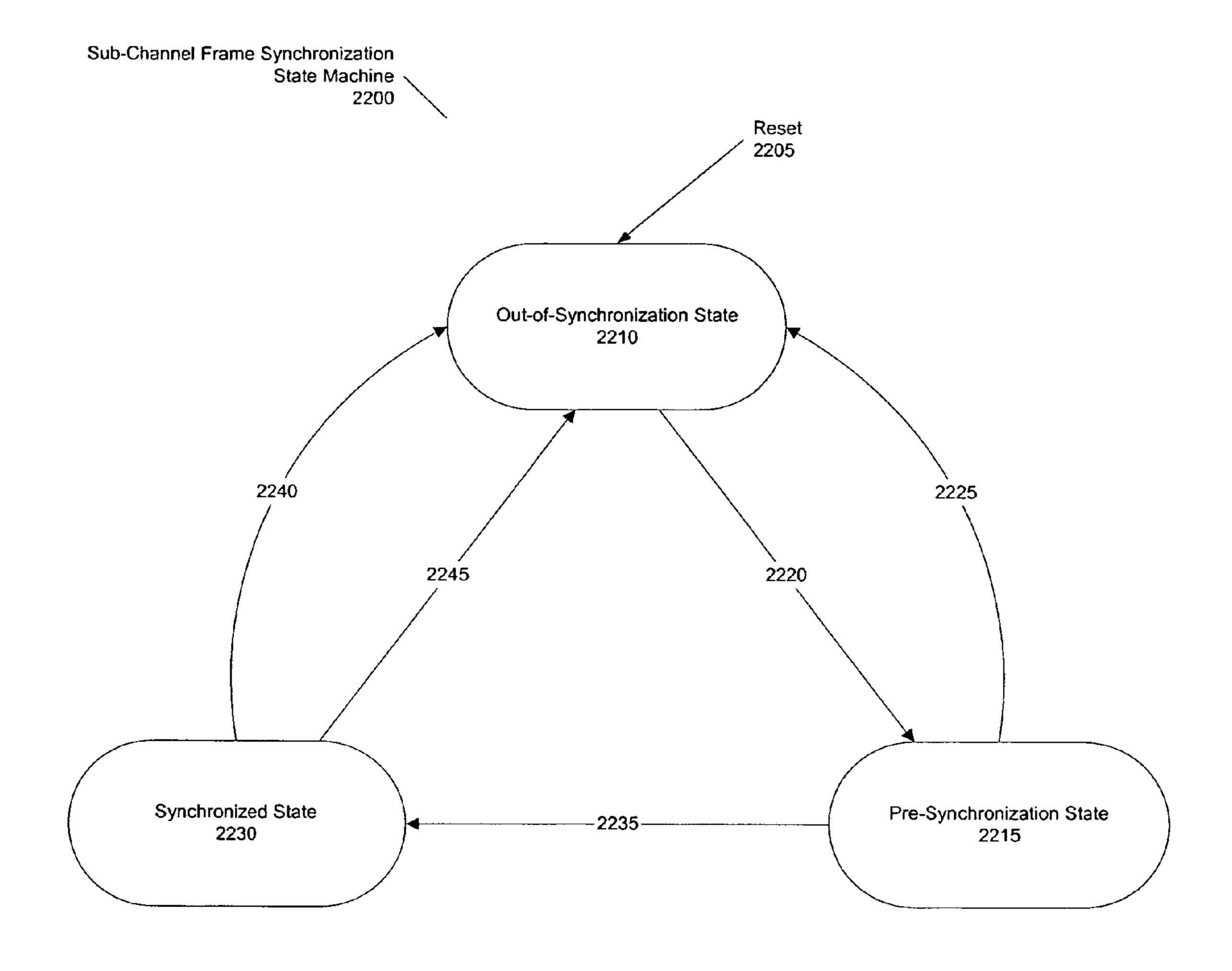

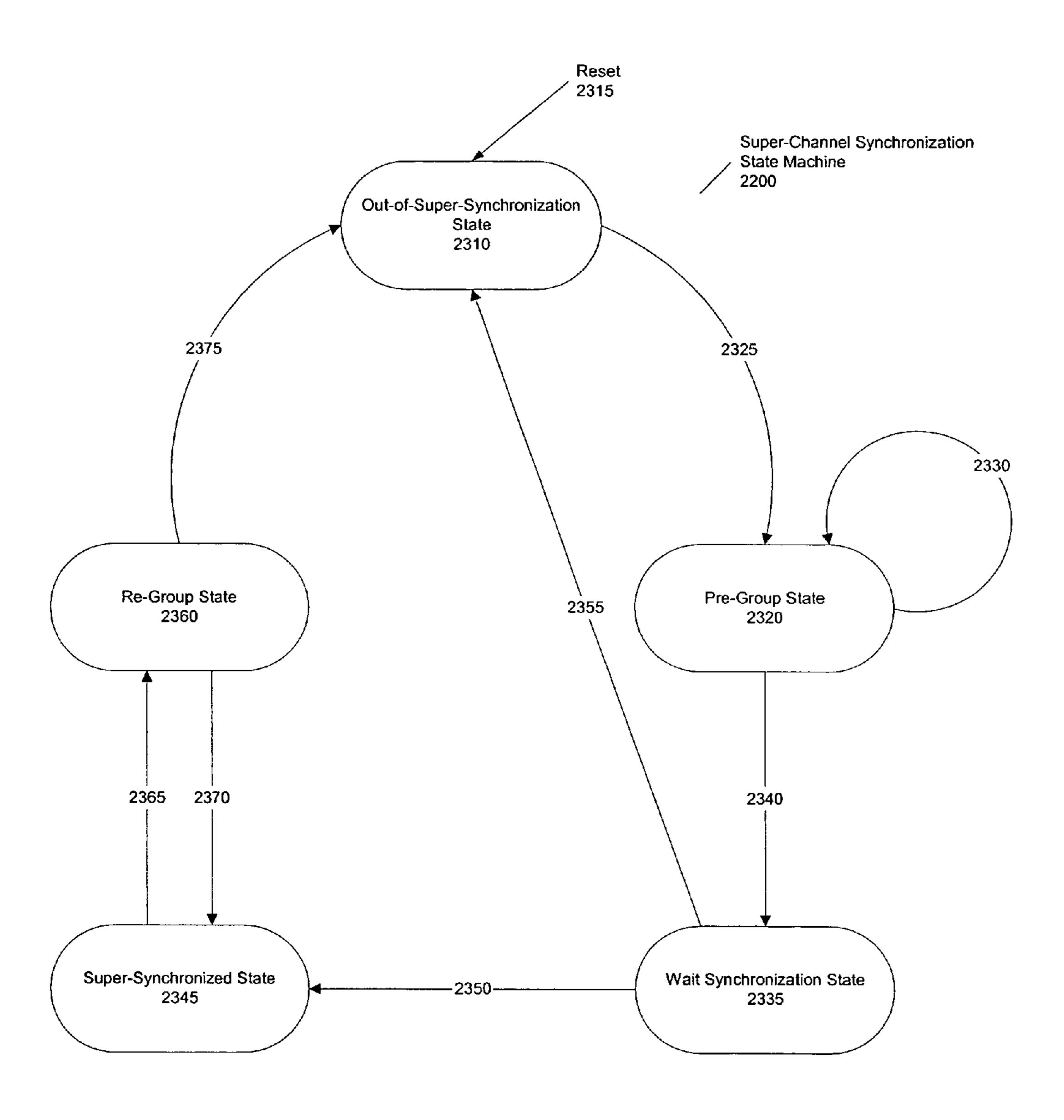

FIG. **22** is a diagram depicting a sub-channel synchronization state machine according to embodiments of the present invention.

FIG. 23 is a diagram depicting a super-channel synchronization state machine according to embodiments of the present invention.

The use of the same reference symbols in different draw- 10 ings indicates similar or identical items.

#### DETAILED DESCRIPTION OF THE INVENTION

The following is intended to provide a detailed description of an example of the invention and should not be taken to be limiting of the invention itself. Rather, any number of variations may fall within the scope of the invention which is defined in the claims following the description.

#### Introduction

The present invention provides a frame structure that takes advantage of the higher speed and lower power silicon technologies to increase the router port throughput beyond 10 Gbps, while keeping the memory requirements to a minimum. This solution is also more economical from the transmission system perspective since the data rate per wavelength is kept at 10 Gbps. In the future, as fiber-optical and transmission technologies evolve to carry higher data rates per wavelength over longer distances, such technologies can be easily incorporated into schemes according to the present invention.

The economy of this solution rests on maximizing the throughput of each of the high-speed ports by utilizing multiple 10 Gbps point-to-point transmission lines more efficiently than the standard SONET framing protocol. A new framing protocol that enhances the throughput over the 10 Gbps point-to-point links by minimizing the overhead requirements for the application is provided by embodiments of the present invention. In addition to overhead efficiency, the framing protocol provides:

- 1. The ability to verify accuracy of super-channel connectivity;

- 2. Support for a super-channel-level 1&1 protection and restoration mechanism architectured into a switch or router;

- 3. The ability to monitor various failure conditions of each transmission link independently;

- 4. The ability to communicate to the far-end switch to start or stop transmitting on a sub-channel based upon one or more error conditions;

- 5. The ability to manually provision a sub-channel in and out of service;

- 6. The ability to allow asymmetric sub-channel connectivity in the forward (W-to-E) and reverse (E-to-W) direction;

- 7. The ability to allow configurable sub-channel burn-in prior to the sub-channel carrying traffic; and

- 8. The ability to allow a user access to a user communication channel from the transmitter to the receiver; and) 9.99% (or better) raw payload throughput.

An Example Network Employing Features of the Present Invention

FIG. 1 is a block diagram illustrating a network 100 that supports and employs the use of a framing technology such as 65 that described in embodiments of the present invention. Network 100 includes packet switches 105, 110 and 115, which

6

are coupled to one another via channels 120, 125 and 130. Each of packet switches 105, 110 and 115 are also coupled to one or more routers (depicted in FIG. 1 as routers 140(1)-(N)). As depicted in FIG. 1, packet switch 105 is coupled to routers 140(1)-(K); packet switch 110 is coupled to routers 140(K+1)-(M); and packet switch 115 is coupled to routers 140(M+1)-(N). Packet switches 105, 110 and 115 provide access to the core of network 100 (represented by channels 120, 125 and 130) to each of routers 140(1)-(N), allowing traffic from each of routers 140(1)-(N) to be communicated over the core of network 100.

Connections to each of routers 140(1)-(N) are exemplified in FIG. 1 by the connections to router 140(K) depicted therein. Local routers 150(1)-(N) are depicted as being coupled to router 140(K), as might be the case in the architecture of a metropolitan area network (MAN) or some other type of regional network. Again, as an example, switches 160(1)-(N) are depicted in FIG. 1 as being coupled to local router 150(1)-(N). Switches 160(1)-(N) might be, for example, located in an entity's building, and serve the local area networks within that building, providing access to the metropolitan area network and to the core of network 100, via the network elements previously discussed. An example of such a local area network is depicted in FIG. 1 as a local area network (LAN)170, coupled to switch 160(1). LAN 170 includes, for example, servers 180(1)-(N) and client terminals 190(1)-(N). LAN 170 not only couples client terminals 190(1)-(N) to servers 180(1)-(N), but also to switch 160(1), thus providing access to the local routers, routers, packet switches and channels of network 100.

FIG. 2 depicts a block diagram of a computer system 210 suitable for implementing the present invention, and exemplary of a computer capable of being coupled to LAN 170, as well as performing processing and control functions throughout network 100. Computer system 210 includes a bus 212 which interconnects major subsystems of computer system 210 such as a central processor 214, a system memory 216 (typically RAM, but which may also include ROM, flash RAM, or the like), an input/output controller 218, an external audio device such as a speaker system 220 via an audio output interface 222, an external device such as a display screen 224 via display adapter 226, serial ports 228 and 230, a keyboard 232 (interfaced with a keyboard controller 233), a storage interface 234, a floppy disk drive 236 operative to receive a floppy disk 238, and a CD-ROM drive 240 operative to receive a CD-ROM 242. Also included are a mouse 246 (or other point-and-click device, coupled to bus 212 via serial port 228), a modem 247 (coupled to bus 212 via serial port 230) and a network interface 248 (coupled directly to bus **212**).

Bus **212** allows data communication between central processor 214 and system memory 216, which may include both read only memory (ROM) or flash memory (neither shown), 55 and random access memory (RAM) (not shown), as previously noted. The RAM is generally the main memory into which the operating system and application programs are loaded and typically affords at least 16 megabytes of memory space. The ROM or flash memory may contain, among other 60 code, the Basic Input-Output system (BIOS) which controls basic hardware operation such as the interaction with peripheral components. Applications resident with computer system 210 are generally stored on and accessed via a computer readable medium, such as a hard disk drive (e.g., fixed disk 244), an optical drive (e.g., CD-ROM drive 240), floppy disk unit 236 or other storage medium. Additionally, applications may be in the form of electronic signals modulated in accor-

dance with the application and data communication technology when accessed via network modem 247 or interface 248.

Storage interface 234, as with the other storage interfaces of computer system 210, may connect to a standard computer readable medium for storage and/or retrieval of information, 5 such as a fixed disk drive 244. Fixed disk drive 244 may be a part of computer system 210 or may be separate and accessed through other interface systems. Many other devices can be connected such as a mouse 246 connected to bus 212 via serial port 228, a modem 247 connected to bus 212 via serial 10 port 230 and a network interface 248 connected directly to bus 212. Modem 247 may provide a direct connection to a remote server via a telephone link or to the Internet via an Internet service provider (ISP). Network interface 248 may provide a direct connection to a remote server via a direct 15 network link to the Internet via a POP (point of presence). Network interface 248 may provide such connection using wireless techniques, including digital cellular telephone connection, Cellular Digital Packet Data (CDPD) connection, digital satellite data connection or the like.

Many other devices or subsystems (not shown) may be connected in a similar manner (e.g., bar code readers, document scanners, digital cameras and so on). Conversely, it is not necessary for all of the devices shown in FIG. 2 to be present to practice the present invention. The devices and 25 subsystems may be interconnected in different ways from that shown in FIG. 2. The operation of a computer system such as that shown in FIG. 2 is readily known in the art and is not discussed in detail in this application. Code to implement the present invention may be operably disposed or stored in computer-readable storage media such as one or more of system memory 216, fixed disk 244, CD-ROM 242, or floppy disk 238. Additionally, computer system 210 may be any kind of computing device, and so is intended to include personal data assistants (PDAs), network appliances, X-window terminals 35 or other such computing devices.

An Example Routing Unit

FIG. 3 is a block diagram illustrating a routing unit 300. A routing unit such as routing unit 300 is included in each of packet switches 105, 110 and 115, and perform the functions 40 that support a framing mechanism according to embodiments of the present invention. Initially, when routing unit 300 receives a datastream, routing unit 300 receives the given datastream at one of fabric ports 305(1)-(N). The datastream is then supplied to a switch fabric 310, which switches the 45 datastream to one of transmit ports 315(1)-(N). Transmit ports 315(1)-(N) output their respective datastreams to an outbound traffic manager 320, which contains a number of input queues (not shown). From the input queues of outbound traffic manager 320, the datastreams are supplied to a framer 50 transmit section 325 of a framing unit 330. Taken together, outbound traffic manager 320 and framer transmit section 325 form, at least in part, a transmit section 327. Framer transmit section 325 assembles pieces of the datastreams (referred to herein as data units) and places the framed data units in output 55 queues within framer transmit section 325 (now shown). These framed data units (or, more simply, frames) are then provided to optical transmitters 335(1)-(N) for transmission over, for example, optical fibers (depicted in FIG. 3 as optical fibers 340(1)-(N)). It will be noted that optical fibers 340(1)- 60 (N) can correspond (e.g., in certain embodiments) to one or more of channels 120, 125 or 130.

In a similar fashion, datastreams are received from optical fibers 345(1)-(N) by optical receivers 350(1)-(N). Optical receivers 350(1)-(N) convert the optical datastreams into 65 electrical datastreams and provide those electrical datastreams to a framer receive section 355 of framing unit 330.

8

Framer receive section 355 reverses the frame generation process performed by the framer transmit section on the transmit side of the network, generating the original datastreams and providing them to an inbound traffic manager 360. Taken together, framer receive section 355 and inbound traffic manager 360 form, at least in part, a receive section 362. Inbound traffic manager 360 includes a number of input queues into which the incoming datastreams are stored. These incoming datastreams, after being queued, are then provided to corresponding ones of receive ports 365(1)-(N). Receive ports 365(1)-(N), in turn, provide these datastreams to switch fabric 310, which switches the incoming datastreams to the proper one of fabric ports 305(1)-(N). Controlling these operations, via control of various of the elements of routing unit 300, is a system processor 370. In this manner, datastreams are both transmitted to and received from the proper packet switches of network 100.

In the example depicted in FIG. 3, the switch fabric port 20 speed (i.e., the speed supported by transmit ports 315(1)-(N) and receive ports 365(1)-(N)) is preferably a multiple of the outgoing sub-channel speeds (data rates) from transmit section 327 (via framer transmit section 325, and subsequently optical transmitters 335(1)-(N)) or the line card (i.e., optical receivers 350(1)-(N) and framer receive section 355), respectively. Framer transmit section 325 receives data from outbound traffic manager 320 and distributes the data across several of the outgoing sub-channels and encapsulates each of the datastreams in a frame as described in regard to FIG. 4. A mirror image of this process is performed by receive section 362 in re-assembling the payloads into their constituent datastreams. In addition to the re-assembly process, receive section 362 communicates with transmit section 327, as well as the line card processor (not shown) to provide protection and restoration of the sub-channels and super-channel.

It will be noted that the variable identifier "N" is used in several instances in FIG. 3 to more simply designate the final element (e.g., transmit ports 315(1)-(N) and receive ports 365(1)-(N)) of a series of related or similar elements (e.g., transmit ports and receive ports). The repeated use of such variable identifiers is not meant to imply a correlation between the sizes of such series of elements, although such correlation may exist. The use of such variable identifiers does not require that each series of elements has the same number of elements as another series delimited by the same variable identifier. Rather, in each instance of use, the variable identified by "N" may hold the same or a different value than other instances of the same variable identifier.

Moreover, regarding the signals described herein, those skilled in the art will recognize that a signal may be directly transmitted from a first block to a second block, or a signal may be modified (e.g., amplified, attenuated, delayed, latched, buffered, inverted, filtered or otherwise modified) between the blocks. Although the signals of the above described embodiment are characterized as transmitted from one block to the next, other embodiments of the present invention may include modified signals in place of such directly transmitted signals as long as the informational and/ or functional aspect of the signal is transmitted between blocks. To some extent, a signal input at a second block may be conceptualized as a second signal derived from a first signal output from a first block due to physical limitations of the circuitry involved (e.g., there will inevitably be some attenuation and delay). Therefore, as used herein, a second signal derived from a first signal includes the first signal or any modifications to the first signal, whether due to circuit

limitations or due to passage through other circuit elements which do not change the informational and/or final functional aspect of the first signal.

The foregoing described embodiment wherein the different components are contained within different other components (e.g., the various elements shown as components of routing unit 300). It is to be understood that such depicted architectures are merely exemplary, and that in fact many other architectures can be implemented which achieve the same functionality. In an abstract, but still definite sense, any 10 arrangement of components to achieve the same functionality is effectively "associated" such that the desired functionality is achieved. Hence, any two components herein combined to achieve a particular functionality can be seen as "associated with" each other such that the desired functionality is 15 achieved, irrespective of architectures or intermediate components. Likewise, any two components so associated can also be viewed as being "operably connected", or "operably coupled", to each other to achieve the desired functionality.

#### An Example Frame Structure

FIG. 4 is a block diagram of an example layout of the frame structure according to embodiments of the present invention. Frame structure 400 can include, for example, information regarding both a primary super-channel and an alternate super-channel (depicted in FIG. 4 as primary super-channel information 401 and alternate super-channel information 402), as well as information regarding sub-channels thereof (depicted in FIG. 4 as sub-channel information 403 and sub-channel information 404). As depicted in FIG. 4, frame structure 400 starts with the information depicted on the right and moves through to the end of the frame with the information depicted on the left.

In one embodiment of the present invention, frame structure 400 is 155,520 bytes in length, and is transmitted in 125 µsec, thereby achieving a data rate of 9.95328×10<sup>9</sup> bps. This structure and transmission rate supports frame transmission that is similar to the familiar SONET OC192 data rate. It should be noted here that there is no inherent limitation on the size or the number of payload data units (PDUs) or overhead (OH) bytes and therefore suitable changes can be made for alternative applications.

Frame structure **400** begins with start-of-frame (SOF) information **405**. SOF information **405** indicates the beginning of the frame. The function of SOF information **405** is to allow receiver section **362** (or, more specifically, framer receive section **355**) to synchronize on the incoming subchannel frame. In one embodiment, the first byte transmitted is 0xAA (10101010), while the second byte transmitted is 0xA5 (10100101). Also, the SOF sequence should not be 50 scrambled before transmission.

Next is the first portion of primary super-channel information 401, which includes primary super-channel identifier 410 and sub-channel identifier **415**. The function of primary super-channel identifier 410 is to allow the receive framer 55 (e.g., framer receive section 355) to verify that the superchannel connection is received from the intended node. This feature is important in the backbone network (e.g., network 100), where the separation between the transmitting node and the receiving node can be 1000 km or more, with several 60 transport network elements between them. The value of super-channel identifier 410 can be, for example, any value between 0 and 65536. In one embodiment, a super-channel identifier value of 0x0000 is reserved for an Alarm Indication Signal (AIS) frame. The AIS frame has an SOF, a super- 65 channel identifier, CRC32 information and BIP8 information as the valid overhead with empty payload data units (PDUs;

10

described subsequently, in connection with FIG. 16D). To maintain connection accuracy across network 100, no two super-channels should have the same super-channel identifier. Typically, super-channel identifier 410 is initialized at startup by the system control software executed by system processor 370.

In certain embodiments, sub-channel identifier 415 is a single byte and contains seven bits of identifying information and an "Active" bit (not shown). The function of sub-channel identifier 415 is to allow framer receive section 355 to identify individual sub-channels within a super-channel. Sub-channel identifier 415 also indicates the round-robin sequence in which the payload units are distributed across the available sub-channels (in embodiments employing a round-robin technique), allowing framer receive section 355 to accurately extract the payload. The Active bit is set by framer transmit section 325 in response to the receipt by framer transmit section 325 of a bitmap from the far-end framer receive 20 framer section (analogous to receive framer section 355) indicating that the sub-channel is tested and can be used. When the Active bit of sub-channel identifier **415** indicates that a sub-channel is in use, framer transmit section 325 sends live data via the PDUs and empty PDUs are sent when there is no data to be sent. Framer transmit section 325 examines the received bitmap every PDU time. If the Active bit changes from 1 to 0, framer transmit section 325 sends an empty PDU immediately following the change. But if the Active bit changes from 0 to 1, framer transmit section 325 begins sending user data only in the following frame after the Active bit is set to 1.

The values used in sub-channel identifier 415 preferably start from 0 and run, in ascending order, up to the maximum number of sub-channels supported by routing unit 300. For example, a maximum of 128 sub-channels can be supported by a 7 bit sub-channel identifier, assuming the preceding arrangement. It will be noted that sub-channel identifiers can be hard-coded in routing unit 300, or can be downloadable (e.g., from the memory (not shown) associated with system processor 370). It will be noted, however, that, although a 7 bit sub-channel identifier can support up to 128 sub-channels, only sub-channels 0 through 63 are valid in an implementation that uses a 64 bit sub-channel bitmap for sub-channel protection. The sub-channel bitmap definition is discuss sub-sequently.

Frame structure **400** also includes a frame counter **420**. The function of frame counter **420** is to keep a count of the number of frames transmitted since power-on or the last counter rollover. The frame count is also used to synchronize all the active sub-channels within a super-channel before the payload is extracted. In one embodiment, frame counter **420** is 4 bytes in length and so can count up to 4 G (4,294,967,296) consecutive frames before roll over. It will be noted that a rollover will occur at approximately 149.131 hours at 10 Gbps frame transmission rate. Because the sub-channel frames are generated and transmitted by the transmit framer (framer transmit section **325**) at the same clock, the sub-channel frames leaving the transmit framer (framer transmit section **325**) at any time should have the same frame count.

Following frame counter 420 are user-accessible bytes (UAB) 425. The function of UAB 425 is to allow the system's user to send and receive information to and from the remote network element. UAB 425 can be directly written to and read from directly accessible registers located in, for example, transmit framer section 325 and receive framer section 362, respectively. A user can choose to send different information

on each sub-channel or the same information on all the subchannels, depending on the user's needs with regard to protection.

The remaining portions of primary super-channel information 401 are shown following. This information includes a primary super-channel (PSC) sub-channel bitmap 430, a set of PSC error condition flags 435 and a PSC label-switched path (LSP) switch byte 440C. An LSP is a routing technique that routes information based on labels. Next is the information contained in alternate super-channel information 402. This information includes an alternate super-channel (ASC) identifier 445, an ASC sub-channel bitmap 450, a set of ASC error condition flags 455 and an ASC LSP enable flag 460.

PSC sub-channel bitmap 430 and ASC sub-channel bitmap **450** are typically configured to implement sub-channel-level <sup>15</sup> fast protection and restoration at layer one by indicating failure to the far-end transmitter. This also allows, for example, the system user to manually take a sub-channel out-of-service, if need be. In one embodiment, the least-significant bit of the first byte transmitted corresponds to a received sub- 20 channel identifier value of 0. The next significant bit corresponds to a received sub-channel identifier value of 1. The least-significant bit of the second byte transmitted corresponds to a received sub-channel identifier value of 8. An error on a received sub-channel is indicated to the far-end <sup>25</sup> transmitter by sending out a bitmap with the bit corresponding to the sub-channel identifier reset to 0. The bitmap carried by the various sub-channels should be identical. This is done to ensure that the bitmap reaches the far-end transmitter, even if only a single working sub-channel is alive in the reverse <sup>30</sup> direction. In the normal case (i.e., with multiple sub-channels alive), framer receive section 355 selects the most conservative sub-channel bitmap. At power-on, the sub-channel bitmap transmitted by the transmitting node is reset to all zeros. The bitmap in the transmitting node is then modified by the receiving node as the receiving node receives good frames on each sub-channel. Each bit in the bitmap received from the receiving node can be individually overridden by the user of the system via dedicated registers. This feature allows the system user to manually take individual sub-channels in and 40 out of service (e.g., for repairs). As currently defined, a 64 bit bitmap supports only 0-63 sub-channels, although sub-channel identifier 415 can support 128 sub-channels. The unused bytes in the frame overhead can also be used to support more than 64 sub-channels. The sub-channel identifier values that 45 are not supported by the bitmap are considered invalid.

The function of the error condition flags (i.e., PSC error condition flags 435 and ASC error condition flags 455) is to inform the far-end network element of error conditions seen by the near-end receiver. The first two bytes transmitted following the sub-channel bitmap (i.e., PSC sub-channel bitmap 430 and ASC sub-channel bitmap 450) are the error condition flags, followed by the LSP switch byte. The bit definitions of these fields are given in Tables 1, 2 and 3.

TABLE 1

|                          |                              | The                     | error cond                       | ition flags                 | byte #1.                   |                                   |                             |

|--------------------------|------------------------------|-------------------------|----------------------------------|-----------------------------|----------------------------|-----------------------------------|-----------------------------|

| MS-<br>Bit<br>Bit<br>0_7 | Bit 06                       | Bit 0_5                 | Bit 0_4                          | Bit 0_3                     | Bit 0_2                    | Bit 0_1                           | LSBit<br>Bit 0_0            |

| CH_<br>ID<br>Error       | Channel ex-<br>cluded due to | RDI in re-sponse to AIS | CRC<br>Error<br>Degra-<br>dation | Loss-of-<br>signal<br>(LOS) | Loss-of-<br>frame<br>(LOF) | BER<br>Degra-<br>dation<br>beyond | Forced-<br>Manual<br>Switch |

12

TABLE 1-continued

|                          |                | The               | error cond | lition fla | gs | byte#         | 1. |                |                  |

|--------------------------|----------------|-------------------|------------|------------|----|---------------|----|----------------|------------------|

| MS-<br>Bit<br>Bit<br>0_7 | Bit 06         | Bit 0_5           | Bit 0_4    | Bit 0_3    | 3  | <b>Bit</b> 0_ | _2 | Bit 0_1        | LSBit<br>Bit 0_0 |

|                          | excess<br>skew | frame<br>received |            |            |    |               |    | thresh-<br>old |                  |

TABLE 2

| , |                  | <u>T</u> :  | he error | condition | flags byte | #2.     |                    |

|---|------------------|-------------|----------|-----------|------------|---------|--------------------|

|   | MSBit<br>Bit 1_7 |             |          | Bit 1_3   | Bit 1_2    | Bit 1_1 | LSBit<br>Bit 1_0   |

| ) | Unused           | Un-<br>used |          | Unused    | Unused     | Unused  | Sub_ch_ID<br>Error |

TABLE 3

|                  |         | Т       | The LSP sv | witch byte |         |             |                  |

|------------------|---------|---------|------------|------------|---------|-------------|------------------|

| MSBit<br>Bit 2_7 | Bit 2_6 | Bit 2_5 | Bit 2_4    | Bit 2_3    | Bit 2_2 |             | LSBit<br>Bit 2_0 |

| 1/0              | 1/0     | Unused  | Unused     | Unused     | Unused  | Un-<br>used | Unused           |

Given the preceding definitions, several points can be made. If more than one sub-channel has different (and distinct) error conditions (e.g., a BER degradation beyond threshold on one channel and LOS on another), the error condition bits (as depict in Tables 1 and 2) are not configured to resolve which of the channels is experiencing which error condition. It will be apparent to one of skill in the art that such information could be included in the overhead bytes (e.g., PSC information 401 and ASC information 402), but this would reduce the efficiency of the frame structure. It will also be noted that, preferably, error condition flags are ordered from the MSBit, which contains an indication of the most severe error, down to the LSBit, which contains an indication of the least severe error.

The function of the LSP switch byte is to inform the far-end line card to switch the guaranteed bandwidth LSPs to an alternate channel, when the capacity of the given super-chan-50 nel drops below the total guaranteed bandwidth traffic through that super-channel. Guaranteed bandwidth traffic is traffic that is designated as having a priority (e.g. quality-ofservice level) that necessitates guaranteeing availability of the necessary bandwidth (i.e., datastream(s)). In the embodi-55 ment depicted herein, the most-significant bit (MSBit) of the LSP switch byte (bit 2\_7) is owned by the primary superchannel (both directions) and the next-most-significant bit (bit 2\_6) is owned by the alternate super-channel (both directions). These bits are externally set in the framer transmit section by the system processor. In response to the bitmap generated by the framer receive section, the system control software executed by the system processor calculates the amount of bandwidth available in that super-channel direction and compares the available bandwidth with the guaran-65 teed bandwidth that is carried through that super-channel. If the total available bandwidth is either close to or smaller than the guaranteed bandwidth traffic, then the bit in the LSP

switch byte corresponding to that super-channel is reset to zero, and is sent out to the far-end line card in the LSP switch byte. Upon receiving the bit in the LSP switch byte belonging to the given super-channel reset to 0, the system processor of the far-end network element initiates a process to inform all the other label forwarding engines to perform layer 2 label lookup to the alternate switch port. The switch-over of the LSPs to the alternate super-channel is done only if the alternate line card receives the bit in the LSP switch byte owned by the primary super-channel set to 1.

Following ASC information 402 are unused bytes 465, 32-bit cyclical redundancy check information (depicted in FIG. 4 as CRC32 470), a payload 480 (that can include a number of payload data units (PDUs) (not shown)) and byteinterleaved parity information (depicted in FIG. 4 as BIP8 15 490). Unused bytes 465 can be assigned for expansion of currently defined bytes, or can be reserved for other uses. The 32-bit cyclical redundancy check information that is depicted in FIG. 4 as CRC32 470 can be, for example, a CCITT standard CRC calculated over the frame header bytes with a 20 divisor=0x04C11DB7 and initial remainder=0xFFFFFFFF. The byte-interleaved parity information depicted in FIG. 4 as BIP8 **490** can be, for example, a SONET-like bit-interleaved parity to set odd parity over the entire previously-transmitted frame (excepting the SOF information). The structure of pay- 25 load 480 is describe in connection with FIGS. 16A-16D.

Example Processes for Building a Frame Structure According to Embodiments of the Present Invention

FIG. 5 is a flow diagram illustrating an example process of generating a frame structure such as frame structure 400. The process begins with the insertion of start-of-frame bytes (depicted in FIG. 4 as SOF information 405) (step 500). Next, a primary super-channel identifier (e.g., PSC identifier 410) is inserted in the frame (step 505). A sub-channel identifier for the primary super-channel is inserted in the frame (e.g., sub-channel identifier 415) (step 510). A frame count is then inserted into the frame (e.g., frame counter 420) (step 515). If the user so desires, any required user-accessible bytes are then inserted into the frame (step 520).

The LSP switch byte is then configured for each superchannel (step **525**). A process for configuring the LSP switch byte is shown in further detail in the flow diagram of FIG. **6**. Error condition flags for each super-channel are also configured (step **530**). The configuration of error condition flags is shown in further detail in the flow diagram of FIG. **8**. Next, the sub-channel identifier bitmap for each super-channel are configured (step **535**). The process of configuring the sub-channel bitmap is described in further detail in regard to FIG. **9**. The sub-channel bitmap for the primary super-channel is then written into the frame (step **540**). Also written into the frame are the error condition flags for the primary super-channel (step **541**). The LSP switch byte for the primary super-channel is then written into the frame (step **542**).

Next, an alternate super-channel identifier (e.g., ASC identifier 445) is inserted in the frame (step 545). The sub-channel bitmap for the alternate super-channel is then written into the frame (step 550). Also written into the frame are the error condition flags for the alternate super-channel (step 551). The LSP switch byte for the alternate super-channel is then written into the frame (step 551).

At this point in the process, if there are unused bytes (step 555), the unused bytes are set to a known value (step 560). The CRC32 divisor value and temporary remainder value are set (step 565) so that a CRC32 remainder value can be generated 65 over the bytes in the header of the frame (step 570). Once the CRC32 check is performed, the payload data units are

14

inserted in the frame (step 575). A byte-interleaved parity value (BIP8 value) is then generated for dip frame (step 580). This BIP8 value will be inserted in the next frame to allow for the detection of errors in the current frame. Finally, the BIP8 value for the previous frame is inserted at the end of the present frame, in a similar fashion. It will be noted that the BIP8 value is actually generated over the frame as the frame is being processed, which is more efficient and potentially simpler than generating the BIP8 value at the end of the frame once the frame has been assembled.

It is appreciated that operations discussed herein with regard to flow diagrams such as that depicted in FIG. 5 may consist of directly entered commands by a computer system user or by steps executed by application specific hardware modules, but the preferred embodiment includes steps executed by software modules. The functionality of steps referred to herein may correspond to the functionality of modules or portions of modules. Moreover, the operations referred to herein may be modules or portions of modules (e.g., software, firmware, hardware or other such modules). For example, although the described embodiment includes software modules and/or includes manually entered user commands, the various example modules may be application specific hardware modules. The software modules discussed herein may include script, batch or other executable files, or combinations and/or portions of such files. The software modules may include a computer program or subroutines thereof encoded on computer-readable media.

Additionally, those skilled in the art will recognize that the boundaries between modules are merely illustrative and alternative embodiments may merge modules or impose an alternative decomposition of functionality of modules. For example, the modules discussed herein may be decomposed into sub-modules to be executed as multiple computer processes. Moreover, alternative embodiments may combine multiple instances of a particular module or sub-module. Furthermore, those skilled in the art will recognize that the operations described in example embodiment are for illustration only. Operations may be combined or the functionality of the operations may be distributed in additional operations in accordance with the invention.

Alternatively, such actions may be embodied in the structure of circuitry that implements such functionality, such as the micro-code of a complex instruction set computer (CISC), firmware programmed into programmable or erasable/programmable devices, the configuration of a field-programmable gate array (FPGA), the design of a gate array or full-custom application-specific integrated circuit (ASIC), or the like.

Each of the blocks of FIG. 5 (as well as those of other the other flow diagrams described herein) may be executed by a module (e.g., a software module) or a portion of a module or a computer system user using, for example, a computer system such as the storage router previously mentioned, or a similar network element, as well as a computer system such as computer system 210. Thus, the above described method, the operations thereof and modules therefor may be executed on a computer system configured to execute the operations of the method and/or may be executed from computer-readable media. The method may be embodied in a machine-readable and/or computer-readable medium for configuring a computer system to execute the method. Thus, the software modules may be stored within and/or transmitted to a computer system memory to configure the computer system to perform the functions of the module.

Such a computer system normally processes information according to a program (a list of internally stored instructions

such as a particular application program and/or an operating system) and produces resultant output information via) I/O devices. A computer process typically includes an executing (running) program or portion of a program, current program values and state information, and the resources used by the operating system to manage the execution of the process. A parent process may spawn other, child processes to help perform the overall functionality of the parent process. Because the parent process specifically spawns the child processes to perform a portion of the overall functionality of the parent process, the functions performed by child processes (and grandchild processes, etc.) may sometimes be described as being performed by the parent process.

Such a computer system typically includes multiple computer processes executing "concurrently." Often, a computer 15 system includes a single processing unit which is capable of supporting many active processes alternately. Although multiple processes may appear to be executing concurrently, at any given point in time only one process is actually executed by the single processing unit. By rapidly changing the process 20 executing, a computer system gives the appearance of concurrent process execution. The ability of a computer system to multiplex the computer system's resources among multiple processes in various stages of execution is called multitasking. Systems with multiple processing units, which by defi- 25 nition can support true concurrent processing, are called multiprocessing systems. Active processes are often referred to as executing concurrently when such processes are executed in a multitasking and/or a multiprocessing environment.

The software modules described herein may be received by 30 such a computer system, for example, from computer readable media. The computer readable media may be permanently, removably or remotely coupled to the computer system. The computer readable media may non-exclusively include, for example, any number of the following: magnetic 35 storage media including disk and tape storage media; optical storage media such as compact disk media (e.g., CD-ROM, CD-R, etc.) and digital video disk storage media; nonvolatile memory storage memory including semiconductor-based memory units such as FLASH memory, EEPROM, EPROM, 40 ROM or application specific integrated circuits; volatile storage media including registers, buffers or caches, main memory, RAM, etc.; and data transmission media including computer network, point-to-point telecommunication, and carrier wave transmission media. In a UNIX-based embodi- 45 ment, the software modules may be embodied in a file which may be a device, a terminal, a local or remote file, a socket, a network connection, a signal, or other expedient of communication or state change. Other new and various types of computer-readable media may be used to store and/or trans- 50 mit the software modules discussed herein.

FIG. 6 is a flow diagram illustrating a process for configuring LSP enable flags for primary and alternate super-channels. First, a determination is made as to whether the primary and alternate super-channels need to be configured (step 600). If the primary and alternate super-channels do not need to be configured, the process waits until such time as such configuration is required. If the primary and alternate super-channels do need to be configured, the number of sub-channels of the primary super-channel which are functional is determined 60 (step 610). Similarly, a determination is made as to the number of sub-channels of the alternate super-channel which are functional (step 620). Once these determinations have been made, a determination is made as to the amount of guaranteed bandwidth traffic that can be accepted (step 630). Next, the 65 bits of the LSP switch byte are set according to the current configuration (step 640). This will typically take into account

**16**

the operational state of the various sub-channels. An example process for performing such configuration is described with regard to FIG. 7. Guaranteed bandwidth traffic is then assigned to the primary and alternate super-channels based on the available capacity of each (step 650).

FIG. 7 is a flow diagram illustrating a process of setting bits of the LSP switch byte according to a current configuration. The process begins with setting the LSP switch bytes of the primary super-channel and alternate super-channel for normal operation (step 700). In the case where the super-channel's LSP switch bytes are being initialized (e.g., during the process depicted in FIG. 6 (step 640)), this is the only action that need be performed. However, during operation of the super-channels, further actions are typically performed.

In such a case, a determination is then made as to whether error conditions exist on enough of the sub-channels of the given super-channel to require switching the guaranteed bandwidth traffic onto the other super-channel (step 710). While error conditions on the sub-channels remain below the given threshold, and so do not require the switching of guaranteed bandwidth, the process awaits the crossing of that threshold, writing LSP switch bytes for a normal operation to the frames currently being generated. Upon the occurrence of a sufficient number of error conditions on one super-channel (e.g., the primary super-channel), the bits in the LSP switch byte are set to indicate switching of the guaranteed bandwidth to the other super-channel (step 720). While the error conditions persist (step 730), the bits in the LSP switch byte remain set to indicate switching of the guaranteed bandwidth to the other super-channel. Once the error condition has been corrected, the process proceeds by setting bits of each LSP switch byte for normal operation for both the primary and alternate super-channels (step 700).

FIG. 8 is a flow diagram illustrating a process of configuring error flags according to embodiments of the present invention. The process begins with a determination as to whether the sub-channel is to be forced to switch (step 800). If the sub-channel is to be forced to switch, a forced/manual switch flag is set, indicating that switching of the sub-channel is to be forced (step 805). Otherwise, the forced/manual switch flag is cleared, indicating that the sub-channel is to be manually switched (step 810). Next, a determination is made as to whether the bit error rate (BER) is unacceptably high (step 815). If the BER is unacceptably high, the BER flag is set (step 820). Otherwise, the BER flag is cleared (step 825). A determination is then made as to whether a loss-of-signal (LOS) has occurred (step 830) If an LOS has occurred, and LOS flag is set (step 835). Otherwise, the LOS flag is cleared (step **840**). In a similar fashion, a determination is made as to whether a loss-of-frame (LOF) has occurred (step **845**). If an LOF has occurred, an LOF flag is set (step 850). Otherwise, the LOF flag is cleared (step 855). Next, a determination is made, using the CRC32 information, as to whether a CRC error has occurred (step 860). If a CRC error has occurred, a CRC error flag is set (step **865**). Otherwise, the CRC error flag is cleared (step 870). Next, a determination is made as to whether to generate a remote defect indicate (RDI) in response to the receipt of an alarm indication signal (AIS) within the frame received (step 875). If an RDI is to be sent, a RDI flag is set (step 880). Otherwise, the RDI flag is cleared (step **885**).

FIG. 9 is a flow diagram illustrating a process of coarse bitmap generation. This process can be carried out, for example, in making a determination as to the degradation of sub-channels, in deciding whether or not to switch guaranteed bandwidth to another super-channel (e.g., step 710 of FIG. 7). The process begins with a selection of a sub-channel (step

900). A determination is then made as to whether the selected sub-channel is degraded (step 910). If the selected sub-channel is degraded, a bit corresponding to the selected sub-channel is set (step 920). Otherwise, the bit corresponding to the selected sub-channel is cleared (step 930). The process continues until all sub-channels have been examined (step 940).

Example Network Segment Illustrating Sub-Channel Protection and Restoration

FIG. 10 is a block diagram illustrating a portion of network  $_{10}$ 100 in further detail that illustrates structure supporting a sub-channel bitmap protection mechanism. In this view, a super-channel 1000 connects packets switches 1010 and 1020. Packet switch 1010 communicates with packet switch 1020 via a line card 1030, while packet switch 1020 communications with packet switch 1010 via a line card 1040. It will be noted that, applying terms of art currently in use, that packet switch 1010 is the "west" packet switch, while packet switch 1020 can be referred to as the "east" packet switch. It will also be noted that, in fact, line card 1030 can actually be considered as part of packet switch 1010. Similarly, line card 1040 can be viewed as being incorporated in packet switch 1020. Taking the perspective of packet switch 1010 (i.e., the "west" packet switch), super-channel 1000 includes a number of transmit sub-channels (depicted in FIG. 10 as sub-channels 25 1050(1)-(N)) and receive sub-channels (depicted in FIG. 10 as sub-channels 1060(1)-(N)). Conversely, packet switch 1020 receives sub-channels 1050(1)-(N), while transmitting sub-channels **1060**(1)-(N).

FIG. 11 is a flow diagram depicting a process of sub- 30 channel protection using a sub-channel bitmap protection mechanism that employs, for example, the information provided by PSC sub-channel bitmap 430 of frame 400 in FIG. 4, in an environment such as that depicted in FIG. 10. Fundamentally, this process, in one embodiment, responds to an 35 incoming bitmap indicating that one or more sub-channels are degraded, by inserting empty payloads in outgoing frames. The process begins with a determination as to whether any of the sub-channels (e.g., one of sub-channels 1050(1)-(N)) is degraded (step 1100). It will be noted that, for  $_{40}$ the sake of generality, the terms "near-end" and "far-end" are used in the present discussion, corresponding to the "east"/ "west" terminology used previously (and in the stead of other possible terminologies), so that the discussion may be relative to the ends of the sub-channel that is experiencing errors. 45 Thus, for example, an error on one of sub-channels 1050(1)-(N) would have packet switch 1010 as the "near-end" packet switch, and packet switch 1020 as the "far-end" packet switch. Upon the detection of a degraded sub-channel (step 1100), the far-end switch identifies the sub-channel experiencing degradation (step 1105). The far-end switch then sets the appropriate error condition flag (or flags) for the subchannel experiencing degradation in frames transmitted from the far-end switch (step 1110). The far-end switch also sets a bit in the sub-channel bitmap corresponding to the sub-chan- 55 nel experiencing degradation in frames that are transmitted from the far-end switch (step 1115). Correspondingly, the near-end switch receives the sub-channel bitmap indicating that the given sub-channel is experiencing degradation (step **1120**). The near-end switch then transmits frames containing 60 empty payloads on the sub-channel experiencing degradation (step **1125**).

Next, a determination is made as to whether the sub-channel bitmap still indicates that the given sub-channel is experiencing degradation (step 1130). If the sub-channel continues to experience degradation, the far-end switch continues to set the appropriate air condition flags and bit (or bits) in the

**18**

sub-channel bitmap to indicate to the near-end switch that such degradation continues to occur (steps 1110 and 1115), and the near-end switch receives this information and continues to act upon that information appropriately (steps 1120 and 1125). Once the given sub-channel is no longer experiencing degradation (step 1130), the far-end switch clears the appropriate error condition flag for the given sub-channel in frames transmitted from the far-end switch (step 1140). The far-end switch also clears the appropriate bit (or bits) in the subchannel bit map corresponding to the given sub-channel in frames transmitted from the far-end switch (step 1150). Correspondingly, the near-end switch receives the sub-channel bit map indicating that the given sub-channel is no longer experiencing degradation (step 1160). The near-end switch 15 then transmits frames having payloads containing data on the given (and now recovered) sub-channel (step 1170).

Referring to FIGS. 10 and 11, an example of the operation of such a sub-channel bitmap protection mechanism can be demonstrated. The following example shows the mechanism behind sub-channel protection and restoration using a sub-channel bitmap. In this example, the West-to-East direction of the super-channel (i.e., super-channel 1000) has three sub-channels (i.e., sub-channels 1050(1)-(3)) and the East-to-West direction as four sub-channels (i.e., sub-channels 1050 (1)-(4)), that are in use. Propagation of the sub-channel bitmap during the "Normal" state, "Errored" sub-channel state and the "Restored" state is now discussed. The corresponding error condition flags are also discussed, for reference. The LSP switch byte and error condition flags operate as described previously.

In the normal operating state, the framer transmit section of the West-side packet switch (packet switch 1010) transmits a sub-channel bitmap having its four least-significant bits (LS-Bits) set to 1 (00001111). The framer transmit section of the East-side packet switch (packet switch 1020) transmits a sub-channel bitmap having its three LSBits set to 1 (00000111). At power-on, the framer receive sections of both the West-side and East-side packet switches are configured to send a sub-channel bitmap having all their bits reset to 0.

An error condition is experienced by sub-channel 1050(1) (e.g., a BER above a user specified threshold), while sub-channel 1050(3) experiences an LOF condition. In this case, the sub-channel bitmap sent by the framer receive section of packet switch 1020 has the LSBit and the third LSBit reset to 0 (00000010). This sub-channel bitmap is sent to the framer transmit section of packet switch 1020, which in turn sends this sub-channel bitmap to the framer transmit section of packet switch 1010 via the framer receive section of packet switch 1010. The bitmap sent to the framer transmit section of packet switch 1010 is not modified.

As soon as the framer transmit section of packet switch 1010 receives a modified bitmap from the framer receive section of packet switch 1010, the framer transmit section of packet switch 1010 searches for 3 consecutive identical subchannel bitmaps and correlates those sub-channel bitmaps to the sub-channel bitmaps received from the alternate superchannel and authenticates the new sub-channel bitmap state. The new authenticated sub-channel bitmap is then used to send empty payloads into the corresponding sub-channels. The system processor of packet switch 1020 modifies the LSP switch byte (10000000) and error condition flags (byte #1=00000110 and byte #2=00000000) to be sent out by the framer transmit section of packet switch 1020.

When sub-channels 1050(1) and 1050(3) recover from their error conditions, the framer receive section of packet switch 1020 sets the sub-channel bitmap to indicate a normal condition (00000111) and transmits the sub-channel bitmap

to the framer transmit section of packet switch 1020 to be transmitted to the framer transmit section of packet switch 1010 via the framer receive section of packet switch 1010. In response to the new sub-channel bitmap, the framer transmit section of packet switch 1010 begins sending live data on 5 sub-channels 1050(1) and 1050(3).

Example Network Segment Illustrating a 1&1 Protection Mechanism

FIG. 12 is a block diagram illustrating a portion of network 10 100 in which a channel 1200 supports communications between a packet switch 1210 and a packet switch 1220. It will be noted that channel 1200 can be viewed as an example of one of channels 120, 125 and 130 of FIG. 1. In a fashion similar to that depicted in FIG. 10, packet switches 1210 and  $_{15}$ 1220 communicate over channel 1200 using line cards (depicted in FIG. 12 as line cards 1230(1,1)-(N2)). Channel 1200 can be further divided into a number of primary super-channels and alternate super-channels, which are paired together logically to form super-channel pairs that include a primary 20 super-channel and an alternate super-channel. These superchannels are depicted in FIG. 12 as primary super-channels 1240(1)-(N) and alternate super-channels 1250(1)-(N). In certain embodiments of the present invention, the super-channel configuration depicted in FIG. 12 can be used to support 25 a protection scheme referred to herein as a 1&1 super-channel protection scheme.

FIG. 13 is a flow-diagram illustrating a procedure for switching guaranteed bandwidth traffic between a primary super-channel and an alternate super-channel. In a fashion 30 similar to that of the discussion of FIG. 11, the terms "nearend" and "far-end" are determined by the primary super-channel's transmit channel that is experiencing errors. Moreover, it will be noted that the process is controlled at the system processing level (described in further detail with regard to FIG. 14) in response to the bitmaps generated by the far-end packet switch, and in particular, the framer receive section thereof (e.g., framer receive section 355 of FIG. 3).

The process begins with a determination as to whether the far-end switch has detected errors on a primary super-channel that requires the use of the corresponding alternate super-channel (step 1300). It will be noted that the discussion of FIG. 13 is in terms of guaranteed bandwidth being switched from a primary super-channel to an alternate super-channel. However, the converse is also possible, and should be considered as part of the present discussion. If no such errors are detected (step 1300), the process simply waits for such errors to occur. Upon the occurrence of such errors (step 1300), the far-end switch indicates to the near-end switch that the near-end switch's primary super-channel transmissions are experiencing errors and so will not be used (step 1310).

Next, the near-end switch transmits frames having guaranteed bandwidth traffic on the alternate super-channel in order

**20**

to provide that guaranteed bandwidth traffic with the bandwidth thus guaranteed (step 1320). The near-end switch continues to transmit best-effort traffic on the primary superchannel, maintaining the bandwidths for the best-effort traffic as is possible (step 1325). The far-end switch, in turn, receives the frames transmitted by the near-end switch on the alternate super-channel (step 1330).

While shifting guaranteed bandwidth to the other superchannel (e.g., the alternate super-channel), the near-end switch continues to transmit frames of best-effort traffic on the original super-channel (the primary super-channel), as best as can be accomplished (step 1325). Correspondingly, the far-end switch receives this best-effort traffic on the primary super-channel (step 1327). As these actions proceed, a determination is made by the far-end switch as to whether the near-end switch's transmit primary super-channel is still experiencing errors (step 1340). If the near-end switch's transmit primary super-channel is still experiencing errors, the alternate super-channel is used to transmit guaranteed bandwidth (steps 1310, 1320 and 1330). Otherwise, the farend switch indicates to the near-end switch that the transmissions of the near-end switch's primary super-channel are no longer experiencing errors and can once again be used to communicate guaranteed traffic (step 1350). At this point, the near-end switch resumes transmitting data on the now-restored primary super-channel (step 1360). Similarly, the farend switch begins receiving frames transmitted by the nearend switch on the given primary super-channel (step 1370). The process then proceeds to await further errors (step 1300).

Referring to FIGS. 12 and 13, an example of the operation of such a 1 & 1 protection mechanism using LSP switch bytes can be demonstrated. As noted, the use of LSP switch bytes (e.g., PSC LSP switch bytes 440 and ASC LSP switch bytes 460) allow guaranteed bandwidth to be switched between super-channels (e.g., from a primary super-channel to an alternate super-channel). Guaranteed bandwidth is bandwidth that is guaranteed to be available to a user of the network, and is guaranteed to be available notwithstanding certain (and even most) network failures. An example of a mechanism that employs LSP switch bytes to allow the switching of guaranteed bandwidth label-switched paths (LSPs) between a primary super-channel and an alternate super-channel in a 1&1 super-channel protection scheme is now described.

Table 4 shows the exchange of LSP switch bytes across primary super-channel 1240(1) and alternate super-channel 1250(1), in the case where an error condition (e.g., BER) causes all three operating sub-channels from the transmit side of LC 1230(1,2) to the receive side of LC 1230(1,1) to be inactive. The recovery from the error is then shown for one of the three sub-channels. Finally, all three sub-channels recover.

TABLE 4

| Exchange of LSP switch byte and error condition flags across primary and alternate super-channels in the present example. |                              |                              |                              |  |  |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|------------------------------|--|--|

| Error                                                                                                                     | Sub-channel Bitmap           | LSP Switch Byte              | Error Condition Flags        |  |  |

| Condition                                                                                                                 | (Transmit Side)              | (Transmit Side)              | (Transmit Side)              |  |  |

| Normal Operation (3 sub-channels operating)                                                                               | LC $1230(1,1) = [00000111]$  | LC $1230(1,1) = [100000000]$ | LC $1230(1,1) = [000000000]$ |  |  |

|                                                                                                                           | LC $1230(1,2) = [00000111]$  | LC $1230(1,2) = [100000000]$ | LC $1230(1,2) = [000000000]$ |  |  |

|                                                                                                                           | LC $1230(2,1) = [00000111]$  | LC $1230(2,1) = [010000000]$ | LC $1230(2,1) = [000000000]$ |  |  |

|                                                                                                                           | LC $1230(2,2) = [00000111]$  | LC $1230(2,2) = [010000000]$ | LC $1230(2,2) = [000000000]$ |  |  |

| BER on all sub-                                                                                                           | LC $1230(1,1) = [000000111]$ | LC 1230(1,1) = [10000000]    | LC $1230(1,1) = [000000000]$ |  |  |