#### US007732342B2

## (12) United States Patent

Balseanu et al.

## (54) METHOD TO INCREASE THE COMPRESSIVE STRESS OF PECVD SILICON NITRIDE FILMS

(75) Inventors: Mihaela Balseanu, Sunnyvale, CA (US); Li-Qun Xia, Santa Clara, CA (US); Vladimir Zubkov, Mountain View, CA (US); Mei-Yee Shek, Mountain View, CA (US); Isabelita

Rolfox, Union City, CA (US); Hichem M'Saad, Santa Clara, CA (US)

(73) Assignee: **Applied Materials, Inc.**, Santa Clara, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 11/398,146

(22) Filed: **Apr. 5, 2006**

### (65) Prior Publication Data

US 2006/0269692 A1 Nov. 30, 2006

#### Related U.S. Application Data

- (60) Provisional application No. 60/685,365, filed on May 26, 2005, provisional application No. 60/701,854, filed on Jul. 21, 2005.

- (51) Int. Cl. H01L 21/302 (2006.01)

See application file for complete search history.

## (45) Date of Patent:

(10) Patent No.:

#### (56) References Cited

U.S. PATENT DOCUMENTS

US 7,732,342 B2

Jun. 8, 2010

### (Continued)

#### FOREIGN PATENT DOCUMENTS

JP 63-261571 10/1998

#### (Continued)

#### OTHER PUBLICATIONS

"Atomic layer controlled deposition of silicon nitride with self-limiting mechanism", Applied Physics Letters, AIP, American Institute of Physics, Melville NY, vol. 6, No. 23, Jun. 3, 1996, pp. 3257-3259.

#### (Continued)

Primary Examiner—Lan Vinh (74) Attorney, Agent, or Firm—Townsend and Townsend and Crew

## (57) ABSTRACT

Compressive stress in a film of a semiconductor device may be controlled utilizing one or more techniques, employed alone or in combination. A first set of embodiments increase silicon nitride compressive stress by adding hydrogen to the deposition chemistry, and reduce defects in a device fabricated with a high compressive stress silicon nitride film formed in the presence of hydrogen gas. A silicon nitride film may comprise an initiation layer formed in the absence of a hydrogen gas flow, underlying a high stress nitride layer formed in the presence of a hydrogen gas flow. A silicon nitride film formed in accordance with an embodiment of the present invention may exhibit a compressive stress of 2.8 GPa or higher.

### 13 Claims, 45 Drawing Sheets

#### U.S. PATENT DOCUMENTS

|    | 6,720,097   | B2         | 4/2004  | Ohwawa et al.          |

|----|-------------|------------|---------|------------------------|

|    | 6,759,100   | B2         | 7/2004  | Fukuda et al.          |

|    | 6,808,991   | B1*        | 10/2004 | Tung 438/275           |

|    | 6,919,282   | B2         | 7/2005  | Sakama et al.          |

|    | 6,929,831   | B2*        | 8/2005  | Patel et al 427/579    |

|    | 6,953,609   | B2*        | 10/2005 | Carollo 427/579        |

| 20 | 002/0016084 | A1*        | 2/2002  | Todd 438/791           |

| 20 | 002/0040847 | A1*        | 4/2002  | Ohmi et al 204/192.22  |

| 20 | 002/0164890 | A1         | 11/2002 | Kwan et al.            |

| 20 | 002/0168828 | A1*        | 11/2002 | Cheng et al 438/303    |

| 20 | 003/0228770 | A1         | 12/2003 | Lee et al.             |

| 20 | 004/0029323 | A1         | 2/2004  | Shimizu et al.         |

| 20 | 004/0175883 | A1*        | 9/2004  | Kim 438/244            |

| 20 | 004/0266083 | A1*        | 12/2004 | Hareland et al 438/199 |

| 20 | 006/0105106 | A1         | 5/2006  | Balseanu et al.        |

| 20 | 07/0007548  | <b>A</b> 1 | 1/2007  | Conti et al.           |

#### FOREIGN PATENT DOCUMENTS

JP 2000-339837 12/2000 WO WO 2005-043623 A 5/2005

#### OTHER PUBLICATIONS

Patil et al. "Deposition of Silicon films in presence of nitrogen plasma feasibility study", Bulletin of Materials Science Indian Acad. Sci. India, vol. 25, No. 5, Oct. 2002, pp. 399-402.

Saito et al. "A study of low temperature formation of stress-free silicon nitride films", Record of Electrical and Communication Engineering Converazione Tohoku University, Tokuku Univ. Japan, vol. 72, No. 1, Nov. 2003, pp. 302-303.

Dharmadhikari et a). "UV-assisted processing for advanced dielectric films", Solid State Technology, Mar. 2005 pp. 43-44,46,48.

Banerjee et al., "Characterization of CVD Deposited Amorphous Fluorocarbons for Low k Interlayer Dielectrics", 1 *Electrochem. Soc.*. 146, 2219 (1999).

Charles, "Role of ions in SiO 2 deposition with pulsed and continuous helicon plasma", Pure And Applied Chemistry, 2002 -vol. 74, No. 3, pp. 401-405, 2002. IUPAC 401.

Cruden et al., "Thermal Decomposition of Low-k Pulsed Plasma Fluorocarbon Films. I. Effects of Precursors and Substrate Temperature", J. Electrochem. Soc. 146,4590 (1999).

Cruden et al., "Thermal Decomposition of Low-k Pulsed Plasma Fluorocarbon Films. II. Effect of Post-Deposition Annealing and Ambients", J. Electrochem. Soc. 146,4597 (1999).

Labelle et al., "Pulsed Plasma Enhanced Chemical Vapor Deposition from CH2F2, C2H2F4, and CHCIF/" *T. Vac. Sci. Techno!*. *A*, 17,445 (1999).

Labelle et al., "Fourier Transform Infrared Spectroscopy of Effluents from Pulsed Plasmas of 1,I,2,2-Tetrafluoroethane, Hexafluoropropylene, and Difluoromethane", *T. Vac. Sci. Techno!. A.* 76, 3419 (1999).

Lau et al., "Solid-State NMR of Low Dielectric Constant Films from Pulsed Hydrofluorocarbon Plasmas", *T. Electrochem. Soc.*. 146,2652 (1999).

Limb et al.," Molecular Design of Fluorocarbon Film Architecture by Pulsed Plasma Enhanced and Pyrolytic Chemical Vapor Deposition", *Plasmas and Polymers* 4(1),21 (1999).

Ma et al. "Investigation on processing of industrial set-up plasma enhanced chemical vapor deposition with pulsed d.c. power", *Surface and Coatings Technology*, vol. 131, No. 1, Sep. 1, 2000, pp. 131-135(5).

Ma et al. "Parametric effects of residual stress in pulsed d.c. plasma enhanced CVD TiN coatings", *Surface & Coatings Technology*, vol. 142, 2001, pp. 1023-1027.

Pedrow "Deposition of Plasma-Polymerized Acetylene by an Intense Pulsed RF Plasma Source", IEEE Transactions on Plasma Science, 1990 vol. 18, No. 6. December 1990.

Smith, "Mechanism of  $SiN_xH_y$  deposition from  $N_2$ -Si $H_4$  plasma" Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures—May 1990—vol. 8, Issue 3, pp. 551-557. U.S. Appl. No. 11/055,936 Tensile and Comp Ressive Stressed Materials for Semiconductor filed on Feb. 11, 2005.

<sup>\*</sup> cited by examiner

FIG. 1

FIG. 2

FIG. 4C

FIG. 4D

FIG. 5A

FIG. 5B

FIG. 8

FIG. 9

FIG. 10

FIG. 12A

FIG. 12B

FIG. 12C

FIG. 12D

FIG. 13A

FIG. 13B

FIG. 13C

FIG. 13D

FIG. 13E

FIG. 13F

FIG. 14

FIG. 15

FIG. 16

FIG. 17

Jun. 8, 2010

1500 Before 1000 **– S** After 500 Stress (Mpa) -500 -1000 -1500 -2000 <del>L</del> TS-5min CS-5min CS-10min TS-10min

Fig. 19

FIG. 22A

FIG. 22B

FIG. 23

FIG. 24

# NH<sub>3</sub> Plasma

FIG. 25A

# N<sub>2</sub> + Ar Plasma

FIG. 25B

## Wafer Temperature = 430°C (Heater Set-point = 500°C)

FIG. 25C

FIG. 25D

FIG. 26A

FIG. 26B

FIG. 28A

FIG. 28B

FIG. 29G

Fig. 29H

FIG. 29E

-1G. 29F

FIG. 30

FIG. 31

FIG. 32

Fig. 33

Fig. 34A

FIG. 35

FIG. 36

FIG. 37A

FIG. 37B

FIG. 38A

FIG. 38B

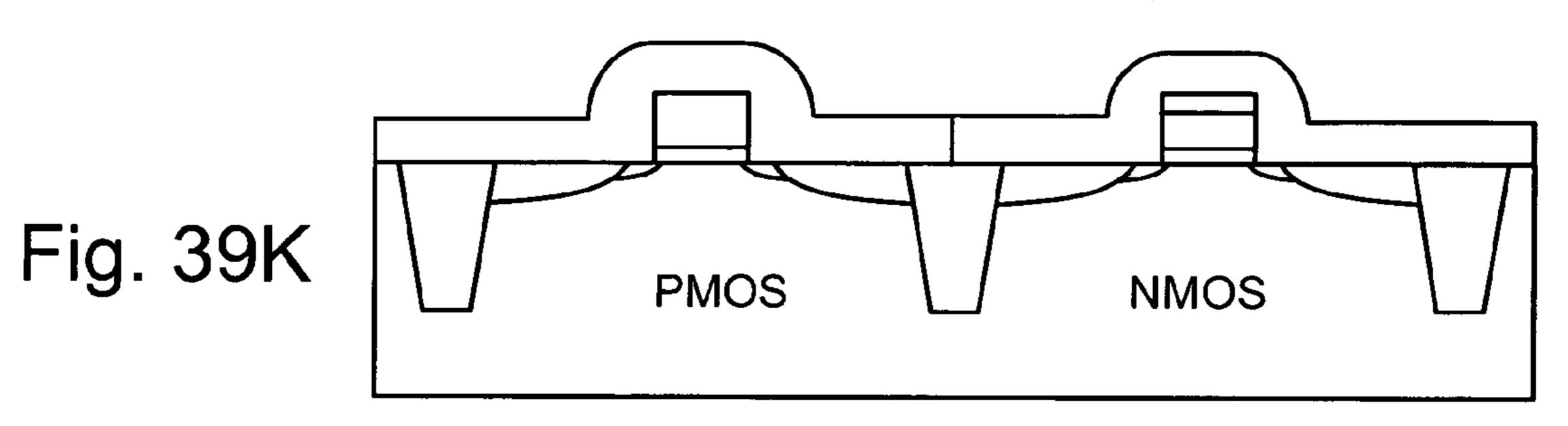

1. Gate stack deposition (gate dielectric and poly)

2. Litho to define the NMOS gate

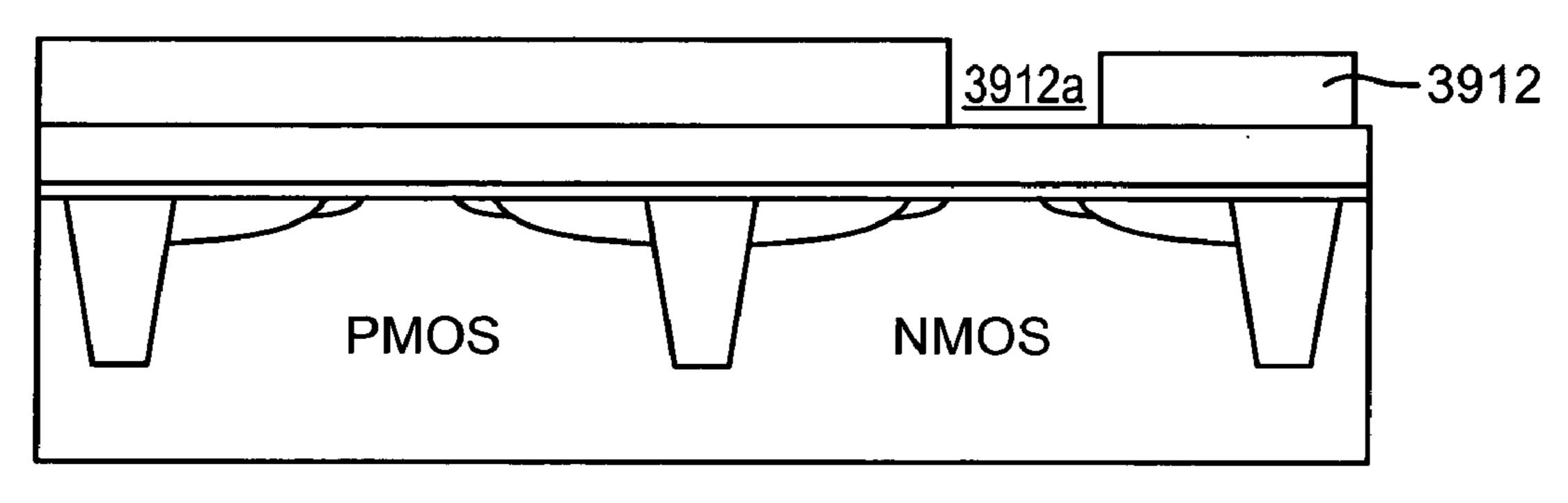

Fig. 39B

- 3. NMOS poly pre-am orphization Ge implant/growth

- recess NMOS poly gate followed by selective SiGe deposition (may require oxide mask)

- b. Ge implantation in NMOS Poly

Fig. 39C

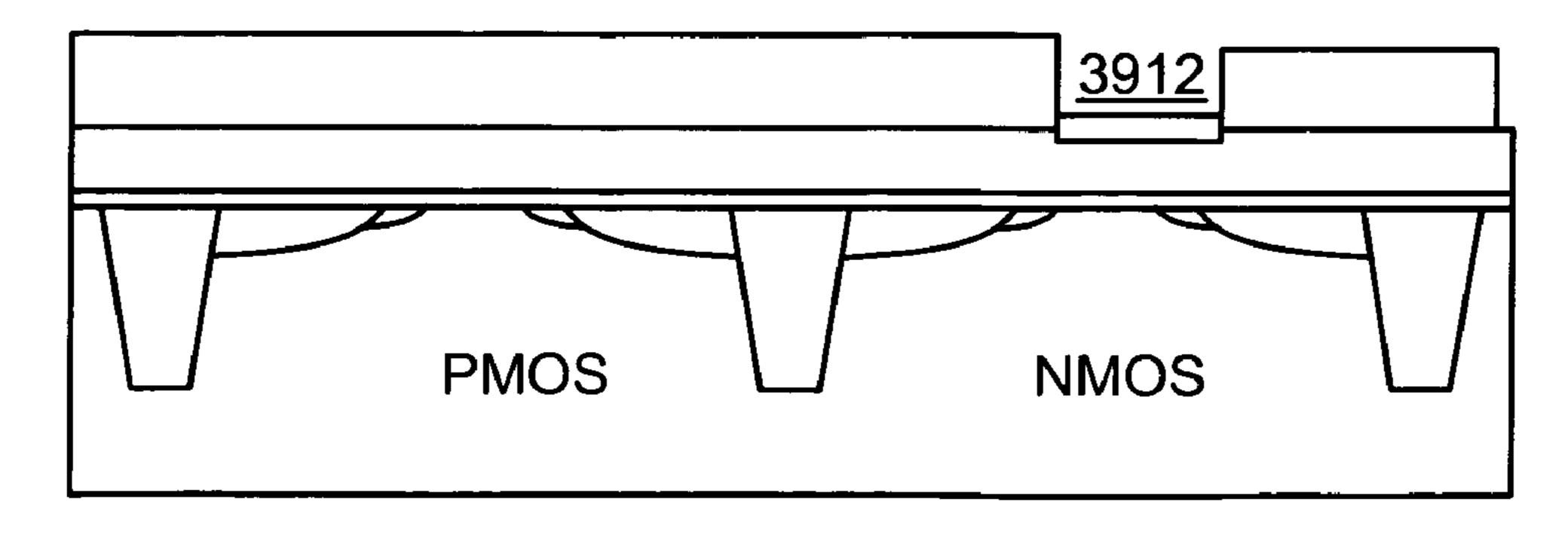

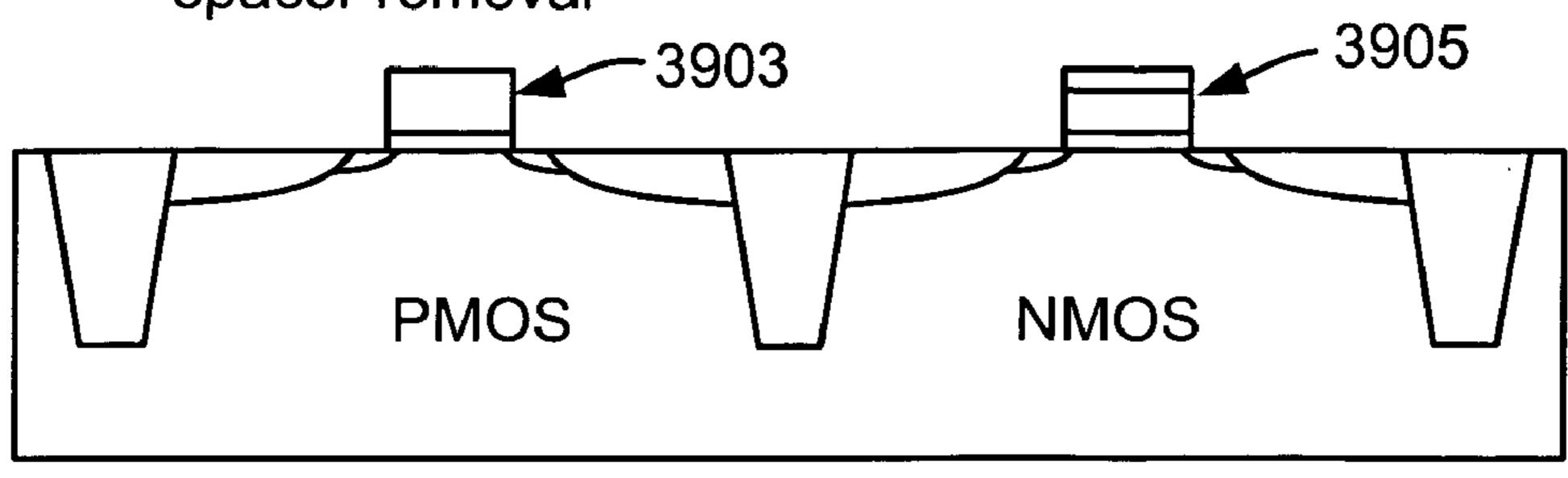

4. Gate etch/S/D Ext and Halo implant; Sacrificial spacer removal

Fig. 39D

5. Tensile nitride dep (pre-RTP)

Jun. 8, 2010

FIg. 39E

6. Litho and Etch to remove the nitride from the PMOS side

Fig. 39F

Jun. 8, 2010

Fig. 39G

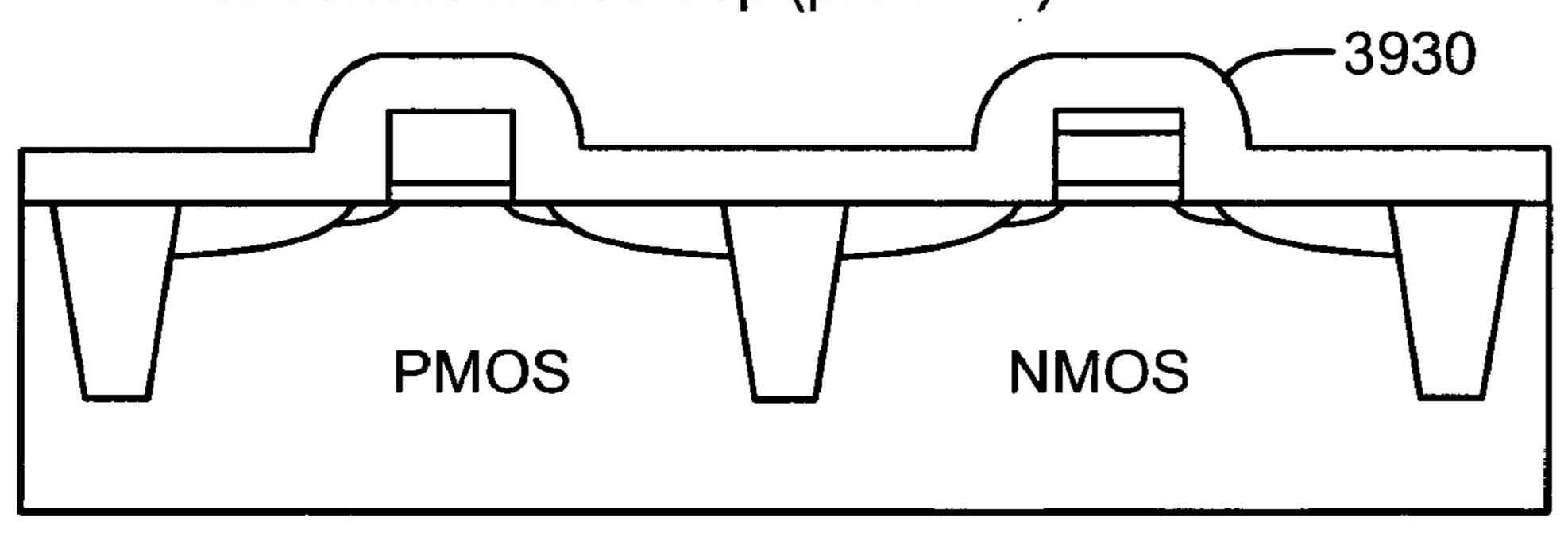

8. RTP spike or soak anneal / DSA to activate dopants; re-crystalize poly-silicon and increase the nitride stress to 2.0GPa (any other annealing method)

Fig. 39H

9. Spacer nitride deposition (neutral or compressive stress) with or w/o a pre-oxide layer

Fig. 391

10. Litho and etch to remove the nitride from NMOS side

**PMOS** NMOS

Jun. 8, 2010

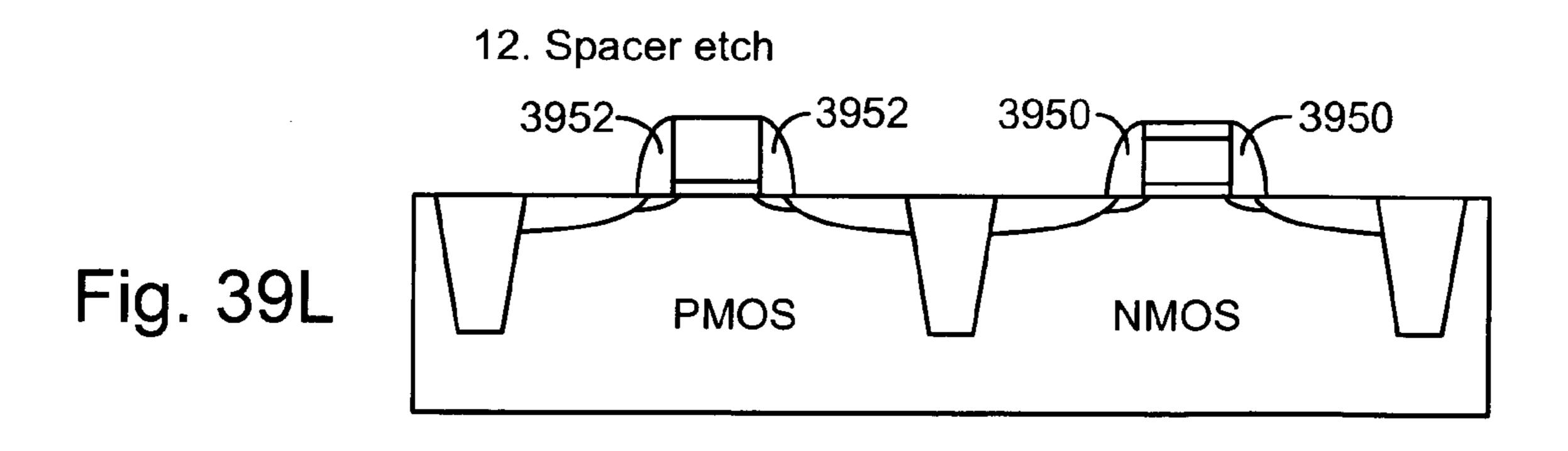

11. Nitride etch from NMOS side (only last layer - compressive or neutral)

13. Dual stresses layer integration from this point on

FIG. 40

FIG. 41

FIG. 42

# METHOD TO INCREASE THE COMPRESSIVE STRESS OF PECVD SILICON NITRIDE FILMS

# CROSS-REFERENCE TO RELATED APPLICATION

This instant nonprovisional application claims priority to commonly assigned U.S. patent application Ser. No. 60/685, 365, filed on May 26, 2005 and U.S. patent application Ser. No. 60/701,854, filed on Jul. 21, 2005, the entire disclosure of which is incorporated herein by reference.

### BACKGROUND OF THE INVENTION

In the processing of a substrate to fabricate circuits and displays, the substrate is typically exposed to an energized process gas capable of depositing or etching material on the substrate. In chemical vapor deposition (CVD) processes, process gas energized by a high frequency voltage or microwave energy is used to deposit material on the substrate, which may be a layer, a filling of contact holes, or other selective deposition structures. The deposited layer can be etched or otherwise processed to form active and passive devices on the substrate, such as for example, metal-oxidesemiconductor field effect transistors (MOSFETs) and other devices. A MOSFET typically has a source region, a drain region, and a channel region between the source and drain. In the MOSFET device, a gate electrode is formed above and separated from the channel by a gate dielectric to control conduction between the source and drain.

The performance of such devices can be improved by, for example, reducing supply voltage, gate dielectric thickness, or channel length. However, such conventional methods face mounting problems as the size and spacing of the devices become ever smaller. For example, at very small channel lengths, the advantages of reducing channel length to increase the number of transistors per unit area and saturation current are offset by undesirable carrier velocity saturation effects. Similar benefits which are obtained from reducing gate dielectric thickness, such as decreased gate delay, are limited in small devices by increased gate leakage current and charge tunneling through the dielectric which can damage the transistor over time. Reducing supply voltage allows lower operating power levels but such reductions are also limited by the threshold voltage of the transistor.

In a relatively newly developed method of enhancing transistor performance, the atomic lattice of a deposited material is stressed to improve the electrical properties of the material 50 itself, or of underlying or overlying material that is strained by the force applied by a stressed deposited material. Lattice strain can increase the carrier mobility of semiconductors, such as silicon, thereby increasing the saturation current of the doped silicon transistors to thereby improve their perfor- 55 mance. For example, localized lattice strain can be induced in the channel region of the transistor by the deposition of component materials of the transistor which have internal compressive or tensile stresses. For example, silicon nitride materials used as etch stop materials and spacers for the silicide 60 materials of a gate electrode can be deposited as stressed materials which induce a strain in the channel region of a transistor. The type of stress desirable in the deposited material depends upon the nature of the material being stressed. For example, in CMOS device fabrication, negative-channel 65 (NMOS) doped regions are covered with a tensile stressed material having positive tensile stress; whereas positive chan2

nel MOS (PMOS) doped regions are covered with a compressive stressed material having negative stress values.

Thus, it is desirable to form stressed materials that have predetermined types of stresses, such as tensile or compressive stresses. It is further desirable to control the level of stress generated in the deposited material. It is also desirable to deposit such stressed materials to generate uniform localized stresses or strains in the substrate. It is also desirable to have a process that can form stressed materials over active or passive devices on the substrate without damaging the devices. It is still further desirable that the deposited films be highly conformal to underlying topography.

#### BRIEF SUMMARY OF THE INVENTION

A plurality of techniques may be employed alone or in combination, to form stressed films having desirable properties. Compressive stress in a film of a semiconductor device may be controlled utilizing one or more techniques, employed alone or in combination. A first set of embodiments increase silicon nitride compressive stress by adding hydrogen to the deposition chemistry, and reduce defects in a device fabricated with a high compressive stress silicon nitride film formed in the presence of hydrogen gas. A silicon nitride film may comprise an initiation layer formed in the absence of a hydrogen gas flow, underlying a high stress nitride layer formed in the presence of a hydrogen gas flow. A silicon nitride film formed in accordance with an embodiment of the present invention may exhibit a compressive stress of 2.8 GPa or higher.

An embodiment of a method in accordance with the present invention for forming silicon nitride, comprises, disposing a workpiece including a surface in a processing chamber, exposing the surface to a plasma in the absence of deposition conditions to remove contamination, and depositing a silicon nitride layer over the plasma-treated surface in the presence of a hydrogen gas flow.

An alternative embodiment of a method in accordance with the present invention for forming silicon nitride, comprises, disposing a workpiece including a surface in a processing chamber, forming a buffer layer over the surface, and depositing a silicon nitride layer over the buffer layer in the presence of a hydrogen gas flow.

Another alternative embodiment of a method in accordance with the present invention for forming silicon nitride, comprises, disposing a workpiece including a surface in a processing chamber, and depositing on the surface a film stack comprising a silicon nitride initiation layer formed in the absence of the hydrogen gas flow, followed by a high compressive stress silicon nitride layer formed in the presence of the hydrogen gas flow.

An embodiment of a method in accordance with the present invention for preventing defects in a device, comprises, treating a surface with a plasma, and depositing a silicon nitride layer on the treated surface in the presence of a flow of hydrogen gas.

An alternative embodiment of a method in accordance with the present invention for preventing defects in a device, comprises, depositing a buffer layer on a surface, and depositing a silicon nitride layer on the buffer layer in the presence of a flow of hydrogen gas.

Another alternative embodiment of a method in accordance with the present invention for preventing defects in a device, comprises, depositing a silicon nitride initiation layer on a surface in the absence of a flow of hydrogen gas, and depositing a high compressive stress silicon nitride layer on the initiation layer in a presence of a flow of hydrogen gas.

An embodiment of a film stack in accordance with the present invention comprises an oxide buffer layer, and an overlying silicon nitride layer deposited in the presence of hydrogen gas and exhibiting a high compressive stress.

Another embodiment of a film stack in accordance with the present invention comprises a silicon nitride initiation layer interposed between a oxide buffer layer and a high compressive stress silicon nitride layer, the initiation layer exhibiting a lower compressive stress than the overlying silicon nitride layer.

A further understanding of the objects and advantages of the present invention can be made by way of reference to the ensuing detailed description taken in conjunction with the accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

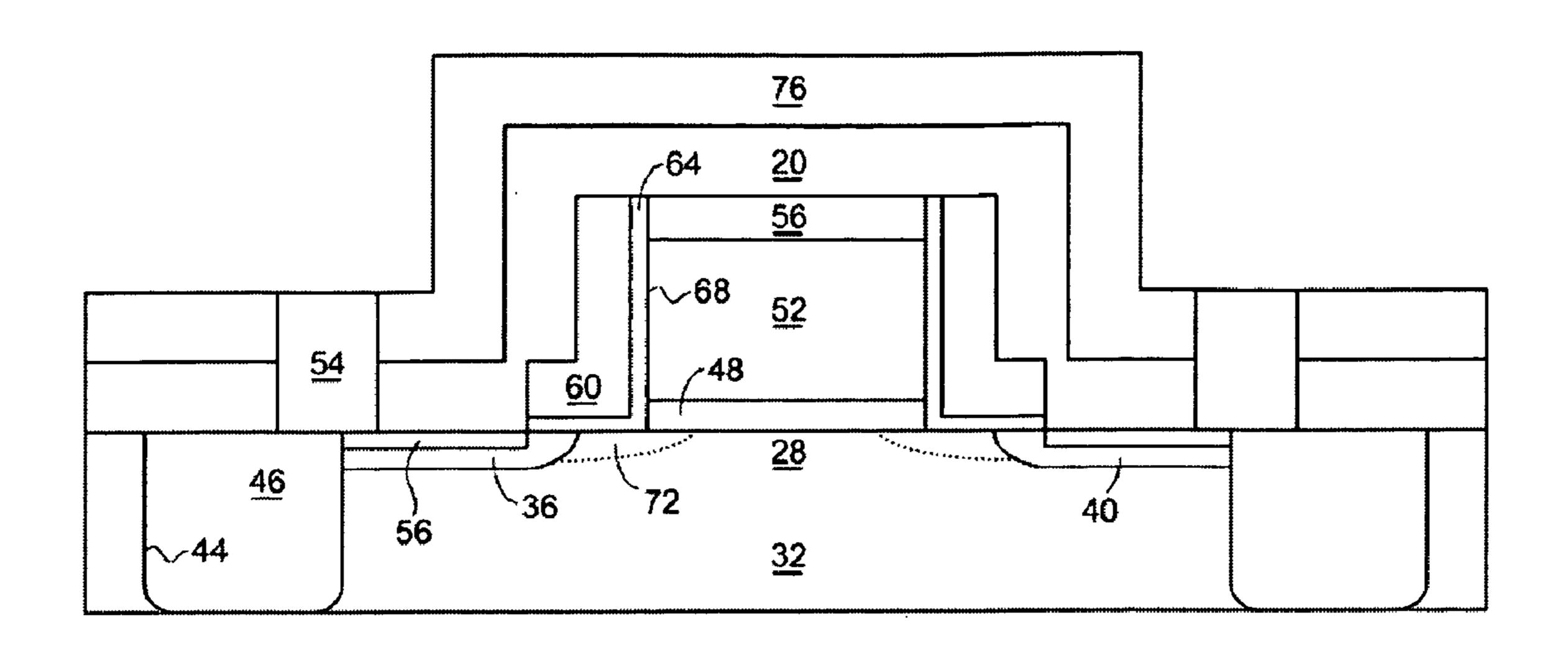

- FIG. 1 is a simplified cross-sectional view of a substrate showing a partial view of a transistor structure with an overlying deposited tensile stressed silicon nitride material;

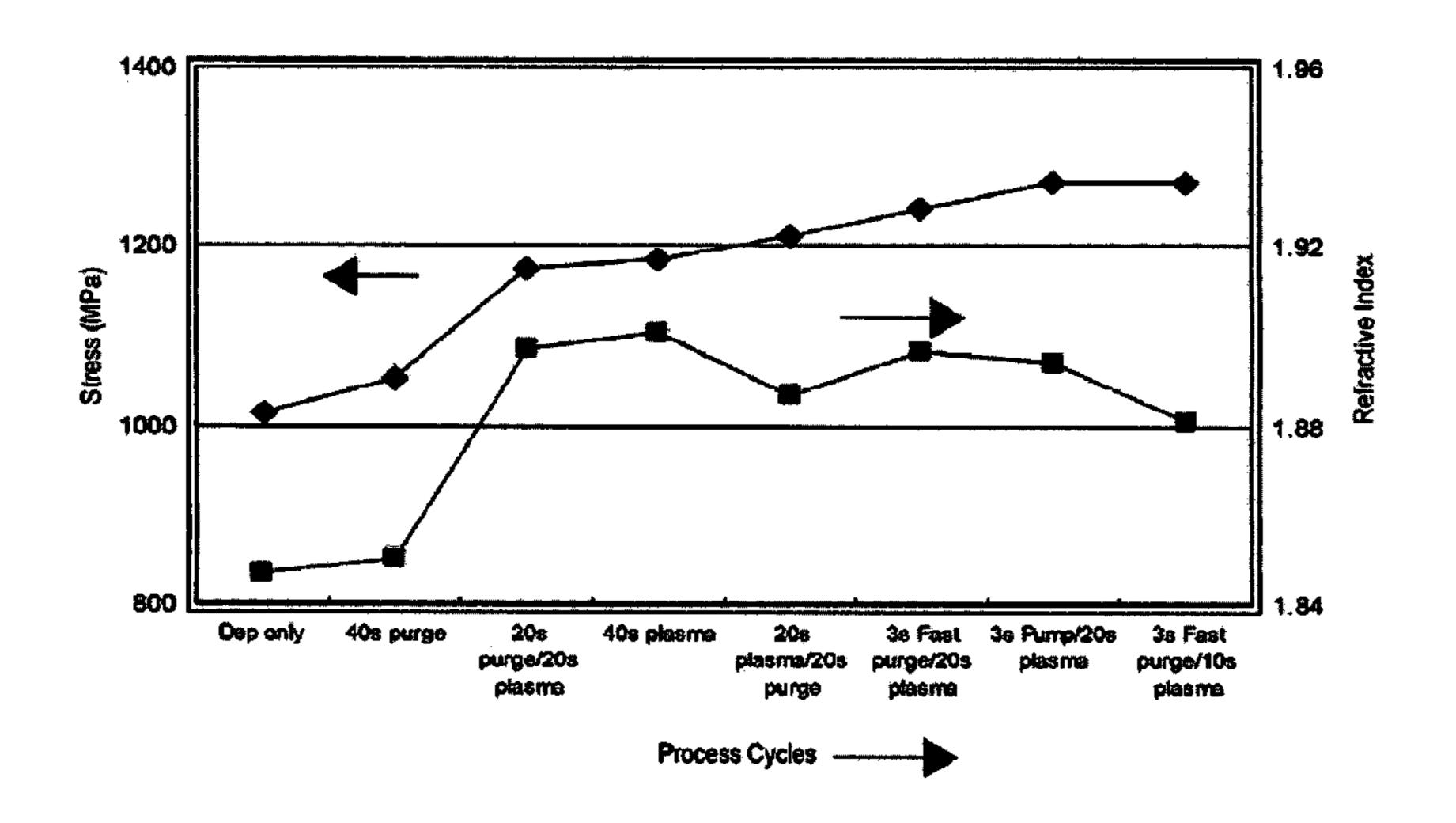

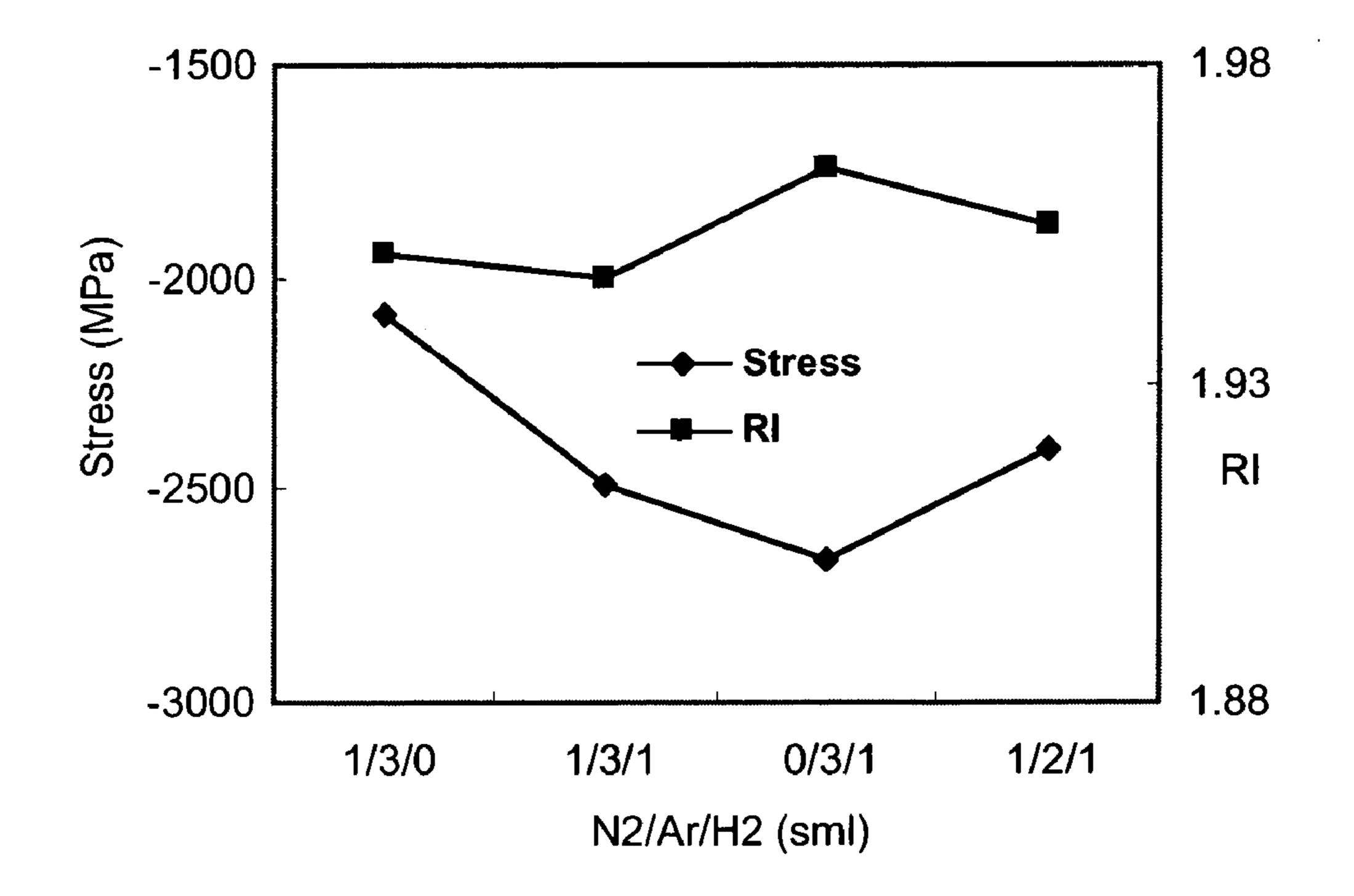

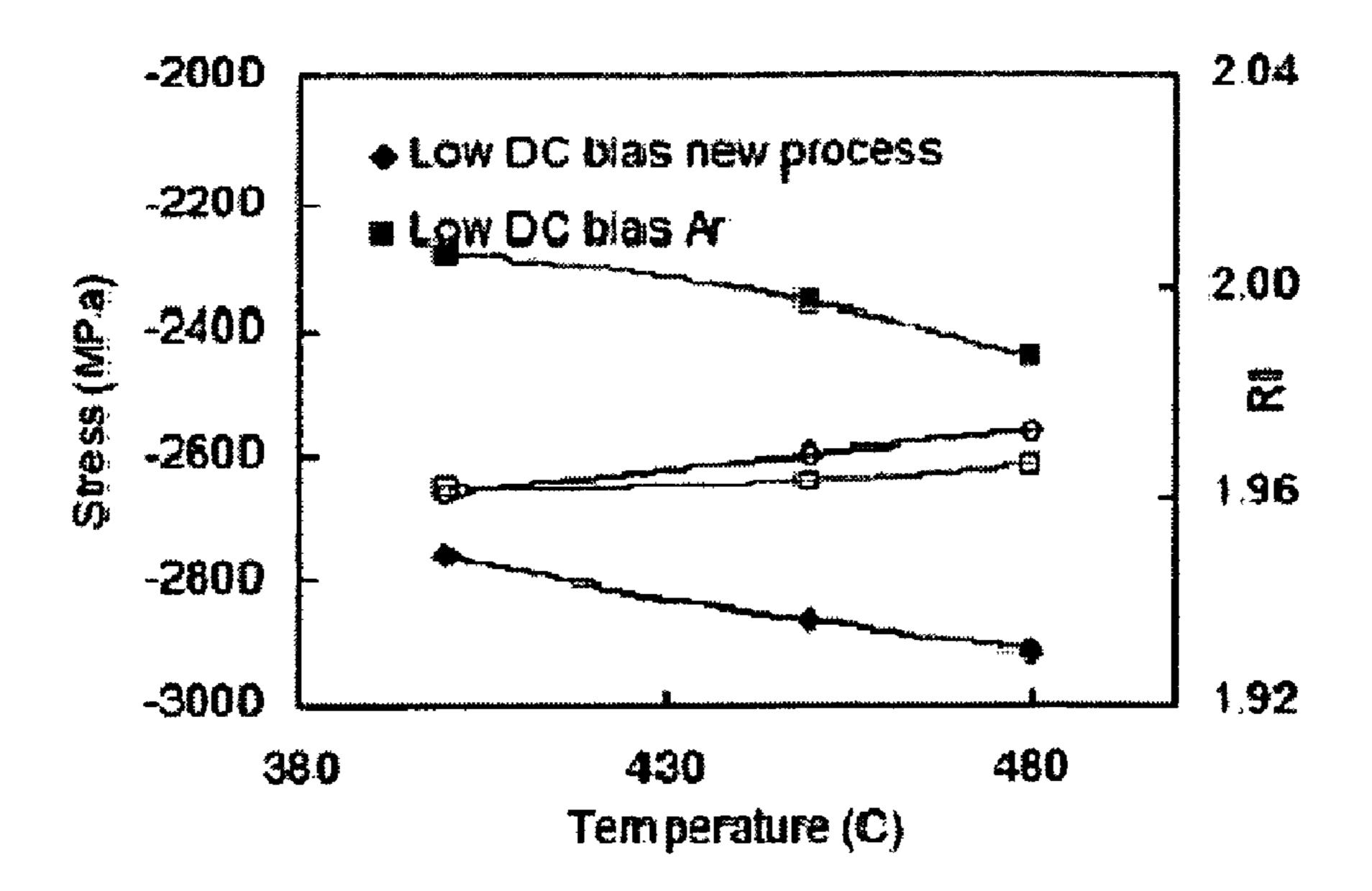

- FIG. 2 plots compressive stress and refractive index for CVD SiN films formed under a number of different process conditions;

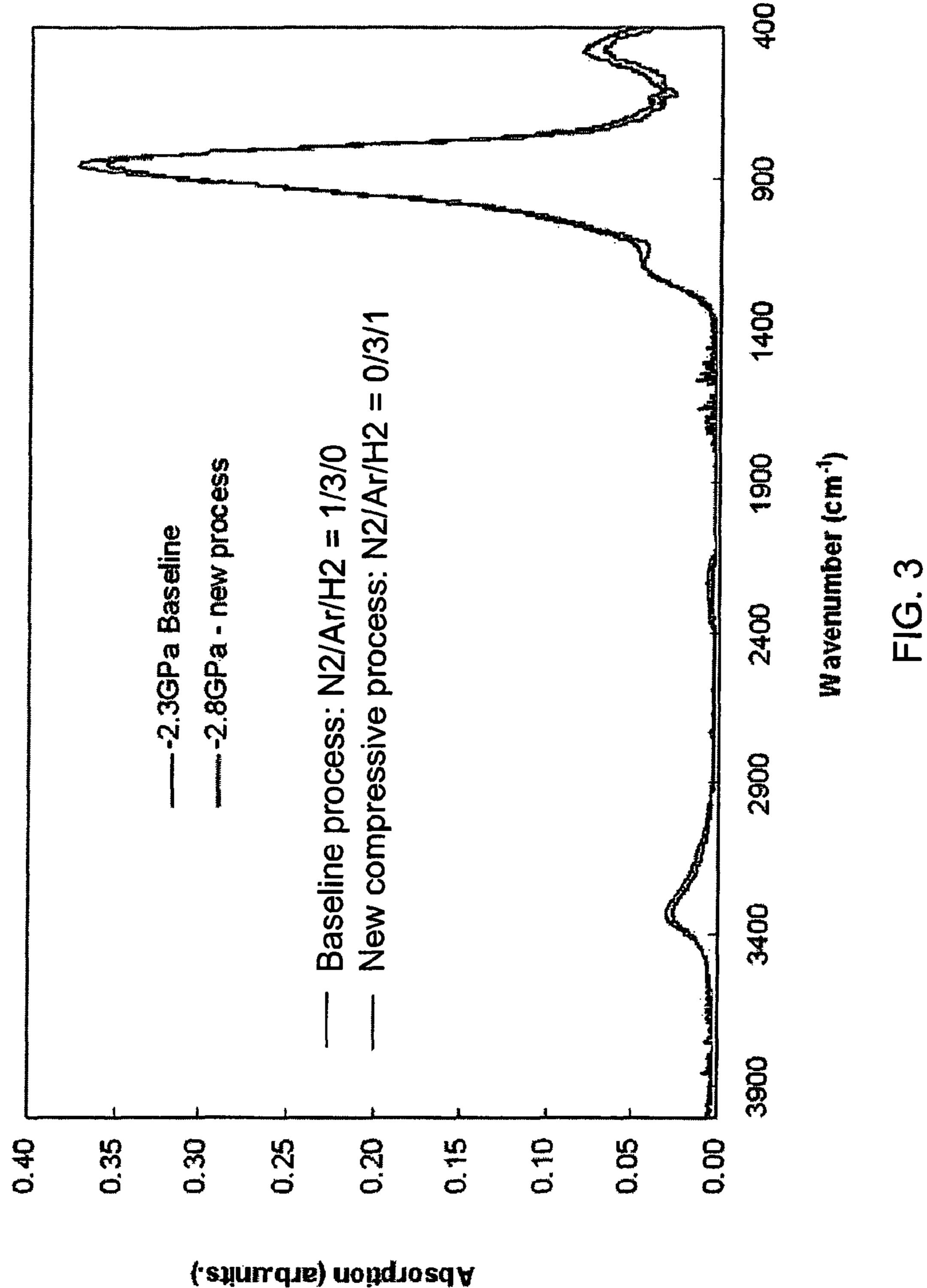

- FIG. 3 shows FT-IR spectra for CVD SiN films formed under a number of different process conditions;

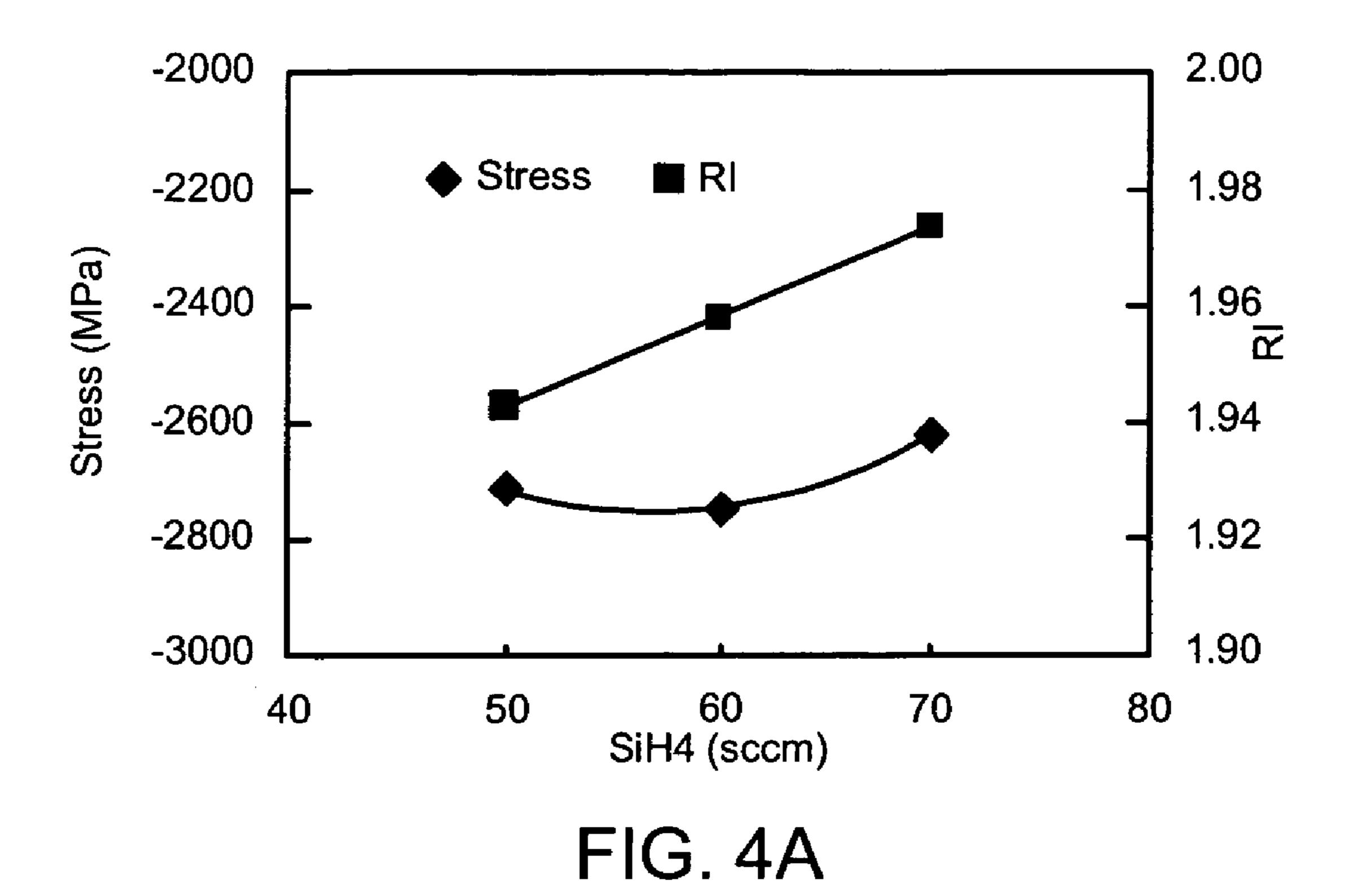

- FIG. 4A plots compressive stress and refractive index for CVD SiN films deposited with different silane flow rates;

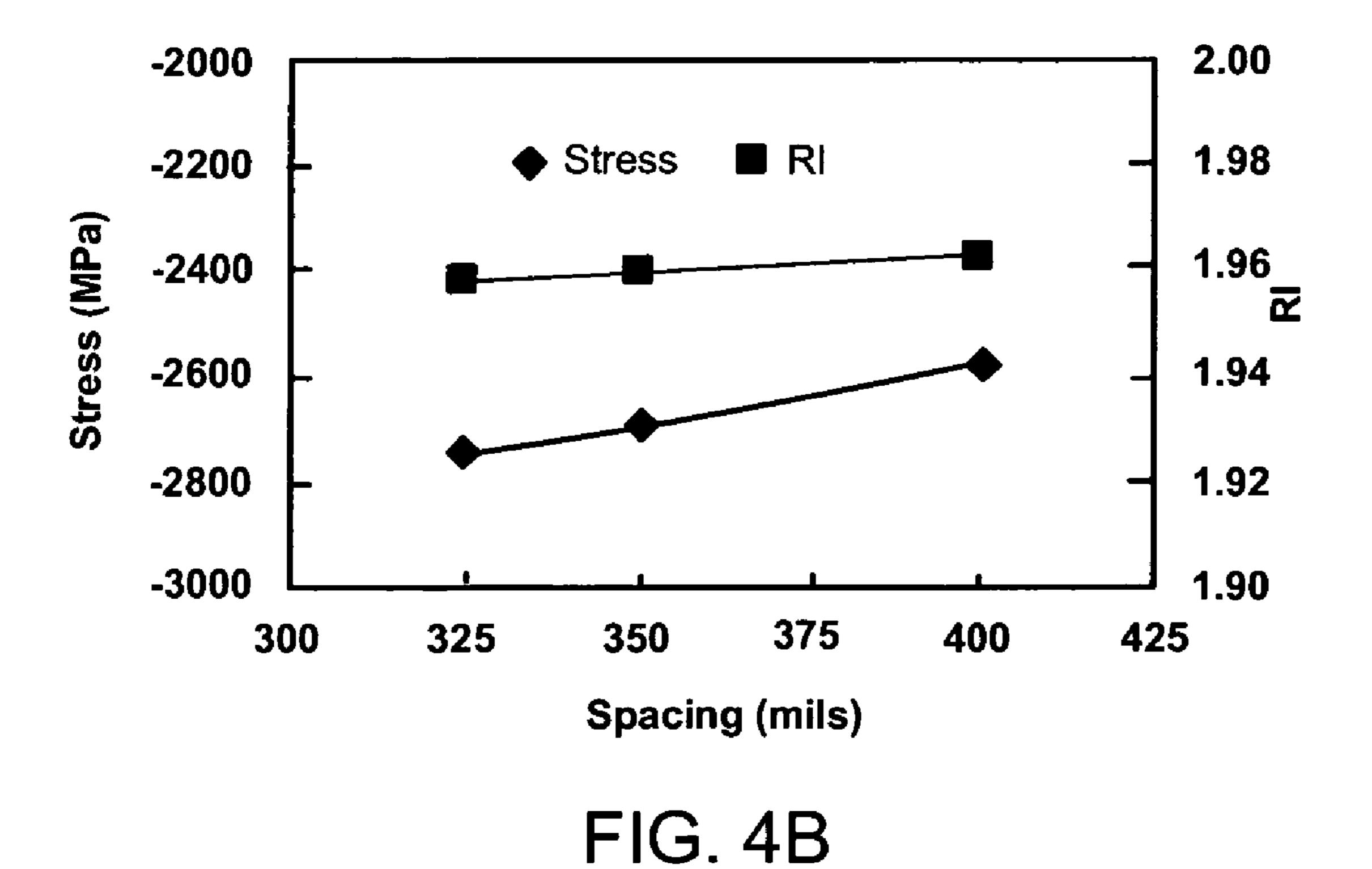

- FIG. 4B plots compressive stress and refractive index for CVD SiN films deposited with different faceplate-to-wafer spacings;

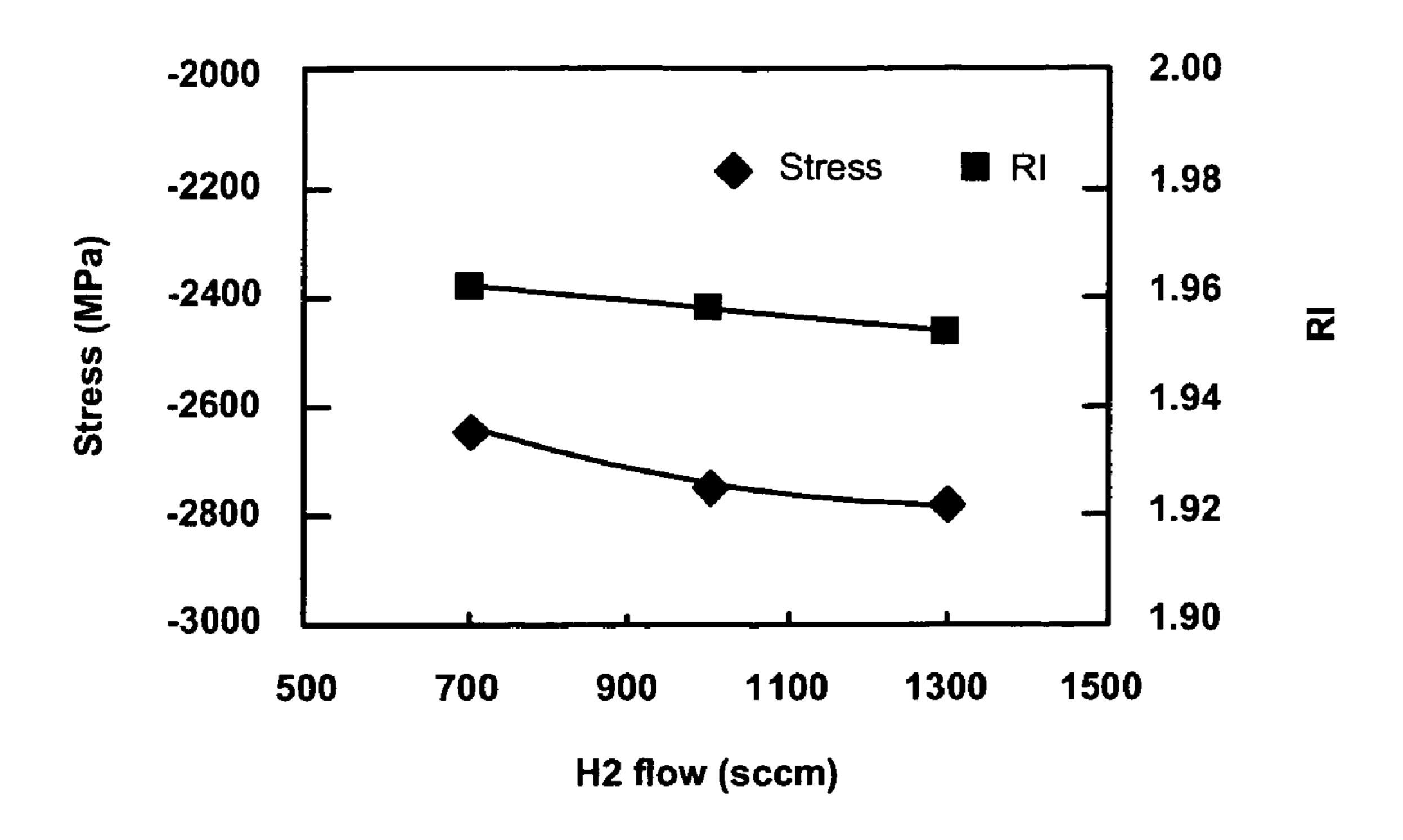

- FIG. 4C plots compressive stress and refractive index for CVD SiN films deposited with different hydrogen gas flow rates;

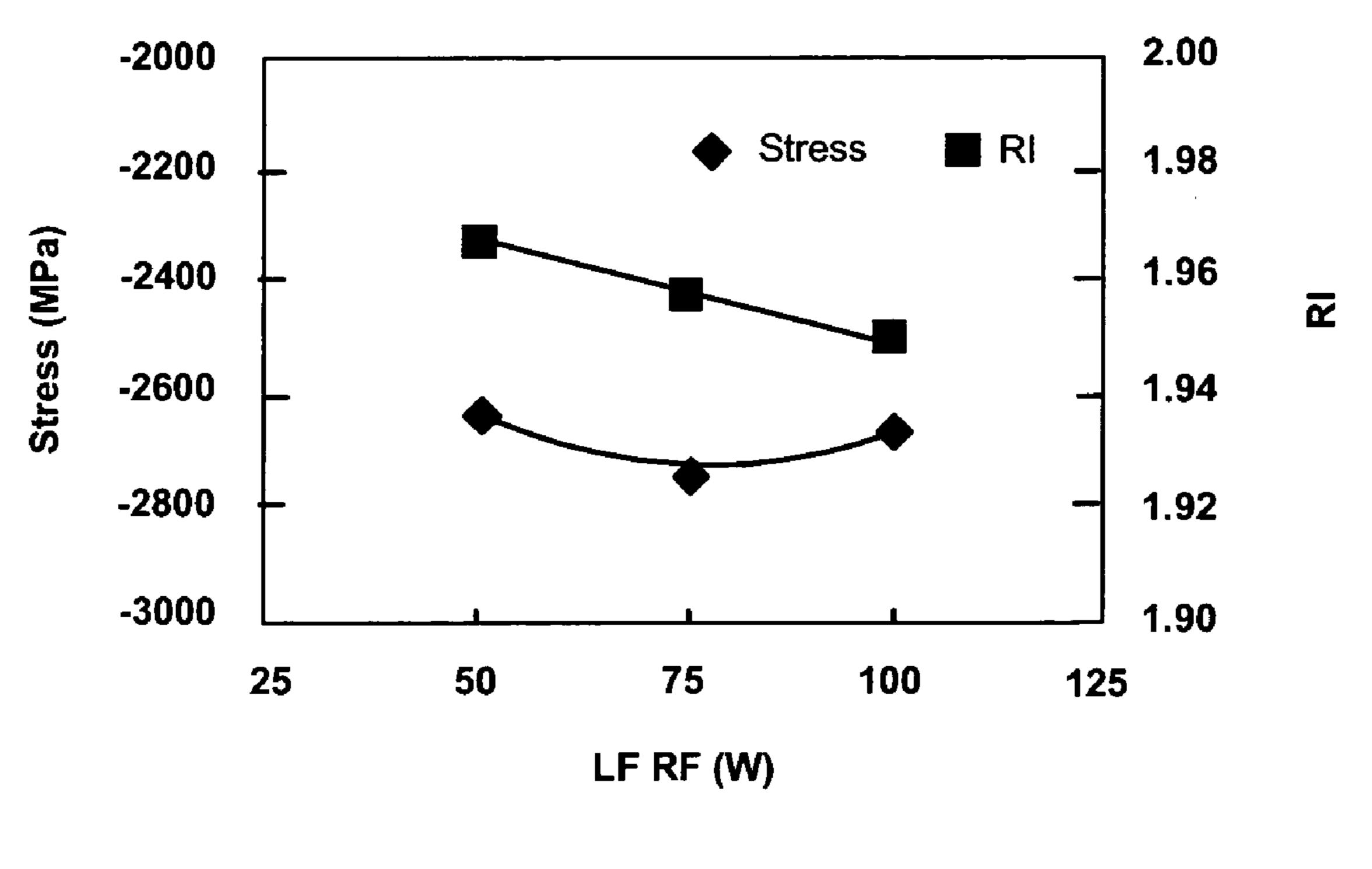

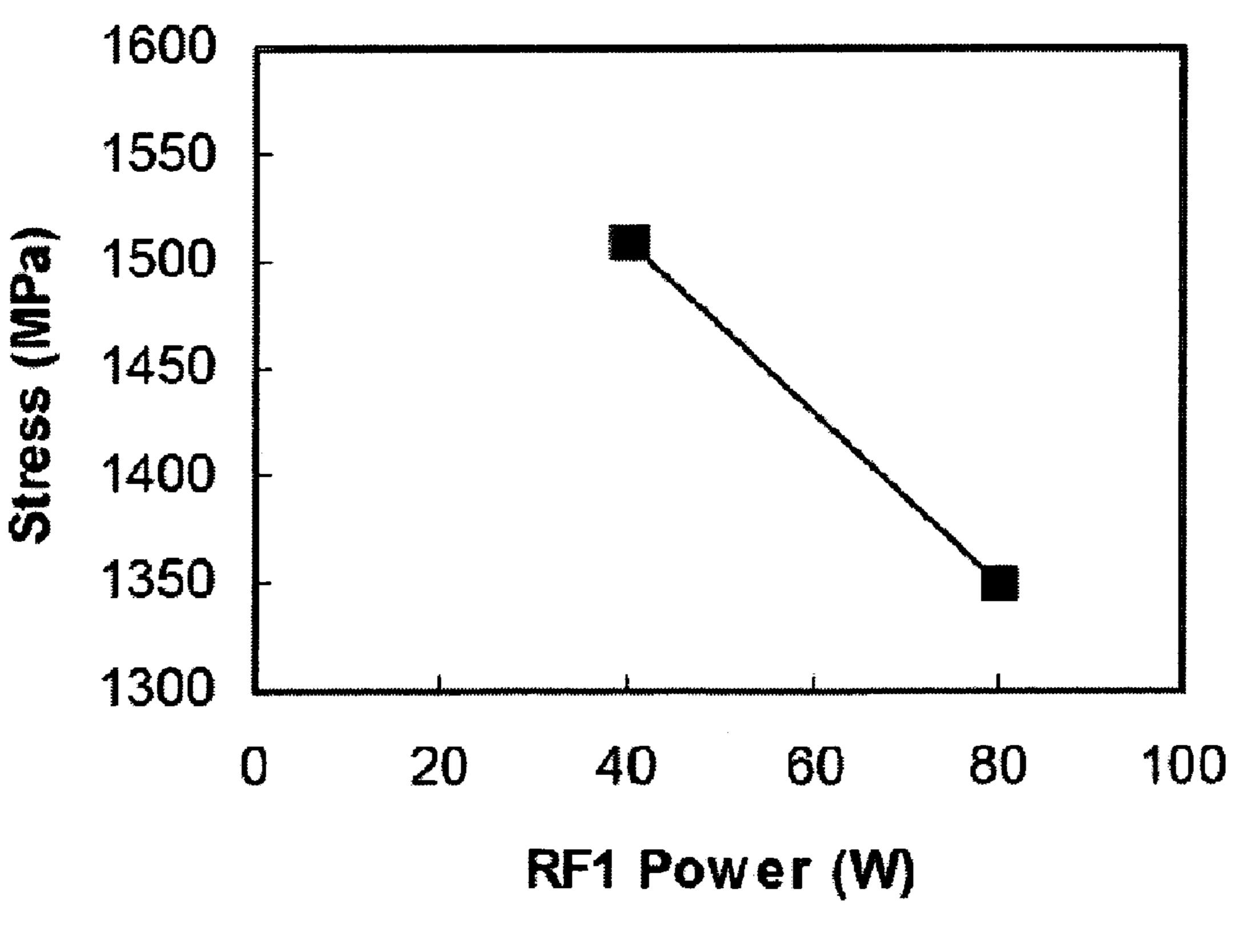

- FIG. 4D plots compressive stress and refractive index for CVD SiN films deposited at different applied power levels;

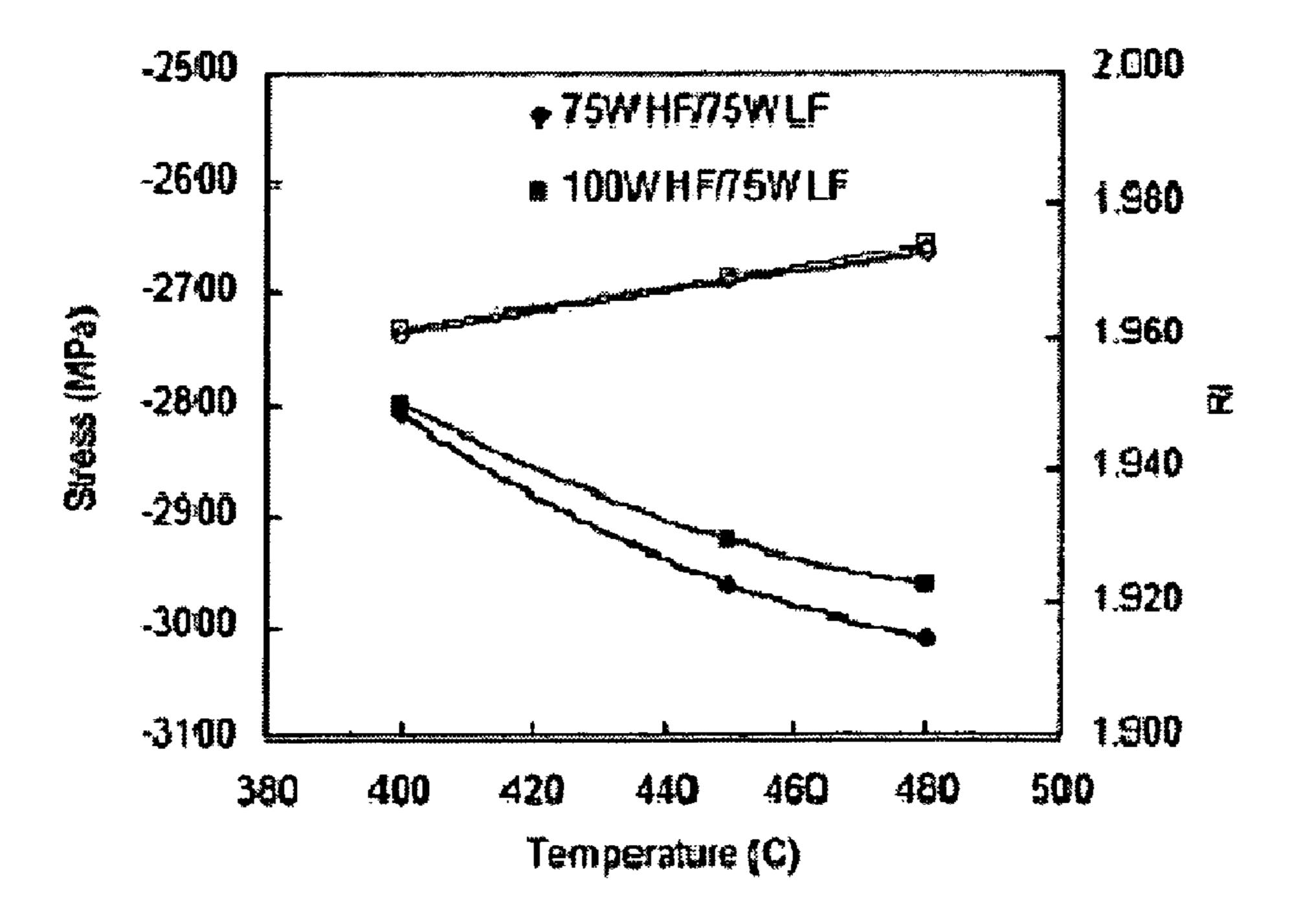

- FIG. **5**A plots compressive stress and refractive index for CVD SiN films deposited with and without hydrogen gas;

- FIG. **5**B plots compressive stress and refractive index for CVD SiN films deposited at different powers and at different temperatures;

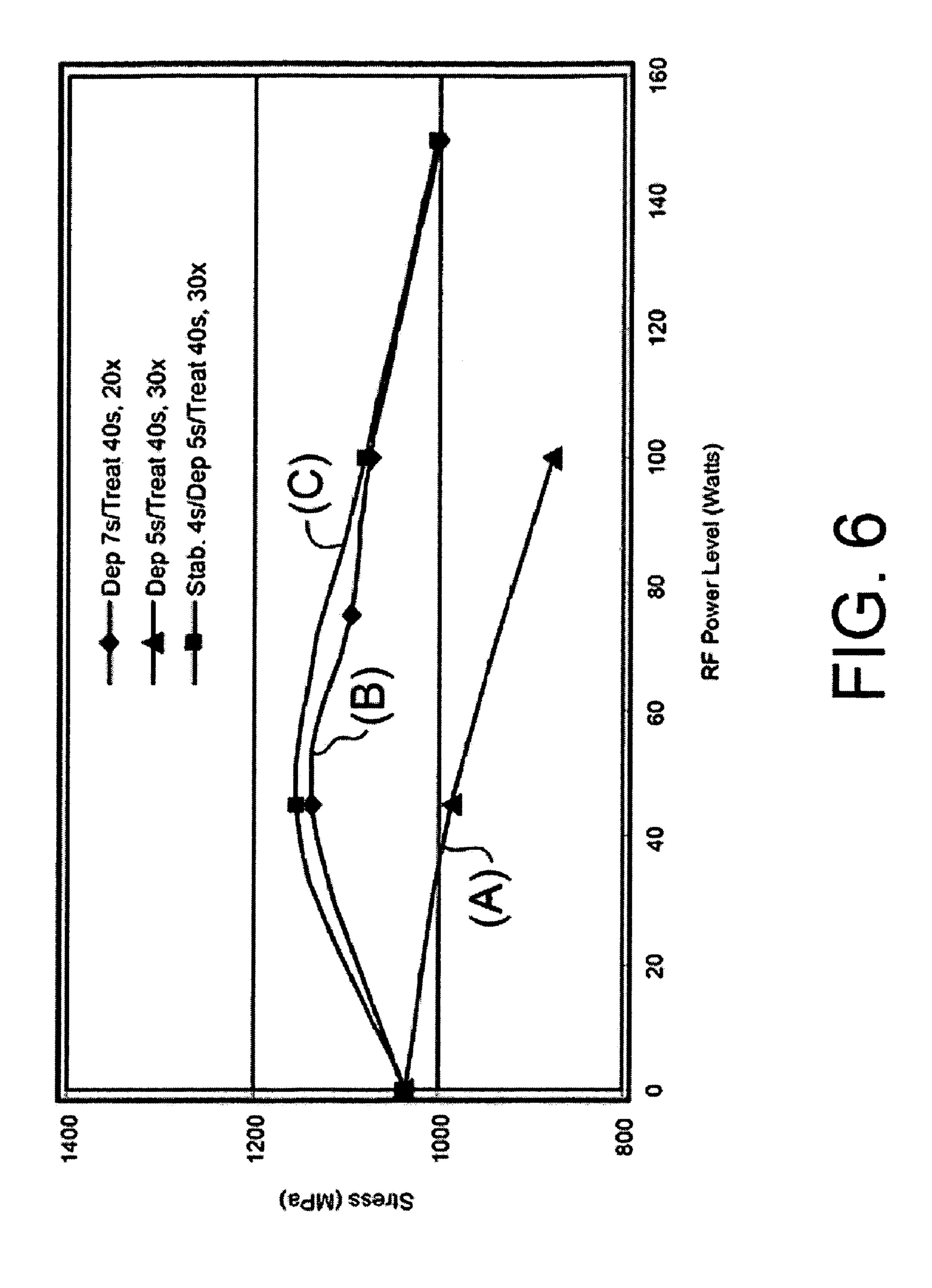

- FIG. 6 is a graph showing measured tensile stresses for increasing power level of the high RF voltage and different nitrogen plasma treatment process cycles;

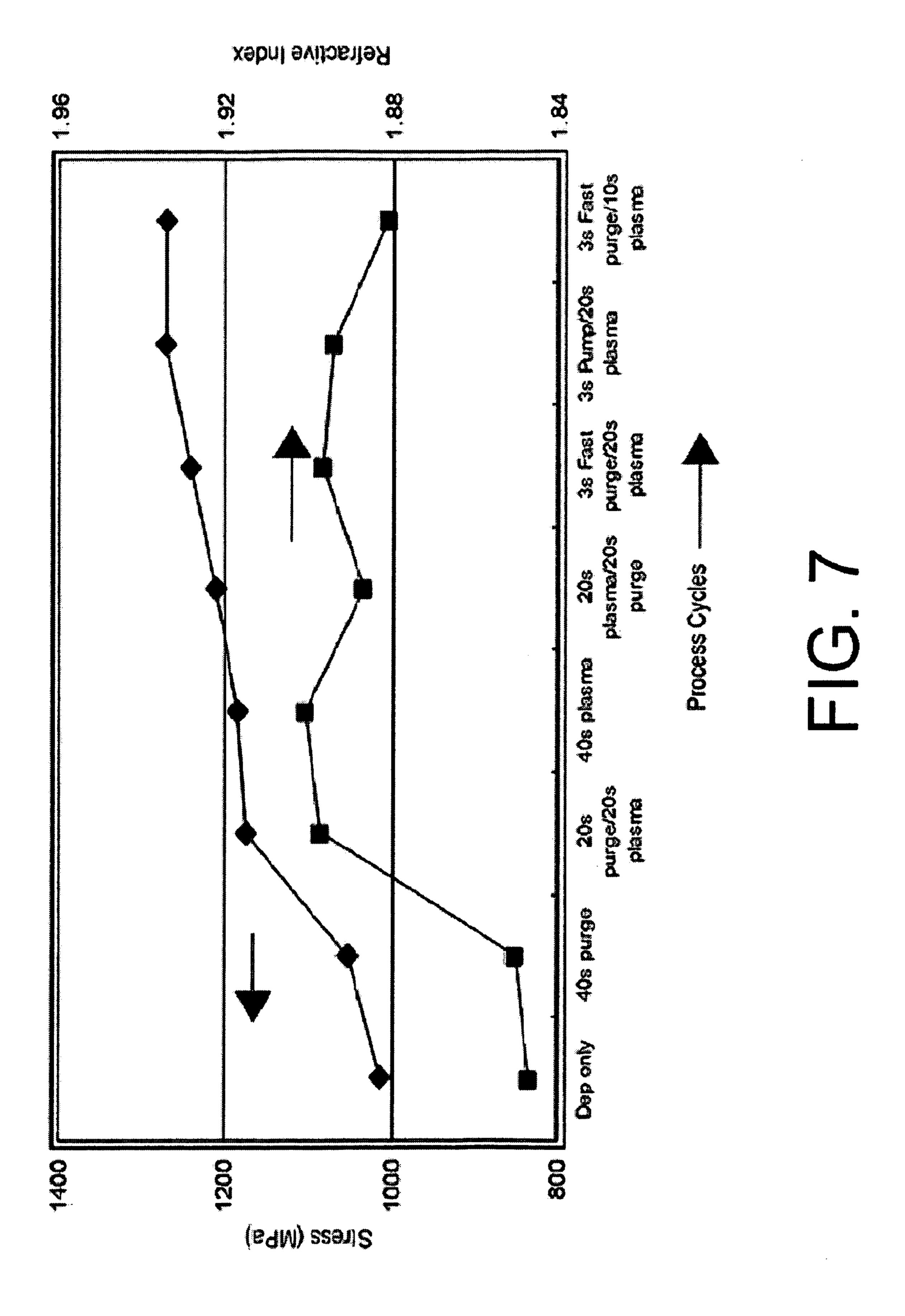

- FIG. 7 is a graph showing the tensile stress values and refractive indices obtained for layers deposited under different deposition and nitrogen plasma treatment process cycles;

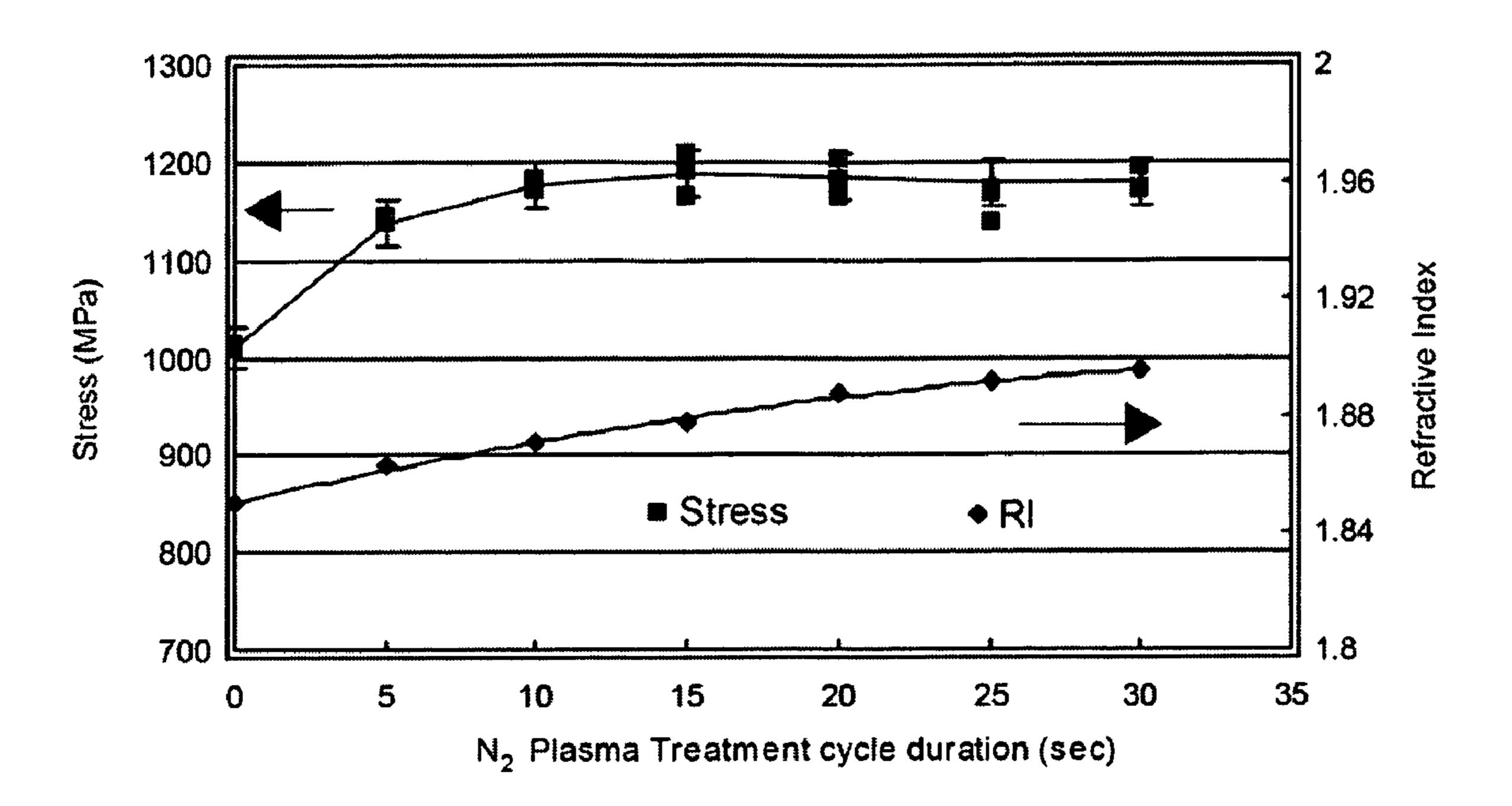

- FIG. 8 is a graph showing the change in tensile stress values of deposited materials with N<sub>2</sub> plasma treatment time;

- FIG. 9 is a graph showing the effect of N<sub>2</sub> plasma treatment time on the tensile stress value for processes having different purge and pump cycles;

SiN films of FIG. 22A;

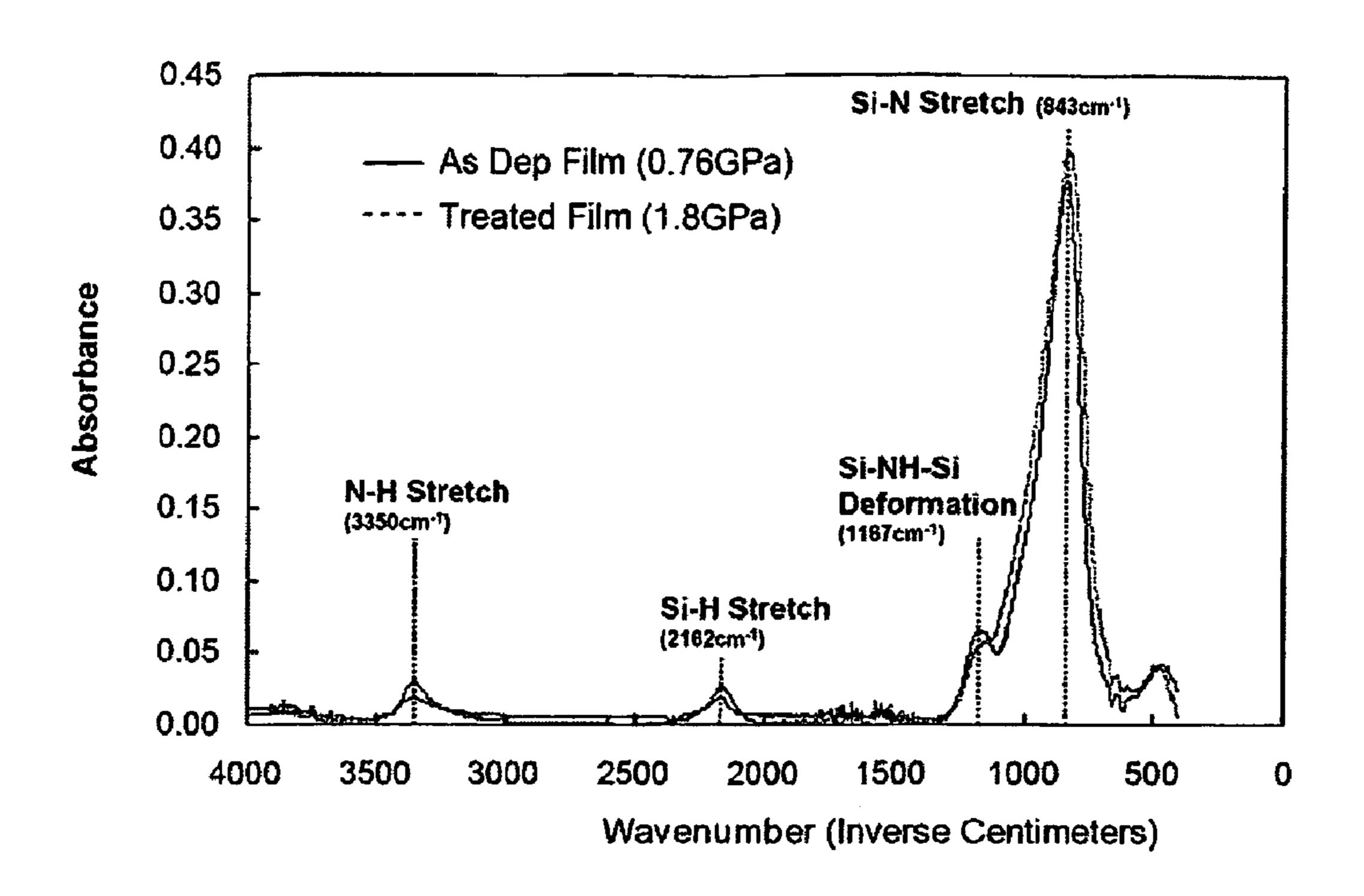

FIG. 23 shows FT-IR ited, and after treatment

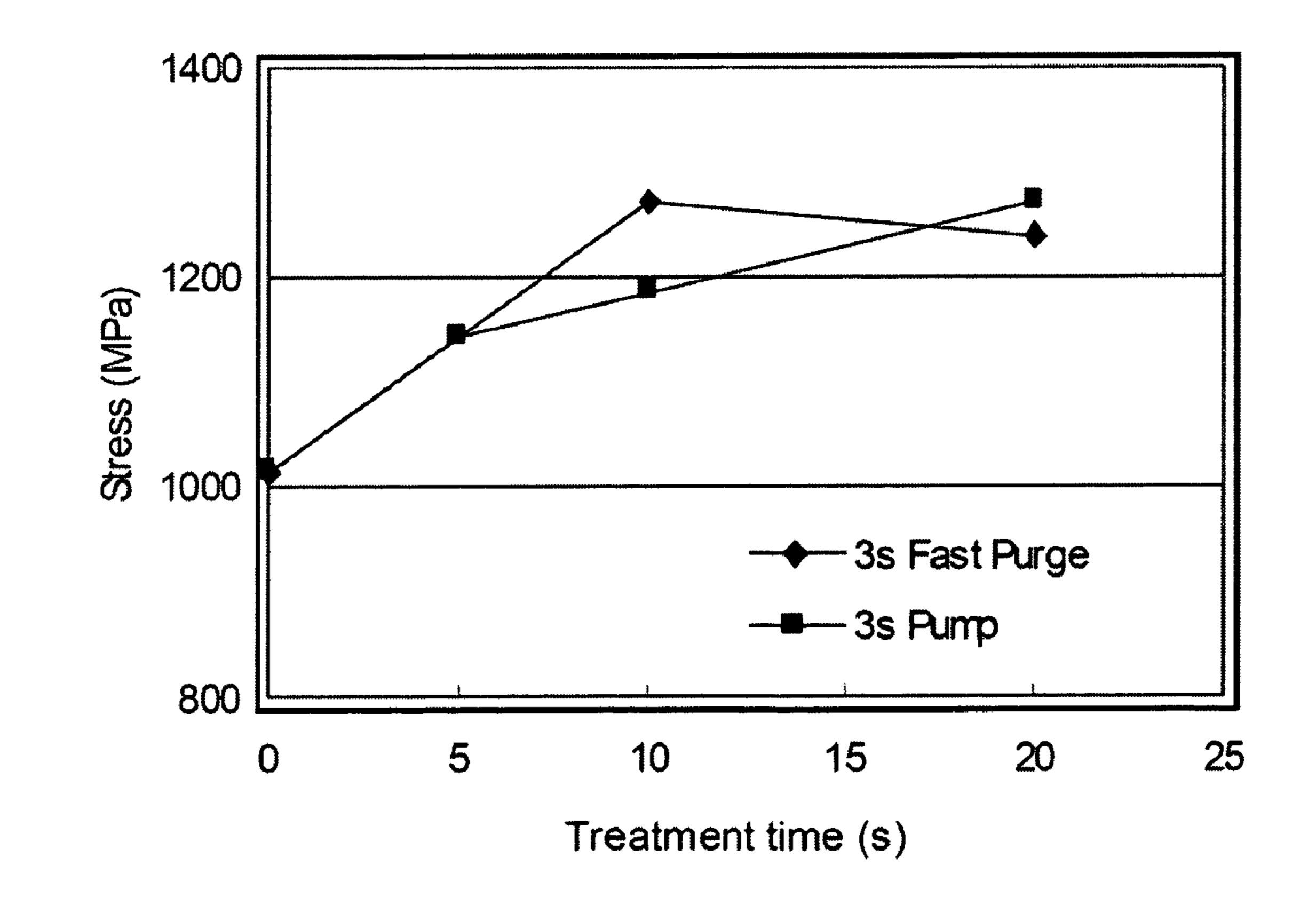

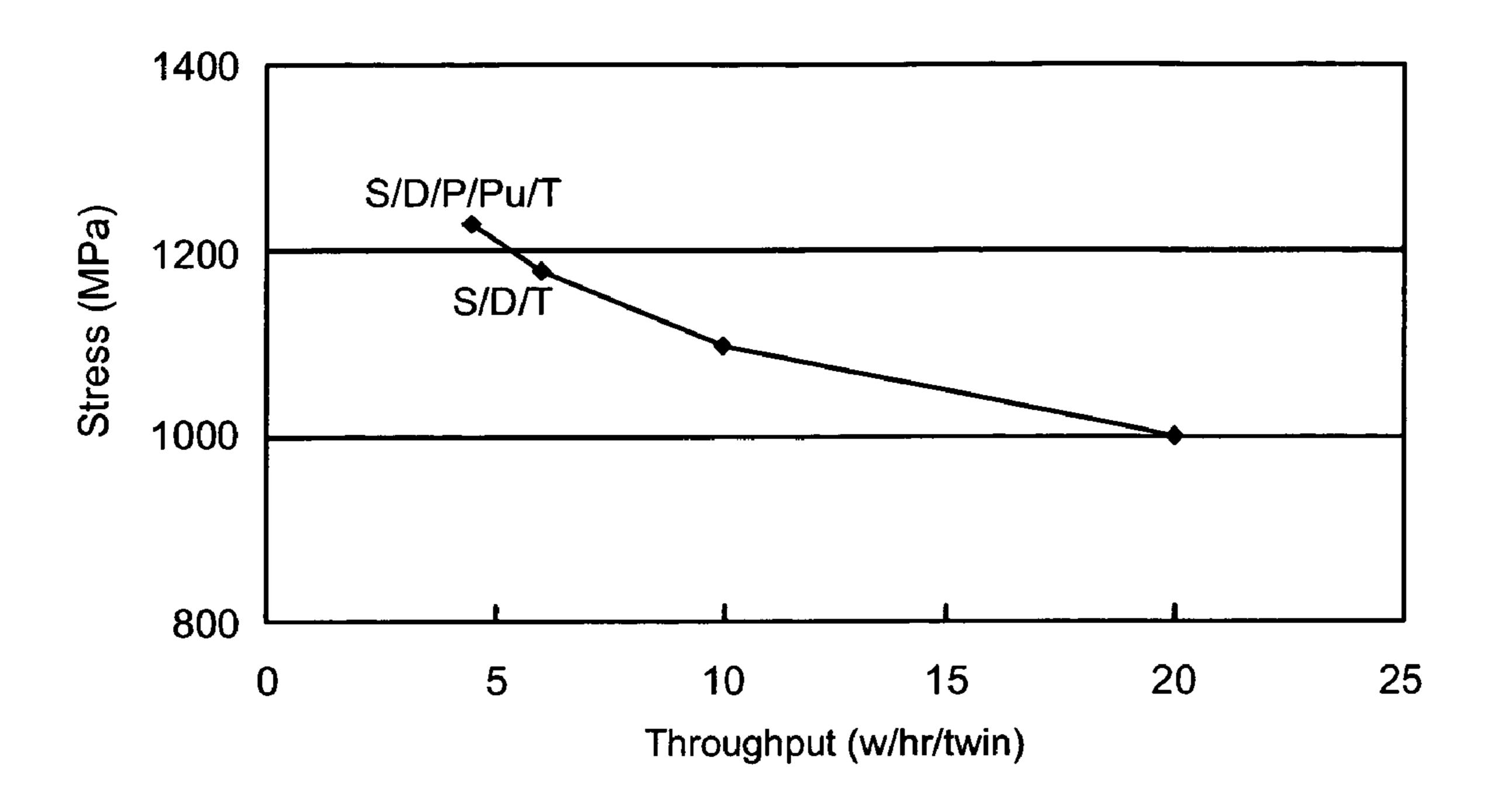

- FIG. 10 plots film tensile film stress versus throughput for CVD SiN films formed with different dep/treat cycles;

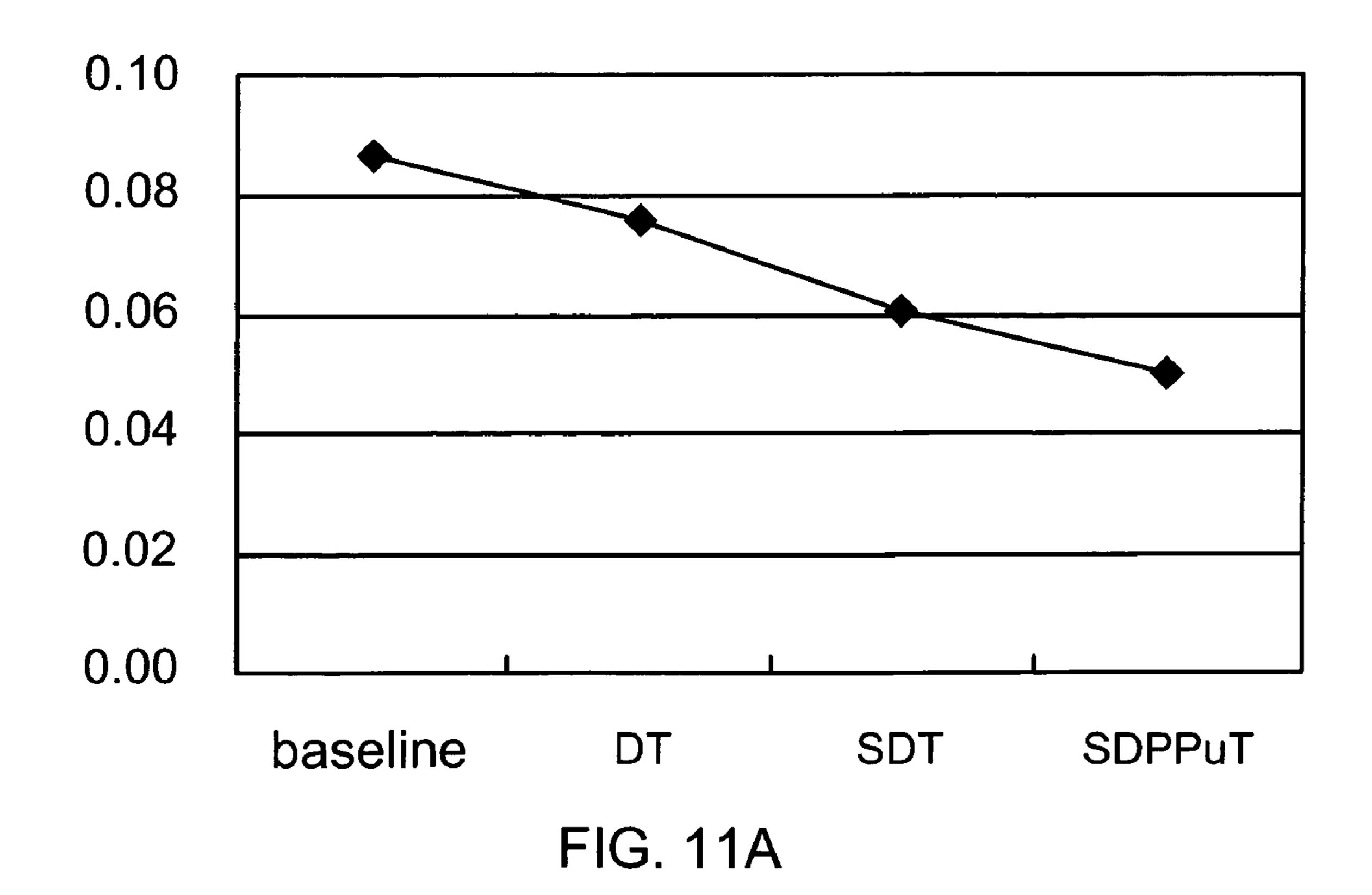

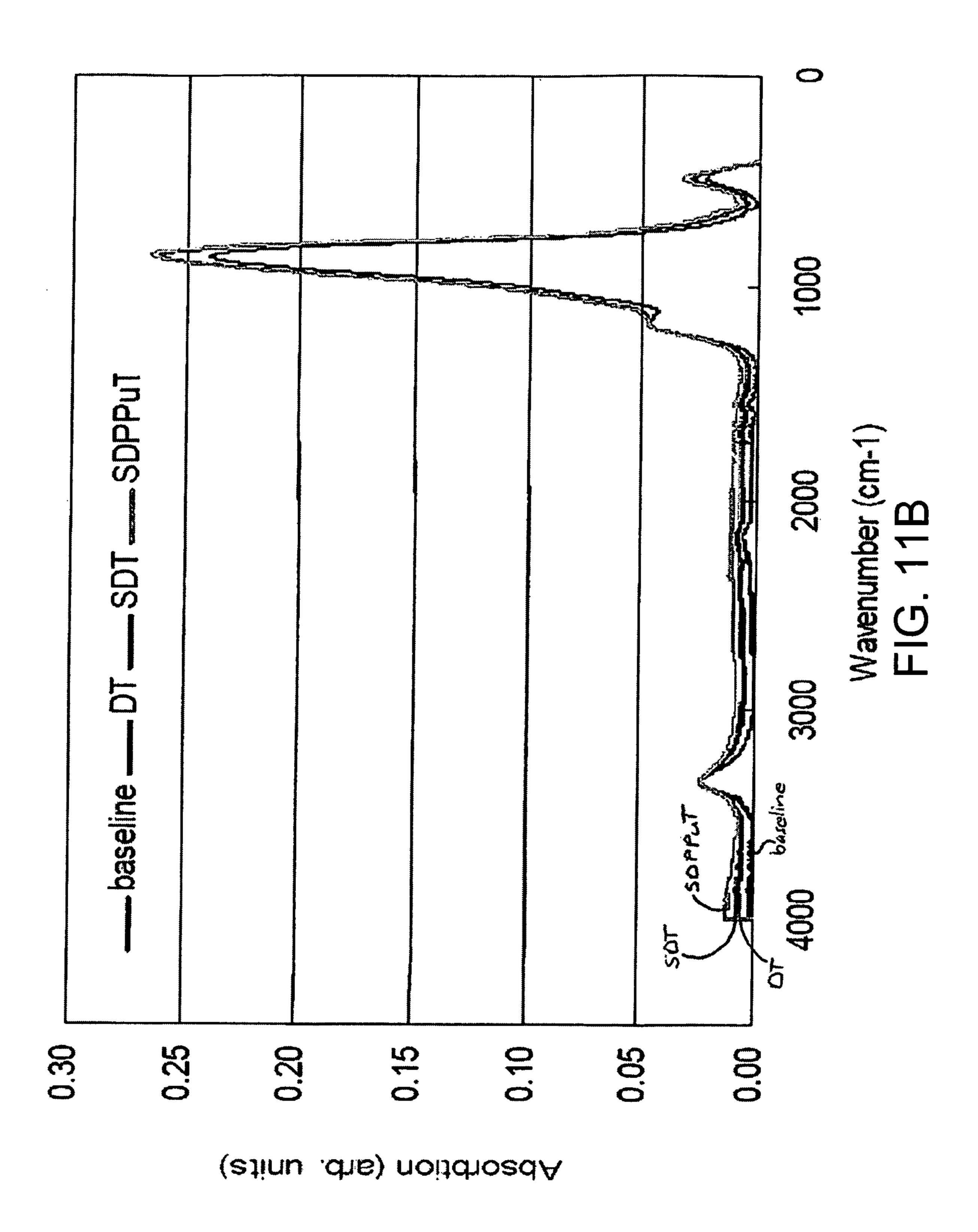

- FIG. 11A shows FT-IR spectra for a CVD SiN film result- 55 gas mixtures; ing from deposition at 400° C. under the various cycle and times shown in Table IV. gas mixtures; showing conference of the sho

- FIG. 11B plots the ratio of N—H:Si—N bonds of the CVD SiN films resulting from deposition under the various cycle conditions shown in Table IV.

- FIGS. 12A-D plotting film stress of a CVD SiN film formed at 450° C. under a variety of different process conditions.

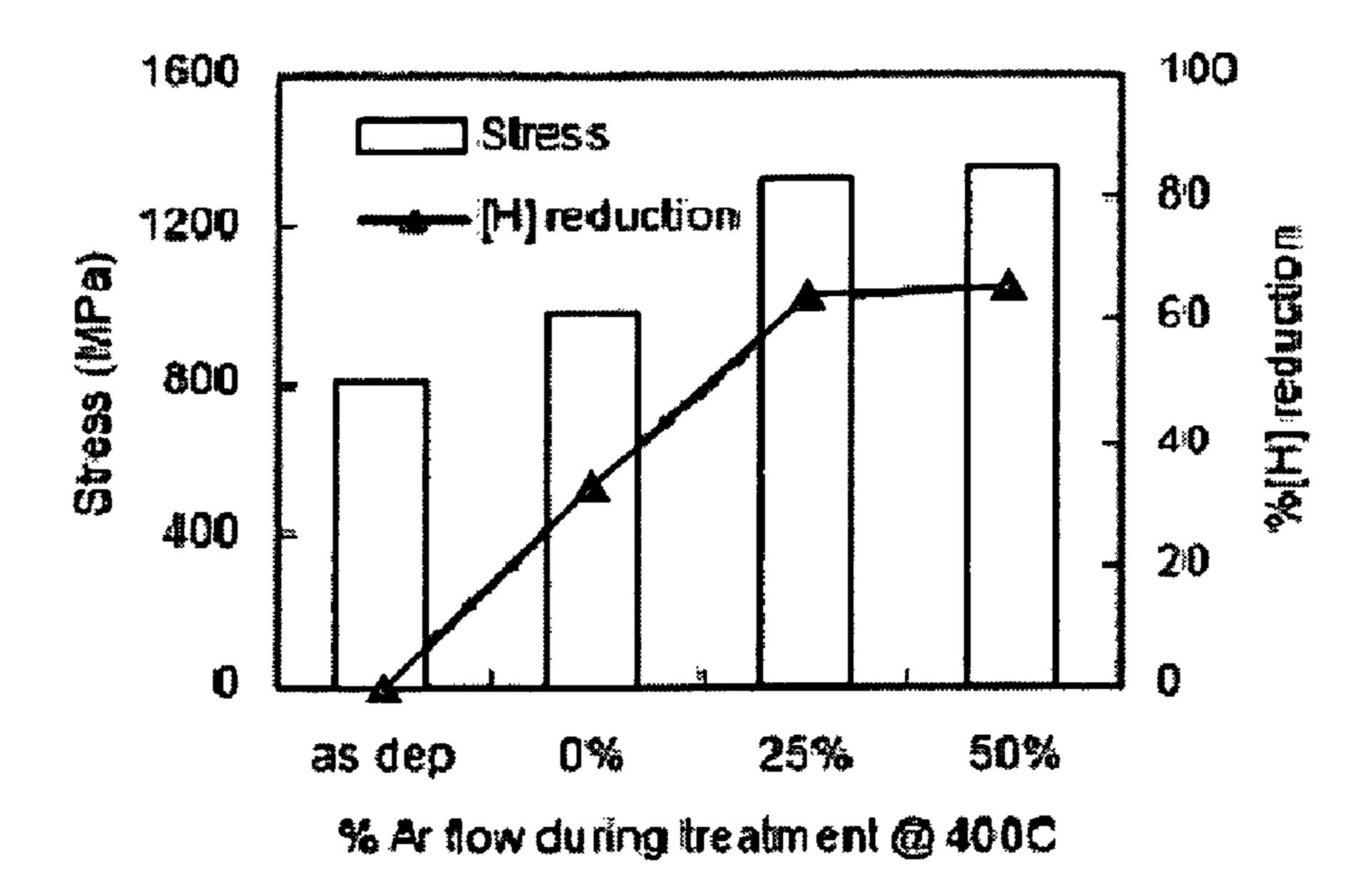

- FIG. 13A charts tensile stress and plots reduction in hydrogen content for CVD SiN films exposed to post-deposition 65 treatment with plasma formed from gases containing different levels of Argon, at 400° C.;

4

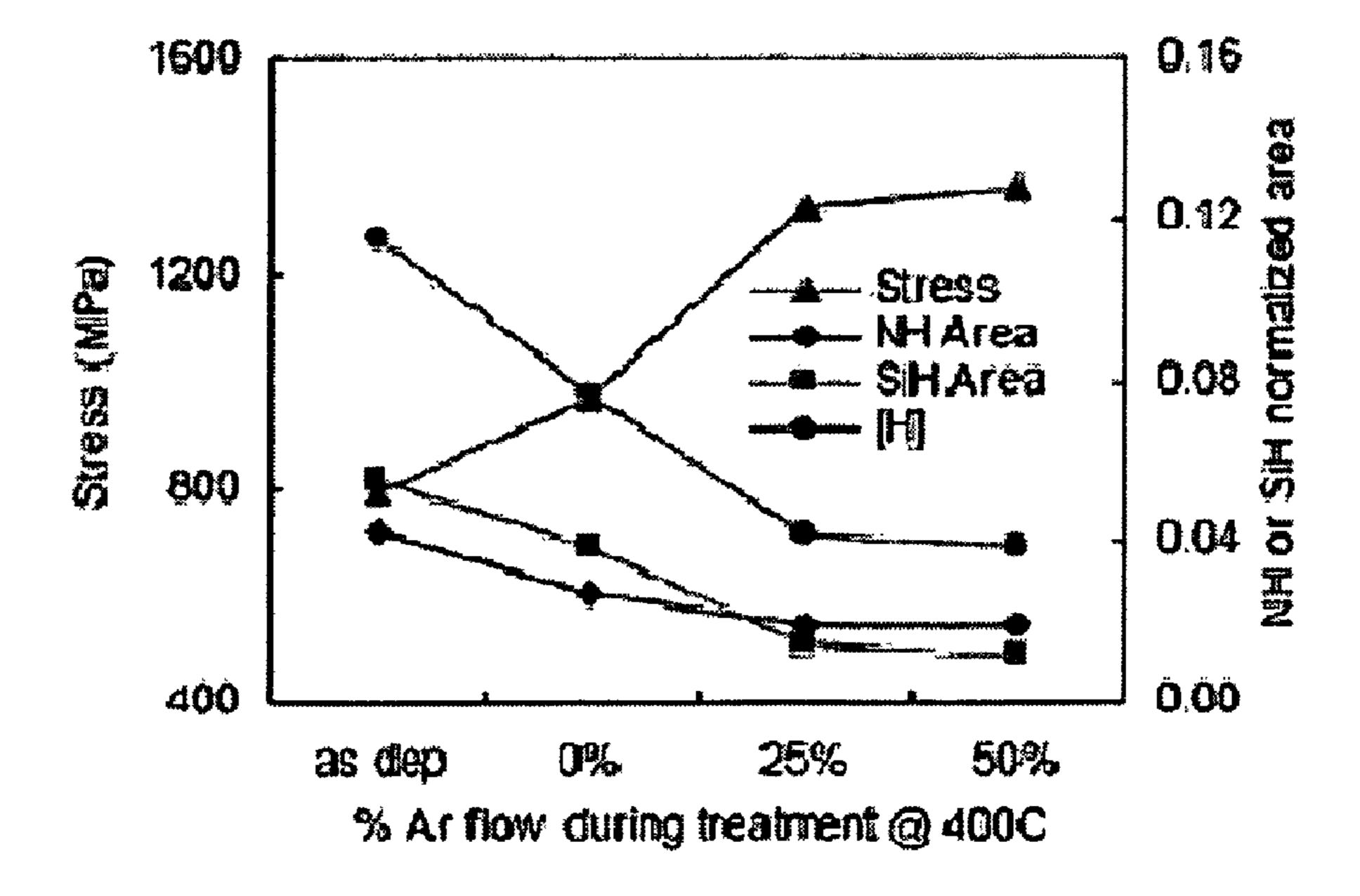

- FIG. 13B plots tensile stress, H content, and FT-IR spectrum peak area for N—H and Si—H bonds, for the CVD SiN films deposited in FIG. 13A;

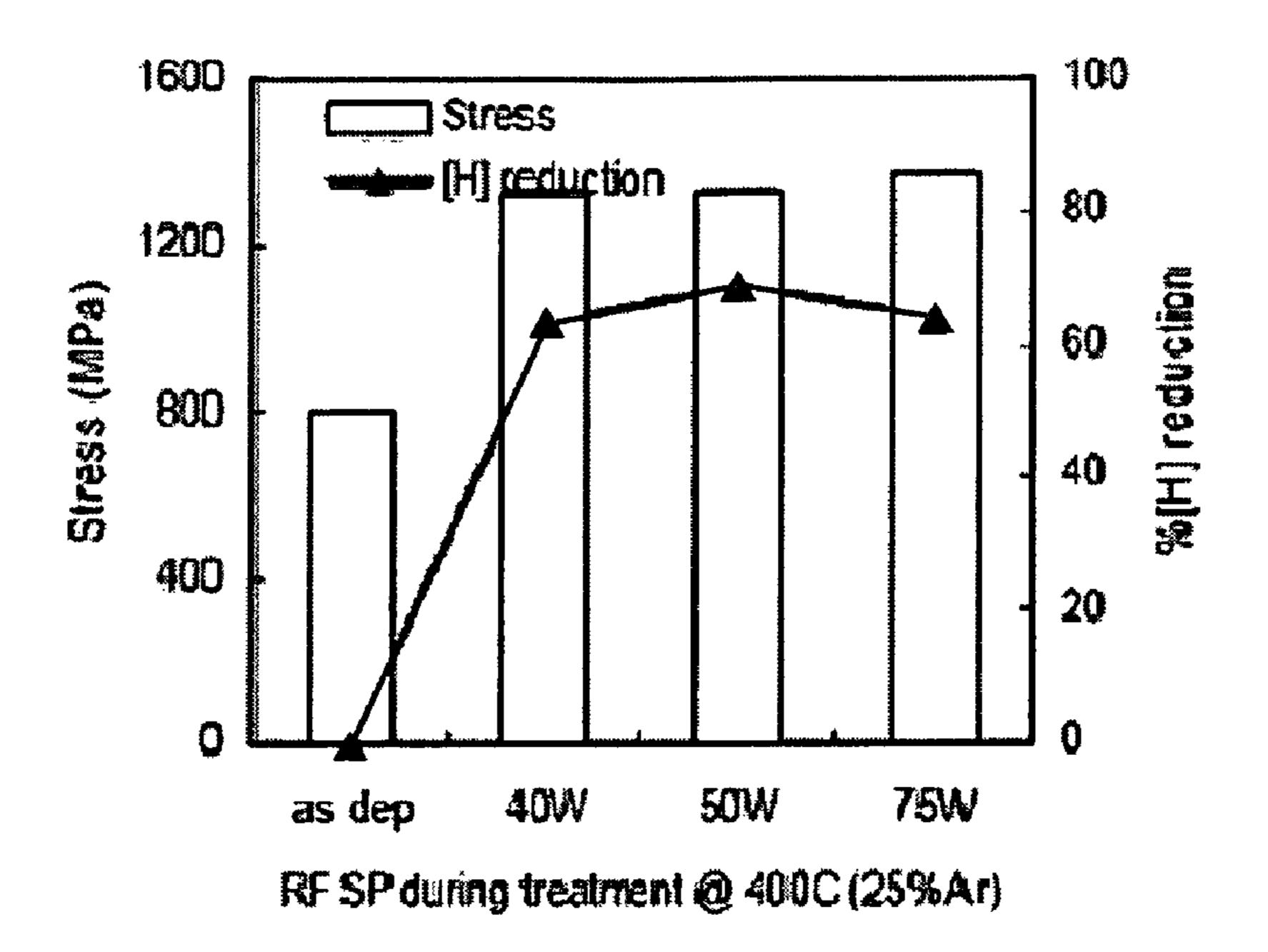

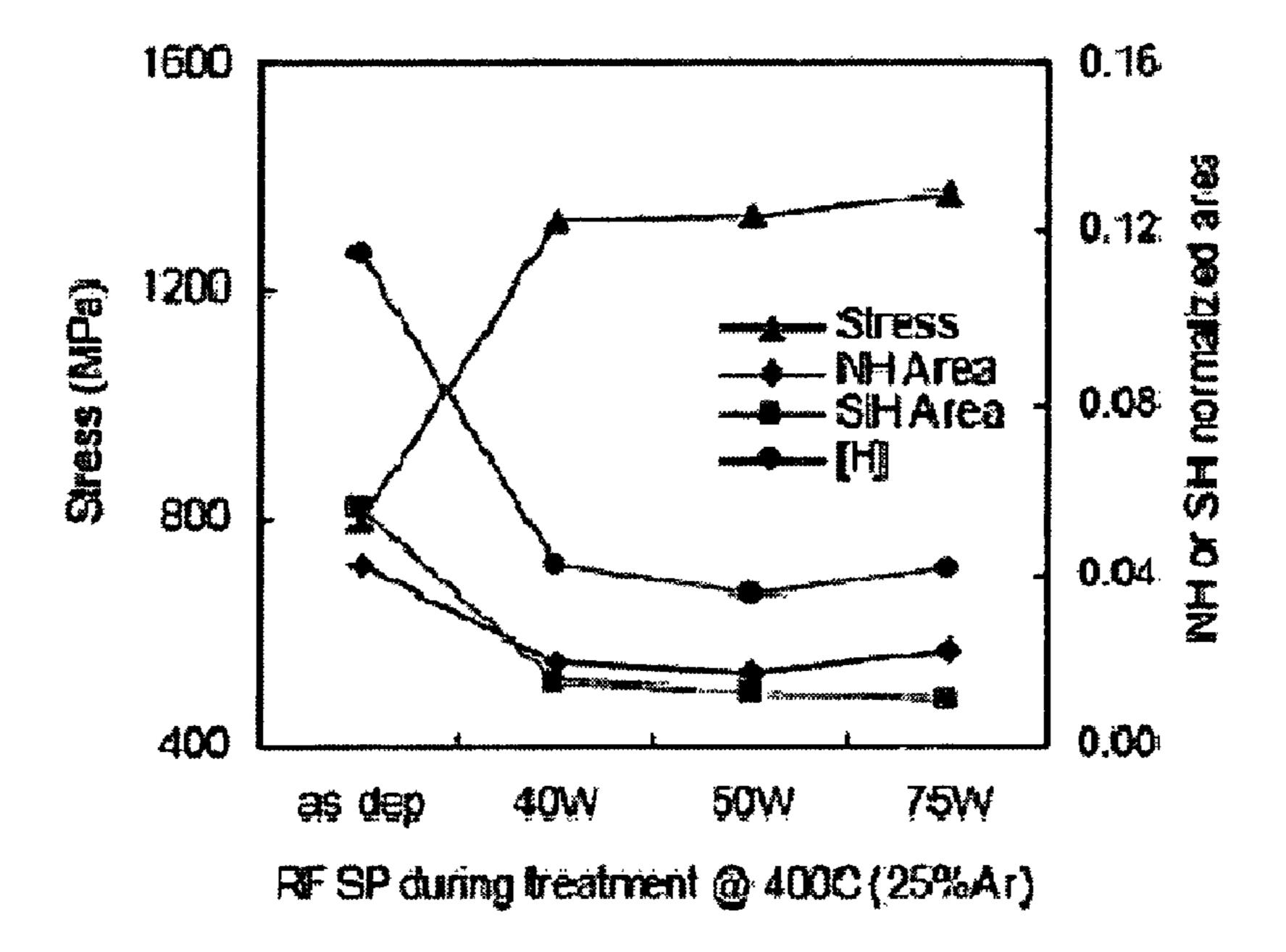

- FIG. 13C charts tensile stress and plots reduction in hydrogen content for CVD SiN films exposed to post-deposition treatment with an Ar plasma at different power levels;

- FIG. 13D plots tensile stress, H content, and FT-IR spectrum peak area for N—H and Si—H bonds, for the CVD SiN films deposited in FIG. 13C;

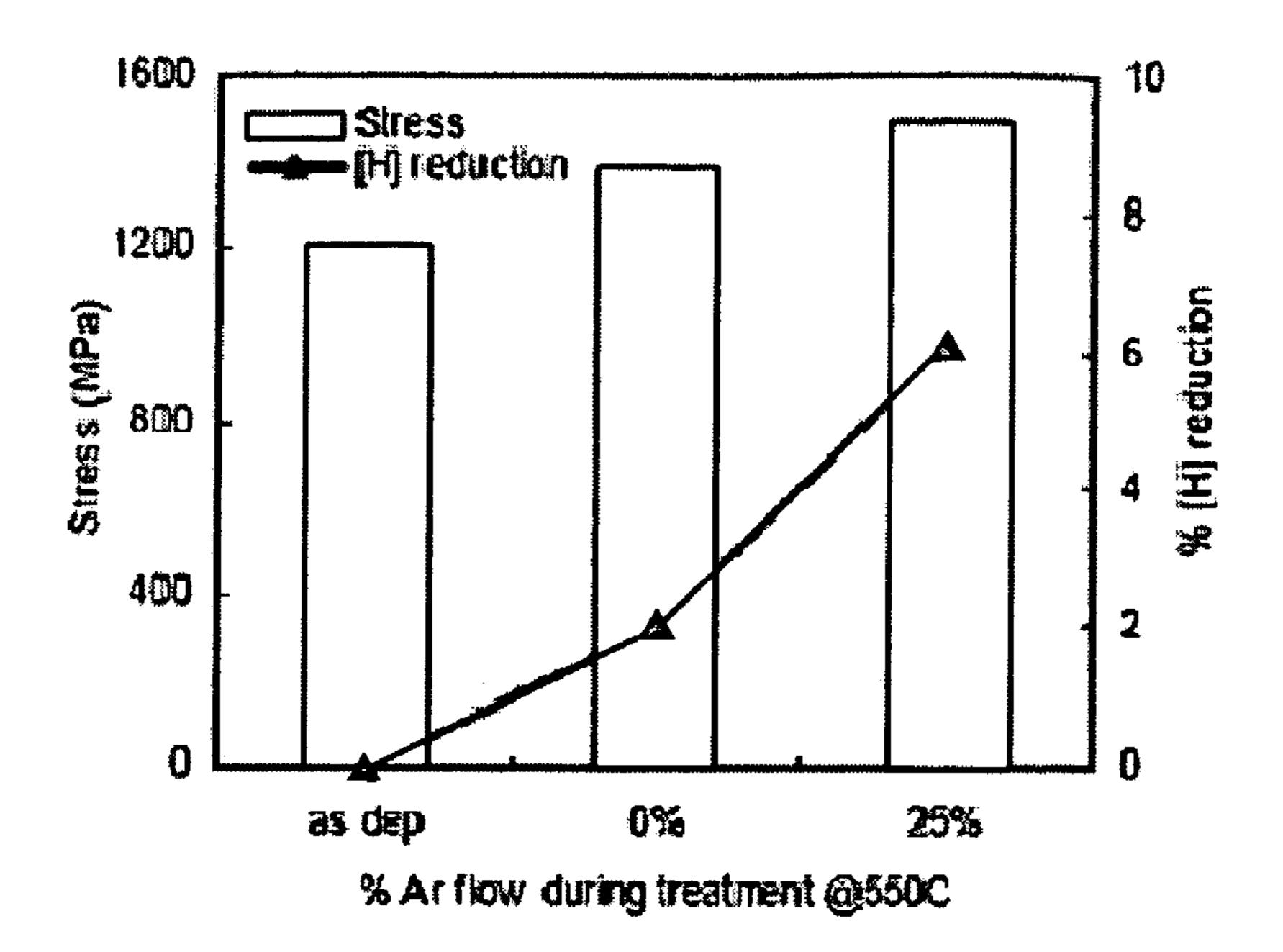

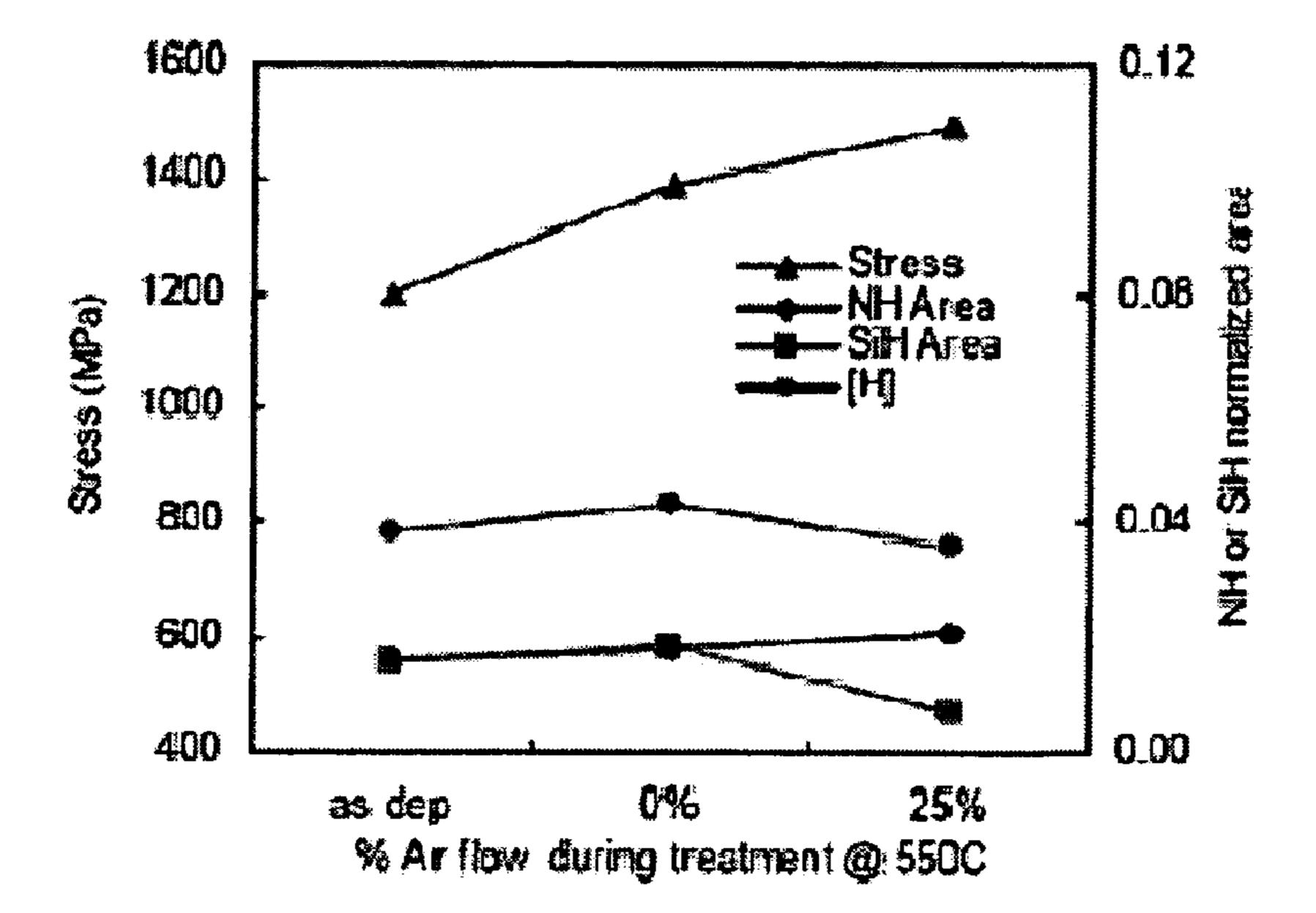

- FIG. 13E charts tensile stress and plots reduction in hydrogen content for CVD SiN films exposed to post-deposition treatment with plasma formed from gases containing different levels of Argon, at 550° C.;

- FIG. 13F plots tensile stress, H content, and FT-IR spectrum peak area for N—H and Si—H bonds, for the CVD SiN films deposited in FIG. 13F;

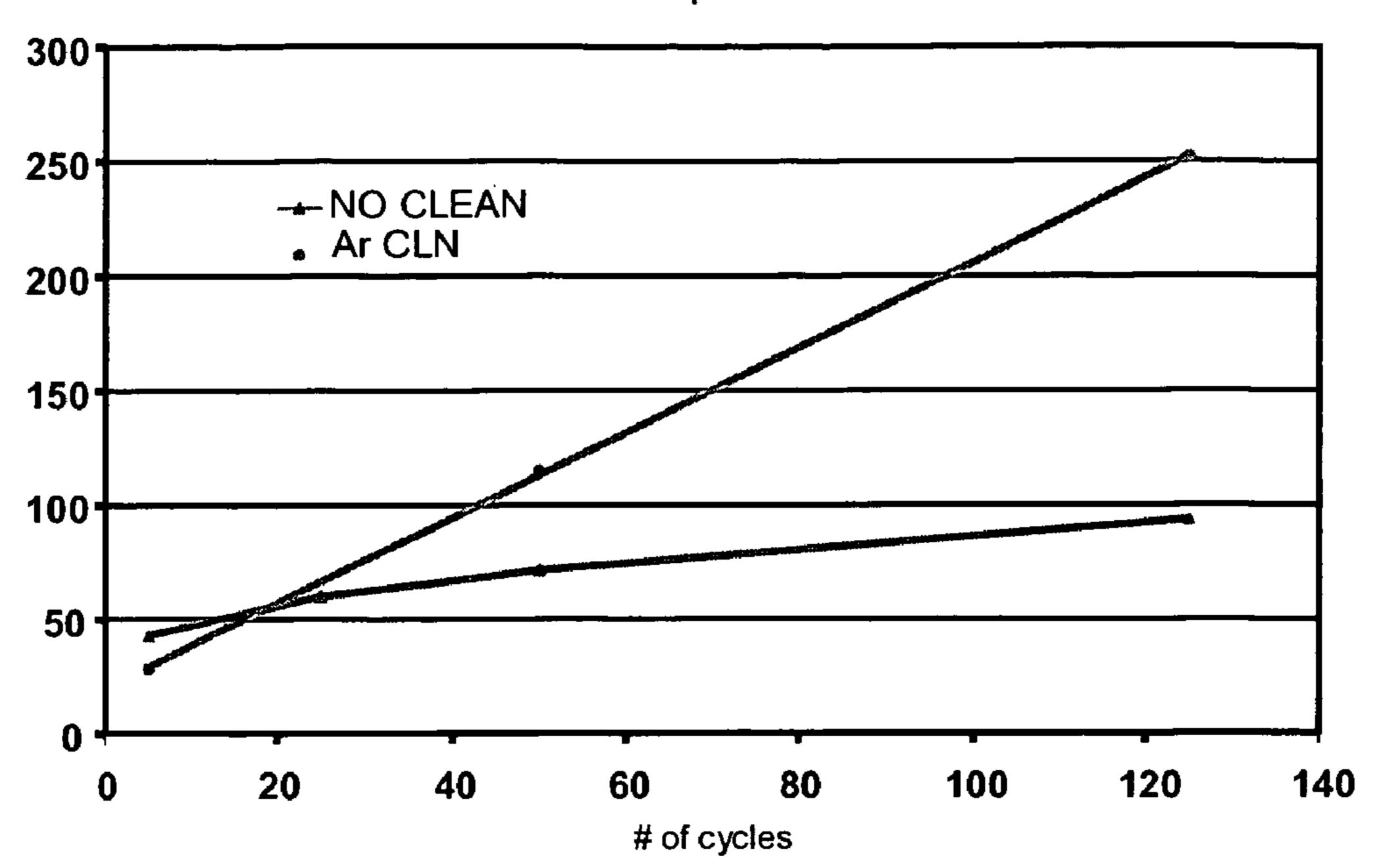

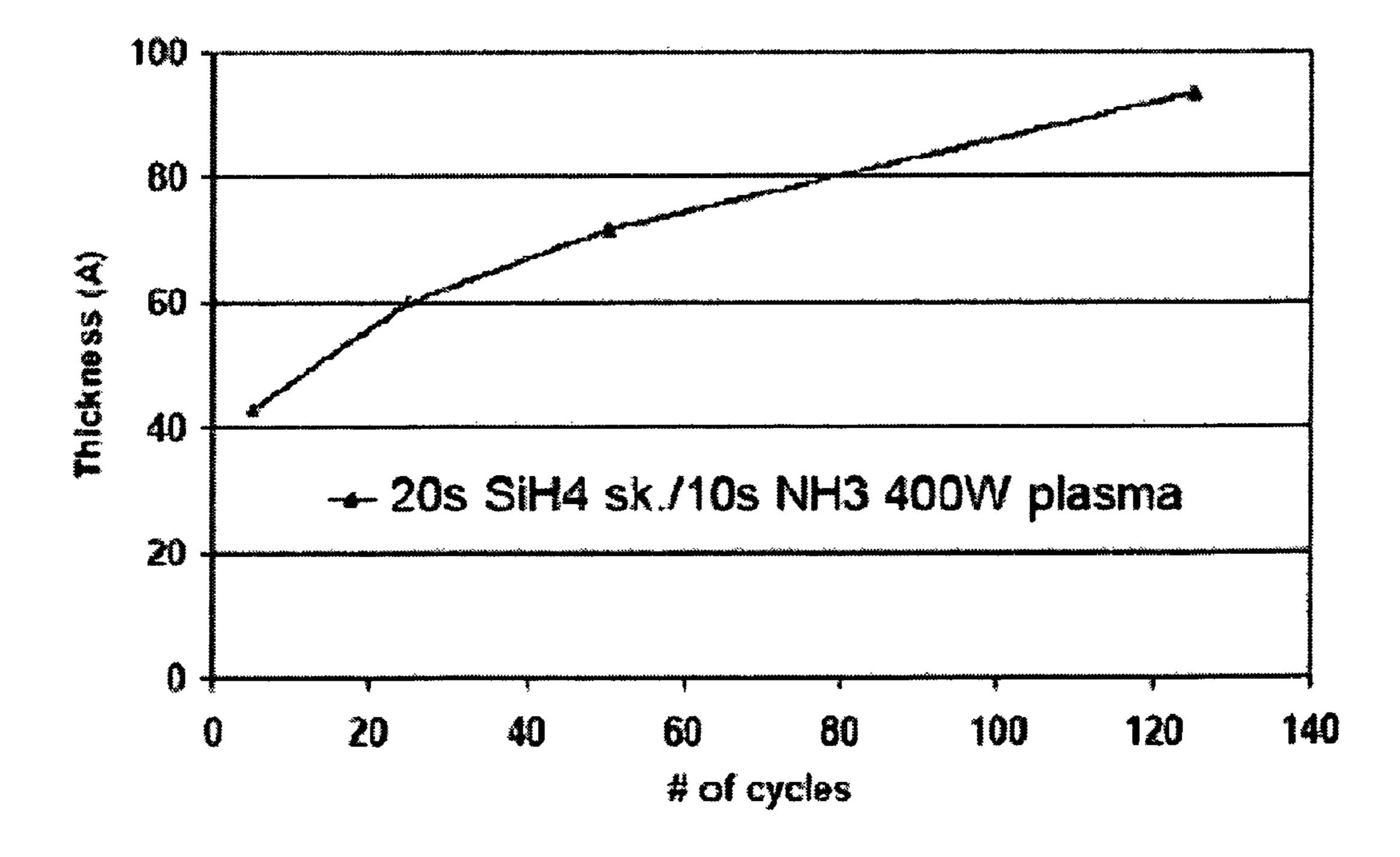

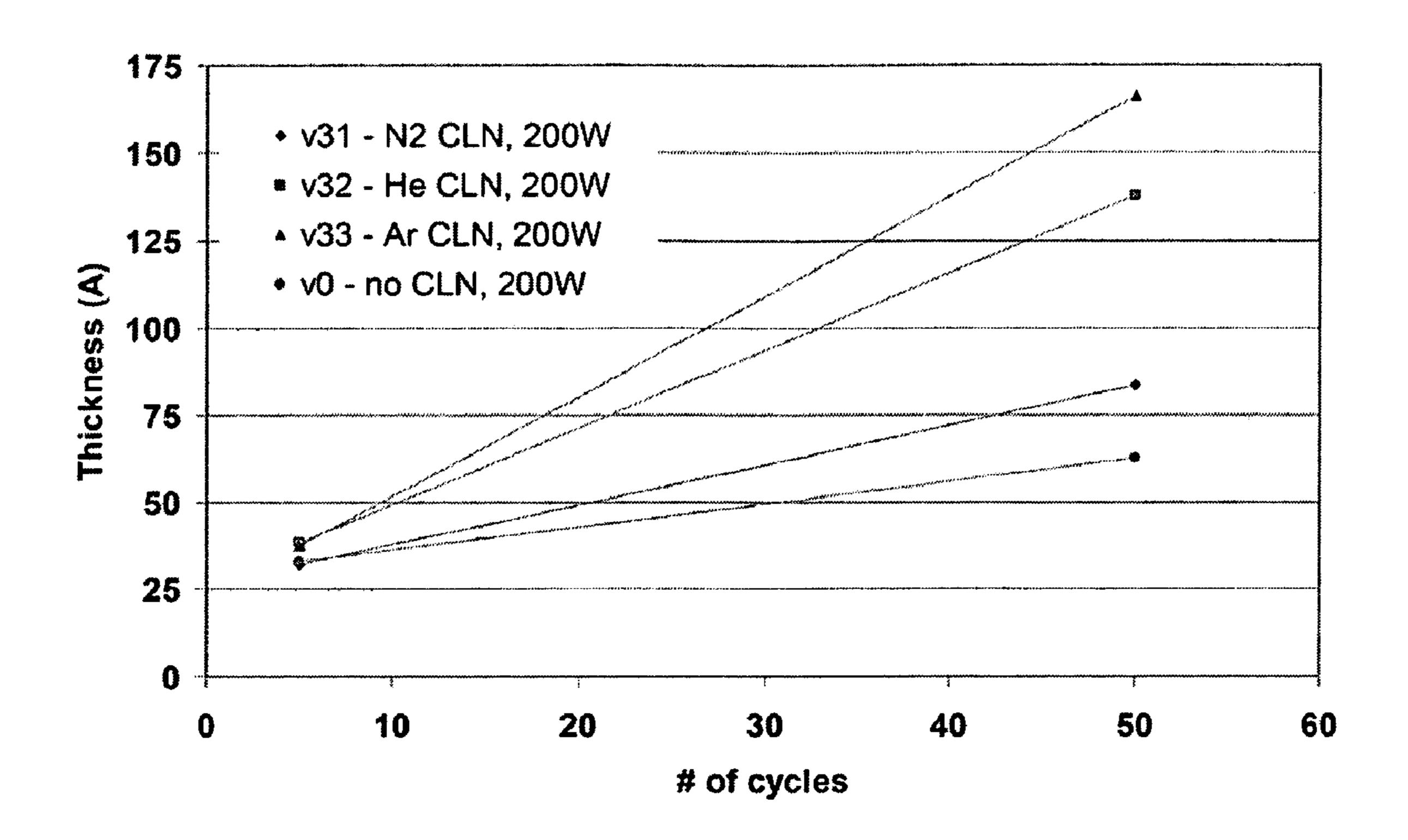

- FIG. 14 plots film thickness versus number of dep/treatment cycles, for CVD SiN films deposited with and without Ar plasma cleaning between each cycle;

- FIG. 15 plots film thickness versus number of dep/treatment cycles for, CVD SiN films deposited without Ar plasma cleaning between each cycle;

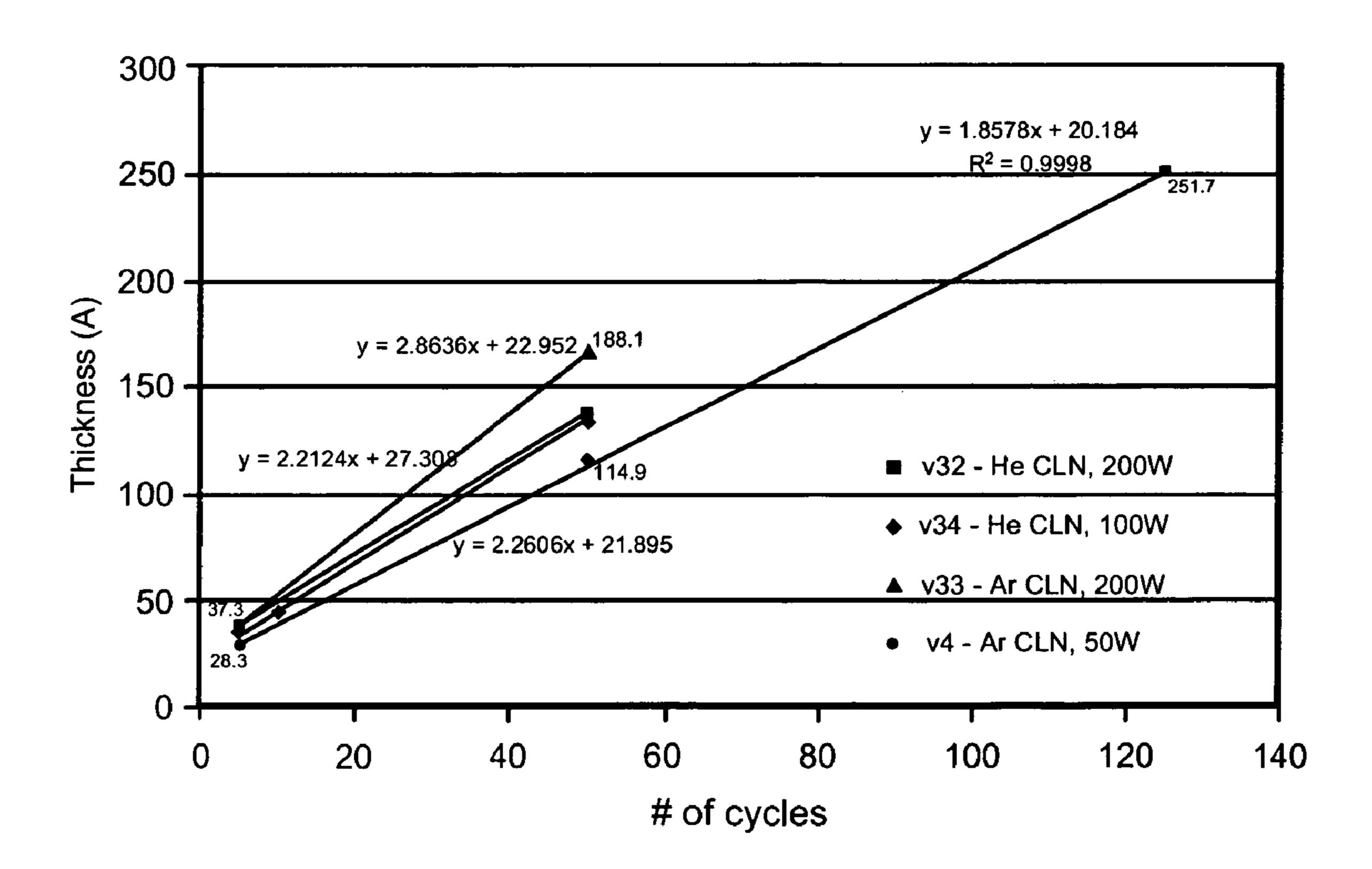

- FIG. **16** plots film thickness versus number of dep/treatment cycles, for CVD SiN films formed under a number of conditions between successive cycles;

- FIG. 17 plots films thickness versus number of dep/treatment cycles, for CVD SiN films formed under a number of conditions between successive cycles;

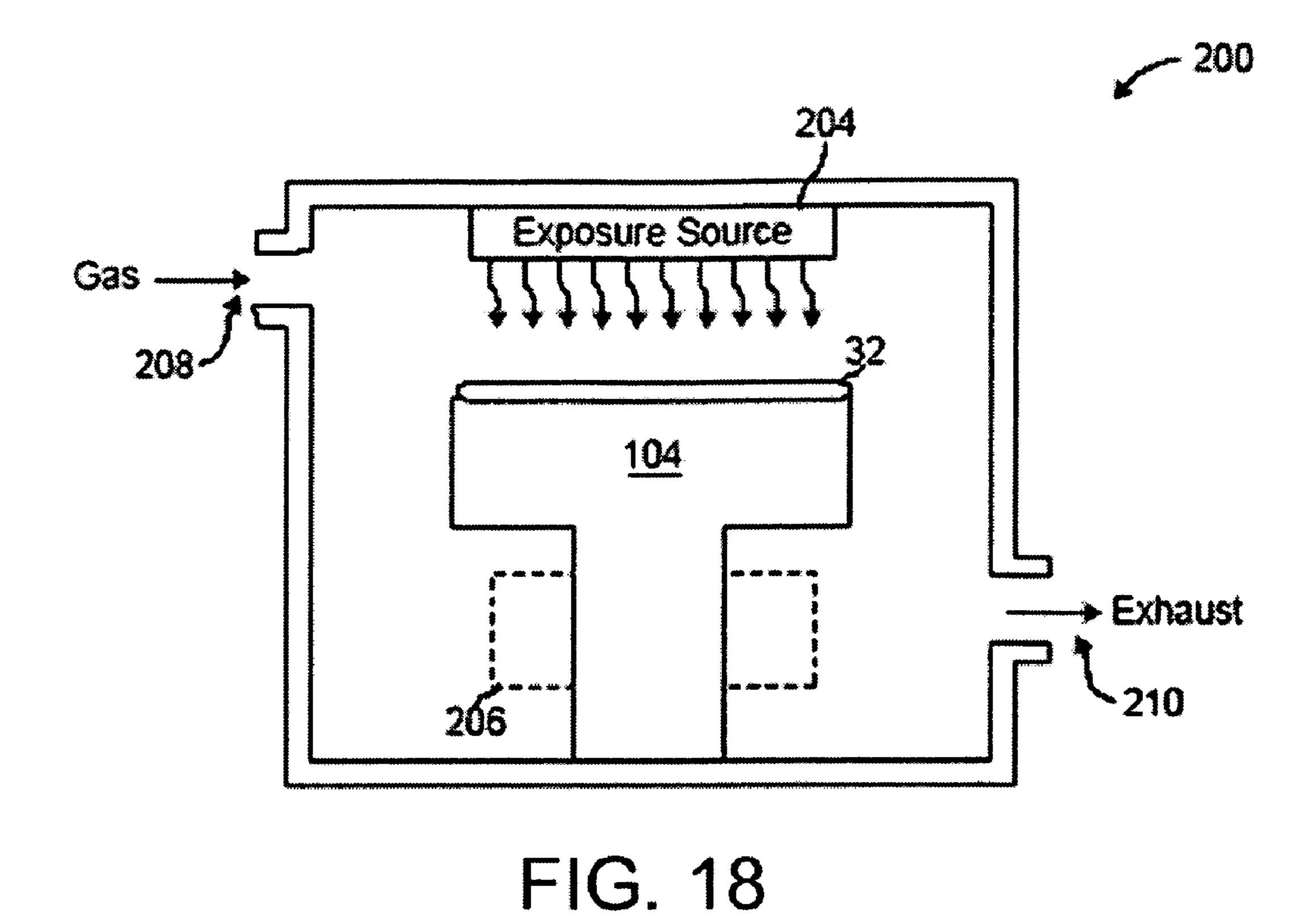

- FIG. **18** is a schematic view of an exposure chamber suitable for exposing a silicon nitride material to a suitable energy beam source;

- FIG. 19 is a bar graph showing the change in tensile stress values of material deposited at different process conditions (A, and B) for increasing ultraviolet radiation exposure time;

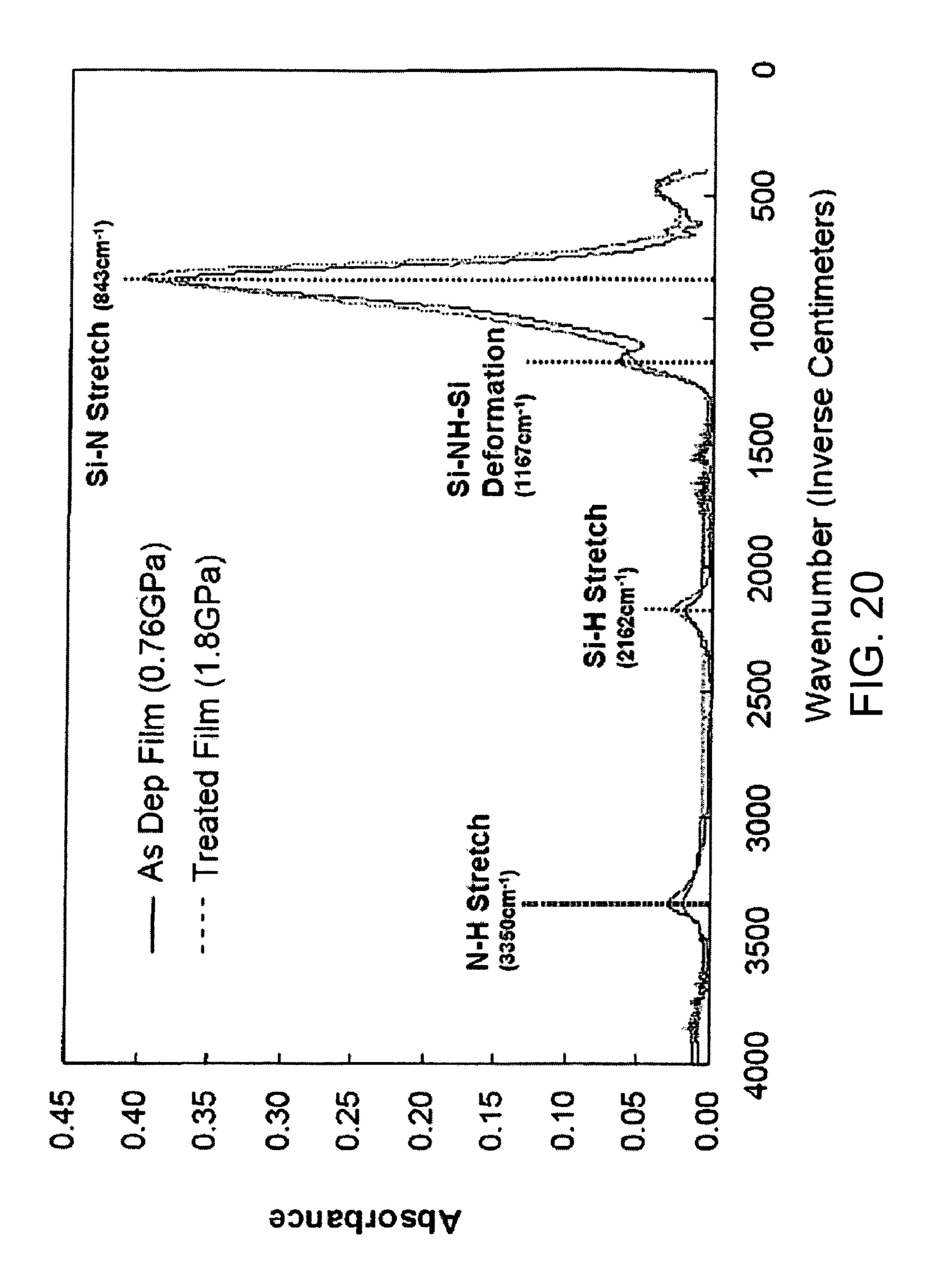

- FIG. 20 is a graph showing a Fourier Transformed Infrared (FT-IR) spectrum of a stressed silicon nitride material in the as-deposited state (as dep.-continuous line), and after treatment with ultraviolet radiation (treated film—dashed line);

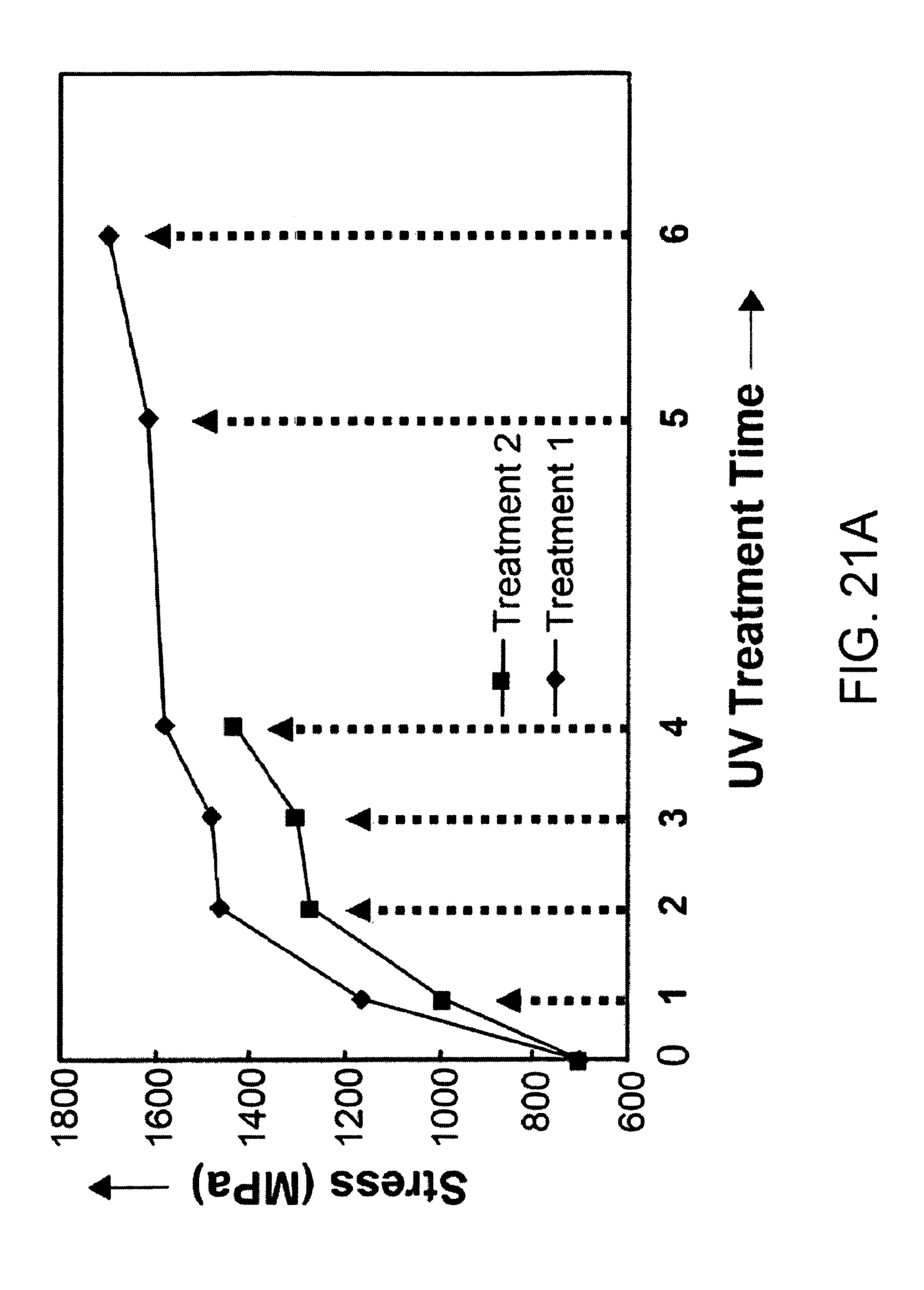

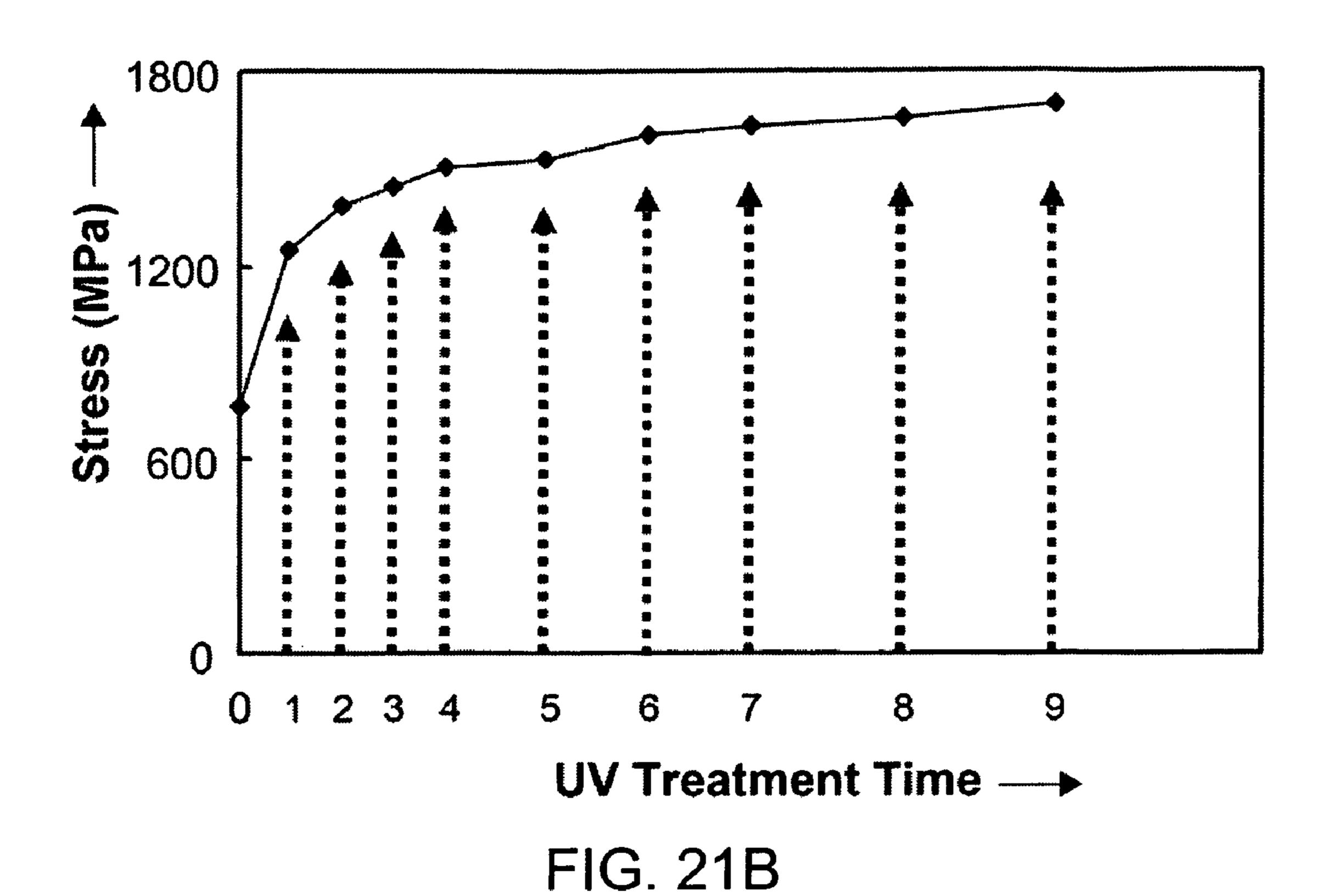

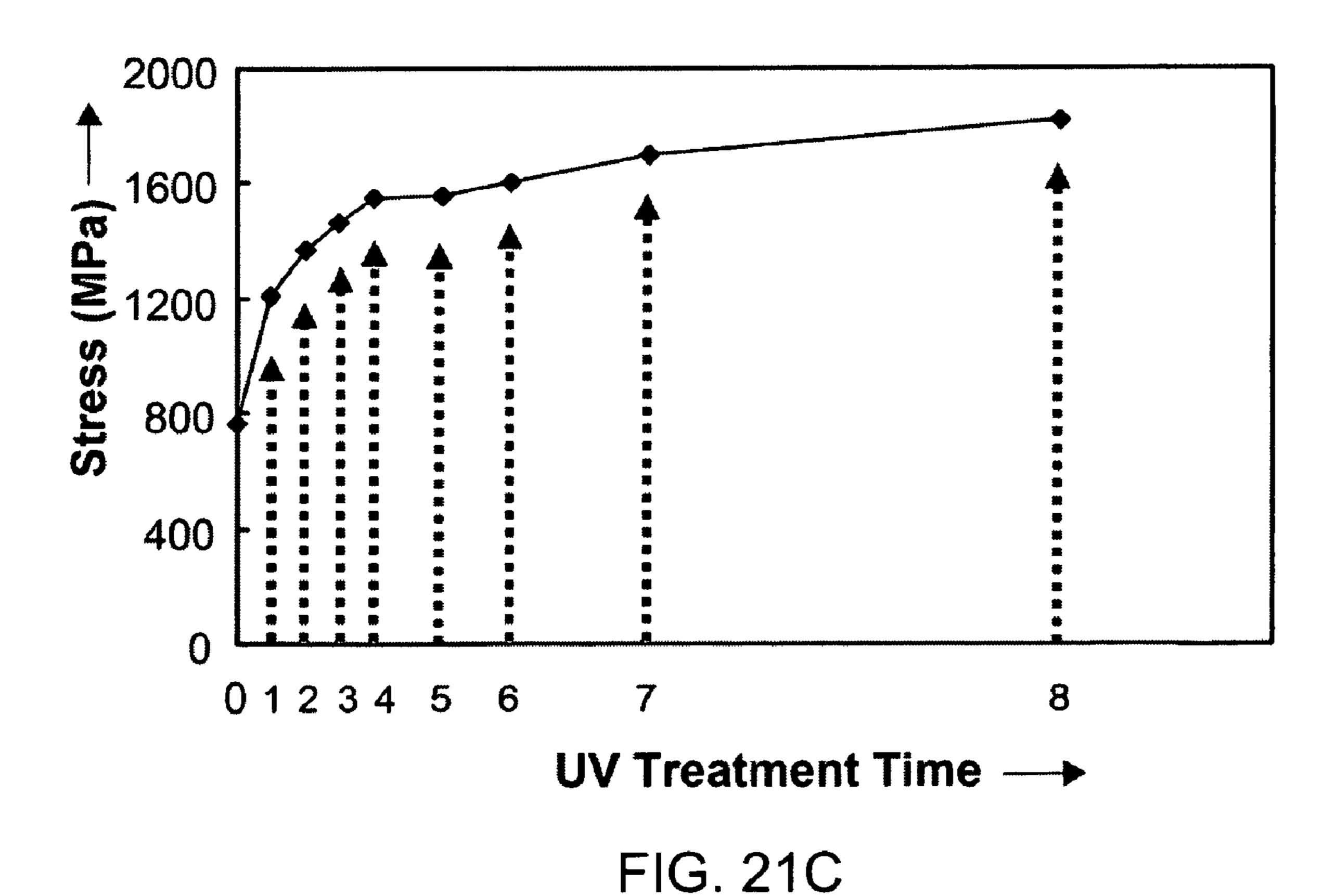

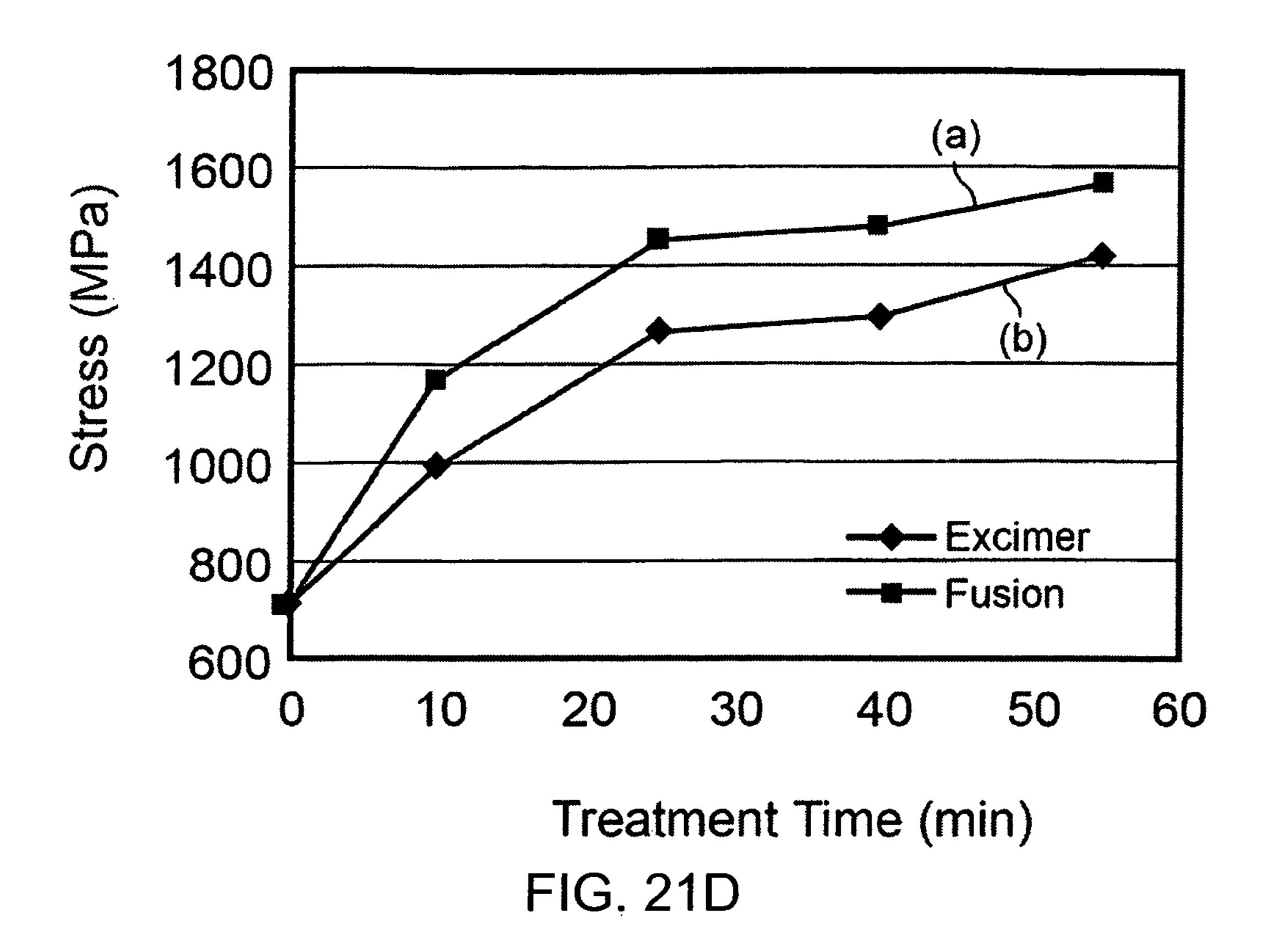

- FIGS. 21A to 21E are graphs showing the increase in tensile stress of deposited silicon nitride materials with time of ultraviolet radiation exposure, and in FIG. 21A, to both single wavelength (Treatment 1) and broadband (Treatment 2) ultraviolet exposure;

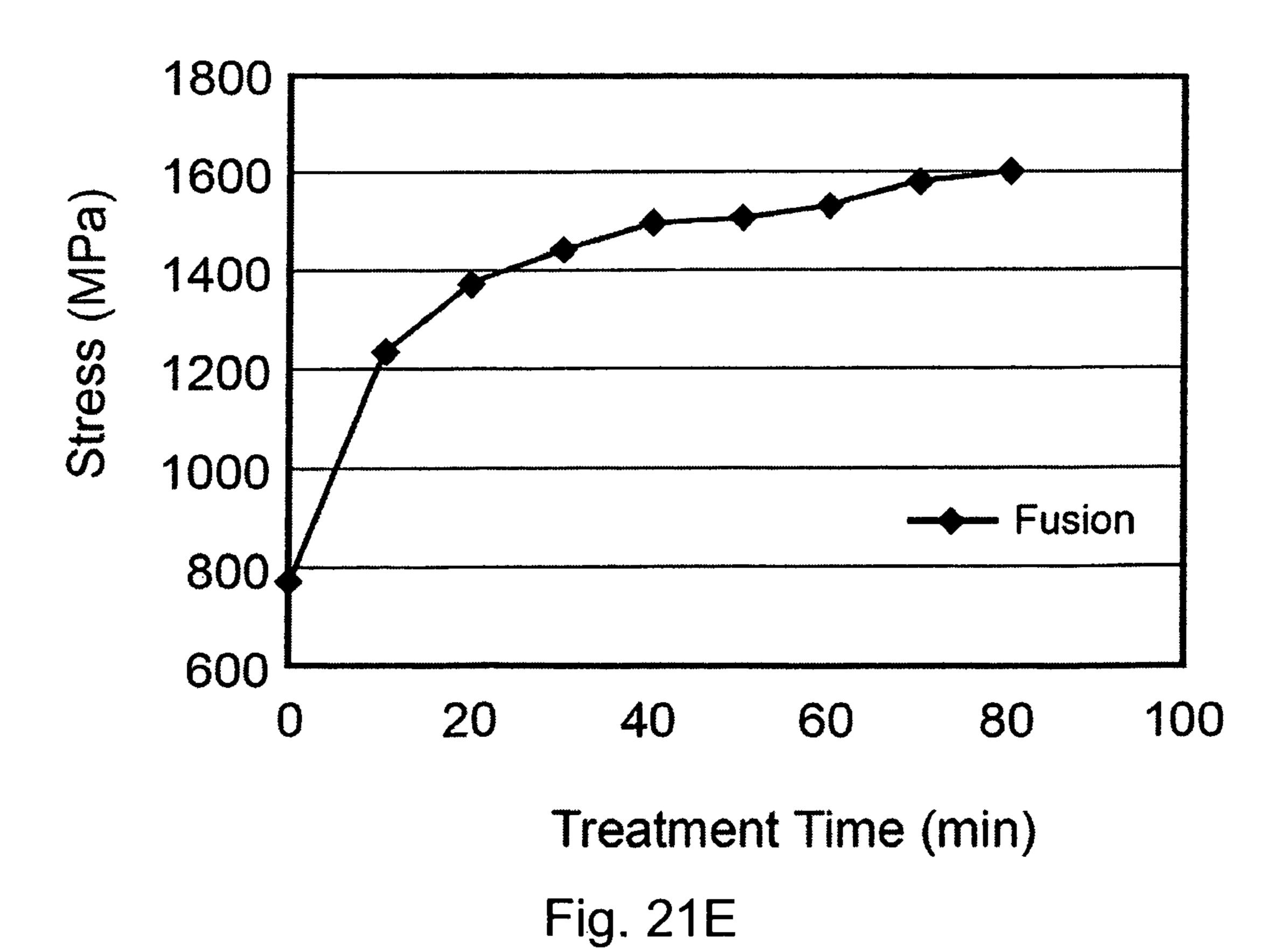

- FIG. **22**A plots tensile stress and shrinkage versus deposition temperature for CVD SiN films exposed to post-deposition treatment with UV radiation;

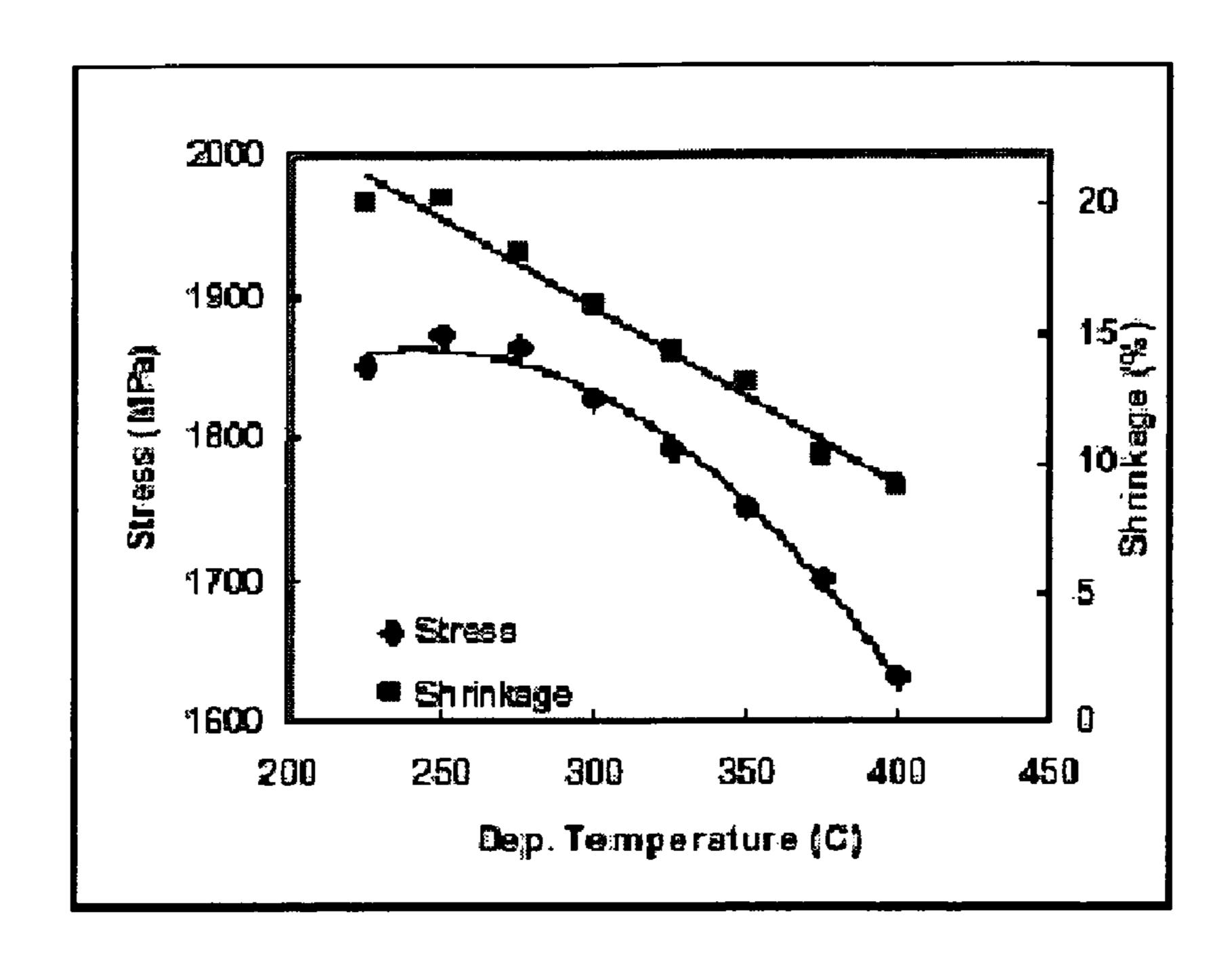

- FIG. 22B plots total H content, and the ratio of FT-IR spectrum peak areas of Si—H and N—H bonds, for the CVD SiN films of FIG. 22A:

- FIG. 23 shows FT-IR spectra of a CVD SiN film as-deposited, and after treatment with UV radiation;

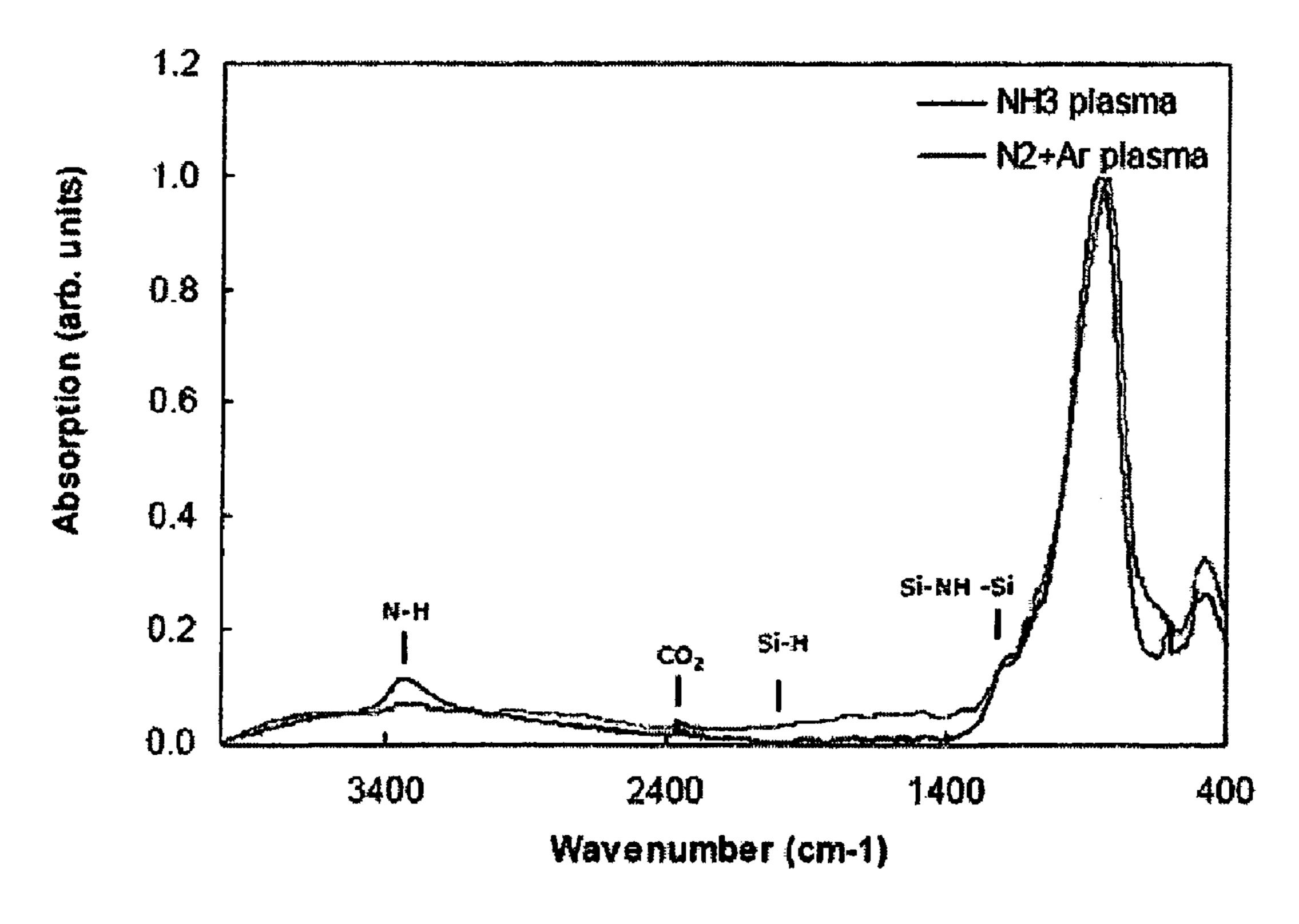

- FIG. 24 shows FT-IR spectra of CVD SiN films exposed to post-deposition treatment plasma as generated from different gas mixtures;

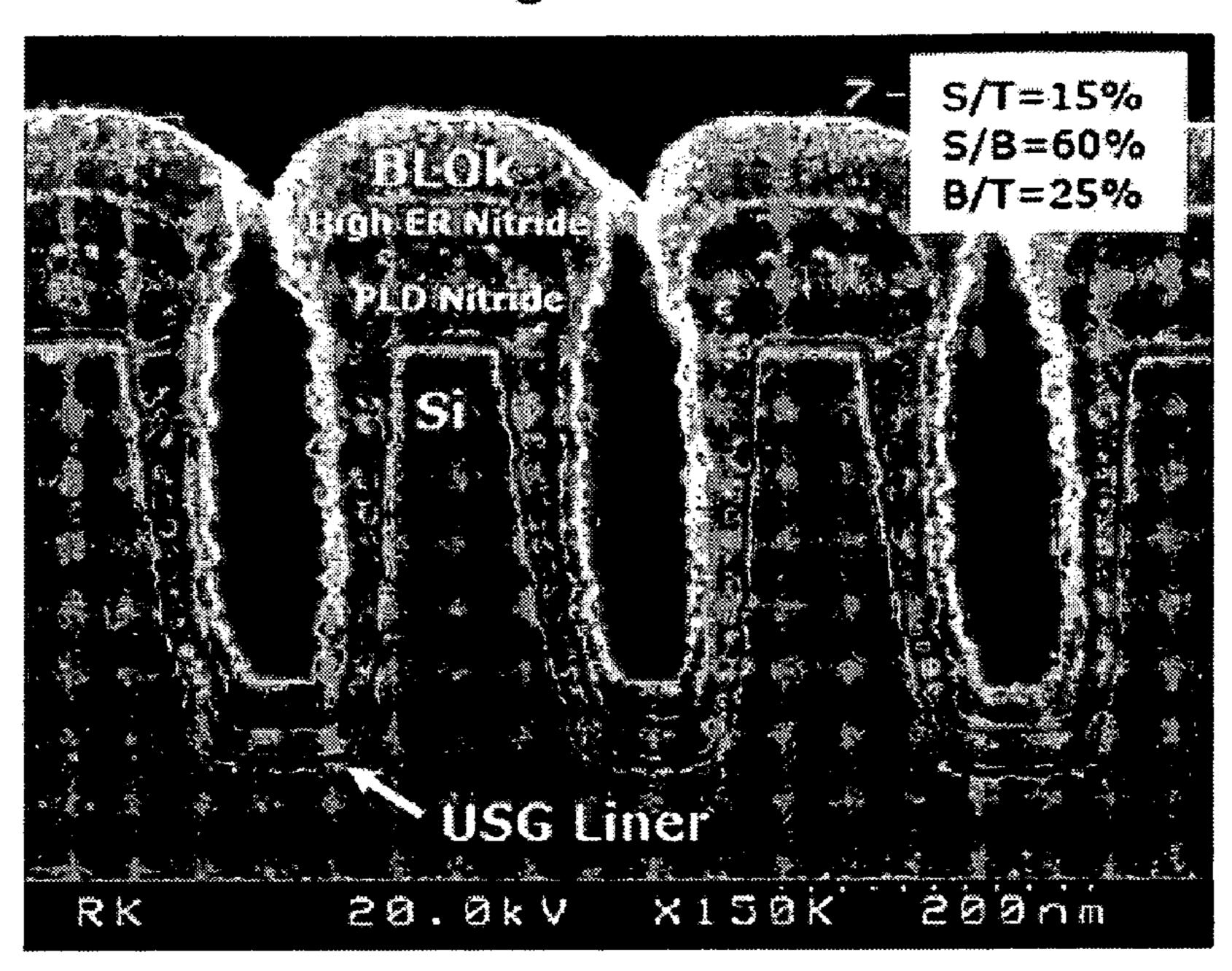

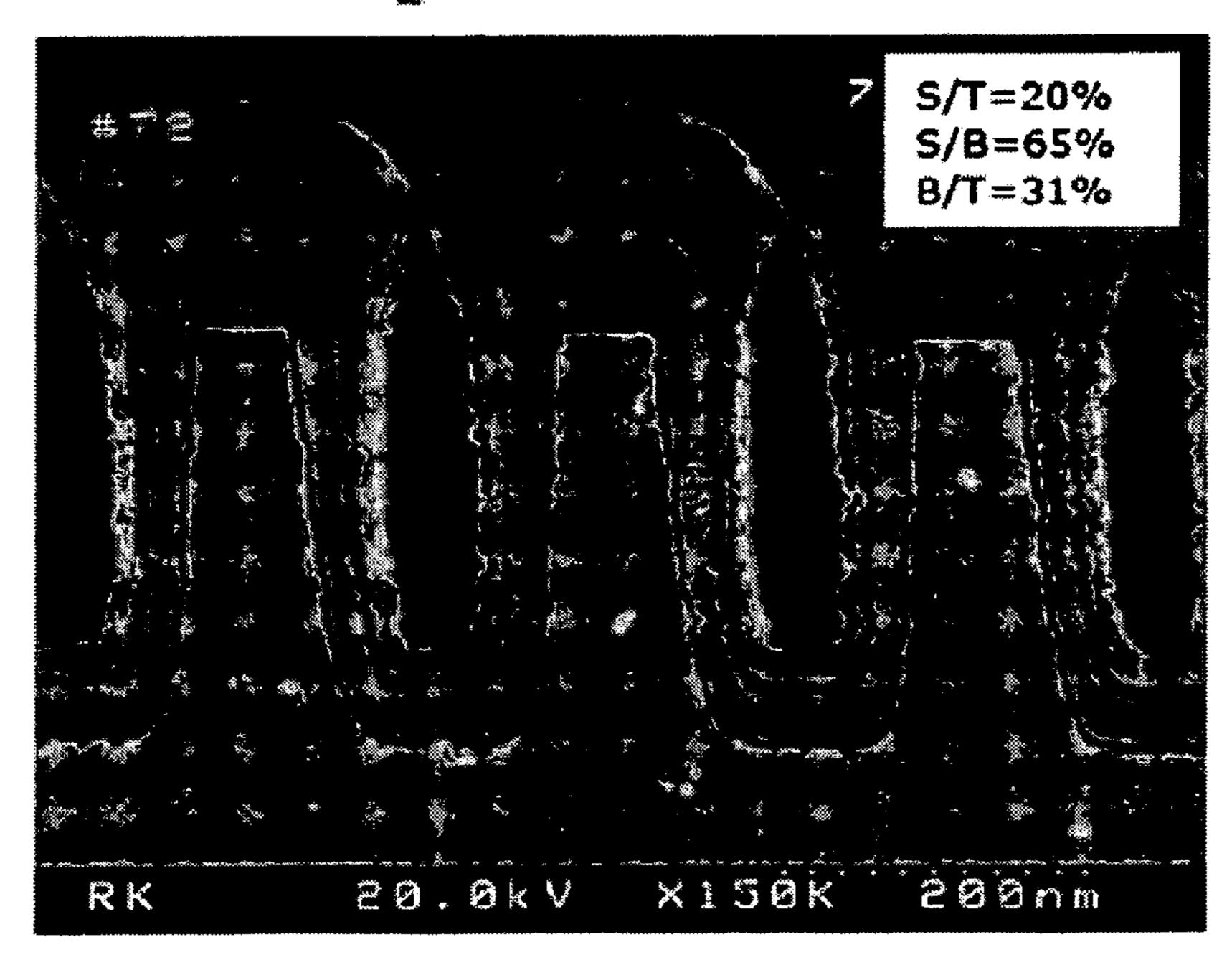

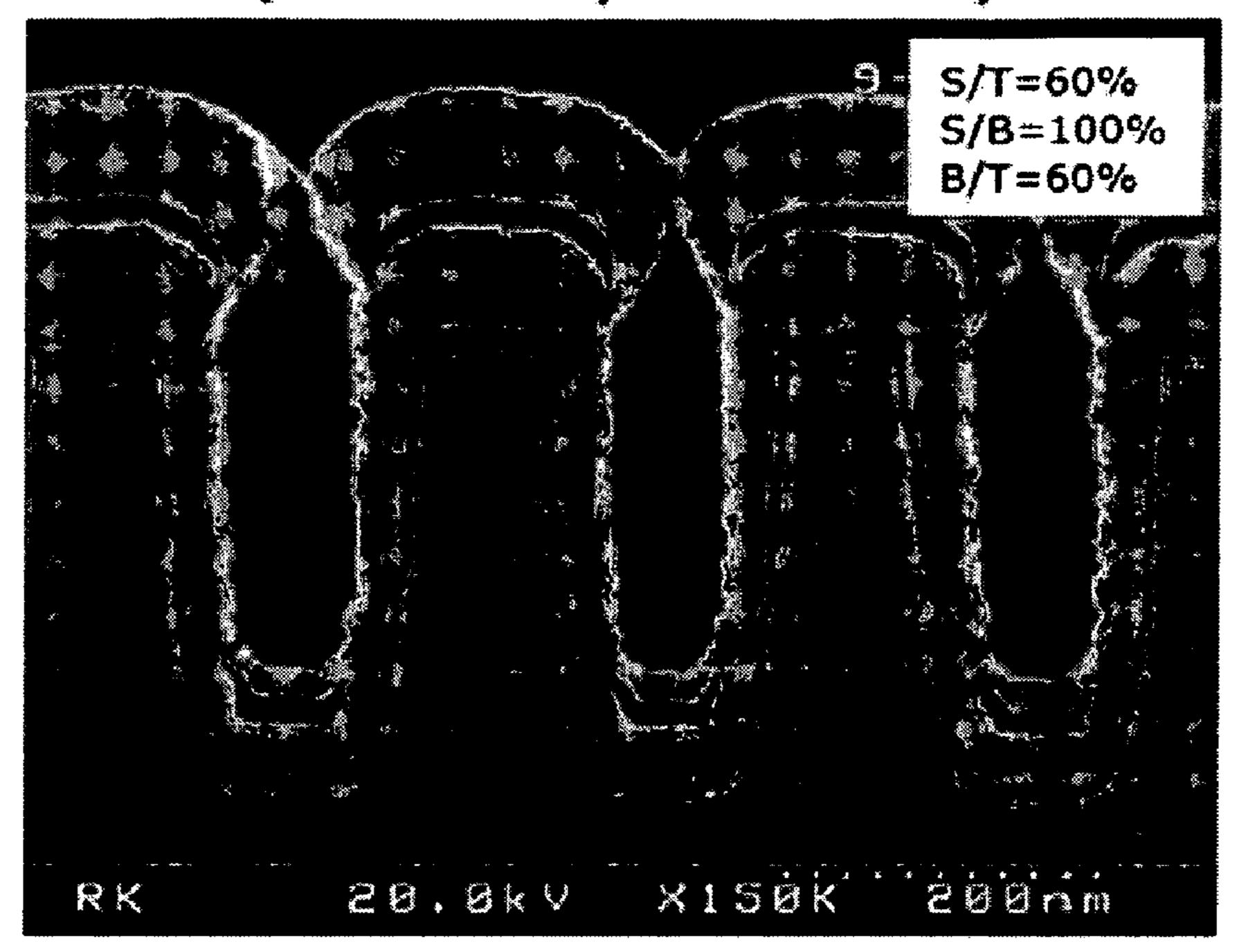

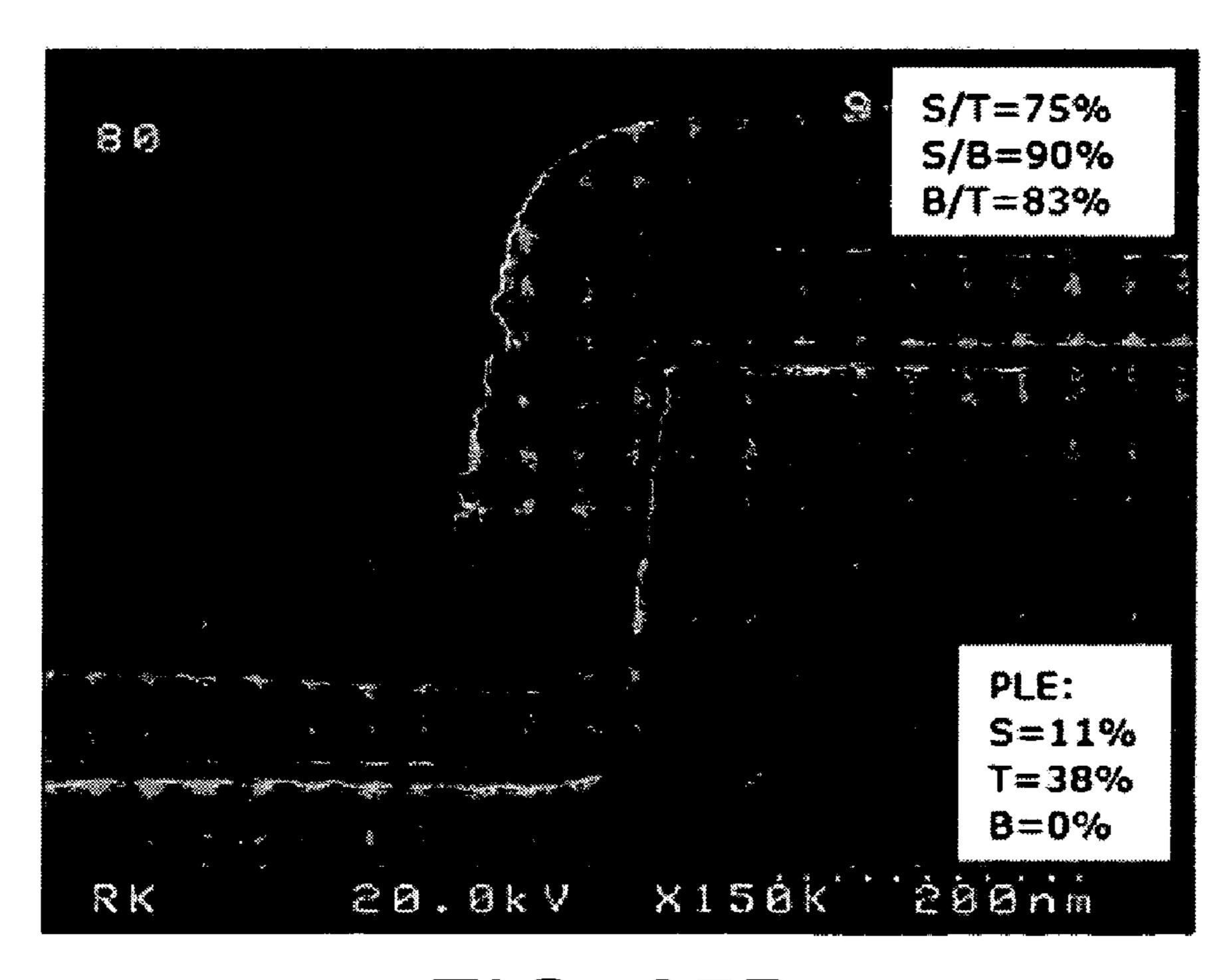

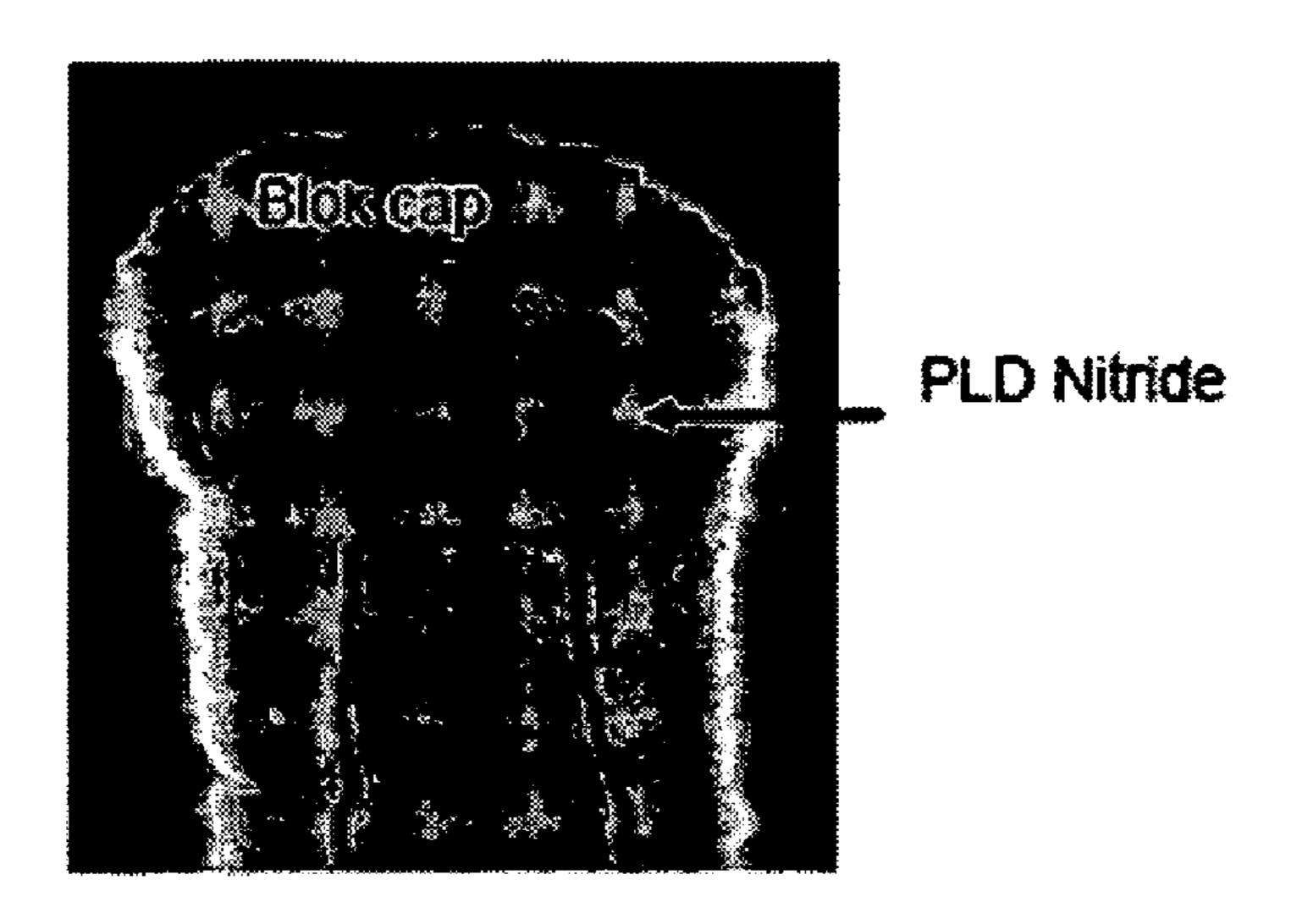

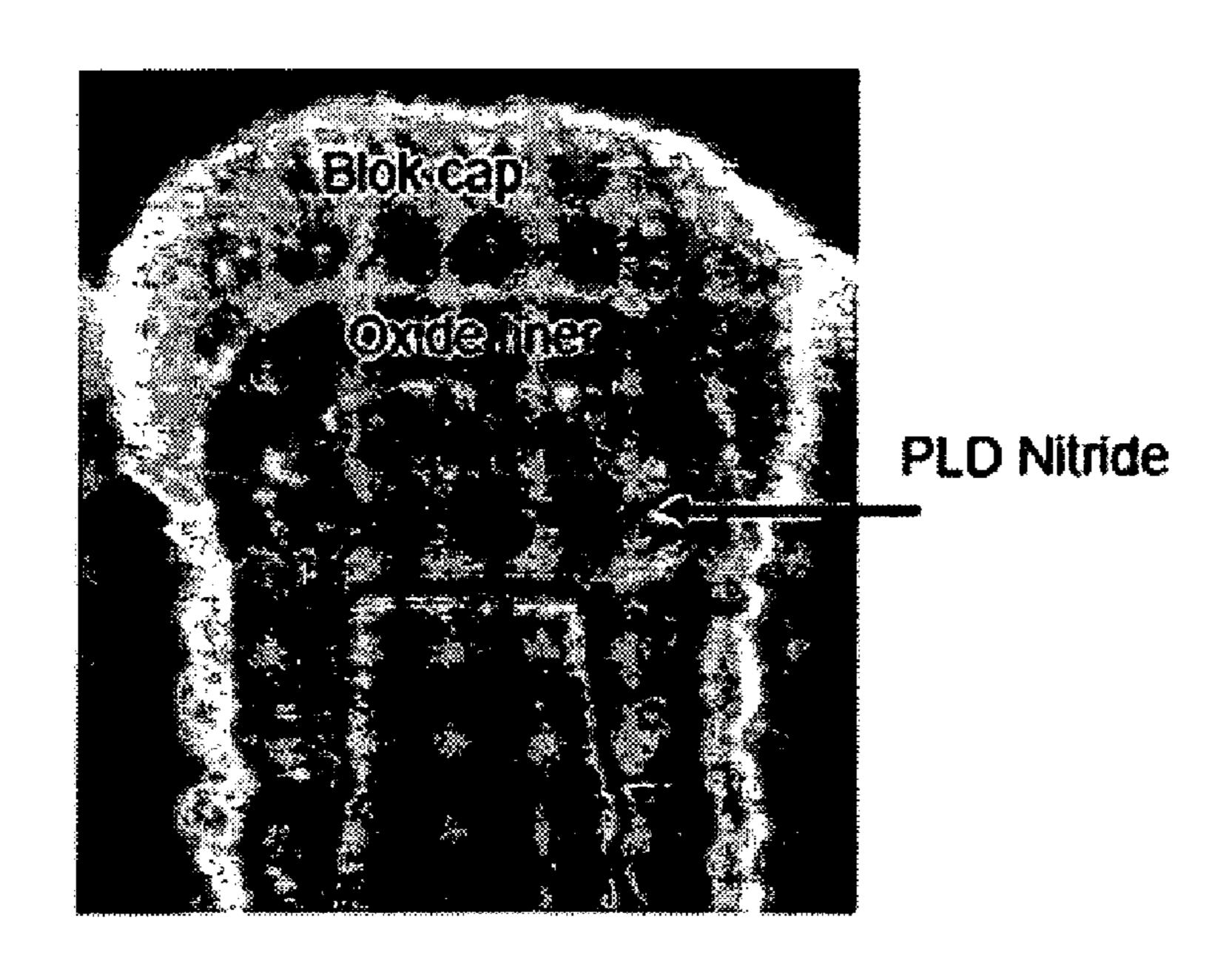

- FIGS. 25A-D are cross-sectional electron micrographs showing conformality of CVD SiN films formed under different processing conditions;

- FIGS. **26**A-B are enlarged cross-sectional electron micrographs showing morphology of CVD SiN films formed under different processing conditions;

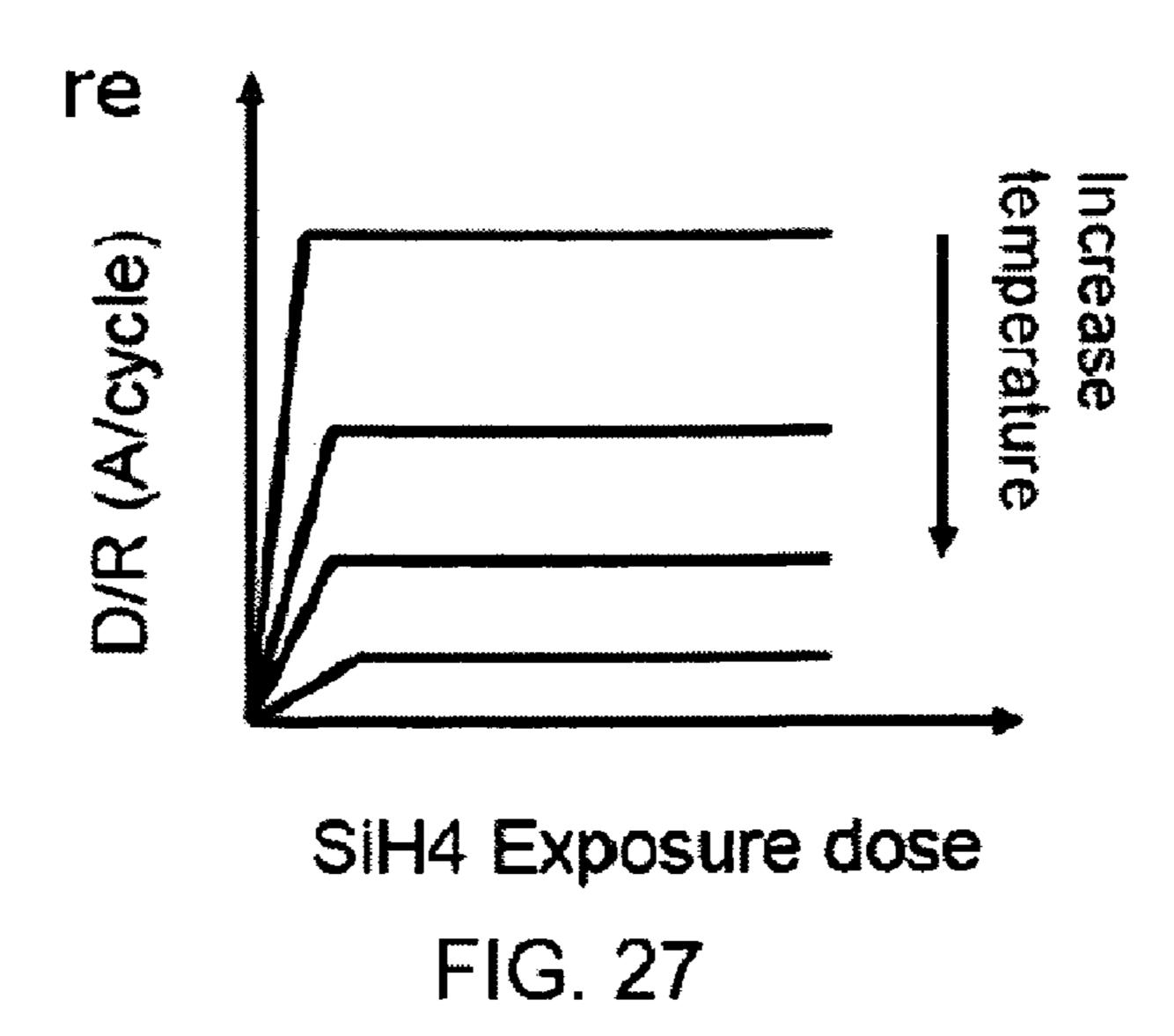

- FIG. 27 plots the rate of deposition of material versus exposure dose.

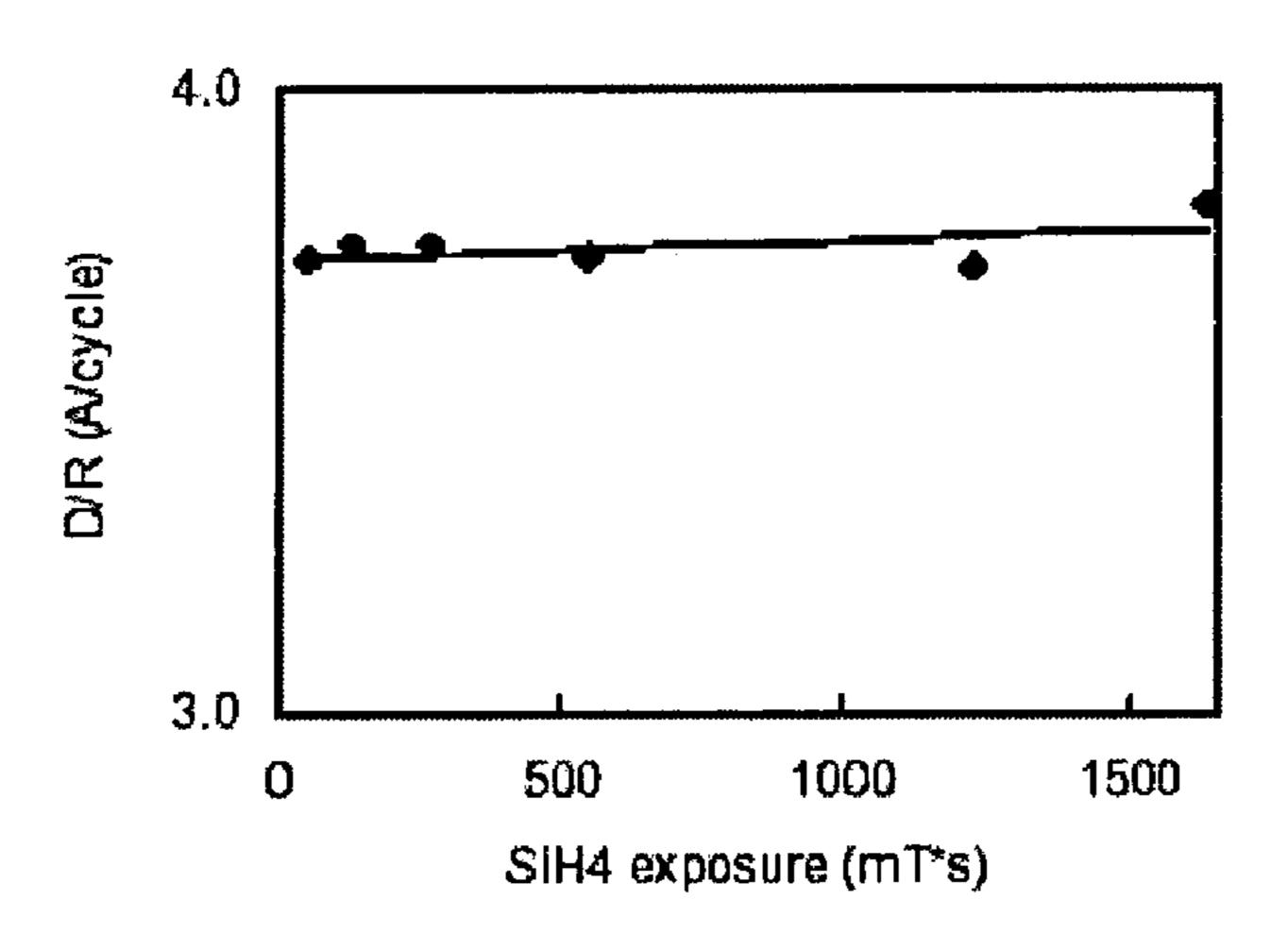

- FIG. 28A plots deposition rate versus exposure dose. FIG. 28B shows a cross-sectional micrograph showing a feature bearing a layer deposited after a SiH<sub>4</sub> exposure dose of 500 mT\*s.

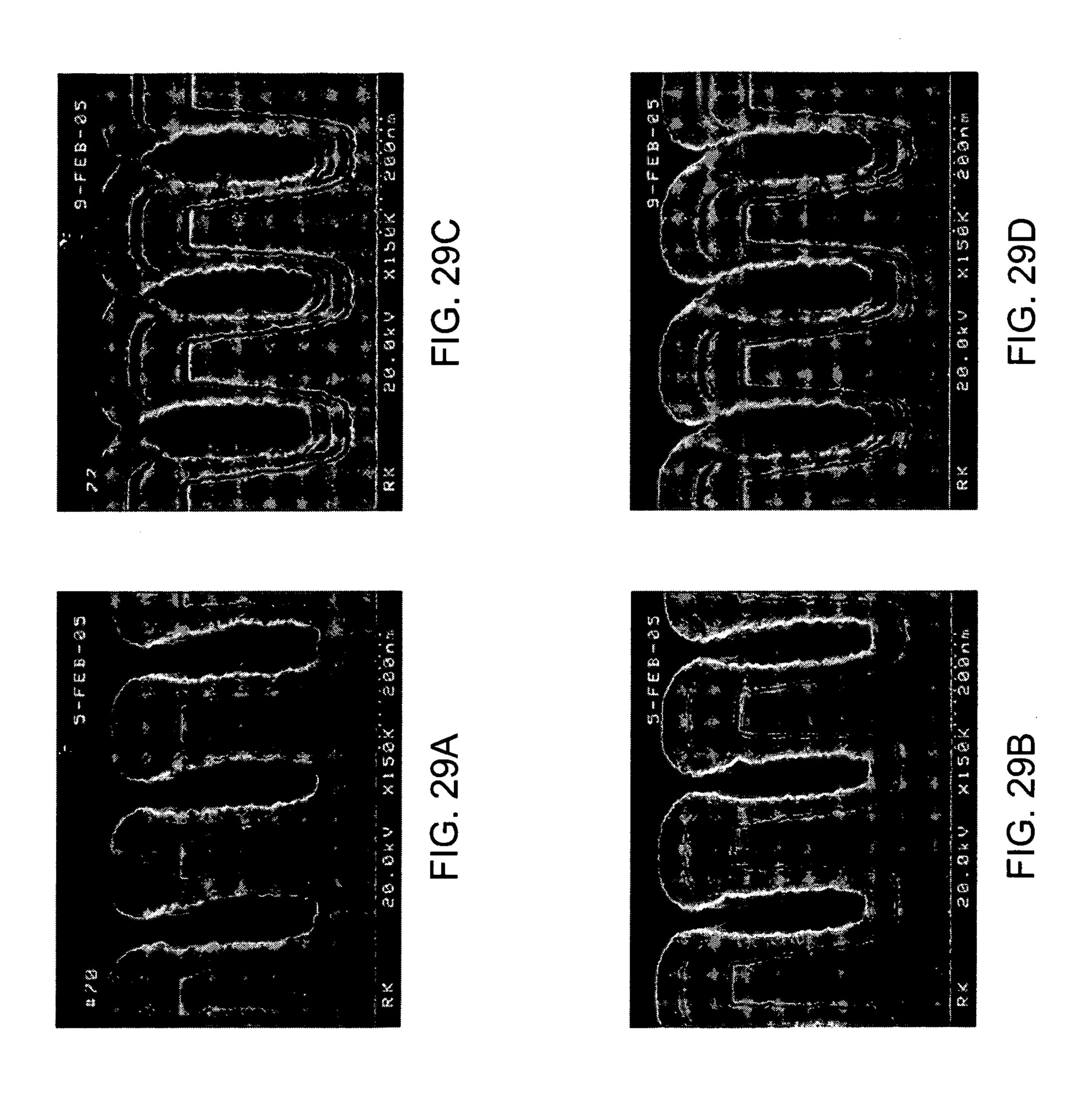

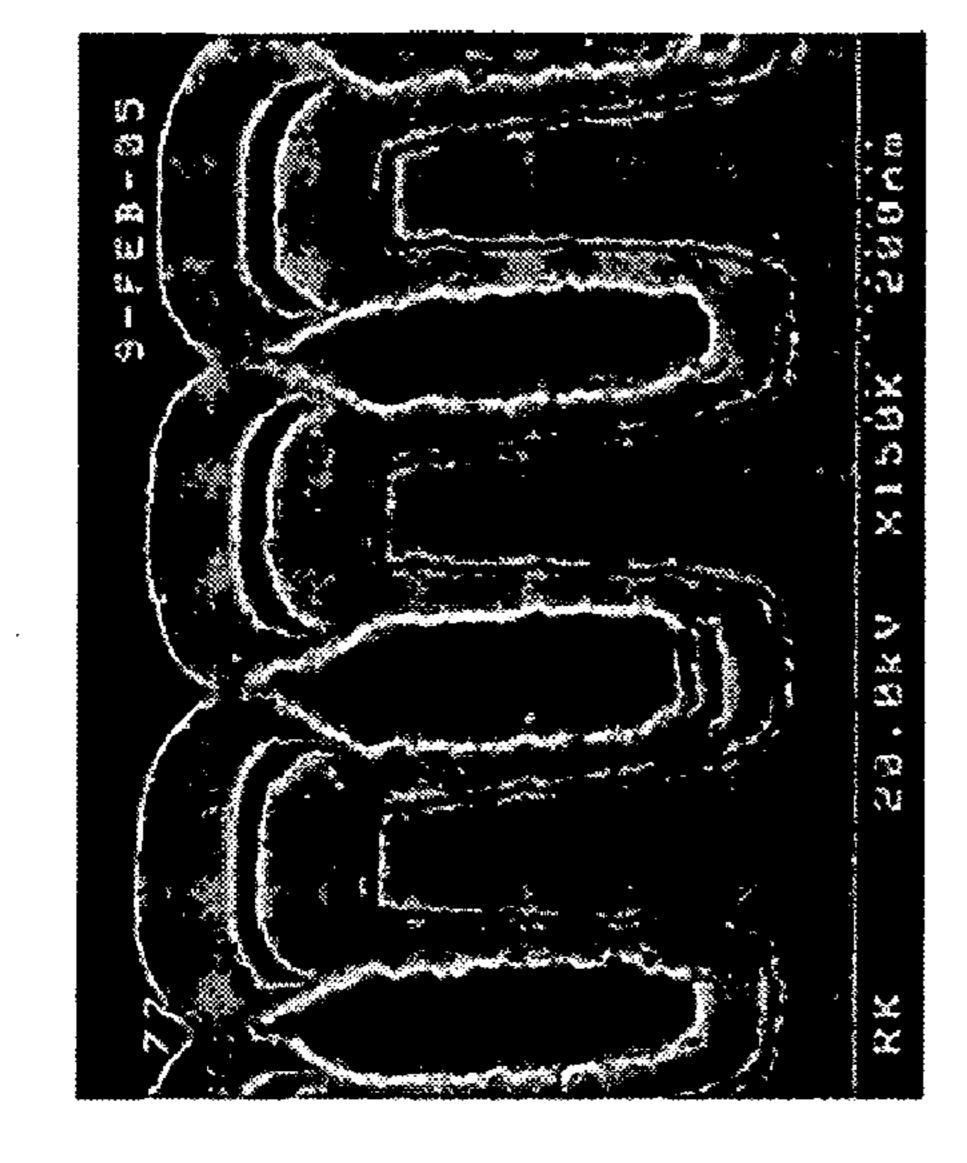

FIGS. 29A-H are cross-sectional electron micrographs showing morphology of CVD SiN films formed under different processing conditions;

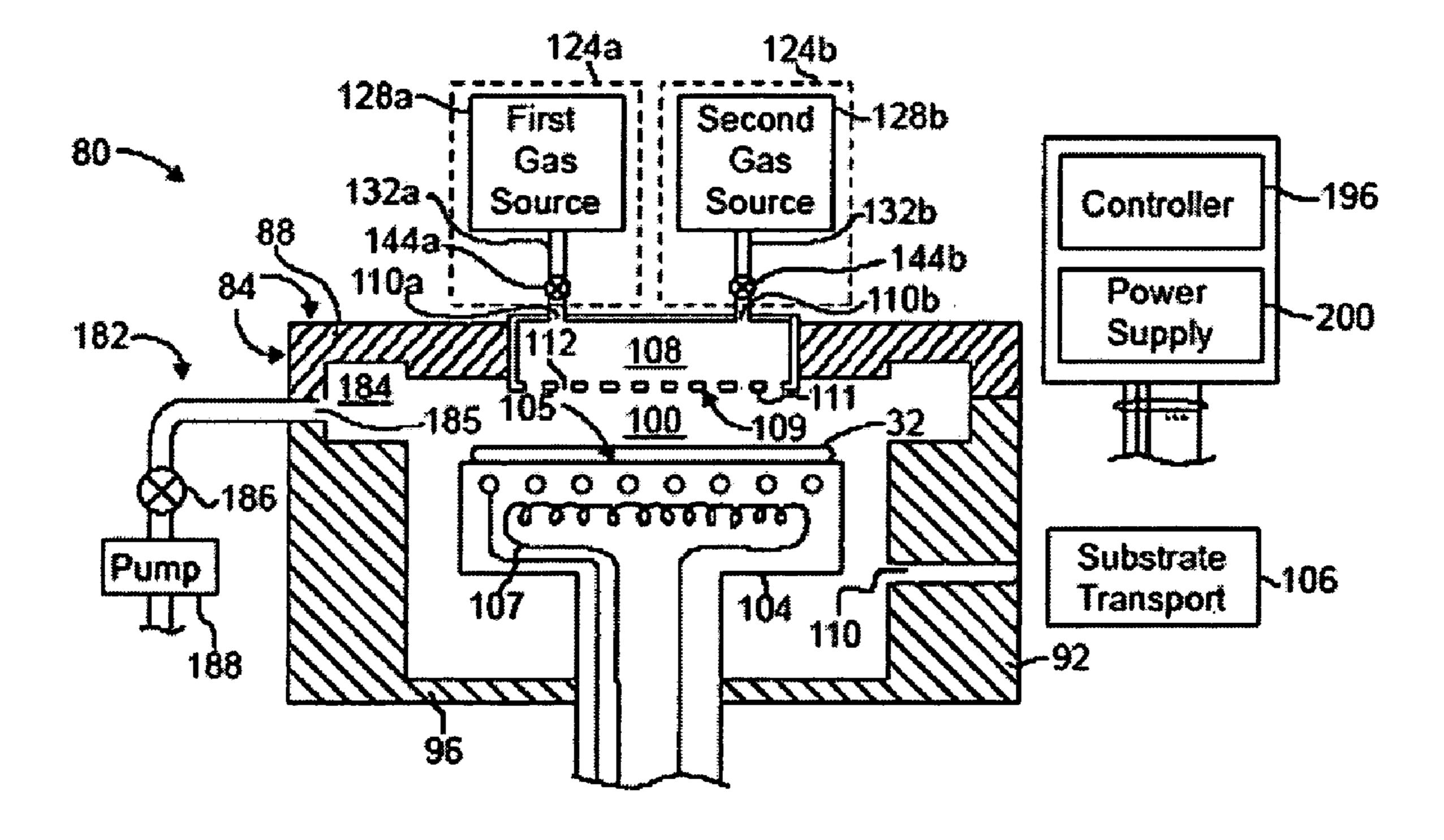

FIG. 30 is a schematic view of an embodiment of a substrate processing chamber that is a PECVD deposition cham- 5 ber;

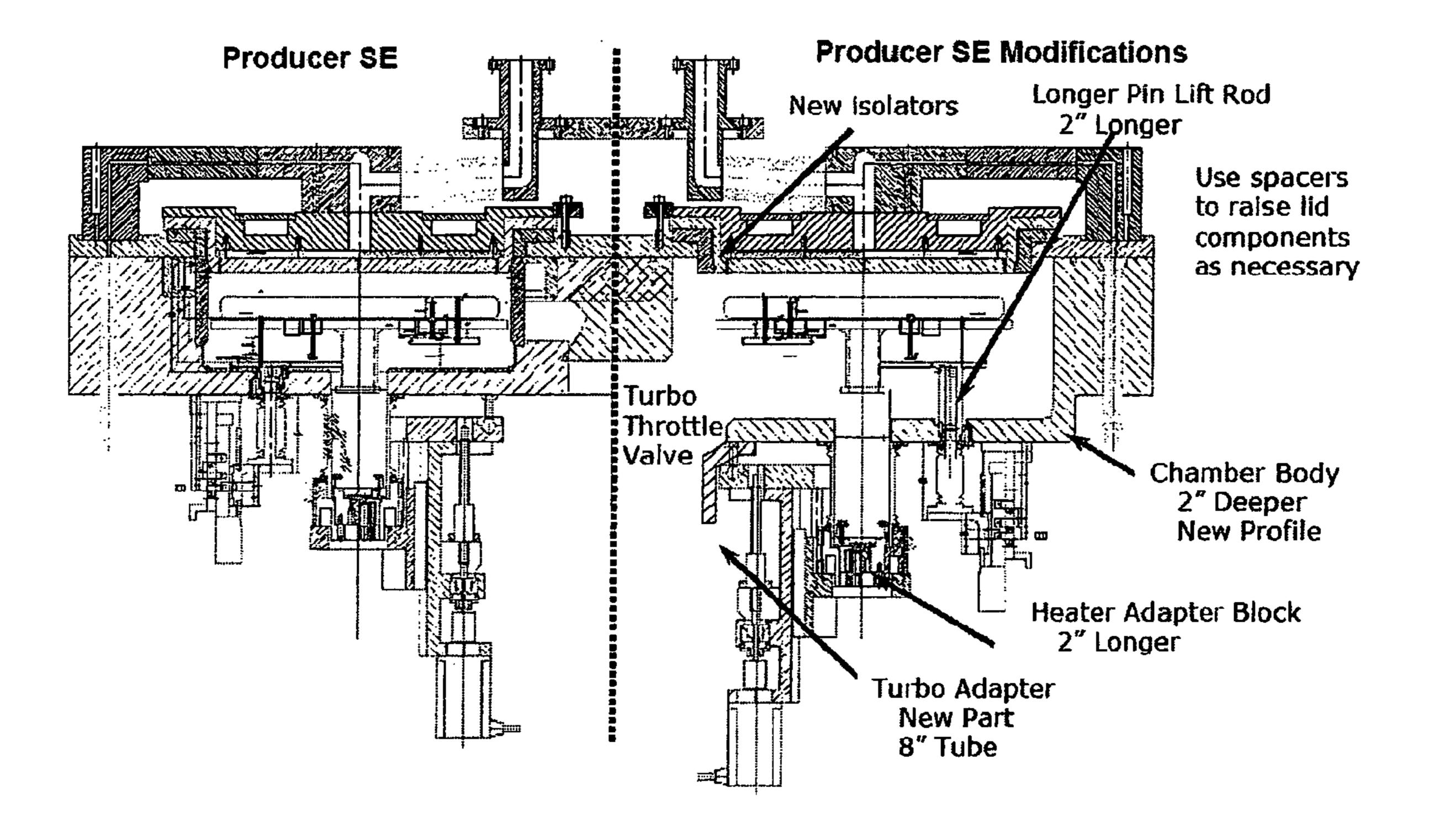

FIG. 31 is a simplified cross-sectional view of a conventional higher pressure processing chamber, and a chamber modified in accordance with an embodiment of the instant invention to operate at lower pressures;

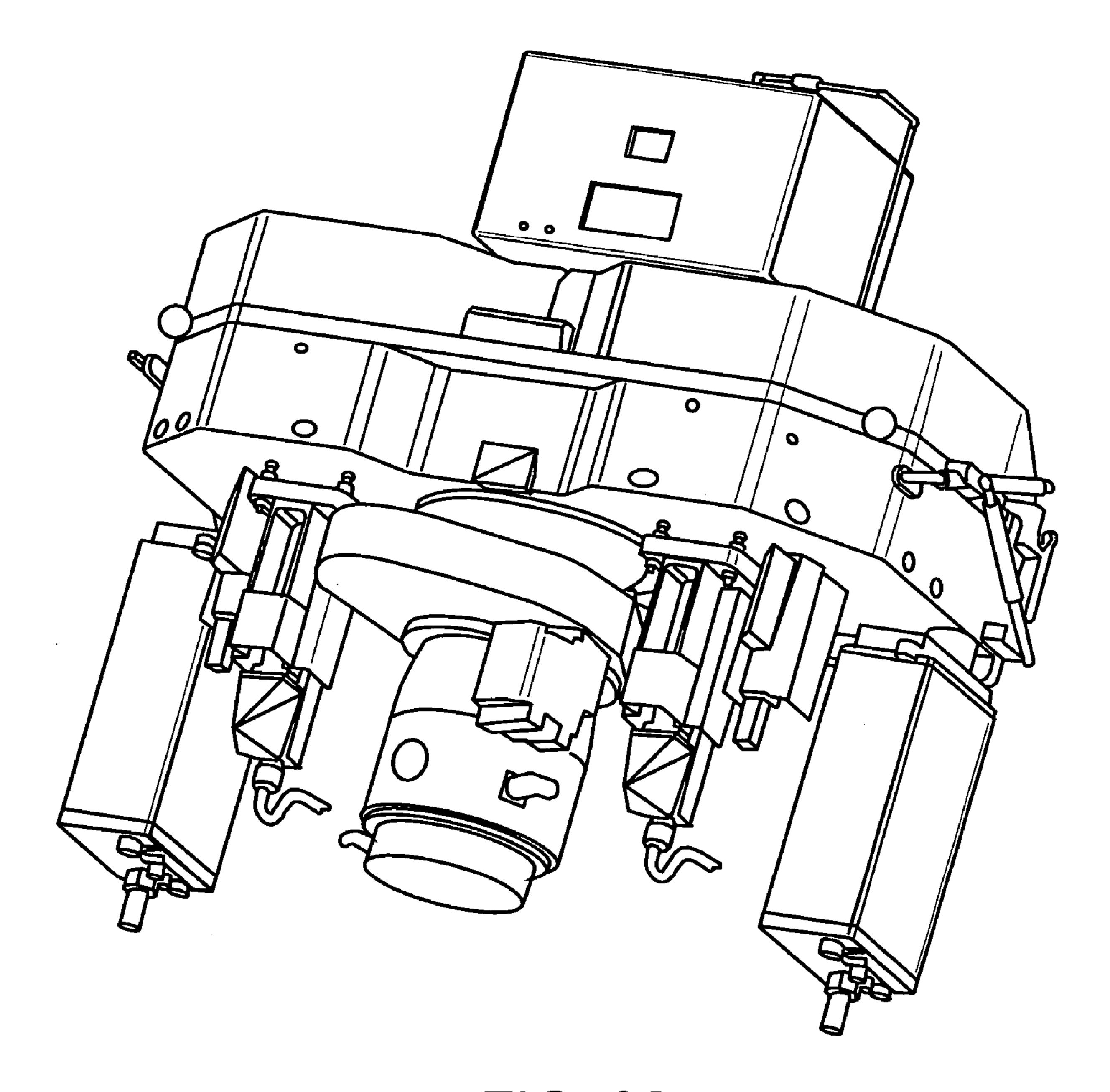

FIG. 32 is a perspective view of the modified chamber shown in cross-sectional in FIG. 31.

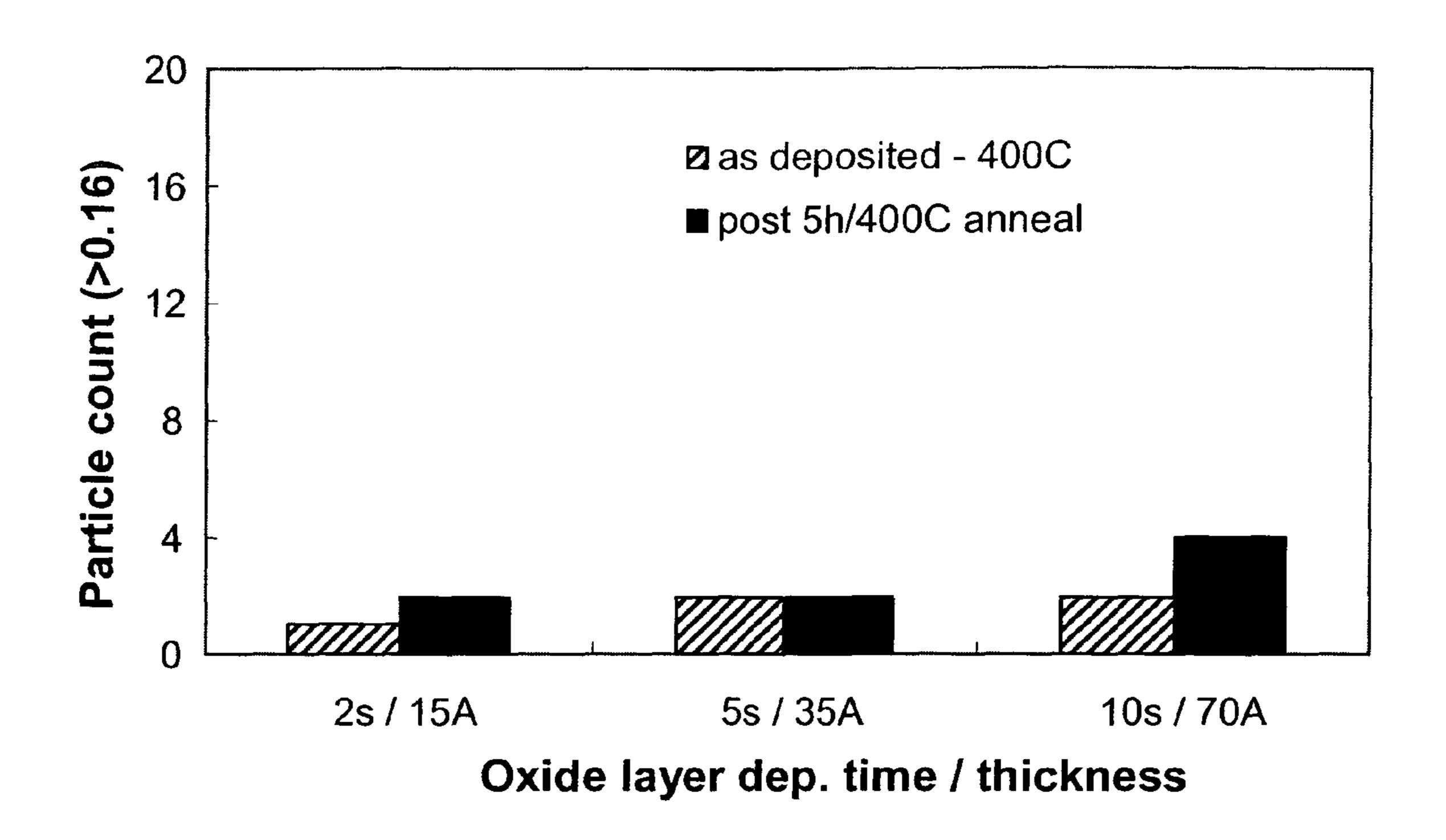

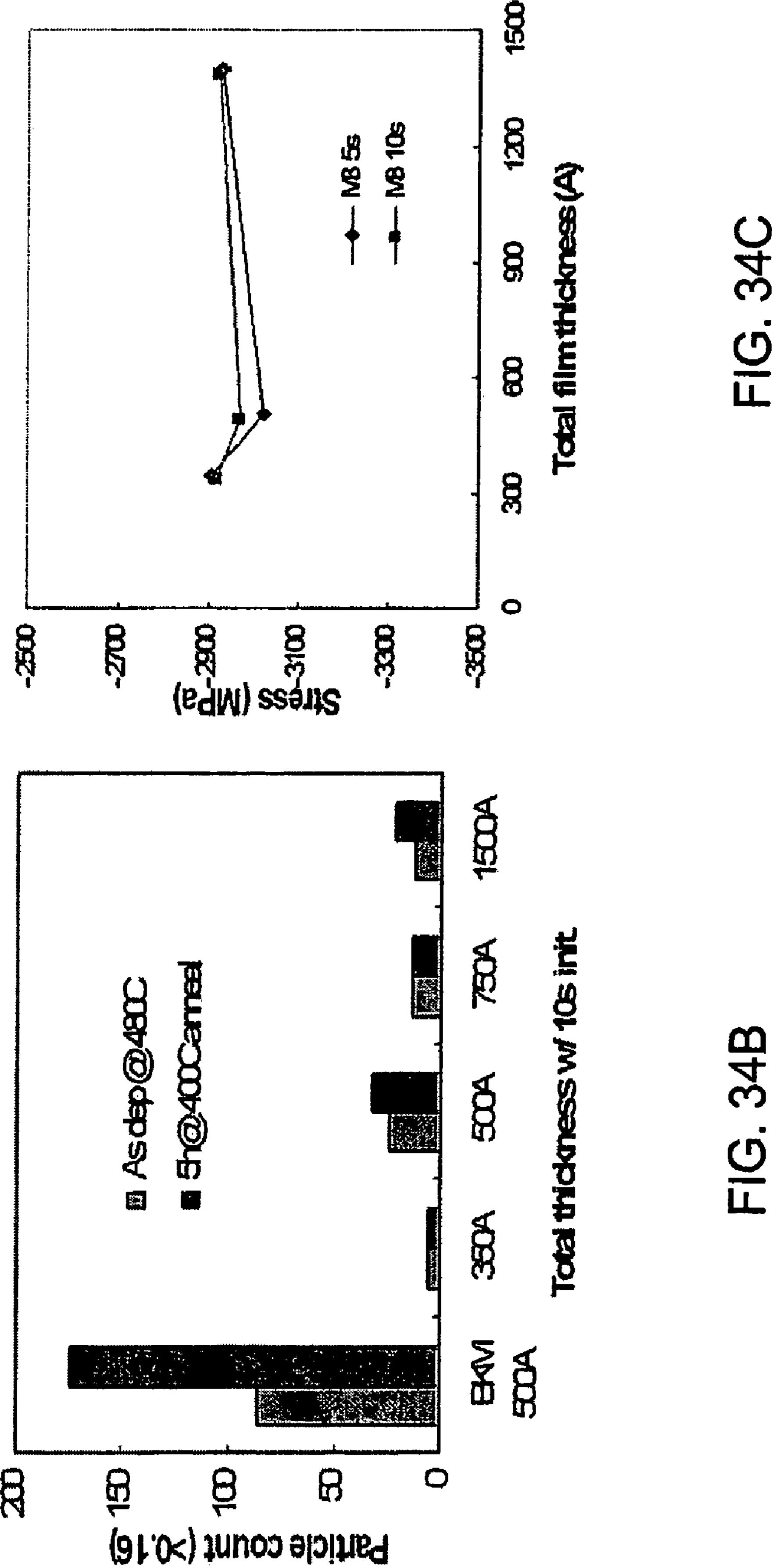

FIG. 33 is a bar graph showing deposited and post annealed particle performance with the addition of an oxide layer.

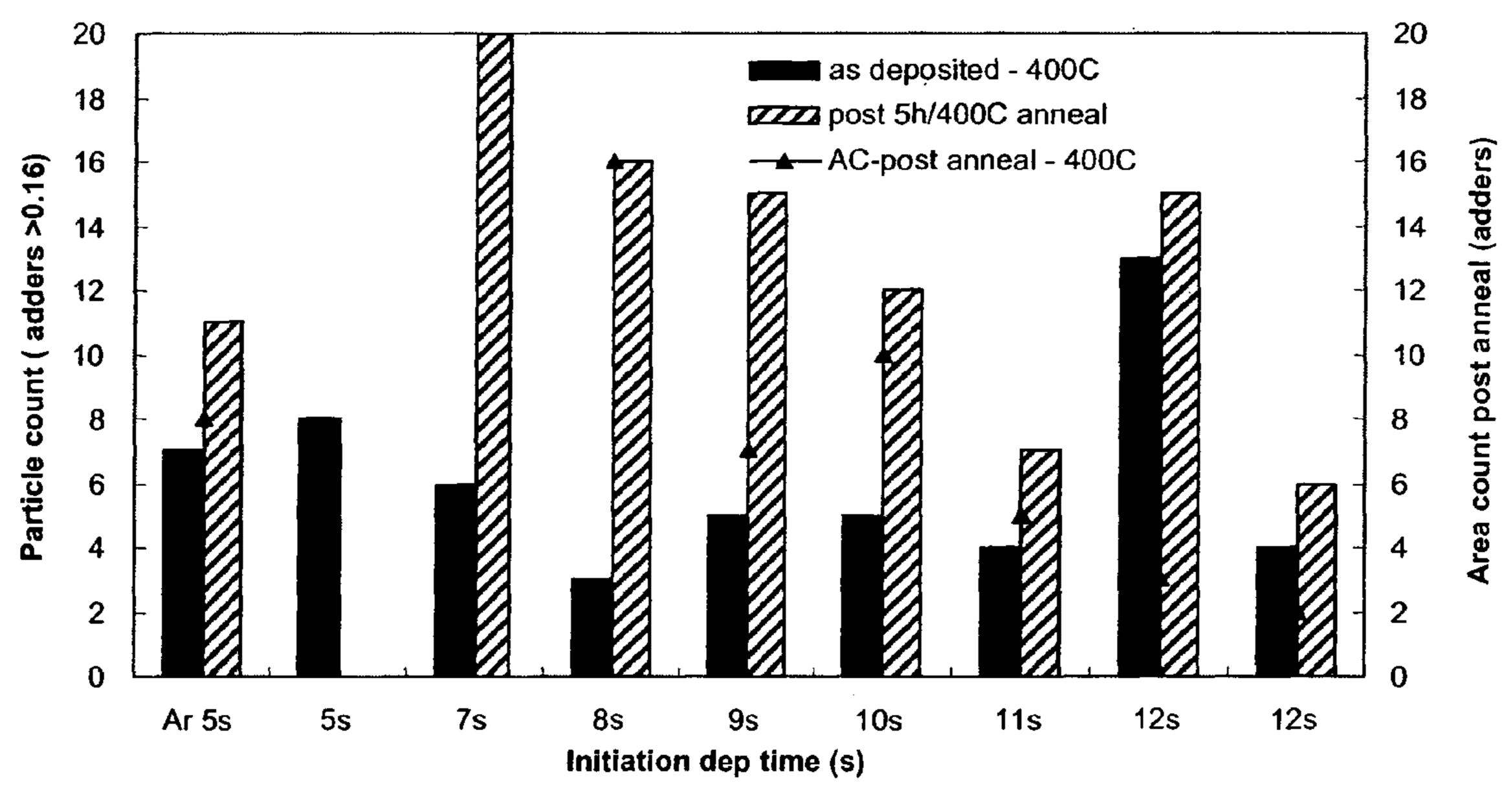

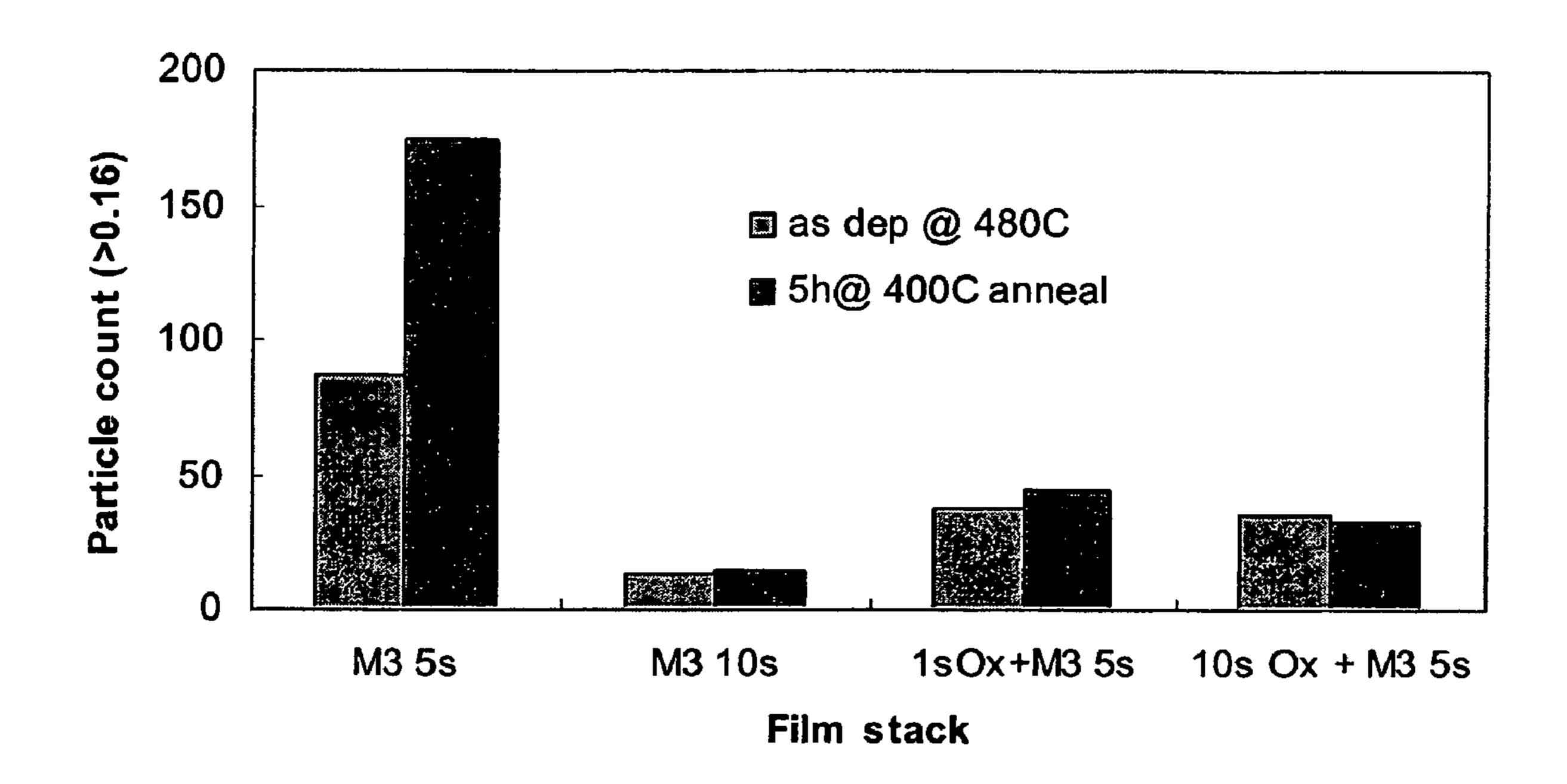

FIGS. 34A-C are graphs showing deposited and post 15 annealed particle performance when an increased initiation layer is used.

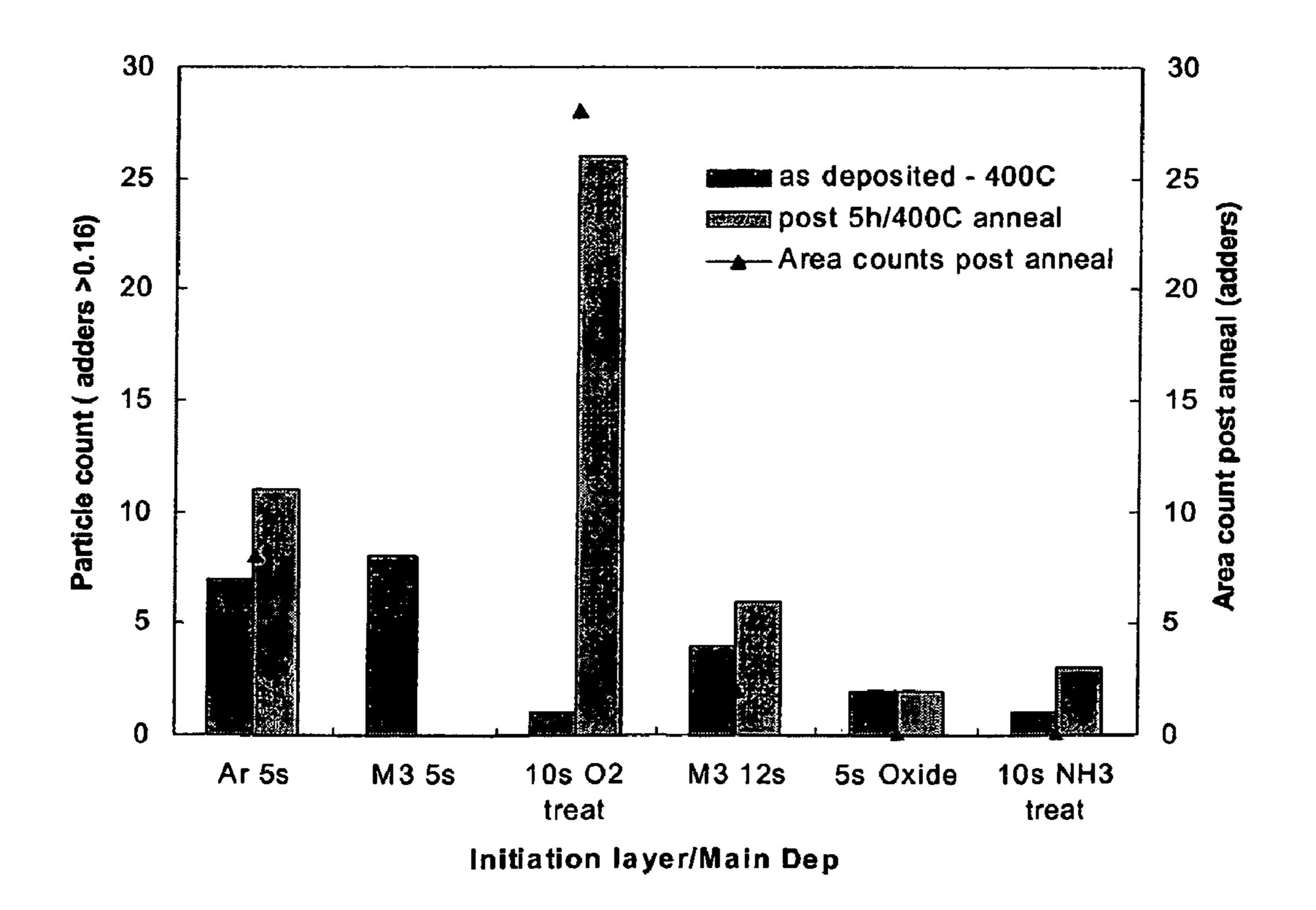

FIG. 35 is a bar graph showing deposited and post annealed particle performance when an oxide layer is used in combination with an increased initiation layer.

FIG. 36 is a bar graph showing deposited and post annealed particle performance when various approaches are used to improve compressive stress reliability.

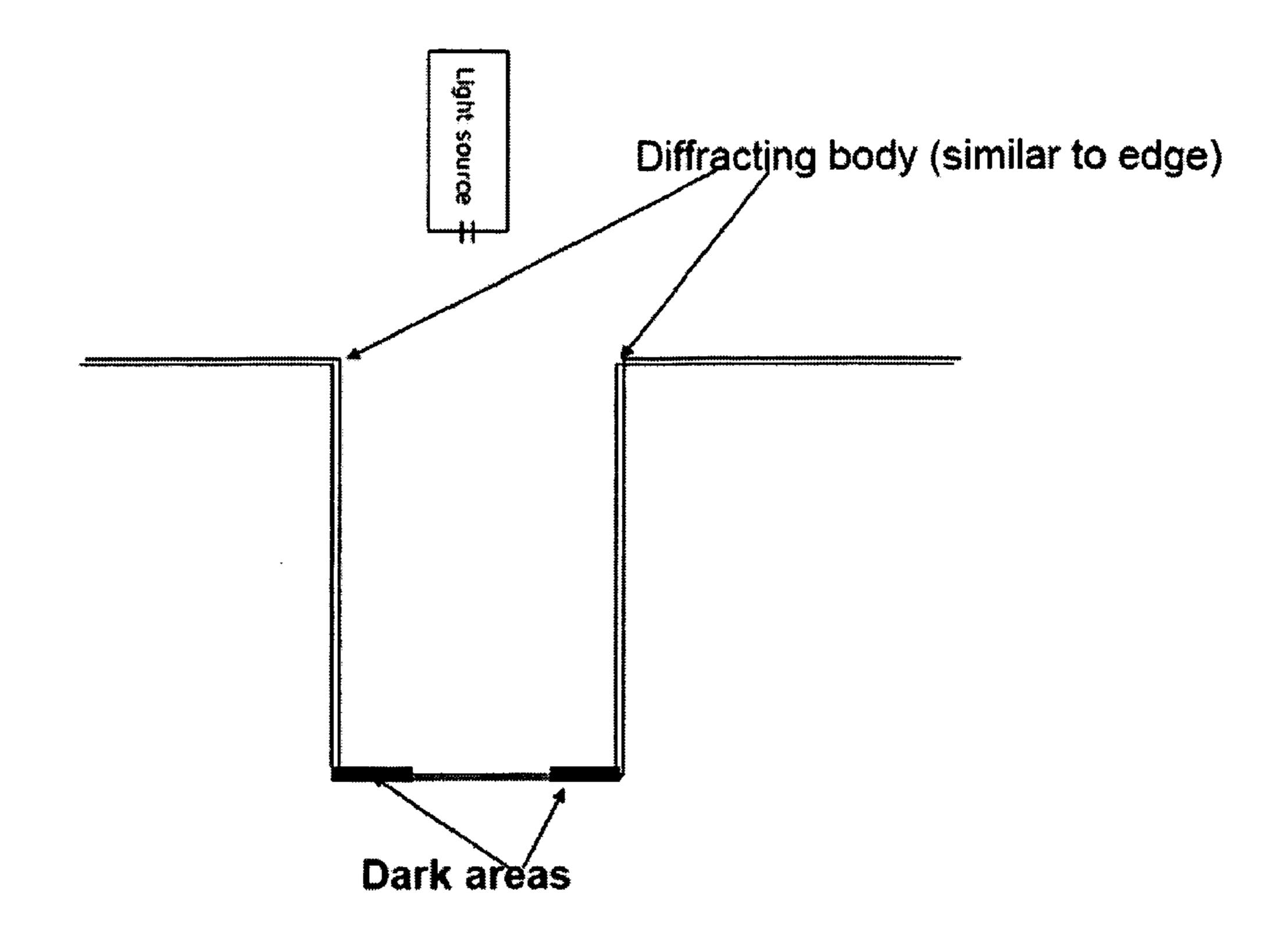

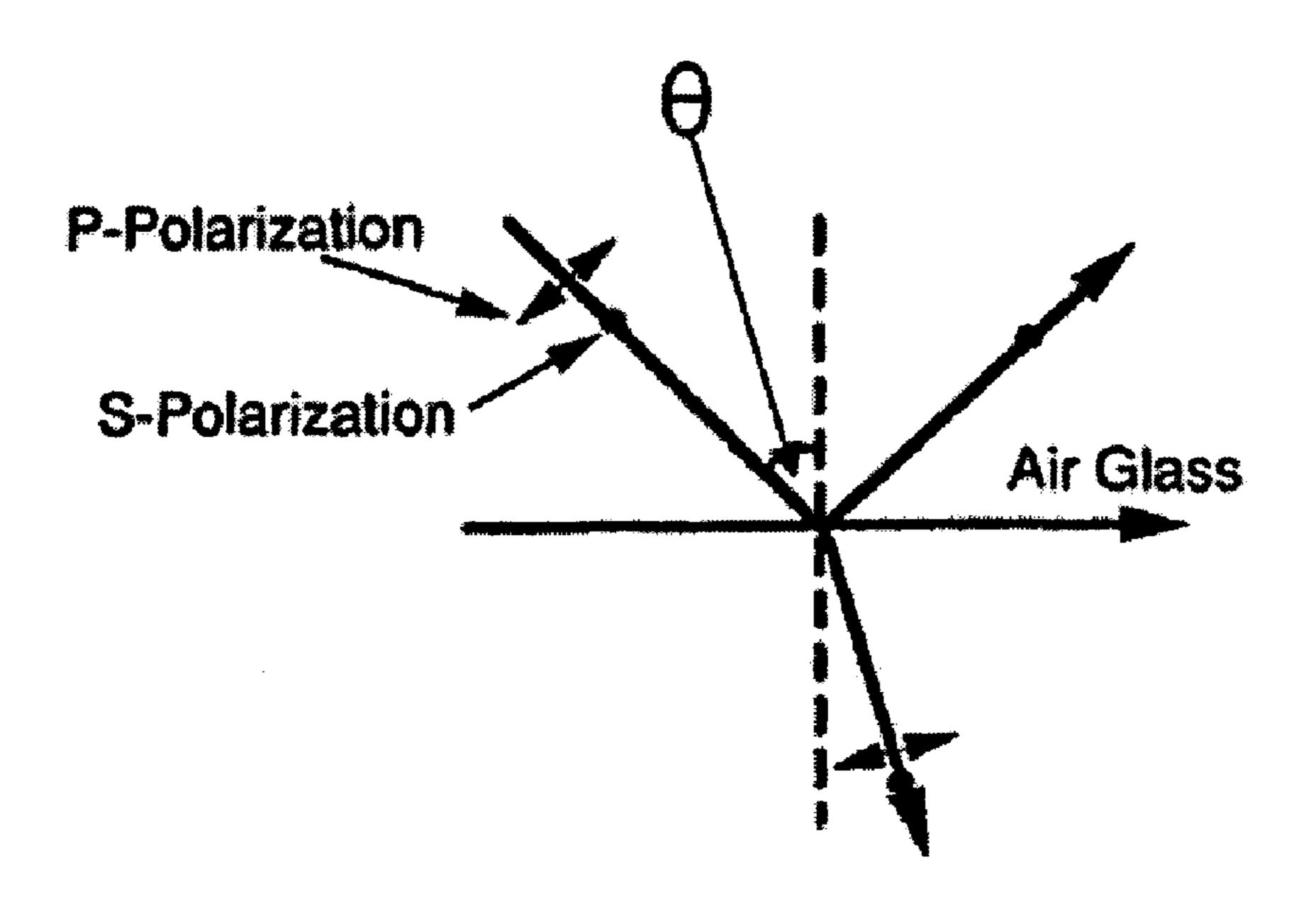

FIG. 37A is a drawing highlighting the Fresnel Principle.

FIG. 37B is a cross sectional micrograph illustrating the 25 Fresnel Principle.

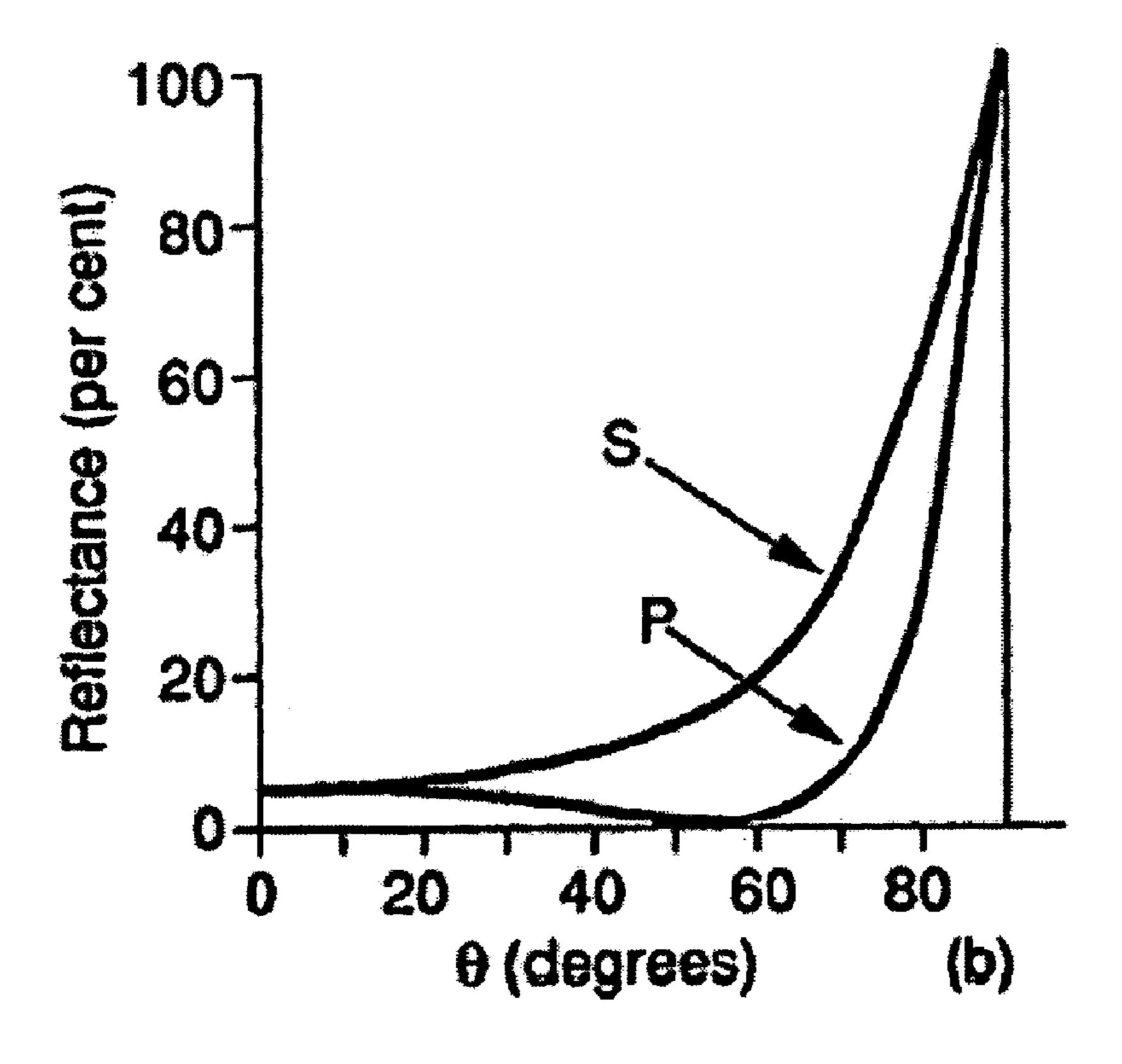

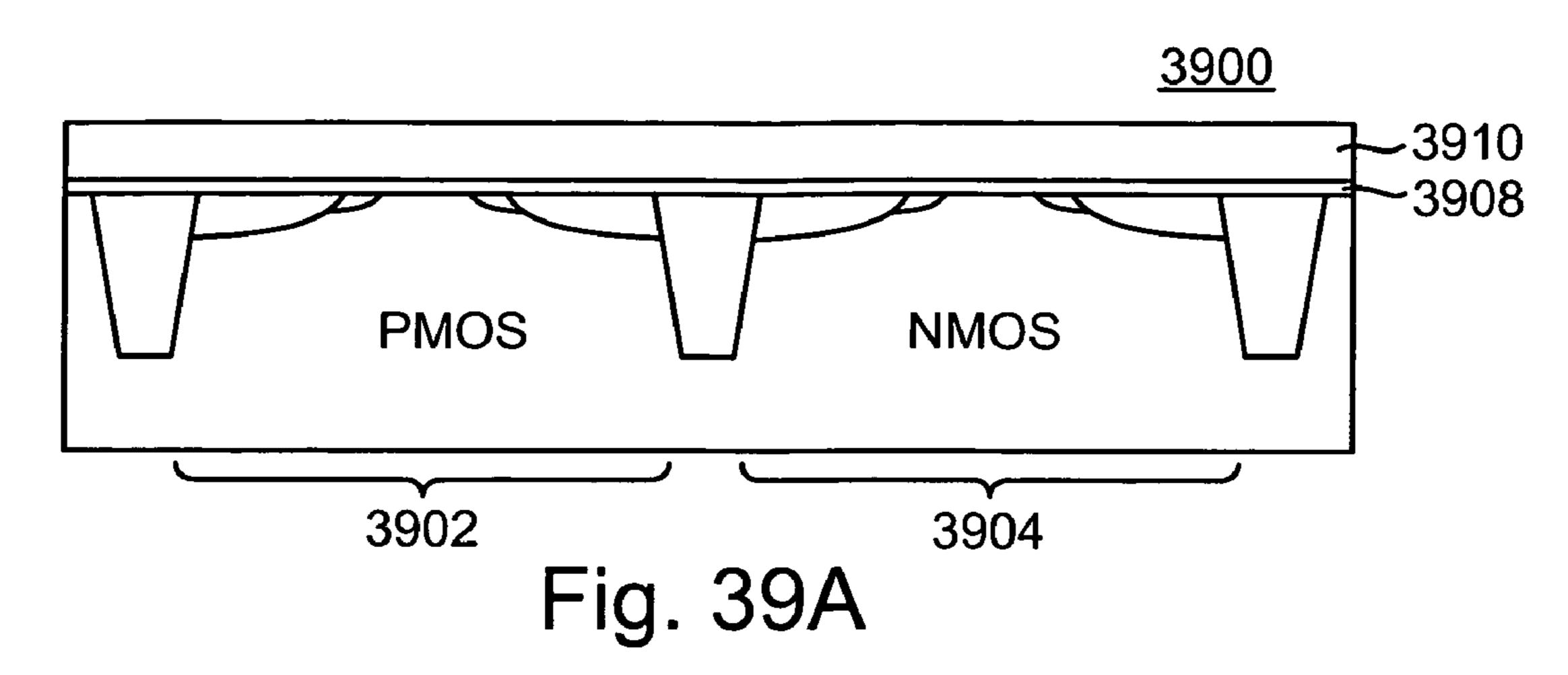

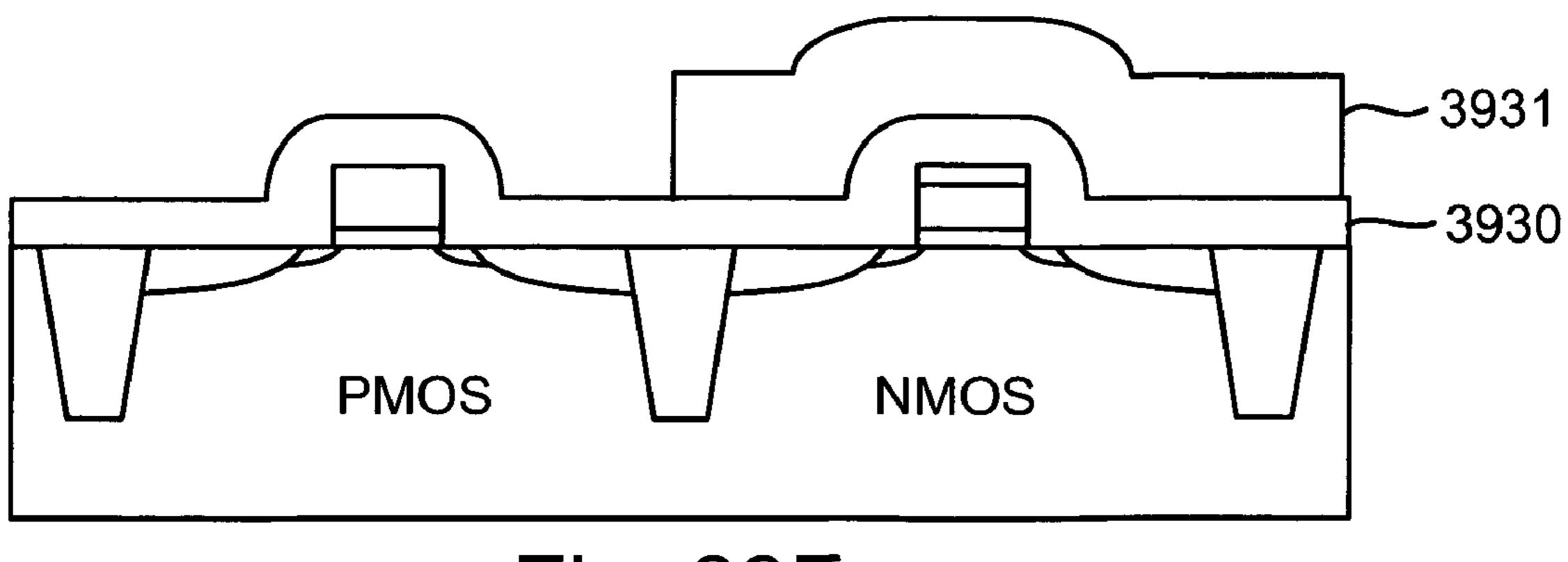

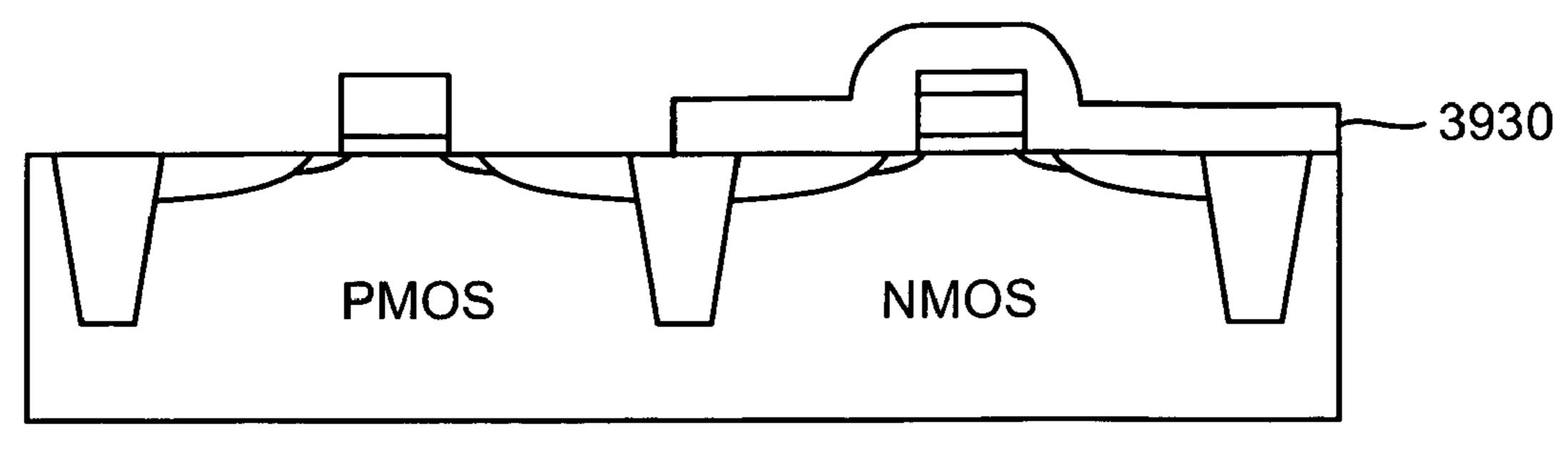

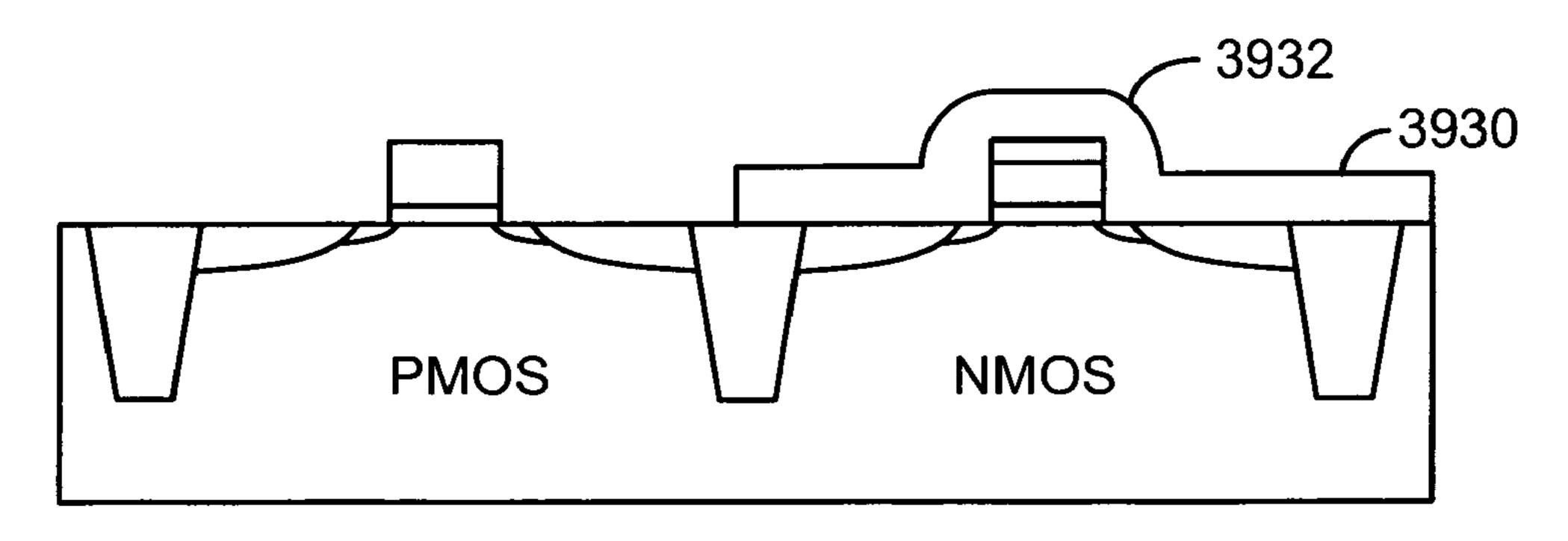

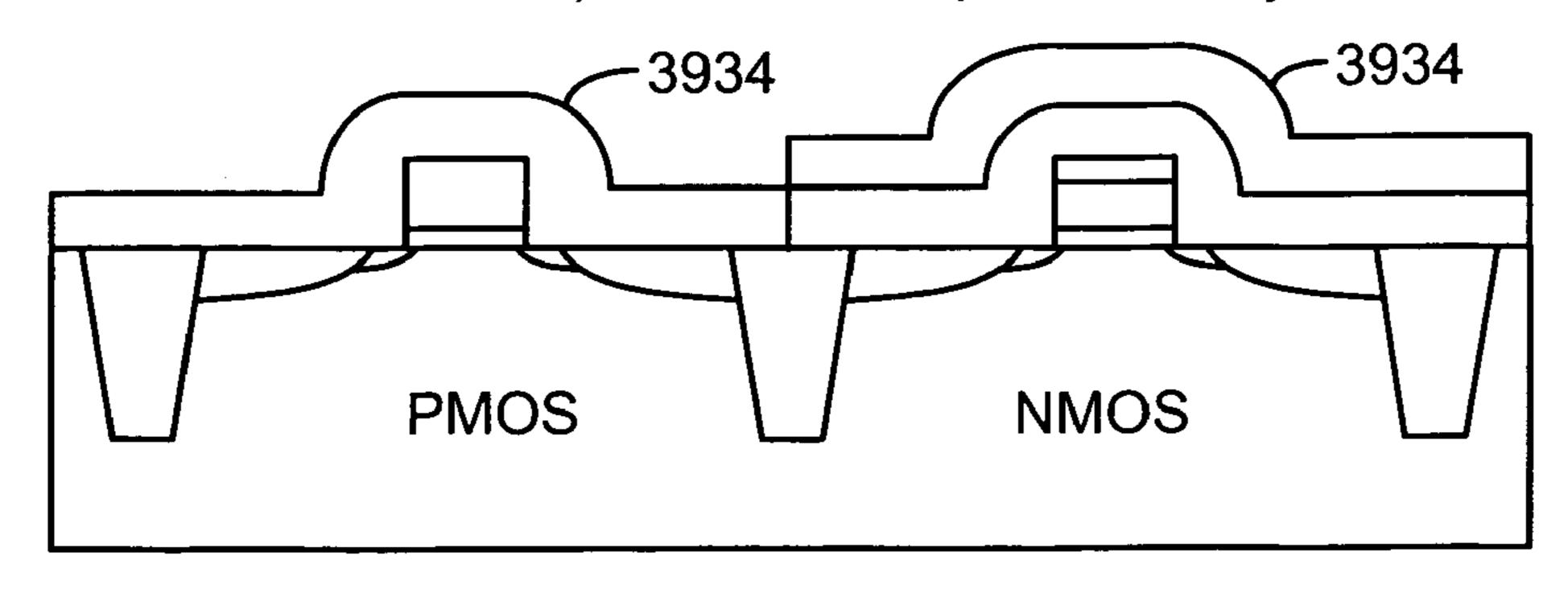

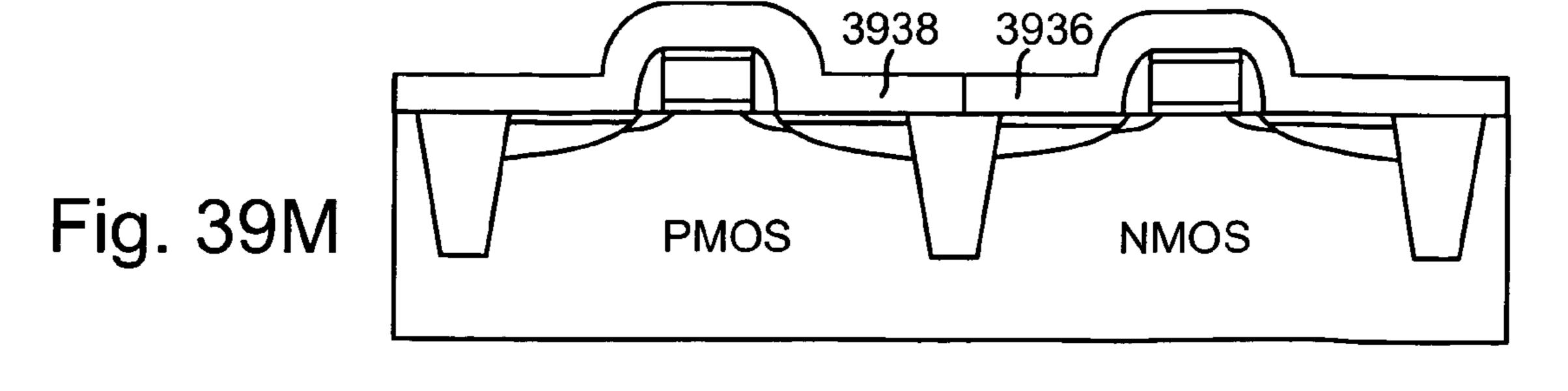

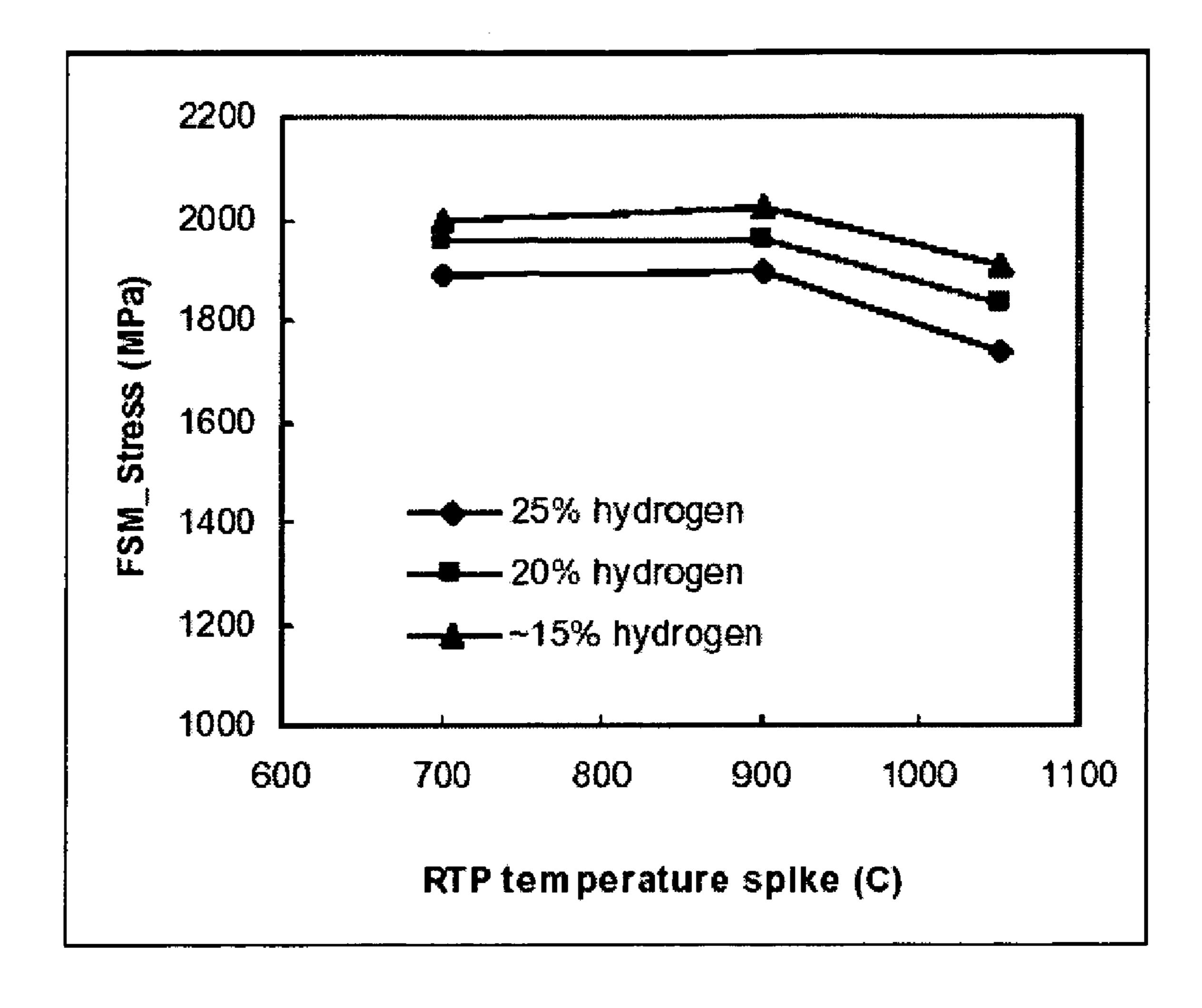

FIG. 38A-B are graphs showing the Brewster angle theory. FIGS. 39A-M illustrate simplified cross-sectional views of an integration process flow employing stress from a plurality of sources to enhance device performance.

FIG. 40 is graph showing the response of stressed nitride films when used with Rapid Thermal Processing versus the composition (Si—H/N—H) and total hydrogen content of the film.

areas for a post deposition NF<sub>3</sub> etch-back process.

FIG. 42 is an electron micrograph showing profile changes and Pattern Loading Effect (PLE) improvement after an NF<sub>3</sub> etch-back process in accordance with an embodiment of the present invention.

#### DETAILED DESCRIPTION OF THE INVENTION

A plurality of techniques may be employed alone or in combination, to enhance conformality and stress in a film 45 formed by chemical vapor deposition (CVD). Embodiments in accordance with the present invention are particularly suited for forming conformal layers exhibiting tensile or compressive stress which impose strain on an underlying silicon lattice.

In one exemplary application, the tensile or compressive stressed silicon nitride material is formed on a substrate or workpiece 32 in the fabrication of a MOSFET structure 392—which is illustrated in the simplified cross-sectional diagram of FIG. 1. The relatively high internal stress of the 55 deposited and treated silicon nitride material 20 induces a strain in a channel region 28 of the transistor 24. The induced strain improves carrier mobility in the channel region 28 which improves transistor performance, such as for example, by increasing the saturation current of the transistor **24**. The 60 silicon nitride material 20 can also have other uses within the MOSFET 24, for example, as an etch stop material. The highly stressed silicon nitride material 20 is also useful in other structures, such as other transistors including without limitation, bipolar junction transistors, capacitors, sensors, 65 and actuators. The substrate or workpiece can be a silicon wafer or can be made from other materials such as germa-

nium, silicon germanium, gallium arsenide and combinations thereof. The substrate or workpiece 32 can also be a dielectric, such as glass, which is used in the fabrication of displays.

The transistor **24** illustrated in FIG. **1** is a negative channel, or n-channel, MOSFET (NMOS) having source and drain regions 36, 40 that are formed by doping the substrate 32 with a Group VA element to form an n-type semiconductor. In the NMOS transistor, the substrate 32 outside of the source and drain regions 36, 40 is typically doped with a Group IIIA 10 element to form a p-type semiconductor. For the NMOS channel regions, the overlying stressed silicon nitride material is fabricated to have a tensile stress.

In another version, the MOSFET transistor **24** comprises a positive channel or p-channel MOSFET (PMOS), (not shown) which has source and drain regions that are formed by doping the substrate with a Group IIIA element to form a p-type semiconductor. In a PMOS transistor, the transistor 24 may comprise a substrate 32 comprising an n-type semiconductor or may have a well region (not shown) comprising an 20 n-type semiconductor formed on a substrate or workpiece 32 comprising a p-type semiconductor. The PMOS channel regions are covered with a compressive stressed silicon nitride.

In the version shown, the transistor **24** comprises a trench 44 to provide isolation between transistors 24 or groups of transistors 24 on the substrate 32, a technique known as shallow trench isolation. The trench **44** is typically formed prior to the source and drain regions 36, 40 by an etch process. A trench side wall liner material (not shown) may be formed in the trench 44 by, for example, a rapid thermal oxidation in an oxide/oxinitride atmosphere, which may also round sharp corners on the trench 44 (and elsewhere). In one version, the trench 44 may be filled with material 46 having a tensile stress, which can also be used to provide a tensile stress to the FIG. 41 is graph showing a higher etch rate on isolated 35 channel region 28. The deposition of the trench material 46 which may include the use of a High Aspect Ratio Process (HARP), which may include using an O<sub>3</sub>/tetraethoxy silane (TEOS) based sub-atmospheric chemical vapor deposition (SACVD) process. Excess trench material 46 may be 40 removed by, for example, chemical mechanical polishing.

The transistor comprises a gate oxide material 48 and a gate electrode 52 on top of the channel region 28 between the source and drain regions 36, 40. In the version shown, the transistor 24 also comprises silicide materials 56 on top of the source and drain regions 36, 40 as well as the gate electrode **52**. The silicide materials **56** are highly conductive compared to the underlying source and drain regions 36, 40 and gate electrode 52, and facilitate the transfer of electric signals to and from the transistor 24 through metal contacts 54. Depend-50 ing on the materials and formation processes used, the silicide materials 56 may also comprise a tensile stress and produce tensile strain in the channel region 28. The transistor shown also comprises spacers 60 and oxide-pad materials 64 which may be located on opposite sidewalls 68 of the gate electrode 52 to keep the silicide materials 56 separated during a silicidation process to form the silicide materials 56. During silicidation, a continuous metal material (not shown) is deposited over the oxide-containing source and drain regions 36, 40 and gate electrode 52, as well as the nitride containing spacers **60**. The metal reacts with the underlying silicon in the source and drain regions 36, 40 and gate electrode 52 to form metalsilicon alloy silicide materials, but are less reactive with the nitride materials in spacers 60. Thus, the spacers 60 allow the overlying, unreacted metal to be etched away while not affecting the metal alloy in silicide materials 56.

The length of the channel region 28 is shorter than the length of the gate oxide material 48. The length of the channel

region 28 measured between the edges of the source region 36 and the drain region 40 may be about 90 nm or less, for example, from about 90 nm to about 10 nm. As the length of channel region 28 gets smaller, implants 72, also known as halos, may be counter-doped into the channel region 28 to prevent charge carriers from uncontrollably hopping from the source region 36 to the drain region 40 and vice versa.

In the version shown in FIG. 1, the silicon nitride material 20 is formed above the silicide materials 56. The silicon nitride material 20 typically acts as a contact-etch stop material as well as providing strain to the channel region 28. The silicon nitride material 20 is capable of being deposited to have a stress values ranging from compressive to tensile stresses. Selection of stress in the silicon nitride material 20 15 selects the type of strain provided to the channel region 28 of the transistor 24.

As just described, film stress and conformality are two key characteristics of a film that is designed to impose strain on an underlying silicon lattice. Incorporated by reference herein 20 for all purposes is U.S. nonprovisional patent application No. 11/055,936, filed Feb. 11, 2005 and entitled "TENSILE AND COMPRESSIVE STRESSED MATERIALS FOR SEMI-CONDUCTORS". This previously-filed patent application describes a number of techniques which may be employed to 25 control stress of a deposited film.

The instant provisional application describes additional techniques for controlling stress and conformality of a film formed by chemical vapor deposition (CVD). It has been discovered that both types of stress, namely tensile or compressive, and the stress value of the deposited silicon nitride stressed material can be set in the deposited material by controlling processing parameters or by treating the deposited material, as described below. The processing parameters are described separately or in particular combinations; however, the invention should not be limited to the exemplary separate or combinations described herein, but may include other separate or combinations of parameters as would be apparent to one of ordinary skill in the art.

The following sections address controlling over compressive film stress, tensile film stress, and film conformality, respectively.

#### I. Compressive Stressed Materials

Deposition process and treatment conditions can be tai- 45 lored to deposit a compressive stressed material on the substrate or to treat a material during or after deposition to increase its compressive stress value. Without being limited by the explanation, it has been discovered that a silicon nitride stressed material having higher compressive stress values can 50 be obtained by increasing the RF bombardment to achieve higher film density by having more Si—N bonds in the deposited material and reducing the density of Si—H and N—H bonds. Higher deposition temperatures and RF power improved the compressive stress levels of the deposited film. 55 In addition, higher compressive stresses levels were obtained in the deposited material at higher kinetic energy levels of plasma species. It is believed that bombardment of energetic plasma species, such as plasma ions and neutrals, generates compressive stresses in the deposited material because film density increases.

The process gas used to deposit compressive stressed silicon nitride includes the silicon-containing and nitrogen-containing gases described below in connection with the formation of tensile stressed materials. Also the general deposition 65 process conditions, such as radio frequency type and power levels, gas flow rates and pressure, substrate temperature and 8

other such process are about the same as those used for the deposition of tensile stressed materials, unless otherwise specified.

To deposit a compressive stressed silicon nitride material, the process gas introduced into the chamber comprises a first component that includes a silicon-containing gas, a second component that includes a nitrogen-containing gas, and a third component containing carbon, boron, or germanium. The silicon-containing compound can be, for example, silane, disilane, trimethylsilyl (TMS), tris(dimethylamino)silane (TDMAS), bis(tertiary-butylamino)silane (BTBAS), dichlorosilane (DCS), and combinations thereof. The carbon-containing compound can be, in addition to the compounds mentioned above, ethylene (C<sub>2</sub>H<sub>2</sub>), propylene (C<sub>3</sub>H<sub>6</sub>), toluene  $(C_7H_8)$ , and combinations thereof. The boron and germanium containing compounds can be dibhorane (B<sub>2</sub>H<sub>6</sub>), boron chlorides  $(B_2C_{14})$ , and germane  $(GeH_4)$ , respectively. For example, a suitable silane flow rate is from about 10 to about 200 sccm. The nitrogen-containing gas can be, for example, ammonia, nitrogen, and combinations thereof. A suitable ammonia flow rate is from about 50 to about 600 sccm. The process gas can also include a diluent gas that is provided in a much larger volume than the reactive gas components. The diluent gas can also serve both as a diluent and at least partially as a reactant nitrogen-containing gas, for example, nitrogen in a flow rate of from about 500 to about 20,000 sccm. Other gases that can be included can be inert gases, such as for example, helium or argon, in a flow rate of from about 100 to about 5,000 sccm. The process gas may also contain additional gases such as an oxygen-containing gas, for example, oxygen, when depositing silicon oxy-nitride materials. Unless otherwise specified, in these processes, the electrode power level is typically maintained at from about 100 to about 400 Watts; electrode spacing is from about 5 mm (200 mils) to about 12 mm (600 mils); process gas pressure is from about 1 Torr to about 4 Torr; and substrate temperature is from about 300 to about 600° C.

It has been discovered that the introduction of  $H_2$  gas into the deposition chemistry may substantially increase compressive stress in the resulting films that are formed. Table I below lists three separate conditions for deposition of silicon nitride films.

TABLE I

| FILM | # SiH <sub>4</sub> (secm) | NH <sub>3</sub> (sccm) | $N_2(L)$ | Ar (L) | $H_2(L)$ |

|------|---------------------------|------------------------|----------|--------|----------|

| 1 2  | 60<br>60                  | 30<br>30               | 1<br>1   | 3<br>3 | 0<br>1   |

| 3    | 60                        | 30                     | 0        | 3      | 1        |

FIG. 2 plots film stress and refractive index for SiN films deposited under the three separate deposition conditions listed above in Table I. FIG. 2 shows the effect of adding H<sub>2</sub> upon the compressive stress exhibited by the resulting film. FIG. 2 shows that the highest compressive stress is achieved when the SiH<sub>4</sub>/NH<sub>3</sub> ratio is optimized for given H<sub>2</sub> and Ar flows, with an N<sub>2</sub>/Ar/H<sub>2</sub> ratio of 0/3/1.

FIG. 3 plots FT-IR absorption spectra for silicon nitride film #'s 1 and 3 listed above in Table I. The FT-IR spectrum for CVD SiN film #3 may fairly be contrasted with that of CVD SiN film #1. The spectra of FIG. 2 indicate that the nitride film #3 deposited in the presence of hydrogen gas, exhibits an increase in intensity at about wavenumber 3330 cm<sup>-1</sup>. This region of the spectrum corresponds to N—H deformation characteristic of tensile stress, indicating an increase in compressive stress.

Within given relative ratios of process gases, other parameters can be varied to further enhance compressive stress. For example, SiN films were deposited by CVD at the 0/3/1 N<sub>2</sub>/Ar/H<sub>2</sub> flow rate ratio just described, under different flow rates of SiH<sub>4</sub> and NH<sub>3</sub>. These experiments revealed a center point of maximum compressive stress (G~-2.8 GPa) with a SiH<sub>4</sub> flow rate of 60 sccm, and a NH<sub>3</sub> flow rate of 150 sccm.

FIGS. 4A-D indicate that the level of compressive stress in the deposited film can be further enhanced to above about –2.8 GPa by varying other process parameters. For example, 10 FIG. 4A plots stress and refractive index for CVD SiN films deposited at three different SiH<sub>4</sub> flow rates. FIG. 4A shows that SiH<sub>4</sub> flow rate may be optimized to enhance compressive stress.

FIG. 4B plots stress and refractive index for CVD SiN films 15 deposited at three different wafer-to-faceplate spacing distances. FIG. 4B also shows that this spacing difference may be optimized to enhance compressive stress.

FIG. 4C plots stress and refractive index for CVD SiN films deposited at three different H<sub>2</sub> flow rates. FIG. 4C shows that 20 the H<sub>2</sub> flow rate parameter may be optimized to enhance compressive stress.

FIG. 4D plots stress and refractive index for CVD SiN films deposited at three different RF powers. FIG. 4D shows that a maximum compressive stress may be achieved by controlling this process parameter.

FIGS. **5**A and **5**B show that variation of a number of process parameters in combination, may allow for a CVD SiN film to exhibit a compressive stress approaching –3.0 GPa. Specifically, FIG. **5**A plots stress and refractive index of SiN 30 films deposited with and without hydrogen gas, at three different temperatures. FIG. **5**A shows that the film deposited at 480° C. with hydrogen gas, exhibited a compressive film stress approaching –3 GPa. **5**B plots stress and refractive index for SiN film deposited with H<sub>2</sub> and Ar at 480° C, with a 35 high frequency power of either 75W or 100W. FIG. **5**B shows that the film deposited with a low frequency of 75W achieved a compressive stress of –3 GPa. For this combination of gases/pressure/spacing, the optimum power of 75W resulted in a film having the highest compressive stress.

As just described, deposition of silicon nitride in the presence of hydrogen gas can produce a desirable enhancement in the compressive stress exhibited by the resulting SiN film. However, it is well known that hydrogen gas can easily diffuse through dielectric materials. Moreover, the penetration of such hydrogen into semiconducting regions can degrade reliability of the device, especially at the transistor level. This phenomenon is even more pronounced when high stress films are used as etch stop layers.

It has also been observed that hydrogen may accumulate at the nitride/device (NiSix) interface, and this accumulated hydrogen can also create physical defects, such as blistering and delamination during subsequent processing steps. An analysis of the residue at the delamination site revealed a presence of Zn and Na, typical metal contaminants. The probability of such physical defects increases with the level of compressive stress, and is more pronounced when the nitride film is deposited at a lower temperature.

In accordance with various embodiments of the present invention, three approaches may be utilized alone or in combination, to eliminate the occurrence of defects and thus improve the device reliability when high compressive stress nitride films are formed by deposition in the presence of hydrogen gas. In accordance with one embodiment, defects may be reduced by pre-deposition plasma treatment of the 65 surface that is to receive the high compressive stress silicon nitride. In accordance with another embodiment, defects may

10

be reduced by forming a buffer layer over the surface that this to receive the high compressive stress nitride layer, prior to deposition of that nitride layer. In accordance with still a further embodiment of the present invention, defects may be reduced by forming a SiN layer in the absence of hydrogen, prior to deposition of an overlying high stress SiN film in the presence of hydrogen gas. Each of these approaches is now discussed in turn below.

In accordance with the first embodiment just mentioned, a plasma pre-treatment step prior to deposition of silicon nitride in the presence of hydrogen can be employed. This pre-deposition plasma treatment cleans the wafer surface, removing contamination that could render the surface susceptible to penetration by hydrogen, such as residual silane or metallic contaminants such as Zn and Na. The plasma utilized for this pre-treatment step may be formed from a number of different ambients, including but not limited to N<sub>2</sub>O, O<sub>2</sub> and NH<sub>3</sub>-containing plasmas which have been successfully used to reduce the number of defects of the nitride film post anneal. The pre treatment may be applied in the same or in a different processing chamber in which the SiN is deposited. The plasma treatment may conclude prior to the subsequent deposition step, or may be continuous and extend into the SiN deposition step. The specific parameters of this plasma pretreatment, such as duration, power, temperature, and ambient, may vary according to the particular application in order to achieve the desired effects.

In accordance with the second embodiment of the present invention mentioned above, defects can be reduced and reliability improved, by forming a buffer layer on the surface that is to receive the high compressive stress nitride. Such a buffer layer, typically comprising oxide, will then be located at the nitride/NiSix interface. This oxide serves as a buffer layer, blocking hydrogen diffusing through the deposited SiN film. Atomic hydrogen reaching the oxide buffer will attempt to combine with other hydrogen atoms to form molecular hydrogen, but will be unsuccessful in doing so owing to the strength of the Si—N, Si—H, and N—H bonds. Specifically, hydrogen diffuses by hopping from one Si—H or N—H bond 40 to another. To migrate out of the nitride layer into the oxide layer, and Si—O bond needs to break and an Si—N bond will form. This reaction id not energetically favorable, so the hydrogen will remain trapped in the nitride layer. In this manner, the oxide buffer layer acts as a wall, preventing gas accumulation at the Si/SiN interface, and decreasing blistering and post anneal delamination.

FIG. 33 compares contamination exhibited by high compressive stress silicon nitride layers deposited over oxide buffer layers of three different thicknesses. FIG. 33 shows that even the use of a very thin oxide buffer layers results in a post-anneal area count of about 2 adders (defects per wafer) or less.

In accordance with the third embodiment of the present invention mentioned above, defect count may be reduced, and reliability enhanced, by forming an initiation layer prior to introduction of the hydrogen gas utilized to form the high compressive stress nitride layer. As described above, the desired high compressive stress characteristic of the nitride layer derives from the presence of hydrogen gas during deposition. In accordance with this third embodiment, the penetration of this hydrogen gas may be reduced by performing the initial stages of the deposition in the absence of hydrogen, such that the resulting silicon nitride initiation layer does not exhibit high compressive stress. Once the initiation layer is formed, hydrogen gas is introduced into the deposition gas mixture to imbue the overlying silicon nitride with the desired level of compressive stress.

The role of the initiation layer is to protect the devices from the potential surges of electrons occurring in the plasma during the deposition of the high compressive stress. Proper adjustment of the initiation layer thickness can also allow it to serve as a barrier for hydrogen diffusion. The initiation layer essentially forms a barrier which aids in eliminating hydrogen accumulation.

FIG. 34A shows the number of adders observed by a high compressive stress silicon nitride layer is formed at 400° C. and annealed for 5 hours at 400° C., over initiation layers of 10 different thicknesses. FIG. 34A shows that use of a thicker initiation layer improves particle performance post-anneal. FIG. 34A also shows that the post-anneal area count decreases to less than about 3 adders only for initiation layer thicknesses larger than about 90 Å (deposited for 12 sec), as 15 compared with initiation layers having a thickness of about 35 Å (deposited for 5 sec).

FIG. 34B shows particle performance of high compressive stress films of varying thicknesses formed at 480° C., over an initiation layer of the same thickness (deposited for 10 sec- 20 onds). FIG. 34B shows that deposition of an initiation layer for 10 seconds improved particle performance for films up to at least 1500 Å in thickness.

FIG. 34C plots film stress versus film thickness for high compressive stress films including an initiation layer deposited for 5 seconds or 10 seconds. FIG. 34C reveals that increasing the initiation from 5 seconds to 10 seconds does not significantly change the stress for film having a thickness of greater than about 350 Å.

Though the three aforementioned approaches for increasing compressive stress reliability have been explained separately, they may also be used in various combinations with one another. For example, FIG. **35** plots particle count for four different high compressive stress silicon nitride film stacks deposited at 480° C. and then annealed for 5 hours at 400° C. 35 The first and second film stacks include initiation layers deposited for 5 and 10 seconds, respectively. The third and fourth films include initiation layers formed over oxide layers deposited for the times indicated.

FIG. 35 shows that use of the thicker initiation layer 40 resulted in good particle performance in the "as deposited" film. FIG. 35 shows that film stacks utilizing an oxide buffer layer (having a thickness of 30-50 Å) under the initiation layer, also exhibited improved particle performance.

FIG. 35 plots particle count and area count for high compressive stress silicon nitride layers formed under a variety of different conditions. FIG. 35 shows that pre-deposition plasma treatment with ammonia (NH3) is the most efficient technique for improving resistance to blistering. The use of an oxide buffer layers and initiation layers also showed good 50 results.

The three embodiments of the present invention just described, can be employed to solve integration-related issues with other dielectric films such as low-k dielectrics and high tensile stress silicon nitride using hydrogen or deuterium 55 in the deposition. In accordance with still other embodiments of the present invention, Deuterium can also be utilized instead of hydrogen during deposition, in order to form silicon nitride films with compressive stress greater than 3 GPa.

Post Deposition NF<sub>3</sub> Etch-back Process

As described above, silicon nitride dielectric films may be used as a barrier or etch stop layer for various applications.

The film thickness non-uniformity across the wafer (e.g., bottom vs. top vs. sidewall thickness) can negatively impact the drive current improvement from one device to another. 65 tion.

PECVD dielectric films may suffer from a high deposition rate in isolated areas as well as at the poly-gate upper corner process.

12

(e.g., bread-loafing). Modulating process parameters may not significantly improve step coverage or pattern loading.

In accordance with one embodiment of the present invention, an NF<sub>3</sub> etch-back process modulates a PECVD nitride step coverage and pattern loading. Diluted NF<sub>3</sub> plasma can be used to etch back the nitride film after deposition to modulate the step coverage profile. This etch-back process results in a low etch rate and desired etch uniformity. The etch-back profile may be similar to that of a PECVD deposition profile. In one embodiment, the NF<sub>3</sub> etch-back process is performed in the same chamber as the deposition process and can be run at the end of the deposition. Alternatively, the etch-back process can be run in a deposition/etch sequence. NF<sub>3</sub> process parameters may be adjusted so that the etch profile can be modulated to match the deposition profile.

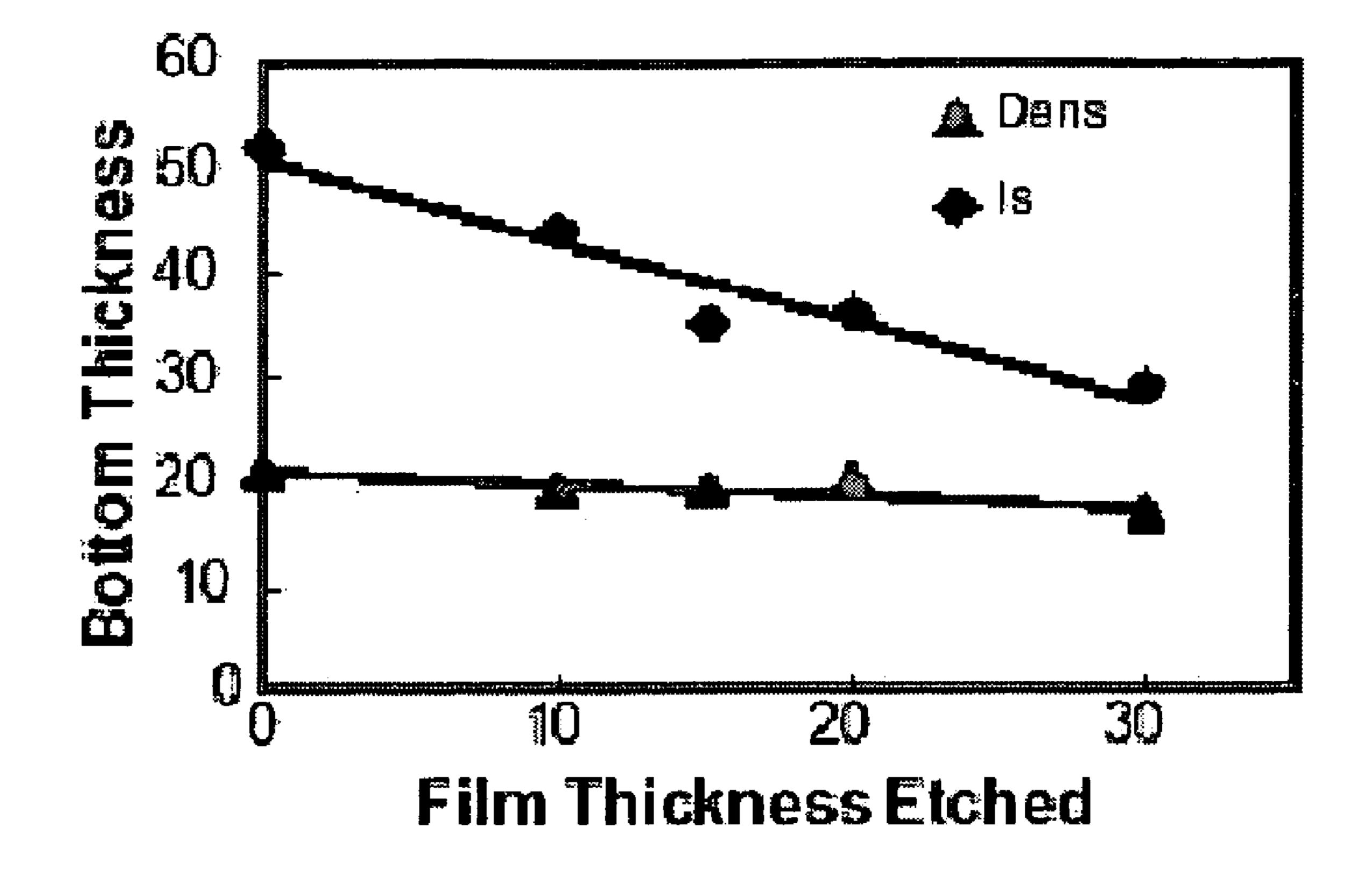

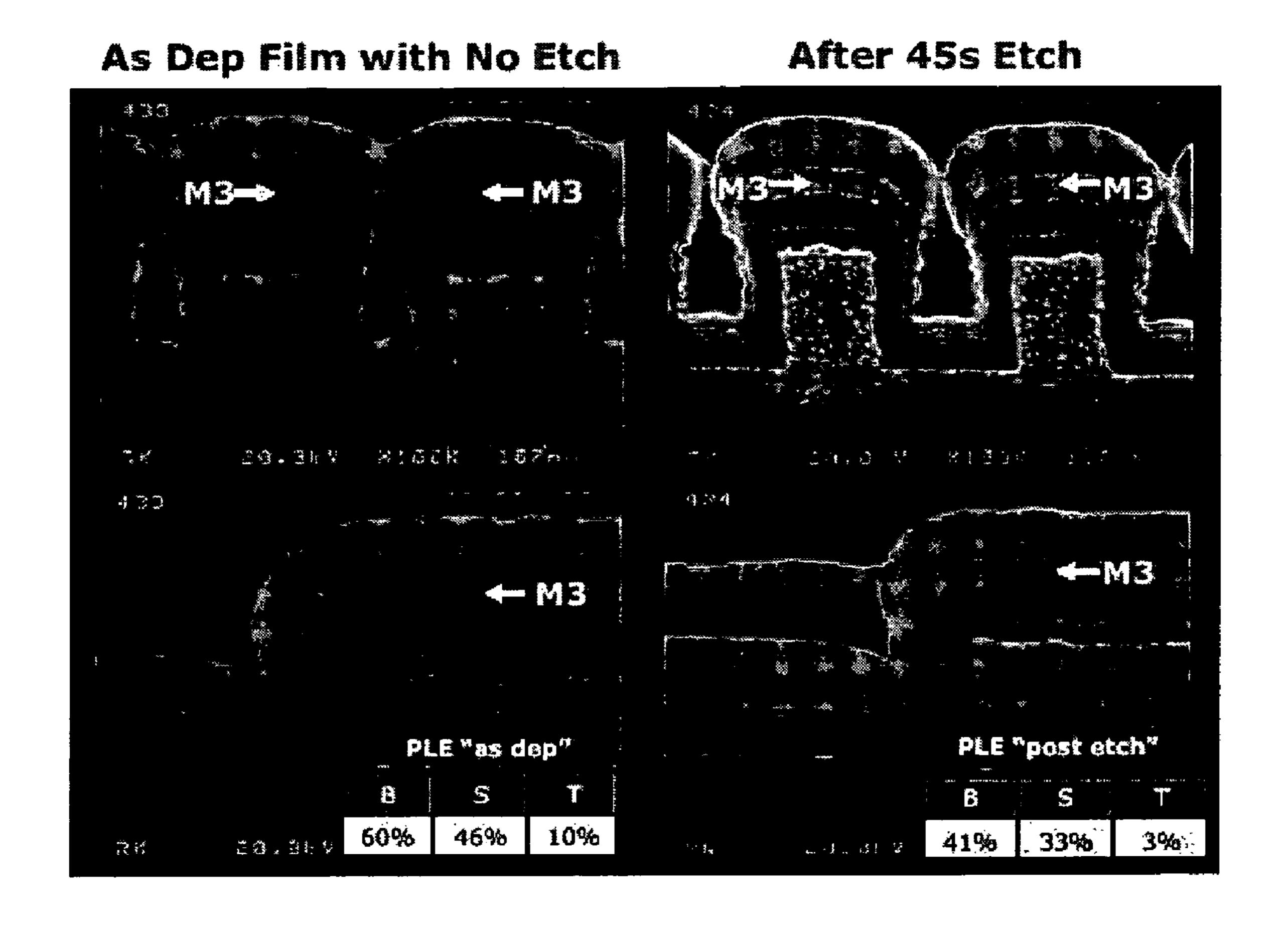

FIG. 41 illustrates results of a post deposition NF<sub>3</sub> etchback process. In FIG. 41, a higher etch rate is shown for the isolated areas. Furthermore, a diluted NF<sub>3</sub> etch-back reduces bottom coverage loading by about 30% without affecting film stress. This can potentially be used to modulate the step coverage for other PECVD dielectric films.

FIG. 42 shows the profile change and Pattern Loading Effect (PLE) improvement after NF<sub>3</sub> etch-back of the silicon nitride layer labeled M3. M3 illustrates the nitride breadloafing profile. The M3 profile has been changed after an NF<sub>3</sub> etch-back process. After post deposition NF<sub>3</sub> etch-back of the M3 compressive nitride, the PLE is improved.

H. Tensile Stressed Materials

Without being limited by an explanation, it has been discovered that a silicon nitride stressed material having higher tensile stress values can be obtained by a number of techniques employed alone or in combination reducing the net hydrogen content, or the amount of silicon-hydrogen and nitrogen-hydrogen bonds (Si—H and N—H bonds respectively) in the deposited silicon nitride material. It is believed that lowering the hydrogen content in the deposited material, which results in a detectably smaller amount of Si—H and N—H bonds in the silicon nitride material, gives rise to higher tensile stress values in the deposited material. It has further been discovered that several different deposition process parameters, treatments of deposited material, or combinations thereof, can be used to achieve lower hydrogen content in the deposited material, as described herein.

Incorporated by reference herein for all purposes is "Mechanism of SiN<sub>x</sub> Deposition from NH<sub>3</sub>-SiH<sub>4</sub> Plasma", Smith et al., *J. Electrochem. Soc.*, Vol. 137, No. 2 (February 1990). This article attributes the formation of tensile stress in a CVD SiN film, to densification of the film in a subsurface zone by the elimination of the volatile ammonia (NH<sub>3</sub>) species. Specifically, nitrogen radicals in the plasma may abstract hydrogen to release the ammonia, leaving dangling Si and N bonds separated by voids. Stretched Si—N bonds then form and are detectable by FT-IR analysis by a characteristic peak at 840 cm<sup>-1</sup>. Constrained by the surrounding material, these stretched Si—N bonds cannot relax, resulting in tensile stress.

Various techniques may be employed to enhance the level of the tensile stress that is created. As described in detail below, in accordance with one technique, tensile stress may be enhanced by forming the material in multiple layers in a plurality of successive deposition/treatment (dep/treat) cycles. In accordance with still another embodiment, tensile stress may be enhanced by depositing the material at a lower temperature prior to subsequent curing by exposure to radiation.

To deposit a tensile stressed silicon nitride material, the process gas introduced into the chamber may comprise a first

component that includes a silicon-containing gas, a second component that includes a nitrogen-containing gas, and a third component containing carbon, boron, or phosphorus. The silicon-containing gas can be, for example, silane, disilane, trimethylsilyl (TMS), tris(dimethylamino)silane (TD- <sup>5</sup> MAS), bis(tertiary-butylamino)silane (BTBAS), dichlorosilane (DCS), and combinations thereof. The carboncontaining compound can be, in addition to the gases mentioned above, ethylene ( $C_2H_4$ ), propylene ( $C_3H_6$ ), toluene ( $C_7H_8$ ), and combinations thereof. The boron and phosphorus containing compounds can be dibhorane (B<sub>2</sub>H<sub>6</sub>), boron chlorides ( $B_2C_{14}$ ), and phosphine ( $PH_3$ ), respectively. For example, a suitable silane flow rate is from about 5 to about 100 sccm. The nitrogen-containing gas can be, for example, ammonia, nitrogen, and combinations thereof. A 15 suitable ammonia flow rate is from about 10 to about 200 sccm. The process gas can also include a diluent gas that is provided in a much larger volume that the reactive gas components. The diluent gas can also serve both as a diluent and at least partially as a reactant nitrogen-containing gas, for example, nitrogen in a flow rate of from about 5000 to about 30,000 sccm. The process gas may also contain additional gases such as an oxygen-containing gas, for example, oxygen, when depositing silicon oxy-nitride materials. Unless otherwise specified, in these processes, typical gas pressures <sup>25</sup> are from about 3 to about 10 Torr; substrate temperatures are from about 300 to 600° C.; electrode spacing is from about 5 mm (200 mils) to about 12 mm (600 mils); and RF power levels are from about 5 to about 100 Watts.

## A. Nitrogen Plasma Treatment Cycles

It was further discovered that the stress values of the asdeposited silicon nitride material could be increased by treating the deposited silicon nitride film with a nitrogen plasma treatment step (treat). Such a treatment cycle can be per- 35 formed by modifying the deposition process to have two process steps. In the first or deposition process step (dep), a process gas comprising a first component comprising siliconcontaining gas and nitrogen-containing gas, and a second component comprising a diluent nitrogen gas, is introduced 40 into the chamber and a plasma is formed from the process gas by applying a high or low frequency voltage to the chamber electrodes. In the second or nitrogen plasma treatment cycle, the flow of the first component of the process gas which includes the silicon-containing gas and the nitrogen-containing gas is shut off or substantially terminated; while the flow of the second component comprising the diluent nitrogen gas is still left on, and the high or low frequency voltage supplied to the electrodes to form the plasma is also maintained. These two process cycles are repeated a number of times during 50 deposition of the silicon nitride material.

Again, without being limited by the explanation, it is believed that the nitrogen plasma cycles further reduce the hydrogen content in the deposited silicon nitride. It is believed that the nitrogen plasma cycle promotes the forma- 55 tion of silicon-nitrogen bonds in the deposited silicon nitride material by removing silicon-hydrogen bonds from the deposited material. However, since the nitrogen plasma treatment can only affect a thin surface region of the deposited silicon nitride film, a nitrogen treatment cycle is formed after 60 short deposition process cycles in which only a film of silicon nitride is deposited on the substrate that is sufficiently thin to allow nitrogen plasma treatment to penetrate substantially the entire thickness of the deposited film. If the nitrogen plasma treatment was performed after deposition of the entire thick- 65 ness of the silicon nitride film, only a thin surface region of the deposited material would be properly treated.

**14**

The modified deposition process comprises a sufficient number of deposition cycles followed by plasma treatment cycles to achieve the desired film thickness. For example, a deposition process comprising twenty (20) process cycles that each comprises a first deposition cycle and a second nitrogen plasma treatment cycle, deposited a tensile stressed silicon nitride material having a thickness of 500 angstroms. Each deposition cycles was performed for about 2 to about 10 seconds and more typically about 5 seconds; and each nitrogen plasma treatment cycle was performed for about 10 to about 30 seconds, and more typically 20 seconds. The resultant deposited tensile stressed silicon nitride material had a thickness of 500 angstroms, and the tensile stress value of the deposited material was increased by the nitrogen plasma treatment to 1.4 GPa. This represented a 10 to 20% improvement over the tensile stress of the as-deposited silicon nitride material, as shown below in Table II.

TABLE II

|   |                                        | Tensile Film Stress (GPa)  Temperature |              |             |             |              |  |  |

|---|----------------------------------------|----------------------------------------|--------------|-------------|-------------|--------------|--|--|

|   |                                        | 400° C.                                | 430° C.      | 450° C.     | 480° C.     | 500° C.      |  |  |

| 5 | Baseline<br>(Single Material)          | 1.0                                    | 1.1          | 1.2         | 1.3         | 1.35         |  |  |

|   | NPT (1)-20s Treat<br>NPT (2)-10s Treat | 1.3<br>1.3                             | 1.35<br>1.35 | 1.44<br>1.4 | 1.44<br>1.4 | 1.43<br>1.43 |  |  |

NPT = Nitrogen Plasma Treatment

Table II shows the improvement in tensile stress of a deposited silicon nitride material with increased substrate temperature during deposition, and with/without multiple nitrogen plasma treatment cycles. The baseline (single material) silicon nitride film was deposited in a single deposition process cycle using the process conditions described above, without nitrogen plasma treatment cycles. The baseline film showed an increase in tensile stress from 1 GPa to about 1.35 GPa as the substrate temperature was increased from 400 to 500° C. The NPT (nitrogen plasma treatment) films were deposited with multiple deposition and nitrogen plasma process cycles—where NPT (1) corresponds to 20 second nitrogen plasma treatment cycles and NPT (2) corresponds to 10 second nitrogen plasma treatment cycles. It is seen that for both NPT films, the tensile stress increased from the baseline film with the nitrogen plasma treatment and also increased with substrate temperature.

FIG. 6 shows the effect of increasing power level of the high RF voltage applied to the electrodes 105, 109, for different nitrogen plasma treatment process conditions, on the tensile stress values of the deposited materials. The first process (A) comprised a deposition stage for 7 seconds, followed by a plasma treatment stage of 40 seconds, repeated for 20 cycles. The second process (B) involved a deposition stage for 5 seconds, followed by plasma treatment for 40 seconds, repeated for 30 cycles. The third process involved plasma stabilizing stage for 4 seconds, deposition for 5 seconds, and plasma treatment for 40 seconds, for 30 cycles. The first and third processes resulted in the highest tensile stress values, when the high radio frequency was set to a power level of a little over 40 Watts, with tensile stress values decreasing on either side of that peak level. The third process steadily decreased in tensile stress value for increasing power levels from a tensile stress value of a little over a 1000 MPa at a power of 0 Watts to 900 MPa at a power of 100 Watts. Thus a power level of 20 to 60 watts, and more preferably 45 watts, was selected for nitrogen plasma/deposition processes.

FIG. 7 shows the tensile stress values and refractive indices obtained for layers deposited under different deposition processes and different nitrogen plasma treatment cycles. The top line indicates the measured tensile stress values and the bottom line indicated the measured refractive indices. The processes included: a deposition only process; a process with a 40 second purge to see the effect without RF power, that is only thermal impact; a process with a 20 second purge then 20 second plasma step; a process with a 40 second plasma step; a process with a 20 second plasma step; a process with a 3 second fast purge than 20 second plasma step; a process with a 3 second pump and 20 second plasma step, and a process with a 3 second fast purge and 10 second plasma step. The layers were formed by a performing a sequence of 30 consecutive cycles.

The highest tensile stress values were achieved with the 3 second pump, 20 second plasma and 3 second fast purge, 10 second plasma processes. The lowest tensile stress values were measured for the deposition only and 10 second purge processes. Generally, the stress value obtained maximizes and evens out for plasma treatment durations longer than 10 sec; however, the stress values do not saturate for treatment durations that were longer than 20 sec when a pump down cycle was added.

Table III below illustrates the exemplary process conditions for each step during the cycle shown in FIG. 7.

TABLE III

| STEP       | SiH <sub>4</sub><br>(sccm) | NH <sub>3</sub> (sccm) | N <sub>2</sub><br>(L) | Press. | Power (W) | Duration (sec) |

|------------|----------------------------|------------------------|-----------------------|--------|-----------|----------------|

| Stabilize  | 25                         | 50                     | 20                    | 6      | 0         | 4              |

| Deposit    | 25                         | 50                     | 20                    | 6      | 45        | 5              |

| Pump       | 0                          | 0                      | 0                     | TFO    | 0         | 30             |

| Fast Purge | 0                          | 0                      | 20                    | TFO    | 0         | 30             |

| Purge      | 0                          | 0                      | 20                    | 6      | 0         | 5-40           |

| Treat      | O                          | 0                      | 20                    | 6      | 45        | 20-40          |

All steps performed at  $400^{\circ}$  C., with a wafer-to-faceplate spacing of 430 mils TFO = throttle valve fully open.

FIG. **8** shows the effect of the duration of N<sub>2</sub> plasma treatment on the tensile stress values of deposited materials. The tensile stress values increase until a treatment duration of about 10 seconds is reached, after which the tensile stress values appears to "saturate" and do not get much larger. The refractive index increases slightly with increasing treatment time.

FIG. 9 shows the effect of the treatment duration on the tensile stress value for processes having a 3 second fast purge and a 3 second pump. The tensile stress values in FIG. 9 do not appear to "saturate" as much as those in FIG. 8, even for treatment times up to about 20 seconds.

It has been discovered that the implementation of additional steps in the nitrogen plasma treatment can result in an even greater enhancement of the level of tensile stress in the resulting film. Table IV summarizes the process sequence for various different cycles of  $N_2$  plasma exposure.

TABLE IV

| Process<br>Sequence             | Step Time<br>(× # cycles)<br>(sec) | Thickness<br>(Å) | RI    | Stress<br>(MPa) | Throughput<br>Twin Tool<br>(Wafers/hr) |

|---------------------------------|------------------------------------|------------------|-------|-----------------|----------------------------------------|

| Dep only                        | 134                                | 500              | 1.847 | 1000            | 20                                     |

| (Baseline)<br>Dep/Treat<br>(DP) | 10/20<br>(×5)                      | 525              | 1.874 | 1100            | 10                                     |

**16**

TABLE IV-continued

|                 | ocess<br>equence                       | Step Time<br>(x # cycles)<br>(sec) | Thickness<br>(Å) | RI    | Stress<br>(MPa) | Throughput<br>Twin Tool<br>(Wafers/hr) |

|-----------------|----------------------------------------|------------------------------------|------------------|-------|-----------------|----------------------------------------|

|                 | ab/Dep/<br>eat (SDT)                   | 4/5/20<br>(×25)                    | 580              | 1.892 | 1180            | 6                                      |

| Sta<br>Pu<br>Tr | ab/Dep/<br>imp/Purge/<br>eat<br>DPPuT) | 4/5/3/5/20<br>(×30)                | 510              | 1.891 | 1230            | 4.5                                    |

FIG. 10 plots film stress versus process throughput, for a twin chamber tool, for each of the N<sub>2</sub> plasma exposure cycles shown in Table IV. FIG. 10 shows that the addition of steps to each cycle reduces process throughput.

FIG. 11 shows FT-IR spectra for a 2800 Å-thick CVD SiN film resulting from deposition at 400° C. under the various cycles and times shown in Table IV. FIG. 11 shows that the N<sub>2</sub> treatment removes hydrogen from both Si—H and N—H bonds, and the peaks at 2200 cm<sup>-1</sup> and 3330 cm<sup>-1</sup> respectively decrease. An additional indication that N—H is reduced by the N<sub>2</sub> treatment is the decrease in the peak/ shoulder at 1167 cm<sup>-1</sup>, which corresponds to the Si—NH—Si bond. This peak 1167 cm<sup>-1</sup> becomes more pronounced when there are a significant number of N—H bonds in the film.

Without wishing to be limited by any particular theory, it is believed that N<sub>2</sub> treatment reduces the hydrogen content in the film leading to the formation of strained Si—N bonds. By introducing additional steps (such as purge and/or pump) after deposition, the effect of the N<sub>2</sub> treatment is enhanced because there are no more deposition gases in the chamber. By contrast, where residual SiH<sub>4</sub> and NH<sub>3</sub> remains in the chamber during treatment, some deposition continues and treatment is not able to penetrate as well into the material already deposited.

FIG. 11A plots the ratio of N—H:Si—N bonds of the CVD SiN films resulting 20 from deposition under the various cycle conditions shown in Table IV. FIG. 11A shows that the addition of steps to the N<sub>2</sub> plasma exposure cycle can reduce N—H content by up to about 40%.

Table V presents stress results for CVD SiN films formed at increasing temperatures utilizing a Producer® SE tool.

TABLE V

|            | Tensile Film Stress (GPa) Temperature (° C.) |     |             |  |  |

|------------|----------------------------------------------|-----|-------------|--|--|

| Cycle      | 400                                          | 430 | <b>45</b> 0 |  |  |

| Baseline   | 1.0                                          | 1.1 | 1.2         |  |  |

| D/T        | 1.1                                          | 1.2 |             |  |  |

| S/D/T      | 1.2                                          | 1.  | 1.44        |  |  |

| S/D/P/Pu/T | 1.3                                          |     | 1.4         |  |  |

Table V shows that a CVD SiN film having a tensile stress of 1.5 GPa may be formed within a thermal budget of 450° C., utilizing the modified tensile process regime.

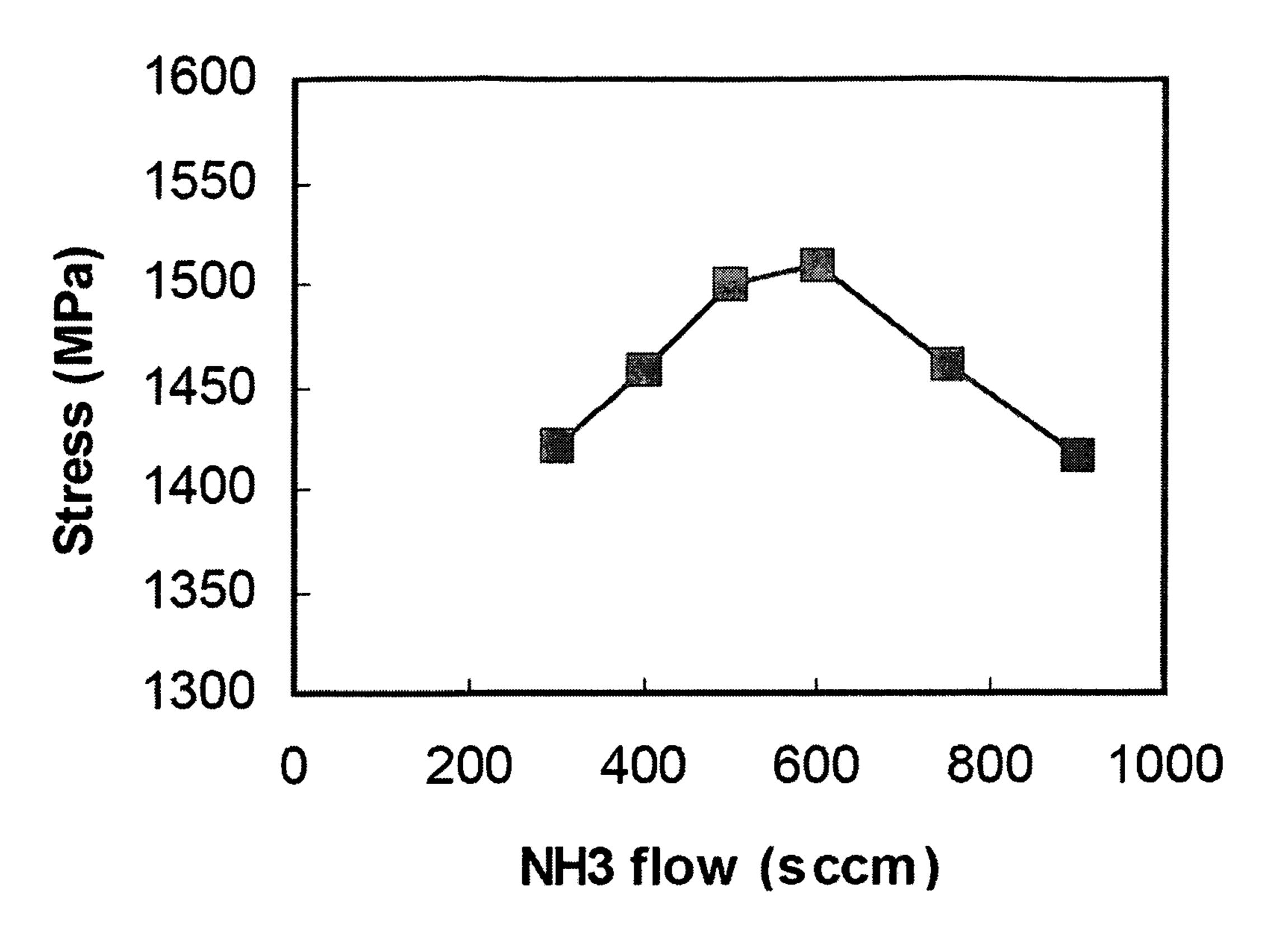

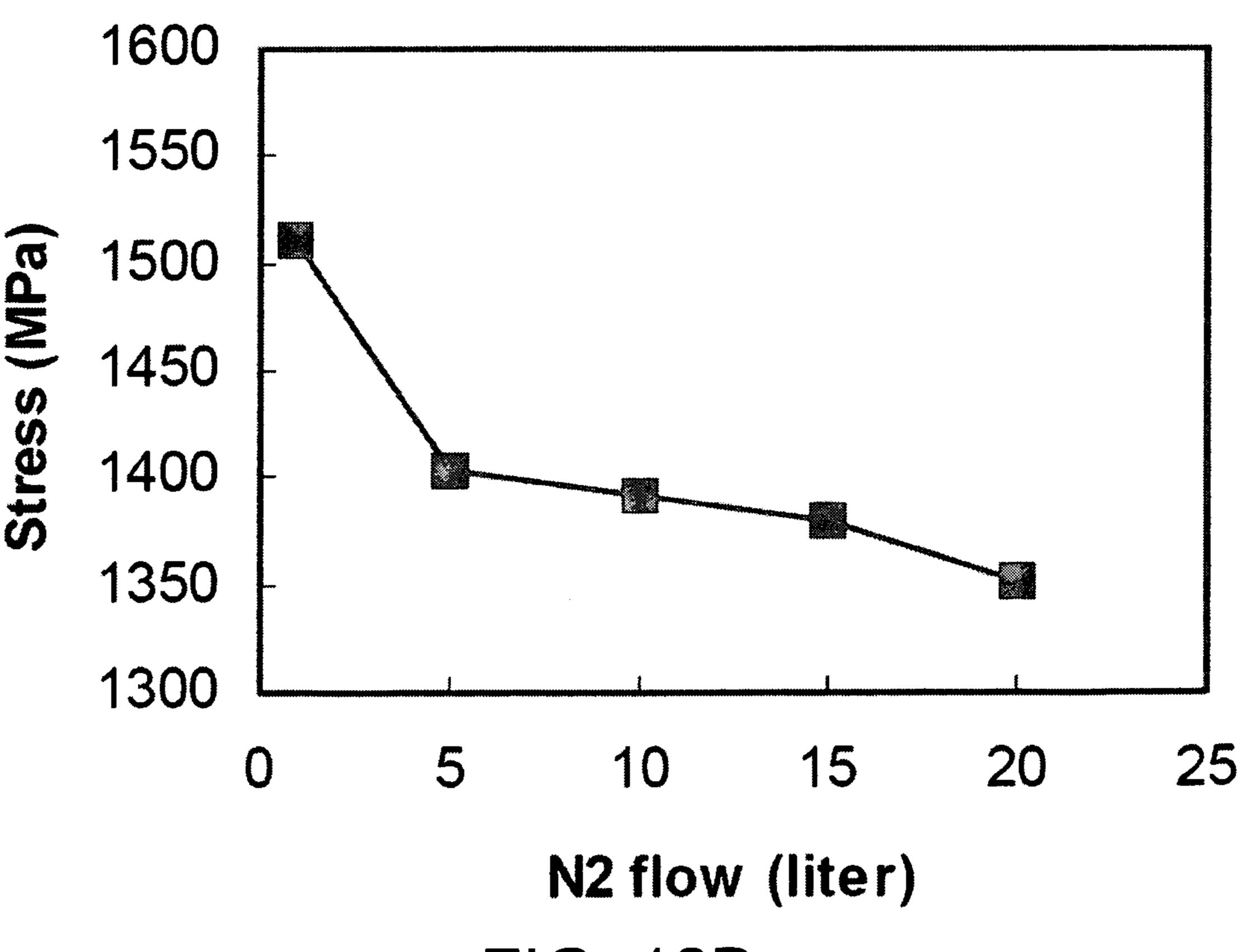

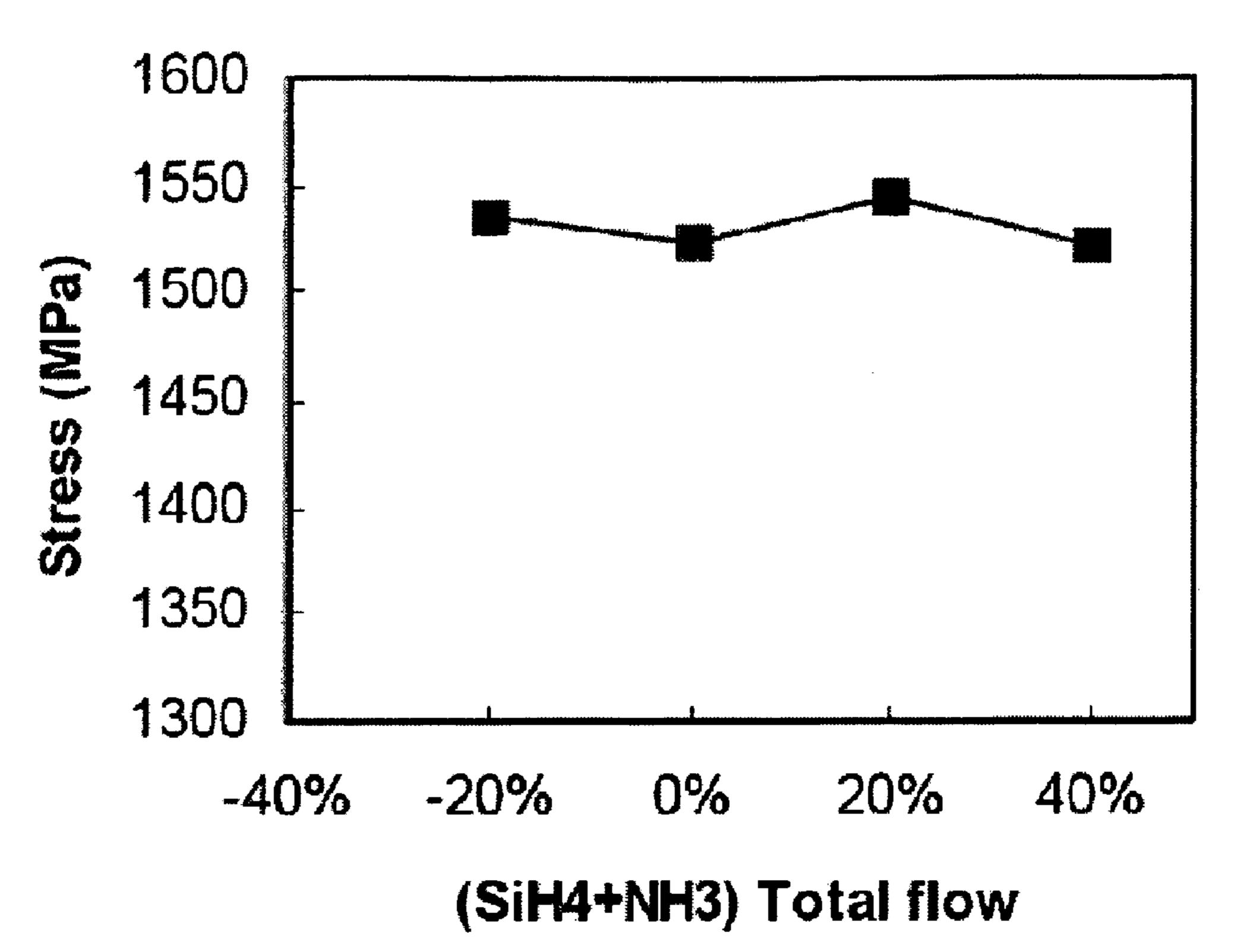

60 FIGS. 12A-D confirm this result, plotting various attributes of a CVD SiN film formed at 450° C. under different process conditions. FIG. 12A plots film stress versus NH<sub>3</sub> flow and indicates that a tensile stress of 1.5 GPa was achieved. FIG. 12B plots film stress versus N<sub>2</sub> flow, and indicates that a tensile stress of 1.5 GPa was achieved with lower N<sub>2</sub> flow rates. FIG. 12C plots film stress versus the total SiH<sub>4</sub> and NH<sub>3</sub> flow rate, and shows that film stress is not a strong function of

this process parameter. FIG. 12D plots film stress versus applied RF power, and shows that a tensile film stress of 1.5 GPa was achieved with a lower RF power.

#### B. Argon (Plasma Treatment)

As described above, exposure of a CVD film to a plasma 5 including a nitrogen containing gas may enhance tensile stress of the film. In accordance with another embodiment of the present invention, stress of a CVD film may also be enhanced by exposing the film during and/or after deposition to a plasma including Argon gas.

FIGS. 13A-F illustrate properties of a CVD SiN film formed by a dep/treat cycle under the conditions shown below in Table VI:

TABLE VI

| CYCLE STEP                            | SiH <sub>4</sub><br>(sccm) | NH <sub>3</sub> (seem) | N <sub>2</sub><br>(L) | N <sub>2</sub> + Ar<br>(L) | RF Power<br>(W) |

|---------------------------------------|----------------------------|------------------------|-----------------------|----------------------------|-----------------|

| Deposition (Dep)<br>Treatment (Treat) | 60<br>0                    | 900<br>0               | 1                     | <del></del>                | 100<br>varied   |

Pressure = 8.5 Torr Wafer-to-faceplate spacing = 300 mils

FIGS. 13A-B show the effect of varying the % of Ar gas flowed during the post deposition treatment, where deposition and treatment are performed at 400° C. FIGS. 13A-B show that the amount of tensile stress resulting in the deposited film directly correlates with reduction in hydrogen content ([H]) in the resulting film. FIGS. 13A-B also show that the increase in tensile stress is a function of Argon gas content and saturates at a % Ar of greater than about 25%.

FIGS. 13C-D show the effect of varying the RF power level applied during the post-deposition Ar treatment, where Ar is 25% of the gas flow and both the deposition and treatment take place at 400° C. FIGS. 13C-D show that the increase in 35 tensile stress is fairly insensitive to the treatment RF power.

FIGS. 13E-F show the effect of varying the temperature upon deposited films treated with plasma including varying amounts of Argon. Specifically, the dep/treat cycles of FIGS. 13E-F were performed at 550° C. FIGS. 13E-F confirm that 40 the increase is tensile stress of the resulting film directly correlates with reduction in hydrogen content of the film. FIGS. 13E-F also indicate that the treatment is less effective when the deposition takes place at a higher temperature (i.e., 550° C. vs. 400° C.). FIGS. 13E-F show the total hydrogen 45 content in the "as deposited" film is lower when compared to the film deposited at 400° C. (FIGS. 13A-B) which leads to a lower reduction in total hydrogen content during plasma treatment.

# C. Ultraviolet Radiation Exposure

The tensile stress of an as-deposited silicon nitride material can be further increased by treating the deposited material with exposure to a suitable energy beam, such as ultraviolet radiation or electron beams. It is believed that ultraviolet and electron beam exposure can be used to further reduce the 55 hydrogen content in the deposited material. The energy beam exposure can be performed within the CVD chamber itself or in a separate chamber. For example, a substrate having the deposited stressed material could be exposed to ultraviolet or electron beam radiation inside the CVD processing chamber. 60 In such an embodiment, the exposure source could be protected from the CVD reaction by a shield or by introducing the exposure source into the chamber subsequent to the flow of process gas. The ultraviolet or electron beams could be applied to the substrate, in-situ in the CVD deposition cham- 65 ber during a CVD reaction to deposit the stressed material. In this version, it is believed that ultraviolet or e-beam exposure

18

during the deposition reaction would disrupt undesirable bonds as they are formed, thereby enhancing the stress values of the deposited stressed material.

FIG. 18 shows an exemplary embodiment of an exposure chamber 200 which can be used to expose a substrate 32 to ultraviolet radiation or electron beam treatment. In the version shown, the chamber 200 includes a substrate support 104 moveable between a released position distal from the exposure source 204, and a lifted position proximate to the source 10 **204** to allow adjustment of the spacing therebetween. A substrate support 104 supports the substrate 32 in the chamber **200**. During insertion and removal of the substrate **32** from the exposure chamber 200, the substrate support 104 can be moved to a loading position, and thereafter, during exposure of the substrate **32** having the deposited silicon nitride material to ultraviolet radiation or electron beams, the support 104 is raised into the lifted position to maximize exposure levels. The chamber 200 further comprises a heater 206, such as a resistive element, which can be used to heat the substrate 32 to a desired temperature during exposure of the substrate 32. A gas inlet 208 is provided to introduce a gas into the exposure chamber 200 and a gas outlet 210 is provided to exhaust the gas from the chamber 200.

The exposure chamber 200 further includes an exposure source 204 that provides a suitable energy beam, such as ultraviolet radiation or electron beams. A suitable ultraviolet radiation source can emit a single ultraviolet wavelength or a broadband of ultraviolet wavelengths. A suitable single wavelength ultraviolet source comprises an excimer ultraviolet source that provides a single ultraviolet wavelength of 172 nm or 222 nm. A suitable broadband source generates ultraviolet radiation having wavelengths of from about 200 to about 400 nm. Such ultraviolet sources can be obtained from Fusion Company, USA or Nordson Company, USA. The stressed silicon nitride material may be exposed to ultraviolet radiation having other wavelengths that are generated by lamps that contain gas that radiates at specific wavelengths when electrically stimulated. For example, suitable ultraviolet lamp may comprise Xe gas, which generates ultraviolet radiation having a wavelength of 172 nm. In other versions, the lamp may comprise other gases having different corresponding wavelengths, for example, mercury lamps radiate at a wavelength of 243 nm, deuterium radiates at a wavelength of 140 nm, and KrCl<sub>2</sub> radiates at a wavelength of 222 nm. Also, in one version, generation of ultraviolet radiation specifically tailored to modify the stress value in the deposited stressed material can be accomplished by introducing a mixture of gases into the lamp, each gas capable of emitting radiation of a characteristic wavelength upon excitation. By varying the 50 relative concentration of the gases, the wavelength content of the output from the radiation source can be selected to simultaneously expose all of the desired wavelengths, thus minimizing the necessary exposure time. The wavelength and intensity of the ultraviolet radiation can be selected to obtain predetermined tensile stress value in the deposited silicon nitride material.

The CVD deposition chamber 80 and exposure chamber 200 may also be integrated together on a multi-chamber processing platform (not shown) served by a single robot arm. The exposure source 204 and the support of the exposure chamber 200, and the components of the CVD deposition chamber 80 that include the substrate support 104, motor, valves or flow controllers, gas delivery system, throttle valve, high frequency power supply, and heater 206, and the robot arm of the integrated processing system, may all be controlled by a system controller over suitable control lines. The system controller relies on feedback from optical sensors to deter-

mine the position of movable mechanical assemblies such as the throttle valve and substrate support 104 which are moved by appropriate motors under the control of the controller.

For exposure treatment in the described exposure chamber **200**, a substrate having a silicon nitride material according to 5 any of the deposition processes described or other deposition processes known in the art, is inserted into the exposure chamber 200 and placed upon the substrate support 104 in the lowered position. The substrate support 104 is then raised to a lifted position, the optional heater 206 in the support pow- 10 ered on, and the exposure source 204 is activated. During exposure, a gas may be circulated through the exposure chamber 200, such as helium, to improve thermal heat transfer rates between the substrate and the support. Other gases may also be used. After a period of radiation exposure, the exposure 15 source 204 is deactivated and the substrate support 104 is lowered back into the released position. The substrate bearing the exposed silicon nitride stressed material is then removed from the exposure chamber 200.