US007722146B2

# (12) United States Patent

# Walmsley

# (10) Patent No.:

US 7,722,146 B2

(45) **Date of Patent:**

\*May 25, 2010

# (54) PRINTING SYSTEM HAVING CONTROLLED MULTI-LENGTH PRINTHEAD ICS

## (75) Inventor: Simon Robert Walmsley, Balmain (AU)

# (73) Assignee: Silverbrook Research Pty Ltd,

Balmain, New South Wales (AU)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 12/436,129

(22) Filed: May 6, 2009

#### (65) Prior Publication Data

US 2009/0251502 A1 Oct. 8, 2009

## Related U.S. Application Data

(63) Continuation of application No. 12/050,941, filed on Mar. 19, 2008, now Pat. No. 7,540,579, which is a continuation of application No. 10/727,245, filed on Dec. 2, 2003, now Pat. No. 7,399,043.

#### (30) Foreign Application Priority Data

| Dec. 2, 2002 | (AU) | ••••• | 2002953134 |

|--------------|------|-------|------------|

| Dec. 2, 2002 |      | ••••• |            |

(51) **Int. Cl.**

**B41J 29/38** (2006.01) **B41J 2/155** (2006.01)

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,198,054    | A   | 3/1993  | Drake et al.       |       |

|--------------|-----|---------|--------------------|-------|

| 5,543,828    | A   | 8/1996  | Minowa             |       |

| 5,719,602    | A   | 2/1998  | Hackleman et al.   |       |

| 6,168,251    | B1  | 1/2001  | Imanaka et al.     |       |

| 6,354,689    | B1  | 3/2002  | Couwenhoven et al. |       |

| 6,637,860    | B1  | 10/2003 | Madeley            |       |

| 6,669,331    | B2  | 12/2003 | Teshigawara et al. |       |

| 6,775,022    | B2  | 8/2004  | Noyes et al.       |       |

| 6,831,753    | B1  | 12/2004 | Tsuchitoi          |       |

| 6,857,724    | B2  | 2/2005  | Silverbrook        |       |

| 7,278,697    | B2* | 10/2007 | Plunkett           | 347/5 |

| 2002/0060707 | A1  | 5/2002  | Yu et al.          |       |

| 2002/0075339 | A1  | 6/2002  | Kamoshida et al.   |       |

| 2002/0158934 | A1  | 10/2002 | Oshima             |       |

| 2002/0171709 | A1  | 11/2002 | Teshigawara et al. |       |

|              |     |         |                    |       |

|              |     |         |                    |       |

#### (Continued)

#### FOREIGN PATENT DOCUMENTS

EP 0863004 A2 9/1998

(Continued)

Primary Examiner—Julian D Huffman Assistant Examiner—Jason S Uhlenhake

## (57) ABSTRACT

Printing system is provided which has a plurality of printhead integrated circuits of different lengths and a controller configured to supply print data to the printhead integrated circuits. The printhead integrated circuits are arranged to define a pagewidth printhead having rows of nozzles formed by adjacent nozzle rows of the adjacent printhead integrated circuits. The nozzle rows of the printhead are configured so that there is at least one row for printing each ink color of a plurality of ink colors. The controller supplies the print data at a rate which is proportional to a ratio of the different lengths of the printhead integrated circuits.

#### 10 Claims, 65 Drawing Sheets

# US 7,722,146 B2 Page 2

| U.S. PATENT DOCUMENTS             | EP 0983855 A2 3/2000     |  |  |

|-----------------------------------|--------------------------|--|--|

|                                   | EP 1157840 A2 11/2001    |  |  |

| 2002/0180816 A1 12/2002 Haflinger | JP 01-216852 A 8/1989    |  |  |

|                                   | WO WO 98/40222 A1 9/1998 |  |  |

| FOREIGN PATENT DOCUMENTS          | WO WO 99/08875 A1 2/1999 |  |  |

| EP 0963854 A 12/1999              | WO WO 00/64679 A 11/2000 |  |  |

| EP 0974467 A1 1/2000              | * cited by examiner      |  |  |

F1G. 1

F16. 2

五 の の

| high speed | low speed

F169. 4

下 の の

high speed low speed

F169.10

F16. 11

F1G. 12

F16. 14

F16. 15

Note: Paper passes under printhead

五 (の) (の)

F169. 21

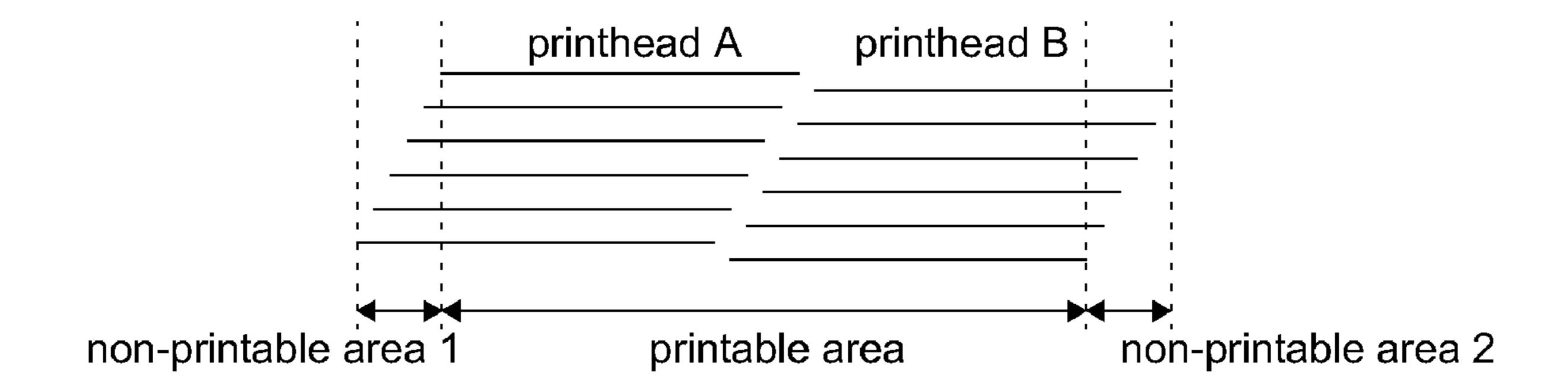

non-printable area 1 = inverted non-printable area 2

F16. 22

| printhead A | printhead B |  |

|-------------|-------------|--|

|             |             |  |

|             |             |  |

|             |             |  |

FIG. 23

# Even Dot Storage in DRAM (Increasing Sense)

F16. 25

# Even Dot Storage in DRAM (Decreasing Sense)

FIG. 26

F169.

s otherwise stated Machine remains in same All outputs are zero unles

State Description:

Idle state wait for active request Idle:

update ColorSelect: Select

requesting to DIU

Request: Request issued wait for

Data word 0 transfer Data0:

Data word 1 transfer Data1:

Data word 2 transfer Data2:

transfer

Data word 3

May 25, 2010

下(G. 24

May 25, 2010

Generate dot

五 の の

万 (の)

State Description:

wait for active request Idle state

update before color to requesting to DIU ColorSclect: Select the

Request: Request issued wait for acknowledge

transfer

Data word 0

May 25, 2010

transfer Data word Data1:

transfer Data word Data2:

transfer Data word 3 Data3:

F16. 42

F16. 43

F169: 44

F169. 45

Generate dot order (from the LLU

F169. 40

F169. 48

F1G. 50

F1G. 51

F16. 53

FIG. 54

F16. 58

F16. 62

F16. 63

F1G. 64

F16. 65

FIG. OI

.00011 ...000001 1110000000 1111111....11100000000....000111111 100....0000000100....0000000100....0 000000....0001000000....0001000000....000 11111....1110000000....000111111....111 ..000000...001 ..1000000...0001

Right Print Head Fire/Sel

Fire/Select

Head

Left Print

F1G. 70

F1G. 71

F16. 73

F1G. 74

# PRINTING SYSTEM HAVING CONTROLLED MULTI-LENGTH PRINTHEAD ICS

# CROSS REFERENCE TO RELATED APPLICATIONS

The present application is a continuation of U.S. application Ser. No. 12/050,941 filed on Mar. 19, 2008, which is a continuation of U.S. application Ser. No. 10/727,245 filed Dec. 2, 2003, now issued U.S. Pat. No. 7,399,043 the entire 10 contents of which are herein incorporated by reference.

#### FIELD OF INVENTION

The present invention relates to techniques for providing data to a printhead such that the requirements of different length printhead modules comprising the printhead are taken in to account.

The invention has primarily been developed for use with a printhead comprising one or more printhead modules constructed using microelectromechanical systems (MEMS) techniques, and will be described with reference to this application. However, it will be appreciated that the invention can be applied to other types of printing technologies in which analogous problems are faced.

### BACKGROUND OF INVENTION

Manufacturing a printhead that has relatively high resolution and print-speed raises a number of problems.

Difficulties in manufacturing pagewidth printheads of any substantial size arise due to the relatively small dimensions of standard silicon wafers that are used in printhead (or printhead module) manufacture. For example, if it is desired to make an 8 inch wide pagewidth printhead, only one such printhead can be laid out on a standard 8-inch wafer, since such wafers are circular in plan. Manufacturing a pagewidth printhead from two or more smaller modules can reduce this limitation to some extent, but raises other problems related to providing a joint between adjacent printhead modules that is precise enough to avoid visible artefacts (which would typically take the form of noticeable lines) when the printhead is used. The problem is exacerbated in relatively high-resolution applications because of the tight tolerances dictated by the small spacing between nozzles.

The quality of a joint region between adjacent printhead modules relies on factors including a precision with which the abutting ends of each module can be manufactured, the accuracy with which they can be aligned when assembled into a single printhead, and other more practical factors such as 50 management of ink channels behind the nozzles. It will be appreciated that the difficulties include relative vertical displacement of the printhead modules with respect to each other.

Whilst some of these issues may be dealt with by careful design and manufacture, the level of precision required renders it relatively expensive to manufacture printheads within the required tolerances. It would be desirable to provide a solution to one or more of the problems associated with precision manufacture and assembly of multiple printhead modules to form a printhead, and especially a pagewidth printhead.

In some cases, it is desirable to produce a number of different printhead module types or lengths on a substrate to maximise usage of the substrate's surface area. However, 65 different sizes and types of modules will have different numbers and layouts of print nozzles, potentially including dif-

2

ferent horizontal and vertical offsets. Where two or more modules are to be joined to form a single printhead, there is also the problem of dealing with different seam shapes between abutting ends of joined modules, which again may incorporate vertical or horizontal offsets between the modules. Printhead controllers are usually dedicated application specific integrated circuits (ASICs) designed for specific use with a single type of printhead module, that is used by itself rather than with other modules. It would be desirable to provide a way in which different lengths and types of printhead modules could be accounted for using a single printer controller.

Printer controllers face other difficulties when two or more printhead modules are involved, especially if it is desired to send dot data to each of the printheads directly (rather than via a single printhead connected to the controller). One concern is that data delivered to different length controllers at the same rate will cause the shorter of the modules to be ready for printing before any longer modules. Where there is little difference involved, the issue may not be of importance, but for large length differences, the result is that the bandwidth of a shared memory from which the dot data is supplied to the modules is effectively left idle once one of the modules is full and the remaining module or modules is still being filled. It would be desirable to provide a way of improving memory bandwidth usage in a system comprising a plurality of printhead modules of uneven length.

In any printing system that includes multiple nozzles on a printhead or printhead module, there is the possibility of one or more of the nozzles failing in the field, or being inoperative due to manufacturing defect. Given the relatively large size of a typical printhead module, it would be desirable to provide some form of compensation for one or more "dead" nozzles. Where the printhead also outputs fixative on a per-nozzle basis, it is also desirable that the fixative is provided in such a way that dead nozzles are compensated for.

A printer controller can take the form of an integrated circuit, comprising a processor and one or more peripheral hardware units for implementing specific data manipulation functions. A number of these units and the processor may need access to a common resource such as memory. One way of arbitrating between multiple access requests for a common resource is timeslot arbitration, in which access to the resource is guaranteed to a particular requester during a predetermined timeslot.

One difficulty with this arrangement lies in the fact that not all access requests make the same demands on the resource in terms of timing and latency. For example, a memory read requires that data be fetched from memory, which may take a number of cycles, whereas a memory write can commence immediately. Timeslot arbitration does not take into account these differences, which may result in accesses being performed in a less efficient manner than might otherwise be the case. It would be desirable to provide a timeslot arbitration scheme that improved this efficiency as compared with prior art timeslot arbitration schemes.

Also of concern when allocating resources in a timeslot arbitration scheme is the fact that the priority of an access request may not be the same for all units. For example, it would be desirable to provide a timeslot arbitration scheme in which one requestor (typically the memory) is granted special priority such that its requests are dealt with earlier than would be the case in the absence of such priority.

In systems that use a memory and cache, a cache miss (in which an attempt to load data or an instruction from a cache fails) results in a memory access followed by a cache update. It is often desirable when updating the cache in this way to

update data other than that which was actually missed. A typical example would be a cache miss for a byte resulting in an entire word or line of the cache associated with that byte being updated. However, this can have the effect of tying up bandwidth between the memory (or a memory manager) and the processor where the bandwidth is such that several cycles are required to transfer the entire word or line to the cache. It would be desirable to provide a mechanism for updating a cache that improved cache update speed and/or efficiency.

Most integrated circuits an externally provided signal as 10 (or to generate) a clock, often provided from a dedicated clock generation circuit. This is often due to the difficulties of providing an onboard clock that can operate at a speed that is predictable. Manufacturing tolerances of such on-board clock generation circuitry can result in clock rates that vary by 15 a factor of two, and operating temperatures can increase this margin by an additional factor of two. In some cases, the particular rate at which the clock operates is not of particular concern. However, where the integrated circuit will be writing to an internal circuit that is sensitive to the time over which 20 system a signal is provided, it may be undesirable to have the signal be applied for too long or short a time. For example, flash memory is sensitive to being written too for too long a period. It would be desirable to provide a mechanism for adjusting a rate of an on-chip system clock to take into account the impact 25 of manufacturing variations on clockspeed.

A number of other aspects, features, preferences and embodiments are disclosed in the Detailed Description of the Preferred Embodiment below.

#### SUMMARY OF THE INVENTION

In accordance with the invention, there is provided a printhead controller for supplying print data to a plurality of printhead integrated circuits of different lengths, the printhead integrated circuits being arranged to define a pagewidth printhead having rows of nozzles formed by adjacent nozzle rows of the adjacent printhead integrated circuits, the nozzle rows of the printhead being configured so that there is at least one row for printing each ink color of a plurality of ink colors, the printhead controller being configured to supply the print data to the printhead integrated circuits in accordance with their respective lengths, such that the difference in the lengths is at least partially compensated for in printing across the pagewidth.

Optionally, the printhead controller is configured to supply the print data to the nozzle rows in serial form.

Optionally, each of the printhead integrated circuits comprises one or more parallel pairs of the rows, the printhead controller being configured to serially supply the print data to a first of each of the rows in the or each pair of rows, the print data being serially clocked through the first row of the or each pair of rows, then through a second row of the or each pair or rows, until all nozzles have received their respective print data.

Optionally, the data is clocked through the second row in a direction substantially opposite to that in which it was clocked through the first row.

Optionally, the printer controller comprises a printhead <sub>60</sub> interface in communication with a line loader unit.

Optionally, the printhead interface accepts two streams of print data from the line loader unit.

Optionally, the line loader unit includes two print data generator units.

Optionally, the line loader unit compensates for any vertical misalignment between the printhead integrated circuits.

4

Optionally, the print data is transferred to either the printhead integrated circuits from a memory under the control of the printhead controller.

Optionally, the printhead controller is configured to manipulate the supply of print data to each of the printhead integrated circuits such that usage of a memory bandwidth is substantially constant during a printhead loading cycle.

### BRIEF DESCRIPTION OF THE DRAWINGS

Preferred and other embodiments of the invention will now be described, by way of example only, with reference to the accompanying drawings, in which:

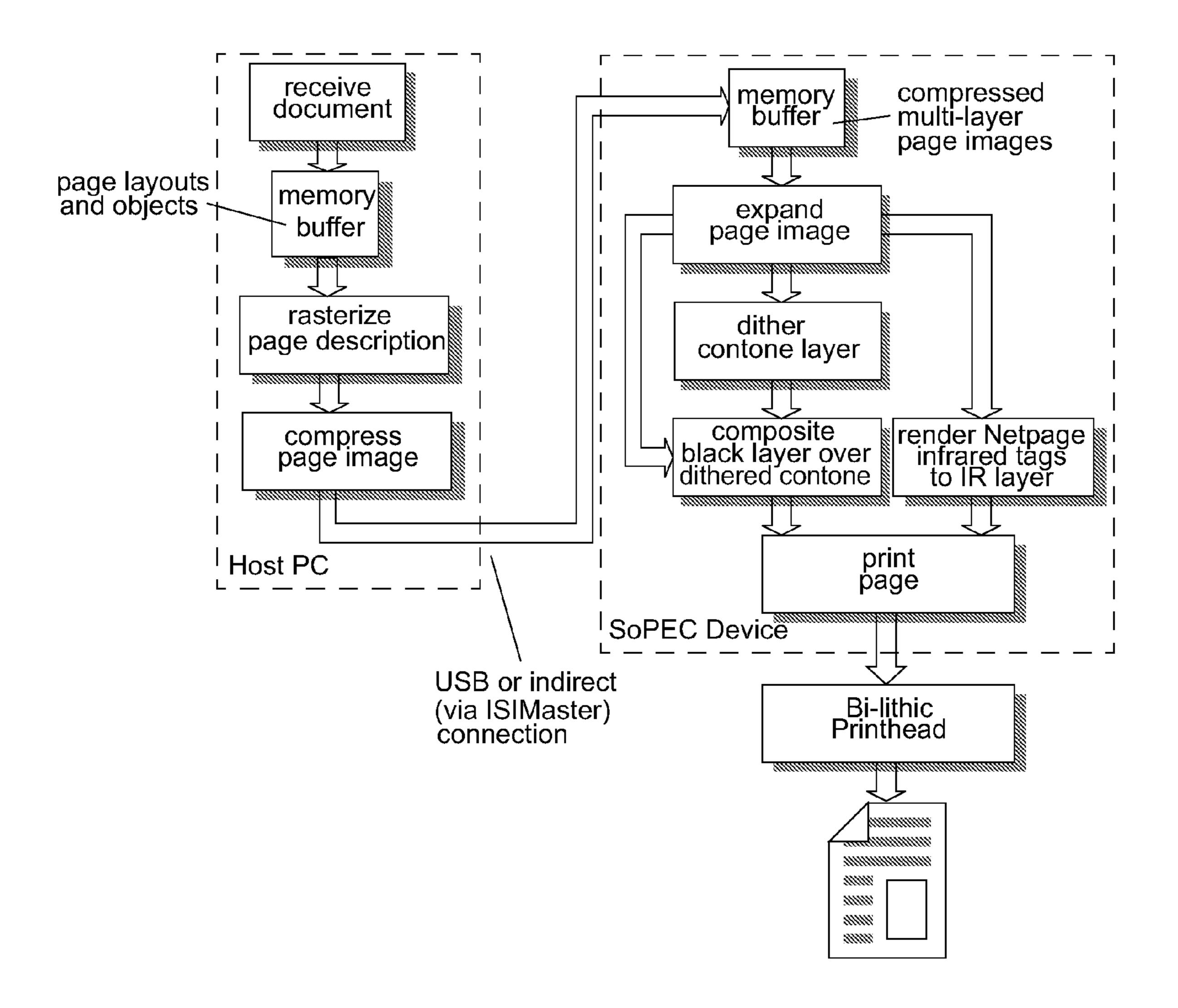

FIG. 1 shows document data flow in a printer

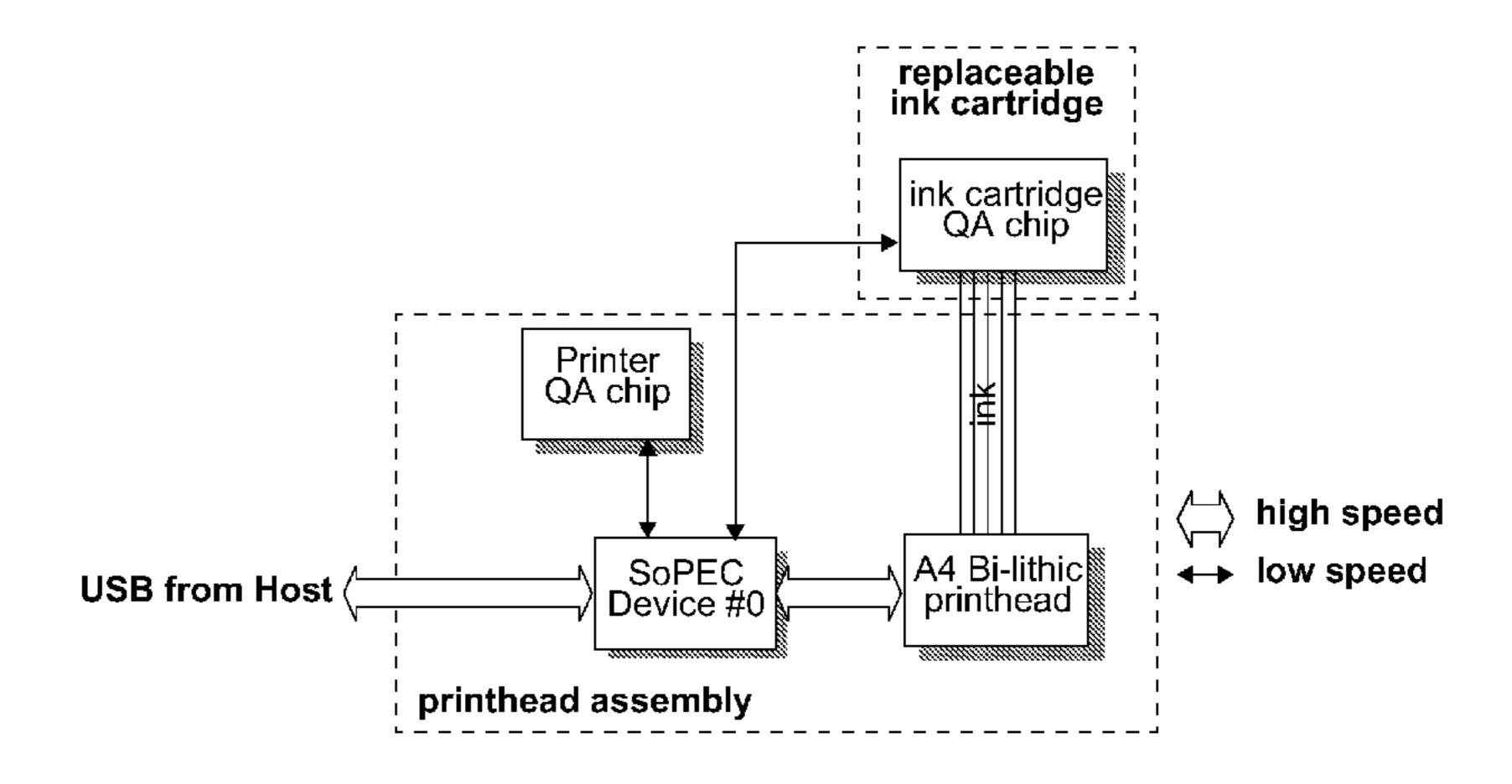

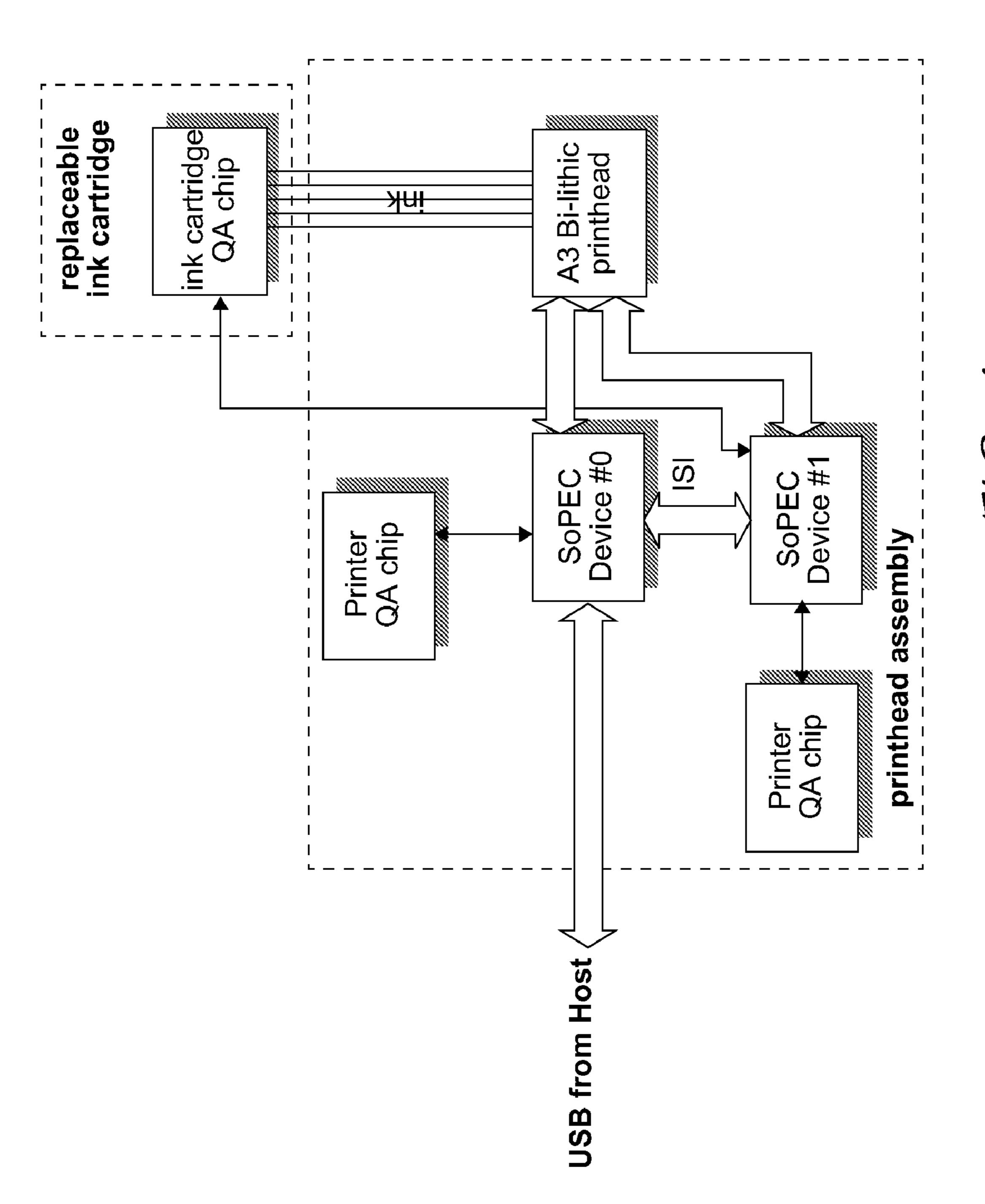

FIG. 2 is an example of a single printer controller (hereinafter "SoPEC") A4 simplex printer system

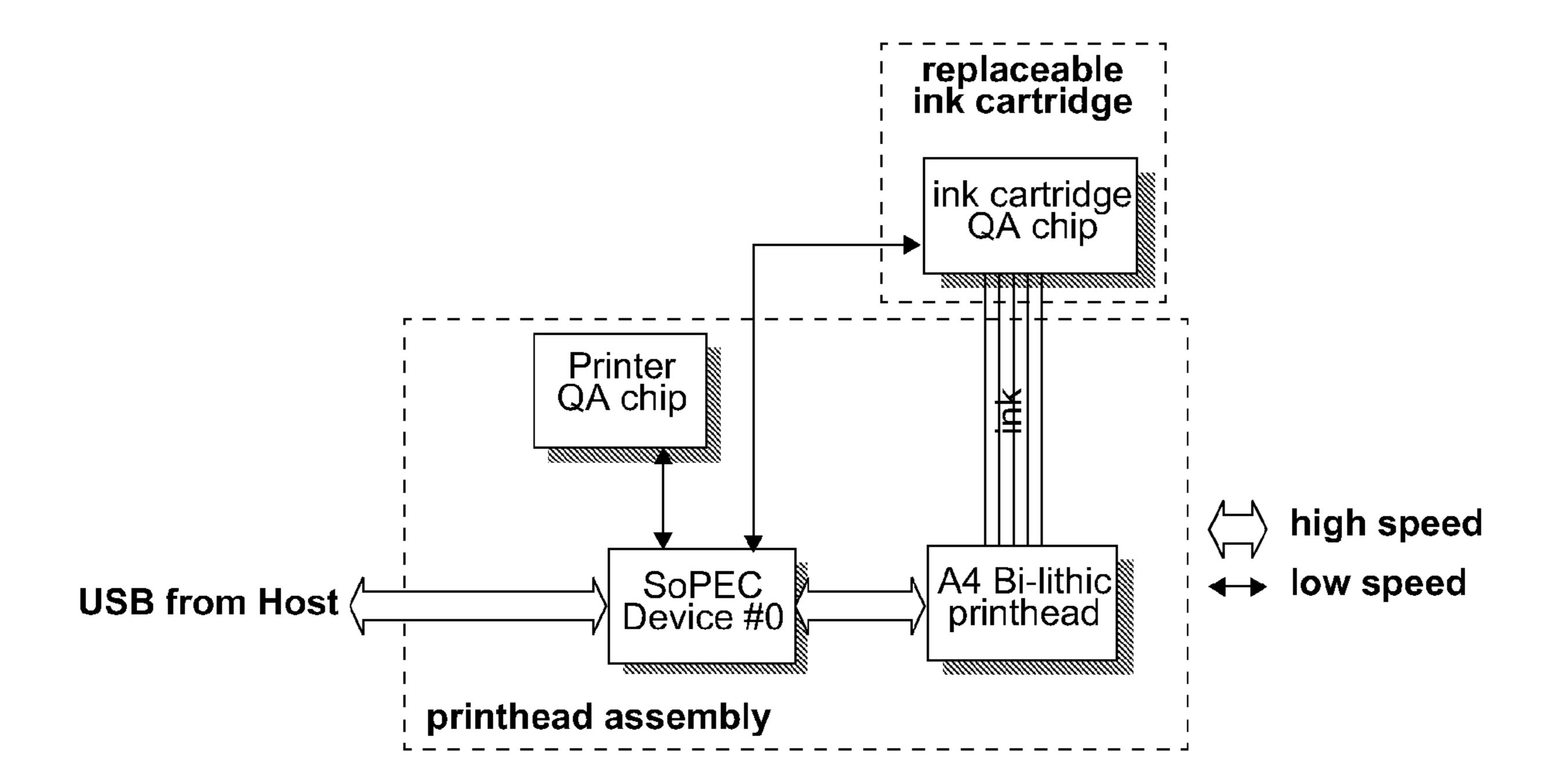

FIG. 3 is an example of a dual SoPEC A4 duplex printer system

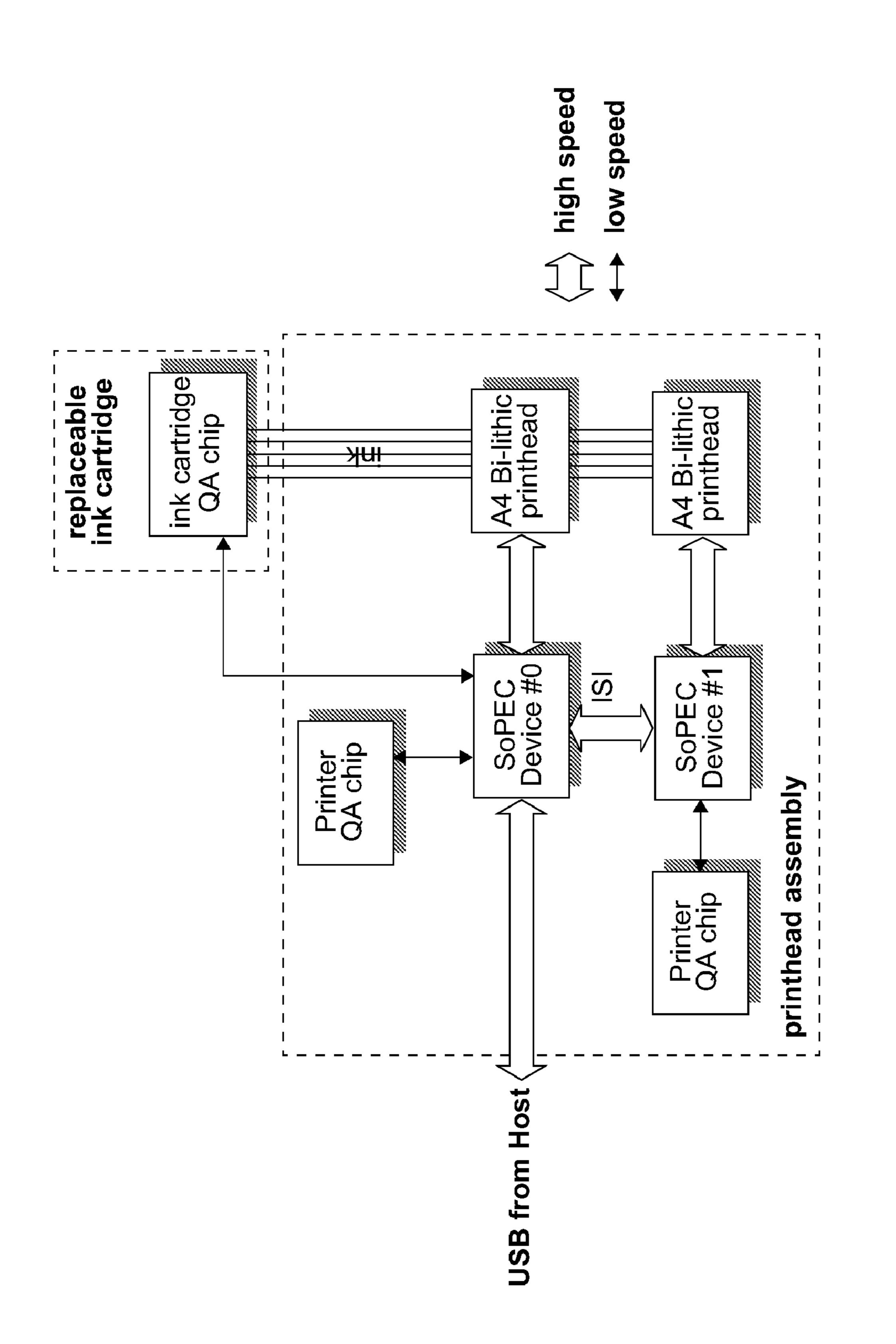

FIG. 4 is an example of a dual SoPEC A3 simplex printer system

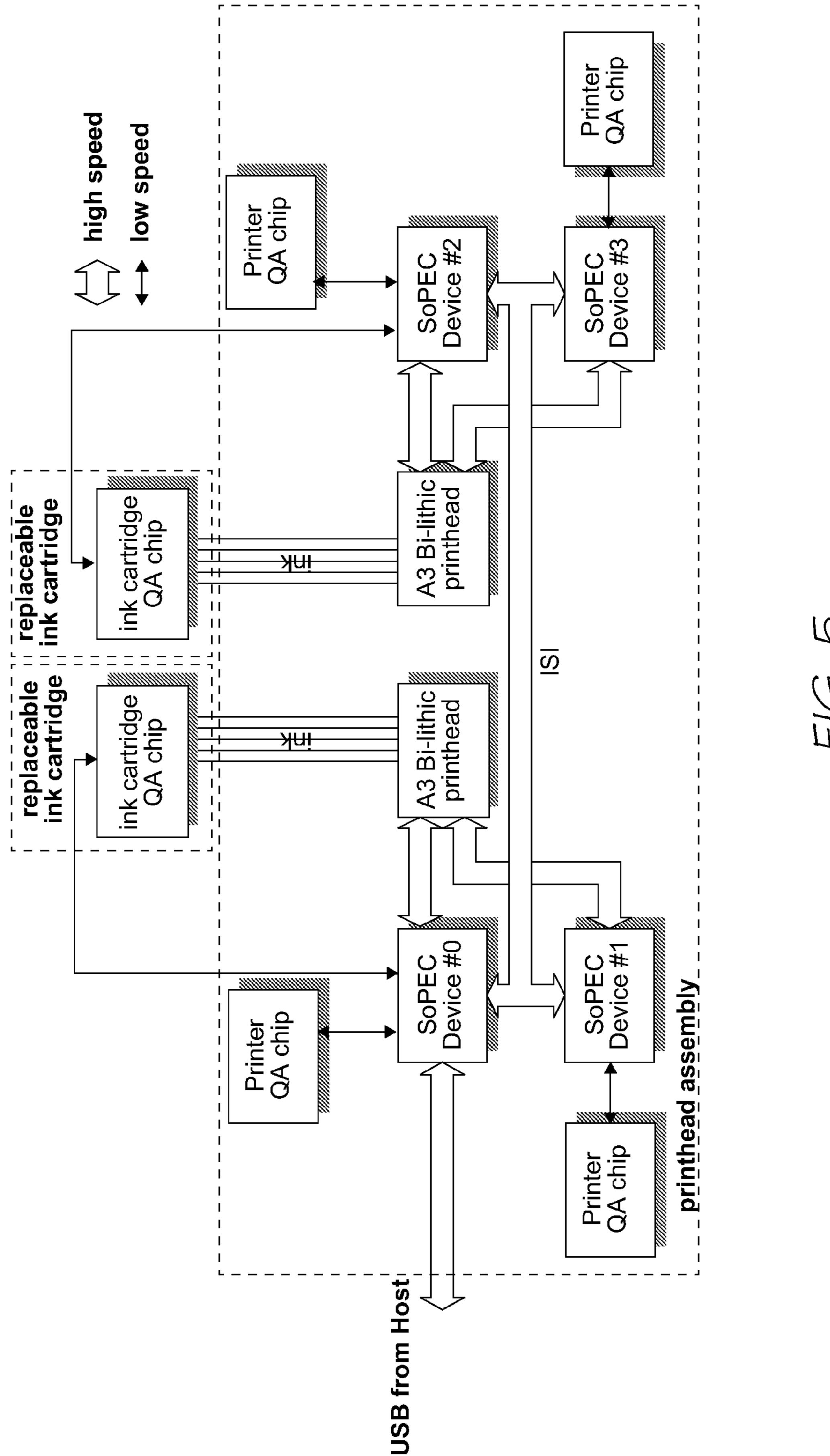

FIG. 5 is an example of a quad SoPEC A3 duplex printer system

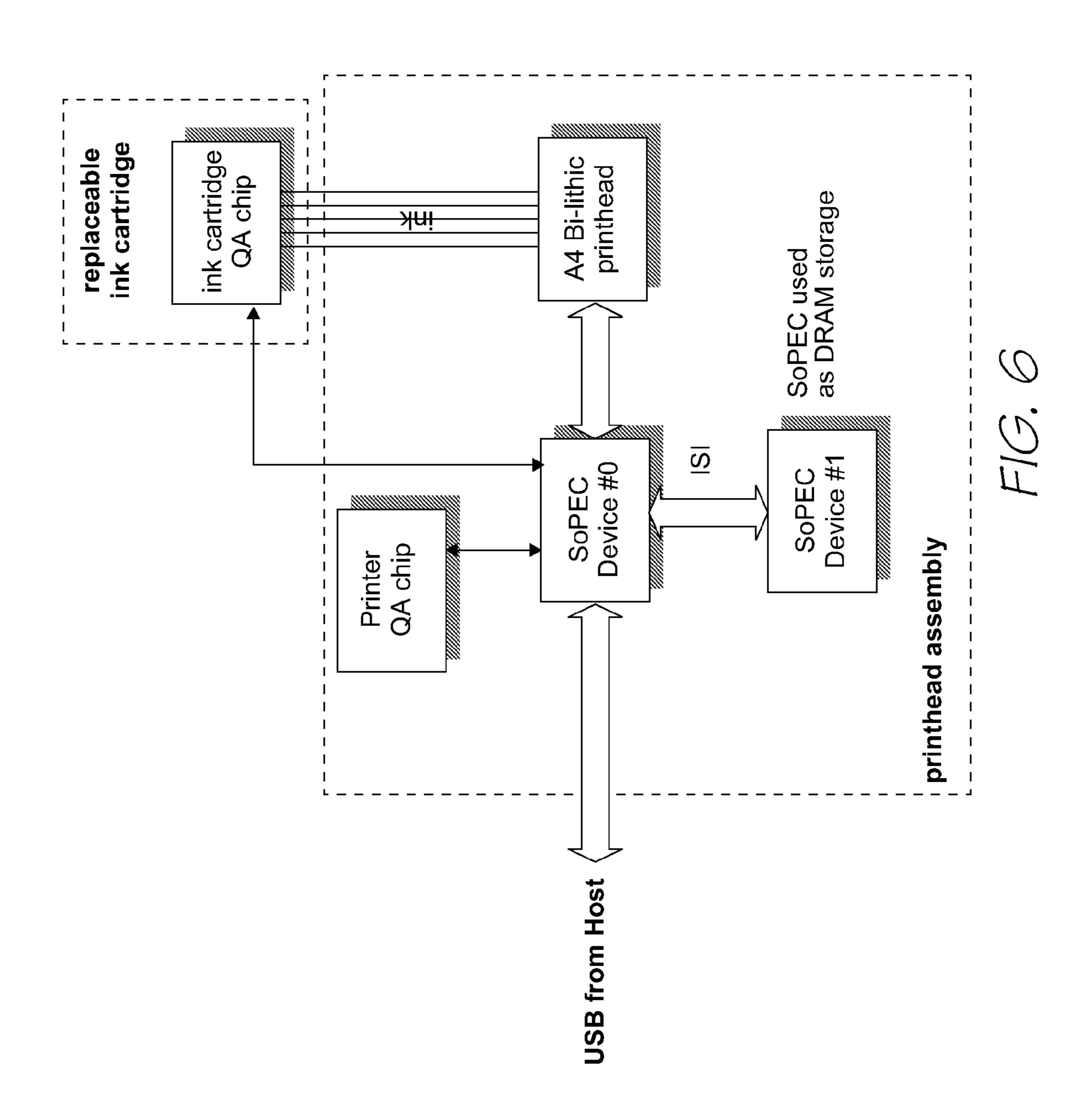

FIG. 6 is an example of a SoPEC A4 simplex printing system with an extra SoPEC used as DRAM storage

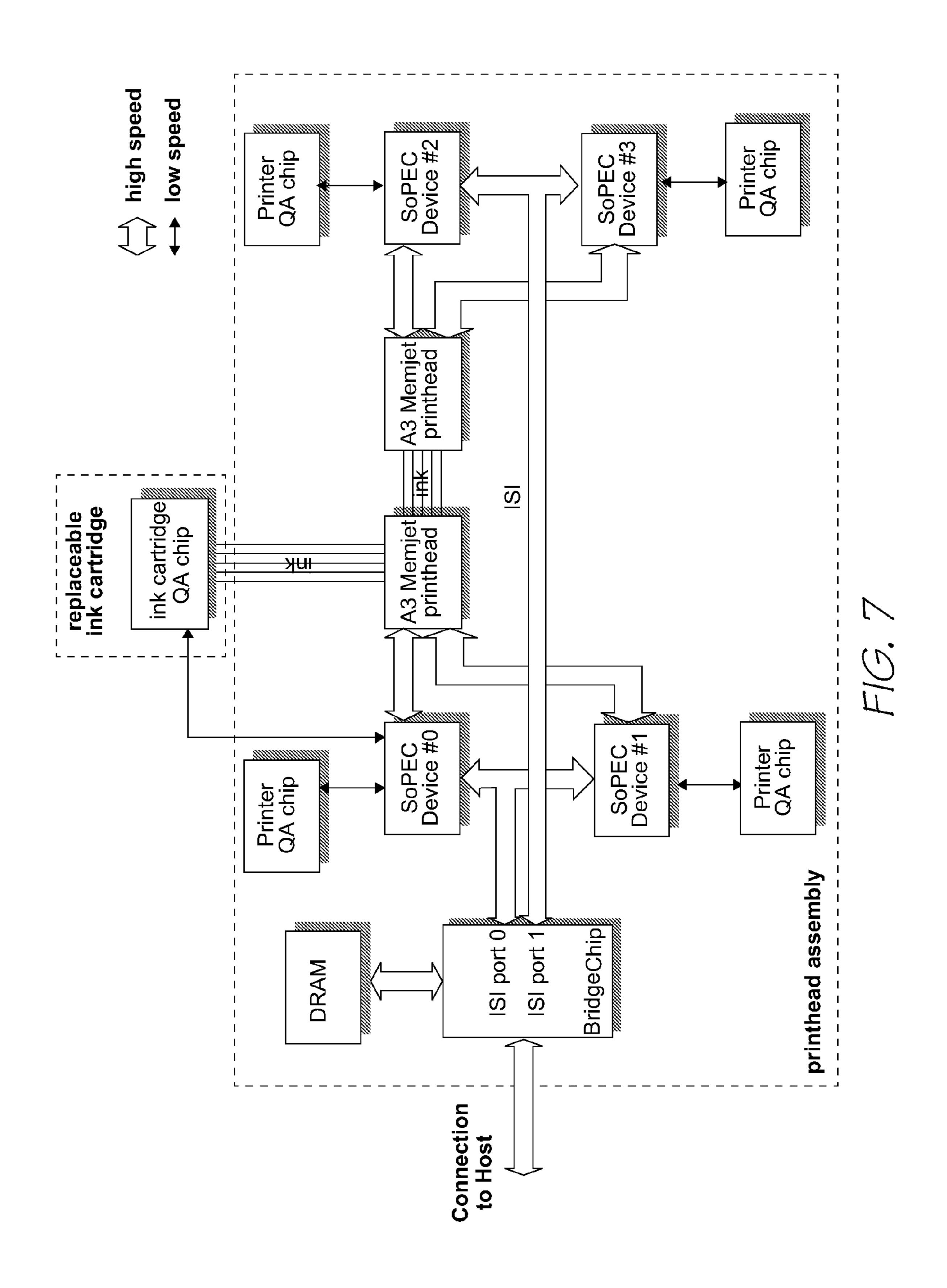

FIG. 7 is an example of an A3 duplex printing system featuring four printing SoPECs

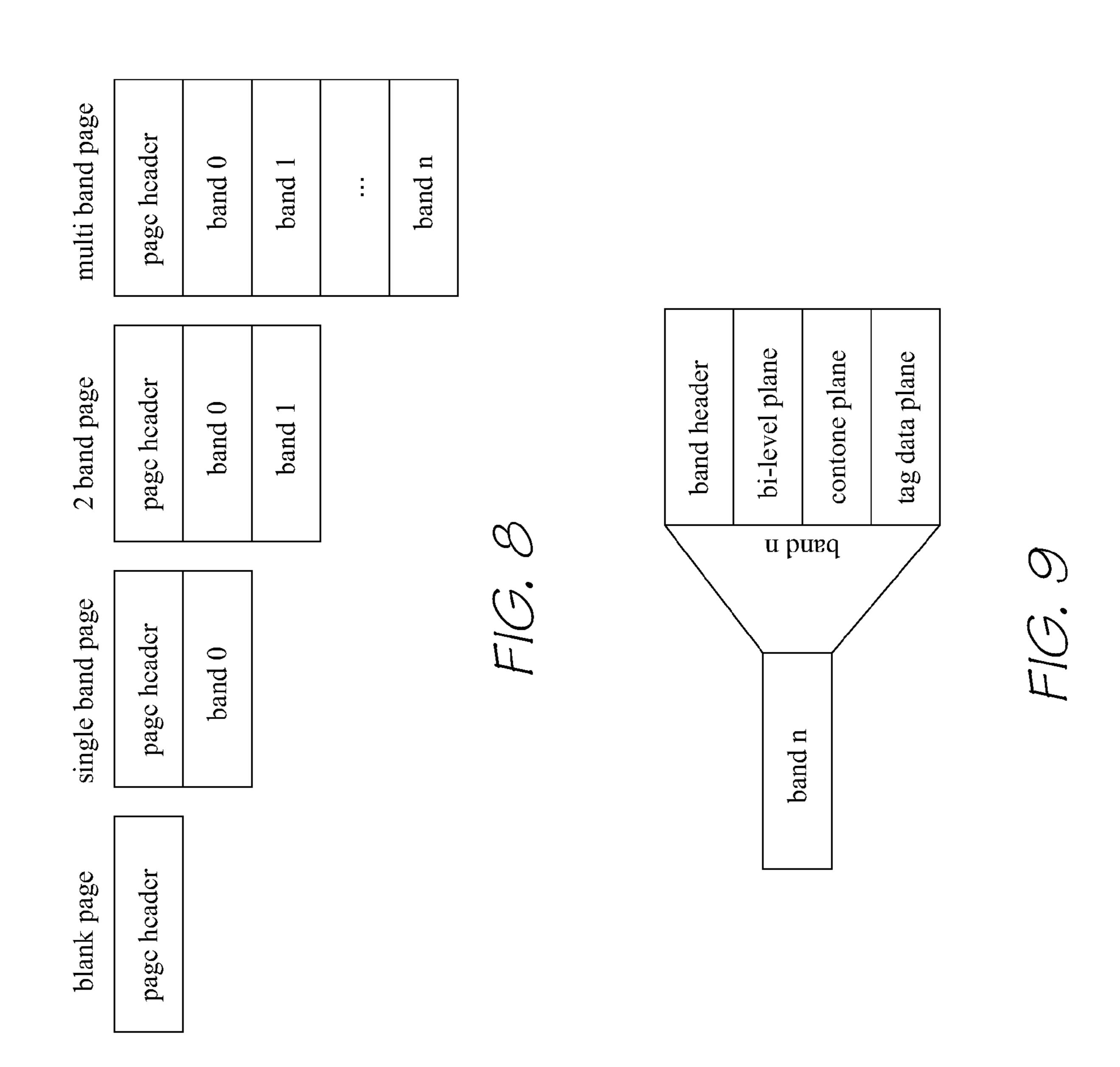

FIG. 8 shows pages containing different numbers of bands

FIG. 9 shows the contents of a page band

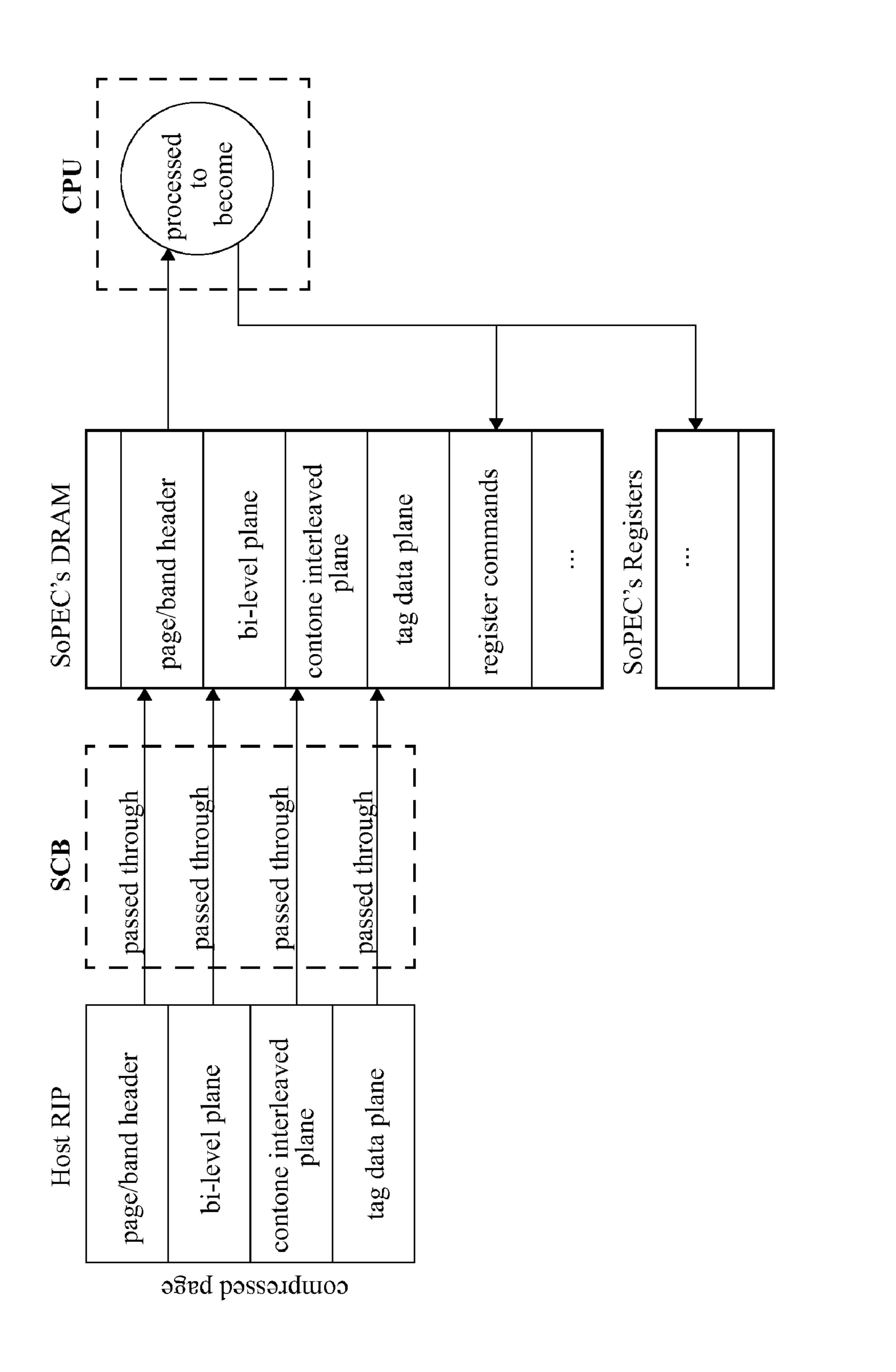

FIG. 10 illustrates a page data path from host to SoPEC

FIG. 11 shows a page structure

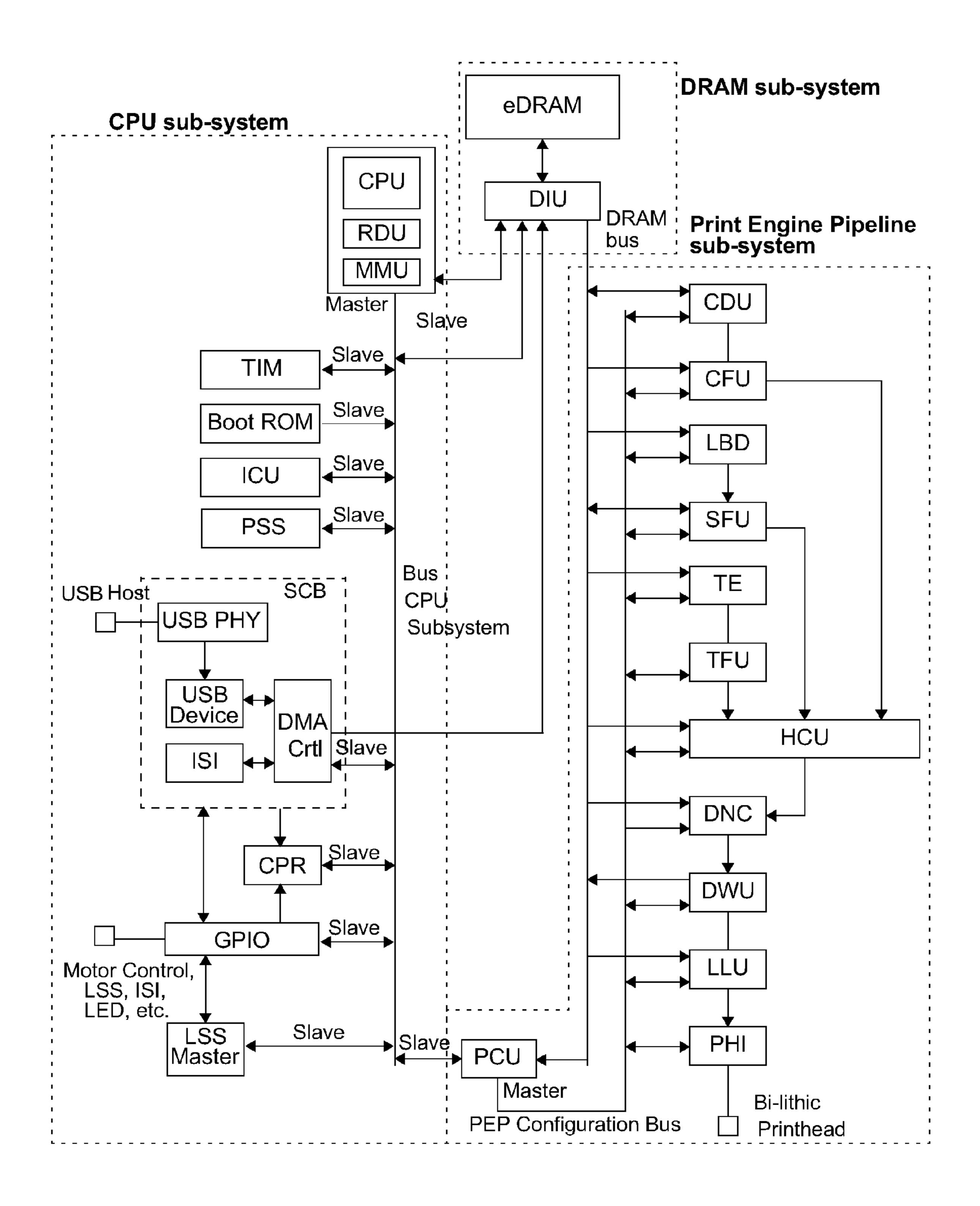

FIG. 12 shows a SoPEC system top level partition

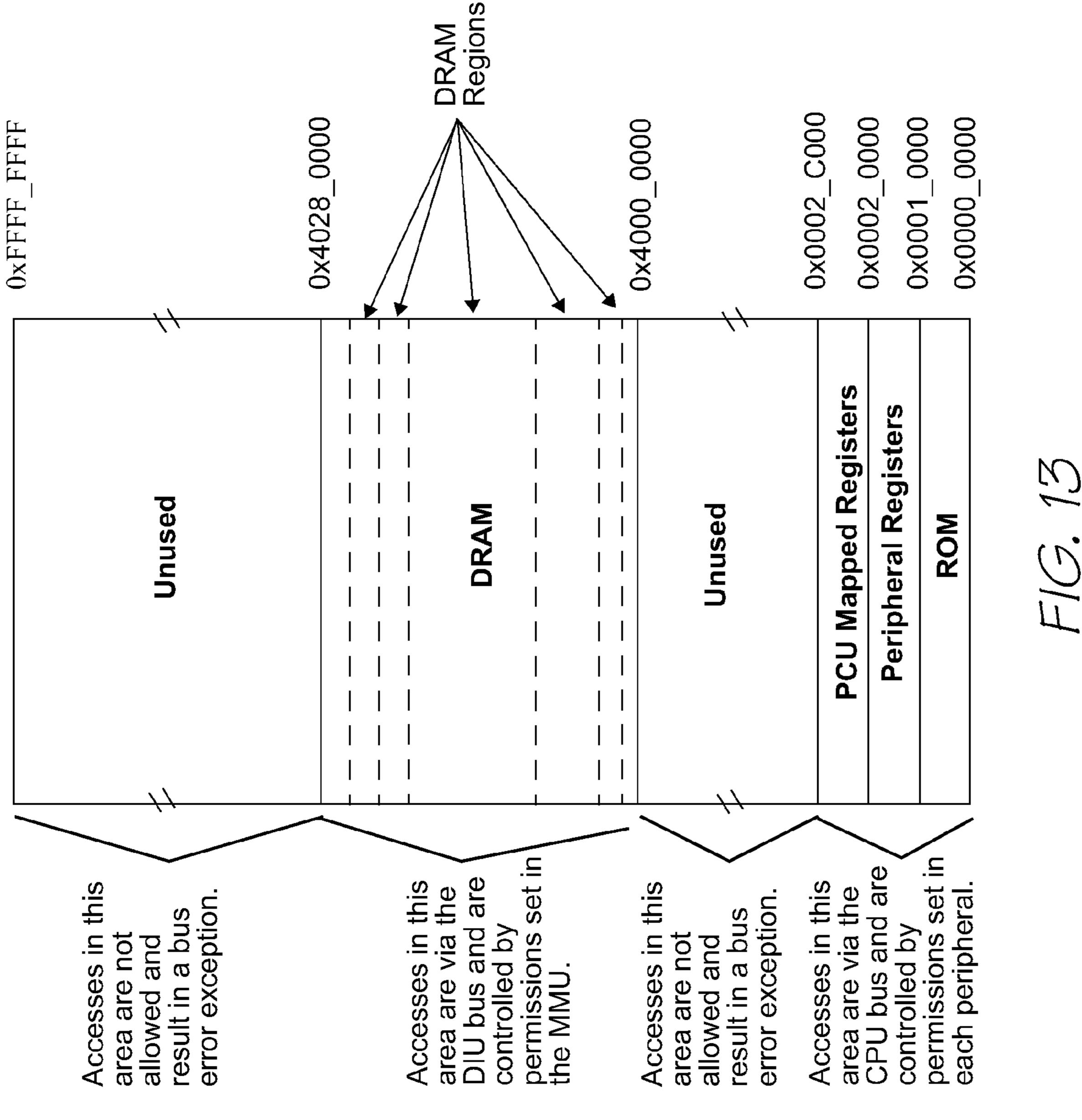

FIG. 13 shows a SoPEC CPU memory map (not to scale)

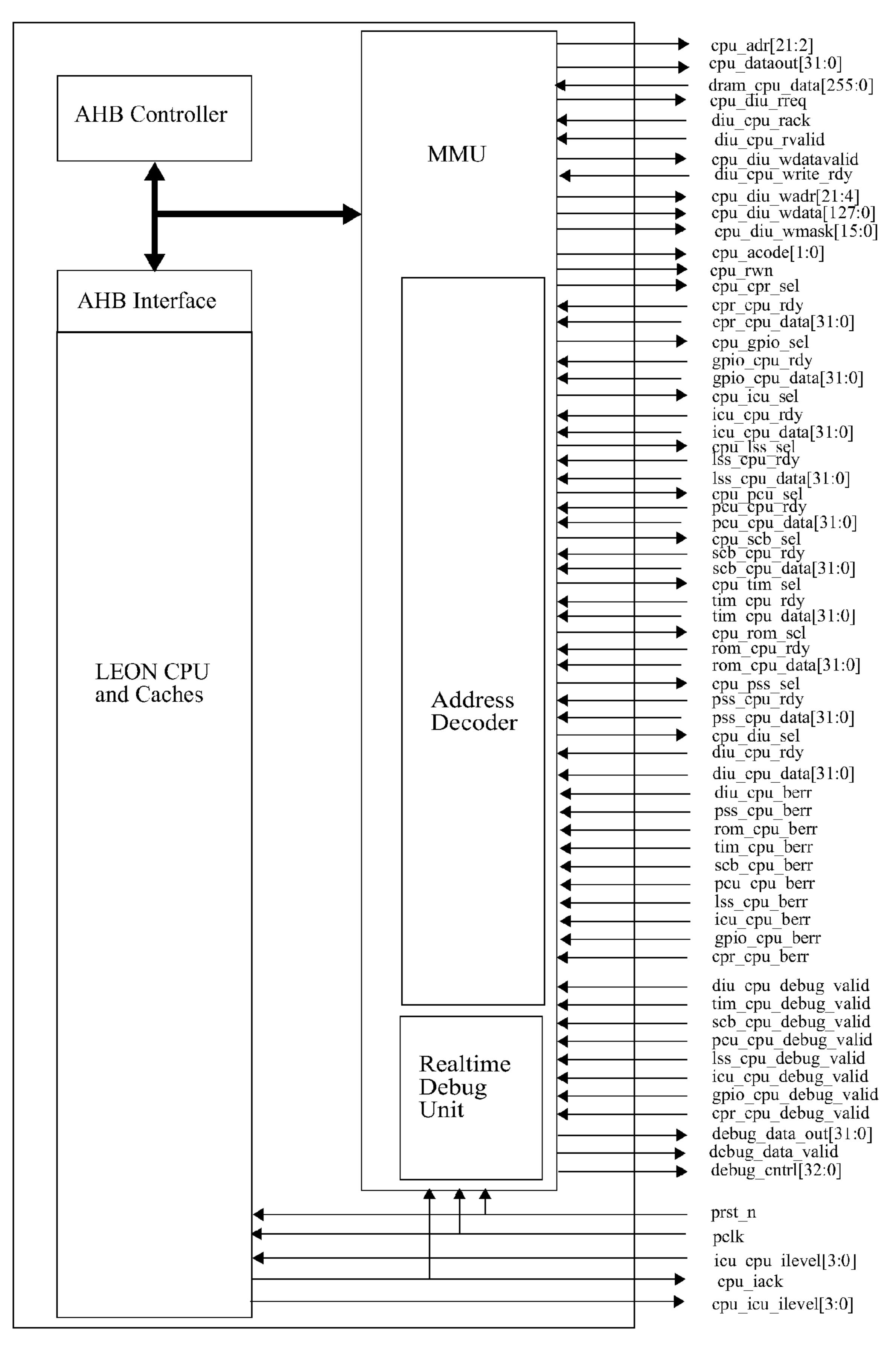

FIG. 14 is a block diagram of CPU

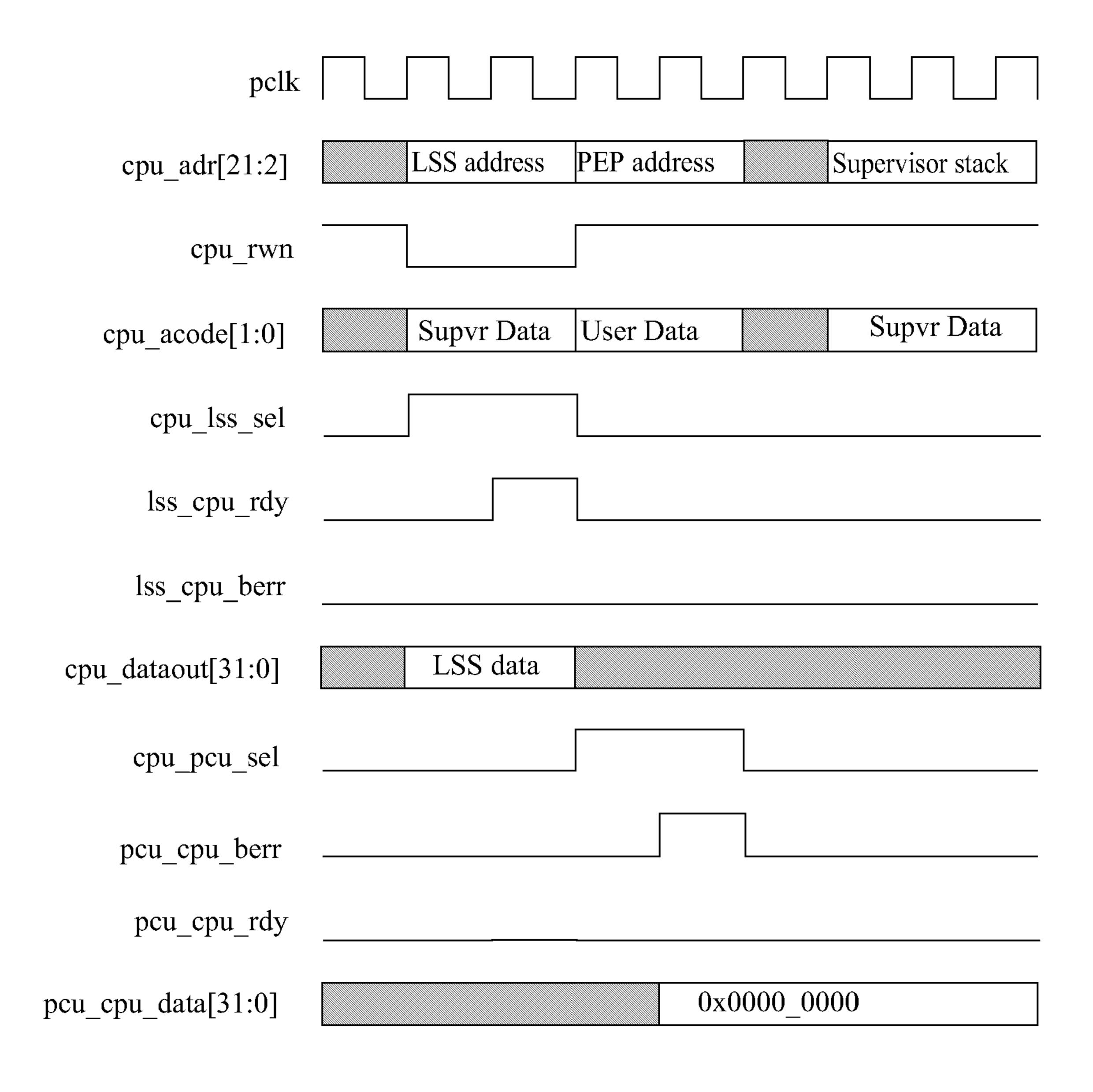

FIG. 15 shows CPU bus transactions

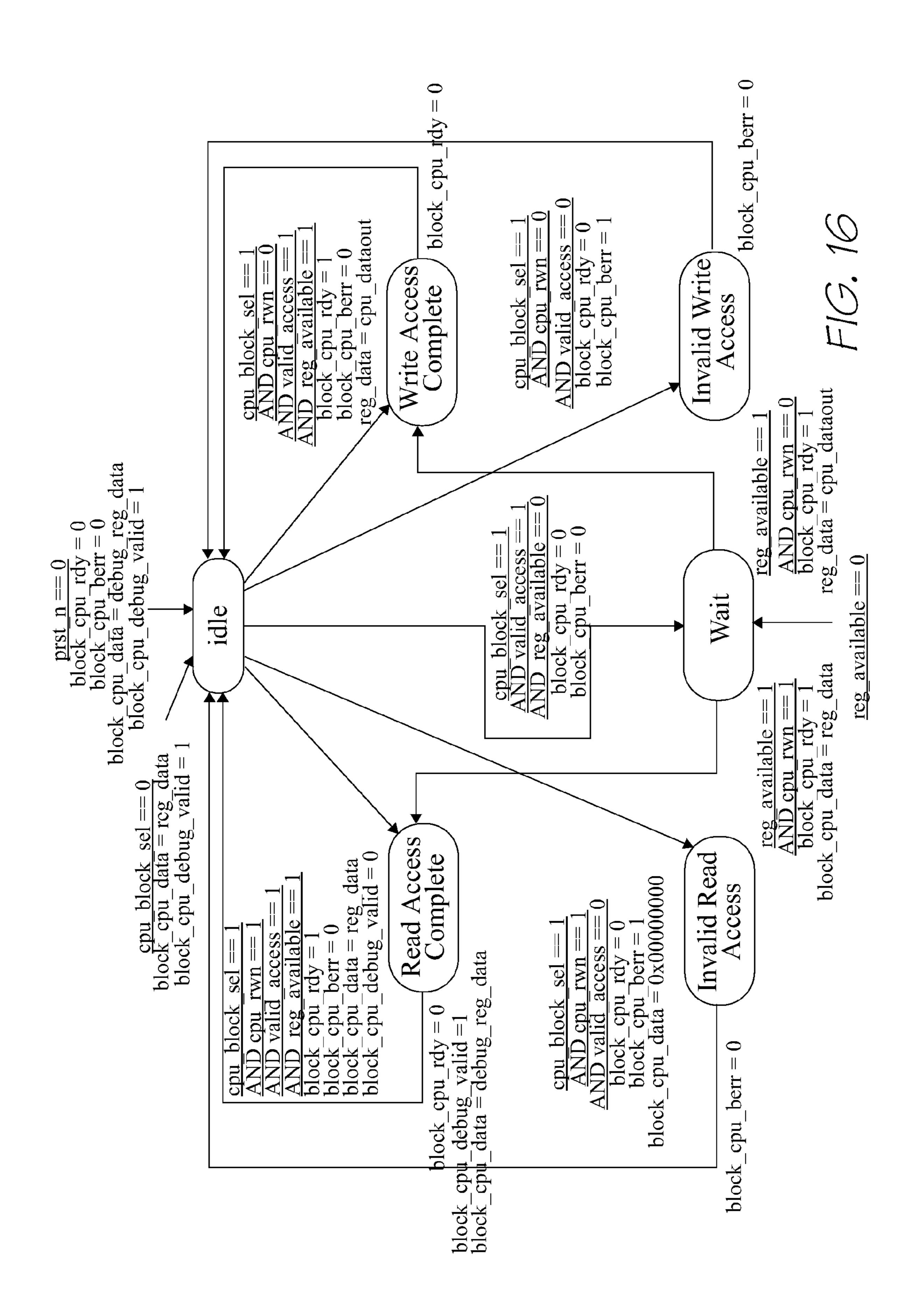

FIG. 16 shows a state machine for a CPU subsystem slave

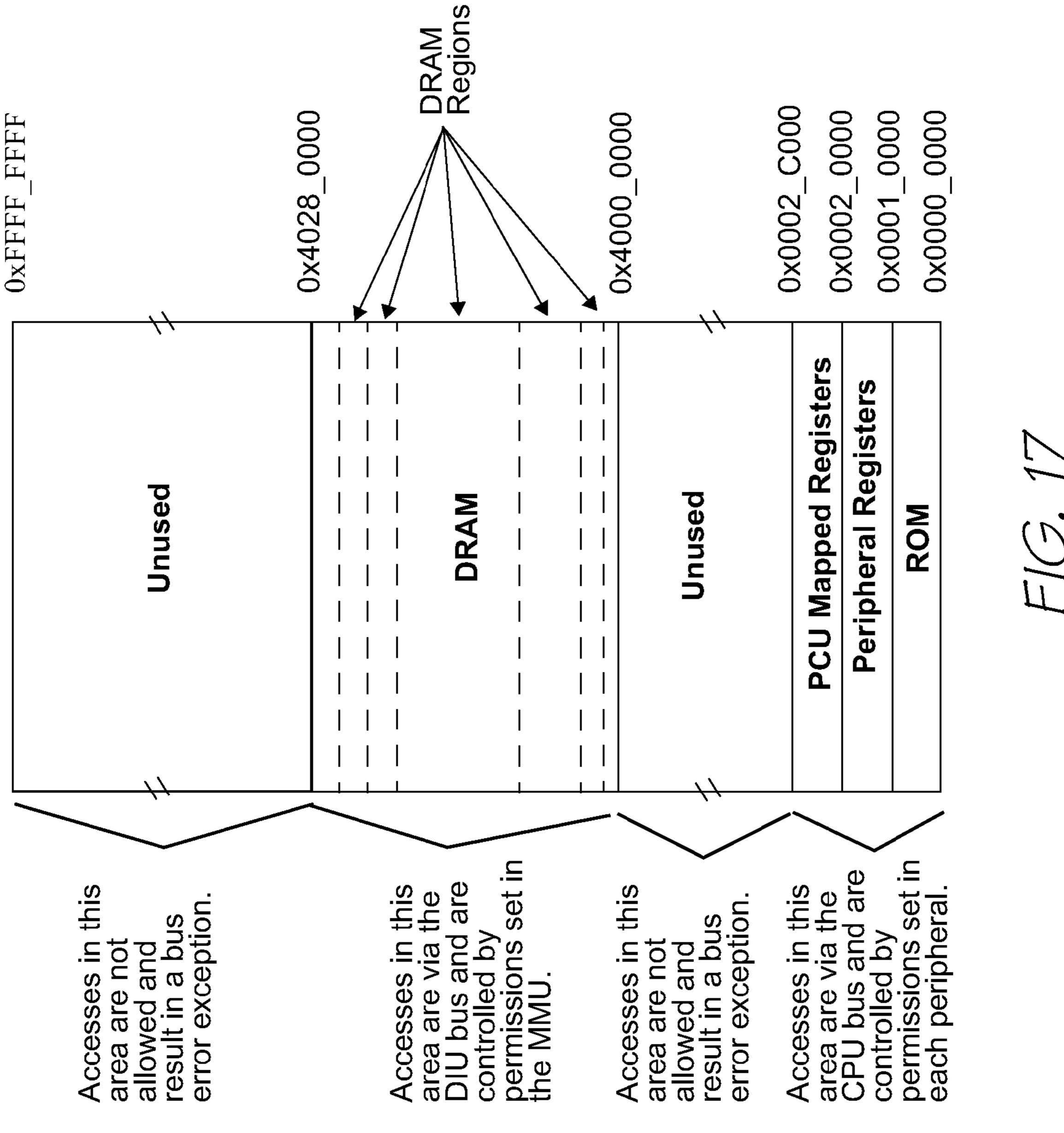

FIG. 17 shows a SoPEC CPU memory map (not to scale)

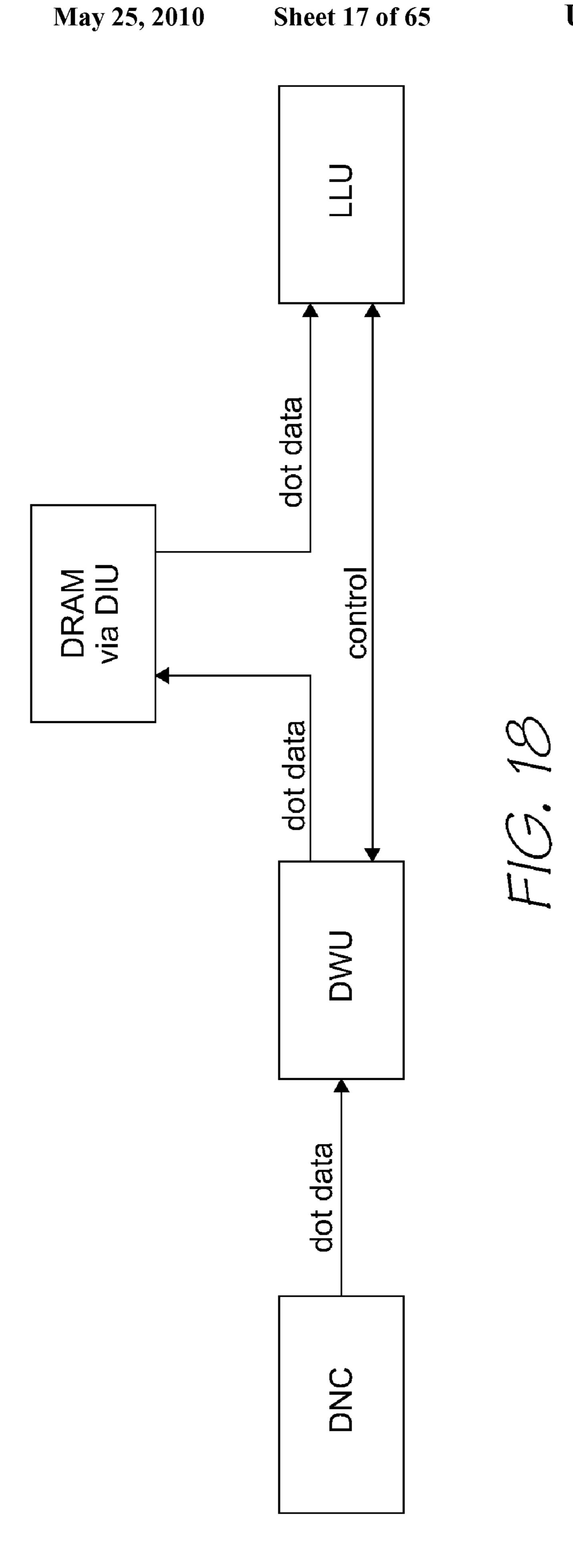

FIG. 18 shows a high-level data flow diagram of DWU in context

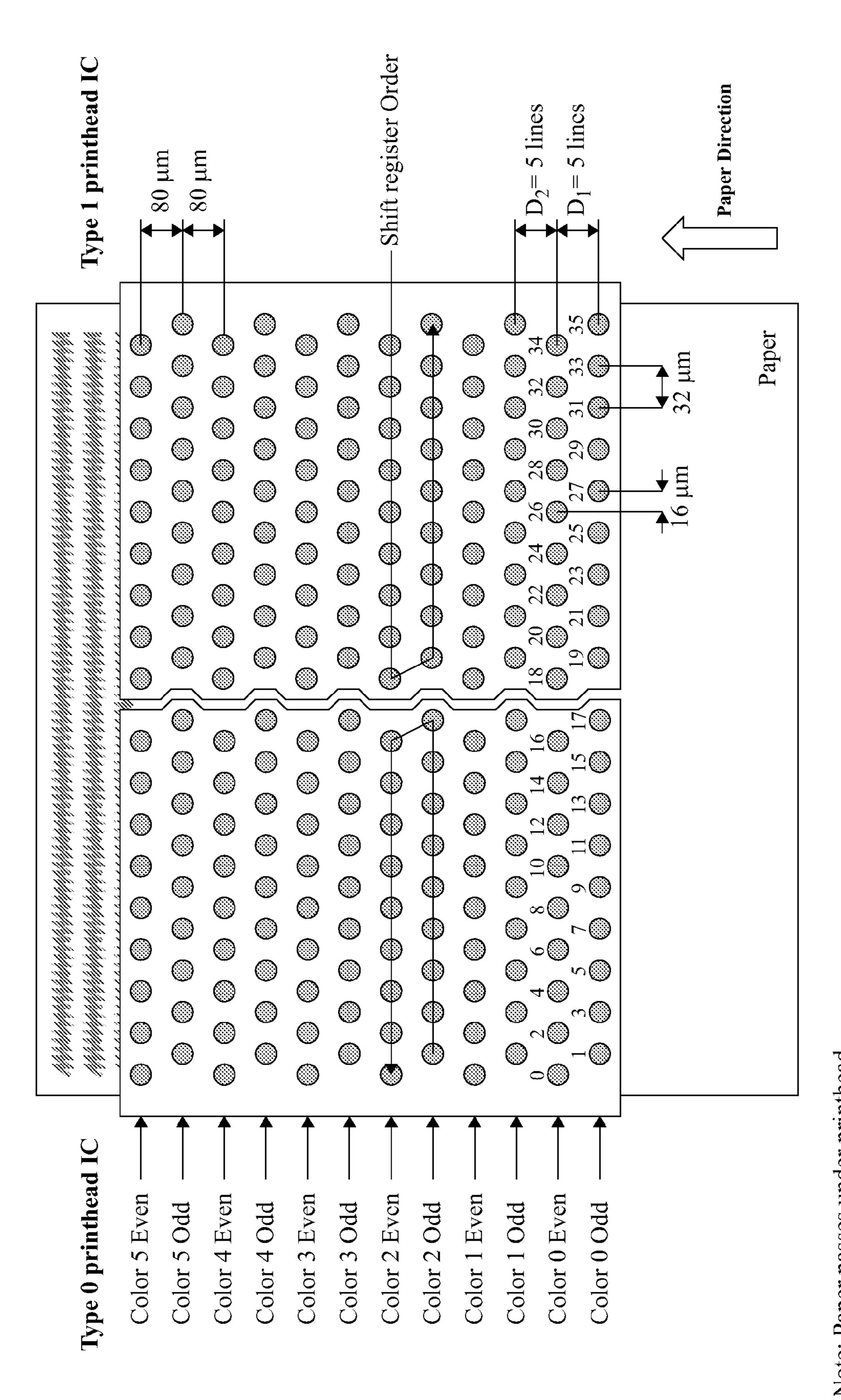

FIG. **19** shows a printhead nozzle layout for 36-nozzle bi-lithic printhead

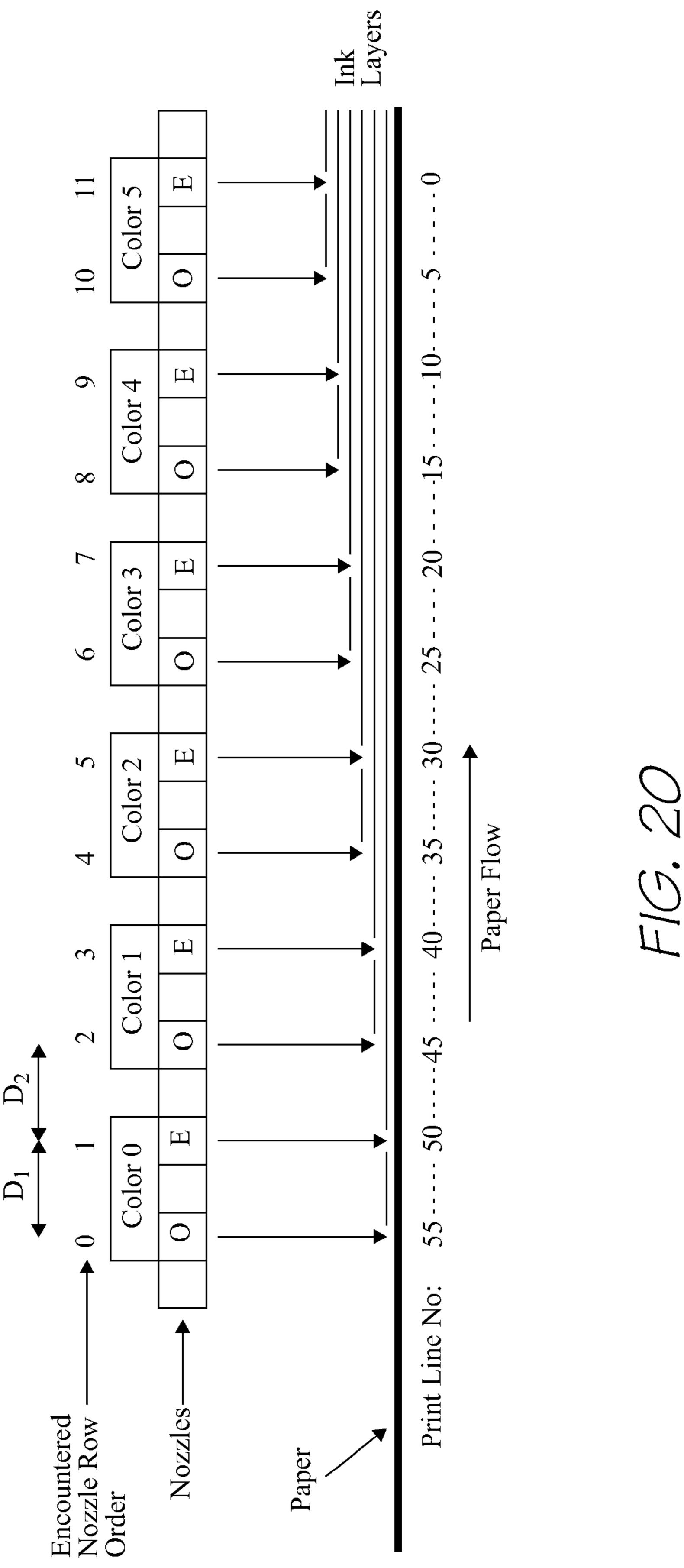

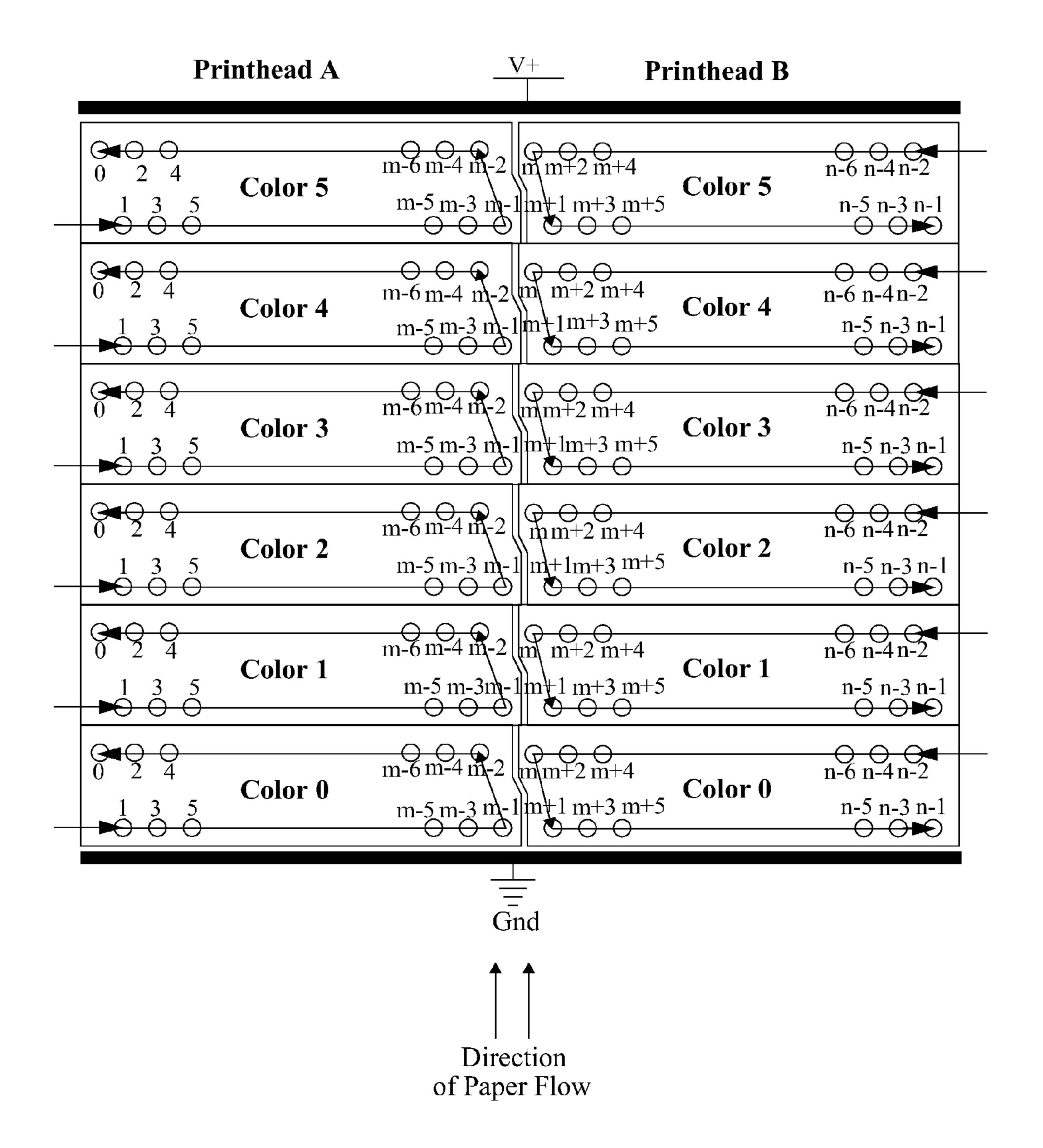

FIG. 20 shows a printhead nozzle layout for a 36-nozzle bi-lithic printhead

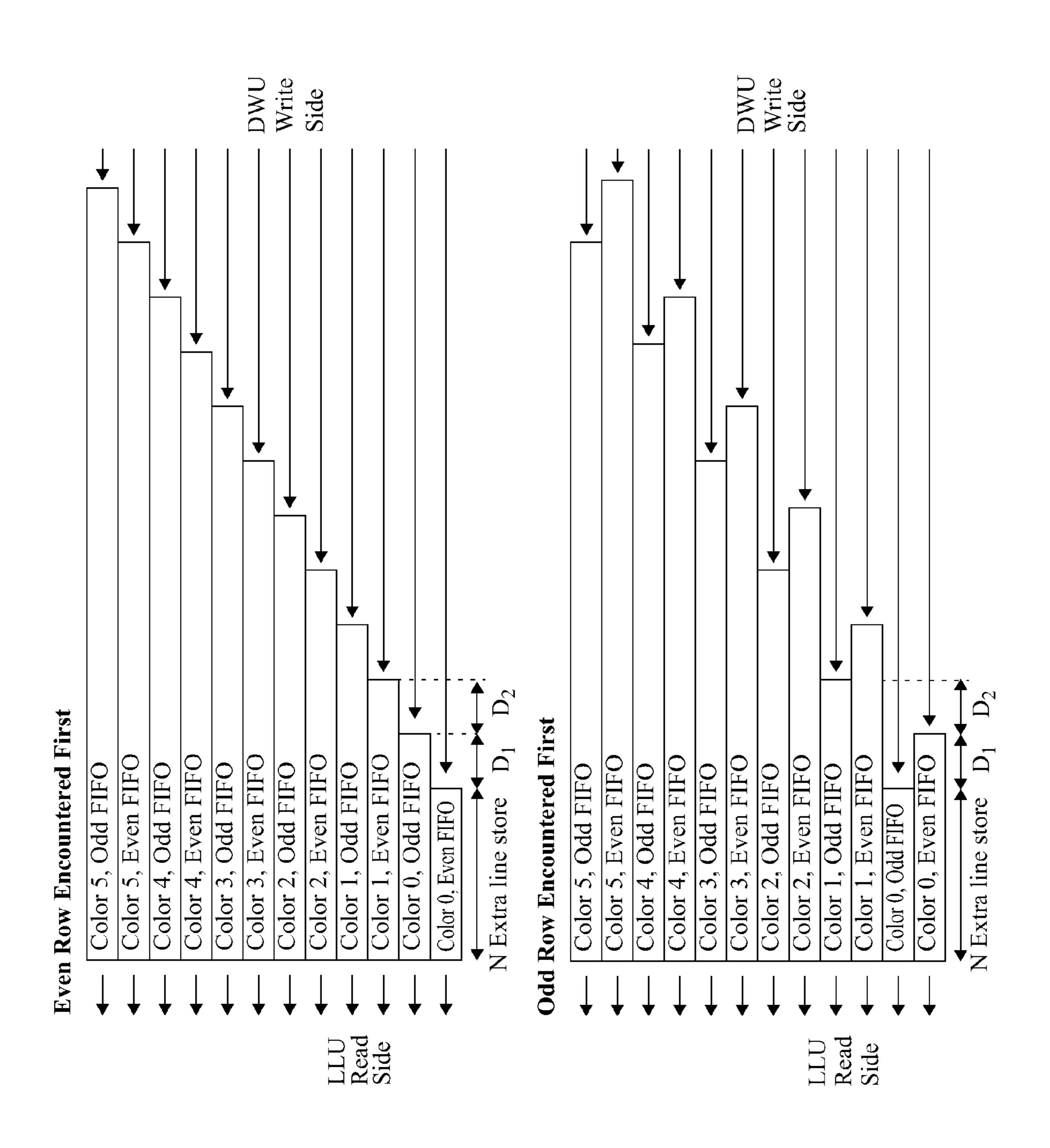

FIG. 21 shows a dot line store logical representation

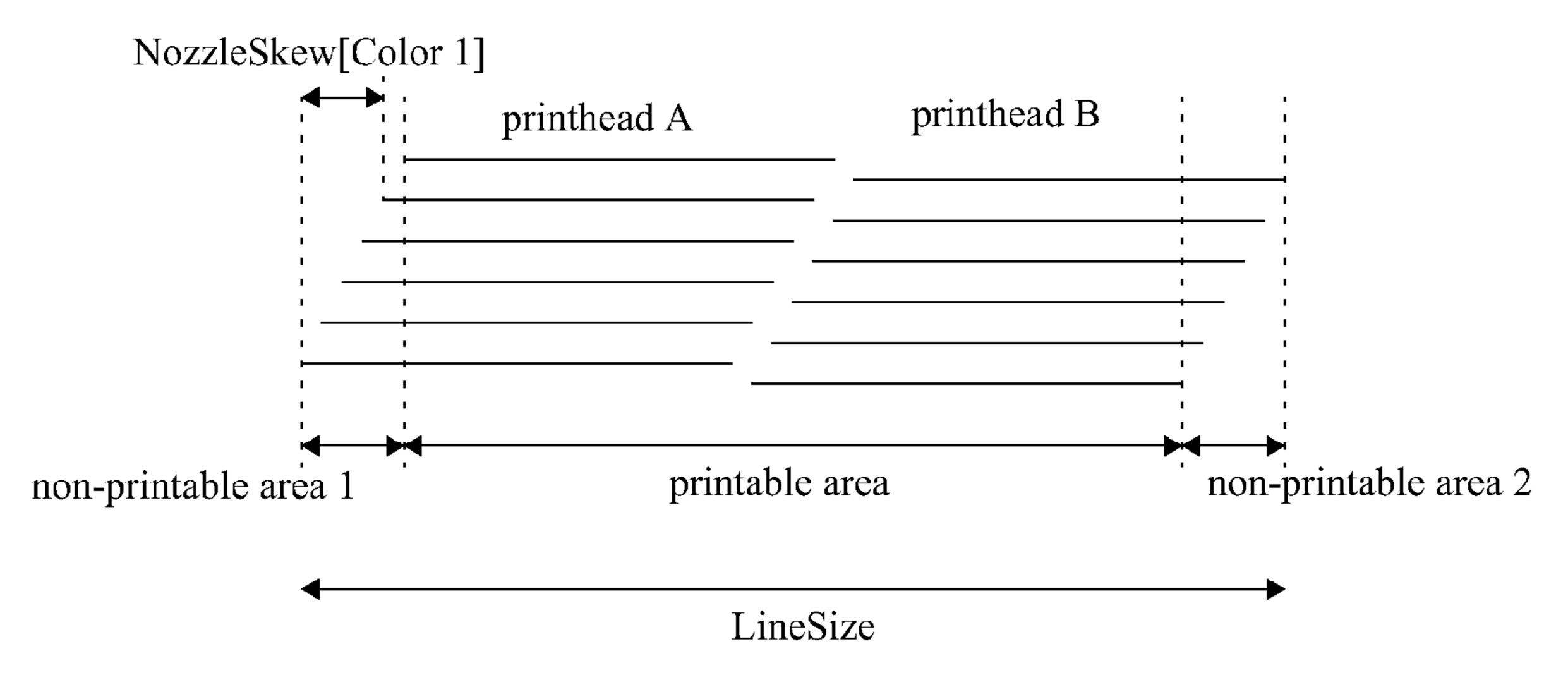

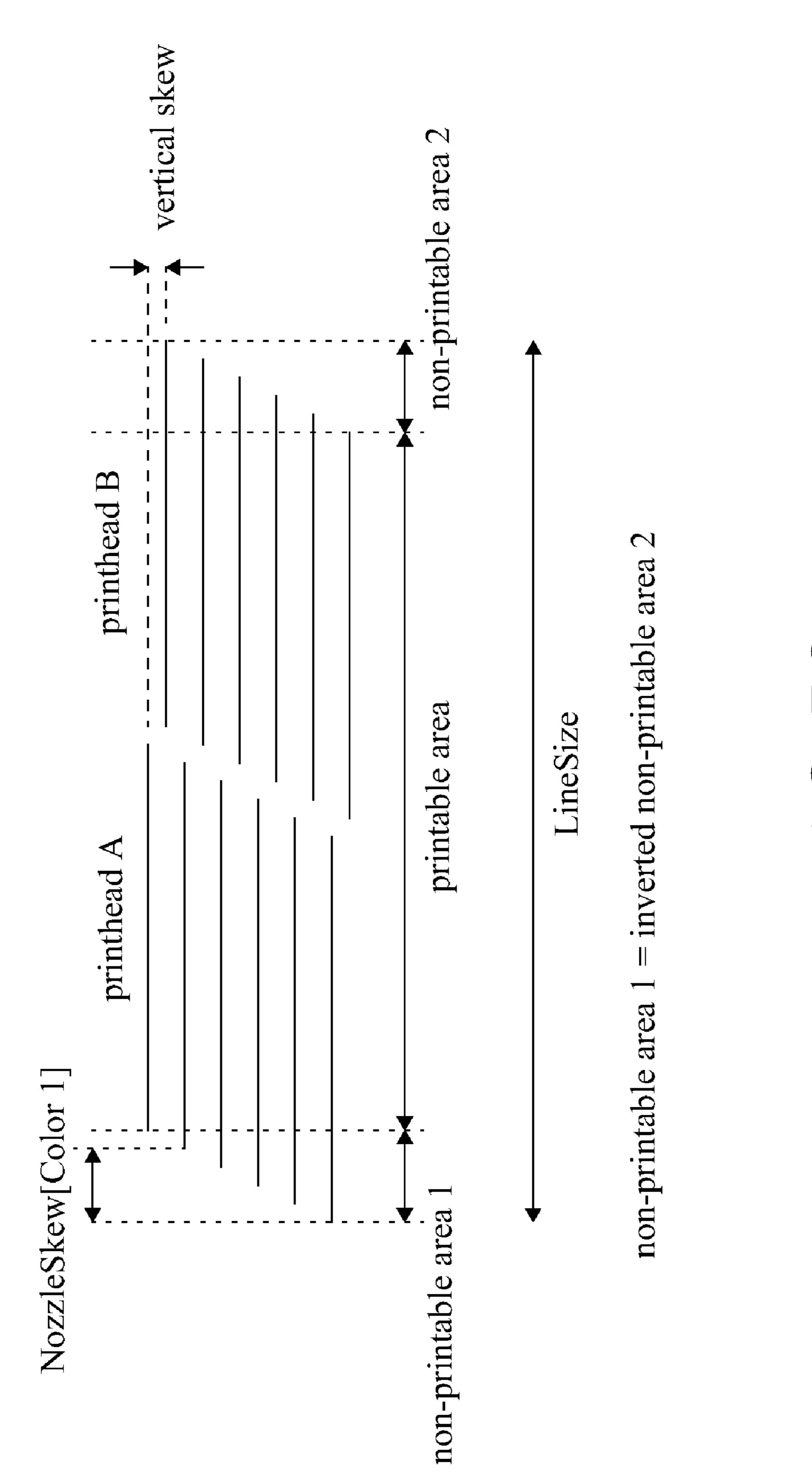

FIG. 22 shows a conceptual view of printhead row alignment

FIG. 23 shows a conceptual view of printhead rows (as seen by the LLU and PHI)

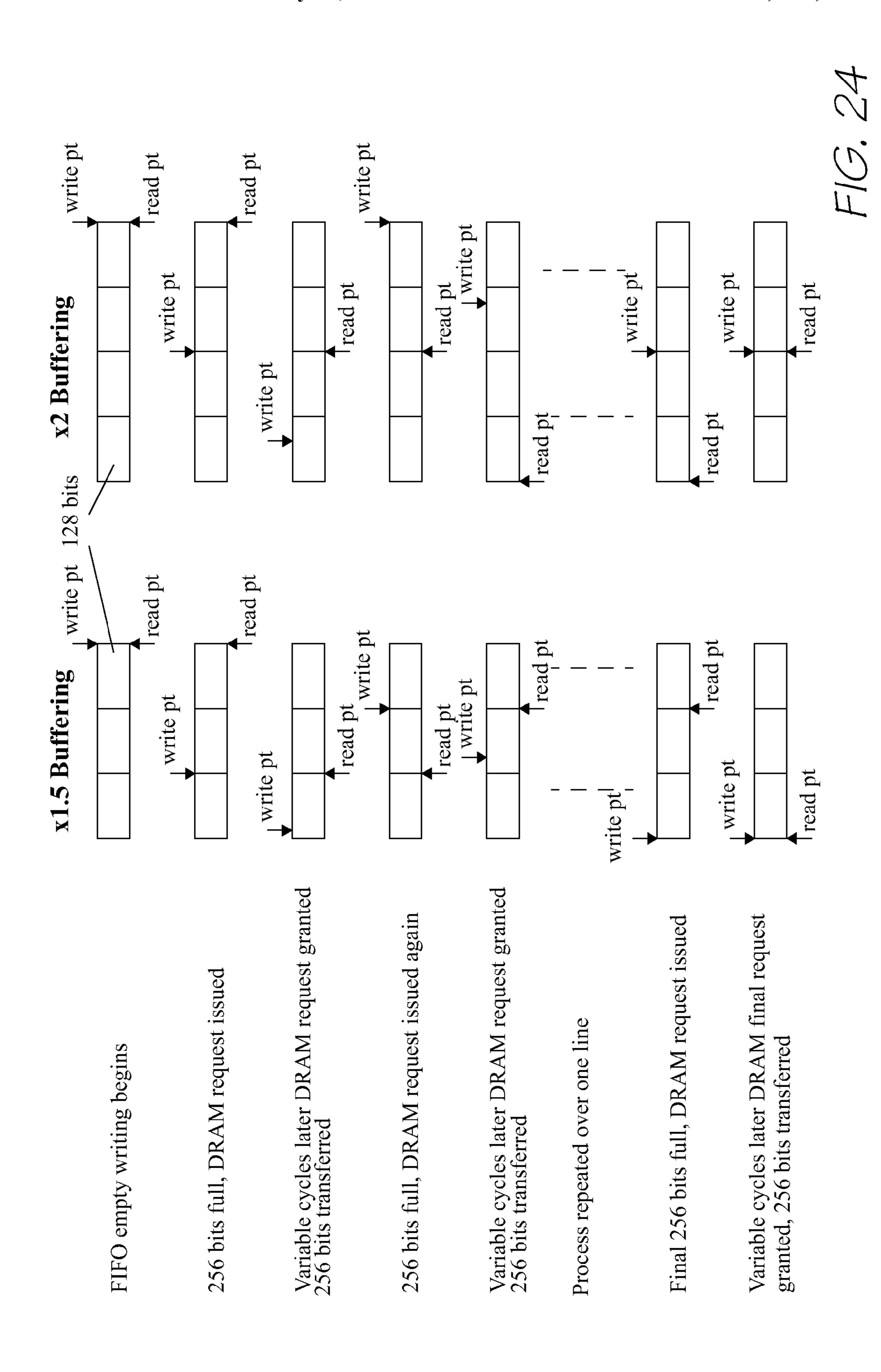

FIG. **24** shows a comparison of 1.5×v 2× buffering

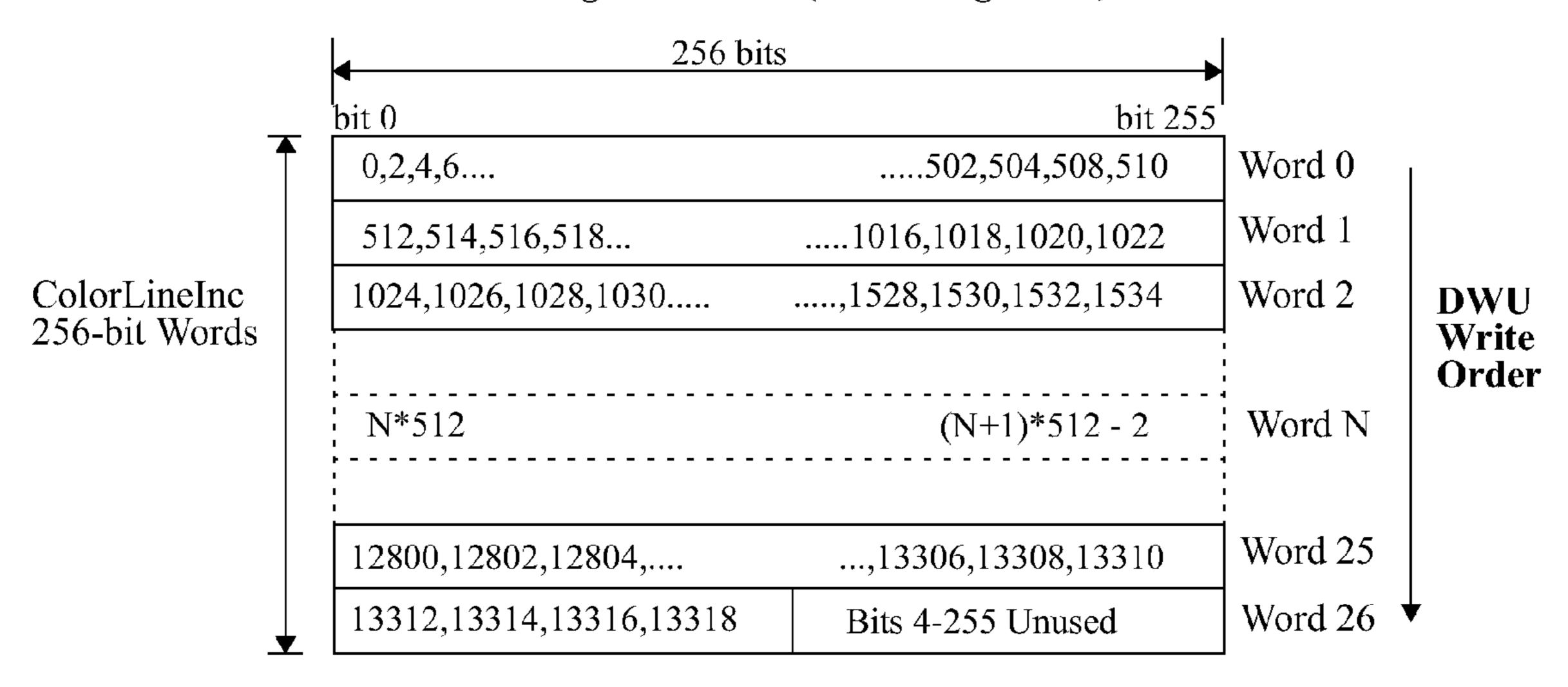

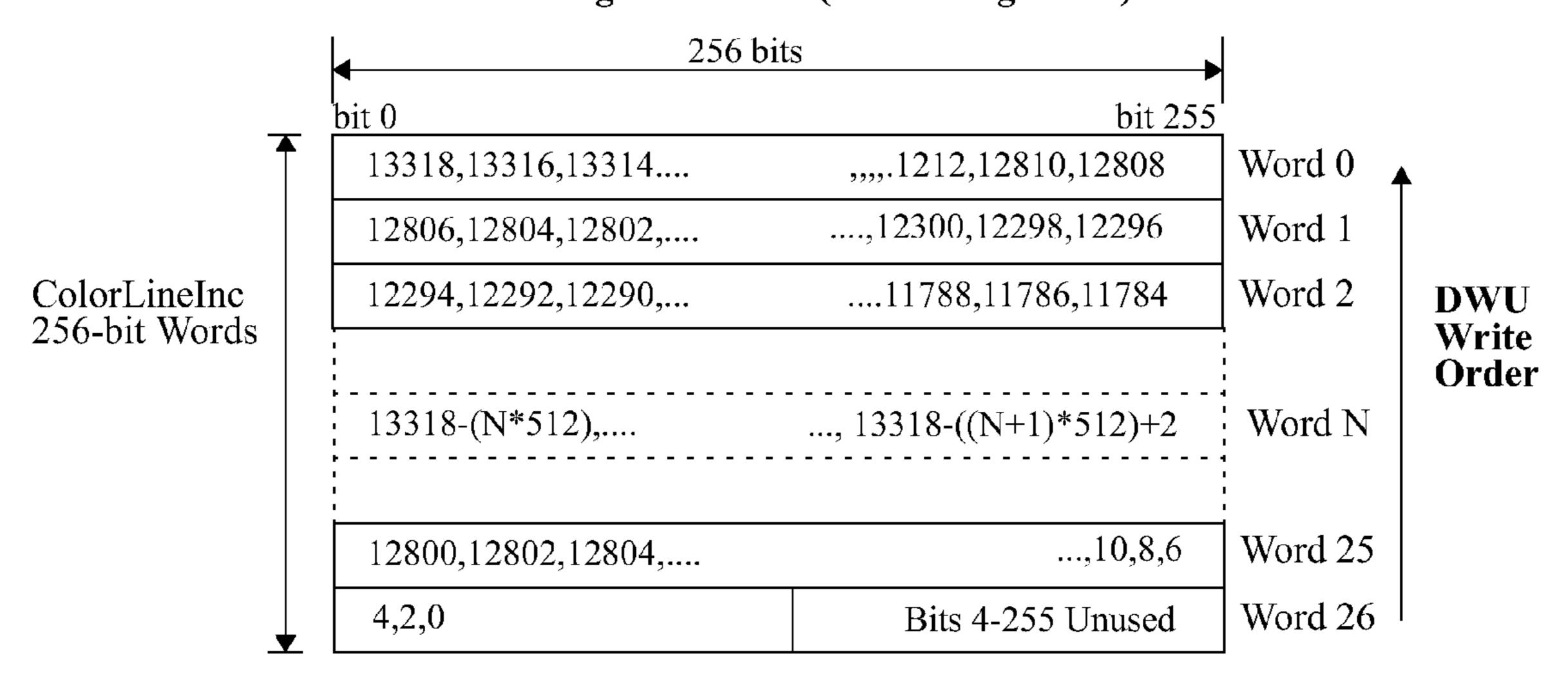

FIG. **25** shows an even dot order in DRAM (increasing sense, 13320 dot wide line)

FIG. **26** shows an even dot order in DRAM (decreasing sense, 13320 dot wide line)

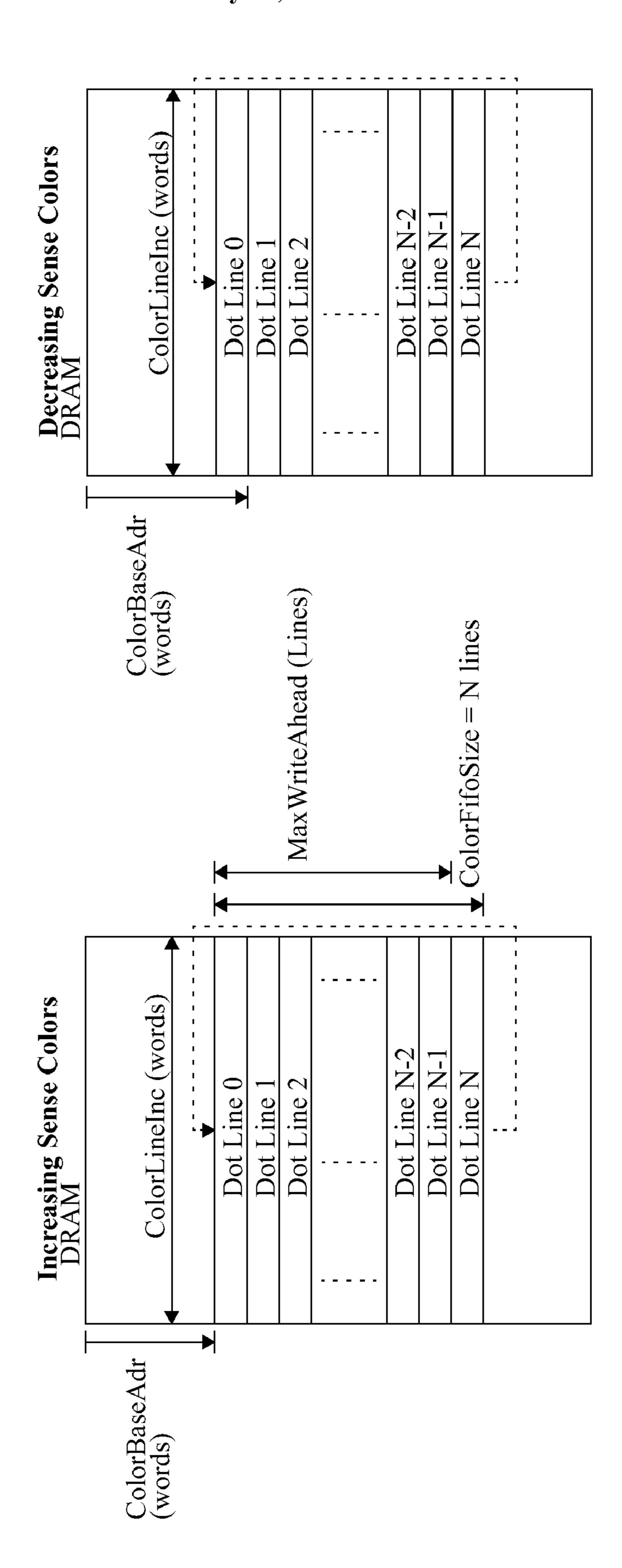

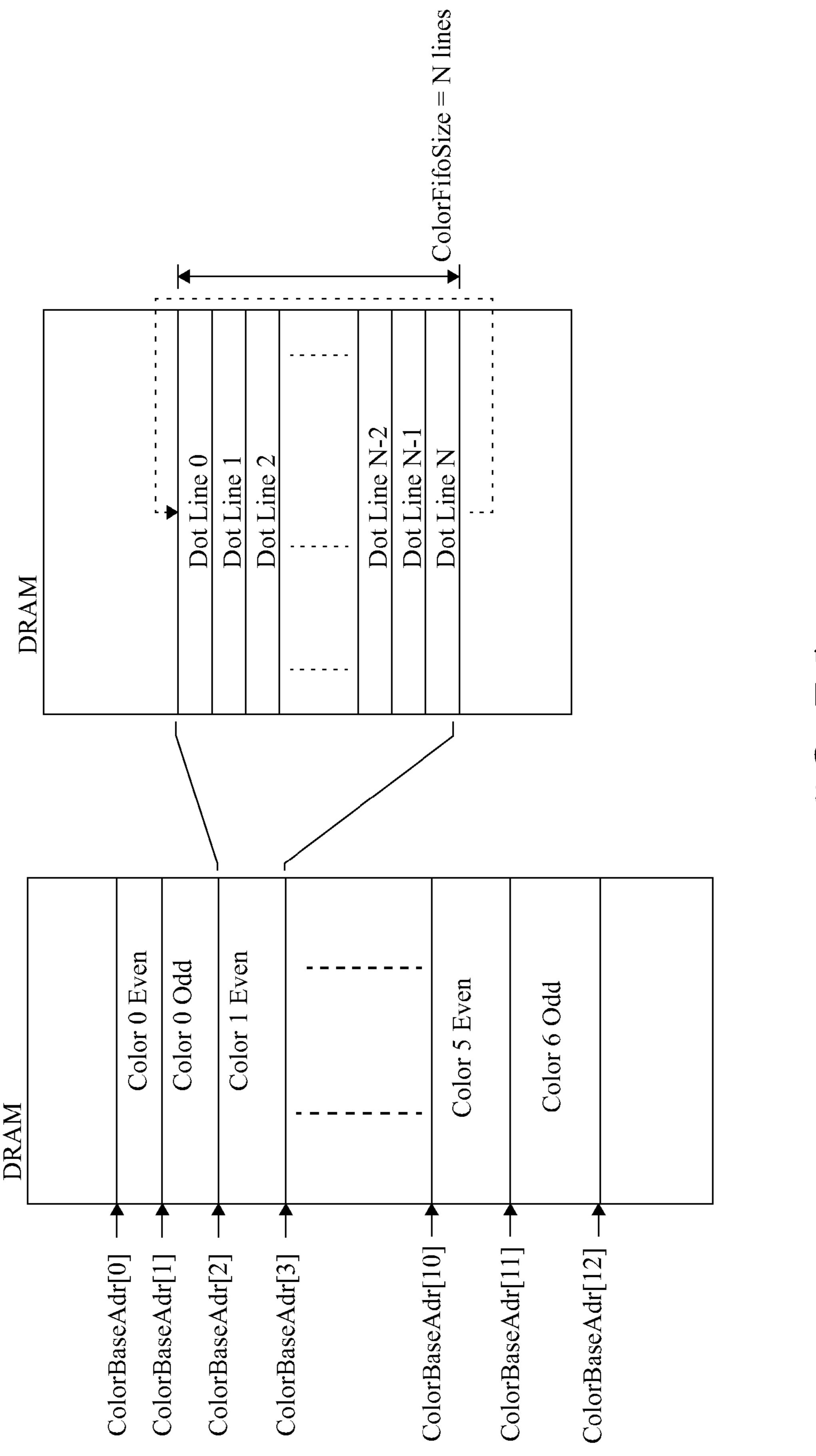

FIG. 27 shows a dotline FIFO data structure in DRAM

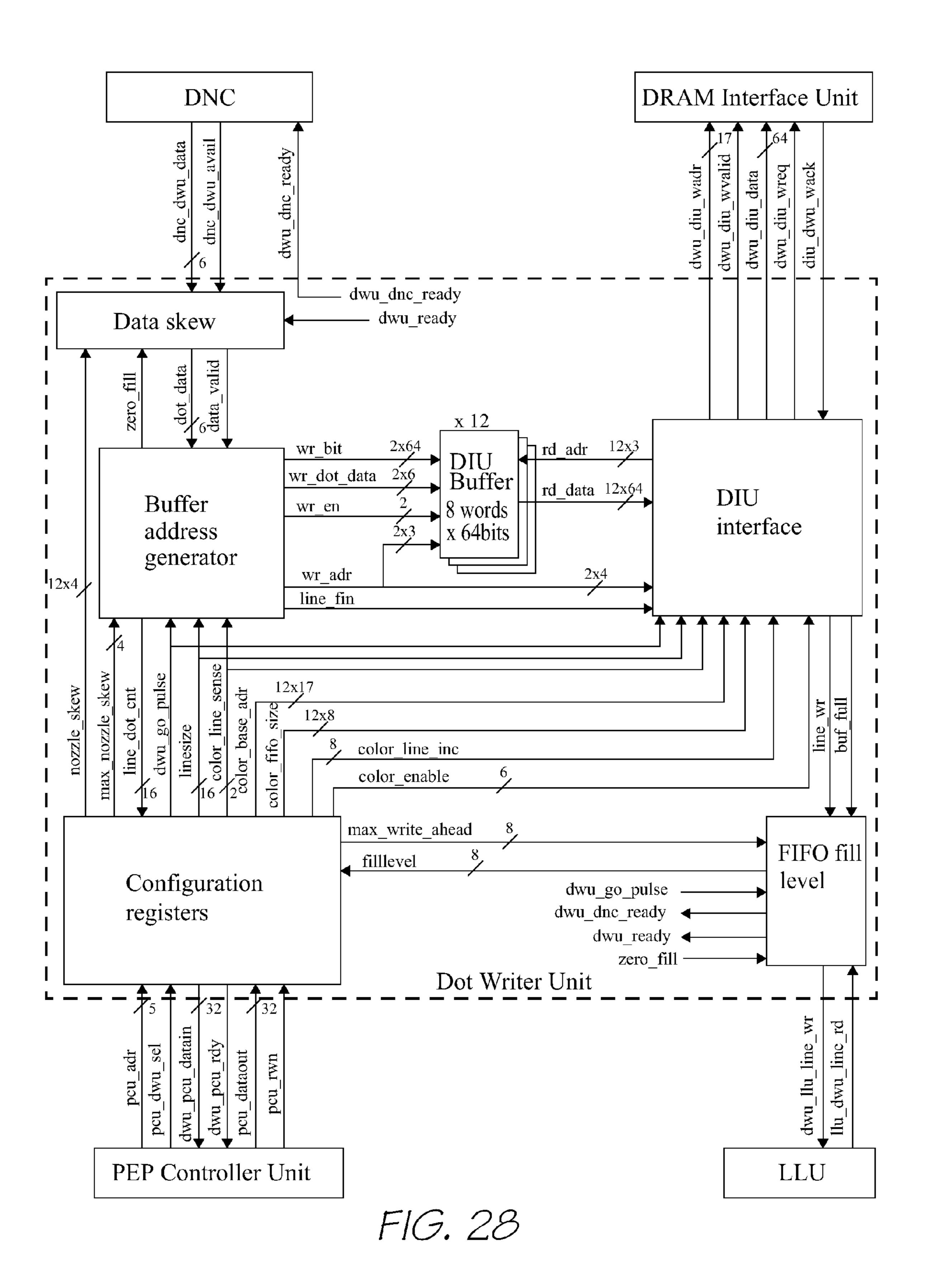

FIG. 28 shows a DWU partition

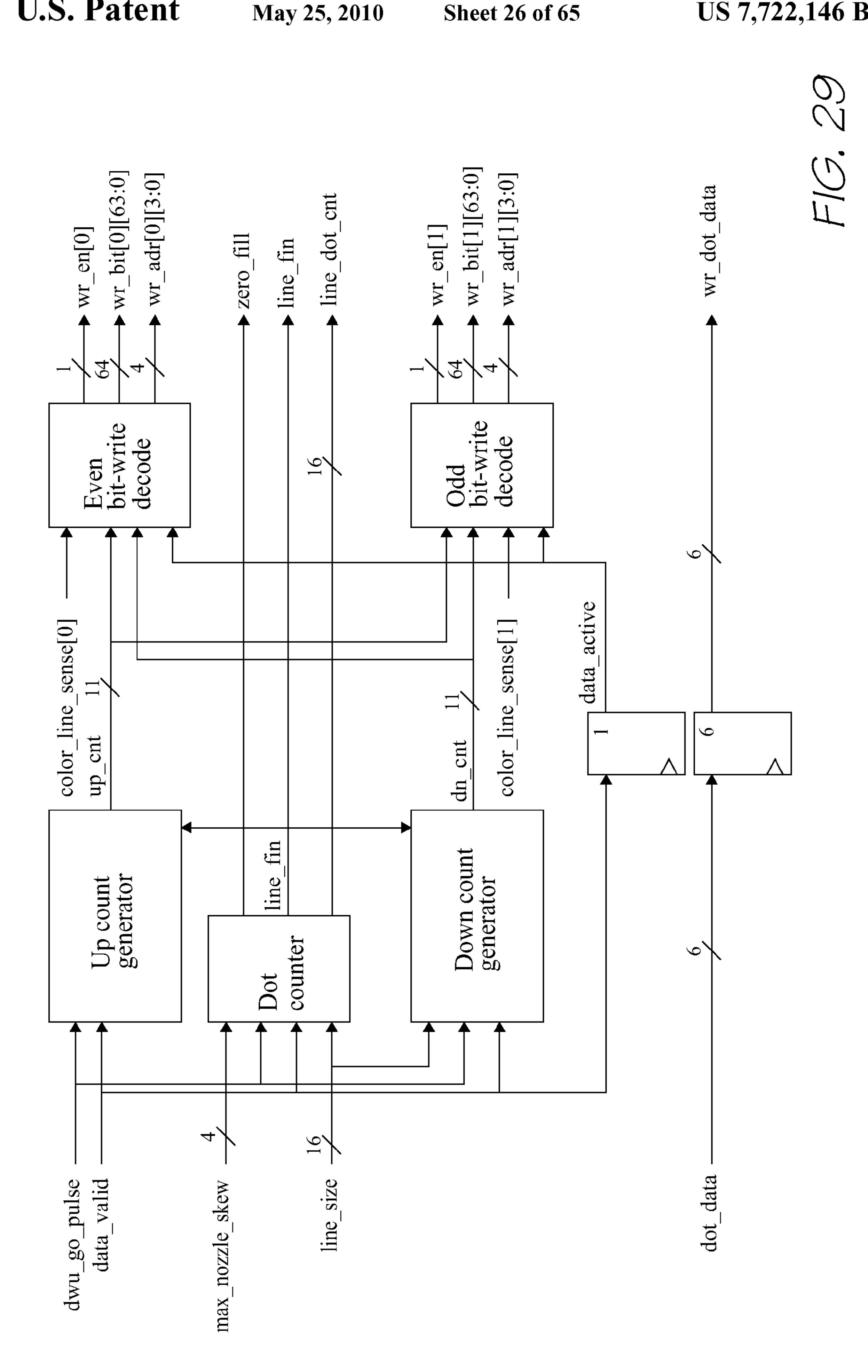

FIG. 29 shows a buffer address generator sub-block

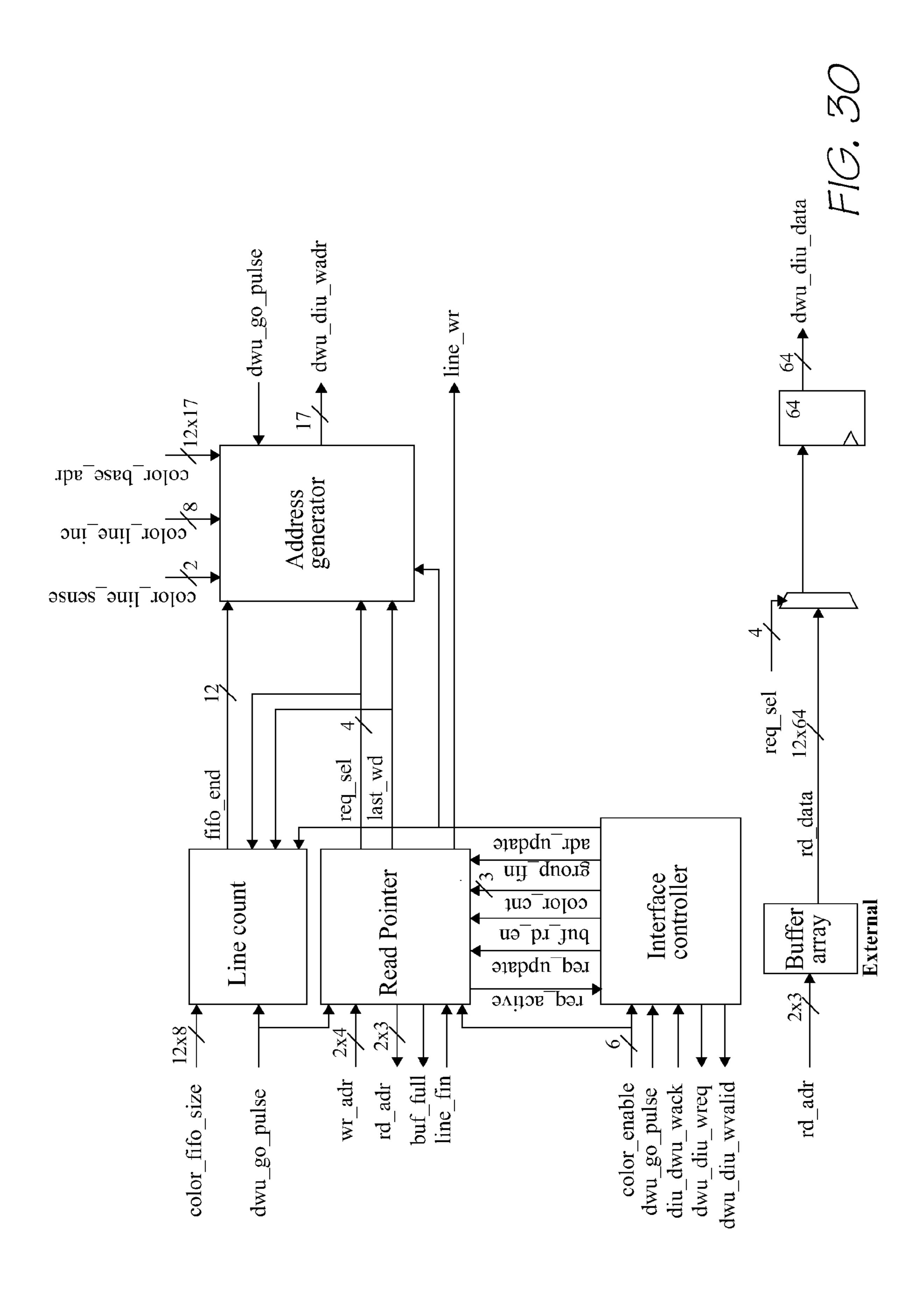

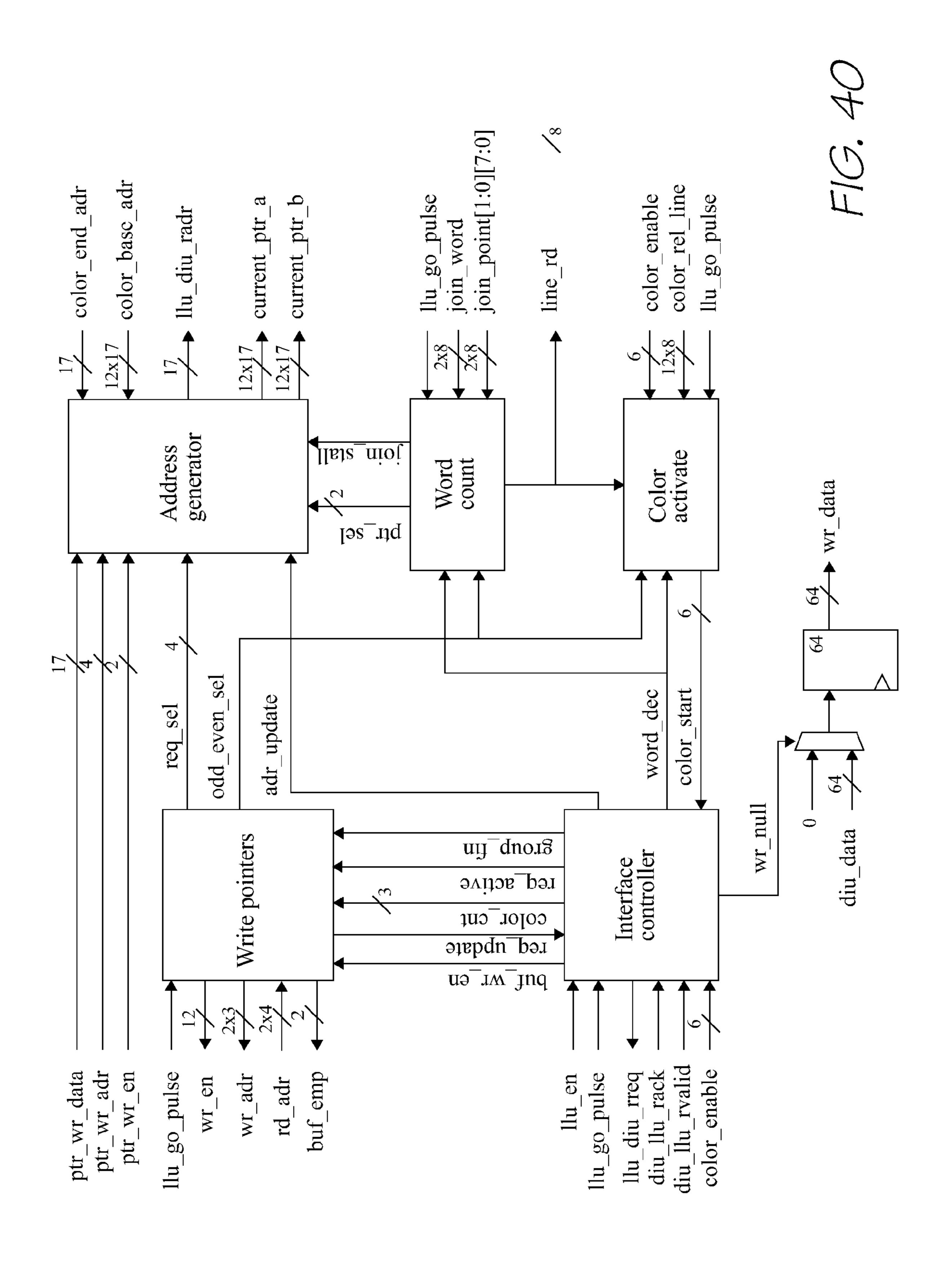

FIG. 30 shows a DIU Interface sub-block

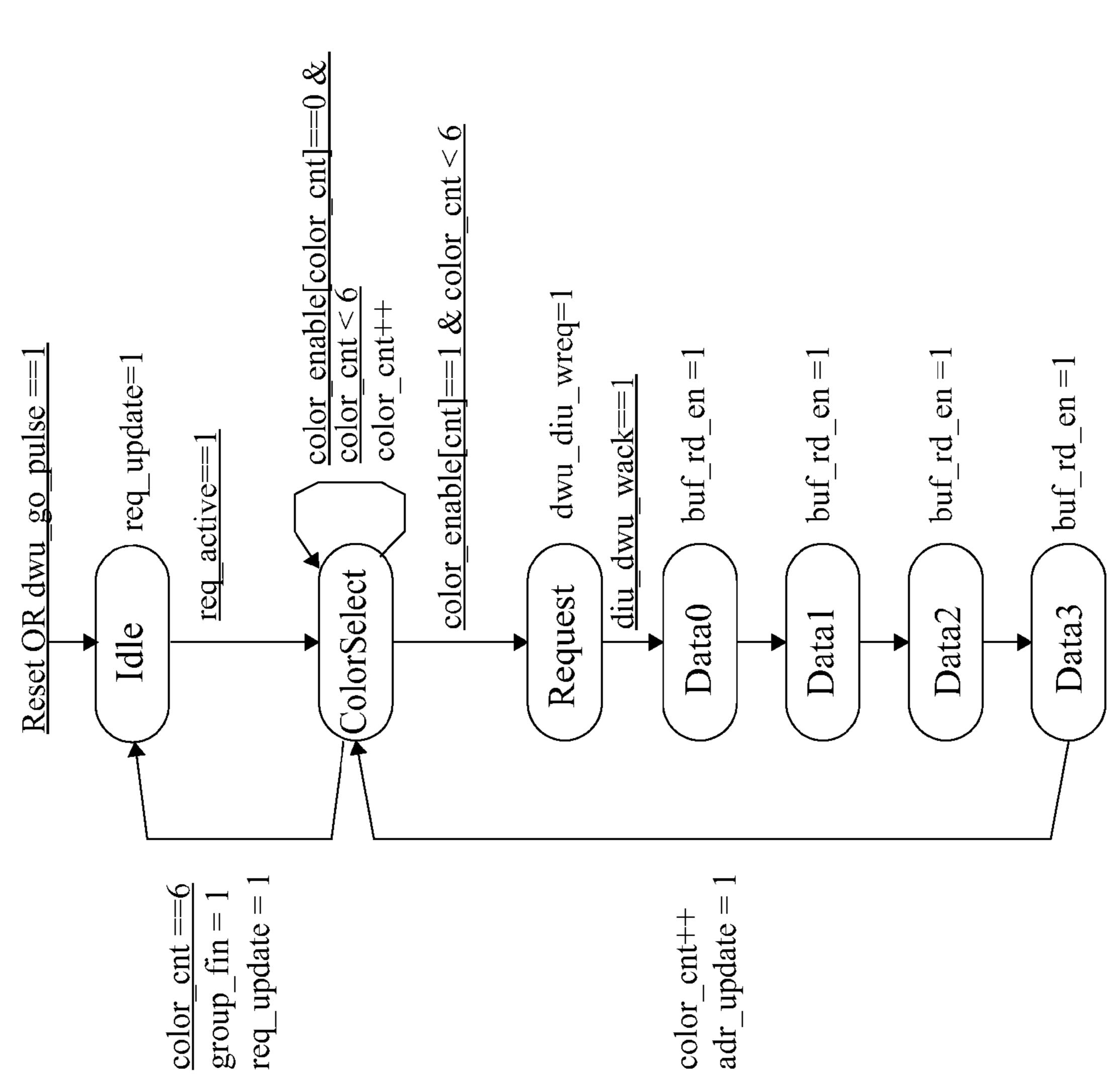

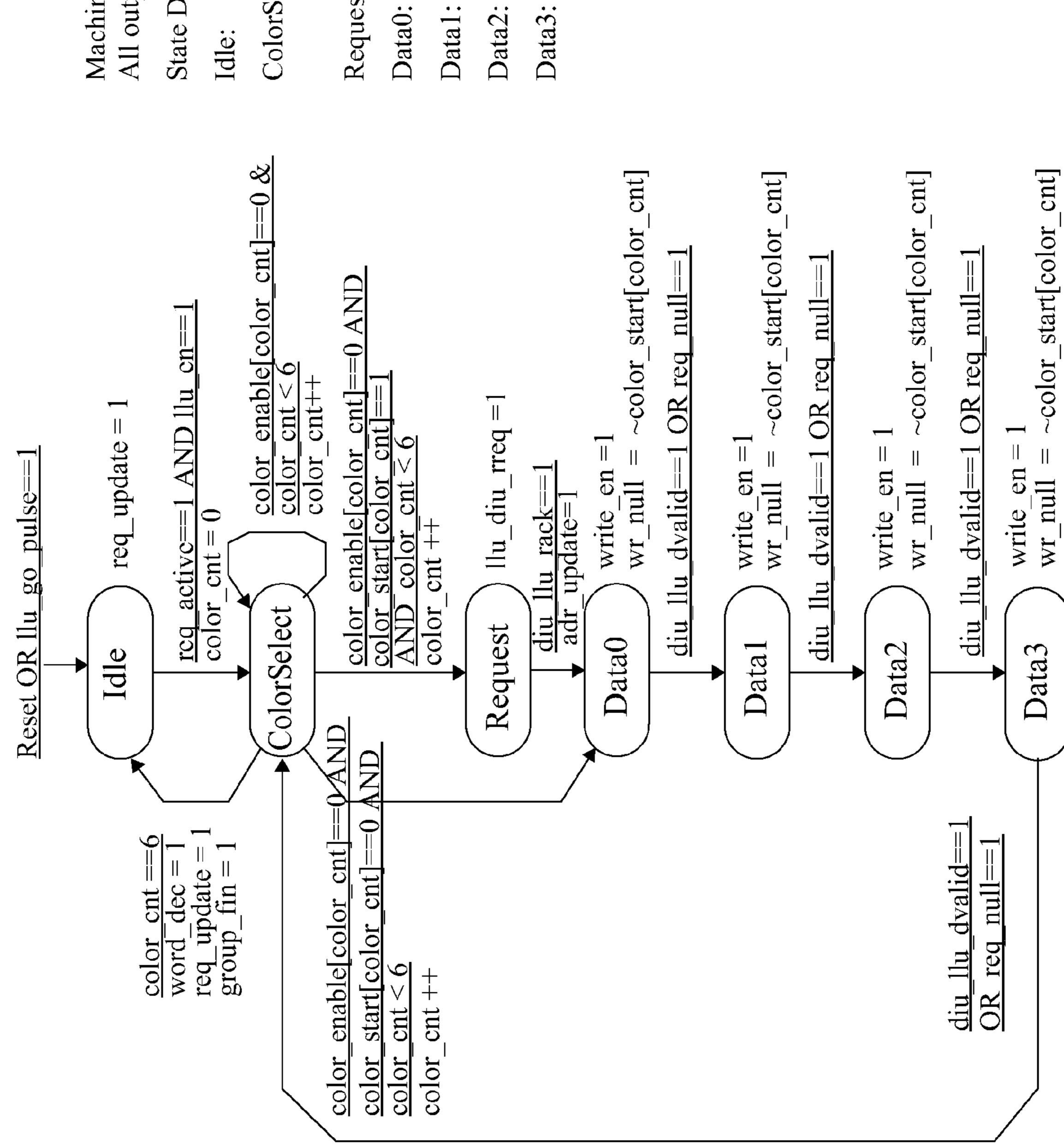

FIG. 31 shows an interface controller state diagram

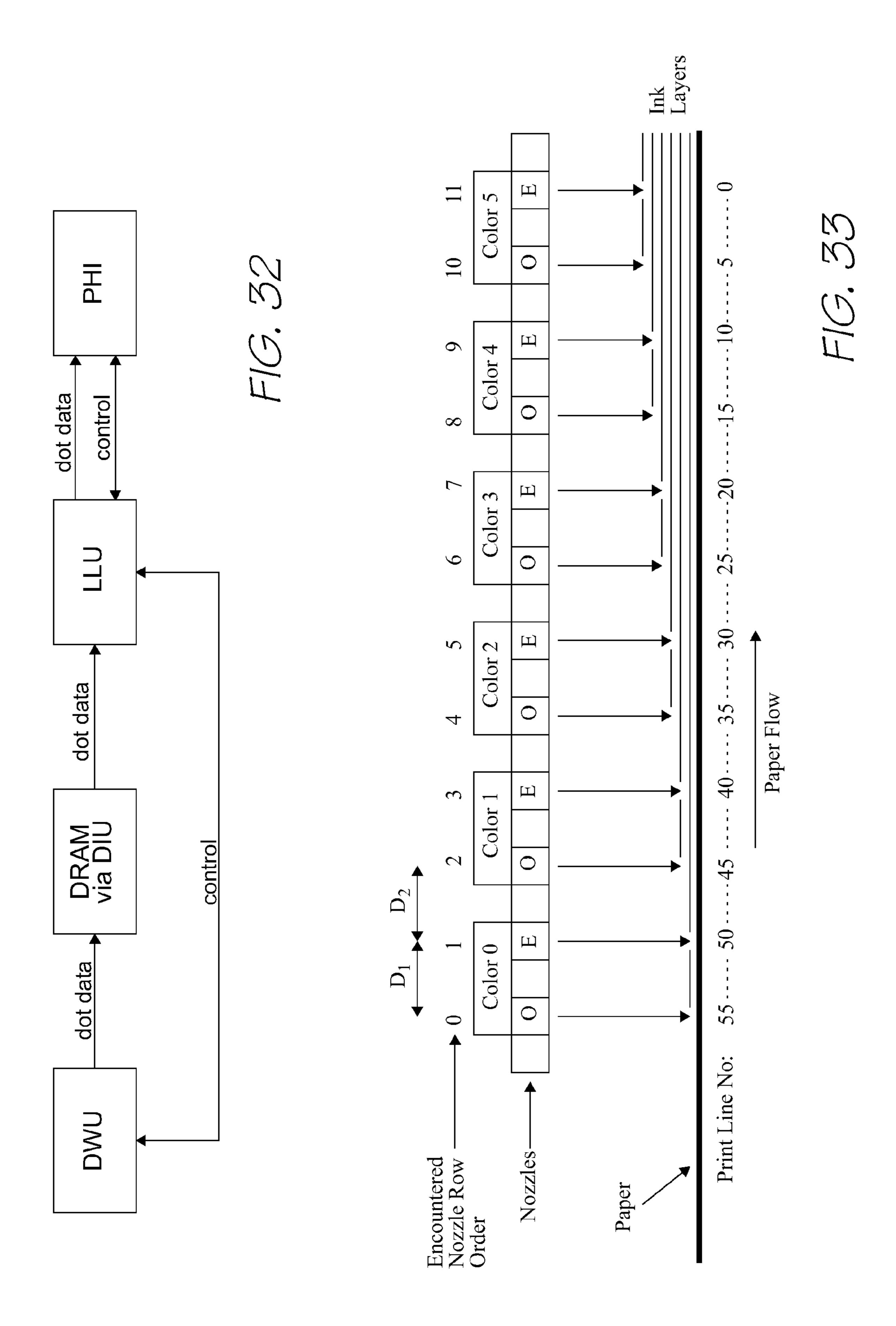

FIG. 32 shows a high level data flow diagram of LLU in context

FIG. 33 shows paper and printhead nozzles relationship (example with  $D_1=D_2=5$ )

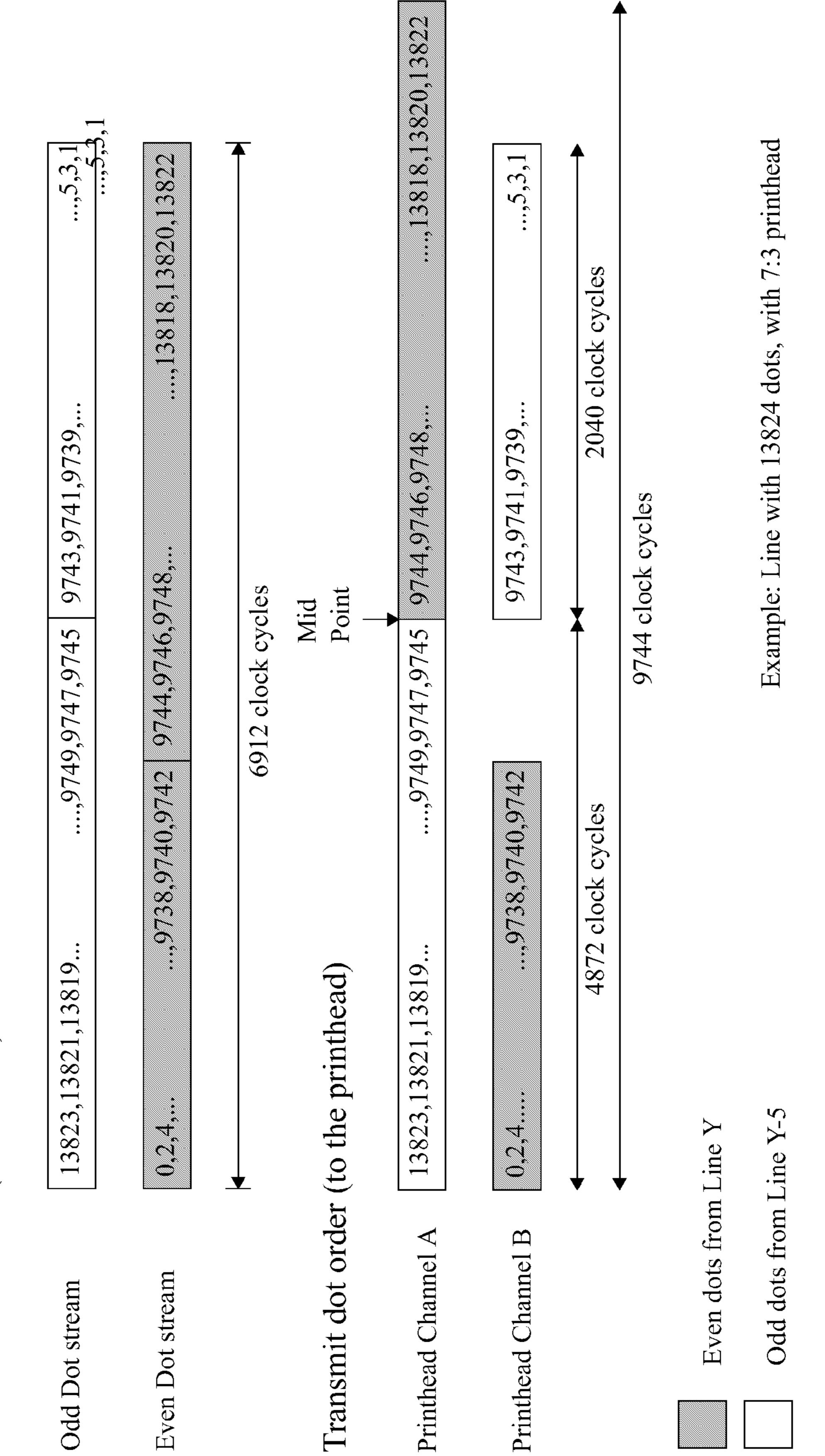

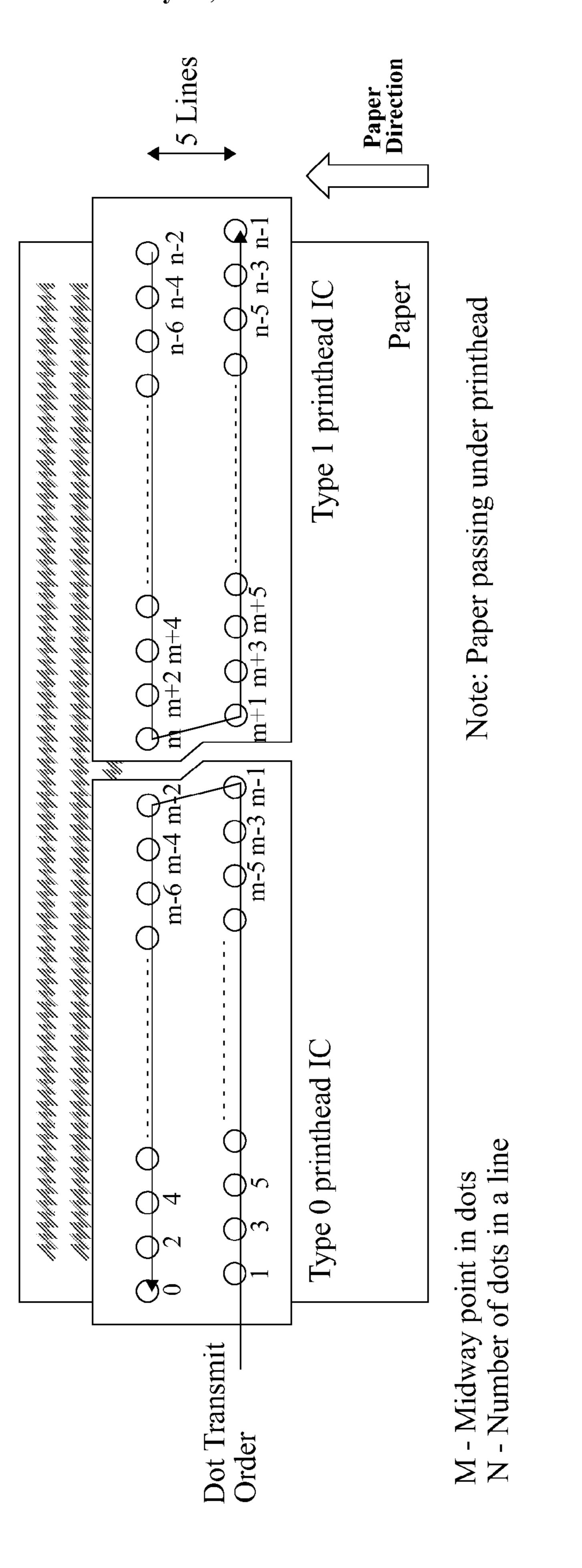

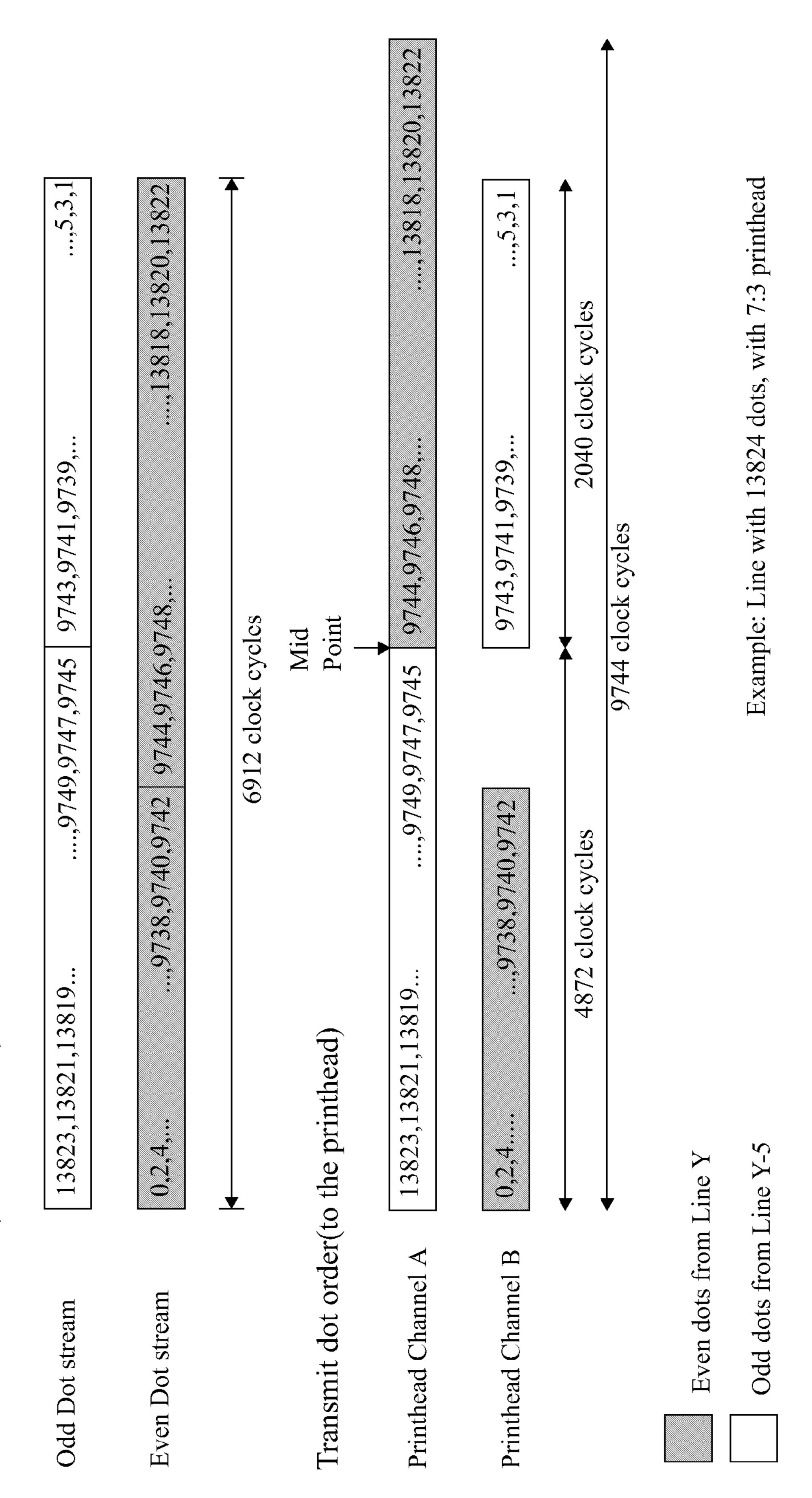

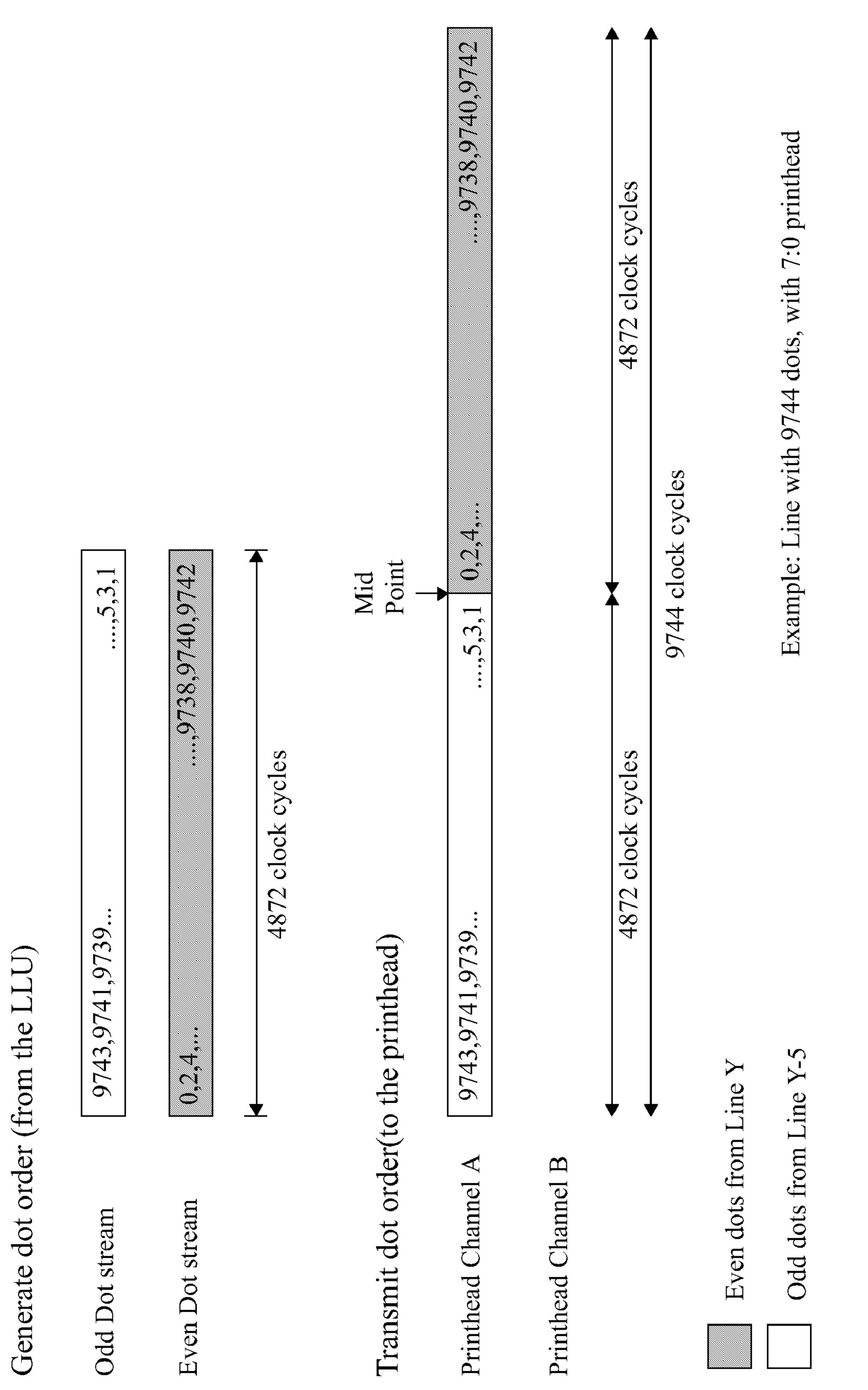

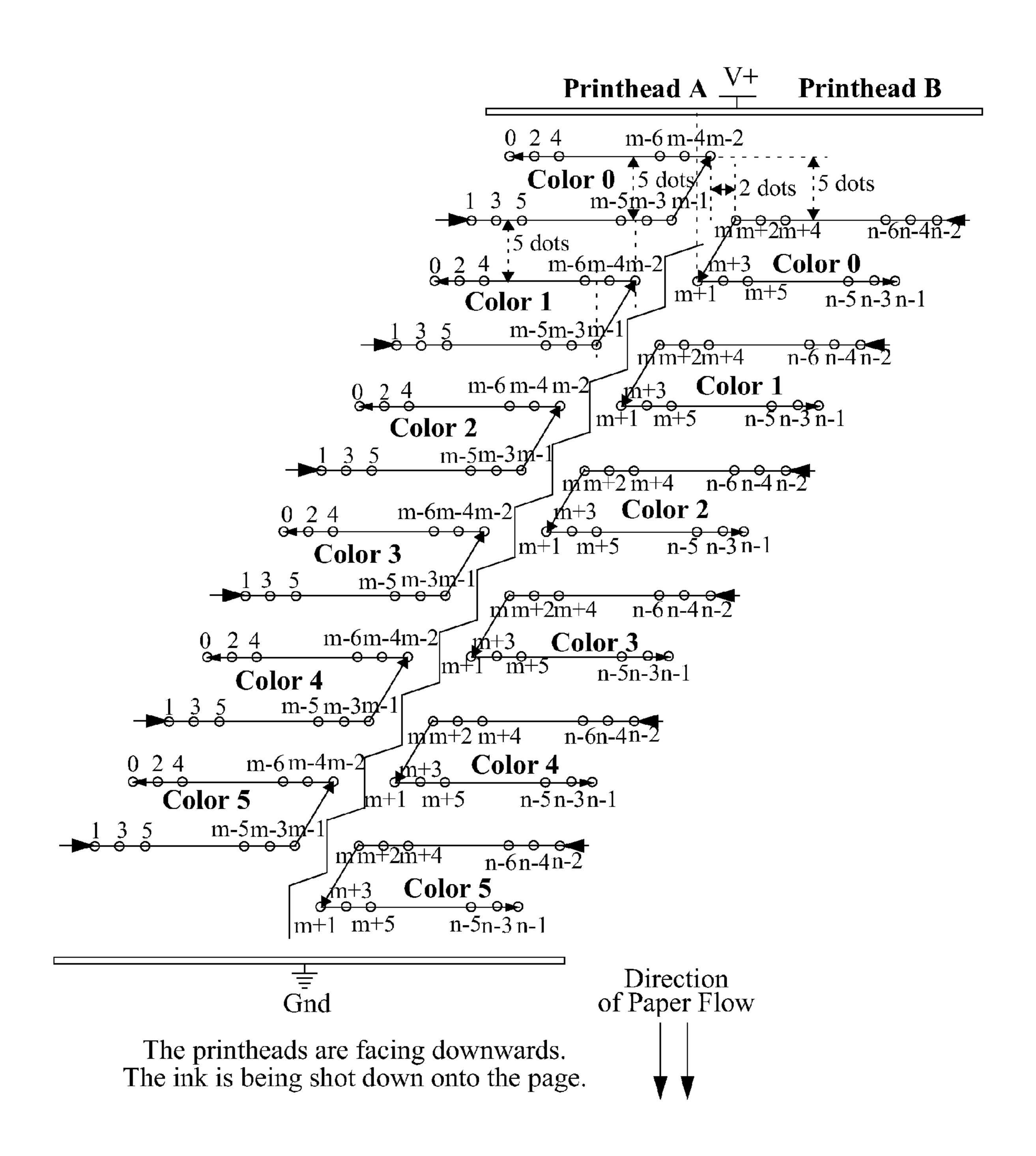

FIG. **34** shows printhead structure and dot generate order FIG. **35** shows an order of dot data generation and transmission

FIG. 36 shows a conceptual view of printhead rows

FIG. 37 shows a dotline FIFO data structure in DRAM (LLU specification)

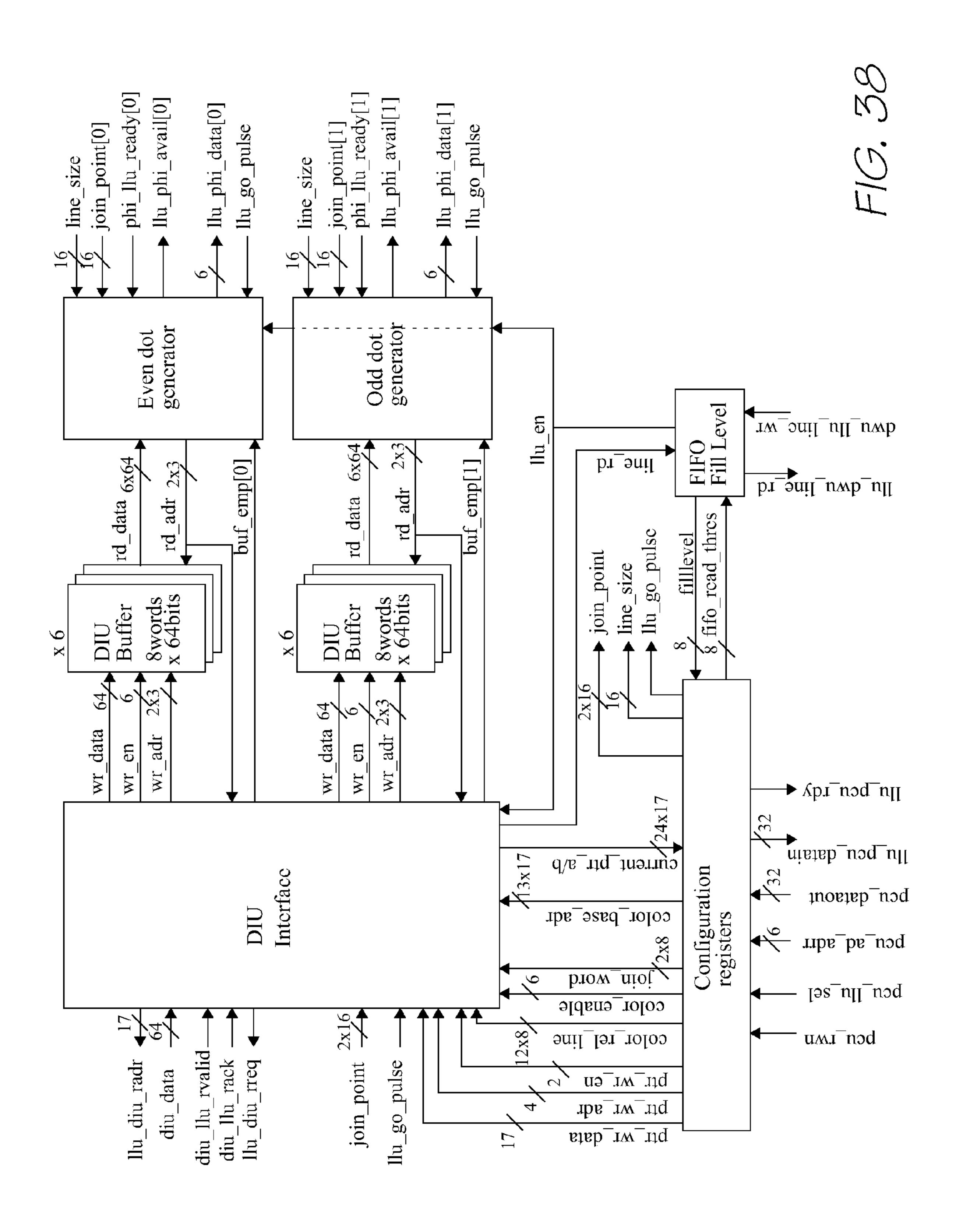

- FIG. 38 shows an LLU partition

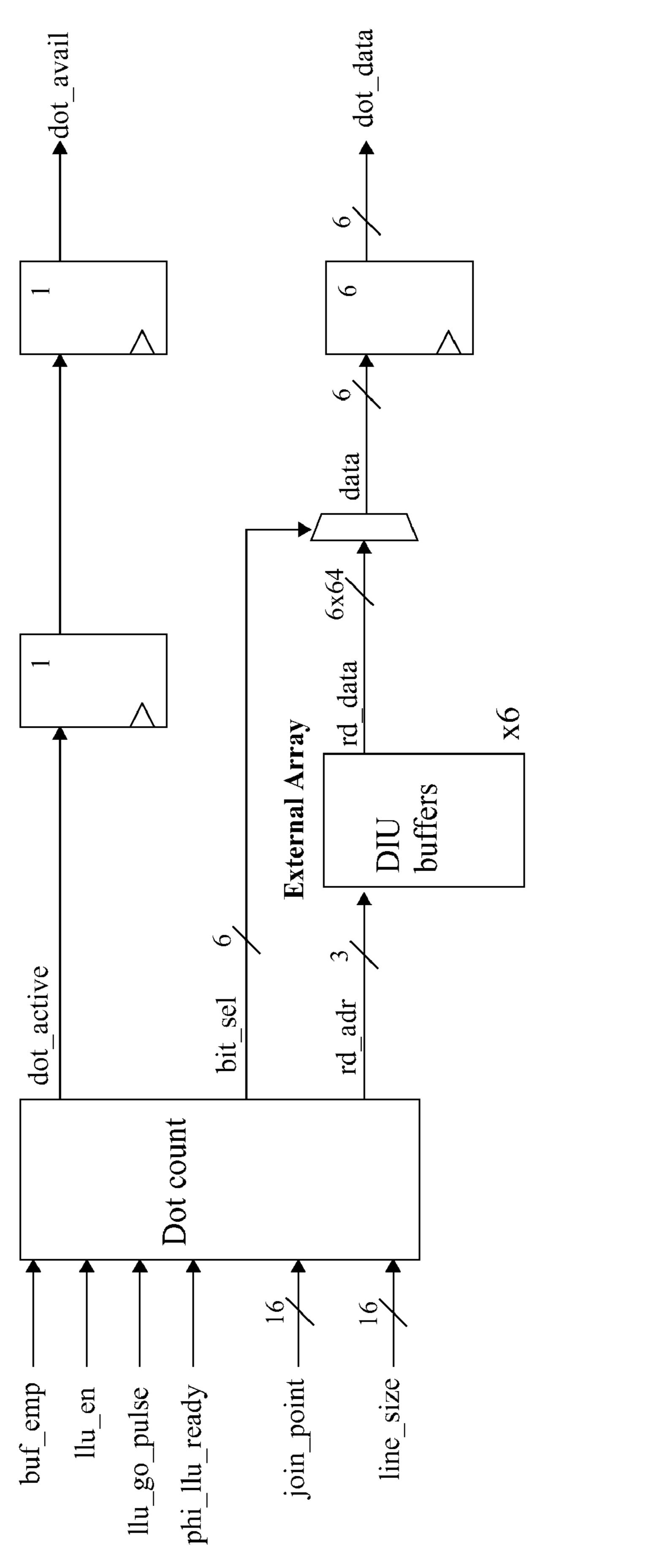

- FIG. 39 shows a dot generator RTL diagram

- FIG. 40 shows a DIU interface

- FIG. 41 shows an interface controller state diagram

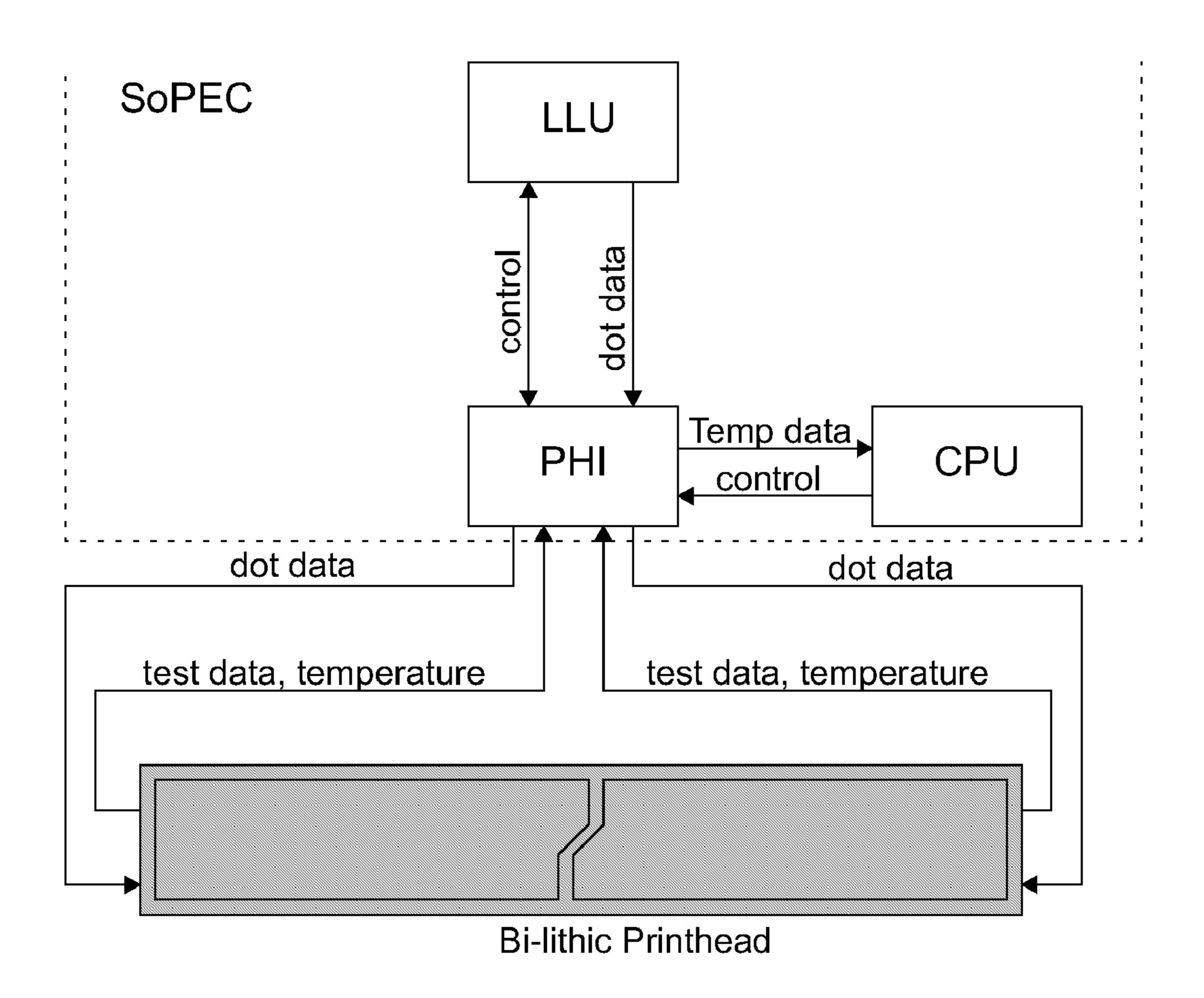

- FIG. 42 shows high-level data flow diagram of PHI in 5 context

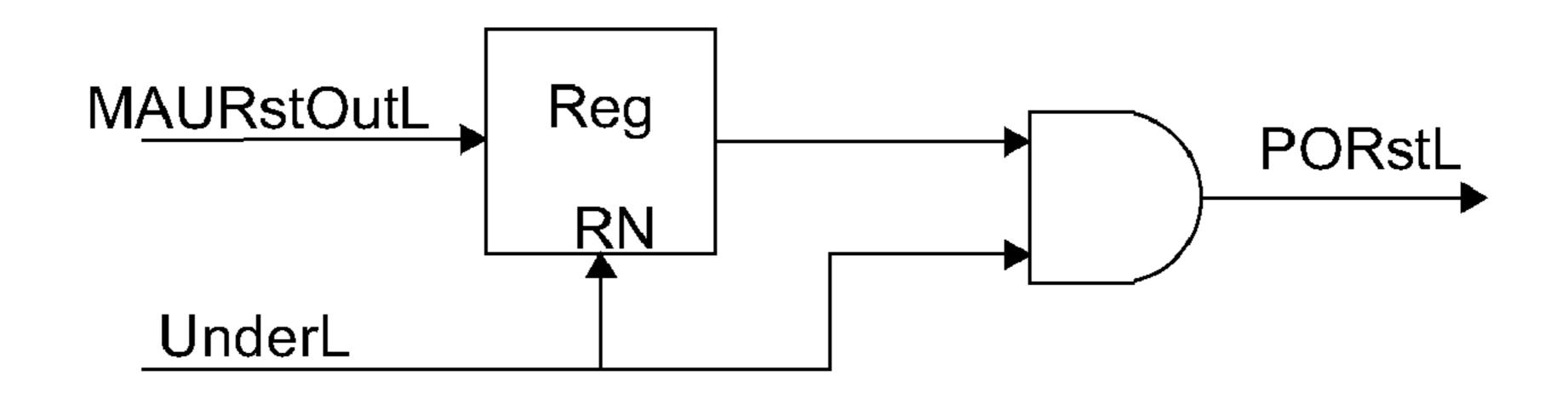

- FIG. 43 shows power on reset

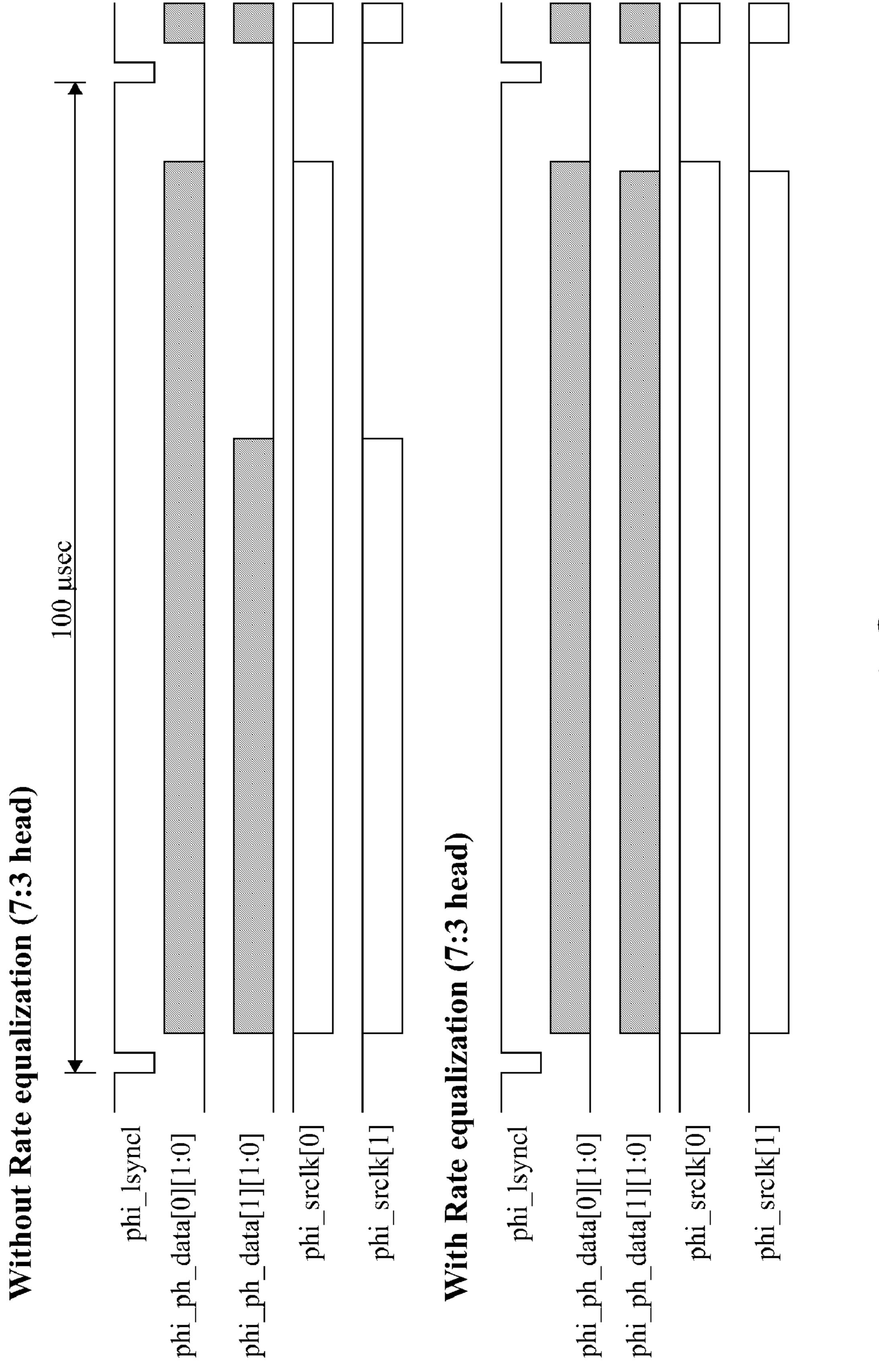

- FIG. 44 shows printhead data rate equalization

- FIG. 45 shows a printhead structure and dot generate order

- FIG. **46** shows an order of dot data generation and trans- 10 mission

- FIG. 47 shows an order of dot data generation and transmission (single printhead case)

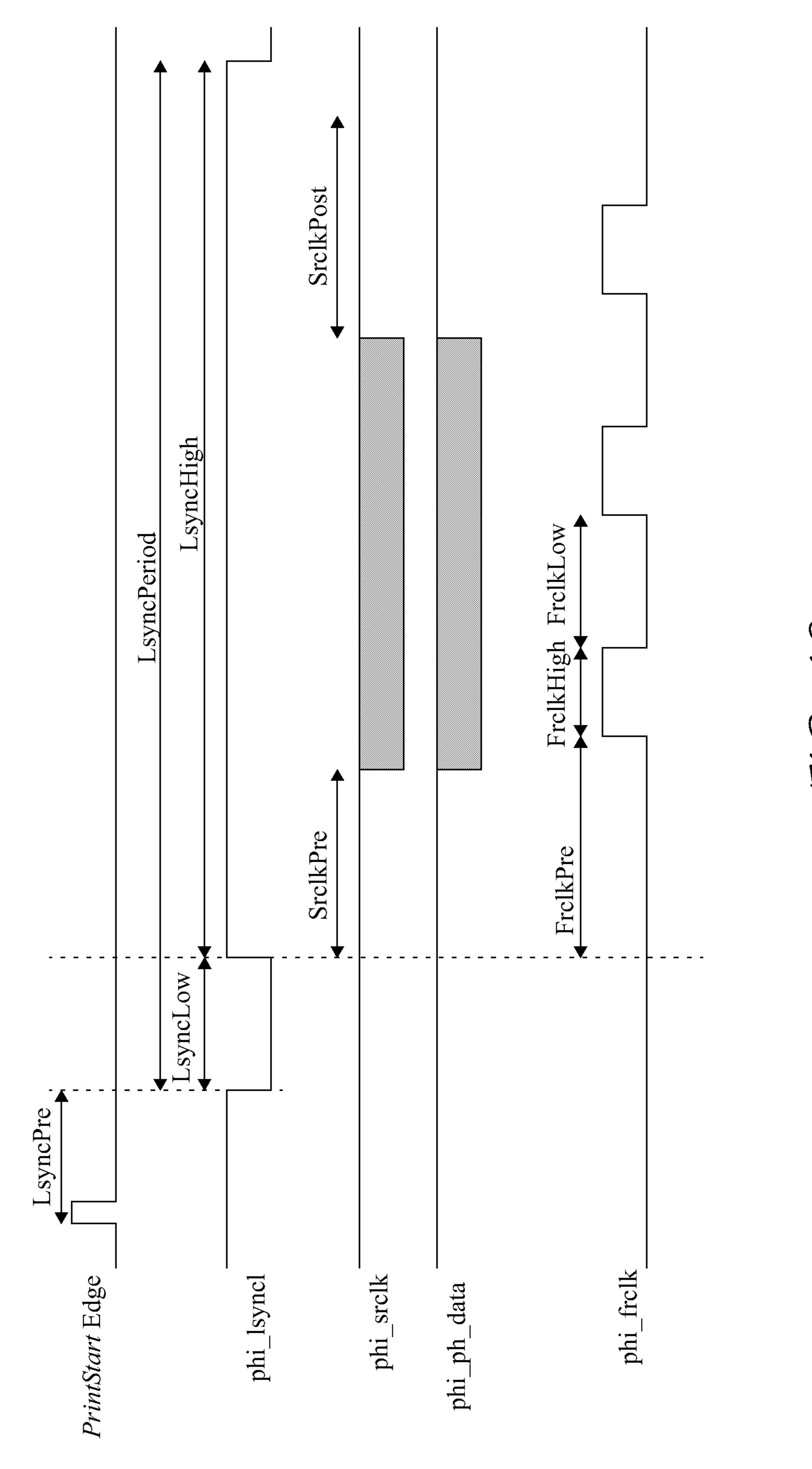

- FIG. 48 shows printhead interface timing parameters

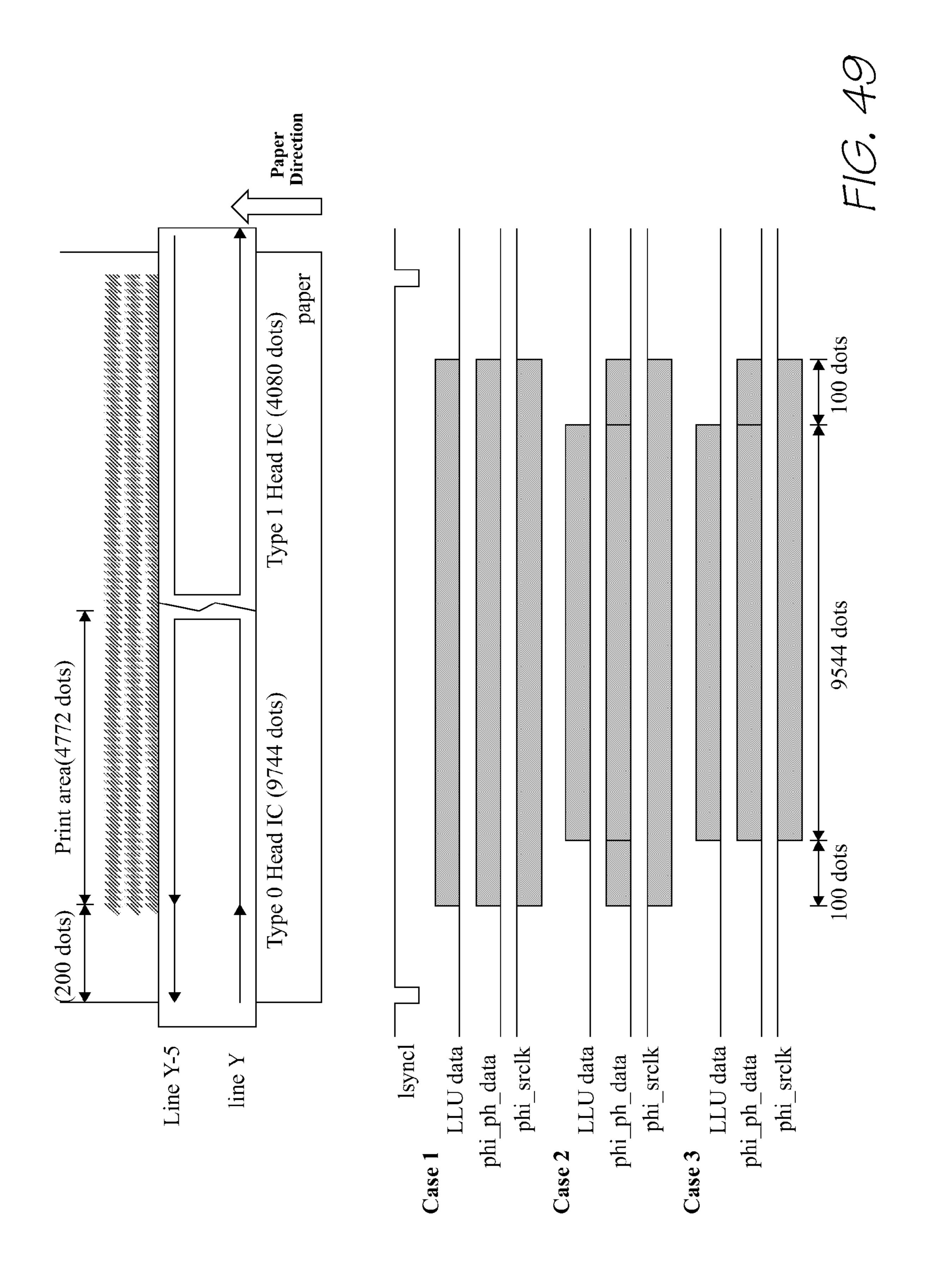

- FIG. 49 shows printhead timing with margining

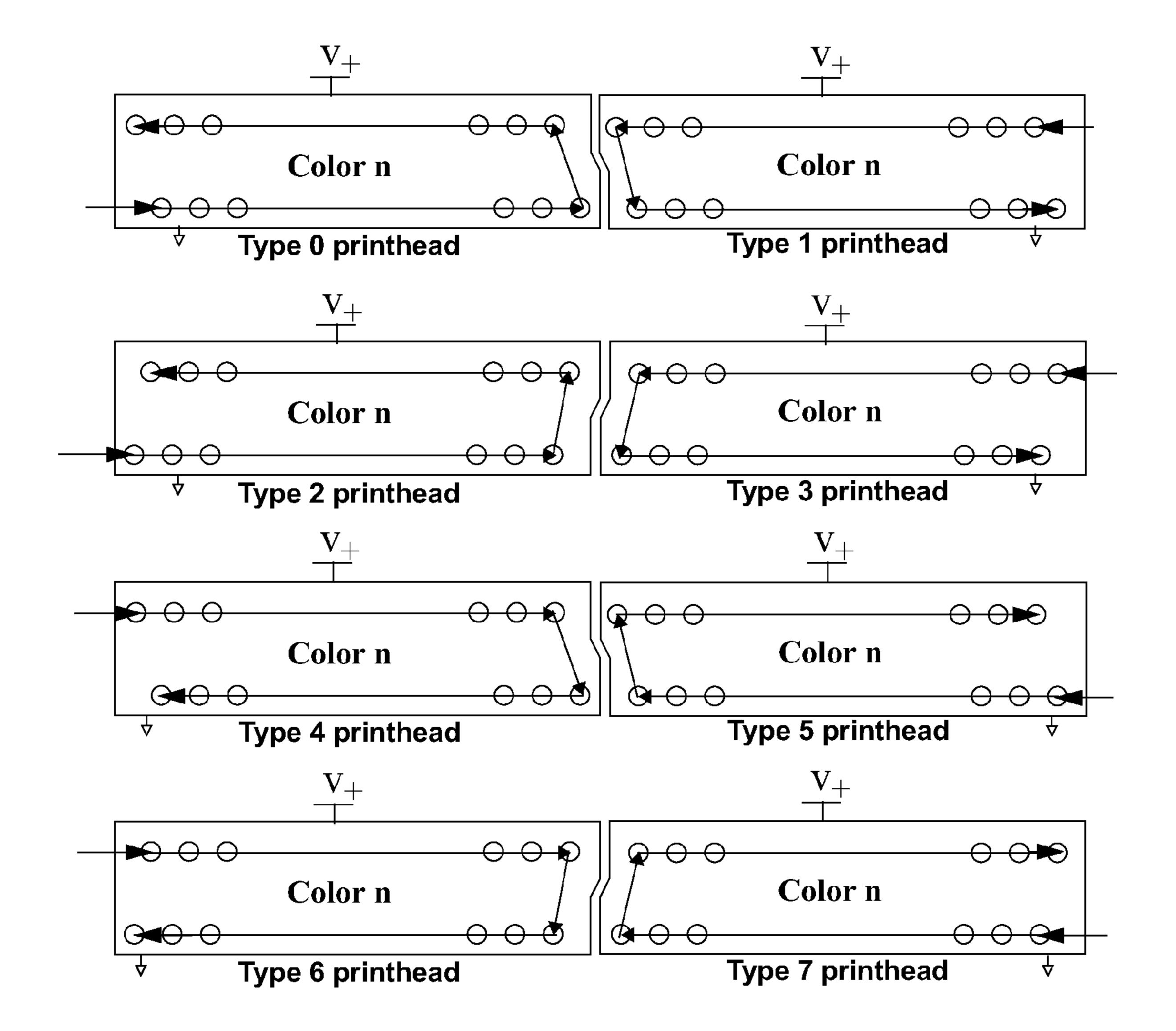

- FIG. 50 shows printhead types 0 to 7

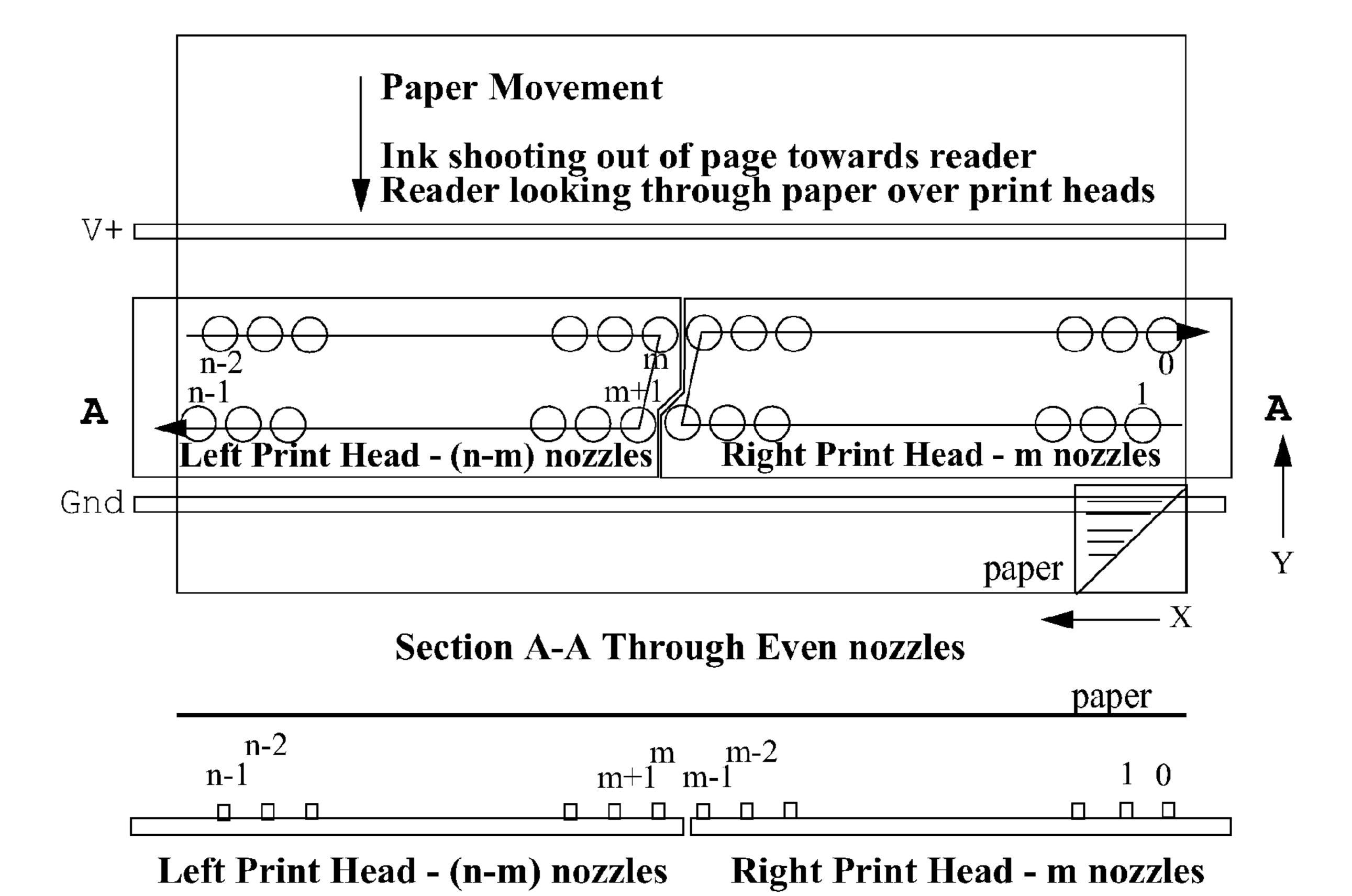

- FIG. **51** shows an ideal join between two dilithic printhead segments

- FIG. **52** shows an example of a join between two bilithic printhead segments

- FIG. **53** shows printable vs non-printable area under new definition (looking at colors as if 1 row only)

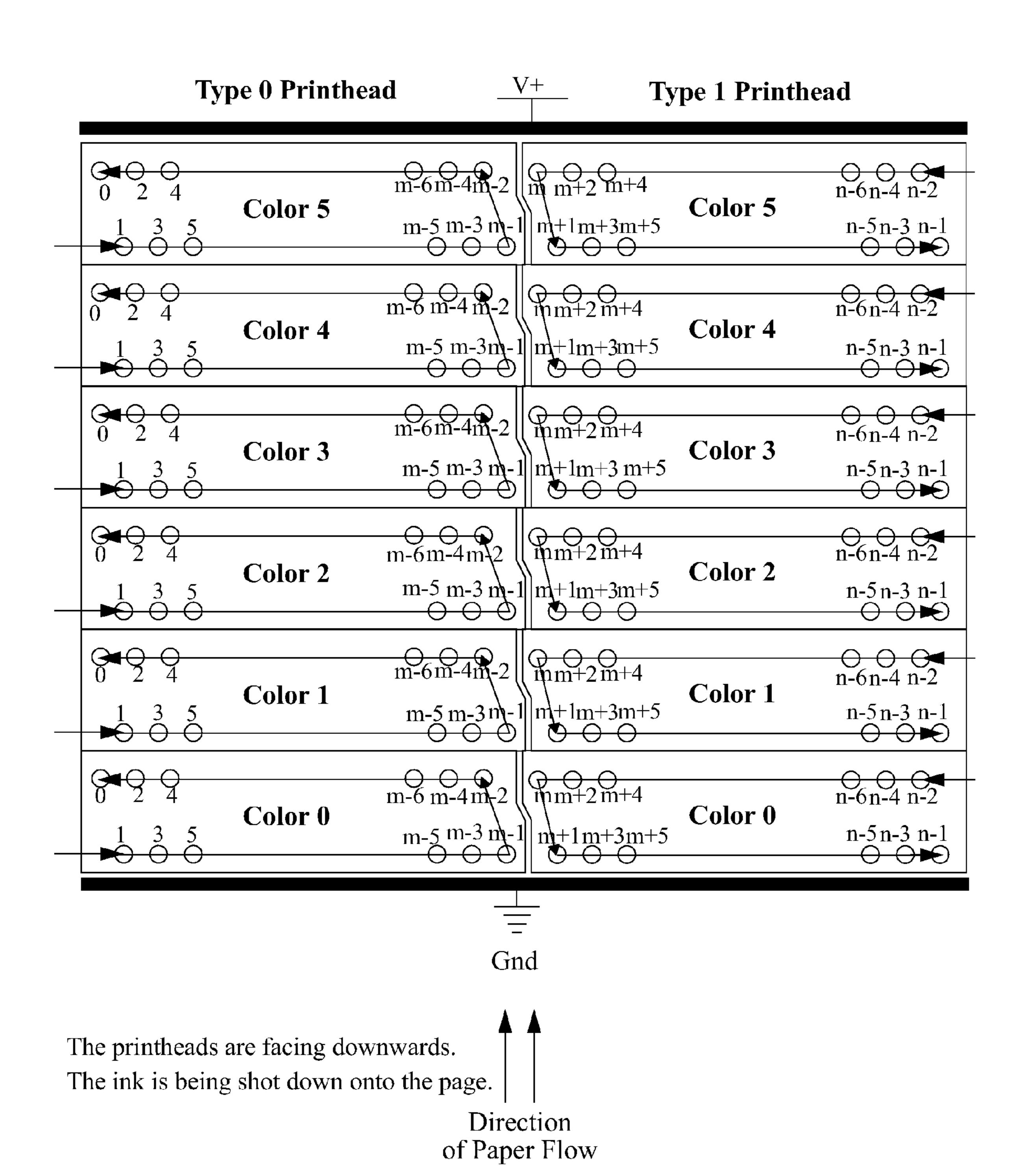

- FIG. **54** shows identification of printhead nozzles and shift-register sequences for printheads in arrangement 1

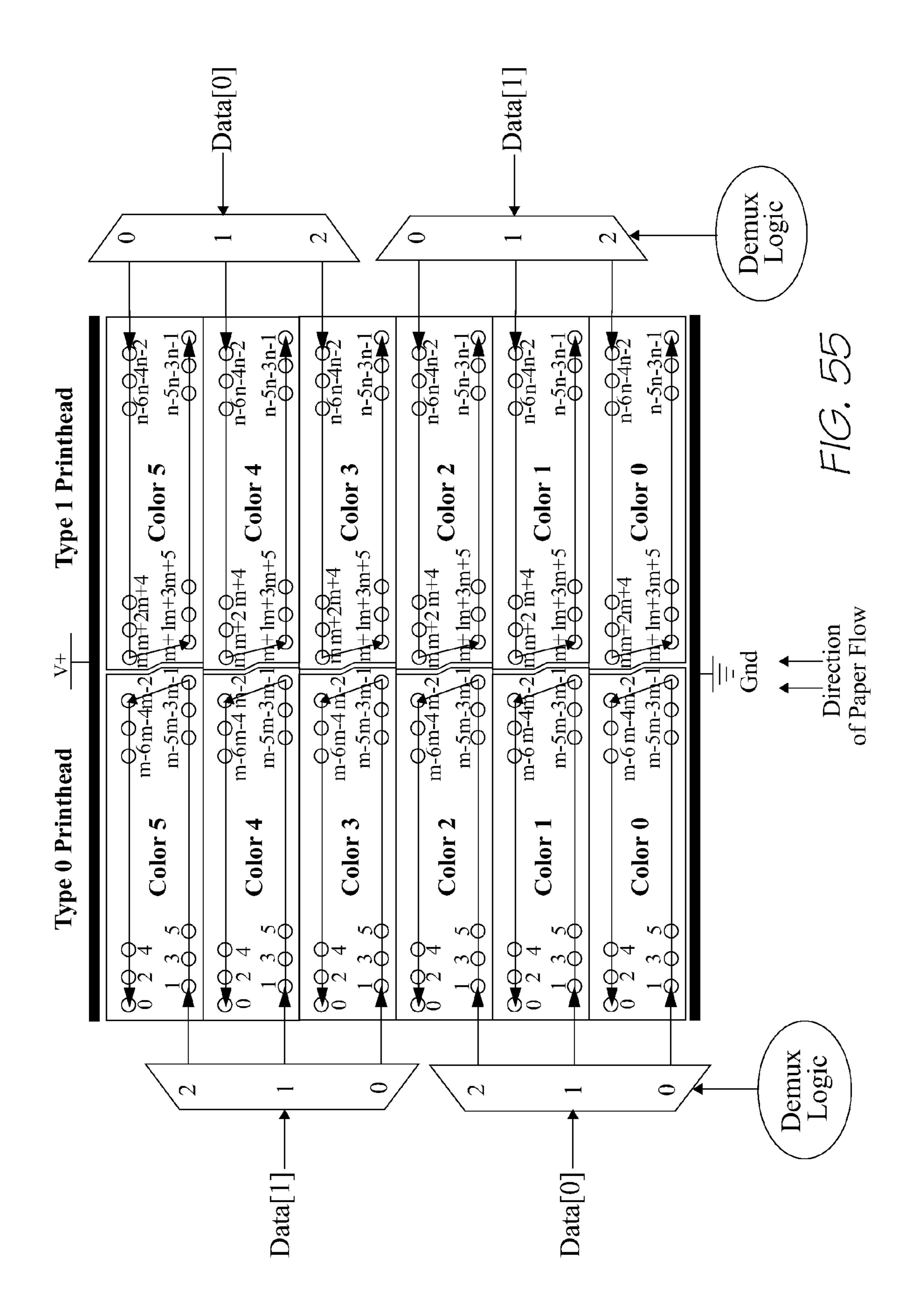

- FIG. **55** shows demultiplexing of data within the print- 25 heads in arrangement 1

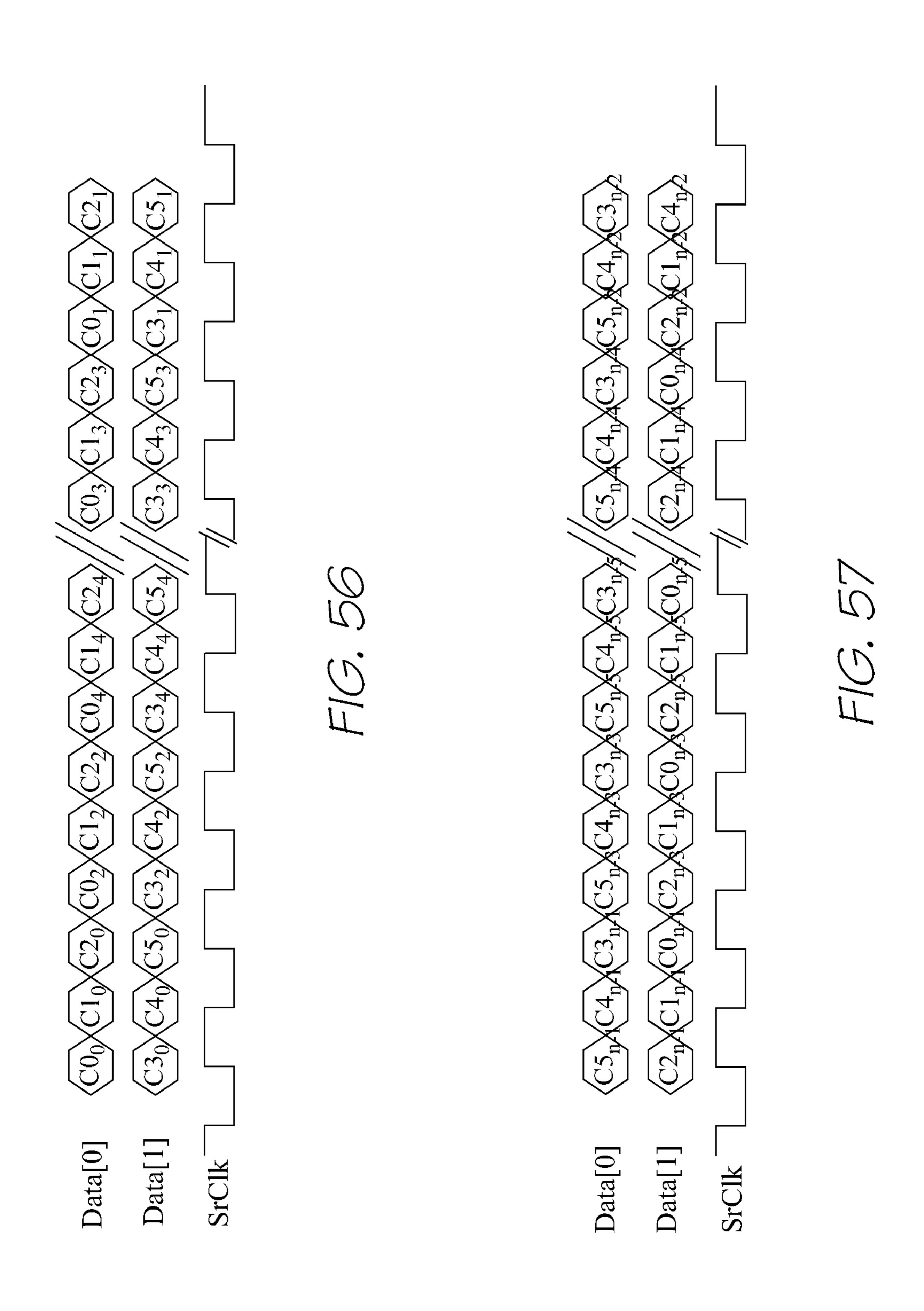

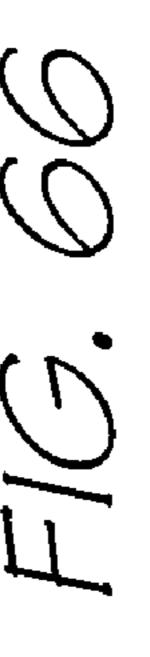

- FIG. **56** shows double data rate signalling for a type 0 printhead in arrangement 1

- FIG. **57** shows double data rate signalling for a type 1 printhead in arrangement 1

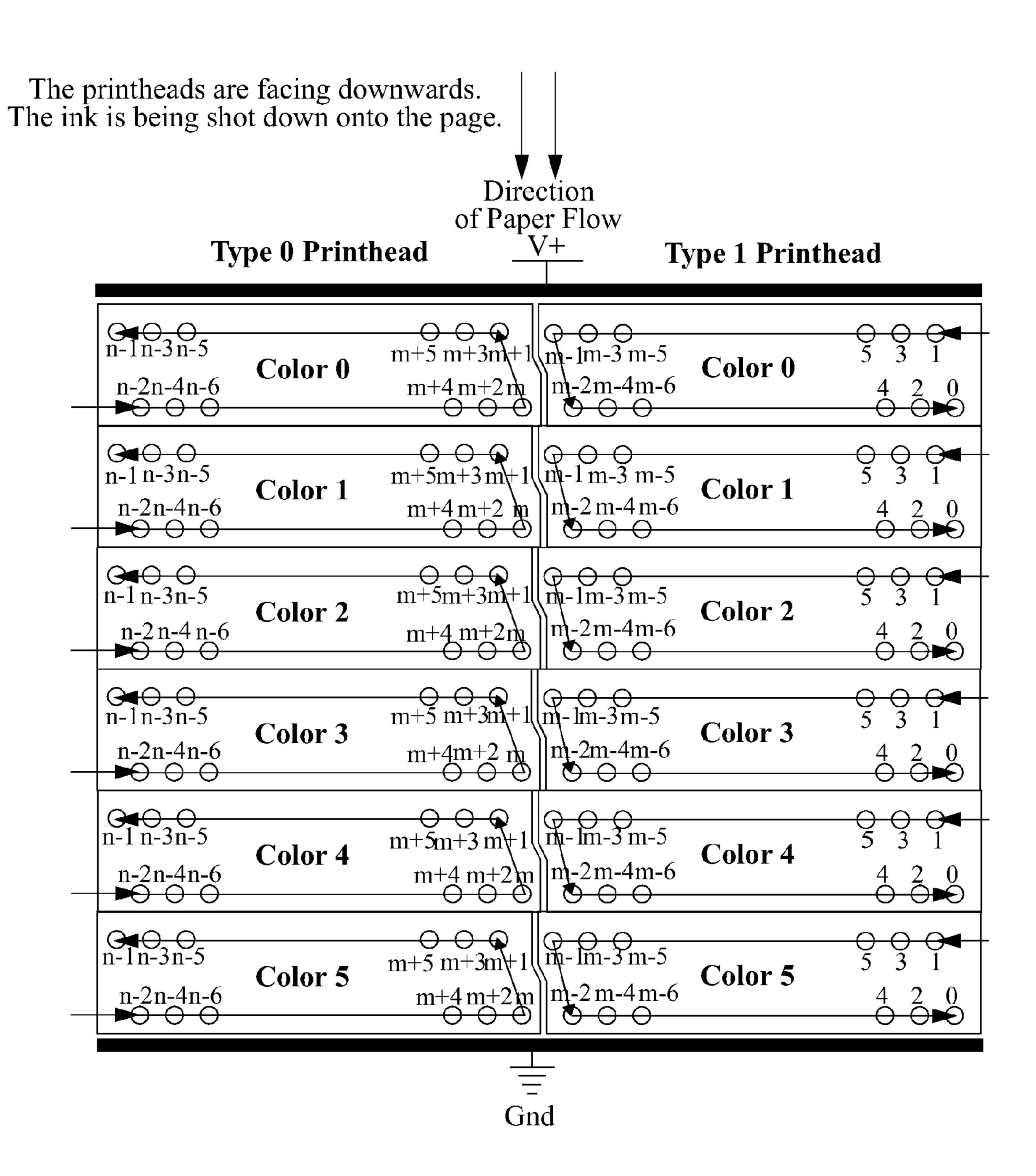

- FIG. **58** shows identification of printheads nozzles and shift-register sequences for printheads in arrangement 2

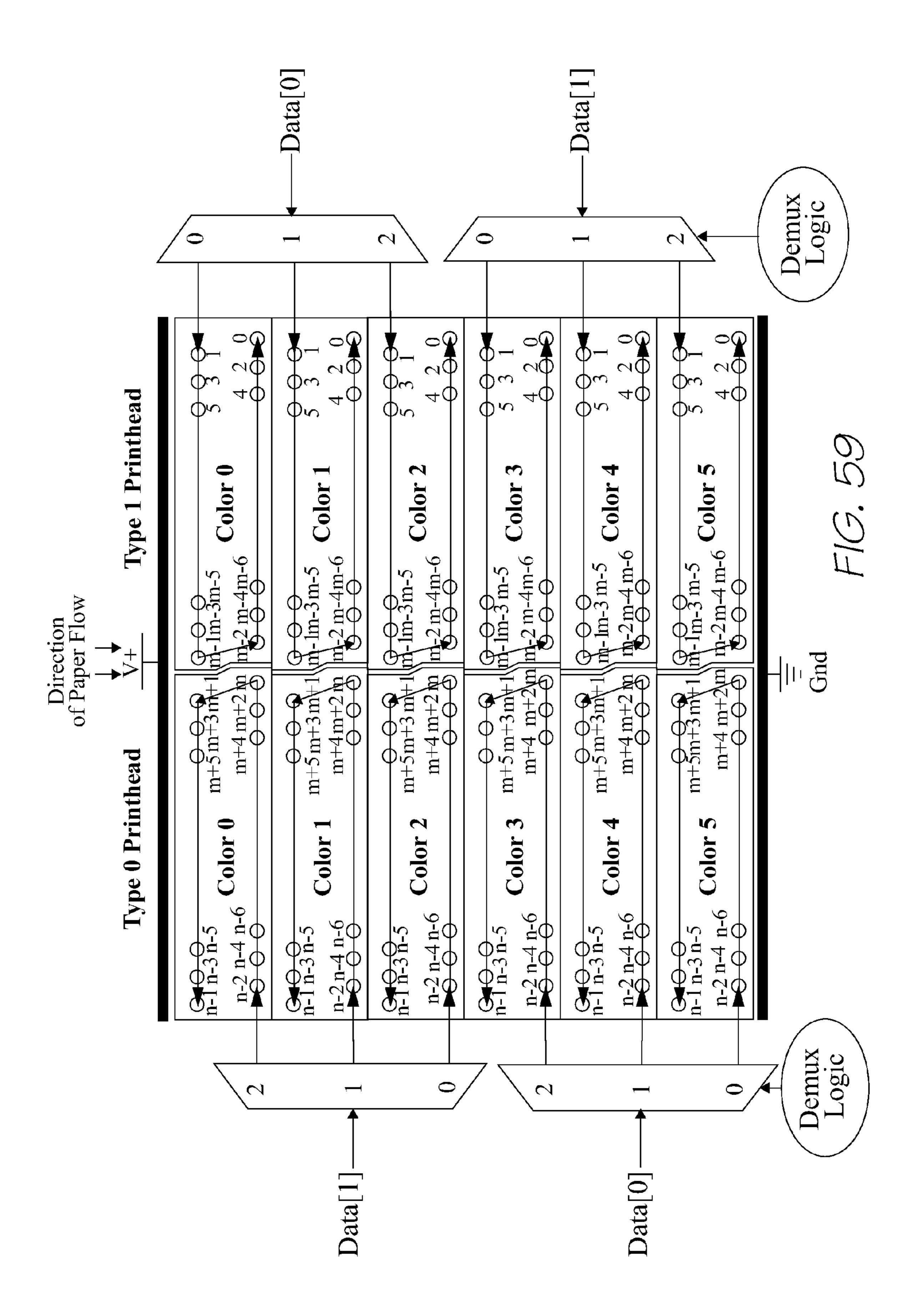

- FIG. **59** shows demultiplexing of data within the printheads in arrangement 2

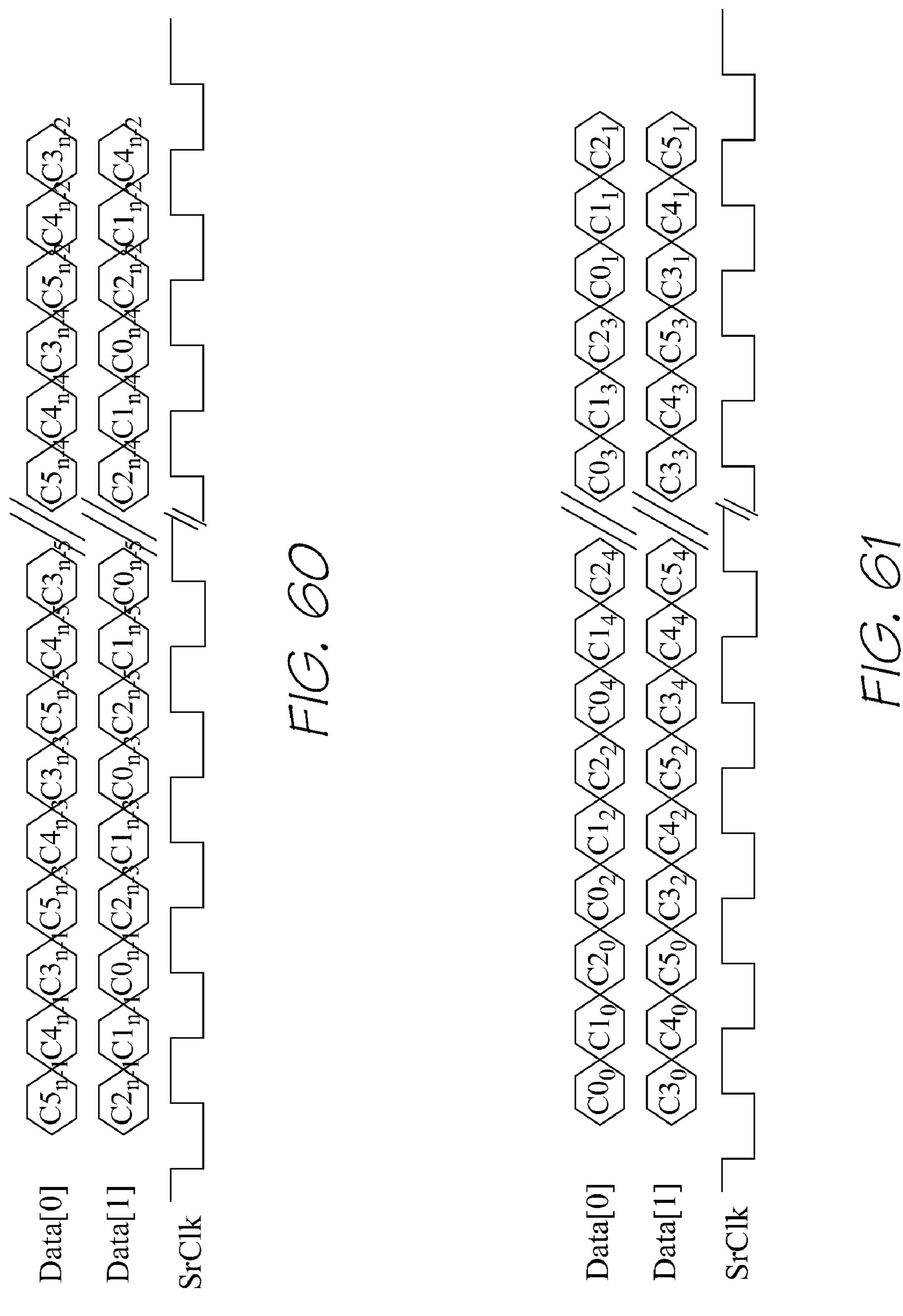

- FIG. **60** shows double data rate signalling for a type 0 35 printhead in arrangement 2

- FIG. **61** shows double data rate signalling for a type 1 printhead in arrangement 2

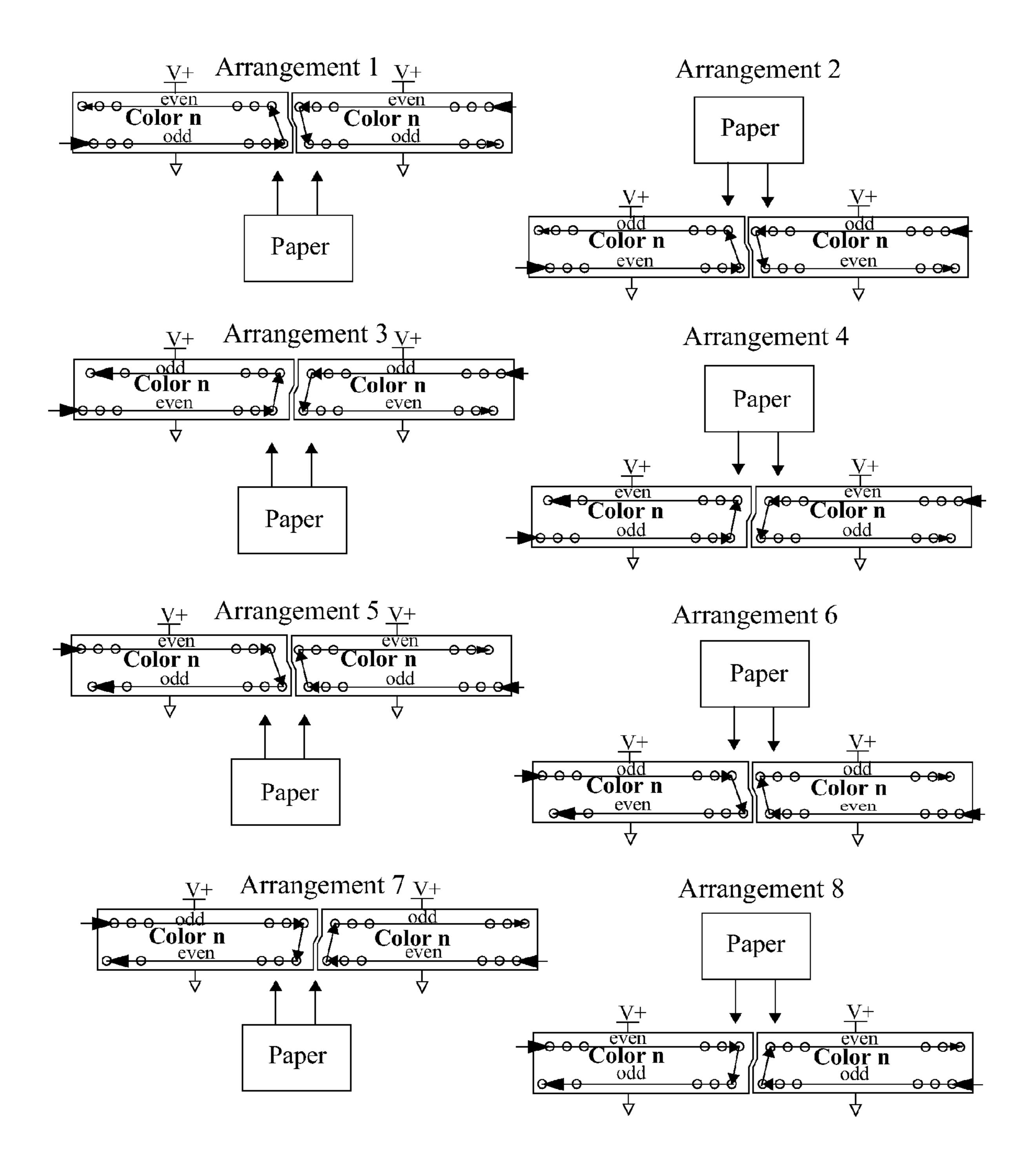

- FIG. 62 shows all 8 printhead arrangements

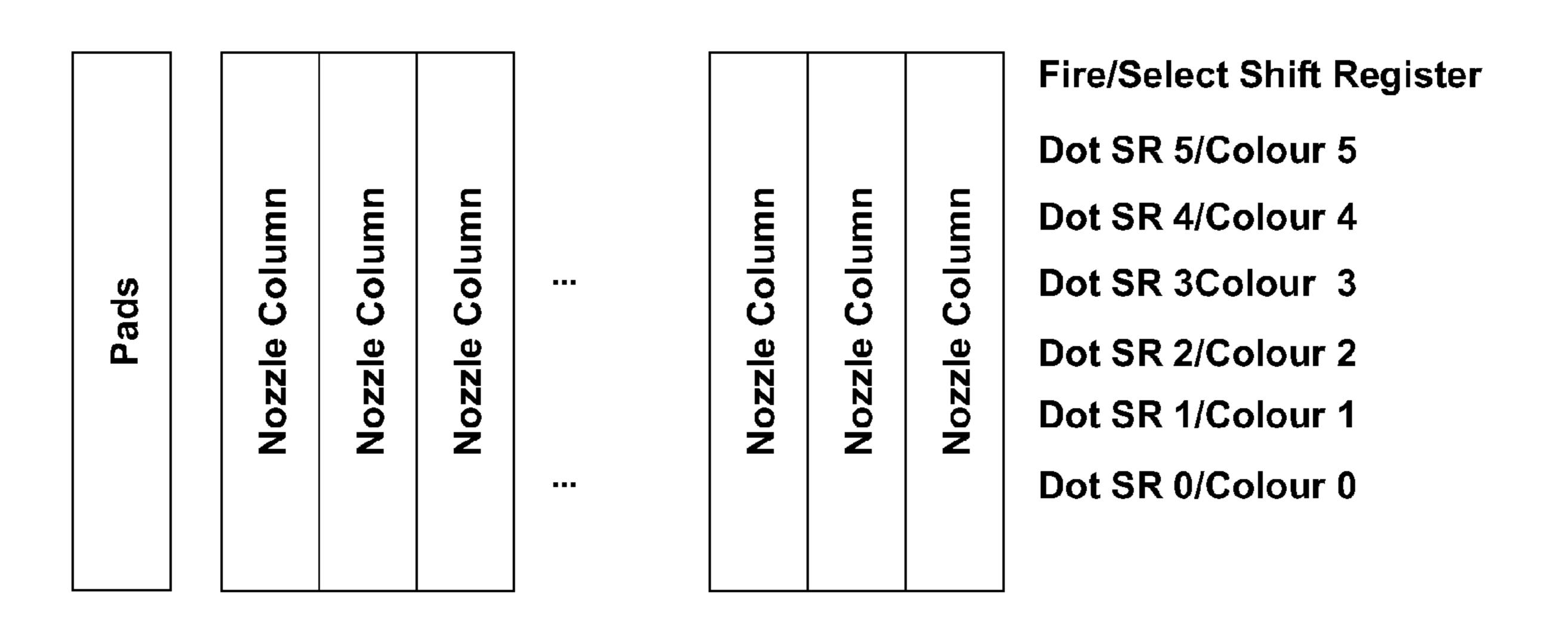

- FIG. 63 shows a printhead structure

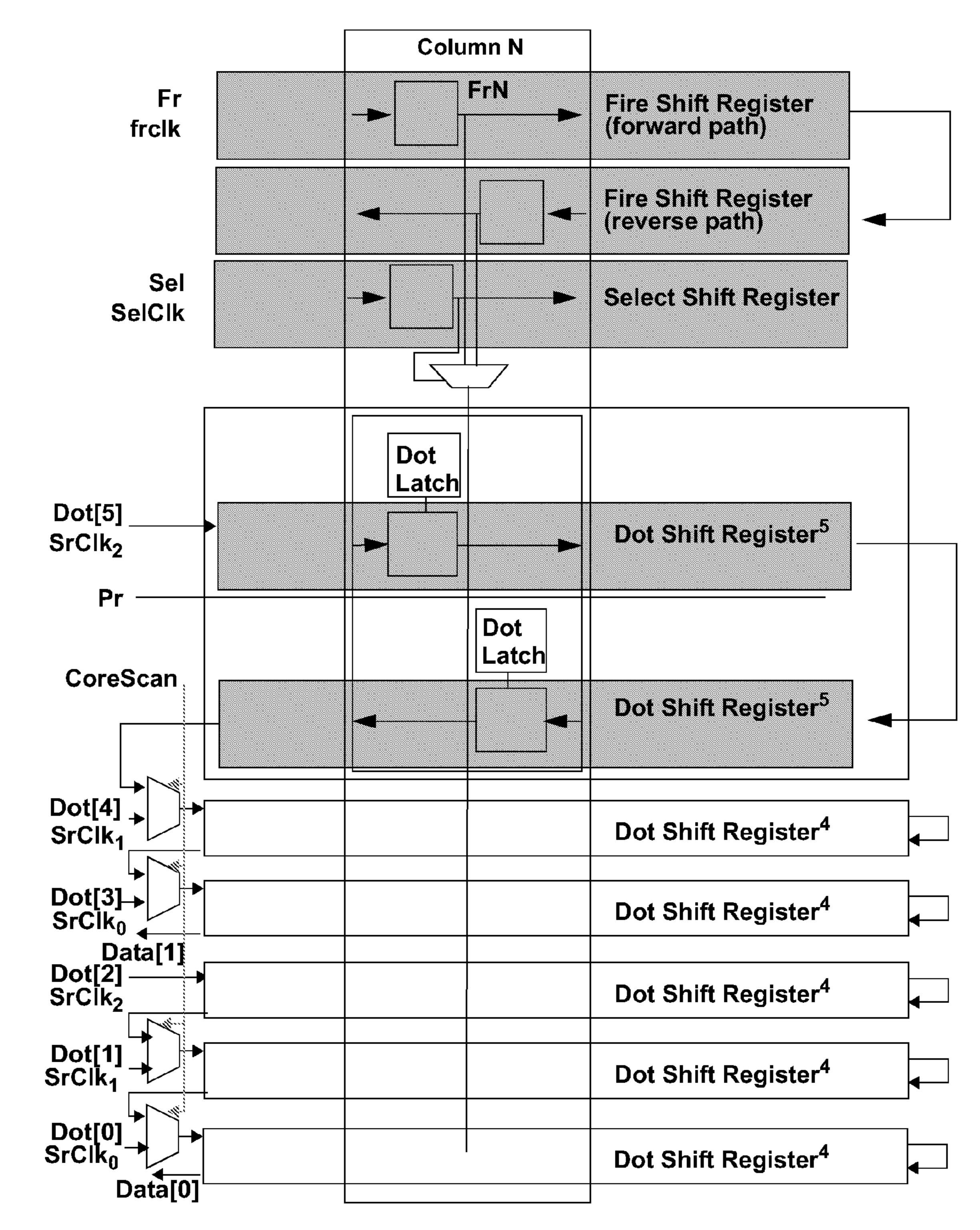

- FIG. 64 shows a column Structure

- FIG. **65** shows a printhead dot shift register dot mapping to page

- FIG. 66 shows data timing during printing

- FIG. 67 shows print quality

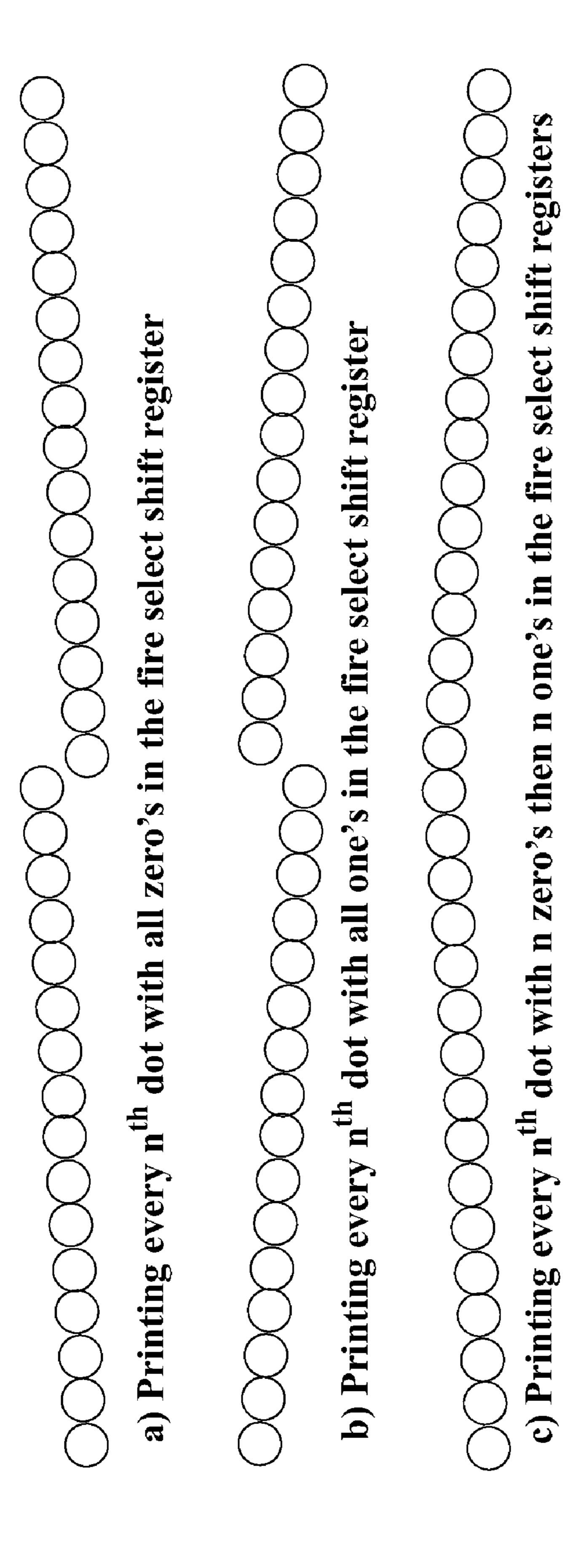

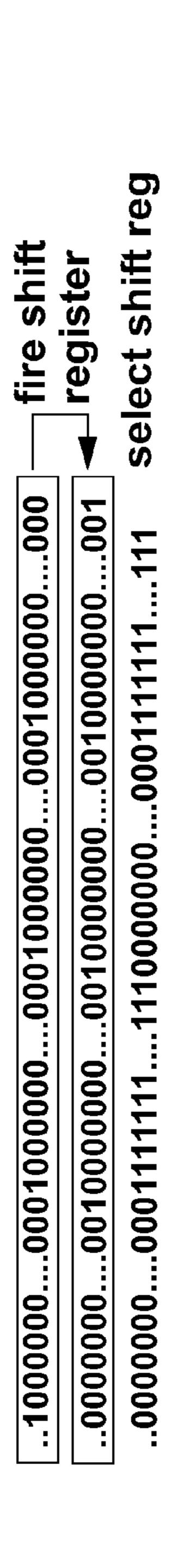

- FIG. **68** shows fire and select shift register setup for printing

- FIG. **69** shows a fire pattern across butt end of printhead chips

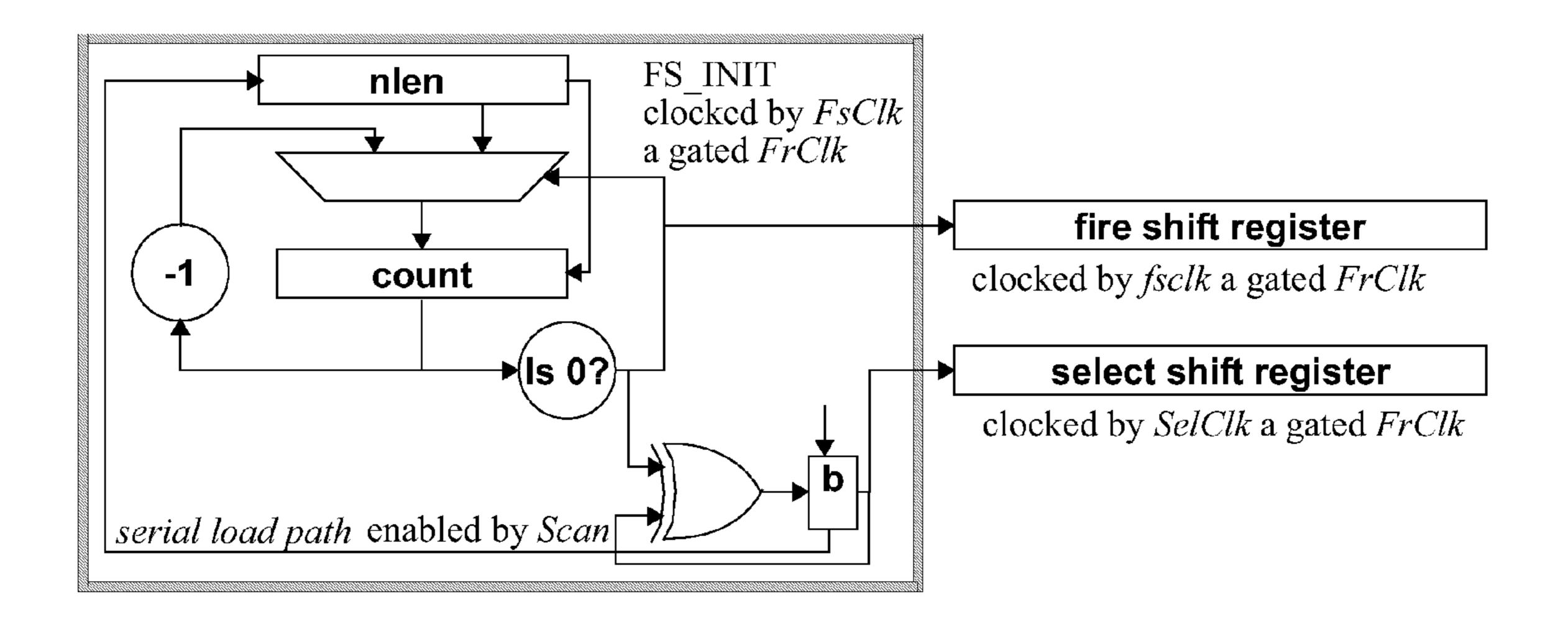

- FIG. 70 shows fire pattern generation

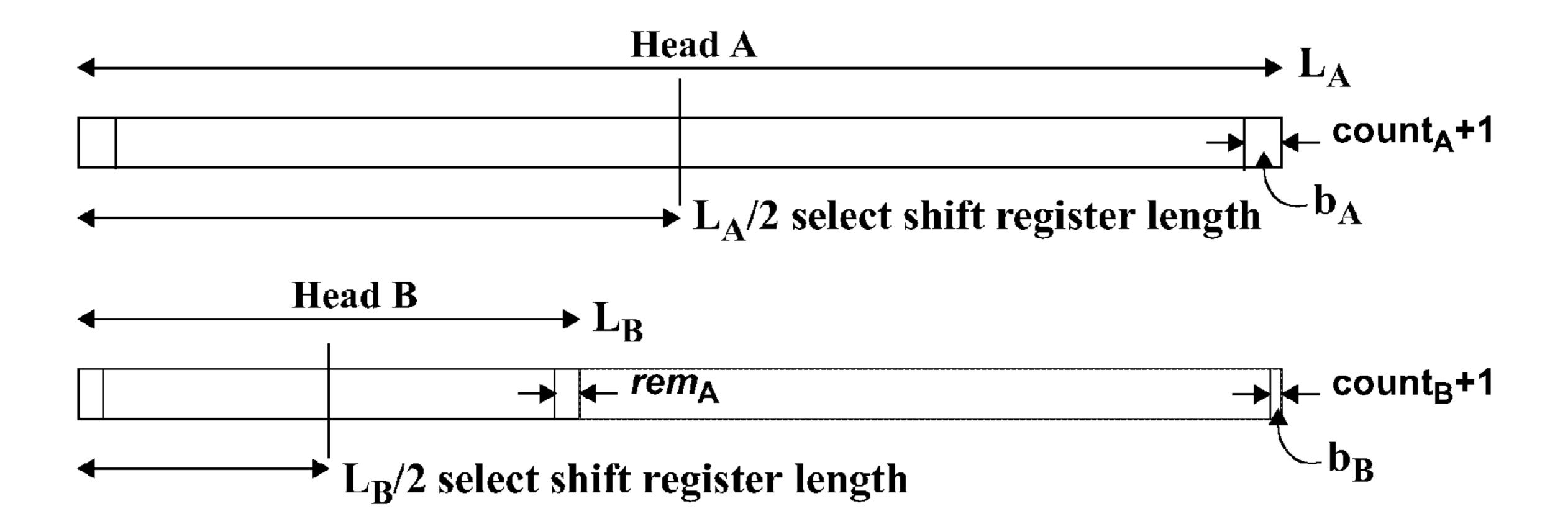

- FIG. 71 shows determination of select shift register value

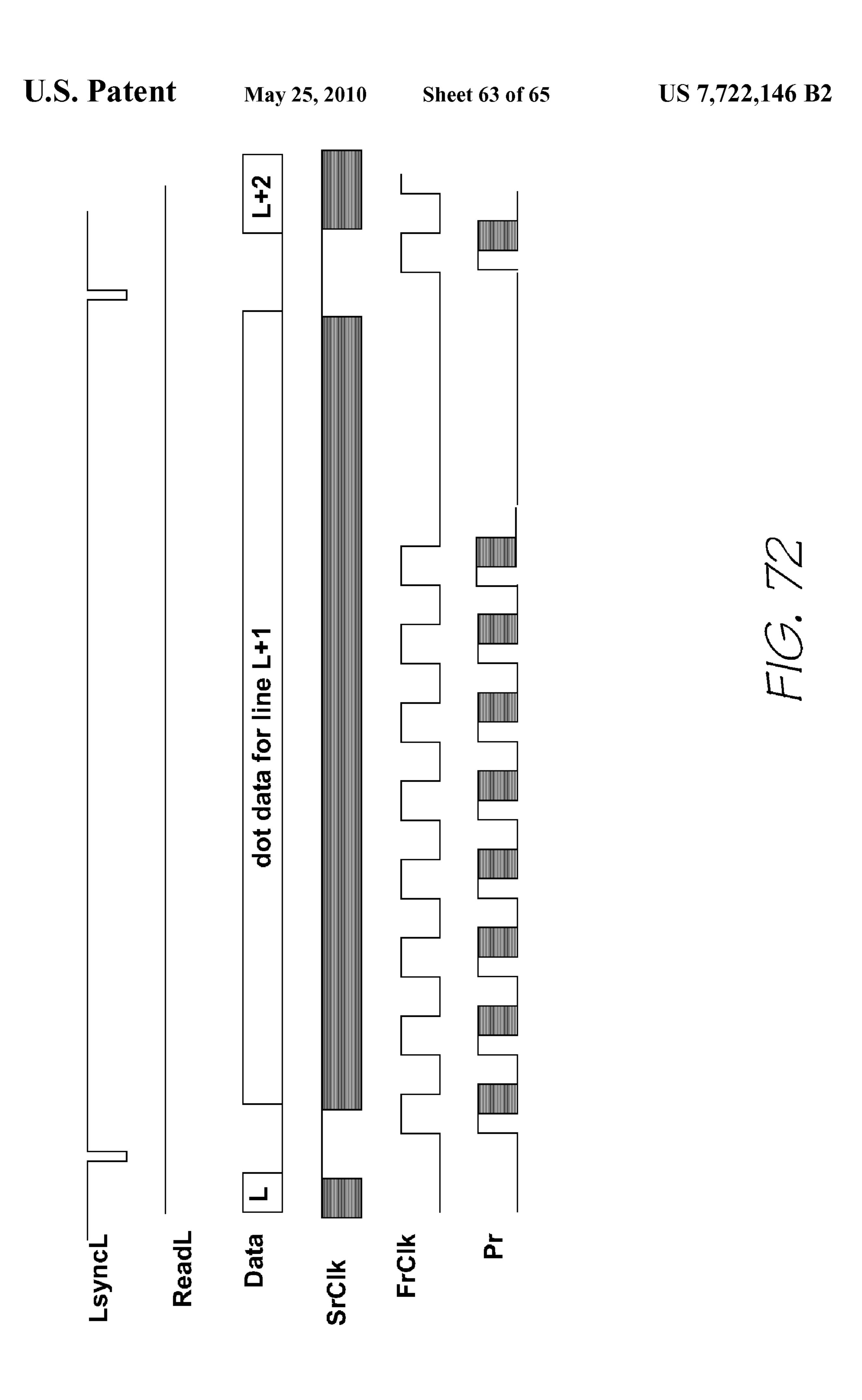

- FIG. 72 shows timing for printing signals

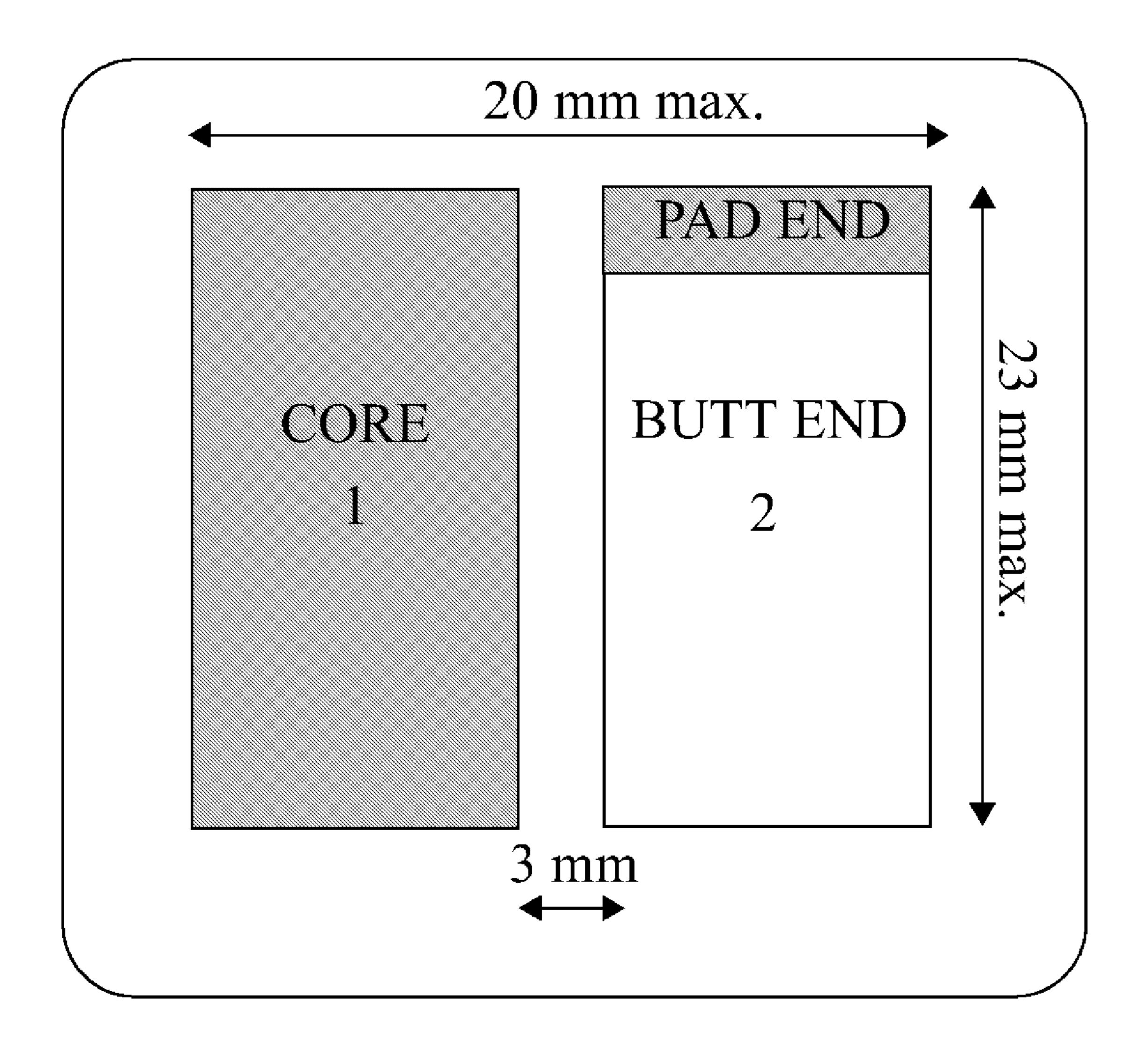

- FIG. 73 shows a reticle layout

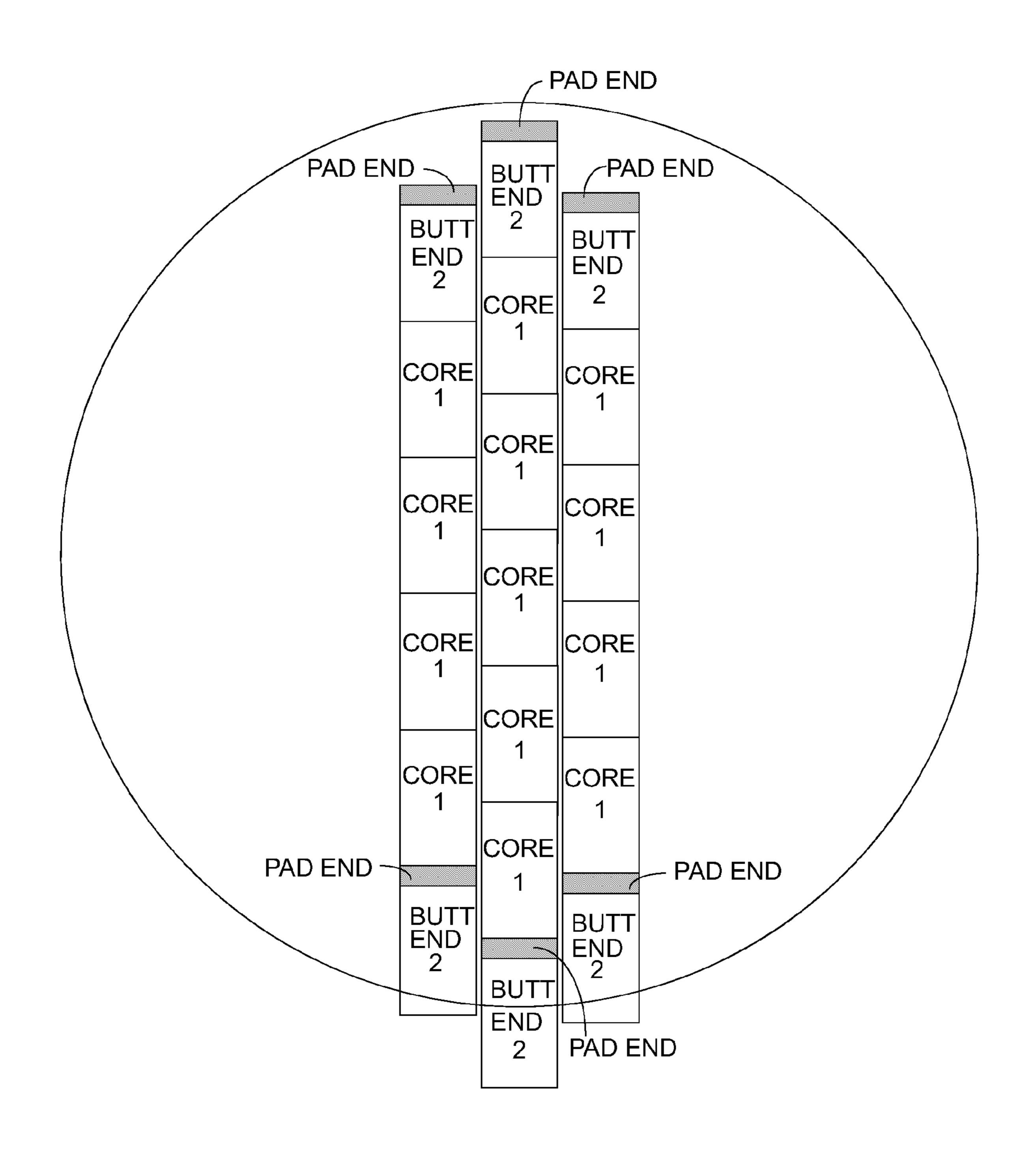

- FIG. 74 shows a stepper pattern on Wafer

## DETAILED DESCRIPTION OF THE EMBODIMENTS

Imperative phrases such as "must", "requires", "necessary" and "important" (and similar language) should be read 60 as being indicative of being necessary only for the preferred embodiment actually being described. As such, unless the opposite is clear from the context, imperative wording should not be interpreted as such. Nothing in the detailed description is to be understood as limiting the scope of the invention, 65 which is intended to be defined as widely as is defined in the accompanying claims.

6

The present invention provides a printer using microelectromechanical systems (MEMS) printheads. The printer can receive data from, for example, a personal computer such as an IBM compatible PC or Apple computer. In other embodiments, the printer can receive data directly from, for example, a digital still or video camera. The particular choice of communication link is not important, and can be based, for example, on USB, Firewire, Bluetooth or any other wireless or hardwired communications protocol.

The SoPEC (Small office home office Print Engine Controller) ASIC (Application Specific Integrated Circuit) suitable for use in, for example, SoHo printer products is described. The SoPEC ASIC is intended to be a low cost solution for bi-lithic printhead control, replacing the multichip solutions in larger more professional systems with a single chip. The increased cost competitiveness is achieved by integrating several systems such as a modified PEC1 printing pipeline, CPU control system, peripherals and memory sub-system onto one SoC ASIC, reducing component count and simplifying board design.

A bi-lithic based printhead is constructed from 2 printhead ICs of varying sizes. The notation M:N is used to express the size relationship of each IC, where M specifies one printhead IC in inches and N specifies the remaining printhead IC in inches.

The following terms are used throughout this specification: Bi-lithic printhead Refers to printhead constructed from 2 printhead ICs

CPU Refers to CPU core, caching system and MMU.

ISI-Bridge chip A device with a high speed interface (such as USB2.0, Ethernet or IEEE1394) and one or more ISI interfaces. The ISI-Bridge would be the ISIMaster for each of the ISI buses it interfaces to.

ISIMaster The ISIMaster is the only device allowed to initiate communication on the Inter Sopec Interface (ISI) bus. The ISIMaster interfaces with the host.

ISISlave Multi-SoPEC systems will contain one or more ISISlave SoPECs connected to the ISI bus. ISISlaves can only respond to communication initiated by the ISIMaster.

LEON Refers to the LEON CPU core.

LineSyncMaster The LineSyncMaster device generates the line synchronisation pulse that all SoPECs in the system must synchronise their line outputs to.

Multi-SoPEC Refers to SoPEC based print system with multiple SoPEC devices

Netpage Refers to page printed with tags (normally in infrared ink).

PEC1 Refers to Print Engine Controller version 1, precursor to SoPEC used to control printheads constructed from multiple angled printhead segments.

Printhead IC Single MEMS IC used to construct bi-lithic printhead

PrintMaster The PrintMaster device is responsible for coordinating all aspects of the print operation. There may only be one PrintMaster in a system.

QA Chip Quality Assurance Chip

Storage SoPEC An ISISlave SoPEC used as a DRAM store and which does not print.

Tag Refers to pattern which encodes information about its position and orientation which allow it to be optically located and its data contents read.

The following acronyms and abbreviations are used in this specification

CFU Contone FIFO Unit

**CPU Central Processing Unit**

DIU DRAM Interface Unit

DNC Dead Nozzle Compensator

DRAM Dynamic Random Access Memory

DWU DotLine Writer Unit

GPIO General Purpose Input Output

HCU Halftoner Compositor Unit

ICU Interrupt Controller Unit

ISI Inter SoPEC Interface

LDB Lossless Bi-level Decoder

LLU Line Loader Unit

LSS Low Speed Serial interface

MEMS Micro Electro Mechanical System

MMU Memory Management Unit

PCU SoPEC Controller Unit

PHI PrintHead Interface

PSS Power Save Storage Unit

RDU Real-time Debug Unit

**ROM Read Only Memory**

SCB Serial Communication Block

SFU Spot FIFO Unit

SMG4 Silverbrook Modified Group 4.

SoPEC Small office home office Print Engine Controller

SRAM Static Random Access Memory

TE Tag Encoder

TFU Tag FIFO Unit

TIM Timers Unit

USB Universal Serial Bus

A bi-lithic printhead produces 1600 dpi bi-level dots. On low-diffusion paper, each ejected drop forms a 22.5 m diameter dot. Dots are easily produced in isolation, allowing dispersed-dot dithering to be exploited to its fullest. Since the bi-lithic printhead is the width of the page and operates with a constant paper velocity, color planes are printed in perfect registration, allowing ideal dot-on-dot printing. Dot-on-dot printing minimizes 'muddying' of midtones caused by intercolor bleed.

A page layout may contain a mixture of images, graphics 50 and text. Continuous-tone (contone) images and graphics are reproduced using a stochastic dispersed-dot dither. Unlike a clustered-dot (or amplitude-modulated) dither, a dispersed-dot (or frequency-modulated) dither reproduces high spatial frequencies (i.e. image detail) almost to the limits of the dot 55 resolution, while simultaneously reproducing lower spatial frequencies to their full color depth, when spatially integrated by the eye. A stochastic dither matrix is carefully designed to be free of objectionable low-frequency patterns when tiled across the image. As such its size typically exceeds the minimum size required to support a particular number of intensity levels (e.g.  $16 \times 16 \times 8$  bits for 257 intensity levels).

Human contrast sensitivity peaks at a spatial frequency of about 3 cycles per degree of visual field and then falls off logarithmically, decreasing by a factor of 100 beyond about 65 40 cycles per degree and becoming immeasurable beyond 60 cycles per degree [25][25]. At a normal viewing distance of

8

12 inches (about 300 mm), this translates roughly to 200-300 cycles per inch (cpi) on the printed page, or 400-600 samples per inch according to Nyquist's theorem.

In practice, contone resolution above about 300 ppi is of limited utility outside special applications such as medical imaging. Offset printing of magazines, for example, uses contone resolutions in the range 150 to 300 ppi. Higher resolutions contribute slightly to color error through the dither.

Black text and graphics are reproduced directly using bilevel black dots, and are therefore not anti-aliased (i.e. low-pass filtered) before being printed. Text should therefore be supersampled beyond the perceptual limits discussed above, to produce smoother edges when spatially integrated by the eye. Text resolution up to about 1200 dpi continues to contribute to perceived text sharpness (assuming low-diffusion paper, of course).

A Netpage printer, for example, may use a contone resolution of 267 ppi (i.e. 1600 dpi 6), and a black text and graphics resolution of 800 dpi. A high end office or departmental printer may use a contone resolution of 320 ppi (1600 dpi/5) and a black text and graphics resolution of 1600 dpi. Both formats are capable of exceeding the quality of commercial (offset) printing and photographic reproduction.

Because of the page-width nature of the bi-lithic printhead, each page must be printed at a constant speed to avoid creating visible artifacts. This means that the printing speed can't be varied to match the input data rate. Document rasterization and document printing are therefore decoupled to ensure the printhead has a constant supply of data. A page is never printed until it is fully rasterized. This can be achieved by storing a compressed version of each rasterized page image in memory.

This decoupling also allows the RIP(s) to run ahead of the printer when rasterizing simple pages, buying time to rasterize more complex pages.

Because contone color images are reproduced by stochastic dithering, but black text and line graphics are reproduced directly using dots, the compressed page image format contains a separate foreground bi-level black layer and background contone color layer. The black layer is composited over the contone layer after the contone layer is dithered (although the contone layer has an optional black component). A final layer of Netpage tags (in infrared or black ink) is optionally added to the page for printout.

FIG. 1 shows the flow of a document from computer system to printed page.

At 267 ppi for example, a A4 page (8.26 inches×11.7 inches) of contone CMYK data has a size of 26.3 MB. At 320 ppi, an A4 page of contone data has a size of 37.8 MB. Using lossy contone compression algorithms such as JPEG, contone images compress with a ratio up to 10:1 without noticeable loss of quality, giving compressed page sizes of 2.63 MB at 267 ppi and 3.78 MB at 320 ppi.

At 800 dpi, a A4 page of bi-level data has a size of 7.4 MB. At 1600 dpi, a Letter page of bi-level data has a size of 29.5 MB. Coherent data such as text compresses very well. Using lossless bi-level compression algorithms such as SMG4 fax, ten-point plain text compresses with a ratio of about 50:1. Lossless bi-level compression across an average page is about 20:1 with 10:1 possible for pages which compress poorly. The requirement for SoPEC is to be able to print text at 10:1 compression. Assuming 10:1 compression gives compressed page sizes of 0.74 MB at 800 dpi, and 2.95 MB at 1600 dpi.

Once dithered, a page of CMYK contone image data consists of 116 MB of bi-level data.

Using lossless bi-level compression algorithms on this data is pointless precisely because the optimal dither is stochastic—i.e. since it introduces hard-to-compress disorder.

Netpage tag data is optionally supplied with the page image. Rather than storing a compressed bi-level data layer for the Netpage tags, the tag data is stored in its raw form. Each tag is supplied up to 120 bits of raw variable data (combined with up to 56 bits of raw fixed data) and covers up to a 6 mm×6 mm area (at 1600 dpi). The absolute maximum number of tags on a A4 page is 15,540 when the tag is only 2 mm×2 mm (each tag is 126 dots×126 dots, for a total coverage of 148 tags×105 tags). 15,540 tags of 128 bits per tag gives a compressed tag page size of 0.24 MB.

The multi-layer compressed page image format therefore exploits the relative strengths of lossy JPEG contone image compression, lossless bi-level text compression, and tag encoding. The format is compact enough to be storage-efficient, and simple enough to allow straightforward real-time expansion during printing.

Since text and images normally don't overlap, the normal worst-case page image size is image only, while the normal best-case page image size is text only. The addition of worst case Netpage tags adds 0.24 MB to the page image size. The worst-case page image size is text over image plus tags. The average page size assumes a quarter of an average page contains images.

The SoPEC device can be used in several printer configurations and architectures.

In the general sense every SoPEC based printer architecture will contain:

One or more SoPEC devices.

One or more bi-lithic printheads.

Two or more LSS busses.

Two or more QA chips.

USB 1.1 connection to host or ISI connection to Bridge Chip.

ISI bus connection between SoPECs (when multiple SoPECs are used).

The SoPEC device contains several system on a chip (SoC) components, as well as the print engine pipeline control application specific logic.

The PEP reads compressed page store data from the 45 interfaces to. embedded memory, optionally decompresses the data and formats it for sending to the printhead. The print engine pipeline functionality includes expanding the page image, dithering the contone layer, compositing the black layer over the contone layer, rendering of Netpage tags, compensation for dead nozzles in the printhead, and sending the resultant image to the bi-lithic printhead. SoPEC contains an embedded CPU for general purpose system configuration and management. The CPU performs page and band header processing, motor control and sensor monitoring (via the GPIO) and other system control functions. The CPU can perform buffer management or report buffer status to the host. The CPU can optionally run vendor application specific code for general print control such as paper ready monitoring and LED status update.

A 2.5 Mbyte embedded memory buffer is integrated onto the SoPEC device, of which approximately 2 Mbytes are available for compressed page store data. A compressed page is divided into one or more bands, with a number of bands stored in memory. As a band of the page is consumed by the 65 PEP for printing a new band can be downloaded. The new band may be for the current page or the next page.

**10**

Using banding it is possible to begin printing a page before the complete compressed page is downloaded, but care must be taken to ensure that data is always available for printing or a buffer underrun may occur.

The embedded USB 1.1 device accepts compressed page data and control commands from the host PC, and facilitates the data transfer to either embedded memory or to another SoPEC device in multi-SoPEC systems.

The printhead is constructed by abutting 2 printhead ICs together. The printhead ICs can vary in size from 2 inches to 8 inches, so to produce an A4 printhead several combinations are possible. For example two printhead ICs of 7 inches and 3 inches could be used to create a A4 printhead (the notation is 7:3). Similarly 6 and 4 combination (6:4), or 5:5 combination.

For an A3 printhead it can be constructed from 8:6 or an 7:7 printhead IC combination. For photographic printing smaller printheads can be constructed.

Each SoPEC device has 2 LSS system buses for communication with QA devices for system authentication and ink usage accounting. The number of QA devices per bus and their position in the system is unrestricted with the exception that PRINTER\_QA and INK\_QA devices should be on separate LSS busses.

Each SoPEC system can have several QA devices. Normally each printing SoPEC will have an associated PRINT-ER\_QA. Ink cartridges will contain an INK\_QA chip. PRINTER\_QA and INK\_QA devices should be on separate LSS busses. All QA chips in the system are physically identical with flash memory contents defining PRINTER\_QA from INK\_QA chip.

The Inter-SoPEC Interface (ISI) provides a communication channel between SoPECs in a multi-SoPEC system. The ISIMaster can be SoPEC device or an ISI-Bridge chip depending on the printer configuration. Both compressed data and control commands are transferred via the interface.

A device, other than a SoPEC with a USB connection, which provides print data to a number of slave SoPECs. A bridge chip will typically have a high bandwidth connection, such as USB2.0, Ethernet or IEEE1394, to a host and may have an attached external DRAM for compressed page storage. A bridge chip would have one or more ISI interfaces. The use of multiple ISI buses would allow the construction of independent print systems within the one printer. The ISI-Bridge would be the ISIMaster for each of the ISI buses it interfaces to

Several possible SoPEC based system architectures exist. The following outline some possible architectures. It is possible to have extra SoPEC devices in the system used for DRAM storage. The QA chip configurations shown are indicative of the flexibility of LSS bus architecture, but not limited to those configurations.

In FIG. 2, a single SoPEC device can be used to control two printhead ICs. The SoPEC receives compressed data through the USB device from the host. The compressed data is processed and transferred to the printhead.

In FIG. 3, two SoPEC devices are used to control two bi-lithic printheads, each with two printhead ICs. Each bi-lithic printhead prints to opposite sides of the same page to achieve duplex printing. The SoPEC connected to the USB is the ISIMaster SoPEC, the remaining SoPEC is an ISISlave. The ISIMaster receives all the compressed page data for both SoPECs and re-distributes the compressed data over the Inter-SoPEC Interface (ISI) bus. It may not be possible to print an A4 page every 2 seconds in this configuration since the USB 1.1 connection to the host may not have enough bandwidth. An alternative would be for each SoPEC to have its own USB 1.1 connection. This would allow a faster average print speed.

In FIG. 4, two SoPEC devices are used to control one A3 bi-lithic printhead. Each SoPEC controls only one printhead IC (the remaining PHI port typically remains idle). This system uses the SoPEC with the USB connection as the ISIMaster. In this dual SoPEC configuration the compressed page store data is split across 2 SoPECs giving a total of 4 Mbyte page store, this allows the system to use compression rates as in an A4 architecture, but with the increased page size of A3. The ISIMaster receives all the compressed page data for all SoPECs and re-distributes the compressed data over the Inter-SoPEC Interface (ISI) bus.

It may not be possible to print an A3 page every 2 seconds in this configuration since the USB 1.1 connection to the host will only have enough bandwidth to supply 2 Mbytes every 2 seconds. Pages which require more than 2 MBytes every 2 seconds will therefore print more slowly. An alternative would be for each SoPEC to have its own USB 1.1 connection. This would allow a faster average print speed.

In FIG. **5** a 4 SoPEC system is shown. It contains 2 A3 bi-lithic printheads, one for each side of an A3 page. Each printhead contain 2 printhead ICs, each printhead IC is controlled by an independent SoPEC device, with the remaining PHI port typically unused. Again the SoPEC with USB 1.1 connection is the ISIMaster with the other SoPECs as ISISlaves. In total, the system contains 8 Mbytes of compressed page store (2 Mbytes per SoPEC), so the increased page size does not degrade the system print quality, from that of an A4 simplex printer. The ISIMaster receives all the compressed page data for all SoPECs and re-distributes the compressed data over the Inter-SoPEC Interface (ISI) bus.

It may not be possible to print an A3 page every 2 seconds in this configuration since the USB 1.1 connection to the host will only have enough bandwidth to supply 2 Mbytes every 2 seconds. Pages which require more than 2 MBytes every 2 seconds will therefore print more slowly. An alternative would be for each SoPEC or set of SoPECs on the same side of the page to have their own USB 1.1 connection (as ISISlaves may also have direct USB connections to the host). This would allow a faster average print speed.

Extra SoPECs can be used for DRAM storage e.g. in FIG. 6 an A4 simplex printer can be built with a single extra SoPEC used for DRAM storage. The DRAM SoPEC can provide guaranteed bandwidth delivery of data to the printing SoPEC. SoPEC configurations can have multiple extra SoPECs used for DRAM storage.

In FIG. 7, an ISI-Bridge chip provides slave-only ISI connections to SoPEC devices. FIG. 7 shows a ISI-Bridge chip with 2 separate ISI ports. The ISI-Bridge chip is the ISIMaster on each of the ISI busses it is connected to. All connected SoPECs are ISISlaves. The ISI-Bridge chip will typically have a high bandwidth connection to a host and may have an attached external DRAM for compressed page storage.

12

An alternative to having a ISI-Bridge chip would be for each SoPEC or each set of SoPECs on the same side of a page to have their own USB 1.1 connection. This would allow a faster average print speed.

The SoPEC is a page rendering engine ASIC that takes compressed page images as input, and produces decompressed page images at up to 6 channels of bi-level dot data as output. The bi-level dot data is generated for the Memjet bi-lithic printhead. The dot generation process takes account of printhead construction, dead nozzles, and allows for fixative generation.

A single SoPEC can control 2 bi-lithic printheads and up to 6 color channels at 10,000 lines/sec<sup>1</sup>, equating to 30 pages per minute. A single SoPEC can perform full-bleed printing of A3, A4 and Letter pages. The 6 channels of colored ink are the expected maximum in a consumer SOHO, or office Bi-lithic printing environment:

<sup>1</sup>10,000 lines per second equates to 30 A4/Letter pages per minute at 1600 dpi CMY, for regular color printing.

K, for black text, line graphics and gray-scale printing. IR (infrared), for Netpage-enabled [5] applications.

F (fixative), to enable printing at high speed. Because the bi-lithic printer is capable of printing so fast, a fixative may be required to enable the ink to dry before the page touches the page already printed. Otherwise the pages may bleed on each other. In low speed printing environments the fixative may not be required.

SoPEC is color space agnostic. Although it can accept contone data as CMYX or RGBX, where X is an optional 4th channel, it also can accept contone data in any print color space. Additionally, SoPEC provides a mechanism for arbitrary mapping of input channels to output channels, including combining dots for ink optimization, generation of channels based on any number of other channels etc. However, inputs are typically CMYK for contone input, K for the bi-level input, and the optional Netpage tag dots are typically rendered to an infra-red layer. A fixative channel is typically generated for fast printing applications.

SoPEC is resolution agnostic. It merely provides a mapping between input resolutions and output resolutions by means of scale factors. The expected output resolution is 1600 dpi, but SoPEC actually has no knowledge of the physical resolution of the Bi-lithic printhead. SoPEC is page-length agnostic. Successive pages are typically split into bands and downloaded into the page store as each band of information is consumed and becomes free. SoPEC provides an interface for synchronization with other SoPECs. This allows simple multi-SoPEC solutions for simultaneous A3/A4/Letter duplex printing. However, SoPEC is also capable of printing only a portion of a page image. Combining synchronization functionality with partial page rendering allows multiple SoPECs to be readily combined for alternative printing requirements including simultaneous duplex printing and wide format printing. Table 1 lists some of the features and corresponding benefits of SoPEC.

TABLE 1

| Features and Benefits of SoPEC           |                                                                        |  |  |

|------------------------------------------|------------------------------------------------------------------------|--|--|

| Feature                                  | Benefits                                                               |  |  |

| Optimised print architecture in hardware | 30 ppm full page photographic quality color printing from a desktop PC |  |  |

| 0.13 micron CMOS                         | High speed                                                             |  |  |

| (>3 million transistors)                 | Low cost<br>High functionality                                         |  |  |

TABLE 1-continued

| IABLE 1-continued                                  |                                                                                      |  |  |

|----------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| Features and Benefits of SoPEC                     |                                                                                      |  |  |

| Feature                                            | Benefits                                                                             |  |  |

| 900 Million dots per second                        | Extremely fast page generation                                                       |  |  |

| 10,000 lines per second at 1600                    | 0.5 A4/Letter pages per SoPEC chip per second                                        |  |  |

| dpi                                                |                                                                                      |  |  |

| 1 chip drives up to 133,920                        | Low cost page-width printers                                                         |  |  |

| nozzles                                            | 0004 of Salla printara can usa 1 SaDEC davice                                        |  |  |

| 1 chip drives up to 6 color planes                 | 99% of SoHo printers can use 1 SoPEC device                                          |  |  |

| Integrated DRAM                                    | No external memory required, leading to low cost                                     |  |  |

|                                                    | systems                                                                              |  |  |

| Power saving sleep mode                            | SoPEC can enter a power saving sleep mode to reduce                                  |  |  |

|                                                    | power dissipation between print jobs                                                 |  |  |

| JPEG expansion                                     | Low bandwidth from PC                                                                |  |  |

|                                                    | Low memory requirements in printer                                                   |  |  |

| Lossless bitplane expansion                        | High resolution text and line art with low bandwidth                                 |  |  |

| <b>3.</b> T                                        | from PC (e.g. over USB)                                                              |  |  |

| Netpage tag expansion                              | Generates interactive paper                                                          |  |  |

| Stochastic dispersed dot dither                    | Optically smooth image quality  No moire effects                                     |  |  |

| Hardware compositor for 6                          | Pages composited in real-time                                                        |  |  |

| image planes                                       | rages composited in rear-time                                                        |  |  |

| Dead nozzle compensation                           | Extends printhead life and yield                                                     |  |  |

|                                                    | Reduces printhead cost                                                               |  |  |

| Color space agnostic                               | Compatible with all inksets and image sources                                        |  |  |

|                                                    | including RGB, CMYK, spot, CIE L * a * b *, hexachrome,                              |  |  |

|                                                    | YCrCbK, sRGB and other                                                               |  |  |

| Color space conversion                             | Higher quality/lower bandwidth                                                       |  |  |

| Computer interface                                 | USB1.1 interface to host and ISI interface to ISI-Bridge                             |  |  |

|                                                    | chip thereby allowing connection to IEEE 1394,                                       |  |  |

| Cagaadahla in magalutian                           | Bluetooth etc.                                                                       |  |  |

| Cascadable in resolution                           | Printers of any resolution  Special color sets a grabove chrome can be used          |  |  |

| Cascadable in color depth Cascadable in image size | Special color sets e.g. hexachrome can be used Printers of any width up to 16 inches |  |  |

| Cascadable in pages                                | Printers can print both sides simultaneously                                         |  |  |

| Cascadable in speed                                | Higher speeds are possible by having each SoPEC print                                |  |  |

|                                                    | one vertical strip of the page.                                                      |  |  |

| Fixative channel data                              | Extremely fast ink drying without wastage                                            |  |  |

| generation                                         |                                                                                      |  |  |

| Built-in security                                  | Revenue models are protected                                                         |  |  |

| Undercolor removal on dot-by-                      | Reduced ink usage                                                                    |  |  |

| dot basis                                          |                                                                                      |  |  |

| Does not require fonts for high                    | No font substitution or missing fonts                                                |  |  |

| speed operation                                    | Many configurations of printhoods are supported by                                   |  |  |

| Flexible printhead configuration                   | Many configurations of printheads are supported by one chip type                     |  |  |

| Drives Bi-lithic printheads                        | No print driver chips required, results in lower cost                                |  |  |

| directly                                           | 1.0 prime direct onipo required, results in 10 mer cost                              |  |  |

| Determines dot accurate ink                        | Removes need for physical ink monitoring system in                                   |  |  |

| usage                                              | ink cartridges                                                                       |  |  |

|                                                    |                                                                                      |  |  |

The required printing rate for SoPEC is 30 sheets per minute with an inter-sheet spacing of 4 cm. To achieve a 30 sheets per minute print rate, this requires:

300 mm×63 (dot/mm)/2 sec=105.8 seconds per line, with no inter-sheet gap.

340 mm×63 (dot/mm)/2 sec=93.3 seconds per line, with a 4 cm inter-sheet gap.

A printline for an A4 page consists of 13824 nozzles across the page. At a system clock rate of 160 MHz 13824 dots of data can be generated in 86.4 seconds. Therefore data can be generated fast enough to meet the printing speed requirement. It is necessary to deliver this print data to the print-heads.

Printheads can be made up of 5:5, 6:4, 7:3 and 8:2 inch printhead combinations [2]. Print data is transferred to both print heads in a pair simultaneously. This means the longest time to print a line is determined by the time to transfer print data to the longest print segment. There are 9744 nozzles 65 across a 7 inch printhead. The print data is transferred to the printhead at a rate of 106 MHz (2/3 of the system clock rate)

per color plane. This means that it will take 91.9 s to transfer a single line for a 7:3 printhead configuration. So we can meet the requirement of 30 sheets per minute printing with a 4 cm gap with a 7:3 printhead combination. There are 11160 across an 8 inch printhead. To transfer the data to the printhead at 106 MHz will take 105.3 s. So an 8:2 printhead combination printing with an inter-sheet gap will print slower than 30 sheets per minute.

From the highest point of view the SoPEC device consists of 3 distinct subsystems

CPU Subsystem

DRAM Subsystem

Print Engine Pipeline (PEP) Subsystem

See FIG. 12 for a block level diagram of SoPEC.

The CPU subsystem controls and configures all aspects of the other subsystems. It provides general support for interfacing and synchronising the external printer with the internal print engine. It also controls the low speed communication to the QA chips. The CPU subsystem contains various peripherals to aid the CPU, such as GPIO (includes motor control),

14

interrupt controller, LSS Master and general timers. The Serial Communications Block (SCB) on the CPU subsystem provides a full speed USB1.1 interface to the host as well as an Inter SoPEC Interface (ISI) to other SoPEC devices.

The DRAM subsystem accepts requests from the CPU, 5 Serial Communications Block (SCB) and blocks within the PEP subsystem. The DRAM subsystem (in particular the DIU) arbitrates the various requests and determines which request should win access to the DRAM. The DIU arbitrates based on configured parameters, to allow sufficient access to 10 DRAM for all requesters. The DIU also hides the implementation specifics of the DRAM such as page size, number of banks, refresh rates etc.

The Print Engine Pipeline (PEP) subsystem accepts compressed pages from DRAM and renders them to bi-level dots 15 for a given print line destined for a printhead interface that communicates directly with up to 2 segments of a bi-lithic printhead.

The first stage of the page expansion pipeline is the CDU, LBD and TE. The CDU expands the JPEG-compressed contone (typically CMYK) layer, the LBD expands the compressed bi-level layer (typically K), and the TE encodes Netpage tags for later rendering (typically in IR or K ink). The output from the first stage is a set of buffers: the CFU, SFU, and TFU. The CFU and SFU buffers are implemented in 25 DRAM.

**16**

The second stage is the HCU, which dithers the contone layer, and composites position tags and the bi-level spot0 layer over the resulting bi-level dithered layer. A number of options exist for the way in which compositing occurs. Up to 6 channels of bi-level data are produced from this stage. Note that not all 6 channels may be present on the printhead. For example, the printhead may be CMY only, with K pushed into the CMY channels and IR ignored. Alternatively, the position tags may be printed in K if IR ink is not available (or for testing purposes).

The third stage (DNC) compensates for dead nozzles in the printhead by color redundancy and error diffusing dead nozzle data into surrounding dots.

The resultant bi-level 6 channel dot-data (typically CMYK-IRF) is buffered and written out to a set of line buffers stored in DRAM via the DWU.

Finally, the dot-data is loaded back from DRAM, and passed to the printhead interface via a dot FIFO. The dot FIFO accepts data from the LLU at the system clock rate (pclk), while the PHI removes data from the FIFO and sends it to the printhead at a rate of  $\frac{2}{3}$  times the system clock rate.

Looking at FIG. 12, the various units are described here in summary form:

TABLE 2

| Units within SoPEC |                 |                                       |                                                                                                                                                                                      |  |

|--------------------|-----------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Subsystem          | Unit<br>Acronym | Unit Name                             | Description                                                                                                                                                                          |  |

| DRAM               | DIU             | DRAM interface unit                   | Provides the interface for DRAM read and write access for the various SoPEC units, CPU and the SCB block. The DIU provides arbitration between competing units controls DRAM access. |  |

| CPU                | DRAM<br>CPU     | Embedded DRAM Central Processing Unit | 20 Mbits of embedded DRAM,<br>CPU for system configuration and control                                                                                                               |  |

|                    | MMU             | Memory<br>Management Unit             | Limits access to certain memory address areas in CPU user mode                                                                                                                       |  |

|                    | RDU             | Real-time Debug<br>Unit               | Facilitates the observation of the contents of most of the CPU addressable registers in SoPEC in addition to some pseudo-registers in realtime.                                      |  |

|                    | TIM             | General Timer                         | Contains watchdog and general system timers                                                                                                                                          |  |

|                    | LSS             | Low Speed Serial<br>Interfaces        | Low level controller for interfacing with the QA chips                                                                                                                               |  |

|                    | GPIO            | General Purpose IOs                   | General IO controller, with built-in Motor control unit, LED pulse units and de-glitch circuitry                                                                                     |  |

|                    | ROM             | Boot ROM                              | 16 KBytes of System Boot ROM code                                                                                                                                                    |  |

|                    | ICU             | Interrupt Controller<br>Unit          | General Purpose interrupt controller with configurable priority, and masking.                                                                                                        |  |

|                    | CPR             | Clock, Power and<br>Reset block       | Central Unit for controlling and generating<br>the system clocks and resets and<br>powerdown mechanisms                                                                              |  |

|                    | PSS             | Power Save Storage                    | Storage retained while system is powered down                                                                                                                                        |  |

|                    | USB             | Universal Serial Bus<br>Device        | USB device controller for interfacing with the host USB.                                                                                                                             |  |

|                    | ISI             | Inter-SoPEC<br>Interface              | ISI controller for data and control communication with other SoPEC's in a multi-SoPEC system                                                                                         |  |

|                    | SCB             | Serial<br>Communication<br>Block      | Contains both the USB and ISI blocks.                                                                                                                                                |  |

TABLE 2-continued

|                             | Units within SoPEC |                              |                                                                                                                                                                                                                                          |

|-----------------------------|--------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Subsystem                   | Unit<br>Acronym    | Unit Name                    | Description                                                                                                                                                                                                                              |

| Print Engine Pipeline (PEP) | PCU                | PEP controller               | Provides external CPU with the means to read and write PEP Unit registers, and read and write DRAM in single 32-bit chunks.                                                                                                              |

| (I LI)                      | CDU                | Contone decoder unit         | Expands JPEG compressed contone layer and writes decompressed contone to DRAM                                                                                                                                                            |

|                             | CFU                | Contone FIFO Unit            | Provides line buffering between CDU and HCU                                                                                                                                                                                              |

|                             | LBD                | Lossless Bi-level<br>Decoder | Expands compressed bi-level layer.                                                                                                                                                                                                       |

|                             | SFU                | Spot FIFO Unit               | Provides line buffering between LBD and HCU                                                                                                                                                                                              |

|                             | TE<br>TFU          | Tag encoder<br>Tag FIFO Unit | Encodes tag data into line of tag dots. Provides tag data storage between TE and HCU                                                                                                                                                     |

|                             | HCU                | Halftoner compositor unit    | Dithers contone layer and composites the bi-level spot 0 and position tag dots.                                                                                                                                                          |

|                             | DNC                | Dead Nozzle<br>Compensator   | Compensates for dead nozzles by color redundancy and error diffusing dead nozzle data into surrounding dots.                                                                                                                             |

|                             | DWU                | Dotline Writer Unit          | Writes out the 6 channels of dot data for a given printline to the line store DRAM                                                                                                                                                       |

|                             | LLU                | Line Loader Unit             | Reads the expanded page image from line store, formatting the data appropriately for the bi-lithic printhead.                                                                                                                            |

|                             | PHI                | PrintHead Interface          | Is responsible for sending dot data to the bilithic printheads and for providing line synchronization between multiple SoPECs.  Also provides test interface to printhead such as temperature monitoring and Dead Nozzle Identification. |

The CPU block consists of the CPU core, MMU, cache and associated logic. The principal tasks for the program running on the CPU to fulfill in the system are:

## Communications:

Control the flow of data from the USB interface to the DRAM and ISI

Communication with the host via USB or ISI Running the USB device driver

## PEP Subsystem Control:

Page and band header processing (may possibly be performed on host PC)

Configure printing options on a per band, per page, per job or per power cycle basis

Initiate page printing operation in the PEP subsystem Retrieve dead nozzle information from the printhead interface (PHI) and forward to the host PC

Select the appropriate firing pulse profile from a set of predefined profiles based on the printhead characteristics

Retrieve printhead temperature via the PHI

## Security:

Authenticate downloaded program code

Authenticate printer operating parameters

Authenticate consumables via the PRINTER\_QA and INK\_QA chips

Monitor ink usage

Isolation of OEM code from direct access to the system resources

## Other:

Drive the printer motors using the GPIO pins Monitoring the status of the printer (paper jam, tray empty etc.) Driving front panel LEDs

Perform post-boot initialisation of the SoPEC device Memory management (likely to be in conjunction with the

viemory management (likely to be in conjunction with the host PC)

Miscellaneous housekeeping tasks

To control the Print Engine Pipeline the CPU is required to provide a level of performance at least equivalent to a 16-bit Hitachi H8-3664 microcontroller running at 16 MHz. An as yet undetermined amount of additional CPU performance is needed to perform the other tasks, as well as to provide the potential for such activity as Netpage page assembly and processing, RIPing etc. The extra performance required is dominated by the signature verification task and the SCB (including the USB) management task. An operating system is not required at present. A number of CPU cores have been evaluated and the LEON P1754 is considered to be the most appropriate solution. A diagram of the CPU block is shown in FIG. 14.

Memory Management Units are typically used to protect certain regions of memory from invalid accesses, to perform address translation for a virtual memory system and to maintain memory page status (swapped-in, swapped-out or unmapped)

The SoPEC MMU is a much simpler affair whose function is to ensure that all regions of the SoPEC memory map are adequately protected. The MMU does not support virtual memory and physical addresses are used at all times. The SoPEC MMU supports a full 32-bit address space. The SoPEC memory map is depicted in FIG. 17.

The MMU selects the relevant bus protocol and generates the appropriate control signals depending on the area of memory being accessed. The MMU is responsible for performing the address decode and generation of the appropriate block select signal as well as the selection of the correct block

**18**

read bus during a read access. The MMU will need to support all of the bus transactions the CPU can produce including interrupt acknowledge cycles, aborted transactions etc.

When an MMU error occurs (such as an attempt to access a supervisor mode only region when in user mode) a bus error is generated. While the LEON can recognise different types of bus error (e.g. data store error, instruction access error) it handles them in the same manner as it handles all traps i.e it will transfer control to a trap handler. No extra state information is be stored because of the nature of the trap. The location of the trap handler is contained in the TBR (Trap Base Register). This is the same mechanism as is used to handle interrupts.

The DIU provides the interface between the on-chip 20 Mbit embedded DRAM and the rest of SoPEC. In addition to outlining the functionality of the DIU, this chapter provides a top-level overview of the memory storage and access patterns of SoPEC and the buffering required in the various SoPEC blocks to support those access requirements.

The main functionality of the DIU is to arbitrate between requests for access to the embedded DRAM and provide read or write accesses to the requesters. The DIU must also implement the initialisation sequence and refresh logic for the embedded DRAM.

The arbitration scheme uses a fully programmable timeslot mechanism for non-CPU requesters to meet the bandwidth <sup>25</sup> and latency requirements for each unit, with unused slots re-allocated to provide best effort accesses. The CPU is allowed high priority access, giving it minimum latency, but allowing bounds to be placed on its bandwidth consumption.

The interface between the DIU and the SoPEC requesters is <sup>30</sup> similar to the interface on PEC1 i.e. separate control, read data and write data busses.

The embedded DRAM is used principally to store:

CPU program code and data.

PEP (re)programming commands.

Compressed pages containing contone, bi-level and raw tag data and header information.

Decompressed contone and bi-level data.

Dotline store during a print.

Print setup information such as tag format structures, dither matrices and dead nozzle information.

The slots for blocks with a service requirement greater than 1 bit/cycle are distributed as follows. Calculations are included to check that such blocks will not suffer more than one stall per rotation.

45

The SFU has 2 bits/cycle on read but this is two separate channels of 1 bit/cycle sharing the same DIU interface so it is effectively 2 channels each of 1 bit/cycle so allowing the same margins as the LBD will work.

The DWU has 12 double buffers in each of the 6 colour planes, odd and even. These buffers are filled by the DNC and will request DIU access when double buffers fill. The DNC supplies 6 bits to the DWU every cycle (6 odd in one cycle, 6 even in the next cycle). So the service deadline is 512 cycles, given 6 accesses per 256-cycle rotation.

For the CFU the requirement is that the DIU stall should be less than the time taken for the CFU to consume one third of its triple buffer. The total DIU stall=refresh latency+extra CDU(W) latency+read circuit latency=3+5 (for 4 cycle timeslots)+10=18 cycles. The CFU can consume its data at 8 bits/cycle at SF=4. Therefore 256 bits of data will last 32 cycles so the triple buffer is safe. In fact we only need an extra 144 bits of buffering or 3×64 bits. But it is safer to have the full extra 256 bits or 4×64 bits of buffering.

The LLU has 2 channels, each of which could request at 6 65 bits/106 MHz channel or 4 bits/160 MHz cycle, giving a total of 8 bits/160 MHz cycle. The service deadline for each chan-

**20**

nel is 256×106 MHz cycles, i.e. all 6 colours must be transferred in 256 cycles to feed the printhead. This equates to 384×160 MHz cycles.

Over a span of 384 cycles, there will be 6 CDU(W) accesses, 4 refreshes and one read latency encountered at most. Assuming CPU pre-accesses for these occurrences, this means the number of available cycles is given by  $384-6\times6-4\times6-10=314$  cycles.

For a CPU pre-access slot rate of 50%, 314 cycles implies 31 CPU and 63 non-CPU accesses (31×6+32×4=314). For 12 LLU accesses interspersed amongst these 63 non-CPU slots, implies an LLU allocation rate of approximately one slot in 5.

If the CPU pre-access is 100% across all slots, then 314 cycles gives 52 slots each to CPU and non-CPU accesses, (52×6=312 cycles). Twelve accesses spread over 52 slots, implies a 1-in-4 slot allocation to the LLU.

The same LLU slot allocation rate (1 slot in 5, or 1 in 4) can be applied to programming slots across a 256-cycle rotation window. The window size does not affect the occurrence of LLU slots, so the 384-cycle service requirement will be fulfilled.

The DNC has a 2.4 bits/cycle bandwidth requirement. Each access will see the DIU stall of 18 cycles. 2.4 bits/cycle corresponds to an access every 106 cycles within a 256 cycle rotation. So to allow for DIU latency we need an access every 106-18 or 88 cycles. This is a bandwidth of 2.9 bits/cycle, requiring 3 timeslots in the rotation.

The Dotline Writer Unit (DWU) receives 1 dot (6 bits) of color information per cycle from the DNC. Dot data received is bundled into 256-bit words and transferred to the DRAM. The DWU (in conjunction with the LLU) implements a dot line FIFO mechanism to compensate for the physical placement of nozzles in a printhead, and provides data rate smoothing to allow for local complexities in the dot data generate pipeline.

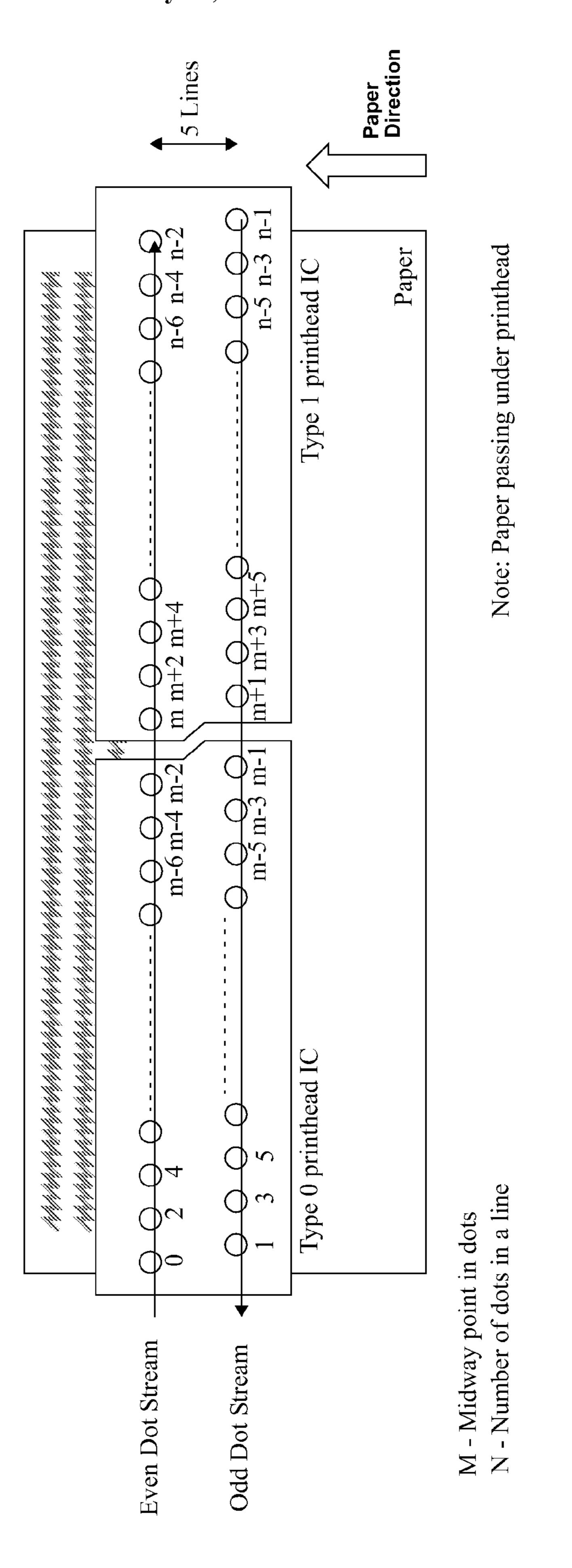

The physical placement of nozzles in the printhead means that in one firing sequence of all nozzles, dots will be produced over several print lines. The printhead consists of 12 rows of nozzles, one for each color of odd and even dots. Odd and even nozzles are separated by D<sub>2</sub> print lines and nozzles of different colors are separated by D<sub>1</sub> print lines. See FIG. 19 for reference. The first color to be printed is the first row of nozzles encountered by the incoming paper. In the example this is color 0 odd, although is dependent on the printhead type. Paper passes under printhead moving downwards.

For example if the physical separation of each half row is  $80 \,\mathrm{m}$  equating to  $\mathrm{D_1} = \mathrm{D_2} = 5 \,\mathrm{print}$  lines at  $1600 \,\mathrm{dpi}$ . This means that in one firing sequence, color 0 odd nozzles will fire on dotline L, color 0 even nozzles will fire on dotline L-D<sub>1</sub>, color 1 odd nozzles will fire on dotline L-D<sub>1</sub>-D<sub>2</sub> and so on over 6 color planes odd and even nozzles. The total number of lines fired over is given as  $0+5+5\ldots+5=0+11\times 5=55$ . See FIG. 20 for example diagram. It is expected that the physical spacing of the printhead nozzles will be  $80 \,\mathrm{m}$  (or 5 dot lines), although there is no dependency on nozzle spacing. The DWU is configurable to allow other line nozzle spacings.

The DWU block is required to compensate for the physical spacing between lines of nozzles. It does this by storing dot lines in a FIFO (in DRAM) until such time as they are required by the LLU for dot data transfer to the printhead interface. Colors are stored separately because they are needed at different times by the LLU. The dot line store must store enough lines to compensate for the physical line separation of the printhead but can optionally store more lines to allow system level data rate variation between the read (printhead feed) and write sides (dot data generation pipeline) of the FIFOs.

A logical representation of the FIFOs is shown in FIG. 21, where N is defined as the optional number of extra half lines

in the dot line store for data rate de-coupling. For an arbitrary page width of d dots (where d is even), the number of dots per half line is d/2.

For interline spacing of  $D_2$  and inter-color spacing of  $D_1$ , with C colors of odd and even half lines, the number of half 5 line storage is  $(C-1)(D_2+D_1)+D1$ .

For N extra half line stores for each color odd and even, the storage is given by (N\*C\*2). The total storage requirement is  $((C-1)(D_2+D_1)+D_1+(N*C*2))*d/2$  in bits.