# (12) United States Patent

# Kobayashi

# (10) Patent No.: US 7,681,111 B2 (45) Date of Patent: Mar. 16, 2010

# DISK ARRAY DEVICE, PARITY DATA GENERATING CIRCUIT FOR RAID AND GALOIS FIELD MULTIPLYING CIRCUIT

(75) Inventor: **Eiji Kobayashi**, Tokyo (JP)

(73) Assignee: **NEC Corporation**, Tokyo (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 12/190,306

(22) Filed: Aug. 12, 2008

#### (65) Prior Publication Data

US 2009/0024879 A1 Jan. 22, 2009

# Related U.S. Application Data

(62) Division of application No. 10/989,439, filed on Nov. 17, 2004, now Pat. No. 7,437,658.

## (30) Foreign Application Priority Data

(51) **Int. Cl.**

G06F 11/00 (2006.01)

See application file for complete search history.

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

5,499,253 A 3/1996 Lary

| 6,148,430    | A    | 11/2000 | Weng                        |

|--------------|------|---------|-----------------------------|

| 6,523,054    | B1   | 2/2003  | Kamijo                      |

| 7,003,715    | B1   | 2/2006  | Thurston                    |

| 7,133,889    | B2 * | 11/2006 | Parthasarathy et al 708/492 |

| 2004/0078643 | A1*  | 4/2004  | Ghosh et al                 |

#### FOREIGN PATENT DOCUMENTS

| JP | 9-218877    | 8/1997 |

|----|-------------|--------|

| JΡ | 2000-259359 | 9/2000 |

#### OTHER PUBLICATIONS

Plank, "A Tutorial on Reed-Solomon Coding for Fault-Tolerance in RAID-like Systems", Software-Practice and Experience, John Wiley & Sons, Ltd., USA, vol. 27(9), Sep. 1997, pp. 995-1012.

\* cited by examiner

Primary Examiner—Esaw T Abraham (74) Attorney, Agent, or Firm—Young & Thompson

## (57) ABSTRACT

In this parity data generating circuit, a Galois field multiplying calculation is realized by performing data conversion by index table information generated from a Galois field multiplying table so that data for RAID6 are generated. A table check circuit inspects nonconformity of the index table information in advance by using results in which the Galois field multiplying table is indexed from different directions constructed by the longitudinal direction and the transversal direction. Data and parity for making the multiplying calculation are decomposed into plural data and parities by using this table check circuit, and index table information different from each other are allocated to these data and parities. Thus, a longitudinal index table making circuit and a transversal index table making circuit themselves are checked.

#### 15 Claims, 28 Drawing Sheets

FIG. 7

Mar. 16, 2010

R2 CONVERSION TABLE

# DISK ARRAY DEVICE, PARITY DATA GENERATING CIRCUIT FOR RAID AND GALOIS FIELD MULTIPLYING CIRCUIT

This application claims priority to prior application JP 5 2003-386997, the disclosure of which is incorporated herein by reference.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a disk array device, a parity data generating circuit for RAID (Redundant Array of Independent Disks) and a Galois field multiplying circuit, and particularly, relates to a disk array device of RAID6, a parity data generating circuit for RAID and a Galois field multiplying circuit requiring high reliability and high performance.

#### 2. Description of the Related Art

In the disk array device for storing important data, reliability is increased by a RAID technique or the like conventionally known, and plural RAID systems of RAID0 to RAID5 have been defined. However, in recent years, a system of RAID6 improving these plural RAID systems has appeared and a further improvement of reliability is required.

The reliability of hardware of the disk array device itself is also required. In data transfer, a mechanism for adding a check code of data guarantee such as parity and ECC (Error Correcting Code) and preventing the transfer data from being changed into another code has been indispensable.

In particular, in the RAID6 recently defined, it is necessary to multiply the Galois field upon treating data. With respect to its arithmetic results, a new mechanism for improving reliability such as reflection of parity for securing the justifying property of data is required.

For example, a RAID device for realizing the RAID6 by using an extension Galois field GF(2<sup>4</sup>) capable of treating 16 kinds of data in the calculation of parity is known (see Japanese Unexamined Patent Publication (JP-A) No. 2000-259359). Hereinafter, the extension Galois field is suitably <sup>40</sup> simply called Galois field.

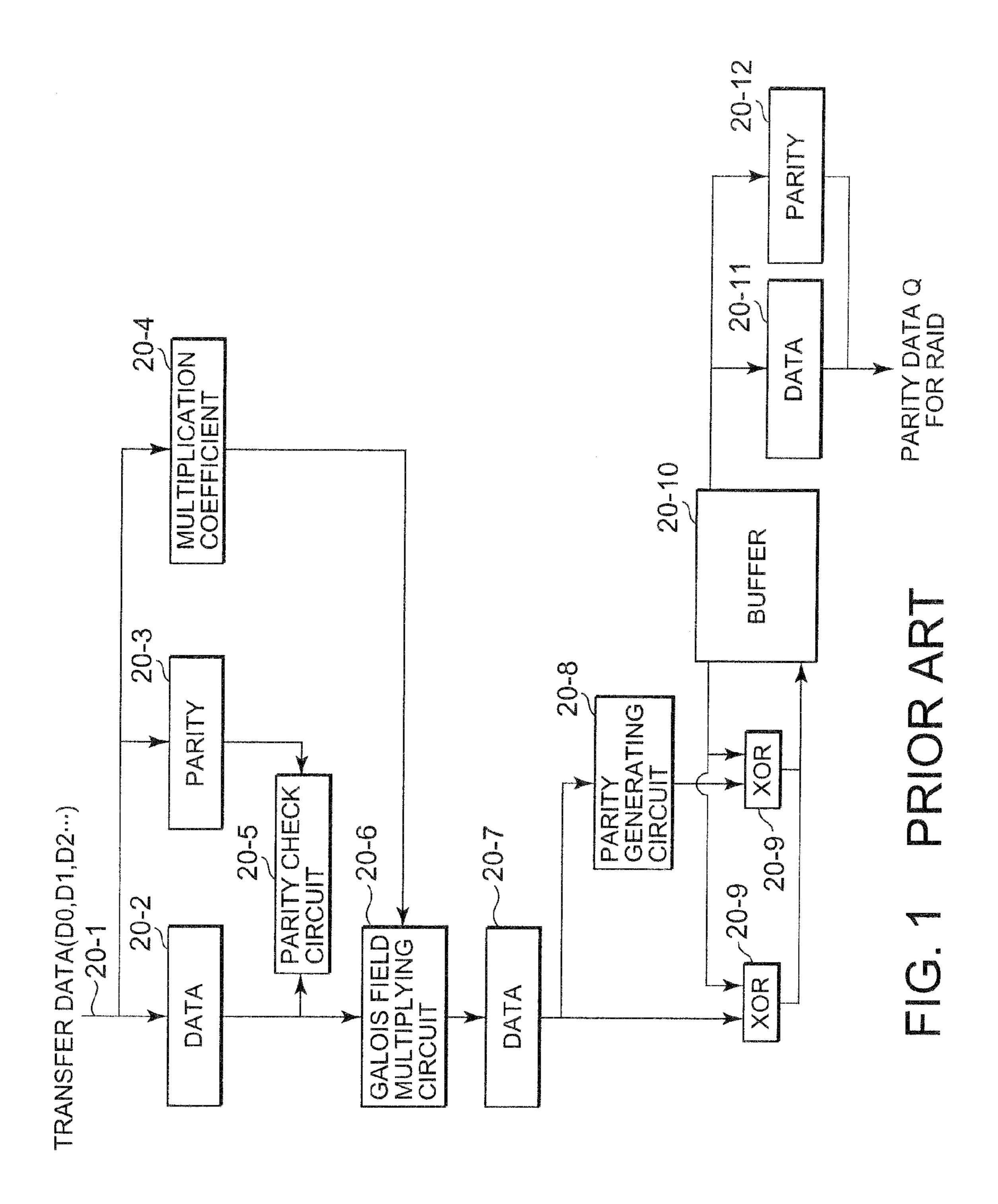

FIG. 1 shows a circuit construction for generating parity data for RAID in the prior art. In transfer data 20-1 from a memory, the circuit is constructed such that data 20-2, parity 20-3 and a multiplication coefficient 204 of the Galois field with respect to these data 20-2 are transferred. With respect to the data 20-2 themselves, a parity check is made by a parity check circuit 20-5 (see "A Tutorial on Reed-Solomon Coding for Fault-Tolerance in RAID-like System" James S. Plank, Department of Computer Science University of Tennessee, Feb. 19, 1999)

An arithmetic calculation using a Galois field multiplying circuit 20-6 is made by designating the multiplication coefficient 20-4 for these data 20-2 so that data 20-7 for RAID are generated. After this generation, the parity for the data 20-7 is generated by a parity generating circuit 20-8. Thus, the justifying property of the data 20-2 from the memory is guaranteed by the parity check circuit 20-5.

In a data guaranteeing circuit in the conventional method as shown in FIG. 1, there is an effect in a logic failure or the like. However, no failure of hardware can be found when a breaking point is narrowed down to a certain one point as in deterioration due to a change with the passage of time within LSI (Large Scaled Integration) and a short circuit.

This problem will be explained in the circuit construction of FIG. 1. Specifically, a state guaranteeing no data 20-2 is

2

attained because no parity error can be detected even if the parity error is generated when the parity check circuit **20-5** for guaranteeing data is broken.

Further, data having no problem are used upon checking the error. However, when the Galois field multiplying circuit **20-6** is broken, its arithmetic result is converted into data except for an object and parity **20-12** is simultaneously newly given again by the parity generating circuit **20-8** existing after this conversion. No parity error is detected even when the data **20-7** are converted in error. The parity data Q for RAID finally generated cause a data changing state, which becomes a fatal wound as a disk array system.

In order to avoid such a problem, proposal has been made of a conventional technique for doubling the Galois field multiplying circuit **20-6** itself and comparing the mutual arithmetic results. However, when an error signal itself showing the comparing result is broken by a short circuit, no effect can be shown at all.

In the disk array device of RAID6 requiring high reliability, the event that these abnormal data are considered as effective data should not be caused.

#### SUMMARY OF THE INVENTION

It is a first object of the present invention to provide a disk array device of RAID6 of high reliability capable of reliably guaranteeing data by parity with respect to the data, a check code of ECC even in the Galois field multiplying circuit.

It is a second object of the present invention to provide a parity data generating circuit for RAID for realizing the disk array device of RAID6 and reliably preventing the data change including a failure and checking the justifying property of the data.

It is a third object of the present invention to provide a Galois field multiplying circuit suitably used in the parity data generating circuit for RAID for realizing the disk array device of RAID6.

It is a fourth object of the present invention to provide a parity data generating method for RAID for realizing the disk array device of RAID6 and reliably preventing the data change including a failure and checking the justifying property of the data.

A disk array device of the present invention is characterized in that data are converted by using a Galois field multiplying table symmetrical longitudinally and transversally and made by a multiplying calculation of the Galois field of GF(2<sup>4</sup>), and index table information of the transversal direction and index table information of the longitudinal direction are extracted from the Galois field multiplying table, and a failure of a circuit is detected by comparing both the index table information.

The disk array device of the present invention is also characterized in that two kinds of index table information for data for making the multiplying calculation and index table information for a check code annexed to these data are generated as the index table information.

The disk array device of the present invention is further characterized in that the failure of the circuit is detected by arithmetically performing an XOR logic operation of a bit unit of the index table information, and detecting that it is a value except for zero.

Furthermore, the disk array device of the present invention is characterized in that the data for making the multiplying calculation of the Galois field are decomposed into plural data, and processing is performed by dividing these data into decomposing data for performing the conversion by using the index table information of the longitudinal direction, and

decomposing data for performing the conversion by using the index table information of the transversal direction.

The disk array device of the present invention is also characterized in that the check code annexed to the data for making the multiplying calculation of the Galois field is decomposed into plural check codes, and processing is performed by dividing these check codes into a decomposing check code for performing the conversion by using the index table information of the longitudinal direction, and a decomposing check code for performing the conversion by using the index table information of the transversal direction.

The disk array device of the present invention is further characterized in that the decomposing check code with respect to the decomposing data is converted by using the index table information of the longitudinal direction when 15 these decomposing data are converted by using the index table information of the transversal direction, and the decomposing check code with respect to the decomposing data is converted by using the index table information of the transversal direction when these decomposing data are converted by using the index table information of the longitudinal direction, so that the decomposing data and the decomposing check code as a pair are converted by using the index table information different from each other.

Furthermore, the disk array device of the present invention 25 is characterized in that the index table information of the longitudinal direction is a longitudinal conversion table for data, and the index table information of the transversal direction is a transversal conversion table for data.

The disk array device of the present invention is also characterized in that the index table information of the longitudinal direction is a longitudinal conversion table for data and a longitudinal inverting table for a check code, and the index table information of the transversal direction is a transversal conversion table for data and a transversal inverting table for 35 a check code.

Further, the disk array device of the present invention is characterized in that the check code is parity with respect to the data.

Furthermore, the disk array device of the present invention 40 is characterized in that the check code is ECC with respect to the data.

On the other hand, the disk array device of the present invention is characterized in that data are converted by using a Galois field multiplying table symmetrical longitudinally 45 and transversally and made by a multiplying calculation of the Galois field of  $GF(2^4)$ , and index table information of the transversal direction and index table information of the longitudinal direction are extracted from the Galois field multiplying table, and a failure of a circuit is detected by comparing 50 both the index table information.

The parity data generating circuit for RAID in the present invention is also characterized in that two kinds of index table information for data for making the multiplying calculation and index table information for a check code annexed to these 55 data are generated as the index table information.

The parity data generating circuit for RAID in the present invention is further characterized in that the failure of the circuit is detected by arithmetically performing an XOR logic operation of a bit unit of the index table information, and 60 detecting that it is a value except for zero.

Furthermore, the parity data generating circuit for RAID in the present invention is characterized in that the data for making the multiplying calculation of the Galois field are decomposed into plural data, and processing is performed by dividing these data into decomposing data for performing the conversion by using the index table information of the longi4

tudinal direction, and decomposing data for performing the conversion by using the index table information of the transversal direction.

The parity data generating circuit for RAID in the present invention is also characterized in that the check code annexed to the data for making the multiplying calculation of the Galois field is decomposed into plural check codes, and processing is performed by dividing these check codes into a decomposing check code for performing the conversion by using the index table information of the longitudinal direction, and a decomposing check code for performing the conversion by using the index table information of the transversal direction.

The parity data generating circuit for RAID in the present invention is further characterized in that the decomposing check code with respect to the decomposing data is converted by using the index table information of the longitudinal direction when these decomposing data are converted by using the index table information of the transversal direction, and the decomposing check code with respect to the decomposing data is converted by using the index table information of the transversal direction when these decomposing data are converted by using the index table information of the longitudinal direction, so that the decomposing data and the decomposing check code as a pair are converted by using the index table information different from each other.

Furthermore, the parity data generating circuit for RAID in the present invention is characterized in that the Galois field multiplying circuit has a Galois field multiplying table; a longitudinal index table making circuit for generating the index table information of the longitudinal direction by indexing the Galois field multiplying table from the longitudinal direction by using a multiplication coefficient; a transversal index table making circuit for generating the index table information of the transversal direction by indexing the Galois field multiplying table from the transversal direction by using the multiplication coefficient; a table check circuit for checking whether the generated index table information is correct; an upper order data converting circuit and a lower order data converting circuit for dividing data from the generated index table information into an upper order data portion and a lower order data portion and converting these data into data for RAID; and an upper order parity inverting circuit and a lower order parity inverting circuit for dividing parity with respect to the data from the generated index table information into an upper order parity portion and a lower order parity portion and converting this parity into parity with respect to the data for RAID.

The parity data generating circuit for RAID in the present invention is also characterized in that the Galois field multiplying circuit has a Galois field multiplying table; a longitudinal index table making circuit for generating the index table information of the longitudinal direction by indexing the Galois field multiplying table from the longitudinal direction by using a multiplication coefficient; a transversal index table making circuit for generating the index table information of the transversal direction by indexing the Galois field multiplying table from the transversal direction by using the multiplication coefficient; a table check circuit for checking whether the generated index table information is correct; an even data converting circuit and an odd data converting circuit for dividing data from the generated index table information into an even data position and an odd data position and converting these data into data for RAID; and an even parity inverting circuit and an odd parity inverting circuit for dividing parity with respect to the data from the generated index

table information into an even parity position and an odd parity position and converting this parity into parity with respect to the data for RAID.

The parity data generating circuit for RAID in the present invention is further characterized in that the Galois field multiplying circuit has a Galois field multiplying table; a longitudinal index table making circuit for generating the index table information of the longitudinal direction by indexing the Galois field multiplying table from the longitudinal direction by using a multiplication coefficient; a transversal index 10 table making circuit for generating the index table information of the transversal direction by indexing the Galois field multiplying table from the transversal direction by using the multiplication coefficient; a table check circuit for checking whether the generated index table information is correct; an 15 upper order data converting circuit and a lower order data converting circuit for dividing data from the generated index table information into an upper order data portion and a lower order data portion and converting these data into data for RAID; and an ECC converting circuit for converting ECC 20 with respect to the data into ECC with respect to the data for RAID.

Furthermore, the parity data generating circuit for RAID in the present invention is characterized in that the index table information of the longitudinal direction is a longitudinal 25 conversion table for data, and the index table information of the transversal direction is a transversal conversion table for data.

The parity data generating circuit for RAID in the present invention is also characterized in that the index table information of the longitudinal direction is a longitudinal conversion table for data and a longitudinal inverting table for a check code, and the index table information of the transversal direction is a transversal conversion table for data and a transversal inverting table for a check code.

The parity data generating circuit for RAID in the present invention is further characterized in that the check code is parity with respect to the data.

Furthermore, the parity data generating circuit for RAID in the present invention is characterized in that the check code is ECC with respect to the data.

The parity data generating circuit for RAID in the present invention is also characterized in that the parity data generating circuit for RAID comprises:

- a Galois field multiplying table having a conversion table for data and a conversion table for parity;

- a longitudinal index table making circuit for generating a longitudinal inverting table for parity and a longitudinal converting table for data by indexing the Galois field multiplying table from the longitudinal direction by using a multiplication coefficient;

- a transversal index table making circuit for generating a transversal converting table for data and a transversal inverting table for parity by indexing the Galois field multiplying 55 table from the transversal direction by using the multiplication coefficient;

- an upper order data converting circuit for selecting the longitudinal converting table for data generated by the longitudinal index table making circuit by each decomposing data of an upper order data portion of data, and obtaining a multiplying result of the Galois field;

- a lower order data converting circuit for selecting the transversal converting table for data generated by the transversal index table making circuit by each decomposing data of a 65 lower order data portion of data, and obtaining a multiplying result of the Galois field;

6

an upper order parity inverting circuit for obtaining an inverting result of an upper order parity portion in which an XOR logic operation is performed with respect to each decomposing parity of the upper order parity portion of the parity and the multiplying result of the Galois field obtained by selecting the transversal inverting table for parity generated by the transversal index table making circuit by each decomposing data of the upper order data portion of the data;

a lower order parity inverting circuit for obtaining an inverting result of the lower order parity in which the XOR logic operation is performed with respect to each decomposing parity of the lower order parity portion of the parity and the multiplying result of the Galois field obtained by selecting the longitudinal inverting table for parity generated by the longitudinal index table making circuit by each decomposing data of the upper order data portion of the data;

a table check circuit for data conversion for comparing and checking the longitudinal converting table for data generated by the longitudinal index table making circuit and the transversal converting table for data generated by the transversal index table making circuit;

a table check circuit for parity inversion for comparing and checking the longitudinal inverting table for parity generated by the longitudinal index table making circuit, and the transversal inverting table for parity generated by the transversal index table making circuit;

a first table zero check circuit for checking that the XOR logic of each bit series of the longitudinal converting table for data generated by the longitudinal index table making circuit, or the transversal converting table for data generated by the transversal index table making circuit is zero;

a second table zero check circuit for checking that the XOR logic of a bit series of the longitudinal inverting table for parity generated by the longitudinal index table making circuit, or the transversal inverting table for parity generated by the transversal index table making circuit is zero;

a parity check circuit for checking the parity of data by using the data generated by the upper order data converting circuit and the lower order data converting circuit, and the parity generated by the upper order parity inverting circuit and the lower order parity inverting circuit;

an XOR circuit for performing the XOR logic arithmetic operation with respect to the data generated by the upper order data converting circuit and the lower order data converting circuit, and the parity generated by the upper order parity inverting circuit and the lower order parity inverting circuit; and

a buffer for accumulating the arithmetic result of the XOR circuit as parity data for RAID.

The parity data generating circuit for RAID in the present invention is further characterized in that the parity data generating circuit for RAID comprises:

- a Galois field multiplying table having a conversion table for data and a conversion table for parity;

- a longitudinal index table making circuit for generating a longitudinal inverting table for parity and a longitudinal converting table for data by indexing the Galois field multiplying table from the longitudinal direction by using a multiplication coefficient;

- a transversal index table making circuit for generating a transversal converting table for data and a transversal inverting table for parity by indexing the Galois field multiplying table from the transversal direction by using the multiplication coefficient;

an even data converting circuit for selecting the longitudinal converting table for data generated by the longitudinal

index table making circuit by each decomposing data of an even data position of data, and obtaining a multiplying result of the Galois field;

an odd data converting circuit for selecting the transversal converting table for data generated by the transversal index 5 table making circuit by each decomposing data of an odd data position of data, and obtaining a multiplying result of the Galois field;

an even parity inverting circuit for obtaining an inverting result of the even parity in which an XOR logic operation is performed with respect to each decomposing parity of the upper order parity portion of the parity and the multiplying result of the Galois field obtained by selecting the transversal inverting table for parity generated by the transversal index table making circuit by each decomposing data of the even data position of the data;

an odd parity inverting circuit for obtaining an inverting result of the odd parity in which the XOR logic operation is performed with respect to each decomposing parity of the lower order parity portion of the parity and the multiplying <sup>20</sup> result of the Galois field obtained by selecting the longitudinal inverting table for parity generated by the longitudinal index table making circuit by each decomposing data of the odd data position of the data;

a table check circuit for data conversion for comparing and checking the longitudinal converting table for data generated by the longitudinal index table making circuit and the transversal converting table for data generated by the transversal index table making circuit;

a table check circuit for parity inversion for comparing and checking the longitudinal inverting table for parity generated by the longitudinal index table making circuit, and the transversal inverting table for parity generated by the transversal index table making circuit;

a first table zero check circuit for checking that the XOR logic of each bit series of the longitudinal converting table for data generated by the longitudinal index table making circuit, or the transversal converting table for data generated by the transversal index table making circuit is zero;

a second table zero check circuit for checking that the XOR logic of a bit series of the longitudinal inverting table for parity generated by the longitudinal index table making circuit, or the transversal inverting table for parity generated by the transversal index table making circuit is zero;

a parity check circuit for checking the parity of data by using the data generated by the upper order data converting circuit and the lower order data converting circuit, and the parity generated by the upper order parity inverting circuit and the lower order parity inverting circuit;

an XOR circuit for performing the XOR logic arithmetic operation with respect to the data generated by the upper order data converting circuit and the lower order data converting circuit, and the parity generated by the upper order parity inverting circuit and the lower order parity inverting circuit; and

a buffer for accumulating the arithmetic result of the XOR circuit as parity data for RAID.

Furthermore, the parity data generating circuit for RAID in the present invention is characterized in that the parity data generating circuit for RAID comprises:

a Galois field multiplying table having a conversion table for data and a conversion table for parity;

an ECC converting table corresponding to each decomposing data of the data;

a longitudinal index table making circuit for generating a longitudinal inverting table for parity and a longitudinal con-

8

verting table for data by indexing the Galois field multiplying table from the longitudinal direction by using a multiplication coefficient;

a transversal index table making circuit for generating a transversal converting table for data and a transversal inverting table for parity by indexing the Galois field multiplying table from the transversal direction by using the multiplication coefficient;

an ECC index table making circuit for generating a conversion table for ECC by indexing the ECC converting table by using the multiplication coefficient;

an upper order data converting circuit for selecting the longitudinal converting table for data generated by the longitudinal index table making circuit by each decomposing data of an upper order data portion of data, and obtaining a multiplying result of the Galois field;

a lower order data converting circuit for selecting the transversal converting table for data generated by the transversal index table making circuit by each decomposing data of a lower order data portion of data, and obtaining a multiplying result of the Galois field;

an ECC converting circuit for selecting the ECC converting table generated by the ECC index table making circuit by each decomposing data of the data, and converting the ECC with respect to the data into ECC with respect to data for RAID;

a table check circuit for data conversion for comparing and checking the longitudinal converting table for data generated by the longitudinal index table making circuit and the transversal converting table for data generated by the transversal index table making circuit;

a table check circuit for parity inversion for comparing and checking the longitudinal inverting table for parity generated by the longitudinal index table making circuit, and the transversal inverting table for parity generated by the transversal index table making circuit;

a first table zero check circuit for checking that the XOR logic of each bit series of the longitudinal converting table for data generated by the longitudinal index table making circuit, or the transversal converting table for data generated by the transversal index table making circuit is zero;

a second table zero check circuit for checking that the XOR logic of a bit series of the longitudinal inverting table for parity generated by the longitudinal index table making circuit, or the transversal inverting table for parity generated by the transversal index table making circuit is zero;

an ECC check circuit for checking the ECC with respect to the data by using the data generated by the upper order data converting circuit and the lower order data converting circuit and the ECC generated by the ECC converting circuit;

an XOR circuit for performing the XOR logic arithmetic operation with respect to the data generated by the upper order data converting circuit and the lower order data converting circuit and the ECC generated by the ECC converting circuit; and

a buffer for accumulating the arithmetic result of the XOR circuit as parity data for RAID.

On the other hand, a Galois field multiplying circuit of the present invention is characterized in that the Galois field multiplying circuit comprises a Galois field multiplying table; a longitudinal index table making circuit for generating the index table information of the longitudinal direction by indexing the Galois field multiplying table from the longitudinal direction by using a multiplication coefficient; a transversal index table making circuit for generating the index table information of the transversal direction by indexing the Galois field multiplying table from the transversal direction

by using the multiplication coefficient; an upper order data converting circuit and a lower order data converting circuit for dividing data from the generated index table information into an upper order data portion and a lower order data portion and converting these data into data for RAID; and an upper order parity inverting circuit and a lower order parity inverting circuit for dividing parity with respect to the data from the generated index table information into an upper order parity portion and a lower order parity portion and converting this parity into parity with respect to the data for RAID.

The Galois field multiplying circuit of the present invention is also characterized in that the Galois field multiplying circuit comprises a Galois field multiplying table; a longitudinal index table making circuit for generating the index table information of the longitudinal direction by indexing the 15 Galois field multiplying table from the longitudinal direction by using a multiplication coefficient; a transversal index table making circuit for generating the index table information of the transversal direction by indexing the Galois field multiplying table from the transversal direction by using the mul- 20 tiplication coefficient; an even data converting circuit and an odd data converting circuit for dividing data from the generated index table information into an even data position and an odd data position and converting these data into data for RAID; and an even parity inverting circuit and an odd parity 25 inverting circuit for dividing parity with respect to the data from the generated index table information into an even parity position and an odd parity position and converting this parity into parity with respect to the data for RAID.

The Galois field multiplying circuit of the present invention is further characterized in that the Galois field multiplying circuit comprises a Galois field multiplying table; a longitudinal index table making circuit for generating the index table information of the longitudinal direction by indexing the Galois field multiplying table from the longitudinal direc- <sup>35</sup> tion by using a multiplication coefficient; a transversal index table making circuit for generating the index table information of the transversal direction by indexing the Galois field multiplying table from the transversal direction by using the multiplication coefficient; an upper order data converting cir- 40 cuit and a lower order data converting circuit for dividing data from the generated index table information into an upper order data portion and a lower order data portion and converting these data into data for RAID; and an ECC converting circuit for converting ECC with respect to the data into ECC 45 with respect to the data for RAID.

Furthermore, the Galois field multiplying circuit of the present invention is characterized in that the Galois field multiplying circuit comprises:

- a Galois field multiplying table having a conversion table for data and a conversion table for parity;

- a longitudinal index table making circuit for generating a longitudinal inverting table for parity and a longitudinal converting table for data by indexing the Galois field multiplying table from the longitudinal direction by using a multiplication coefficient;

- a transversal index table making circuit for generating a transversal converting table for data and a transversal inverting table for parity by indexing the Galois field multiplying 60 table from the transversal direction by using the multiplication coefficient;

an upper order data converting circuit for selecting the longitudinal converting table for data generated by the longitudinal index table making circuit by each decomposing data of an upper order data portion of data, and obtaining a multiplying result of the Galois field;

10

a lower order data converting circuit for selecting the transversal converting table for data generated by the transversal index table making circuit by each decomposing data of a lower order data portion of data, and obtaining a multiplying result of the Galois field;

an upper order parity inverting circuit for obtaining an inverting result of an upper order parity portion in which an XOR logic operation is performed with respect to each decomposing parity of the upper order parity portion of the parity and the multiplying result of the Galois field obtained by selecting the transversal inverting table for parity generated by the transversal index table making circuit by each decomposing data of the upper order data portion of the data; and

a lower order parity inverting circuit for obtaining an inverting result of the lower order parity in which the XOR logic operation is performed with respect to each decomposing parity of the lower order parity portion of the parity and the multiplying result of the Galois field obtained by selecting the longitudinal inverting table for parity generated by the longitudinal index table making circuit by each decomposing data of the upper order data portion of the data.

The Galois field multiplying circuit of the present invention is also characterized in that the Galois field multiplying circuit comprises:

- a Galois field multiplying table having a conversion table for data and a conversion table for parity;

- a longitudinal index table making circuit for generating a longitudinal inverting table for parity and a longitudinal converting table for data by indexing the Galois field multiplying table from the longitudinal direction by using a multiplication coefficient;

- a transversal index table making circuit for generating a transversal converting table for data and a transversal inverting table for parity by indexing the Galois field multiplying table from the transversal direction by using the multiplication coefficient;

an even data converting circuit for selecting the longitudinal converting table for data generated by the longitudinal index table making circuit by each decomposing data of an even data position of data, and obtaining a multiplying result of the Galois field;

an odd data converting circuit for selecting the transversal converting table for data generated by the transversal index table making circuit by each decomposing data of an odd data position of data, and obtaining a multiplying result of the Galois field;

an even parity inverting circuit for obtaining an inverting result of the even parity in which an XOR logic operation is performed with respect to each decomposing parity of the upper order parity portion of the parity and the multiplying result of the Galois field obtained by selecting the transversal inverting table for parity generated by the transversal index table making circuit by each decomposing data of the even data position of the data; and

an odd parity inverting circuit for obtaining an inverting result of the odd parity in which the XOR logic operation is performed with respect to each decomposing parity of the lower order parity portion of the parity and the multiplying result of the Galois field obtained by selecting the longitudinal inverting table for parity generated by the longitudinal index table making circuit by each decomposing data of the odd data position of the data.

The Galois field multiplying circuit of the present invention is further characterized in that the Galois field multiplying circuit comprises:

a Galois field multiplying table having a conversion table for data and a conversion table for parity;

an ECC converting table corresponding to each decomposing data of the data;

a longitudinal index table making circuit for generating a longitudinal inverting table for parity and a longitudinal converting table for data by indexing the Galois field multiplying table from the longitudinal direction by using a multiplication coefficient;

a transversal index table making circuit for generating a transversal converting table for data and a transversal inverting table for parity by indexing the Galois field multiplying table from the transversal direction by using the multiplication coefficient;

an ECC index table making circuit for generating a conversion table for ECC by indexing the ECC converting table by using the multiplication coefficient;

an upper order data converting circuit for selecting the longitudinal converting table for data generated by the longitudinal index table making circuit by each decomposing data of an upper order data portion of data, and obtaining a multiplying result of the Galois field;

a lower order data converting circuit for selecting the transversal converting table for data generated by the transversal index table making circuit by each decomposing data of a lower order data portion of data, and obtaining a multiplying result of the Galois field; and

an ECC converting circuit for selecting the ECC converting table generated by the ECC index table making circuit by each decomposing data of the data, and converting the ECC with respect to the data into ECC with respect to data for RAID.

In addition, a parity data generating method for RAID in the present invention is characterized in that data are converted by using a Galois field multiplying table symmetrical longitudinally and transversally and made by a multiplying calculation of the Galois field of GF(2<sup>4</sup>), and index table information of the transversal direction and index table information of the longitudinal direction are extracted from the Galois field multiplying table, and a failure of a circuit is detected by comparing both the index table information.

The parity data generating method for RAID in the present invention is also characterized in that two kinds of index table information for data for making the multiplying calculation and index table information for a check code annexed to these data are generated as the index table information.

The parity data generating method for RAID in the present invention is further characterized in that the value of zero is detected by arithmetically performing an XOR logic operation of a bit unit of the index table information.

Furthermore, the parity data generating method for RAID in the present invention is characterized in that the data for making the multiplying calculation of the Galois field are decomposed into plural data, and processing is performed by dividing these data into decomposing data for performing the conversion by using the index table information of the longitudinal direction, and decomposing data for performing the conversion by using the index table information of the transversal direction.

The parity data generating method for RAID in the present invention is also characterized in that the check code annexed to the data for making the multiplying calculation of the Galois field is decomposed into plural check codes, and processing is performed by dividing these check codes into a 65 decomposing check code for performing the conversion by using the index table information of the longitudinal direc-

12

tion, and a decomposing check code for performing the conversion by using the index table information of the transversal direction.

The parity data generating method for RAID in the present invention is further characterized in that the decomposing check code with respect to the decomposing data is converted by using the index table information of the longitudinal direction when these decomposing data are converted by using the index table information of the transversal direction, and the decomposing check code with respect to the decomposing data is converted by using the index table information of the transversal direction when these decomposing data are converted by using the index table information of the longitudinal direction, so that the decomposing data and the decomposing check code as a pair are converted by using the index table information different from each other.

Furthermore, the parity data generating method for RAID in the present invention is characterized in that the parity data generating method includes a process for generating the index table information of the longitudinal direction by indexing the Galois field multiplying table from the longitudinal direction by using a multiplication coefficient; a process for generating the index table information of the transversal direction by indexing the Galois field multiplying table from 25 the transversal direction by using the multiplication coefficient; a process for checking whether the generated index table information is correct; a process for dividing data from the generated index table information into an upper order data portion and a lower order data portion and converting these data into data for RAID; and a process for dividing parity with respect to the data from the generated index table information into an upper order parity portion and a lower order parity portion and converting this parity into parity with respect to the data for RAID.

The parity data generating method for RAID in the present invention is also characterized in that the parity data generating method includes a process for generating the index table information of the longitudinal direction by indexing the Galois field multiplying table from the longitudinal direction by using a multiplication coefficient; a process for generating the index table information of the transversal direction by indexing the Galois field multiplying table from the transversal direction by using the multiplication coefficient; a process for checking whether the generated index table information is correct; a process for dividing data from the generated index table information into an even data position and an odd data position and converting these data into data for RAID; and a process for dividing parity with respect to the data from the generated index table information into an even parity position and an odd parity position and converting this parity into parity with respect to the data for RAID.

The parity data generating method for RAID in the present invention is further characterized in that the parity data generating method includes a process for generating the index table information of the longitudinal direction by indexing the Galois field multiplying table from the longitudinal direction by using a multiplication coefficient; a process for generating the index table information of the transversal direction by indexing the Galois field multiplying table from the transversal direction by using the multiplication coefficient; a process for checking whether the generated index table information is correct; a process for converting data from the generated index table information into data for RAID; and a process for converting ECC with respect to the data into ECC with respect to the data for RAID.

Furthermore, the parity data generating method for RAID in the present invention is characterized in that the index table

information of the longitudinal direction is a longitudinal conversion table for data, and the index table information of the transversal direction is a transversal conversion table for data.

The parity data generating method for RAID in the present 5 invention is also characterized in that the index table information of the longitudinal direction is a longitudinal conversion table for data and a longitudinal inverting table for a check code, and the index table information of the transversal direction is a transversal conversion table for data and a 10 transversal inverting table for a check code.

The parity data generating method for RAID in the present invention is further characterized in that the check code is parity with respect to the data.

Furthermore, the parity data generating method for RAID 15 in the present invention is characterized in that the check code is ECC with respect to the data.

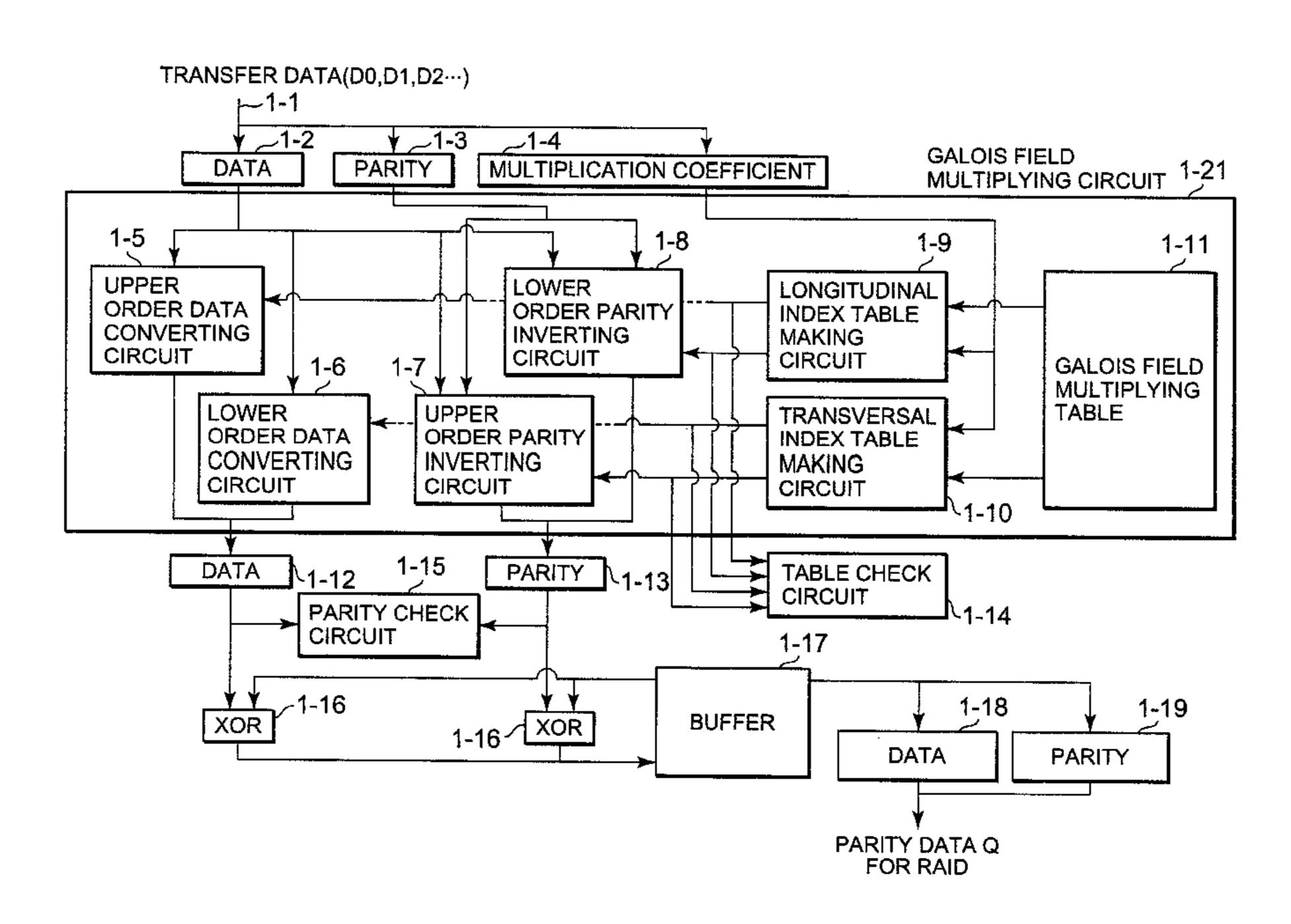

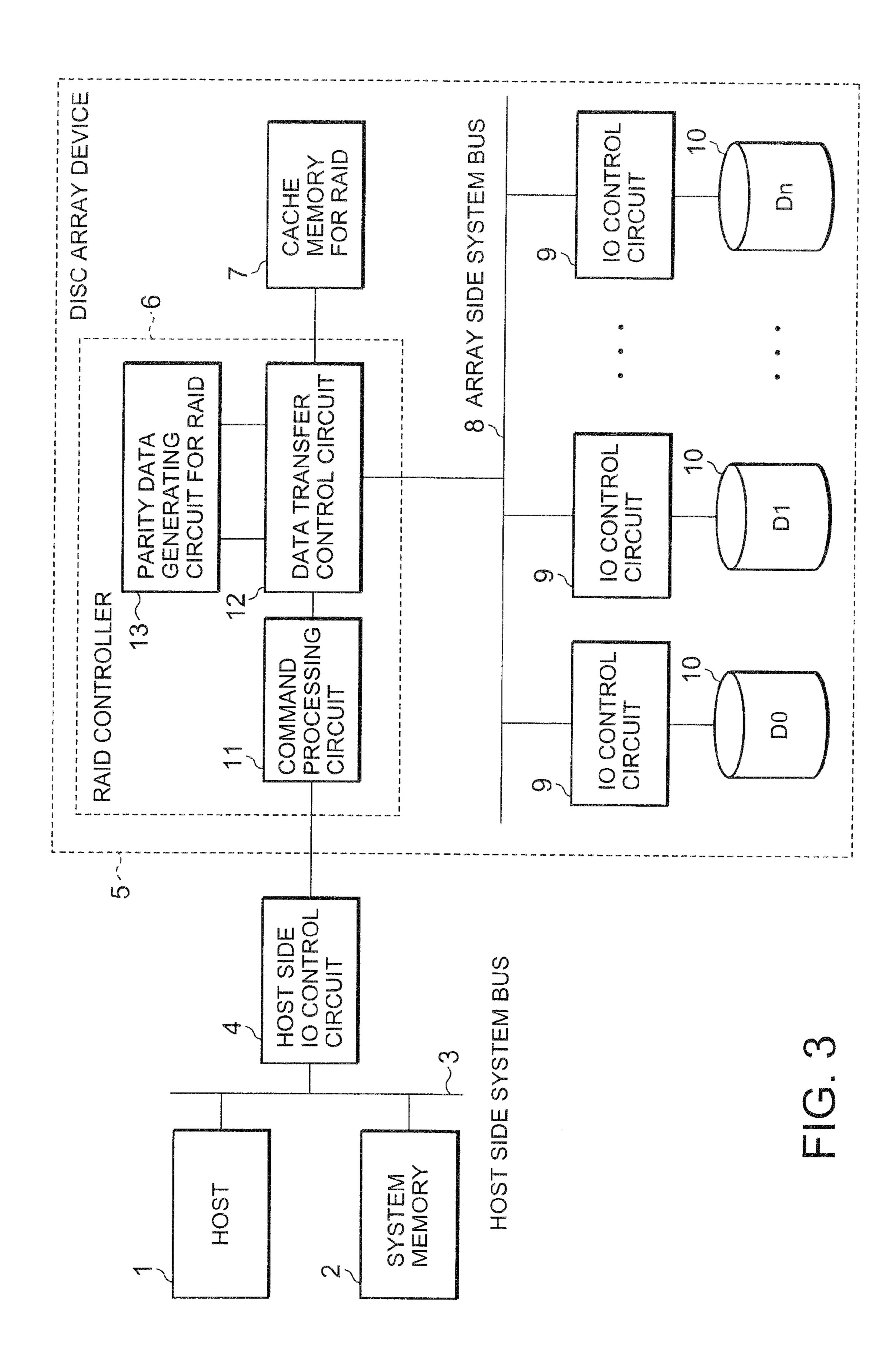

FIG. 2 shows the construction of a parity data generating circuit for RAID for realizing RAID6 of the present invention.

The present invention is characterized in the following construction. Namely, the Galois field multiplying circuit **1-21** has the Galois field multiplying table **1-11** therein. The Galois field multiplying circuit 1-21 also has a longitudinal index table making circuit 1-9 for generating the index table 25 information of the longitudinal direction by indexing the Galois field multiplying table 1-11 from the longitudinal direction by using the multiplication coefficient 1-4; a transversal index table making circuit 1-10 for generating the index table information of the transversal direction by similarly indexing the Galois field multiplying table 1-11 from the transversal direction by using the multiplication coefficient 1-4; an upper order data converting circuit 1-5 and a lower order data converting circuit 1-6 for converting data 1-2 from the generated index table information into data 1-12 for 35 RAID; and an upper order parity inverting circuit 1-7 and a lower order parity inverting circuit 1-8 for similarly converting parity 1-3 with respect to the data 1-2 into parity 1-13 with respect to the data 1-12 for RAID. In addition, the Galois field multiplying circuit 1-21 has a table check circuit 1-14 for 40 checking whether the generated index table information is correct.

Then, it is characterized in that the present invention has the parity check circuit 1-15 for converting the upper order data portion of the data 1-12 and the lower order parity portion of the parity 1-3 by the index table information indexed from the longitudinal direction, and inspecting the data 1-12 and the parity 1-13 as converting results of the lower order data portion of the data 1-12 and the upper order parity portion of the parity 1-3 by the index table information indexed from the transversal direction. Thus, it is possible to check that the multiplying calculation of the Galois field is made without any error. Accordingly, the parity data generating circuit for RAID able to generate reliable data for RAID6 is provided.

With respect to an arithmetic formula of RAID6 itself in the present invention, the following arithmetic formulas (formulas 1 and 2) are used as a base. However, the definitions of these formulas themselves, etc. are already known by the non-patent literature 1, etc. Simultaneously, the arithmetic formulas themselves in the multiplying calculation of the Galois field are generally known arithmetic calculations. Therefore, the detailed proofs and contents of these formulas are not described here.

Formula for realizing RAID6:

When n data series are set to D0, D1, D2, . . . , D(n-1), its two parity data P and Q use the following two formulas.

14

P=D0+D1+D2+...+D(n-1) [Formula 1]

Q=D0+2D1+3D2+...+nD(n-1) [Formula 2]

In the notation of the above formulas 1 and 2, the multiplying calculation shows the multiplying calculation of the Galois field, and the adding calculation shows exclusive OR using the XOR logic.

The parity data generating circuit for RAID realizing RAID6 of high reliability for making the multiplying calculation of the Galois field can be provided by the circuit construction of the present invention.

A hardware failure of the Galois field multiplying circuit itself can be found by the construction for simultaneously indexing one Galois field multiplying table in the longitudinal direction and the transversal direction and comparing the index results.

Further, even when one of the index results is broken, the hardware failure can be reliably found by an error such as a parity error, an ECC error, etc. by the construction using the index table information indexed from a different direction in the conversion of data, its parity, a check code such as ECC, etc.

Further, even when the parity check circuit, etc. for checking the result of the multiplying calculation of the Galois field are broken and the failure of the Galois field multiplying circuit itself is generated at this breaking time, the check code before the conversion is propagated in shape and all the failure factors are reflected in the generated check code. Therefore, output data and the check code are perfectly guaranteed, and a circuit for judging no output data as correct data in error by the circuit failure is obtained. Thus, the parity data generating circuit for RAID of higher reliability can be provided.

Further, in a flowing path of data, the Galois field multiplying circuit itself is realized by one stage of selectors. Therefore, the Galois field multiplying circuit can also resist data transfer of very high speed.

### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a view showing the construction of a circuit for generating parity data for RAID in the prior art.

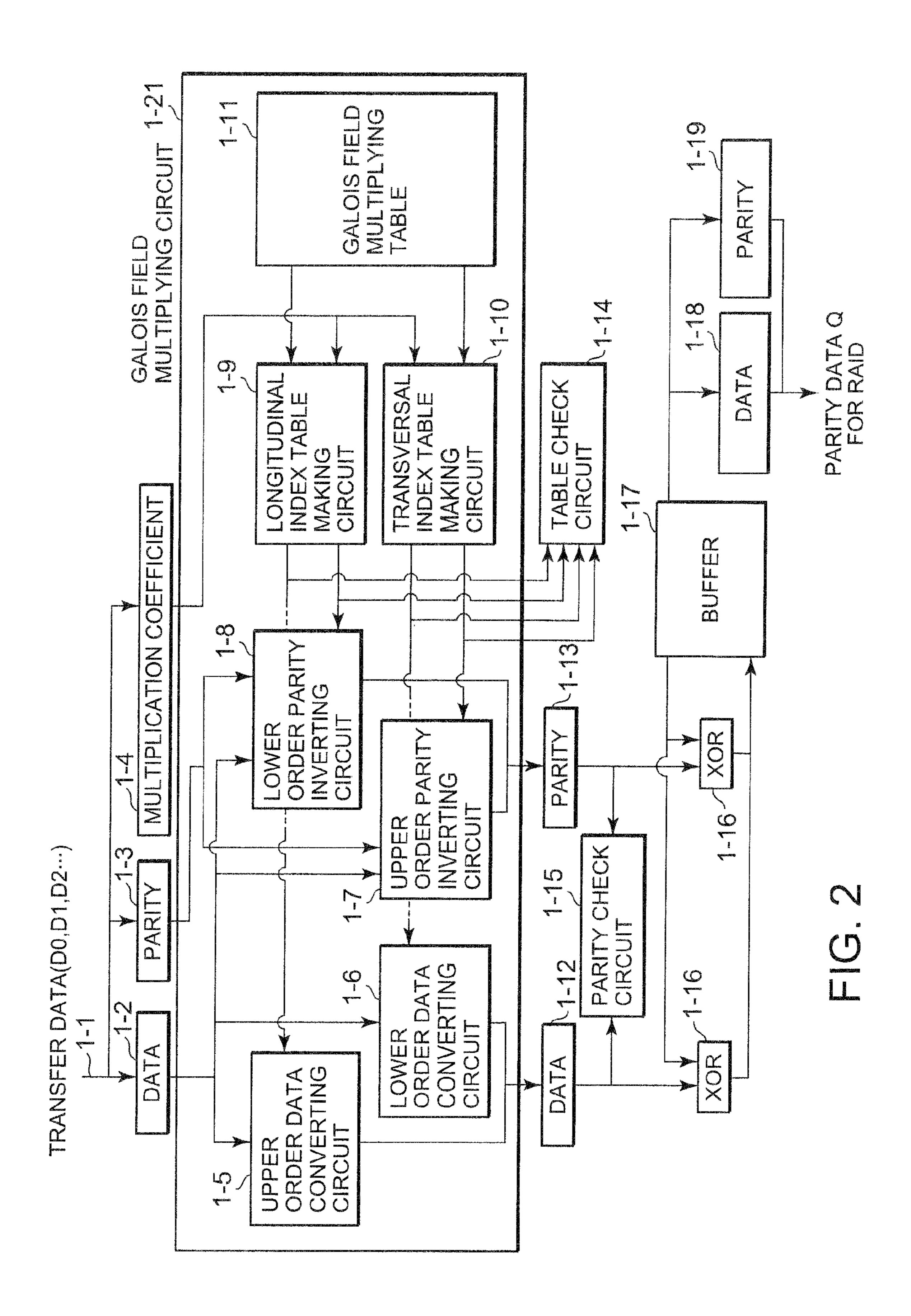

FIG. 2 is a circuit block diagram showing the construction of a parity data generating circuit for RAID in accordance with an embodiment 1 of the present invention.

FIG. 3 is a circuit block diagram showing the construction of a disk array system in which the parity data generating circuit for RAID in the present invention is arranged.

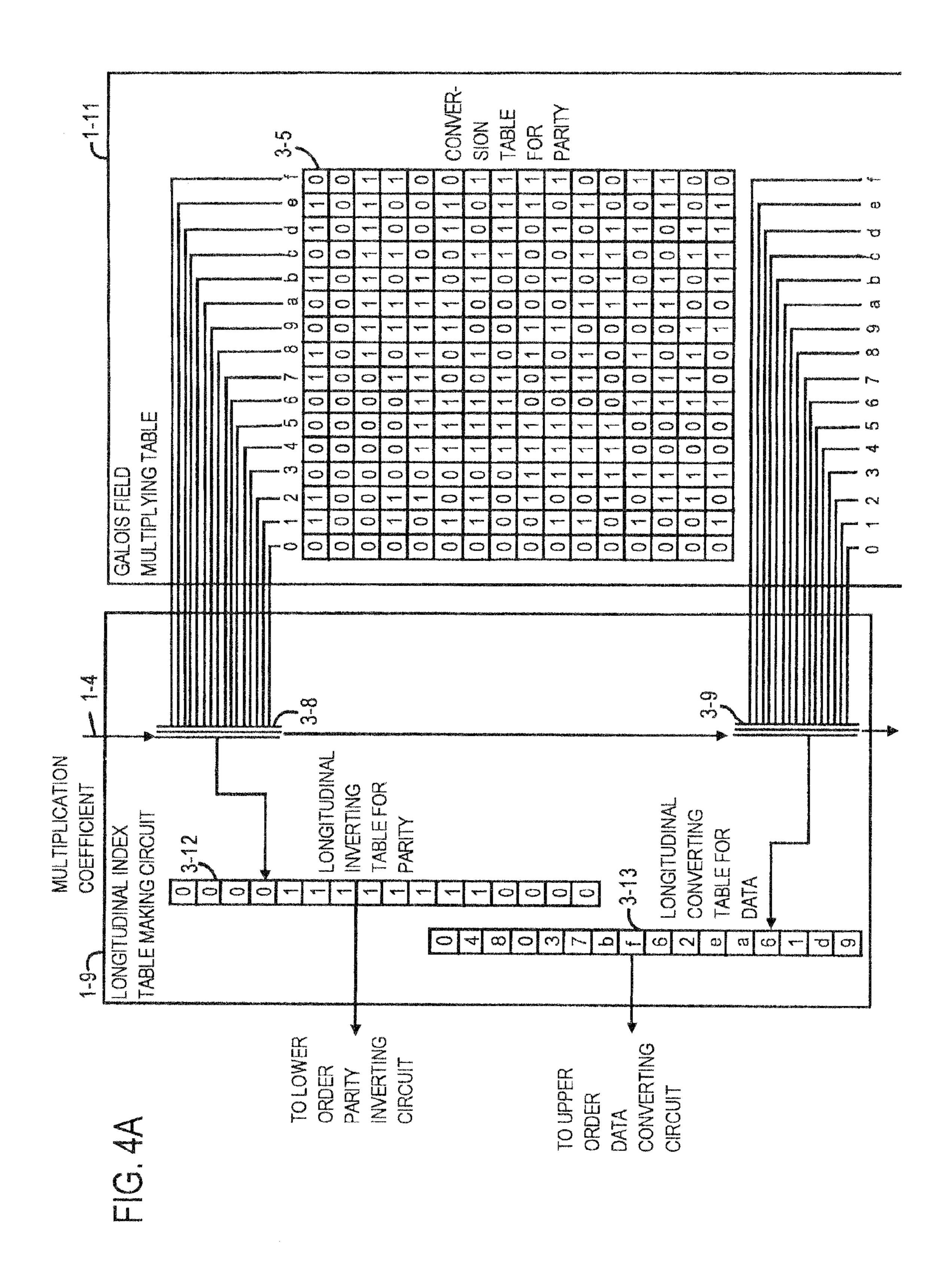

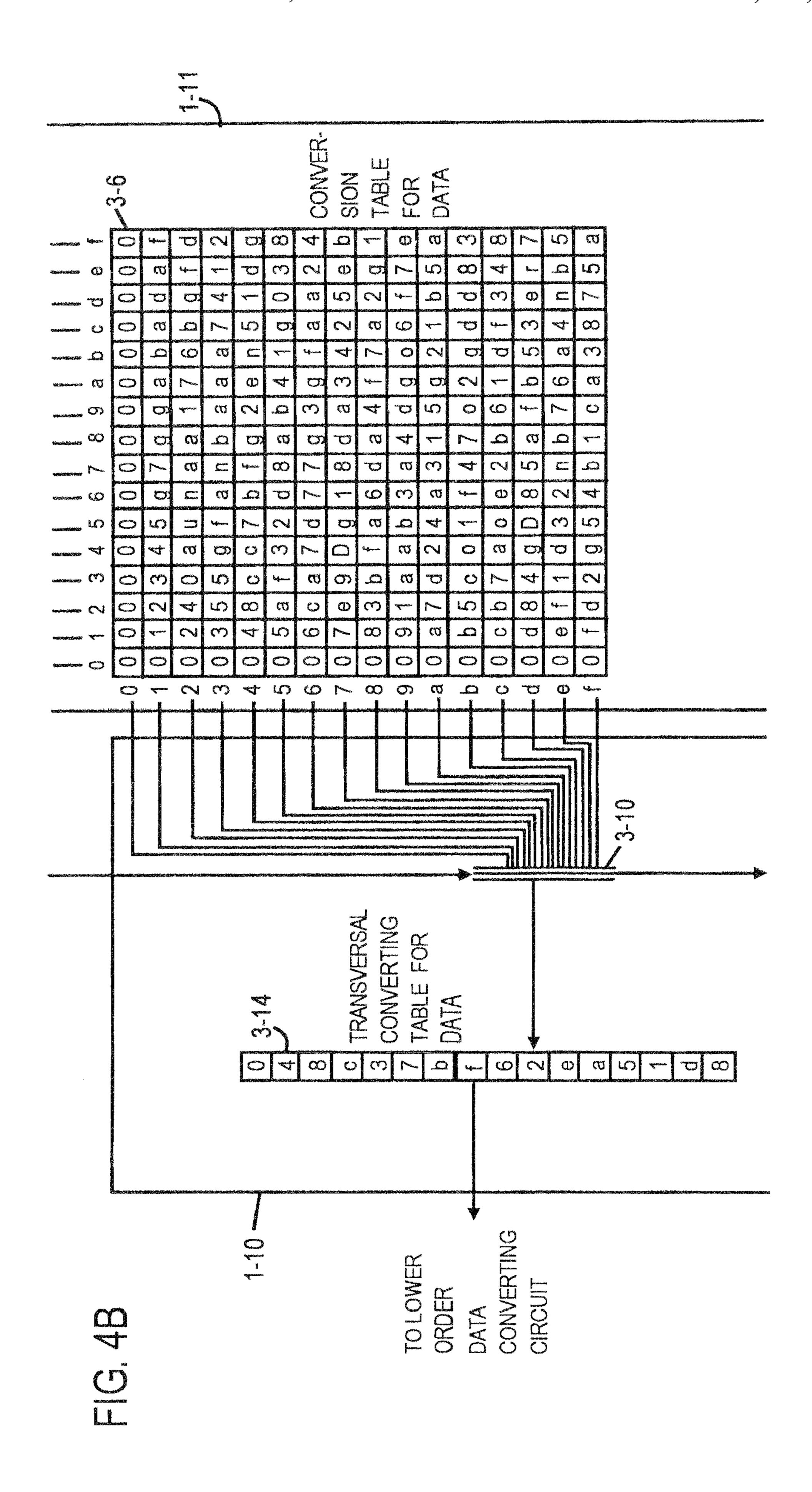

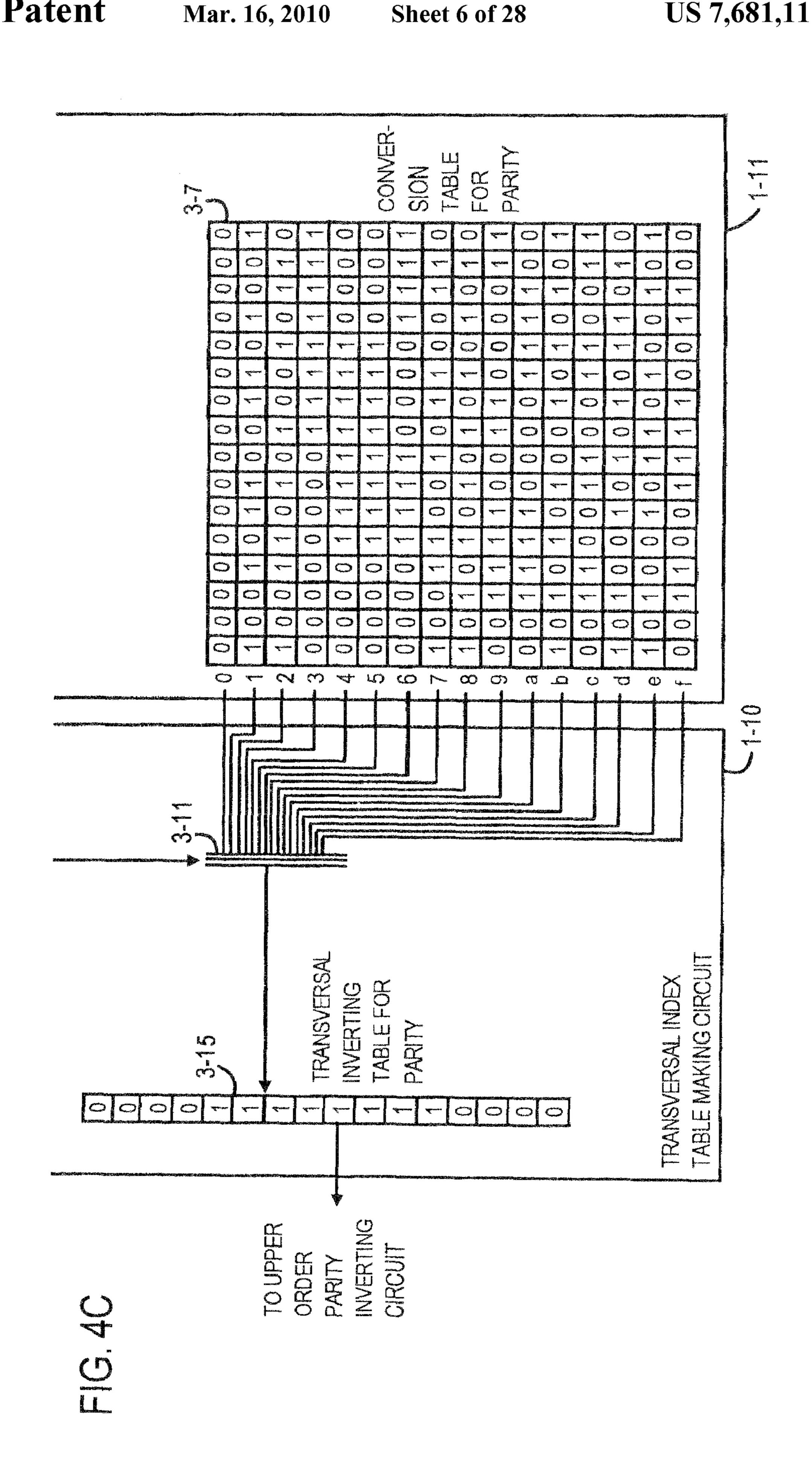

FIG. 4 is a view showing the details of a Galois field multiplying table, a longitudinal index table making circuit and a transversal index table making circuit shown in FIG. 2.

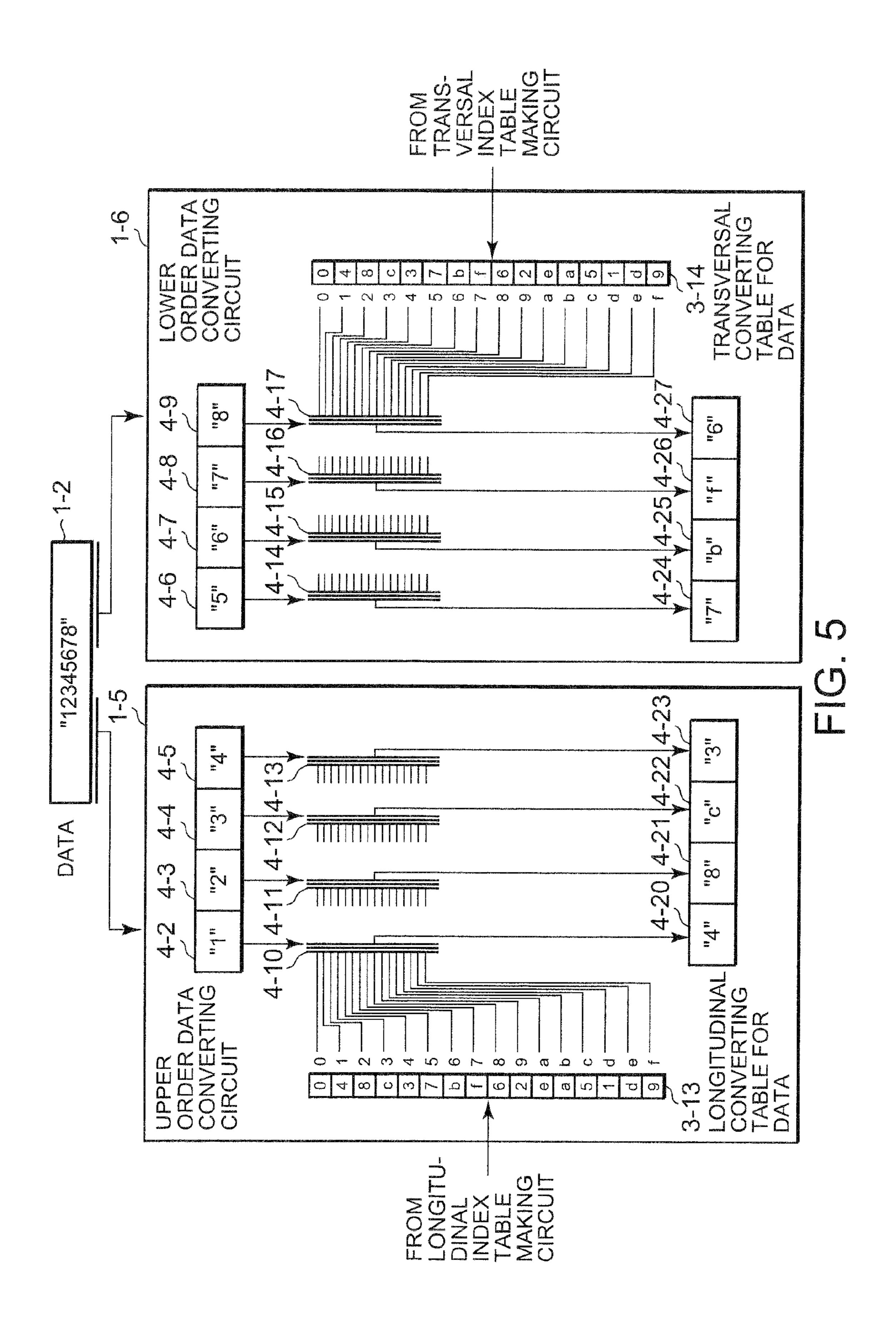

FIG. 5 is a view showing the details of an upper order data converting circuit and a lower order data converting circuit shown in FIG. 2.

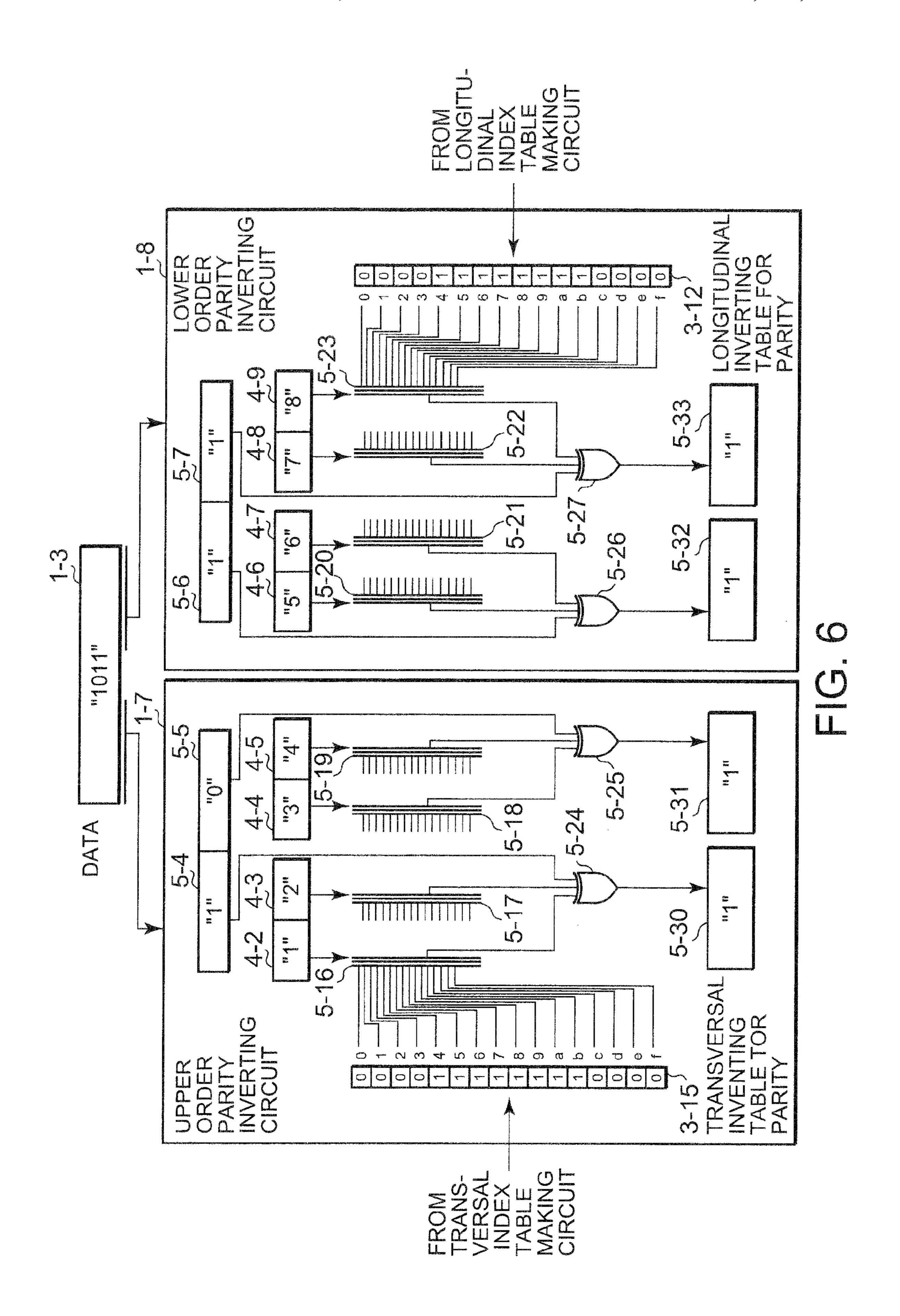

FIG. 6 is a view showing the details of an upper order parity inverting circuit and a lower order parity inverting circuit shown in FIG. 2.

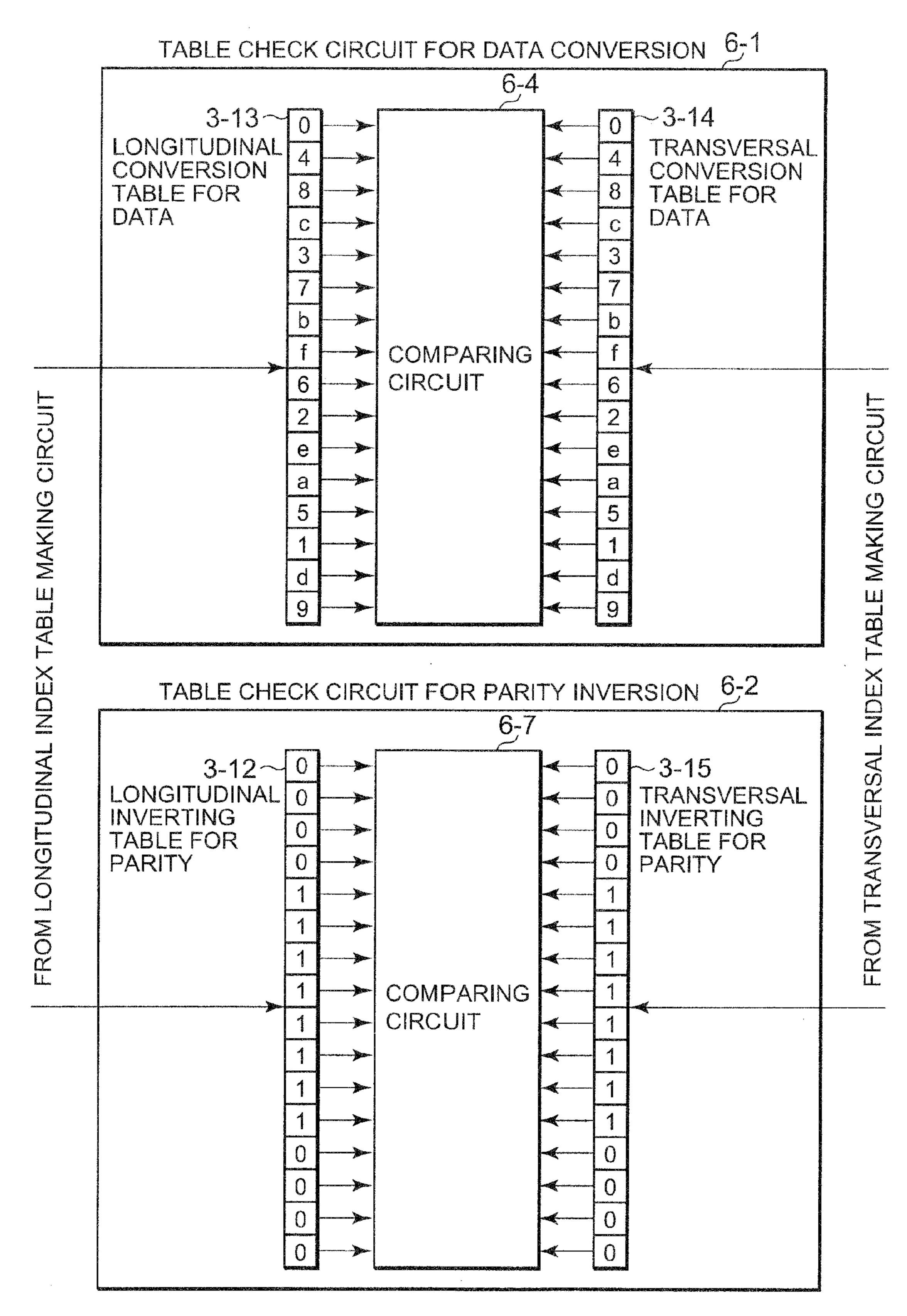

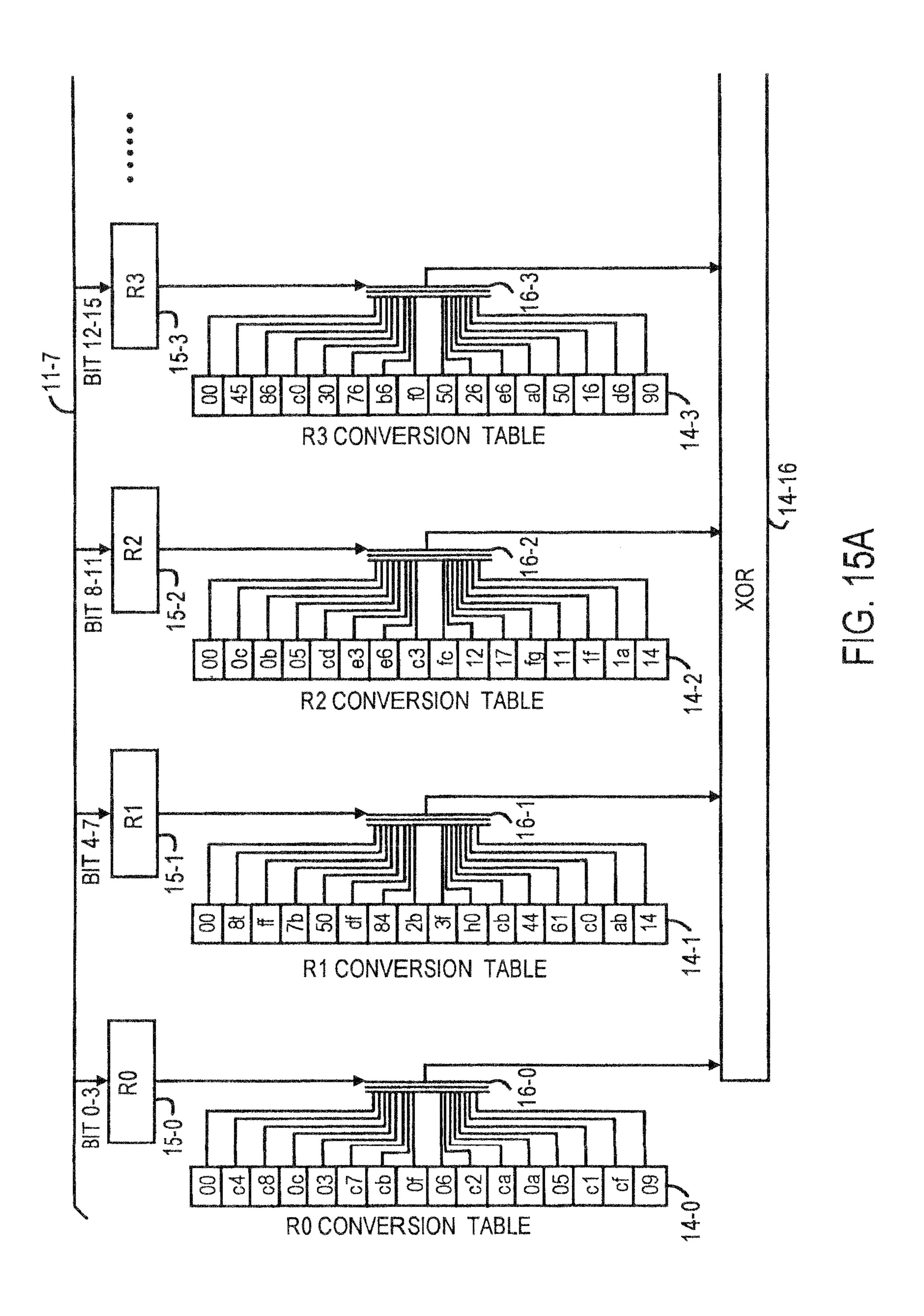

FIG. 7 is a view showing the details of a table check circuit for data conversion and a table check circuit for parity inversion in a table check circuit shown in FIG. 2.

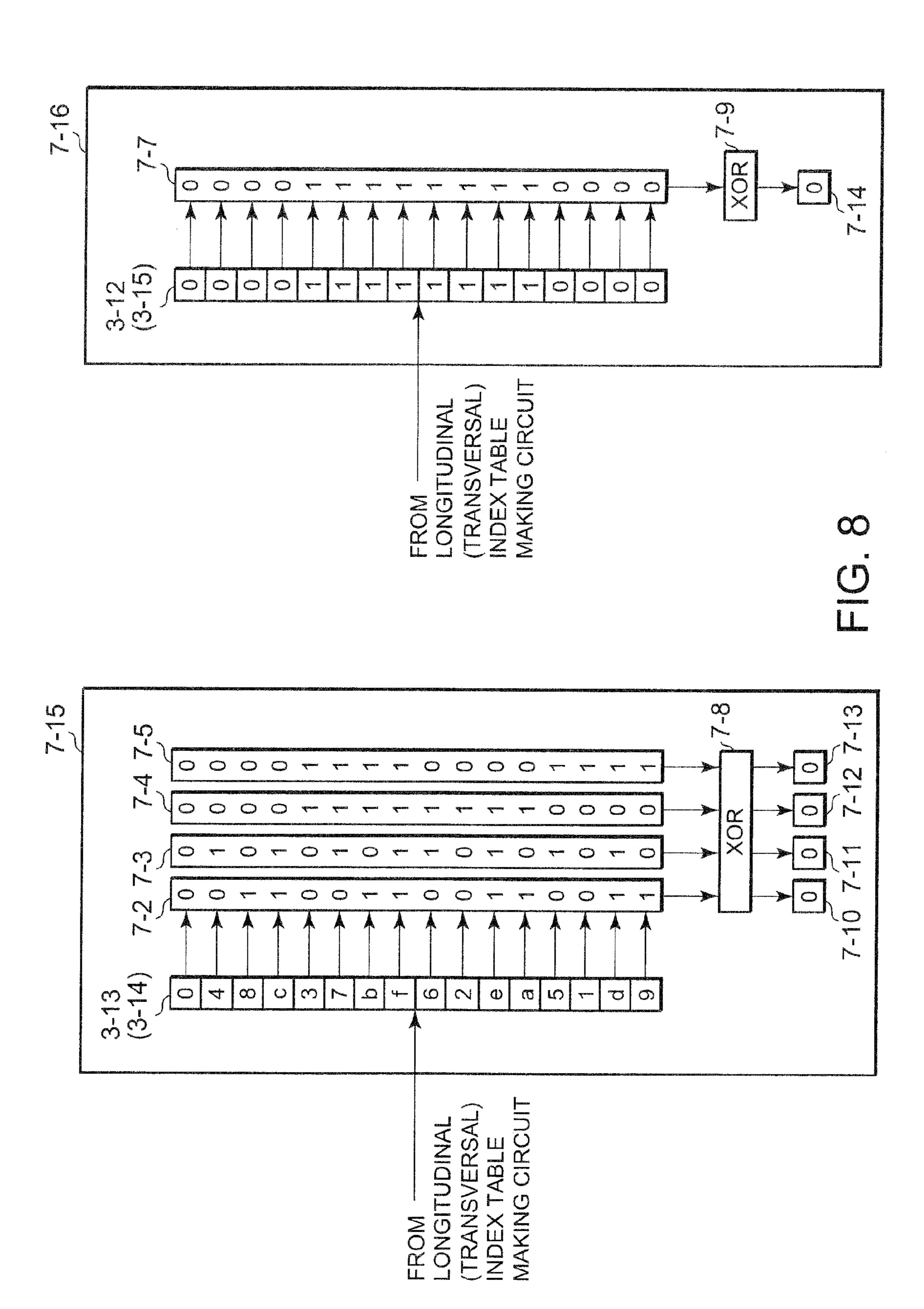

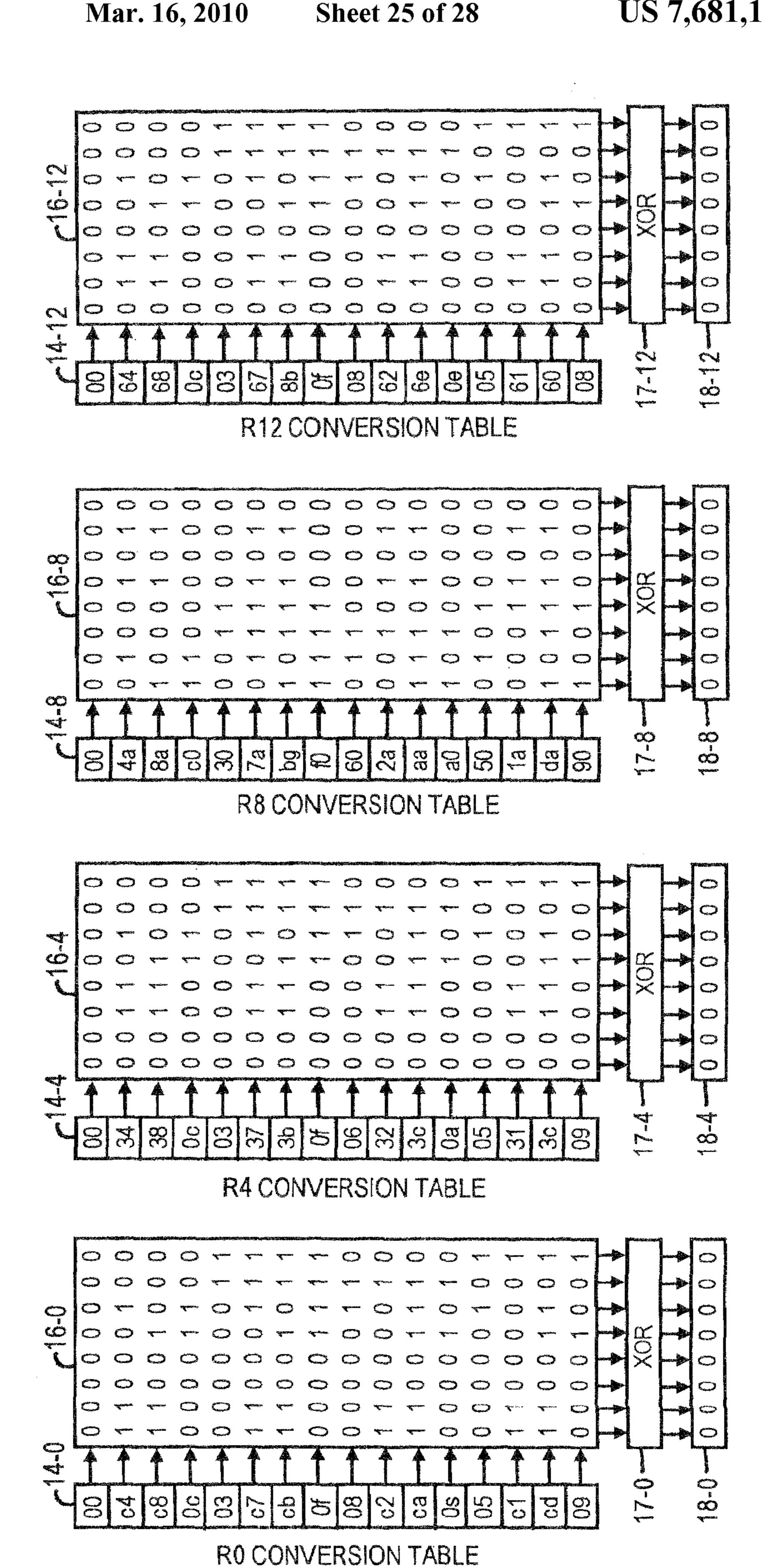

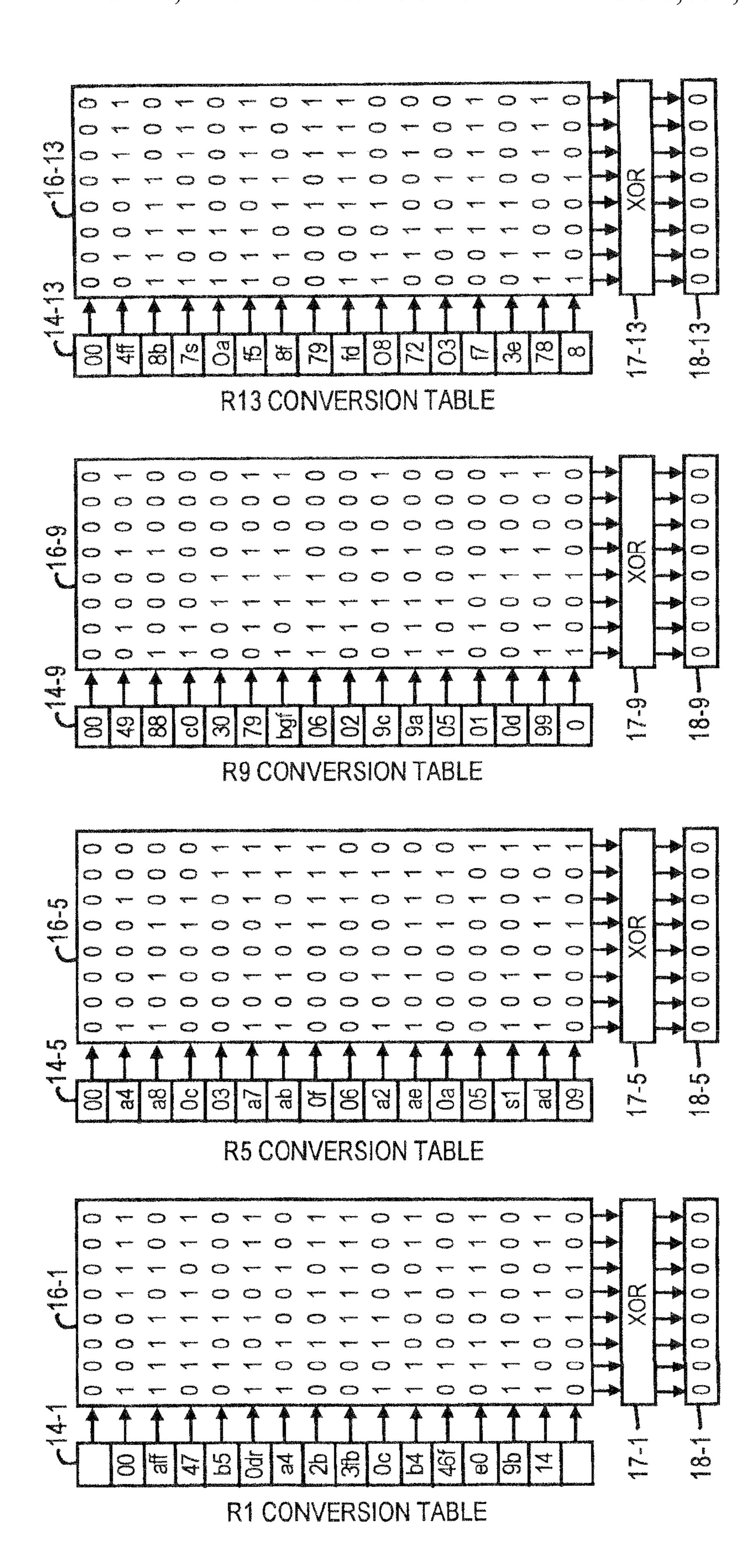

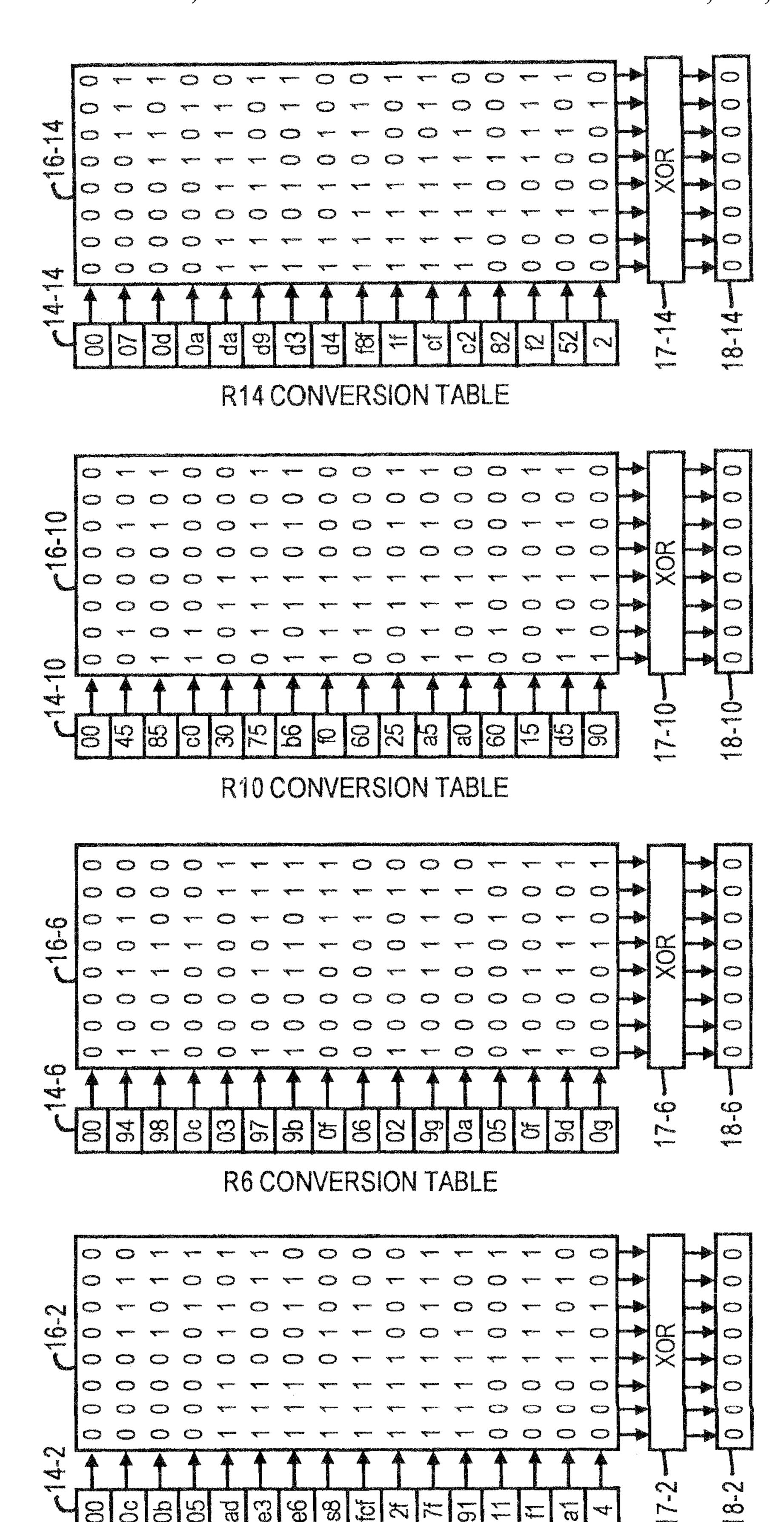

FIG. 8 is a view showing the details of a table zero check circuit in the table check circuit shown in FIG. 2.

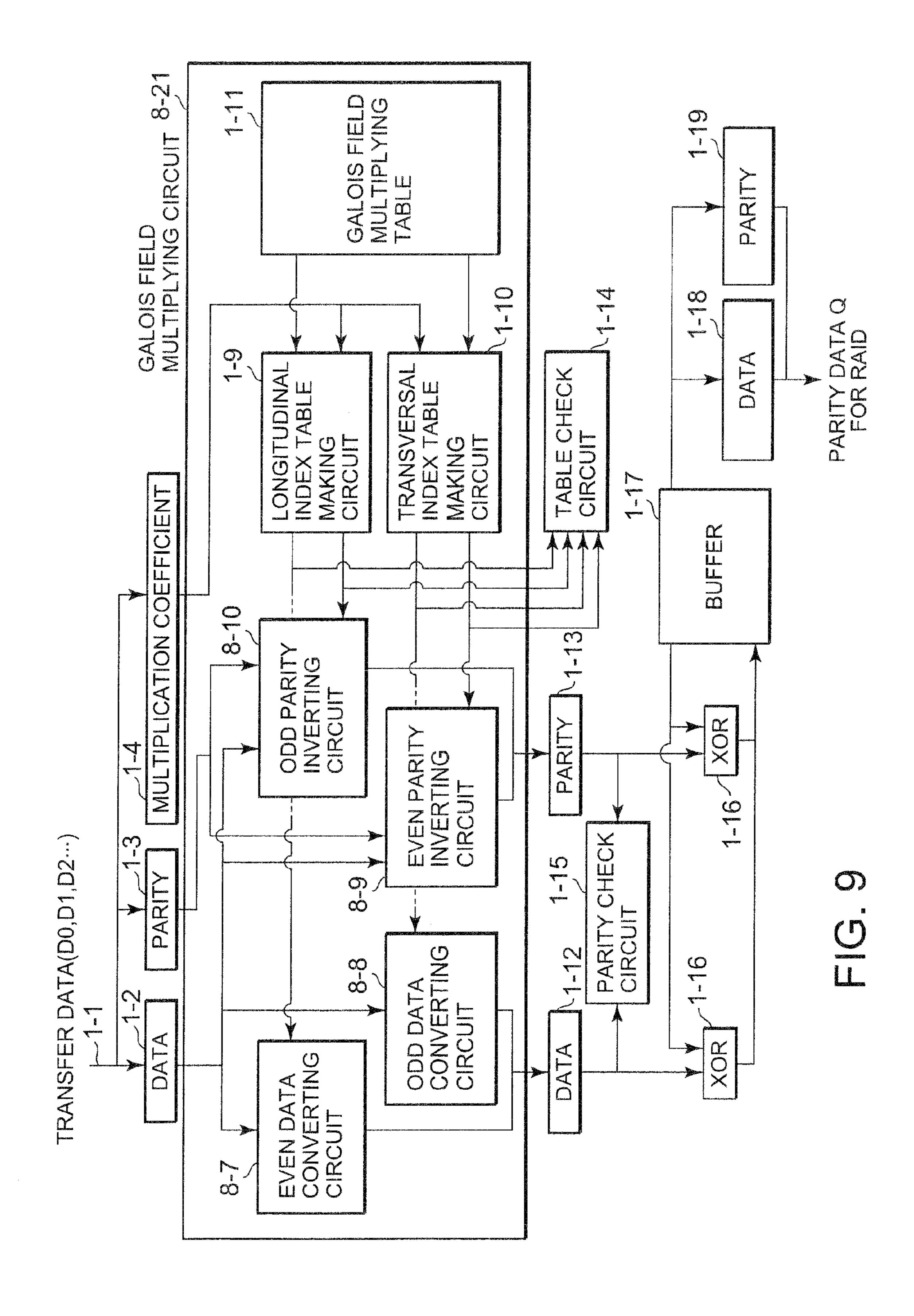

FIG. 9 is a circuit block diagram showing the construction of a parity data generating circuit for RAID in accordance with an embodiment 2 of the present invention.

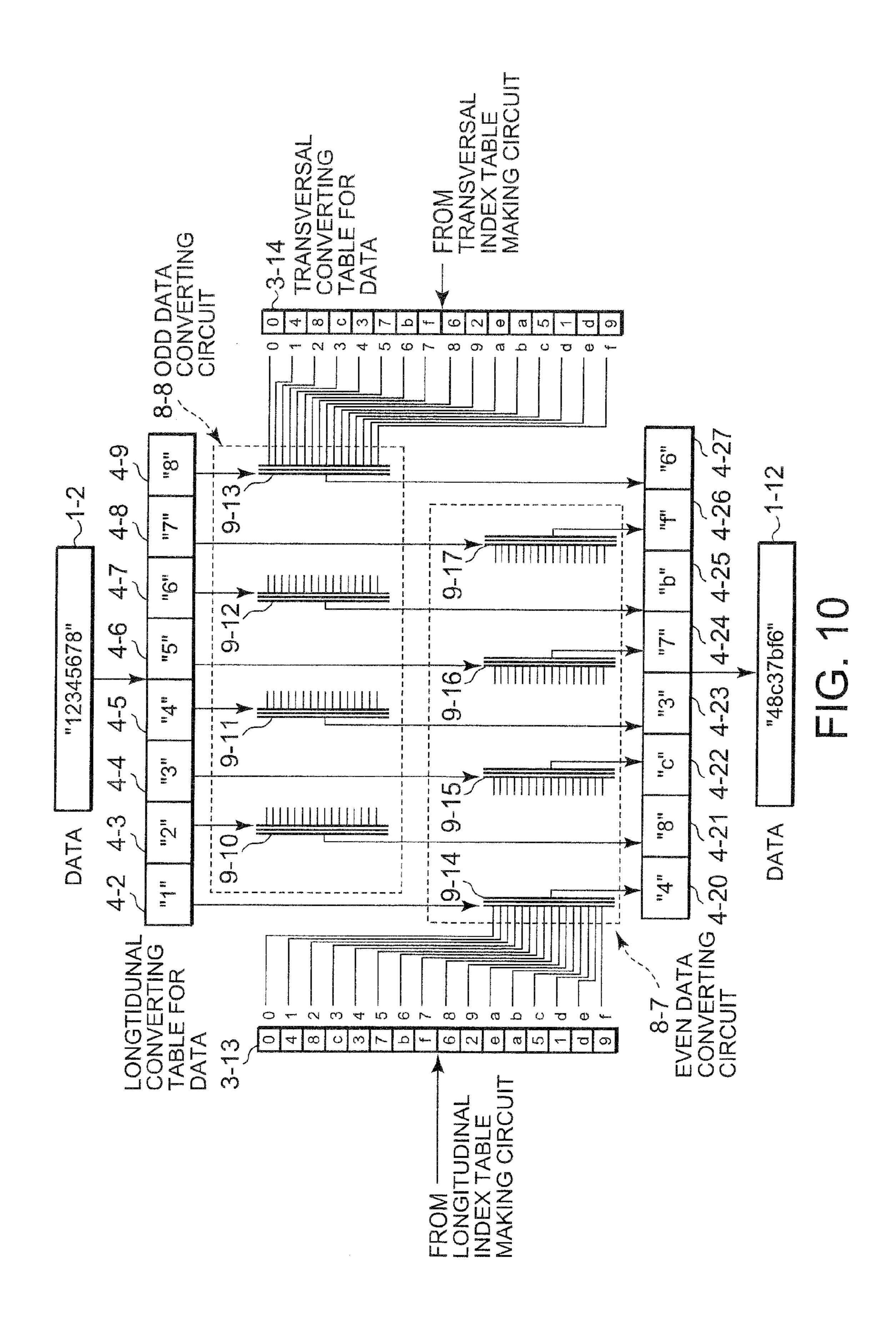

FIG. 10 is a view showing the details of an even data converting circuit and an odd data converting circuit shown in FIG. 9.

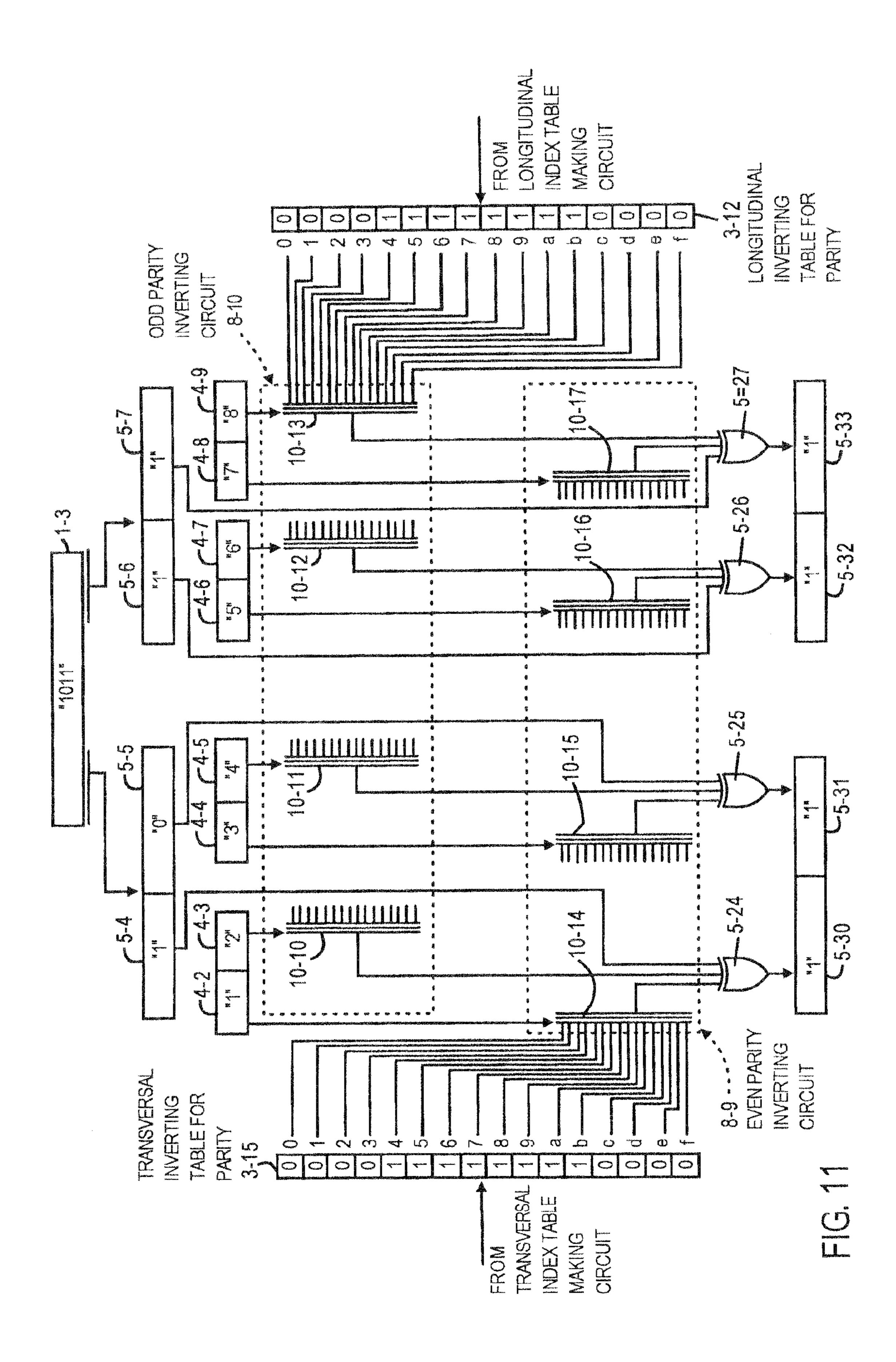

FIG. 11 is a view showing the details of an even parity inverting circuit and an odd parity inverting circuit shown in FIG. 9.

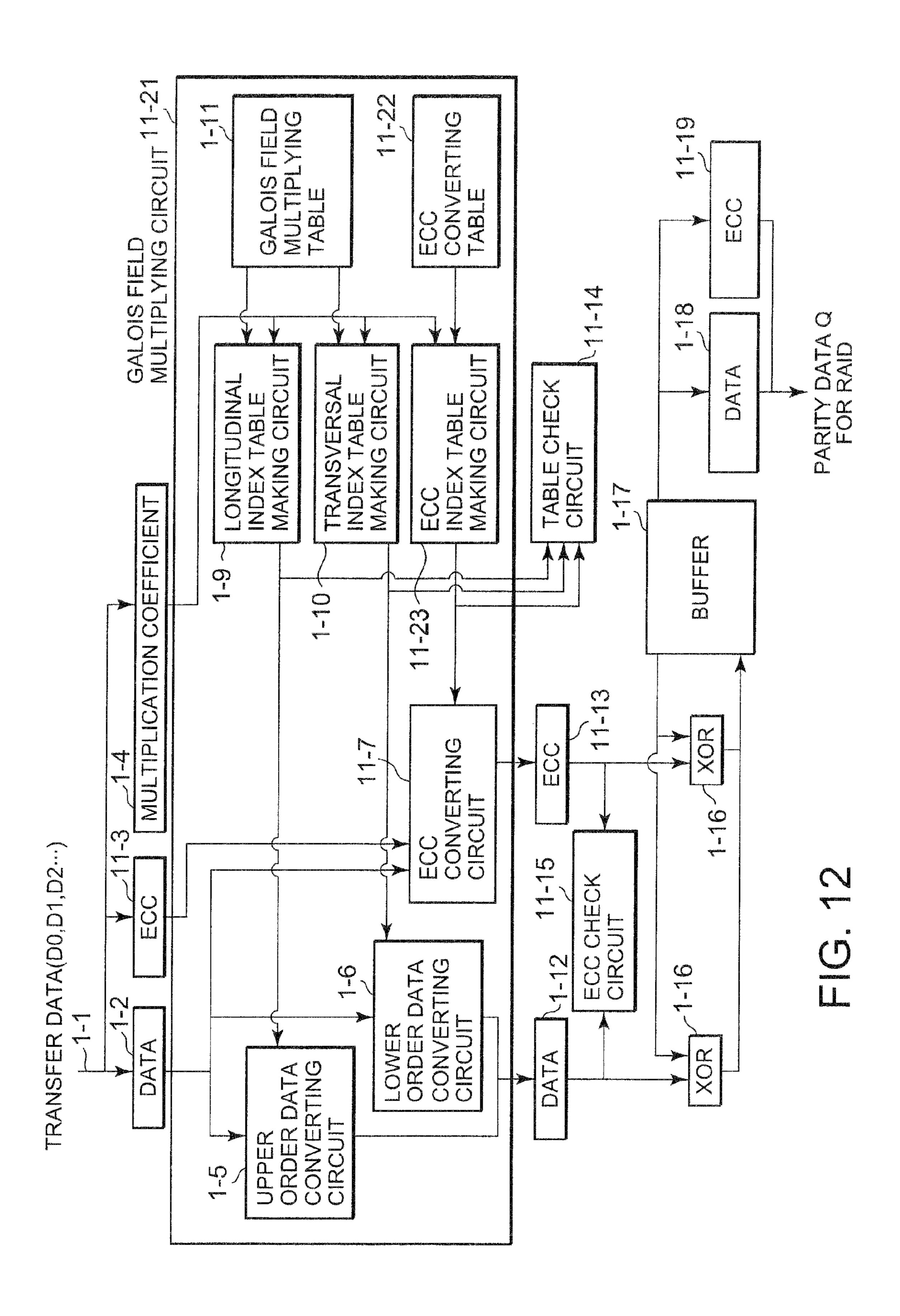

FIG. 12 is a circuit block diagram showing the construction of the parity data generating circuit for RAID when check coding in accordance with an embodiment 3 of the present invention is performed by ECC.

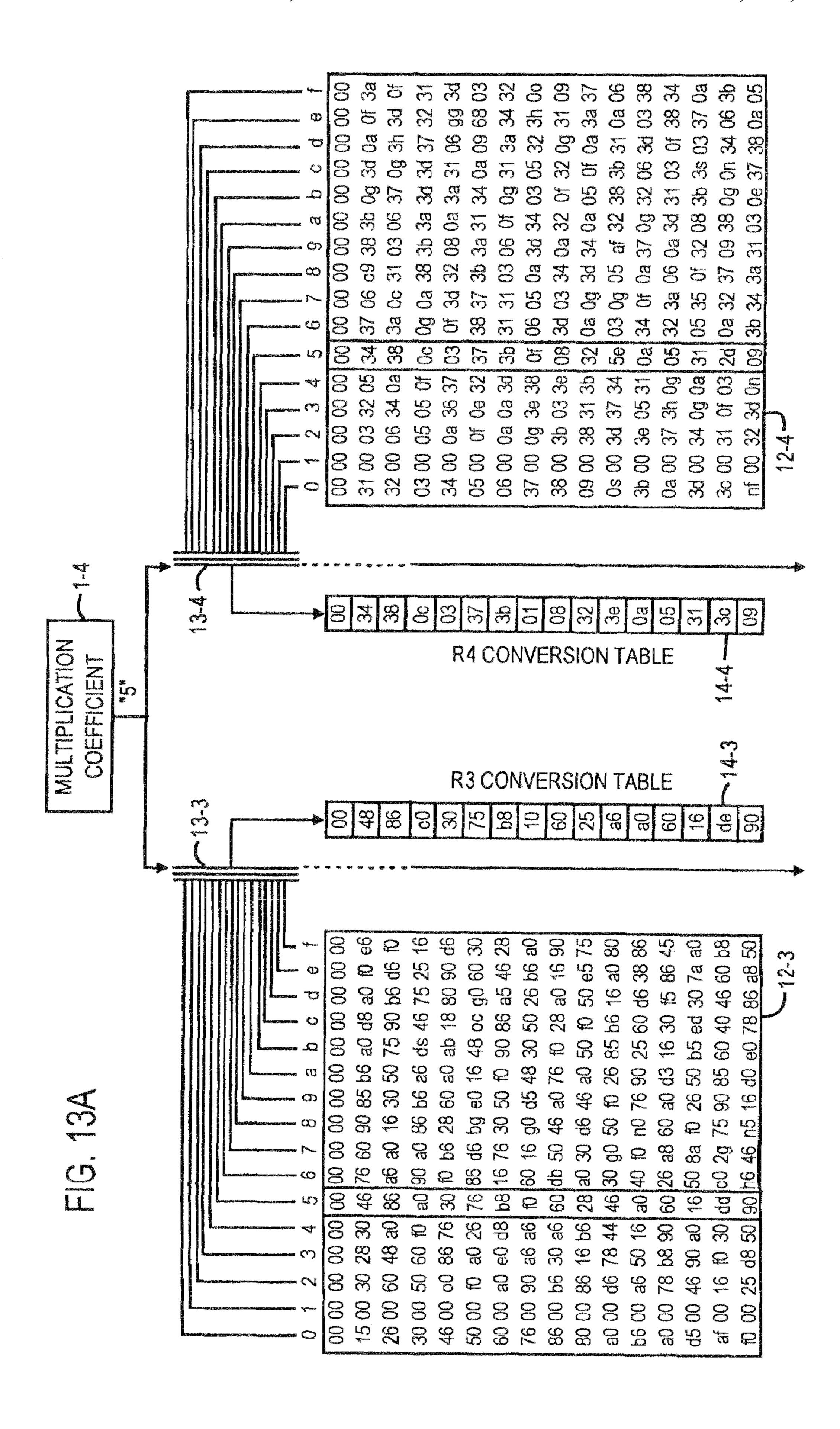

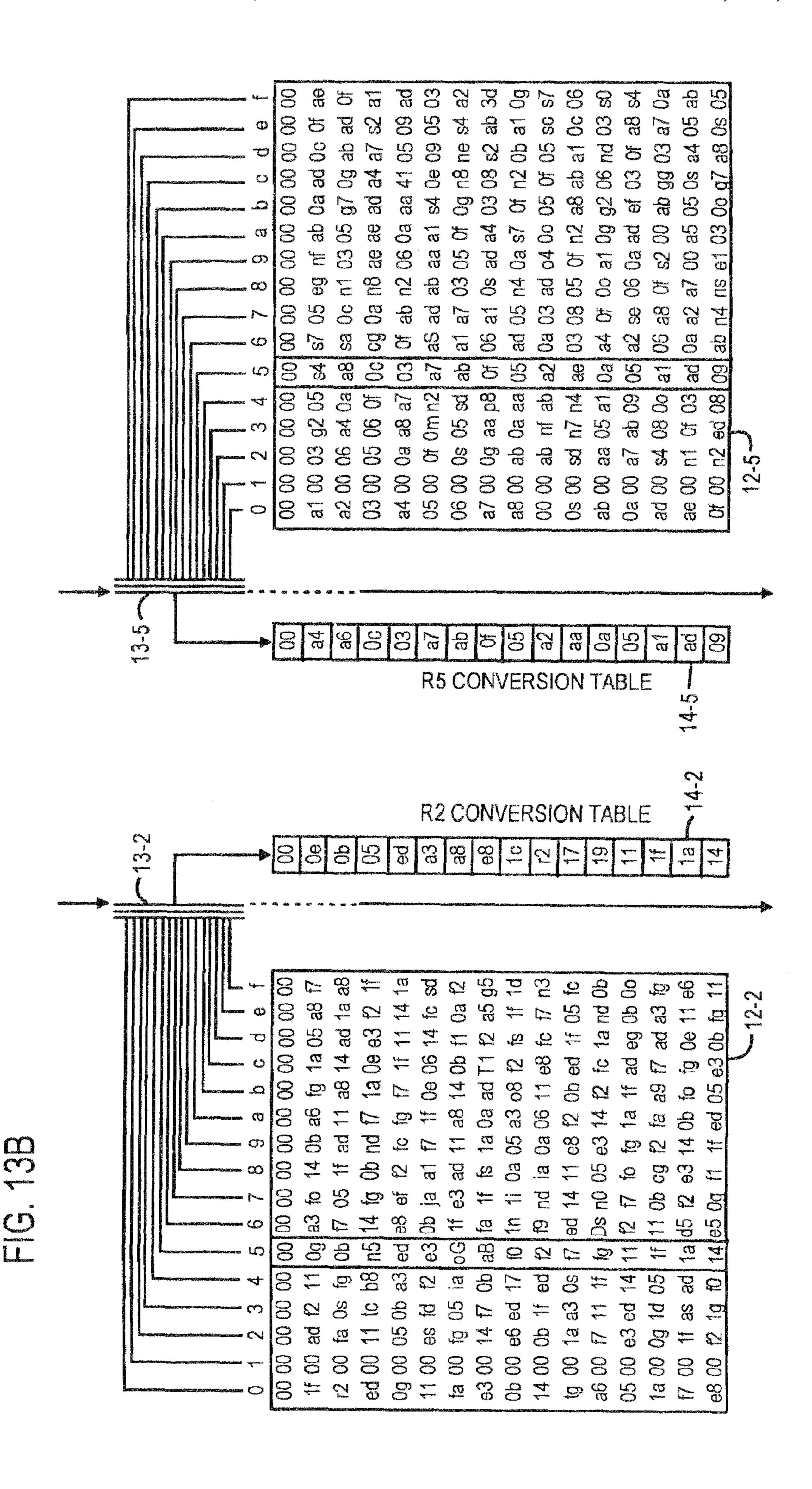

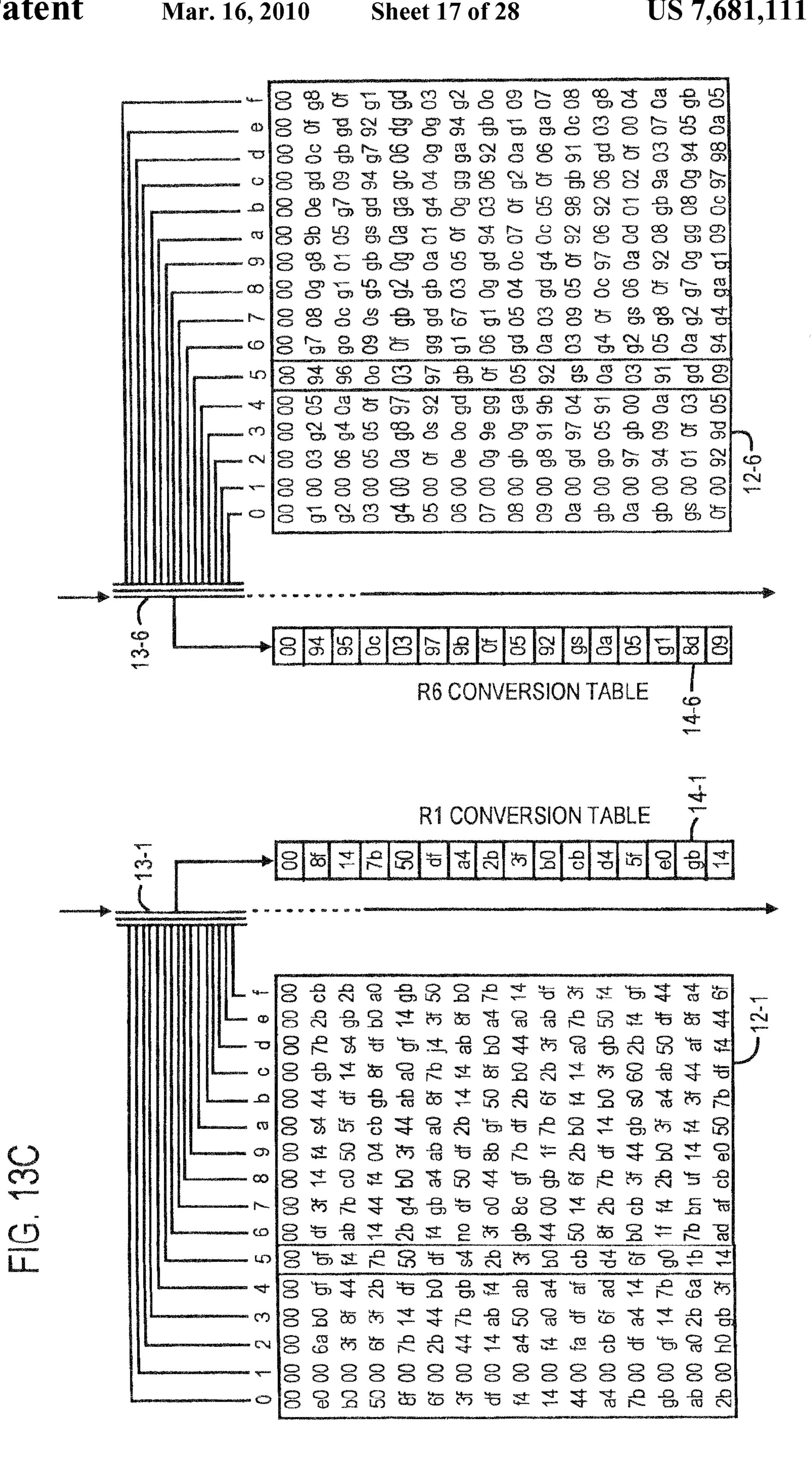

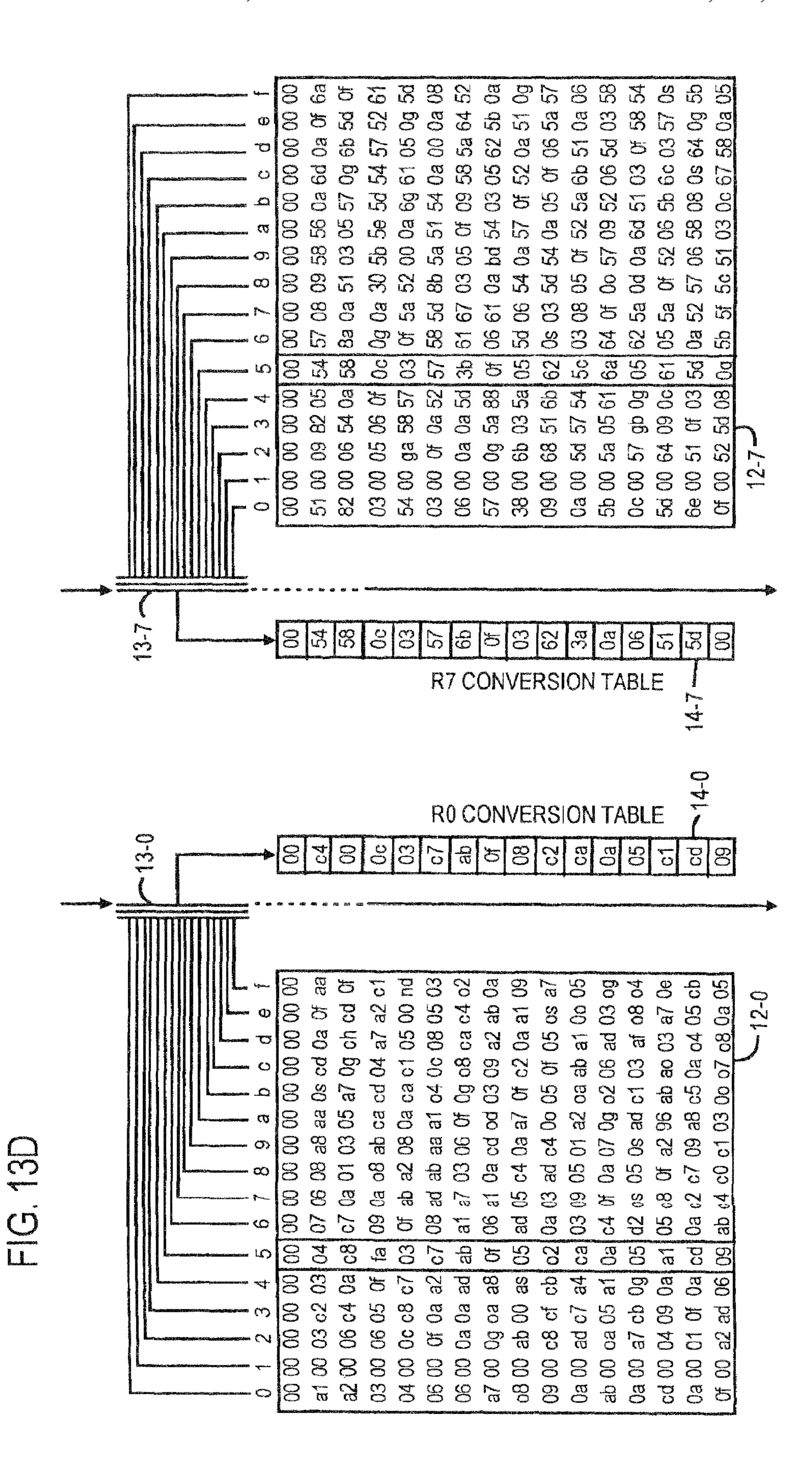

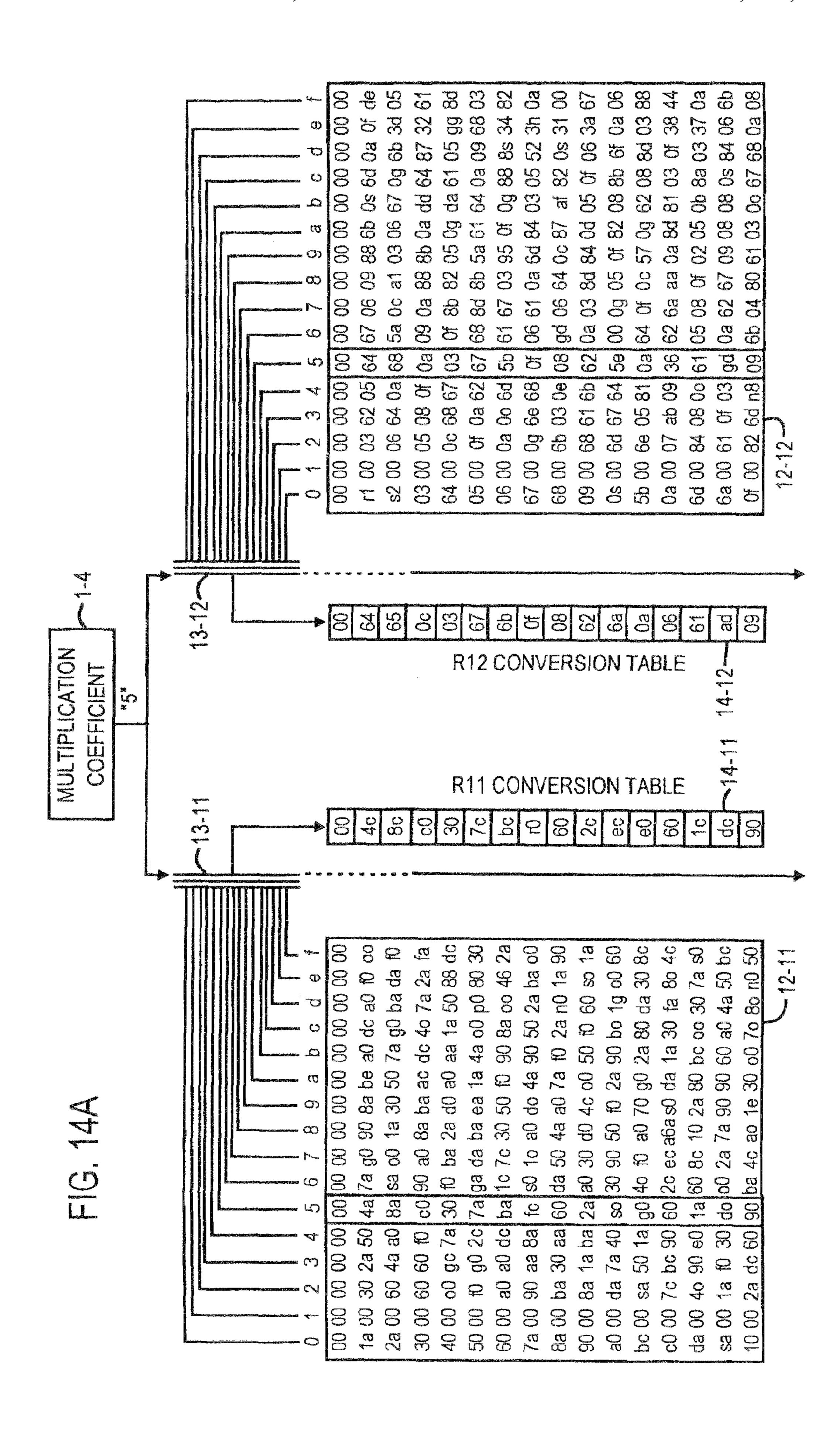

FIG. 13 is a view showing the details of an index table making circuit shown in FIG. 12.

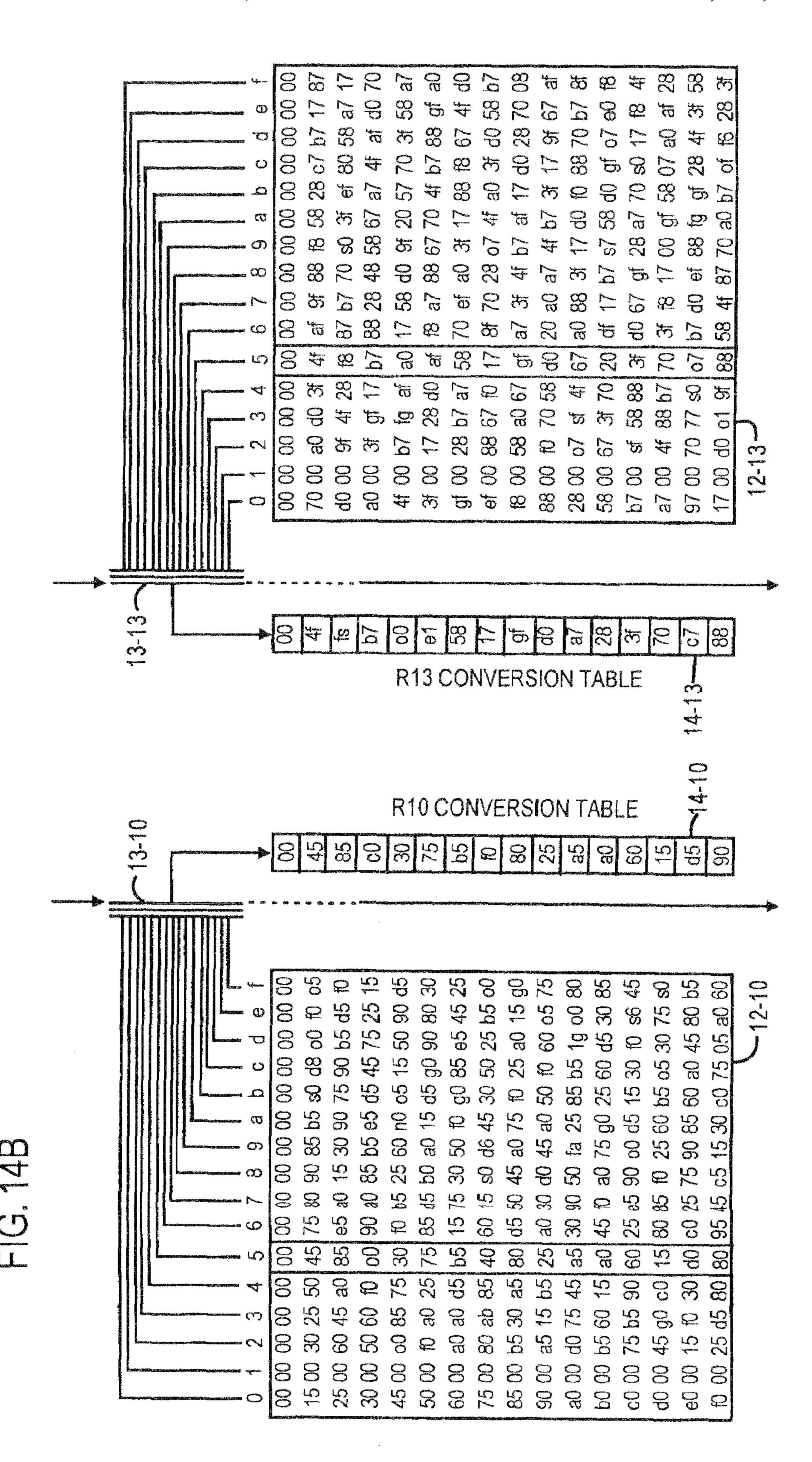

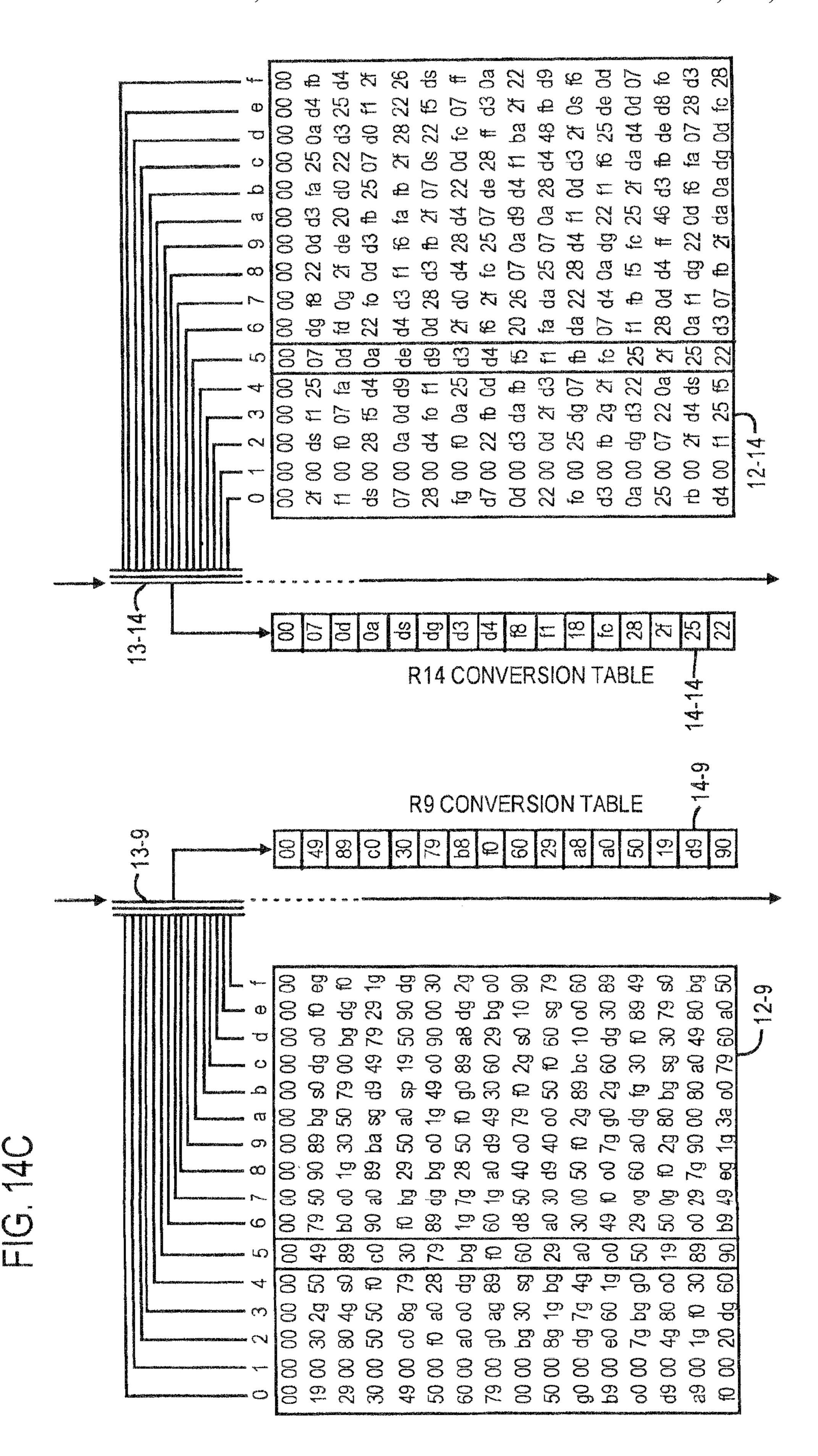

FIG. **14** is a view showing the details of the index table making circuit shown in FIG. **12**.

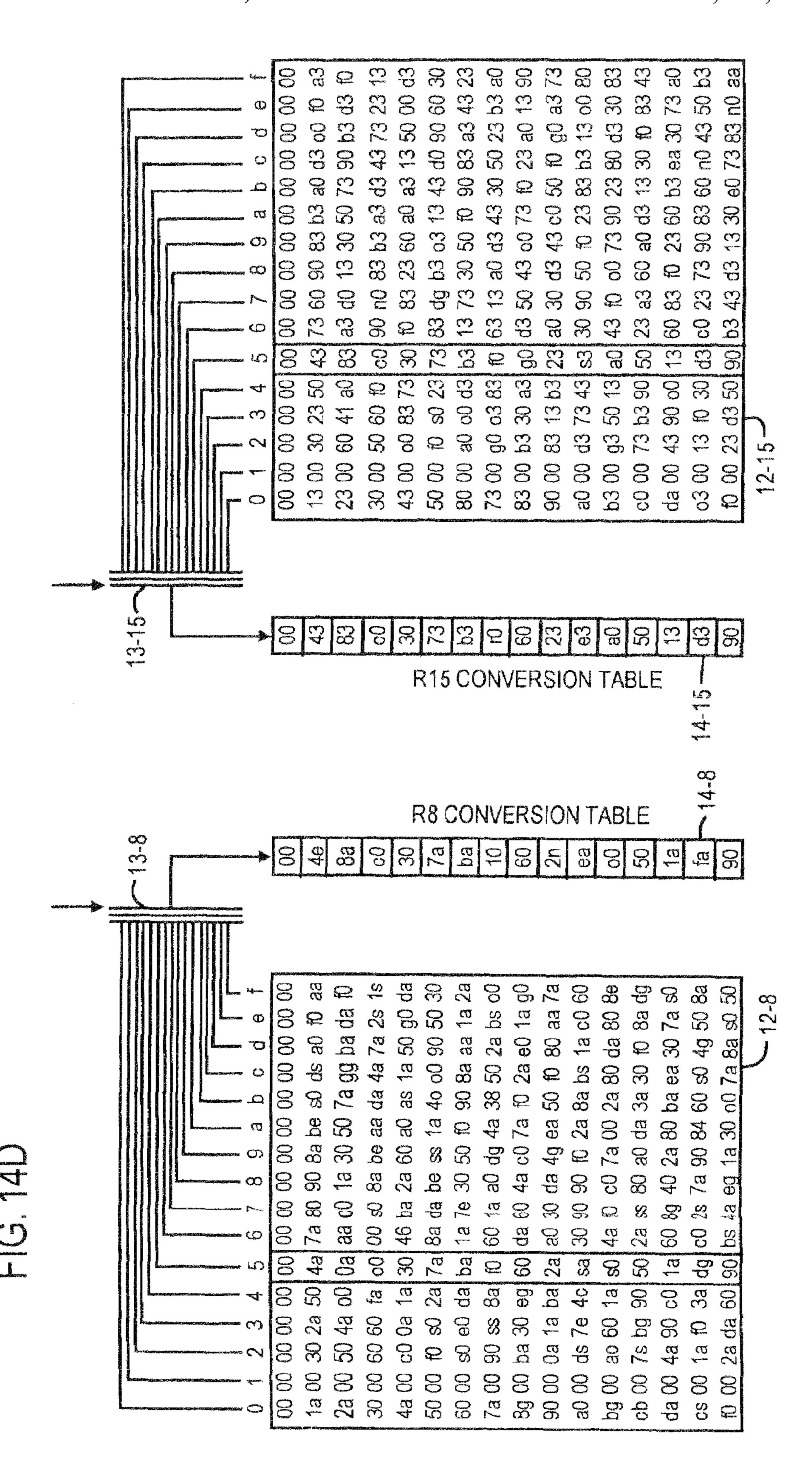

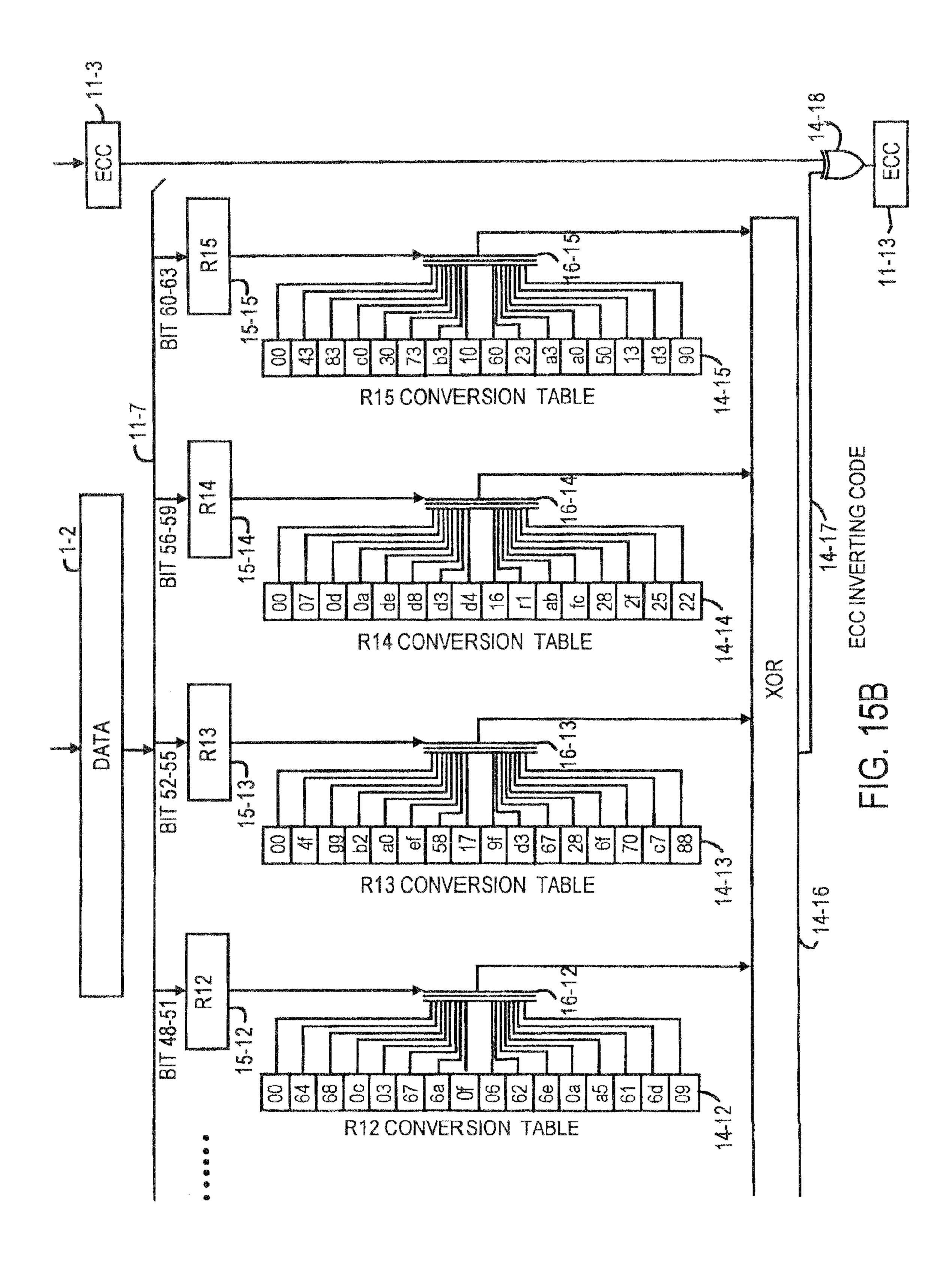

FIG. 15 is a view showing the details of an ECC converting circuit shown in FIG. 12.

FIG. **16** is a view showing the details of a table check circuit shown in FIG. **12**.

## DESCRIPTION OF THE PREFERRED EMBODIMENTS

The embodiments of the present invention will next be explained in detail with reference to the drawings.

## Embodiment 1

Referring to FIG. 3, a main portion of a disk array system according to an embodiment 1 of the present invention comprises a host 1, a system memory 2, a host side system bus 3 connected to the host 1 and the system memory 2, a host side IO control circuit 4 connected to the host side system bus 3, and a disk array device 5 connected to the host side IO control circuit 4.

The disk array device 5 comprises a RAID controller 6 connected to the host side IO control circuit 4, a cache memory 7 for RAID connected to the RAID controller 6, an array side system bus 8 connected to the RAID controller 6, n (n is plural) IO control circuits 9 such as SCSI (Small Computer System Interface) connected to the array side system bus 8, and n hard disk devices 10 respectively connected to each IO control circuit 9.

The RAID controller 6 includes a command processing circuit 11 connected to the host side IO control circuit 4, a data transfer control circuit 12 connected to the command processing circuit 11, the array side system bus 8 and the cache memory 7 for RAID, and a parity data generating circuit 13 for RAID connected to the data transfer control circuit 12.

FIG. 2 is a circuit block diagram showing the construction of the parity data generating circuit 13 for RAID for realizing RAID6 in accordance with the embodiment 1 of the present 50 invention.

The parity data generating circuit 13 for RAID comprises a Galois field multiplying circuit 1-21, a table check circuit 1-14, a parity check circuit 1-15, two XOR circuits 1-16 and a buffer 1-17. The Galois field multiplying circuit 1-21 inputs 55 data 1-2, parity 1-3 and a multiplication coefficient 1-4 thereto and makes a Galois field multiplying calculation. The table check circuit 1-14 checks whether index table information (a longitudinal inverting table 3-12 for parity, a longitudinal converting table 3-13 for data, a transversal converting 60 table 3-14 for data, and a transversal inverting table 1-15 for parity shown in FIG. 4) generated in the Galois field multiplying circuit 1-21 is correct. The parity check circuit 1-15 checks the parity by using data 1-12 and parity 1-13 generated by the Galois field multiplying circuit 1-21. The XOR circuit 65 1-16 performs an XOR logic arithmetic operation with respect to the data 1-12 and the parity 1-13 generated by the

**16**

Galois field multiplying circuit 1-21. The buffer 1-17 accumulates the arithmetic result of the XOR circuit 1-16 as parity data Q for RAID.

The Galois field multiplying circuit 1-21 comprises a Galois field multiplying table 1-11, a longitudinal index table making circuit 1-9, a transversal index table making circuit 1-10, an upper order data converting circuit 1-5, a lower order data converting circuit 1-6, an upper order parity inverting circuit 1-7 and a lower order parity inverting circuit 1-8. The longitudinal index table making circuit 1-9 indexes the Galois field multiplying table 1-11 from the longitudinal direction by using the multiplication coefficient 1-4 and generates index table information of the longitudinal direction. Similarly, the transversal index table making circuit 1-10 indexes the Galois field multiplying table 1-11 from the transversal direction by using the multiplication coefficient 1-4 and generates index table information of the transversal direction. The upper order data converting circuit 1-5 and the lower order data converting circuit 1-6 convert the data 1-2 into the data 1-12 for RAID from the generated index table information. Similarly, the upper order parity inverting circuit 1-7 and the lower order parity inverting circuit 1-8 convert the parity 1-3 with respect to the data 1-2 into the parity 1-13 with respect to the data 1-12 <sub>25</sub> for RAID.

FIG. 4 shows the concrete circuit construction of the Galois field multiplying table 1-11, the longitudinal index table making circuit 1-9 and the transversal index table making circuit 1-10.

A calculating example of the parity will first be explained. Since each hard disk device **10** is divided into blocks in a four-bit unit, sixteen kinds of data from 0 to 15 can be stored to each block.

Therefore, the parity is calculated by using the extension Galois field  $GF(2^4)$  cable of treating the sixteen kinds of data. This extension Galois field  $GF(2^4)$  can make adding (subtracting), multiplying and dividing calculations within the defined kind of data. The adding (subtracting) calculation is made by using XOR logic. The multiplying calculation is made by the use of a conversion table 3-6 for data as multiplying results of the extension Galois field  $GF(2^4)$ . The dividing calculation is quoted by performing a reverse subtracting operation with respect to the conversion table 3-6 for data.

The conversion table 3-6 for data is a table in which the extension Galois field  $GF(2^4)$  is calculated by using  $X^4+X+1$  as an irreducible polynomial of the fourth order on a Galois field GF(2).

A brief explanation of the extension Galois field  $GF(2^4)$  and a making example of the conversion table 3-6 for data will next be explained.

In the Galois field GF(2), two kinds of 0 and 1 are elements, and the adding, subtracting, multiplying and dividing calculations can be made therebetween. In contrast to this, in the extension Galois field  $GF(2^m)$ , there are 2m elements, and the adding, subtracting, multiplying and dividing calculations can be made freely therebetween.  $2^m$  represents the m-th power of 2.

The multiplying calculation of the fourth order in the extension Galois field will be next defined.

When roots of the irreducible polynomial

$X^4 + X + 1 = 0$

of the fourth order on GF(2) as a multiplying result are considered in the elements of the two kinds of 0 and 1 as a field of the Galois field GF(2), no root exists even when any element

of 0 and 1 is substituted. Therefore, one of such roots of the irreducible polynomial is defined as and the field is enlarged on trial.

As its result, since  $\alpha$  satisfies  $\alpha^4 + \alpha + 1 = 0$ ,

the relation of

$\alpha^4 = \alpha + 1$

is obtained, and all relation formulas of the fourth order or more represented by  $\alpha$  can be replaced with relation formulas  $^{10}$  of the fourth order or less.

Therefore, when the sixteen kinds of data are considered by the n-th order of  $\alpha$ , these data can be represented by the relation formulas as shown below, and do not appear except for the relation formulas of fifteen kinds.

$$\alpha^{2}$$

$$\alpha^{3}$$

$$\alpha^{4}=\alpha+1$$

$$\alpha^{5}=\alpha^{2}+\alpha$$

$$\alpha^{6}=\alpha^{3}+\alpha^{2}$$

$$\alpha^{7}=\alpha^{4}+\alpha^{3}=\alpha^{3}\alpha+1$$

$$\alpha^{8}=\alpha^{4}+\alpha^{2}+\alpha=\alpha^{2}+1$$

$$\alpha^{9}=\alpha^{3}+\alpha$$

$$\alpha^{10}=\alpha^{4}+\alpha^{2}=\alpha^{2}+\alpha+1$$

$$\alpha^{11}=\alpha^{3}+\alpha^{2}+\alpha$$

$$\alpha^{12}=\alpha^{4}+\alpha^{3}+\alpha^{2}=\alpha^{3}+\alpha^{2}+\alpha+1$$

$$\alpha^{13}=\alpha^{4}+\alpha^{3}+\alpha^{2}+\alpha=\alpha^{3}+\alpha^{2}+1$$

$$\alpha^{14}=\alpha^{4}+\alpha^{3}+\alpha=\alpha^{3}+1$$

$$\alpha^{15}=\alpha^{4}+\alpha+1$$

When data of the n-th orders of  $\alpha$  are multiplied, the multiplied data are represented by any one of the relation formulas of the fifteen kinds from the above relation formulas. For example,

$$\alpha^7 + \alpha^{14} = \alpha^{21} = \alpha^6 = \alpha^3 + \alpha^2$$

is formed and is represented by the formula  $\alpha^6$  within the fifteen kinds. Since one cycle is formed by the kinds 1 to F of data from these relation formulas,  $\alpha^{16}=\alpha$  is formed and it is returned to 1.

Herein, with respect to the above-mentioned relation formulas of the fifteen kinds, the conversion table 3-6 for data can be made by making these formulas correspond to 1 to F. The conversion table 3-6 for data is numerically expressed by making the index number of  $\alpha$  correspond to the digit of a binary number. The conversion table 3-6 for data includes zero in addition to 1 to F and shows multiplying results of 0 to F.

Accordingly, the conversion table 3-6 for data shows the multiplying results using the extension Galois field  $GF(2^4)$  by 65 using the irreducible polynomial  $X^4+X+1$  of the fourth order on the Galois field GF(2). However, it is supposed that all

**18**

congruence expressions described below are also calculated by the extension Galois field  $GF(2^4)$  as long as it is emphatically said.

The Galois field multiplying table 1-11 has the conversion table 3-6 for data which is made by the Galois field multiplying calculation of the extension Galois field GF(2<sup>4</sup>) and is symmetrical longitudinally and transversally. The Galois field multiplying table 1-11 also has conversion tables 3-5 and 3-7 for parity. In the Galois field multiplying table 1-11, one column or one row shown by the multiplication coefficient 1-4 of the Galois field is indexed by selectors 3-8, 3-9, 3-10 and 3-11 as a longitudinal inverting table 3-12 for parity, a longitudinal converting table 3-13 for data, a transversal converting table 3-14 for data and a transversal inverting table 3-15 for parity.

The conversion table 3-6 for data is a table in which the index of the longitudinal direction and the index of the transversal direction are the same result from the characteristics of this conversion table 3-6 for data. The longitudinal index table making circuit 1-9 generates the longitudinal converting table 3-13 for data by the selector 3-9 from the conversion table 3-6 for data, and transfers this longitudinal converting table 3-13 for data to the upper order data converting circuit 1-5. Further, the transversal index table making circuit 1-10 generates the transversal converting table 3-14 for data by the selector 3-10 from the conversion table 3-6 for data, and transfers this transversal converting table 3-14 for data to the lower order data converting circuit 1-6.

The conversion tables **3-5** and **3-7** for parity have values mutually replaced with respect to the longitude and the transverse. The longitudinal index table making circuit **1-9** generates the longitudinal inverting table **3-12** for parity by the selector **3-8** from the conversion table **3-5** for parity, and transfers this longitudinal inverting table **3-12** for parity to the lower order parity inverting circuit **1-8**. Further, the transversal inverting table **3-15** for parity by the selector **3-11** from the conversion table **3-7** for parity, and transfers this transversal inverting table **3-15** for parity to the upper order parity inverting table **3-15** for parity to the upper order parity inverting circuit **1-7**.

Referring to FIG. 5, the upper order data converting circuit 1-5 performs the conversion of an upper order data portion with respect to the data 1-2. The upper order data portion of the data 1-2 is decomposed into respective decomposing data 4-2 to 4-5 of a four-bit unit, and becomes select signals of selectors 4-10 to 4-13. The upper order data converting circuit 1-5 is constructed so as to obtain an arithmetic result with respect to the multiplication coefficient 1-4 of the Galois field by selecting the longitudinal converting table 3-13 for data generated by the longitudinal index table making circuit 1-9.

The lower order data converting circuit 1-6 also has a circuit similar to the upper order data converting circuit 1-5. A lower order data portion of the data 1-2 is decomposed into respective decomposing data 4-6 to 4-9 of a four-bit unit, and becomes select signals of selectors 4-14 to 4-17. The lower order data converting circuit 1-6 is constructed so as to obtain an arithmetic result with respect to the multiplication coefficient 1-4 of the Galois field by selecting the transversal converting table 3-14 for data generated by the transversal index table making circuit 1-10.

Referring to FIG. 6, the upper order parity inverting circuit 1-7 performs the conversion of an upper order parity portion with respect to the parity 1-3. The upper order parity portion of the parity 1-3 is decomposed into parity bits 5-4 to 5-5 of a one-bit unit, and is given to XOR circuits 5-24 to 5-25. On the other hand, the upper order data portion of the data 1-2 is decomposed into respective decomposing data 4-2 to 4-5 of

the four-bit unit, and becomes select signals of selectors 5-16 to 5-17. A result obtained by selecting the transversal inverting table 3-15 for parity generated by the transversal index table making circuit 1-10 is inputted to the XOR circuits 5-24 to 5-25. The outputs of the XOR circuits 5-24 to 5-25 become parity bits 5-30 to 5-31 of a one-bit unit in which the upper order parity portion is inverted.

The lower order parity inverting circuit 1-8 also has a circuit structure similar to the upper order parity inverting circuit 1-7, and performs the conversion of a lower order parity portion with respect to the parity 1-3. In the lower order parity portion of the parity 1-3, parity bits 5-6 to 5-7 of a one-bit unit are given to XOR circuits 5-26 to 5-27. On the other hand, the lower order data portion of the data 1-2 is decomposed into respective decomposing data 4-6 to 4-9 of the four-bit unit, and becomes select signals of selectors 5-20 to 5-23. A result obtained by selecting the longitudinal inverting table 3-12 for parity generated by the longitudinal index table making circuit 1-9 is inputted to XOR circuits 5-26 to 5-27. The outputs of the XOR circuits 5-24 to 5-25 become parity bits 5-32 to 5-33 of a one-bit unit in which the lower order parity portion of the parity 1-3 is inverted.

Thus, when each of the decomposing data 4-2 to 4-9 is incorrect, its parity bits 5-30 to 5-33 are also incorrect and an error is confirmed upon checking the parity.

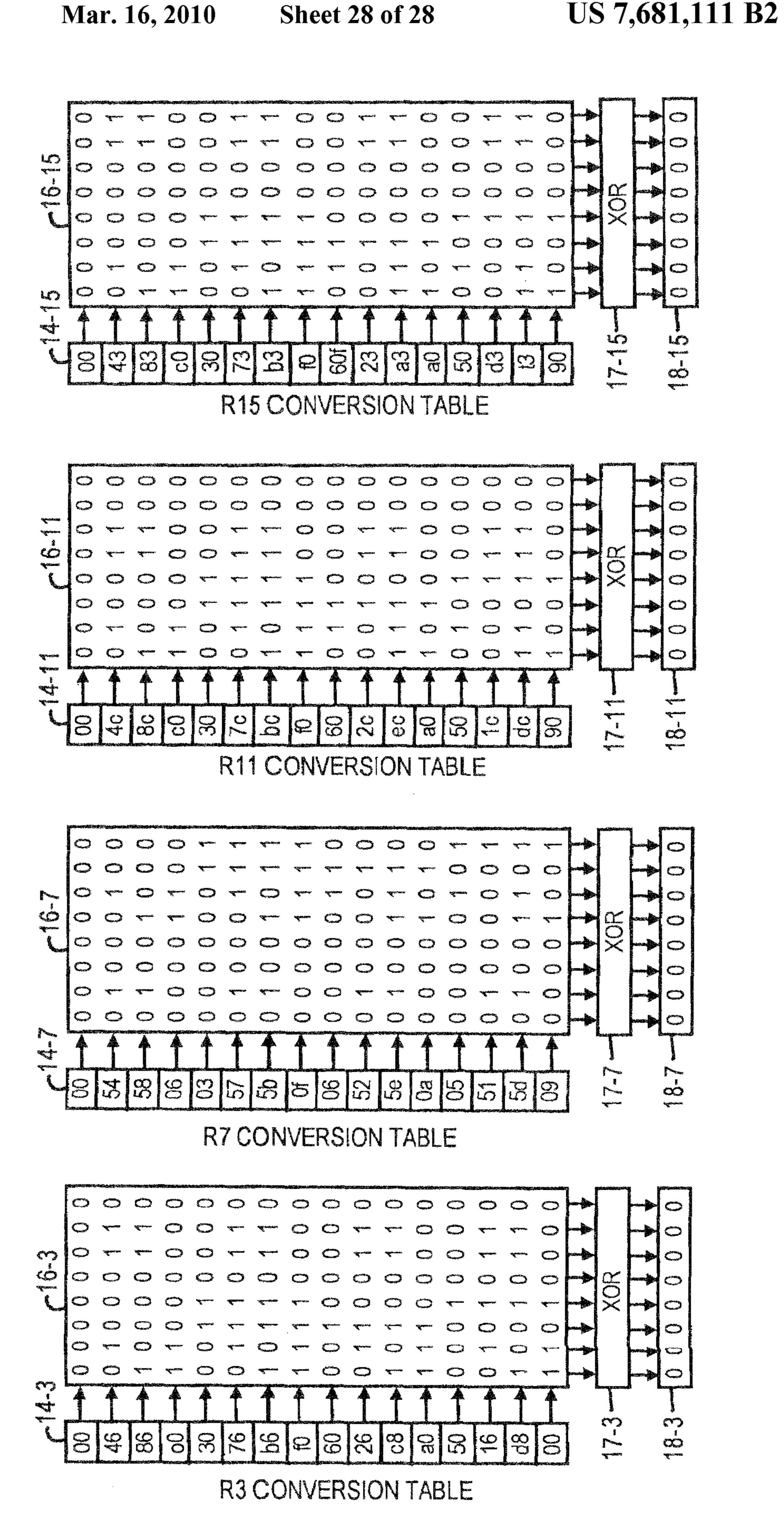

FIGS. 7 and 8 show the detailed circuit construction of the table check circuit 1-14.

FIG. 7 shows a table check circuit 6-1 for data conversion for comparing and checking the longitudinal converting table 3-13 for data and the transversal converting table 3-14 for data. FIG. 7 also shows a table check circuit 6-2 for parity inversion for comparing and checking the longitudinal inverting table 3-12 for parity and the transversal inverting table 3-15 for parity.

The table check circuit 6-1 for data conversion serves to inspect conformity of the longitudinal converting table 3-13 for data generated by the longitudinal index table making circuit 1-9 and the transversal converting table 3-14 for data generated by the transversal index table making circuit 1-10 by a comparing circuit 6-4. The table check circuit 6-2 for parity inversion serves to inspect conformity of the longitudinal inverting table 3-12 for parity generated by the longitudinal index table making circuit 1-9 and the transversal inverting table 3-15 for parity generated by the transversal index 45 "12345678". table making circuit 1-10 by a comparing circuit 6-7. It is possible to inspect whether the longitudinal converting table 3-13 for data, the transversal converting table 3-14 for data, the longitudinal inverting table 3-12 for parity and the transversal inverting table 3-15 for parity themselves at the converting times of data and parity are correct by the above two kinds of the table check circuit 6-1 for data conversion and the table check circuit 6-2 for parity inversion.

FIG. 8 shows table zero check circuits 7-15 and 7-16. The table zero check circuit 7-15 inspects that an XOR logic of each bit unit becomes "0" by inputting the longitudinal converting table 3-13 for data or the transversal converting table 3-14 for data. The table zero check circuit 7-16 inspects that the XOR logic of the bit unit becomes "zero" by inputting the longitudinal inverting table and table 3-12 for parity or the transversal for parity inverting circuit 1-9 se table making circuit 1-9 se "4" of the multiplication co table 3-5 for parity by the longitudinal inverting table "00001111111110000" (bin longitudinal inverting table parity inverting circuit 1-8. Further, similar to the longitudinal to the longitudinal to the longitudinal inverting circuit 1-8.

The table zero check circuit 7-15 respectively decomposes respective data of the longitudinal converting table 3-13 for data and the transversal converting table 3-14 for data generated by the longitudinal index table making circuit 1-9 and the 65 transversal index table making circuit 1-10 into bits 7-2 to 7-5. The table zero check circuit 7-15 further performs all the

**20**

XOR logic operations of the same bit series by an XOR circuit 7-8 and inspects that all their XOR logic results 7-10 to 7-13 become "0".

The table zero check circuit 7-16 decomposes the longitudinal inverting table 3-12 for parity or the transversal inverting table 3-15 for parity generated by the longitudinal index table making circuit 1-9 and the transversal index table making circuit 1-10 into a bit unit 7-7. The table zero check circuit 7-16 further performs all the XOR logic operations of a bit series by an XOR circuit 7-9, and inspects that its XOR logic result 7-14 becomes "0". Thus, the table zero check circuit 7-16 is constructed so as to inspect whether the Galois field multiplying table 1-11 itself has correct values.

Subsequently, explanation will be made of the operation of the parity data generating circuit 13 for RAID according to the embodiment 1 having the above-mentioned structure with reference to FIGS. 2 to 8.

In FIGS. 2 to 8, this operation will be explained in the case of 32 bits in data and four bits in parity. However, these bit numbers are one example, and the bit numbers are not restricted in the present invention.

When RAID5 and RAID6 are constructed, parity data for RAID are generated by the XOR logic for a data series constituting a group of the RAID from its characteristics.

In this event, when the parity data for RAID6 are generated, two kinds of parity data P and Q are required as already mentioned above. One case relates to generation of the parity data P equal to that of RAID5 conventionally used. Its generating method is sufficiently widened by a known technique. Therefore, this generating method is not described here, and the generation of the parity data Q specialized and required in RAID6 will be described.

The arithmetic calculation of the parity data Q specialized for RAID6 is shown by the above formula 2.

In FIG. 2, the multiplication coefficient 1-4 of the Galois field is transferred together with the data 1-2 and the parity 1-3. Herein, the data 1-2 have a value of 32 bits of "12345678" in the hexadecimal notation, and its parity 1-3 has a value of odd parity of four bits of "B". The multiplication coefficient 1-4 at this time will be explained as "4".

This explanation is made when the arithmetic calculation of a term "4D5" within the formula 2 is intended to be performed, and is an explanation of the multiplying calculation of the Galois field when "D5" becomes the value of "12345678".

Since the multiplication coefficient 1-4 is "4", the longitudinal index table making circuit 1-9 selects a column corresponding to "4" of the multiplication coefficient 1-4 from the conversion table 3-6 for data by the selector 3-9, and generates the longitudinal converting table 3-13 for data having a value of "048C37BF62EA51D9", and transfers this longitudinal converting table 3-13 for data to the upper order data converting circuit 1-5. Simultaneously, the longitudinal index table making circuit 1-9 selects a column corresponding to "4" of the multiplication coefficient 1-4 from the conversion table 3-5 for parity by the selector 3-8, and generates the longitudinal inverting table 3-12 for parity having a value of "0000111111110000" (binary notation), and transfers this longitudinal inverting table 3-12 for parity to the lower order parity inverting circuit 1-8.

Further, similar to the longitudinal index table making circuit 1-9, the transversal index table making circuit 1-10 selects a row corresponding to "4" of the multiplication coefficient 1-4 from the conversion table 3-6 for data by the selector 3-10, and generates the transversal converting table 3-14 for data having a value of "048C37BF62EA51D9" and transfers this transversal converting table 3-14 for data to the

lower order data converting circuit 1-6. Simultaneously, the transversal index table making circuit 1-10 selects a row corresponding to "4" of the multiplication coefficient 1-4 from the conversion table 3-7 for parity by the selector 3-11, and generates the transversal inverting table 3-15 for parity having a value of "00001111111110000" (binary notation) and transfers this transversal inverting table 3-15 for parity to the upper order parity inverting circuit 1-7.

Thus, the longitudinal converting table 3-13 for data and the transversal converting table 3-14 for data, and the longitudinal inverting table 3-12 for parity and the transversal inverting table 3-15 for parity are generated. The right property of values is confirmed by the table check circuit 6-1 for data conversion and the table check circuit 6-2 for parity inversion in the table check circuit 1-14, and the table zero 15 check circuits 7-15 and 7-16.

In the table check circuit 1-14, the table check circuit 6-1 for data conversion respectively compares the longitudinal converting table 3-13 for data and the longitudinal inverting table 3-12 for parity generated by the longitudinal index table making circuit 1-9, and the transversal converting table 3-14 for data and the transversal inverting table 3-15 for parity generated by the transversal index table making circuit 1-10. When these tables are not conformed to each other, this unconformity is detected as a failure of the disk array system.

Similarly, in the table check circuit 1-14, the table zero check circuit 7-15 inspects whether all XOR arithmetic results 7-10 to 7-13 of a bit unit of the longitudinal converting table 3-13 for data and the transversal converting table 3-14 for data are zero. When these results become values except for zero, this case is also detected as a failure of the disk array system. Further, the table zero check circuit 7-16 inspects whether the XOR arithmetic result 7-9 of the longitudinal inverting table 3-12 for parity and the transversal inverting table 3-15 for parity is zero. When this arithmetic result becomes a value except for zero, this case is also detected as a failure of the disk array system.

When no error is detected in the table check circuit 6-1 for data conversion and the table check circuit 6-2 for parity inversion and the table zero check circuits 7-15 and 7-16, the actual parity data Q for RAID are generated and the data 1-2 and the parity 1-3 are transferred to the upper order data converting circuit 1-5, the lower order data converting circuit 1-6, the upper order parity inverting circuit 1-7 and the lower order parity inverting circuit 1-8.

The upper order data converting circuit 1-5 receives a value of "1234" as upper order 16 bits of the data 1-2 of 32 bits, and decomposes this value into respective decomposing data 4-2 to 4-5 of a four-bit unit.

These respective decomposing data 4-2 to 4-5 of the fourbit unit become select signals of respective selectors 4-10 to 4-13. The selectors 4-10 to 4-13 select respective values of the longitudinal converting table 3-13 for data.