## US007625786B2

## (12) United States Patent

## Makita et al.

# (10) Patent No.: US 7,625,786 B2 (45) Date of Patent: Dec. 1, 2009

## (54) SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME

(75) Inventors: **Naoki Makita**, Nara (JP); **Misako Nakazawa**, Kanagawa (JP); **Hideto Ohnuma**, Kanagawa (JP); **Takuya**

Matsuo, Osaka (JP)

(73) Assignees: Semiconductor Energy Laboratory

Co., Ltd., Kanagawa-Ken (JP); Sharp Kabushiki Kaisha, Osaka (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 437 days.

(21) Appl. No.: 11/088,888

(22) Filed: Mar. 25, 2005

(65) Prior Publication Data

US 2005/0170573 A1 Aug. 4, 2005

## Related U.S. Application Data

(62) Division of application No. 10/183,056, filed on Jun. 27, 2002, now Pat. No. 6,998,641.

## (30) Foreign Application Priority Data

(51) **Int. Cl.**

(58)

$H01L\ 21/84$  (2006.01)

438/151–166, 154, 176, 195, 301, 476; 257/88, 257/213, E21.561

See application file for complete search history.

## (56) References Cited

## U.S. PATENT DOCUMENTS

5,501,989 A 3/1996 Takayama et al. 5,563,426 A 10/1996 Zhang et al.

| 5,589,694 | A   | 12/1996 | Takayama et al.        |

|-----------|-----|---------|------------------------|

| 5,643,826 | A   | 7/1997  | Ohtani et al.          |

| 5,744,822 | A   | 4/1998  | Takayama et al.        |

| 5,904,509 | A   | 5/1999  | Zhang et al.           |

| 6,031,249 | A   | 2/2000  | Yamazaki et al.        |

| 6,072,193 | A   | 6/2000  | Ohnuma et al.          |

| 6,197,626 | B1  | 3/2001  | Yamazaki et al.        |

| 6,218,219 | B1* | 4/2001  | Yamazaki et al 438/149 |

| 6.251.712 | B1  | 6/2001  | Tanaka et al.          |

## (Continued)

## FOREIGN PATENT DOCUMENTS

EP 0 862 201 A2 9/1998

## (Continued)

### OTHER PUBLICATIONS

Search Report for Application No. 02013449.0; EP5732; dated Feb. 11, 2005.

## (Continued)

Primary Examiner—Richard A. Booth (74) Attorney, Agent, or Firm—Nixon Peabody LLP; Jeffrey L. Costellia

## (57) ABSTRACT

Problems in prior art regarding an n-channel TFT in the source/drain gettering method are solved. In the n-channel TFT, its source/drain regions contain only an n-type impurity. Therefore, compared to a p-channel TFT whose source/drain regions contain an n-type impurity and a higher concentration of p-type impurity, the gettering efficiency is inferior in a channel region of the n-channel transistor. Accordingly, the problem of inferior gettering efficiency in the n-channel TFT can be solved by providing at an end of its source/drain regions a highly efficient gettering region that contains an n-type impurity and a p-type impurity both with the concentration of the p-type impurity set higher than the concentration of the n-type impurity.

## 14 Claims, 16 Drawing Sheets

#### U.S. PATENT DOCUMENTS FOREIGN PATENT DOCUMENTS 6,278,131 B1 8/2001 Yamazaki et al. EP 0 862 201 A3 10/1999 EP 6,278,132 B1 8/2001 Yamazaki et al. 1 020 920 A2 7/2000 EP 9/2001 Yamazaki 7/2000 6,294,441 B1 1006589 5/2002 Zhang et al. EP 4/2002 6,391,694 B1 1 020 920 A3 7/2002 Kawasaki et al. JP 6,424,012 B1 07-130652 5/1995 JP 6,465,288 B1 10/2002 Ohnuma 07-202213 8/1995 Tanaka et al. 6,518,102 B1 08-330602 2/2003 12/1996 6,620,711 B2 JP Yamazaki 9/2003 10-125926 5/1998 Yamazaki et al. ...... 257/72 JP 6,639,244 B1\* 11-054760 10/2003 2/1999 1/2004 Kawasaki et al. JP 6,677,221 B2 2000-133594 5/2000 2/2004 Yamazaki et al. 8/2000 6,693,299 B1 2000-228527 6,727,124 B2\* 4/2004 Nakajima et al. ...... 438/154 9/2000 2000-269512 8/2004 Yamazaki et al. ...... 257/88 6,777,716 B1\* 1/2001 2001-007342 6,855,580 B2 JP 2001-155995 6/2001 2/2005 Tanaka et al. 7,008,828 B2 \* 7,157,753 B2\* OTHER PUBLICATIONS 2001/0016376 A1 8/2001 Yamazaki et al. 10/2001 Yamazaki et al. 2001/0029070 A1 U.S. Appl. No. 09/123,000, filed Jul. 28, 1998 (740756-1845). 11/2001 Yamazaki et al. 2001/0038127 A1 Intellectual Property Office of Singapore "Search Report and Written 2001/0048115 A1 12/2001 Yamazaki et al. Opinion for Application No. 200203262-1"; dated Mar. 24, 2004. 2002/0004291 A1 1/2002 Yamazaki Office Action (U.S. Appl. No. 2002-0036280; Our Ref.: KR5732), 2002/0053671 A1 5/2002 Koyama dated Nov. 14, 2008 with English translation. 5/2002 Nakajima et al. 2002/0053674 A1 \* cited by examiner

2002/0142525 A1\*

FIG. 4A

FIG. 4B

FIG. 4C

FIG. 7A

FIG. 7B

FIG. 7C

FIG. 13

US 7,625,786 B2

1303

1508

1502

1506

FIG. 14C

FIG. 14D

FIG. 14E

FIG. 14F

FIG. 16B

1901

1902

1903

to screen

1905

## SEMICONDUCTOR DEVICE AND METHOD OF MANUFACTURING THE SAME

### BACKGROUND OF THE INVENTION

## 1. Field of the Invention

The present invention relates to a semiconductor device using a crystalline semiconductor film that contains silicon and to a method of manufacturing the semiconductor device. Specifically, the present invention relates to a semiconductor device having an n-channel thin film transistor (hereinafter referred to as TFT) formed from a crystalline semiconductor film that contains silicon and to a method of manufacturing the semiconductor device.

## 2. Description of the Related Art

In recent years, the technique of making a semiconductor circuit from TFTs formed on an insulating substrate such as a glass substrate has rapidly progressed and is utilized to manufacture active matrix liquid crystal display devices and other electrooptical devices. An active matrix liquid crystal display 20 device is a monolithic liquid crystal display device in which a pixel matrix circuit and a driver circuit are placed on the same substrate. The above technique is also utilized to develop a system on panel incorporating logic circuits such as a  $\gamma$  correction circuit, a memory circuit, and a clock generating 25 circuit.

Driver circuits and logic circuits as above need to operate at high speed. Therefore, it is inappropriate to use an amorphous silicon film for the semiconductor layer that serves as an active layer of a TFT of these circuits. TFTs whose active 30 layers are polycrystalline silicon films are thus becoming the mainstream. There is a need for a glass substrate as a substrate on which TFTs are formed because of its inexpensiveness, and a low temperature process applicable to a glass substrate is actively being developed.

One of the low temperature process techniques that have been developed is a technique for forming a crystalline silicon film on a glass substrate, which is disclosed in Japanese Patent Application Laid-open No. Hei 7-130652. According to the technique described in the publication, an amorphous 40 silicon film is provided with a catalytic element that accelerates crystallization and the amorphous silicon film is then crystallized by heat treatment. This crystallization technique makes it possible to lower the temperature at which an amorphous silicon film is crystallized and shorten the crystallization time. The technique allows a glass substrate with a low heat resistance to have a large area crystalline silicon film on its surface, opening the gate to employment of glass substrate of crystalline silicon film in TFTs.

This technique of crystallizing an amorphous silicon film 50 uses as the catalytic element Ni (nickel), Co (cobalt), or the like. Therefore, when used in a TFT, a crystalline silicon film obtained by this crystallization technique can affect electric characteristics and reliability of the TFT. In fact, it has been confirmed that the catalytic element remaining in the crystal- 55 line silicon film segregates irregularly in a grain boundary and that the grain boundary region in which the catalytic element segregates serves as a leak path of a weak current to cause an eruptive increase in OFF current in the TFT. Then, a technique of gettering a catalytic element by a halogen element 60 has been developed (See Japanese Patent Application Laidopen No. Hei 10-125926). This gettering technique requires high temperature heat treatment at 800° C. or higher and is not applicable to a glass substrate having a low heat resistance. Although the technique is capable of lowering the crystalli- 65 zation temperature for obtaining a crystalline silicon film than the heat resistance temperature of a glass substrate, the tem2

perature during gettering of catalytic element by the technique is no lower than 800° C. to make it practically impossible to apply the low temperature process using a catalytic element to a glass substrate.

Against this background, a highly efficient catalytic element gettering technique has been developed and disclosed in Japanese Patent Application Laid-open No. Hei 11-054760. According to the technique described in the publication, catalytic elements in a gettering subject region (a region that is not doped with a Group 13 element and a Group 15 element) are thermally diffused and moved to a gettering region, and the catalytic elements are then gettered in the gettering region by a Group 13 element (typically boron (B)) and a Group 15 element (typically, phosphorus (P)). This technique consists of the following three steps.

The first step is to obtain a crystalline silicon film by crystallizing an amorphous silicon film using a catalytic element. The second step is to form a gettering region by selectively doping the crystalline silicon film with a Group 13 element (typically B) and a Group 15 element (typically P). The third step is to move catalytic elements in a gettering subject region to a gettering region through thermal diffusion induced by heat treatment for gettering.

In applying the above gettering technique to a process of manufacturing a TFT, there are three major application modes given below.

According to Application Mode 1, a gettering subject region is a region including a semiconductor layer formed from a crystalline silicon film and composed of a source region, drain region, and channel region of a TFT. A region in the periphery of the gettering subject region is selectively doped with both a Group 13 element (typically B) that imparts the p-type conductivity and a Group 15 element (typically P) that imparts the n-type conductivity, thereby forming a gettering region. Then, heat treatment is conducted for gettering.

According to Application Mode 2, the entire region of a crystalline silicon film except a channel region is a gettering region. In other words, a source region and a drain region, and regions other than a semiconductor layer make the gettering region. Specifically, this application mode is comprised of: a step of forming a resist mask on a region that serves as the channel region of the TFT after the crystalline silicon film is formed using a catalytic element (before the semiconductor layer is formed); a doping step using both a Group 13 element (typically B) that imparts the p-type conductivity and a Group 15 element (typically P) that imparts the n-type conductivity; a step of removing the resist mask; and a gettering step for gettering the catalytic element from the region serving as the channel region through heat treatment. Since the gettering region includes a part of the source region and drain region, Application Mode 2 can have a larger gettering region as compared to Application Mode 1.

According to Application Mode 3, a channel region in a semiconductor layer that is formed from a crystalline silicon film is a gettering subject region whereas a source region and a drain region in the semiconductor layer alone make a gettering region. Impurity elements in the source region and drain region double as gettering sources. Specifically, this application mode is comprised of: a step of forming the semiconductor layer after the crystalline silicon film is formed using a catalytic element; a step of forming a gate electrode; a step of doping the semiconductor layer with a Group 13 element (typically B) that imparts the p-type conductivity and a Group 15 element (typically P) that imparts the n-type conductivity while using the gate electrode as a mask to form the source region and the drain region; and a step of thermally activating impurity elements in the source region and drain

region and simultaneously gettering the catalytic element in the channel region through heat treatment. Since the gettering region is confined to the semiconductor layer and is smaller in surface area as compared to Application Mode 2, Application Mode 3 is that much less effective in gettering the catalytic element in the channel region. On the other hand, Application Mode 3 integrates the step of introducing a gettering source for forming a gettering region with the impurity doping step for forming a source region and a drain region and is therefore advantageous in improving throughput.

Application Mode 3 improves the degree of integration of TFT as well as throughput and is therefore convenient and useful. However, when Application Mode 3 is employed in manufacture of an n-channel TFT and a p-channel TFT, the catalytic element gettering efficiency in a channel region is lower in the n-channel TFT than in the p-channel TFT. The problem of Application Mode 3 regarding the low gettering efficiency of the n-channel TFT will be described in detail below.

Semiconductor layers of the n-channel TFT and p-channel 20 TFT are doped with an n-type impurity element that imparts the n-type conductivity while using gate electrodes as masks. Thereafter, the semiconductor layer of the p-channel TFT alone is doped with a p-type impurity element that imparts the p-type conductivity in an amount large enough to convert the 25 layer's conductivity while using the gate electrode as a mask. Thus formed are source regions and drain regions of the n-channel TFT and p-channel TFT. The source region and drain region of the p-channel TFT therefore contain an element that imparts the n-type conductivity and an element that 30 imparts the p-type conductivity with the amount of p-type impurity exceeding the amount of n-type impurity. On the other hand, the source region and drain region of the n-channel TFT contain only an element that imparts the n-type conductivity. During the gettering treatment that doubles as 35 impurity ion activation treatment, the catalytic element in the channel region of the p-channel TFT is gettered by the element that imparts the n-type conductivity and the element that imparts the p-type conductivity and is contained in an amount exceeding the amount of n-type impurity. The catalytic ele- 40 ment in the n-channel TFT, on the other hand, is gettered solely by the element that imparts the n-type conductivity.

It has been confirmed that the gettering efficiency is higher when an element that imparts the n-type conductivity and an element that imparts the p-type conductivity and is contained 45 in a concentration exceeding the concentration of n-type impurity both participate in gettering than when the gettering source consists solely of the element that imparts the n-type conductivity (See Japanese Patent Application Laid-open No. Hei 11-054760). In other words, an n-channel TFT with the 50 gettering source consisting of the element that imparts the n-type conductivity alone is inferior to a p-channel TFT in terms of efficiency in gettering catalytic element of its channel region.

When the effect of gettering catalytic element in a channel 55 region is lower in an n-channel TFT than in a p-channel TFT, gettering in the n-channel TFT could be insufficient and it may be necessary to change gettering treatment conditions so as to avoid insufficient gettering. Therefore, it can be said that the problem regarding gettering efficiency of an n-channel 60 TFT is accompanied with a process margin problem of gettering treatment.

## SUMMARY OF THE INVENTION

The present invention has been made in view of the above, and an object of the present invention is therefore to solve the

4

above problems in prior art. More specifically, an object of the present invention is to solve the problem of inferior efficiency in gettering of catalytic element in a channel region of an n-channel TFT to the gettering efficiency in a p-channel TFT. Another object of the present invention is to solve a process margin problem of gettering treatment which accompanies the gettering efficiency problem.

## [Structure of n-Channel TFT]

First, means to solve the problems of prior art will be described from the aspect of the structure of n-channel TFT.

It has been disclosed in Japanese Patent Application Laidopen No. Hei 11-054760 that the presence of both an element that imparts the n-type conductivity and an element that imparts the p-type conductivity and contained in a concentration larger than the concentration of the n-type impurity in a gettering region is effective in improving the gettering efficiency. The publication studies the gettering efficiency of when a gettering region has both an element that imparts the n-type conductivity (n-type impurity) and an element that imparts the p-type conductivity (p-type impurity), and discloses conclusions about a proper concentration range for improving the gettering efficiency. The conclusions are summarized as follows.

The first conclusion is that a preferable catalytic element gettering efficiency is obtained by setting the dose of an element that imparts the n-type conductivity (typically P) and of an element that imparts the p-type conductivity (typically B) both to  $1 \times 10^{15}$  ions/cm<sup>2</sup> or higher in a doping device when the concentration of catalytic element (typically Ni) is  $1 \times 10^{19}$  to  $2 \times 10^{19}$  atoms/cm<sup>3</sup>. The second conclusion is that a preferable catalytic element (typically Ni) gettering efficiency is obtained by setting the dose of an element that imparts the p-type conductivity (typically B) equal to or larger than the dose of an element that imparts the n-type conductivity (typically P), and that 1 to 3 times larger dose is suitable considering the productivity.

From the first conclusion and the second conclusion, an appropriate range of the dose of element that imparts the n-type conductivity (typically P) is  $1\times10^{14}$  to  $1\times10^{16}$  ions/cm<sup>2</sup>, and an appropriate range of the dose of element that imparts the p-type conductivity (typically B) is  $1\times10^{14}$  to  $3\times10^{16}$  ions/cm<sup>2</sup>. When an element that imparts the p-type conductivity and an element that imparts the n-type conductivity are used in the above ranges of dose and the conditions in the second conclusion are met, the gettering efficiency can be improved.

The above study shows that an n-channel TFT, whose source region and drain region contain only an element that imparts the n-type conductivity, has an inferior gettering efficiency in a channel region to the gettering efficiency of a p-channel TFT whose source region and drain region contain an element that imparts the n-type conductivity and an element that imparts the p-type conductivity with the concentration of the p-type impurity higher than the concentration of the n-type impurity. One measure to counter the problem of inferior gettering efficiency in the n-channel TFT is to provide in a part of the source region and drain region a highly efficient gettering region containing an element that imparts the n-type conductivity and an element that imparts the p-type conductivity with the concentration of the p-type impurity higher than the concentration of the n-type impurity.

In this countermeasure, the gettering efficiency in the channel region of the n-channel TFT basically depends on the area of the highly efficient gettering region. Accordingly, a larger area is better for the highly efficient gettering region in principal. It is necessary to form as large a highly efficient getter-

ing region as possible within the confines of the semiconductor layer that is composed of the channel region, the source region, and the drain region.

The highly efficient gettering region on the whole has the p-type conductivity since the concentration of p-type impurity that imparts the p-type conductivity is higher than the concentration of n-type impurity that imparts the n-type conductivity in the region. When the highly efficient gettering region is provided in a part of the source region and drain region of the n-channel TFT, unwanted pn junction is formed 10 region). between the highly efficient gettering region because the rest of the source region and drain region has the n-type conductivity. If the pn junction is positioned to obstruct a current that flows between the source region and the drain region, electric characteristics of the n-channel TFT can be affected. For that 15 reason, the pn junction, namely, the highly efficient gettering region has to be located at a given place in the source region and drain region which does not affect the flow of the current. Specifically, it is necessary to avoid placing the highly efficient gettering region in a region between a contact portion 20 that is connected to the source region and a contact portion that is connected to the drain region because the current that flows between the source region and the drain region flows through the contact portions.

From the reason above, the regions suitable to hold the highly efficient gettering region extend from an end of the semiconductor layer and are ended in front of the contact portions connected to the source region and the drain region. The highly efficient gettering region may be very close to a contact portion to give the highly efficient gettering region as large surface area as possible. In this situation, there is a possibility that the highly efficient gettering region overlaps the contact portion due to alignment error in the photolithography step of the manufacturing process. Therefore, it is necessary to set the alignment accuracy such that the highly efficient gettering region overlaps no more than half the contact portion at worst, and to determine the design distance between a contact portion and the highly efficient gettering region.

In view of the above points, the present invention provides 40 an n-channel TFT structured as follows and a semiconductor device (comprised of an n-channel TFT and a p-channel TFT) to solve the problems of prior art. In patent claims, the format for claiming an n-channel TFT alone is different from the format for claiming a semiconductor device (complementary 45) circuit) that has an n-channel TFT and a p-channel TFT both. The application range of semiconductor device can vary depending on the claim format. For instance, when an n-channel TFT alone is claimed, the application range of semiconductor device includes an NMOS semiconductor device in 50 which TFTs used to construct circuits are all n-channel TFTs and a CMOS circuits in which an n-channel TFT and a p-channel TFT are both used to construct a circuit. This is because the claim does not put any technical limitation on a p-channel TFT. On the other hand, when a semiconductor 55 device having both an n-channel TFT and a p-channel TFT is claimed, the application range of semiconductor device includes a CMOS semiconductor device alone. Therefore, the n-channel TFT and the semiconductor device are separately described in the following.

A structure of the present invention is a semiconductor device (specifically an n-channel TFT) comprising a semiconductor layer, a gate insulating film and a gate electrode, the semiconductor layer being formed from a crystalline silicon film obtained through providing of a catalytic element 65 that accelerates crystallization, the gate electrode being placed above the semiconductor layer with the gate insulating

6

film interposed therebetween, the semiconductor layer having a source region and a drain region to the left and right of the gate electrode, the source region and the drain region (first concentration regions) being doped with an element that imparts the n-type conductivity, and the device is characterized in that the source region and the drain region have, apart from a channel region, a region doped with an element that imparts the n-type conductivity and with an element that imparts the p-type conductivity (second concentration region).

Another structure of the present invention is a semiconductor device (specifically an n-channel TFT) comprising a semiconductor layer, a gate insulating film, a gate electrode, and an interlayer insulating film, the semiconductor layer being formed from a crystalline silicon film obtained through providing of a catalytic element that accelerates crystallization, the gate electrode being placed above the semiconductor layer with the gate insulating film interposed therebetween, the semiconductor layer having a source region and a drain region to the left and right of the gate electrode, the source region and the drain region (first concentration regions) being doped with an n-type impurity that imparts the n-type conductivity, the interlayer insulating film covering the gate electrode and having a pair of contact holes that reaches the source region and the drain region, and the device is characterized in that the source region and the drain region have a region doped with an element that imparts the n-type conductivity and with an element that imparts the p-type conductivity (second concentration region), the second concentration region being positioned so as to avoid being sandwiched between the pair of contact holes.

Another structure of the present invention is a semiconductor device (specifically a complementary circuit having an n-channel TFT and a p-channel TFT both) comprising first and second semiconductor layers and first and second gate electrodes, the semiconductor layers being formed from a crystalline silicon film obtained through providing of a catalytic element that accelerates crystallization, the first and second gate electrodes being respectively placed above the first and second semiconductor layers with a gate insulating film interposed therebetween, and the device is characterized in that:

the first semiconductor layer is for forming an n-channel thin film transistor and has a source region and drain region (first concentration regions) doped with an element that imparts the n-type conductivity;

the second semiconductor layer is for forming a p-channel thin film transistor and has a source region and drain region (second concentration regions) doped with an element that imparts the n-type conductivity and with an element that imparts the p-type conductivity;

the source region and drain region of the first semiconductor layer have, apart from a channel region, a region (second concentration region) doped with an element that imparts the n-type conductivity and with an element that imparts the p-type conductivity.

Another structure of the present invention is a semiconductor device (specifically a complementary circuit having an n-channel TFT and a p-channel TFT both) comprising first and second semiconductor layers and first and second gate electrodes, the semiconductor layers being formed from a crystalline silicon film obtained through providing of a catalytic element that accelerates crystallization, the first and second gate electrodes being respectively placed above the first and second semiconductor layers with a gate insulating film interposed therebetween, and the device is characterized in that:

the first semiconductor layer is for forming an n-channel thin film transistor and has a source region and drain region (first concentration regions) doped with an element that imparts the n-type conductivity;

the second semiconductor layer is for forming a p-channel 5 thin film transistor and has a source region and drain region (second concentration regions) doped with an element that imparts the n-type conductivity and with an element that imparts the p-type conductivity;

contact holes respectively reaching the source regions and drain regions of the first and second semiconductor layers are formed in an interlayer insulating film that covers the first and second gate electrodes; and

the source region and drain region of the first semiconductor layer have a region (second concentration region) doped with an element that imparts the n-type conductivity and with an element that imparts the p-type conductivity, the region being positioned so as to avoid being sandwiched between the contact holes.

A second concentration region doped with an element that imparts the n-type conductivity and with an element that imparts the p-type conductivity serves as a highly efficient gettering region. The concentration of catalytic element after gettering is higher in a second concentration region than in a first concentration region.

In the above four structures of the present invention, different formats describe different semiconductor devices and include different semiconductor device application ranges. However, the n-channel TFT and the n-channel TFT in the CMOS semiconductor device have substantially the same structure.

## [Method of Manufacturing an n-Channel TFT]

Next, means to solve the problems of prior art is described from the aspect of n-channel TFT manufacturing method. 35 Again, the format for claiming an n-channel TFT alone is different from the format for claiming a semiconductor device (complementary circuit) that has an n-channel TFT and a p-channel TFT both, and the application range of semiconductor device can vary depending on the claim format. 40 Therefore, descriptions on manufacture of the n-channel TFT and of the semiconductor device are separately given in the following. Crystallization techniques that utilize crystallization accelerating catalytic elements to form crystalline silicon films are classified into longitudinal growth methods and 45 lateral growth methods. Therefore, a longitudinal growth method is separated from a lateral growth method in the following descriptions on n-channel TFT manufacturing method.

Definitions of longitudinal growth method and lateral 50 growth method are clarified here. A longitudinal growth method is a crystal growth method in which the entire surface of an amorphous silicon film is uniformly provided with a catalytic element before thermal crystallization and crystals grow in a longitudinal direction (perpendicular to the sub- 55 strate plane) from the surface of the amorphous silicon film provided with the catalytic element. Therefore, this type is called a longitudinal growth method in this specification. A method called as a lateral growth method in this specification is a crystal growth method in which a part of an amorphous 60 silicon film is provided with a catalytic element through an opening region in a mask insulating film before thermal crystallization, and crystallization advances in a lateral direction (parallel to the substrate plane) through thermal diffusion from the opening region toward the surrounding regions. 65 Therefore, this type is called a lateral growth method in this specification.

8

A structure of the present invention is a method of manufacturing a semiconductor device (longitudinal growth method for manufacturing an n-channel TFT alone), comprising:

- a first step of forming an amorphous silicon film on an insulating substrate such as a glass substrate;

- a second step of providing the entirety of the amorphous silicon film with a catalytic element that accelerates crystallization;

- a third step of subjecting the amorphous silicon film to heat treatment to form a crystalline silicon film;

- a fourth step of patterning the crystalline silicon film to form a semiconductor layer;

- a fifth step of forming a gate insulating film on the semiconductor layer;

an sixth step of forming a gate electrode above the semiconductor layer with the gate insulating film interposed therebetween;

a seventh step of forming an n-type impurity region by doping the semiconductor layer with an n-type impurity that is an element imparting the n-type conductivity while using the gate electrodes as a mask;

an eighth step of forming a resist pattern that places an opening region in the n-type impurity region apart from a channel region; and

an ninth step of using the resist pattern as a mask to dope the n-type impurity region with a p-type impurity that is an element imparting the p-type conductivity.

Another structure of the present invention is a method of manufacturing a semiconductor device (lateral growth method for manufacturing an n-channel TFT alone), comprising:

- a first step of forming an amorphous silicon film on an insulating substrate such as a glass substrate;

- a second step of forming a mask insulating film and forming an opening region in a part of the mask insulating film;

- a third step of providing the top face of the mask insulating film with a catalytic element that accelerates crystallization and selectively providing the catalytic element to a part of the amorphous silicon film through the opening region;

- a fourth step of subjecting the amorphous silicon film to heat treatment to form a crystalline silicon film;

- a fifth step of removing the mask insulating film that has served as a mask during introduction of the catalytic element;

- a sixth step of patterning the crystalline silicon film to form a semiconductor layer;

- a seventh step of forming a gate insulating film on the semiconductor layer;

an eighth step of forming a gate electrode above the semiconductor layer with the gate insulating film interposed therebetween;

a ninth step of forming an n-type impurity region by doping the semiconductor layer with an n-type impurity that is an element imparting the n-type conductivity while using the gate electrodes as a mask;

a tenth step of forming a resist pattern that places an opening region in the n-type impurity region apart from a channel region; and

an eleventh step of using the resist pattern as a mask to dope the n-type impurity region with a p-type impurity that is an element imparting the p-type conductivity.

Another structure of the present invention is a method of manufacturing a semiconductor device (longitudinal growth method for manufacturing a complementary circuit that has an n-channel TFT and a p-channel TFT both), comprising:

a first step of forming an amorphous silicon film on an insulating substrate such as a glass substrate;

a second step of providing the entirety of the amorphous silicon film with a catalytic element that accelerates crystallization;

a third step of subjecting the amorphous silicon film to heat treatment to form a crystalline silicon film;

- a fourth step of patterning the crystalline silicon film to form semiconductor layers for forming an n-channel TFT and a p-channel TFT;

- a fifth step of forming a gate insulating film on the semiconductor layer;

- an sixth step of forming a gate electrode above the semiconductor layers with the gate insulating film interposed therebetween;

- a seventh step of forming an n-type impurity region by doping the semiconductor layers with an n-type impurity that 15 is an element imparting the n-type conductivity while using the gate electrodes as a mask;

an eighth step of forming a resist pattern that places an opening region in the n-type impurity region for forming the n-channel TFT apart from a channel region, and sets the entire 20 region of the semiconductor layer for forming the p-channel TFT as an opening region; and

an ninth step of using the resist pattern as a mask to dope the n-type impurity region with a p-type impurity that is an element imparting the p-type conductivity.

Another structure of the present invention is a method of manufacturing a semiconductor device (lateral growth method for manufacturing a complementary circuit that has an n-channel TFT and a p-channel TFT both), comprising:

a first step of forming an amorphous silicon film on an 30 insulating substrate such as a glass substrate;

a second step of forming a mask insulating film and forming an opening region in a part of the mask insulating film;

a third step of providing the top face of the mask insulating film with a catalytic element that accelerates crystallization 35 and selectively providing the catalytic element to a part of the amorphous silicon film through the opening region;

- a fourth step of subjecting the amorphous silicon film to heat treatment to form a crystalline silicon film;

- a fifth step of removing the mask insulating film that has 40 served as a mask during providing of the catalytic element;

- a sixth step of patterning the crystalline silicon film to form semiconductor layers for forming an n-channel TFT and a p-channel TFT;

- a seventh step of forming a gate insulating film on the 45 semiconductor layer;

an eighth step of forming a gate electrode above the semiconductor layers with the gate insulating film interposed therebetween;

a ninth step of forming an n-type impurity region by doping 50 the semiconductor layers with an n-type impurity that is an element imparting the n-type conductivity while using the gate electrodes as a mask;

a tenth step of forming a resist pattern that places an opening region in the n-type impurity region for forming the 55 n-channel TFT apart from a channel region, and sets the entire region of the semiconductor layer for forming the p-channel TFT as an opening region; and

an eleventh step of using the resist pattern as a mask to dope the n-type impurity region with a p-type impurity that is an 60 element imparting the p-type conductivity.

In the above manufacturing methods, different formats describe different semiconductor devices and include different semiconductor device application ranges. However, the n-channel TFT and the n-channel TFT in the CMOS semi- 65 conductor device are manufactured by substantially the same method.

**10**

[Supplement]

Supplementation is made on unclear points in the above descriptions of the structure and manufacturing method of n-channel TFT.

## (1) Definition of Crystalline Silicon Film

In this specification, a silicon film having a crystallinity which is obtained by utilizing a crystallization accelerating catalytic element is called a crystalline silicon film and is distinguished from a usual polycrystalline silicon film. The crystalline silicon film is distinguished from a usual polycrystalline silicon film because it is characterized in that its grains are oriented in substantially one direction and it has higher field effect mobility than a usual polycrystalline silicon film.

(2) Catalytic Element Having a Crystallization Accelerating Effect

Catalytic elements that accelerate crystallization are described in Japanese Patent Application Laid-open No. Hei 11-054760. Since the present invention includes the use of catalytic element, an explanation is given anew on catalytic elements. A catalytic element is an element used in providing for crystallizing an amorphous silicon film. Typical catalytic elements are Fe (iron), Co (cobalt), Ni (nickel), Pd (palladium), Pt (platinum), Cu (copper), Au (gold), and the like. Usually, one element selected from the above catalytic elements is used but it is possible to employ a combination of two or more catalytic elements. It has been found that Ni is the most suitable catalytic element out of the above catalytic elements.

(3) Gettering Source Consisting of an Element that Imparts the n-Type Conductivity

Using a gate electrode as a mask, a semiconductor layer (including a semiconductor layer for forming an n-channel TFT and a semiconductor layer for forming a p-channel TFT) is doped with an element that imparts the n-type conductivity (gettering source). This element is called an n-type impurity and is selected from the group consisting of P (phosphorus), As (arsenic), Sb (antimony), and Bi (bismuth) (N is excluded here). It has been acknowledged that P is the most suitable gettering source considering the effect as a gettering source (Japanese Patent Application Laid-open No. Hei 11-054760).

(4) Gettering Source Consisting of an Element that Imparts the p-Type Conductivity

An element that imparts the p-type conductivity (gettering source) is called an p-type impurity and is selected from the group consisting of B (boron), Al (aluminum), Ga (gallium), In (indium), and Tl (thallium). It has been acknowledged that B is the most suitable gettering source considering the effect as a gettering source (Japanese Patent Application Laid-open No. Hei 11-054760).

## BRIEF DESCRIPTION OF THE DRAWINGS

In the accompanying drawings:

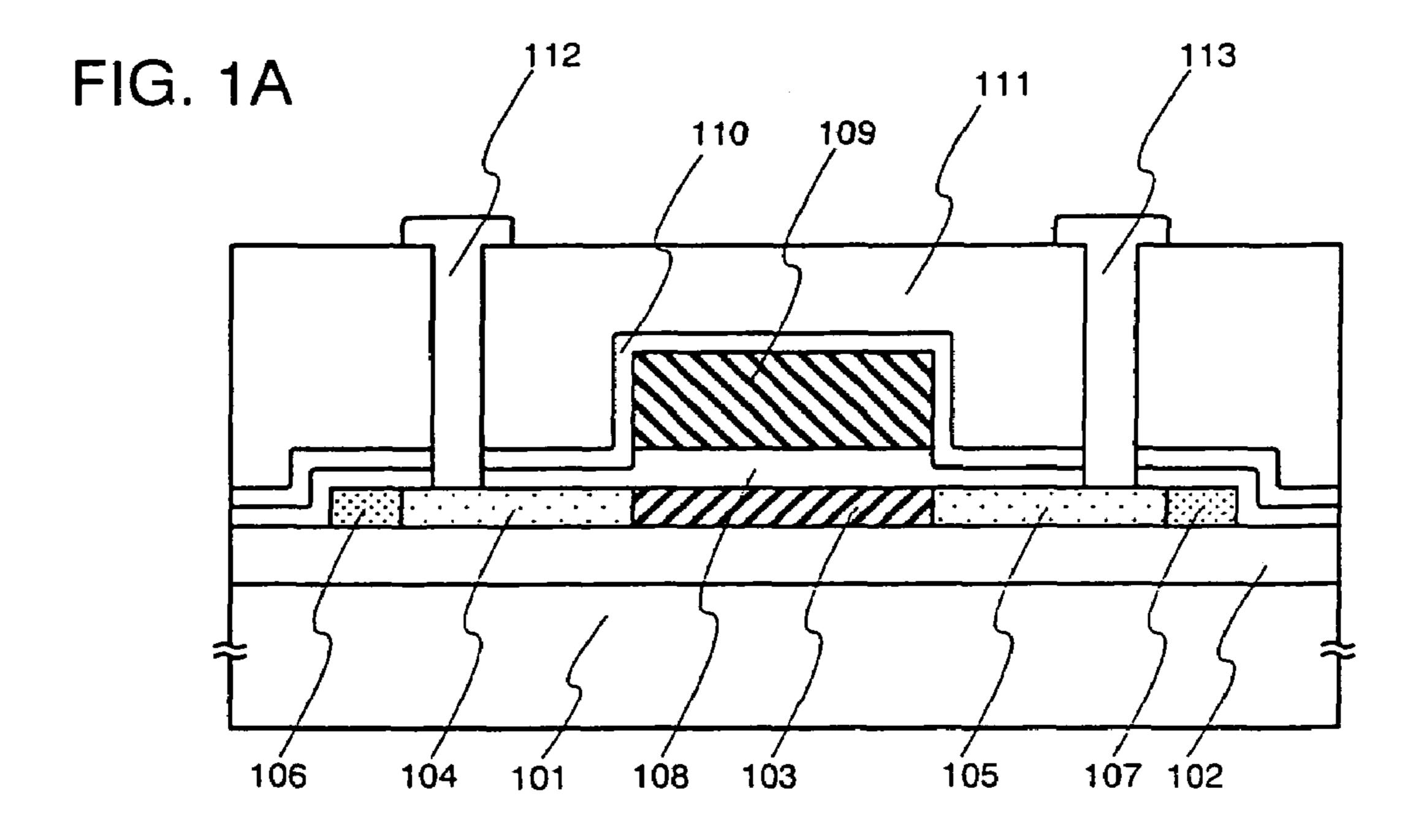

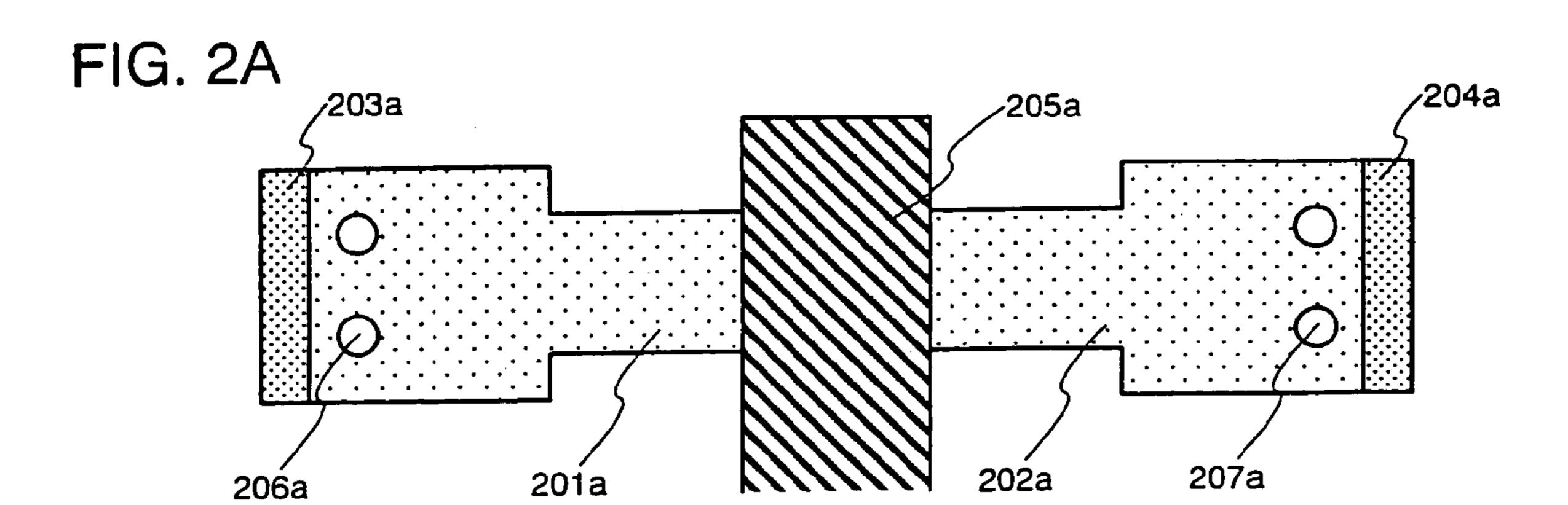

FIGS. 1A and 1B are a sectional view and plan view of an n-channel TFT that has a highly efficient gettering region;

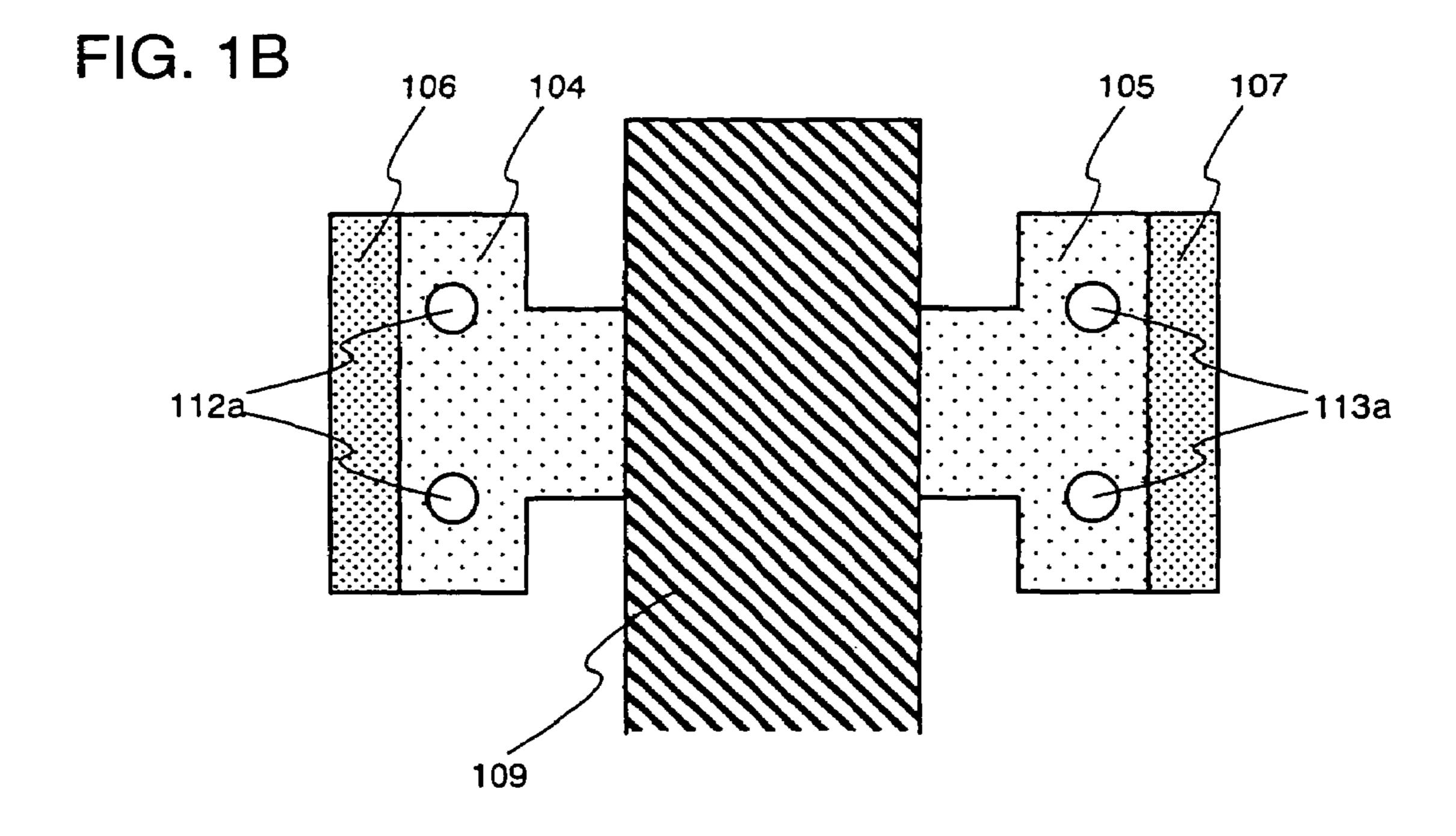

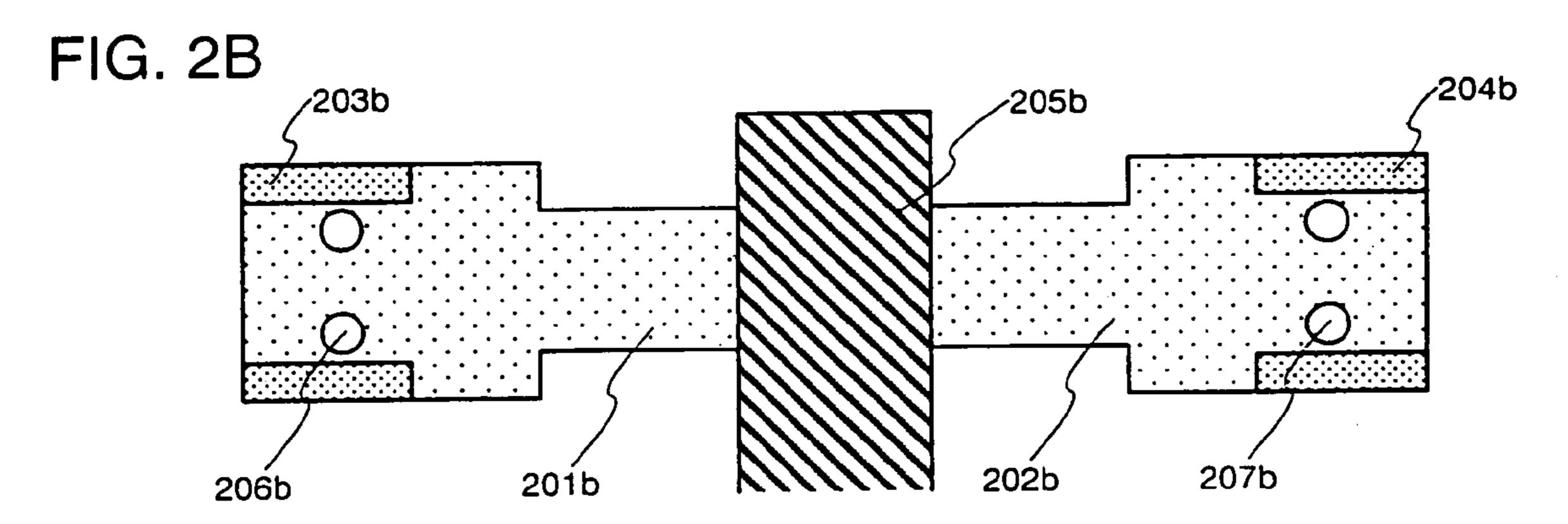

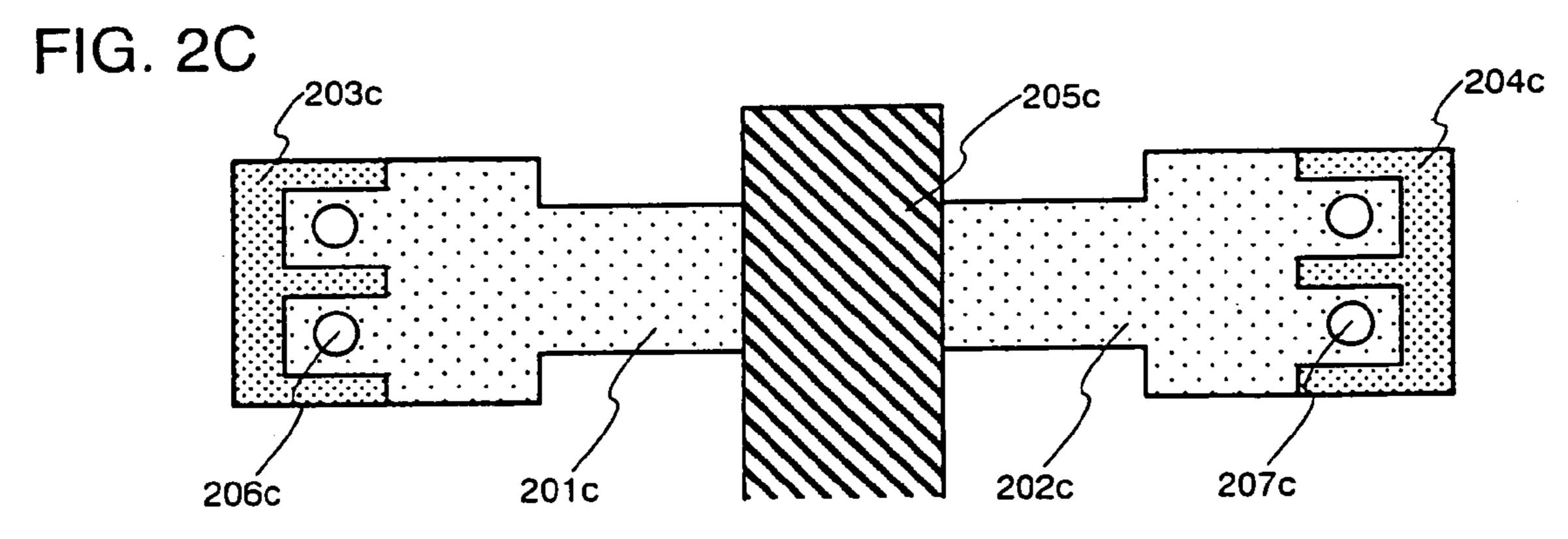

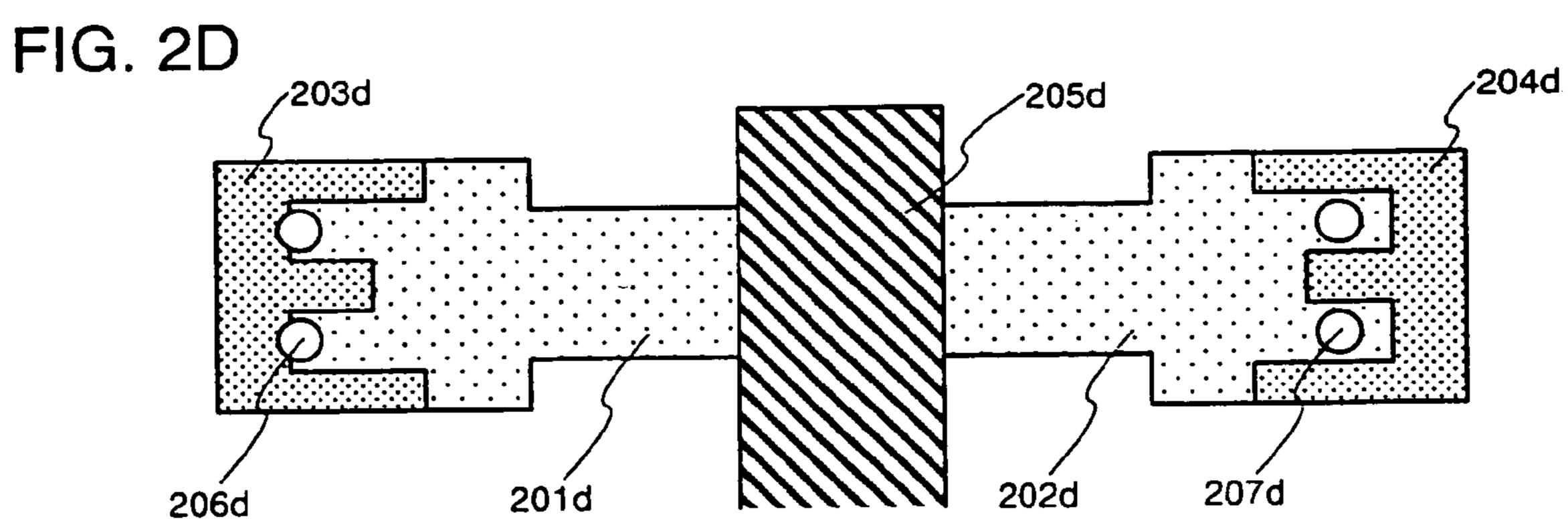

FIGS. 2A to 2D are plan views showing examples of arrangement of highly efficient gettering region in an n-channel TFT;

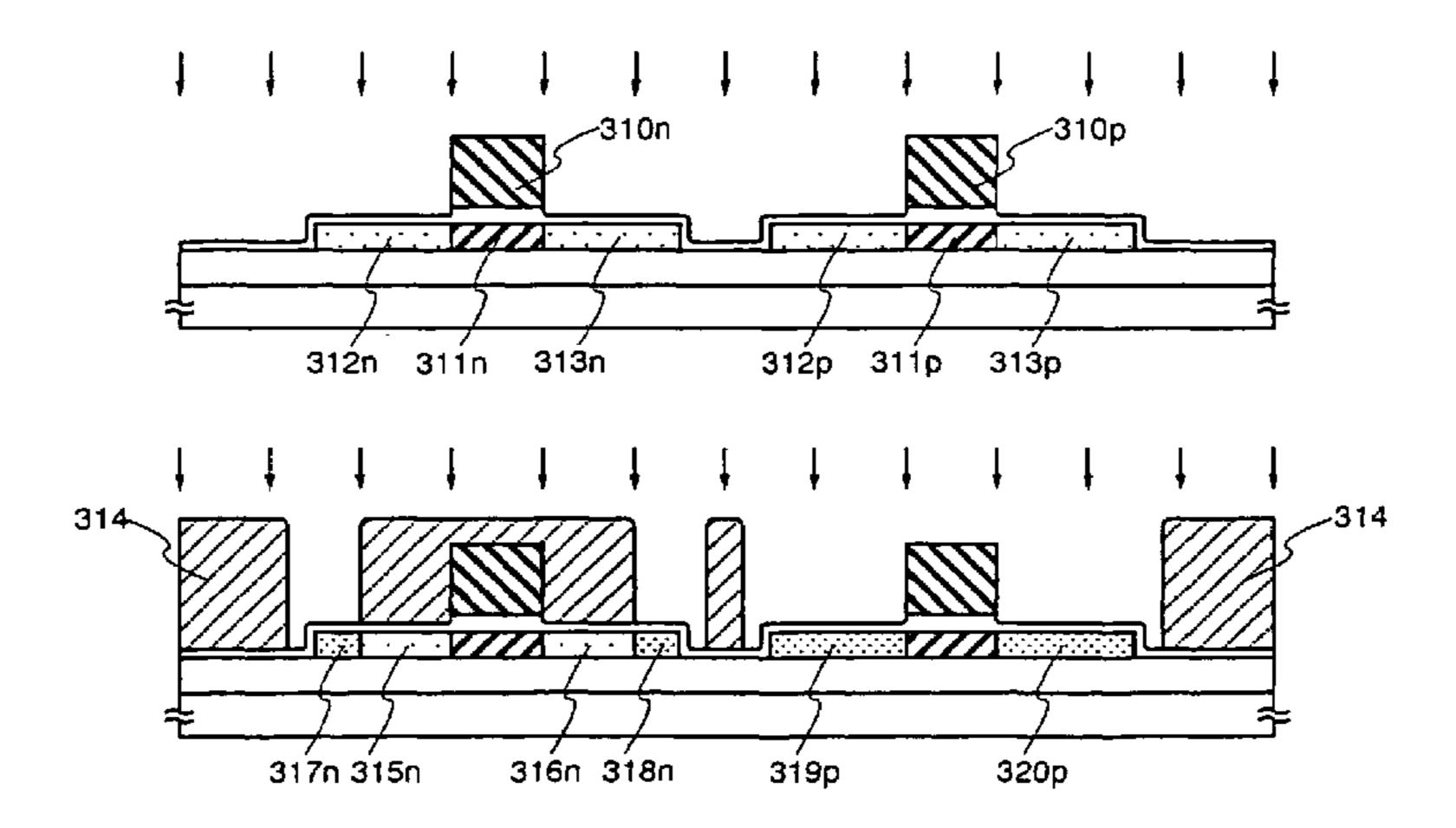

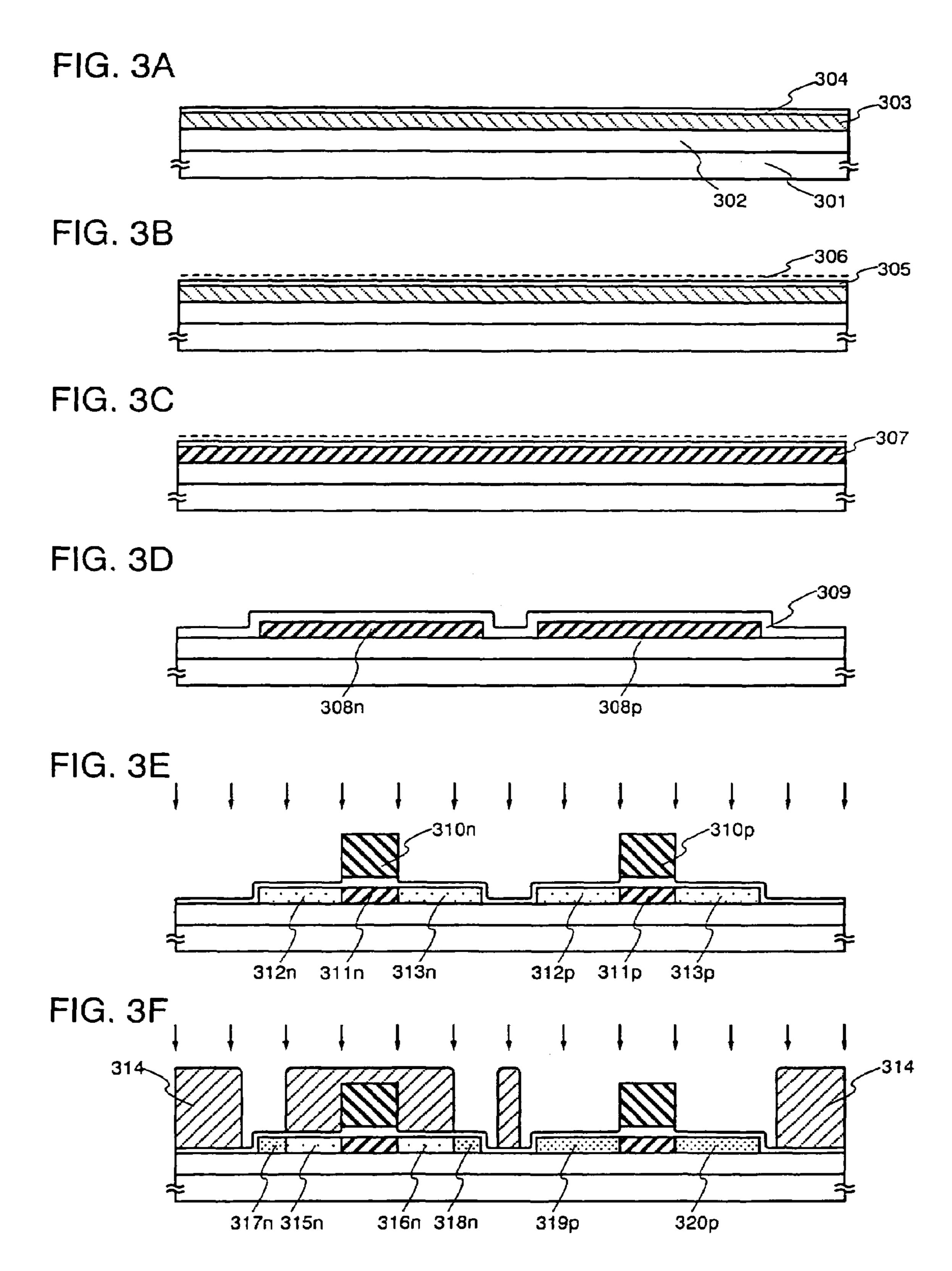

FIGS. 3A to 3F are sectional views showing a process (longitudinal growth method) of manufacturing a semiconductor device that has an n-channel TFT and a p-channel TFT both;

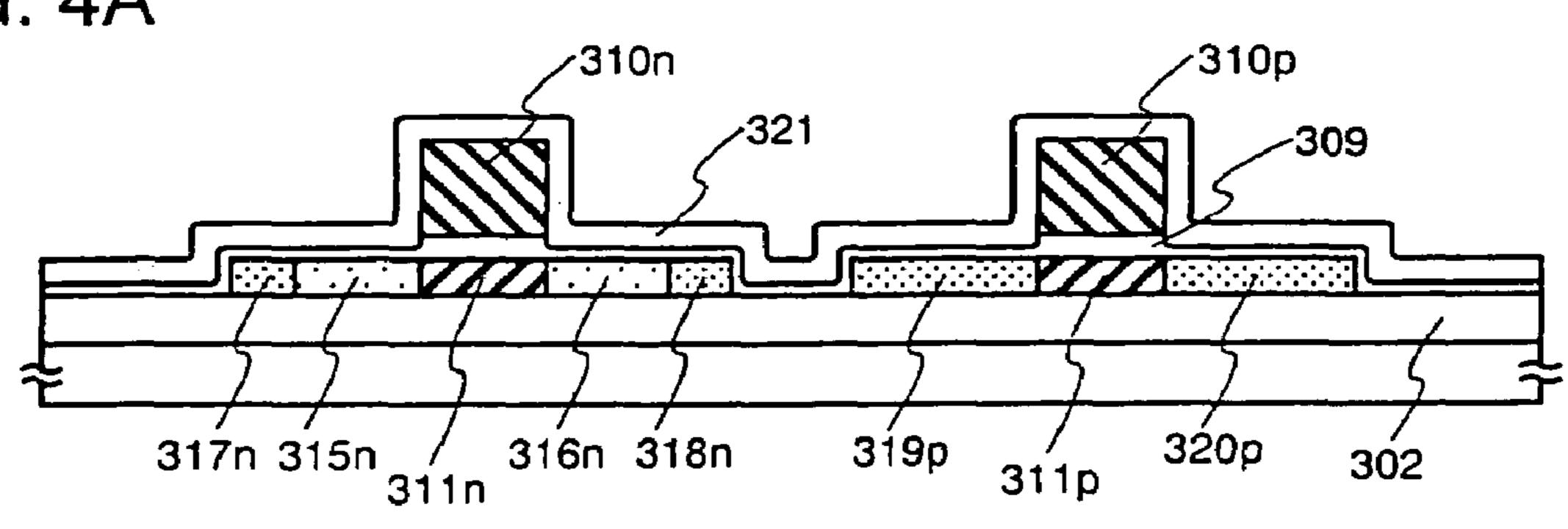

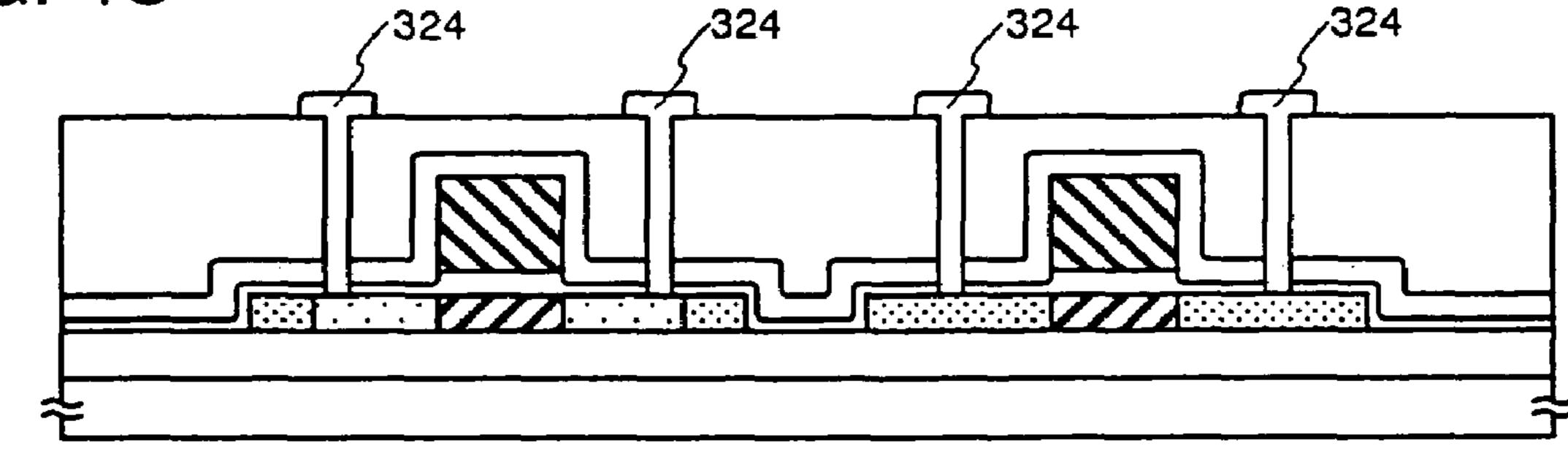

FIGS. 4A to 4C are sectional views showing subsequent steps to the process of FIGS. 3A to 3F for manufacturing a semiconductor device that has an n-channel TFT and a p-channel TFT both;

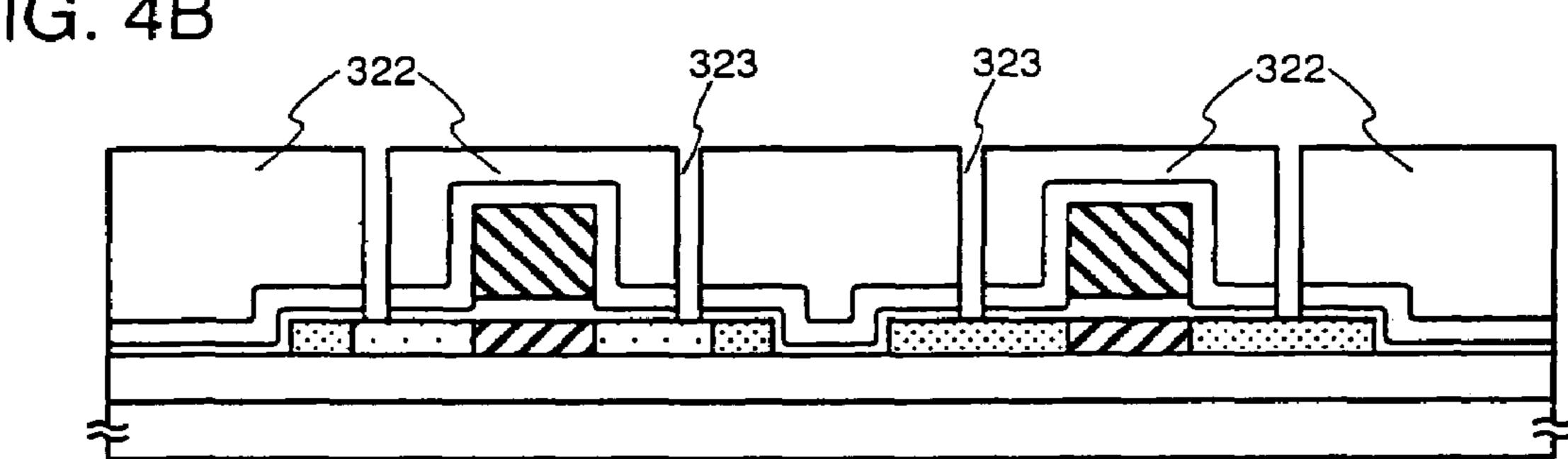

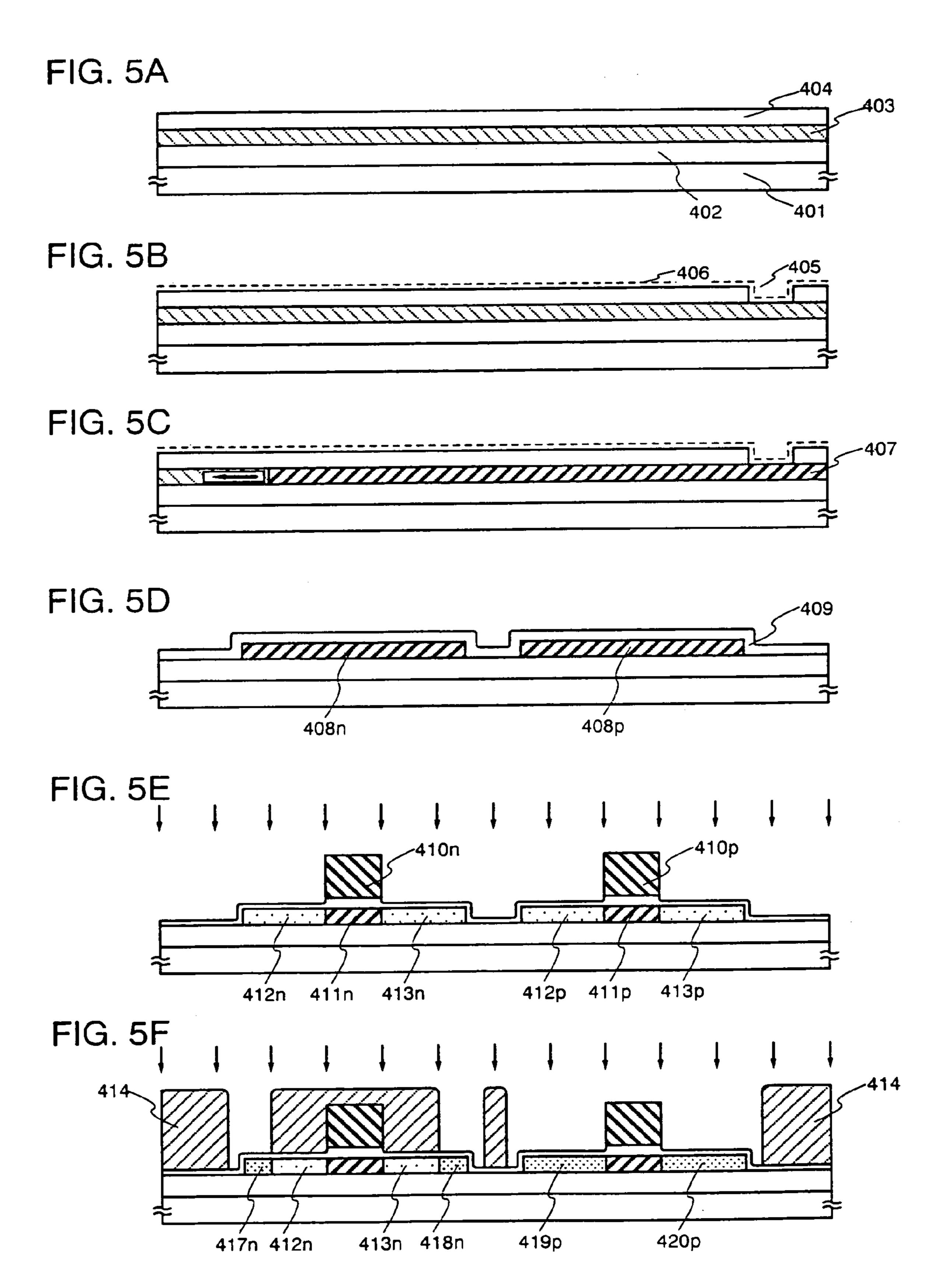

FIGS. **5**A to **5**F are sectional views showing a process (lateral growth method) of manufacturing a semiconductor device that has an n-channel TFT and a p-channel TFT both;

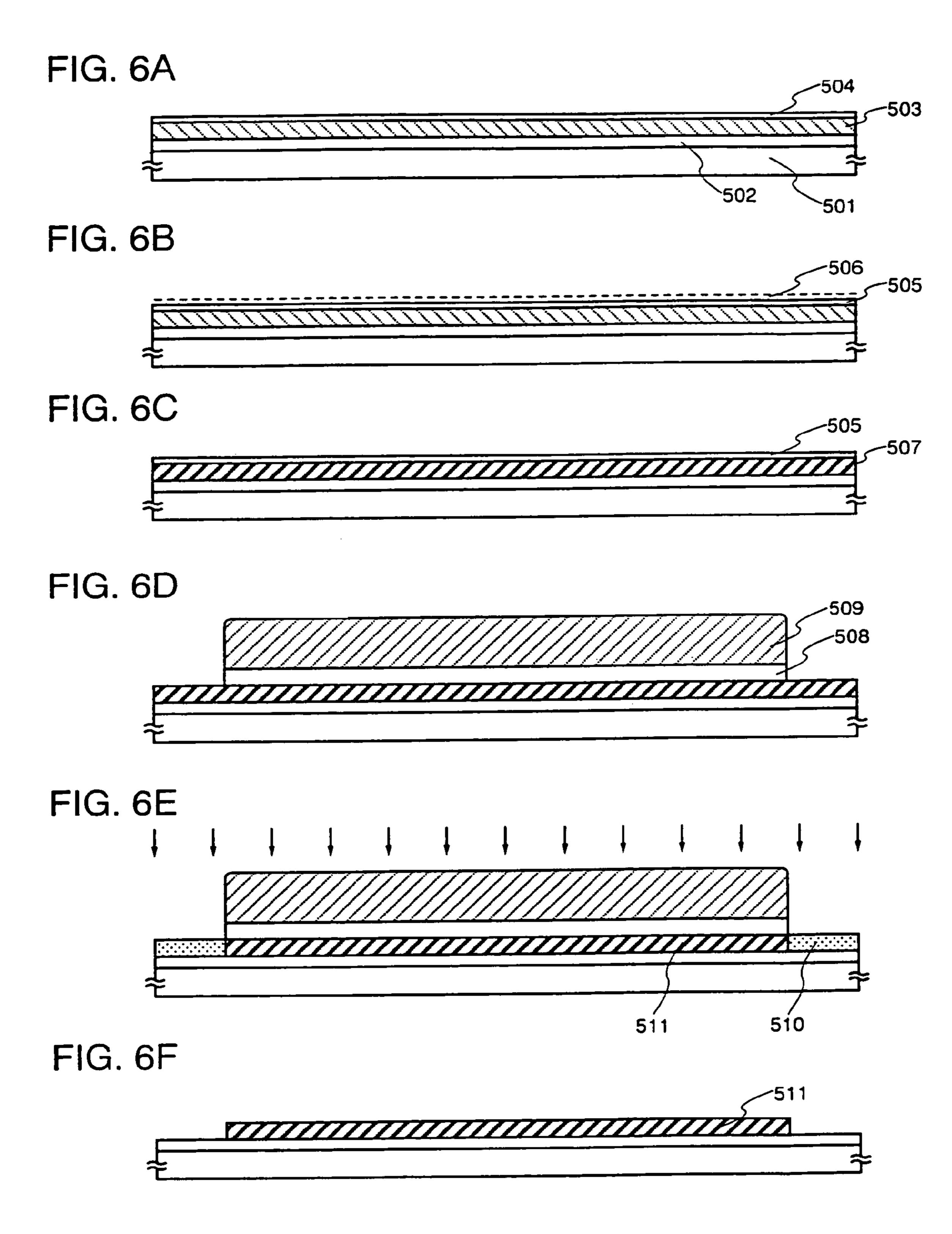

FIGS. **6**A to **6**F are sectional views showing a process (longitudinal growth method) of manufacturing a semiconductor device from crystal growth to formation of a gettering subject region;

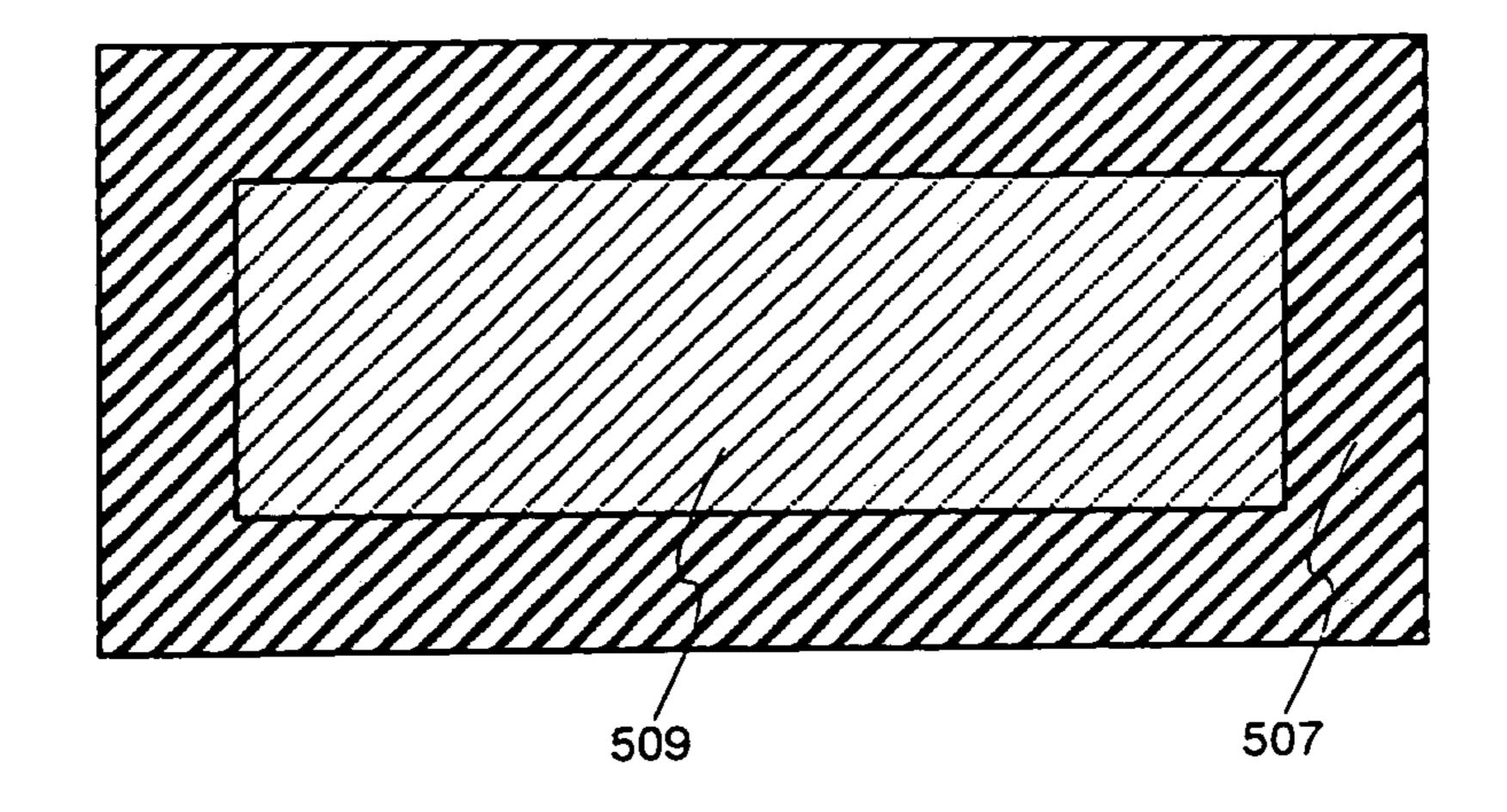

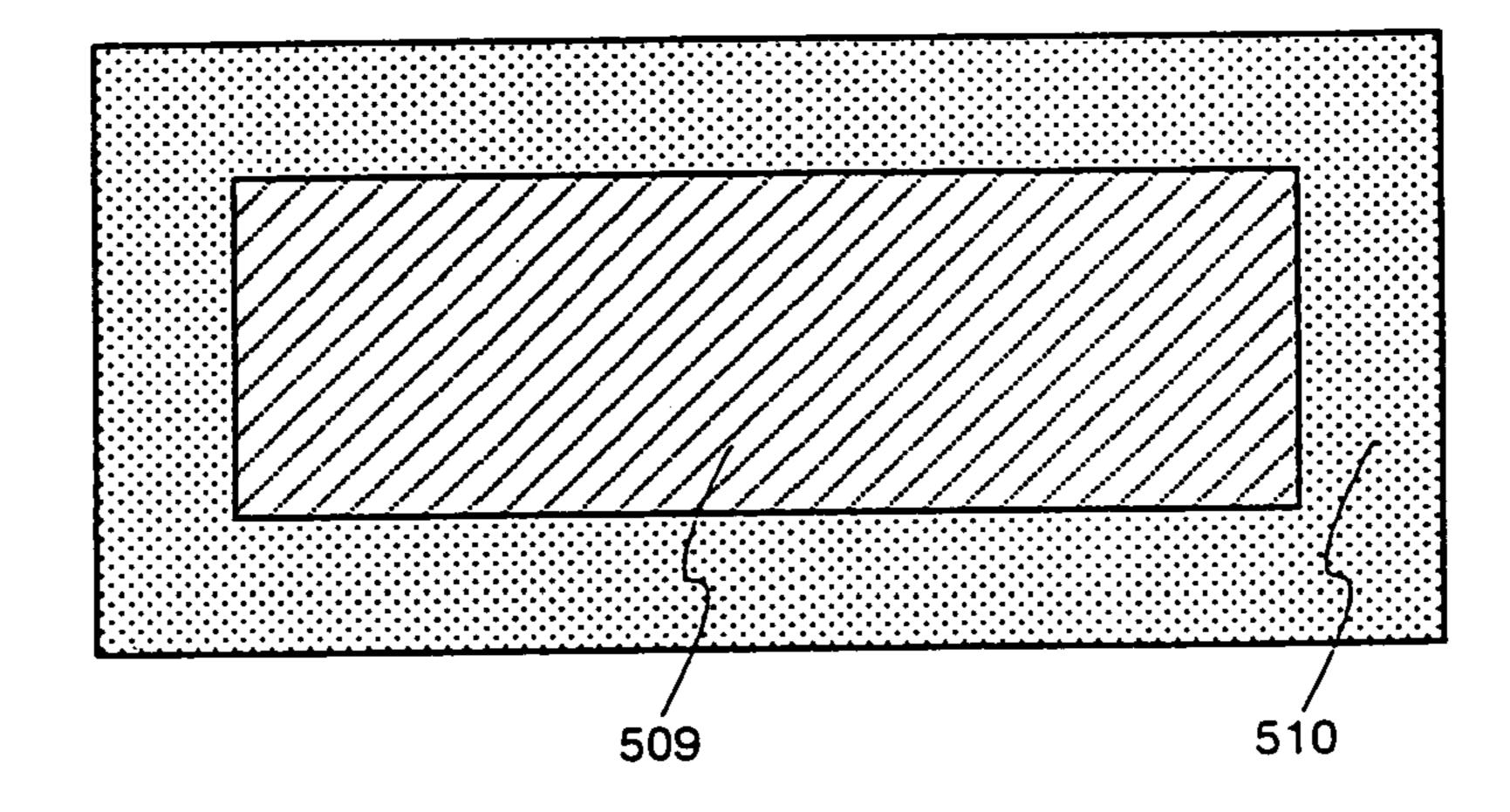

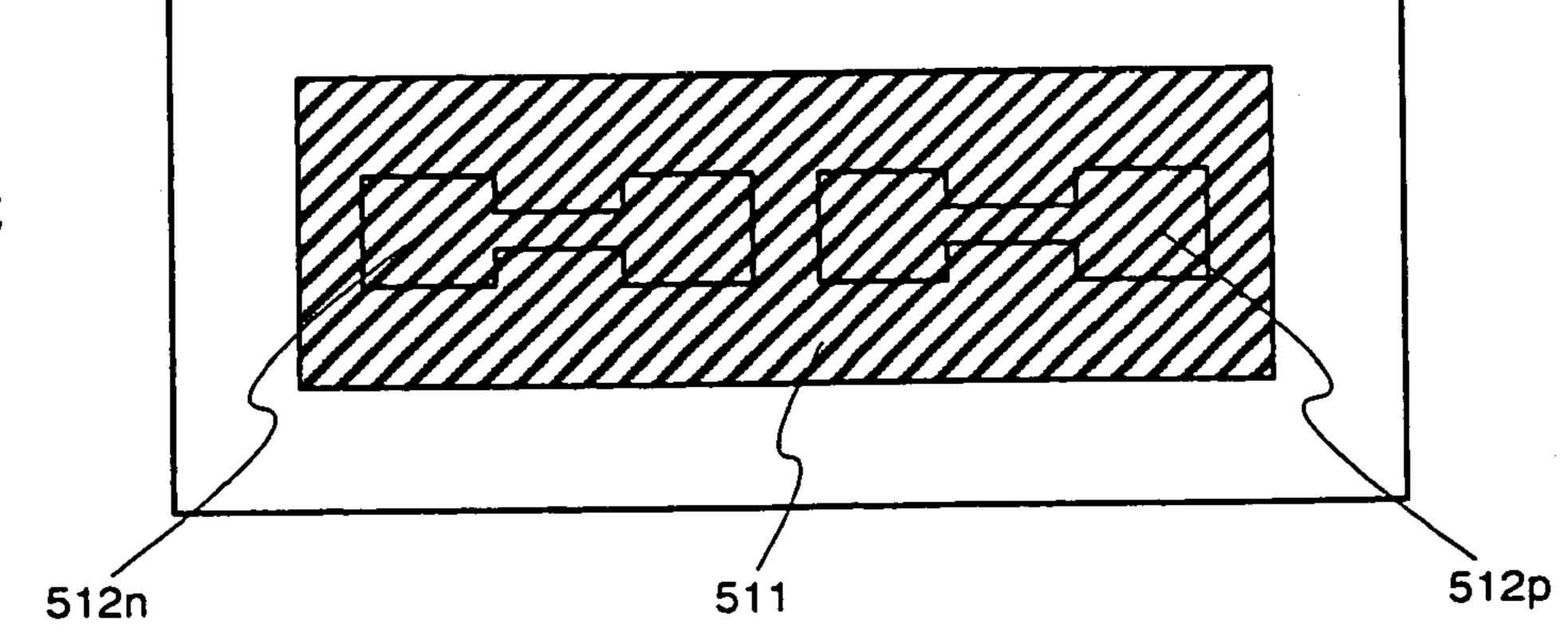

FIGS. 7A to 7C are plan views showing the semiconductor device manufacture process (longitudinal growth method) of FIGS. 6A to 6F;

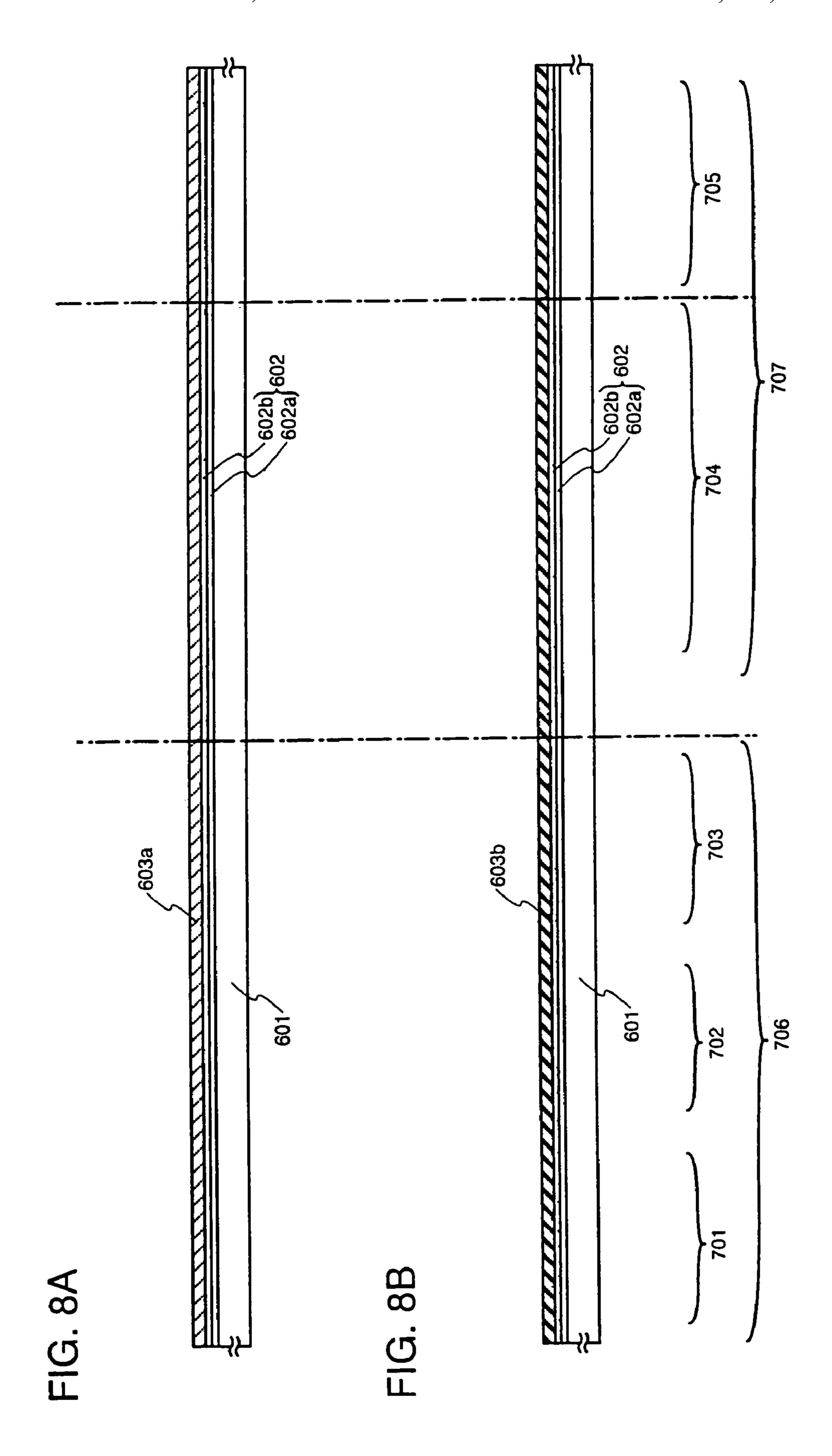

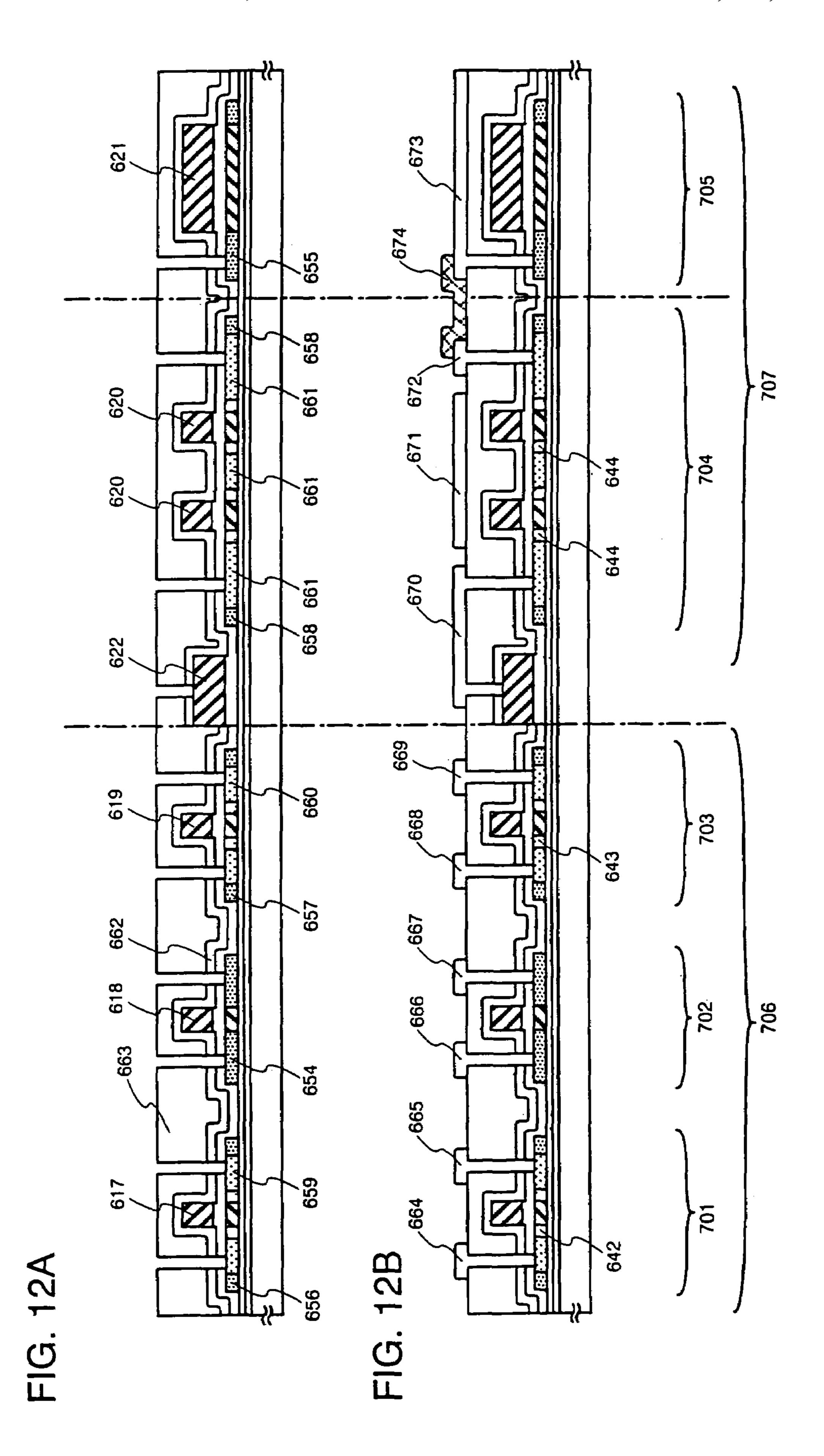

FIGS. 8A and 8B are sectional views showing a process of manufacturing an active matrix liquid crystal display device;

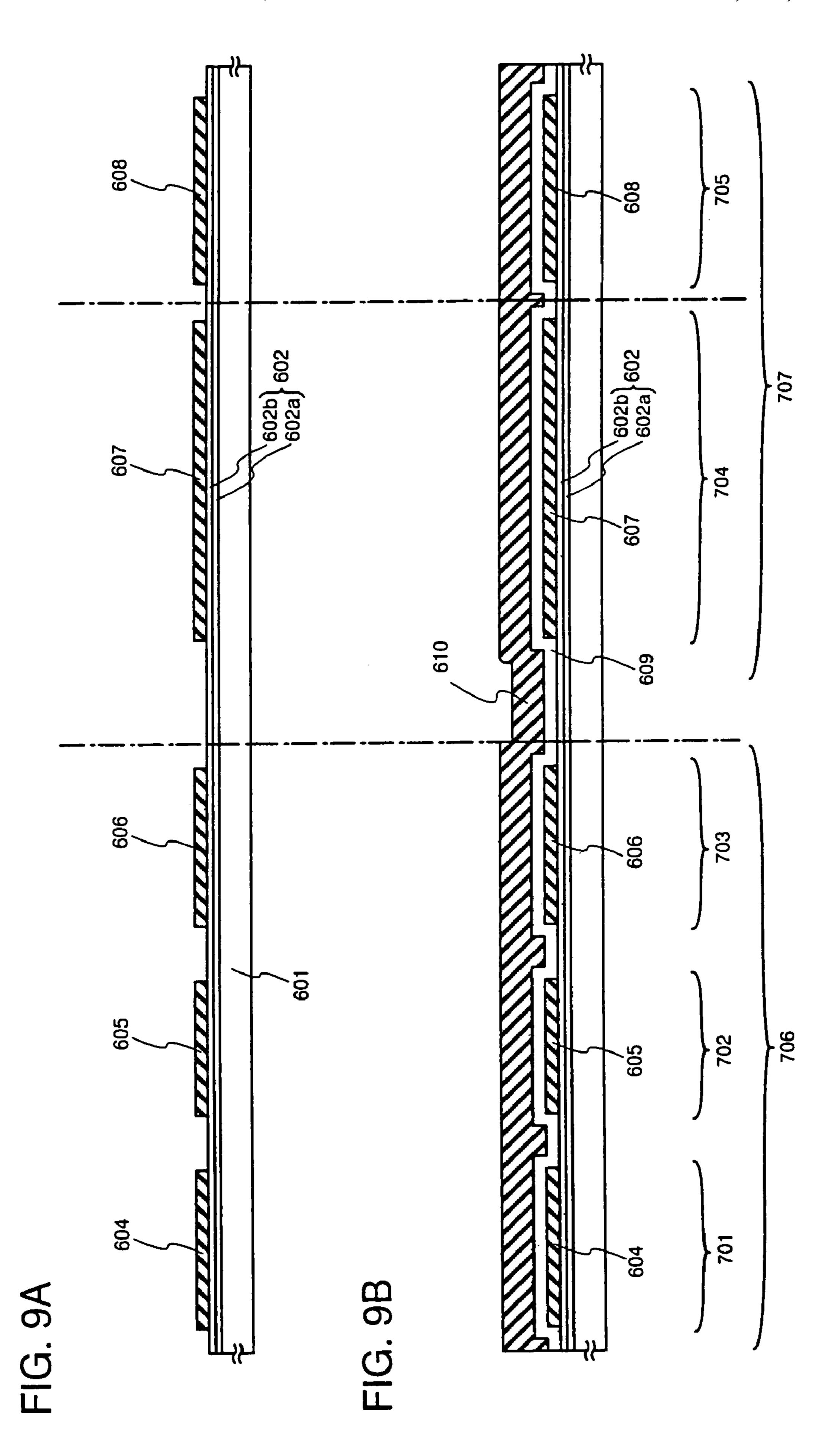

FIGS. 9A and 9B are sectional views showing a process of manufacturing an active matrix liquid crystal display device;

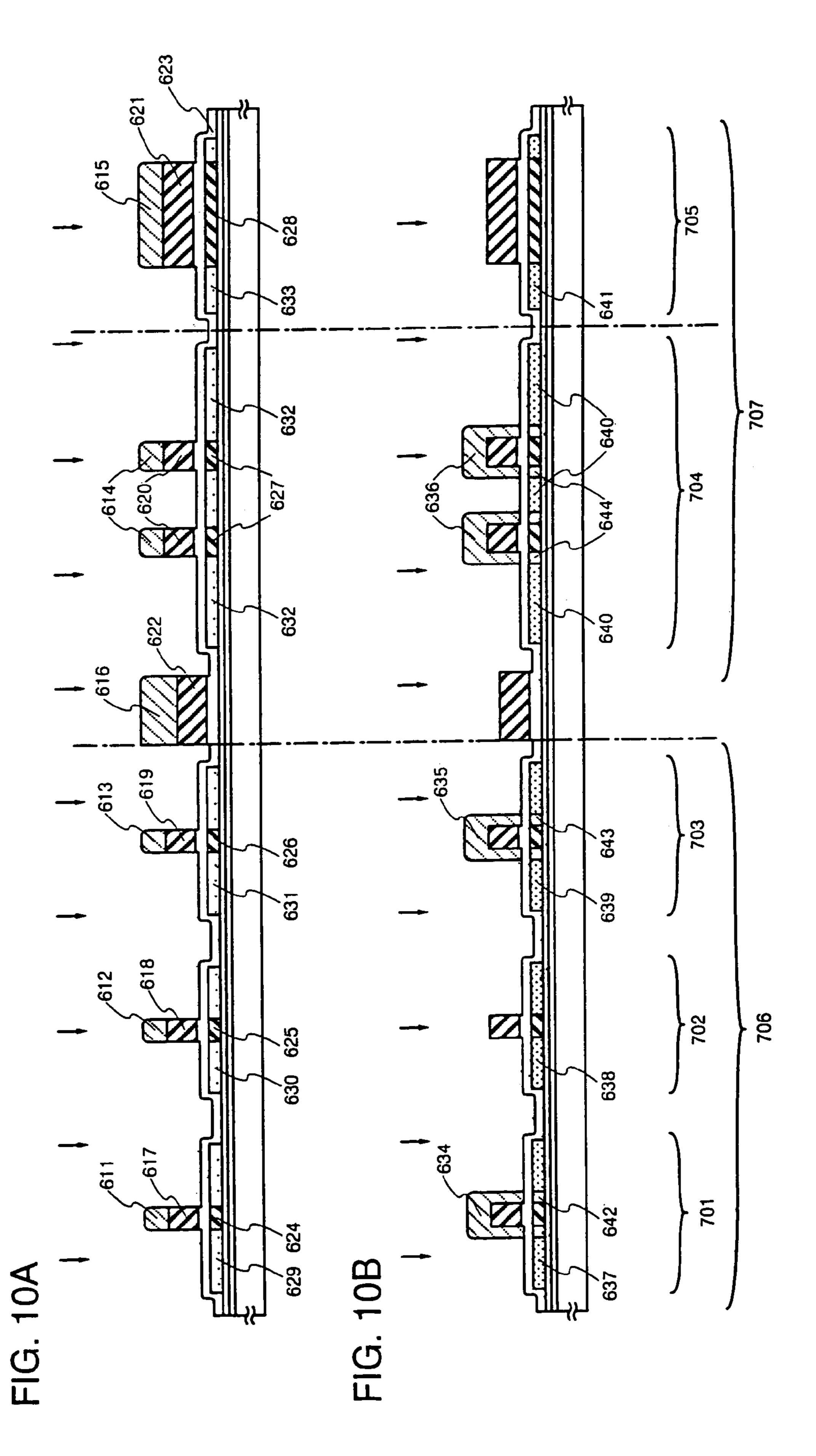

FIGS. 10A and 10B are sectional views showing a process of manufacturing an active matrix liquid crystal display device;

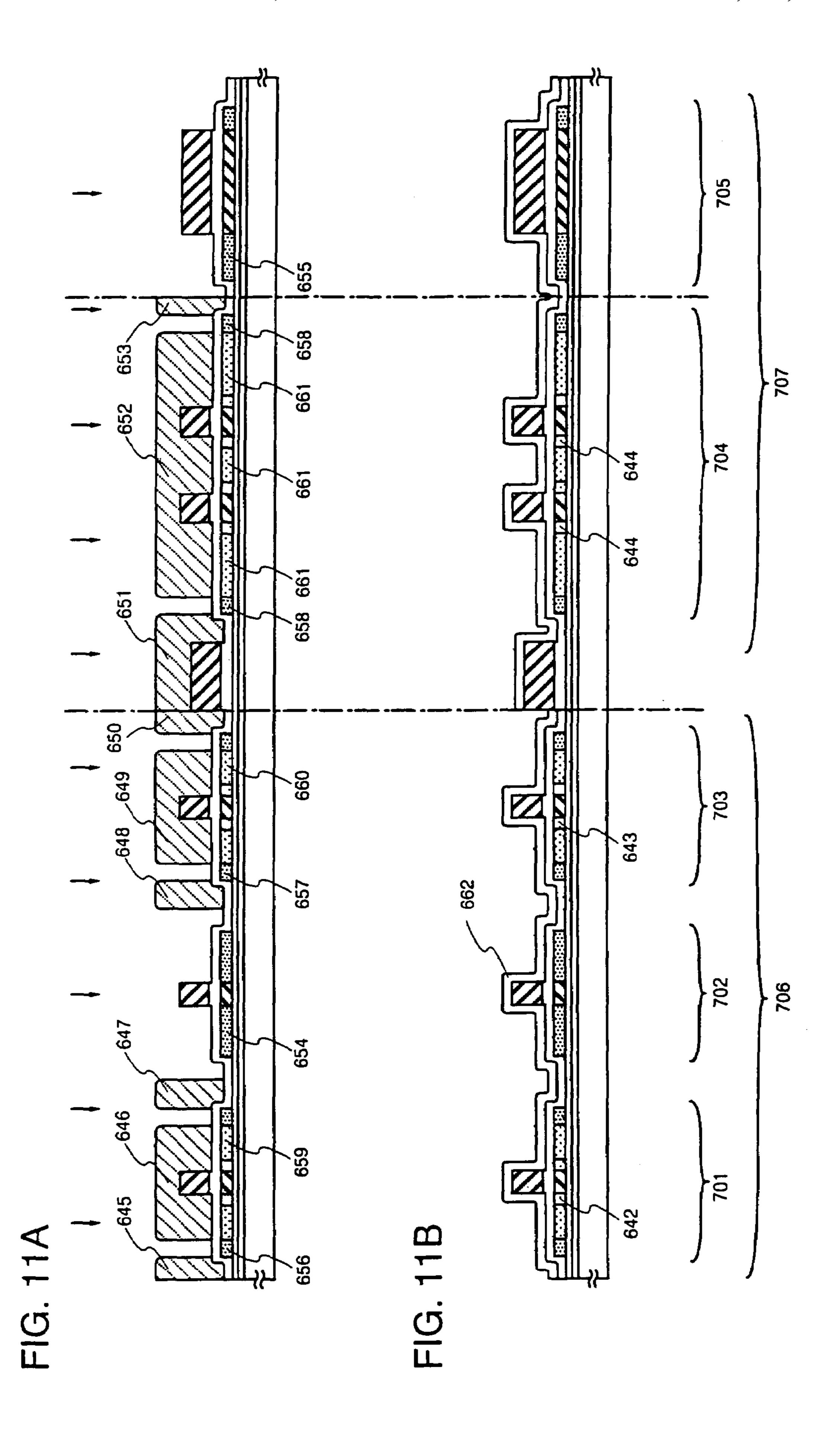

FIGS. 11A and 11B are sectional views showing a process of manufacturing an active matrix liquid crystal display device;

FIGS. 12A and 12B are sectional views showing a process of manufacturing an active matrix liquid crystal display device;

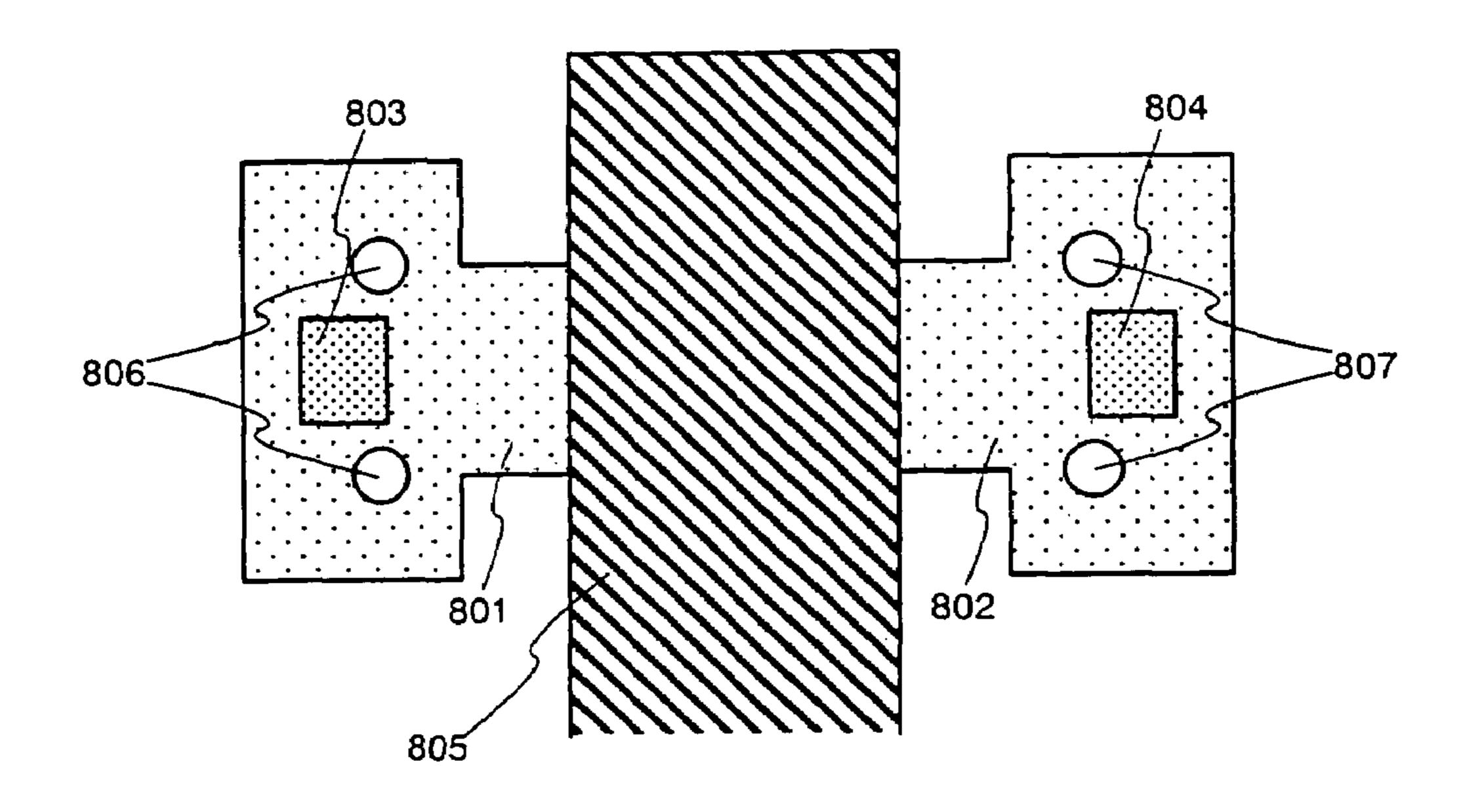

FIG. 13 is a plan view of an n-channel TFT that has a highly efficient gettering region;

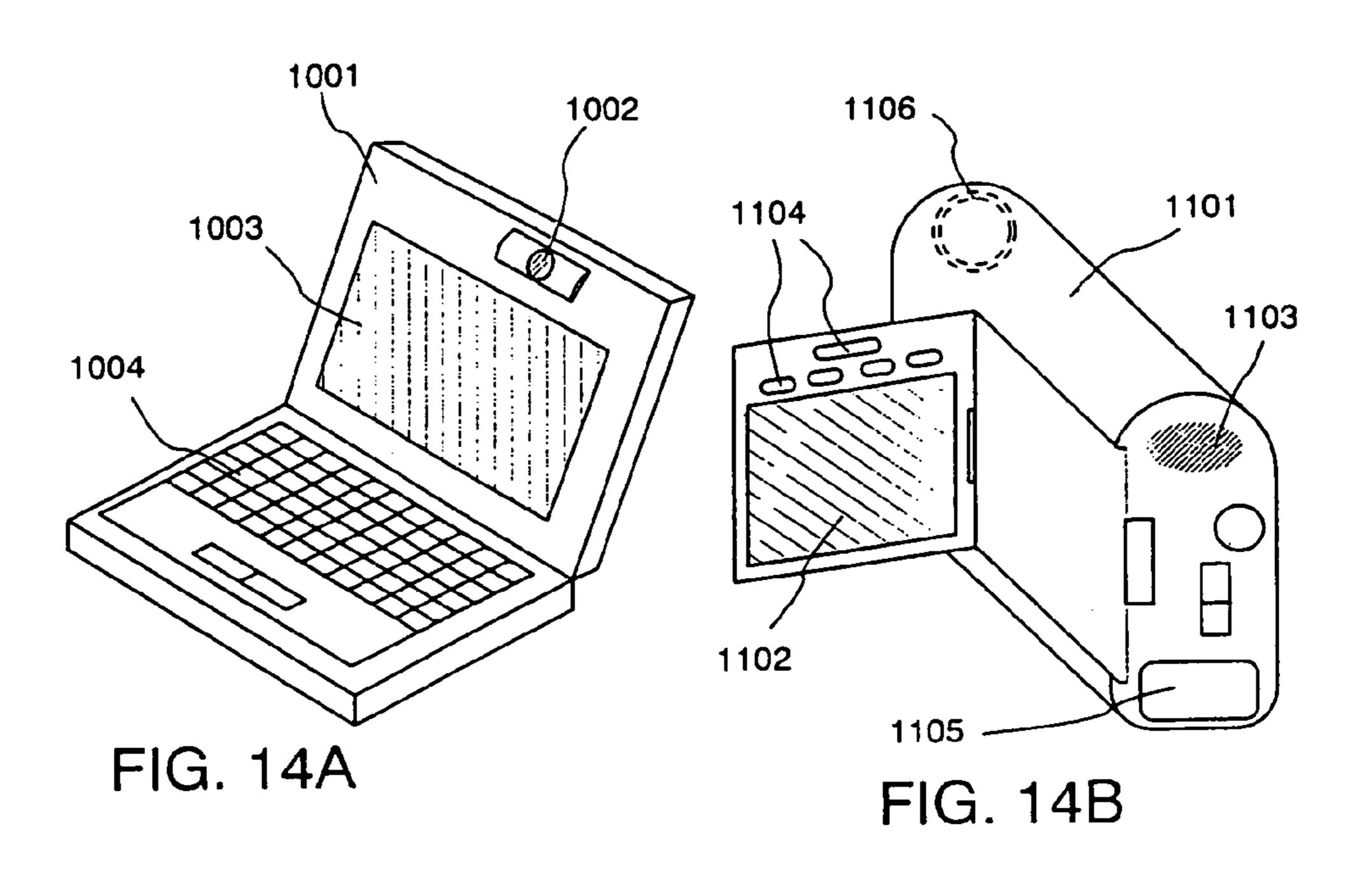

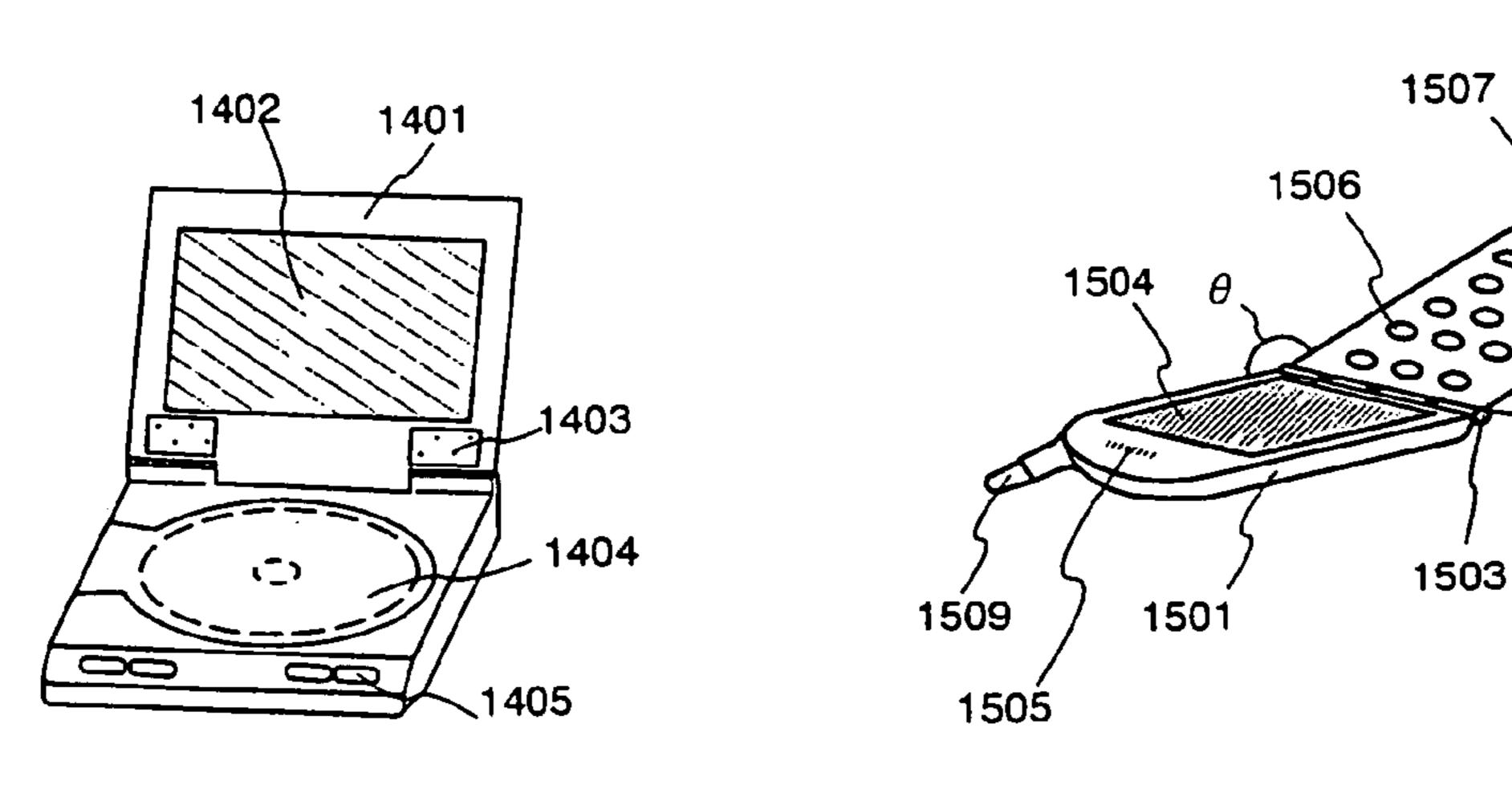

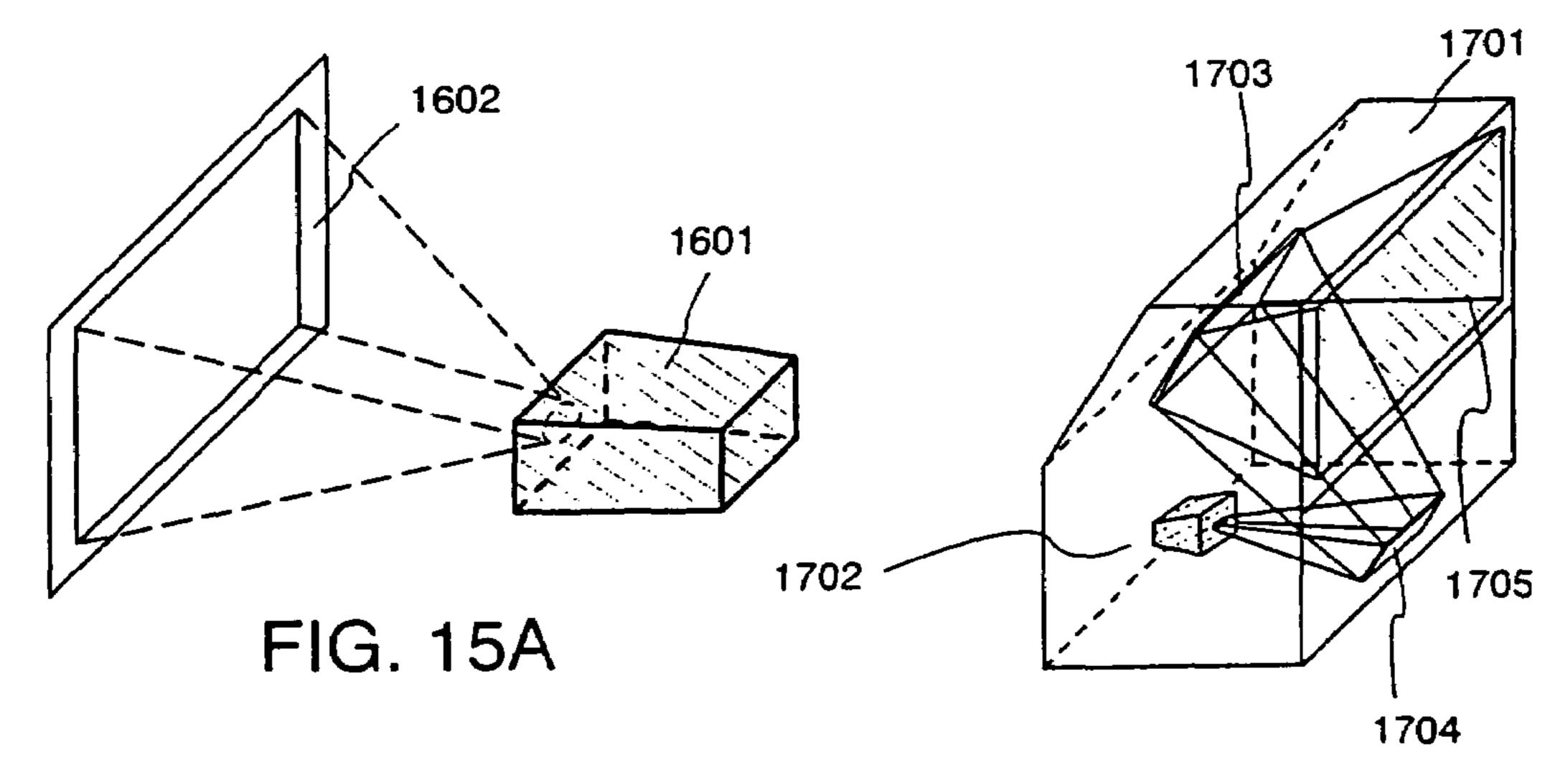

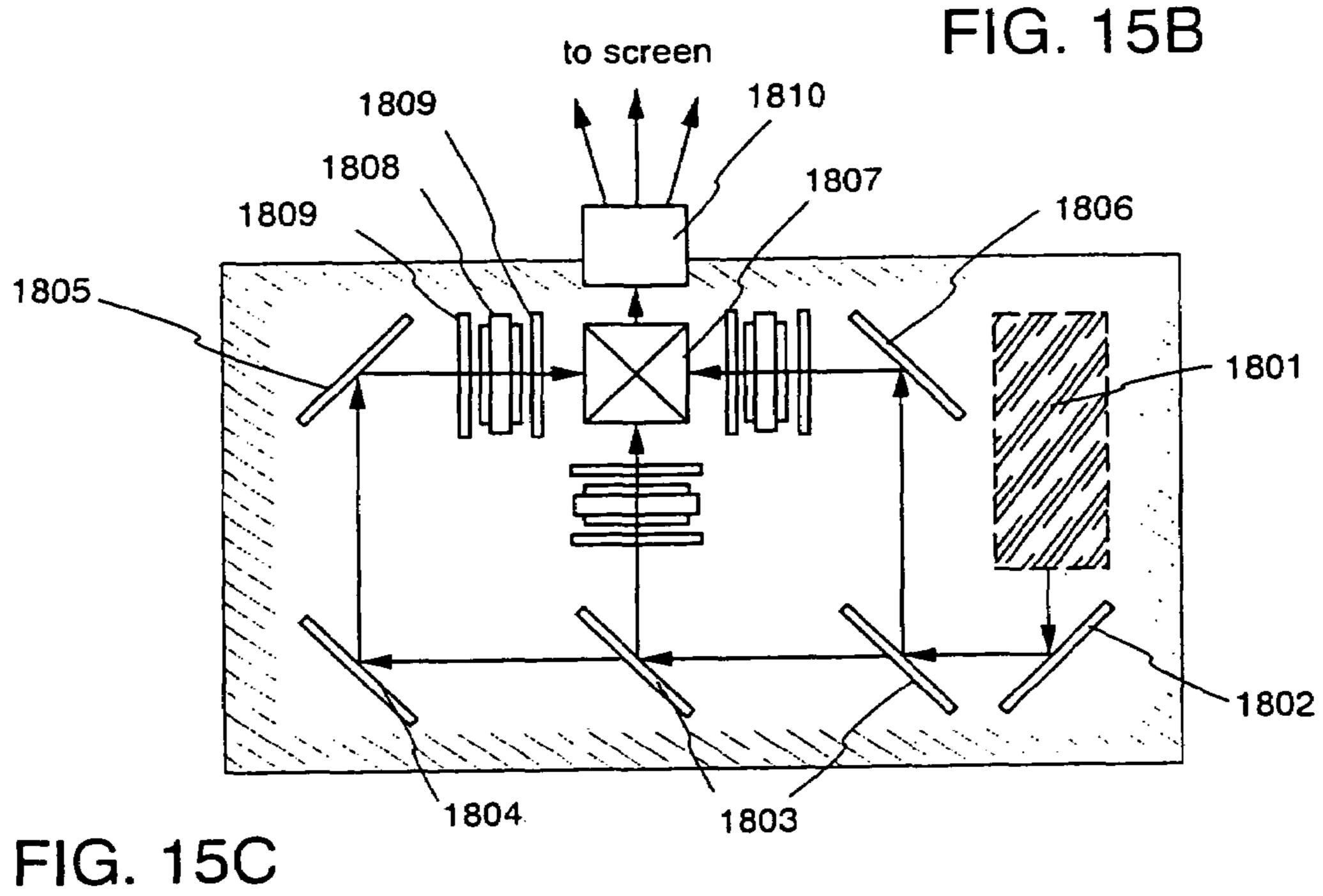

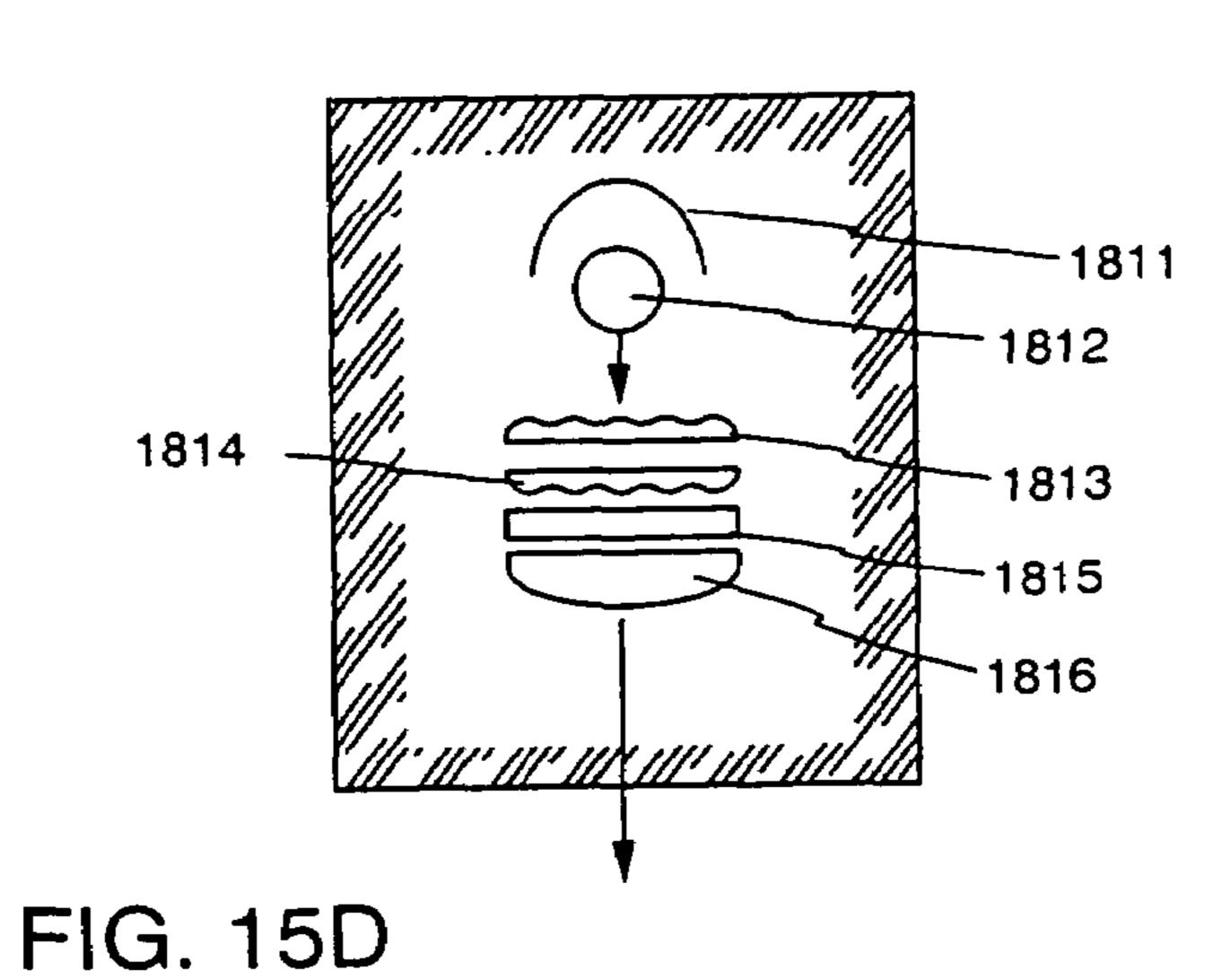

FIGS. 14A to 14F are schematic diagrams of devices showing examples of electronic equipment with a liquid crystal display device incorporated therein;

FIGS. 15A to 15D are schematic diagrams of devices showing examples of electronic equipment with a liquid crys- 30 tal display device incorporated therein; and

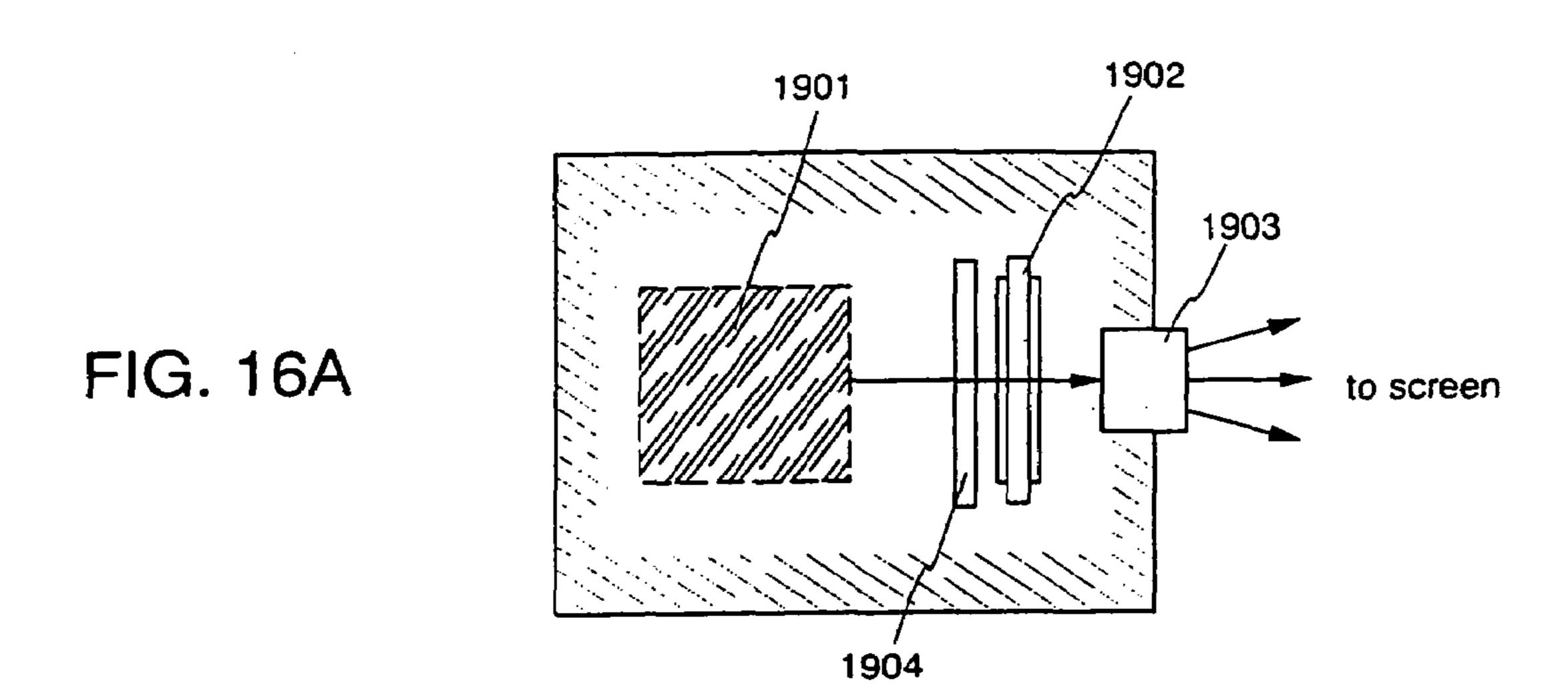

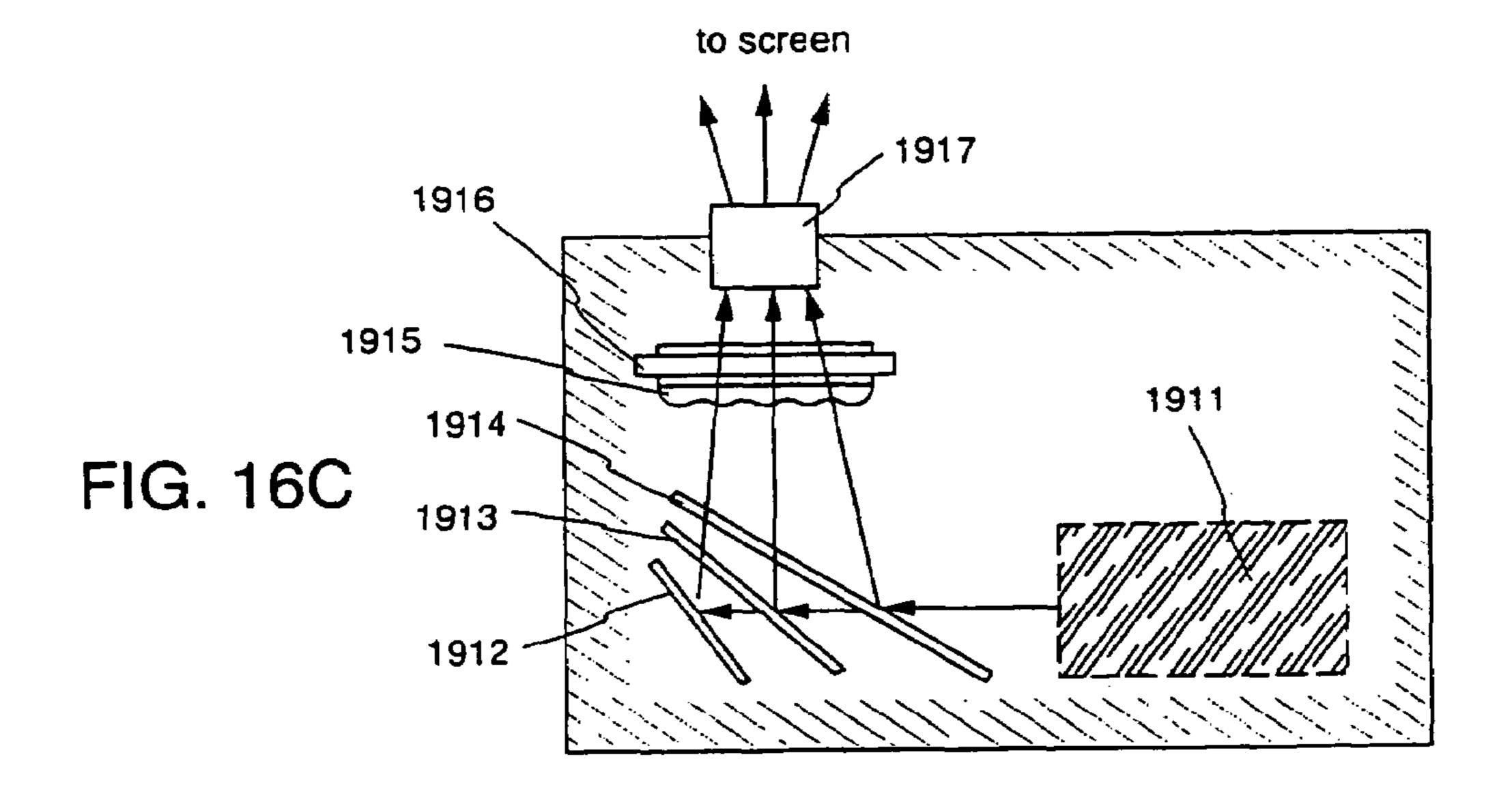

FIGS. 16A to 16C are schematic diagrams of devices showing examples of electronic equipment with a liquid crystal display device incorporated therein.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

## Embodiment Mode 1

This embodiment mode describes an example of semiconductor device that can solve the problem of inferior efficiency in gettering a catalytic element in a channel region of an n-channel TFT to the gettering efficiency in a p-channel TFT. The description is given with reference to FIGS. 1A to 2D.

FIG. 1A is a sectional view of an n-channel TFT. Silicon oxynitride is deposited on a glass substrate 101 to have a thickness of 100 nm to form a base film 102. An n-channel TFT is formed on the base film 102. The n-channel TFT on the base film 102 is composed of a semiconductor layer, a gate insulating film 108, and a gate electrode 109 which are layered with the semiconductor layer as the bottom layer and the gate electrode as the top layer. The semiconductor layer is a crystalline silicon film with a thickness of 50 nm. The gate insulating film 108 is a silicon oxide film with a thickness of 100 nm. The gate electrode 109 is formed from a high melting point metal film (typically a W film) with a thickness of 400 nm. The semiconductor layer is not limited to a crystalline silicon film and may be formed of other materials as long as the obtained semiconductor layer has a crystallinity.

The semiconductor layer formed from a crystalline silicon film has a channel region 103 that is a substantially intrinsic region, a source region (n<sup>+</sup> region) 104 and drain region (n<sup>+</sup> region) 105 that have the n-type conductivity, and highly efficient gettering regions 106 and 107 having the p-type 65 conductivity. The channel region 103 is positioned right below the gate electrode 109. The source region 104 and the

**12**

drain region 105 are to the left and right of the channel region 103. The highly efficient gettering regions 106 and 107 are on the outer sides of the source and drain regions. (See FIG. 1A)

The source region **104** and the drain region **105** are doped with P that is an n-type impurity in a dose of  $1.7 \times 10^{15}$  ions/cm<sup>2</sup>. The highly efficient gettering regions **106** and **107** are doped with P that is an n-type impurity in a dose of  $1.7 \times 10^{15}$  ions/cm<sup>2</sup> at the same time the source region **104** and the drain region **105** are doped with P. Thereafter, the highly efficient gettering regions are doped with B that is a p-type impurity in a dose large enough to invert the conductivity, specifically,  $2.5 \times 10^{15}$  ions/cm<sup>2</sup>. (See FIG. **1A**)

For reference, secondary ion mass spectroscopy (SIMS) results are shown about the relation between the set dose in a doping device and the concentration of impurities in the crystalline silicon film when the crystalline silicon film is doped with P and B. A sample for the spectroscopy is prepared by forming a crystalline silicon film with a thickness of 50 nm (the same thickness as the crystalline silicon film of this 20 embodiment mode) on a glass substrate and doping the film with P and B each in a dose of  $3 \times 10^{15}$  ions/cm<sup>2</sup> at an acceleration voltage of 10 kV using a doping device. Samples thus prepared receive SIMS. As a result, it has been confirmed by SIMS that the crystalline silicon film is doped with about  $1 \times 10^{15}$  ions/cm<sup>2</sup> of P in terms of dose and that the peak concentration in the crystalline silicon film is about  $2 \times 10^{20}$ atoms/cm<sup>3</sup>. SIMS simultaneously performed on B reveals almost the same results as P, namely, it has been confirmed that the crystalline silicon film is doped with about  $1 \times 10^{15}$ ions/cm<sup>2</sup> of B in terms of dose and that the peak concentration in the crystalline silicon film is about  $2 \times 10^{20}$  atoms/cm<sup>3</sup>.

In this embodiment mode, the crystalline silicon film is doped with P in a dose of  $1.7 \times 10^{15}$  ions/cm<sup>2</sup> and with B in a dose of  $2.5 \times 10^{15}$  ions/cm<sup>2</sup>. Consulting the above SIMS results, the concentration by dose and the peak concentration in the crystalline silicon film are obtained by proportion. It is inferred from the calculation that about  $0.6 \times 10^{15}$  ions/cm<sup>2</sup> of P in terms of dose is contained and that the peak concentration of P is about  $1.1 \times 10^{20}$  atoms/cm<sup>3</sup>. It is inferred from the calculation that about  $0.8 \times 10^{15}$  ions/cm<sup>2</sup> of B in terms of dose is contained and that the peak concentration of B is about  $1.7 \times 10^{20}$  atoms/cm<sup>3</sup>.

The thus structured semiconductor layer serves as an active layer of the n-channel TFT. The semiconductor layer is obtained by patterning a crystalline silicon film that is formed by doping an amorphous silicon film having a thickness of 50 nm with a crystallization accelerating catalytic element and then subjecting the amorphous silicon film to heat treatment. Accordingly, a large amount of catalytic elements used during crystallization is contained in the semiconductor layer. The catalytic element employed is a metal element such as Ni or Co. Ni is employed in this embodiment mode. A metal element as a catalytic element forms a deep level in a silicon film to trap carriers. When a crystalline silicon film obtained by using a metal element as a catalytic element forms a semiconductor layer of a TFT, the metal element can affect electric characteristics and reliability of the TFT. Therefore, it is necessary to remove the catalytic element quickly after crystallization or reduce the catalytic element to an amount 60 that does not influence the TFT electrically. (See FIG. 1A)

Based on the above points, a region containing both P that is an n-type impurity and B that is a p-type impurity, namely, the highly efficient gettering regions 106 and 107 are placed apart from channel region 103 in the semiconductor layer, in other words, outside of the source region 104 and drain region 105. During heat treatment for impurity activation as well as for gettering, the catalytic element Ni in the channel region

103 is moved through thermal diffusion to the highly efficient gettering regions 106 and 107 for gettering owing to the efficient gettering action of the highly efficient gettering regions 106 and 107. Ni in the channel region 103 is reduced to an amount that does not electrically influence the TFT by 5 the efficient gettering action. (See FIG. 1A)

A first interlayer insulating film 110 that is a silicon oxynitride film with a thickness of 150 nm is formed on the surface of the n-channel TFT. A second interlayer insulating film 111 that is an acrylic resin film with a thickness of 1.6 µm is laid 10 on top of the first interlayer insulating film to form a laminate. The laminate plus the gate insulating film 108 below the first interlayer insulating film 110 are pierced by contact holes. Metal wiring lines 112 and 113 are formed so as to bury the contact holes. The metal wiring line 112 is electrically connected to the source region 104 whereas the metal wiring line 113 is electrically connected to the drain region 105. (See FIG. 1A)

As has been described, the concentration of B that is a p-type impurity is higher than the concentration of P that is an 20 n-type impurity in the highly efficient gettering regions 106 and 107 to give the regions the p-type conductivity. When the highly efficient gettering regions 106 and 107 are provided in a part of the source region 104 and drain region 105 of the n-channel TFT, unwanted pn junction is formed between the 25 highly efficient gettering regions and the rest of the source region and drain region having the n-type conductivity. If the pn junction is positioned to obstruct a current that flows between the source region 104 and the drain region 105, electric characteristics of the n-channel TFT can be affected. 30 For that reason, the highly efficient gettering regions **106** and 107 have to be located at a position that does not obstruct a current flowing between the source region 104 and the drain region 105, namely, a position that does not block a current flowing through the metal wiring line **112** connected to the 35 source region 104 and through the metal wiring line 113 connected to the drain region 105. (See FIG. 1A)

FIG. 1B is a plan view of the n-channel TFT. Symbols used to denote the respective components in FIG. 1B are basically the same as those in the sectional view of the n-channel TFT 40 (FIG. 1A). As shown in FIG. 1B, the highly efficient gettering regions 106 and 107 where both the n-type impurity and p-type impurity are present are positioned so as to avoid obstructing a current flowing through a contact portion 112a that is connected to the source region 104 and through a 45 contact portion 113a that is connected to the drain region 105, namely, on the outer sides of the contact portions 112a and 113a. (See FIG. 1B)

FIGS. 2A to 2D are plan views of n-channel TFTs, showing examples of arrangement of highly efficient gettering regions 50 apart from channel regions in semiconductor layers.

In the example shown in FIG. 2A, highly efficient gettering regions 203a and 204a where an n-type impurity and a p-type impurity are both present are rectangles with their longer sides set parallel to a gate electrode 205a. The rectangles are 55 13) apart from a channel region in the semiconductor layer and the outer corners of the rectangles coincide with the outer corners of the semiconductor layer. This arrangement example is identical with the example of the n-channel TFT shown in FIG. 1B. In the example shown in FIG. 2B, highly 60 efficient gettering regions 203b and 204b are rectangles with their longer sides set perpendicular to a gate electrode 205b. The rectangles are apart from a channel region in the semiconductor layer and one corner of each of the rectangles coincides with one corner of the semiconductor layer. In the 65 example shown in FIG. 2C, highly efficient gettering regions 203c and 204c have a complicate shape obtained by combin14

ing rectangles whose longer sides are parallel to a gate electrode **205**c with rectangles whose longer sides are perpendicular to the gate electrode **205**c. The polygons are apart from a channel region in the semiconductor layer and the outer corners of the polygons coincide with the outer corners of the semiconductor layer. This example is characterized by the highly efficient gettering regions having larger area than those in FIGS. **2A** and **2B**. (See FIGS. **2A** to **2C**)

In any of the above arrangement examples, the highly efficient gettering regions are arranged so as to avoid obstructing a current flowing between the contact portion that is connected to the source region and the contact portion that is connected to the drain region. To elaborate, the highly efficient gettering regions 203a and 204a in FIG. 2A are arranged in positions that do not block a current flowing between contact portions 206a connected to a source region **201***a* and contact portions **207***a* connected to a drain region 202a. The highly efficient gettering regions 203b and 204b in FIG. 2B are arranged in positions that do not block a current flowing between contact portions **206***b* connected to a source region 201b and contact portions 207b connected to a drain region 202b. The highly efficient gettering regions 203c and **204**c in FIG. **2**C are arranged in positions that do not block a current flowing between contact portions 206c connected to a source region 201c and contact portions 207c connected to a drain region 202c. (See FIGS. 2A to 2C)

FIG. 2D shows an arrangement example that is basically the same as the example in FIG. 2C. In the example of FIG. 2D, highly efficient gettering regions 203d and 204d are even larger than the highly efficient gettering regions in FIG. 2C in order to enhance the gettering efficiency, and the highly efficient gettering region 203d partially overlaps contact portions **206***d*. Basically, no problem is caused when the highly efficient gettering regions 203d and 204d partially overlap the contact portions 206d and 207d. However, it is necessary to make sure that the highly efficient gettering regions overlap no more than half the contact portions 206d and 207d at worst. Therefore, the design distances between the contact portions 206d and 207d and the highly efficient gettering regions 203d and 204d has to be set suitably taking into consideration the alignment accuracy of an exposure device that is used in photolithography steps for forming the regions.

The positions of highly efficient gettering regions are not limited to those in this embodiment mode. The highly efficient gettering regions can be provided in any place as long as a current flowing between the source region and the drain region is not affected (as long as the current is not blocked). The highly efficient gettering regions may not always be placed at the ends of the semiconductor layer. The same effect can be obtained when, for instance, highly efficient gettering regions 803 and 804 are placed in regions adjacent to contact portions 806 and 807 that are respectively connected to a source region 801 and a drain region 802 as shown in FIG. 13. A reference numeral 805 denotes a gate electrode. (See FIG. 13)

## Embodiment Mode 2

This embodiment mode describes a method of manufacturing a semiconductor device that can solve the problem of inferior efficiency in gettering a catalytic element in a channel region of an n-channel TFT to the gettering efficiency in a p-channel TFT. The description is given with reference to FIGS. 3A to 4C.

First, a silicon oxynitride film with a thickness of 100 nm is formed as a base film 302 on a glass substrate 301 by plasma CVD. Then, an amorphous silicon film 303 is immediately

formed to have a thickness of 15 to 70 nm, preferably 30 to 60 nm. Plasma CVD is used in this embodiment mode to form the amorphous silicon film 303 to have a thickness of 50 nm, but low pressure CVD may be used instead. During formation of the amorphous silicon film 303, a natural oxide film 304 is formed on the surface by the effect of oxygen in the air. (See FIG. 3A)

The amorphous silicon film 303 is crystallized next. Before crystallization, the contaminated natural oxide film 304 on the surface of the amorphous silicon film 303 is removed by 10 treating the substrate on which the amorphous silicon film 303 is formed with diluted fluoric acid. Then, the amorphous silicon film 303 is irradiated with UV light in an oxygen atmosphere to form a very thin silicon oxide film 305 on the surface of 303. The very thin silicon oxide film 305 has a 15 function of improving the permeability of a Ni aqueous solution that is a catalytic element solution to be applied later by spin coating. (See FIG. 3B)

An aqueous solution of Ni that is a catalytic element is applied to the entire surface of the amorphous silicon film 303 20 (the surface of the silicon oxide film 305, to be exact) by spin coating. The Ni concentration in the Ni aqueous solution is 0.1 to 50 ppm by weight, preferably 1 to 30 ppm by weight. This concentration range is determined to set the Ni concentration in the amorphous silicon film 303 to  $1\times10^{15}$  to  $6\times10^{19}$  25 atoms/cm<sup>3</sup>. Here the Ni concentration in the amorphous silicon film is set to  $1\times10^{15}$  to  $6\times10^{19}$  atoms/cm<sup>3</sup> because it is difficult to obtain the catalytic action of Ni when the concentration thereof is lower than  $1\times10^{15}$  atoms/cm<sup>3</sup>. The above Ni concentration is determined by the maximum measurement 30 value by SIMS. (See FIG. 3B)

In this embodiment mode, a Ni aqueous solution containing 10 ppm of Ni is applied by spin coating. During spin coating, the glass substrate 301 is rotated to shake excess Ni aqueous solution off to form a very thin Ni-containing layer 35 306 on the entire surface of the amorphous silicon film 303 (the surface of the silicon oxide film 305, to be exact). (See FIG. 3B)

Next, the amorphous silicon film 303 is subjected to heat treatment in nitrogen atmosphere at 550° C. for four hours to crystallize the film 303 and form a crystalline silicon film 307. In a crystal growth method like this, where the amorphous silicon film 303 is subjected to heat treatment after applying a Ni aqueous solution to the entire surface of the film 303, crystal growth advances from the surface of the amorphous silicon film 303 doped with Ni toward the base film 302 (longitudinal direction). The method is therefore called a longitudinal growth method in this specification. (See FIG. 3C)

The above heat treatment may be carried out in an electric furnace at 500 to 700° C., preferably 550 to 650° C. The upper limit of the heat treatment temperature has to be set taking into consideration the heat resistance of the substrate used. In the case of the glass substrate 301, for example, glass distortion point is about 600° C. and the glass substrate 301 is 55 noticeably warped or shrunk if heated at a temperature exceeding the glass distortion point. Therefore, the glass substrate 301 has to be subjected to heat treatment at 600° C. or lower. Although this embodiment mode uses an electric furnace for the heat treatment, laser annealing, lamp annealing, or like other heat treatment means may be employed. (See FIG. 3C)

The obtained crystalline silicon film 307 is irradiated with a laser to improve the crystallinity. Heat treatment in an electric furnace only achieves insufficient crystallization of 65 the crystalline silicon film 307, and amorphous components are scatteredly left in the film. Here, insufficient crystallinity

**16**

is improved by irradiating the crystalline silicon film 307 with a pulse oscillation type KrF excimer laser (wavelength: 248 nm). The excimer laser is oscillated ultraviolet light and therefore instantaneous fusing and solidification is repeated in a laser irradiation subject region. This brings a kind of non-equilibrium state to the laser irradiation subject region and makes it very easy for Ni to move. The laser irradiation step may be omitted but it is preferable to include this step since the laser irradiation step has an effect of improving the efficiency in a later gettering step in addition to improving the crystallinity.

Next, the crystalline silicon film 307 is patterned by normal photolithography treatment and dry etching treatment into a semiconductor layer 308n for forming an n-channel TFT and a semiconductor layer 308p for forming a p-channel TFT. The surfaces of the semiconductor layers 308n and 308p have unwanted natural oxide films, which are removed by diluted fluoric acid treatment. Then, a silicon oxide film is formed as a gate insulating film 309 by plasma CVD or low pressure CVD to have a thickness of 100 nm. (See FIG. 3D)

Next, a conductive film as a gate electrode material is formed (to have a thickness of 400 nm) by sputtering or CVD. The conductive film is then patterned by normal photolithography treatment and dry etching treatment into a gate electrode 310n for the n-channel TFT and a gate electrode 310pfor the p-channel TFT. The gate electrode material used here is preferably a heat resistant material that can withstand the temperature (550 to 650° C.) of later heat treatment for gettering as well as for activation of impurity elements. Examples of the heat resistant material include high melting point metals such as Ta (tantalum), Mo (molybdenum), Ti (titanium), W (tungsten), and Cr (chromium), metal silicides that are compounds of high melting point metals and silicon, and polycrystalline silicon having the n-type or p-type conductivity. This embodiment mode employs a metal film (W) with a thickness of 400 nm. (See FIG. 3E)

The gate electrodes 310n and 310p are used as masks to dope the semiconductor layers with P that is an n-type impurity. Doping conditions include setting the acceleration voltage to 60 to 100 kV and the dose to  $1.7 \times 10^{15}$  ions/cm<sup>2</sup>. Through the doping treatment, high concentration impurity regions (n<sup>+</sup> regions) 312n and 313n that have the n-type conductivity and function as a source region and a drain region, and a substantially intrinsic region 311n that functions as a channel region are formed in the semiconductor layer 308n for forming the n-channel TFT. High concentration impurity regions (n<sup>+</sup> regions) 312p and 313p that have the n-type conductivity and a substantially intrinsic region 311p that functions as a channel region are formed through the doping treatment in the semiconductor layer 308p for forming the p-channel TFT. (See FIG. 3E)

Formed next is a resist pattern **314** that places an opening region at an end apart from the channel region 311n in the semiconductor layer 308n for forming the n-channel TFT, and sets the entire region of the semiconductor layer 308p for forming the p-channel TFT as an opening region. Then, the resist pattern 314 and the gate electrode 310p for the p-channel TFT are used as masks to dope the semiconductor layers with B that is a p-type impurity. Doping conditions include setting the acceleration voltage to 60 to 100 kV and the dose to  $2.5\times10^{15}$  ions/cm<sup>2</sup>. Through the doping treatment, the conductivity of the n-type impurity regions 312p and 313p for forming the p-channel TFT is inverted to form high concentration impurity regions (p<sup>+</sup> regions) 319p and 320p having the p-type conductivity. At the same time the p-type impurity regions 319p and 320p are formed, the opening region of the resist pattern 314 that is placed apart from the channel region

311n in the semiconductor layer 308n of the n-channel TFT is used as a mask to form high concentration impurity regions (p<sup>+</sup> regions) 317n and 318n having the p-type conductivity. (See FIG. 3F)

The high concentration impurity regions ( $p^+$  regions) 319p and 320p formed here to have the p-type conductivity are regions functioning as a source region and drain region of the p-channel TFT. Containing the n-type impurity in addition to the p-type impurity, the regions 319p and 320p also function as highly efficient gettering regions for gettering Ni in the substantially intrinsic region 311p that is the channel region. The high concentration impurity regions ( $p^+$  regions) 317n and 318n formed apart from the channel region 311n in the semiconductor layer 308n of the n-channel TFT to have the p-type conductivity also function as highly efficient gettering 15 regions for gettering Ni in the substantially intrinsic region 311n that is the channel region. (See FIG. 3F)

After the resist pattern **314** is removed, an inorganic film with a thickness of 100 to 300 nm is formed as a first interlayer insulating film **321**. The first interlayer insulating film **321** in 20 this embodiment mode is a silicon oxynitride film formed by plasma CVD to have a thickness of 150 nm. Then, heat treatment is conducted in an electric furnace at 600° C. for 12 hours to activate thermally the impurity elements (n-type impurity and p-type impurity) implanted in the semiconduc- 25 tor layers 308n and 308p. This heat treatment for thermal activation of the impurity elements doubles as gettering treatment for gettering unwanted catalytic element (Ni) contained in the substantially intrinsic regions 311n and 311p that function as the channel regions. The unwanted catalytic element 30 (Ni) contained in the substantially intrinsic regions 311n and **311**p that function as the channel regions are thus moved through thermal diffusion to the highly efficient gettering regions 317n, 318n, 319p, and 320p for gettering. A TFT with a crystalline silicon film formed by this method has high field 35 effect mobility and shows excellent electric characteristics including a reduced OFF current value. Thereafter, the semiconductor layers 308n and 308p are subjected to hydrogenation treatment in a nitrogen atmosphere containing 3% of hydrogen at 410° C. for an hour to terminate dangling bonds 40 in the semiconductor layers. (See FIG. 4A)

Next, a transparent organic film is formed as a second interlayer insulating film 322 on the first interlayer insulating film 321 to have a thickness of 1 to 3  $\mu m$ . The second interlayer insulating film 322 in this embodiment mode is an 45 acrylic resin film with a thickness of 1.6  $\mu m$ . Then, contact holes 323 are formed by normal photolithography treatment and dry etching treatment in the second interlayer insulating film 322 and the first interlayer insulating film 321 as well as a gate insulating film 309 below the first interlayer insulating 50 film 321. (See FIG. 4B)

A conductive metal film is formed next to have a thickness of 200 to 800 nm. In this embodiment mode, a laminate of a Ti film with a thickness of 50 nm and an Al—Ti alloy film with a thickness of 500 nm is formed by sputtering. Then, 55 metal wiring lines 324 are formed by normal photolithography treatment and dry etching treatment. The metal wiring lines 324 are respectively connected through the contact holes 323 to the source region 315n and drain region 316n for forming the n-channel TFT and to the source region 319p and 60 drain region 320p for forming the p-channel TFT. (See FIG. 4C)

## Embodiment Mode 3

Embodiment Mode 2 describes a method of manufacturing a semiconductor device which uses a longitudinal growth

18

method to crystallize an amorphous silicon film. As has been mentioned, there is another growth method that can be used to crystallize an amorphous silicon, a lateral growth method. This embodiment mode describes a method of manufacturing a semiconductor device which uses a lateral growth method to crystallize an amorphous silicon film. Specific descriptions on the method are given below with reference to FIGS. 5A to 5F.

First, a silicon oxynitride film with a thickness of 100 nm is formed as a base film **402** on a glass substrate **401** by plasma CVD. Then, an amorphous silicon film **403** is immediately formed to have a thickness of 15 to 70 nm, preferably 30 to 60 nm. Plasma CVD is used in this embodiment mode to form the amorphous silicon film **403** to have a thickness of 50 nm, but low pressure CVD may be used instead. A silicon oxide film is formed as a mask insulating film **404** on the amorphous silicon film **403** by plasma CVD or low pressure CVD to have a thickness of 70 nm. (See FIG. **5**A)

An opening region 405 is formed in a part of the mask insulating film 404 by normal photolithography treatment and wet etching treatment. The opening region 405 formed here is for selectively providing a catalytic element (Ni is used in this embodiment mode too) to the amorphous silicon film 403. The amorphous silicon film 403 is exposed at the bottom of the opening region 405. Then, the substrate is oxidized to form a very thin silicon oxide film 0.5 to 5 nm in thickness (not shown) on the exposed region of the amorphous silicon film 403 in the opening region 405. In this embodiment mode, the oxidization treatment is delivered through ozone water treatment by the spin processing method (single wafer method) continued for a given period of time. Batch processing ozone water treatment using a washing tank may be employed for the oxidization treatment. Alternatively, single wafer method or batch processing hydrogen peroxide water treatment may be employed, or the substrate may be oxidized by ozone generated by ultraviolet (UV) irradiation in an oxygen atmosphere. The very thin silicon oxide film (not shown) in the opening region 405 is formed to improve the permeability of a catalytic element solution (typically, a Ni aqueous solution) to the amorphous silicon film 403. (See FIG. 5B)

Next, a Ni aqueous solution as the catalytic element solution is applied by spin coating to the entire surface of the mask insulating film 404 having the opening region 405 to selectively introduce Ni to the amorphous silicon film 403 at the bottom of the opening region 405. In this embodiment mode, the catalytic element solution used is a nickel acetate aqueous solution containing 10 ppm (by weight) of Ni. A very thin Ni-containing layer 406 is formed through the spin coating. (See FIG. 5B)

Next, the amorphous silicon film 403 is subjected to heat treatment in a nitrogen atmosphere at 600° C. for eight hours to crystallize the film 403 and form a crystalline silicon film 407. During crystallization, Ni selectively introduced through the opening region 405 is diffused from the opening region 405 toward the surrounding regions and crystallization of the amorphous silicon film 403 progresses with the advance of diffusion. The crystallization proceeds in the lateral direction (the direction parallel to the substrate), and this method is therefore called a lateral growth method in this specification. (See FIG. 5C)

The obtained crystalline silicon film 407 is irradiated with a laser to improve the crystallinity. The laser irradiation greatly improves the crystallinity of the crystalline silicon film 407. This embodiment mode employs a pulse oscillation type KrF excimer laser (wavelength: 248 nm). The excimer laser not only improves the crystallinity of the crystalline silicon film 407 but also makes it very easy for Ni to move.

Therefore, the laser irradiation also has an effect of improving the efficiency in gettering by a gettering source.

The substrate is then treated with diluted fluoric acid to remove the mask insulating film 404 that has been used as a mask for selectively providing Ni. After the mask insulating 5 film 404 is removed, the crystalline silicon film 407 is patterned by normal photolithography treatment and dry etching treatment into a semiconductor layer 408n for forming an n-channel TFT and a semiconductor layer 408p for forming a p-channel TFT. A silicon oxide film with a thickness of 100 nm is formed as a gate insulating film 409 by plasma CVD or low pressure CVD. Before forming the gate insulating film 409, the substrate is washed through diluted fluoric acid treatment to remove contaminants (including a natural oxide film) on the surface of the substrate. (See FIG. 5D)

Descriptions of the following steps are substantially the same as the descriptions on FIGS. 3E and 3F and FIGS. 4A to 4C in Embodiment Mode 2. Therefore, summarized version thereof is given.

A film of W that is a conductive high melting point metal is 20 formed by sputtering or CVD to have a thickness of 400 nm. The W film is patterned by normal photolithography treatment and dry etching treatment into a gate electrode **410***n* for the n-channel TFT and a gate electrode **410***p* for the p-channel TFT. Then, the gate electrodes **410***n* and **410***p* are used as 25 masks to dope the semiconductor layers with P that is an n-type impurity. Thus formed are high concentration impurity regions (n<sup>+</sup> region) **412***n*, **413***n*, **412***p*, and **413***p* having the n-type conductivity and substantially intrinsic regions **411***n* and **411***p*. (See FIG. **5**E)

Formed next is a resist pattern **414** that places an opening region at an end apart from the channel region 411n in the semiconductor layer 408n for forming the n-channel TFT, and sets the entire region of the semiconductor layer 408p for forming the p-channel TFT as an opening region. Then, the 35 resist pattern 414 and the gate electrode 410p for the p-channel TFT are used as masks to dope the semiconductor layers with B that is a p-type impurity. Through the doping treatment, high concentration impurity regions (p<sup>+</sup> regions) 419p and 420p having the p-type conductivity are formed in the 40 semiconductor layer 408p for forming the p-channel TFT. At the same time the high concentration impurity regions 419pand 420p are formed, the opening region of the resist pattern 414 which is placed apart from the channel region 411n in the semiconductor layer 408n of the n-channel TFT is used as a 45 mask to form high concentration impurity regions (p<sup>+</sup> regions) 417*n* and 418*n* having the p-type conductivity. Conditions for doping of the n-type impurity and p-type impurity are the same as the doping conditions in Embodiment Mode 2. (See FIG. **5**F)

Interlayer insulating films, contact holes, and metal wiring lines are then formed by the same process illustrated in FIGS.

4A to 4C to complete a semiconductor device having an n-channel TFT and a p-channel TFT both.

As described above, highly efficient gettering regions 55 where an n-type impurity (P) and a p-type impurity (B) are both present, namely, the high concentration impurity regions ( $p^+$  regions) 417n and 418n having the p-type conductivity can be formed apart from the channel region 411n of the n-channel TFT in the semiconductor layer 408n also when the 60 amorphous silicon film is crystallized by a lateral growth method. When a lateral growth method is used to crystallize the amorphous silicon film, the semiconductor layers 408n and 408n contain a catalytic element in a lower concentration than when a longitudinal growth method is used. Accordingly, the use of lateral growth method in crystallizing the amorphous silicon film provides an effect of lowering the

20

gettering treatment temperature, shortening the gettering treatment time, and the like, which increases process margin. Specific embodiments of the present invention will be described in detail below with reference to FIGS. 6A to 15D.

### Embodiment 1

In Embodiment Modes 2 and 3, a region where an n-type impurity and a p-type impurity are both present is formed in at least a part of source region and drain region of a TFT and a catalytic element in a channel region alone is removed by the highly efficient gettering action of this region. These methods of manufacturing a semiconductor device are characterized by shortened process achieved by integrating a step of introducing a gettering source for forming a gettering region and an impurity doping step for forming a source region and a drain region into a single step. On the other hand, these methods can form only a gettering region of limited area and have room for improvement in terms of gettering efficiency. This embodiment describes a method of manufacturing a semiconductor device which can eliminate this drawback.

Specifically, according to the method of this embodiment, a region including a semiconductor layer that is composed of a channel region, a source region, and a drain region of a TFT is the gettering subject region, and highly efficient gettering regions containing an n-type impurity and a p-type impurity both are formed in the periphery of the gettering subject region to getter a catalytic element in the gettering subject region. Through the gettering treatment, the catalytic element in the gettering subject region can be reduced in advance. The method of this embodiment will be described in detail below with reference to FIGS. 6A to 7C. FIGS. 6A to 6F are sectional views showing the manufacturing process and FIGS. 7A to 7C are plan views of FIGS. 6D to 6F.

First, a silicon oxynitride film with a thickness of 100 nm is formed as a base film **502** on a glass substrate **501** by plasma CVD. Then, an amorphous silicon film **503** is immediately formed to have a thickness of 15 to 70 nm, preferably 30 to 60 nm. Plasma CVD is used in this embodiment to form the amorphous silicon film **503** to have a thickness of 50 nm, but low pressure CVD may be used instead. During formation of the amorphous silicon film **503**, a natural oxide film **504** is formed on the surface by the effect of oxygen in the air. (See FIG. **6A**)