#### US007593271B2

# (12) United States Patent Ong

# (10) Patent No.:

# US 7,593,271 B2

# (45) **Date of Patent:**

# Sep. 22, 2009

# (54) MEMORY DEVICE INCLUDING MULTIPLEXED INPUTS

- (75) Inventor: Adrian E. Ong, Pleasanton, CA (US)

- (73) Assignee: Rambus Inc., Los Altos, CA (US)

- (\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 11/744,815

- (22) Filed: May 4, 2007

## (65) Prior Publication Data

US 2007/0263458 A1 Nov. 15, 2007

## Related U.S. Application Data

- (60) Provisional application No. 60/798,113, filed on May 4, 2006.

- (51) Int. Cl. G11C 7/10 (2006.01)

## (56) References Cited

## U.S. PATENT DOCUMENTS

| 5,249,160 A * | 9/1993  | Wu et al 365/230.08       |

|---------------|---------|---------------------------|

| 5,490,113 A * | 2/1996  | Tatosian et al 365/189.05 |

| 5,590,078 A * | 12/1996 | Chatter 365/189.03        |

| 5,594,694 A   | 1/1997  | Roohparvar et al.         |

| 5,600,606 A * | 2/1997  | Rao 365/233.1             |

| 5,734,849 A * | 3/1998  | Butcher 710/305           |

| 5,829,016 A * | 10/1998 | Sharma et al 711/111      |

| 5,898,623 A * | 4/1999  | Clinton et al 365/189.04  |

| 6,031,767 A * | 2/2000  | Schuh et al 365/189.05 |

|---------------|---------|------------------------|

| 6,191,603 B1  | 2/2001  | Muradali et al.        |

| 6,215,704 B1* | 4/2001  | Shimizu 365/189.02     |

| 6,272,053 B1* | 8/2001  | Choi 365/189.03        |

| 6,425,046 B1* | 7/2002  | Leung et al 711/101    |

| 6,519,171 B2  | 2/2003  | Matsuzaki et al.       |

| 6,732,304 B1  | 5/2004  | Ong                    |

| 6,812,726 B1  | 11/2004 | Ong                    |

| 6,825,683 B1  | 11/2004 | Berndt et al.          |

| 6,859,399 B1* | 2/2005  | Azimi et al 365/189.03 |

| 6,882,171 B2  | 4/2005  | Ong                    |

| 6,954,822 B2* | 10/2005 | Bains et al 711/5      |

| 6,967,397 B2  | 11/2005 | Inoue et al.           |

|               |         |                        |

## (Continued)

#### OTHER PUBLICATIONS

Jedec Solid State Technology Association, "Jedec Standard, Double Data Rate (DDR) SDRAM Specification," May 2005, pp. 1-85, Revision of JESD79D, Jedec Solid State Technology Association, Arlington, Virginia, USA.

### (Continued)

Primary Examiner—Huan Hoang (74) Attorney, Agent, or Firm—Park, Vaughan & Fleming LLP

# (57) ABSTRACT

Systems and methods are described for reducing the number of exterior contacts on a semiconductor package without reducing the number of address, data and control signals used by an integrated circuit interior to the semiconductor package. In some embodiments, two signals may be received at a shared conductor accessible by devices exterior to the semiconductor package and communicated to two contacts on the integrated circuit that are inaccessible to the exterior of the semiconductor package. In various embodiments, signals required to support a full set of features of the JEDEC JESD79E standard or the JEDEC JESD79-2C standard are communicated using a reduced number of exterior contacts.

## 20 Claims, 12 Drawing Sheets

# US 7,593,271 B2

# Page 2

| U.S. PATENT DOCUMENTS               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7,313,740 B2*                                               | 12/2007 | Ong 714/718                       |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------|-----------------------------------|

| 6006 <b>-</b> 4 <b>- D</b> 4 - 0(00 | and the second of the second o | 7,336,554 B2*                                               | 2/2008  | Kim et al 365/219                 |

|                                     | 6 Shaylor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7,365,557 B1*                                               | 4/2008  | Ong 324/765                       |

|                                     | 06 Ong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7,370,256 B2*                                               | 5/2008  | Ong 714/731                       |

|                                     | 6 Hong et al 365/230.08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7,404,117 B2*                                               | 7/2008  | Ong et al 714/718                 |

|                                     | 06 Ong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2002/0105522 A1*                                            | 8/2002  | Kolluru et al 345/519             |

| 7,079,445 B2 * 7/20                 | 6 Choi et al 365/189.02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2004/0019841 A1*                                            | 1/2004  | Ong 714/738                       |

| 7,133,798 B1 11/20                  | 06 Ong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2005/0204223 A1                                             | 9/2005  | Ong                               |

| 7,139,945 B2 11/20                  | 06 Ong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2005/0289428 A1*                                            | 12/2005 | Ong 714/742                       |

| 7,184,322 B2 * 2/20                 | 7 Takahashi et al 365/189.02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2007/0013402 A1*                                            |         | Ong et al 324/765                 |

| 7,240,254 B2 7/20                   | 7 Ong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2007/0067687 A1*                                            |         | Ong 714/731                       |

| 7,245,141 B2 7/20                   | 7 Ong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2007/0079204 A1*                                            |         | Ong 714/738                       |

| 7,254,582 B2 8/20                   | 7 Song et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2007/0113126 A1*                                            |         | Ong 714/724                       |

| 7,265,570 B2 9/200                  | 7 Ong                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                             |         |                                   |

| 7,269,524 B1 9/20                   | 7 Ong et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OTI                                                         | HER PU  | BLICATIONS                        |

| 7,269,765 B1 9/200                  | 7 Charlton et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I. J C. 1'. J. C44 T 1.                                     | 1 A _   | :                                 |

| 7,305,595 B2 12/200                 | 7 Goodwin et al.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                             | ~,      | ssociation, "Jedec Standard, DDR2 |

| , ,                                 | 7 Ong 324/765                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                           | •       | 006, pp. 1-110, JESD79-2C, Jedec  |

|                                     | or Ong 324/765                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Sond State Technology Association, Armigion, Virginia, OSA. |         |                                   |

|                                     | 7 Ong 324/765                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | * cited by examiner                                         |         |                                   |

| 7,510,000 152 12/20                 | 77 0115 32-1/703                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | oned by examine                                             |         |                                   |

\*="Don't Care", if A10 is HIGH at this point

PRE = PRECHARGE, ACT = ACTIVE, RA = Row Address

NOP commands are shown for ease of illustration; other commands may be valid at these times Although tDQSS is drawing only for the first DQS rising edge, each rising edge of DQS must fall within the ± 25% window of the corresponding positive clock edge.

Precharge may may be issued before tRAS ns after the ACTIVE command for applicable banks.

Prior Art FIG. 2

tRAS would be limiting

NOP commands are shown for ease of illustration; other commands may be valid at these times

Note that tRCD > tRCD MIN so that the same timing applies if Autoprecharge is enabled (in which case

FIG. 3

FIG. 4

FIG. 5

FIG. 6

Sep. 22, 2009

| <b>T</b>                    |       |       |       |  |  |

|-----------------------------|-------|-------|-------|--|--|

| Mulitplex IO pin definition |       |       |       |  |  |

| CS\=1                       | CS\=0 | CS\≃1 | CS\=0 |  |  |

| 100                         | A0    | 1016  | RAS\  |  |  |

| 101                         | A1    | 1017  | CASI  |  |  |

| 102                         | A2    | 1018  | WE\   |  |  |

| 103                         | A3    | 1019  | DM0   |  |  |

| 104                         | A4    | 1020  | DM1   |  |  |

| 105                         | A5    | 1021  | DM2   |  |  |

| 106                         | A6    | 1022  | DM3   |  |  |

| 107                         | A7    | 1023  |       |  |  |

| 801                         | A8    | 1024  |       |  |  |

| 108                         | A9    | 1025  |       |  |  |

| 1010                        | A10   | 1026  |       |  |  |

| 1011                        | A11   | 1027  |       |  |  |

| 1012                        | A12   | 1028  |       |  |  |

| IO13                        | BA0   | 1029  |       |  |  |

| 1014                        | BA1   | 1030  | }     |  |  |

| 1015                        |       | 1031  |       |  |  |

| Mulitplex Test IO pin definition |        |  |  |  |

|----------------------------------|--------|--|--|--|

| TCS\=1                           | TCS\=0 |  |  |  |

| TDQ0                             | TA10   |  |  |  |

| TDQ1                             | TWE    |  |  |  |

| TDQ2                             | TCAS   |  |  |  |

| TDQ3                             | TRAS   |  |  |  |

| TDQ4                             | LOAD   |  |  |  |

| TDQ5                             | SET    |  |  |  |

| TDQ6                             | TBA1   |  |  |  |

| TDQ7                             | TBA0   |  |  |  |

FIG. 11

# MEMORY DEVICE INCLUDING MULTIPLEXED INPUTS

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application claims benefit of U.S. Provisional Patent Application Ser. No. 60/798,113 filed on May 4, 2006, entitled "Integrated Circuit Testing Module including Multiplexed Inputs." The disclosure of the above application is 10 hereby incorporated herein by reference.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates generally to semiconductor devices, and more particularly to packaging semiconductor devices.

## 2. Description of Related Art

Integrated circuits, for example memory, are used in a wide 20 variety of applications. Typically, memory conforms to accepted standards. For example, many memory standards are defined by the Joint Electron Device Engineering Council, also known as the JEDEC Solid State Technology Association (JEDEC). Designs for memory that conform to standards such as JEDEC standards are well known. Moreover, memory layouts and lithographic masks for standard memories are readily available. It is desirable to use such standard memory designs in an application rather than redesigning the memory specifically for a different application. However, the 30 number of external contacts used for standard memory is determined by the standard for the memory design. The minimal size of the package sometimes is limited by the number and pitch of the contacts. This is a disadvantage of the prior art.

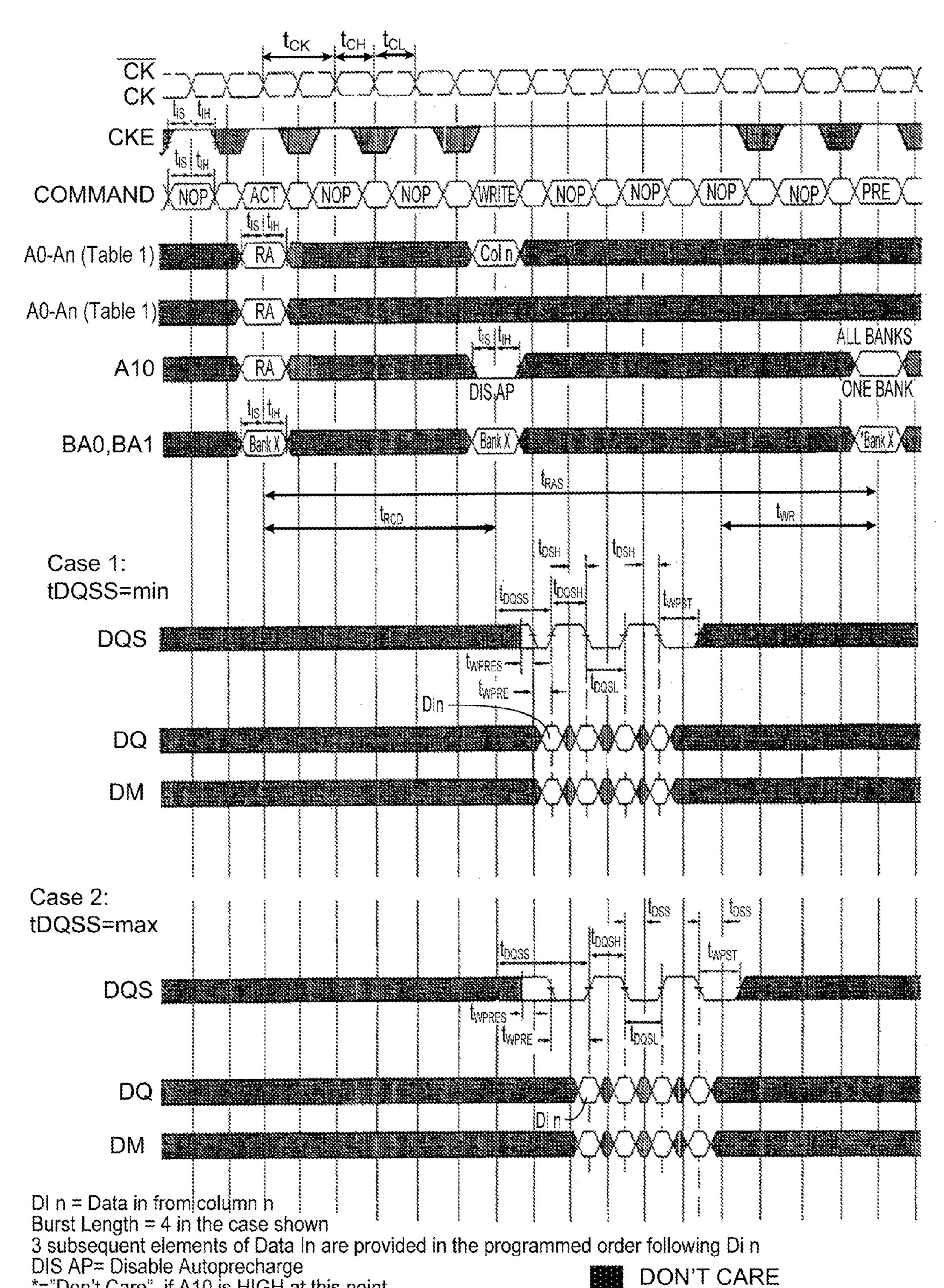

FIG. 1 illustrates a prior art standard (JESD79C) timing diagram for a memory bank write operation. In this standard, a first set of inputs A0-An, A10, BA0 and BA1 are used to input an address and a second set of inputs DQ and DM are used to write data values starting at the address. The data 40 values are written several clock cycles after the address as input.

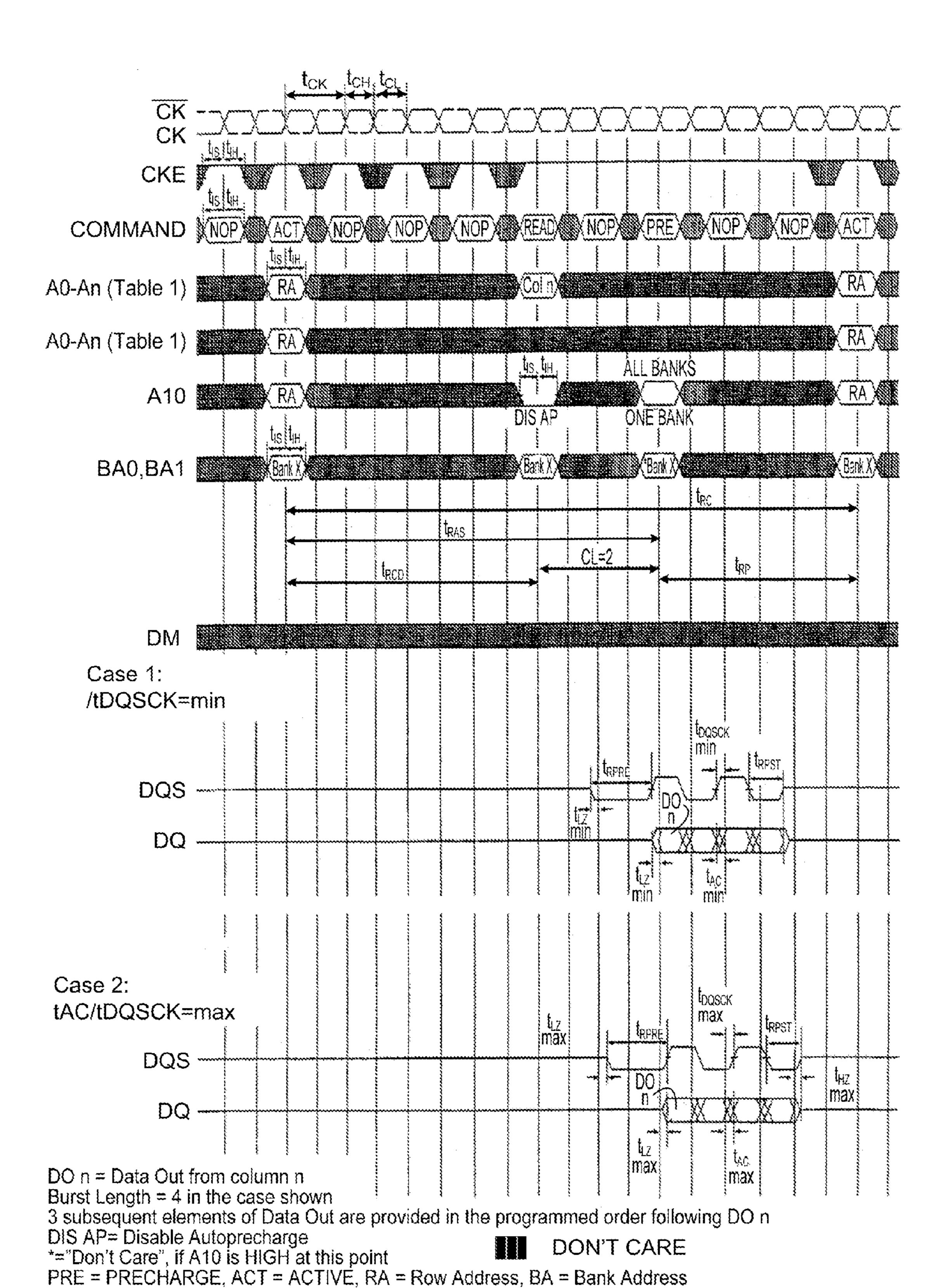

FIG. 2 illustrates a timing diagram for a memory bank read operation according to the prior art standard of FIG. 1. In this operation, inputs A0-An, A10, BA0 and BA1 are used to input 45 an address and DQ and DQS are used to output data stored starting at that address. The data values are read several clock cycles after the address as output.

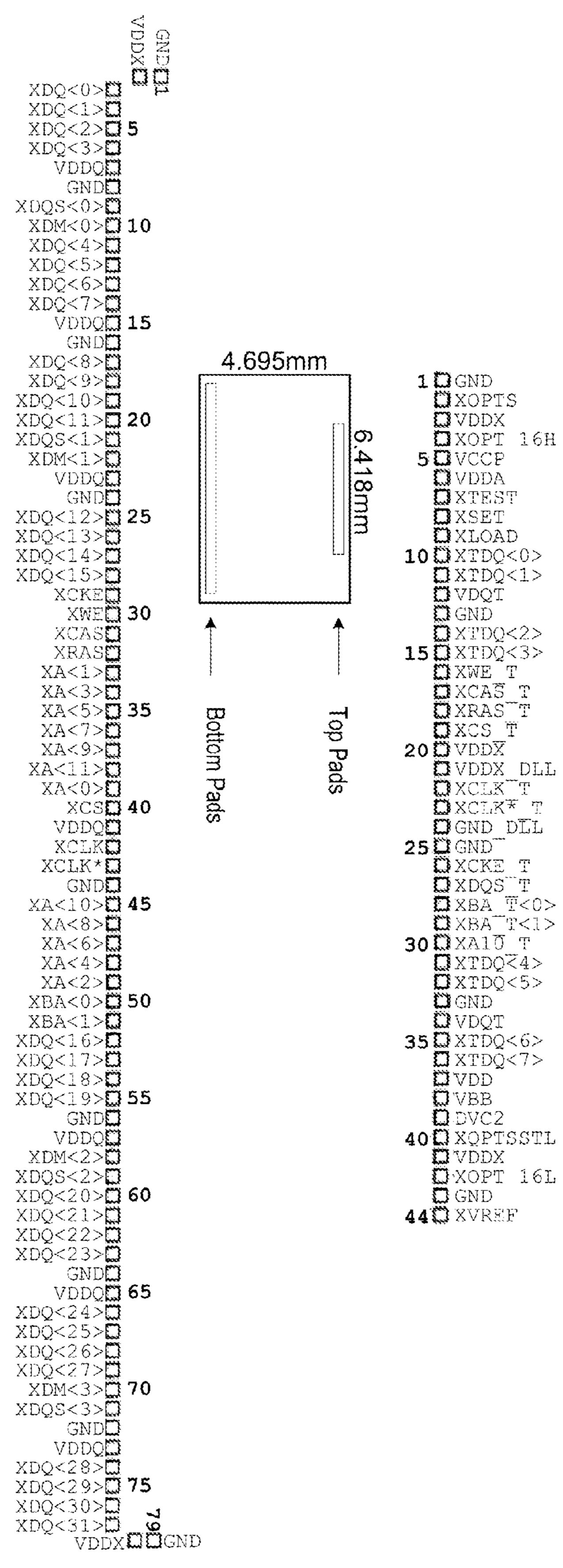

FIG. 3 illustrates a prior art bond pad layout for a memory device proposed by JEDEC. The illustration includes 79 bottom pads and 44 top pads. A variety of data (DQ, DQS and DM), address (A, BA) pads are illustrated. This particular configuration includes 32 DQ pads and, thus, can handle 32-bit data.

# SUMMARY OF THE INVENTION

Various embodiments of the invention include a package having a memory, internal memory contacts on an integrated circuit substrate, and external contacts for communicating 60 signals between the memory contacts and external devices. The internal memory contacts optionally conform to an industry standard such as the JEDEC JESD79E standard or the JEDEC JESD79-2C standard. One or more of the external contacts are shared contacts configured to communicate signals to different members of the memory contacts at different times and/or in different modes. The package may include

2

fewer external contacts than internal memory contacts. By reducing the number of external contacts, smaller package sizes may be achieved.

The package further includes interface circuits disposed between the memory contacts and the shared external contacts. In various embodiments, the interface circuits include latches, multiplexers, PROMs, buffers, and/or the like. In some embodiments, one of the interface circuits is configured to communicate an address signal from an address memory contact to a shared external contact in an address mode, and communicate a data signal between a data memory contact and the shared external contact in a data mode. Alternatively, the interface circuit is configured to communicate an address signal and a control signal, or a data signal and a control signal, between the shared external contact and a respective address memory contact, data memory contact, or control memory contact.

Various embodiments of the invention include a memory device comprising a plurality of memory cells configured to store data, a first memory contact configured to communicate data signals to or from the plurality of memory cells, a second memory contact configured to communicate address signals or command signals to the plurality of memory cells, a shared external contact configured to communicate the data signals in a first mode, and to receive the address signals or the command signals in a second mode, an interface configured to communicate the data signals between the shared external contact and the first memory contact in the first mode, and to communicate the address signals or the command signals from the shared external contact to the second memory contact in the second mode, a control input configured to change a mode of the memory device between the first mode and the second mode, and a semiconductor package including the plurality of memory cells, at least part of the shared electrical 35 conductor, and the interface.

Various embodiments of the invention include a system comprising a semiconductor package, a plurality of memory cells incorporated in the semiconductor package and configured to store data, the memory cells coupled to a first memory contact and a second memory contact, a shared contact at least partially external to the semiconductor package and configured to receive a first signal in a first mode and a second signal in a second mode, a first circuit incorporated in the semiconductor package and configured to communicate the first signal between the shared contact and the first conductor in the first mode, a second circuit incorporated in the semiconductor package and configured to communicate the second signal between the shared contact and the second conductor in the second mode, and a control input to the semiconductor package and configured for changing between the first mode and the second mode.

Various embodiments of the invention include a memory device comprising a plurality of memory cells configured to store data and coupled to a first memory contact and a second memory contact, a shared contact configured to receive a first signal during a first time period and a second signal during a second time period, a circuit configured to communicate the first signal between the shared contact and the first memory contact during the first time period and communicate the second signal between the device contact and the second memory contact during the second time period, and a semi-conductor device package including the plurality of memory cells, at least part of the shared contact, and the circuit.

Various embodiments of the invention include a system comprising a semiconductor package containing a memory configured to store data, a first memory contact electronically coupled to the memory, a second memory contact electroni-

cally coupled to the memory, a first shared contact external to the memory, the first shared contact configured to communicate with a device external to the semiconductor package, and configured to receive a first signal in a first mode and a second signal in a second mode, and at least one multiplexer circuit configured to convey the first signal from the first terminal to the first memory contact when the memory is in the first mode, and to convey the second signal from the first terminal to the second memory contact when the memory is in the second mode.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 illustrates a prior art standard (JESD79C) timing diagram for a memory bank write operation.

FIG. 2 illustrates a timing diagram for a memory bank read operation according to the prior art standard of FIG. 1.

FIG. 3 illustrates a prior art bond pad layout for a memory device proposed by JEDEC.

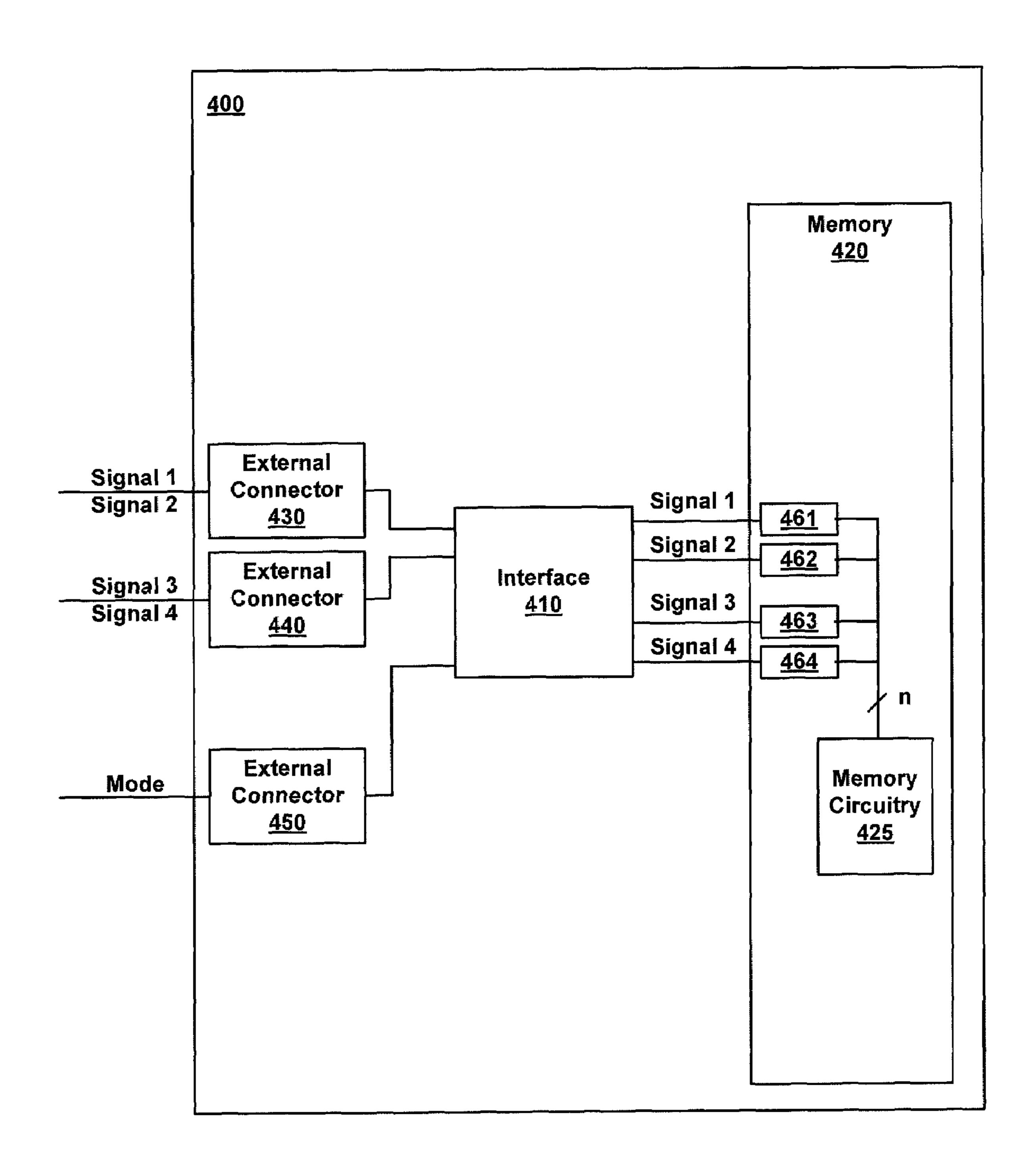

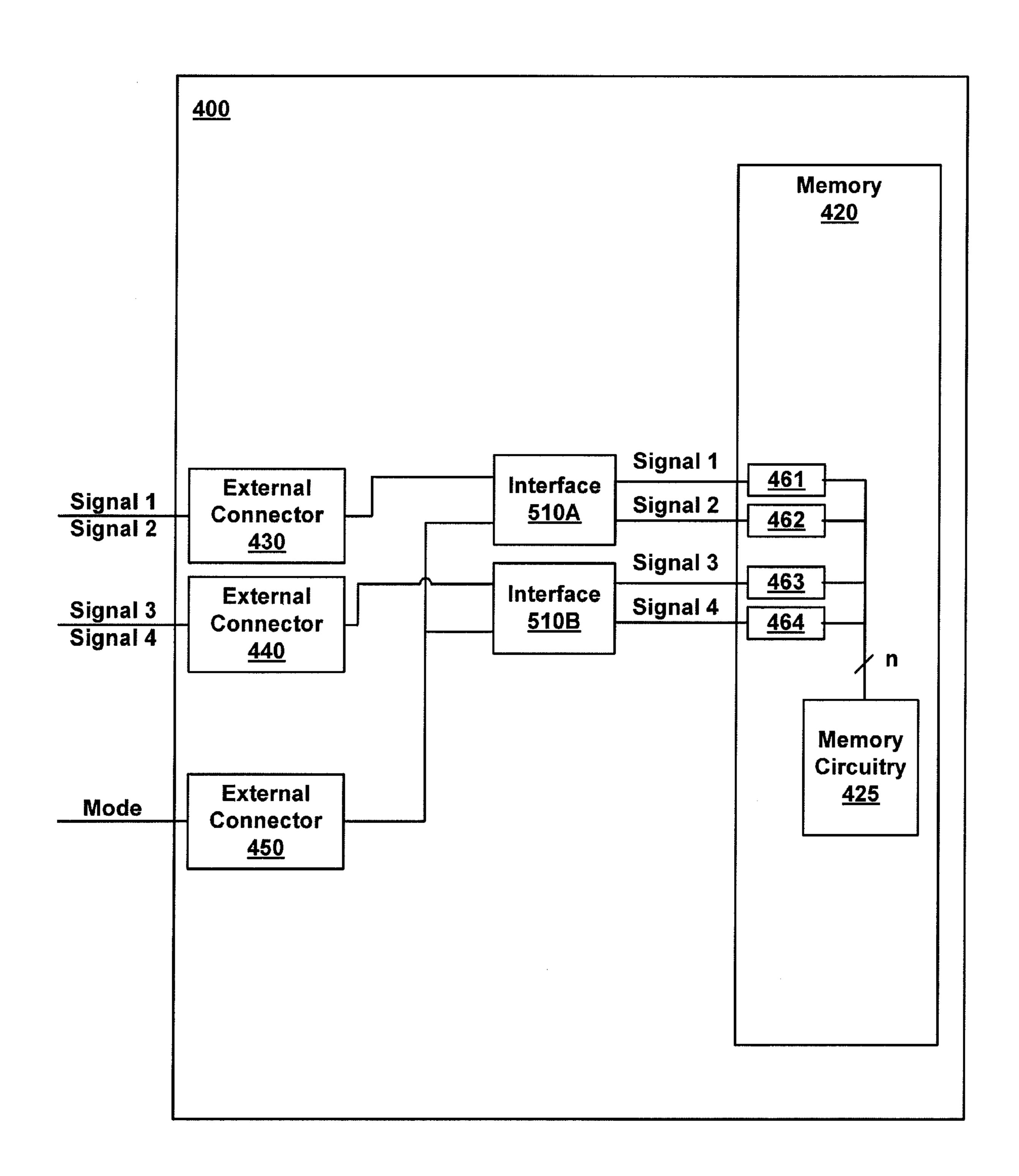

FIG. 4 illustrates a semiconductor package including a memory and an interface in accordance with various embodiments of the invention.

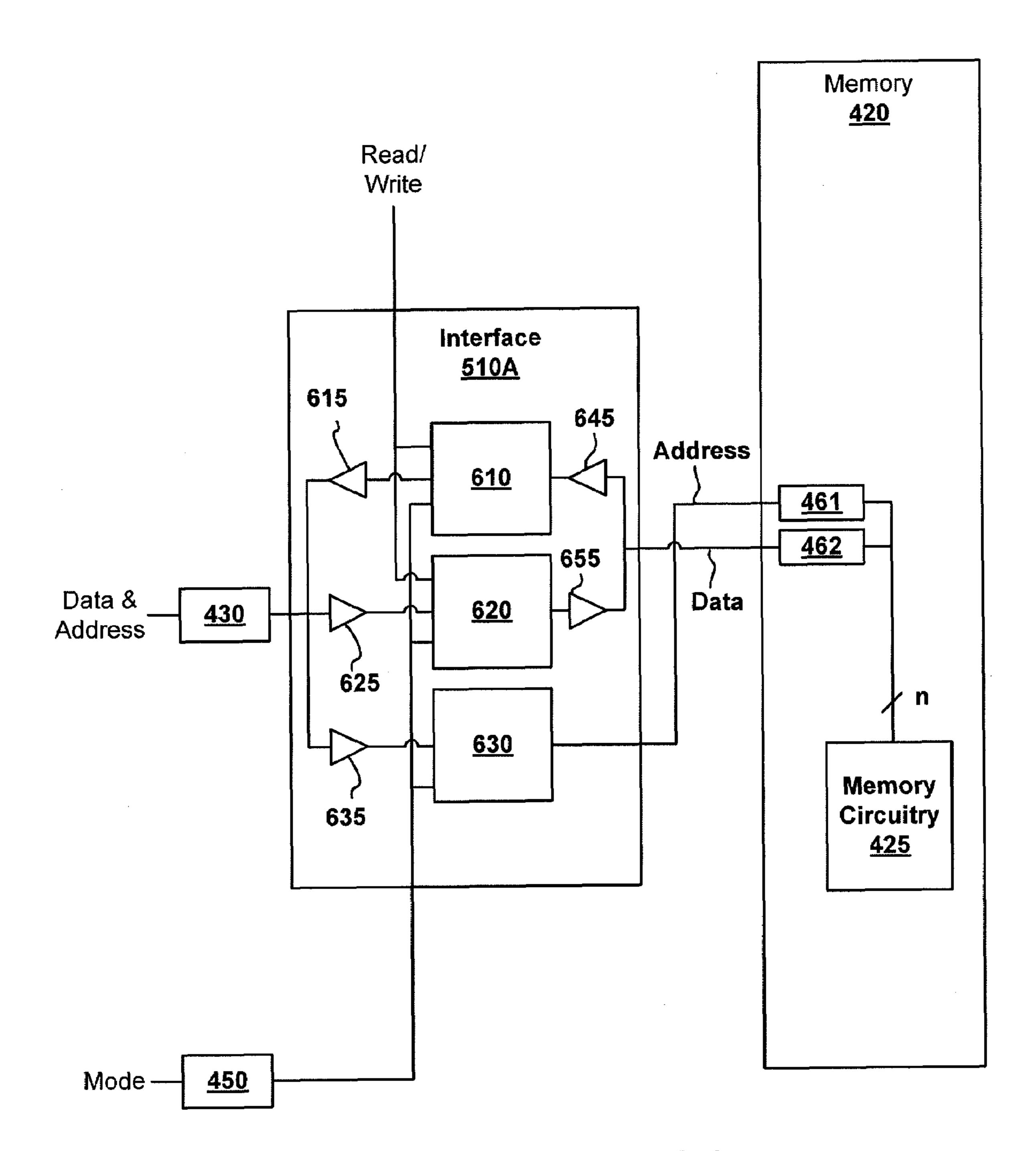

FIG. 5 illustrates the semiconductor package of FIG. 4 including an alternative embodiment of the interface of FIG. 4

FIG. 6 illustrates details of the interface of FIG. 5 according to various embodiments of the invention.

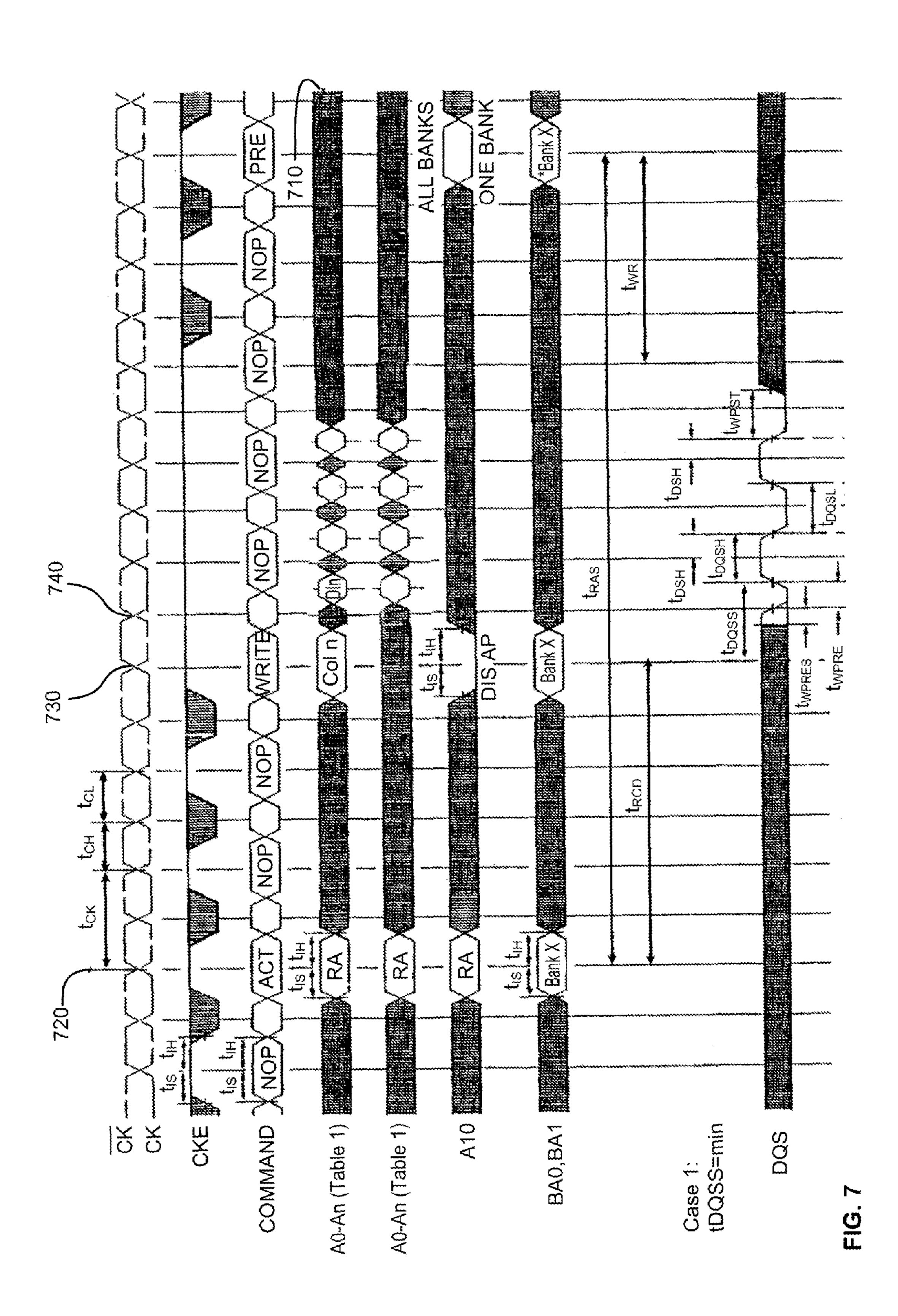

FIG. 7 is a timing diagram illustrating the use of the interface of FIG. 5 for writing data to a memory, according to various embodiments of the invention.

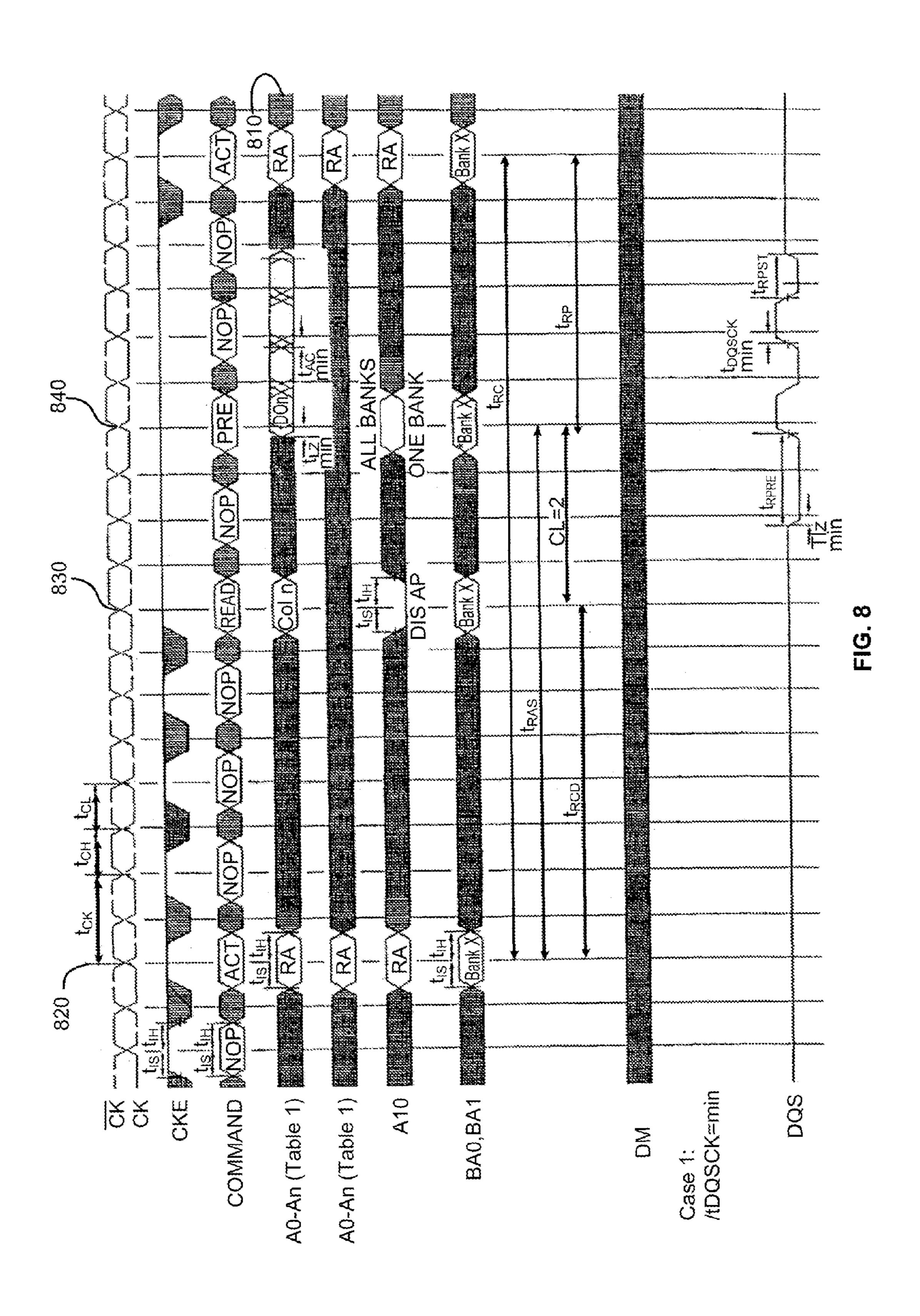

FIG. 8 is a timing diagram illustrating the use of the interface of FIG. 5 for reading data from memory, according to various embodiments of the invention.

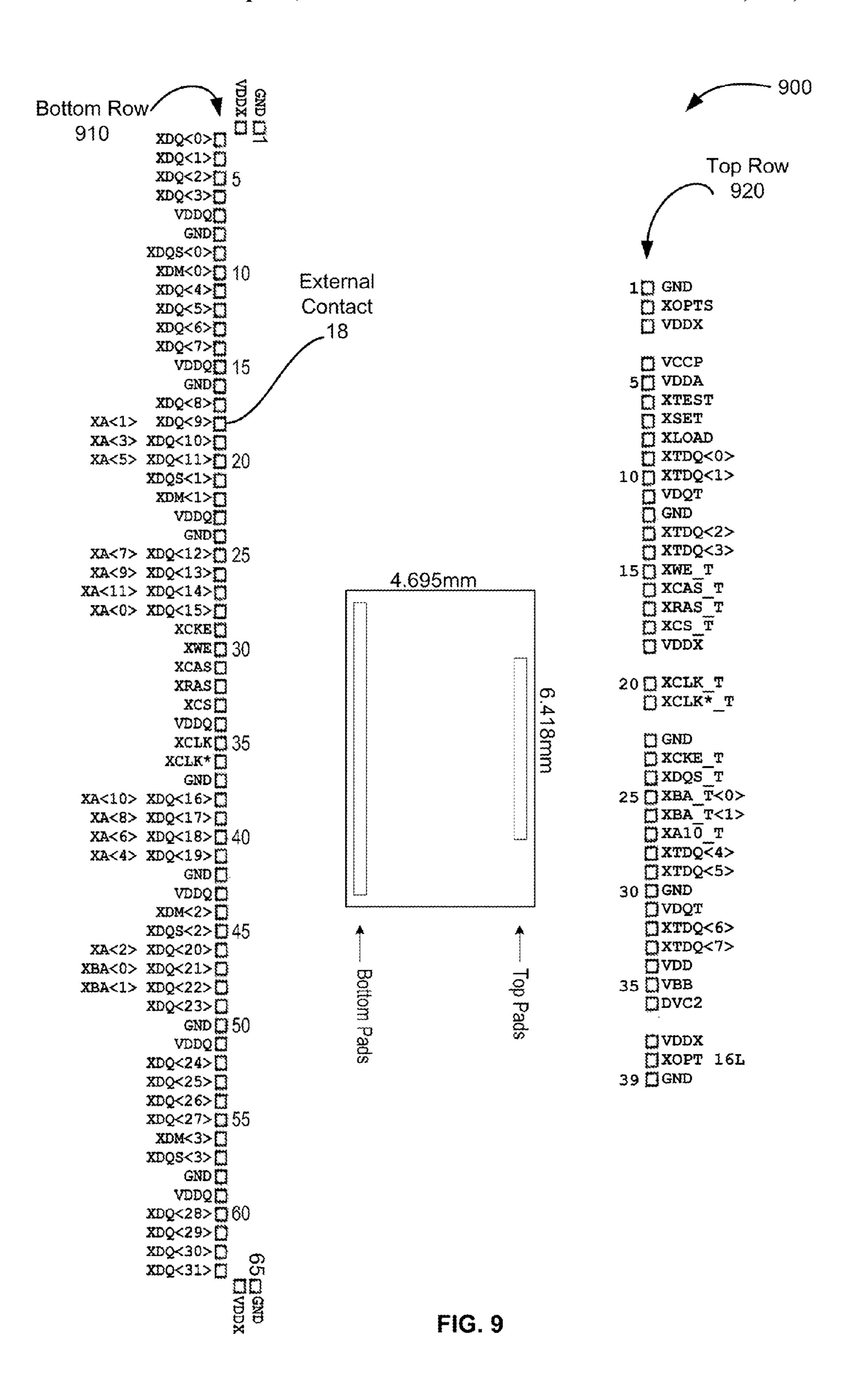

FIG. 9 illustrates an external contact layout for a semiconductor package, according to various embodiments of the invention.

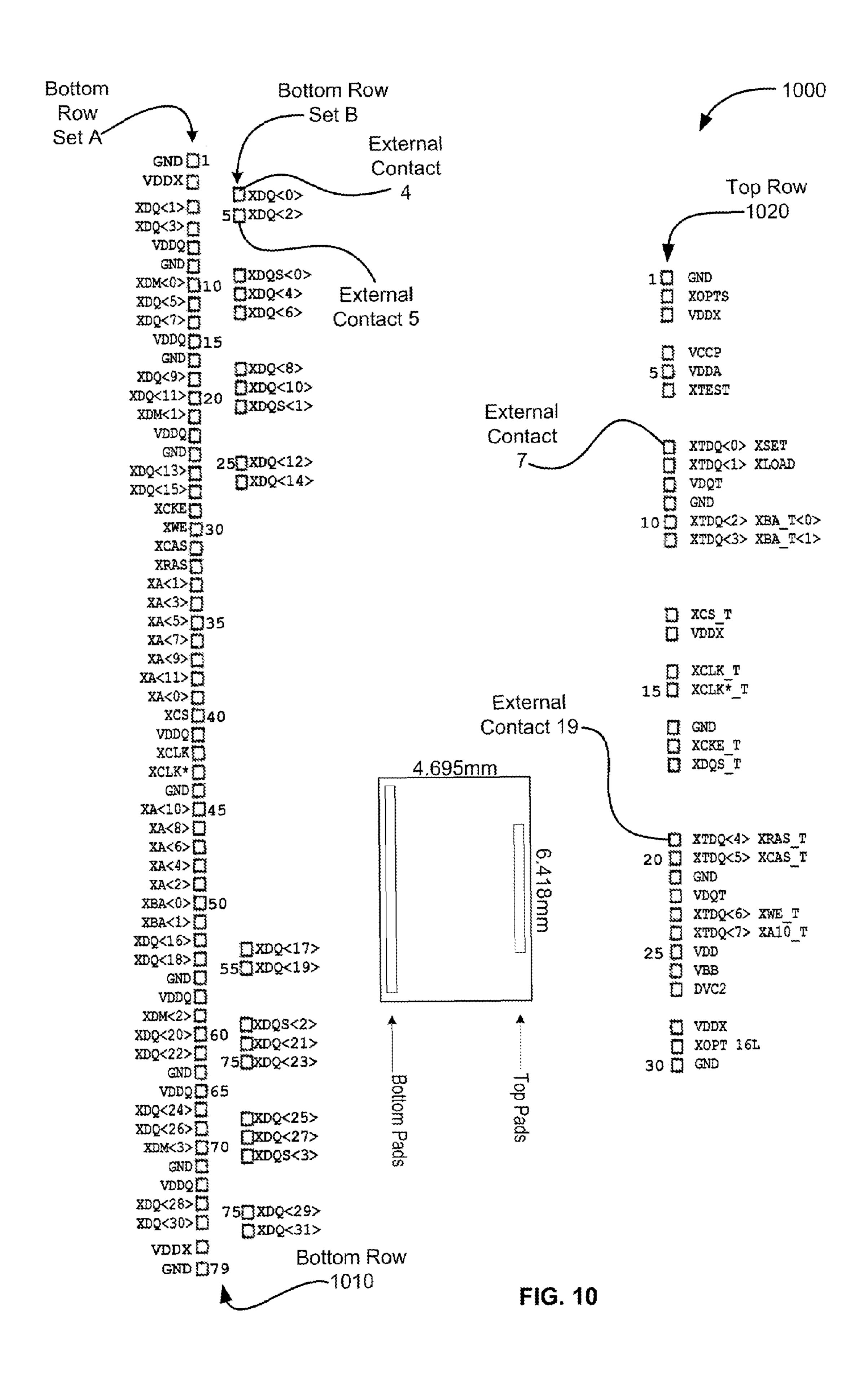

FIG. 10 illustrates an alternative external contact layout for a semiconductor package, according to various embodiments of the invention.

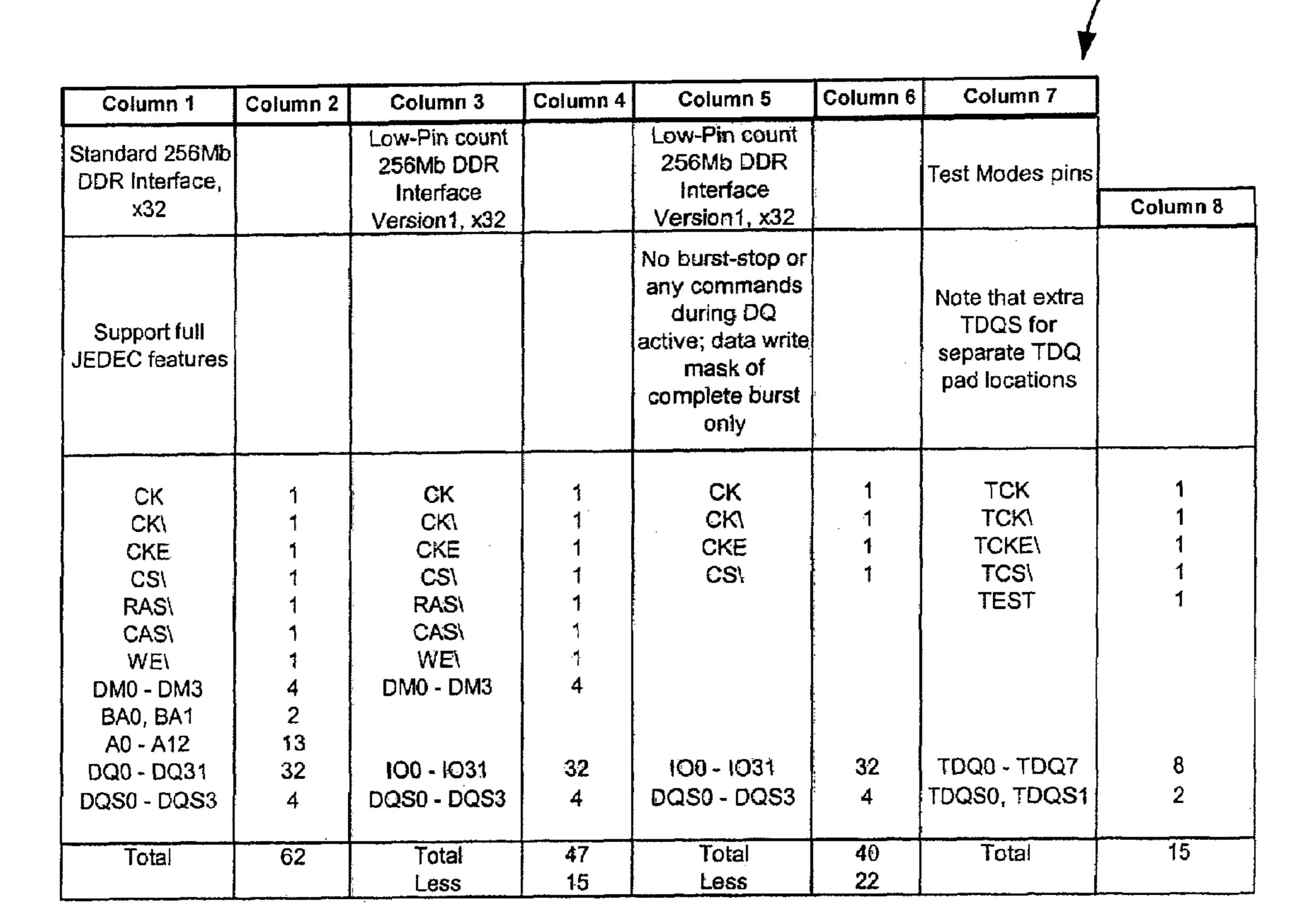

FIG. 11 illustrates an external contact count table, a multiplex I/O pin definition table and a multiplex test I/O pin definition table, according to various embodiments of the invention.

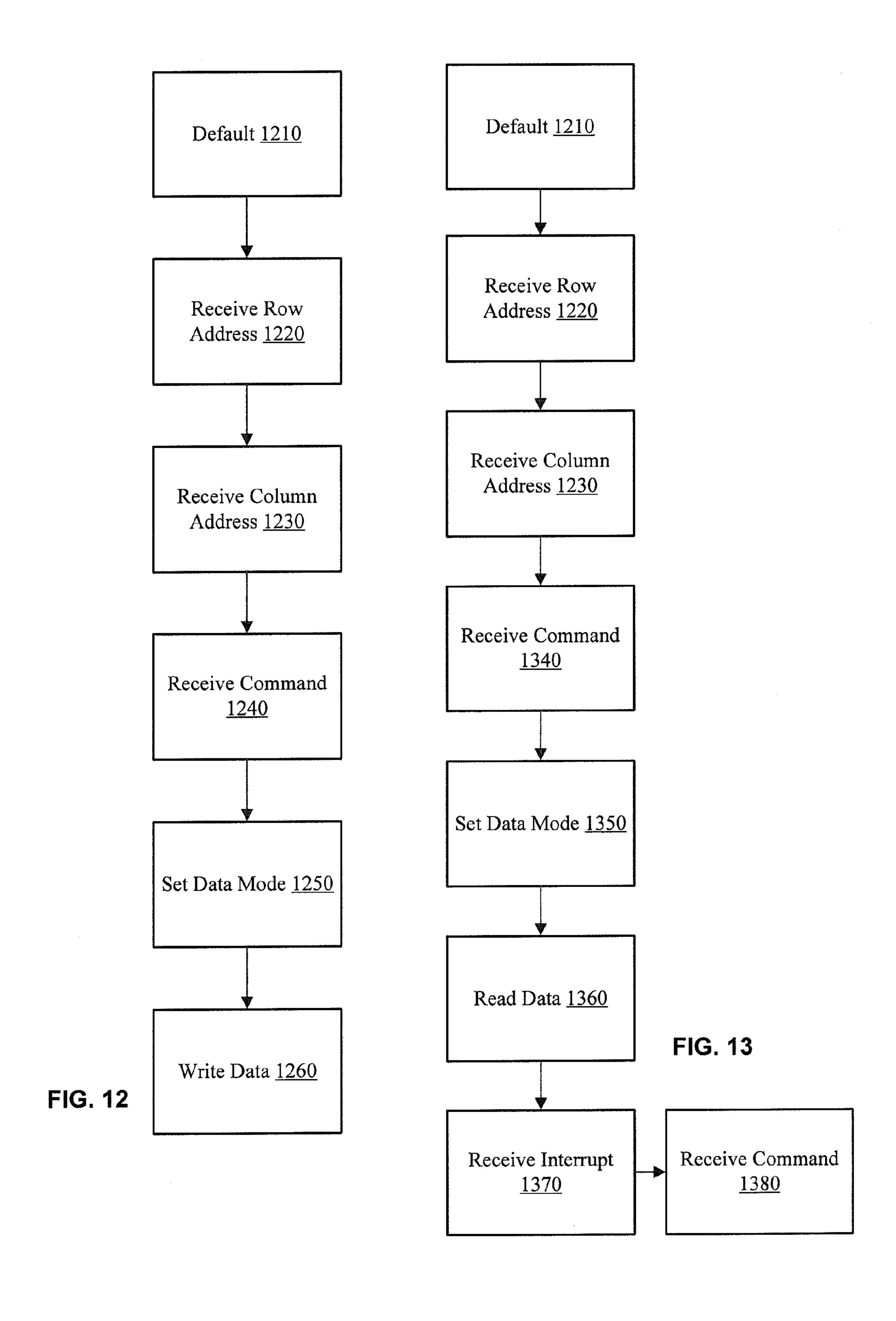

FIG. 12 illustrates methods of writing data to memory 45 according to various embodiments of the invention.

FIG. 13 illustrates methods of reading data from memory according to various embodiments of the invention.

## DETAILED DESCRIPTION

Multiplexing is used to communicate signals between a memory circuit and external contacts. The memory circuit and external contacts may be associated within a SIP (systemin-package), PoP (package-on-package), or the like. In some 55 embodiments the memory circuit includes the testing interface described in U.S. patent application Ser. No. 11/304,445 entitled "Integrated Circuit Testing Module" and filed Dec. 14, 2005, or the testing interface described in U.S. Pat. No. 6,882,171 issued Apr. 19, 2005 both of which are hereby 60 incorporated herein by reference. In various embodiments, the multiplexed signals communicated between the external contacts and the memory circuits include data, addresses, and/or commands. In various embodiments, the multiplexed signals are configured for accessing memory circuits. For 65 example, in some embodiments, addresses and data are communicated through a shared external contact. In various

4

embodiments, addresses and commands, or data and commands are communicated through a shared external contact.

FIG. 4 illustrates a semiconductor package 400 in accordance with various embodiments of the invention. The semiconductor package 400 includes a memory 420, an interface 410 and external contacts, 430, 440 and 450. Although the semiconductor package 400 as illustrated includes an interface 410, a memory 420, and external contacts 430, 440, and 450, the semiconductor package 400 may include fewer or more components and still fall within the scope of various embodiments.

The memory 420 includes memory contacts 461-464 and memory circuitry 425 internal to the memory 420. The memory circuitry includes an array of memory cells and memory interface logic configured to receive signals according to standard communications protocol and provide access to the array of memory cells.

The memory contacts 461-464 are typically physically inaccessible to external devices and are part of the same wafer as the memory circuitry 425. The memory contacts 461-464 are electronically coupled to the memory circuitry 425 via a plurality (e.g., "n") of conductors. The memory contacts 461-464 are configured to communicate signals 1-4 respectively between the interface 410 and the memory circuitry 425 of the memory 420. The memory contacts 461-464 may include a pad, contact, trace, conductor, bond, test point, solder pad, bond pad, contact pad, and/or the like. Although the memory 420 is illustrated as having memory circuitry 425 and memory contacts 461-464, fewer or more memory contacts and/or more memory circuits may be included in the memory 420 and still fall within the scope of various embodiments.

The external contacts 430, 440 and 450 are accessible from outside the semiconductor package 400 and are configured for making electrical contact with one or more external devices (not shown). The external contacts 430, 440 and 450 are not typically part of the wafer on which the memory circuitry 425 is fabricated. The external contacts 430, 440 and 450 may include a connector, pin, post, balls, socket, support balls, wire wrap pin, test point, solder pad, contact pad, and/or the like.

The external contact 430 is configured to communicate a signal 1 and a signal 2 between an external device and the interface 410. The external contact 440 is configured to communicate a signal 3 and a signal 4 between an external device and the interface 410.

External contact **450** is configured to receive a mode signal and couple the mode signal to the interface 410. The mode signal is configured to place the interface 410 alternatively in a first or a second state. In some embodiments, the interface 50 **410** is responsive to the logic state of the mode signal. For example, the interface 410 is placed in the first state when the mode signal is a logical 1 and in the second state when the mode signal is a logical 0. Alternatively, the interface 410 is in the first state unless a logical 1 is asserted by the mode signal. In some embodiments, the interface 410 is responsive to a change of state the mode signal. For example, the interface 410 may default to the first state until receiving a pulse from the mode signal. Then the interface 410 may be placed in the second state for a predetermined period of time and return the first state. The predetermined period of time may be detected using analog circuitry or digital logic (e.g., a clock, a clock and a counter, a clock and a shift register, and/or the like). Alternatively, the interface may change state between the first state and the second state when receiving a pulse from the mode signal. In some embodiments, a serial bit pattern (e.g., 01010) may place the interface 410 in the first state and another logical pattern (e.g., 01100) may place the interface

**410** in the second state. Serial bit patterns may be defined that place the interface **410** in additional states (e.g., 3, 4, 8, 16, or more states).

In some embodiments, external contact 450 is optional. In these embodiments, the interface 410 is by default in a first 5 mode and after receipt of signals in the first mode automatically switches to a second mode. After signals are received in the second mode or after a number of clock cycles, the interface 410 automatically switches back to the first mode. For example, the interface 410 may be by default in an address 10 mode. After address data and a READ or WRITE command are received by the semiconductor package 400, the interface 410 automatically switches to a data mode in which data is communicated through the same shared external contacts as the address data was received. These modes are discussed 15 further elsewhere herein. While the examples discussed herein refer to a mode signal received through the external contact 450, it should be understood that in these examples this mode signal may be generated automatically using circuits within interface 410, and that external contact 450 is 20 optional.

The interface 410 may be a part of the same wafer as the memory circuitry 425. Alternatively, the external contacts 430, 440, and/or 450 may be a part of the interface 410. In some embodiments, the interface 410 includes one or more 25 discrete devices separate from the memory 420 and the external contacts 430, 440, and/or 450. Examples of the interface 410 include multiplexers, buffers, ASICS, and/or the like.

The interface 410 receives the mode signal from the external contact 450. When the mode signal places the interface 30 410 in the first state, the interface 410 is configured to couple signal 1 between the external contact 430 and the memory contact 461 and couple signal 3 between the external contact 440 and the memory contact 463. When the mode signal places the interface 410 in the second state, the interface 410 35 is configured to couple signals 2 and 4 between the external contacts 430 and 440 and the memory contacts 462 and 464 respectively. Thus, one external contact 430 can be shared between the memory contacts 461 and 462. Likewise, one external contact 440 can be shared between the two memory 40 contacts 463 and 464. Thus, the four signals 1-4 can be communicated between memory contacts 461-464 and an external device via two external contacts 430 and 440. In some embodiments, it is assumed that the signal received at external contact 430 is signal 1 unless a received command or 45 other signal (e.g. an internally generated signal or a signal received via external contact 450) indicates otherwise.

In various embodiments, signals 1 and 3 include address signals and signals 3 and 4 include data signals. For example, when mode signal places the interface 410 in the first state, the address signals 1 and 3 are input from the external contacts 430 and 440 via the interface 410 to the memory contacts 461 and 463 respectively. When the mode signal places the interface 410 in the second state during a read operation, the data signals 2 and 4 are output from the memory contacts 462 and 464 via the interface 410 to the external contacts 430 and 440 respectively. Alternatively, during a write operation when the mode signal is in the second state, the data signals 2 and 4 are input to the memory contacts 462 and 464 via the interface 410 from the external contacts 430 and 440 respectively.

In some embodiments, signals 1 and 3 include address signals and signals 2 and 4 included control signals. Alternatively, signals 1 and 3 include data signals and signals 2 and 4 include control signals. In some embodiments, it is assumed that the signal received at external contact 430 is an address signal unless a received command (e.g., a mode signal) or other signal indicates otherwise. While the interface 410 is

6

illustrated as being configured to coupling two shared external contacts to two pair of memory contacts, the interface 410 may be configured to couple more or fewer shared external contacts to pairs of memory contacts and still fall within the scope of various embodiments. For example, the interface 410 may be configured to couple at least 1, 3, 4, 8, 16 or 32 shared external contacts to pairs of memory contacts.

FIG. 5 illustrates the semiconductor package 400 including an alternative embodiment of the interface 410 of FIG. 1. FIG. 5 differs from FIG. 4 in that the interface 410 is shown as two interfaces namely, interface 510A and 510B. External contact 450 is configured to couple the mode signal to both the interface 510A and interface 510B. The mode signal is configured to place the interface 510A and interface 510B alternatively in a first or a second state. As discussed elsewhere herein, the interface 510A and/or 510B may be responsive to the logical state of the mode signal, the change in the mode signal, a serial bit pattern of the mode signal, and/or the like.

The interface 510A is configured to couple the shared external contact 430 to the memory contact 461 while in the first state and couple the shared external contact 430 to the memory contact 462 while in the second state. Likewise, the interface 510B is configured to couple the shared external contact 440 to the memory contact 463 in a first state and to the memory contact 464 in a second state. Thus, the external contact 430 may be shared between the memory contacts 461 and 462 through the interface 510A and the external contact 440 may be shared between the memory contacts 463 and 464 through the interface 510B. Examples of the interface 510A and 510B include gates, multiplexers, latches, buffered latches, ASICS, and/or the like.

In some embodiments, the signals received at external contact 450 are buffered, interpreted or otherwise processed before being used to control the interface 510A. In typical embodiments, the external contacts 430 and 440 are part of a plurality of shared external contacts configured for communicating data in parallel to the memory 420 via a plurality of interfaces 510.

FIG. 6 illustrates details of the interface 510A according to various embodiments of the invention. These embodiments include the external contacts 430, external contact 450, memory contact 461 and memory contact 462. The external contact 440, memory contact 463, and memory contact 464 illustrated in FIGS. 4 and 5 are omitted for clarity. As illustrated in FIG. 6, the external contact 430 is configured to communicate data signals and address signals between an external device (not shown) and the interface 510A. In some embodiments, the external contact 430 is configured to communicate data signals between a first external device and the memory 420, and to communicate address signals between a second external device and the memory 420.

In some embodiments, the mode signal is configured to place the interface 510A in an address mode or a data mode. In the address mode, address signals are communicated from the external device to the memory 420. In the data mode, data signals are communicated between the external device and the memory 420. As discussed elsewhere herein, data may be read and/or written several clock cycles, after the address is sent to the memory 420. Thus, a mode change from the address mode to the data mode may occur one or more clock cycles after the address signals are communicated.

The interface 510A is configured to receive a read/write signal that places the interface 510A in a read state or a write state for controlling whether the data is read from or written to the memory 420. In the read state, data is communicated via the interface 510A from the memory 420 to the external device. In a write state, the data is communicated via the

interface 510A from the external device to the memory 420. In various embodiments, the read/write signal may be received from the memory 420, from another circuit within the semiconductor package 400 or an external device via an external contact (not shown).

The interface **510**A includes latches **610**, **620** and **630**, and buffers **615**, **625**, **645** and **655**. In various embodiments, the buffers **615**, **625**, **645** and/or **655** may be inverting, non-inverting, tri-state, open collector, and/or the like. The latches **610**, **620** and/or **630** may include circuitry (e.g., gates, buffers, counters, multiplexers, and/or the like) for signal manipulation and/or conditioning. The shared external contact **430** is coupled to one or more buffers in the interface **510**A, e.g., the buffers **615**, **625** and **635**. The external contact **450** couples the mode signal to one or more latches **610**, **620**, and **630**.

The mode signal places the interface 510A in the address mode by disabling the latches 610 and 620 and enabling the latch 630. When the interface 510A is in the address mode, the buffer 635 is configured to receive an address signal from the external contact 430 and provide the address signal into the 20 latch 630. The latch 630 is configured to latch the address signal and provide the address signal to the memory contact 461.

After receiving an address signal in the address mode, the mode signal can place the interface 510A in the data mode by disabling the latch 630 and enabling the latches 610 and 620. In the data mode, the interface 510A is configured to either communicate data from the memory 420 to the external device in the read state, or communicate data from the external device to the memory 420 in the write state.

For reading data, the read/write signal is configured to place the interface 510 in a read state by disabling the latch 620 and the leaving latch 610 enabled. While the interface 510A is in the data mode and the read state, the memory contact 462 is configured communicate a data signal from the 35 memory circuitry 425 to the buffer 645 in the interface 510A. The buffer 645 is configured to communicate the data signal to the latch 610, which is configured to latch and provide the data signal to the buffer 615. The external contact 430 is configured to communicate the data signal from the buffer 615 to the external device. During a block read, the interface 510A may remain in the data mode for multiple clock cycles while the memory circuitry 425 provides multiple data signals to the external device through the memory contact 462, buffer 645, latch 610, buffer 615 and external contact 430.

For writing data, the read/write signal is configured to place the interface 510 in the write state by disabling the latch 610 and leaving the latch 620 enabled. While the interface is in the data mode and the write state, the external contact 430 is configured to communicate a data signal from the external device to the buffer 625 in the interface 510A. The buffer 625 is configured to provide the data signal to the latch 620 for output to the buffer 655. The memory contact 462 is configured to communicate the data signal from the buffer 655 to the memory circuitry 425. During a block write, the interface 55 510A may remain in the data mode for multiple clock cycles while the external device provides multiple data signals to the memory circuitry 425 through the external contact 430, buffer 625, latch 620, buffer 655, and memory contact 462.

Thus, the external contact 430 is configured to communicate both address and bidirectional data. The external contact 430 can communicate address signals while the interface 510A is in the address mode, and can communicate both read data and write data while the interface 510A is in the data mode.

FIG. 7 is a timing diagram illustrating the use of the interface 510A for writing data to the memory 420, according to

8

various embodiments of the invention. The address signals and the data signals in FIG. 7 are both communicated through the external contact 430. The signals at the external contact **430** are illustrated by a Timing Trace **710**. At a Third Clock 5 Cycle **720**, an ACT command and row address signals are received. At a Tenth Clock Cycle 730 a WRITE command and column address signals are received. The WRITE command is configured to set latches 610, 620 and 630 in a state for receiving data signals rather than address signals. In some embodiments, external contact 450 is one of the external contacts used to receive the WRITE command. In some embodiments, WRITE command is used by circuitry within semiconductor package 400 to generate a mode signal. At approximately an Eleventh Clock Cycle 740, data signals are received at the external contact 430. Interface 510A is optionally automatically returned to the address mode after the data signals are received. The various clock cycles discussed herein represent different time periods.