#### US007567264B2

### (12) United States Patent

#### Izumiya

## (10) Patent No.: US 7,567,264 B2 (45) Date of Patent: Jul. 28, 2009

## (54) COLLOR IMAGE FORMING APPARATUS HAVING MAGNIFICATION CORRECTION FUNCTION

(75) Inventor: Kenji Izumiya, Hachioji (JP)

(73) Assignee: Konica Minolta Business Technologies,

Inc. (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 239 days.

(21) Appl. No.: 11/438,726

(22) Filed: May 22, 2006

(65) Prior Publication Data

US 2007/0064088 A1 Mar. 22, 2007

(30) Foreign Application Priority Data

(51) Int. Cl.

B41J 17/00 (2006.01)

B41J 2/435 (2006.01)

See application file for complete search history.

(56) References Cited

U.S. PATENT DOCUMENTS

| 6,628,424    | B2         | 9/2003 | Sakurai               |

|--------------|------------|--------|-----------------------|

| 6,839,078    | B2 *       | 1/2005 | Izumiya et al 347/249 |

| 6,856,336    | B2 *       |        | Toyoda 347/116        |

| 2003/0174200 | A1         |        | Izumiya et al.        |

| 2006/0158712 | <b>A</b> 1 |        | Higashi et al.        |

#### FOREIGN PATENT DOCUMENTS

EP 0 291 738 A1 11/1988 JP 09-230273 9/1997

#### OTHER PUBLICATIONS

European Search Report for Application No. 06114356.6-2202 mailed Jan. 19, 2007.

\* cited by examiner

Primary Examiner—Hai C Pham (74) Attorney, Agent, or Firm—Cantor Colburn LLP

#### (57) ABSTRACT

An image forming apparatus for forming color images may include at least two or more colors, having a function of magnification correction of image size by one page unit, the image forming apparatus including: an image carrier; a polygonal mirror rotator independently provided for each color; and a controller which simultaneously conducts first control for changing rotation speed of the polygonal mirror rotator in order for changing image size in a sub-scanning direction perpendicular to a main scanning direction, and second control for correcting a correction amount for color registration error depending on magnification correction of image size, and for adjusting a rotating phase of the polygonal mirror rotator depending on the corrected correction amount for color registration error.

#### 5 Claims, 19 Drawing Sheets

CONFIGURATION EXAMPLE OF COLOR FIG. 1 COPIER 100 AS 1ST EMBODIMENT

Jul. 28, 2009

FIG. 2 CONFIGURATION EXAMPLE OF CONTROL SYSTEM IN COLOR COPIER 100

FIG. 4

# CONFIGURATION EXAMPLE OF POLYGON MIRROR DRIVE SYSTEM FOR EACH COLOR IMAGE FORMATION

OPERATION EXAMPLE AFTEF CONTROL IN IMAGE FORMING

- (Y-COLOR BASIS)

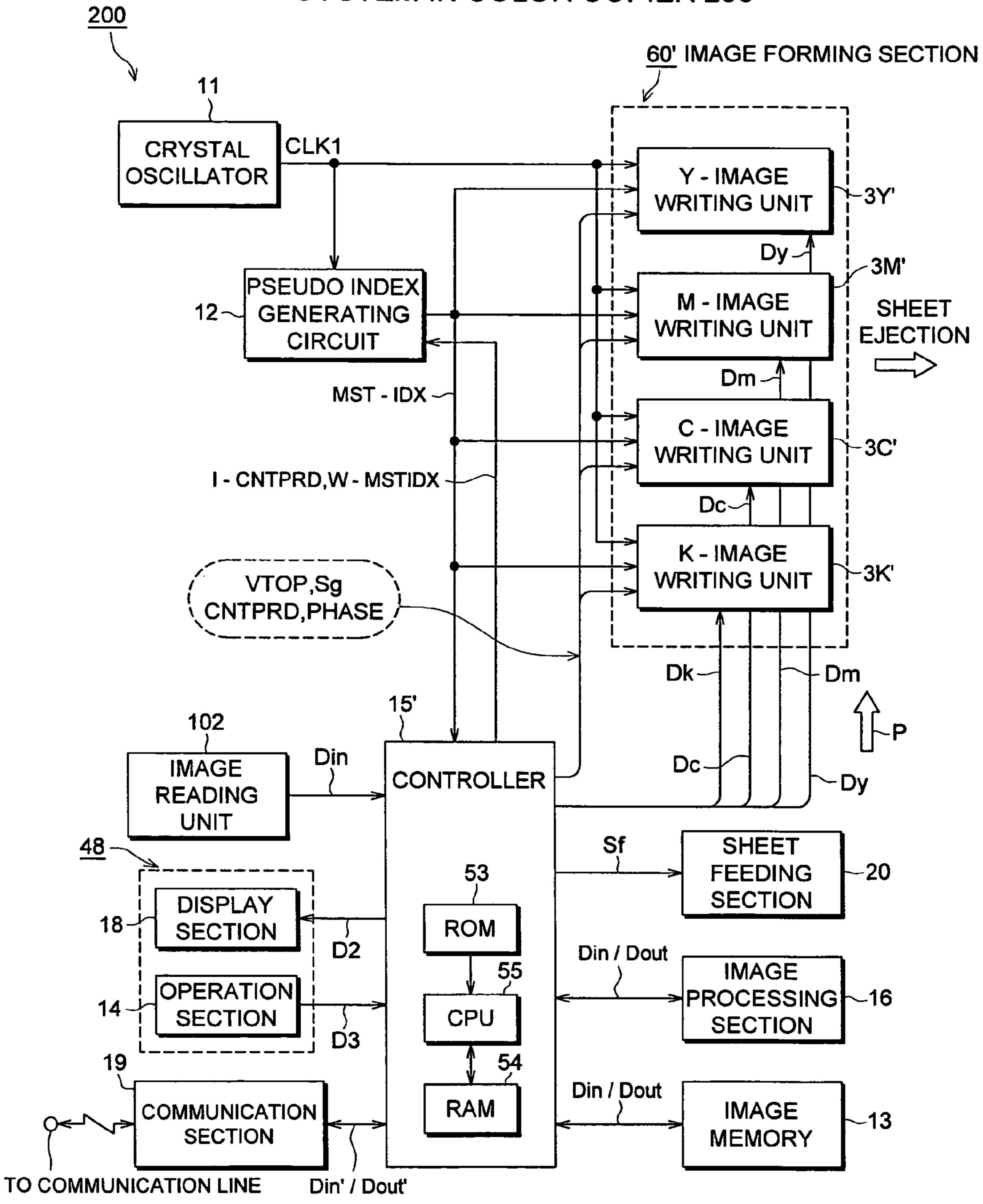

FIG. 8 CONFIGURATION EXAMPLE OF CONTROL SYSTEM IN COLOR COPIER 200

FIG. 10

# CONFIGURATION EXAMPLE OF POLYGON MIRROR DRIVE SYSTEM INCLUDING PSEUDO IDX GENERATING CIRCUIT

OPERATION EXAMPLE BEFORE MAGNIFICATION CONTROL (MST-IDX BASIS)

OPERATION EXAMPLE AFTER MAGNIFICATION CONTROL (MST-IDX BASIS)

FIG. 14

# CONFIGURATION EXAMPLE OF CONTROL SYSTEM IN COLOR COPIER 300 OF 3RD

# EXAMPLE OF PAPER SIZE SHRINKAGE IN DOUBLE FACE IMAGE FORMATION

## FIG. 17

POLYGON DRIVE CLK

$$F = \frac{L}{L'} \cdot F0$$

PIXEL CLK FREQUENCY  $F = \frac{L'}{L} \cdot \frac{W}{W'} \cdot f0$

F0: POLYGON DRIVE CLK FREQUENCY FOR FRONT FACE IMAGE FORMATION

F: POLYGON DRIVE CLK FREQUENCY FOR REAR FACE IMAGE FORMATION

f0: PIXEL CLK FREQUENCY FOR FRONT FACE IMAGE FORMATION

f: PIXEL CLK FREQUENCY FOR REAR FACE IMAGE FORMATION

Jul. 28, 2009

SIZE

## COLLOR IMAGE FORMING APPARATUS HAVING MAGNIFICATION CORRECTION FUNCTION

### CROSS REFERENCE TO RELATED APPLICATION

The present application is based on Japanese Patent Application No. 2005-274553 filed with Japan Patent Office on Sep. 21, 2005, the entire content of which is hereby incorporated by reference.

#### BACKGROUND OF THE INVENTION

#### 1. Technical Field

The present invention relates to an image forming apparatus that is preferably applied to a black-and white or color digital multifunctional machine equipped with copying functions, facsimile functions and printer functions and to a copier.

#### 2. Description of Related Art

In recent years, there has come to be put to practical use a digital color copier that conducts color image forming based on color image data relating to red (R) color, green (G) color and blue (B) color acquired from colored document images. 25 In the copier of this kind, image information of the document is read by a scanner, and color image data relating to image information of the document are acquired.

Further, a laser recording apparatus is mounted on the copier, and a laser beam emitted from a semiconductor laser 30 light source is used for exposure scanning on a photoreceptor drum having thereon prescribed voltage to record images, depending on YMCK image data which are obtained by color-converting RGB image data acquired from a scanner into image data of yellow (Y) color, magenta (M) color, cyan 35 (C) color and black (K) color. Images recorded on the photoreceptor drum are developed by each toner of each color, then, colors are superposed on an intermediate transfer body, for example, and each image is transferred onto a prescribed sheet from the intermediate transfer body, to be fixed. As a 40 result, a color document image can be copied.

In a field of the color image forming apparatus of this kind, an apparatus wherein a color image can be formed on each of both sides of the sheet has been developed and is manufactured. Double-face forming functions are used for forming an image for a front cover on a sheet and for forming an image for a back cover on a sheet, when creating a booklet, for example. In many cases, a sheet that is thicker than a sheet mentioned in the text is used as a sheet for each of the front cover and back cover.

Sheets for the front cover and the back cover after double-face image forming are supposed to be subjected to post-processing such as center-folding and staple processing. In the double-face image forming processing of this kind, it is known that, after an image is formed on one side of a sheet, 55 the sheet shrinks. The reason for this phenomenon is that a sheet onto which a color toner image has been transferred is subjected to thermal shrinkage by fixing processing, and the thicker the sheet is, the more remarkable the shrinkage is.

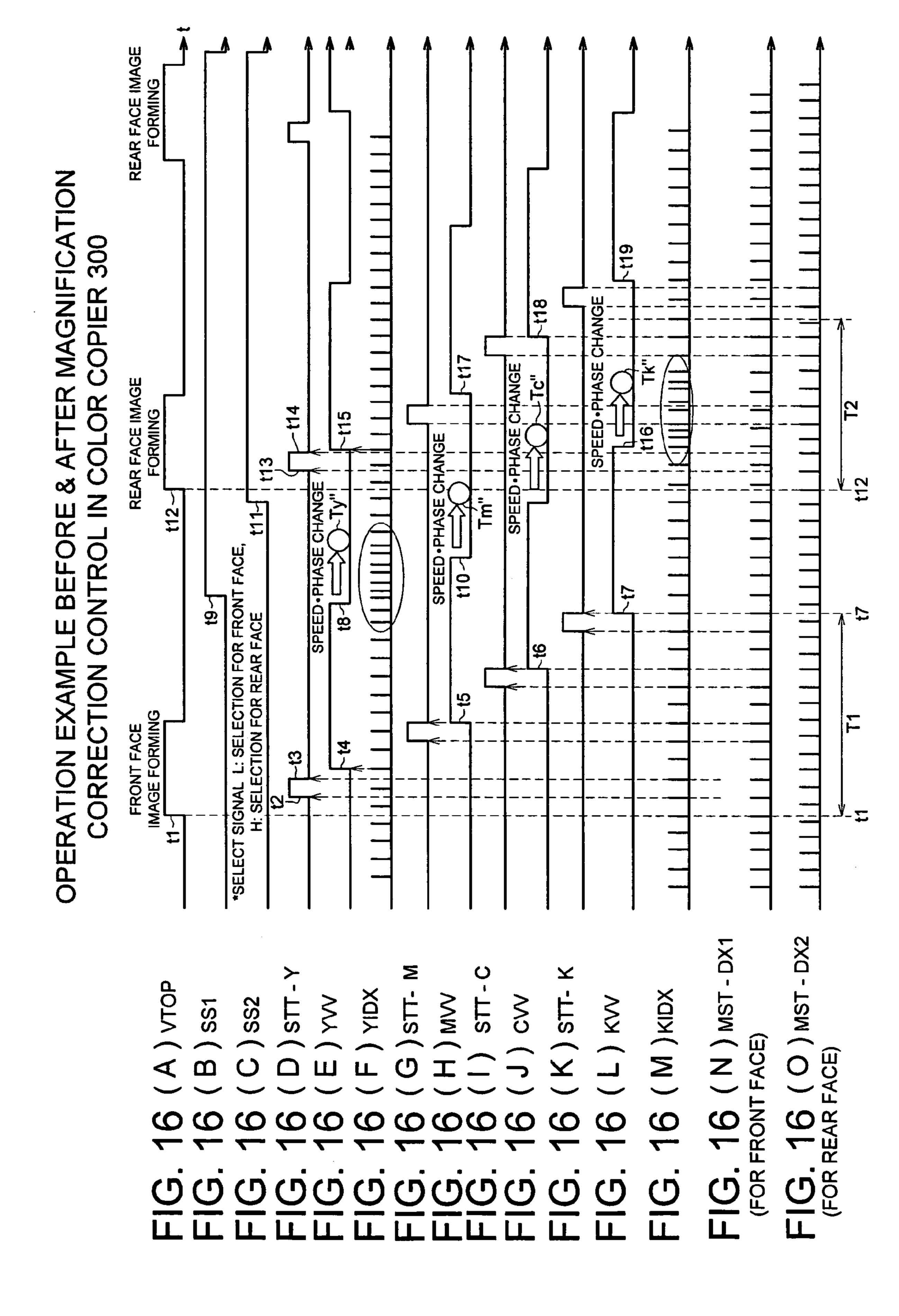

Each of FIGS. 17(A) and 17(B) is a diagram illustrating an 60 example of shrinkage of sheet size in the case of double-face image forming. Sheet P shown in FIG. 17 (A) is in the state before fixing after being subjected to secondary transfer of color toner images. In sheet sizes for sheet P, a longitudinal length is L mm, and a lateral width is W mm. Sheet P' shown 65 in FIG. 17(B) is in the state after fixing of sheet P. In sheet sizes for sheet P', a longitudinal length is constricted to L'

2

mm, and a lateral width is constricted to W' mm. The reason for shrinkage of sheet sizes is considered to be moisture dessipation in the course of fixing. An image needs to be formed on the rear face of the sheet, taking such shrinkage of sheet sizes of sheet P into consideration. Incidentally, if image forming conditions are not adjusted to sheet sizes L' mm×W' mm after shrinkage, an image forming position (size) for the front face is deviated from that for the rear face.

A driving clock (hereinafter referred to as CLK) frequency of a polygon motor is changed, taking such shrinkage of sheet sizes of sheet P into consideration. When F0 represents polygon driving CLK frequency before shrinkage, namely, in the course of image forming on the front face, and F represents polygon driving CLK frequency after shrinkage, namely, in the course of image forming on the rear face, establishment is made so that F=F0×L/L' may hold.

Further, pixel CLK frequency that controls a laser beam is changed. When f0 represents pixel CLK frequency before shrinkage and f represents pixel CLK frequency after shrinkage, establishment is made so that f=(L/L')×(W/W')×f0 may hold. By changing a polygon driving CLK frequency and a pixel CLK frequency, in consideration of shrinkage in sheet sizes for sheet P as stated above, it is possible to obtain images which are well-registered between the front face and the rear face.

Further, when the polygon driving CLK frequency is changed from F0 to F under the assumption that V0 represents a process linear speed before shrinkage, G0 represents a gap between processes before shrinkage, process gap G represents a distance between units and V represents a process linear speed, apparent process linear speed V is changed as shown below.

- (1) Apparent process linear speed V=V0×F0/F=v0×L'/L

- (2) Gap between processes G (pixel)=G0×V0/V=G0×L/L'

In this case, the process linear speed V corresponds to a rotation speed of a photoreceptor representing an image carrier on which an image is formed.

Therefore, correction for an amount of front-face/rear-face magnification change (which is also called front-face/rear-face magnification correction or image size correction, after this) is needed even for a correction amount for color registration error which corresponds to gap between processes G. Accordingly, a polygon mirror which requires plane phase adjustment is subjected to practice of plane phase control when switching between front face and rear face. Control of the rotation speed of the polygon mirror and control of plane phase of a polygon mirror for each color of Y, M and C are practiced not only for double-face image forming processing but also for switching of trays.

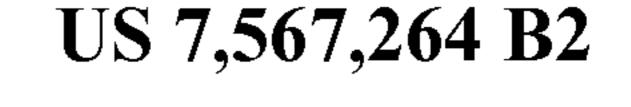

For practicing image size correction in the case of switching between the front face and the rear face of a sheet or between trays, there is employed a method to control a rotation speed and a phase of a polygon mirror. Each of FIGS. **18**(A)-**18**(I) is a time chart showing an example of image forming operations (for Y color) in the case of switching trays in an image writing unit for each of Y, M, C and K, relating to the conventional example.

A VTOP signal shown in FIG. 18(A) is a signal that rises in synchronization with an index signal (hereinafter referred to as KIDX signal) for forming K color images shown in FIG. 18(I), after a leading edge of the sheet fed out of tray 1 is detected by an unillustrated leading edge detection sensor. YVV start timing shown in FIG. 18(B) is for a signal that rises in synchronization with KIDX signal, where an unillustrated KIDX counter is started, and the number of pulses for KIDX signal is counted.

AYVV signal shown in FIG. 18(C) is a signal that rises in synchronization with an index signal (hereinafter referred to as YIDX signal) for forming Y color images shown in FIG. 18(D). During the period of "H" level of the YVV signal, an image in Y color is formed on a sheet coming from tray 1, and after completion of the foregoing, there is made control for changing a rotation speed of a polygon mirror for forming an image in Y color. In this case, a frequency of the YIDX signal is fluctuated-until the rotation speed of the polygon mirror is stabilized. With regard to the sheet for second page fed out of tray 2, image forming for Y color is started after waiting for stabilizing time Ty1 during which a rotation of the polygon mirror is stabilized.

In the same way, during the period of "H" level of the MVV signal shown in FIG. **18**(E), an image in M color is formed on a sheet coming from tray **1**, and after completion of the foregoing, there is made control for changing a rotation speed of a polygon mirror for forming-an image in M color. In this case, a frequency of the MIDX signal is fluctuated until the rotation speed of the polygon mirror for M color is stabilized. Phase change is controlled after waiting for stabilizing time Tm1 during which a rotation of the polygon mirror is stabilized. With regard to the sheet for second page fed out of tray **2**, image forming for M color is started after waiting for stabilizing time Tm2 during which a rotation of the polygon 25 mirror for M color is stabilized.

Further, during the period of "H" level of the CVV signal shown in FIG. 18(F), an image in C color is formed on a sheet coming from tray 1, and after completion of the foregoing, there is made control for changing a rotation speed of a 30 polygon mirror for forming an image in C color. In this case, a frequency of the CIDX signal is fluctuated until the rotation speed of the polygon mirror for C color is stabilized. Phase change is controlled after waiting for stabilizing time Tc1 during which a rotation of the polygon mirror is stabilized. 35 With regard to the sheet for second page fed out of tray 2, image forming for C color is started after waiting for stabilizing time Tc2 during which a rotation of the polygon mirror for C color is stabilized.

Further, KTV start timing shown in FIG. **18**(G) is for a signal that rises in synchronization with KIDX signal, where an unillustrated KIDX counter is started, and the number of pulses for KIDX signal is counted KVV signal shown in FIG. **18**(H) is a signal that rises in synchronization with KIDX signal shown in FIG. **18**(I). During the period of "H" level of the KVV signal, an image in K color is formed on a sheet coming from tray **1**, and after completion of the foregoing, there is made control for changing a rotation speed of a polygon mirror for forming an image in K color.

In this case, a frequency of the KIDX signal is fluctuated 50 until the rotation speed of the polygon mirror for K color is stabilized. Phase change is controlled after waiting for stabilizing time Tk1 during which a rotation of the polygon mirror is stabilized. With regard to the sheet for second page fed out of tray 2, image forming for K color is started after waiting for 55 stabilizing time Tk2 during which a rotation of the polygon mirror for K color is stabilized. In the example of image forming operations in the case of switching trays mentioned above, controls of rotation speed of polygon mirror for forming an image in each of Y, M and C colors and of a phase are 60 practiced after the control of rotation speed of a polygon mirror for forming an image in K color has been completed, because it is carried out based on KIDX signals.

In association with the aforesaid control of a polygon mirror, a laser beam scanning apparatus is disclosed in Patent 65 Document 1. In this laser beam scanning apparatus, there is provided a rotation phase calculating section that calculates a

4

time difference between an optical beam detection signal corresponding to a reference polygon mirror and an optical beam detection signal [corresponding to a polygon mirror other than the reference polygon mirror, and compares phase control data based on the time difference with phase control data corresponding to a reference polygon mirror, to generate a rotation frequency. By providing such rotation phase calculating section, an orientation of the mirror surface of the polygon mirror can be controlled simply.

Patent Document 1: Unexamined Japanese Patent Application Publication NO. 9-230273 (FIG. 1 on page 5)

Incidentally, in the image forming apparatus applied by the inventors of the present invention, there is employed a method to correct magnifications for the front face and the rear face by changing rotation speed and phase of the polygon mirror by the use of pseudo index signals.

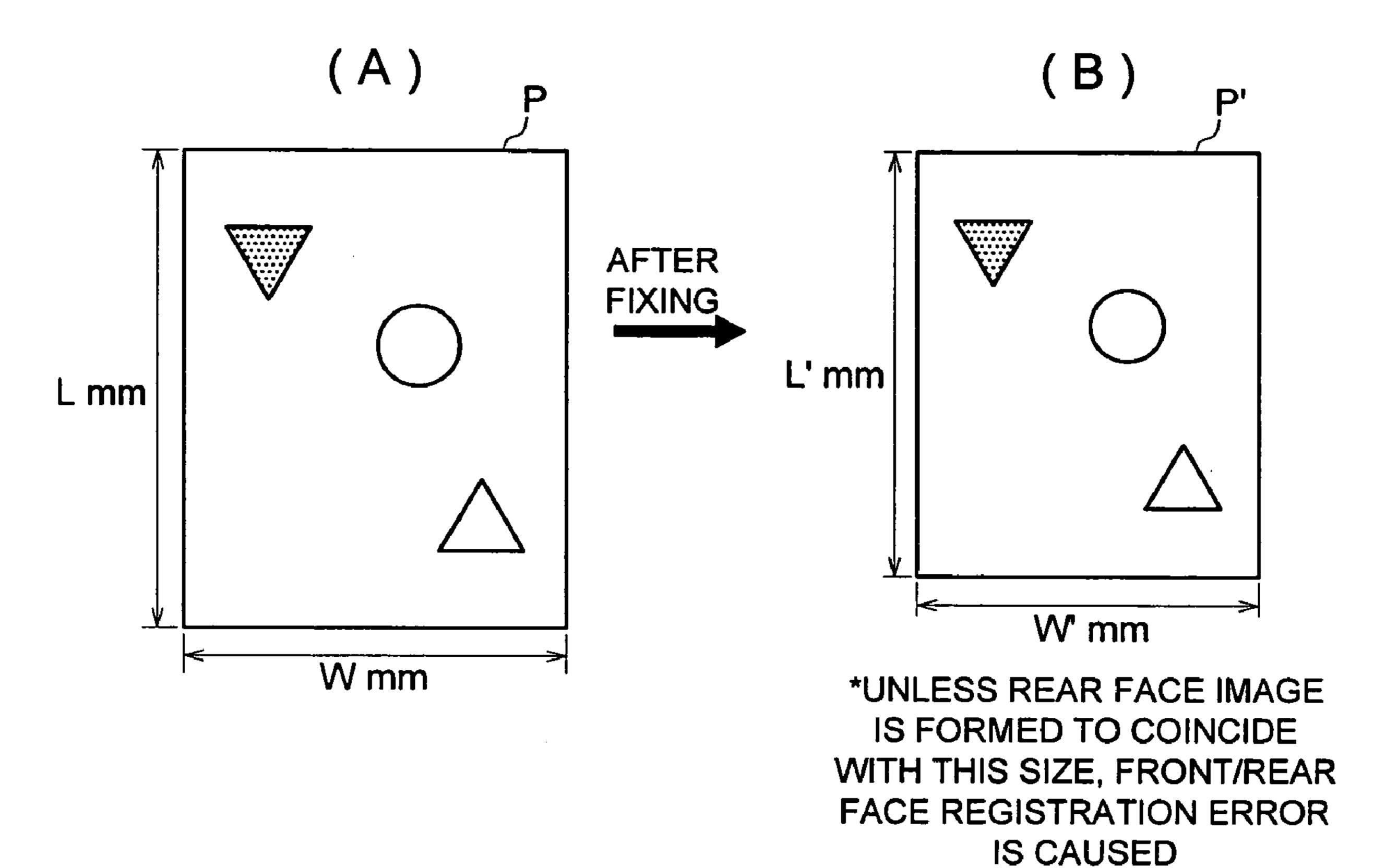

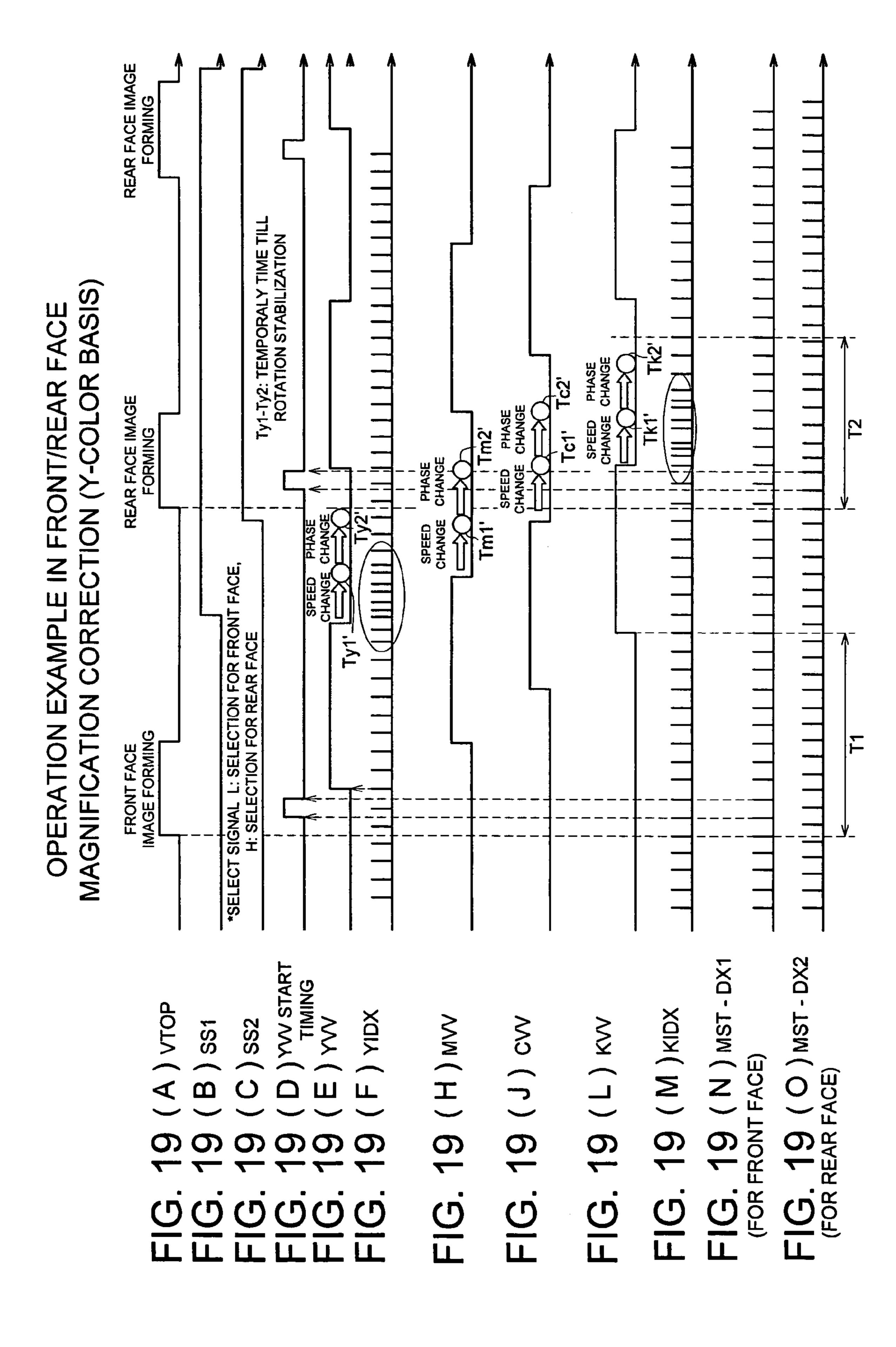

Each of FIGS. 19 (A)-18(O) is a time chart showing an example of operations (for Y color) in the case of correcting magnifications for the front face and the rear face of a color image forming apparatus.

AVTOP signal shown in FIG. **19**(A) is a signal that rises in synchronization with YIDX signal shown in FIG. **19**(F) after a leading edge of the sheet fed out of tray **1** is detected. YVV start timing shown in FIG. **19**(D) is for a signal that rises in synchronization with YIDX signal, where an unillustrated YIDX counter is started, and the number of pulses for YIDX signal is counted. A YVV signal shown in FIG. **19**(E) is a signal that rises in synchronization with YIDX signal shown in FIG. **19**(F). During the period of "H" level of the YVV signal, an image in Y color is formed on a sheet coming from tray **1**.

The control for changing a rotation speed of the polygon mirror for forming an image in Y color is carried out after completion of Y color image forming on the front face of the sheet, namely, after KVV signal shown in FIG. 19(H) has risen. In this case, a frequency of the YIDX signal is fluctuated until the rotation speed of the polygon mirror for Y color is stabilized. Phase change is controlled after waiting for stabilizing time Ty1' during which a rotation of the polygon mirror is stabilized. With regard to the rear face of the sheet, image forming for Y color is started after waiting for stabilizing time Ty2' during which a rotation of the polygon mirror for Y color is stabilized.

During the period of "H" level of the MVV signal shown in FIG. 19(H), an image in M color is formed on the front face of the sheet, and after completion of the foregoing, there is practiced a control for changing a rotation speed of a polygon mirror for forming an image in M color. In this case, a frequency of the MIDX signal is fluctuated until the rotation speed of the polygon mirror for M color is stabilized. Phase change is controlled after waiting for stabilizing time Tm1' during which a rotation of the polygon mirror is stabilized. With regard to the rear face of the sheet, image forming for M color is started after waiting for stabilizing time Tm2' during which a rotation of the polygon mirror for M color is stabilized.

During the period of "H" level of the CVV signal shown in FIG. 19(J), an image in C color is formed on the front face of the sheet, and after completion of the foregoing, there is practiced a control for changing a rotation speed of a polygon mirror for forming an image in C color. In this case, a frequency of the CIDX signal is fluctuated until the rotation speed of the polygon mirror for C color is stabilized. Phase change is controlled after waiting for stabilizing time Tc1' during which a rotation of the polygon mirror is stabilized. With regard to the rear face of the sheet, image forming for C

color is started after waiting for stabilizing time Tc2' during which a rotation of the polygon mirror for C color is stabilized.

KVV start timing shown in FIG. 19(L) is for a signal that rises in synchronization with YIDX signal, where an unillustrated KIDX counter is started, and the number of pulses for YIDX signal is counted. KVV signal shown in FIG. 19(L) is a signal that rises in synchronization with KIDX signal shown in FIG. 19(M). During the period of "H" level of the KVV signal, an image in K color is formed on a sheet coming from 10 tray 1, and after completion of the foregoing, there is made control for changing a rotation speed of a polygon mirror for forming an image in K color.

In this case, a frequency of the KIDX signal is fluctuated until the rotation speed of the polygon mirror for K color is 15 stabilized. Phase change is controlled after waiting for stabilizing time Tk1' during which a rotation of the polygon mirror is stabilized. With regard to the rear face of th sheet, image forming for K color is started after waiting for stabilizing time Tk2' during which a rotation of the polygon mirror for K color 20 is stabilized. Incidentally, T1 shown in FIG. 19(O) shows a period during which the start timing for each of YVV signal, MVV signal and CVV signal in the case of image forming on the front face is determined with MST-IDX1 serving as a count source, while T2 shows a period during which the start 25 timing for each of YVV signal, MVV signal and CVV signal in the case of image forming on the rear face is determined with MST-IDX2 serving as a count source. By using pseudo index signals for correction of magnifications on the front face and the rear face as stated above, productivity is 30 improved.

However, a color image forming apparatus relating to the conventional example has following problems.

when the polygon mirror arrives at its stable rotation by the instruction for changing rotation speed of the polygon mirror. Further, even after practicing the phase changing control, image forming processing cannot be started until the polygon mirror comes to its stable rotation. Therefore, when the magnification is corrected, the switching operation takes time, and productivity for double-face operations is lowered by conducting correction operation for magnifications.

In the example of image size correction in the case of tray switching shown in FIGS. 18(A)-18(I), it is not possible to 45 start succeeding image formation processing for each color, without waiting for stabilizing time Ty1 for stabilizing polygon mirror rotation for Y-color, after Y-color image formation processing, without waiting for stabilizing time Tm1+Tm2 for stabilizing polygon mirror rotation for M-color, after M-color image formation processing, without waiting for stabilizing time Tc1+Tc2 for stabilizing polygon mirror rotation for C-color, after C-color image formation processing and without waiting for stabilizing time Tk1+Tk2 for stabilizing polygon mirror rotation for K-color, after K-color image formation processing. Therefore, high speed image formation processing is hampered by waiting for these stabilizing times Ty1, Tm1+Tm, Tc1+Tc2 and Tk1+Tk2.

(ii) The aforesaid problems are caused equally even in the case of switching image formation processing between the 60 front face and rear face by using pseudo index signals shown in FIGS. 19(A)-19(O). In this case, it is not possible to start succeeding image formation processing for each color, without waiting for stabilizing time Ty1'+Ty2' for stabilizing polygon mirror rotation for Y-color, after Y-color image formation 65 processing, without waiting for stabilizing time Tm1'+Tm2' for stabilizing polygon mirror rotation for M-color, after

M-color image formation processing, without waiting for stabilizing time Tc1'+Tc2' for stabilizing polygon mirror rotation for C-color, after C-color image formation processing and without waiting for stabilizing time Tk1'+Tk2' for stabilizing polygon mirror rotation for K-color, after K-color image formation processing. Therefore, high speed image formation processing is hampered by waiting for these stabilizing times Ty1'+Ty2', Tm1'+Tm2', Tc1'+Tc2' and Tk1'+ Tk2'.

(iii) In the laser beam apparatus seen in Patent Document 1, there is employed a method to generate polygon clock by comparing a counter cycle and a count value with a start-up point value calculated from a phase difference of detector pulse signals (index signals), concerning phase control of a polygon mirror. Even in this method, it is not possible to start color image forming processing for the succeeding page, without waiting stabilizing time after controlling a phase of a polygon mirror until its rotation is stabilized. Therefore, productivity in operations for image size correction is lowered, and continuous high speed processing for color images is prevented.

With the foregoing as a background, the invention has solved the aforesaid problems, and its objective is to provide an image forming apparatus wherein a decline of productivity in the course of correcting image size can be controlled, and continuous high speed processing for color images can be carried out.

#### **SUMMARY**

For solving the problems stated above, the first image forming apparatus reflecting a feature of the present invention is an image forming apparatus for forming color images com-(i) Phase changing control cannot be started until the moment 35 prising at least two or more colors, having a function of magnification correction of image size by one page unit, the image forming apparatus including:

an image carrier;

a polygonal mirror rotator independently provided for each color; and

a controller which simultaneously conducts first control for changing rotation speed of the polygonal mirror rotator in order for changing image size in a sub-scanning direction perpendicular to a main scanning direction, and second control for correcting a correction amount for color registration error depending on magnification correction of image size, and for adjusting a rotating phase of the polygonal mirror rotator depending on the corrected correction amount for color registration error,

where the main scanning direction is a direction in which the image carrier is scanned with an exposure beam coming from the polygonal mirror rotator.

In the first image forming apparatus, when forming images by correcting magnification in terms of image sizes by one 55 page unit, the controller conducts simultaneously control for changing rotation speed of the polygonal mirror rotator for changing image size in the sub-scanning direction and control for correcting a correction amount for color registration error depending on correction of magnification for image sizes, and for adjusting a rotating phase of the polygonal mirror rotator depending on a correction amount for color registration error after the correction.

It is therefore possible to shorten a stabilizing time during which the rotation of the polygonal mirror rotator is stabilized, compared with an occasion wherein speed control and phase control of the polygonal mirror rotator are carried out in succession.

The second image forming apparatus reflecting another aspect of the present invention is an image forming apparatus for continuously forming color images comprising at least two or more colors, having a function of magnification correction of image size by one page unit, the image forming apparatus including:

a polygonal mirror rotator which is provided independently for each color image forming unit;

an image carrier on which a latent image is formed by an exposure beam scanned by the polygonal mirror rotator and 10 the latent image is developed to be a color image; and

a controller comprising:

- a color registration error detecting section which detects color registration error on each color image formed on the image carrier;

- a color registration error correcting section which corrects the color registration error depending on an amount of the color registration error obtained from the color registration error detecting section; and

- a calculating section which calculates a rising edge and a 20 falling edge of a drive clock signal controlling a rotation speed of the polygonal mirror rotator for a succeeding page, based on an amount of phase control calculated by correcting an amount of color registration error correction after correction by the color registration error cor- 25 recting section depending on an amount of magnification correction, on an output value of a counter provided and independently controlled for each color to determine a drive clock signal cycle that controls a rotation speed of the polygonal mirror rotator, on a phase difference between a first main scanning basis signal generated by detecting an exposure beam scanned by the polygonal rotator for a first color image forming unit immediately before conducting magnification correction for image sizes with a sensor arranged in a scanning 35 optical path and the second main scanning basis signal generated by detecting an exposure beam scanned by the polygonal rotator for a second color image forming unit with a sensor arranged in a scanning optical path, and on a phase difference between a first base point of a count 40 cycle of a counter for generating a drive clock signal of the polygonal mirror rotator for each of the first and second color image forming units immediately before conducting magnification correction for image size and a second base point of a count cycle after the magnifi- 45 cation correction for image size,

wherein the controller executes polygonal mirror rotator drive control in a case of magnification correction for image sizes by the drive clock signal, which controls a rotation speed of the polygonal mirror rotator, generated based on an output 50 of the calculating section.

In the second image forming apparatus, when correcting an image size by one page unit, an image is formed on the image carrier by an exposure beam oscillated by the polygonal mirror rotator, and the image is developed to be a color image. 55 The color registration error detection section detects color registration errors of each color image formed on the image carrier. The color registration error correction section corrects color registration errors depending on an amount of detection of color registration errors obtained from the color registra- 60 tion error detection section. On the assumption of the foregoing, the calculating section calculates a rising edge and a falling edge of drive clock signals controlling a rotation speed of the polygonal mirror rotator for the succeeding page based on an amount of phase control calculated by correcting an 65 amount of correction of color registration errors depending on an amount of magnification adjustment, an output value of

8

a counter that is provided independently of each color for determining a cycle of drive clock signal and is controlled independently, a phase difference between the first main scanning basis signal immediately before conducting magnification correction for image sizes and the second main scanning basis signal, and on a phase difference between a base point of a count cycle of the counter for generating drive clock signal of the polygonal mirror rotator and a base point of a count cycle under the condition of count cycle after correction of magnification for image size, in the controller.

For example, when images are formed in the order of the first, second, third and fourth color image forming units wherein the earliest one comes first, the controller controls rotational phase for each polygonal mirror rotator so that the second color image forming unit may use a base point of a count cycle of a counter for generating drive clock signals of the polygonal mirror rotator of the first color image forming unit as a base, the third color image forming unit may use a base point of a count cycle of a counter for generating drive clock signals of the polygonal mirror rotator of the second color image forming unit as a base, and the fourth color image forming unit may use a base point of a count cycle of a counter for generating drive clock signals of the polygonal mirror rotator of the third color image forming unit as a base.

Therefore, compared with a conventional method, it is possible to shorten stabilizing time during which a rotation of the polygonal mirror rotator is stabilized, because speed control and phase control of the polygonal mirror rotator can be carried out simultaneously.

The third image forming apparatus reflecting another aspect of the present invention is a tandem type color image forming apparatus having a function to correct image sizes by one page unit and being capable of forming color images composed of at least two or more colors continuously, the image forming apparatus including:

a polygonal mirror rotator which is provided independently for each color image forming unit;

an image carrier on which a latent image is formed by an exposure beam scanned by the polygonal mirror rotator and the latent image is developed to be a color image; and

a controller comprising:

- a color registration error detecting section which detects color registration error on each color image formed on the image carrier;

- a color registration error correcting section which corrects the color registration error depending on an amount of the color registration error obtained from the color registration error detecting section; and

- a calculating section which calculates a rising edge and a falling edge of a drive clock signal controlling a rotation speed of the polygonal mirror rotator for a succeeding page, based on an amount of phase control calculated by correcting an amount of color registration error correction after correction by the color registration error correcting section depending on an amount of magnification correction, on an output value of a counter provided and independently controlled for each color to determine a drive clock signal cycle that controls a rotation speed of the polygonal mirror rotator, on a phase difference between a first main scanning basis signal generated by detecting an exposure beam scanned by the polygonal rotator for a first color image forming unit immediately before conducting magnification correction for image sizes with a sensor arranged in a scanning optical path and the second main scanning basis signal generated by detecting an exposure beam scanned by the polygonal rotator for a second color image forming unit

9

with a sensor arranged in a scanning optical path, and on a phase difference between a base point of a count cycle for generating a pseudo index signal, which is obtained by dividing a source oscillation signal of an original oscillator used in common with generation of drive clock signal of the polygonal mirror rotator in practicing rotational phase control of the polygonal mirror rotator so that the pseudo index signal agrees with one plane cycle of the polygonal mirror rotator, and a base point of a counter cycle for generating drive clock signal of the polygonal mirror rotator for each color unit,

wherein the controller executes polygonal mirror rotator drive control in a case of magnification correction for image sizes by the drive clock signal, which controls a rotation speed of the polygonal mirror rotator, generated based on an output of the calculating section.

In the third image forming apparatus, when correcting an image size by one page unit, an image is formed on the image carrier by an exposure beam oscillated by the polygonal mirror rotator, and the image is developed to be a color image. The color registration error detection section detects color registration errors of each color image formed on the image carrier. The color registration error correction section corrects color registration errors depending on an amount of detection of color registration errors obtained from the color registration error detection section. On the assumption of the foregoing, the calculating section calculates a rising edge and a falling edge of drive clock signals controlling a rotation speed of the polygonal mirror rotator for the succeeding page based  $_{30}$ on an amount of phase control calculated by correcting an amount of correction of color registration errors depending on an amount of magnification adjustment, an output value of a counter that is provided independently of each color for determining a cycle of drive clock signal and is controlled independently, a phase difference between the first main scanning basis signal immediately before conducting magnification correction for image sizes and the second main scanning basis signal, and on a phase difference between a base point of a count cycle generating pseudo index signal and a base point of a counter cycle for generating drive clock signal for the polygonal mirror rotator of each color unit, in the controller.

Therefore, compared with a conventional method, it is possible to shorten stabilizing time during which a rotation of 45 the polygonal mirror rotator is stabilized, because speed control and phase control of the polygonal mirror rotator can be carried out simultaneously.

#### BRIEF DESCRIPTION OF THE DRAWINGS

These and other objects, advantages and features of the invention will become apparent from the following description thereof taken in conjunction with the accompanying drawings in which:

- FIG. 1 is a conceptual diagram showing an example of configuration of color copier 100 as the first embodiment of the invention;

- FIG. 2 is a block diagram showing an example of configuration of a control system of the color copier 100;

- FIG. 3 is a block diagram showing an example of configuration of image writing unit 3Y for Y-color image forming shown in FIG. 2 and its peripheral circuit;

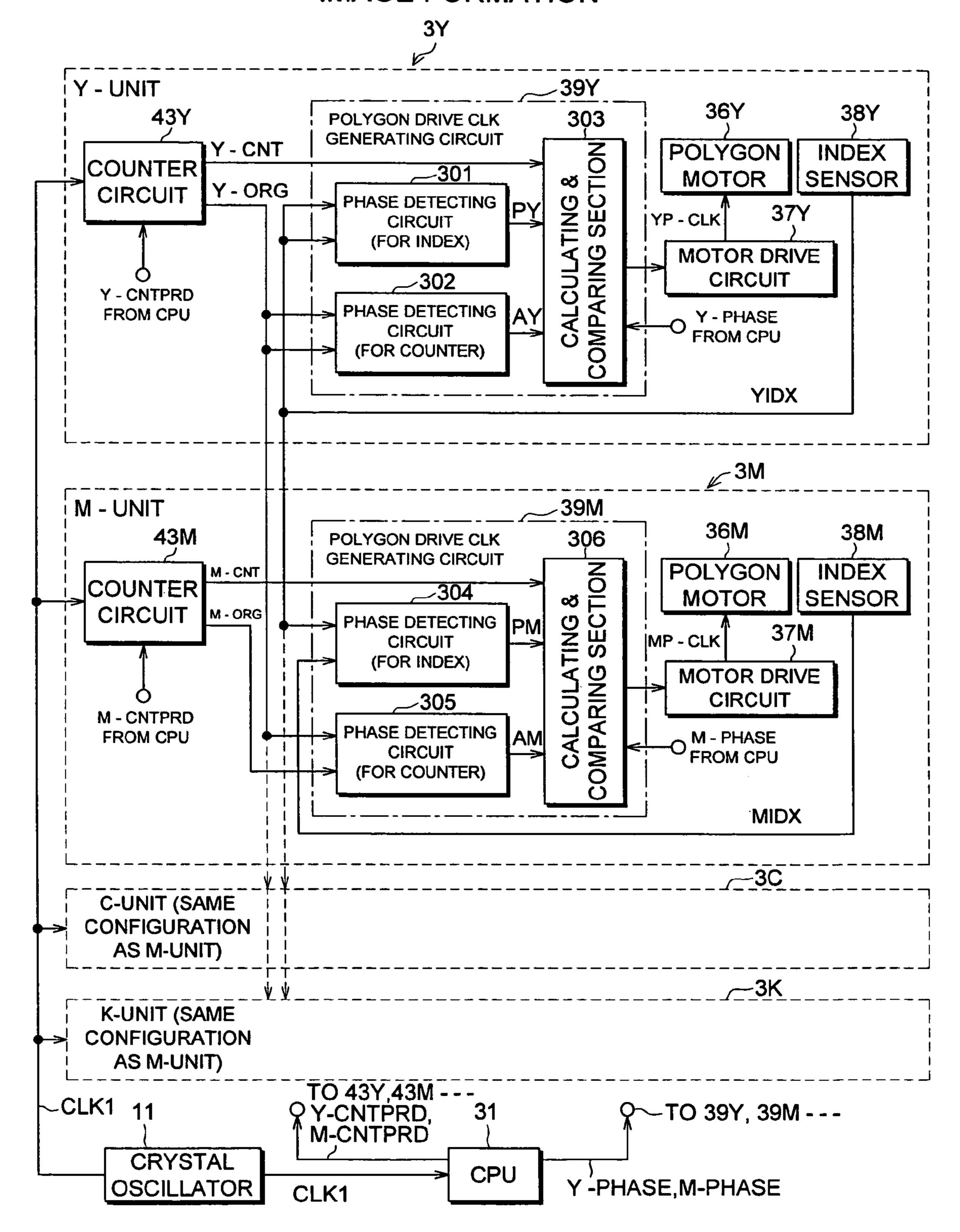

- FIG. 4 is a block diagram showing an example of configu- 65 ration of a polygon mirror drive system for each color image forming;

**10**

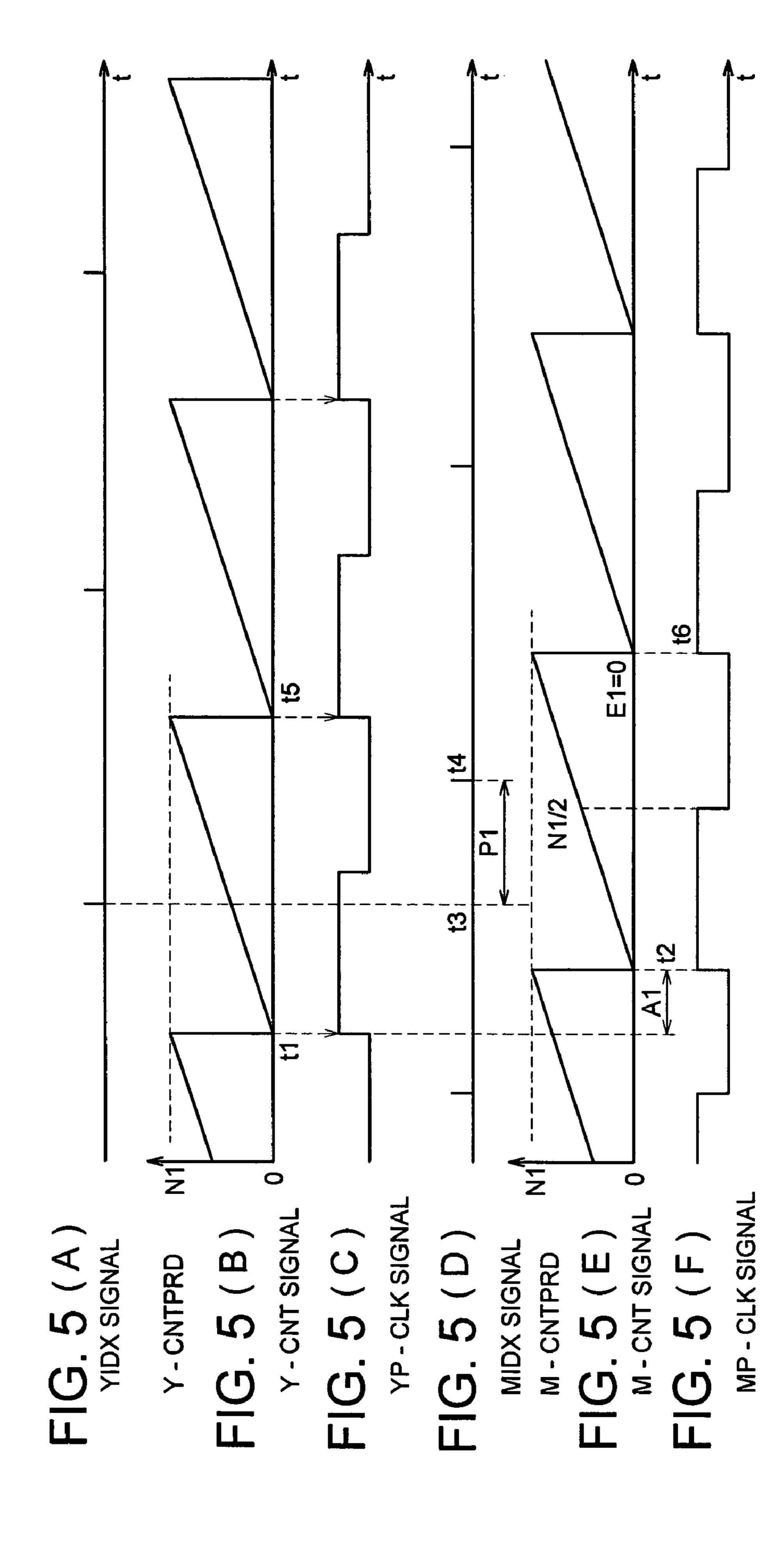

Each of FIGS. 5 (A)-5 (F) is a time chart showing an example of operations (YP-CLK basis time) before magnification correction control in image forming section 60;

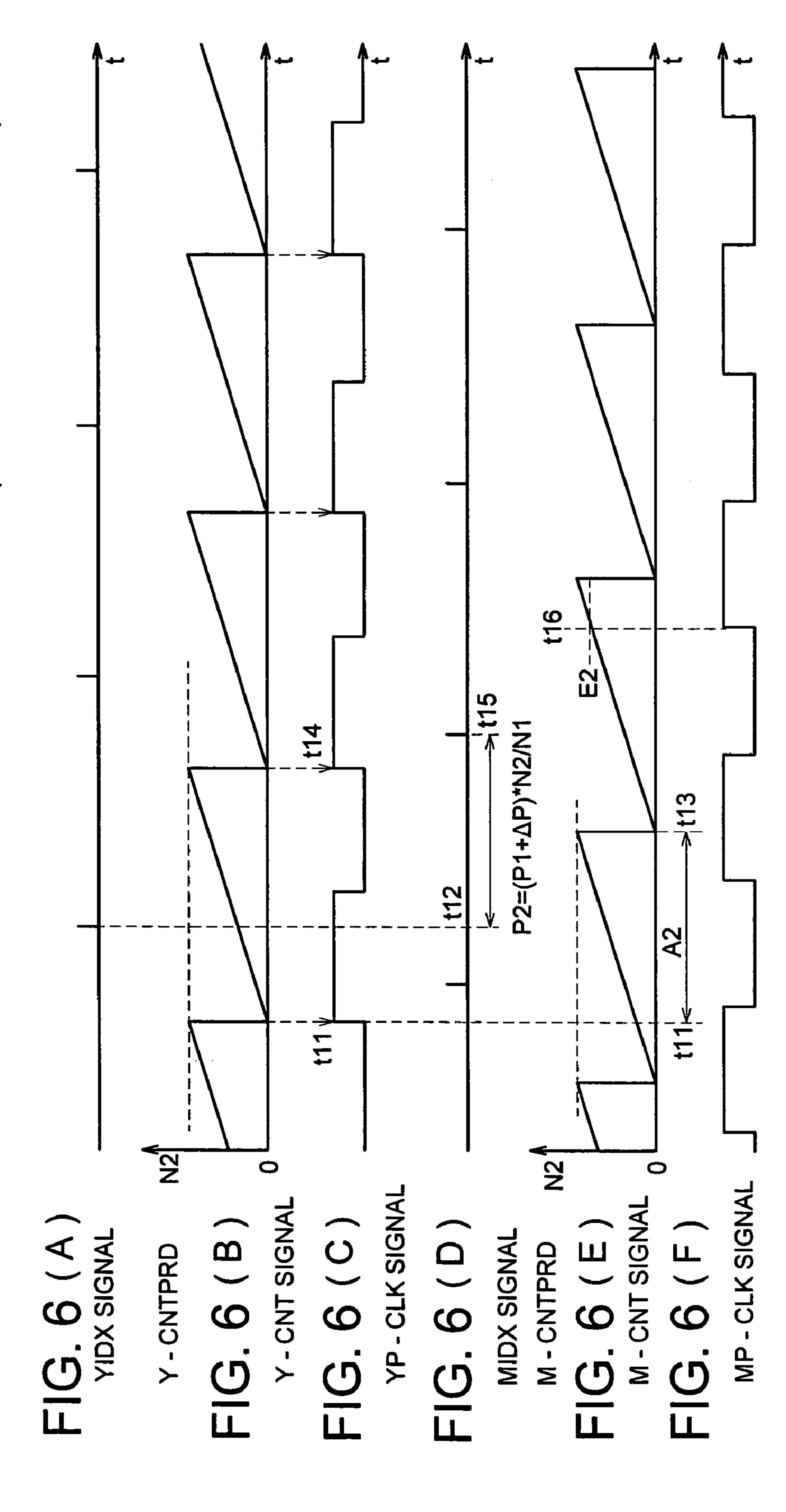

Each of FIGS. 6 (A)-6 (F) is a time chart showing an example of operations (YP-CLK signal basis time) after magnification correction control in image forming section 60;

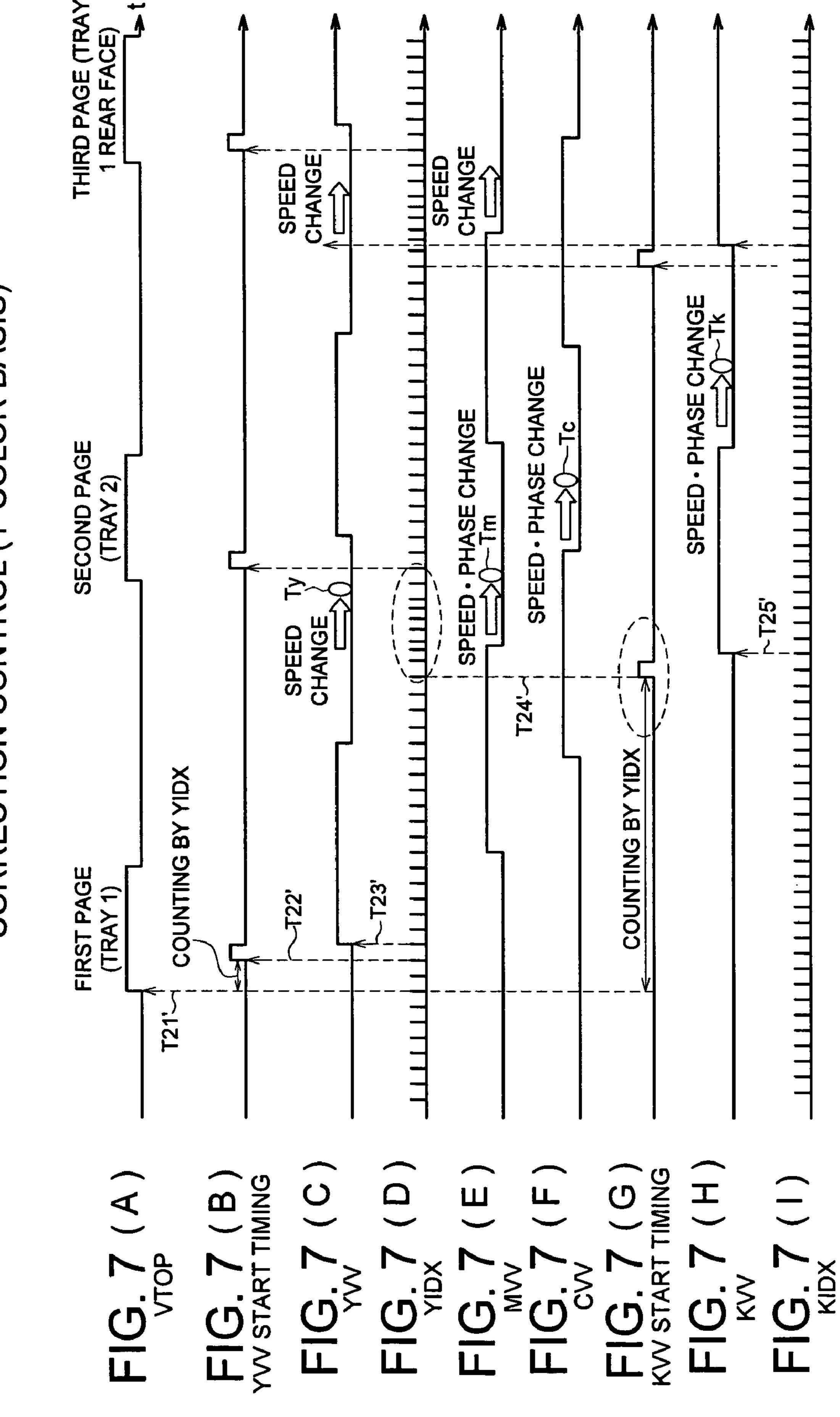

Each of FIGS. 7(A)-7(I) is a time chart showing an example of operations (Y-color basis) after magnification correction control of color copier 100;

FIG. 8 is a block diagram showing an example of configuration of color copier 200 as the second embodiment;

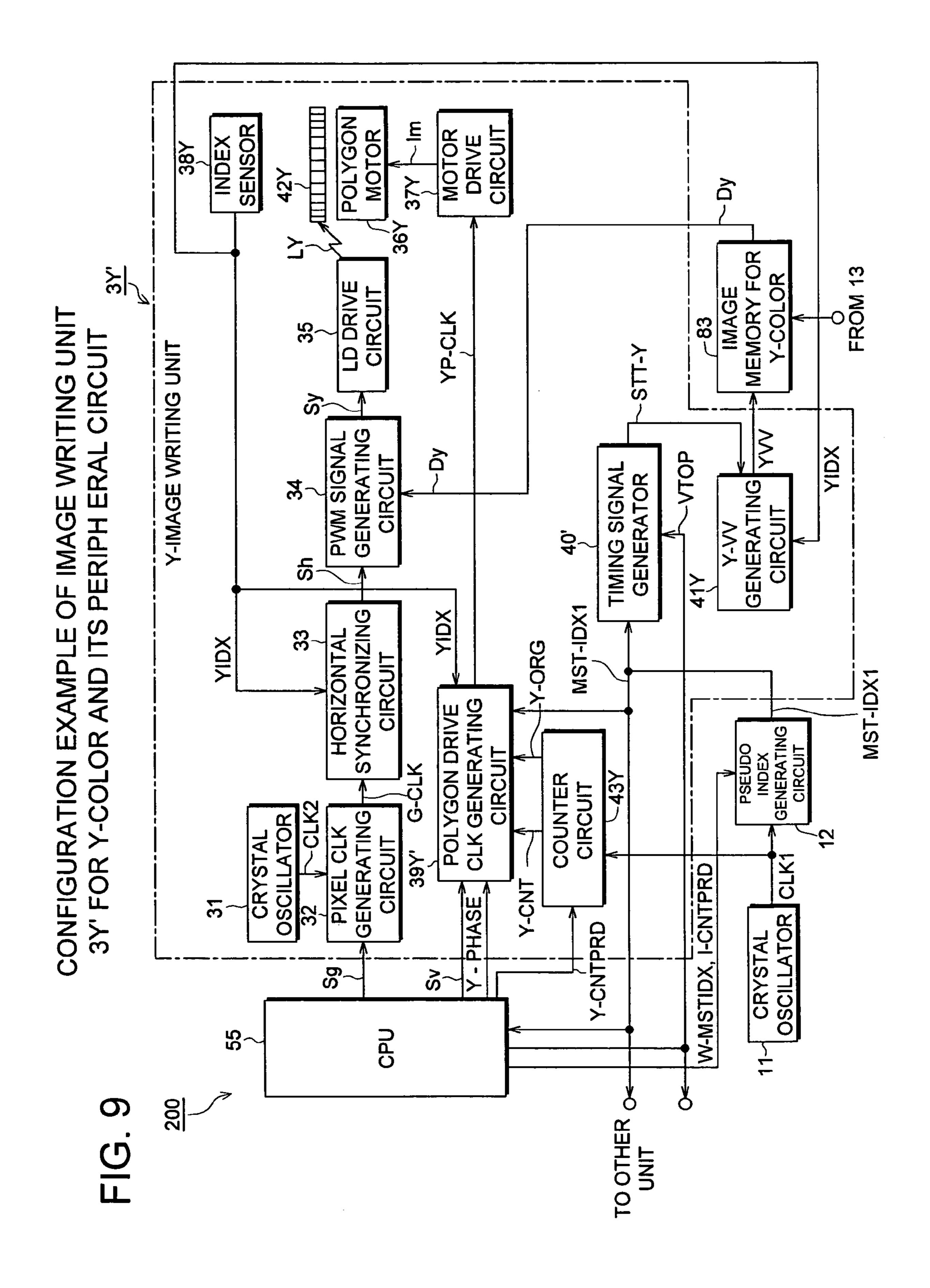

FIG. 9 is a block diagram showing an example of configuration of image writing unit 3Y' for Y-color image forming shown in FIG. 8 and its peripheral circuit;

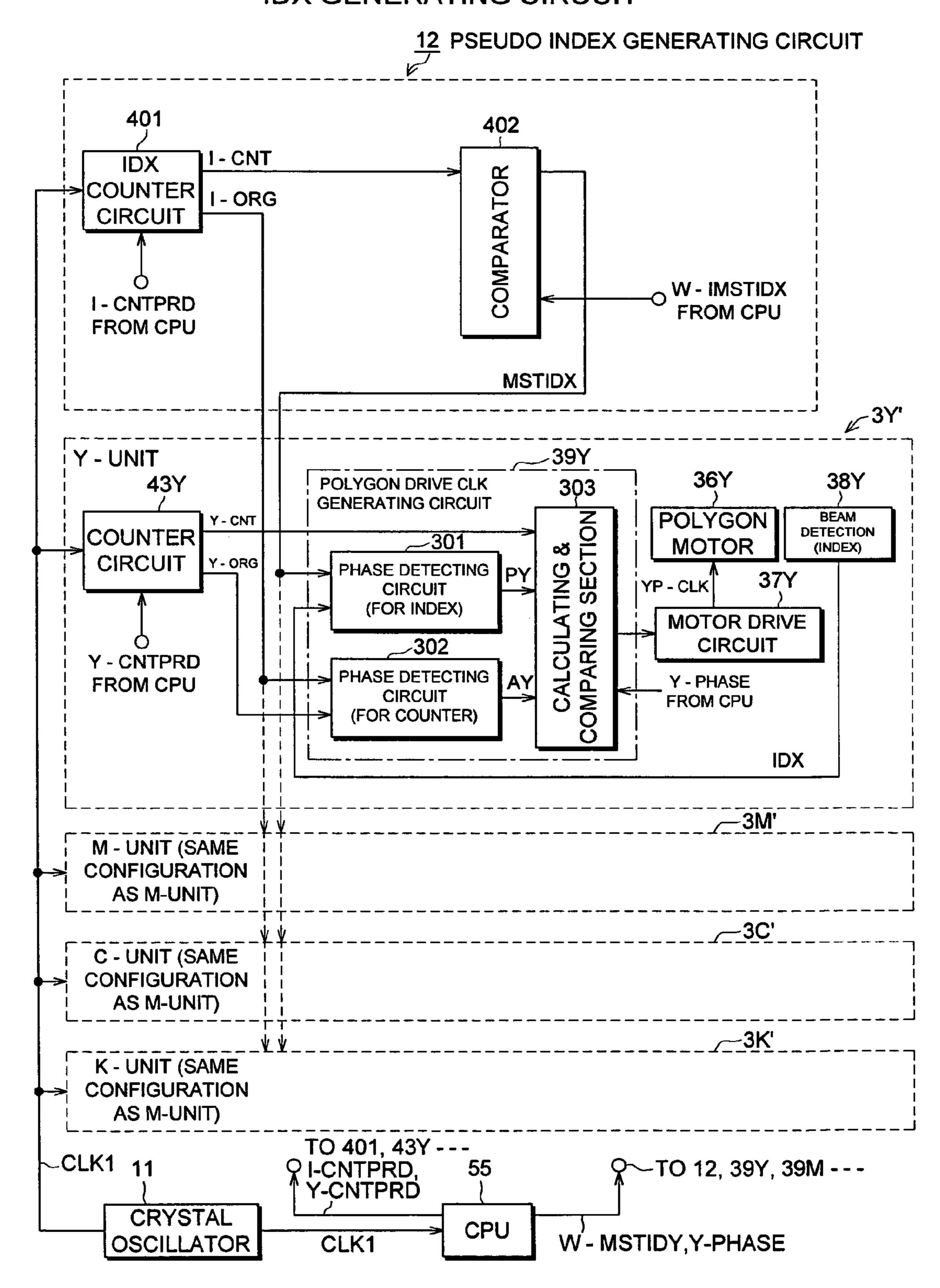

FIG. 10 is a block diagram showing an example of configuration of a polygon mirror drive system including a pseudo IDX generating circuit;

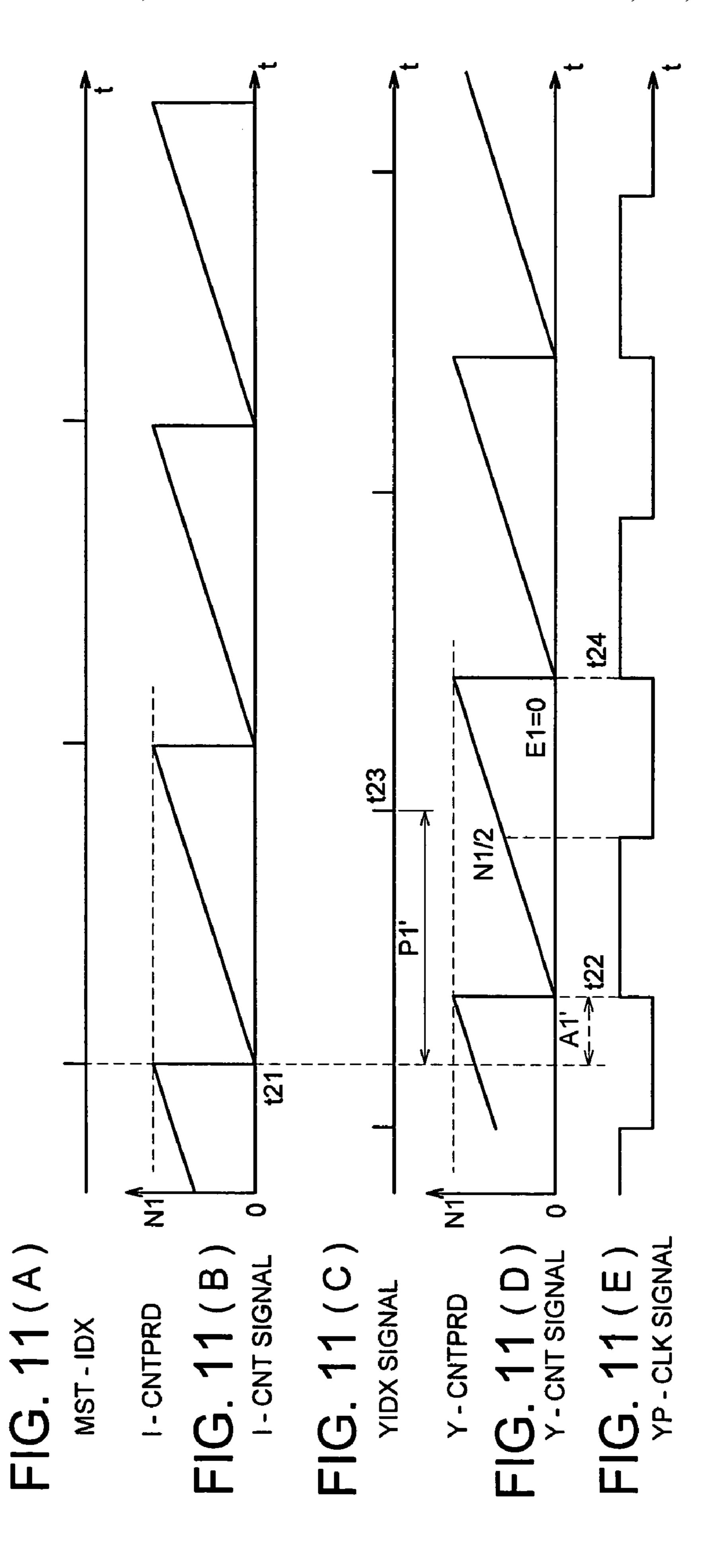

Each of FIGS. 11(A)-11(E) is a time chart showing an example of operations (MST-IDEX basis time) before magnification correction control in image forming section 60';

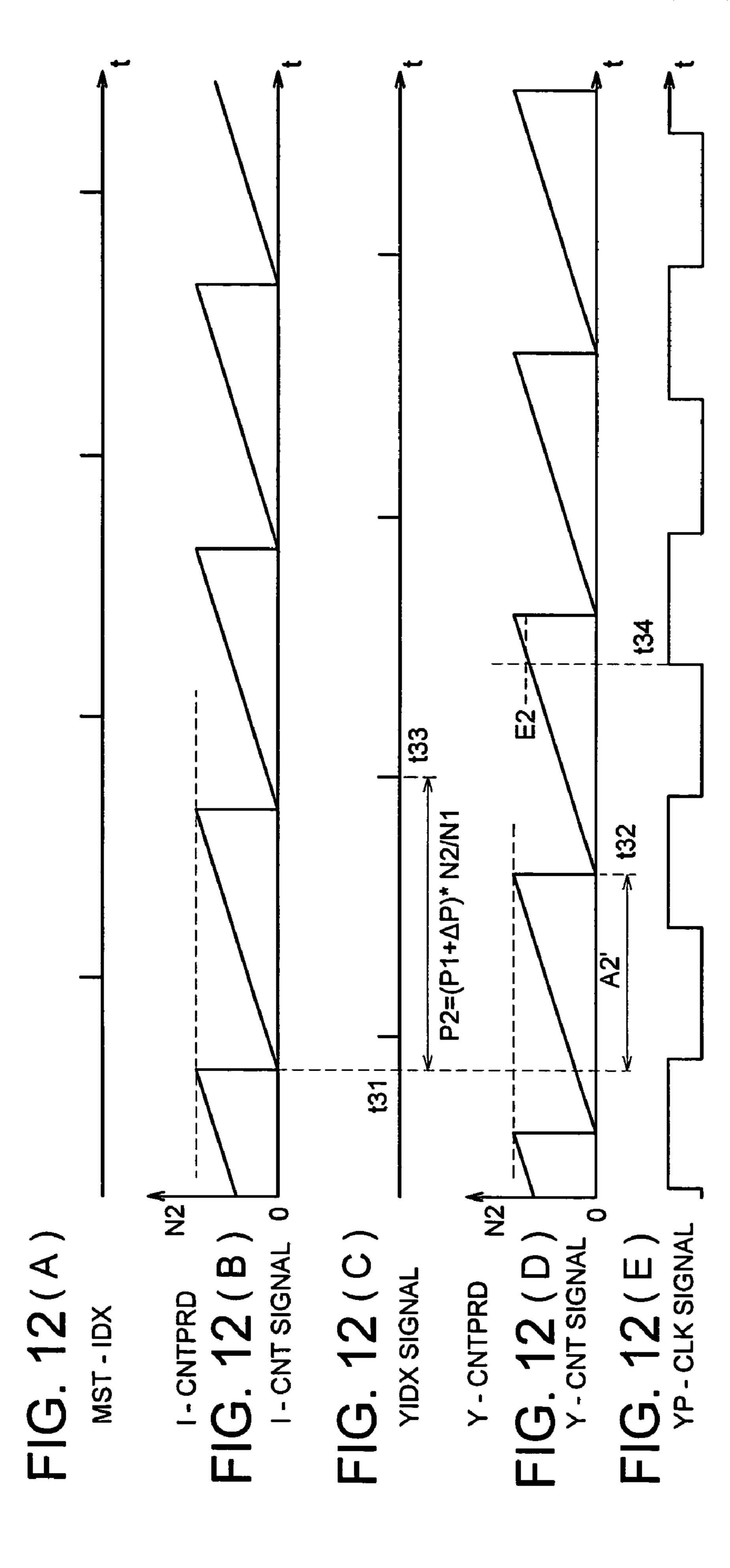

Each of FIGS. 12(A)-12(E) is a time chart showing an example of operations (MST-IDEX basis time) after magnification correction control in image forming section 60';

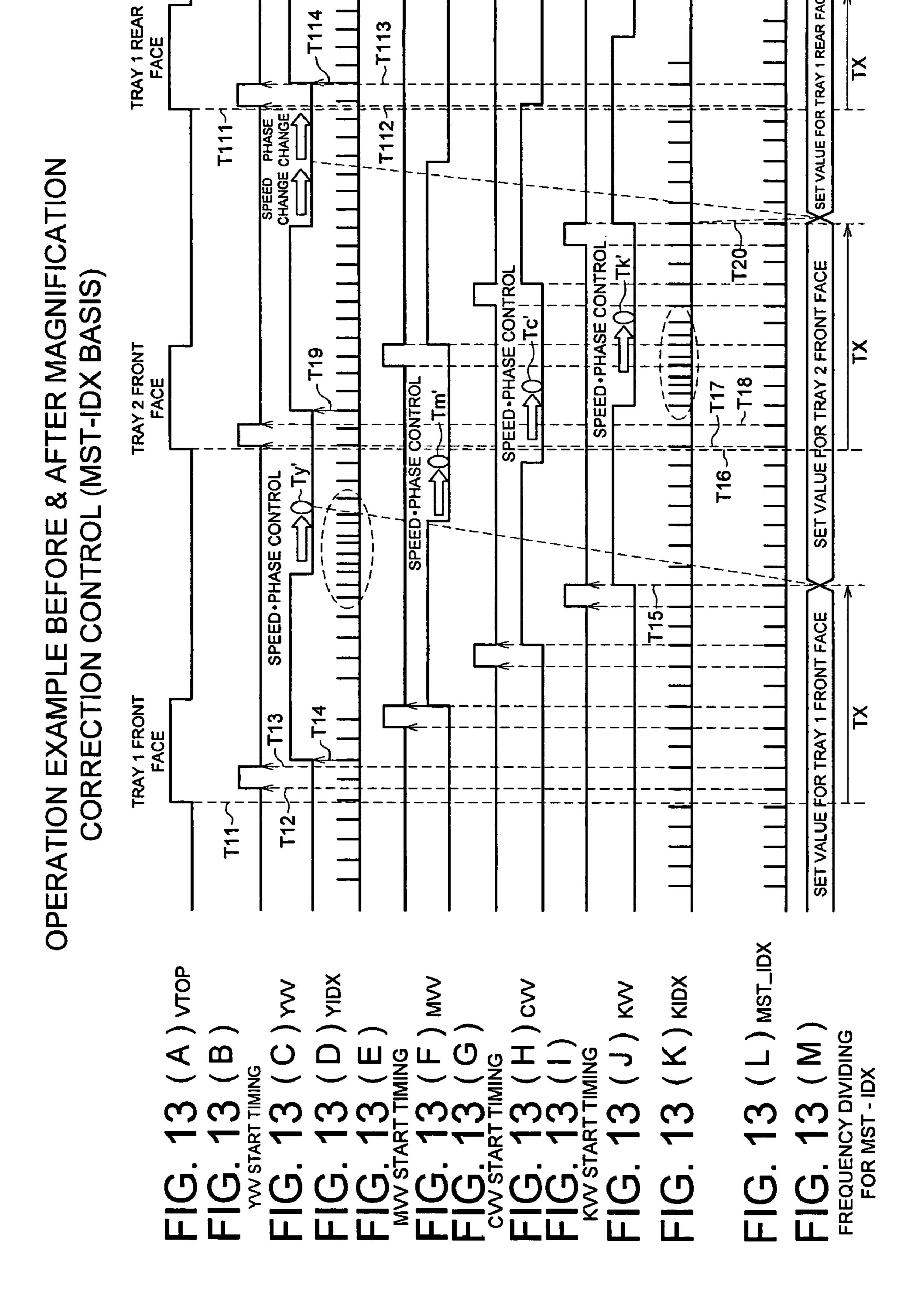

Each of FIGS. 13(A)-13(M) is a time chart showing an example of operations (MST-IDEX signal basis) after magnification correction control of color copier 200;

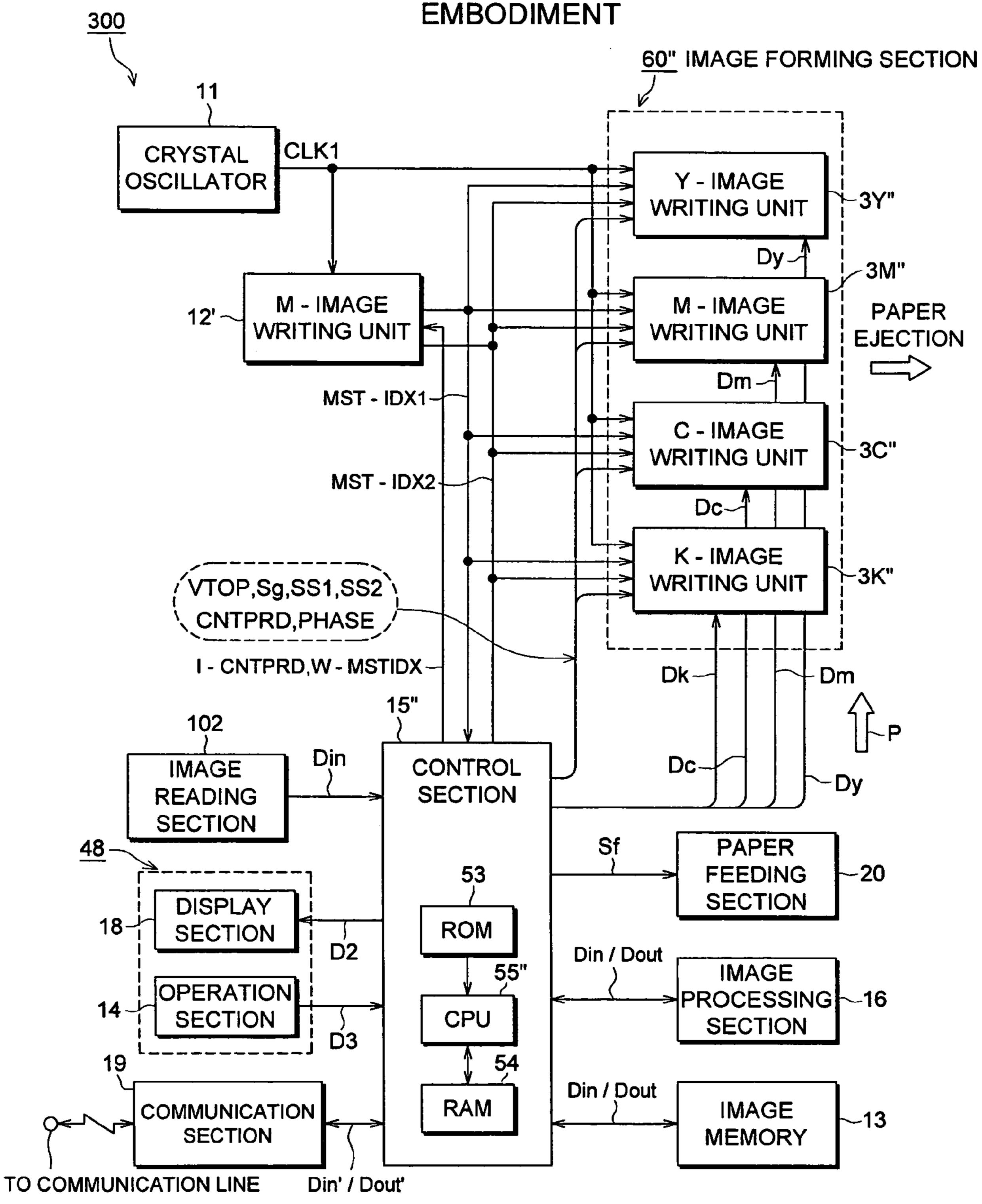

FIG. 14 is a block diagram showing an example of configuration of a control system in color copier 300 relating to the third embodiment;

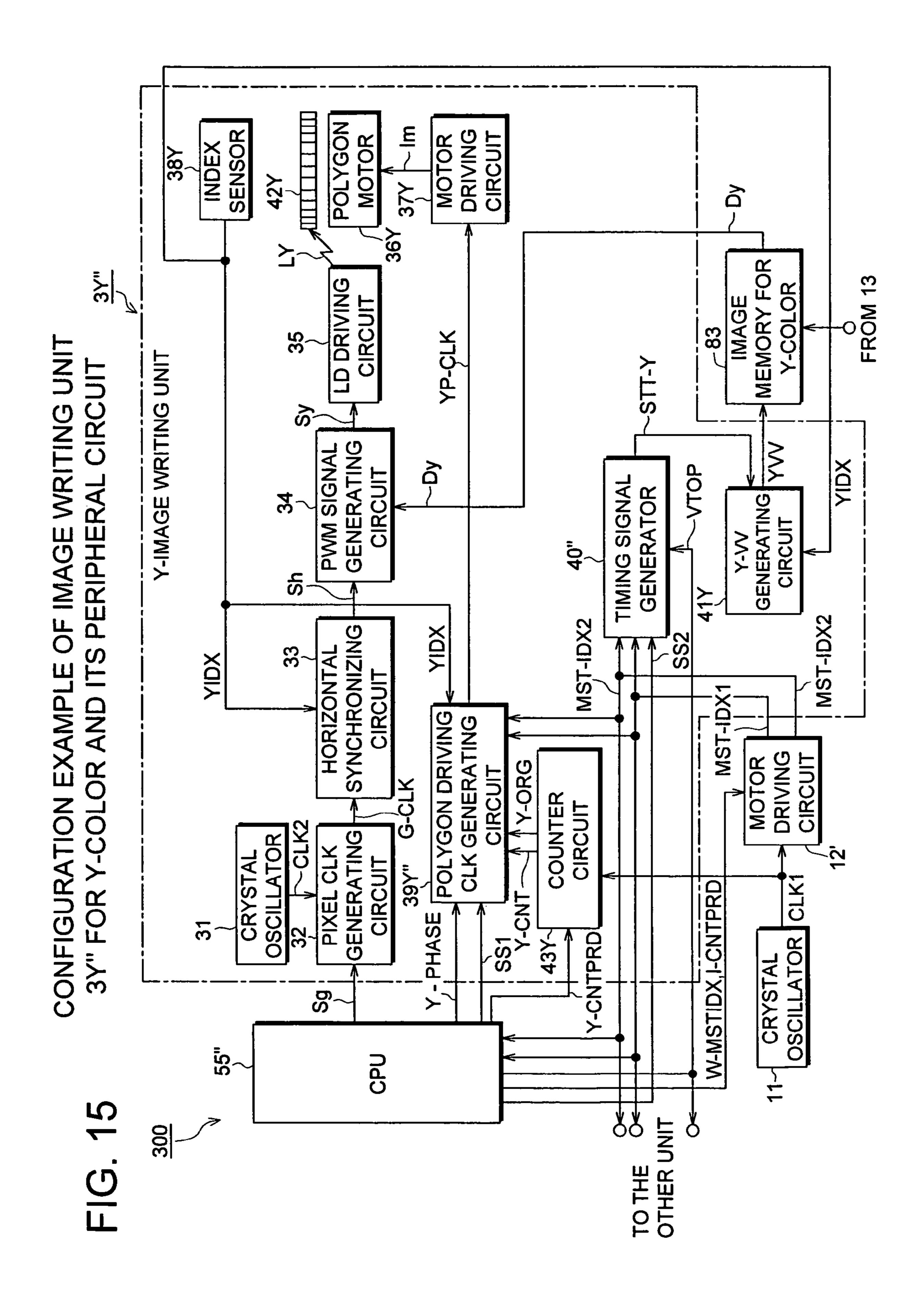

FIG. 15 is a block diagram showing an example of configuration of image writing unit 3Y" for Y-color image forming extracted from FIG. 14 and its peripheral circuit;

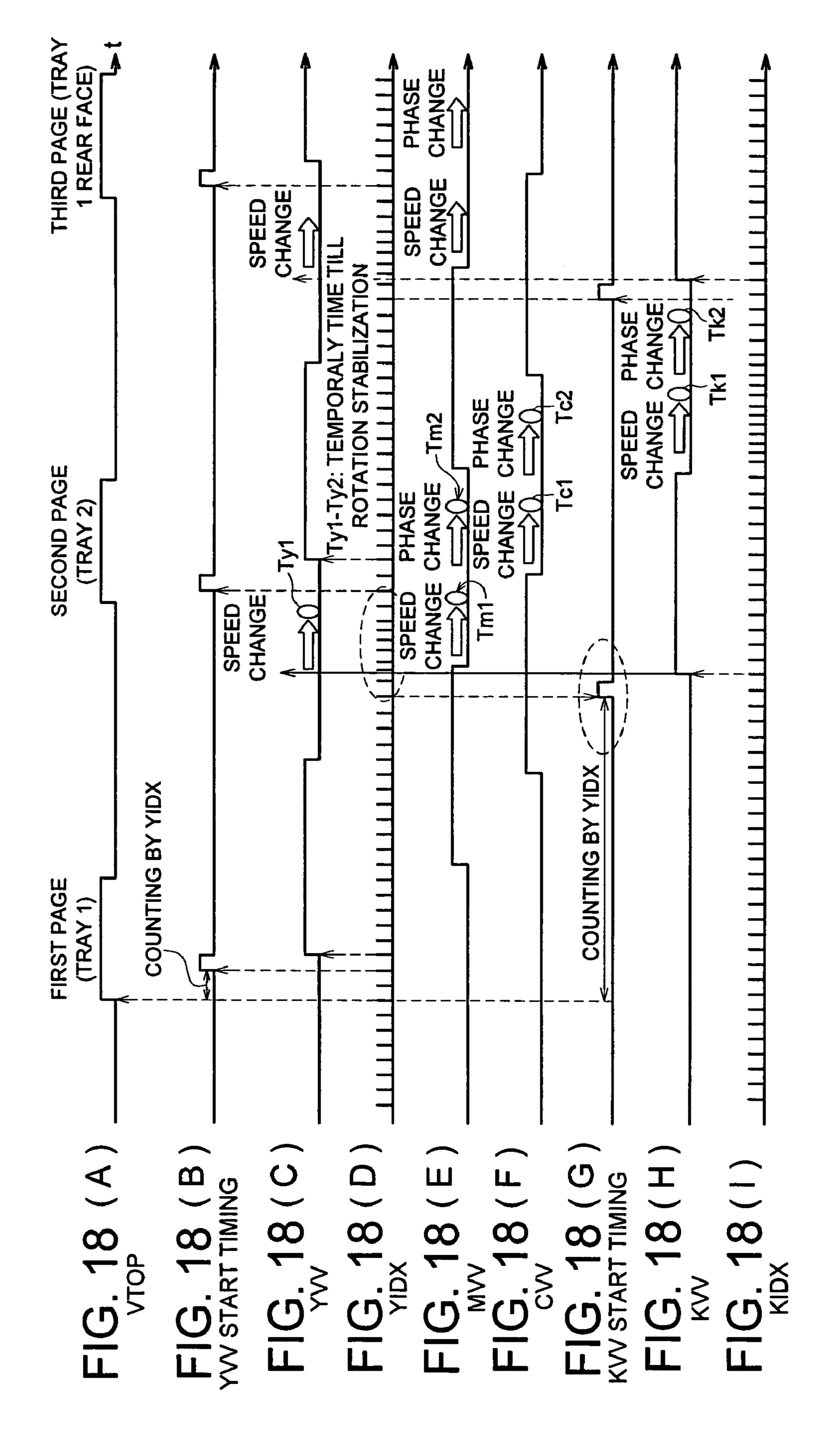

Each of FIGS. 16(A)-16(O) is a time chart showing an example of operations after magnification correction control of color copier 300;

Each of FIGS. 17(A) and 17(B) is a diagram illustrating an example of shrinkage of a sheet size in the case of double-face image forming;

Each of FIGS. **18**(A)-**18**(I) is a time chart showing an example of image size correction (K-color basis) in the case of switching trays in an image writing unit for each of Y-color, M-color, C-color and K-color in conventional examples; and

Each of FIGS. **19**(A)-**19**(O) is a time chart showing an example of operations (Y-color basis) in the case of front-face/rear-face magnification correction of a color image forming apparatus.

### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

An image forming apparatus relating to an example of the invention will be explained as follows, referring to the drawings.

#### Embodiment 1

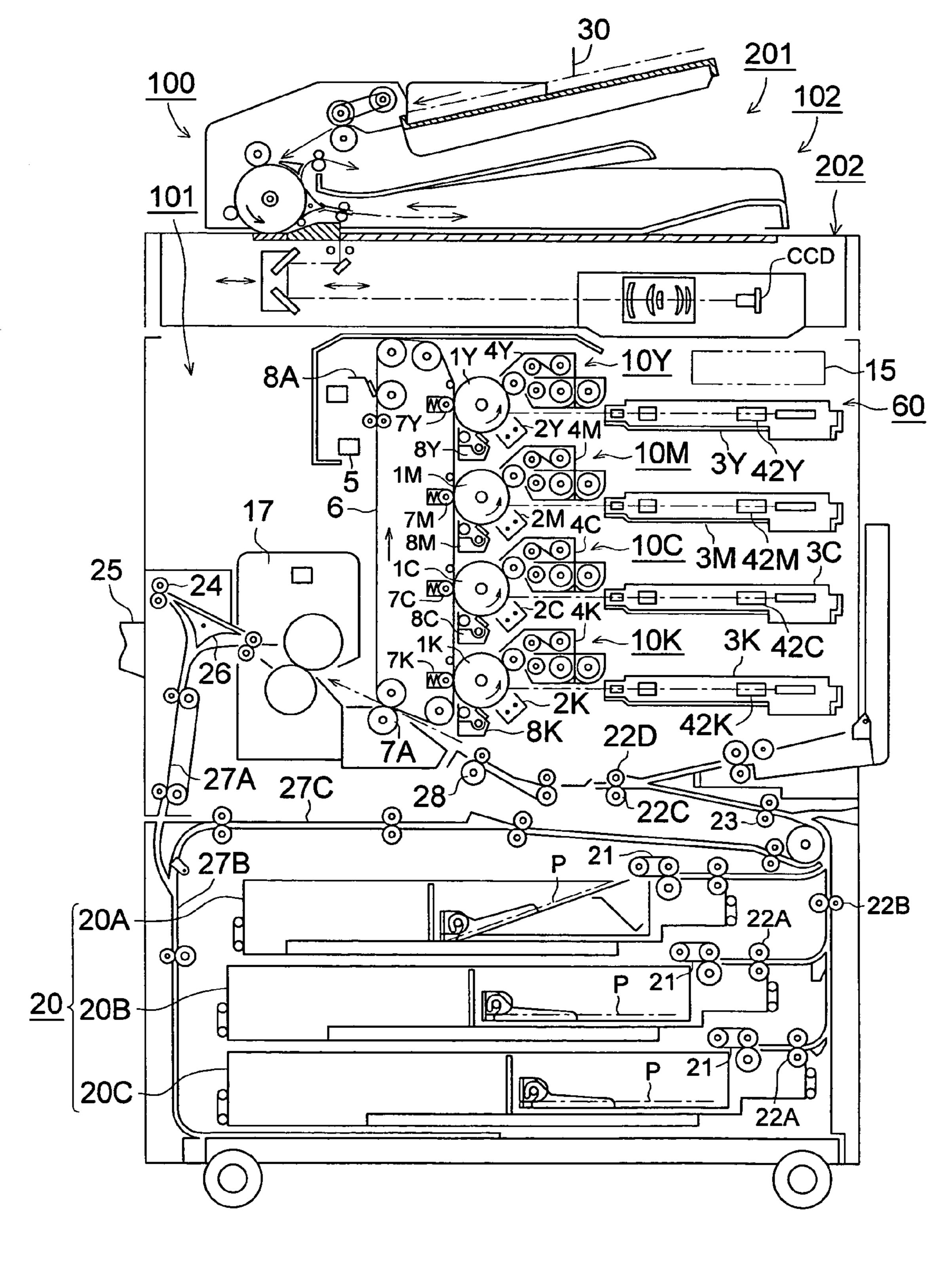

FIG. 1 is a conceptual diagram showing an example of configuration of a section of color copier 100 as the first embodiment of the invention.

Color copier 100 shown in FIG. 1 is an example of the first, second or third image forming apparatus representing an apparatus that has a function to correct image sizes by one page unit and is capable of forming continuously color images composed of at least two or more colors. An image forming apparatus relating to the invention may also be applied to a color printer, a facsimile machine and their multifunctional machine, in addition to the color copier 100.

The color copier 100 is composed of copier main body 101 and image reading unit 102. The image reading unit 102 composed of automatic document feeder 201 and document image scanning exposure unit 202 is arranged on the top of the copier main body 101. Document 30 placed on a document table of the automatic document feeder 201 is conveyed by an unillustrated conveyer, and thereby images on one side or two sides of the document are subjected to scanning exposure by the optical system of the document image scanning exposure unit 202, and an incident light reflecting document images is read by line image sensor CCD.

Analog image signals converted photoelectrically by line image sensor CCD are subjected to analog processing, A/D conversion, shading correction and image compression processing in an unillustrated image processing section, to 15 become digital image data Din. The image data Din are sent to image writing units (laser writing units) 3Y, 3M, 3C and 3K constituting image forming section 60, after being converted to image data Dy, Dm, Dc and Dk for image forming for Y-color, M-color, C-color and K-color.

The aforesaid automatic document feeder 201 reads contents in document 30 fed from the document table by one effort continuously, and accumulates contents of the document in a memory section (electronic RDH function). This electronic RDH function is used conveniently when copying contents of many documents by a copying function, or when sending many documents 30 by a facsimile function.

The copier main body 101 constitutes a tandem type color image forming apparatus, and is provided with four image forming units (image forming systems) 10Y, 10M, 10C and 30 10K, endless intermediate transfer belt 6, a sheet conveying section including a sheet re-feeding mechanism (ADU mechanism), fixing unit 17 for fixing a toner image and with sheet feeding section 20 that feeds a transfer material (hereinafter referred to as a sheet) to an image forming system. The 35 sheet feeding section 20 is provided below the image forming system. The sheet feeding section 20 is composed, for example, of three sheet feeding trays 20A, 20B and 20C. Sheet P fed out of the sheet feeding section 20 us conveyed to the lower part of the image forming unit 10K.

Image forming units 10Y, 10M, 10C and 10K constitute image forming section 60, and a polygon mirror and a photoreceptor drum are provided for each color, and they form color images on prescribed sheet P based on main scanning basis signal (hereinafter referred to as index signal) and/or on 45 pseudo main scanning basis signal).

For example, image forming unit 10Y has polygon mirror 42Y and photoreceptor drum (image carrier) 1Y, image forming unit 10M has polygon mirror 42M and photoreceptor drum (image carrier) 1M, image forming unit 10C has polygon mirror 42C and photoreceptor drum (image carrier) 1C and image forming unit 10K has polygon mirror 42K and photoreceptor drum (image carrier) 1K. Each of the polygon mirrors 42Y-42K is provided independently of others, and scanning beams of the polygon mirrors 42Y-42K form latent 55 images which are developed through development into color images.

In this example, the image forming unit 10Y for forming a yellow (Y) color image has therein photoreceptor drum 1Y for forming a Y-color toner image, charging unit 2Y for 60 Y-color image forming arranged around the photoreceptor drum 1Y, image writing unit 3Y, developing unit 4Y and cleaning section 8Y for the image carrier.

The image forming unit 10M for forming a magenta (M) color image has therein photoreceptor drum 1M for forming 65 a M-color toner image, charging unit 2M for M-color image forming, image writing unit 3M, developing unit 4M and

12

cleaning section 8M for the image carrier. The image forming unit 10C for forming a cyan (C) color image has therein photoreceptor drum 1C for forming a C-color toner image, charging unit 2C for C-color image forming, image writing unit 3C, developing unit 4C and cleaning section 8C for the image carrier. The image forming unit 10K for forming a black (K) color image has therein photoreceptor drum 1K for forming a K-color toner image, charging unit 2K for K-color image forming, image writing unit 3K, developing unit 4K and cleaning section 8K for the image carrier.

A latent image forming section is constituted by a combination of charging unit 2Y and image writing unit 3Y, a combination of charging unit 2M and image writing unit 3M, a combination of charging unit 2C and image writing unit 3C, and a combination of charging unit 2K and image writing unit 3K. Development by each of developing units 4Y, 4M, 4C and **4K** is carried out by reversal development in which developing bias where alternating voltage is superimposed on direct voltage whose polarity is the same as that of working toner (negative polarity in the present example) is impressed. The intermediate transfer belt 6 is trained about plural rollers, to be supported rotatably, and a Y-color toner image, a M-color toner image, a C-color toner image, and a K-color toner image formed respectively on respective photoreceptor drums 1Y, 1M, 1C and 1K are transferred onto the intermediate transfer belt 6.

An outline of image forming process will now be explained as follows. Images each having a different color formed respectively by image forming units 10Y, 10M, 10C and 10K are transferred onto rotating intermediate transfer belt 6(primary transfer) in order by primary transfer rollers 7Y, 7M, 7C and 7K on each of which primary transfer bias (not shown) having polarity opposite to that of working toner (positive polarity in the present example), thus, color toner images are superimposed to form a color image. The color image is transferred onto sheet P from the intermediate transfer belt 6.

Sheet P loaded in each of sheet feeding trays 20A, 20B and 20C is fed by feed out roller 21 and sheet feeding roller 22A which are provided on each of the sheet feeding trays 20A, 20B and 20C to be conveyed to secondary transfer roller 7A through conveyance rollers 22B, 22C, 22D and registration rollers 23 and 28, whereby, color images are transferred collectively onto the surface on one side (front face) of sheet P (secondary transfer).

The sheet P onto which the color image has been transferred is subjected to fixing processing by fixing unit 17, and is interposed by sheet ejection rollers 24 to be conveyed to sheet ejection tray 25. Toner remaining on a circumferential surface on each of photoreceptor drums 1Y, 1M, 1C and 1K after transferring is removed by each of image carrier cleaning sections 8Y, 8M, 8C and 8K, to be ready for the succeeding image forming cycle.

In the case of double-face image forming, sheet P which has been subjected to image forming on the surface (front face) of its one side and has been ejected from fixing unit 17 is branched from a sheet ejecting path by branch section 26, then, passes through lower circulating sheet path 27A to be reversed inside out by reversing conveyance path 27B representing a sheet re-feeding mechanism (ADU mechanism), and passes through sheet re-feeding conveyance section 27C to join at sheet feeding roller 22D. The sheet P which has been reversed and conveyed passes through registration rollers 23 and 28 to be conveyed again to secondary transfer roller 7A where color images (color toner images) are transferred collectively onto the surface (rear face) on the other side of the sheet P.

In the case of image forming stated above, sheet P to be used includes a thin sheet of about 52.3-63.9 kg/m<sup>2</sup> (1000 sheets), a regular sheet of about 64.0-81.4 kg/m<sup>2</sup> (1000 sheets), a thick sheet of about 83.0-130.0 kg/M<sup>2</sup> (1000 sheets) and a super-thick sheet of about 150.0 kg/m<sup>2</sup> (1000 sheets).

The sheet P onto which the color image has been transferred is subjected to fixing processing by fixing unit 17, and is interposed by sheet ejection rollers 24 to be conveyed to sheet ejection tray 25. On the other hand, after a color image is transferred onto sheet P by secondary transfer roller 7A, intermediate transfer belt 6 from which the aforesaid sheet P is separated through curvature is cleaned by cleaning section 8A for an intermediate transfer belt so that residual toner is removed. In this example, registration sensor 5 representing an example of a detection section for color registration error is arranged at the upstream side of the cleaning section 8A, to detect color registration errors of each color image formed on the intermediate transfer belt 6.

Copier main body 100 is equipped with controller 15 that conducts simultaneously controlling to change a rotation speed of polygon mirror 42Y or the like for changing an image size in the sub-scanning direction and controlling to adjust rotation phase of the polygon mirror 42Y depending on an amount of correction for color registration errors after the correction (first image forming apparatus). The controller 15 constitutes a part of a color registration error correcting section, and it corrects color registration errors depending on an amount of detection for color registration error obtained from registration error in the sub-scanning direction can be adjusted by conducting phase control (which is also called plane phase control) for each of polygon mirrors 42Y-42K by the controller 15.

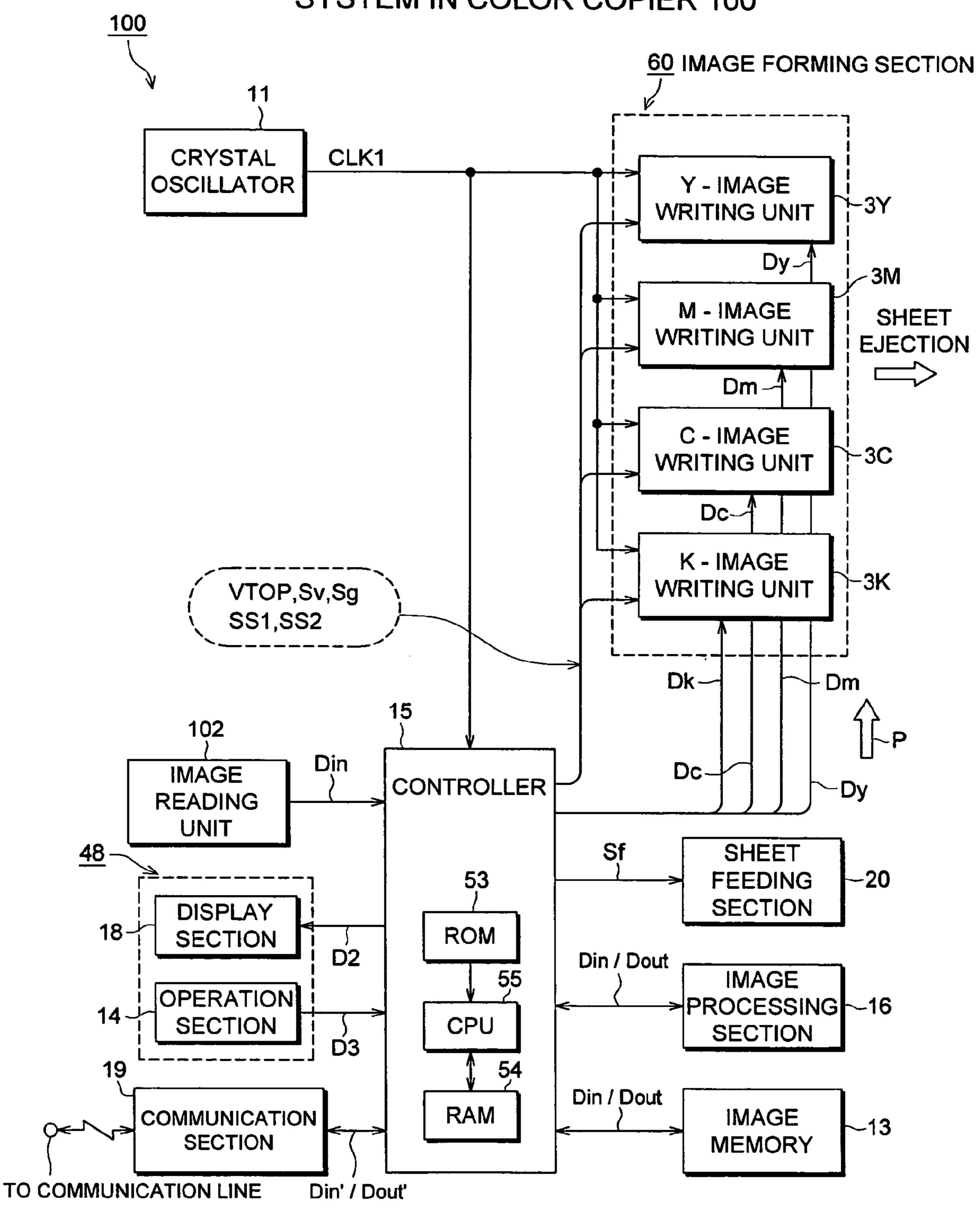

FIG. 2 is a block diagram showing an example of configuration of a control system of the color copier 100. The color copier 100 shown in FIG. 2 has therein controller 15 that determines timing to start image forming on a prescribed surface of sheet P based on basis signal (hereafter, index signal for each color image forming is called YIDX, MIDX, CIDX or KIDX) for forming Y-color image, M-color image, C-color image or K-color image. The basis signal in this case means main scanning basis signal (INDEX signal) to be generated by detecting a laser (exposure) beam oscillated by polygon mirror 42Y of each color image forming unit.

Crystal oscillator (source oscillator) 11, image memory 13, image processing section 16, communication section 19, sheet feeding section 20, operation panel 48, image forming section 60 and image reading unit 102 are connected to the controller 15.

The crystal oscillator 11 oscillates basis clock signal (hereinafter referred to as CLK1 signal) representing a basis signal in the case of color image forming. The CLK1 signals oscillated by the crystal oscillator 11 are outputted, for example, to image writing units 3Y, 3M, 3C and 3K which are respectively for Y-color image forming, M-color image forming, C-color image forming and K-color image forming.

The controller 15 has therein ROM (Read Only Memory) 53, RAM (Random Access Memory) 54 for work and CPU (Central Processing Unit; central processing unit) 55. System 60 program data for controlling the overall copier and information for controlling a rotation speed and a phase of polygon mirror 42 are stored in the ROM 53. These pieces of information include counter control signals (hereinafter referred to as CNTPRD signals) and phase control signals (hereinafter 65 referred to as PHASE signals). The RAM 54 stores temporarily control command in implementation of various modes.

**14**

When power supply is turned on, CPU 55 starts the system by reading system program data from ROM 53, and controls the overall copier. The CPU55, for example, executes control of color image forming on a prescribed surface of sheet P based on CLK1 signal and YIDX signal, when forming a color image on prescribed sheet P on a basis of Y-color. With regard to the YIDX signal, its cycle varies depending on rotation speed control and phase control for polygon mirror 42Y. The CPU 55 determines image leading edge signal in color image forming processing from a front face to a rear face of sheet P (hereinafter referred to as VTOP signal) and VTOP signal in color image forming processing in the case of switching from tray 1 to tray 2. The VTOP signal is a signal for synchronizing timing for conveying sheet P with timing for image forming.

The image forming section 60 is equipped with image writing units 3Y, 3M, 3C and 3K which are respectively for image forming for Y-color, M-color, C-color and K-color. In the color image forming, the CPU 55 establishes frequency control signal Sg, CNTPRD signal and PHASE signal on each of the image writing units 3Y, 3M, 3C and 3K. In Y-image writing unit 3Y, image data Dy for Y-color image forming are inputted from image memory for Y-color image forming, and actions are taken to form Y-color toner images based on frequency control signal Sg, CNTPRD signal, PHASE signal, CLK1 signal and an unillustrated YIDX signal. The YIDX signal is a basis signal in the case of controlling a rotation speed and a phase of polygon mirror 42Y for Y-color image forming and thereby scanning photoreceptor drum 1Y with a laser beam, and it is a signal obtained by detecting a laser beam reflected on polygon mirror 42Y.

Equally, in M-image writing unit 3M, image data Dm for M-color image forming are inputted from image memory for M-color image forming, and actions are taken to form M-color toner images based on frequency control signal Sg, CNTPRD signal, PHASE signal, CLK1 signal and MIDX signal. The MIDX signal is a basis signal in the case of controlling a rotation speed and a phase of polygon mirror 42M for M-color image forming and thereby scanning photoreceptor drum 1M with a laser beam, and it is a signal obtained by detecting a laser beam reflected on polygon mirror 42M.

In C-image writing unit 3C, image data Dc for C-color image forming are inputted from image memory for C-color image forming, and actions are taken to form C-color toner images based on frequency control signal Sg, CNTPRD signal, PHASE signal, CLK1 signal and CIDX signal. The CIDX signal is a basis signal in the case of controlling a rotation speed and a phase of polygon mirror 42C for C-color image forming and thereby scanning photoreceptor drum 1C with a laser beam, and it is a signal obtained by detecting a laser beam reflected on polygon mirror 42C.

In K-image writing unit 3K, image data Dk for K-color image forming are inputted from image memory for K-color image forming, and actions are taken to form K-color toner images based on frequency control signal Sg, CNTPRD signal, PHASE signal, CLK1 signal and KIDX signal. The KIDX signal is a basis signal in the case of controlling a rotation speed and a phase of polygon mirror 42K for K-color image forming and thereby scanning photoreceptor drum 1K with a laser beam, and it is a signal obtained by detecting a laser beam reflected on polygon mirror 42K.

In this example, the controller 15 executes color image forming control on a prescribed surface of sheet P based on YIDX signal and VTOP signal. Due to this, it is possible to correct image size on each of the front face and the rear face of sheet P, even when sheet P shrinks after image forming on

the front face, when forming images on both the front face and the rear face of the sheet. It is further possible to correct an image size on a different sheet, even when a type of a sheet on tray 1 is different from that of a sheet on tray 2, when forming color images after switching sheet feeding from tray 1 to tray 5.

Incidentally, operation panel 48 is connected to the controller 15, and has therein operation section 14 composed of a touch panel and display section 18 composed of liquid crystal display panel, both of which are not illustrated. An input section of a type of GUI (Graphic User Interface) is used for the operation panel 48. A power supply switch is provided on the operation panel 48. The display section 18 conducts display operations, interlocking with, for example, operation section 14.

The operation panel 48 is operated when selecting image forming conditions and selecting sheet feeding trays 20A-20C. For example, operation section 14 is operated when selecting a type of sheet P (sheet type) from a regular sheet, a recycled sheet, coated paper and OHT sheet and when selecting a sheet feeding tray storing therein the selected sheet from sheet feeding trays 20A-20C, thus, image forming conditions are established. Incidentally, the image forming conditions established by the operation panel 48 and information of the selected sheet feeding tray are outputted to the CPU 55 as operation data D3.

The aforesaid controller 15 executes color image forming on a prescribed surface of sheet P based on operation data D3 outputted from operation section 14 or on information received through communication section 19. For example, the aforesaid controller 15 executes processing to adjust an image size between the front face and the rear face of sheet P and processing to adjust a position between the front face and the rear face of sheet P, corresponding to a type of set sheet P or to set sheet feeding trays 20A-20C.

Image reading unit 102 is connected to the controller 15, and it reads images from document 30 shown in FIG. 1 to output image data Din (each color component data for R, G and B) for digital color to the controller 15. In the controller 40 15, image data Din are stored in image memory 13. Image processing section 16 reads image data Din from image memory 13, and conducts processing to convert color component data for R, G and B into image data Dy for Y-color image forming, image data Dm for M-color image forming 45 image data Dc for C-color and image data Dk for K-color image forming. Image data Dy, Dm, Dc and Dk respectively for Y-color image forming, M-color image forming, C-color image forming and K-color image forming are stored in image memory 13 or in an unillustrated image memory for Y-color image forming, M-color image forming, C-color image forming and K-color image forming.

Communication section 19 is connected to a communication line such as LAN, and is used when communicating with outside computers. When the color copier 100 is used as a printer, the communication section 19 is used to receive print data Din' from outside computers, in the mode of printing operation. Incidentally, print data Din' include image forming conditions and information of selecting sheet feeding trays. Those received from outside computers through communication section 19 may also be used as the image data Dy, Dm, Dc and Dk respectively for Y-color, M-color, C-color and K-color image forming.

Sheet feeding section 20 is connected to an unillustrated motor for driving sheet feeding trays 20A-20C, and it controls 65 rotation of the motor based on sheet feeding control signal Sf, and operates to convey sheet P fed out of the sheet feeding tray

**16**

20A, 20B or 20C to the image forming system. The sheet feeding control signal Sf is supplied to sheet feeding section 20 from the controller 15.

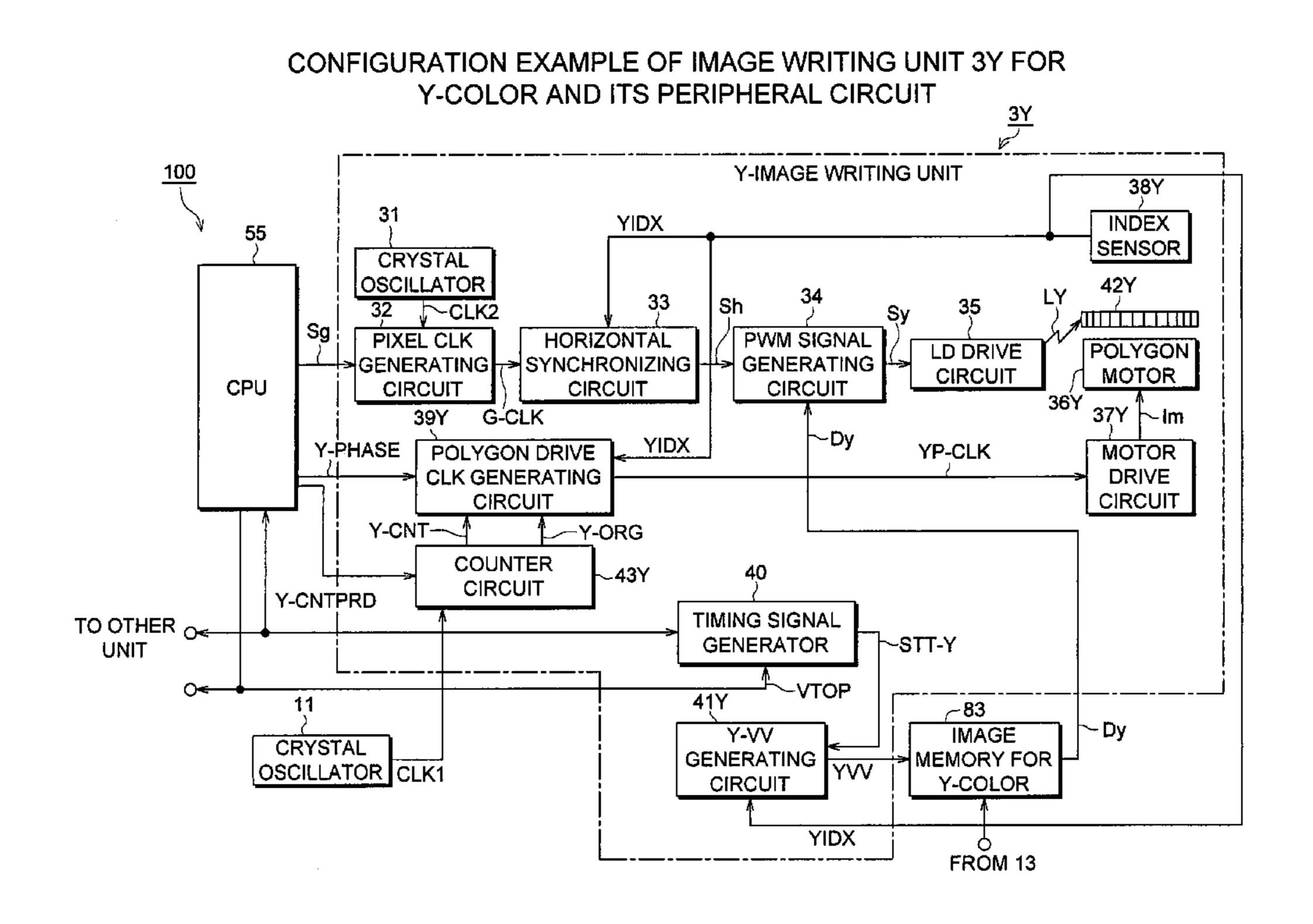

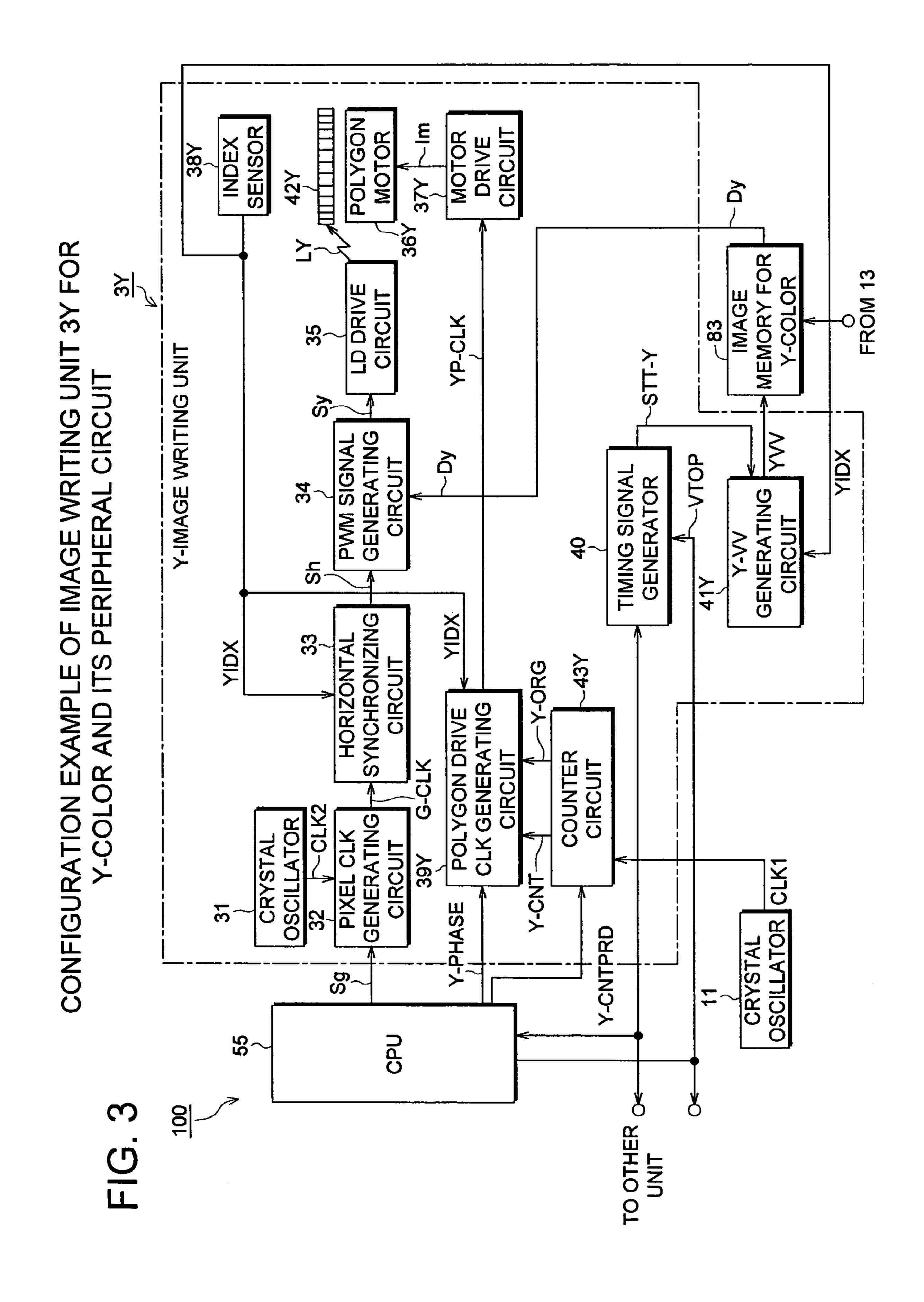

FIG. 3 is a block diagram showing an example of configuration of image writing unit 3Y for Y-color image forming shown in FIG. 2 and its peripheral circuit.

Y-color image writing unit 3Y shown in FIG. 3 is connected to crystal oscillator 11 and to CPU 55. The Y-color image writing unit 3Y is composed, for example, of crystal oscillator 31, pixel CLK generating circuit 32, horizontal synchronizing circuit 33, PWM signal generating circuit 34, laser (LD) drive circuit 35, polygon motor 36Y, motor drive circuit 37Y, index sensor 38Y, polygon drive CLK generating circuit 39Y, timing generator 40, Y-VV (Valid) generating circuit 41 and counter circuit 43Y.

Counter circuit 43Y is one for determining a cycle of YP-CLK signal that controls a rotation speed of polygon mirror 42Y, and it counts the number of pulses of CLK signals based on Y-CNTPRD signal, and outputs Y-CNT signal of the first cycle and Y-ORG signal of the second cycle. CLK1 signal is outputted to counter circuit 43Y from crystal oscillator 11. The Y-CNTPRD signal is a signal to establish a target count value of counter circuit 43Y, and it is a signal to establish a cycle of YP-CLK signal, namely, a speed of polygon motor 36Y. Y-CNTPRD signal is outputted to counter circuit 43Y from CPU 55 in the case of image forming on the front face and the rear face. This signal is used for controlling a rotation speed of polygon mirror 42Y. Y-CNT signal and Y-ORG signal are outputted to polygon drive CLK generating circuit 39Y from counter circuit 43Y.

To counter circuit **43**Y and CPU **55**, there is connected polygon drive CLK generating circuit **39**Y, and Y-PHASE signal, Y-CNT signal, Y-ORG signal and YIDX signal are inputted to be processed to generate polygon drive clock signal (YP-CLK signal) for Y-color image forming. The Y-PHASE signal is a signal that establishes an amount of phase adjustment on the polygon drive CLK generating circuit **39**Y, and it is used for controlling a phase of polygon mirror **42**Y. Further, on the polygon drive CLK generating circuit **39**Y, rotation speeds of polygon mirrors **42**Y-**42**K are changed.

The YIDX signal is outputted to the polygon drive CLK generating circuit 39Y from index sensor 38Y. CLK1 signal is outputted to the polygon drive CLK generating circuit 39Y from crystal oscillator 11. An example of internal configurations of the polygon drive CLK generating circuit 39Y will be explained, referring to FIG. 4.

Motor drive circuit 37Y is connected to the polygon drive CLK generating circuit 39Y. The motor drive circuit 37Y is connected to polygon motor 36Y, to drive the polygon motor 36Y based on YP-CLK signal. Polygon mirror 42Y is mounted on the polygon motor 36Y to be rotated by drive power of the polygon motor 36Y in the main scanning direction.

Laser beam LY radiated from an unillustrated diode is oscillated for main scanning when polygon mirror 42Y is rotated for photoreceptor drum 1Y rotating in the sub-scanning direction, in the aforesaid LD drive circuit 36, whereby an electrostatic latent image is formed on the photoreceptor drum 1Y. The electrostatic latent image formed on the photoreceptor drum 1Y is developed with toner member for Y-color image forming. A Y-color toner image on the photoreceptor drum 1Y is transferred onto intermediate transfer belt 6 rotating in the sub-scanning direction (primary transfer).

In the mean time, crystal oscillator 31 oscillates basis clock signals (hereinafter referred to as CLK2 signals) and outputs

them to pixel CLK generating circuit 32 which is connected to the crystal oscillator 31. The pixel CLK generating circuit 32 constitutes a pixel clock frequency changing section, and operates to generate pixel clock signals for Y-color image forming (hereinafter referred to as G-CLK signals) based on 5 frequency control signal Sg outputted by CPU 55 and thereby to output to horizontal synchronizing circuit 33.

The pixel CLK generating circuit 32 changes a pixel clock frequency depending on an amount of change in rotation speed for each of polygon mirrors 42Y-42K and an amount of adjustment of lateral magnification. For example, a value obtained by multiplying frequency f0 of G-CLK signal in the case of image forming on the front face and (L/L')·(W/W') together is established as Y-color image forming pixel CLK frequency f in the case of image forming on the rear face. The 15 aforesaid pixel CLK generating circuit 32 and the polygon drive CLK generating circuit 39Y constitute a magnification correcting section which corrects magnifications in terms of image sizes by one page unit.

The horizontal synchronizing circuit 33 is connected to the pixel CLK generating circuit 32 and to PMW signal generating circuit 34, and detects horizontal synchronizing signal Sh based on YIDX signal to output to the PMW signal generating circuit 34. The YIDX signal is outputted from index sensor 38Y for Y-color image forming not only to the horizontal 25 synchronizing circuit 33 but also to polygon drive CLK generating circuit 39Y. The index sensor 38Y is composed of a light-receiving element.

The PMW signal generating circuit 34 inputs image data Dy for Y-color image forming from image memory 83 for 30 Y-color image forming, and modulates the image data Dy in terms of pulse width to output laser drive signal Sy for Y-color image forming to LD drive circuit 35. The aforesaid PMW signal generating circuit 34 is connected with LD drive circuit 35. The LD drive circuit 35 is connected with an unillustrated 35 laser diode. The LD drive circuit 35 drives the laser diode based on laser drive signal Sy, and generates laser beam LY for Y-color image forming to radiate to polygon mirror 42Y.

To the aforesaid crystal oscillator 11, connected is timing signal generator 40 for determining image forming start timing for Y-color image forming. The timing signal generator 40 is further connected with CPU 55, and counts the number of pulses of YIDX signals based on VTOP signals outputted from the CPU 55 in the case of image forming on the front face, for example, to determine image forming start timing for 45 Y-color image forming on the front face of the sheet based on the number of the counted pulses. Concurrently with this determining of image forming start timing for Y-color image forming, image forming start signals (hereinafter referred to as STT signals) are outputted to Y-VV creating circuit 41Y.

The Y-VV creating circuit 41Y counts the number of pulses of YIDX signals based on STT signals outputted from the timing signal generator 40 to create sub-scanning effective area signal (hereinafter referred to as YTV signal) for Y-color image forming on the front face of the sheet based on the 55 number of the counted pulses. The YVV signal is outputted to image memory 83 for Y-color image forming.

To the aforesaid PMW signal generating circuit 34, there is connected image memory 83 for Y-color image forming, so that image data Dy for Y-color image forming may be read out 60 based on YVV signal in the case of forming images on both the front face and the rear face of the sheet. With regard to the image data Dy, image data for R, G and B colors are read out from image memory 13 shown in FIG. 2 in image processing section 16, and the image data for R, G and B colors represent 65 one of image data for Y, M, C and K colors converted in terms of a color.

18

Further, the timing signal generator 40 counts the number of pulses of YIDX signals based on VTOP signals outputted from CPU 55, immediately before the start of image forming on the rear face f the sheet, for example, to determine image forming start timing for Y-color image forming on the rear face of the sheet based on the number of the counted pulses. Concurrently with this determining of image forming start timing for Y-color image forming, STT signals (image forming start signals) are outputted to Y-VV creating circuit 41Y.

Y-VV creating circuit 41Y counts the number of pulses of YIDX signals based on STT signals outputted from timing signal generator 40, to create YVV signals for Y-color image forming on the rear face of the sheet based on the number of the counted pulses. YVV signals are outputted to image memory 83 for Y-color image forming.

In the mean time, since each of other image writing units 3M, 3C and 3K has also the configuration and function which are the same as those in the foregoing, descriptions for them will be omitted. In the present example, an explanation has been given by including crystal oscillator 31, pixel CLK generating circuit 32, horizontal synchronizing circuit 33, PWM signal generating circuit 34, polygon drive CLK generating circuit 39Y, timing generator 40, Y-VV generating circuit 41 and counter 43Y in the image writing unit 3Y. However, the invention is not limited to this, and these circuit elements may also be included in image processing section 16 or in controller 15 for the configuration.

In that case, it is also possible to employ a configuration wherein CPU **55** is caused to have functions of the timing generator **40**, VTOP signal is started based on CLK1 signal in the case of image forming on the front face of the sheet, the number of pulses of YIDX signals is counted based on the VTOP signal, and first image forming start timing for Y-color on the front face of the sheet is determined based on the number of counted pulses. Based on the STT signal (image forming start signal) determined here, the number of pulses of YIDX signals for Y-color image forming is counted, and image writing unit **3**Y is controlled so that YVV signal for Y-color image forming on the front face of the sheet may be created based on the number of counted pules.

In the case of image forming on the rear face of the sheet, CPU **55** starts VTOP signal based on CLK1 signal, then, counts the number of pulses of YIDX signals based on the VTOP signal, and determines first image forming start timing for Y-color for the rear face of the sheet based on the number of counted pulses.

The CPU 55 may also be made up to control input and output of image writing unit 3Y so that the number of pulses of YIDX signal for each color image forming are counted based on the determined image forming start timing, and YVV signal for Y-color image forming on the rear face of the sheet is created based on the number of the counted pulses.

In the present example, the CPU 55 controls a frequency of YP-CLK signal for each color in the order wherein image forming on the front face of the sheet for each of respective colors is completed, to establish a rotation speed of polygon mirror 42Y for the rear face of the sheet, and then, executes phase control for the MST-IDX.

If the control is operated as stated above, it is possible to carry out the control such as the rotation speed change and phase change of the polygon mirror 42Y, after completion of image forming for respective colors, based on MST-IDX signal established to a prescribed cycle, without depending on IDX signal of basis color.

Due to this, it is possible to carry out the control such as the rotation speed change and phase change of the polygon mirror for that color image forming, by waiting neither stabili-

zation of the rotation speed of polygon mirror 42K established to the basis color, nor adjustment of timing until the start of image forming for all of other colors.

FIG. 4 is a block diagram showing an example of configuration of a polygon mirror drive system for each color image forming, and it is a diagram wherein polygon mirror drive system (hereinafter referred to simply as Y, M, C or K unit) for each color image forming is extracted from image writing units 3Y, 3M, 3C and 3K for respective colors shown in FIG. 2

Y unit 3Y shown in FIG. 4 is composed of counter circuit 43Y, polygon drive CLK generating circuit 39Y, motor drive circuit 37Y, polygon motor 36Y and index sensor 38Y.

The counter circuit 43Y determines output timing of YP-CLK signal for driving polygon motor **36**Y (polygon mirror 15 42Y). This output timing means a rising edge and falling edge of YP-CLK signal. When Y-color image forming is made to be a basis, CPU 55 determines output timing of YP-CLK signal for the succeeding page, based on output value Y-CNT signal of counter circuit 43Y, a phase difference between YIDX 20 signal and YIDX signal, a phase difference between a base point of count cycle of Y-ORG signal by counter circuit 43Y and a base point of count cycle of Y-ORG signal by counter circuit 43Y, and on Y-PHASE signal showing an amount of phase control of polygon mirror 42Y. The amount of phase 25 control mentioned here means one which is calculated by correcting an amount of correction for color registration errors before correction of magnification for image size in accordance with an amount of adjustment of magnification.

The CPU 55 controls individually a count cycle established independently of each of polygon mirrors 42Y-42K, based on CLK1 signal though counter circuits 43Y, \$#M, 43C and 43K. The CPU 55 controls counter circuits 43Y, 43M, 43C and 43K, based on YP-CLK signal outputted from polygon drive CLK generating circuit 39Y, so that the count cycle may 35 be the same regarding image forming of the same page, when driving polygon motor 36Y, and establishes count cycle individually on each of image forming units 10Y, 10M, 10C and 10K for each color, to execute speed control.

Polygon drive CLK generating circuit 39Y is connected with counter circuit 43Y, and generates YP-CLK, referring to output values of the counter circuit 43Y. The polygon drive CLK generating circuit 39Y has therein phase detection circuit 301 for index use, phase detection circuit 302 for counter use and calculating & comparing section 303.

In the phase detection circuit 301 for index, phase difference PY between YIDX signal for Y-color image forming and YIDX signal is detected. In the phase detection circuit 302 for counter, phase difference AY between a base point of a count cycle of Y-ORG signal by counter circuit 43Y for Y-color 50 image forming and a base point of a count cycle of Y-ORG signal is detected. To the phase detection circuits 301 and 302, there is connected calculating & comparing section 303 constituting an example of a calculation section which carry out an operation for phase difference PY, phase difference AY and 55 Y-PHASE to calculate an amount of phase adjustment. In the present example, "an amount of phase adjustment=0" is outputted because of Y-color image forming basis. The calculating & comparing section 303 executes polygon mirror drive control in the case of magnification correction in terms of an 60 image size, with YP-CLK signal for controlling a rotation speed of polygon mirror 42Y generated based on the result of the operation.

To the counter circuit 43M, there is connected polygon drive CLK generating circuit 39M which generates MP-CLK, 65 referring to the output value of the counter circuit 43M. The polygon drive CLK generating circuit 39M has therein phase

**20**

detection circuit 304 for index, phase detection circuit 305 for counter and calculating & comparing section 306.

In the phase detection circuit 304 for index, phase difference PM between YIDX signal for Y-color image forming and MIDX signal is detected. The phase difference PM between YIDX signal and MIDX signal in this case means a phase difference between a main scanning basis signal for Y-color image writing unit 3Y immediately before conducting magnification correction in terms of an image size and main scanning basis signal for M-color image writing unit 3M. In the phase detection circuit 305 for counter, phase differences AM and AM' each between a base point of a count cycle of Y-ORG signal by counter circuit 43Y for Y-color image forming and a base point of a count cycle of M-ORG signal for M-color image forming is detected. This phase difference AM is one between a base point of a count cycle of counter circuit 43Y for Y-color image writing unit 3Y immediately before conducting magnification correction in terms of an image size and a base point of a count cycle of counter circuit 43M for M-color image writing unit 3M, while, phase difference AM' is a phase difference from a base point of a count cycle in the state where counter circuits 43Y and 43M after magnification correction in terms of an image size arrive at a count cycle.

To the phase detection circuits 304 and 305, there is connected calculating & comparing section 306 which carries out an operation for phase difference PM, phase differences AM and AM' as well as M-PHASE to calculate an amount of phase adjustment. In addition to Y unit 3Y and M unit 3M, C-K units have the same configuration and are equipped with the same functions. Therefore, explanation for them will be omitted here.

Each of FIGS. **5**(A)-**5**(F) is a time chart showing an example of operations (YP-CLK basis time) before magnification correction control in image forming section **60**. In the present example, there is shown the state before magnification correction control in the occasion where YP-CLK signal is a basis (CNTPRD Y=CNTPRD M=N1).

YIDX signals shown in FIG. **5**(A) are outputted from index sensor **38**Y shown in FIG. **4** before magnification correction control to phase detection circuits **301** and **304**. Y-CNT signal shown in FIG. **5**(B) is outputted from counter circuit **43**Y shown in FIG. **4** to calculating & comparing section **303**. In FIG. **5**(B), a counter cycle is set by Y-CNTPRD signal to output value N1.

YP-CLK signal shown in FIG. **5**(C) is outputted from calculating & comparing section **303** shown in FIG. **4** to motor drive circuit **37**Y. In FIG. **5**(C), period (t**5**-t**1**) is a clock cycle of YP-CLK signal before magnification correction control. At the point in time when counter circuit **43**Y counts N**1**/**2**, YP-CLK signal is reversed from a high level to a low level.

MIDX signal shown in FIG. 5(D) is outputted from index sensor 38M shown in FIG. 4 before magnification correction control to phase detection circuit 304. M-CNT signal shown in FIG. 5. (E) is outputted from counter circuit 43M shown in FIG. 4 to calculating & comparing section 306. In FIG. 5 (E), a counter cycle is set by M-CNTPRD signal to output value N1. MP-CLK signal shown in FIG. 5(F) is outputted from calculating & comparing section 306 to motor drive circuit 37Y. In FIG. 5(F), period (t6-t2) is a clock cycle of MP-CLK signal before magnification correction control. At the point in time when counter circuit 43M counts N1/2, MP-CLK signal is reversed from a high level to a low level.

In this example, when Al represents a phase difference between rising time t1 of YP-CLK signal shown in FIG. 5(C), namely, a count base point of counter circuit 43Y for Y-color

image forming and rising time t2 of MC-CLK signal, namely, a count base point of counter circuit 43M for M-color image forming, phase detection circuit 305 detects this phase difference A1.

Further, when P1 represents a phase difference between 5 rising time t3 of YIDX signal shown in FIG. 5(A) and rising time t4 of MIDX signal shown in FIG. 5(D), phase detection circuit 304 detects this phase difference P1. In the mean time, E1 represents a rising edge of MP-CLK signal for M-color image forming before magnification correction control 10 shown in FIG. 5(E). In the present example, E1 equals 1.

Each of FIGS. **6**(A)-**6**(F) is a time chart showing an example of operations (YP-CLK signal basis time) after magnification correction control in image forming section **60**. In this example, there is shown the state after magnification 15 correction control in the occasion where YP-CLK signal is a basis (CNTPRD Y=CNTPRD M=N1).

YIDX signals shown in FIG. **6**(A) are outputted from index sensor **38**Y shown in FIG. **4** after magnification correction control to phase detection circuits **301** and **304**. Y-CNT signal 20 shown in FIG. **6**(B) is outputted from counter circuit **43**Y shown in FIG. **4** to calculating & comparing section **303**. In FIG. **6**(B), a counter cycle is set by Y-CNTPRD signal to output value N2.