#### US007506286B2

# (12) United States Patent

# Beardslee et al.

# (10) Patent No.:

US 7,506,286 B2

(45) Date of Patent:

\*Mar. 17, 2009

# (54) METHOD AND SYSTEM FOR DEBUGGING AN ELECTRONIC SYSTEM

(75) Inventors: **John Mark Beardslee**, Menlo Park, CA

(US); Nils Endric Schubert, Sunnyvale,

CA (US); Douglas L. Perry, San

Ramon, CA (US)

(73) Assignee: **Synopsys, Inc.**, Mountain View, CA

(US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 196 days.

This patent is subject to a terminal dis-

claimer.

(21) Appl. No.: 11/417,355

(22) Filed: May 2, 2006

(65) Prior Publication Data

US 2006/0195822 A1 Aug. 31, 2006

#### Related U.S. Application Data

- (63) Continuation of application No. 09/724,585, filed on Nov. 28, 2000, now Pat. No. 7,072,818.

- (60) Provisional application No. 60/230,068, filed on Aug. 31, 2000, provisional application No. 60/168,266, filed on Nov. 30, 1999.

- (51) Int. Cl. G06F 17/50 (2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

4,306,286 A 12/1981 Cocke et al. 4,590,581 A 5/1986 Widdoes, Jr. 4,635,218 A 1/1987 Widdoes, Jr. 4,675,646 A 6/1987 Lauer

(Continued)

# FOREIGN PATENT DOCUMENTS

DE 4 042 262 7/1992

#### (Continued)

#### OTHER PUBLICATIONS

A. Carbine, D. Feltham, "Pentium® PRO Processor Design for Test and Debug", Proceedings of International Test Conference 1997 (Nov. 1-6, 1997) pp. 294-303.\*

#### (Continued)

Primary Examiner—Jack Chiang Assistant Examiner—Aric Lin (74) Attorney, Agent, or Firm—Blakely, Sokoloff, Taylor & Zafman LLP

## (57) ABSTRACT

Techniques and systems for debugging an electronic system having instrumentation circuitry included therein are disclosed. The techniques and systems facilitate analysis, diagnosis and debugging fabricated hardware designs at a Hardware Description Language (HDL) level. Although the hardware designs (which were designed in HDL) have been fabricated in integrated circuit products with limited input/output pins, the invention enables the hardware designs within the integrated circuit products to be comprehensively analyzed, diagnosed, and debugged at the HDL level at speed. The ability to debug hardware designs at the HDL level facilitates correction or adjustment of the HDL description of the hardware designs.

## 29 Claims, 26 Drawing Sheets

# US 7,506,286 B2 Page 2

| TIC DATENIT                           |                           | C 105 C20 D1 * 2/20                   | 01 D =1 -4 -1 702/17                    |

|---------------------------------------|---------------------------|---------------------------------------|-----------------------------------------|

| U.S. PATENT                           | DOCUMENTS                 |                                       | 01 Bargh et al 703/17                   |

| 4,845,712 A 7/1989                    | Sanner et al.             | , ,                                   | 01 Challier et al.<br>01 Tzori          |

| , ,                                   | Watkins                   | , ,                                   | 01 Ponte                                |

| , ,                                   | Samuels et al.            | , ,                                   | 01 Fonte<br>01 Guccione                 |

| , ,                                   | Beck et al.               | , ,                                   | 01 Stewart et al.                       |

| , ,                                   | Butts et al.              | , ,                                   | 01 Raynaud et al.                       |

| , ,                                   | Ackerman et al.           |                                       | 01 Raynaud et al.<br>01 Beenstra et al. |

|                                       | Hahn et al.               | , ,                                   | 01 Schwarz et al.                       |

| , ,                                   | Phillips et al.           | , ,                                   |                                         |

|                                       | Sample et al.             |                                       | 01 Wong et al.                          |

|                                       | Swoboda et al.            | , ,                                   | 01 Cromer et al. 702/12                 |

| 5,369,593 A 11/1994                   |                           |                                       | 01 Mason et al 703/13                   |

|                                       | Tsui et al.               | , ,                                   | 01 Veenstra et al.                      |

| , ,                                   | Ogino et al.              | , ,                                   | 01 Ho et al.                            |

|                                       | Liu et al.                |                                       | 01 Roy                                  |

|                                       | Giomi et al.              |                                       | 01 Choquette et al.                     |

|                                       | Harenberg et al.          | , ,                                   | 01 Khoche et al.                        |

| 5,546,562 A 8/1996                    |                           |                                       | 02 Burgun et al 703/15                  |

|                                       | Lenkov et al.             | , ,                                   | 02 Smith et al 714/741                  |

| 5,568,437 A 10/1996                   |                           | , ,                                   | 02 Boubezari et al.                     |

| 5,572,712 A 11/1996                   |                           | , ,                                   | 02 Bockhaus et al.                      |

| 5,574,388 A 11/1996                   |                           |                                       | 02 Sample et al.                        |

|                                       | Lin et al.                |                                       | 02 Sample et al.                        |

| 5,596,587 A 1/1997                    |                           | ,                                     | 02 Whetsel                              |

|                                       | Bhat et al.               | 6,389,558 B1 5/20                     |                                         |

| / /                                   | Whitsel et al.            | , ,                                   | 02 McElvain                             |

| , ,                                   | Sample et al.             | , ,                                   | 02 Jeddeloh                             |

|                                       | Butts et al.              | , ,                                   | 02 Garreau                              |

|                                       | Bhandari et al.           | , ,                                   | 02 Warren                               |

|                                       | Haag et al.               | , ,                                   | 02 Watkins                              |

| , ,                                   | Tzori                     | , ,                                   | 02 McElvain et al.                      |

| , ,                                   | Tobin et al.              | , ,                                   | 02 McElvain                             |

| <i>'</i>                              | Barbier et al.            | , ,                                   | 02 Dumbri                               |

| , ,                                   |                           | , ,                                   | 02 Patil et al.                         |

| , ,                                   | Segars<br>Tobin et al.    | · · · · · · · · · · · · · · · · · · · | 02 Veenstra et al.                      |

| , ,                                   | Barbier et al.            | 6,460,174 B1 10/20                    | _                                       |

| , ,                                   |                           | 6,463,392 B1 10/20                    |                                         |

|                                       | Barbier et al.            |                                       | 02 Bargh et al 716/4                    |

|                                       | Kawamura et al 364/489    | 6,484,273 B1 11/20                    |                                         |

|                                       | Giramma et al.            | 6,493,852 B1 12/20                    |                                         |

| , ,                                   | Butts et al.              | 6,499,123 B1 12/20                    |                                         |

| 5,812,562 A 9/1998                    |                           | , ,                                   | 03 Nadeau-Dostie et al.                 |

| , , ,                                 | Chilton et al.            | , ,                                   | 03 Bloom et al.                         |

|                                       | Beausang et al 364/489    |                                       | 03 Eldridge et al 438/14                |

|                                       | Snyder 395/384            | , ,                                   | 03 Mates                                |

|                                       | Dangelo et al.            | , ,                                   | 03 Edwards et al.                       |

| 5,870,410 A 2/1999                    |                           |                                       | 03 Vogt                                 |

|                                       | Kasuya 395/500            | , ,                                   | 03 Schubert et al.                      |

| 5,907,697 A 5/1999                    |                           | , ,                                   | 03 Duboc et al.                         |

| 5,933,356 A 8/1999                    |                           | 6,591,369 B1 7/20                     |                                         |

|                                       | Gregory et al 395/704     | 6,594,802 B1 7/20                     |                                         |

| 5,943,490 A 8/1999                    | •                         | 6,618,839 B1 9/20                     |                                         |

|                                       | Naaseh et al.             | , ,                                   | 03 Mann 717/124                         |

| 5,960,191 A 9/1999                    | -                         | , ,                                   | 03 Baxter et al 716/6                   |

| 5,963,735 A 10/1999                   | ±                         | , ,                                   | 03 Arimilli et al.                      |

| , ,                                   | Williams et al 395/500.19 | 6,690,398 B1 2/20                     |                                         |

| 5,999,725 A 12/1999                   |                           | 6,697,957 B1 2/20                     |                                         |

| , , , , , , , , , , , , , , , , , , , | Rhim et al 395/500.02     | , ,                                   | 04 Veenstra et al.                      |

| 6,009,256 A 12/1999                   | _                         | 6,754,760 B1 6/20                     |                                         |

| 6,014,334 A 1/2000                    |                           |                                       | 04 Hoyer et al.                         |

|                                       | Szeto et al.              | , ,                                   | 04 Edwards et al.                       |

| / /                                   | Lin et al.                | , ,                                   | 04 Jaramillo et al.                     |

| , ,                                   | Shiell Daylaian at al     | · · ·                                 | 04 Slaugh et al.                        |

| , , ,                                 | Barbier et al.            | , ,                                   | 04 Verdoorn et al.                      |

| , , ,                                 | Kelem et al.              | , ,                                   | 04 Andersen et al.                      |

|                                       | Gregory et al.            | , ,                                   | 04 Duff et al.                          |

| , ,                                   | Herrmann et al.           | , ,                                   | 04 Chaudhari                            |

| 6,157,210 A 12/2000                   |                           | , ,                                   | 04 Wood et al.                          |

|                                       | Ly et al.                 |                                       | 04 Draper et al.                        |

| , ,                                   | Herrmann et al.           | 6,839,654 B2 1/20                     | 05 Röllig et al.                        |

| , ,                                   | McElvain                  | 6,839,874 B1 1/20                     | e e e e e e e e e e e e e e e e e e e   |

| 6,188,975 B1 2/2001                   | Gay                       | 6,859,892 B2 2/20                     | 05 Bolding et al.                       |

| 6,191,683 B1 2/2001                   | Nygaard, Jr.              | 6,868,376 B2 3/20                     | 05 Swoboda                              |

|                                       |                           |                                       |                                         |

| 6,894,530    | B1            | 5/2005  | Davidson et al.      |

|--------------|---------------|---------|----------------------|

| 6,895,365    | B2            | 5/2005  | Voorhees et al.      |

| 6,895,372    | B1            | 5/2005  | Knebel et al.        |

| 6,904,577    | B2 *          | 6/2005  | Schubert et al 716/4 |

| 2002/0147939 | $\mathbf{A}1$ | 10/2002 | Wenzel et al.        |

| 2002/0177990 | $\mathbf{A}1$ | 11/2002 | Sample               |

| 2002/0194543 | $\mathbf{A}1$ | 12/2002 | Veenstra et al.      |

| 2003/0154458 | $\mathbf{A}1$ | 8/2003  | Butts et al.         |

| 2004/0111252 | $\mathbf{A}1$ | 6/2004  | Burgun et al.        |

| 2004/0181385 | $\mathbf{A}1$ | 9/2004  | Milne et al.         |

#### FOREIGN PATENT DOCUMENTS

| WO | WO 00/43884 A1 | 7/2000 |

|----|----------------|--------|

| WO | WO 01/63434 A1 | 8/2001 |

| WO | WO 01/71876 A1 | 9/2001 |

#### OTHER PUBLICATIONS

Kirovski, D., et al., "Improving the Observability and Controllability of Datapaths for Emulation-Based Debugging", IEEE Trans. on CAD, vol. 18, Nov. 1999, pp. 1529-1541.

Vermeulen, B., et al., "Silicon debug of a co-processor array for video applications", pp. 6, High-Level Design Validation and Test Workshop, 2000, IEEE Proceedings.

Van Rootselarr, G., et al., "Silicon debug: scan chains alone are not enough", pp. 11, ITC 1999.

Van Rootselaar, G., et al., "Silicon Debug Methodology", pp. 32, Embedded Tutorial, ICCAD, 1999.

Gernot Koch et al., "System Validation by Source Level Emulation of Behavioral VHDL Specifications," 6<sup>th</sup> International Workshop on Rapid System Prototyping, 1995.

Peter Clarke, "DATE99: Temento to launch scan insertion tool," EETimes.com, Mar. 4, 1999.

Alexander Miczo, "Digital Logic Testing and Simulation," Harper & Row, Publishers, 1996.

Xilinx, "ChipScope Software and ILA Cores User Manual," v1.1, Jun. 30, 2000.

Gernot Koch et al., "Breakpoints and Breakpoint Detection in Source Level Emulation," ACM Transactions on Design Automation of Electronic Systems, vol. 3, No. 2, 1998.

Samiha Mourad et al., "123 Logic Analyzers", The Engineering Handbook, pp. 1325-1330, CRC Press, Inc., 1996.

Ableidinger et al., "Multi-Core Embedded Debug for Structured ASIC Systems", DesignCon 2004, Feb. 2004, 23 pgs.

"Actel Corporation," Actel Silicon Explorer II—User's Guide, Mar. 2004; cover page, p. ii and pp. 3-43.

Altera Corporation, "Quartus II Handbook, vol. 3", Section IV-1, May 2005; pp. 9/1-9/14; pp. 10/1-10/46; pp. 11/1-11/46; pp. 12/1-12/10.

Altera Corporation, "SignalTap II Features", http://www.altera.com/products/software/products/quartus2/verification/signaltap2/sigfeature\_descriptions.html, Jun. 2005, pp. 1-4.

ASSET Intertech, Inc., "ScanWorks Diagnostic & Repair Station Bundle", Document 20019-H, Jun. 2005, pp. 1-6.

Automotive DesignLine, "Lattice Semi in-system configuration engine goes into JTAG system", http://www.automotivedesignline. com, Feb. 14, 2005, pp. 1-3.

Bennetts, R.G., "Boundary Scan Tutorial", ASSET Intertech Inc., Sep. 2002, pp. 1-58.

First Silicon Solutions, Technical Data for CLAM System for Actel FPGA Devices, http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Trace Instrumentation and Architectures for OCP Buses", Date Conference 2005, Mar. 2005, 16 pgs.

First Silicon Solutions, Inc., "Getting Started—FS2 System Analyzer for QuickLogic Eclipse Devices", http://www.fs2.com, Jan. 2004, pp. 1-29.

First Silicon Solutions, Inc., "Getting Started—System Analyzer for AMD Geode GX and Geode LX Processors", http://www.fs2.com, May 2005, pp. 1-45.

First Silicon Solutions, Inc., "Technical Data for ISA-ACTEL51 In-Target System Analyzer for Actel Core8051 Microcontroller Cores", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Technical Data for ISA-ARM System Analyzer for ARM Processors and Cores", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Technical Data for ISA-CAST51 In-Target System Analyzer for CAST 8051 Synthesizable Microcontroller Cores", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Technical Data for FS2 System Analyzer for QuickLogic Eclipse FPGA Devices", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Technical Data for System Navigator OE for AMD Geode GX Processors", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Technical Data for System Navigator OE for MIPS32 and MIPS64 Cores", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Technical Data for In-Target System Analyzer for Altera Nios Embedded Processor Systems", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Technical Data for FS2 System Analyzer for QuickLogic QuickMIPS ESP Devices", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Technical Data for In-Target System Analyzer for LSI Logic ZSP500 DSP Core", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Getting Started—ISA-Jazz Debugger", http://www.fs2.com, Apr. 2004, pp. 1-22.

First Silicon Solutions, Inc., "Technical Data for FS2 On-Chip Logic Navigator System for Actel FPGA Devices", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Technical Data for Logic Navigator System for Atmel FPGA Devices", http://www.fs2.com, Jun. 2005, 3 pgs.

First Silicon Solutions, Inc., "Preliminary Technical Data for FS2 MED System for SoC Multi-Core Embedded Debug", http://www.fs2.com, Feb. 2004, 2 pgs.

First Silicon Solutions, Inc., "Technical Data for ISA-M8051EW In-Target System Analyzer for Mentor Grphics M8051EW Synthesizable Microcontroller Core", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Getting Started—System Navigator for MIPS Cores", http://www.fs2.com, Mar. 2005, pp. 1-49.

First Silicon Solutions, Inc., "Preliminary Technical Data for AMBA Navigator AMBA On-Chip Bus Analyzer for AHB Bus Systems", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Preliminary Technical Data for OCP Navigator On-Chip Bus Socket Analyzer for OCP Bus Systems", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Preliminary Technical Data for SiliconBackplane Navigator On-Chip Bus Analyzer for Sonics SiliconBackplane uNetwork", http://www.fs2.com, Jun. 2005, 2 pgs. First Silicon Solutions, Inc., "NIOS II Hardware Reference—System Analyzer for the Nios II Processor Core", http://www.fs2.com, Nov. 2004, pp. 1-33.

First Silicon Solutions, Inc., "NIOS II Software User Guide—System Analyzer for the Nios II Processor Core", http://www.fs2.com, Nov. 2004, pp. 1-34.

First Silicon Solutions, Inc., "Getting Started—FS2 System Analyzer for QuickLogic QuickMIPS Devices", http://www.fs2.com, Feb. 2004, pp. 1-44.

First Silicon Solutions, Inc., "Technical Data for System Navigator for AMD Geode GX Processor", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Technical Data for System Navigator for MIPS32 and MIPS64 Cores", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Technical Data for System Navigator for Tensilica Xtensa Processors", http://www.fs2.com, Jun. 2005, 2 pgs.

First Silicon Solutions, Inc., "Getting Started—VAutomation System Analyzer, VSA-186", Version 1.8.0.2, http://www.fs2.com, Oct. 2002, pp. 1-19.

First Silicon Solutions, Inc., "Technical Data for VSA-8X/18X System Analyzer for ARC International (formerly VAutomation) V186 and Turbo 186 Synthesizable Cores", http://www.fs2.com, Jun. 2005, 2 pgs.

Goel et al., "On-Chip Test Infrastructure Design for Optiomal Multi-Site Testing of System Chips", Date Conference 2005, Mar. 2005, 6 pgs.

Lauterbach, "BDM/JTAG Debuggers", http://www.lauterbach.com, Jan. 2005, pp. 1-51.

Lauterbach, "ICD In-Circuit Debugger", http://www.lauterbach.com, Jan. 2005, pp. 1-23.

Lauterbach, "Lauterbach—Basic Concept", http://www.lauterbach.com, Jan. 2005, pp. 1-15.

Mayer et al., "Debug Support, Calibration and Emulation for Multiple Processor and Powertrain Control SoCs", Date Conference 2005, Mar. 2005, 5 pgs.

S2C Inc., "IP Porter Introduction", http://www.s2cinc.com/aaipi3. asp, Jun. 2005, 9 pgs.

Stollon et al., "Multi-Core Embedded Debug for Structured ASIC Systems", DesignCon 2004, Feb. 2004, pp. 1-23.

Xilinx, Inc., "ChipScope Pro Software and Cores User Guide", UG029, Version v7.1, Feb. 2005, 122 pgs.

Yang et al., "Extraction Error Modeling and Automated Model Debugging in High-Performance Low Power Custom Designs", Date Conference 2005, Mar. 2005, 6 pgs.

Haufe, J., et al., "Ein Debugger fuer ASIC-Prototypen", DASS Dresden Germany, 2000, pp. 10.

PCT International Search Report, re PCT/US 00/32543, Jun. 28, 2001.

U.S. Appl. No. 09/724,840, filed Nov. 28, 2000.

U.S. Appl. No. 09/724,839, filed Nov. 28, 2000.

U.S. Appl. No. 09/724,702, filed Nov. 28, 2000.

Bulent Dervisoglu, "Design for Testability: It is time to deliver it for Time-to-Market," Proceedings of the International Test Conference, 1999.

Keshava Iyengar Satish, "Tutorial on Design For Testability (DFT): An ASIC Design Philosophy for testability from Chips to Systems," Sixth Annual IEEE International ASIC Conference and Exhibit, 1993.

Jan Liband, "Techniques for Real-Time Debugging," Embedded Systems Programming, vol. 8, No. 4, Apr. 1995.

Dr. Vinod Agarwal, "Embedded IC Test: A New Plateau for DFT," Evaluation Engineering, vol. 38, No. 9, Sep. 1999.

Stephen O'Reilly, "Debugging Drivers with Emulators and Logic Analyzers," Embedded Systems Programming, vol. 11, No. 2, Feb. 1998.

Jack G. Ganssle, "Debuggers for Modern Embedded Systems," Embedded Systems Programming, Nov. 1998.

Brent Miller, "Scan Conversion of ASICs," Circuit Design, vol. 7, No. 2, Feb. 1990.

Jerry Bauer et al., "A Reconfigurable Logic Machine for Fast Event-Driven Simulation," Design Automation Conference Proceedings (DAC), Jun. 1998, pp. 668-671.

Synopsys, Inc., "BSD Compiler" datasheet, www.synopsys.com/products/test/bsd\_ds.html.

Synopsys, Inc., "DFT Compiler" Next Generation 1-Pass Test Synthesis Technology Backgrounder, Apr. 2000.

Cynthia Cousineau et al., "Design of a JTAG Based Run Time Reconfigurable System," 7<sup>th</sup> IEEE Symposium on Field Programmable Custom Computing Machines, 1999.

John Andrews, "An Embedded JTAG, System Test Architecture," Proceedings of ELECTRO, 1994.

Shen XuBang et al., "Design and Implementation of a JTAG Boundary-Scan Interface Controller," Proceedings of the 2<sup>nd</sup> IEEE Asian Test Symposium, 1993.

"JTAG for system emulation," Electronic Engineering, vol. 65, No. 794, Feb. 1993.

R.P. van Riessen et al., "Design and Implementation of a Hierarchical Testable Architecture using the Boundary Scan Standard," 1<sup>st</sup> European Test Conference, IEEE, 1989.

Ing-Jer Huang et al., "ICEBERG: An Embedded In-circuit Emulator Synthesizer for Microcontrollers," Proceedings of the 36<sup>th</sup> Design Automation Conference (DAC), 1999.

Ross Bannatyne, "Debugging Aids for Systems-on-a-Chip," Proceedings of North Con, 1998.

Robert J. Hasslen et al., "A Validation Strategy for Embedded Core ASICS," Proceedings of the Third Annual IEEE ASIC Seminar and Exhibit, Sep. 1990.

Max Baron et al., "A Real-Time Performance Analyzer," VLSI Systems Design, May 4, 1987.

Indradeep Ghosh, "A BIST Scheme for RTL Circuits Based on Symbolic Testability Analysis," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 19, No. 1, Jan. 2000. Indradeep Ghosh, "A Design-for-Testability Technique for Register-Transfer Level Circuits Using Control/Data Flow Extraction," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 17, No. 8, Aug. 1998.

Barbara Tuck, "Test-bench tools ease tedious, time-consuming manual efforts," Computer Design, May 1996.

Krzysztof Badzmirowski et al., "Diagnosis of Digital/Analogue Measurement System with Application of Test Bus and Distributed Diagnostic Subsystem," Proceedings of the IEEE Instrumentation and Measurement Technology Conference, 1998.

Stephen Pateras et al., "BIST: A Test & Diagnosis Methodology for Complex, High Reliability Electronics Systems," 1997 IEEE Autotestcon Proceedings.

John Sweeney, "A Method For Using JTAG Boundary Scan For Diagnosing Module Level Functional Failures," Proceedings of WesCon Conference, 1988.

Wen-Jong Fang et al., "A Multi-Level FPGA Synthesis Method Supporting HDL Debugging for Emulation-Based Designs," Proceedings of the Asian and South Pacific Design Automation Conference, 1999.

David Ruimy Gonzales, "Tool Reusable for DSP System Emulation and Board Production Testing," IEEE Technical Applications Conference, Northcon, 1996.

Ray Weiss, "ICEs try to target higher clock rates, more processors," Computer Design, vol. 35, No. 2, Feb. 1996.

Mike Winters, "Using IEEE-1149.1 For In-Circuit Emulation," Proceedings of WesCon, 1994.

Christopher Perez, "Tools for Embedded-Systems Debugging," Dr. Dobbs Journal, Mar. 1993.

Kristen Ahrens, "Test Standard Speeds On-Board Programming," Electronic Design, Nov. 7, 1994.

Oliver Bringmann et al., "Target Architecture Oriented High-Level Synthesis for Multi-FPGA Based Emulation," Proceedings of the Design Automation and Test Conference, DATE, 2000.

Karlheinz Weiß et al., "Exploiting FPGA-Features during the Emulation of a Fast Reactive Embedded System," Proceedings of the 1999 ACM/SIGDA International Symposium on Field Programmable Gate Arrays, ACM, 1999.

Gernot Koch et al., "Breakpoints and Breakpoint Detection in Source Level Emulation," 9<sup>th</sup> International Symposium on System Synthesis, 1996.

Gernot Koch et al., "Co-Emulation and Debugging of HW/SW-Systems," 10<sup>th</sup> International Symposium on System Synthesis (ISSS), 1997.

Gernot Koch et al., "System prototyping in the COBRA Project," International Journal Microprocessors and Microsystems, Elsevier Science, vol. 20, No. 3, 1996.

G. Haug et al., "Behavioral Emulation of Synthesized RT-level Descriptions Using VLIW Architectures," 9<sup>th</sup> International Workshop on Rapid System Prototyping, 1998.

Gernot Koch, "Interaktives Debugging algorithmischer Hardware—Verhaltensbeschreibungen mit Emulation," Dissertation, 1998.

<sup>\*</sup> cited by examiner

FIG. 2

FIG. 4A

FIG. 5B

FIG. 5C

FIG. 7B

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 18

FIG. 21

# METHOD AND SYSTEM FOR DEBUGGING AN ELECTRONIC SYSTEM

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a continuation of U.S. patent application Ser. No. 09/724,585, filed on Nov. 28, 2000 now U.S. Pat. No. 7,072,818. This application also claims the benefit of: (i) U.S. Provisional Patent Application No. 60/168,266, filed 10 Nov. 30, 1999, and entitled "INTERACTIVE DEBUGGING OF HDL SOURCE CODE", and which is hereby incorporated by reference herein; and (ii) U.S. Provisional Patent Application No. 60/230,068, filed Aug. 31, 2000, and entitled "HDL-BASED HARDWARE DEBUGGING", and which is 15 hereby incorporated by reference herein.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to electronic systems and, more particularly, to debugging of electronic systems.

#### 2. Description of the Related Art

Electronic systems are designed by designers to operate in specific ways. Electronic systems are systems that contain 25 digital and/or analog electronic components connected together to perform specific operations or functions. Besides the electronic components, electronic systems may also include software. Once designed, the electronic systems may need to be debugged. Debugging electronic systems is a process which involves detection, diagnosis, and correction of functional failures. In the detection step, the designer of the electronic system observes a functional failure. When the designer is able to gather enough information about the incorrect behavior of the electronic system, the designer of the 35 electronic system can draw the necessary conclusions to diagnose the functional failure. For correction of the functional failure, a fix is applied and subsequently tested. When the design is provided in a Hardware Description Language (HDL), such a fix may be a textual change to the HDL 40 description of the electronic system.

In general, debugging has conventionally been performed by various different approaches. In particular, debugging has been performed by computer software debugging, hardware description language functional verification, hardware logic 45 level analysis, or hardware behavioral source level emulation. These different approaches are discussed below.

Computer software debugging is conventionally performed using a computer software debugger. A computer software debugger is a software tool that allows a software 50 developer to control the execution of a running computer software program by setting break-points, sequentially single-stepping through the execution of the computer software program, and looking at the program's state by examining and displaying variables and expressions. One example 55 of such a software debugging tool is the GNU Debugger (GDB), which can be obtained from Red Hat, Inc. in Sunnyvale, Calif.

Software debuggers usually offer interactive debugging of software programs which are sequentially executed on computers. However, some software debuggers also support limited concurrency such as threaded program execution. Some software debuggers support debugging programs written at different levels of abstraction from high-level computer languages such as C++ down to assembler code and/or machine code. To assist with debugging of programs written in high-level computer languages, the software debugging system can

2

add extra debug information (e.g., symbolic names and references to source code) to the compiled code during compilation of the computer software program. In combination with in-circuit emulators, software debuggers may provide a limited capability to analyze the underlying Central Processing Unit (CPU) of the computer executing the computer software program. A major disadvantage of software debuggers is, however, that they cannot be used for efficiently debugging general hardware of electronic systems.

Hardware description language functional verification is used to verify that the parts of an electronic system which are described using HDL match their functional specification. Such functional verification can be achieved through functional simulation or formal verification.

Functional simulation is performed by a functional simulator. A functional simulator is a software program that runs on a host computer and simulates the operation of an electronic system using its HDL description. Examples of functional simulators include VCS and VSS from Synopsys, Inc. in Mountain View, Calif., and ModelSim from Mentor Graphics Corp. in Wilsonville, Oreg. To increase simulation performance some functional simulators additionally make use of special purpose hardware which acts as a co-processor and accelerates the simulation. An example of a hardware-accelerated functional simulator is the Hammer system from Tharas Systems, Inc. in Santa Clara, Calif. Unfortunately, one major disadvantage of functional simulation is the need for simulation models. In order to be able to simulate, there must exist a simulation model with the proper functional behavior for each component of the HDL design for the electronic system. For some components such simulation models may not be readily available and must be generated. Additionally, the HDL design must be stimulated by a testbench. Since the ideal testbench must correctly and exhaustively match the behavior of the target environment, creation of a testbench can be very difficult and time consuming. On the other hand, a testbench that is too simple will not provide the necessary coverage to find all the design errors. Although functional simulation is useful, using functional simulation to debug design errors is too burdensome. Not only are the testbenches difficult to create, but also the more complex the HDL design is, the lower the performance of functional simulation. For state-of-the-art HDL designs simulation is now a million times slower than the fabricated hardware. Hardware-acceleration can typically speedup functional simulation by a factor on the order of one-hundred. Accordingly, its low performance makes it impractical to use functional simulation either to debug real-time applications or to concurrently debug hardware and software of complex electronic systems.

Formal verification is performed by a formal verification tool. Formal verification can help with the problem of incomplete coverage in functional simulation due to testbench limitations. One approach checks the HDL description for properties. Such properties may be explicitly provided by the designer of the electronic system or implicitly extracted from the HDL description by the formal verification tool. An example of such a formal verification tool is Solidify from Averant, Inc. in Sunnyvale, Calif. One disadvantage of formal verification is that it is impractical to use to re-produce functional failures observed in a running electronic system.

Both techniques, functional simulation and formal verification, have the major disadvantage that they do not operate on fabricated hardware. Instead, both techniques operate on a model of the electronic system and a model of the environment in which the electronic system runs, i.e., a testbench. Thus, their use is limited to debugging design errors. As such, neither technique is applicable for debugging manufacturing

faults, environment errors, timing errors and/or tool errors. Also, inadequacies in the testbench have the potential to hide or introduce design errors in the HDL design during functional simulation which can later, when the HDL design is fabricated, show up as functional failures of the running electronic system.

Hardware logic level analysis is a technique that works at the logic level of a fabricated electronic system. The logic level of abstraction is also referred to as gate-level. Since electronic systems have been designed at the logic level for many years (for example using schematic entry of logic gates and flip-flops), there exists a wide variety of different techniques for debugging at logic level, including: digital logic analyzers, in-circuit emulators, Design-For-Test (DFT) techniques, and hardware emulation, each of these different techniques are discussed below.

Digital logic analyzers operate to probe a limited number of digital signals and record their logic values. Probing is accomplished by physically connecting probes of the digital logic analyzer to exposed pins and/or circuitry on the fabri- 20 cated design. Recording is controlled by trigger conditions, which are conditional expressions built upon the values of the recorded signals provided by the probes. The values for the recorded signals are stored in dedicated memory inside the digital logic analyzer so as to be available for subsequent 25 display. Digital logic analyzers can be external devices or blocks embedded inside the digital circuits of an electronic system. An example of an external digital logic analyzer is the Agilent 16715A from Agilent Technologies, Inc. in Palo Alto, Calif. Examples of embedded logic analyzers are SignalTap 30 from Altera Corporation in San Jose, Calif., or ChipScope from Xilinx, Inc. in San Jose, Calif. Another example of an embedded logic analyzer was presented at the 1999 IEEE International Test Conference by Bulent Dervisoglu in "Design for Testability: It is time to deliver it for Time-to- 35 Market". Since embedded logic analyzers are added to the circuitry of the design, they can probe internal signals. Thus, embedded digital logic analyzers overcome the limited access to internal signals problem of external logic analyzers because access to the internal signals is not restricted by the 40 pins of the fabricated circuits.

An in-circuit emulator is a specialized piece of hardware that connects to a CPU for debugging the CPU and the software that runs on the CPU. An example of an in-circuit emulator is visionICE from Windriver in Alameda, Calif. 45 However, since in-circuit emulators only work for the specific target CPU for which they were built, in-circuit emulators are inappropriate for debugging general digital circuits.

DFT techniques, such as boundary scan and built-in self test, provide access to the internal registers of a running 50 fabricated digital circuit. An example of such technique is described in the IEEE 1149.1 JTAG standard available from the Institute of Electrical and Electronic Engineers in Piscataway, N.J. DFT techniques are also described in "Digital Logic Testing and Simulation" by Alexander Miczo, published by Wiley, John and Sons Inc., 1985. DFT techniques were originally developed for and applied to testing of manufacturing faults and have the major disadvantage that they do not relate back to the HDL description.

Hardware emulation systems map a synthesized HDL 60 design onto special emulation hardware. Such emulation hardware comprises many re-programmable FPGA devices and/or special purpose processors. The emulation hardware then executes a model of the HDL design. Thus hardware emulation has the same disadvantage as functional simula-65 tion, namely, that it works on a model of the electronic system and not on the fabricated hardware. As a result, hardware

4

emulation systems are limited to design error debugging, and cannot be used for diagnosing manufacturing faults, tool errors, timing errors, etc. An example of such a hardware emulation system is System Realizer from Quickturn Systems, in San Jose, Calif. Specially built prototyping systems comprising FPGAs/PLDs can also be seen as hardware emulation systems. Since hardware emulation is usually much faster than functional simulation, hardware emulation systems may enable use of the software that is supposed to run on the HDL design to be used as a testbench. Even so, hardware emulation typically runs at speeds below one MegaHertz (MHz) while the HDL design is supposed to run at many hundred MegaHertz. In some cases the emulator speed may allow the user to connect the HDL design to the target environment which makes the design of testbenches unnecessary. Even so, with the high speeds of state-of-the-art HDL designs, hardware emulation is not capable of debugging the majority of real-time applications. Another disadvantage is that the special synthesis, mapping, and multi-chip partitioning steps required to bring an HDL design into a hardware emulation system are very complicated and time consuming.

A major drawback of all logic level debugging techniques is that they work at the logic level of abstraction. Since the HDL-based design methodology of electronic systems is much more efficient for todays complex designs, HDL designs have largely replaced logic level designs. Application of logic level debugging techniques to HDL design methodology is highly inefficient. Since logic level debugging does not relate back to the HDL description, it normally would not provide the designer of the electronic system with sufficient information to correctly diagnose a functional failure.

Hardware behavioral source level emulation provides hardware emulation of source level designs. One technique for debugging HDL designs described at the behavioral level HDL using hardware emulation is described in "Interaktives Debugging algorithmischer Hardware-Verhaltensbeschreibungen mit Emulation" by Gemot H. Koch, Shaker Verlag, Germany, 1998. Some of which is also described in Koch et al., "Breakpoints and Breakpoint Detection in Source Level Emulation," ACM Transactions on Design Automation of Electronic Systems, Vol. 3, No. 2, 1998. The therein described technique is referred to as Source Level Emulation (SLE) and offers an approach for emulating HDL designs, however only if such designs are described in behavioral VHDL. During behavioral synthesis a behavioral HDL design is enhanced for debugging by generating and adding additional circuitry for break-point detection. The behavioral synthesis tool writes out synthesized VHDL which contains a register transfer level description of the enhanced HDL design. The register transfer level description is then synthesized, mapped, and multi-chip partitioned into the emulation hardware. During hardware emulation with a hardware model of the HDL design, the user is able to examine particular variables in the behavioral HDL description.

Control is provided via break-points which are detected using the additional circuitry inside the running hardware model. Break-points in SLE have a very specific meaning. In particular, such break-points are closely tied to behavioral operations in the data-flow of the behavioral HDL description, and are associated with particular states of a controller which is generated by the behavioral synthesis. Additionally, break-points can be made conditioned upon particular values of data-path registers. When a break-point is detected, the execution of the hardware model is stopped. This is done by halting some or all of the system clocks and prevents the registers from changing their current values. Once halted,

-

internal registers can be read. These registers form a scanchain such that their values can be read by an emulation debugging tool.

Examination of variables in the behavioral HDL description is done in two ways. For variables which are mapped by 5 the behavioral synthesis into registers in the hardware model, their values can be read and related back to HDL identifiers. This is done using map files which keep track of the transformations in behavioral synthesis, register transfer level synthesis, mapping, and multi-chip partitioning. For variables 10 which have not been mapped to registers in the hardware model, their values are computed using a functional model of the behavioral HDL design. This functional model is created during behavioral synthesis and requires the existence of functional models of its components. The values, either read 15 or computed, are then displayed in the behavioral HDL description. Optionally, by overwriting some or all of the registers of the hardware model while the hardware model is halted, the behavior of the HDL design can be modified once the execution of the hardware model is resumed.

Although source level emulation provides a debugging method which works at the level of the HDL description (in this case behavioral VHDL), it has various drawbacks which limits its use in practice. Several of the drawbacks are as follows. First, enhancements for source level emulation must 25 be done inside a behavioral synthesis tool, since it needs special information about the behavioral HDL design which is only available during the behavioral synthesis process. Second, source level emulation does not allow the designer to perform customization. For example, a designer is not able to 30 select trade-offs between hardware overhead and debugging support. Third, source level emulation cannot handle HDL descriptions on levels of abstraction other than the one provided by behavioral VHDL. Explicitly, source level emulation is not applicable for the most commonly used levels of <sup>35</sup> abstraction of RTL HDL and gate-level HDL. Fourth, source level emulation supports neither hierarchy nor re-use of predesigned blocks. Fifth, there are various limitations and difficulties in relating registers back to behavioral HDL source code. Sixth, in order to examine the state of the hardware 40 model, it is required that some or all of the system clocks be halted and the hardware stopped, which makes source level emulation inapplicable for debugging the majority of today's electronic systems which are not to be stopped.

Thus, there is a need for efficient and effective approaches for debugging HDL-based electronic system designs.

### SUMMARY OF THE INVENTION

Broadly speaking, the invention relates to techniques and systems for debugging an electronic system having instrumentation circuitry included therein. The invention facilitates analysis, diagnosis and debugging fabricated hardware designs at a Hardware Description Language (HDL) level. Although the hardware designs (which were designed in HDL) have been fabricated in integrated circuit products with limited input/output pins, the invention enables the hardware designs within the integrated circuit products to be comprehensively analyzed, diagnosed, and debugged at the HDL level at speed. The ability to debug hardware designs at the HDL level facilitates correction or adjustment of the HDL description of the hardware designs.

The invention can be implemented in numerous ways including, a method, system, device, and a computer readable 65 medium. Several embodiments of the invention are discussed below.

6

As a method for debugging an electronic system having instrumentation circuitry included therein, wherein the electronic system is described with an HDL, one embodiment of the invention includes at least the acts of: activating certain design visibility, design patching or design control aspects of the instrumentation circuitry available for examining or modifying the electronic system via the instrumentation circuitry; determining configuration information based on the certain design visibility, design patching or design control aspects that are activated; configuring the instrumentation circuitry in accordance with the configuration information; receiving debug data from the configured instrumentation circuitry operating within the integrated circuit product; translating the debug data into HDL-related debug information; and relating the HDL-related debug information to the HDL description.

As a method for debugging an integrated circuit product having instrumentation circuitry included therein, wherein the integrated circuit product was designed with a high-level HDL description, one embodiment of the invention includes at least the acts of: activating certain aspects available for examining or modifying by the instrumentation circuitry; determining configuration information based on the certain aspects that are activated; configuring the instrumentation circuitry in accordance with the configuration information; receiving debug data from the configured instrumentation circuitry operating within the integrated circuit product; translating the debug data into HDL-related debug information; relating the HDL-related debug information to the highlevel HDL description; thereafter retrieving circuit status information for the integrated circuit product via the instrumentation circuitry; and displaying state information concerning the integrated circuit product based on the retrieved circuit status information.

As a computer readable medium including at least computer program code for debugging an electronic system having instrumentation circuitry included therein, wherein the electronic system is described with an HDL, one embodiment of the invention includes at least: computer program code for activating certain design visibility, design patching or design control aspects of the instrumentation circuitry available for examining or modifying the electronic system via the instrumentation circuitry; computer program code for determining configuration information based on the certain design visibility, design patching or design control aspects that are activated; computer program code for configuring the instrumentation circuitry in accordance with the configuration information; computer program code for receiving debug data from the configured instrumentation circuitry operating within the integrated circuit product; computer program code for translating the debug data into HDL-related debug information; and computer program code for relating the HDLrelated debug information to the HDL description.

Other aspects and advantages of the invention will become apparent from the following detailed description taken in conjunction with the accompanying drawings which illustrate, by way of example, the principles of the invention.

### BRIEF DESCRIPTION OF THE DRAWINGS

The invention will be readily understood by the following detailed description in conjunction with the accompanying drawings, wherein like reference numerals designate like structural elements, and in which:

FIG. 1A is a block diagram of a hardware debugging system according to one embodiment of the invention;

- FIG. 1B is a block diagram of a hardware debugging system according to another embodiment of the invention;

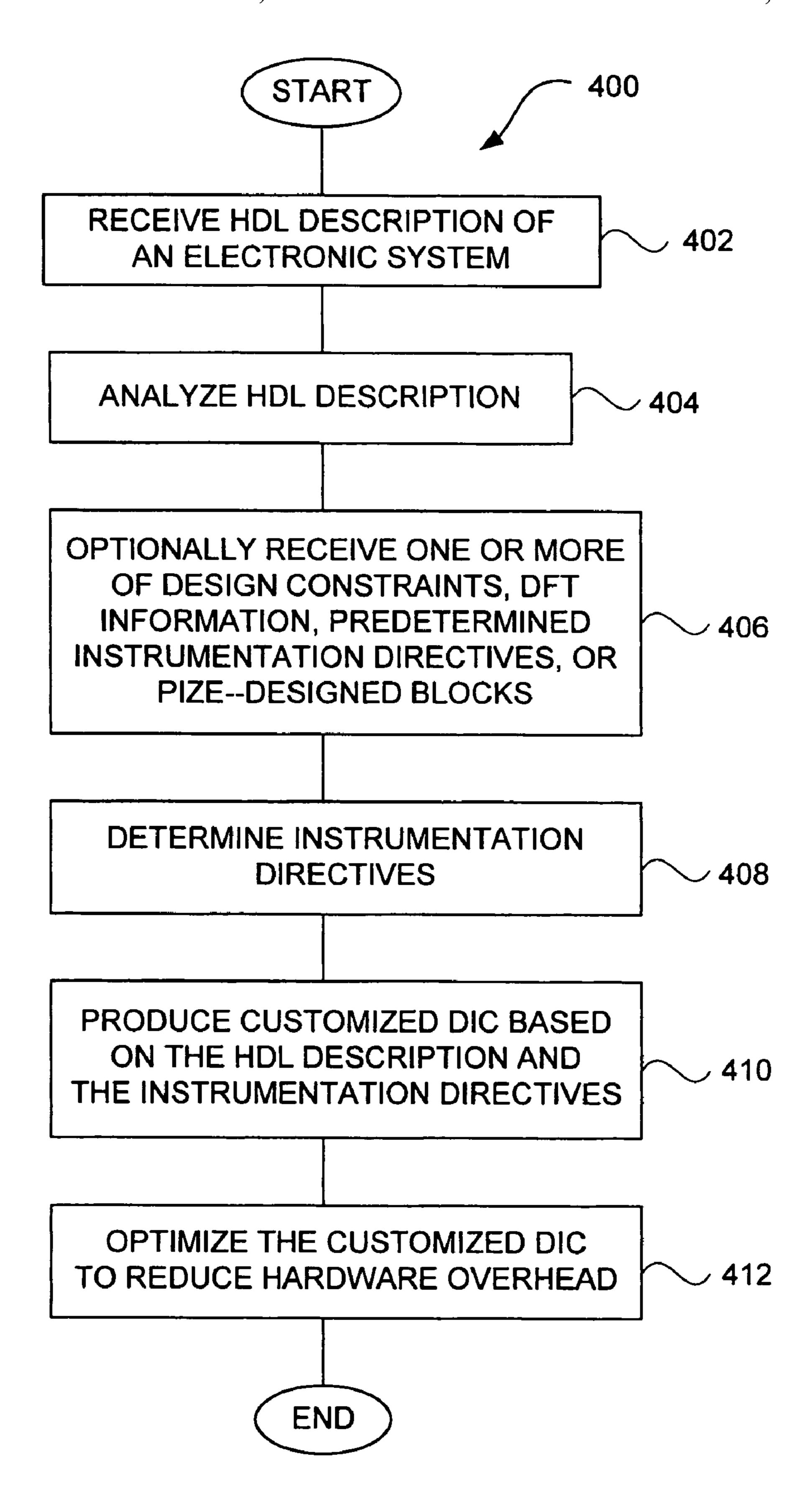

- FIG. 2 is a flow diagram of basic instrumentation processing according to one embodiment of the invention;

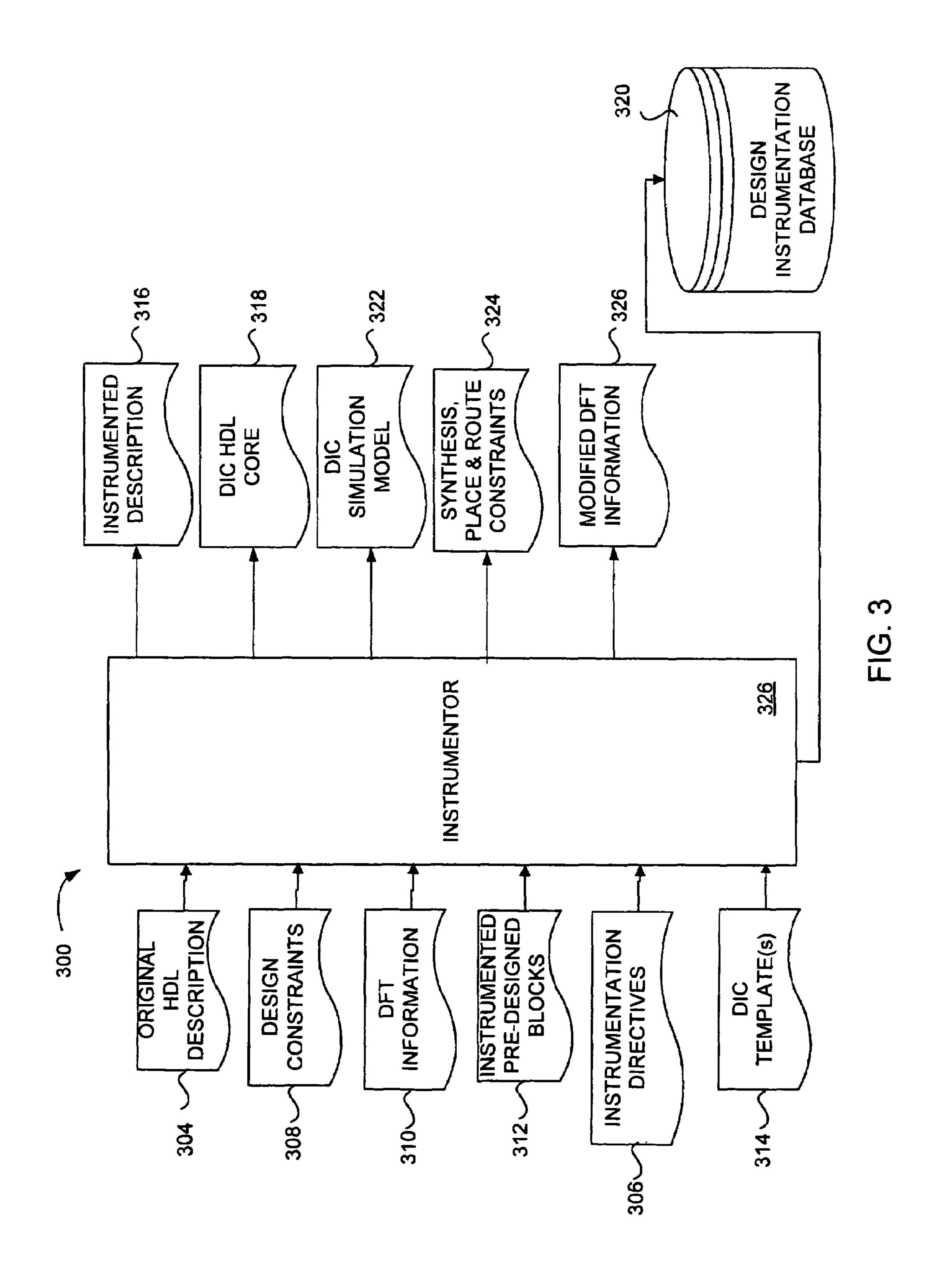

- FIG. 3 is a block diagram of an instrumentation system 5 according to one embodiment of the invention;

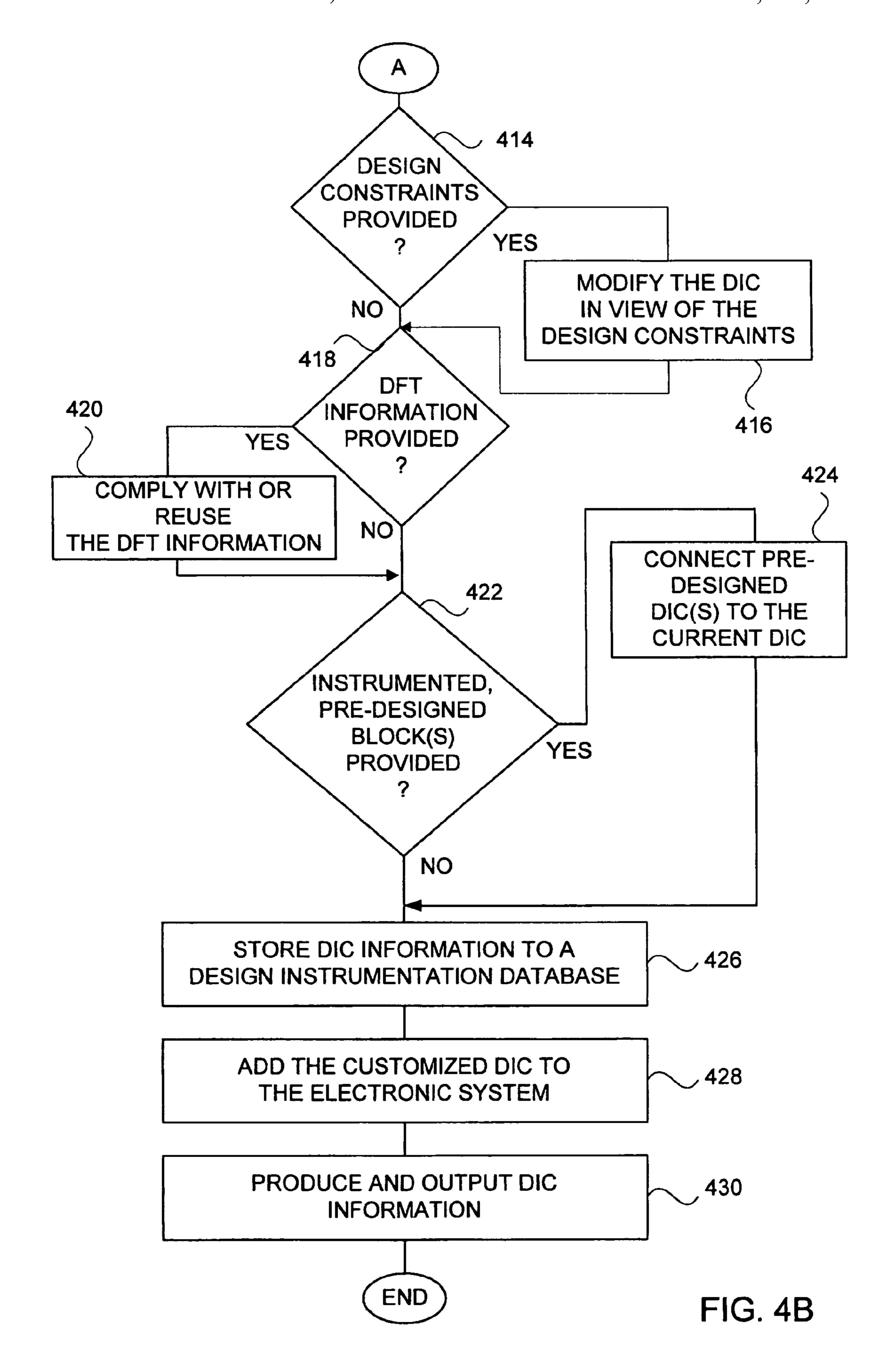

- FIGS. 4A and 4B are flow diagrams of detailed design instrumentation processing according to one embodiment of the invention;

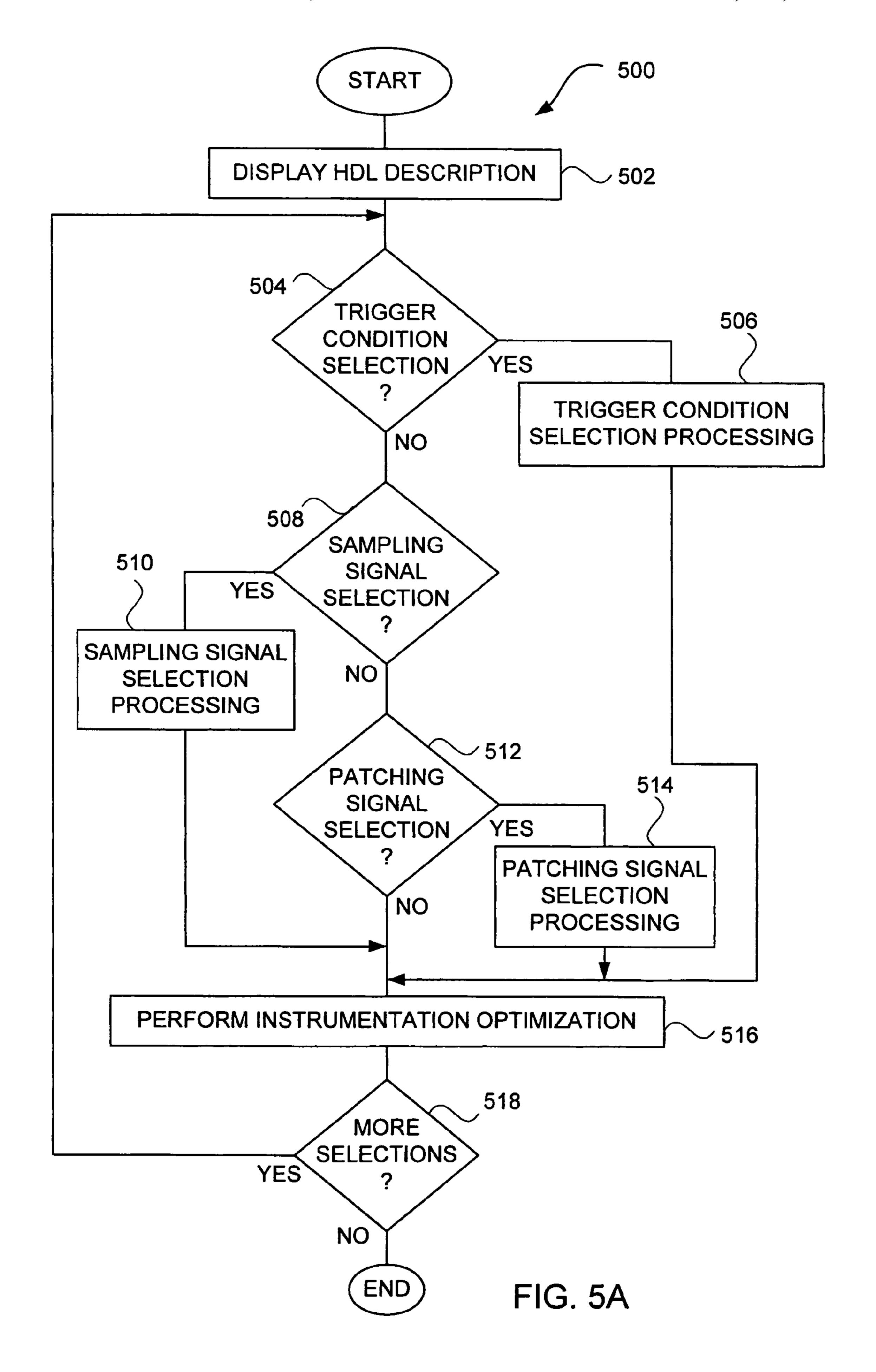

- FIG. 5A is a flow diagram of selection processing according to one embodiment of the invention;

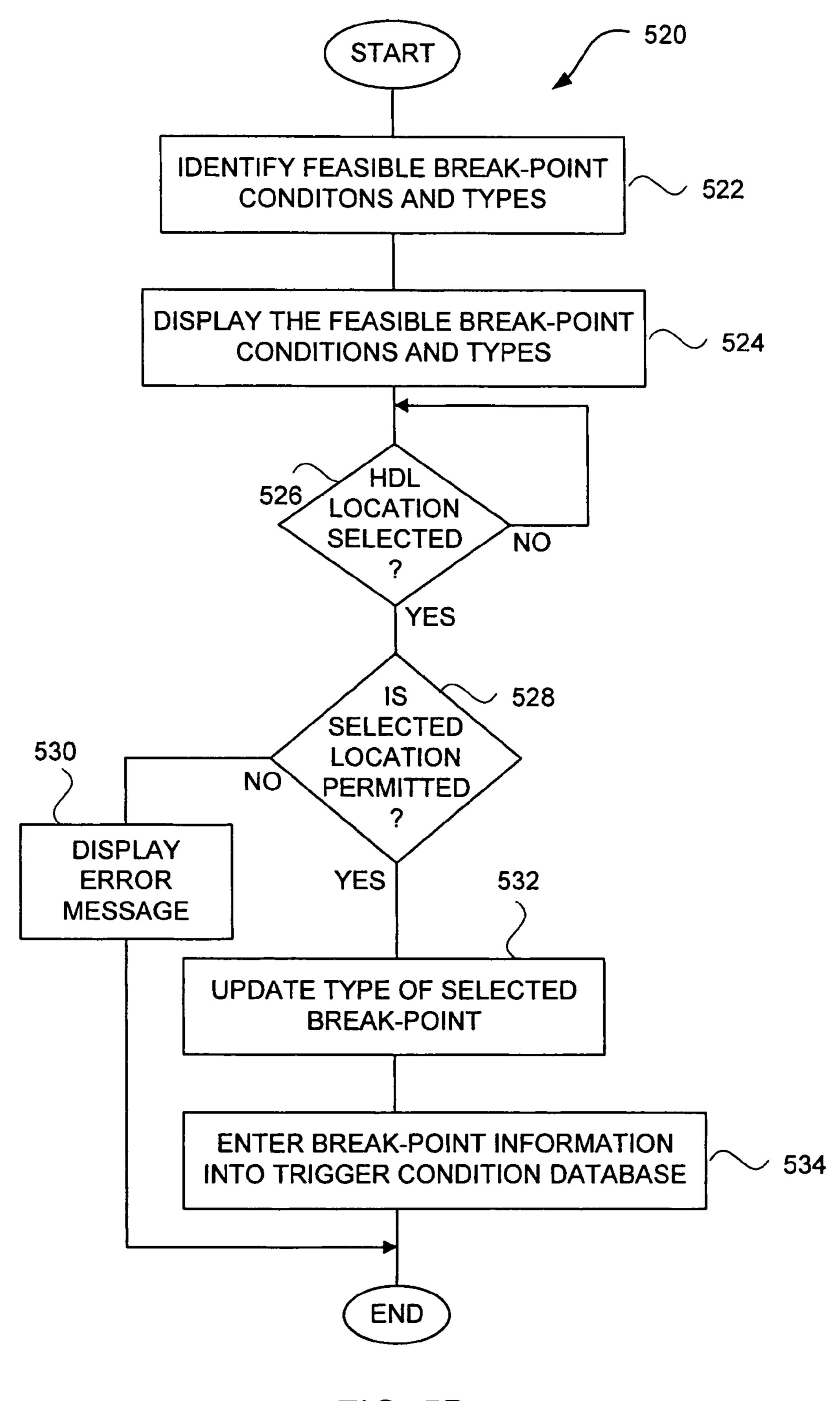

- FIG. 5B is a flow diagram of break-point processing according to one embodiment of the invention;

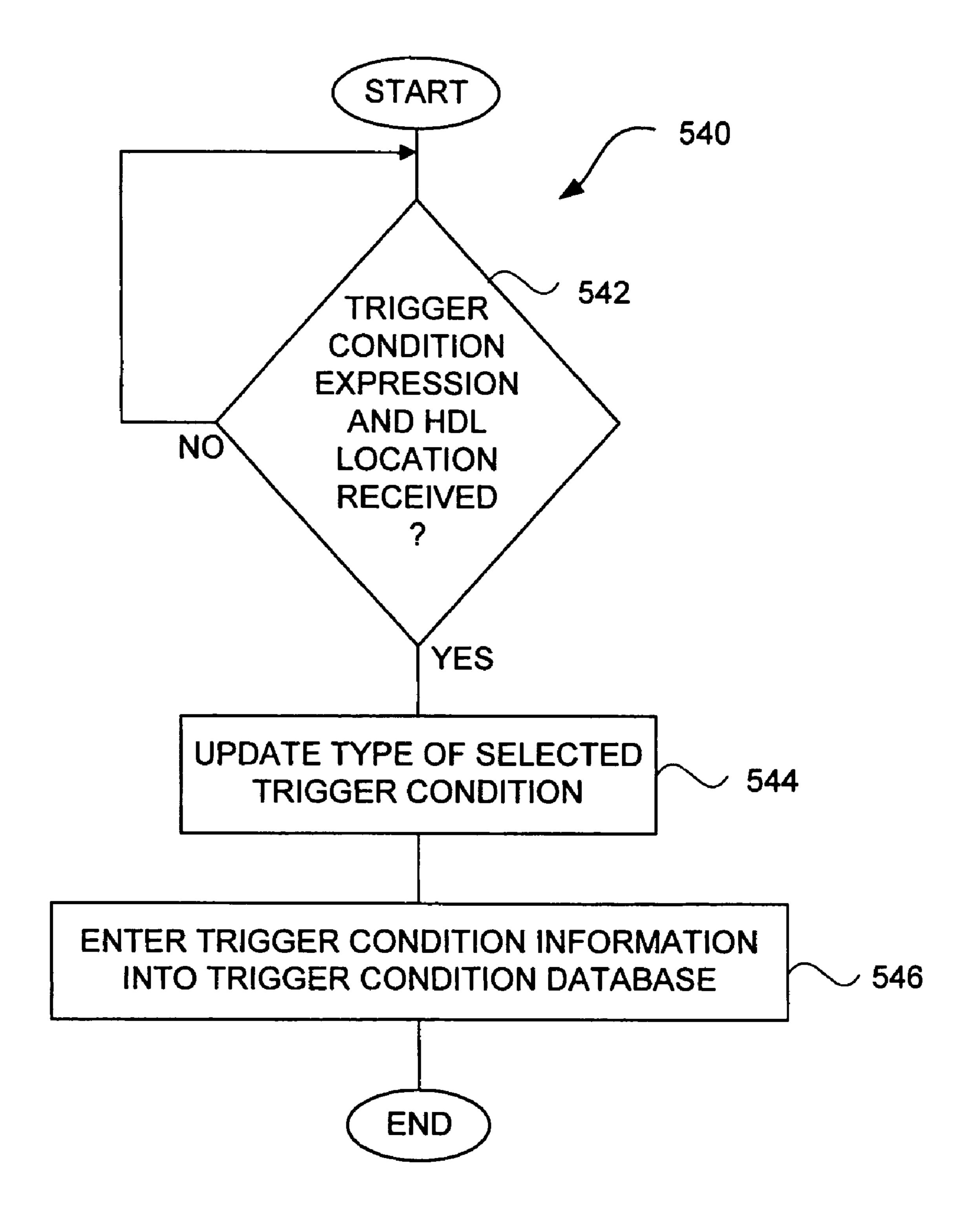

- FIG. 5C is a flow diagram of explicit trigger condition selection processing according to one embodiment of the invention;

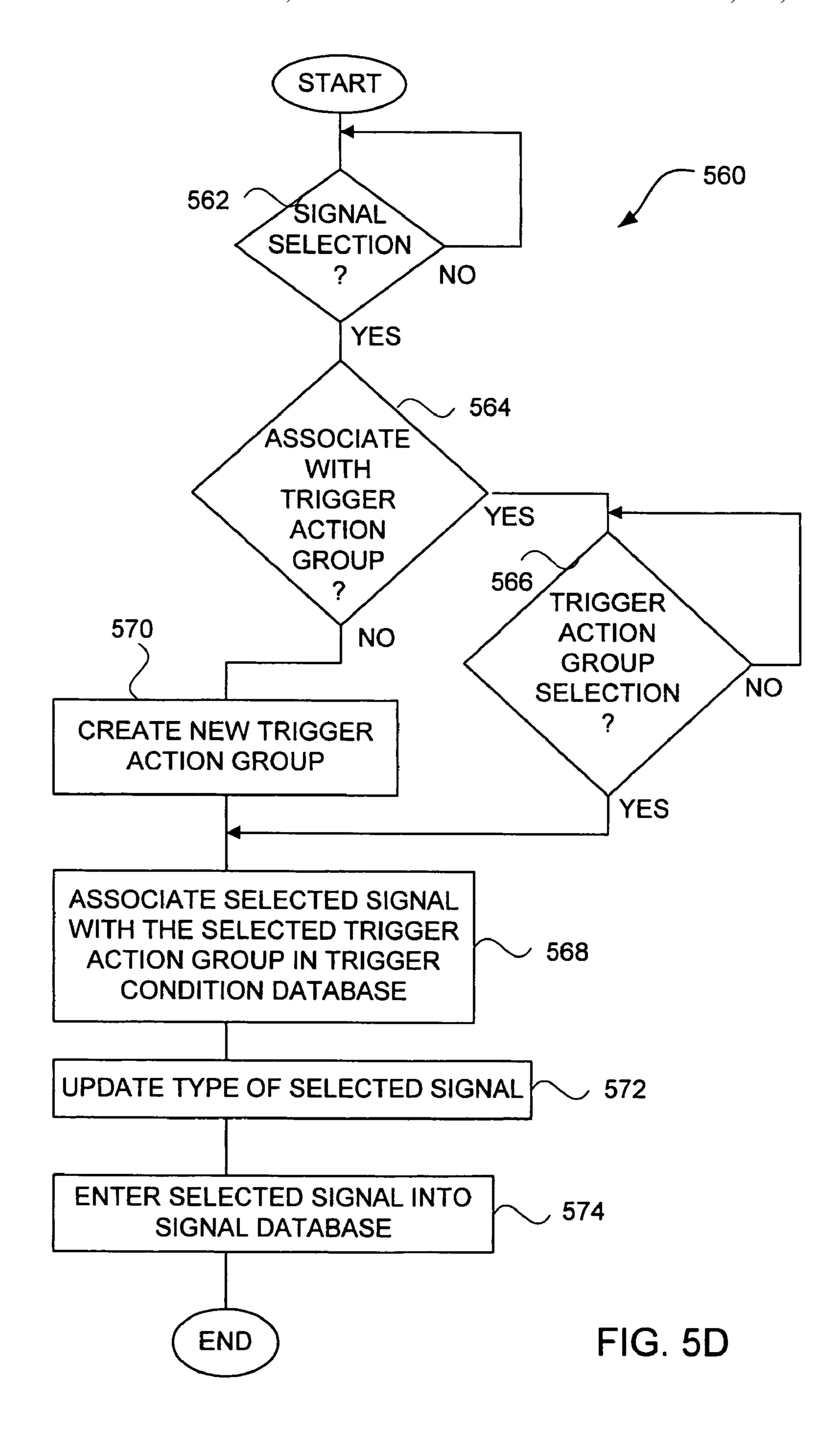

- FIG. 5D is a flow diagram of sampling signal selection processing according to one embodiment of the invention;

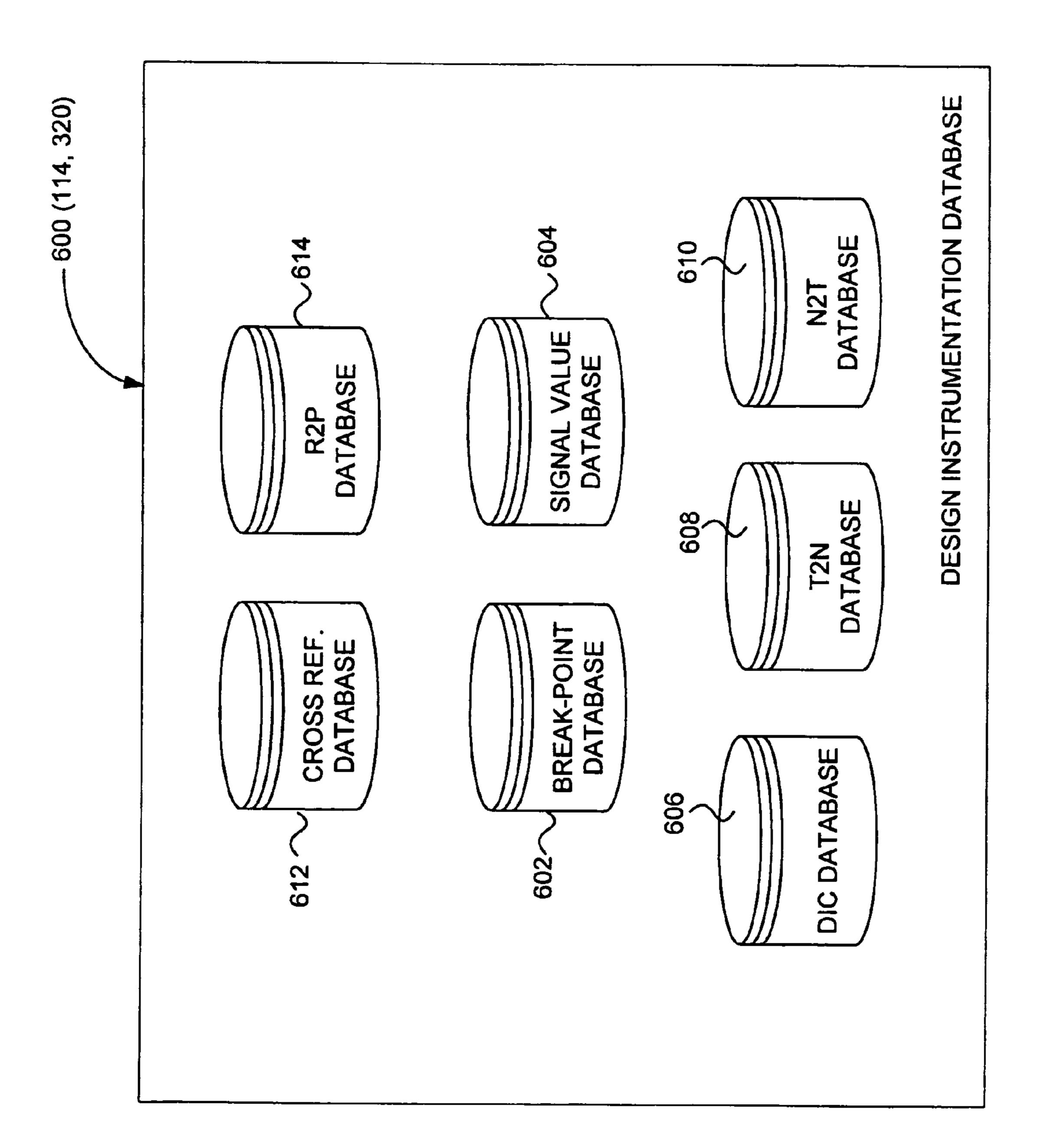

- FIG. 6 is a diagram of a design instrumentation database according to one embodiment of the invention;

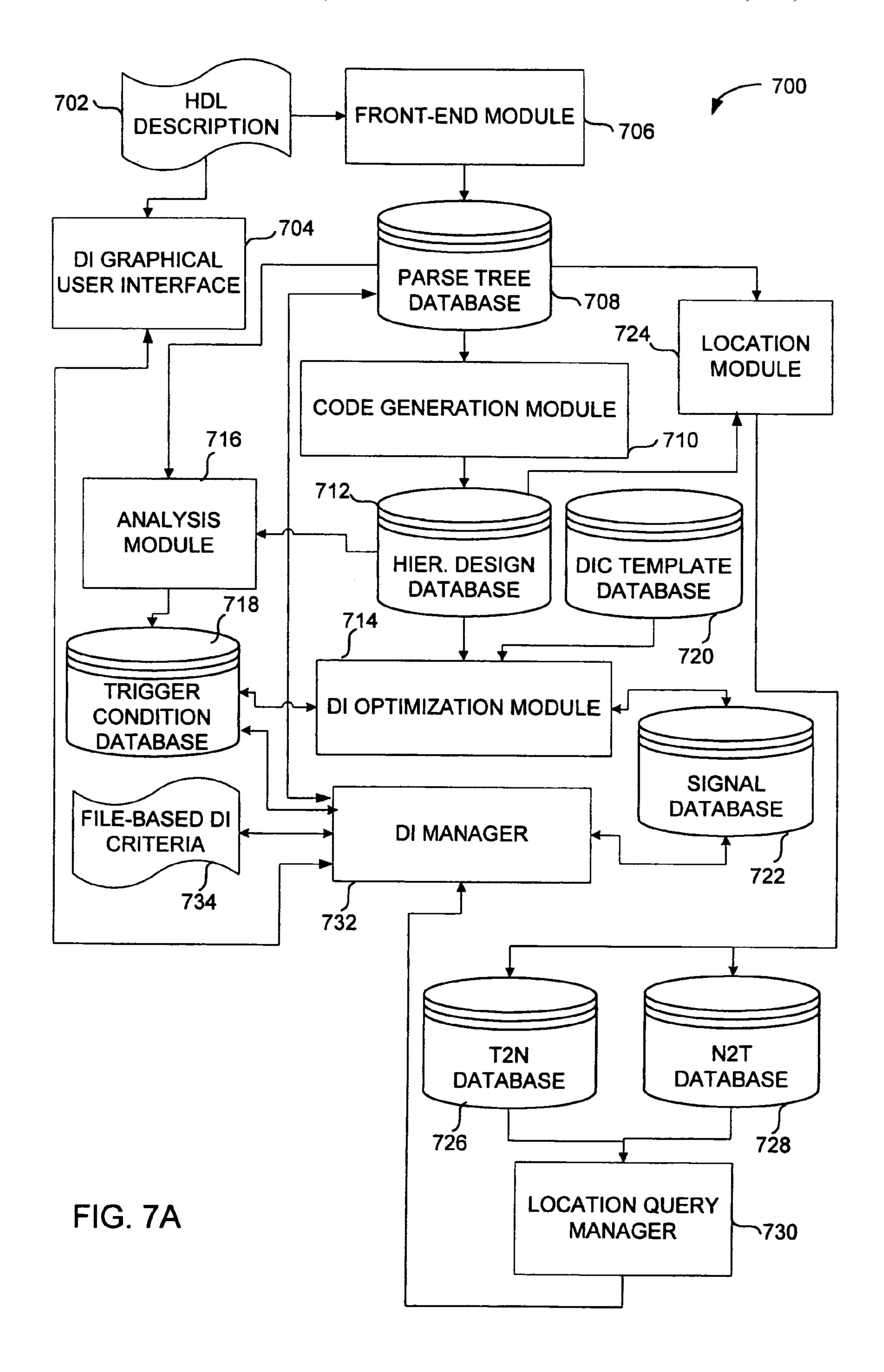

- FIG. 7A is a block diagram of an instrumentation system according to one embodiment of the invention;

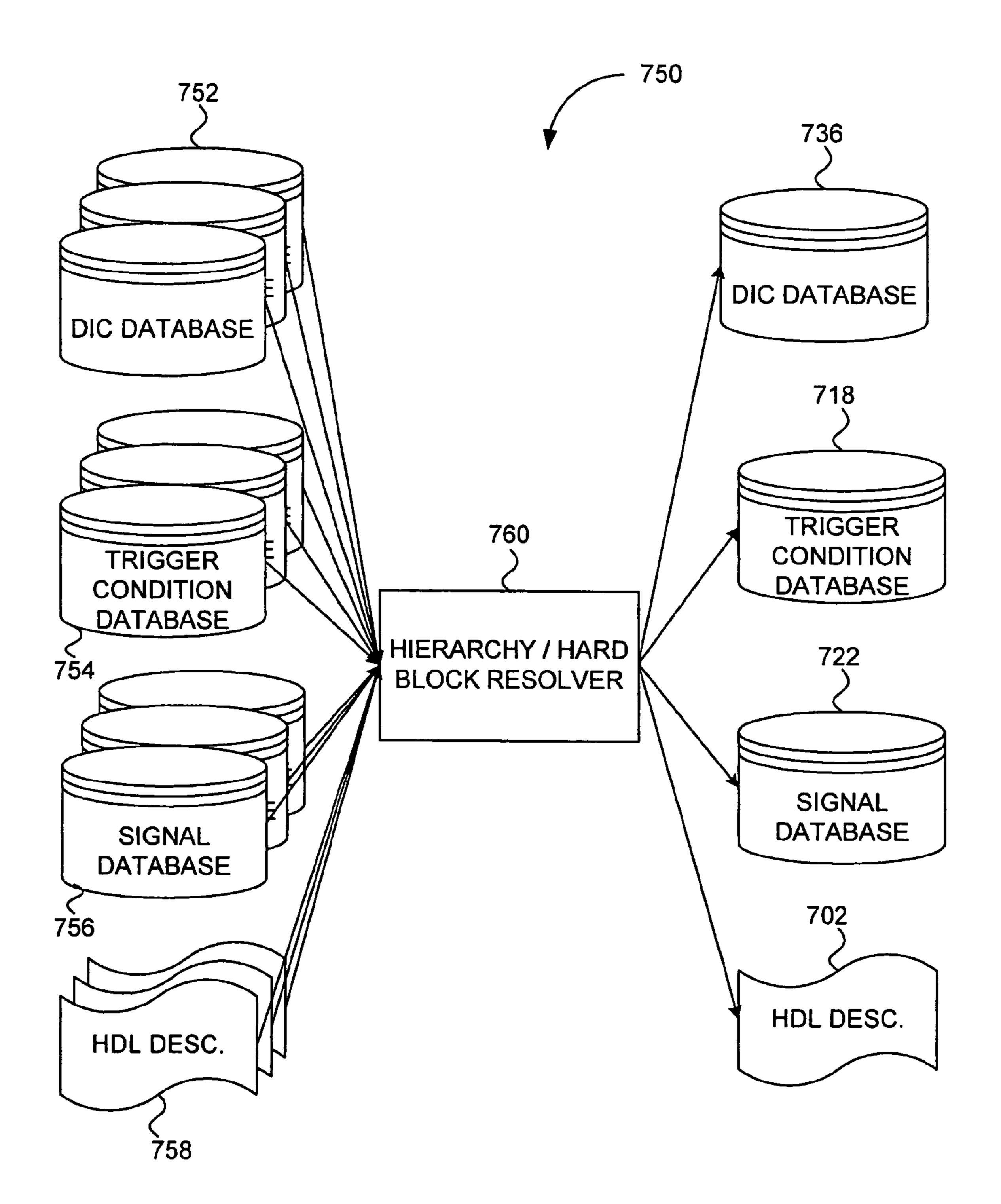

- FIG. 7B is a diagram of a hard block resolution system according to one embodiment of the invention;

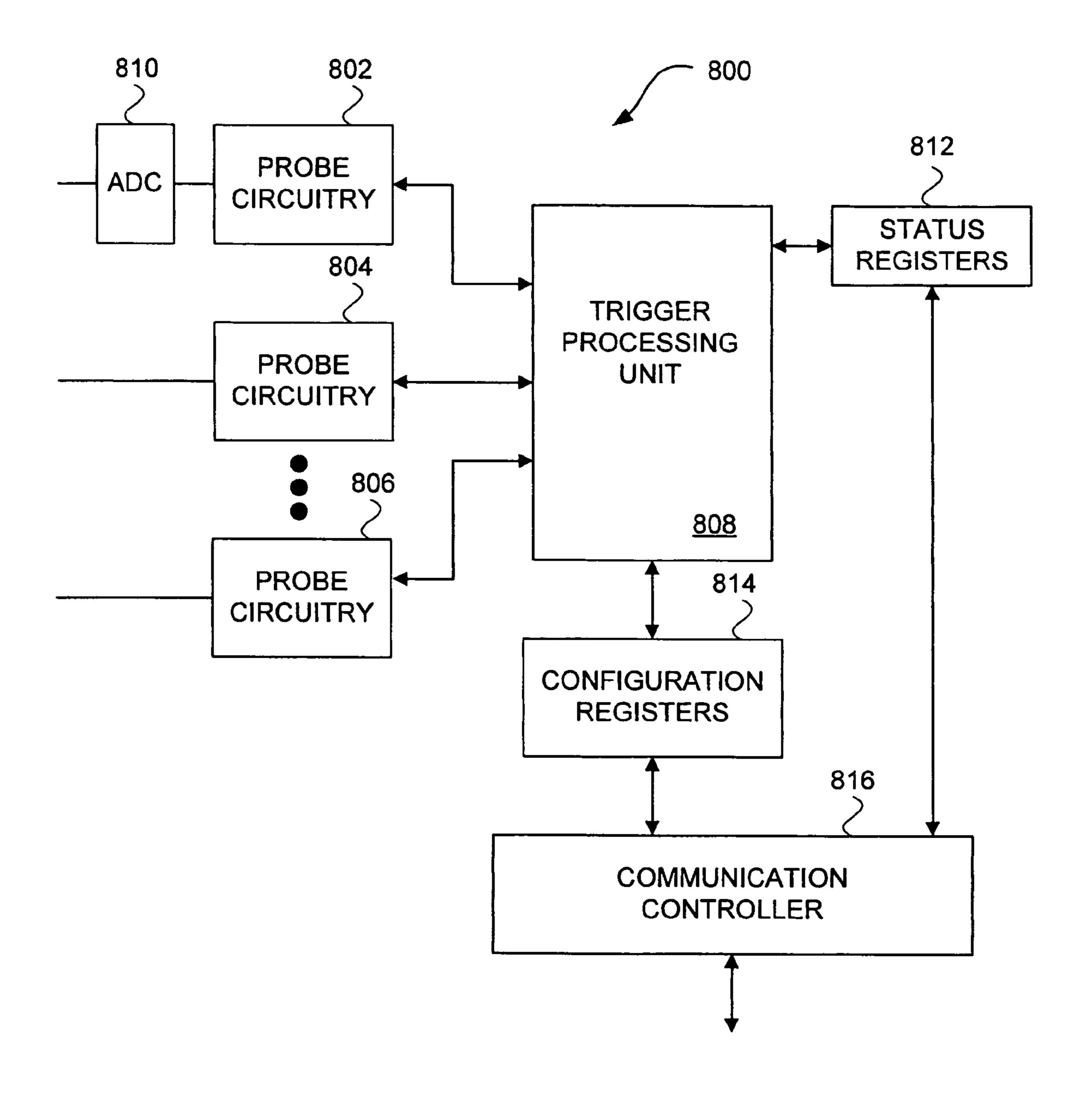

- FIG. 8 is a block diagram of a representative Design Instrumentation Circuit (DIC) according to one embodiment of the invention;

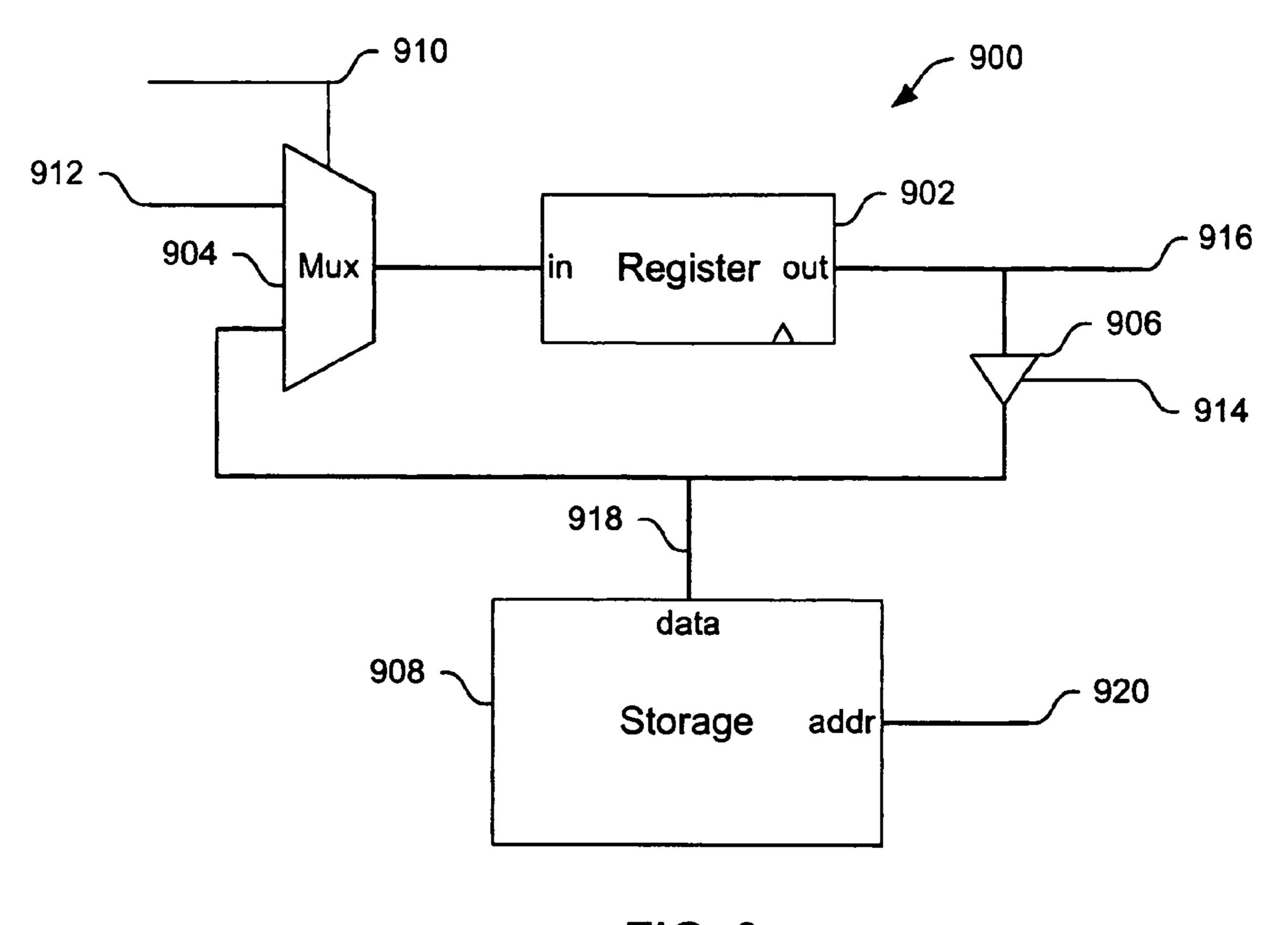

- FIG. 9 describes a representative generic configurable circuitry which can implement design sampling and design 30 patching according to one embodiment of the invention;

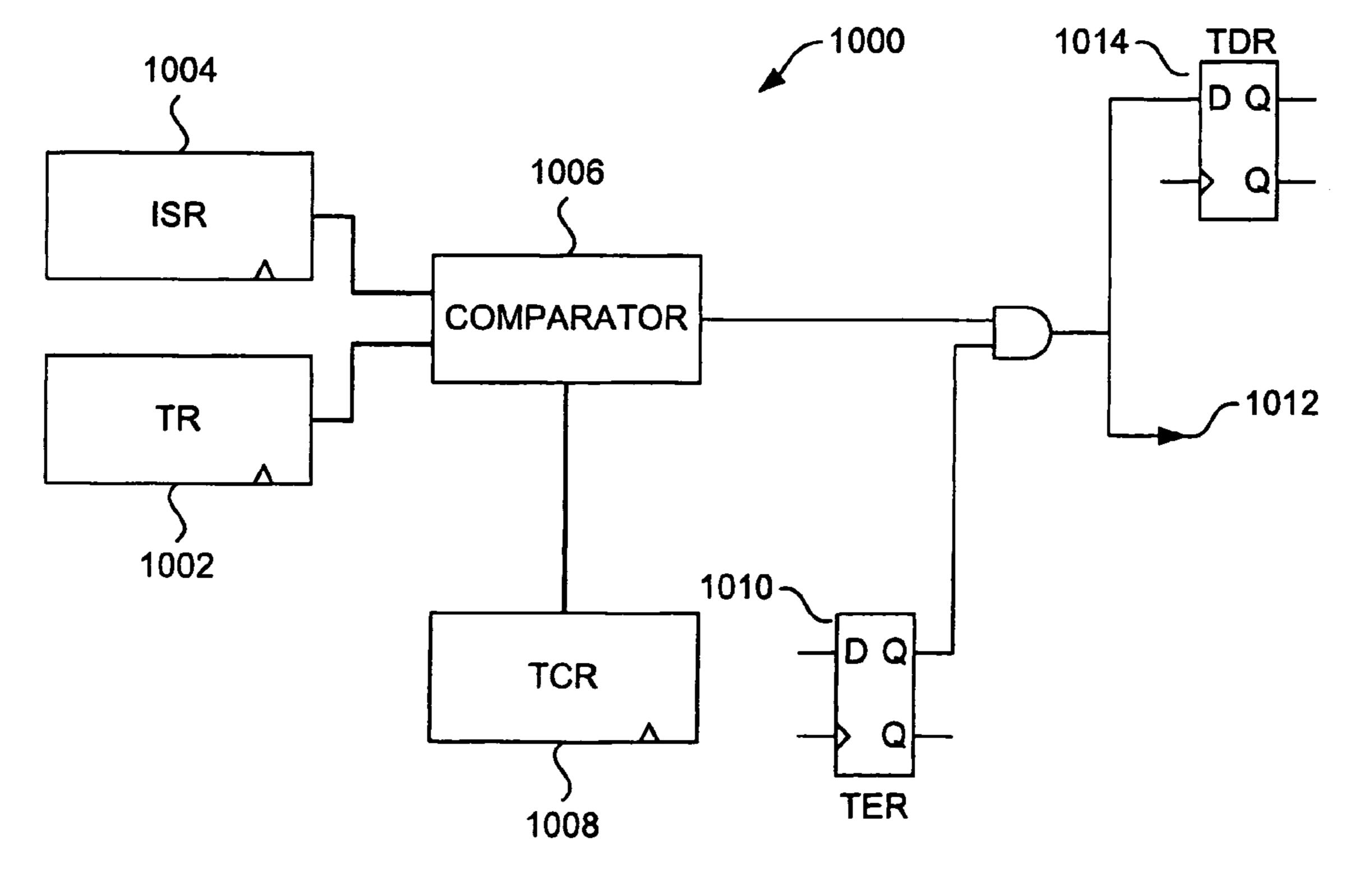

- FIG. 10 illustrates a representative generic configurable trigger detection circuit according to one embodiment of the invention;

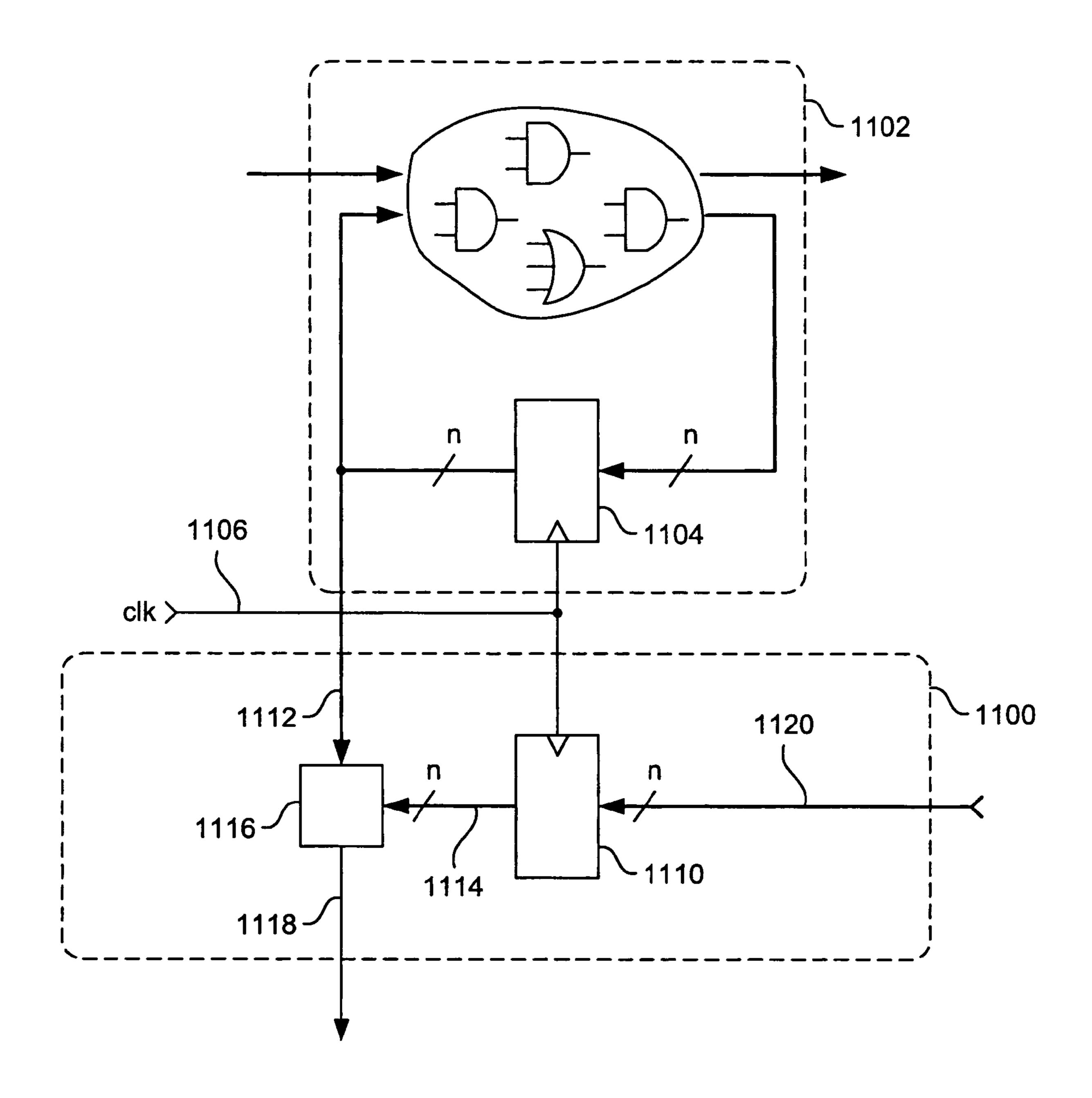

- Machine design control circuit according to one embodiment of the invention;

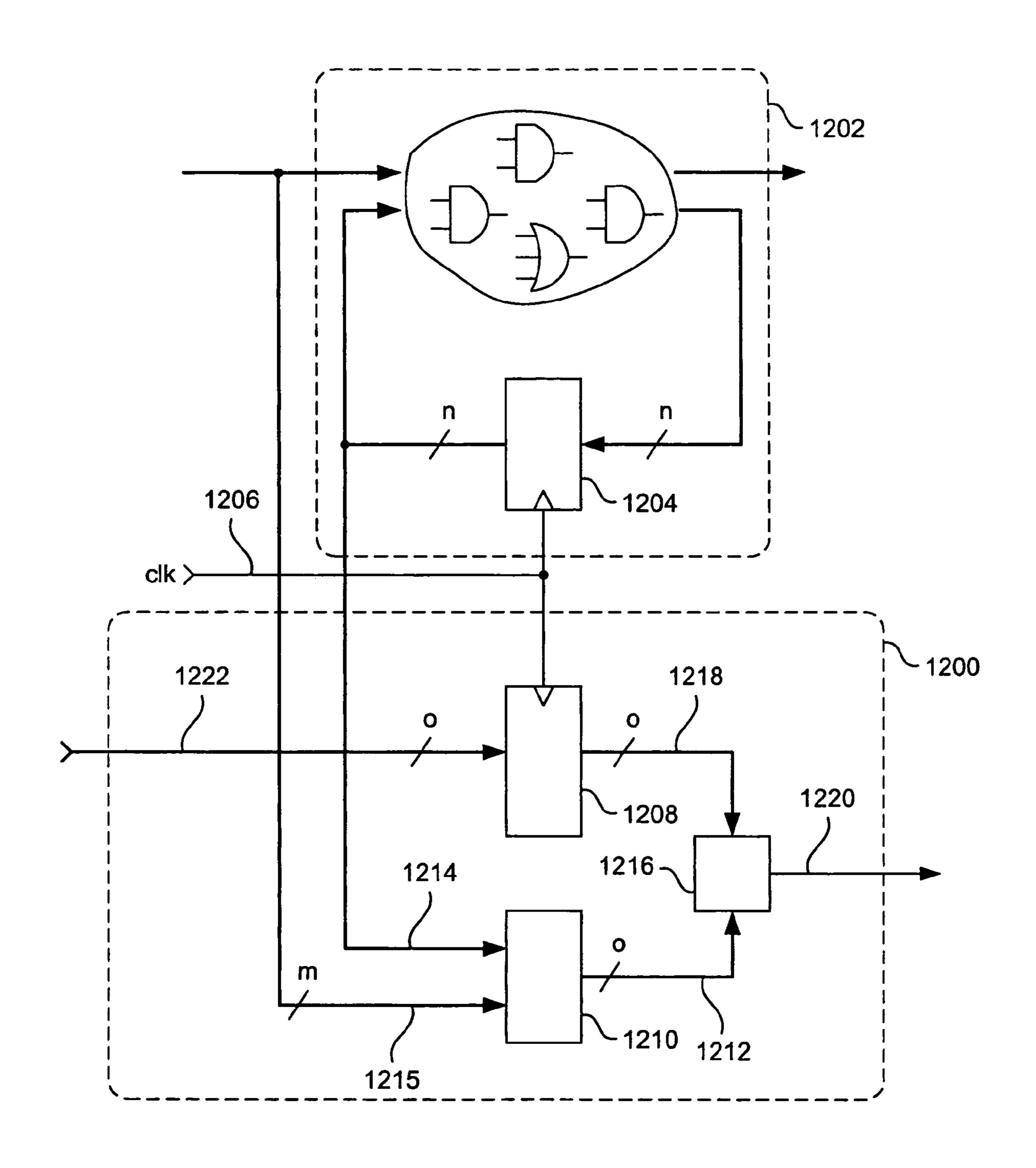

- FIG. 12 illustrates a representative transition based Finite State Machine design control circuit according to one embodiment of the invention;

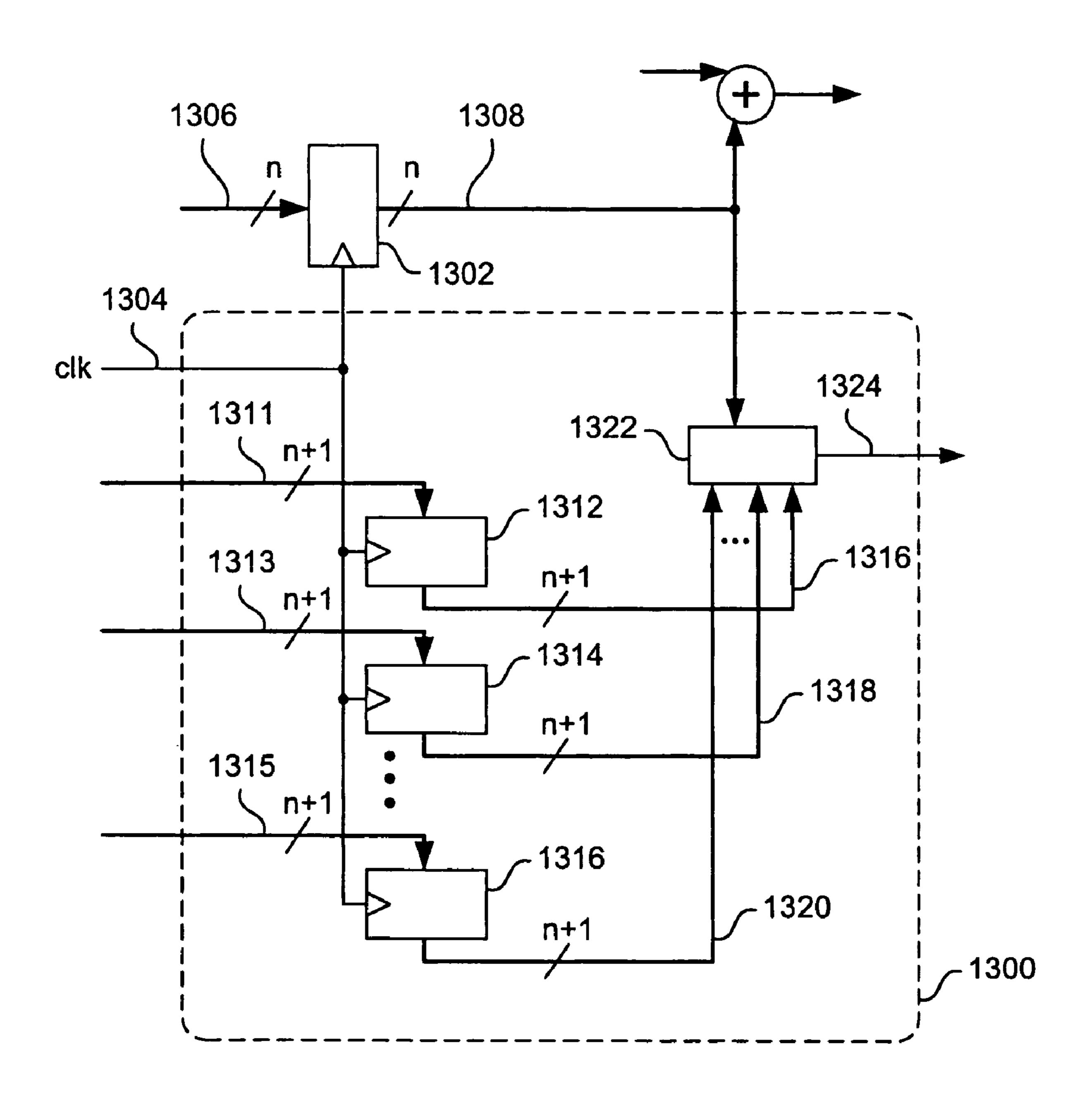

- FIG. 13 illustrates a representative data-path register design control circuit according to one embodiment of the invention;

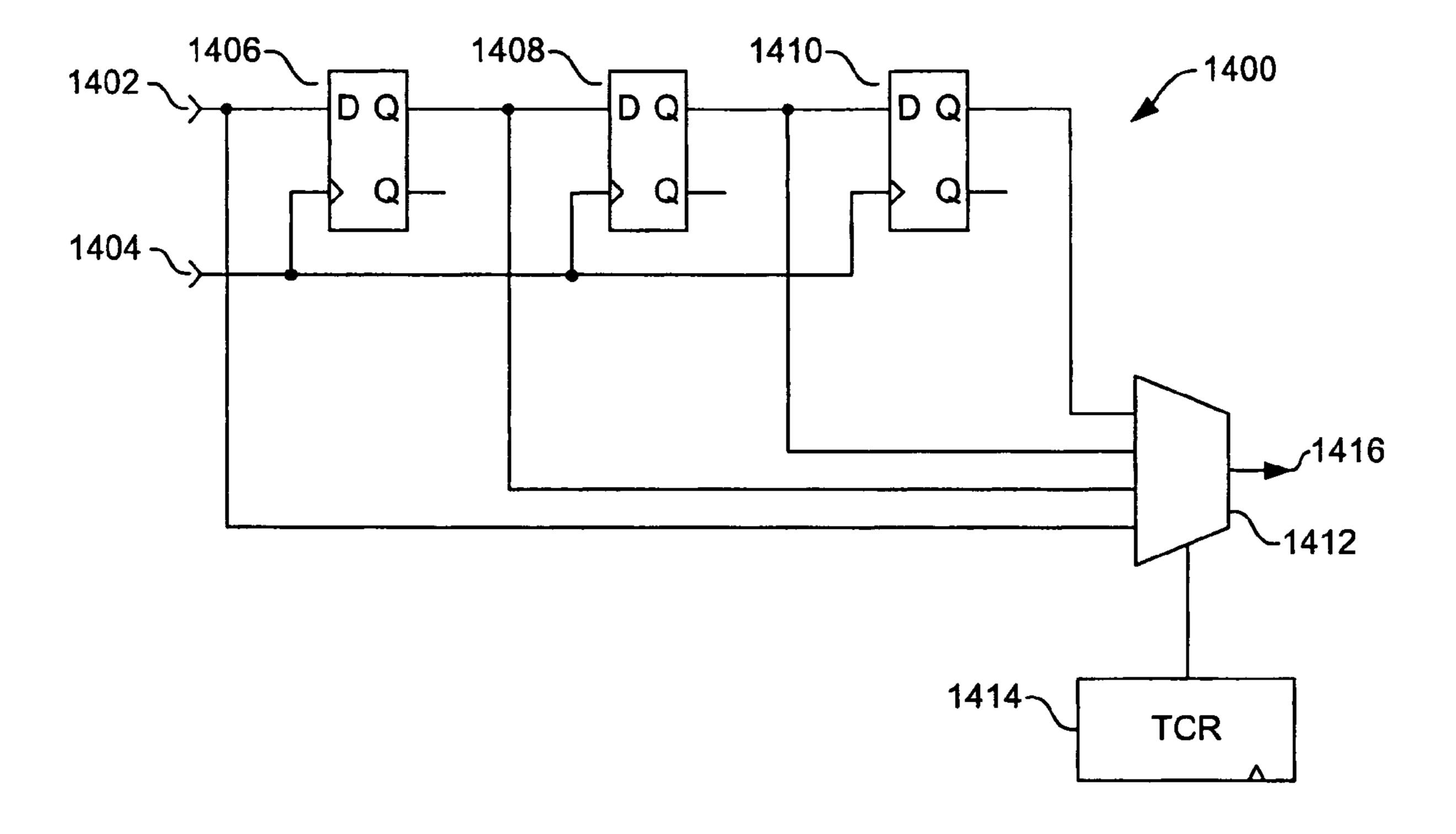

- FIG. 14 illustrates a representative part of the design control circuit according to one embodiment of the invention;

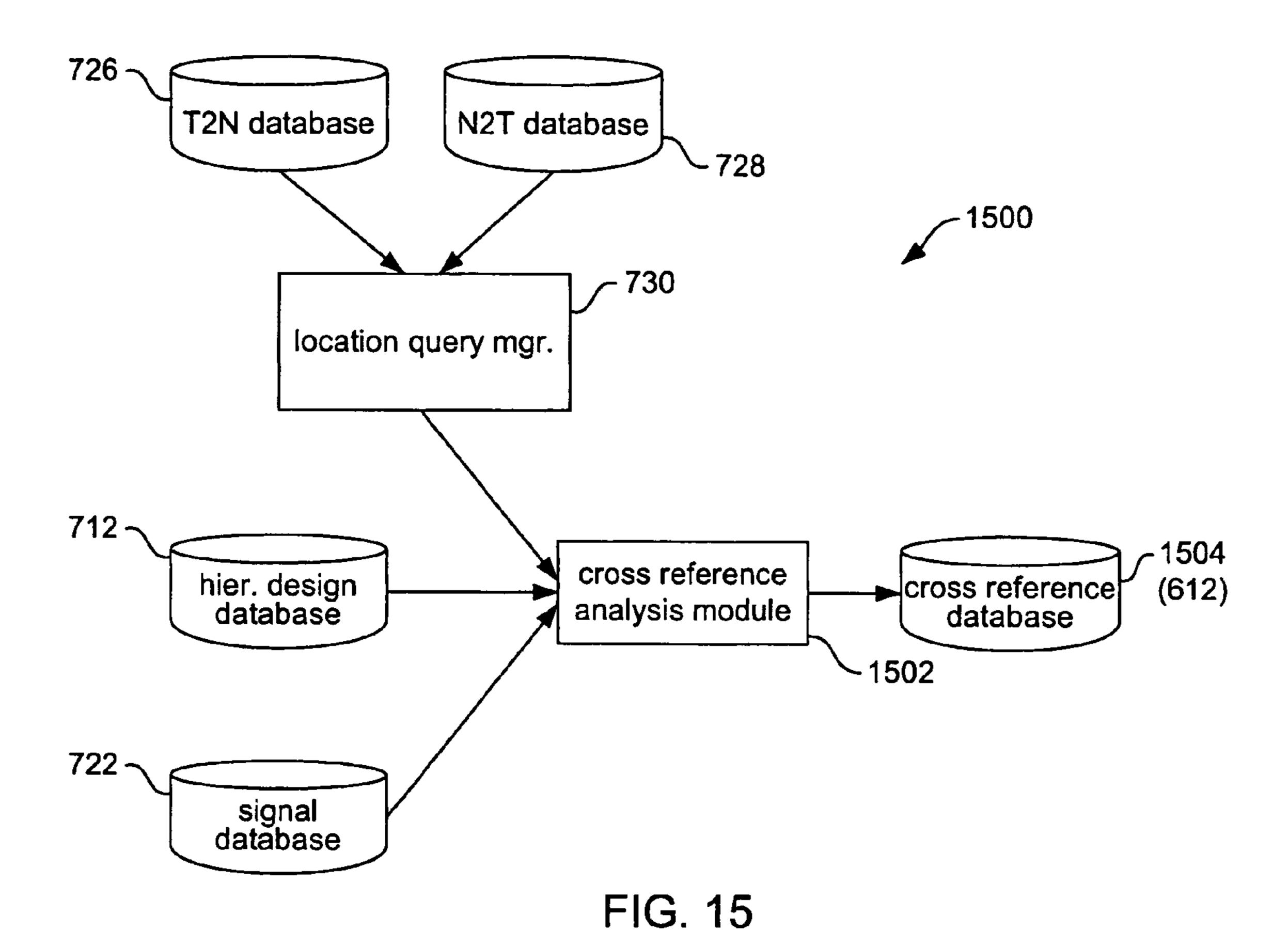

- FIG. 15 is a block diagram of a portion of an instrumentation system which includes a cross-reference analysis module and a cross-reference database according to one embodiment of the invention;

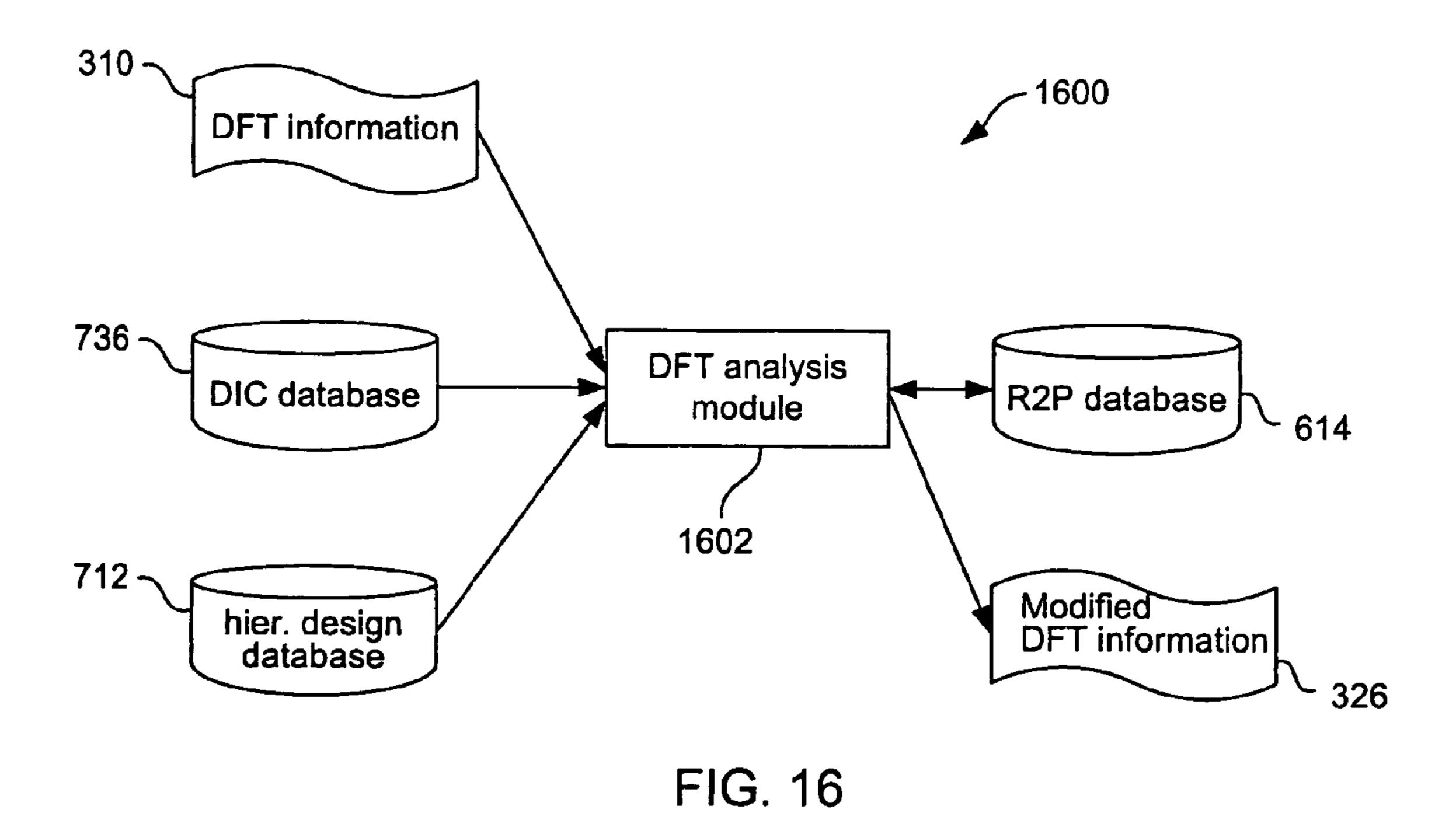

- FIG. 16 is a block diagram of a portion of an instrumentation system which includes a DFT analysis module according to one embodiment of the invention;

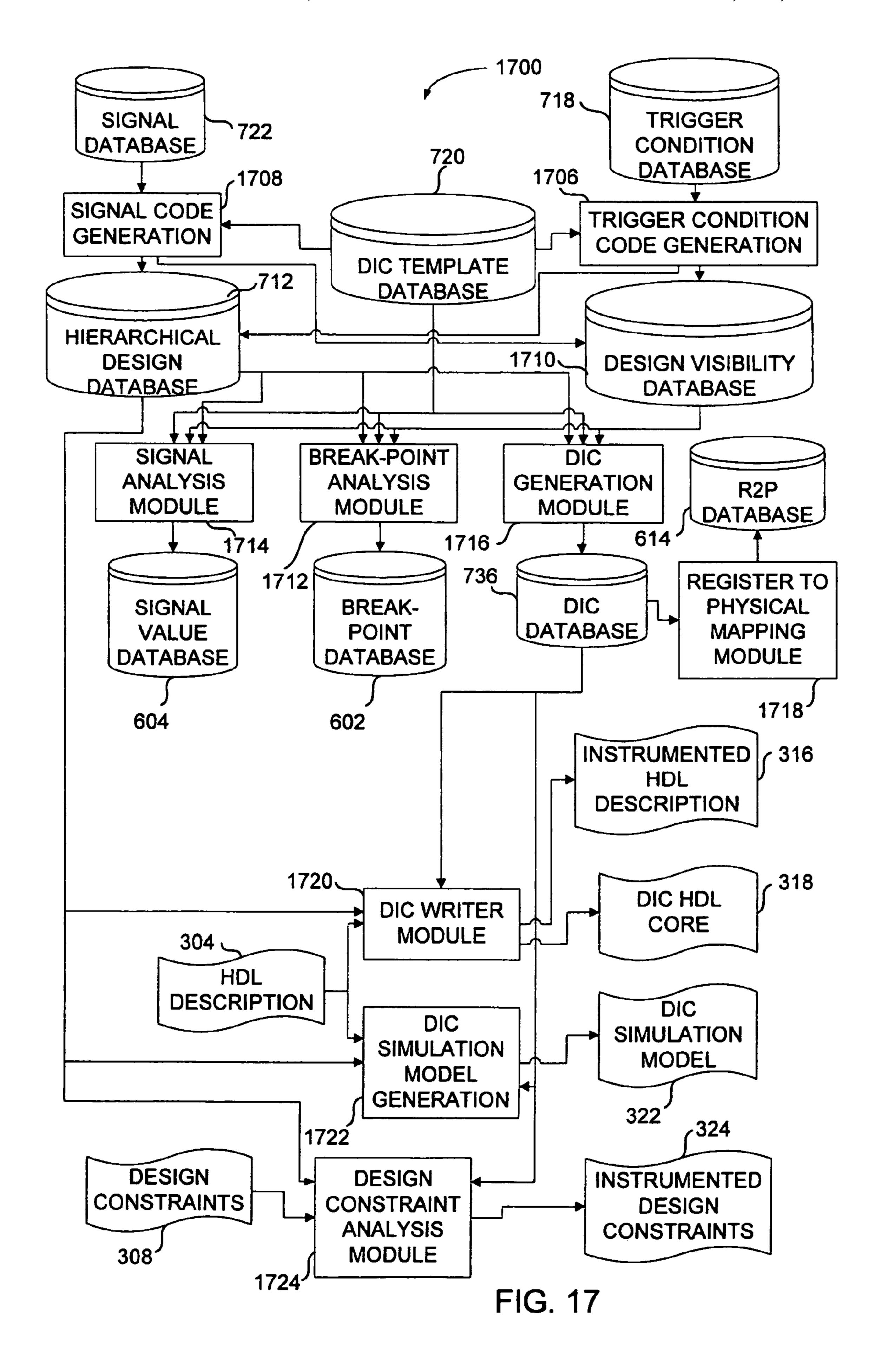

- FIG. 17 is a data flow diagram illustrating DIC creation processing according to one embodiment of the invention;

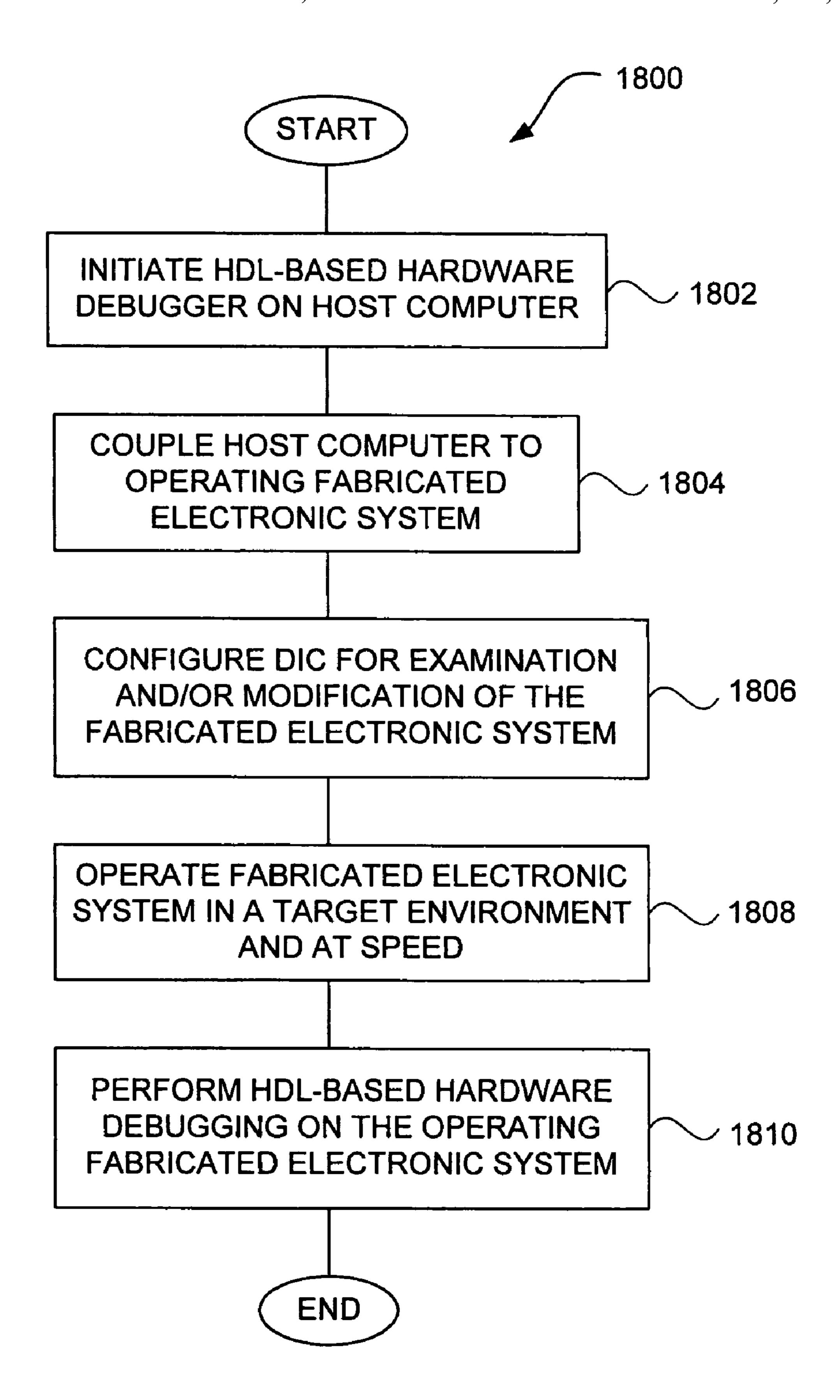

- FIG. 18 is a flow diagram of HDL-based hardware debugging processing according to one embodiment of the invention;

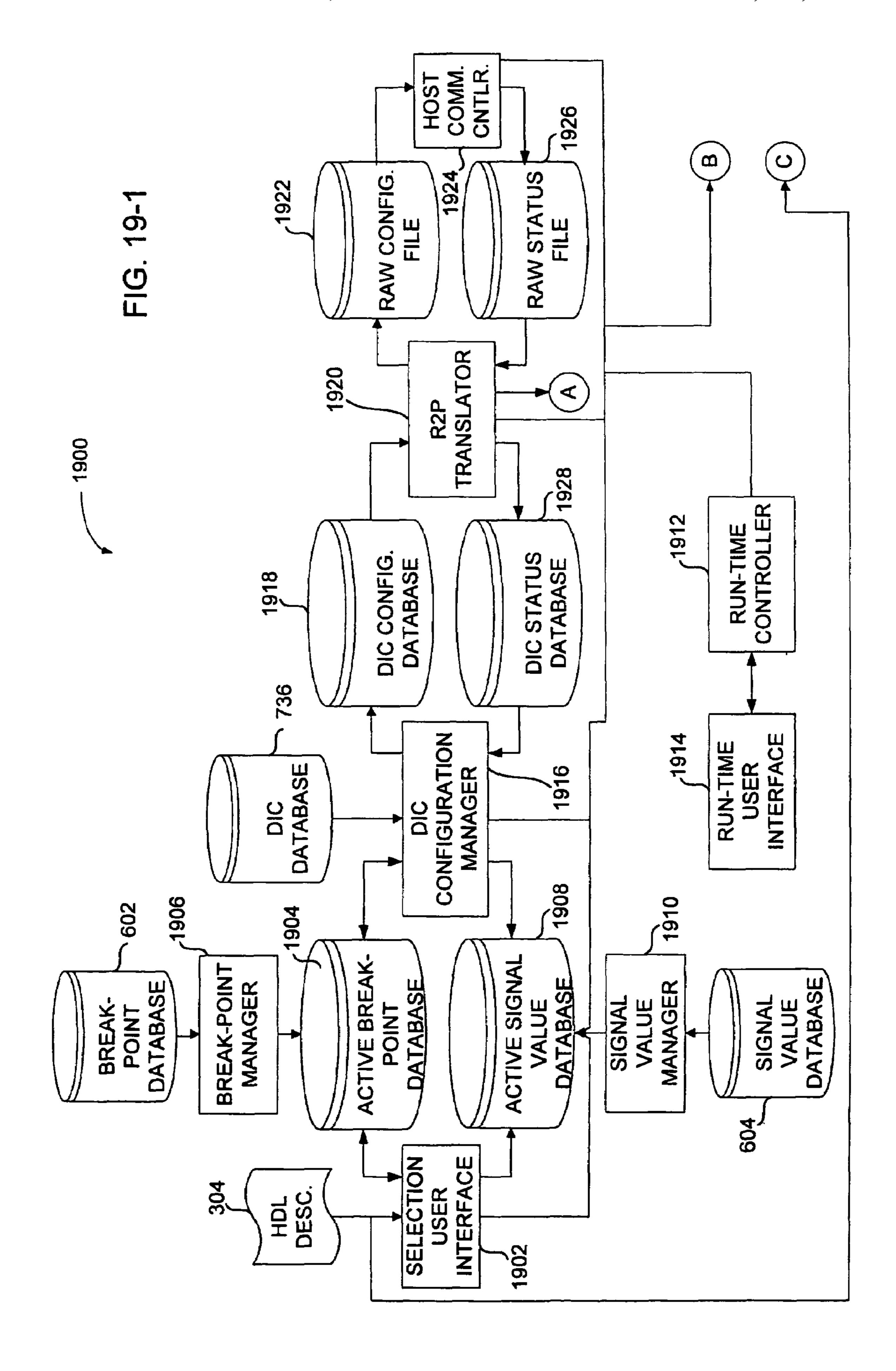

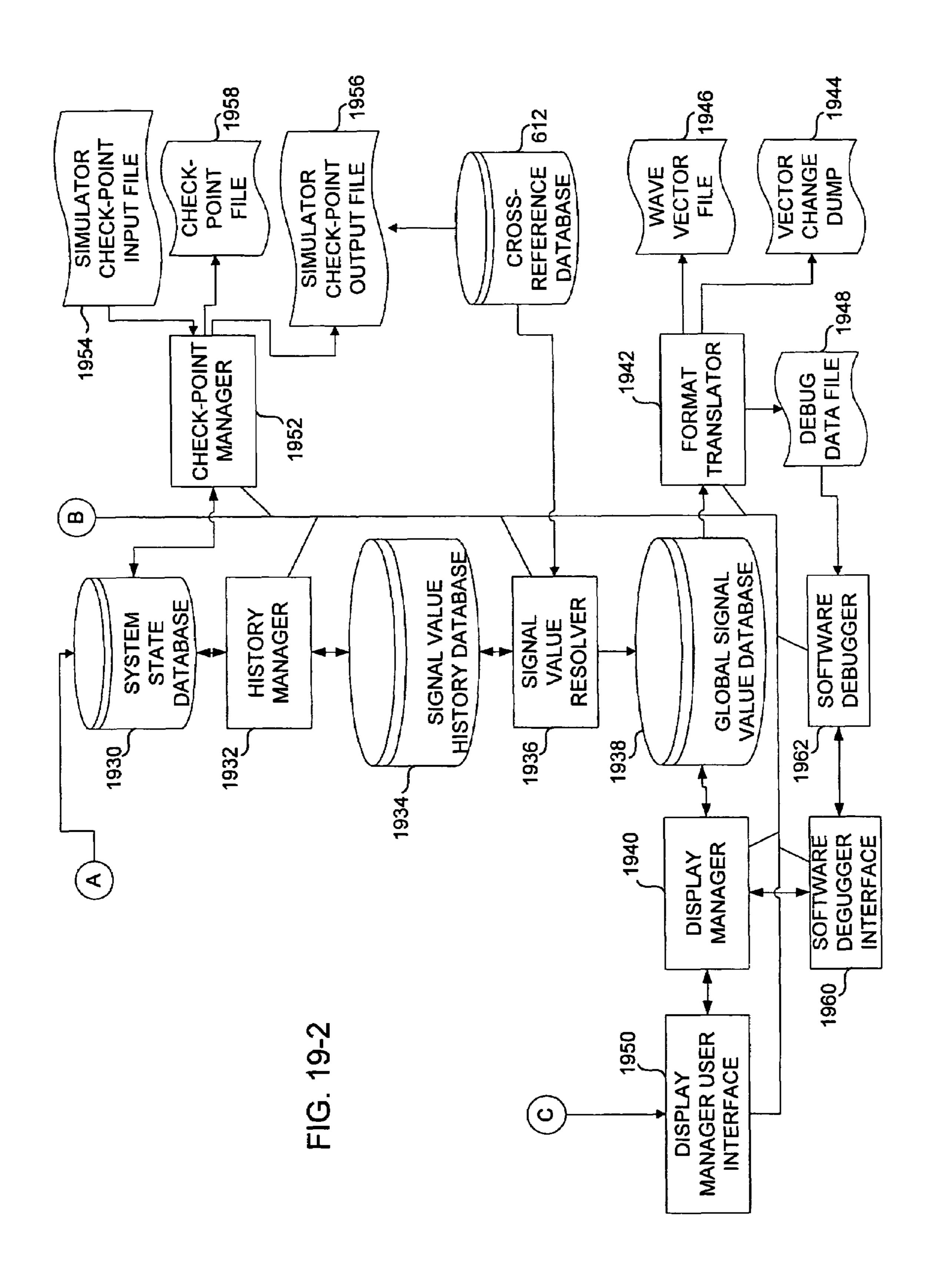

- FIG. 19 is a data flow diagram of a debugging process performed by a HDL-based hardware debugger according to 60 sis. one embodiment of the invention;

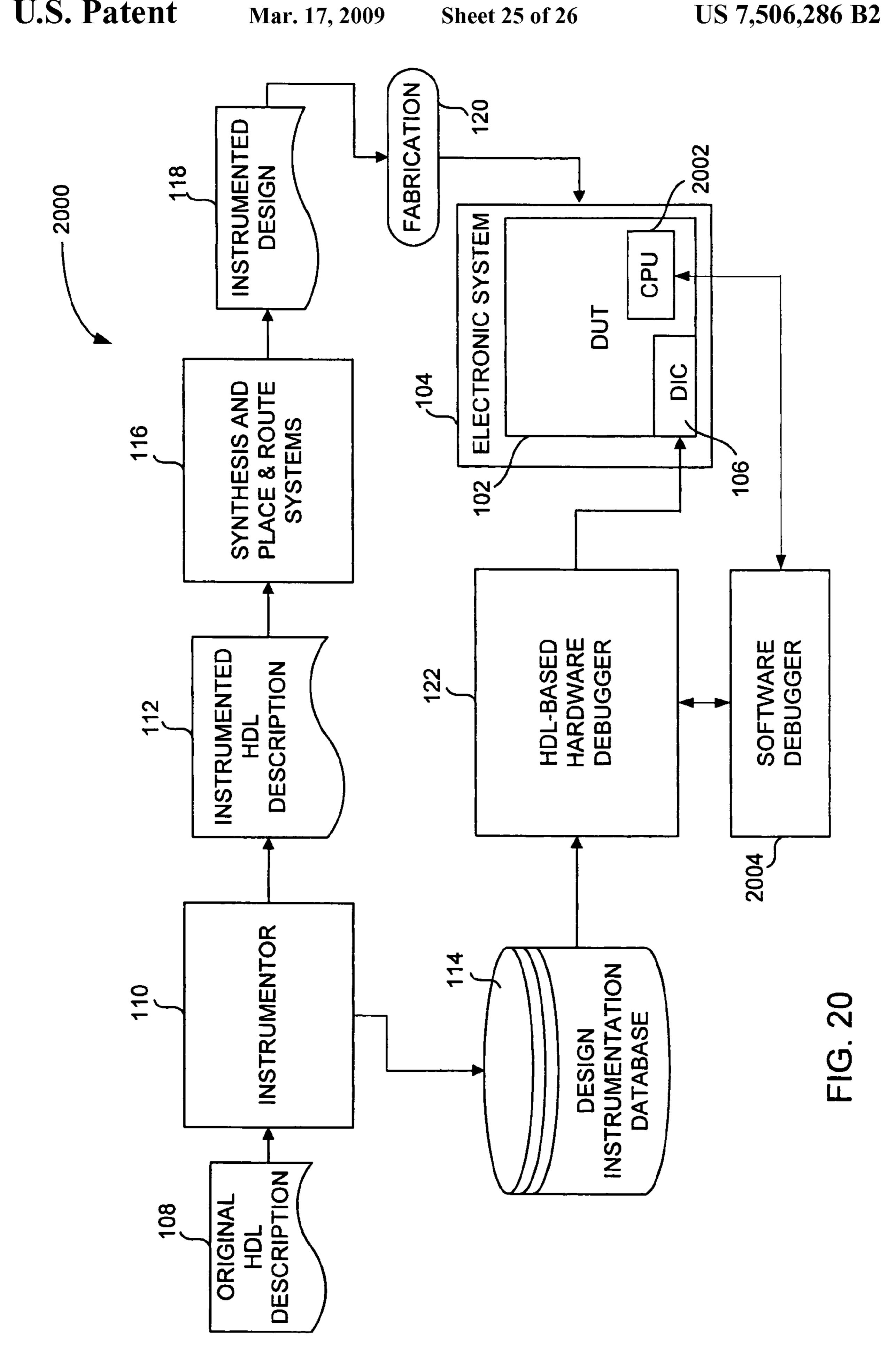

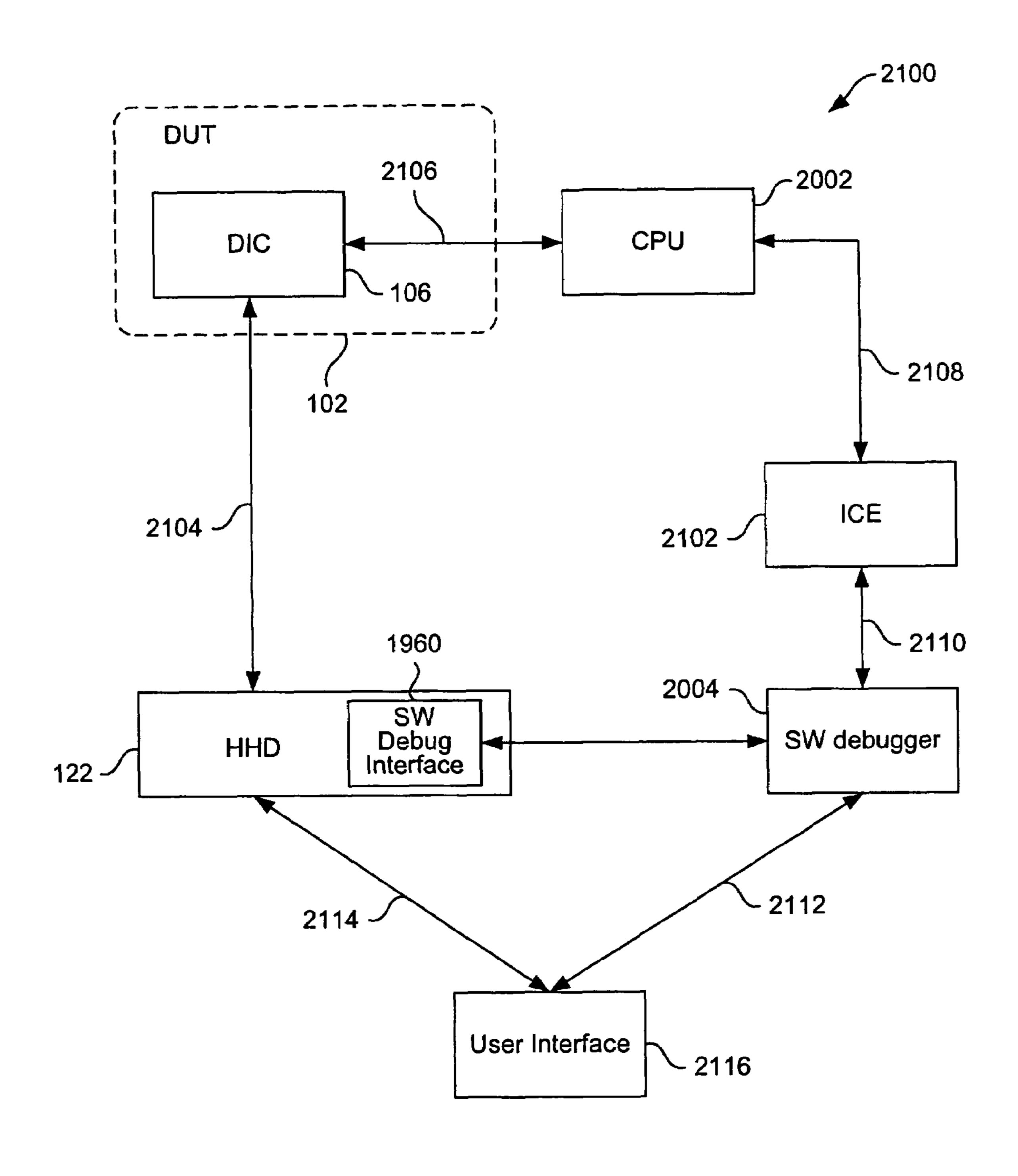

- FIG. 20 is a block diagram of a hardware/software codebugging system according to one embodiment of the invention; and

- FIG. 21 is a block diagram of a hardware/software co- 65 debugging system according to one embodiment of the invention.

#### DETAILED DESCRIPTION OF THE INVENTION

The present invention relates to techniques and systems for debugging an electronic system having instrumentation circuitry included therein. The invention facilitates analysis, diagnosis and debugging fabricated hardware designs at a Hardware Description Language (HDL) level. Although the hardware designs (which were designed in HDL) have been fabricated in integrated circuit products with limited input/ output pins, the invention enables the hardware designs within the integrated circuit products to be comprehensively analyzed, diagnosed, and debugged at the HDL level at speed. The ability to debug hardware designs at the HDL level facilitates correction or adjustment of the HDL description of the 15 hardware designs.

The following discussions will be made clearer by a brief review of the relevant terminology as it is typically (but not exclusively) used. Accordingly, to assist readers in understanding the terminology used herein, the following defini-20 tions are provided.

"Software" is deemed as but not limited to programming language content written using a programming language. Examples of programming languages include C, C++, Basic, assembly, and Java.

"HDL" is a Hardware Description Language. A hardware description language is defined as any programming language that can describe the hardware portion of an electronic system. Examples of HDLs include VHDL which is described in the IEEE Standard VHDL Language Reference Manual available from the Institute of Electrical and Electronic Engineers in Piscataway, N.J., which is hereby incorporated by reference; Verilog HDL which is described in Hardware Modeling with Verilog HDL by Eliezer Sternheim, Rajvir Singh, and Yatin Trivedi, published by Automata Pub-FIG. 11 illustrates a representative state based Finite State 35 lishing Company, Palo Alto, Calif., 1990, which is hereby incorporated by reference; and SystemC which stems from the Open SystemC Initiative (OSCI) originally started by Synopsys, Inc. of Mountain View, Calif. General purpose programming languages such as C++, C, and assembly languages may also be used as a HDL.

A "high level HDL description" is a HDL description in which at least a portion of the description is at register transfer level (RTL) or higher. For VHDL this synthesizable, register transfer level subset is described in the EEE 1076.6-1999 Standard for VHDL Register Transfer Level (RTL) Synthesis, available from the Institute of Electrical and Electronic Engineers in Piscataway, N.J., which is hereby incorporated by reference. The synthesizable register transfer level subset of the Verilog HDL is described in "Verilog HDL: A Guide to 50 Digital Design and Synthesis" by Samir Palnitkar, SunSoft Press, 1996.

A "RAM" is a Random Access Memory—defined as an electronic component capable of storing data.

"ASIC" is an Application Specific Integrated Circuit. An 55 ASIC device is an electronic component of a system. ASICs are custom devices created for a specific purpose within the electronic system. ASIC devices are easier and faster to create with respect to a full custom semiconductor device. An ASIC may be described using HDL and implemented using synthe-

An "FPGA" is a Field Programmable Gate Array. FPGAs are electronic components that have a configurable function. These devices are able to change their functionality via an information stream transferred to the device. These electronic components are available from a number of different suppliers in a wide range of sizes and speeds. One example of these devices are the Virtex FPGA devices from Xilinx, Inc. located

in San Jose, Calif. An FPGA design may be described using HDL and implemented using synthesis.

A "Central Processing Unit" or "CPU" is circuitry controlling the interpretation and execution of software programmed instructions, performs arithmetic and logical operations on data, and controls input/output functions. For the following descriptions the term CPU will be used to also denote other processing elements such as microprocessors, digital signal processors, microcontrollers, etc.

A "register" is an element in digital circuitry which can <sup>10</sup> store one or more bits. Examples for registers are the various types of flip-flops and latches.

A "PLD" is an Programmable Logic Device. PLDs are electronic components that have a configurable function. These devices are able to change their functionality via an information stream transferred to the device. These electronic components are available from a number of different suppliers in a wide range of sizes and speeds. One example of these devices are the Apex PLD devices from Altera Corporation in San Jose, Calif. A PLD design may be described using HDL 20 and implemented using synthesis.

"Electronic Components" are defined as but not limited to, transistors, logic gates, integrated circuits, semi-custom integrated circuits, full custom integrated circuits, application specific integrated circuits (ASICs), gate arrays, programmable logic devices (PLDs), field programmable gate arrays (FPGAs), CPUs, Random Access Memory (RAM), mixed signal integrated circuits, systems on a chip (SOC), and systems on a printed circuit board.

An "Electronic System" is defined as a system that contains one or more digital and/or analog Electronic Components connected together to perform specific operations or functions. An Electronic System can be implemented entirely of hardware (Electronic Components) or consist of a mix of hardware and software (programming language content).

"Mixed-signal designs" are defined as Electronic System designs which incorporate both digital and analog signals.

The "HDL Design" is referred to as the portion of the electronic system which is described in HDL and implemented in hardware. It is also referred to as the "Design under Test" (DUT).

An "SOC" is a System On Chip. A SOC is defined as a device large enough to contain an entire electronic system implementation. SOC devices can integrate a number of electronic devices into one device.

An "HDL description" is the textual description of an HDL Design.

"HDL source code" is referring to the text files which contain the HDL description.

An "HDL identifier" is an object in an HDL description which represents a signal, a set of signals, a storage element, or a set of storage elements and which can take a value from a set of possible values. Each HDL identifier is associated with a particular scope defined by the syntax of the underlying 55 hardware description language.

A "Technology Mapping Process" is defined as the process of transforming a particular representation of an electronic design into a design consisting entirely of primitive electronic elements from a design library for a target technology. The 60 representation of said electronic design from which the Technology Mapping Process begins is dependent on the particular Technology Mapping Process being employed. However, said representation usually consists of simple boolean elements. For example, said representation may consist entirely 65 of an interconnected set of 2-input/1-output logic elements with each said element performing the NAND function. An

**10**

example of a tool that performs the Technology Mapping Process is Design Compiler from Synopsys in Mountain View, Calif.

"Synthesis" is defined as the process of creating an electronic implementation from the functional description of a system. An example of a tool that performs this operation is Design Compiler from Synopsys in Mountain View, Calif. which reads electronic system descriptions written in a synthesizable subset of VHDL and Verilog and produces a technology mapped design as an output.

"Behavioral HDL" is an HDL description at an algorithmic level of abstraction in which neither the timing behavior nor the structure of the HDL Design is explicitly described.

"Behavioral synthesis" transforms a behavioral HDL description into a register transfer level (RTL) description where the timing behavior and the structure of the HDL Design is fixed. This RTL description is then processed in synthesis and technology mapping. An example of a tool that performs behavioral synthesis is Behavioral Compiler from Synopsys, Inc. of Mountain View, Calif.

A "System Clock" is defined as a main timekeeping signal in a design. All operations that are relative to the System Clock will proceed when the System Clock becomes active.

"Constraints" are defined as limits placed on parameters for the implementation of an electronic system. Parameters of an electronic system can include but are not limited to register to register propagation delay, system clock frequency, primitive element count, and power consumption. These constraints can be used by synthesis tools to guide the implementation of the electronic design.

"Fabrication" is the process of transforming a synthesized and technology mapped design into one or more devices of the target technology. For example, the fabrication of ASICs involves manufacturing and the fabrication of FPGAs and PLDs involves device configuration.

"DFT" is Design-for-test. DFT is defined as a process in which an electronic system designer will include structures in the electronic system that facilitates manufacturing testing.

"Design Rule Check" (DRC) are checks performed before integrated circuit manufacturing to ensure that in the placed and routed technology mapped design none of the rules of the target technology process is violated. Examples for such DRC are checks for shorts, spacing violations, or other design-rule problems between logic cells. An example for a tool that does DRC is Dracula from Cadence Design Systems, Inc. in San Jose, Calif.

A "Functional Specification" is defined as the documentation that describes the necessary features and operations of a system.

A "functional failure" is a behavior of a design which does not meet the functional specification which was used in the creation of the design. Every step in the design process can potentially cause a functional failure. Functional failures can be classified depending on which step of the design process caused the functional failure.

A "fault" is a specific type of functional failure. This type of failure is due to one or more manufacturing defects causing a functional failure in the fabricated design.

A "design error" is a specific type of functional failure where the HDL description's behavior did not match the functional specification.

A "tool error" is a specific type of functional failure which was introduced by design tools because the HDL description was not properly processed such that the functional specification is not met by the implementation.

An "environment error" is a specific type of functional failure caused by a particular combination of environmental parameters such as temperature, humidity, pressure, etc.

A "Functional Simulator" is a tool that mimics the functional behavior of a model of an electronic system which is described using HDL.

A "Testbench" is defined as an electronic system description that presents stimulus to and/or gathers information from the target electronic system design to be verified. In some cases the testbench ignores the response from the target electronic system design. A testbench is used to mimic the behavior of the target environment in which the electronic system being developed will operate. A testbench may comprise both hardware and software.

A "Target Environment" is the system the electronic sys- 15 tem is specified to interact with and/or to run in. A target environment may comprise both hardware and software.

The "Target Speed" of an electronic system is the speed and/or the speed range the electronic system is specified to run at. Examples for measures for the target speed and the 20 speed range are clock frequency, response time, time to propagate, and cycle time.

"Debugging" is the process of comparing the behavior of an implementation of the electronic system to the electronic system functional specification. The purpose of debugging is 25 to find causes and remedies for functional failures.

"Co-Debugging" or "hardware/software co-debugging" is defined as the process of debugging the software and hardware of an electronic system concurrently.

A "FSM" is Finite State Machine—defined as an electronic 30 system control structure. The design and implementation of FSM is described in great detail in Synthesis and Optimization of Digital Circuits, by Giovanni DeMicheli, McGraw Hill, 1994.

A "HDL Building Block" is a functional unit of an HDL Design from which the HDL Design is constructed. A HDL Building Block (BB) performs calculations on the signals to which it is connected and communicates with other BBs in the design. The communication is through connecting internal signals of a BB to communication ports of the BB and/or 40 connecting internal signals of the BB to communication ports of other BBs in the HDL Design. Examples of BBs are Entities in the VHDL language and Modules in the Verilog language.

A "Hard Block" is an electronic system which has a predefined functionality and which can be incorporated into another electronic system. Commonly, the form of the Hard Block is such that the functionality of the Hard Block can not be altered. An example of a hard block is an HDL Design which implements a industry standard bus controller.

A "Design State" is defined as the logical values taken by the storage elements of the design at a particular time, combined with the logical values taken by the inputs of the design taken at the same particular time.

The "System State" or "State of the System" is a synonym 55 device configuration. for "Design State."

At this point, the

"Real-time" means a task, process or response occurs substantially immediately. The term is used to describe a number of different computer features. For example, real-time operating systems are systems that respond to input immediately. 60 Real-time is also used for describing tasks in which the computer must react to a steady flow of new information without interruption. Real-time can also refer to events simulated by a computer at the same speed that they would occur in real life.

Embodiments of this aspect of the invention are discussed 65 below with reference to FIGS. 1-21. However, those skilled in the art will readily appreciate that the detailed description

12

given herein with respect to these figures is for explanatory purposes as the invention extends beyond these limited embodiments.

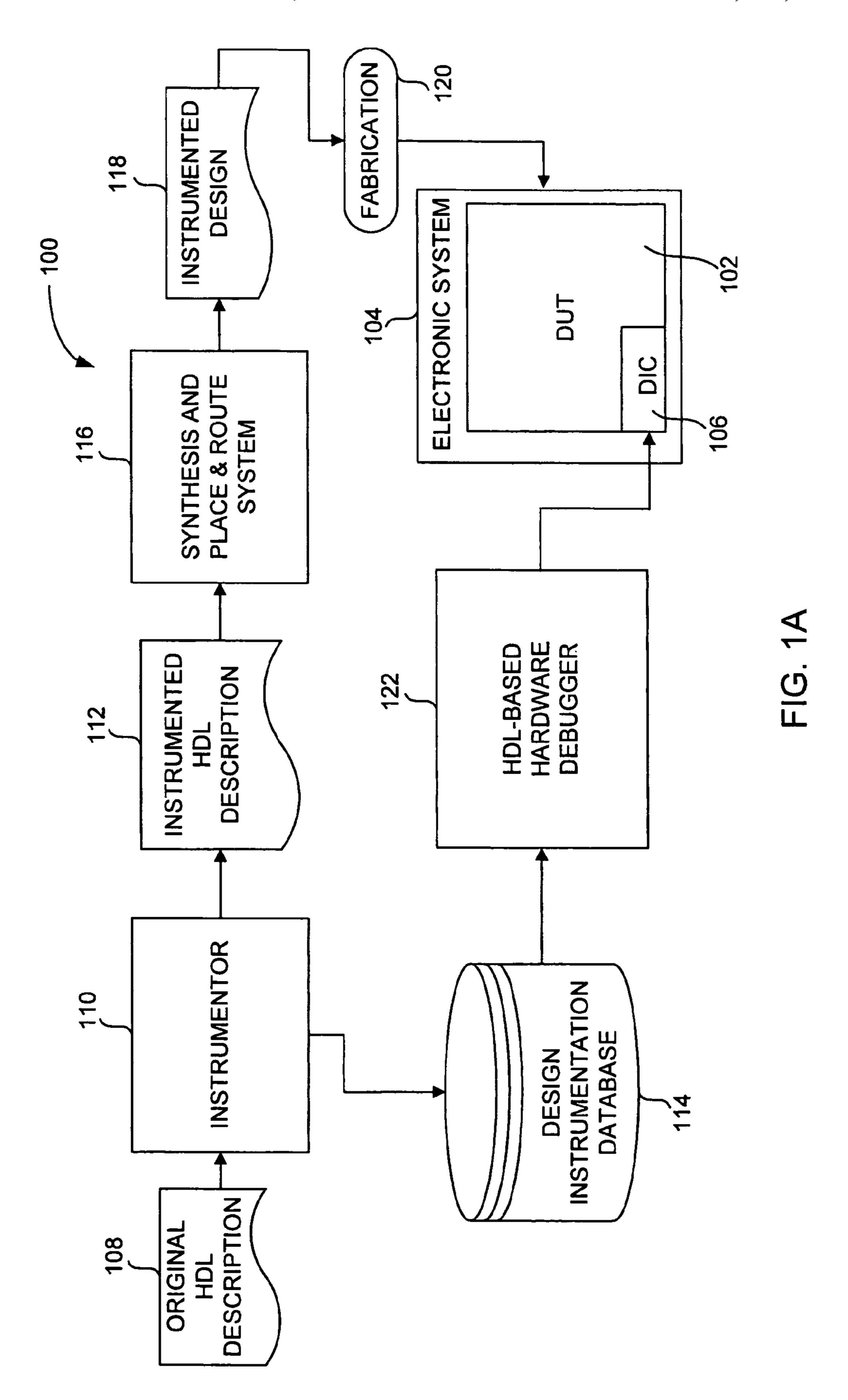

FIG. 1A is a block diagram of a hardware debugging system 100 according to one embodiment of the invention. The hardware debugging system 100 operates to debug a hardware product referred to herein as a Device Under Test (DUT) 102. The DUT 102 is typically part of a larger hardware product referred to as an electronic system 104. The DUT 102 can pertain to a single integrated circuit chip, multiple integrated circuit chips, a system on a chip, or a system on a printed circuit board.

According to the invention, the DUT 102 includes Design Instrumentation Circuitry (DIC) 106. The DIC 106 is provided within the DUT 102 in order to facilitate debugging of the DUT 102. The DIC 106 can be provided within the DUT 106 in either a centralized or distributed manner.

The hardware debugging system 100 operates to determine the DIC 106 that is provided within the DUT 102. In this regard, an original HDL description 108 of the electronic system 104 is received at an instrumentor 110. The instrumentor 110 modifies or alters the original HDL description 108 to produce an instrumented HDL description 112. The instrumented HDL description 112 represents not only the electronic system 104 with the DUT 102 provided therein, but also the DIC 106 that is provided within the DUT 102. The instrumentor 110 also stores DIC information to a design instrumentation database 114. By storing the DIC information in the design instrumentation database 114, the hardware-based debugging of the DUT 102 is facilitated.

The hardware debugging system 100 also includes synthesis and place & route systems 116. The synthesis and place & route systems 116 receives the instrumented HDL description 112 and performs conventional synthesis as well as place & route operations in order to produce an instrumented design 118. Although not shown in FIG. 1A, other additional tools can be utilized to produce or enhance the instrumented design 118. Examples of additional tools include a Design-For-Test (DFT) tool or a Design Rule Check (DRC) tool. The instrumented design 118 represents a description (e.g., design files) of the electronic system 104 that would be thereafter fabricated. Hence, once the instrumented design 118 is available, fabrication 120 can be performed. The fabrication 120 produces the electronic system 104 having the DUT 102 with the DIC 106 provided therein. Fabrication is the process of transforming a synthesized and technology mapped design (e.g., the instrumented design 118) into one or more devices of the target technology. For example, if the target technology is Application Specific Integrated Circuits (ASICs) then the fabrication involves manufacturing, and if the target technology is Field Programmable Gate Arrays (FPGAs) or Programmable Logic Devices (PLDs) the fabrication involves

At this point, the electronic system 104 is a hardware product that has been produced. This hardware product can then be debugged using a HDL-based hardware debugger 122. More particularly, the HDL-based hardware debugger 122 couples to the DIC 106 so that it is able to communicate with the DIC 106 when debugging the DUT 102. The HDL-based hardware debugger 122 also couples to the design instrumentation database 114 so that access to the DIC information is available. As a result, the HDL-based hardware debugger 122 enables a user to debug the DUT 102 and/or hardware and/or software interacting with the DUT 102 in close relation to the original HDL description 108. Further, in

one embodiment, debugging can be performed while the electronic system 104 and the DUT 102 operate in the target environment, at target speed.

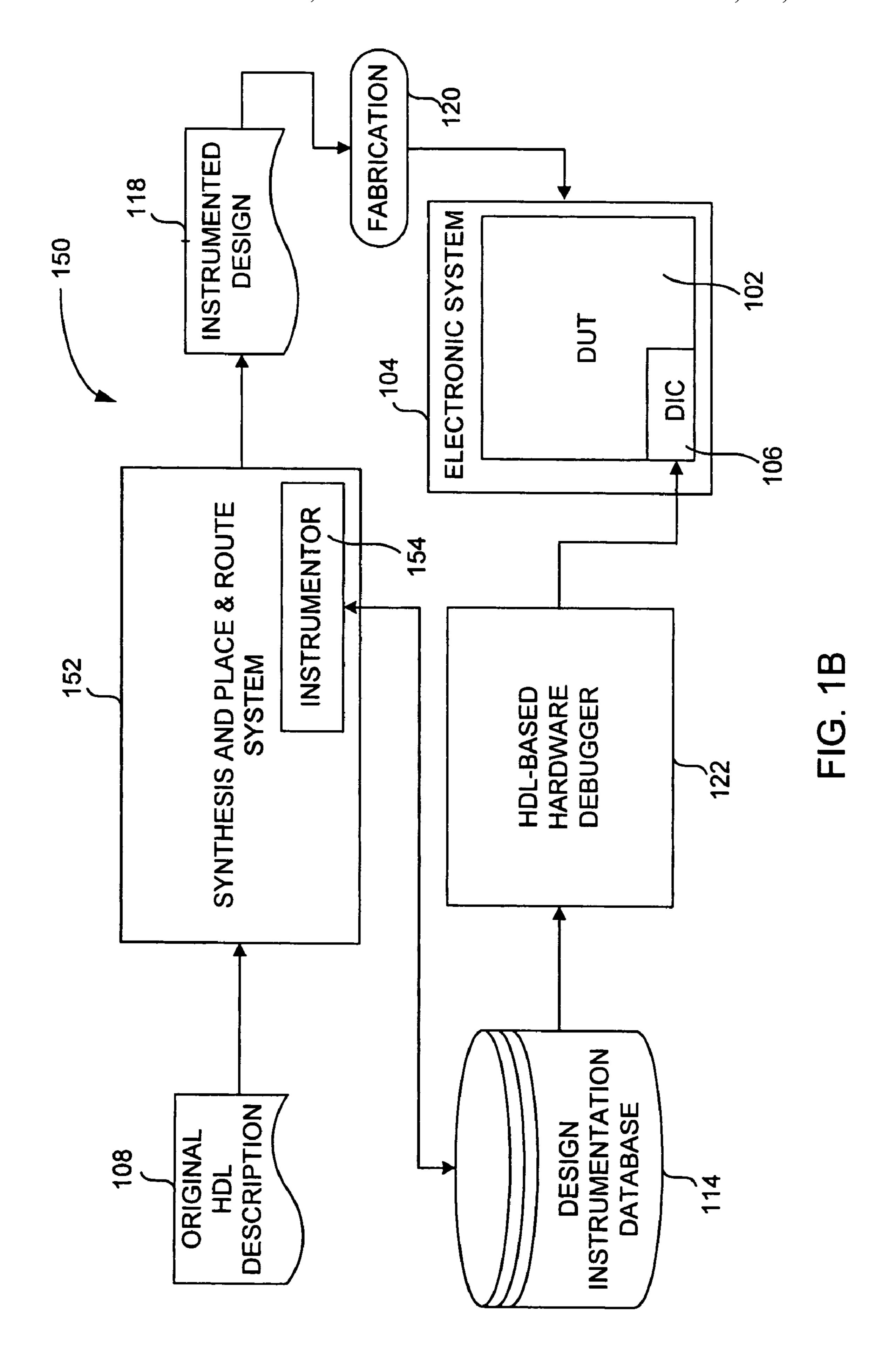

FIG. 1B is a block diagram of a hardware debugging system **150** according to another embodiment of the invention. 5 The hardware debugging system 150 is similar to the hardware debugging system 100 and includes many of the same components. Hence, the hardware debugging system 150 enables a user of the HDL-based hardware debugger 122 to debug the DUT 102 of the electronic system 104 and/or 10 hardware and/or software interacting with the DUT 102, as noted above. However, the hardware debugging system 150 includes a synthesis and place & route system 152 that includes an instrumentor 154. Hence, the original HDL description 108 is supplied to the synthesis and place & route 15 system 152. The synthesis and place & route system 152 can then produce the instrumented design 118 while using not only synthesis and place & route tools but also the instrumentor 154. In this embodiment, the instrumentor 154 is able to be embedded within synthesis and place & route system 152. 20 Here, the instrumentor **154** assists with producing the instrumented design 118 which represents the electronic system 104 having the DIC 106 provided within the DUT 102. However, with the hardware debugging system 150, the original HDL description 108 need not be modified to produce an 25 instrumented HDL description.

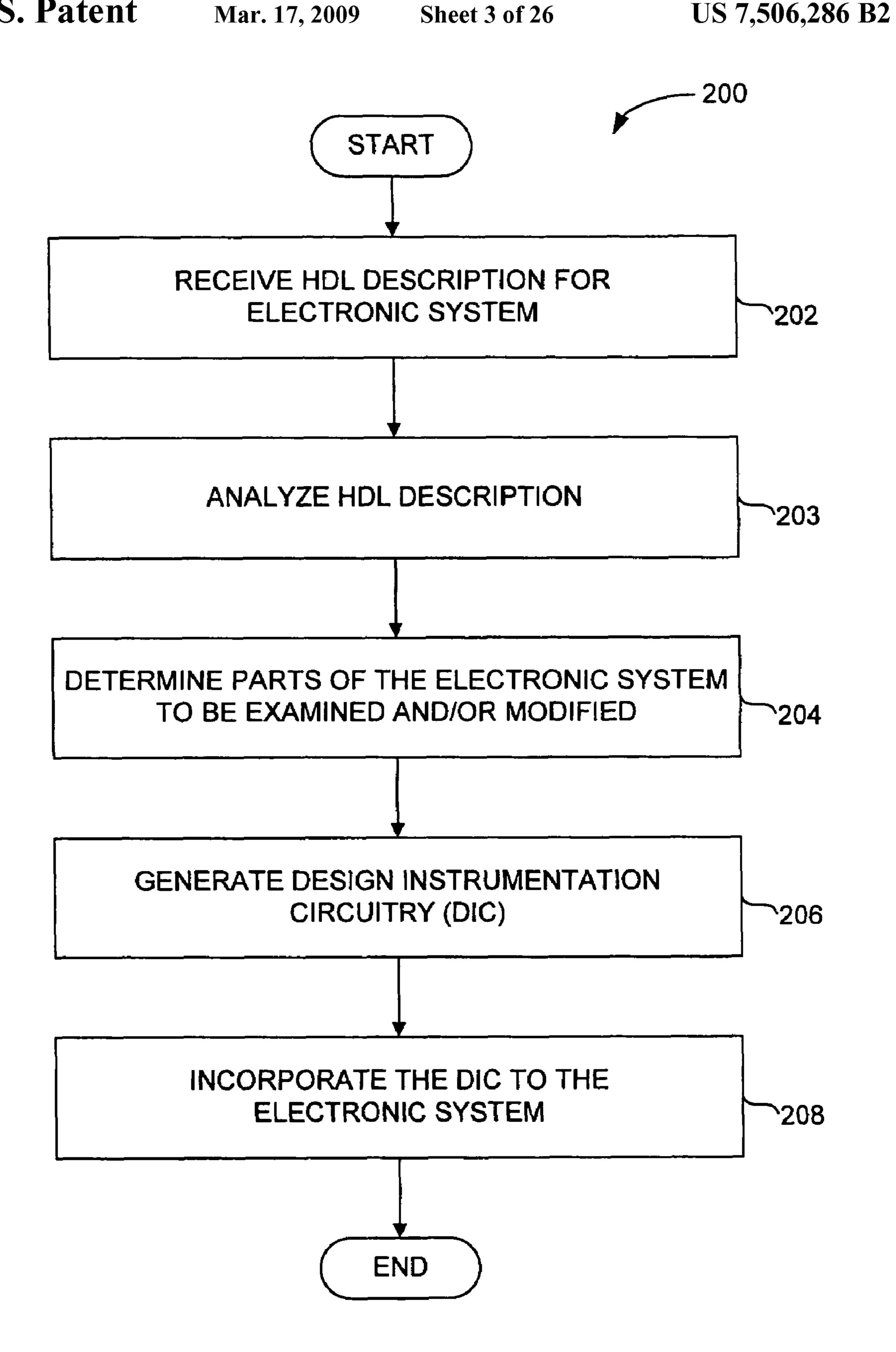

FIG. 2 is a flow diagram of basic instrumentation processing 200 according to one embodiment of the invention. The basic instrumentation processing 200 is, for example, performed by the instrumentor 110 illustrated in FIG. 1A or the 30 instrumentor 154 illustrated in FIG. 1B.

The basic instrumentation processing 200 initially receives 202 a HDL description for an electronic system. The HDL description is then analyzed 203 to understand the characteristics of the electronic system. Next, parts (or portions) of the 35 electronic system that are to be examined and/or modified are determined 204. Typically, the parts of the electronic system to be examined and/or modified (e.g., instrumented) are within a DUT such as the DUT 102 illustrated in FIGS. 1A and 1B. Hence, the parts of the electronic system to be exam- 40 ined and/or modified represent various signals and/or components within the DUT. After the parts of the electronic system to be examined and/or modified have been determined **204**, design instrumentation circuitry (DIC) is generated **206**. Preferably, the DIC is determined **204** based on the parts of 45 the electronic system to be examined and/or modified. In this regard, the DIC can be at least partially customized to the application such as the amount or degree of testing or debugging desired. Thereafter, the DIC is incorporated 208 into the electronic system. The DIC can be incorporated 208 into the 50 electronic system (namely, the DUT) in various ways. In one embodiment, the DIC can be incorporated by adding HDL to the original HDL for the electronic system. In another embodiment, the DIC can be incorporated by modifying a netlist description for the electronic system. Following the 55 operation 208, the basic instrumentation processing 200 is complete and ends.

Design instrumentation (DI) is a process by which a HDL description of an electronic system is analyzed, and then a DIC computed. The DIC is thereafter incorporated (e.g., 60 added) into the electronic system to facilitate debugging. The DIC can be added to the electronic system in a variety of ways. In one embodiment, DIC can be added to the electronic system by adding an HDL description of the DIC to the HDL description of the electronic system. In another embodiment, 65 the DIC can be added to the electronic system during synthesis. The DIC provides mechanisms to control the examination

14

and/or modification of a running electronic system. Thus, the DIC allows to analyze, diagnose, and/or debug the DUT by giving detailed and accurate information about its current state of operation, as well as the state history.

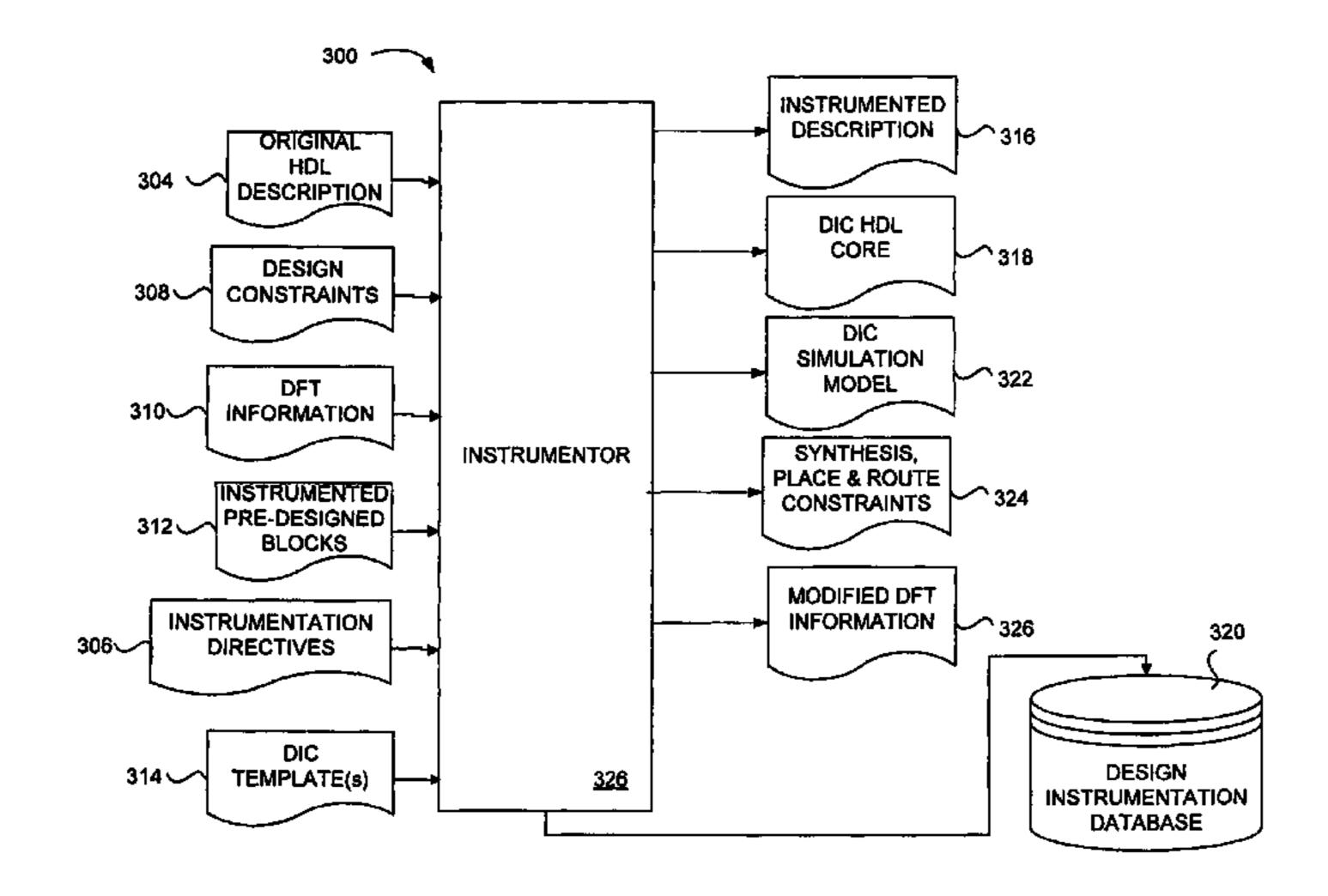

FIG. 3 is a block diagram of an instrumentation system 300 according to one embodiment of the invention. The instrumentation system 300 operates to perform design instrumentation operations to produce an appropriate DIC.

The instrumentation system 300 includes an instrumentor 302. The instrumentor 302 operates to determine the appropriate DIC for the electronic system (namely, the DUT) that is to be eventually hardware debugged. The instrumentor 302 receives an original HDL description 304 as well as instrumentation directives 306. The instrumentation directives 306 are instructions to the instrumentor 302 that inform the instrumentor 302 of the portions, parts or areas of the original HDL description 304 that are to be examined and/or modified. The instrumentation directives 306 can be predetermined or interactively provided by a user through a user interface. Additionally, the instrumentor 302 can further receive design constraints 308, Design For Test (DFT) information 310, instrumented pre-designed blocks 312 and DIC template(s) 314.

The design constraints 308 are constraints on the particular design associated with the original HDL description 304. More particularly, design constraints are limits placed on parameters for an implementation of an electronic system. Some examples of the parameters that can be limited by design constraints include register-to-register propagation delay, system clock frequency, primitive element count, and power consumption. The constraints on the parameters are used by synthesis and place & route tools to guide the implementation of the electronic design.

The DFT information 310 is information about features (e.g., structures) of the original HDL description 304 that pertain to testing. The DFT information is used to facilitate manufacturing testing. For example, the DFT information 310 can provide a description of a scan-chain provided within the original HDL description 304. The instrumentor 302 can utilize portions of the DFT information 310 to reduce the circuitry required for the DIC.