#### US007498246B2

# (12) United States Patent Kim

# (10) Patent No.:

US 7,498,246 B2

(45) **Date of Patent:**

Mar. 3, 2009

# (54) METHOD OF MANUFACTURING A SEMICONDUCTOR DEVICE HAVING A STEPPED GATE STRUCTURE

# (75) Inventor: **Hyun Jung Kim**, Kyoungki-do (KR)

# (73) Assignee: Hynix Semiconductor Inc.,

Kyoungki-do (KR)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 11/923,817

(22) Filed: Oct. 25, 2007

# (65) Prior Publication Data

US 2008/0044993 A1 Feb. 21, 2008

## Related U.S. Application Data

(62) Division of application No. 11/157,580, filed on Jun. 21, 2005, now Pat. No. 7,361,945.

# (30) Foreign Application Priority Data

Mar. 15, 2005 (KR) ...... 10-2005-0021389

(51) Int. Cl.

**H01L 21/4763** (2006.01)

**U.S. Cl.** 438/585; 438/206

See application file for complete search history.

## (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,300,988 B1*    | 10/2001 | Ishihara et al 349/43 |

|------------------|---------|-----------------------|

| 7,244,650 B2*    | 7/2007  | Suh 438/253           |

| 7,268,391 B2*    | 9/2007  | Park 257/330          |

| 2003/0013221 A1* | 1/2003  | Kimura et al 438/30   |

| 2005/0110074 A1* | 5/2005  | Jang et al 257/327    |

## \* cited by examiner

Primary Examiner—Thao P. Le

(74) Attorney, Agent, or Firm—Ladas & Parry LLP

# (57) ABSTRACT

Disclosed herein are a method of manufacturing a semiconductor device, which can prevent a stepped gate from leaning and increase the channel length of the device, thus contributing to an increase in the degree of integration of the device, as well as a semiconductor device manufactured thereby. The method comprises the steps of: forming in a silicon substrate an isolation film defining an active region; selectively etching each of both sides of the active region to form a first recess and a first protrusion surrounded by the first recess and located at the central portion of the active region; selectively etching the bottom of the first recess and either side of the first protrusion to form a second recess and a second central protrusion surrounded by the second recess; and forming a gate on a portion of the active region extending from each of both edges of the second central protrusion to a portion of the second recess of the active region.

# 6 Claims, 8 Drawing Sheets

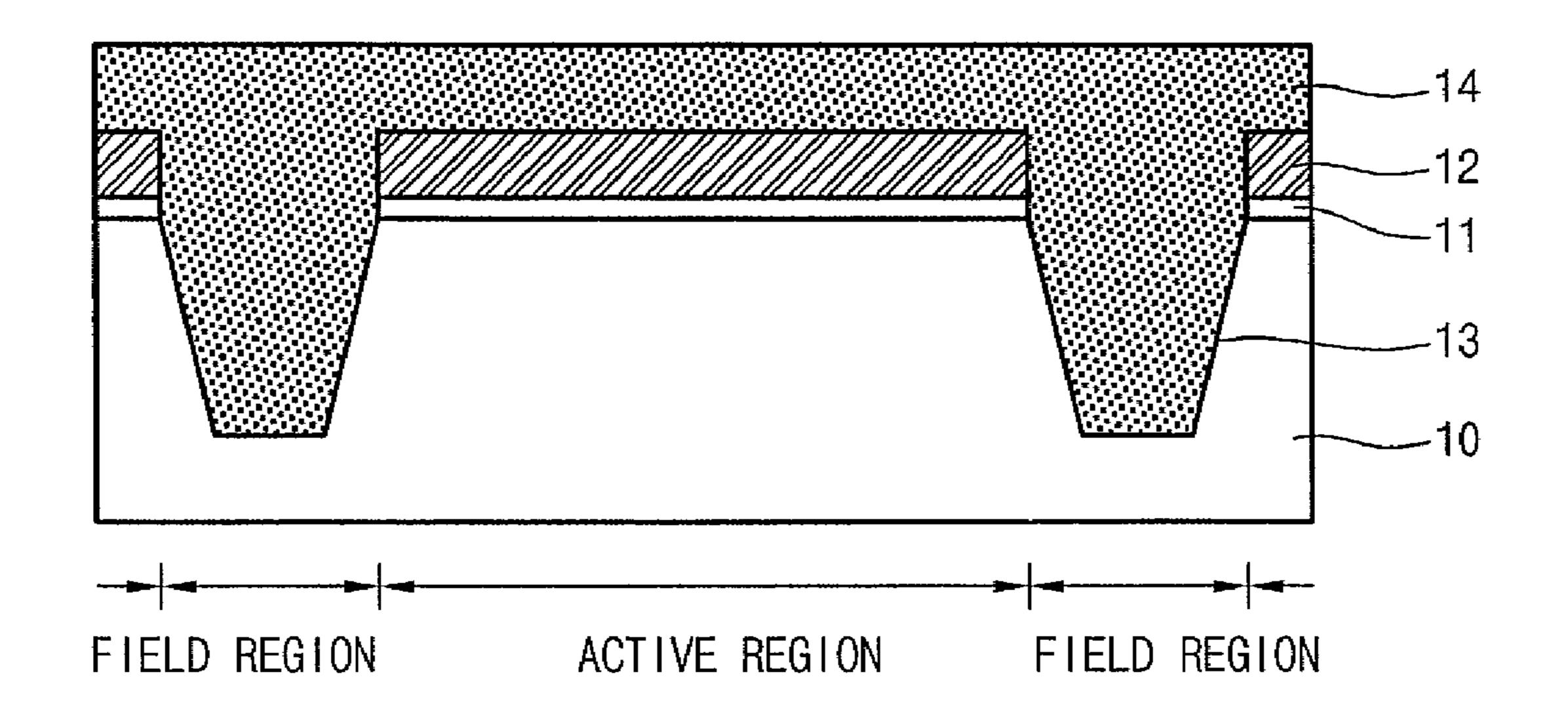

FIG.1A

(PRIOR ART)

FIG.1B

(PRIOR ART)

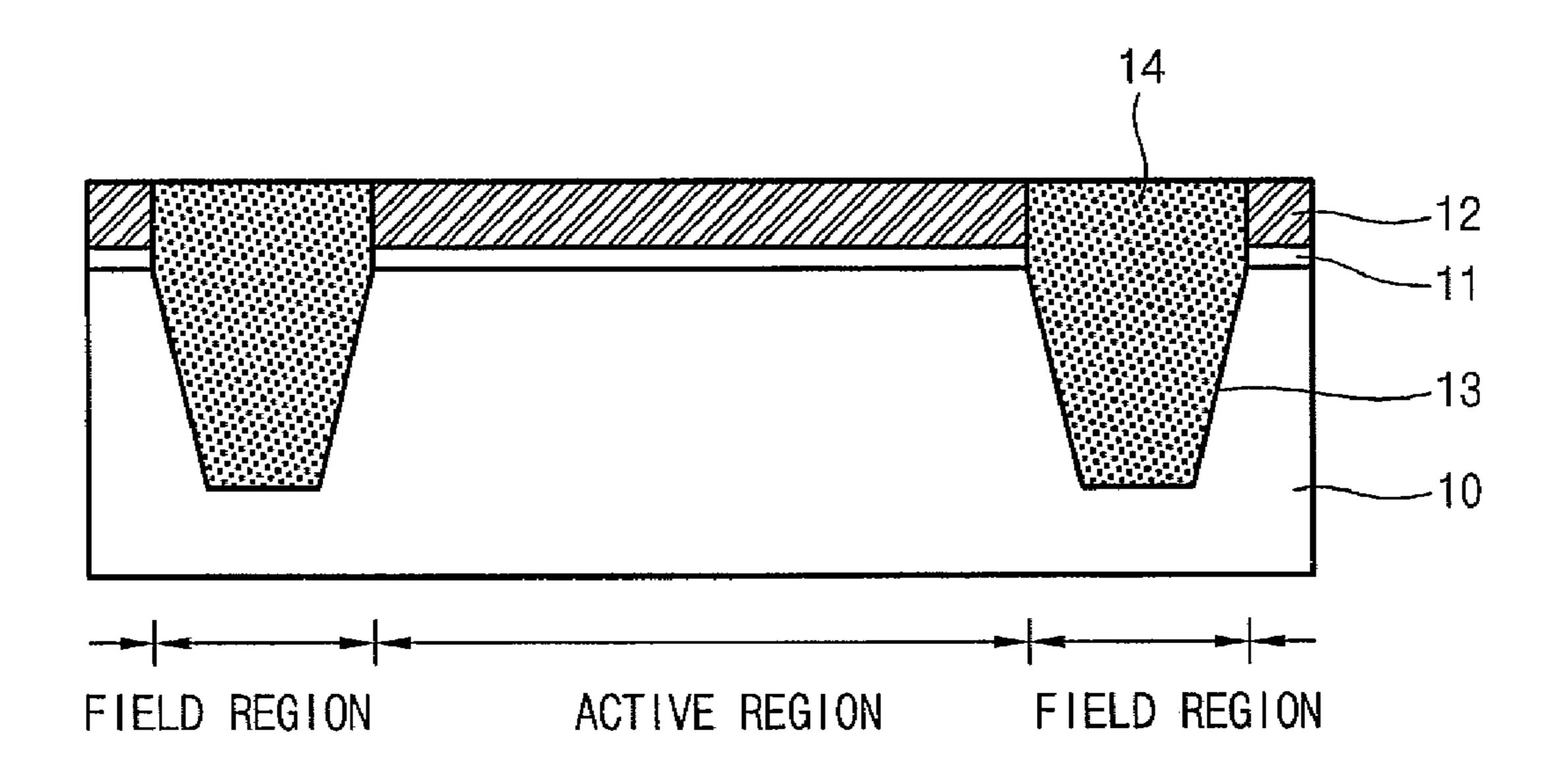

FIG.1C

(PRIOR ART)

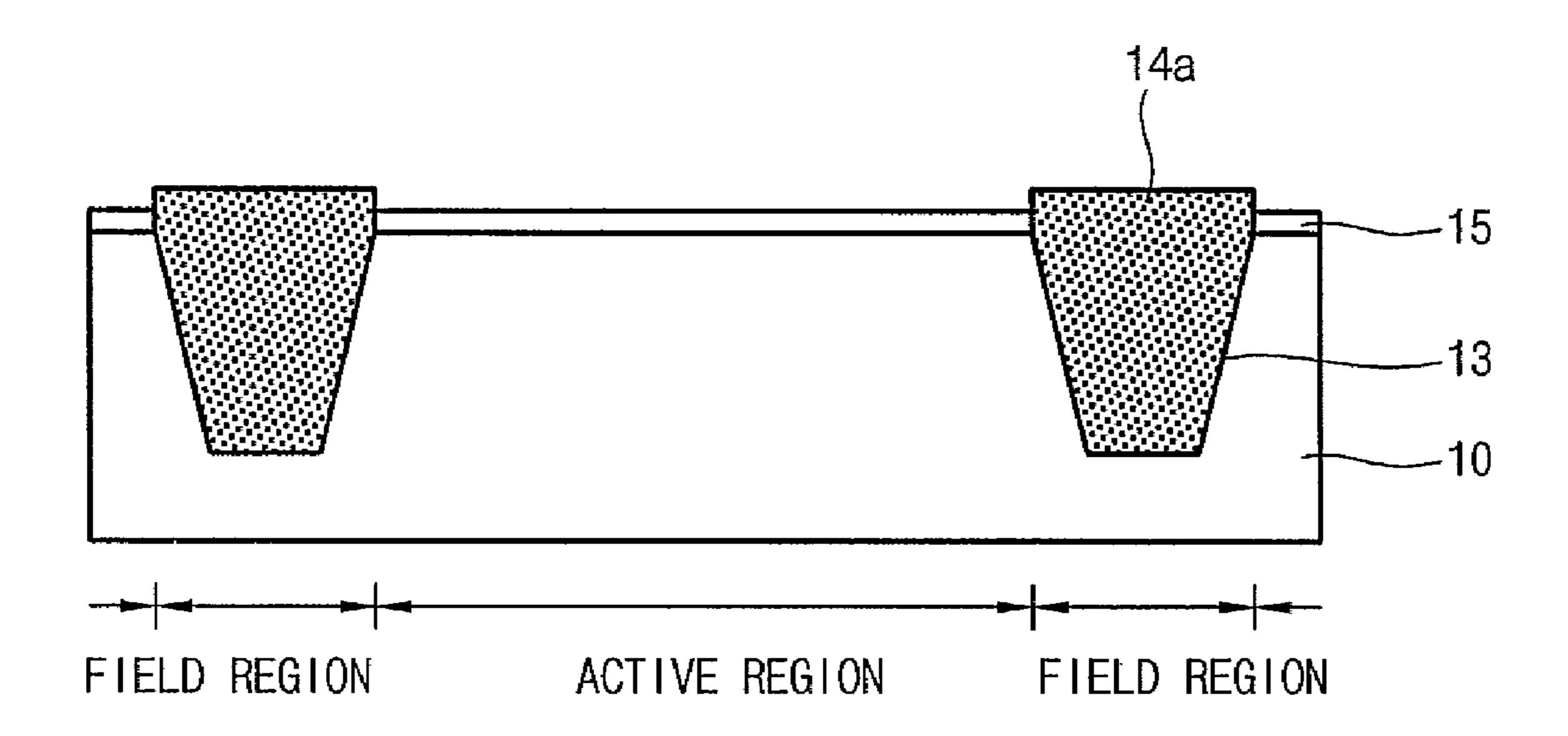

FIG. 1D

(PRIOR ART)

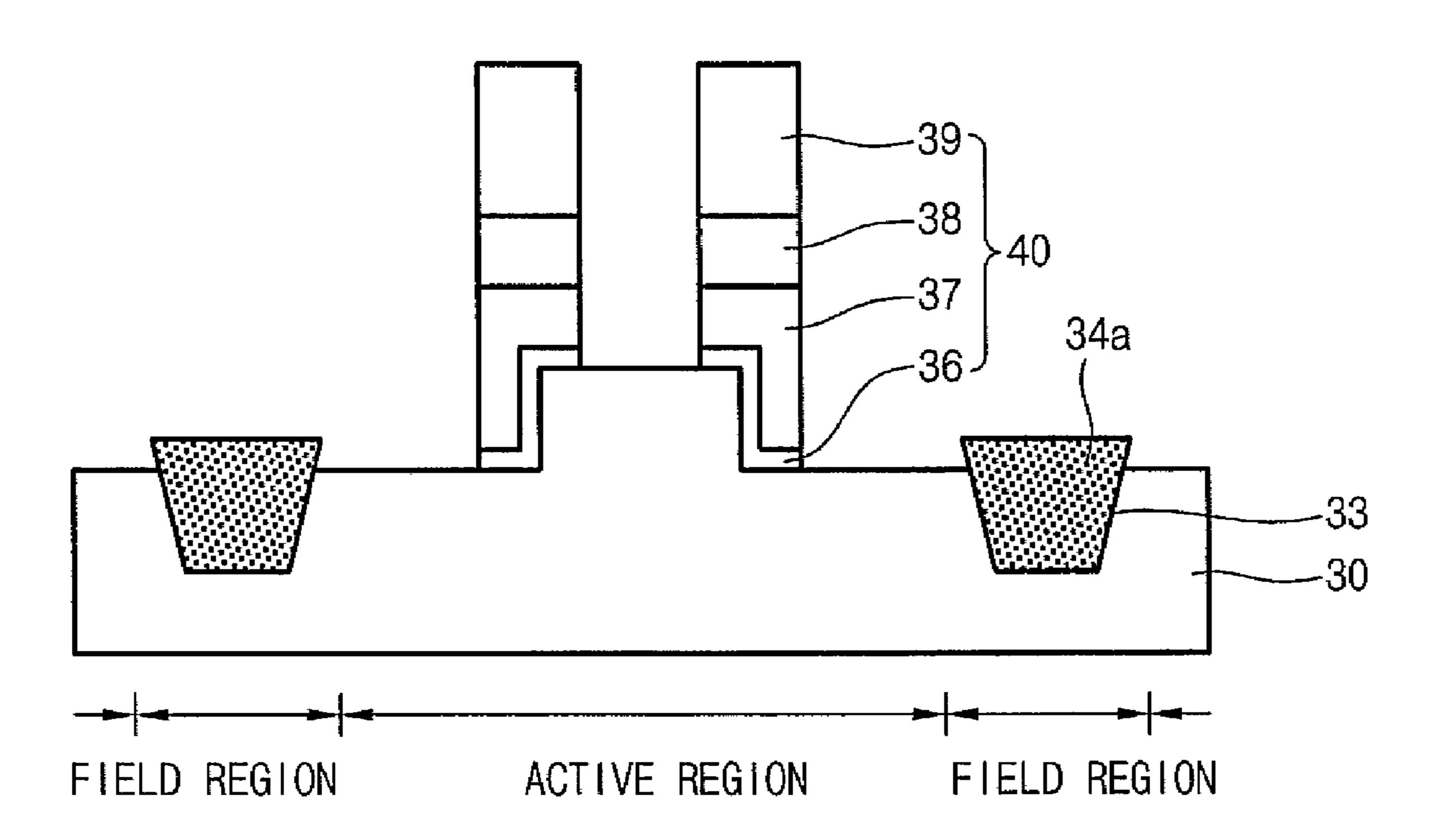

FIG.1E

(PRIOR ART)

FIG.1F

(PRIOR ART)

FIG.2A

Mar. 3, 2009

FIG.2B

FIG.2C

FIG.2D

FIG.2E

FIG.2F

FIG.2G

FIG.3

FIG.4

FIG.5

1

# METHOD OF MANUFACTURING A SEMICONDUCTOR DEVICE HAVING A STEPPED GATE STRUCTURE

# CROSS-REFERENCE TO RELATED APPLICATIONS

The present application claims priority to Korean patent application No. 10-2005-0021389 filed on Mar. 15, 2005 and U.S. patent application Ser. No. 11/157,580 filed on Jun. 21, 10 2005, both of which are incorporated herein by reference in their entirety.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a method of manufacturing a semiconductor device having a stepped gate, which can prevent the stepped gate from leaning and increase the channel length of the device, thus contributing to an increase in the degree of integration of the device, as well as a semiconductor device manufactured thereby.

## 2. Description of the Prior Art

Currently, as the size of a semiconductor device becomes smaller, it is more and more difficult to secure the capacity of a capacitor. Also, as the magnitude of electric field in the junction regions of a transistor becomes larger, it is more and more difficult to secure the refresh characteristics of a cell area. For this reason, a method is used which makes the effective channel length of a transistor long by the use of a 30 three-dimensional cell other than a planar cell.

Particularly, a stepped gate structure was recently proposed which is obtained by forming a recess in a portion both sides of the substrate's active region and then forming a stepped gate on a portion of the active region extending from each edge of the non-recessed portion of the active region to a portion of the recess of the active region. This structure provides an increase in the effective channel length required for the operation of the gate, resulting in an increase in the threshold.

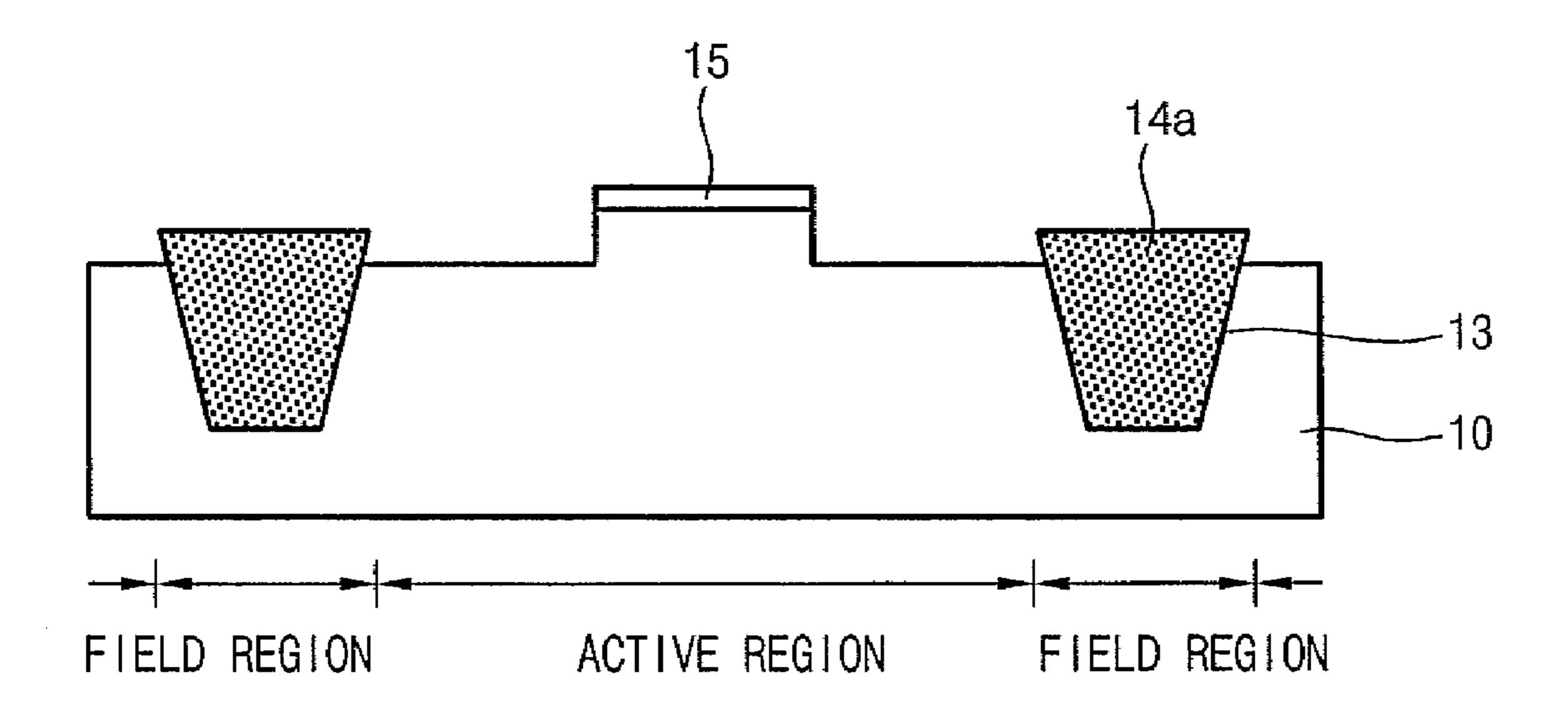

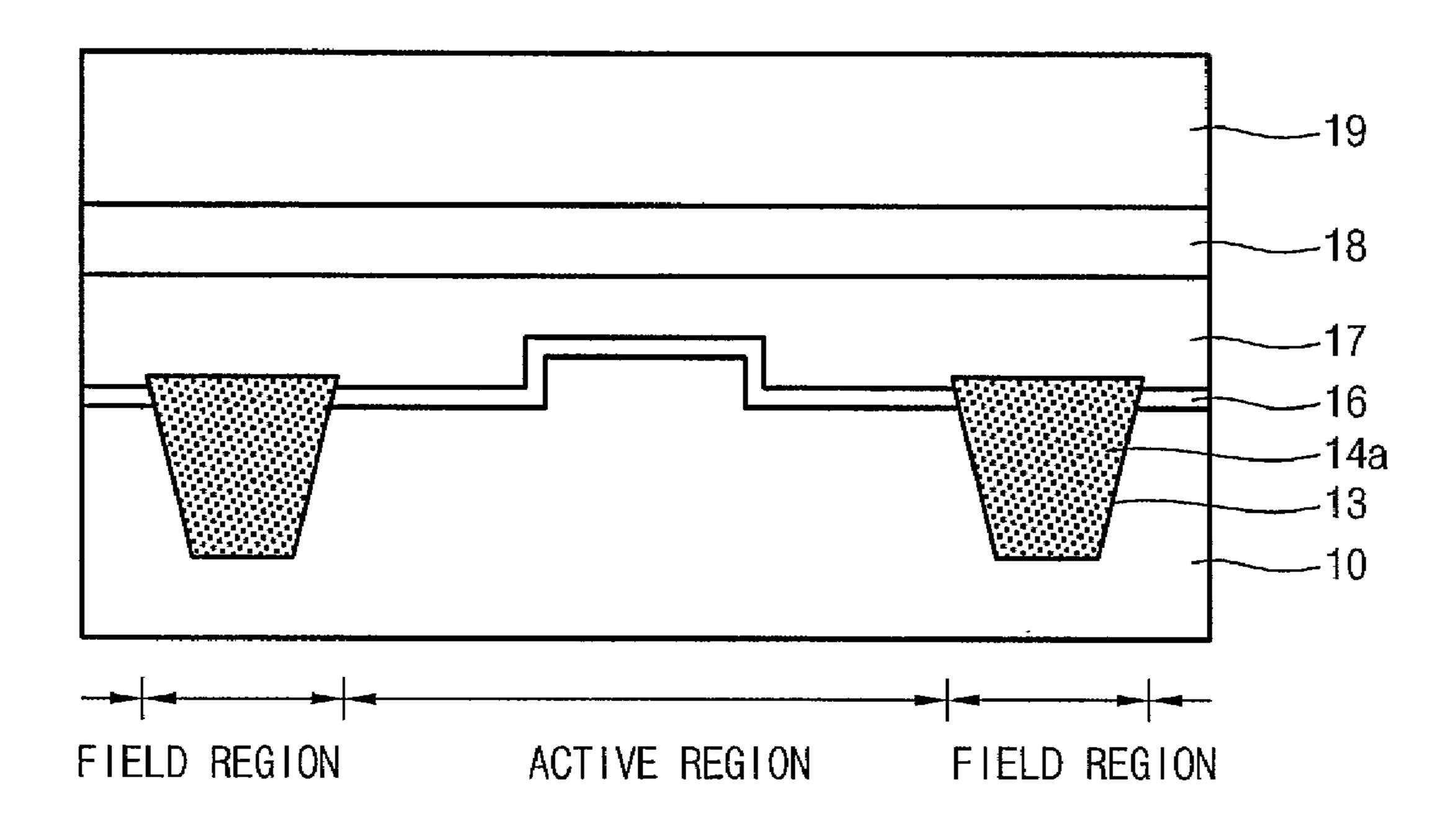

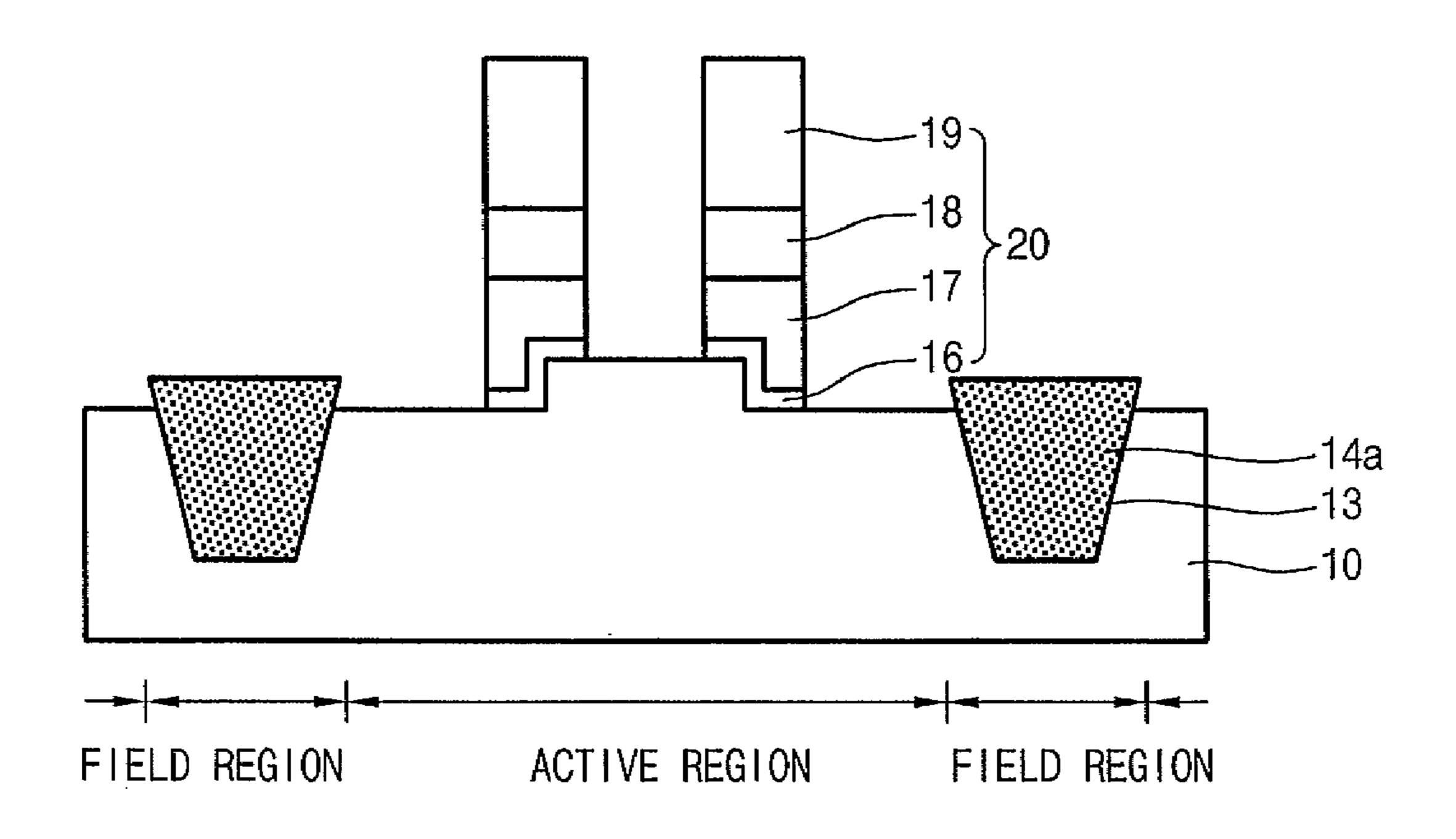

FIGS. 1A to 1F are cross-sectional views for explaining each step of a method of manufacturing a semiconductor device having a stepped gate.

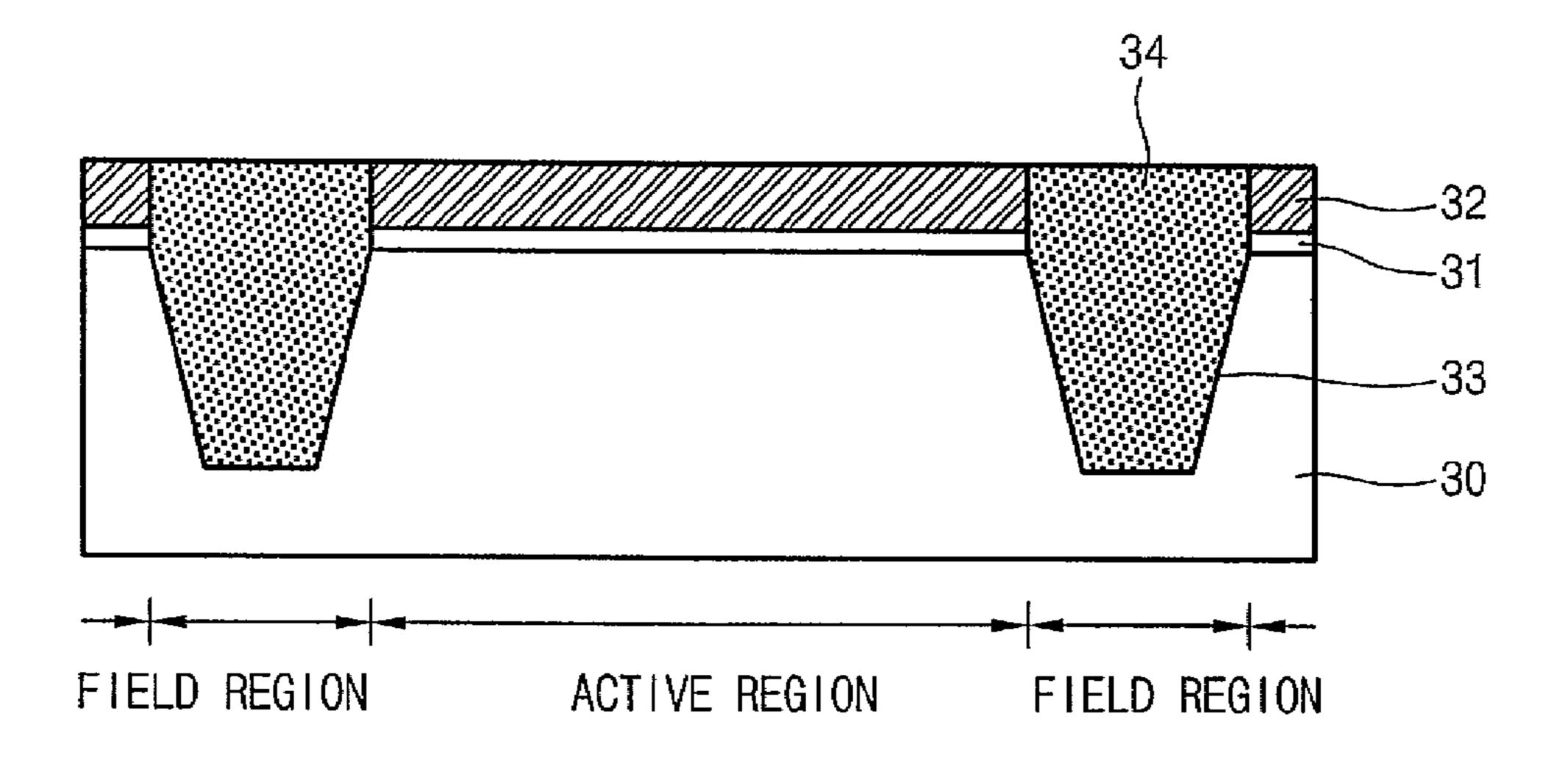

As shown in FIG. 1A, the pad oxide film 11 and the pad nitride film 12 are sequentially formed on the silicon substrate 45 10 having an active region and a field region. Then, the pad nitride film 12 is etched so as to expose the field region, and the pad oxide film 11 and the silicon substrate 10 are etched using the remaining pad nitride film 12 as an etch barrier so as to form the trench 13 in the field region. Then, on the resulting 50 substrate, the gap-fill oxide 14 is formed to fill the trench 13.

As shown in FIG. 1B, the gap-fill oxide film 14 is subjected to chemical mechanical polishing (hereinafter, also referred to as "CMP") until the pad nitride film 12 is exposed.

As shown in FIG. 1C, the remaining pad nitride film 12 and 55 pad oxide film 11 are then removed to form the isolation film 14a, after which the hard mask oxide film 15 is formed on the active region of the substrate 10.

As shown in FIG. 1D, the hard mask oxide film 15 is then etched so as to expose both sides of the active region. Next, 60 both exposed sides of the active region are etched using the remaining hard mask film 15 as an etch barrier so as to form a recess in the active region.

As shown in FIG. 1E, the remaining hard mask oxide film is then removed. Then, the gate oxide film 16 is formed on the active region of the substrate 10. Next, the doped polycrystalline silicon film 17, the tungsten silicide film 18 and the

2

gate hard mask film 19 are sequentially formed on the entire surface of the substrate 10 including the gate oxide film 16.

As shown in FIG. 1F, the gate hard mask film 19 is then etched, leaving a gate pattern. Next, the tungsten silicide film 18, the doped polycrystalline film 17 and the gate oxide film 16 are selectively etched using the remaining gate hard mask film as an etch barrier, thus forming the stepped gate 20 on a portion of the active region extending from each of both edges of the non-recessed central portion and a portion of the recess of the active region.

Although not shown in the drawings, a thermal oxidation process is then performed on the substrate 10 including the gate 20, in order to recover from damage caused by the etching process for forming the gate 20.

However, in the method of manufacturing the semiconductor device having the stepped gate 20 according to the prior art, the volume of the doped polycrystalline film 17 and the tungsten silicide film 18 in the gate 20 shrinks in the hightemperature thermal oxidation process conducted after the formation of the gate 20. Also, since the thickness of a portion of the doped polycrystalline silicon film 17 and the tungsten silicide film 18 placed on the recessed portion of the substrate 10 is greater than the thickness of a portion of the doped polycrystalline silicon film 17 and the tungsten silicide film 18 placed on the non-recessed portion of the substrate 10, then the volume of a portion of the films 17 and 18 placed on the recessed portion of the substrate 10 shrink more. Thus, the gates 20 lean inwardly towards the recessed portion of the substrate 10. Accordingly, the interval between the adjacent gates 20 becomes narrower, and thus, contact open failure in the formation of a landing plug contact may occur. Also, an interlayer insulating film to be formed later may not completely fill the interval between the gates 20 so that the bridge between plugs can occur. As a result, the characteristics of the device will be deteriorated.

And, as the degree of integration of the device continuously increases, there is a limitation in increasing the channel length of the device. Therefore, it will be difficult to fabricate a highly integrated device by the above-described prior method

## SUMMARY OF THE INVENTION

Accordingly, the present invention has been made to solve the above-mentioned problems occurring in the prior art, and it is an object of the present invention to provide a method of manufacturing a semiconductor device, which can prevent the gate from leaning and can increase the channel length of the device, thus contributing to an increase in the degree of integration of the device, as well as a semiconductor device manufactured thereby.

To achieve the above object, in one aspect, the present invention provides a semiconductor device comprising: a silicon substrate; a isolation film formed in the silicon substrate; an active region defined by the isolation film and having a central protrusion which extends over the central portion of the length of a channel and either side of the width of the channel, the central protrusion being formed by etching both sides of the active region so as to form a first recess while leaving a first protrusion surrounded by the first recess and located at the central portion of the active region, and then selectively etching the bottom of the first recess of the active region and either side of the first protrusion to form a second recess surrounding the central protrusion; and a stepped gate formed on a portion of the active region extending from each of both edges of the central protrusion to a portion of the second recess of the active region.

3

In the inventive semiconductor device, the first recess preferably has a depth of 100-400 Å, and the second recess preferably has a depth of 100-400 Å.

In another aspect, the present invention provides a method of manufacturing a semiconductor device, the method comprising the steps of: forming in a silicon substrate a isolation film defining an active region; selectively etching each of both sides of the active region to form a first recess while leaving a first protrusion surrounded by the first recess and located at the central portion of the active region; selectively etching the bottom of the first recess and either side of the first protrusion to form a second recess while leaving a second protrusion surrounded by the second recess; and forming a gate on a portion of the active region extending from each of both edges of the central protrusion to a portion of the second recess of the active region.

As shown in FIG. 2A, the nitride film 32 are sequential 30 having an active region a film 31 is formed to a thick pad nitride film 32 is formed. A. Then, the pad nitride film 32 as an etch barrier so a region. The trench 33 is form the central protrusion to a portion of the second recess of 15 formed to fill the trench 33.

As shown in FIG. 2A, the nitride film 32 are sequential 30 having an active region a film 31 is formed to a thick pad nitride film 32 is formed. A. Then, the pad nitride film 32 as an etch barrier so a region. The trench 33 is form the central protrusion to a portion of the second recess of 15 formed to fill the trench 33.

As shown in FIG. 2B, the protrusion of the second recess of 15 formed to fill the trench 33.

In the inventive method, the step of forming the isolation film preferably comprises the sub-steps of: sequentially forming a pad oxide film and a pad nitride film on the substrate; etching the pad nitride film so as to expose the field region of the substrate; etching the pad oxide film and the substrate using the remaining pad nitride film as an etch barrier so as to form a trench; forming a gap-fill oxide film on the resulting substrate to fill the trench; subjecting the gap-fill oxide film to chemical mechanical polishing (CMP) until the pad nitride film and pad oxide film.

Also, the trench is preferably formed to a depth of 2,000-3,000 Å.

Also, the first recess of the active region is preferably 30 formed to a depth of 100-400 Å.

Also, the second recess of the active region is preferably formed to a depth of 100-400 Å.

Also, the step of forming the gate preferably comprises the sub-steps of: forming a gate oxide film on the two-step- 35 recessed active region of the substrate; sequentially forming a doped polycrystalline silicon film, a tungsten silicide film and a gate hard mask film on the entire surface of the substrate including the gate oxide film; etching the gate hard mask film so as to leave a gate pattern; and etching the tungsten silicide 40 film and the doped polycrystalline silicon film using the remaining gate hard mask film as an etch barrier.

## BRIEF DESCRIPTION OF THE DRAWINGS

The above and other objects, features and advantages of the present invention will be more apparent from the following detailed description taken in conjunction with the accompanying drawings, in which:

FIGS. 1A to 1F are cross-sectional views for explaining each step of a method of manufacturing a semiconductor device having a stepped gate, according to the prior art;

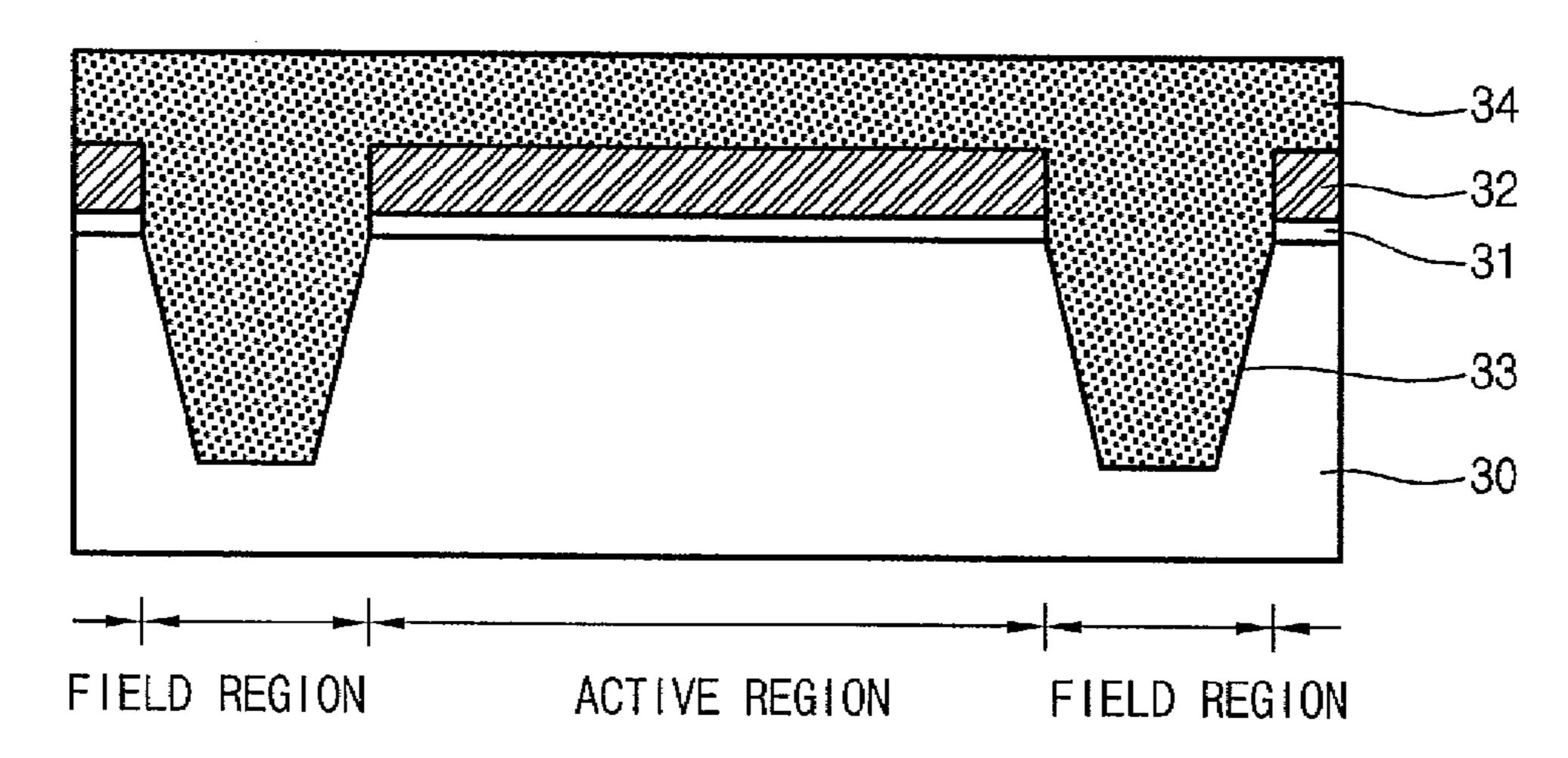

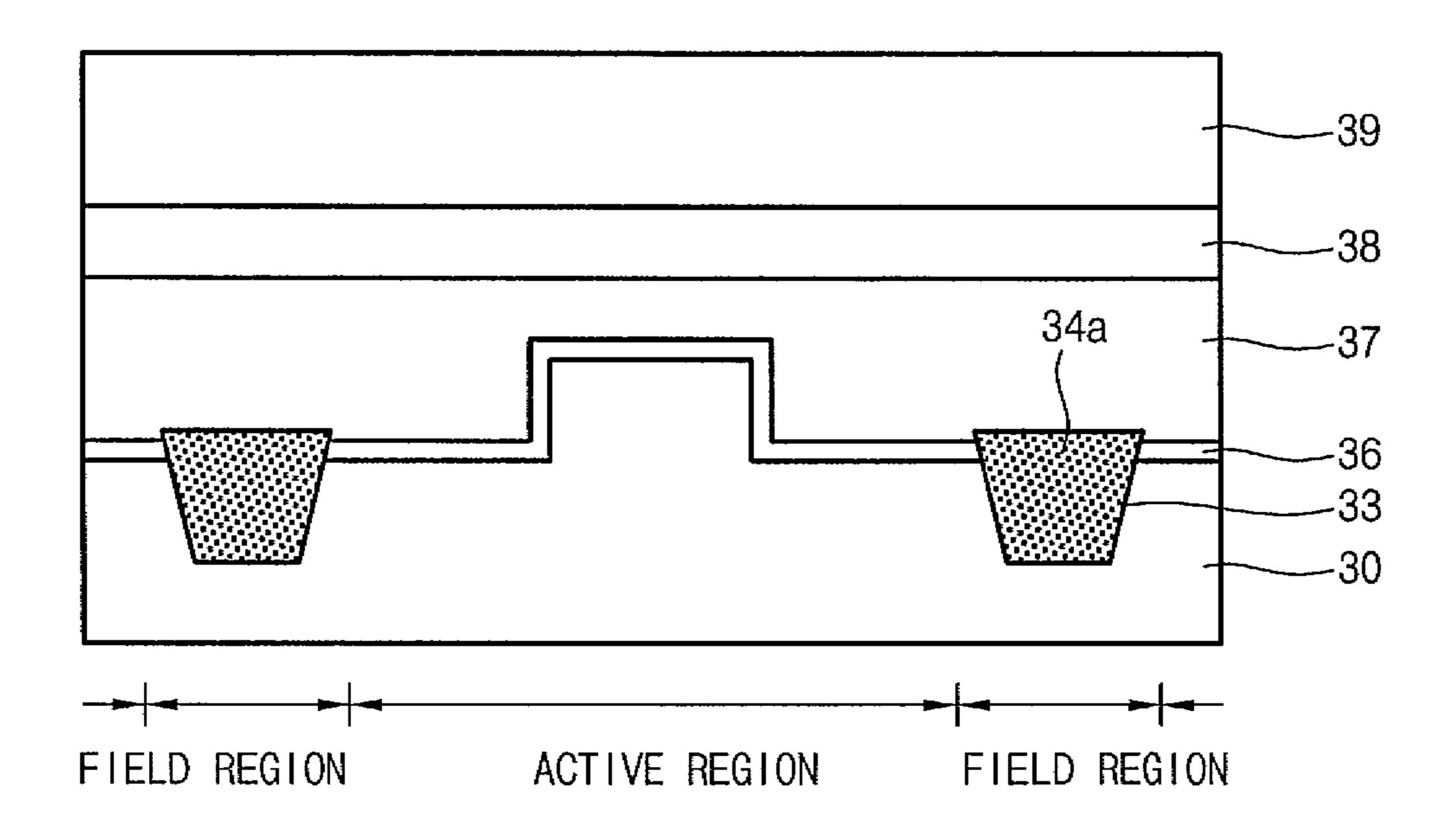

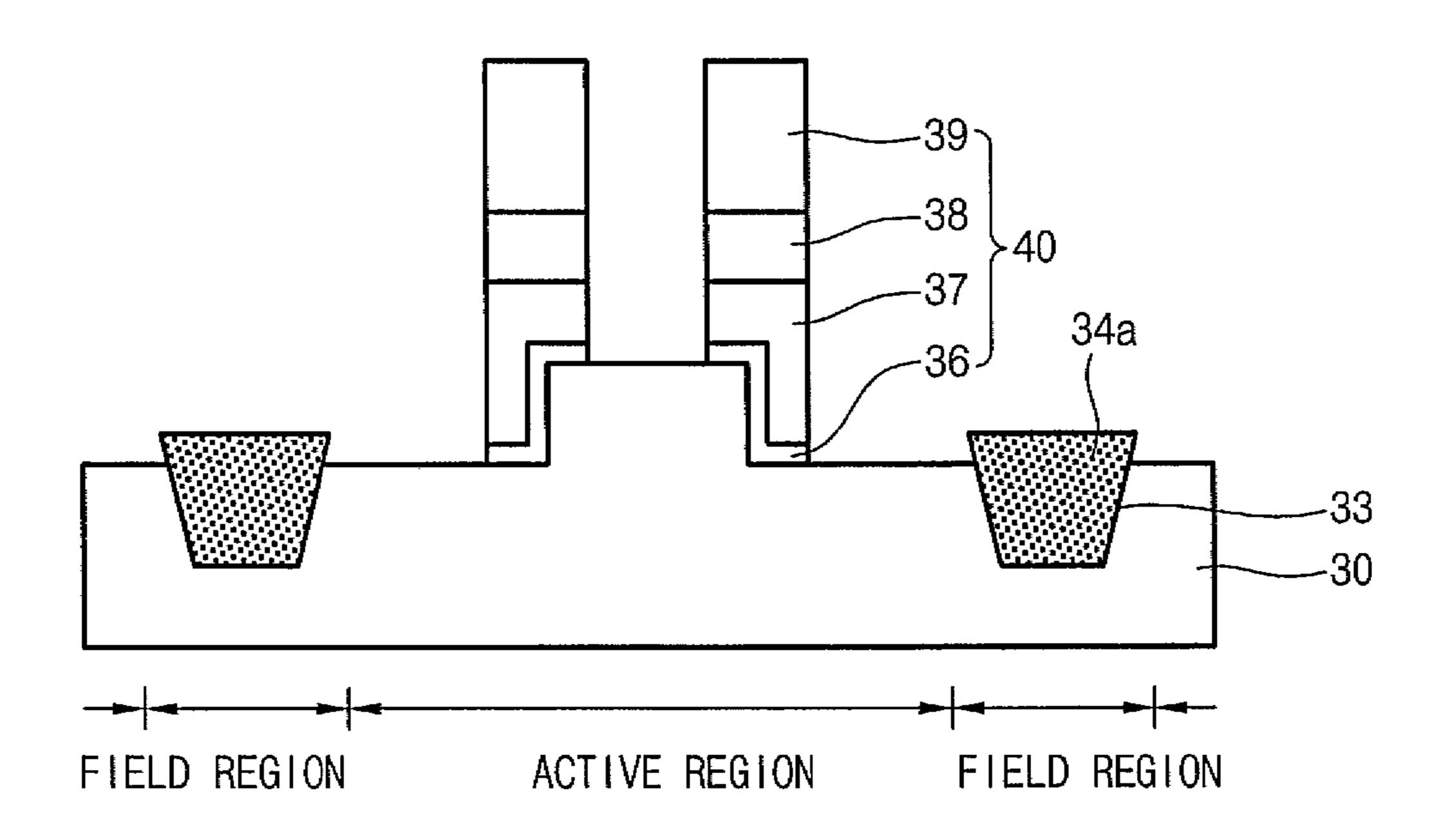

FIGS. 2A to 2G are cross-sectional views for explaining each step of a method of manufacturing a semiconductor device according to the present invention;

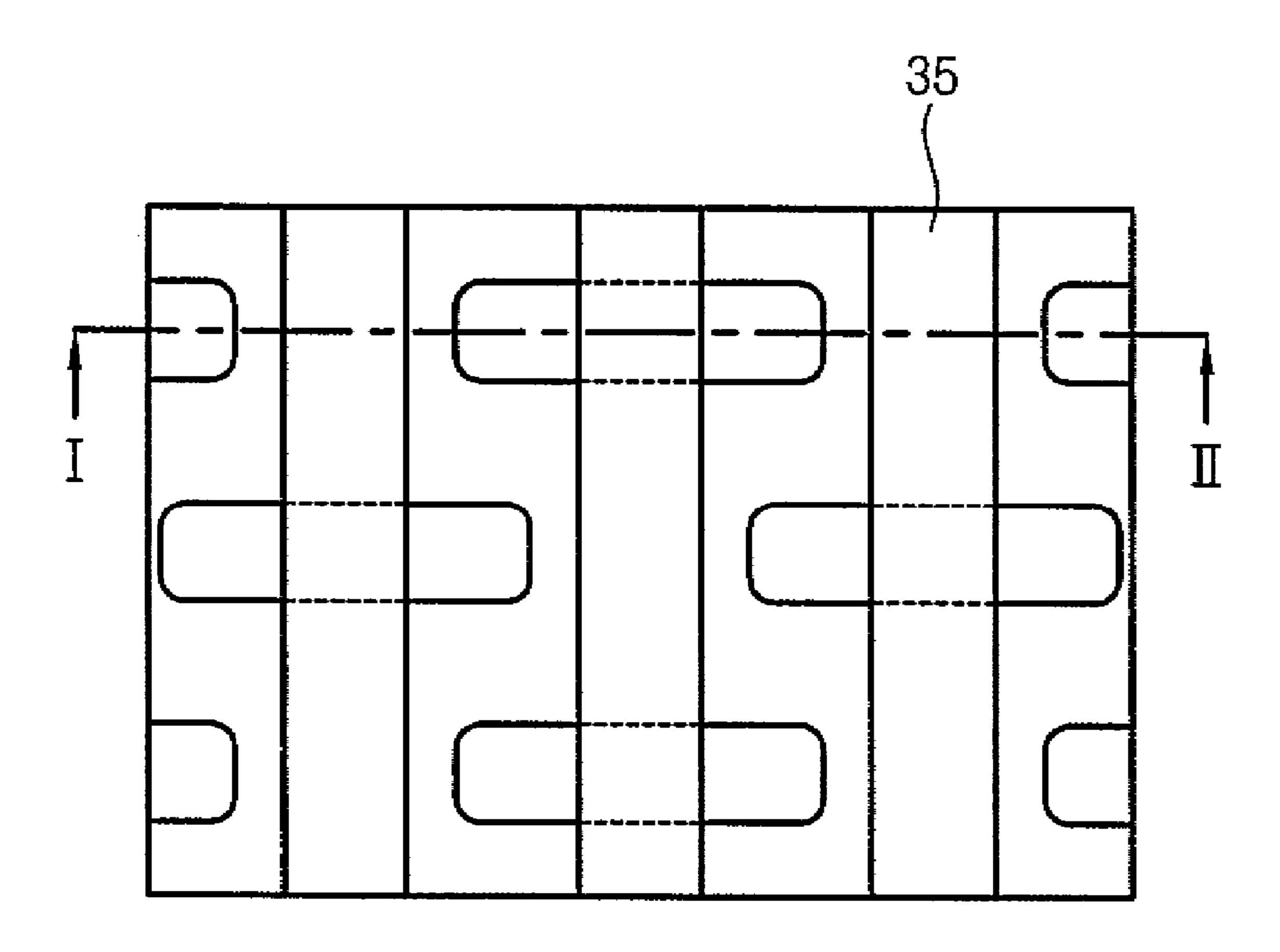

FIG. 3 is a top view of FIG. 2D;

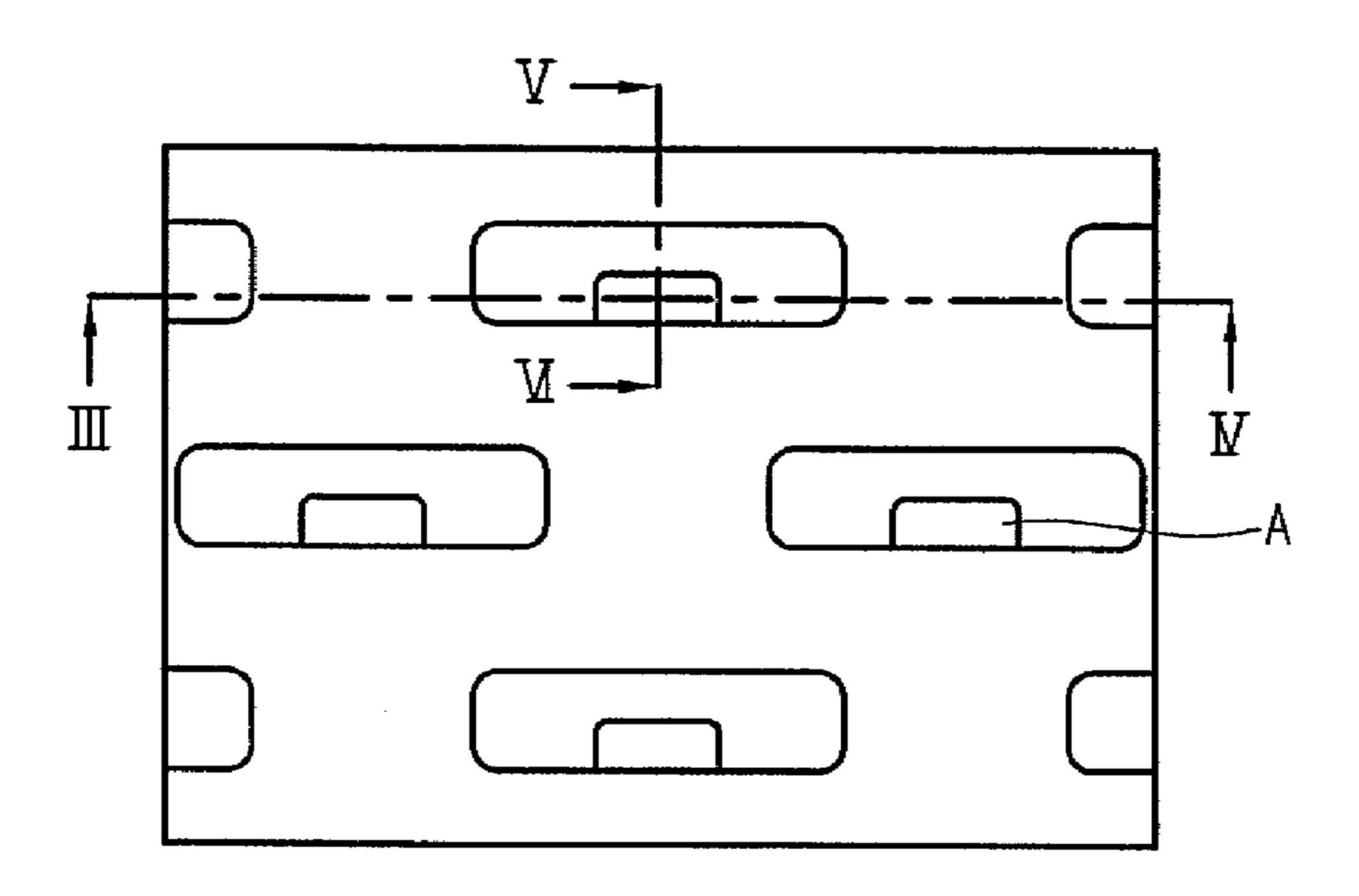

FIG. 4 is a top view of FIG. 2E; and

FIG. 5 is a cross-sectional view taken along line V-VI in FIG. 4.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

Hereinafter, the present invention will be described in detail with reference to the accompanying drawings.

FIGS. 2A to 2G are cross-sectional views for explaining each step of a method of manufacturing a semiconductor

4

device having a stepped gate, according to the present invention, FIG. 3 is a top view of FIG. 2D, and FIG. 4 is a top view of FIG. 2E.

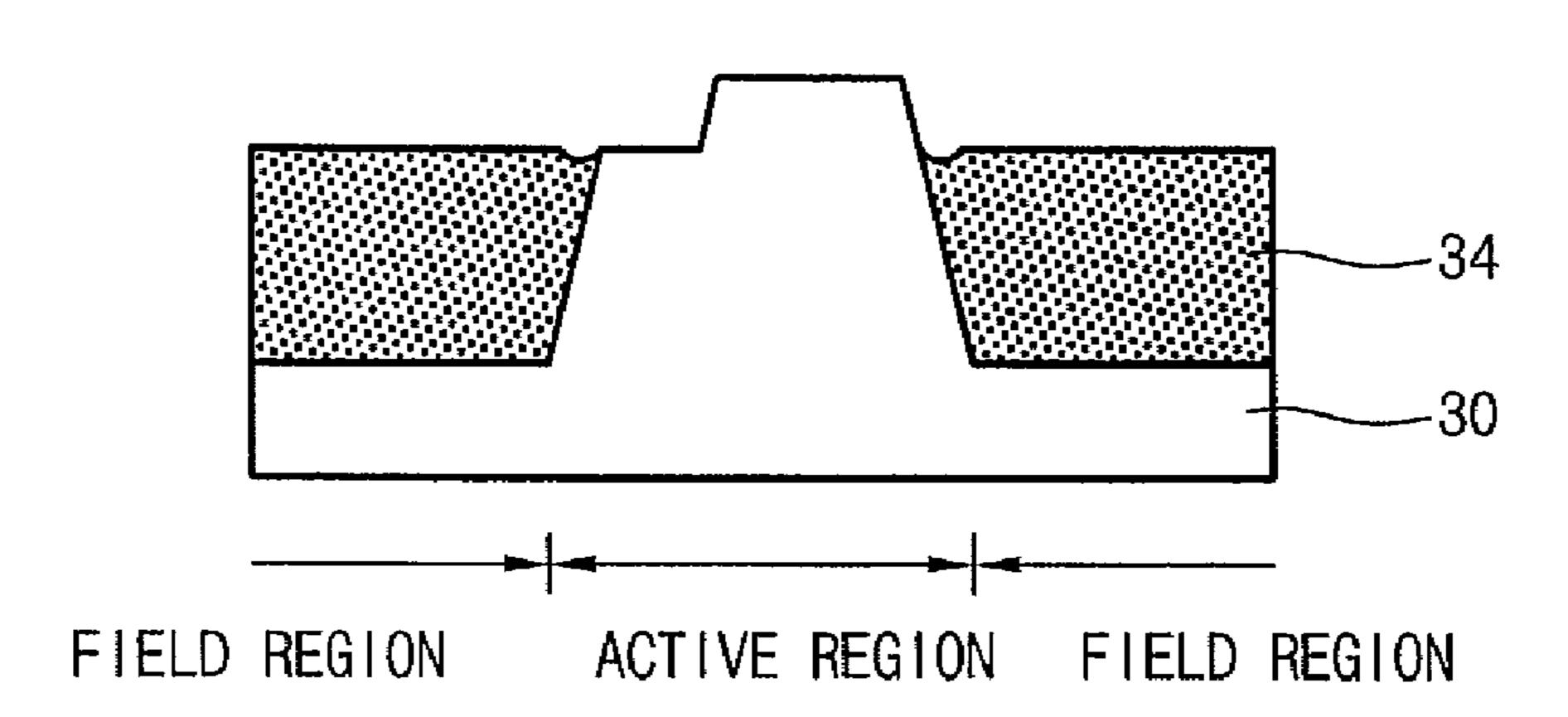

As shown in FIG. 2A, the pad oxide film 31 and the pad nitride film 32 are sequentially formed on the silicon substrate 30 having an active region and a field region. The pad oxide film 31 is formed to a thickness of about 50-100 Å, and the pad nitride film 32 is formed to a thickness of about 500-800 Å. Then, the pad nitride film 32 is partially etched so as to expose the field region, and the pad oxide film 31 and the silicon substrate 30 is etched using the remaining pad oxide film 32 as an etch barrier so as to form the trench 33 in the field region. The trench 33 is formed to a depth of 2,000-3,000 Å. Then, on the resulting substrate, the gap-fill oxide film 34 is formed to fill the trench 33.

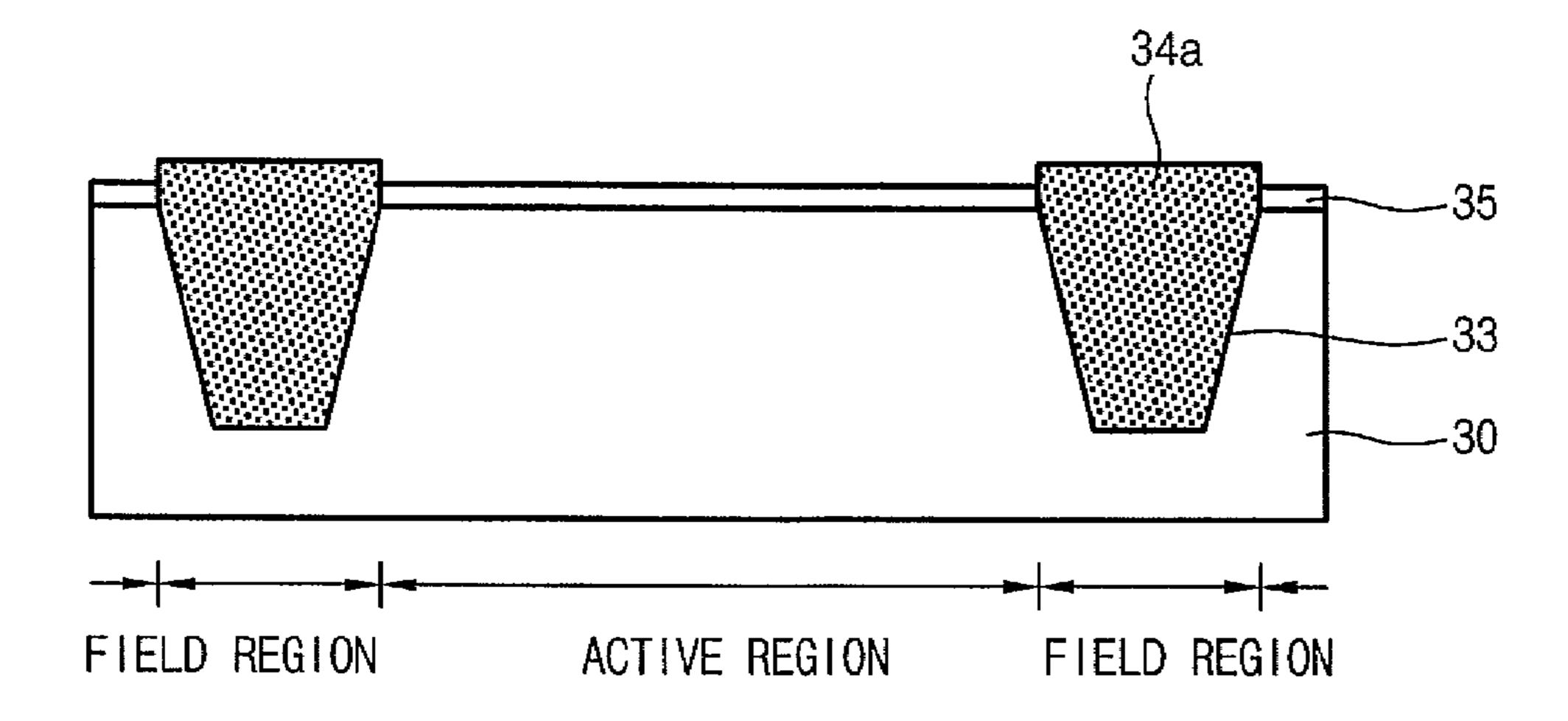

As shown in FIG. 2B, the gap-fill oxide film 34 is then subjected to chemical mechanical polishing (CMP) until the pad nitride film 32 is exposed.

As shown in FIG. 2C, the remaining pad nitride film 32 and pad oxide film 31 are then removed, thus forming the isolation film 34a. Then, the hard mask oxide film 35 is formed on the active region of the substrate 30. Alternatively, the remaining pad oxide film 31 may also be substituted for the hard mask oxide film 35 without removal.

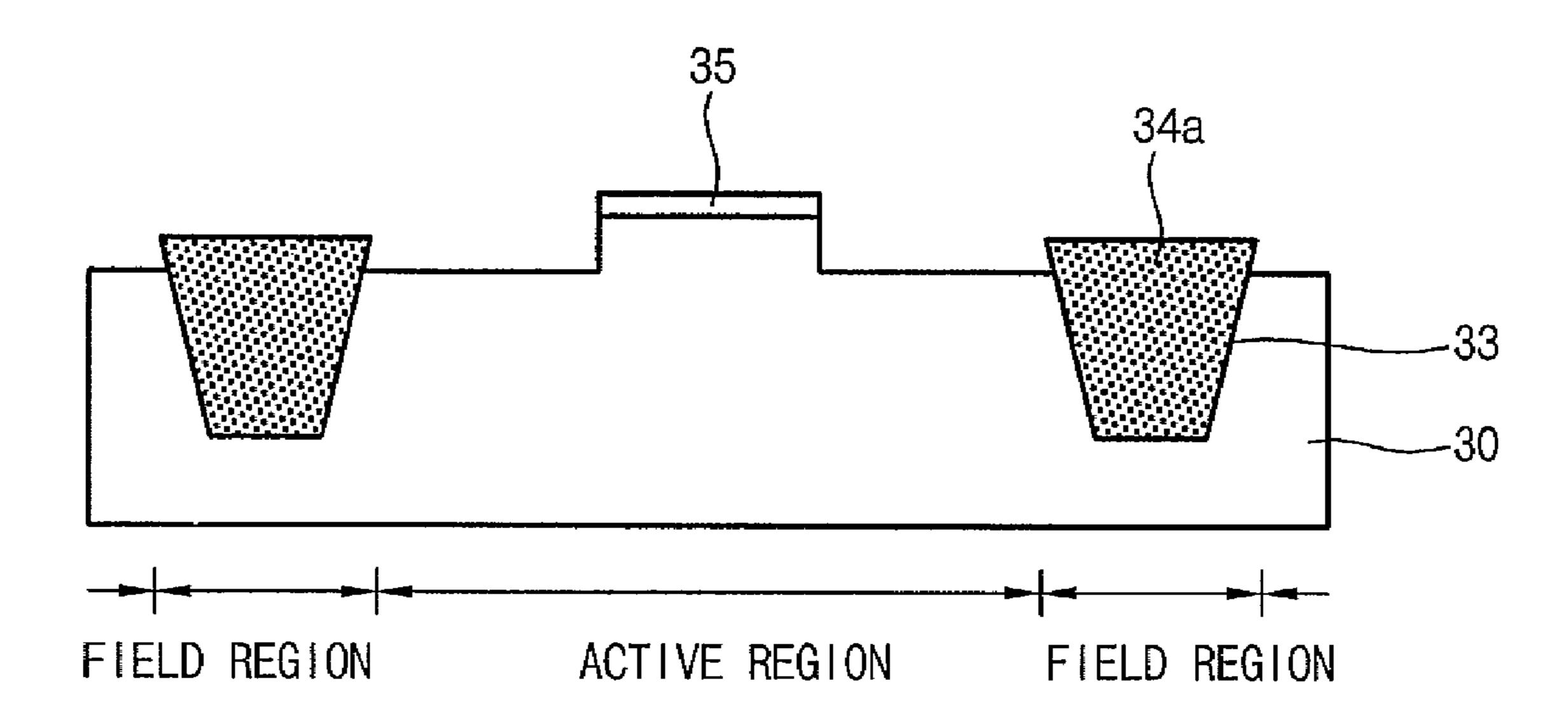

As shown in FIGS. 2D and 3, the hard mask oxide film 35 is then partially etched so as to expose both sides of the active region. Then, both exposed sides of the active region are etched using the remaining hard mask oxide film 35 as an etch barrier, thus forming a first recess and a first protrusion surrounded by the first recess and located at the central portion of the active region.

In this regard, FIG. 2D is a cross-sectional view taken along line I-II (channel length direction) in FIG. 3. The first recess of the active region of the substrate 30 is etched to a depth of 100-400 Å, and thus, the channel length of the device is increased.

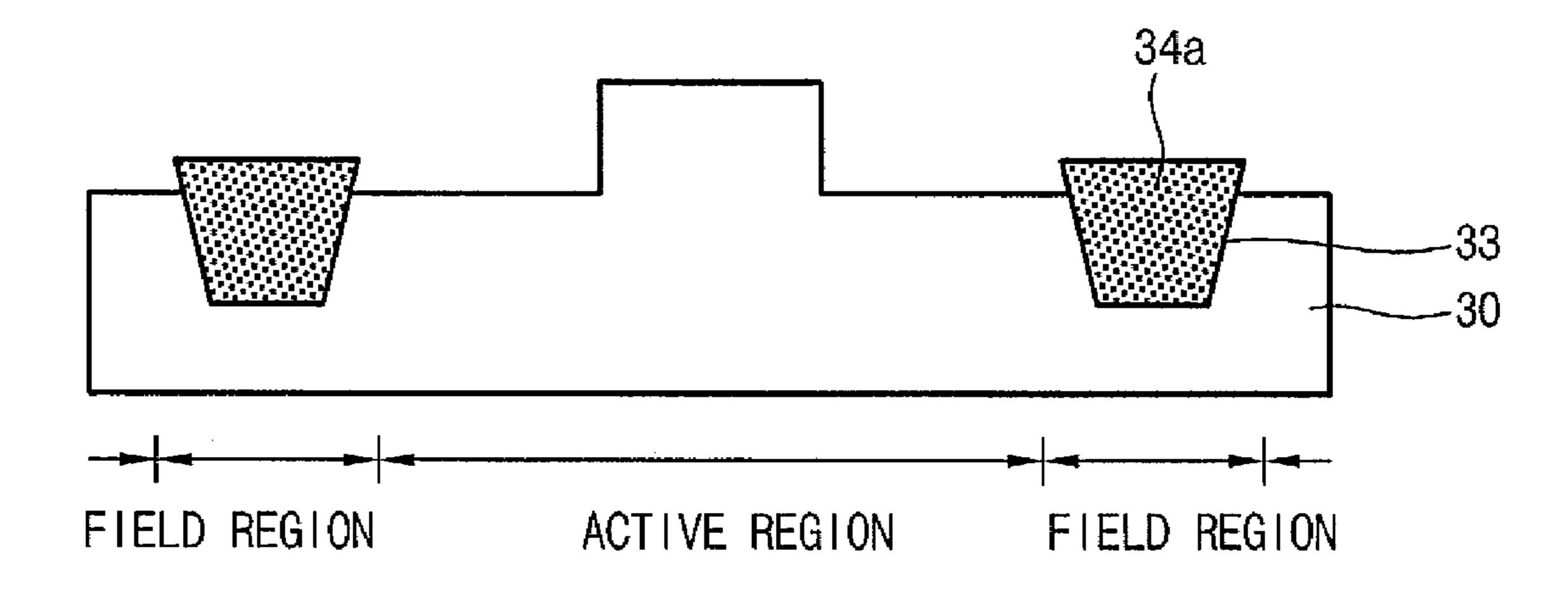

As shown in FIGS. 2E, 4 and 5, the remaining hard mask oxide film 35 is removed. Thereafter, the bottom of the first recess and either side of the first protrusion are selectively etched to form a second protrusion which extends over the central portion of the length of the channel and either side of the width of the channel.

In this regard, FIG. **2**E is a cross-sectional view taken along line III-IV (channel length direction) in FIG. **4**, and FIG. **5** is a cross-sectional view taken along line V-VI (channel width direction) in FIG. **4**. The second recess of the active region is formed to a depth of 100-400 Å, and thus, the channel length and width of the device are additionally increased.

Thereafter, although not shown in the drawings, a screen oxide film (not shown) is formed on the two-step-recessed active region of the substrate 30. Following this, a well ion implantation process and a channel ion implantation process into the substrate 30 are sequentially performed.

As shown in FIG. 2F, the gate oxide film 36 is then formed on the active region of the resulting substrate 30. The gate oxide film 36 is formed to a thickness of 30-50 Å. Then, the doped polycrystalline silicon film 37, the tungsten silicide film 38 and the gate hard mask film 39 are sequentially formed on the entire surface of the substrate 30 including the gate oxide film 36. The doped polycrystalline silicon film is formed to a thickness of 400-700 Å, the tungsten silicide film 38 is formed to a thickness of 1,000-1,500 Å, and the gate hard mask film 39 is formed to a thickness of 2,000-2,500 Å.

As shown in FIG. 2G, the gate hard mask film 39 is partially etched, leaving a gate pattern. Then, the tungsten silicide film 38 and the doped polycrystalline silicon film 37 are etched using the remaining gate hard mask film as an etch barrier,

5

thus forming the stepped gate 40 on the active region of the substrate 30. In this regard, the stepped gate 40 is located at a portion of the active region extending from each of both edges of the central protrusion to a portion of the second recess.

Thereafter, although not shown in the drawings, the silicon substrate 30 including the gate 40 is subjected to a thermal oxidation process in order to recover from damage caused by the etching process for forming the gate 40. Following this, a series of known subsequent processes are sequentially performed, thus completing the manufacturing of the inventive semiconductor device.

As described above, according to the present invention, the stepped gate 40 is formed in a state where the recessed area of the substrate 30 has been increased by the two-step-recess process as compared to that in the prior art. For this reason, the 15 stepped gate 40 can be prevented from leaning due to the thermal oxidation process conducted after the formation of the stepped gate 40, and the length of channel can be further increased, resulting in improvements in the refresh characteristics and operating speed of the device.

As can be seen from the foregoing, according to the present invention, a portion of the active region of the substrate is recessed so as to increase the channel length, and then, additionally recessed. Accordingly, the present invention can prevent the stepped gate from leaning and can improve the 25 refresh characteristics and operating speed of the device, thus contributing to an increase in the degree of integration of the device.

Although a preferred embodiment of the present invention has been described for illustrative purposes, those skilled in 30 the art will appreciate that various modifications, additions and substitutions are possible, without departing from the scope and spirit of the invention as disclosed in the accompanying claims.

What is claimed is:

1. A method of manufacturing a semiconductor device, the method comprising the steps of:

forming in a silicon substrate an isolation film defining an active region;

selectively etching each of both sides of the active region to form a first recess while leaving a first protrusion surrounded by the first recess and located at the central portion of the active region;

6

selectively etching the bottom of the first recess and either side of the first protrusion to form a second recess while leaving a second protrusion surrounded by the second recess; and

forming a gate on a portion of the active region extending from each of both edges of the second central protrusion to a portion of the second recess of the active region.

2. The method of claim 1, wherein the step of forming the isolation film comprises the sub-steps of:

sequentially forming a pad oxide film and a pad nitride film on the substrate;

etching the pad nitride film so as to expose the field region of the substrate;

etching the pad oxide film and the substrate using the remaining pad nitride film as an etch barrier so as to form a trench;

forming a gap-fill oxide film on the resulting substrate to fill the trench;

subjecting the gap-fill oxide film to chemical mechanical polishing until the pad nitride film is exposed; and

removing the remaining pad nitride film and pad oxide film.

- 3. The method of claim 2, wherein the trench is formed to a depth of 2,000-3,000 Å.

- 4. The method of claim 1, wherein the first recess is formed to a depth of 100-400 Å.

- 5. The method of claim 1, wherein the second recess of the active region is formed to a depth of 100-400 Å.

- 6. The method of claim 1, wherein the step of forming the gate comprises the sub-steps of:

forming a gate oxide film on the two-step-recessed active region of the substrate;

sequentially forming a doped polycrystalline silicon film, a tungsten silicide film and a gate hard mask film on the entire surface of the substrate including the gate oxide film;

etching the gate hard mask film so as to leave a gate pattern; and

etching the tungsten silicide film and the doped polycrystalline silicon film using the remaining gate hard mask film as an etch barrier.

\* \* \* \* \*