### US007473999B2

# (12) United States Patent

Lin et al.

(10) Patent No.: US 7,473,999 B2 (45) Date of Patent: Jan. 6, 2009

# (54) SEMICONDUCTOR CHIP AND PROCESS FOR FORMING THE SAME

(75) Inventors: **Mou-Shiung Lin**, Hsin-Chu (TW); **Chien-Kang Chou**, Tainan Hsien (TW); **Hsin-Jung Lo**, Taipei County (TW)

(73) Assignee: MEGICA Corporation, Hsinchu (TW)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 163 days.

(21) Appl. No.: 11/534,672

(22) Filed: Sep. 24, 2006

(65) Prior Publication Data

US 2007/0069347 A1 Mar. 29, 2007

(30) Foreign Application Priority Data

(51) Int. Cl. H01L 21/44 (2006.01)

# (56) References Cited

### U.S. PATENT DOCUMENTS

| 2005/0250255 A | A1* | 11/2005 | Chen 438/127      |

|----------------|-----|---------|-------------------|

| 2005/0101116 A | A1* | 5/2006  | Tseng 438/622     |

| 2007/0246834   | A1* | 10/2007 | Lin et al         |

| 2008/0012132   | A1* | 1/2008  | Lin 257/738       |

| 2008/0045007   | A1* | 2/2008  | Lin et al 438/644 |

\* cited by examiner

Primary Examiner—Michael S Lebentritt (74) Attorney, Agent, or Firm—Winston Hsu

# (57) ABSTRACT

A semiconductor chip comprises a first MOS device, a second MOS device, a first metallization structure connected to said first MOS device, a second metallization structure connected to said second MOS device, a passivation layer over said first and second MOS devices and over said first and second metallization structures, and a third metallization structure connecting said first and second metallization structures.

### 20 Claims, 36 Drawing Sheets

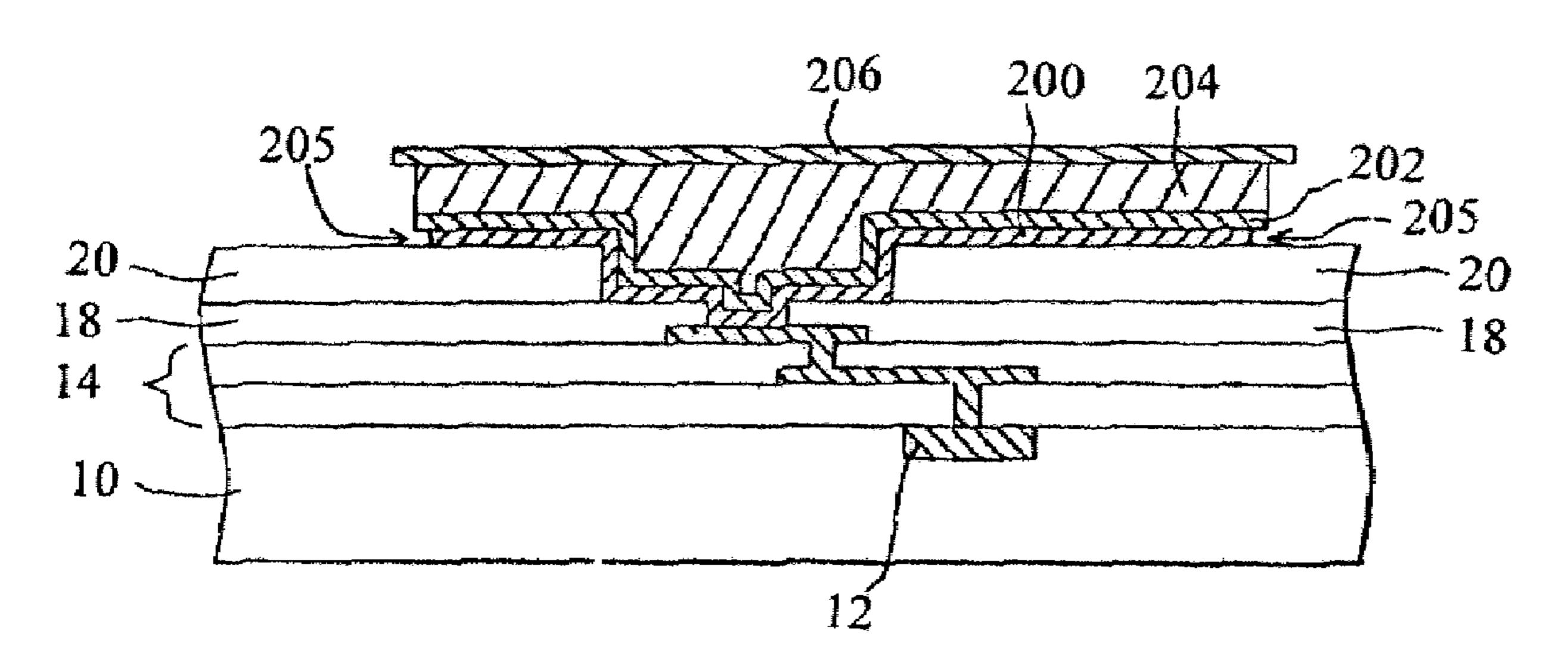

FIG 1a

202 200 18 14 10 FIG 2b

FIG 2e

FIG 2f

FIG 2g

FIG 2h

FIG 2i

FIG 2j

FIG 2k

FIG 21

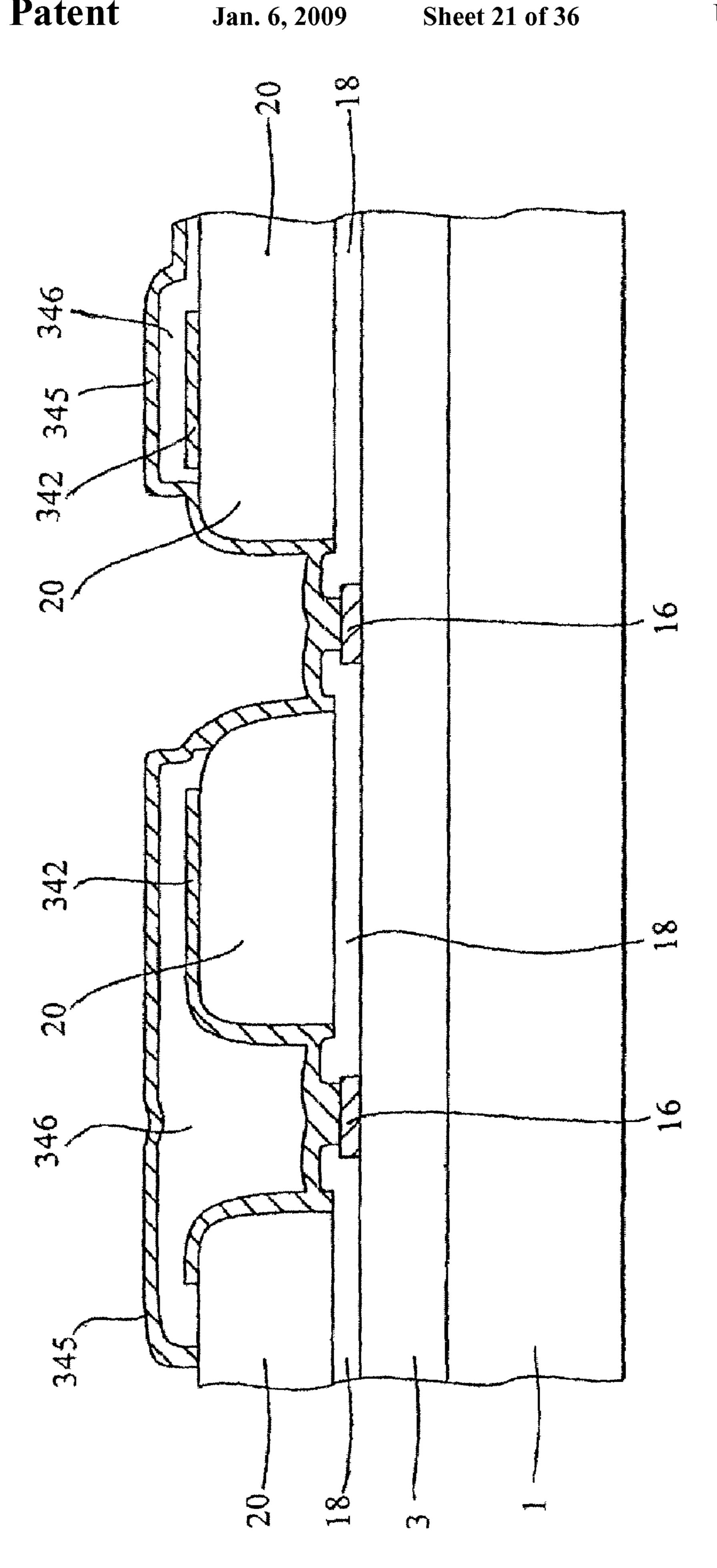

FIG 3d

FIG 4a

FIG 4b

FIG 5a

FIG 5b

FIG 6a

FIG 6b

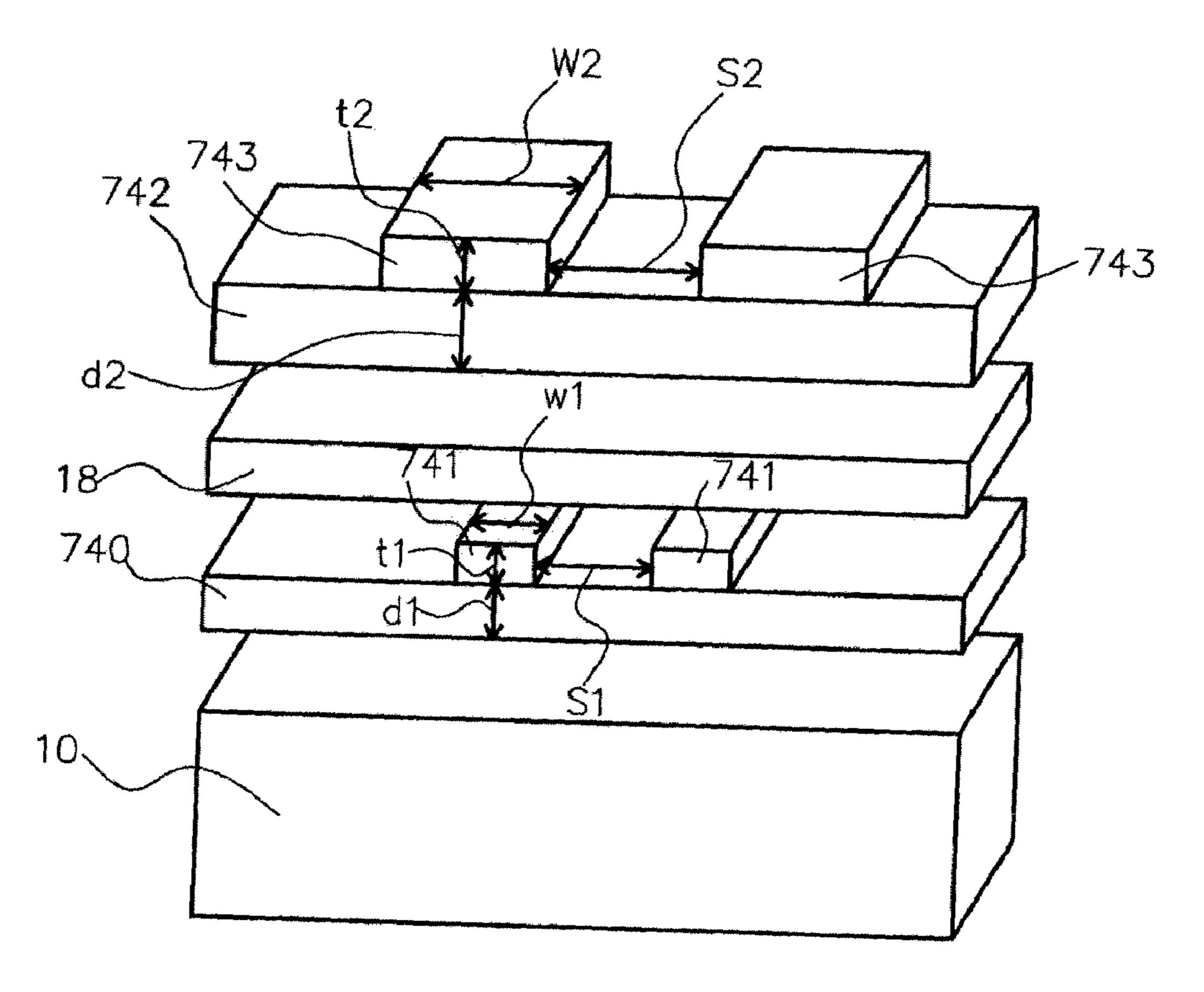

FIG 7a

FIG 7b

Jan. 6, 2009

FIG 8a

FIG 8b

FIG 9b

FIG 9c

FIG 9d

FIG 10a

FIG 10b

FIG 11a

FIG 11b

FIG 11c

Jan. 6, 2009

FIG 13b

FIG 13c

FIG 14a

FIG 14b

FIG 14c

FIG 14e

FIG 14g

FIG 14h

FIG 15b

FIG 15c

FIG 15d

Jan. 6, 2009

FIG 16

FIG 17

Table 1 PPT RC Constant

| Metal        |           |                      | Dielectric        |                  | R(Ohm/mm) | C (pF/mm) | C (pF/mm) | RC (ps/mm) | RC (ps/mm) |

|--------------|-----------|----------------------|-------------------|------------------|-----------|-----------|-----------|------------|------------|

| Width(µm) W2 | Space(µm) | Thickness ( $\mu$ m) | PI Thickness (μm) | BCB<br>Thickness |           | with PI   | with BCB  | with PI    | with BCB   |

|              |           |                      |                   |                  |           |           |           |            |            |

|              |           |                      |                   | d2               |           |           |           |            |            |

| 3            | 3         | 3                    | 3                 | 3                | 2.00      | 1.00      | 0.76      | 2.0000     | 1.5152     |

| 5            | 5         | 5                    | 5                 | 5                | 0.72      | 1.00      | 0.76      | 0.7200     | 0.5455     |

| 10           | 10        | 5                    | 5                 | <b>5</b> .       | 0.36      | 1.00      | 0.76      | 0.3600     | 0.2727     |

| 20           | 10        | 5                    | 5                 | 5                | 0.18      | 2.00      | 1.52      | 0.3600     | 0.2727     |

| 20           | 20        | 5                    | 5                 | 5                | 0.18      | 1.00      | 0.76      | 0.1800     | 0.1364     |

| 10           | 10        | 5                    | 10                | 10               | 0.36      | 0.50      | 0.38      | 0.1800     | 0.1364     |

| 10           | 10        | 10                   | 10                | 10               | 0.18      | 1.00      | 0.76      | 0.1800     | 0.1364     |

| 20           | 10        | 10                   | 10                | 10               | 0.09      | 2.00      | 1.52      | 0.1800     | 0.1364     |

| 20           | 20        | 10                   | 10                | 10               | 0.09      | 1,00      | 0.76      | 0.0900     | 0.0682     |

| 20           | 10        | 20                   | 20                | 20               | 0.05      | 2.00      | 1.52      | 0.0900     | 0.0682     |

| 20           | 20        | 20                   | 20                | 20               | 0.05      | 1.00      | 0.76      | 0.0450     | 0.0341     |

| 20           | 20        | 10                   | 30                | 30               | 0.09      | 0.33      | 0.25      | 0.0300     | 0.0227     |

| 40           | 40        | 20                   | 20                | 20               | 0.02      | 1.00      | 0.76      | 0.0225     | 0.0170     |

| 40           | 40        | 10                   | 30                | 30               | 0.05      | 0.33      | 0.25      | 0.0150     | 0.0114     |

| 50           | 50        | 10                   | 30                | 30               | 0.04      | 0.33      | 0.25      | 0.0120     | 0.0091     |

| 50           | 50        | 10                   | 30                | 30               | 0.04      | 0.33      | 0.25      | 0.0120     | 0.0091     |

| 60           | 60        | 10                   | 30                | 30               | 0.03      | 0.33      | 0.25      | 0.0100     | 0.0076     |

| 50           | 50        | 10                   | 60                | 60               | 0.04      | 0.17      | 0.13      | 0.0060     | 0.0045     |

| 60           | 120       | 10                   | 30                | 30               | 0.03      | 0.17      | 0.13      | 0.0050     | 0.0038     |

| 60           | 60        | 10                   | 60                | 60               | 0:03      | 0.17      | 0.13      | 0.0050     | 0.0038     |

# SEMICONDUCTOR CHIP AND PROCESS FOR FORMING THE SAME

The present application claims priority benefit of Taiwan Application Serial No. 94,133,248, filed Sep. 23, 2005.

## BACKGROUND OF THE INVENTION

## 1. Field of the Invention

The invention relates in general to a chip structure and a process for forming the same. More particularly, the invention relates to the process with simplified steps and its corresponding chip structure.

## 2. Description of the Related Art

The way to improve the performance of a semiconductor device is usually to reduce the geometric dimensions of the Integrated Circuits. It results in the reduction in the cost per die and the improvement of performance. A metal connection between Integrated Circuits and other circuits or between Integrated Circuits and system components is becoming relatively important and has an increasingly negative impact on the circuit performance, while Integrated Circuits are more miniaturized.

The increase of the parasitic capacitance and resistance 25 induced by the metal interconnections increase degrades the chip performance significantly. Of most concerns are the voltage drop along power and ground buses and the RC delay of critical signal paths. Attempts to reduce the resistance by using wider metal lines result in higher parasitic capacitance induced by these wider metal lines. To solve this problem, a metal of low resistance, such as copper, is introduced as the conducting wires and a dielectric material with low dielectric constant (k) is used between the signal lines. According to the historical point of view of the metallization structure for IC, since 60s the sputtered aluminum dominated as the material for connecting metal. An aluminum thin-film layer is formed to cover the whole chip by using a sputtering process and then patterned by a photolithography process and a dry or wet formed by a sputtering process, the technique for forming an aluminum circuit with a thickness of more than 2 microns is very difficult and expensive.

In about 1995, a damascene copper became another material for connecting metal in IC. According to the damascene copper process, after patterning an insulating layer, a copper layer is formed by an electroplating process inside the opening in the insulating layer and on the insulating layer. Then, the copper layer outside the opening in the insulating layer is removed by using a Chemical Mechanical Polishing/Planarization (CMP). As a result, the copper trace can be formed inside the opening in the insulating layer.

However, the thick metal layer electroplated onto the whole chip has a relatively large inner stress and the thickness of the damascene copper layer depends on the thickness of the insulating layer made of, for example, a Chemical-Vapor-Deposition (CVD) oxide. Because of the concern about the inner stress and the cost, the damascene copper process can not form a thicker copper trace. In other words, it is difficult in aspect of technology and expensive in cost to form a copper wire that is thicker than 2 microns.

Nakanishi (U.S. Pat. No. 5,212,403) discloses a method of forming wiring connections both inside and outside in a wiring substrate, especially a logic design varying with the length of the wiring connections.

Gehman, Jr. et al. (U.S. Pat. No. 5,501,006) shows a structure with an insulating layer between integrated circuits (IC)

2

and a wiring substrate. A distribution lead connects the bonding pads of the IC to the bonding pads of a circuit board.

Jacobs (U.S. Pat. No. 5,055,907) discloses an integrated semiconductor structure allowing manufacturers to integrate circuitry beyond a chip by forming multiple thin-film wiring layers over a support substrate and over the chip.

Volfson et al. (U.S. Pat. No. 5,106,461) teaches a multilayer interconnect structure with alternating an insulating layers of polyimide, formed over a chip, and with a TAB structure.

Wenzel et al. (U.S. Pat. No. 5,635,767) teaches a method for reducing RC delay by a PBGA with multiple separate metal layers.

Fulcher (U.S. Pat. No. 5,686,764) shows a flip-chip substrate that reduces RC delay by separating the power traces from I/O traces.

In the book of "Silicon Processing for the VLSI Era" (Vol. 2, pp. 214-217, Lattice Press, Sunset Beach, Calif. c. 1990), written by Stanley Wolf, it is discussed that polyimide is used as an insulating layer between metals in 80s. However, due to some disadvantages in polyimide, polyimide has not been used for that purpose.

#### SUMMARY OF THE INVENTION

The main objective of the invention is to provide a thick metal layer over a passivation on layer of a semiconductor chip.

In accordance with the above objectives, the invention provides a semiconductor chip comprising a first MOS device, a second MOS device, a first metallization structure connected to said first MOS device, a second metallization structure connected to said second MOS device, a passivation layer over said first and second MOS devices and over said first and second metallization structures, and a third metallization structure connecting said first and second metallization structures.

In accordance with the above objectives, the invention provides a semiconductor chip comprising a first circuit, a etching process. Due to the cost and the thin-film stress formed by a sputtering process, the technique for forming an aluminum circuit with a thickness of more than 2 microns is very difficult and expensive.

In about 1995, a damascene copper became another material for connecting metal in IC. According to the damascene copper process, after patterning an insulating layer, a copper layer is formed by an electroplating process inside the open-

## BRIEF DESCRIPTION OF THE DRAWINGS

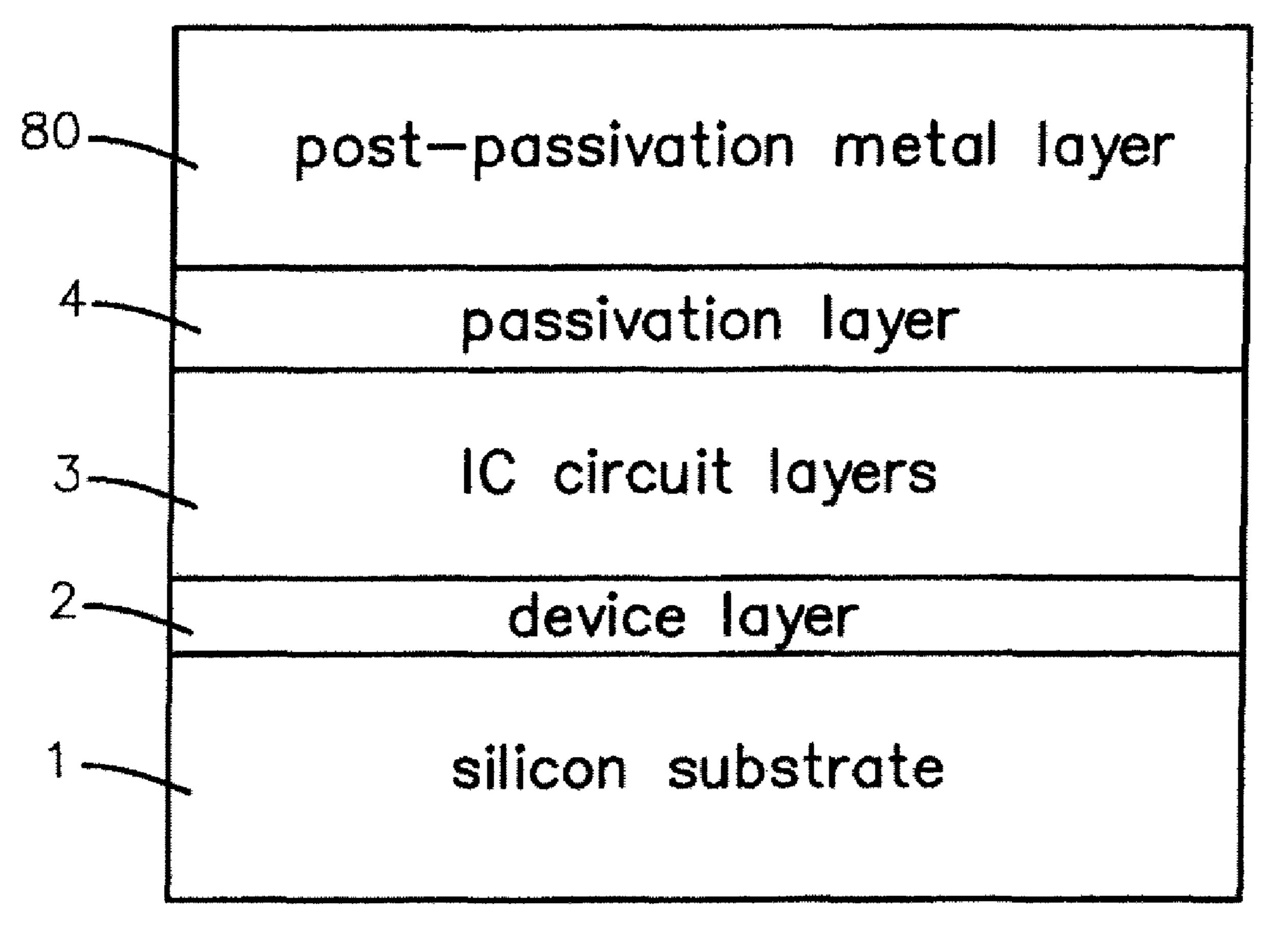

FIG. 1a shows a simplified cross-sectional view of a semiconductor chip according to the present invention.

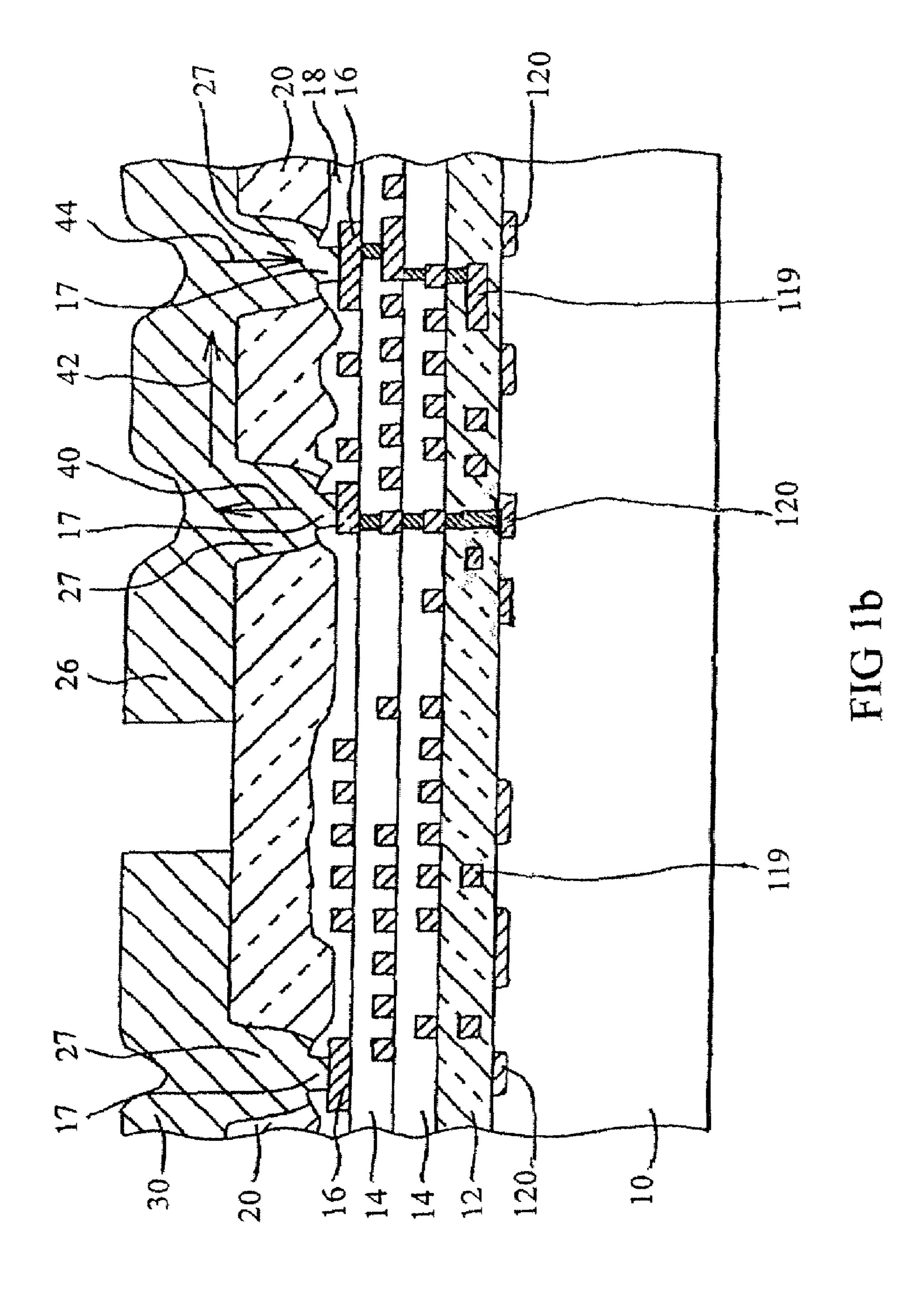

FIG. 1b is a schematically cross-sectional view of a semiconductor chip in an embodiment of the present invention.

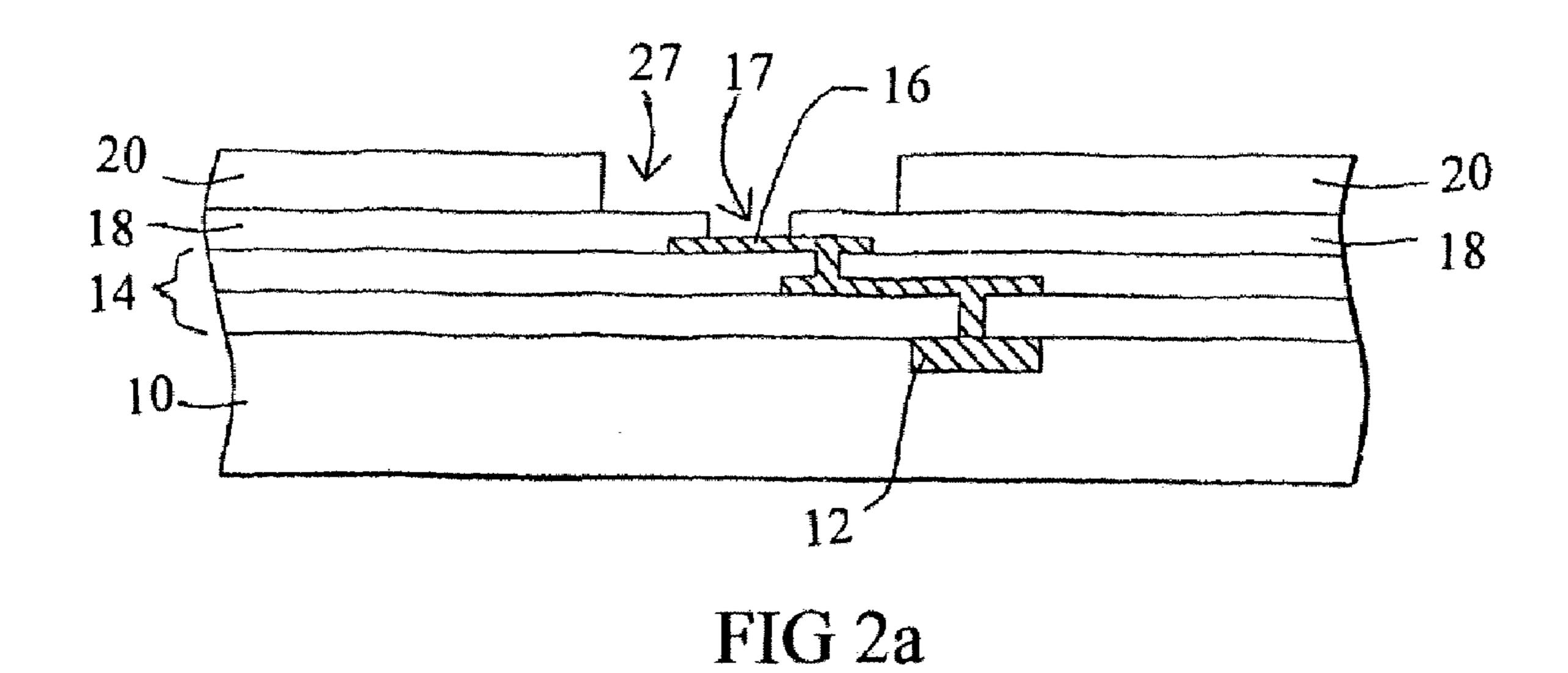

FIGS. 2*a*-2*m* are schematically cross-sectional views of various processes for fabricating a thick circuit layer over a passivation layer

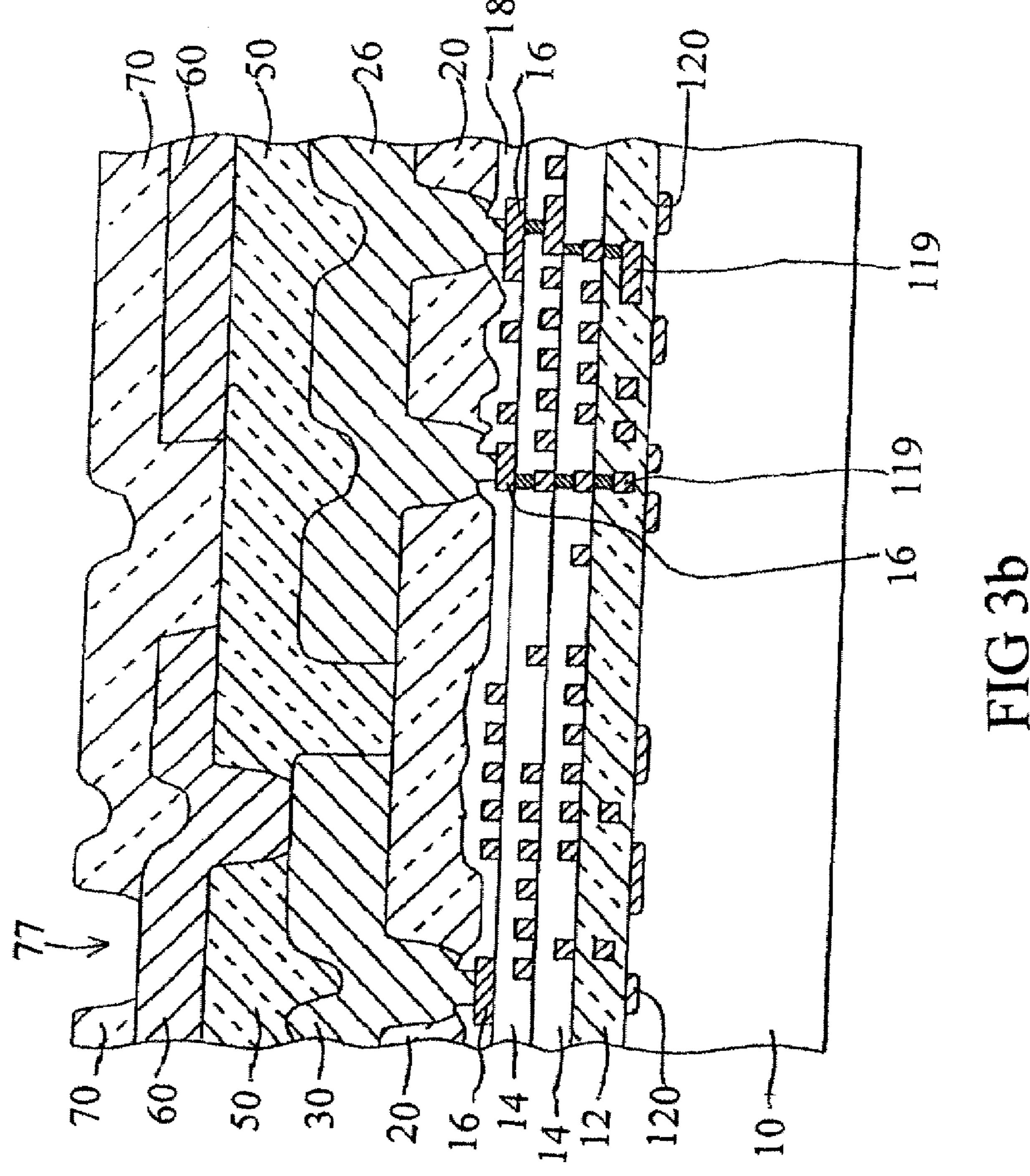

FIGS. 3a and 3b are schematically cross-sectional views of a semiconductor chip having multiple thick circuit layers over a passivation layer.

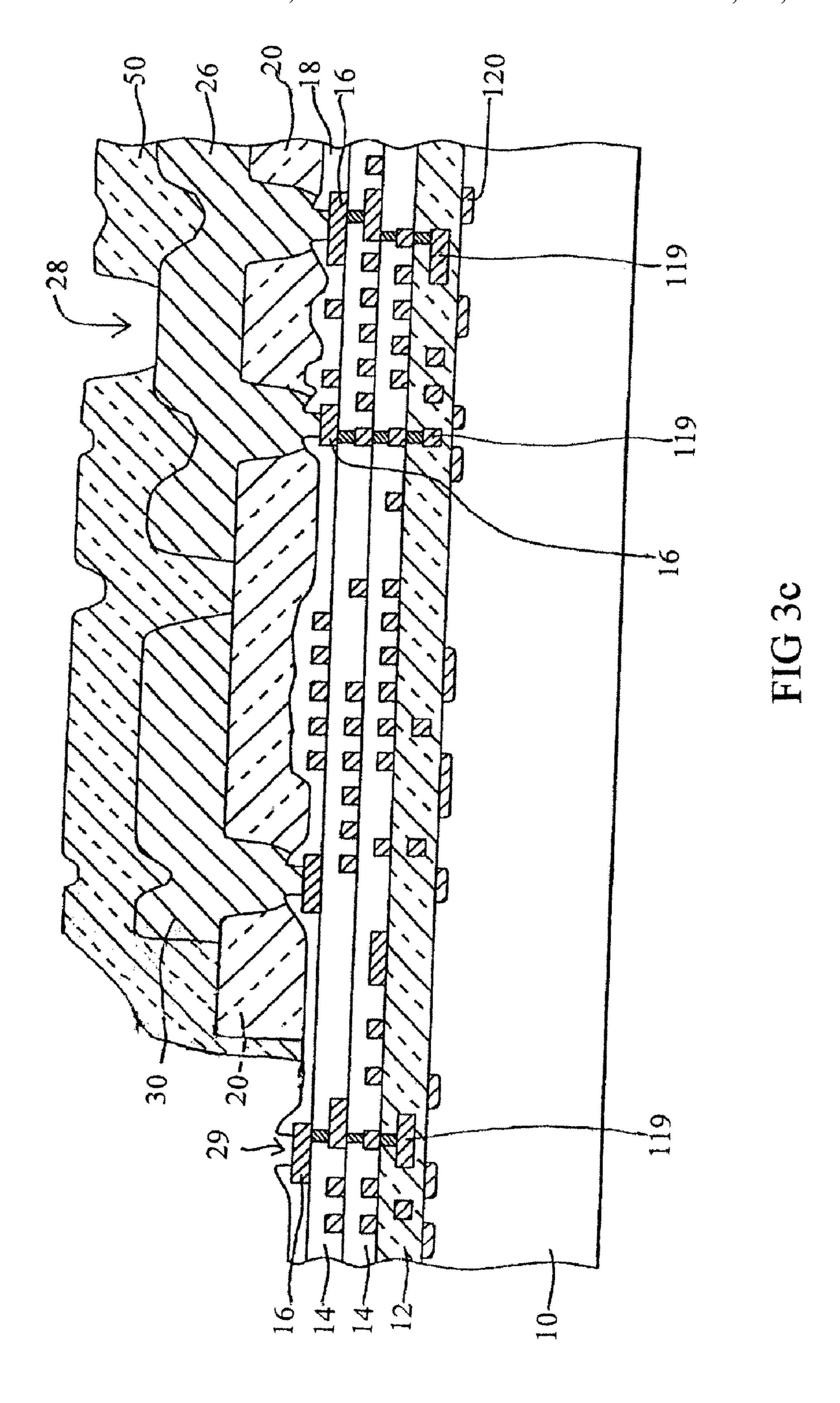

FIG. 3c is a schematically cross-sectional view showing a semiconductor chip having an exposed pad used to be wire-bonded thereto or to have a gold bump or solder bump formed thereon being connected to a thick circuit layer over a passivation layer through a trace under the passivation layer.

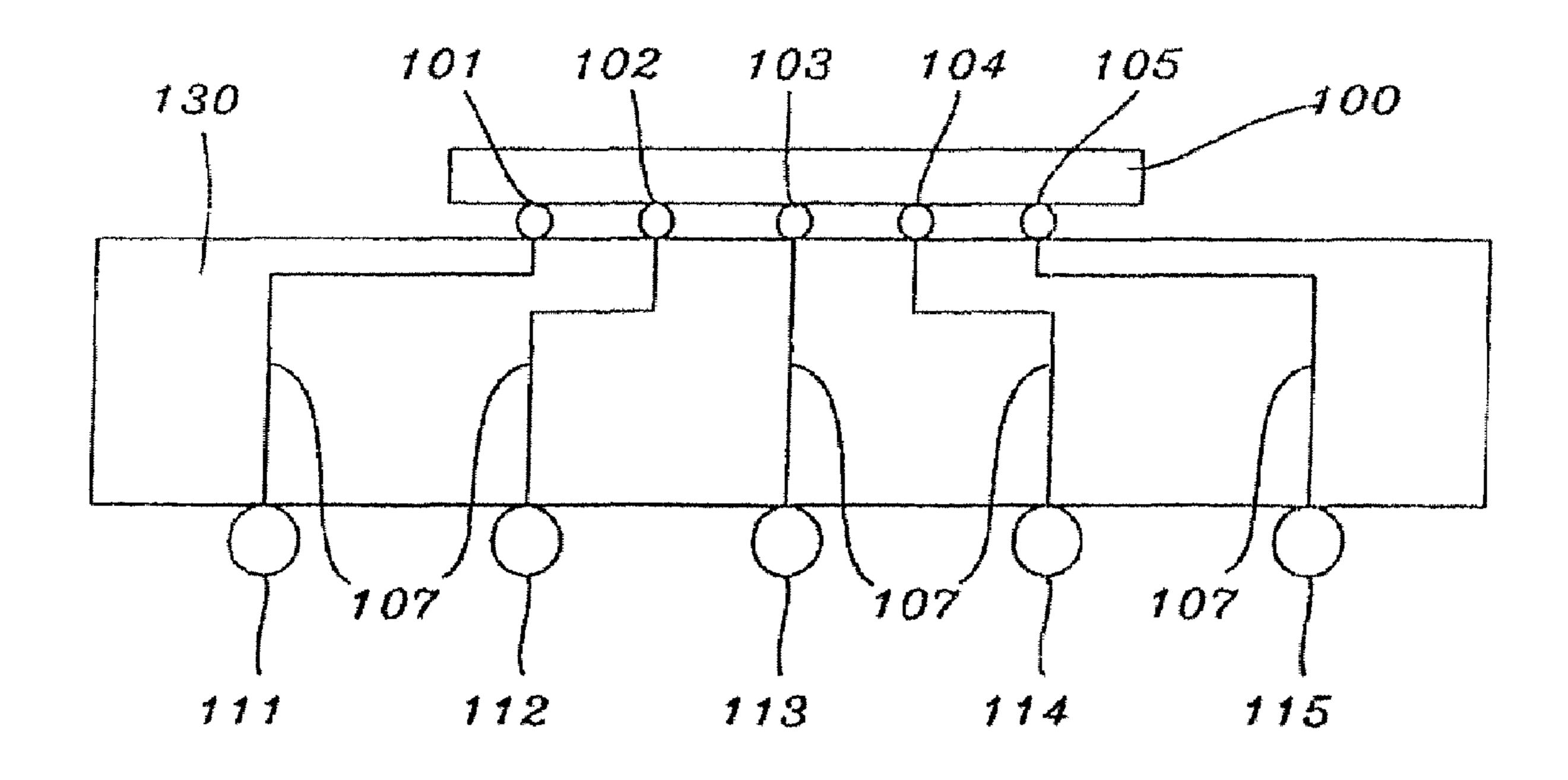

FIG. 4a shows the concept of fanning out a BGA substrate employed in a flip chip package.

FIG. 4b shows that the thick metal line has the function of fanning out bond pads.

FIG. 5a shows the concept of relocating input/output contact points applied for the connection with a BGA substrate in a flip chip package.

FIG. 5b shows that the above-mentioned thick metal lines have the function of relocating input/output positions and sequence.

FIG. 6a shows the concept of reducing the total number of the input/output count applied for the connection with a BGA 10 substrate in a flip chip package.

FIG. 6b shows that the thick metal lines have the function of reducing the total number of the input/output count.

FIG. 7a shows the concept of enhancing the Input/Output contact points applied to the connection with a BGA substrate 15 in a flip chip package.

FIG. 7b shows that the thick metal lines have the function of enhancing the total number of the input/output count for a semiconductor chip.

FIGS. 8a and 8b are schematically cross-sectional views 20 showing a semiconductor chip having an inductor over a passivation layer.

FIGS. 9a-9d are schematically cross-sectional views showing a semiconductor chip having a transformer over a passivation layer.

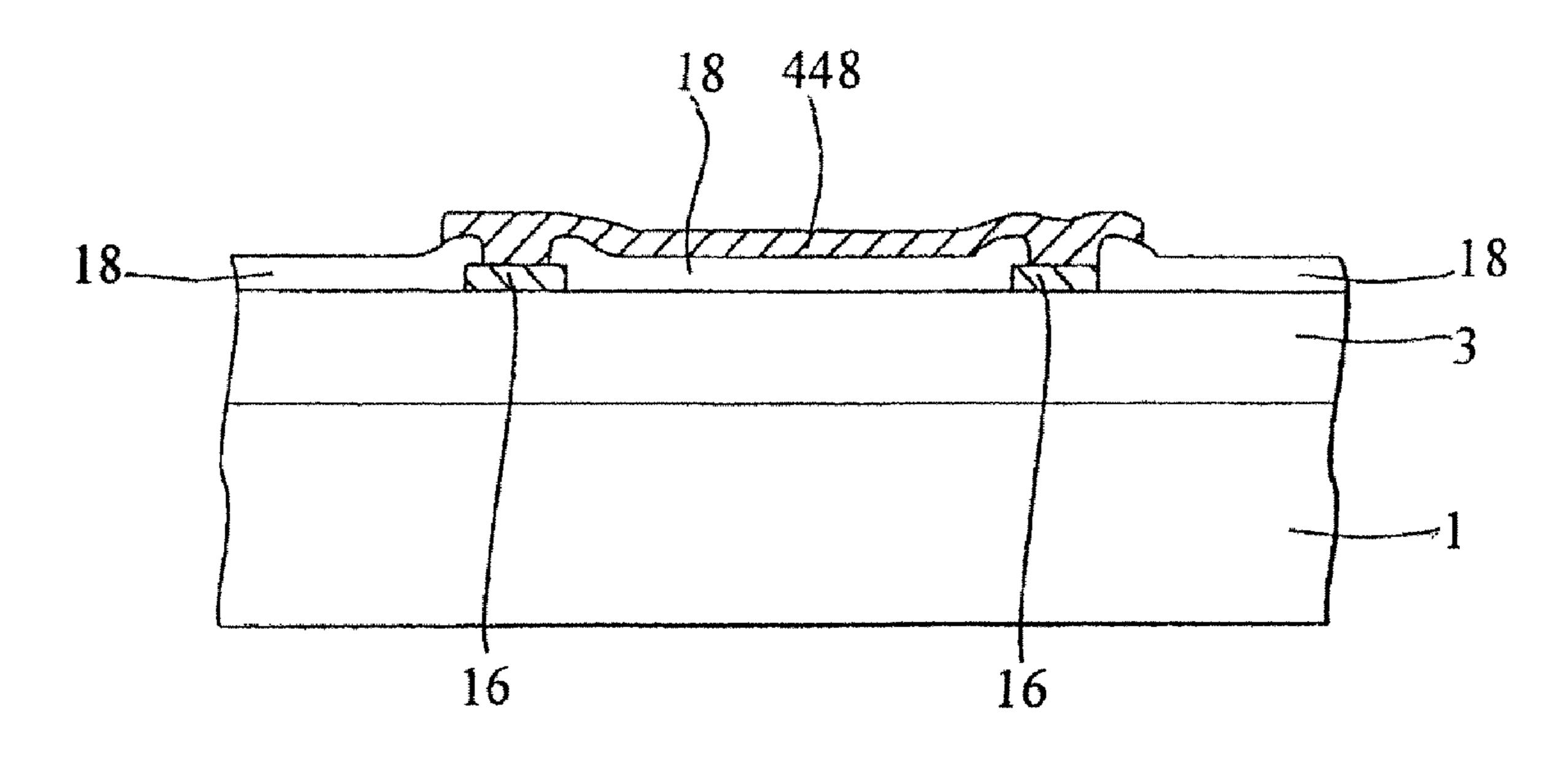

FIGS. 10*a*-10*c* are schematically cross-sectional views showing a semiconductor chip having a capacitor over a passivation layer.

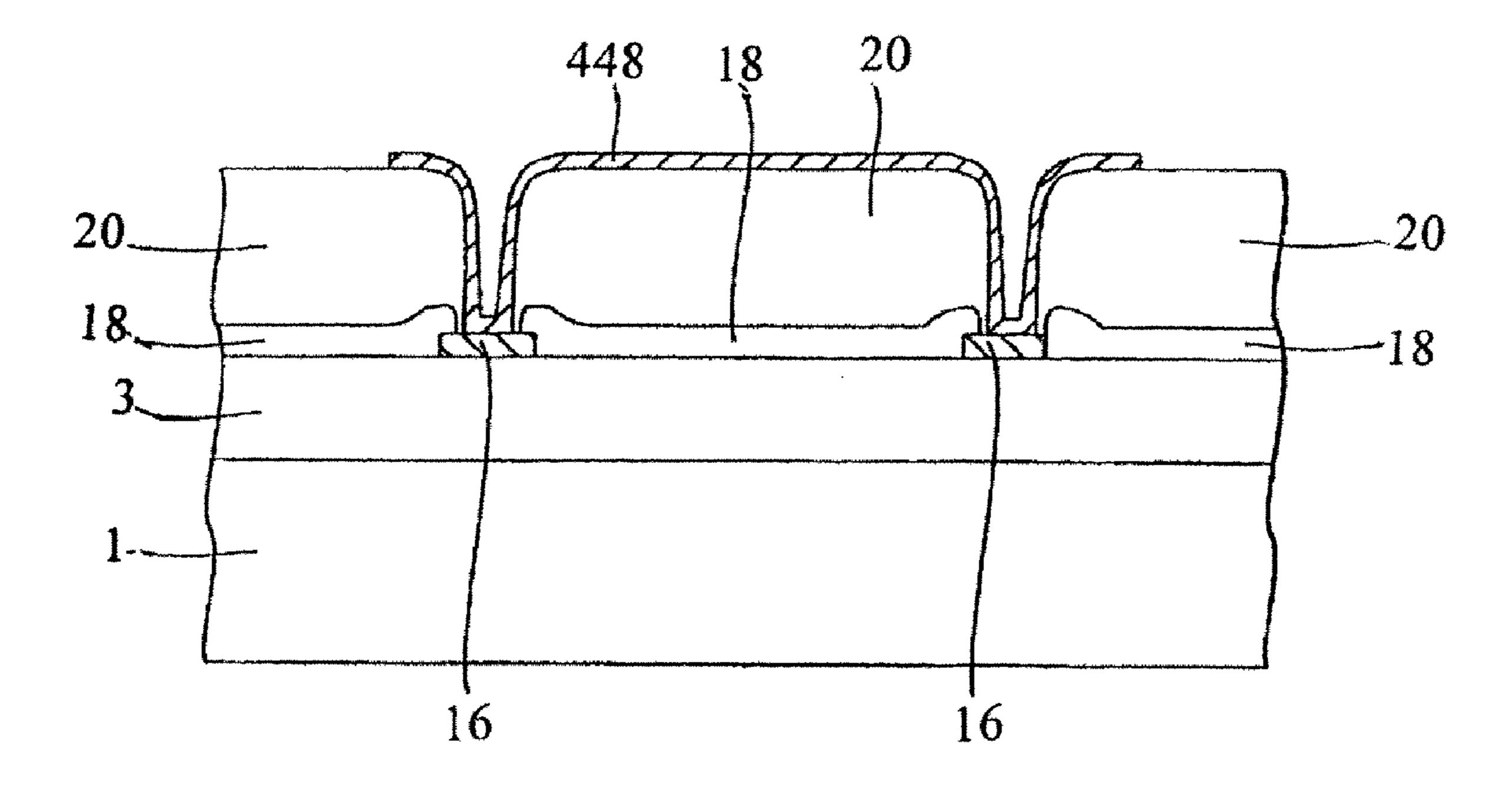

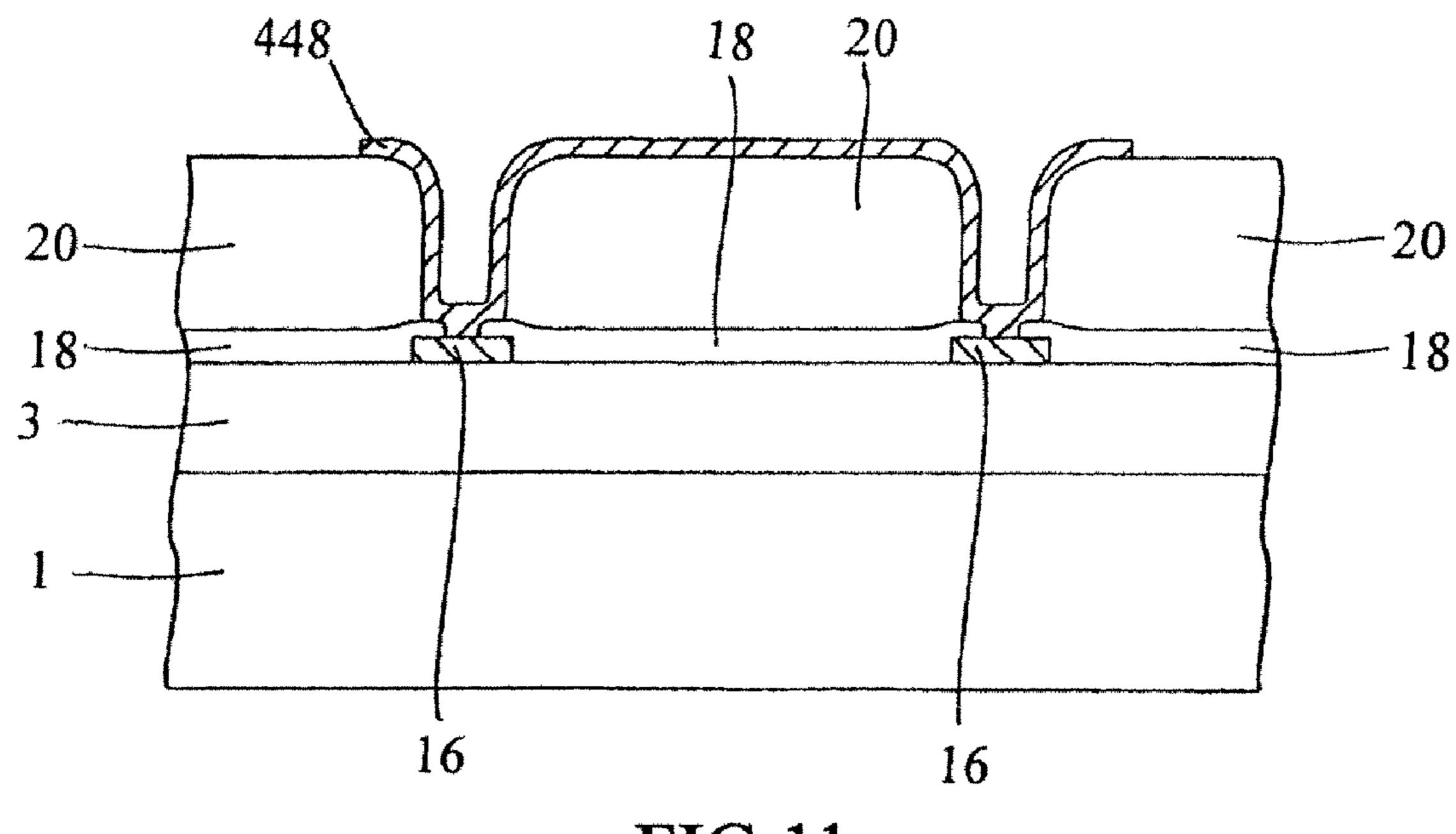

FIGS. 11*a*-11*c* are schematically cross-sectional views showing a semiconductor chip having a resistor over a passi- 30 vation layer.

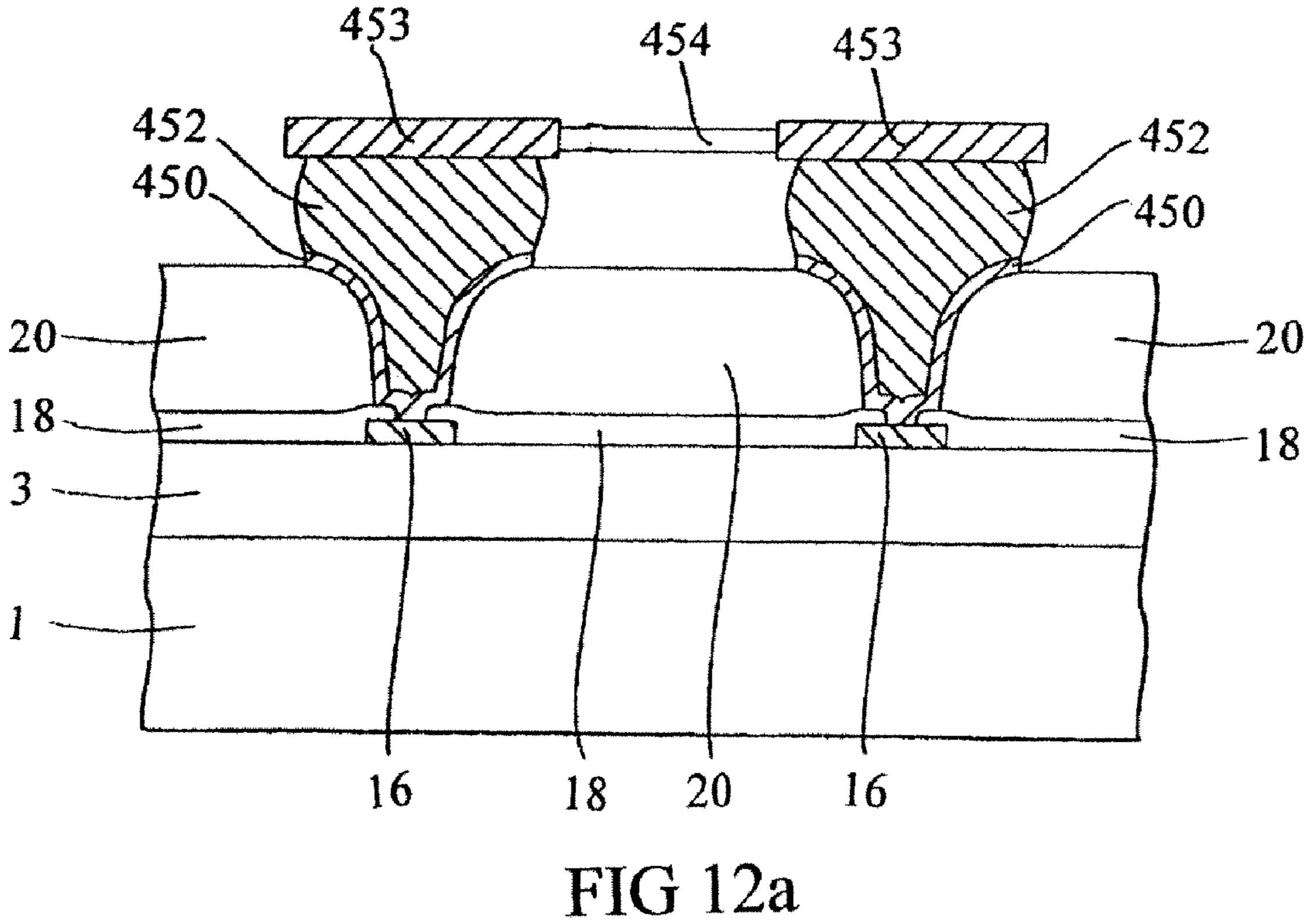

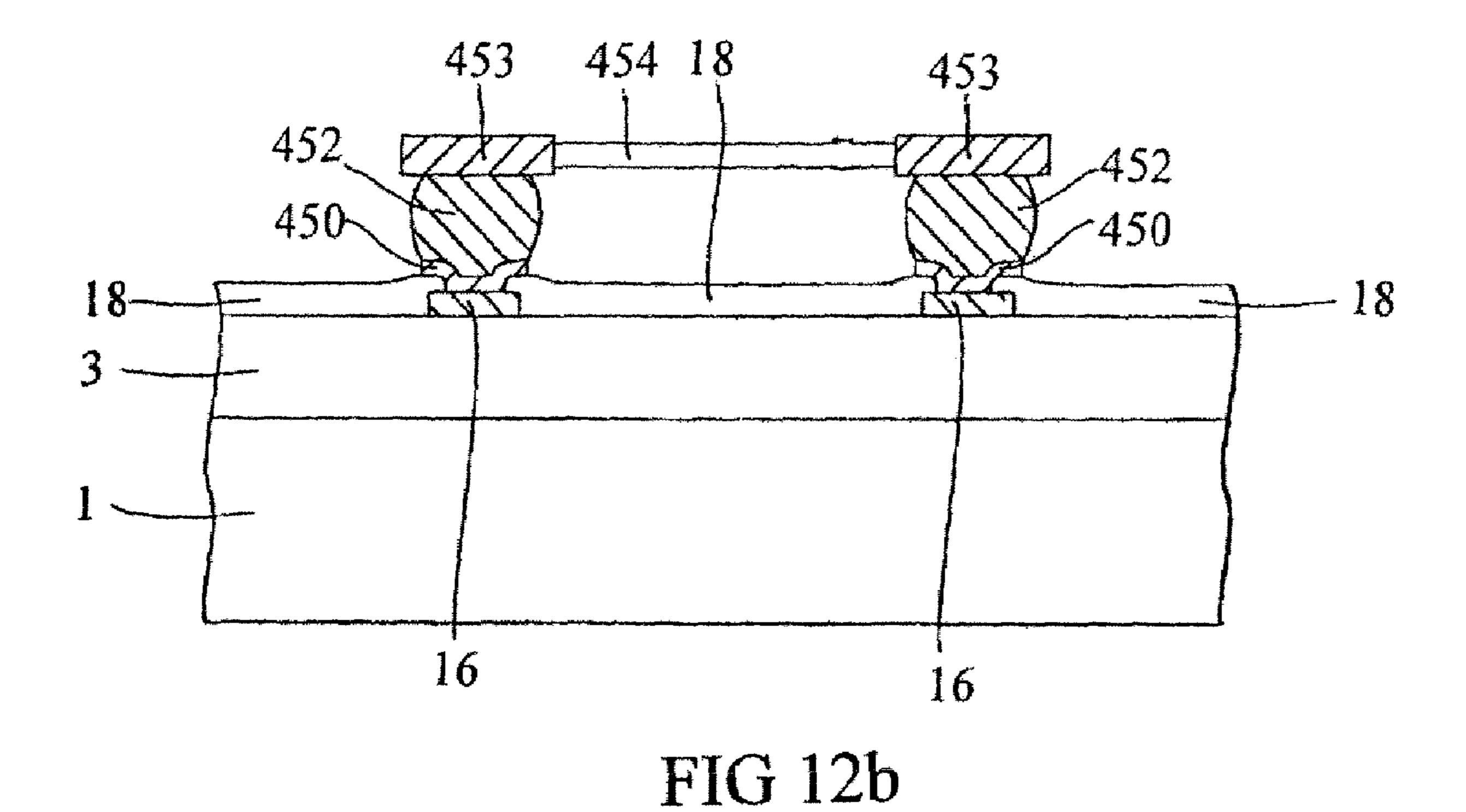

FIG. 12a is a schematically cross-sectional view showing a semiconductor chip having a discrete passive device over a passivation layer.

FIG. 12b is a schematically cross-sectional view showing a 35 semiconductor chip having a discrete passive device over a passivation layer.

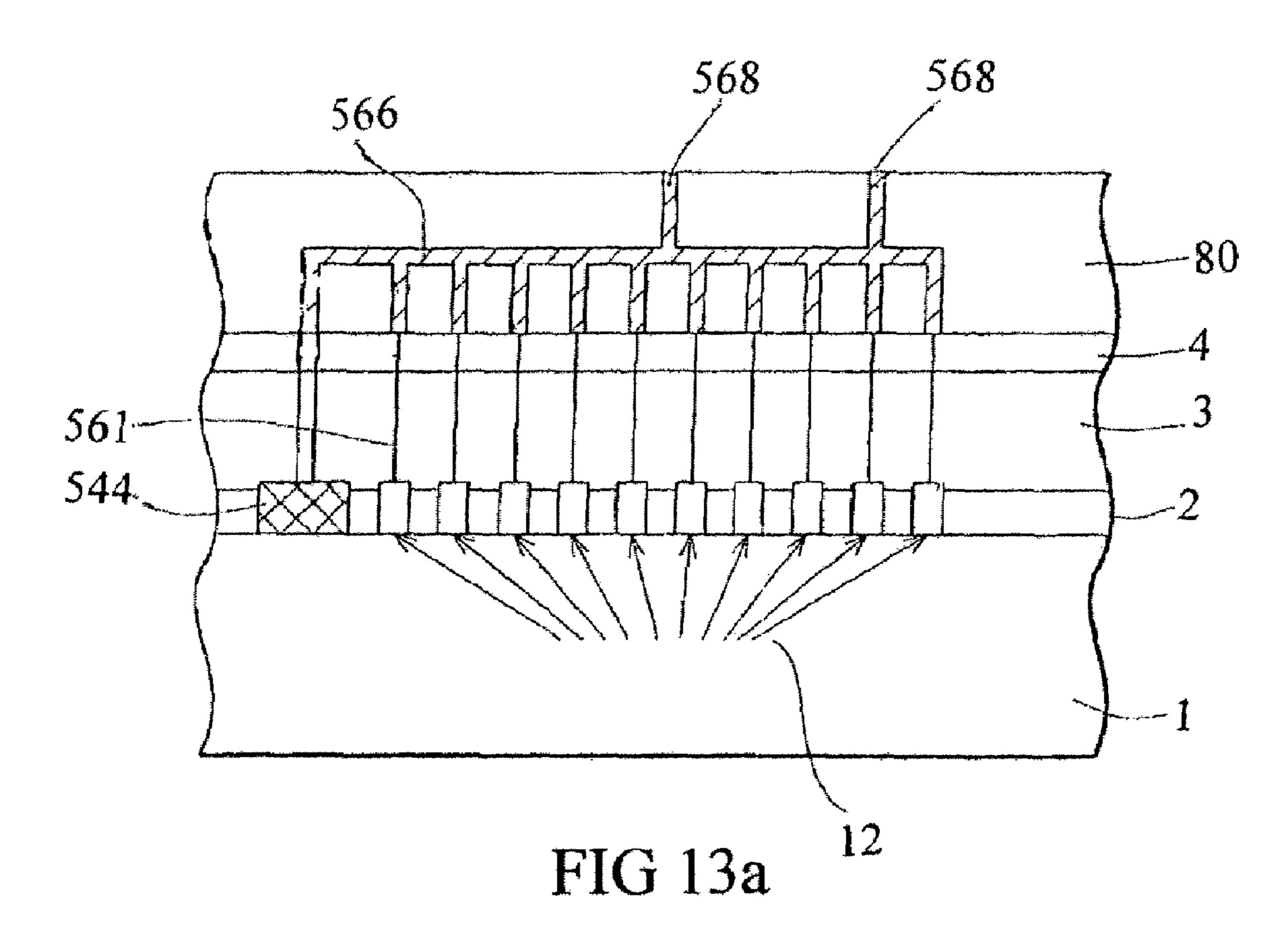

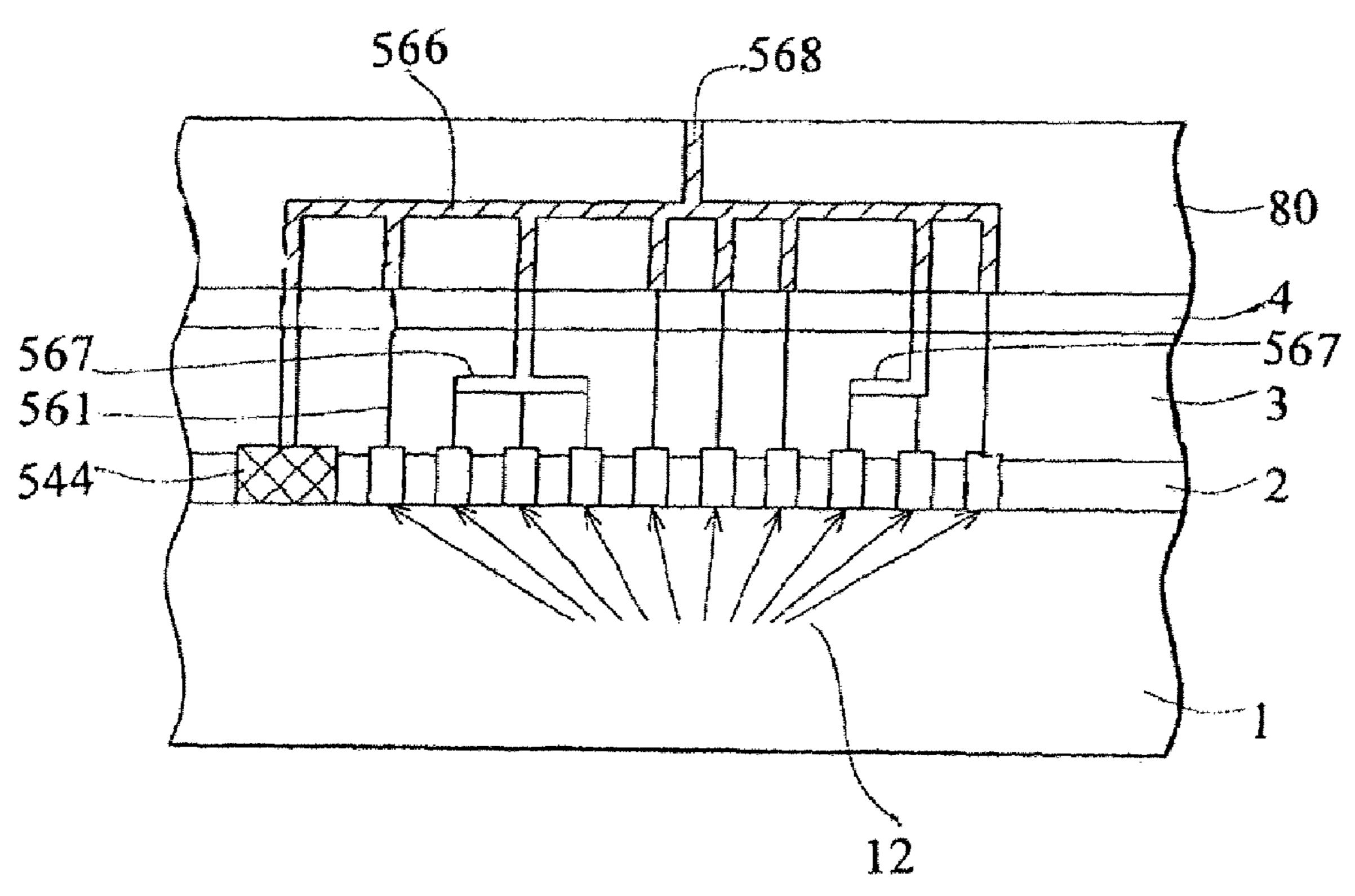

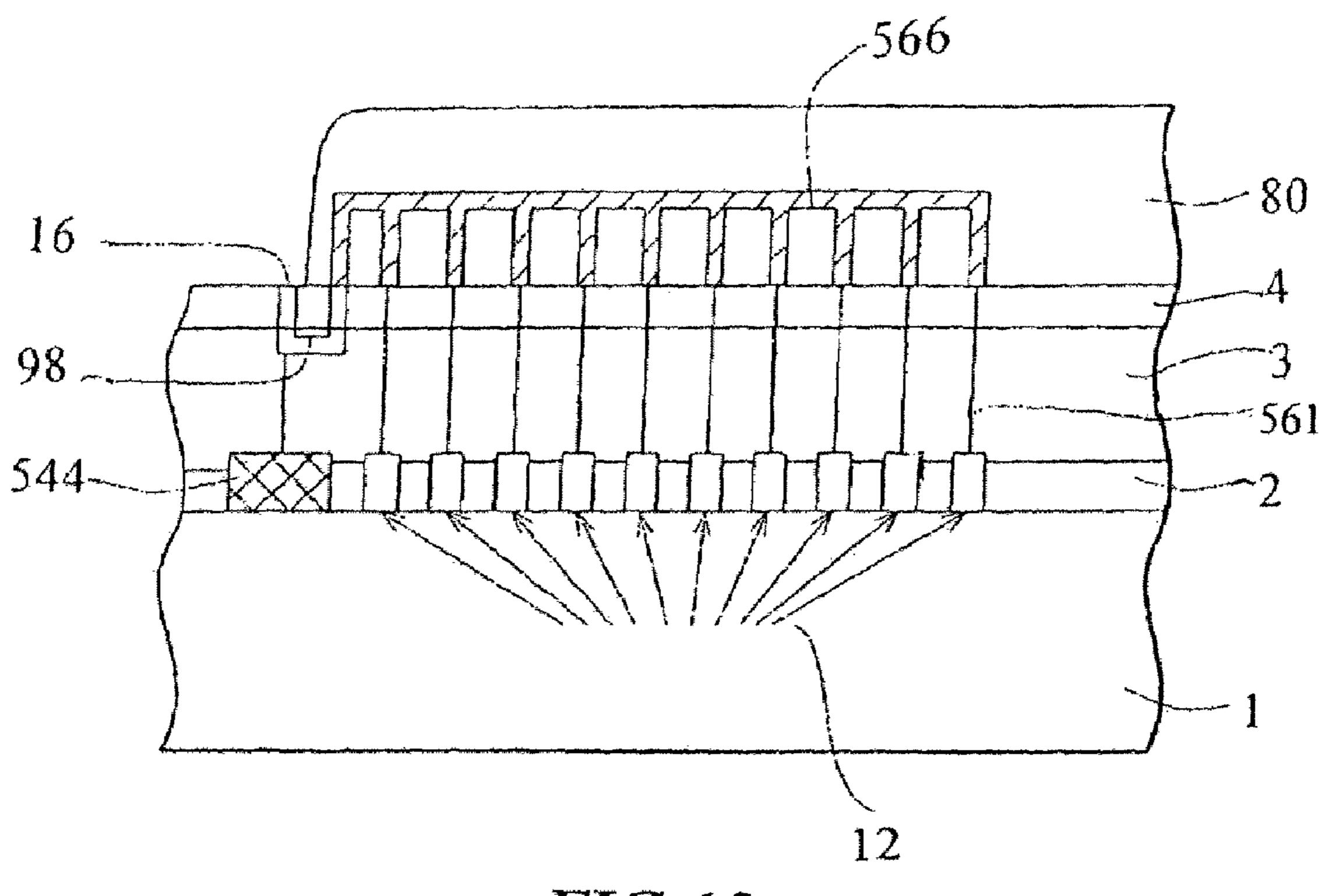

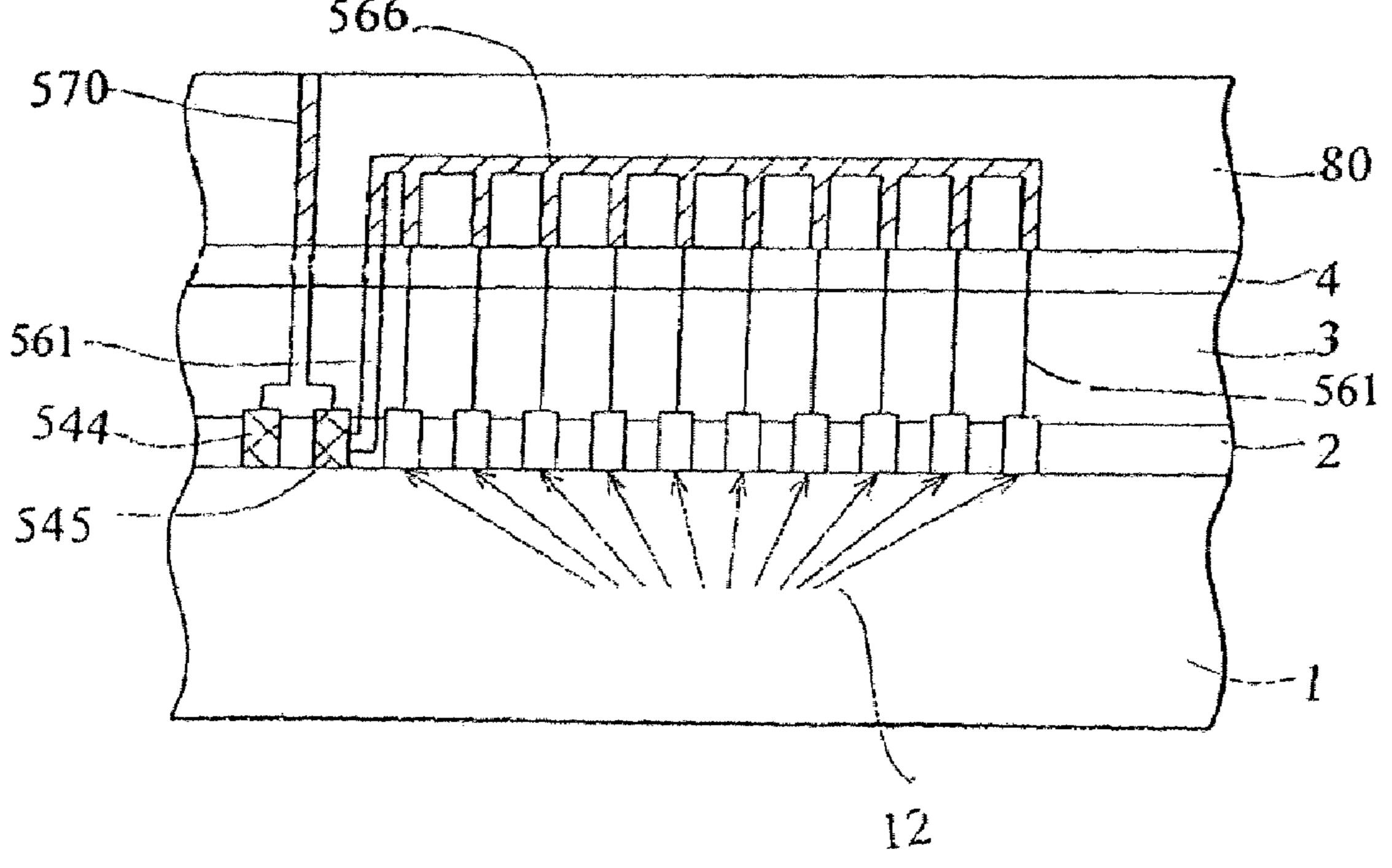

FIGS. 13*a*-13*c* show circuitry architectures having a thick circuit trace or plane over a passivation layer connecting an ESD circuit and multiple internal circuits.

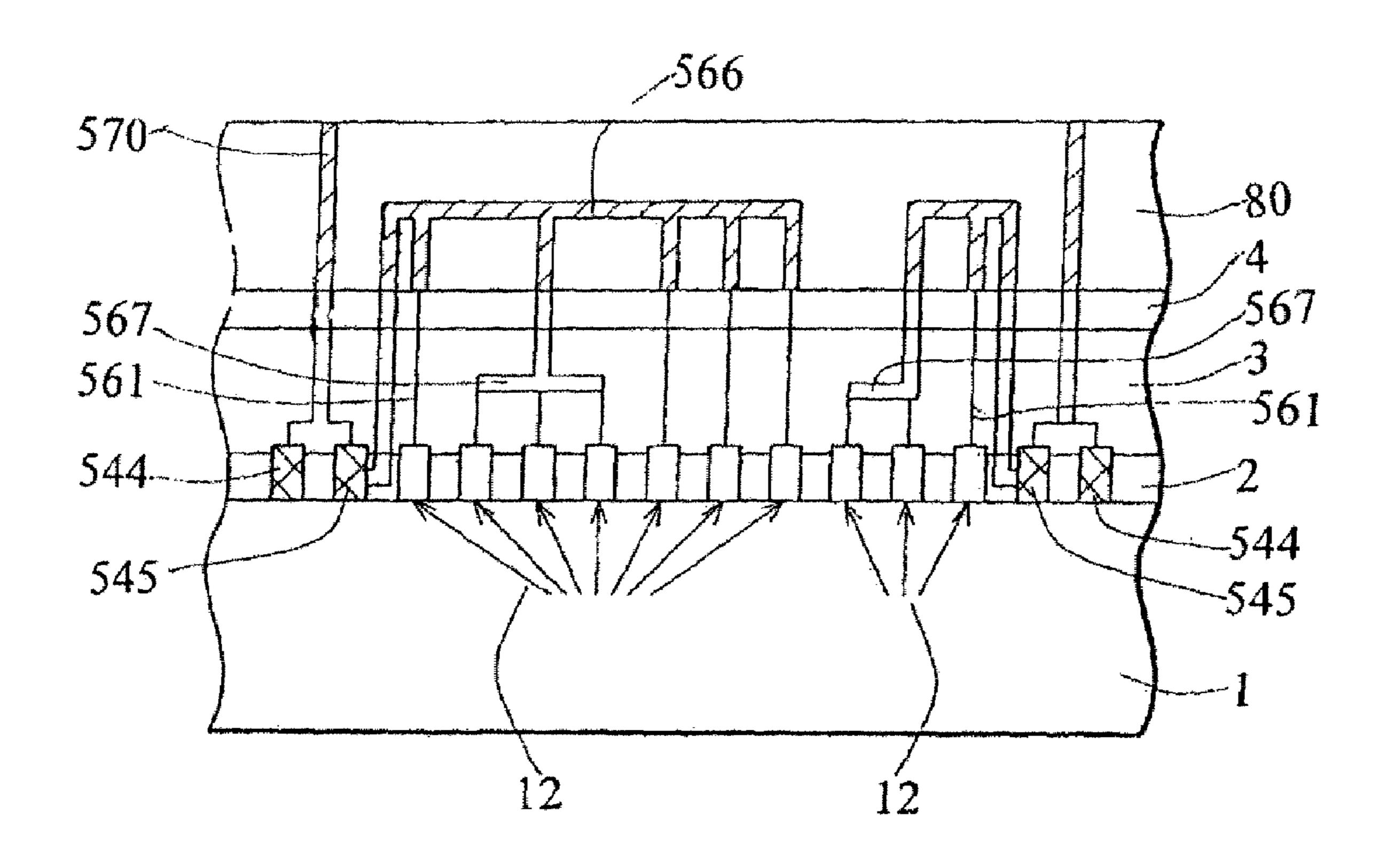

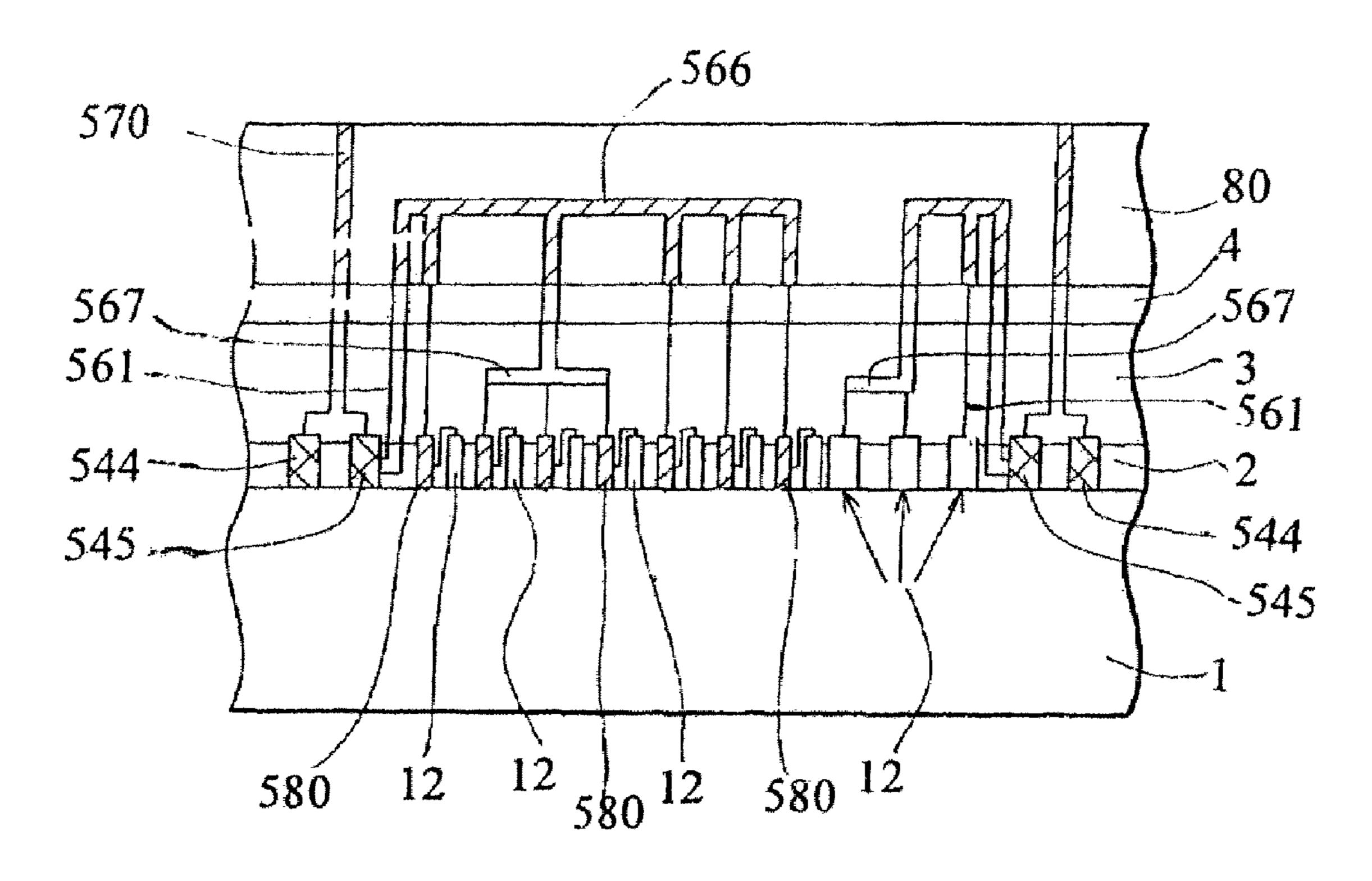

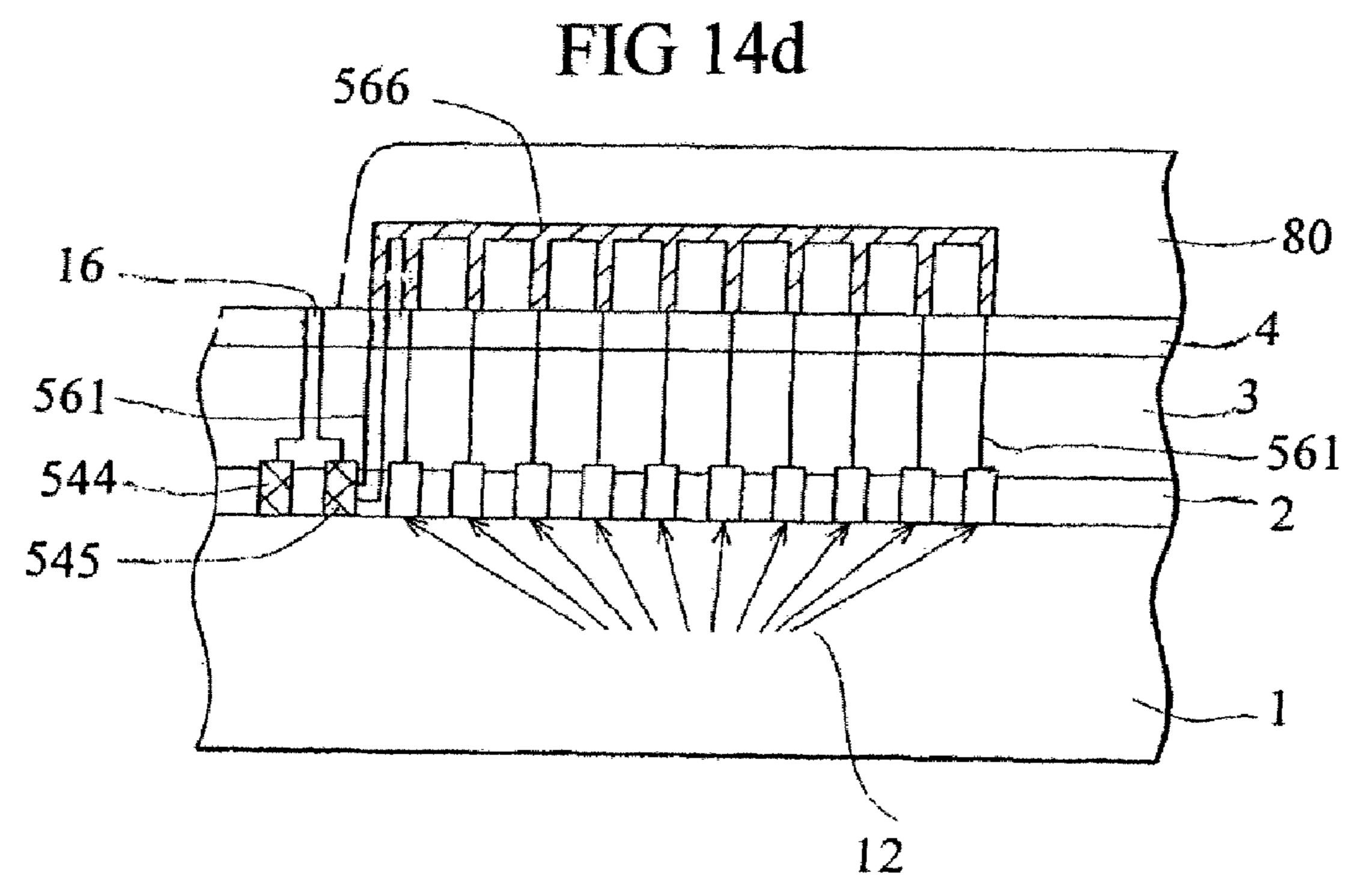

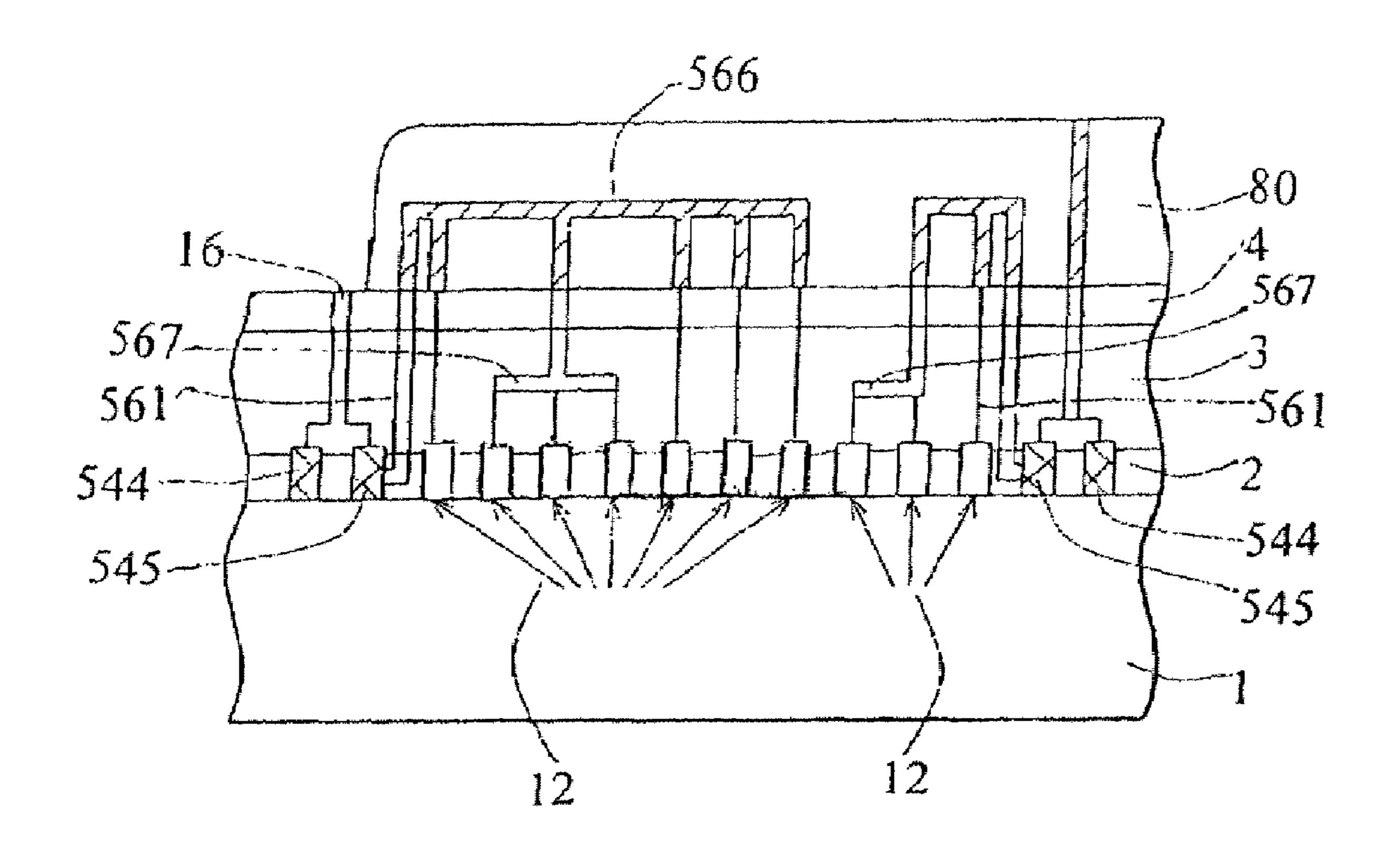

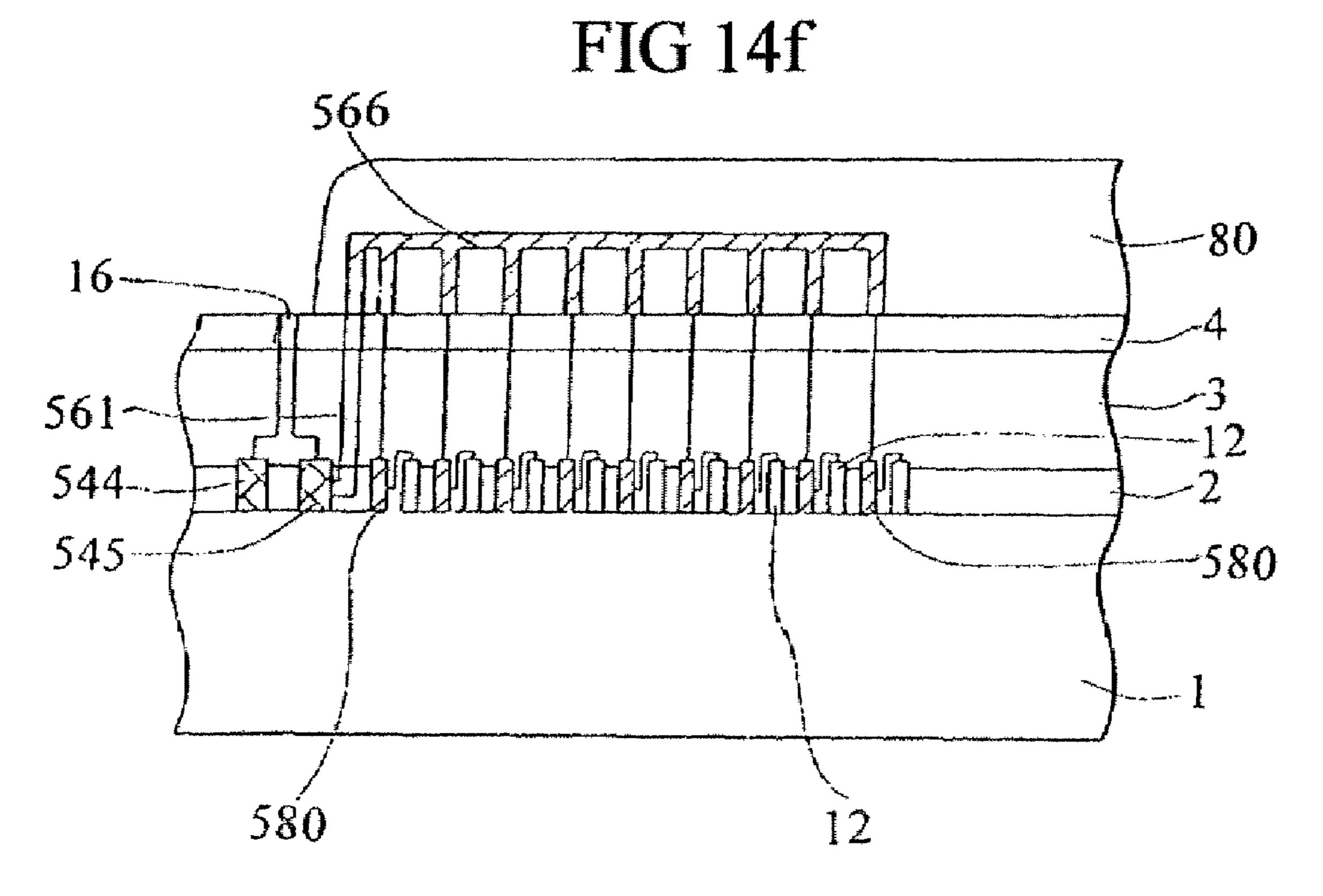

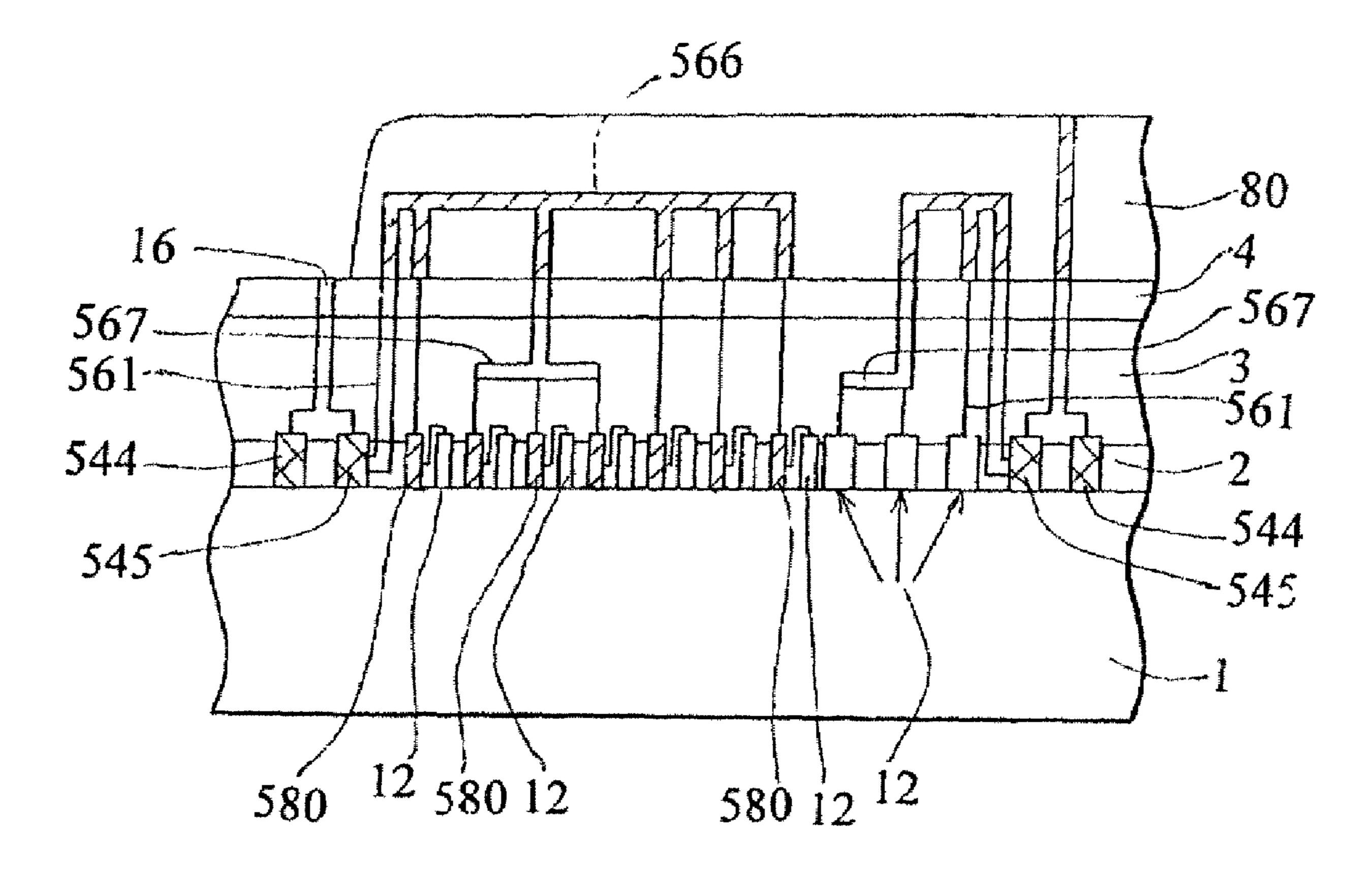

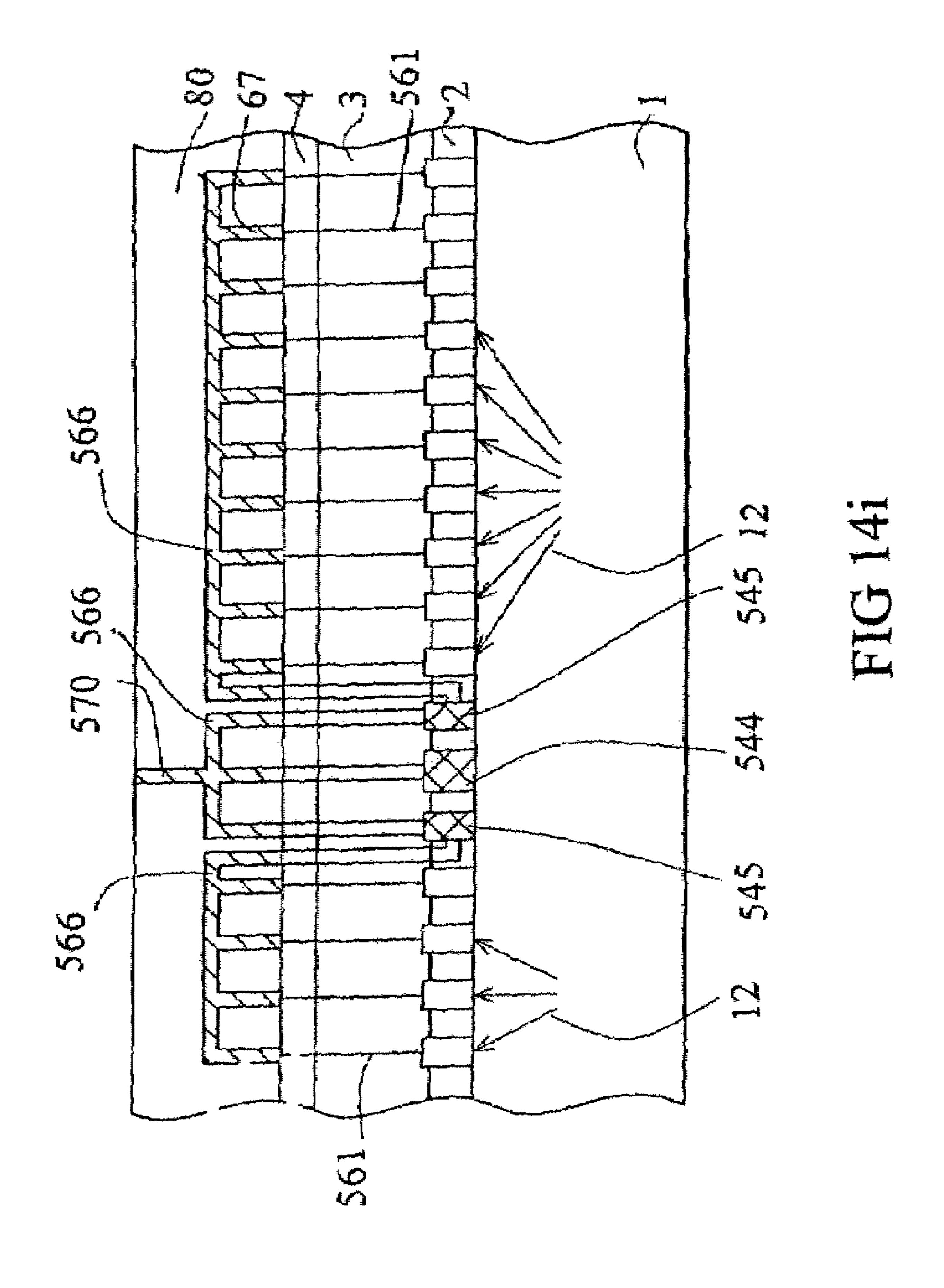

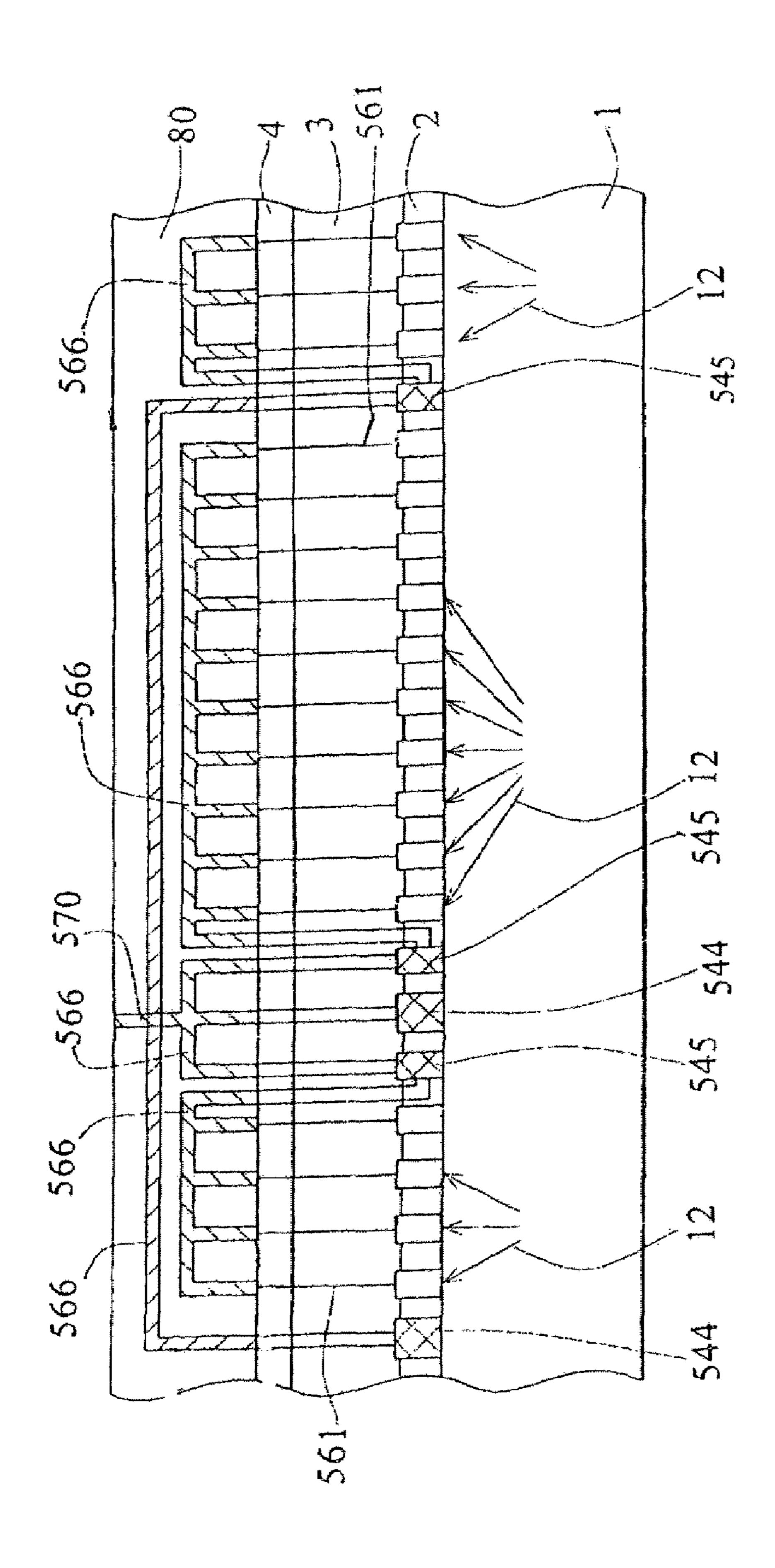

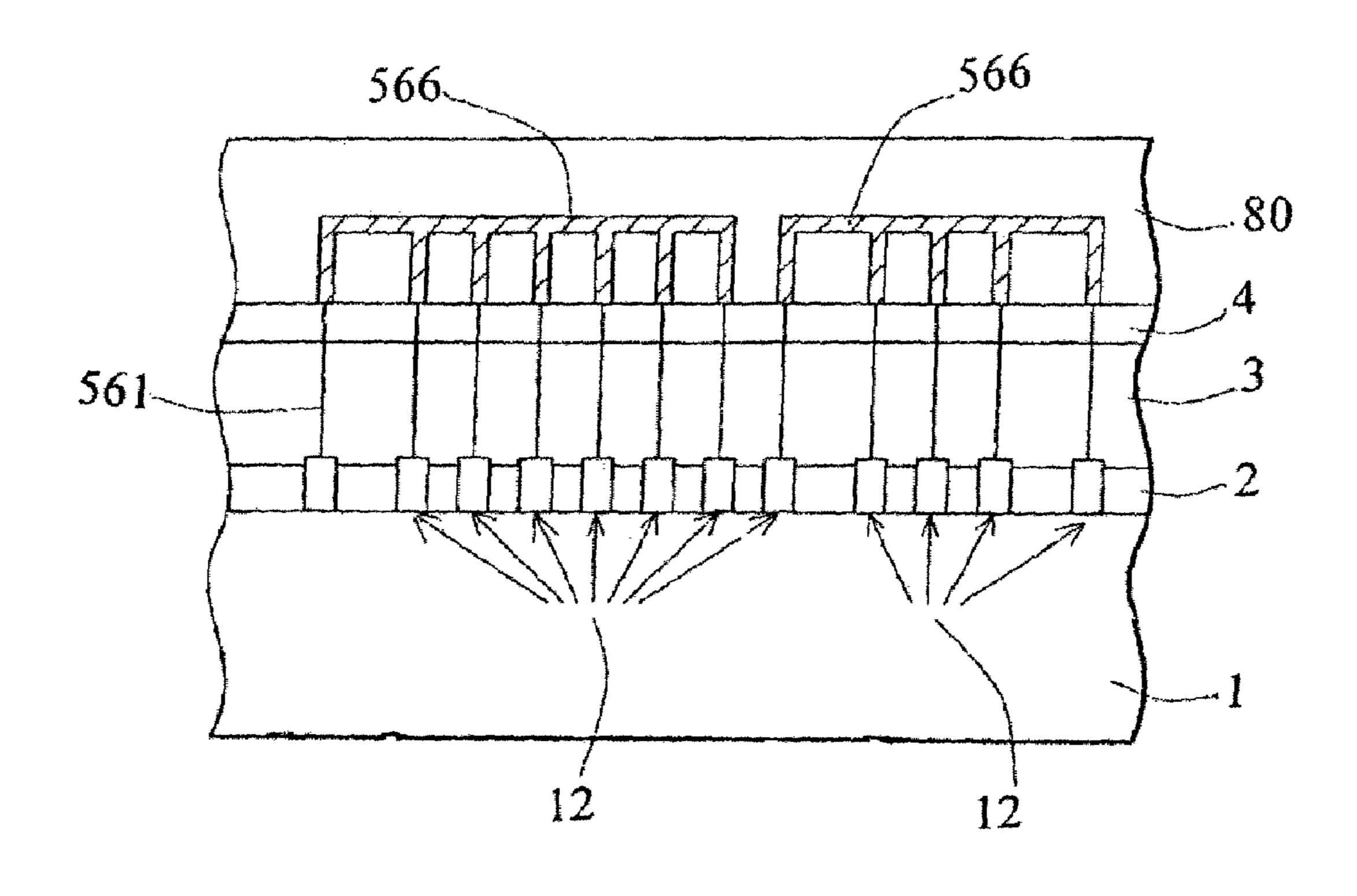

FIGS. 14*a*-14*j* show circuitry architectures having a thick circuit trace or plane over a passivation layer connecting an off-chip I/O circuit and multiple internal circuits or connecting an off-chip I/O circuit and multiple intra-chip drivers or receivers.

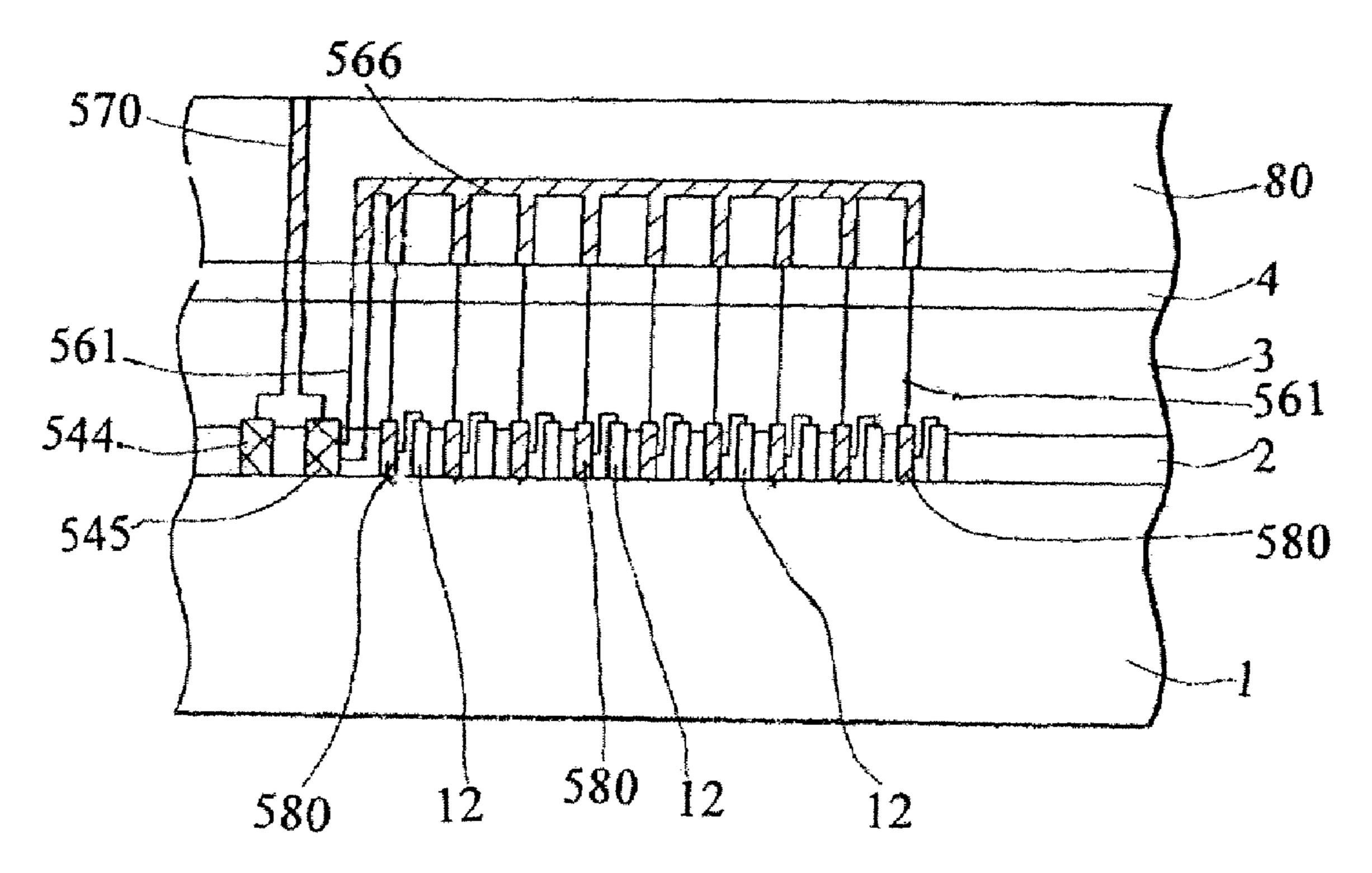

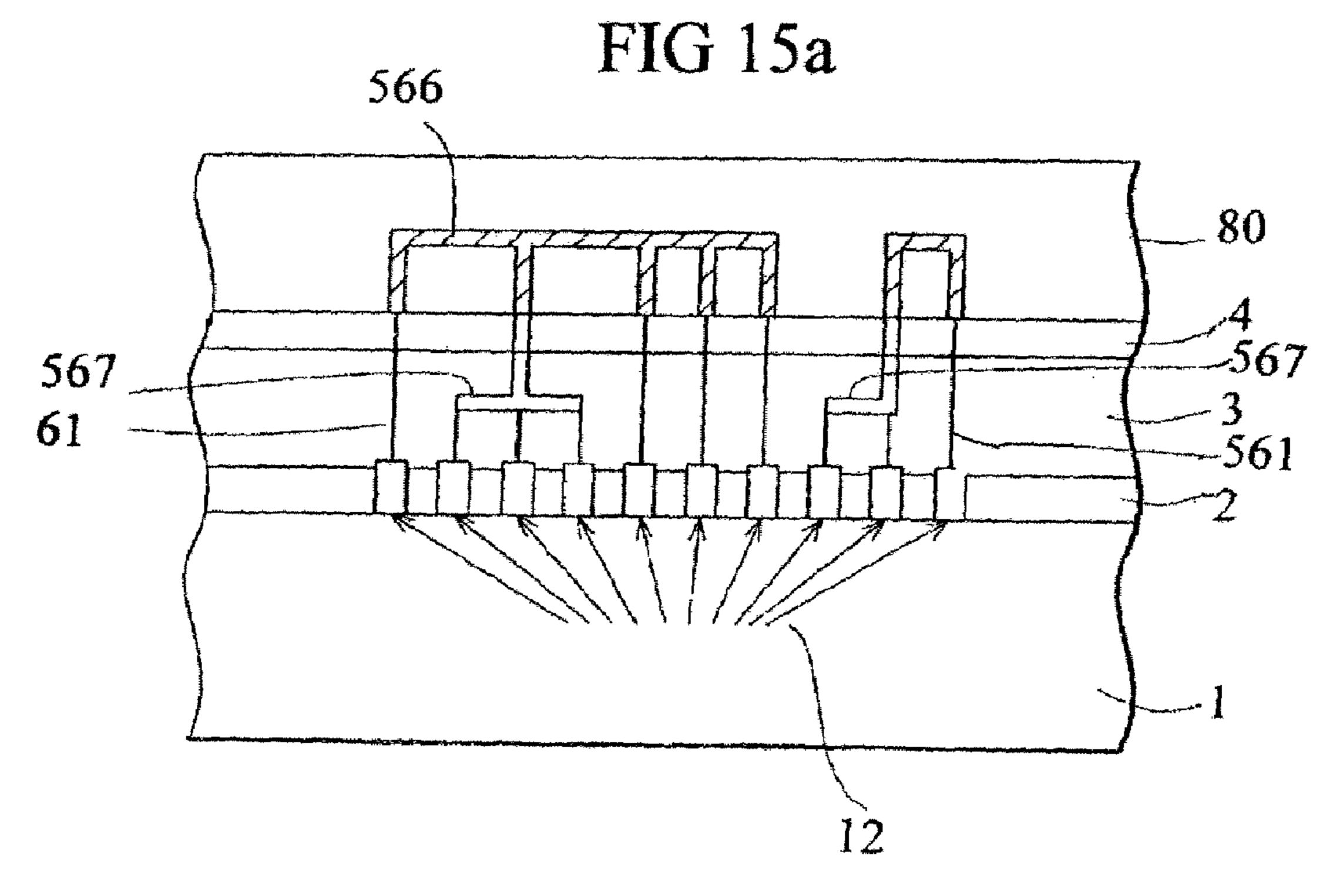

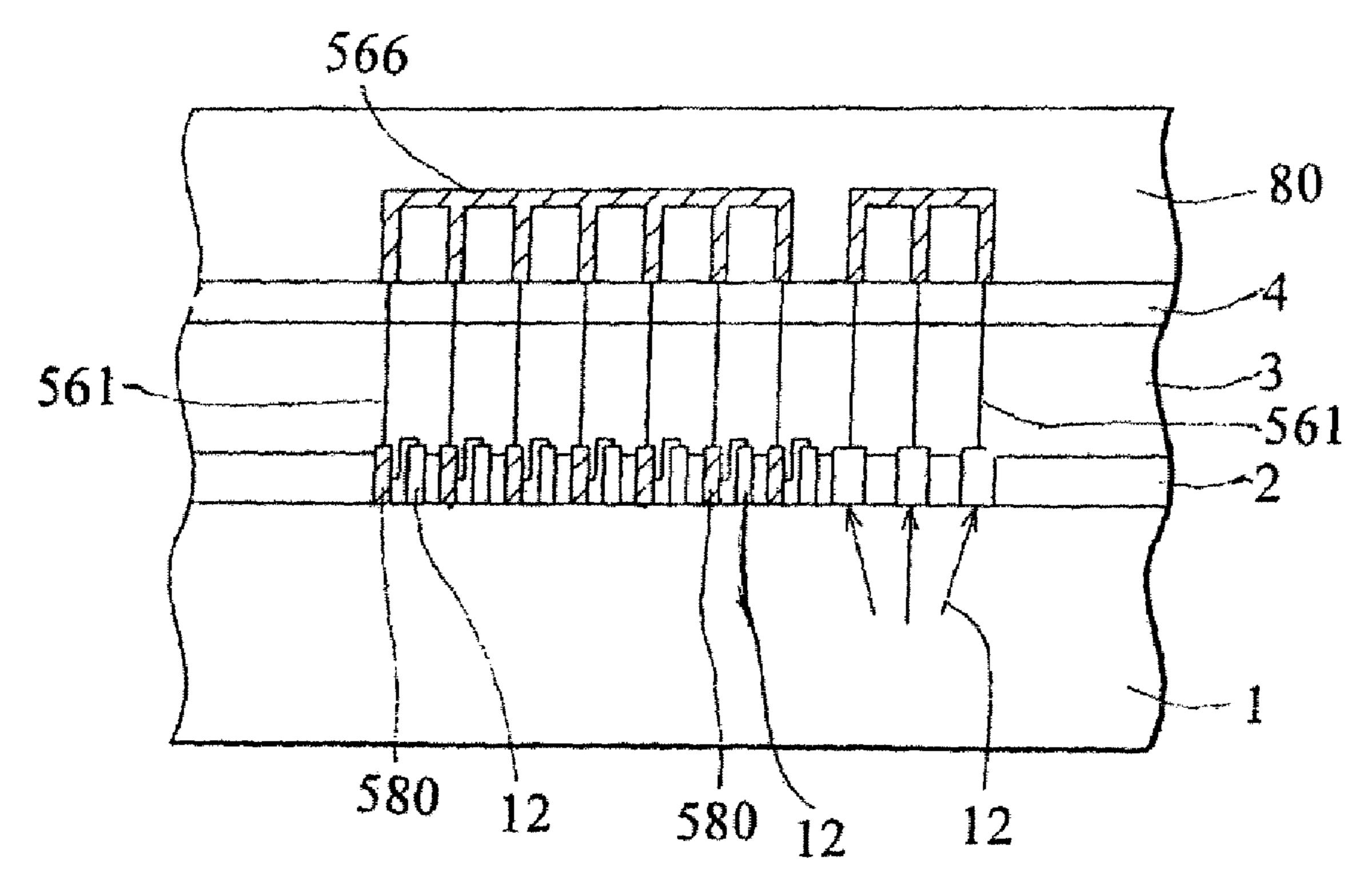

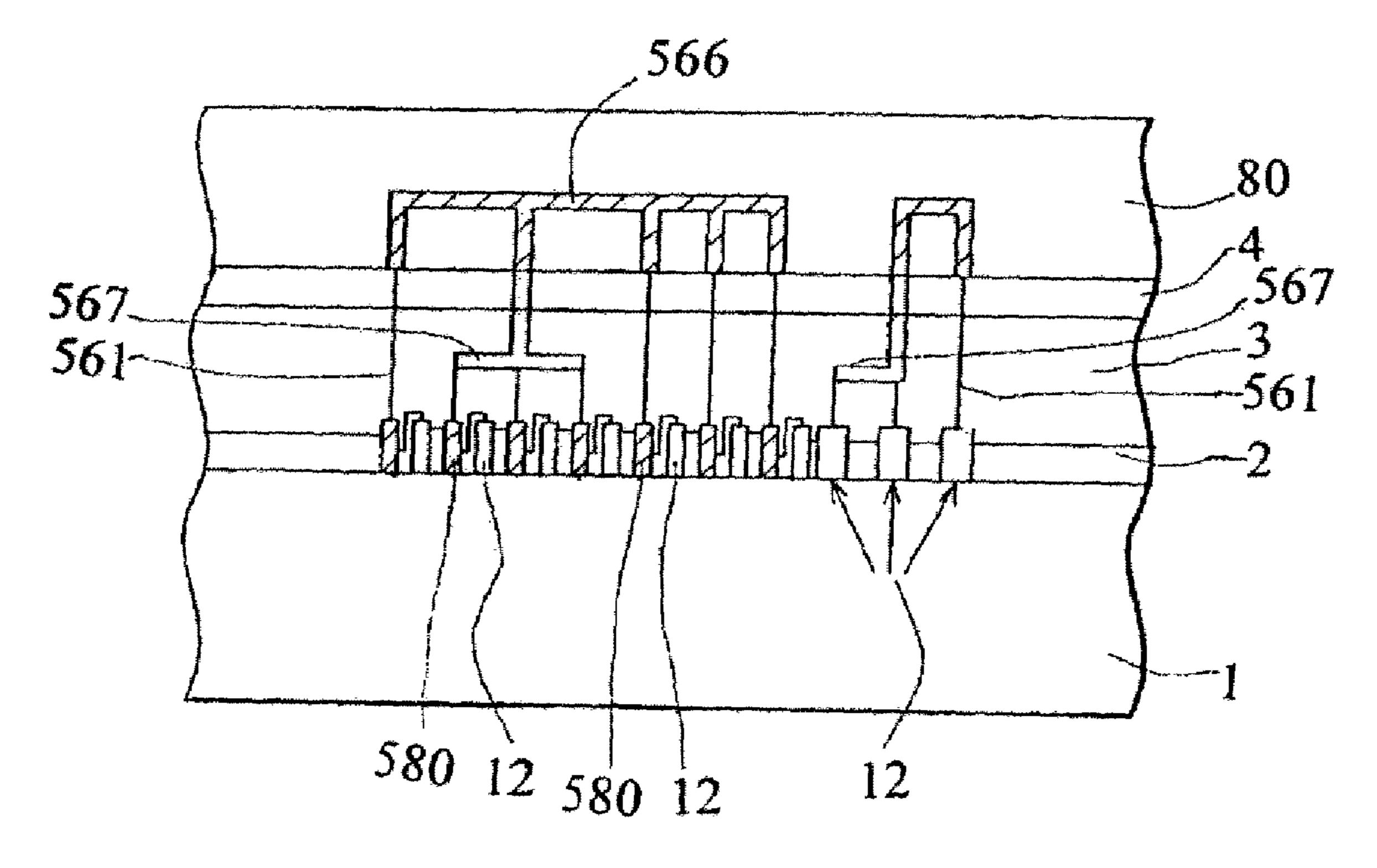

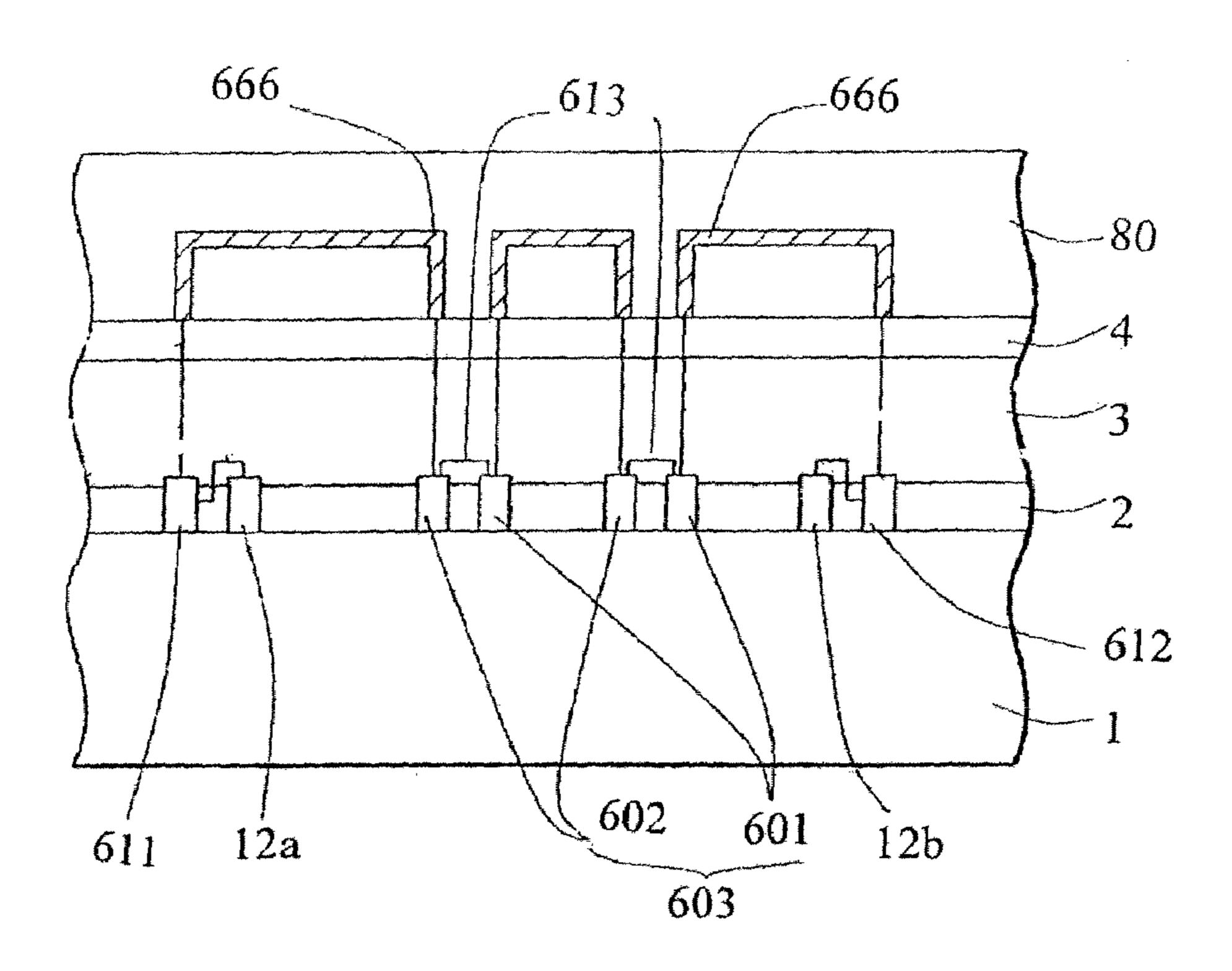

FIGS. 15*a*-15*d* show circuitry architectures having a thick circuit trace or plane over a passivation layer connecting multiple internal circuits or connecting multiple intra-chip drivers or receivers.

FIG. 16 shows a circuitry architecture having a thick circuit 50 trace or plane over a passivation layer connecting multiple repeaters.

FIG. 17 shows a semiconductor chip having a thick circuit layer over a passivation layer.

Table 1 shows products of resistance times capacitance for 55 various cases.

## DESCRIPTION OF THE PREFERRED EMBODIMENTS

## First Embodiment

The present invention discloses an Integrated Circuit structure, wherein a redistribution circuit layer and a polymer layer are formed over the passivation layer of a conventional IC. 65 Wide and thick metal lines are used for the redistribution circuit layer, so that RC Delay can be declined. Alternatively,

4

a thick and wide metal line located over the passivation layer may connect two separate electrical bond pads exposed by the openings in the passivation layer. Alternatively, inductors, capacitors and resistors can be formed with a thick metal layer located over the passivation layer.

Referring to the FIG. 1a showing a simplified cross-sectional view of a semiconductor chip according to the present invention. A semiconductor substrate 1, for instance, silicon substrate, germanium substrate or gallium-arsenide substrate is provided. Multiple electronic devices are formed by doping ions with pendat valence electrons or trivalence electrons, such as phosphorus ions or boron ions, into the semiconductor substrate 1, which is shown as a device layer 2 in FIG. 1a. These electronic devices include, for instance, metal oxide semiconductor (MOS) devices, transistor, poly silicon resistor and poly-to-poly capacitor . . . etc.

An IC interconnection layer 3 located on the device layer 2 is formed with alternating depositions of thin-film metal layers and thin-film insulating layers. In general, the materials of the thin-film insulating layer between the thin-film metal layers include an oxide containing silicon, such as a CVD silicon oxide, a CVD Tetraethoxysilane (TEOS), a spin-on glass (SOG), a Fluorinated silica Glass (FSG) and a CVD oxide formed through high density plasma. The thin-film insulating layers can be a composit or a single layer made of above mentioned materials.

The general thickness of the thin-film metal layer each ranges, for instance, from 1000 microns to 10,000 microns. In general, the thin-film metal layer is formed by patterning a sputtered aluminum or aluminum alloy, such as aluminum-copper alloy, to form fine metal lines. In one case, an aluminum-copper alloy, which has less than 5 weight percent of copper, may be employed for forming the thin-film metal layer below the passivation layer.

In the process for forming said fine aluminum lines, an aluminum layer is firstly sputtered on a thin-film insulating layer, such as silicon dioxide or an insulating layer with a dielectric constant of lower than 2.5. Next, the aluminum layer is patterned by photolithography and etching processes. Next, another thin-film insulating layer, such as silicon dioxide or an insulating layer with a dielectric constant of lower than 2.5, is formed on the patterned aluminum layer by a Chemical Vapor Deposition (CVD) process. Next, said another thin-film insulating layer is patterned by photolithog-45 raphy and etching processes such that multiple openings can be formed through said another thin-film insulating layer and expose the patterned aluminum layer thereunder. Thereafter, the above-mentioned process may be a sequent repeat for depositing the IC interconnection structure 3. In addition, the above-mentioned fine aluminum lines may be replaced by other kind metal lines formed by a damascene copper process.

In the damascene copper process, a copper line is protected by an adhesion/barrier layer, which is located under the copper line and around the side wall of the copper line, avoiding copper ions of the copper line from migrating to affect other active components.

In the copper damascene process, a thin-film insulating layer, such as silicon dioxide or material with dielectric constant of less than 2.5, is formed by a CVD process. Then, the thin-film insulating layer is patterned by photolithography and etching processes such that multiple openings can be formed in the thin-film insulating layer and expose an underlying metal layer. Next, an adhesion/barrier layer, such as tantalum, tantalum nitride (TaN) or titanium, or titanium nitride (TiN), can be sputtered over the thin-film insulating layer and in the openings in the thin-film insulating layer. Then, a metal layer, such as copper layer, can be formed over

the adhesion/barrier layer and in the openings in the thin-film insulating layer by an electroplating process, a sputtering process or a CVD process, wherein the metal layer has, for example, greater than 95 weight percent of copper. Next, the metal layer and the adhesion/barrier layer outside the openings in the thin-film insulating layer are removed by using a chemical-mechanical-polishing (CMP) process. Thereby, the adhesion/barrier layer covers the bottom and the side wall of the metal layer. The above-mentioned process may be a sequent repeat for depositing the IC interconnection structure 10

In general, the thickness of the above-mentioned thin-film metal layer under a passivation layer 4 is about between 1000 and 10,000 Angstroms. The metal line of the thin-film metal layer is required to be fabricated in the clean room of less than 15 or equal to Class 10 that means that the number of the airborne particles, whose size are larger than 0.5 microns, can not exceed 10 per cubic inch in air. The metal line of the thin-film metal layer should be formed using a 5x stepper or a scanner or better equipment and using a photoresist layer having a 20 thickness of less than 5 microns. The IC metal interconnection in the IC interconnection structure 3 connects different electronic devices in the device layer 2 to form an operation circuit. The topmost thin-film metal layer under the passivation layer 4 is provided with metal contact points for external 25 electrical connection, such as bond pads. These bond pads provide the electrical connection between IC interconnection layer 3 and an external circuitry.

The passivation layer 4 is disposed on the IC interconnection structure 3 and is provided with multiple openings exposing the bond pads of the IC interconnection structure 3. The passivation layer is formed by depositing oxide and nitride using Plasma Enhanced Chemical Vapor Deposition PECVD process. The passivation layer 4 is formed by first, depositing one layer of silicon oxide layer with the thickness of 0.5 microns using a PECVD process and, then forming a silicon nitride layer with the thickness of greater than 0.3 microns and preferably of 0.7 microns.

The above mentioned passivation layer 4 is quite important. It can protect the device layer 2 and the IC interconnection structure 3 from being damaged by the moisture, by the transition metal such as gold, silver, copper, etc and by the foreign ion contamination such as sodium ion.

To attain the goal of the protection, the thickness of the layer of silicon nitride of the passivation layer 4 is usually 45 greater than 0.3 microns. The passivation layer 4 between the IC interconnection structure 3, which contains thin-film fine lines of Integrated Circuits formed with a sub-micron (less than 1 micron) order thickness, and the post passivation structure 80, which contains a thick and wide metal interconnection lines formed with a micron order (greater than 1 micron) process, is a key point. Due to the protection of the passivation layer 4, the post passivation structure 80 with a thick and wide metal interconnections and a thick polymer layer can be allowed to be formed by a cheaper process in a clean room 55 with lower cleanliness.

The thickness of the passivation layer 4 is, for example, more than 0.35 microns. The passivation layer may be silicon oxynitride, phosphosilicate (PSG), borosilicate glass BSG borophosphosilicate glass BPSG or a composite formed of at 60 least one of the above mentioned materials.

In one case, the passivation layer 4 includes one layer of silicon nitride and one layer of silicon oxide, wherein the layer of silicon nitride lies on the layer of silicon oxide. The thickness of the layer of silicon nitride ranges, for instance, 65 from 0.2 microns to 1.2 microns. The thickness of the layer of silicon oxide ranges, for instance, from 0.1 microns to 0.8

6

microns. In general, a passivation layer 4 includes the top-most layer of silicon nitride and the topmost layer of silicon oxide of the finished chip structure. The passivation layer 4 includes the topmost CVD-formed insulating layer of the chip structure. Multiple openings in the passivation layer 4 expose the topmost one of the thin-film metal layers in the IC interconnection layer 3. The largest transverse dimension of the openings in the passivation layer may range from 0.1 to 25 microns.

The below mentioned selective deposition process can be employed to form the wide and thick metal interconnection lines over the passivation layer 4. The product of resistance created by a first section of the wide and thick metal interconnection line over the passivation layer 4 times capacitance created by said first section is far smaller than that of resistance created by a second section of the thin-film fine line under the passivation layer 4 times capacitance created by said second section by 5 times, 50 times, 1000 times or 10000 times, for example.

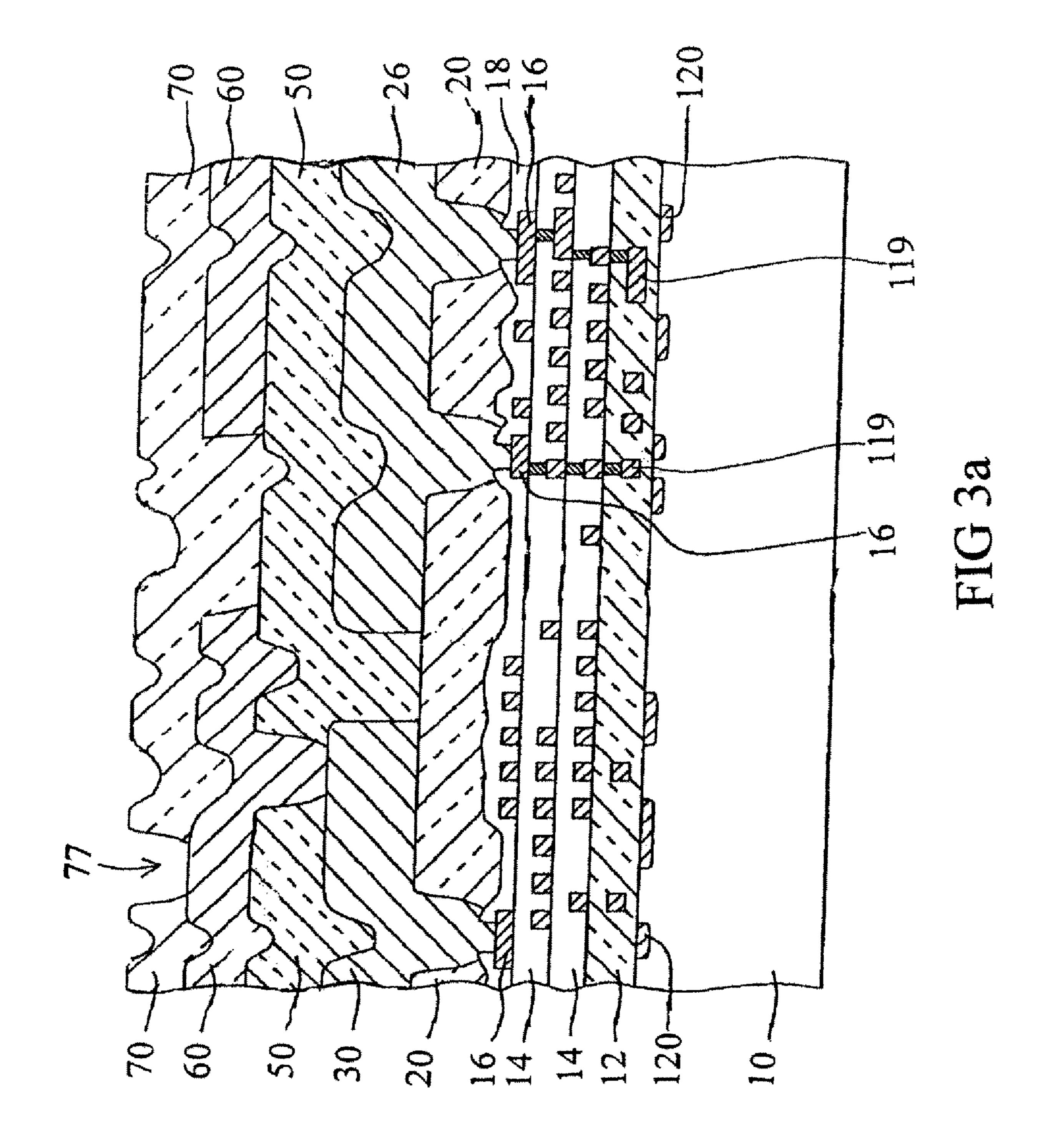

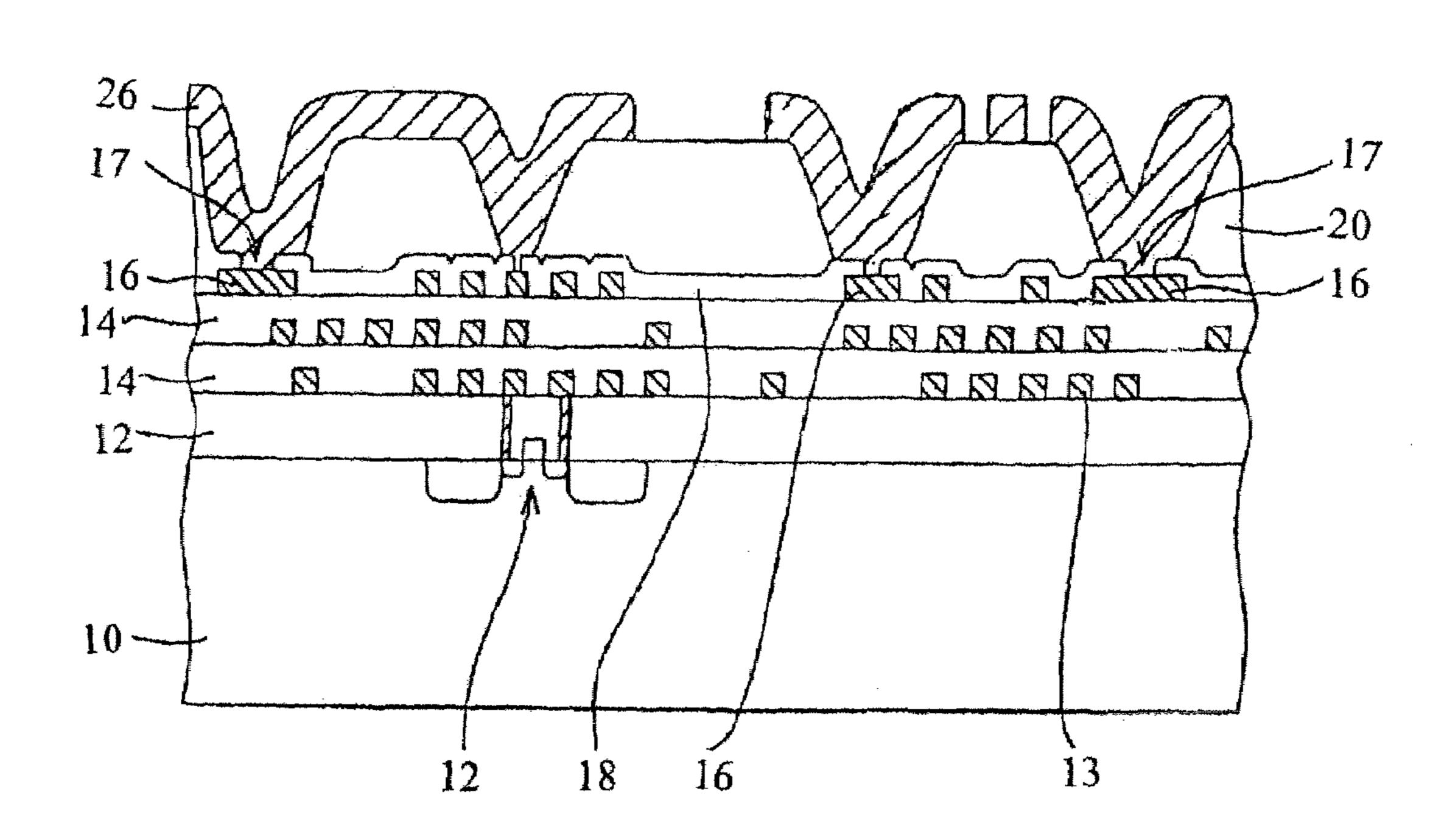

FIG. 1b is a cross-sectional view of a semiconductor chip in an embodiment of the present invention. A semiconductor substrate 10 contains electronic devices, such as transistors or MOS (Metal Oxide Semiconductor) devices having a source, drain and gate. A thin film insulating layer 12 is formed over the semiconductor substrate 10 and over these electronic devices. The diffusion layer 120 of source or drain lies inside the semiconductor substrate 10. The bottommost one of the thin film insulating layers 12 may include a gate 119 over the semiconductor substrate 10 between the source and the drain, so that the channel can be formed in the semiconductor substrate 10 under the gate 119, and between the diffusion layer 120 of source or drain.

An interconnection structure 14 comprising multiple thinfilm metal layers and thin-film insulating layers lies over the thin film insulating layer 12, wherein the thin-film metal layers of the structure **14** is formed by previously mentioned sputtering aluminum process or damascene copper process. The main material of the thin-film insulating layers is, for instance, silicon oxide formed by CVD. A passivation layer 18 is deposited over the interconnection structure 18. The topmost thin-film metal layer under a passivation layer 18 is formed, for instance, by previously mentioned sputtering aluminum process or damascene copper process. Multiple openings in the passivation layer 18 expose the electrical bond pads 16 of the topmost one of the thin-film metal layers of the interconnection structure 14. The structure and function of the passivation layer 18 can be referred to as that of the passivation layer 4 in FIG. 1a.

As below, eleven methods for depositing the passivation layer 42 are to be introduced.

## Method 1

A silicon oxide layer with a thickness of between 0.2 and 1.2 microns is formed with a CVD method; and next, a silicon nitride layer with a thickness of between 0.2 and 1.2 microns is formed on the silicon oxide with a CVD method.

## Method 2

A silicon oxide layer with a thickness of between 0.2 and 1.2 microns is formed with a CVD method; next, a silicon oxy-nitride layer with a thickness of between 0.05 and 0.15 microns is formed on the silicon oxide with a plasma-enhanced CVD method; and next, a silicon nitride layer with a thickness of between 0.2 and 1.2 microns is formed on the silicon oxy-nitride layer with a CVD method.

#### Method 3

A silicon oxy-nitride layer with a thickness of between 0.05 and 0.15 microns is formed with a CVD method; next, a silicon oxide layer with a thickness of between 0.2 and 1.2 microns is formed on the silicon oxy-nitride layer with a CVD 5 method; and next, a silicon nitride layer with a thickness of between 0.2 and 1.2 microns is formed on the silicon oxide layer with a CVD method.

### Method 4

A first silicon oxide layer with a thickness of between 0.2 and 0.5 microns is formed with a CVD method; next, a second silicon oxide layer with a thickness of between 0.5 and 1 microns is formed on the first silicon oxide layer with a spin-coating method; next, a third silicon oxide layer with a thickness of between 0.2 and 0.5 microns is formed on the second silicon oxide layer with a CVD method; and next, a silicon nitride layer with a thickness of between 0.2 and 1.2 microns is formed on the third silicon oxide layer with a CVD method.

## Method 5

A silicon oxide layer with a thickness of between 0.5 and 2 microns is formed with a HDP-CVD (High Density Plasma-Chemical Vapor Deposition) method; and next, a silicon nitride layer with a thickness of between 0.2 and 1.2 microns is formed on the silicon oxide layer with a CVD method.

#### Method 6

A USG (Undoped Silicate Glass) layer with a thickness of between 0.2 and 3 microns is firstly formed; next, an insulating layer with a thickness of between 0.5 and 3 microns, such as TEOS, BPSG (Borophosphosilicate Glass) or PSG (Borophosphosilicate Glass), is formed on the USG layer; and next, a silicon nitride layer with a thickness of between 0.2 and 1.2 microns is formed on the insulating layer with a CVD method.

## Method 7

A first silicon oxy-nitride layer with a thickness of between 0.05 and 0.15 microns is optionally formed with a CVD method; next, a silicon oxide layer with a thickness of 40 between 0.2 and 1.2 microns is formed on the first silicon oxy-nitride layer with a CVD method; next, a second silicon oxy-nitride layer with a thickness of between 0.05 and 0.15 microns is optionally formed on the silicon oxide layer with a CVD method; next, a silicon nitride layer with a thickness of 45 between 0.2 and 1.2 microns is formed on the second silicon oxy-nitride layer or on the silicon oxide layer with a CVD method; next, a third silicon oxy-nitride layer with a thickness of between 0.05 and 0.15 microns is optionally formed on the silicon nitride layer with a CVD method; and next, a silicon oxide layer with a thickness of between 0.2 and 1.2 microns is formed on the third silicon oxy-nitride layer or on the silicon nitride layer with a CVD method.

## Method 8

A first silicon oxide layer with a thickness of between 0.2 and 1.2 microns is formed with a PECVD (Plasma Enhanced Chemical Vapor Deposition) method; next, a second silicon oxide layer with a thickness of between 0.5 and 1 microns is formed on the first silicon oxide layer with a spin-coating method; next, a third silicon oxide layer with a thickness of 60 between 0.2 and 1.2 microns is formed on the second silicon oxide layer with a CVD method; next, a silicon nitride layer with a thickness of between 0.2 and 1.2 microns is formed on the third silicon oxide layer with a CVD method; and next, a fourth silicon oxide layer with a thickness of between 0.2 and 65 1.2 microns is formed on the silicon nitride layer with a CVD method.

8

#### Method 9

A first silicon oxide layer with a thickness of between 0.5 and 2 microns is formed with a HDP-CVD method; next, a silicon nitride layer with a thickness of between 0.2 and 1.2 microns is formed on the first silicon oxide layer with a CVD method; and next, a second silicon oxide layer with a thickness of between 0.5 and 2 microns is formed on the silicon nitride layer with a HDP-CVD method

## Method 10

A first silicon nitride layer with a thickness of between 0.2 and 1.2 microns is formed with a CVD method; next, a silicon oxide layer with a thickness of between 0.2 and 1.2 microns is formed on the first silicon nitride layer with a CVD method; and next, a second silicon nitride layer with a thickness of between 0.2 and 1.2 microns is formed on the silicon oxide layer with a CVD method.

#### Method 11

A silicon oxy-nitride layer with a thickness of between 0.05 and 0.15 microns is formed with a CVD method; next, a first silicon oxide layer with a thickness of between 0.2 and 1.2 microns is formed on the silicon oxy-nitride layer with a CVD method; next, a silicon nitride layer with a thickness of between 0.2 and 1.2 microns is formed on the first silicon oxide layer with a CVD method; and next, a second silicon oxide layer with a thickness of between 0.2 and 1.2 microns is formed on the silicon nitride layer with a CVD method.

After forming the passivation layer 18, MOS components and the interconnection structure 14 formed before the formation of the passivation layer 18 can be protected from being damaged by the moisture, by the transmit metals or by the foreign ion contamination. Therefore, it is allowed to employ cheaper process to form the thick and wide metal interconnections and thick polymer layer over the passivation layer 18. And they can be manufactured in the clean room with low class of purity, such as class 100 or over class 100, wherein the definition of the class 100 is that the number of the particles with the diameter of more than 0.5 microns is equal to or exceeds 100 per cubic inch.

After forming the passivation layer 18, a layer of polymer 20 can be deposited over the passivation layer 18. The material for forming the polymer layer is, for example, polyimide from Hitachi-Dupont (HD2732 or HD2734), or polyimide from Asahi (LS800, 1-83005 or 8124). Another material forming the polymer layer 20 may be BenzoCycloButene (BCB), manufactured by Dow Chemical. It is trend that BCB is going to be replaced with polyimide. Parylene, porous insulating material or elastomer, etc can be the material for forming the polymer layer 20.

The material containing epoxy, such as photosensitive epoxy SU-8 manufactured by Sotec Microsystems, can be the material of forming the polymer layer 20 as well. The polymer layer 20 can be deposited by spin-on coating and curing process, as mentioned below: An ester-type precursory polymer layer made of, for example, photosensitive polyimide, is coated over the passivation layer 18 and electrical bond pads 16 by a spin-on coating process; next, the precursory polymer layer can be patterned by a photolithography process such that openings can be formed in the precursory polymer layer and expose the electrical bond pads 16; next, the precursory polymer layer us cured at 380 degrees centigrade for 4 hours in a vacuum or nitrogen ambient.

Alternatively, another process can be employed, as mentioned below: An ester cursory polymer layer made of, for example, non-photosensitive polyimide is first coated over the passivation layer 18 and electric bond pads 16 by spin-on coating process; next, the precursory polymer layer is cured at

380 degree C. for 4 hours in a vacuum or nitrogen ambient; next, the cured polymer layer is patterned by photolithography and etching processes such that openings can be formed in the cured polymer layer and expose the electrical bond pads 16.

If a thicker polymer layer 20 is needed, more than one ester-type precursory polymer layers, such as photosensitive polyimide, can be coated over the passivation layer 18, then patterned by a photolithography process, and then cured at 380 degree C. for 4 hours in a vacuum or nitrogen ambient. 10 Thereby, the polymer layer 20 comprising multiple layers of polymer can be formed over the passivation layer 18.

Alternatively, if a thicker polymer layer 20 is needed, one or more ester-type precursory polymer layers, such as non-photosensitive polyimide, can be coated over the passivation 1 layer 18, then cured at 380 degree C. for 4 hours in a vacuum or nitrogen ambient, and then patterned by photolithography and etching processes. Thereby, the polymer layer 20 comprising multiple layers of polymer can be formed over the passivation layer 18.

Besides, the polymer layer **20** can be formed by screen printing an ester-type precursory polymer layer over the passivation layer **18**. While the precursory polymer layer is printed, an area, which is not printed, can be left for forming the openings in the precursory polymer layer exposing the electrical bond pads **16**. So, the step of the photolithography process and/or the etching processes can be saved. The material of the precursory polymer layer is, for example, polyimide. Thereafter, the screen-printed precursory polymer layer is cured at 380 degree C. for 4 hours in a vacuum or nitrogen 30 ambient.

Alternatively, the polymer layer 20 can be formed by pressing with heat a dry film with multiple openings formed therein over the passivation layer 18, so that the openings in the polymer layer 20 can be formed not through photolithography or etching process. The openings in the polymer layer 20 expose the electrical bond pads 16. Therefore, the step of the photolithography process and/or the etching process can be saved. Alternatively, the polymer layer 20 can be formed by pressing with heat a dry film without openings formed therein 40 over the passivation layer 18. Next, multiple openings are formed in the pressed dry film by a photolithography process and/or an etching process. The openings in the pressed dry film can expose the electrical bond pads 16.

In another embodiment, The precursory polymer formed 45 by spin-on coating or screen printing can be cured at the highest temperature of lower than 320 degree C. Alternatively, the precursory polymer formed by spin-on coating or screen printing can be cured over 320 degree C. for less than 40 minutes, or even less than 20 minutes.

The thickness of the polymer layer **20**, after being cured, may exceed 2 microns, or, for example, range from 2 to 150 microns. It is dependant on the requirement of electronic design. The polymer layer **20**, after being cured, should be thicker than any one of the thin film insulating layers or any one of the thin-film metal layers of the interconnection structure **14** by 2 to 500 times. After the curing process, the sidewall of the openings in the polymer layer **20** is sloping. The angle between the sidewall and the horizon is, for instance, 45 degrees or more, such as between 50 and 60 degrees. Basically, the angle is greater than 20 degrees, so that the openings in the polymer layer **20** is shaped like half cones.

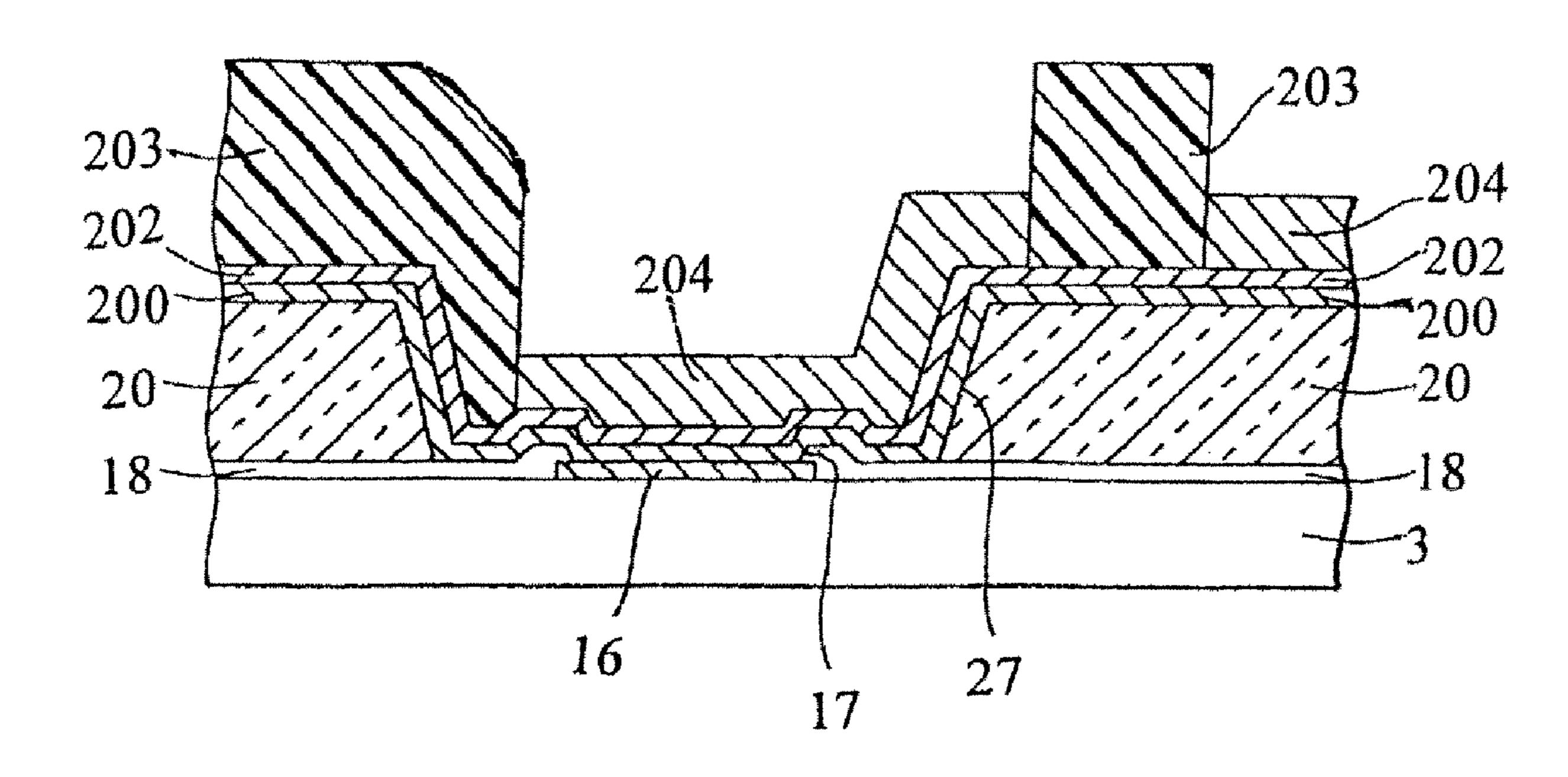

Referring to 1b, the greatest transverse dimension of the openings 27 in the polymer layer 20 is greater than that of the corresponding openings 17 in the passivation layer 18, 65 wherein the greatest transverse dimension of the openings 17 of the passivation layer 18 is, for instance, between 0.1 and 50

**10**

microns and preferably between 0.5 and 20 microns. The greatest transverse dimension of the electrical bond pads 16 lies, for instance, between 0.1 and 50 microns and preferably between 0.5 and 20 microns. The greatest transverse dimension of the openings 27 in the polymer layer 20 lies, for instance, between 1 micron and 100 microns and preferably between 2 and 30 microns. Thereby, the electrical bond pads 16 exposed by the openings 17 and 27 can be made very small, so the routing ability of the topmost thin-film metal layer under the passivation layer 18 can be enhanced. Furthermore, the parasitic capacitance generated between the electric bond pads 16 and the underlying thin-film metal layer.

Referring to FIG. 1b, after forming the polymer layer 20, a thick metal layer 30 is formed over the polymer layer 20 and inside the openings 27 in the polymer layer 20. A thick and wide metal line 26 of the patterned thick metal layer 30 may connect multiple electric bond pads 16. Referring to FIG. 1b, a signal output from the source 120 of a semiconductor device may be transmitted to one of the electrical bond pads 16 through the thin-film metal layers of the interconnection structure 14, and then passes through the thick and wide metal line 26 to another one of the electrical bond pad 16 (transmission path as indicated by the arrows 40, 42, 44), and finally is transmitted to the gate 119 of another semiconductor device through the thin-film metal layers of interconnection structure 14.

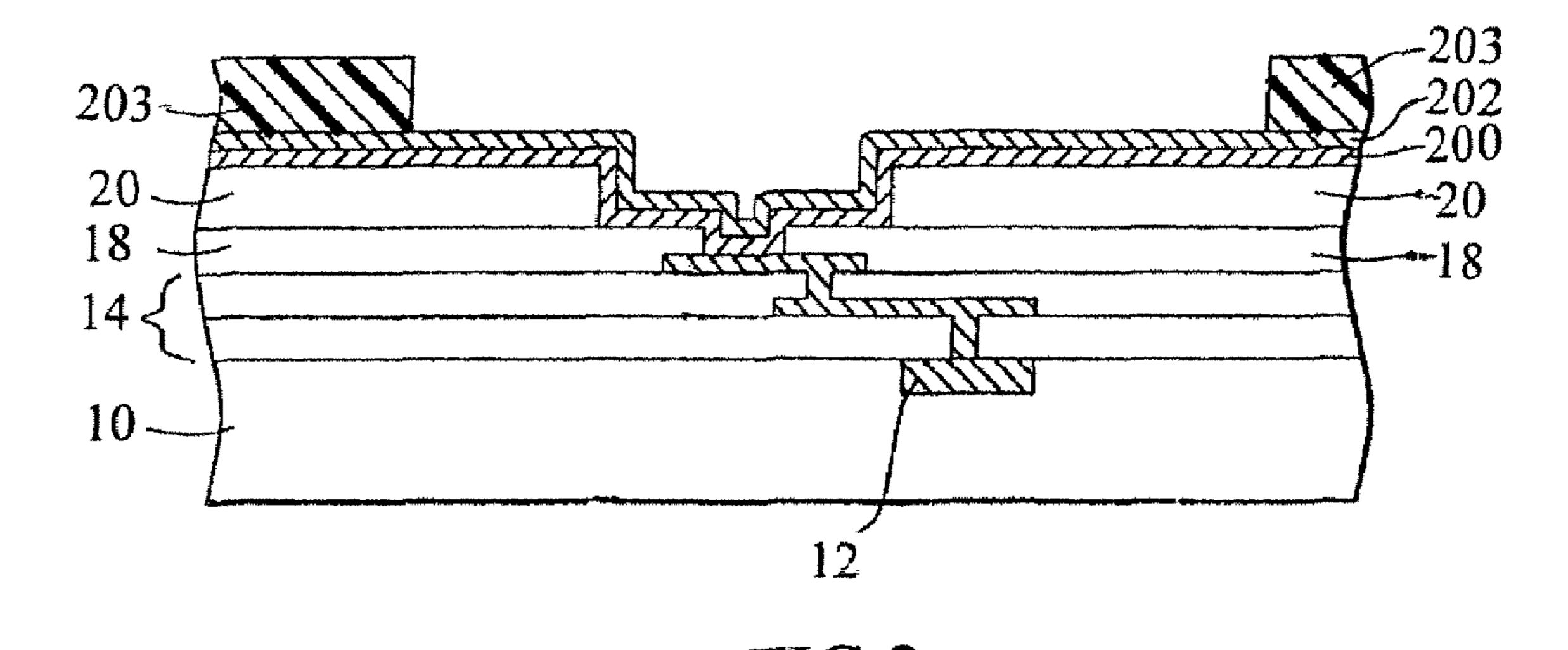

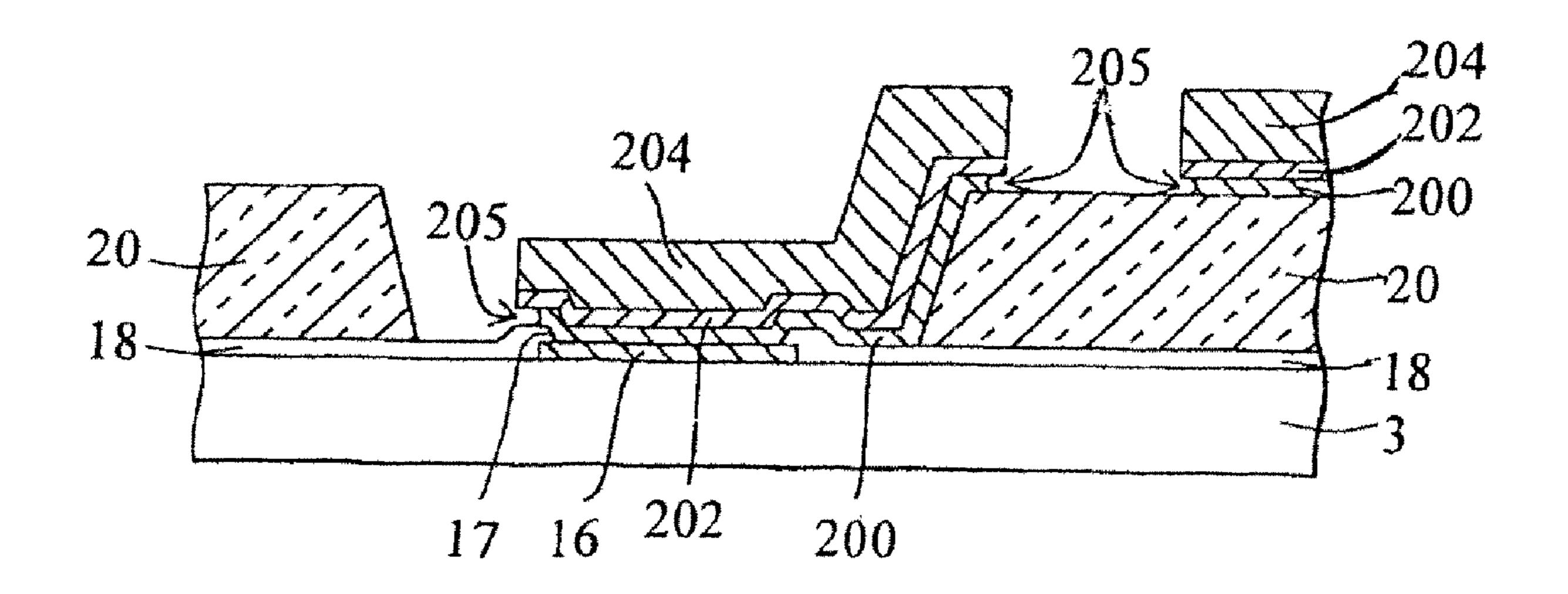

The process for forming the patterned thick metal layer 30 as shown in FIG. 1b can be referred to as shown in FIGS. 2a-2f. To simplify the figures, number 12 represents MOS devices containing gate, source and drain, or passive devices, wherein the semiconductor devices 12 can be connected to the electrical bond pads 16 through the interconnection structure 14. The openings 17 in the passivation layer 18 expose the electrical bond pads 16. The polymer layer 20 is formed onto the passivation layer 18 by the above mentioned process. The openings 27 in the polymer layer 20 expose the electrical bond pads 16, as shown in FIG. 2a.

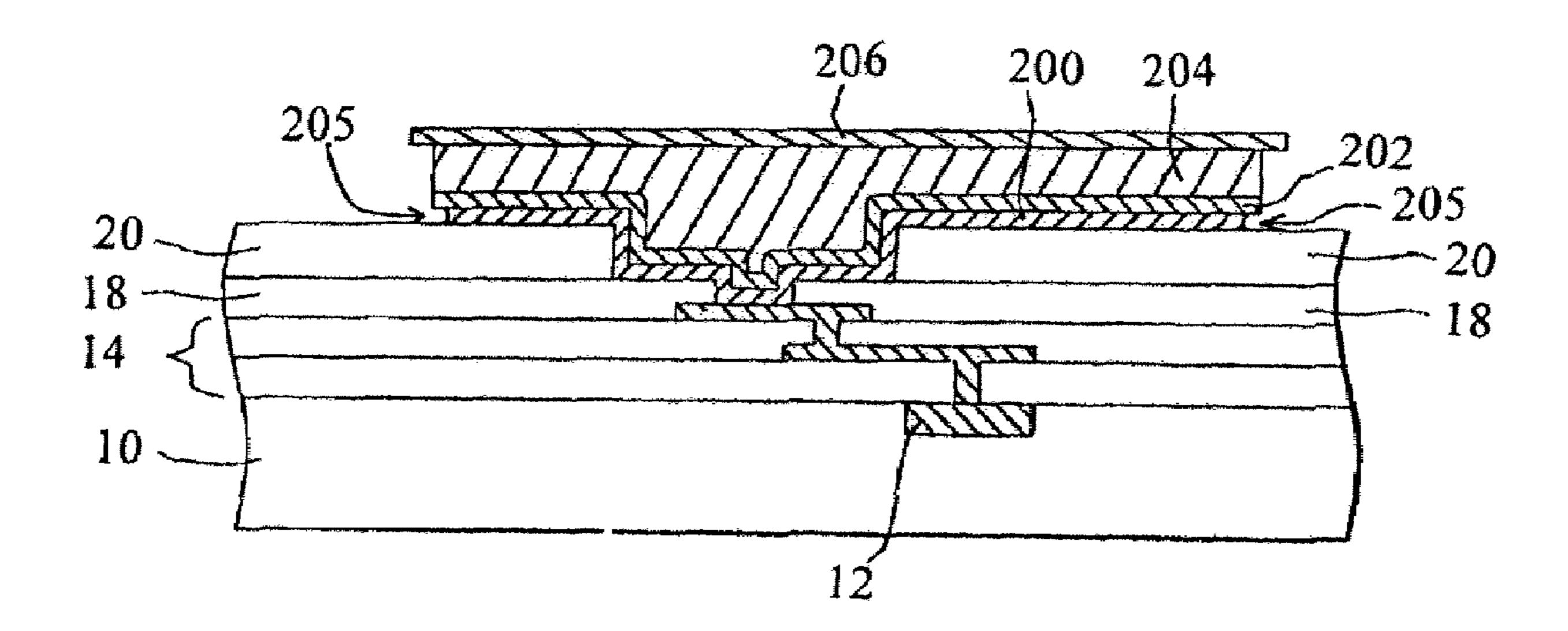

Next, referring to the FIG. 2b, after forming the polymer layer 20 onto the passivation layer 18, an adhesion/barrier layer 200, such as titanium-tungsten alloy, chromium, chromium-copper alloy, titanium, tantalum, tantalum nitride or titanium nitride, having a thickness ranging from 0.01 microns to 3 microns and preferably ranging from 200 angstroms to 5000 angstroms, can be sputtered onto the polymer layer 20, in the openings 17 in the polymer layer 20 and onto the electrical bond pads 16.

Next, a seed layer **202**, such as copper, gold, silver, palladium, platinum, rhodium, ruthenium, rhenium, or nickel, having a thickness ranging from 0.01 microns to 3 microns and preferably ranging from 300 angstroms to 10000 angstroms, is formed onto the adhesion/barrier layer **200** by a sputtering process or an electroless plating process.

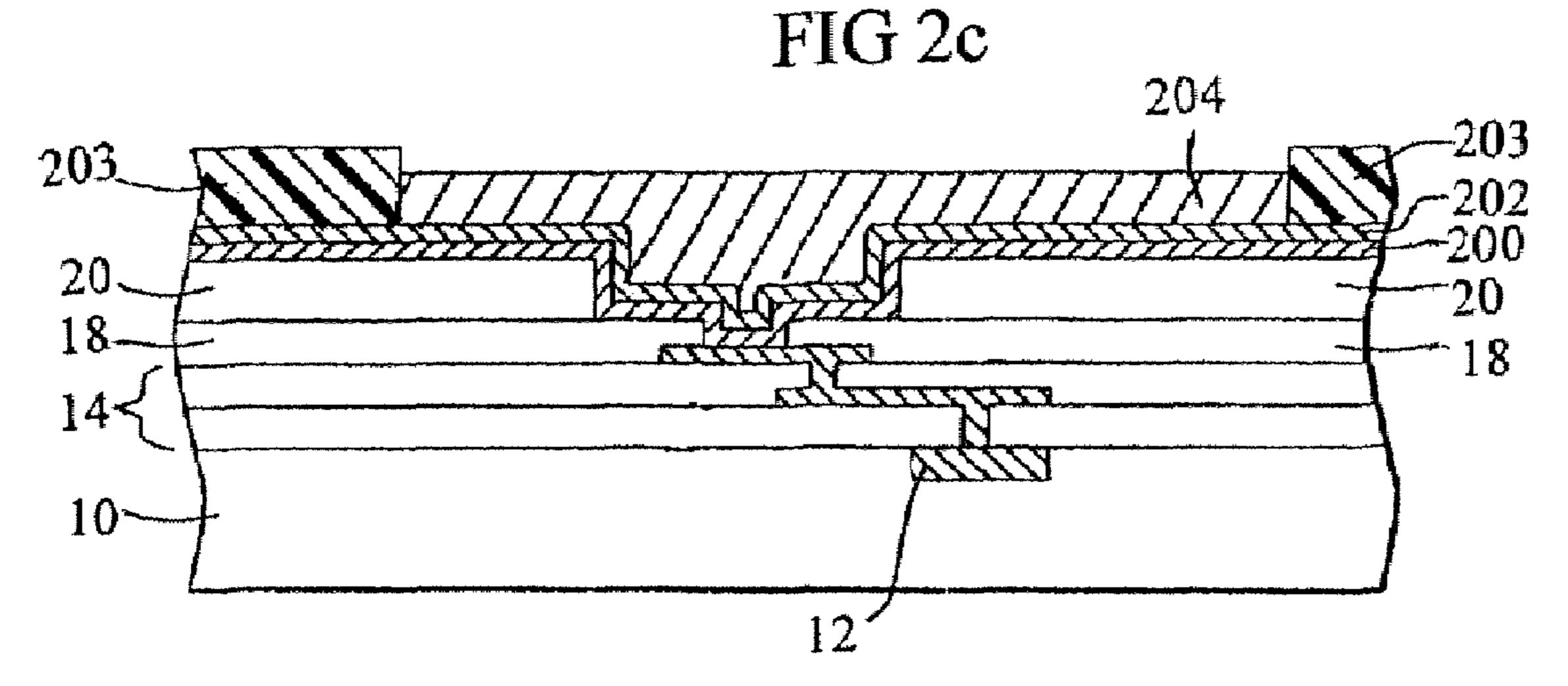

Subsequently, referring to FIG. 2c, a thick photoresist layer 203, such as positive photoresist, napthoquinone diazide, having a thickness of between 8 and 50 microns, can be spin coated onto the seed layer 202, wherein the thickness of the photoresist layer 203 may range from 1 micron to 100 microns. Next, the thick photoresist layer 203 is patterned by a photolithography process including exposing and developing steps to form multiple openings in the thick photoresist layer 203 exposing the seed layer 202, wherein a light (G-line) with a wavelength of between 434 nanometers and 437 nanometers may be used for performing the exposing step. A light (H-line) with a wavelength of between 403 nanometers and 406 nanometers may be used for performing the exposing step. A light (I-line) with a wavelength of

between 364 nanometers and 366 nanometers may be used for performing the exposing step. A 1× stepper or aligner is preferably used for performing the exposing step.

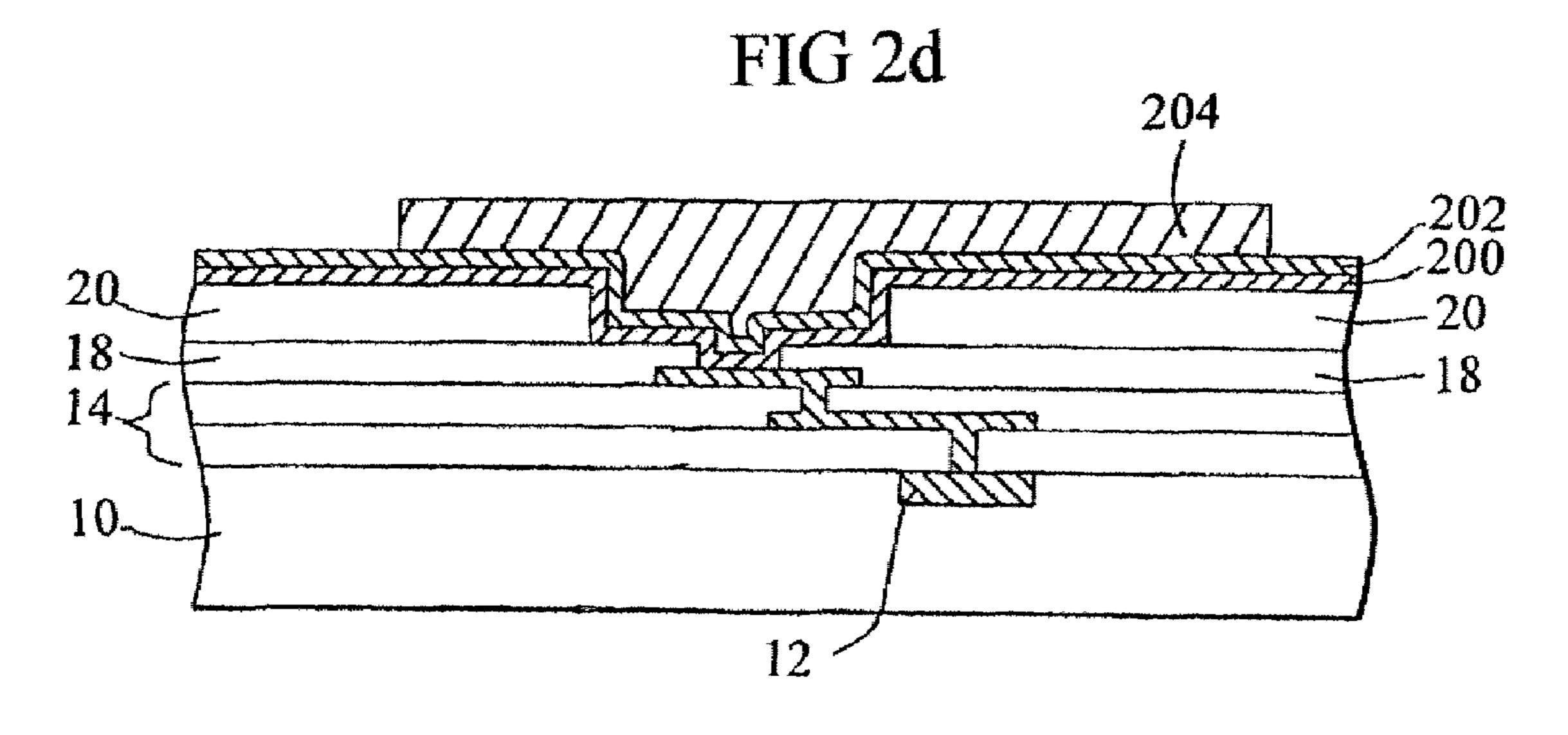

Referring to FIG. 2d, a metal layer 204, such as copper, gold, silver, palladium, platinum, rhodium, rhenium, ruthenium or nickel, having a thickness ranging from 1 micron to 100 microns, and preferably ranging from 2 microns to 10 microns, can be formed onto the seed layer 202 exposed by the openings in the thick photoresist layer 203 by using electroplating or electroless plating process. When the metal layer 10 204 has greater than 90 or even 99 weight percent of copper and formed by electroplating, the seed layer 202 preferably has greater than 90 or even 99 weight percent of copper.

When the metal layer **204** has greater than 90 or even 99 weight percent of gold and formed by electroplating, the seed 15 layer **202** preferably has greater than 90 or even 99 weight percent of gold.

When the metal layer **204** has greater than 90 or even 99 weight percent of silver and formed by electroplating, the seed layer **202** preferably has greater than 90 or even 99 20 weight percent of silver.

When the metal layer **204** has greater than 90 or even 99 weight percent of palladium and formed by electroplating, the seed layer **202** preferably has greater than 90 or even 99 weight percent of palladium.

When the metal layer 204 has greater than 90 or even 99 weight percent of platinum and formed by electroplating, the seed layer 202 preferably has greater than 90 or even 99 weight percent of platinum.

When the metal layer **204** has greater than 90 or even 99 weight percent of ruthenium and formed by electroplating, the seed layer **202** preferably has greater than 90 or even 99 weight percent of ruthenium.

When the metal layer **204** has greater than 90 or even 99 weight percent of rheniumnum and formed by electroplating, the seed layer **202** preferably has greater than 90 or even 99 weight percent of rhenium.

When the metal layer **204** has greater than 90 or even 99 weight percent of nickel and formed by electroplating, the seed layer **202** preferably has greater than 90 or even 99 40 weight percent of nickel.

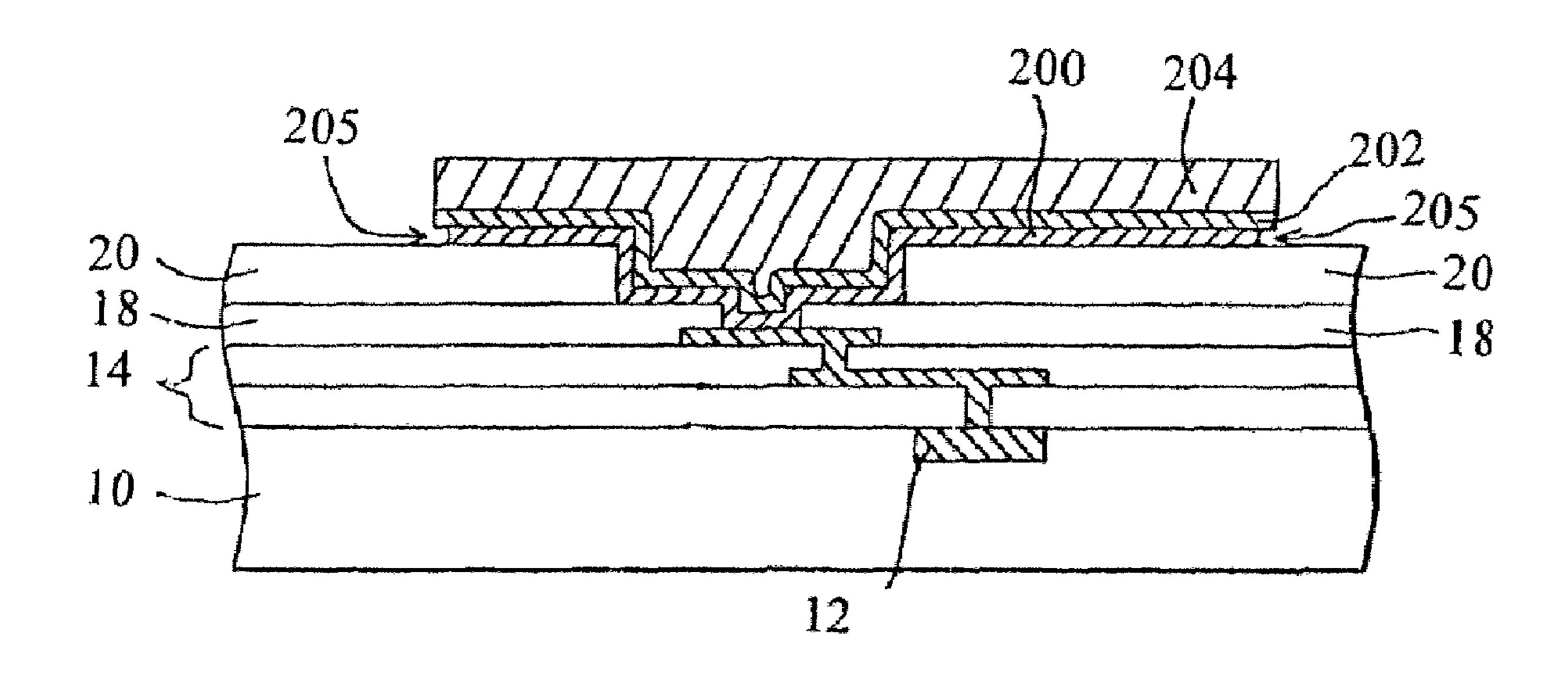

Next, Referring to the FIG. 2e, after forming the metal layer 204, the photoresist layer 203 can be removed. Thereafter, referring to the FIG. 2f, the seed layer 202 and adhesion/barrier layer 200 not under the metal layer 204 are sequently 45 removed by etching process.

The adhesion/barrier layer 200 is removed by self-aligned wet etching process. An undercut 205 can be formed around the adhesion/barrier layer 200 and under the metal layer 204. The lateral depth of the undercut 205 basically ranges about 50 from 0.03 microns to 2 microns and depends on the etching factors and etching time. An interface between the seed layer 202 formed by sputtering process and the metal layer 204 formed by electroplating process is a clear demarcation which can be observed by Transmission Electron microscope 55 (TEM).

Referring to FIG. 2g, in the above mentioned process, if the material of the metal layer 204 is copper, another metal layer 206 can be formed onto the metal layer 204 in order to protect the metal layer 204 of copper from being corroded, wherein 60 the material of the metal layer 206 may be gold, silver, palladium, platinum, rhodium, ruthenium, rhenium or nickel. The thickness of the metal layer 206 ranges, for example, from 1 micron to 100 microns, and preferably from 2 microns to 10 microns. The thickness of the metal layer 204 ranges, for example, from 1 micron to 100 microns, and preferably from 2 microns to 10 microns to 10 microns.

12

After the metal layer 204 is formed onto the seed layer 202 exposed by the openings in the photoresist layer 203, as shown in FIG. 2d, the metal layer 206 can be formed onto the metal layer 204 by using electroplating or electroless plating process. Next, a process for removing the photoresist layer 203 can be performed. Next, the seed layer 202 and adhesion/barrier layer 200 not under the metal layers 204 and 206 can be sequently removed by a wet etching process or a dry etching process. Thereby, the bottom surface of the metal layer 206 close to the edge thereof can be exposed after etching the the seed layer 202 and adhesion/barrier layer 200 not under the metal layers 204 and 206.

The thickness of the thick and wide metal line formed over the passivation layer **18** using above mentioned process ranges from 1 micron to 100 microns. The pitch between the neighboring wide and thick metal lines at same a same patterned metal layer can be greater than 2 microns.

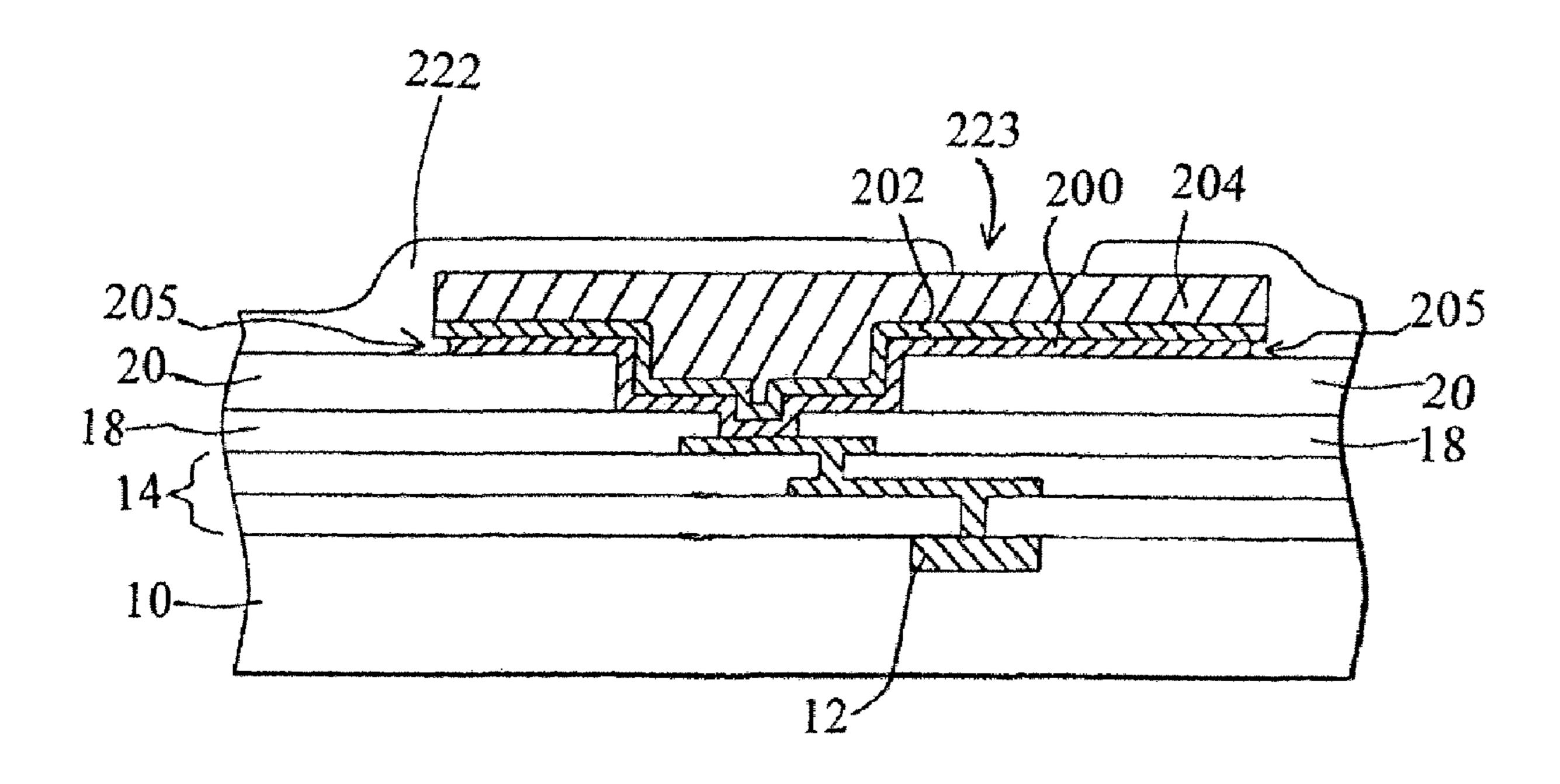

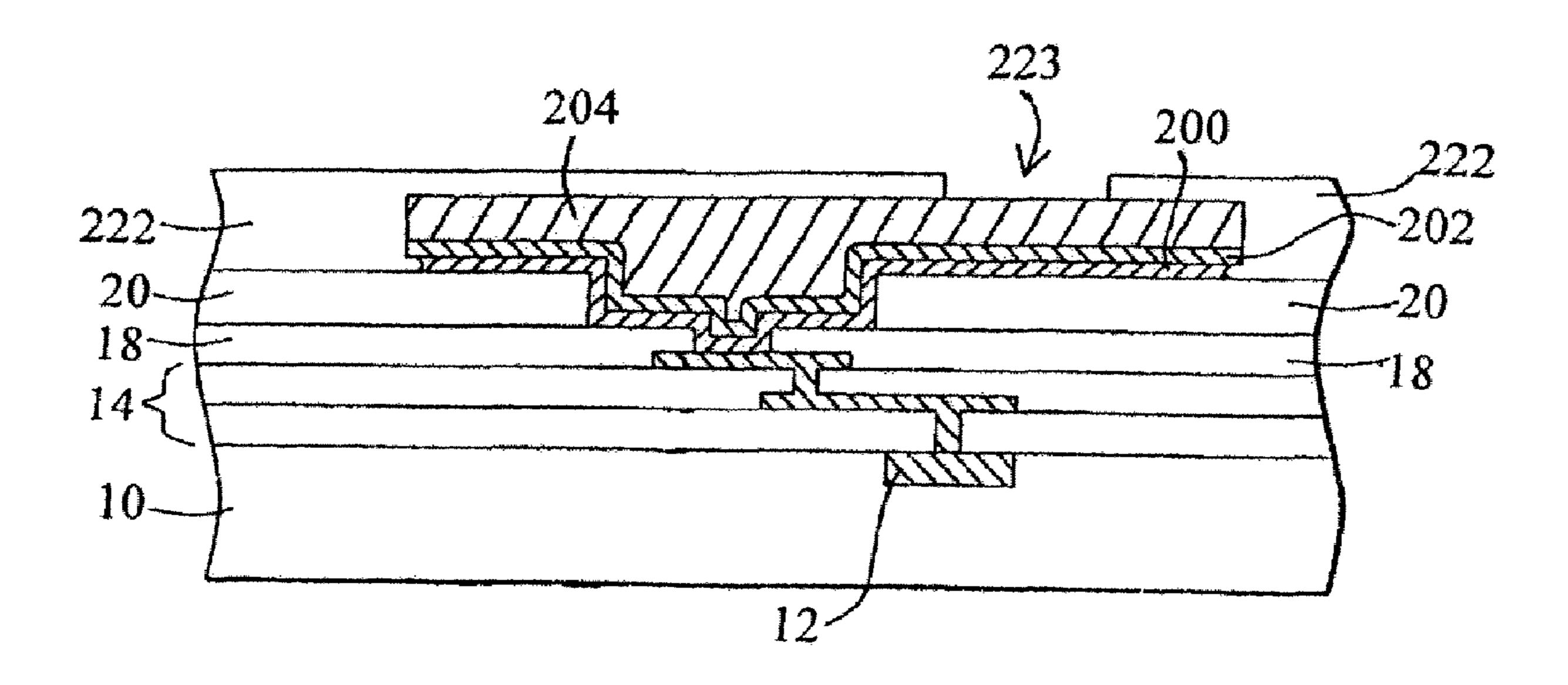

Referring to FIG. 2h, after forming the thick and wide metal line composed of the metal layers 200, 202 and 204 over the polymer layer 20, another polymer layer 222 can be formed onto the thick and wide metal line and the polymer layer 20 in order to protect the thick and wide metal line formed before, wherein the method of forming the polymer layer 222 can be referred to as the previous mentioned method of forming the polymer layer 20. The openings 223 in the polymer layer 222 may expose the bond pads of the thick and wide metal line. Next, tin-containing bumps, such as tin-lead alloy or tin-silver alloy, and gold bumps can be formed over the bond pads exposed by the openings 223 in the polymer layer 222, or gold wires formed by a wire bonding process can be bonded over the bond pads exposed by the openings 223 in the polymer layer 222.

Due to the projecting thick and wide metal line composed of the metal layers 200, 202 and 204, the polymer layer 222 can not be formed with a flat top surface. To resolve the issue, a process for planarizating the polymer layer 222 can cause the polymer layer 222 have a flat top surface, as shown in FIG. 2i, wherein the material of the polymer layer 222 may be, for instance, BenzoCycloButene (BCB), polyimide, parylene, porous dielectric or elastomer, etc.

Referring to FIG. 2i, the detailed process, for example, is as follows: After forming the polymer layer 222 over the polymer layer 20 and over the thick metal line composed of the metal layers 200, 202 and 204 by spin-on coating process, the polymer layer 222 can be cured by a heating process, followed by planarizing the top surface of the polymer layer 222 using a Mechanical polishing process (MP) or Chemical mechanical polishing process (CMP), followed by forming the openings 223 in the polymer layer 222 using photolithography and etching processes, the openings 223 exposing the bond pads of the thick and wide metal line composed of the metal layers 200, 202 and 204.

Alternatively, after forming the polymer layer 222 over the polymer layer 20 and over the thick metal line composed of the metal layers 200, 202 and 204 by a spin-on coating process, the top surface of the polymer layer 222 can be planarizated by using a Mechanical polishing process (MP) or a Chemical mechanical polishing process (CMP), followed by forming the openings 223 in the polymer layer 222 using photolithography and/or etching processes, the openings 223 exposing the bond pads of the thick and wide metal line composed of the metal layers 200, 202 and 204, followed by curing the polymer layer 222 using a heating process.

Alternatively, after forming the polymer layer 222 over the polymer layer 20 and over the thick metal line composed of the metal layers 200, 202 and 204 by spin-on coating process, the openings 223 in the polymer layer 222 are formed using

photolithography and etching processes, the openings 223 exposing the bond pads of the thick and wide metal line composed of the metal layers 200, 202 and 204, followed by planarizing the top surface of the polymer layer 222 using a Mechanical polishing process (MP) or a Chemical mechanical polishing process (CMP), followed by curing the polymer layer 222 using a heating process.

Alternatively, after forming the polymer layer 222 over the polymer layer 20 and over the thick metal line composed of the metal layers 200, 202 and 204 by a spin-on coating process, the openings 223 may be formed in the polymer layer 222 using photolithography and/or etching processes, the openings 223 exposing the bond pads of the thick and wide metal line composed of the metal layers 200, 202 and 204, followed by curing the polymer layer 222 using a heating 15 process, followed by planarizing the top surface of the polymer layer 222 using a Mechanical polishing process (MP) or a Chemical-mechanical polishing process (CMP).

In the above mentioned process for forming the flat polymer layer 222, the conditions of curing the polymer layer 222 can be referred to those for curing the polymer layer 20, as shown in FIG. 1b.

The method for forming the polymer layer 222 disclosed in FIGS. 2h and 2i can be employed to form a polymer layer on the thick and wide metal line composed of metal layers 20, 25 202, 204 and 206, as shown in FIG. 2g, over the passivation layer 18.

Alternatively, the above-mentioned thick metal line over the passivation layer 18 may only cover partial side wall of the openings in the polymer layer 20. The related process can be 30 referred to the FIGS. 2j and 2k.

Referring to FIG. 2*j*, after forming the adhesion/barrier layer 200 and seed layer 202 onto the polymer layer 20, onto the side wall of the openings 27 in the polymer layer 20, and onto the electric bond pads 16 exposed by the openings of the 35 passivation layer 18, A patterned photoresist layer 203 can be formed onto the seed layer 202. A part of the patterned photoresist layer 203 is located in the openings 27 in the polymer layer 20 and covers the seed layer 202 on the side wall of the openings 27, and then, the metal layer 204 can be formed on 40 the seed layer 202 exposed by the openings in the photoresist layer 203.

In this embodiment, the method for forming the adhesion/barrier layer 200, the seed layer 202 and the metal layer 204 and their corresponding material and thickness can be 45 referred to as the above-mentioned elements indicated by a same reference number, as shown in FIGS. 2*a*-2*f*.

Referring to FIG. 2k, next, the patterned photoresist layer 203 can be removed, and then the seed layer 202 and adhesion/barrier layer 200 not under the metal layer 204 can be 50 removed, wherein an undercut 205 exists below the seed layer and around the adhesion/barrier layer 200. In this embodiment, the size of the undercut 205 can be referred to the description of that shown in FIG. 2f. As a result, the thick metal line located on the passivation layer 18 can only cover 55 a part of the side wall of the openings 27 in the polymer layer 20

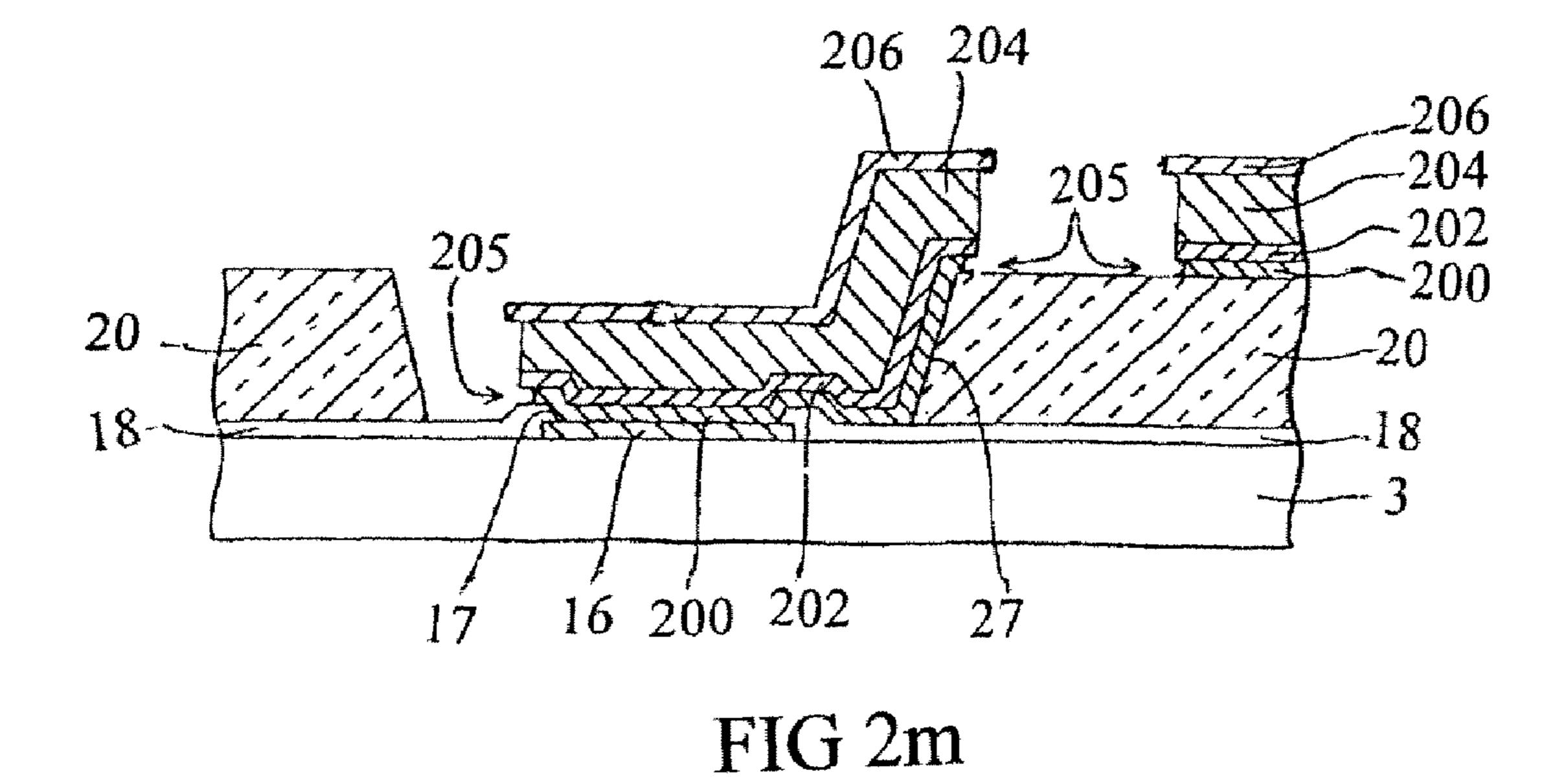

Besides, if the material of the metal layer 204 is copper, another metal layer 206 can be formed onto the metal layer 204 in order to protect the metal layer 204 of copper from 60 being corroded, wherein the material of the metal layer 206 may be, for example, gold, silver, palladium, platinum, rhodium, ruthenium rhenium, or nickel. The thickness of the metal layer 206 ranges, for example, from 1 micron to 100 microns and the thickness of the metal layer 204 ranges, for 65 example, from 1 micron to 100 microns, as shown in FIGS. 21-2m.

**14**

Referring to the FIG. 21, after the metal layer 204 is formed onto the seed layer 202 exposed by the openings in the photoresist layer 203, as shown in FIG. 2j, the metal layer 206 can also be formed on the metal layer 204 using an electroplating or electroless plating process, followed by, referring to the FIG. 2m, removing the photoresist layer 203. Next, the patterned photoresist layer 203 can be removed, and then the seed layer 202 and adhesion/barrier layer 200 not under the metal layer 204 can be removed, wherein an undercut 205 exists below the seed layer and around the adhesion/barrier layer 200. In this embodiment, the method for forming the adhesion/barrier layer 200, the seed layer 202 and the metal layers 204 and 206 and their corresponding material and thickness can be referred to as the above-mentioned elements indicated by a same reference number, as shown in FIGS. 2a-2g.

Referring to the FIGS. 2*j*-2*m*, the greatest transverse dimension of the openings 27 in the polymer layer 20 is greater than that of the openings in the passivation layer 18, wherein the 1 greatest transverse dimension of the openings 17 in the passivation layer 18 ranges, for example, from 0.1 microns to 50 microns and, preferably, from 0.5 microns to 20 microns. The greatest transverse dimension of the openings 27 in the polymer layer 20 ranges, for example, from 1 micron to 100 microns, and preferably from 2 microns to 30 microns.

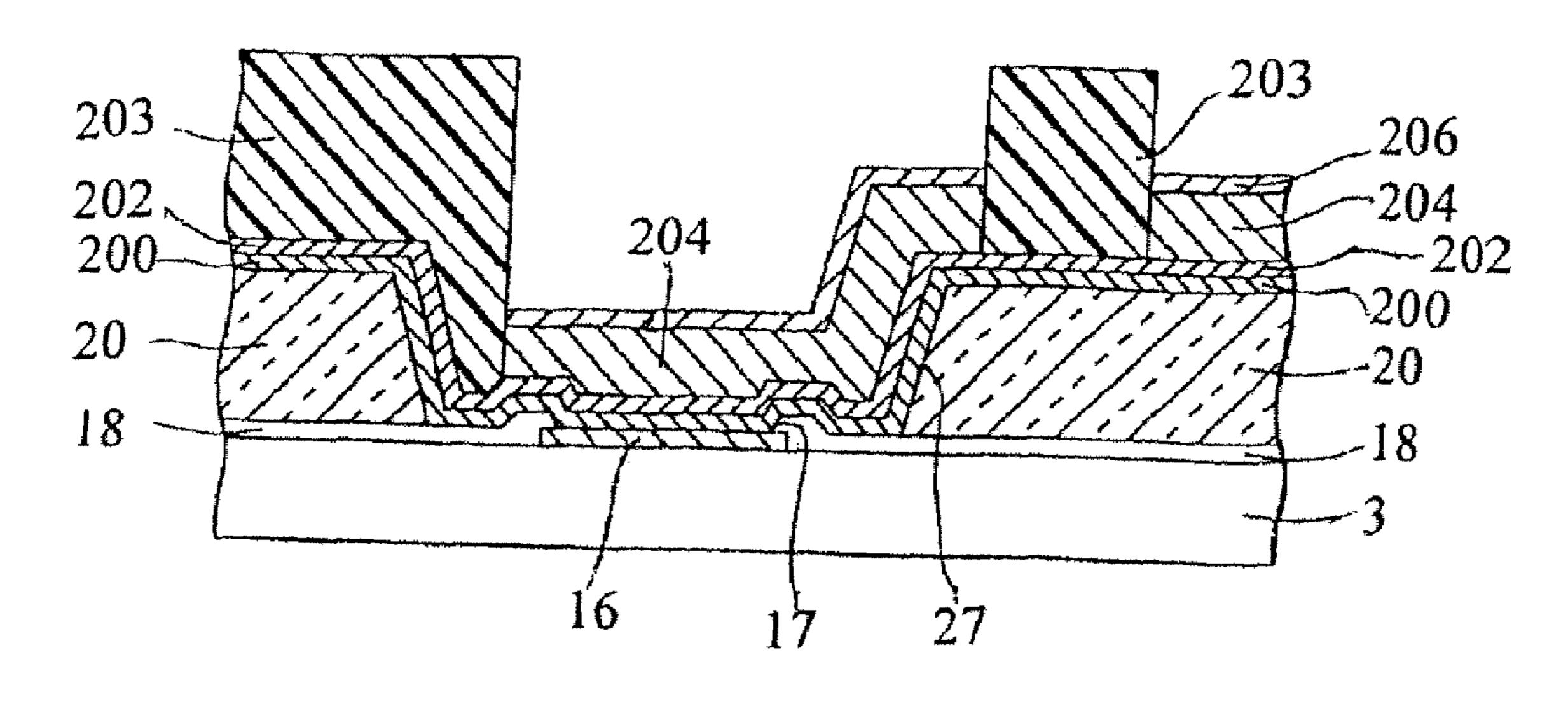

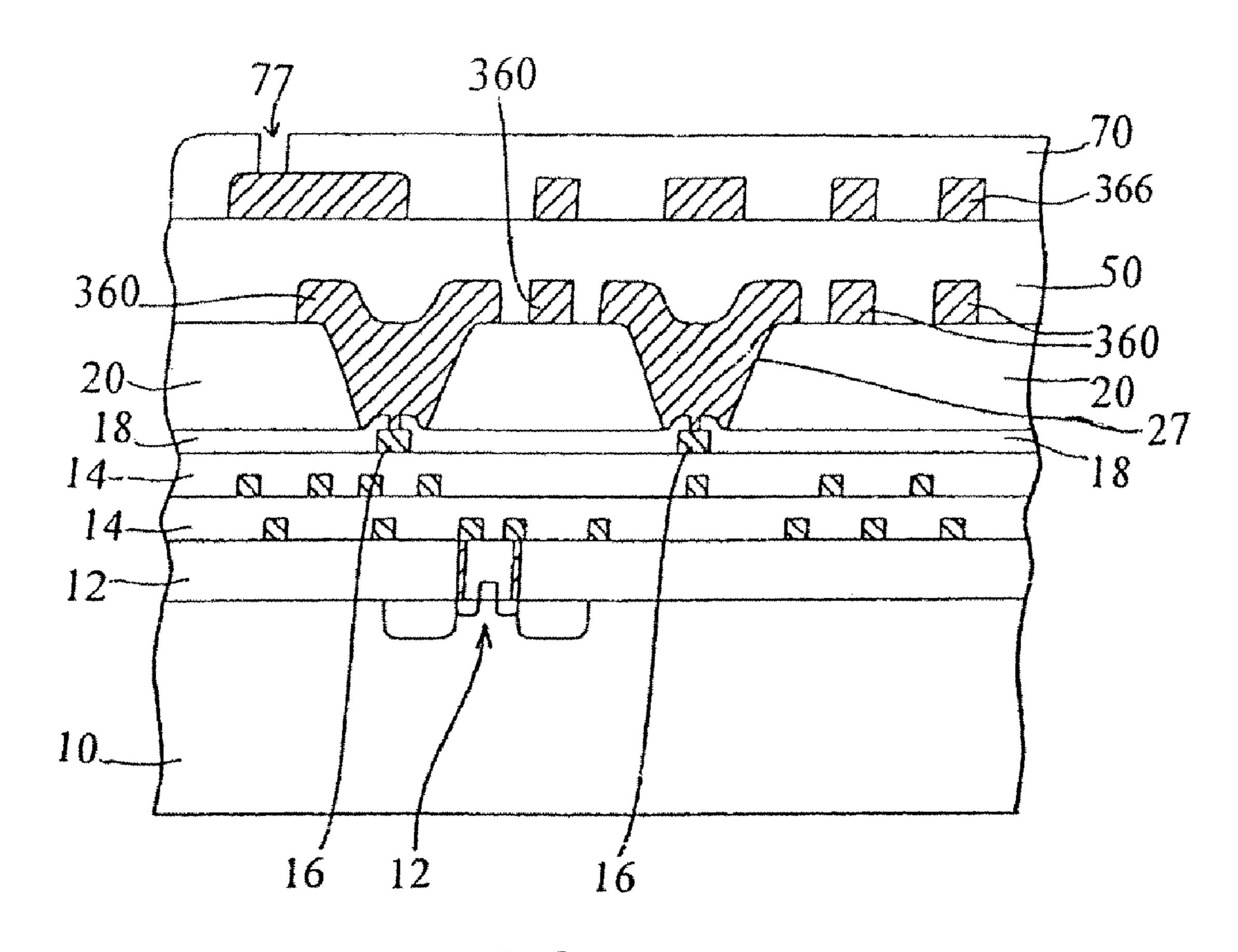

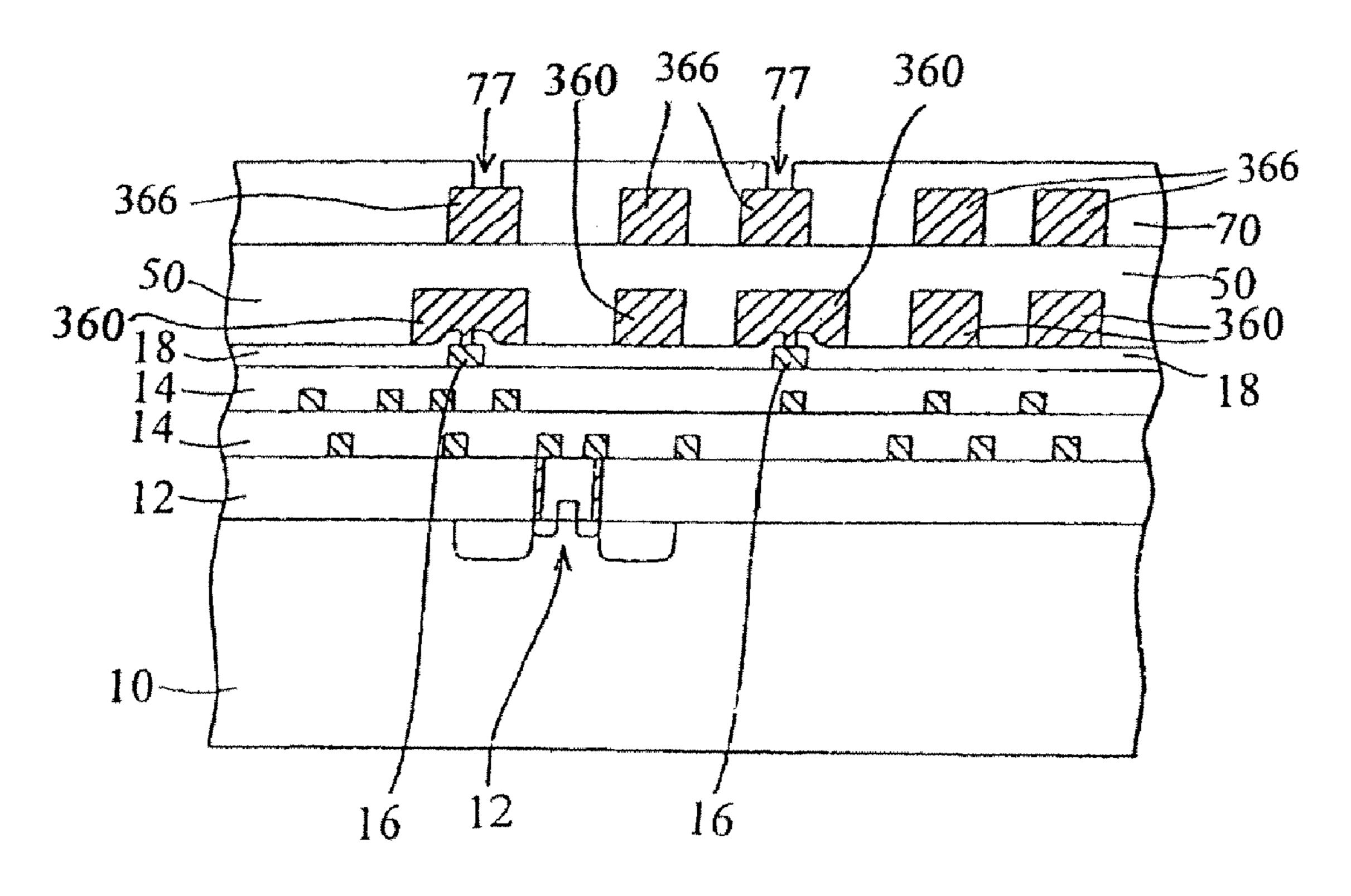

In an embodiment, multiple thick metal layers and multiple thick polymer layers may be formed over the passivation layer, as shown in FIGS. 3a and 3b. Referring to FIG. 3a, a polymer layer 20 is formed on the passivation layer 18. The method of forming the polymer layer 20 and the material thereof can be referred to the above disclosure of the polymer layer 20 shown in FIG. 1b. Next, a thick metal layer 30 is formed on the polymer layer 20 and connected to the electrical bond pads 16 through the openings in the polymer layer 20 and in the passivation layer 18. The method for forming the thick metal layer 30 and the structure thereof can be referred to the above disclosure of the thick metal layer as shown in FIGS. 2a-2g and 2j-2m.

Next, a polymer layer 50 is formed onto the polymer layer 20 and onto the thick metal layer 30, wherein the method for forming the polymer layer 50 and the structure thereof can be referred to the above disclosure of the polymer layer 20 shown in FIG. 1b. Next, a thick metal layer 60 is formed onto the polymer layer 50 and connected to the thick metal layer 30 through the openings of the polymer layer 50. The method for forming the thick metal layer 50 and the structure thereof can be referred to the above disclosure of the thick metal layer as shown in FIGS. 2a-2g and 2j-2m.

Next, a polymer layer 70 is formed onto the polymer layer 50 and onto the thick metal layer 60, wherein the method for forming the polymer layer 70 and the structure thereof can be referred to the above disclosure of the polymer layer 20 shown in FIG. 1b. Openings in the polymer layer 70 may expose the bonding pads of the thick metal layer 60. Next, a tin-containing bump or gold bump can be formed over the bonding pads of the thick metal layer 60. Alternatively, gold wires formed by a wirebonding process can be bonded over bonding pads the thick metal layer 60 exposed by the openings in the polymer layer 70. Thereby, the above-mentioned polymer layer and the above-mentioned thick metal layer can be alternately and repeatedly deposited to form multiple polymer layers and multiple thick metal layers over the passivation layer 18.

In another embodiment, referring to FIG. 3c, a polymer layer 20 is formed on the passivation layer 18. The method of forming the polymer layer 20 and the material thereof can be referred to the above disclosure of the polymer layer 20

shown in FIG. 1b. Next, a thick metal layer 30 is formed on the polymer layer 20 and connected to the electrical bond pads 16 through the openings in the polymer layer 20 and in the passivation layer 18. The method for forming the thick metal layer 30 and the structure thereof can be referred to the 5 above disclosure of the thick metal layer as shown in FIGS. 2a-2g and 2j-2m. Next, a polymer layer 50 is formed onto the polymer layer 20 and onto the thick metal layer 30, wherein the polymer layer 50 covers the sidewall of the polymer layer 20. The polymer layer 50 can be formed by spin-coating a 10 precursory polymer layer on the thick metal layer 30, on the polymer layer 20, on the passivation layer 18 and on the electrical contact pad 16 exposed by the opening 29 in the passivation layer 18, next patterning the polymer layer 50 to remove the precursory polymer layer on the passivation layer 15 18, to remove the precursory polymer layer on the electrical bonding pads 16 exposed by the opening 29 in the passivation layer 18, and to form an opening 28 in the precursory polymer layer exposing the bonding pad of the thick metal layer 30. The method for forming the polymer layer **50** and the struc- 20 ture thereof can be referred to the above disclosure of the polymer layer 20 shown in FIG. 1b. Next, a tin-containing bump or gold bump can be formed over the bonding pads of the thick metal layer 30 exposed by the openings 28 in the polymer layer 50, or over the bonding pad exposed by the 25 openings 29 in the passivation layer 18. Alternatively, gold wires formed by a wirebonding process can be bonded over the bonding pads of the thick metal layer 30 exposed by the openings 28 in the polymer layer 50, or over the bonding pad exposed by the openings 29 in the passivation layer 18.

Referring to FIGS. 3a, 3b and 3c, the thick metal trace 26 of the thick metal layer 30 over the passivation layer may connect the gates of two MOS devices. The thick metal trace 26 may have a function to transmit a signal, or may be a power bus or a ground bus distributing power and connected to the 35 power bus or ground bus of the thin-film metal layers under the passivation layer 18. The thick metal layers 30 and 60 formed over the passivation layer 18 may be used as a signal trace, power bus or ground bus, which leads an external circuitry, such as printed circuit board, connected with the 40 thick metal layers 30 and 60 to be designed with simple routing.

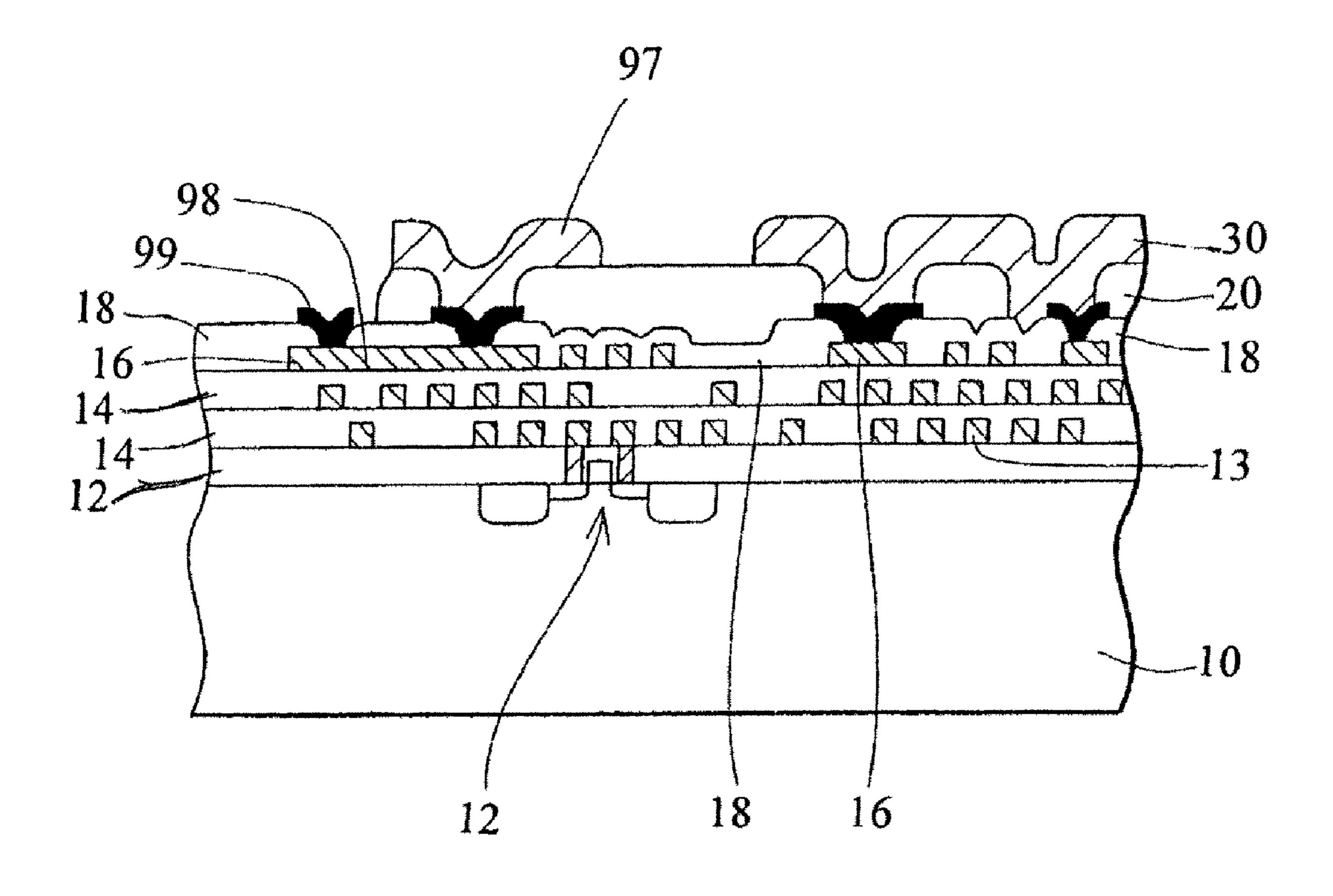

Referring to FIG. 3d, A metal cap 99 (the leftmost one) over the bonding pad exposed by the opening in the passivation layer 18 may be connected to the thick metal line 97 over the 45 passivation layer 18 through an interconnection trace 98 under the passivation layer 18 and with a short distance. The interconnection trace 98 may be formed by, for example, sputtering aluminum or damascening copper. The routing length of the interconnection trace 98 ranges, for instance, 50 from 50 microns to 1000 microns. After forming the thick metal layer 30, tin-containing bumps, such as tin-lead alloy or tin-silver alloy, gold bumps or wires formed by a wire bonding process can be formed onto the metal cap 99 and can connect the metal cap 99 to an external circuitry, such as 55 printed circuit board.

Alternatively, as illustrated in FIGS. 3a, 3b, 3c and 3d, the step of forming the polymer layer 20 can be omitted and thereby the thick metal layer 30 can be formed directly onto and in contact with the passivation layer 18.

FIGS. 4a, 5a, 6a and 7a show the concept of fanning out bond pads, relocating bond pads, reducing the number of bond pads, and increasing the number of bond pads through the printed circuit board PCB, wherein the bond pads are, for example, used for transmitting signals, connecting ground 65 voltage or power voltage. FIGS. 4b, 5b, 6b and 7b show the concept of fanning out bond pads, relocating bond pads,

**16**

reducing the number of bond pads, and increasing the number of bond pads through the thick and wide metal lines over the passivation layer, wherein the bond pads are, for example, used for transmitting signals, connecting ground voltage or power voltage.

FIG. 4a shows the concept of fanning out a BGA substrate employed in a flip chip package. For example, an Integrated Circuit 100 contains five tin-lead bumps 101-105. Through the metal traces 107 within the BGA substrate 130, the tinlead bump 101 and the planted solder ball 111 having different input/output layouts from a bottom perspective view can be electrically connected with each other. The tin-lead bump 102 and the planted solder ball 112 having different input/ output layouts from a bottom perspective view can be electrically connected with each other. The tin-lead bump 104 and the planted solder ball 114 having different input/output layouts from a bottom perspective view can be electrically connected with each other. The tin-lead bump 105 and the planted solder ball 115 having different input/output layouts from a bottom perspective view can be electrically connected with each other. The distance between the neighboring planted solder balls 111-115 is greater than that between the neighboring tin-lead bumps 101-105. The closer to the middle of the semiconductor chip 100 a planted solder ball is, the smaller the lateral distance from a bottom perspective view between the tin-lead bump and the planted solder ball connected with each other is. For instance, the lateral distance from a bottom perspective view between the tin-lead bump 103 and the planted solder ball 113 is smaller than that of the tin-lead bump 101 relating to the planted solder ball 111.

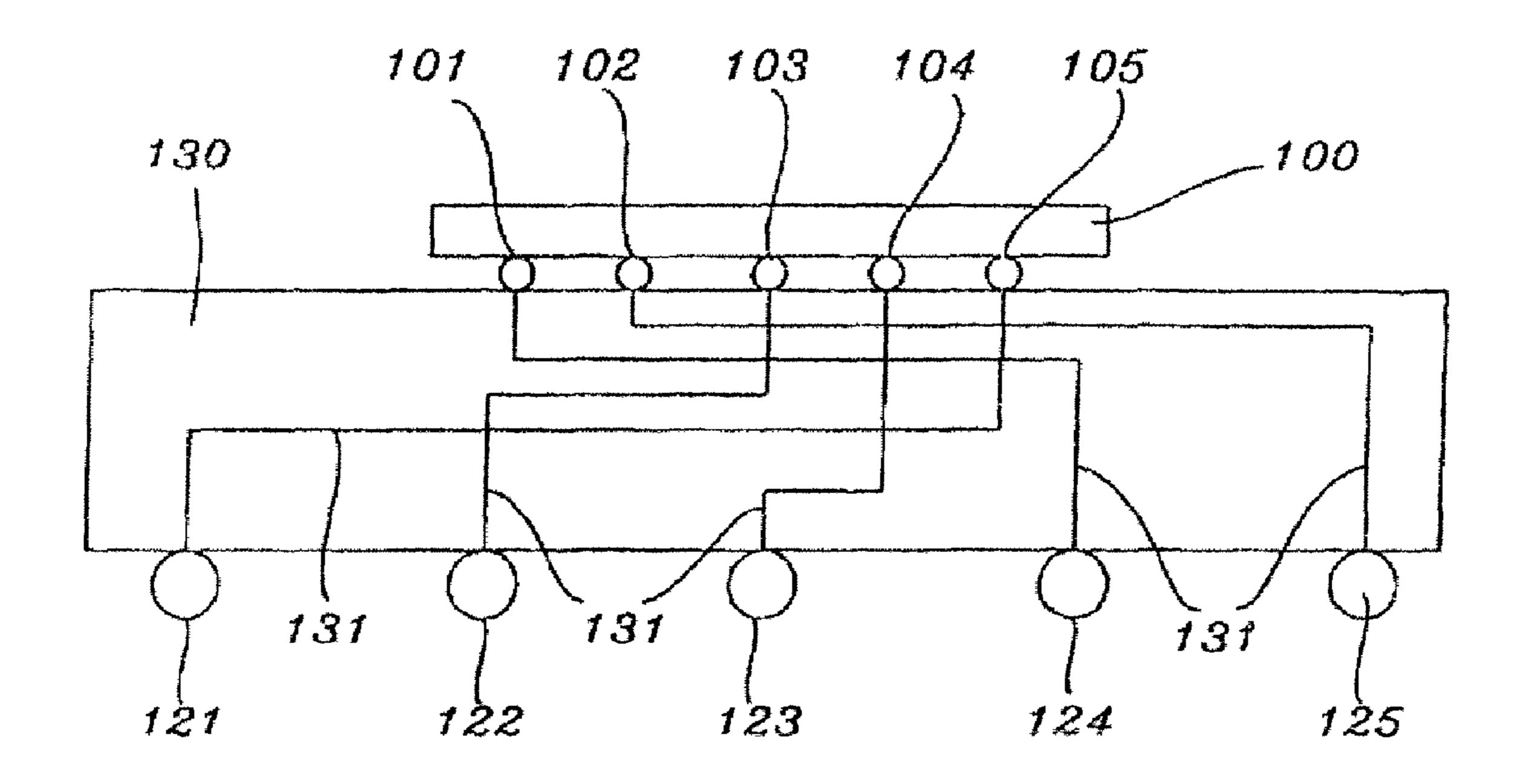

FIG. 5a shows the concept of relocating input/output contact points applied for the connection with a BGA substrate in a flip chip package. For example, an Integrated Circuit 100 contains five tin-lead bumps 101-105. Through the metal traces 131 within the BGA substrate 130, the positions of the tin-lead bumps 101-105 can be relocated to other positions of the planted solder balls 124, 125, 122, 123 and 121, respectively. For example, the leftmost tin-lead bump 101 can be connected to the second right planted solder ball 124 under the BGA substrate 130 through one of the metal traces 131 within the BGA substrate 130.

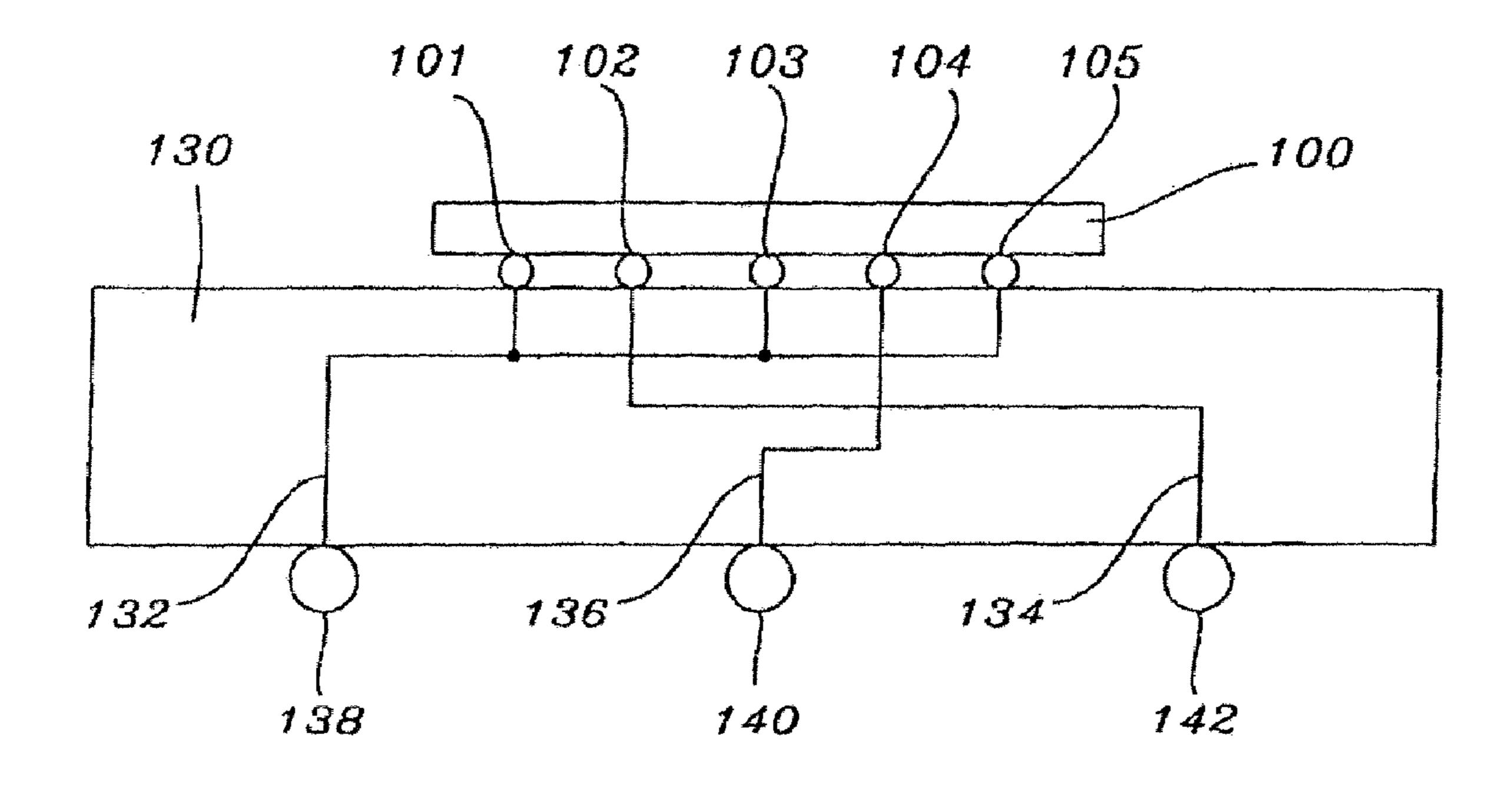

FIG. 6a shows the concept of reducing the total number of the input/output count applied to the connection with a BGA substrate in a flip chip package. For example, an Integrated Circuit 100 contains five tin-lead bumps 101-105, wherein the tin-lead bumps 101-105 can be connected to a BGA substrate 130. As shown in FIG. 6a, the BGA substrate 130 contains three trace units 132, 134 and 136 used for, for instance, the power distribution, ground distribution and signal distribution of the IC, respectively.

The tin-lead bumps 101, 103 and 105 can be connected to a planted solder ball 138 under the BGA substrate 130 through the trace unit 132 within a BGA substrate 130. Other tin-lead bumps 102 and 104 can be relocated to other planted solder balls 142 and 140, respectively. In this embodiment, through the BGA substrate, the total number of the Input/Output contact points used to be connected to the IC 100 can be reduced from 5 to 3.

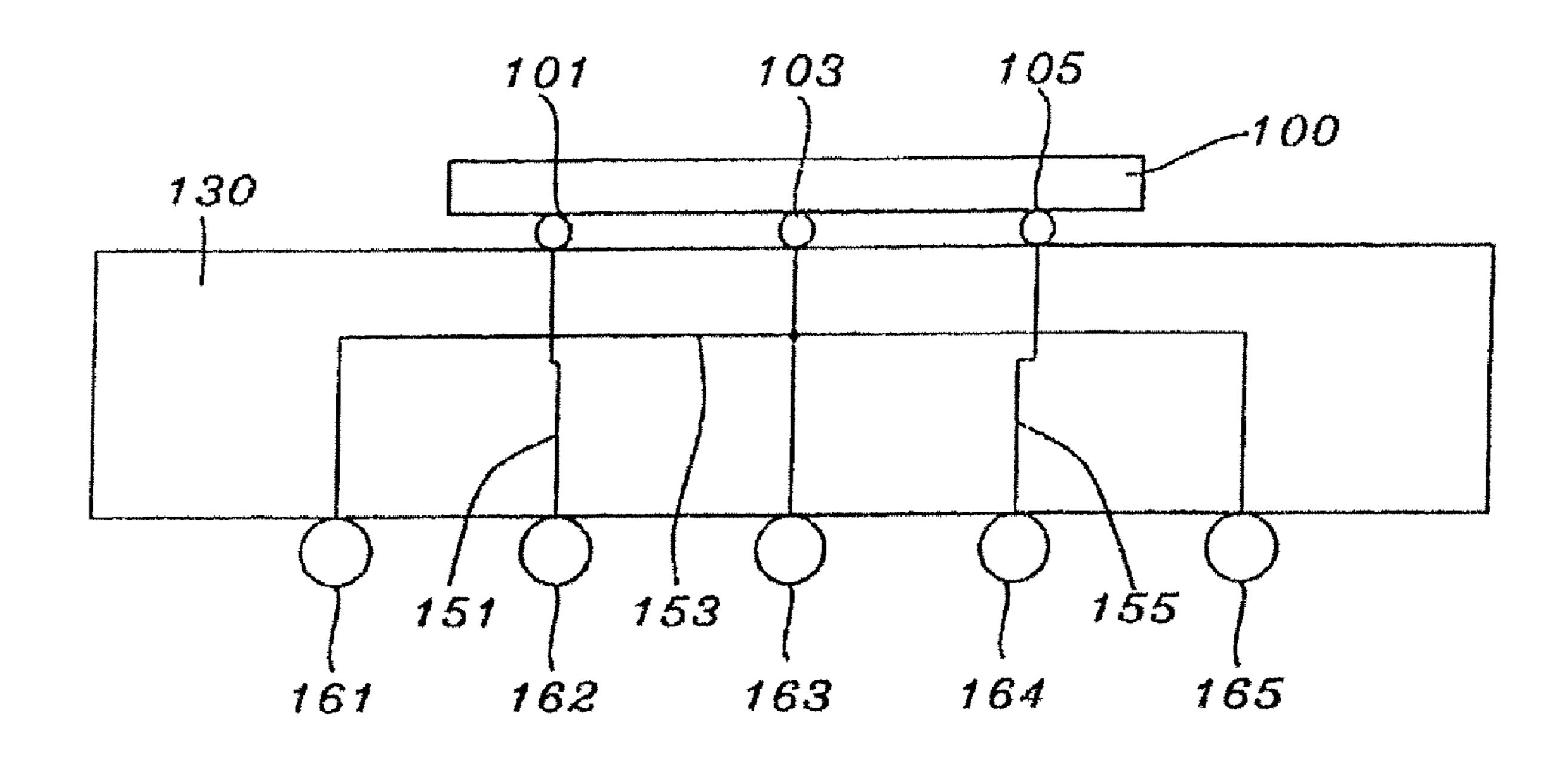

FIG. 7a shows the concept of enhancing the Input/Output contact points applied to the connection with a BGA substrate in a flip chip package. For example, an IC 100 contains three tin-lead bumps 101-103. As shown in FIG. 7a, the BGA substrate 130 contains three trace units 151, 153 and 155, which are used for the power distribution, ground distribution and signal distribution, respectively.

The tin-lead bump 103 can be connected to three planted solder balls 161, 163 and 165 under the BGA substrate

through the trace unit 153 within the BGA substrate 130. Other tin-lead bumps 101 and 105 can be connected to other planted solder balls 162 and 164, respectively. In this embodiment, the total number of the Input/Output contact points used to be connected to the IC 100 can be enhanced from 3 to 5

The above mentioned functions of the BGA substrate 130 including fanning out layout, relocating layout, reducing the total number of Input/Output counts and enhancing the total number of Input/Output counts, can be realized through forming the above mentioned thick metal lines over the passivation layer 4. According to FIGS. 4b, 5b, 6b and 7b, the concepts of fanning out bond pads, relocating bond pads, reducing or enhancing the total number of Input/Output counts can be realized by forming the above-mentioned thick metal line 15 over the passivation layer 4, mentioned as follows.

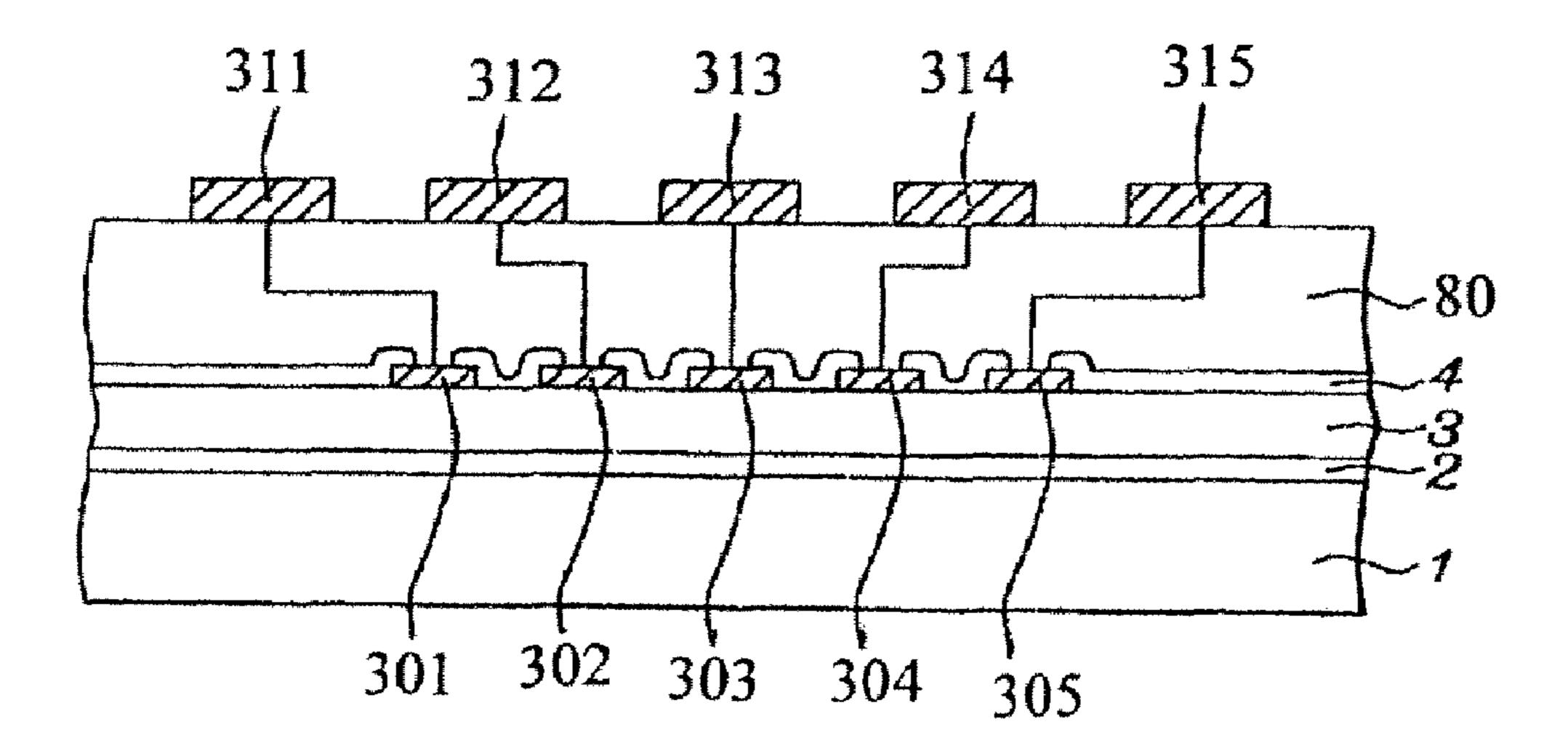

The thick metal lines formed over the passivation layer 4 may have the function of fanning out bond pads, as shown in FIG. 4b. FIG. 4b shows that the thick metal line has the function of fanning out bond pads. The metal bond pads 20 301-305 exposed by the openings in the passivation layer 4 can be fanned out to external contact points 311-315 respectively through the above mentioned thick metal lines over the passivation layer 4. Multiple tin-lead bumps, gold bumps or wires formed by a wirebonding process can be connected to 25 the external contact points 311-315.

The metal bond pads 301-305 exposed by the openings in the passivation layer 4 can be arranged as an array. In this embodiment, only one row of the array is shown. The metal bond pads 301-305 can be fanned out to external contact 30 points 311-315 in sequence through the above mentioned thick metal lines over the passivation layer 4. The fanned out external contact points 311-315 can also be arranged in an array. This embodiment shows only one row **311-315** of the array of the external contact points. The distance between the 35 neighboring external contact points 311-315 can be greater than that between the neighboring metal bond pads 301-305. The closer to the middle of the semiconductor chip an external contact point is, the smaller the lateral distance from a bottom view between the external contact point and the metal 40 bond pad connected with each other is. For example, the lateral distance from a bottom perspective view between the external contact point 313 and the metal bond pad 303 is smaller than that between the external contact point 311 and the metal bond pad 301.

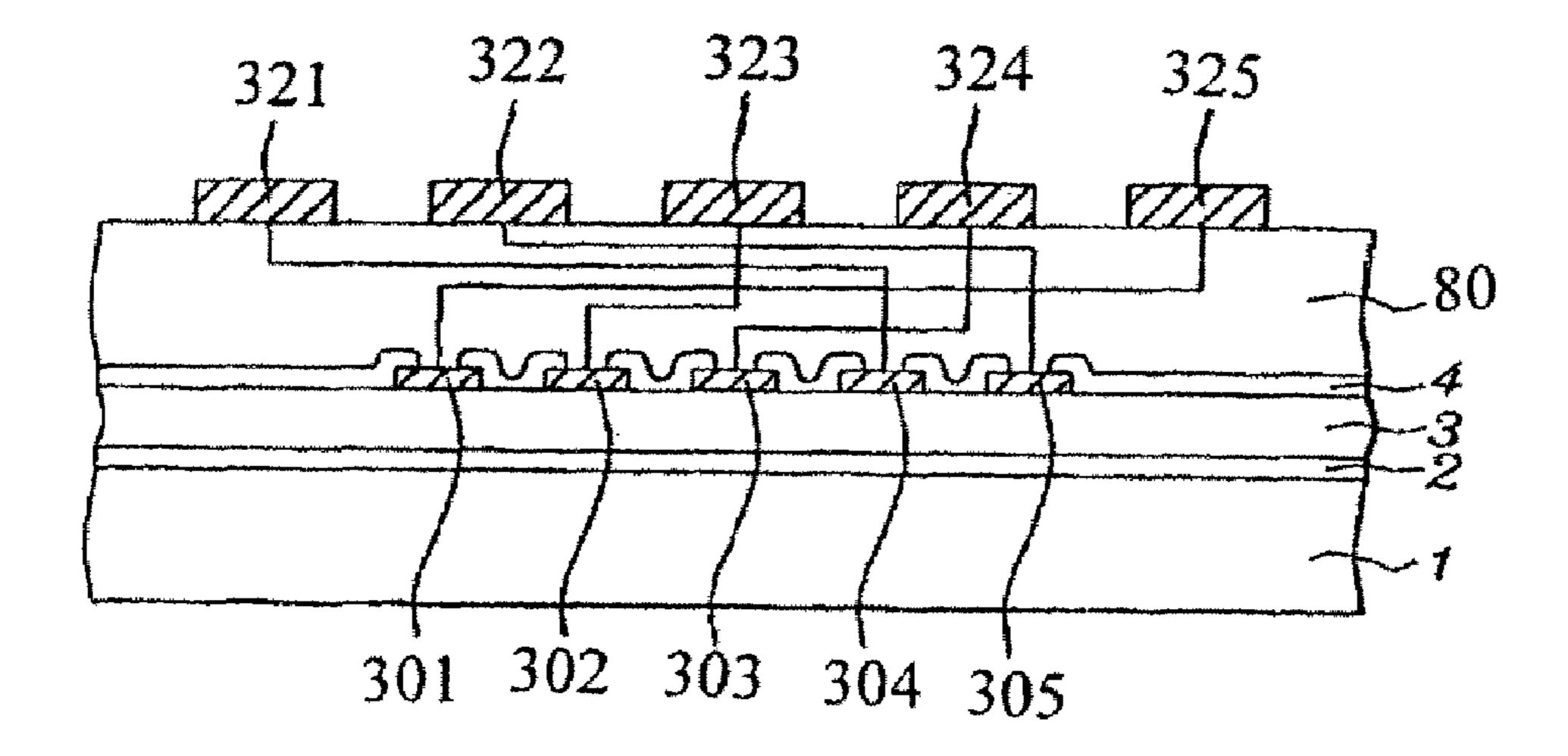

The above-mentioned thick metal line formed over the passivation layer 4 may have the function of relocating input/ output positions and sequence, as shown in FIG. 5b. FIG. 5b shows that the above-mentioned thick metal lines have the function of relocating input/output positions and sequence. 50 Through the previous mentioned thick metal lines over the passivation layer 4, the metal bond pads 301-305 exposed by the openings of the passivation layer 4 can be connected respectively to the external contact points 325, 323, 324, 321 and **322** whose positions and sequence are different from 55 those of the metal bond pads 301-305. Tin-containing bumps, such as tin-lead alloy or tin-silver alloy, or gold bumps can be formed over the external contact points 321-325. Alternatively, wires formed by a wirebonding process can be bonded over the external contact points 321-325. The distance 60 between the neighboring external contact points 321-325 can be greater than that between the neighboring metal bond pads **301-305**.

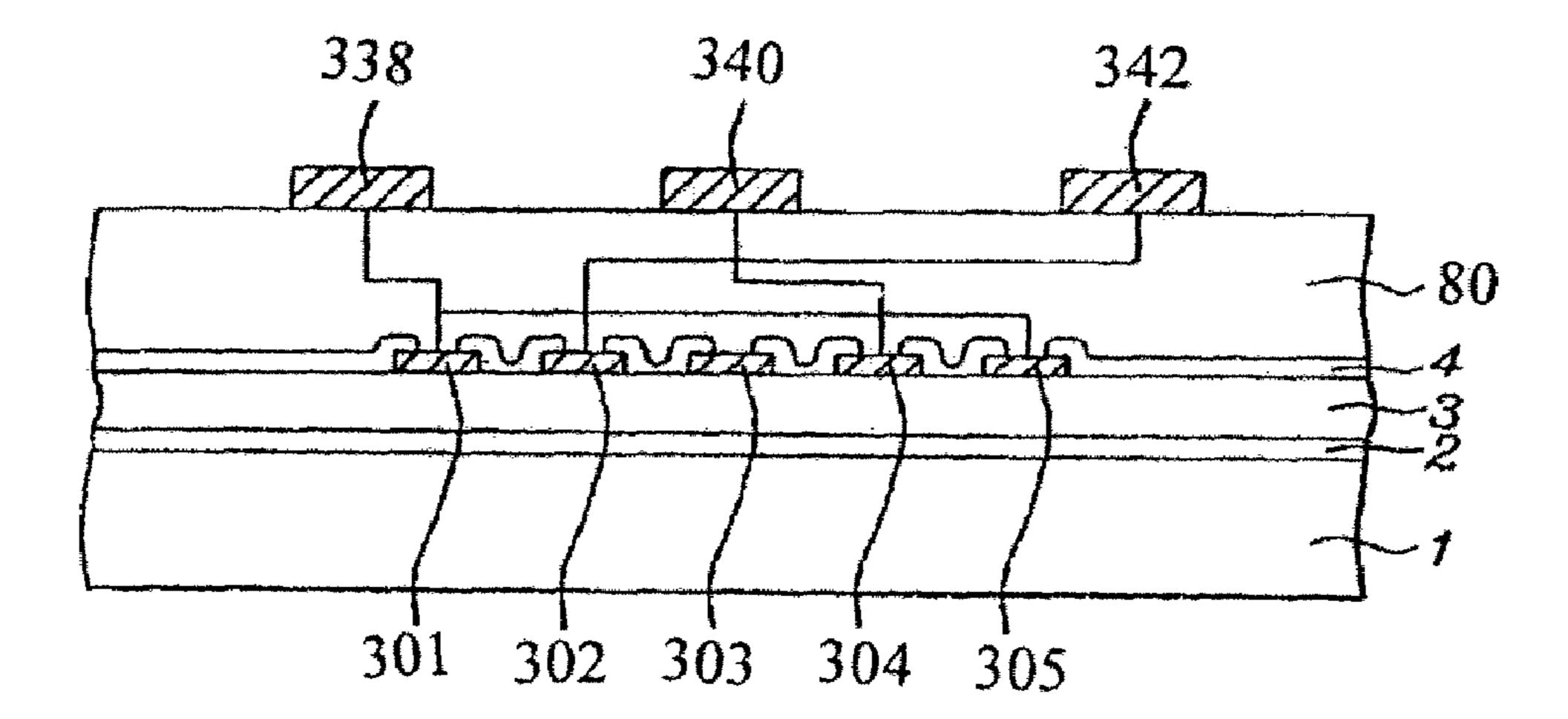

The thick metal lines formed over the passivation layer 4 may have a function of reducing the total number of the 65 input/output count of a semiconductor chip, as shown in FIG. 6b. FIG. 6b shows that the thick metal lines have the function

18

of reducing the total number of the input/output count. Through the previous mentioned thick metal lines over the passivation layer 4, the metal bond pads 301 and 305 exposed by the openings of the passivation layer 4 can be connected respectively to one external contact point 338 in order to perform the same function, such as being used for distribution of power voltage, distribution of ground voltage or distribution of signal. The metal bond pads 302 and 304 can be connected respectively to the external contact points 342 and 340. Tin-containing bumps, such as tin-lead alloy or tin-silver alloy, or gold bumps can be formed over the external contact points 338, 340 and 342. Alternatively, wires formed by a wirebonding process can be bonded over the external contact points 338, 340 and 342. In this embodiment, the total number of the external contact points 338, 340 and 342 can be less than that of the metal bond pads 301-305 exposed by the openings in the passivation layer 4. Thereby, the total number of the input/output count for the semiconductor chip can be reduced.

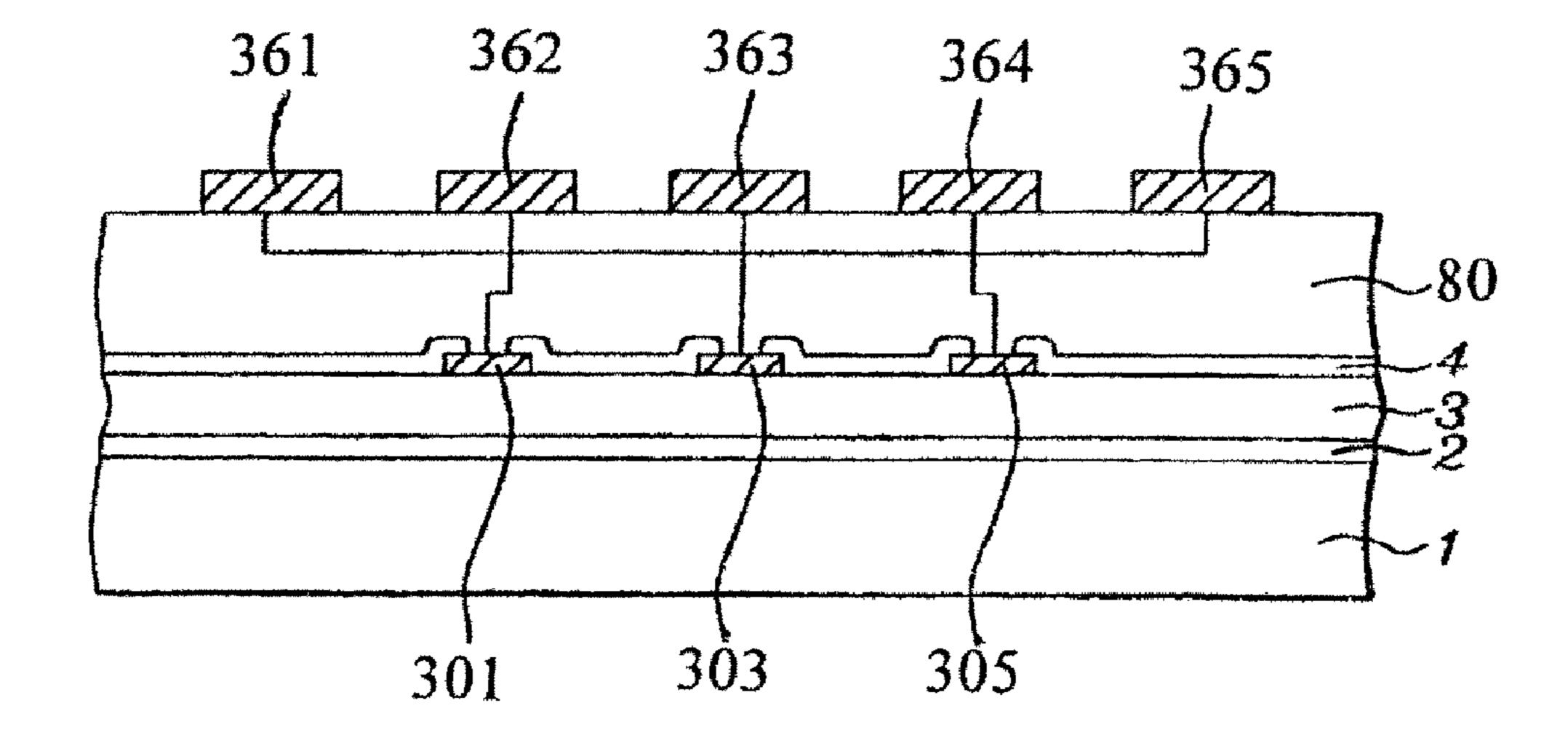

The thick metal lines formed over the passivation layer 4 may have the function of enhancing the total number of the input/output count for a semiconductor chip, as shown in FIG. 7b. FIG. 7b shows that the thick metal lines have the function of enhancing the total number of the input/output count for a semiconductor chip. Through the previous mentioned thick metal lines over the passivation layer 4, one metal bond pad 303 exposed by the openings in the passivation layer 4 can be connected to multiple external contact points 361, 363 and 365 in order to perform the same function, such as being used for the distribution of power voltage, the distribution of ground voltage or the distribution of signal. The metal bond pads 301 and 305 can be connected respectively to the external contact points 362 and 364. Tin-containing bumps, such as tin-lead alloy or tin-silver alloy, or gold bumps can be formed over the external contact points 361-365. Alternatively, wires formed by a wirebonding process can be bonded over the external contact points 361-365. In this embodiment, the total number of the external contact points 361-365 is more than that of the metal bond pads 301, 303 and 305 exposed by the openings in the passivation layer 4. Thereby, the total number of the input/output count for the semiconductor chip can be increased.

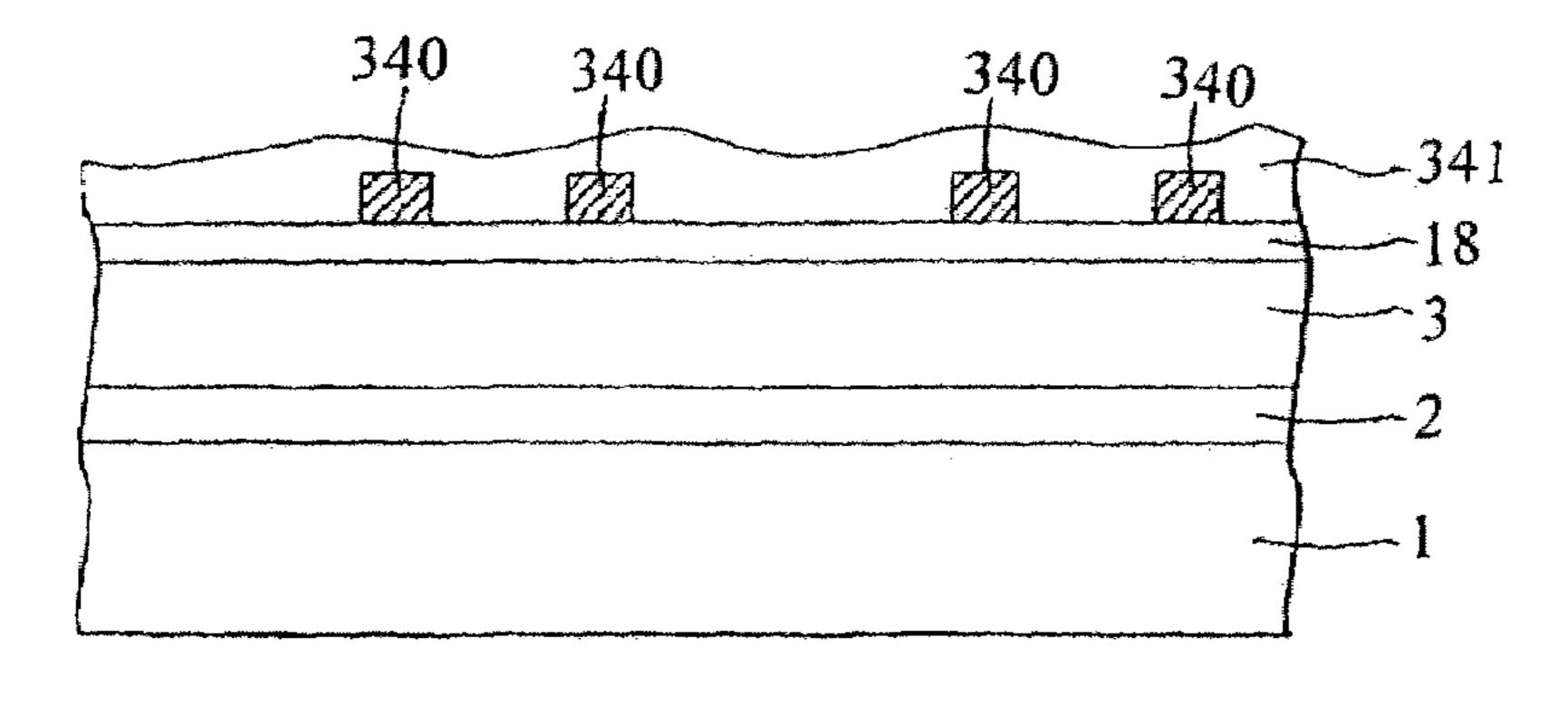

In other cases, the above mentioned process of forming the thick metal line over the passivation layer can be used to form an inductor over the passivation layer, as shown in FIG. 8a, wherein the inductor is a horizontally spread coil, for example. After forming a polymer layer 20 onto the passivation layer 18, a thick metal layer can be formed onto the polymer layer 20, whose material and the method for forming the same can be referred to as those of the polymer layer 20 shown in FIG. 1b.

Next, the thick metal layer containing a thick metal line 26 and an inductor 340 is formed on the polymer layer 20 and connected to the electrical bond pads 16 through the openings in the polymer layer 20 and in the passivation layer 18. The detailed structure of the thick metal layer over the passivation layer 18 and the method for forming the same can be referred to as those of the thick metal layer shown in FIGS. 2a-2g and 2j-2m.

In this case, the inductor 340 is a form of a plane, which is parallel to the top surface of the semiconductor substrate 10. The magnetic field created by the inductor or coil 340 is directed in an upper direction vertical to the top surface of the semiconductor substrate 10. The interconnecting structure 14, the passivation layer 18 and the thick polymer layer 20 leads the inductor 340 to be far away from the silicon substrate 10, and thereby an eddy current effect in the semicon-

ductor substrate 10, induced by the inductor 340, can be declined. Therefore, the inductor 340 may have an enhanced quality factor. The inductor 340 can be formed by electroplating metal with low resistance, such as gold, silver or copper, as illustrated in FIGS. 2a-2g and 2j-2m. The thickness of the turns of the inductor 340 can be, for instance, greater than 1 micron and preferably ranges from 2 microns to 10 microns. The space between the neighboring turns of the inductor 340 can be, for instance, greater than 4 microns, and in general, ranges from 0.5 microns to 50 microns. In addition, another 10 polymer layer can be formed on the thick metal line 26 and the inductor 340.

Referring to FIG. 8*a*, the inductor 340 may have two contact points, both of which are connected to the electrical bond pads 16 exposed by openings in the passivation layer 18. 15 Alternatively, the inductor 340 may have two contact points, one of which is connected to the electrical bond pad 16 exposed by an opening in the passivation layer 18 and the other one of which is connected to an external circuitry, such as printed circuit board or semiconductor chip, through a 20 tin-lead bump, gold bump or a wire formed by a wire bonding process. Alternatively, the inductor 340 may have two contact points, both of which are connected to an external circuitry through tin-lead solder bumps, gold bumps or wires formed by a wire bonding process.

Referring to FIG. 8a, the inductor 340 is formed over the polymer layer 20 and the passivation layer 18. Alternatively, the polymer layer 20 can be saved such that the inductor 340 can be formed directly onto and in touch with the passivation layer 18, as shown in FIG. 8b. The detailed structure of the 30 inductor 340 and the method for forming the same can be referred to as those of the thick metal layer shown in FIGS. 2a-2g and 2j-2m. After forming the inductor 340, a polymer layer 341 can be formed onto the inductor 340 and the passivation layer 18. The material of the polymer 341 and the 35 method of forming the polymer 341 can be referred to as those of the polymer layer 20 shown in FIG. 1b.

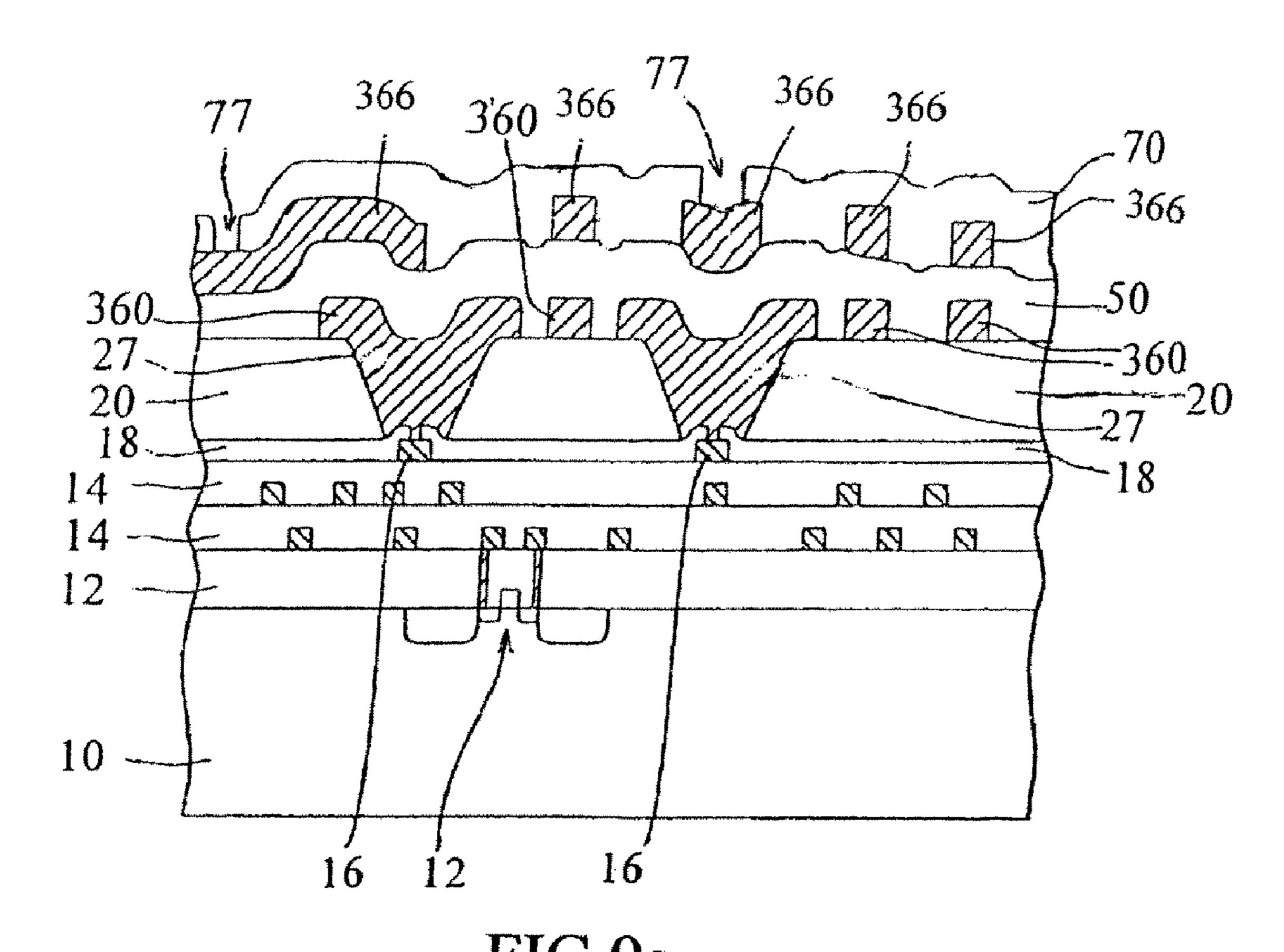

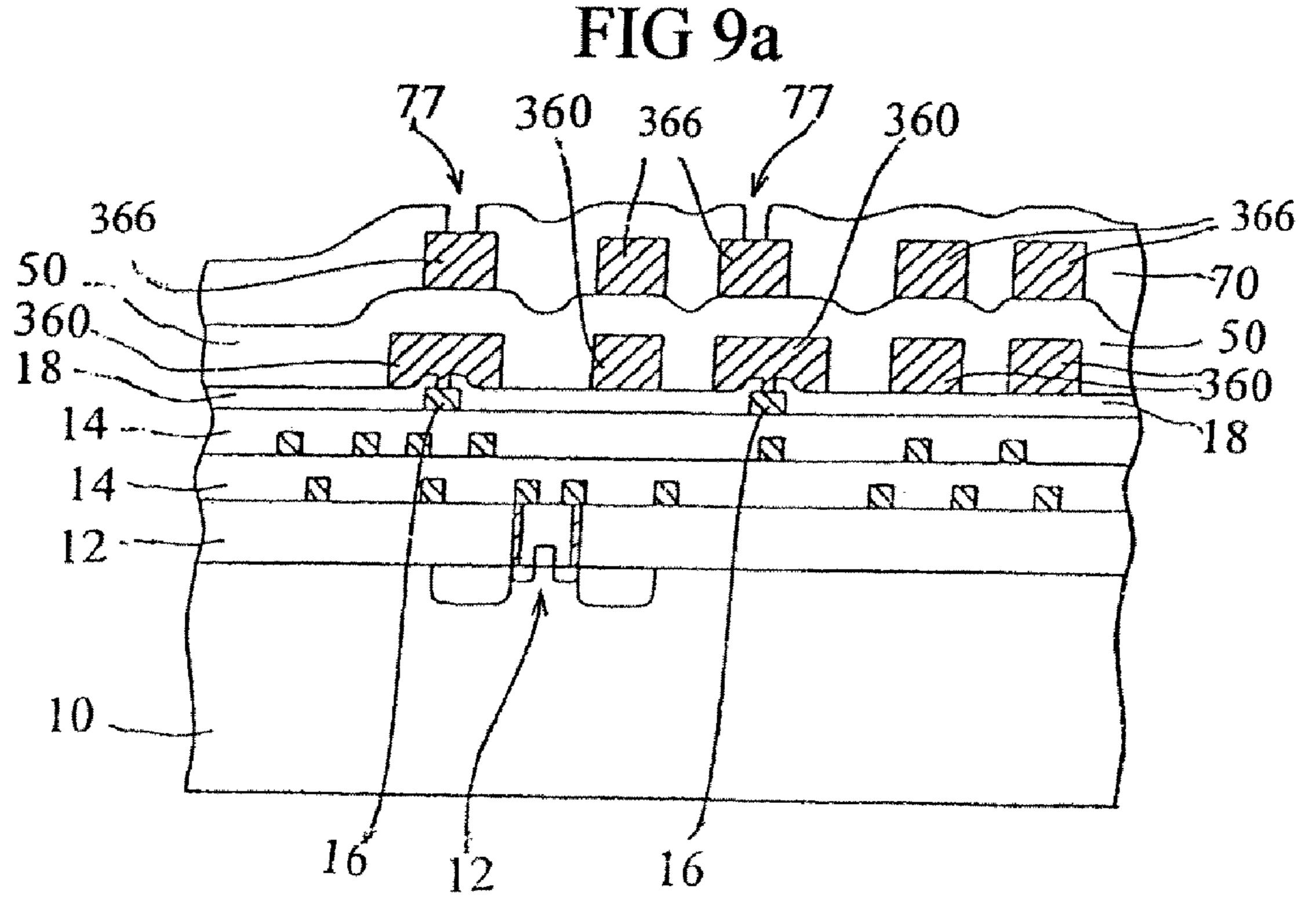

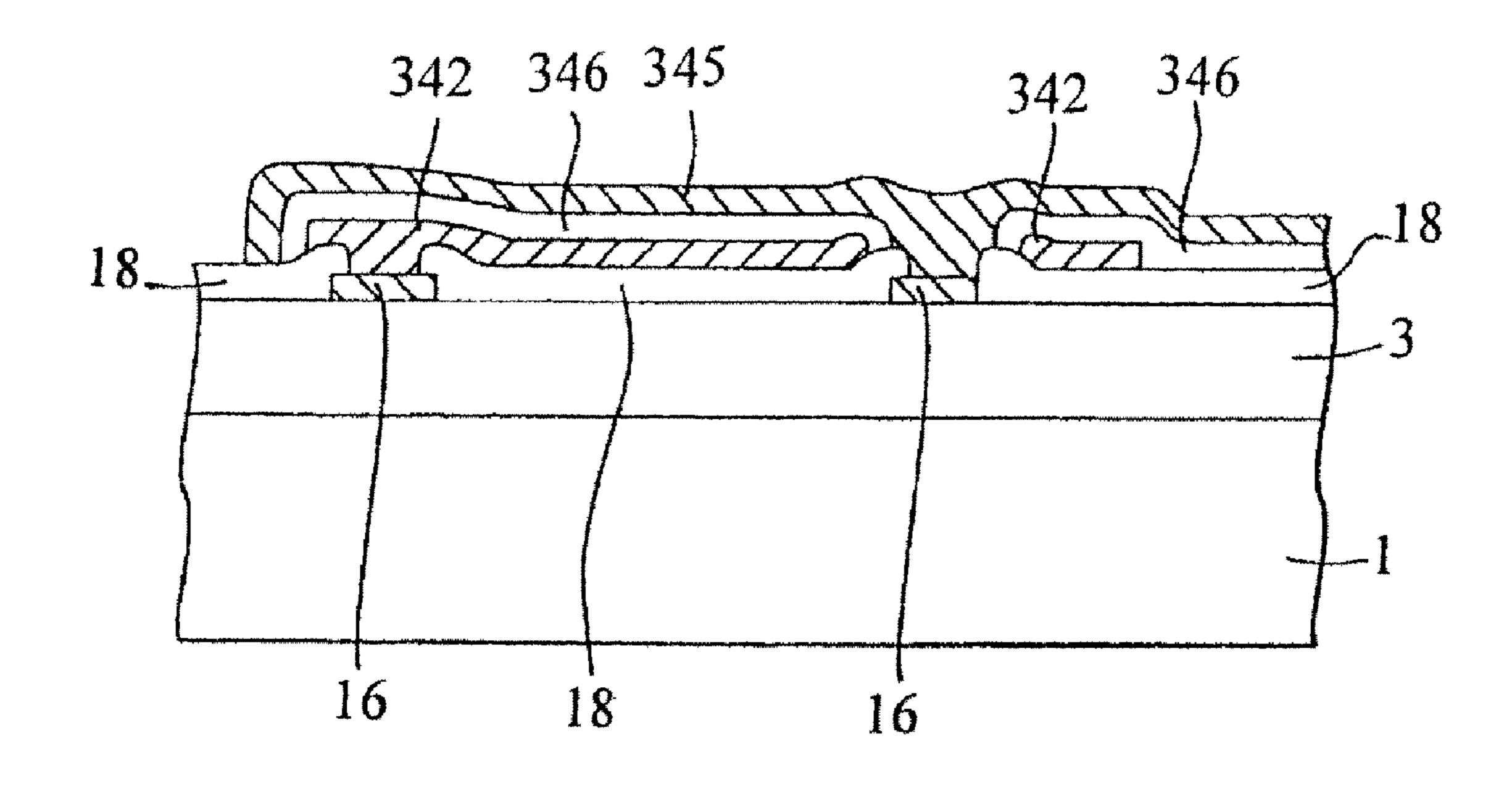

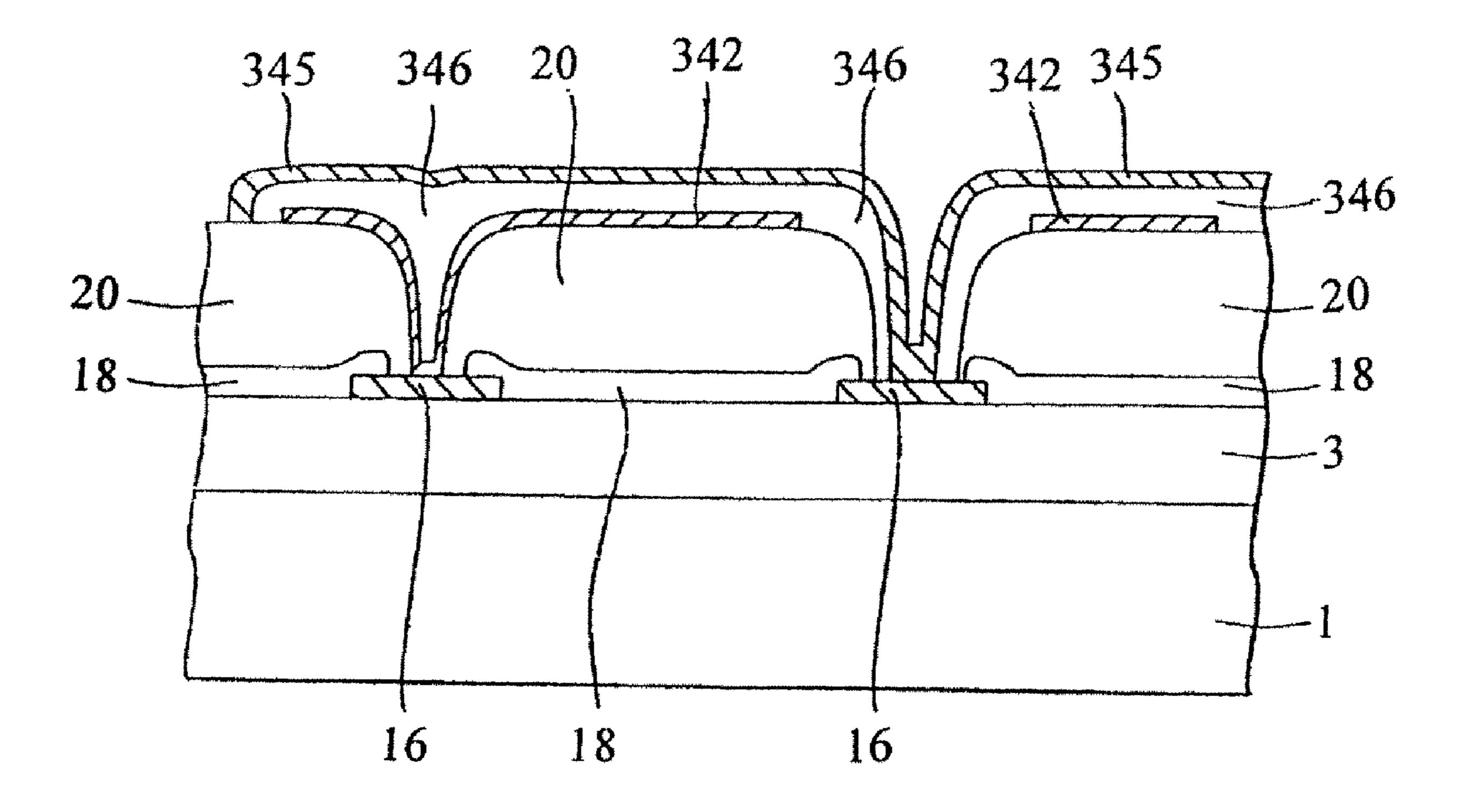

FIGS. 9*a*-9*b* show a cross-sectional view of a transformer formed over the passivation layer. The transformer is provided with a bottom coil 360 and a top coil 362, wherein the 40 bottom coil 360 and the top coil 362 can be formed, for example, by using the process for forming the metal line shown in FIGS. 2a-2f or 2j-2k. Alternatively, both are formed by using the process for forming the metal line shown in FIGS. 2g or 2l-2m. Alternatively, the bottom coil 360 is 45 formed, for example, by using the process for forming the metal line shown in FIGS. 2a-2f or 2j-2k and the top coil 362 is formed, for instance, by using the process for forming the metal line shown in FIG. 2g or FIGS. 2l-2m. Alternatively, the bottom coil 360 is formed, for example, by using the process 50 for forming the metal line shown in FIG. 2g or FIGS. 2l-2m and the top coil 362 is formed, for example, by using the process for forming metal line shown in FIGS. 2a-2f or 2j-2k.

Two contact points connected to the bottom coil **360** are connected, for example, to the metal bond pads **16** exposed by 55 the openings in the passivation layer **18**. Two contact points connected to the top coil **362** can be connected, for instance, to an external circuitry, such as a printed circuit board (PCB), or another semiconductor chip, through tin-lead bumps or gold bumps formed on the two contact points, or alternatively 60 through gold wires formed by a wire bonding process.

In this embodiment, the bottom coil 360 can be formed, for instance, on the polymer layer 20 on the passivation layer 18, as shown in FIGS. 9a and 9c, wherein the material of the polymer layer 20 and the method for forming the same can be 65 referred to as those of the polymer 20 shown in FIG. 1b. Alternatively, the polymer layer 20 can be saved such that the

**20**

bottom coil 360 can be formed directly onto and in touch with the passivation layer 18, as shown in FIGS. 9b and 9d.

After forming the bottom coil 360 onto the passivation layer 18 or onto the polymer layer 20, a polymer layer 50 can be formed onto the bottom coil 360, as shown in FIGS. 9a-9d. If a high-precision process is not needed for forming the transformer or coupler, the material and the method of forming the polymer layer 50 can be referred to those of the polymer layer 20 shown in FIG. 1b and the above mentioned step of planarizing the top surface of the polymer layer 50 can be saved. The polymer layer **50** is provided with a relatively uneven top surface. Because the following-formed top coil 362 is formed onto the uneven top surface of the polymer layer 50, the transformer or coupler can not reach a relatively high precision, as shown in FIGS. 9a and 9b. If a highprecision process is needed for forming the transformer or coupler, the material of the polymer layer 50 and the method for forming the same can be referred to as those of the polymer layer 222 shown in FIG. 2i. The step of planarizing the top surface of the polymer layer 50 can be performed by a Mechanical Polishing (MP) process or a Chemical Mechanical Polishing (CMP) process. Because the following formed top coil **362** is formed onto the flat top surface of the polymer layer 50, the transformer can reach a relatively high precision, as shown in FIGS. 9c and 9d.