#### US007459379B2

## (12) United States Patent

#### Kokubo et al.

### (10) Patent No.:

US 7,459,379 B2

#### (45) **Date of Patent:**

Dec. 2, 2008

## (54) METHOD FOR MANUFACTURING SEMICONDUCTOR DEVICE

(75) Inventors: Chiho Kokubo, Tochigi (JP); Shunpei

Yamazaki, Tokyo (JP); Tamae Takano, Kanagawa (JP); Hiroaki Irie, Kanagawa

(JP)

(73) Assignee: Semiconductor Energy Laboratory

Co., Ltd., Kanagawa-Ken (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 403 days.

(21) Appl. No.: 11/089,055

(22) Filed: Mar. 25, 2005

(65) Prior Publication Data

US 2005/0221545 A1 Oct. 6, 2005

#### (30) Foreign Application Priority Data

(51) **Int. Cl.**

$H01L\ 21/20$  (2006.01)

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,256,681 A | 3/1981  | Lindmayer       |

|-------------|---------|-----------------|

| 4,814,292 A | 3/1989  | Sasaki et al.   |

| 5,529,937 A | 6/1996  | Zhang et al.    |

| 5,569,610 A | 10/1996 | Zhang et al.    |

| 5,639,698 A | 6/1997  | Yamazaki et al. |

| 5,643,826 A | 7/1997  | Ohtani et al.   |

| 5,663,077 A | 9/1997  | Adachi et al.   |

| 5,773,327 A | 6/1998  | Yamazaki et al. |

| 5,824,573 A | 10/1998 | Zhang et al.    |

5,854,096 A 12/1998 Ohtani et al. 5,879,977 A 3/1999 Zhang et al.

#### (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 1373503 10/2002

#### (Continued)

#### OTHER PUBLICATIONS

Abe et al., "AM-LCD '98 Digest of Technical Papers, High-Performance Poly-Crystalline Silicon TFTs Fabricated Using the SPC and ELA Methods", TFT3-2, pp. 85-88, Jan. 1, 1998.

#### (Continued)

Primary Examiner—Stephen W Smoot (74) Attorney, Agent, or Firm—Nixon Peabody LLP; Jeffrey L. Costellia

#### (57) ABSTRACT

When a semiconductor film is irradiated with laser light, the semiconductor film is instantaneously melted and expand locally. In order to reduce internal stress generated by this expansion, strain is locally generated in the semiconductor film. Accordingly, a variation is caused among portions with strain and portions without strain, and a variation is caused also by a difference in extent of strain.

According to the present invention, after laser light irradiation, an oxide film (referred to as a chemical oxide) is formed by using a solution containing ozone (typically, ozone water) to form an oxide film of 1 to 10 nm in total, and further, a heat treatment for reducing strain of a semiconductor film (a heat treatment of heating the semiconductor film instantaneously to approximately 400 to 1000° C.) is performed.

30 Claims, 13 Drawing Sheets

# US 7,459,379 B2 Page 2

|                       | U.S. I        | PATENT         | DOCUMENTS              |                                                                                                    | 89909 A1        |         | Miyairi et al.                      |  |  |

|-----------------------|---------------|----------------|------------------------|----------------------------------------------------------------------------------------------------|-----------------|---------|-------------------------------------|--|--|

| 5 004 770             | •             | <b>5</b> /1000 | O1.4                   |                                                                                                    | 09086 A1*       |         | Arao                                |  |  |

| 5,904,770             |               |                | Ohtani et al.          | 2004/02                                                                                            | 259389 A1       | 12/2004 | Yamazaki et al.                     |  |  |

| 5,923,962             |               |                | Ohtani et al.          | 2005/00                                                                                            | )32336 A1       | 2/2005  | Yamazaki et al.                     |  |  |

| 5,923,997             |               |                | Mitanaga et al.        | 2006/02                                                                                            | 276012 A1       | 12/2006 | Yamazaki et al.                     |  |  |

| 5,948,496             |               |                | Kinoshita et al.       |                                                                                                    | EODEIC          | SEDATES | NIT DOCT IN ADNITO                  |  |  |

| 5,953,597             |               |                | Kusumoto et al.        | FOREIGN PATENT DOCUMENTS                                                                           |                 |         |                                     |  |  |

| 6,014,944             |               |                | Aklufi et al.          | CN                                                                                                 | 1401            | 1142    | 3/2003                              |  |  |

| 6,066,516             |               |                | Miyasaka               | EP                                                                                                 |                 | 431 A2  | 5/1995                              |  |  |

| 6,184,068             |               |                | Ohtani et al.          | EP                                                                                                 |                 | 259 A1  | 8/2002                              |  |  |

| 6,281,057             |               |                | •                      | JP                                                                                                 | 06-163          |         | 6/1994                              |  |  |

| 6,285,042             |               |                | Ohtani et al.          | JP                                                                                                 | 07-183          |         | 7/1995                              |  |  |

| ·                     |               |                | Zhang et al.           | JP                                                                                                 | 11-074          |         | 3/1999                              |  |  |

| 6,326,248             |               |                | Ohtani et al.          | JP                                                                                                 | 2000-150        |         | 5/2000                              |  |  |

| 6,335,541             |               |                | Ohtani et al.          | JP                                                                                                 | 2000-130        |         | 5/2000                              |  |  |

| 6,455,360             |               |                | Miyasaka               | JP                                                                                                 | 2000-303        |         | 3/2000                              |  |  |

| 6,509,579             |               |                | Takeya et al.          | JP                                                                                                 | 2002-070        |         | 9/2002                              |  |  |

| 6,716,768             |               | 4/2004         |                        | JP                                                                                                 | 2002-201        |         | 9/2002                              |  |  |

| 6,770,518             |               |                | Yamazaki et al.        | JP                                                                                                 | 2002/201        |         | 10/2002                             |  |  |

| 6,808,968             |               |                | Yamazaki et al.        | JP                                                                                                 | 2002-303        |         | 11/2002                             |  |  |

| 6,872,638             | B2            | 3/2005         | Yamazaki et al.        | JI                                                                                                 | 2002-323        | 7008    | 11/2002                             |  |  |

| 7,160,784             | B2            | 1/2007         | Yamazaki et al.        |                                                                                                    | OTI             | HER PUI | BLICATIONS                          |  |  |

| 2001/0003659          | $\mathbf{A}1$ | 6/2001         | Aya et al.             |                                                                                                    |                 |         |                                     |  |  |

| 2002/0098628          | $\mathbf{A}1$ | 7/2002         | Hamada et al.          |                                                                                                    |                 |         | gest of Technical Papers", "Device  |  |  |

| 2002/0119585          | $\mathbf{A}1$ | 8/2002         | Yamazaki et al.        | Simulation of Interface Roughness in Laser-crystallized p-Si TFTs",                                |                 |         |                                     |  |  |

| 2002/0119633          | <b>A</b> 1    | 8/2002         | Yamazaki et al.        | 1 1                                                                                                | 266, Jan. 1, 19 |         |                                     |  |  |

| 2002/0125480          | $\mathbf{A}1$ | 9/2002         | Nakamura et al.        |                                                                                                    |                 |         | Report & Written Opinion, issued in |  |  |

| 2002/0127827          | $\mathbf{A}1$ | 9/2002         | Yamazaki et al.        | Singapore, (Application No. 2002-00835-7; SG5551) Dated Apr. 20,                                   |                 |         |                                     |  |  |

| 2002/0134981          | $\mathbf{A}1$ | 9/2002         | Nakamura et al.        | 2004.                                                                                              |                 |         |                                     |  |  |

| 2002/0146868          | <b>A</b> 1    | 10/2002        | Miyasaka               |                                                                                                    |                 |         | Report & Written Opinion, issued in |  |  |

| 2002/0151120          |               |                | Yamazaki et al.        | Singapore, (Application No. 2002-00837-3; SG5561/5562) Dated                                       |                 |         |                                     |  |  |

| 2002/0164843          |               |                | Yamazaki et al.        | Apr. 20, 2004.<br>Office Action of U.S. Appl. No. 10/078,240 dated Jun. 19, 2003.                  |                 |         |                                     |  |  |

| 2002/0197785          |               |                | Yamazaki et al.        |                                                                                                    |                 |         |                                     |  |  |

| 2002/0197783          |               |                | Horikoshi et al 257/48 | Office Action from Chinese Patent Office for Application No. 200510076232.6, Dated: Dec. 14, 2007. |                 |         |                                     |  |  |

| 2003/0042484          |               |                |                        |                                                                                                    |                 |         |                                     |  |  |

|                       |               |                | Takemura               | * ~:4~ -1 1-                                                                                       |                 |         |                                     |  |  |

| 200 <i>3</i> /0082839 | Al *          | 5/2003         | Ichijo et al 438/166   | " citea b                                                                                          | y examiner      |         |                                     |  |  |

|                       |               |                |                        |                                                                                                    |                 |         |                                     |  |  |

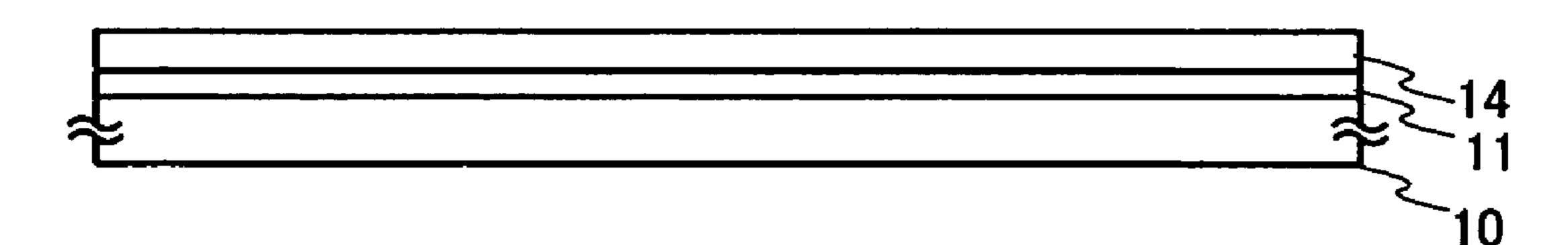

FIG. 1A

Dec. 2, 2008

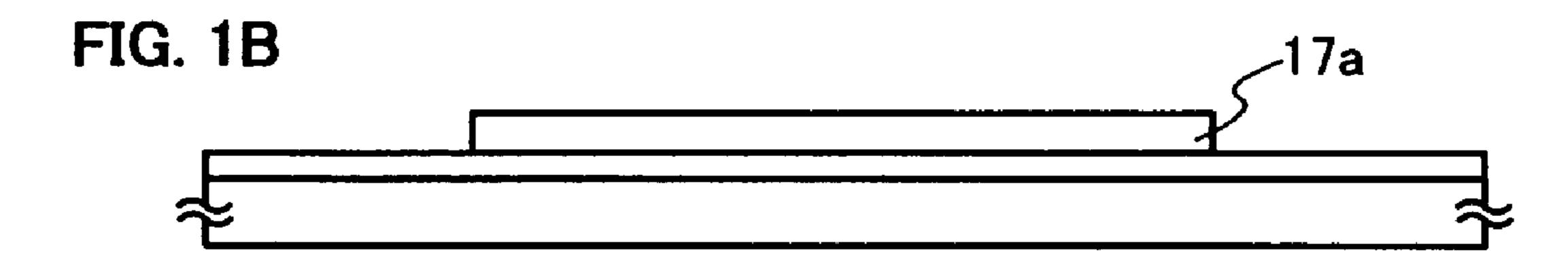

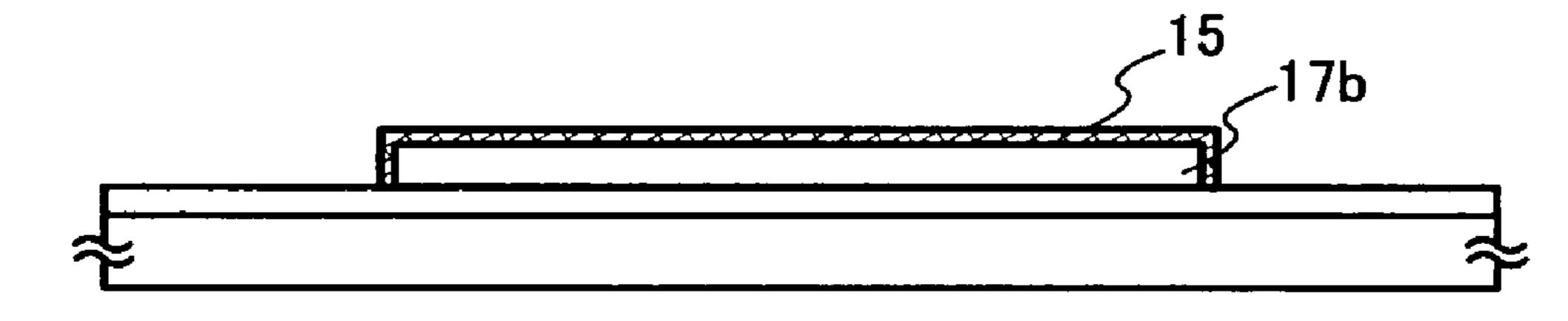

FIG. 1C

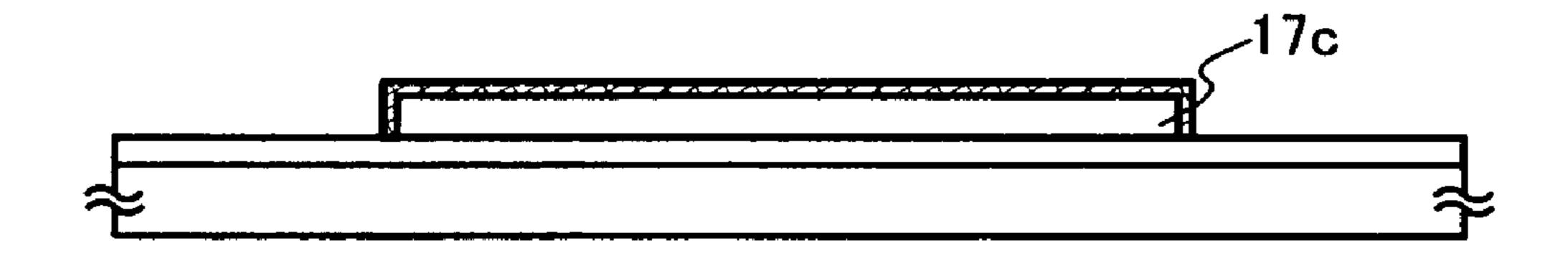

FIG. 1D

FIG. 1E

FIG. 1F

FIG. 8A

FIG. 8B

pixel portion

828

834

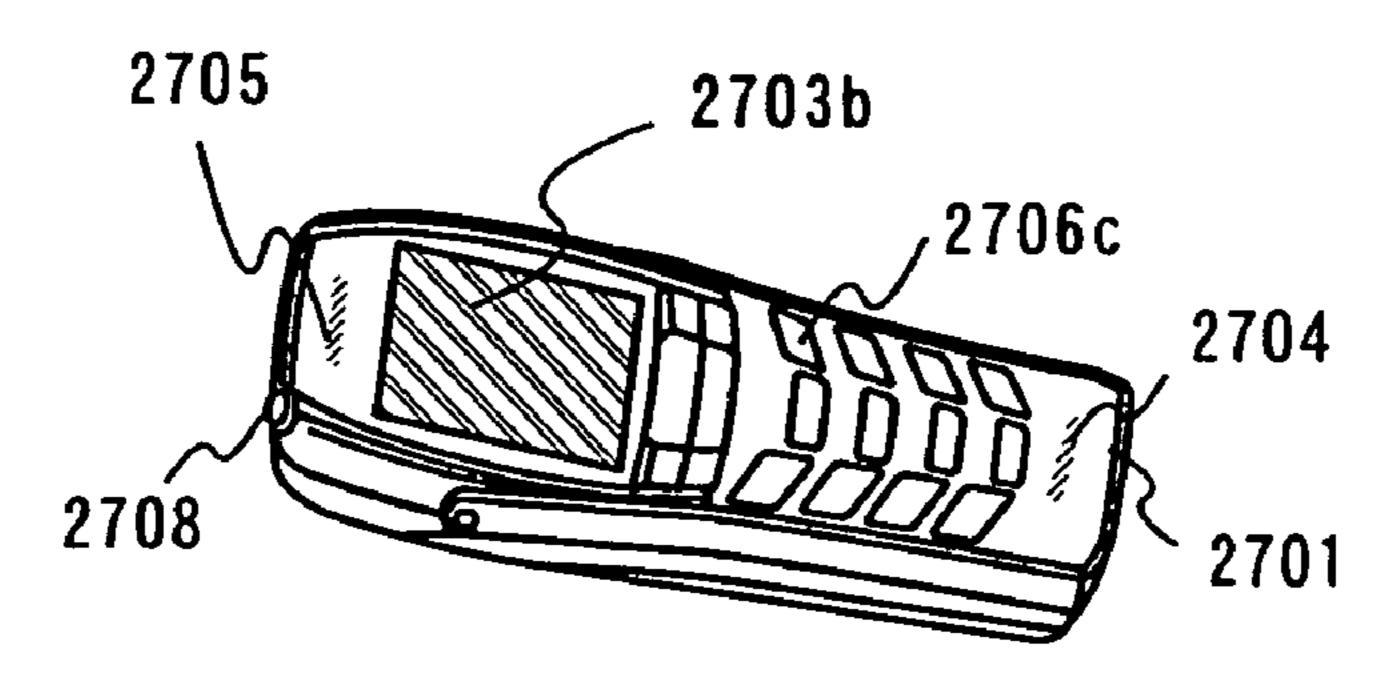

FIG. 13E folded state

## METHOD FOR MANUFACTURING SEMICONDUCTOR DEVICE

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention relates to a semiconductor device that has a circuit comprising a thin film transistor (hereinafter, referred to as a TFT) and a method for manufacturing the semiconductor device. For example, the invention relates to an electronic device carrying an electro-optical device typified by a liquid crystal display panel or a light-emitting display device that has an organic light-emitting element as a part thereof.

Note that the semiconductor device in the specification <sup>15</sup> indicates overall devices that can function by using semiconductor properties, and electro-optical devices, semiconductor circuits, and electronic devices are all included in the semiconductor device.

#### 2. Description of the Related Art

Recently, a technique for manufacturing a thin film transistor (TFT) with the use of a semiconductor film (approximately several to several hundred nm in thickness) formed over a substrate with an insulating surface has been attracting attention. The thin film transistor is widely applied to electronic devices such as an IC and an electro-optical device, and in particular, has been developed quickly as a switching element for image display devices.

As a material for a crystalline semiconductor film to be used for a TFT, silicon is mainly used. As a silicon film including a crystalline structure (hereinafter, referred to as a crystalline silicon film), a film obtained in such a way that an amorphous silicon film deposited on a substrate such as glass or quartz by plasma CVD or low-pressure CVD is crystallized by a heat treatment or laser light irradiation (hereinafter, referred to as a laser treatment in the specification) has been used.

In the laser treatment, high productivity can be obtained by forming a relatively large spot shape, for example, a square spot shape several cm square or a linear spot shape of 10 cm or more in length, at an irradiated surface. In particular, when the linear spot shape is used, the whole area of an irradiated surface can be irradiated with laser by scanning only in a direction perpendicular to the longitudinal direction of the linear laser light so that the productivity is higher, as compared with a case of using spot-shaped laser light requiring scanning back and forth and from side to side.

However, in crystallization by laser light irradiation, a precipitous temperature gradient may be generated between a substrate and a semiconductor film to lower the quality of a semiconductor film obtained after the laser light irradiation.

Consequently, the applicant has proposed Patent Reference 1, Patent Reference 2, Patent Reference 3, and Patent Reference 4 mentioned below.

In Patent Reference 3, a technique of reducing strain generated by laser light irradiation in such a way that a heat treatment is performed after crystallizing a semiconductor film by using laser light is described.

(Patent Reference 1) Japanese Patent Laid-Open No. 2002-305148

(Patent Reference 2) Japanese Patent Laid-Open No. 2002-329668

(Patent Reference 3) Japanese Patent Laid-Open No. 2002-261007

(Patent Reference 4) Japanese Patent Laid-Open No. 2002-261008 2

When a semiconductor film is irradiated with laser light, the semiconductor film is instantaneously melted and expand locally. In order to reduce internal stress generated by this expansion, strain is locally generated in the semiconductor film. Accordingly, a variation of the semiconductor film is caused among portions with strain and portions without strain, and a variation of the semiconductor film is caused also by a difference in extent of strain.

In addition, the semiconductor film is densified by crystallization. This densification can be confirmed by reduction in film thickness. The semiconductor film is contracted by crystallization, which contributes to generation of strain.

In a TFT, when there is strain in a semiconductor film to serve as an active layer, a potential barrier and a trap level are formed due to this strain. Accordingly, the interface state between the active layer and a gate insulating film becomes high. In addition, when there is strain in a semiconductor film to serve as an active layer, defects in operation of a TFT are caused because an electric field is not added to the semiconductor film uniformly.

Further, strain at the surface of a semiconductor film damages the flatness of a gate insulating film deposited by sputtering or CVD. Thus, insulation failure and the like is caused, which is one of causes of lowering the reliability of a TFT. As one of factors of determining field effect mobility, surface scattering is known, and the flatness at the interface between an active layer and a gate insulating film of a TFT has a great influence on the field effect mobility. The flatter the interface is, the less the field effect mobility is affected by scattering so that a higher field effect mobility can be obtained.

#### SUMMARY OF THE INVENTION

The present invention provides a method for reducing strain generated in a semiconductor film (to serve as an active layer of a TFT) due to laser light irradiation.

According to the present invention, after laser light irradiation, a heat treatment for reducing strain of a semiconductor film (a heat treatment of heating a semiconductor film instantaneously to approximately 400 to 1000° C.) is performed. Further, an oxide film (referred to as a chemical oxide) is formed by using a solution containing ozone (typically, ozone water) to form an oxide film of 1 to 10 nm in total thickness. Alternatively, by using an aqueous solution obtained by mixing a hydrogen peroxide solution with an acid such as sulfuric acid, hydrochloric acid, or nitric acid instead of the solution containing ozone, a chemical oxide can be formed similarly. After that, the formed oxide film is removed and a semiconductor film reduced in strain is obtained.

Before removing the oxide film, a heat treatment for reducing strain of the semiconductor film may be performed again, and then, the formed oxide film may be removed.

Alternatively, the following step may be performed for obtaining a semiconductor film reduced in strain, after laser light irradiation, an oxide film is formed by using a solution containing ozone to form an oxide film of 1 to 10 nm in thickness. After that, a heat treatment for reducing strain of the semiconductor film (a heat treatment of heating a semiconductor film instantaneously to approximately 400 to 1000° C.) is performed. Then, the formed oxide film may be removed. When the heat treatment is performed after forming the oxide film, an impurity such as a metal included in the film can be moved into the oxide film or the interface thereof, and also, the semiconductor film in which the impurity is reduced can be obtained by removing the oxide film.

Alternatively, after laser light irradiation, a patterning step of a semiconductor film, a heat treatment step for reducing

strain of the semiconductor film, a step of forming an oxide film by using a solution containing ozone to form an oxide film of 1 to 10 nm in total thickness, and a step of removing the oxide film may be performed sequentially. In order to reduce the number of steps, a gate insulating film may be formed 5 without removing the oxide film.

Alternatively, after laser light irradiation, a patterning step of a semiconductor film, a step of forming an oxide film of 1 to 10 nm by using a solution containing ozone, a heat treatment step for reducing strain of the semiconductor film, and a step of removing the oxide film may be performed sequentially. In order to reduce the number of steps, a gate insulating film may be formed over the oxide film without removing the oxide film.

The applicant discloses a technique of manufacturing a semiconductor film including a crystalline structure by adding a metal element (for example, nickel) for promoting crystallization of a semiconductor film to a semiconductor film including an amorphous structure (Japanese Patent Laid-Open No. 7-183540). This technique has not only the advantage of decreasing a heating temperature required for crystallization, but also the advantage of being able to improve the orientation in a certain direction. When the semiconductor film including such a crystalline structure is used to form a TFT, the subthreshold factor (s-factor) becomes smaller as 25 well as improving the field effect mobility so that the electrical characteristics can be improved dramatically.

Because nucleation in crystallization can be controlled by using the metal element for promoting crystallization, an obtained film is more uniform as compared with a film 30 obtained by another crystallization method involving random nucleation. It is desirable to reduce the metal element completely or reduce the metal element into the allowable range of density. However, since the metal element for promoting crystallization is added, the metal element remains in the 35 semiconductor film including the crystalline structure or at the surface of the film to result in problems such as variations in obtained-device characteristics. As an example thereof, there is a problem that the OFF current of a TFT is increased to result in a variation among individual devices. Namely, the 40 metal element for promoting crystallization becomes unnecessary when the semiconductor film including the crystalline structure is formed once.

Consequently, gettering for removing the metal element is performed. If gettering is not performed sufficiently within a 45 substrate and a variation in gettering level is unignorable, slight differences among respective TFT characteristics, that is, a variation of characteristics is generated. In the case of a transmissive liquid crystal display device, when TFTs arranged in a pixel portion show a variation in electrical 50 characteristics, a variation in threshold voltages of the TFTs is generated. Therefore, a variation in transmitted light intensity is generated, which is seen by viewer's eyes as display unevenness.

For a light-emitting device that has a layer including an organic compound as a light-emitting layer (a light-emitting device that has an EL element), a TFT is an essential element to realize an active matrix driving method. Accordingly, in a light-emitting device using an EL element, at least a TFT that serves as a switching element and a TFT for supplying current to the EL element are provided in each pixel. Independently of the circuit structure of a pixel and a driving method, the luminance of the pixel is determined by the ON current  $(I_{on})$  when las of the TFT connected to the EL element for supplying current to the EL element. Therefore, for example, in the case of overall white display, there is a problem that a variation in luminance is generated unless the ON current is constant.

4

The present invention also provides a technique for removing the metal element remaining in the film effectively after obtaining a semiconductor film including a crystalline structure with the use of a metal element for promoting crystallization of a semiconductor film.

The present invention has a feature of performing at least one of a step of performing a heat treatment for reducing strain of a semiconductor film (a heat treatment of heating a semiconductor film instantaneously to approximately 400 to  $1000^{\circ}$  C.) and a step of forming an oxide film (a barrier layer) to serve as an etching stopper by using a solution containing ozone before forming a second semiconductor film (a gettering site) including a rare gas element. By performing these steps, the metal element can be gettered more effectively so that the density of the metal element in the semiconductor film can be reduced to suppress the variation of the characteristics of the TFTs.

A configuration of the invention disclosed in the specification includes a step of forming a first semiconductor film including a crystalline structure over an insulating surface with the use of a metal element, a step of irradiating the first semiconductor film with laser light, a step of performing a heat treatment for reducing strain of the first semiconductor film (a heat treatment of heating the first semiconductor film instantaneously to approximately 400 to 1000° C.), a step of forming an oxide film (a barrier layer) to serve as an etching stopper by using a solution containing ozone, a step of forming a second semiconductor film (a gettering site) including a rare gas element, a step of moving the metal element into the gettering site (the second semiconductor film) by a heat treatment, a step of removing the second semiconductor film, and a step of removing the oxide film.

When a semiconductor film is irradiated with laser light for crystallization or improving the crystallinity, the semiconductor film is melted instantaneously from the surface, and then, by heat conduction to a substrate, the melted semiconductor film is cooled and solidify from the substrate side. In this solidification step, the semiconductor film is crystallized and becomes a semiconductor film including a crystalline structure having a larger grain size. However, since the semiconductor film is melted once, cubical expansion is generated and a convexity referred to as a ridge at the surface of the semiconductor film. In particular, in the case of a top gate TFT, device characteristics are influenced significantly since the surface with the ridge is an interface between a gate insulating film and the semiconductor film. In addition, a thin oxide film is formed at the surface of the semiconductor film by oxygen in an atmosphere when laser light irradiation is performed. Because the thickness and the uniformity of this oxide film are not predictable, it is preferable to remove the oxide film. However, because a watermark is easily generated in drying of the water-shedding surface, it is preferable that an oxide film is formed by using a solution containing ozone after the removal of the oxide film to prevent generation of a

However, because the surface oxide film formed by laser light irradiation is harder than an oxide film formed by using a solution containing ozone, the surface oxide film is superior as an oxide film (a barrier layer) to serve as an etching stopper. Accordingly, it is not particularly necessary to remove the surface oxide film formed by laser light irradiation since the number of steps can also be reduced.

When laser light irradiation is performed after adding a metal element (for example, nickel), the metal element tends to segregate more at the ridge. At the ridge with more nickel, NiSix is formed, and solidifies last in melting. NiSix easily dissolves in diluted hydrofluoric acid and an alkali etchant.

Therefore, when there are portions with more nickel in places and the oxide film (barrier layer) to serve as an etching stopper is insufficient in thickness, there is a risk that NiSix is removed by etching for removing the second semiconductor film and a minute hole (also referred to as a pinhole) is formed in the first semiconductor film.

In addition, at the ridge with more nickel, NiOx is also easily formed. NiOx is soft and has acid solubility. When the oxide film (barrier layer) to serve as an etching stopper is insufficient, there is a risk that NiOx is removed in a step to be performed later (etching for removing the second semiconductor film or a treatment before forming a gate insulating film) and a minute hole (a pinhole) is formed in the first semiconductor film.

When a minute hole (a pinhole) is formed in a semiconductor film to serve as an active layer, a defective state of covering the semiconductor film by a gate insulating film is generated, which results in a display defect such as a point defect.

In the present invention, after laser light irradiation, a first semiconductor film is heated instantaneously to approximately 400 to 1000° C. to reduce strain and ridges, and then, an oxide film (a barrier layer) that is uniform in film thickness is formed by using a solution containing ozone. This oxide film (barrier layer) serves as to protect the first semiconductor film during etching for removing the second semiconductor film. When the first semiconductor film is heated instantaneously to approximately 400 to 1000° C., strain is removed so as to easily perform gettering of nickel in a gettering step later.

Additionally, before performing a treatment before forming a gate insulating film, it is preferable that an oxide film (a barrier layer) that is uniform in film thickness is formed again by using a solution containing ozone to protect the first semiconductor film.

Note that methods for forming the second semiconductor film described above include sputtering and plasma CVD. Plasma CVD needs less maintenance as compared with sputtering because the inside of a deposition chamber (also referred to as a chamber) can be cleaned with the use of gas. 40 Accordingly, it is said that plasma CVD is suitable for mass production. The film thickness of the oxide film (the barrier layer) is as thin as 1 to 10 nm. Therefore, when the second semiconductor film is formed on the oxide film (the barrier layer) by plasma CVD, there is a risk that the oxide film (the 45 barrier layer) is partially destroyed by, for example, plasma generated during deposition. When the oxide film (the barrier layer) is partially destroyed, the oxide film (the barrier layer) insufficiently functions as an etching stopper in removing the second semiconductor film by etching to be performed later 50 so that defects such as a variation in film thickness of the first semiconductor film and holes formed in the first semiconductor film are caused.

Consequently, a heat treatment (heating instantaneously to approximately 400 to 1000° C.) is performed to the oxide film 55 (the barrier layer) to form a hard oxide film, by which the first semiconductor film is protected from damage of plasma. By damaging intentionally only the oxide film (the barrier layer) with protecting the first semiconductor film by plasma during forming the second semiconductor film to form strain and a dangling bond in the oxide film (the barrier layer), the metal element moving in such a direction as to reduce the strain can be made to pass effectively through the oxide film, move into and be trapped in the gettering site (the second semiconductor film). In case of damaging intentionally the oxide film (the 65 barrier layer) by plasma during forming the second semiconductor film, it is preferable to increase the RF power density

6

in plasma CVD. For example, the RF power may be controlled to be  $300 \, \text{W} \, (0.052 \, \text{W/cm}^2), 400 \, \text{W} \, (0.069 \, \text{W/cm}^2), \text{ or } 400 \, \text{W}$  or more.

Alternatively, when the flow ratio (SiH<sub>4</sub>:rare gas) of a rare gas to monosilane introduced into a deposition chamber, the RF power density, and the pressure are controlled to form the second semiconductor film by plasma CVD, damage to the oxide film (the barrier layer) can be also reduced and variation in the film thickness of the first semiconductor film and defects of holes formed in the first semiconductor film can be suppressed. For example, the RF power may be controlled to be 100 W (0.017 W/cm<sup>2</sup>), or 100 W or less.

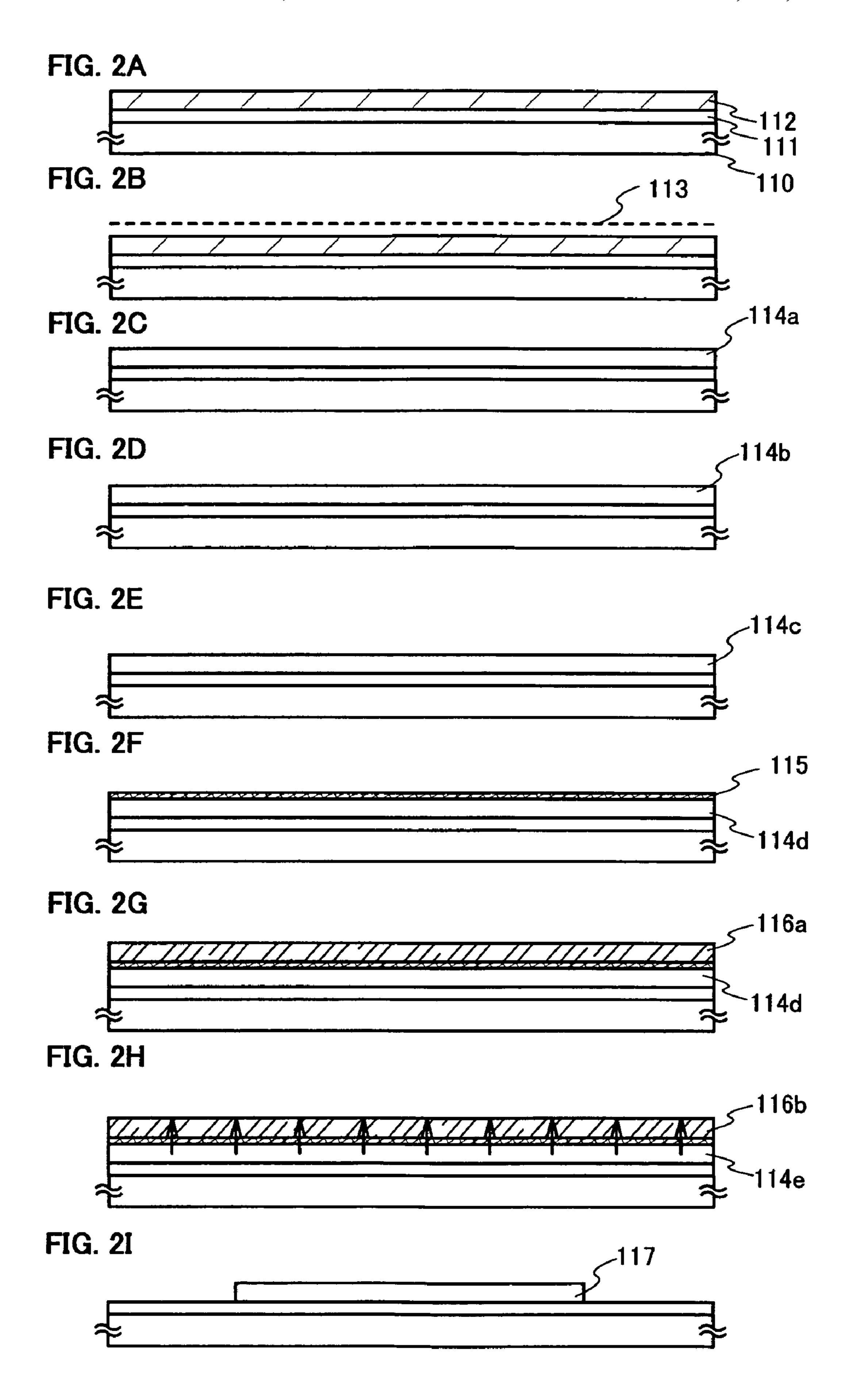

A more detailed configuration of the invention is a method for manufacturing a semiconductor device, which includes a first step of forming a first semiconductor film including an amorphous structure on an insulating surface, a second step of adding a metal element to the first semiconductor film including the amorphous structure, a third step of crystallizing the first semiconductor film to form a first semiconductor film including a crystalline structure, a fourth step of irradiating the first semiconductor film with laser light, a fifth step of performing a first heat treatment to the first semiconductor film to reduce strain thereof, a sixth step of oxidizing a surface of the first semiconductor film by using a solution including ozone to form a barrier layer, a seventh step of forming a second semiconductor film including a rare gas element on the barrier layer, an eighth step of performing a second heat treatment to remove or reduce metal element in the first semiconductor film by moving the metal element into the second semiconductor film, a ninth step of removing the second semiconductor film; and a tenth step of removing the barrier layer, as shown in FIGS. 2A to 2I.

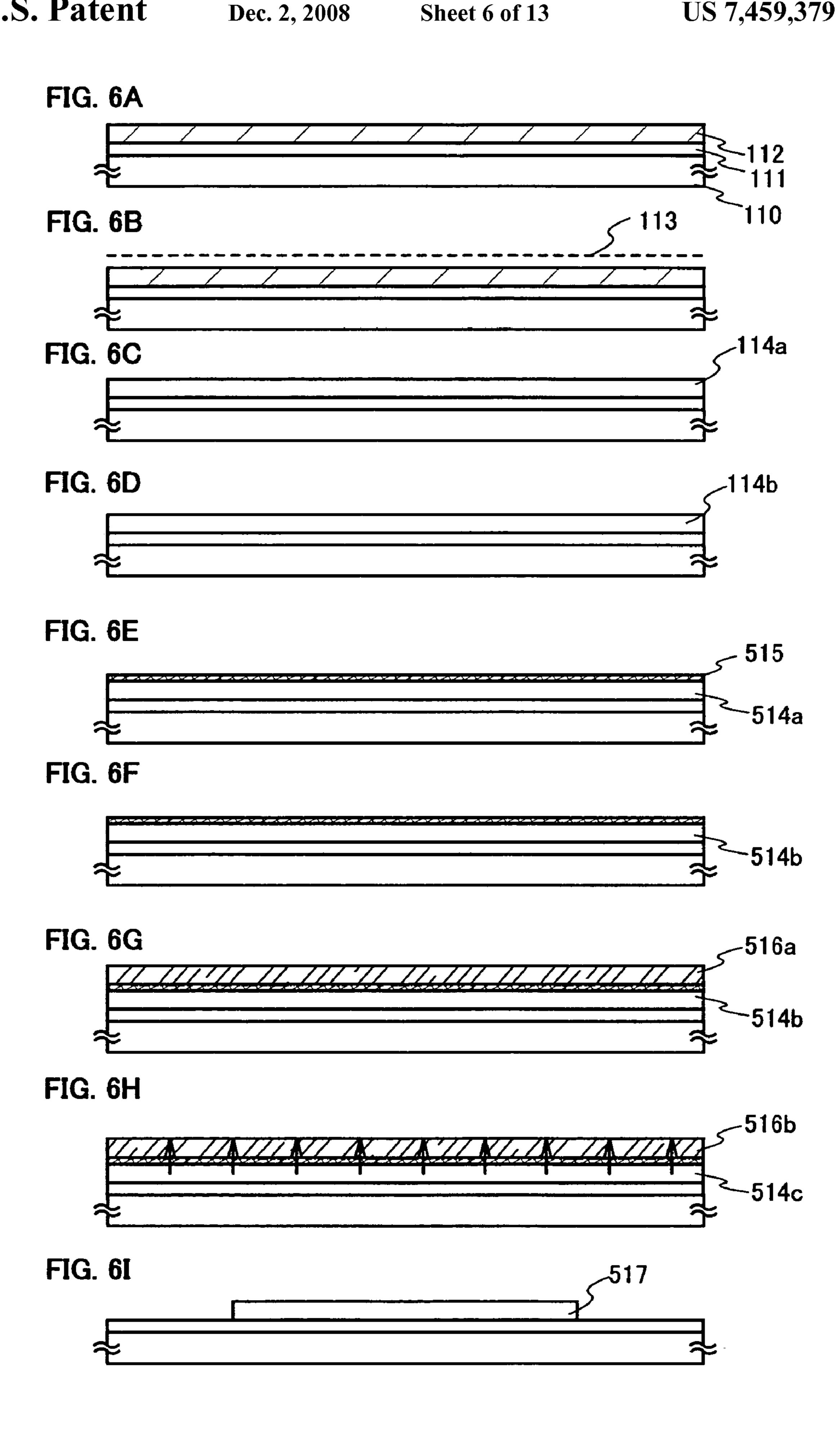

The first heat treatment may be performed after the step of forming the oxide film (the barrier layer) by the using the solution including ozone. Therefore, another configuration of the invention is a method for manufacturing a semiconductor device, which includes a first step of forming a first semiconductor film including an amorphous structure on an insulating surface, a second step of adding a metal element to the first semiconductor film including the amorphous structure, a third step of crystallizing the first semiconductor film to form a first semiconductor film including a crystalline structure, a fourth step of irradiating the first semiconductor film with laser light, a fifth step of oxidizing a surface of the first semiconductor film by using a solution including ozone to form a barrier layer, a sixth step of performing a first heat treatment to reduce strain of the first semiconductor film, a seventh step of forming a second semiconductor film including a rare gas element on the barrier layer, an eighth step of performing a second heat treatment to remove or reduce the metal element in the first semiconductor film by moving the metal element into the second semiconductor film, a ninth step of removing the second semiconductor film, and a tenth step of removing the barrier layer, as shown in FIGS. 6A to 6I.

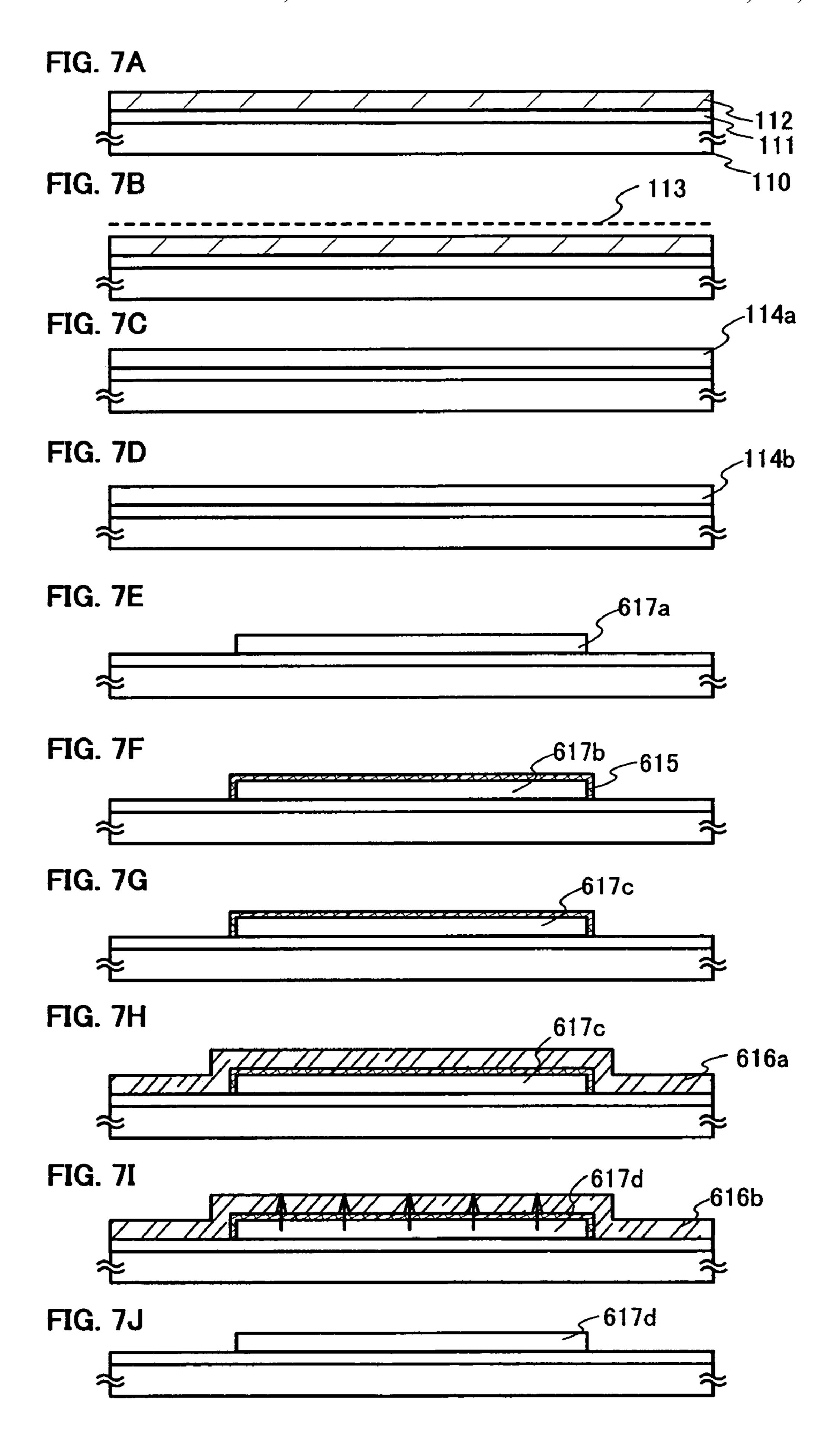

A heat treatment for reducing strain of a semiconductor film may be performed twice before and after the step of forming the oxide the oxide film (the barrier layer) by the using the solution including ozone. Therefore, another configuration of the invention is a method for manufacturing a semiconductor device, which includes a first step of forming a first semiconductor film including an amorphous structure on an insulating surface, a second step of adding a metal element to the first semiconductor film including the amorphous structure, a third step of crystallizing the first semiconductor film to form a first semiconductor film including a crystalline structure, a fourth step of irradiating the first semiconductor film with laser light, a fifth step of performing a

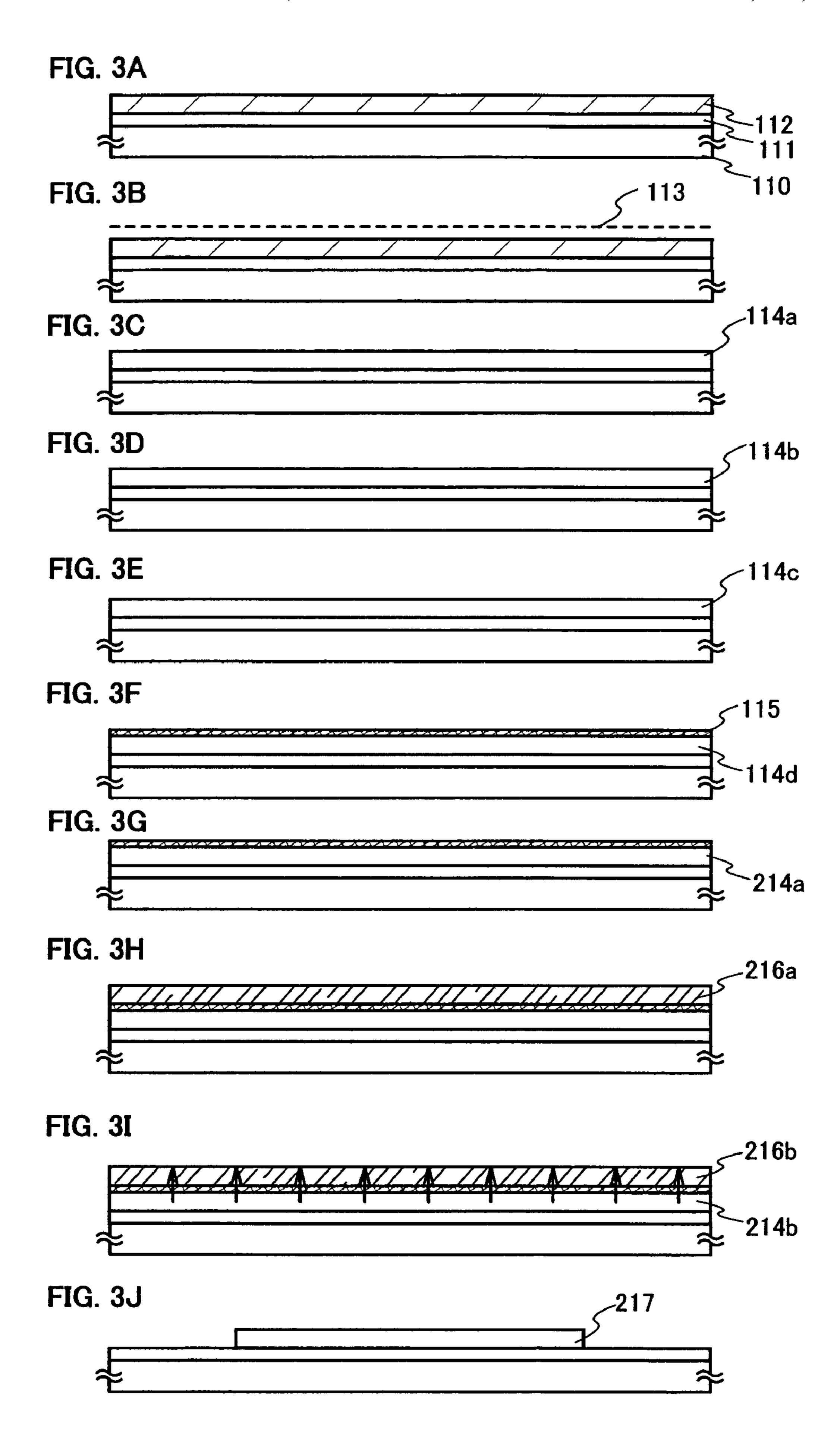

first heat treatment to reduce strain of the first semiconductor film, a sixth step of oxidizing a surface of the first semiconductor film by using a solution including ozone to form a barrier layer, a seventh step of performing a second heat treatment to further reduce strain of the first semiconductor 5 film, an eighth step of forming a second semiconductor film including a rare gas element on the barrier layer, a ninth step of performing a third heat treatment to remove or reduce the metal element in the first second semiconductor film by moving the metal element into the second semiconductor film, a 10 tenth step of removing the second semiconductor film, and an eleventh step of removing the barrier layer, as shown in FIGS. 3A to 3J.

In each configuration described above, a native oxide film formed at the surface of the first semiconductor film may be 15 removed by cleaning the surface of the semiconductor film before the step of irradiating the first semiconductor film with laser light.

Further, in each configuration described above, a surface oxide film formed by the laser light irradiation may be <sup>20</sup> removed after the step of irradiating the first semiconductor film with laser light.

Further, in each configuration described above, the barrier layer is one of a silicon oxide film and a silicon oxynitride film of 1 to 10 nm in film thickness. Note that the barrier layer indicates all oxide film formed at the surface of the first semiconductor film before forming the gattering site (the second semiconductor film). When there is no step of removing an oxide film before forming the gattering site (the second semiconductor film), the native oxide film, the surface oxide film by the laser light irradiation, and the oxide film (chemical oxide) formed by using the solution including ozone may be all included with being mixed or laminated.

Further, in each configuration described above, the metal element for promoting crystallization is one or more kinds selected from the group consisting of Fe, Ni, Co, Ru, Rh, Pd, Os, Ir, Pt, Cu, and Au.

Further, in each configuration described above, the rare gas element is one or more kinds selected from the group consisting of He, Ne, Ar, Kr, and Xe. Above all, argon (Ar), which is an inexpensive gas, is preferable for mass production.

The present invention can reduce strain generated in a semiconductor film (to serve as an active layer of a TFT) by laser light irradiation.

In the case of adding a metal element for crystallization to the first semiconductor film, a condition under which the metal element easily moves to a gettering site can be obtained by performing a heat treatment for reducing strain of a semiconductor film by laser light irradiation before a heat treatment for gettering.

In addition, an oxide film obtained according to the present invention protects the first semiconductor film from an etchant including an acid and the like in steps performed after laser light irradiation (for example, etching for removing the second semiconductor film and a treatment before forming the gate insulating film) so that a minute hole (also referred to as a pinhole) can be prevented from being formed. Accordingly, the present invention can reduce defective pixels such as point defects to improve a yield.

#### BRIEF DESCRIPTION OF THE DRAWINGS

In the accompanying drawings:

FIGS. 1A to 1F are diagrams illustrating a manufacturing 65 process according to the present invention (Embodiment Mode 1);

8

FIGS. 2A to 2I are diagrams illustrating a manufacturing process according to the present invention (Embodiment Mode 2);

FIGS. 3A to 3J are diagrams illustrating a manufacturing process according to the present invention (Embodiment Mode 3);

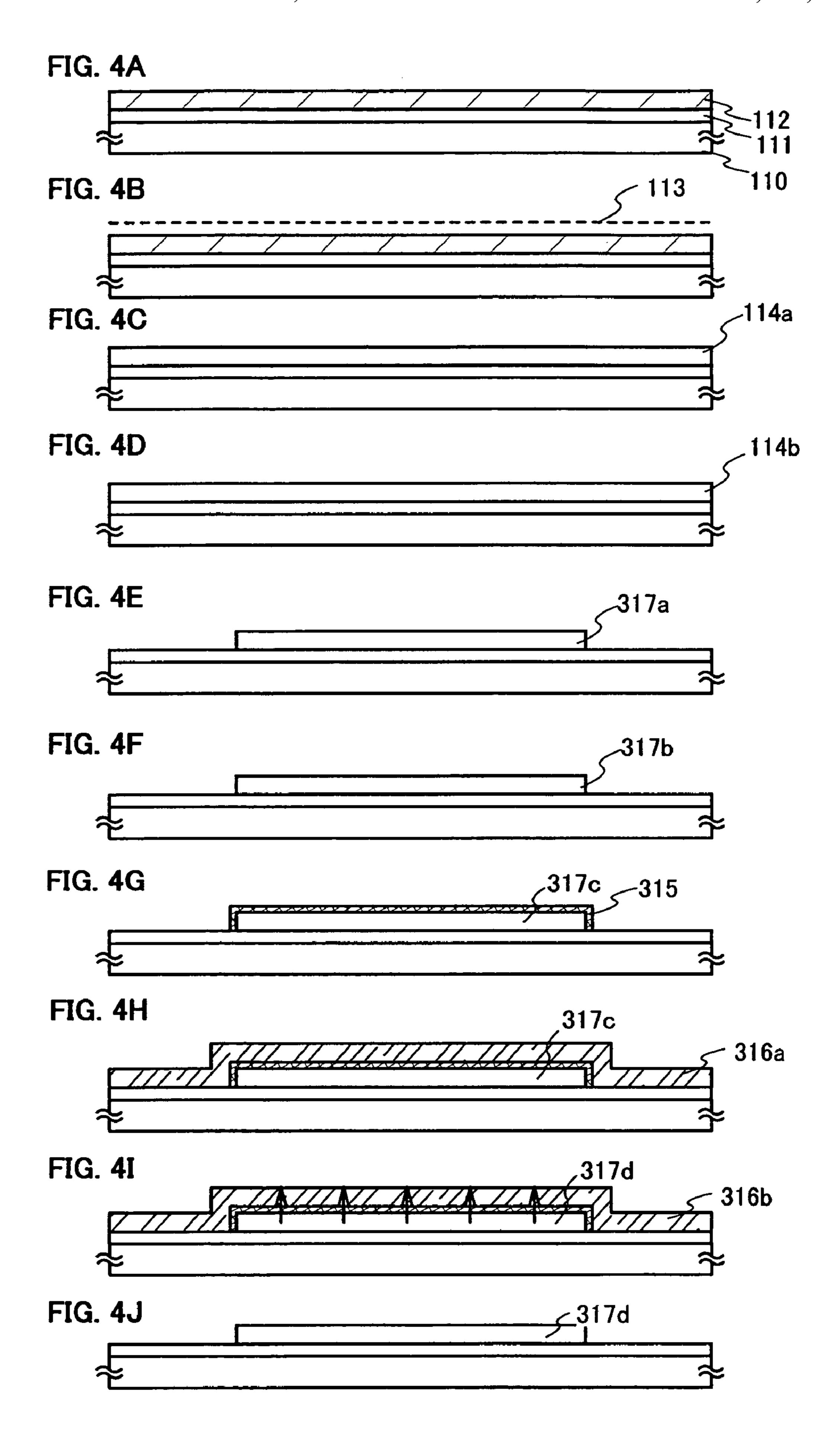

FIGS. 4A to 4J are diagrams illustrating a manufacturing process according to the present invention (Embodiment Mode 4);

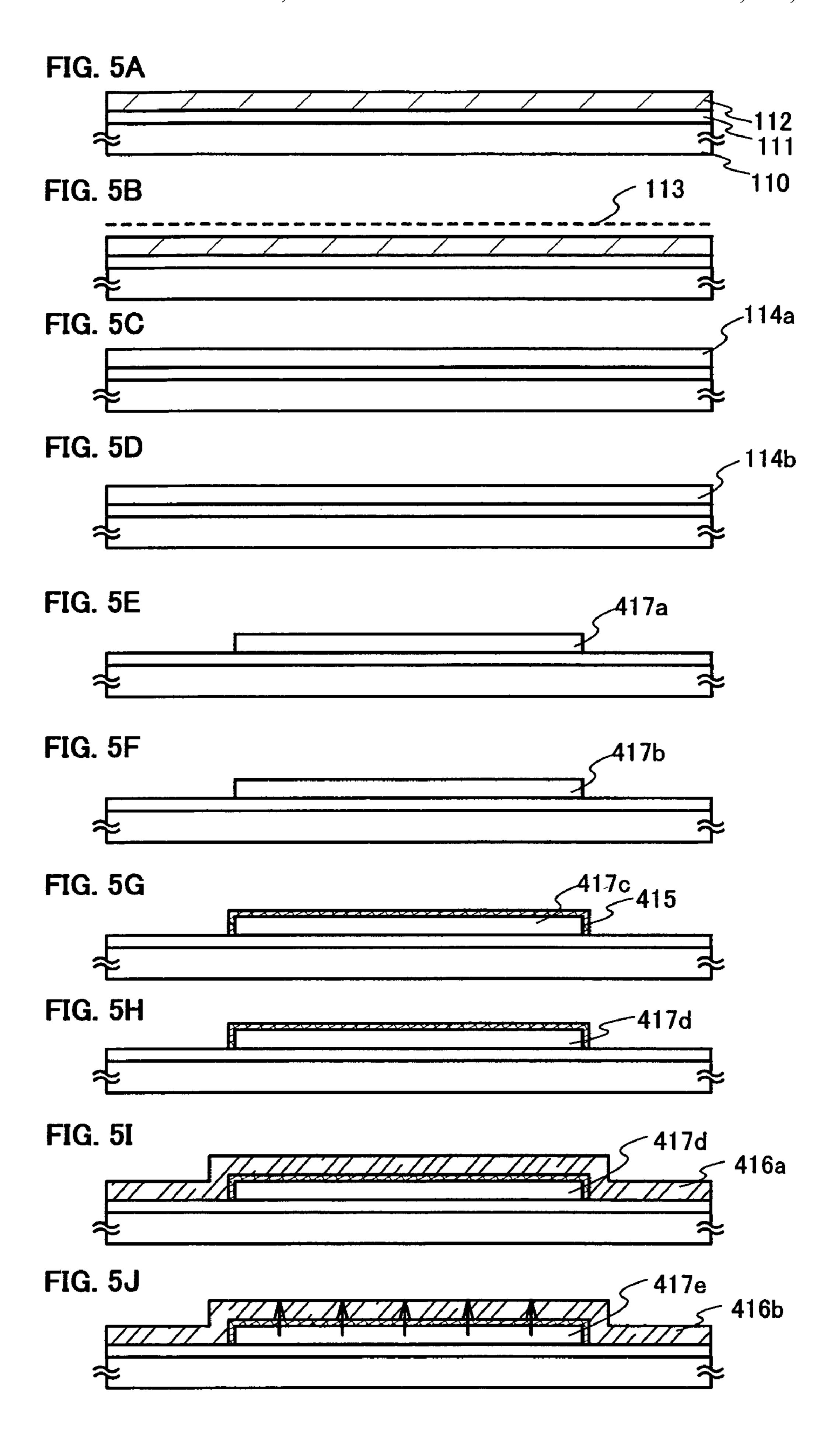

FIGS. **5**A to **5**J are diagrams illustrating a manufacturing process according to the present invention (Embodiment Mode 5);

FIGS. 6A to 6I are diagrams illustrating a manufacturing process according to the present invention (Embodiment Mode 6);

FIGS. 7A to 7J are diagrams illustrating a manufacturing process according to the present invention (Embodiment Mode 7);

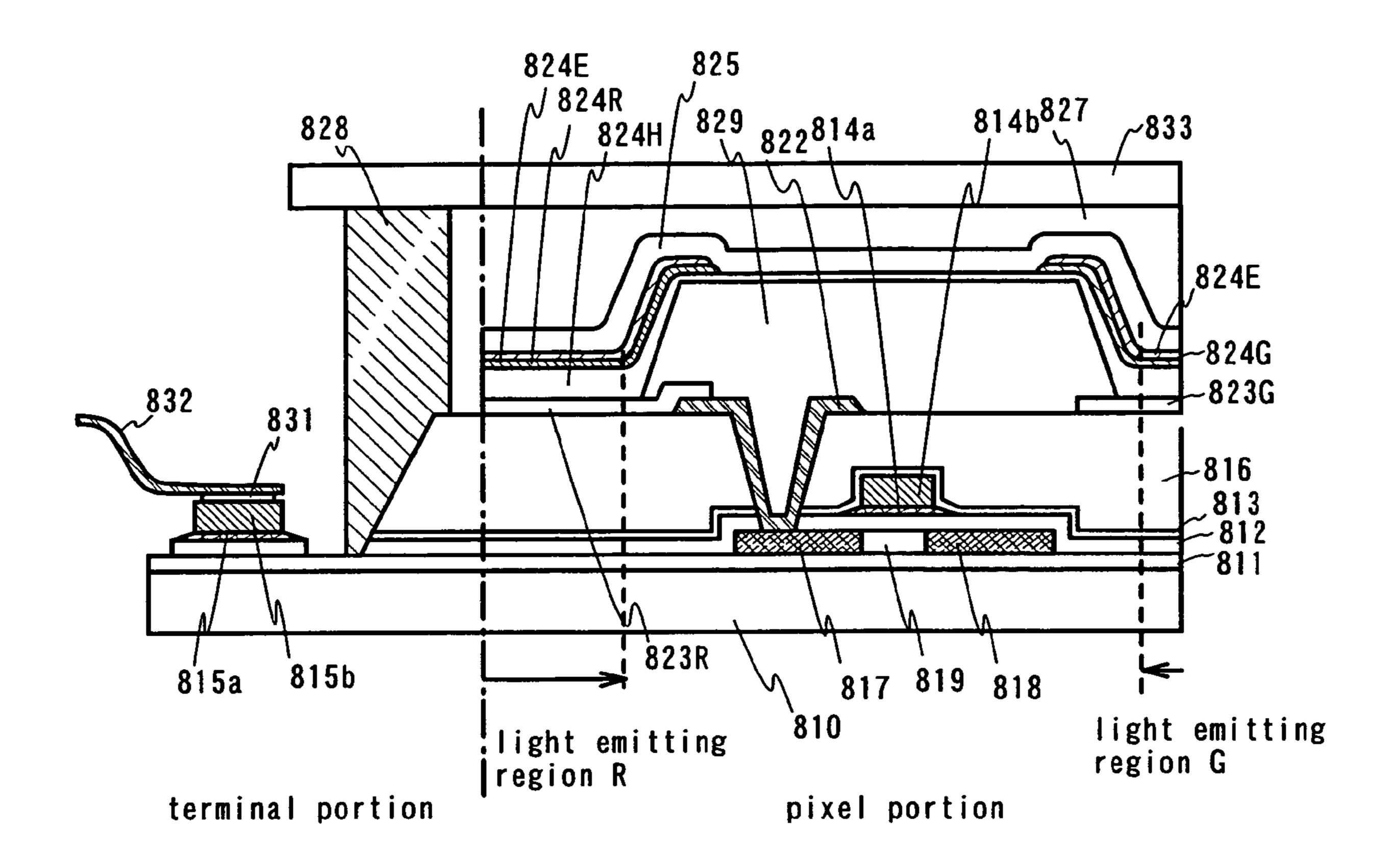

FIGS. 8A and 8B are diagrams illustrating the structure of an active matrix EL display device (Embodiment 1);

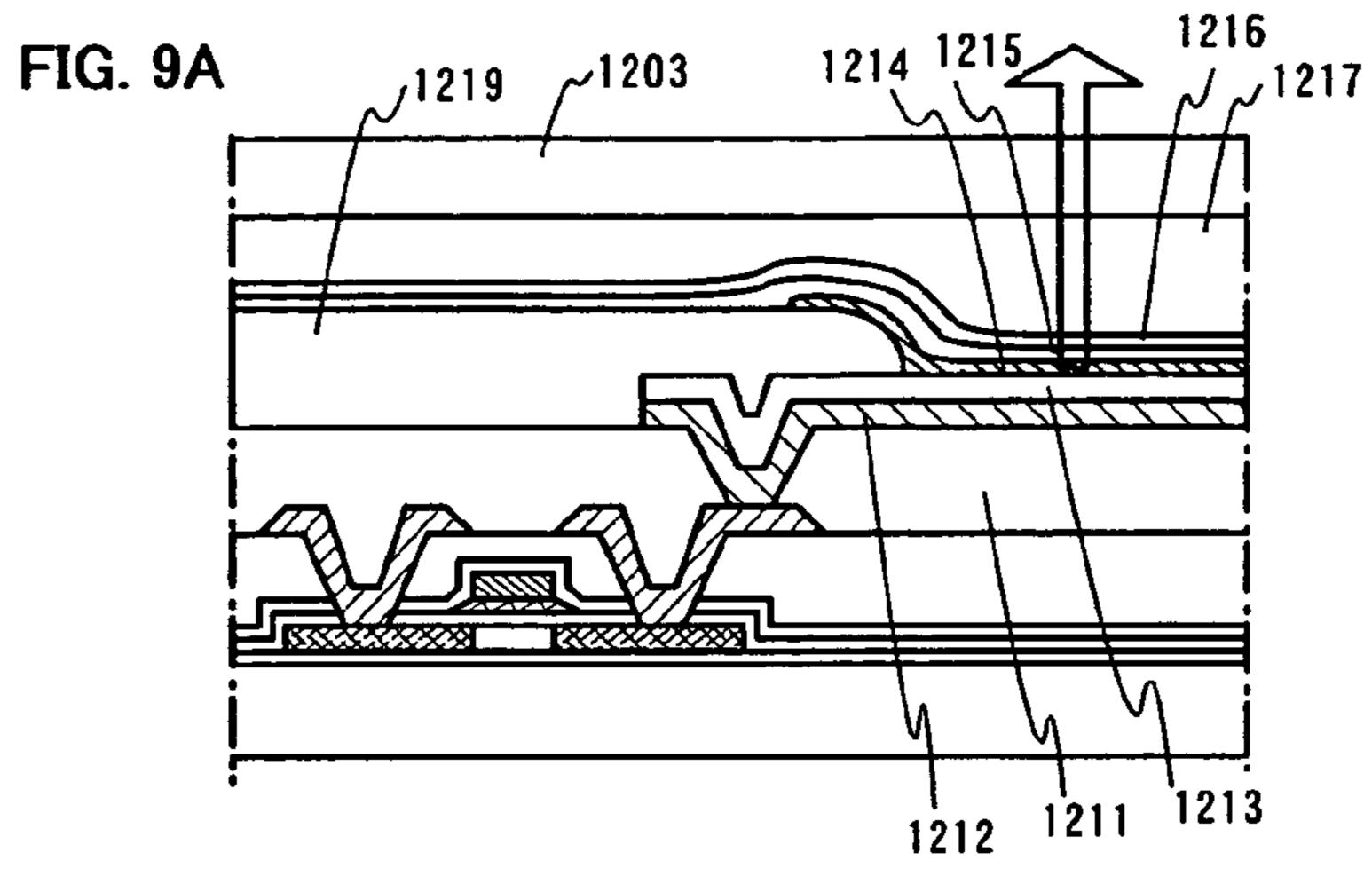

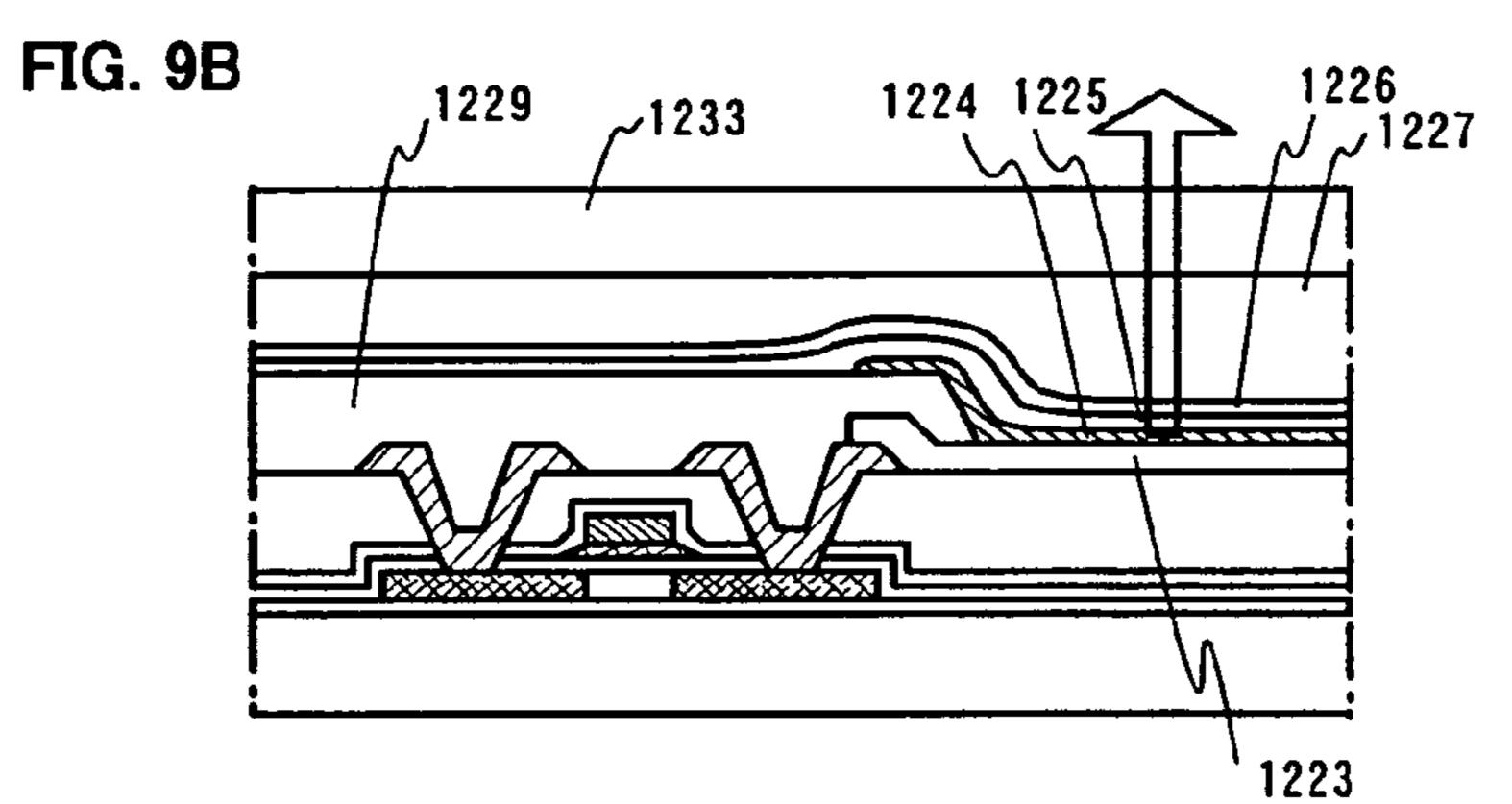

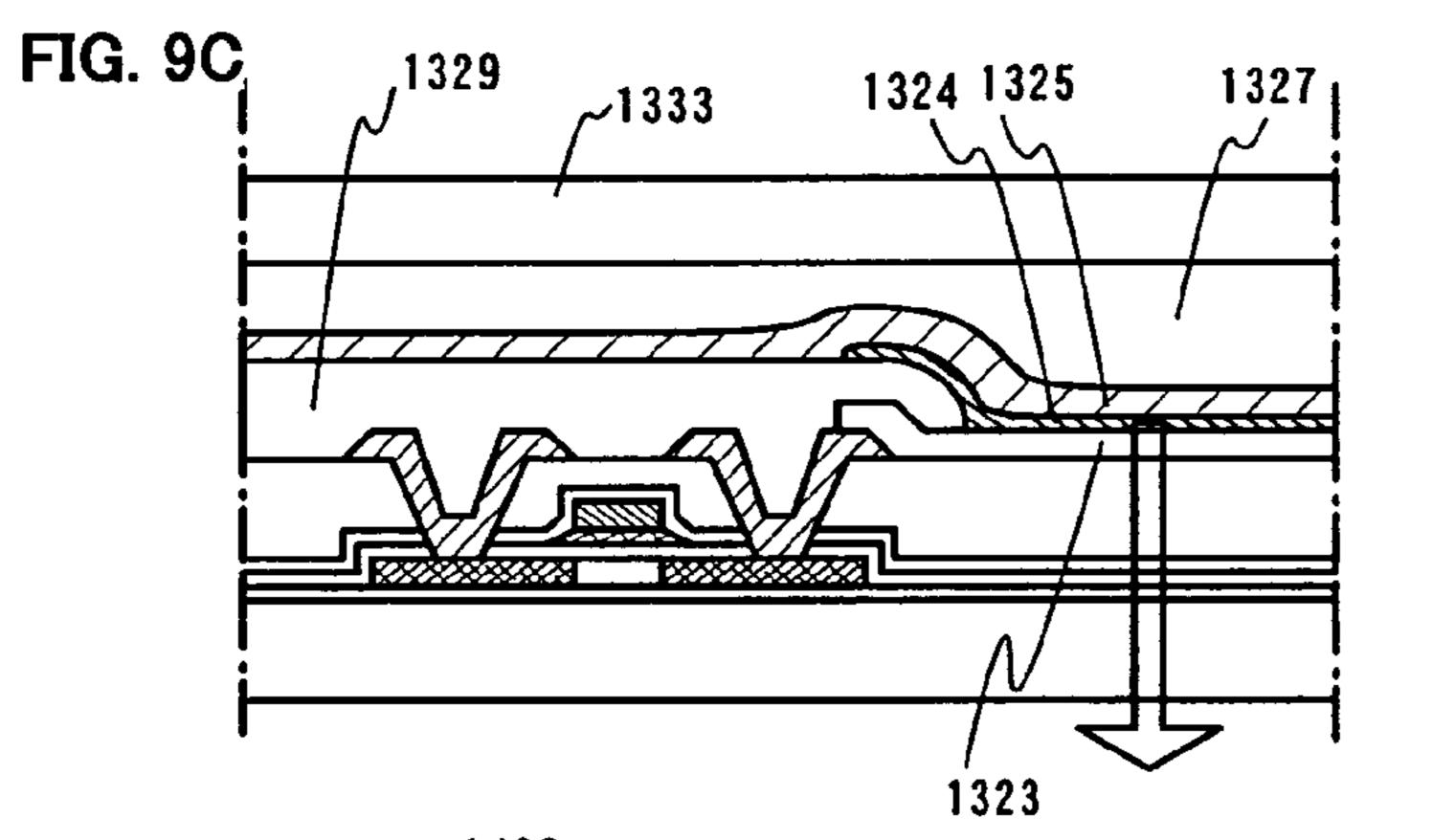

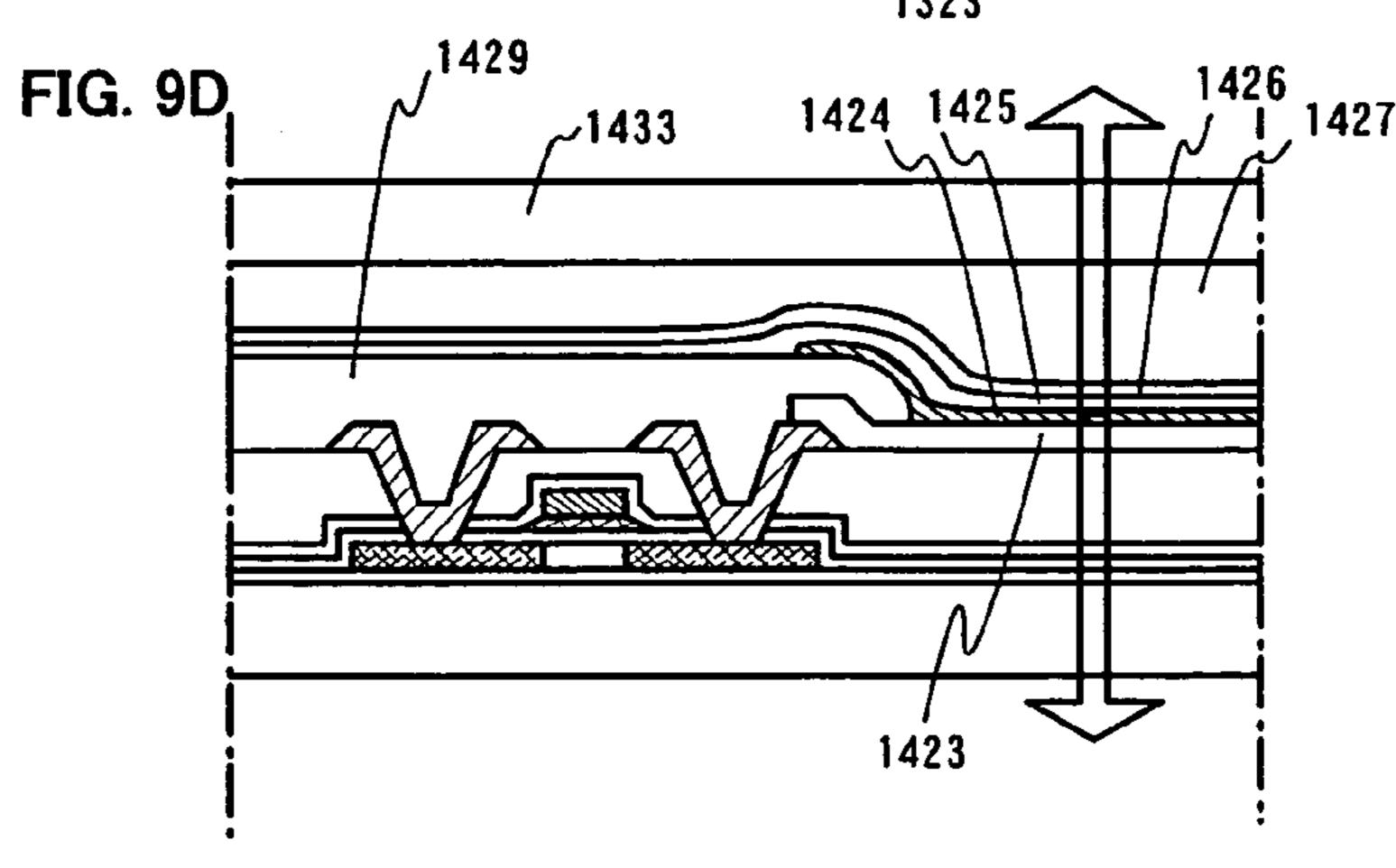

FIGS. 9A to 9D are cross-sectional views illustrating variations of pixel structures;

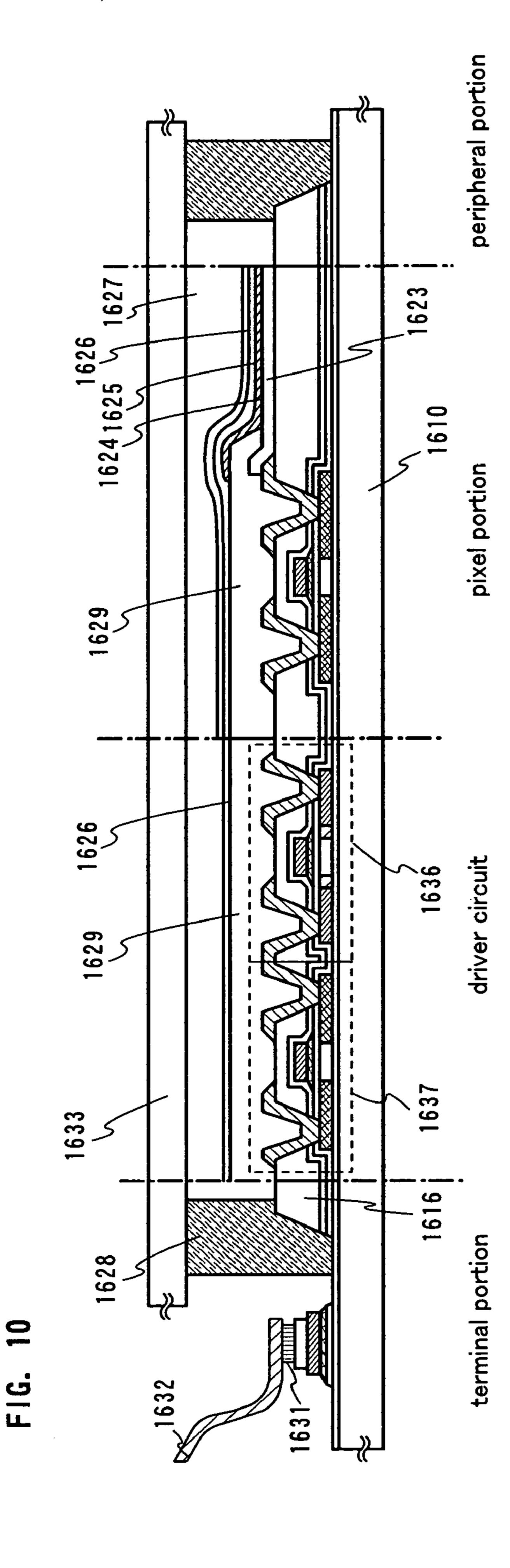

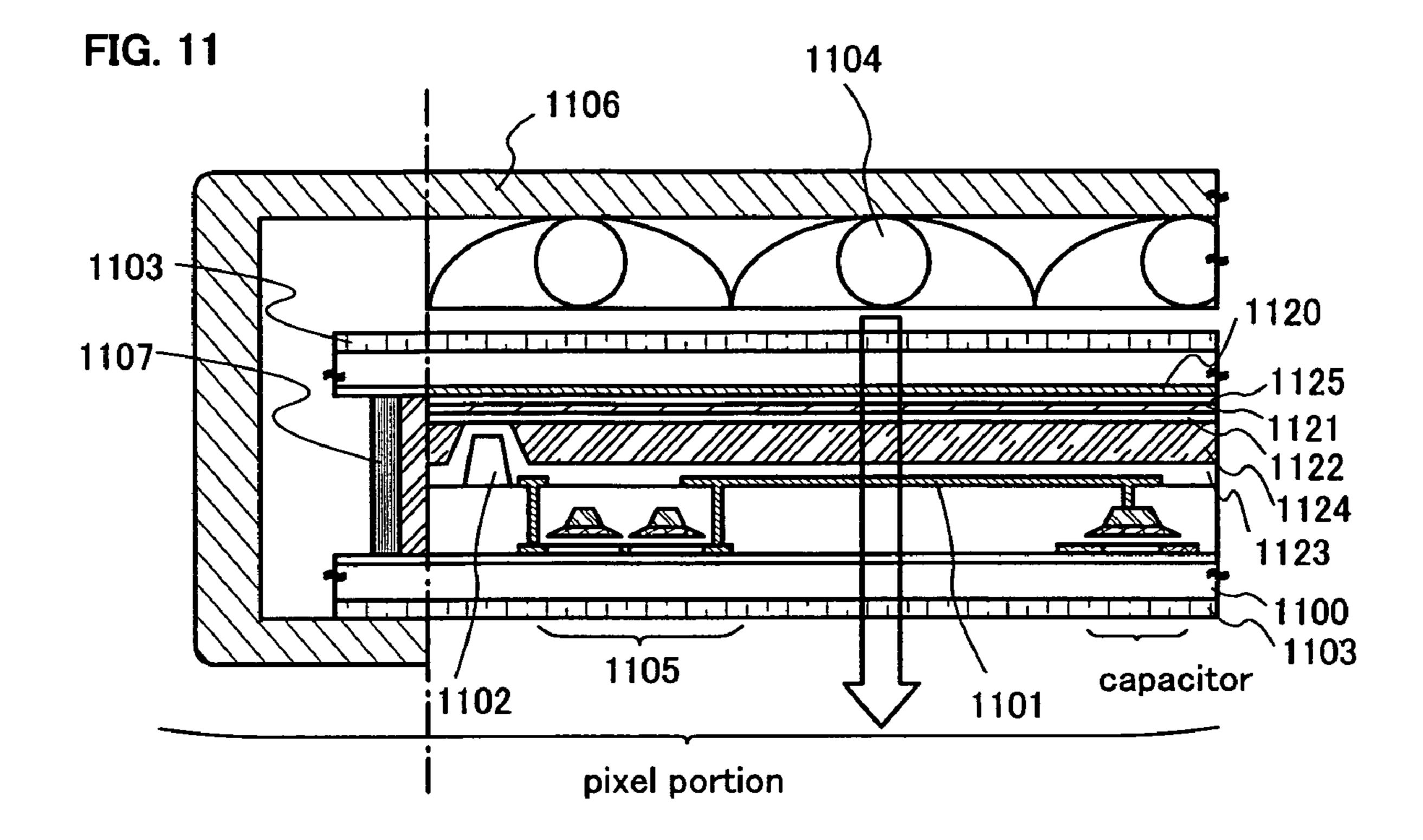

FIG. 10 is a cross-sectional view of an EL display device; FIG. 11 is a diagram illustrating a cross-sectional structure of an active matrix liquid crystal display device;

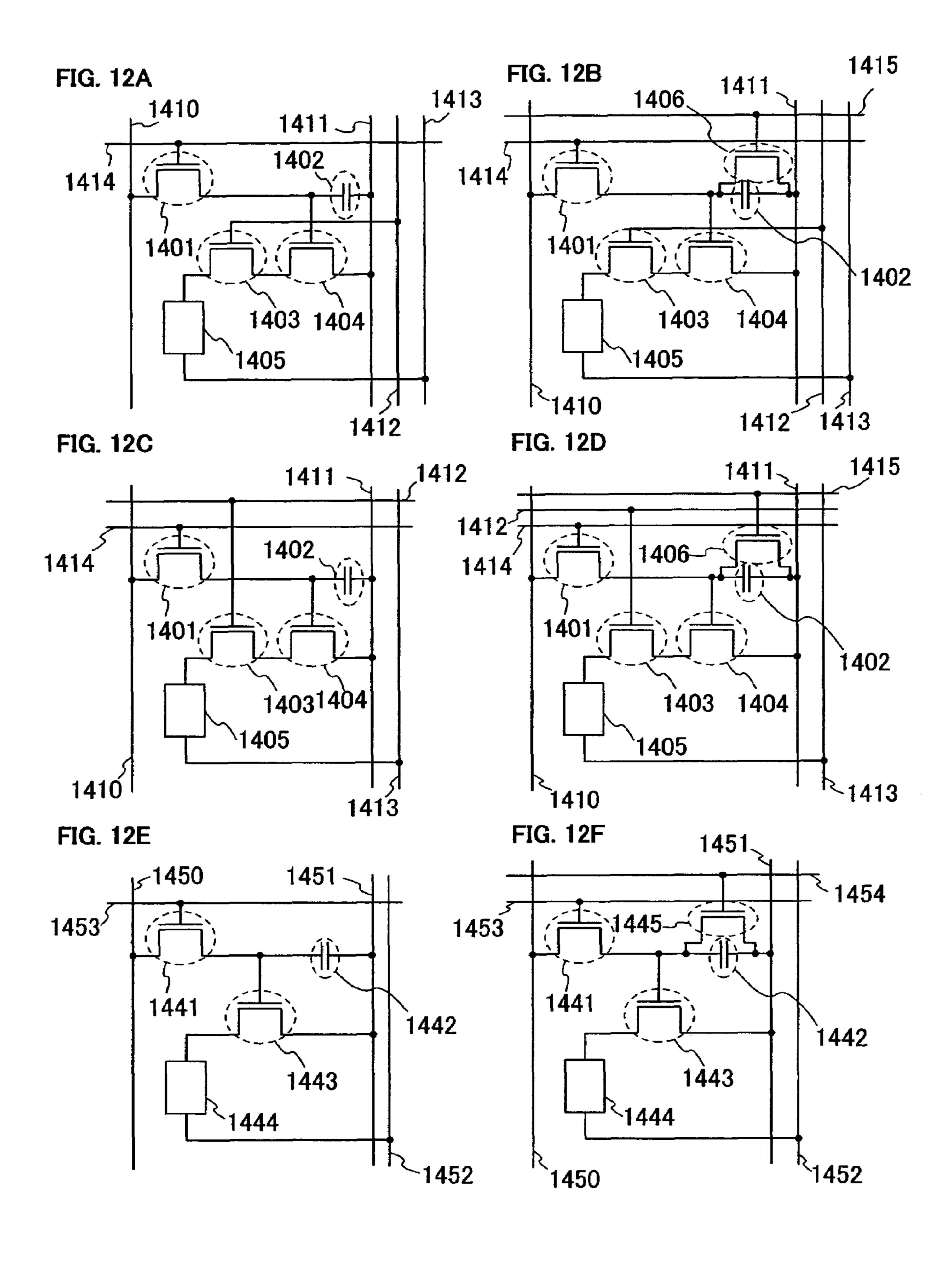

FIGS. 12A to 12F are diagrams illustrating pixel structures that can be applied to an EL display panel according to the present invention; and

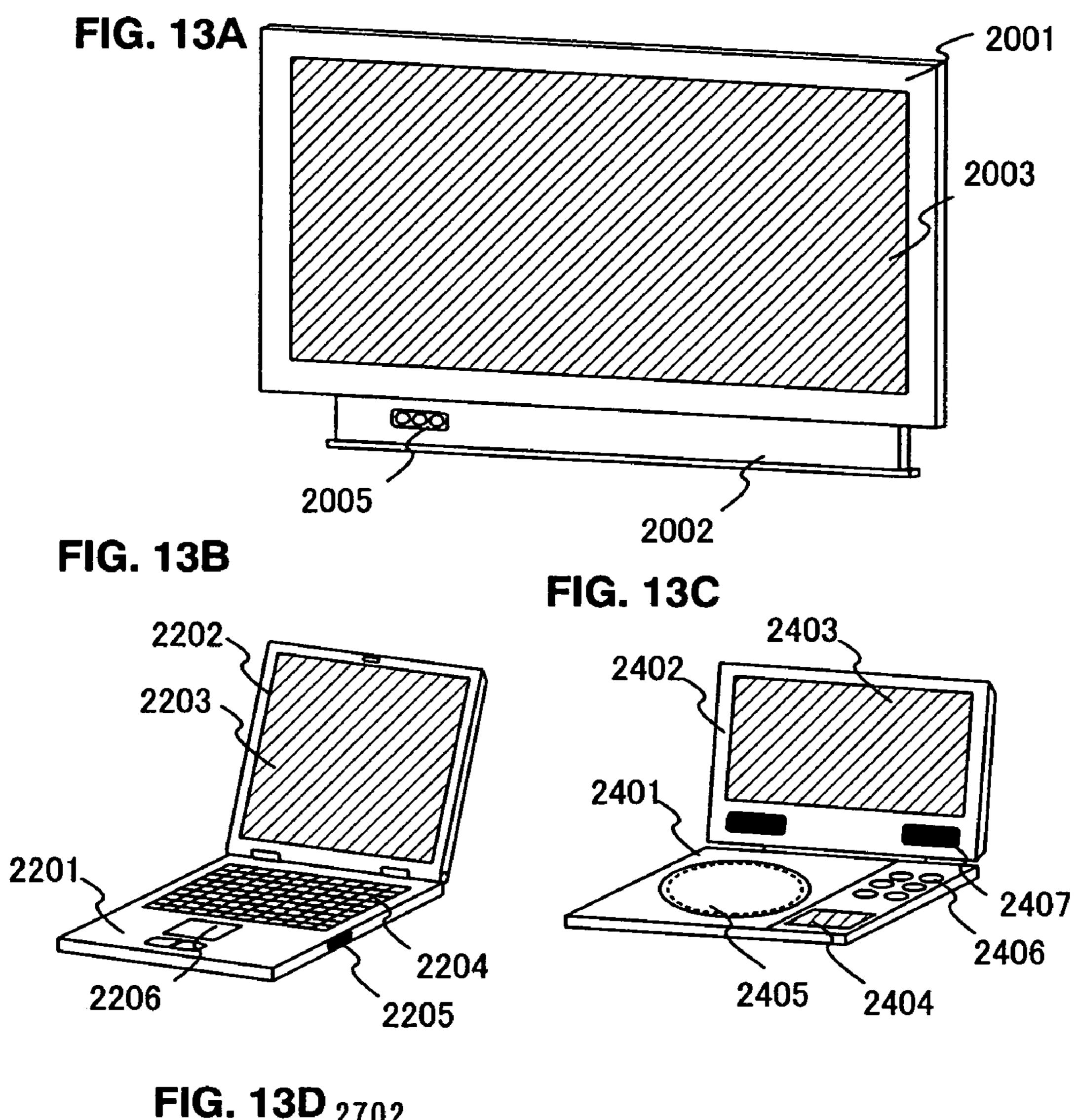

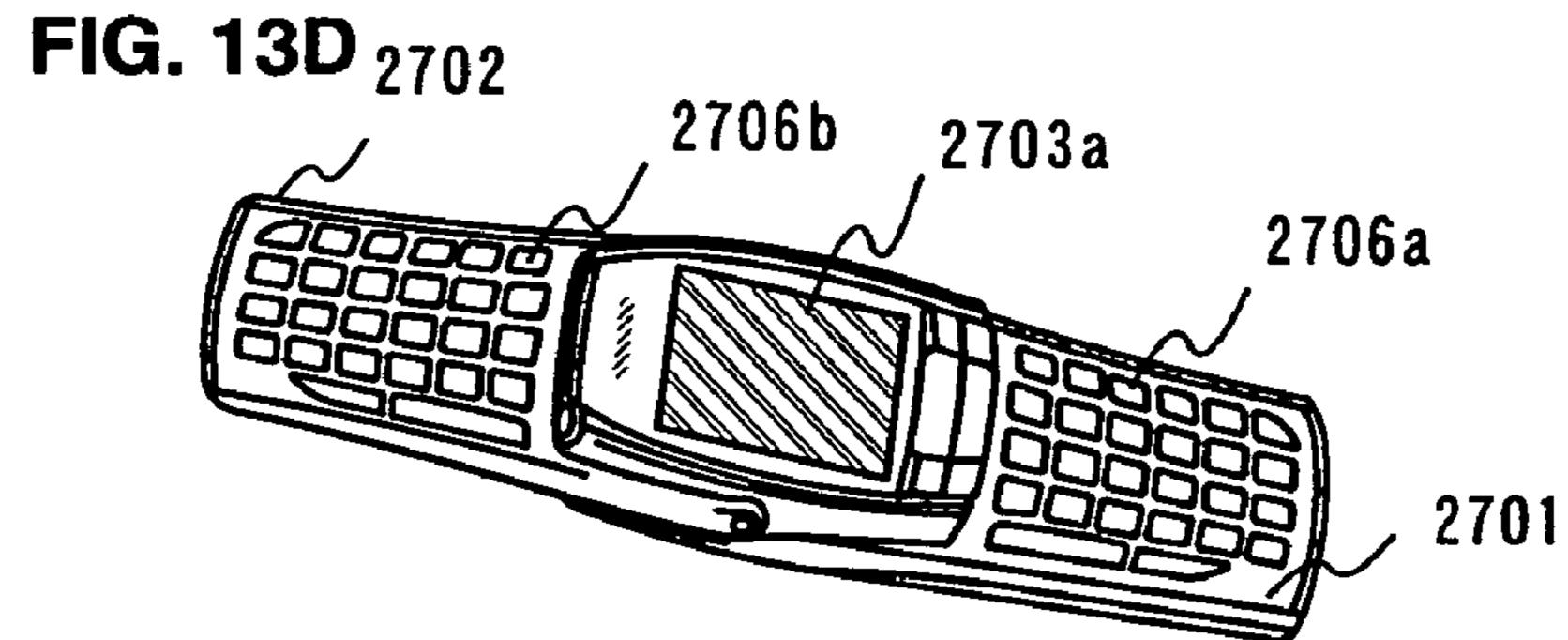

FIGS. 13A to 13E are diagrams illustrating examples of electronic devices.

#### DETAILED DESCRIPTION OF THE INVENTION

Embodiment modes of the present invention will be described below.

#### Embodiment Mode 1

A typical process for manufacturing a TFT by using the present invention will be briefly described below with reference to FIGS. 1A to 1F. An example of performing an oxidation treatment with a solution containing ozone and a heat treatment for reducing strain after patterning of a semiconductor film into a desired shape is shown here.

In FIG. 1A, reference numeral 10 denotes a substrate that has an insulating surface, reference numeral 11 denotes a base insulating film, and reference numeral 14 denotes a semiconductor film having a crystalline structure by laser light irradiation.

In FIG. 1A, a glass substrate, a quartz substrate, a ceramic substrate, and the like can be used as the substrate 10. Also, a silicon substrate, a metal substrate, or a stainless substrate with an insulating film formed on the surface thereof may be used. In addition, a heat-resistant plastic substrate that can withstand processing temperatures in the process may be used.

First, as shown in FIG. 1A, the base insulating film 11 formed of an insulating film such as a silicon oxide film, a silicon nitride film, or a silicon oxynitride film (SiO<sub>x</sub>N<sub>y</sub>) is formed on the substrate 10. In a representative example, the base insulating film 11 has a two layer structure, for which a silicon nitride oxide film having a thickness of 50 to 100 nm formed by using SiH<sub>4</sub>, NH<sub>3</sub>, and N<sub>2</sub>O as reaction gases and a silicon oxynitride film having a thickness of 100 to 150 nm formed by using SiH<sub>4</sub> and N<sub>2</sub>O as reaction gases are laminated. As one layer of the base insulating film 11, it is preferable to use a silicon nitride film (SiN film) or a silicon

oxynitride film (SiO<sub>x</sub>N<sub>y</sub> (X>Y) film) of 10 nm or less in film thickness. In gettering, nickel tends to move easily to a region including a higher density of oxygen. Therefore, it is highly effective to use a silicon nitride film as the base insulating film 11 in contact with the semiconductor film 14. Alternatively, a 5 three layer structure in which a silicon nitride oxide film, a silicon oxynitride film, and a silicon nitride film are sequentially laminated may be used.

Next, a semiconductor film including an amorphous structure is formed on the base insulating film 11. For the semiconductor film, a semiconductor material containing silicon as its main component is used. Typically, after forming an amorphous silicon film or an amorphous silicon-germanium film by a known method (for example, sputtering, LPCVD, or plasma CVD), a known crystallization treatment (laser crystallization, thermal crystallization using a catalyst such as nickel) is performed to obtain a semiconductor film including a crystalline structure.

Alternatively, by controlling the deposition condition appropriately, a semiconductor film including a crystalline structure (for example, a polycrystalline silicon film, a microcrystalline semiconductor film (also referred to as a semi-amorphous semiconductor film)) may be obtained only by performing deposition. For example, a semiconductor film including a crystalline structure is formed directly on a substrate to be processed by introducing a silicide gas (for example, monosilane, disilane, or trisilane) and fluorine (or a halogen fluoride gas) into a deposition chamber as material gases and generating plasma.

FIG. 1A is a cross-sectional view after a step of irradiating the semiconductor film 14 with laser light. In the case of obtaining a semiconductor film including a crystalline structure by laser crystallization, the step indicates a crystallization step. FIG. 1A also shows a cross-sectional view of a step in the case of laser light irradiation for enhancing a degree of crystallinity of a semiconductor film including a crystalline structure obtained by a method other than laser crystallization. In the case of laser light irradiation for enhancing the degree of crystallinity, it is preferable to remove a native oxide film formed on the surface in a crystallization step before the laser light irradiation.

In any case, when laser light irradiation is performed, strain and ridges are formed in the semiconductor film, and a thin surface oxide film is formed at the surface of the semiconductor film 14. Since a film thickness and uniformity of this thin oxide film are not predictable, it is preferable to remove the oxide film. However, since a watermark is easily generated in drying of the water-shedding surface, it is preferable that another oxide film is formed by using a solution containing ozone after removing the surface oxide film to prevent generation of a water mark. In order to reduce the number of steps, the removal of the surface oxide film formed by the laser light irradiation may be unnecessary.

As a laser oscillator to be used for the laser light irradiation, a laser oscillator capable of emitting ultraviolet light, visible light, or infrared light can be used. As the laser oscillator, an excimer laser oscillator using KrF, ArF, XeCl, Xe, or the like, a gas laser oscillator using He, He—Cd, Ar, He—Ne, HF, or the like, a solid laser oscillator using a crystal such as YAG, GdVO<sub>4</sub>, YV<sub>4</sub>, YLF, or YAlO<sub>3</sub> doped with Cr, Nd, Er, Ho, Ce, Co, Ti, or Tm, and a semiconductor laser oscillator using GaN, GaAs, GaAlAs, InGaAsP, or the like can be used. In the case of the solid laser oscillator, it is preferable to apply the first to fifth harmonics of the fundamental wave.

Typically, excimer laser light with a wavelength of 400 nm or less or the second or third harmonic of a YAG laser is used

10

as the laser light. For example, pulsed laser light with a repetition frequency of 10 Hz to 100 MHz is used.

Next, patterning is performed with the use of a photolithography technique to obtain a semiconductor film 17a (FIG. 1B). Before forming a resist mask in the patterning, an oxide film is formed by using solution containing ozone or generating ozone by UV irradiation in an oxygen atmosphere to form an oxide film in order to protect the semiconductor film. The oxide film here is also effective in improving wettability of the resist.

If necessary, before the patterning, doping with a slight amount of impurity element (boron or phosphorous) is performed through the oxide film described above in order to control the threshold voltage of a TFT. When the doping is performed though the oxide film described above, the oxide film is removed, and another oxide film is formed by using a solution containing ozone.

Then, after cleaning is performed for removing undesired substances (for example, resist left and a solution for stripping resist) produced during the patterning, a solution containing ozone (typically, ozone water) is used to form an oxide film (referred to as a chemical oxide) 15 at the surface of the semiconductor film 17b in order to protect the patterned semiconductor film (FIG. 1C).

Next, a heat treatment for reducing strain of the semiconductor film (a heat treatment of heating the semiconductor film instantaneously to approximately 400 to 1000° C.) is performed in a nitrogen atmosphere to obtain a flat semiconductor film 17c (FIG. 1D). As the heat treatment of instantaneous heating, a heat treatment of intense light irradiation or a heat treatment of putting the substrate into heated gas and taking the substrate out after being left for several minutes may be used. Depending on the condition of this heat treatment, defects remaining in crystal grains can be repaired, that is, the crystallinity can be improved while reducing the strain.

In the case of performing an instantaneous heat treatment by intense light irradiation, any one of infrared light, visible light, and ultraviolet light or a combination thereof can be used. Typically, light emitted from a halogen lamp, a metal halide lamp, a xenon arc lamp, a carbon arc lamp, a high-pressure sodium vapor lump, or a high-pressure mercury vapor lump is used. The semiconductor film may be heated by turning on the lamp for a required time or instantaneously heated to approximately 400 to 1000° C. by turning on the light source once to ten times, in which each period of turning on the light source may be 10 to 60 seconds, preferably 30 to 60 seconds.

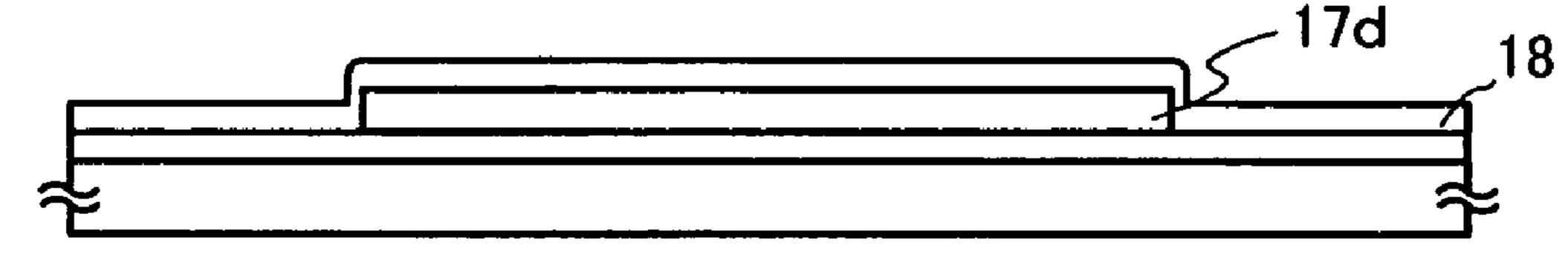

Next, an insulating film containing silicon as its main component to serve as a gate insulating film 18 is formed over the surface of a semiconductor film 17d (FIG. 1E). In order to reduce the number of steps, the gate insulating film 18 is formed without removing the oxide film here. Before forming the gate insulating film 18, the oxide film may be removed by using an etchant including hydrofluoric acid. In addition, it is not particularly necessary to remove the oxide film of the semiconductor film 17d completely, and the oxide film may be left thinly. When the semiconductor film 17d is exposed by overetching, the surface is likely to be contaminated with impurities.

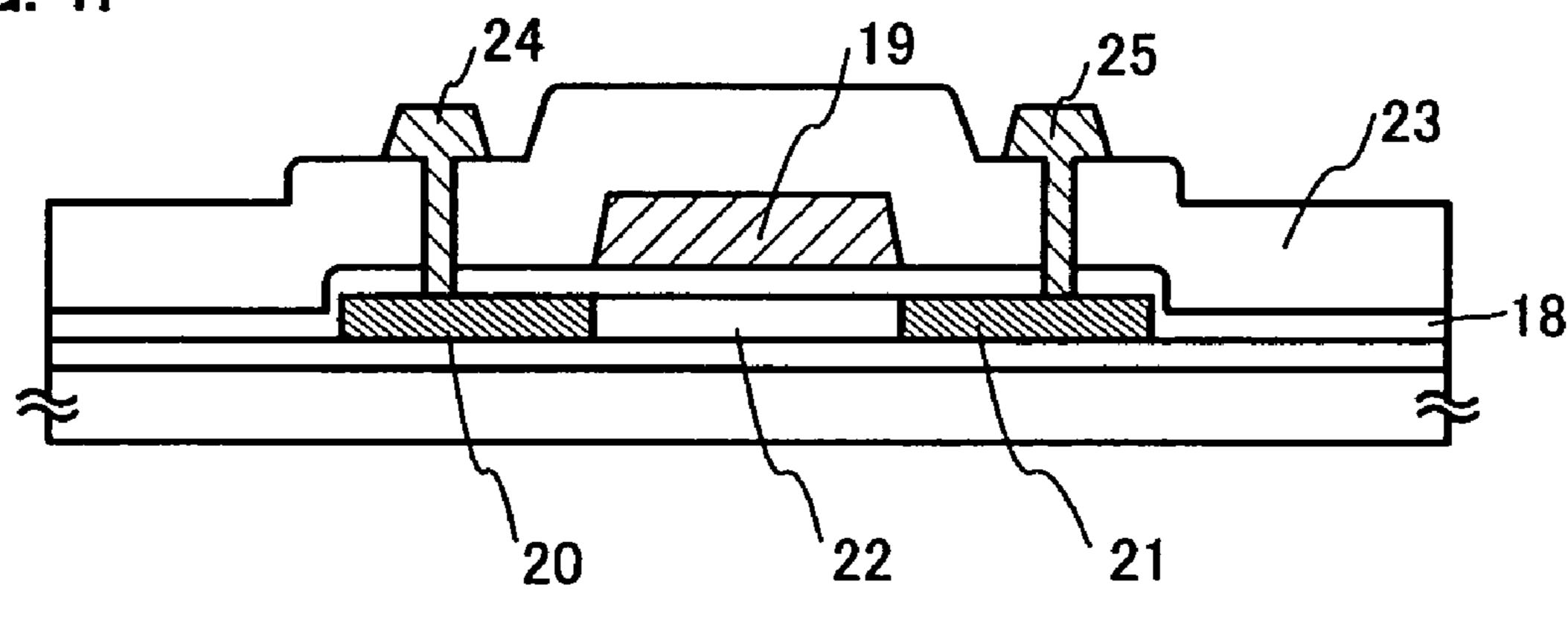

Next, after cleaning the surface of the gate insulating film 18, a gate electrode 19 is formed thereover. Then, the semiconductor film 17d is doped appropriately with an impurity element (for example, P or As) that gives n-type conductivity, phosphorous here, to form a source region 20 and a drain region 21. After the doping, a heat treatment, intense light irradiation, or laser light irradiation is performed in order to activate the impurity element. In addition, as well as activa-

tion, plasma damage to the gate insulating film and plasma damage to the interface between the gate insulating film and the semiconductor film can be recovered. In particular, it is quite effective to activate the impurity element by irradiation with the second harmonic of YAG laser from the surface or rear surface side of the semiconductor film in an atmosphere at room temperature to 300° C. The YAG laser is preferable activation means because less maintenance is required.

According to subsequent steps of forming an interlayer insulating film 23, performing hydrogenation, forming contact holes reaching the source region 20 and the drain region 21, forming a conductive film, and forming a source electrode 24 and a drain electrode 25 by patterning the conductive film, a TFT (n-channel TFT) is completed (FIG. 1F). The source electrode 24 and the drain electrode 25 are formed by using a 15 single layer comprising an element selected from the group consisting of Mo, Ta, W, Ti, Al, and Cu, or an alloy material or a compound material containing the element as its main component, or by using a lamination layer of these. For example, a three layer structure of a Ti film, a pure-Al film, and a Ti 20 film, or a three layer structure of a Ti film, an Al alloy film containing Ni and C, and a Ti film is used. Further, in consideration of forming an interlayer insulating film and the like in subsequent steps, it is preferable that the cross section of the electrode has a tapered shape.

A channel forming region 22 of the thus obtained TFT is relatively flat, and strain can be reduced.

Further, the present invention is not limited to the TFT structure in FIG. 1F. If necessary, a lightly doped drain (LDD) structure that has an LDD region between a channel forming region and a drain region (or a source region) may be employed. In this structure, a region doped with an impurity element at a lower density is provided between a channel forming region and a source region or a drain region formed by doping with an impurity element at a higher density, and 35 this region is referred to as an LDD region. Further, a so-called GOLD (Gate-drain Overlapped LDD) structure, in which an LDD region is overlapped with a gate electrode with a gate insulating film interposed therebetween, may be employed.

The description is given with reference to an n-channel TFT here. However, it will be obvious that a p-channel TFT can be formed by using a p-type impurity element instead of an n-type impurity element.

In addition, the description is given with reference to a top 45 gate TFT as an example here. The present invention can be applied regardless of the TFT structure, and can be applied to for example, a bottom gate TFT (an inversely staggered TFT) and a staggered TFT.

#### Embodiment Mode 2

Further, FIGS. 2A to 2I show an example of performing a heat treatment for reducing strain and an oxidation treatment with a solution containing ozone after crystallization of a 55 semiconductor film added with a metal element.

In FIG. 2A, reference numeral 110 denotes a substrate that has an insulating surface, reference numeral 111 denotes a base insulating film, and reference numeral 112 denotes a semiconductor film including an amorphous structure.

First, as shown in FIG. 2A, the base insulating film 111 comprising an insulating film such as a silicon oxide film, a silicon nitride film, or a silicon oxynitride film ( $SiO_xN_y$ ) is formed on the substrate 110.

Next, the first semiconductor film 112 with the amorphous 65 structure is formed on the base insulating film 111. For the first semiconductor film 112, a semiconductor material con-

12

taining silicon as its main component is used. Typically, an amorphous silicon film, an amorphous silicon-germanium film, or the like is applied, which is formed by plasma CVD, low-pressure CVD, or sputtering to be 10 to 100 nm in thickness. In order to obtain a semiconductor film including a high-quality crystalline structure in subsequent crystallization, the density of impurities such as oxygen and nitrogen contained in the first semiconductor film 112 with the amorphous structure is preferably reduced to  $5\times10^{18}/\text{cm}^3$  (an atomic density measured by secondary ion mass spectrometry (SIMS)) or less. These impurities become factors for interfering with subsequent crystallization, and factors for increasing density of trapping centers and recombination centers also after crystallization. Therefore, as well as using a high-purity material gas, it is preferable to perform mirror polishing such as electrolytic polishing or use a CVD system equipped with an oil-free vacuum evacuation system, by which super high vacuum can be obtained.

Next, as a technique for crystallizing the first semiconductor film 112 with the amorphous structure, the technique described in Japanese Patent Laid-Open No. 8-78329 is used here for crystallization. In the technique described there, a metal element for promoting crystallization is selectively added to an amorphous silicon film, and a semiconductor film 25 including a crystalline structure that spreads from the region to which the metal element is added is formed by performing a heat treatment. First, a nickel acetate solution including a metal element (nickel here) that has catalytic activity of promoting crystallization at 1 to 100 ppm by weight is applied with a spinner to the surface of the first semiconductor film 112 including the amorphous structure to form a layer containing nickel 113 (FIG. 2B). As another method other than the method of forming a layer containing nickel 113 by application of a solution including a metal element, a method of forming an extremely thin film by sputtering, an evaporation method, or a plasma treatment may be employed. Although an example of application all over the first semiconductor film 112 is shown here, a mask may be formed to form a layer containing nickel selectively.

Next, a heat treatment is performed for crystallization. In this case, crystallization proceeds with silicide formed as a nucleus at a portion of the semiconductor film in contact with the metal element which promotes crystallization of a semiconductor. In this way, a first semiconductor film 114a including a crystalline structure, shown in FIG. 2C, is formed. Note that it is preferable that the density of oxygen included in the first semiconductor film 114a after crystallization is made to be  $5 \times 10^{18}$  atoms/cm<sup>3</sup> or less. After a heat treatment (450° C. for 1 hour) for dehydrogenation, a heat treatment (550 to 650°) 50 C. for 2 to 24 hours) for crystallization is performed here. In the case of performing crystallization by intense light irradiation, any one of infrared light, visible light, and ultraviolet light, or a combination thereof can be used. If necessary, before intense light irradiation, a heat treatment may be performed for releasing hydrogen contained in the first semiconductor film 112 including the amorphous structure. Alternatively, a heat treatment and intense light irradiation may be performed at the same time for crystallization. In light of productivity, it is preferable to perform crystallization by 60 intense light irradiation.

In the thus obtained first semiconductor film 114a, the metal element (nickel here) is remaining at a density over  $1\times10^{19}$  atoms/cm<sup>3</sup> as an average density even if the metal element is not distributed uniformly in the film. Of course, even in this state, various semiconductor elements typified by a TFT can be formed. However, the metal element is removed by gettering described subsequently.

Before performing laser light irradiation, a native oxide film formed in the crystallization step is removed here. Because this native oxide film includes nickel at a high density, it is preferable to remove the native oxide film.

Next, in order to increase degree of crystallinity (ratio of a 5 volume of crystalline part to the whole volume of the film) and repair defects remaining in crystal grains, the first semiconductor film 114a including the crystalline structure is irradiated with laser light (FIG. 2D). Thus, a first semiconductor film 114b is formed. By laser light irradiation, the 10 semiconductor film 114b has strain and ridges formed, and a thin surface oxide film (not shown) is formed at the surface of the semiconductor film 114b. As this laser light, excimer laser light with a wavelength of 400 nm or less emitted from a pulse oscillating laser or the second or third harmonic of a YAG 15 laser may be used. Alternatively, as the laser light, the second to fourth harmonics of the fundamental wave of a continuous wave solid laser may be used. Typically, the second harmonic (532 nm) or the third harmonic (355 nm) of Nd: YVO<sub>4</sub> laser (fundamental wave: 1064 nm) may be applied.

Next, a heat treatment for reducing strain of the first semiconductor film 114b (heating the semiconductor film instantaneously to approximately 400 to 1000° C.) is performed in a nitrogen atmosphere to obtain a flat semiconductor film 114c (FIG. 2E). As the heat treatment of instantaneous heating, intense light irradiation or a treatment of putting a substrate into heated gas and taking the substrate out after being left for several minutes may be used. Depending on the condition of this heat treatment, a defect remaining in a crystal grain can be repaired, that is, the crystallinity can be improved 30 while reducing the strain. In addition, this heat treatment reduces strain so that nickel is easily gettered in a subsequent gettering step. When the temperature in this heat treatment is lower than the melting point of the semiconductor, nickel would move into a silicon film with the first semiconductor 35 film **114***c* in a solid phase.

Next, at a surface of a semiconductor film 114d, an oxide film (also referred to as a barrier layer) 115 to serve as an etching stopper is formed by using a solution containing ozone (typically, ozone water) to have a film thickness of 1 to 40 10 nm (FIG. 2F). Since this oxide film 115 is formed by oxidizing the semiconductor film 114c reduced in strain, the oxide film also has favorable characteristics (for example, flatness and uniformity in film thickness).

Next, a second semiconductor film 116a including a rare 45 gas element is formed on this oxide film 115 (FIG. 2G).

The second semiconductor film 116a including the rare gas element, which is formed on the oxide film (barrier layer) 115, is formed by plasma CVD or sputtering to form a gettering site of 10 to 300 nm in film thickness. It is preferable 50 that the film thickness of the second semiconductor film 116a is thin since the deposition time and subsequent etching time both can be shortened. As the rare gas element, one or more kinds selected from the group consisting of helium (He), neon (Ne), argon (Ar), krypton (Kr), and xenon (Xe) are used. 55 Above all, argon (Ar) that is an inexpensive gas is preferable.

Plasma CVD is used here to form the second semiconductor film **116***a* with the use of monosilane and argon as a material gas at the ratio (monosilane:argon) of 0.1:99.9 to 1:9, preferably 1:99 to 5:95. It is preferable that the RF power 60 density during the deposition is controlled to be 0.0017 to 0.48 W/cm<sup>2</sup>. It is preferable that the RF power density is as high as possible since the quality of the film is improved enough to obtain a gettering effect and the deposition rate is improved. In addition, it is preferable that the pressure during 65 the deposition is controlled to be 1.333 Pa (0.01 Torr) to 133.322 Pa (1 Torr). It is preferable that the pressure is as high

14

as possible since the deposition rate is improved. Further, it is preferable that the deposition temperature is controlled to be  $300 \text{ to } 500^{\circ} \text{ C}$ . In this way, the second semiconductor film 116a can be formed by plasma CVD, which includes argon at a density of  $1\times10^{18}$  to  $1\times10^{22}$  atoms/cm<sup>3</sup>, preferably  $1\times10^{20}$  to  $1\times10^{21}$  atoms/cm<sup>3</sup>, and with which a gettering effect can be obtained. By controlling the deposition condition for the second semiconductor film within the ranges described above, damage to the oxide film (barrier layer) 115 during the deposition can be reduced so that variation in film thickness of the first semiconductor film and defects of holes formed in the first semiconductor film can be suppressed.

The inclusion of ions of a rare gas element that is an inert gas in the film has two meanings. One is that a dangling bond is formed to give strain to the semiconductor film, and the other is that strain is given among lattices of the semiconductor film. In order to give strain among the lattices of the semiconductor film, it is remarkably effective to use an element that has a larger atomic radius than silicon, such as argon (Ar), krypton (Kr), or xenon (Xe). In addition, the inclusion of the rare gas element in the film forms not only lattice strain but also an unpaired electron to contribute to a gettering action.

Next, a heat treatment is performed for gettering in order to reduce the density of the metal element (nickel) in the first semiconductor film or to remove the metal element (FIG. 2H). As the heat treatment for gettering, a heat treatment of intense light irradiation, a heat treatment using a furnace, or a heat treatment of putting a substrate into heated gas and taking the substrate out after being left for several minutes may be used. This gettering makes the metal element move in the direction of arrows in FIG. 2H (that is, the direction from the substrate side toward the surface of the second semiconductor film) to remove the metal element included in a first semiconductor film 114e covered with the oxide film 115 or reduce the density of the metal element. The moving distance of the metal element in the gettering may be a distance almost as long as the thickness of the first semiconductor film, and gettering can be completed for a relatively short time. The nickel is all moved into a second semiconductor film 116b here so as to prevent segregation to perform adequate gettering such that there is almost no nickel included in the first semiconductor film 114e, that is, the nickel density in the film is  $1 \times 10^{18}$  atoms/cm<sup>3</sup> or less, preferably  $1 \times 10^{17}$  atoms/cm<sup>3</sup> or less. Note that the oxide film 115 also functions as a gettering site in addition to the second semiconductor film.

Next, with the oxide film 115 as an etching stopper, only the second semiconductor film 116b is selectively removed. As a method for etching only the second semiconductor film 116b selectively, dry etching with ClF<sub>3</sub> without the use of plasma or wet etching with an alkali solution such as a solution including hydrazine or tetramethyl ammonium hydroxide (chemical formula: (CH<sub>3</sub>)<sub>4</sub>NOH; abbreviation: TMAH) can be employed. In the etching here, overetching takes less time in order to prevent a pin hole from being formed in the first semiconductor film. According to measurement of the nickel density at the surface of the oxide film (barrier layer) 115 by TXRF after removing the second semiconductor film 116b, nickel is detected in concentrated amounts. Therefore, it is preferable to remove the oxide film (barrier layer) 115 in a subsequent step.

Next, the oxide film 115 is removed by using an etchant including hydrofluoric acid.

Next, the first semiconductor film 114e is subjected to patterning with the use of a known patterning technique to form a semiconductor film 117 in a desired shape (FIG. 2I).

After removing the oxide film (barrier layer) 115, it is preferable to form a thin oxide film at the surface of the first semiconductor film 114e by using ozone water before forming a mask comprising resist.

If necessary, before the patterning, doping with a slight 5 amount of impurity element (boron or phosphorous) is performed through the oxide film described above in order to control the threshold voltage of a TFT. When the doping is performed though the oxide film described above, the oxide film is removed, and another oxide film is formed by using a solution containing ozone.

After completing the step of forming the semiconductor film 117 in the desired shape, the surface of the semiconductor film 117 is cleaned with the use of an etchant including hydrofluoric acid, and an insulating film containing silicon as its main component is formed to serve as a gate insulating film. It is preferable to clean the surface and form the gate insulating film continuously without exposing to the air. In order to reduce the number of steps, this surface cleaning step may be omitted to form the gate insulating film and a conductive film (a gate electrode material) continuously.

The subsequent steps are the same as those of Embodiment Mode 1. Therefore, the detailed description thereof is omitted here.

#### Embodiment Mode 3

FIGS. 3A to 3J show here an example of performing a heat treatment more than once. The steps in FIGS. 3A to 3F are the same as the steps in FIGS. 2A to 2F. Therefore, the detailed description thereof is omitted here.

After performing the steps of FIGS. 3A to 3F in accordance with Embodiment Mode 2, the heat treatment for reducing strain of the first semiconductor film is again performed in a nitrogen atmosphere to obtain a flatter first semiconductor film 214a (FIG. 3G). In addition, the oxide film (barrier layer) 115 also becomes denser by the heat treatment.

Next, a second semiconductor film **216***a* including a rare gas element is formed on the oxide film (barrier layer) **115** (FIG. **3**H). The second semiconductor film **216***a* including the rare gas element is formed by plasma CVD or sputtering to form a gettering site of 10 to 300 nm in film thickness.

Next, a heat treatment is performed to perform genering for reducing the density of the metal element (nickel) in the first semiconductor film or removing the metal element (FIG. 3I). As the heat treatment for gettering, a heat treatment of intense light irradiation, a heat treatment using a furnace, or a heat treatment of putting a substrate into heated gas and taking the substrate out after being left for several minutes may be used. This gettering makes the metal element move in the direction of arrows in FIG. 3I (that is, the direction from the substrate side toward the surface of the second semiconductor film) to remove the metal element included in a first semiconductor film 214b covered with the oxide film (barrier layer) 115 or reduce the density of the metal element.

Next, with the oxide film (barrier layer) 115 as an etching stopper, only a second semiconductor film denoted by reference numeral 216b is selectively removed. Then, the oxide film (barrier layer) 115 is removed.

Next, the first semiconductor film **214***b* is subjected to patterning with the use of a known patterning technique to form a semiconductor film **217** in a desired shape (FIG. **3**J). After removing the oxide film (barrier layer) **115**, it is preferable to form a thin oxide film at the surface of the first 65 semiconductor film **214***b* by using ozone water before forming a mask comprising resist.

**16**

If necessary, before the patterning, doping with a slight amount of impurity element (boron or phosphorous) is performed through the oxide film described above in order to control the threshold voltage of a TFT. When the doping is performed though the oxide film described above, the oxide film is removed, and an oxide film is again formed by using a solution containing ozone.

After completing the step of forming the semiconductor film 217 in the desired shape, the surface of the semiconductor film 217 is cleaned with the use of an etchant including hydrofluoric acid, and an insulating film containing silicon as its main component is formed to serve as a gate insulating film. It is preferable to clean the surface and form the gate insulating film continuously without exposing to the air.

The subsequent steps are the same as those of Embodiment Mode 1. Therefore, the detailed description thereof is omitted here.

#### Embodiment Mode 4

FIGS. 4A to 4J show here an example of performing gettering after pattering of a semiconductor film. The steps in FIGS. 4A to 4F are the same as the steps in FIGS. 2A to 2D. Therefore, the detailed description thereof is omitted here.

After performing the steps of FIGS. 4A to 4D in accordance with Embodiment Mode 2, the first semiconductor film 114b is subjected to patterning with the use of a known patterning technique to form a semiconductor film 317a in a desired shape (FIG. 4E). It is preferable to form a thin oxide film at the surface of the first semiconductor film 114b by using ozone water before forming a mask comprising resist.

If necessary, before the patterning, doping with a slight amount of impurity element (boron or phosphorous) is performed through the oxide film described above in order to control the threshold voltage of a TFT. When the doping is performed though the oxide film described above, the oxide film is removed, and another oxide film is again formed by using a solution containing ozone.

Next, a heat treatment for reducing strain of the semiconductor film (a heat treatment of heating the semiconductor film instantaneously to approximately 400 to 1000° C.) is performed in a nitrogen atmosphere to obtain a flat semiconductor film 317b (FIG. 4F). Depending on the condition of this heat treatment, a defect remaining in a crystal grain can be repaired, that is, the crystallinity can be improved while reducing the strain.

Next, at the surface of the semiconductor film 317b, an oxide film (also referred to as a barrier layer) 315 to serve as an etching stopper is formed by using a solution containing ozone to have a film thickness of 1 to 10 nm (FIG. 4G). Since the oxide film 315 is formed by oxidizing the semiconductor film 317b reduced in strain, the oxide film also has favorable characteristics (for example, flatness and uniformity in film thickness). In addition, the formation of the oxide film makes it possible to keep an interface of the semiconductor film 317b further stable.

Next, a second semiconductor film 316a including a rare gas element is formed on this oxide film 315 (FIG. 4H).

Next, a heat treatment is performed for gettering in order to reduce the density of the metal element (nickel) in the first semiconductor film or to remove the metal element (FIG. 4I). As the heat treatment for gettering, a heat treatment of intense light irradiation, a heat treatment using a furnace, or a heat treatment of putting a substrate into heated gas and taking the substrate out after being left for several minutes may be used. This gettering makes the metal element move in the direction of arrows in FIG. 4I (that is, the direction from the substrate

side toward the surface of the second semiconductor film) to remove the metal element included in a first semiconductor film 317d covered with the oxide film 315 or reduce the density of the metal element.

Next, with the use of the barrier layer 315 as an etching stopper, only a second semiconductor film denoted by reference numeral 316b is selectively removed. Then, the oxide film 315 is removed.

Next, an insulating film containing silicon as its main component is formed to serve as a gate insulating film.  $^{10}$

The subsequent steps are the same as those of Embodiment Mode 1. Therefore, the detailed description thereof is omitted here.

#### Embodiment Mode 5

FIGS. 5A to 5J show here an example of performing a heat treatment more than once after pattering of a semiconductor film, and then performing gettering. The steps in FIGS. 5A to 5F are the same as the steps in FIGS. 2A to 2D. Therefore, the detailed description thereof is omitted here.

After performing the steps of FIGS. **5**A to **5**D in accordance with Embodiment Mode 2, the first semiconductor film 114b is subjected to patterning with the use of a known patterning technique to form a semiconductor film **417**a in a desired shape (FIG. **5**E). It is preferable to form a thin oxide film at the surface of the first semiconductor film **114**b by using ozone water before forming a mask comprising resist. 30

If necessary, before the patterning, doping with a slight amount of impurity element (boron or phosphorous) is performed through the oxide film described above in order to control the threshold voltage of a TFT. When the doping is performed though the oxide film described above, the oxide 35 film is removed, and another oxide film is formed by using a solution containing ozone.

Next, a heat treatment for reducing strain of the semiconductor film (a heat treatment of heating the semiconductor film instantaneously to approximately 400 to 1000° C.) is 40 performed in a nitrogen atmosphere to obtain a flat semiconductor film **417***b* (FIG. **5**F).

Next, at the surface of a semiconductor film 417c, an oxide film (also referred to as a barrier layer) 415 to serve as an etching stopper is formed by using a solution containing ozone to have a film thickness of 1 to 10 nm (FIG. 5G).

Next, the heat treatment for reducing strain of the semiconductor film is again performed in a nitrogen atmosphere to obtain a flatter semiconductor film 417d (FIG. 5H). In addition, the oxide film 415 also becomes denser by the heat treatment.

Next, a second semiconductor film **416***a* including a rare gas element is formed on this oxide film **415** (FIG. **5**I).

Next, a heat treatment is performed for gettering in order to reduce the density of the metal element (nickel) in the first semiconductor film or to remove the metal element (FIG. 5J). As the heat treatment for gettering, a heat treatment of intense light irradiation, a heat treatment using a furnace, or a heat treatment of putting a substrate into heated gas and taking the substrate out after being left for several minutes may be used. This gettering makes the metal element move in the direction of arrows in FIG. 5J (that is, the direction from the substrate side toward the surface of the second semiconductor film) to remove the metal element included in a first semiconductor film 417e covered with the oxide film 415 or reduce the density of the metal element.

**18**

Next, with the oxide film **415** as an etching stopper, only a second semiconductor film denoted by reference numeral **416***b* is selectively removed. Then, the oxide film **415** is removed.

Next, an insulating film containing silicon as its main component is formed to serve as a gate insulating film.

The subsequent steps are the same as those of Embodiment Mode 1. Therefore, the detailed description thereof is omitted here.

#### Embodiment Mode 6

FIGS. **6**A to **6**I show here an example that is partially different in step sequence from Embodiment Mode 2, specifically an example of performing a heat treatment for reducing strain after an oxidation treatment. The steps in FIGS. **6**A to **6**D are the same as the steps in FIGS. **2**A to **2**D. Therefore, the detailed description thereof is omitted here.

After performing the steps of FIGS. **6**A to **6**D in accordance with Embodiment Mode 2, at the surface of a semiconductor film **514***a*, an oxide film (also referred to as a barrier layer) **515** to serve as an etching stopper is formed by using a solution containing ozone to have a film thickness of 1 to 10 nm (FIG. **6**E).

Before forming the oxide film **515** by using the solution containing ozone, a surface oxide film formed by laser light irradiation may be removed.

Next, a heat treatment for reducing strain of the semiconductor film (a heat treatment of heating the semiconductor film instantaneously to approximately 400 to 1000° C.) is performed in a nitrogen atmosphere to obtain a semiconductor film **514***b* (FIG. **6**F).

Next, a second semiconductor film **516***a* including a rare gas element is formed on this oxide film **515** (FIG. **6**G).